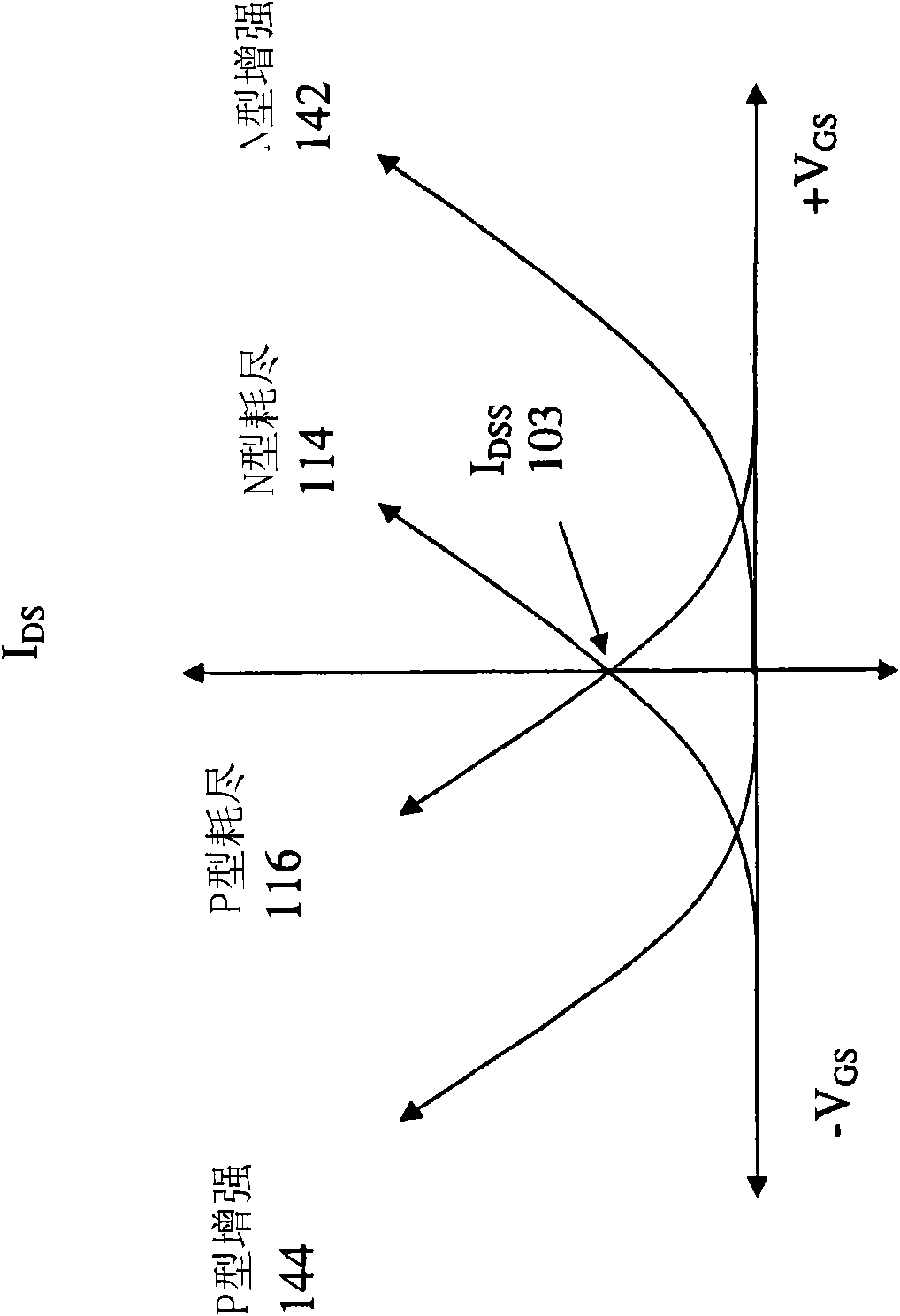

Depletion-mode MOSFET circuit and applications

A positive voltage, single resistance technology, applied in the analog field of depletion mode MOSFET, can solve the problem that "positive logic" circuit cannot be used

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

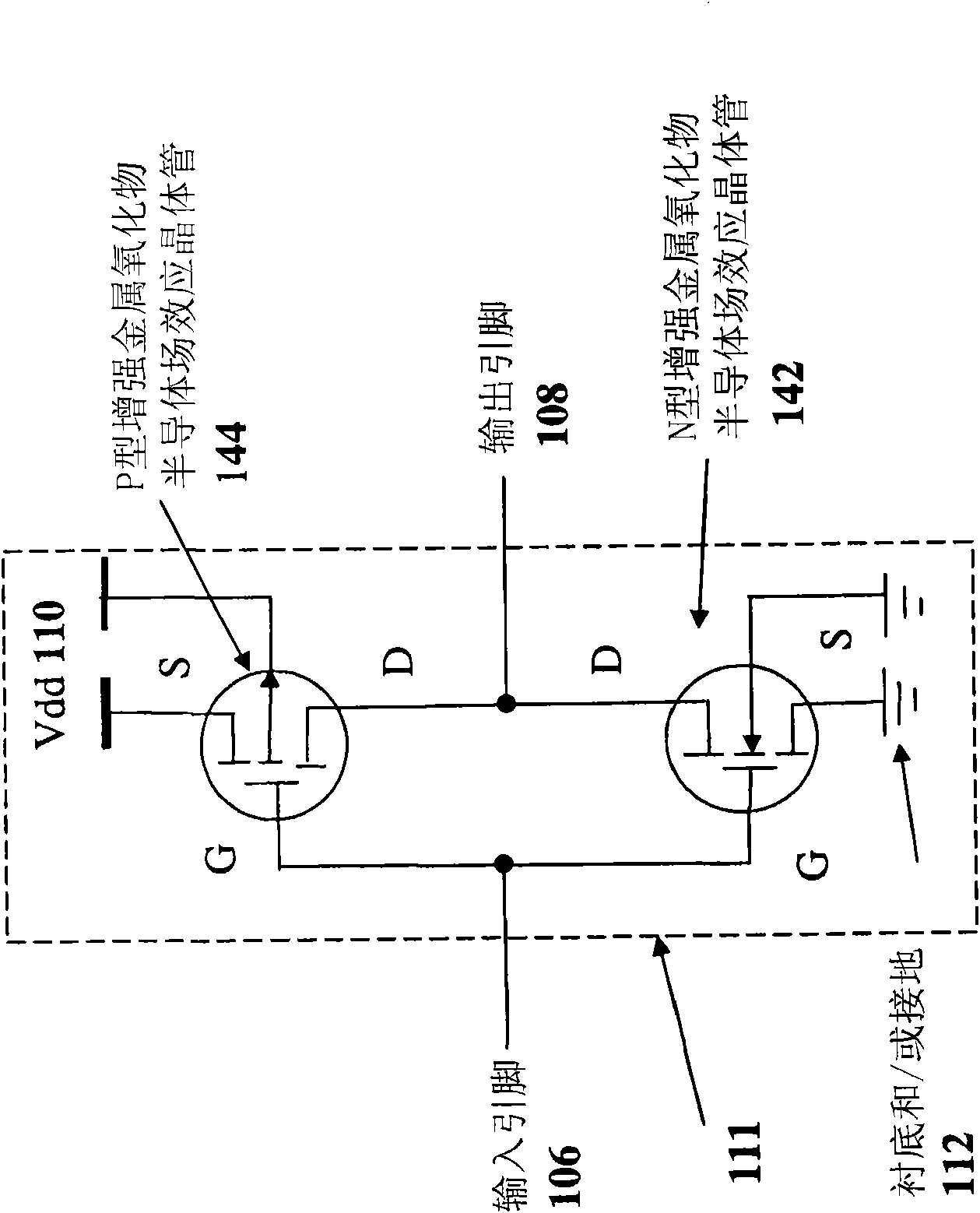

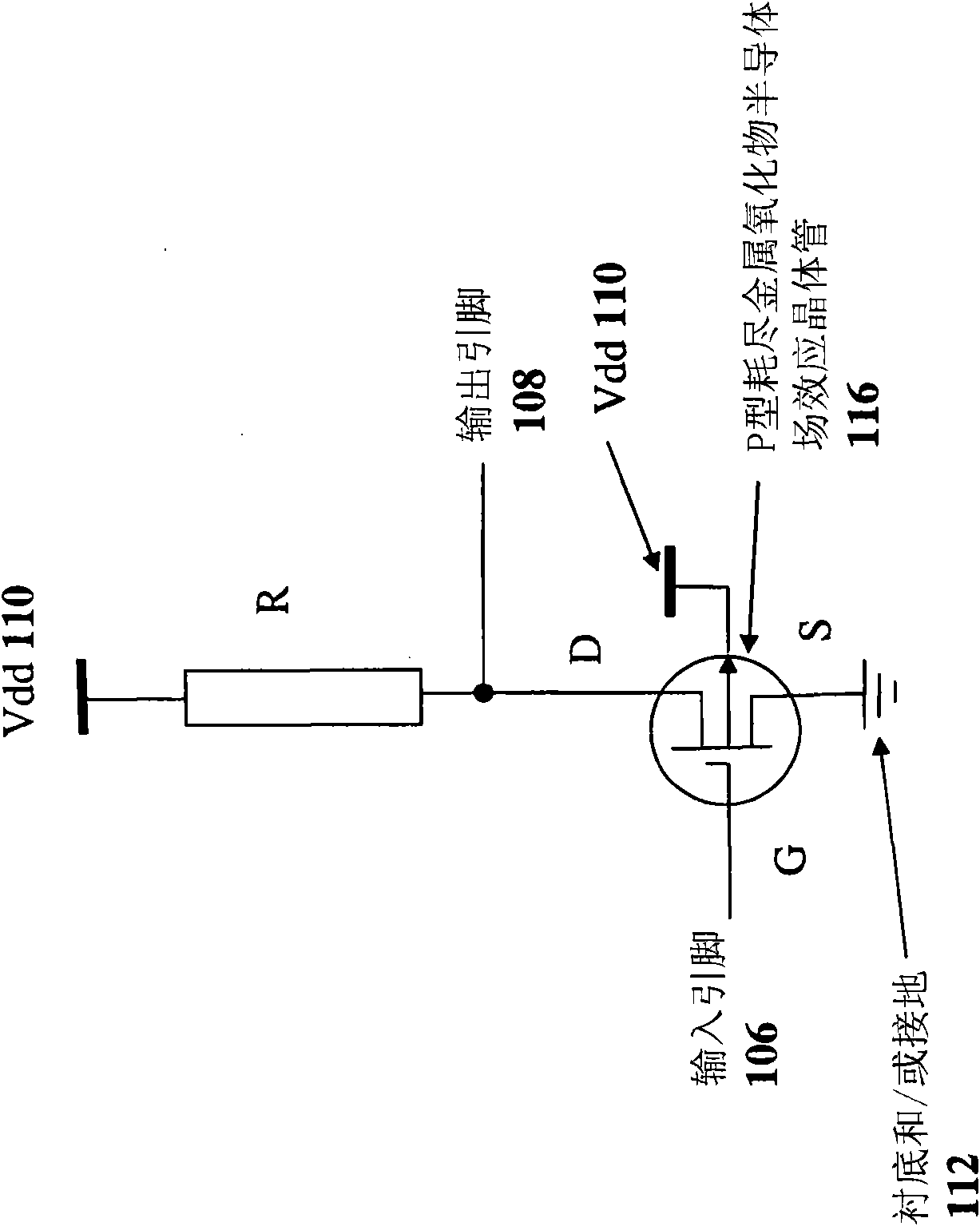

[0060] Computer simulation techniques for MOSFETs present fundamental difficulties regarding the definition of the source and drain pins; due to the symmetrical structure of the MOSFET, these two pins are practically interchangeable, and the source and drain The definition of the name is just naming and doesn't matter. However, in a computer simulation program, both types of pins must be precisely defined before calculations can begin. Traditionally, there are two methods to define the pins of MOSFETs by using DC voltage or majority carriers. For the voltage method, the pin with the lower DC voltage is generally considered the source, and the pin with the higher DC voltage is considered the drain. Another conventional method to identify the source and drain is to use the majority carrier concept that considers the pin supplying the majority carriers as the source. Unfortunately, both of these methods are imperfect.

[0061] Consider a conventional inverter 111 made of N-typ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com