Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

63 results about "Physical synthesis" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

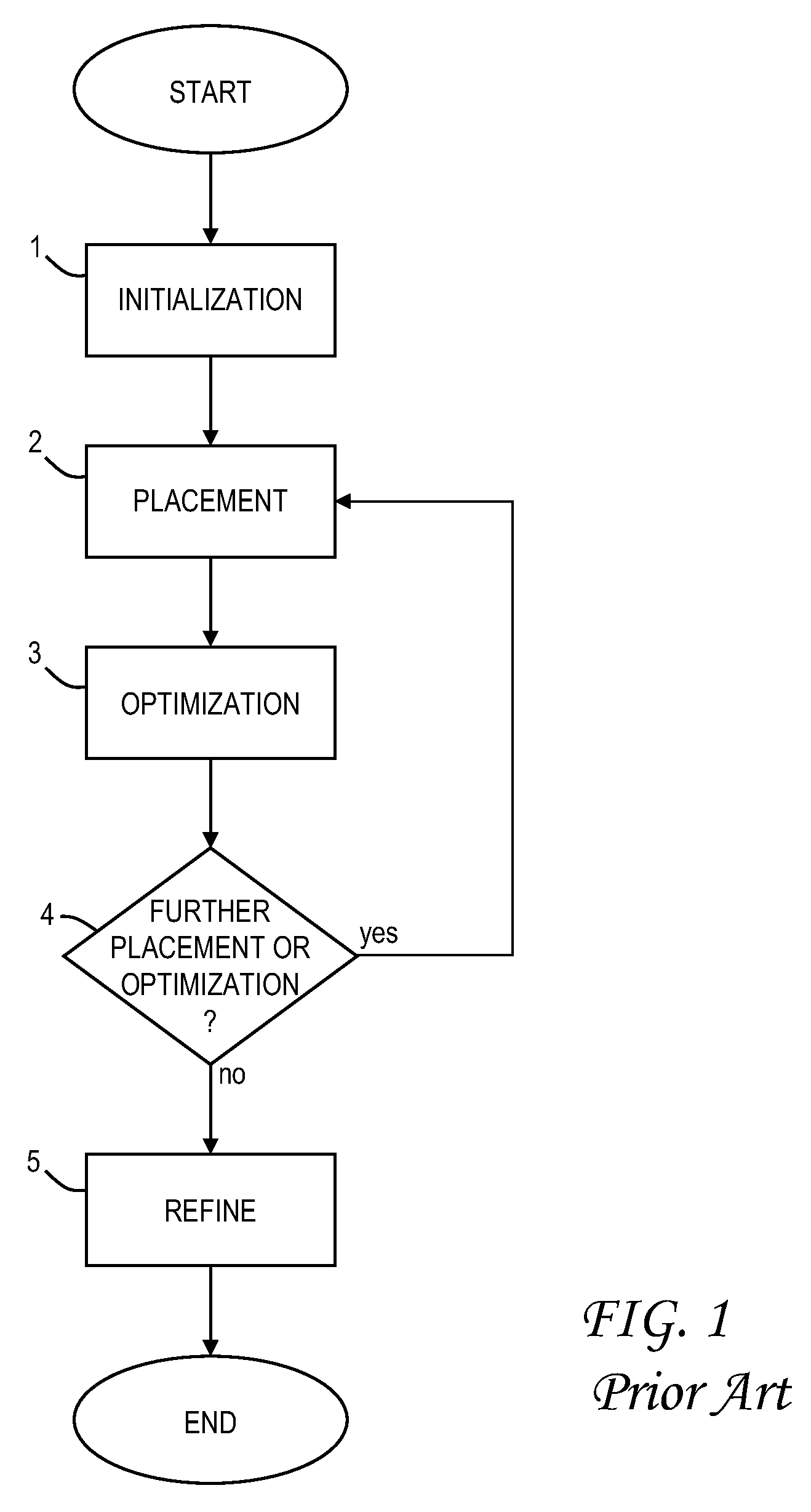

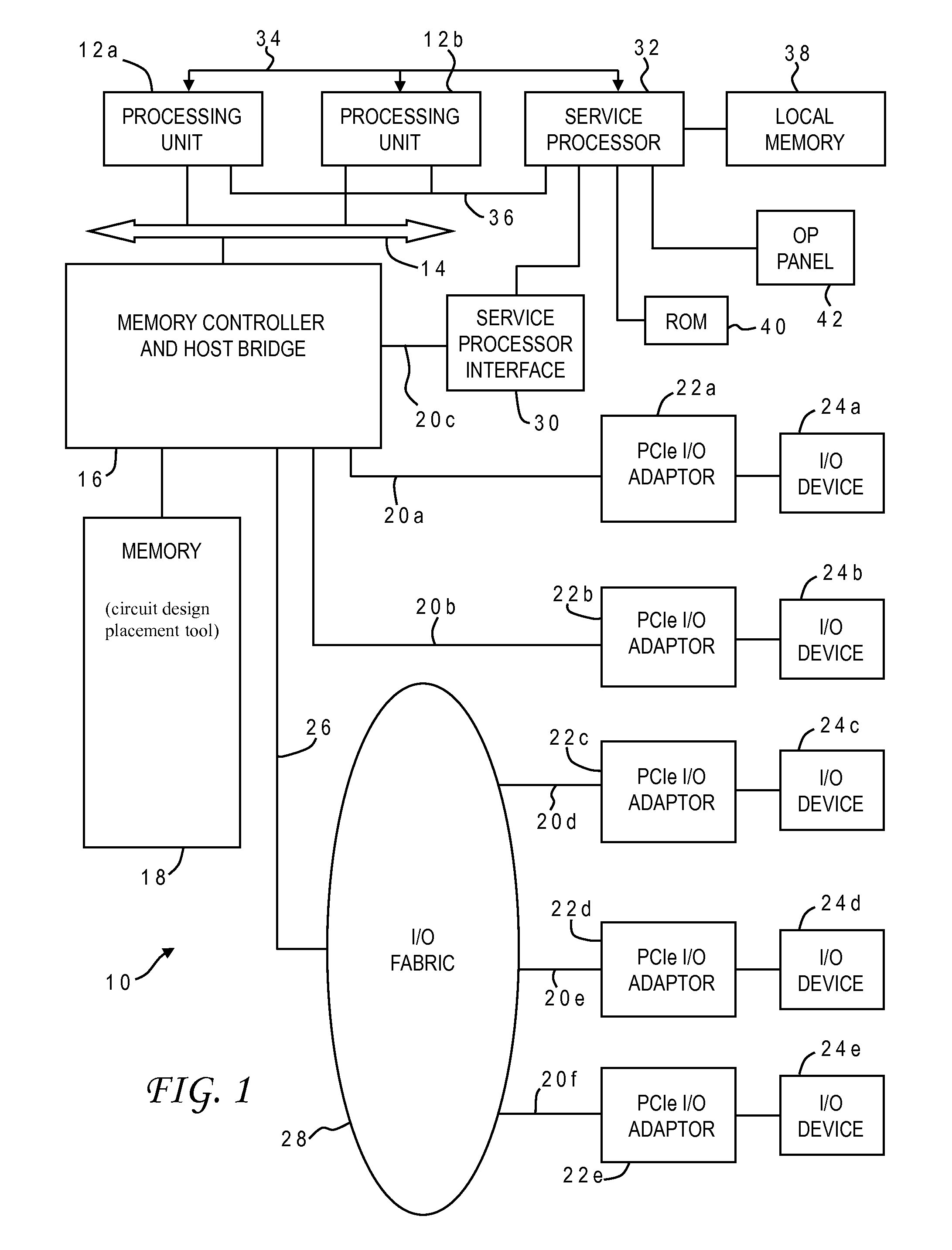

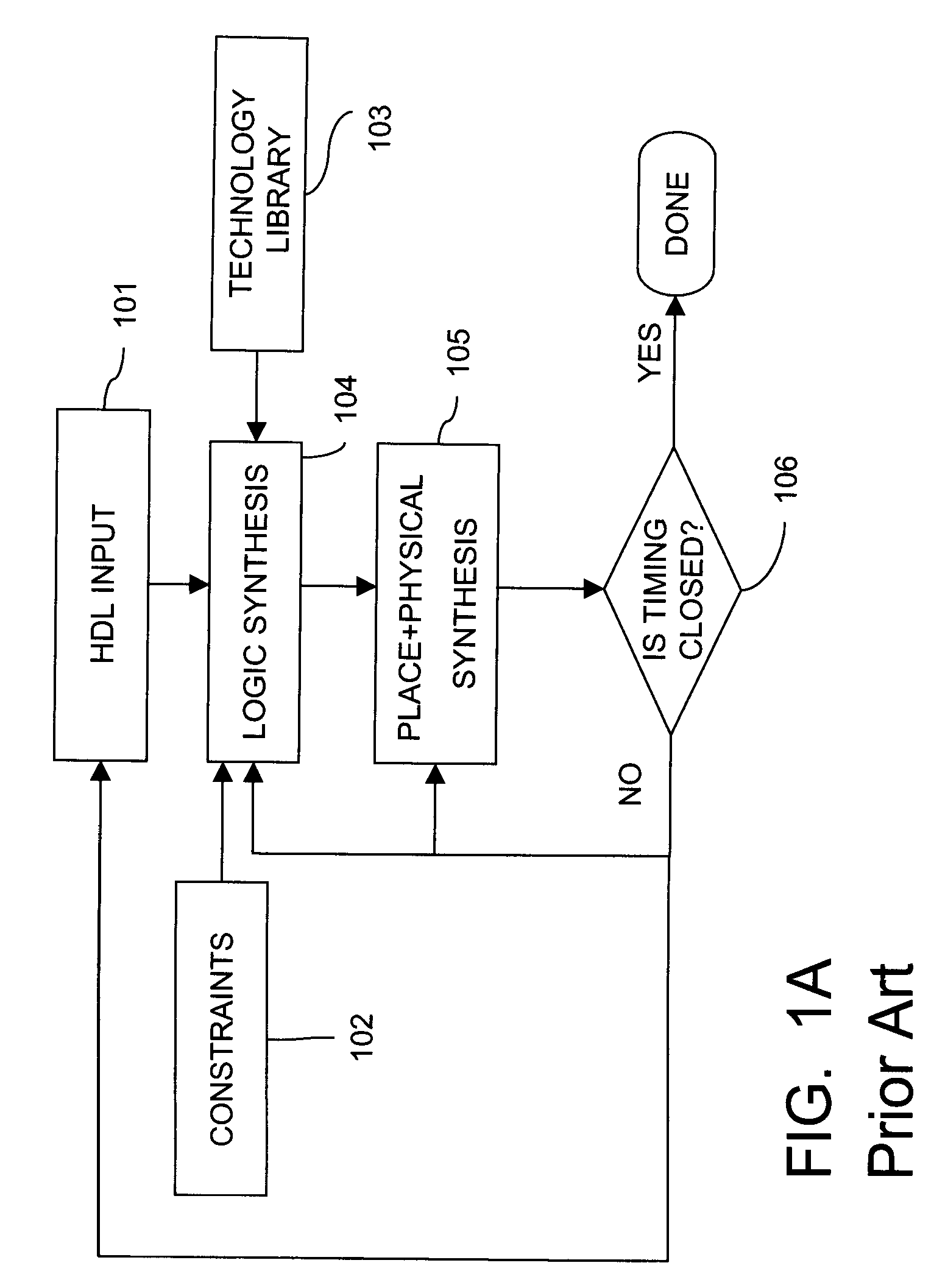

Architectural physical synthesis

ActiveUS20090031278A1Quality improvementEasy to placeComputer aided designSpecial data processing applicationsLocal congestionResource utilization

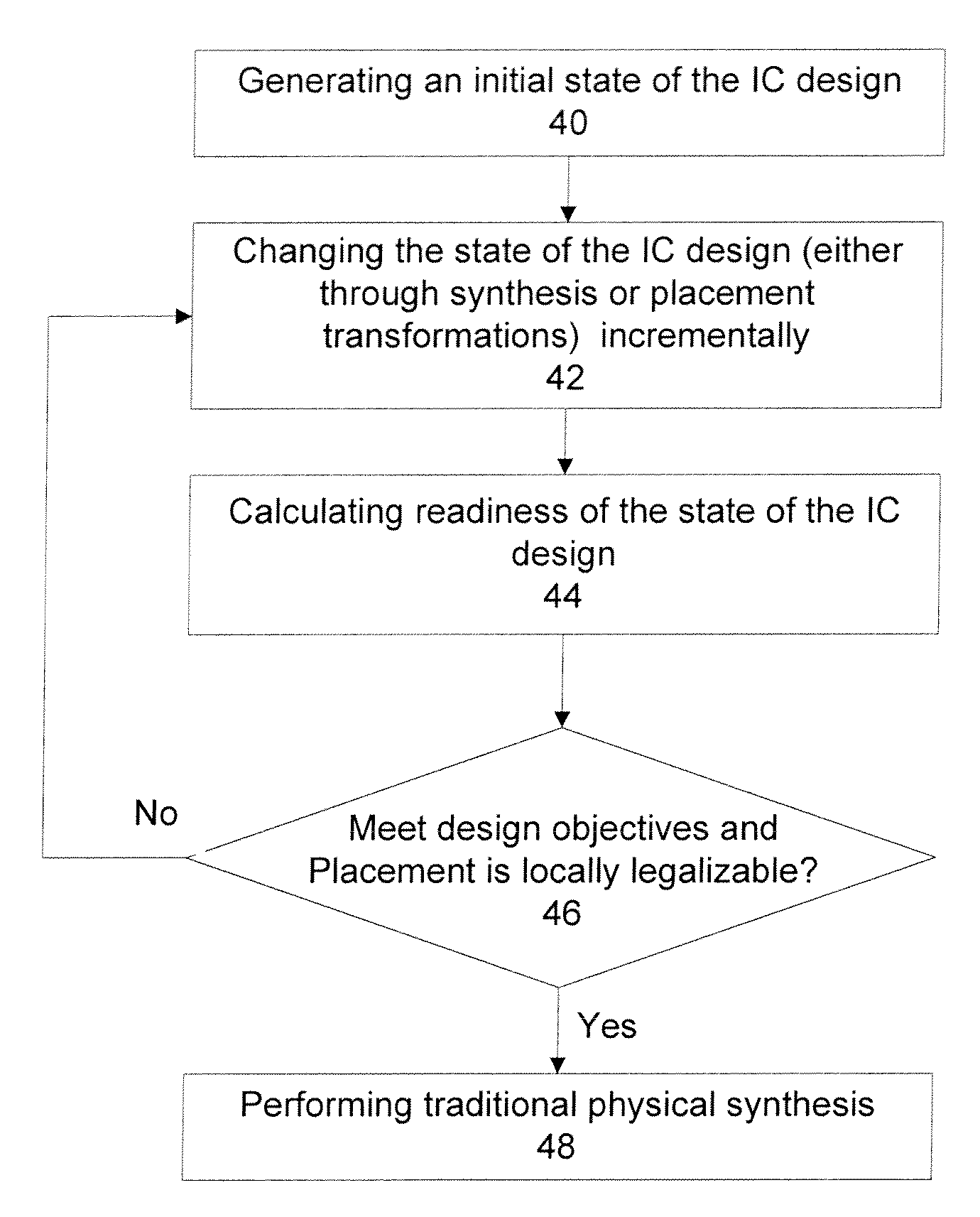

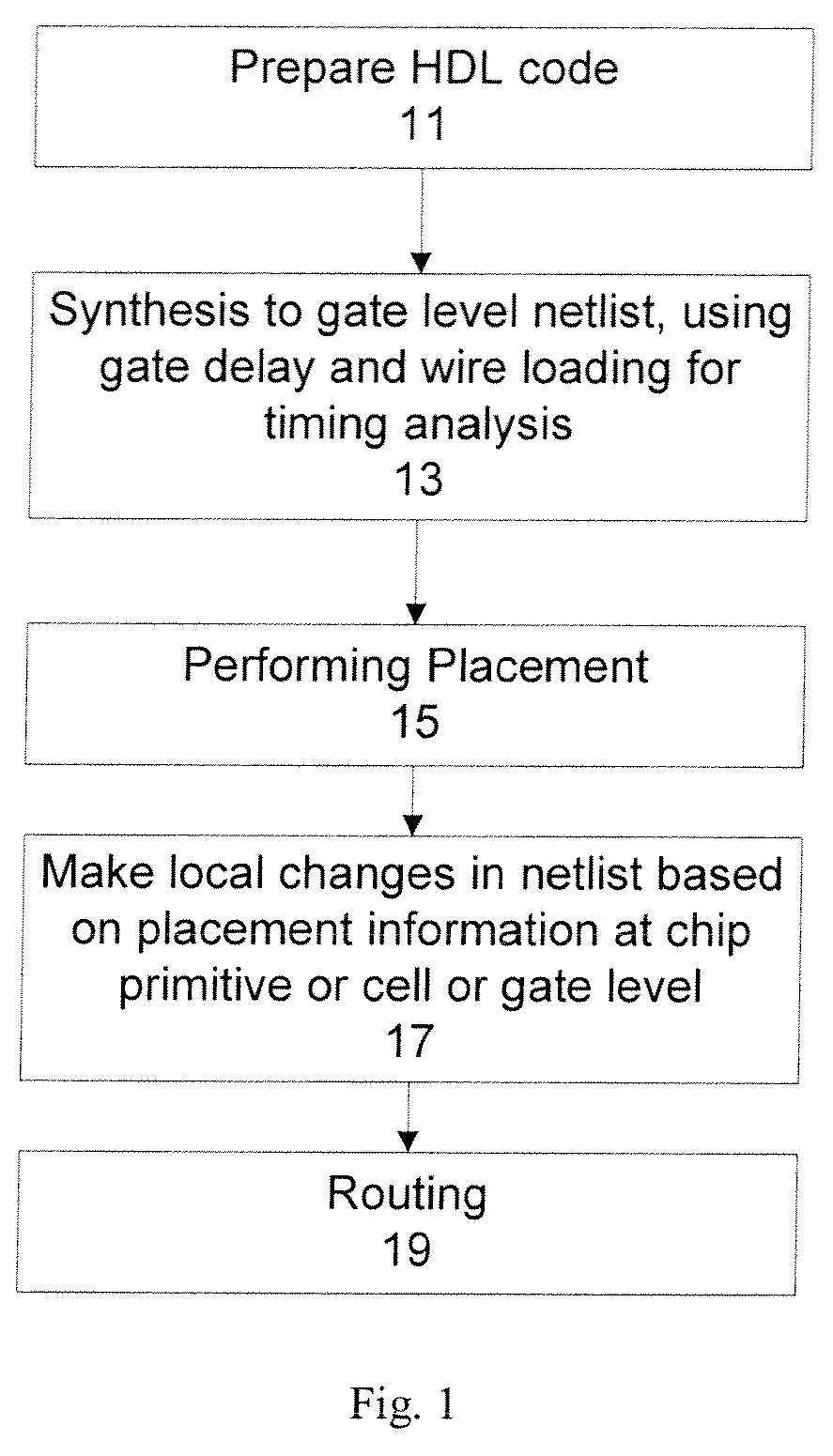

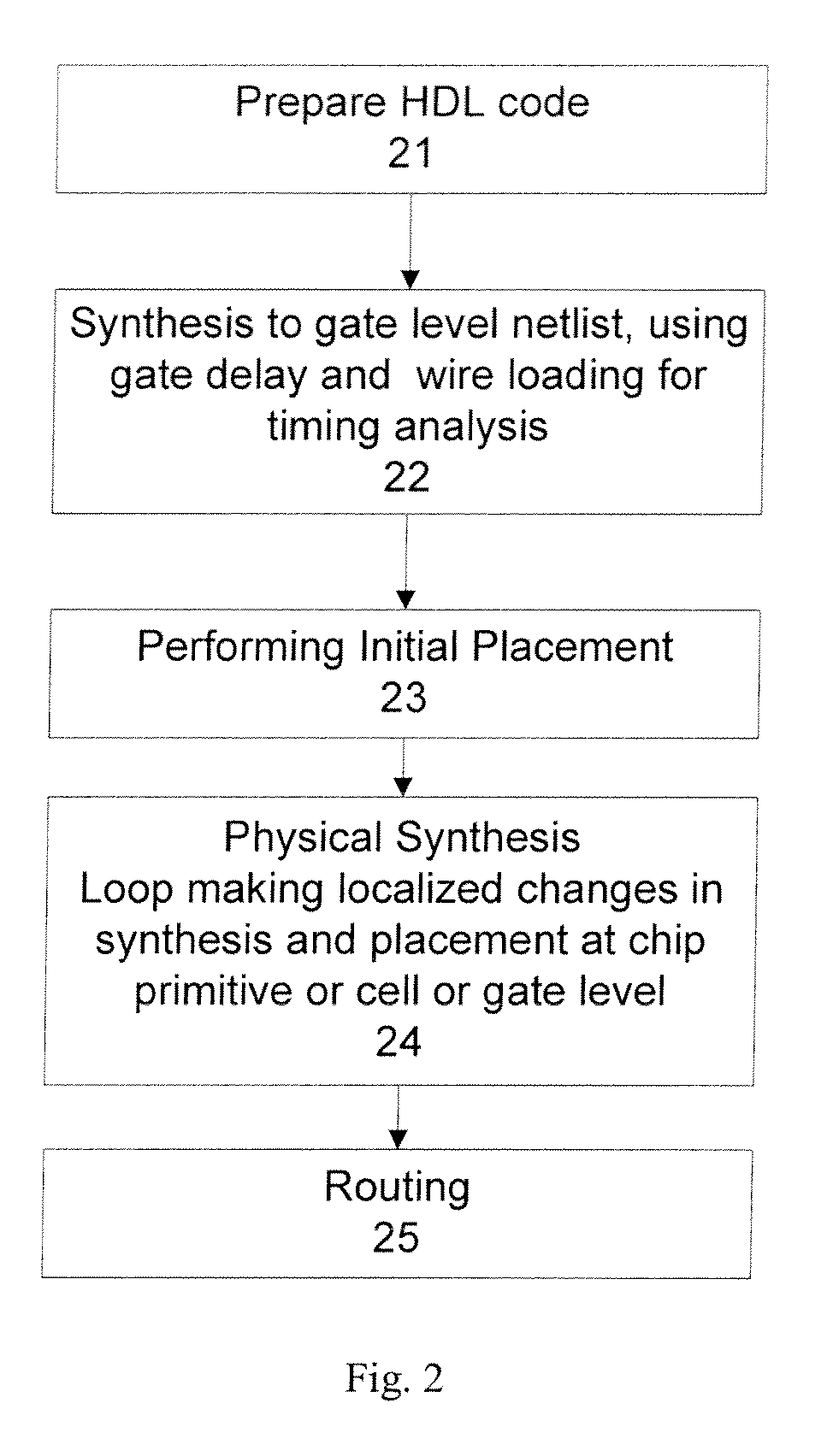

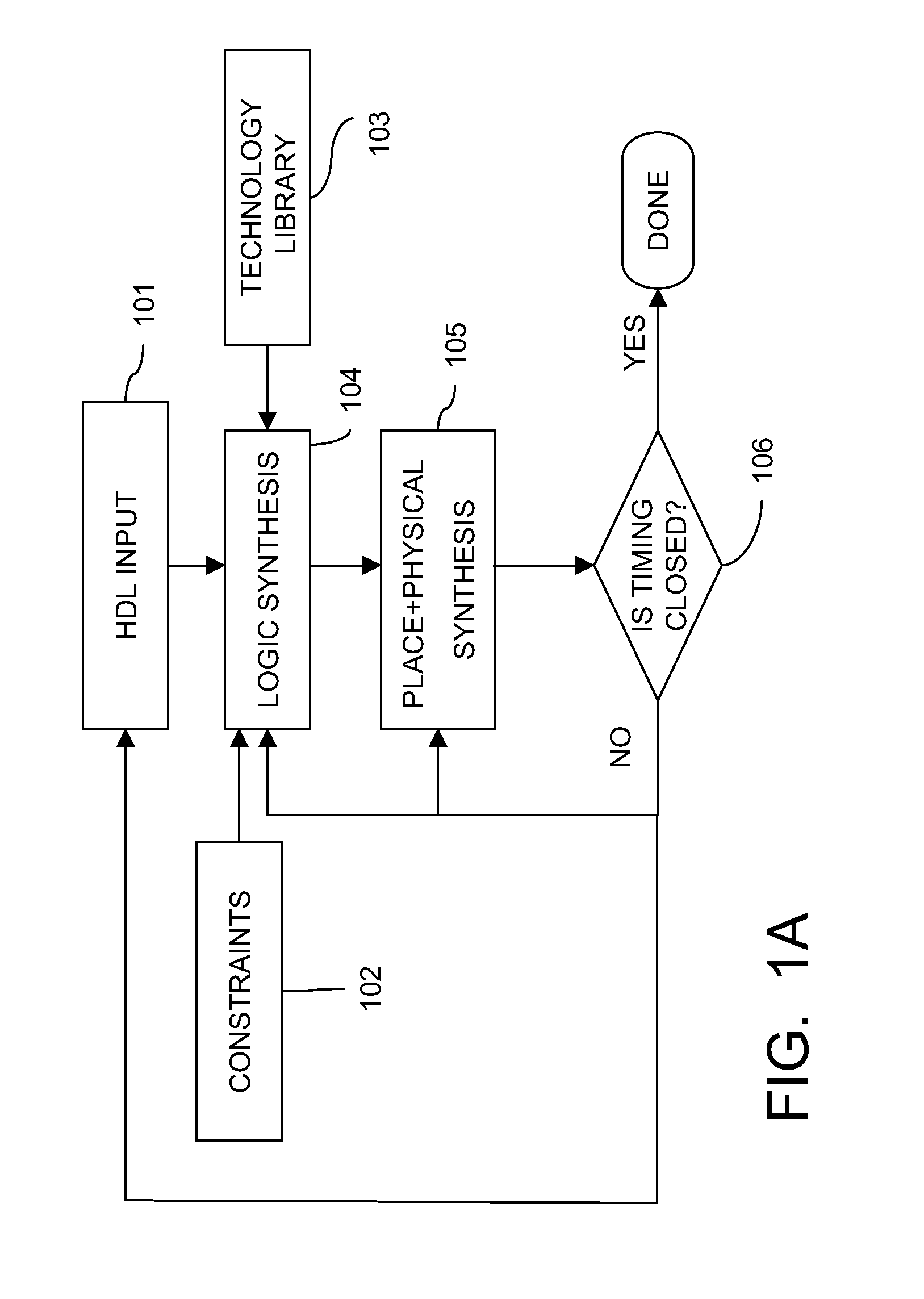

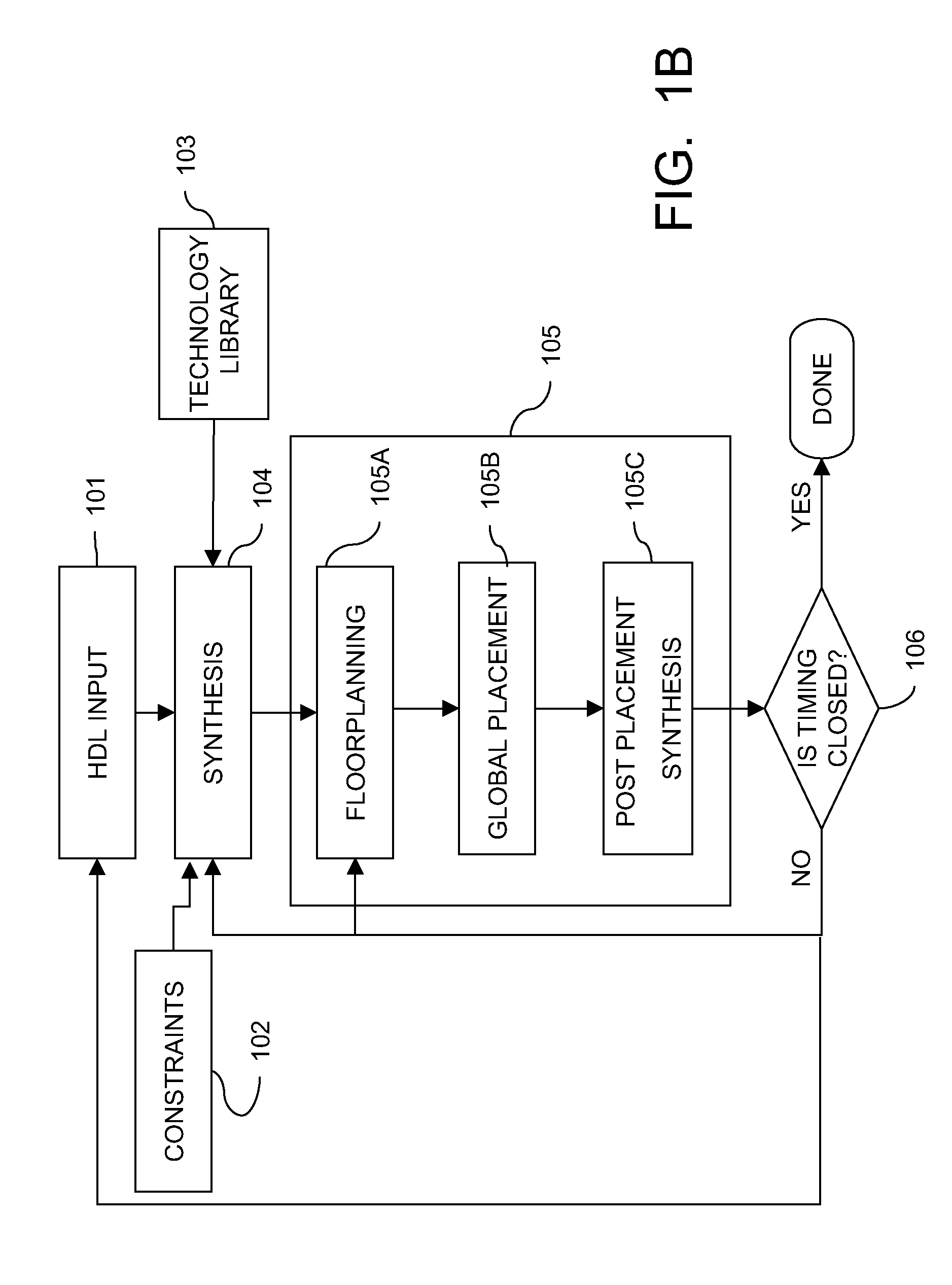

The present invention discloses methods and apparatuses to design an integrated circuit. According to one aspect, the present invention circuit design discloses an iterative process of synthesis and placement where each iteration provides incremental changes on the design of the integrated circuit. The incrementally iterative approach of the present invention provides a continuous advancement from synthesis to placement and vice versa, with the incremental improvements on synthesis made with knowledge of current instance placement, and the incremental improvements on placement made with knowledge of current circuit logic. According to another aspect, the present invention circuit design discloses incremental force directed placement transforms utilizing resource layers to address the heterogeneous resource distribution problem, where the force on an instance can be a weighted average of the forces from its resource layers based on the local congestion of those resources. In addition, incremental area removal method can be utilized to address resource utilization problem through a quality metric based on force directed placement transforms, such as a resource demand topological mapping.

Owner:SYNOPSYS INC

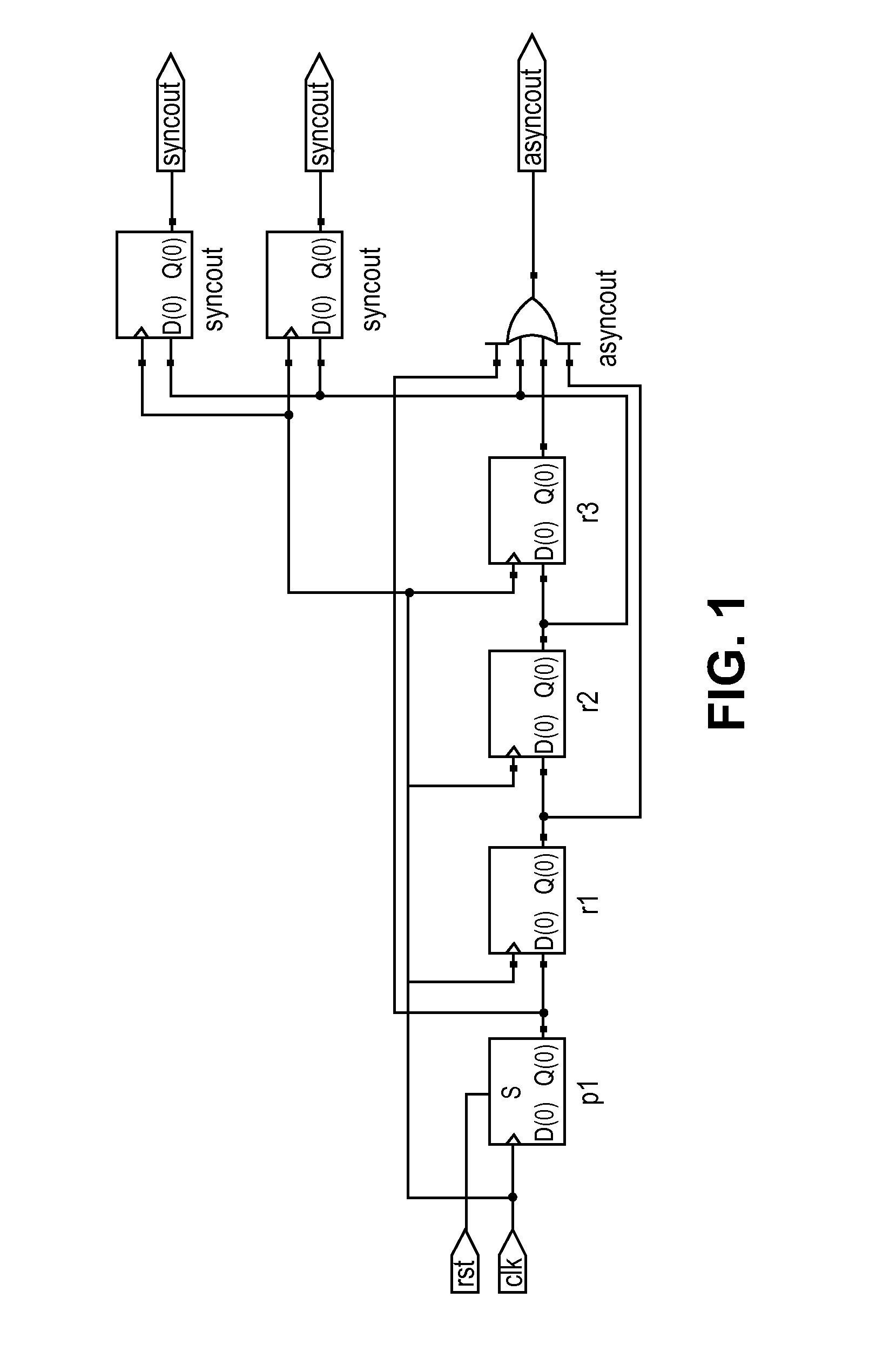

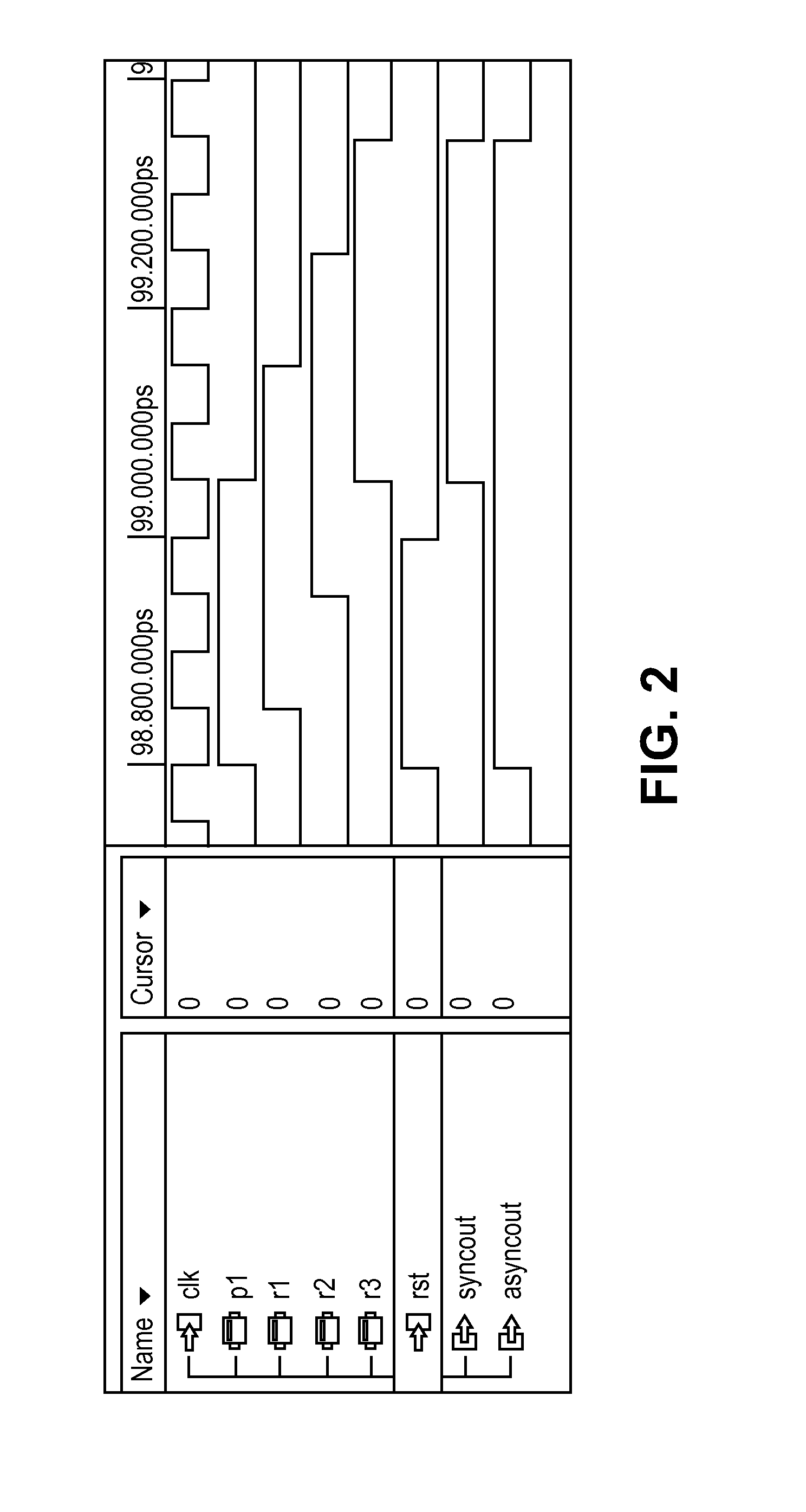

Methods and apparatuses for reset conditioning in integrated circuits

ActiveUS7594211B1Reduce metastability problemReliable signalData resettingComputer aided designPropagation delayProcessor register

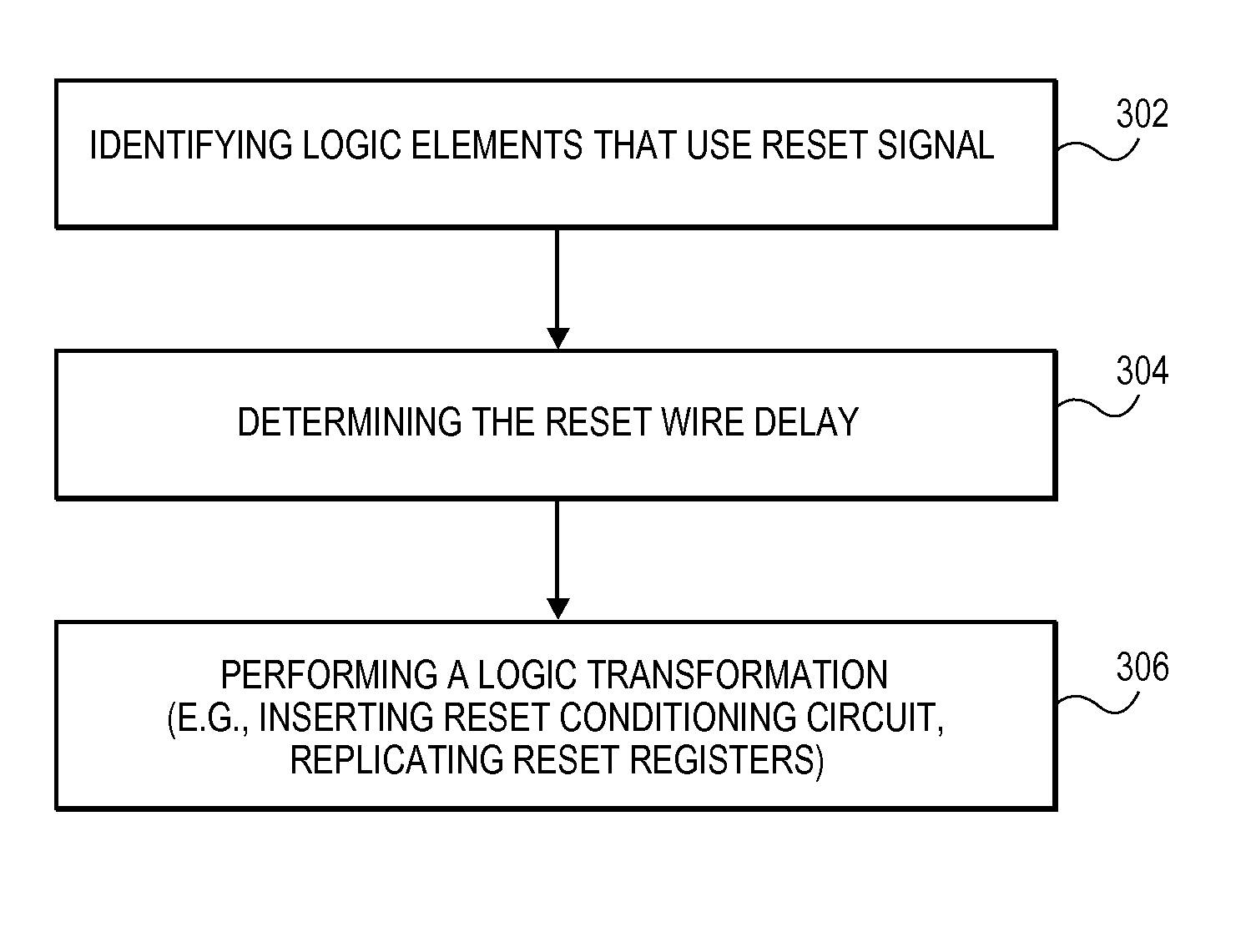

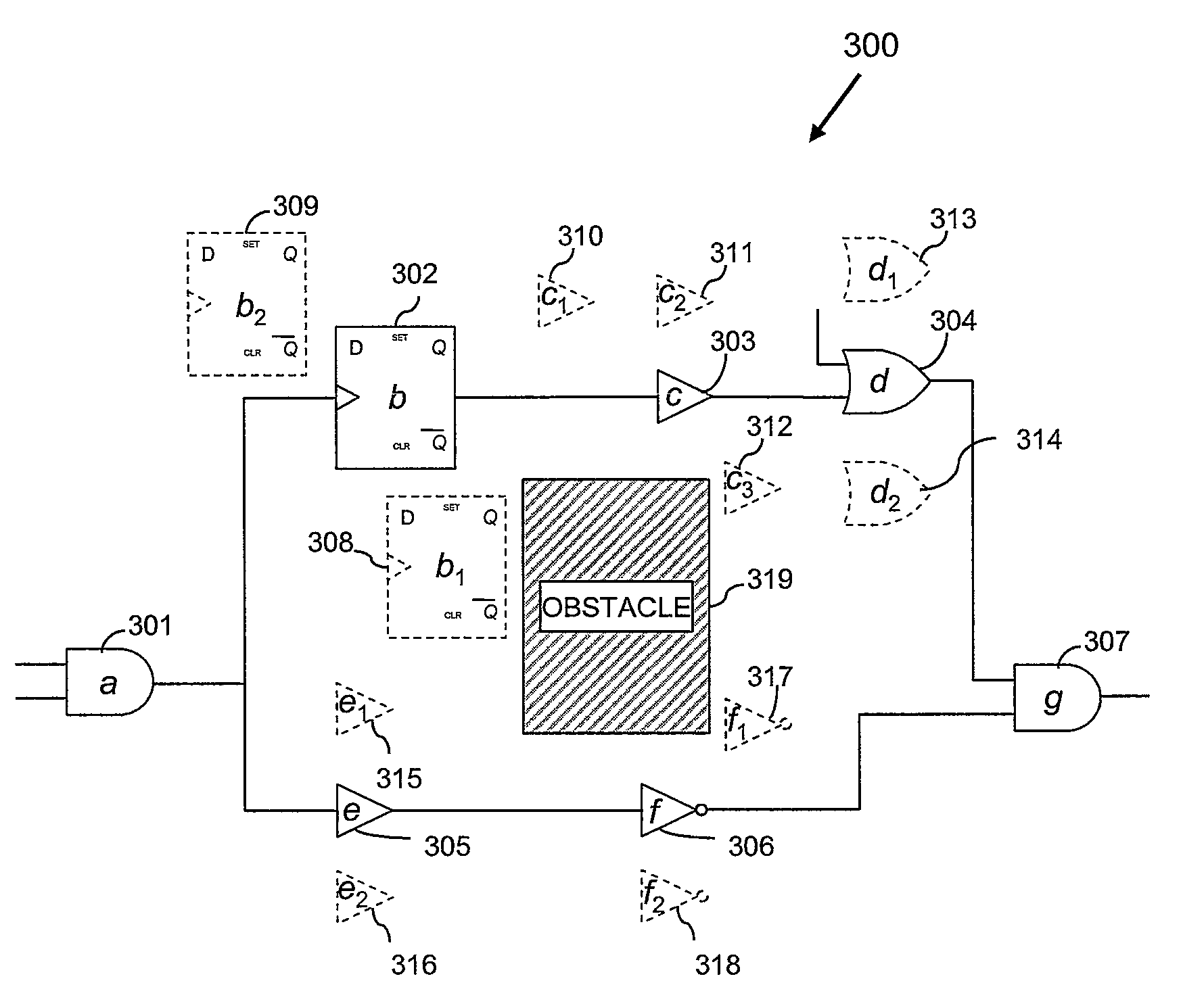

Embodiments of the present invention disclose methods and apparatuses to reduce metastability problem related to propagation delay of reset signals in integrated circuits, with preferred applications in automatic physical synthesis for RTL (register transfer level) netlist. In an embodiment, a reset conditioning circuit is inserted into the original integrated circuit to make the reset behavior more reliable to avoid unpredictable states, especially for the de-assertion state of the reset signal. The reset conditioning circuit can provide an asynchronous reset signal output with extended duration so that all the load registers employing asynchronous reset signal will get the reset properly. Further, the reset conditioning circuit can modify the timing of the reset signal so that its de-assertion edge is synchronized with a rising clock edge. In another embodiment, the reset conditioning circuit replicates a synchronous reset signal to provide a reset signal closer to loads or registers at a plurality of circuit modules or partitions. The generation of the reset conditioning circuit is well suitable for physical synthesis of RTL netlists, especially for automatic physical synthesis.

Owner:SYNOPSYS INC

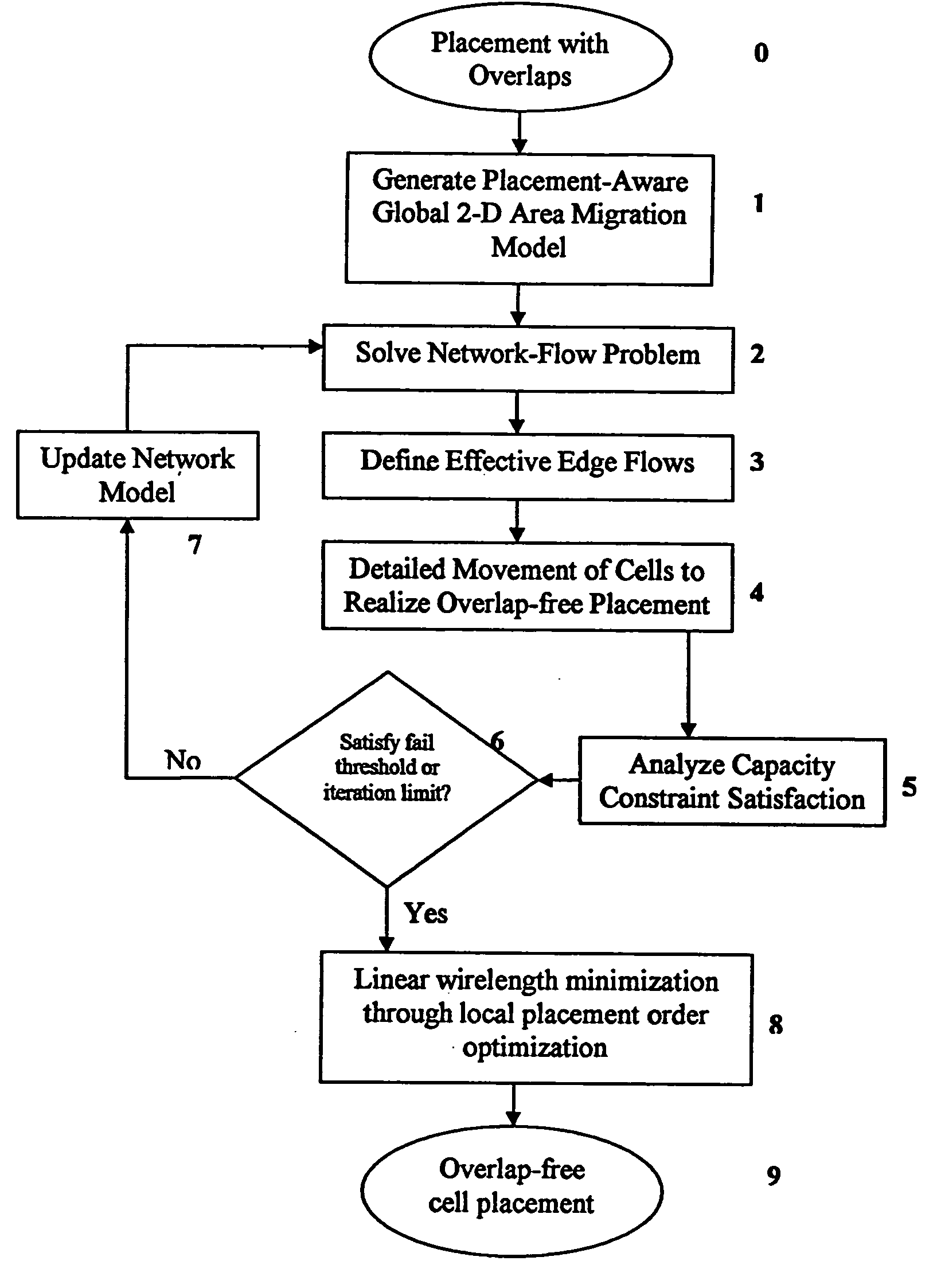

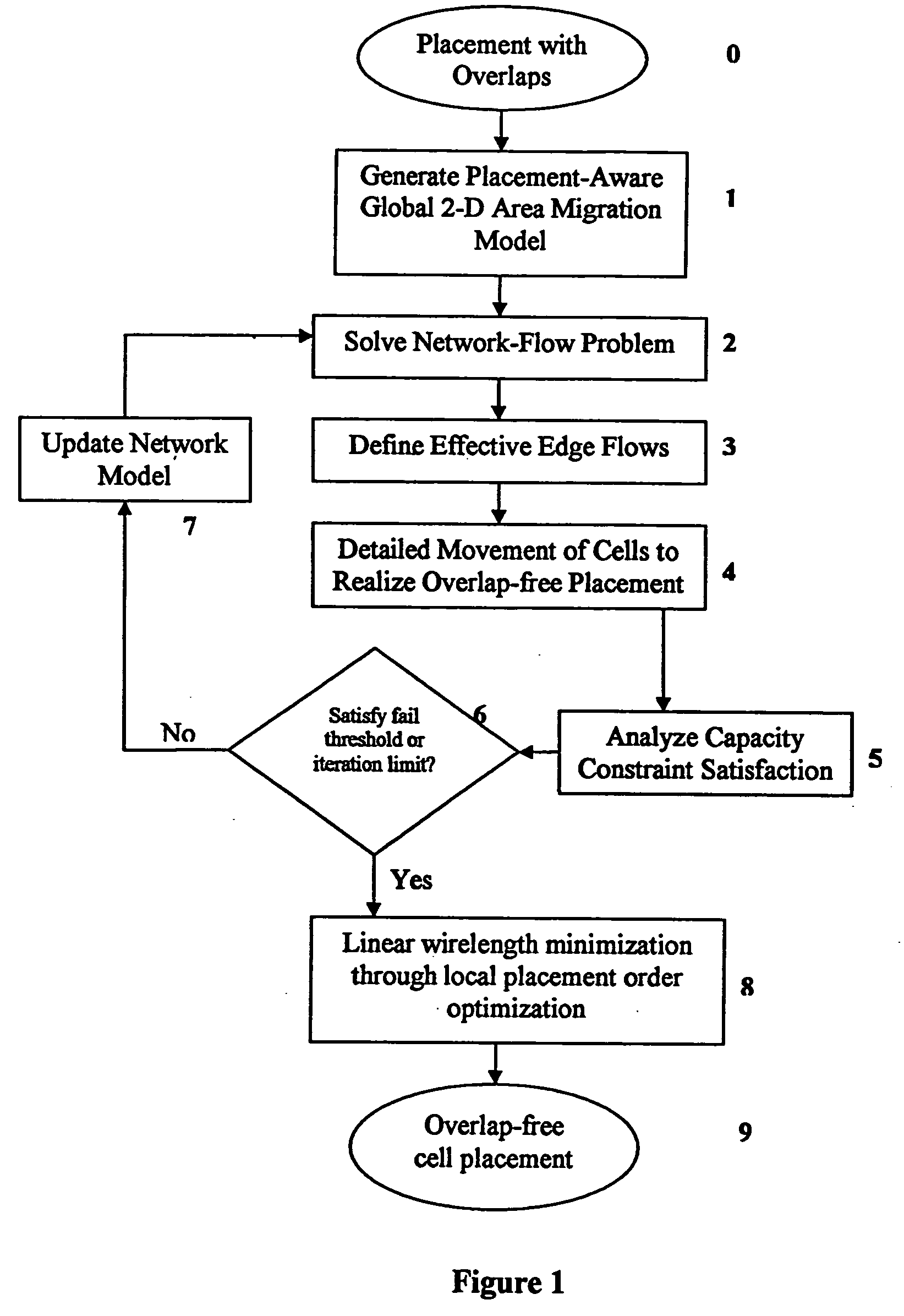

Method for legalizing the placement of cells in an integrated circuit layout

InactiveUS20050166169A1Maintain qualityAutomatically resolve cell overlapsComputer aided designSoftware simulation/interpretation/emulationHigh cellIntegrated circuit layout

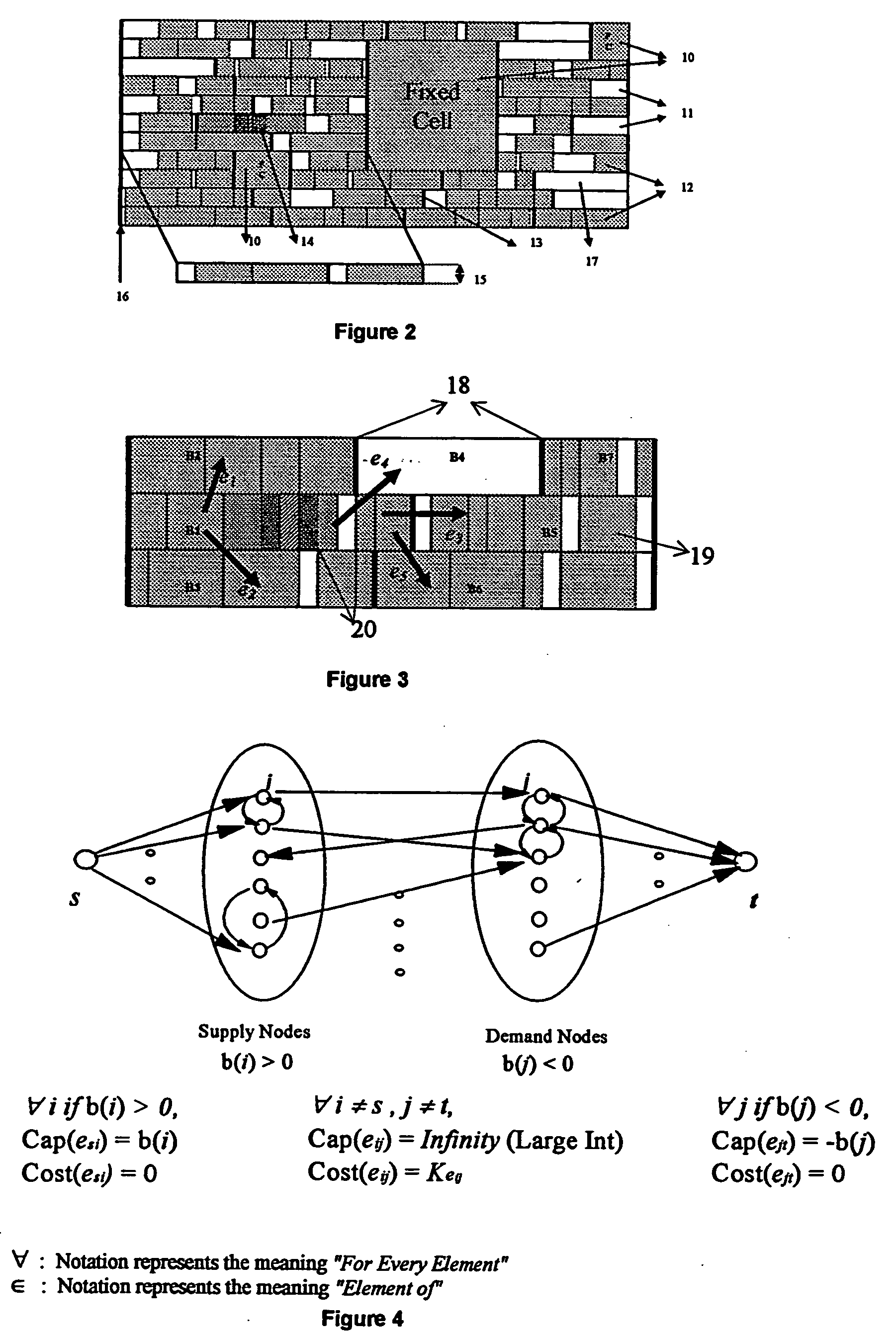

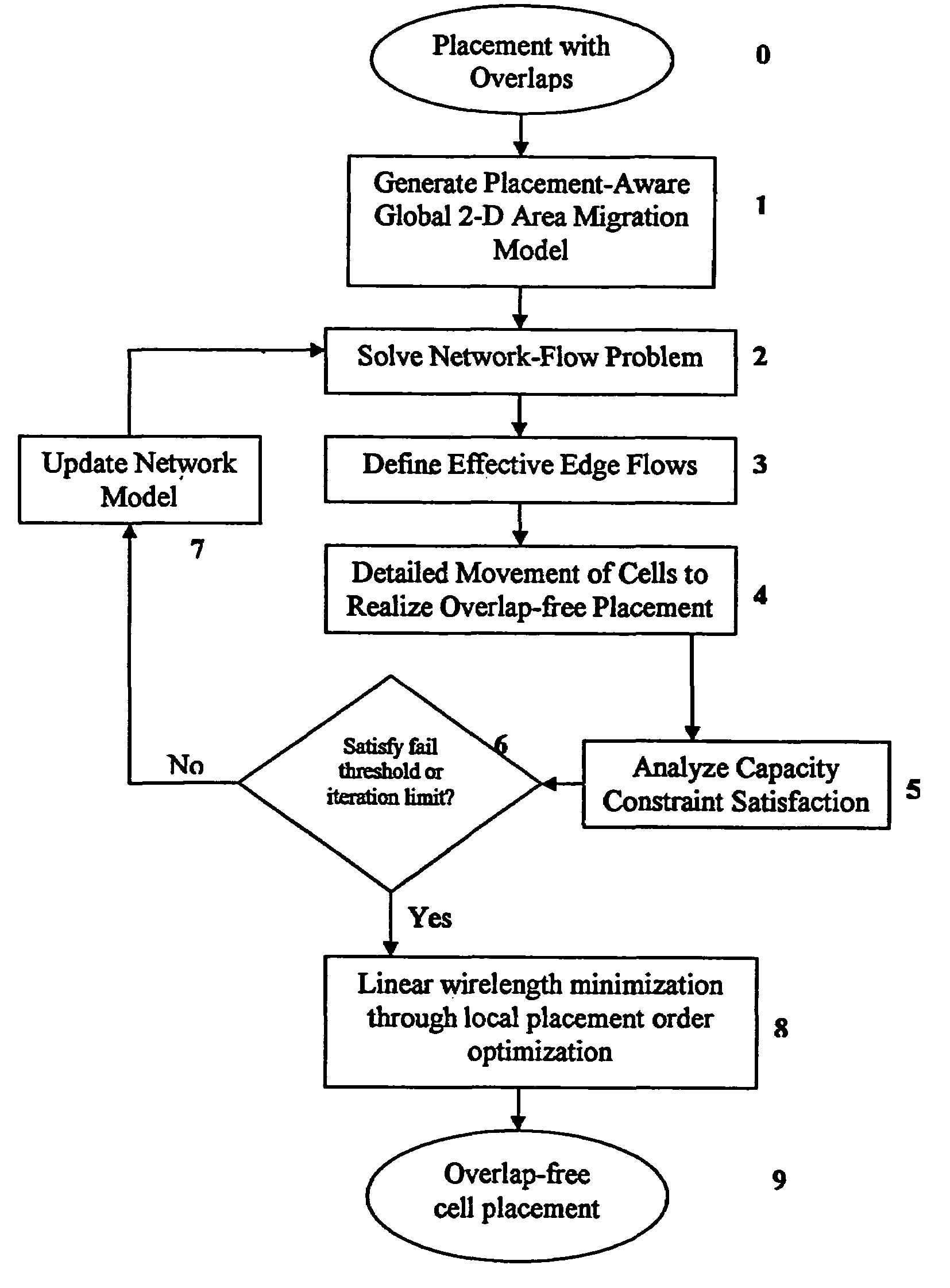

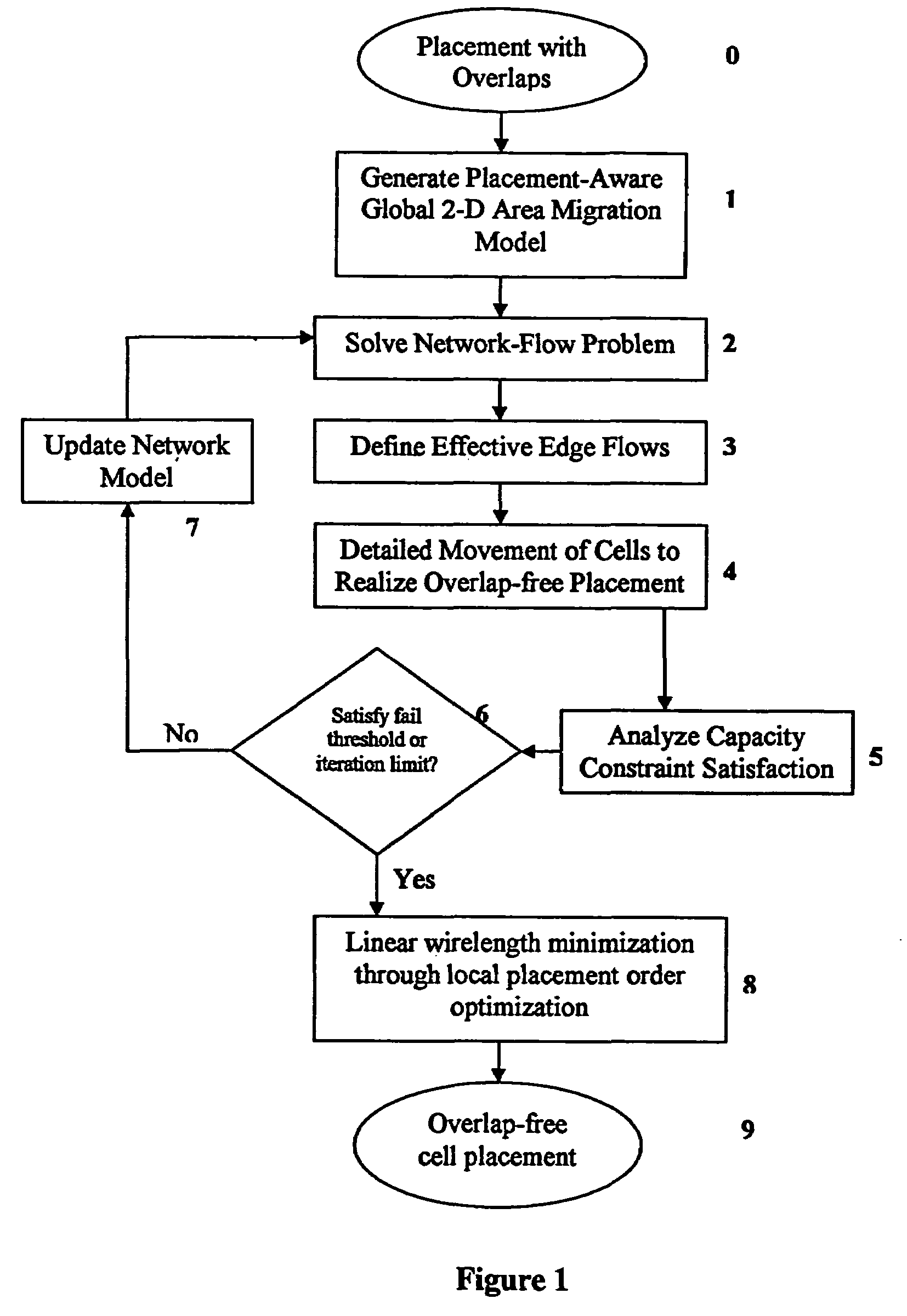

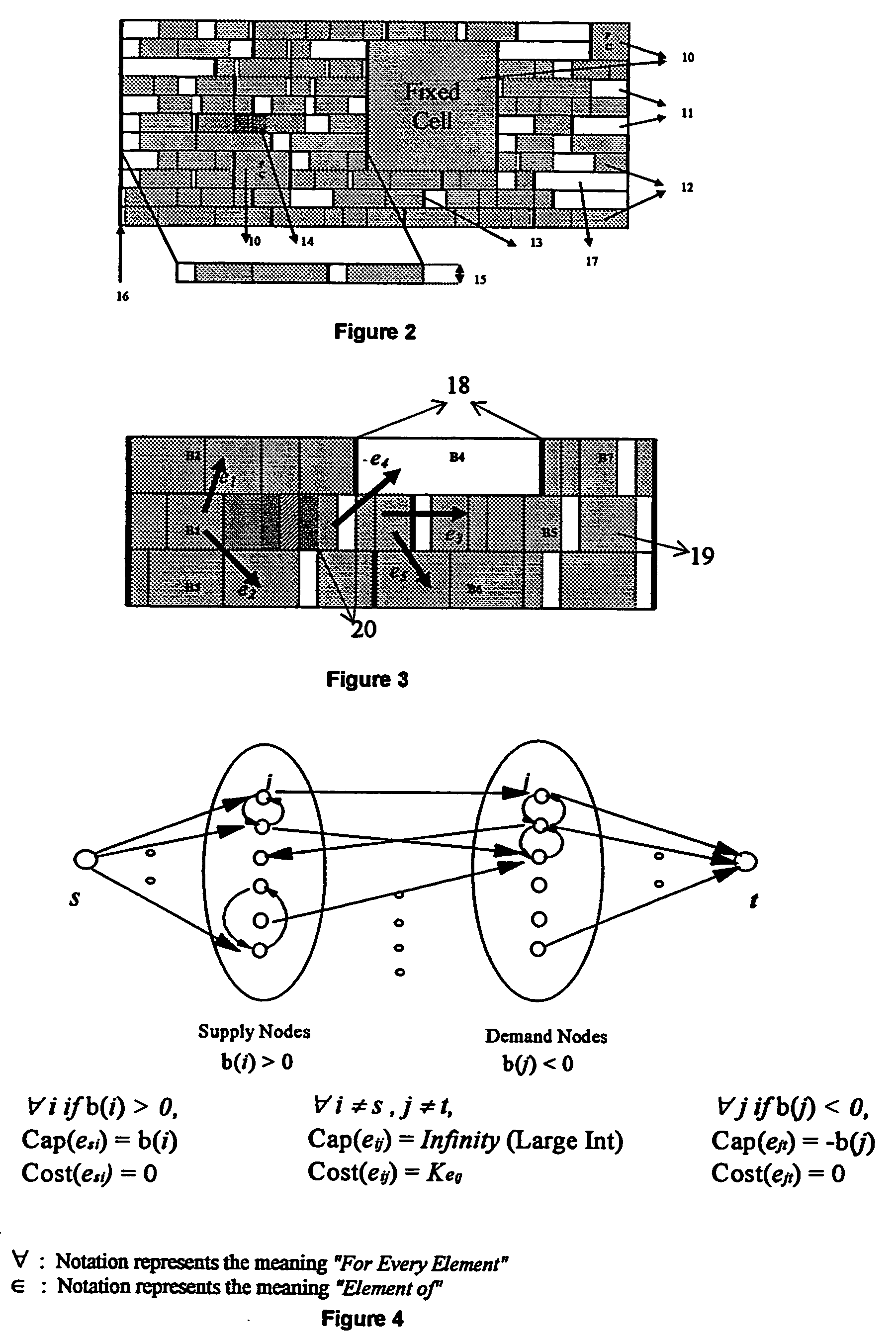

A method for resolving overlaps in the cell placement (placement legalization) during the physical design phase of an integrated chip design is described. This problem arises in several contexts within the physical design automation area including global and detailed placement, physical synthesis, and ECO (Engineering Change Order) mode for timing / design closure The method involves capturing a view of a given placement, solving a global two-dimensional area migration model and locally perturbing the cells to resolve the overlaps with minimal changes to the given placement. The method first captures a two-dimensional view of the placement including blockage-space, free-space and the given location of cells by defining physical regions. The desired global area migration across the physical regions of the placement image is determined such that it satisfies area capacity-demand constraints. The method also provides moving the cells between physical regions along previously computed directions of migration to minimize the movement cost. Also provided is an approximate method to model the movement of multi-row high cells.

Owner:IBM CORP

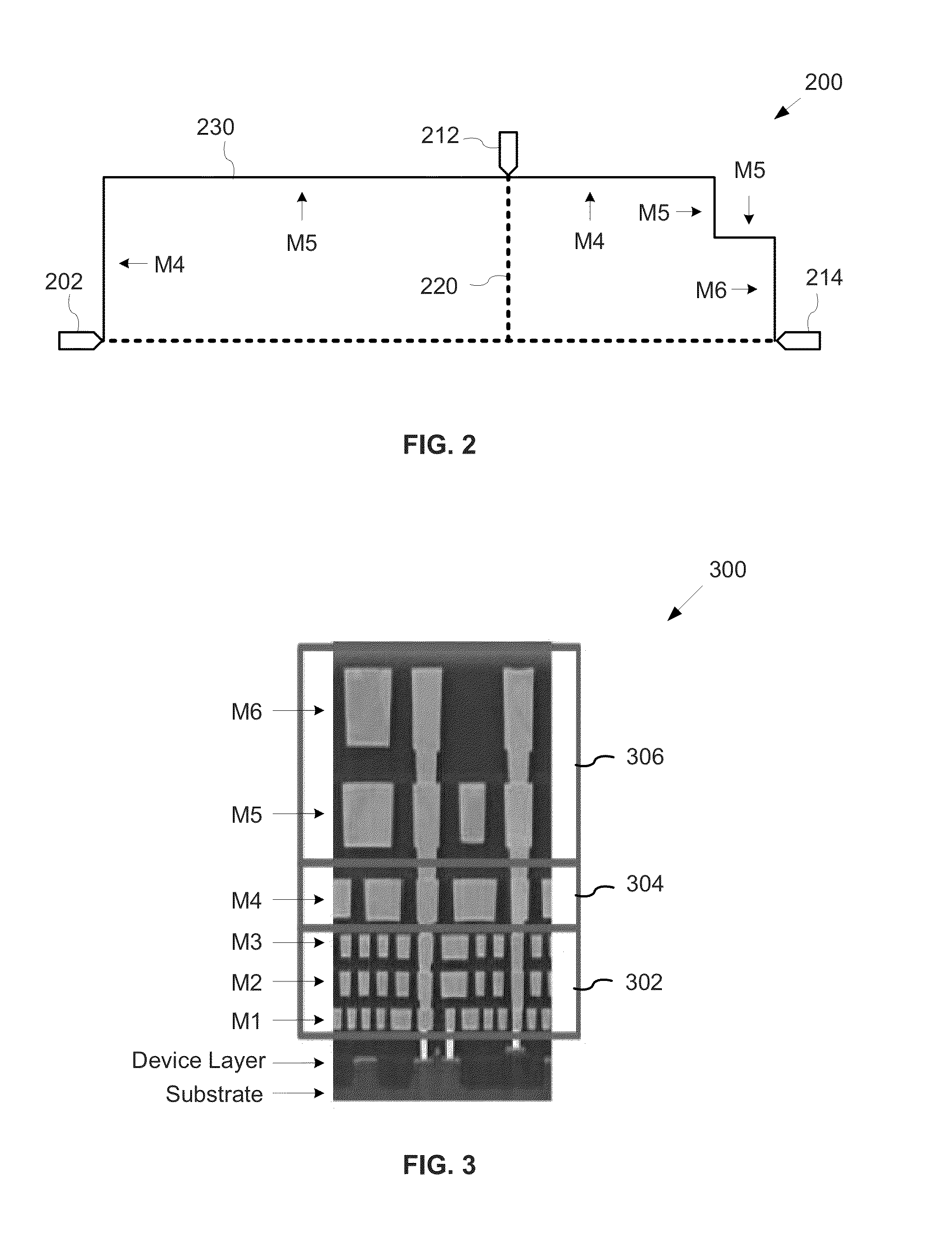

Evaluating routing congestion based on average global edge congestion histograms

InactiveUS20130086545A1Computer aided designSpecial data processing applicationsHorizontal and verticalRouting congestion

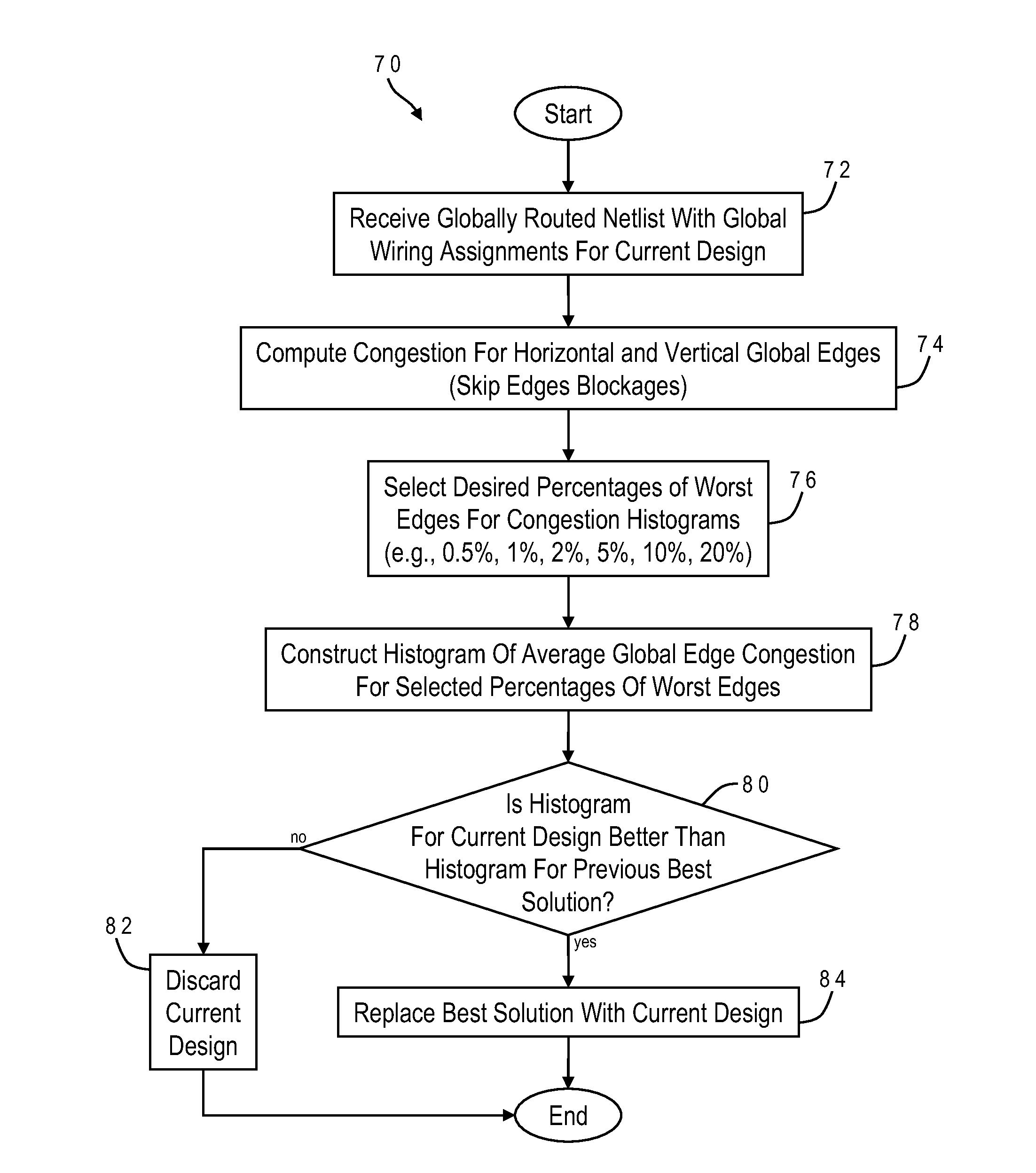

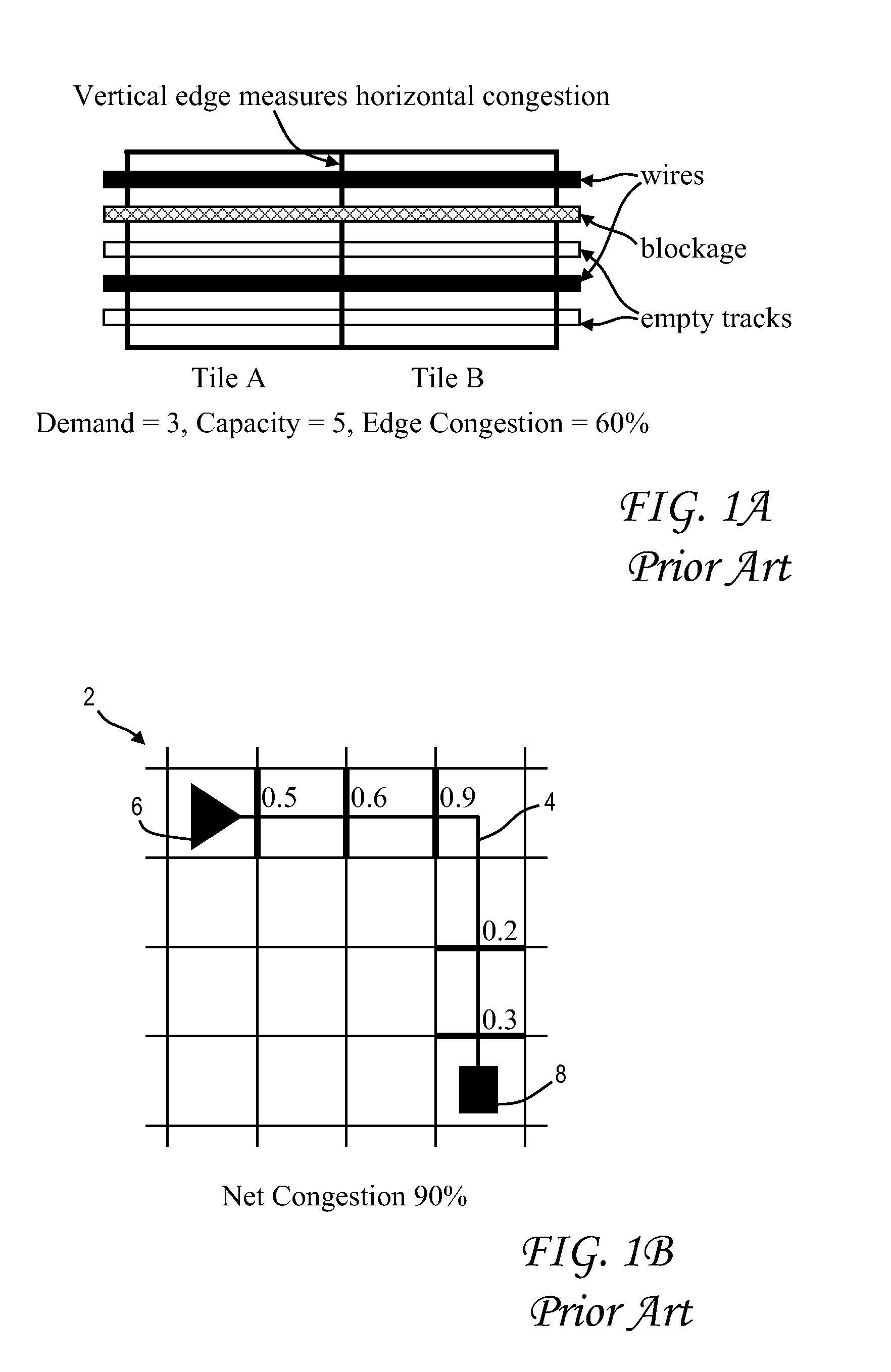

Global routing congestion in an integrated circuit design is characterized by computing global edge congestions and constructing a histogram of averages of the global edge congestions for varying percentages of worst edge congestion, e.g., 0.5%, 1%, 2%, 5%, 10% and 20%. Horizontal and vertical global edges are handled separately. Global edges near blockages can be skipped to avoid false congestion hotspots. The histogram of the current global routing can be compared to a histogram for a previous global routing to select a best routing solution. The histograms can also be used in conjunction with congestion-driven physical synthesis tools.

Owner:GLOBALFOUNDRIES US INC

Method for legalizing the placement of cells in an integrated circuit layout

InactiveUS7089521B2Guaranteed preservation qualityEfficient solutionComputer aided designSoftware simulation/interpretation/emulationHigh cellControl engineering

Owner:INT BUSINESS MASCH CORP

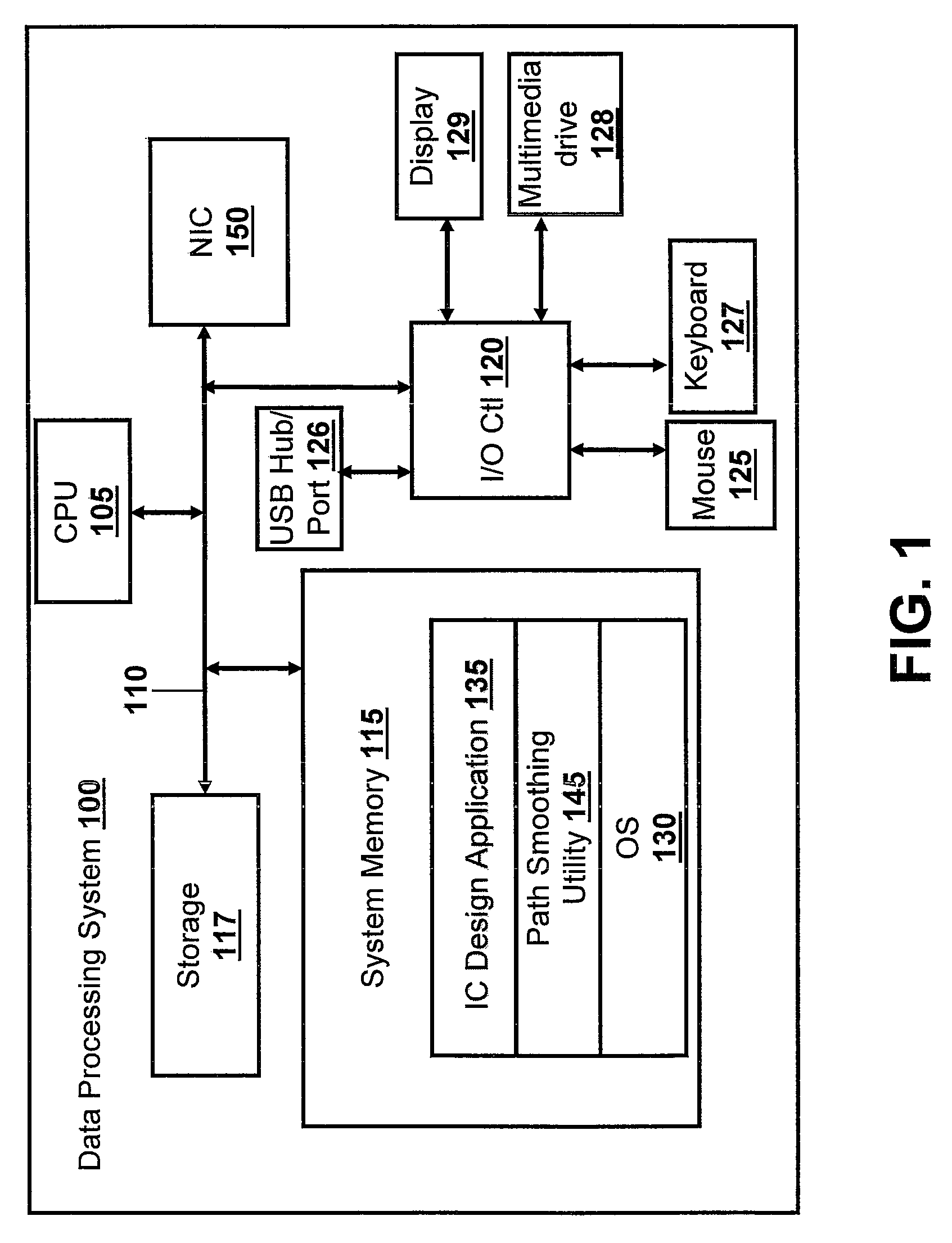

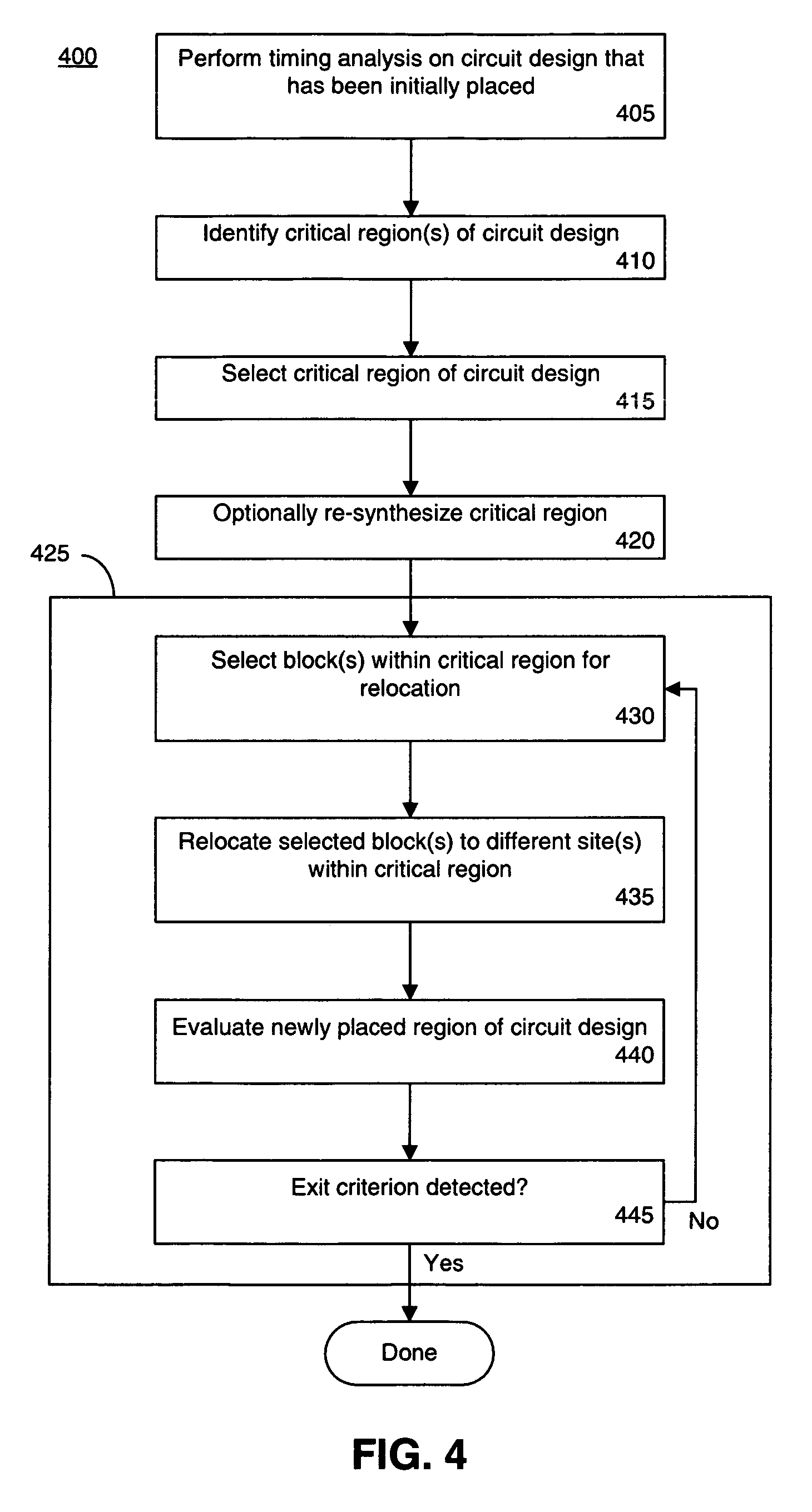

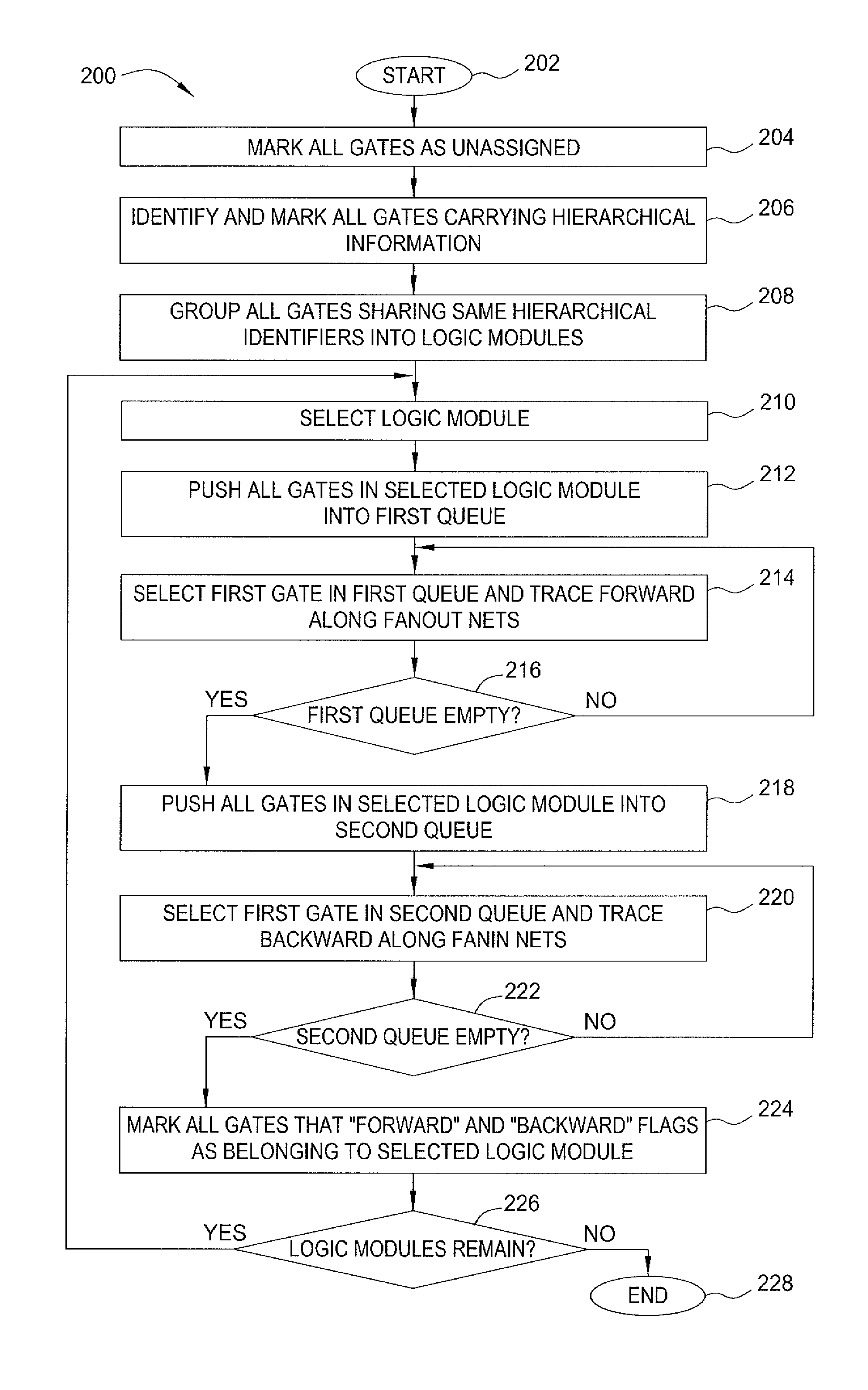

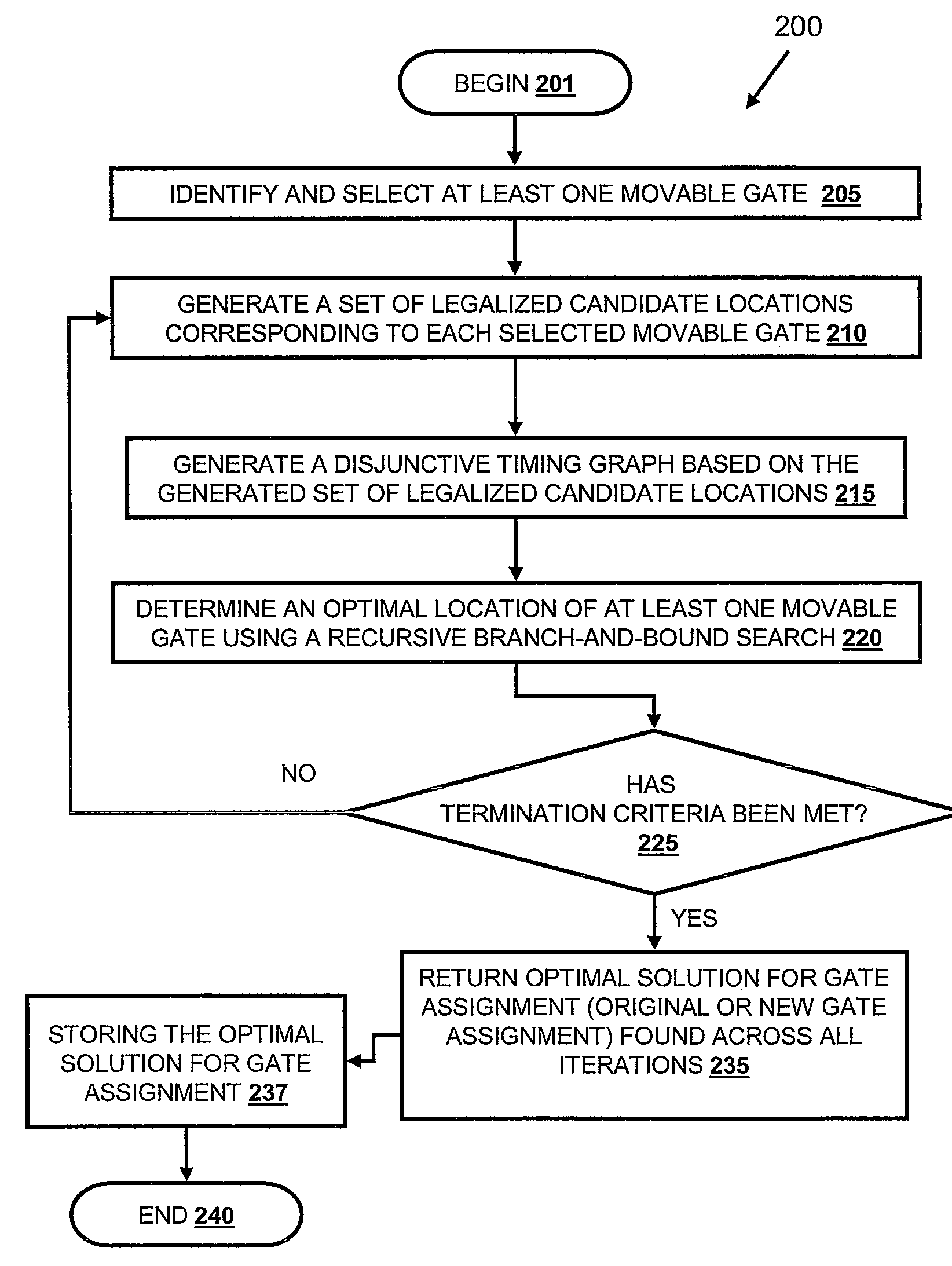

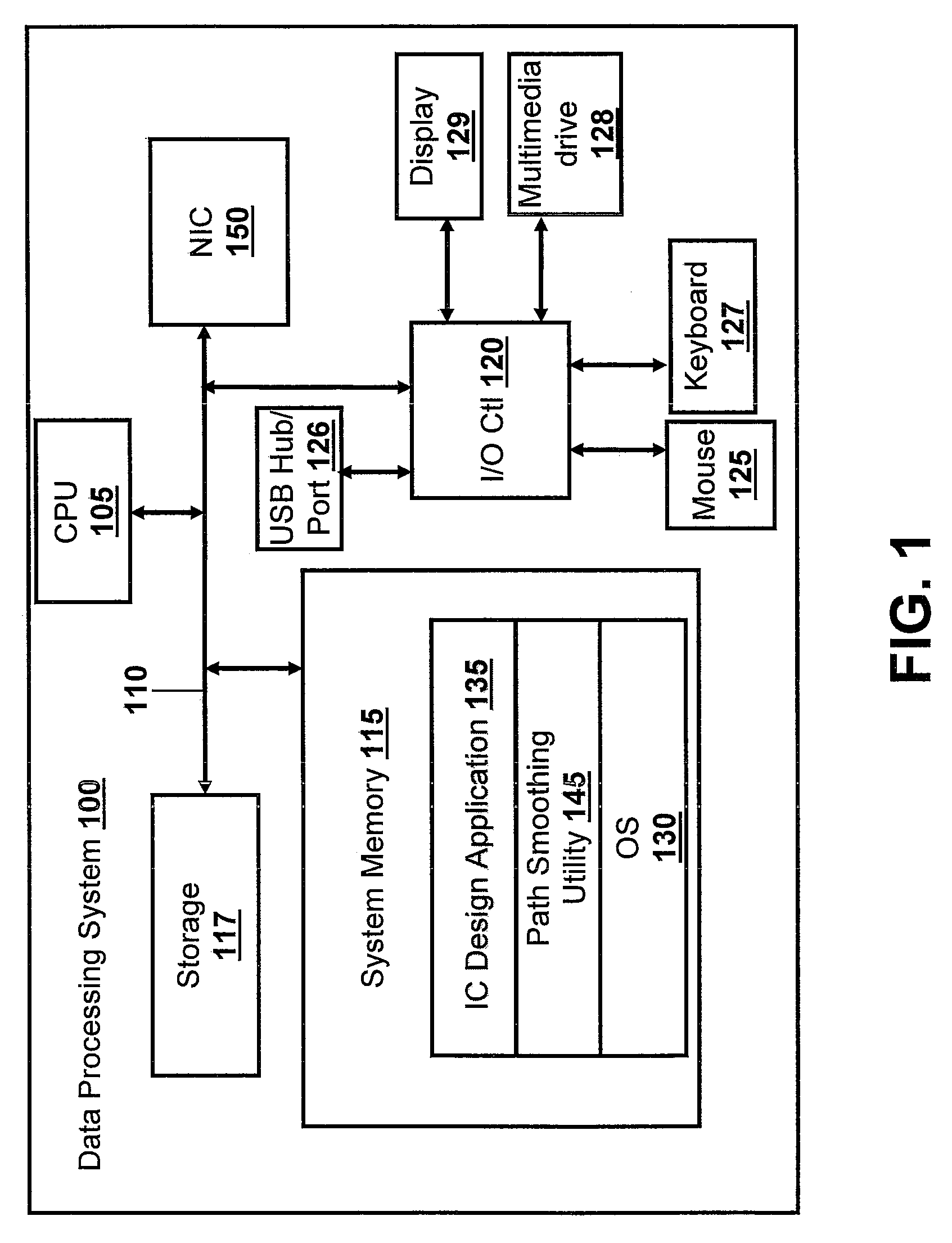

Incremental timing-driven, physical-synthesis using discrete optimization

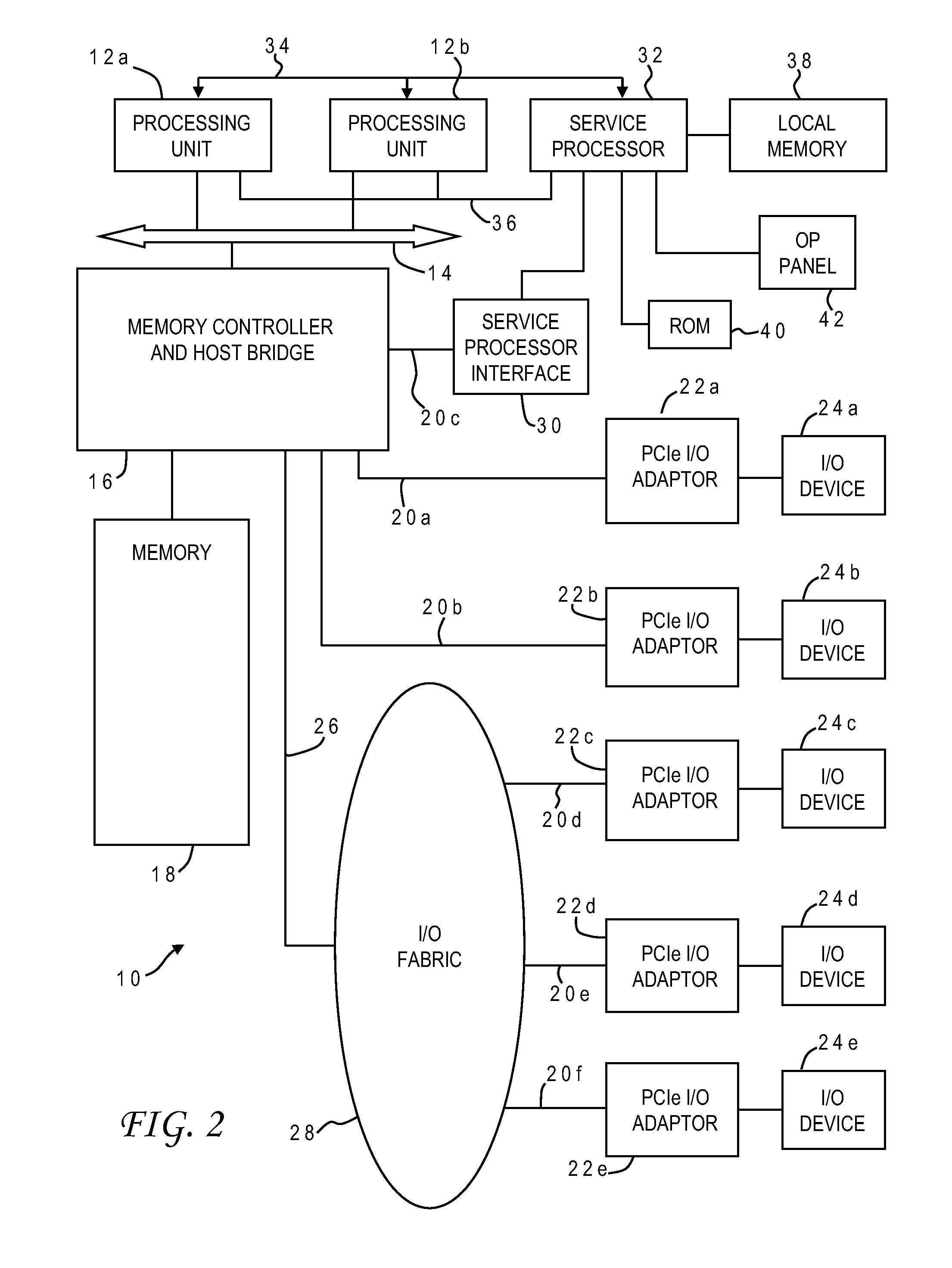

ActiveUS7707530B2Analogue computers for electric apparatusComputer aided designData processing systemSelection criterion

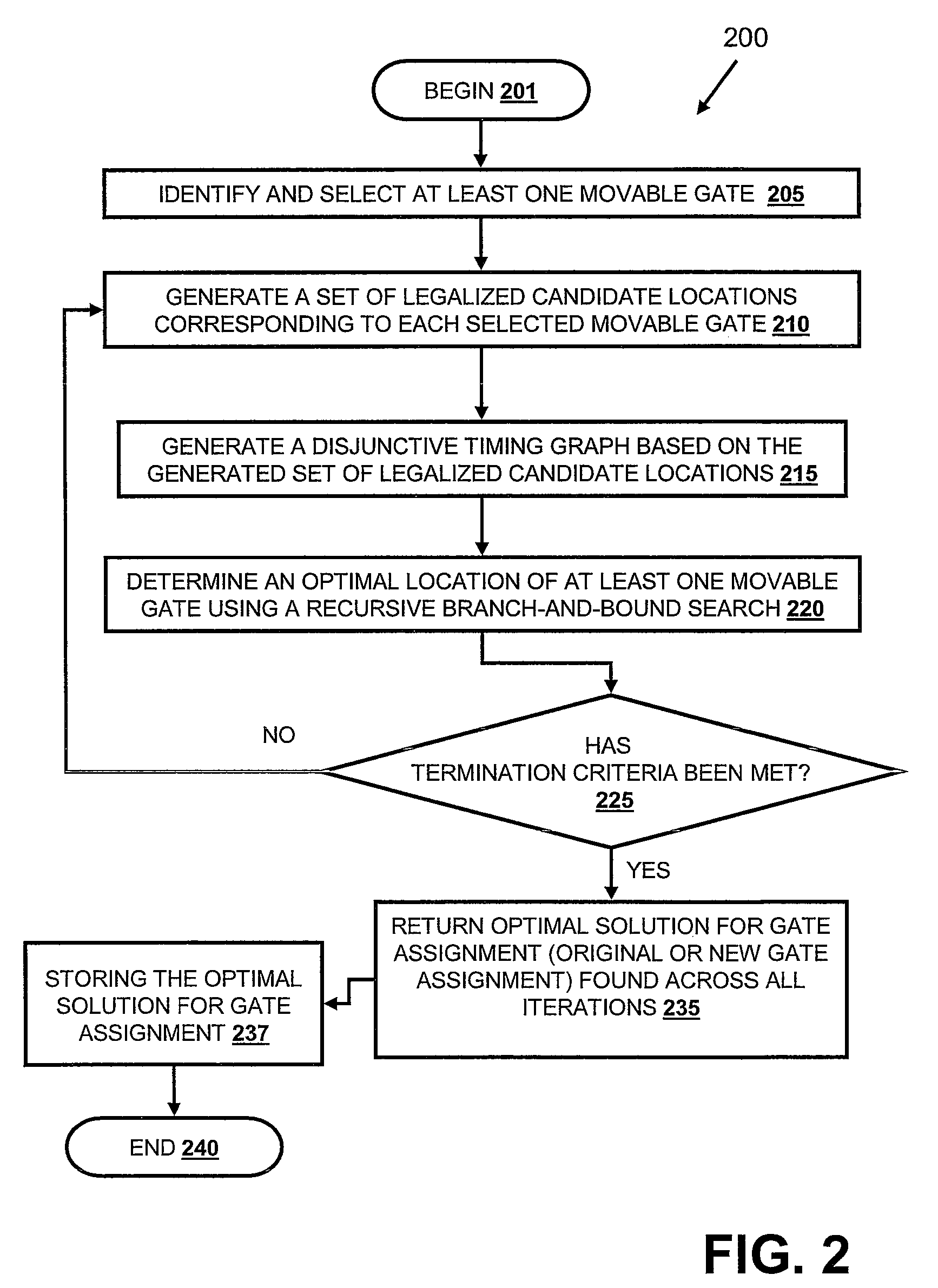

A method, data processing system and computer program product for optimizing the placement of logic gates of a subcircuit in a physical synthesis flow. A Path Smoothing utility identifies one or more movable gates based on at least one selection criteria. A set of legalized candidate locations corresponding to one or more identified movable gates is generated. A disjunctive timing graph based on the generated set of legalized candidate locations is then generated. An optimal location of one or more movable gate(s) is determined using a recursive branch-and-bound search and stored in the computing device.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

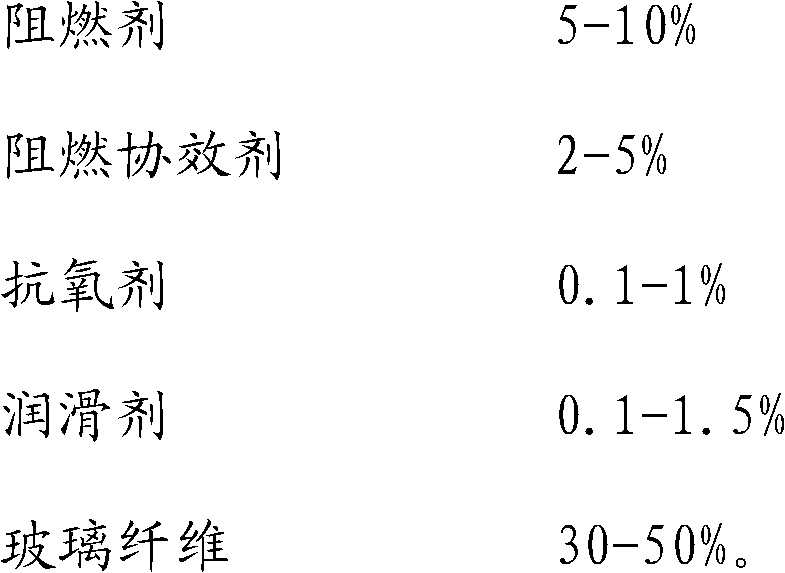

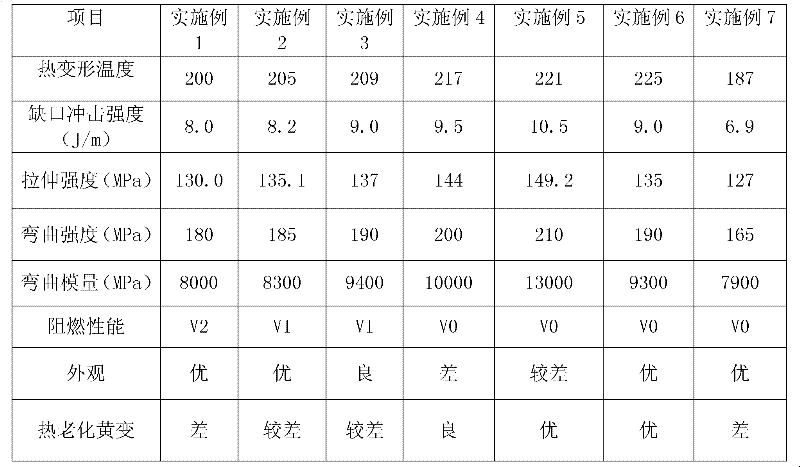

Thermal aging resistant PET modified material and its preparation method

The invention discloses a thermal aging resistant PET modified material and its preparation method. The PET modified material provided by the invention comprises the following components of: by weight, 38-62% of PET, 0.3-0.1% of a nucleating agent, 5-10% of a flame retardant, 2-5% of a flame-retardant synergist, 0.1-1% of an anti-oxidant, 0.1-1.5% of a lubricant and 30-50% of glass fibre. The thermal aging resistant PET modified material prepared in the invention has advantages of high temperature resistance, thermal aging resistance, good physical comprehensive properties and good surface glossiness without no floating fibre, and can be widely applied in the field of electronic and electrical products such as coil winders, integrated circuit packages, timer packages, relays and the like,in the field of automobile spare and accessory parts such as automobile headlight decorative loops, heatproof automobile wheel covers, midget electric motor cover casing and the like, and in the field of household electrical appliances such as straight hair device shells, electric iron pedestals, straight hair device heat spacers and the like.

Owner:SHENZHEN KEJU NEW MATERIAL

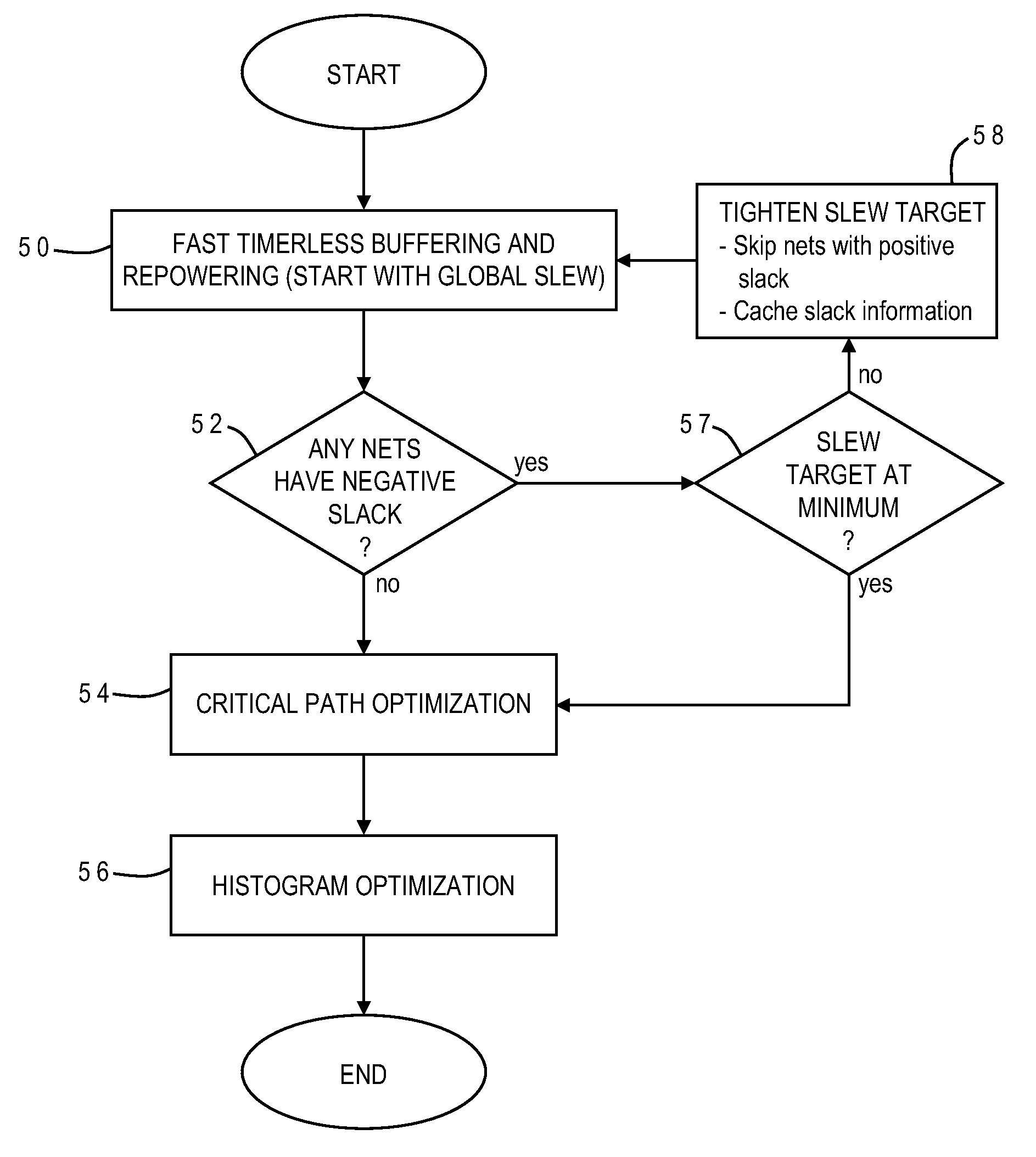

Techniques for fast area-efficient incremental physical synthesis

InactiveUS20100257499A1Simple methodMeet cutting requirementsCAD circuit designSoftware simulation/interpretation/emulationRepoweringComputer science

A fast technique for circuit optimization in a physical synthesis flow iteratively repeats slew-driven (timerless) buffering and repowering with a changing slew target. Buffers are added as necessary with each iteration to bring the nets in line with the new slew target, but any nets having positive slack from the previous iteration are skipped, and that slack information is cached for future timing analysis. Buffer insertion is iteratively repeated with incrementally decreasing slew until a minimum slew is reached, or when none of the nets have negative slack. Iteratively repeating the timerless buffering and repowering while gradually decreasing the slew constraint in this manner results in a design structure which retains high quality of results with significantly smaller area and wire length, and with only a small computational overhead.

Owner:GLOBALFOUNDRIES INC

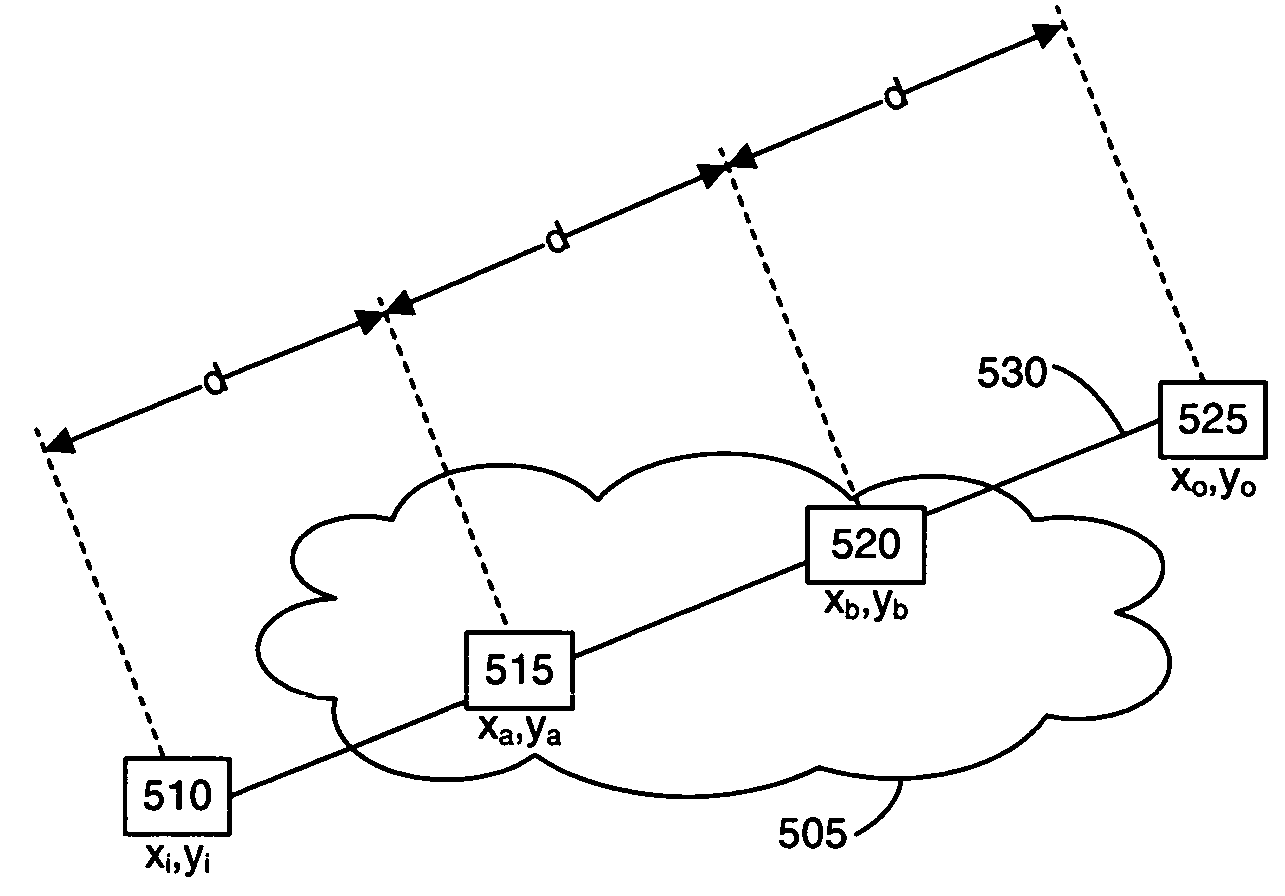

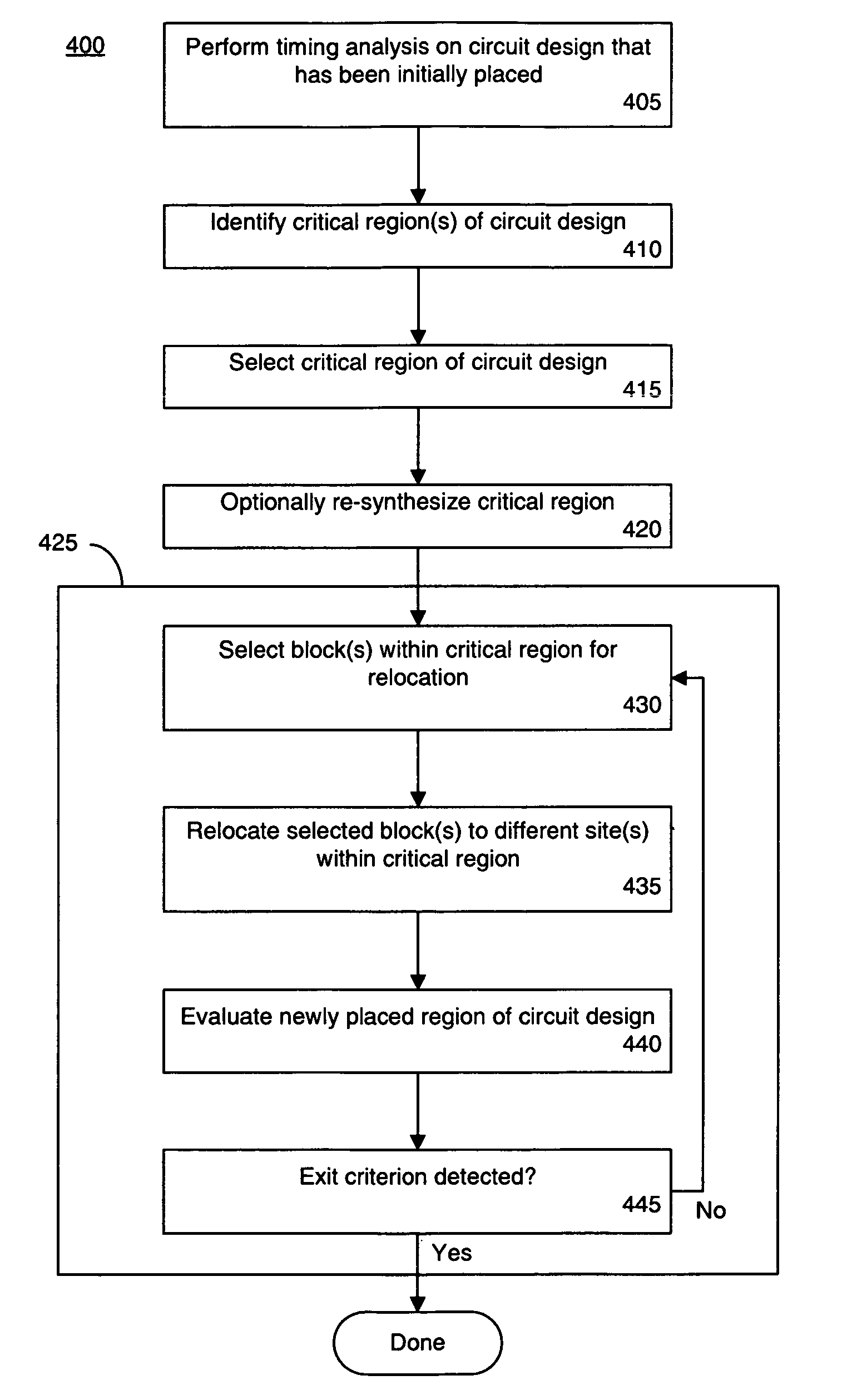

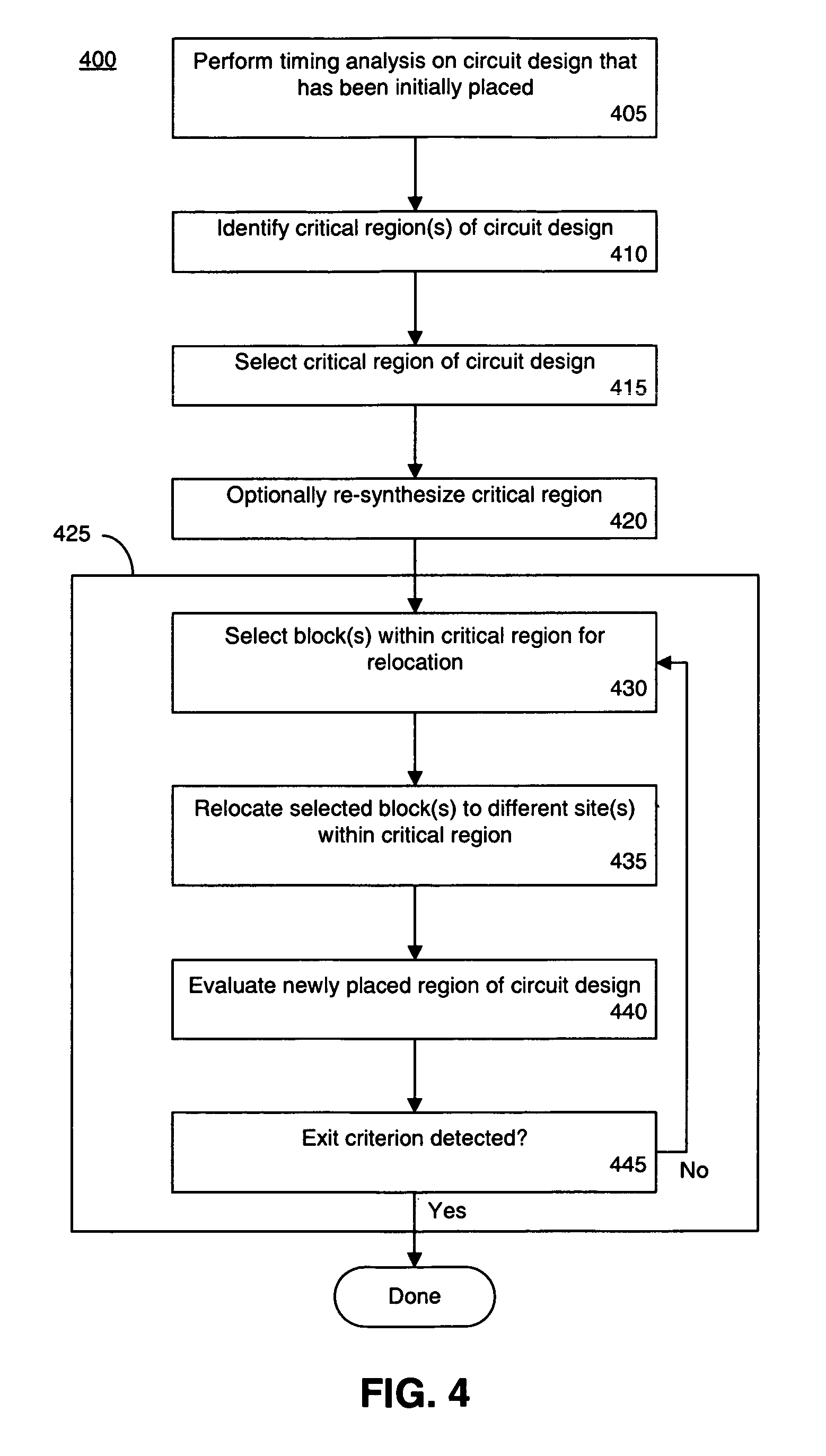

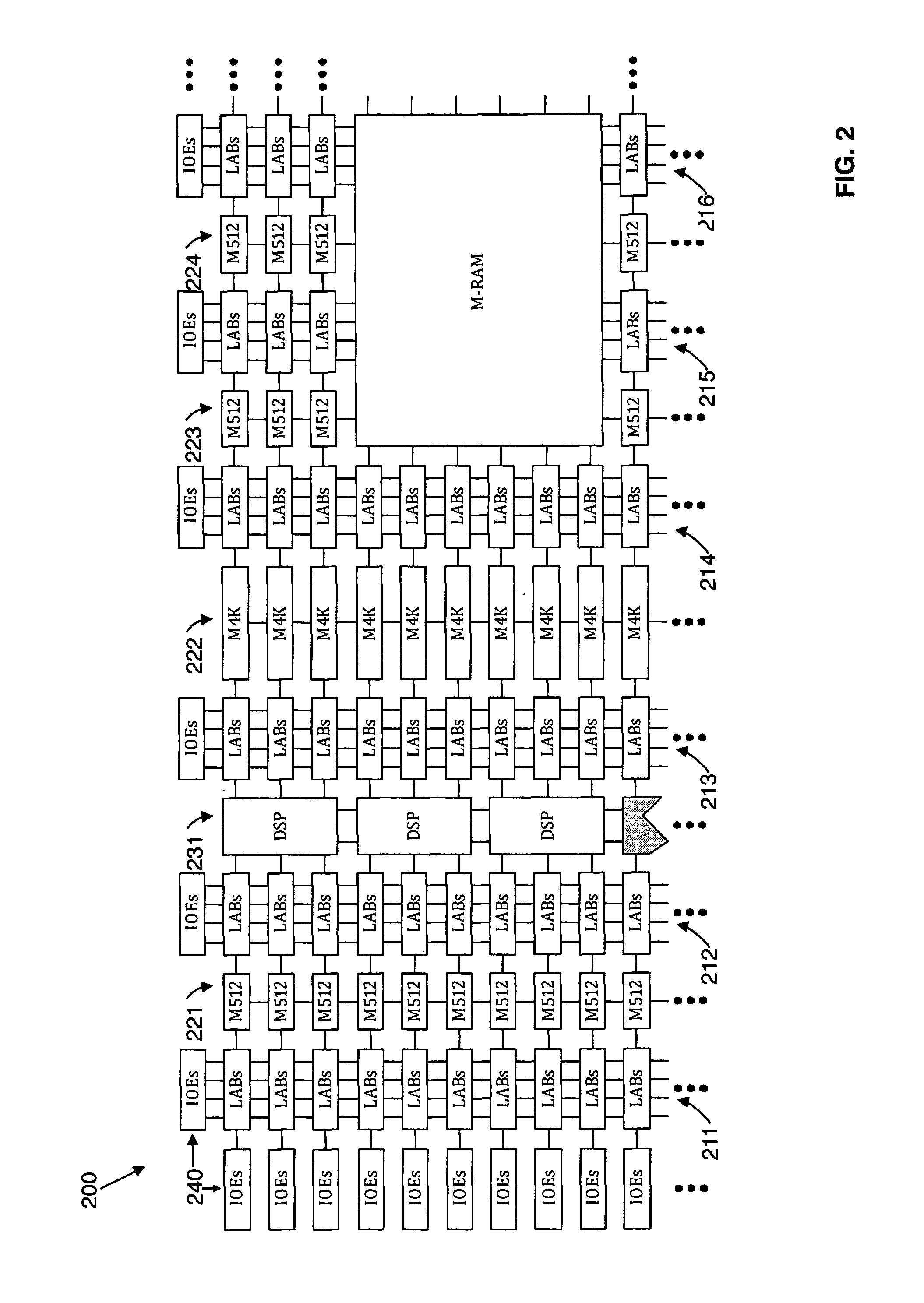

Incremental placement during physical synthesis

ActiveUS7536661B1Software simulation/interpretation/emulationSpecial data processing applicationsParallel computingCritical section

A method of optimizing a portion of a circuit design for a target device can include identifying a critical region from a plurality of regions after an initial placement of the circuit design. The critical region can be defined, at least in part, by at least one input block and at least one output block. Blocks of the critical region can be relocated to different sites within the critical region. The method further can include evaluating the relocation of blocks of the critical region according to a cost function and continuing to relocate blocks and evaluate the relocation of blocks in the critical region until at least one exit criterion is met.

Owner:XILINX INC

High-quality oligomeric proanthocyanidins and preparation method thereof

ActiveCN108997294AEasy to operateImprove antioxidant capacityOrganic chemistryDepolymerizationProanthocyanidin

The invention relates to the technical field of natural plant extraction processing, and concretely relates to a high-quality oligomeric proanthocyanidins and a preparation method thereof. The high-quality oligomeric proanthocyanidins can be obtained by the steps of extraction, concentration, purification, re-concentration, water dissolution, depolymerization, and spray drying. The raw materials and auxiliary materials selected by the method are natural materials, the method employs physical synthesis and biological fermentation methods, the oligomeric proanthocyanidins can be completely usedfor food processing and is safe and quality-assured, the operation is simple, the prepared oligomeric proanthocyanidins has strong anti-oxidizability.

Owner:HUNAN DASANXIANG TEA OIL CO LTD

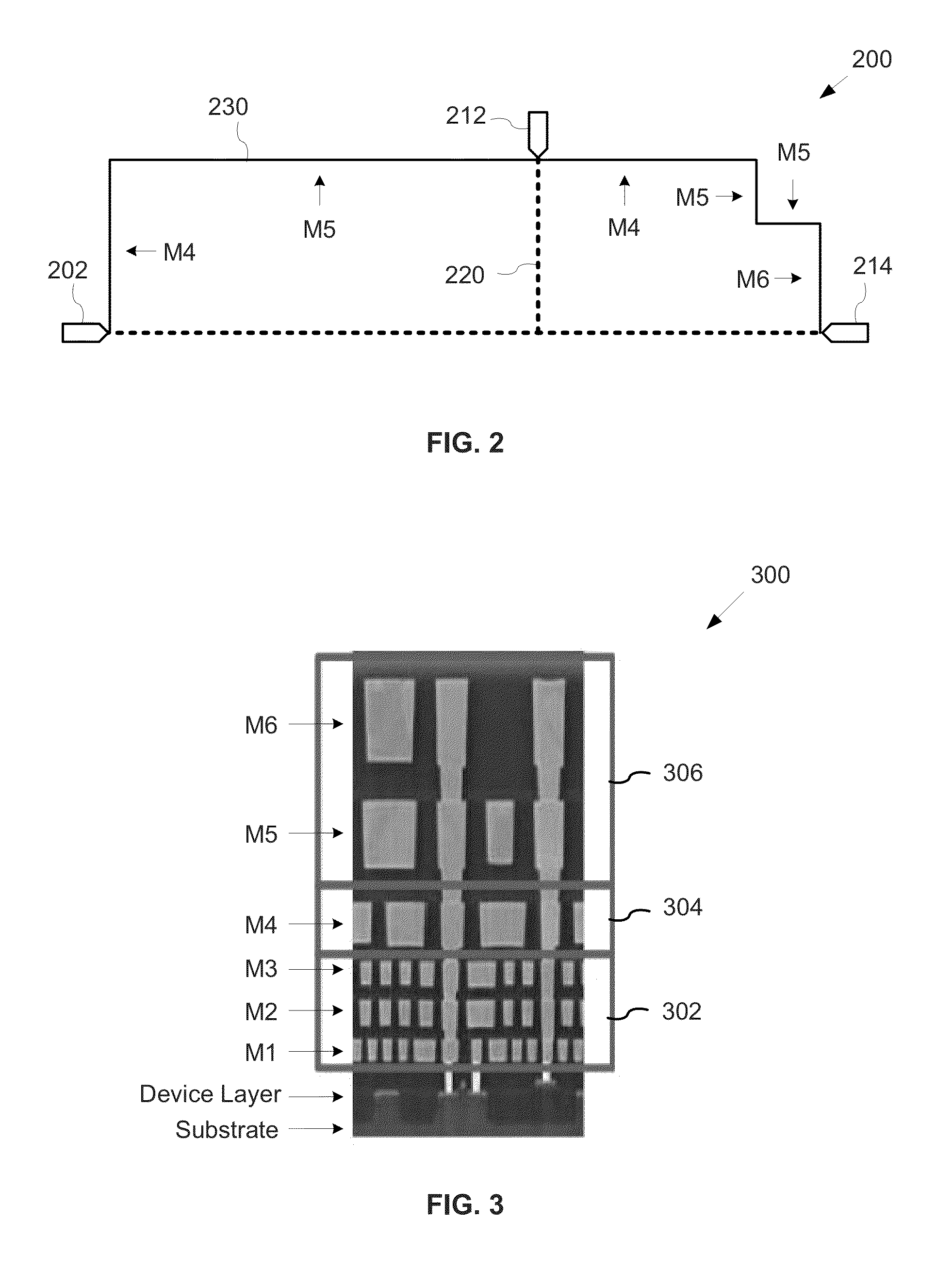

Method and apparatus to generate pattern-based estimated rc data with analysis of route information

ActiveUS20130346937A1Good correlationImprove estimation accuracyComputer aided designSpecial data processing applicationsPattern matchingTime critical

A method and apparatus for improving physical synthesis of a circuit design is described. In one exemplary embodiment, preliminary routing information of nets in the circuit design is analyzed. The preliminary routing information includes track assignment information. Timing-critical nets are identified based on statistical distribution of the preliminary routing information of the nets. The identified timing-critical nets are assigned to a set of routing layers and removed from future net pattern matching. The remaining nets are clustered into multiple net patterns based on their physical attributes. The scaling factor for each net pattern is updated based on the scaling factor standard deviation and net length of the net pattern. Nets that are outside multiple standard deviations of a net pattern are assigned to routing layers. The scaling factors of the net patterns and the layer assignments are applied to the next phase of placement-based optimizations.

Owner:SYNOPSYS INC

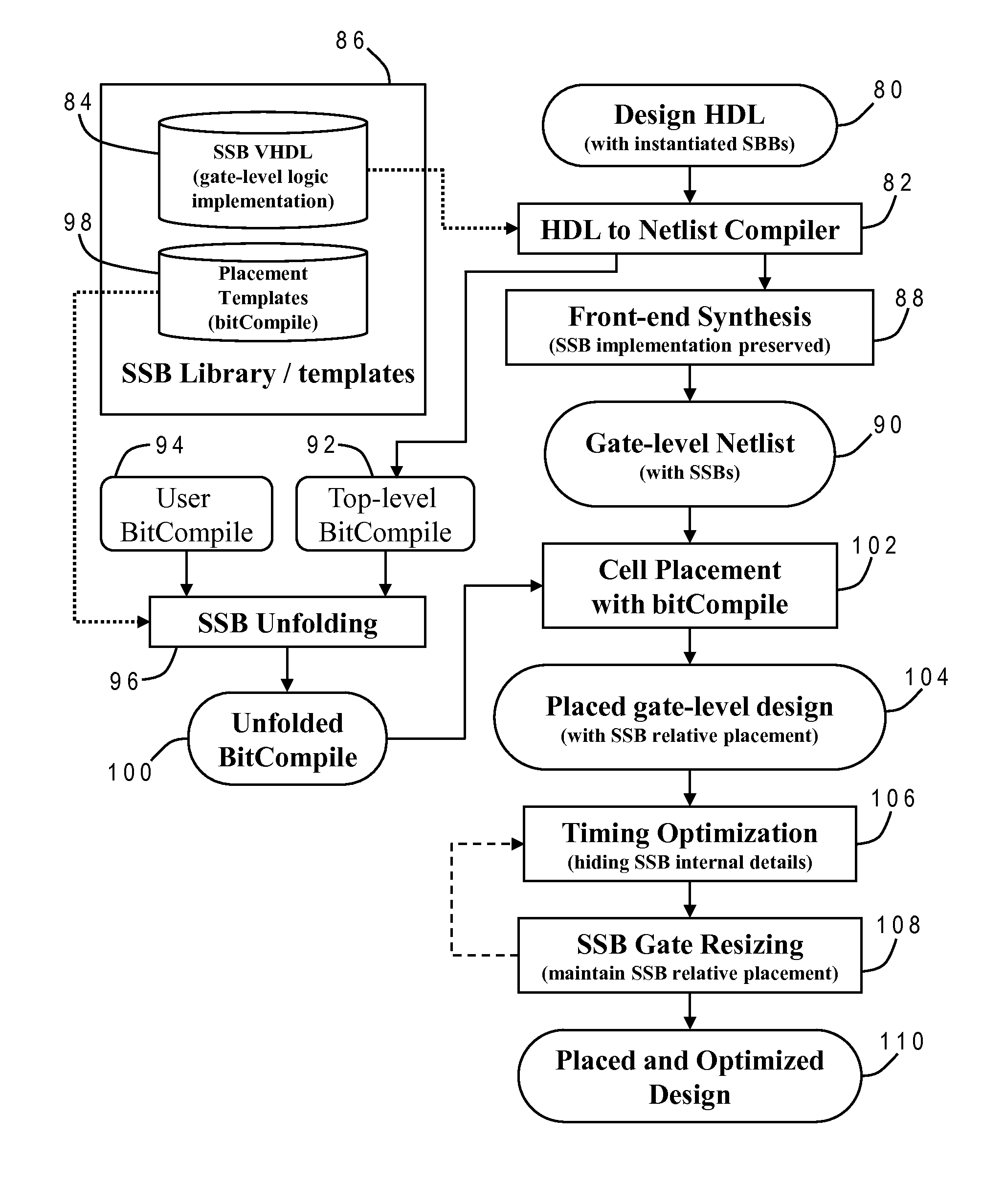

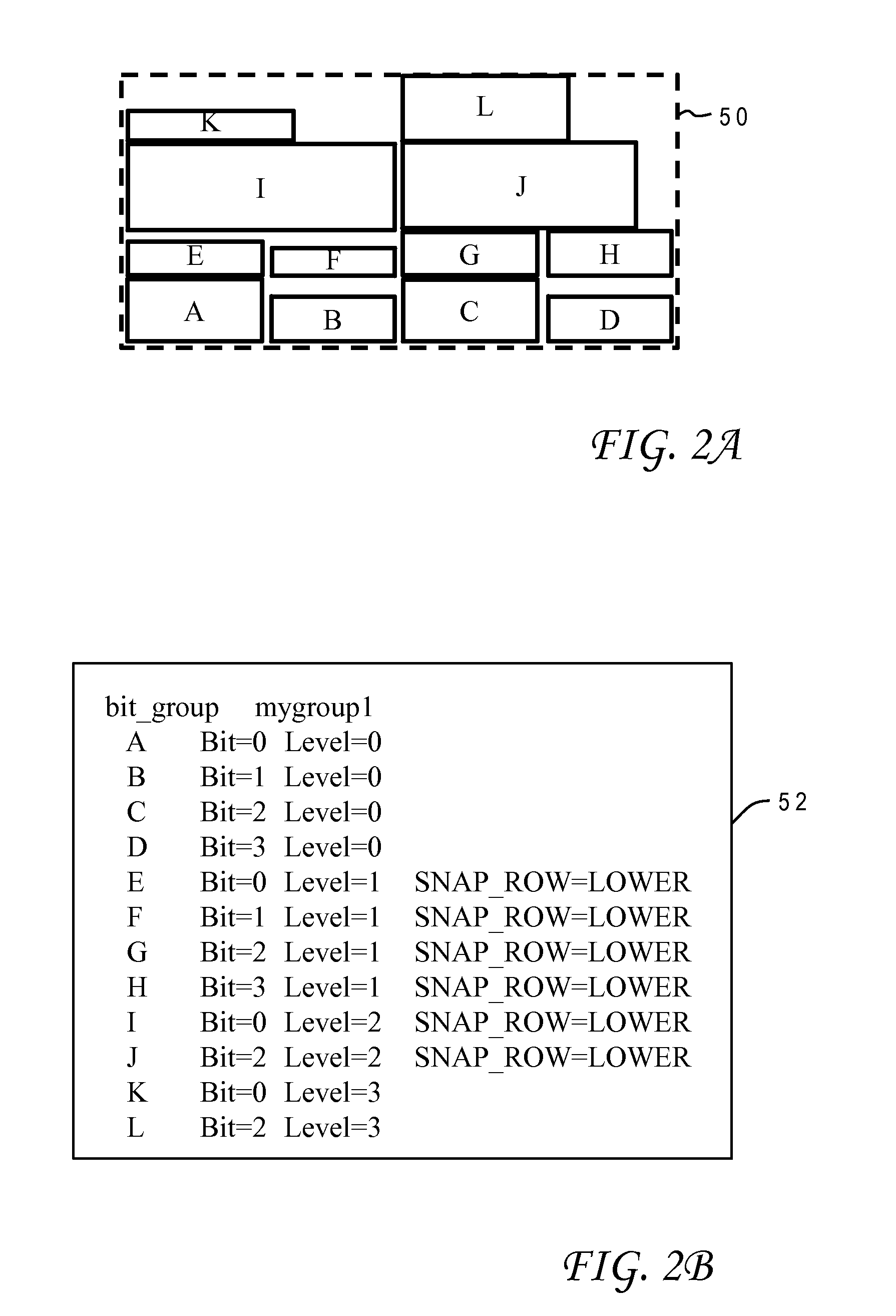

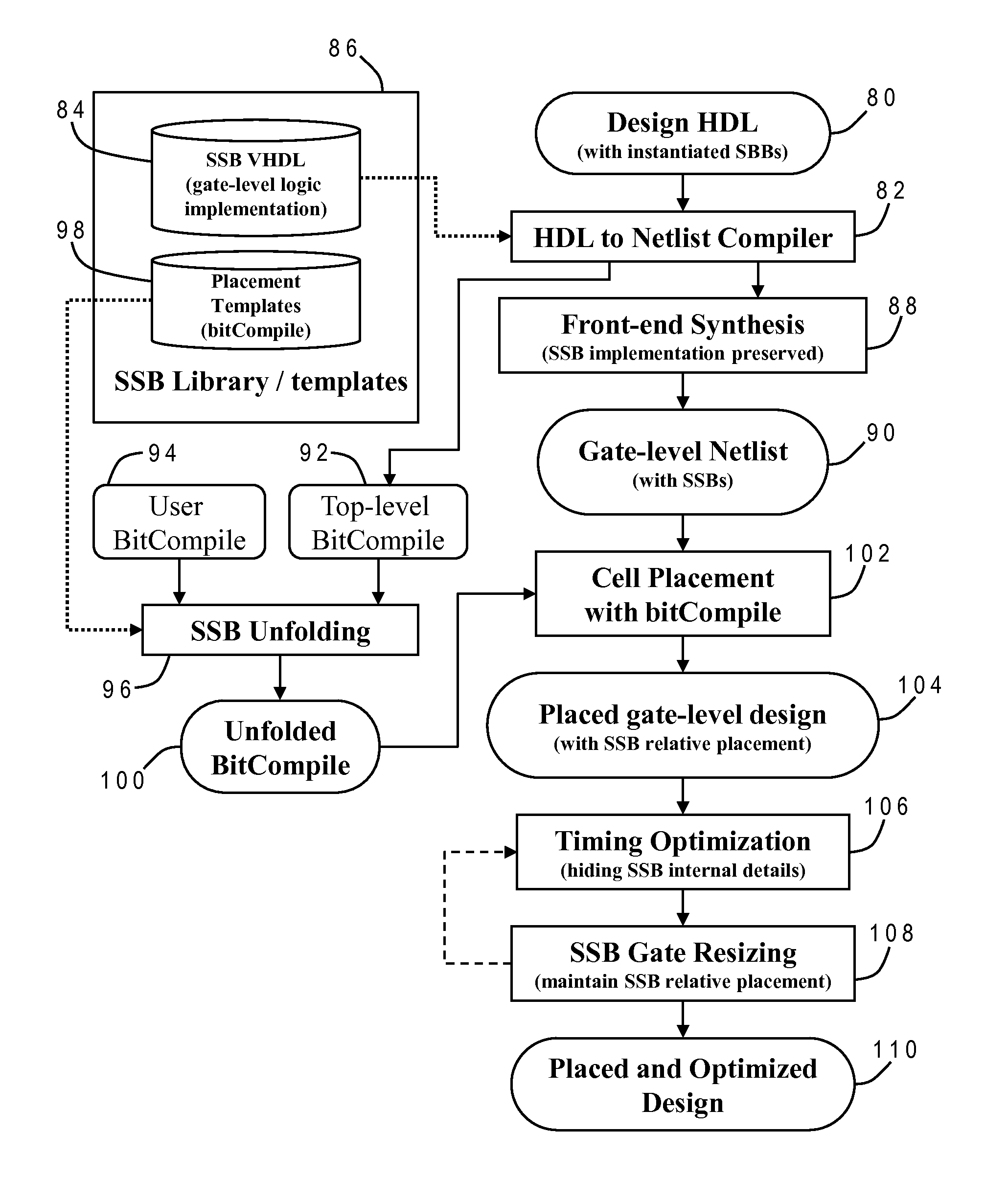

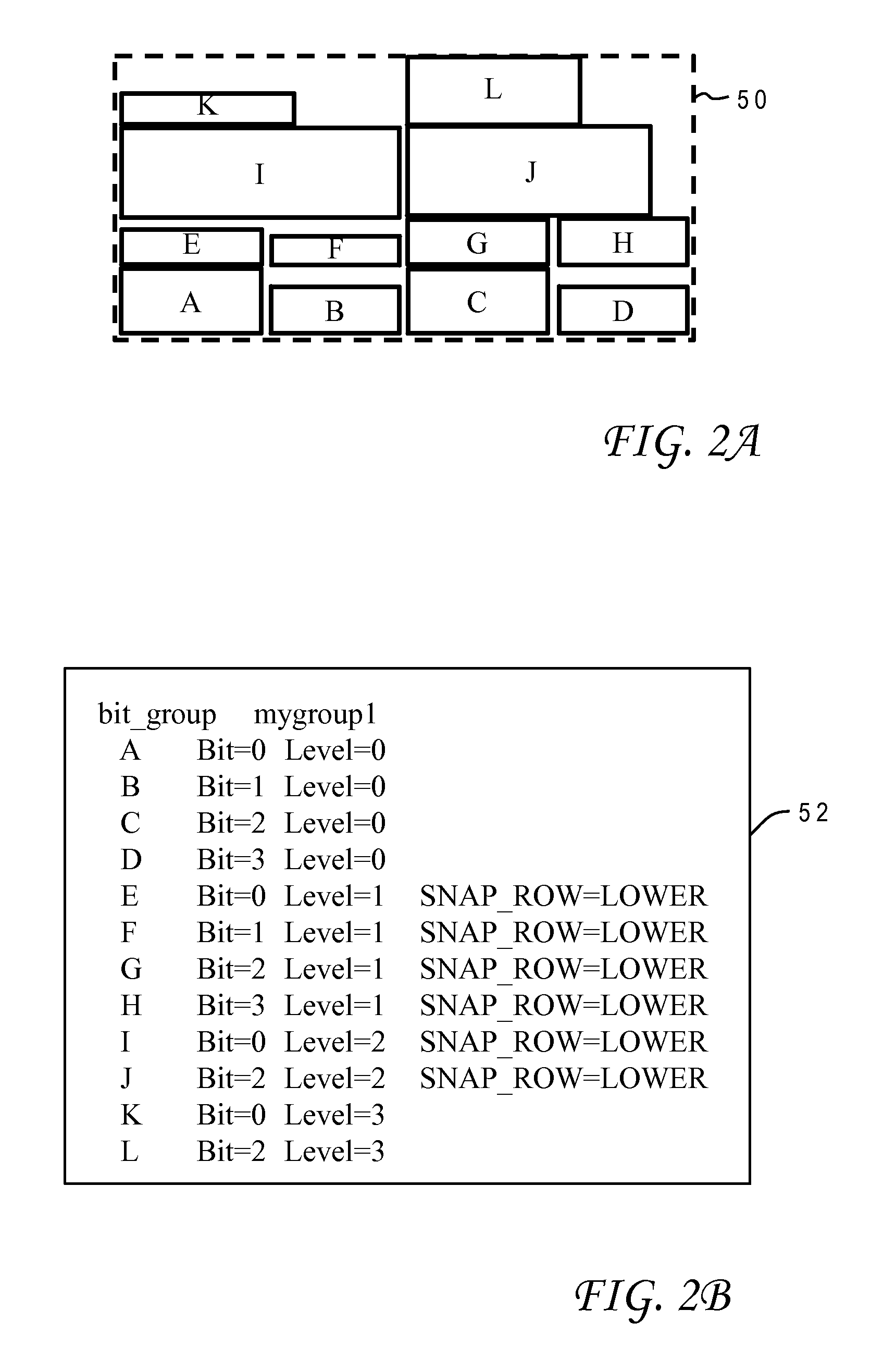

Structured placement of hierarchical soft blocks during physical synthesis of an integrated circuit

InactiveUS20140359546A1Easy to placeAvoid changeCAD circuit designSpecial data processing applicationsComputer architectureLogic implementation

Integrated circuit design uses a library of structured soft blocks (SSBs) composed of pre-defined sets of cells with their logic implementation and placement templates with their relative placement information. A compiler receives a circuit description which includes an instance of an SSB and unfolds the instance according to the placement template to generate a modified circuit description which includes the relative placement information. The placement of circuit objects is optimized while maintaining relative locations for cells of the SSB instance according to the relative placement information. The SSB may be hierarchical. Gate resizing of cells in the SSB instance may result in a change in its bounds. A timing optimization procedure for the modified circuit description may be carried out while hiding internal details of the SSB instance. For example, buffers may be inserted in nets external to the SSB instance while preventing insertion of buffers in any internal nets.

Owner:IBM CORP

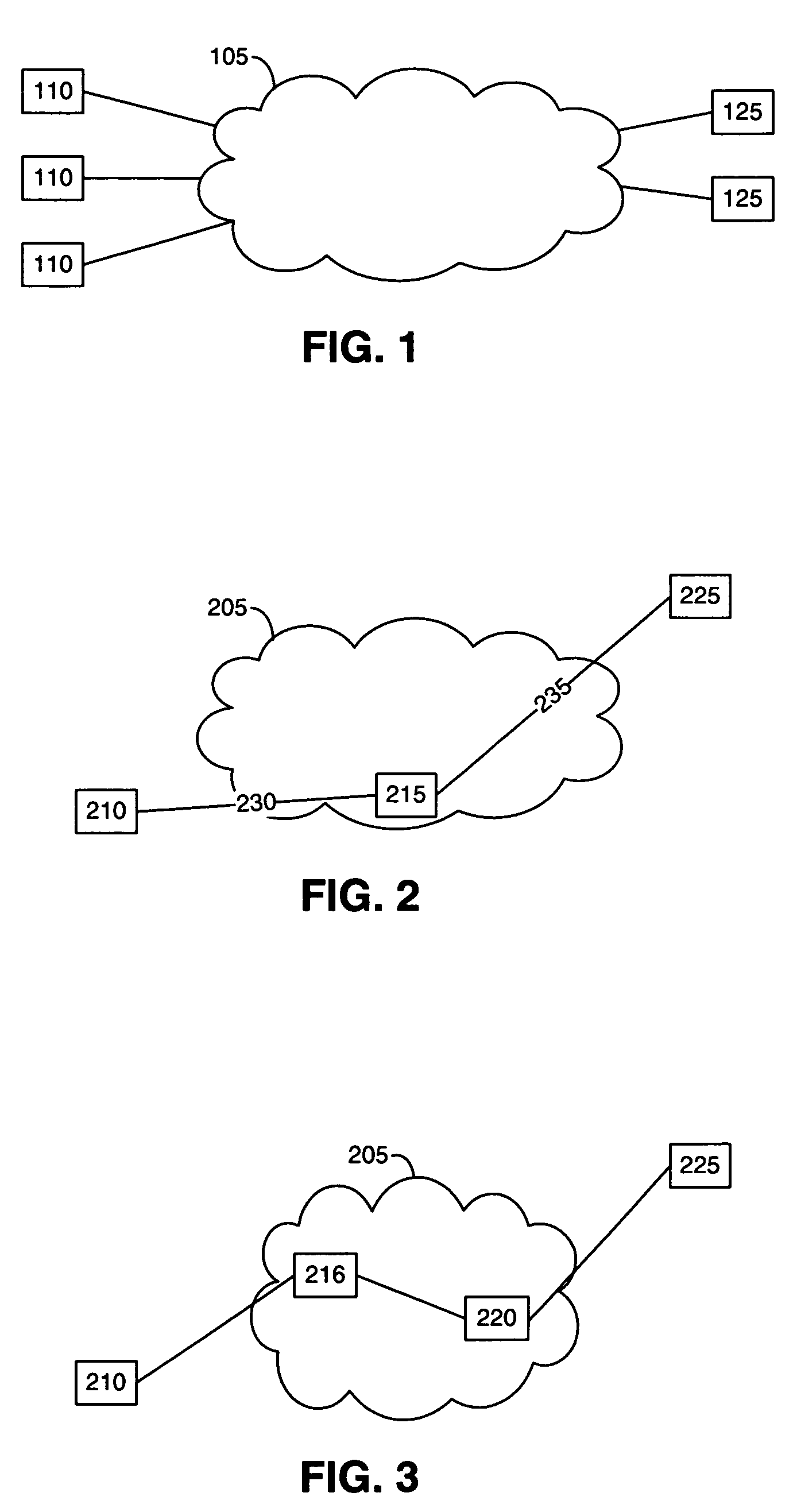

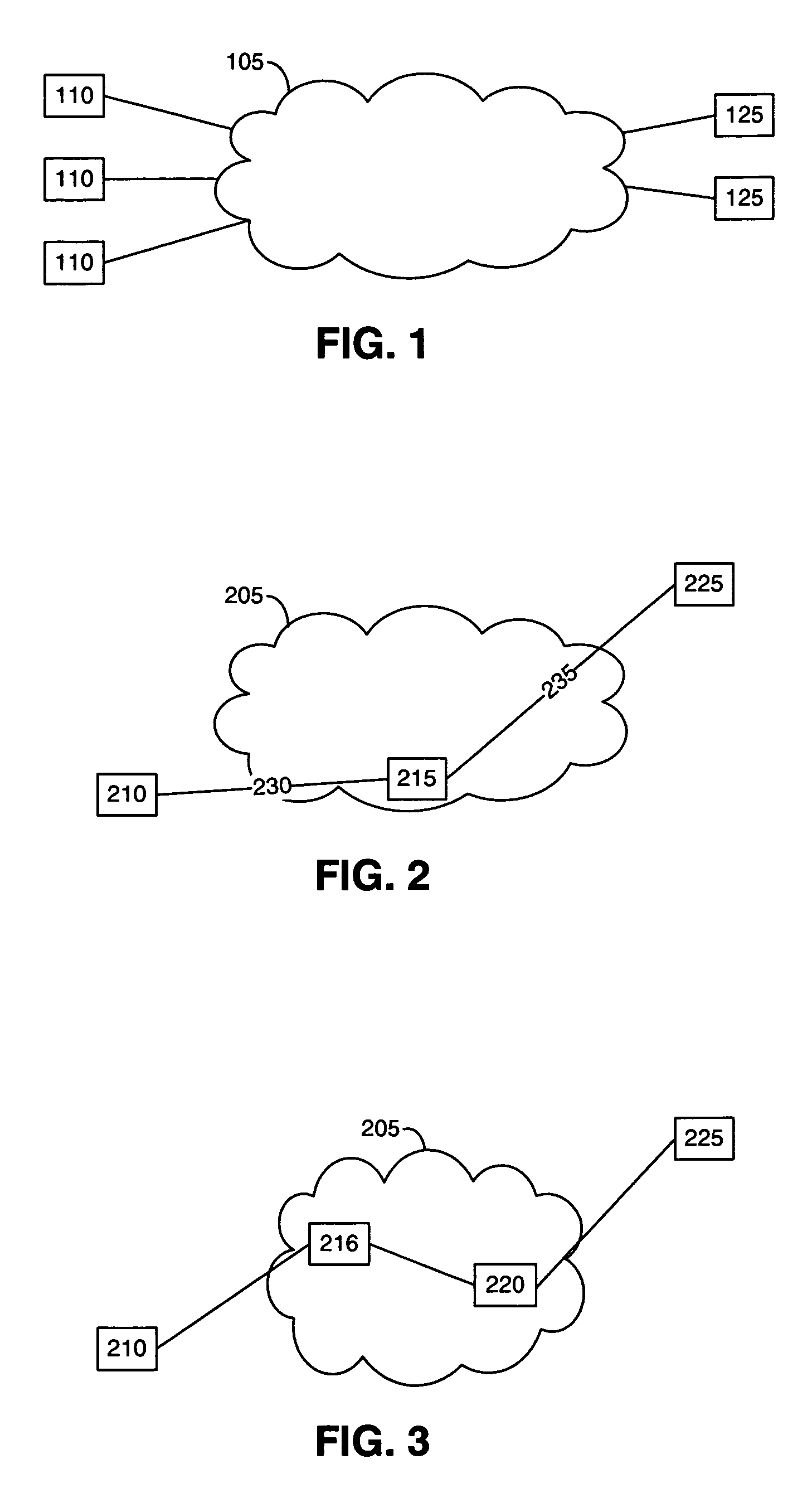

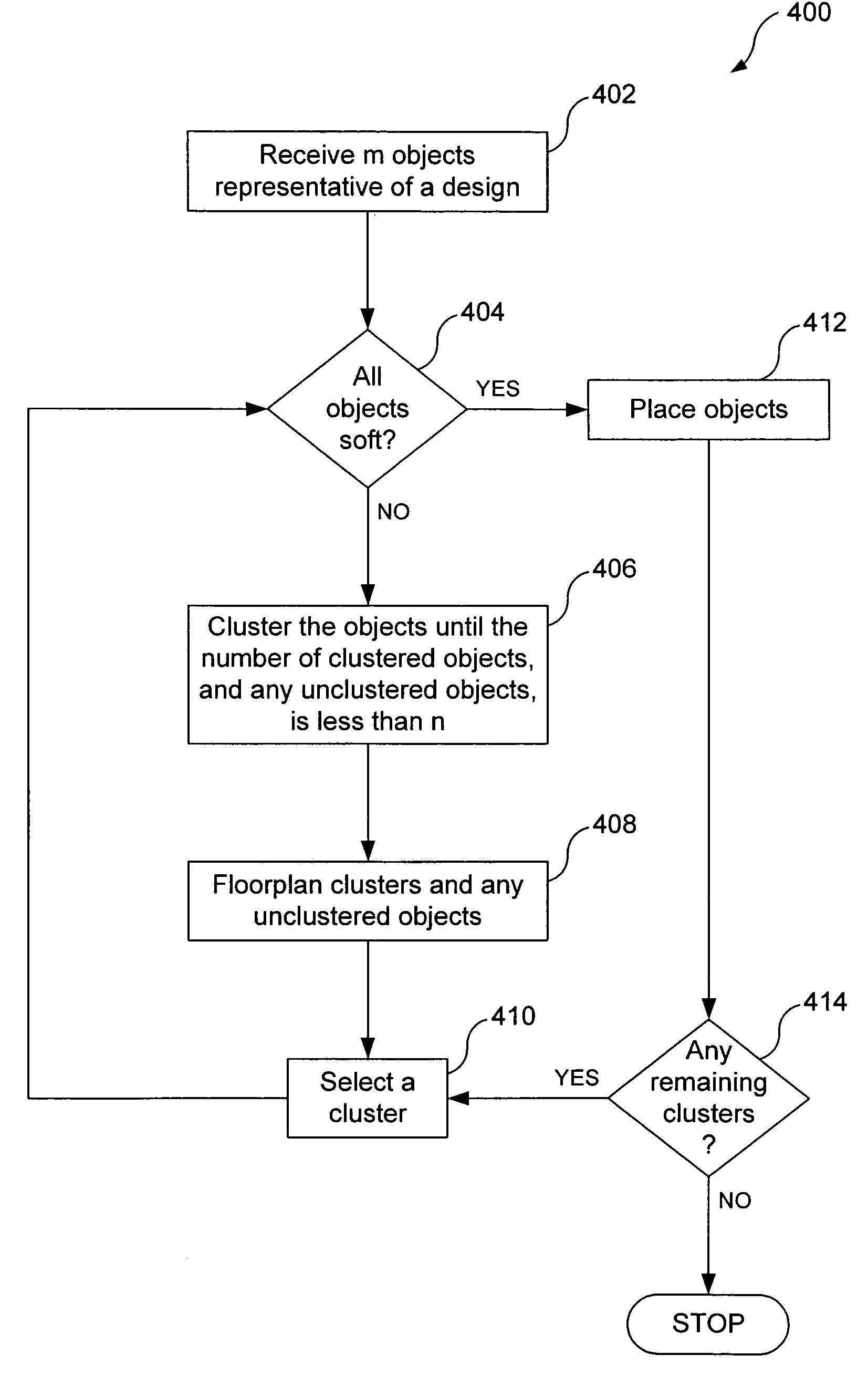

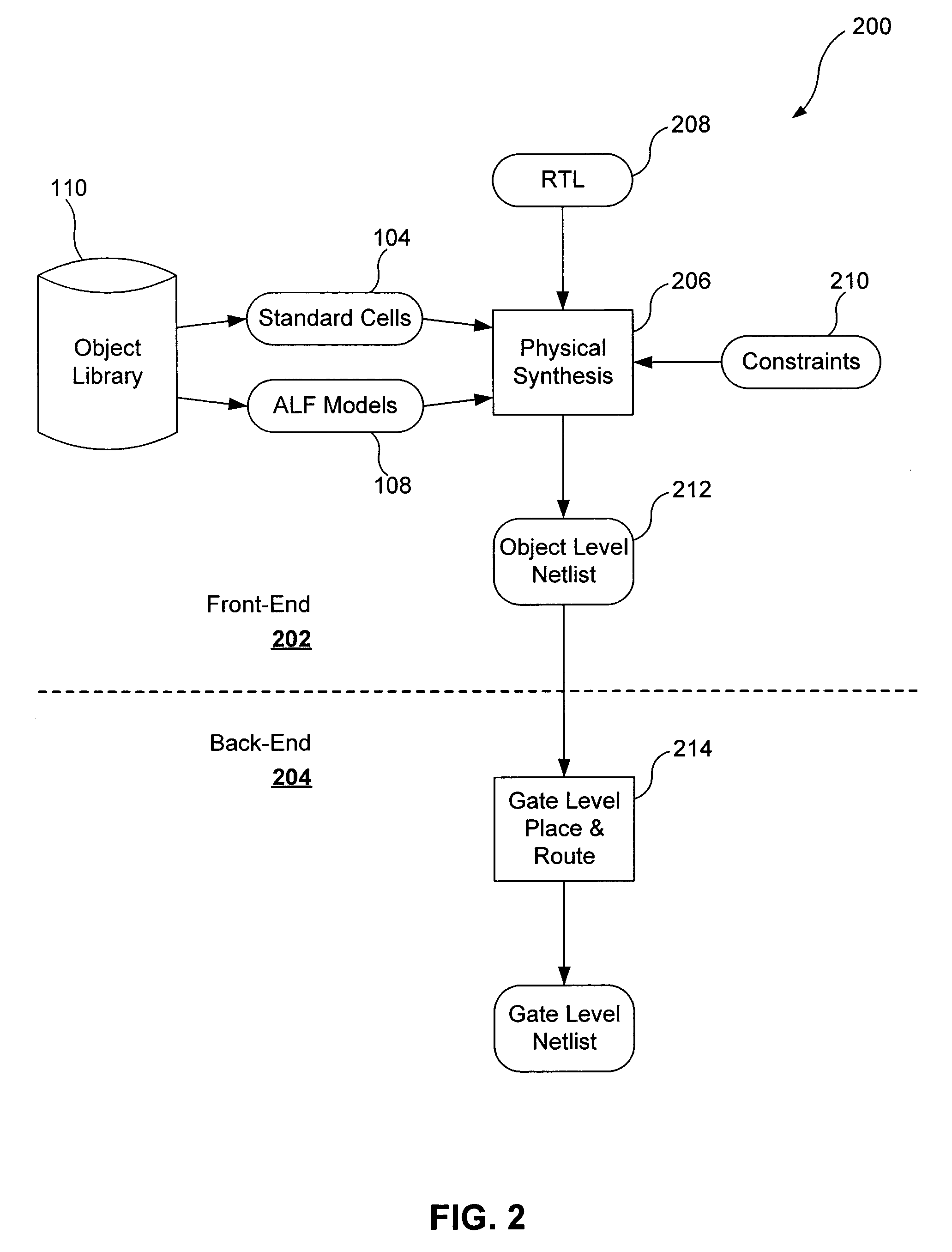

Methods and systems for mixed-mode physical synthesis in electronic design automation

ActiveUS20050268267A1Shorten the lengthAccurately predict timingCAD circuit designProgram controlLoad modelInterconnection

Methods and systems for electronic design automation includes clustering objects into more manageable numbers of objects. Clustering is optionally performed to reduce or minimize interconnections between clusters. Clustering optionally includes multi-level clustering. The clusters, and any unclustered objects, are floorplanned. Floorplanning positions the clusters so as to reduce or minimize the length of interconnections between the clusters. Objects within the clusters are then placed within the area assigned to the corresponding clusters. Placement optionally utilizes placement-based wire load models to accurately predict timing issues. A bottoms-up procedure is optionally performed during clustering and / or floorplanning, whereby area and / or size constraints of clustered objects are taken into account.

Owner:SYNOPSYS INC

Enhanced incremental placement during physical synthesis

A method of placing a circuit design for a target device can include identifying a critical region having at least one input block and at least one output block and determining a line starting at the input block and extending to the output block. Blocks of the critical region can be assigned to sites located on, or proximate to, the line according to connectivity.

Owner:XILINX INC

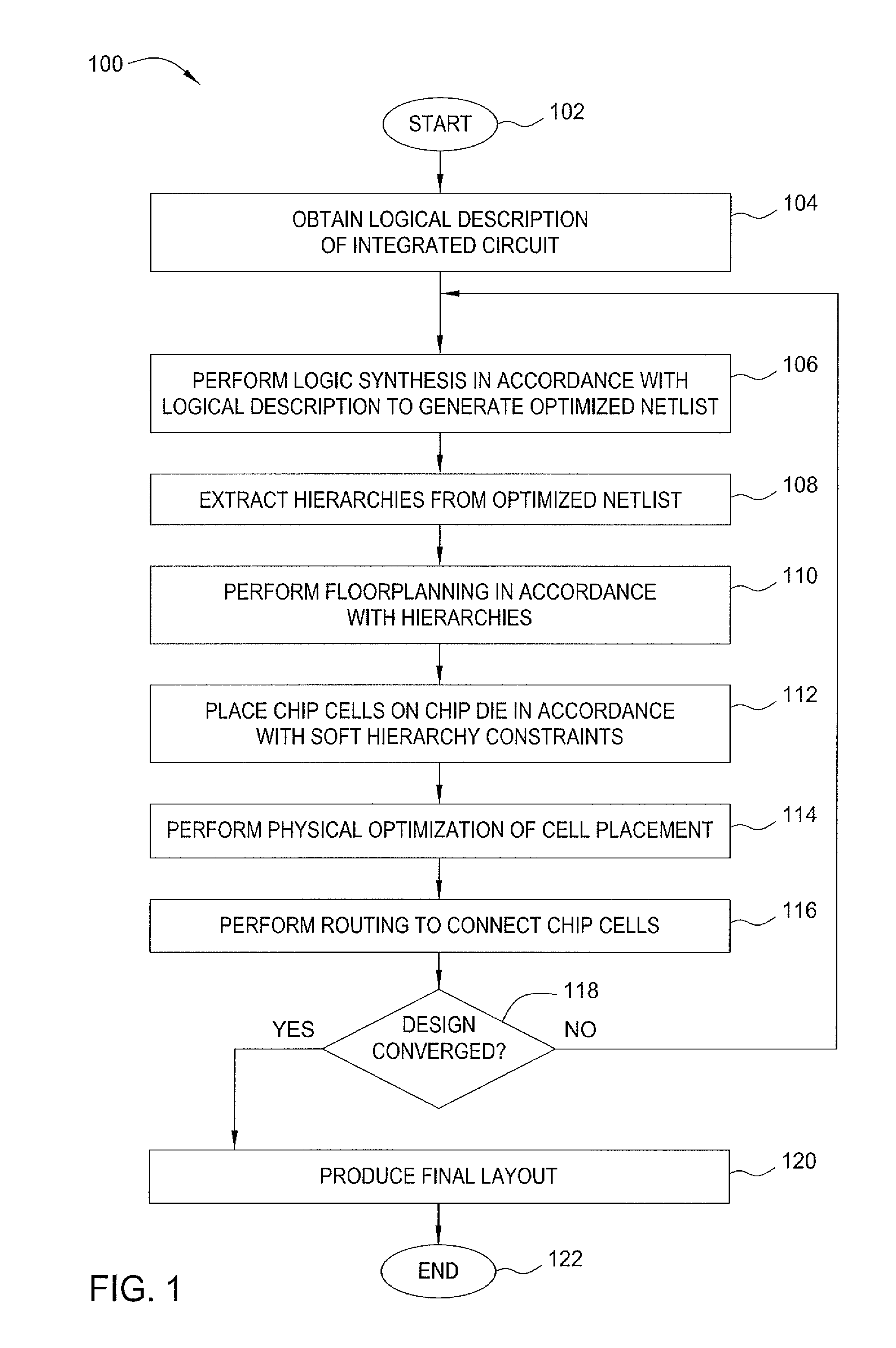

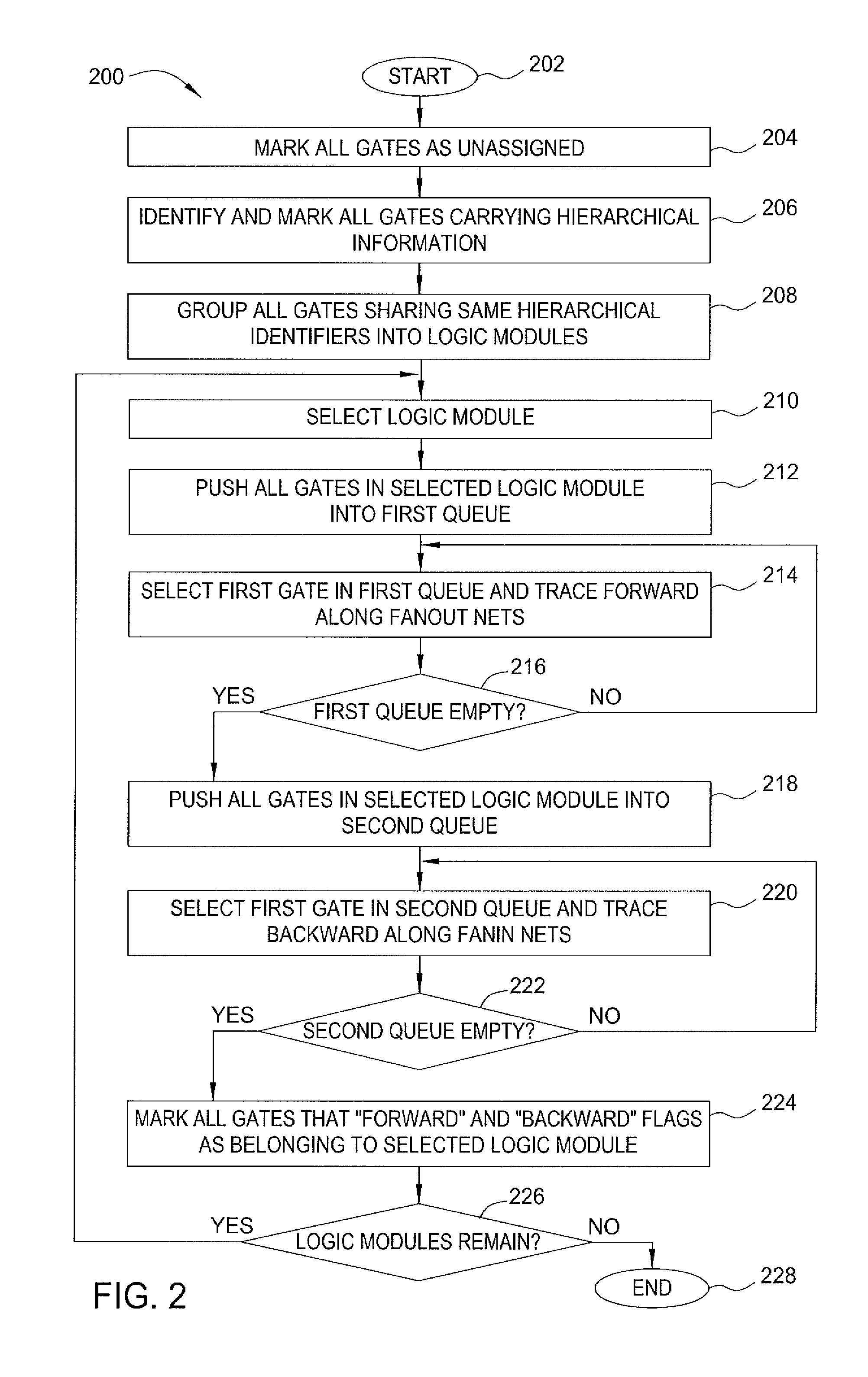

Soft hierarchy-based physical synthesis for large-scale, high-performance circuits

In one embodiment, the invention is a method and apparatus for soft hierarchy-based synthesis for large-scale, high-performance circuits. One embodiment of a method for physically synthesizing a design of an integrated circuit includes compiling a logical description of the design into a flattened netlist, extracting a soft hierarchy from the flattened netlist, wherein the soft hierarchy defines a boundary on a die across which cells of the integrated circuit are permitted to move, and placing a cell of the integrated circuit on the die in accordance with the soft hierarchy.

Owner:GLOBALFOUNDRIES INC

Method for Incremental, Timing-Driven, Physical-Synthesis Using Discrete Optimization

ActiveUS20090132981A1Easy to placeAnalogue computers for electric apparatusComputer aided designData processing systemSelection criterion

A method, data processing system and computer program product for optimizing the placement of logic gates of a subcircuit in a physical synthesis flow. A Path Smoothing utility identifies one or more movable gates based on at least one selection criteria. A set of legalized candidate locations corresponding to one or more identified movable gates is generated. A disjunctive timing graph based on the generated set of legalized candidate locations is then generated. An optimal location of one or more movable gate(s) is determined using a recursive branch-and-bound search and stored in the computing device.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Method for eliminating negative slack in a netlist via transformation and slack categorization

ActiveUS20090070715A1Extension of timeEliminating negative slackCAD circuit designSoftware simulation/interpretation/emulationTime informationTheoretical computer science

A method for eliminating negative slack in a netlist representing a chip design uses a contrived timing environment to overlay information onto the design environment during logic and physical synthesis phase. The overlaid timing information determines which netlist transformation provides a maximum leverage for the negative slack elimination and a way for creating a dynamic transformation recipe tuned for each design. The method further provides upper bounds on the negative slack elimination to prevent the netlist transforms from being applied to situations exceeding the capabilities for improving the design.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

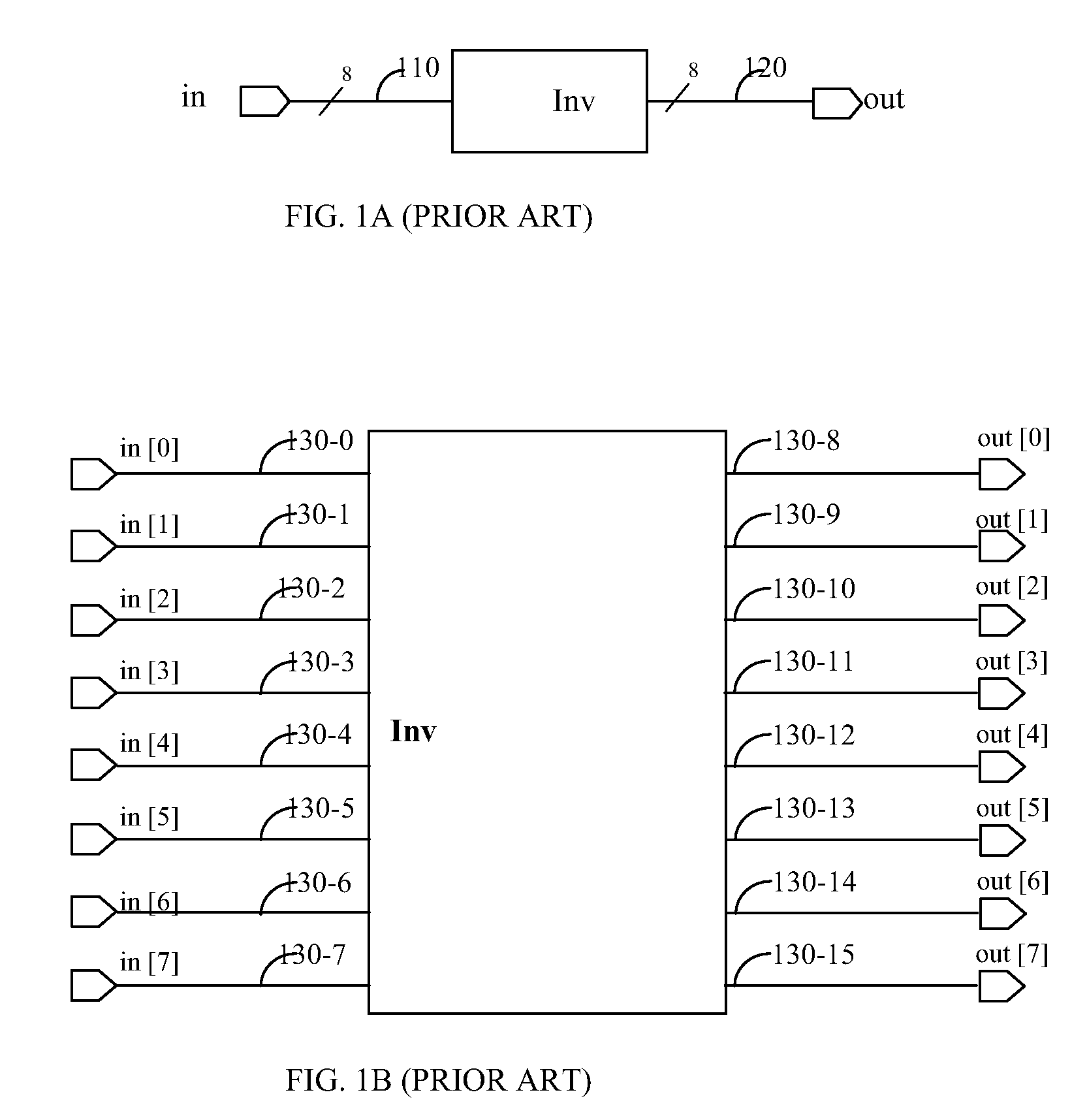

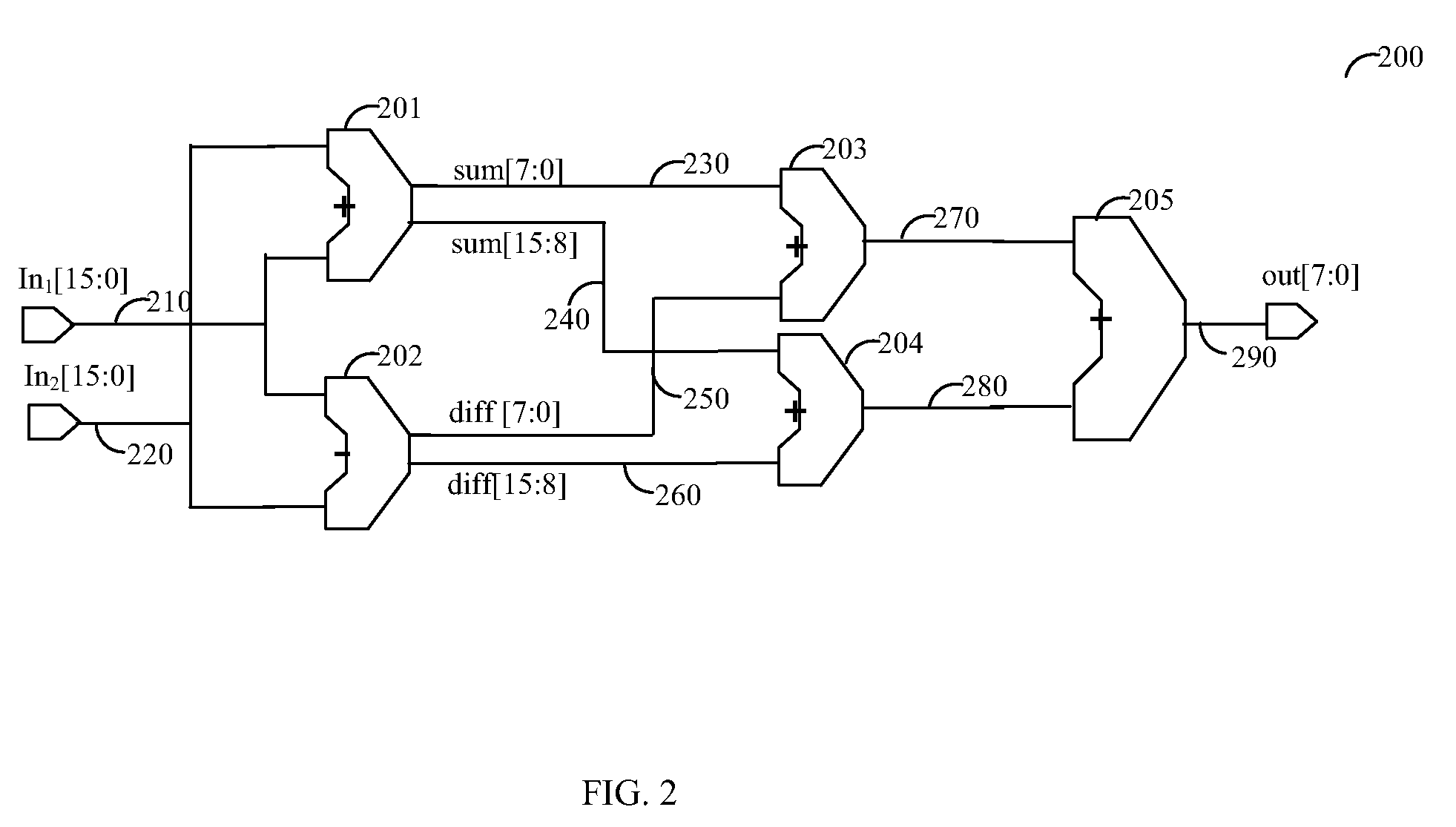

Bus representation for efficient physical synthesis of integrated circuit designs

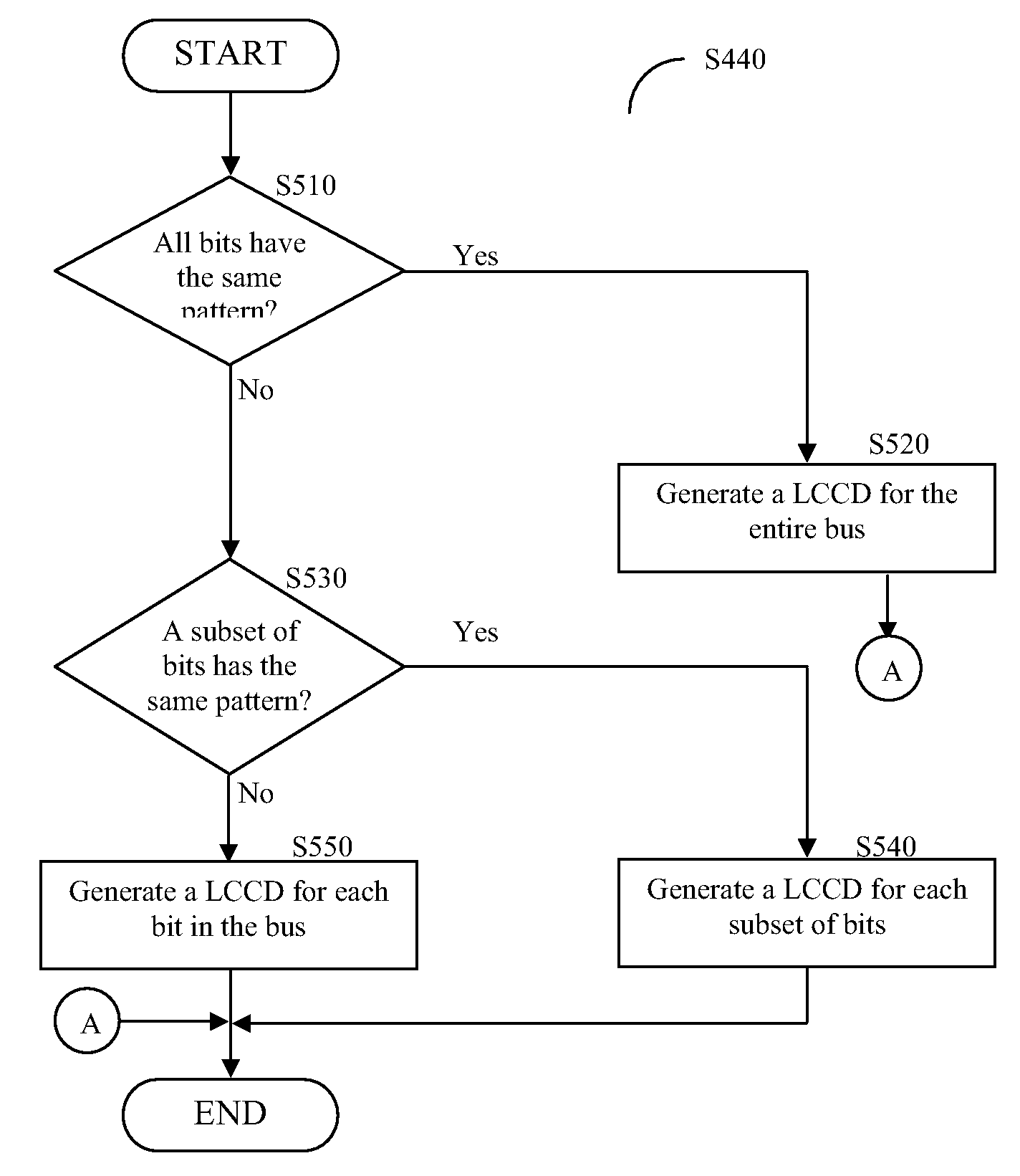

ActiveUS7451427B2CAD circuit designSoftware simulation/interpretation/emulationComputer architectureComputer science

A method for the abstraction of connectivity that provides an intermediate data path representation of integrated circuit (IC) designs is provided. The connectivity abstraction maintains the compactness of a bus level representation as well as the uniqueness of a bit level representation. Connectivity abstraction significantly reduces network complexity, i.e., the number of wires in a design and the execution time of physical synthesis of IC designs.

Owner:SYNOPSYS INC

Methods and systems for mixed-mode physical synthesis in electronic design automation

ActiveUS7409658B2Shorten the lengthAccurate timingCAD circuit designProgram controlLoad modelInterconnection

Methods and systems for electronic design automation includes clustering objects into more manageable numbers of objects. Clustering is optionally performed to reduce or minimize interconnections between clusters. Clustering optionally includes multi-level clustering. The clusters, and any unclustered objects, are floorplanned. Floorplanning positions the clusters so as to reduce or minimize the length of interconnections between the clusters. Objects within the clusters are then placed within the area assigned to the corresponding clusters. Placement optionally utilizes placement-based wire load models to accurately predict timing issues. A bottoms-up procedure is optionally performed during clustering and / or floorplanning, whereby area and / or size constraints of clustered objects are taken into account.

Owner:SYNOPSYS INC

Generating pattern-based estimated RC data with analysis of route information

ActiveUS9003344B2Good correlationImprove estimation accuracyComputer aided designSoftware simulation/interpretation/emulationPattern matchingTime critical

A method and apparatus for improving physical synthesis of a circuit design is described. In one exemplary embodiment, preliminary routing information of nets in the circuit design is analyzed. The preliminary routing information includes track assignment information. Timing-critical nets are identified based on statistical distribution of the preliminary routing information of the nets. The identified timing-critical nets are assigned to a set of routing layers and removed from future net pattern matching. The remaining nets are clustered into multiple net patterns based on their physical attributes. The scaling factor for each net pattern is updated based on the scaling factor standard deviation and net length of the net pattern. Nets that are outside multiple standard deviations of a net pattern are assigned to routing layers. The scaling factors of the net patterns and the layer assignments are applied to the next phase of placement-based optimizations.

Owner:SYNOPSYS INC

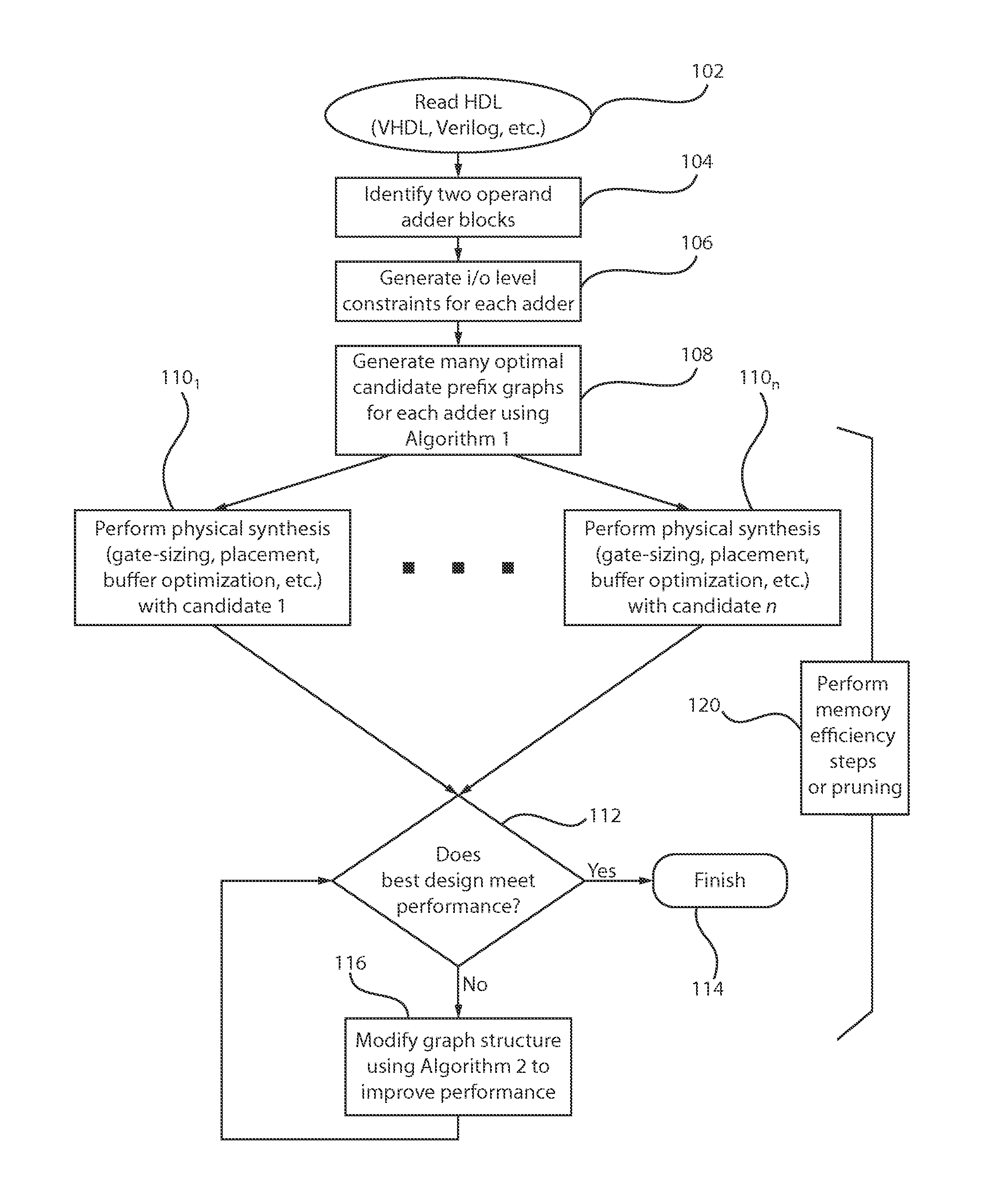

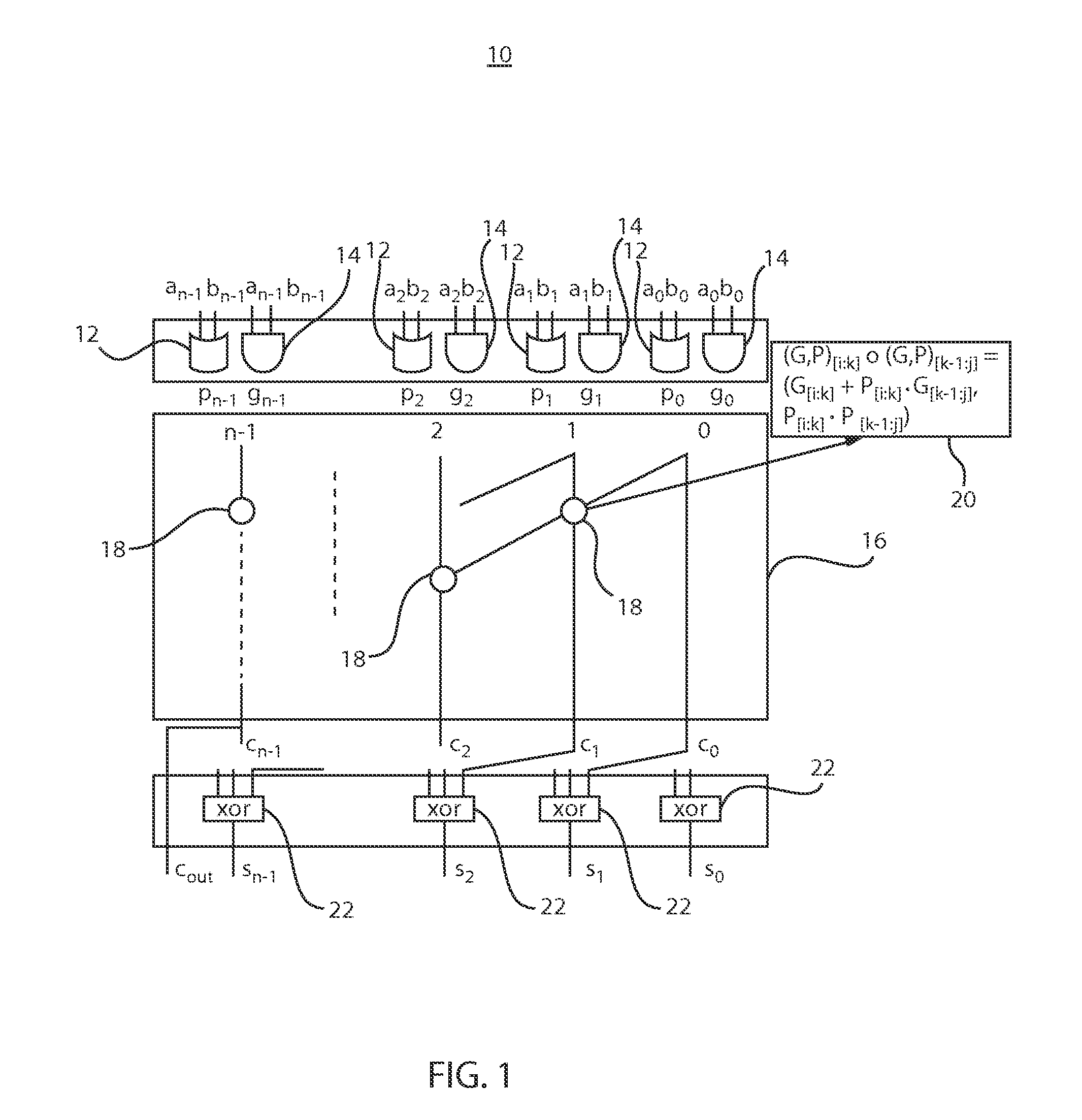

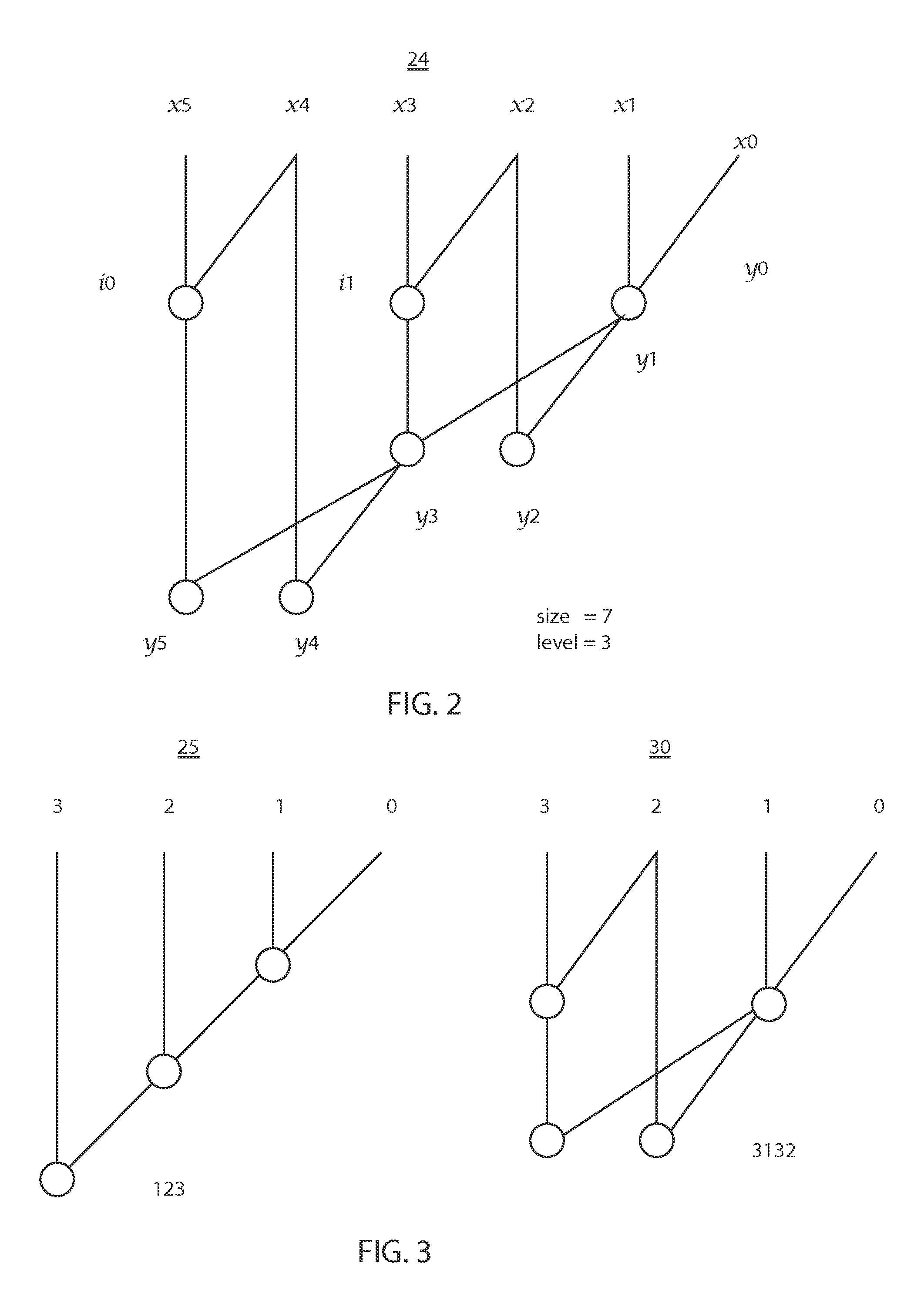

Automated synthesis of high-performance two operand binary parallel prefix adder

InactiveUS8527920B1Improve performanceComputer aided designSpecial data processing applicationsTheoretical computer scienceOperand

A method for automated synthesis of a parallel prefix device includes determining structural constraints for a given parallel prefix device; generating a plurality of candidate prefix graphs for the parallel prefix device by performing a search of possible prefix graphs meeting the constraints; performing physical synthesis of each of the plurality of candidate prefix graphs to generate performance information for each candidate prefix graph; and determining one or more of the plurality of candidate prefix graphs that meet performance criteria for incorporation into the parallel prefix device.

Owner:GLOBALFOUNDRIES INC

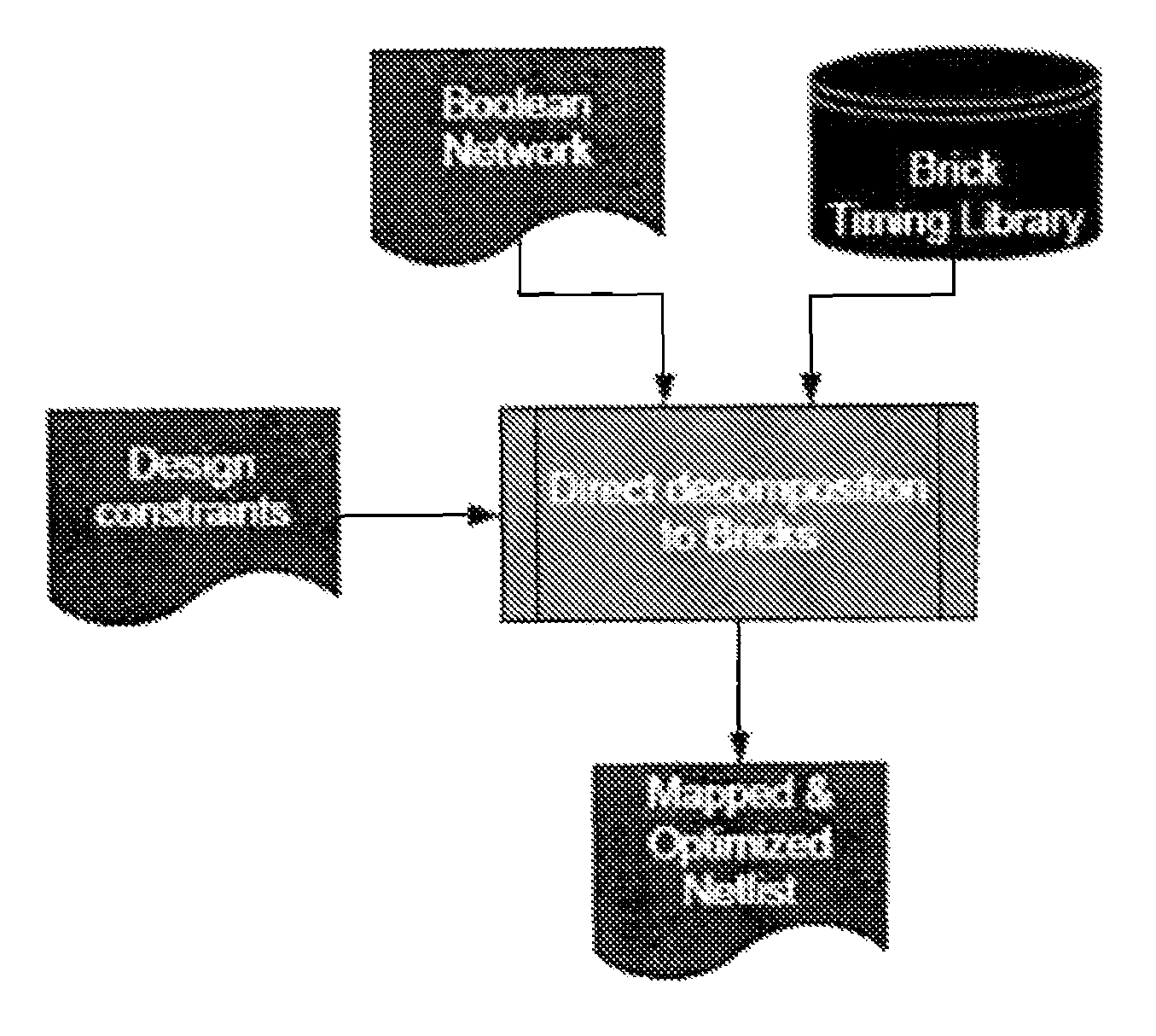

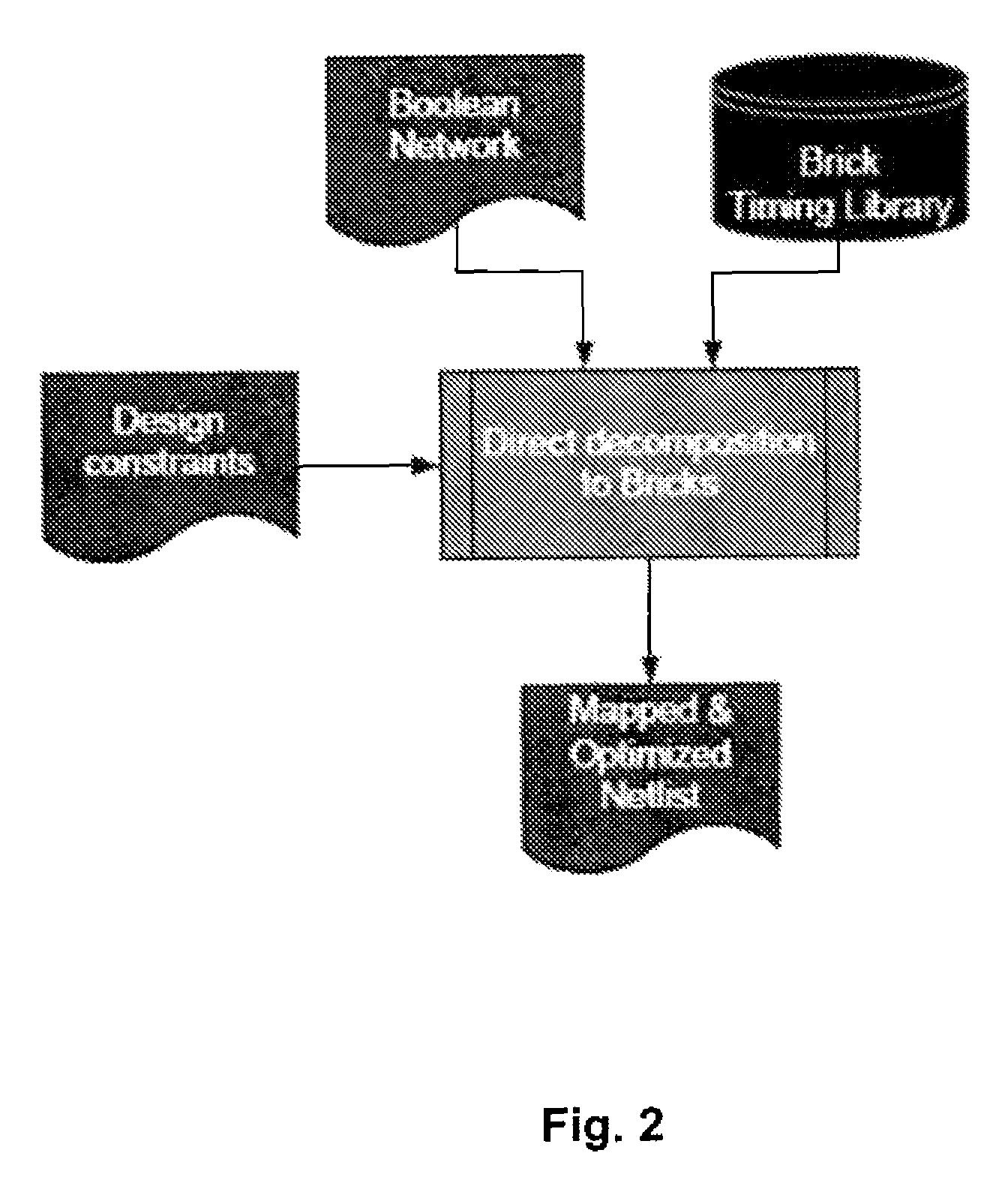

Method And System For Mapping A Boolean Logic Network To A Limited Set Of Application-Domain Specific Logic Cells

InactiveUS20080163152A1Computer aided designSoftware simulation/interpretation/emulationBrickLogic cell

A method and system is described for mapping a system-level description of an integrated system directly to a technology-specific set of logic cells that are comprised primarily of large complex cells (bricks). The invention is based on applying aggressive Boolean operations that would be of impractical runtime complexity for a large library, but are applicable for the targeted brick libraries which typically contain a small number of complex cells, along with a much smaller number of simple cells. This invention is modular such that it can be applied in the context of incremental netlist optimization as well as optimization during physical synthesis.

Owner:PDF SOLUTIONS INC

Method for mapping a Boolean logic network to a limited set of application-domain specific logic cells

A method and system is described for mapping a system-level description of an integrated system directly to a technology-specific set of logic cells that are comprised primarily of large complex cells (bricks). The invention is based on applying aggressive Boolean operations that would be of impractical runtime complexity for a large library, but are applicable for the targeted brick libraries which typically contain a small number of complex cells, along with a much smaller number of simple cells. This invention is modular such that it can be applied in the context of incremental netlist optimization as well as optimization during physical synthesis.

Owner:PDF SOLUTIONS INC

Structured placement of hierarchical soft blocks during physical synthesis of an integrated circuit

InactiveUS8954915B2Easy to placeAvoid changeCAD circuit designSoftware simulation/interpretation/emulationComputer architectureLogic implementation

Integrated circuit design uses a library of structured soft blocks (SSBs) composed of pre-defined sets of cells with their logic implementation and placement templates with their relative placement information. A compiler receives a circuit description which includes an instance of an SSB and unfolds the instance according to the placement template to generate a modified circuit description which includes the relative placement information. The placement of circuit objects is optimized while maintaining relative locations for cells of the SSB instance according to the relative placement information. The SSB may be hierarchical. Gate resizing of cells in the SSB instance may result in a change in its bounds. A timing optimization procedure for the modified circuit description may be carried out while hiding internal details of the SSB instance. For example, buffers may be inserted in nets external to the SSB instance while preventing insertion of buffers in any internal nets.

Owner:IBM CORP

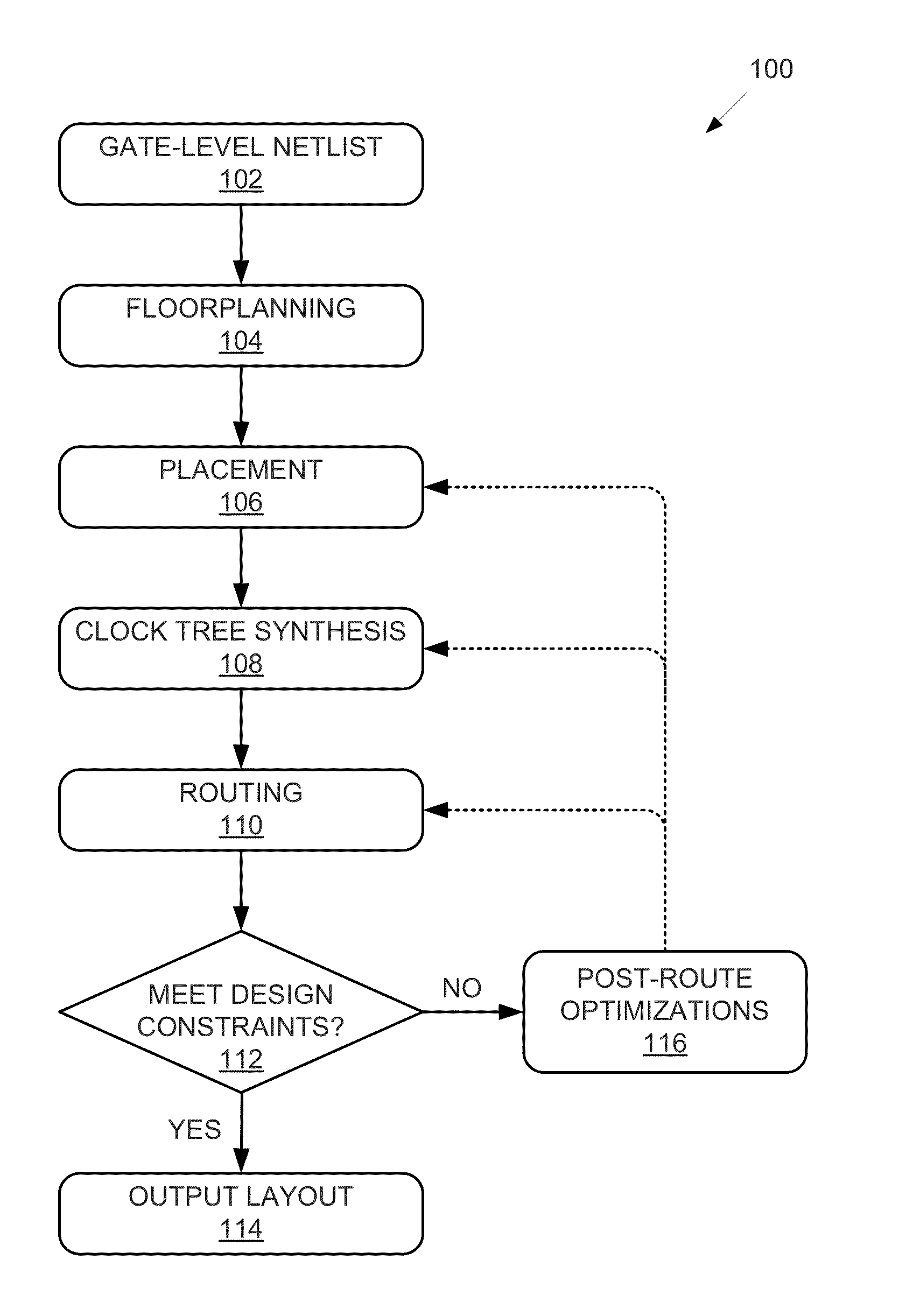

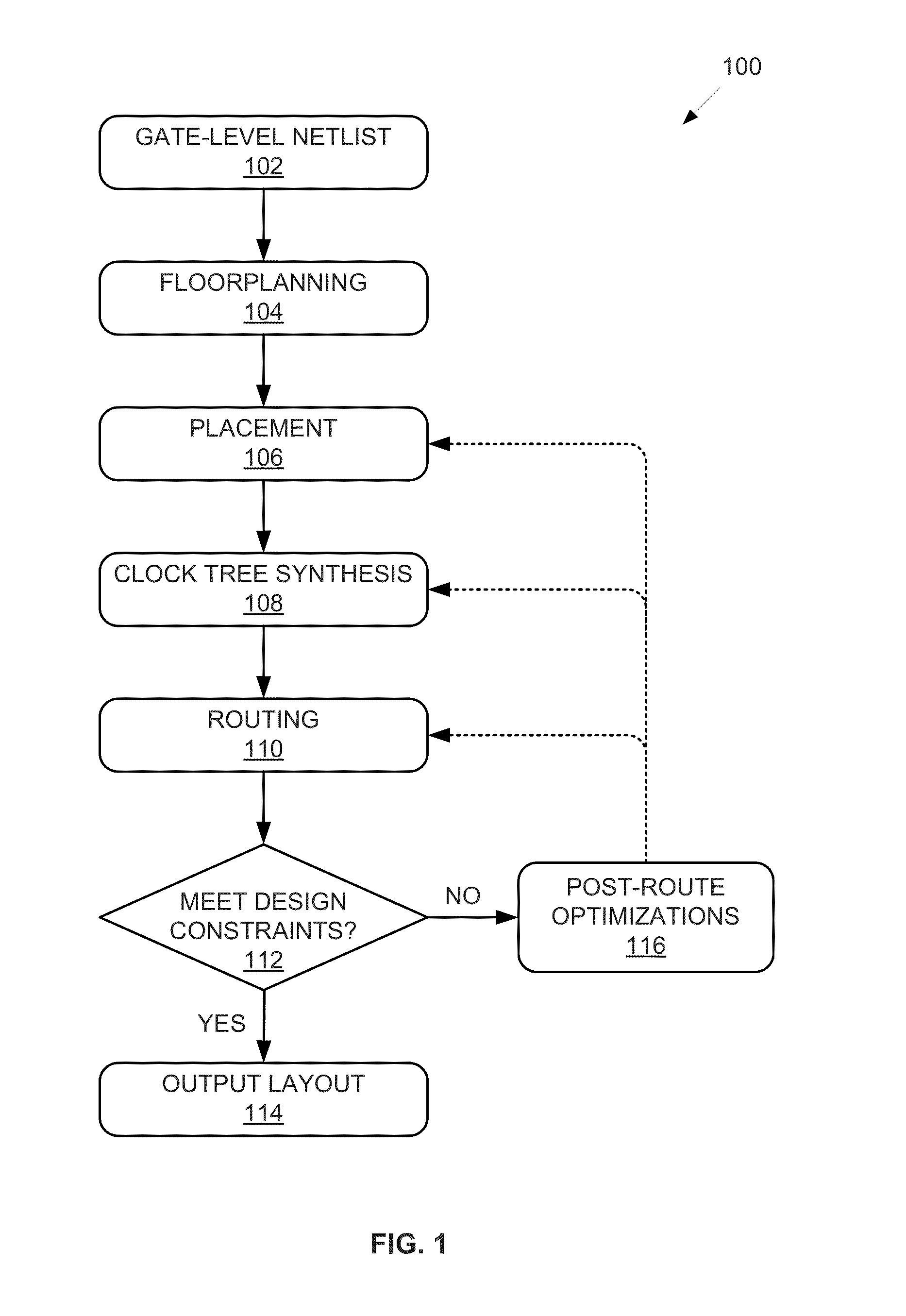

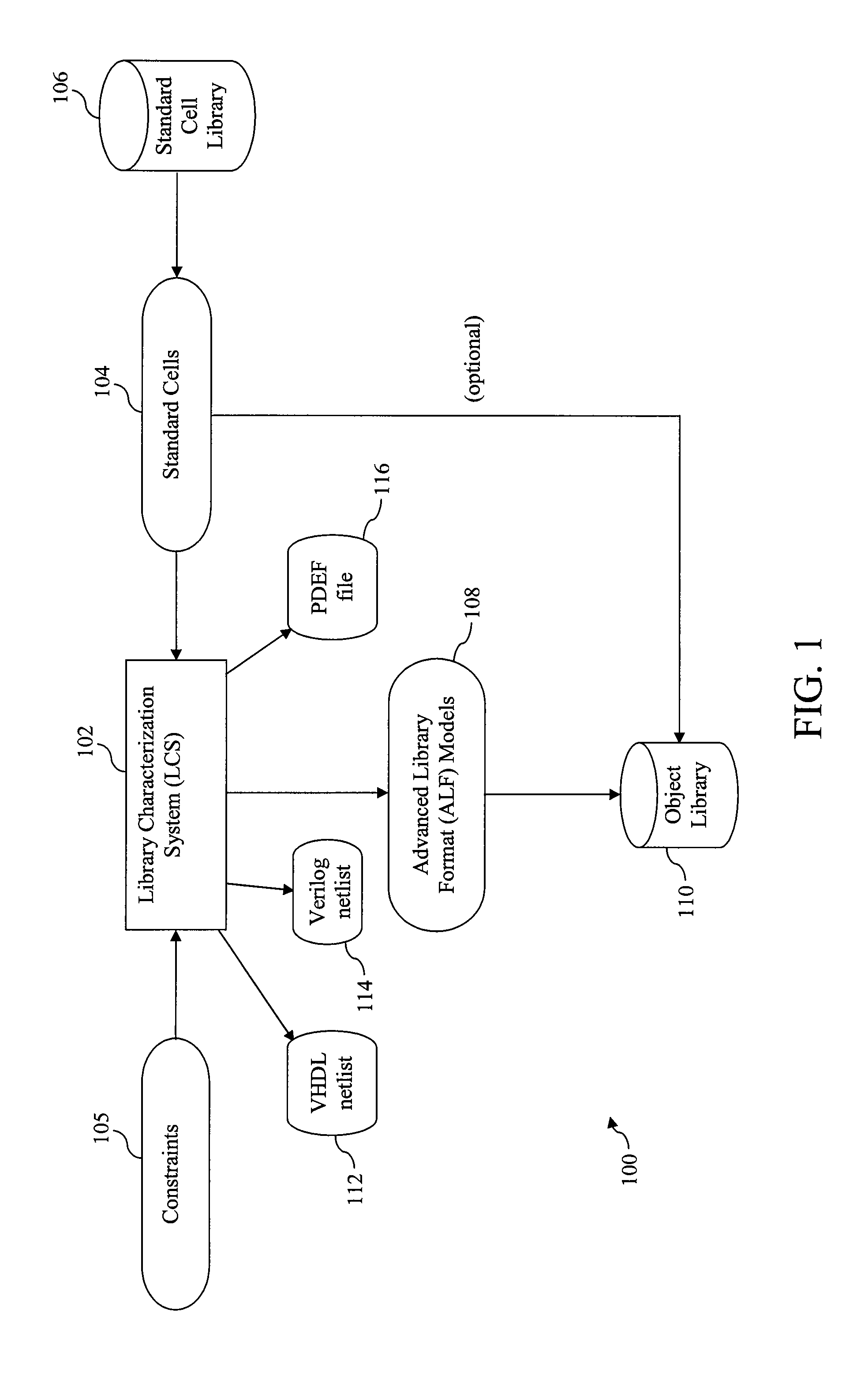

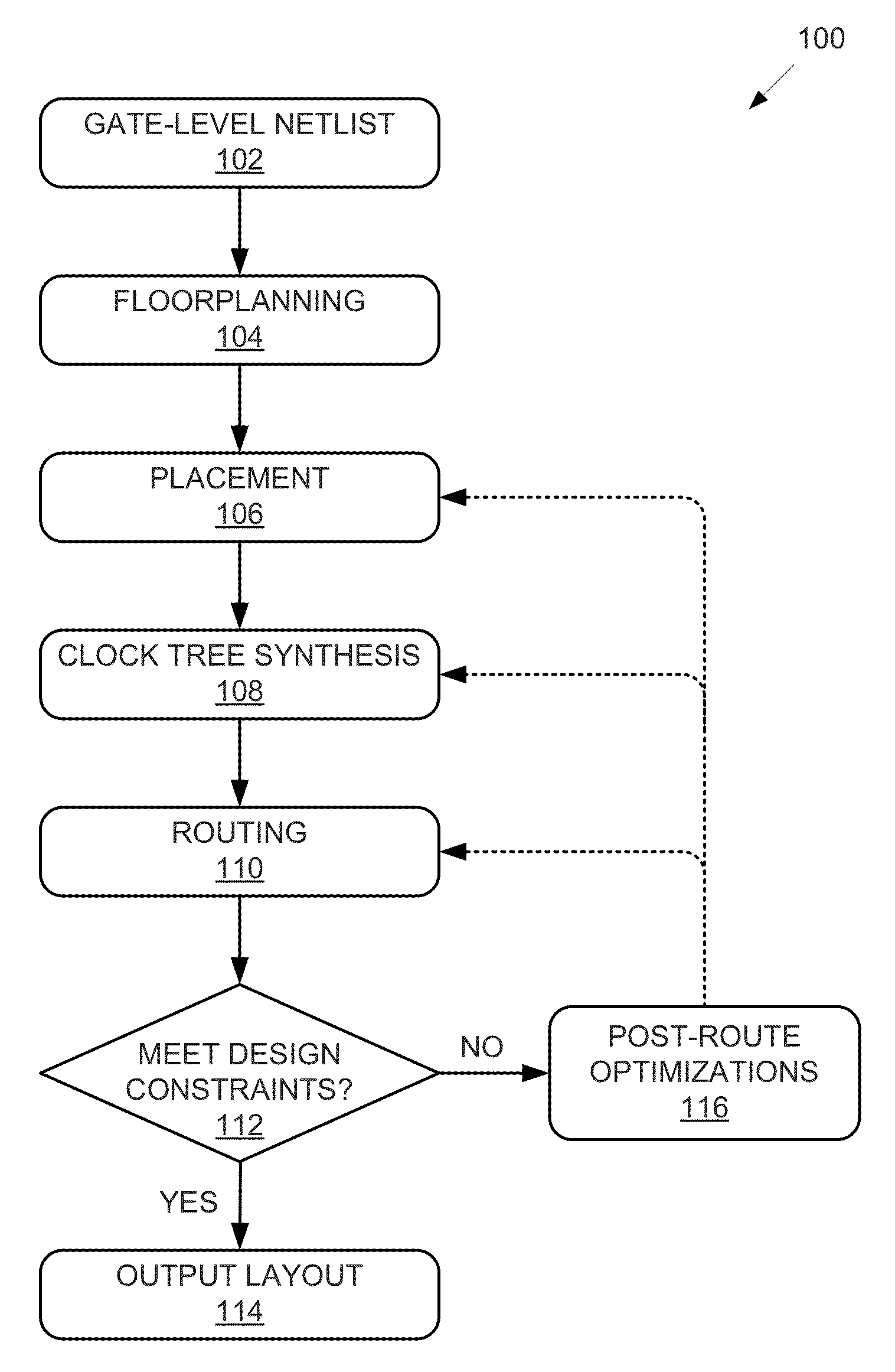

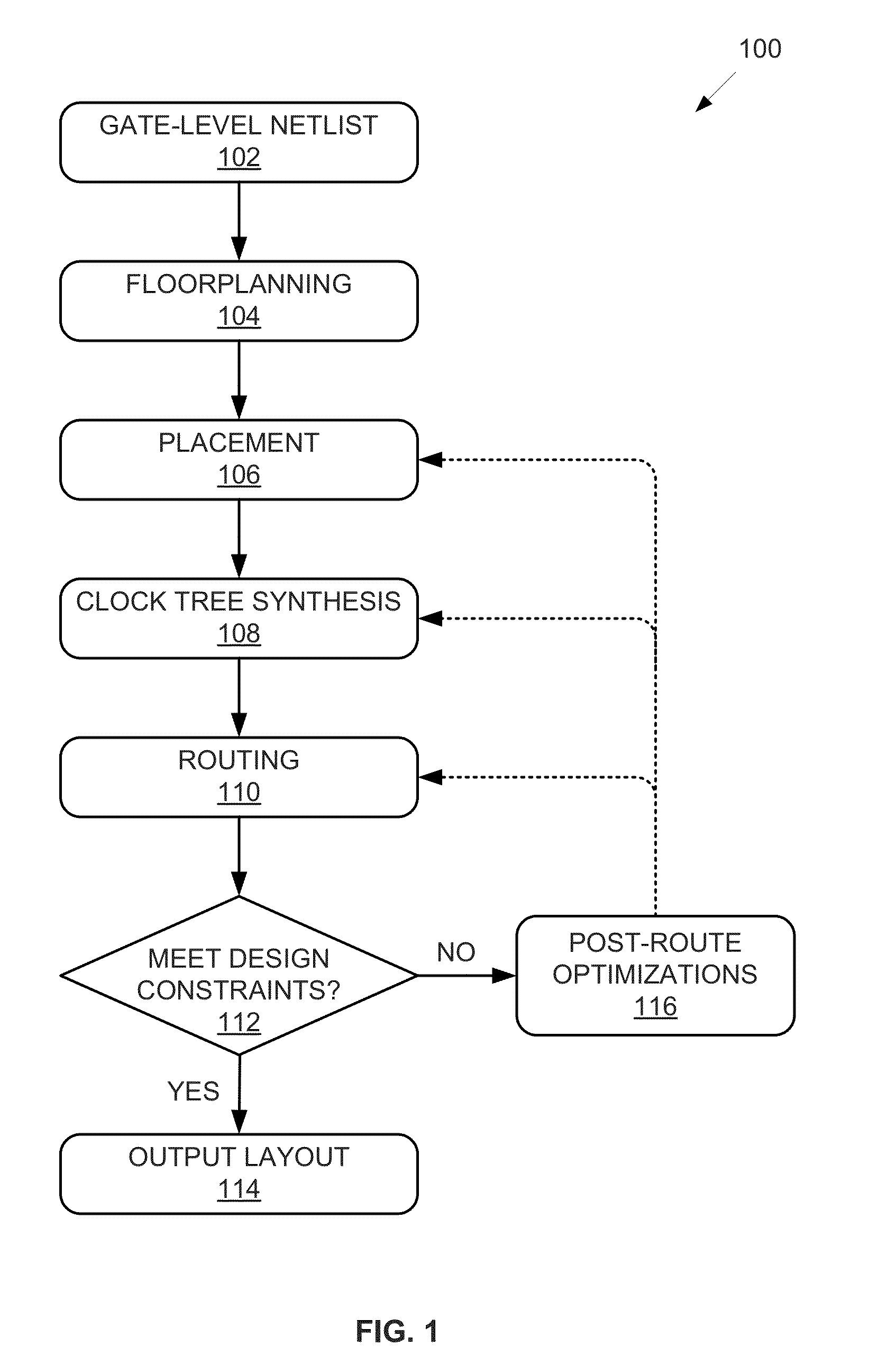

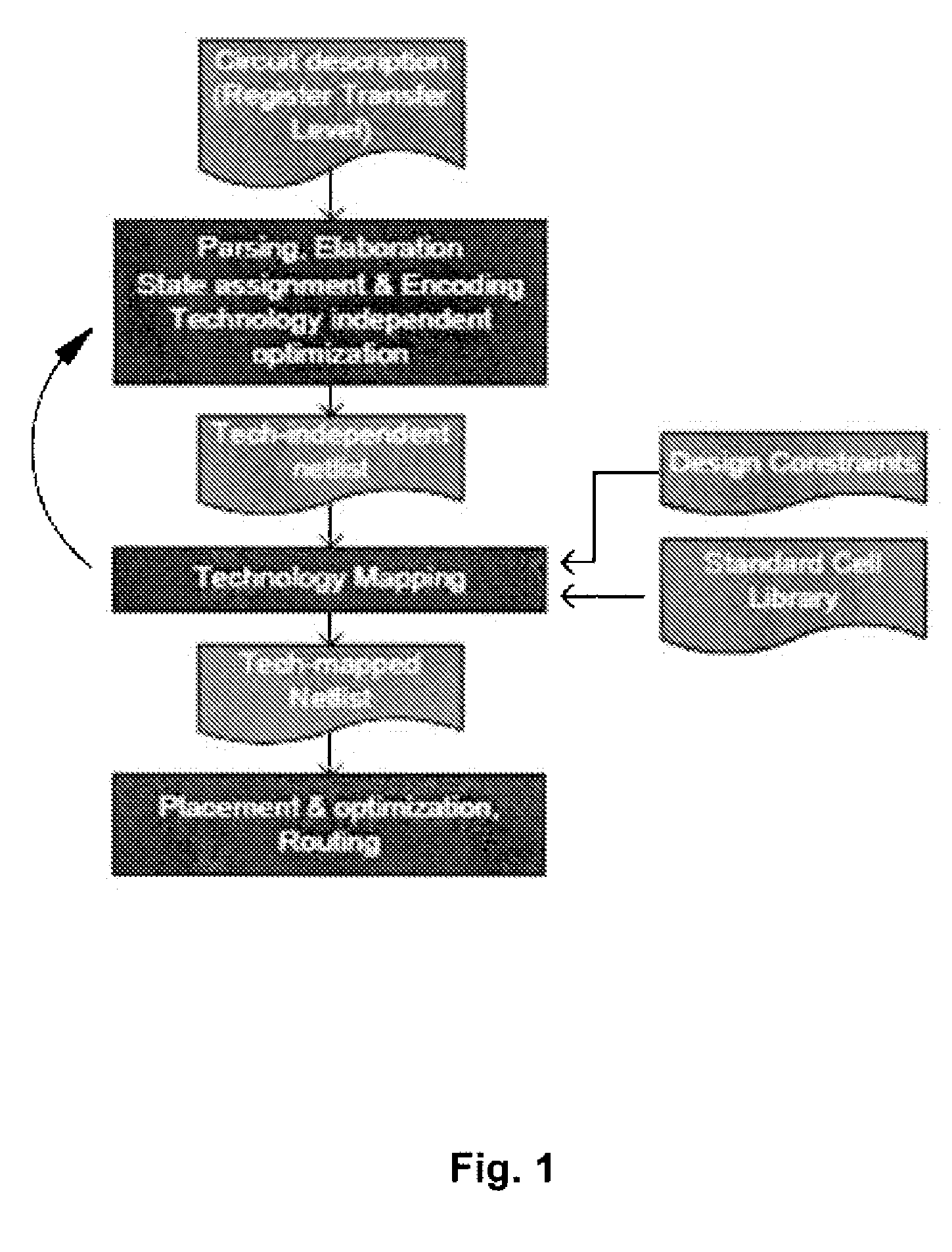

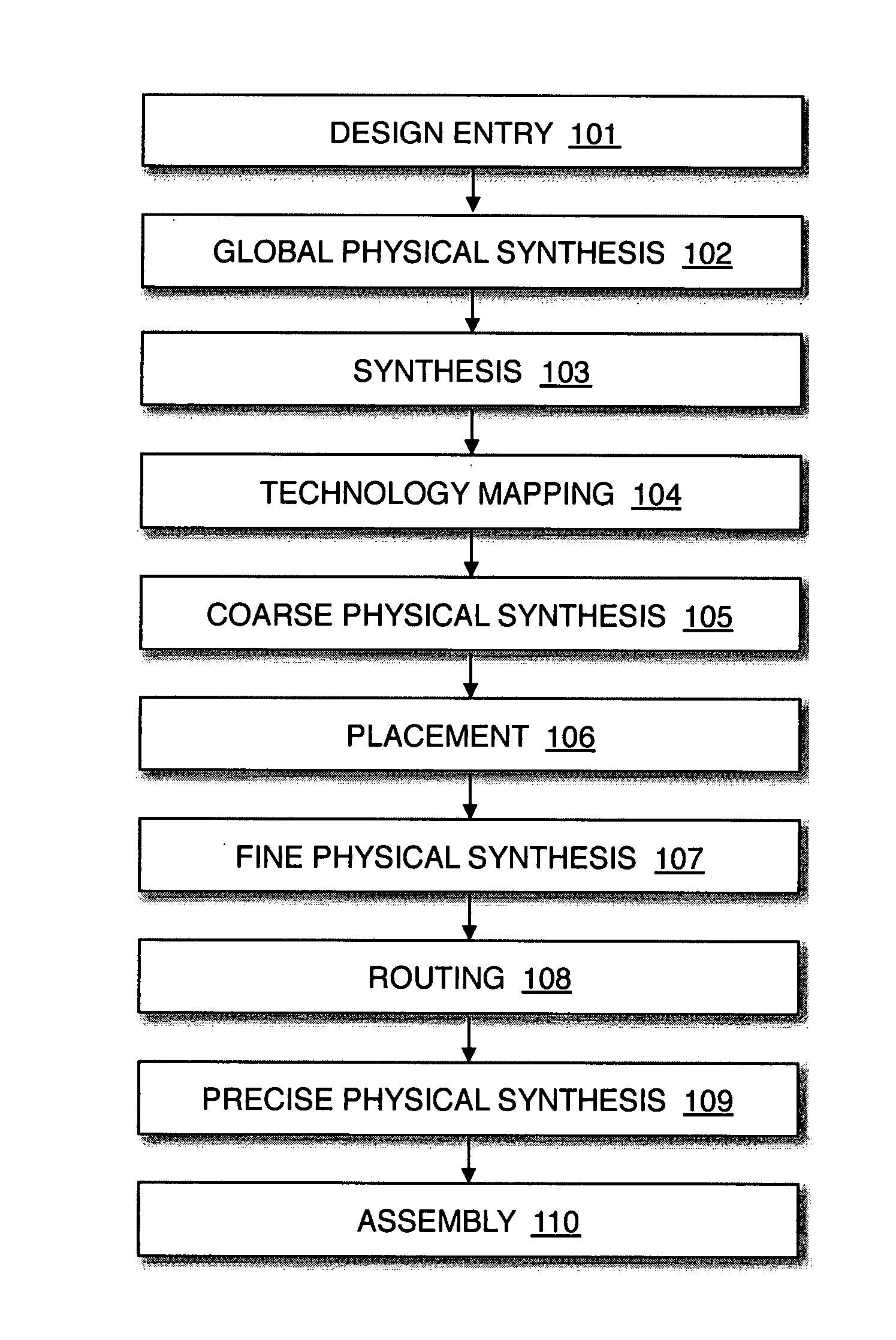

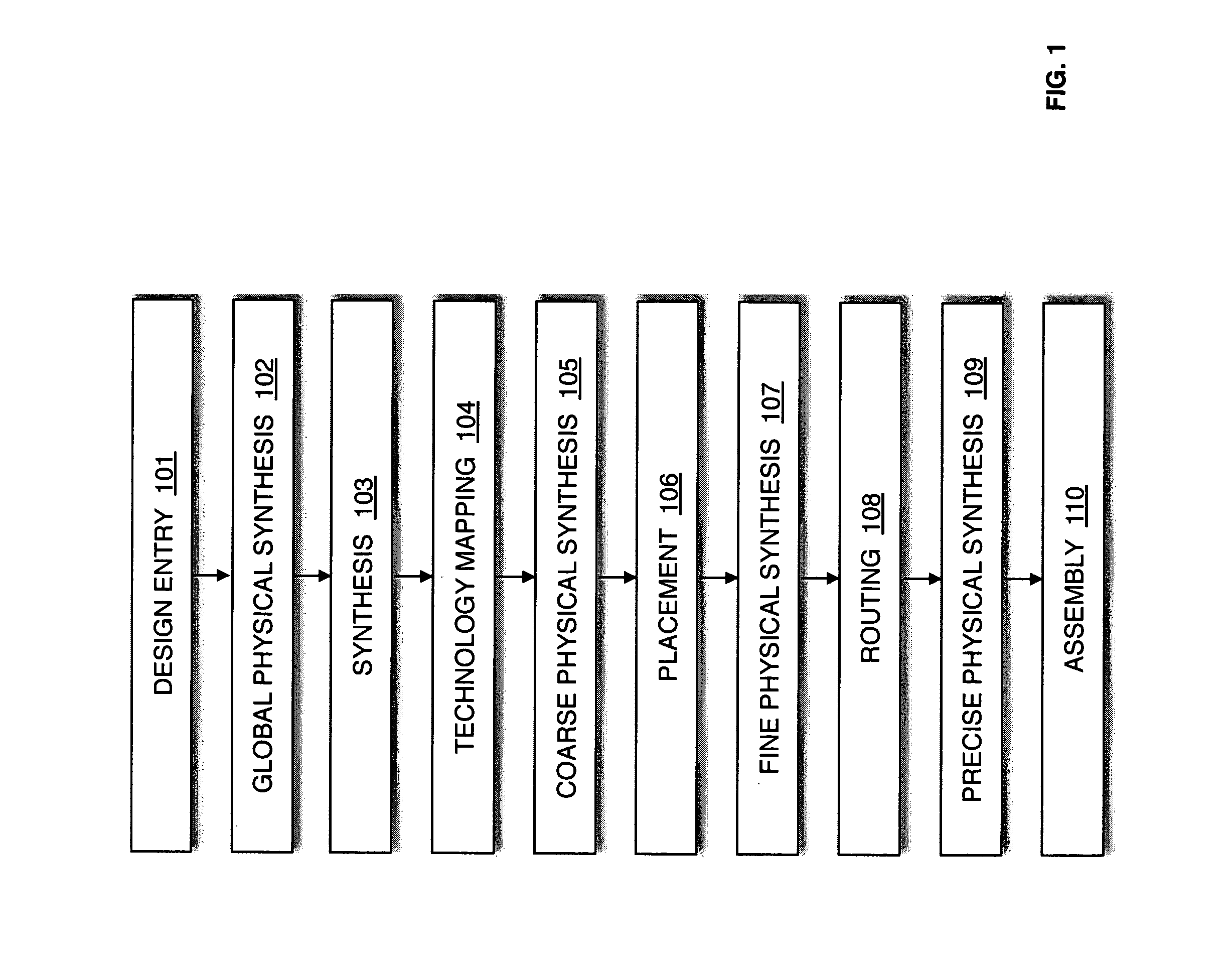

Method and apparatus for performing multiple stage physical synthesis

ActiveUS8510688B1Reduce delaysImprove routabilityCAD circuit designSoftware simulation/interpretation/emulationEngineeringPhysical synthesis

A method for designing a system on a target device includes entering the system. The system is synthesized. The system is mapped. The system is placed on the target device. The system is routed. Physical synthesis is performed on the system immediately after more than one of the entering, synthesizing, mapping, placing and routing procedures.

Owner:ALTERA CORP

Method for eliminating negative slack in a netlist via transformation and slack categorization

ActiveUS7810062B2Extension of timeEliminating negative slackCAD circuit designSoftware simulation/interpretation/emulationTime informationTheoretical computer science

A method for eliminating negative slack in a netlist representing a chip design uses a contrived timing environment to overlay information onto the design environment during logic and physical synthesis phase. The overlaid timing information determines which netlist transformation provides a maximum leverage for the negative slack elimination and a way for creating a dynamic transformation recipe tuned for each design. The method further provides upper bounds on the negative slack elimination to prevent the netlist transforms from being applied to situations exceeding the capabilities for improving the design.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

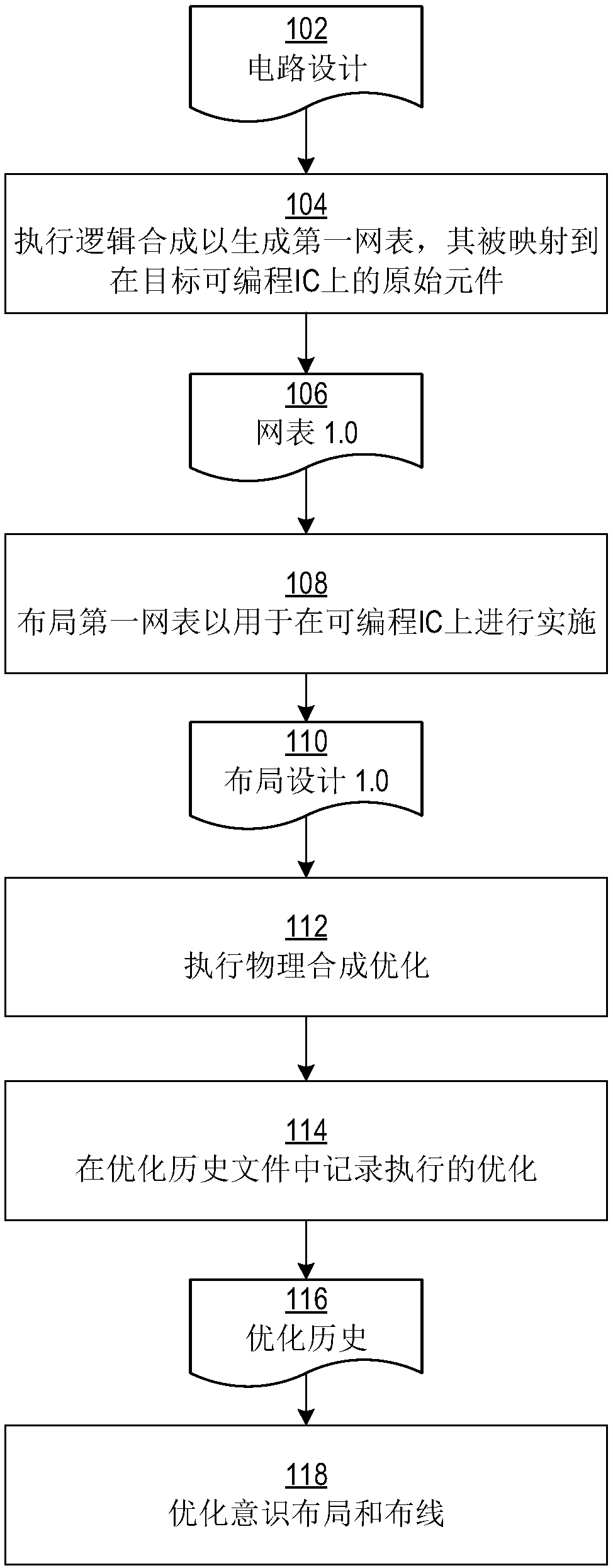

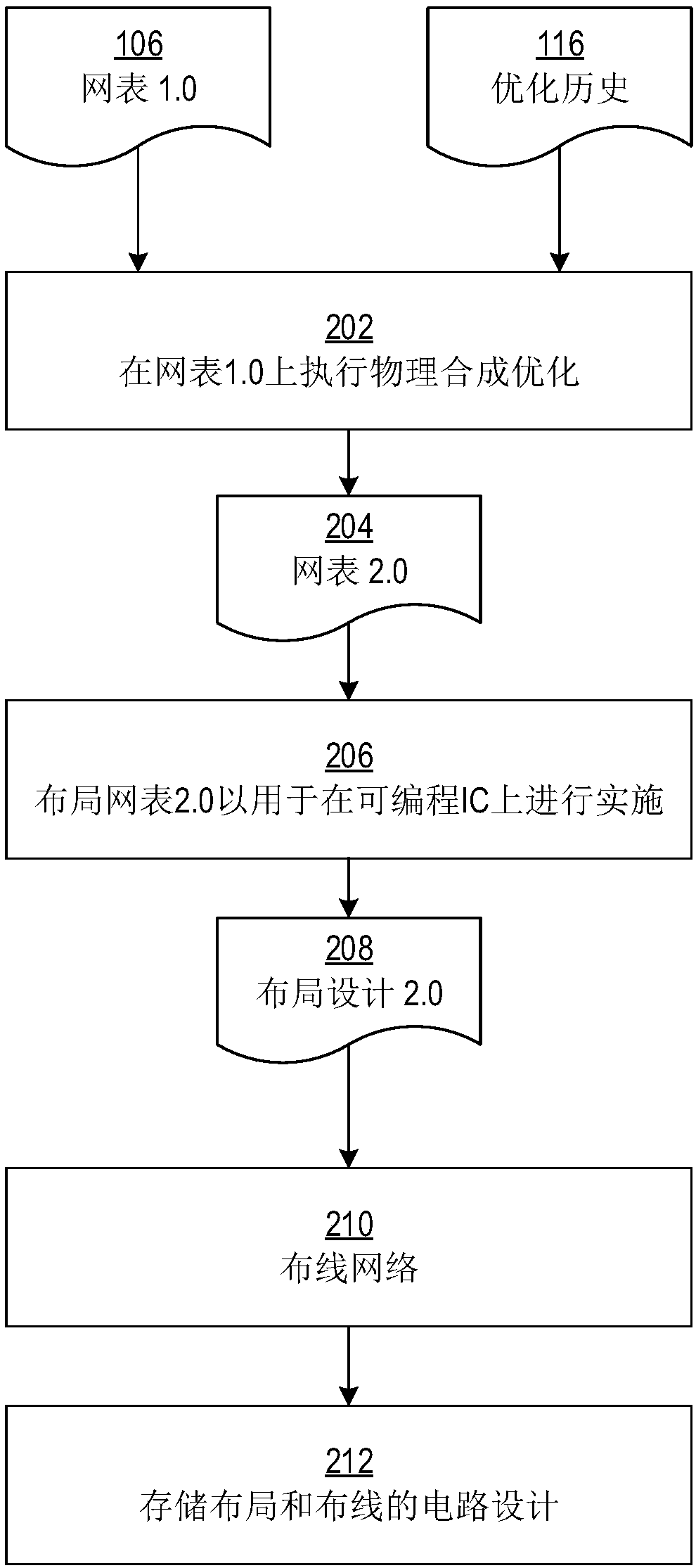

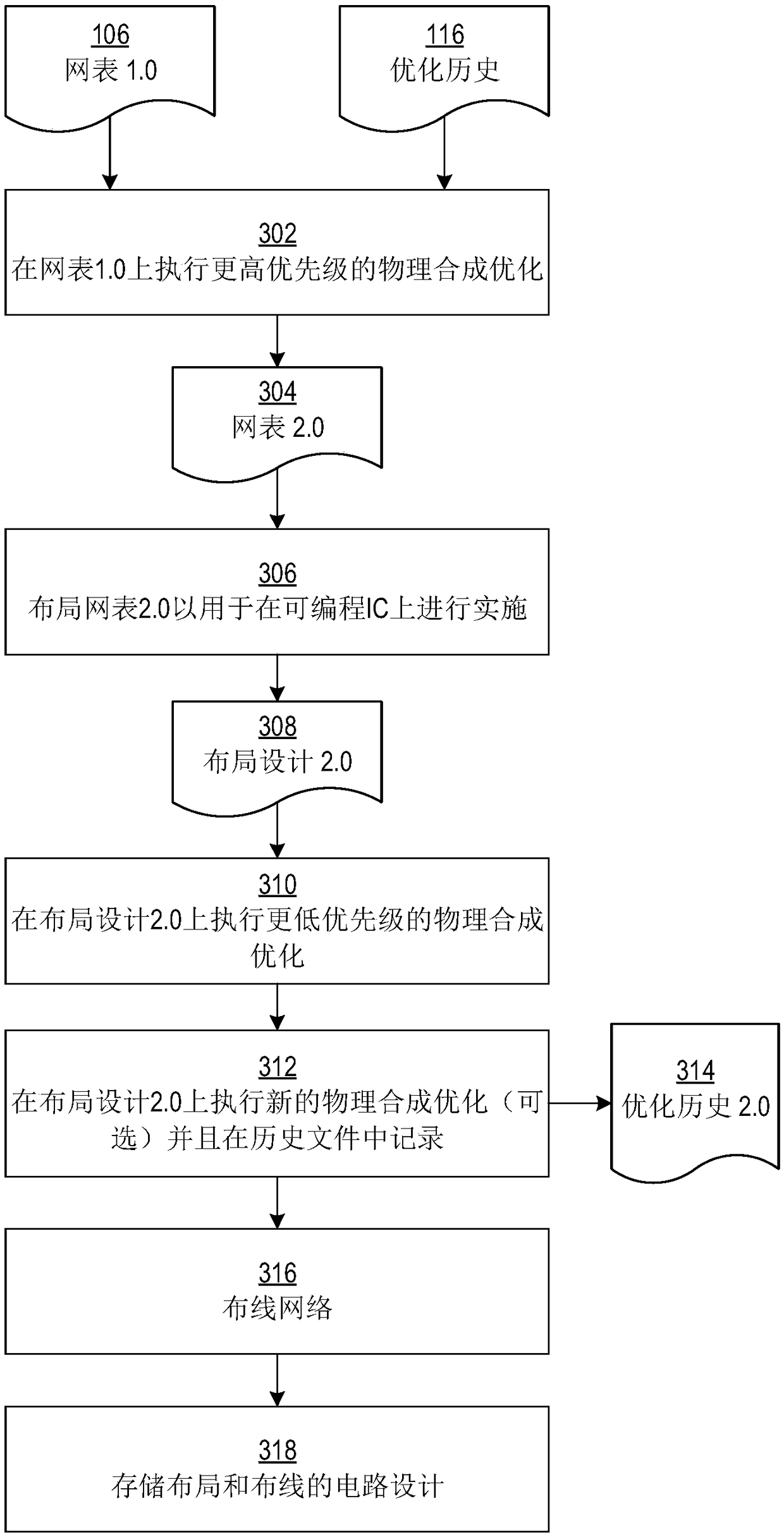

Interactive multi-step physical synthesis

In one embodiment of the invention, a processor-implemented method is provided for placing and routing a circuit design (102). A first netlist is generated for a circuit design. Placement is performed(108) for the first netlist (106) on a target IC to produce a first placed design (1 10). A set of optimizations are performed (1 12) on the first placed design. The set of optimizations are recorded(1 14) in an optimization history file (1 16). One or more optimizations specified in the optimization history file are performed (1 18 / 202) on the first netlist to produce a second netlist that is different than the first netlist. Placement is performed (206) for the second netlist on the target IC to produce a second placed design (208) that is different than the first placed design. Nets of the second placed design are routed (210) to produce a placed and routed circuit design.

Owner:XILINX INC

Physical synthesis method for preventing cage reared chick from vent pecking

InactiveCN105532567AReduce concentrationLowered for its pecking, fromAnimal feeding stuffAccessory food factorsZoologyVent pecking

The invention discloses a physical synthesis method for preventing cage reared chicks from vent pecking, and belongs to a chick breeding method, and an objective is to provide a method for preventing cage reared chicks from vent pecking. The technical scheme comprises hanging red strips of cloth, or melon vine plants, or tuberous plants for chicks to peck in a cage; using red light in a brooding room; and mixing gravels in size of rice grain in forage. The method is simple and feasible, and is low in cost and convenient in operation, and would not hurt the chicks. The method can effectively reduce occurrence of vent pecking, and is a method for preventing cage reared chicks from vent pecking.

Owner:GUIZHOU ZHONGYAO POULTRY IND CO LTD

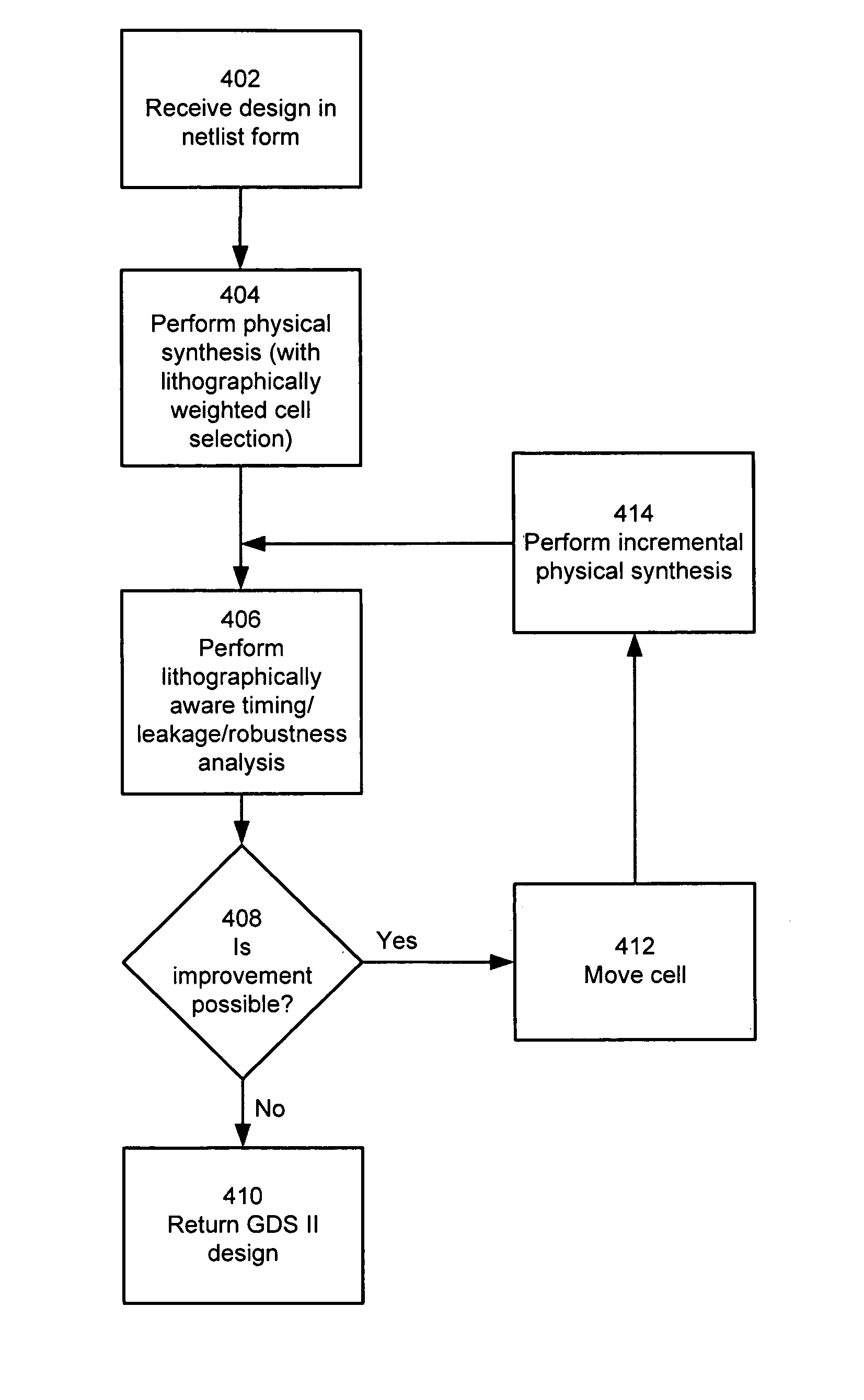

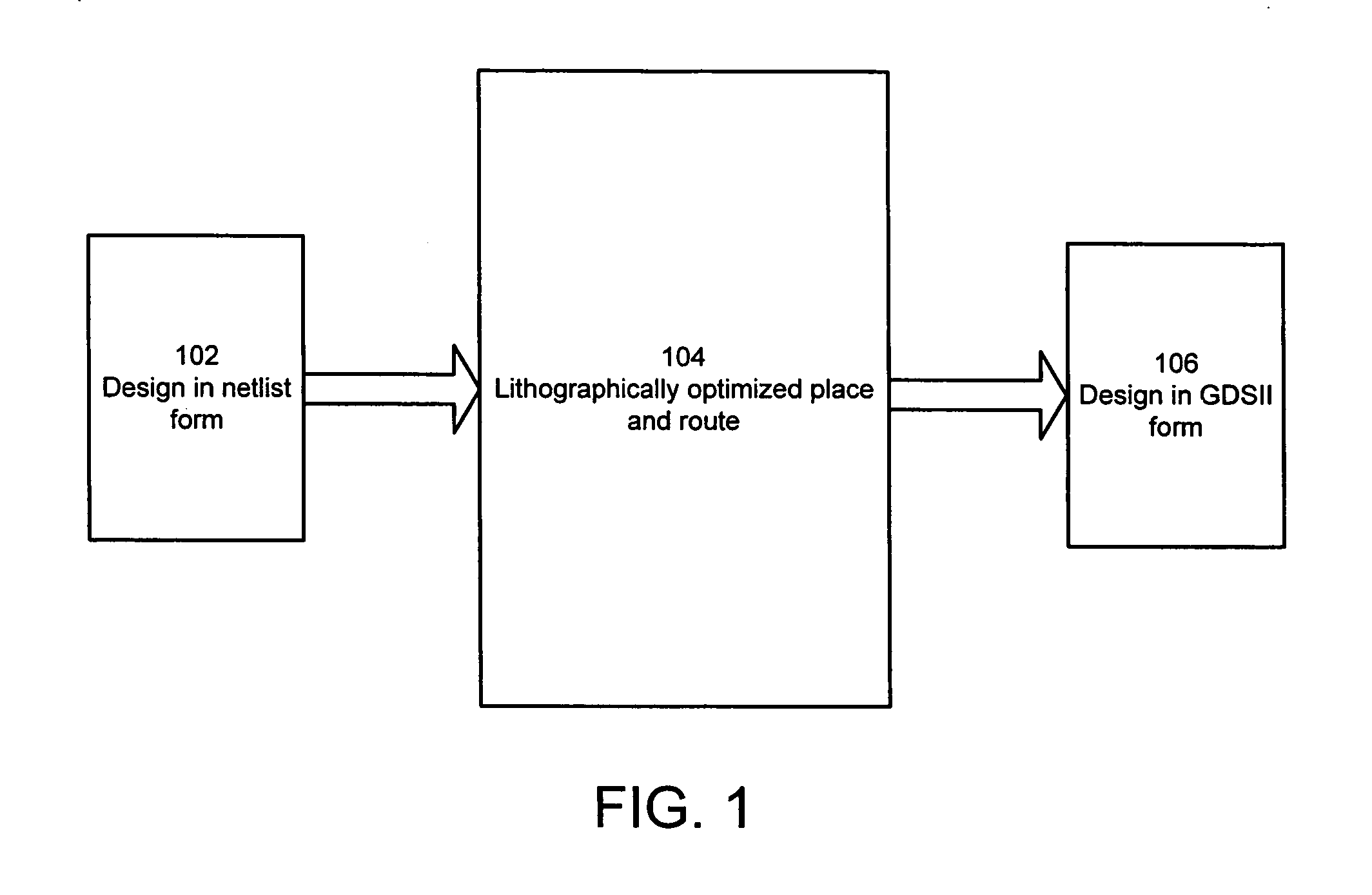

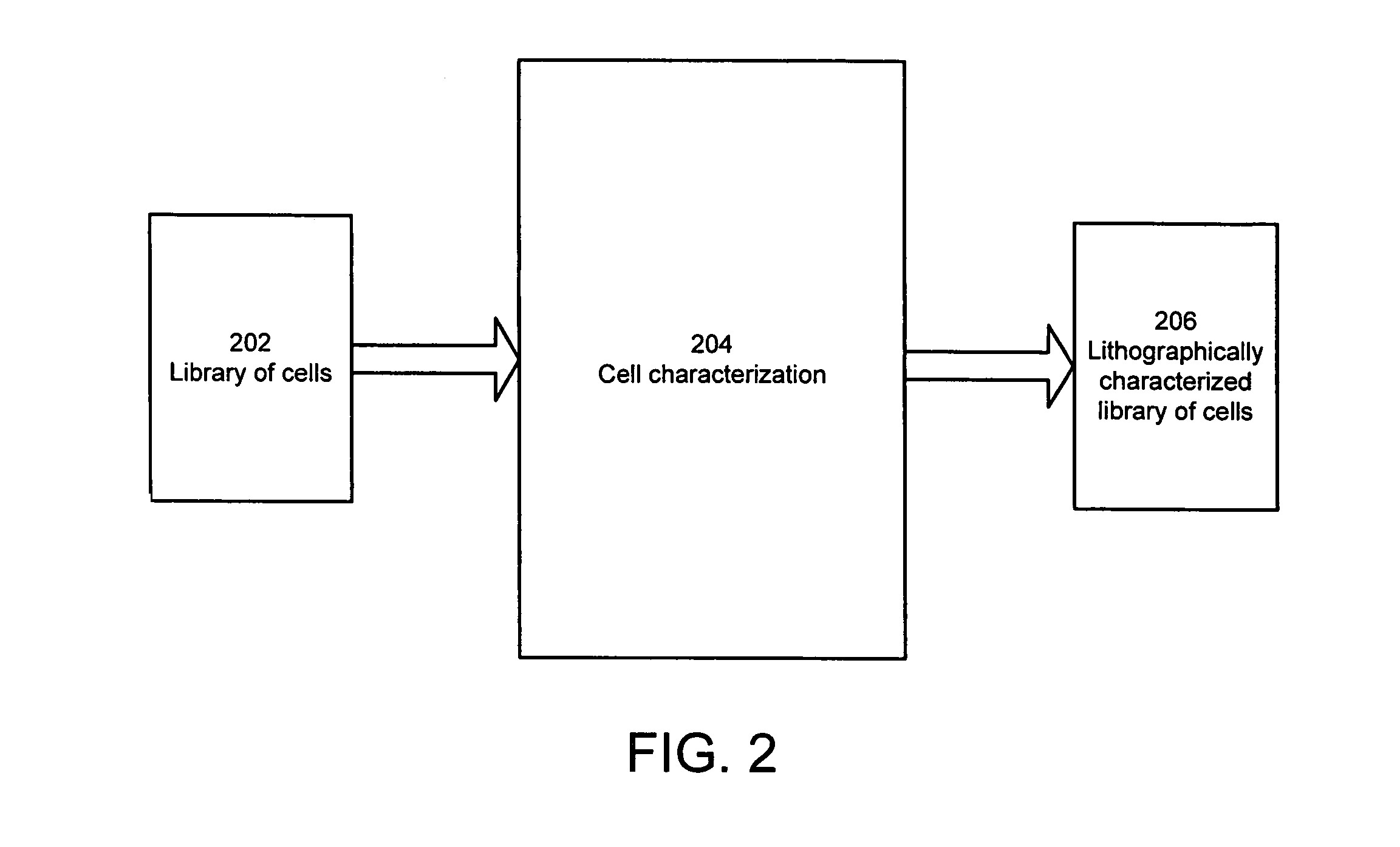

Lithographically optimized placement tool

ActiveUS7434188B1Improve circuit performanceComputer aided designSoftware simulation/interpretation/emulationSimulationPhotolithography

A system and a method are disclosed for integrating the results of lithographic simulation into the physical synthesis process. The effects of lithographic variation are considered when selecting a cell from among a group of cells having equivalent function. Circuit design elements are placed and routed with consideration of the effects of lithographic variation on robustness, timing performance, and leakage current. Cells may be simulated under a variety of conditions and environments and the simulation results stored in a library for efficient lithographically optimized placements.

Owner:SYNOPSYS INC

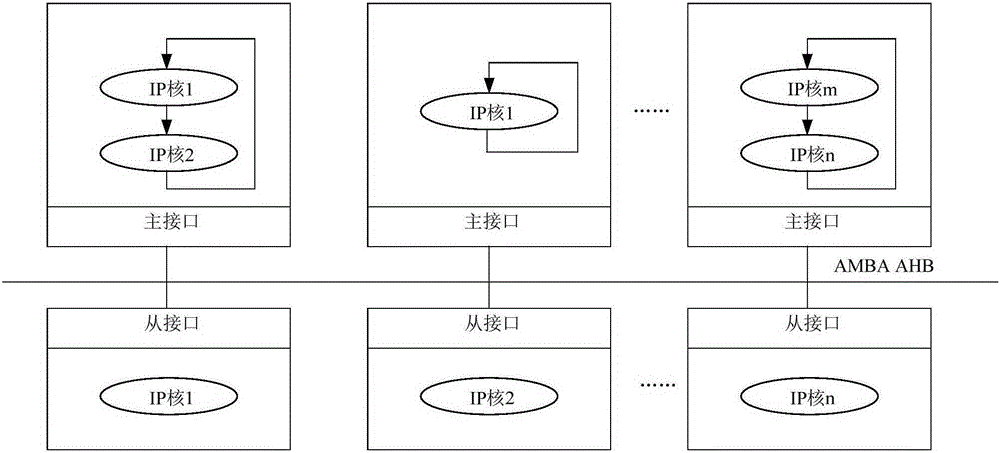

Method and device for generating RTL (Register Transfer Logic)-level IP (Intellectual Property) core

ActiveCN106709116ABest performance ratioGuaranteed performanceSpecial data processing applicationsIntellectual propertyHigh-level programming language

The invention provides a method and a device for generating an RTL (Register Transfer Logic)-level IP core, and belongs to the field of application specific integrated circuits. The method comprises the following steps that: firstly, carrying out high-level synthesis on an advanced language program to obtain a plurality of behavior level IP cores; then, obtaining the compromising curve of each behavior level IP core, wherein the compromising curve is the area and task load relation curve of the each behavior level IP core; according to the compromising curve, obtaining an optimized RTL-level IP core corresponding to each behavior level IP core; and carrying out physical synthesis on all optimized RTL-level IP cores to obtain a data structure netlist. Through the method and the device for generating the RTL-level IP core, each obtained optimized RTL-level IP core has an optimal performance ratio, and an area is reduced while overall performance is guaranteed.

Owner:SHENZHEN BOJUXING IND DEV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com