Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

220 results about "Pattern space" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

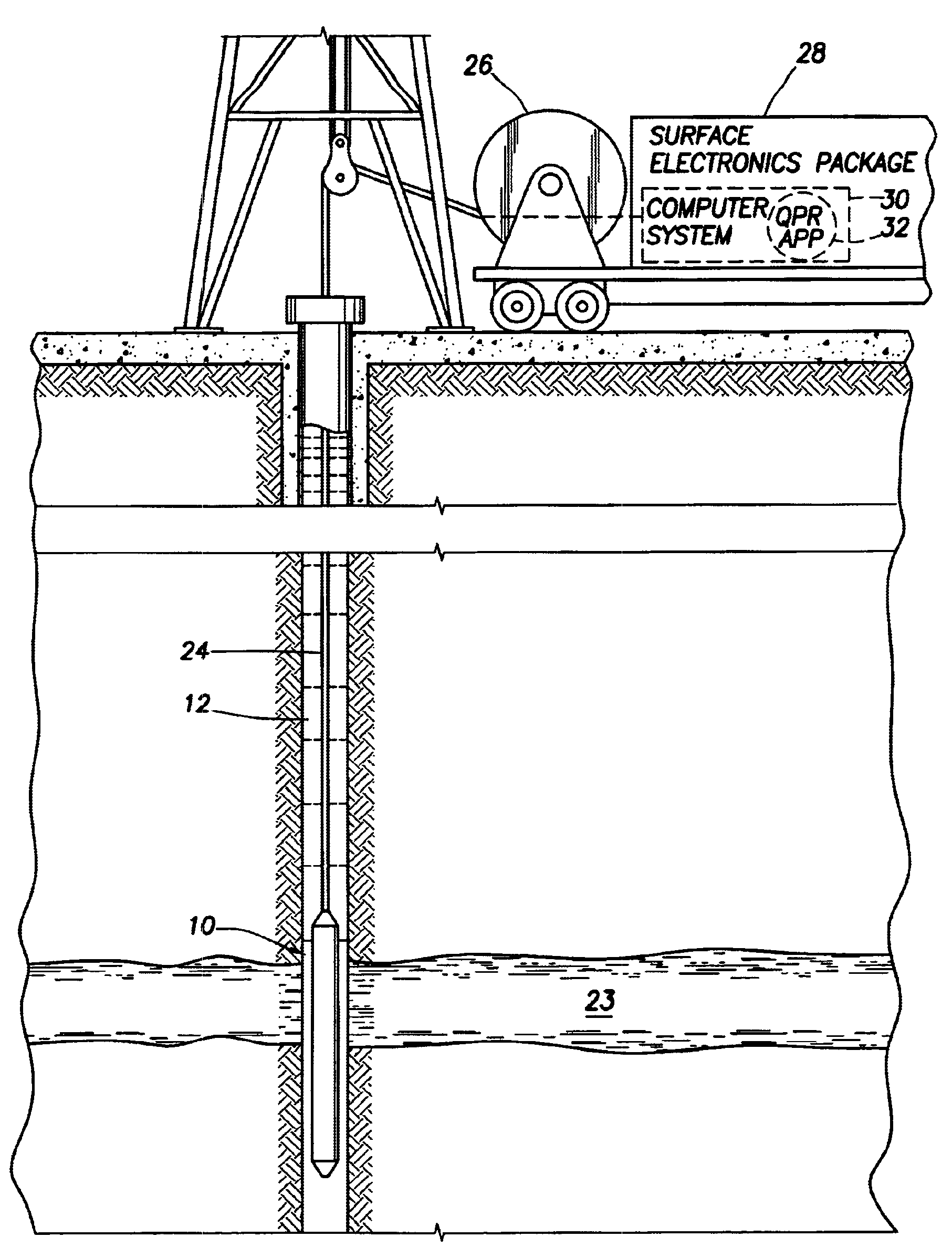

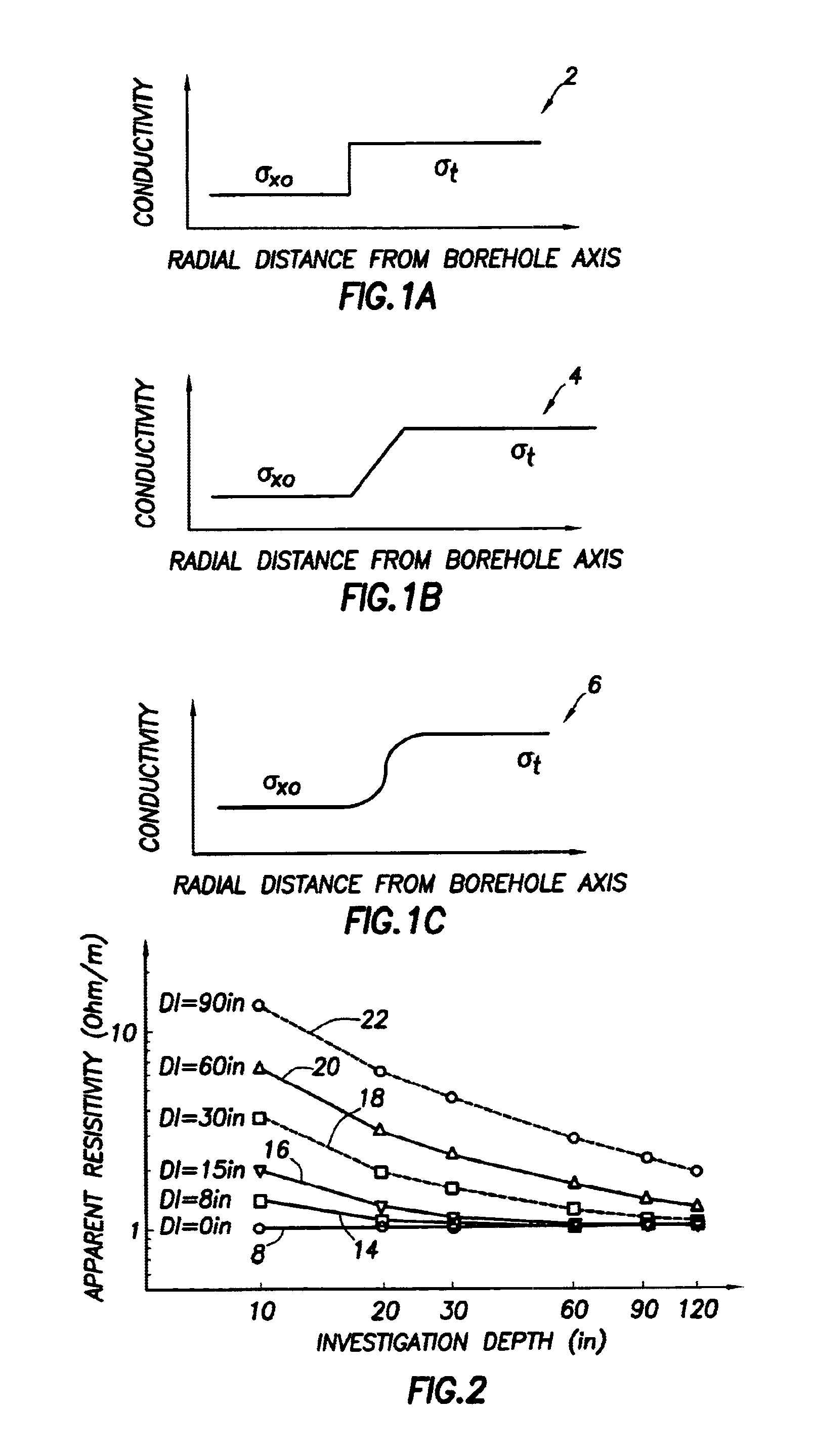

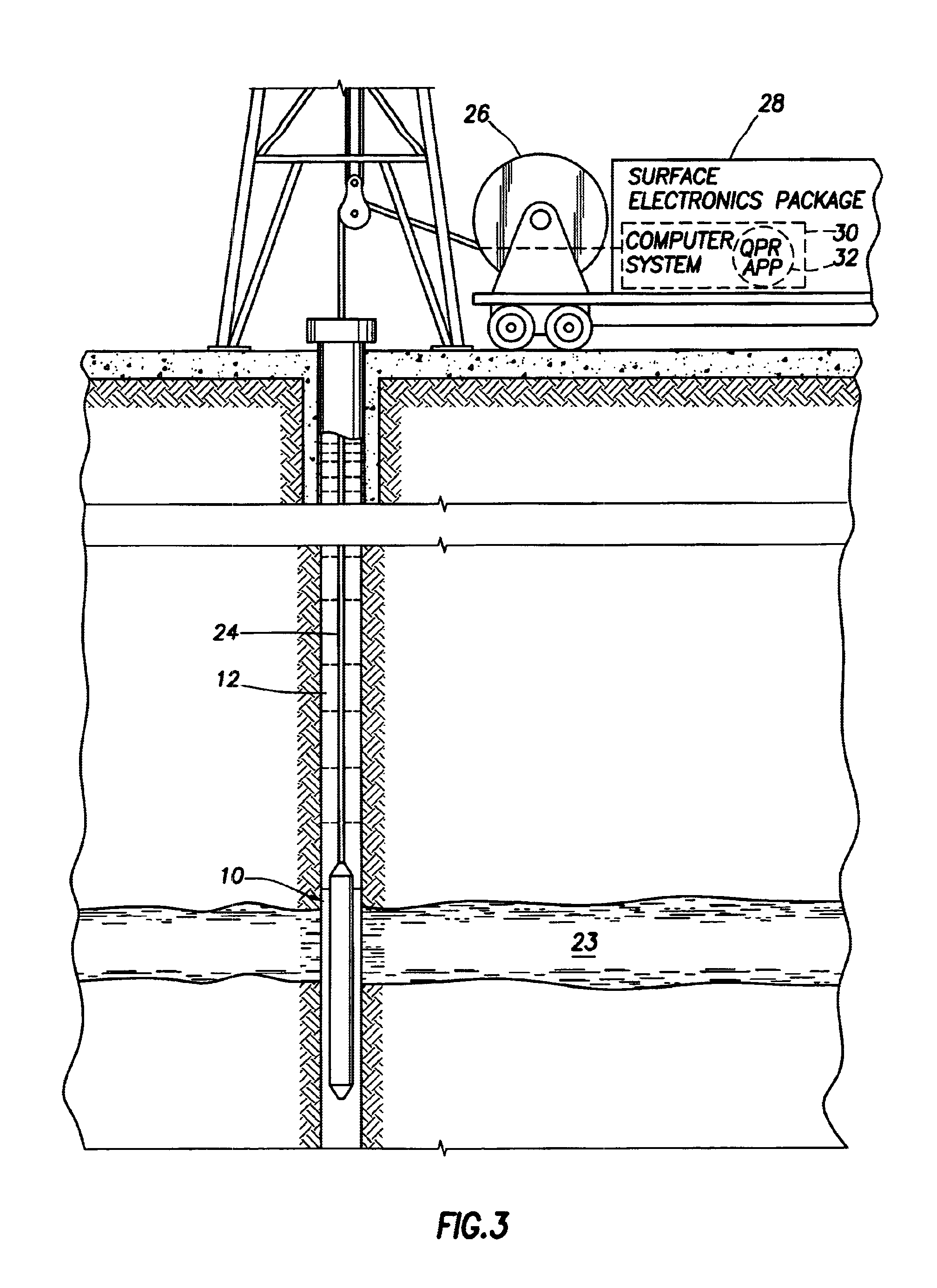

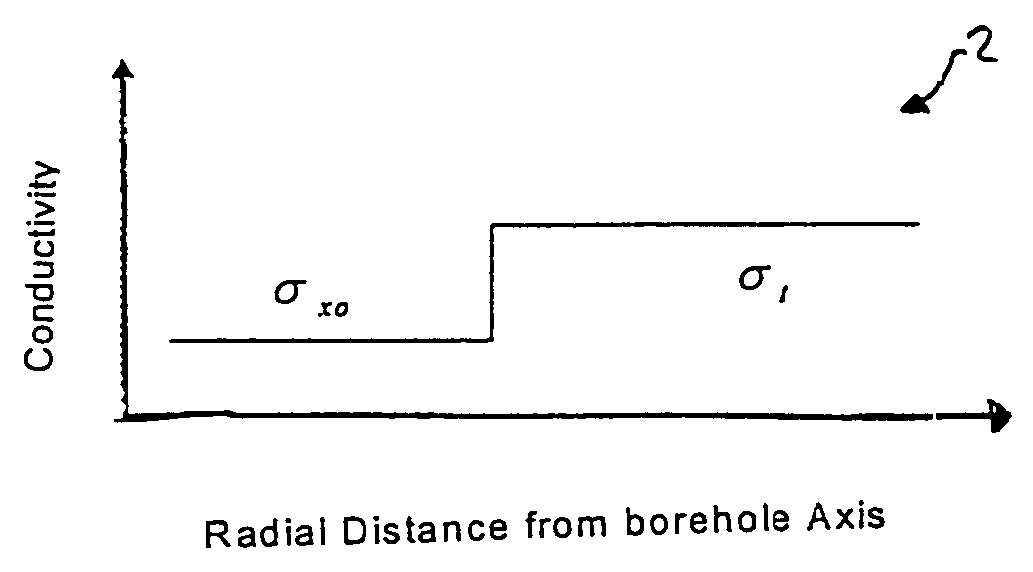

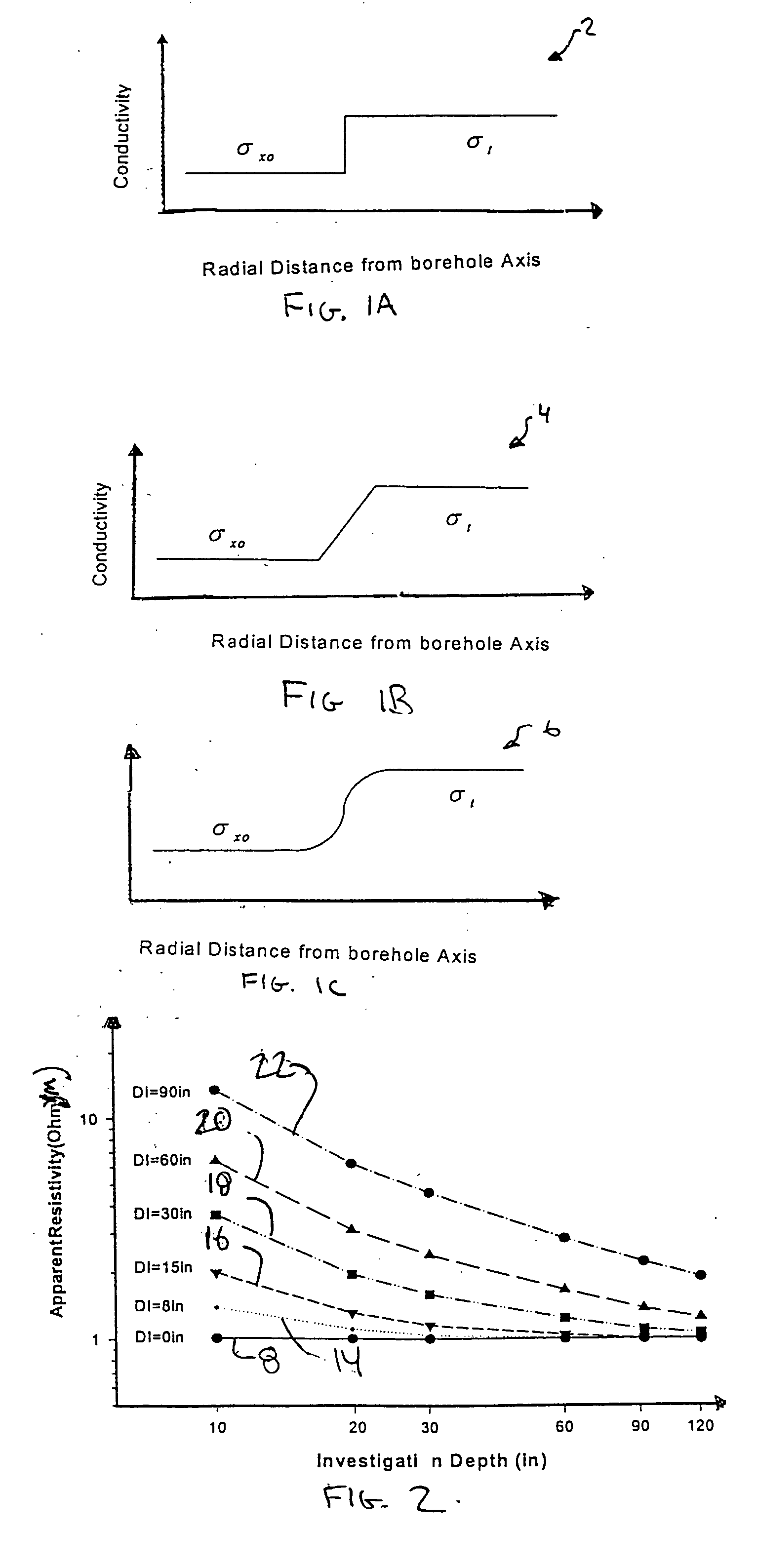

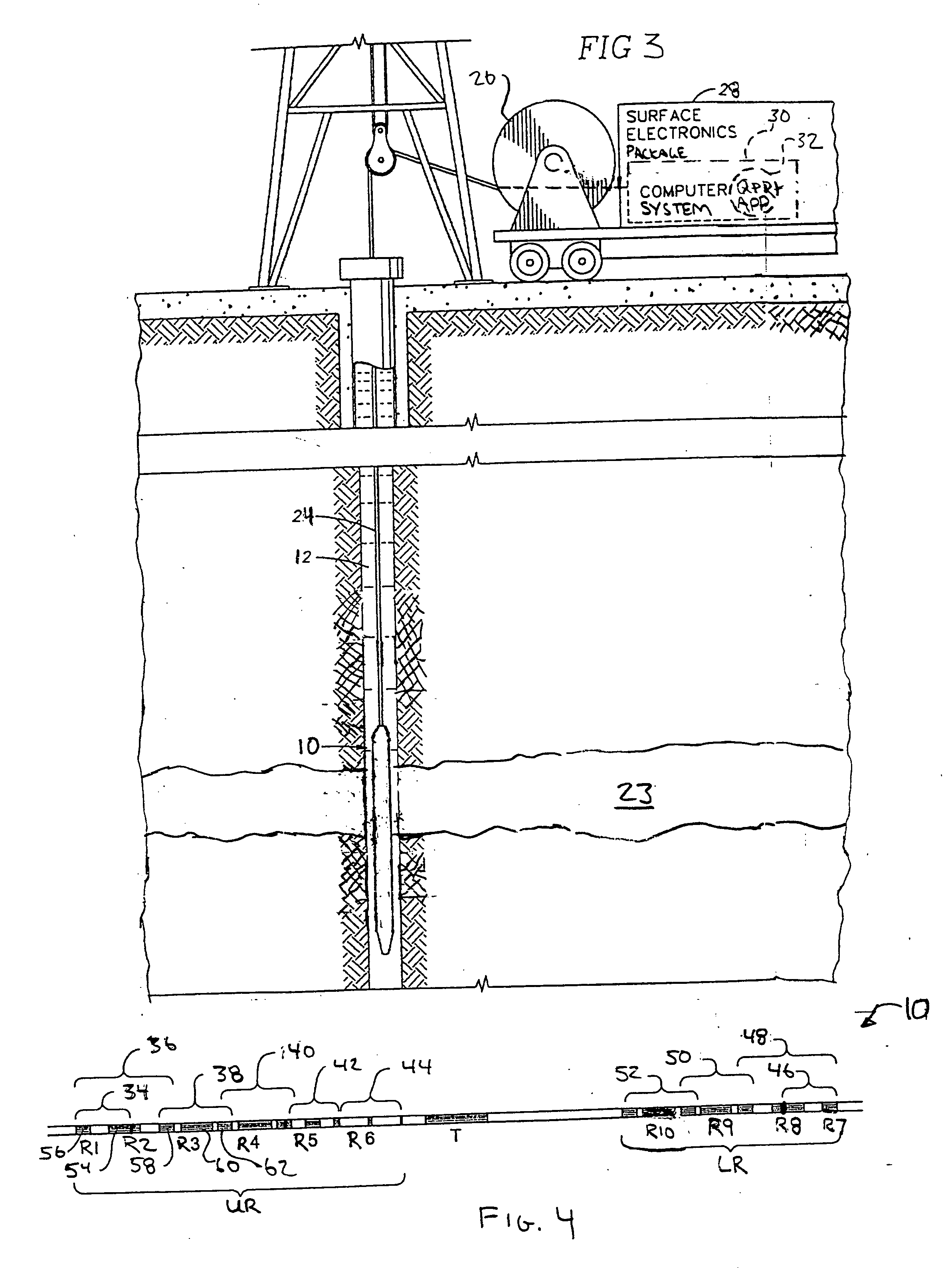

Method and apparatus for inversion processing of well logging data in a selected pattern space

ActiveUS6944546B2Electric/magnetic detection for well-loggingAnalogue computers for heat flowWell loggingPattern space

Method and apparatus for deriving information regarding a subsurface geophysical formation. Well logging data is acquired for the subsurface geophysical formation. Geometrical parameters for the subsurface geophysical formation are determined by inversion processing of the acquired well logging data in a pattern space while formation conductivities for the subsurface geophysical formation are determined by inversion processing of the acquired well logging data in a measurement space. The processing may be iteratively applied until satisfied formation parameters are achieved.

Owner:HALLIBURTON ENERGY SERVICES INC

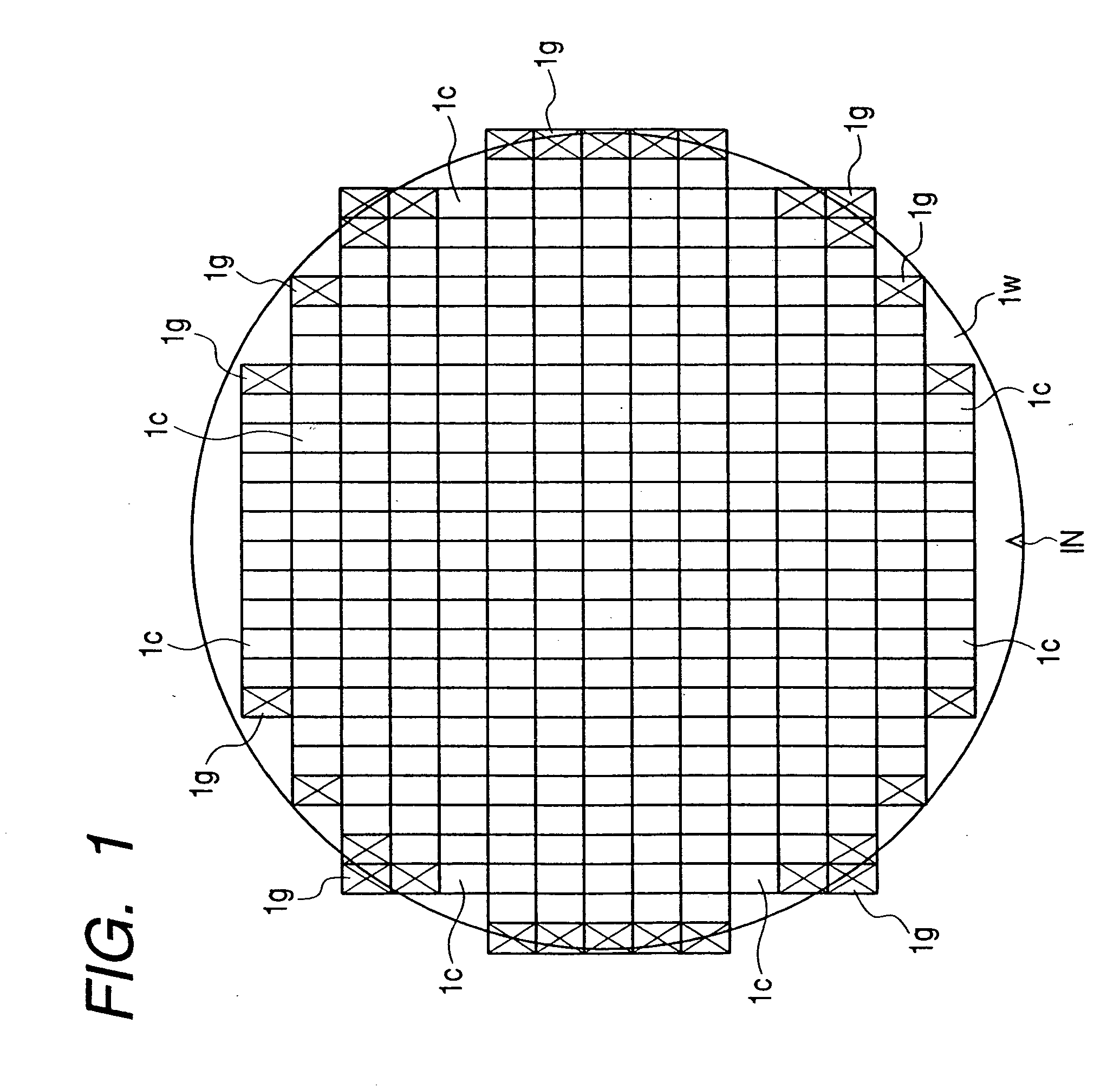

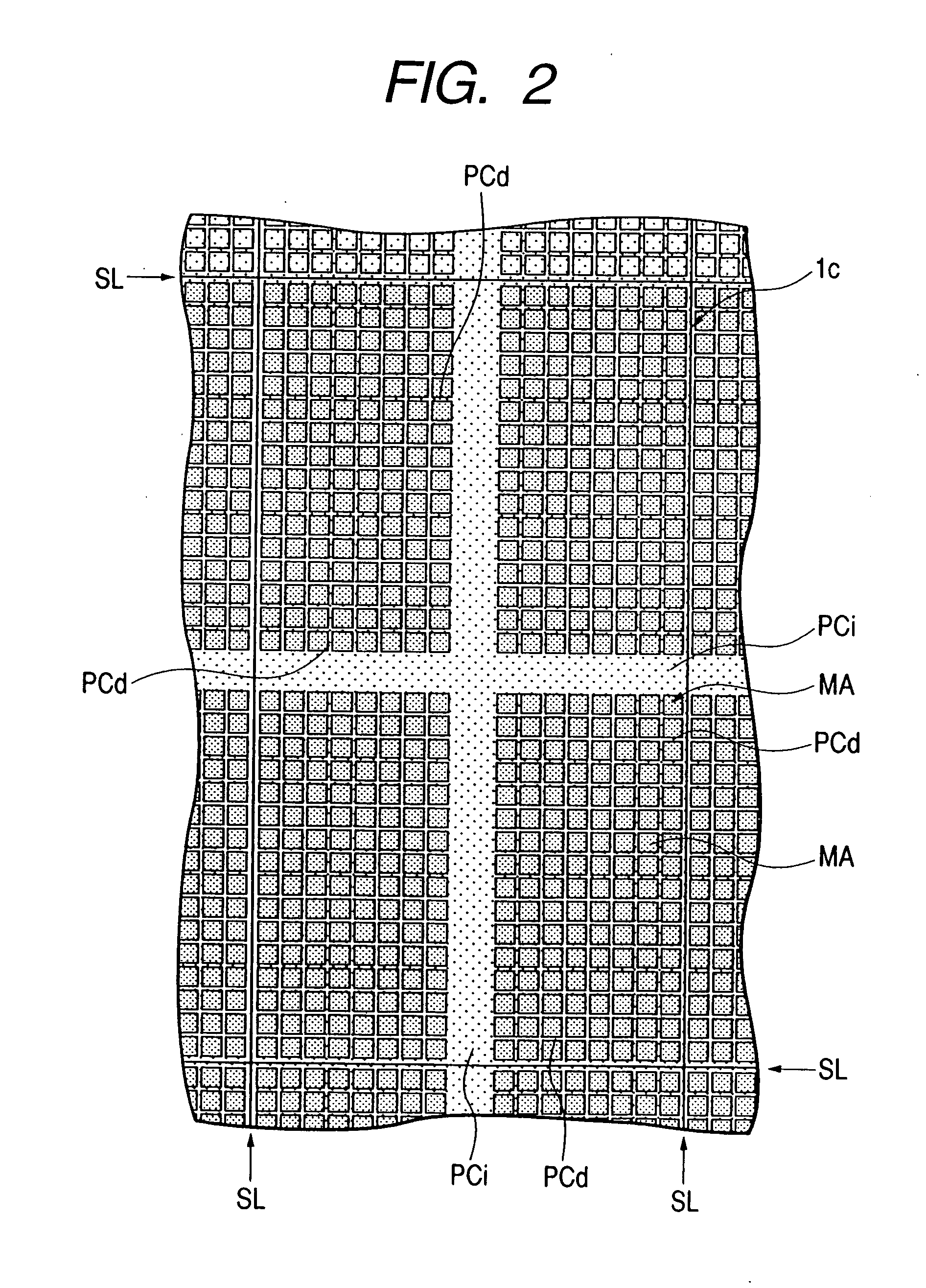

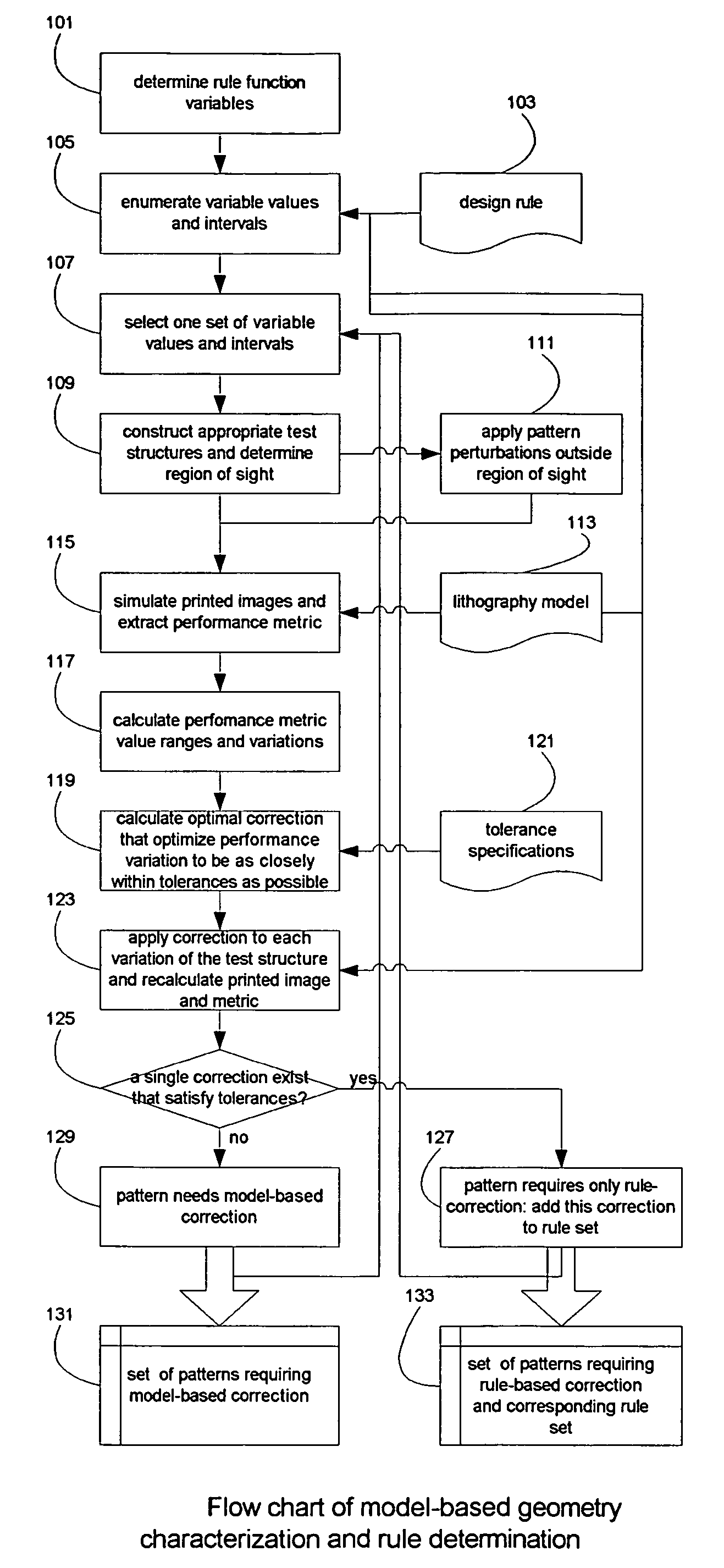

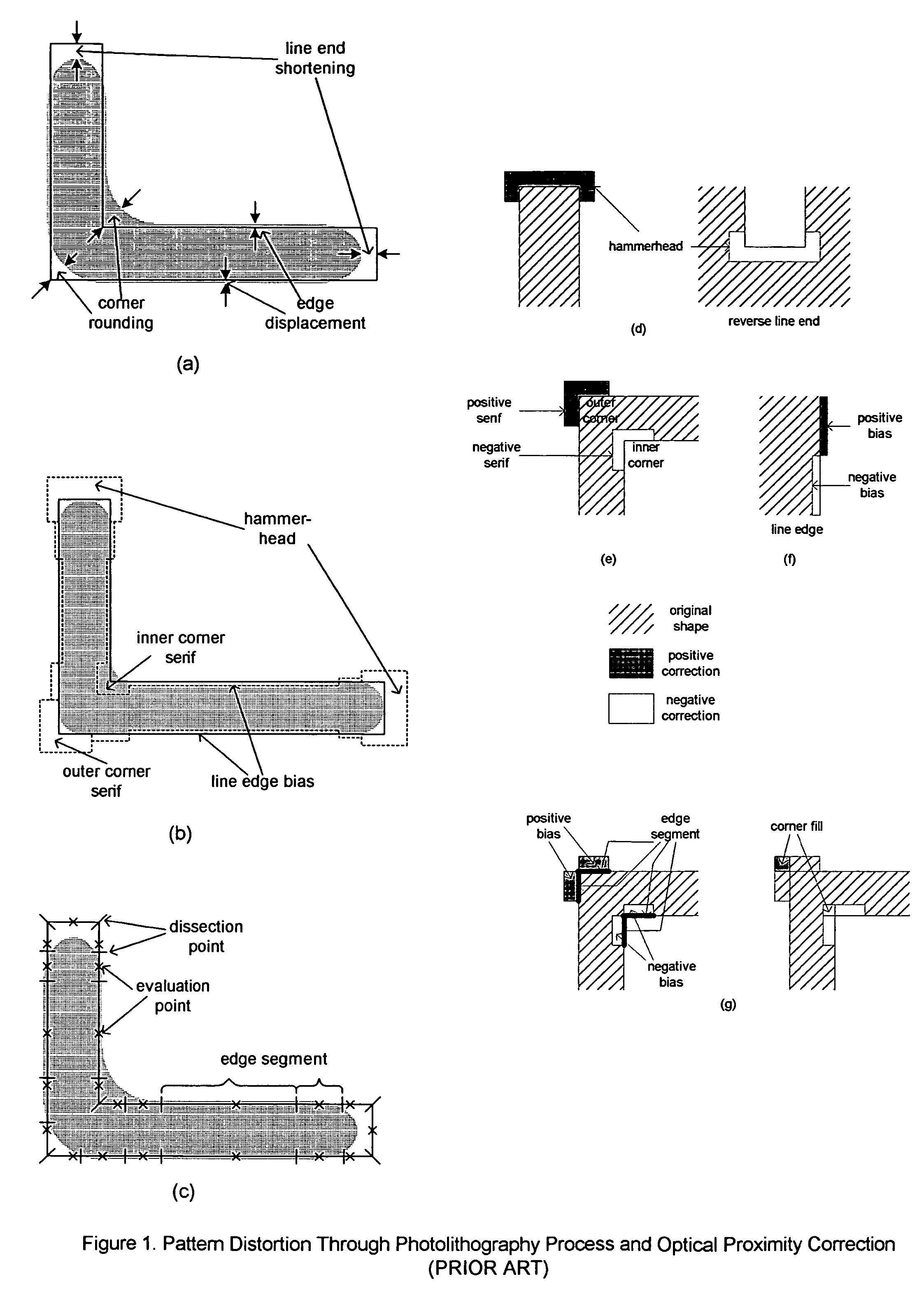

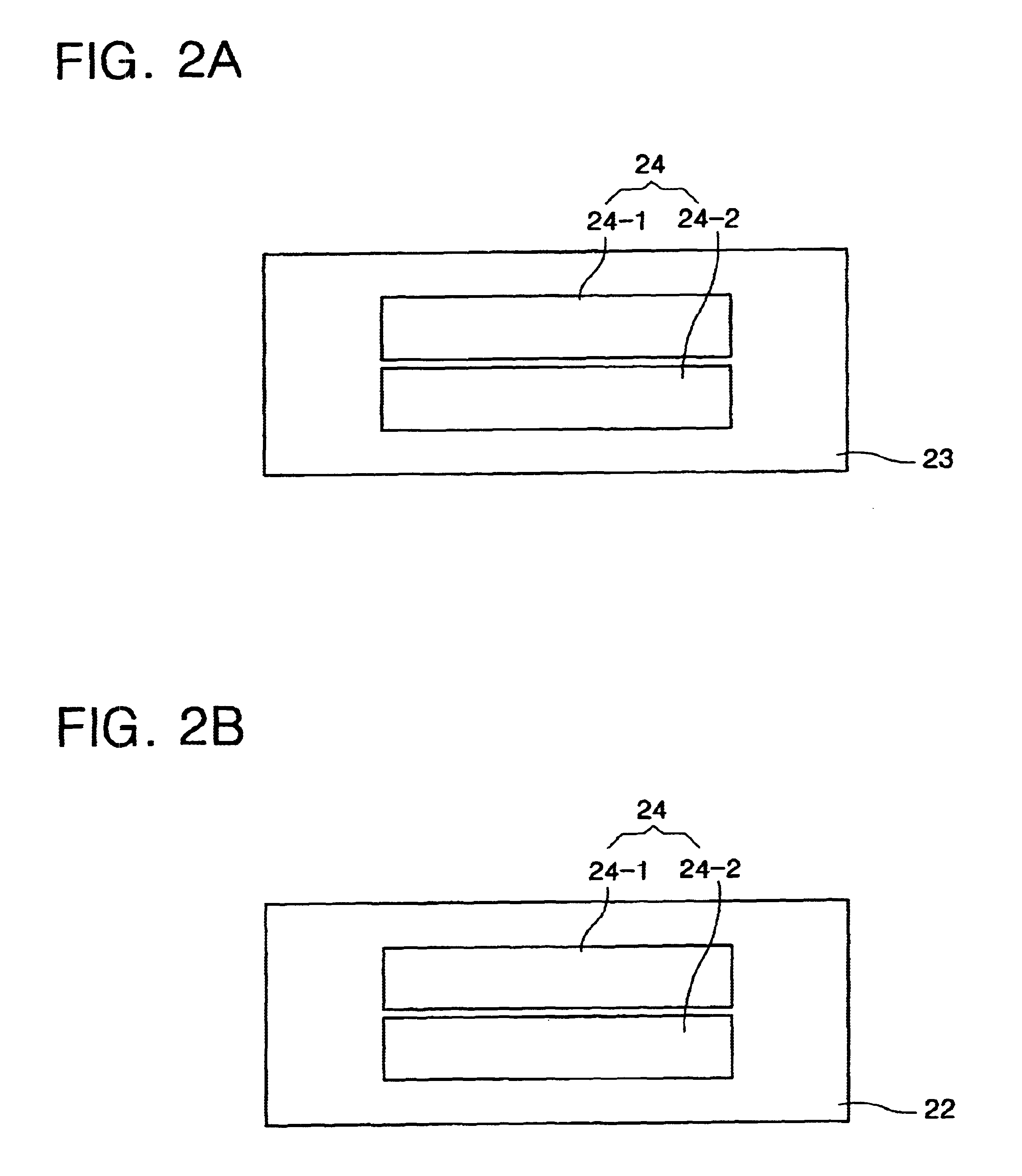

Model-based pattern characterization to generate rules for rule-model-based hybrid optical proximity correction

ActiveUS20060085772A1Photomechanical apparatusOriginals for photomechanical treatmentHybrid systemLithographic artist

A system and method are provided for analyzing layout patterns via simulation using a lithography model to characterize the patterns and generate rules to be used in rule-based optical proximity correction (OPC). The system and method analyze a series of layout patterns conforming to a set of design rules by simulation using a lithography model to obtain a partition of the pattern spaces into one portion that requires only rule-based OPC and another portion that requires model-based OPC. A corresponding hybrid OPC system and method are also introduced that utilize the generated rules to correct an integrated circuit (IC) design layout which reduces the OPC output complexity and improves turnaround time.

Owner:APPLIED MATERIALS INC

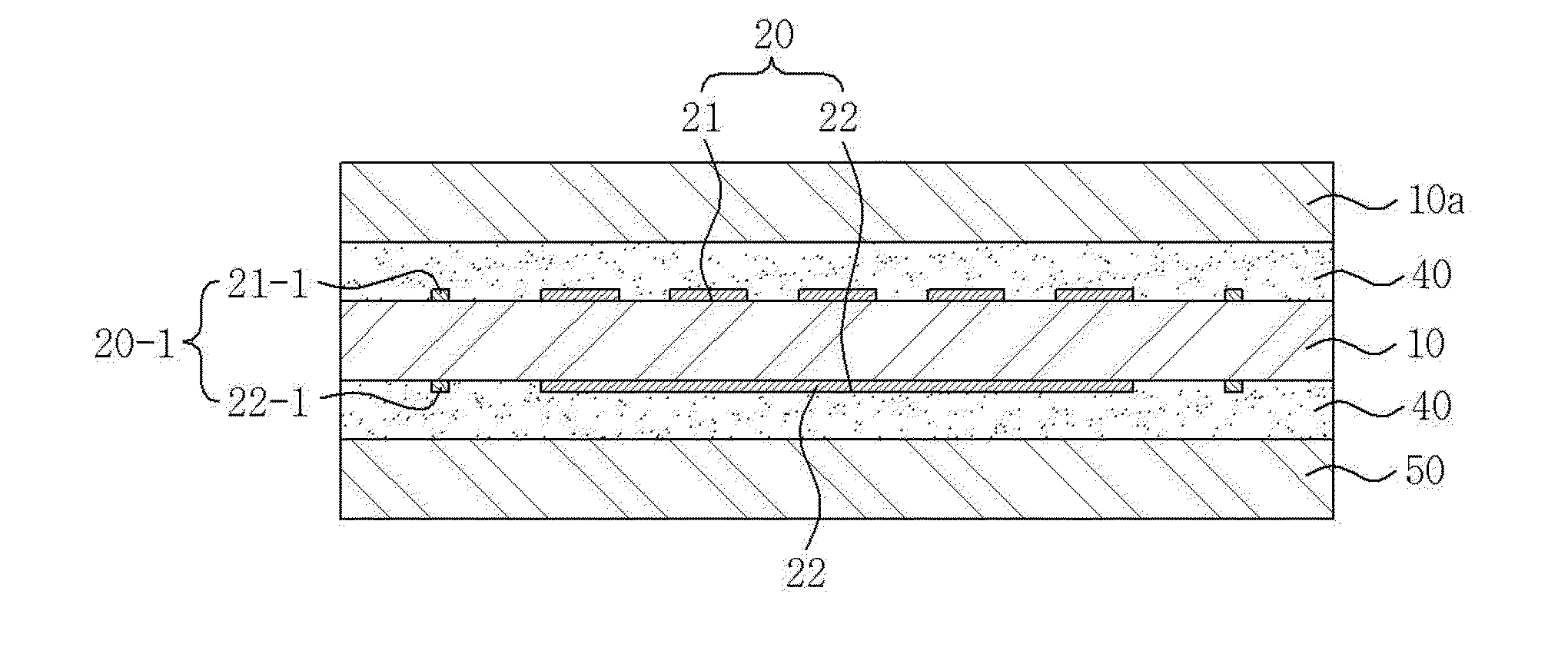

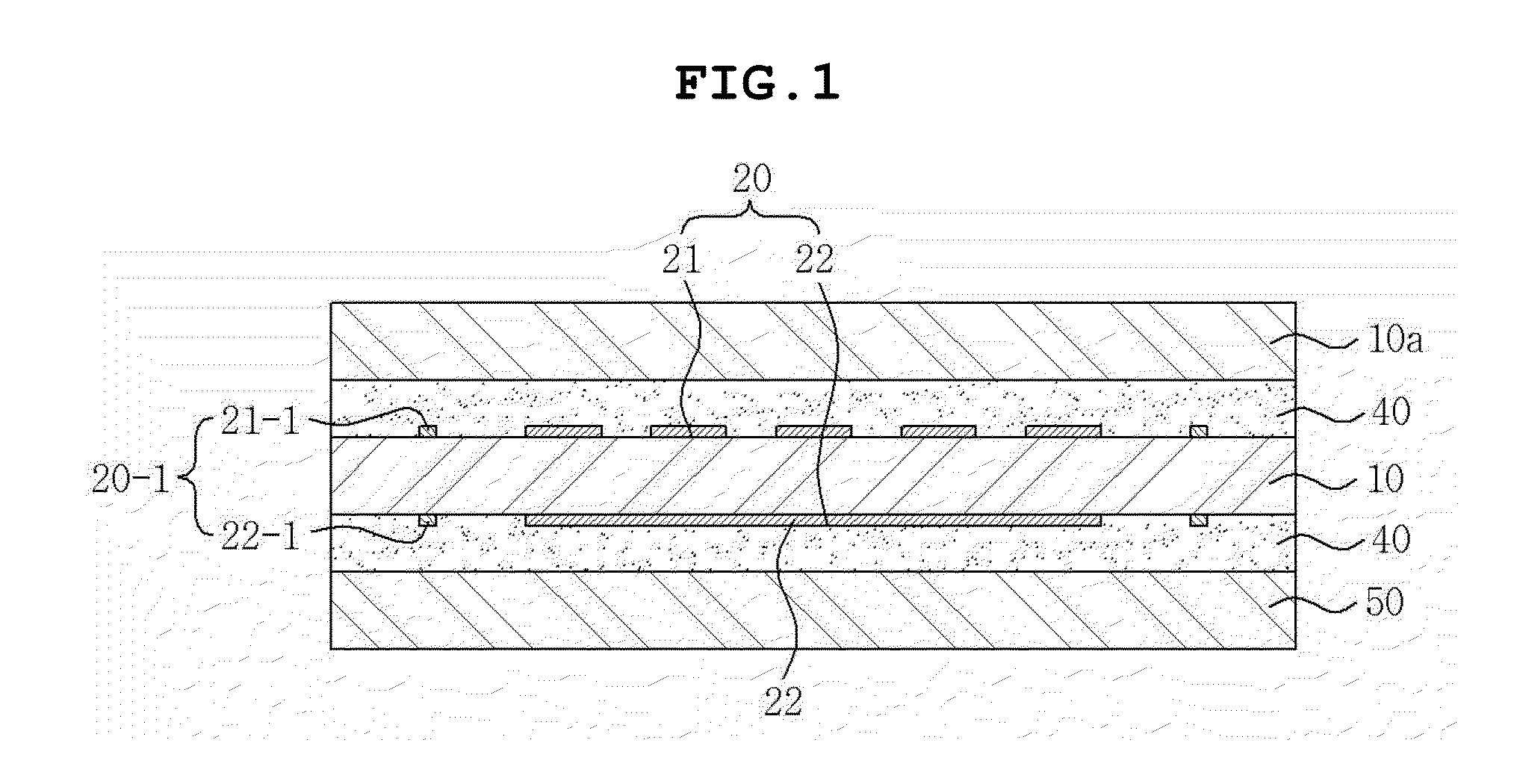

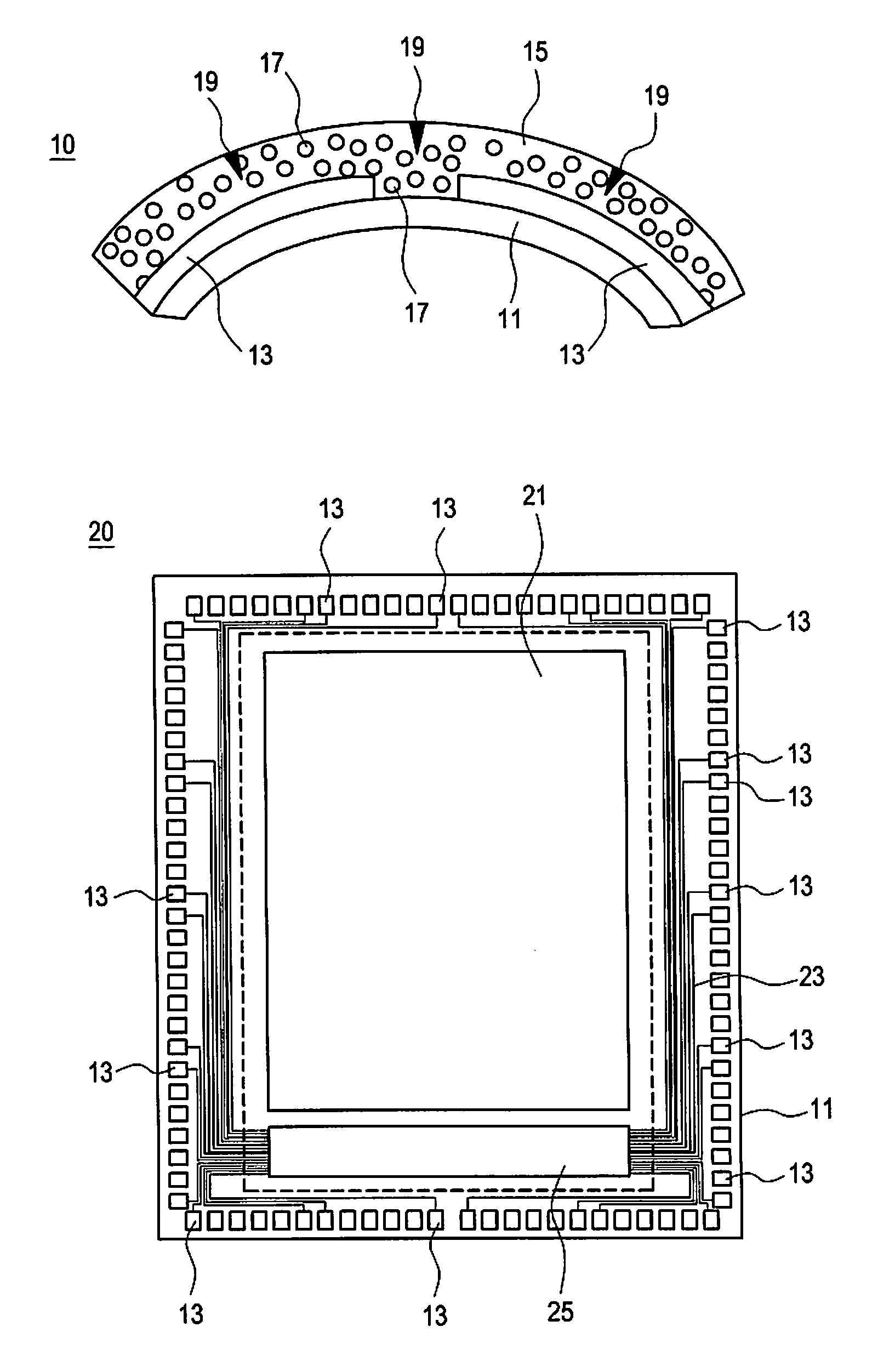

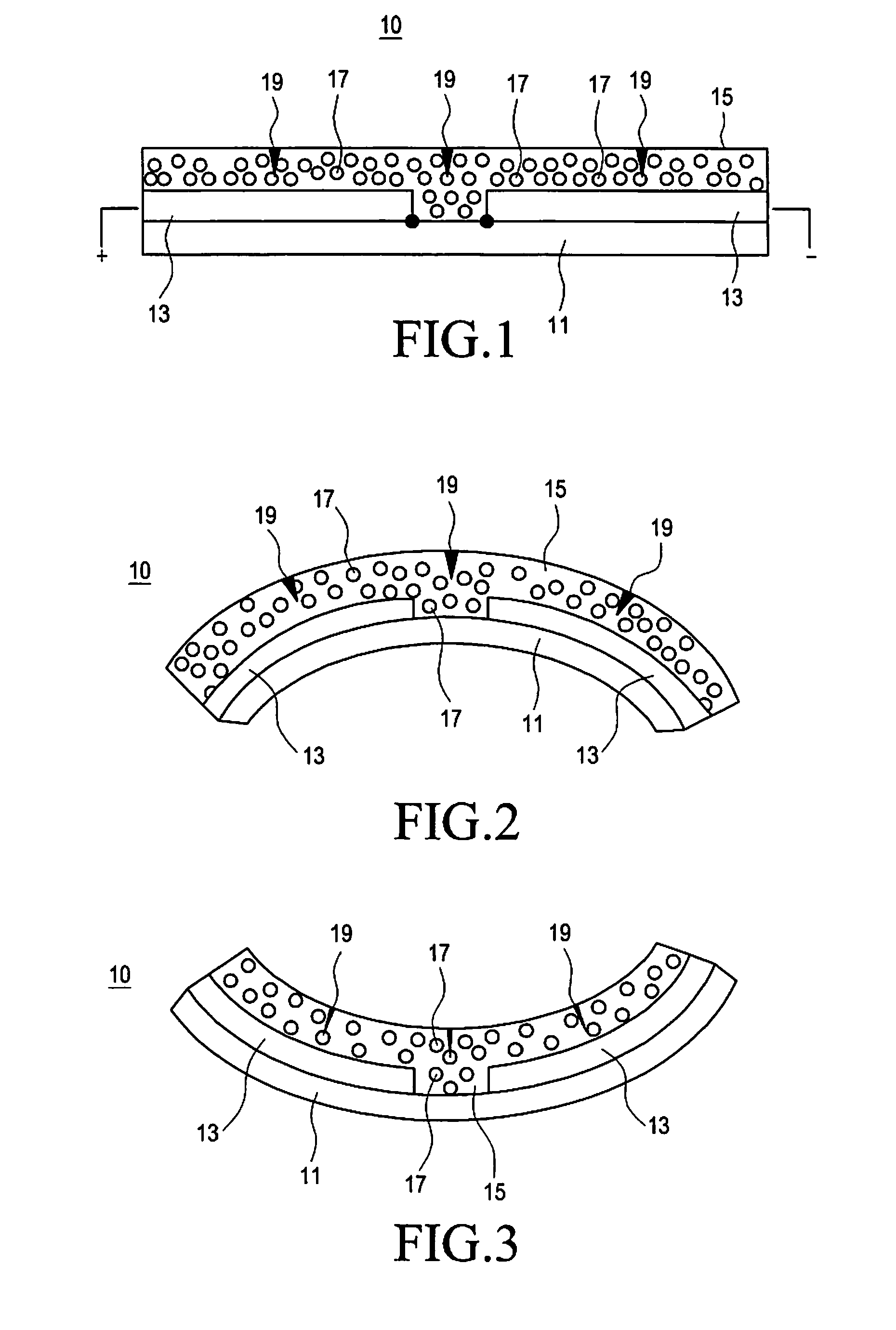

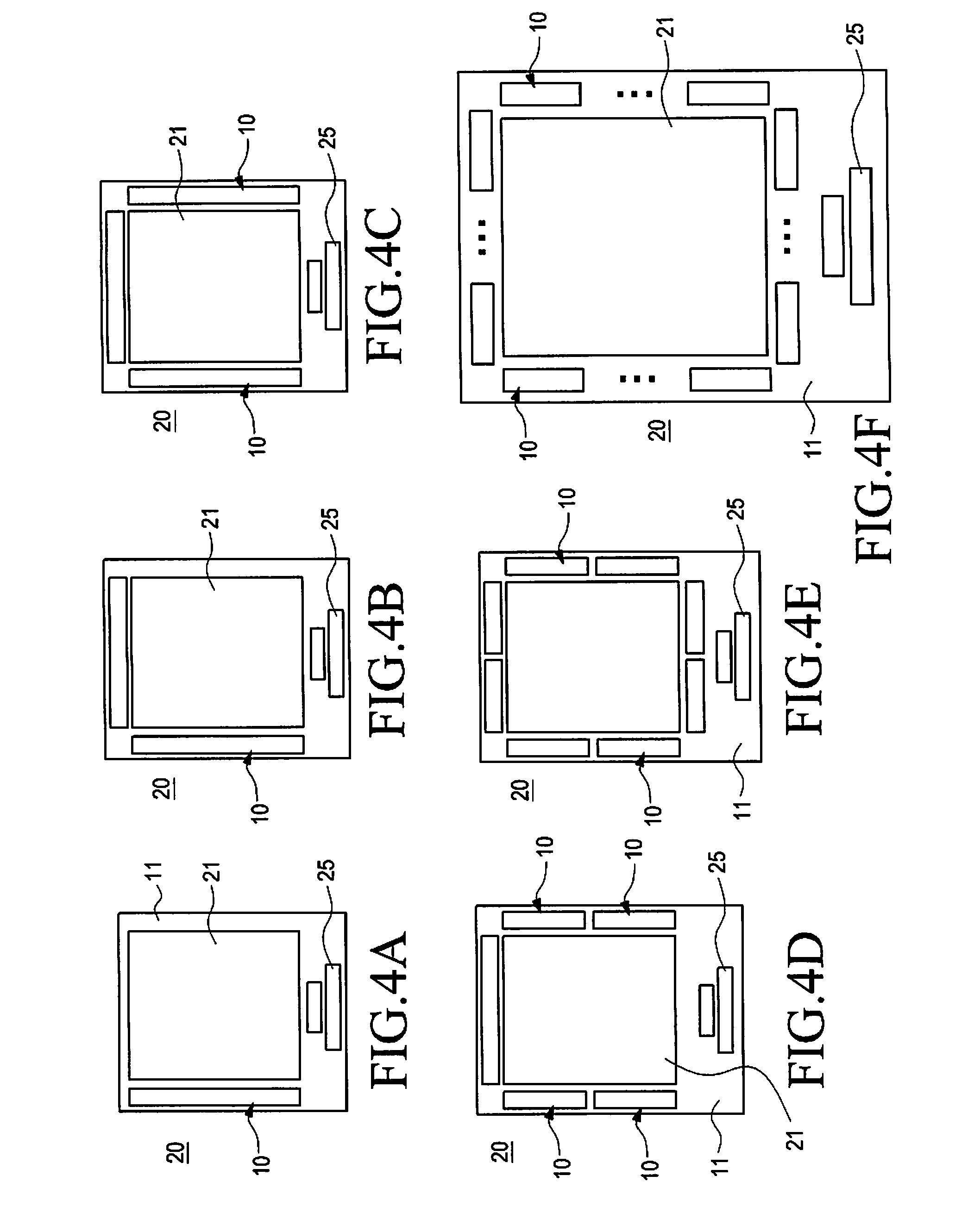

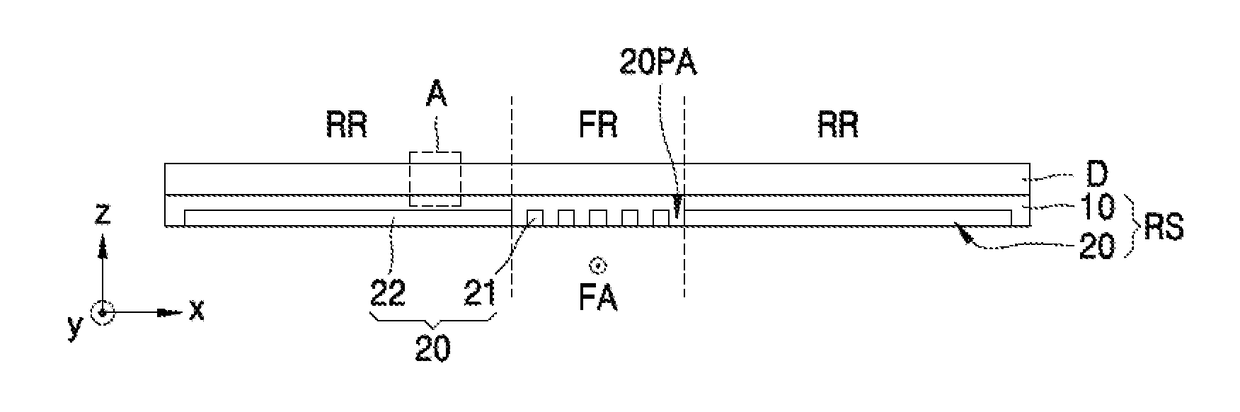

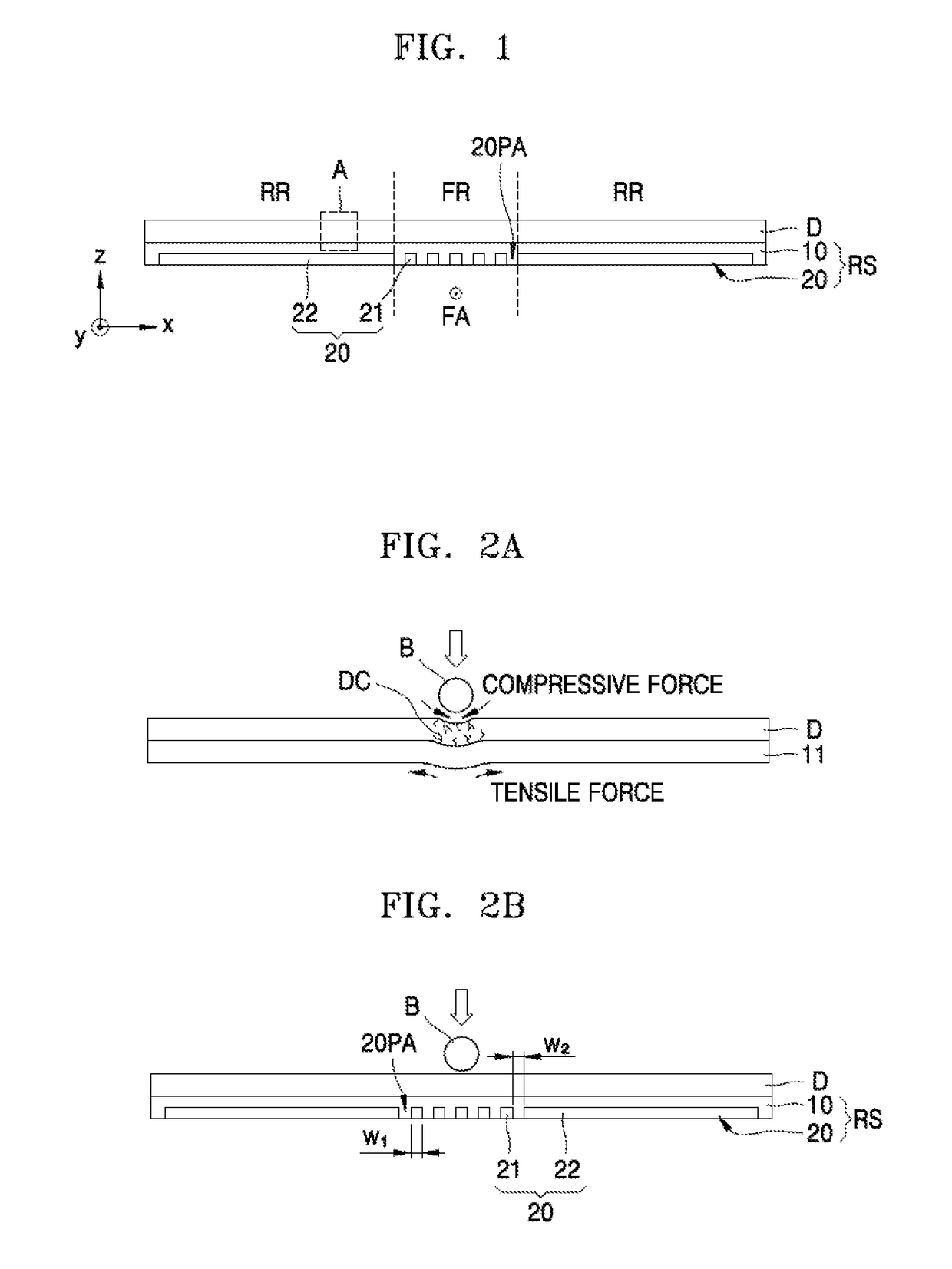

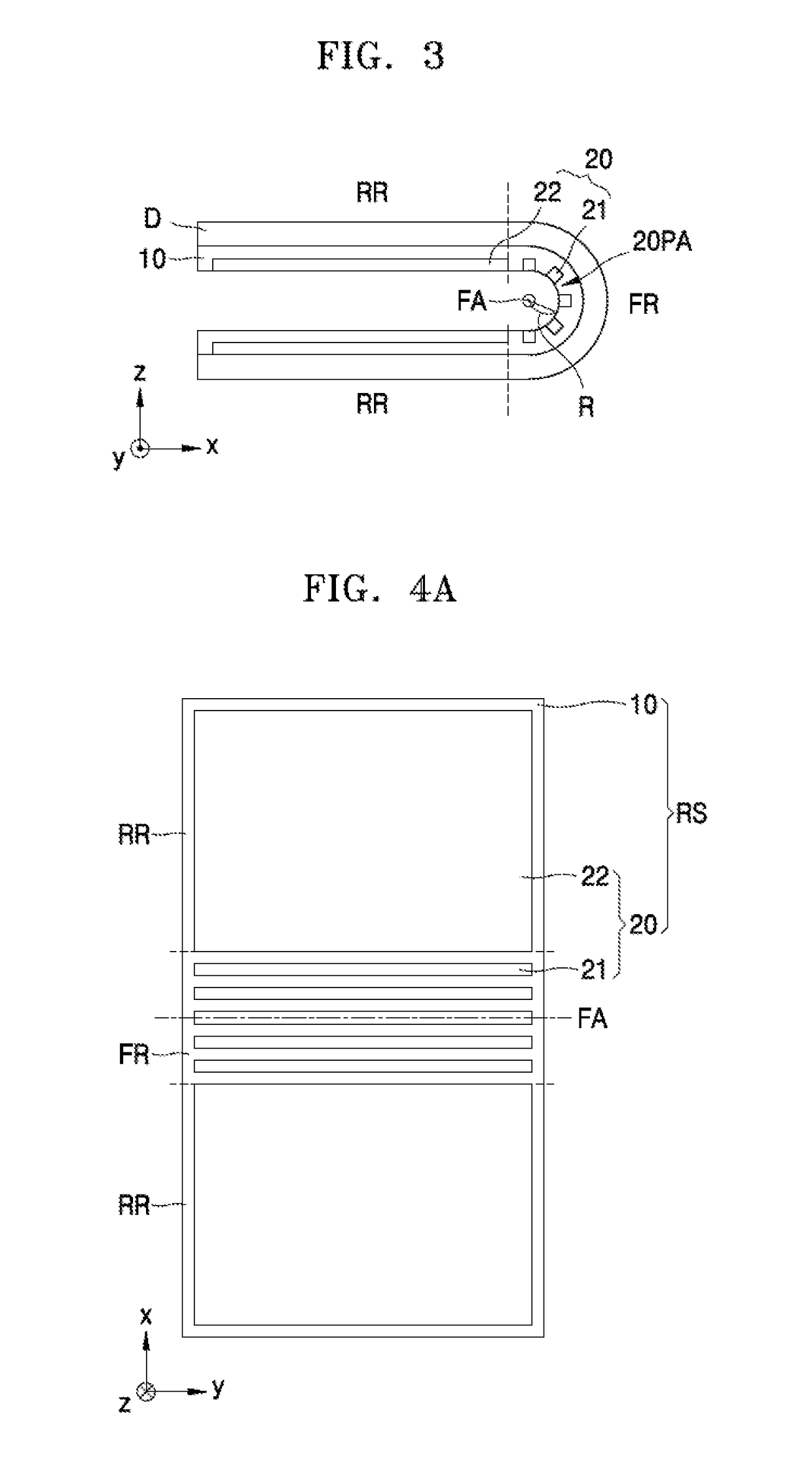

Bending sensor and method for fabricating the same

InactiveUS20120256720A1Small sizeResistance/reactance/impedenceForce measurementEngineeringFlexible display

A bend-detecting (bending) sensor is provided, including a flexible substrate, at least a pair of electrode patterns spaced apart from each other provided on the flexible substrate, and a paste layer containing conductive particles. The paste layer is coated onto the flexible substrate where the electrode patterns are formed, such that when the flexible substrate is bent, the density of the conductive particles between the electrode patterns changes and an electric resistance between the electrode patterns also changes, thereby sensing deformation of the flexible substrate, and eventually, a target to which the flexible display element or the flexible substrate is attached. When the bending sensor is applied to the flexible display device, the electrode patterns and the paste layer may be formed on the flexible substrate which is to form the flexible display element, thus forming a bending sensing structure with a thickness of the flexible display element or less.

Owner:SAMSUNG ELECTRONICS CO LTD

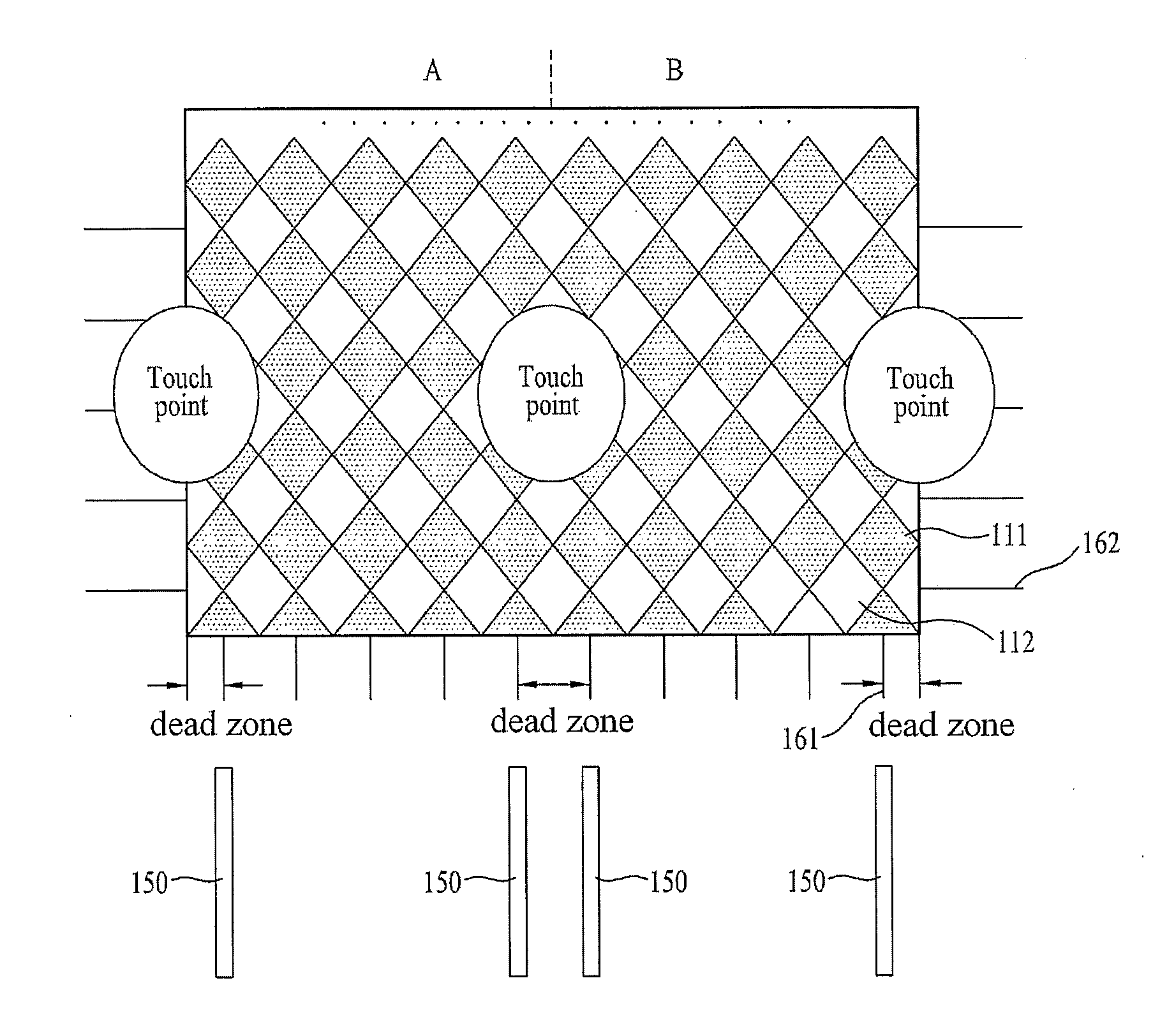

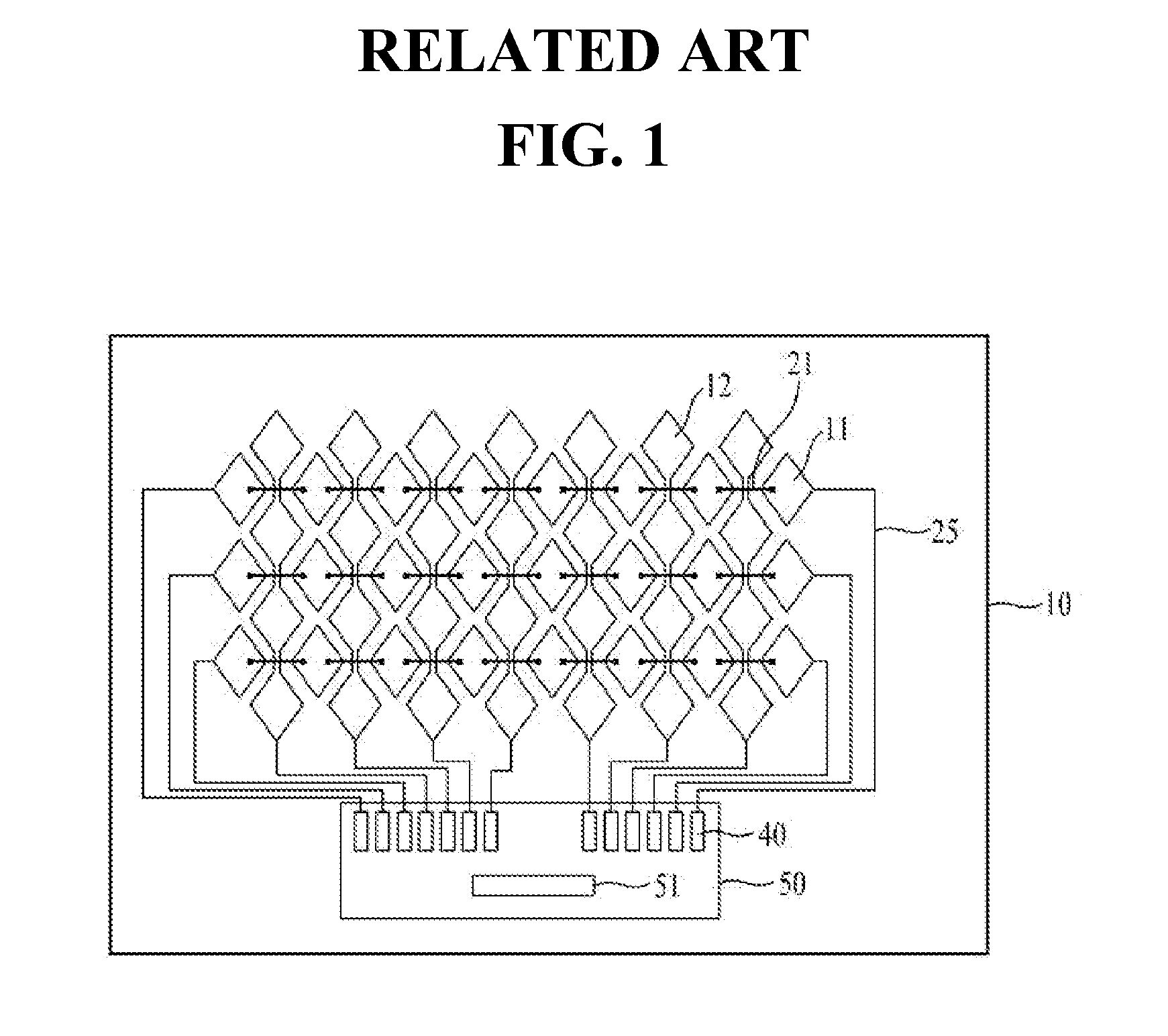

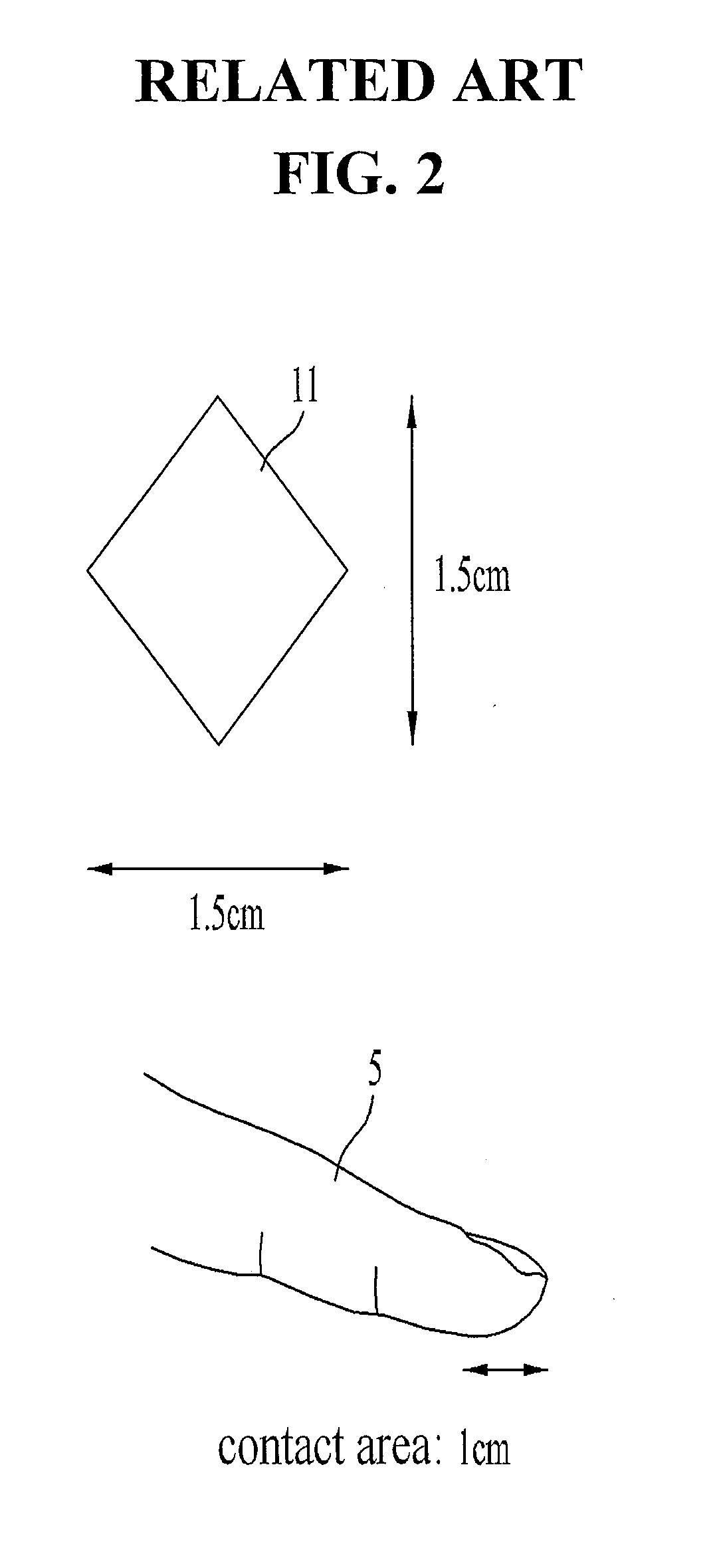

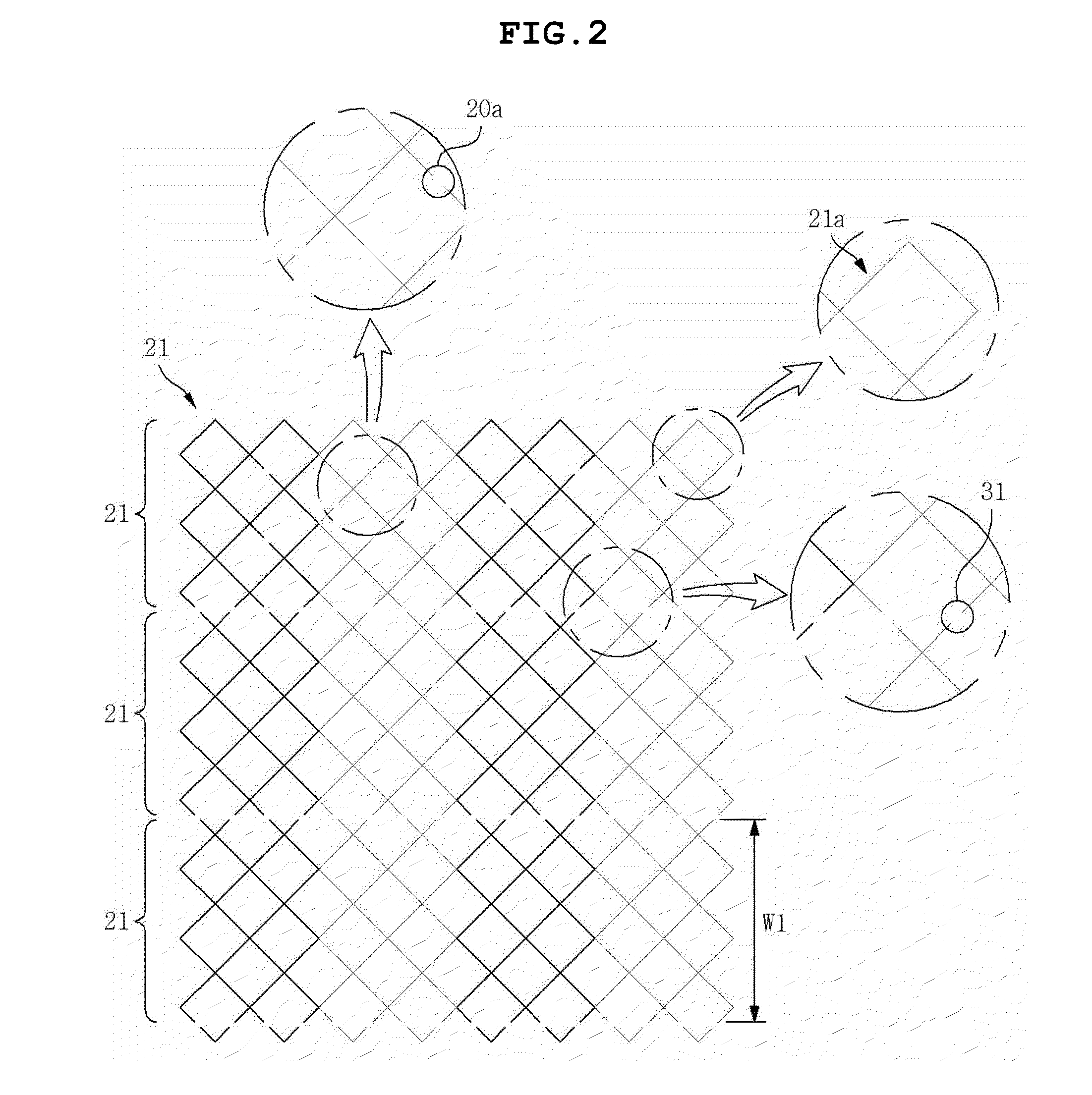

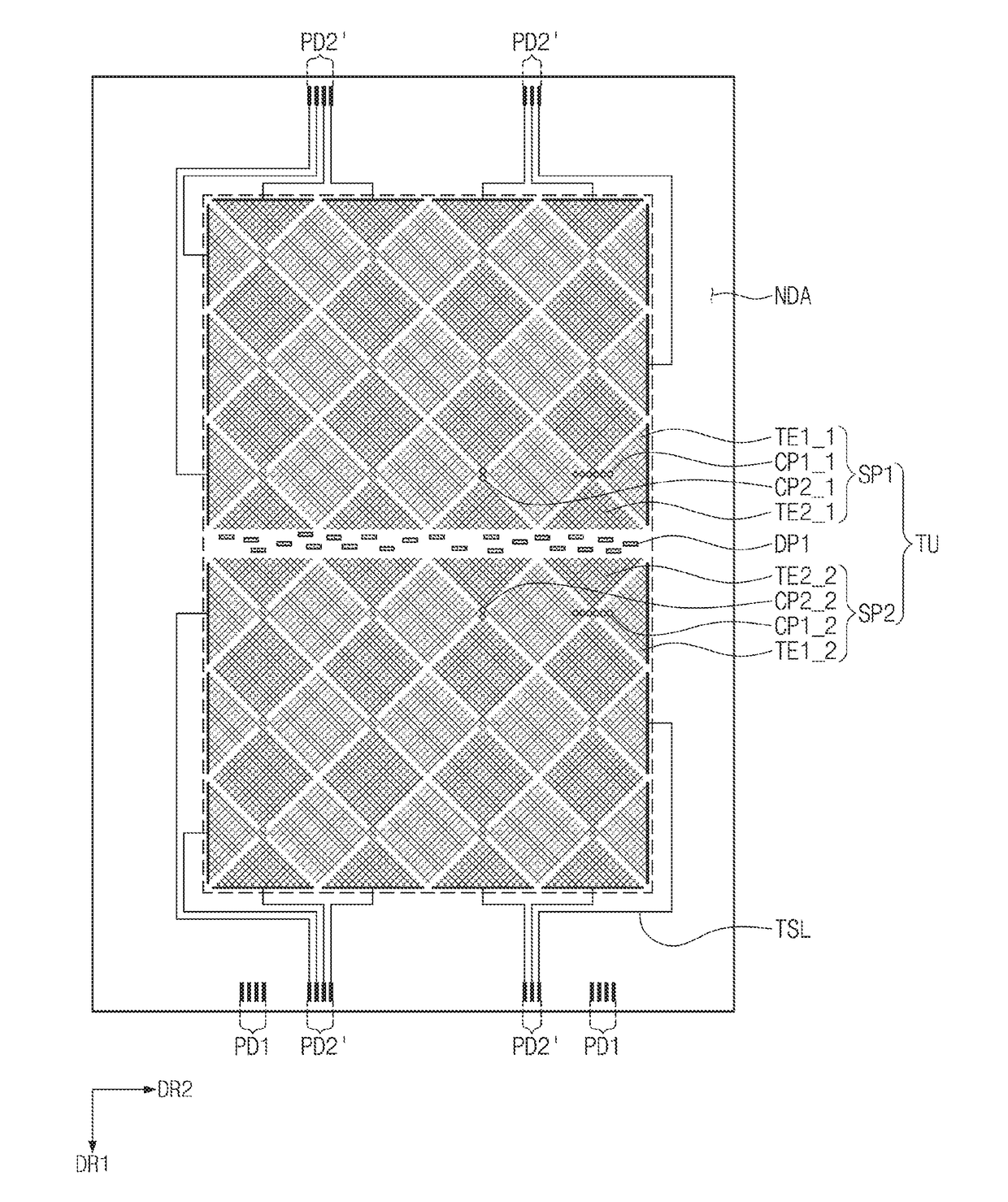

Touch panel and liquid crystal display device including the same

ActiveUS20110141040A1Without deterioration of touch sensitivitySmall sizeNon-linear opticsInput/output processes for data processingLiquid-crystal displayEngineering

A touch panel includes a substrate comprising divided regions; first electrodes, each of the first electrodes comprising first rhombus patterns spaced apart a predetermined distance from each other in a predetermined first direction and first connection patterns configured to connect the first rhombus patterns second electrodes, each of the second electrodes comprising second rhombus patterns spaced apart a predetermined distance from each other in the second direction and second connection patterns configured to connect the second rhombus patterns; third electrodes formed in border areas between the divided regions and outer areas of the divided regions; a touch controller formed in each of the divided regions correspondingly; and pad electrodes connected with the touch controller.

Owner:LG DISPLAY CO LTD

Touch sensor and electronic device having the same

InactiveUS20140333555A1Easy to controlIncrease in sizeInput/output processes for data processingEngineeringElectrical and Electronics engineering

A touch sensor includes a transparent substrate, first electrode patterns formed on one surface of the transparent substrate, second electrode patterns formed to intersect with the first electrode patterns, the second electrode patterns spaced apart from the first electrode patterns, wiring parts formed on one end or both ends of the first electrode patterns and the second electrode patterns to electrically connect between the first electrode patterns and the second electrode patterns. The first and second electrode patterns comprise thin metallic wires conducting with the wiring parts. An area occupied by the thin metallic wire per unit area on the first electrode pattern may be different from an area occupied by the thin metallic wire per unit area on the second electrode pattern.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

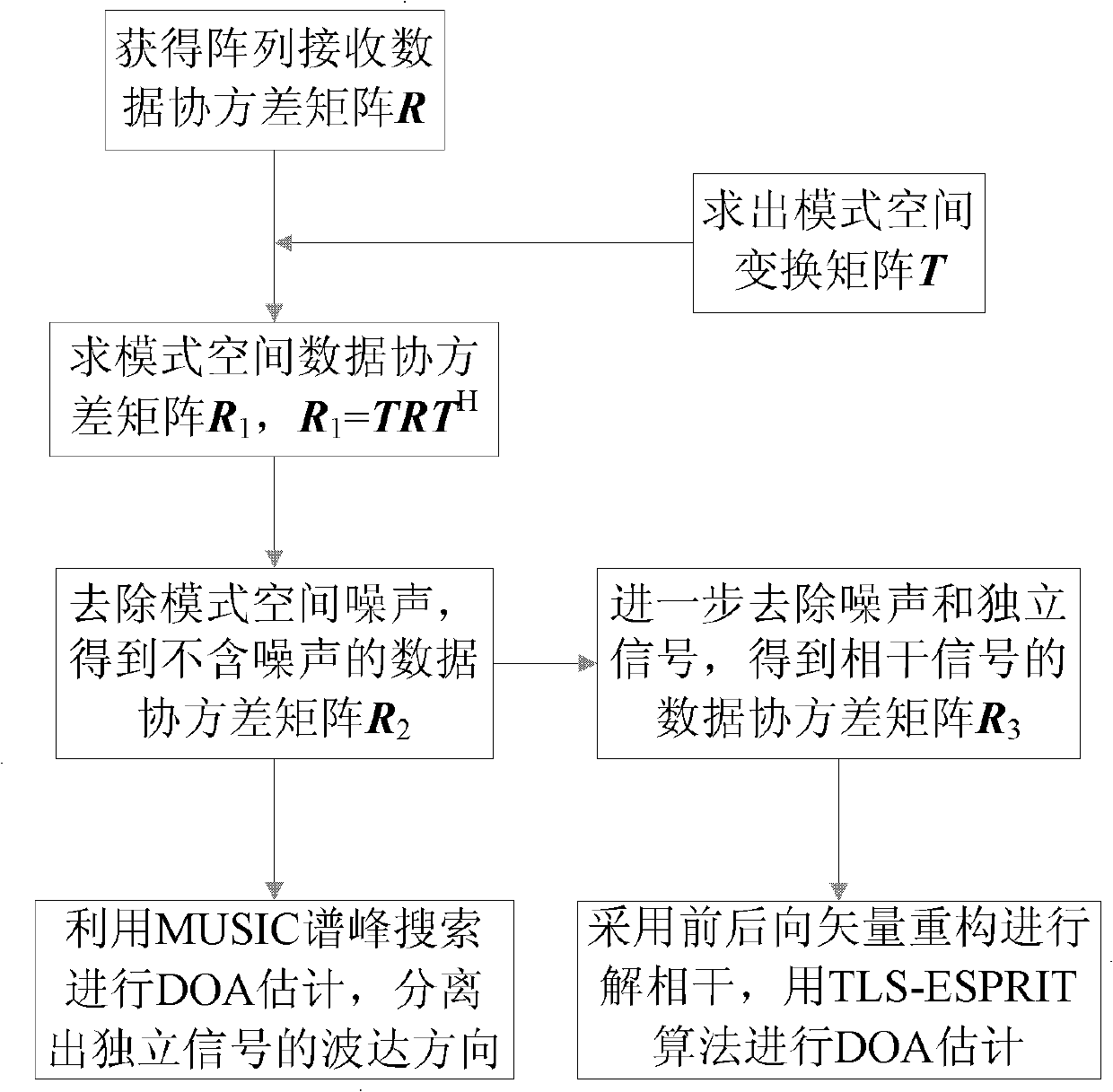

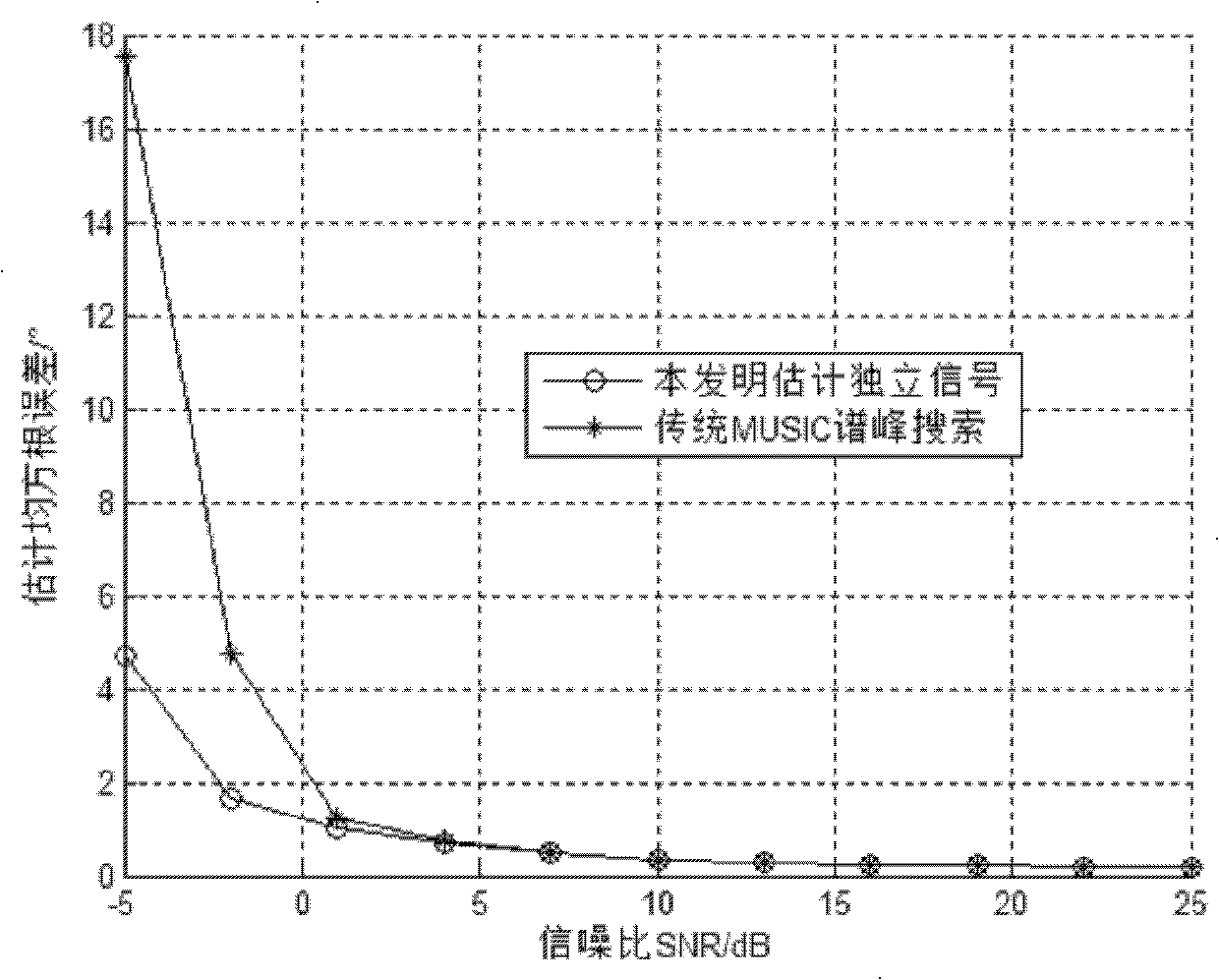

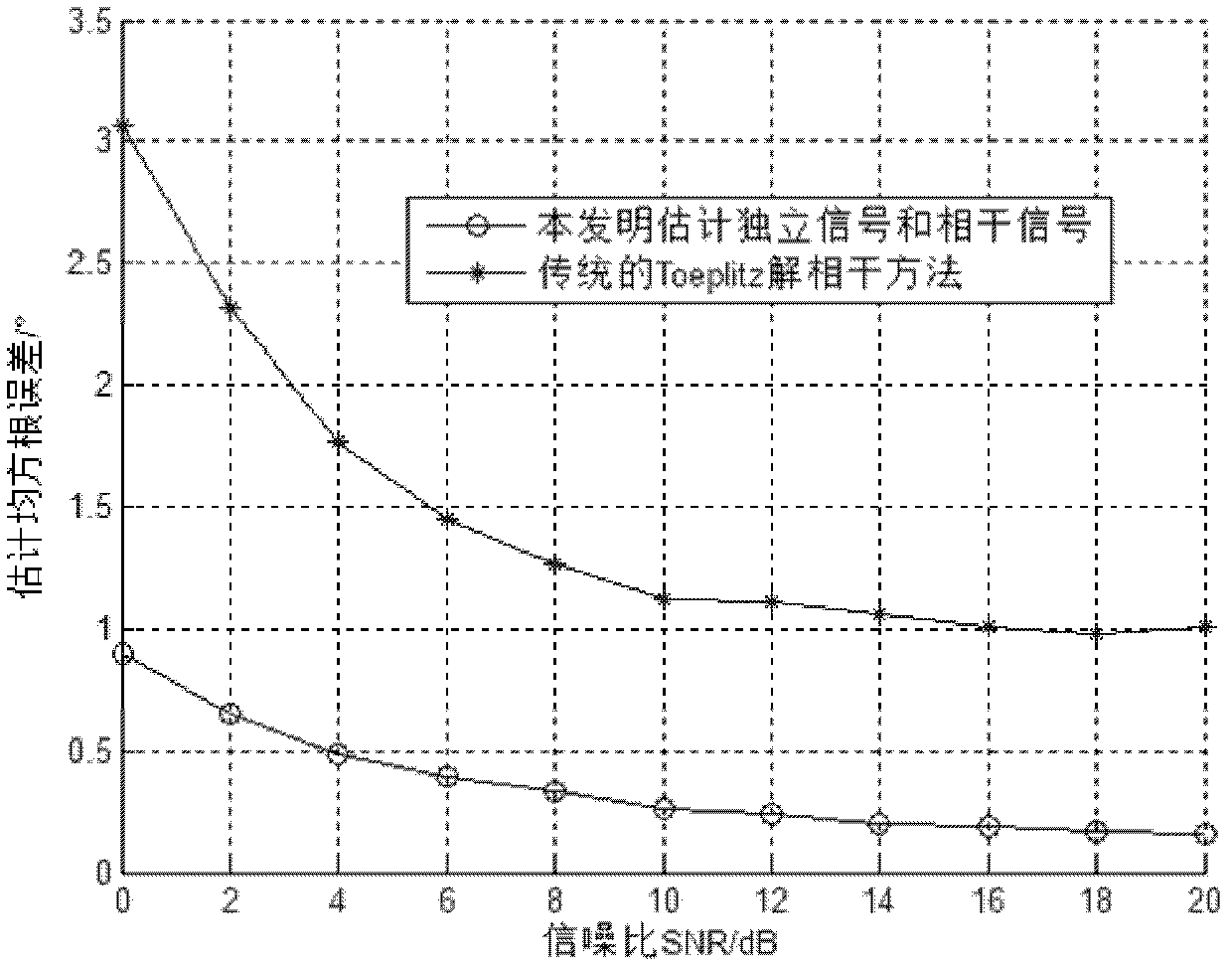

Direction-of-arrival estimation method on basis of uniform circular array

InactiveCN102608565ATake advantage ofImprove estimation accuracyRadio wave finder detailsRadio wave direction/deviation determination systemsEstimation methodsSignal on

The invention relates to a direction-of-arrival estimation method on the basis of a uniform circular array, in particular to a direction-of-arrival estimation method for independent signals and coherent signals on the basis of the uniform circular array. The direction-of-arrival estimation method on the basis of the uniform circular array includes: preprocessing estimation parameters of direction-of-arrival; removing noise of pattern space; increasing aperture of the array and performing direction-of-arrival estimation to independent signals; and eliminating independent signals and performing direction-of-arrival estimation to coherent signals. The direction-of-arrival estimation method has higher estimation precision, the aperture of the array can be utilized more sufficiently, the loss of the aperture of the array due to array transformation of a virtual array is recovered, estimation performance can be improved further, calculation is simple and calculation quantity is low.

Owner:HARBIN ENG UNIV

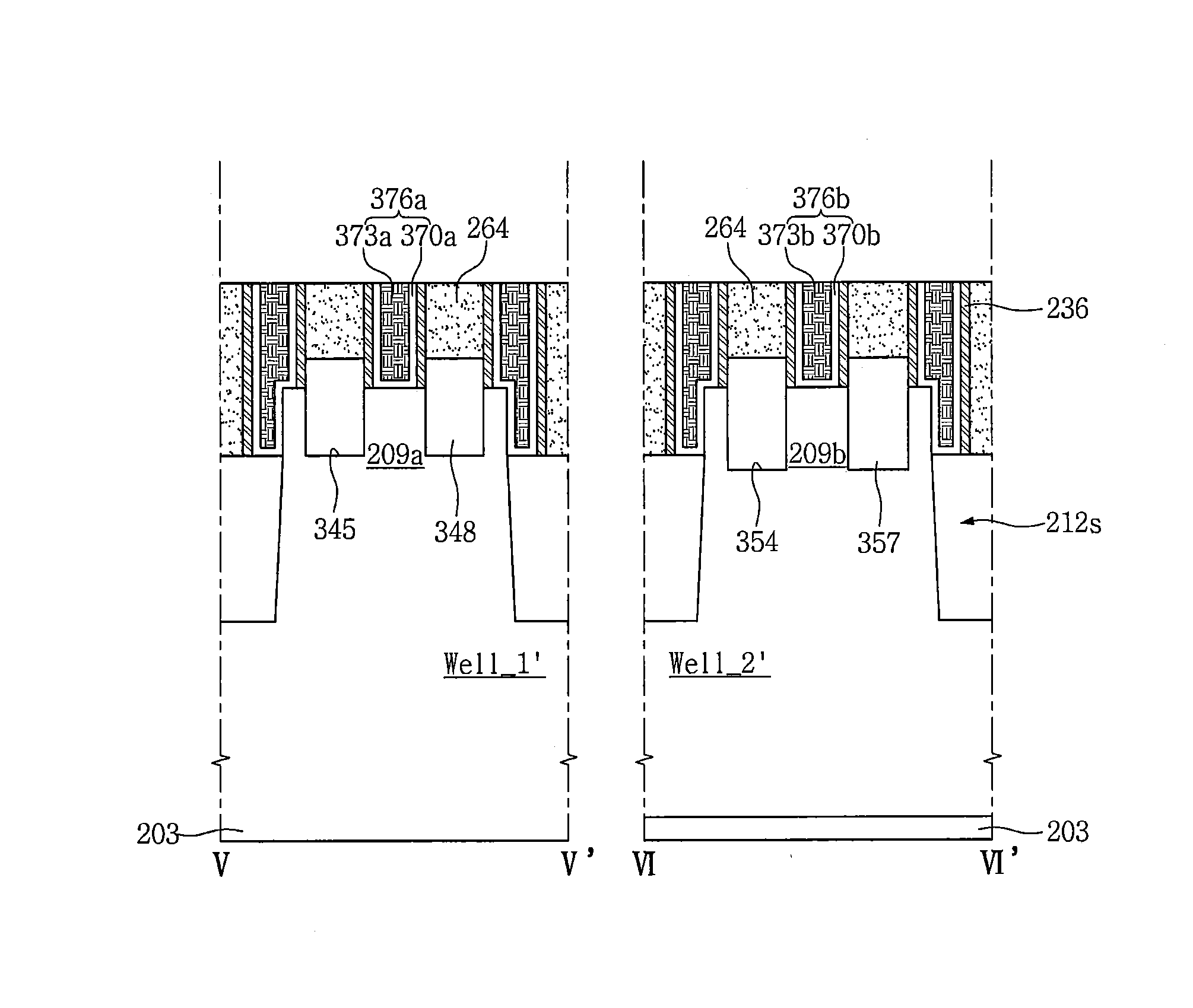

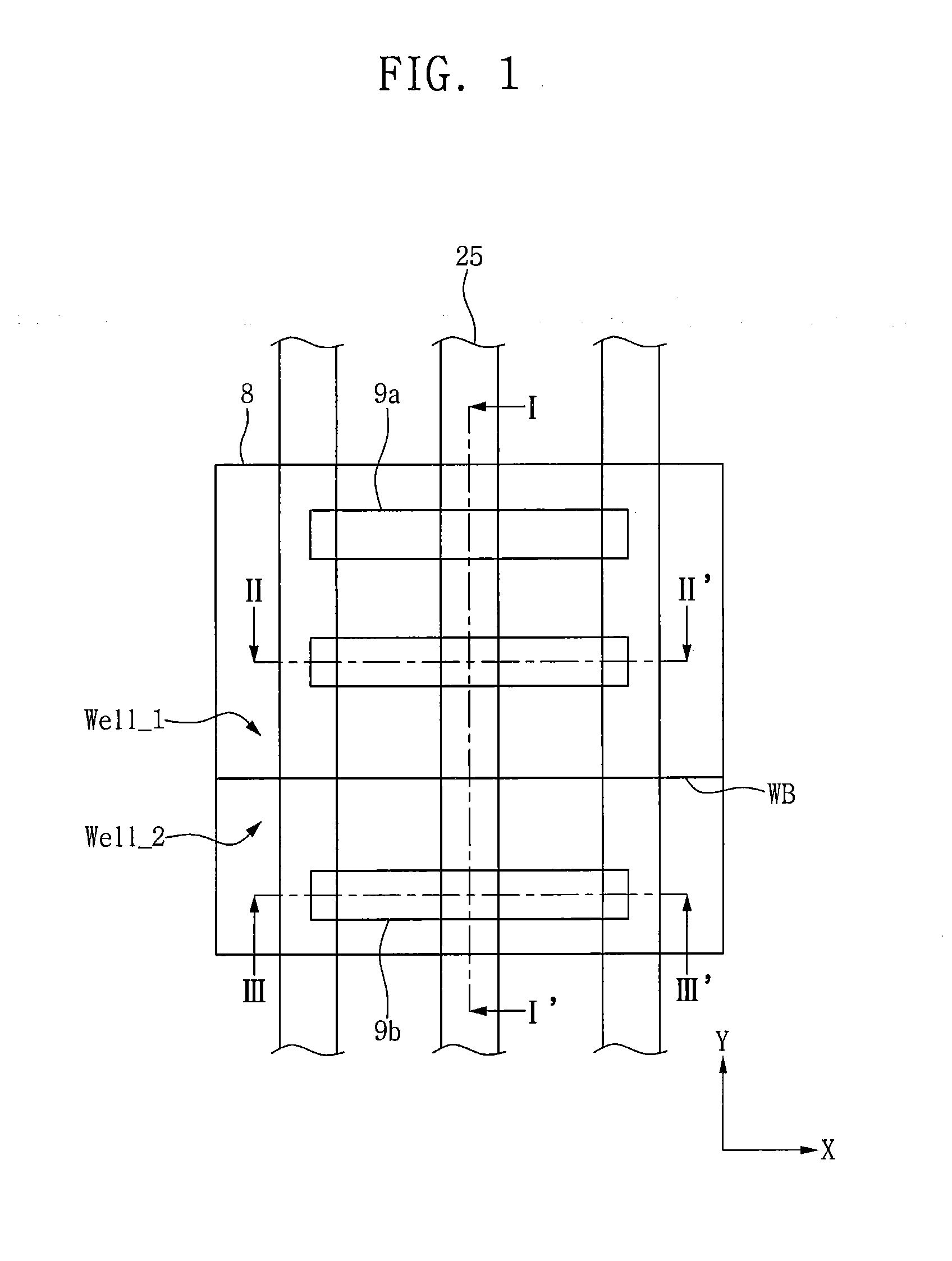

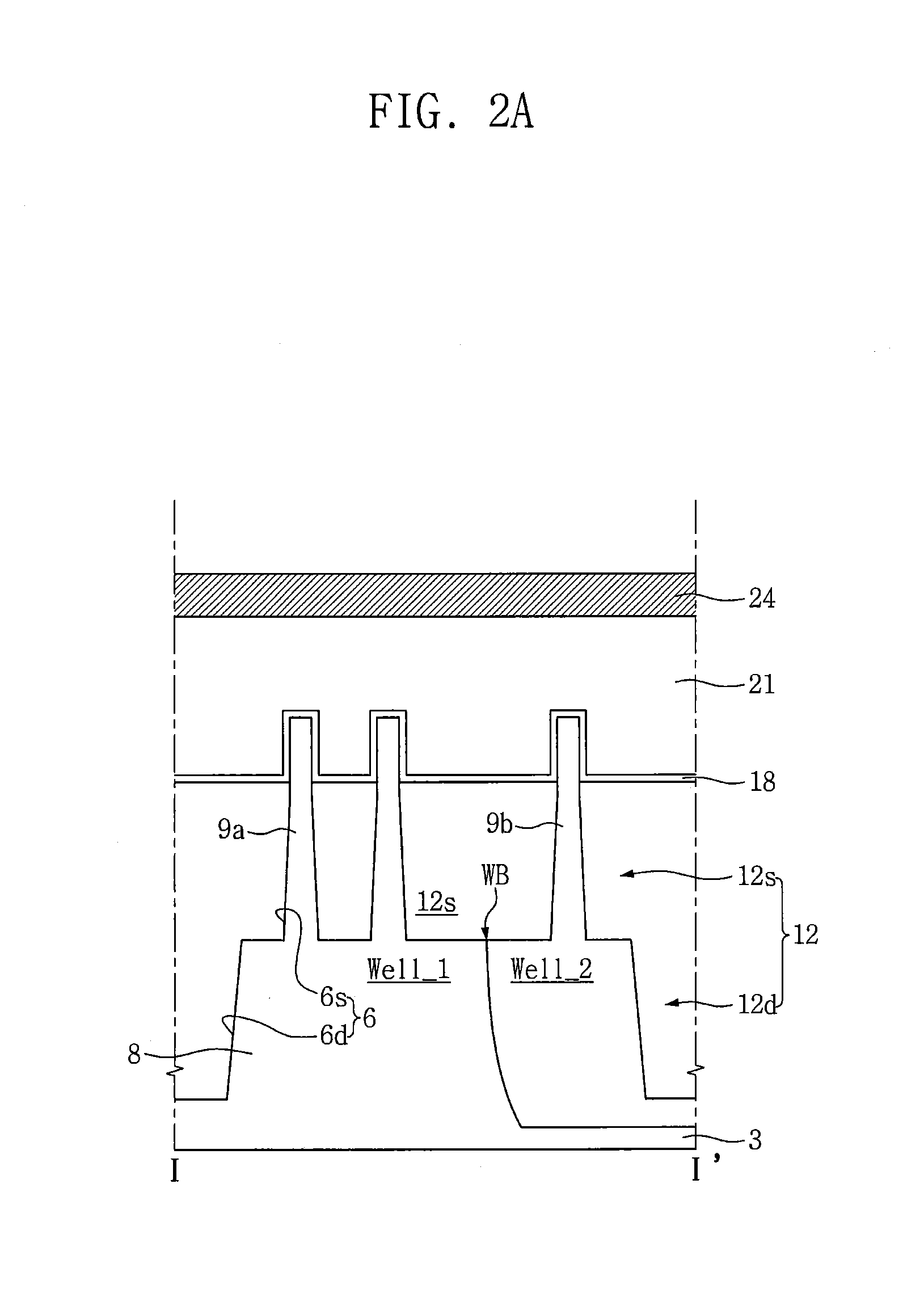

Method of fabricating semiconductor device

ActiveUS20160247728A1Semiconductor/solid-state device manufacturingSemiconductor devicesDevice materialSemiconductor

A method of fabricating a semiconductor device includes forming a first well region and a second well region in a semiconductor substrate, forming an isolation region defining a first fin active region and a second fin active region on the semiconductor substrate, forming a sacrificial gate layer on the semiconductor substrate having the first and second fin active regions and the isolation region, forming a hardmask line on the sacrificial gate layer, forming a gate cut mask having a gate cut opening on the hardmask line, and forming first and second hardmask patterns spaced apart from each other by etching the hardmask line using the gate cut mask as an etching mask. The gate cut opening overlaps a boundary between the first and second well regions formed between the first and second fin active regions, and has a line shape in a direction intersecting the hardmask line.

Owner:SAMSUNG ELECTRONICS CO LTD

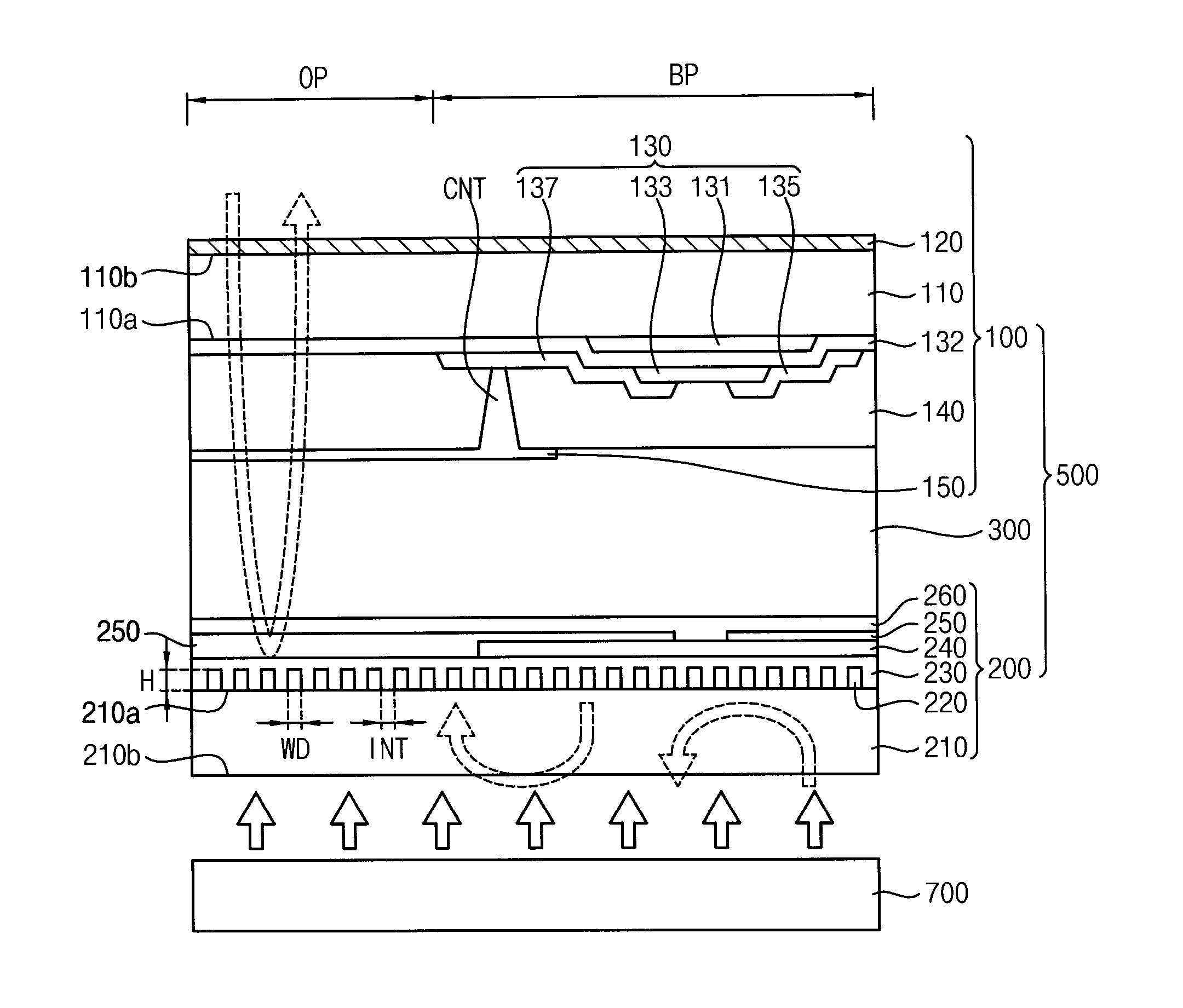

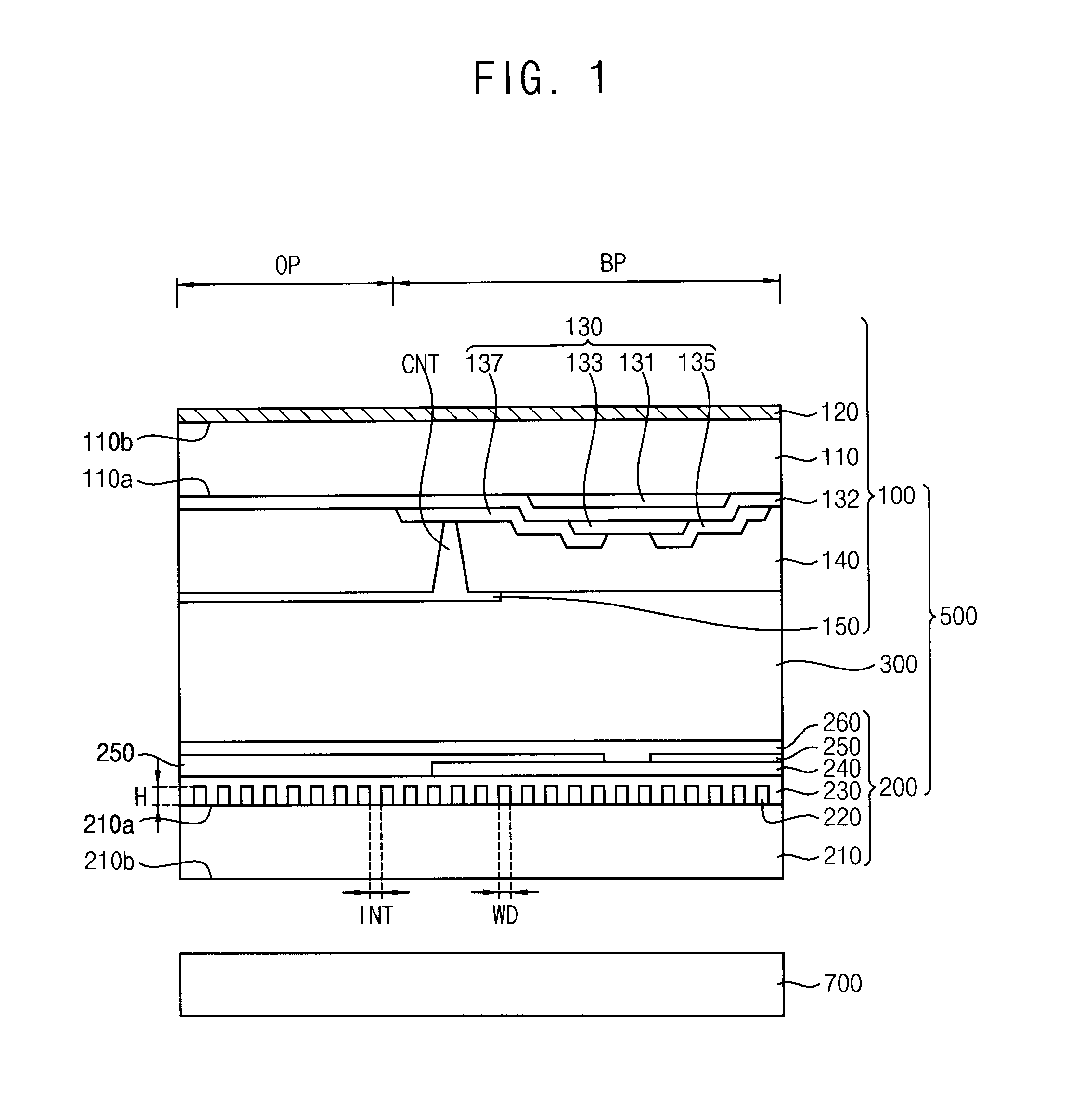

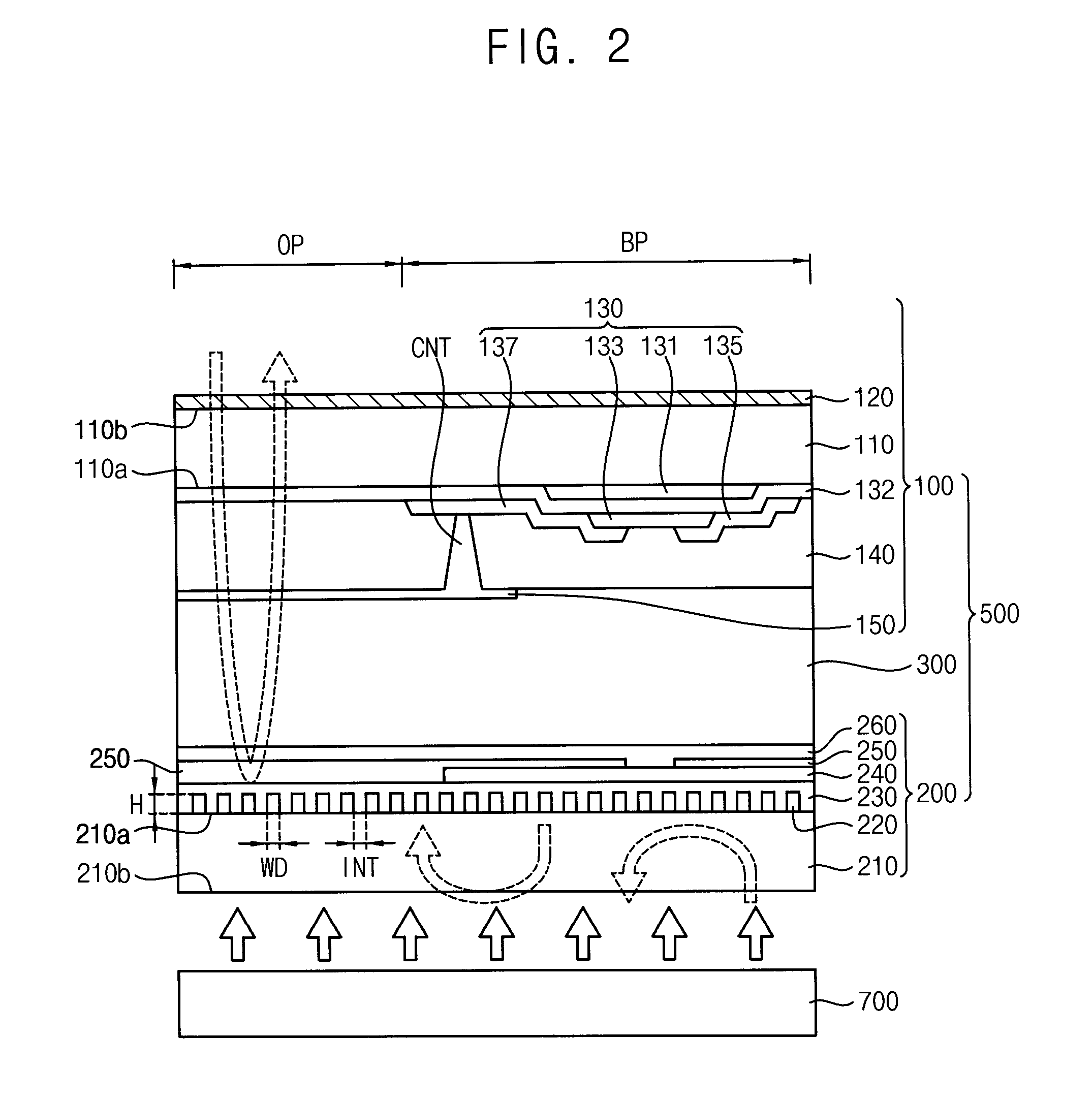

Liquid crystal display device

ActiveUS20140293187A1Eliminate side effectsImprove lighting efficiencyNon-linear opticsOptical elementsLiquid-crystal displayPolarizer

A liquid crystal display device includes a liquid crystal display panel and a backlight unit providing light to the liquid crystal display panel. The liquid crystal display panel includes a first substrate on which a thin film transistor is disposed, a second substrate facing the first substrate, a liquid crystal layer disposed between the first substrate and the second substrate, and a first polarizer disposed on the second substrate having a plurality of metal patterns spaced apart from each other by an interval. The backlight unit faces the second substrate.

Owner:SAMSUNG DISPLAY CO LTD

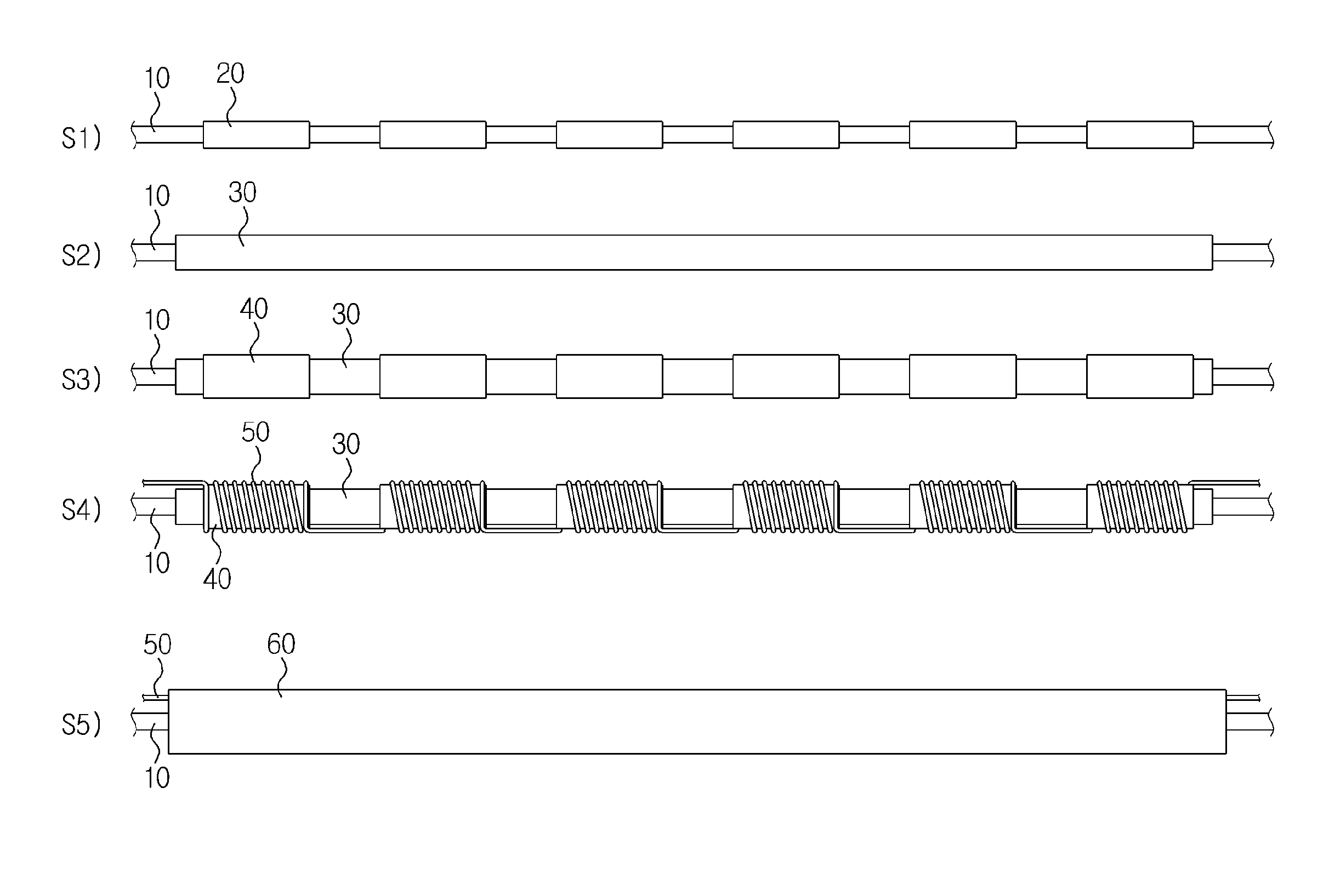

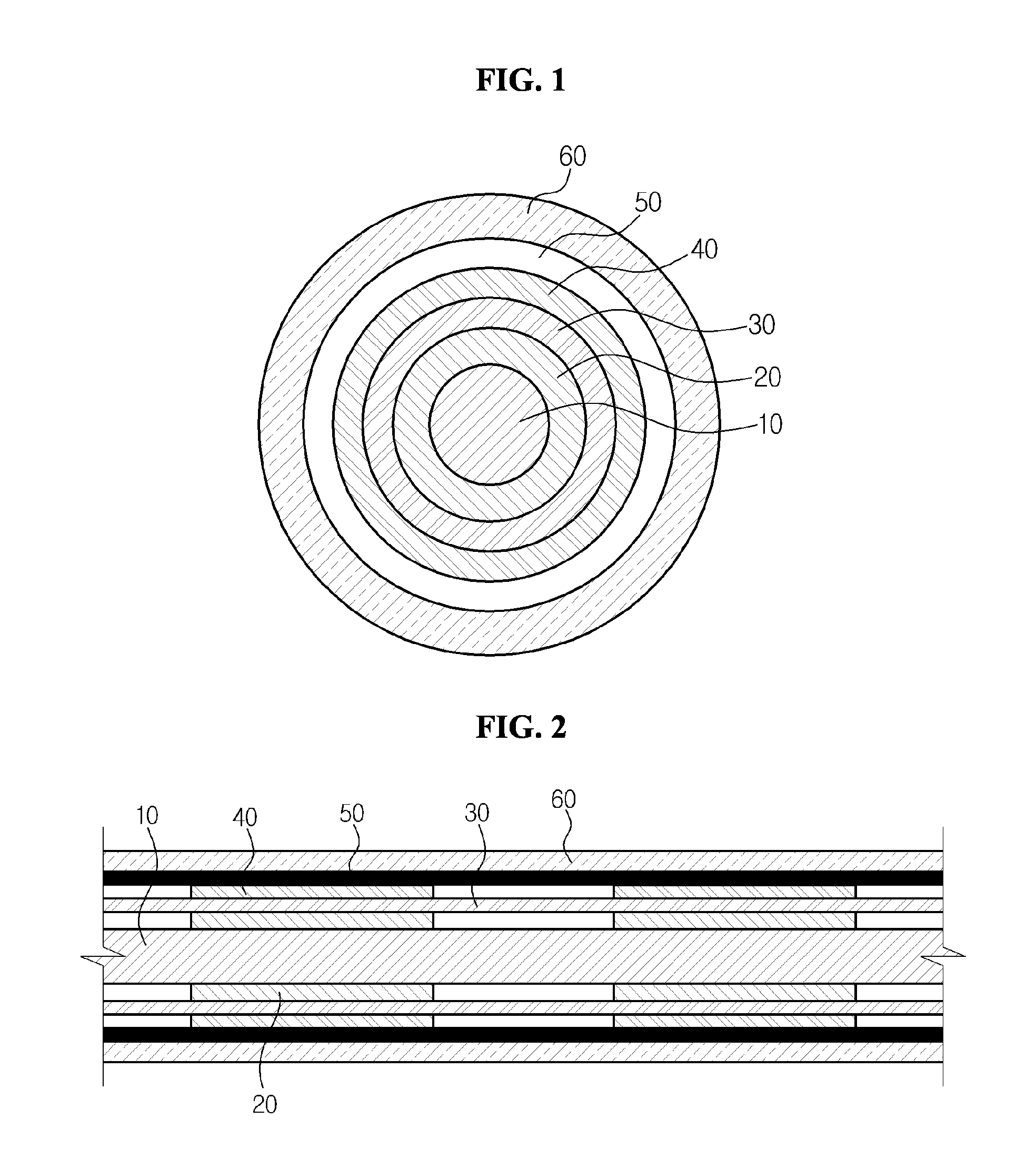

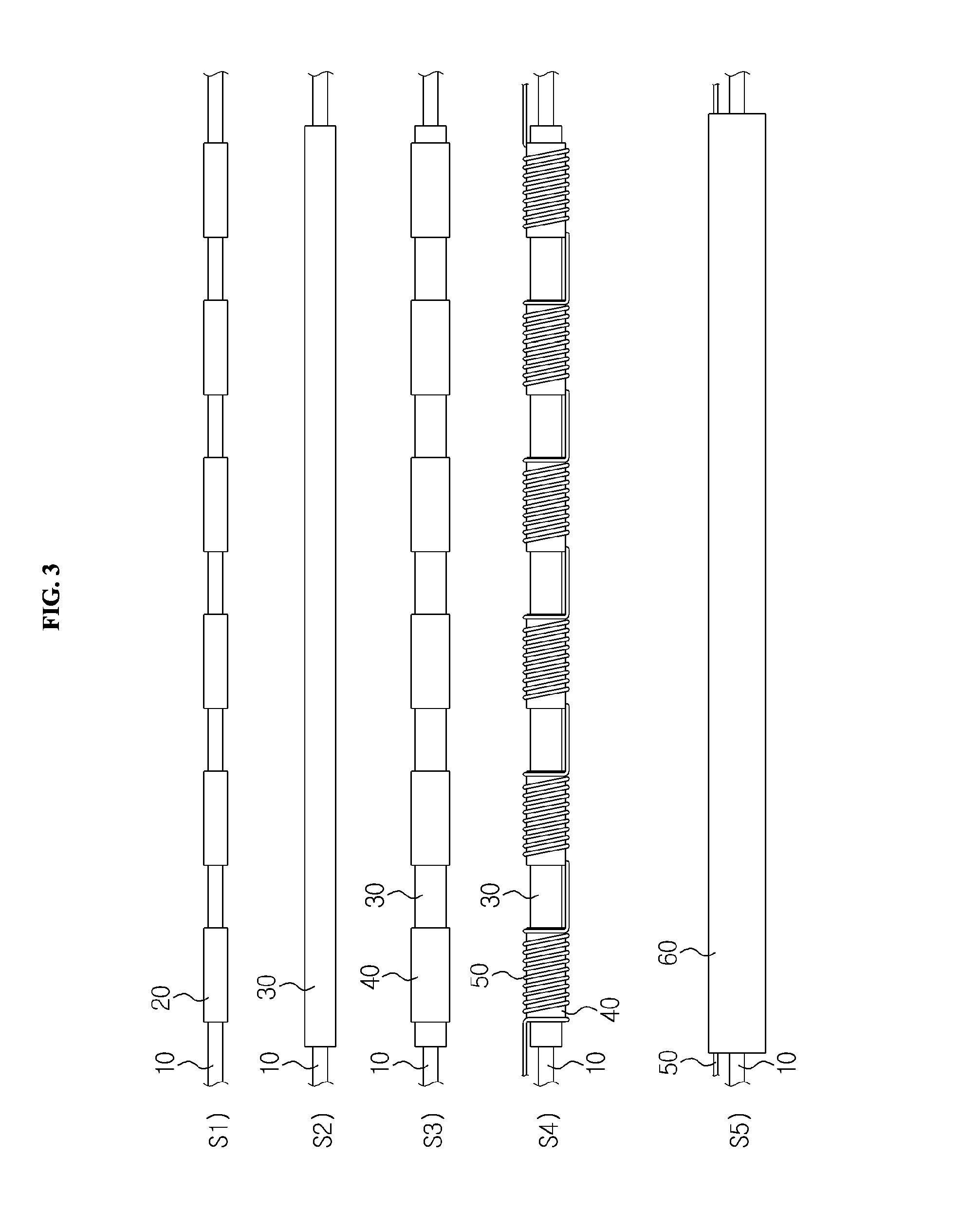

Cable-type secondary battery

ActiveUS20120107658A1Increase flexibilityAvoid deformationFinal product manufactureSmall-sized cells cases/jacketsEngineeringIon channel

Provided is a cable-type secondary battery including an anode current collector having a horizontal cross section of a predetermined shape and extending longitudinally, an anode active material pattern layer having anode active material patterns spaced away at a predetermined interval on the anode current collector, an electrolyte layer surrounding the anode active material pattern layer and serving as an ion channel, a cathode active material pattern layer having cathode active material patterns spaced away at a predetermined interval on the electrolyte layer at locations corresponding to those of the anode active material patterns, and a cathode current collector surrounding the cathode active material pattern layer.The cable-type secondary battery having the active material patterns has excellent flexibility to prevent the active material from falling off from the active material layer.

Owner:LG ENERGY SOLUTION LTD

Method and apparatus for inversion processing of well logging data in a selected pattern space

ActiveUS20050075789A1Electric/magnetic detection for well-loggingAnalogue computers for heat flowWell loggingElectrical resistivity and conductivity

Method and apparatus for deriving information regarding a subsurface geophysical formation. Well logging data is acquired for the subsurface geophysical formation. Geometrical parameters for the subsurface geophysical formation are determined by inversion processing of the acquired well logging data in a pattern space while formation conductivities for the subsurface geophysical formation are determined by inversion processing of the acquired well logging data in a measurement space. The processing may be iteratively applied until satisfied formation parameters are achieved.

Owner:HALLIBURTON ENERGY SERVICES INC

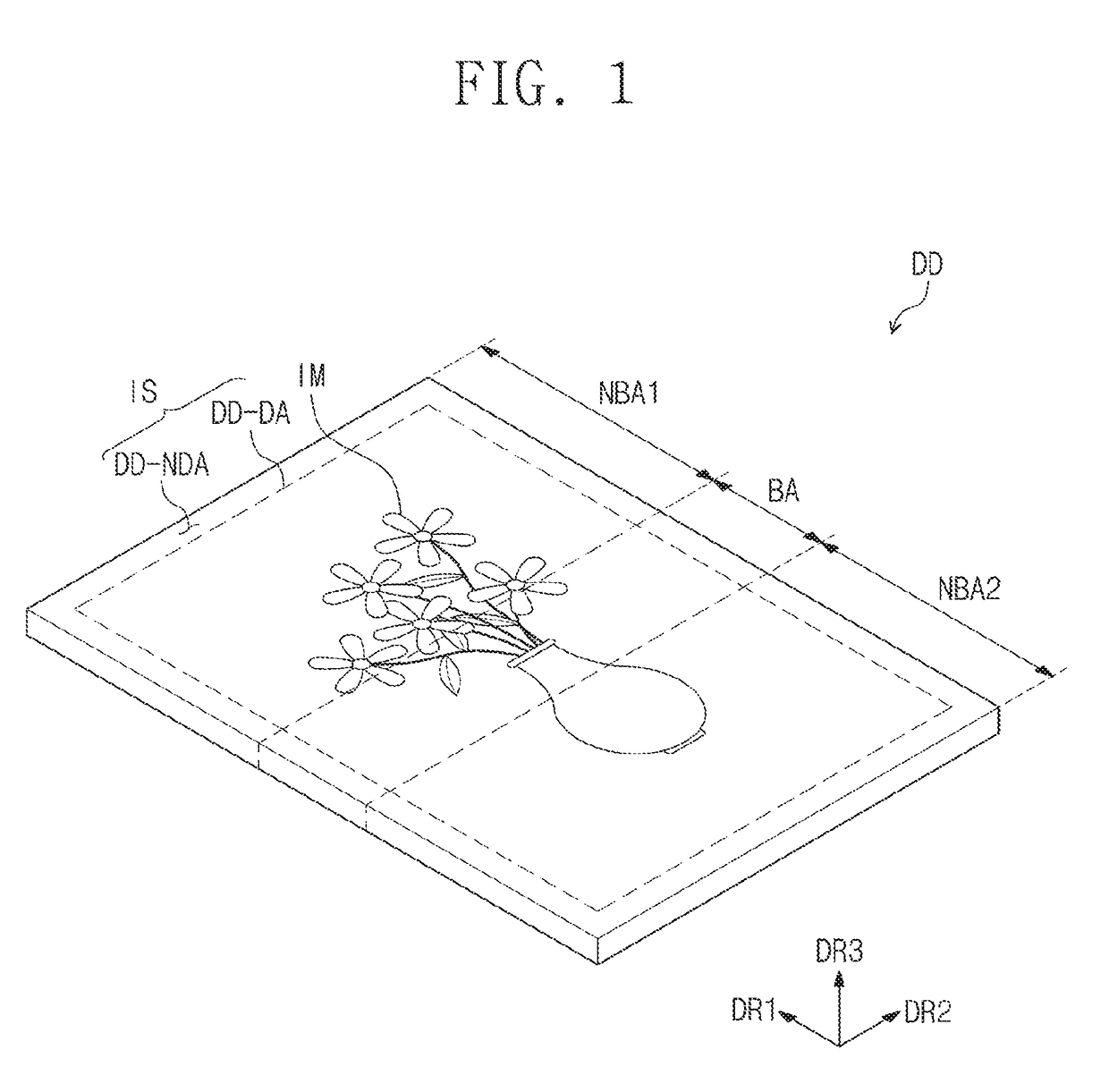

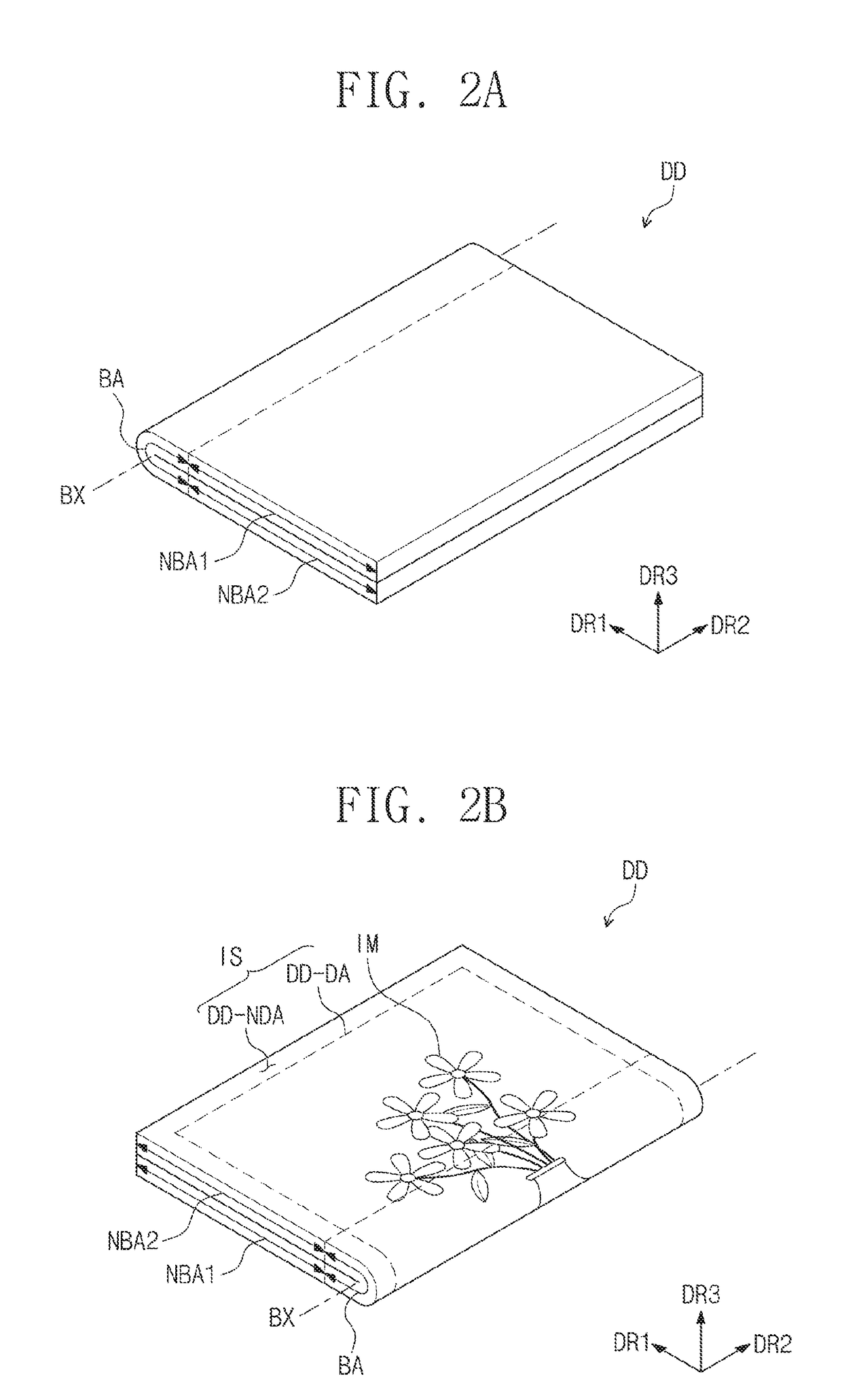

Display device

ActiveUS20180081219A1Improve visibilityRobust displayDetails for portable computersNon-linear opticsDisplay deviceNon functional

A display device including a display panel having a first area, a second area spaced from the first area, and a bending area disposed between the first and second areas, a first sensing pattern overlapped with the first area, a second sensing pattern spaced apart from the first sensing pattern and overlapped with the second area, and a first non-functional pattern overlapped with the bending area and spaced apart from each of the first and second sensing patterns

Owner:SAMSUNG DISPLAY CO LTD

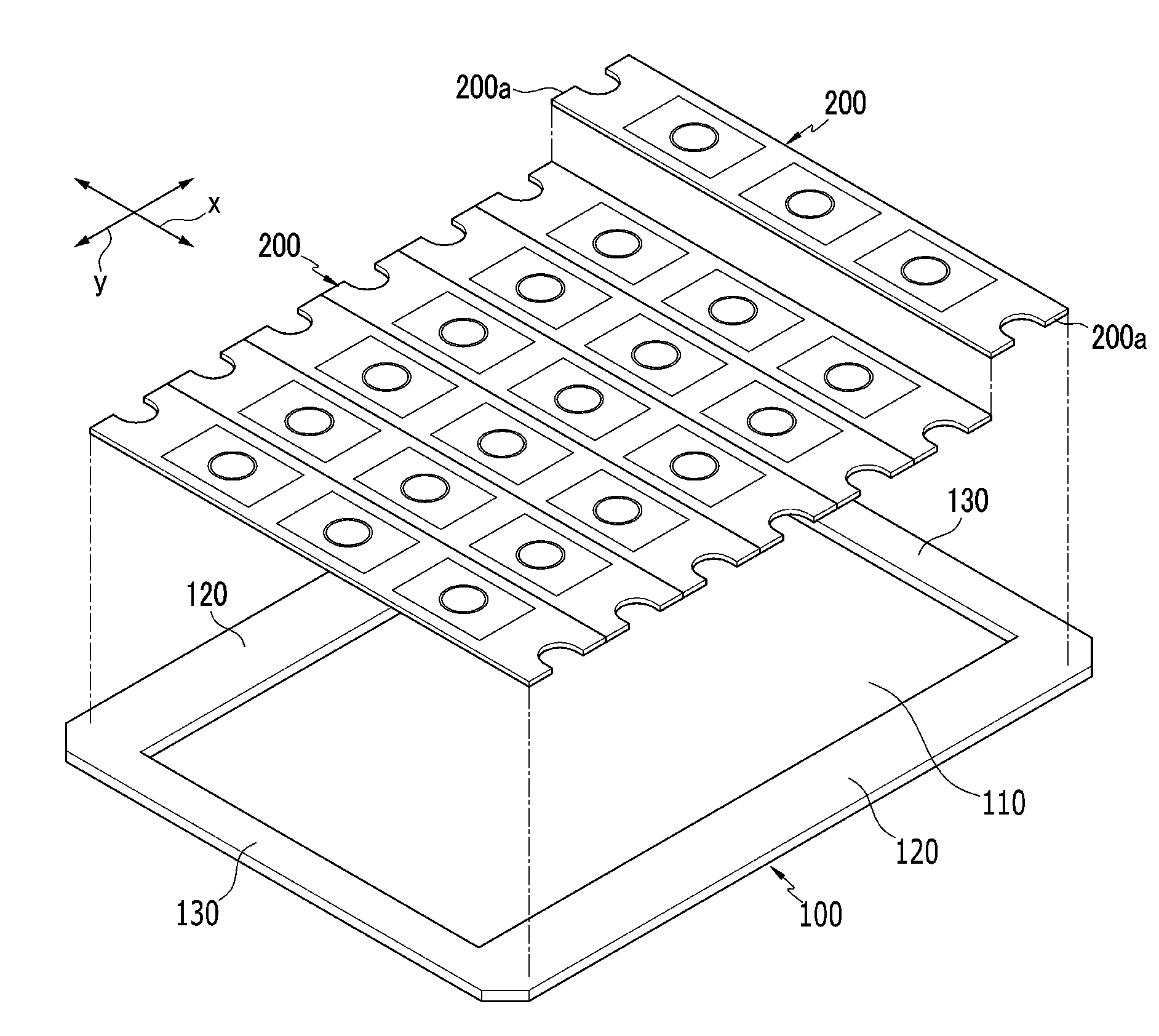

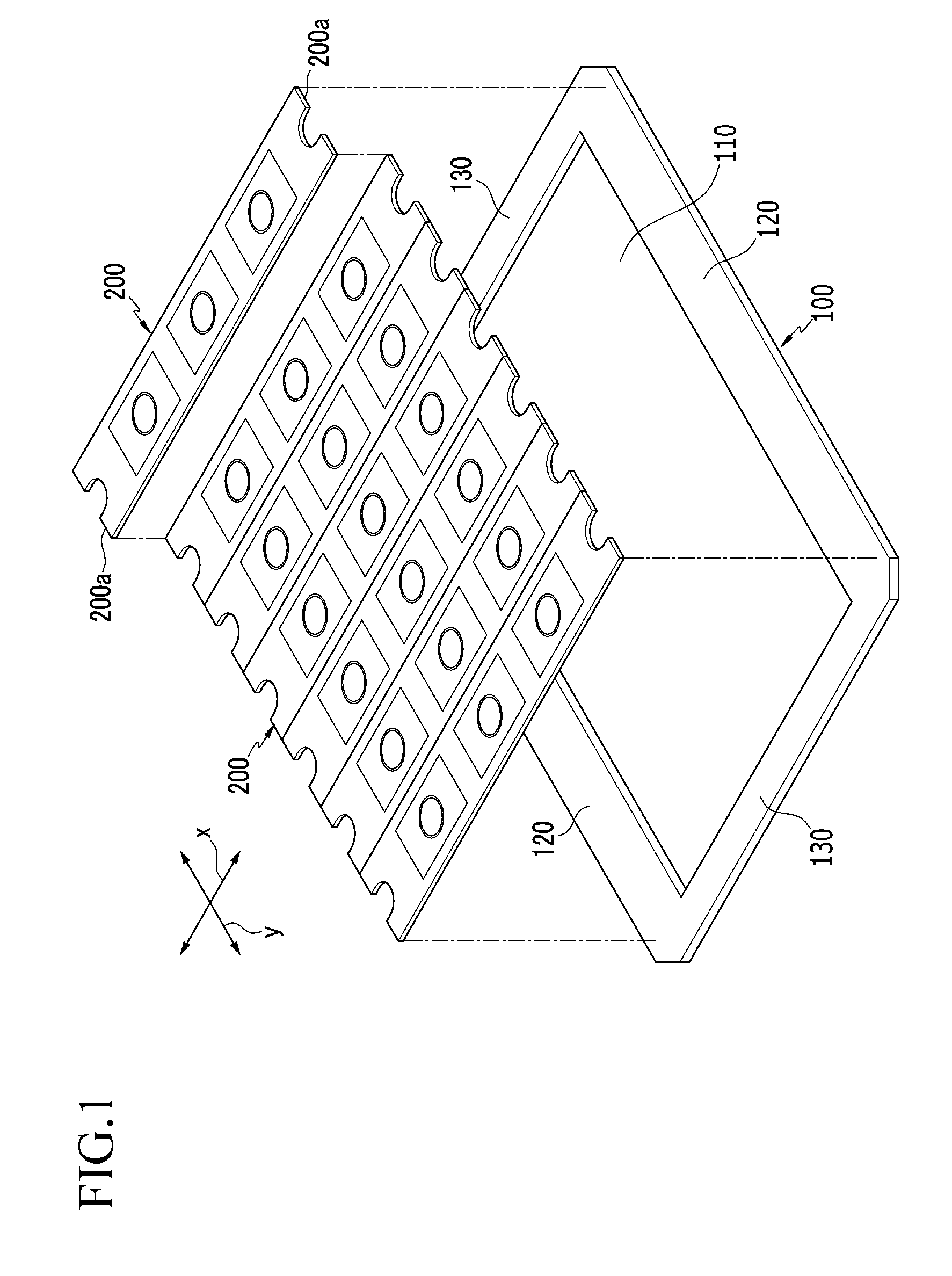

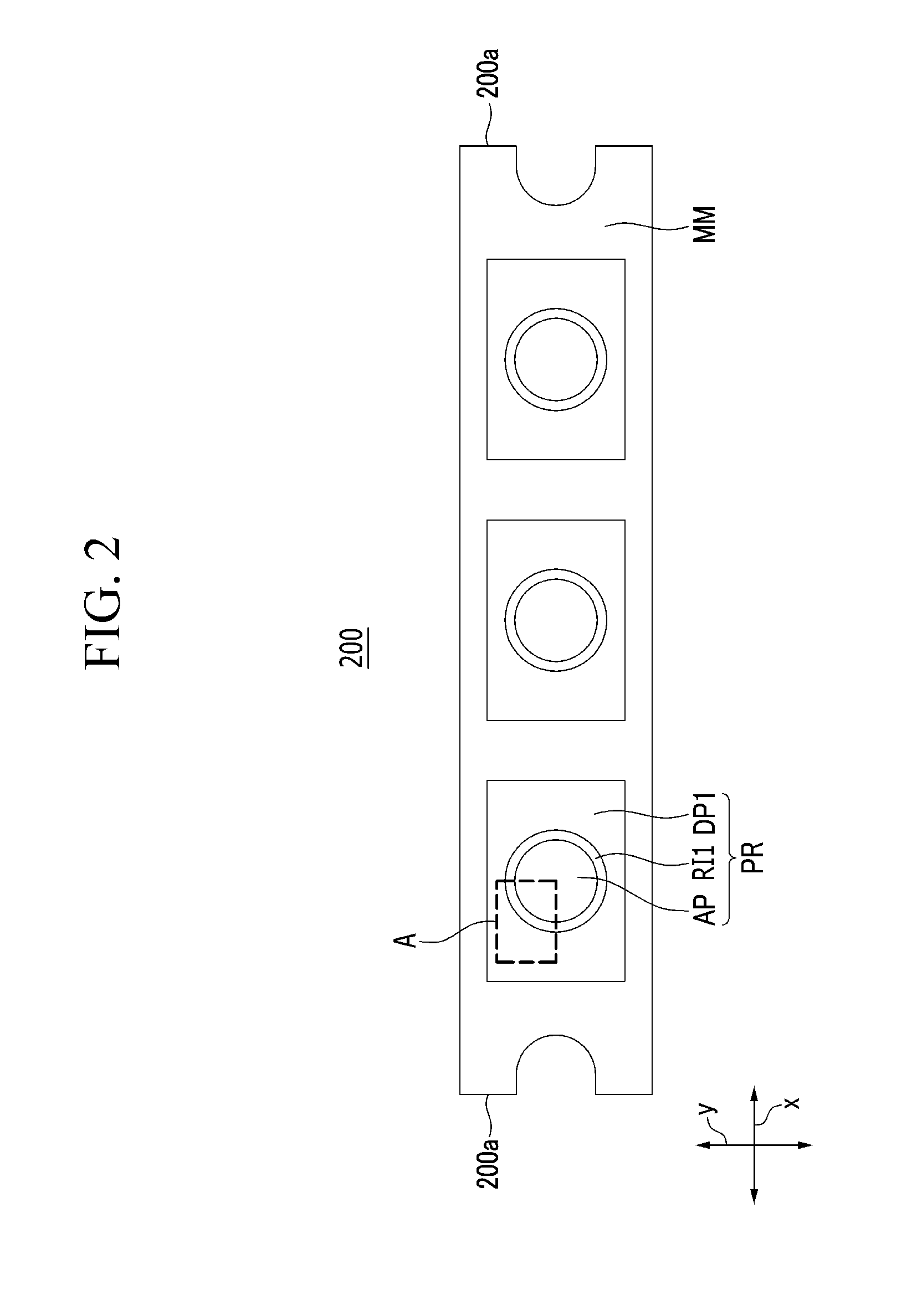

Mask and mask assembly

ActiveUS20150165464A1Handling easiness is improvedLiquid surface applicatorsSpraying apparatusEngineeringPattern space

Owner:SAMSUNG DISPLAY CO LTD

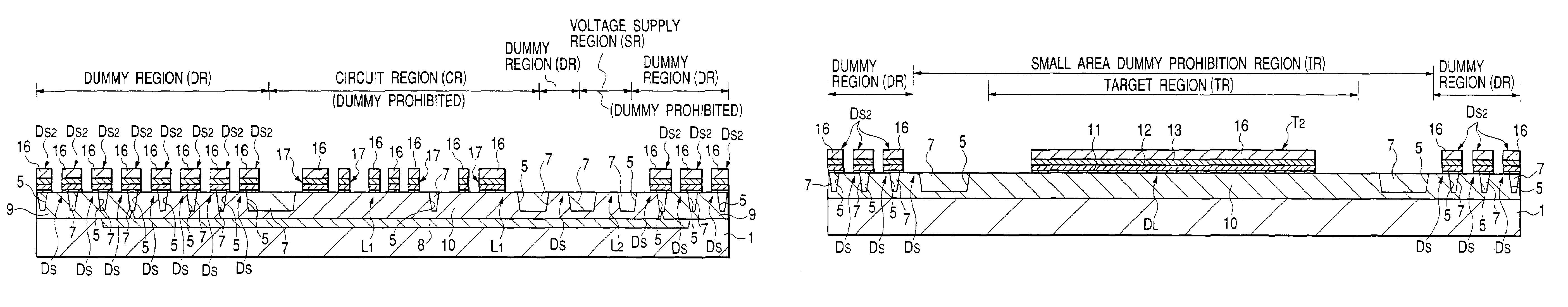

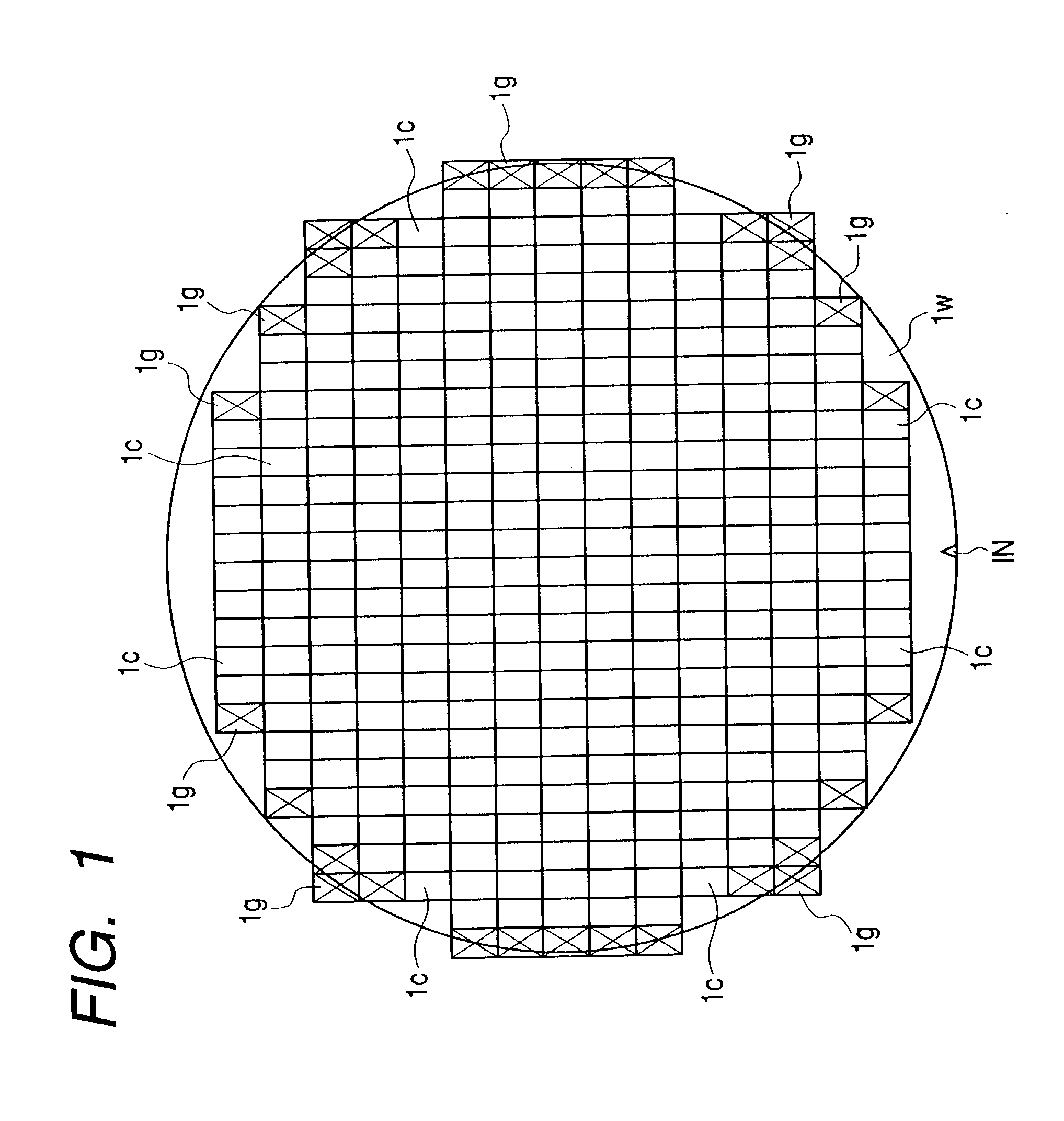

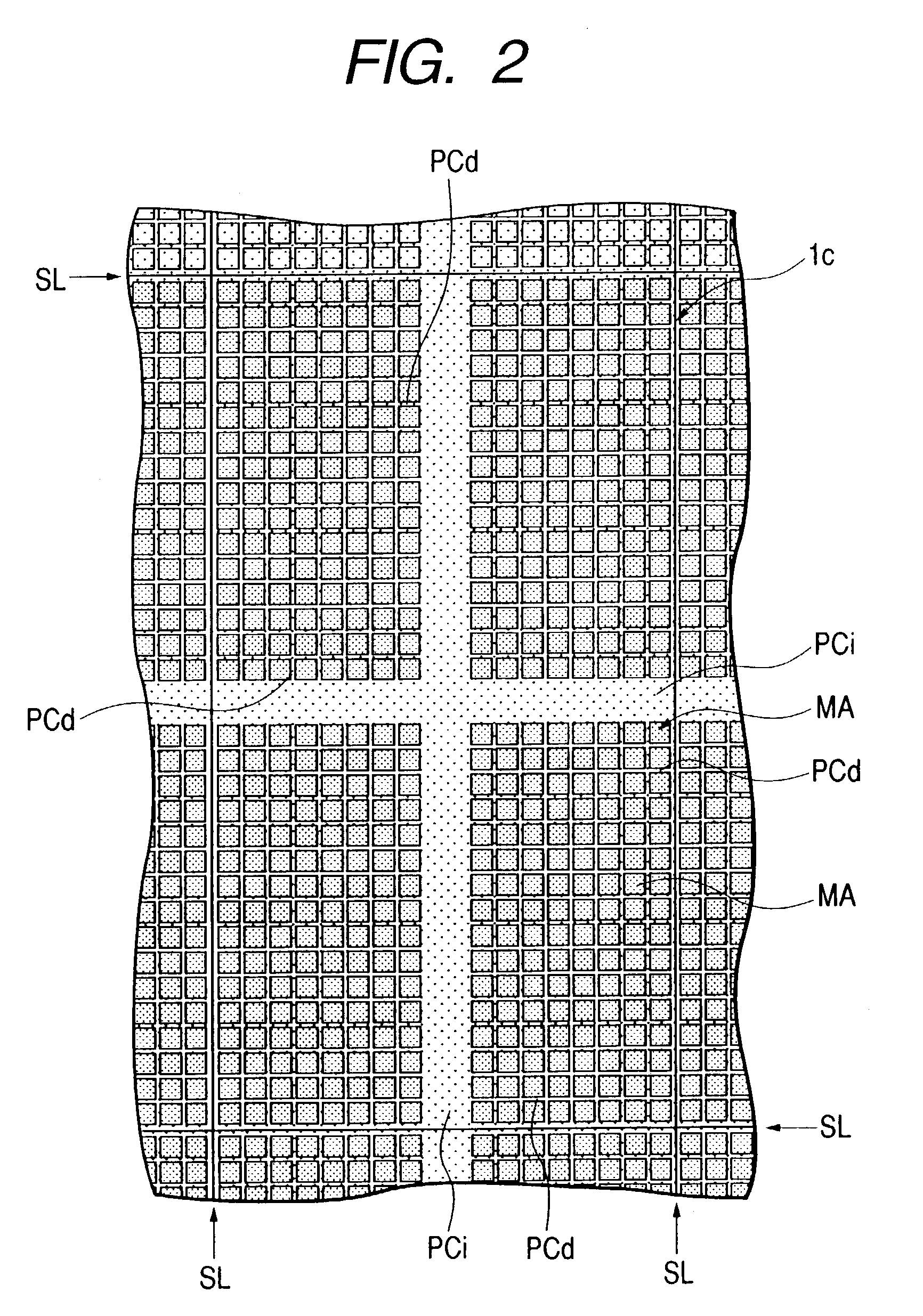

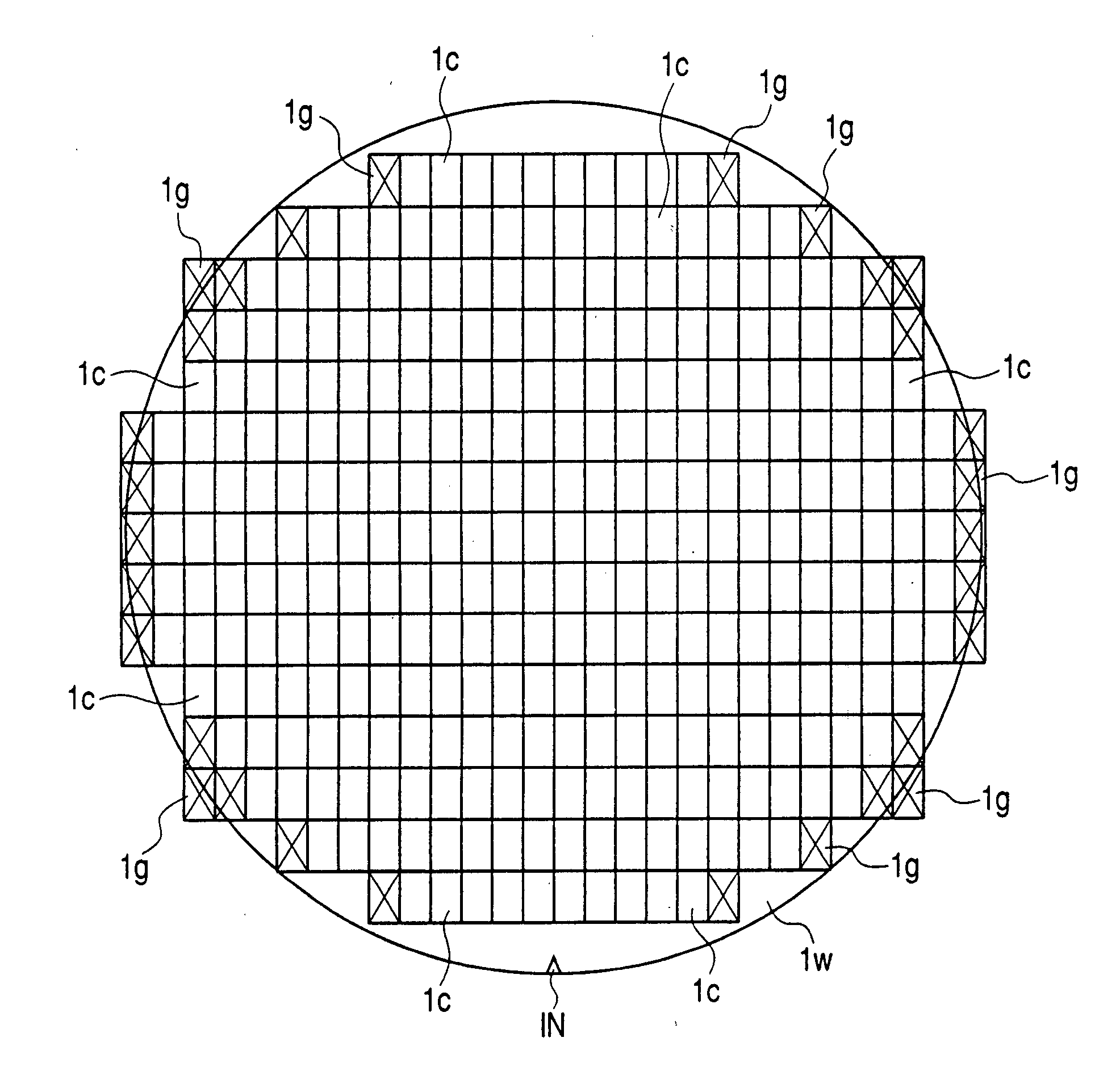

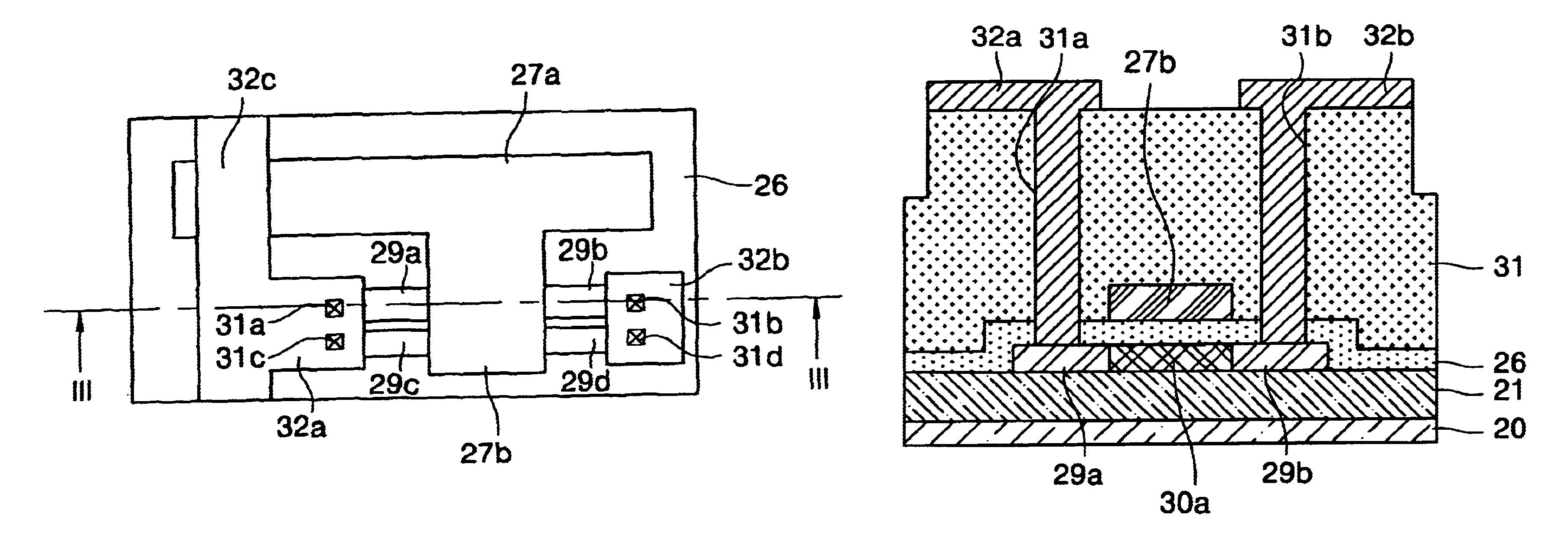

Semiconductor integrated circuit device including dummy patterns located to reduce dishing

InactiveUS7009233B2Decrease the pattern intervalReduce areaTransistorSemiconductor/solid-state device testing/measurementEngineeringSemiconductor

Owner:RENESAS ELECTRONICS CORP

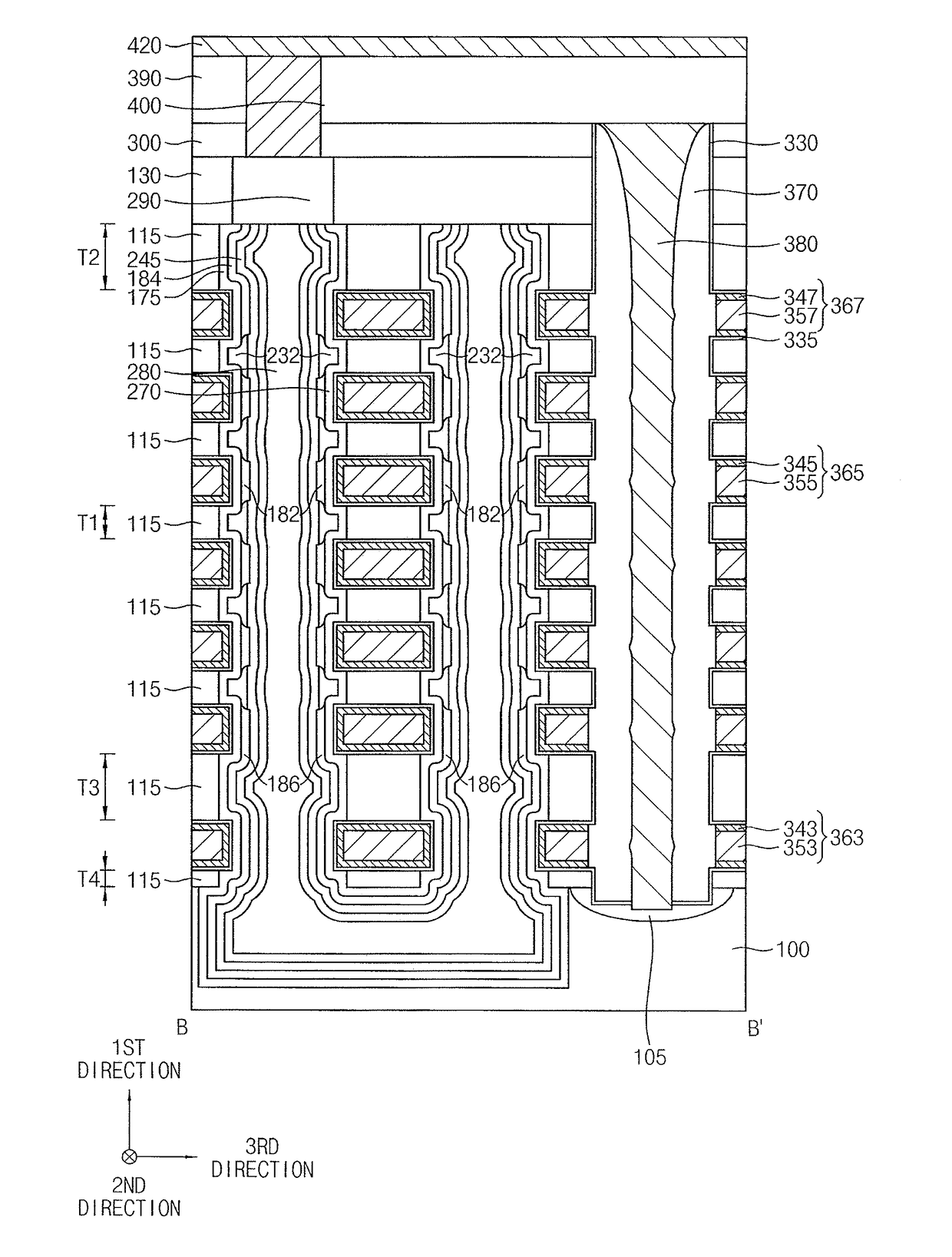

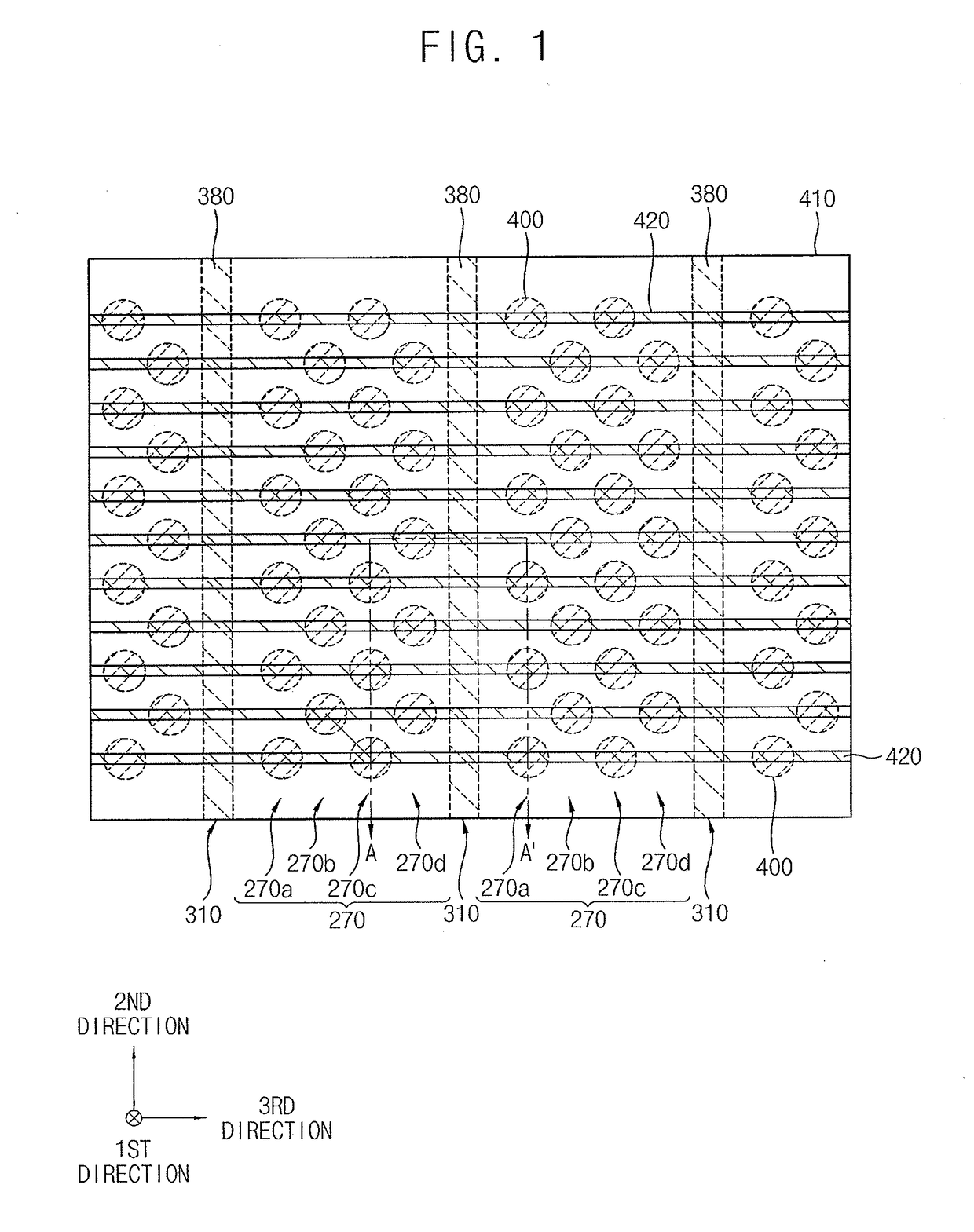

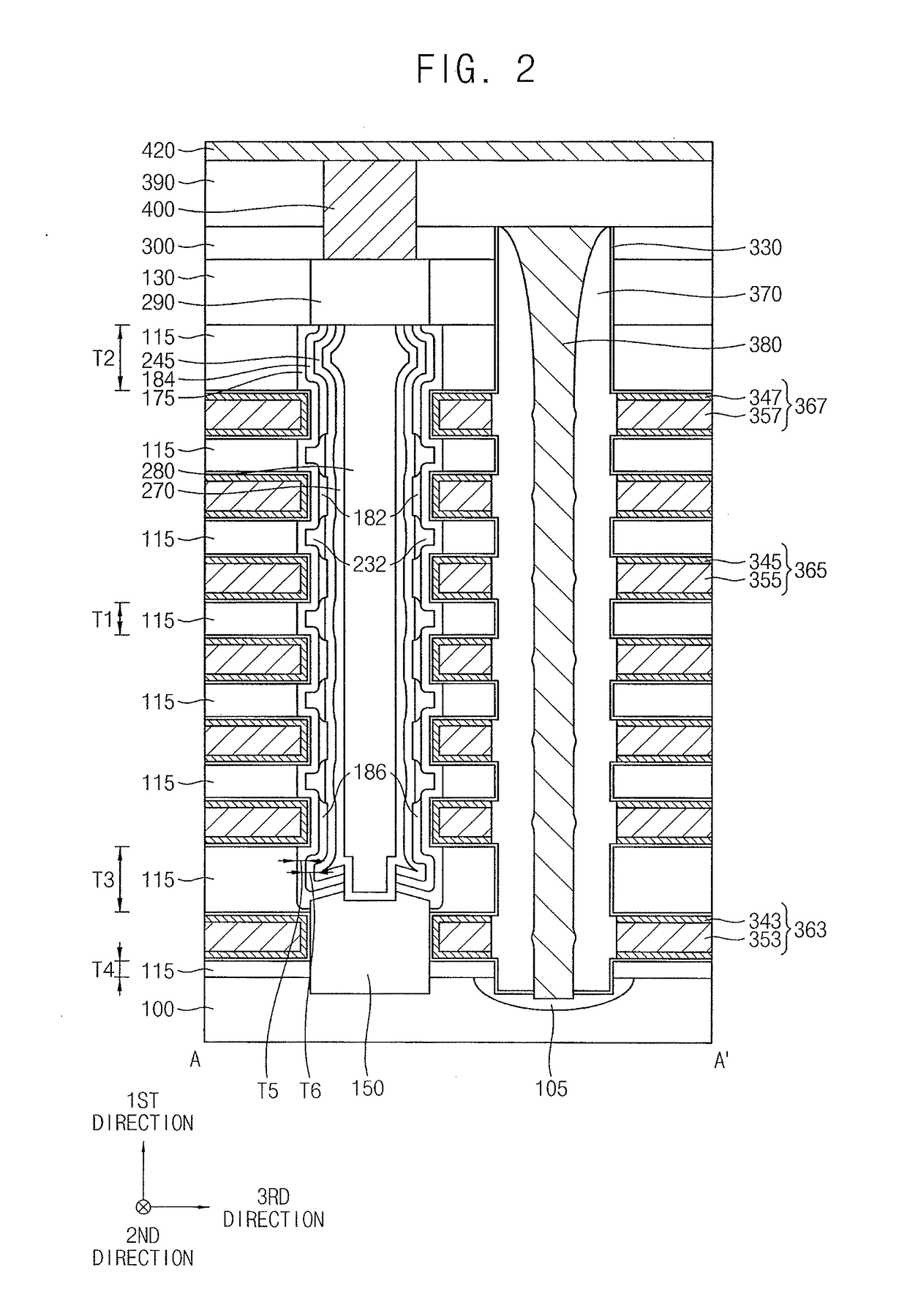

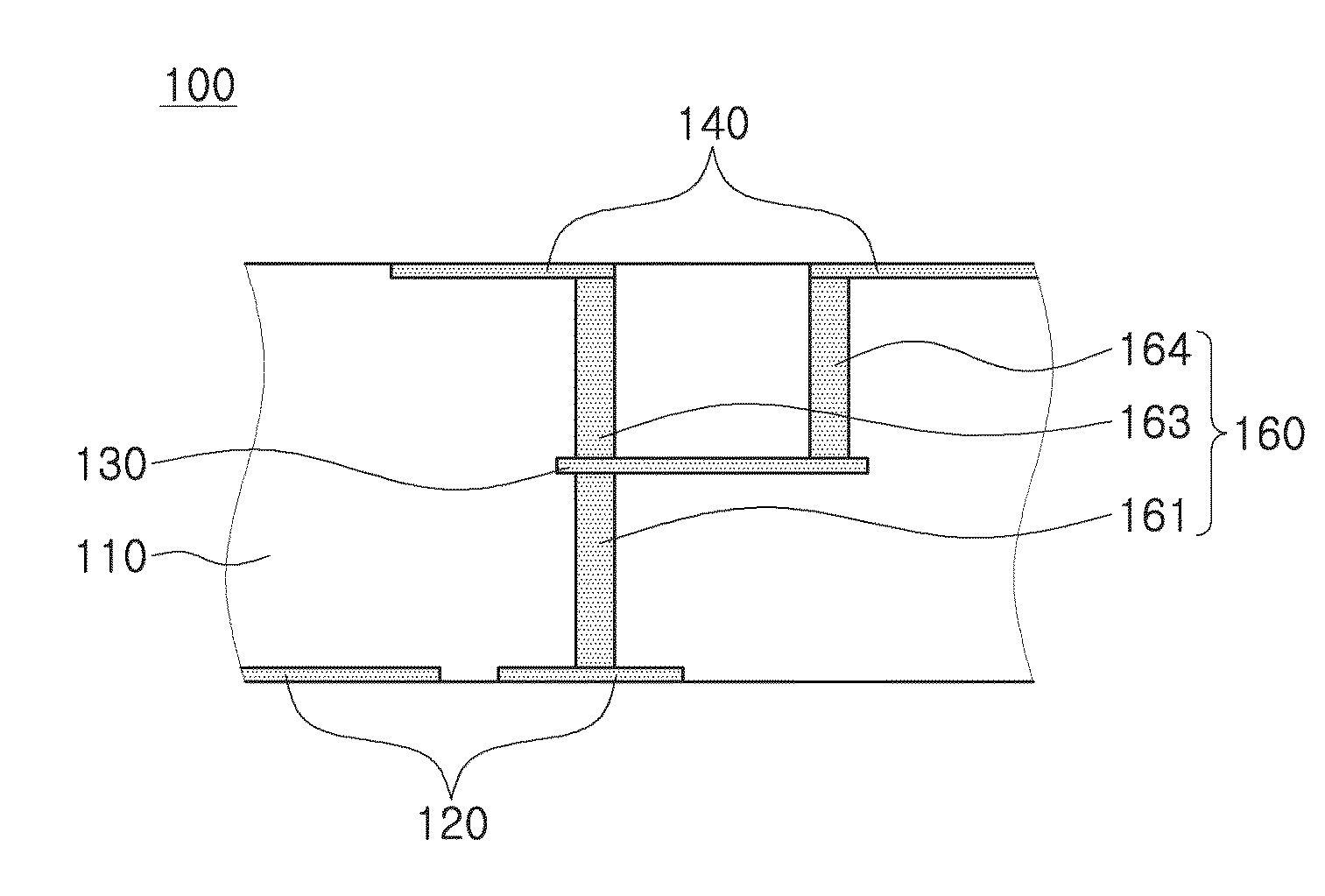

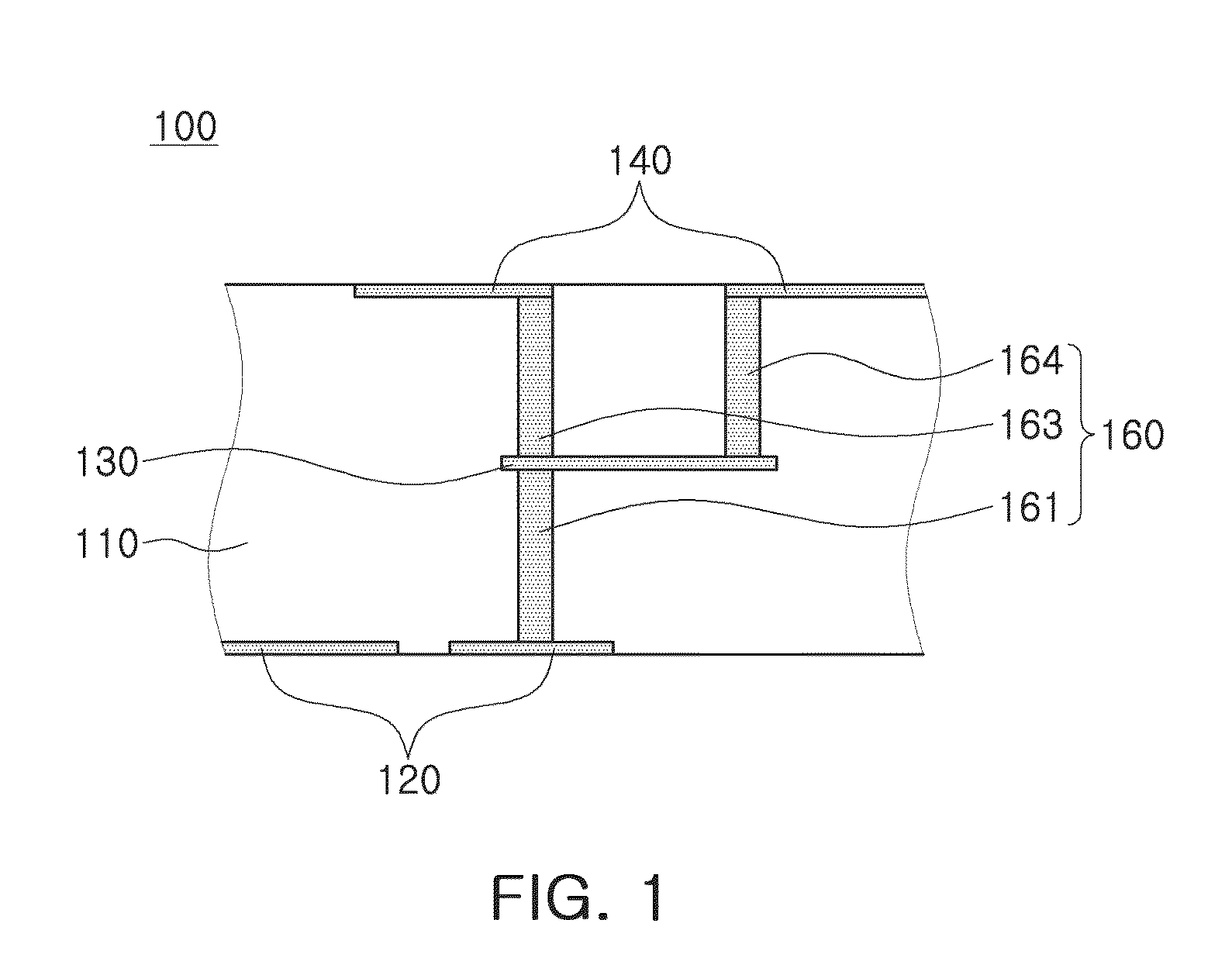

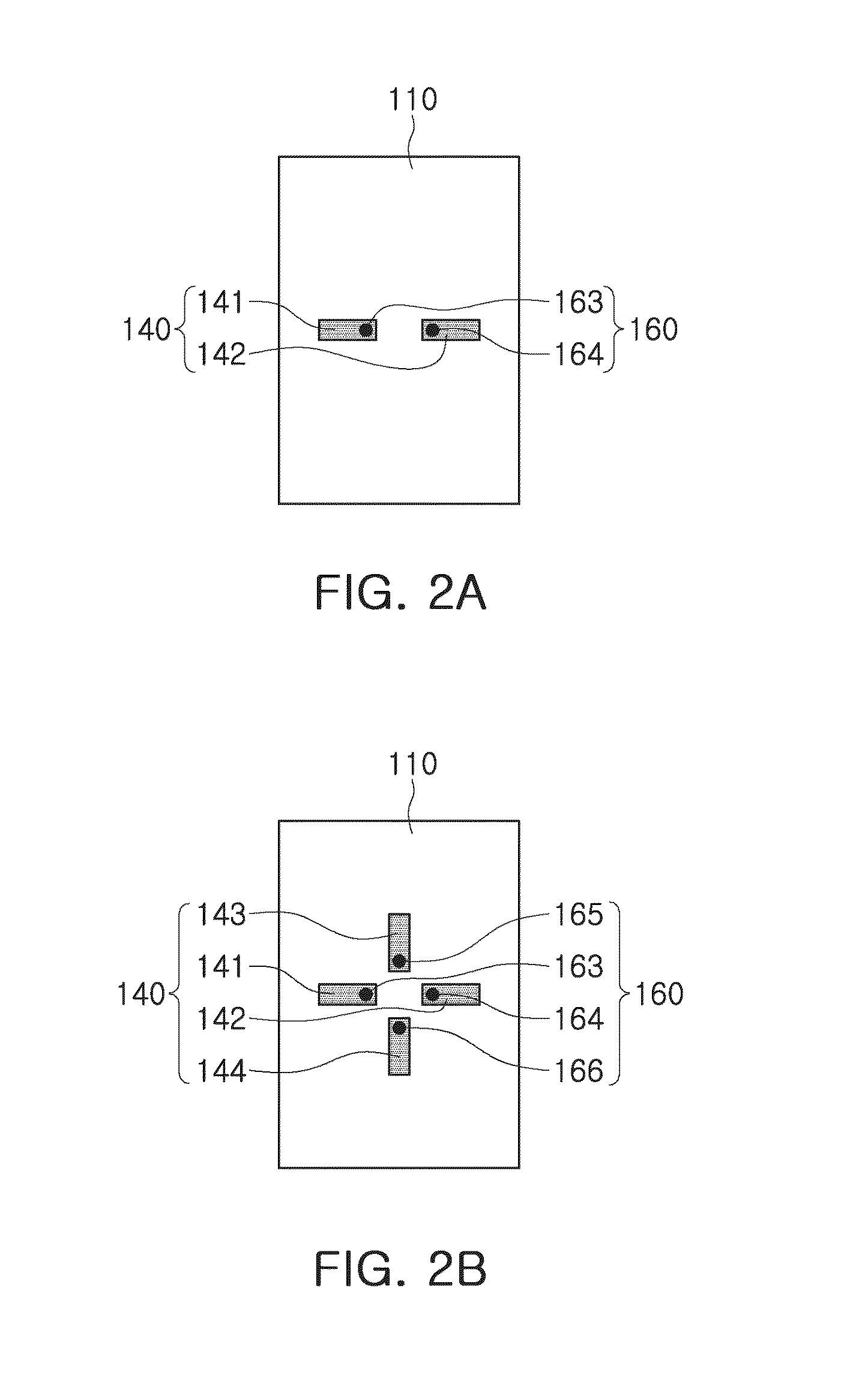

Vertical memory devices and methods of manufacturing the same

A vertical memory device includes insulating interlayer patterns, of gate electrodes, a channel, and a charge storage pattern structure. The insulating interlayer patterns are spaced in a first direction. The gate electrodes between are neighboring insulating interlayer patterns, respectively. The channel extends through the insulating interlayer patterns and the gate electrodes in the first direction. The charge storage pattern structure includes a tunnel insulation pattern, a charge trapping pattern structure, and a blocking pattern sequentially stacked between the channel and each of the gate electrodes in a second direction. The charge trapping pattern structure includes charge trapping patterns spaced in the first direction. The charge trapping patterns are adjacent to sidewalls of first gate electrodes, respectively. A first charge trapping pattern extends in the first direction along a sidewall of a first insulating interlayer pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

Antenna, antenna package, and communications module

InactiveUS20160104934A1Well formedSimultaneous aerial operationsPrinted electric component incorporationComputer moduleEngineering

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Semiconductor integrated circuit device including dummy patterns located to reduce dishing

InactiveUS20050110065A1Decrease pattern intervalReduce areaTransistorSemiconductor/solid-state device testing/measurementEngineeringSemiconductor

A large area dummy pattern DL is formed in a layer underneath a target T2 region formed in a scribe region SR of a wafer. A small area dummy pattern in a lower layer and a small area dummy pattern Ds2 in an upper layer are disposed in a region where the inter-pattern space of a pattern (active regions L1, L2, L3, gate electrode 17), which functions as an element of a product region PR and scribe region SR, is wide. The small area dummy pattern Ds2 in the upper layer is offset by ½ pitch relative to the small area dummy pattern Ds in the lower layer.

Owner:RENESAS ELECTRONICS CORP

Model-based pattern characterization to generate rules for rule-model-based hybrid optical proximity correction

ActiveUS7627837B2Photomechanical apparatusOriginals for photomechanical treatmentHybrid systemAlgorithm

A system and method are provided for analyzing layout patterns via simulation using a lithography model to characterize the patterns and generate rules to be used in rule-based optical proximity correction (OPC). The system and method analyze a series of layout patterns conforming to a set of design rules by simulation using a lithography model to obtain a partition of the pattern spaces into one portion that requires only rule-based OPC and another portion that requires model-based OPC. A corresponding hybrid OPC system and method are also introduced that utilize the generated rules to correct an integrated circuit (IC) design layout which reduces the OPC output complexity and improves turnaround time.

Owner:APPLIED MATERIALS INC

Bending sensor and method for fabricating the same

InactiveUS8547197B2Small sizeResistance/reactance/impedenceForce measurementEngineeringFlexible display

A bend-detecting (bending) sensor is provided, including a flexible substrate, at least a pair of electrode patterns spaced apart from each other provided on the flexible substrate, and a paste layer containing conductive particles. The paste layer is coated onto the flexible substrate where the electrode patterns are formed, such that when the flexible substrate is bent, the density of the conductive particles between the electrode patterns changes and an electric resistance between the electrode patterns also changes, thereby sensing deformation of the flexible substrate, and eventually, a target to which the flexible display element or the flexible substrate is attached. When the bending sensor is applied to the flexible display device, the electrode patterns and the paste layer may be formed on the flexible substrate which is to form the flexible display element, thus forming a bending sensing structure with a thickness of the flexible display element or less.

Owner:SAMSUNG ELECTRONICS CO LTD

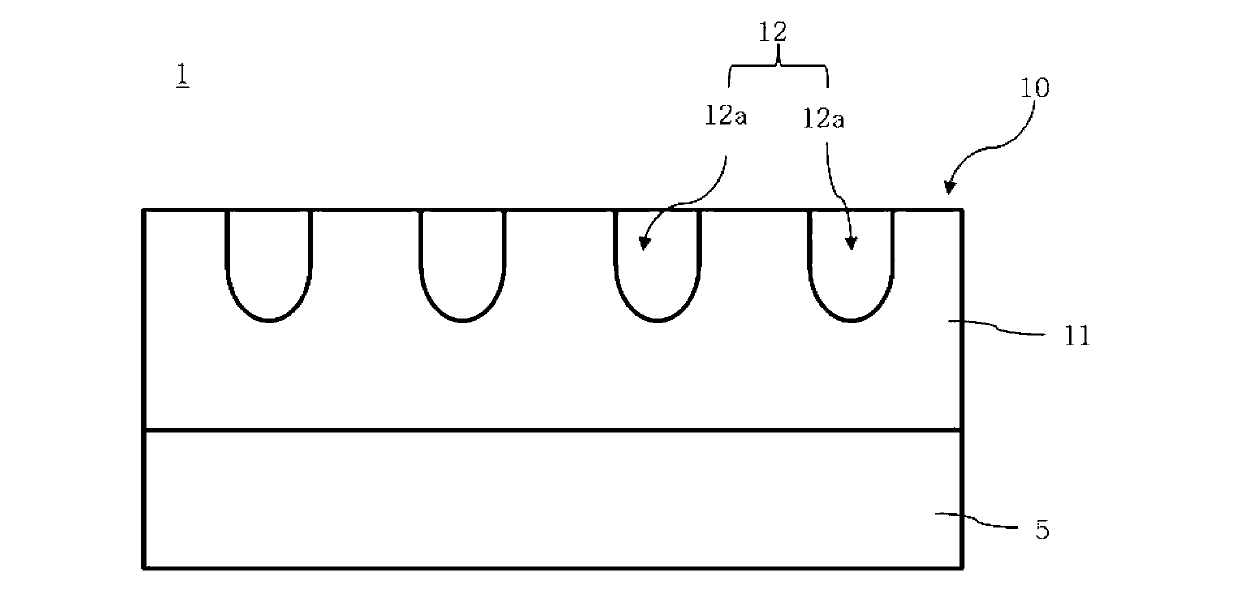

Display device and method of manufacturing the same

PendingUS20180175310A1Increase stiffnessModulus of elasticityFinal product manufactureDigital data processing detailsDisplay deviceComputer science

A display device includes a reinforced substrate; and a display layer disposed on the reinforced substrate and configured to display an image, wherein the reinforced substrate includes a first reinforced layer including a flexible region including a plurality of patterns spaced apart from one another; and a first substrate disposed on the first reinforced layer and has flexibility. A modulus of elasticity of the first reinforced layer is greater than a modulus of elasticity of the first substrate.

Owner:SAMSUNG DISPLAY CO LTD

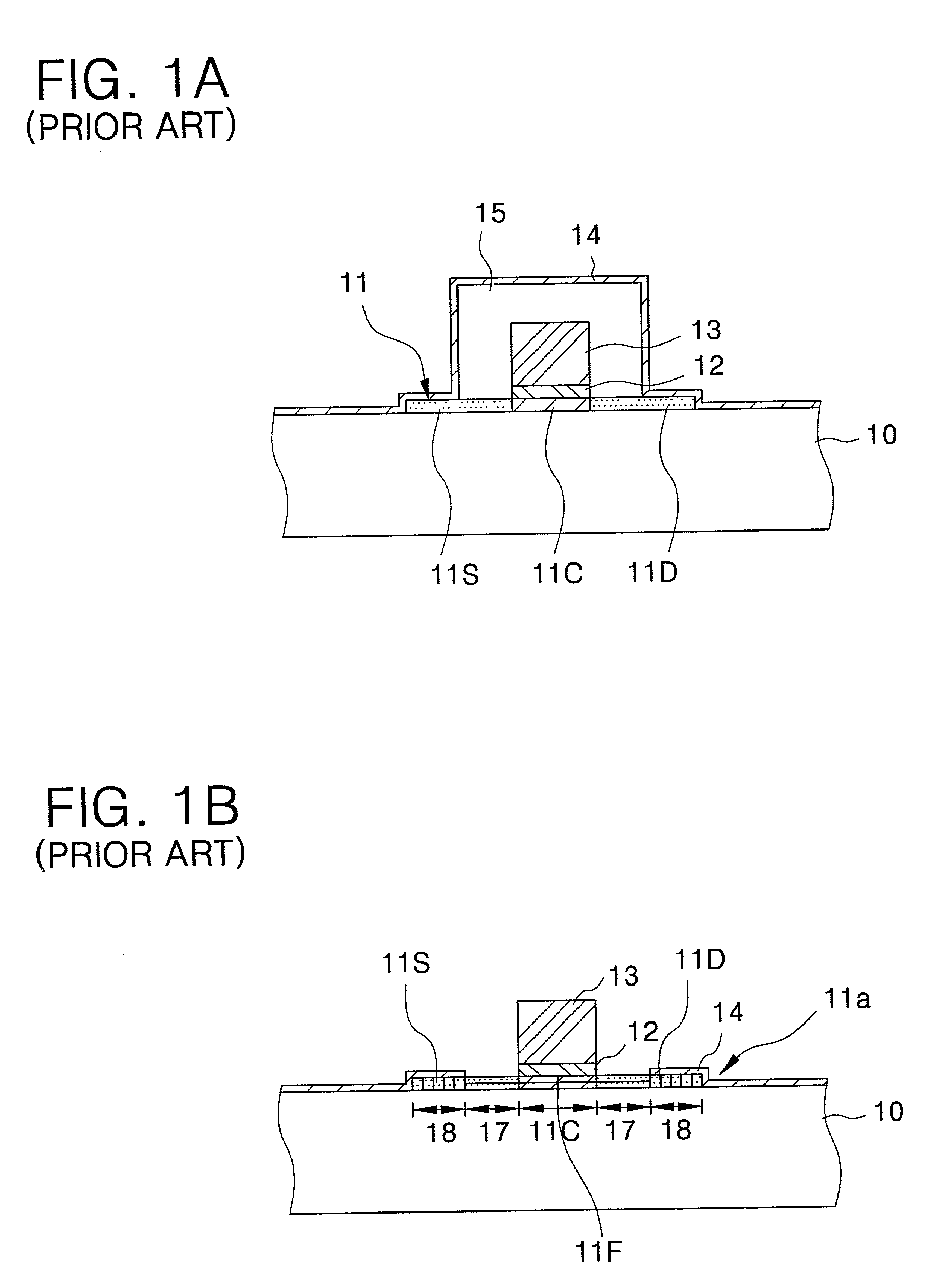

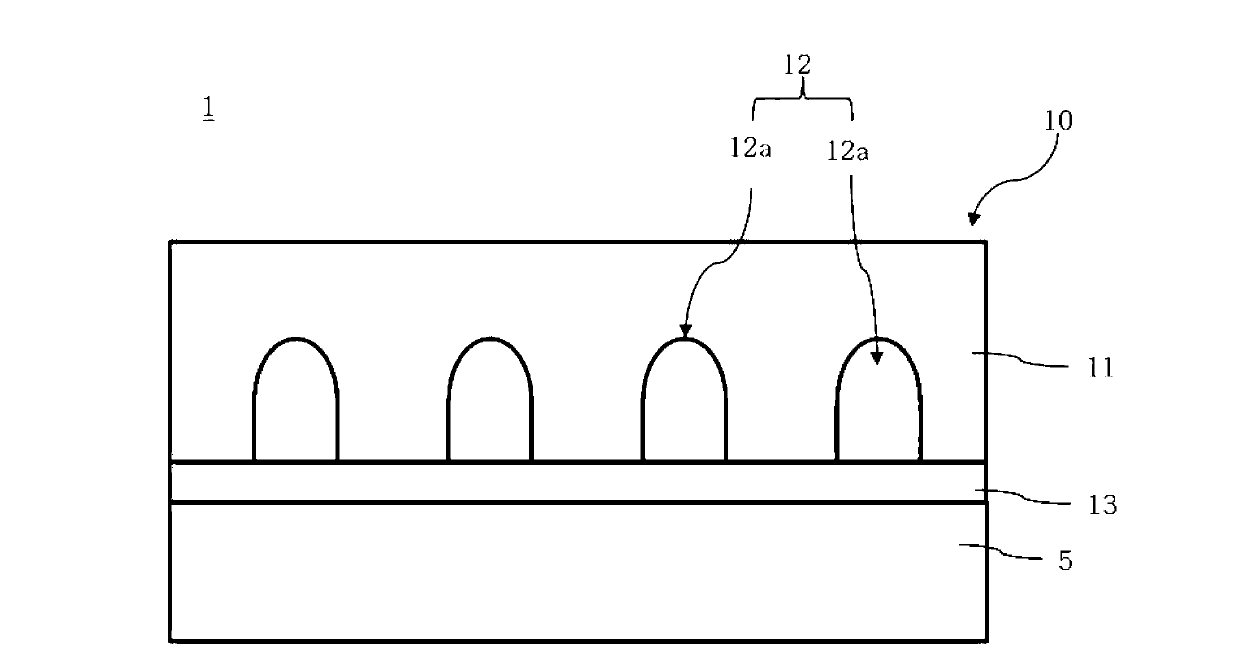

Thin film transistor and method of manufacturing the same

InactiveUS20020146869A1Improve mobilityImprove productivityTransistorSolid-state devicesElectrical conductorMetal-induced crystallization

A method of manufacturing a thin film transistor that provides high electric field mobility is disclosed. The method comprising: a) forming an amorphous silicon layer and a blocking layer on an insulating substrate; b) forming a photoresist layer having first and second photoresist patterns on the blocking layer, the first and second photoresist patterns spaced apart from each other; c) etching the blocking layer using the first photoresist pattern as a mask to form first and second blocking patterns; d) reflowing the photoresist layer, so that the first and second photoresist patterns abut on each other to entirely cover the first and second blocking patterns; e) forming a metal layer over the entire surface of the insulating substrate; f) removing the photoresist layer to expose the blocking layer and an offset region between the blocking layer and the metal layer; g) crystallizing the amorphous silicon layer to form a poly silicon layer, wherein a portion of the amorphous silicon layer directly contacting the first metal layer is crystallized through a metal induced crystallization (MIC), and the remaining portion of the amorphous silicon layer is crystallized through a metal induced lateral crystallization (MILC), so that a MILC front exists on a portion of the poly silicon layer between the first and second blocking patterns; h) etching the poly silicon layer using the first and second blocking patterns as a mask to form first and second semiconductor layers and to remove the MILC front; and i) removing the first and second blocking patterns.

Owner:SAMSUNG DISPLAY CO LTD

Overlay measurement for a double patterning

ActiveUS20130084655A1High sensitivitySemiconductor/solid-state device testing/measurementPhotomechanical apparatusReflectivity measurementErrors measurement

A multi-patterning method of manufacturing a patterned wafer provides test structures designed to enhance overlay error measurement sensitivity for monitoring and process control. One or more patterns are overlaid on a first pattern, each of a given pitch, with the elements interleaved. Test structure is formed with elements of the overlaid patterns spaced away from respective mid-positions more closely toward elements of the first pattern. In some embodiments, test structure elements of the second pattern are overlaid midway between mid-positions of elements of the first pattern and measured by scatterometry. In other embodiments, test structure elements of the second pattern are overlaid at a slightly different pitch than the elements of the first pattern and measured by reflectivity. Measurements are compared with library measurements to identify the error, which may be fed back to control the patterning process. The multi-patterning may be formed by LELE, LLE, LFLE, or other methods.

Owner:TOKYO ELECTRON LTD

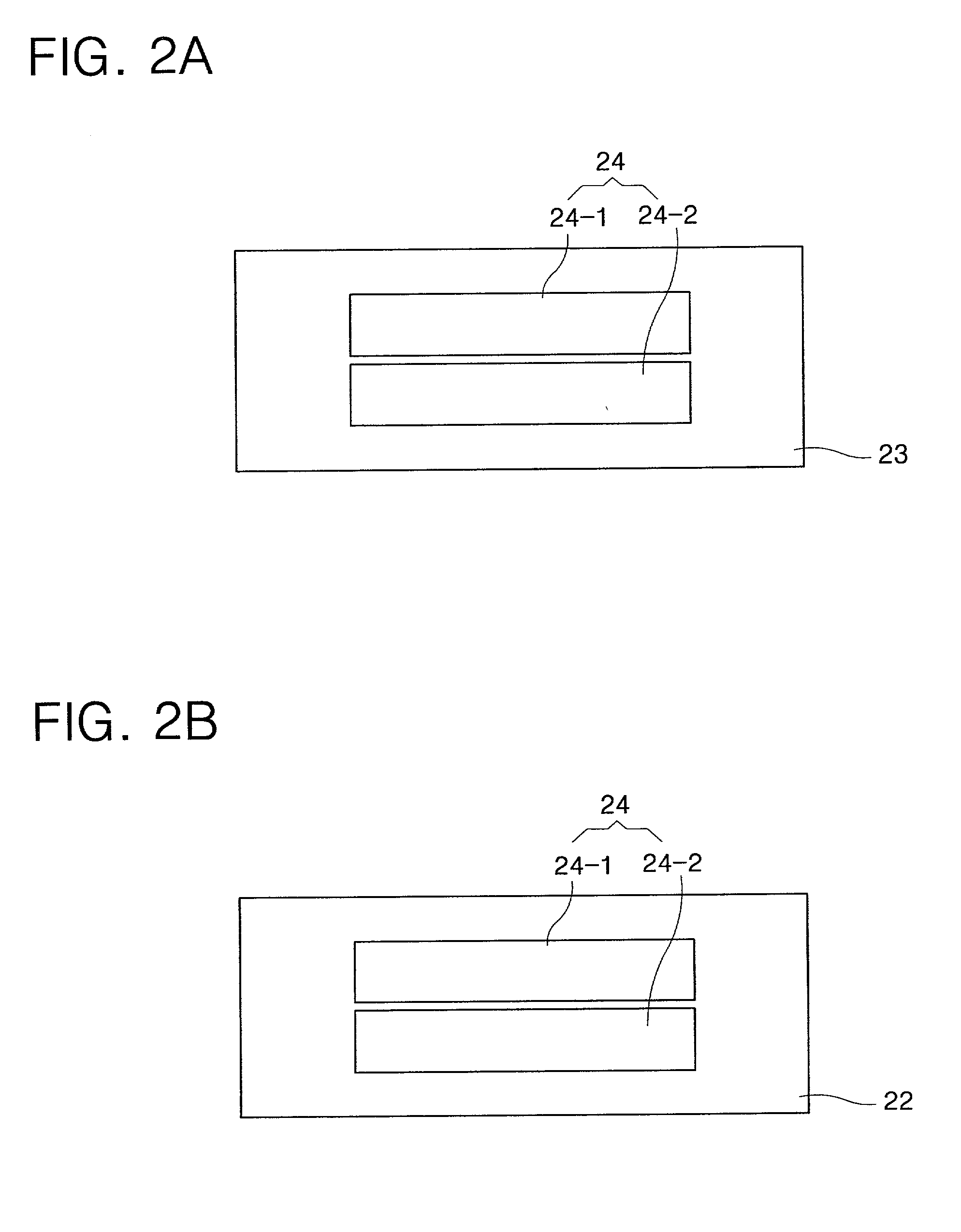

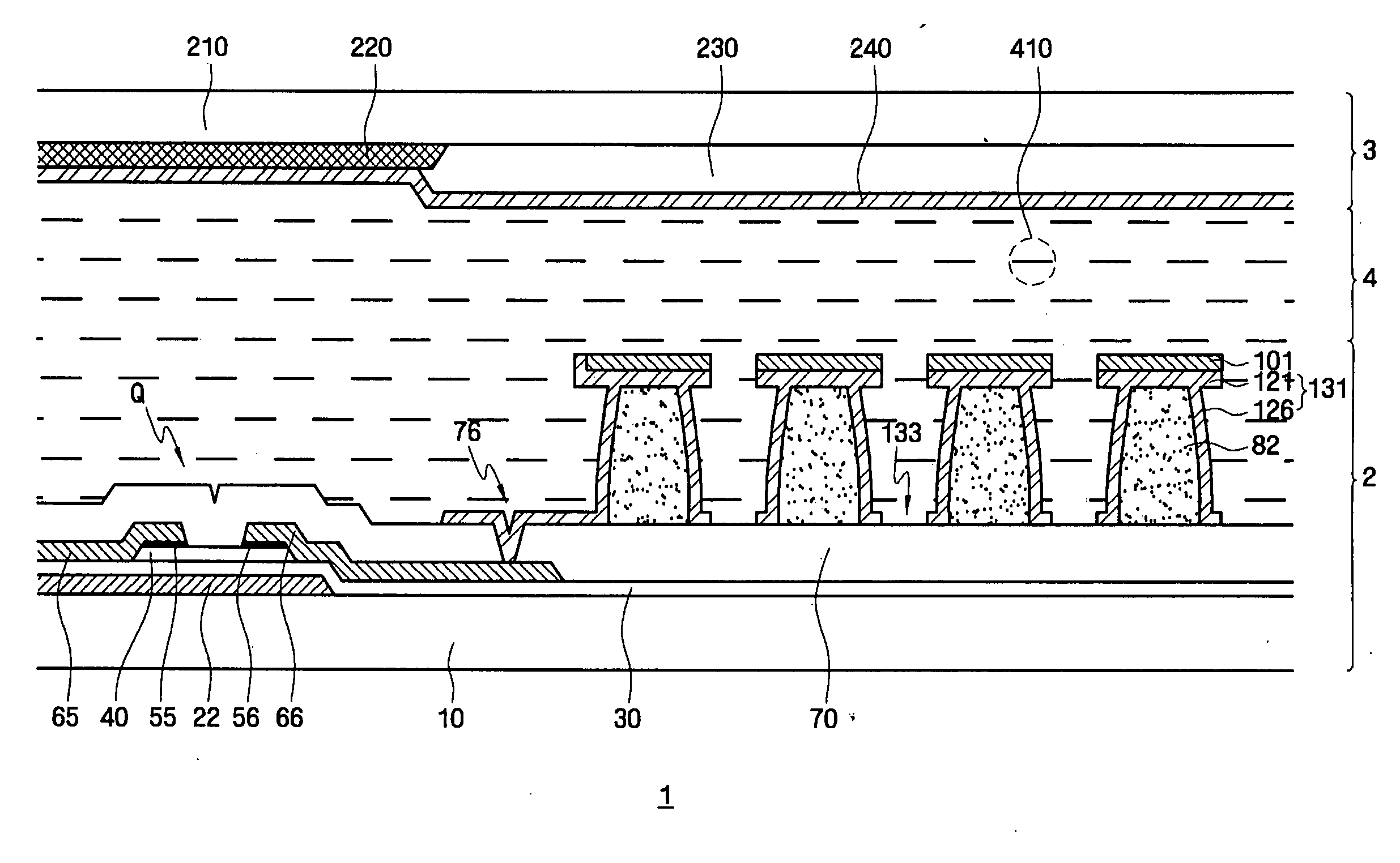

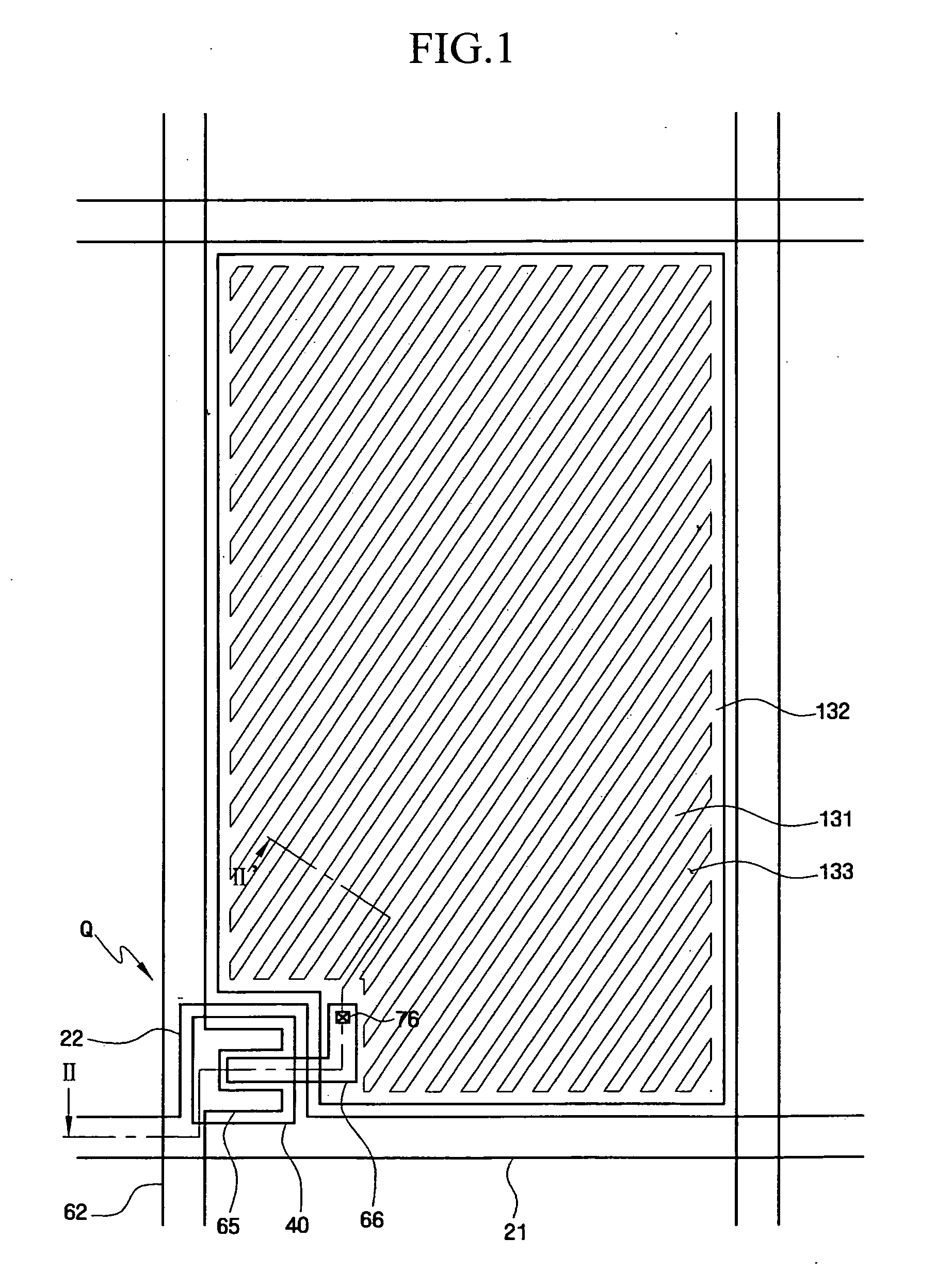

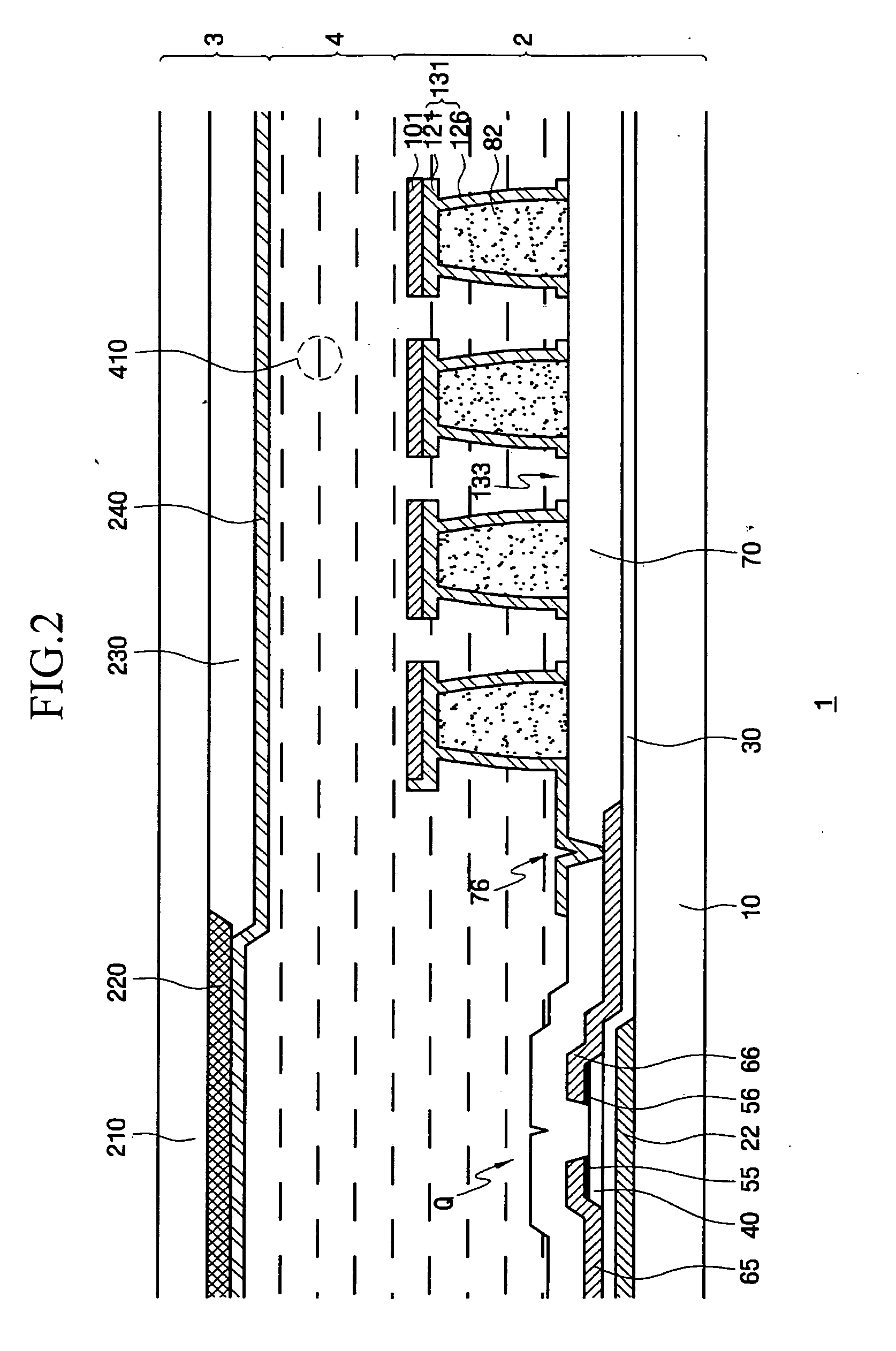

Liquid crystal display device and method of manufacturing the same comprising a plurality of seal patterns between a plurality of supporting patterns and a plurality of compensating patterns disposed below and aligned with the plurality of supporting patterns

A liquid crystal display device includes a first substrate having a first region and a second region, wherein the second region surrounds the first region, a plurality of patterned spacers over the first substrate in the first region, a plurality of supporting patterns spaced apart from each other over the first substrate in the second region, a seal pattern in the second region including the plurality of supporting patterns, a second substrate spaced apart from and attached to the first substrate by the seal pattern, and a liquid crystal layer between the first and second substrates.

Owner:LG DISPLAY CO LTD

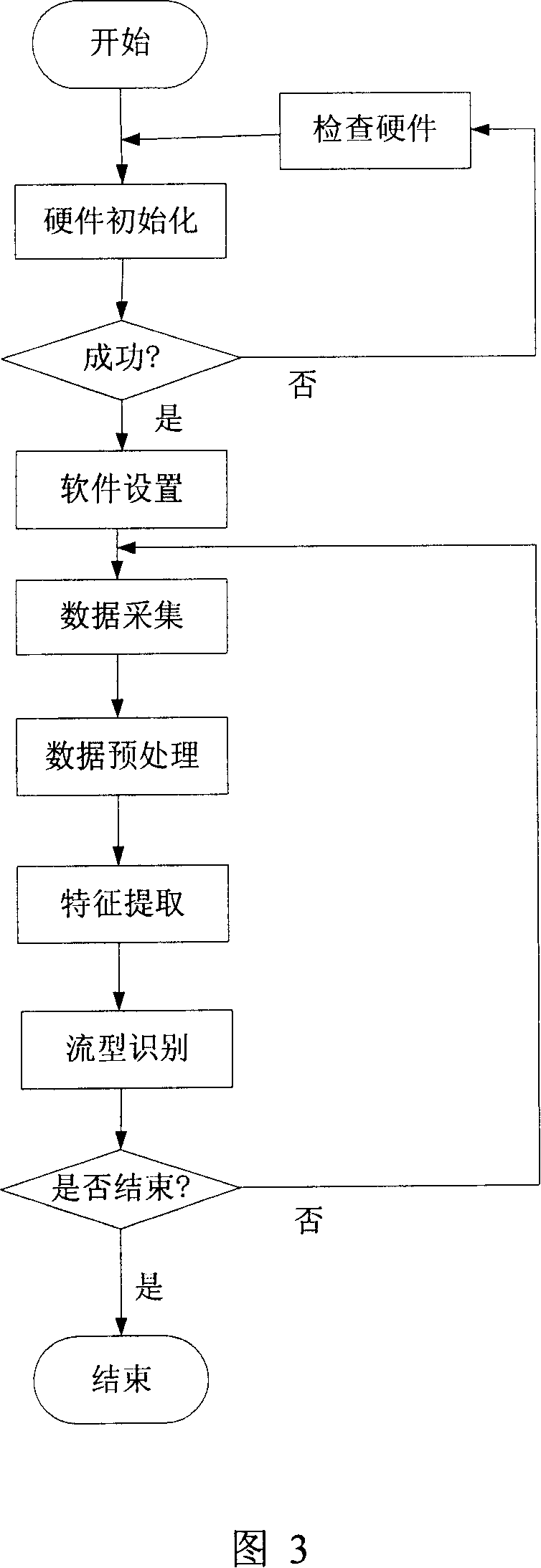

Gas-liquid two-phase flow type recognition method based on digital graphic processing technique

InactiveCN101140216ARealize non-contact measurementClear stream imageFlow propertiesCharacter and pattern recognitionCharacteristic spaceRough set

The invention relates to a gas-liquid two-phase flow pattern recognition method based on digital image processing technology, which is characterized in that the method uses a high-speed camera to gain the gas-liquid two-phase flow image in a horizontal pipeline under the different working conditions; the characteristics of invariant moment and gray level co-occurrence matrix of the image are extracted by the image processing technology; the characteristic fusion is implemented by using a rough set theory to reduce the characteristic dimensions, and the characteristic vector forms a flow pattern sample to implement the training for a support vector machine in order to complete the mapping from the characteristic space to the flow pattern space and finally realize the flow pattern recognition. The adopted rough set theory fuses image texture information and shape information, improves the recognition precision of a classifier, simultaneously reduces the training time, and can roundly reflect the characteristics of flow pattern image; the dependent degree and the generalization capacity of the flow pattern recognition method of the support vector machine for the sample data are better than the BP neural network; the invention has the shorter training time, and is applied to the flow pattern online recognition.

Owner:NORTHEAST DIANLI UNIVERSITY

Thin film transistor and method of manufacturing the same

InactiveUS6706573B2Improve mobilityImprove productivityTransistorSolid-state devicesElectrical conductorMetal-induced crystallization

A method of manufacturing a thin film transistor that provides high electric field mobility is disclosed. The method comprising: a) forming an amorphous silicon layer and a blocking layer on an insulating substrate; b) forming a photoresist layer having first and second photoresist patterns on the blocking layer, the first and second photoresist patterns spaced apart from each other; c) etching the blocking layer using the first photoresist pattern as a mask to form first and second blocking patterns; d) reflowing the photoresist layer, so that the first and second photoresist patterns abut on each other to entirely cover the first and second blocking patterns; e) forming a metal layer over the entire surface of the insulating substrate; f) removing the photoresist layer to expose the blocking layer and an offset region between the blocking layer and the metal layer; g) crystallizing the amorphous silicon layer to form a poly silicon layer, wherein a portion of the amorphous silicon layer directly contacting the first metal layer is crystallized through a metal induced crystallization (MIC), and the remaining portion of the amorphous silicon layer is crystallized through a metal induced lateral crystallization (MILC), so that a MILC front exists on a portion of the poly silicon layer between the first and second blocking patterns; h) etching the poly silicon layer using the first and second blocking patterns as a mask to form first and second semiconductor layers and to remove the MILC front; and i) removing the first and second blocking patterns.

Owner:SAMSUNG DISPLAY CO LTD

Polarizer, display substrate, display panel having the same and method of manufacturing the same

ActiveUS20160170261A1Improve lighting efficiencyDecorative surface effectsSolid-state devicesPolarizerWhite area

A display panel includes a light blocking pattern and a polarizer. The light blocking pattern is disposed on a base substrate. A plurality of opening areas is defined based on the light blocking pattern. The polarizer includes a plurality of linear patterns spaced apart from each other. The plurality of opening areas includes a color area transmitting color light and a white area transmitting white light. The polarizer overlaps the color area and the white area.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

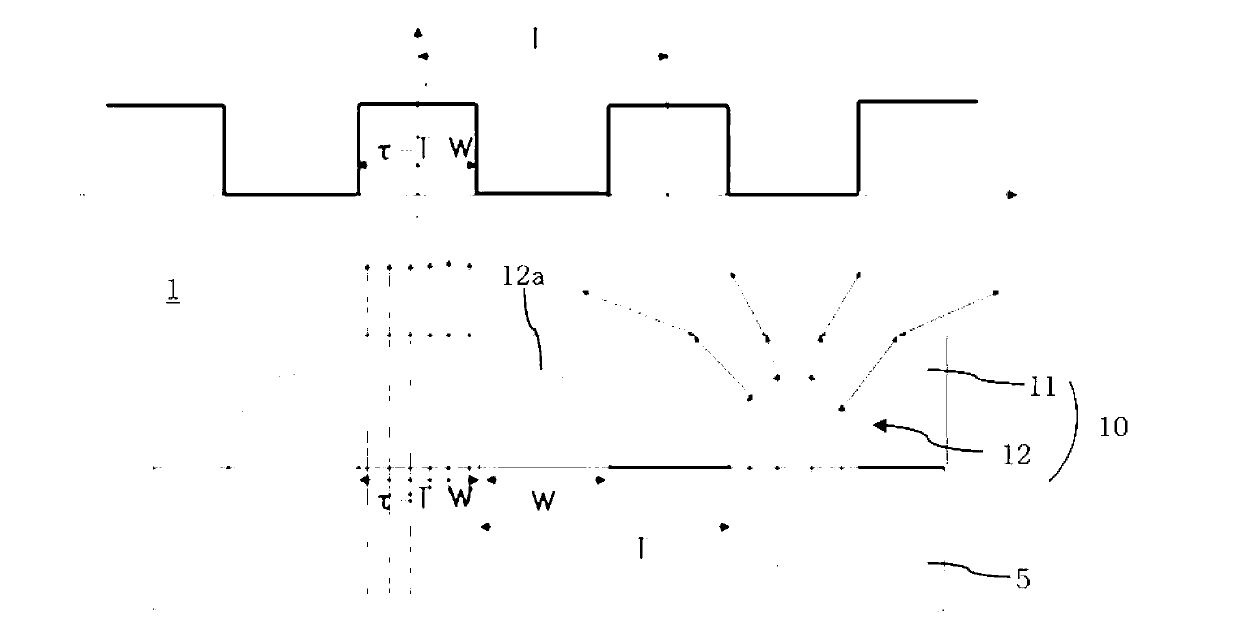

Display device

InactiveCN102809846APreventing Image Quality DeteriorationImprove image qualitySolid-state devicesNon-linear opticsColor shiftDisplay device

A display device that can reduce color shift and prevent the quality of an image from degrading due to Moire. The display device includes a display panel and an optical film, which includes a background layer disposed in front of the display panel, and a lens section formed on the background layer. The lens section has a plurality of patterns spaced apart from each other to diffuse incident light. The spacing [tau] and pitch T of the patterns are determined by the following m value in the following formulae, and m = P / T, p / P is an aperture ratio of sub-pixels of the display panel, [tau] / T is an aperture ratio of the lens section, I is an intensity of light exiting the optical film after being diffused through the sub-pixels, P and p are a pitch and a width of the sub-pixels, T is a pitch of the patterns, and [tau]=T-W.

Owner:SAMSUNG CORNING PRECISION MATERIALS CO LTD

Method of fabricating resistance variable memory device and devices and systems formed thereby

InactiveUS20130040408A1High densityEasy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingLine structureVariable resistance

An exemplary method of forming a variable resistance memory may include forming first source / drain regions in a substrate, forming gate line structures and conductive isolation patterns buried in the substrate with the first source / drain regions interposed therebetween, and forming lower contact plugs on the first source / drain regions. The forming of lower contact plugs may include forming a first interlayer insulating layer, including a first recess region exposing the first source / drain regions adjacent to each other in a first direction, forming a conductive layer in the first recess region, patterning the conductive layer to form preliminary conductive patterns spaced apart from each other in the first direction, and patterning the preliminary conductive patterns to form conductive patterns spaced apart from each other in a second direction substantially orthogonal to the first direction.

Owner:SAMSUNG ELECTRONICS CO LTD

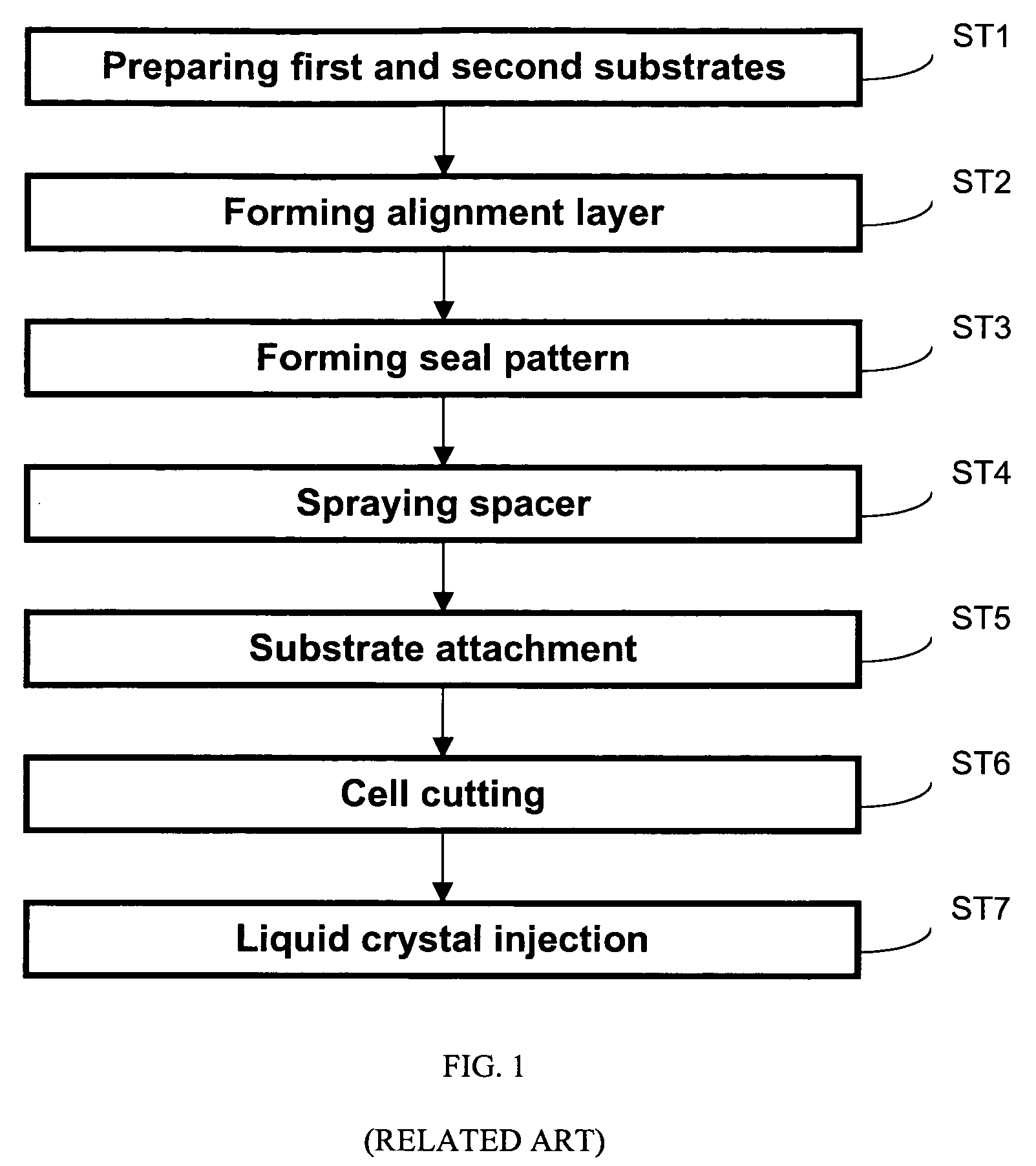

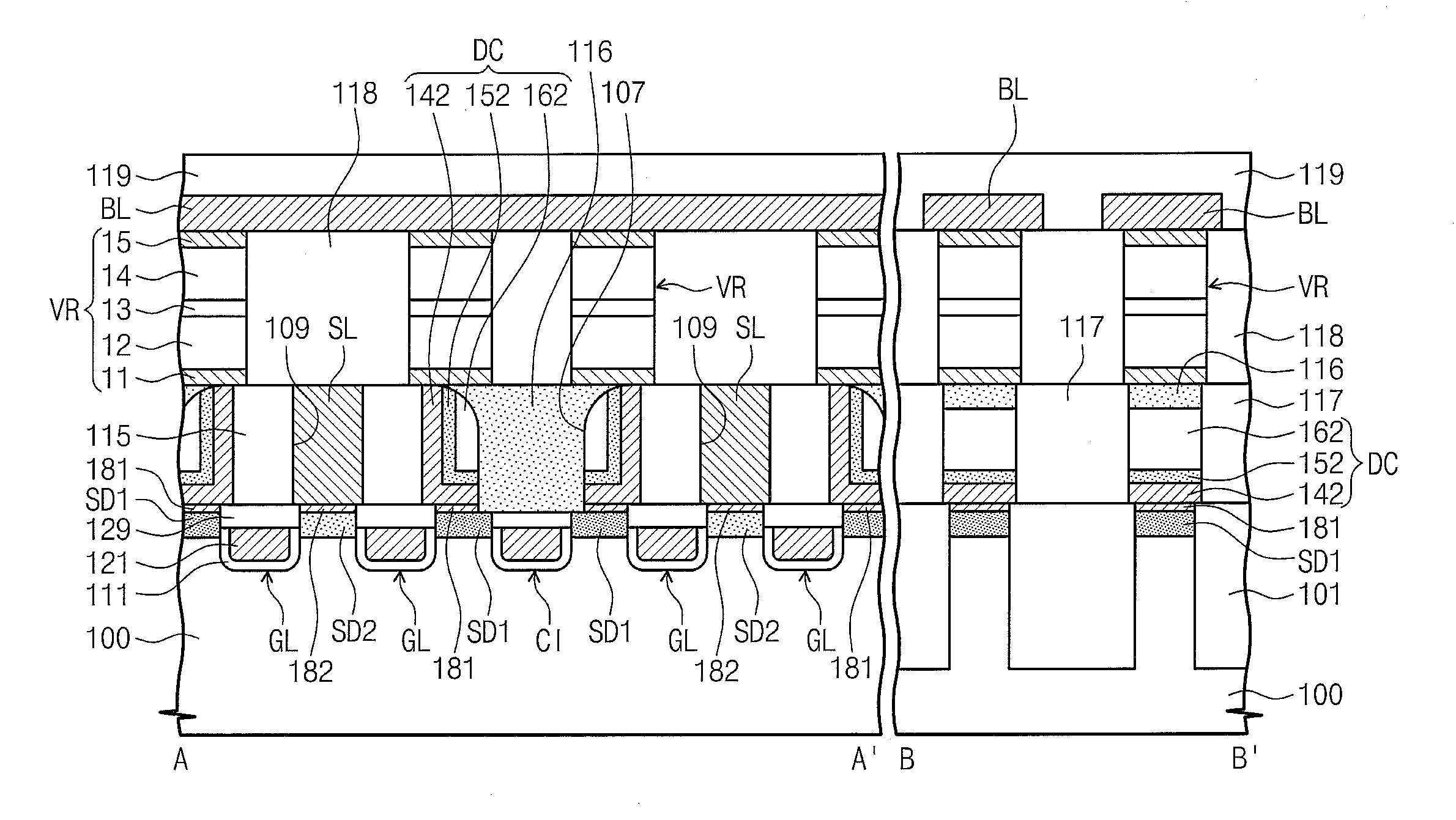

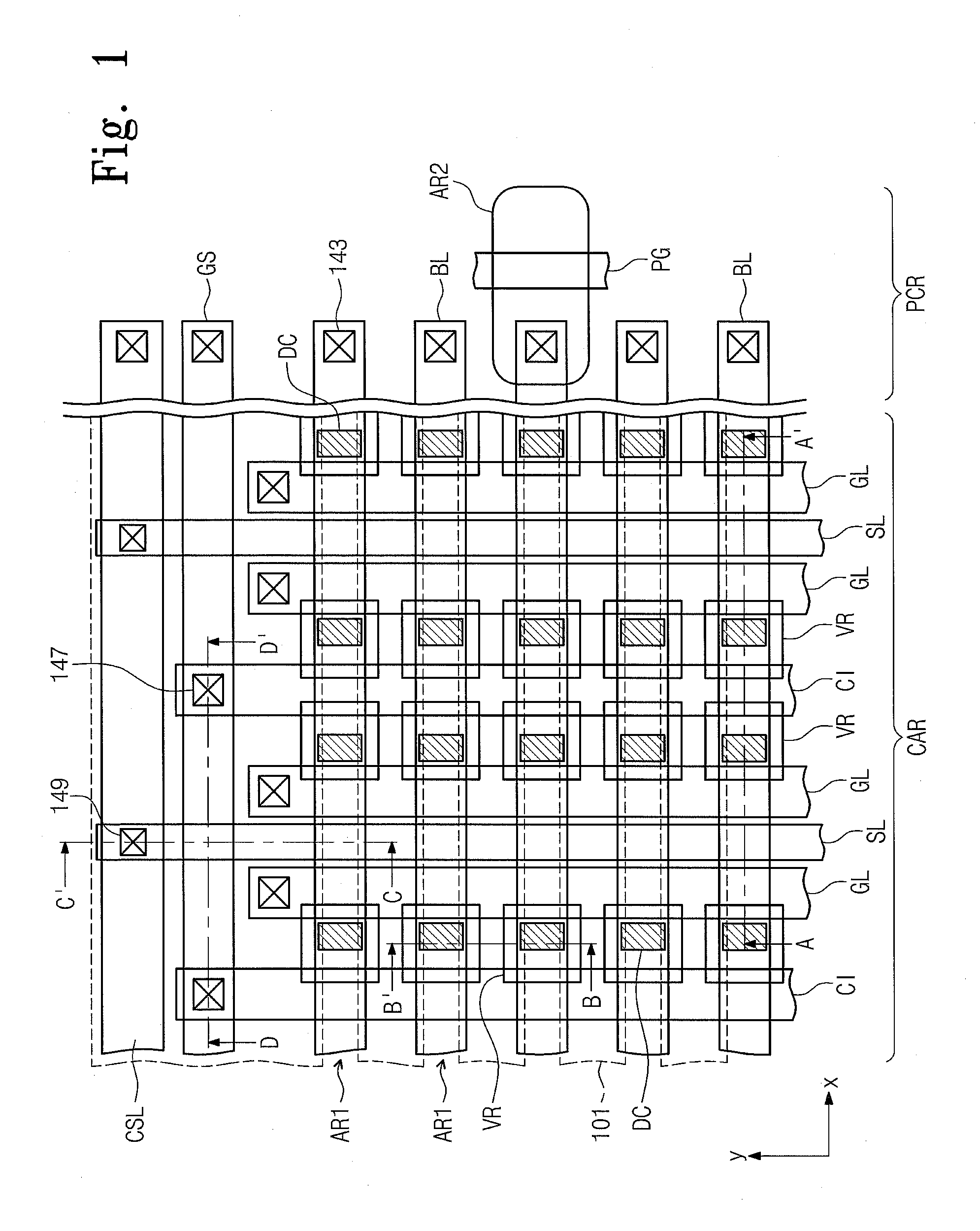

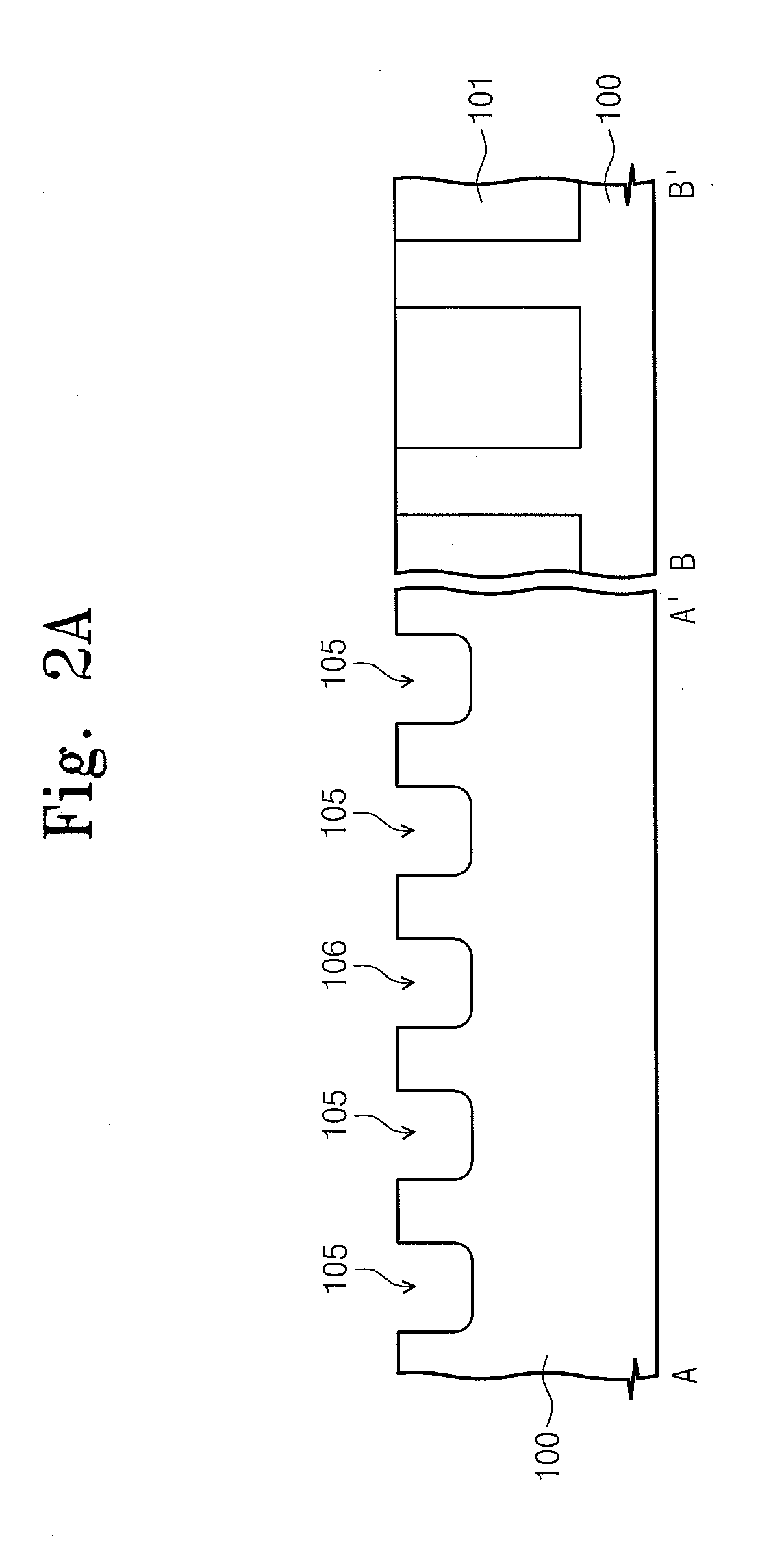

Liquid crystal display and method of fabricating the same

ActiveUS20100091228A1Increase the driving voltageLiquid crystal compositionsNon-linear opticsLiquid-crystal displayEngineering

A liquid crystal display (“LCD”) and a method of fabricating the same are provided. The LCD includes a first insulating substrate, protrusion patterns spaced apart from each other on the first insulating substrate, pixel electrodes disposed on the protrusion patterns and having a cutout between the protrusion patterns, metal patterns disposed on the protrusion patterns and overlapping top surfaces of the protrusion patterns, a second insulating substrate facing the first insulating substrate, and a liquid crystal layer interposed between the first insulating substrate and the second insulating substrate.

Owner:SAMSUNG DISPLAY CO LTD

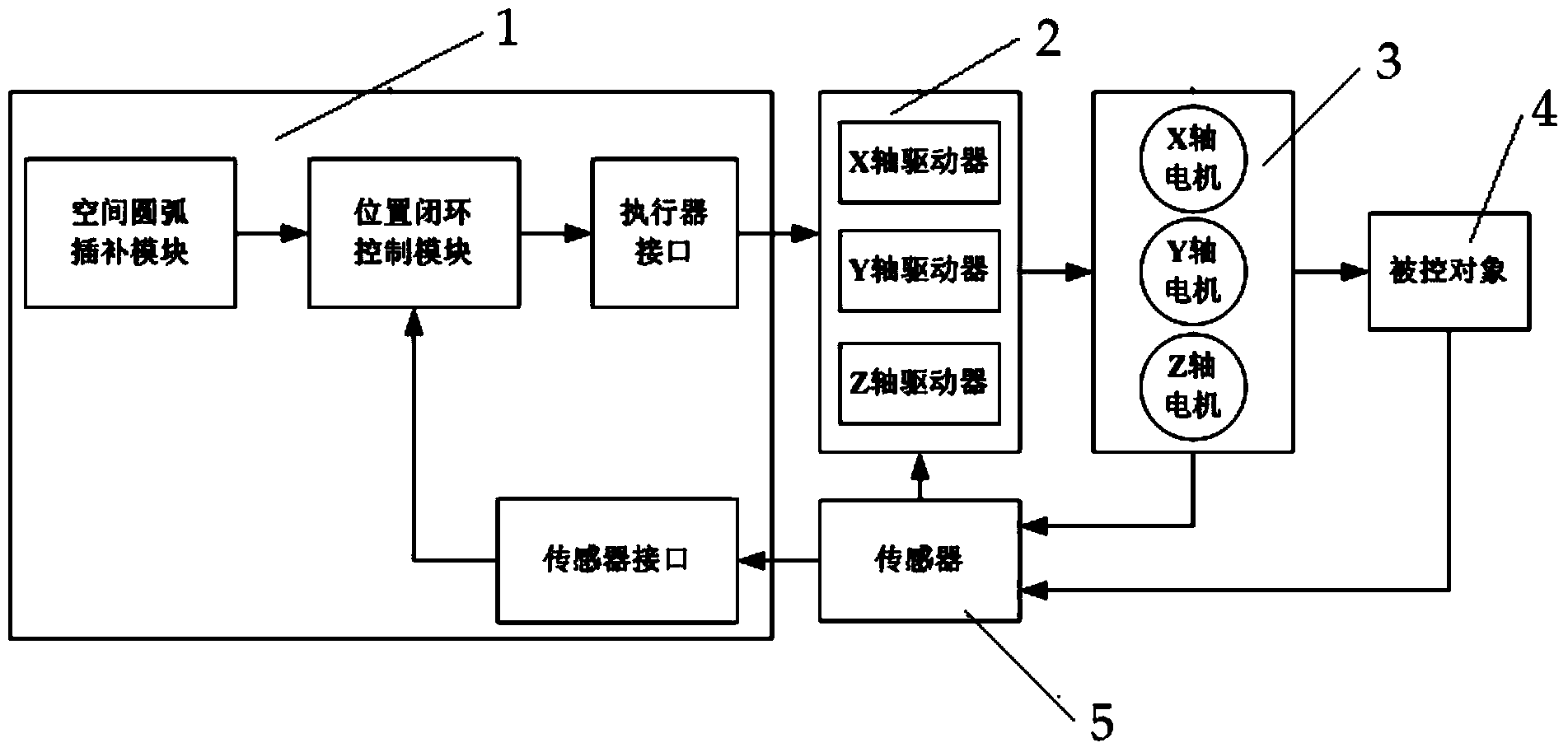

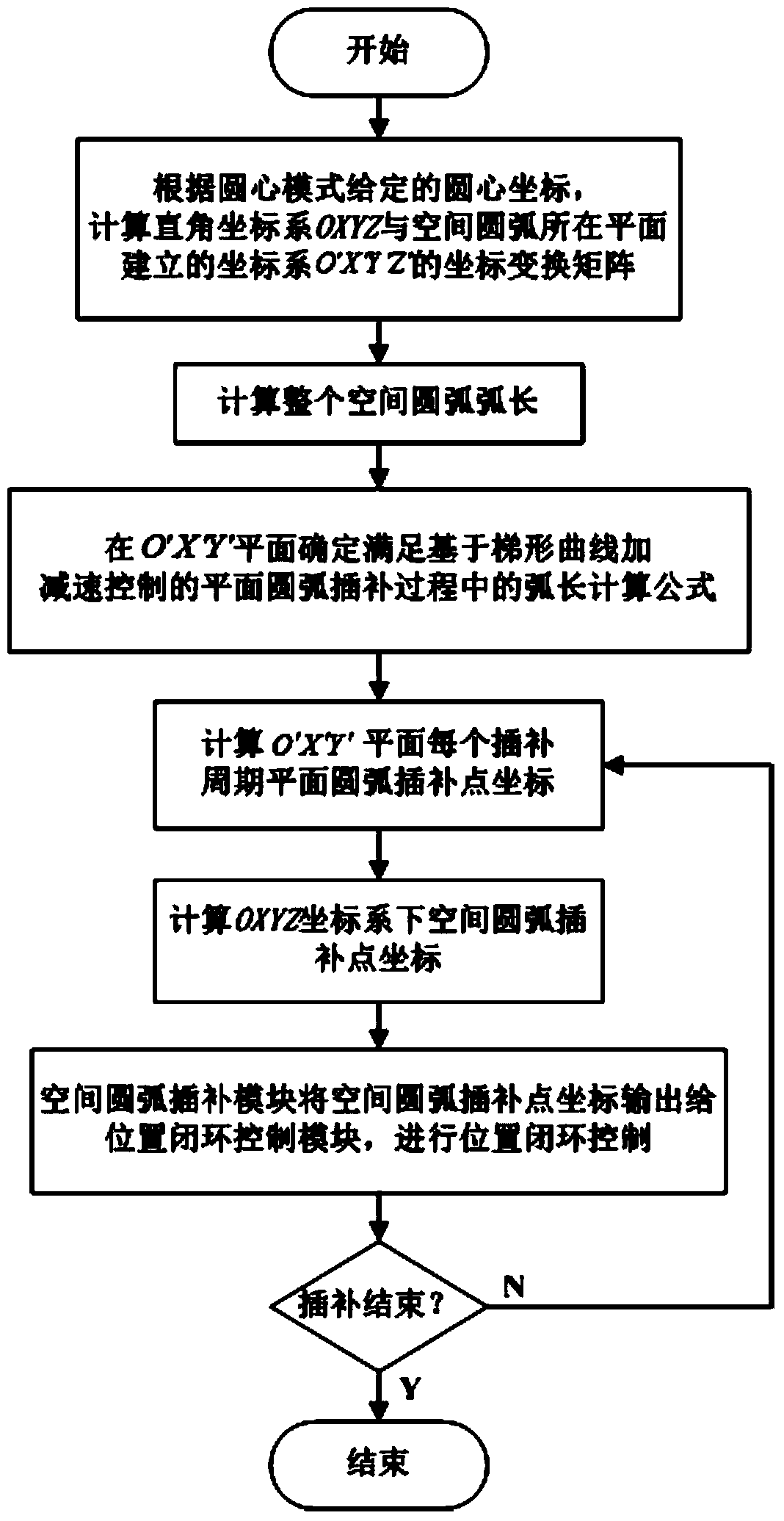

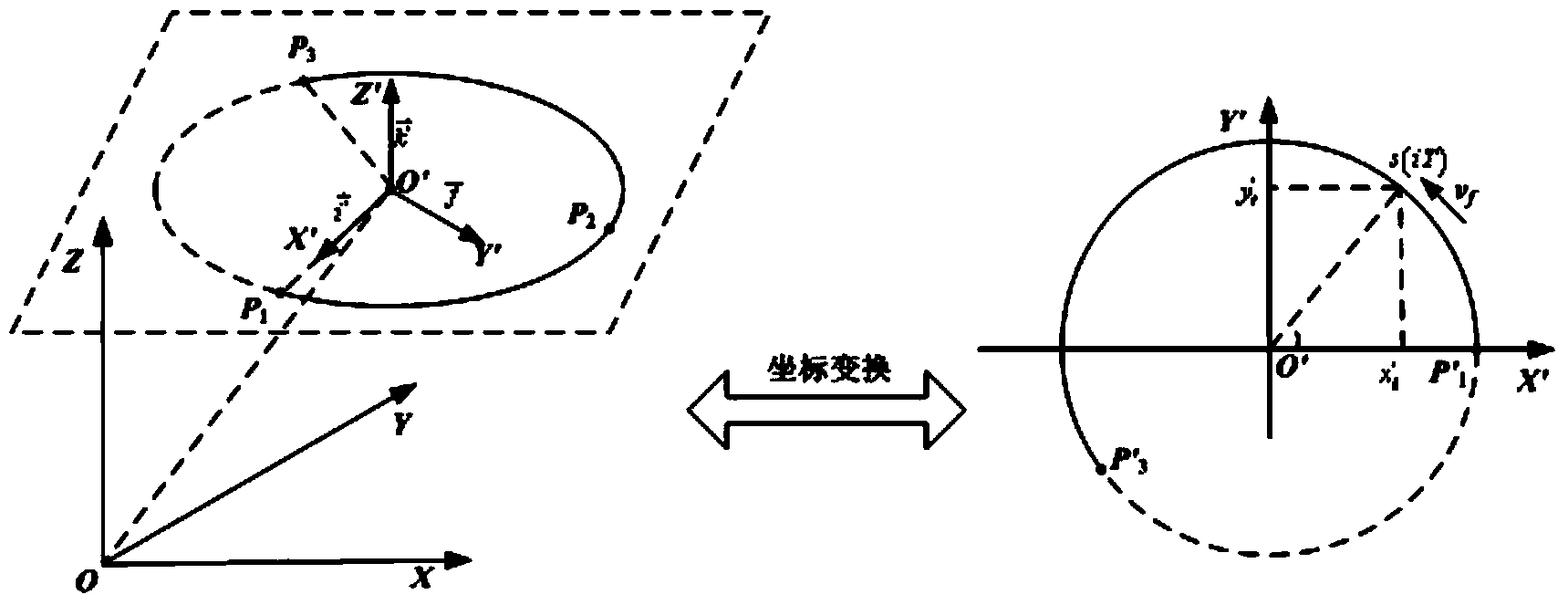

Circle center mode space circular interpolation method applied to motion control system

ActiveCN103676787ASmall amount of calculationImprove computing efficiencyProgramme controlComputer controlLoop controlControl system

The invention relates to a circular interpolation method, in particular to a circle center mode space circular interpolation method applied to a motion control system. The circle center mode space circular interpolation method applied to the motion control system comprises the following steps that a coordinate transformation matrix of a rectangular coordinate system OXYZ and an O'X'Y'Z' coordinate system built in the plane where a space circular arc is located is calculated according to circle center coordinates given by a circle center mode; the length of the whole space circular arc is calculated; an arc length calculation formula satisfying the plane circular arc interpolation process based on trapezoid curve acceleration and deceleration control is determined in an O'X'Y' plane; the coordinates of a plane circular arc interpolation point of each interpolation period in the O'X'Y' plane are calculated; the coordinates of a space circular arc interpolation point under the OXYZ coordinate system are calculated; a space circular arc interpolation module outputs the coordinates of the space circular arc interpolation point to a position closed loop control module to carry out position closed loop control. The circle center mode space circular interpolation method applied to the motion control system reduces the calculation amount of space circular arc parameters, and improves calculation efficiency and interpolation accuracy.

Owner:大连爱智控制系统有限公司

Two-phase fluid flow pattern identification method based on time sequence and neural net pattern identification

InactiveCN1664555AAvoid the influence of human subjective factorsAccurately getFlow propertiesFlags/bannersFrequency functionData treatment

The invention relates to a method for identifying the flow pattern of the two-phase, which combines the nerval net pattern identifying technology with the traditional time series frequency function statistical method and identifies on line, real time and automatically. The method comprise the following steps: a)processing the flow parameter time series of different flow pattern and getting the characteristic parameters of the frequency function of different flow pattern, b) setting the characteristic parameters as input samples, c) mapping from the measuring space to the flow pattern space by the nerval net identifying technology and identifying the flow pattern.

Owner:SHANGHAI JIAO TONG UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com