Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

43 results about "Overflow flag" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer processors, the overflow flag (sometime called V flag) is usually a single bit in a system status register used to indicate when an arithmetic overflow has occurred in an operation, indicating that the signed two's-complement result would not fit in the number of bits used for the operation (the ALU width). Some architectures may be configured to automatically generate an exception on an operation resulting in overflow.

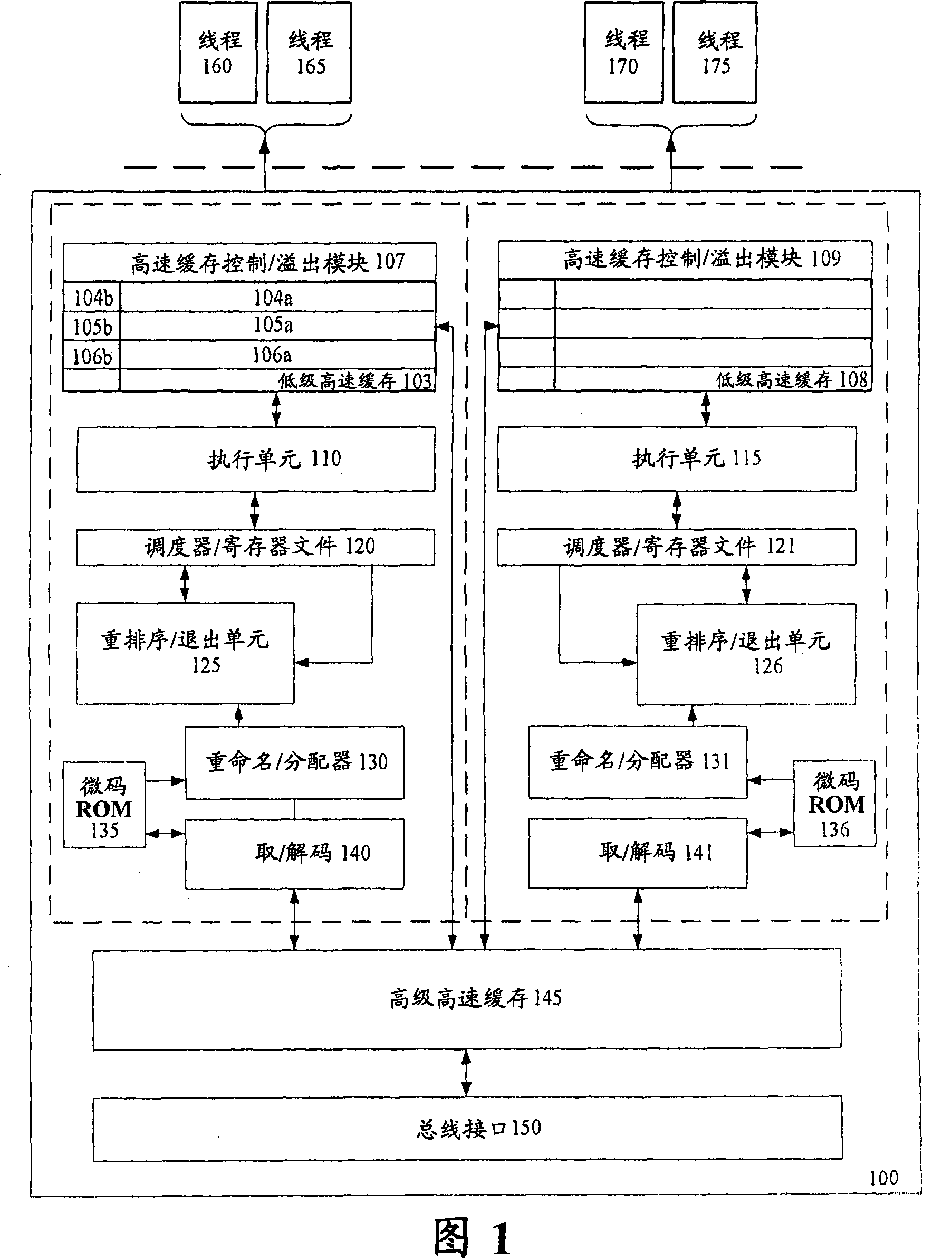

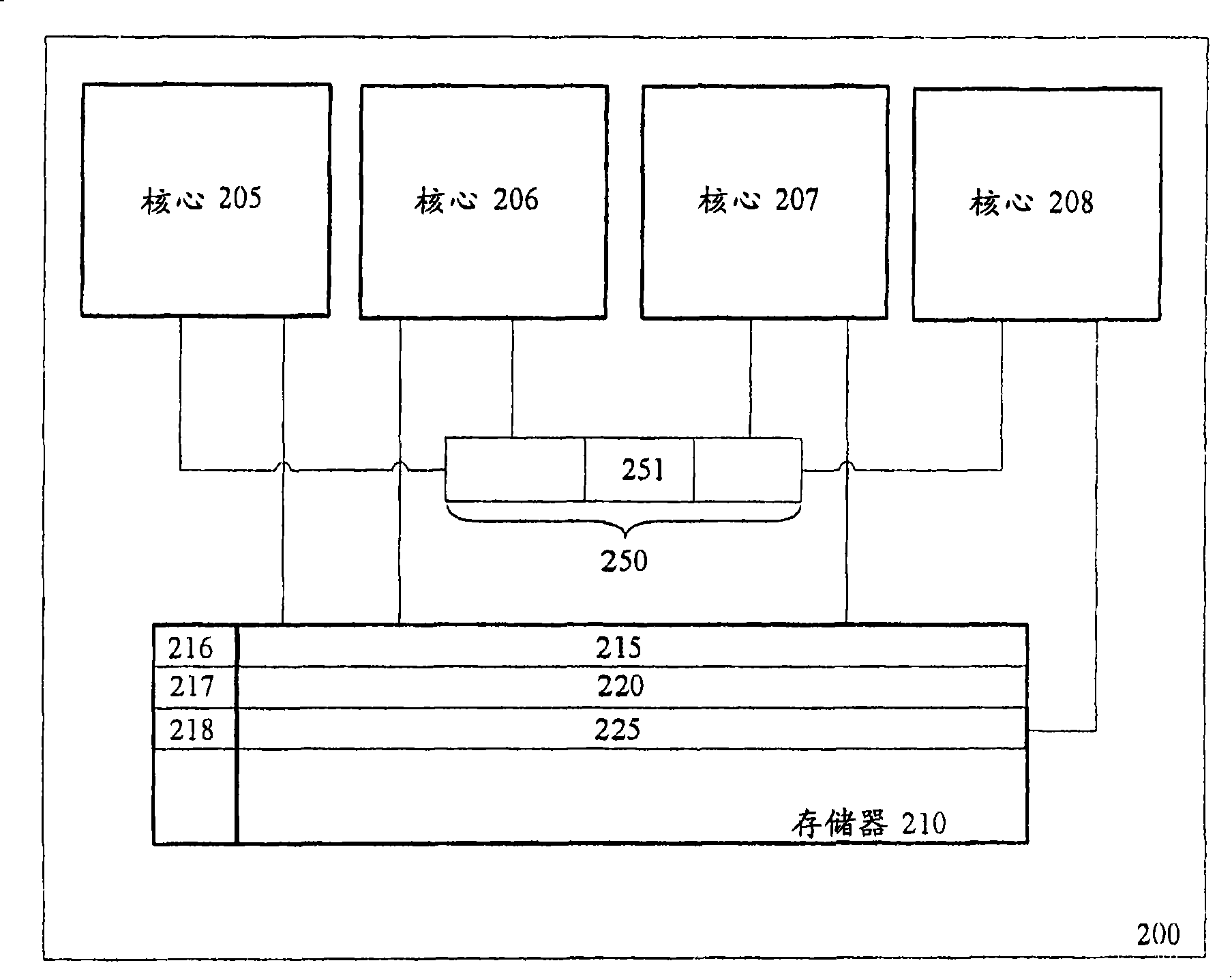

Global overflow method for virtualized transactional memory

InactiveCN101097544AMemory adressing/allocation/relocationMicrocontrol arrangementsVirtualizationParallel computing

A method and apparatus for virtualizing and / or extending transactional memory is described herein. Transactions are executed using local shared transactional memory, such as a cache memory. Upon overflowing the shared transactional memory, the transactional memory is virtualized and / or extended into a higher-level memory, such as a system memory. Upon an overflow event, such as an eviction of a cache line previously accessed during a currently pending transaction, an overflow flag is set to notify processors / cores that the transactional memory is to be virtualized in a global overflow table. A base address of the global overflow table is also potentially stored to reference the base of the global overflow table in the higher-level memory.

Owner:INTEL CORP

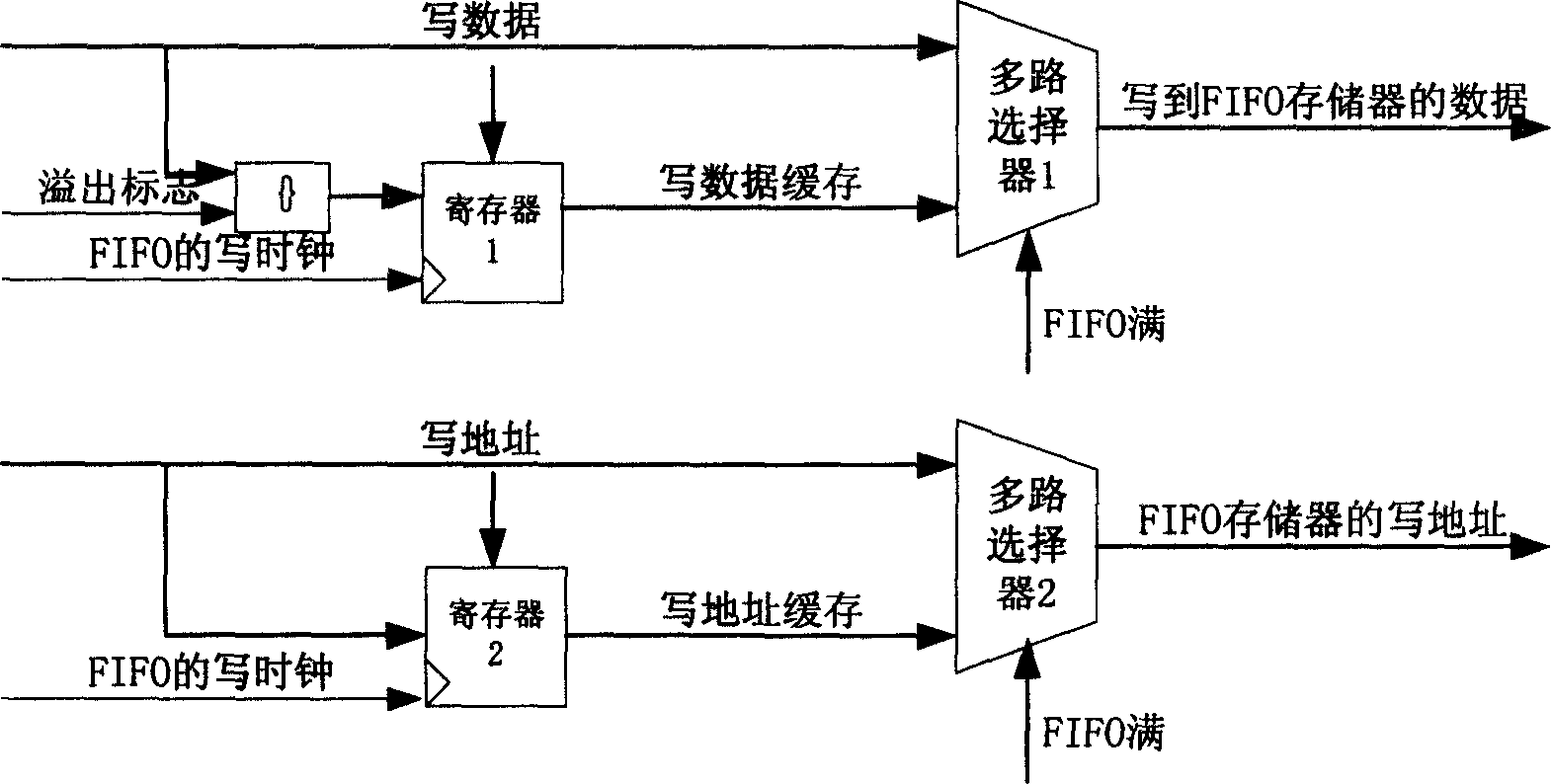

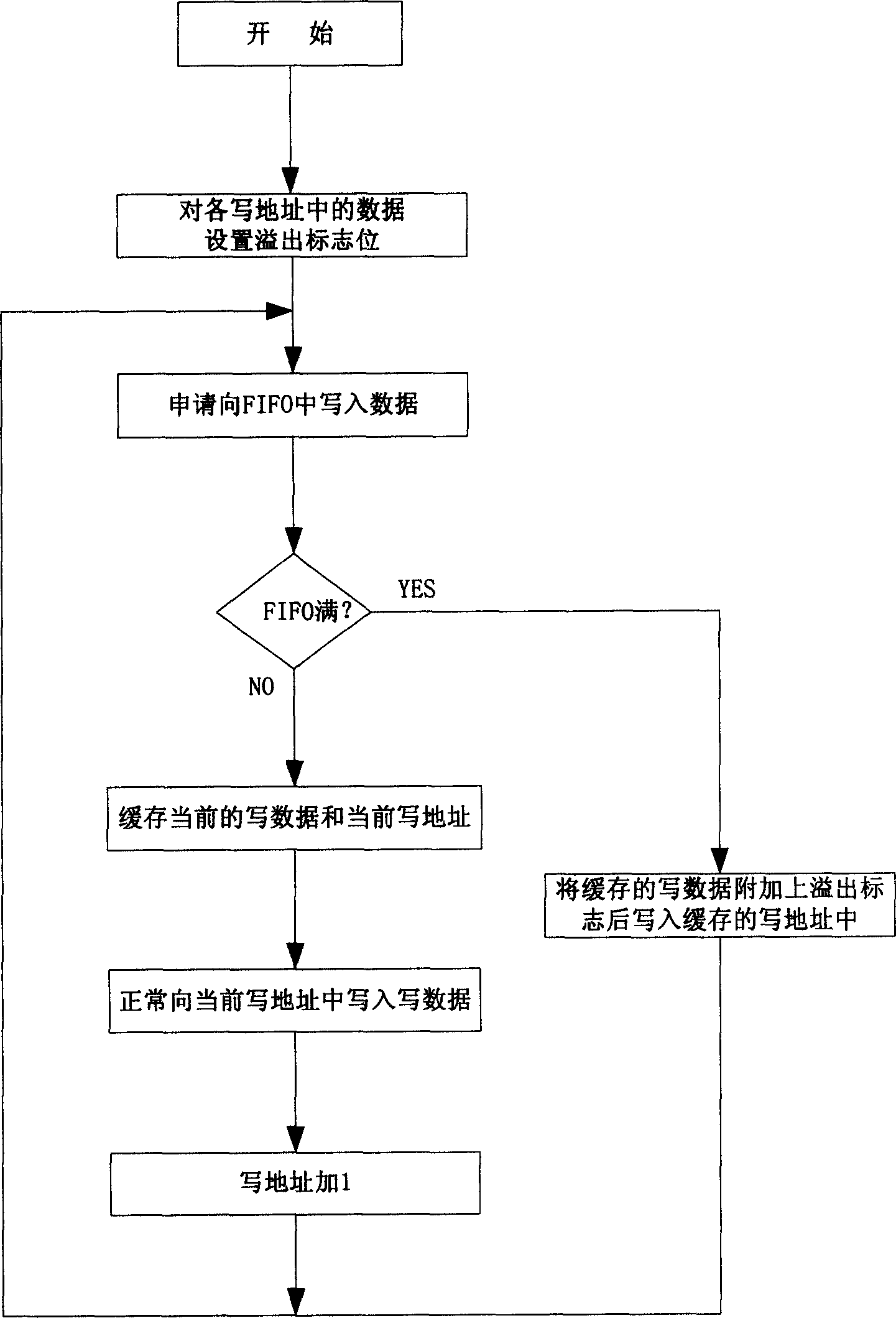

Data handling method of FIFO memory device

InactiveCN1545031AEffective protectionImprove efficiencyUnauthorized memory use protectionFifo memoryComputer science

The invention discloses the data processing method of a FIFO memory, and its kernel ideas: a write module internally buffers write data and address of FIFO, which make the buffered data and address lag the actual ones by a beat, and thus when the overflow occurs, it is able to write the buffered data added with an overflow flag in the position the buffered address points to, accordingly avoiding the data of the current read pointer. It is especially applied to the occasion of using FIFO to store the data with frame structure, able to correct the errors caused by asynchronism and effectively protect the data, furthest enhancing efficiency and utilization ratio of data storage.

Owner:ZTE CORP

Fully digital conference audio mixing apparatus and method

The present invention discloses a fully digital conference audio mixing apparatus and method. Multi-channel audio data which are input is subjected to audio data preprocessing and then are sent to a summation module for summation, so as to obtain a multi-channel audio mixing digital sequence. After the multi-channel audio mixing digital sequence enters a gain adjustment module, the audio gain output is adjusted according to an adjustment factor parameter which is updated in real time. An overflow detection module detects whether overflow appears or not and feeds back an overflow flag to an adaptive adjustment factor calculation module. The adaptive adjustment factor calculation module calculates and updates adjustment factor parameters in real time according to the overflow flag value, and provides them to the gain adjustment module. Therefore, adaptive adjustment characteristics are achieved. The present invention realizes little noise, solves the problem of digital mixing overflow while retaining high sound quality, and has the benefits of high real-time capability and short delay.

Owner:GUANGZHOU BAOLUN ELECTRONICS CO LTD

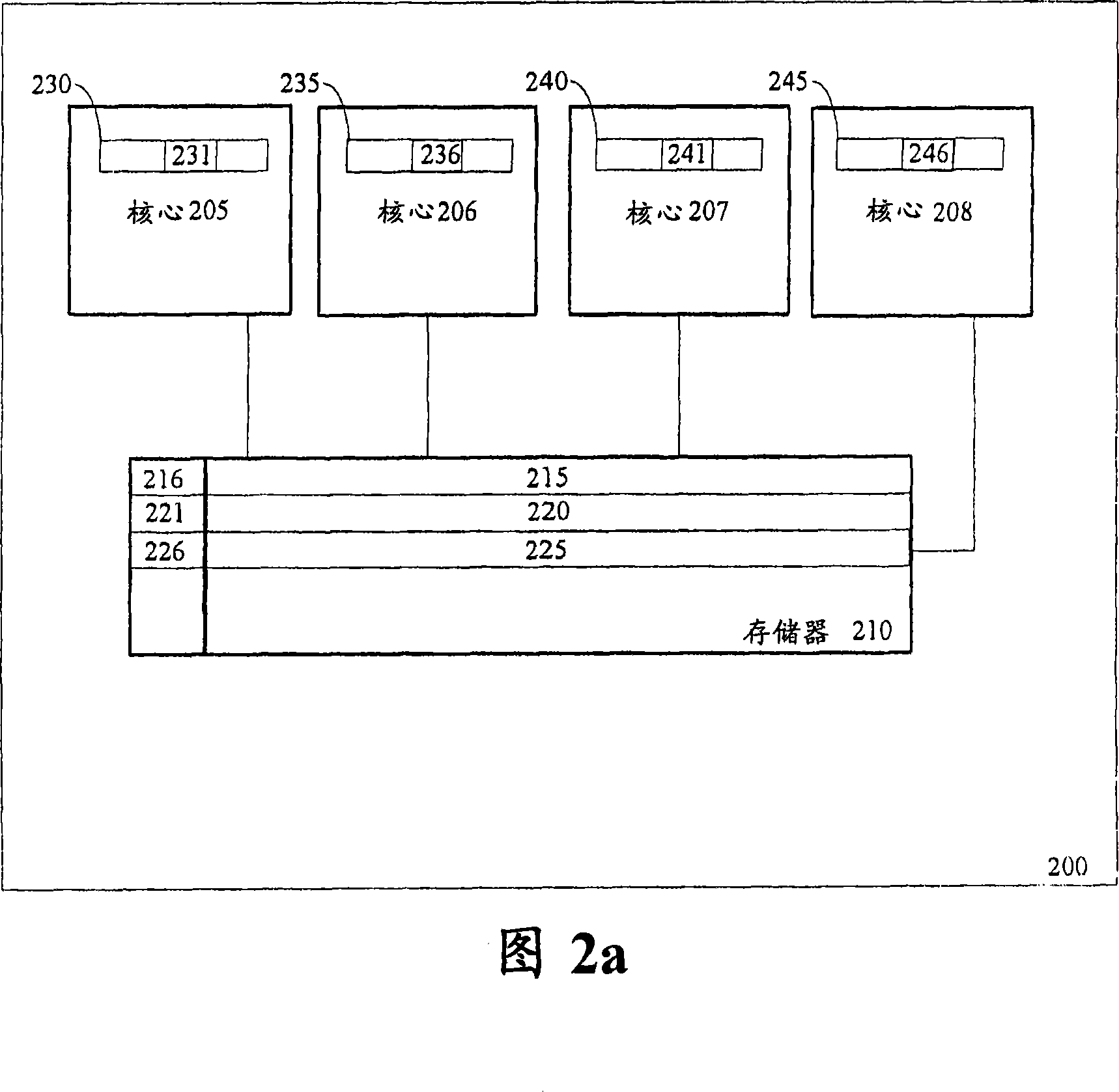

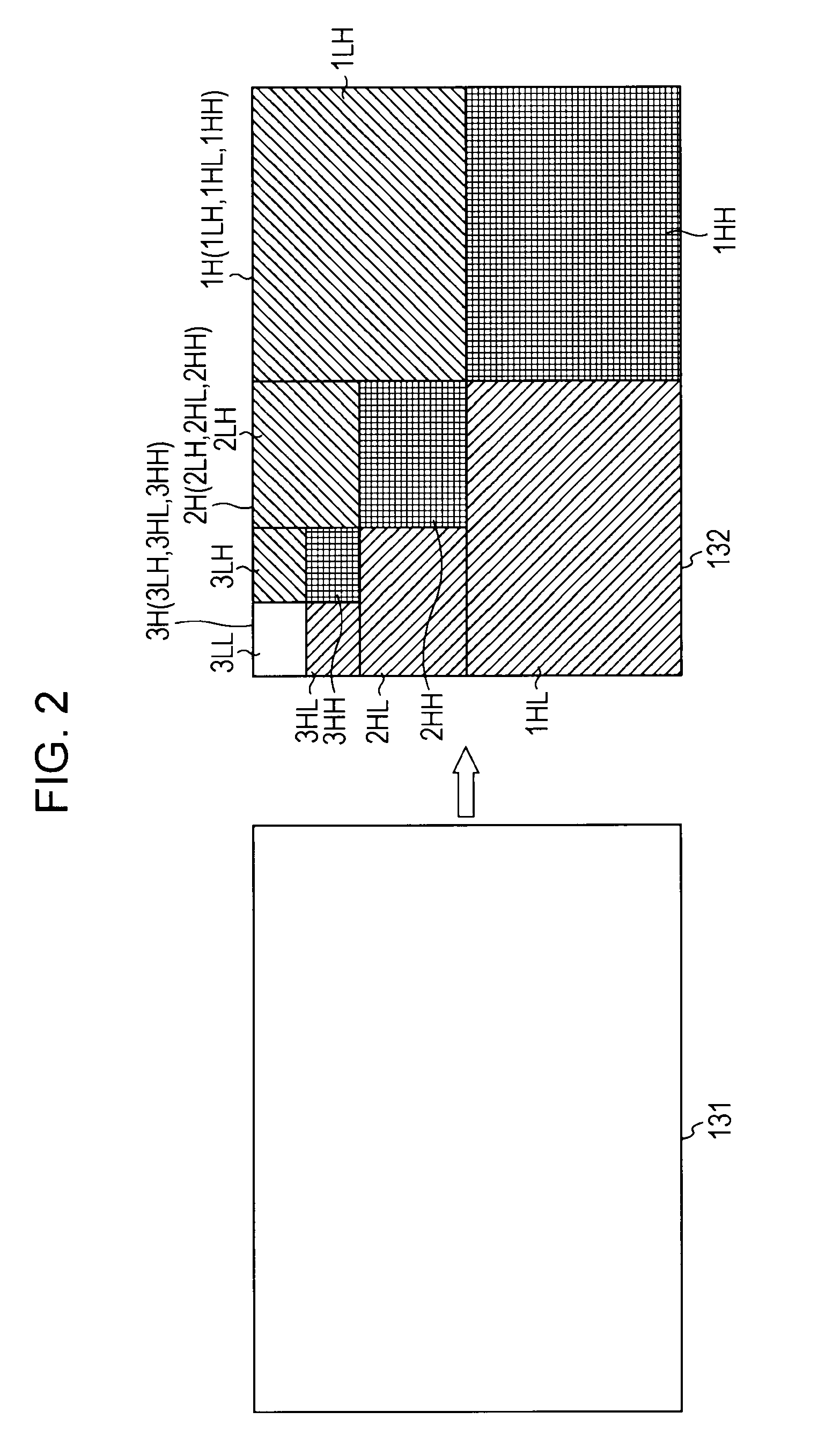

Information processing apparatus and method

InactiveUS20100064091A1Appropriately processedQuality improvementTelevision system detailsMemory adressing/allocation/relocationInformation processingOverflow flag

An information processing apparatus includes bank overflow flag confirming means for confirming whether a bank overflow flag is set, the bank overflow flag notifying the occurrence of a bank-full state where, in a storage area including plural banks formed therein to store data, not-yet-read data is stored in all the banks, read pointer control means for, upon confirming that the bank overflow flag is set, moving a location designated by a read pointer cyclically designating each of the banks as a bank, from which the data is to be read, to a bank positioned next to a bank at a location designated by a write pointer cyclically designating each of the banks as a bank, into which the data is to be written, and reading means for reading the data from the bank designated by the read pointer after the location designated by the read pointer has been updated.

Owner:SONY CORP

Data processor

InactiveUS20080046697A1Avoid dataUndesirable operationProgram initiation/switchingRegister arrangementsData treatmentOverflow flag

Owner:RENESAS TECH CORP

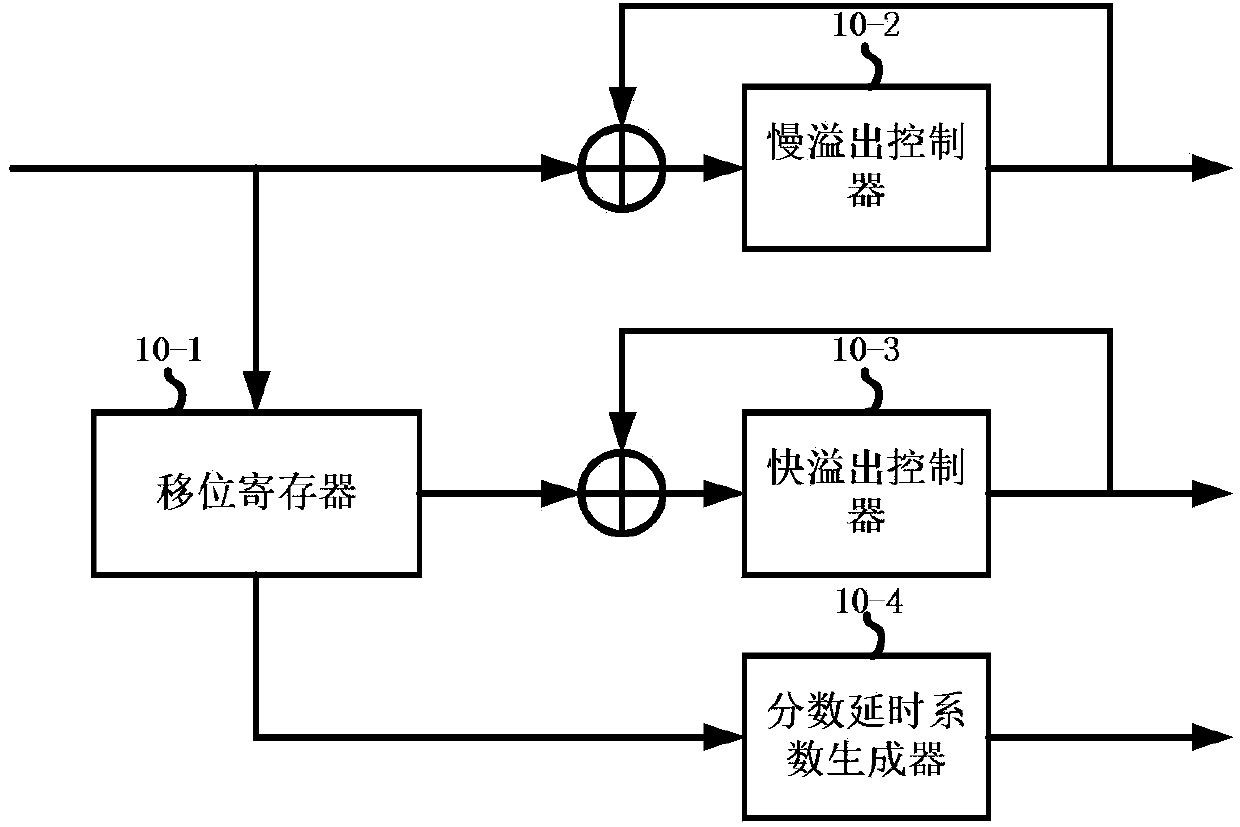

Fractional-multiple interpolation shaping filter and implementation method thereof

ActiveCN104218919ASmart structureSimple interfaceDigital technique networkData synchronizationTime delays

The invention provides a fractional-multiple interpolation shaping filter and an implementation method thereof. The fractional-multiple interpolation shaping filter comprises a data synchronization module, a segmented filtering module, a resampling module and a numerically controlled oscillator control module. The numerically controlled oscillator control module generates a slow overflow flag according to baseband modulation rate input and sends the slow overflow flag to the data synchronization module to generate slow synchronous data output; the slow synchronous data output is processed by the segmented filtering module to generate a filter group output; the filter group output and a fast overflow flag as well as the time delay of a fractional time delay filter are processed by the resampling module to generate shaped filtered data. The fractional-multiple interpolation shaping filter is used for realizing fractional-multiple conversion between a user input rate and the rate after interpolation shaping filtering, and is adaptive to the ksps grade real-time adjustment of the user rate and capable of breaking through the traditional limitation on the user input rate; besides, the fractional-multiple interpolation shaping filter is light and ingenious in structure, simple in interface, and high in flexibility and applicability; the fractional-multiple interpolation shaping filter can be migrated to a programmable logic device or designed into a special integrated circuit, and the variable rate range of the filter can be expanded according to requirements.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

High-precision timing method of 51 singlechip microcomputer

ActiveCN103605279AAchieving high-precision timekeepingFix timing errorsElectric unknown time interval measurementMicrocomputerOverflow flag

The invention relates to a high-precision timing method of a 51 singlechip microcomputer. The method is performed by consecutively reading a timer and appropriately shielding the timer, wherein consecutive two-time value reading of the timer solves timing errors due to lower 8-bit overflow carry-in of the timer; appropriate timer shielding in cooperation with timer overflow flag bit reading solves the timing errors due to lower 16-bit overflow carry-in of the timer, and accordingly high-precision timing of the 51 singlechip microcomputer is achieved. Meanwhile, the high-precision timing method of the 51 singlechip microcomputer is achieved simply through the timer in the 51 singlechip microcomputer instead of external complex timing circuits, thereby being relatively low in cost, simple, easy to achieve and highly practical.

Owner:BEIJING INST OF CONTROL ENG

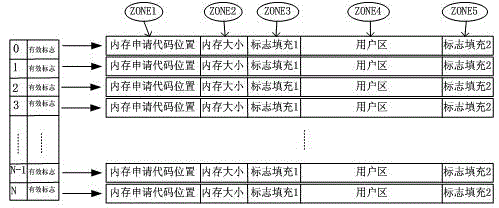

Single-process dynamic storage management method based on Hash table

ActiveCN105094710AImprove debugging efficiencyImprove test efficiencyInput/output to record carriersResource allocationMessage queueIdle time

The present invention discloses a single-process dynamic storage management method based on a Hash table, which comprises: initializing the Hash table; applying for a dynamic memory; releasing the dynamic memory; carrying out real-time routing inspection; creating an empty Hash table; and storing dynamic storage applying information. In the dynamic memory applying process, related information of applying for the memory is stored into the Hash table and overflow flags are set; in the dynamic memory releasing process, the Hash table is searched, the memory is released if related pointers are searched, or an alarm is given; and in the real-time routing inspection and calling process, whether overflow of the dynamic memory exists or not is judged; by checking overflow flag words in memory areas in Hash table nodes one by one, the sizes of all memory spaces in the Hash table are added, the sum of the memory spaces is stored according to the frequency of storing for once at intervals of one hour, and whether the memory overflow risk exists or not is judged. According to the present invention, progress idle time is used to monitor and check the use condition of the dynamic memory in real time, a monitoring result is sent to a frame by a message queue, the frame takes charge of carrying out organizing and providing an inquiring function, and the single-process dynamic storage management method has wide application prospect.

Owner:NARI TECH CO LTD +1

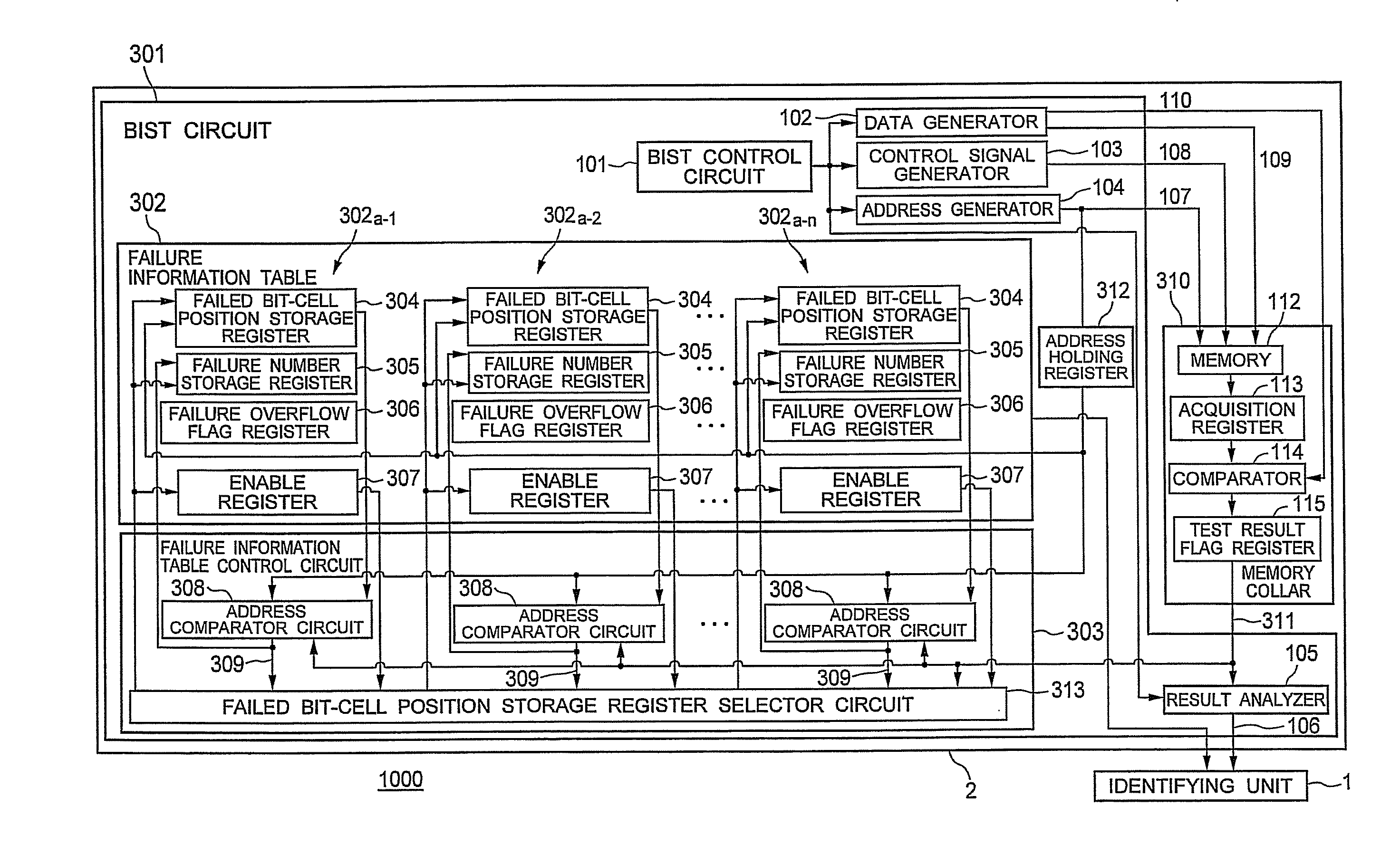

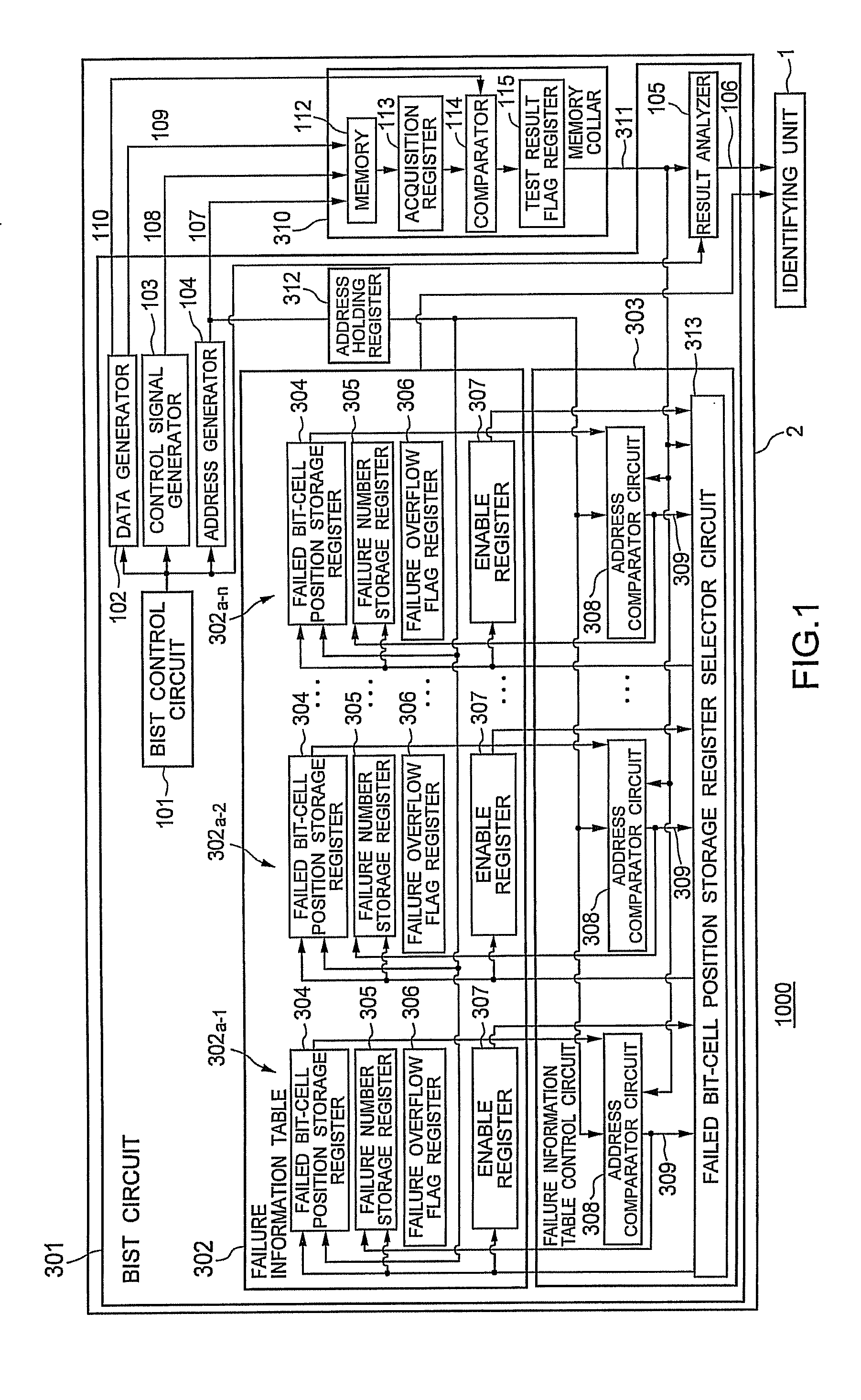

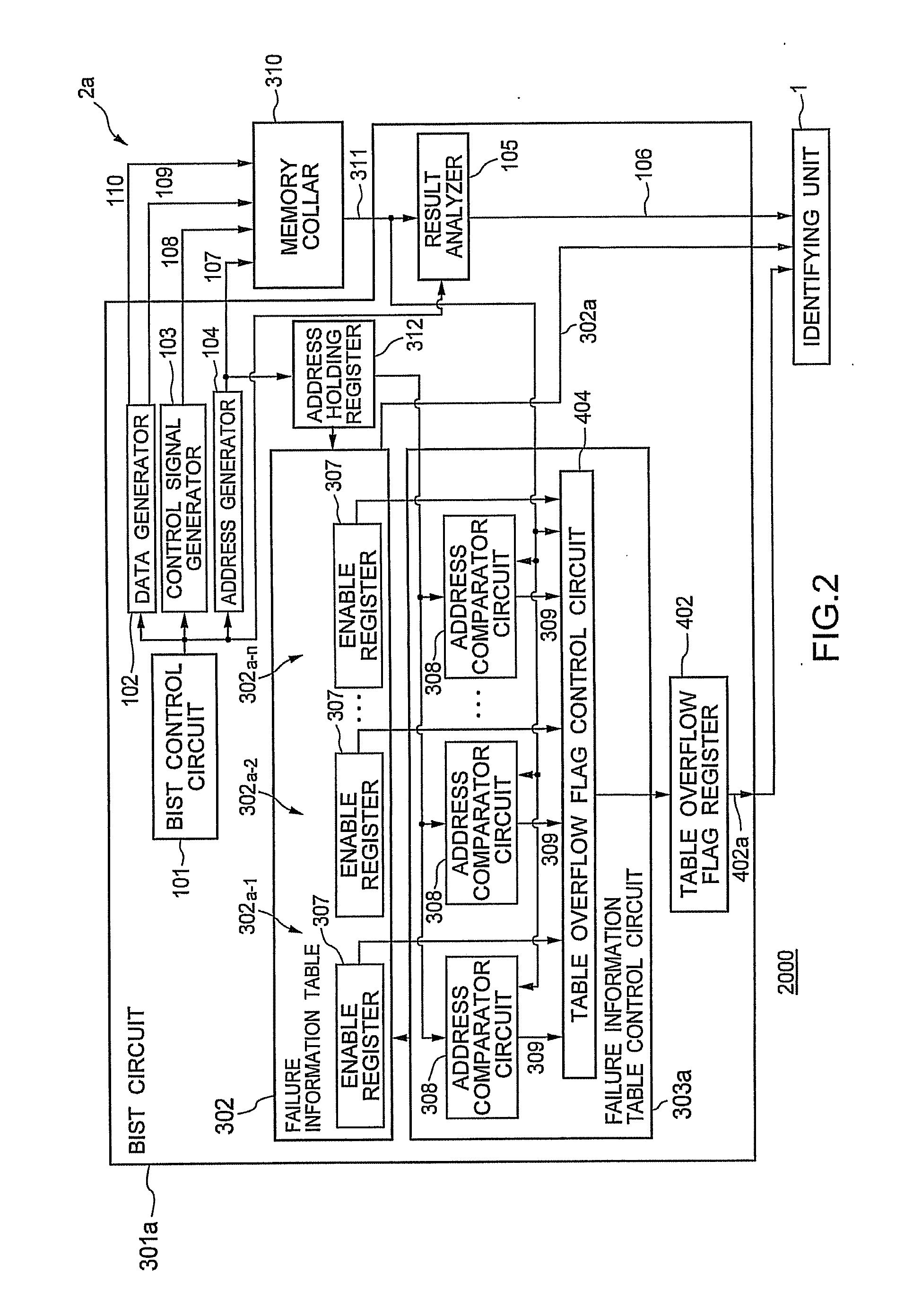

Semiconductor integrated circuit, failure diagnosis system and failure diagnosis method

A semiconductor integrated circuit includes a memory containing multiple memory bits that store predetermined data placed in a first address direction and a second address direction. The semiconductor integrated circuit includes a BIST (Built-in Self-Test) circuit that diagnoses a failure of the memory.The BIST circuit includes a BIST control circuit that controls a BIST on the memory. The BIST circuit includes a failure information table storing: a failed bit-cell position that is an address of a bit cell identified in the first address direction as a failed bit cell by the BIST conducted in the first address direction; the number of bit cell failures at the failed bit-cell position; and a failure overflow flag indicating whether the number of failures exceeds a predetermined upper value or not. The BIST circuit includes a result analyzer that outputs a BIST result obtained by the BIST on the memory.

Owner:KK TOSHIBA

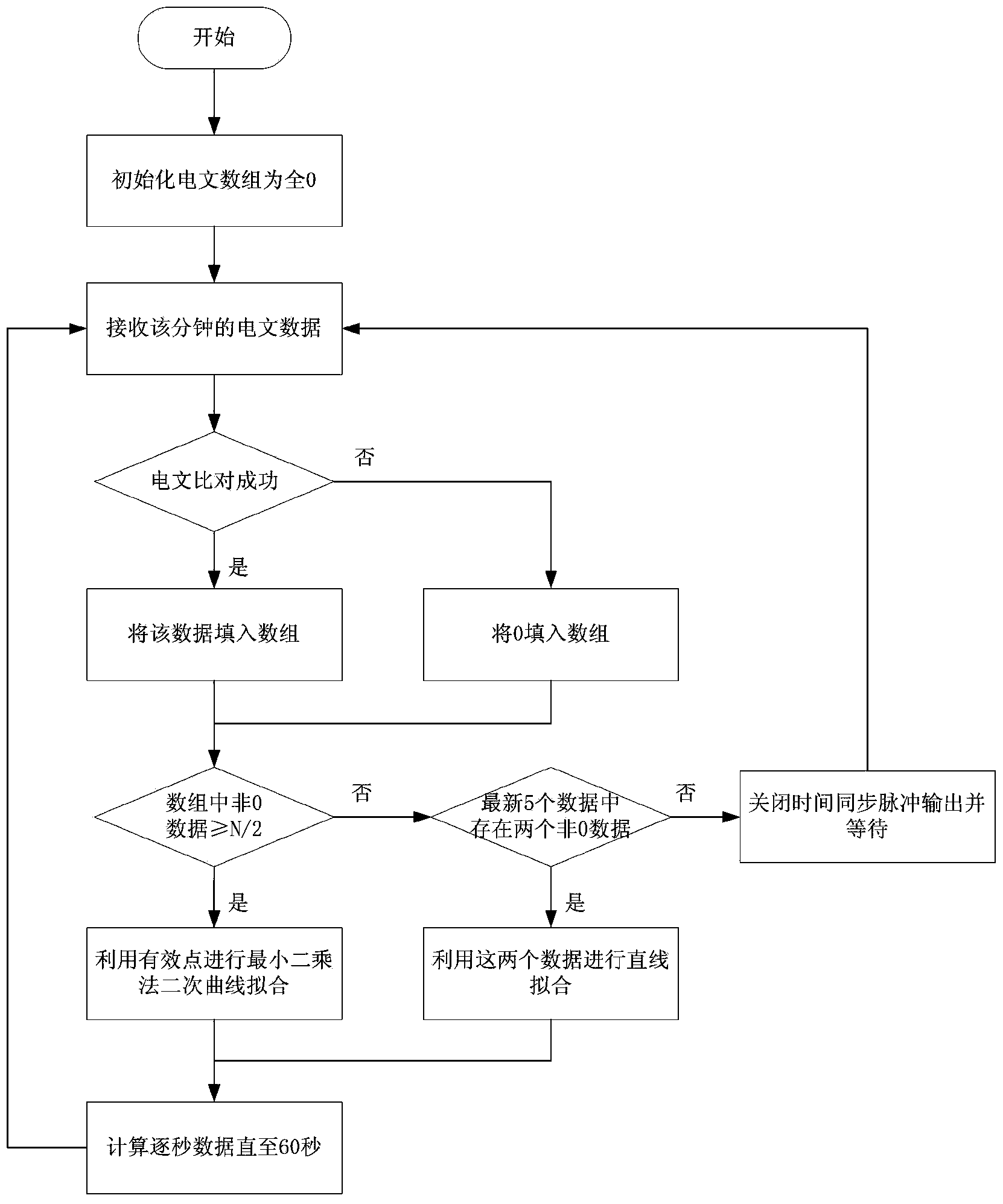

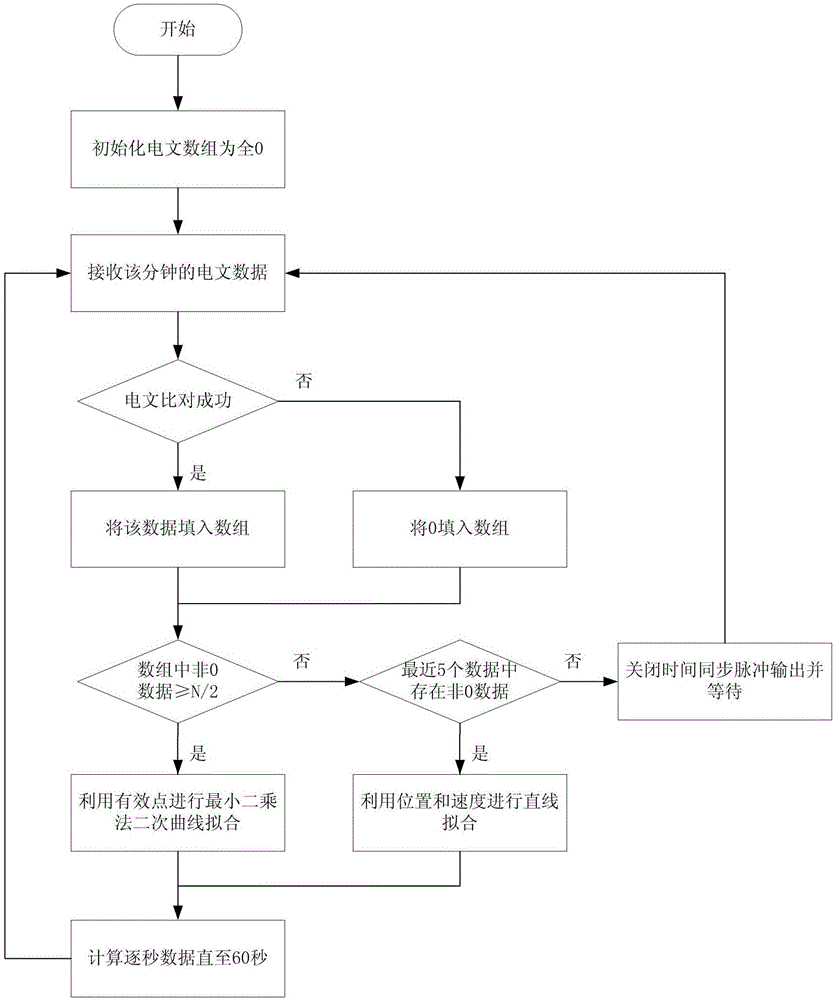

Time pulse synchronization method based on RDSS satellite navigation system

ActiveCN103676634AIncreased resilienceGuaranteed Time AccuracyRadio-controlled time-piecesTime deviationNavigation system

The invention discloses a time pulse synchronization method based on an RDSS satellite navigation system. According to the method, based on a local clock, time deviation between the local clock and BDT is worked out according to time stamps and deviation adjustment information which are carried by RDSS downlink signals; the time deviation is adjusted to an output local clock overflow flag, and a pulse per second is output at the overflow moment. Because the local clock is adopted as reference in the adjustment process, time synchronization reliability is effectively improved.

Owner:NO 54 INST OF CHINA ELECTRONICS SCI & TECH GRP

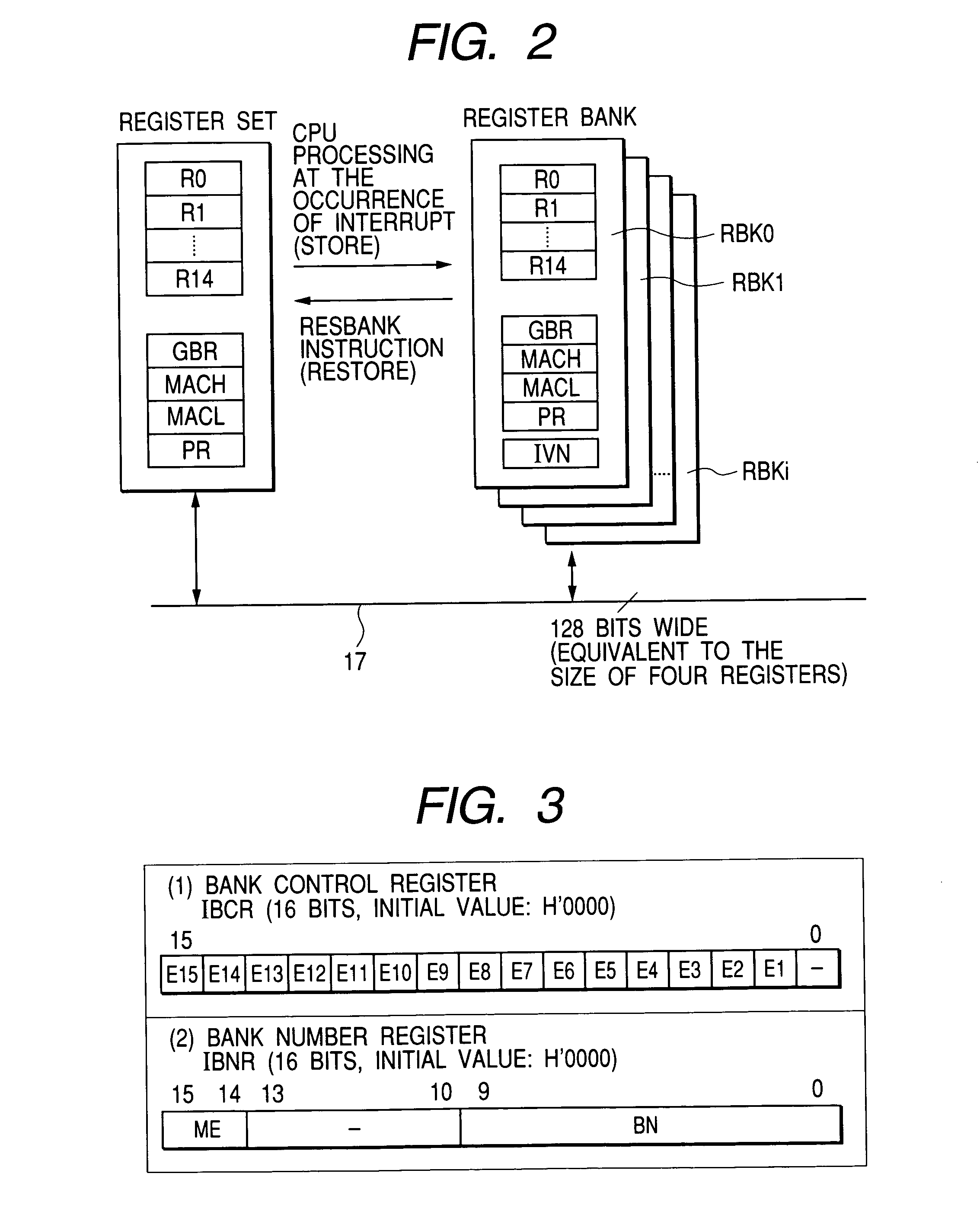

Data processor employing register banks with overflow protection to enhance interrupt processing and task switching

ActiveUS7290124B2Performed smoothly and efficientlyExcellent in applicability to multitask processingProgram initiation/switchingRegister arrangementsProcessor registerData treatment

The present invention prevents a data processor from undesirable operation stop due to an overflow of a plurality of register banks. A status register includes an overflow flag to indicate an overflow of the plurality of register banks. When an interrupt exception occurs in a state in which data has been saved to all banks of the register banks, and the accepted interrupt exception is permitted to use the register banks, a central processing unit saves data of a register set to a stack area and reflects an overflow state in the overflow flag. When the overflow flag indicates an overflow state, if data restoration from the register banks to the register set is directed, the central processing unit restores the data from the stack area to the register set.

Owner:RENESAS ELECTRONICS CORP

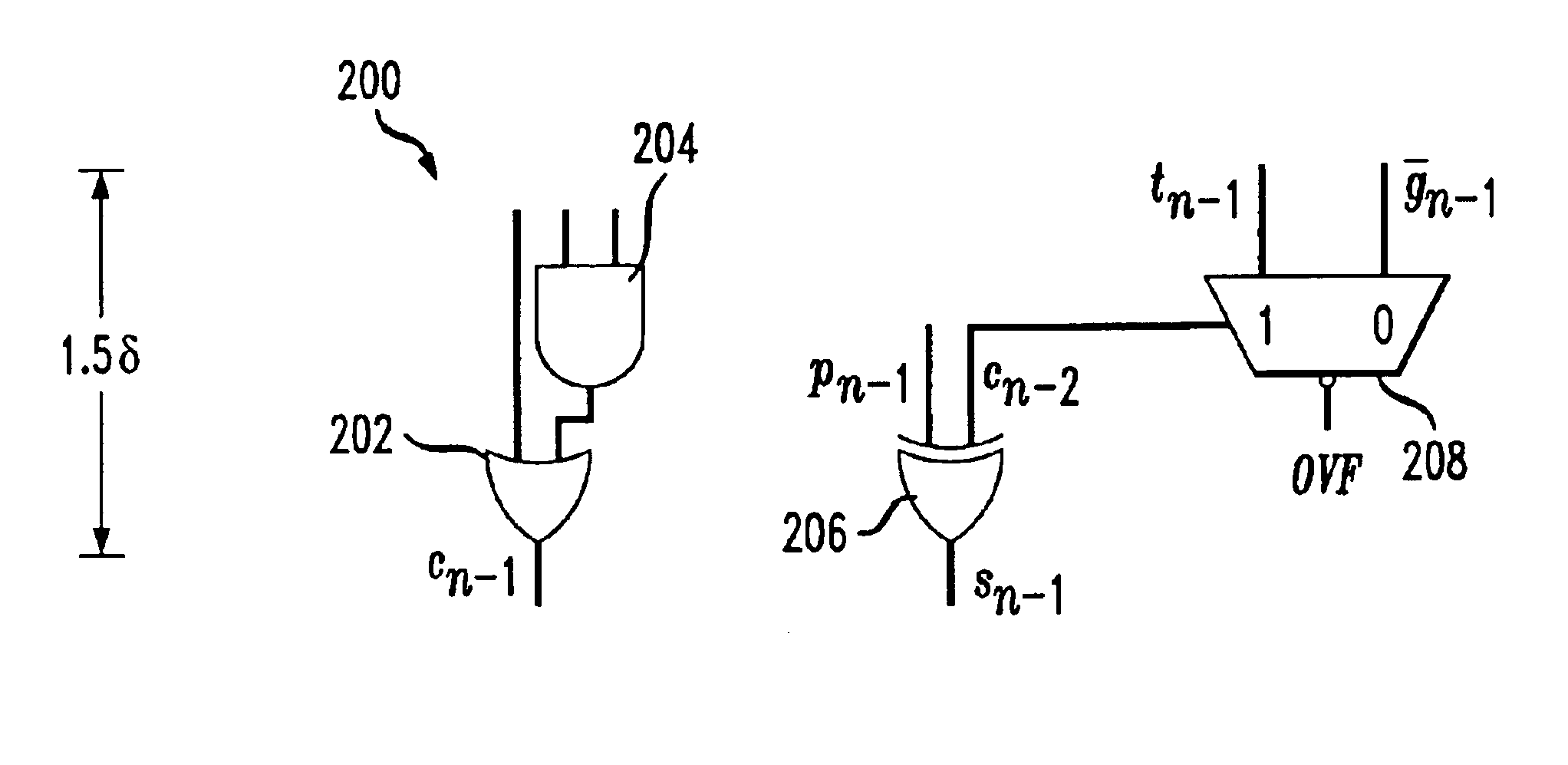

Adder with improved overflow flag generation

InactiveUS6912560B2Reduce delaysIncrease generationComputation using non-contact making devicesDigital computer detailsParallel computingHemt circuits

An adder includes a number of computational stages each associated with one or more bit positions. Particular ones of the computational stages generate a sum output signal and a primary carry-output signal of the adder. A flag generation circuit is coupled to at least one of the stages and is operative to generate an overflow flag for the adder substantially in parallel with the generation of the sum output signal and the primary carry-output signal of the adder. Advantageously, the invention substantially reduces the computational delay associated with generation of the overflow flag, relative to that of conventional adders, without requiring an increase in transistor count or circuit area.

Owner:LUCENT TECH INC +1

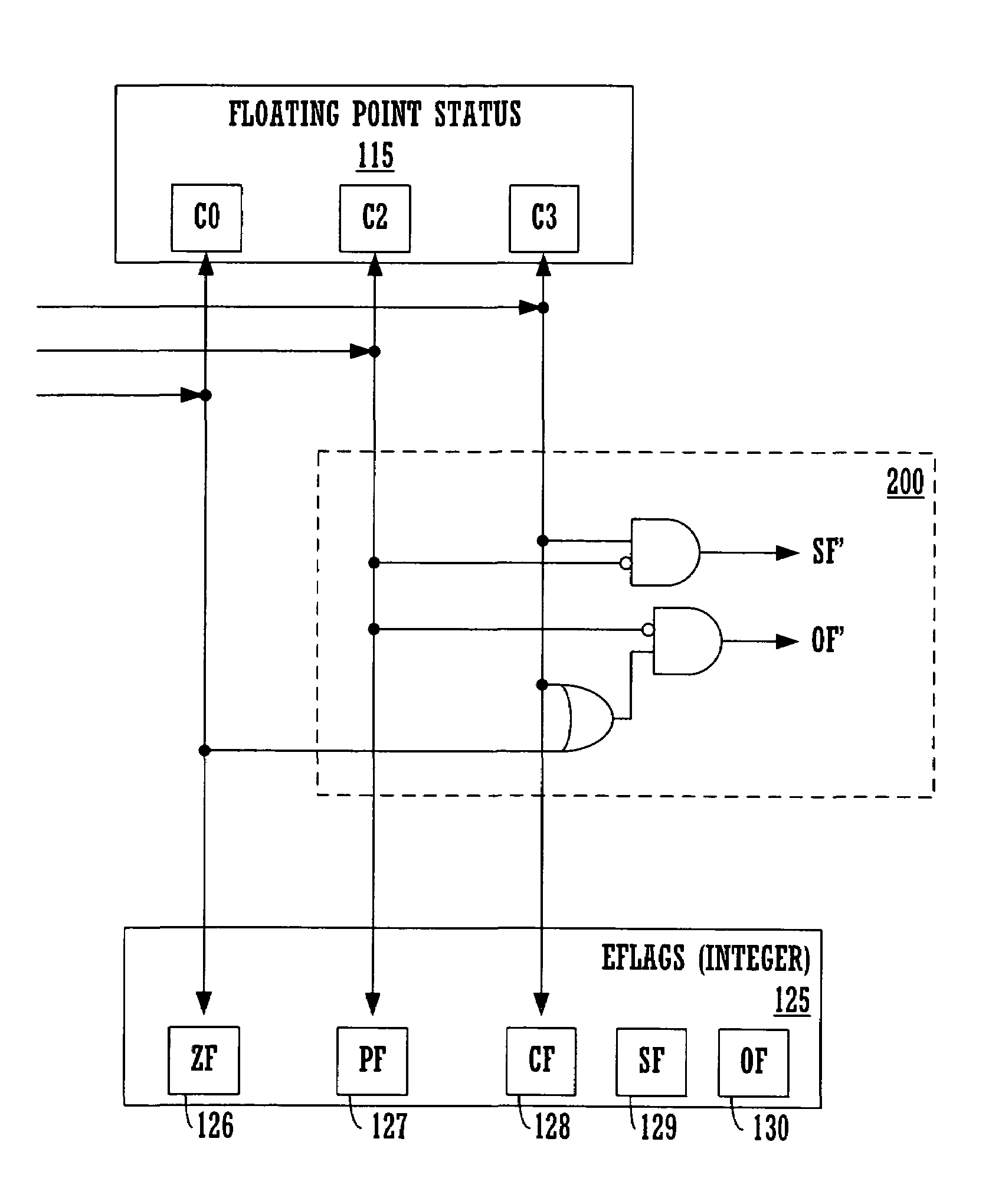

Method and system for implementing a floating point compare using recorded flags

ActiveUS7039792B1Digital computer detailsComparison of digital valuesFloating-point unitOverflow flag

A method and system for implementing a floating point compare operation in an x86 compatible processor. The method includes the step of comparing a first bit pattern and a second bit pattern using a floating point unit of an x86 compatible processor. The EFLAGS register is set in accordance with a result of the comparison. A sign flag and an overflow flag of the EFLAGS register are encoded with information derived from the result of the comparison.

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

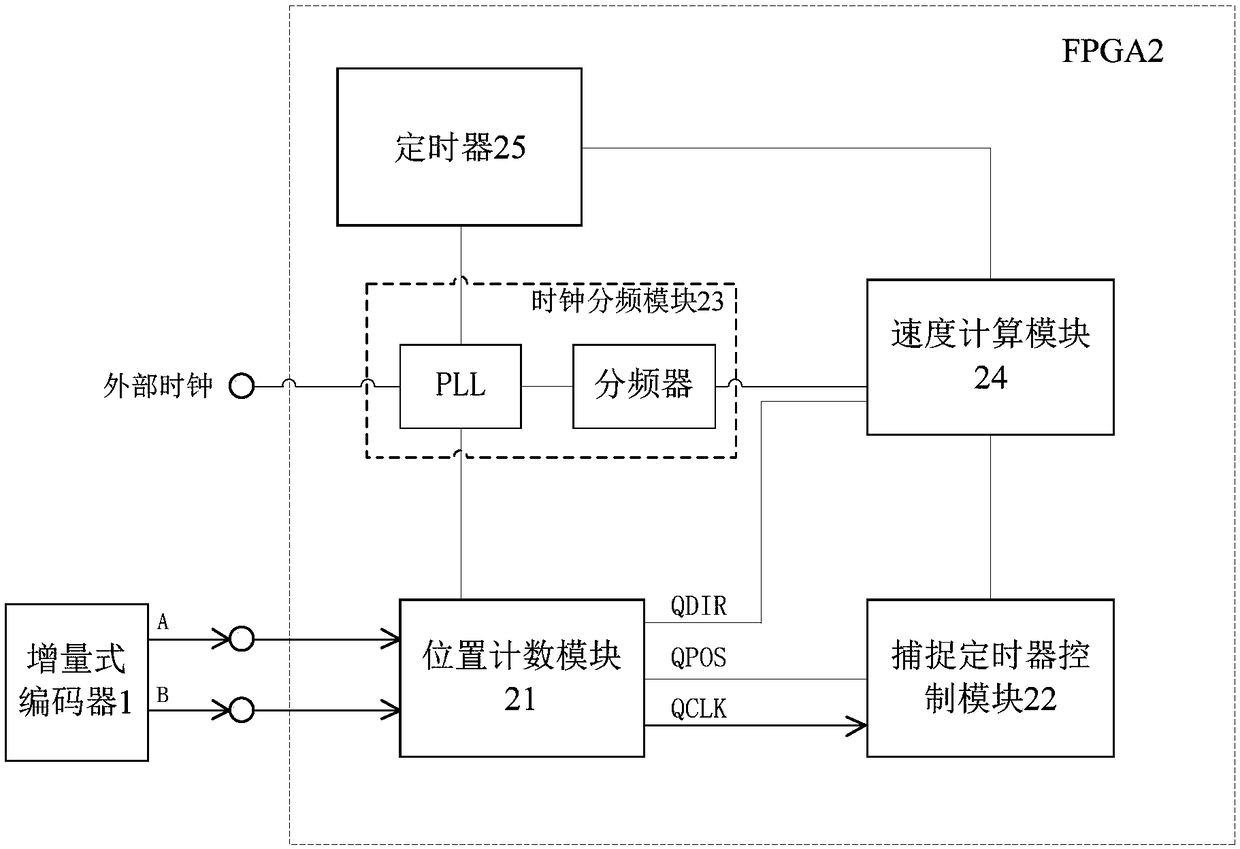

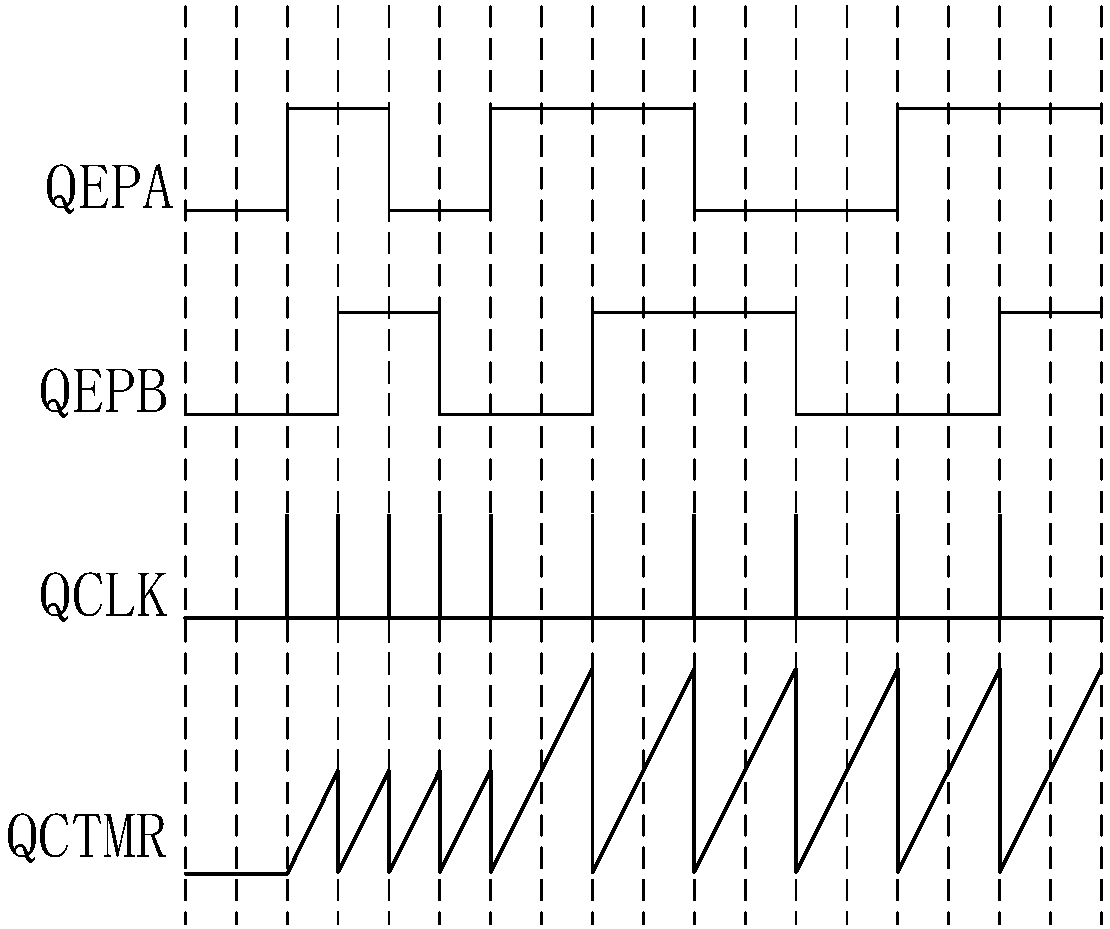

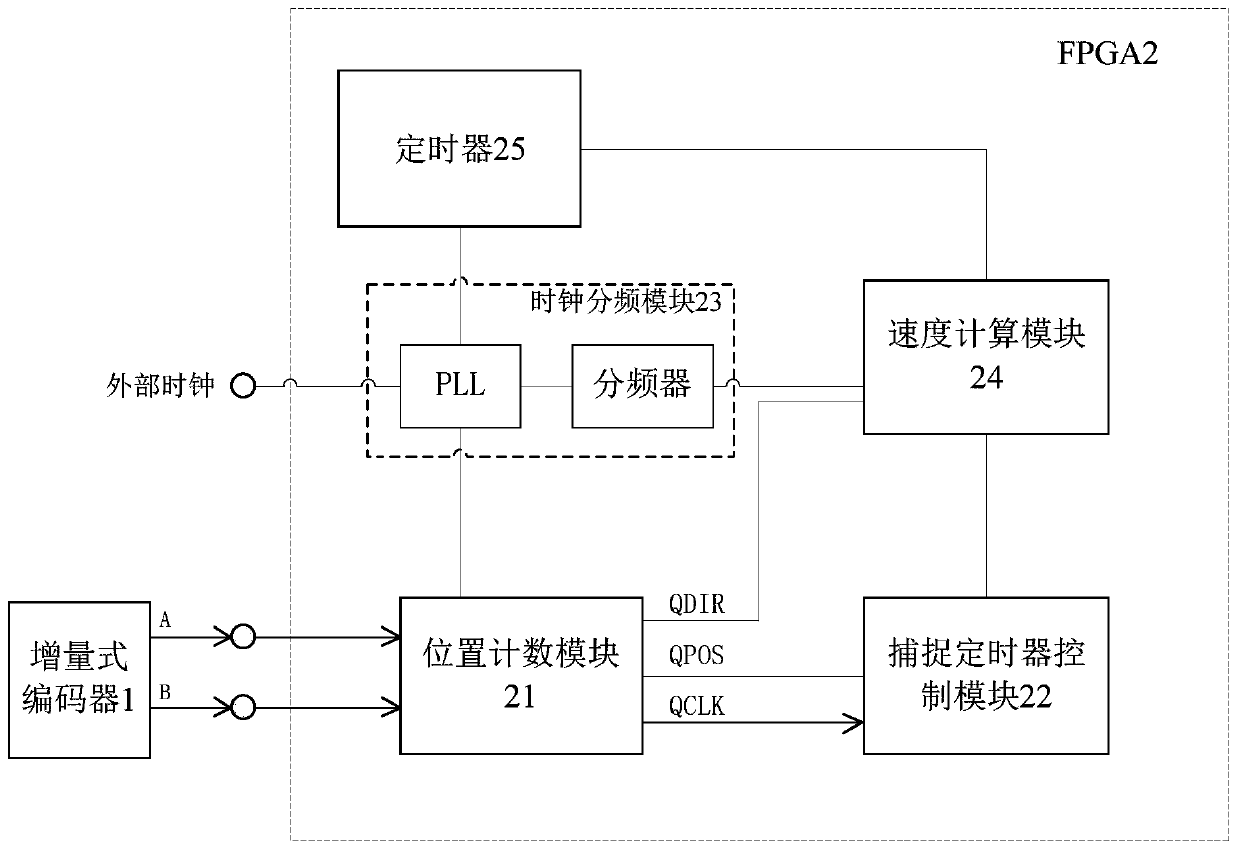

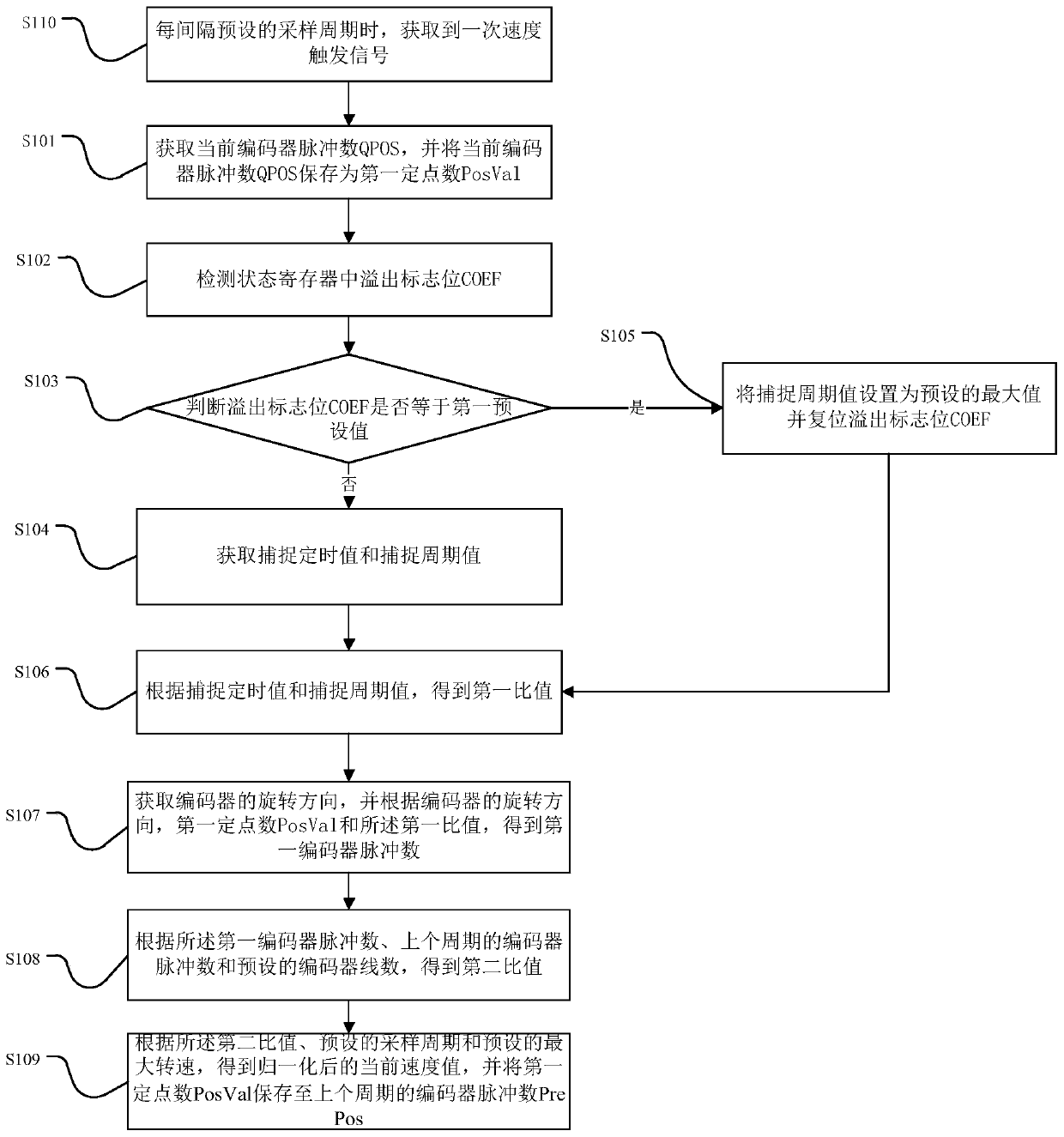

A prediction M/T speed measurement system and method

ActiveCN108549024AGood speed measurement abilityLinear/angular speed measurementDynamo-electric machine testingProcessor registerPulse number

The invention provides a prediction M / T speed measurement method. The speed measurement method includes the following steps: obtaining a current encoder pulse number QPOS; detecting the overflow flagbit COEF of a state register, and judging whether the overflow flag bit COEF is equal to the first preset value; when the overflow flag bit COEF is equal to the first preset value, arranging the capture period value as the preset maximum value and resetting the flag bit COEF; when the overflow flag bit is not equal to the first preset value, obtaining the capture timing value and the capture period value; obtaining the first ratio according to the capture timing value and the capture period value; obtaining the rotation direction of the encoder, and obtaining the a first encoder pulse number according to the rotation direction of the encoder, the first fixed point number PosVal and the first ratio; obtaining the second ratio according to the first encoder pulse number, the encoder pulse number of the last period and a preset encoder line number; and obtaining the current speed value after normalization according to the second ratio, the preset sampling period and the preset maximum rotating speed.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

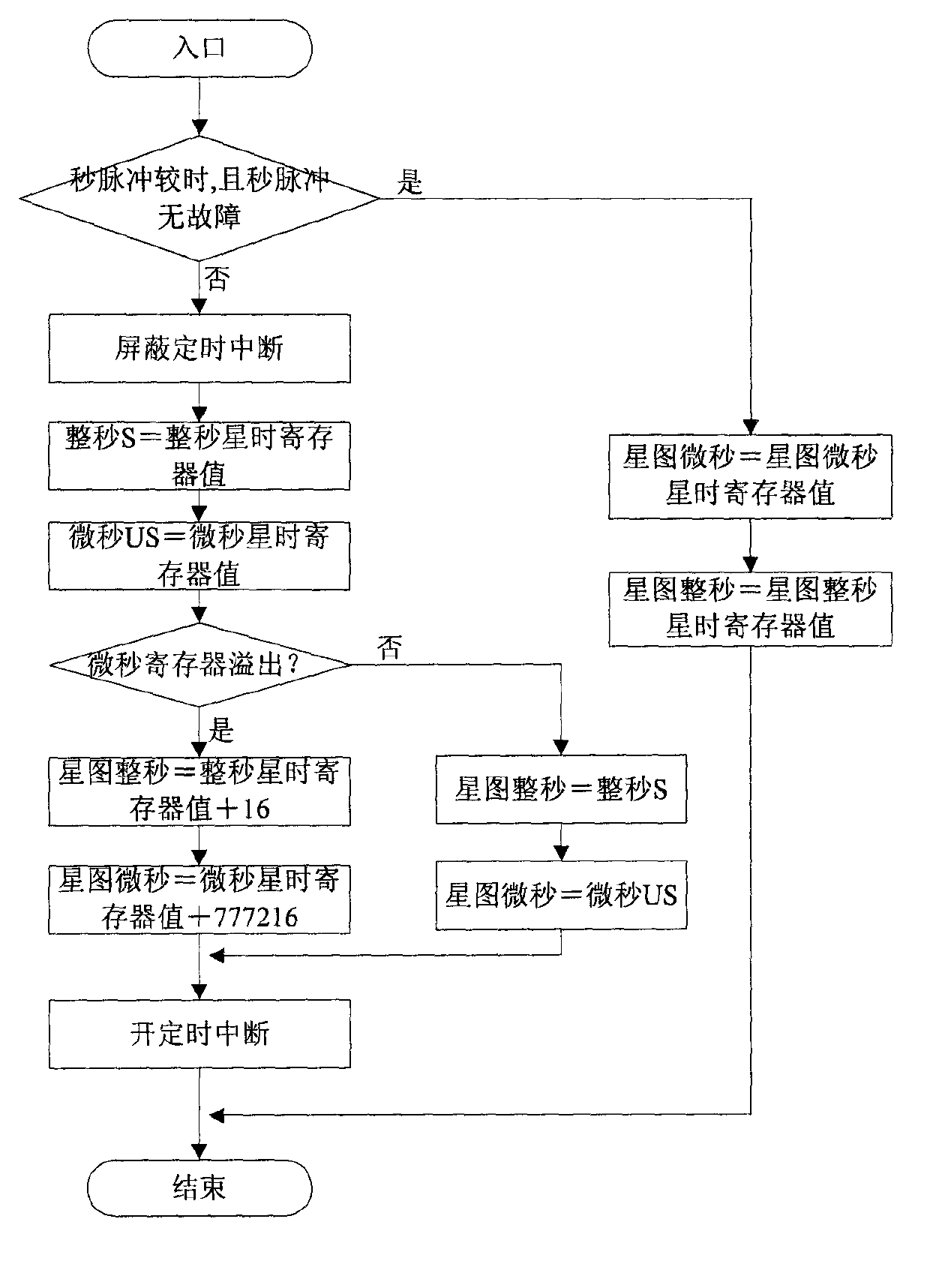

Method for accurately obtaining star image sidereal time

ActiveCN102981430AAvoid the risk of inaccurate lock timesHigh locking precisionProgramme controlComputer controlProcessor registerRead through

The invention discloses a method for accurately obtaining star image sidereal time. When a microsecond sidereal time register overflows, star image sidereal time information locked through hardware and deposited in a star image second sidereal time register and a star image microsecond sidereal time register is not directly used through software, but the value of the star image second sidereal time register and the value of the star image microsecond sidereal time register are read through the software, second sidereal time and microsecond sidereal time are obtained, and then the value of a microsecond overflow flag register is read. Whether the second sidereal time and the microsecond sidereal time need correction is judged, if the correction is not needed, the second sidereal time and the microsecond sidereal time directly serve as star image second sidereal time and star image microsecond sidereal time; and otherwise, corrected second sidereal time and corrected microsecond sidereal time serve as the star image second sidereal time and the star image microsecond sidereal time. The method is not affected by interruption of a processor and overflowing of the microsecond sidereal time register, and therefore locking accuracy of star image time is improved.

Owner:BEIJING INST OF CONTROL ENG

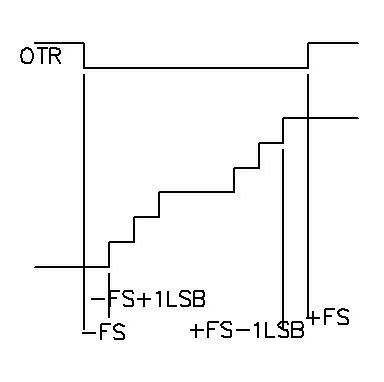

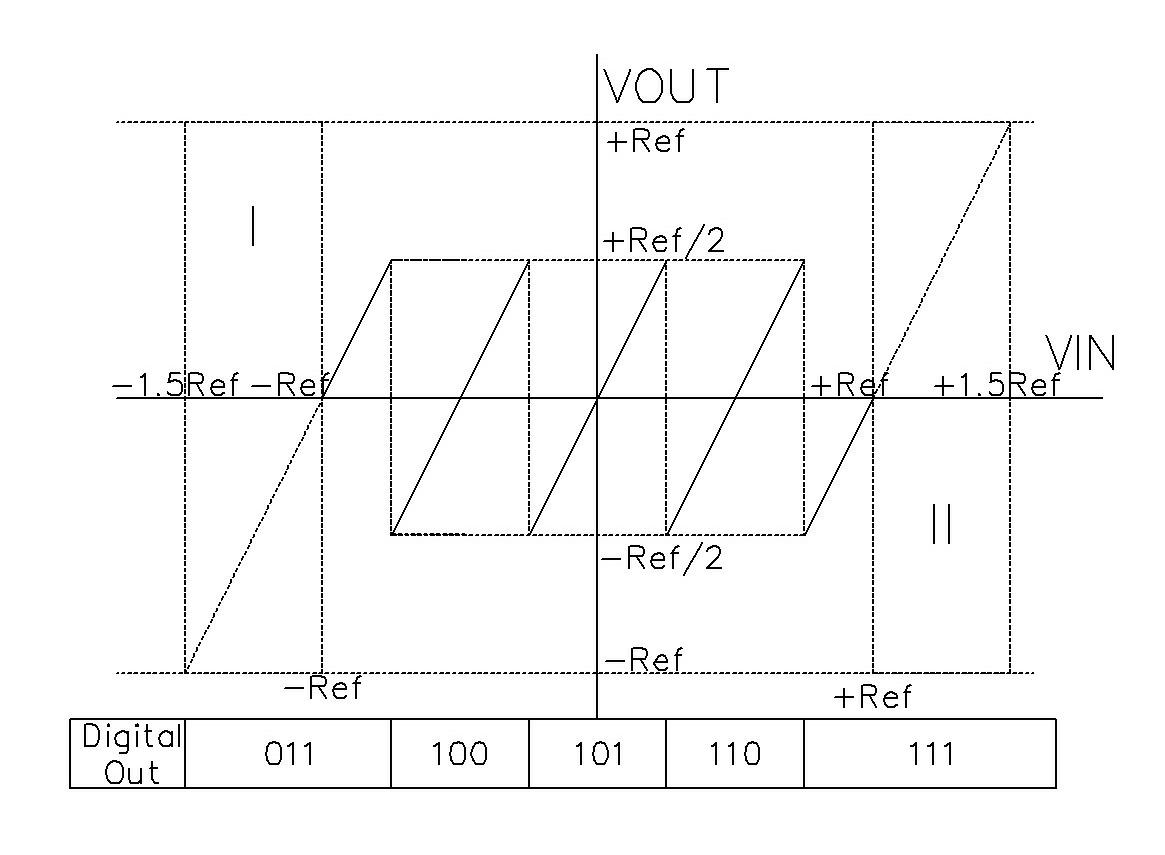

Method for judging input overflowing amplitude of pipelining type analog-to-digital converter

ActiveCN102104383AShorten the timeImprove efficiencyAnalogue-digital convertersDigital down converterAnalog-to-digital converter

The invention relates to a method for judging the input overflowing amplitude of a pipelining type analog-to-digital converter, which has the advantages of shortening adjusting time and improving efficiency. A pipelining type analog-to-digital converter of 1.5 bit is adopted in a first level. The method is characterized by comprising the steps of: inputting a signal into the pipelining type analog-to-digital converter, enabling a first-level digital circuit to adopt a 3-bit digital encoding mode and enabling other digital circuits to output in a traditional digital encoding mode; adding the initial bit of the later level and the last bit of the former level to finish the output of added digits, wherein the output initial bit of the first-level digit does not participate in an addition process and is an internal overflowing judging bit; judging on negative overflowing or positive overflowing when digit output after programming settings are added, the internal overflowing judging bit, and the corresponding highest bit of the sum of the output rest levels except the first level meet corresponding conditions; and then, setting an overflowing flag signal to be 1, fully negating the data subjected to output of the added digits to acquire final digit output, i.e. to acquire accurate amplitude in a measuring range within 0.5 time.

Owner:杭州思泰微电子有限公司

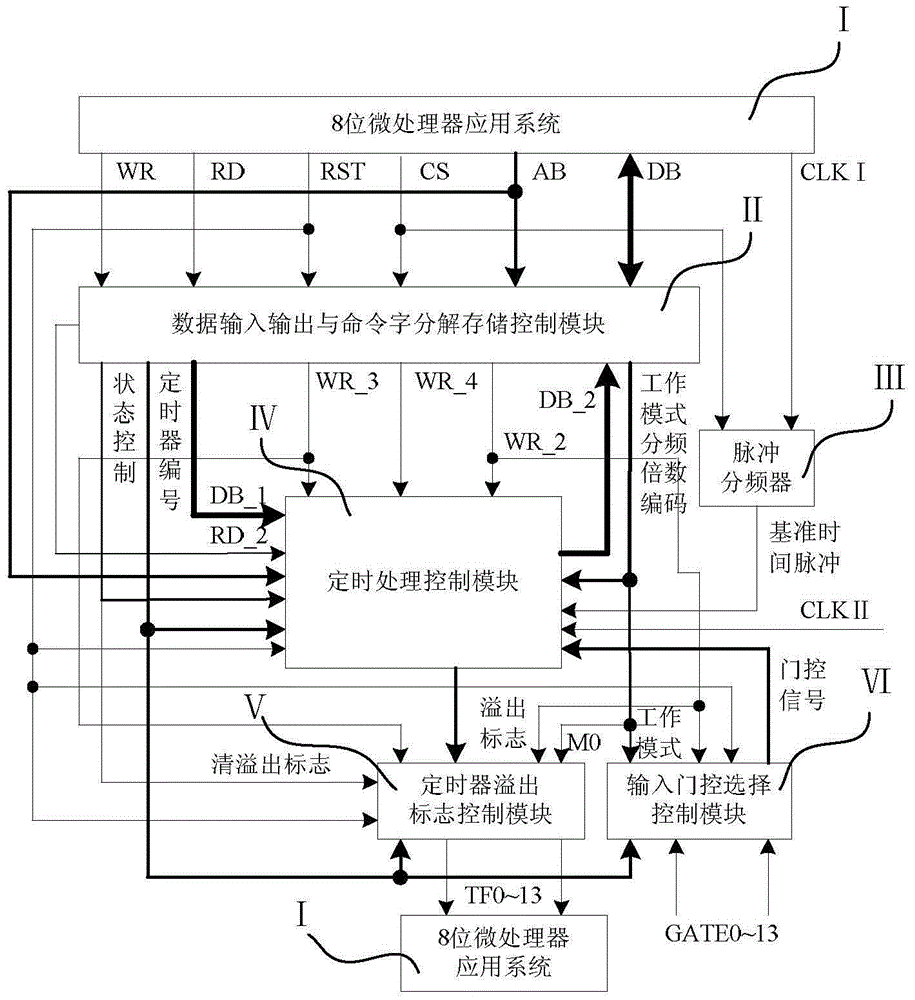

Timer IP (Intellectual Property) core connected with 8-bit microprocessor application system and method thereof for realizing timing control of timer

InactiveCN105183430AEasy to program controlHigh time accuracyMachine execution arrangementsDecompositionIntellectual property

The invention discloses a timer IP (Intellectual Property) core connected with an 8-bit microprocessor application system. The timer IP core comprises a data input / output and command word decomposition storage control module, a pulse 12 frequency divider, a timing processing control module, a timer overflow flag control module and an input gating selection control module. An FPGA (Field Programmable Gate Array) is applied to design the timer IP core formed by a hard connection control circuit, the timer IP core is provided with fourteen 16-bit timers, wherein twelve 16-bit timers can form six 32-bit timers, one command word sets a working mode and selects the reference clock frequency division multiple of the timer, and the other command word controls a working state. The program execution time of the 8-bit microprocessor is not occupied except that the 8-bit microprocessor carries out the operations, including function and state setting, timing parameter transmission and current timing value reading, on the timer. Each 16-bit / 32-bit timer has a function of automatically reloading the timing parameter, so that timing precision is improved. The requirements of the timing of a plurality of timers and the timing control of a system can be met.

Owner:LUSHAN COLLEGE OF GUANGXI UNIV OF SCI & TECH +1

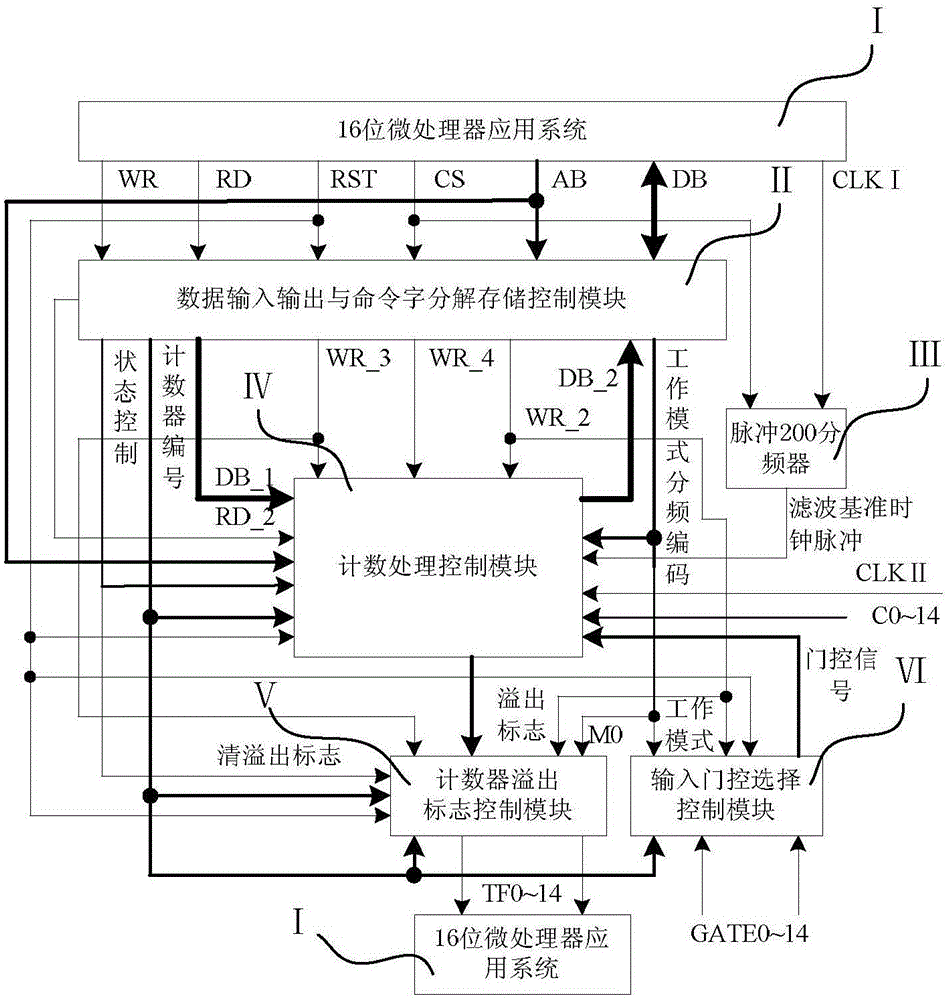

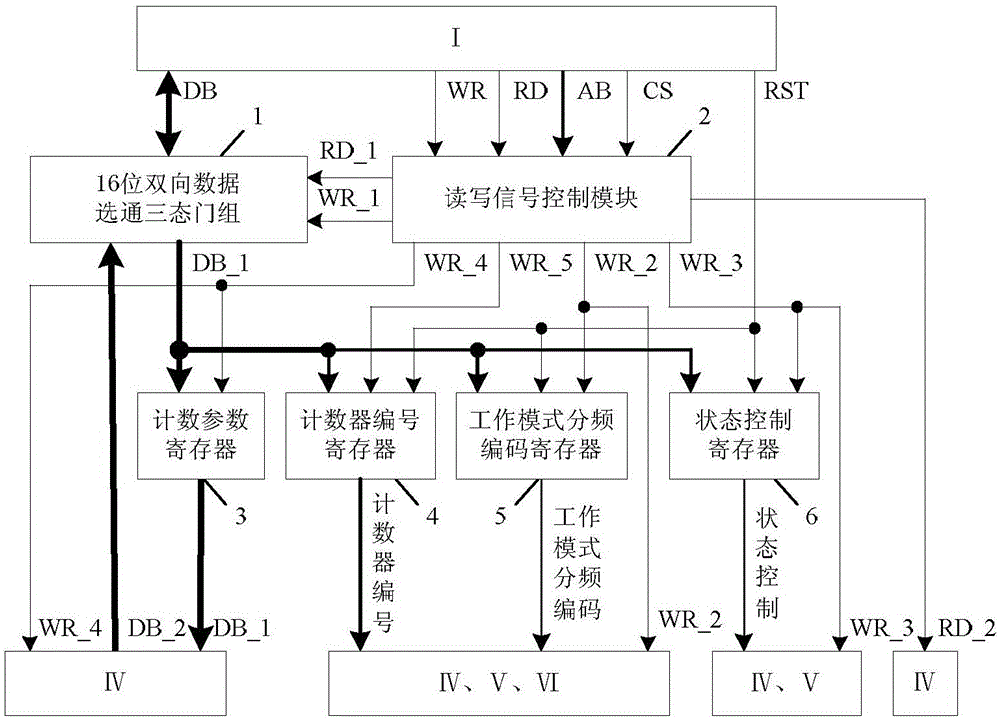

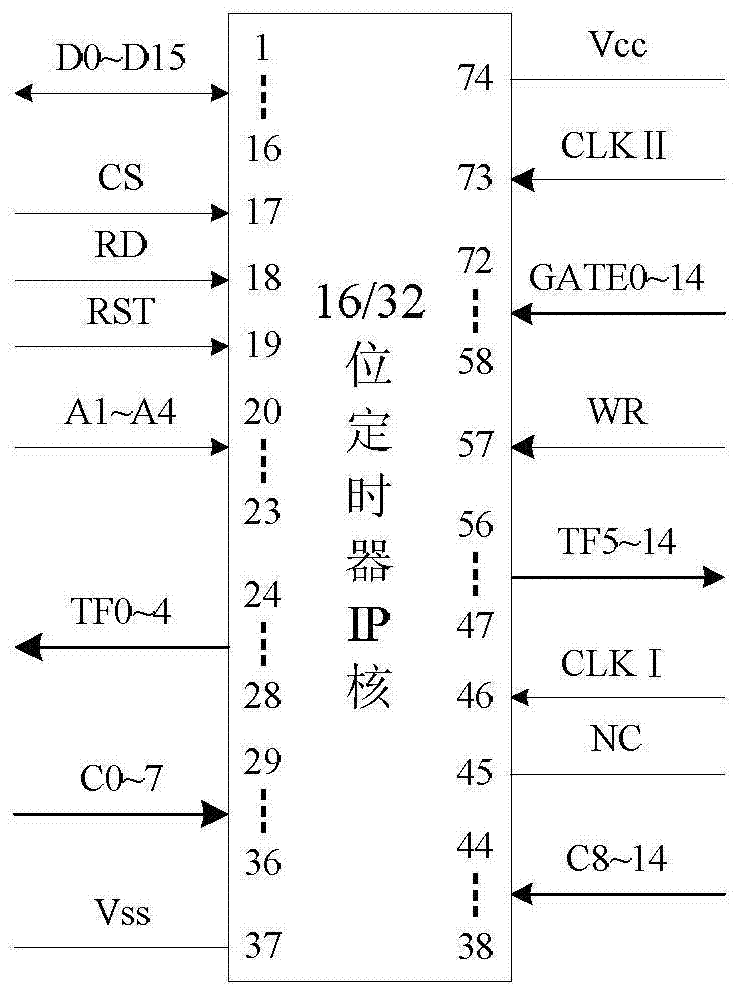

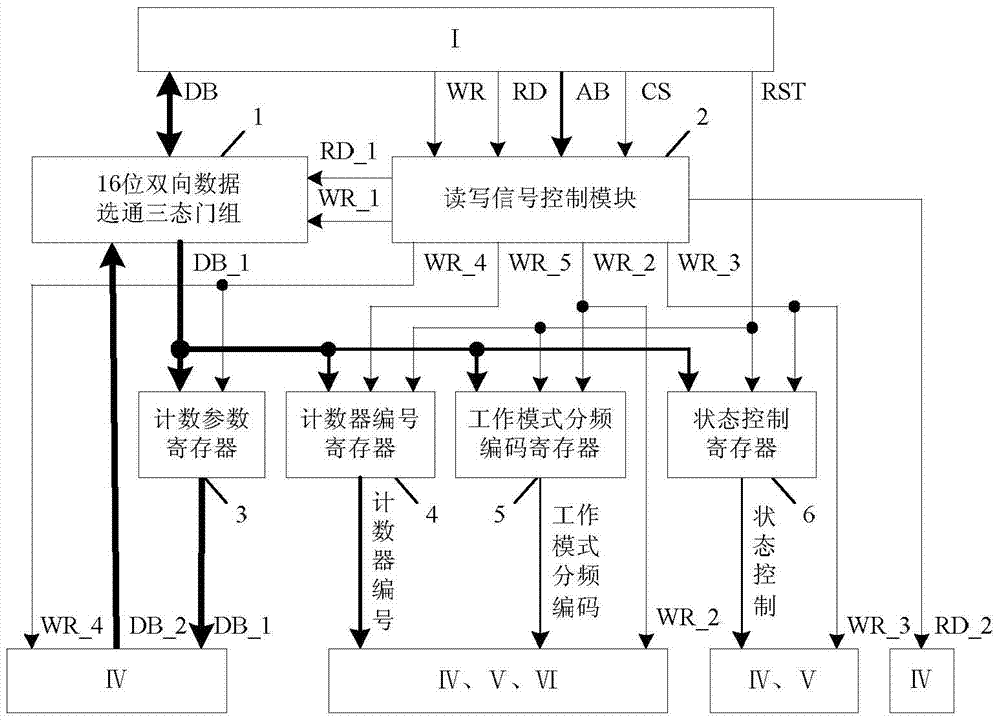

Counter IP core connected with 16-bit microprocessor application system, and counter counting control realization method thereof

InactiveCN105117200AEasy to program controlGood value for moneyMachine execution arrangementsComputer architectureDecomposition

A counter IP core connected with a 16-bit microprocessor application system comprises a data input / output and command word decomposition storage control module, a pulse 200 frequency divider, a counting processing control module, a counter overflow sign control module and an input gated selection control module; the FPGA design counter IP core is in hard connection with a control circuit; the counter IP core comprises 15 16-bit counters, wherein 14 counters can form 7 32-bit counters; one command word sets the work mode of the counter, sets counting filtering reference clock frequency division times, and controls the work state; the counter IP core only uses the 16-bit microprocessor to set functions and states, counting parameter transmission and read counting present value operation of the counters, so program execution time of the 16-bit microprocessor is not used by other programs; each 16 / 32 bit counter has a counting parameter automatic afresh loading function, thus satisfying counting and counting control system demands of many counters.

Owner:GUANGXI UNIVERSITY OF TECHNOLOGY

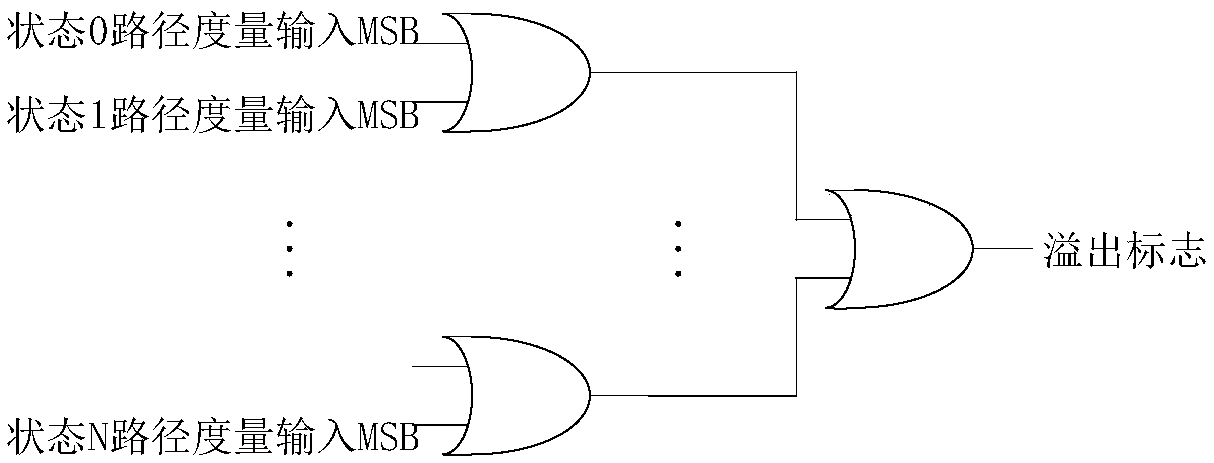

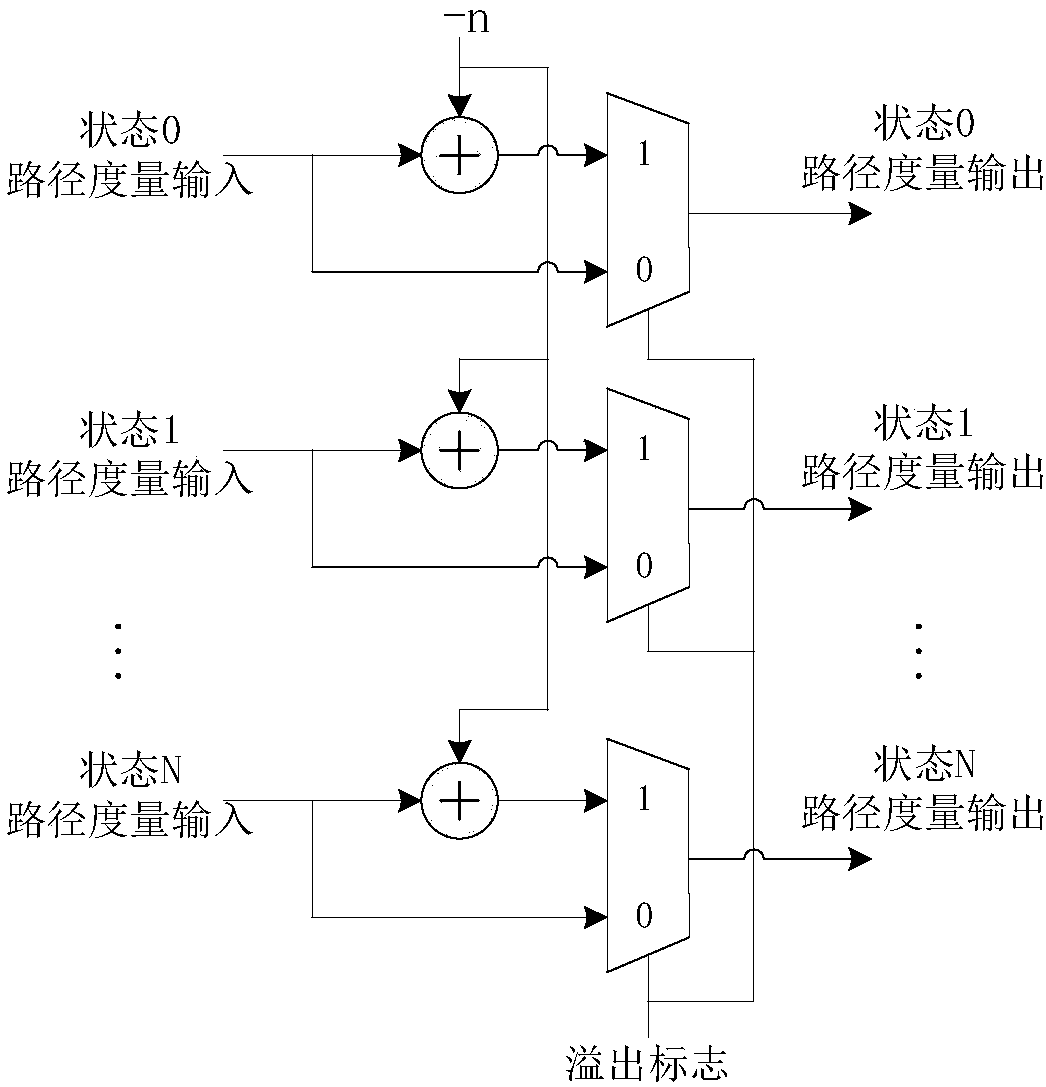

Viterbi decoding path measurement anti-overflow method and device

ActiveCN108540264AResolve overflowError preventionOther decoding techniquesFree distanceOverflow flag

The application provides a Viterbi decoding path measurement anti-overflow method. The method comprises the following steps: computing a path measurement bit wide spreading parameter by using free distance and a convolutional code parameter; obtaining the path measurement total bit wide according to the path measurement bit wide spreading parameter and the Viterbi decoding input information bit wide; respectively selecting the highest bit of each state path measurement value according to the path measurement total bit wide so as to obtaining an overflow zone bit by performing OR operation according to the selected highest bit; and performing the anti-overflow processing when the overflow zone bit satisfies the first preset condition. Through the method provided by the application, a Viterbi decoding path measurement accumulation result can be realized through an OR gate, a selector switch and like simple hardware, the non-overflow is represented by the bit wide W, and the overflow problem existent in the Viterbi decoding path measurement can be solved through low complexity and hardware source overhead.

Owner:深圳昂瑞微电子技术有限公司

A predictive m/t speed measuring system and method

ActiveCN108549024BGood speed measurement abilityLinear/angular speed measurementDynamo-electric machine testingCurrent velocityProcessor register

The present invention provides a predictive M / T speed measurement method, said speed measurement method comprising the following steps: obtaining the current encoder pulse number QPOS; detecting the overflow flag COEF in the status register, and judging whether the overflow flag COEF is equal to the first preset Set a value; when the overflow flag COEF is equal to the first preset value, the capture cycle value is set to a preset maximum value and reset the overflow flag COEF; when the overflow flag COEF is not equal to the first preset value, capture timing value and capture period value; according to the capture timing value and capture period value, the first ratio is obtained; the rotation direction of the encoder is obtained, and according to the rotation direction of the encoder, the first fixed-point number PosVal and the first ratio, the first ratio is obtained An encoder pulse number; according to the first encoder pulse number, the encoder pulse number of the last cycle and the preset encoder line number, a second ratio is obtained; according to the second ratio, the preset sampling period and the preset maximum speed to get the normalized current speed value.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

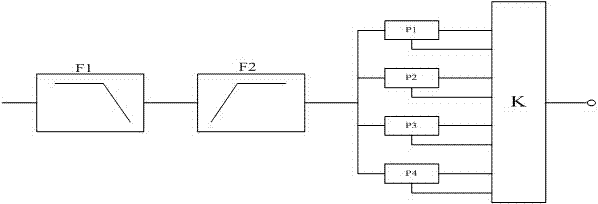

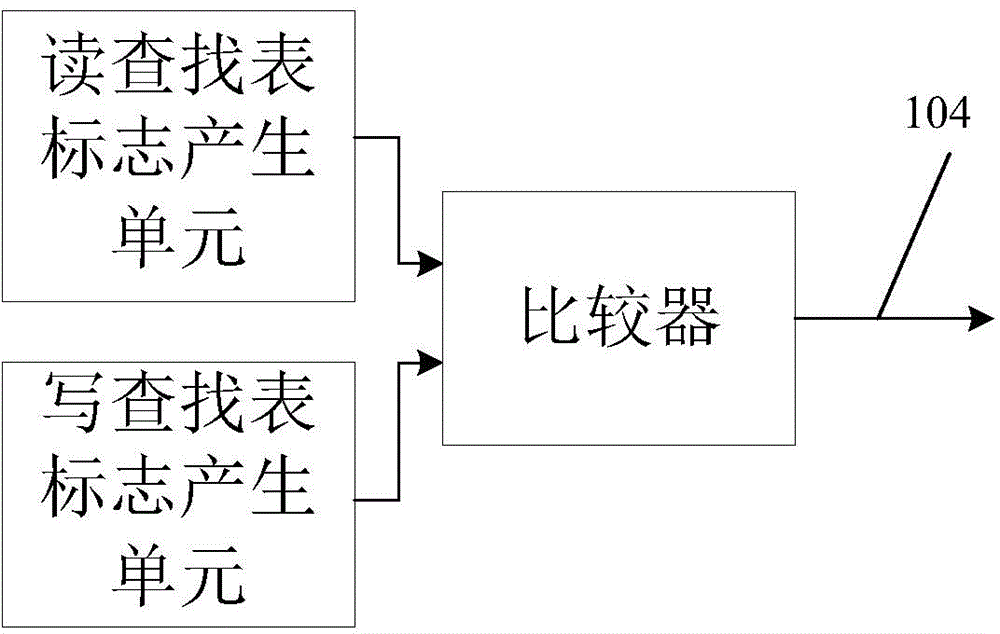

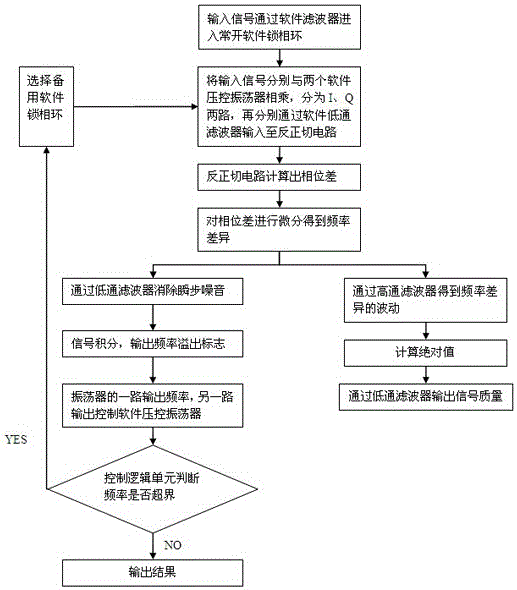

High-reliability and low-calculation rhythm recognition circuit and high-reliability and low-calculation rhythm recognition method suitable for wearable device

ActiveCN104224157ALow signal to noise ratioLower requirementSensorsMeasuring/recording heart/pulse rateSignal-to-noise ratio (imaging)Open software

The invention discloses a high-reliability and low-calculation rhythm recognition circuit and a high-reliability and low-calculation rhythm recognition method suitable for a wearable device. The high-reliability and low-calculation rhythm recognition circuit comprises at least one software filter, a normally-opened software phase locked loop, at least one standby software phase locked loop and a control logic unit K, wherein all standby software phase locked loops are respectively connected with the normally-opened software phase locked loop in parallel; signal output ends of all the software filters are respectively connected with the normally-opened software phase locked loop and the standby software phase locked loops; the normally-opened software phase locked loop and the standby software phase locked loops respectively comprise rhythm signal output ends and frequency overflow flag output ends; the rhythm signal output ends and the frequency overflow flag output ends are respectively connected with the control logic unit K. The circuit disclosed by the invention has the advantages of low requirement on signal-noise ratio of signals, good robustness and wide recognition range; the method has the advantages of low requirement on a processor, low power consumption, high reliability and low calculation, and is suitable for the wearable device.

Owner:CHENGDU VCARE QINYUAN HEALTH TECH

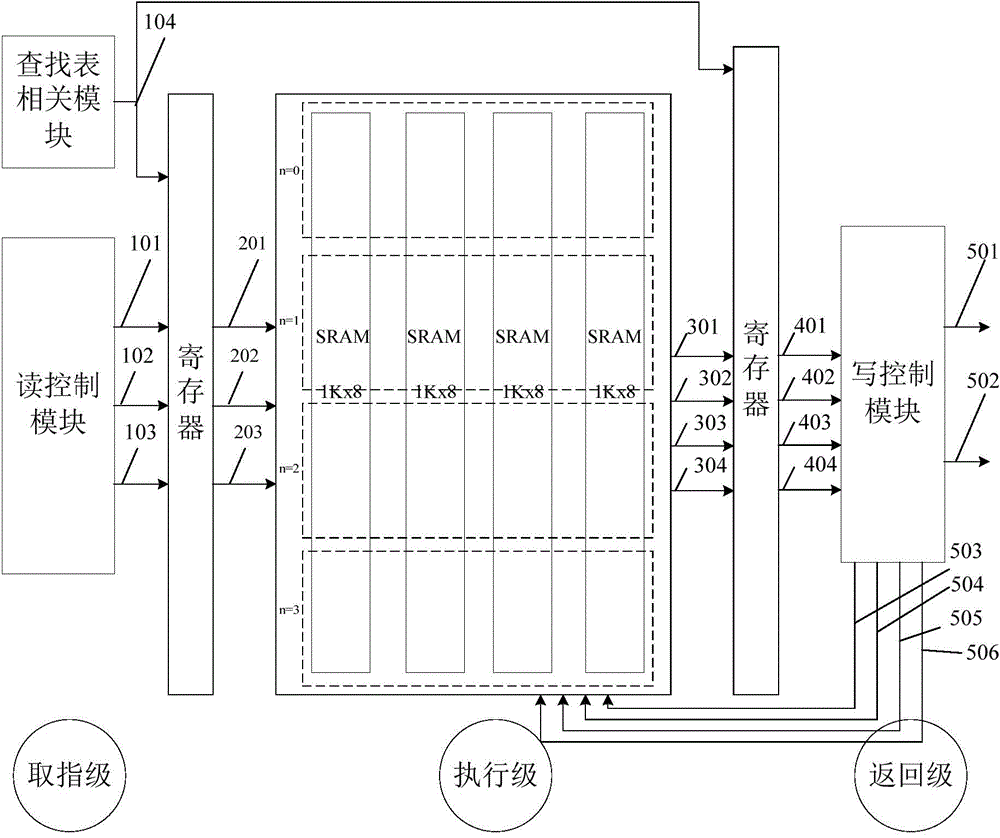

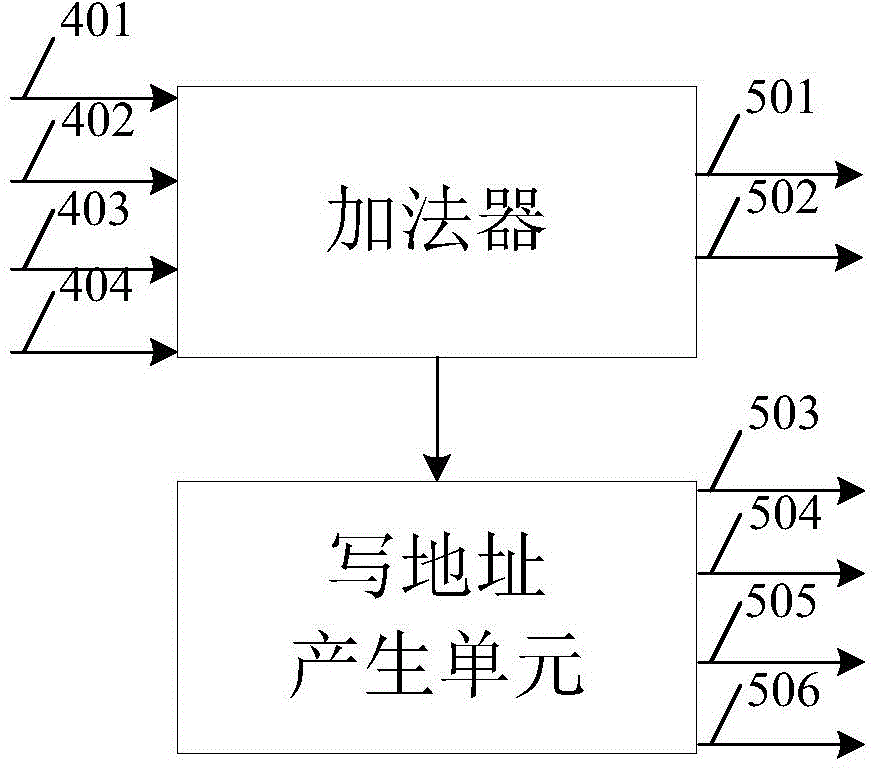

Histogram statistic realization device and method applied to DSP (digital signal processor)

ActiveCN104361587AMeet various needsLow efficiencyImage analysisProcessor architectures/configurationDigital signal processingStatic random-access memory

A histogram statistic realization device applied to a DSP (digital signal processor) comprises a lookup table module, a read control module, a write control module, a lookup table correlation module and a register block. The read control module and the lockup table correlation module are on a fetching level, the lockup table module is on an executive level, the write control module is on a return level, and the lockup table module is composed of four SRAMs (static random access memories); the read control module generates an address and enabling and chip selection signals for reading the lock-up table module; the write control module is used for additive operation and generation of an address, data and enabling and chip selection signals for writing the lock-up table module; the lookup table correlation module generates correlation flags for write operation and read operation; the register block is used for registration of control signals and data and pipeline stall. The invention further provides a histogram statistic realization method applied to the DSP. The method and the device have the advantages that a user can randomly expand bits of pixel numbers according to overflow flags, various requirements are met, a pipeline structure is adopted, and execution efficiency is improved.

Owner:安徽芯纪元科技有限公司

Heart rhythm recognition circuit and method with high reliability and low calculation load suitable for wearable devices

ActiveCN104224157BLow signal to noise ratioLower requirementSensorsMeasuring/recording heart/pulse rateSignal-to-noise ratio (imaging)Parallel computing

A highly reliable and low computational load heart rhythm recognition circuit and method applicable in a wearable device. The circuit comprises at least one software filter, one normally open software phase-locked loop, at least one backup software phase-locked loop, and at least one control logical unit K. Each backup software phase-locked loop is connected in parallel to the normally open software phase-locked loop. A signal output end of the software filter is connected respectively to the normally open software phase-locked loop and the backup software phase-locked loop. The normally open software phase-locked loop and each backup software phase-locked loop respectively comprise a heart rhythm signal output end and a frequency overflow flag output end. The heart rhythm signal output ends and the frequency overflow flag output ends respectively are connected to control logical unit K. The circuit has a lowered requirement on the signal-to-noise ratio of a signal, great robustness, and a broad recognition range. The method has an extremely low requirement on a processor, low power consumption, high reliability, and low computational load and is applicable in a wearable device.

Owner:CHENGDU VCARE QINYUAN HEALTH TECH

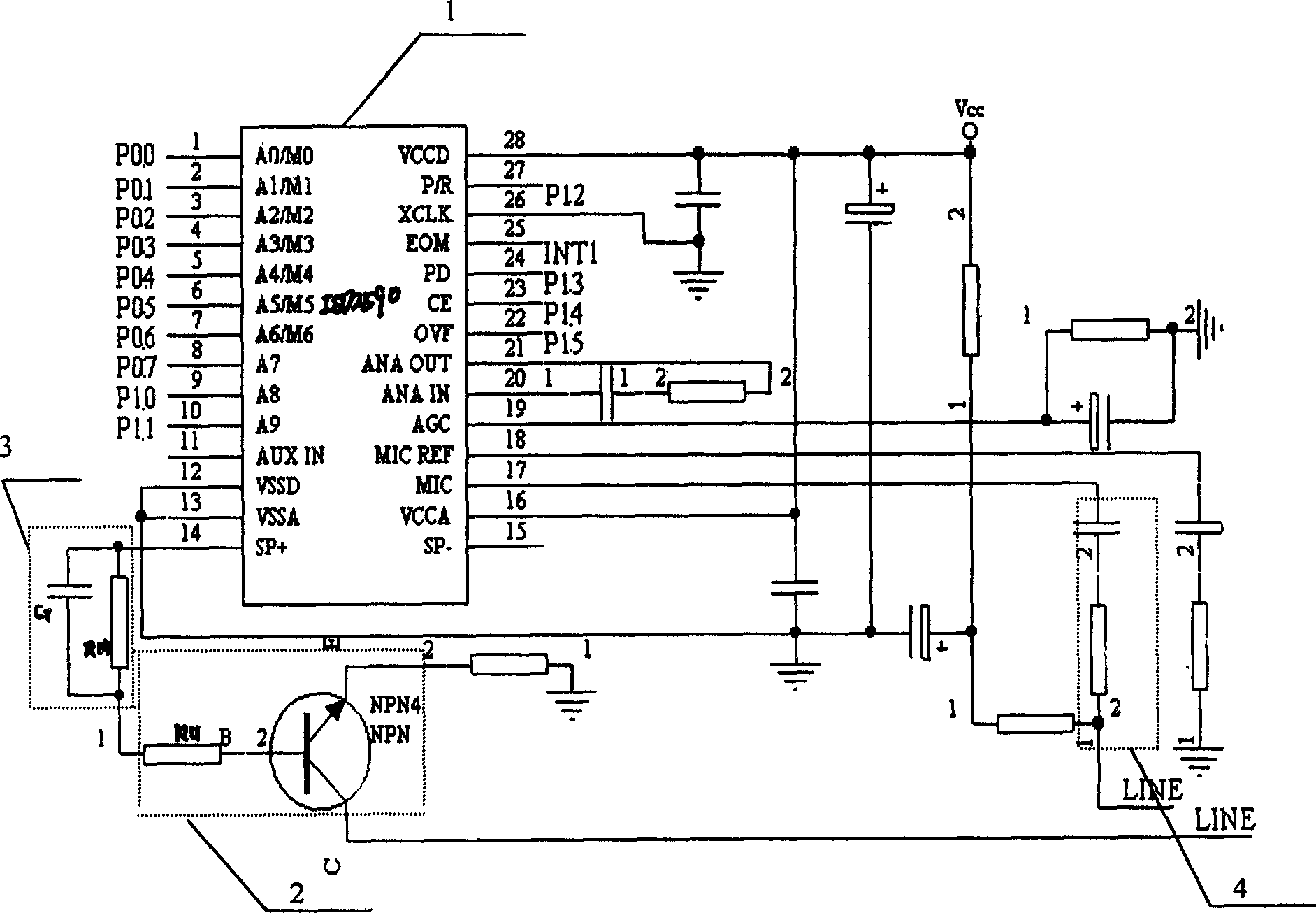

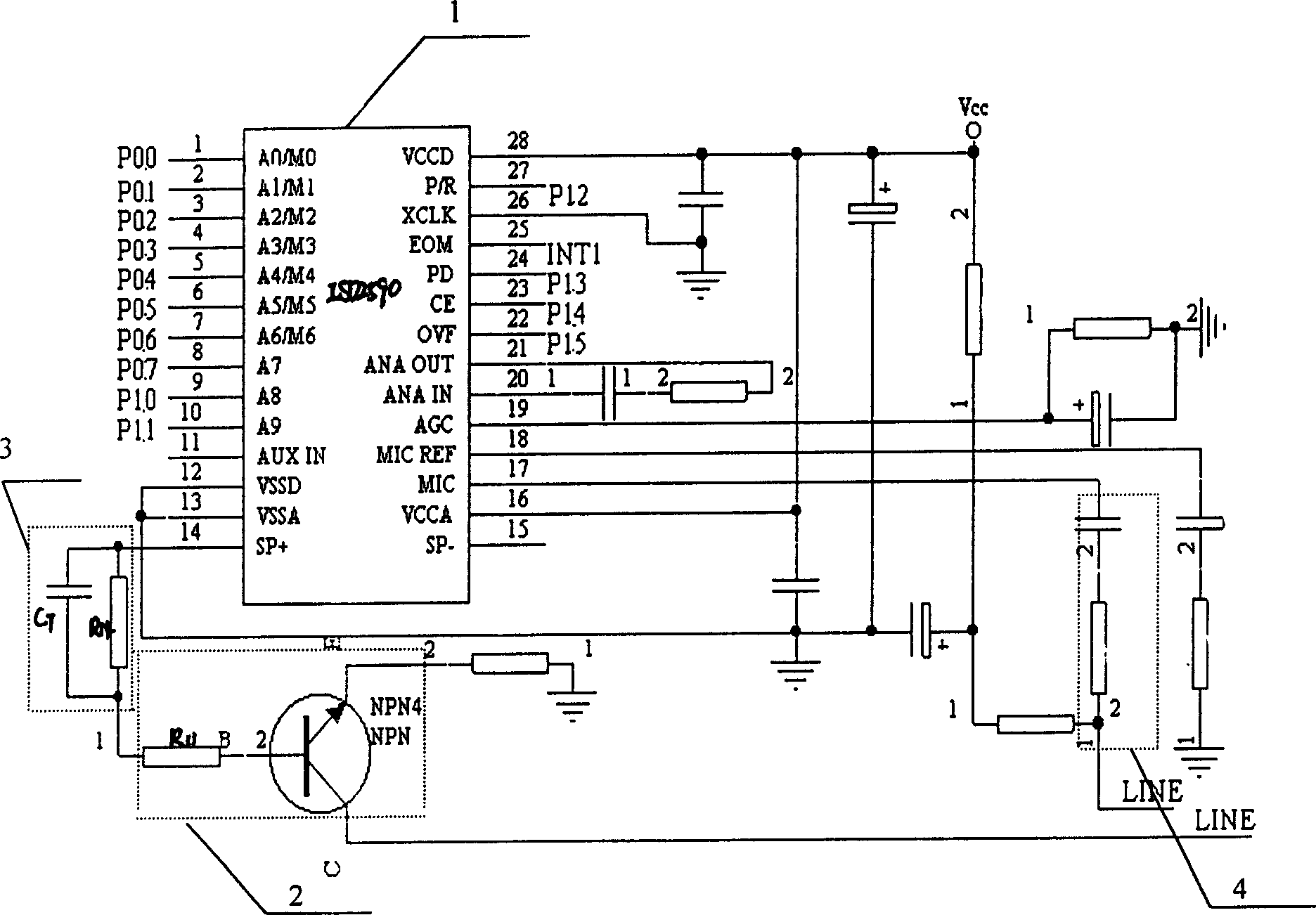

Phonetic prompt device for intelligent phone set

InactiveCN1453976AAvoid misuseImprove securitySpeech amplifier applicationsSubstation speech amplifiersMicrocontrollerControl system

In the present invention, voice chip address line AO-A9 is connected with PO mouth P0.0-P0.7 and P1 mouth P1.0-1.1 of monolithic computer, input end P / R of voice chip record-playback mode selection control, input end of energy saving mode control, input end CE of wafer selective signal and input end OVE of overflow flag are connected with P1 mouth P1.2-1.5 of the monolithic computer separately; output end EOM of voice chip information end flag is connected with external interrupt input INT1 of the monolithic computer, output signal of voice chip is conencted with phone line via capacity coupler 1 by its SP+ end together with signal amplifying circuit and phone line input signal is connected to MIC end of ISD2590 chip via capacity coupler 2.

Owner:TSINGHUA UNIV +1

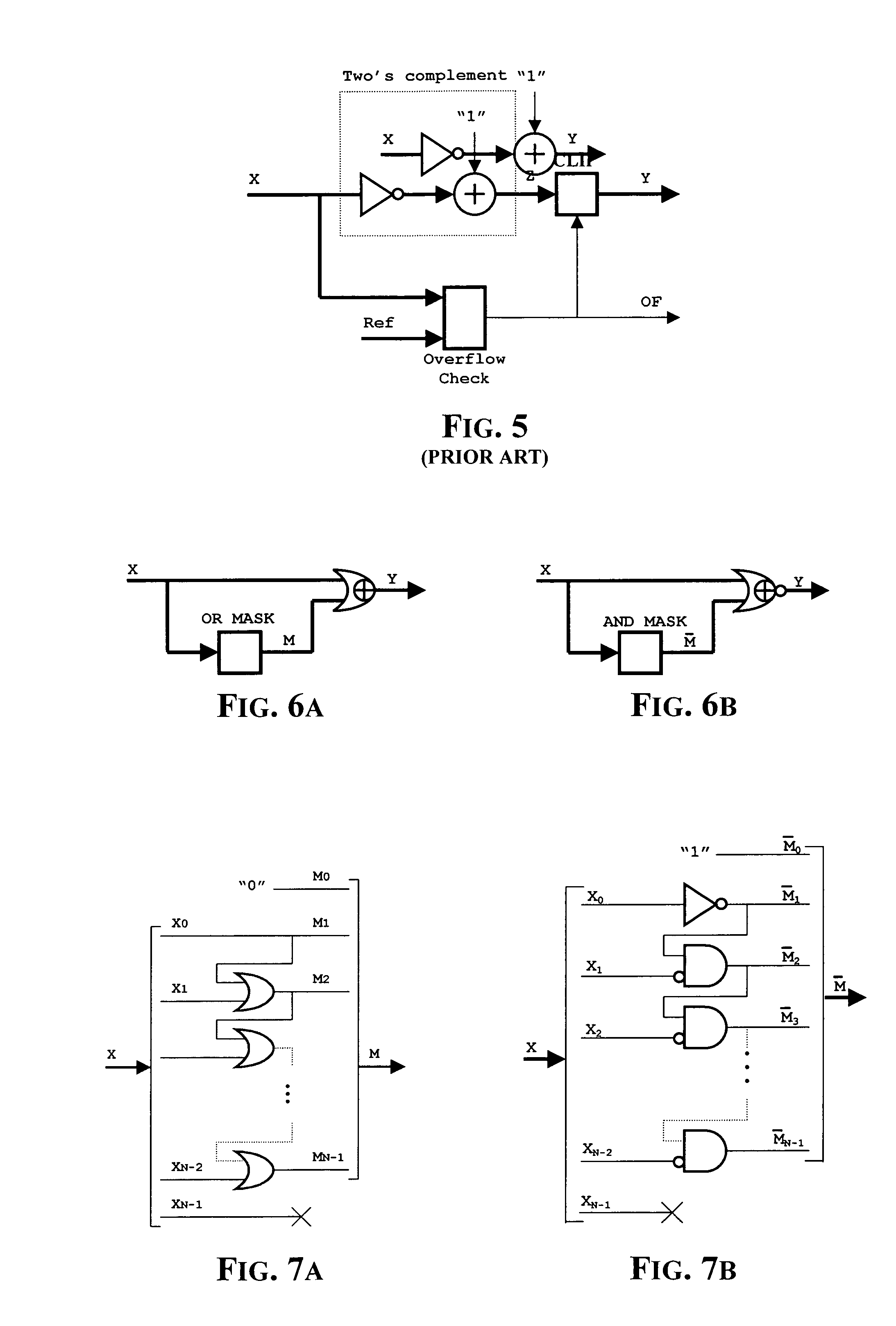

Method and relative circuit for incrementing, decrementing or two's complementing a bit string

InactiveUS7395305B2Conveniently generatedComputation using non-contact making devicesLeast significant bitTheoretical computer science

A method for incrementing, decrementing or two's complementing a first string of bits includes generating an auxiliary string of bits as a function of the first string, and logically combining the auxiliary string with the first string to generate a corresponding output string. A least significant bit of the auxiliary string is independent from the bits of the first string, and any other bit of the auxiliary string. The method is particularly convenient for generating an overflow flag when the number to be output exceeds the representation interval. An overflow flag is generated by logically combining the most significant bits of the first and auxiliary strings.

Owner:STMICROELECTRONICS SRL

Time pulse synchronization method in rdss satellite navigation system

ActiveCN103676634BGuaranteed Time AccuracyOutput time synchronization pulseRadio-controlled time-piecesTime deviationNavigation system

The invention discloses a time pulse synchronization method based on an RDSS satellite navigation system. According to the method, based on a local clock, time deviation between the local clock and BDT is worked out according to time stamps and deviation adjustment information which are carried by RDSS downlink signals; the time deviation is adjusted to an output local clock overflow flag, and a pulse per second is output at the overflow moment. Because the local clock is adopted as reference in the adjustment process, time synchronization reliability is effectively improved.

Owner:NO 54 INST OF CHINA ELECTRONICS SCI & TECH GRP

Global overflow method for virtualized transactional memory

InactiveCN101097544BMemory adressing/allocation/relocationMicrocontrol arrangementsVirtualizationParallel computing

A method and apparatus for virtualizing and / or extending transactional memory is described herein. Transactions are executed using local shared transactional memory, such as a cache memory. Upon overflowing the shared transactional memory, the transactional memory is virtualized and / or extended into a higher-level memory, such as a system memory. Upon an overflow event, such as an eviction of a cache line previously accessed during a currently pending transaction, an overflow flag is set to notify processors / cores that the transactional memory is to be virtualized in a global overflow table. A base address of the global overflow table is also potentially stored to reference the base of the global overflow table in the higher-level memory.

Owner:INTEL CORP

Speech prompt device for intelligent phone set

InactiveCN1210929CAvoid misuseImprove securitySpeech amplifier applicationsSubstation speech amplifiersMicrocontrollerMode control

Owner:TSINGHUA UNIV +1

A counter ip core connected with a 16-bit microprocessor application system and a method for realizing counter counting control

InactiveCN105117200BEasy to program controlGood value for moneyMachine execution arrangementsControl system16-bit

A counter IP core connected with a 16-bit microprocessor application system, including data input and output and command word decomposition storage control module, pulse 200 frequency divider, counting processing control module, counter overflow flag control module and input gate selection control Module; the present invention uses FPGA design counter IP core hard connection control circuit, counter IP core has 15 16-bit counters, 14 of which can form 7 32-bit counters, one command word sets the operating mode of a counter, and counts and filters the reference clock Frequency division multiple, working state control; the present invention does not occupy 16-bit microprocessor program execution time except that the 16-bit microprocessor performs function and state setting, counting parameter transmission, and counting current value operation on the counter; each 16 The bit / 32-bit counter has the function of automatically reloading counting parameters; it can meet the needs of a large number of counter counting and counting control systems.

Owner:GUANGXI UNIVERSITY OF TECHNOLOGY

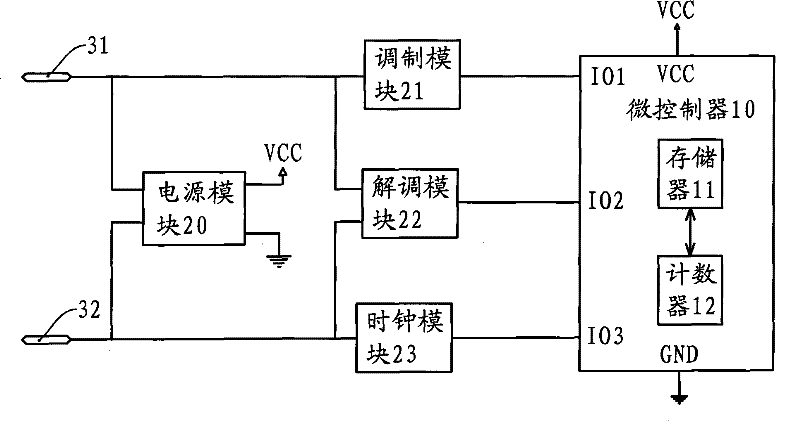

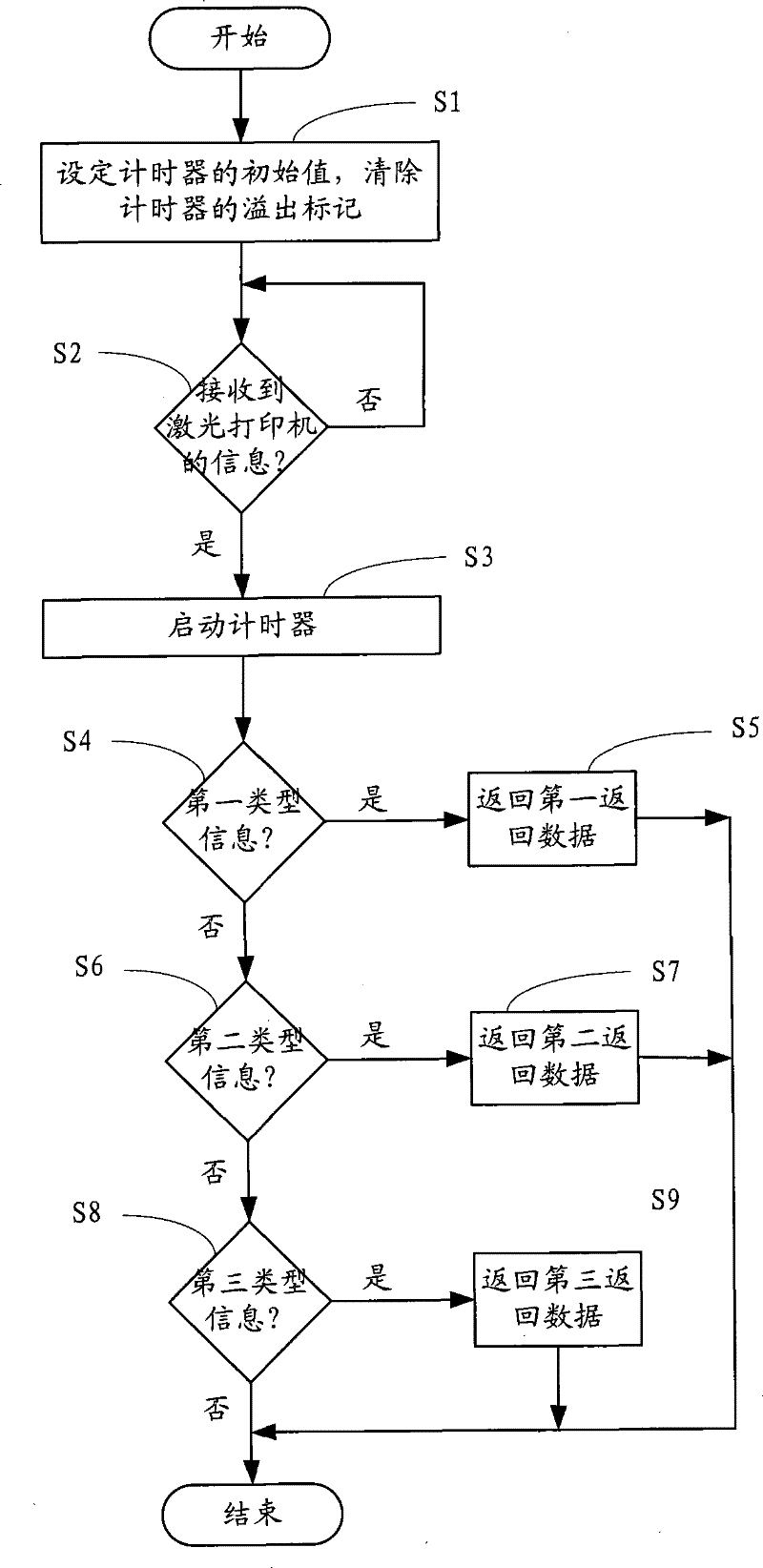

Synchronization method for printing consumable chip data transmission

InactiveCN101609297BReduce manufacturing costError preventionElectrography/magnetographyMicrocontrollerTimer

The invention provides a method for synchronizing data transmission of printing consumable chips. The data is stored in the memory of the electronic module of the printing consumable chip. The electronic module is provided with a micro-controller which can exchange information with the outside. The return time of returning data to the outside. There is a counter in the microcontroller. The method includes determining the reference time, applying the integer multiple of the reference time setting and a remaining time accumulation result to represent the return time, and the reference time, reference time The integer multiple of the time setting and the remaining time are stored in the memory. The microcontroller judges whether the information transmitted from the outside is received. If it is to start the counter and generate the returned data, it judges the number of times the counter overflow flag is set and the integer set by the reference time. The times are equal, so the return data is sent when the counter counts to the end of the remaining time. The present invention can use the counter with fewer digits to realize the timing of the return time and reduce the production cost of the electronic module.

Owner:ZHUHAI TIANWEI TECH DEV CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com