Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

159 results about "Memory copy" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Memory Copy can be used to quickly make the tower of blocks. Start with a set of three blocks, each a component. Then make a component from the three components. (Memory Copy only works on components.)

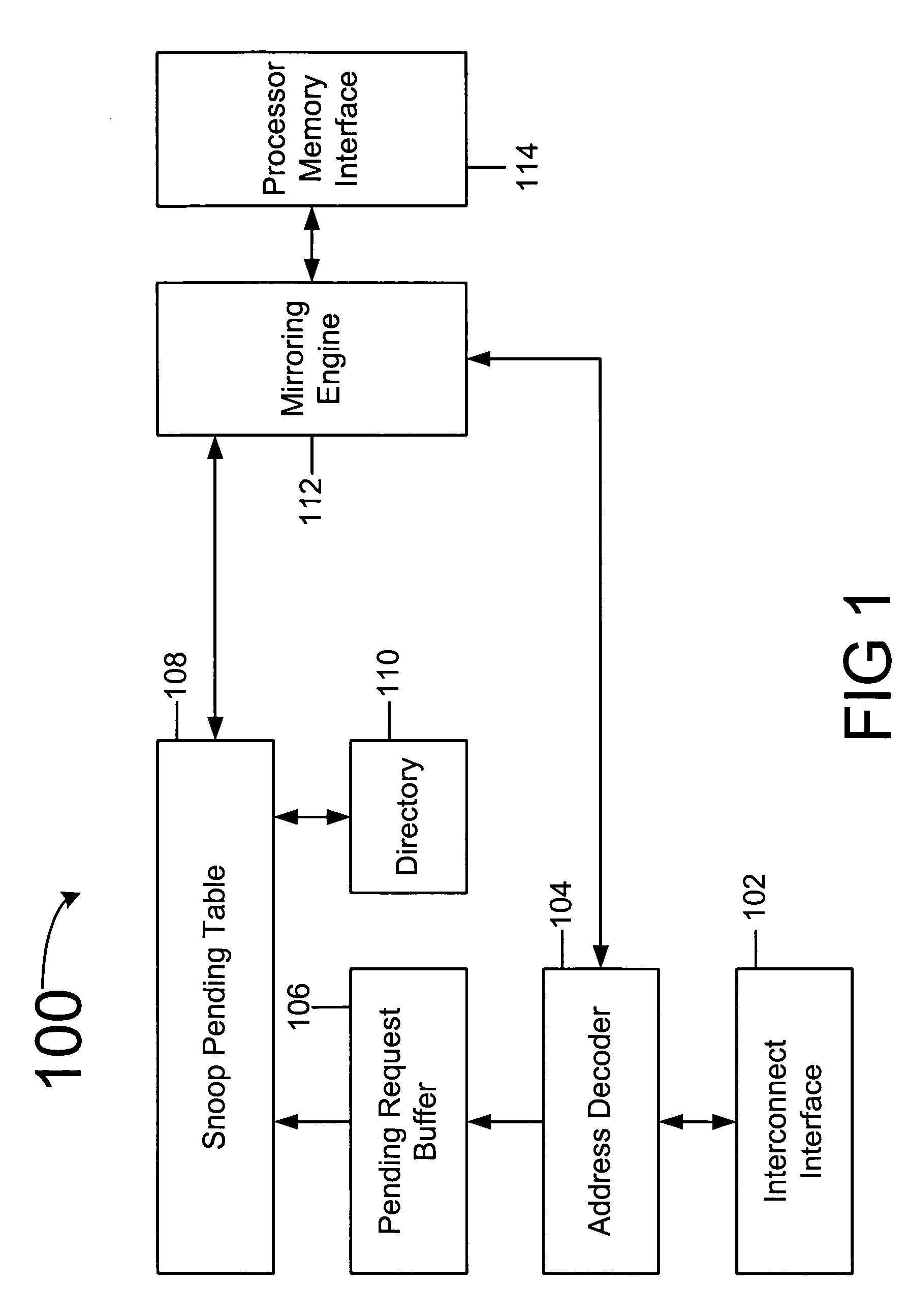

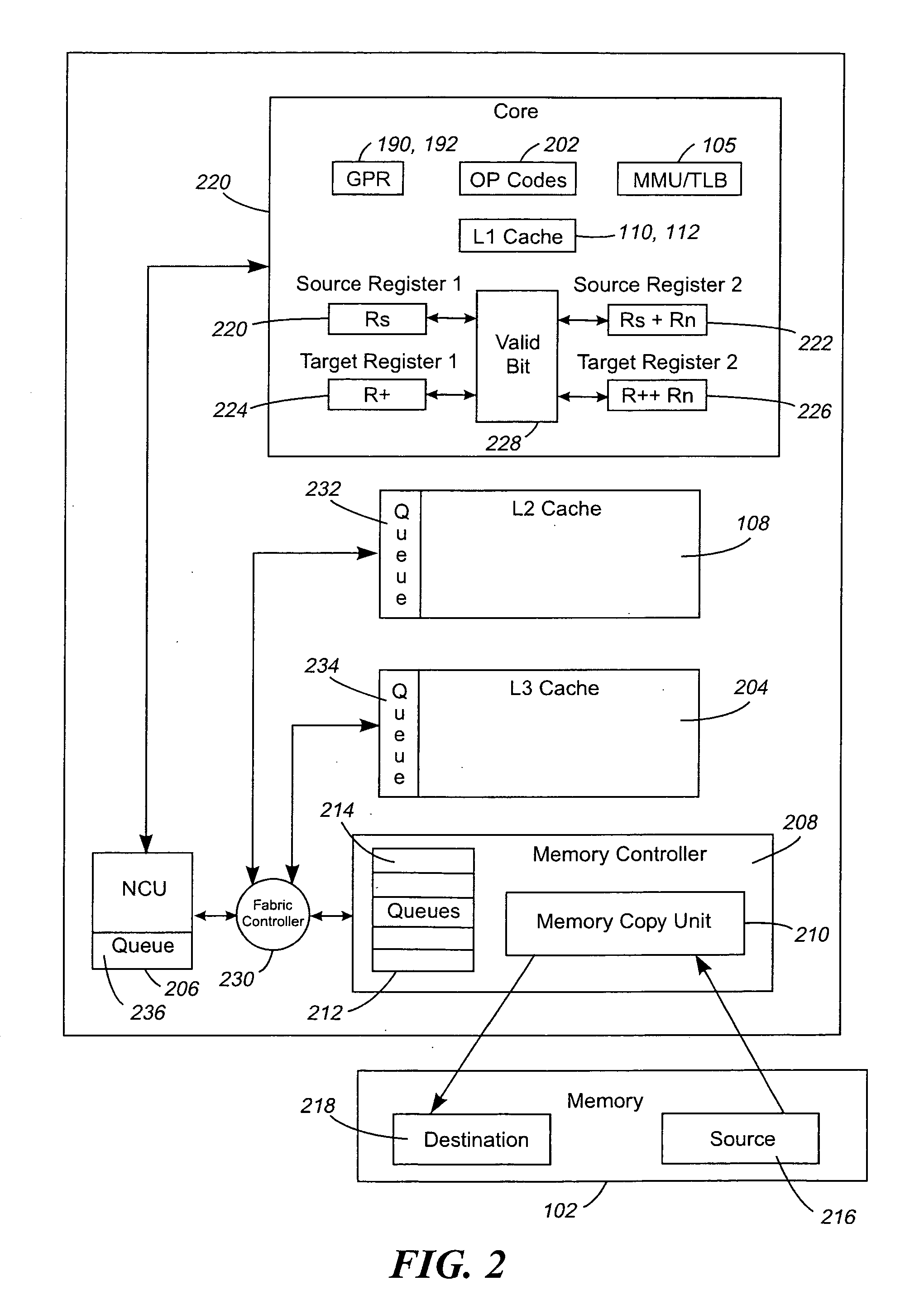

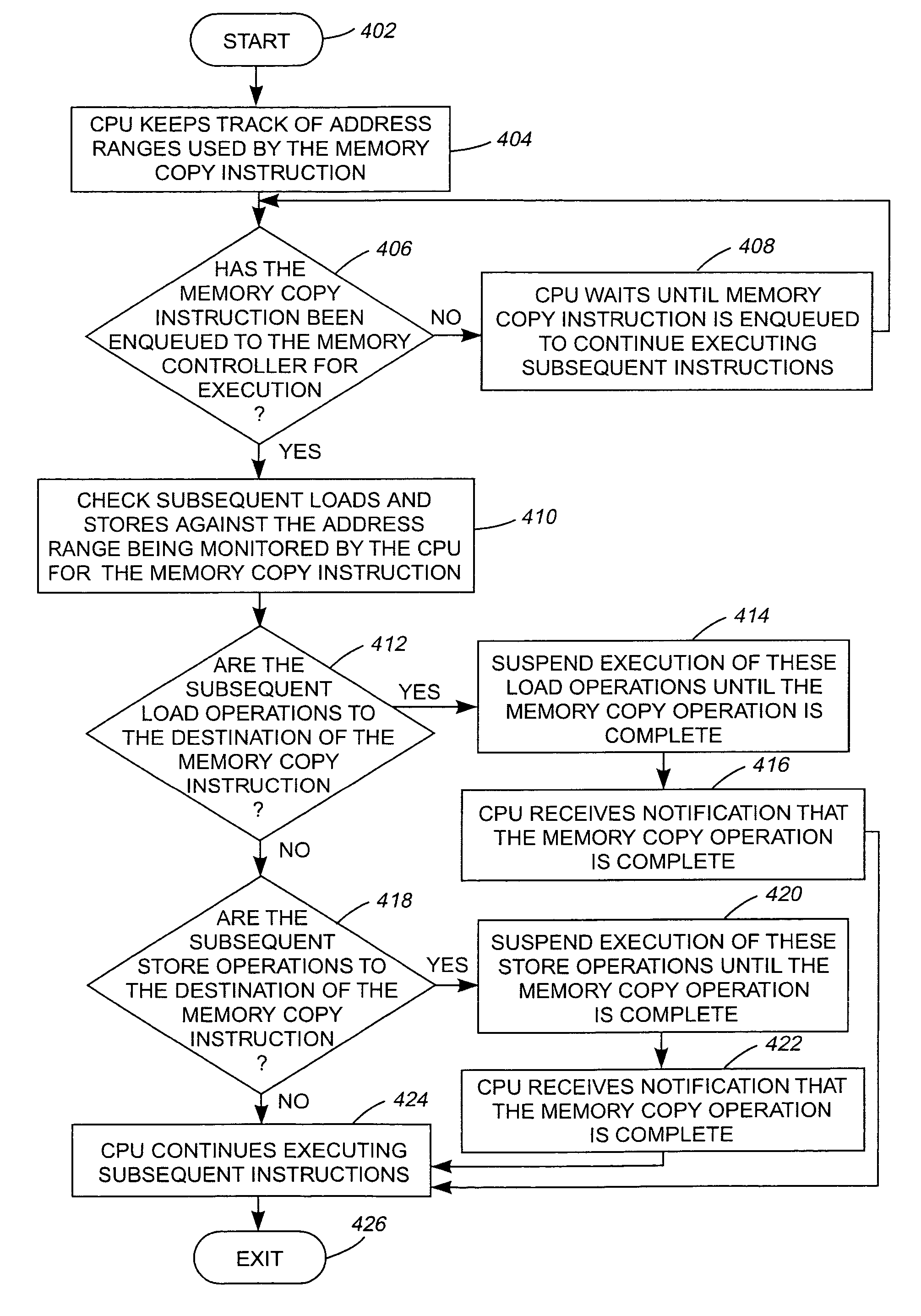

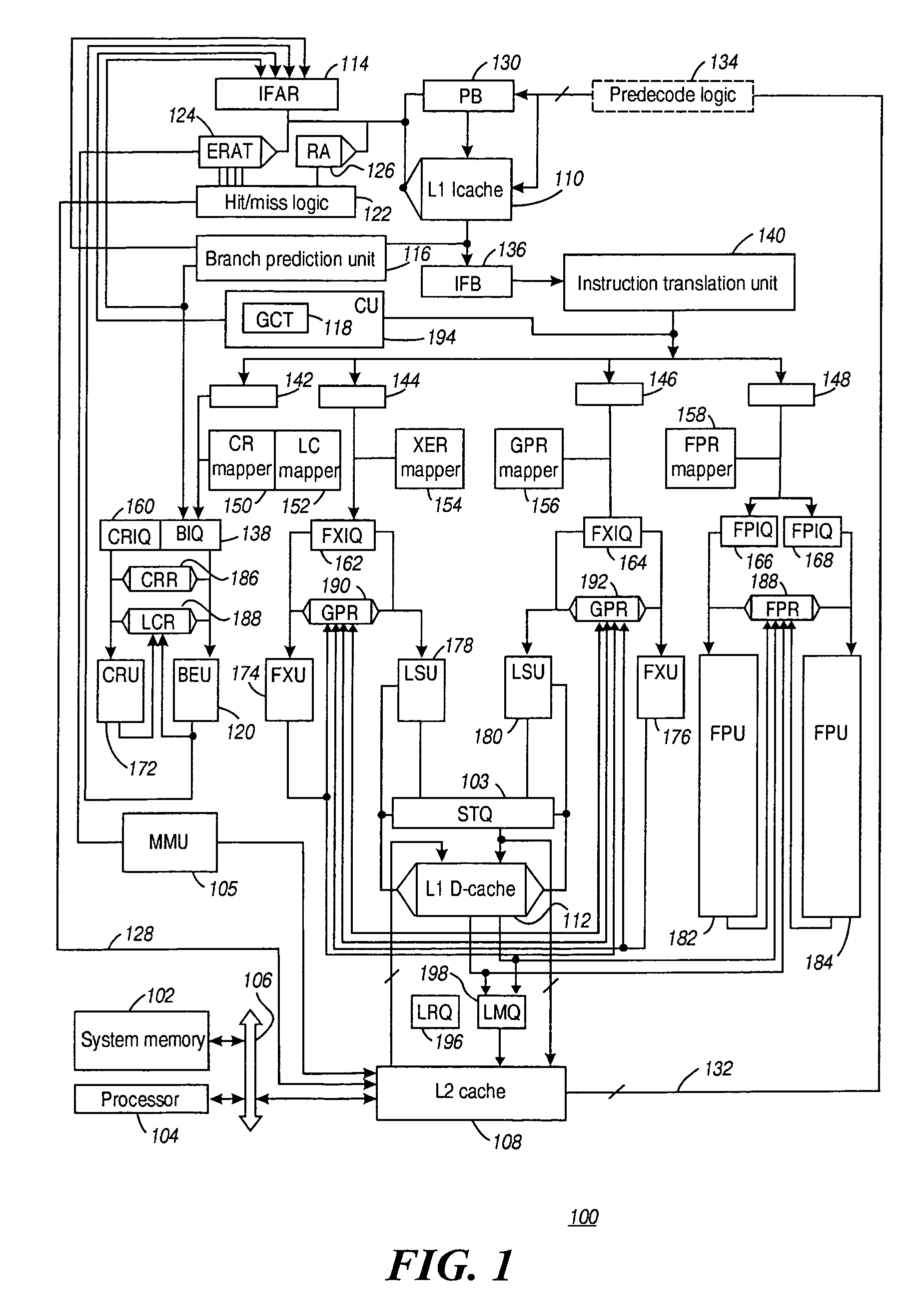

Synchronizing memory copy operations with memory accesses

In some embodiments, a comparator compares an incoming memory address with a memory address currently being copied by a memory copy operation. A holding buffer holds the incoming address prior to forwarding it to a memory read / write queue if the incoming memory address is the same as the memory address currently being copied by the memory copy operation, forwards the buffered incoming memory address to the read / write queue once the memory copy operation for the memory address currently being copied has finished. Other embodiments are described and claimed.

Owner:INTEL CORP

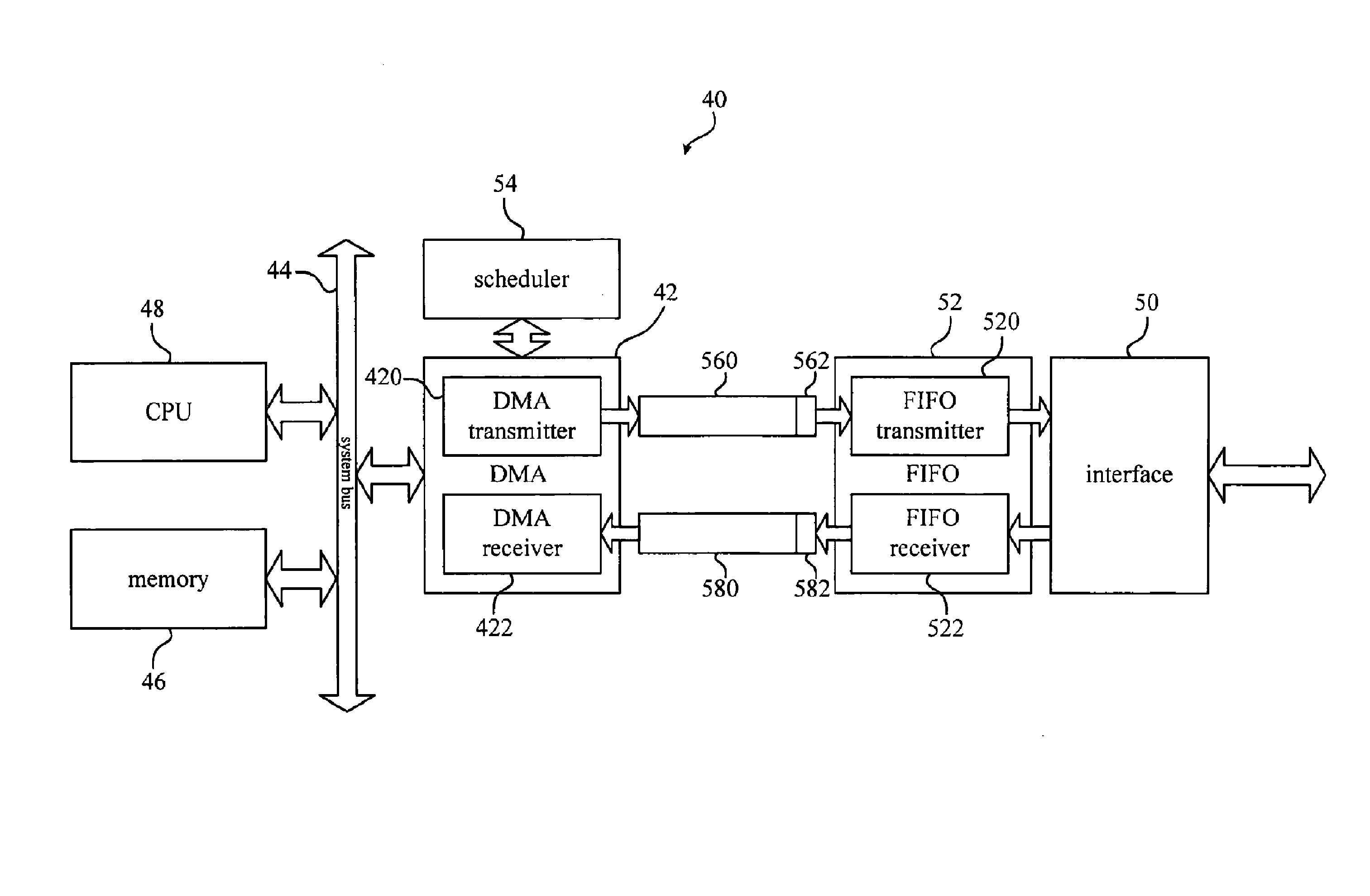

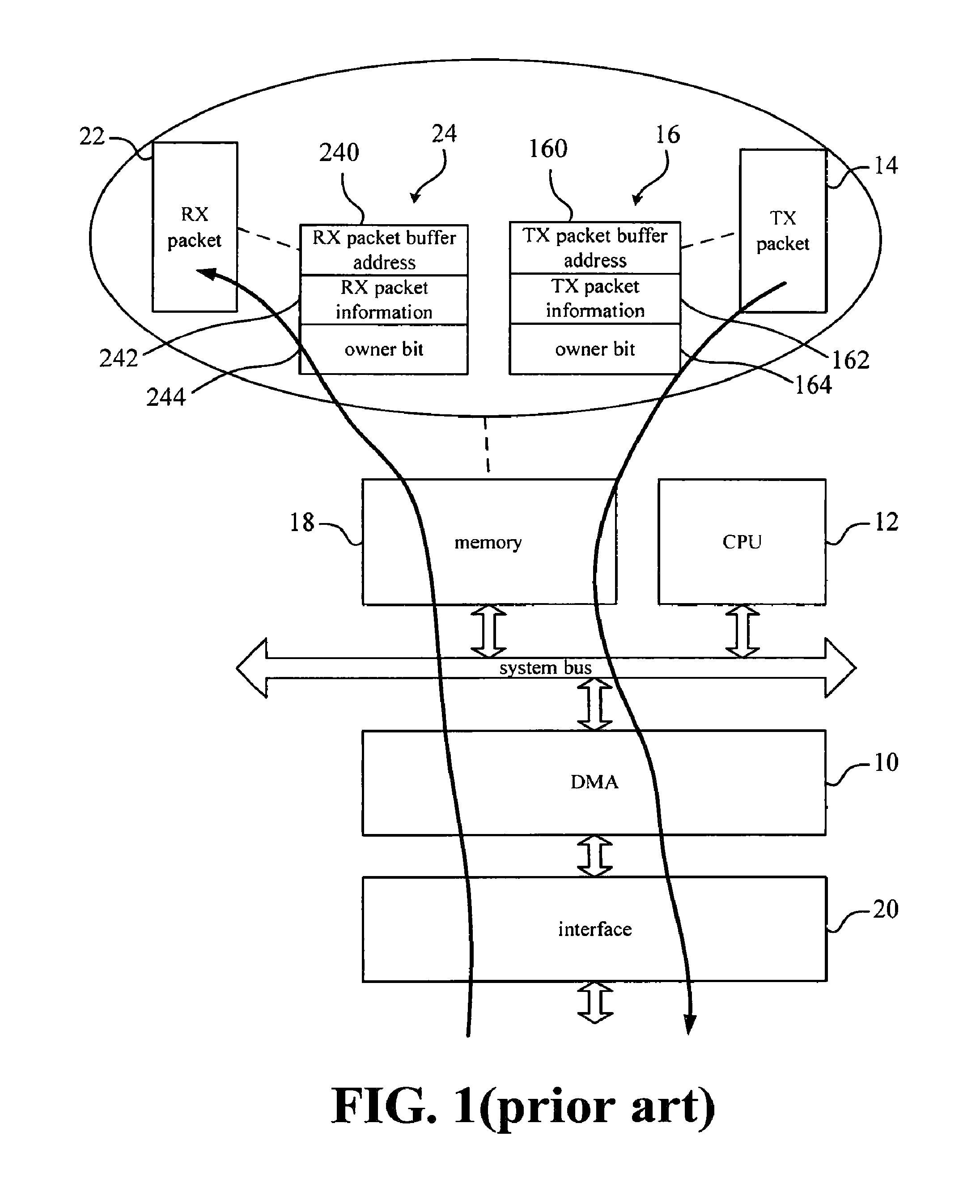

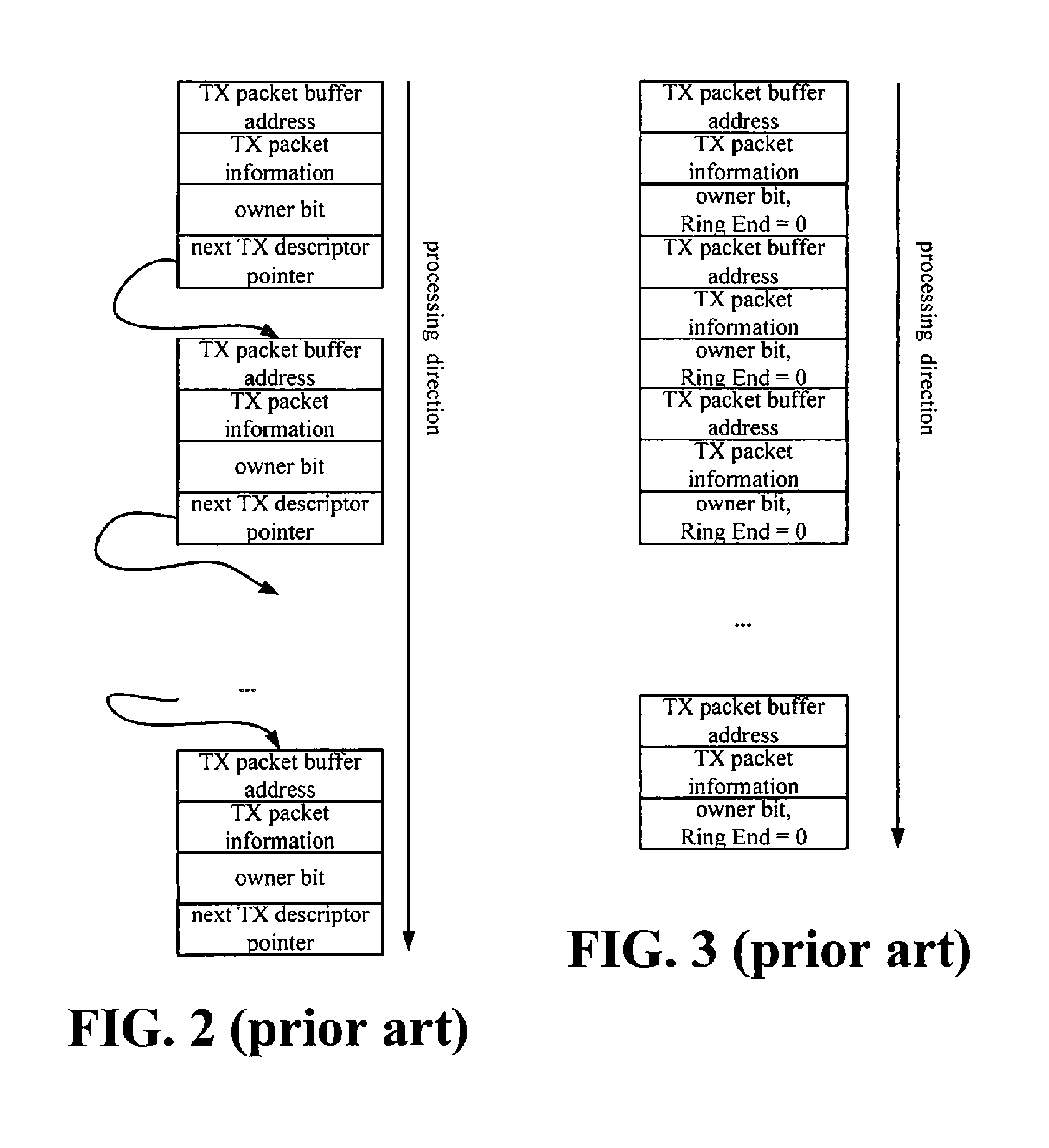

Direct memory access system and method using the same

ActiveUS9021153B2Multiple digital computer combinationsElectric digital data processingComputer architectureDirect memory access

The invention discloses a DMA system capable of being adapted to various interfaces. The DMA system includes the following advantages: 1) the software porting effort can be reduced when different interfaces are integrated into a SoC; 2) a flexible DMA that could provide protocol transparency and could be ported into different interfaces easily; 3) a scalable DMA that can support unlimited TX / RX scattering / gathering data segments; 4) a reusable DMA that provides user defined TX information (or RX information) and TX message (or RX message) field; and 5) a high performance DMA that support unaligned segment data pointers and unlimited scattering / gathering data segments, so as to reduce extra memory copies by CPU.

Owner:MEDIATEK INC

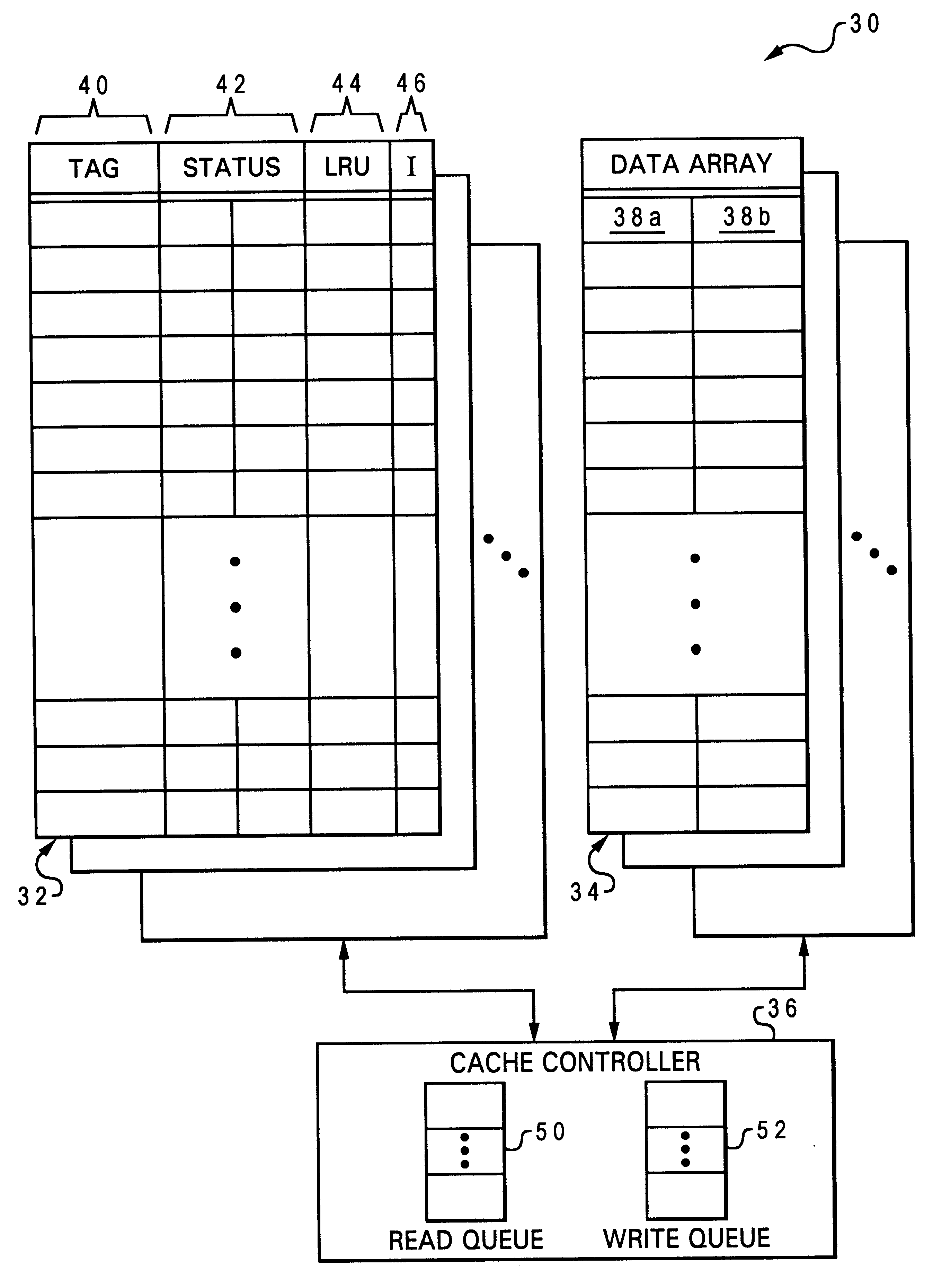

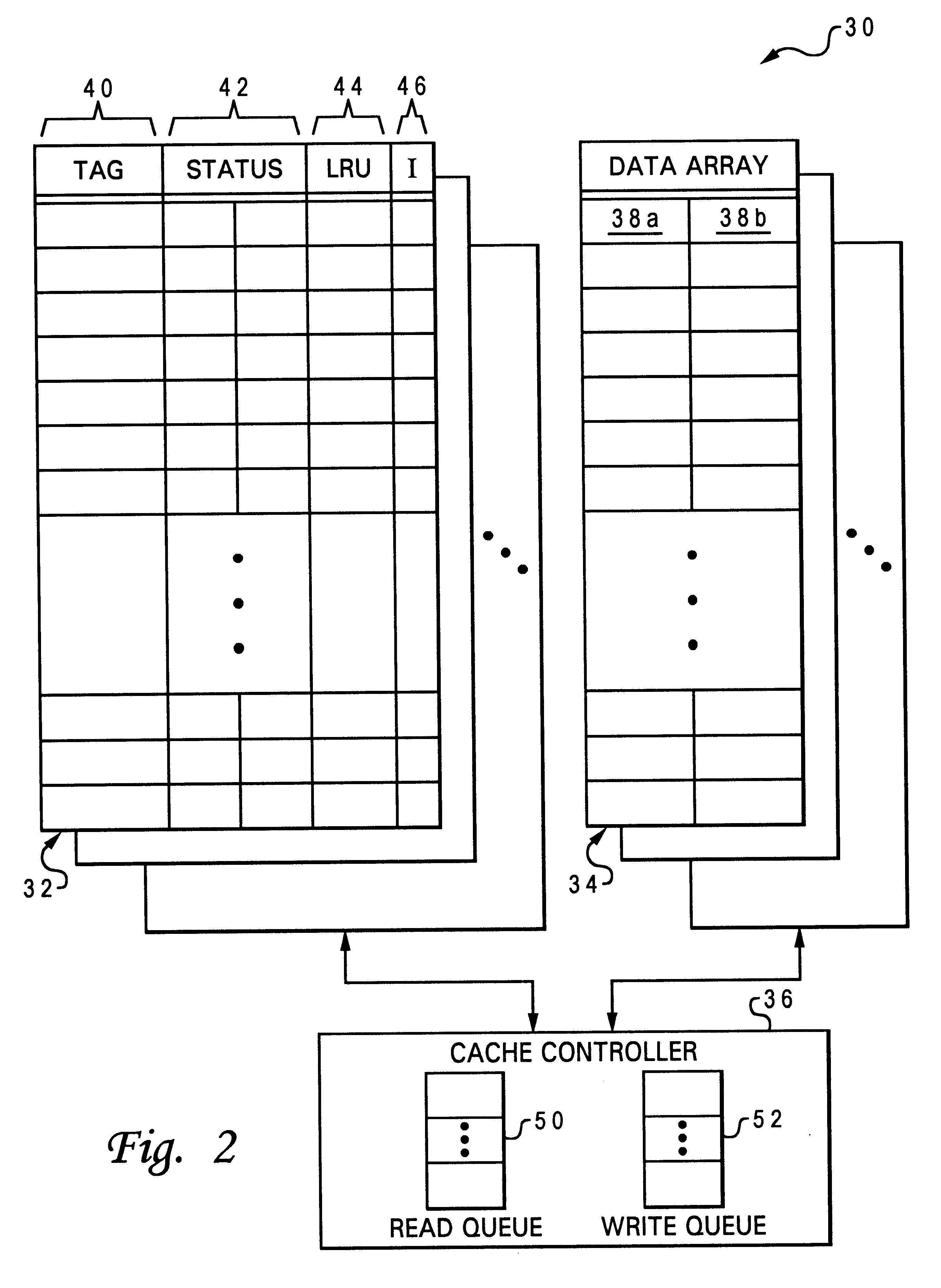

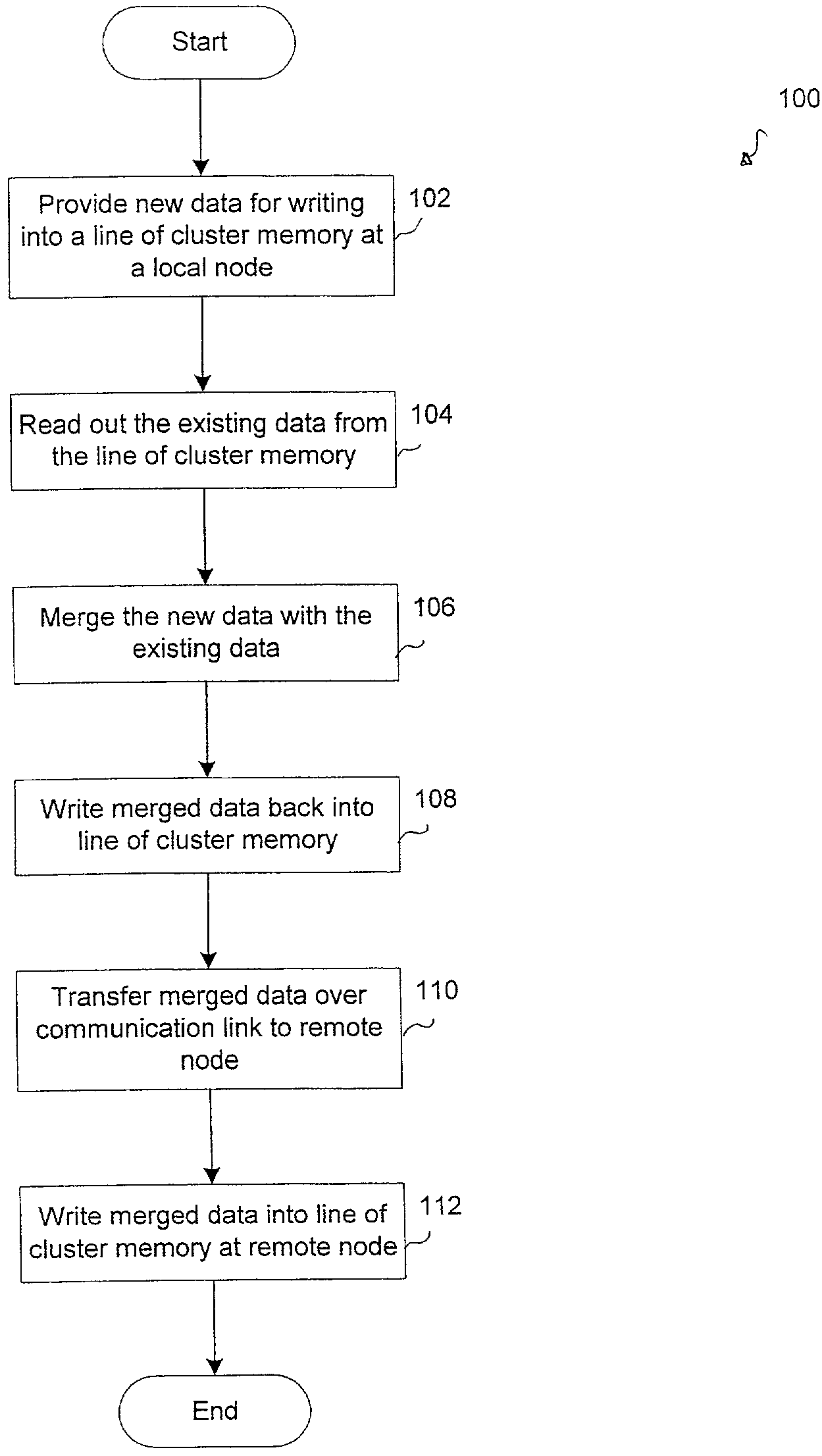

Data processing system, cache, and method that select a castout victim in response to the latencies of memory copies of cached data

A data processing system includes a processing unit, a distributed memory including a local memory and a remote memory having differing access latencies, and a cache coupled to the processing unit and to the distributed memory. The cache includes a congruence class containing a plurality of cache lines and a plurality of latency indicators that each indicate an access latency to the distributed memory for a respective one of the cache lines. The cache further includes a cache controller that selects a cache line in the congruence class as a castout victim in response to the access latencies indicated by the plurality of latency indicators. In one preferred embodiment, the cache controller preferentially selects as castout victims cache lines having relatively short access latencies.

Owner:IBM CORP

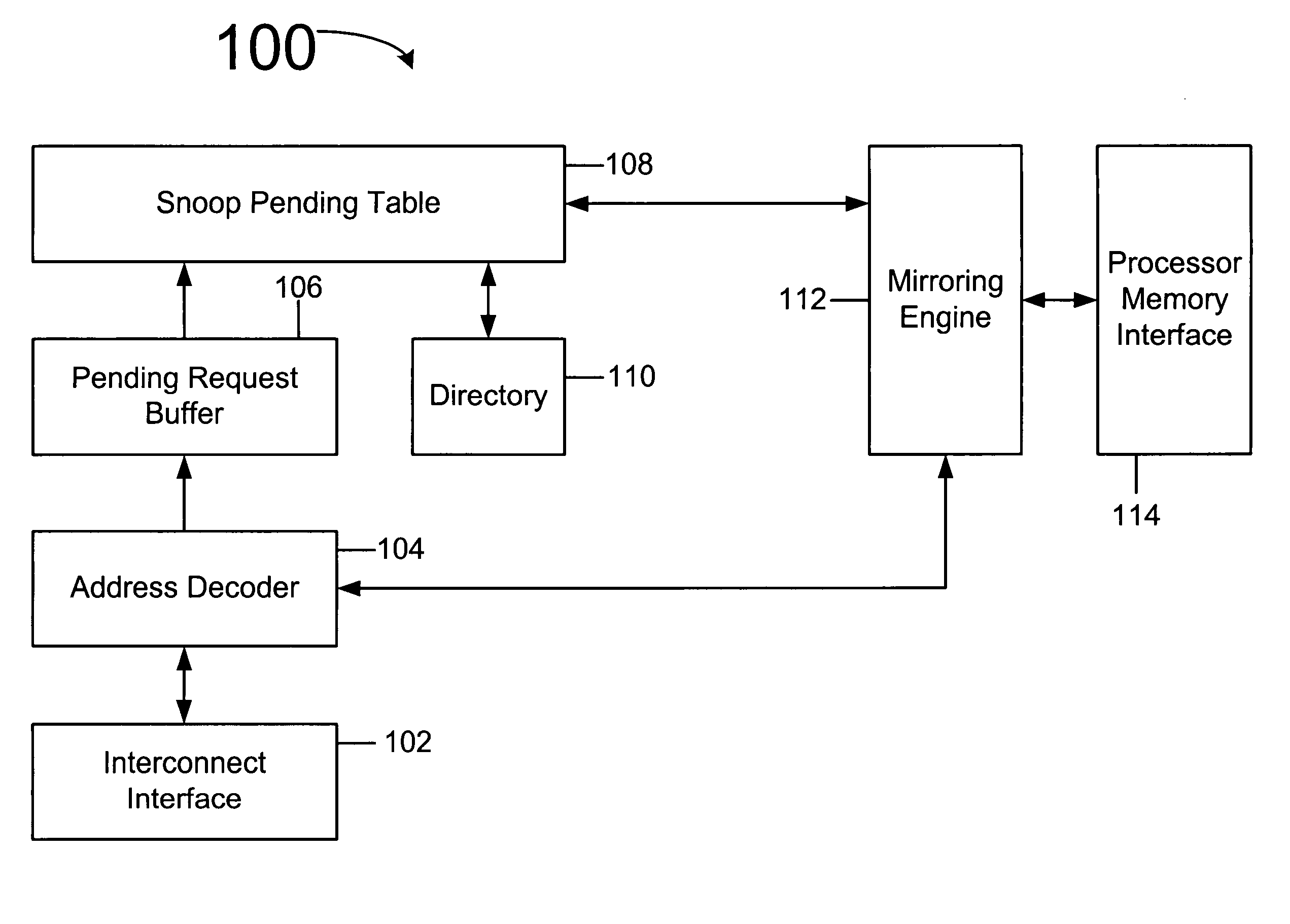

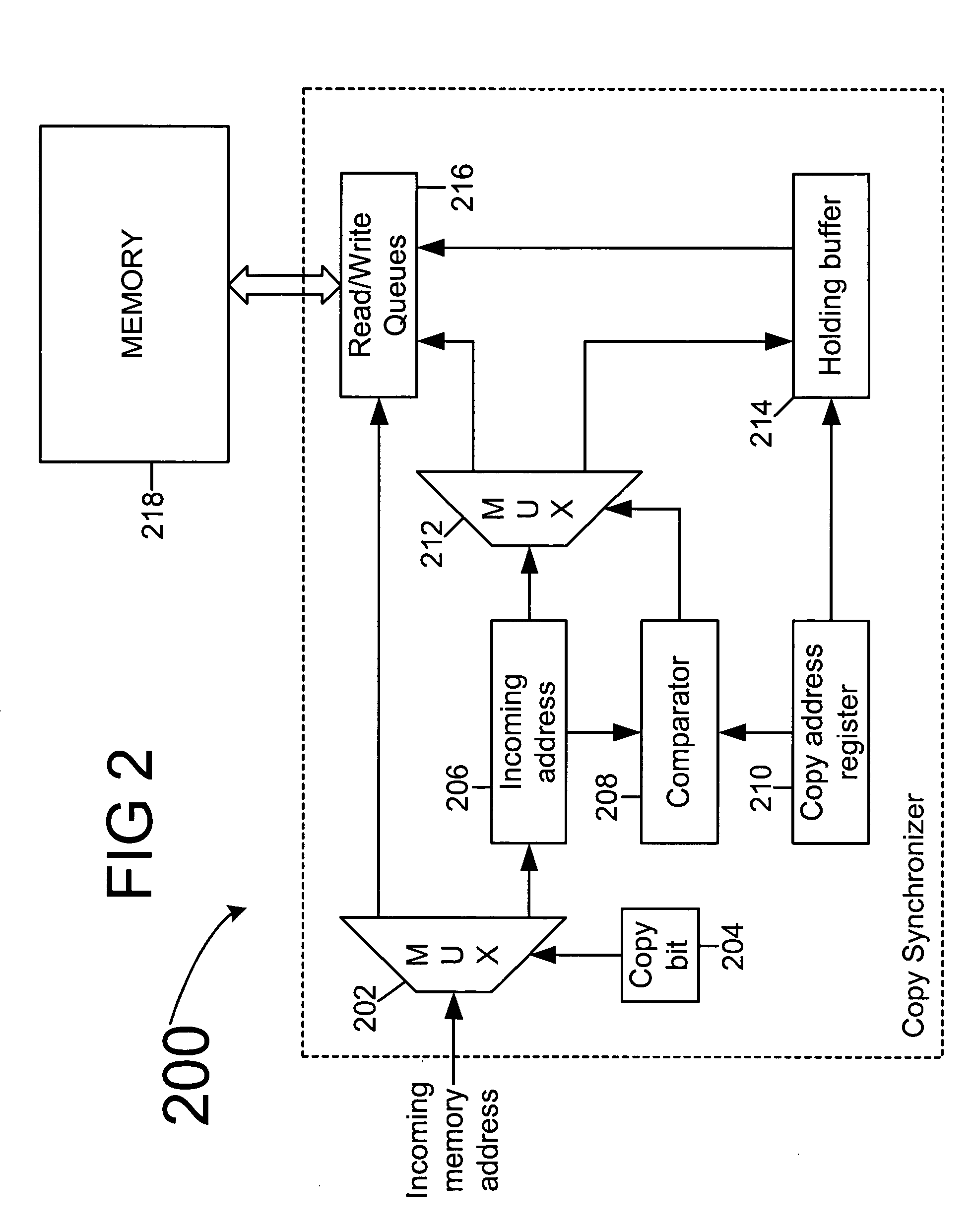

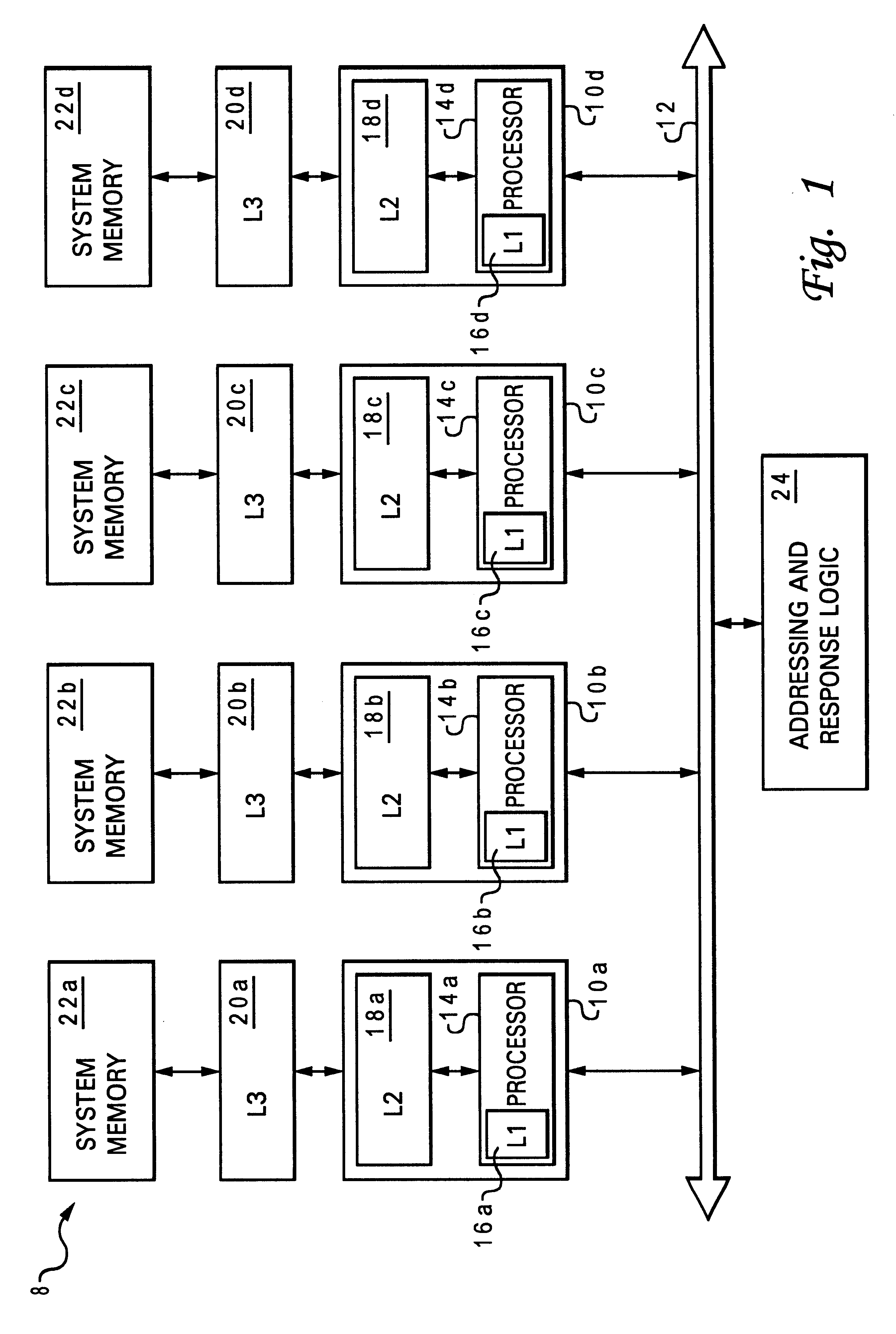

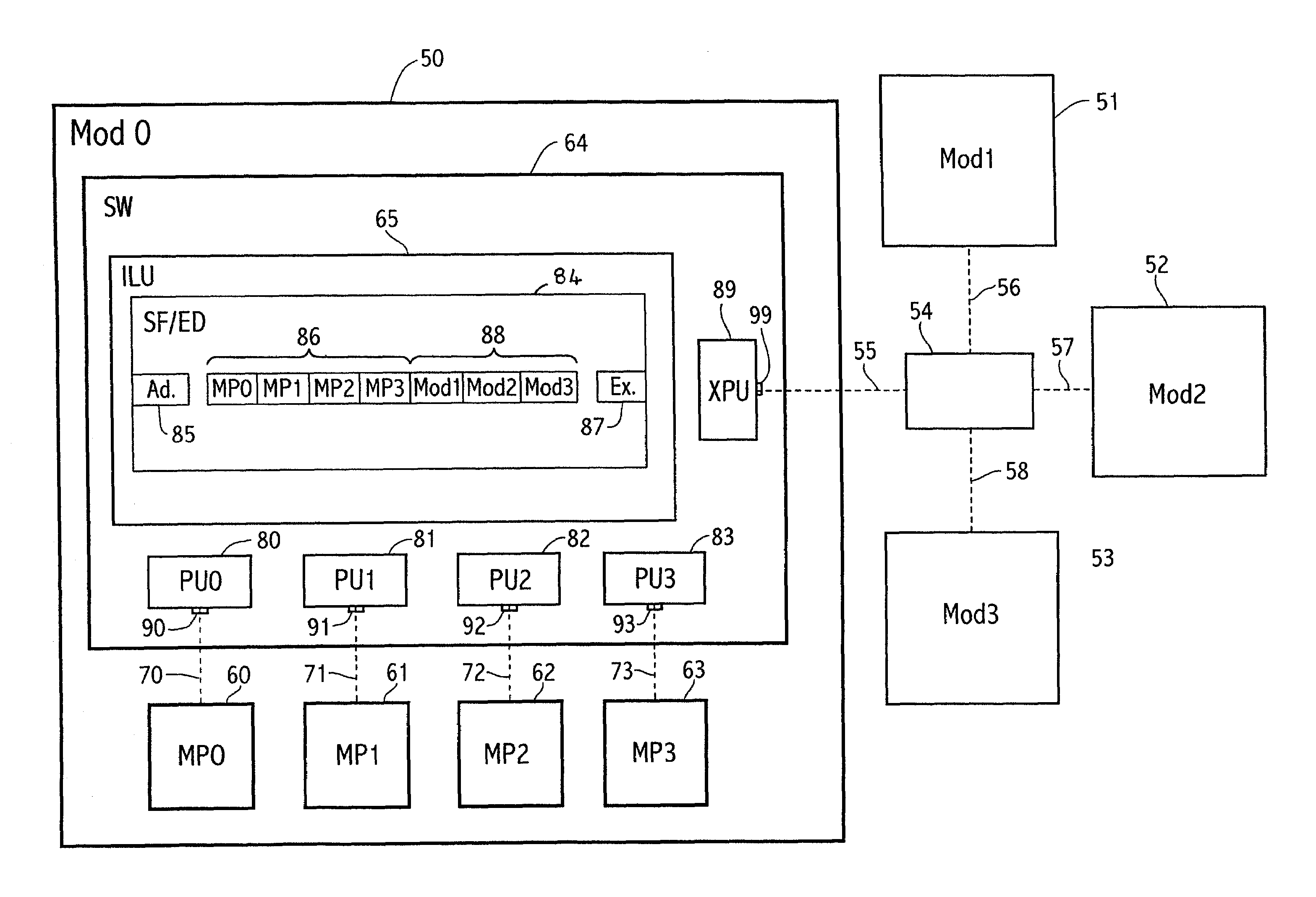

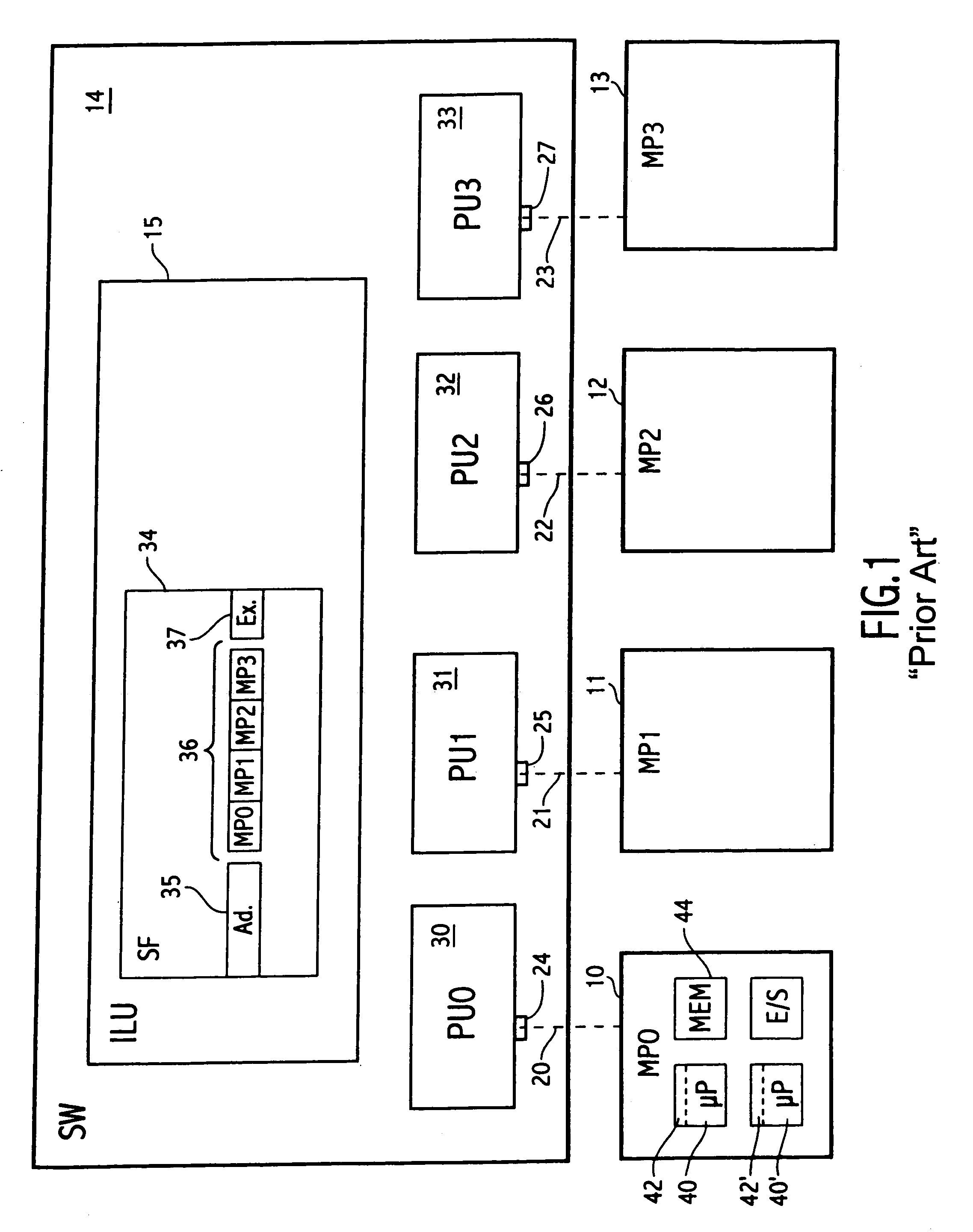

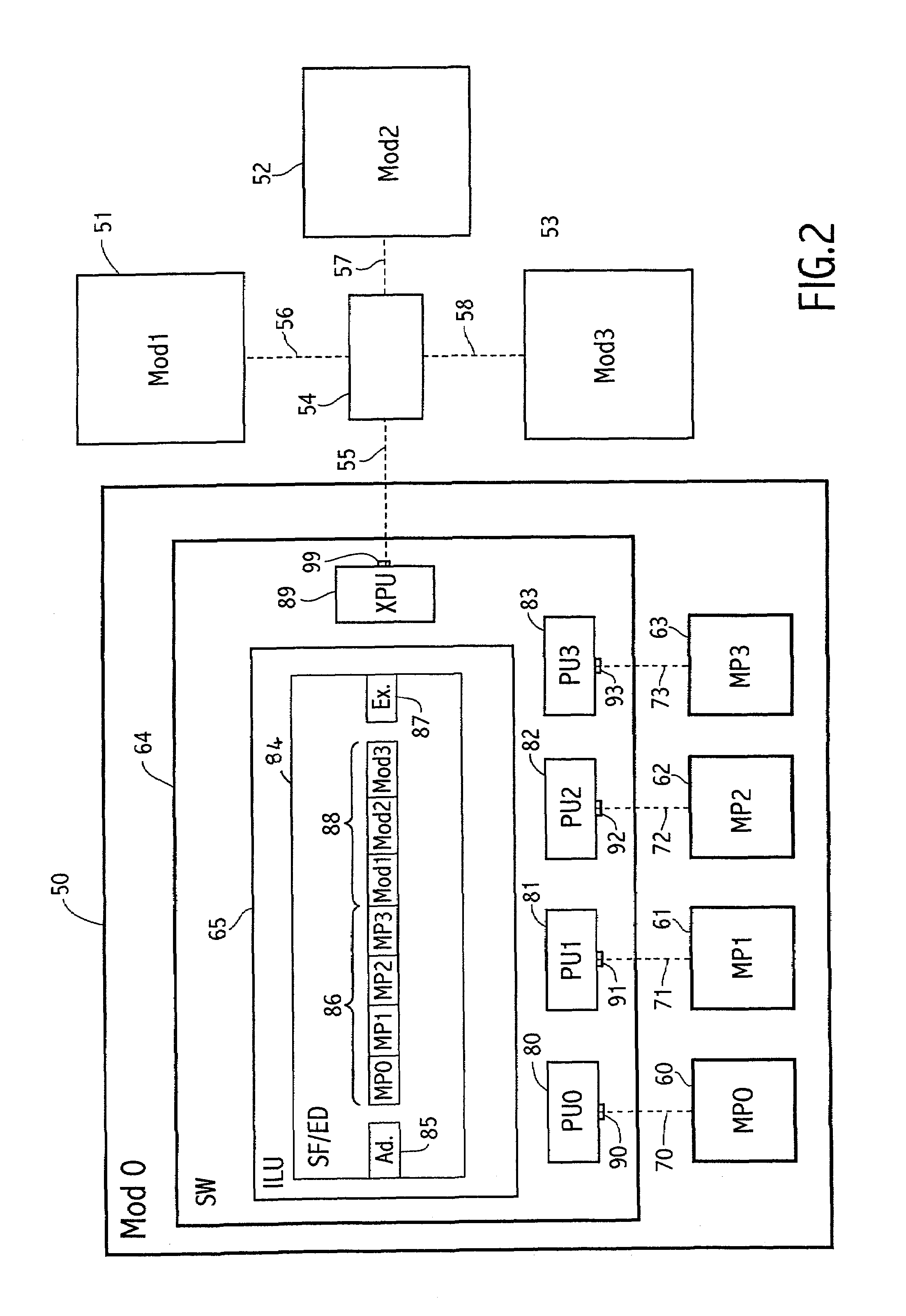

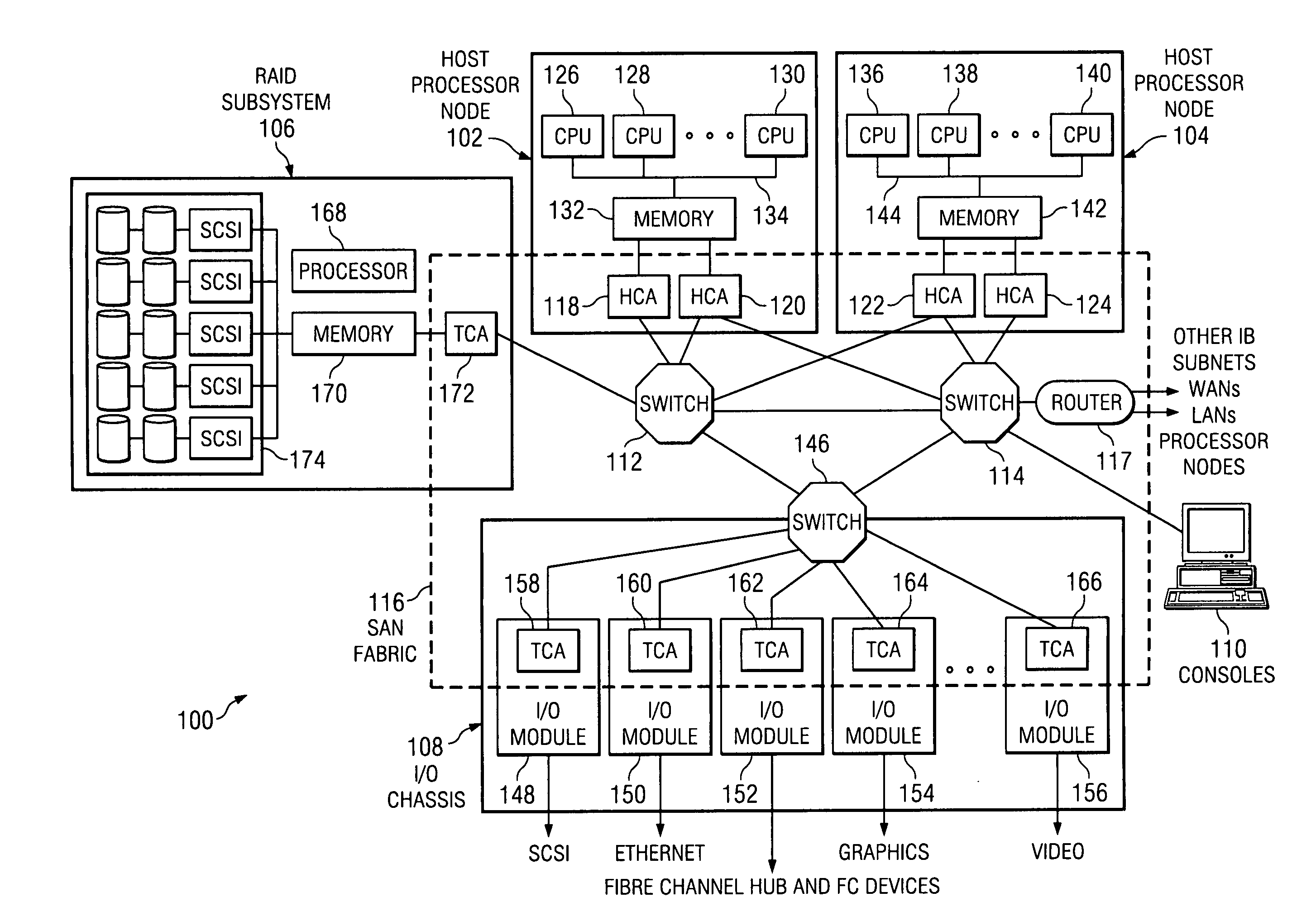

Coherence controller for a multiprocessor system, module, and multiprocessor system with a multimodule architecture incorporating such a controller

InactiveUS7017011B2Improve performanceDrawback can be obviatedMemory systemsMulti processorParallel computing

A coherence controller is included in a module which includes a plurality of multiprocessor units, each of which contains a main memory and processors equipped with respective cache memories. The module may be one of a plurality of similarly constructed modules connected by a router or other type of switching device. The coherence controller in each module includes a cache filter directory having a first filter directory for guaranteeing coherence between the local main memory and the cache memory in each of the processors of the module, and an external port connected to at least one of the other modules. The cache filter directory also includes a complementary filter directory, which tracks locations of lines or blocks of the local main memory copied from the module into other modules, and for guaranteeing coherence between the local main memory and the cache in each of the processors of the module and the other modules.

Owner:BULL SA

Zero-copy data sharing by cooperating asymmetric coprocessors

ActiveUS8645634B1Reduce data duplicationGeneral purpose stored program computerMemory systemsCoprocessorZero-copy

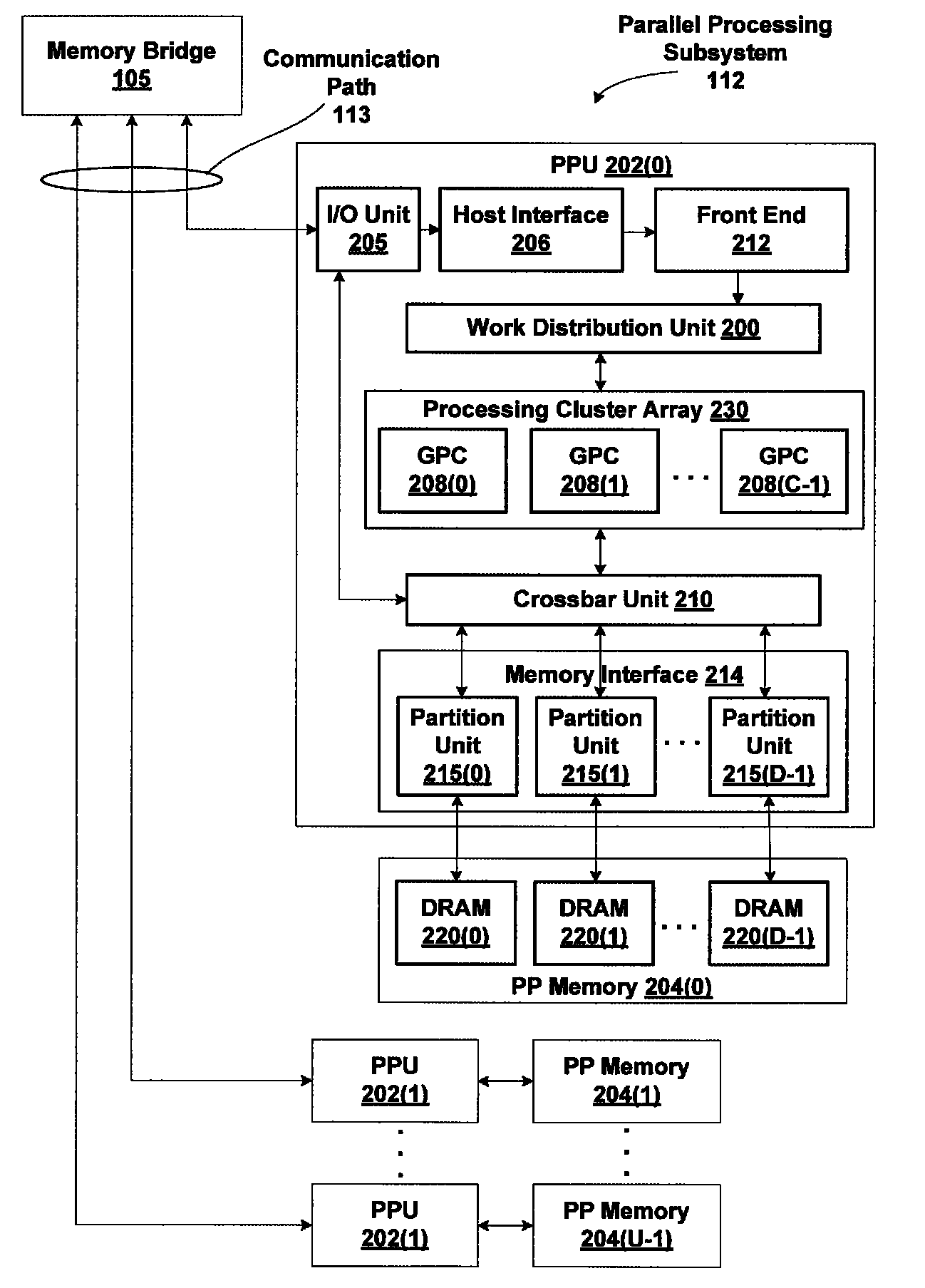

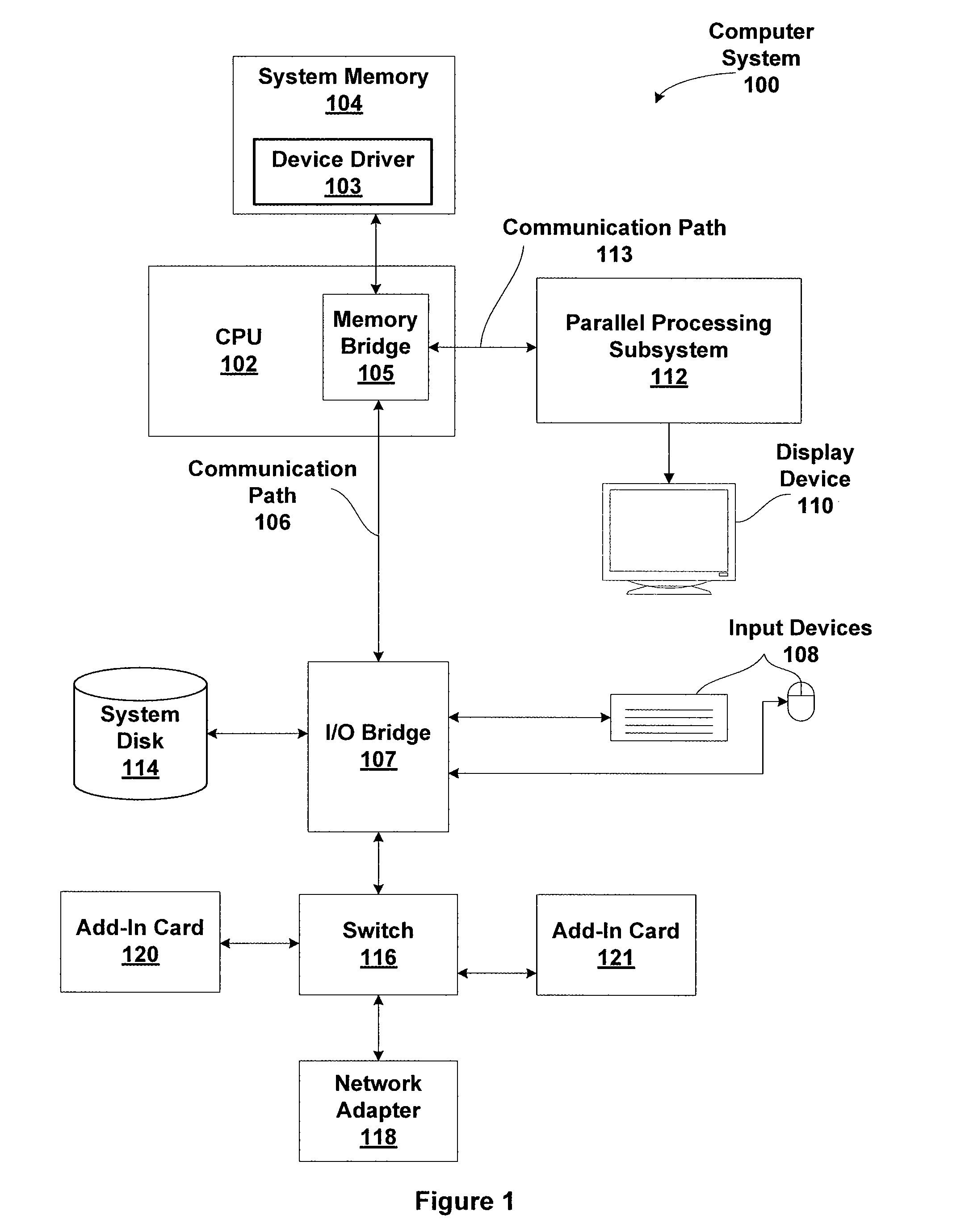

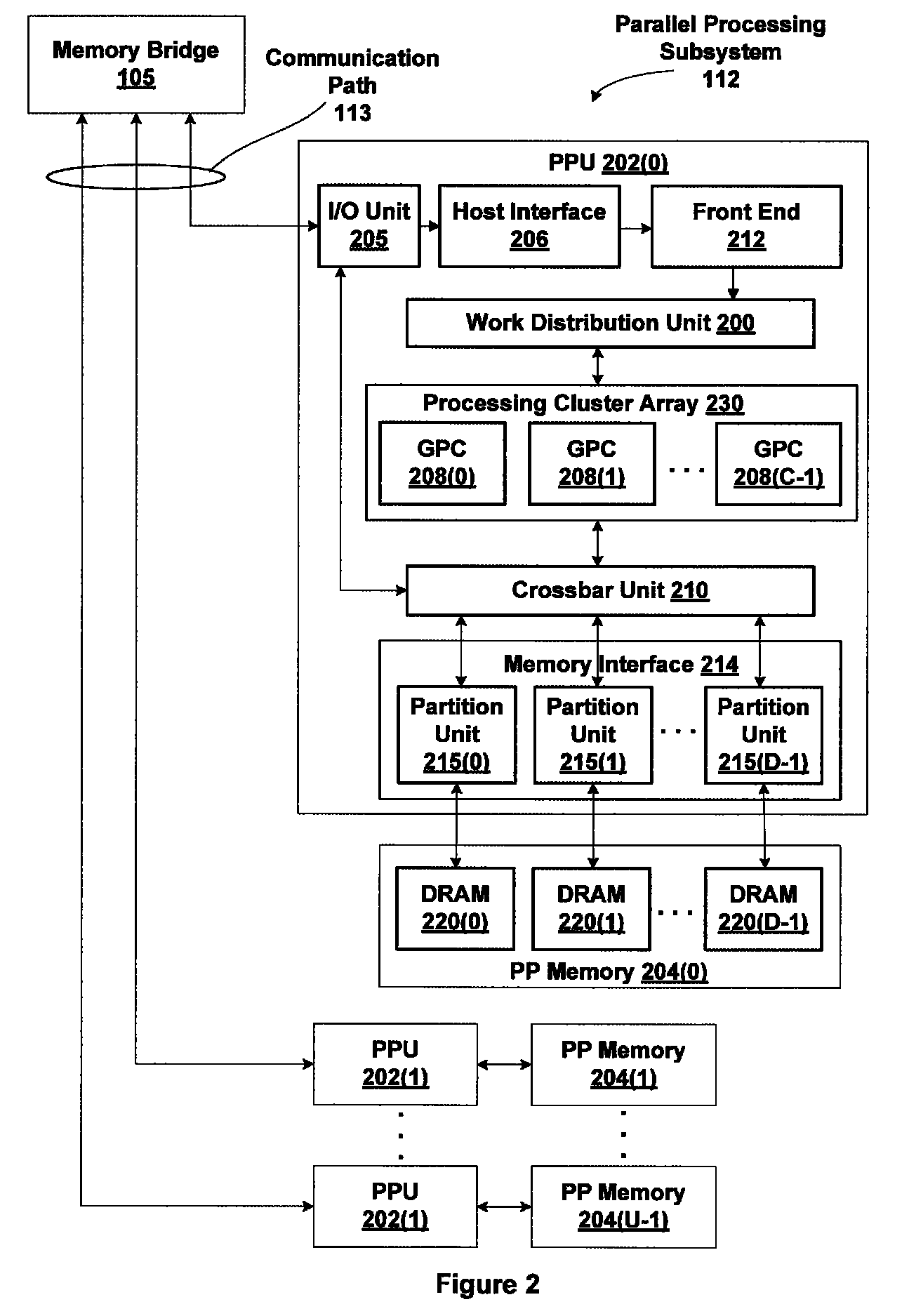

One embodiment of the present invention sets forth a technique for reducing the copying of data between memory allocated to a primary processor and a coprocessor is disclosed. The system memory is aliased as device memory to allow the coprocessor and the primary processor to share the same portion of memory. Either device may write and / or read the shared portion of memory to transfer data between the devices rather than copying data from a portion of memory that is only accessible by one device to a different portion of memory that is only accessible by the other device. Removal of the need for explicit primary processor memory to coprocessor memory and coprocessor memory to primary processor memory copies improves the performance of the application and reduces physical memory requirements for the application since one portion of memory is shared rather than allocating separate private portions of memory.

Owner:NVIDIA CORP

Method and apparatus for efficient determination of memory copy versus registration in direct access environments

ActiveUS20070239905A1TransmissionElectric digital data processingAbstraction layerDirect memory access

A memory registration abstraction layer includes decision logic for dynamic, efficient determination of memory copy versus registration. The exemplary embodiments apply to direct memory access environments. The memory registration abstraction layer also includes tracking logic for monitoring the usage history for certain ranges of memory registration requests. The registration logic chooses to copy memory or map memory based on training and observation of application behavior, taking the more efficient performance path without requiring changes to the application.

Owner:TWITTER INC

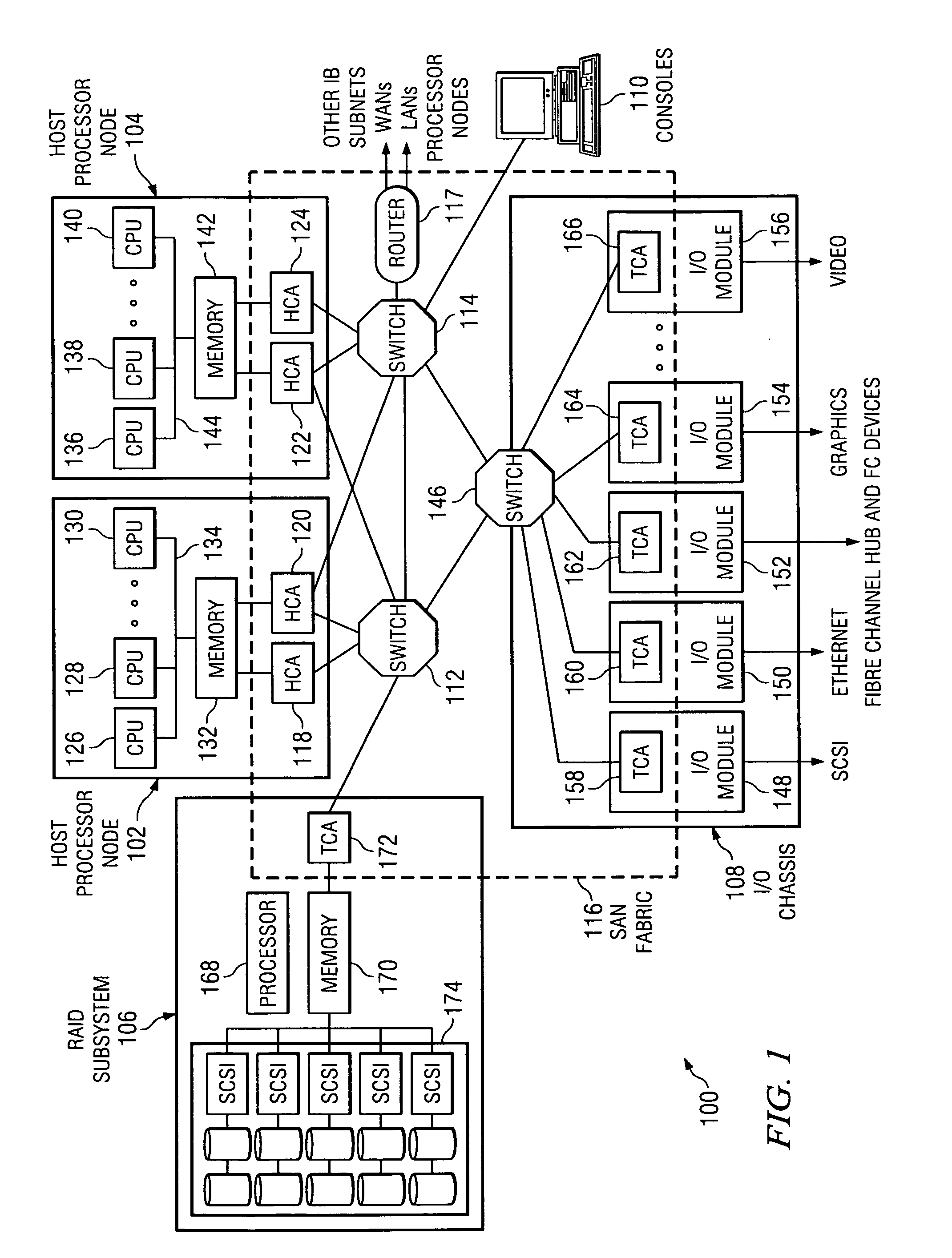

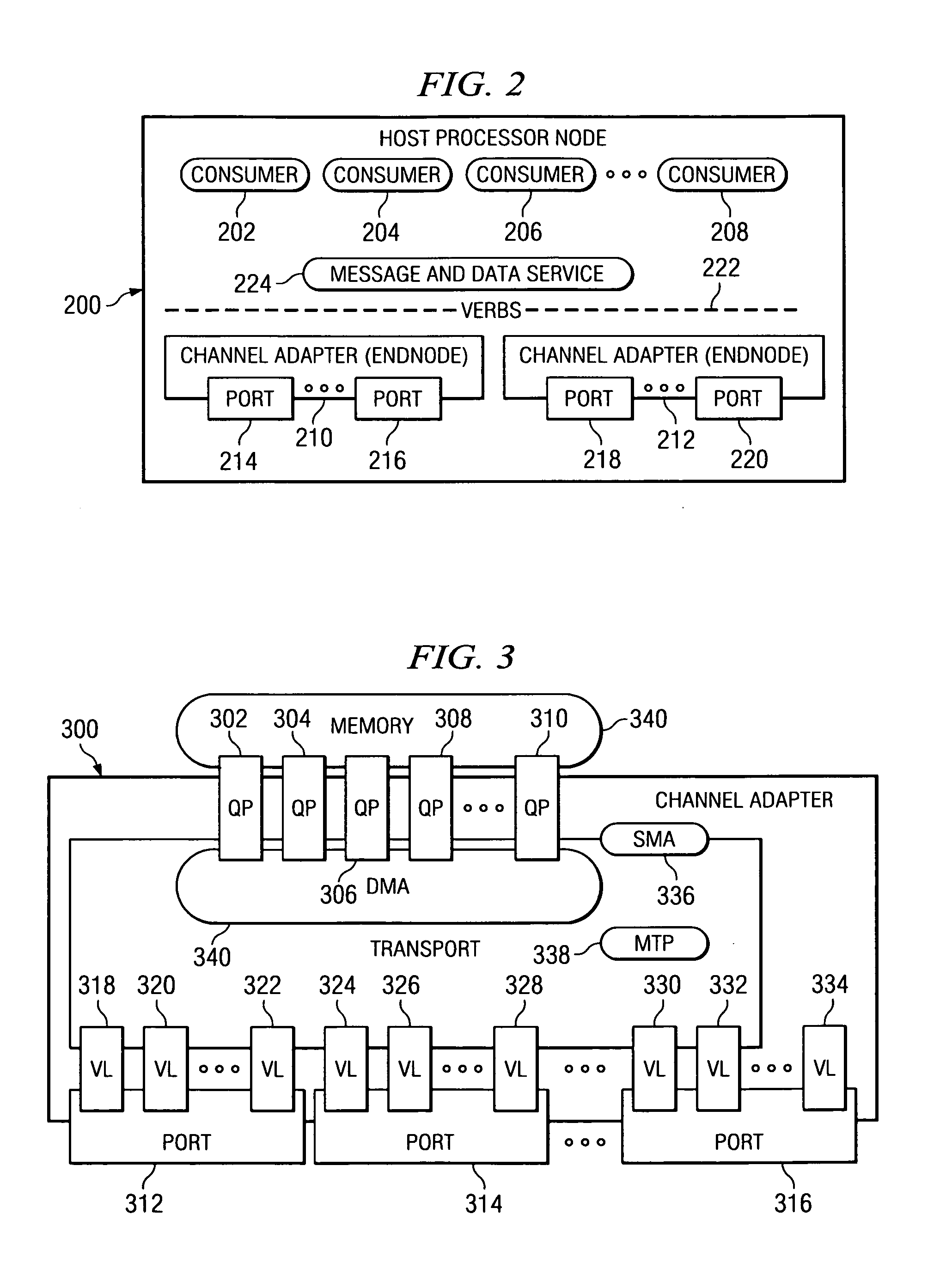

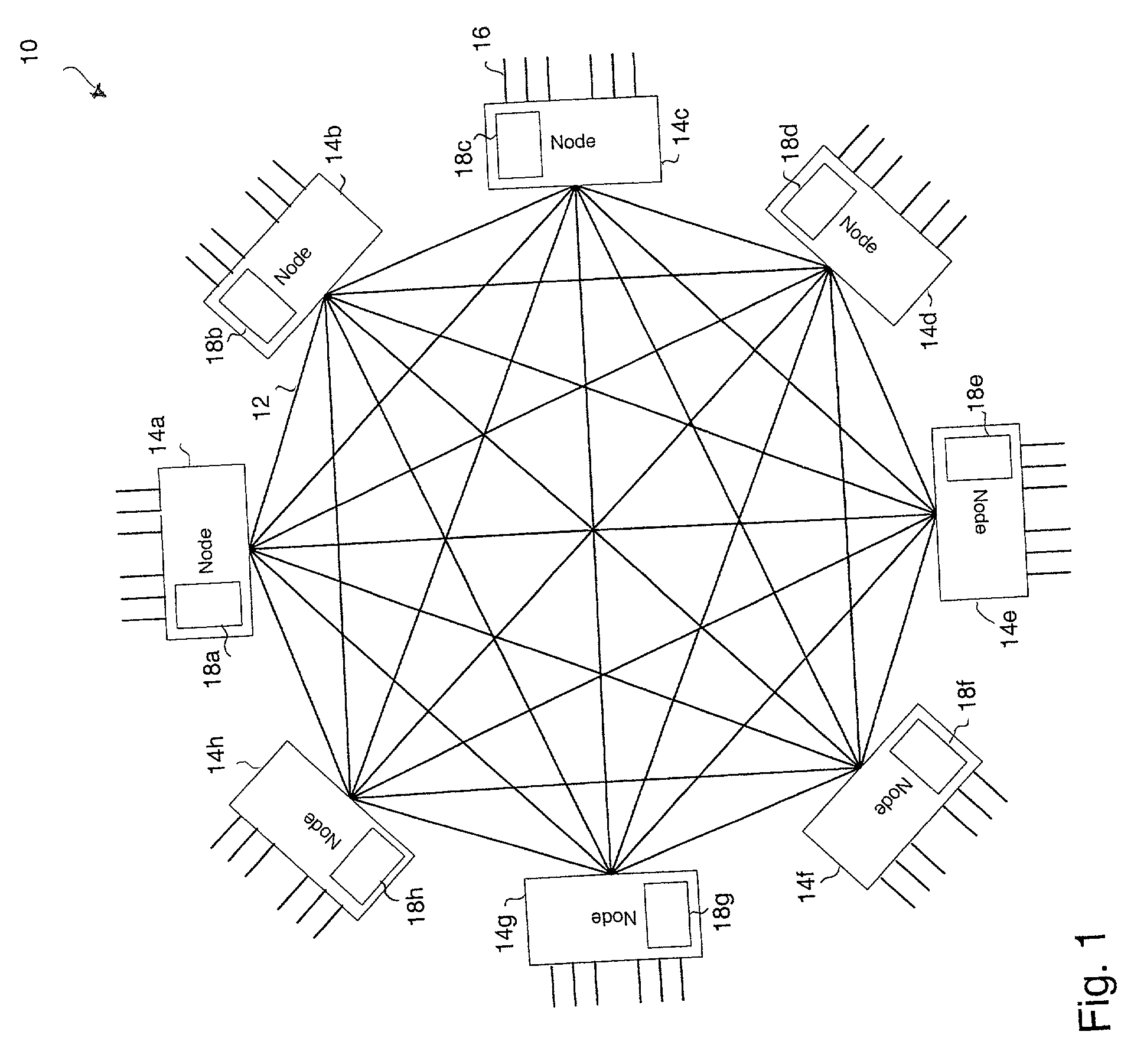

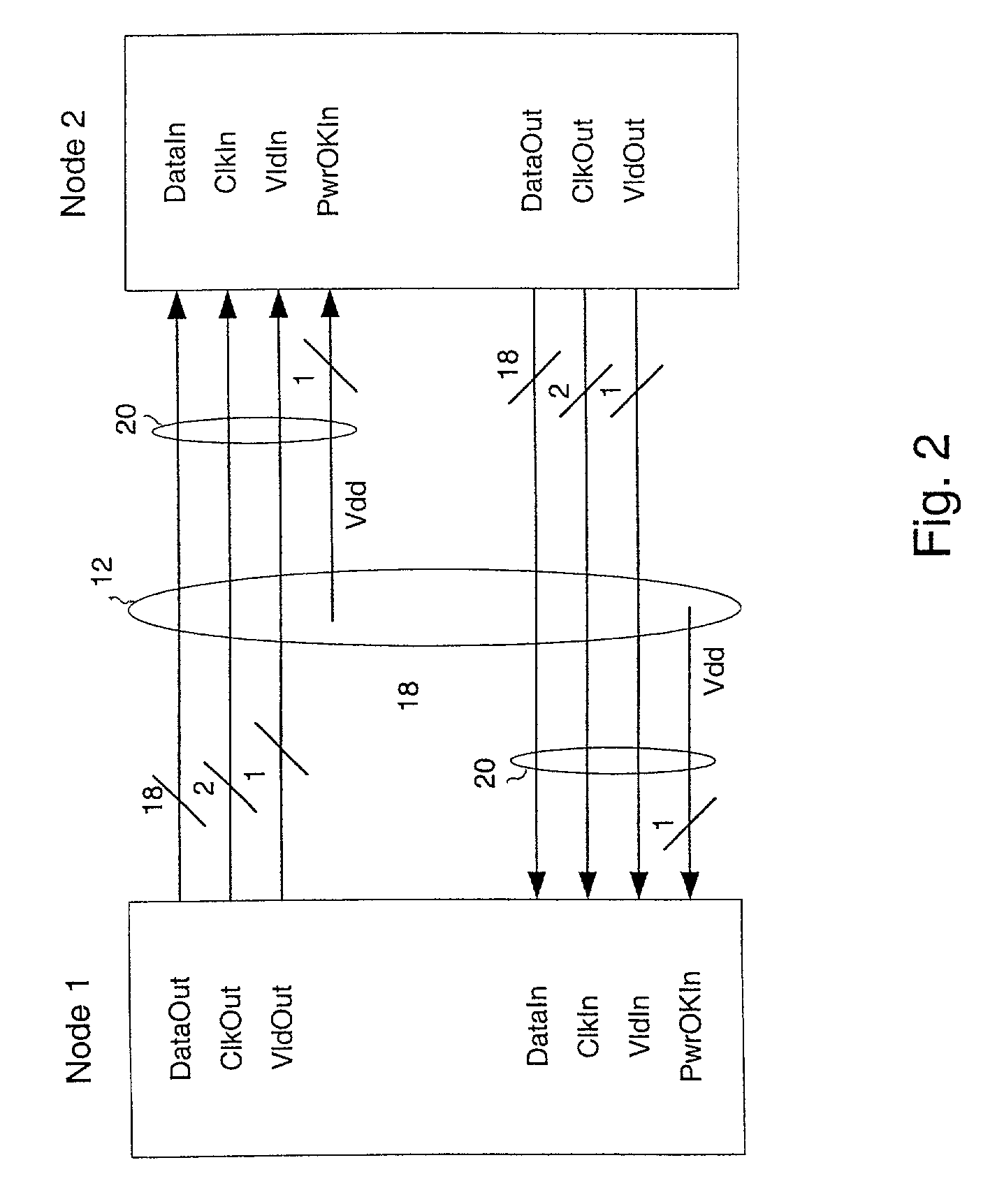

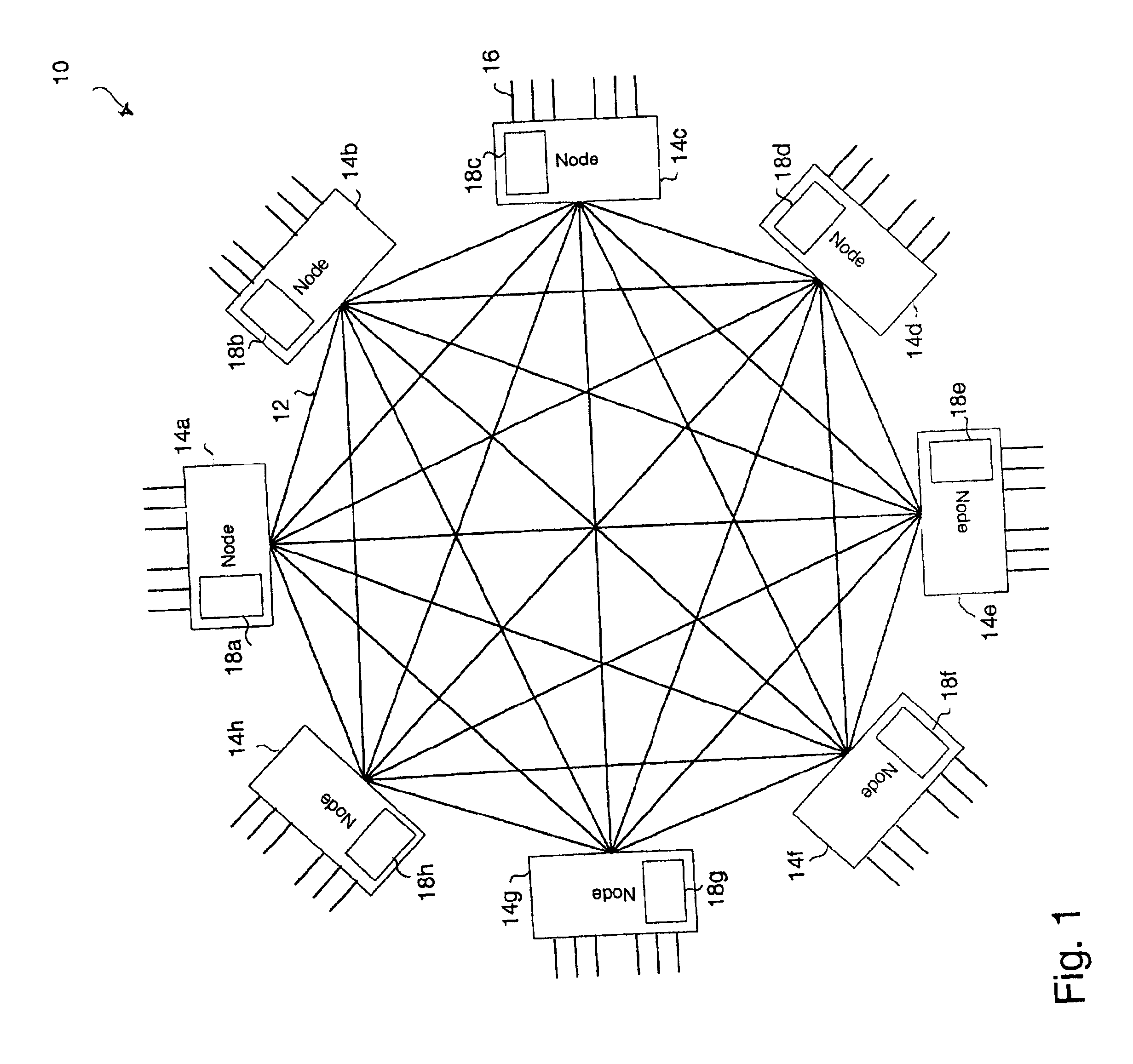

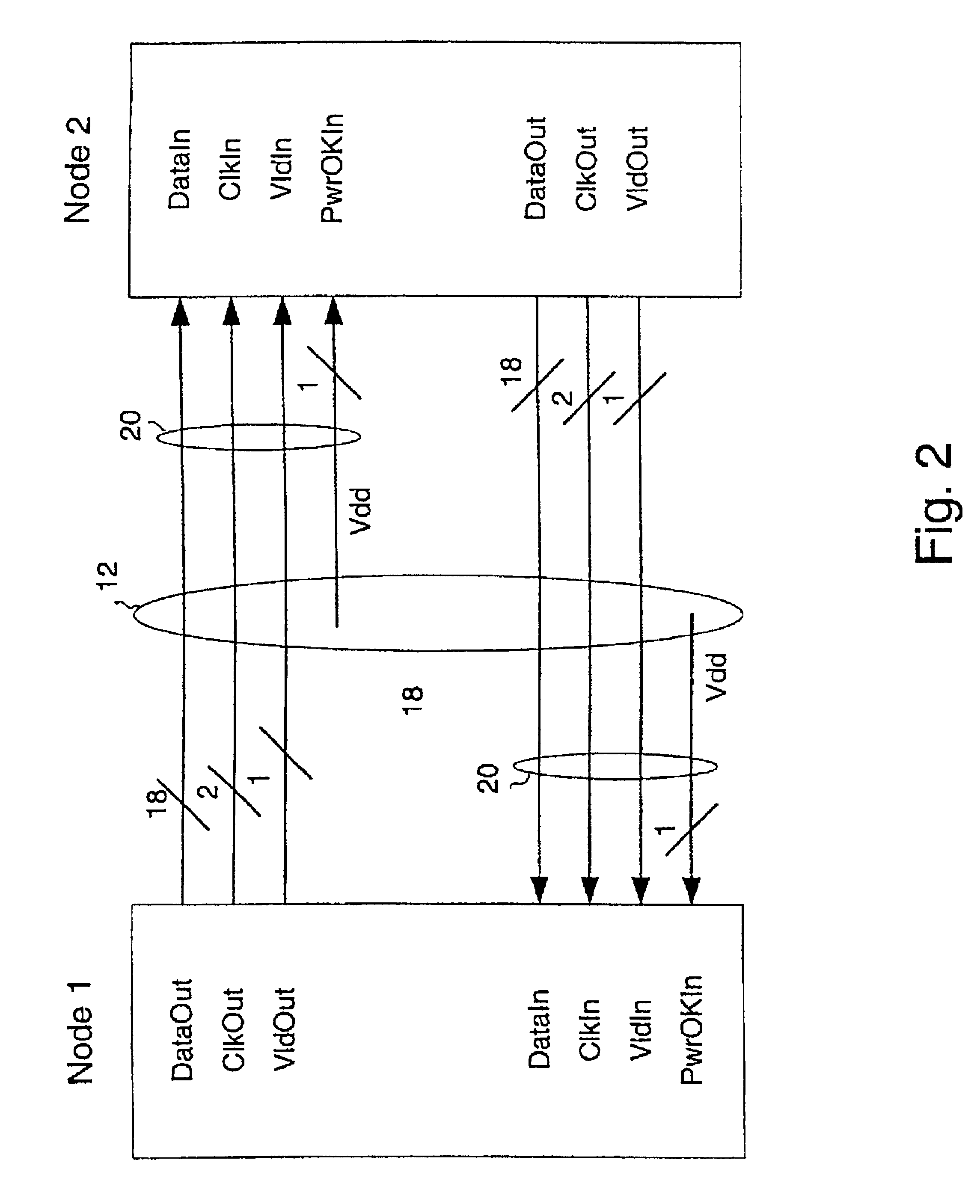

Method of communicating data in an interconnect system

InactiveUS6973484B1Optimizes and improves performanceMemory adressing/allocation/relocationDigital computer detailsDirect memory accessMemory copy

A method is provided for communicating data in an interconnect system comprising a plurality of nodes. In one aspect, the method includes: issuing a command packet from a first node, the command packet comprising a respective header quadword and at least one respective data quadword for conveying a command to a second node, wherein the command is selected from a group comprising a direct memory access (DMA) command, an administrative write command, a memory copy write command, and a built in self test (BIST) command; receiving the command packet at the second node; issuing an acknowledgement packet from the second node, the acknowledgement packet comprising a respective header quadword for conveying an acknowledgement that the command packet has been received at the second node.

Owner:HEWLETT PACKARD DEV CO LP

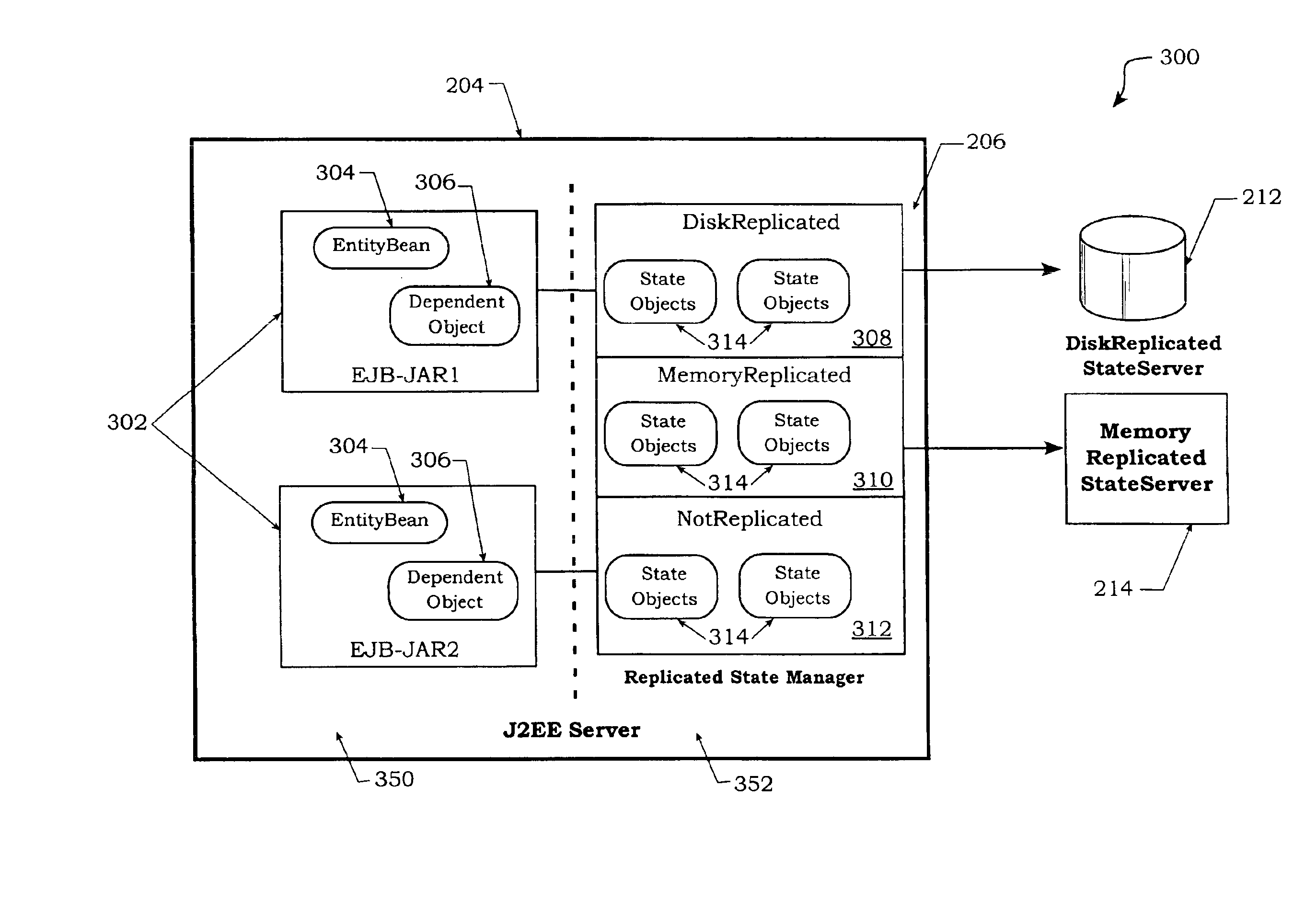

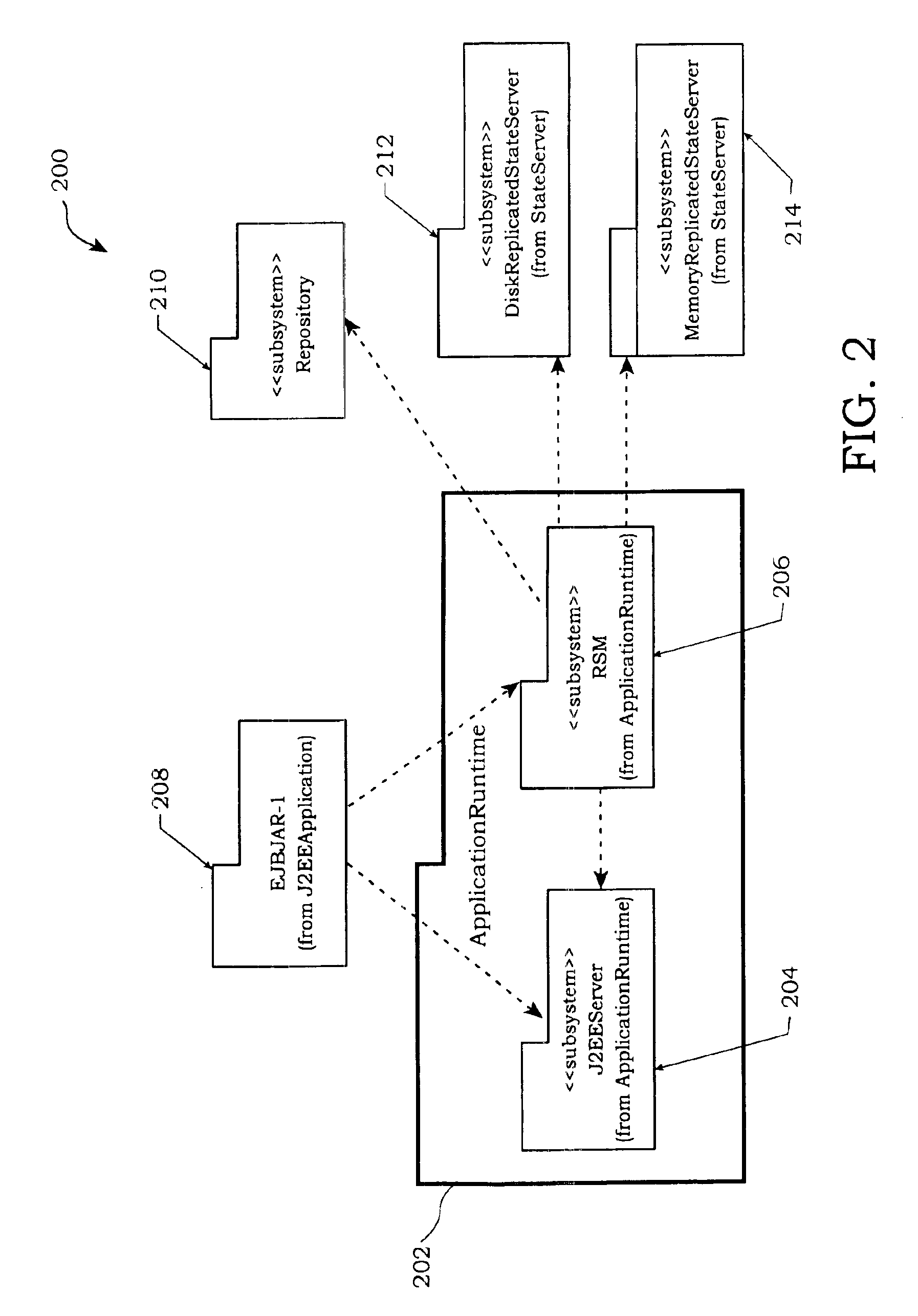

Method and apparatus for migration of managed application state for a Java based application

InactiveUS6912569B1Serious impact performanceResource allocationMultiple digital computer combinationsFistObject store

An invention for migrating managed application state for a Java based application is disclosed. A first Java module is executed on a first server. The first Java module includes a first entity bean and a first state object in communication with the first entity bean. The first state object stores a state of the first entity bean. The first state object is replicated to a state server or stored in-memory and made capable of migration by replicated state manager. Then, a second Java module is started on a second server as part of the module migration by a control module. The second Java module includes a second state object that is populated with state by either recovering from replica of fist state object stored on the state server or by getting transferred state of an in-memory copy of first state object managed on first server.

Owner:ORACLE INT CORP

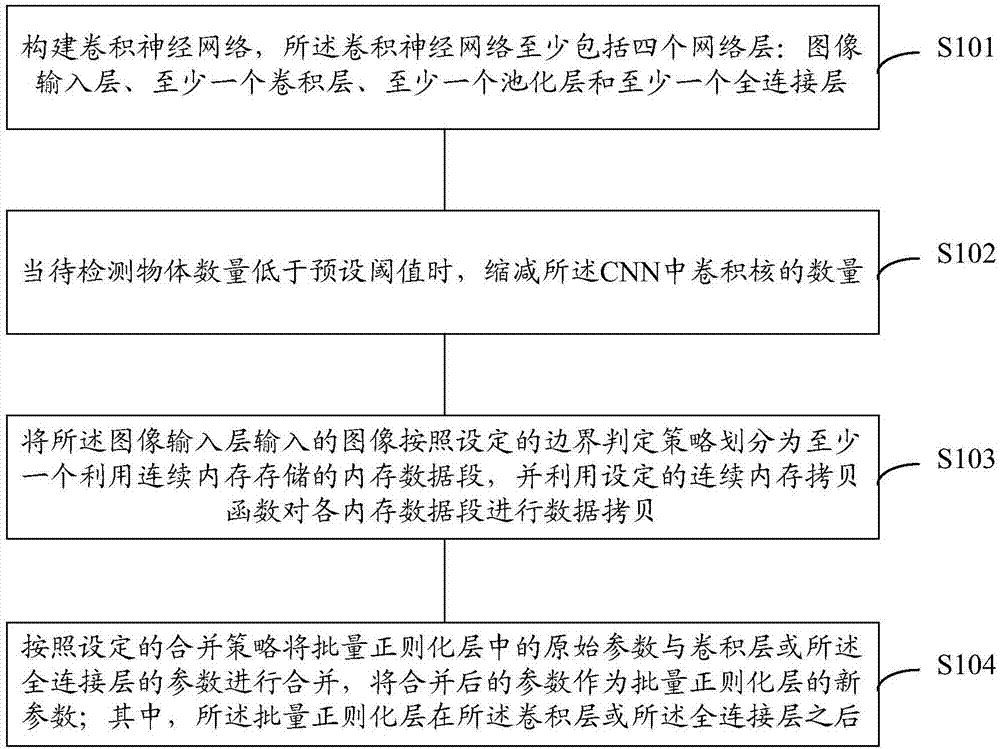

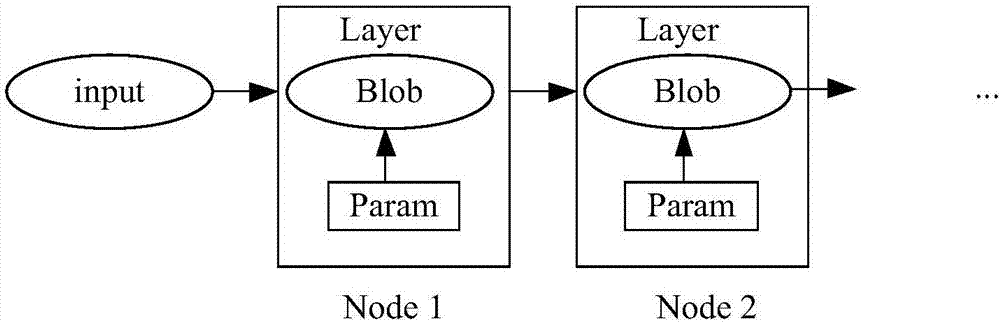

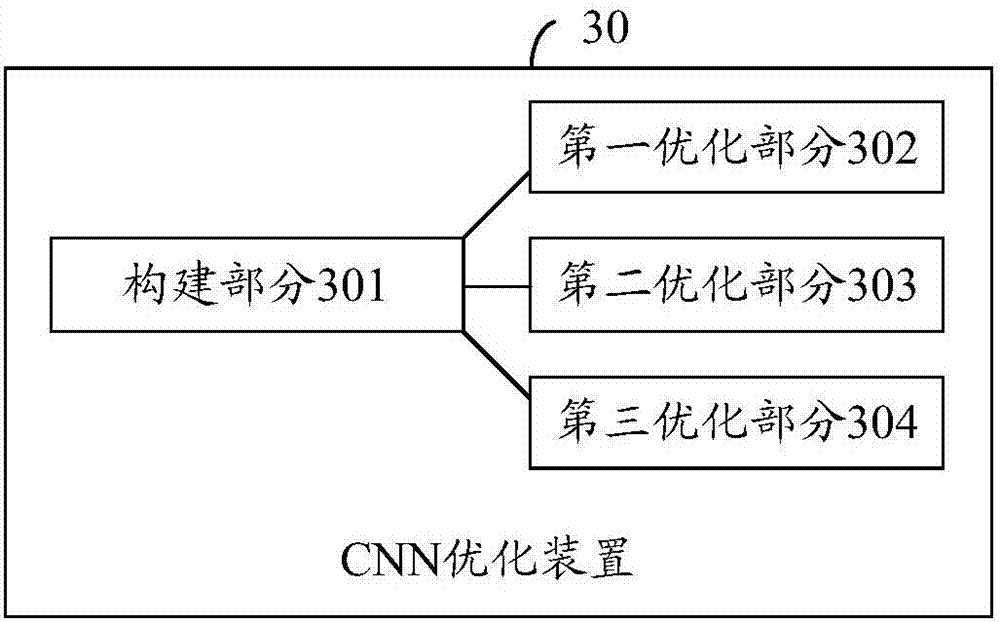

Optimization method and device of convolutional neural network (CNN) and computer storage medium

The embodiment of the invention discloses an optimization method and device of a convolutional neural network (CNN) and a computer storage medium. The method includes: constructing the convolutional neural network, wherein the convolutional neural network includes at least four network layers of an image input layer, at least one convolutional layer, at least one pooling layer and at least one fully connected layer; decreasing the number of convolution kernels in the CNN when the number of to-be-detected objects is less than a preset threshold value; dividing an input image of the image inputlayer into at least one memory data segment, which is stored by utilizing continuous memory, according to a set border determination strategy, and utilizing a set continuous memory copy function to carry out data copying on each memory data segment; and merging original parameters in a batch normalization (BN) layer and parameters of the convolutional layer or the fully connected layer according to the set merging strategy, and using merged parameters as new parameters of the batch normalization layer, wherein the batch normalization layer is after the convolutional layer or the fully connected layer. Calculation consumption in carrying out detection through the CNN is reduced.

Owner:MIDEA GRP CO LTD

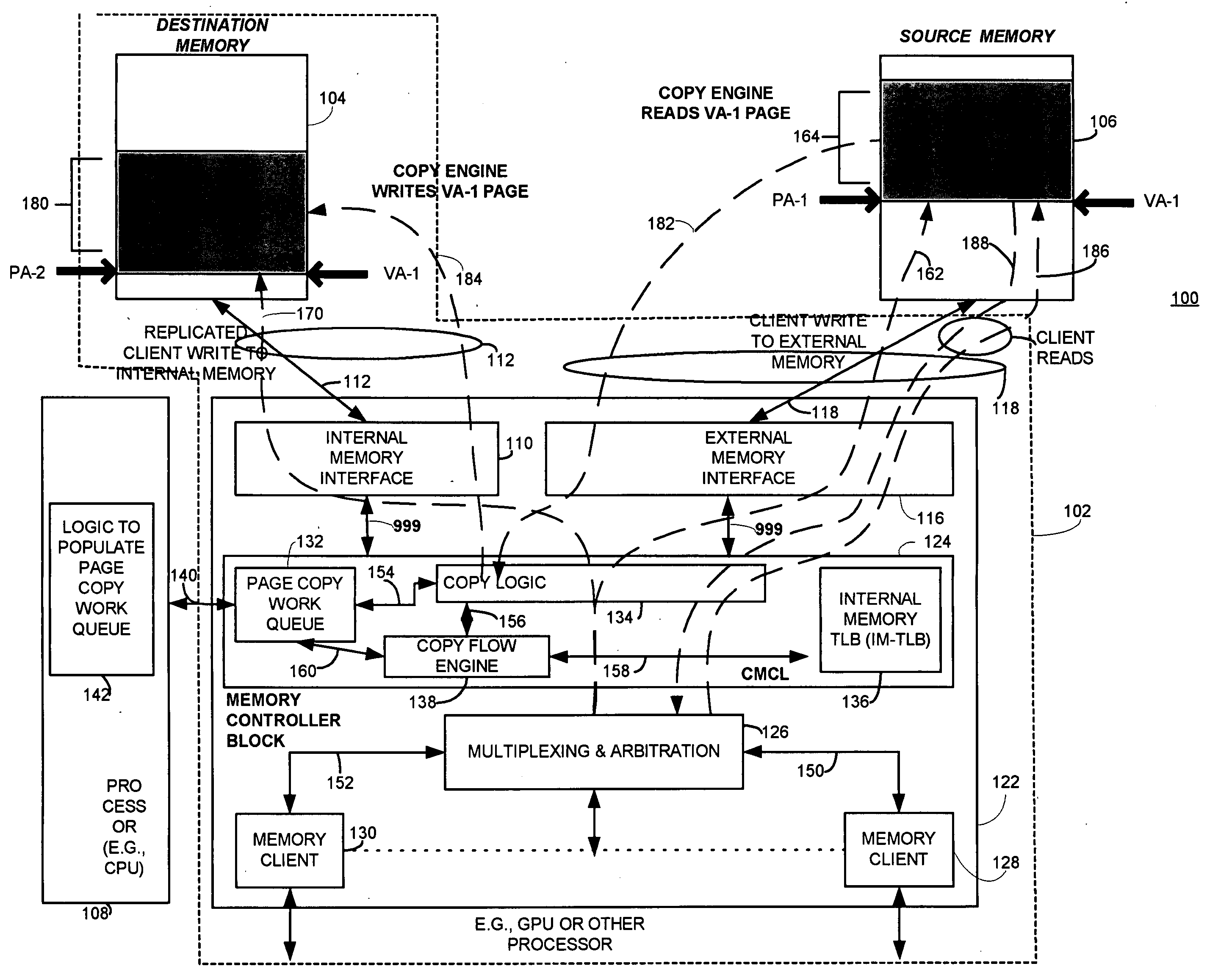

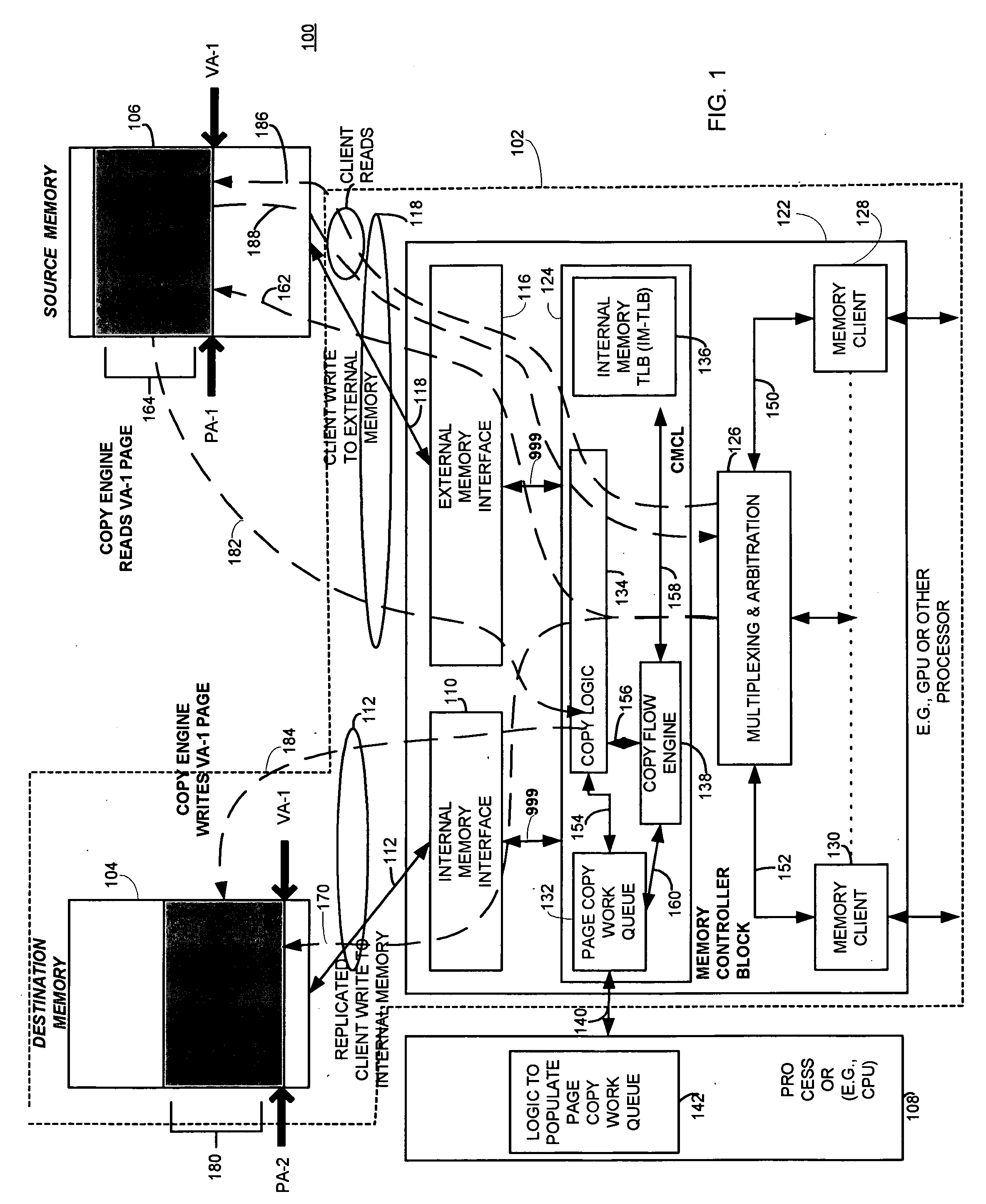

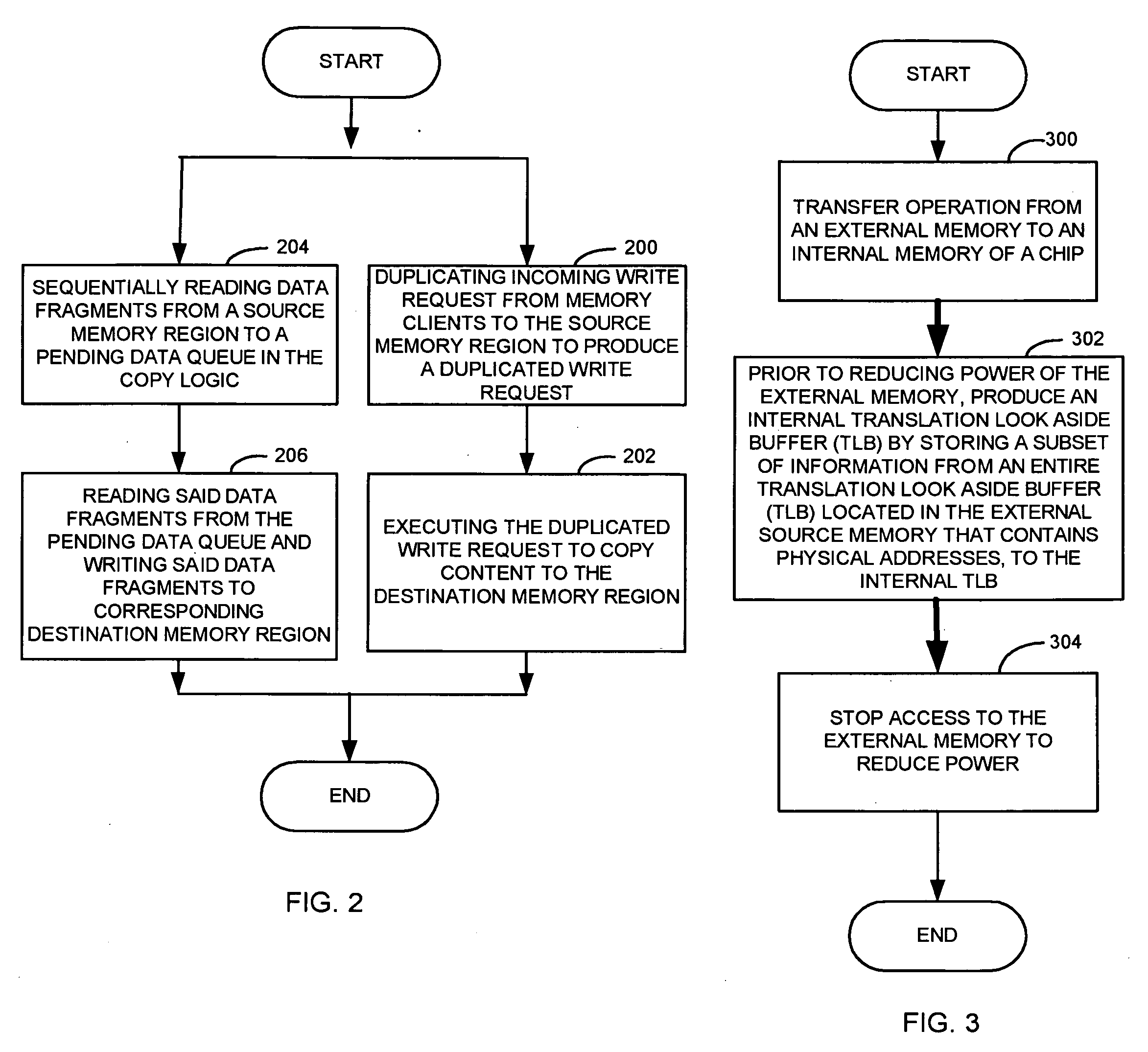

Method and apparatus for reallocating memory content

ActiveUS20100161923A1Memory architecture accessing/allocationEnergy efficient ICTInternal memoryExternal storage

Coherent memory copy logic is operative to copy data from a source memory location to a destination memory location and duplicate a write request to a source memory region to produce a duplicated write request. Coherent memory copy logic is also operative to execute the duplicated write request to copy content from the external memory region to the destination memory region. Power to the source memory can then be reduced to save power while the internal memory is being used. Accordingly, a type of “hardware memory mover” does not require the use of any complex software synchronization and does not result in any service interruption during a memory move. The coherent memory copy logic reallocates the application memory space from, for example, external memory to internal memory within a chip in a manner that is transparent to the application software and the user. Corresponding methods are also set forth.

Owner:ATI TECH INC

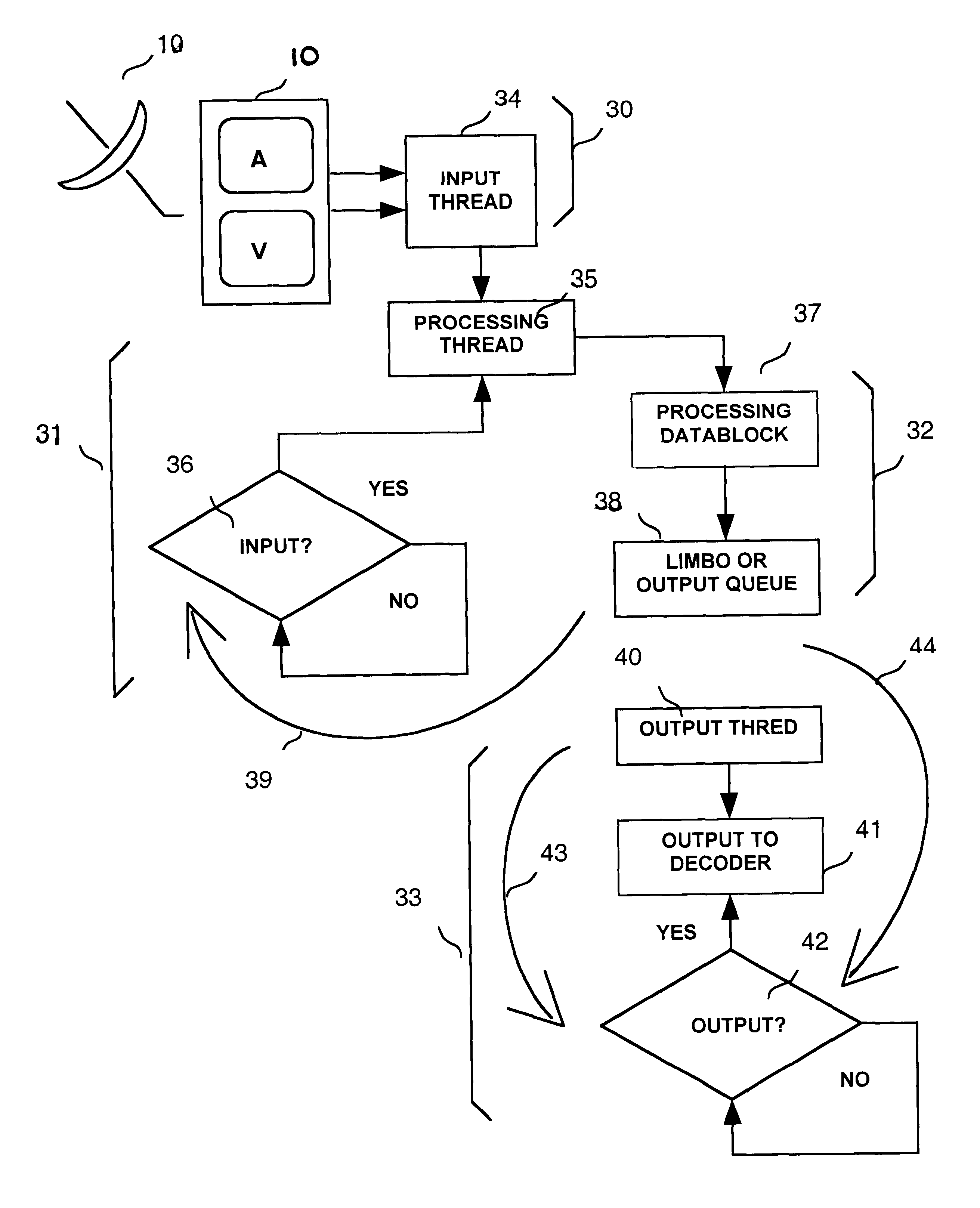

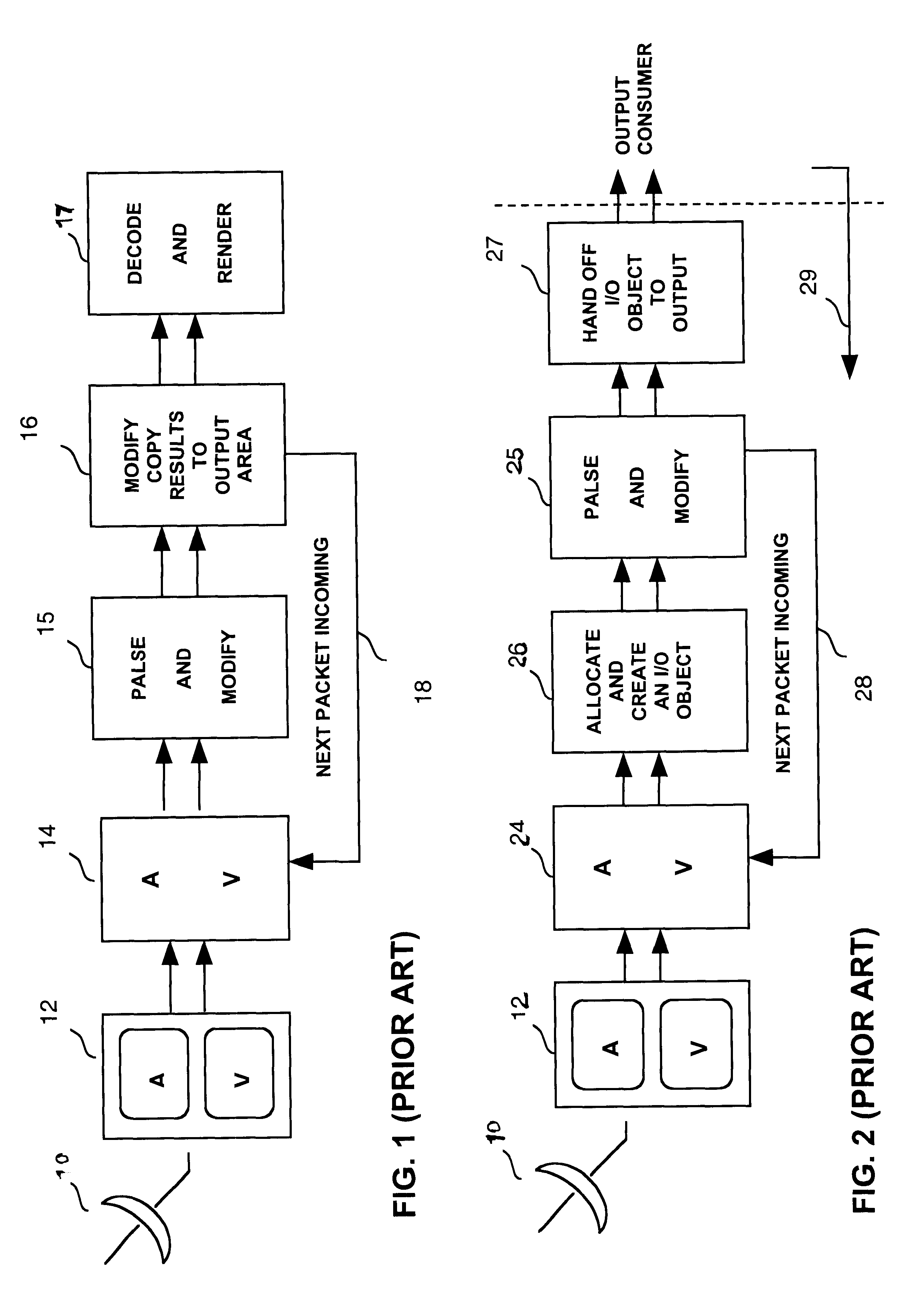

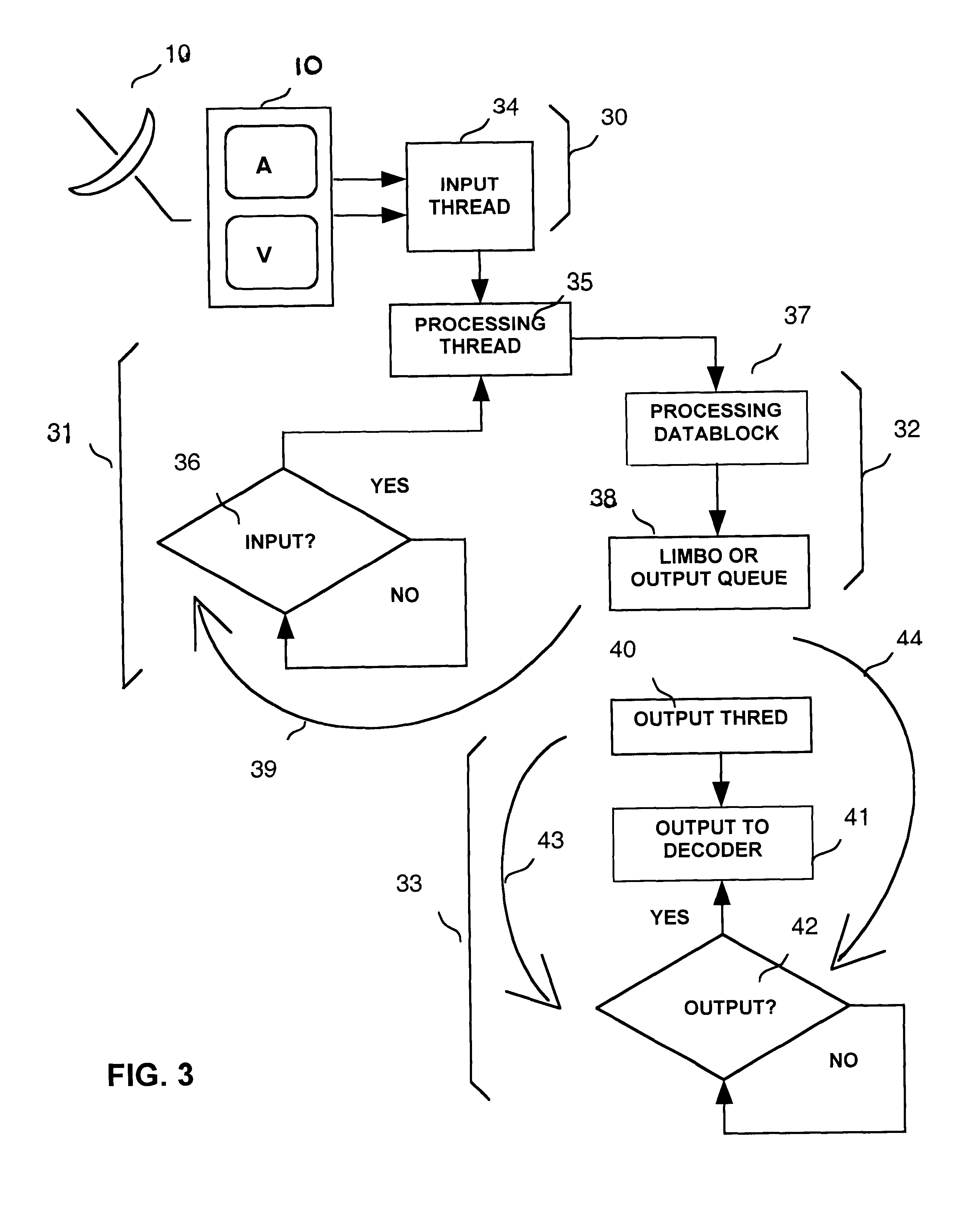

Optimal handling and manipulation of high-speed streaming media in a computing device

InactiveUS6366970B1Reduce in quantityMultiple digital computer combinationsTelevision systemsStreaming dataHigh bandwidth

A method and apparatus for optimal handling of high bandwidth streaming data in a computer system minimizes computational activities to achieve maximal performance. This performance improvement is accomplished by minimizing the amount of memory copying and also by minimizing the number of allocation and deallocations of objects which occur. Memory copying is a CPU / bandwidth intense operation when there is high speed streaming data on the input. The allocation and deallocation of objects is a system resource intense activity and requires a very significant amount of CPU processing per invocation in a computing device. Using a combination of techniques, the invention provides a technique that reduces both the number of memory copies as well as the number of objects which get allocated and deallocated during the course of operating on the streaming media data.

Owner:ROVI TECH CORP

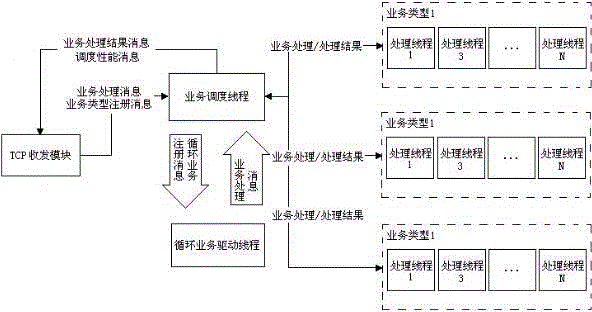

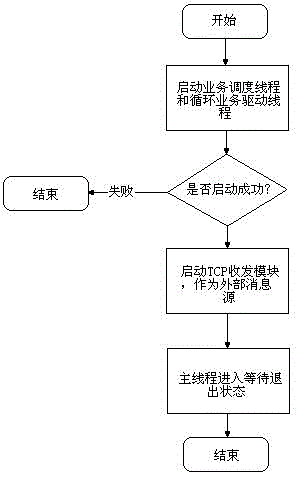

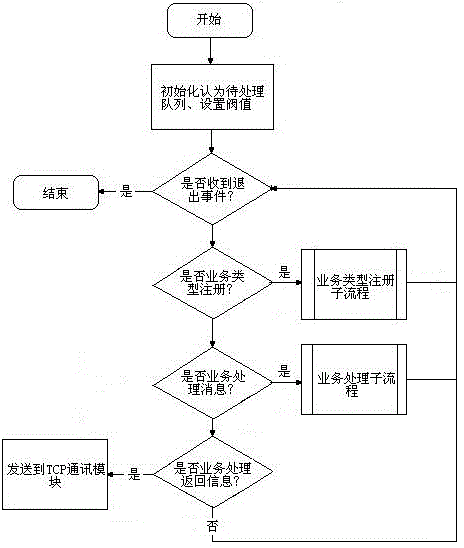

Method for processing business application through multiple threads

ActiveCN104834506AReduce usageImprove scalabilityConcurrent instruction executionProcessing typeResource utilization

The invention relates to a method for processing business application through multiple threads. The method simply includes the steps of creating a business scheduling thread, creating an activation circulating business drive thread, registering a scheduling state detection task, starting a default or assigned processing thread number for business processing types, distributing a lockless queue for each business processing thread, selecting the business processing thread which is not busy relatively, obtaining business processing information from the lockless queue of the selected business processing thread for processing, setting the reference count of a data area in the business processing information to be zero through the business processing thread, and feeding back the information when the business scheduling thread receives the information indicating that processing is finished. The method has the advantages that according to current processing capacity, the concurrence number of the threads is controlled, unnecessary memory copy is reduced, use of a system lock is reduced, new business processing types can be added in the running period, business expansibility of a system is improved, system operation efficiency is improved, resource utilization flexibility of the system is improved, and the development period of the business system is shortened.

Owner:BEIJING VRV SOFTWARE CO LTD

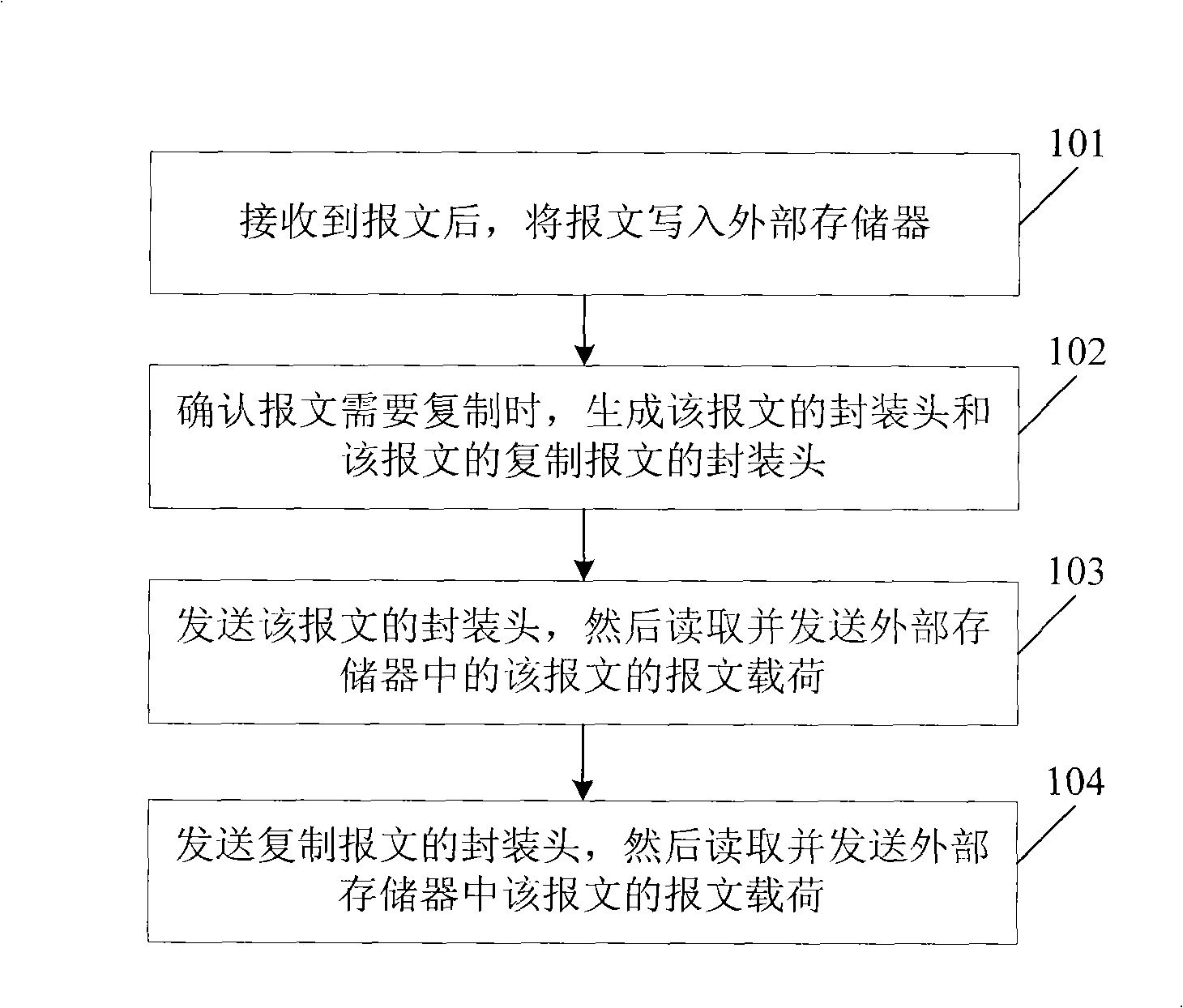

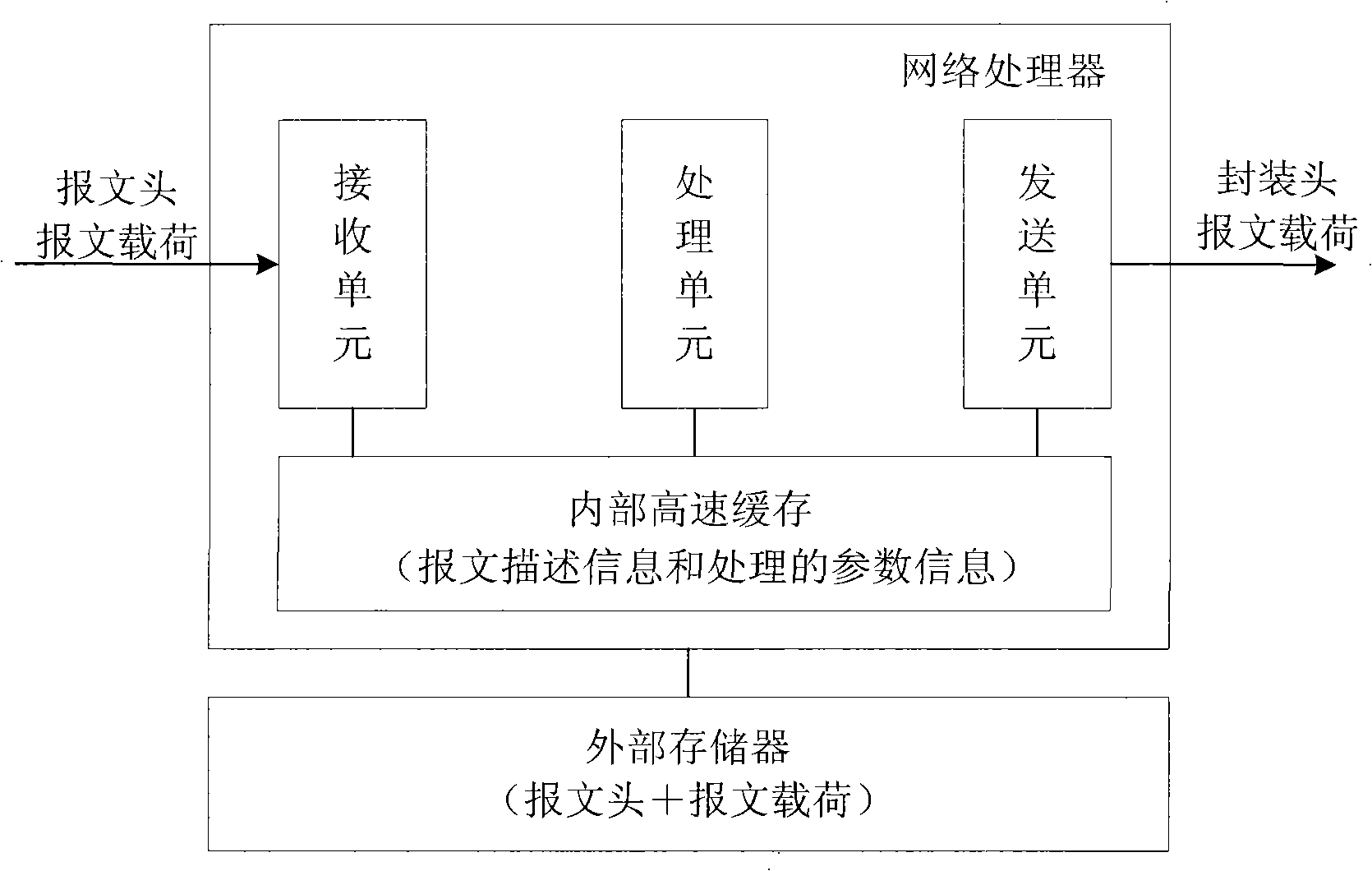

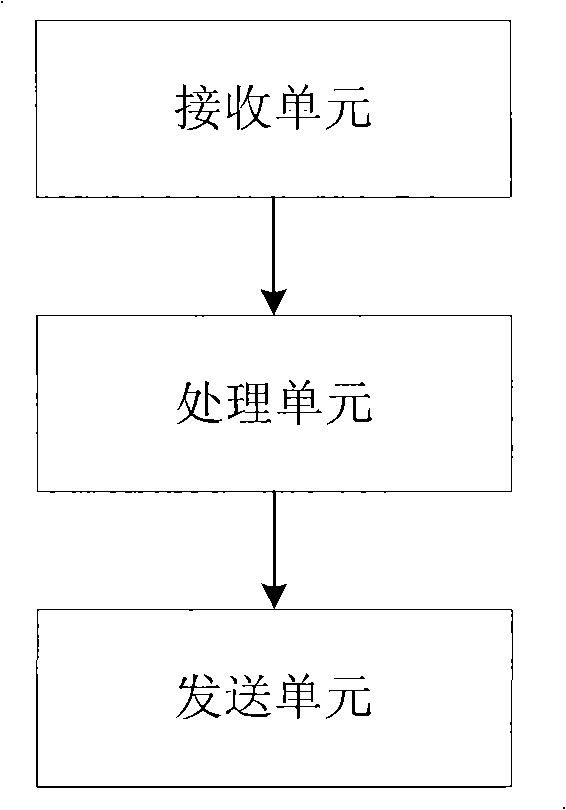

Method for network processor to copy packet and network processor

InactiveCN101257457AAchieved goalsImprove performanceData switching networksExternal storageResource block

The invention discloses a method of network processor for copying the message and a network processor, belonging to the communication field. The method includes: after receiving the message, the message is written into the external memory; when determining that the message is needed to be copied, the packaging head of the message and copied message of the message are generated; transmitting the packaging head of the message, then reading and transmitting the message load of the message. The network processor includes: a receiving unit, a processing unit ad a transmitting unit. The invention realizes the aim of copying the message through transmitting the packaging head and the message load for two times, meanwhile no memory copy is processed when processing the message, and no new resource blocks is applied, which advances the performance of copying the message, further strengthening the transmitting capability to bear the operations for the network processor.

Owner:HUAWEI TECH CO LTD

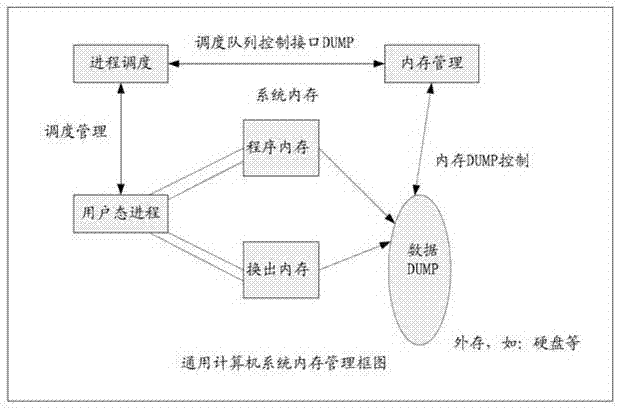

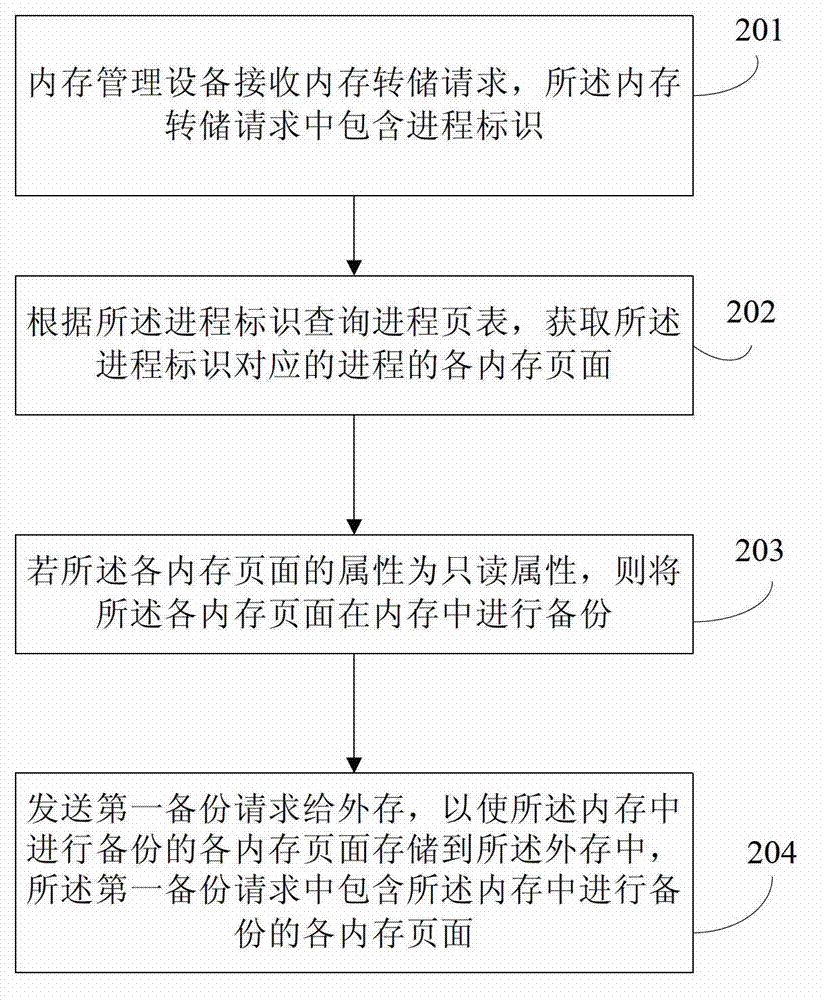

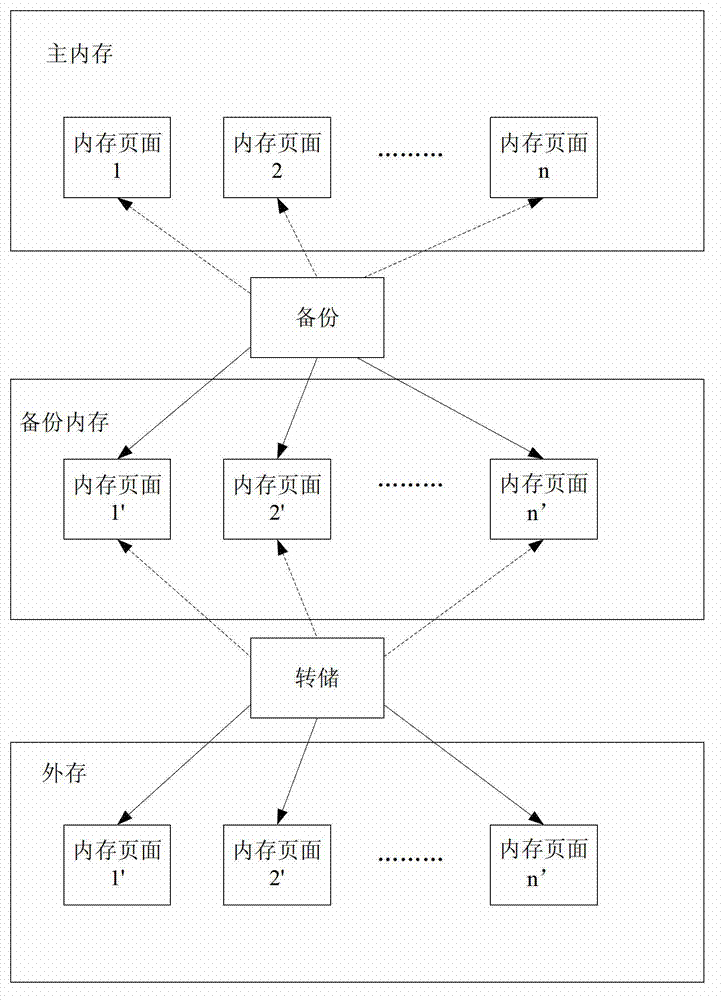

Memory processing method and memory management equipment

InactiveCN102831069AEnsure consistencyMemory adressing/allocation/relocationRedundant operation error correctionMemory processingIn-Memory Processing

The embodiment of the invention discloses a memory processing method and memory management equipment. The method comprises the steps: receiving a memory dump request by the memory management equipment, wherein the memory dump request contains a process identification (PID), and memory pages of the process corresponding to the PID are needed dump memory pages; according to the PID, querying a process page table, and acquiring the memory pages of the process corresponding to the PID; if the attributes of the memory pages are read only attributes, carrying out backups of the memory pages in a memory; and sending a first backup request to external memory so that the external memory copies the backup memory pages into the external memory, wherein the first backup request contains the memory pages of the backups, and can ensure the data consistency while realizing online memory dump.

Owner:HUAWEI TECH CO LTD

Validity of address ranges used in semi-synchronous memory copy operations

InactiveUS20070150675A1Avoiding unnecessary processor downtimeAvoid overheadMemory loss protectionMicro-instruction address formationParallel computingTerm memory

A system, method, and a computer readable for protecting content of a memory page are disclosed. The method includes determining a start of a semi-synchronous memory copy operation. A range of addresses is determined where the semi-synchronous memory copy operation is being performed. An issued instruction that removes a page table entry is detected. The method further includes determining whether the issued instruction is destined to remove a page table entry associated with at least one address in the range of addresses. In response to the issued instruction being destined to remove the page table entry, the execution of the issued instruction is stalled until the semi-synchronous memory copy operation is completed.

Owner:IBM CORP

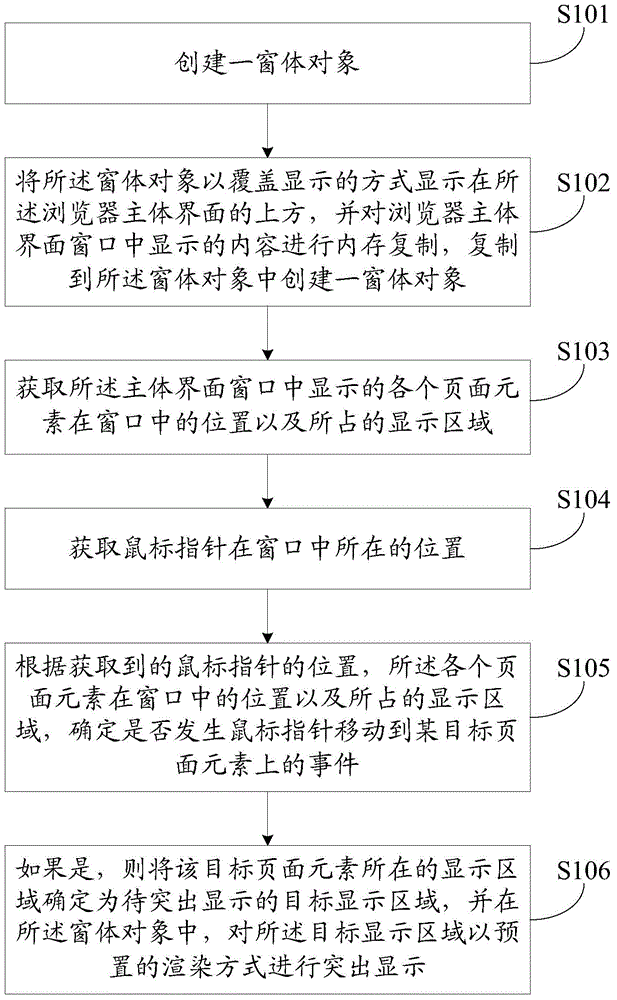

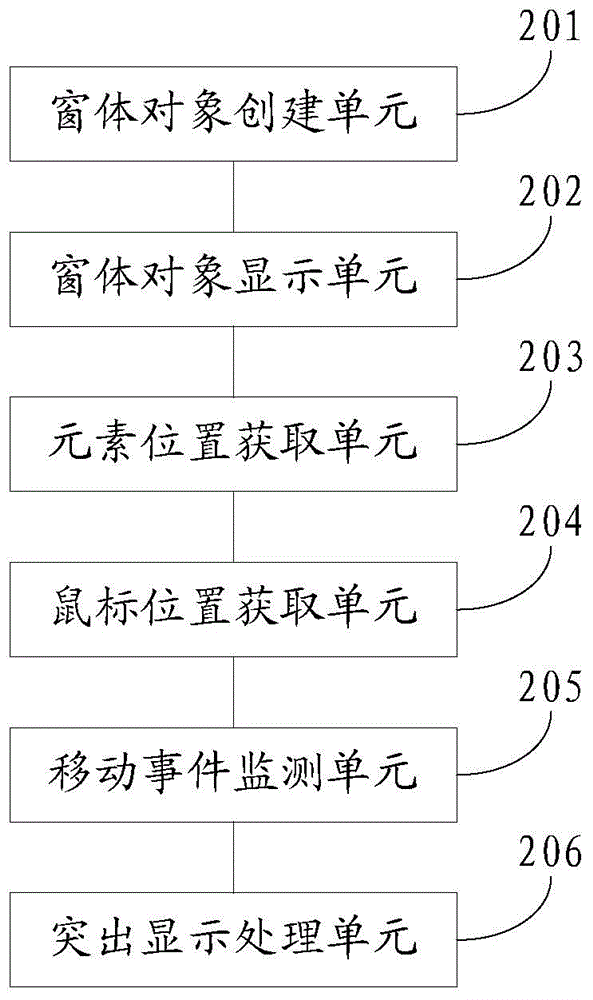

Page element real-time highlighted display method and apparatus

ActiveCN105242817AAvoid confictAdaptableInput/output processes for data processingComputer graphics (images)Memory copy

The application discloses a page element real-time highlighted display method and apparatus. The method comprises: creating a window object; displaying the window object above a browser main body interface in a manner of overlay display, and performing memory copy on the content displayed in a window of the browser main body interface to copy the content into the window object; obtaining the position and an occupied display region of each page element displayed in the window of the main body interface, in the window; obtaining the position of a mouse pointer in the window; according to the obtained position of the mouse pointer as well as position and occupied display region of each page element in the window, determining whether an event of moving the mouse pointer to a target page element occurs or not; and if so, determining a display region whether the target page element is as a target display region, and performing highlighted display on the target display region in a preset rendering mode in the window object. With the method, the highlighted display timeliness and adaptability of page elements are improved.

Owner:ALIBABA GRP HLDG LTD

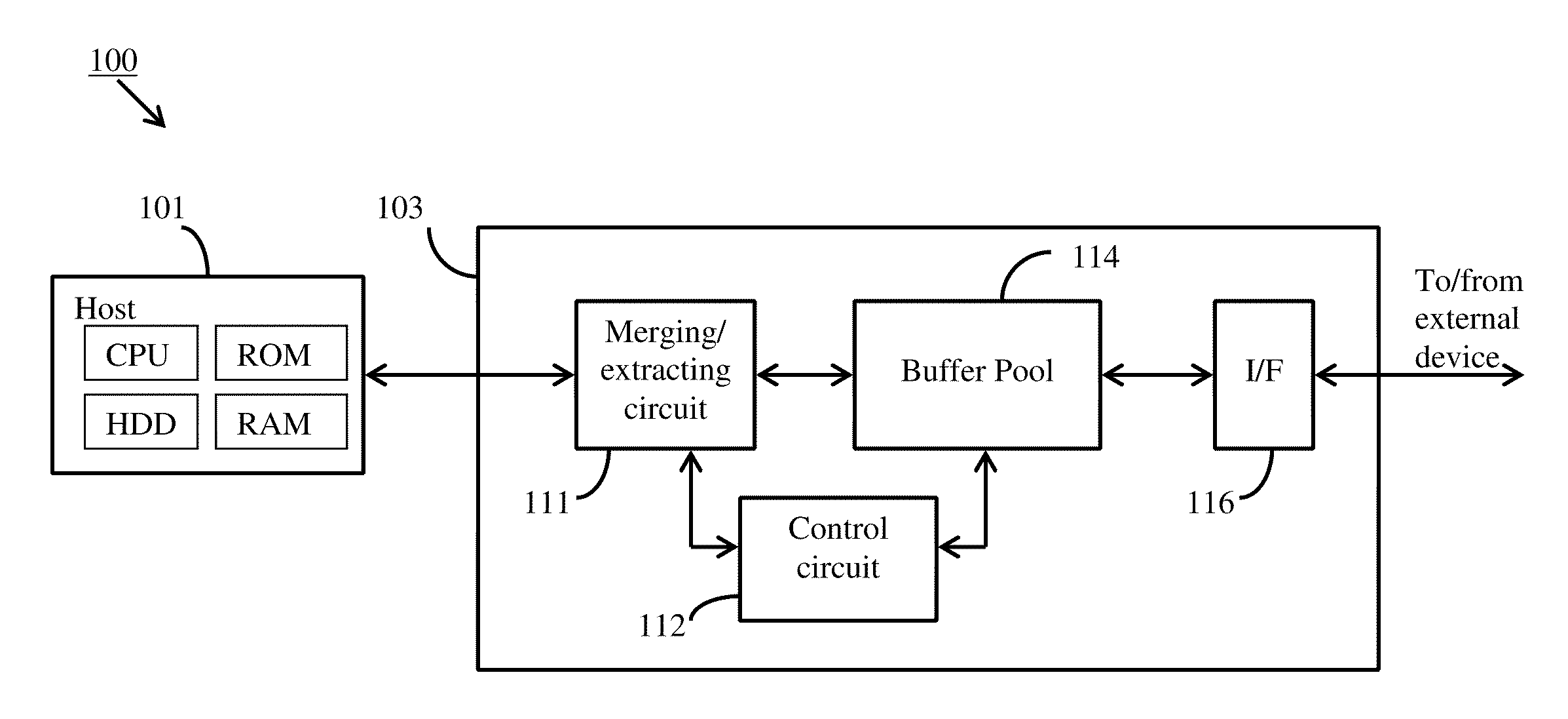

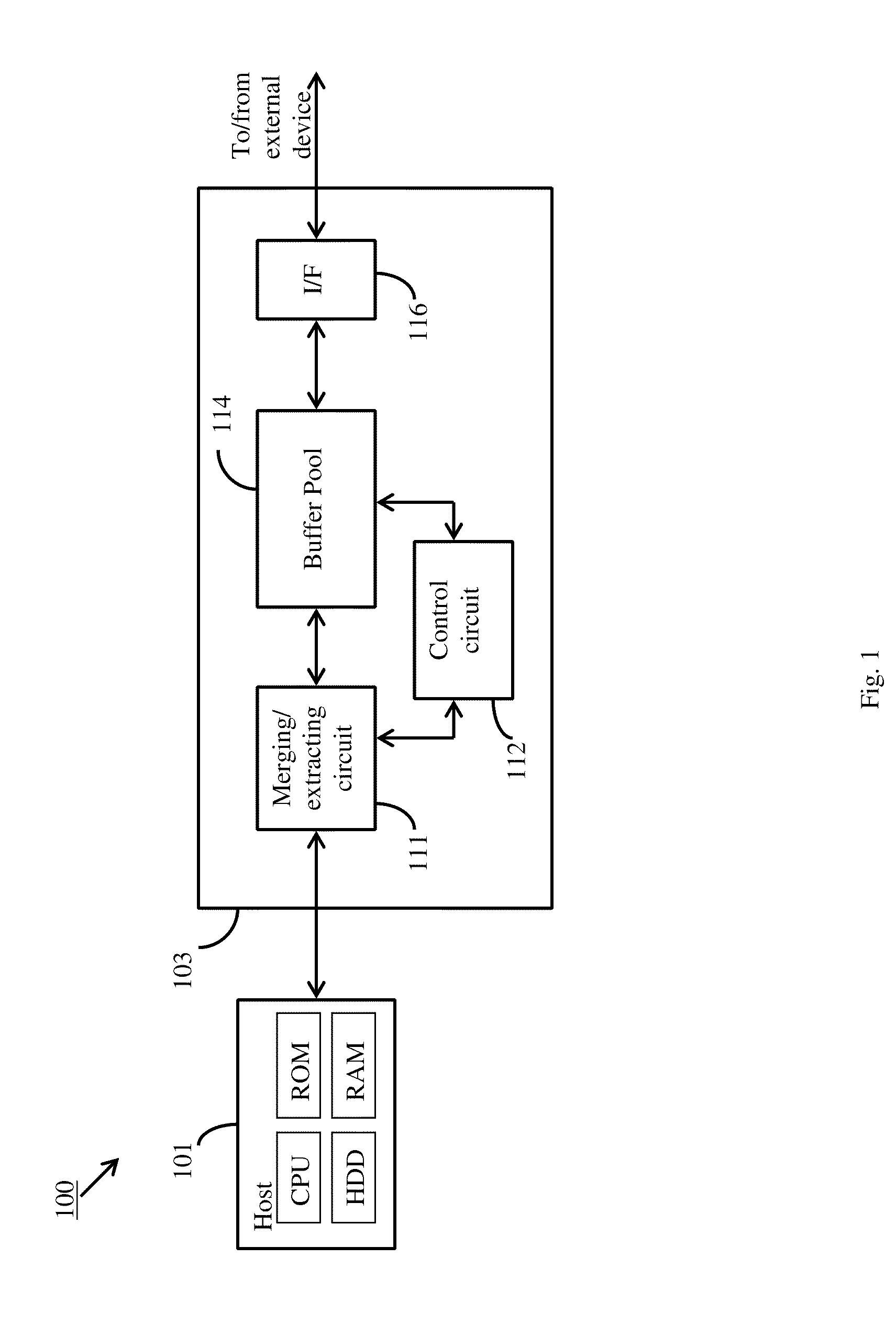

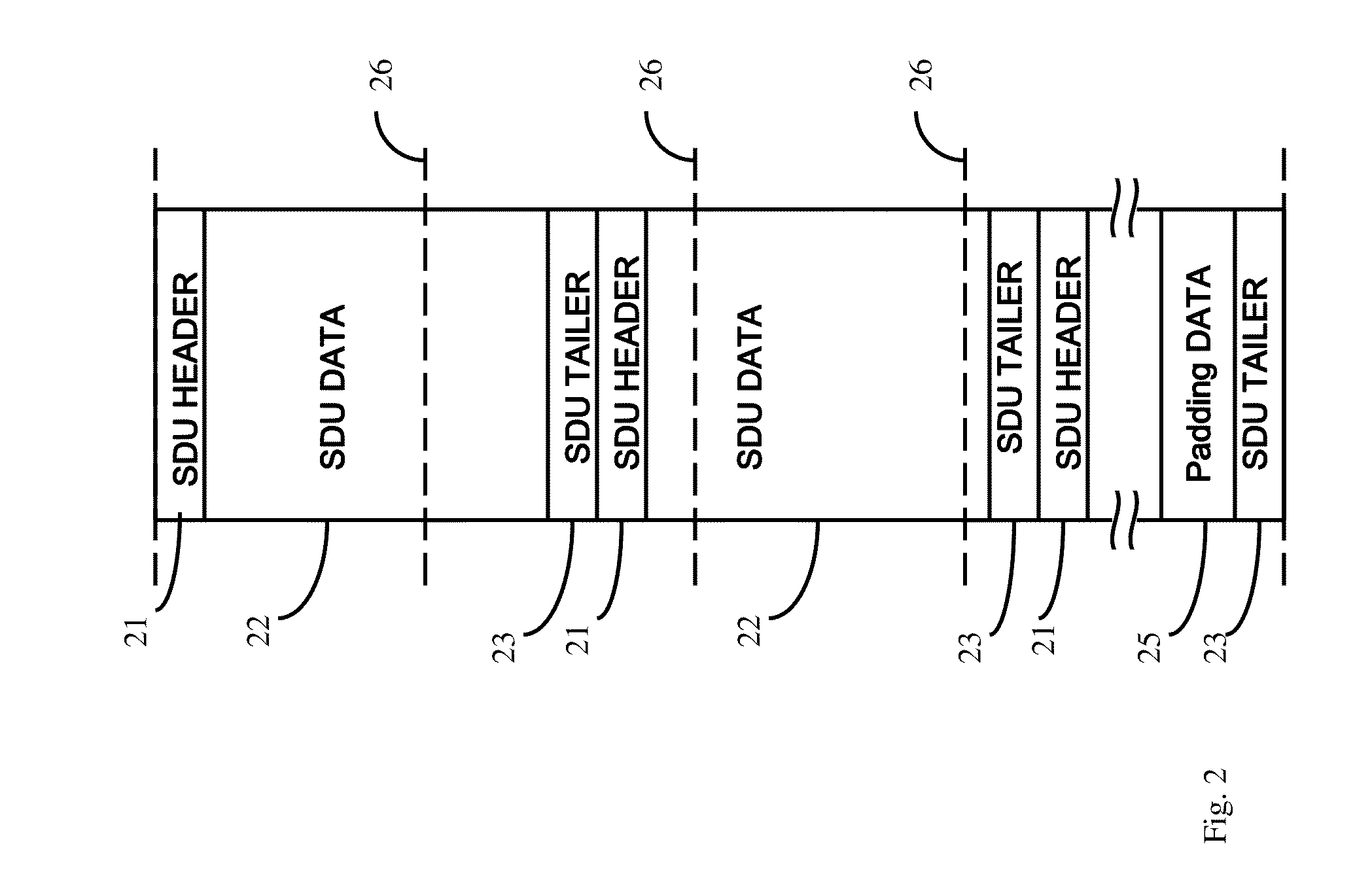

Packet based data transfer system and method for host-slave interface

ActiveUS20110276730A1Efficient data transferTransmissionInput/output processes for data processingDirect memory accessData stream

In a host-slave data transfer system, the slave device receives packet based data from an external device and stores the packet content in a buffer as data segments. The slave merges a plurality of data segments into data streams and transmits the data streams to the host. The host uses direct memory access (DMA) to unpack the data stream from the slave into individual data segments without memory copy. To enable the host to set up DMA, the slave transmits information regarding sizes of the data segments to the host beforehand via an outband channel, e.g. by transmitting the size information in headers and / or tailers inserted into previous data streams. The host utilizes the data segment size information to program descriptor tables, such that each descriptor in the descriptor tables causes one data segment in the data stream to be stored in the system memory of the host.

Owner:MEDIATEK INC

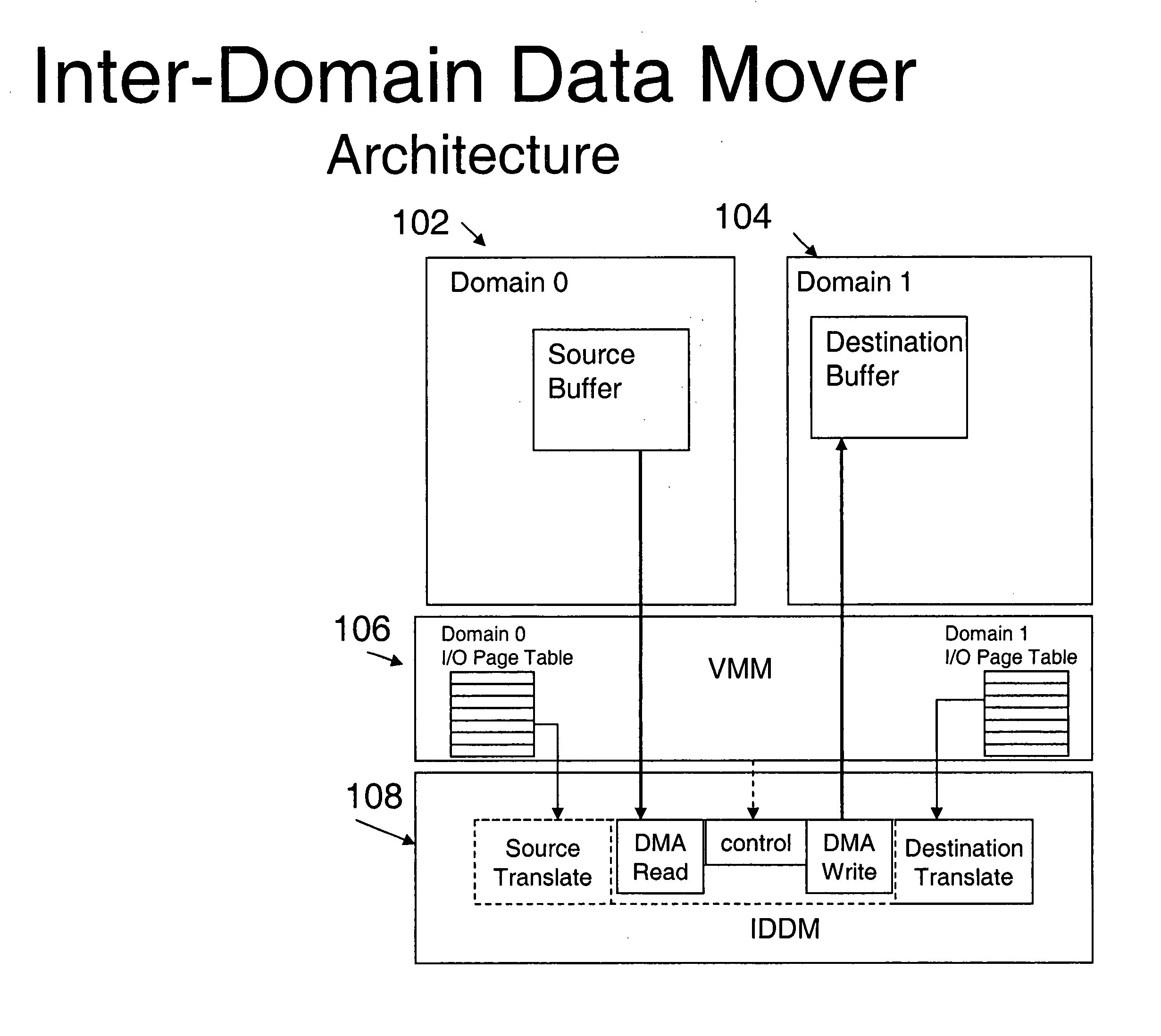

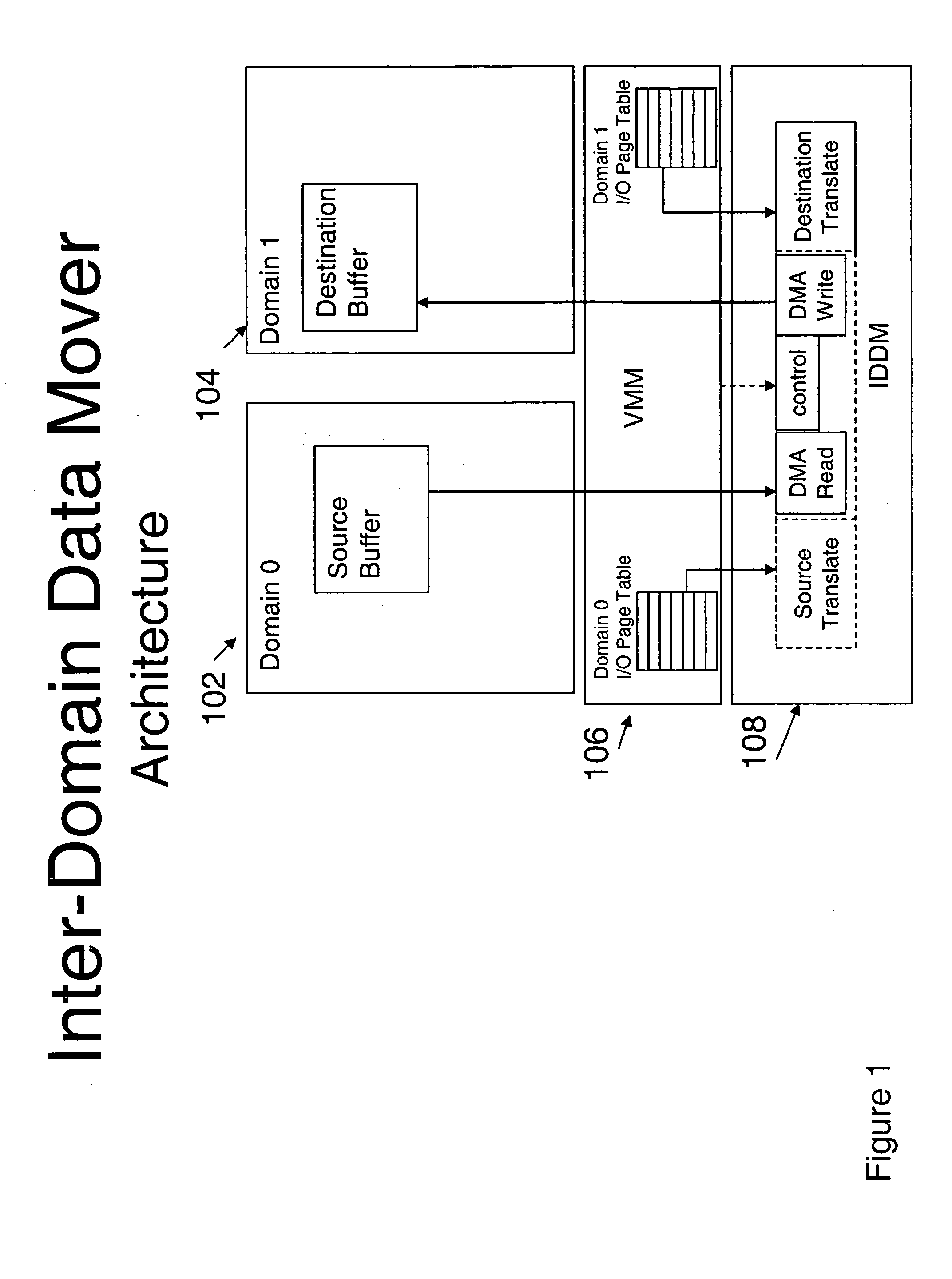

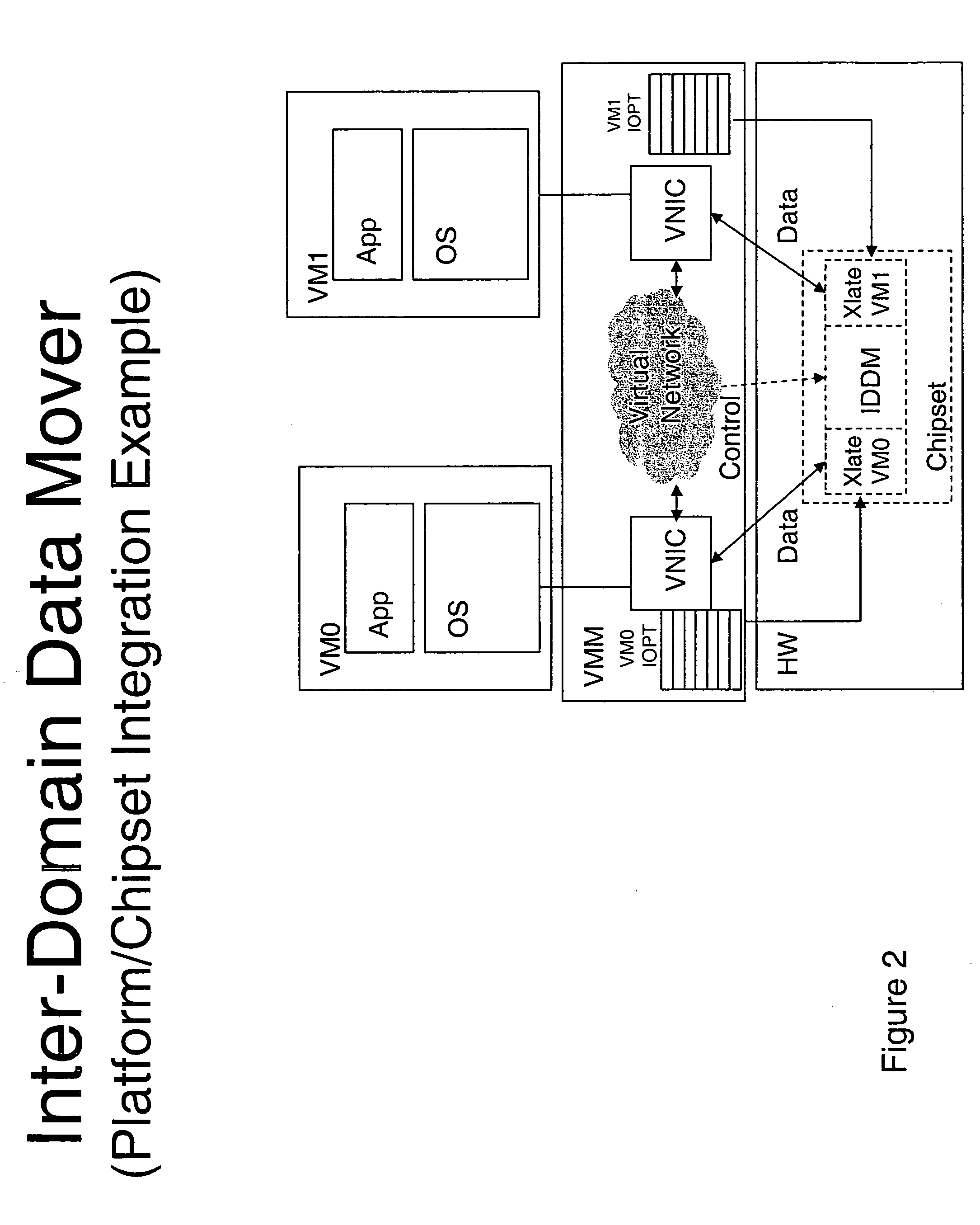

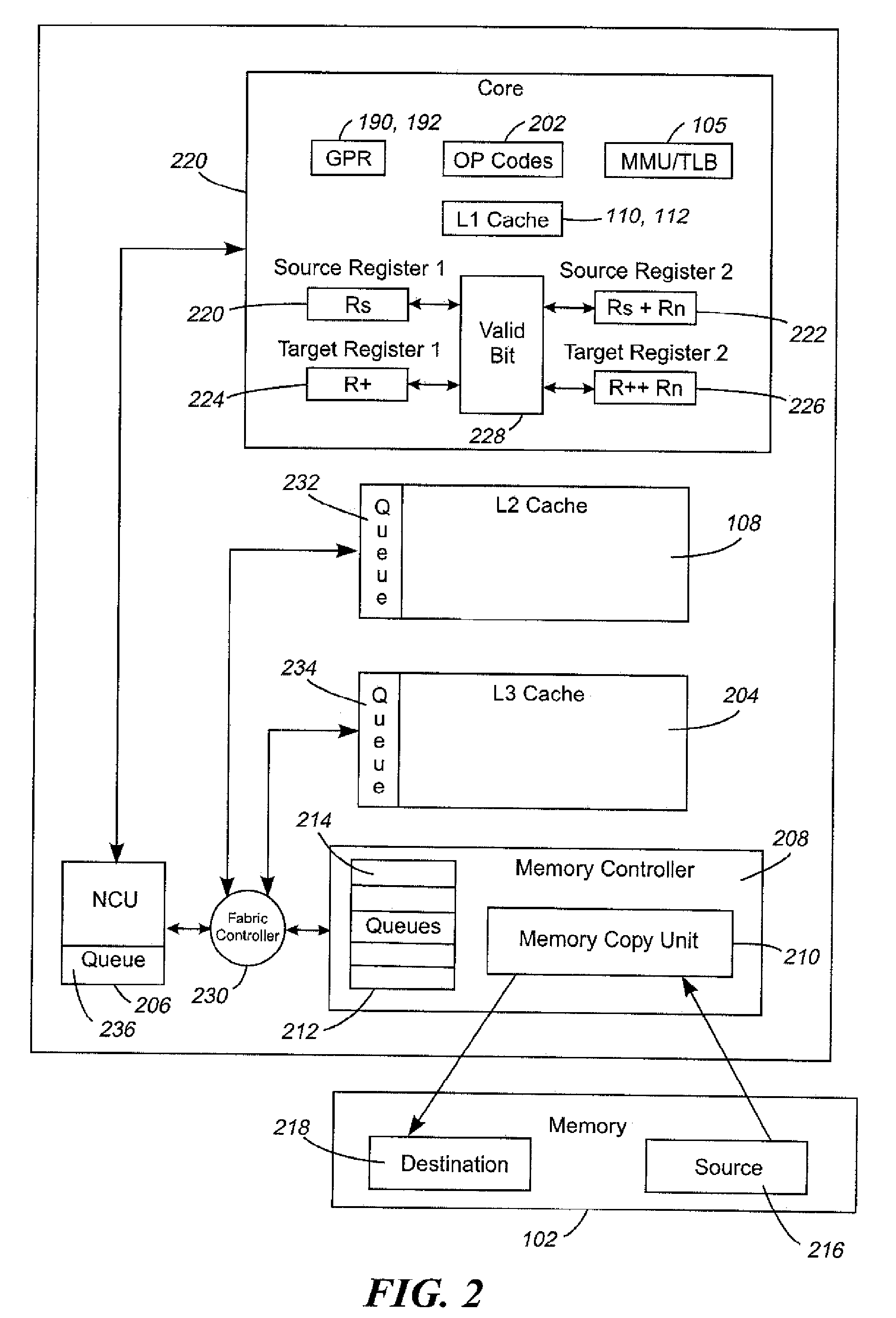

Inter-domain data mover for a memory-to-memory copy engine

An discussion of an address translation for a source and a destination of the data that utilizes different page tables. For example, a direct memory access (DMA) engine is used as a memory-to-memory copy engine by utilizing a page-table walk and address translation for a source side of the copy, and an independent page-table walk and address translation for a destination side of the copy.

Owner:INTEL CORP

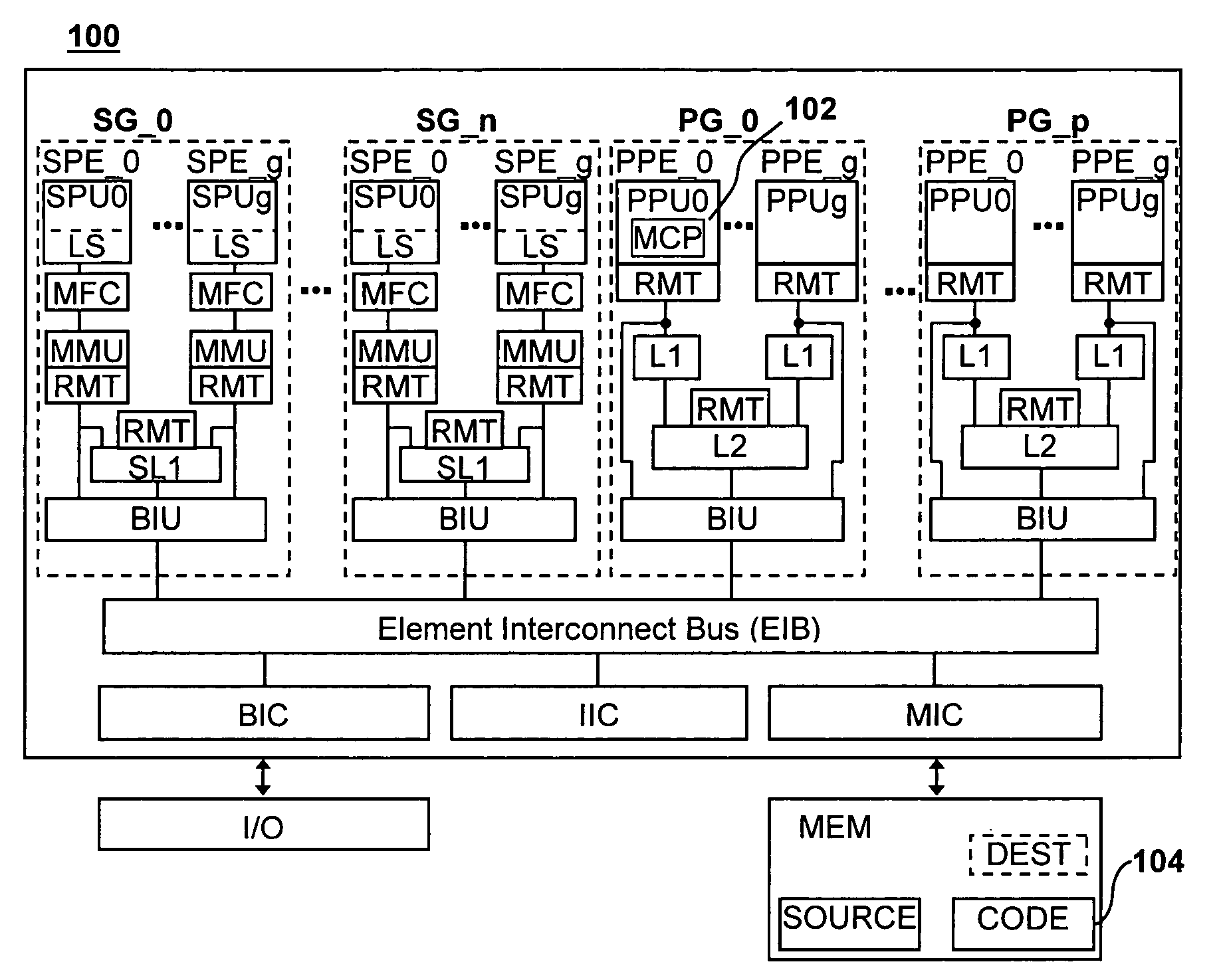

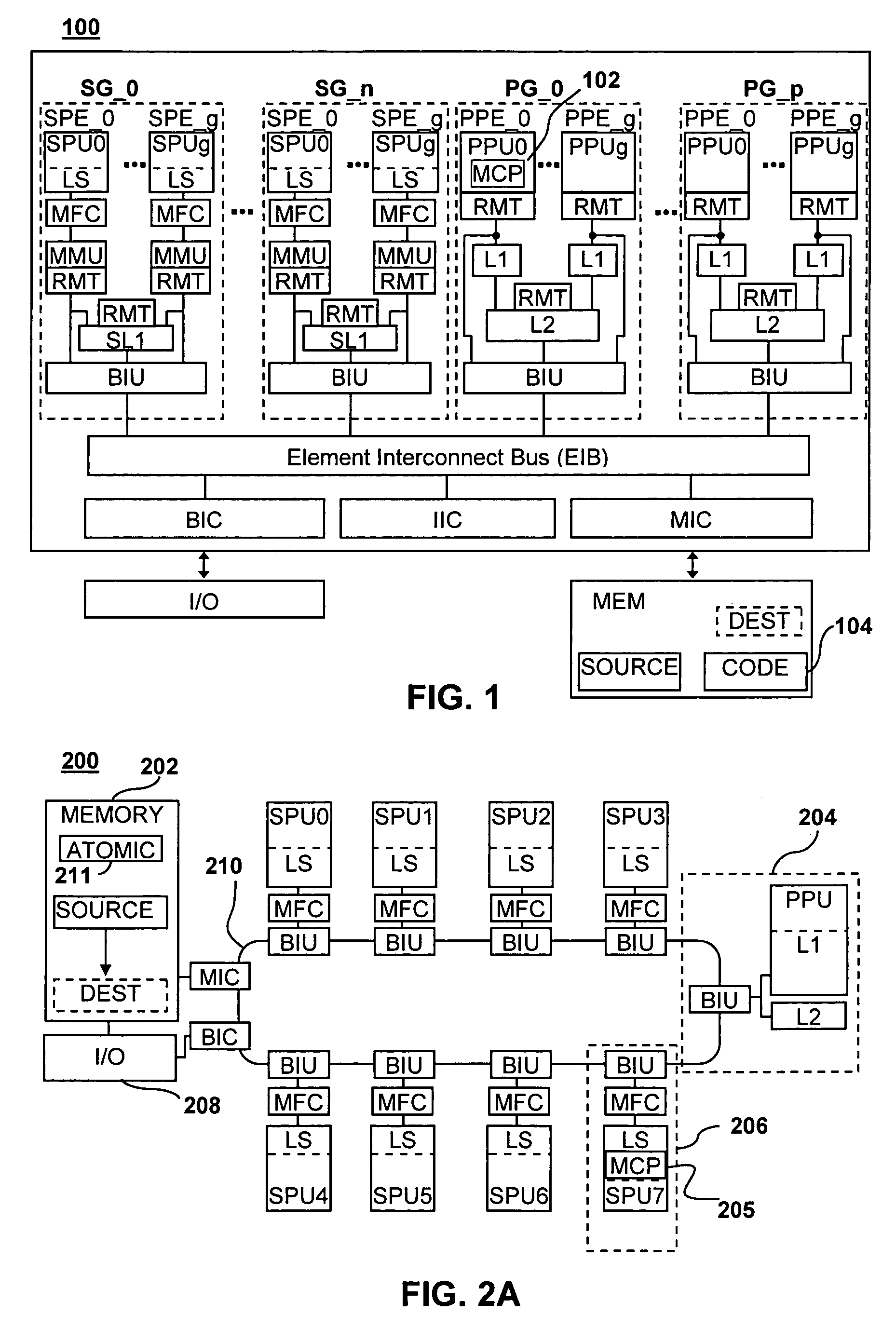

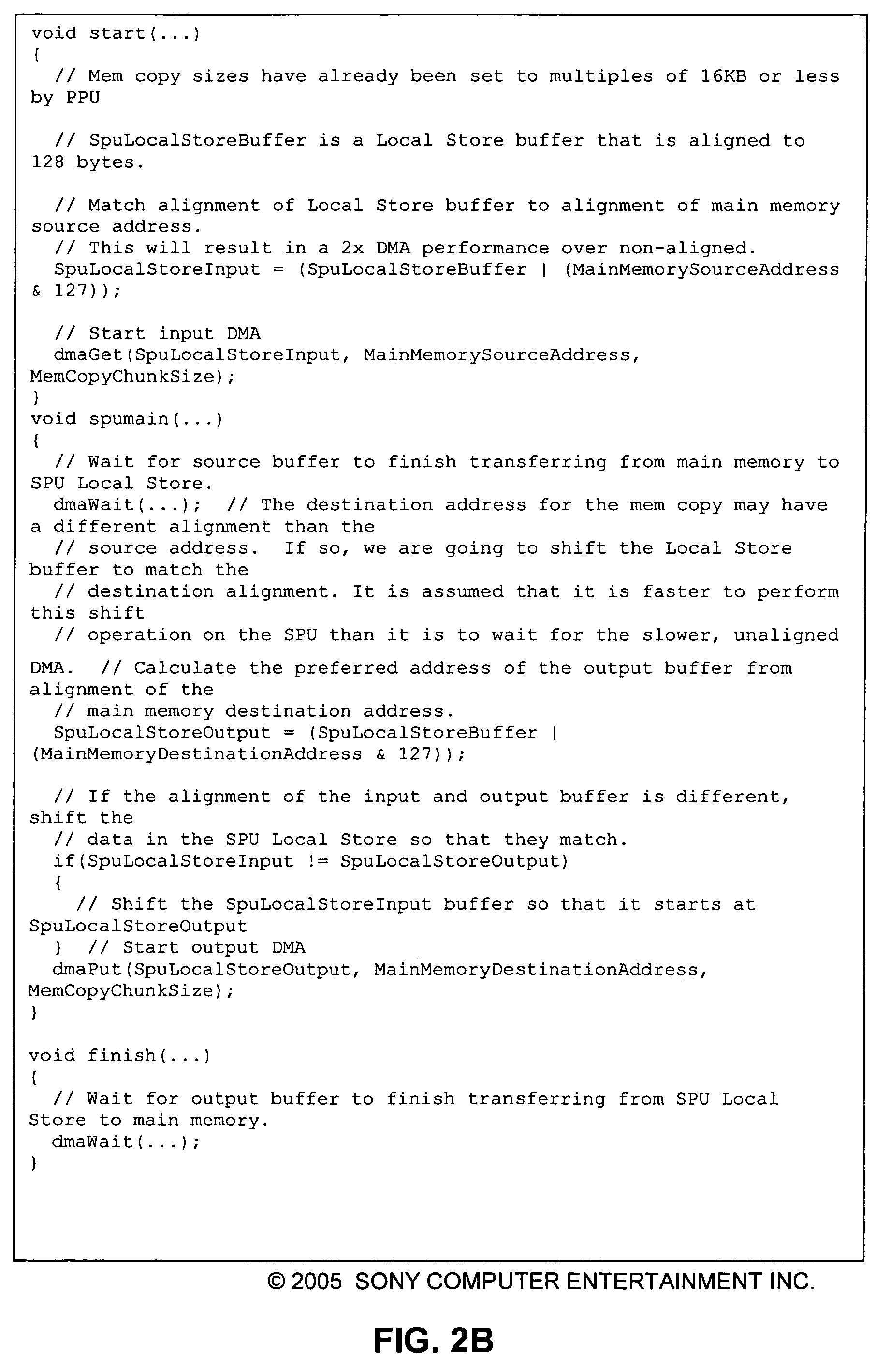

Method and system for performing memory copy function on a cell processor

Owner:SONY COMPUTER ENTERTAINMENT INC

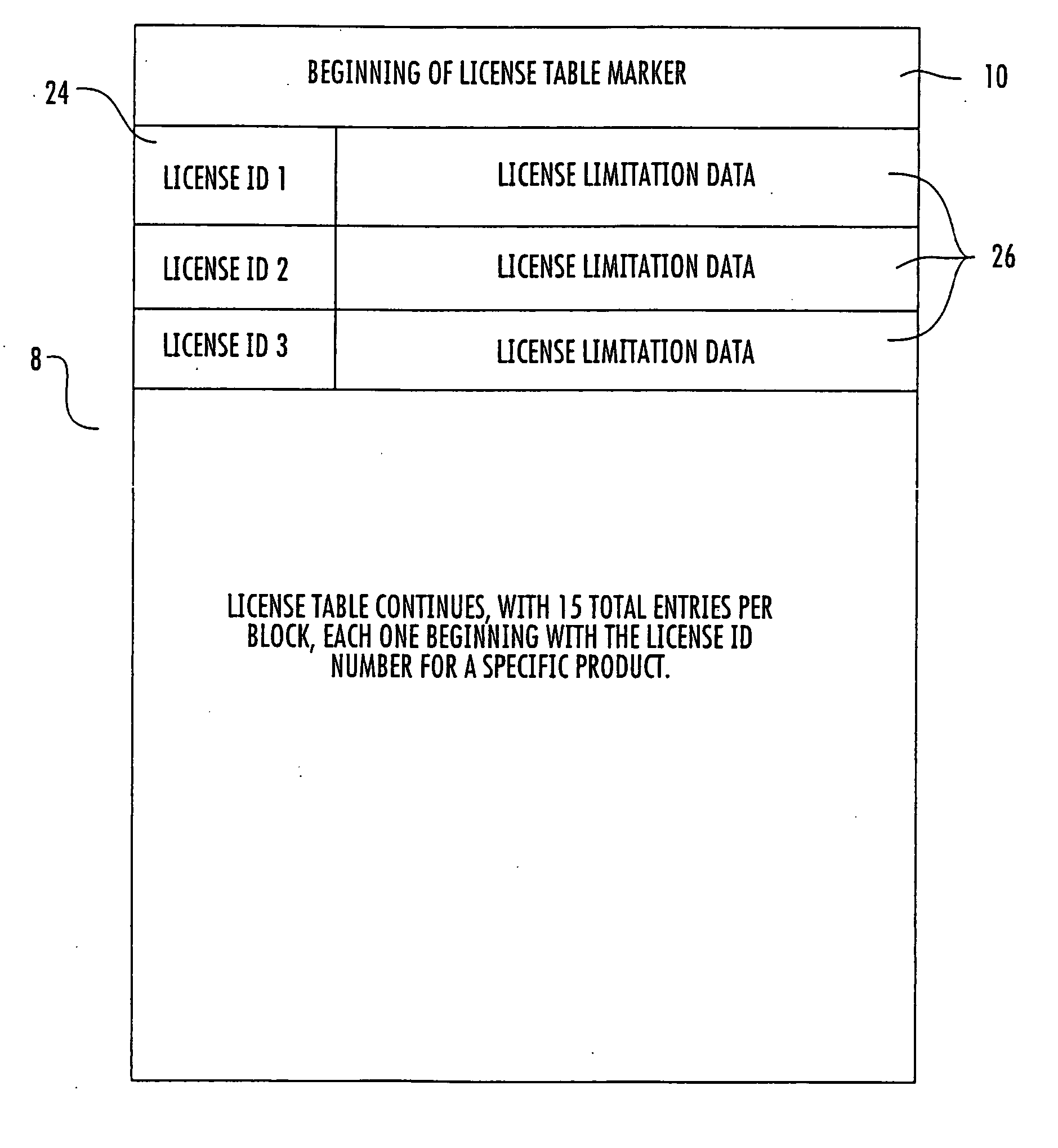

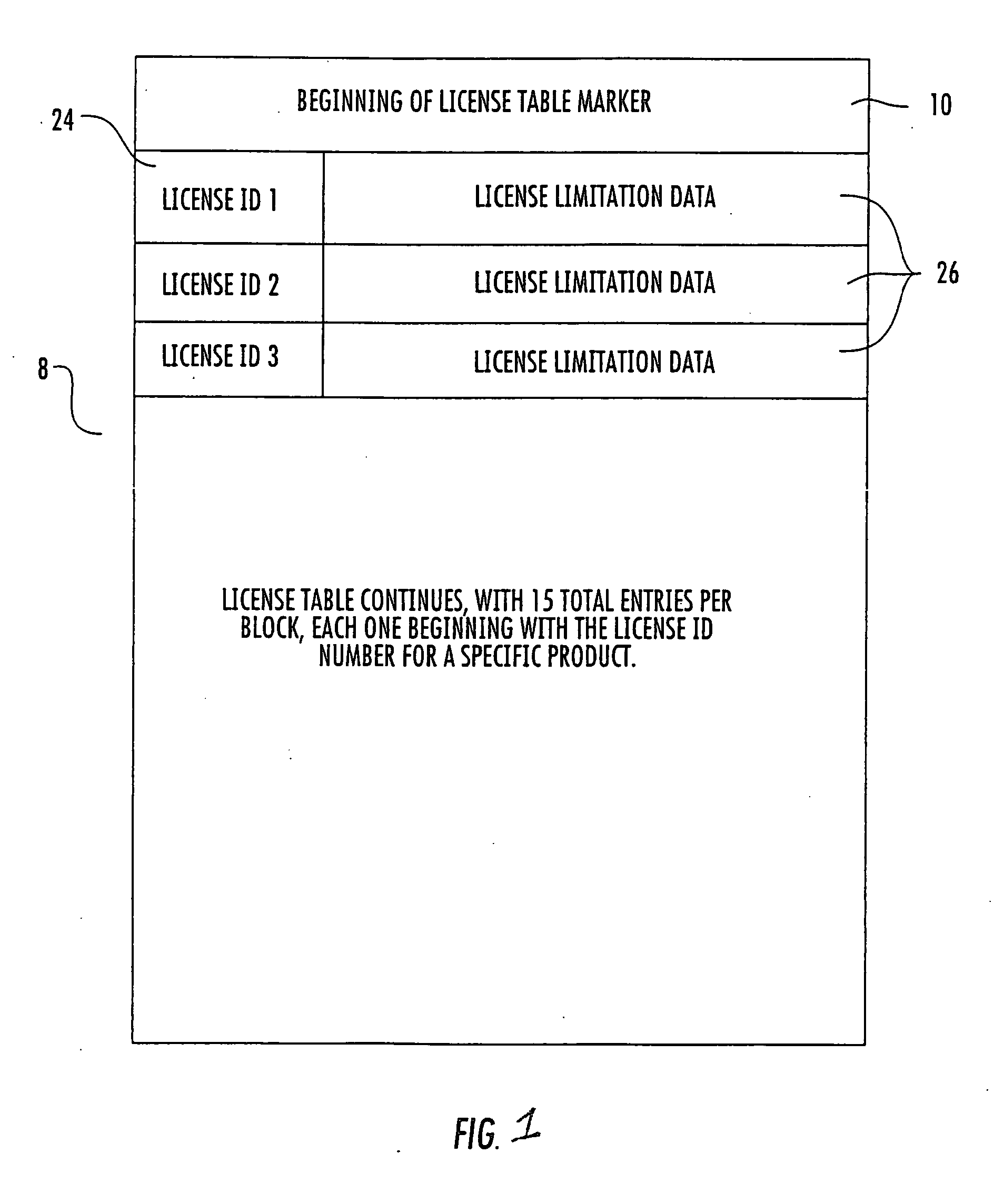

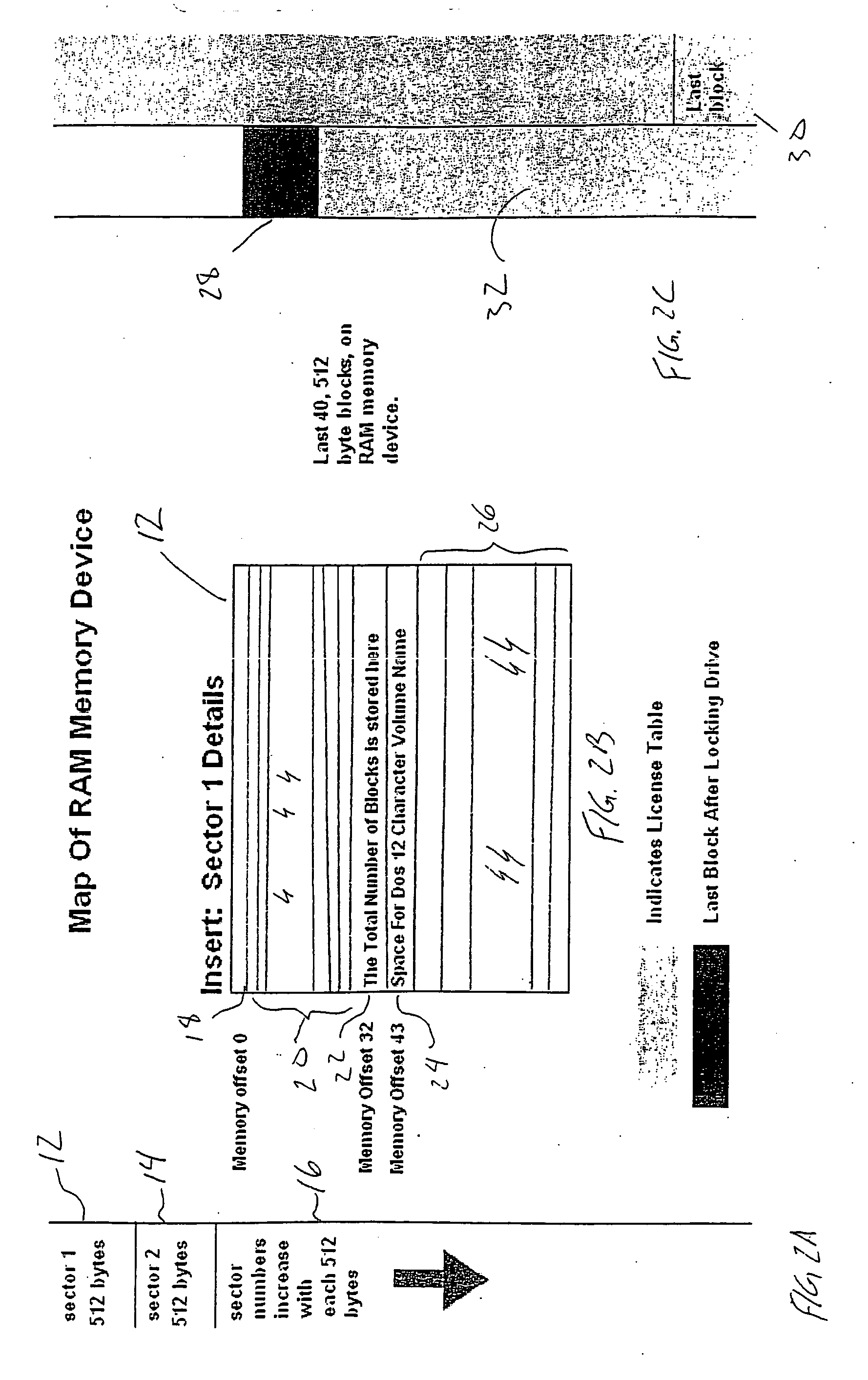

Methods of copy protecting software stored on portable memory

InactiveUS20060200414A1Avoid accessSmall sizeData processing applicationsRecord information storageOriginal dataData storing

Memory copy protection by structuring the sector arrangement of memory devices in such a way as to allow access to the data stored in the sectors of the device without compromising the protection of the data is disclosed. Methods of protecting data stored in nonvolatile RAM memory from access and copying are disclosed, and methods that will enable software to distinguish between originals data and illegal or unauthorized copies of the nonvolatile memory. A method and device for securely authorizing the use of a computer program is also provided.

Owner:NALPEIRON

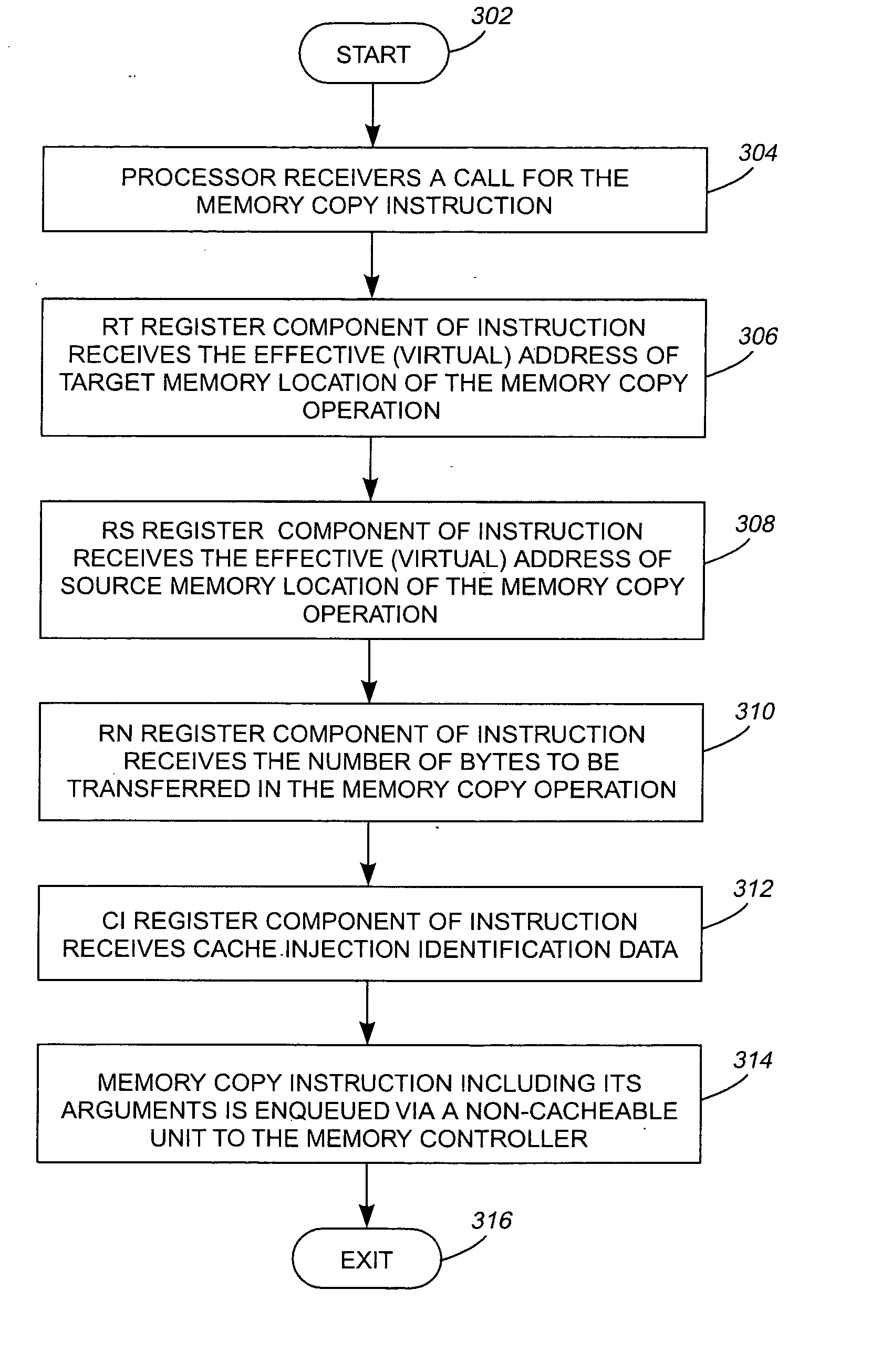

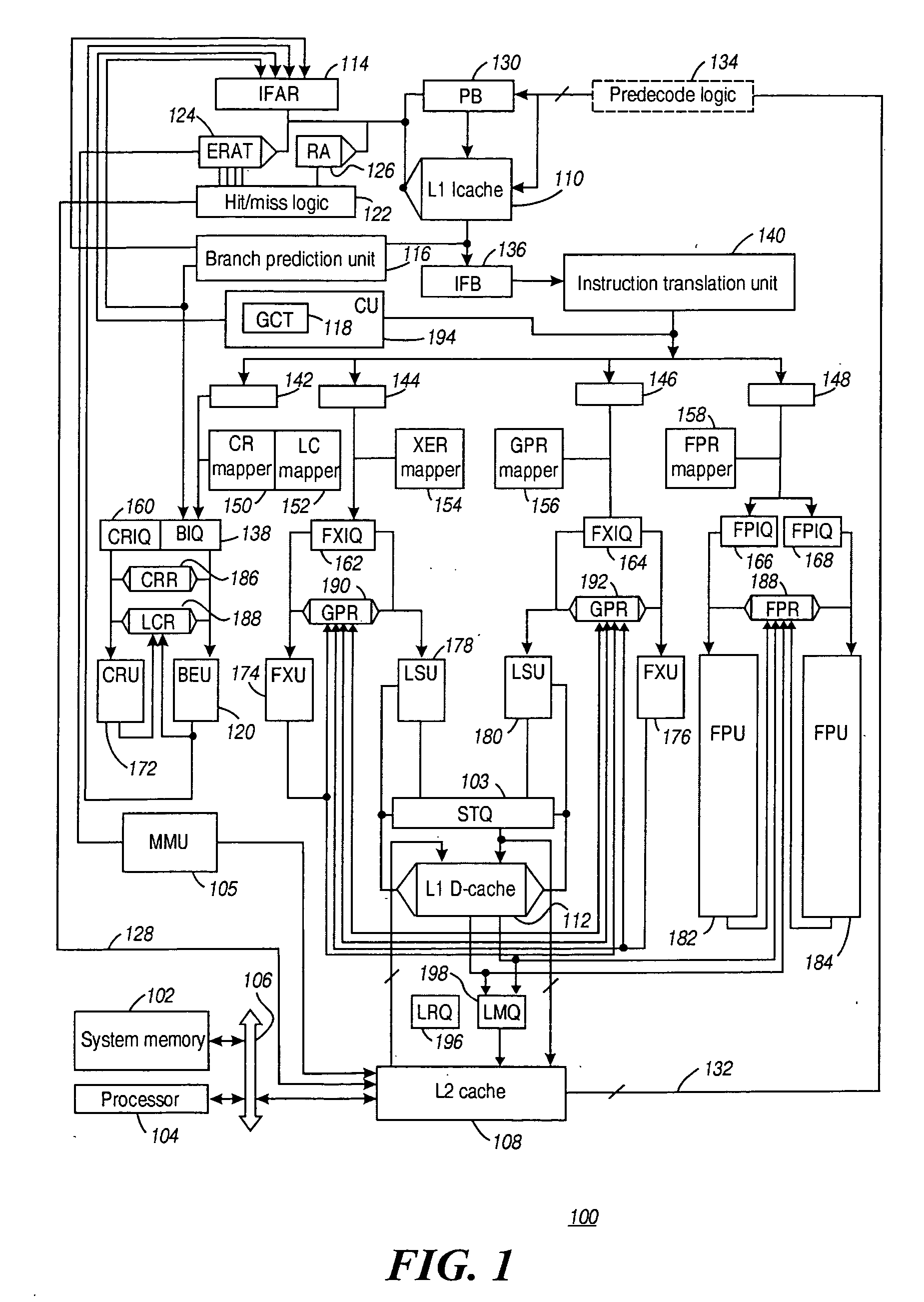

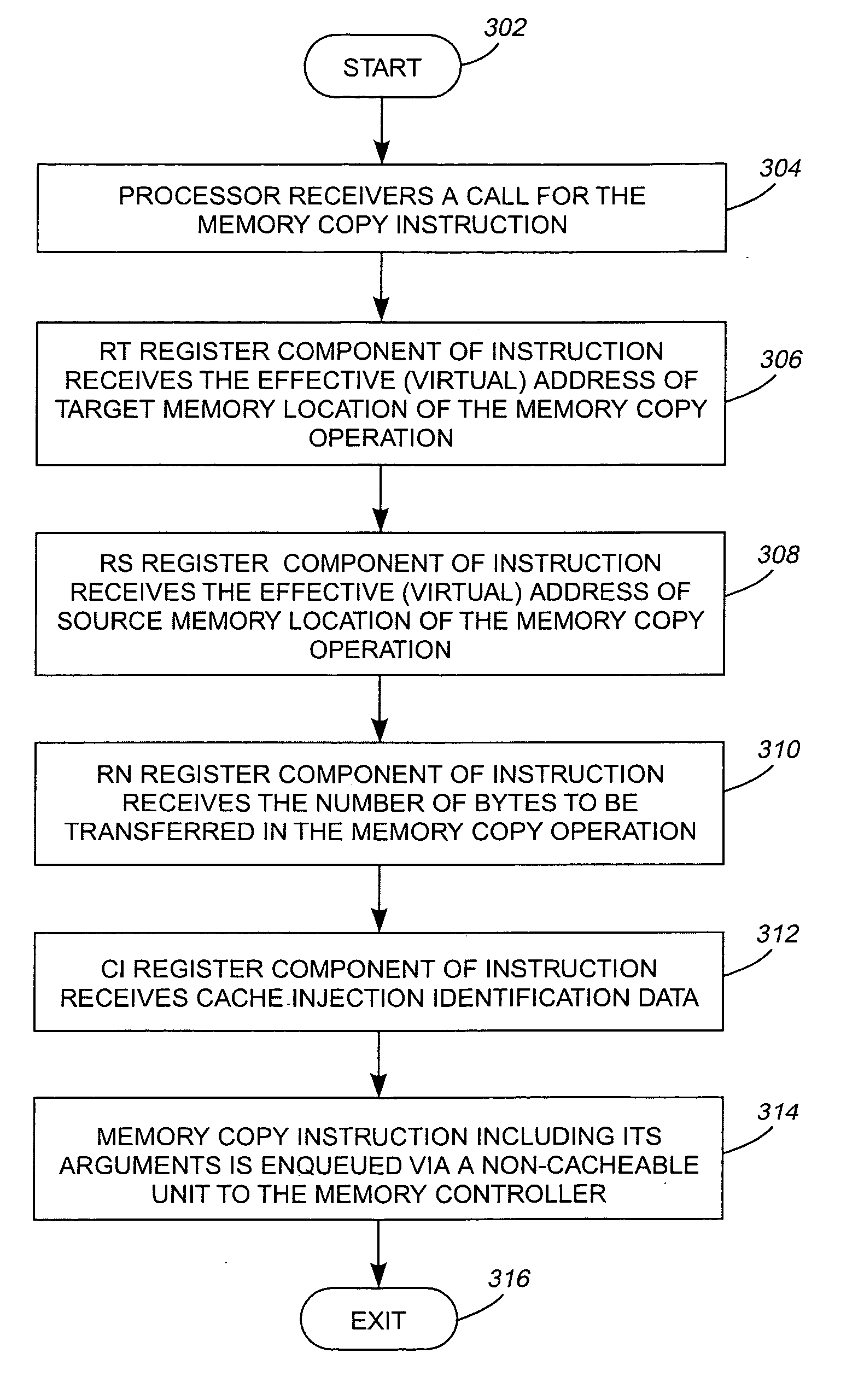

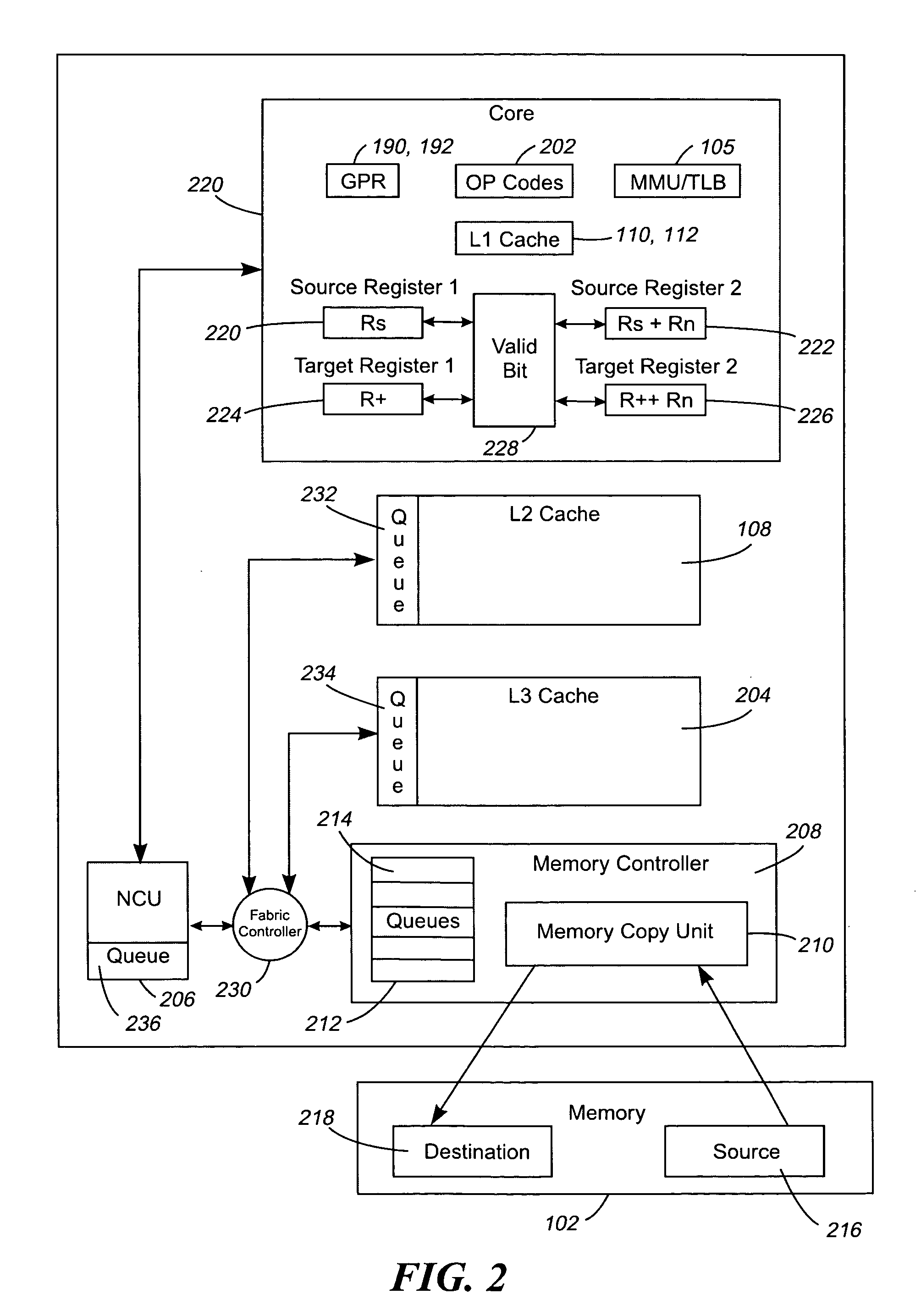

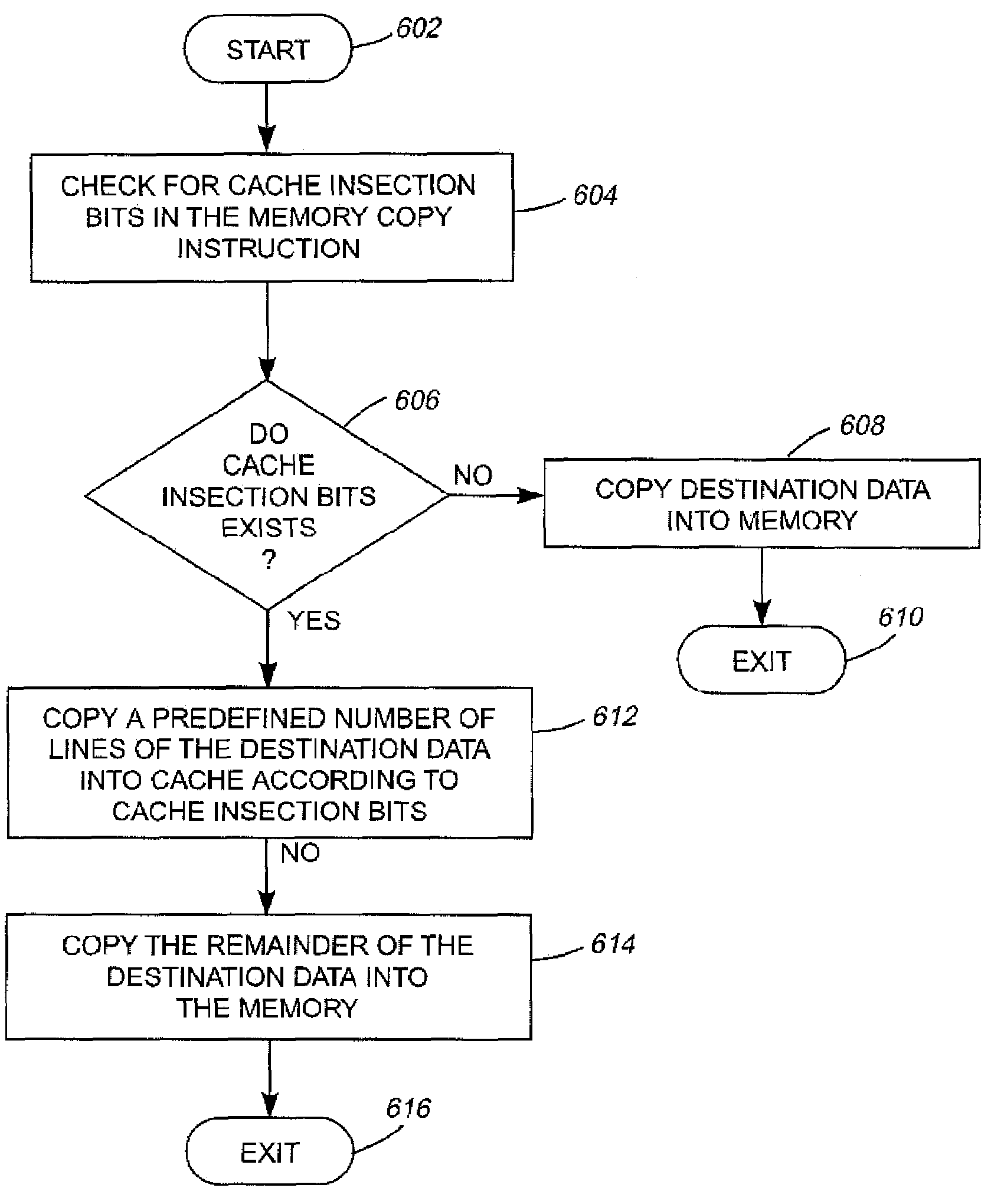

Cache injection semi-synchronous memory copy operation

InactiveUS20070150659A1Avoiding unnecessary processor downtimeAvoid overheadMemory architecture accessing/allocationProgram controlParallel computingTerm memory

A system, method, and a computer readable for inserting data into a cache memory based on information in a semi-synchronous memory copy instruction are disclosed. The method comprises determining a start of a semi-synchronous memory copy operation. The semi-synchronous memory copy operation is checked for a given value in at least one cache injection bit. In response to the given value in the cache injection bit, a predefined number of lines of destination data is copied into at least one level of cache memory.

Owner:IBM CORP

Method of communicating data in an interconnect system

InactiveUSRE40877E1Optimizes and improves performanceMemory adressing/allocation/relocationDigital computer detailsDirect memory accessMemory copy

A method is provided for communicating data in an interconnect system comprising a plurality of nodes. In one aspect, the method includes: issuing a command packet from a first node, the command packet comprising a respective header quadword and at least one respective data quadword for conveying a command to a second node, wherein the command is selected from a group comprising a direct memory access (DMA) command, an administrative write command, a memory copy write command, and a built in self test (BIST) command; receiving the command packet at the second node; issuing an acknowledgement packet from the second node, the acknowledgement packet comprising a respective header quadword for conveying an acknowledgement that the command packet has been received at the second node.

Owner:HEWLETT PACKARD DEV CO LP

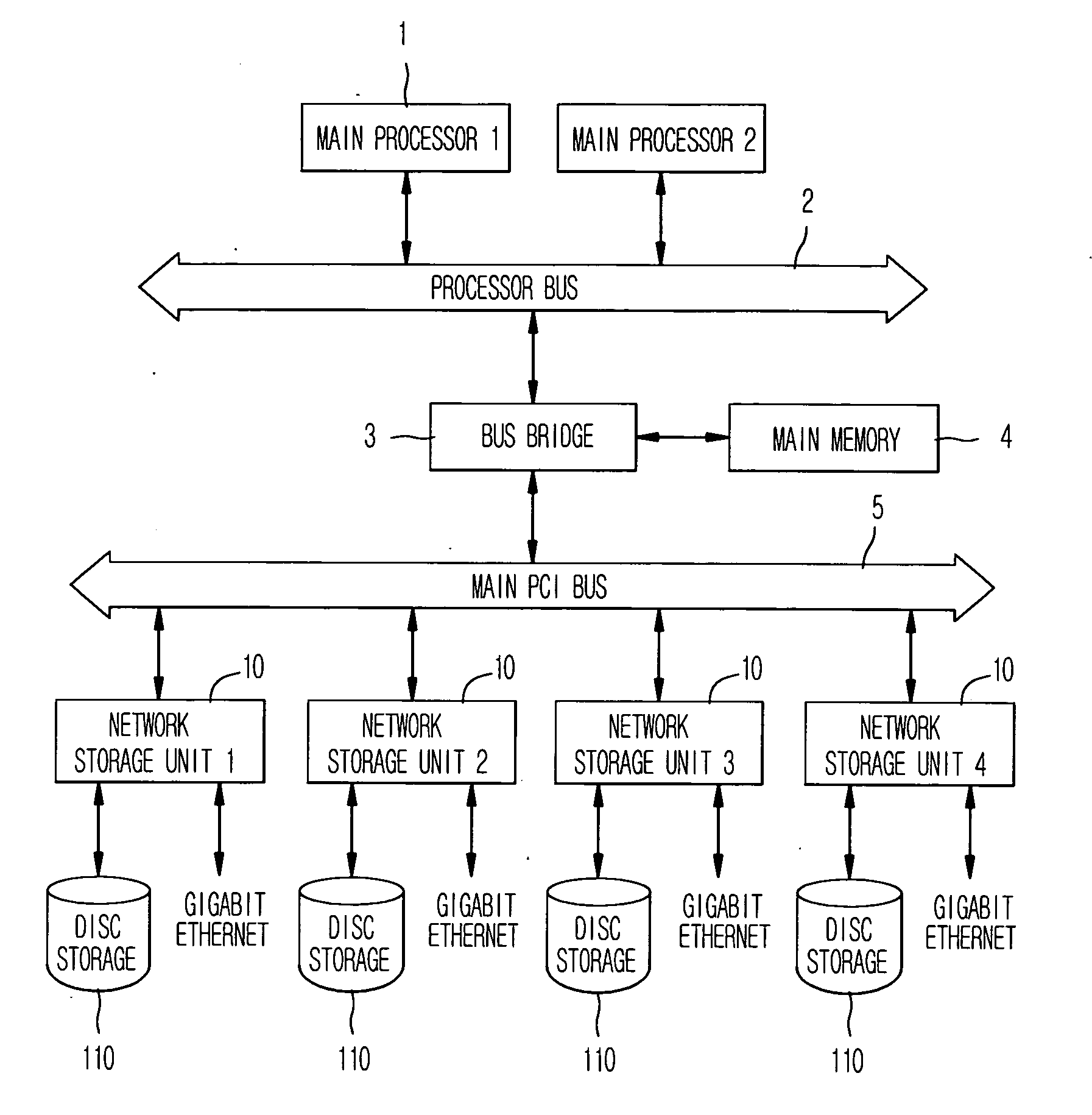

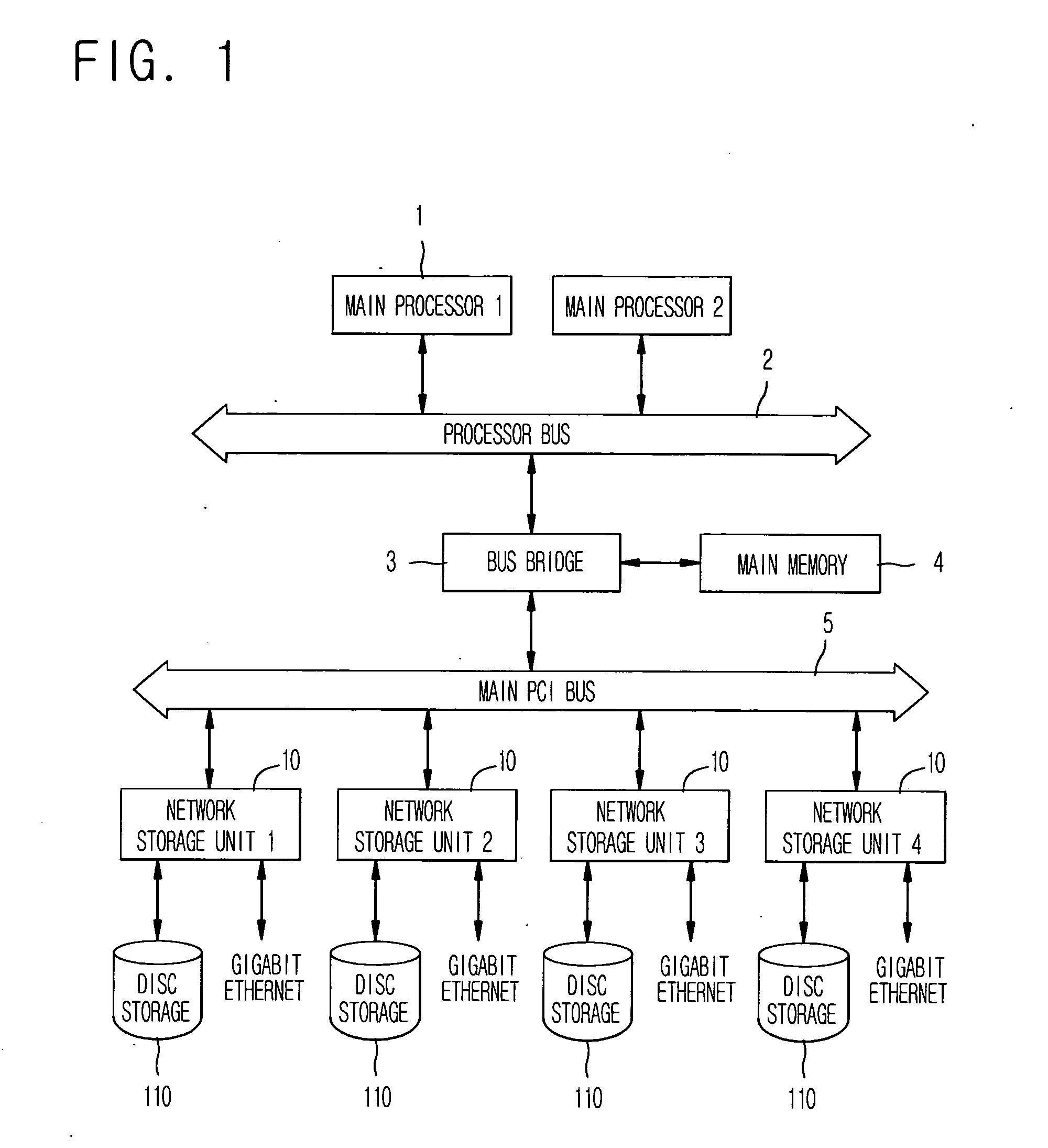

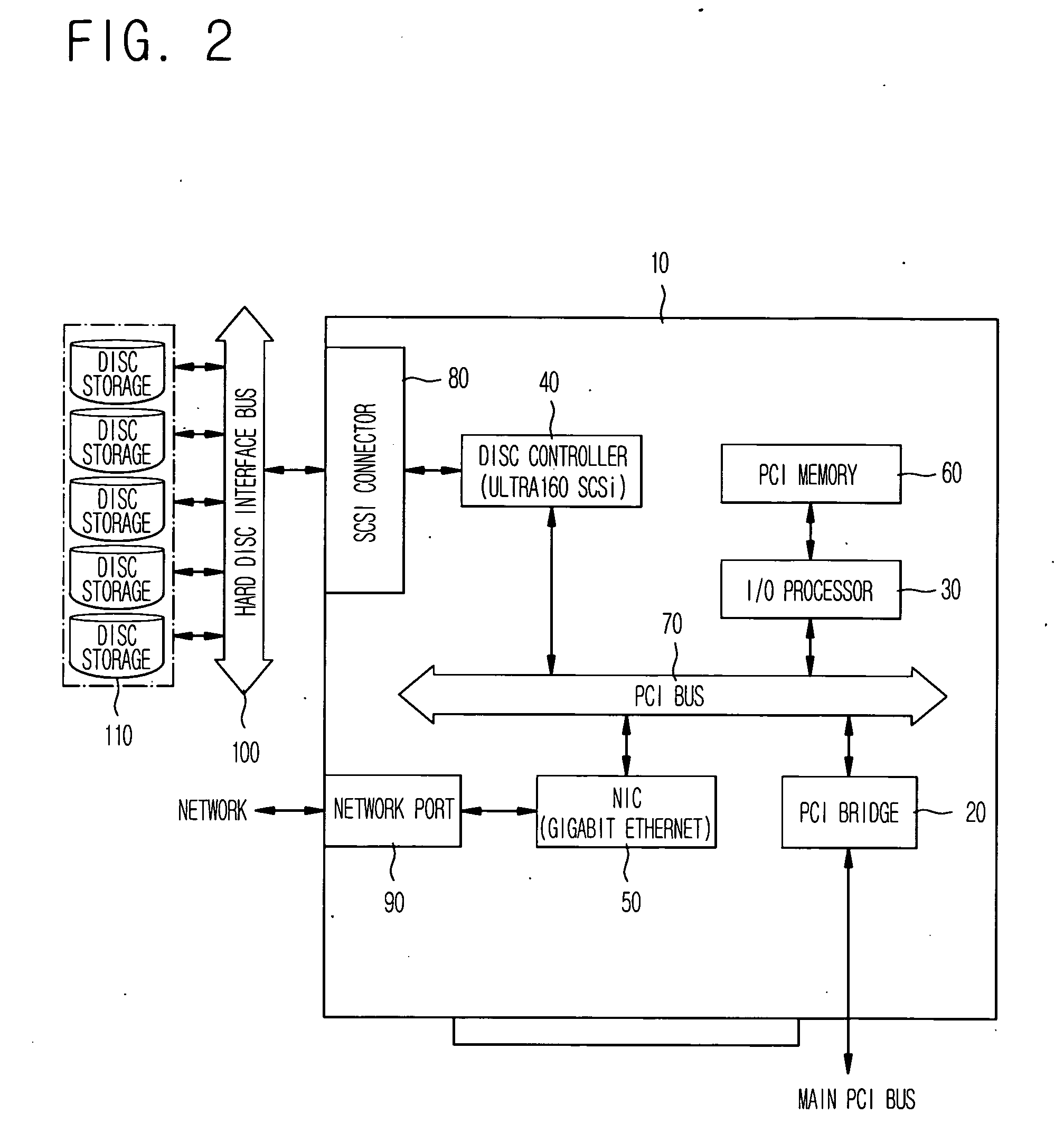

Apparatus for high-speed streaming data transmission using PMEM controller and method thereof

InactiveUS20050273649A1Eliminate the problemError detection/correctionMultiple digital computer combinationsStreaming dataTerm memory

Disclosed are an apparatus for a high-speed streaming data transmission using a PMEM controller and a method thereof. The PMEM controller (i.e., an I / O processor) transmits data stored in a storage device to a network through a process for a PMEM to local copy of the data between a large-capacity PM (Peripheral Memory) and a main memory or for a PMEM to PMEM copy of the data in the PM. According to this process, the data transmission speed can be improved. Also, by reducing the memory copy of disc streaming data, the interference with the main processor can be minimized, and thus high-quality streaming data can be supported.

Owner:ELECTRONICS & TELECOMM RES INST

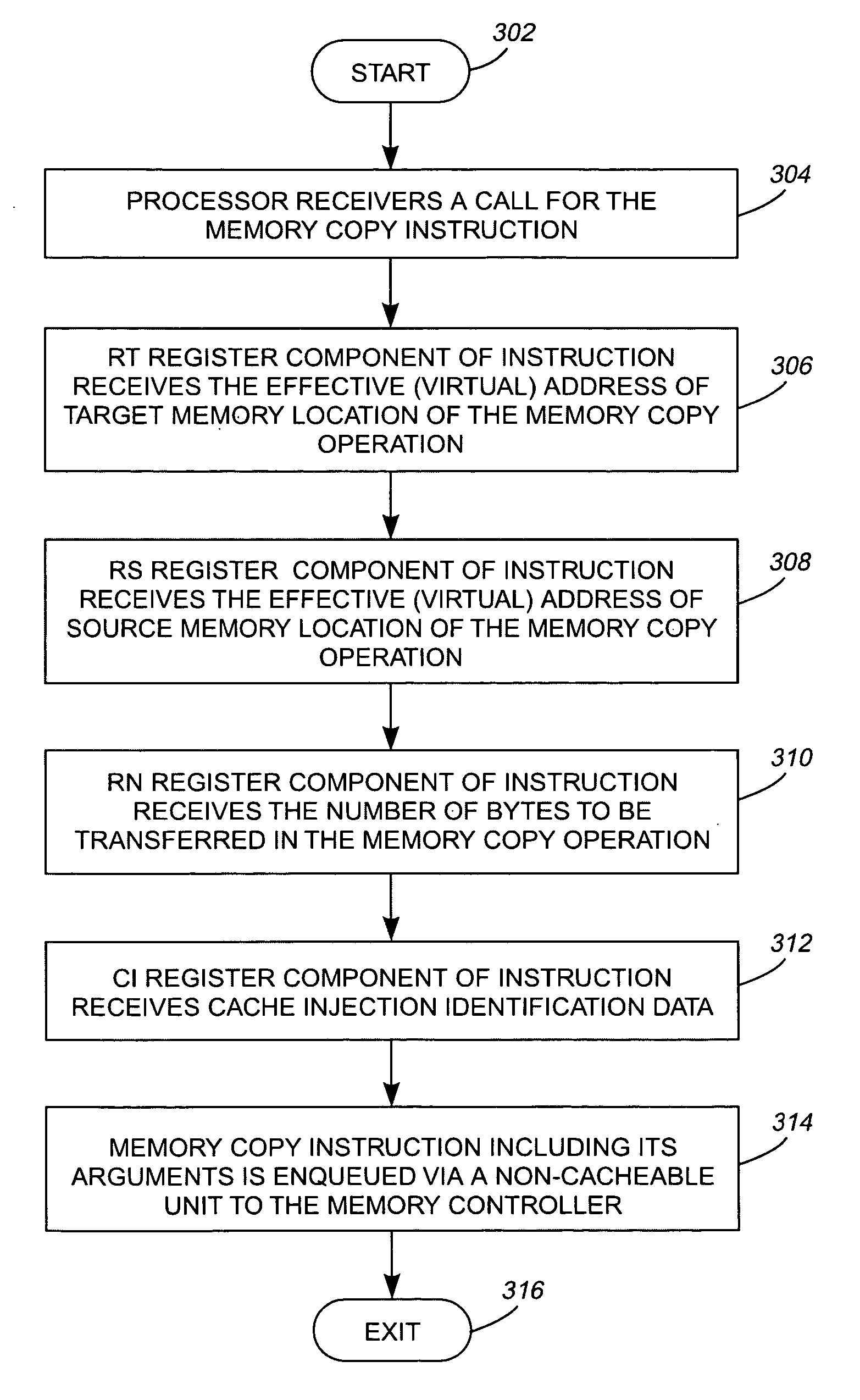

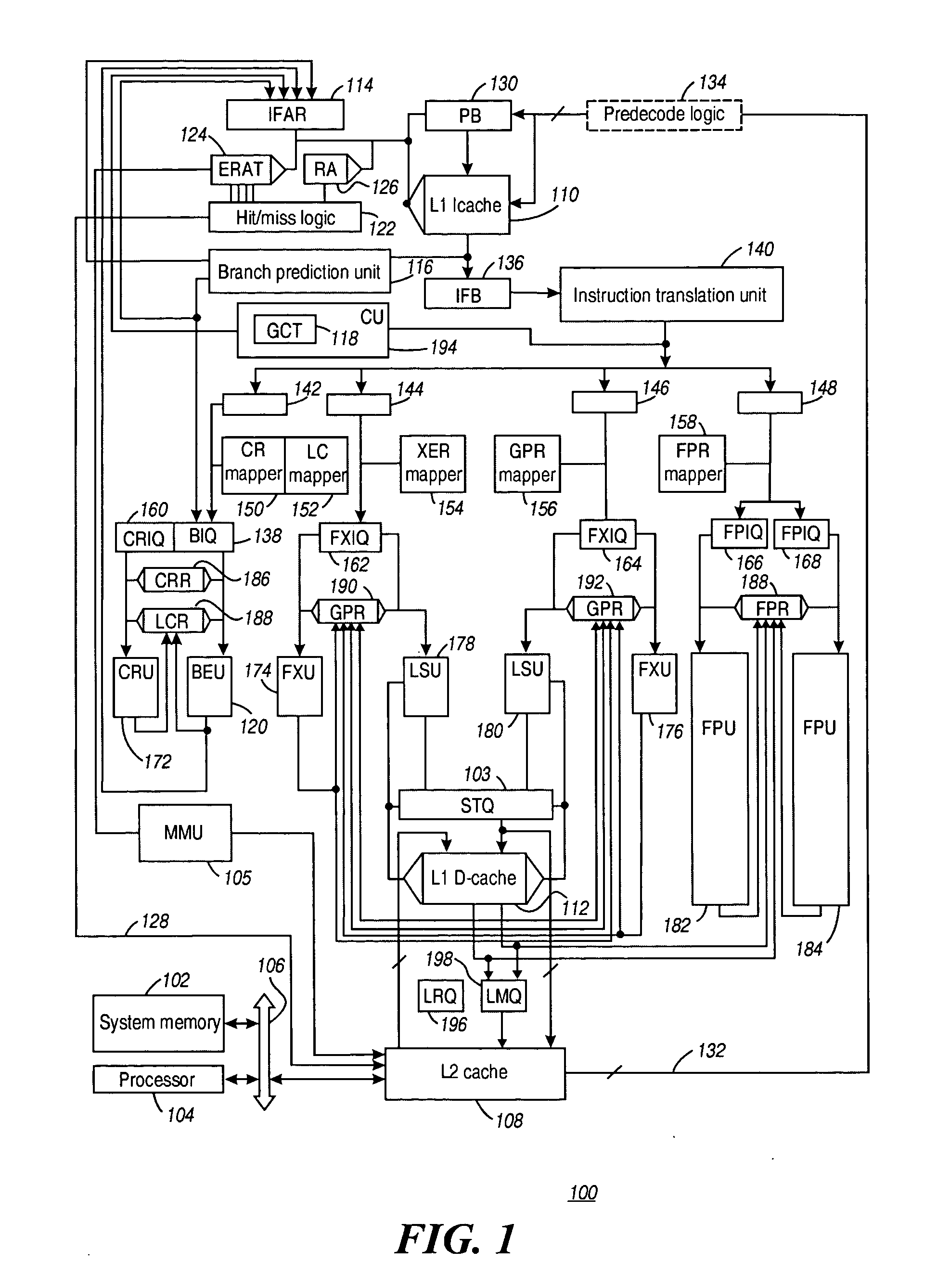

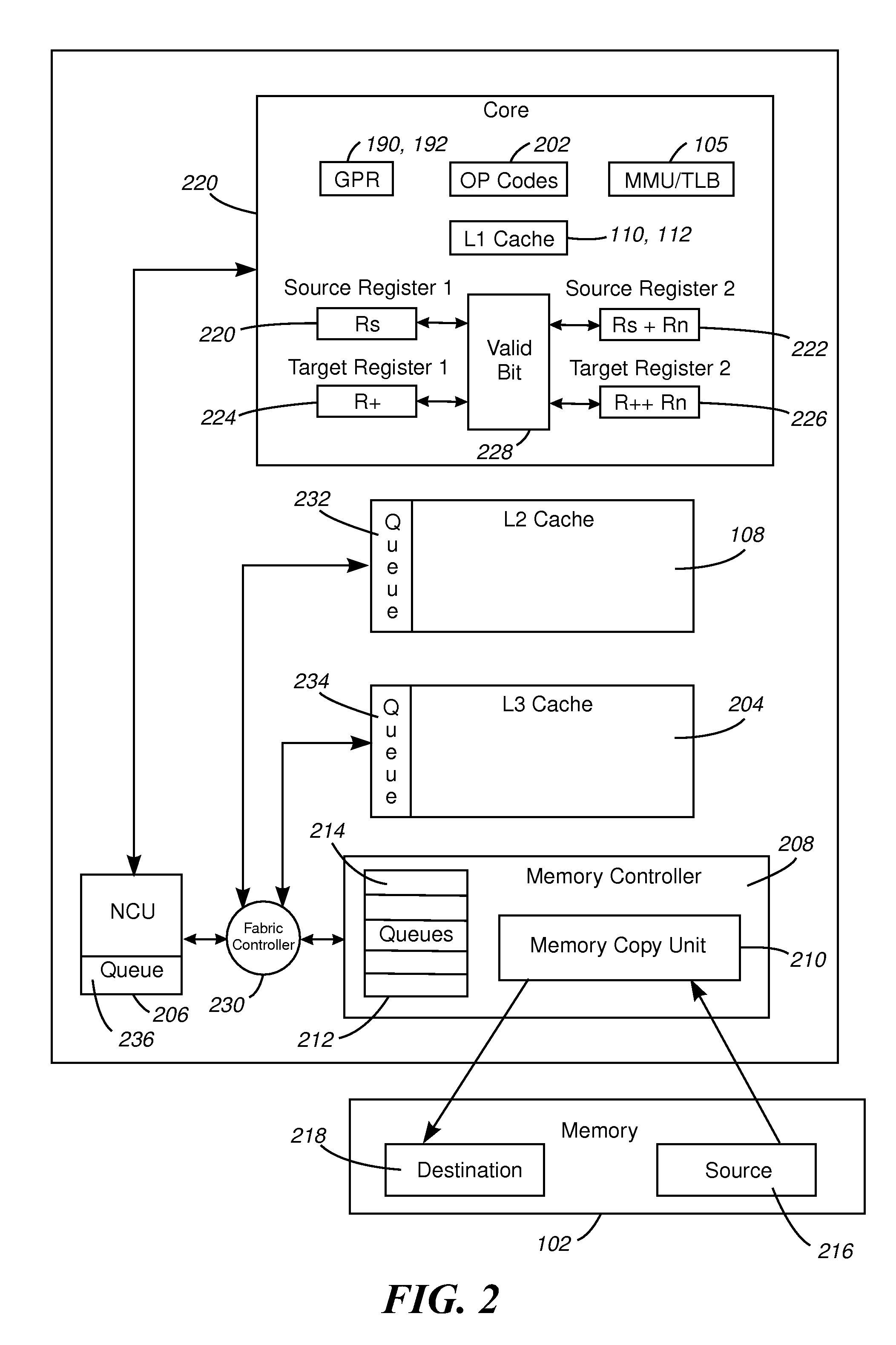

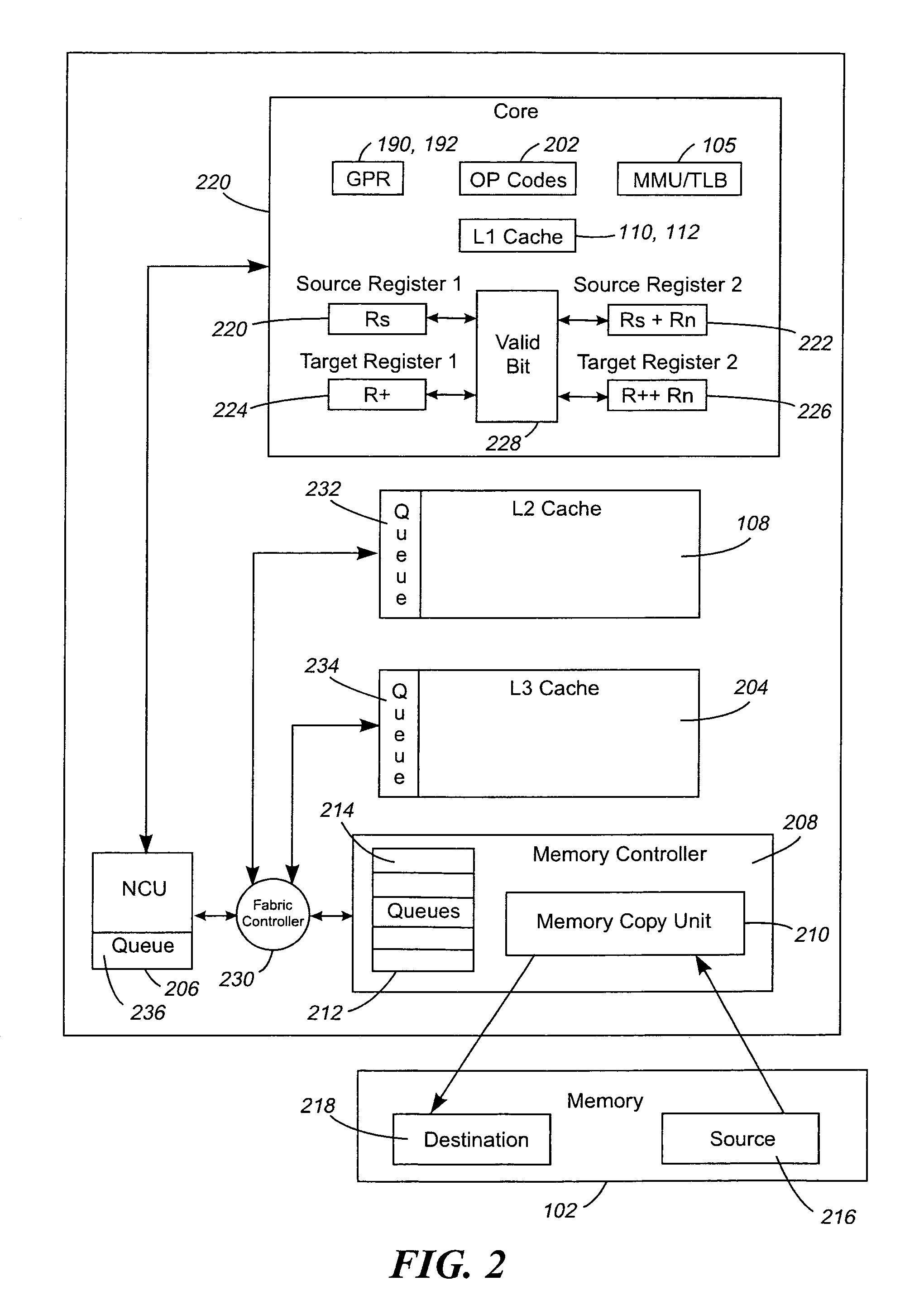

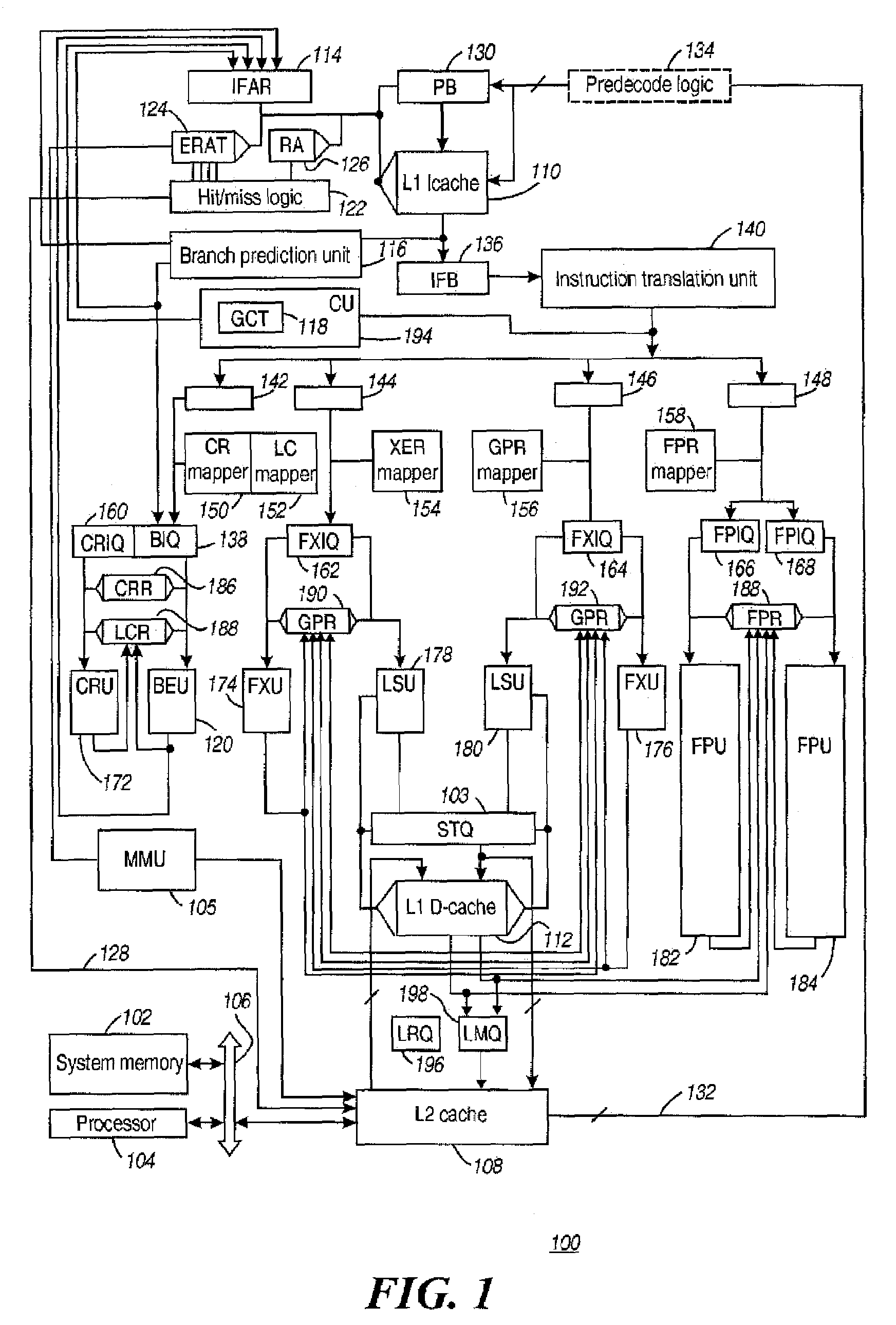

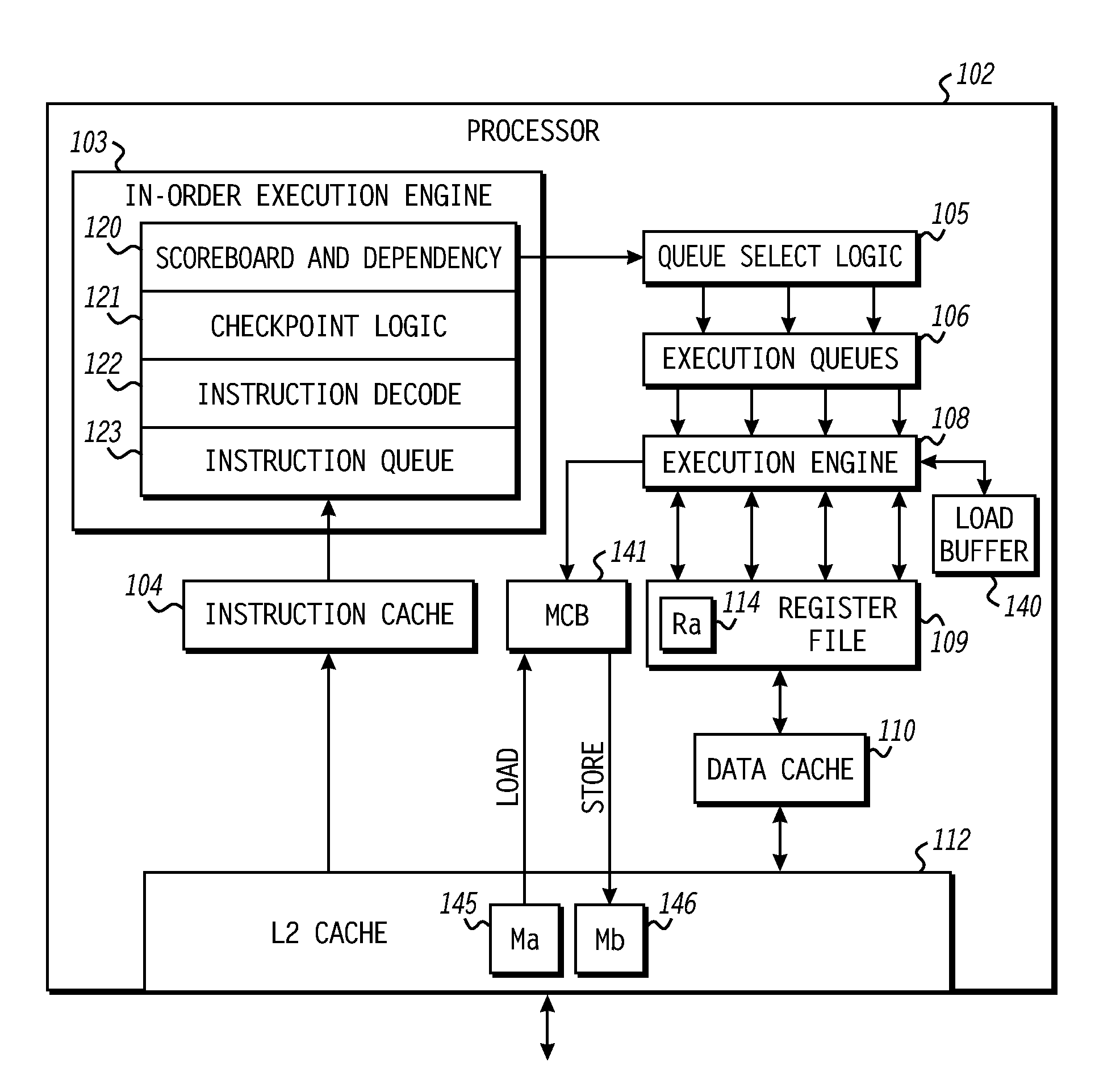

Efficient and flexible memory copy operation

InactiveUS20070150676A1Avoiding unnecessary processor downtimeAvoid overheadMemory loss protectionConcurrent instruction executionVirtual targetTerm memory

A system, method, and computer program product for semi-synchronously copying data from a first portion of memory to a second portion of memory are disclosed. The method comprises receiving, in a processor, a call for a semi-synchronous memory copy operation. The semi-synchronous memory copy operation preserves temporal persistence of validity for a virtual source address corresponding to a source location in a memory and a virtual target address corresponding to a target location in the memory by setting a flag bit. The call includes at least the virtual source address, the virtual target address, and an indicator identifying a number of bytes to be copied. The memory copy operation is placed in a queue for execution by a memory controller. The queue is coupled to the memory controller. At least one subsequent instruction is continued to be executed as the subsequent instruction becomes available from an instruction pipeline.

Owner:IBM CORP

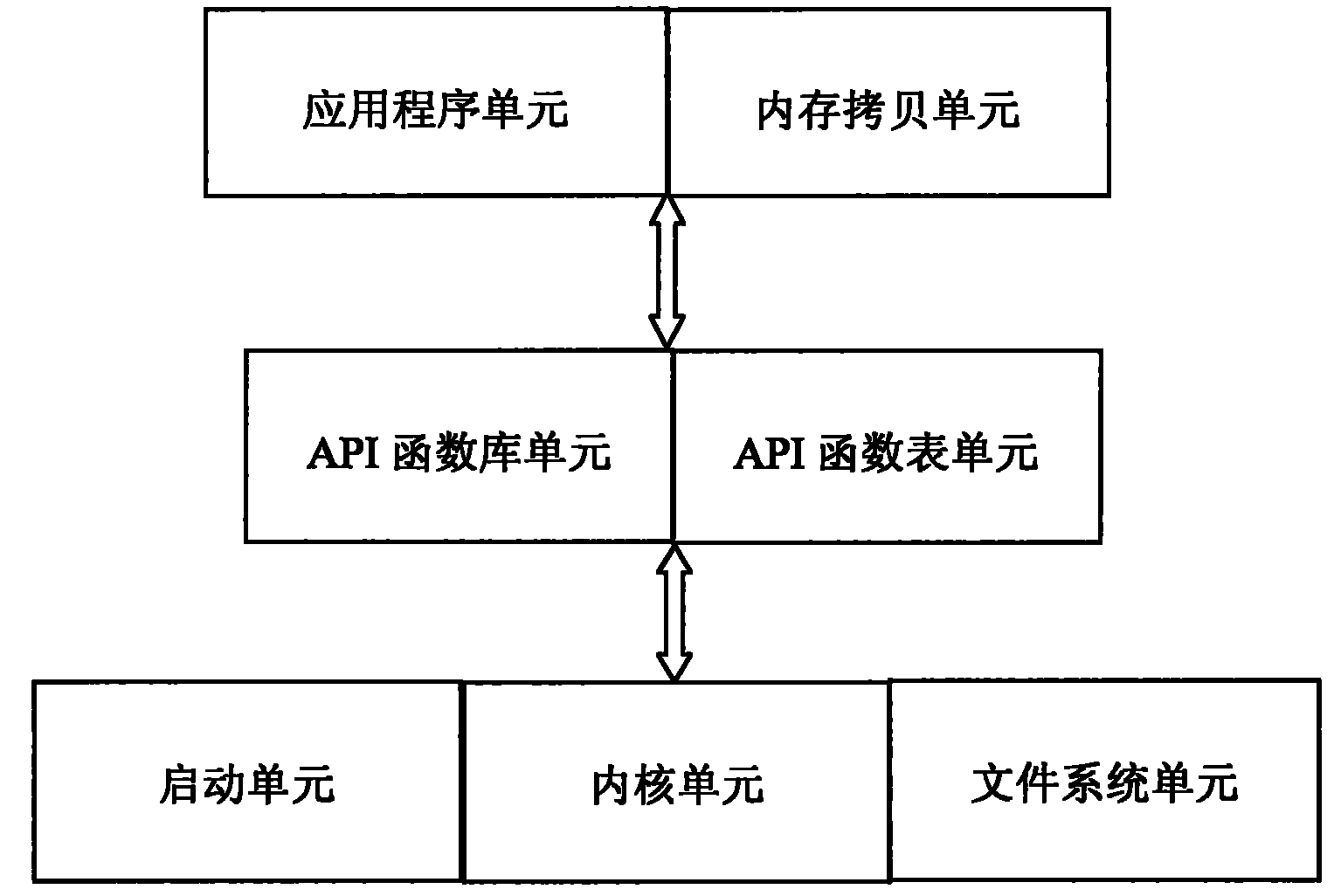

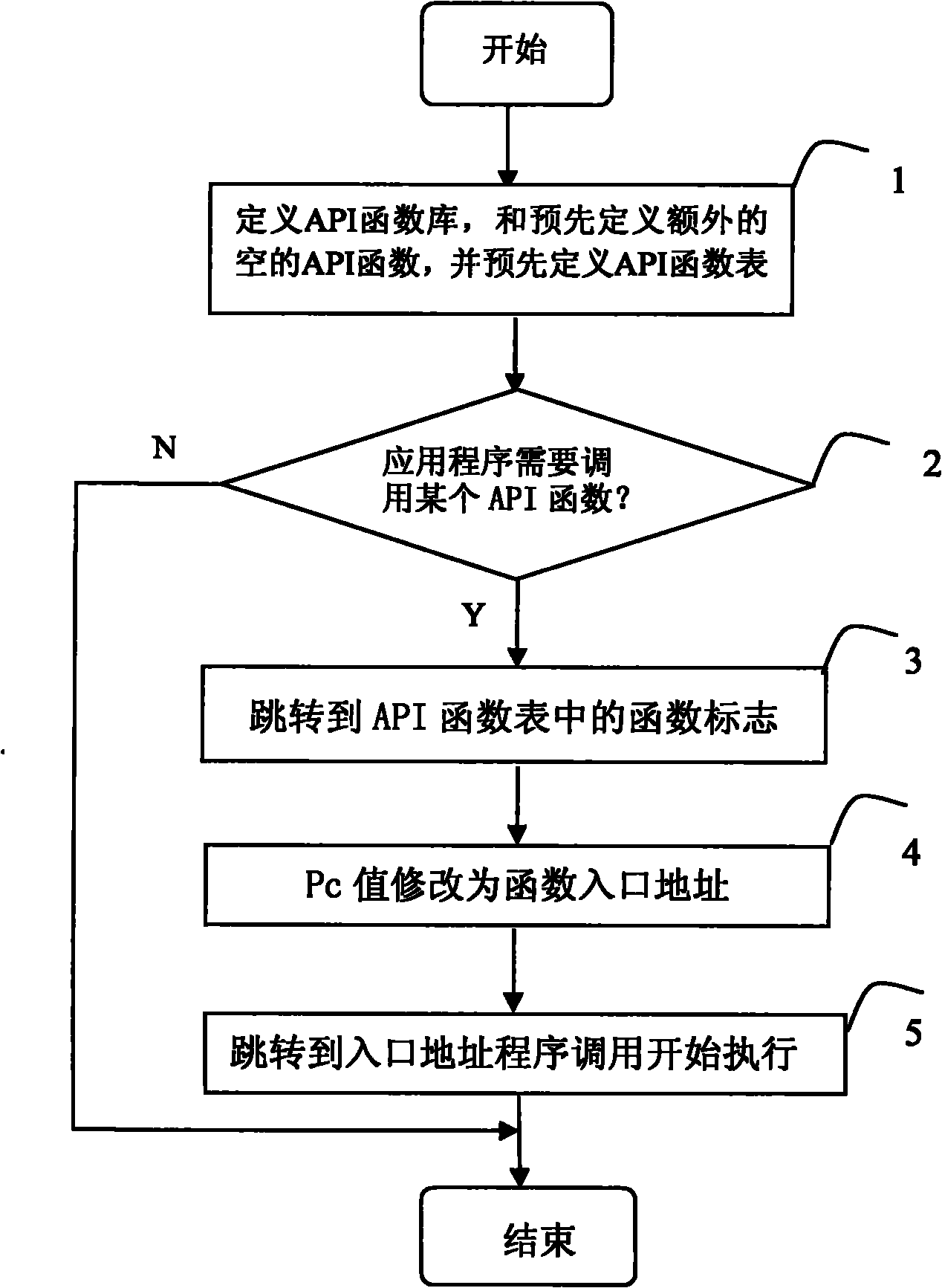

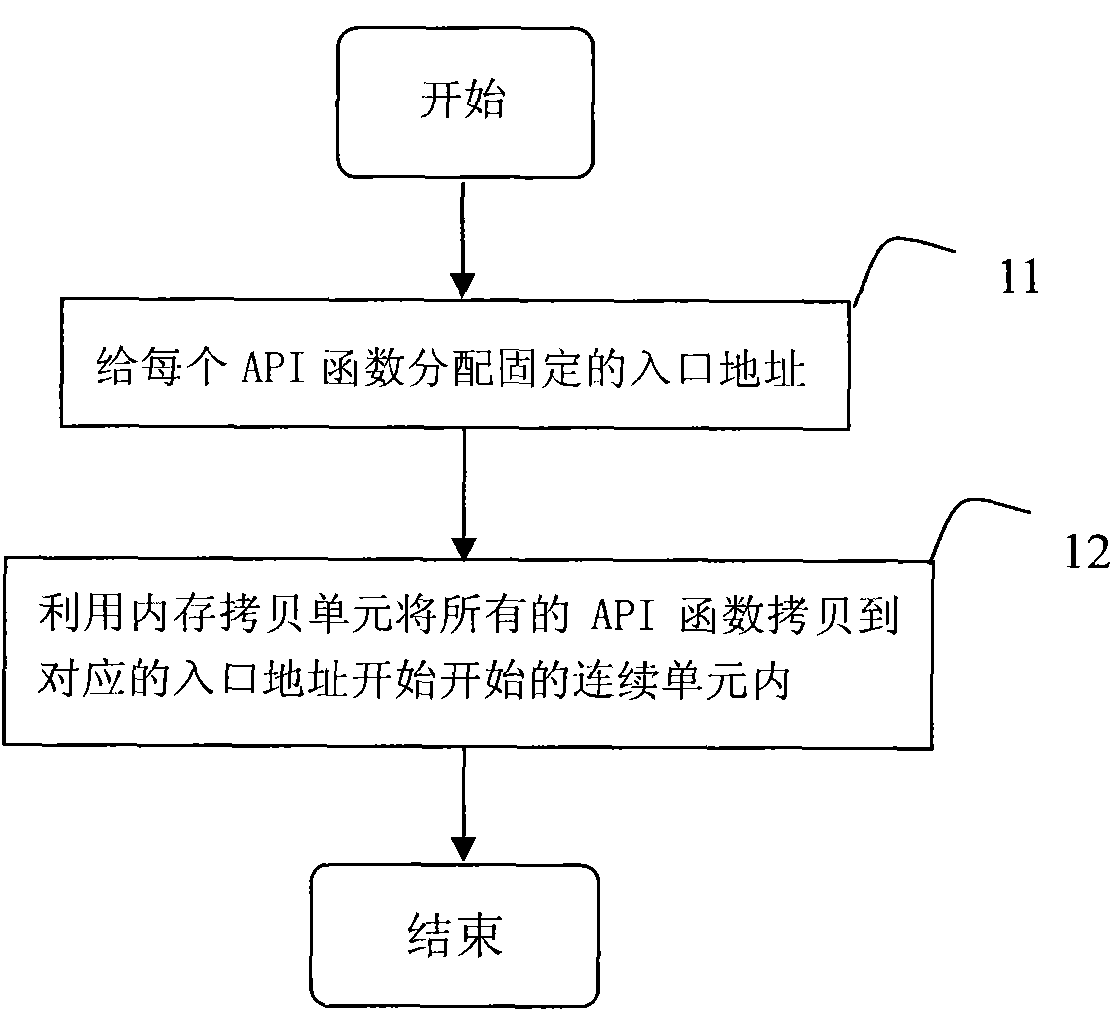

Rapid implementation method based on embedded program and system thereof

InactiveCN101814020AEfficient executionSimplify the dynamic loading processConcurrent instruction executionMemory systemsOperational systemFile system

Owner:CHANGSHA UNIVERSITY OF SCIENCE AND TECHNOLOGY

Efficient and flexible memory copy operation

InactiveUS20080307182A1Avoiding unnecessary processor downtimeAvoid overheadMemory loss protectionConcurrent instruction executionVirtual targetMemory controller

Owner:INT BUSINESS MASCH CORP

Validity of address ranges used in semi-synchronous memory copy operations

InactiveUS7506132B2Avoiding unnecessary processor downtimeAvoid overheadMemory loss protectionMicro-instruction address formationParallel computingPage table

A system, method, and a computer readable for protecting content of a memory page are disclosed. The method includes determining a start of a semi-synchronous memory copy operation. A range of addresses is determined where the semi-synchronous memory copy operation is being performed. An issued instruction that removes a page table entry is detected. The method further includes determining whether the issued instruction is destined to remove a page table entry associated with at least one address in the range of addresses. In response to the issued instruction being destined to remove the page table entry, the execution of the issued instruction is stalled until the semi-synchronous memory copy operation is completed.

Owner:INT BUSINESS MASCH CORP

Cache injection semi-synchronous memory copy operation

InactiveUS7484062B2Avoiding unnecessary processor downtimeAvoid overheadMemory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingMemory copy

A system, method, and a computer readable for inserting data into a cache memory based on information in a semi-synchronous memory copy instruction are disclosed. The method comprises determining a start of a semi-synchronous memory copy operation. The semi-synchronous memory copy operation is checked for a given value in at least one cache injection bit. In response to the given value in the cache injection bit, a predefined number of lines of destination data is copied into at least one level of cache memory.

Owner:INT BUSINESS MASCH CORP

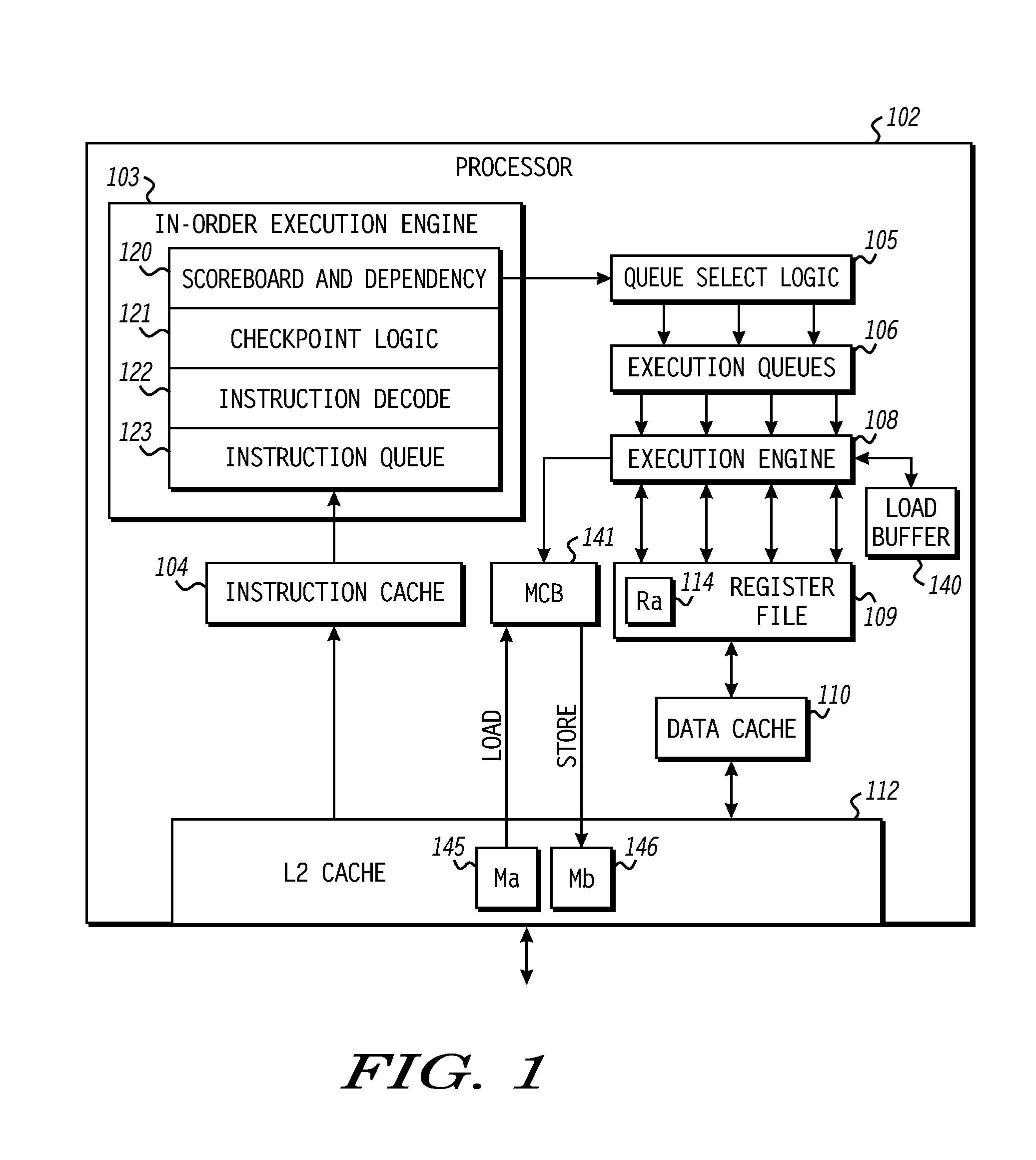

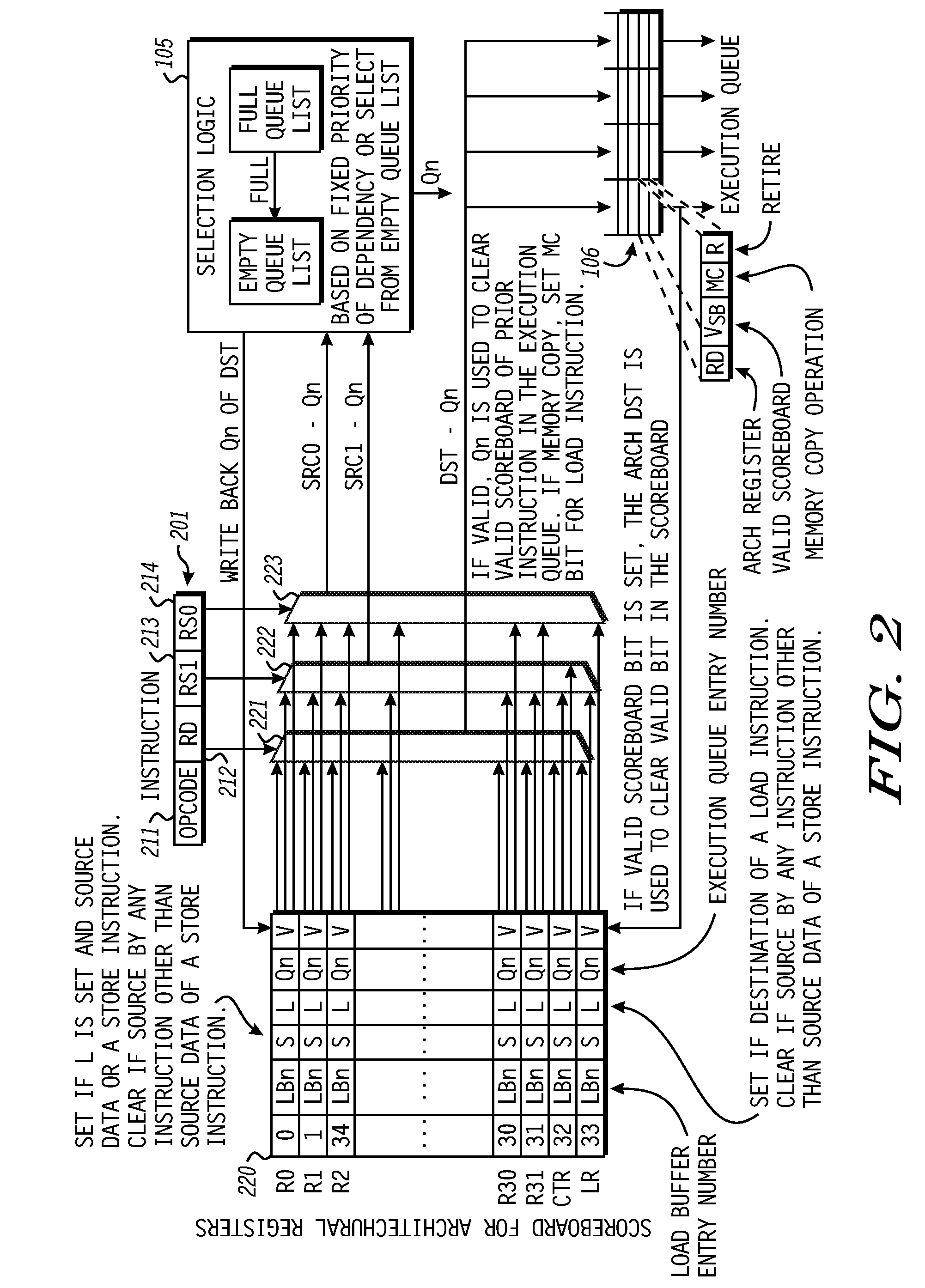

Apparatus and method for memory copy at a processor

ActiveUS20130290639A1Memory adressing/allocation/relocationProgram controlLoad instructionProcessor register

Owner:NXP USA INC

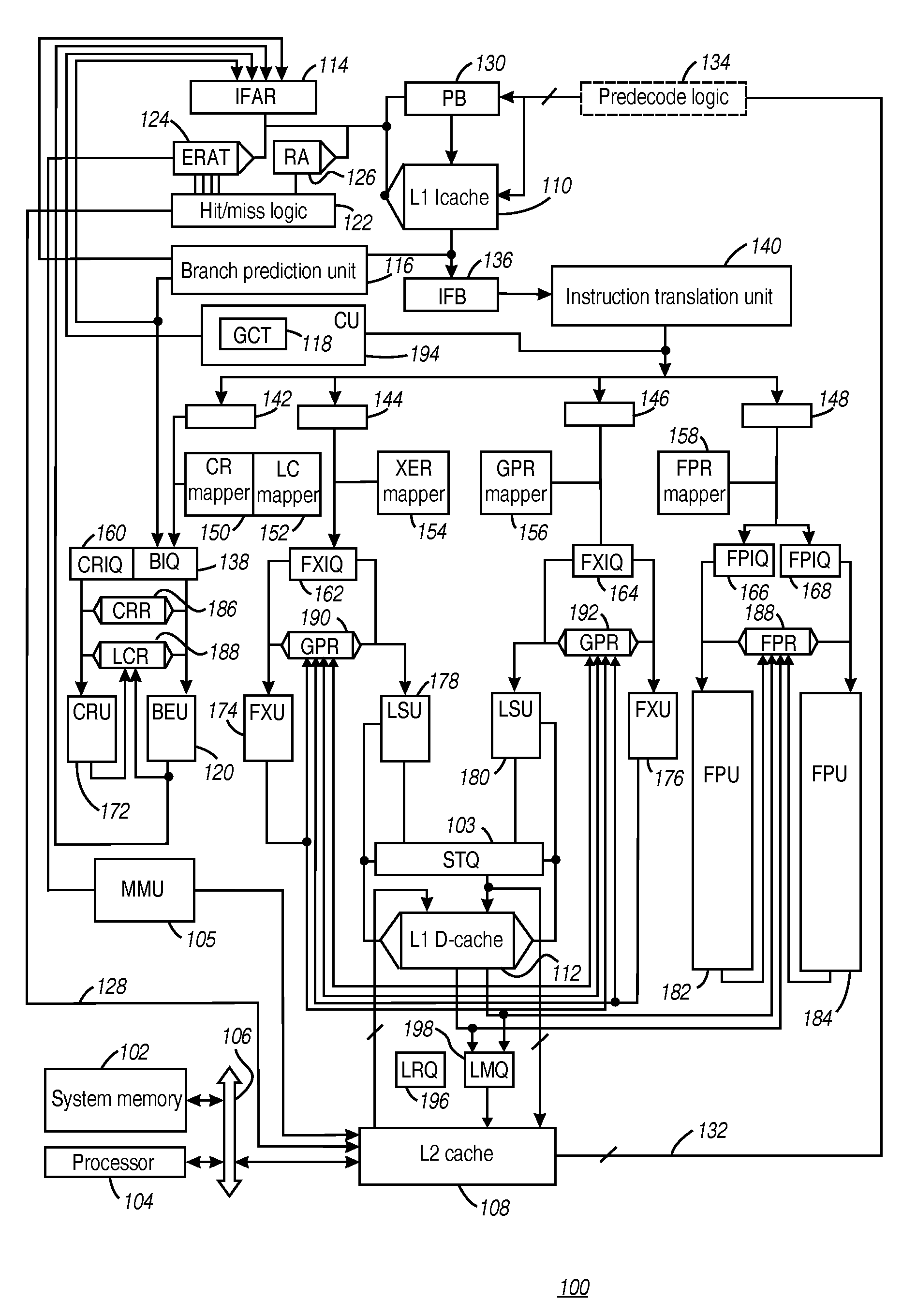

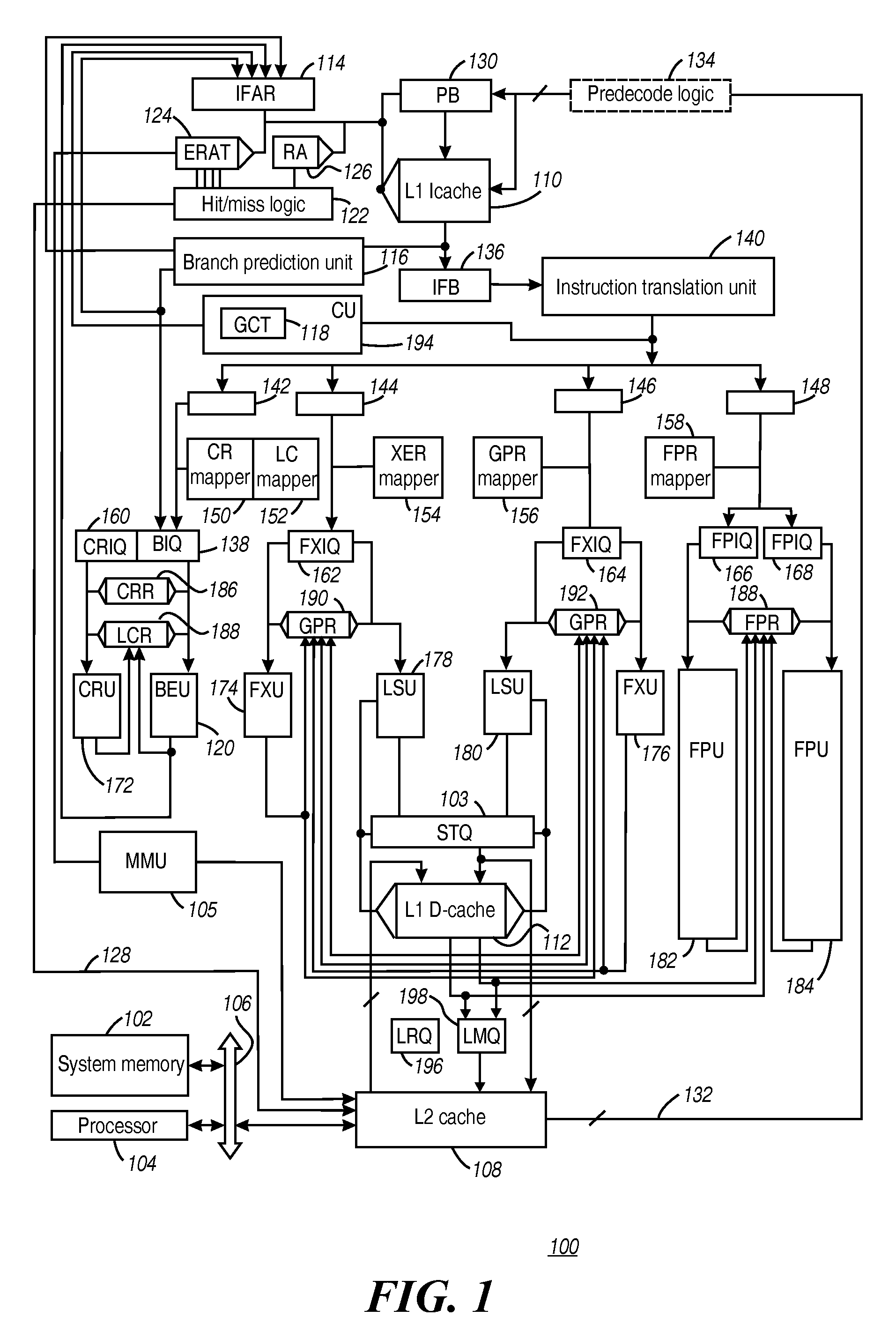

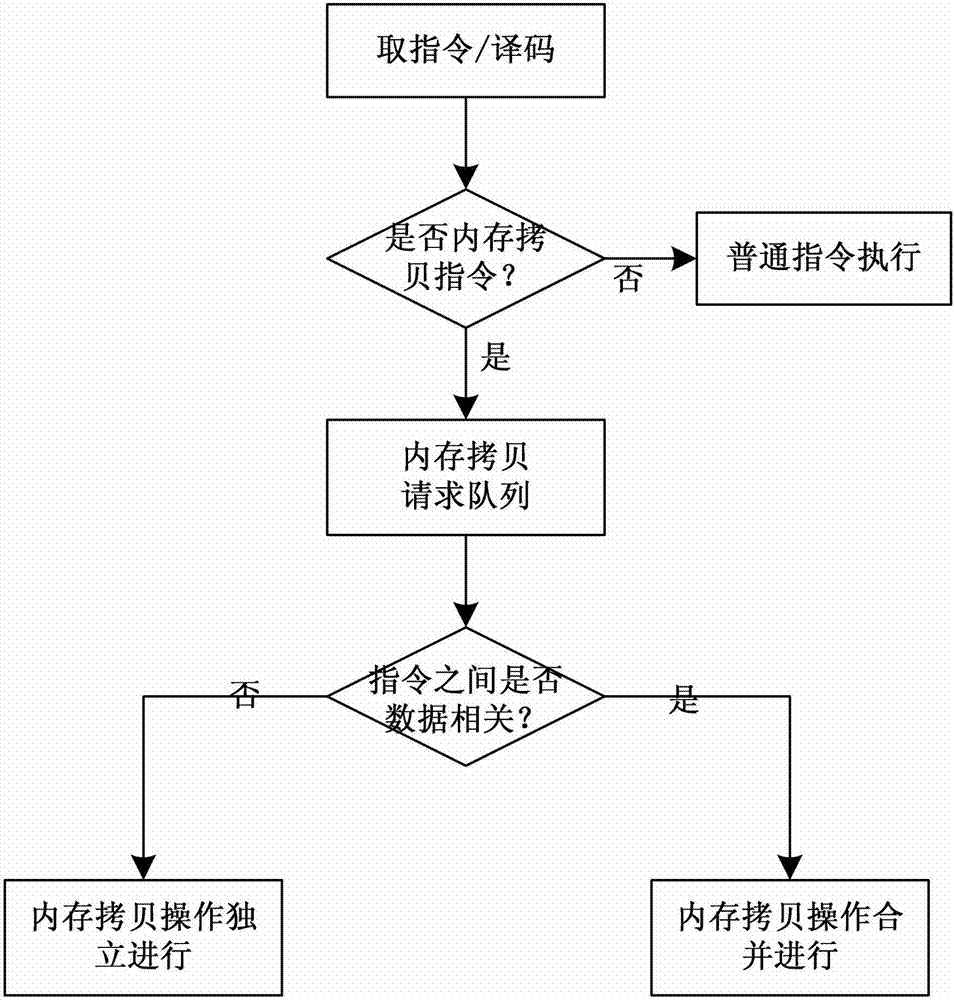

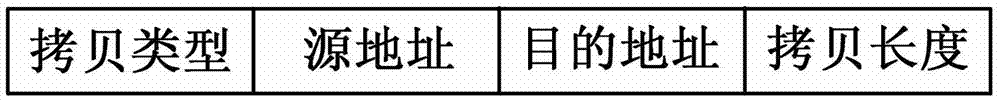

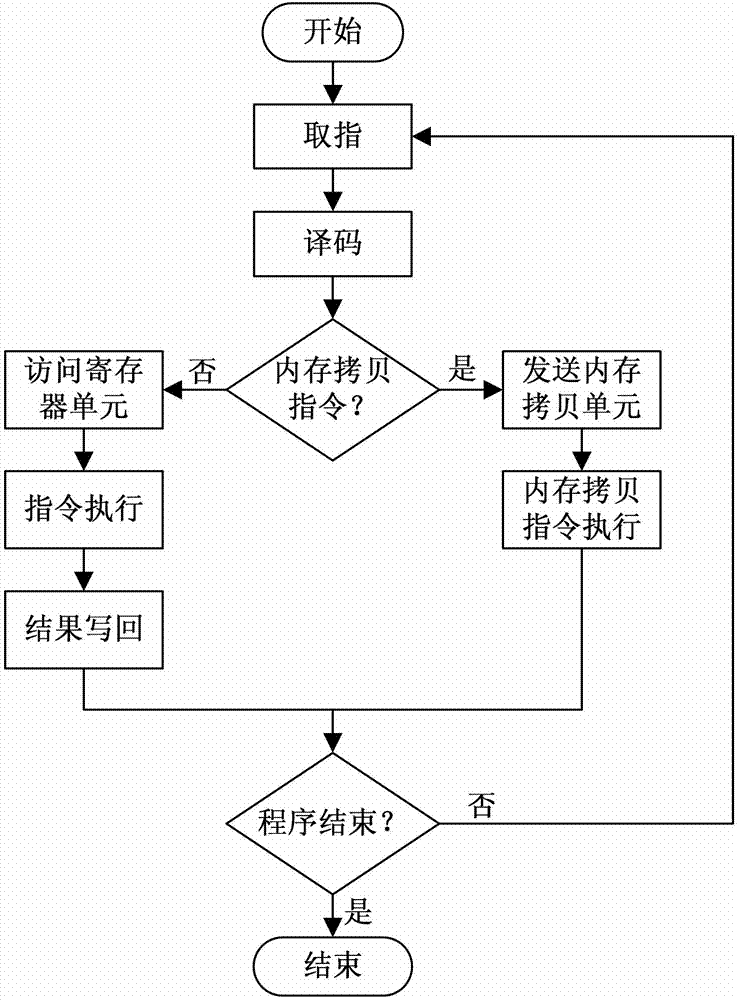

Method and device for accelerating memory copy of microprocessor

ActiveCN102968395AImprove efficiencyImprove concurrencyEnergy efficient ICTConcurrent instruction executionComputer architectureAccess frequency

The invention discloses a method and a device for accelerating a memory copy of a microprocessor. The method comprises the following steps : firstly, adding a memory copy unit in the microprocessor; secondly, transmitting a memory copy instruction obtained by decoding according to a decoding logic to the memory copy unit; and detecting the correlation between a new memory copy request and other memory copy requests by the memory copy unit through a correlated detection part and caching the new memory copy request and the correlation thereof to a request queue; and thirdly, performing the current memory copy request with pages as unit and cooperatively performing the correlated memory copy requests. The device comprises the memory copy unit special for performing the memory copy request and the correlated detection part for detecting the correlation between the new memory copy request and the other memory copy requests in the queue. The method and the device disclosed by the invention have the advantages of high performance of the memory copy, simpleness in realization of hardware, small cost, excellent expansibility, strong compatibility, favorable concurrency, low access frequency and low power consumption.

Owner:NAT UNIV OF DEFENSE TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com