Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

64 results about "Interrupt flag" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The Interrupt flag (IF) is a system flag bit in the x86 architecture's FLAGS register, which determines whether or not the central processing unit (CPU) will handle maskable hardware interrupts. The bit, which is bit 9 of the FLAGS register, may be set or cleared by programs with sufficient privileges, as usually determined by the operating system. If the flag is set to 1, maskable hardware interrupts will be handled. If cleared (set to 0), such interrupts will be ignored. IF does not affect the handling of non-maskable interrupts (NMIs) or software interrupts generated by the INT instruction.

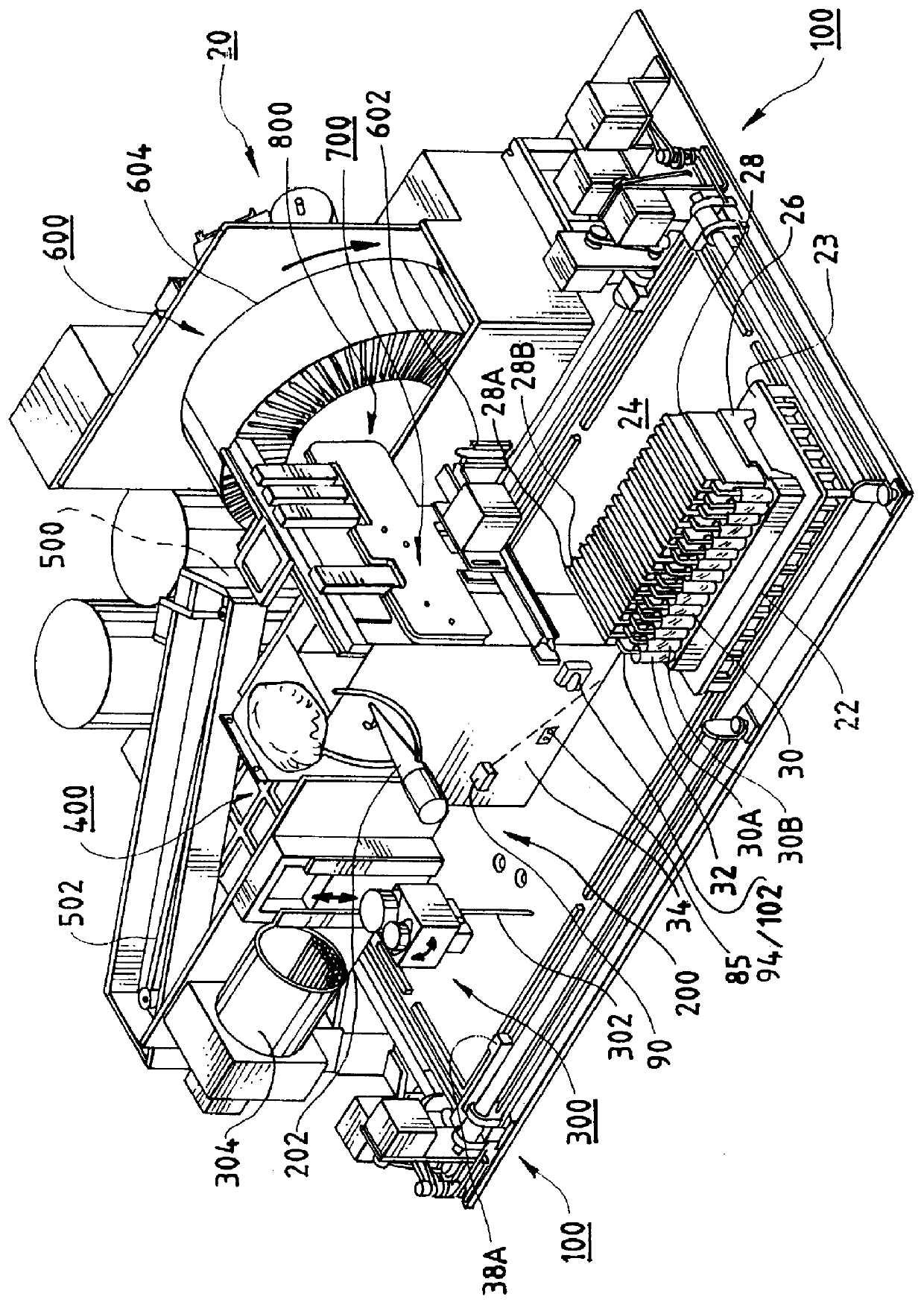

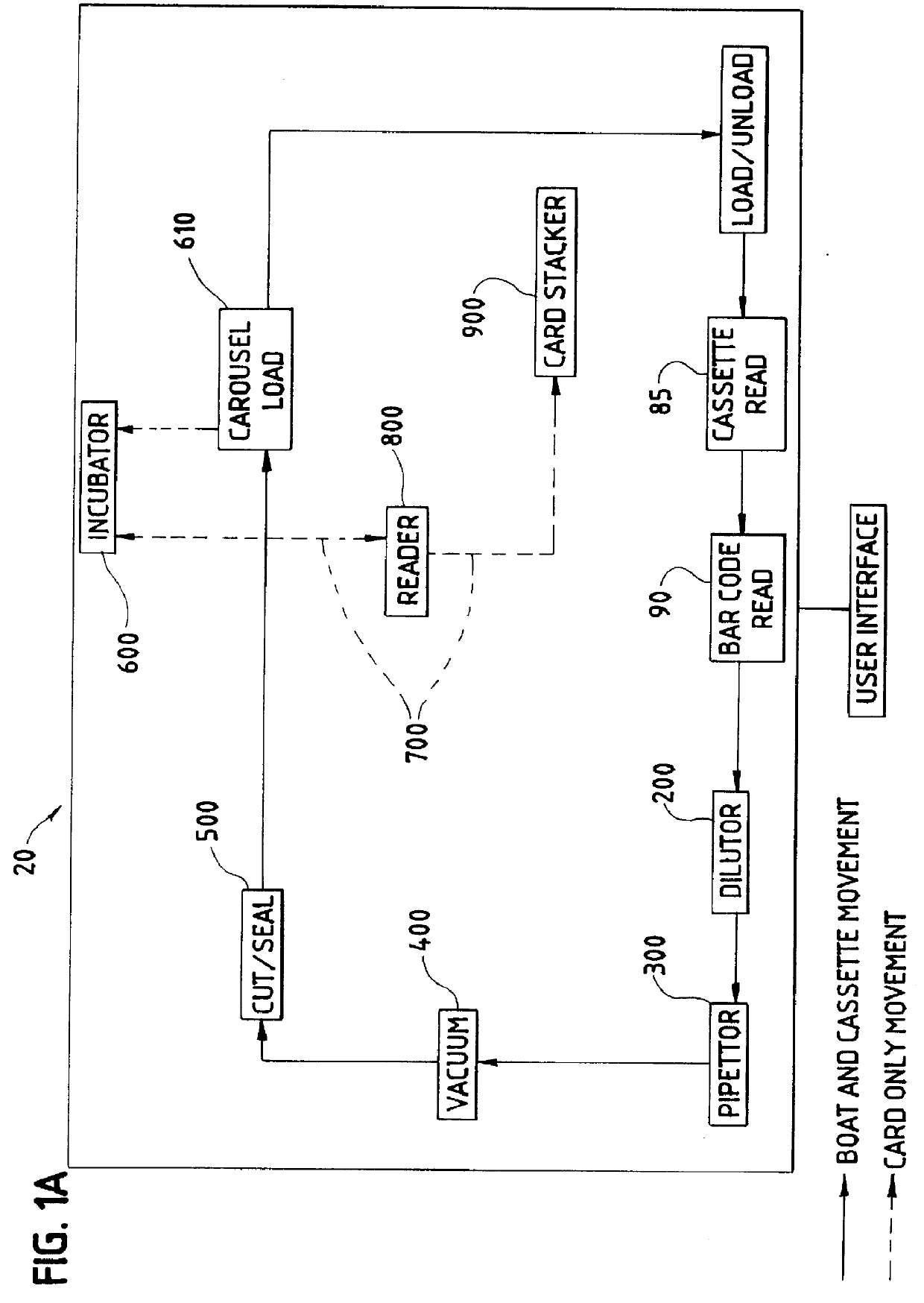

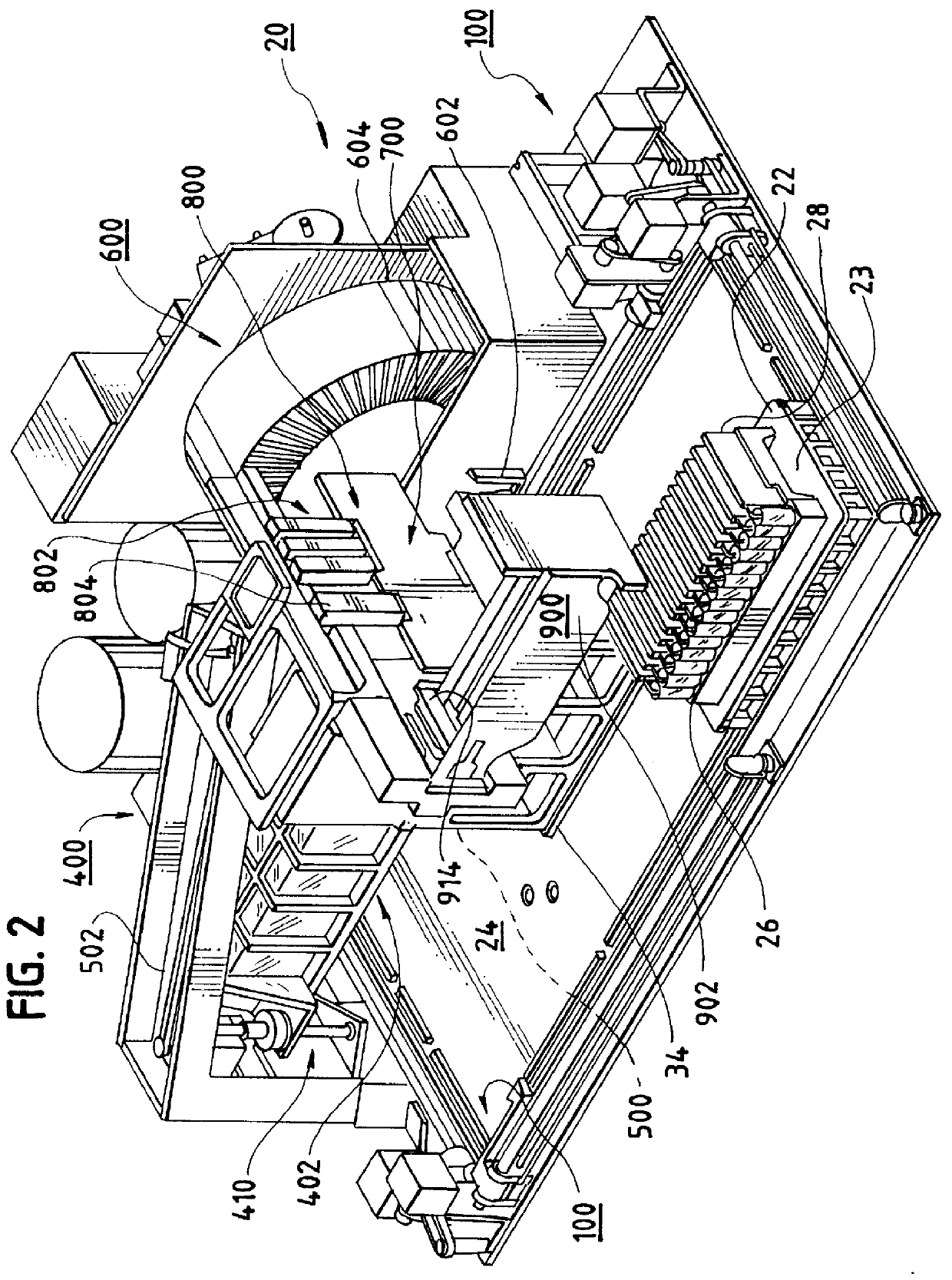

Incubation station for test sample cards

InactiveUS6024921ABioreactor/fermenter combinationsBiological substance pretreatmentsReciprocating motionTest sample

Test sample cards containing biological samples are moved through an analytical instrument past a card detection device and detected by the device. The card detection device has an actuator that reciprocates relative to a housing between first and second positions. The actuator has a surface that comes into contact with the card as the card is moved past the device. The actuator carries an optical interrupt flag which is used in conjunction with an optical sensor placed in proximity to the actuator. When the card comes into contact with the actuator, the actuator is moved from the first position to the second, or retracted position. This action moves the flag relative to the optical sensor, triggering the optical sensor and a detection of the card. In one possible embodiment, multiple cards are placed in a cassette for movement around the instrument. The cassette has a number of slots for the cards, one card per slot. Each card has placed thereon indicia such as bar codes that are used for identification purposes by the instrument. The card detection device, in addition to performing the detection functions for each of the cards, also rocks the cards within the cassette slots so as to place the bar codes or other indicia into a better position for reading by a bar code reader or other appropriate reading device for the indicia.

Owner:BIOMERIEUX INC

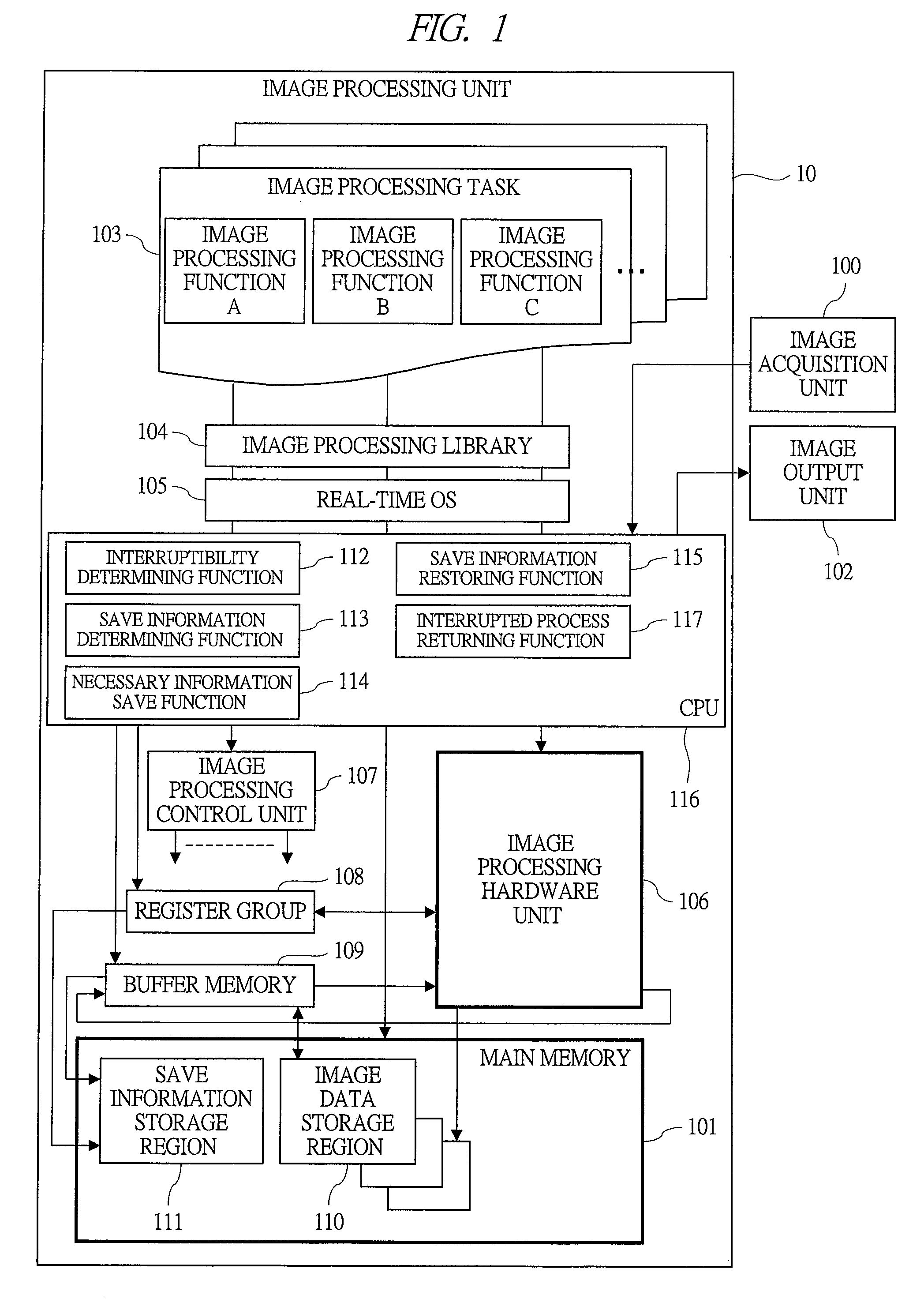

Data processing unit

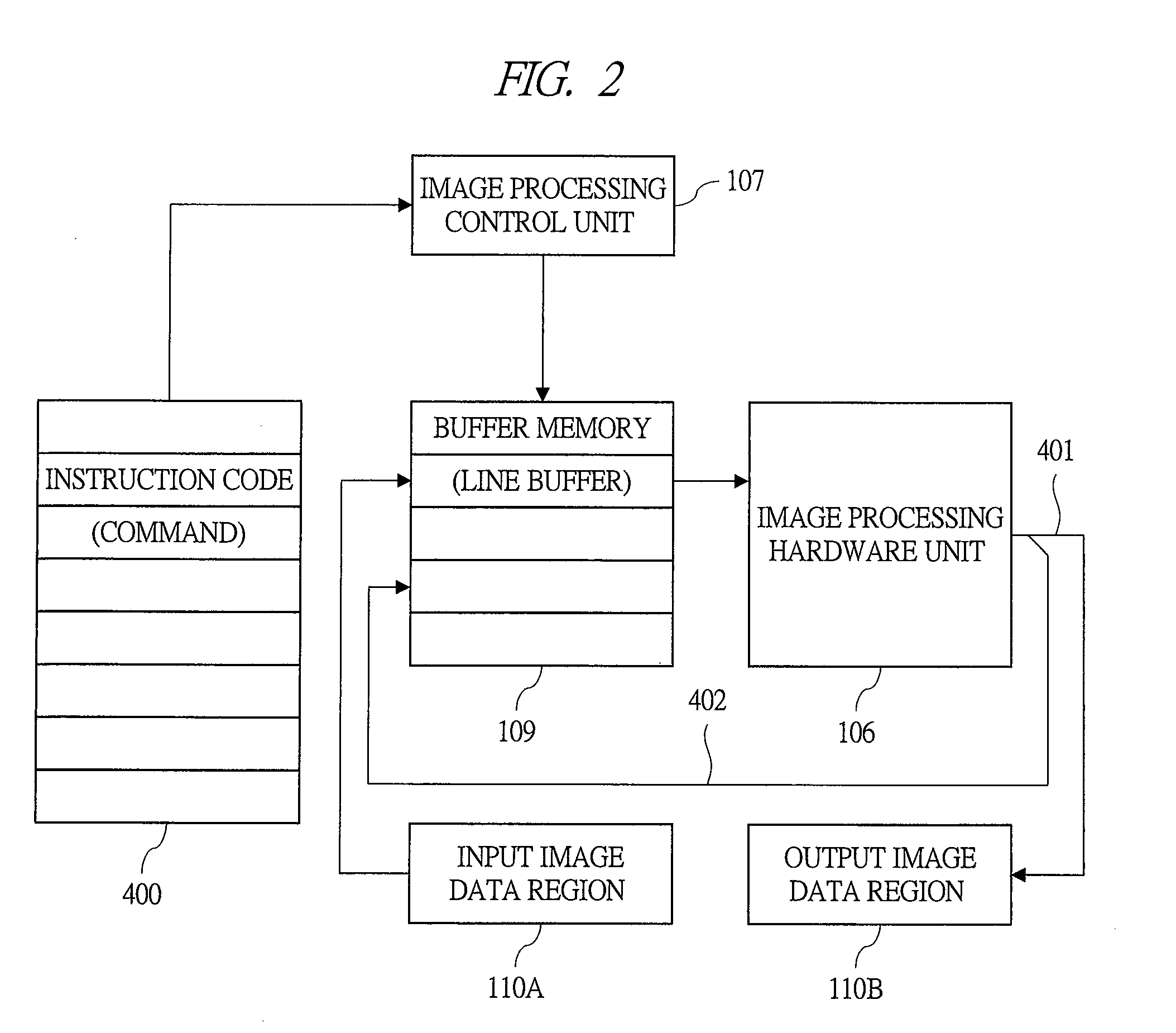

InactiveUS20100199283A1Reduce overheadReduce overhead timeProgram initiation/switchingResource allocationImaging processingInterrupt flag

When a CPU is processing a first task by using an accelerator for use in image processing, if a request for allocating the accelerator to a process of a second task is issued, the CPU sets an interruption flag when the process of the second task is prioritized over a process of the first task, and the accelerator is allowed to be used for the process of the second task when a state in which the interruption flag is set is detected at a timing predetermined in accordance with a process stage of the accelerator for the first task. Since the timing of detecting the set interruption flag is determined in accordance with a progress state of the process of the task to be interrupted, task switching can be made at a timing of reducing overhead for save and return for the process of the task to be interrupted.

Owner:RENESAS ELECTRONICS CORP

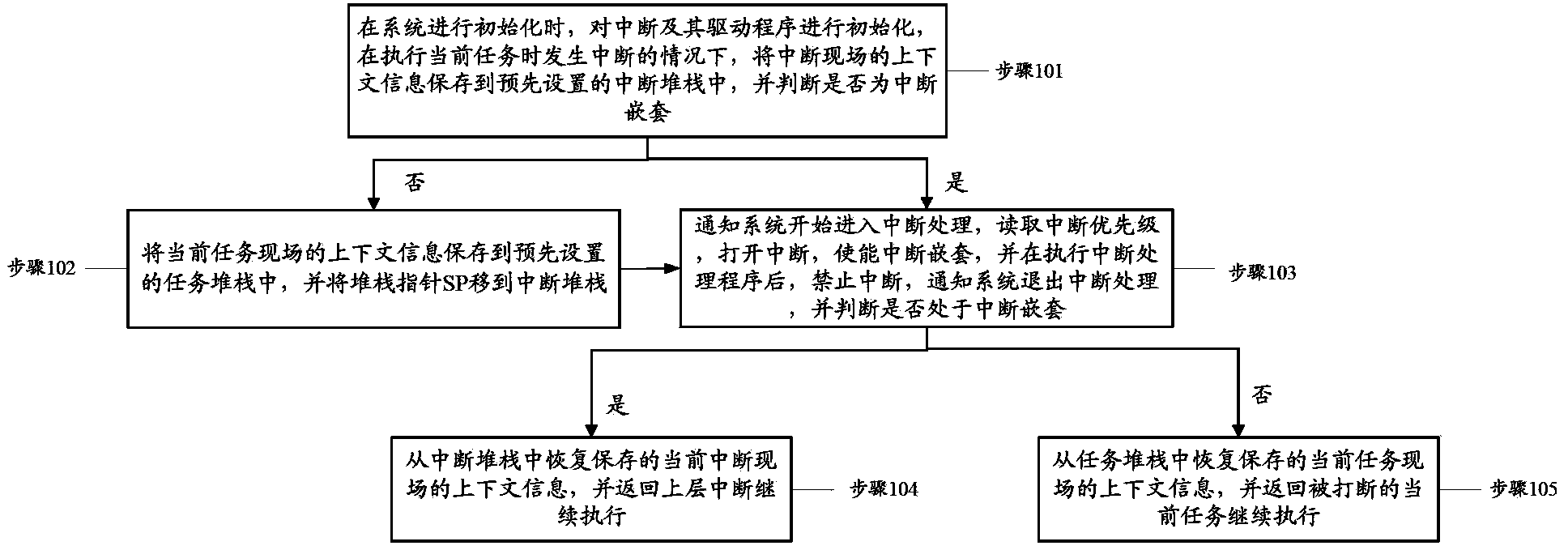

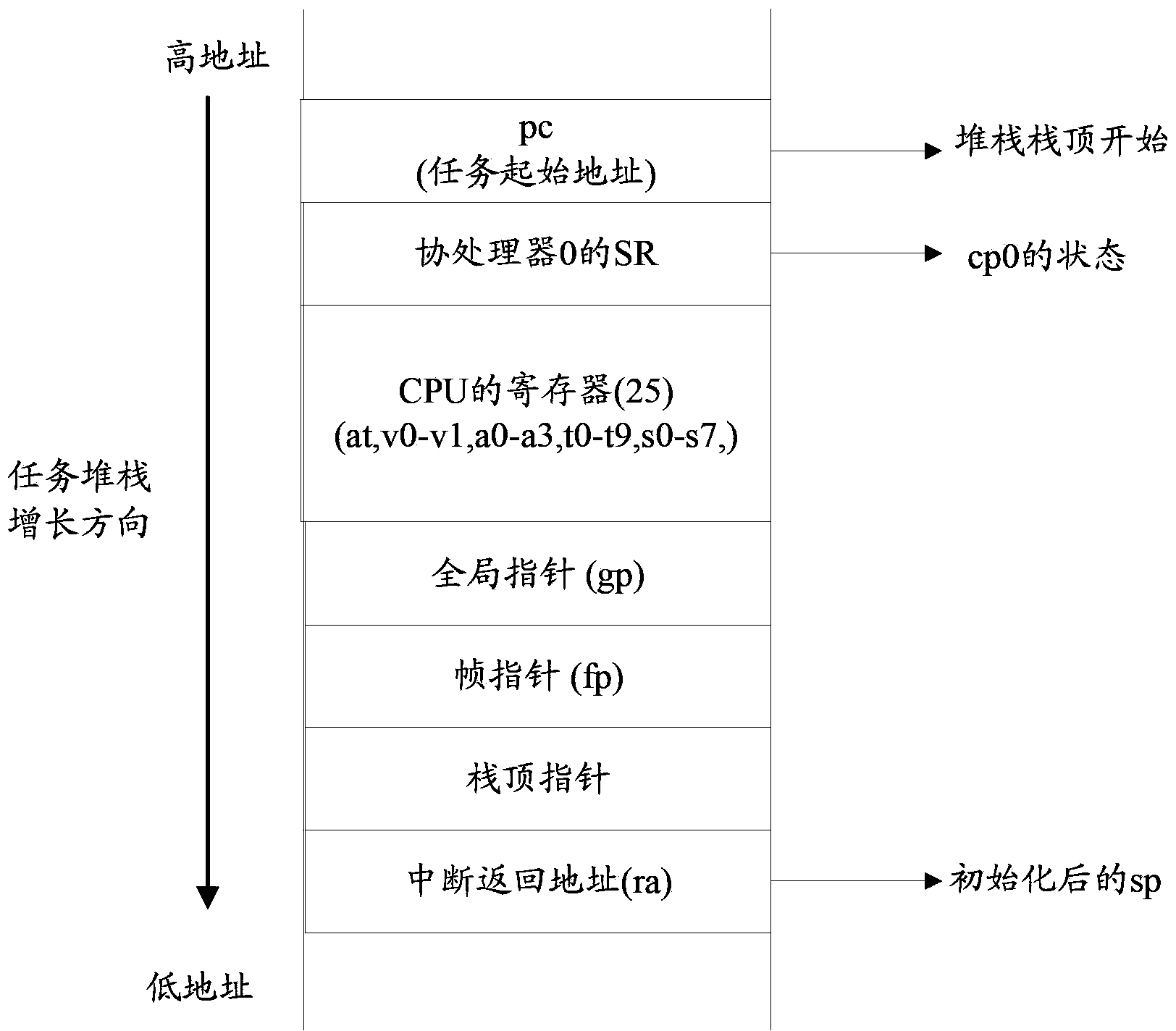

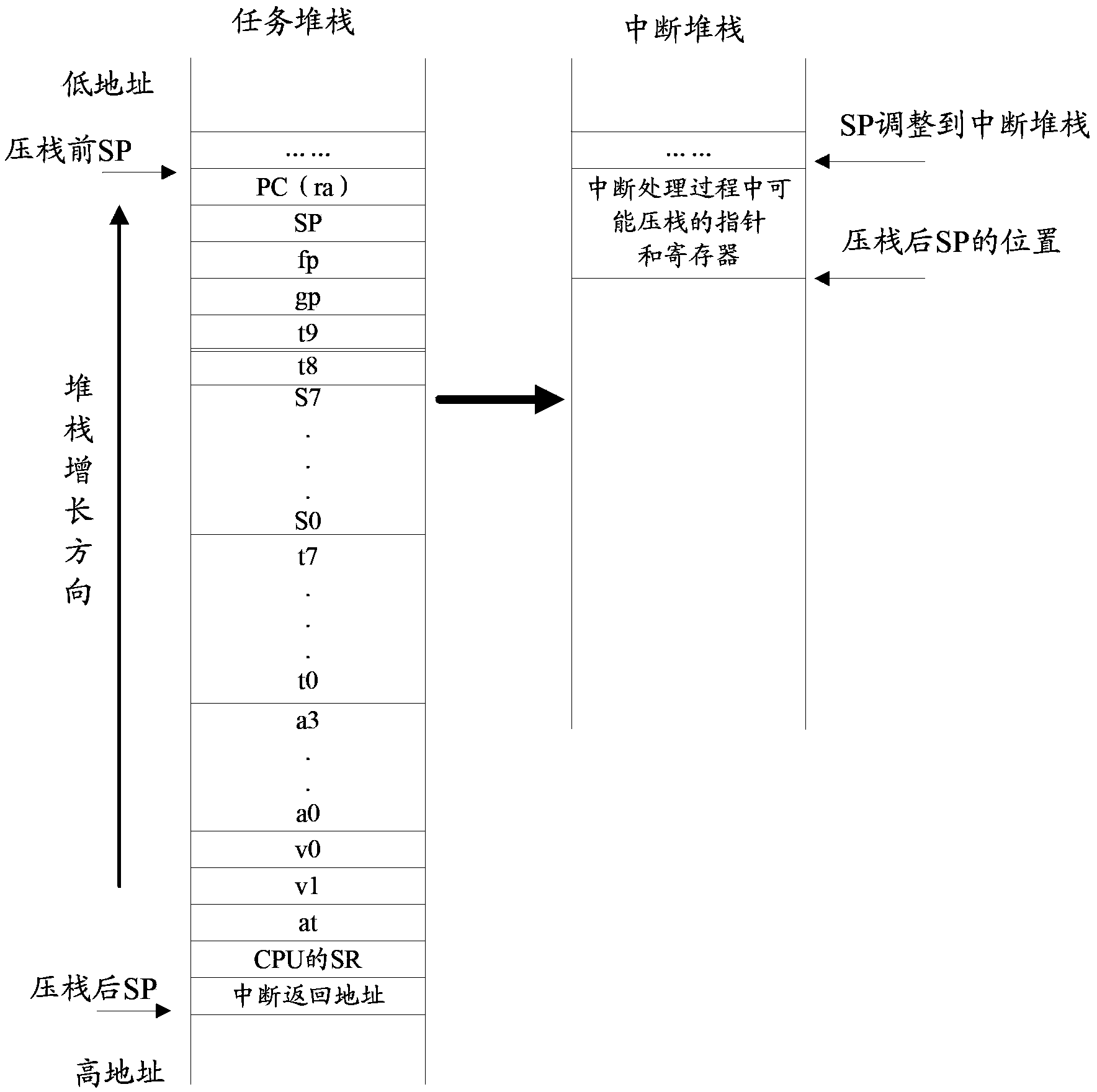

Interrupt processing method and device

InactiveCN103778009AImprove efficiencyReduce memory size requirementsProgram initiation/switchingEmbedded systemNotification system

The invention discloses an interrupt processing method and device. The method comprises the steps of step 1, initializing interrupt and the drive program of the interrupt when a system is initialized, and when the interrupt occurs during execution of a current task, storing the context information of the interrupt field into a preset task stack and determining whether the interrupt is a interrupt nesting; step 2, storing the context information of a current task field into the preset task stack and moving a stack pointer (SP) to an interrupt stack; step 3, informing the system to start entering interrupt processing, reading interrupt priority levels, opening the interrupt, enabling the interrupt nesting, and after executing an interrupt processing program, prohibiting the interrupt, informing the system to exit the interrupt processing and determining whether the system is in the interrupt nesting; step 4, recovering the context information of the stored current interrupt field and returning to upper-layer interrupt; step 5, recovering the context information of the stored current task field and returning to the current task.

Owner:SANECHIPS TECH CO LTD

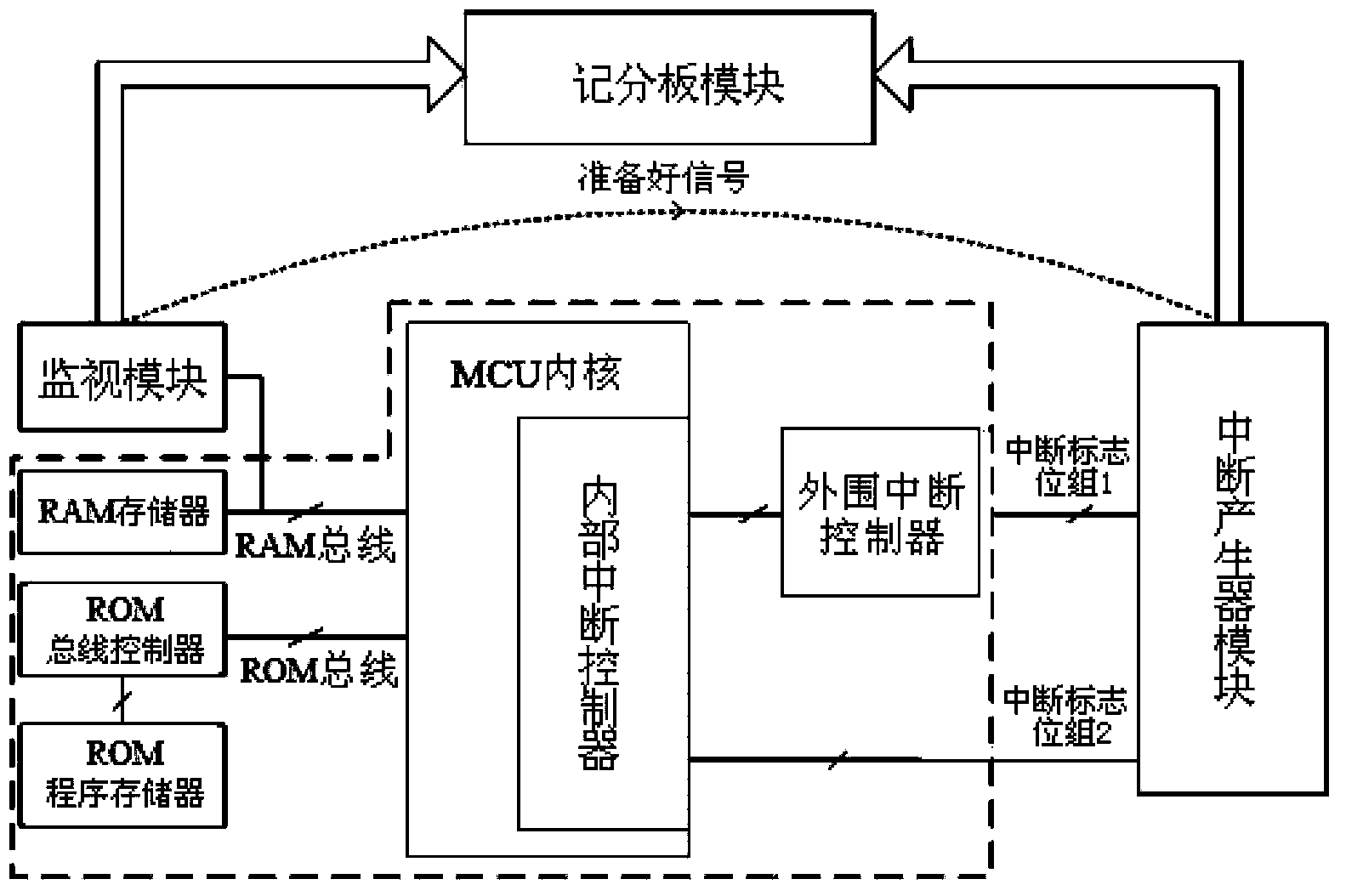

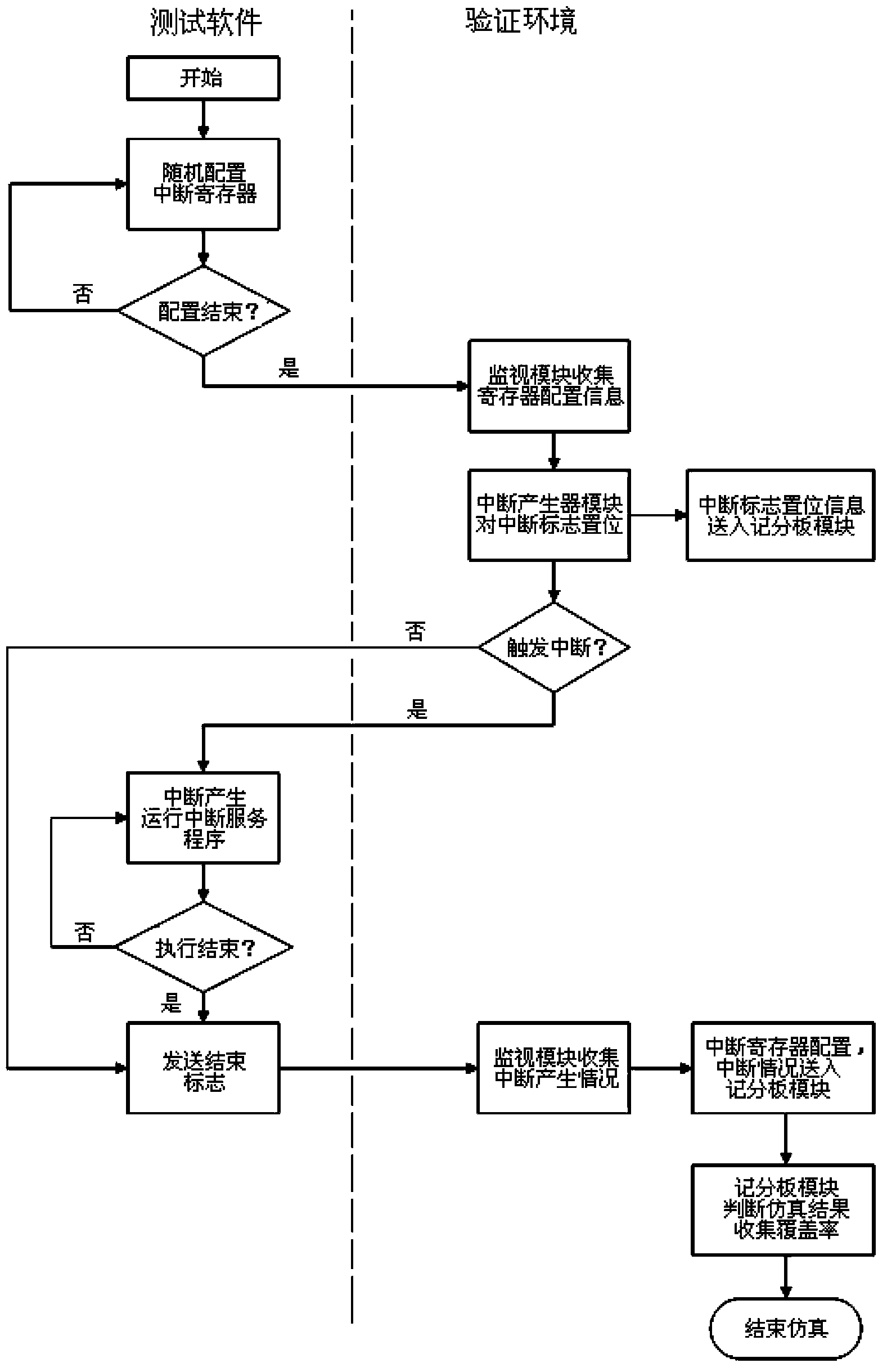

Simulation verification system and method for interrupt controller of hard-core MCU

ActiveCN103838899AImprove reusabilityIncrease coverageSpecial data processing applicationsRegister allocationValue assignment

The invention discloses a simulation verification system for an interrupt controller of a hard-core MCU. The simulation verification system comprises testing software and a simulation verification environment module. The testing software comprises a main program and an interrupt service routine. Value assignment is performed on a relevant interrupt register by the main program in a random mode, and the main program transmits interrupt register configuration, interrupt processing information and a software ready signal to the simulation verification environment module; the interrupt service routine records an interrupt mark number and an interrupt sequence; the simulation verification environment module produces interrupt setting information in a random mode and directly sets all interrupt flag bits in the simulation verification system; the testing software obtains the interrupt processing information in cooperation with the simulation verification environment module, and simulation verification of the interrupt controller is collaboratively completed under a certain flow control. The invention further discloses a simulation verification method for the interrupt controller of the hard-core MCU. According to the simulation verification system and method for the interrupt controller of the hard-core MCU, verification efficiency can be enhanced, the coverage rate can be increased, and reusability is quite high.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

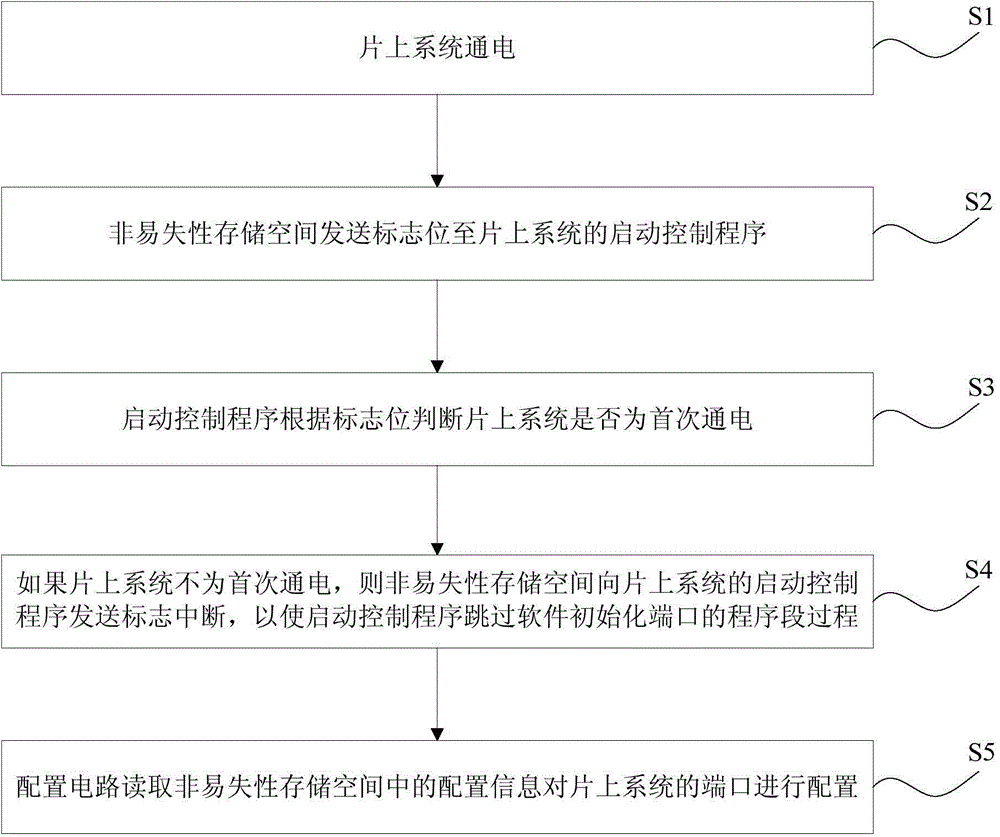

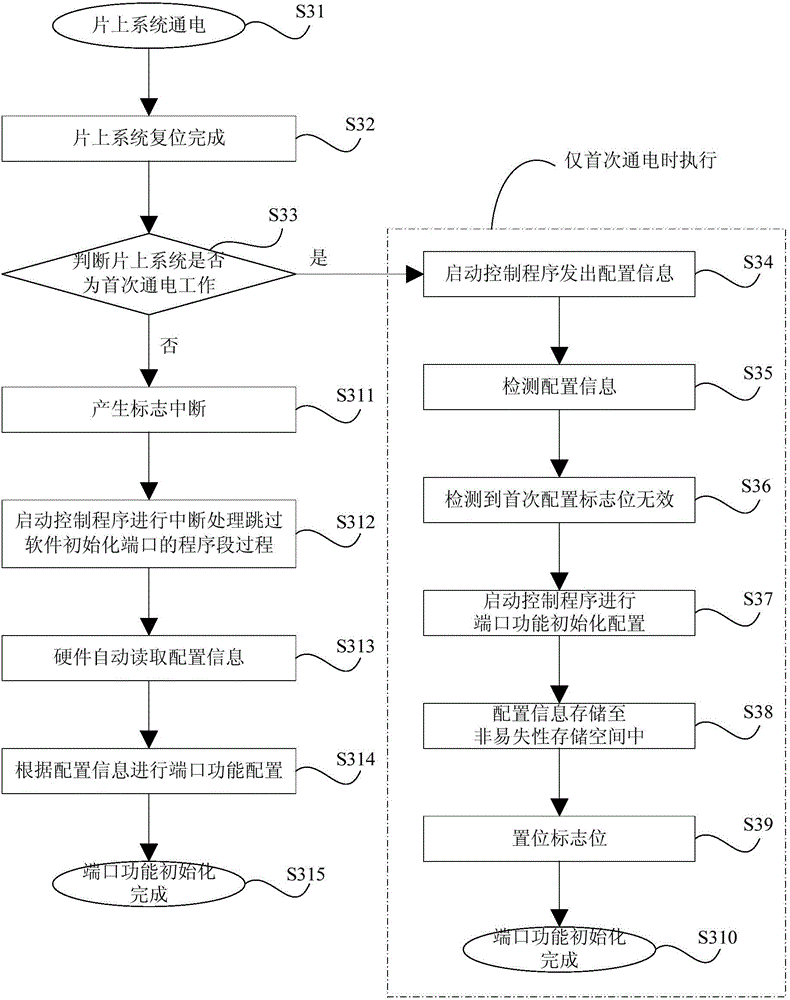

System on chip, and method and apparatus for port function initialization for system on chip

ActiveCN105718248AImplement initializationAvoid multiple redundant operationsSpecific program execution arrangementsProgram segmentEmbedded system

The invention discloses a method for port function initialization for a system on chip. The method comprises the steps that the system on chip is powered on; a nonvolatile storage space sends a zone bit to a start control program of the system on chip; the start control program judges whether the system on chip is powered on initially or not according to the zone bit; if the system on chip is not powered on initially, the nonvolatile storage space sends an interrupt flag to the start control program of the system on chip to enable the start control program to skip a program segment process of port initialization by software; and a configuration circuit reads the configuration information in the nonvolatile storage space to configure the port of the system on chip. According to the method, when the system on chip is powered on for more than one time, hardware rapid response is executed and the port function initialization is carried out, so that the efficiency of the system from powering on to the port function initialization is improved, and the instantaneity and the reliability of the system are reinforced. The invention also discloses an apparatus for port function initialization for the system on chip and the system on chip including the apparatus.

Owner:BYD SEMICON CO LTD

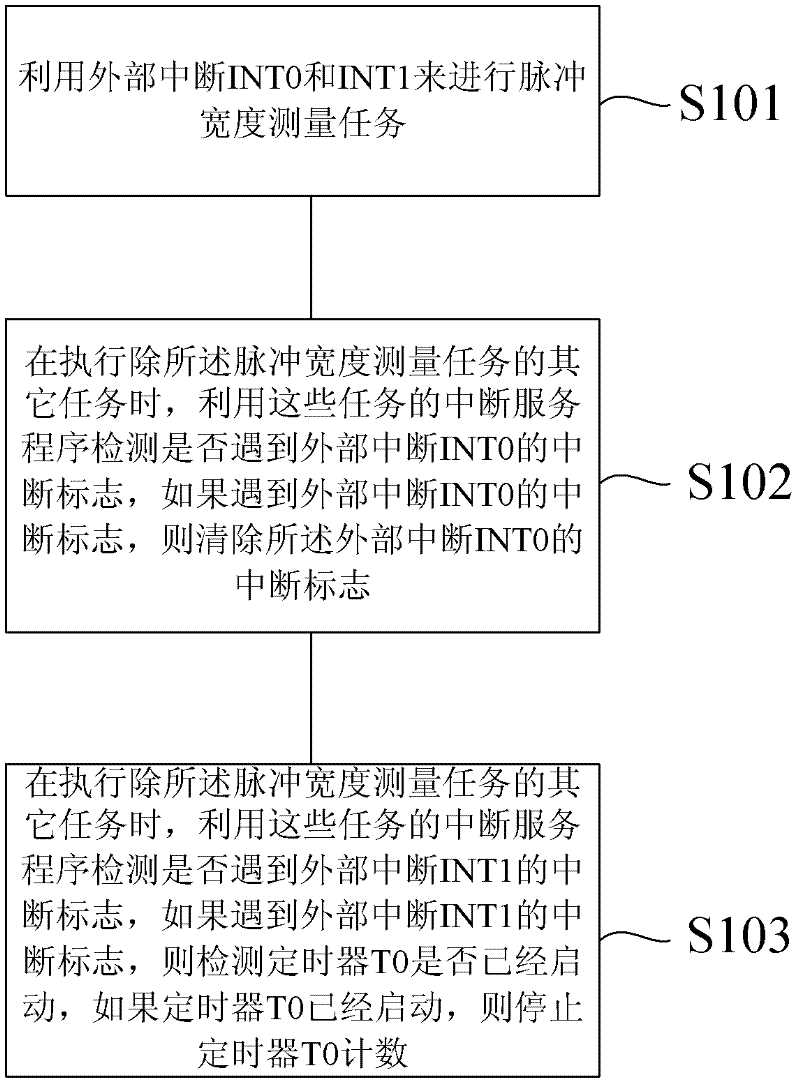

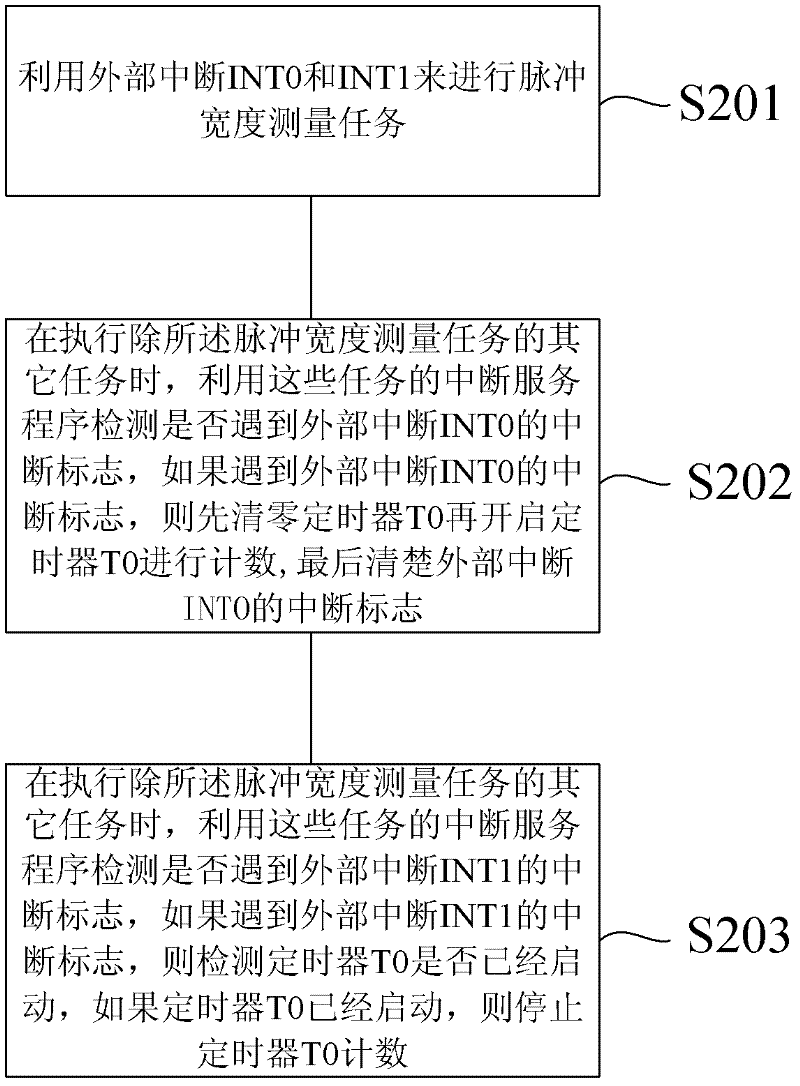

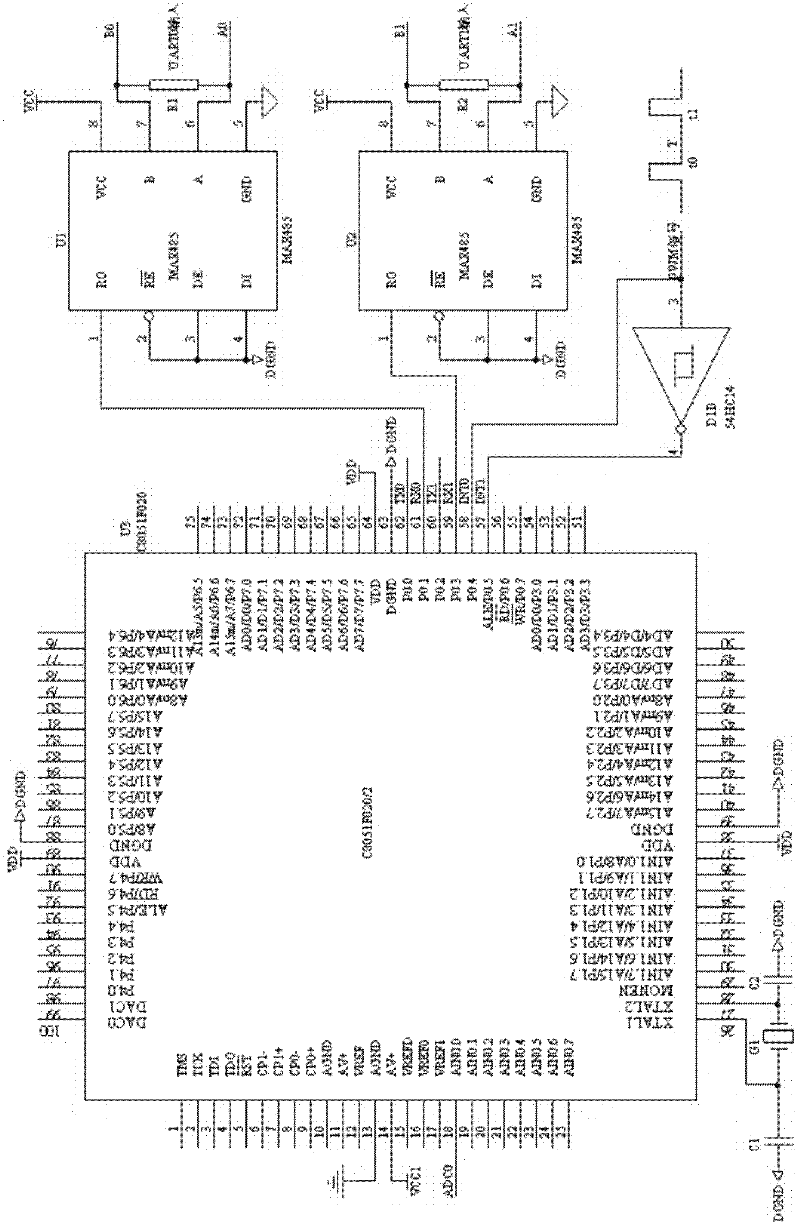

Method for ensuring accurate measurement on pulse width in multi-task singlechip system and device

The embodiment of the invention provides a method for ensuring accurate measurement on pulse width in a multi-task singlechip system and a device. The method comprises the following steps: carrying out a pulse width measurement task by utilizing external interrupts INT0 and INT1; when other tasks are executed, by utilizing the interrupt service routines of the tasks, detecting whether the interrupt identification of the external interrupt INT0 is met or not; if the interrupt identification of the external interrupt INT0 is met, clearing the interrupt identification of the external interrupt INT0; and by utilizing the interrupt service routines of the tasks, detecting whether the interrupt identification of the external interrupt INT1 is met or not; if the interrupt identification of the external interrupt INT1 is met, detecting whether a timer T0 is started or not; and if the timer T0 is started, stopping the counting of the timer T0. In the method and the device for ensuring the accurate measurement on the pulse width in the multi-task singlechip system, a judgment on starting and stopping the pulse width measurement task is introduced into the interrupt service routines of other tasks, and the timer T0 is controlled according to the judgment, thereby, the accuracy of pulse width measurement data in a singlechip is ensured.

Owner:CHINA AERO GEOPHYSICAL SURVEY & REMOTE SENSING CENT FOR LAND & RESOURCES

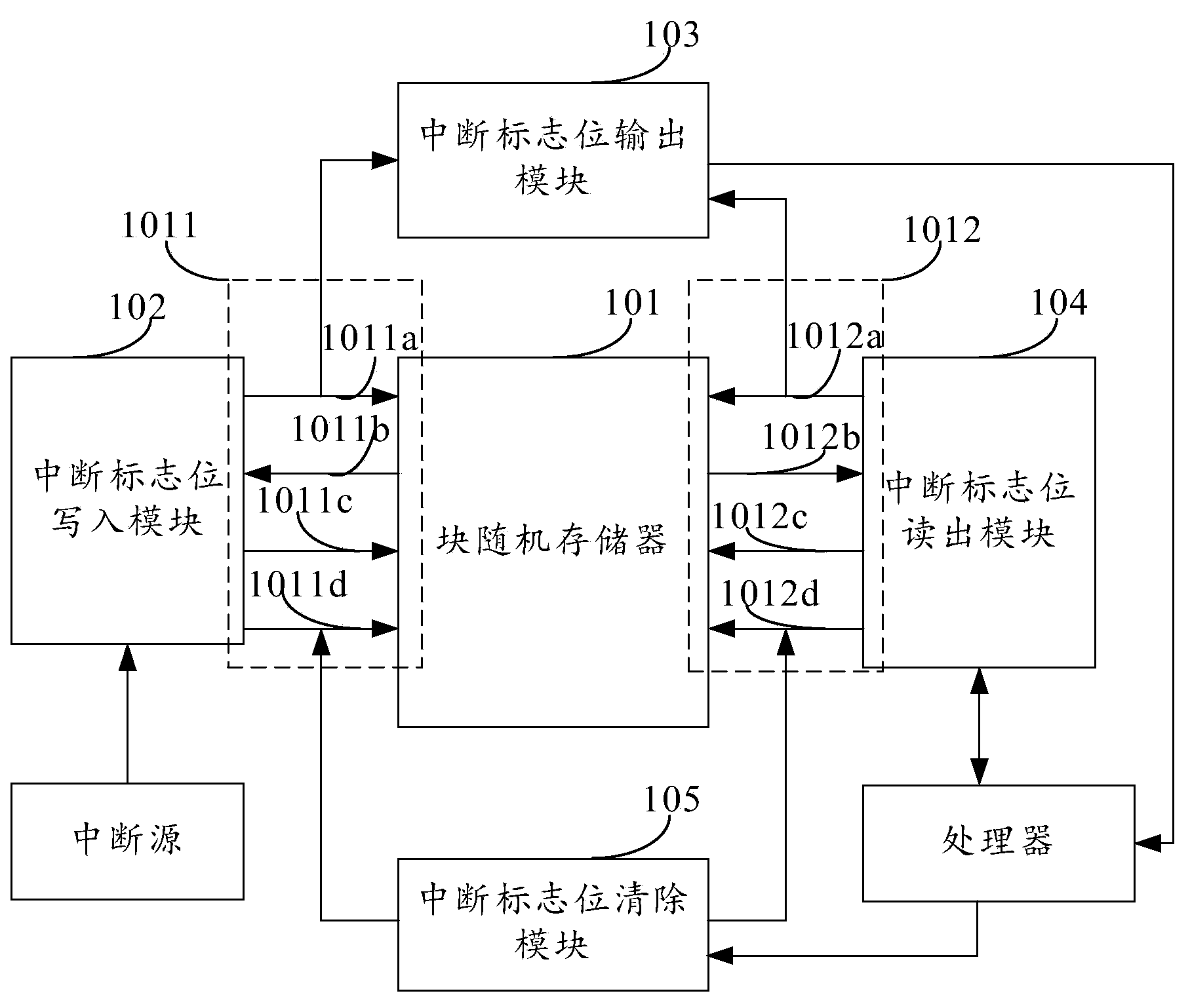

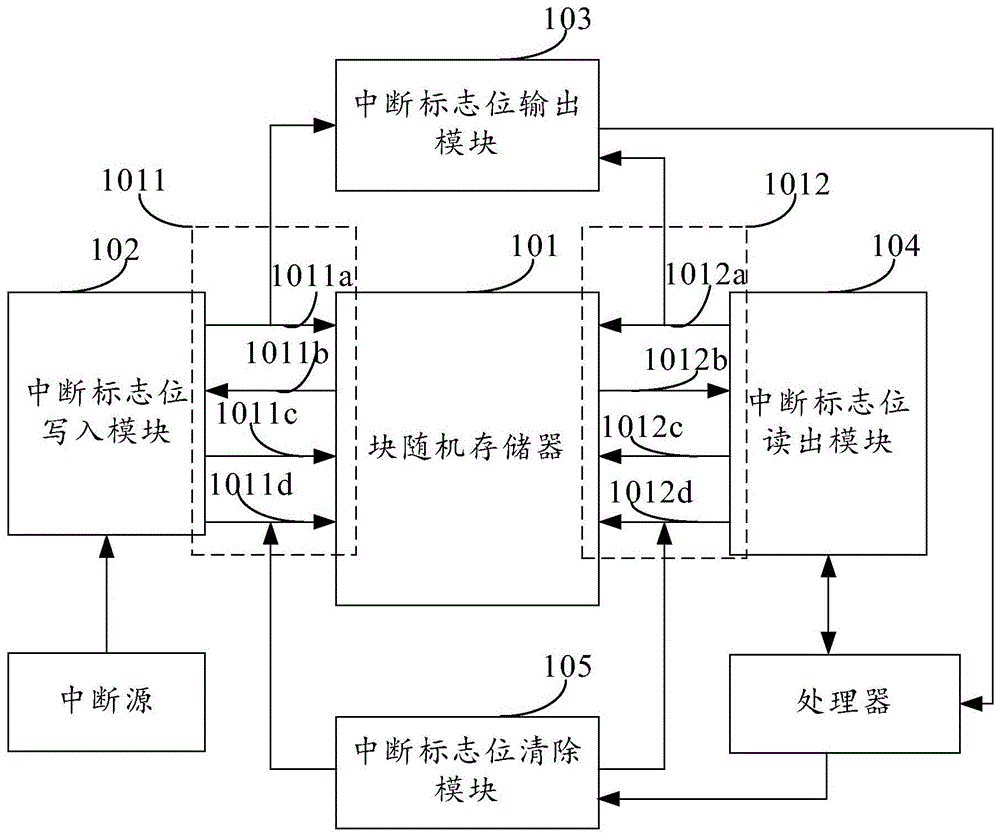

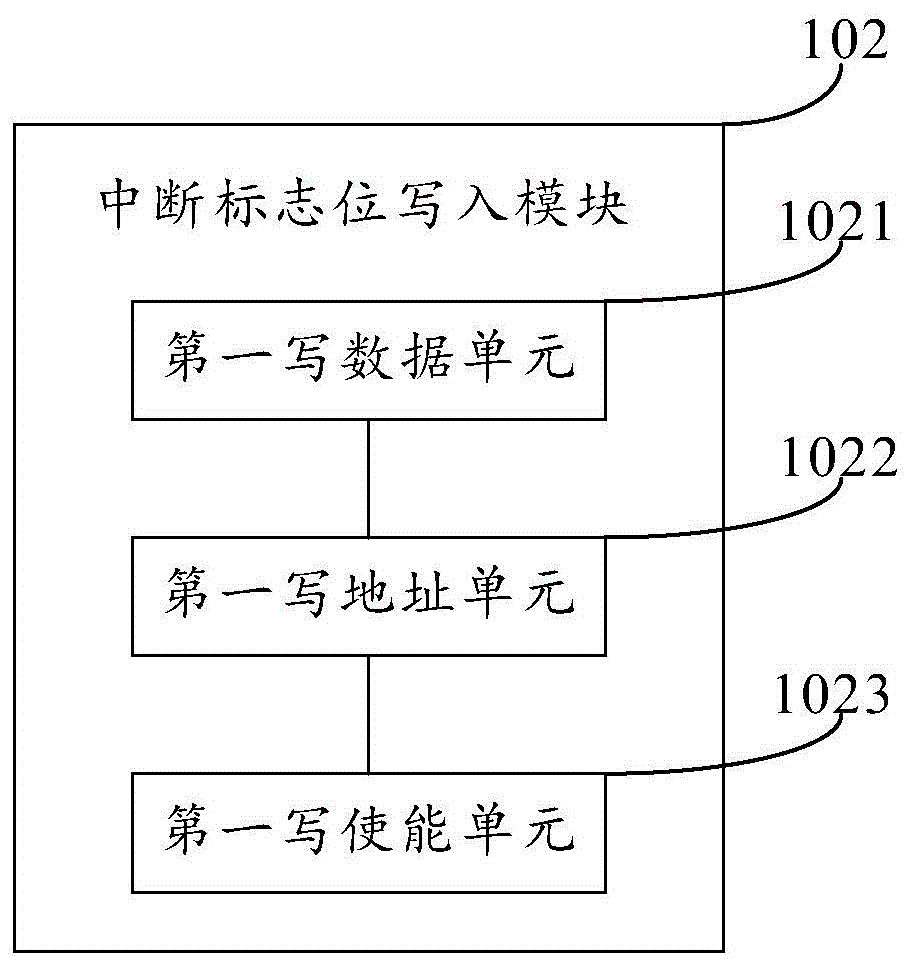

Interrupt processing device and method

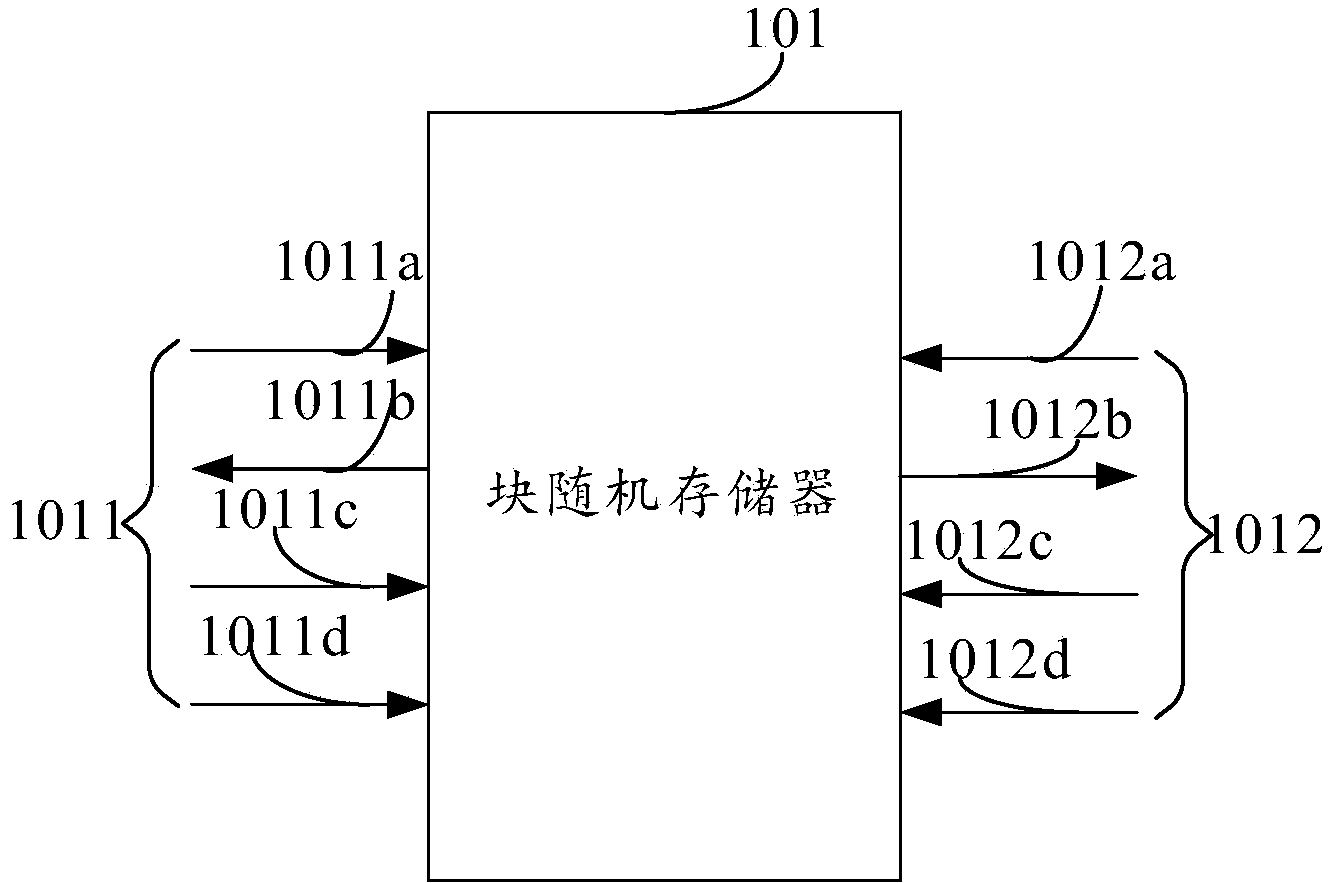

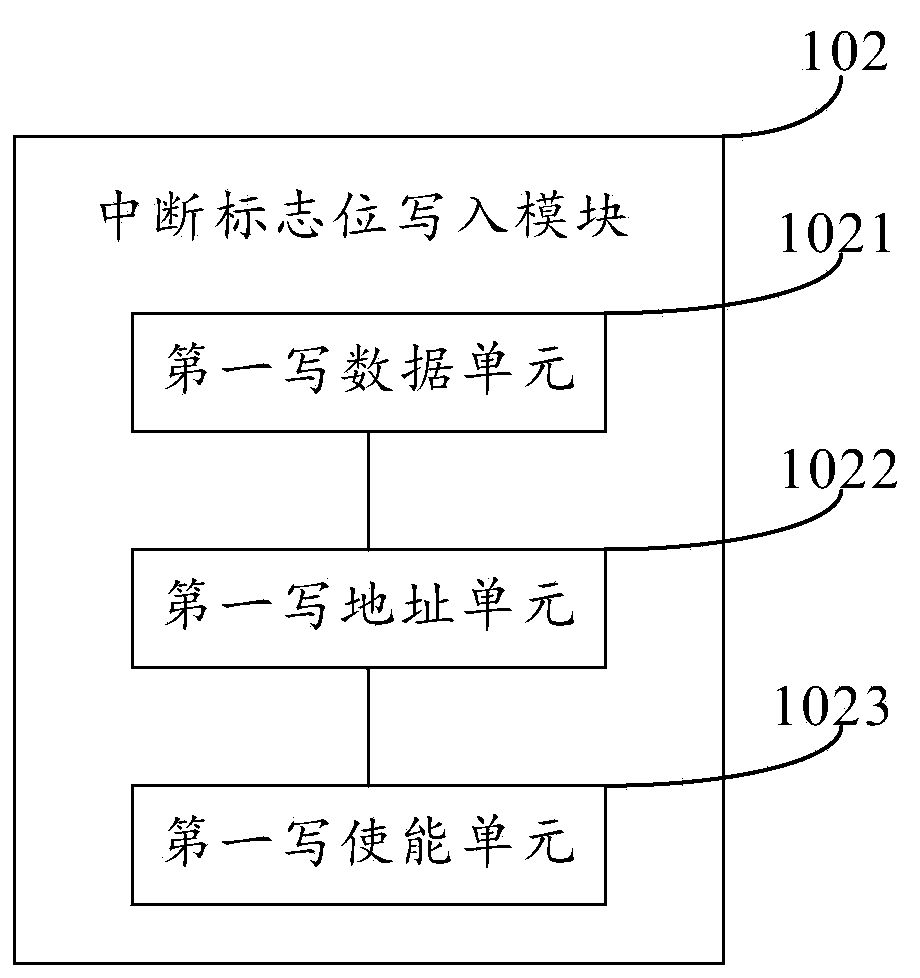

The embodiment of the invention provides an interrupt processing device and method. The interrupt processing device and method are applied to the technical field of interrupt control, can save hardware resources, and can reduce hardware cost. The interrupt processing device comprises a block random access memory, an interrupt flag bit write-in module, an interrupt flag bit output module, an interrupt flag bit read-out module and an interrupt flag bit removal module, wherein the block random access memory at least comprises m memory cell groups; the interrupt flag bit write-in module is used for writing interrupt flag bit information of any function module in the memory cell group corresponding to the function module; the interrupt flag bit output module is used for generating an interrupt event processing request and sending the interrupt event processing request to a processor; the interrupt flag bit read-out module is used for obtaining the interrupt flag bit information of the memory cell group corresponding to the function module and sending the interrupt flag bit information to the processor; the interrupt flag bit removal module is used for removing effective information corresponding to an interrupt source. The interrupt processing device is used for processing an interrupt event.

Owner:RUIJIE NETWORKS CO LTD

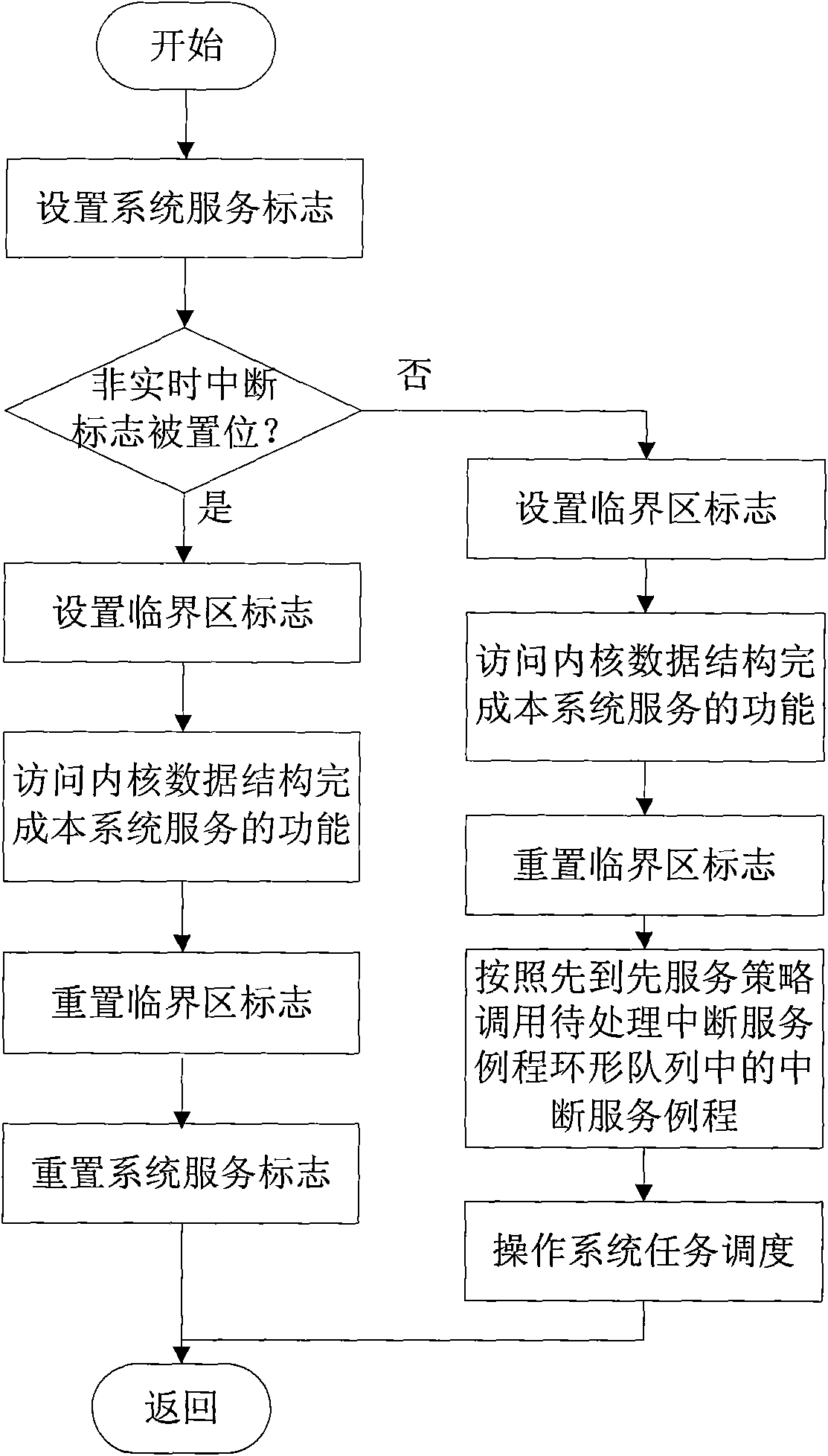

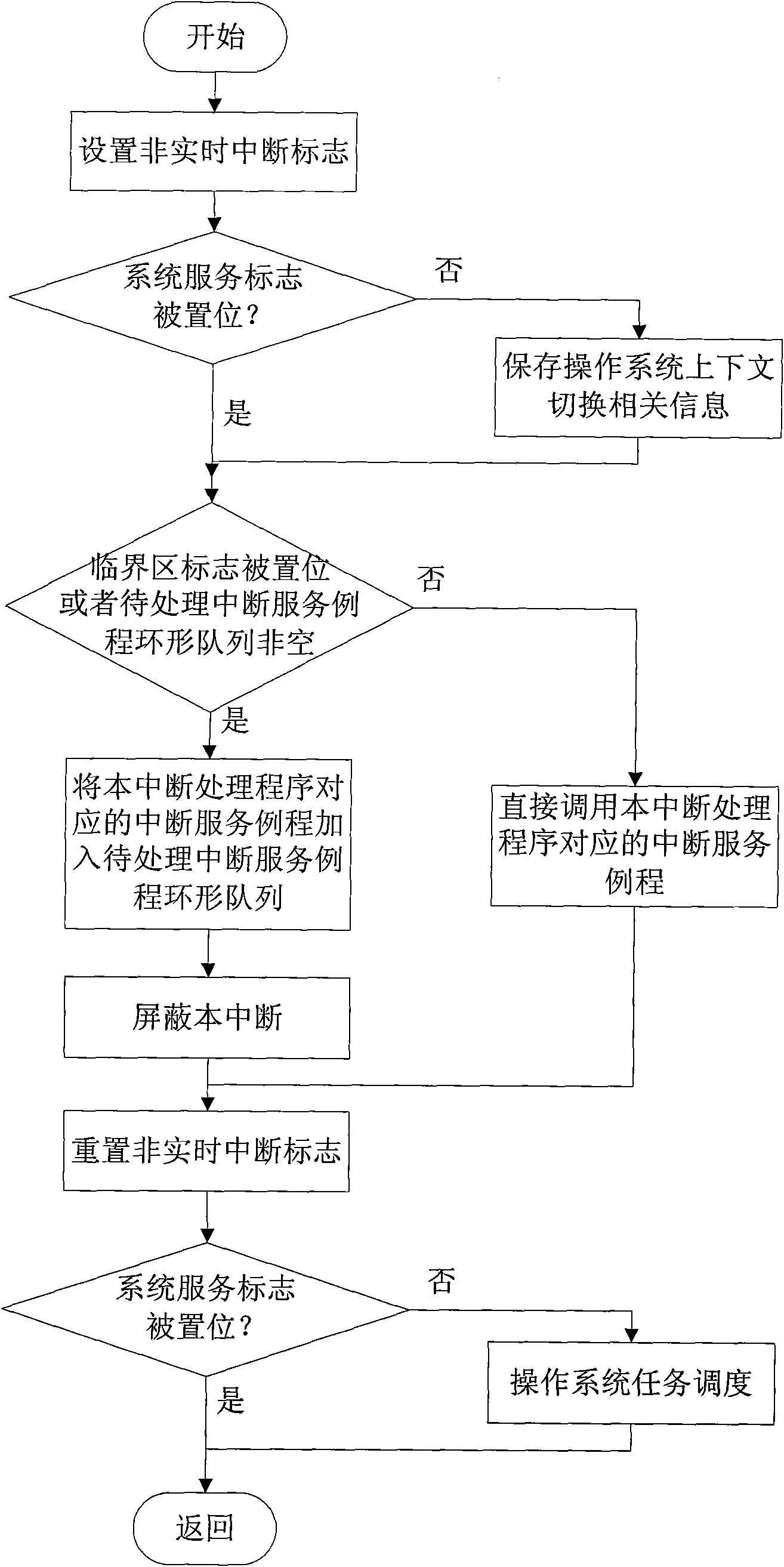

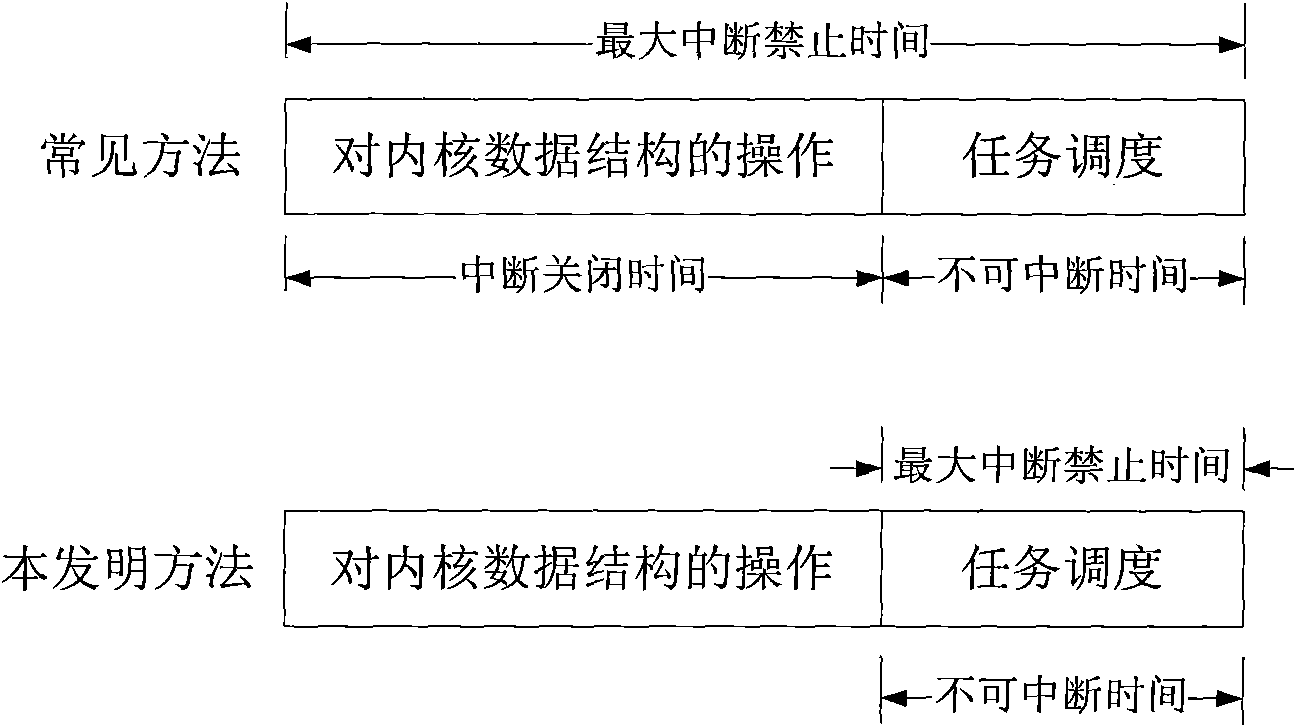

Method for improving interruption delay of embedded type real-time operation system

InactiveCN101639791AImprove the interrupt delay problemReduce execution overheadProgram initiation/switchingNon real timeOperational system

The invention discloses a method for improving the interruption delay of an embedded type real-time operation system. The method comprises the following steps: creating a system service mark, a critical section mark, a non-real time interruption mark and an interruption service routine annular array to be processed; programming an arbitrary operation system service, an interruption processing program of non-real time interruption and the task scheduling of an operation system by specific steps: finally registering the interruption processing program of non-real time interruption into an interruption vector table and registering an interruption service routine of real-time interruption into the interruption vector table. The invention does not perform closing interruption operation at all in the realizing process of the system service of the operation system, and can shorten the maximal interruption prohibited time and reduce the interruption delay, thereby improving the instantaneity of the embedded type real-time operation system. The invention has less time and space cost needed by realizing interruption management and is quite suitable for a microkernel embedded type real-time operation system.

Owner:ZHEJIANG UNIV

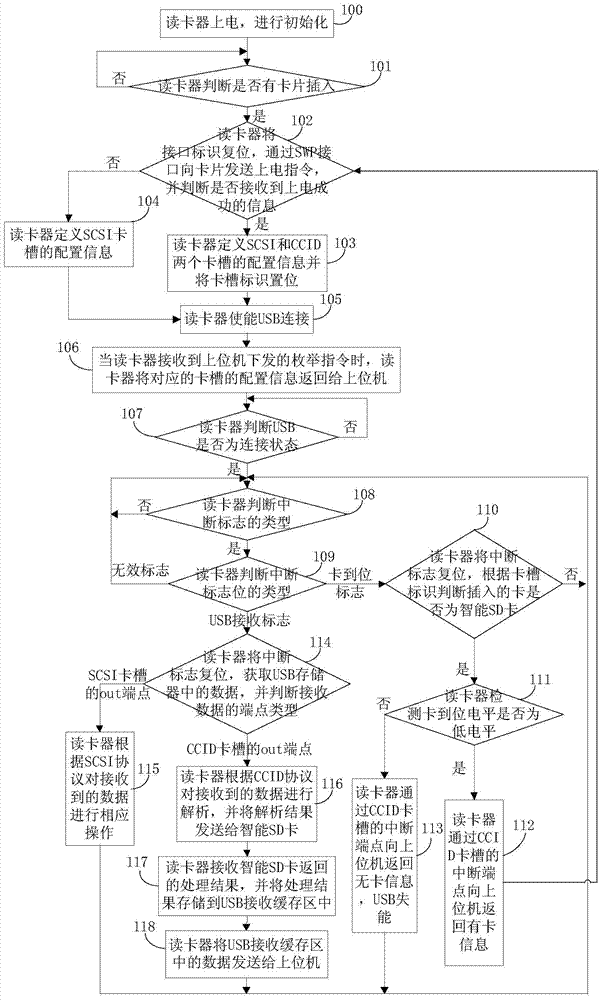

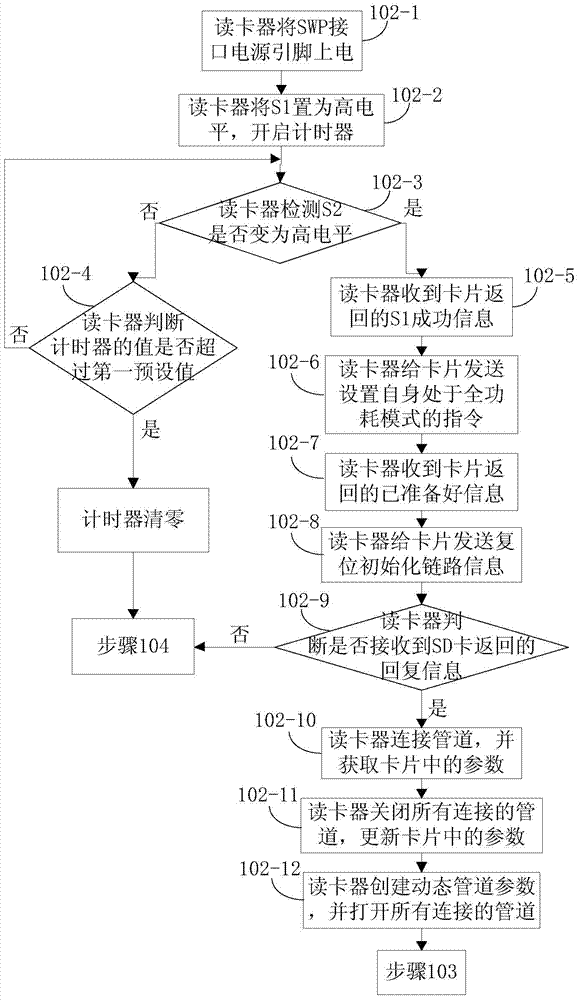

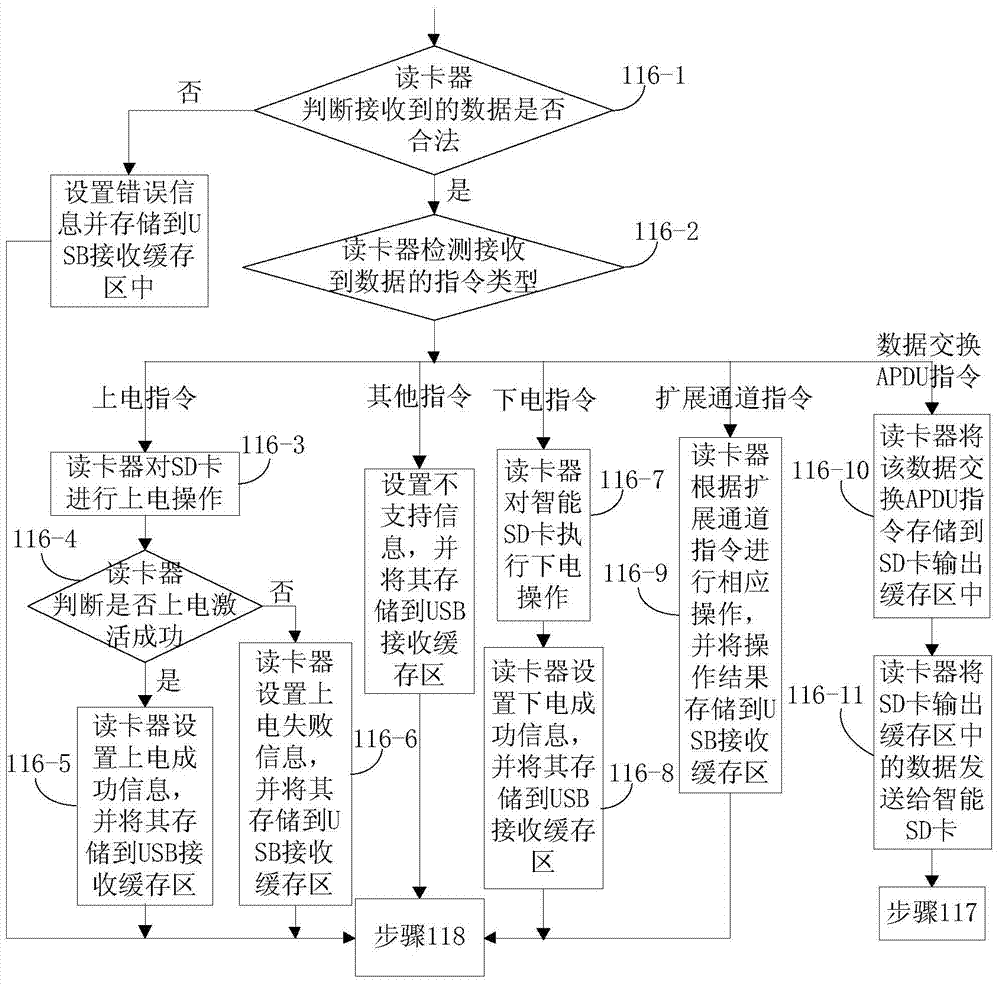

Working method of card reader based on intelligent SD card

The invention discloses a working method of a card reader based on an intelligent SD card. The method comprises the steps of electrifying the card reader and conducting initialization; judging whether the intelligent SD card is inserted in, defining the configuration information of an SCSI card slot and a CCID card slot if yes, and defining the configuration information of the SCSI card slot if not; enabling USB connection; feeding corresponding card slot information back to an upper computer according to an enumeration command, resetting an interrupt flag when the card reader detects that the interrupt flag is set to be a USB receiving flag, analyzing received data according to a CCID protocol if the terminal receiving the data is an out terminal of the CCID, and sending an analyzing result to the intelligent SD card; waiting for and receiving a processing result fed back by the intelligent SD card, and sending the data in a USB receiving cache region to the upper computer through an in terminal of the CCID card slot. By the adoption of the method, communication between the intelligent SD card and the upper computer is achieved.

Owner:FEITIAN TECHNOLOGIES

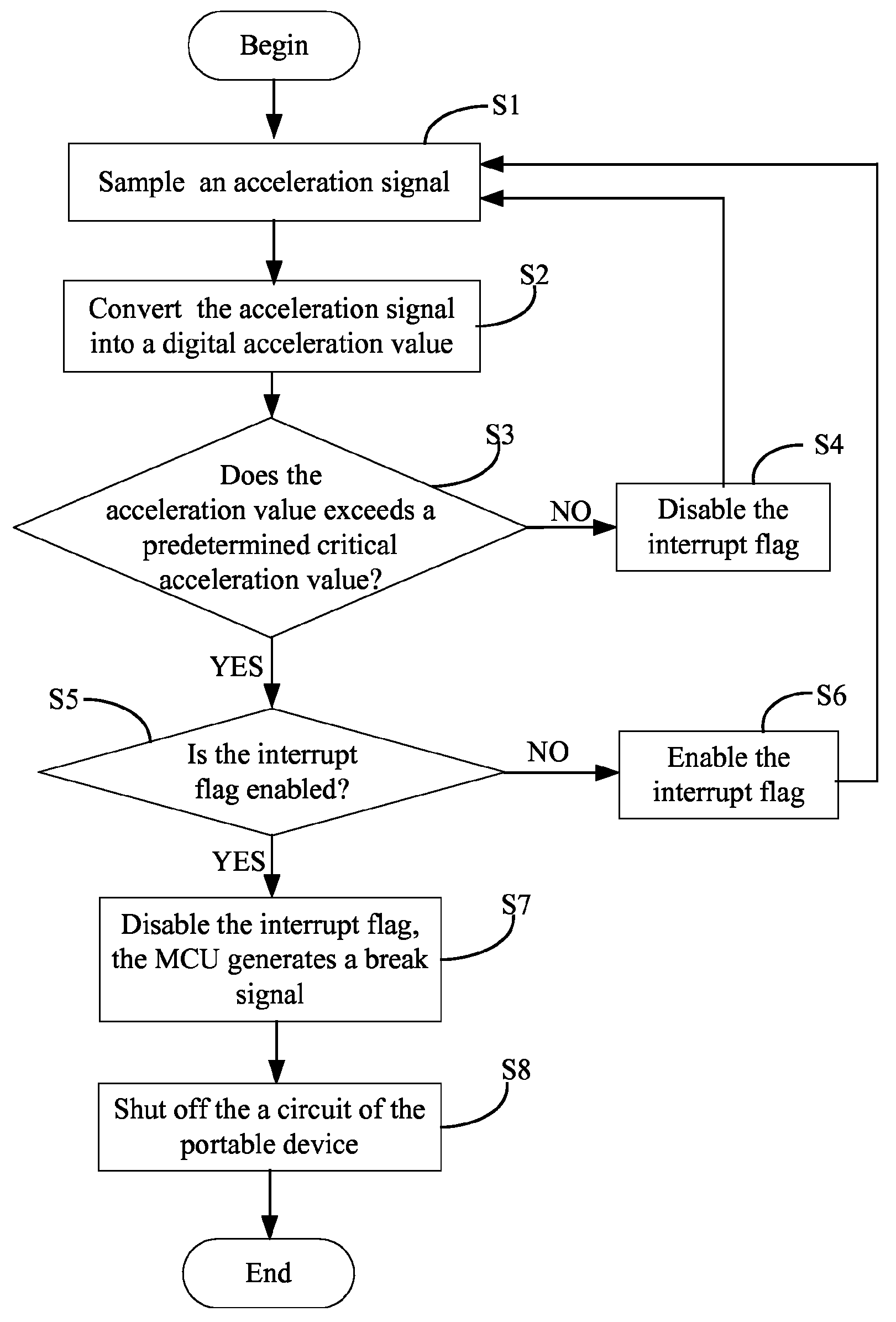

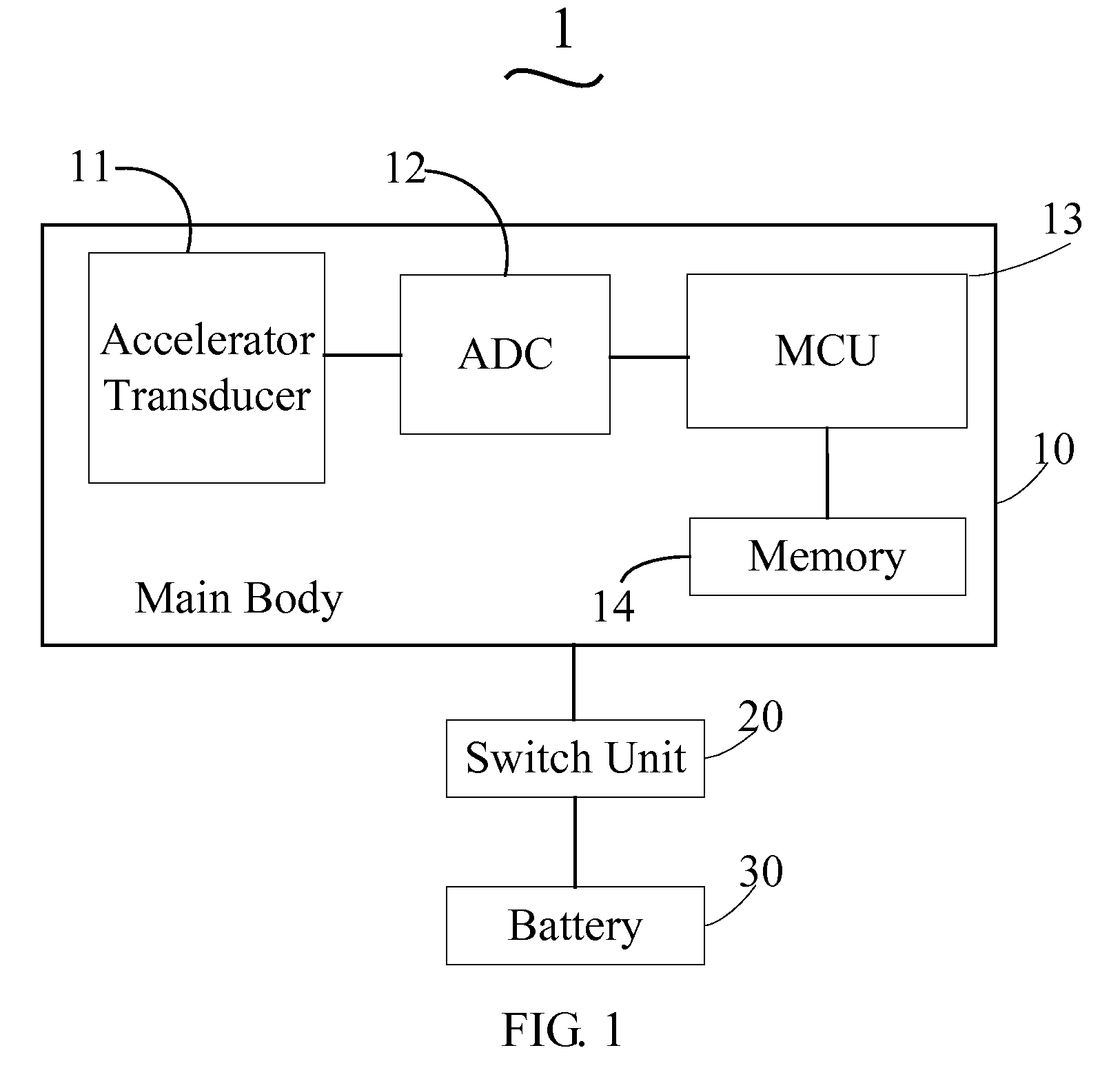

Portable device with an automatic power off protection and method for same

InactiveUS7827420B2Protection from damageReduce harmDriving/moving recording headsVolume/mass flow measurementElectrical batteryTransducer

A portable device with an automatic power off protection and a method of achieving such a protection are related. The portable device circuit comprises a switch unit, a main body, and a battery. The main body includes an acceleration transducer that samples an analog acceleration signal; an analog-to-digital converter (ADC) that converts the sampled analog acceleration signal into a digital acceleration value; a memory that stores a critical acceleration value and an interrupt flag; and a micro-control unit (MCU) that compares the digital acceleration values with the critical acceleration value and the comparing result which may or may not change the value of the interrupt flag. When the acceleration of the portable device is greater than the critical acceleration and the interrupt flag is enable, the MCU sends a break signal to the switch unit to power off the portable device.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

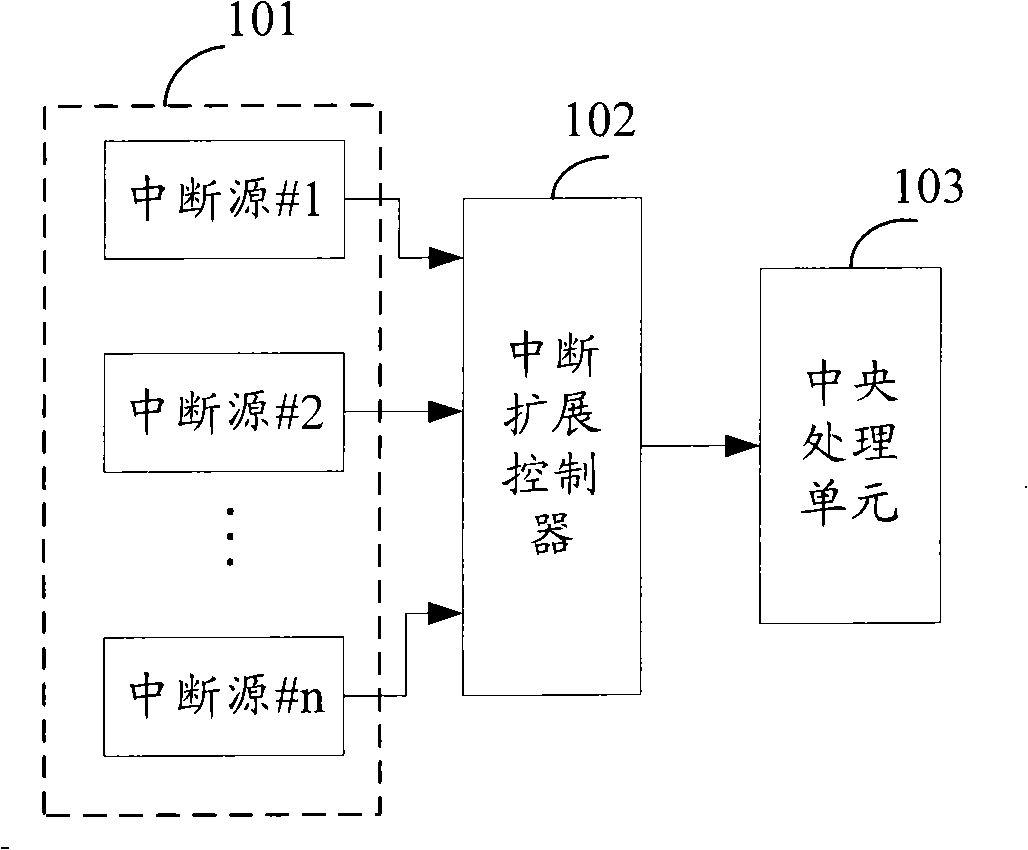

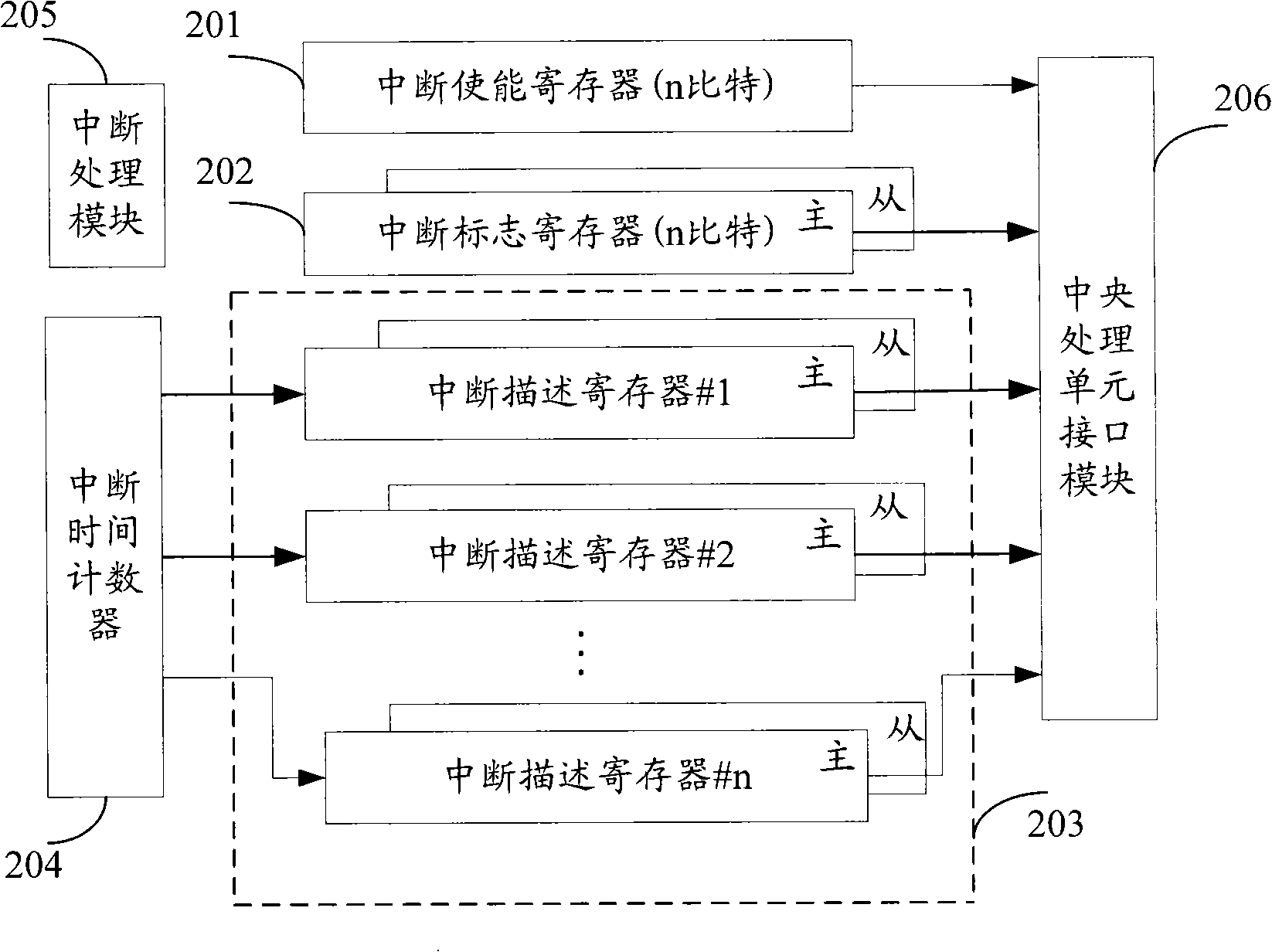

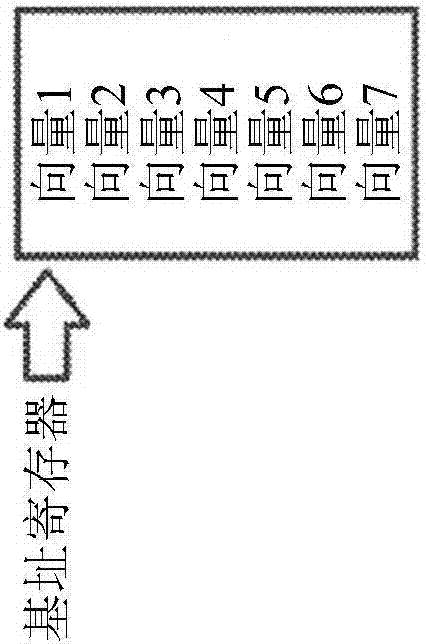

Method and apparatus for realizing interrupt acquisition

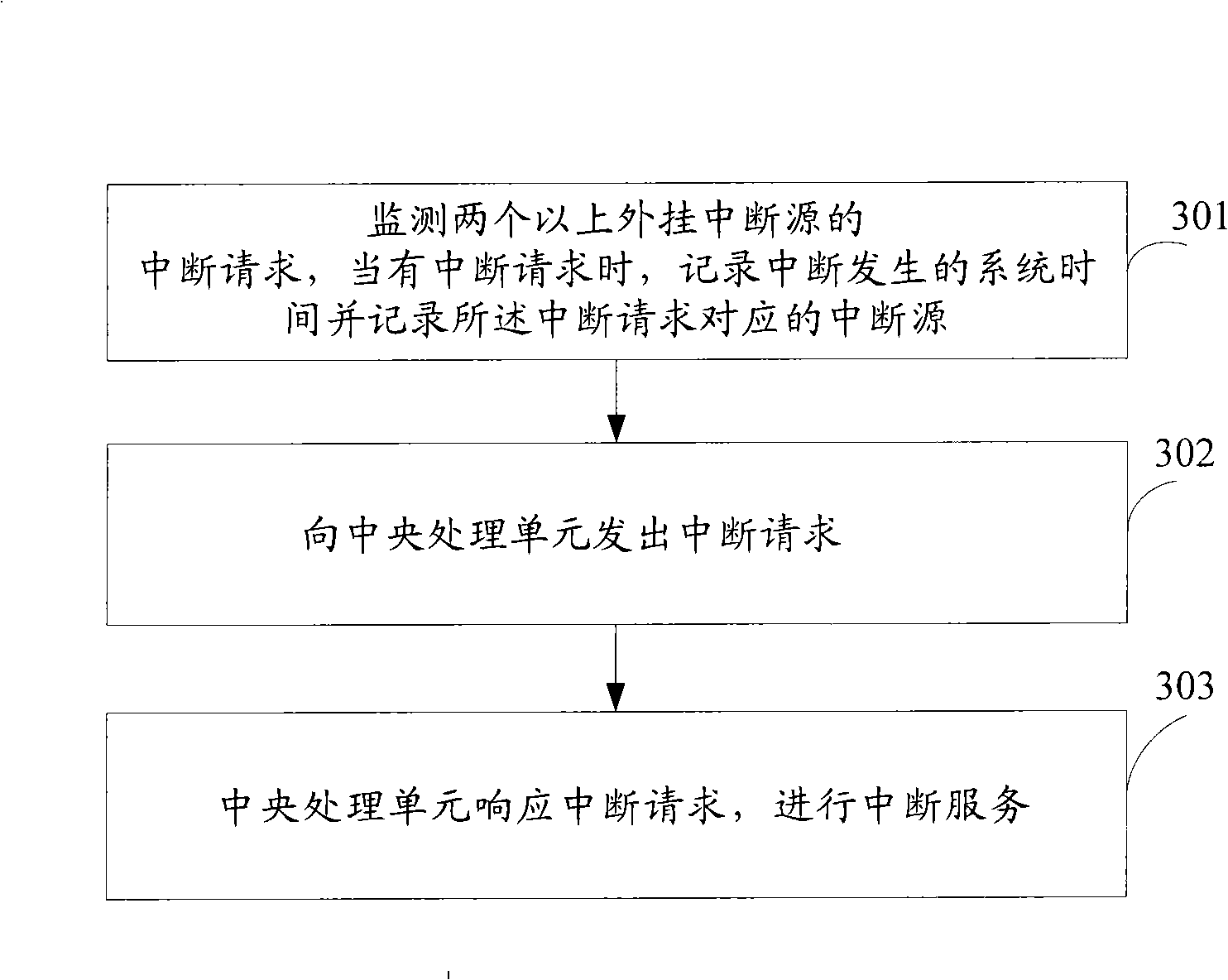

ActiveCN101299206AImplement interrupt servicingSolve the problem of insufficient interrupt pinsElectric digital data processingProcessor registerSystem time

The invention discloses an interrupt capture implementing method, which includes: monitoring the interrupt request of the more than two external hanging interruption sources, if the interrupt request is received, and if the interruption is enabled and no interruption collision takes place, recording the interruption generating system time and recording the interrupt source corresponding to the interrupt request, and then sending out interrupt request to the central processing unit; the central processing unit responds to the interrupt request, and executes interrupt service. The present invention also discloses an interrupt capture implementing apparatus, including: an interrupt flag register, an interrupt information recording module, an interrupt processing module, a central processing unit interface module and an interrupt enable register and central processing unit, for the realization of interrupt request capture to a plurality of external hanging interrupt sources and effective servings to the interruption.

Owner:ZTE CORP

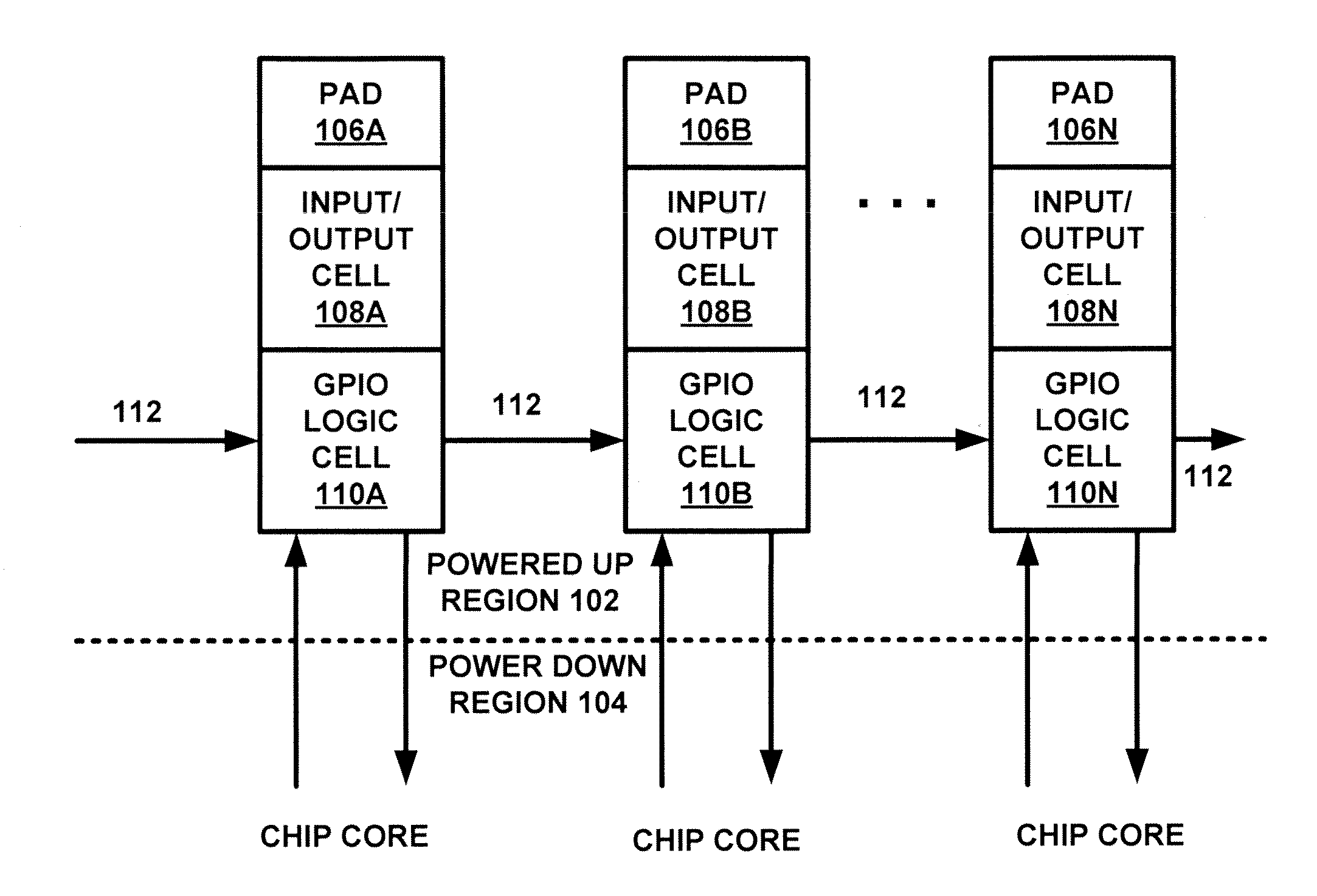

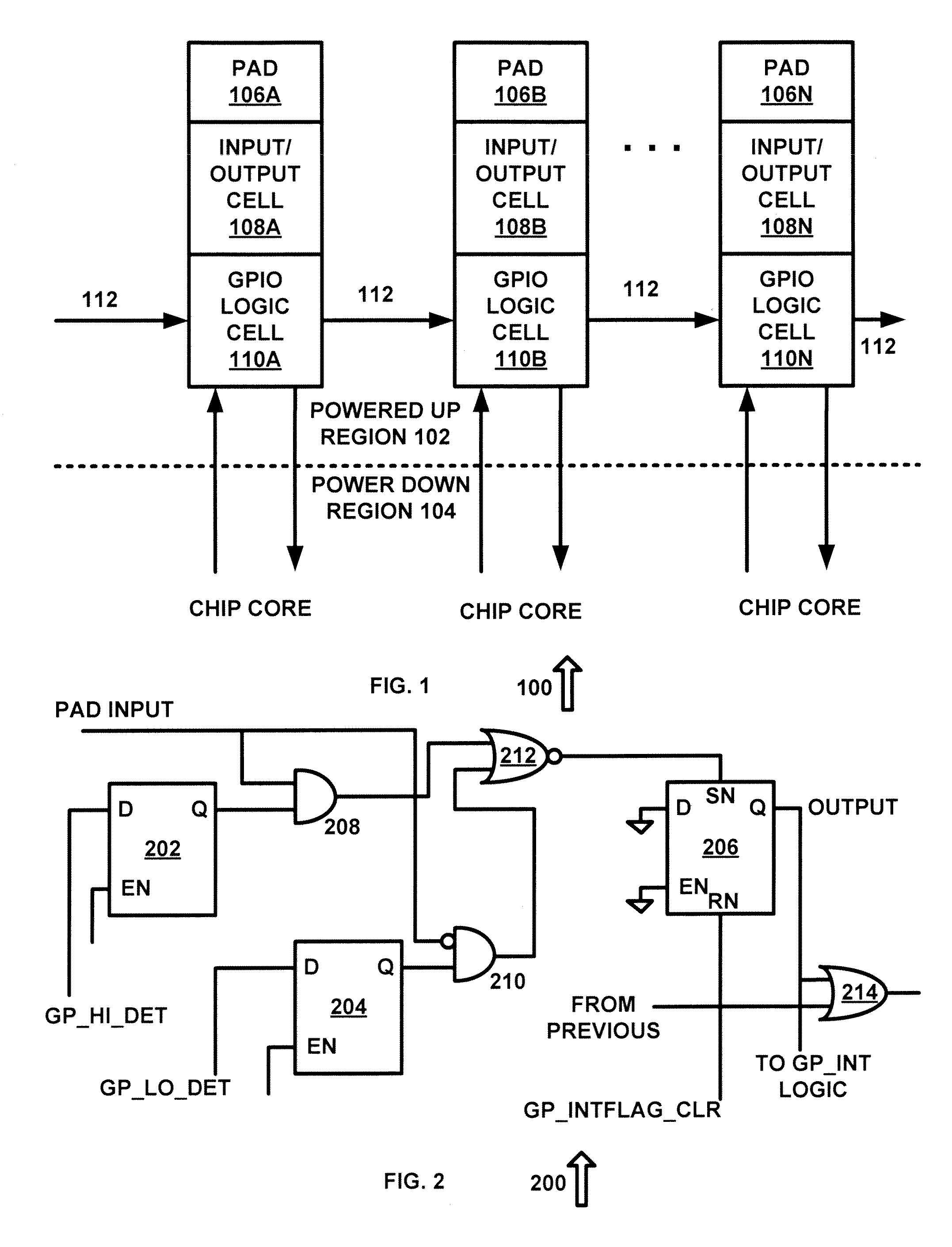

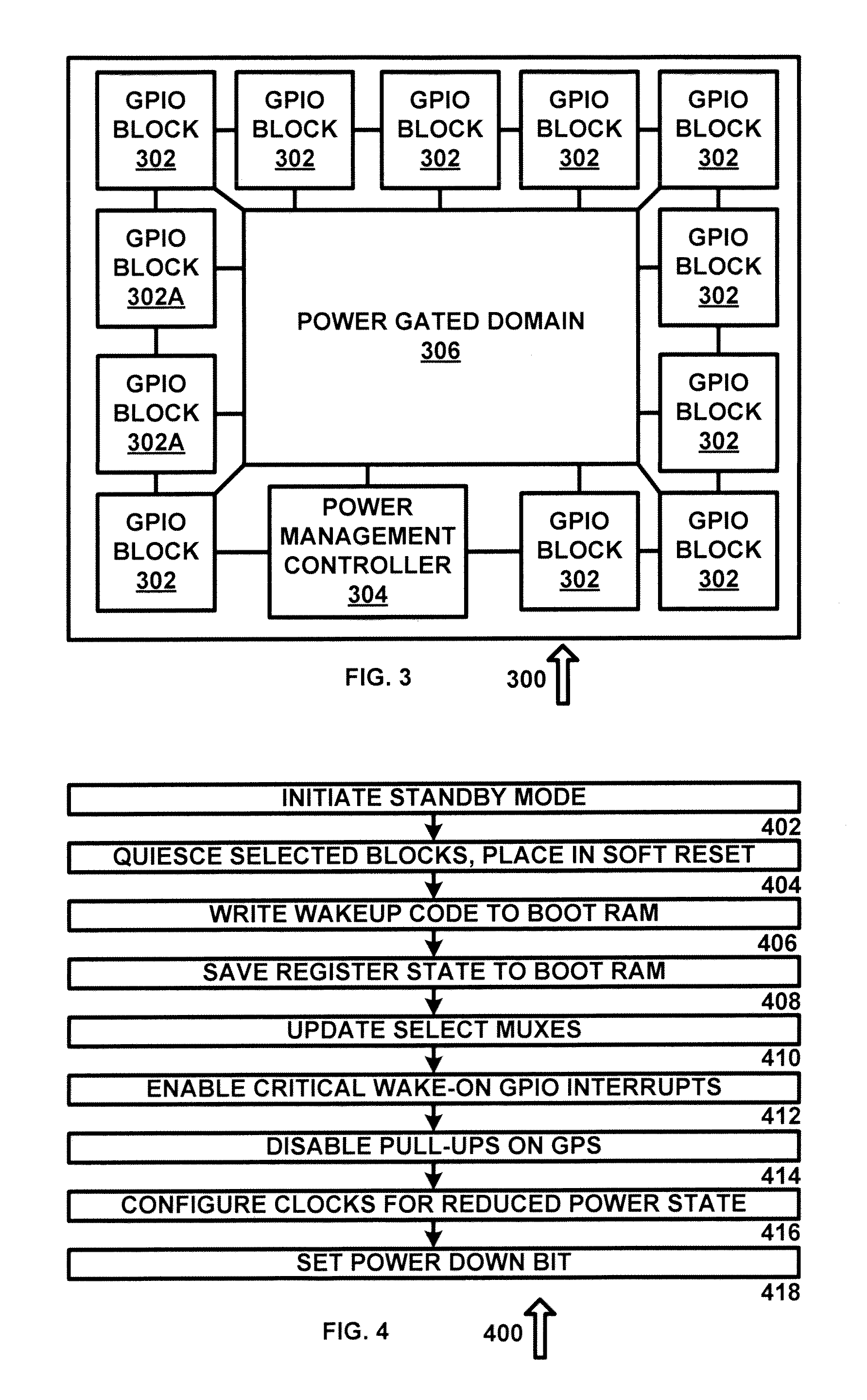

Method and system for waking on inuput/output interrupts while powered down

A system for power management. The system includes a plurality of input / output pads and a plurality of input / output cells, where each input / output cell is coupled to one of the input / output pads. The system further includes a plurality of interrupt observe circuits, where each interrupt observe circuit is coupled to one of the input / output cells, and where the interrupt observe circuits are configured to generate an interrupt flag during a low power mode.

Owner:SYNAPTICS INC

Device for realizing wireless sensor network access protocol

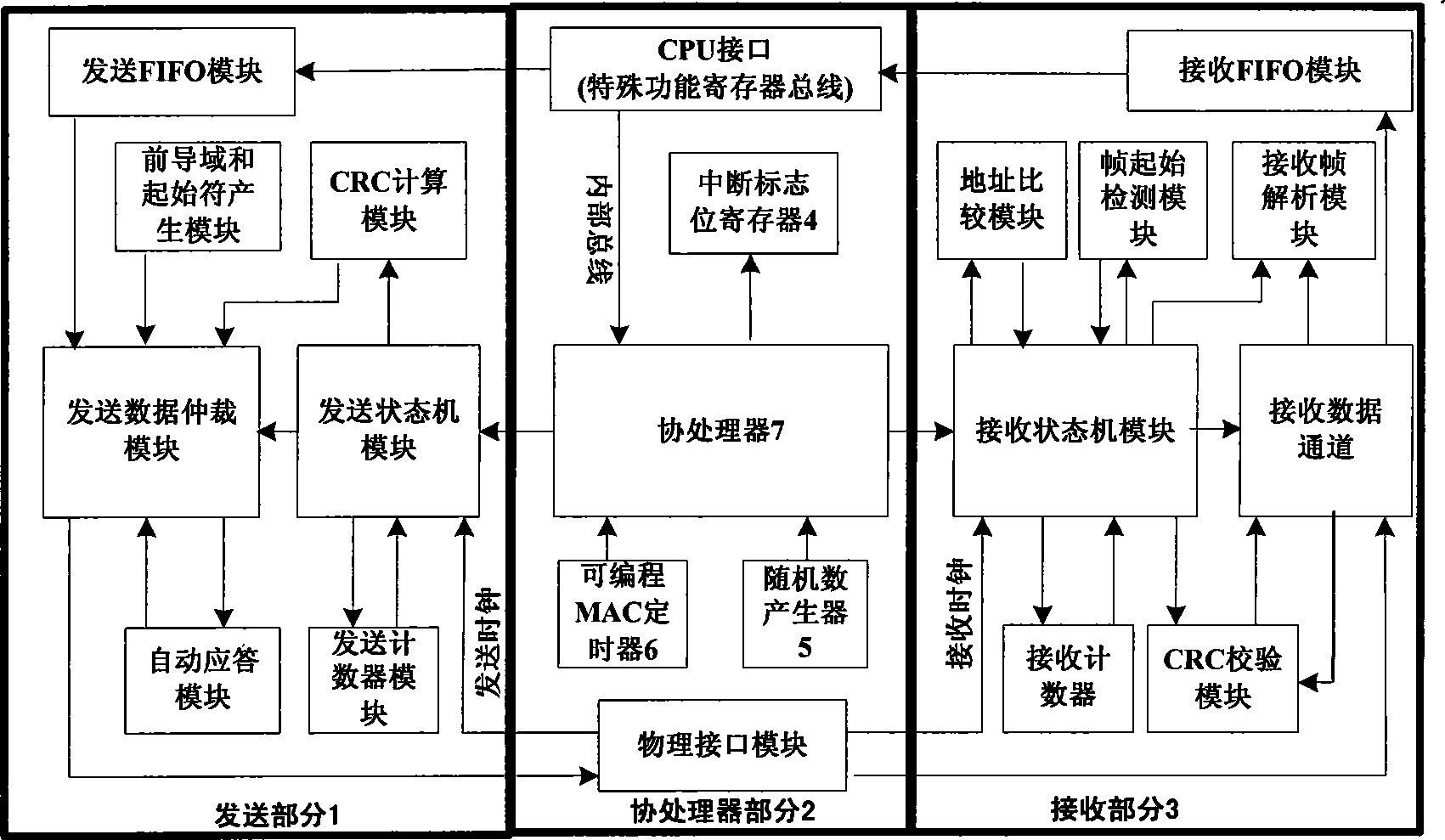

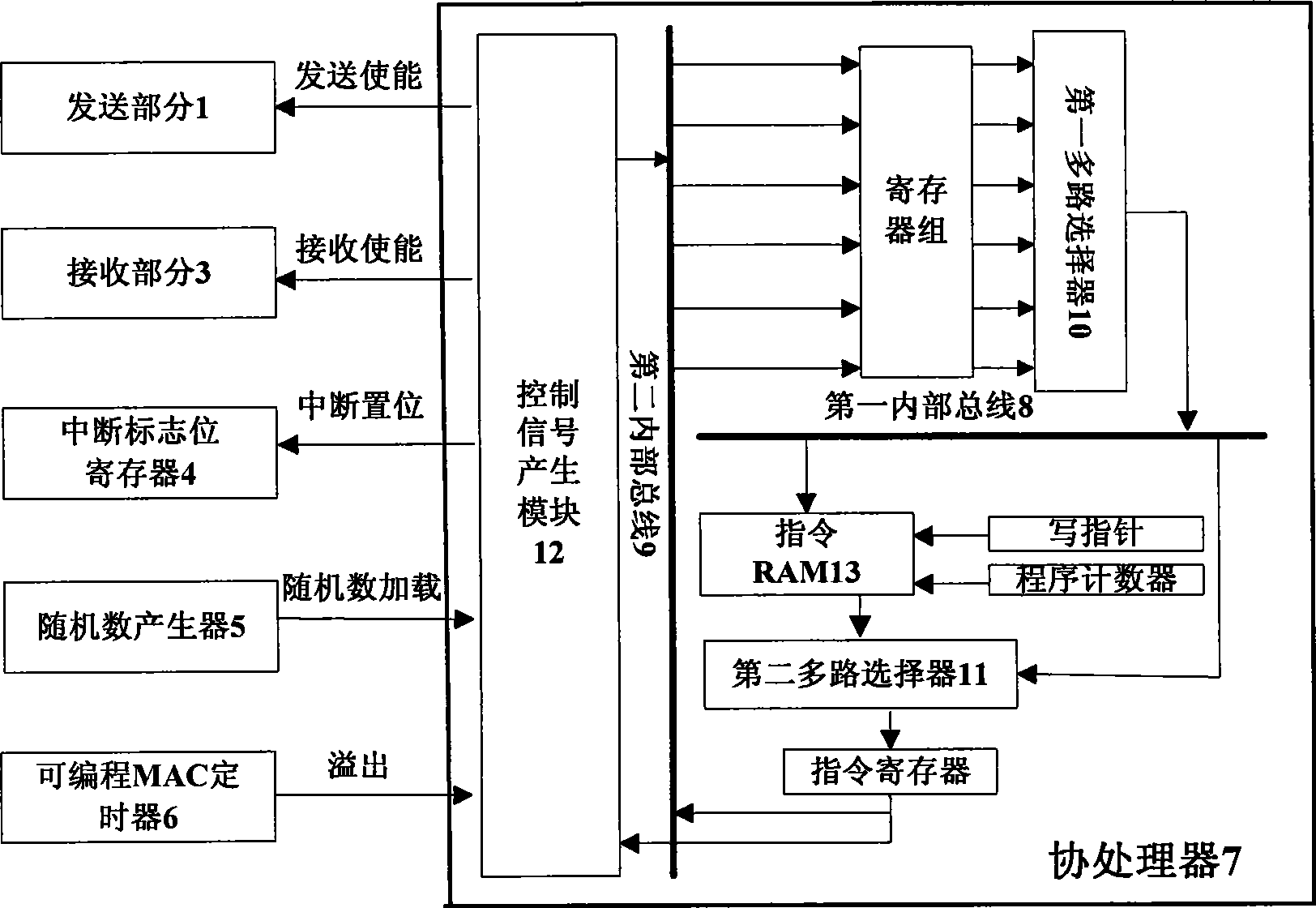

InactiveCN101521952AReduce processing burdenEasy to controlError preventionWireless network protocolsCoprocessorNetworking protocol

The invention discloses a device for realizing a wireless sensor network access protocol. The channel contention mechanisms with different MAC protocols are mapped as the software programs inside a coprocessor, the reusability of the MAC can be enhanced by using the programmable flexibility of the coprocessor, the flexibility of the hardware is promoted, and the design cost of the hardware is reduced. The device comprises a sending part, a coprocessor part and a receiving part, wherein the coprocessor part comprises an interrupt flag register, a random number generator, a programmable MAC timer and a coprocessor; the coprocessor receives a signal from a CPU interface through an internal bus, the sending part, the receiving part and the interrupt flag register are controlled according to the generated control command, and the switching control between the receiving state and the sending state as well as the realization of the CSMA / CA algorithm are finished. The FPGA verification shows that the invention has simple design structure and small occupied area, can support the 20-250kbps communication rate, fully considers the feasibility of communication under the different wireless sensor network protocols and is especially suitable for the node chip of the wireless sensor network.

Owner:HUAZHONG UNIV OF SCI & TECH

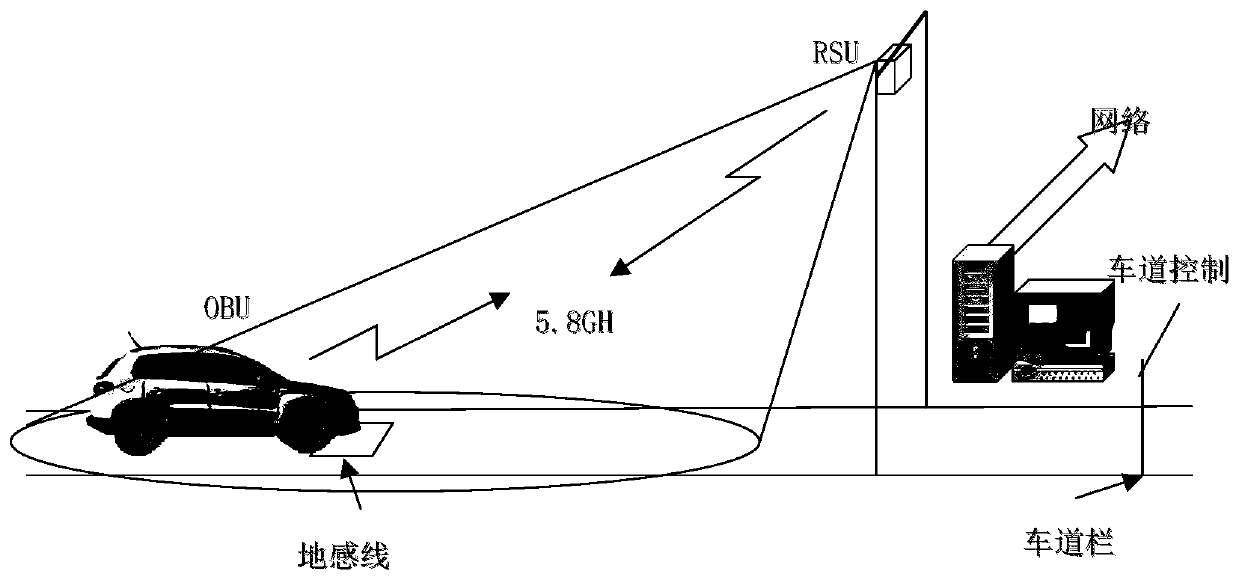

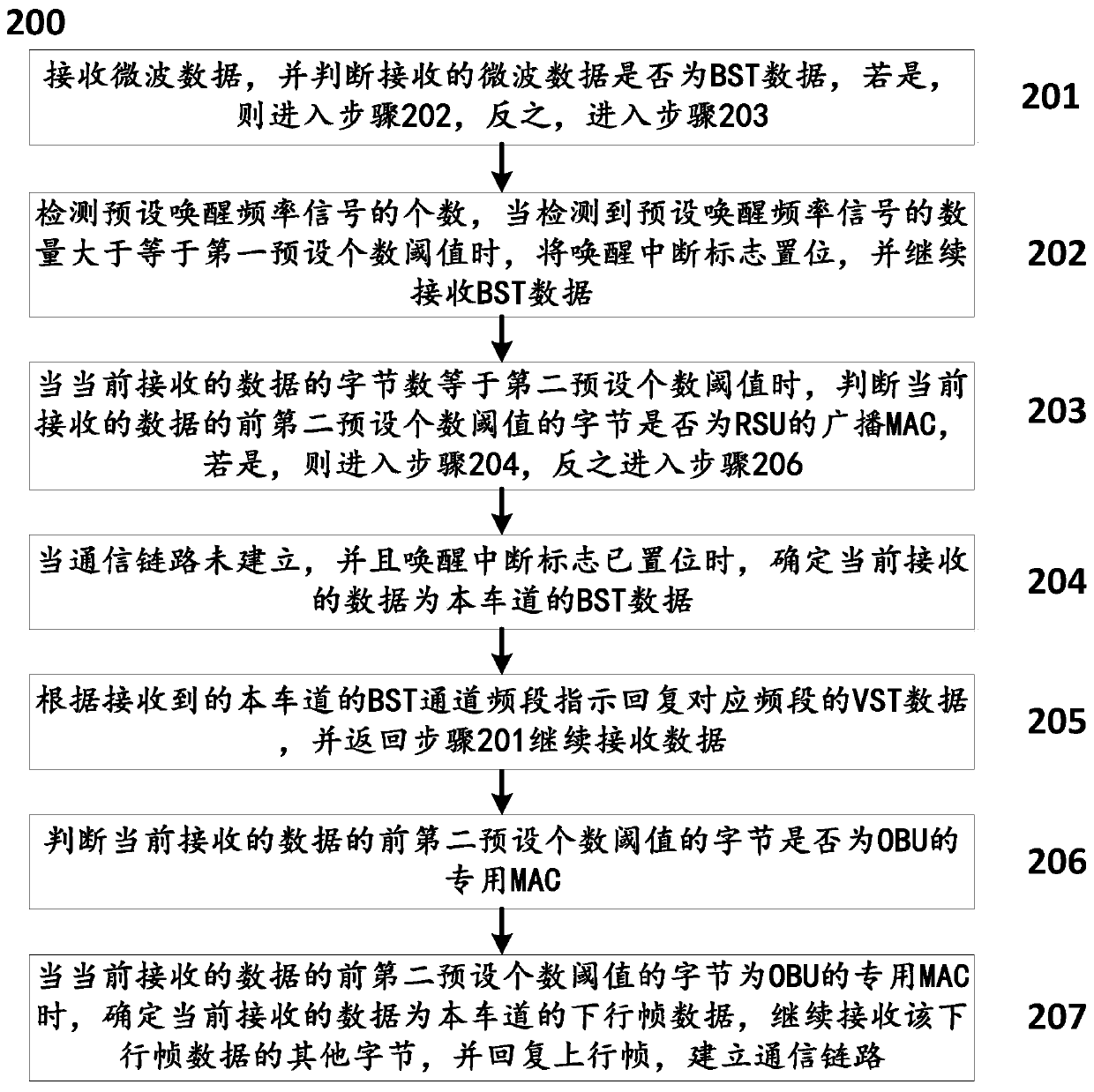

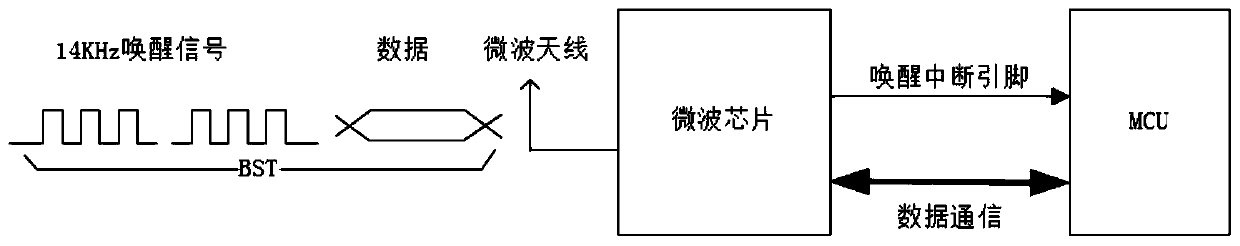

A method and a system for resisting adjacent channel interference transaction of an OBU electronic tag

ActiveCN109831764AImprove transaction success rateEnhanced anti-adjacent channel interferencePower managementTicket-issuing apparatusAdjacent-channel interferenceTelecommunications link

The invention discloses an anti-adjacent channel interference transaction method and system suitable for an OBU electronic tag, the OBU can only receive the awakening interruption generated by the lane awakening signal to serve as a judgment basis for identification.The method comprises the following steps: when bytes of a second preset number of front thresholds of received data are broadcast MACof an RSU and a wake-up interrupt flag is set, determining the BST data as BST data of a lane under the condition that a link is not established, and continuously receiving and replying VST data of acorresponding frequency band; and when the bytes of the first preset number threshold value and the second preset number threshold value of the received data are special MAC of the OBU, determining the bytes as downlink frame data of the lane, continuously receiving other bytes of the downlink frame data and replying to an uplink frame, and establishing a communication link. According to the technical scheme provided by the invention, the OBU receives the lane wake-up signal and then the received BST data is identified as the effective signal of the lane, so that the adjacent lane interference resistance of the OBU can be effectively enhanced; and the received downlink data is compared with preset numeric nodes in advance, so that the transaction time can be greatly shortened.

Owner:BEIJING YUNXINGYU TRAFFIC SCI & TECH

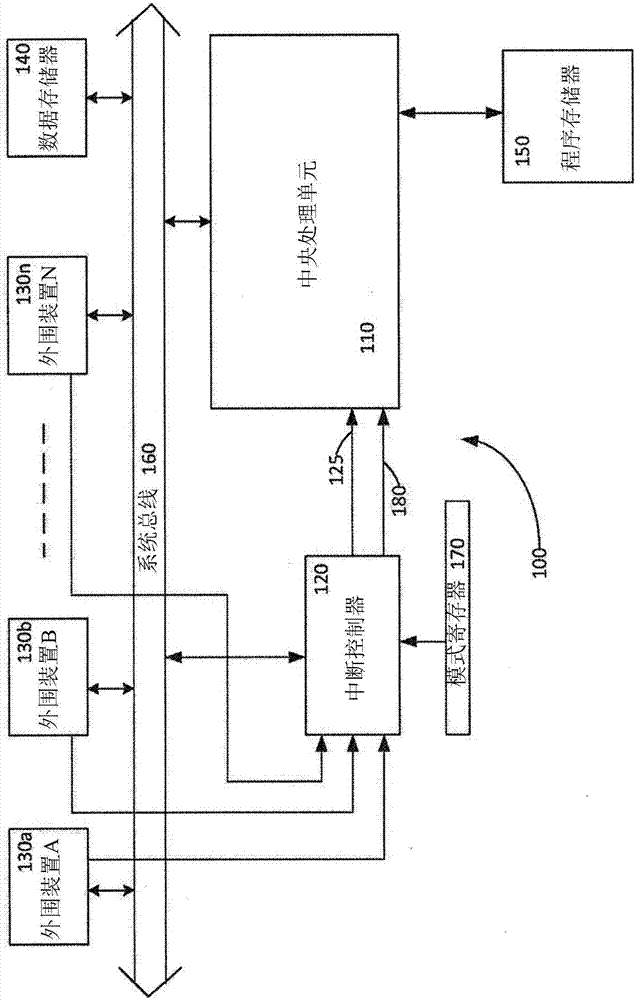

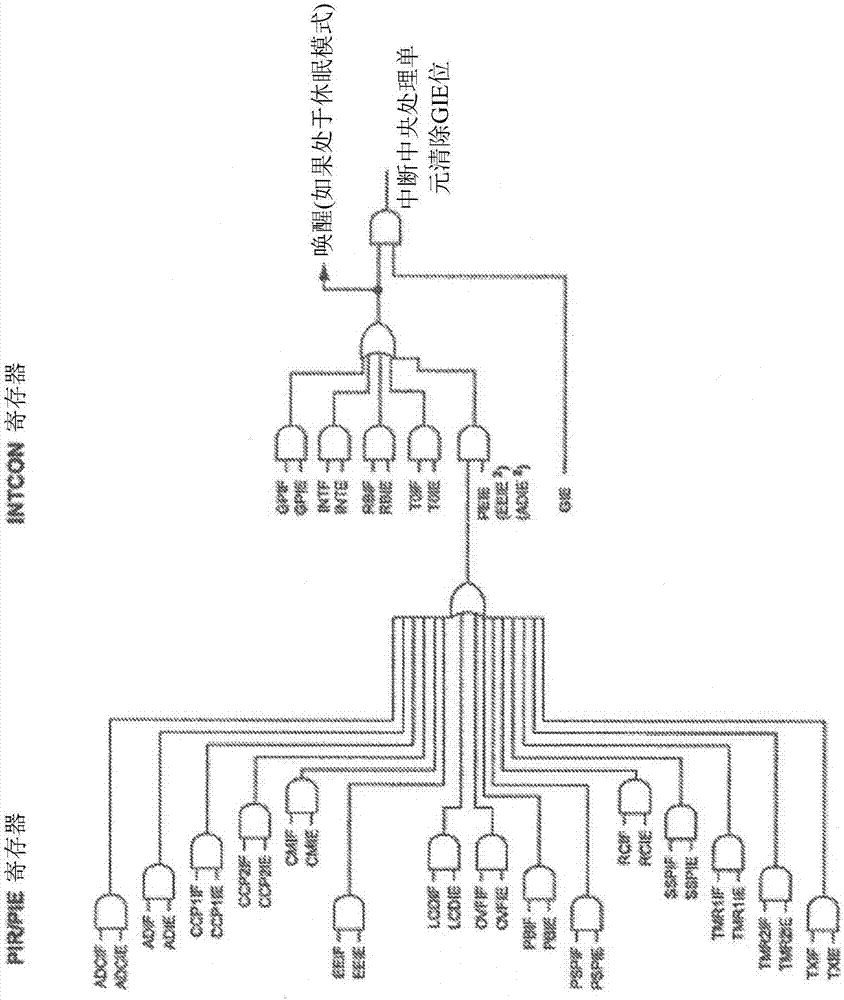

Microcontroller or microprocessor with dual mode interrupt

A microcontroller has a CPU with at least one interrupt input coupled with an interrupt controller, a plurality of peripherals, and a mode register comprising at least one bit controlling an operating mode of the microcontroller. The microcontroller is configured to operate in a first operating mode wherein upon assertion of an interrupt by a peripheral of the microcontroller, the interrupt controller forwards an interrupt signal to the CPU and the peripheral sets an associated interrupt flag, wherein the interrupt causes the CPU to branch to a predefined interrupt address associated with the interrupt input. In a second operating mode, upon assertion of an interrupt by a peripheral of the microcontroller, the interrupt controller forwards an interrupt signal to the CPU and the CPU receives additional interrupt information from the peripheral that generated the interrupt, wherein the additional interrupt information is used to generate a vector address.

Owner:MICROCHIP TECH INC

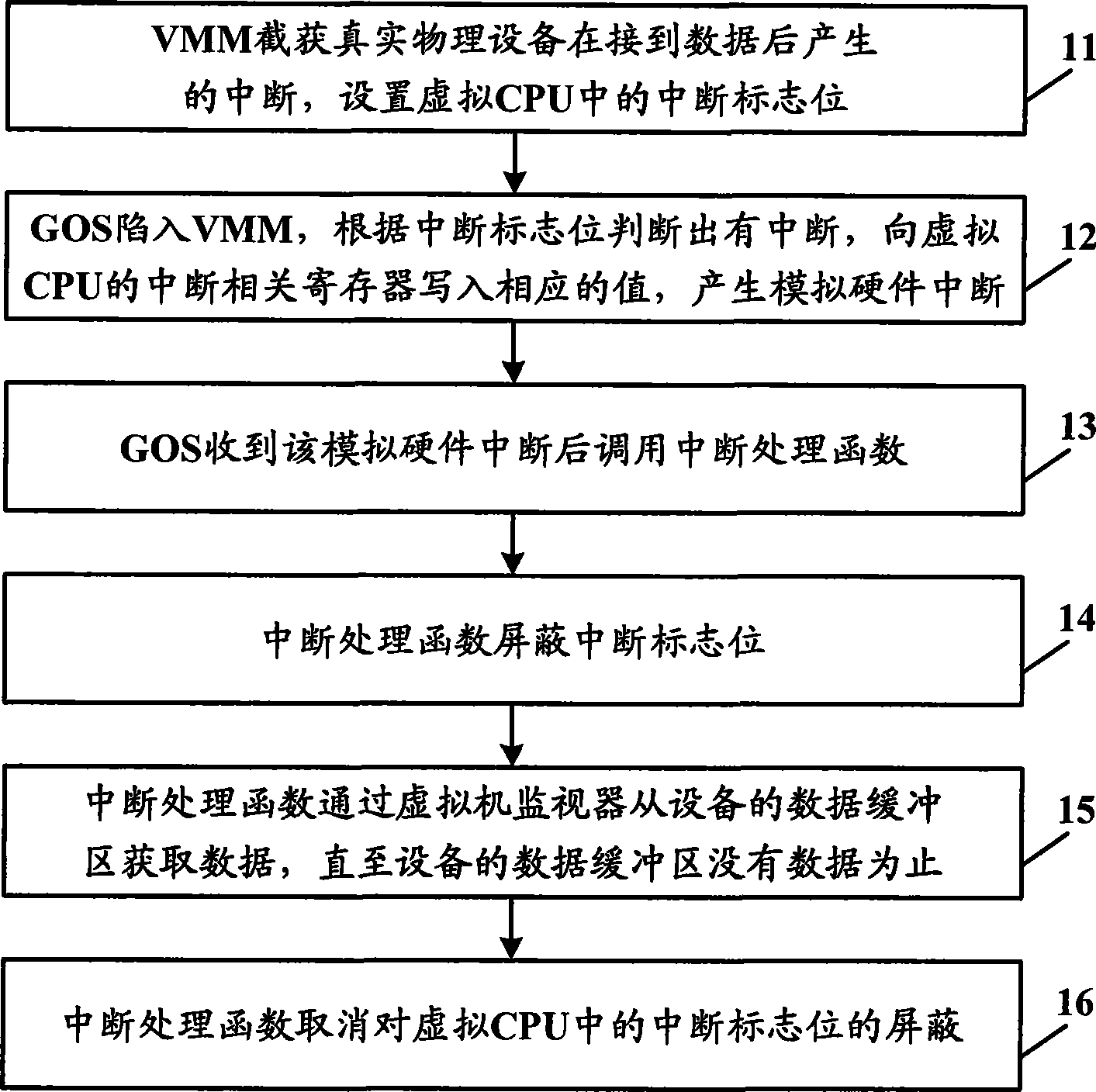

Virtual machine system and interrupt handling method for customer operating system of the virtual machine system

ActiveCN101382923AEasy to receiveImprove performanceSoftware simulation/interpretation/emulationOperational systemInterrupt flag

The invention provides a virtual machine system and an interruption handling method for the client operation system thereof, wherein, the interruption handling method for the client operation system of the virtual machine system comprises the following steps: step A, an interruption flag bit in virtual CPU is set after a virtual machine monitor intercepts and captures interruption generated by real physical equipment; step B, the invocation of an interruption handling function of a drive is interrupted according to the simulated hardware of the virtual CPU after the client operation system gets into the virtual machine monitor; step C, the interruption flag bit is shielded by the interruption handling function; and step D, the interruption handling function obtains data from a data buffering zone through the virtual machine monitor till no data is left in the data buffering zone of the equipment. With the adoption of the virtual machine system and the interruption handling method, data receiving process is accelerated and system performance is improved.

Owner:LENOVO (BEIJING) LTD

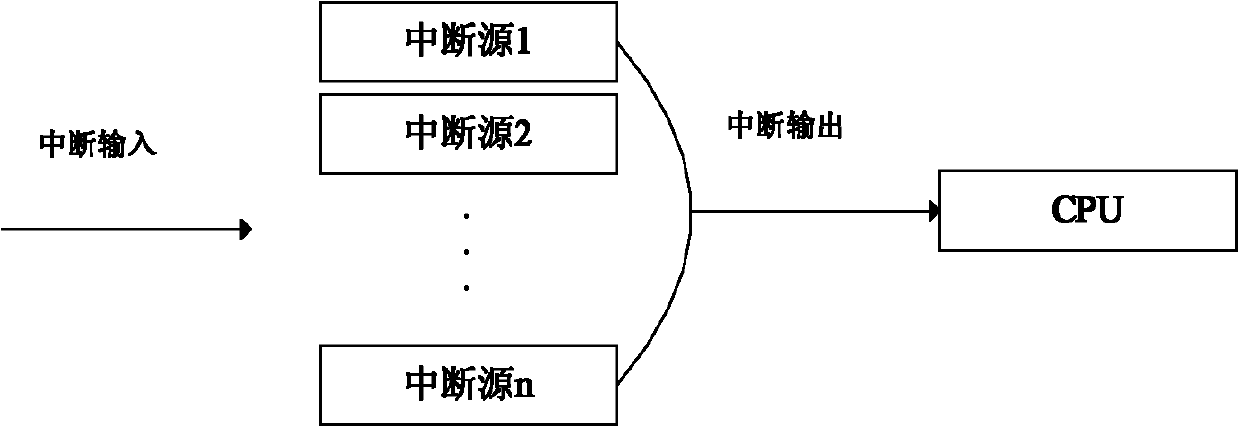

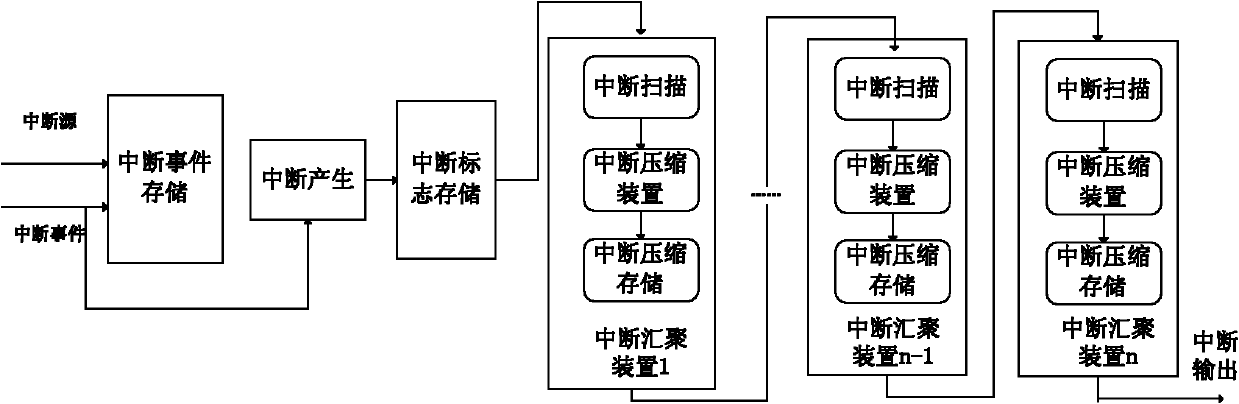

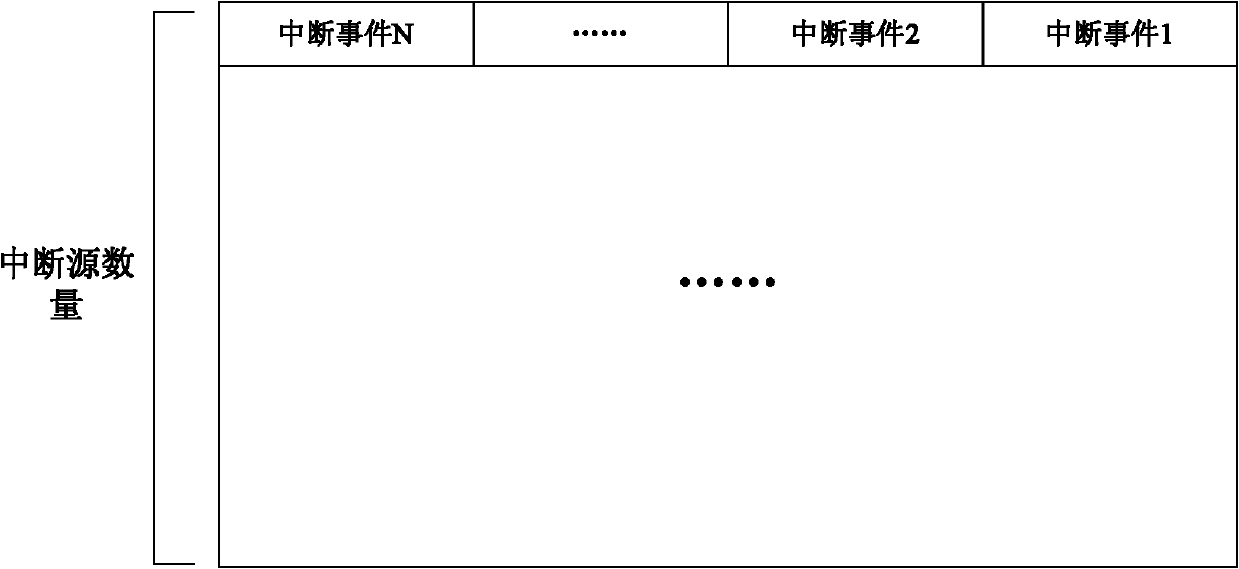

Quick interrupt graded processing device and method

InactiveCN102495816AReduce occupancyQuickly Locate the Source of InterruptionProgram initiation/switchingOccupancy rateComputer science

The invention provides a quick interrupt graded processing device and a method. The quick interrupt graded processing device comprises an interrupt event memory device, an interrupt generating device, an interrupt identification memory device and an interrupt convergence device, wherein the interrupt event memory device is used for storing interrupt events generated by interrupt sources, the interrupt generating device is used for converting the interrupt events of the same interrupt source into 1 bit interrupt identification, the interrupt identification memory device is used for storing all the generated interrupt identifications, the interrupt convergence device is used for compressing the interrupt identifications in a graded manner, storing the compressed interrupt identifications and leading the compressed interrupt identifications to be processed by a CPU (central processing unit), N stages of interrupt convergence device units cascade to form the interrupt convergence device, structures of the interrupt convergence device units are identical, n represents the bit width of data read and written by the CPU, and S represents the total amount of the interrupt source of a circuit system. By the aid of the device and the method, after the CPU receives an interrupt request, only an interrupt identification needs to be searched reversely so as to find a corresponding interrupt event, the corresponding interrupt source can be quickly positioned, processing time is shortened, and the occupancy rate of the CPU is reduced.

Owner:武汉众邦领创技术有限公司

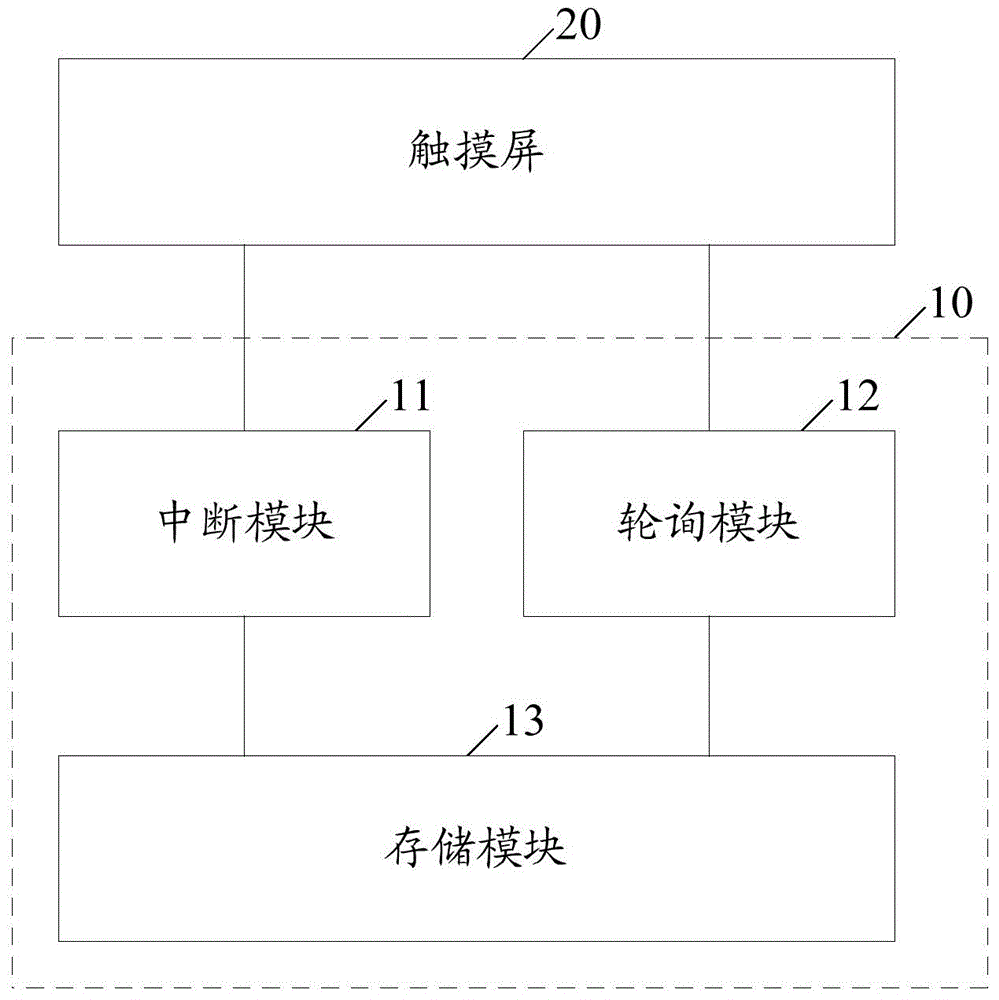

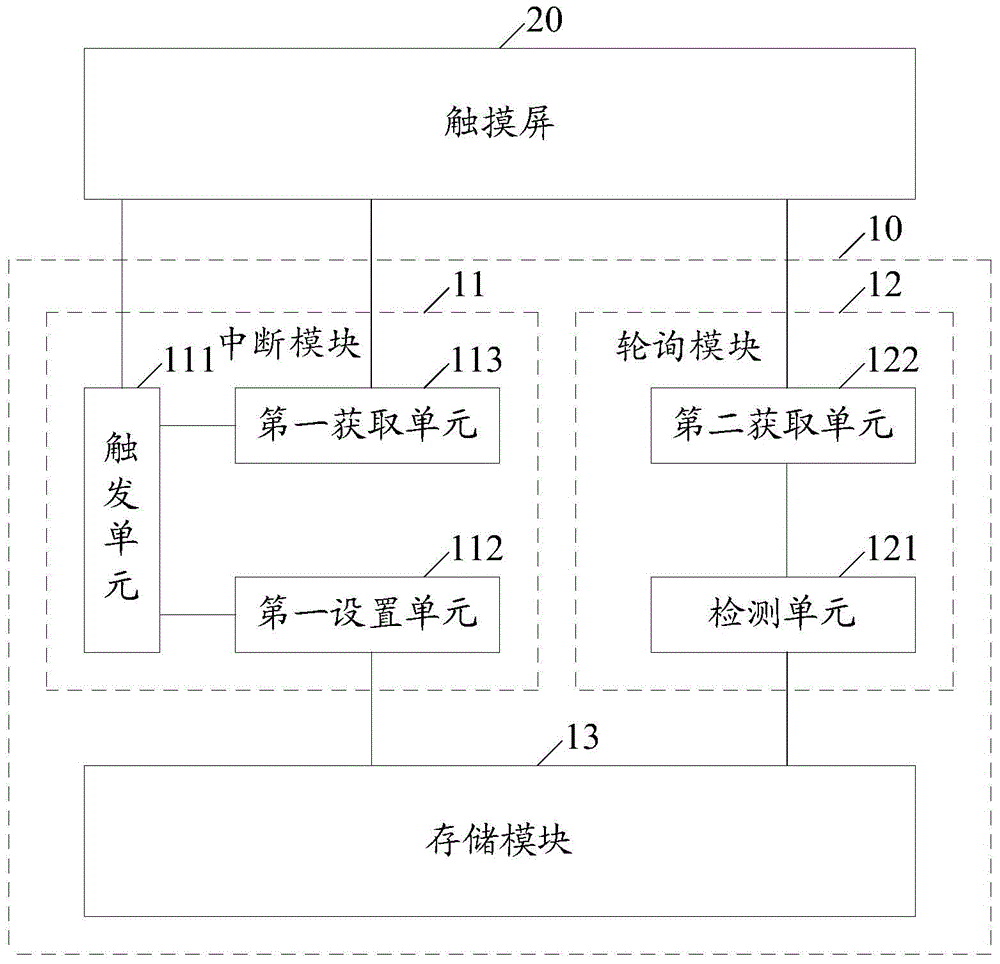

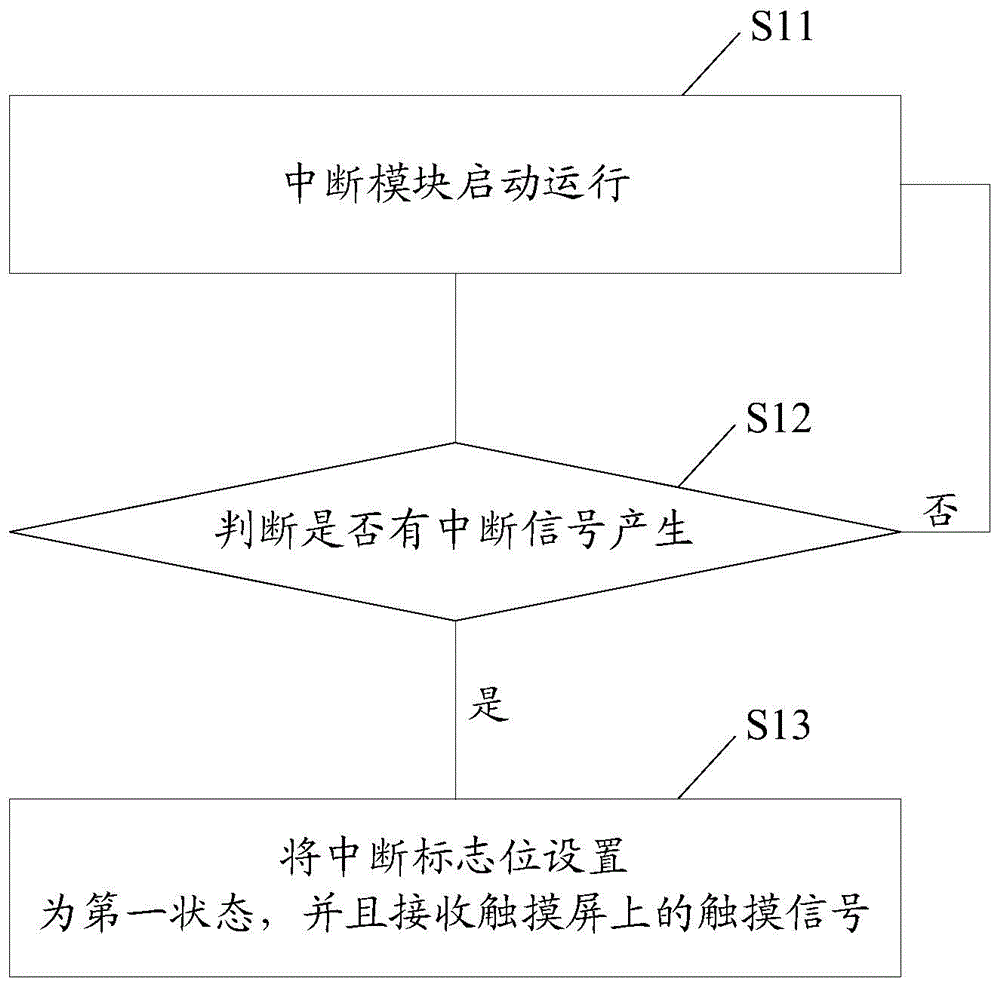

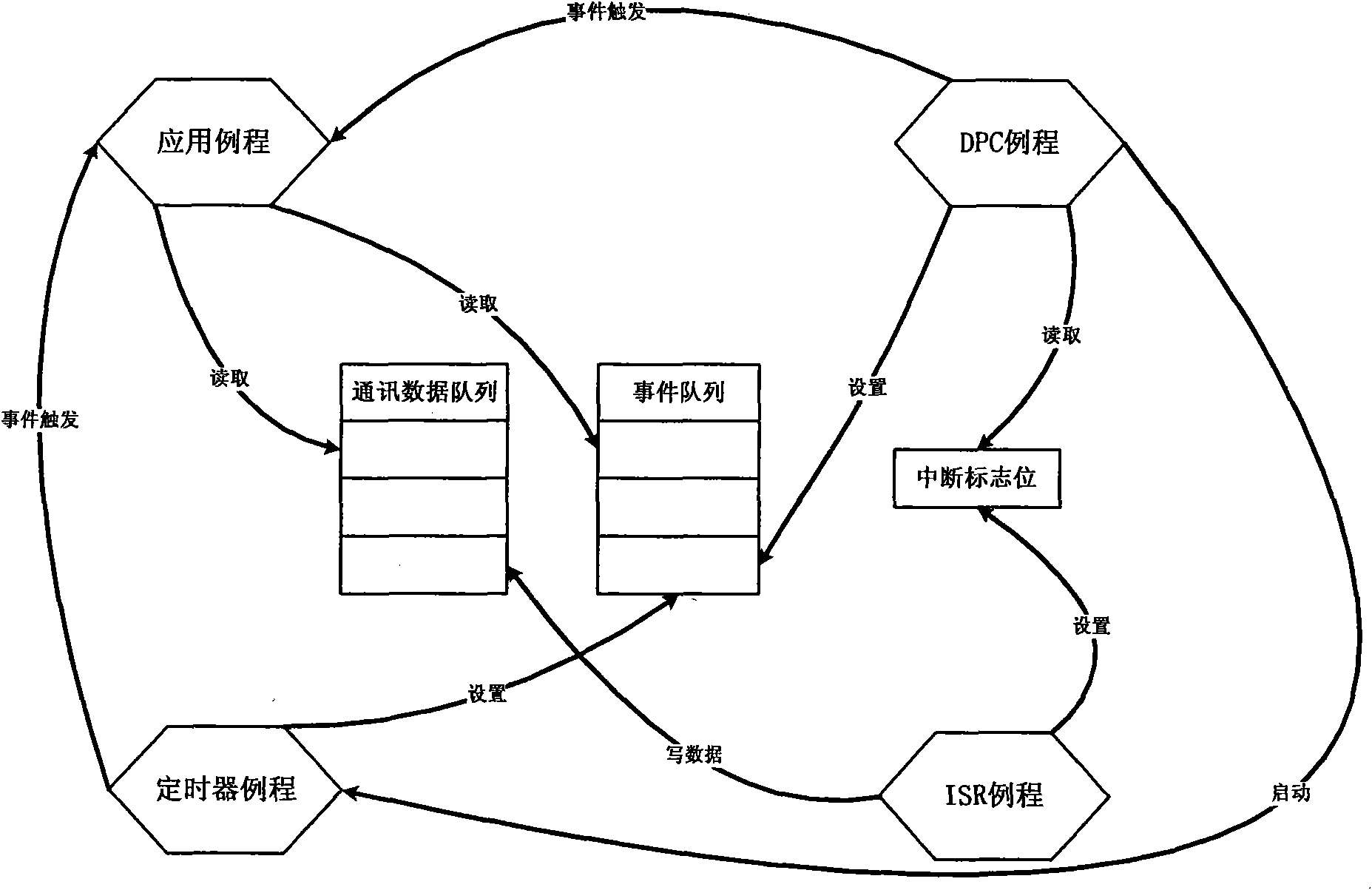

Data acquisition device and mobile terminal

ActiveCN104636287AImprove stabilitySave powerInput/output processes for data processingSignal onData acquisition

Provided are a data acquisition device and a mobile terminal. The data acquisition device is suitable for being connected with a touch screen to obtain touch signals on the touch screen, and comprises an interrupt module, a roll poling module and a storage module, wherein the storage module is suitable for storing interrupt flag bits which comprise a first state and a second state. The interrupt module is suitable for setting the interrupt flag bits at the first state after receiving interrupt signals and for obtaining the touch signals on the touch screen. The roll poling module is suitable for detecting the states of the interrupt flag bits in a preset interval time, and obtaining the touch signals on the touch screen when the interrupt flag bits are at the second state. According to the data acquisition device and the mobile terminal, the roll poling module and the interrupt flag bits are arranged additionally so that touch signals on the touch screen can be obtained through the roll poling module after the touch screen loses efficacy, and the stability of a system is improved.

Owner:宋易霄

Integrated-equipment driving system and application method thereof

ActiveCN101526929ALow costSimple designElectric digital data processingBus masteringApplication module

The invention discloses an integrated-equipment driving system and an application method thereof. A processing unit of the system comprises an interrupt processing module, an interrupt-latency calling module and an application module; an integrated driving unit of the system comprises a PCI controller, a communication-port controller and at least one bus controller of IO signals; the PCI controller is connected with the communication-port controller and every bus controller of input / output signals respectively, and is connected with the interrupt processing module through a Slave mode; the system is also provided with an interrupt register for saving interrupt marks; the interrupt processing module is used for receiving and managing the interrupt marks and communication data; the interrupt-latency calling module is used for managing events corresponding to the interrupt marks respectively; and the application module is used for processing the communication data and the events. The system is simple in software driving model, safe in interrupt processing and higher in efficiency, thereby increasing the reliability of system operation, reducing hardware cost and simplifying hardware design.

Owner:SHENZHEN MINDRAY BIO MEDICAL ELECTRONICS CO LTD +1

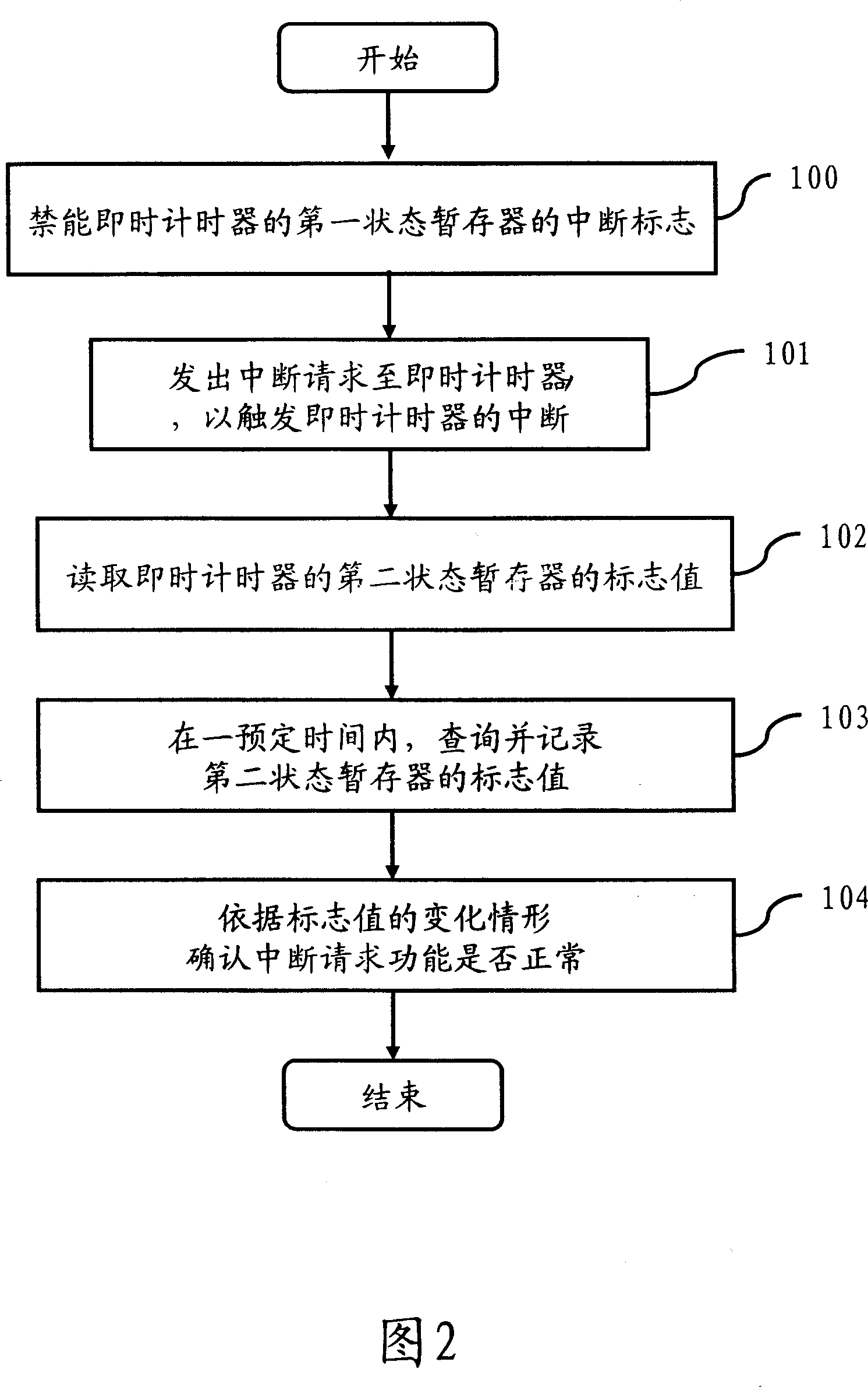

Method for interrupting request inspection of realtime timing service under Linux or Windows operation system

InactiveCN1983200ADoes not affect the processing mechanismShorten test timeError detection/correctionProcess mechanismGNU/Linux

A method for detecting demand timer interruption request under Linux or Window operation system includes energizing interruption mark of the first state working storage on demand timer to issue an interruption request to demand timer for triggering up interruption of demand timer, fetching mark value of the second state working storage on demand time and judging whether interruption request function of demand timer is normal or not according to said mark value.

Owner:INVENTEC CORP

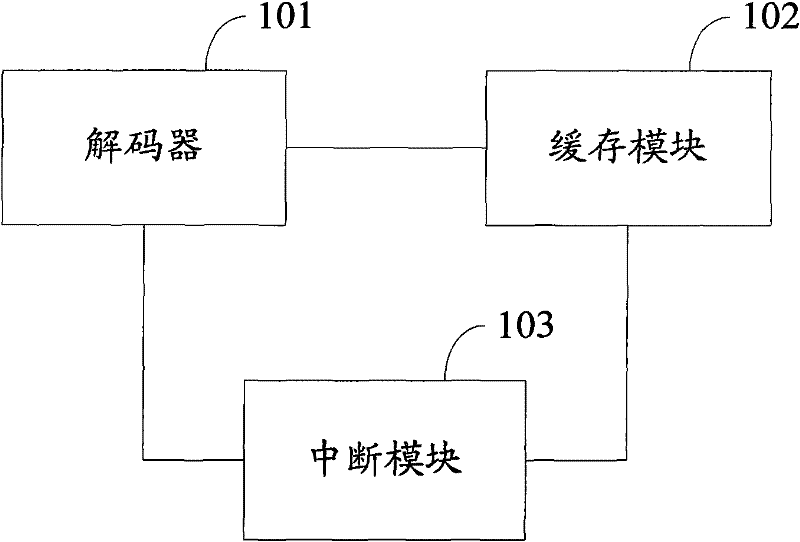

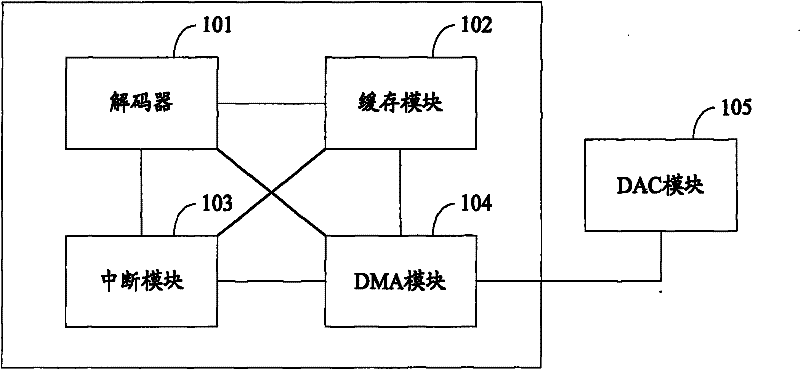

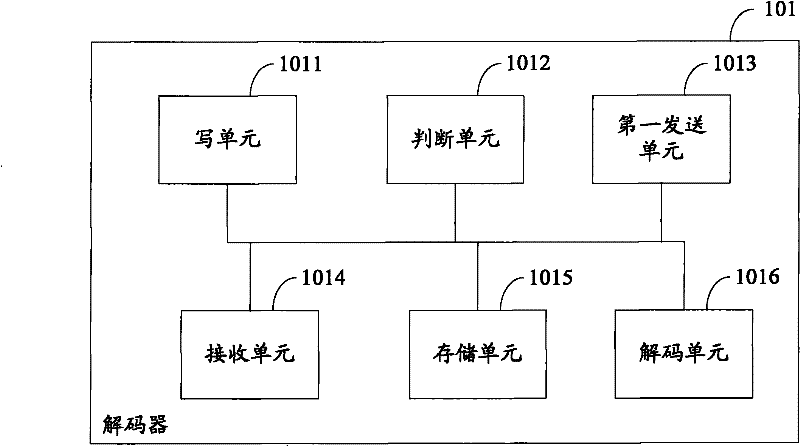

Method and device for transmitting audio data

ActiveCN102290050AReduce the burden onSave storage spaceSpeech analysisDirect memory accessComputer module

The invention discloses an audio data transmission method, which is used for carrying out audio data transmission without occupying an extra memory in order to save the memory space and reduce the burden of a CPU (central processing unit). The method includes the following steps that: a decoder writes audio data into a cache unit; when the cache unit is full, the decoder judges whether an interrupt flag exists; after audio transmission is interrupted, the decoder receives an interrupt flag transmitted by an interrupt module; and when a judgement result is yes, the decoder triggers DMA (Direct Memory Access) transmission. The invention also discloses a device used for carrying out the method.

Owner:VIMICRO ELECTRONICS CORP

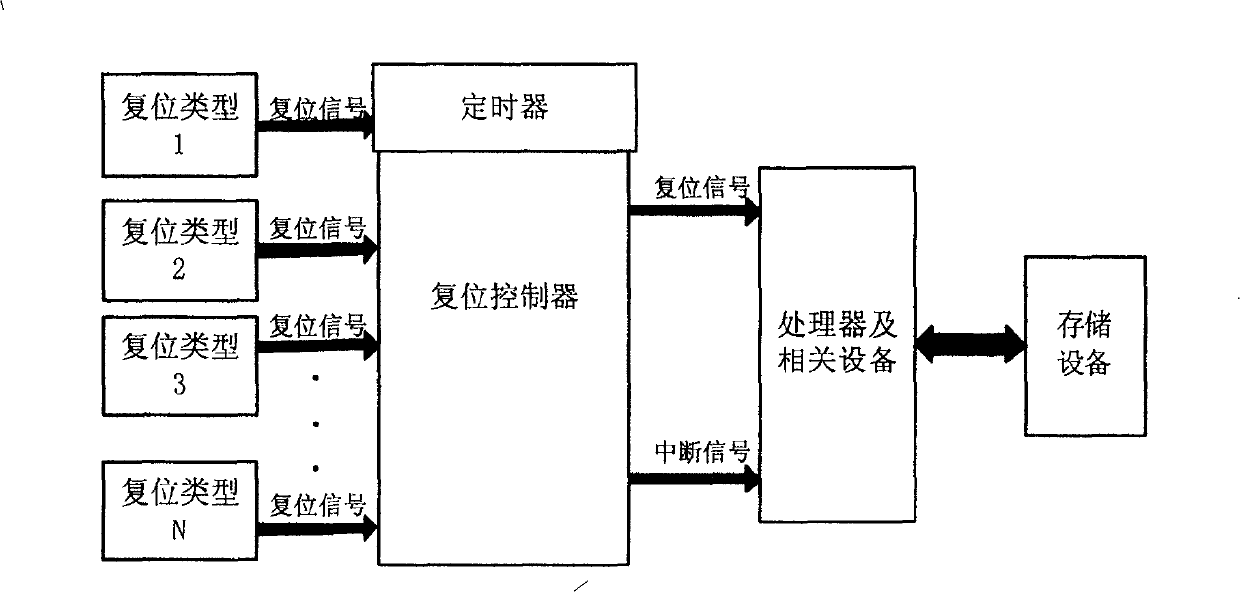

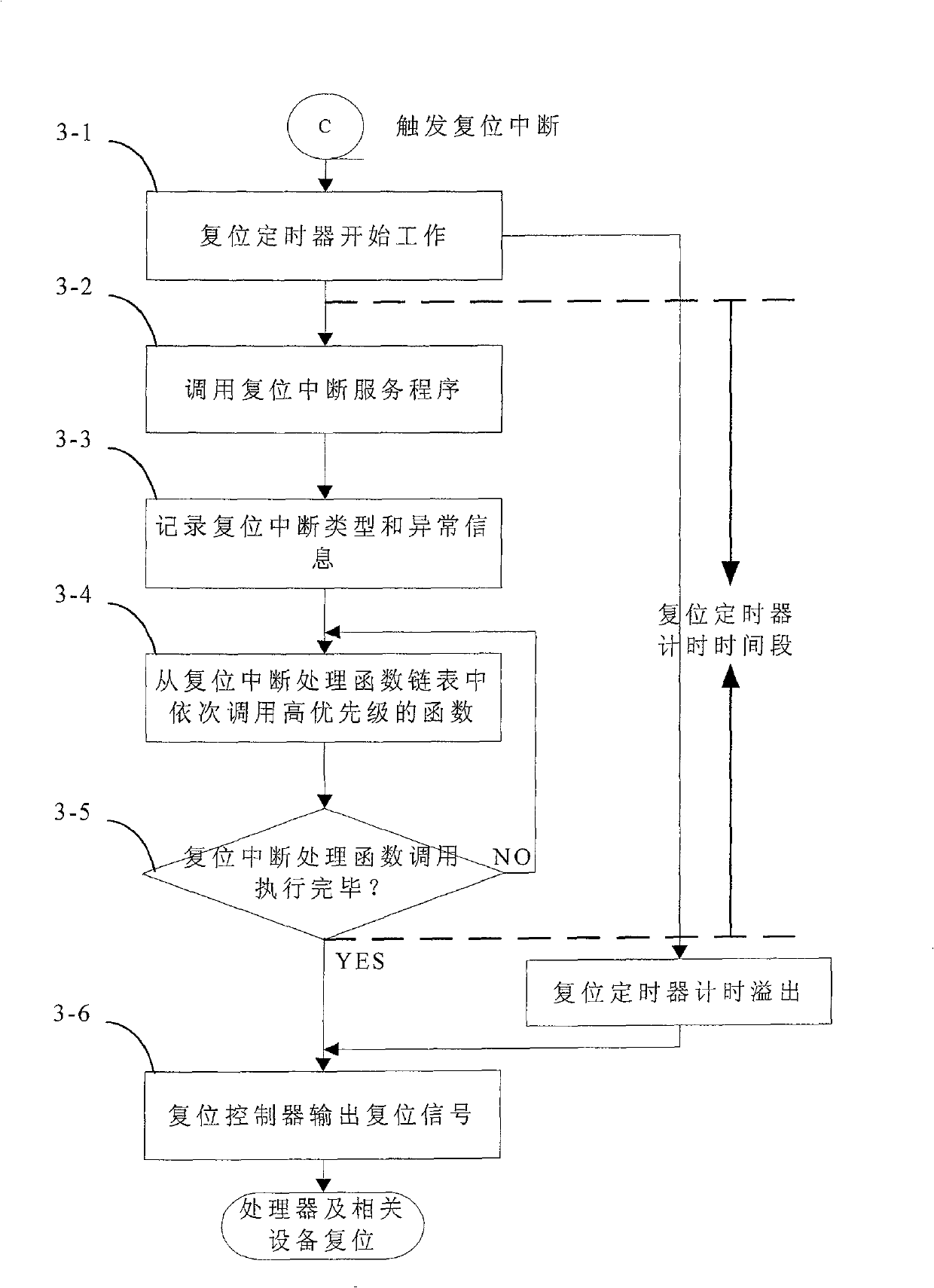

Combined type reset system processing method and device

InactiveCN100517177CFlexible handlingShorten the timeData resettingInterrupt handlerProtection system

Owner:ZTE CORP

An interrupt processing device and interrupt processing method

The embodiment of the invention provides an interrupt processing device and method. The interrupt processing device and method are applied to the technical field of interrupt control, can save hardware resources, and can reduce hardware cost. The interrupt processing device comprises a block random access memory, an interrupt flag bit write-in module, an interrupt flag bit output module, an interrupt flag bit read-out module and an interrupt flag bit removal module, wherein the block random access memory at least comprises m memory cell groups; the interrupt flag bit write-in module is used for writing interrupt flag bit information of any function module in the memory cell group corresponding to the function module; the interrupt flag bit output module is used for generating an interrupt event processing request and sending the interrupt event processing request to a processor; the interrupt flag bit read-out module is used for obtaining the interrupt flag bit information of the memory cell group corresponding to the function module and sending the interrupt flag bit information to the processor; the interrupt flag bit removal module is used for removing effective information corresponding to an interrupt source. The interrupt processing device is used for processing an interrupt event.

Owner:RUIJIE NETWORKS CO LTD

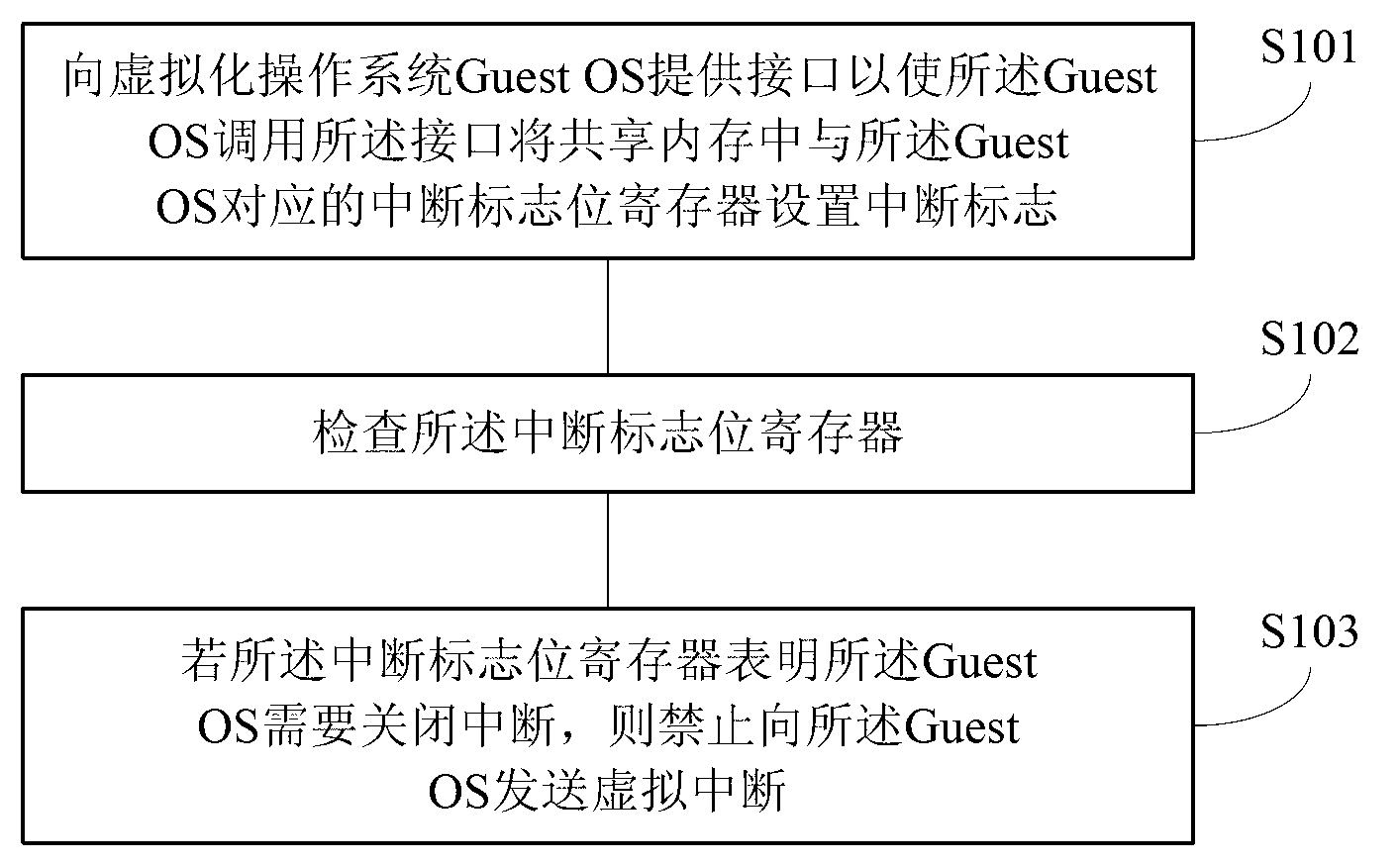

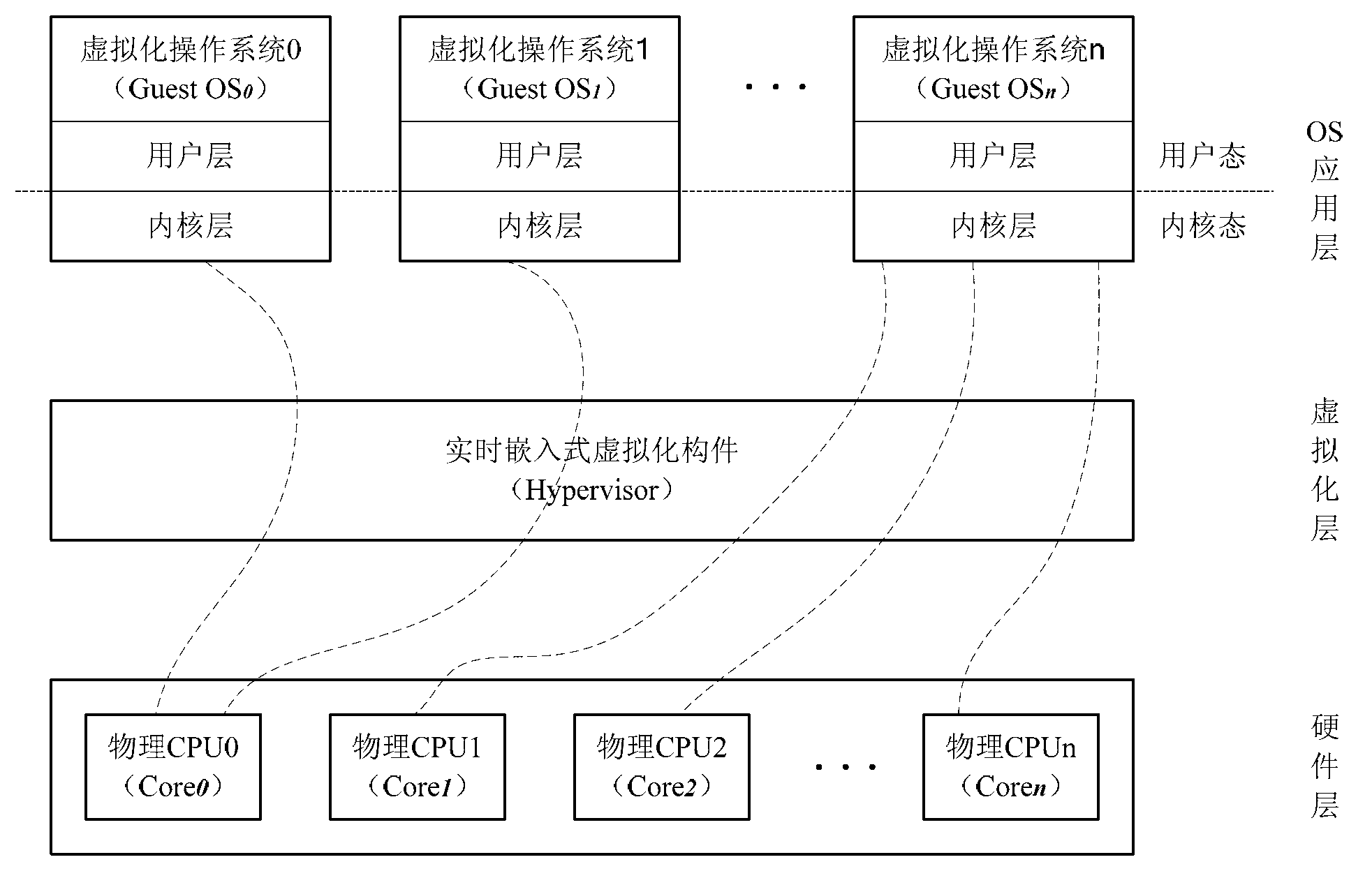

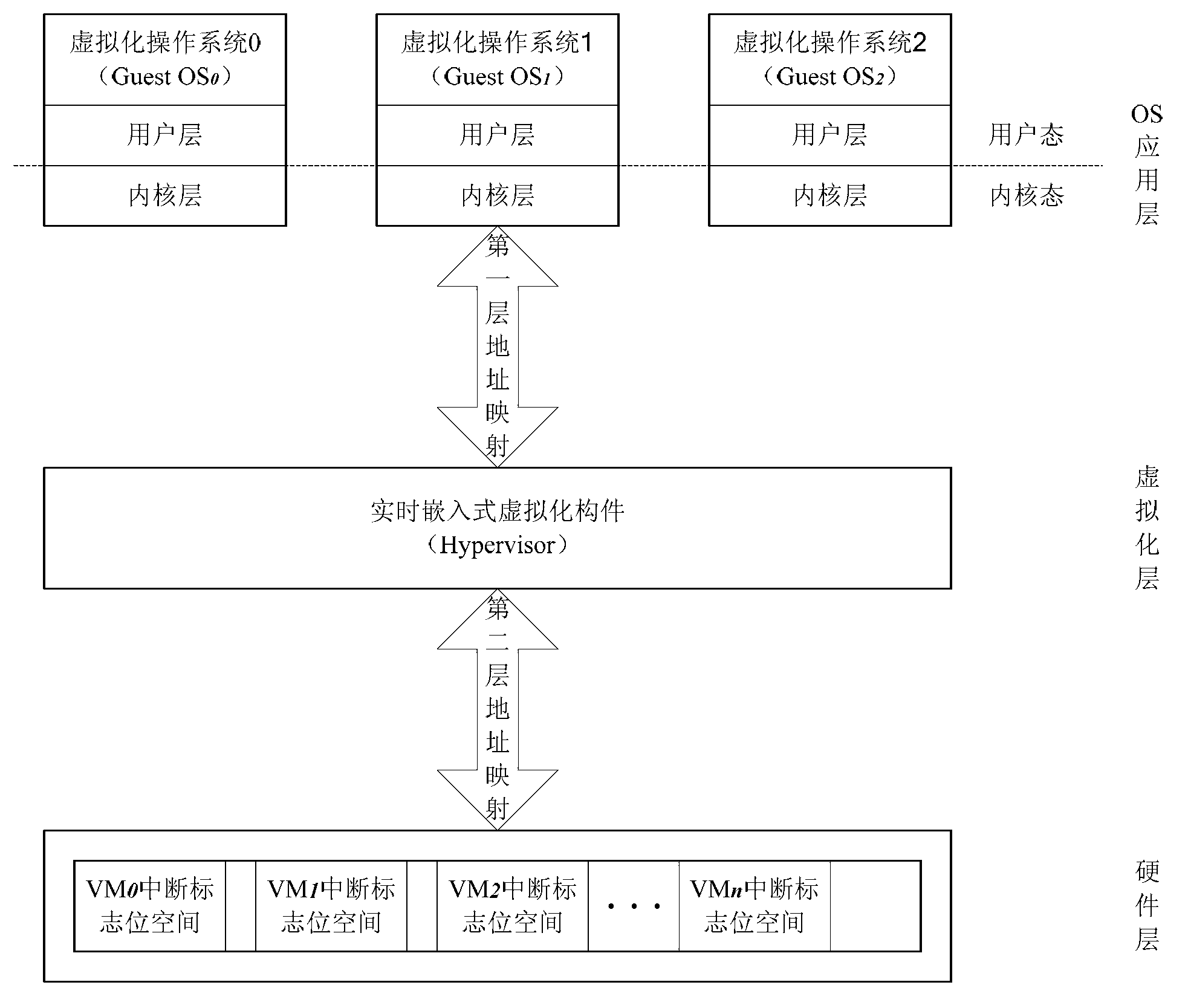

Method and device for closing interrupt in virtualization system

ActiveCN102799480AHigh speedImprove operational efficiencyProgram initiation/switchingSoftware simulation/interpretation/emulationOperational systemInterrupt flag

The invention provides a method and device for closing interrupt in a virtualization system, which aim to better support the open / close interrupt of a Guest OS (Operating System) and reduce the influence on system operating efficiency. The method comprises the following steps of: offering an interface to the Guest OS of the virtualization operating system so as to allow the Guest OS to call the interface to set an interrupt flag for an interrupt flag register corresponding to the Guest OS in shared memory; checking the interrupt flag register; and avoiding sending virtual interrupt to the Guest OS if the interrupt flag register indicates that the Guest OS requires interrupt closing. The method provided by the invention does not rely on co-compiling of Hypervisor and the Guest OS, the Hypervisor has no need of sharing code sections with the Guest OS, and the access to the shared memory is realized through a virtual address, so that the interrupt closing / opening is quick, and the system operating efficiency is high.

Owner:NANTONG HANGDA ELECTRONICS TECH

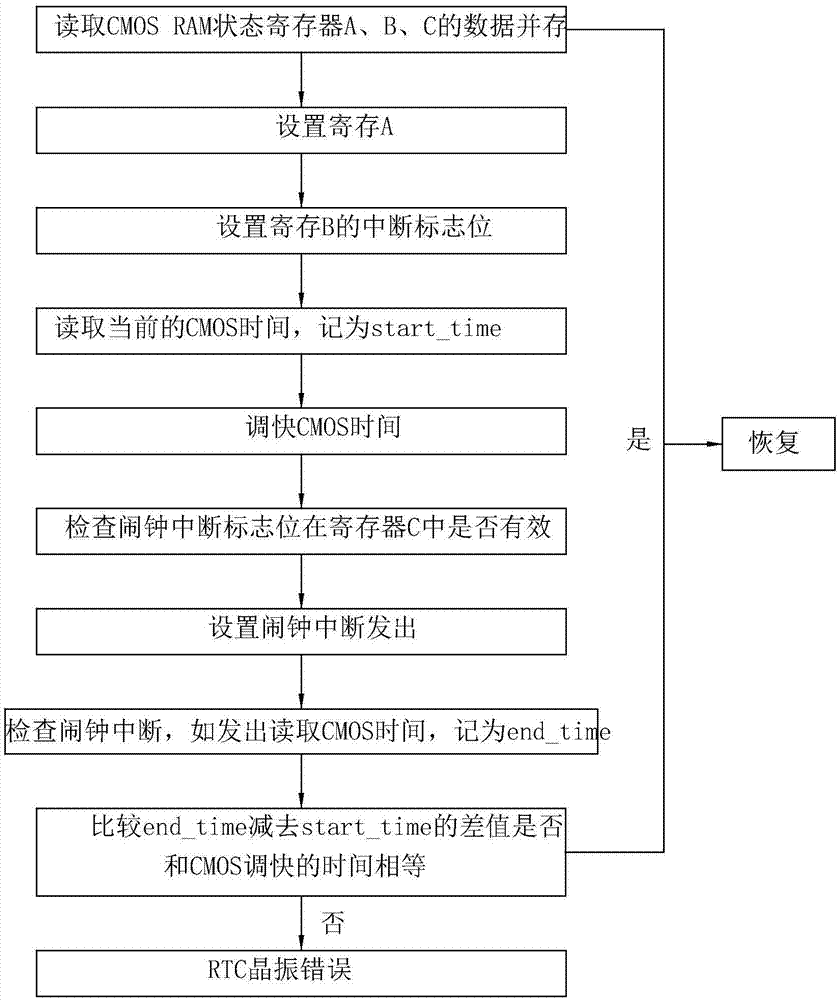

RTC crystal oscillator detection method

ActiveCN107219395AEffective detectionEffective identificationFrequency measurement arrangementCMOSProcessor register

The invention discloses an RTC crystal oscillator detection method. The method comprises steps that setting of state registers A, B and C is read, and the read data is saved; interruption flag bits of the register A and the register B are set, so interruption of an alarm clock is made to be valid; the present CMOS time is read and is marked as start_time; the CMOS time is set one second faster; whether an interruption flag bit of the alarm clock is valid in the register C is checked; interruption of the alarm clock is set and emitted; whether interruption of the alarm clock is emitted is checked, if yes, the CMOS time is read and is marked as end_time; if (end_time)-(start_time) is not equal to 1, shock of the RTC crystal oscillator is proved to be in a fault, otherwise, shock of the RTC crystal oscillator is qualified. The method is advantaged in that the method is convenient for operation, a problem that frequency of the crystal oscillator drifts out of the scope can be effectively detected and identified, material management cost is reduced, and a test coverage rate is improved.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

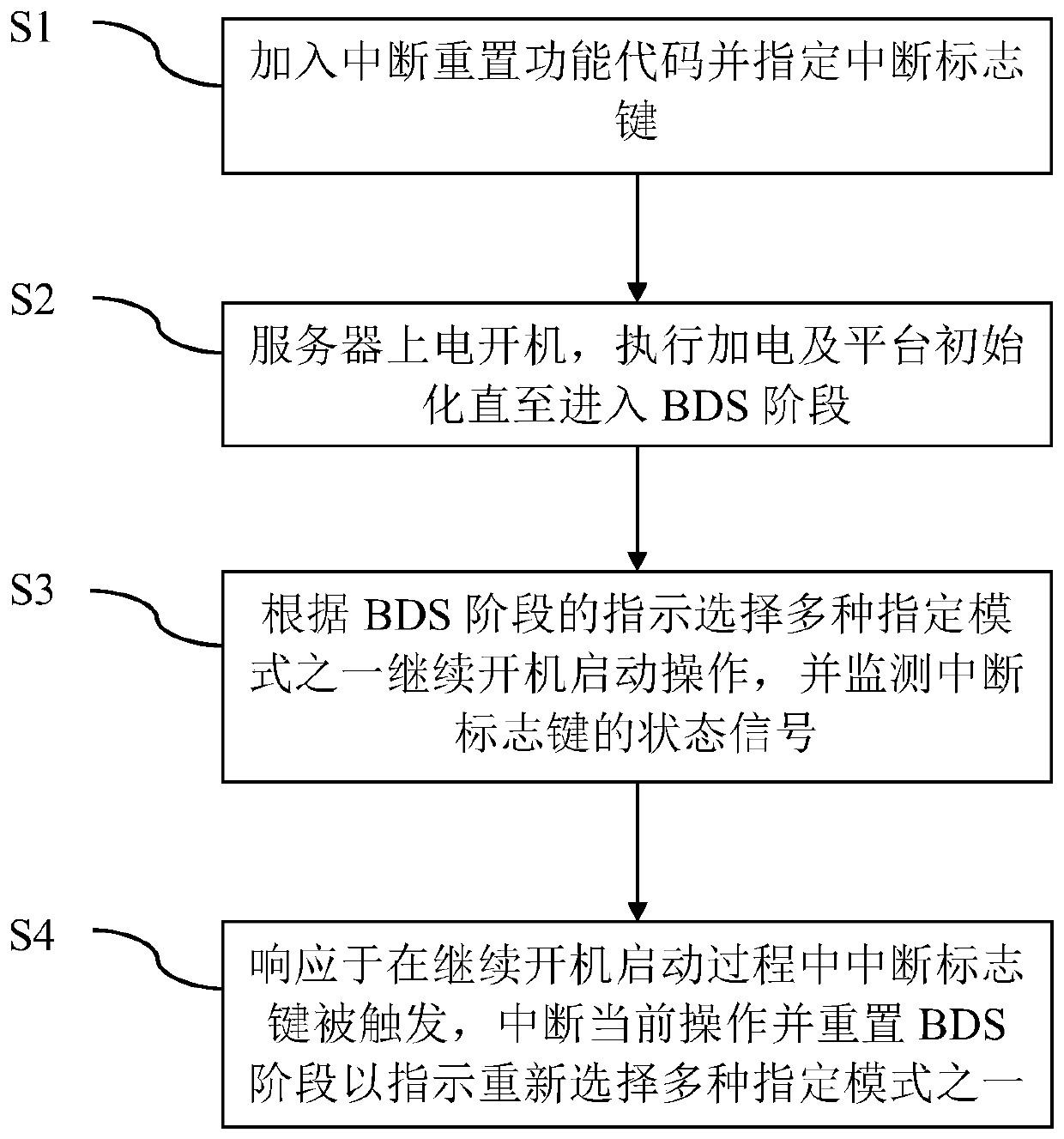

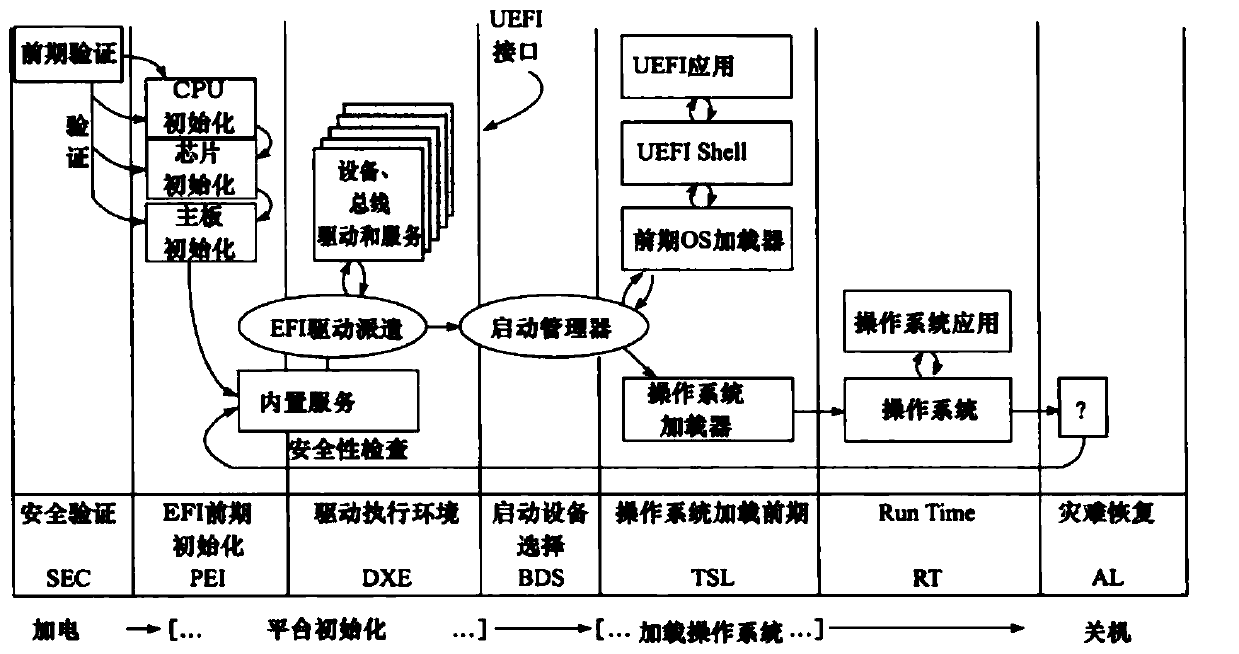

Method and device for optimizing UEFI to guide startup

The invention relates to a method and a device for optimizing a UEFI to guide startup. The method comprises: an interrupt reset function instruction is added, and an interrupt flag key is specified;the server is powered on and started, and power-on and platform initialization are executed until a BDS stage is entered; one of a plurality of specified modes is selected to continue the startup operation according to the indication of the BDS stage, and the state signal of the interrupt flag key is monitored; and, in response to the interrupt flag key being triggered during continued booting, the current operation is interrupted and the BDS stage is reset to indicate reselection of one of a plurality of specified modes. According to the invention, an existing UEFI boot startup process is optimized; under the condition that the mode needs to be reselected, restarting is not needed, and the current operation can be interrupted and the BDS stage reselection mode can be returned only by triggering a pre-assigned interruption flag key, so the flexibility and operability of server starting are guaranteed, and the efficiency of server starting is improved.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

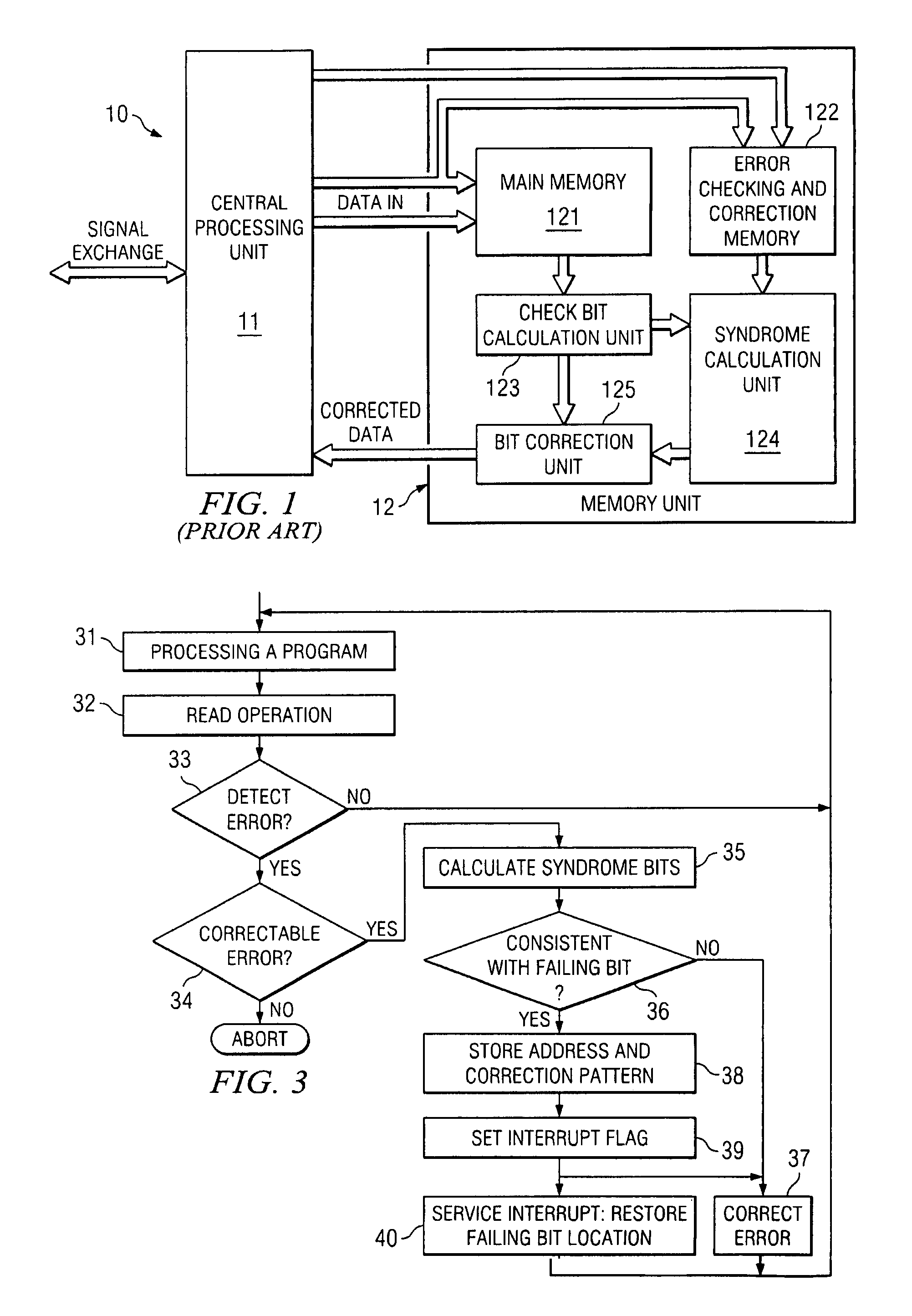

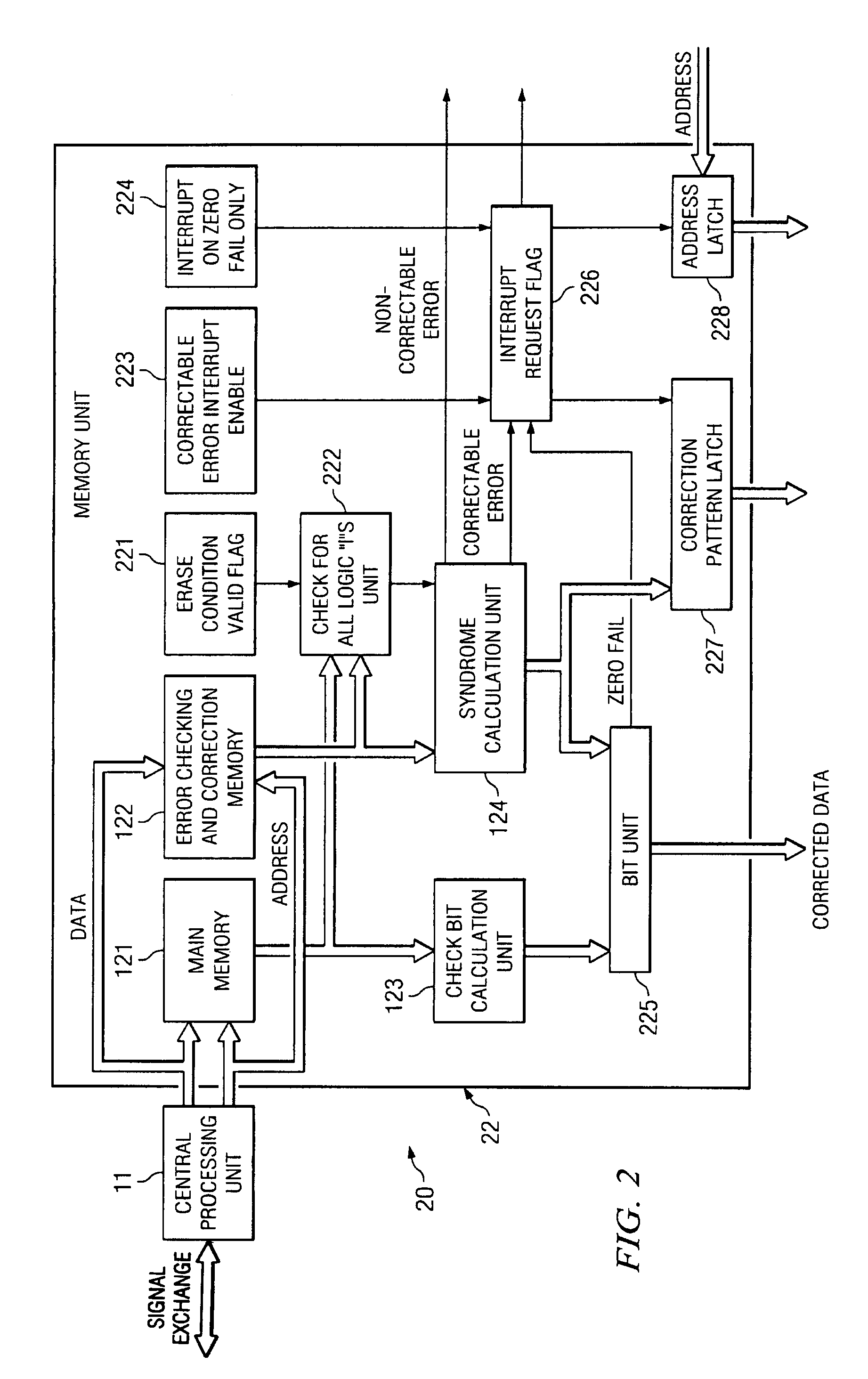

Apparatus and method for responding to data retention loss in a non-volatile memory unit using error checking and correction techniques

ActiveUS7496822B2Positioning failureError preventionTransmission systemsError checkingCorrection technique

In a non-volatile memory unit such as a flash memory unit, the degradation of charge can result in an error during a read operation. By using the error checking and correction techniques, a determination can be made whether a detected error can be corrected and, if correctable, is the consistent with charge degradation at that bit position displaying the error. When a correctable error is detected, the signal group address and the correction pattern are stored and an interrupt request flag applied to the central processing unit. When the interrupt flag is processed, the central processing unit, using the signal group address and the correction pattern, restores the charge of the bit position in the memory unit. In this manner, further read operations involving the restored bit position will not repeat the corrected error.

Owner:TEXAS INSTR INC

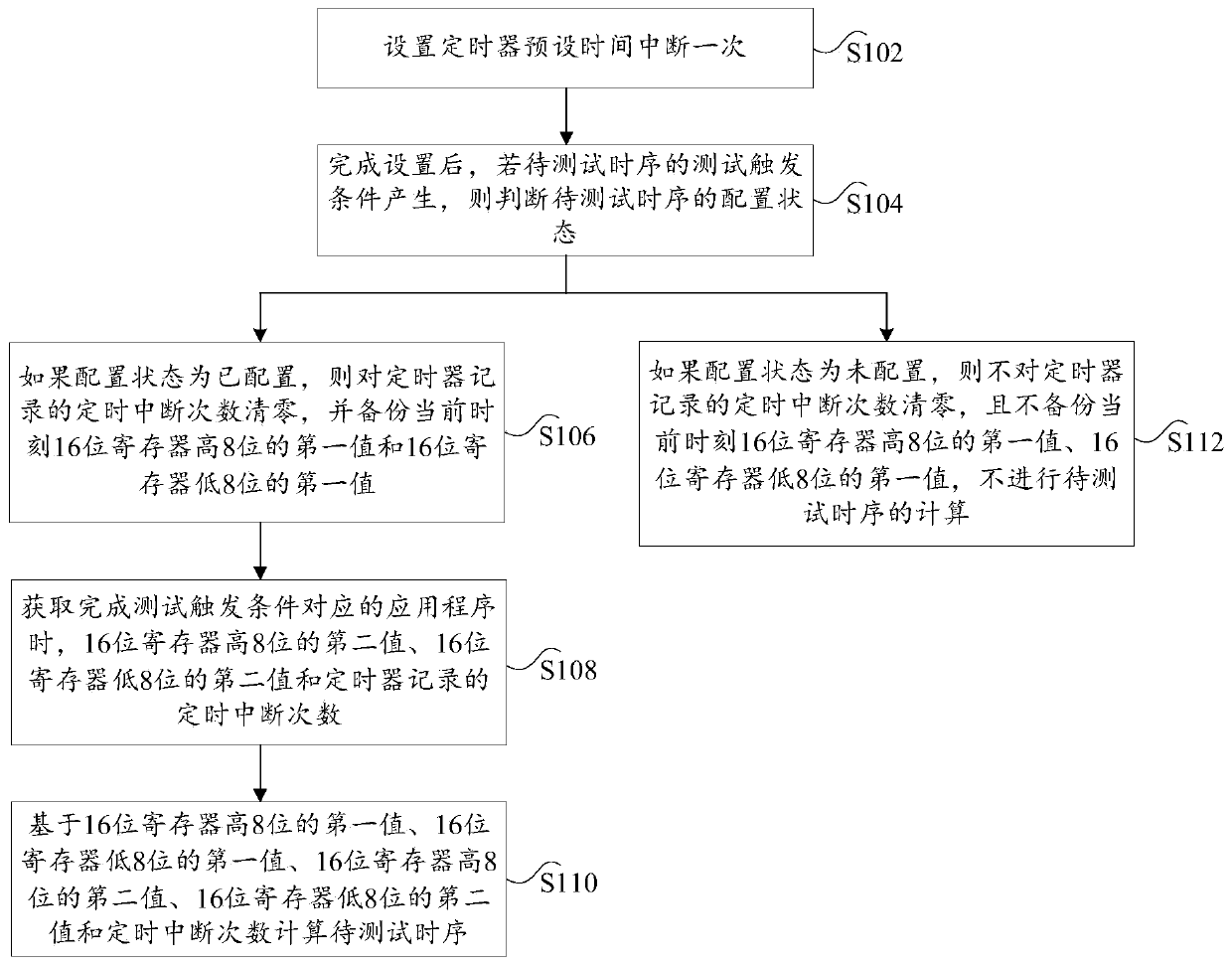

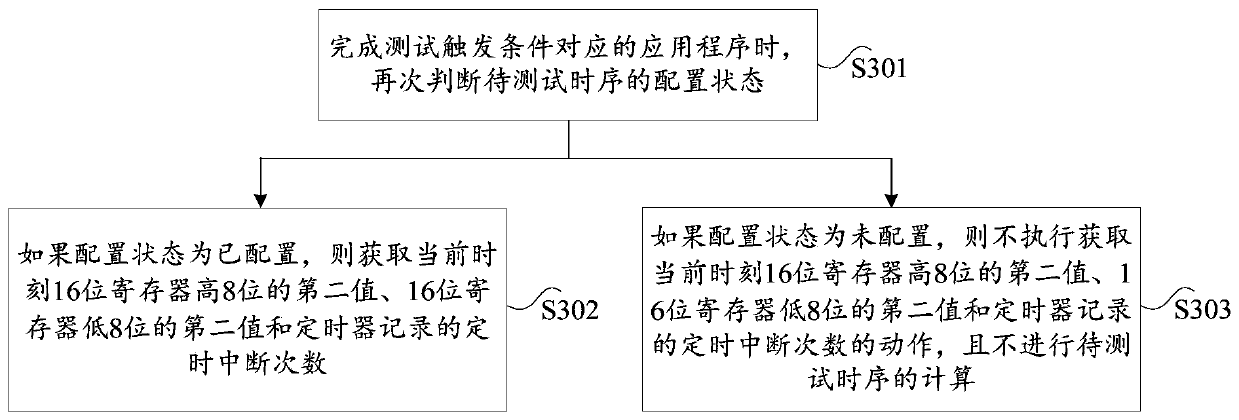

Time sequence measurement method and device

ActiveCN110489292AImprove test efficiencyEasy to operateDetecting faulty computer hardwareEnergy efficient computingTest efficiencyProcessor register

The invention provides a time sequence measurement method and device. The time sequence measurement method comprises the following steps: setting a timer to be interrupted once at preset time; if thetest triggering condition of the to-be-tested time sequence is generated, judging the configuration state of the to-be-tested time sequence; if the to-be-tested time sequence is configured, resettingthe interrupt flag of the timer, resetting the timing interrupt times recorded by the timer, and backing up a first value of a 16-bit register with 8 higher bits and a first value of a 16-bit registerwith 8 lower bits at the current moment; when the application program corresponding to the test triggering condition is completed, obtaining a second value of the 16-bit register with 8 higher bits,a second value of the 16-bit register with 8 lower bits and the timing interruption times recorded by the timer; and calculating the to-be-tested time sequence based on the values. The purpose of automatically measuring the to-be-tested time sequence can be achieved through software, operation is easy, and the testing efficiency is high.

Owner:DONGGUAN MENTECH OPTICAL & MAGNETIC CO LTD

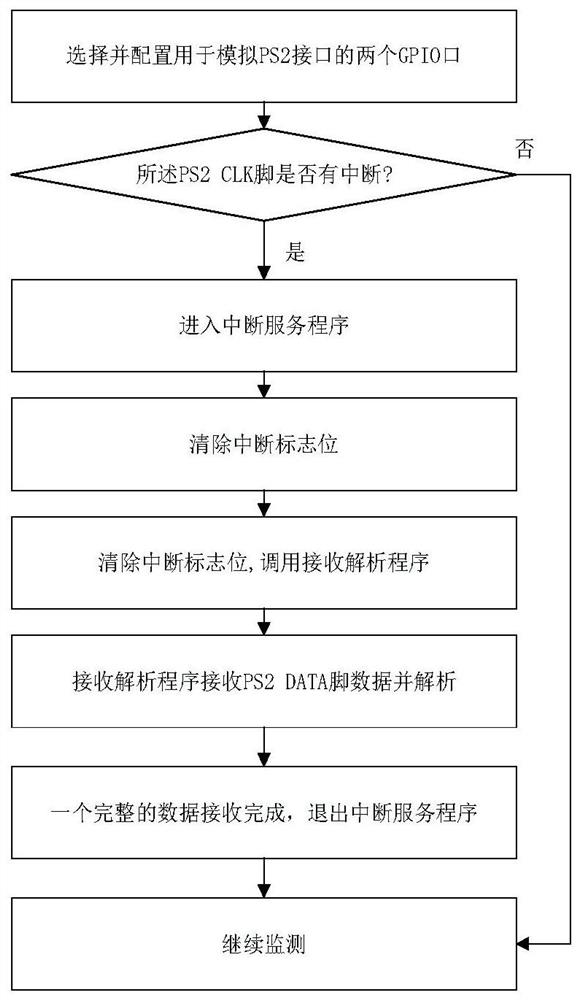

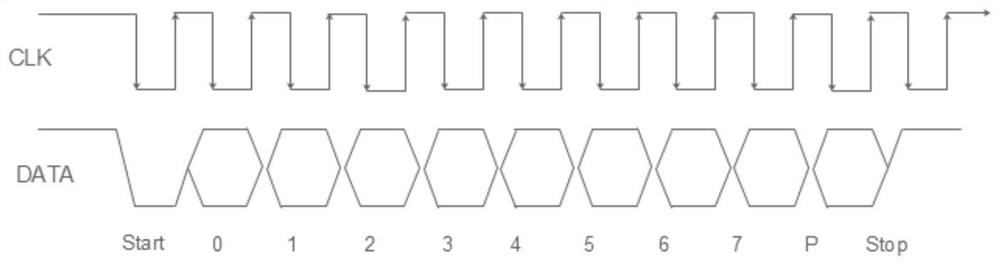

Method for simulating PS2 interface through GPIO port of single-chip microcomputer, single-chip microcomputer and system

PendingCN112835821ALow costImprove compatibilitySoftware testing/debuggingComplete dataComputer architecture

The invention provides a method for simulating a PS2 interface through a GPIO port of a single-chip microcomputer, the single-chip microcomputer and a system, and belongs to the field of communication. The method for simulating the PS2 interface through the GPIO port of the single-chip microcomputer comprises the following steps that two GPIO ports used for configuring and simulating the PS2 interface are selected and configured; an interrupt processing module of the single chip microcomputer judges whether the PS2 CLK pin is interrupted or not, if not, monitoring continues, and if yes, the next step is executed, and an interrupt service program is entered; the interrupt service program clears an interrupt flag bit, and then calls a receiving and analyzing program to receive and analyze PS2 DATA pin data; and after a complete data is received, quitting the interrupt service program, and continuing monitoring. The invention also provides a single-chip microcomputer and a system for realizing the method. The method has the beneficial effects that the function of the hardware PS2 interface is realized by a pure software method, and the cost is low.

Owner:深圳市国科亿道科技有限公司

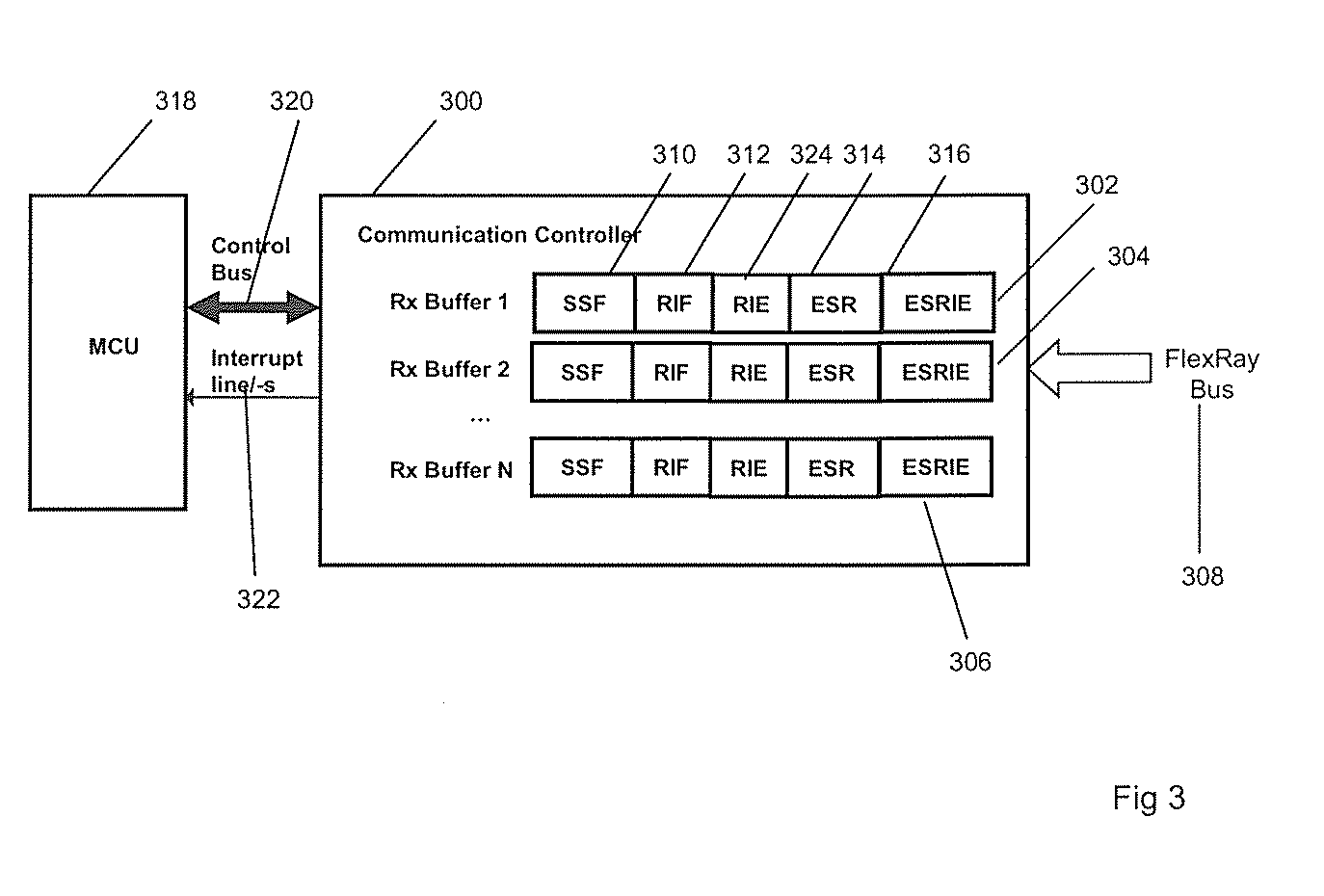

Buffer management

ActiveUS20100002658A1Error detection/correctionTime-division multiplexComputer scienceInterrupt flag

A receive buffer of the type that receives information at regular time slots and is required to indicate any status changes to a micro control unit (MCU), the receive buffer including: a slot status field for storing slot status information at each timeslot for the receive buffer; a receive interrupt flag for sending a signal to the MCU for indicating a change of the slot status field on receipt of the information at each timeslot; characterised in that the receive buffer also includes: an empty slot recognition bit for determining if an empty slot is received and generating an indicator thereof, wherein the indicator is passed to the MCU instead of the useless empty slot status field.

Owner:NXP USA INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com