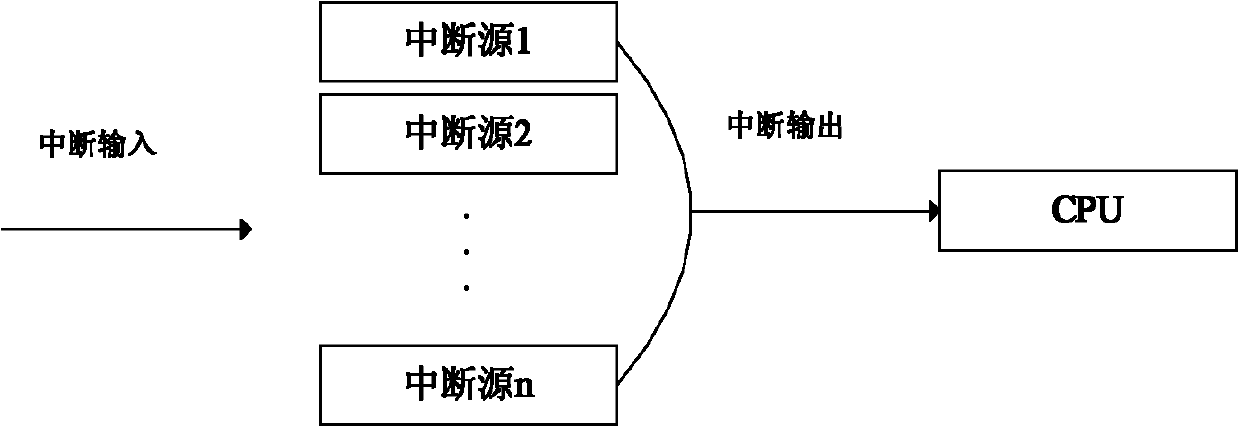

Quick interrupt graded processing device and method

A hierarchical processing and fast technology, applied in the field of data communication, can solve the problems of CPU response speed requirements, increased CPU occupancy, excessive time consumption, etc., to achieve fast positioning, speed up processing time, and save CPU occupancy.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The present invention will be further elaborated below according to the drawings and specific embodiments.

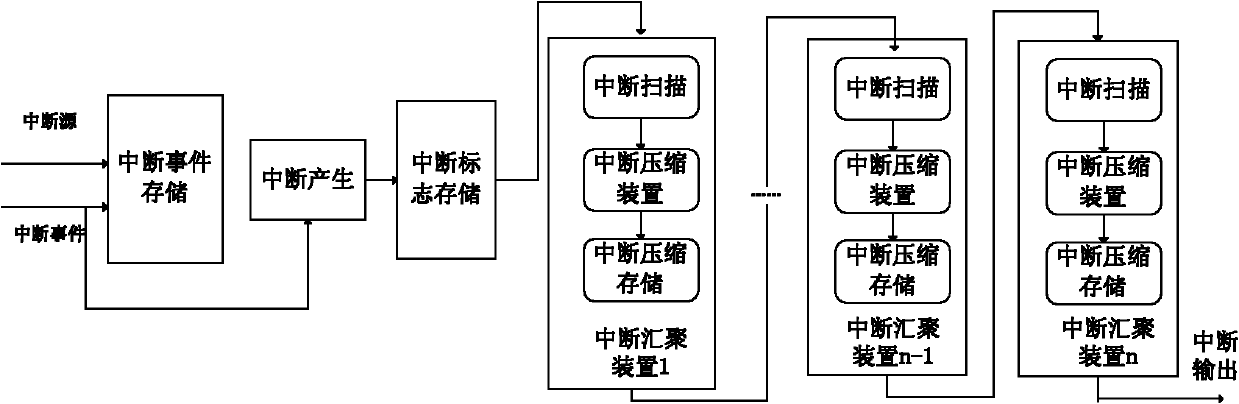

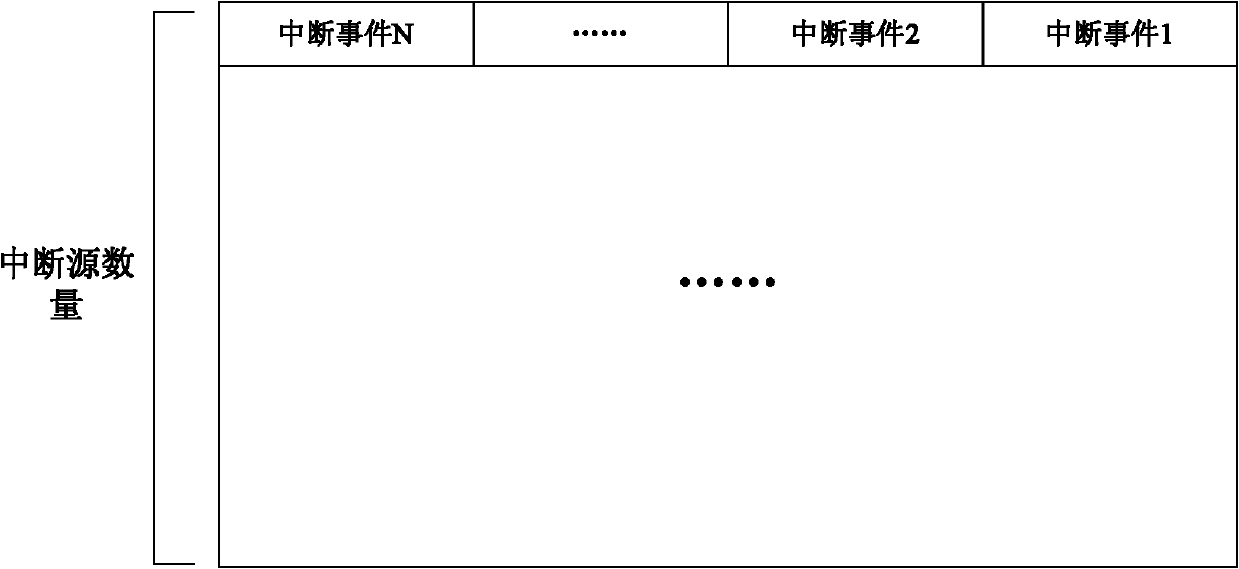

[0041] figure 2 It is an overall structure diagram of the embodiment of the present invention, which includes: an interrupt event storage device, which is used to store the interrupt event generated by the interrupt source; an interrupt generating device, which is used to convert the interrupt event of the same interrupt source into a 1-bit interrupt flag; the interrupt flag The storage device is used for storing all generated interrupt flags; and the interrupt aggregation device is used for compressing and storing the interrupt flags in stages, and handing over the interrupt flags to the CPU for processing.

[0042] The interrupt aggregation device is composed of N levels of cascading, and the structure of each level of interrupt aggregation device is the same. Considering the bit width of CPU read and write data, all interrupts will eventually converge into a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com