Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

104 results about "Input output controller" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Input/output controller. Alternatively referred to as an input/output interface, IOC, or PIOC for Peripheral input/output controller. The input/output controller is a device that interfaces between an input or output device and the computer or hardware device. The input/output controller on a computer is commonly located on the motherboard.

Integrated input/output controller

An integrated I / O controller in an integrated circuit is provided for centralized data management. The integrated circuit includes a host interface, a disk interface, and a mapping controller implemented in hardware to speed data processing and provide fault tolerance as exemplified with RAID configurations. The mapping controller provides block mapping across a plurality of peripherals or disk drives in a disk array. The integrated I / O controller can be utilized in storage area network systems and network area storage systems as well as other networking systems or devices.

Owner:ADAPTEC

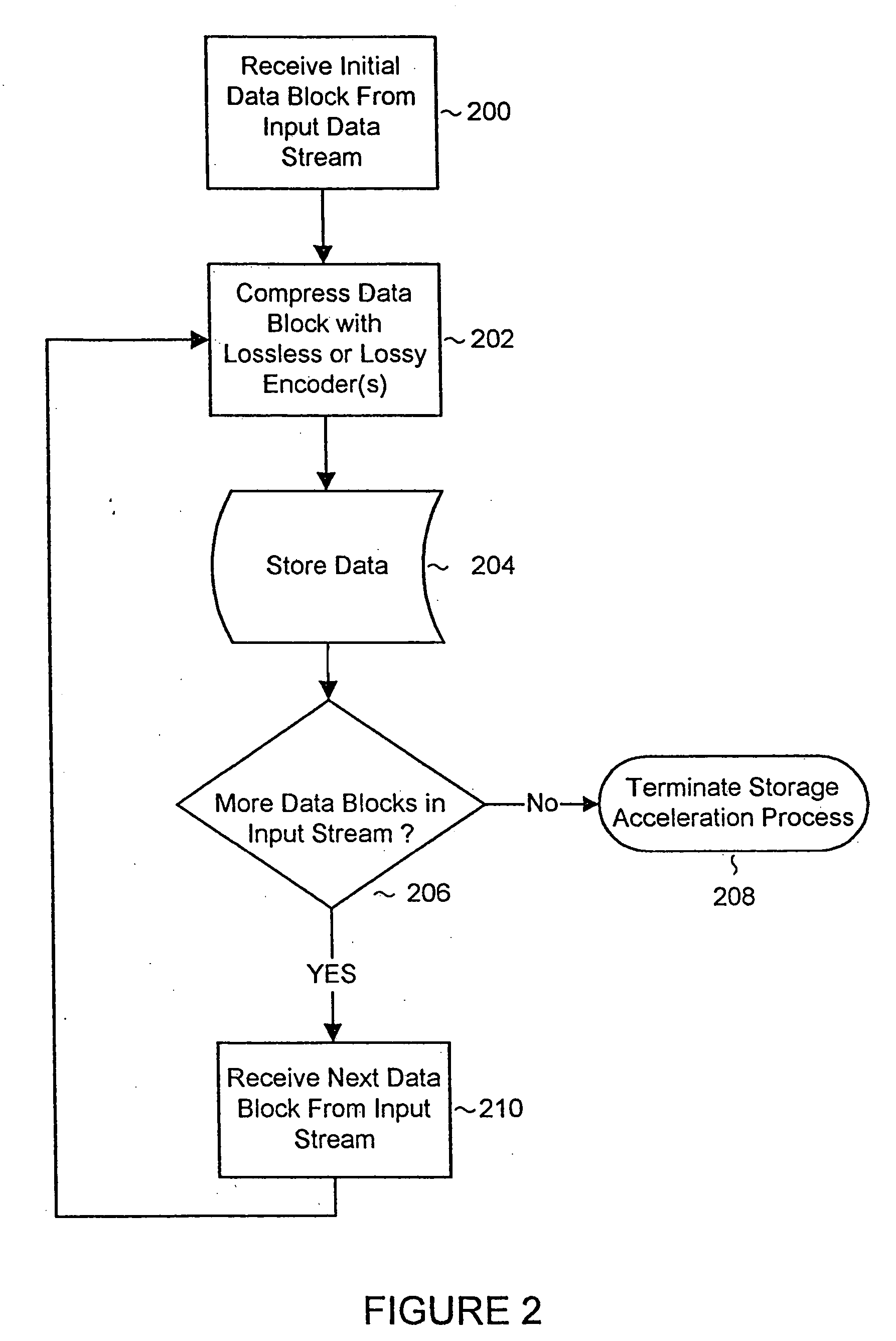

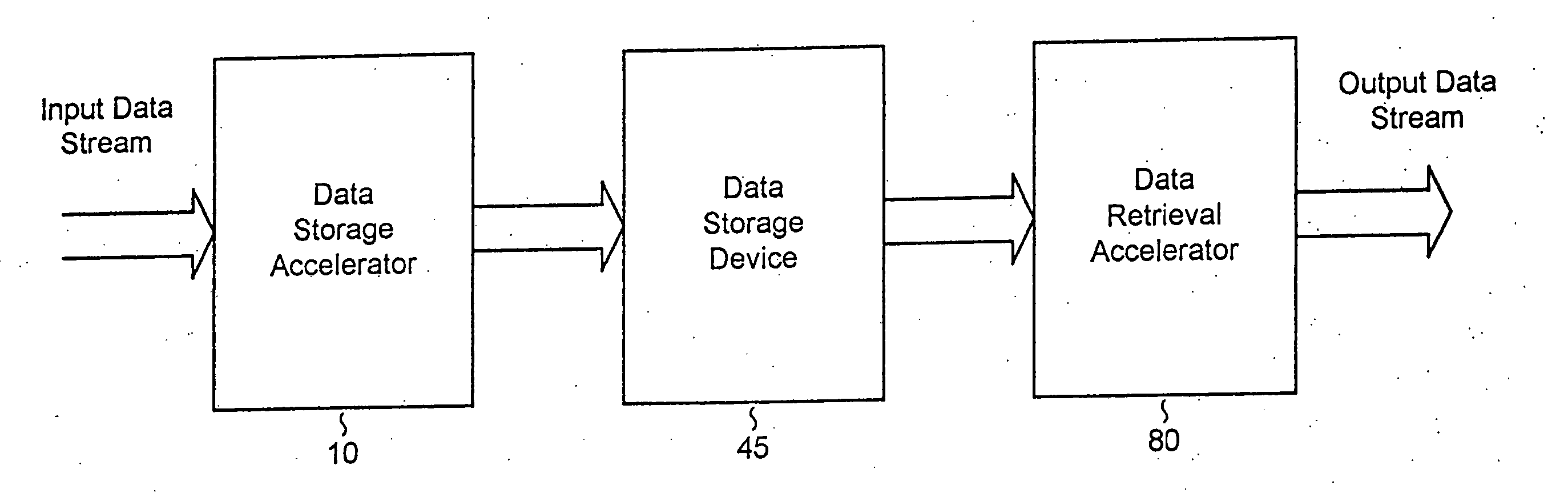

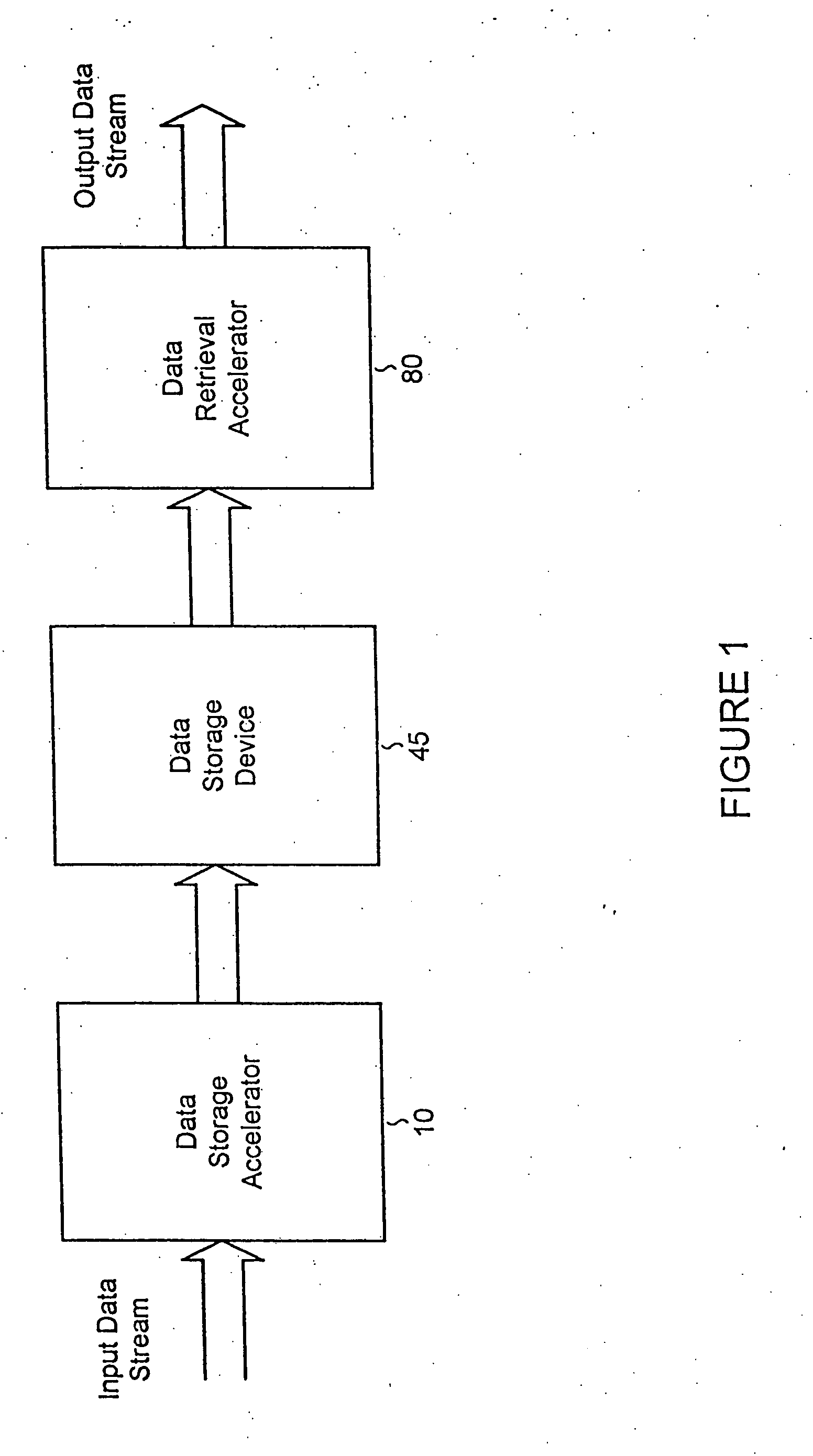

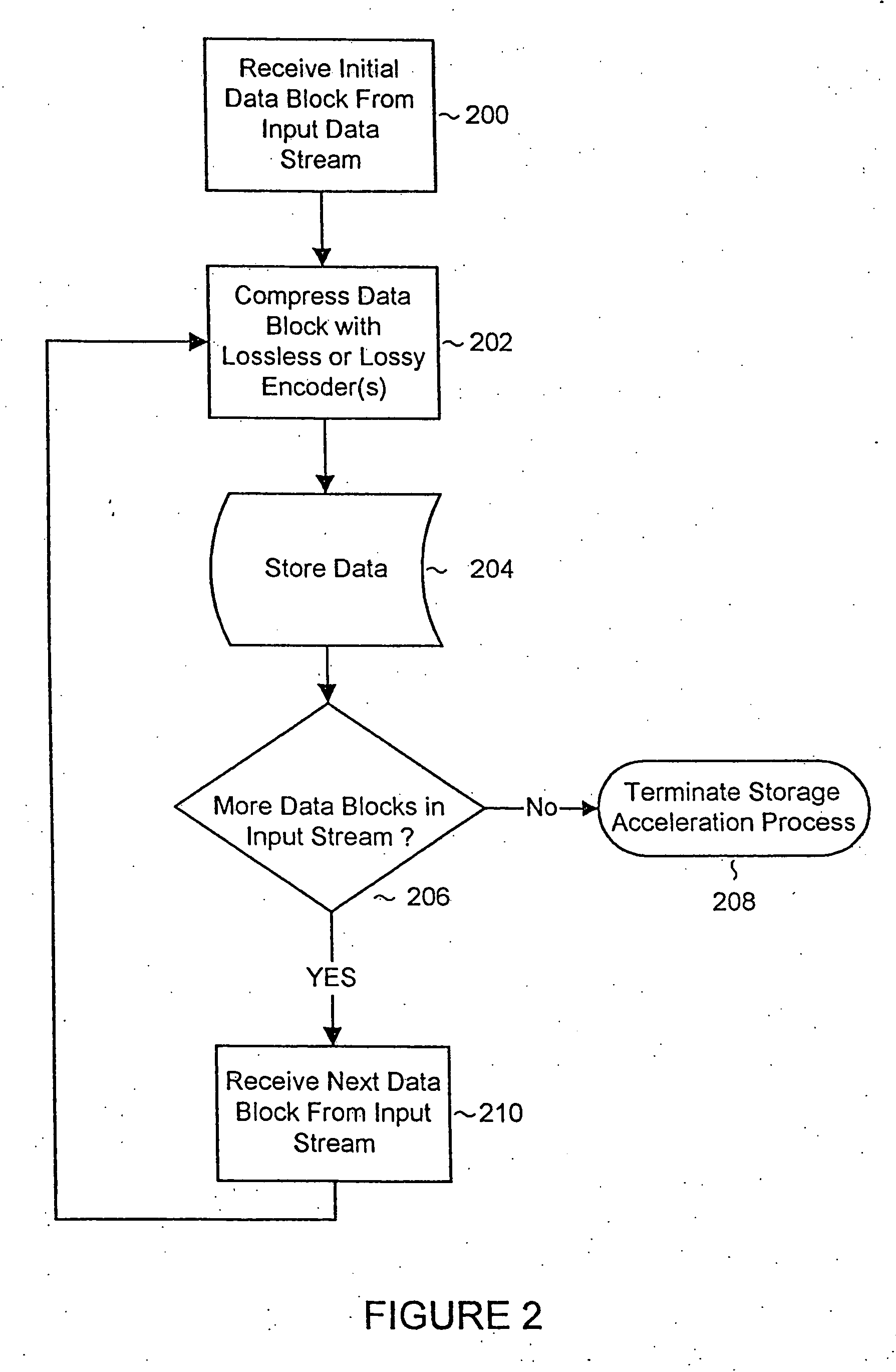

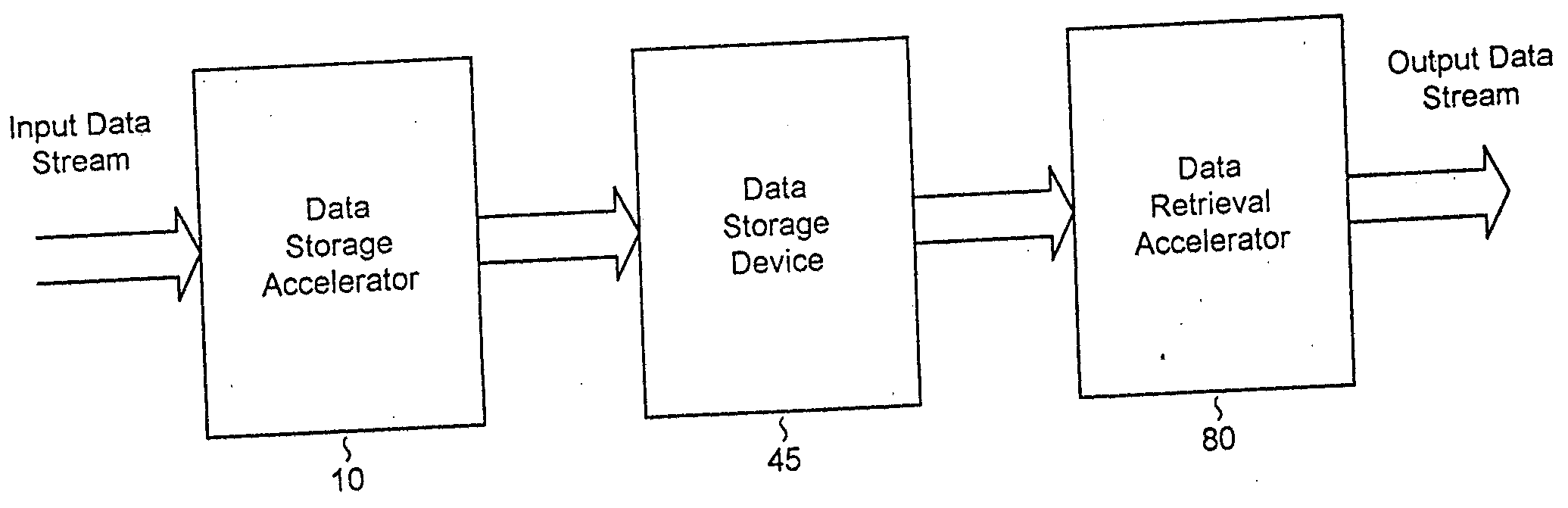

System and methods for accelerated data storage and retrieval

InactiveUS20060015650A1Shorten the timeIncrease data storageTelevision system detailsInput/output to record carriersData compressionData stream

Systems and methods for providing accelerated data storage and retrieval utilizing lossless and / or lossy data compression and decompression. A data storage accelerator includes one or a plurality of high speed data compression encoders that are configured to simultaneously or sequentially losslessly or lossy compress data at a rate equivalent to or faster than the transmission rate of an input data stream. The compressed data is subsequently stored in a target memory or other storage device whose input data storage bandwidth is lower than the original input data stream bandwidth. Similarly, a data retrieval accelerator includes one or a plurality of high speed data decompression decoders that are configured to simultaneously or sequentially losslessly or lossy decompress data at a rate equivalent to or faster than the input data stream from the target memory or storage device. The decompressed data is then output at rate data that is greater than the output rate from the target memory or data storage device. The data storage and retrieval accelerator method and system may employed: in a disk storage adapter to reduce the time required to store and retrieve data from computer to disk; in conjunction with random access memory to reduce the time required to store and retrieve data from random access memory; in a display controller to reduce the time required to send display data to the display controller or processor; and / or in an input / output controller to reduce the time required to store, retrieve, or transmit data.

Owner:FALLON JAMES J

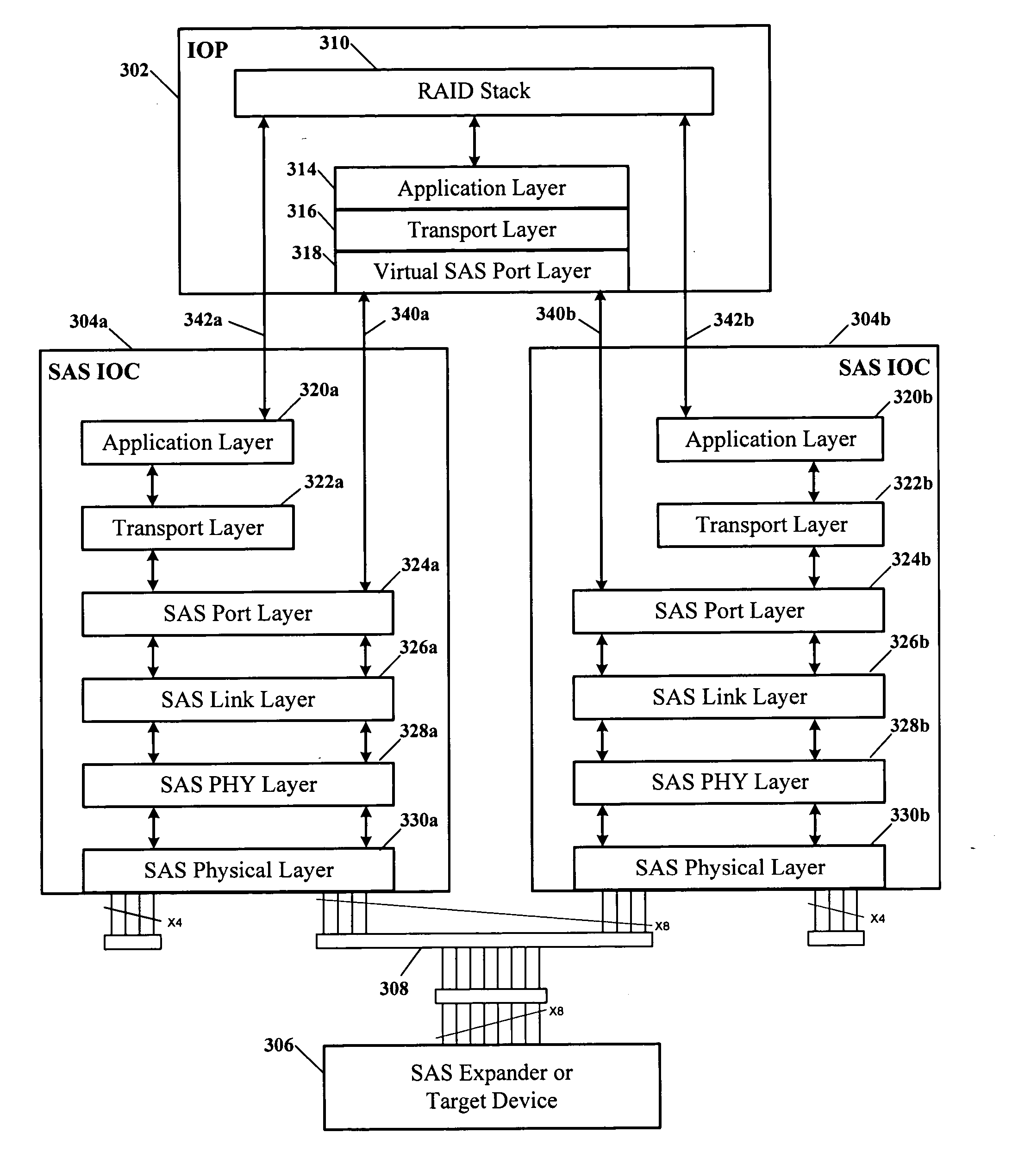

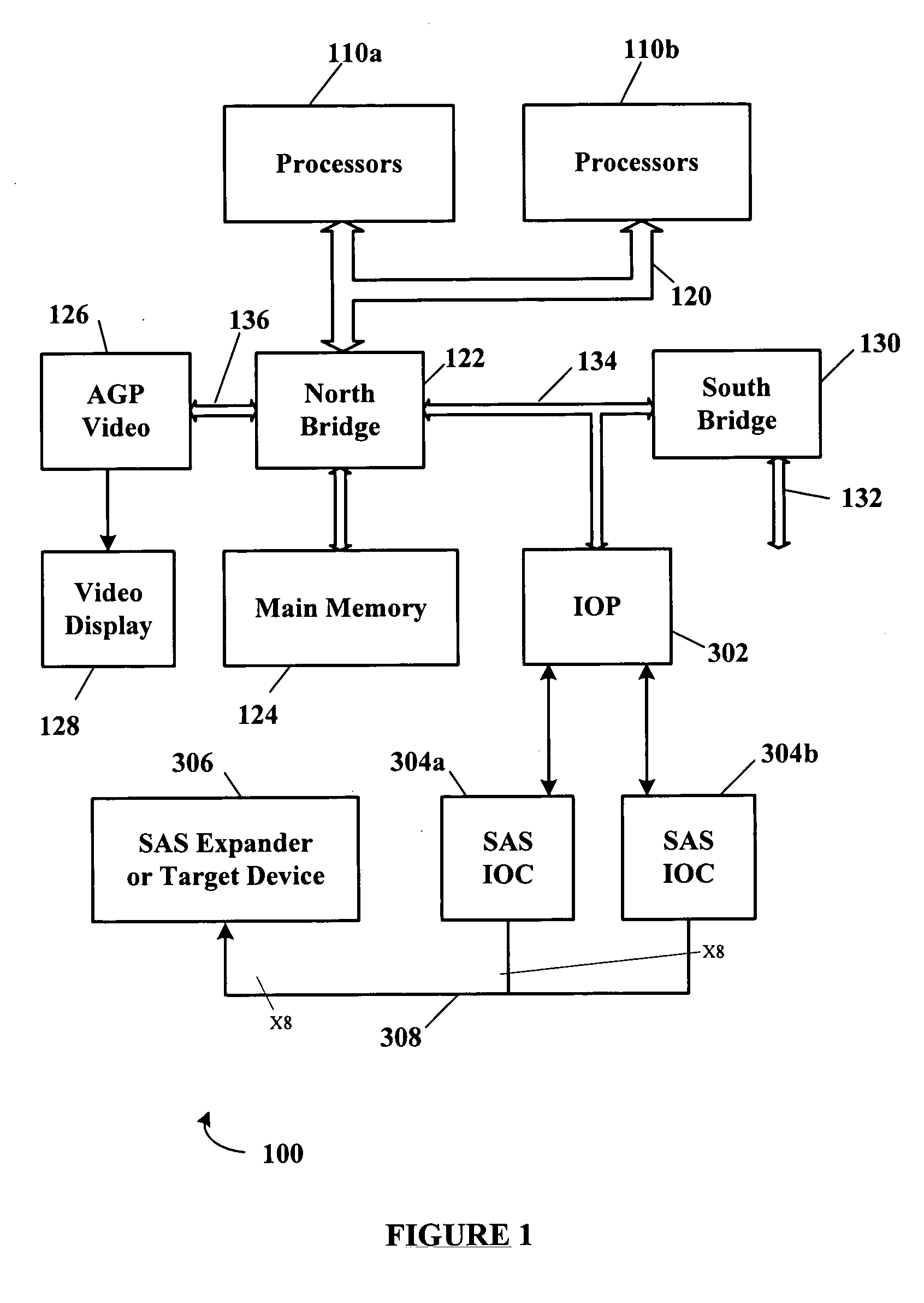

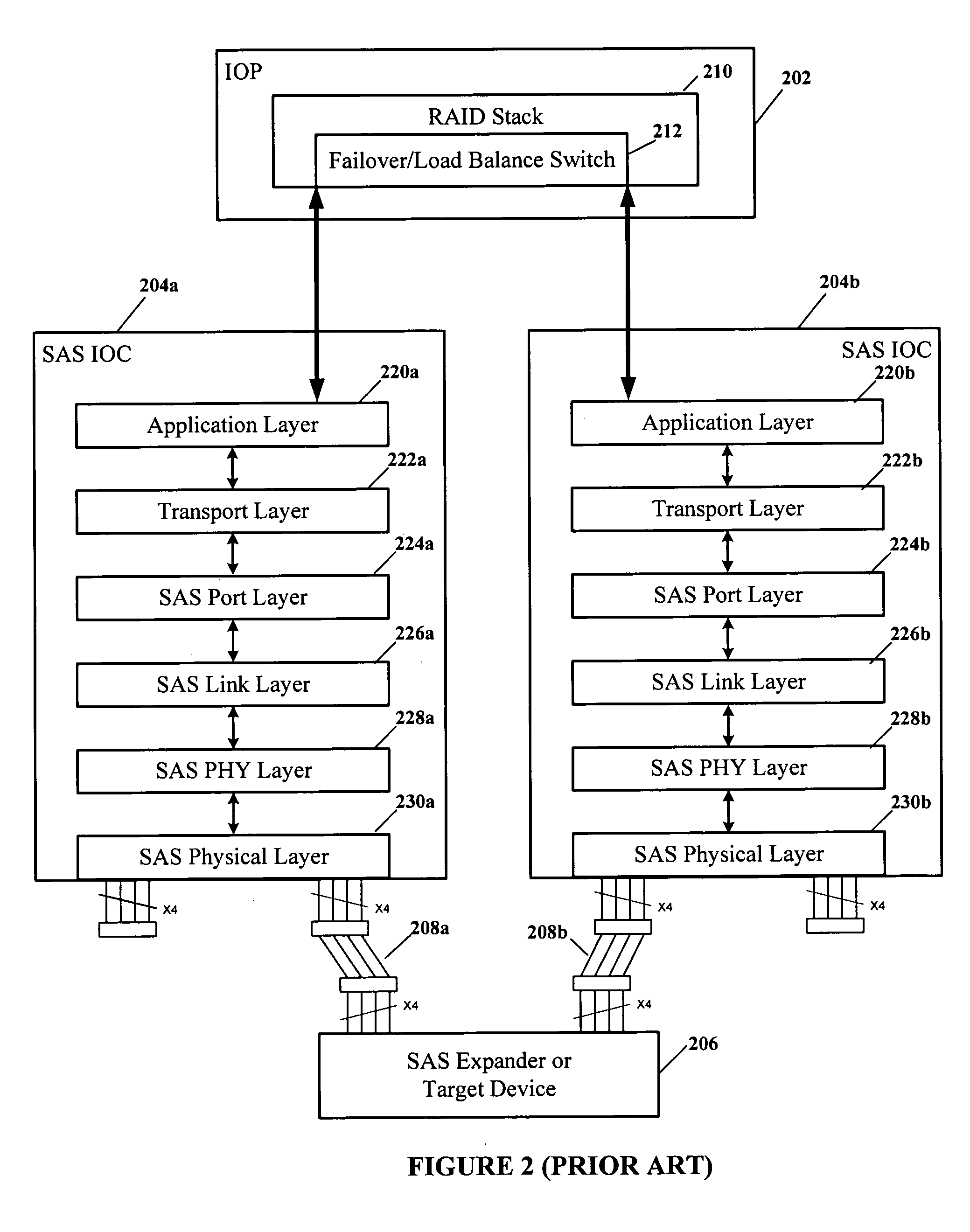

Method and apparatus for supporting port aggregation of serial attached SCSI wide ports via virtual ports

InactiveUS20060194386A1Improve performanceLower latencyError detection/correctionSemiconductor/solid-state device manufacturingRAIDFailover

An SAS RAID adapter comprises an input-output processor (IOP) and at least two SAS input-output controllers (IOCs). Wherein SAS links coupled to each of the IOCs form “virtual ports” in order to increase performance and maintain availability. The virtual ports across the at least two IOCs have wide port SAS link capability so as to provide performance enhancements similar to a standard SAS wide port. Even if a single IOC failure occurs, downshifting to N / 2 links is provided with degraded aggregated bandwidth (data throughput) instead of a failover and / or system shutdown.

Owner:DELL PROD LP

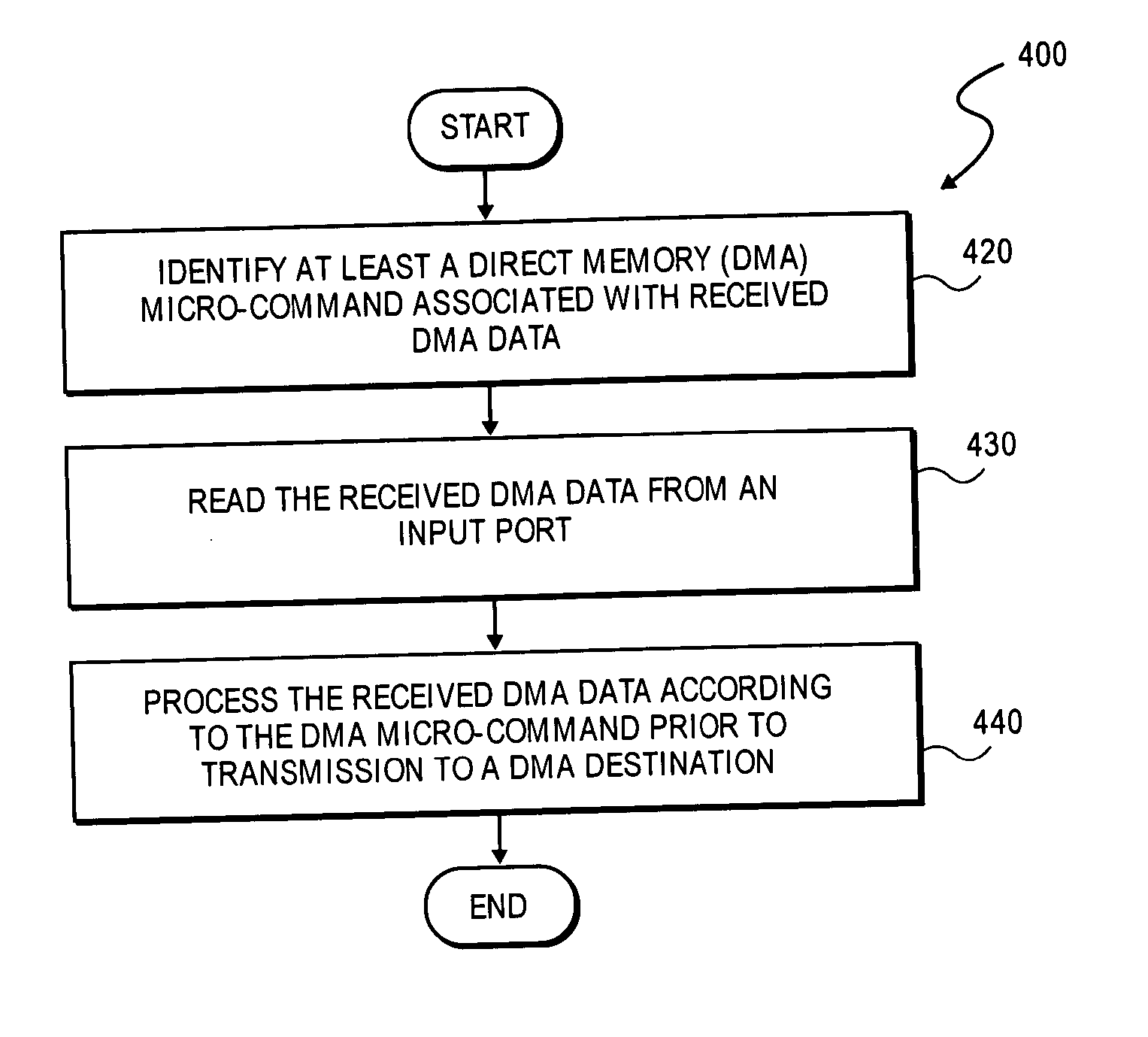

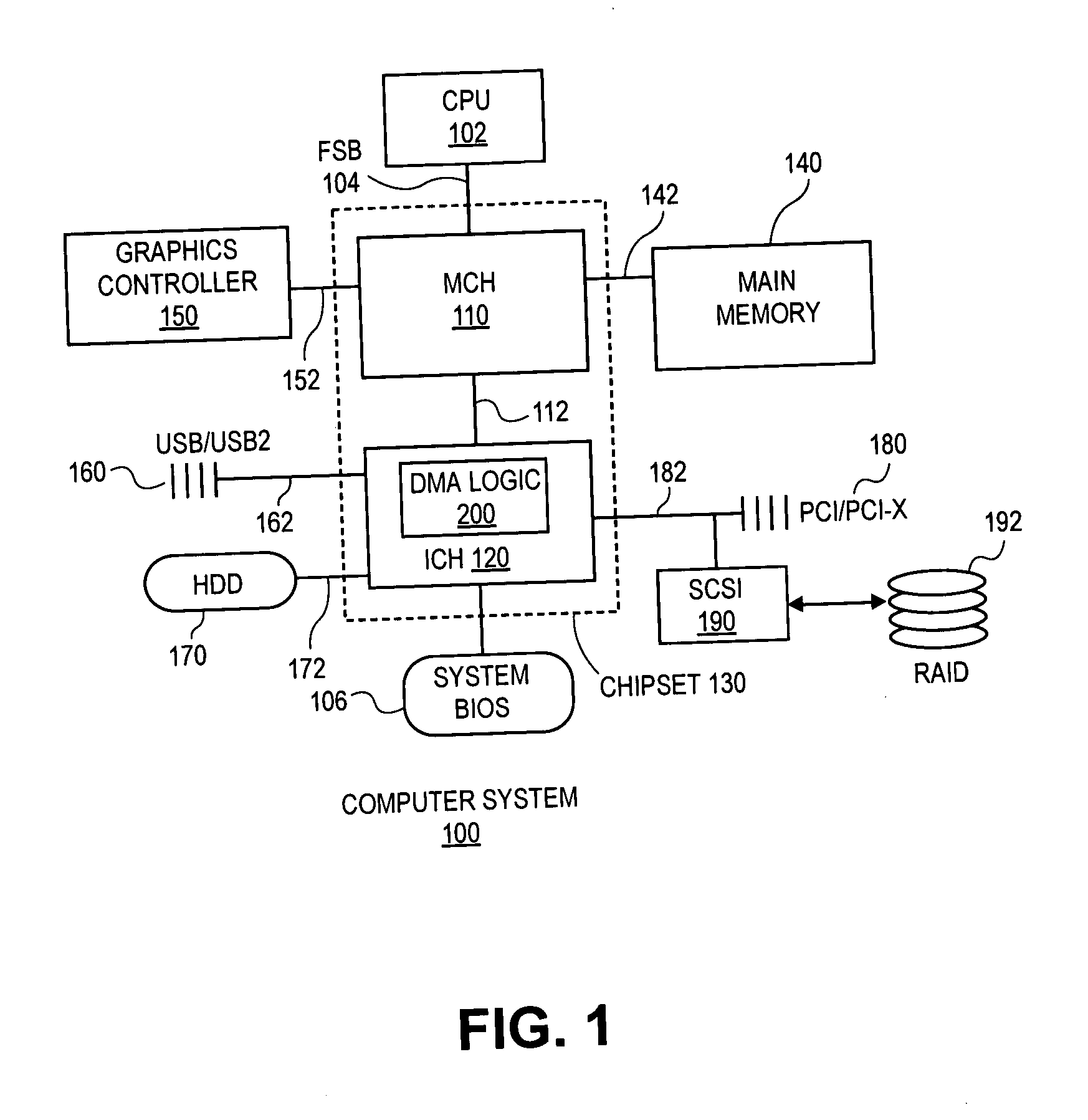

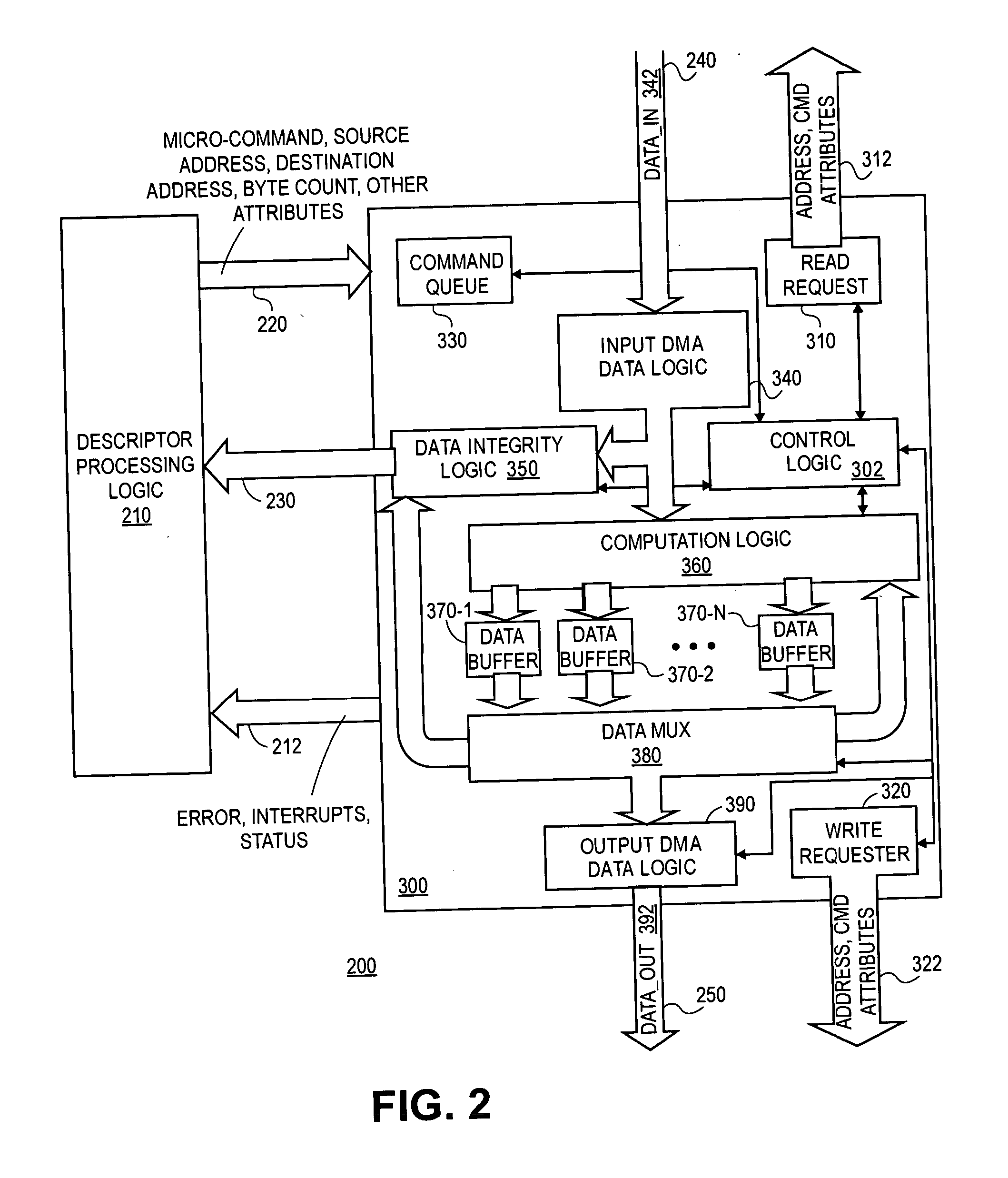

Apparatus and method for a multi-function direct memory access core

A method and apparatus for a multi-function direct memory access core are described. In one embodiment, the method includes the reading of a direct memory access (DMA) descriptor having associated DMA data to identify at least one micro-command. Once the micro-command is identified, the DMA data is processed according to the micro-command during DMA transfer of the data. In one embodiment, a DMA engine performs an operation on the DMA data in transit within the DMA controller according to the identified micro-command. Hence, by defining a primitive set of micro-commands, the DMA engine within, for example, an input / output (I / O) controller hub (ICH), can be used to perform a large number of complex operations on data when data is passing through the ICH without introducing latency into the DMA transfer. Other embodiments are described and claimed.

Owner:INTEL CORP

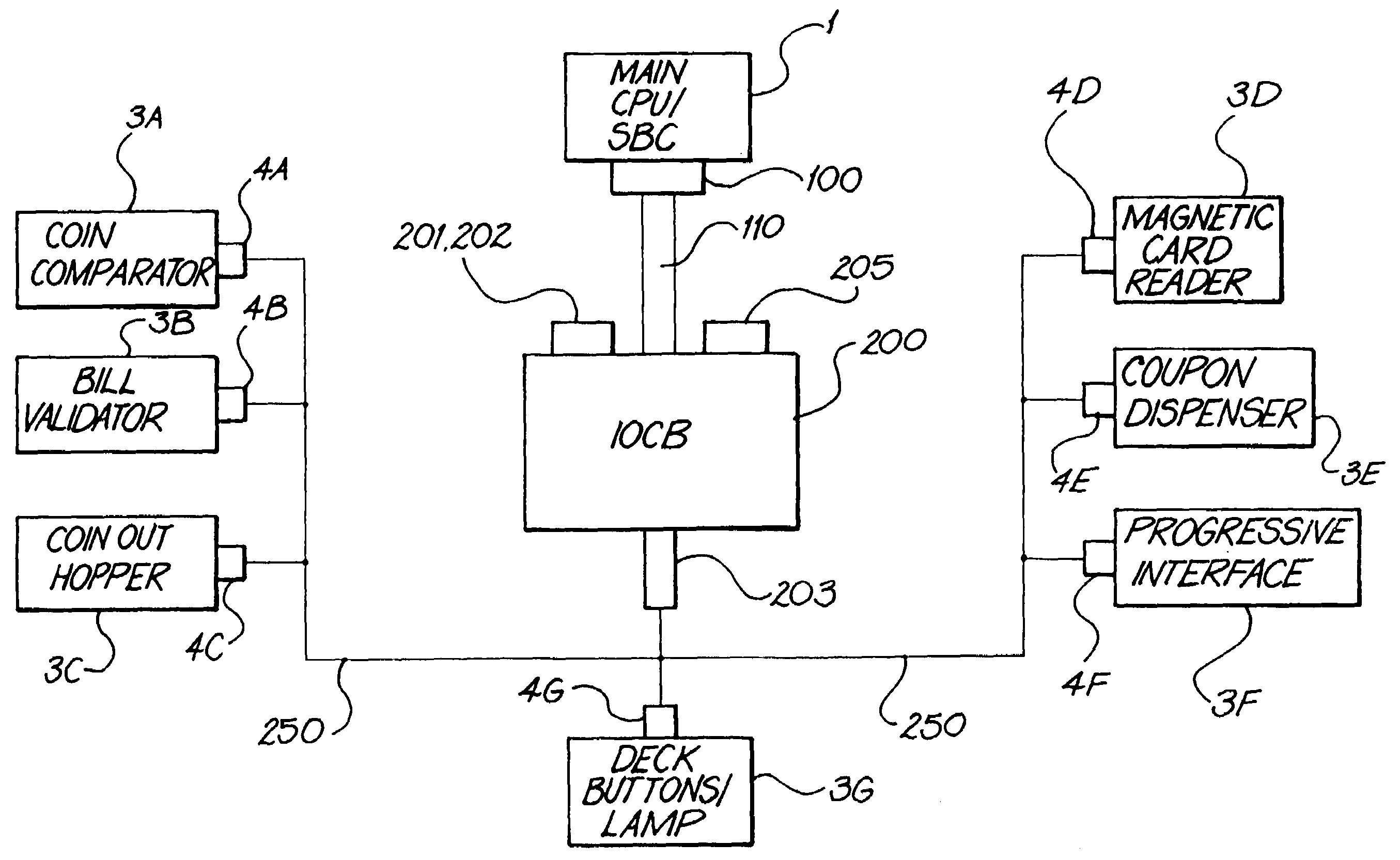

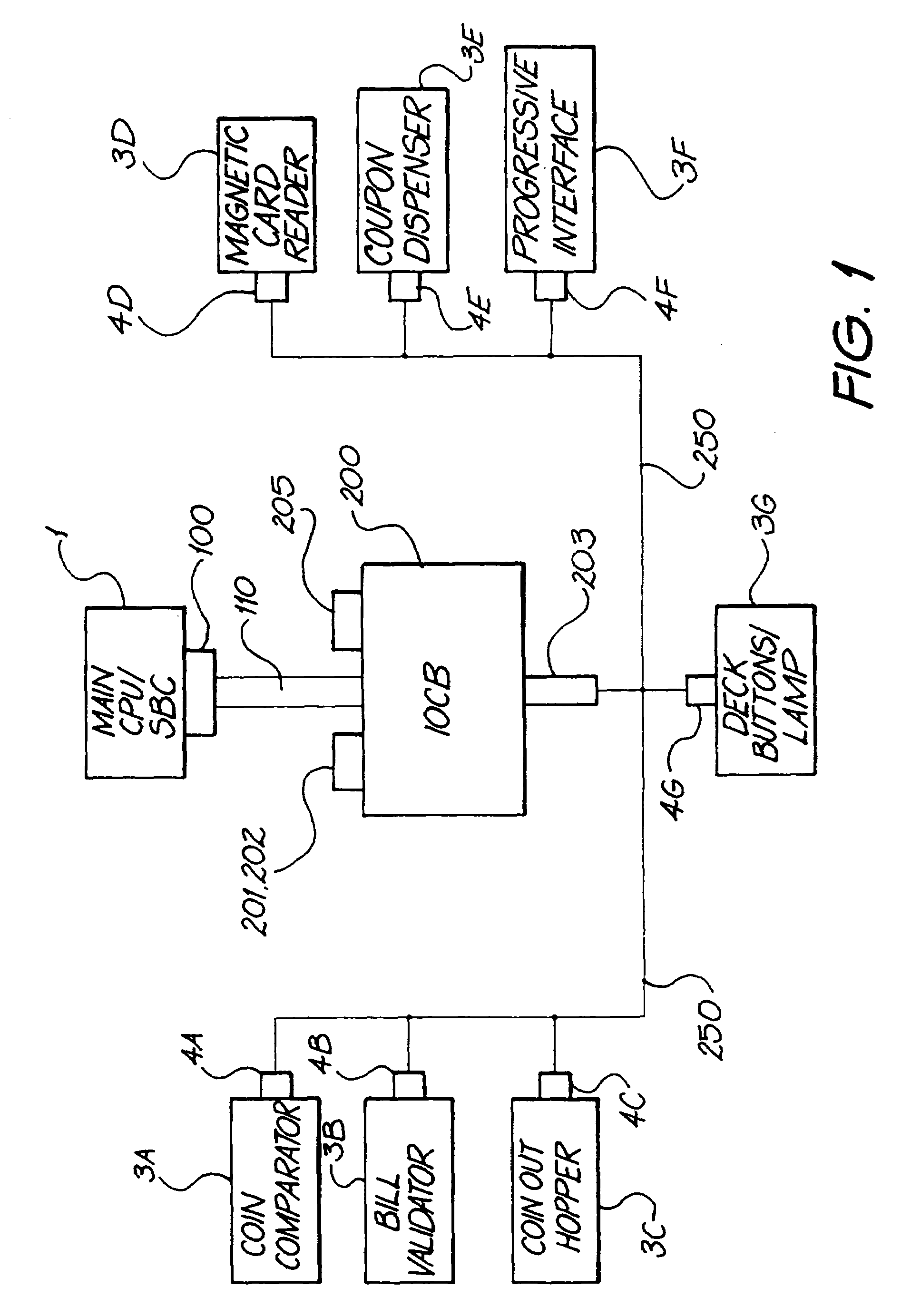

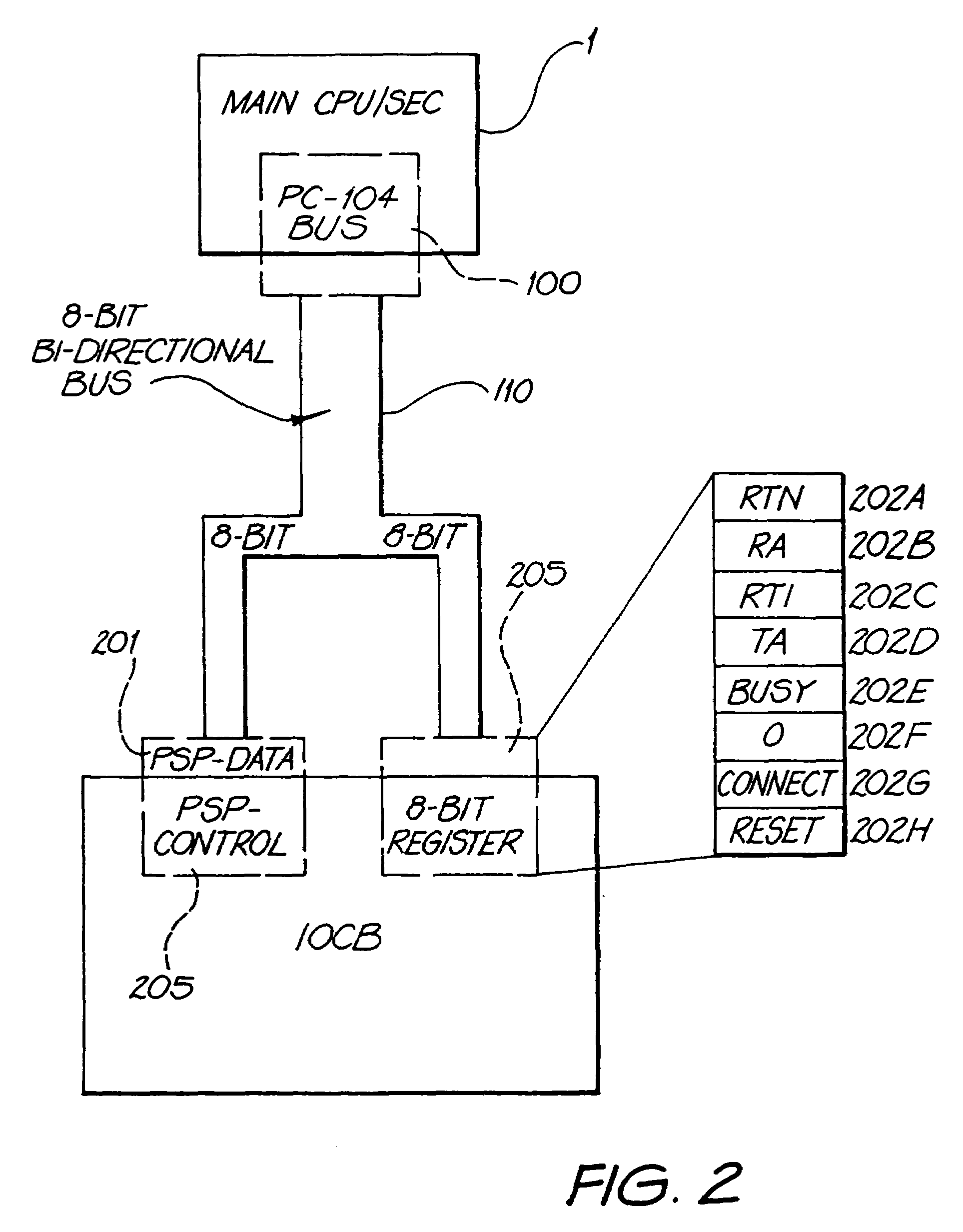

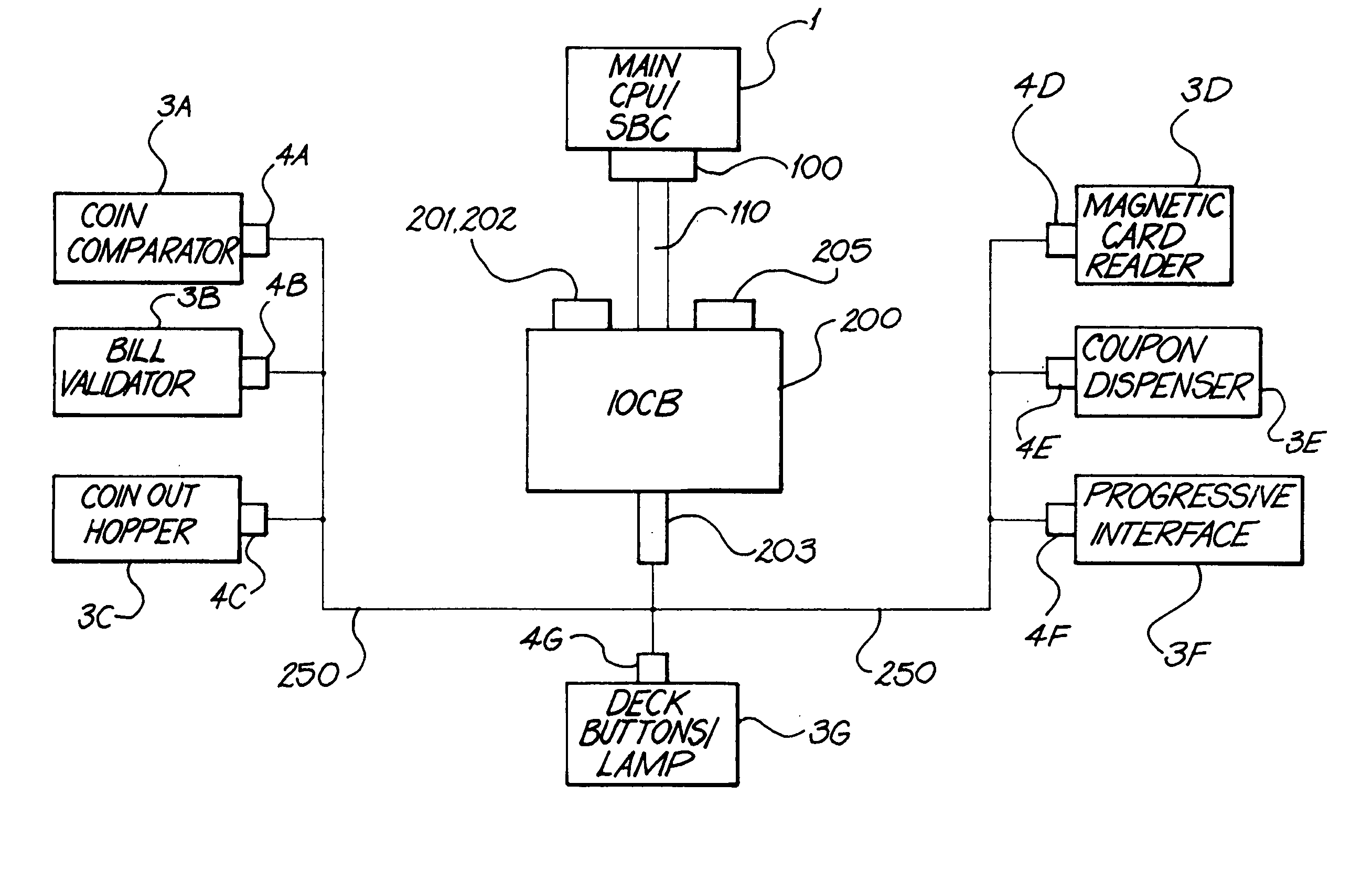

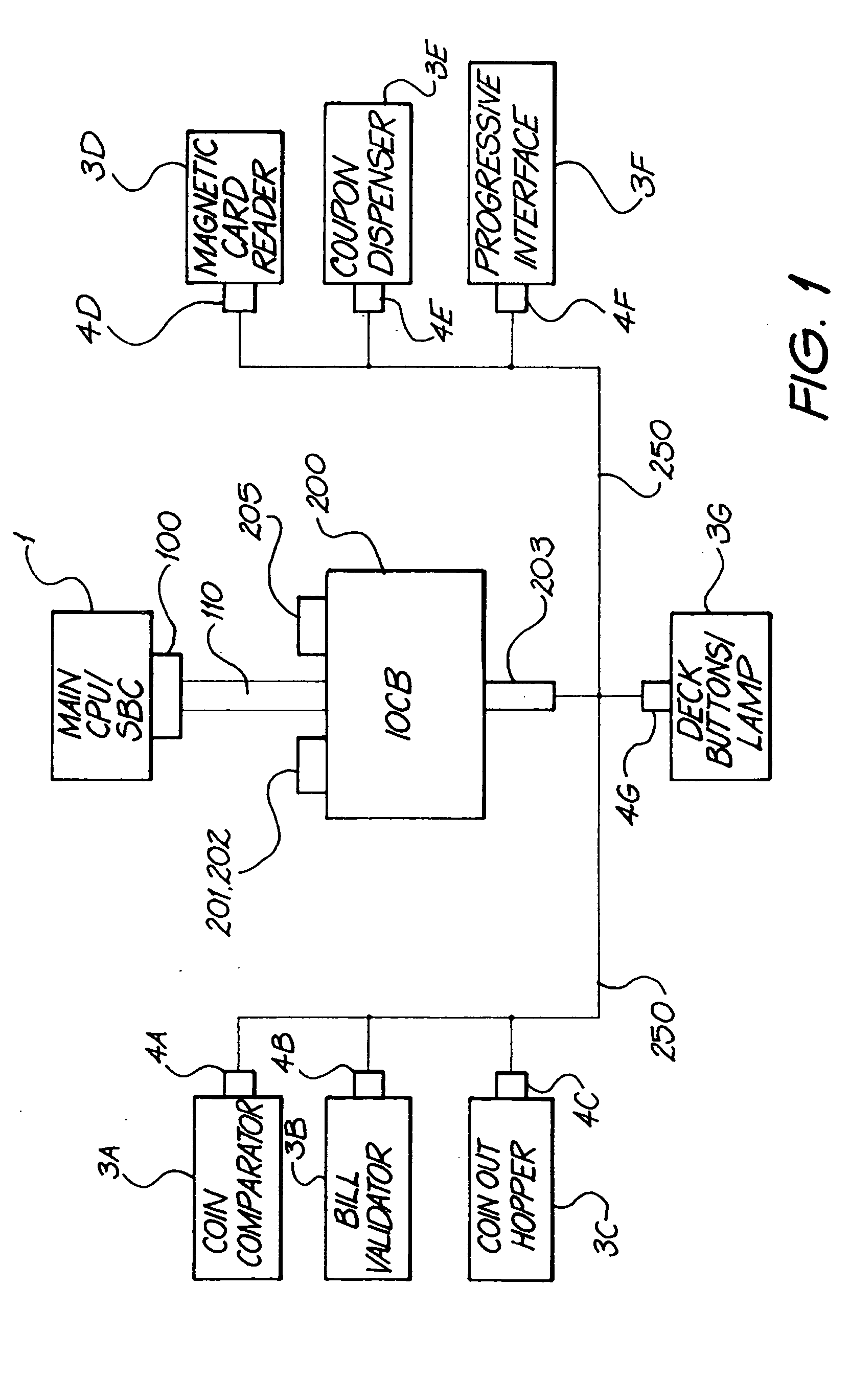

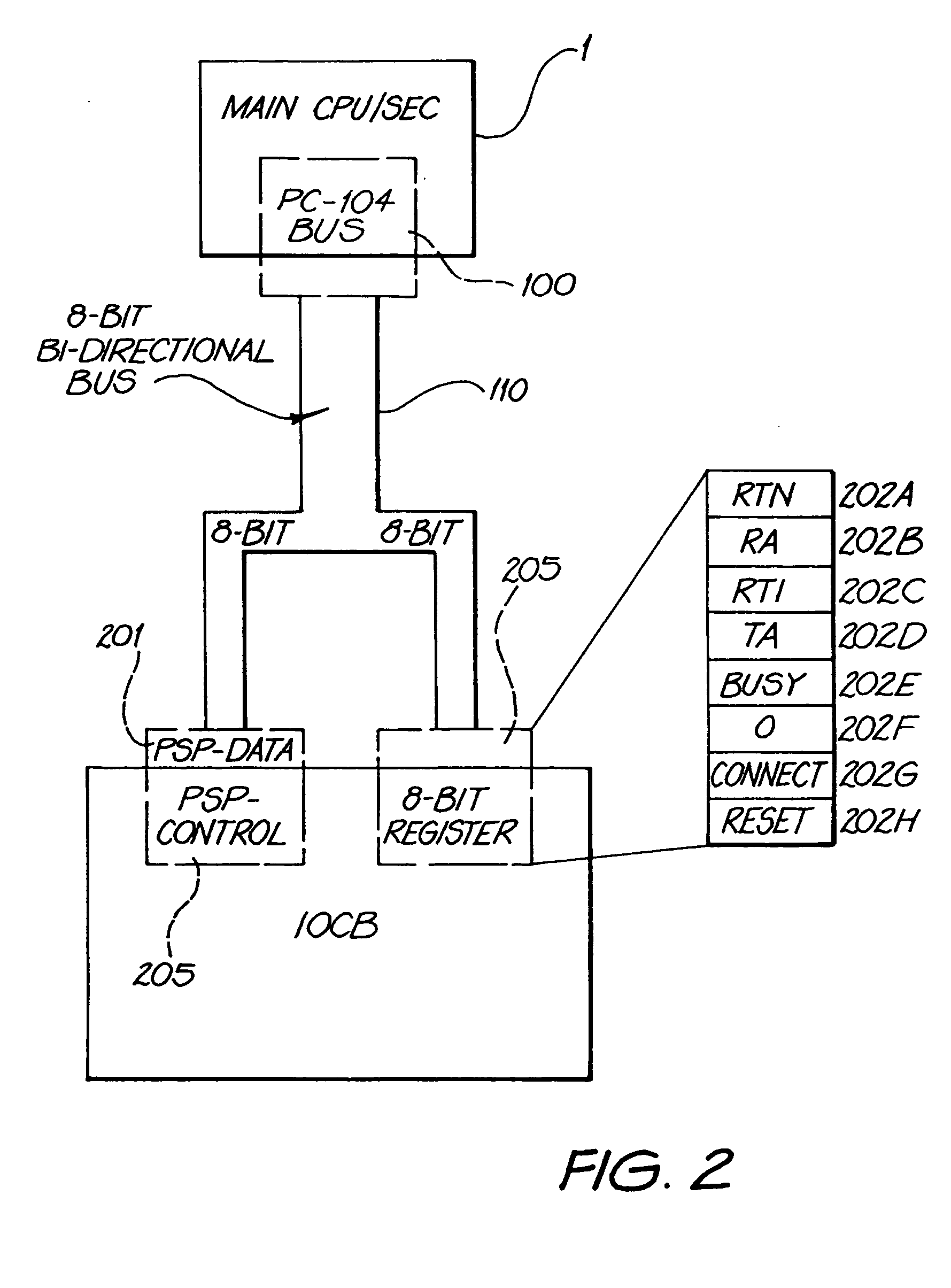

Secured inter-processor and virtual device communications system for use in a gaming system

InactiveUS7093040B1Reliable dataFacilitate communicationDigital computer detailsInternal/peripheral component protectionCommunications systemMultidrop bus

The invention comprises an electronically secured inter-processor and virtual device communications system, with an input / output controller board, a multi-drop bus interface to multiple devices, and a parallel interface to an industry standard single board computer. The invention assigns a bus address and virtual identification number to each device and controls communications between the main central processing unit and the devices through a Plug-n-Play protocol.

Owner:ARISTOCRAT TECH AUSTRALIA PTY LTD

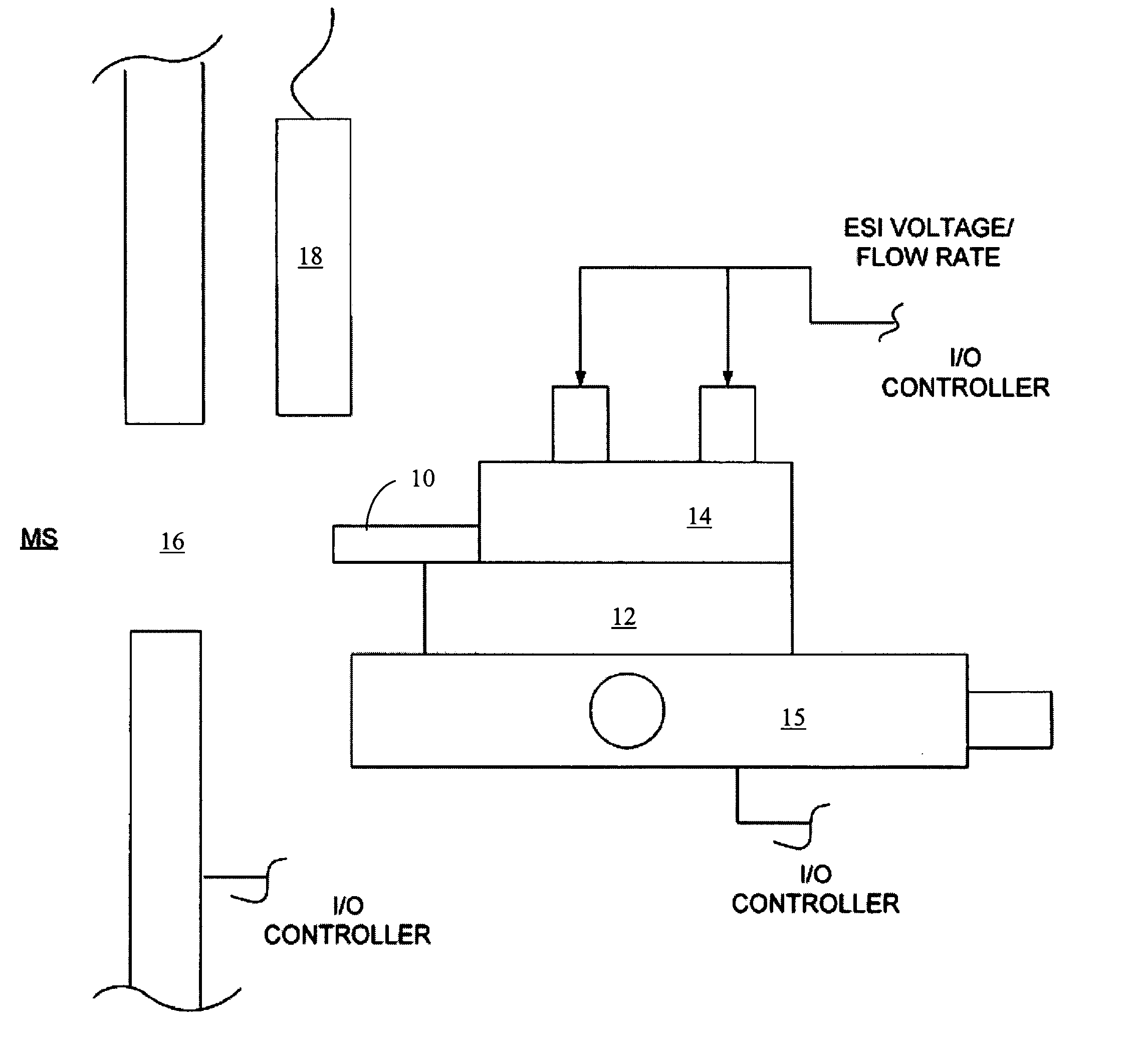

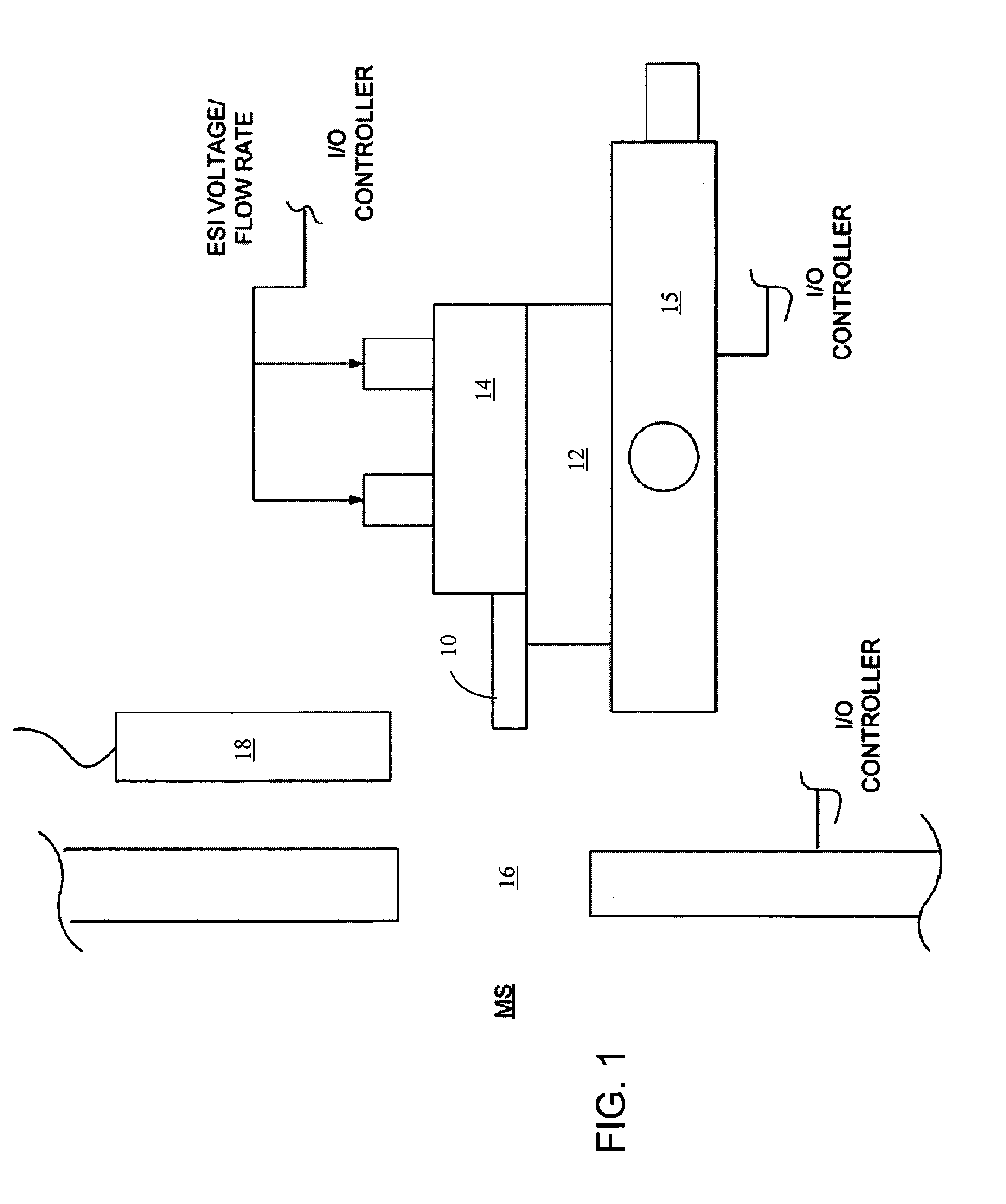

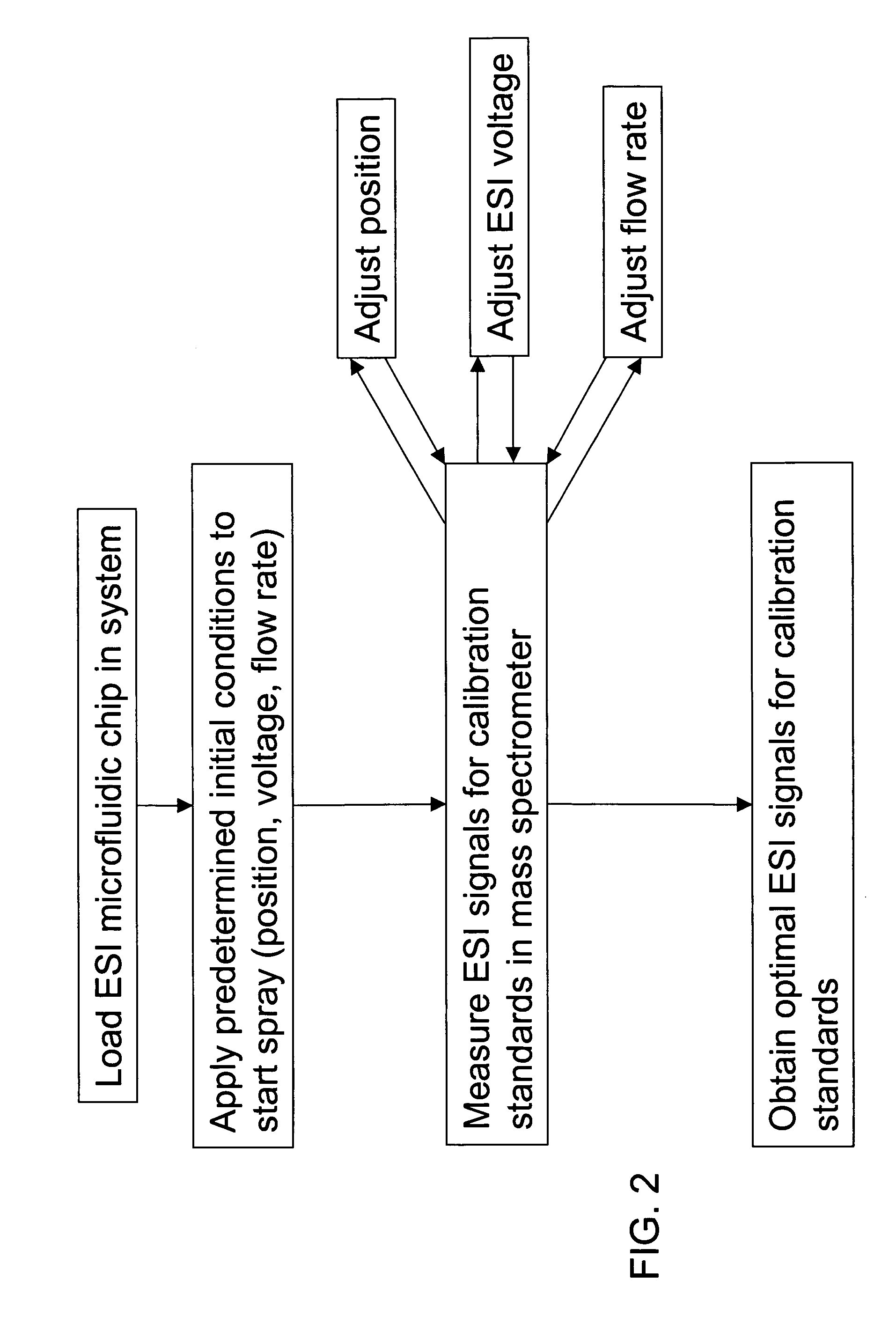

Methods and apparatus for self-optimization of electrospray ionization devices

InactiveUS20050072915A1Efficient interfaceSamples introduction/extractionIsotope separationMass spectrometricSpectrometer

An automated electrospray ionization (ESI) device and related methods to optimize electrospray interface conditions for mass spectrometric analysis. The optimization process can be performed with calibration or optimization solutions that produce expected ESI parameters such as an ESI signal or an ion current. The ESI device may include an input / output (I / O) controller that is coupled to an electrospray assembly including an XYZ stage for positioning an electrospray emitter relative to a mass spectrometer orifice. The I / O controller may be connected to a power supply for applying an adjustable electrospray ionization voltage, and an adjustable flow regulator that alters the flow of solution by modifying applied voltage and / or pressure. A central processing unit instructs the I / O controller to control selectively the electrospray assembly based on the resultant signals from the mass spectrometer or the ion currents within the mass spectrometer in accordance with a predetermined optimization algorithm. The resulting ESI signal or ion currents are monitored and provide feedback to the I / O controller which can automatically instruct selected system components to make adjustments as needed to attain optimal settings that produce expected ESI signals or ion currents in the mass spectrometer for selected solutions.

Owner:NORVIEL VERN

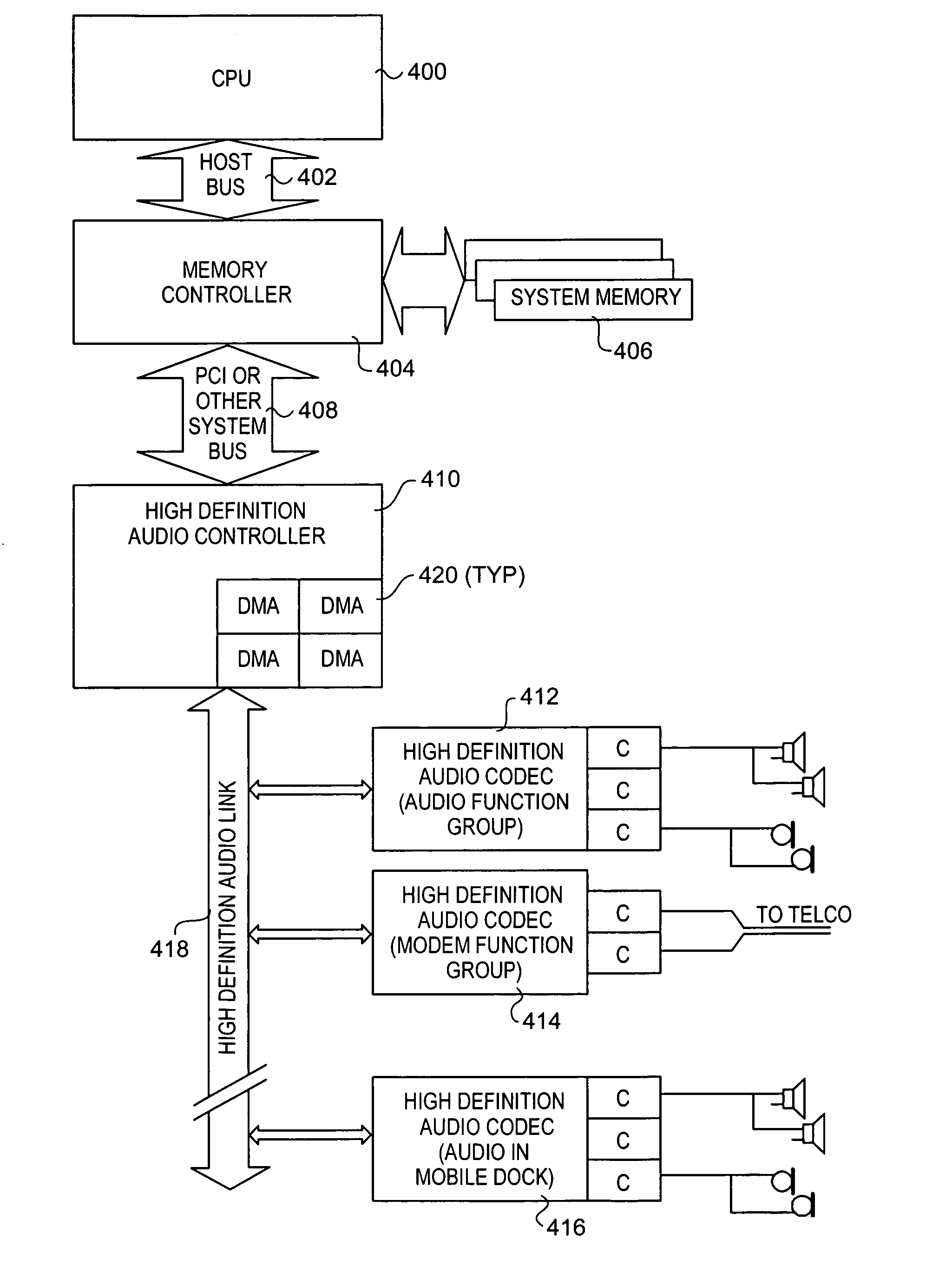

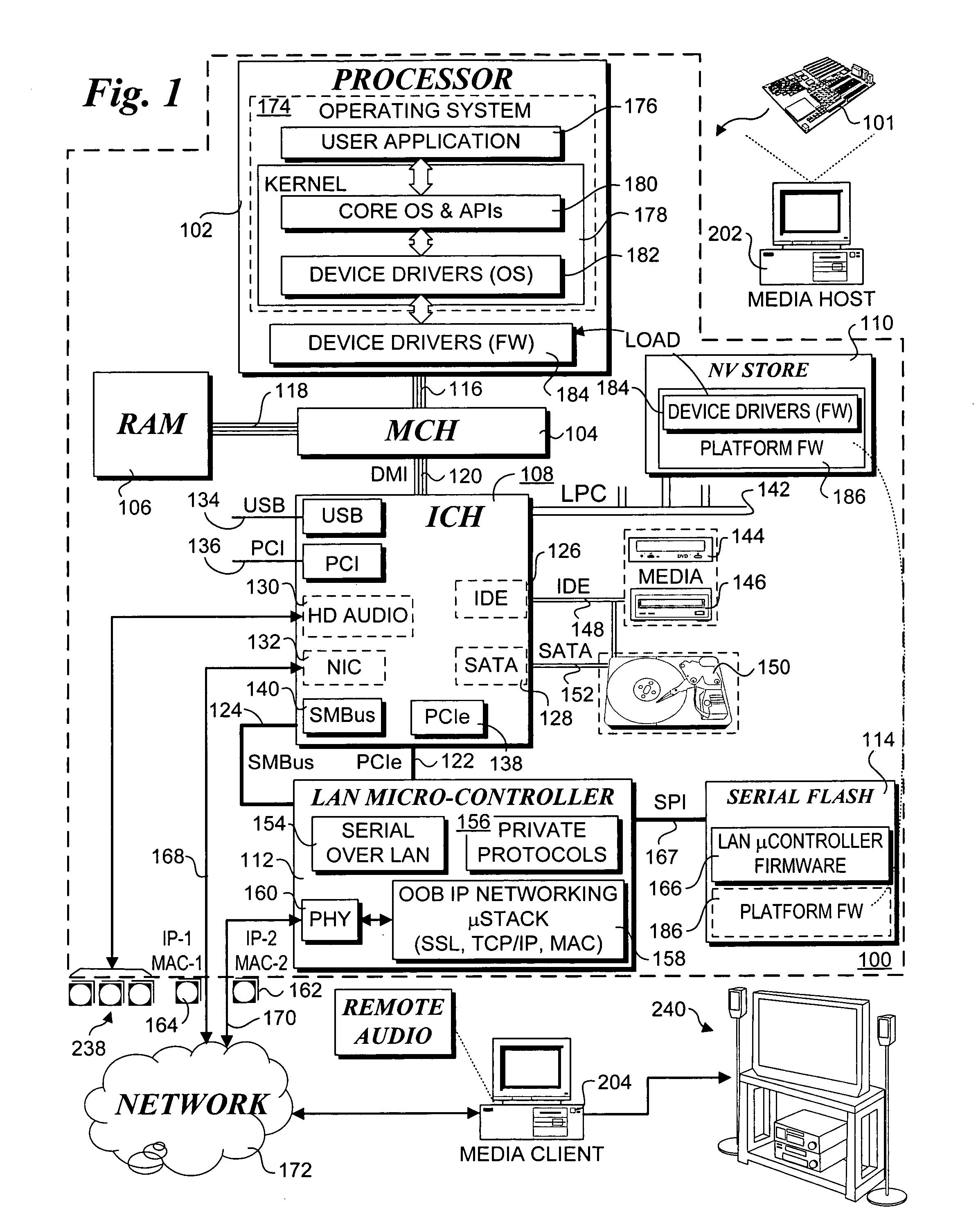

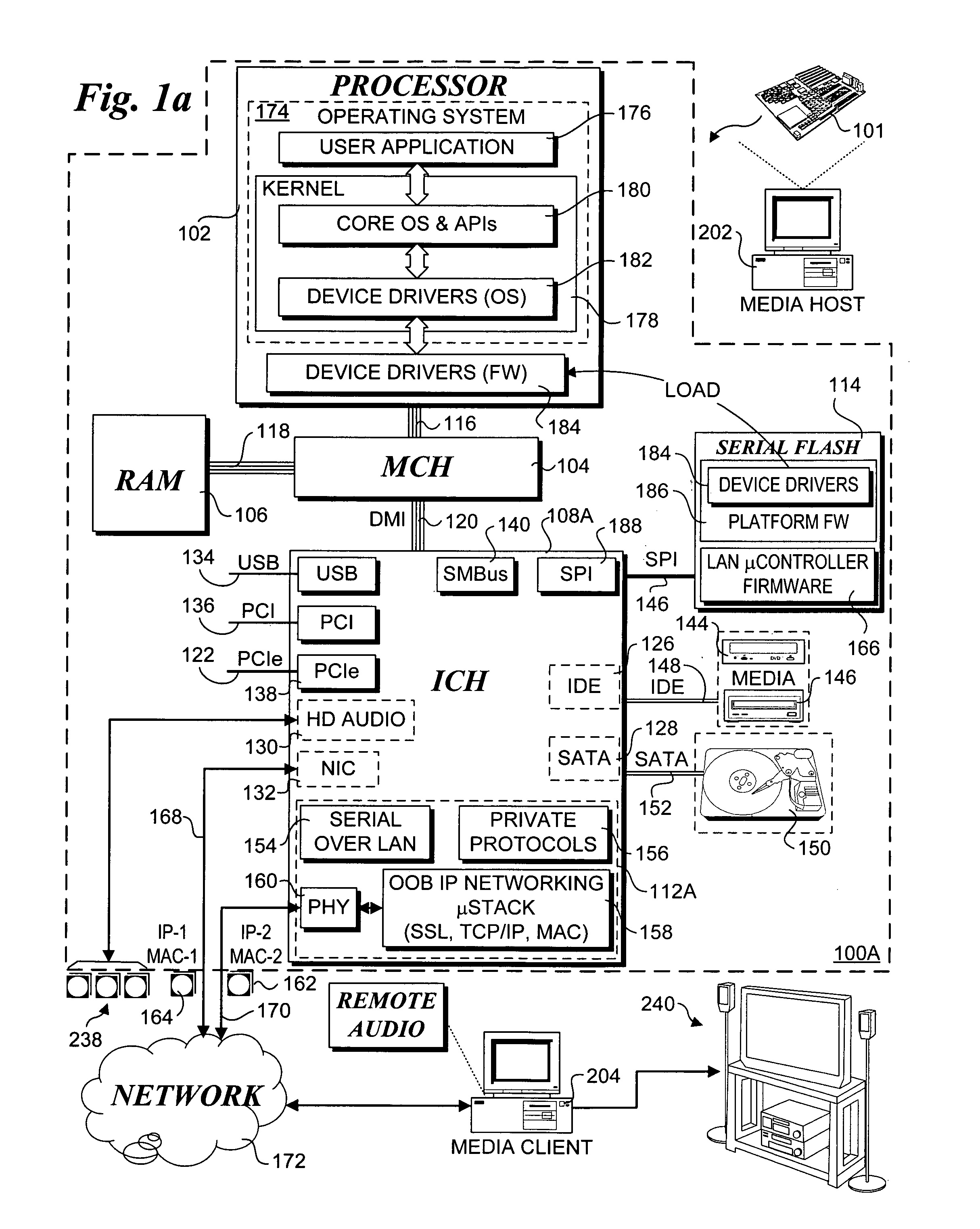

Method and apparatus for providing remote audio

InactiveUS20060206618A1Broadcast with distributionMultiple digital computer combinationsMicrocontrollerHard disc drive

A method and apparatus for providing remote audio using an out-of-band (OOB) communication channel. The method enables audio content to be broadcast from a media host to multiple media clients using an OOB communication channel that is transparent to operating systems running on the media host and clients. Audio content (data) is read from media, such as a CD-ROM, DVD, or hard disk drive, at the media host. The audio data is packetized using an OOB networking stack and transferred to the media clients, whereupon the packets are processed by a client-side OOB networking stack. The audio data is then extracted from the packets and provided to an audio sub-system to be rendered. In one embodiment, the apparatus comprises an input / output controller hub (ICH) including an embedded High Definition audio sub-system and a separate LAN microcontroller. In another embodiment, the ICH includes an embedded LAN microcontroller.

Owner:INTEL CORP

System and methods for accelerated data storage and retrieval

InactiveUS20060184696A1Increases effective data access rateHigh bandwidthTelevision system detailsInput/output to record carriersData compressionData stream

Systems and methods for providing accelerated data storage and retrieval utilizing lossless and / or lossy data compression and decompression. A data storage accelerator includes one or a plurality of high speed data compression encoders that are configured to simultaneously or sequentially losslessly or lossy compress data at a rate equivalent to or faster than the transmission rate of an input data stream. The compressed data is subsequently stored in a target memory or other storage device whose input data storage bandwidth is lower than the original input data stream bandwidth. Similarly, a data retrieval accelerator includes one or a plurality of high speed data decompression decoders that are configured to simultaneously or sequentially losslessly or lossy decompress data at a rate equivalent to or faster than the input data stream from the target memory or storage device. The decompressed data is then output at rate data that is greater than the output rate from the target memory or data storage device. The data storage and retrieval accelerator method and system may employed: in a disk storage adapter to reduce the time required to store and retrieve data from computer to disk; in conjunction with random access memory to reduce the time required to store and retrieve data from random access memory; in a display controller to reduce the time required to send display data to the display controller or processor; and / or in an input / output controller to reduce the time required to store, retrieve, or transmit data.

Owner:REALTIME DATA

System and methods for accelerated data storage and retrieval

InactiveUS20060184687A1Lower requirementShorten the timeTelevision system detailsColor television detailsData streamData retrieval

Systems and methods for providing accelerated data storage and retrieval utilizing lossless data compression and decompression. A data storage accelerator includes one or a plurality of high speed data compression encoders that are configured to simultaneously or sequentially losslessly compress data at a rate equivalent to or faster than the transmission rate of an input data stream. The compressed data is subsequently stored in a target memory or other storage device whose input data storage bandwidth is lower than the original input data stream bandwidth. Similarly, a data retrieval accelerator includes one or a plurality of high speed data decompression decoders that are configured to simultaneously or sequentially losslessly decompress data at a rate equivalent to or faster than the input data stream from the target memory or storage device. The decompressed data is then output at rate data that is greater than the output rate from the target memory or data storage device. The data storage and retrieval accelerator method and system may employed: in a disk storage adapter to reduce the time required to store and retrieve data from computer to disk; in conjunction with random access memory to reduce the time required to store and retrieve data from random access memory; in a display controller to reduce the time required to send display data to the display controller or processor; and / or in an input / output controller to reduce the time required to store, retrieve, or transmit data.

Owner:REALTIME DATA

Data storage system with integrated switching

ActiveUS7107337B2Cost complexityComplexity of data storageDigital computer detailsElectric digital data processingElectricityExternal data

According to one embodiment of the present invention, a network adapter is provided that is used in the system to permit data communication among external data exchanging devices and an input / output (I / O) controller residing in the system. The adapter includes one or more interfaces that may be coupled to an electrical backplane in the system. The backplane is coupled to the controller, and is configured to permit communication between the controller and the adapter when the interfaces are coupled to the backplane. The adapter also includes an integrated switching system that has a first set of ports that may be coupled to the data exchanging devices and a second set of ports that may couple the switching system to the controller when the one or more interfaces are coupled to the backplane.

Owner:EMC IP HLDG CO LLC

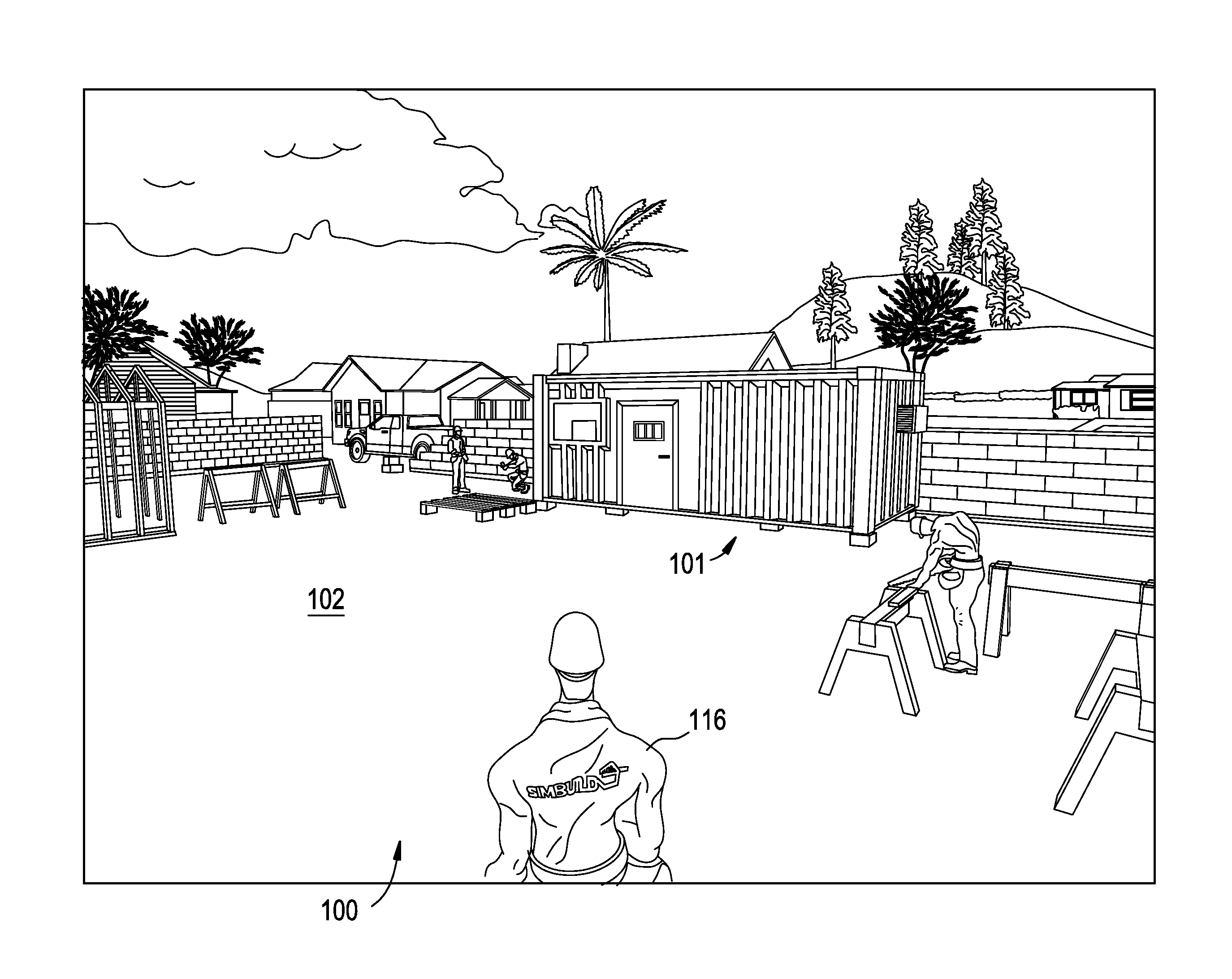

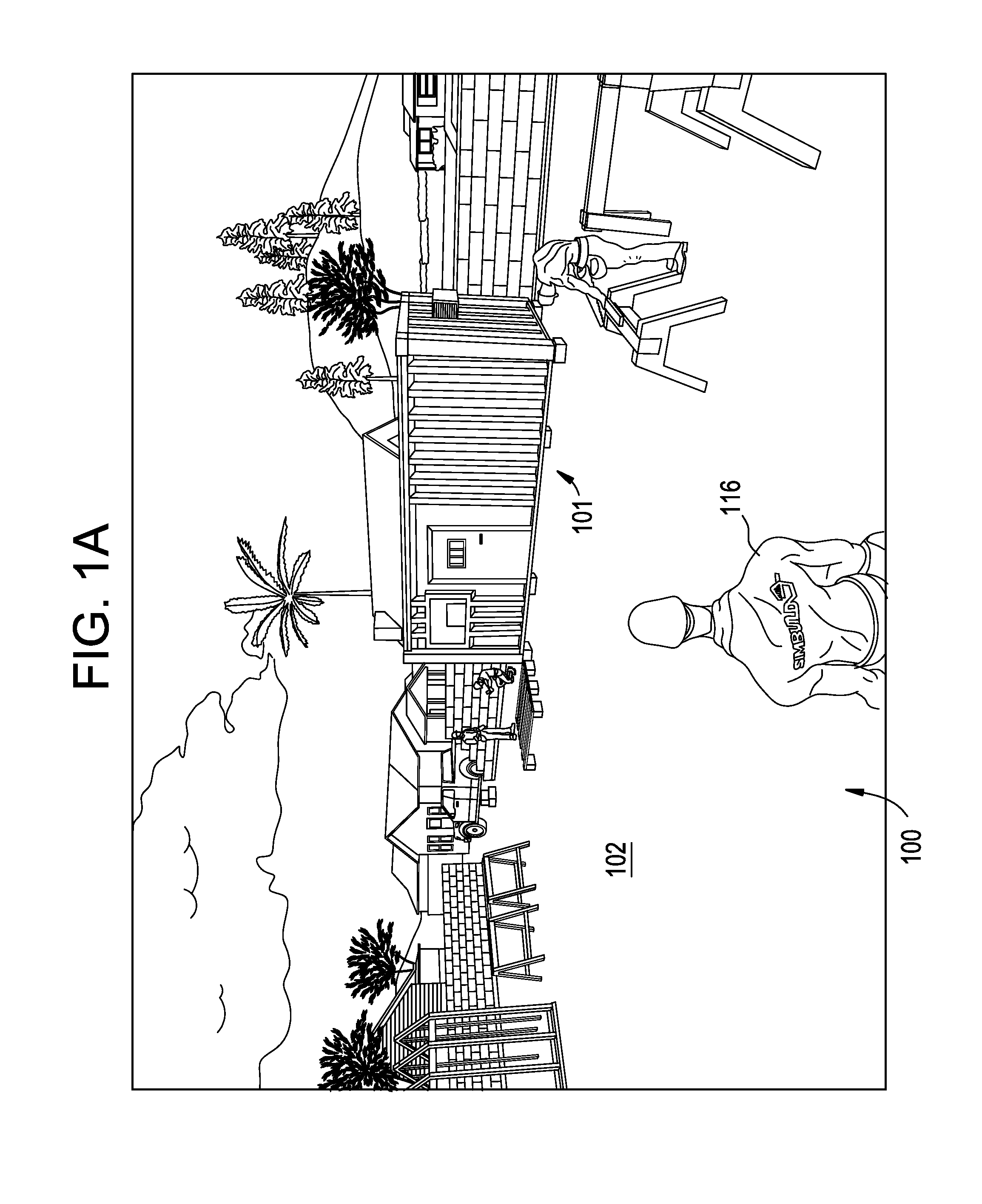

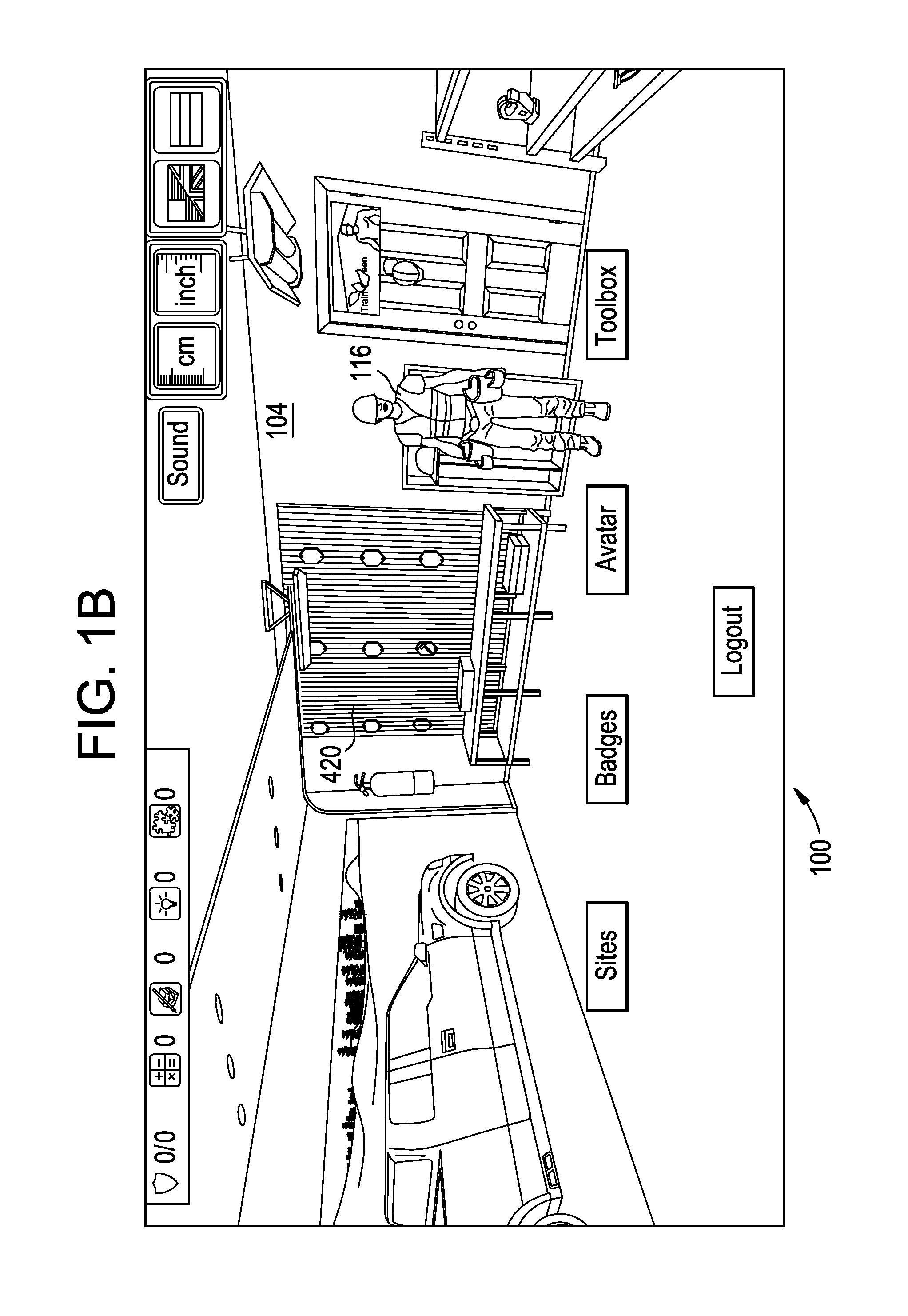

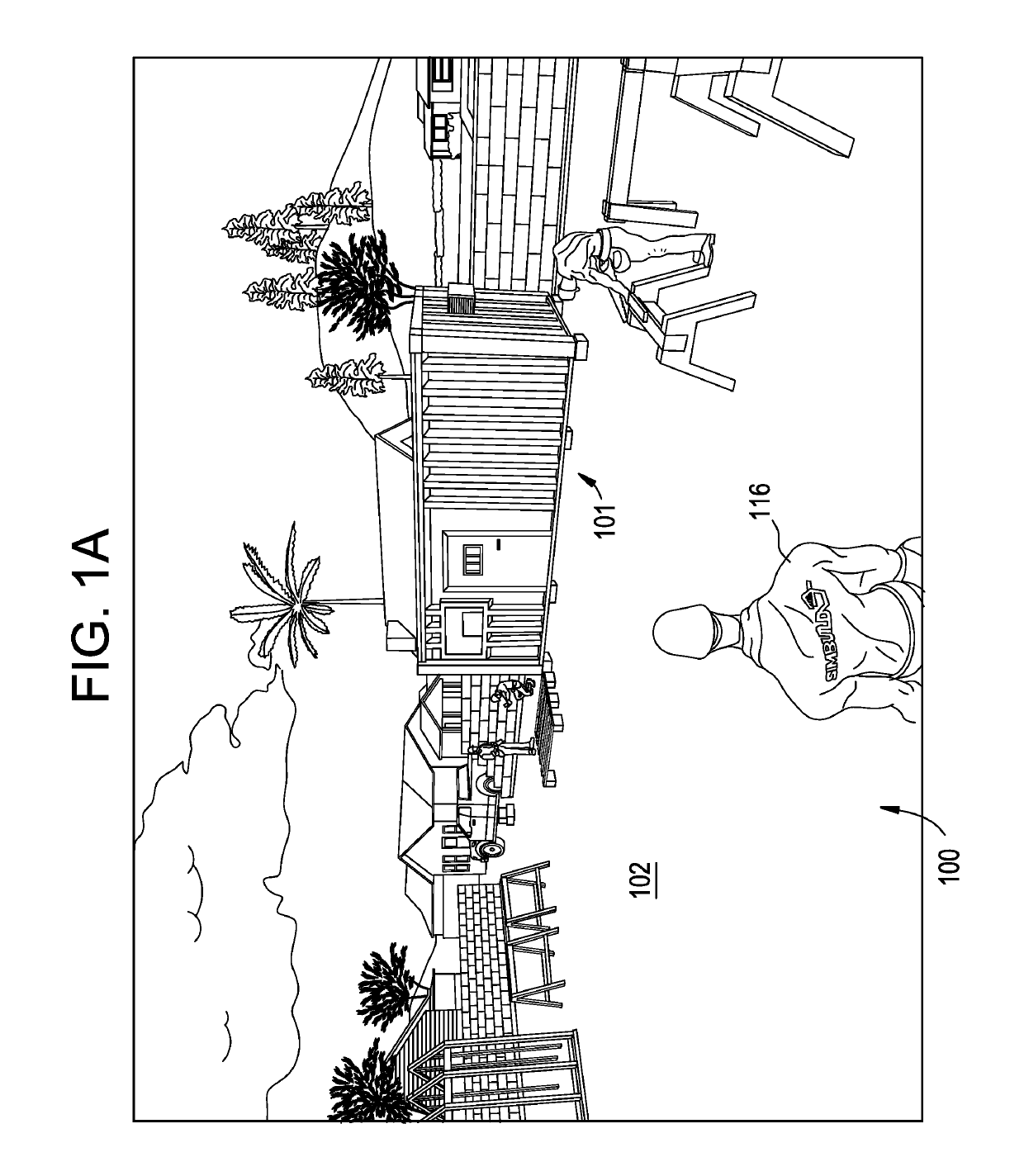

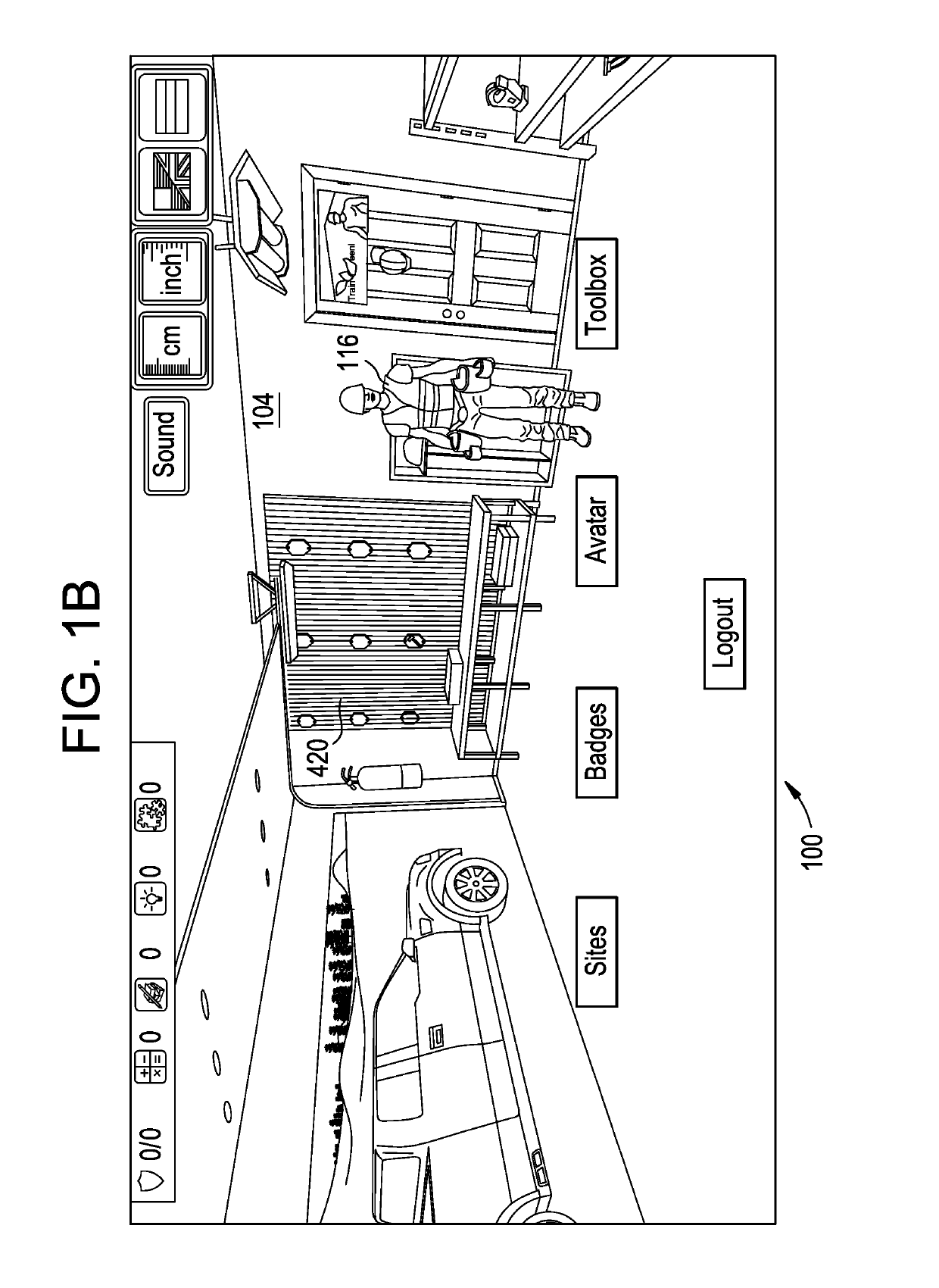

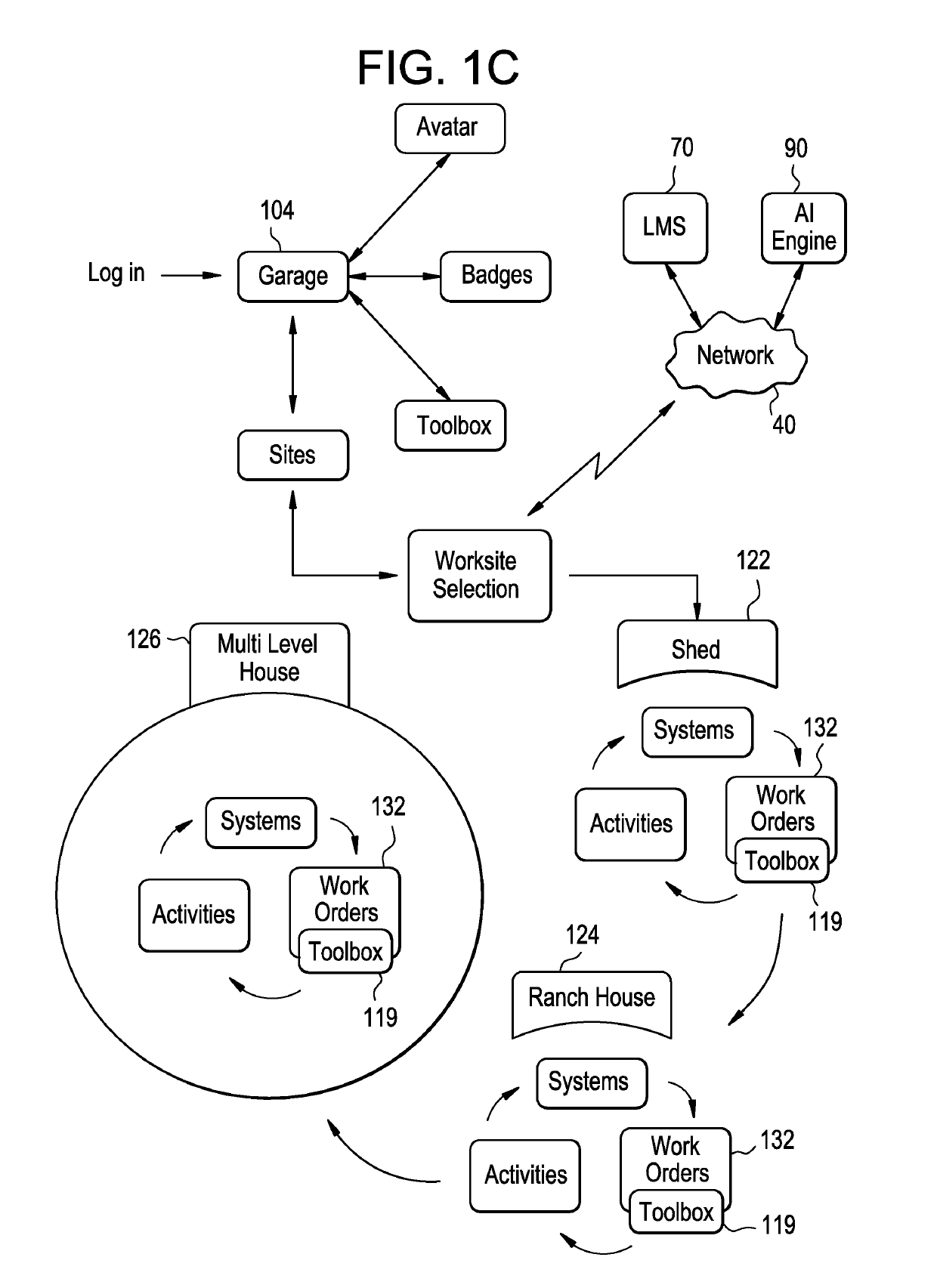

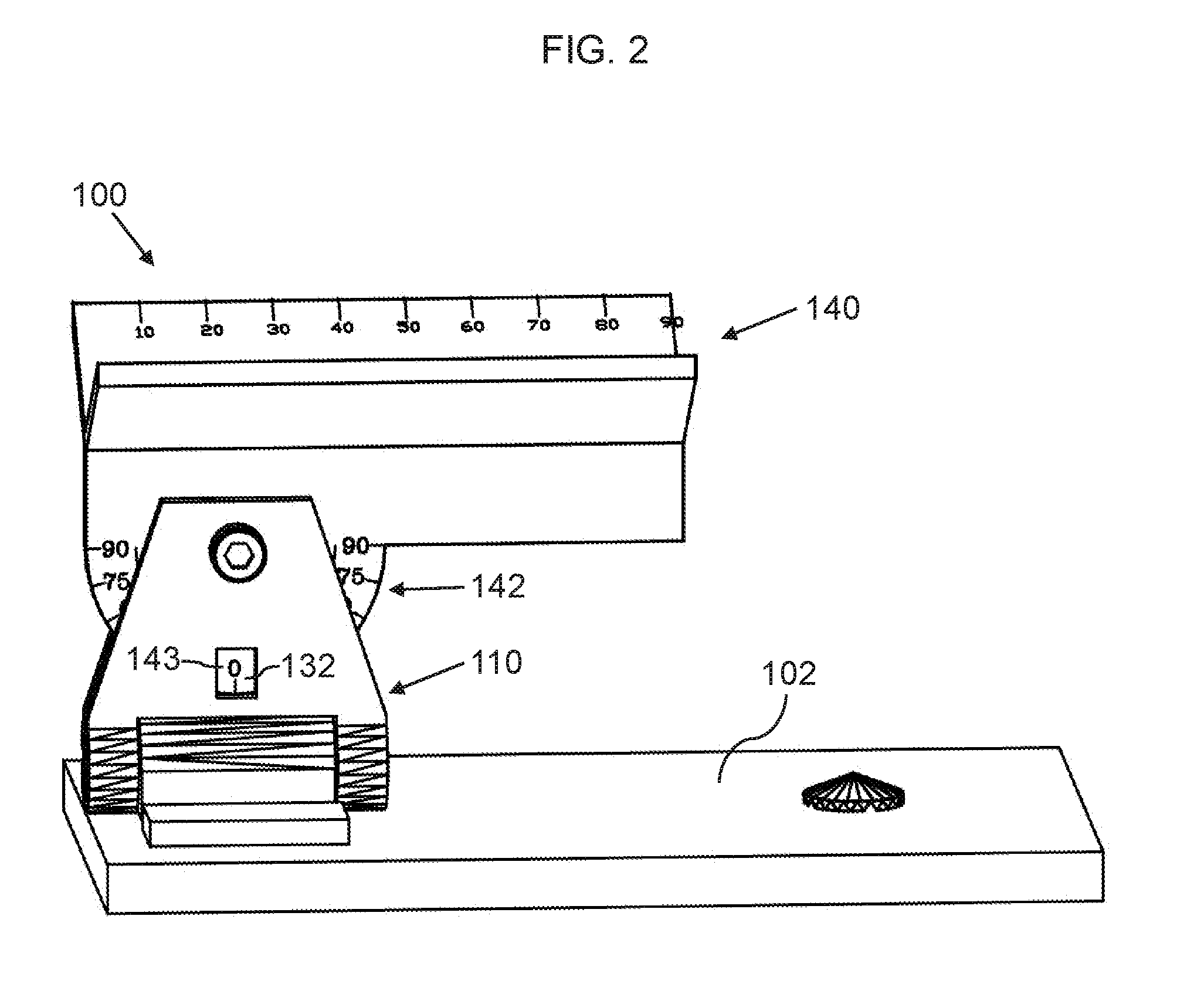

Simulator for skill-oriented training

ActiveUS20140162224A1Easy inputHigh outputSoil-shifting machines/dredgersDesign optimisation/simulationVirtual trainingSkill sets

A skill-based training system includes a processing system having a processor, memory coupled to the processor with executable instructions stored therein, and an input-output controller coupled to the processor and to input and output devices. The memory includes lesson plans that outline skill-based tasks and activities, and predetermined performance criteria. The processor is configured by the instructions to present interfaces on the output devices simulating a virtual training environment. The processor is configured to receive input signals representative of performing the tasks and activities in the virtual environment, and to evaluate the performance by comparing the performed tasks and activities to the criteria, to determine a score and to present the score on the output devices. The system includes work orders categorized by the lesson plans and defining within an increasing progression of a degree of skill, knowledge, critical thinking and problem solving needed to complete the tasks and activities.

Owner:VRSIM

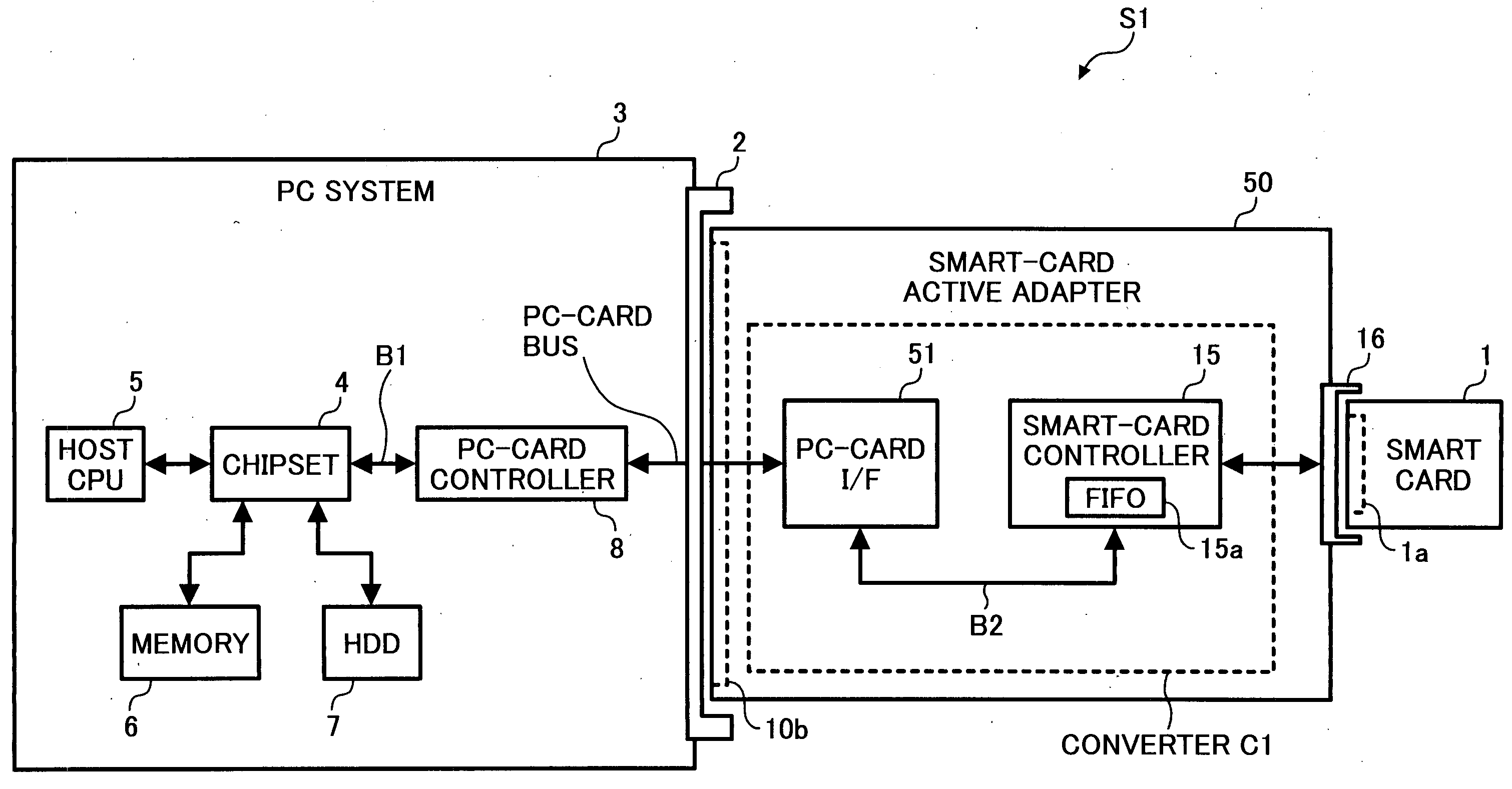

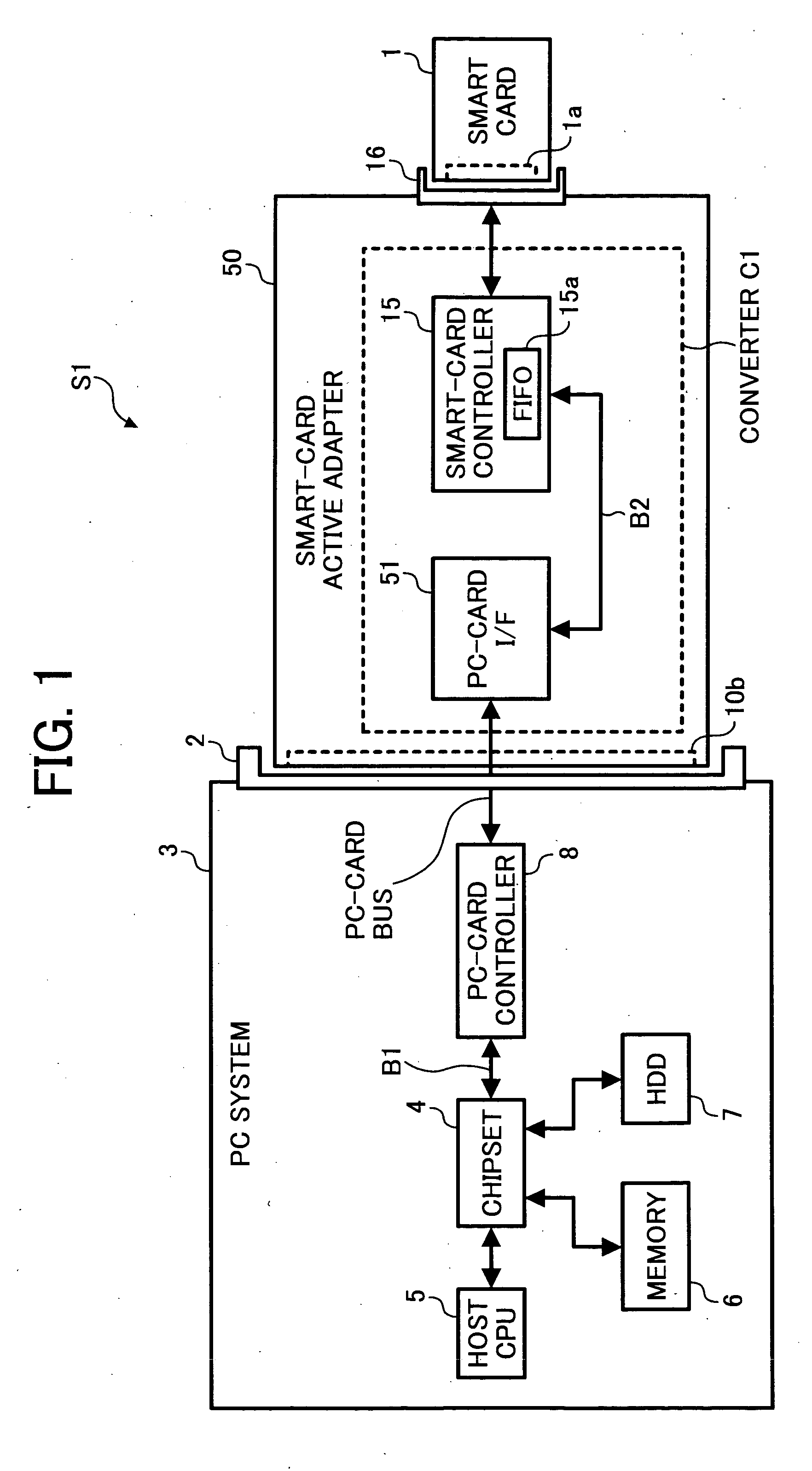

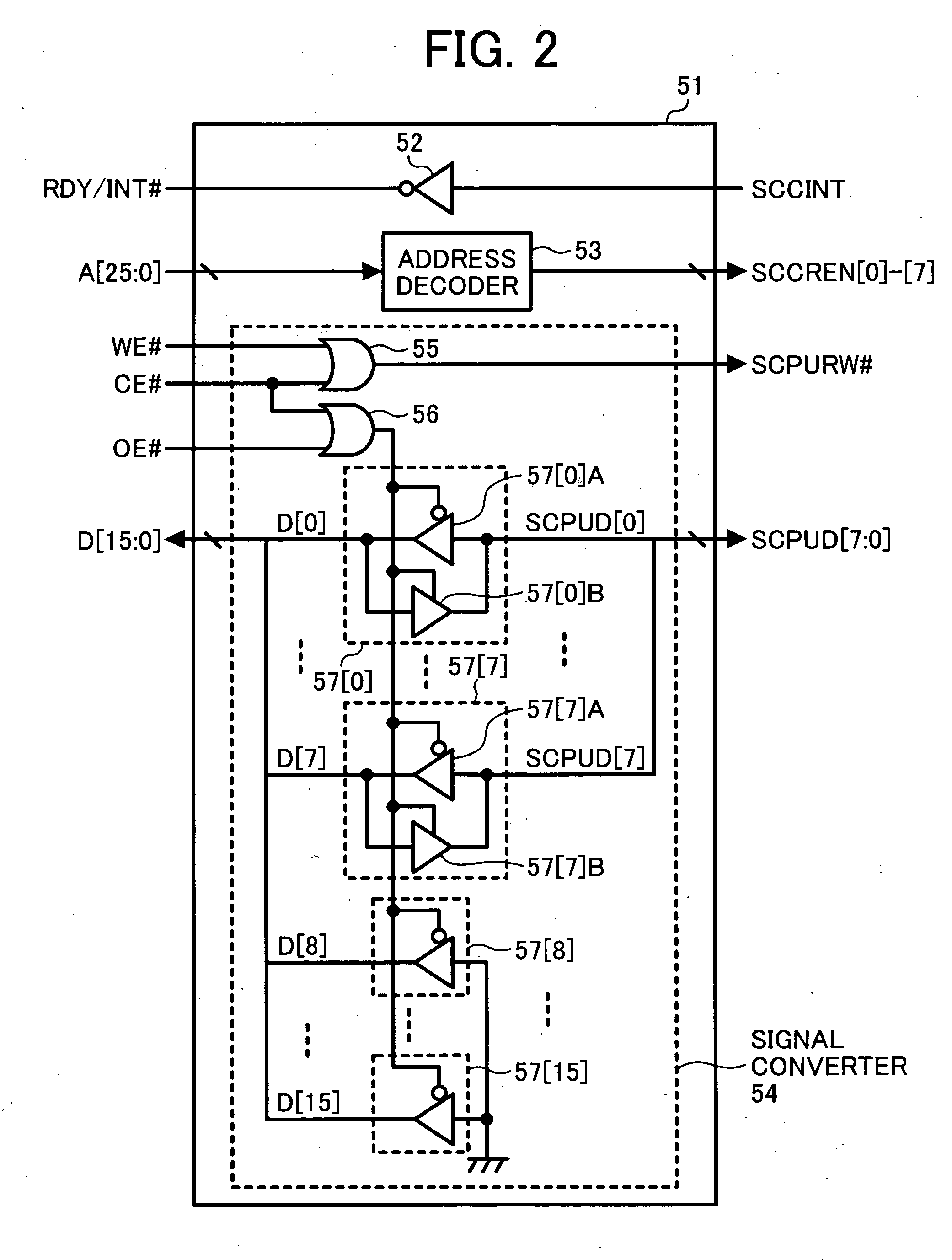

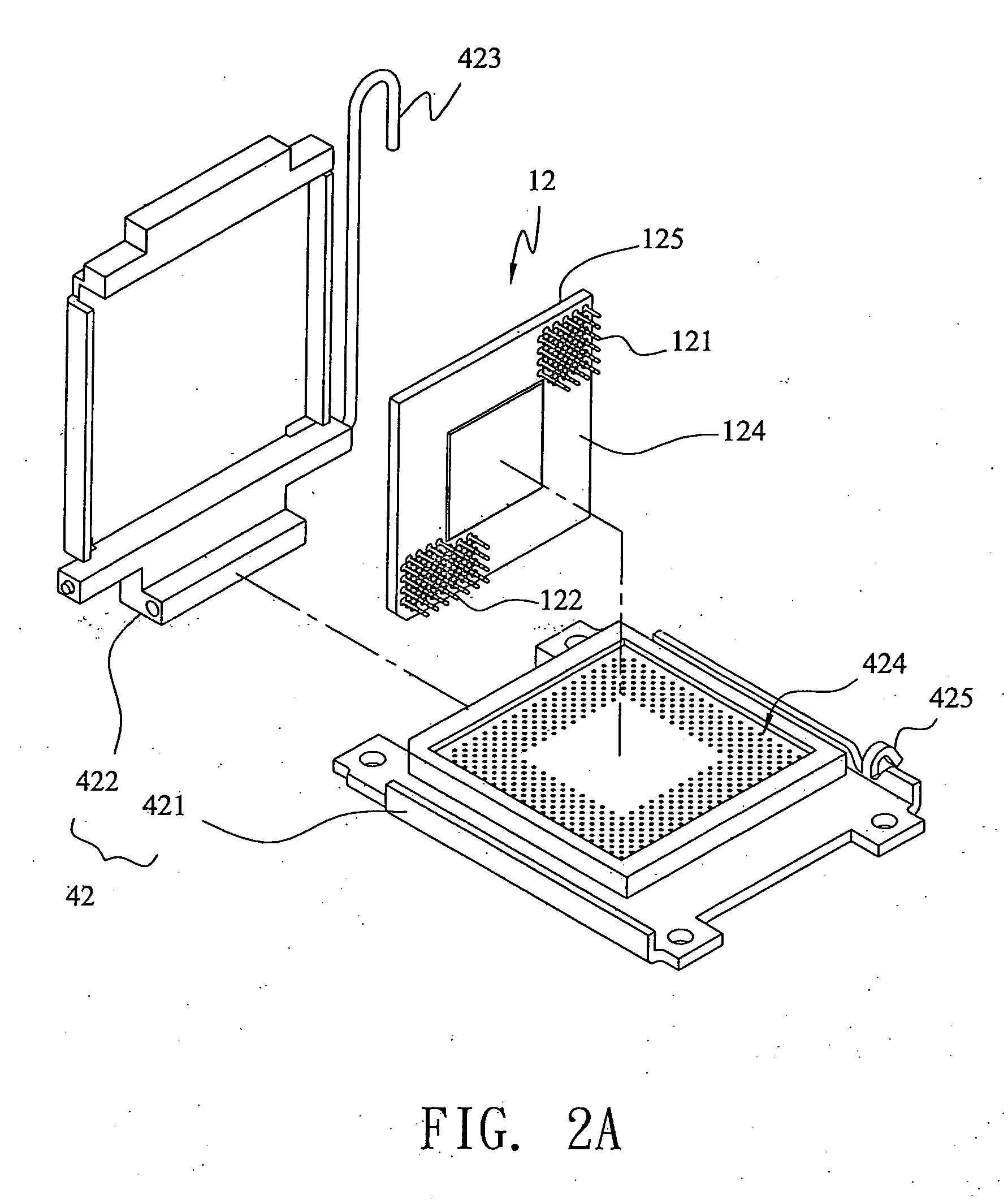

Card recognition system for recognizing standard card and non-standard card

InactiveUS20050077355A1Sensing record carriersRecord carriers used with machinesData conversionRecognition system

A novel card recognition system includes a computer having a card controller for exchanging data with a standard card that is compliant with a standard and a non-standard card that is not compliant with the standard, and a card adapter for connecting the non-standard card to the computer so that the non-standard card is recognized. The computer or card adapter includes a data converter having an input / output controller for the non-standard card and converting data of the non-standard card into data for the standard card, and an interface having an input / output controller for the standard card and connected to the data converter via a dedicated transmission path.

Owner:RICOH KK

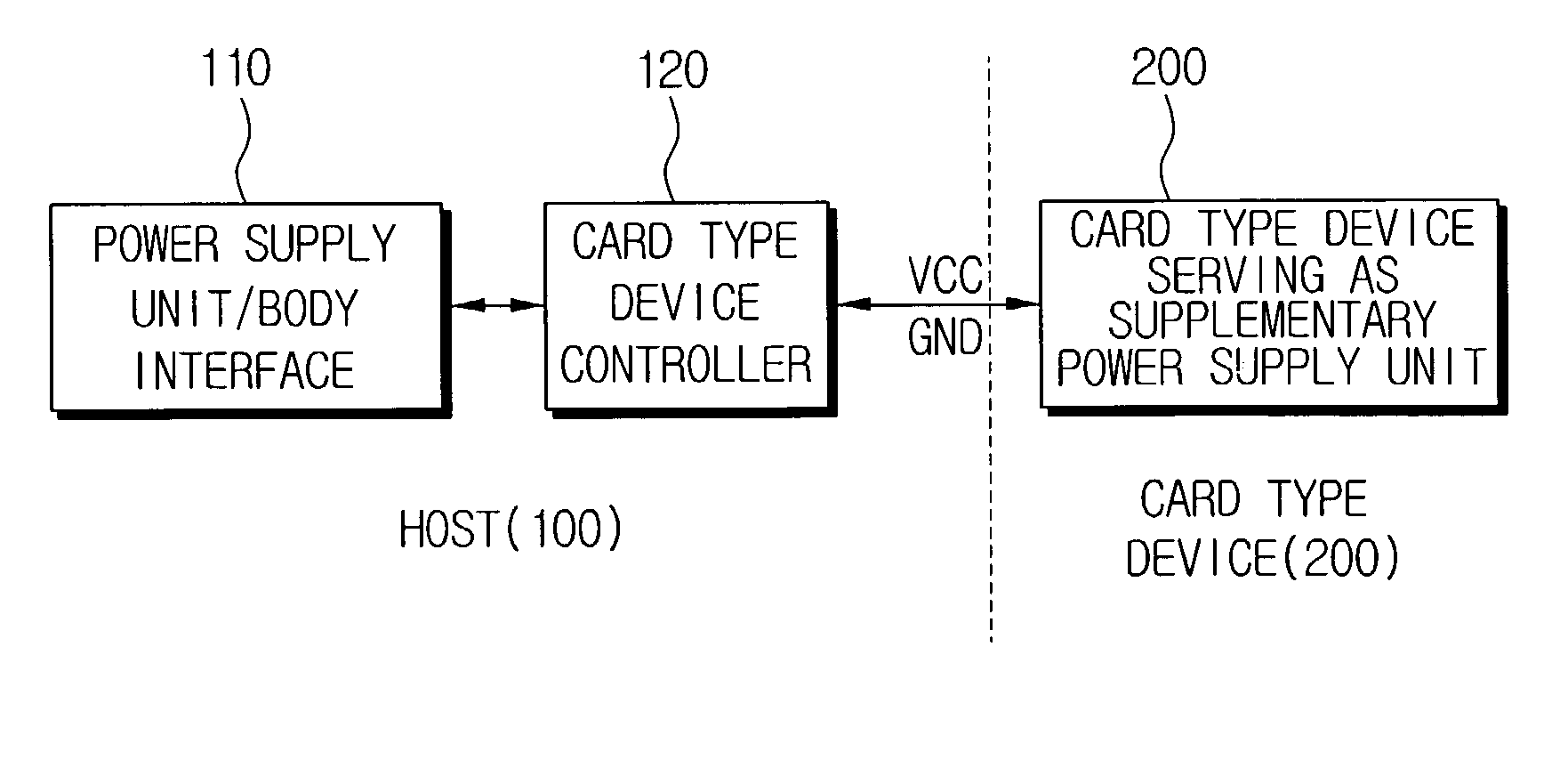

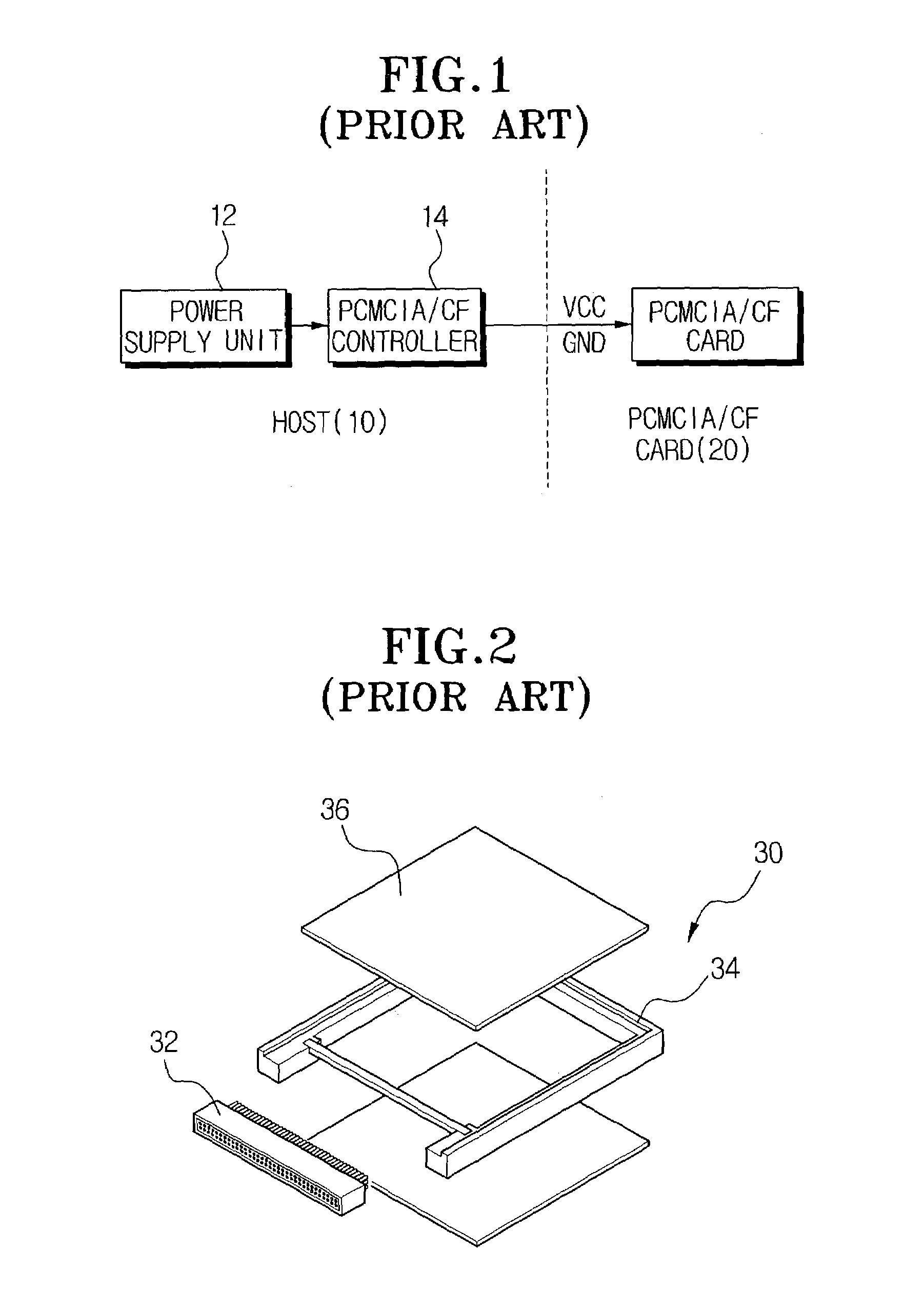

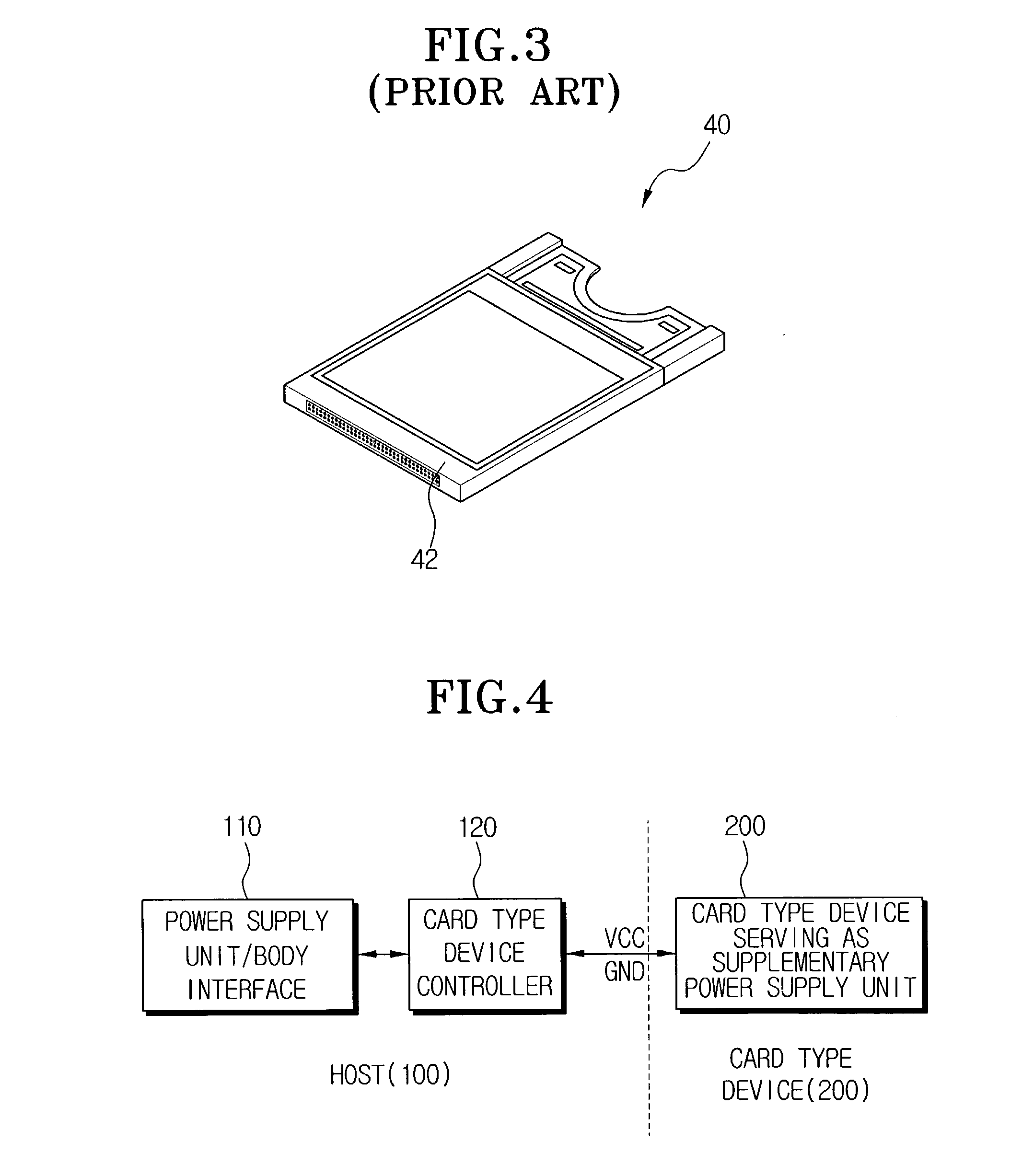

Card type device serving as supplementary battery and host using the same

InactiveUS7170257B2Long operating timeVolume/mass flow measurementCells structural combinationData connectionBattery charge

A card type device serving as a supplementary power supply device, and a host using the same. The card type device may include a battery provided in a frame to serve as a supplementary power supply to the host, a connector to connect to the host for an interfacing of power and data to and / or from the host, a battery charging / discharging circuit to charge the battery with an input power supplied via the connector, and to output the power of the battery via the connector. A power input / output controller provides the host with information of attributes of the battery during a connection to the host, with the power input / output controller to control the battery charging / discharging circuit so that the power of the battery is supplied to the host when a request for power supply is transmitted from the host. The power input / output controller controls the battery charging / discharging circuit so that the battery is charged with the input power when the battery is completely discharged. Further, the battery charging / discharging circuit is a smart battery circuit, and the smart battery circuit provides the host with information of attributes of the battery via an address pin of the connector. The information of the attributes of the battery, provided to the host, include at least one of a battery voltage, a battery remnant, battery charging times, a battery manufacturer, and a battery manufacturing period.

Owner:SAMSUNG ELECTRONICS CO LTD

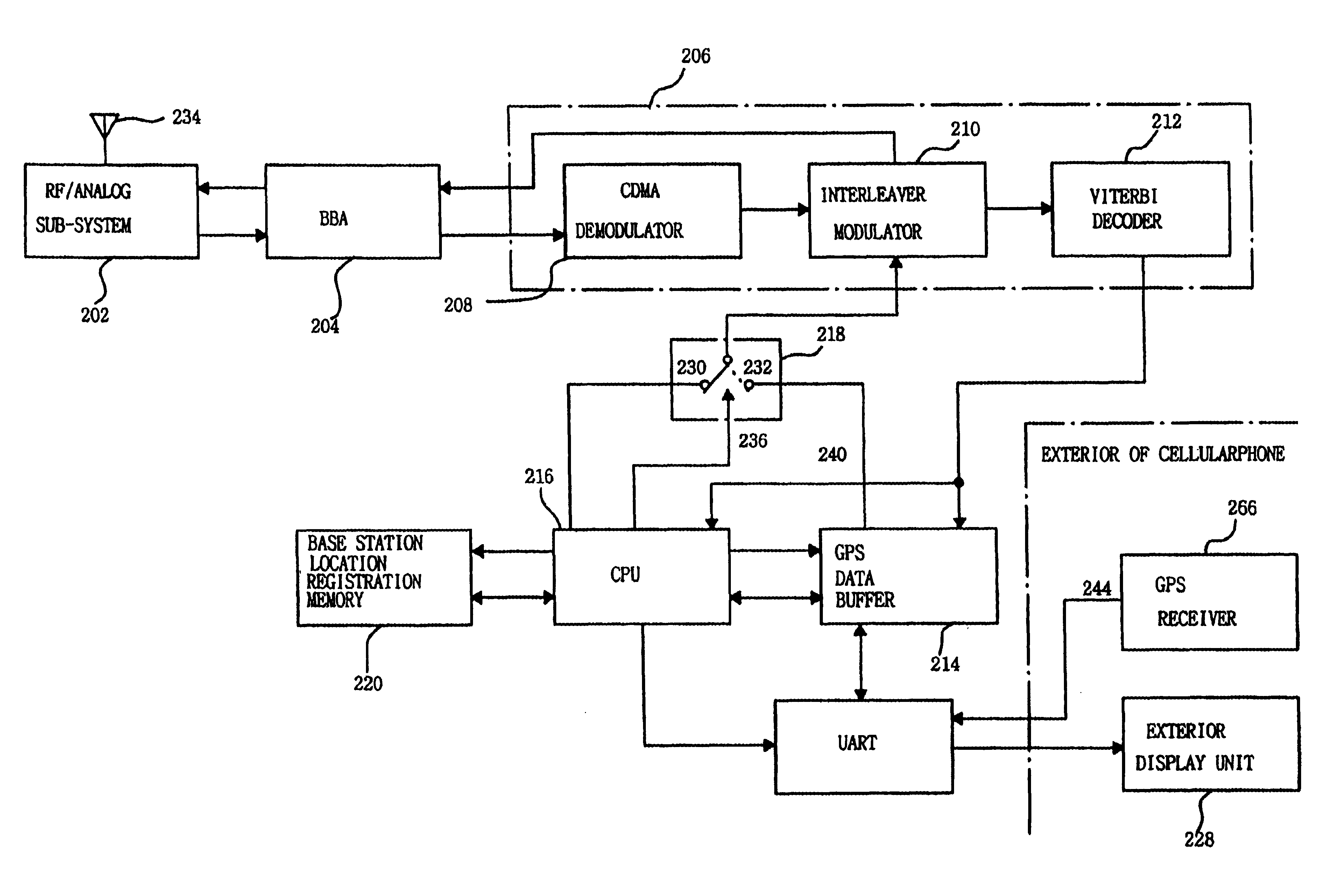

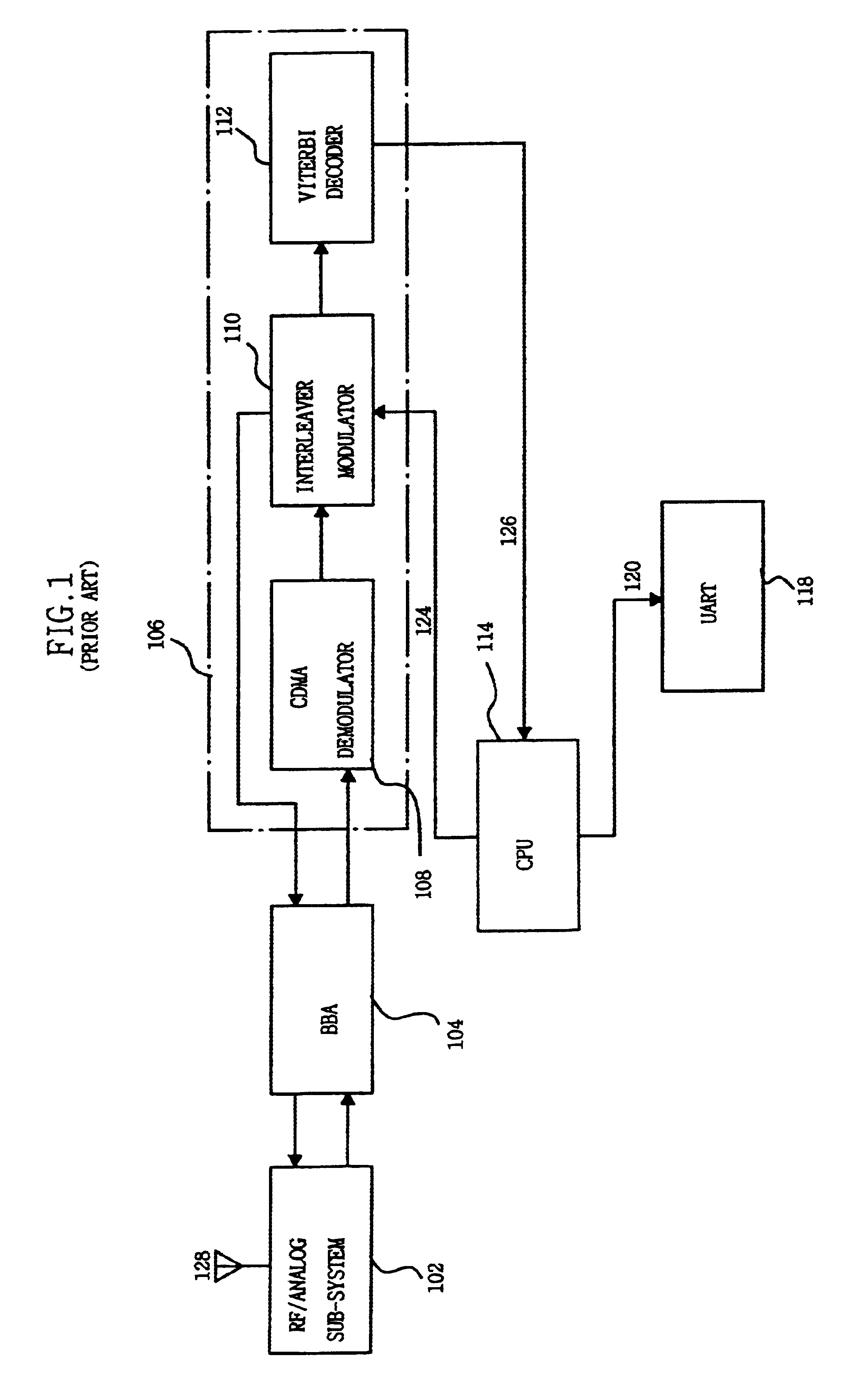

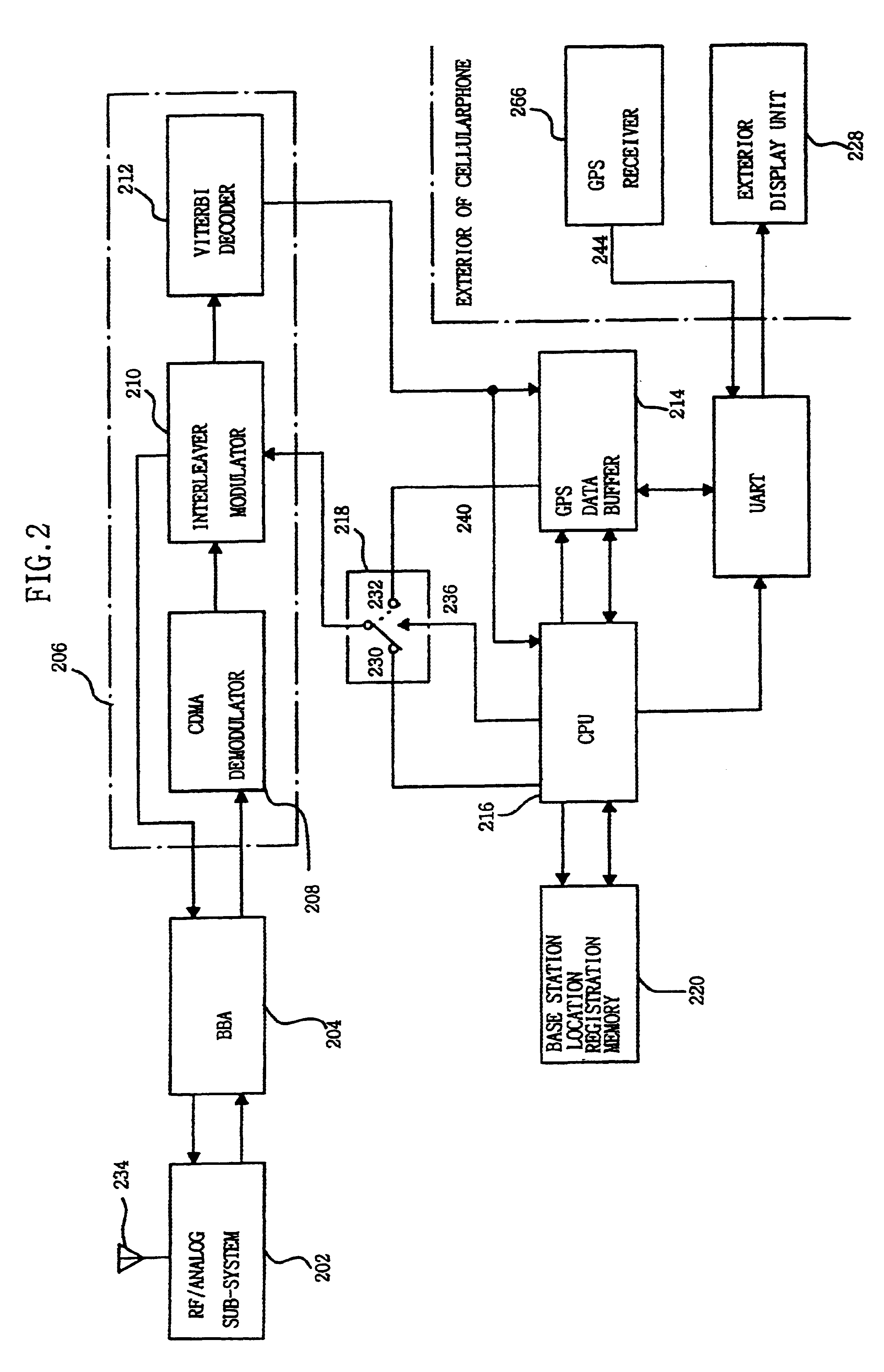

GPS data controller in mobile communication system and control method thereof

InactiveUS6684078B1Radio/inductive link selection arrangementsRadio transmission for post communicationTime informationGps receiver

A mobile communication system includes a signal processor, a first memory, a controller, and an input-output controller. The signal processor receives first forward GPS data and transmits backward GPS data. The first memory has a preamble area, a base station information area, a time information area, and a location information area and stores the backward GPS data, the first forward GPS data, and second forward GPS data received by an exterior GPS receiver. The controller controls data input and output over the first memory and controls transmission of the backward GPS data stored in the first memory to the signal processor. The input-output controller is controlled by the controller and transmits the second forward GPS data to the first memory.

Owner:MAGNACHIP SEMICONDUCTOR LTD

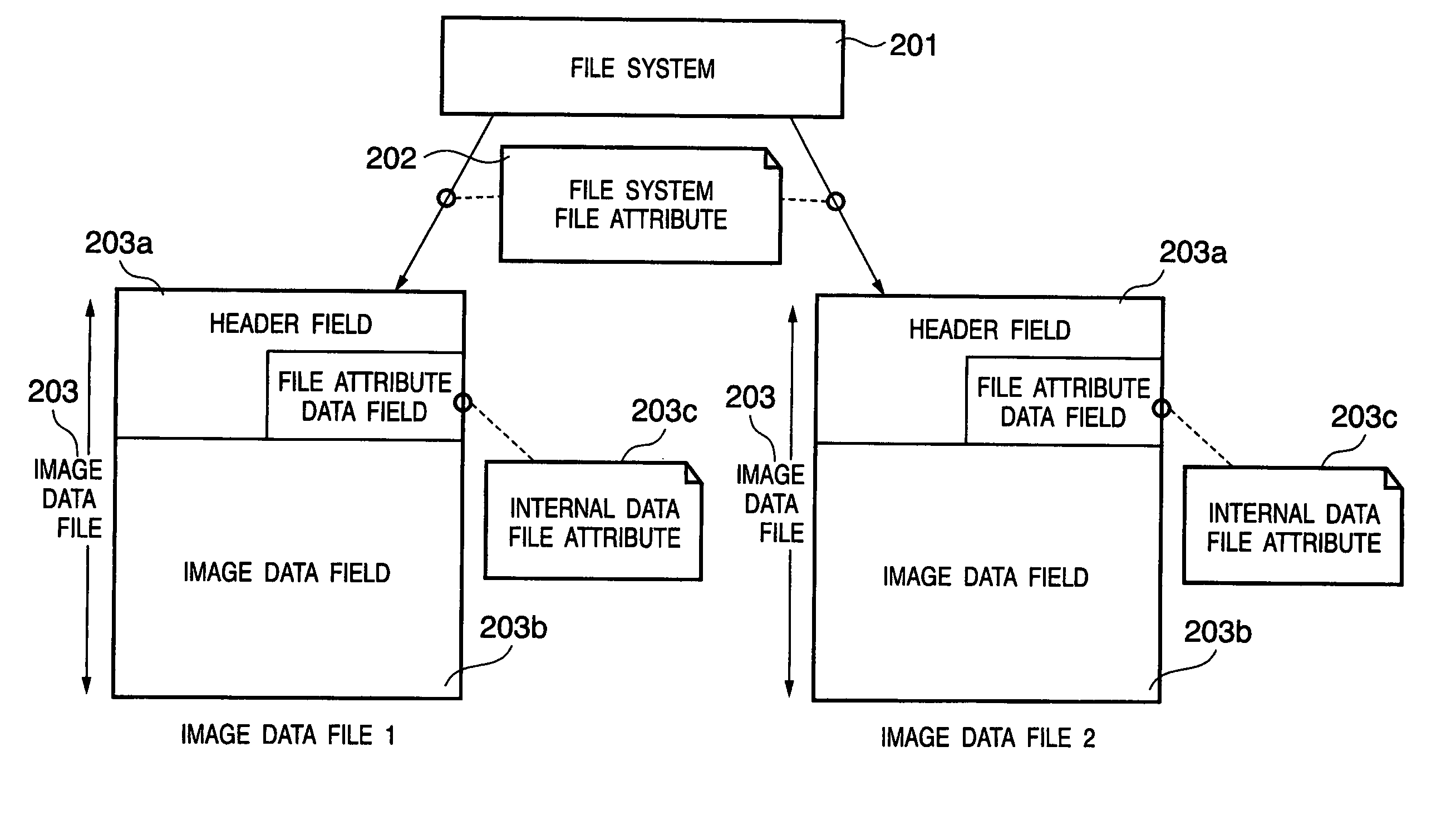

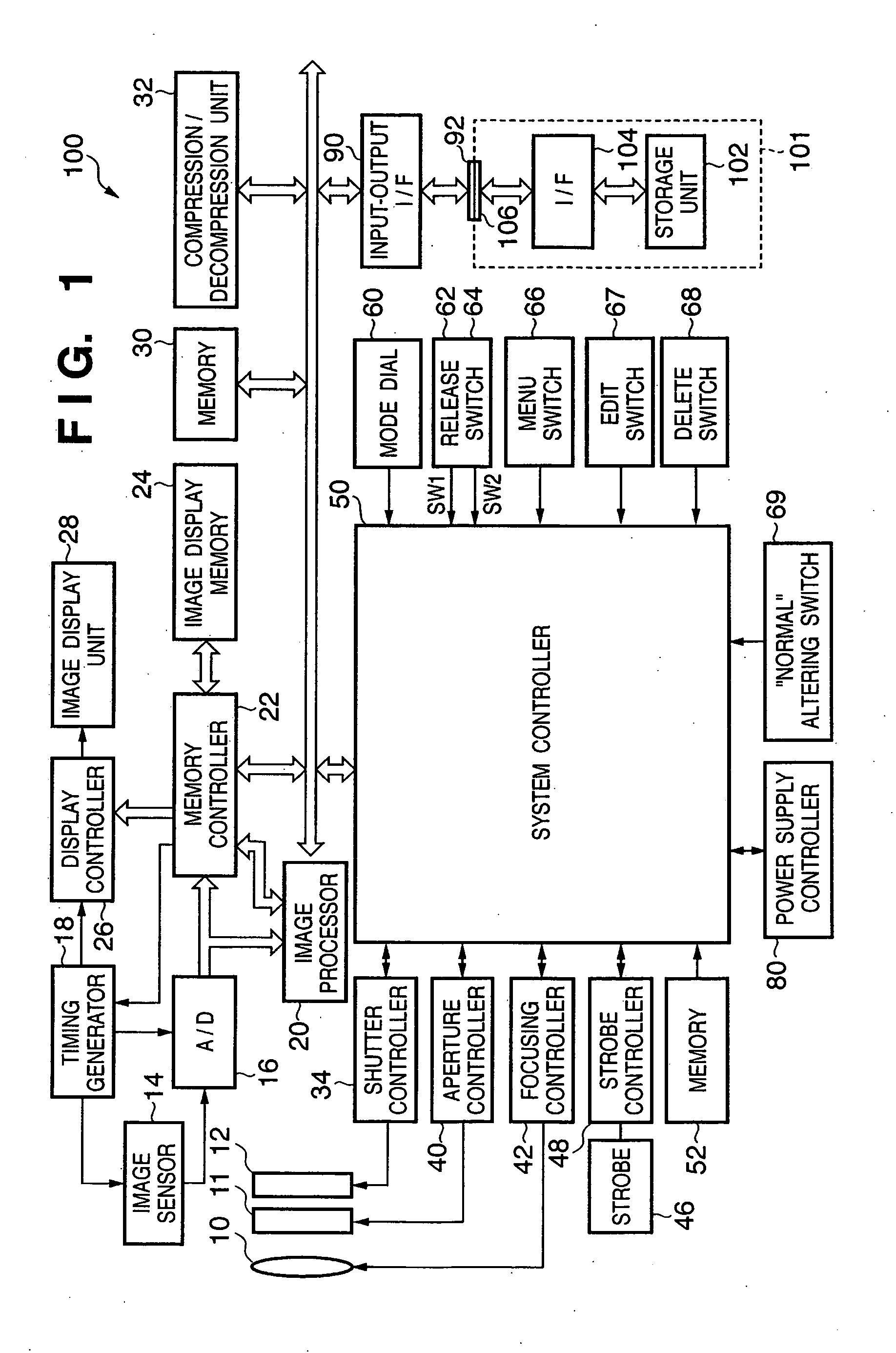

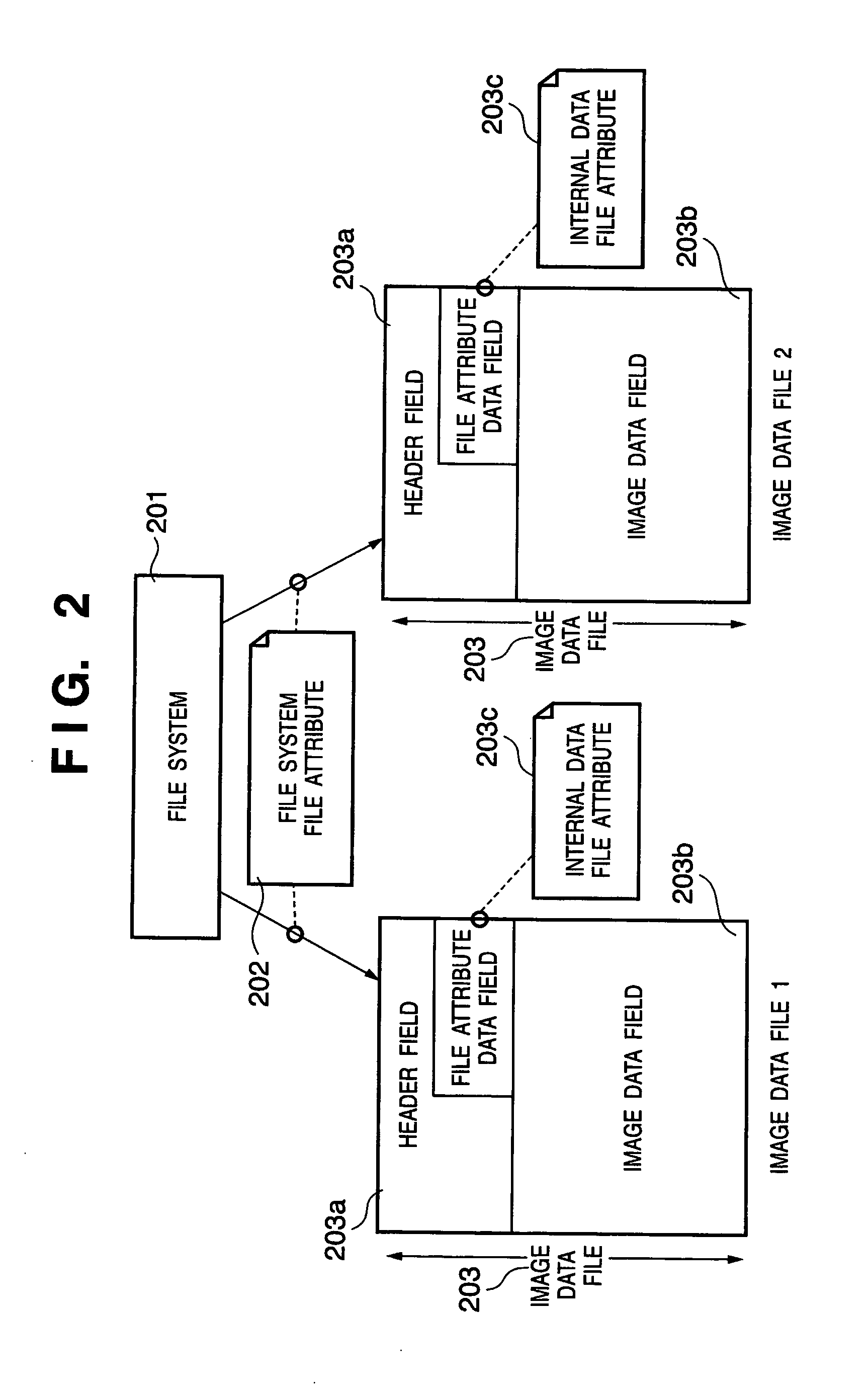

Image processing apparatus, image processing method, computer program, and storage medium

InactiveUS20070198546A1Digital data processing detailsDigital data protectionImaging processingExternal storage

An apparatus has a first attribute setting unit which sets first attribute information of image data, a second attribute setting unit which sets second attribute information of the image data, and an input-output controller which writes and reads out image data to and from an external storage medium. The first attribute information is stored in the image data, and the second attribute information is stored in an area in the external storage medium, which is used to manage the image data to be written in the external storage medium.

Owner:CANON KK

Secured inter-processor and virtual device communications system

InactiveUS20050172101A1Reliable dataFacilitate communicationGeneral purpose stored program computerInternal/peripheral component protectionBus interfaceElectronic security

The invention comprises an electronically secured inter-processor and virtual device communications system, with an input / output controller board, a multi-drop bus interface to multiple devices, and a parallel interface to an industry standard single board computer. The invention assigns a bus address and virtual identification number to each device and controls communications between the main central processing unit and the devices through a Plug-n-Play protocol.

Owner:ARISTOCRAT TECH AUSTRALIA PTY LTD

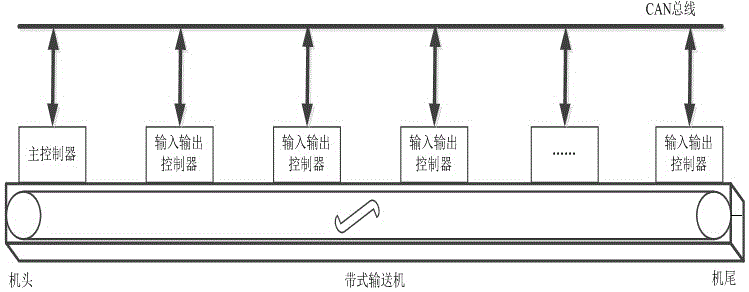

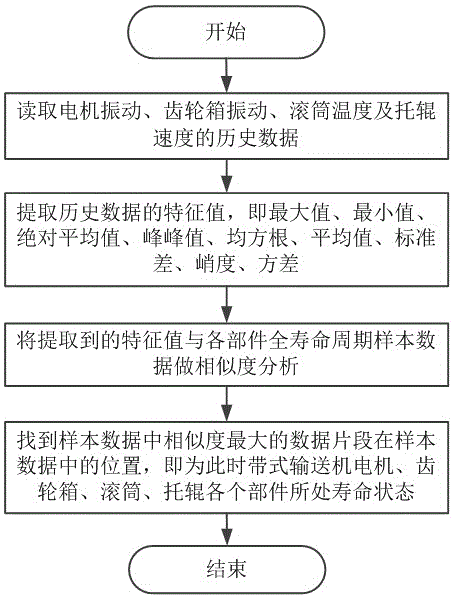

Monitoring and service life managing system for belt conveyor

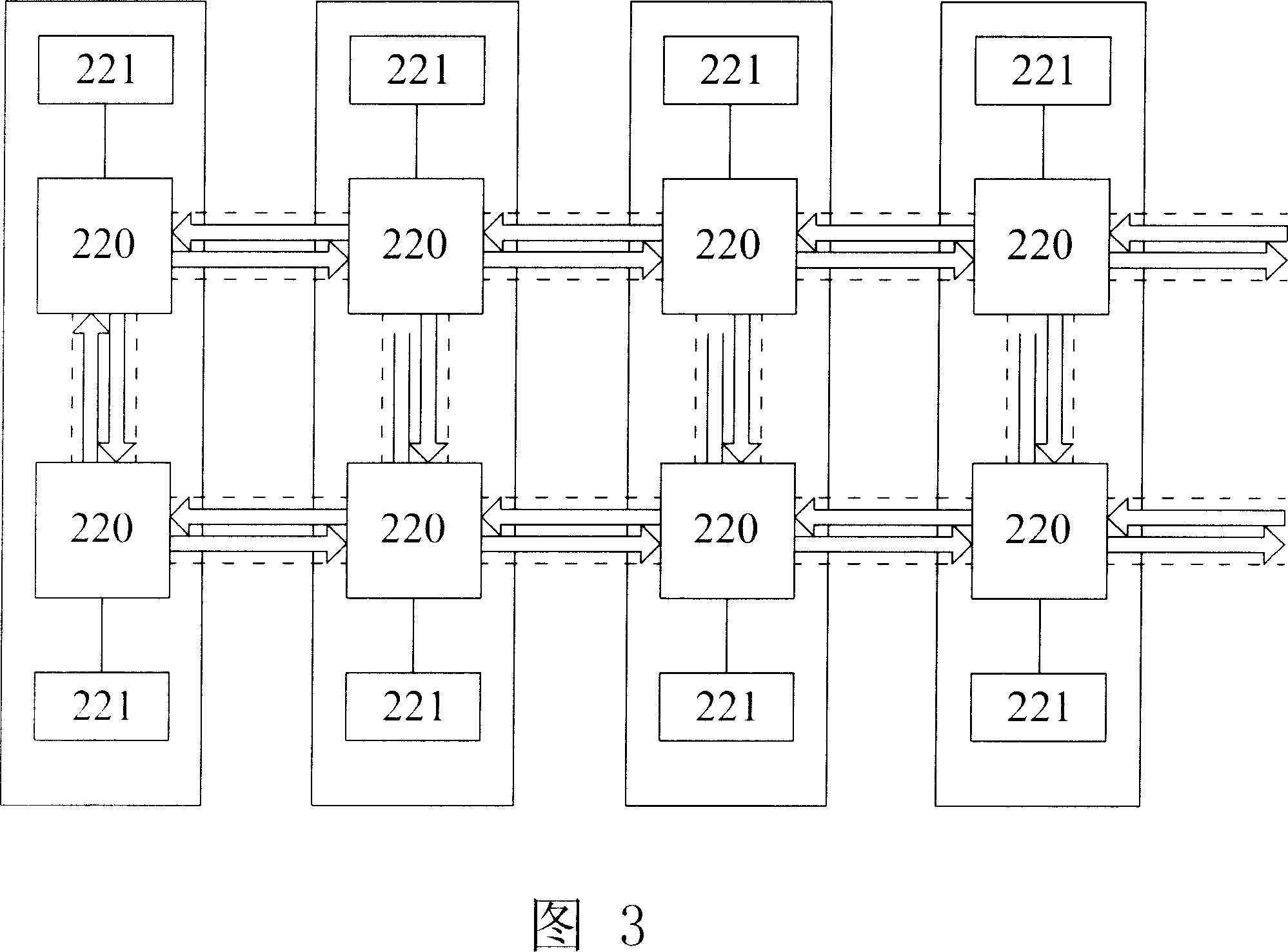

InactiveCN106241270ARealize monitoringAchieving condition-based maintenanceConveyorsControl devices for conveyorsPower flowHuman–machine interface

The invention discloses a monitoring and service life managing system for a belt conveyor. A master controller positioned on the machine head of the belt conveyor communicates with a plurality of input and output controllers which are positioned on a plurality of joints along the belt conveyor, the input and output controllers acquire fault signals of off-tracking, over-temperature, smoke, coal piling, tearing and slipping of the belt conveyor as well as temperature signals of a motor, a gearbox and a roller, an adhesive tape operation speed signal, a motor current signal, and vibration signals of the motor and the gearbox, and the master controller analyzes, computes and processes acquired information through a human-computer interface based on VB, so that comprehensive monitoring, in an operation process, of the belt conveyor as well as service life management on the motor, the gearbox, the roller and a carrier roller part is realized. According to the monitoring and service life managing system disclosed by the invention, the operation state of the belt conveyor is monitored in real time, corresponding control signals can be output according to monitored information, and management is carried out on service life of the motor, service life of the gearbox, service life of the roller and service life of the carrier roller, so that safety, stability and continuity of operation of the belt conveyor are improved.

Owner:TAIYUAN UNIV OF TECH

Simulator for skill-oriented training

ActiveUS10388176B2Easy inputHigh outputSoil-shifting machines/dredgersDesign optimisation/simulationVirtual trainingSkill sets

A skill-based training system includes a processing system having a processor, memory coupled to the processor with executable instructions stored therein, and an input-output controller coupled to the processor and to input and output devices. The memory includes lesson plans that outline skill-based tasks and activities, and predetermined performance criteria. The processor is configured by the instructions to present interfaces on the output devices simulating a virtual training environment. The processor is configured to receive input signals representative of performing the tasks and activities in the virtual environment, and to evaluate the performance by comparing the performed tasks and activities to the criteria, to determine a score and to present the score on the output devices. The system includes work orders categorized by the lesson plans and defining within an increasing progression of a degree of skill, knowledge, critical thinking and problem solving needed to complete the tasks and activities.

Owner:VRSIM

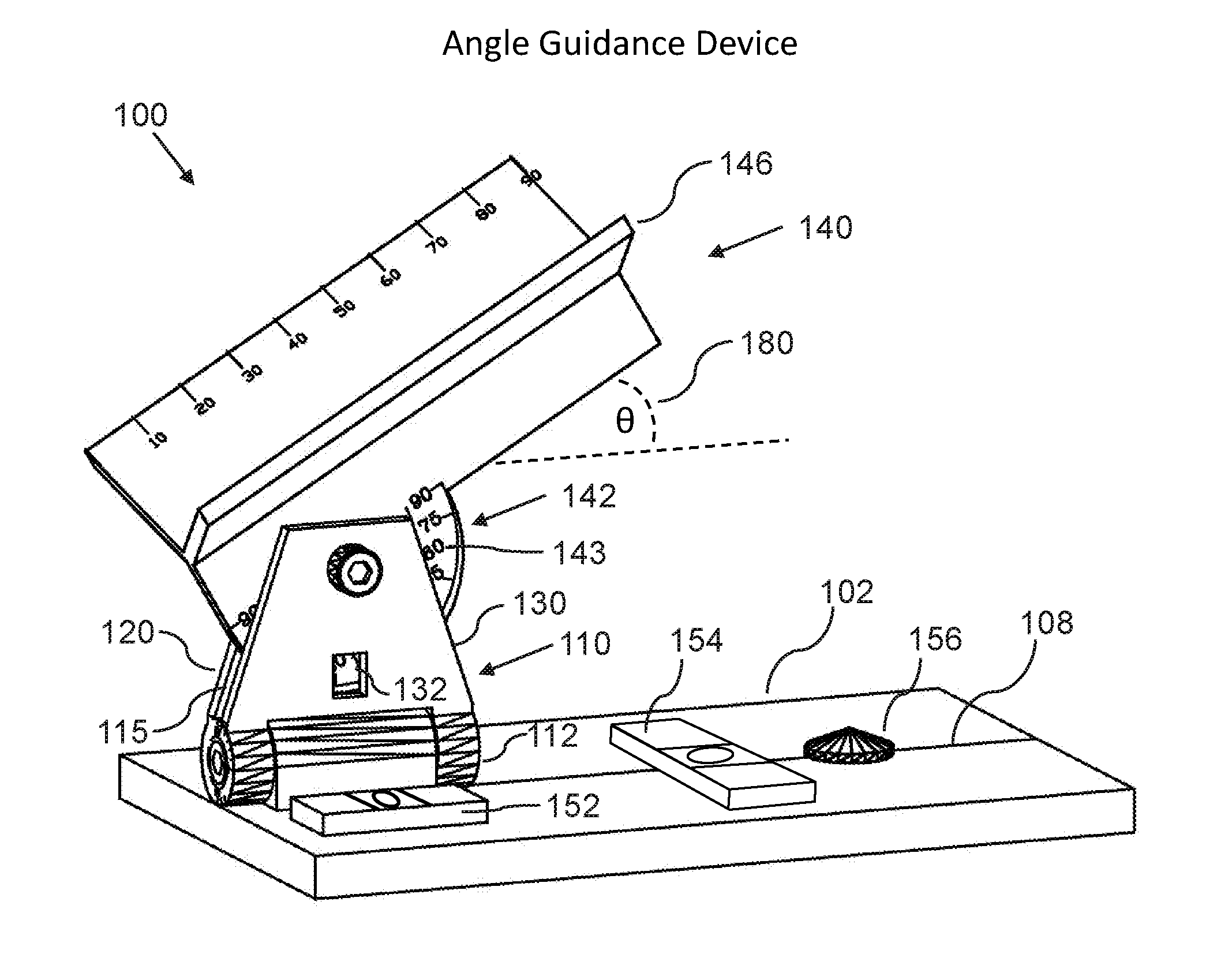

Angle-guidance device and method for CT guided drainage and biopsy procedures

An angle guidance device includes a base, which can be flexible and self-adhesive; a connector piece, including a rotatable connection, which is tiltable to a left or right side, and right and left connector plates, each including center and protractor cutouts; and a guidance piece, including an insert or protractor piece, and v-shaped needle guide, such that the v-shaped needle guide can be adjusted to a predetermined device inclination angle relative to the base. Optionally included are longitudinal and lateral level components, a bullseye level, a laser pointer, a screen, and an angle-guidance control unit, including a processor, a non-transitory memory, an input / output, a CT controller, an angle sensor, an angle viewer, a 3-axis accelerometer, and a data bus. Also disclosed is an angle-guidance method, including obtaining CT images, measuring angle and depth, setting biopsy angle, marking entry point, positioning angle-guidance device, marking position, inserting procedure needle.

Owner:RAHMAN AKM A

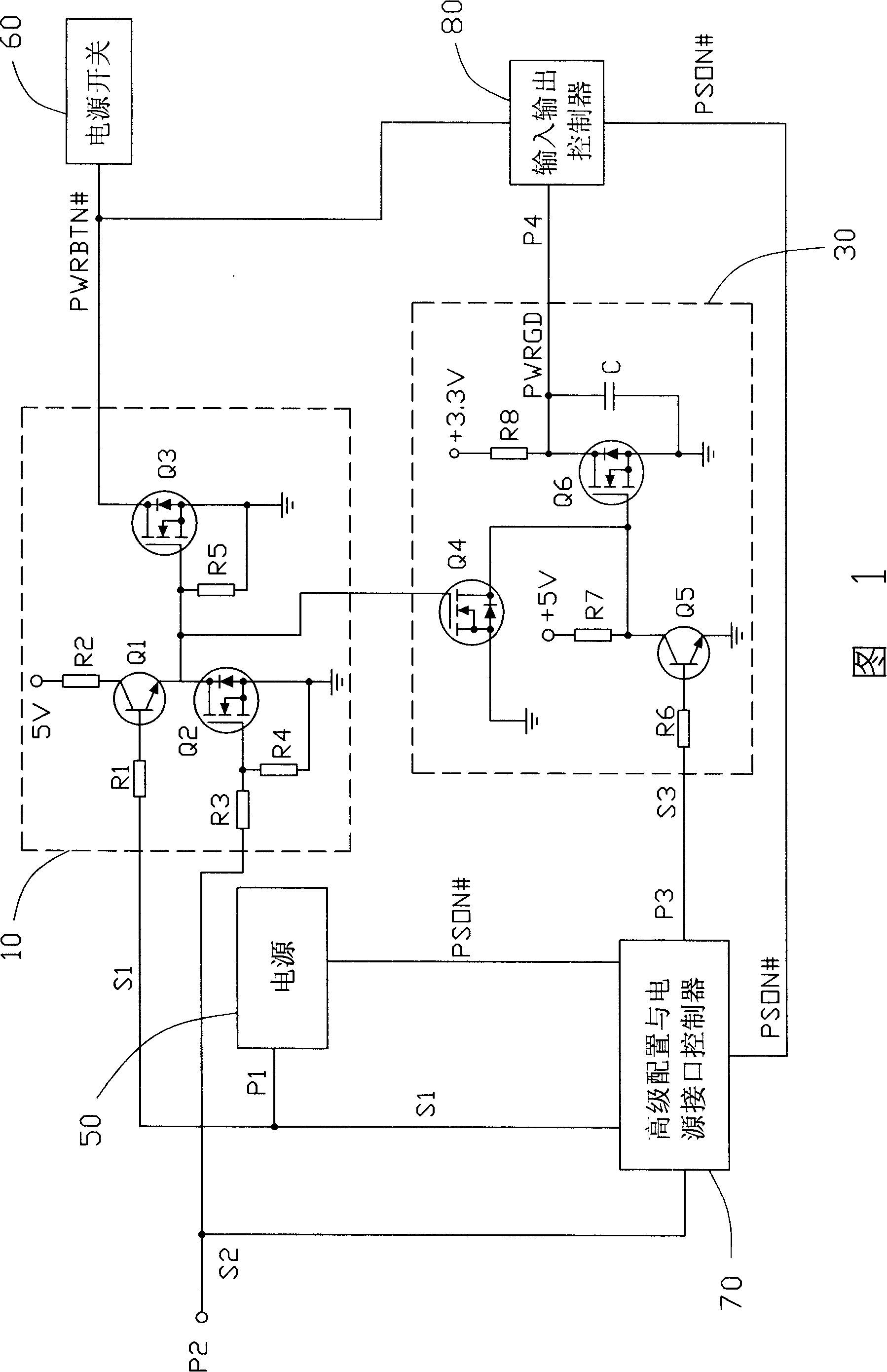

Main board power supply protection circuit

InactiveCN101212139ATimely protectionQuickly detect power supply statusVolume/mass flow measurementEmergency protective circuit arrangementsAdvanced Configuration and Power InterfaceControl signal

The invention relates to a power supply protection circuit for a main board used for protecting the main board of a power cord in an unconnected central processor unit. The power supply protection circuit for the main board comprises an input and output controller, an advanced configuration and a power interface controller. The power supply protection circuit for the main board also comprises a controlling signal generation circuit and an enabling signal generating circuit. The controlling signal generation circuit generates a controlling signal according to the power supply condition of the central processor unit and the signal is sent into the input and output controller. At the same time, the enabling signal generating circuit generates an enabling signal which causes the input and output controller to process the controlling signal normally. When the power cord of the central processor is wrongly connected, the controlling signal causes the input and output controller to send a shutdown signal to the advanced configuration and the power interface controller to stop power supply. The power supply protection circuit of the main board can carry out protection for the main board with an occurrence of abnormal power state on the central processor unit.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

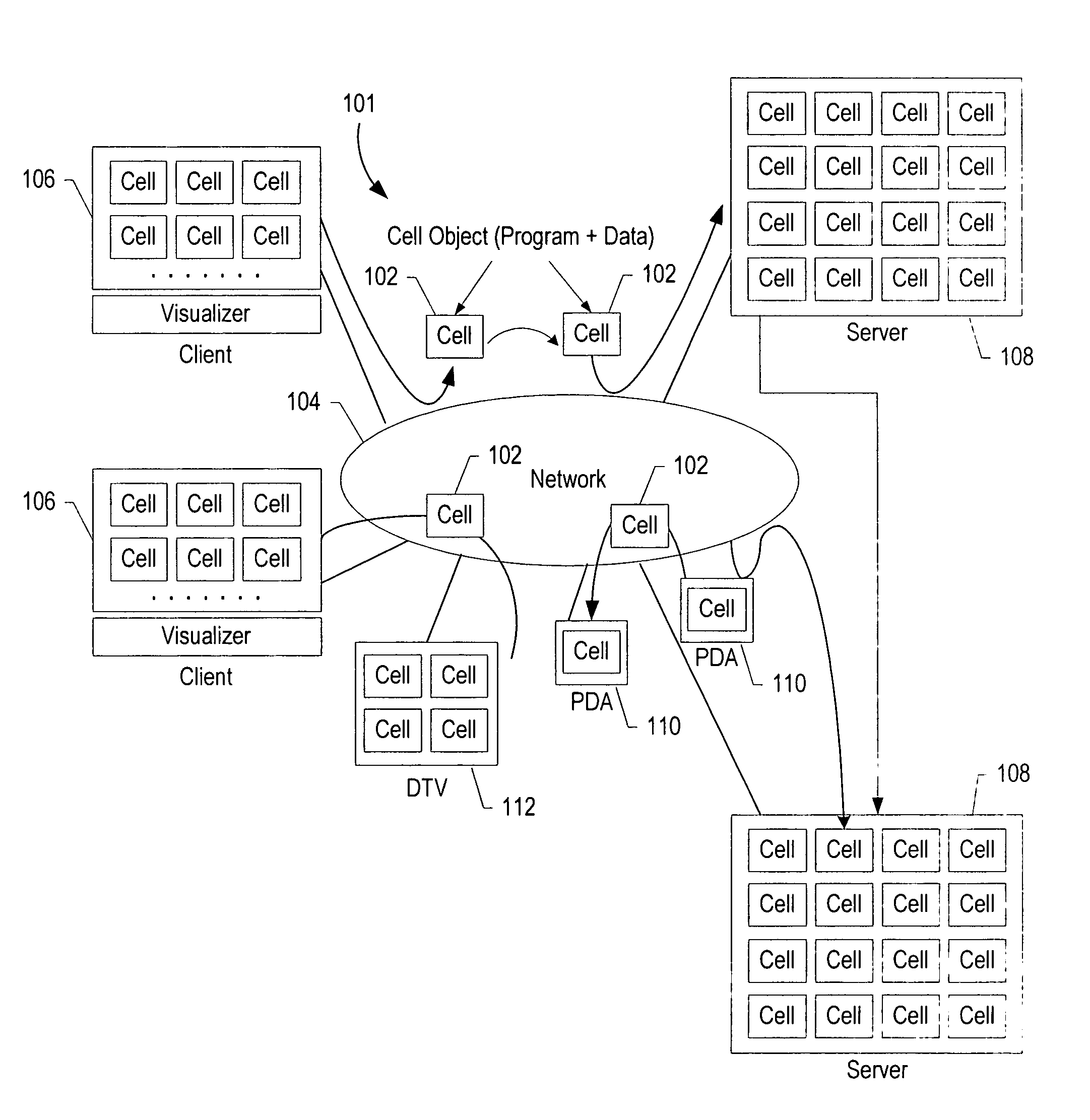

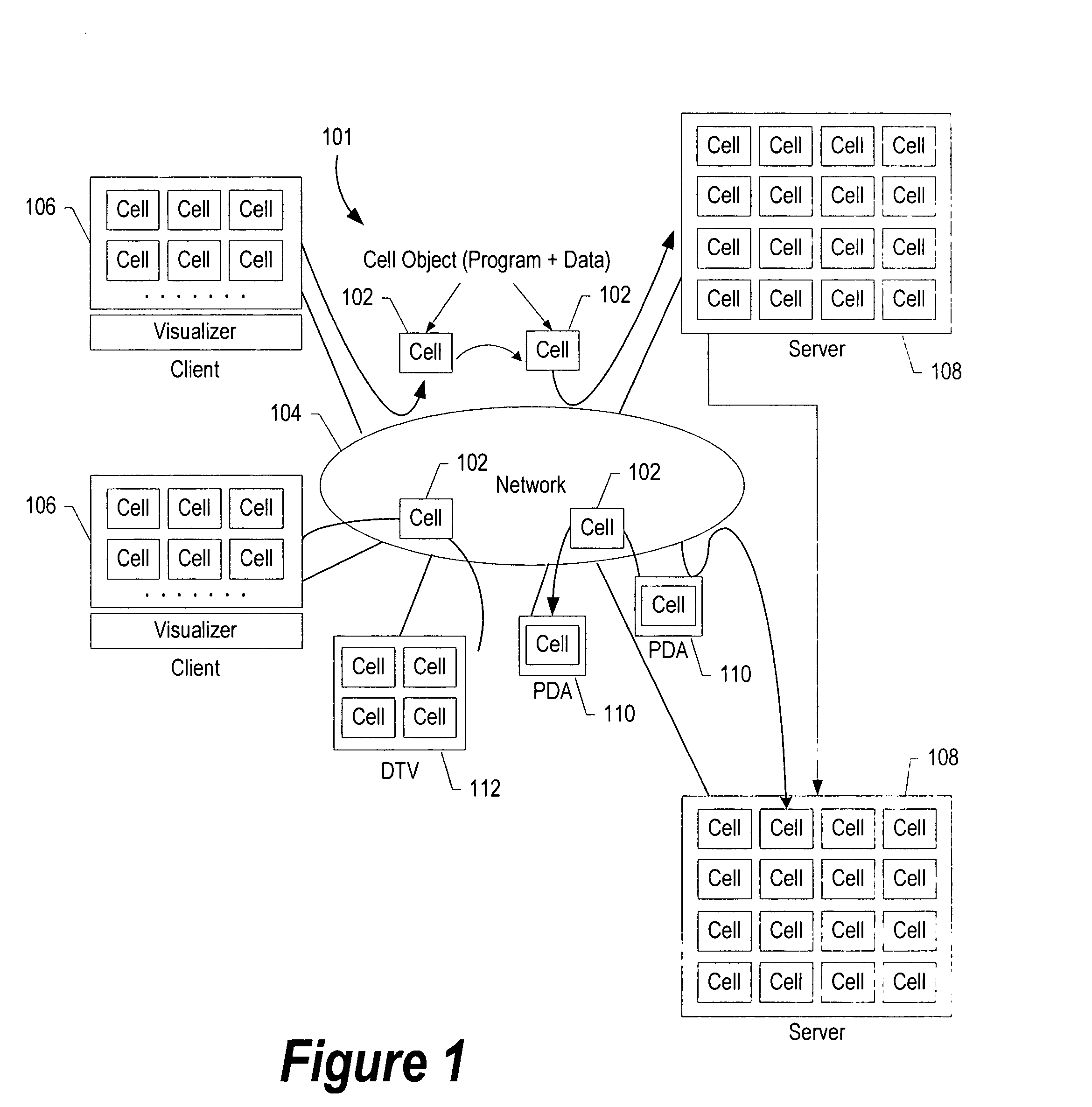

System and method for a configurable interface controller

ActiveUS20050097231A1Cathode-ray tube indicatorsDigital output to display deviceComputer hardwareInput output controller

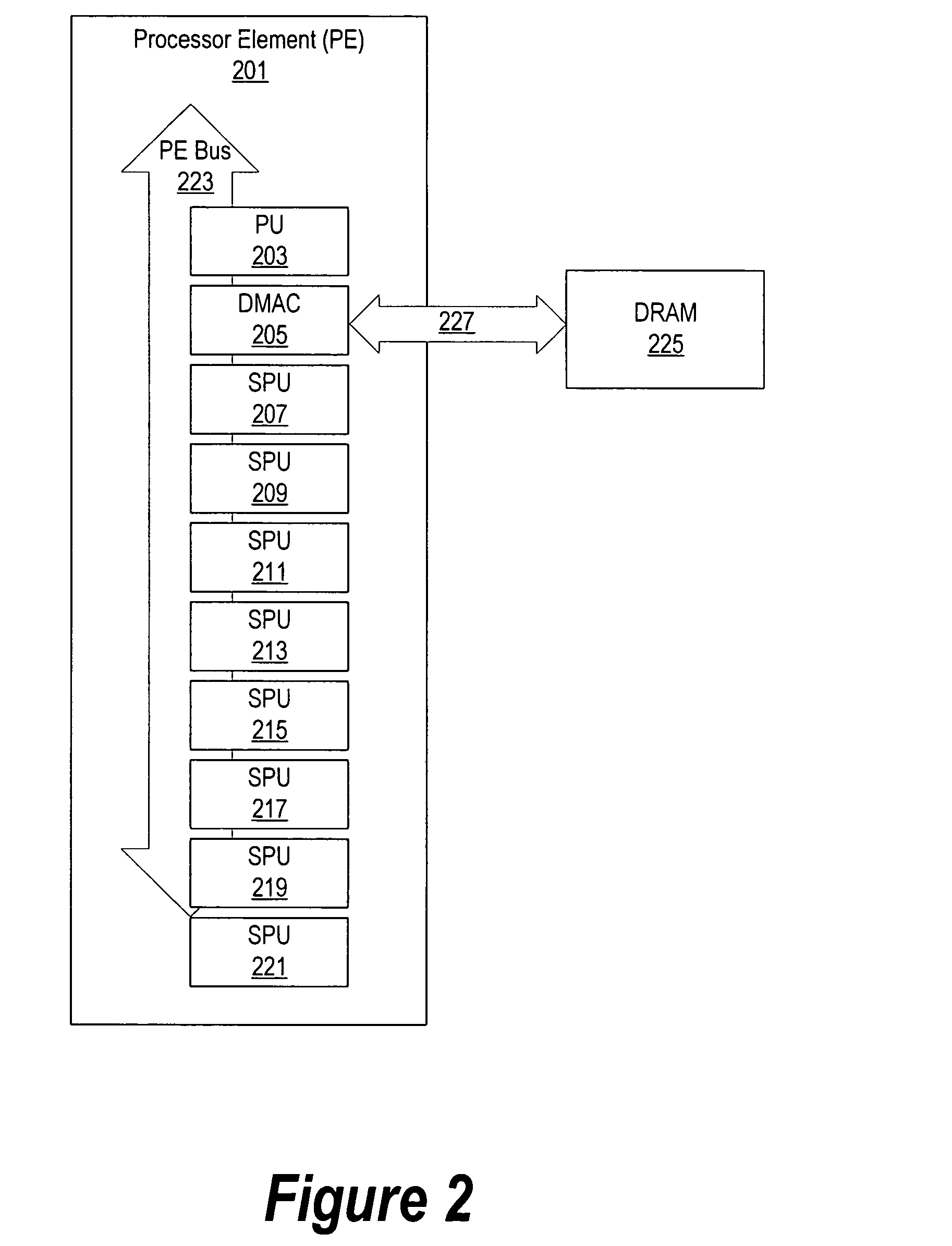

A flexible input / output controller logic interfaces with existing input / output controllers (IOC's) in order to configure the amount of data sent to and received from the IOC's. The flexible I / O interface receives data from a component at a rate determined by the particular component. The flexible I / O interface then feeds the received data to a traditional I / O controller at a rate suitable for the I / O controller. Thus, the interface to the individual I / O controllers is maintained. The flexible I / O logic balances bandwidth between a plurality of individual I / O controllers in order to better utilize the overall system I / O bandwidth. In one embodiment, the I / O configuration managed by the flexible I / O logic is determined during system-build, while in another embodiment, the I / O configuration is set during system initialization.

Owner:IBM CORP

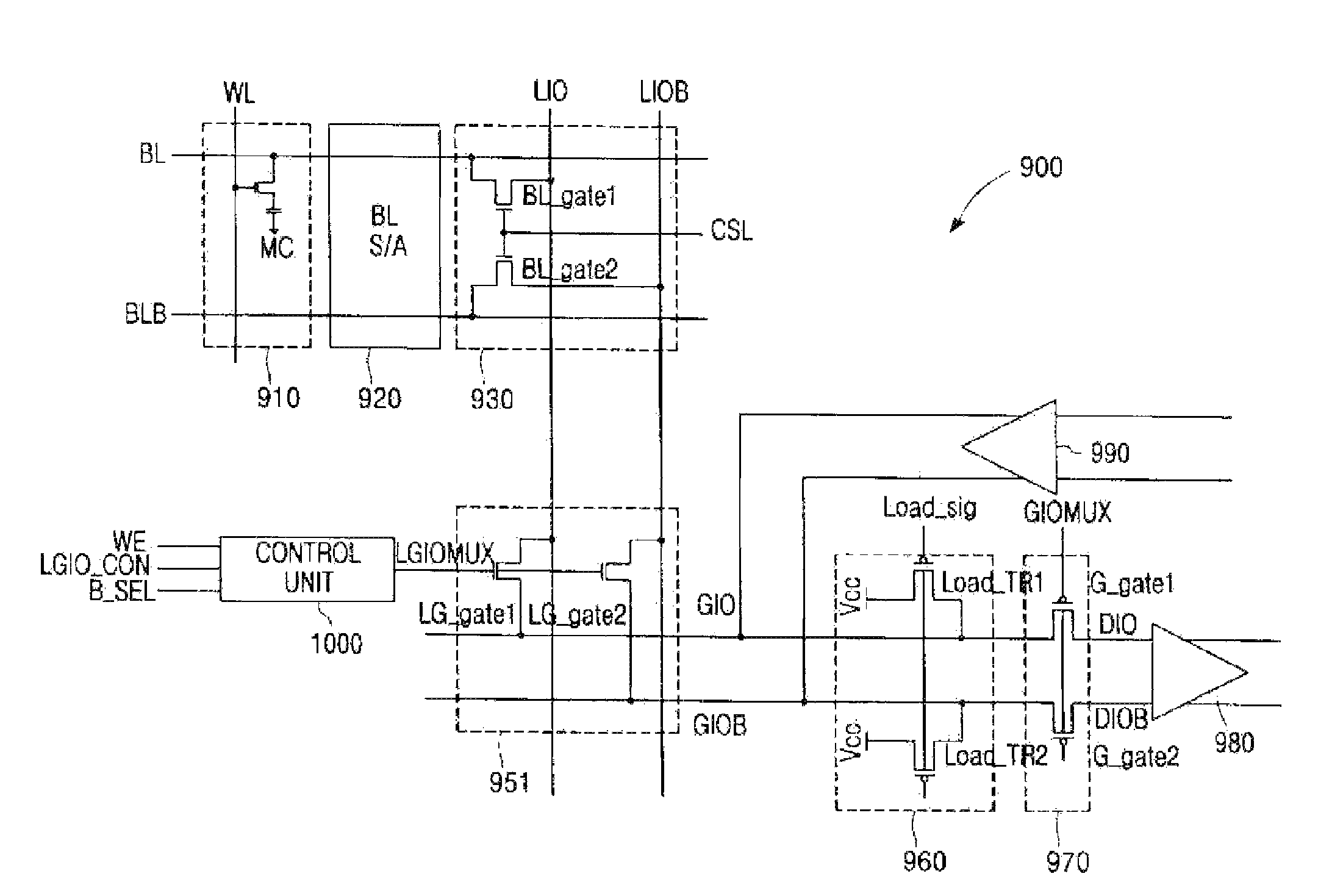

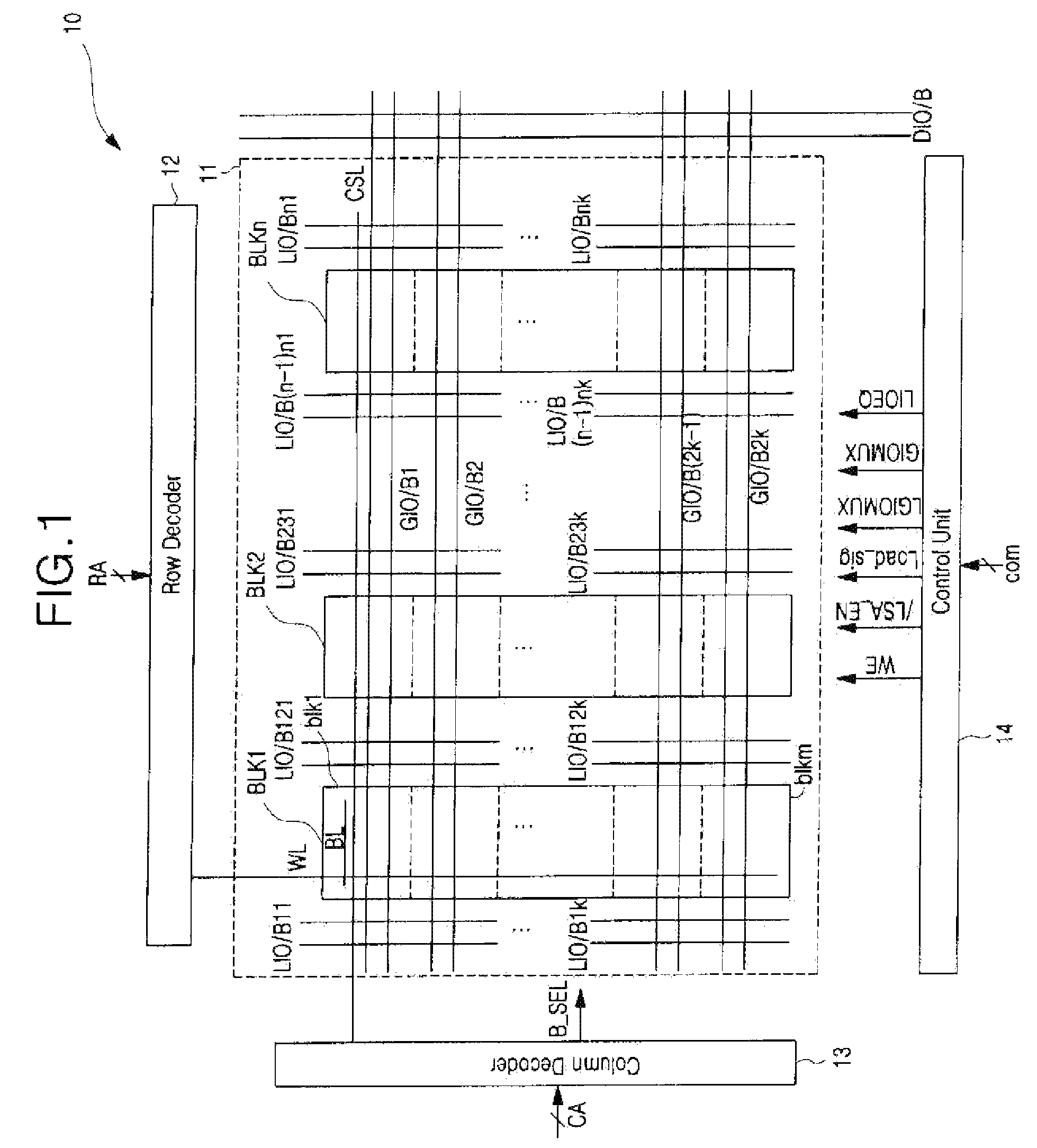

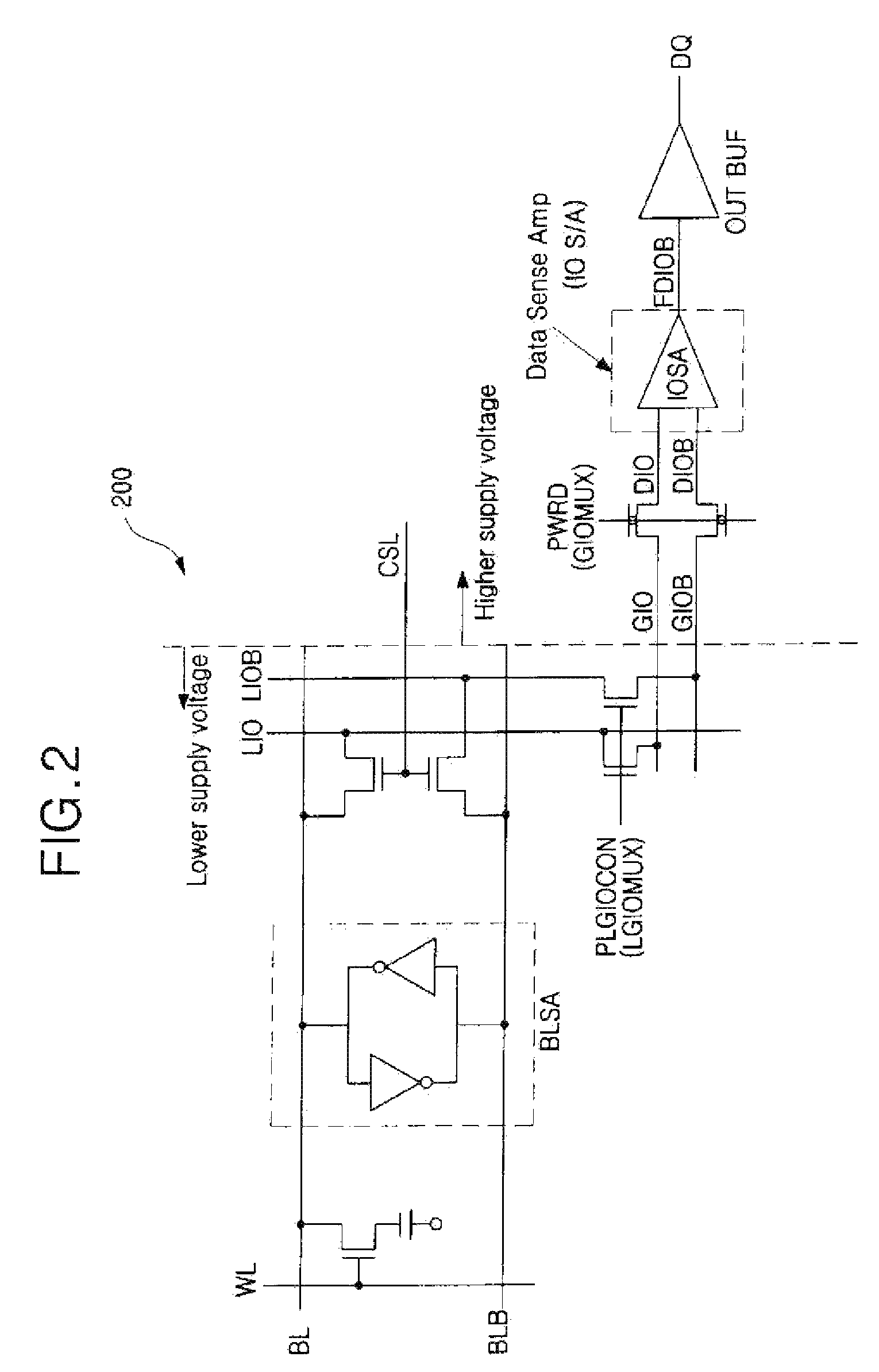

Memory device with separate read and write gate voltage controls

A circuit and method are provided for controlling the gate voltage of a transistor acting between local and global input / output lines of a memory device, the circuit including a local input / output line, a local from / to global input / output multiplexer in signal communication with the local input / output line, a global input / output line in signal communication with the local from / to global input / output multiplexer, and a local from / to global input / output controller having an input node and an output node, the input node disposed for receiving a signal indicative of an input or output operation, and the output node in signal communication with a gate of the local from / to global input / output multiplexer for providing a gate signal of a first or second level in the presence of the output operation, and a gate signal of a third level in the presence of the input operation.

Owner:SAMSUNG ELECTRONICS CO LTD

Automatic file generating apparatus, method, program and record medium

InactiveUS20050010548A1Low costShorten the timeDigital data processing detailsNatural language data processingComputer printingData file

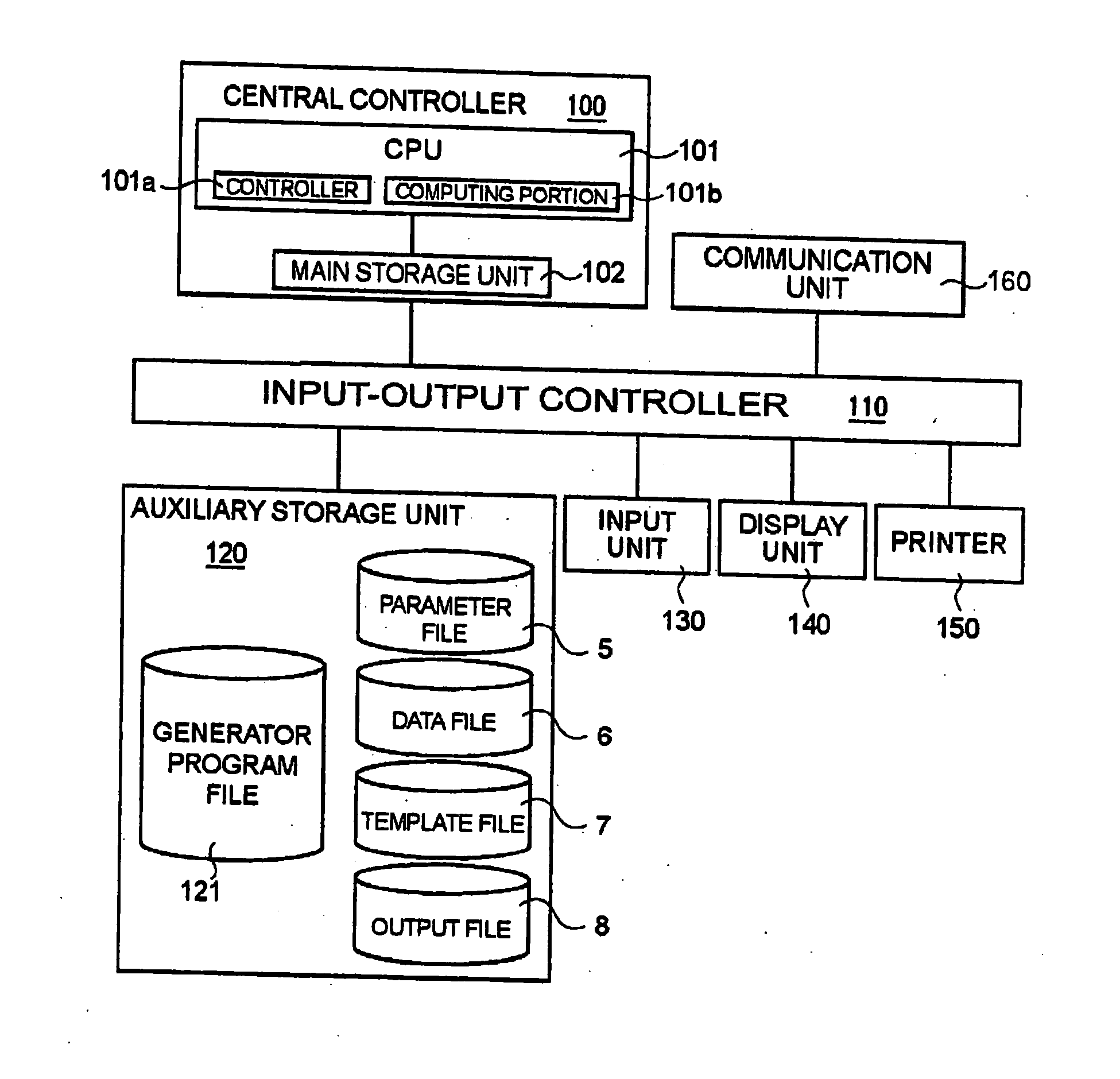

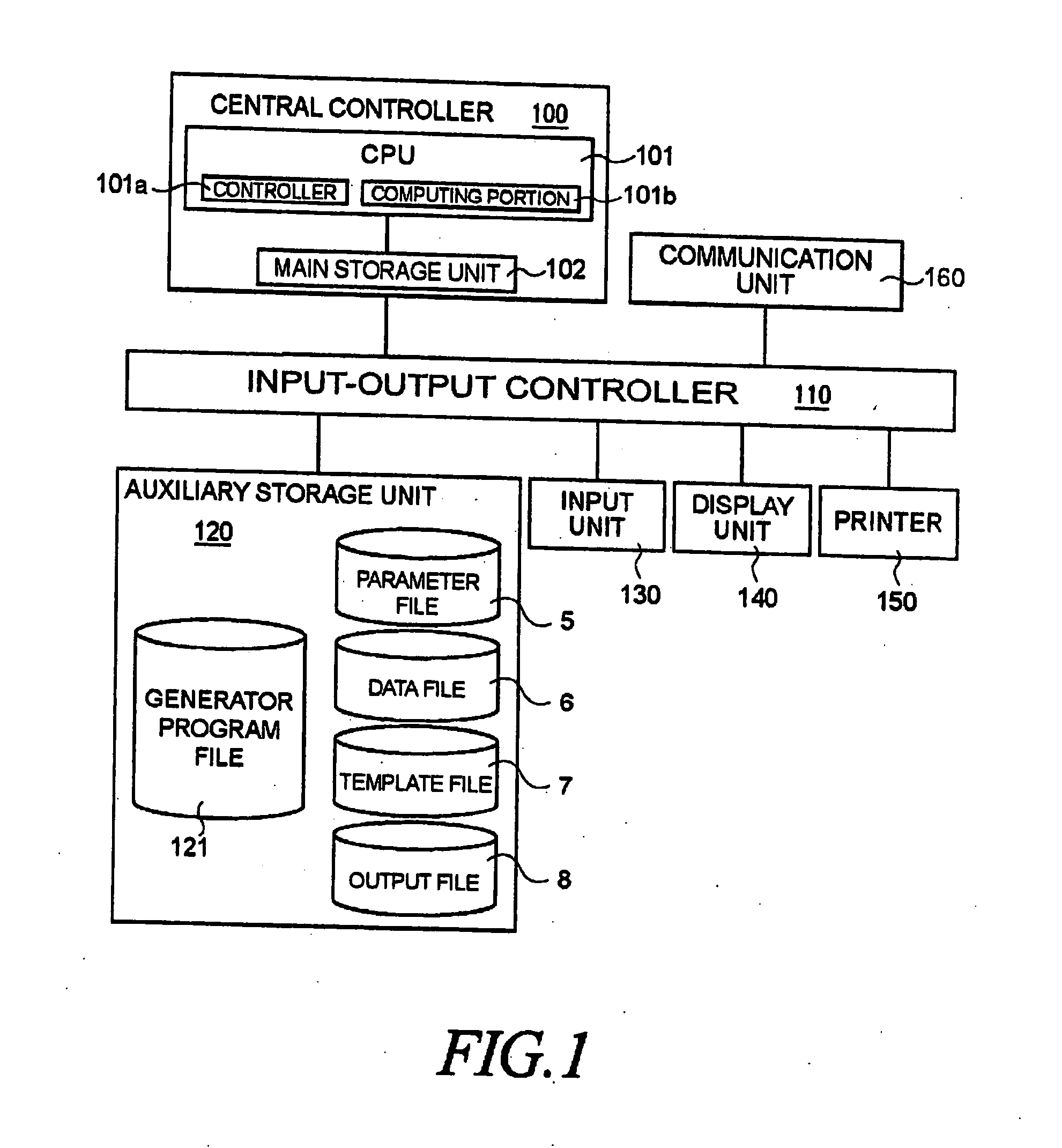

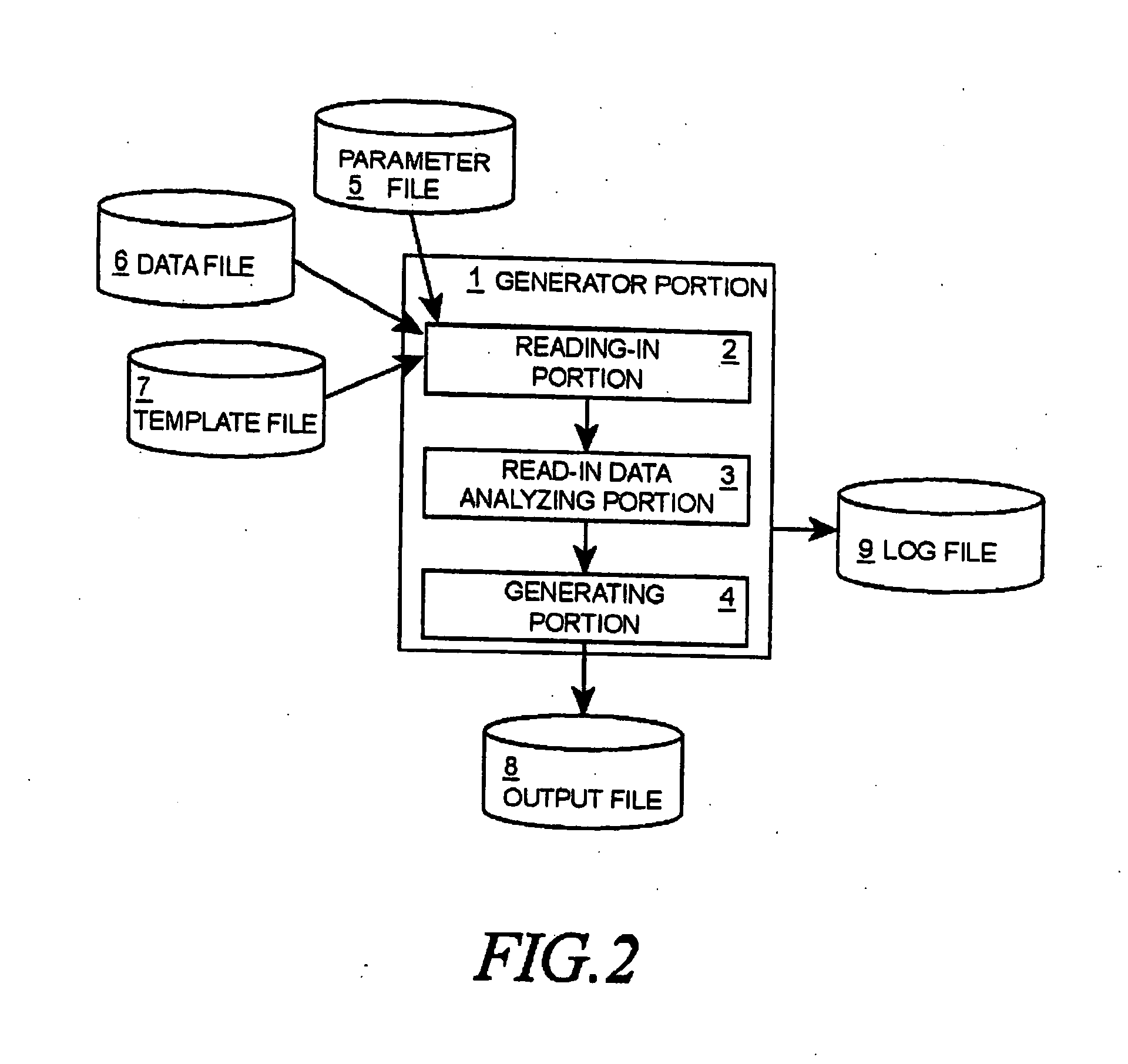

An automatic file generating apparatus, method, program and record medium that can handle requirements for output data by simple additions and alterations without restriction on the format of the input data file. A central controller 100 is connected via an input-output controller 110 to an auxiliary storage unit 120, an input unit 130, a display unit 140, and a printer 150. The auxiliary storage unit 120 stores a generator program file 121, a parameter file 5, a data file 6, a template file 7, and an output file 8. The central controller 100 loads a copy of the generator program file 121 stored in the auxiliary storage unit 120 into a main storage unit, and has a CPU 101 execute the program.

Owner:KAZUTOMO

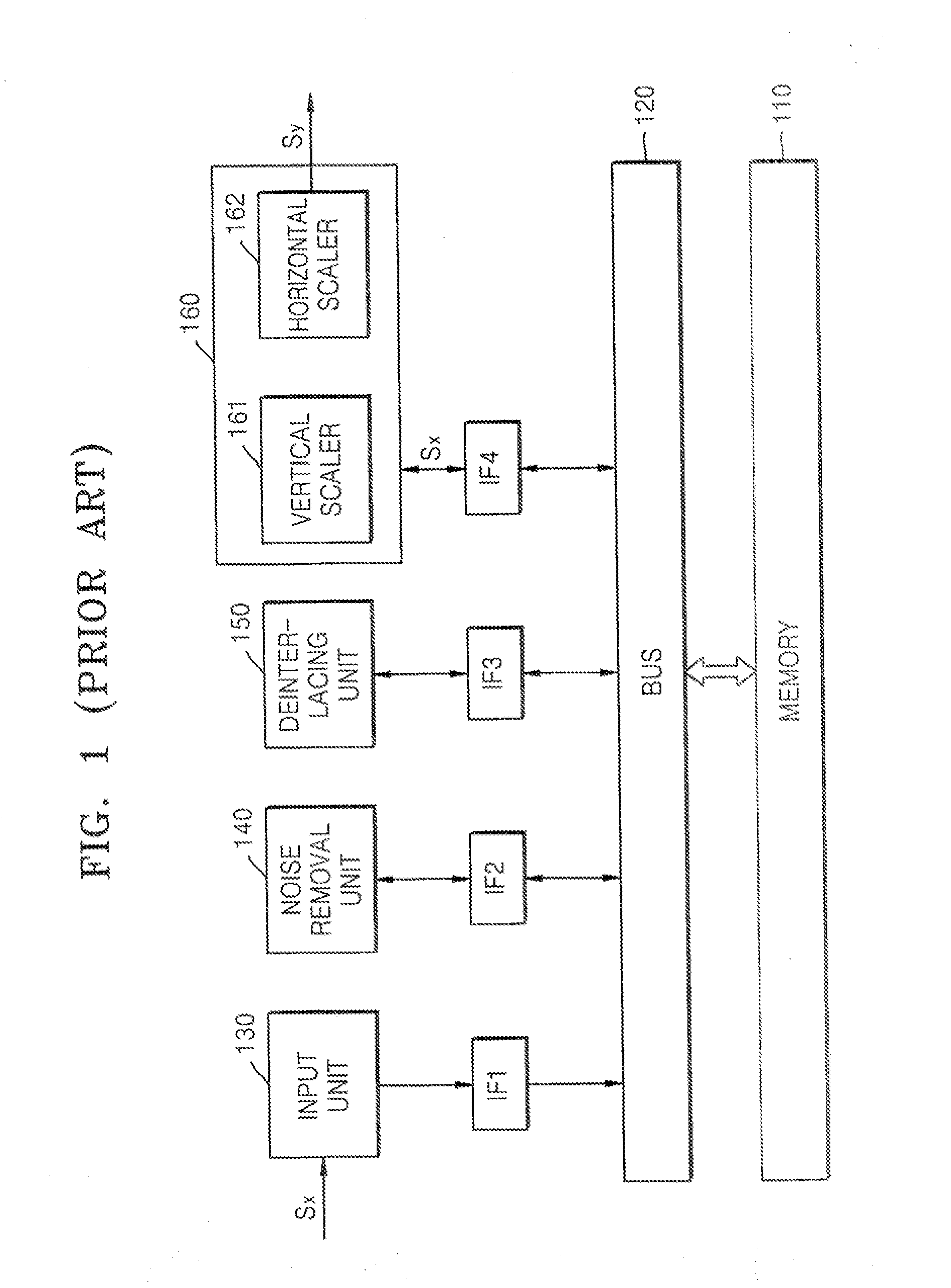

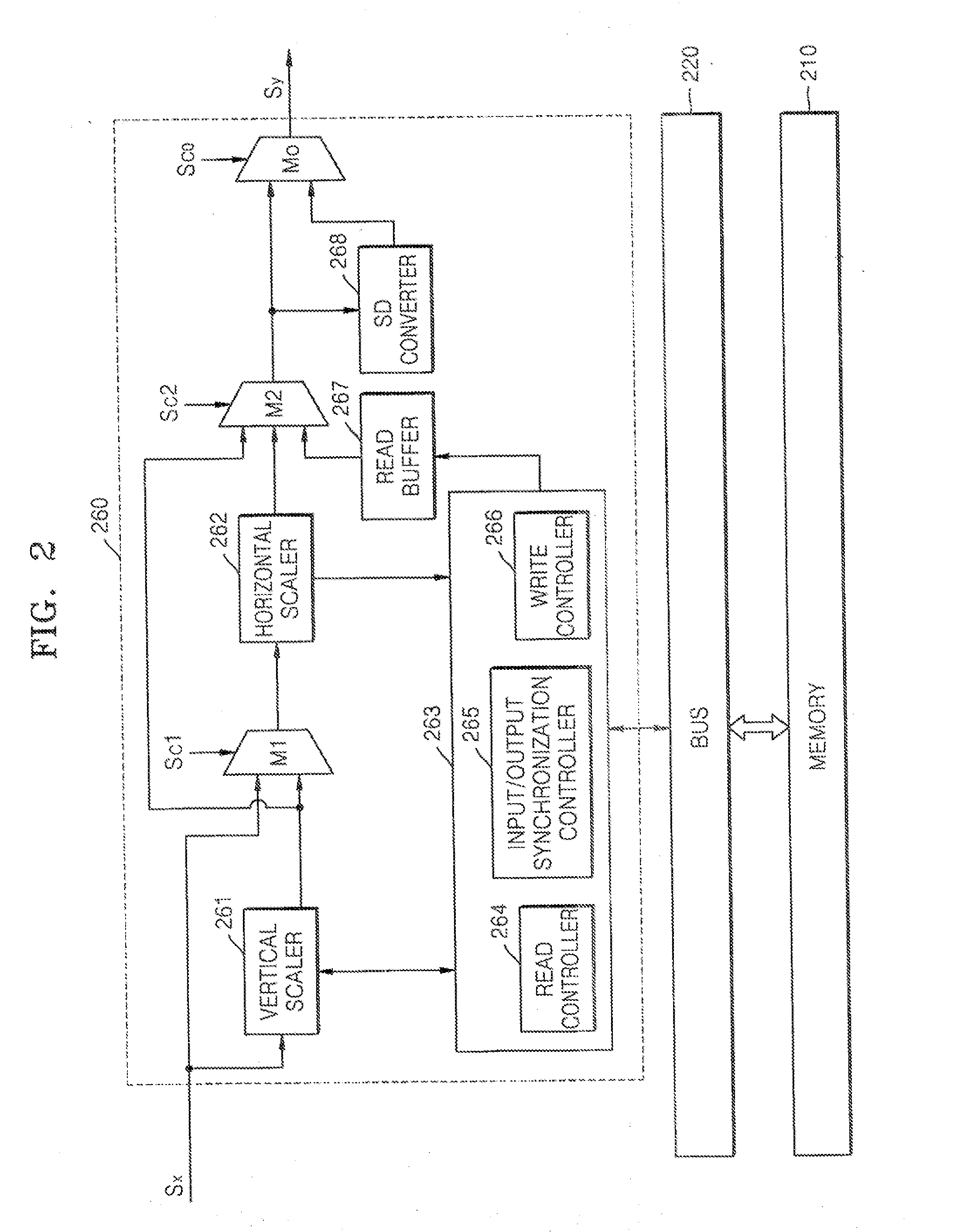

Image signal scaler and image signal processor including the same

InactiveUS20100172599A1High bandwidthCharacter and pattern recognitionImage data processing detailsMultiplexerImage signal

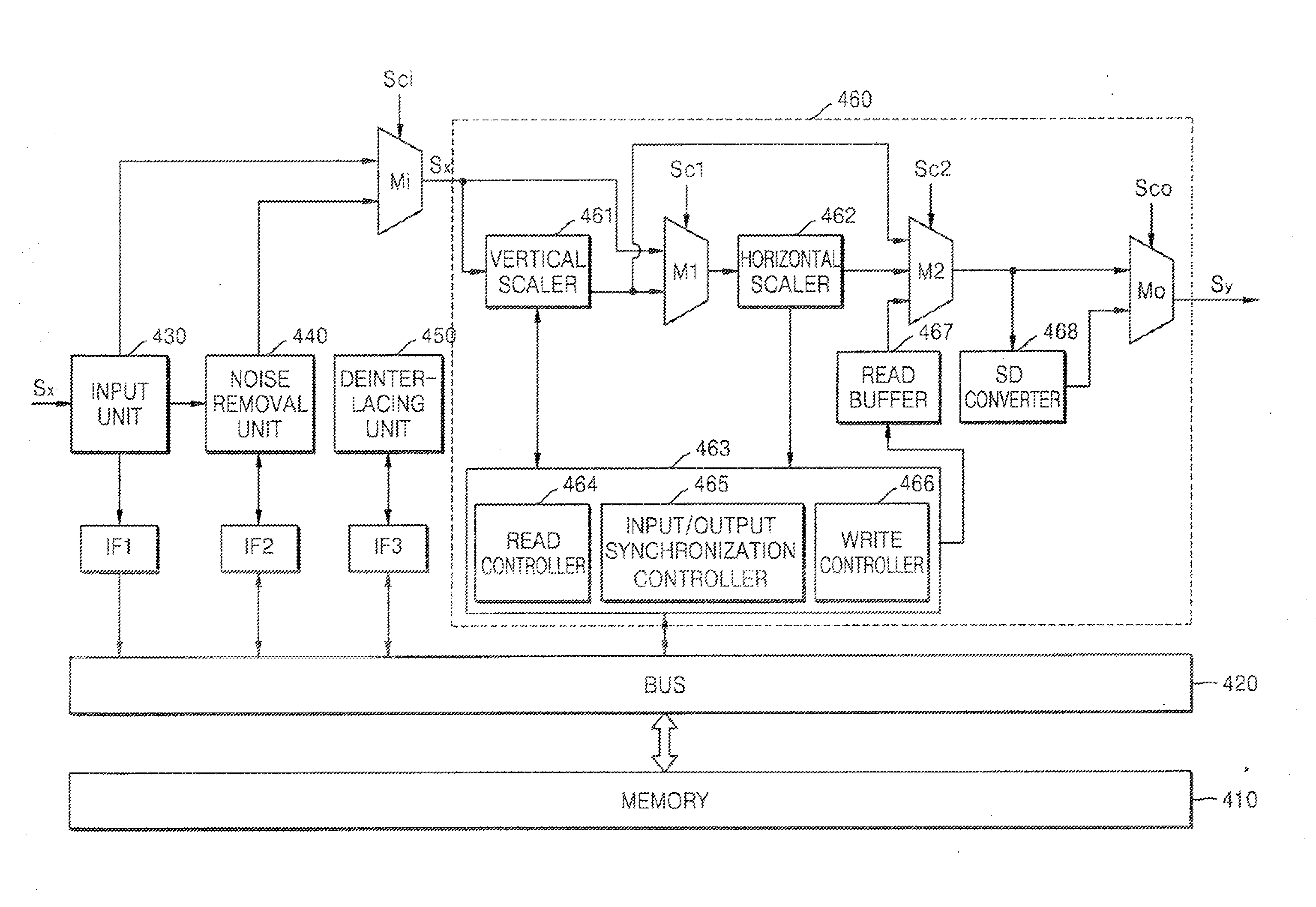

An image signal scaler and an image signal processor including the image signal scaler in which the image signal scaler includes a vertical scaler controlling a vertical image size of an input image signal, a horizontal scaler controlling a horizontal image size of the input image signal, an input / output controller controlling the vertical scaler and the horizontal scaler to transmit / receive an image signal to / from a memory, a read buffer reading an image signal stored in the memory through the input / output controller, a first multiplexer controlling a route of the input image signal, and a second multiplexer receiving an image signal from the vertical scaler, the horizontal scaler or the read buffer and outputting an output image signal. The vertical scaler or the horizontal scaler reduces the vertical image size or the horizontal image size of the input image signal and stores the input image signal in the memory through the input / output controller when the vertical image size or the horizontal image size of the input image signal is larger than the vertical image size or the horizontal image size of the output image signal.

Owner:SAMSUNG ELECTRONICS CO LTD

Bridge, computer system and method for initialization

An indicator pin of an input / output controller is used to identifying whether a processor or a bridge is configured in a processor. When a predetermined voltage level of the indicator pin is confirmed, a base input / output system of the computer system renews a coherent / non-coherent HyperTransport link table. Then an initialization procedure is performed in accordance with the renewed coherent / non-coherent HyperTransport link table.

Owner:MITAC INT CORP

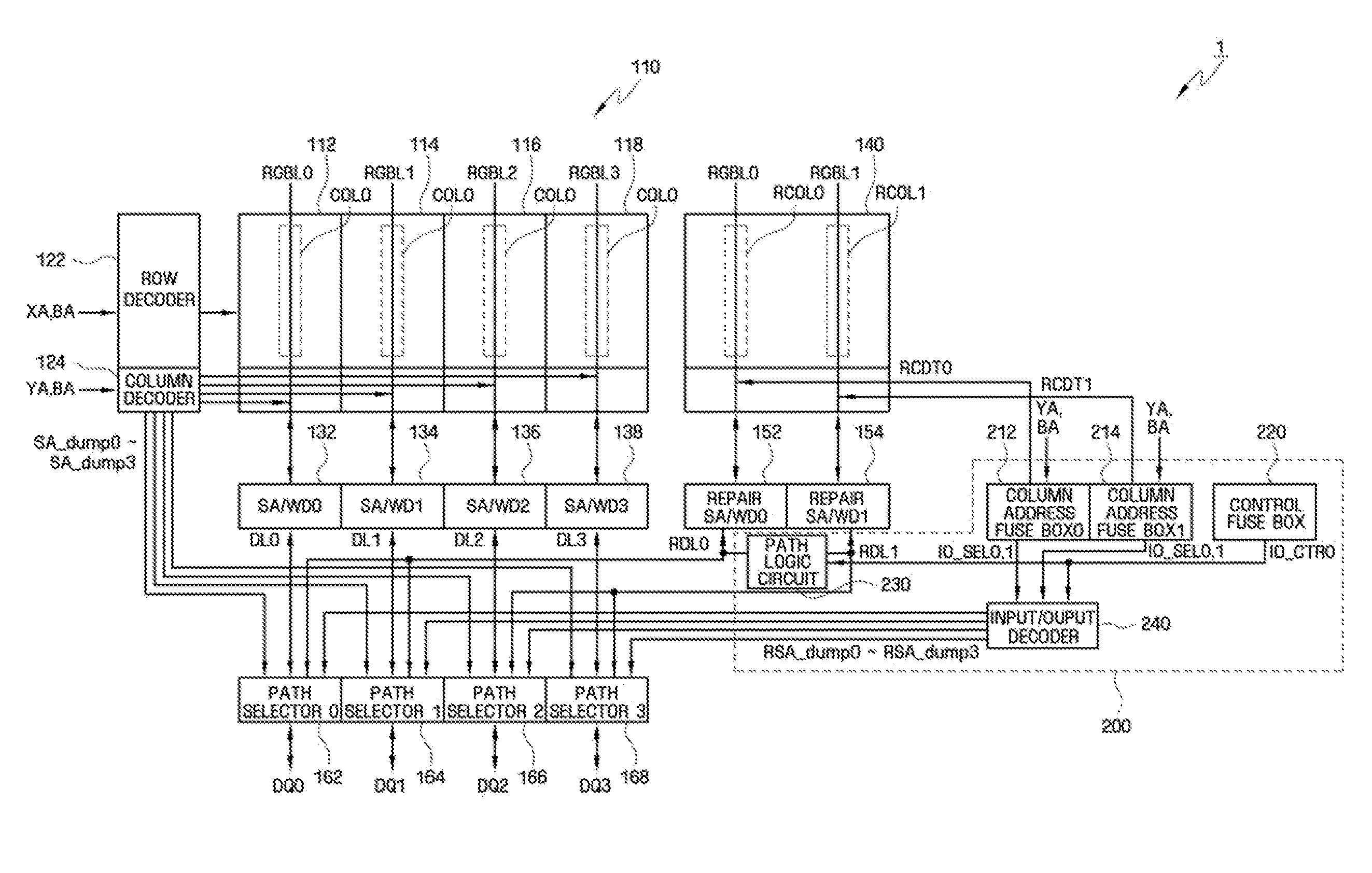

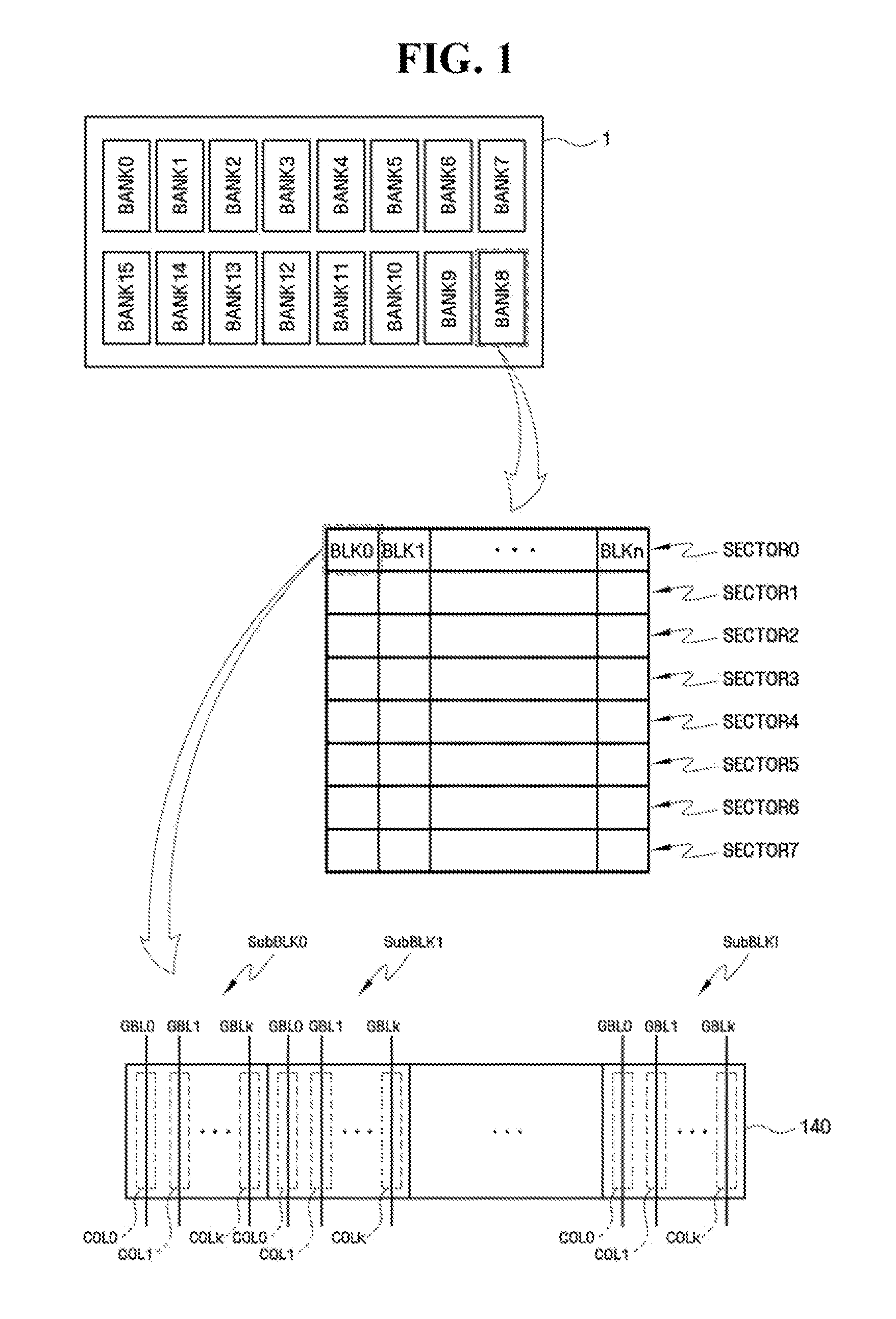

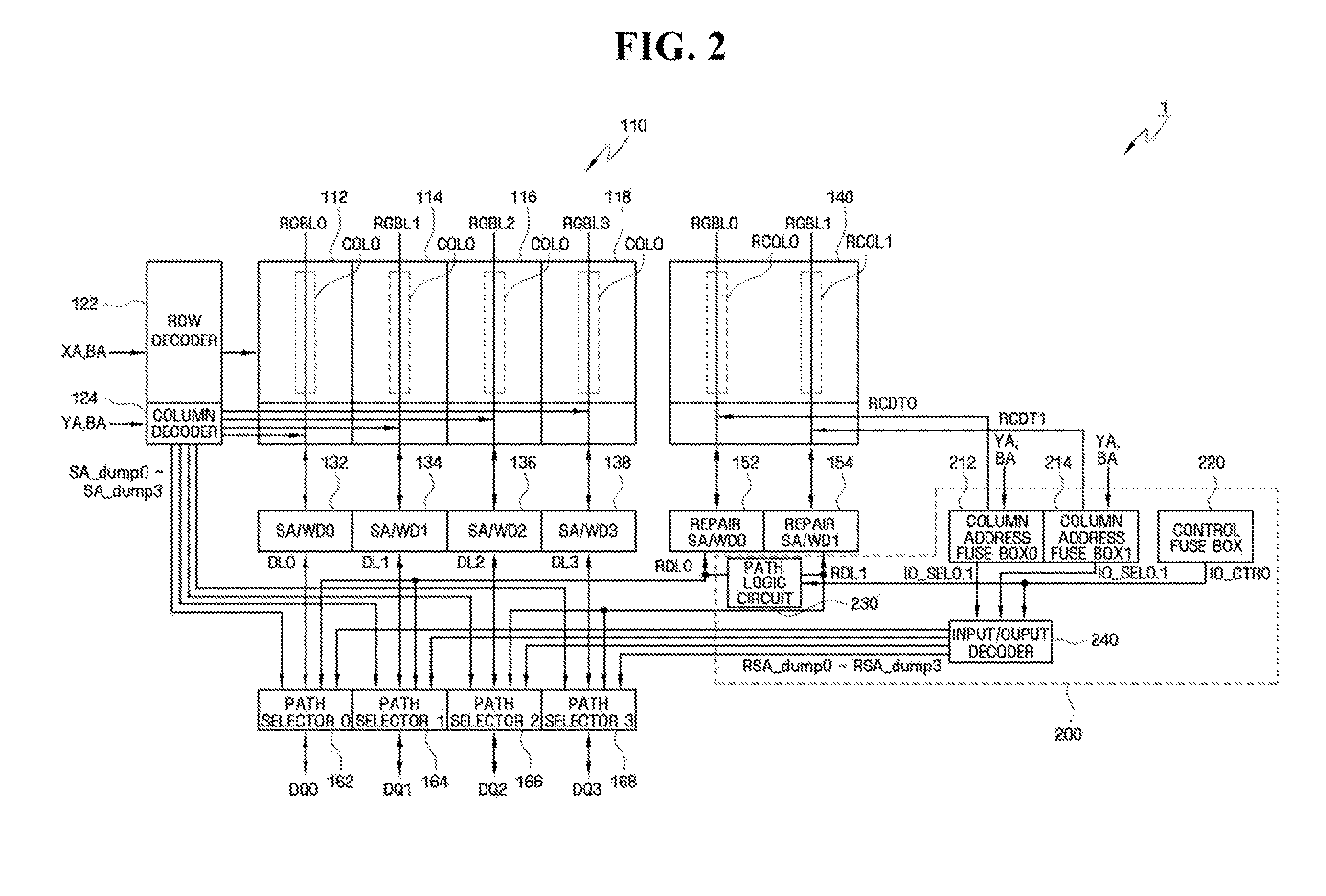

Phase-change random access memory

ActiveUS20070217273A1Improve efficiencyImprove reliabilityElectric analogue storesRead-only memoriesMode controlControl signal

A phase-change random access memory includes a memory block including a plurality of memory columns corresponding to the same column address and using different input / output paths; a redundancy memory block including a plurality of redundancy memory columns using different input / output paths; and an input / output controller repairing at least one of the plurality of memory columns using at least one of the plurality of redundancy memory columns, and controlling the number of memory columns simultaneously repaired using redundancy memory columns in response to an input / output repair mode control signal.

Owner:SAMSUNG ELECTRONICS CO LTD

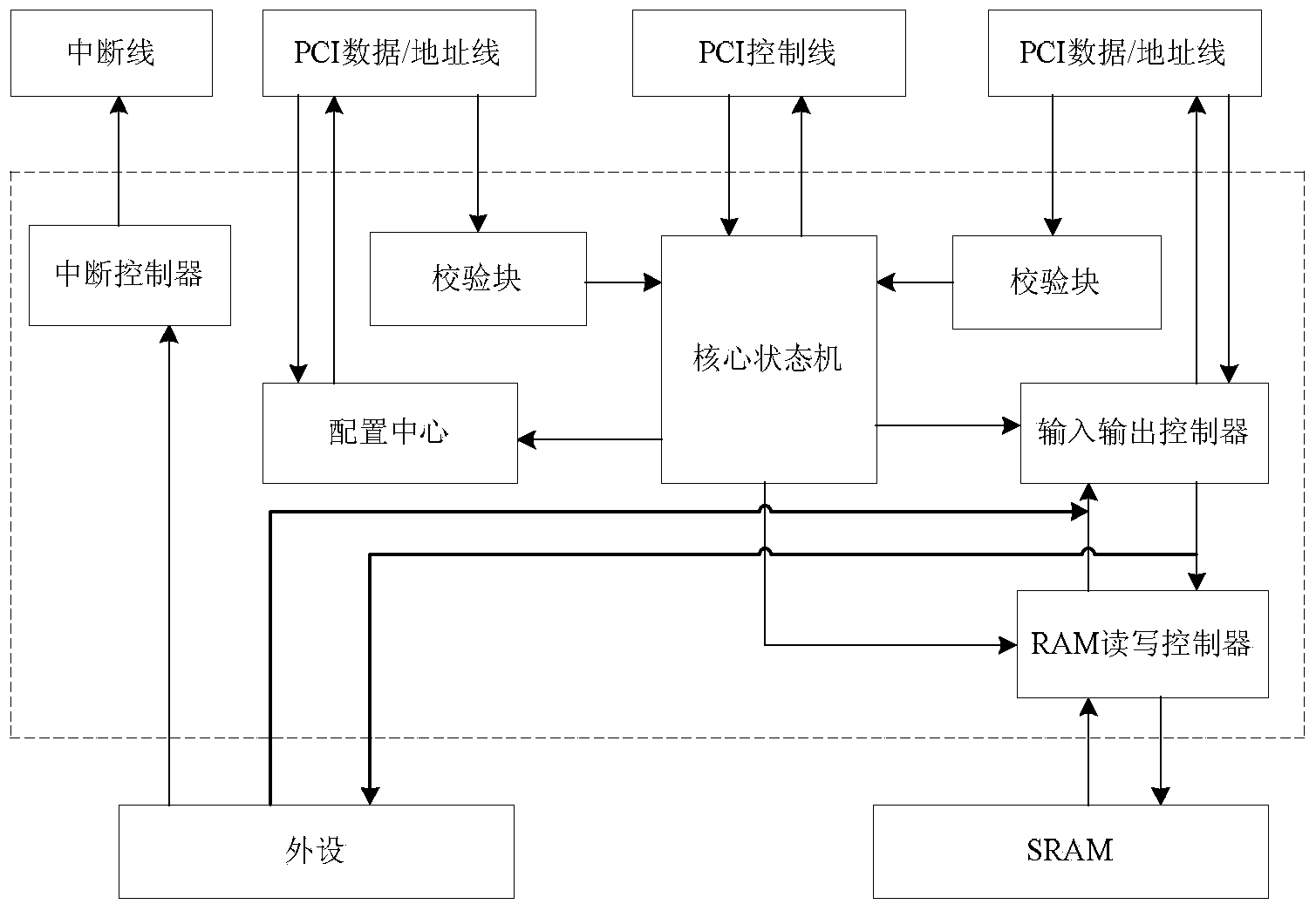

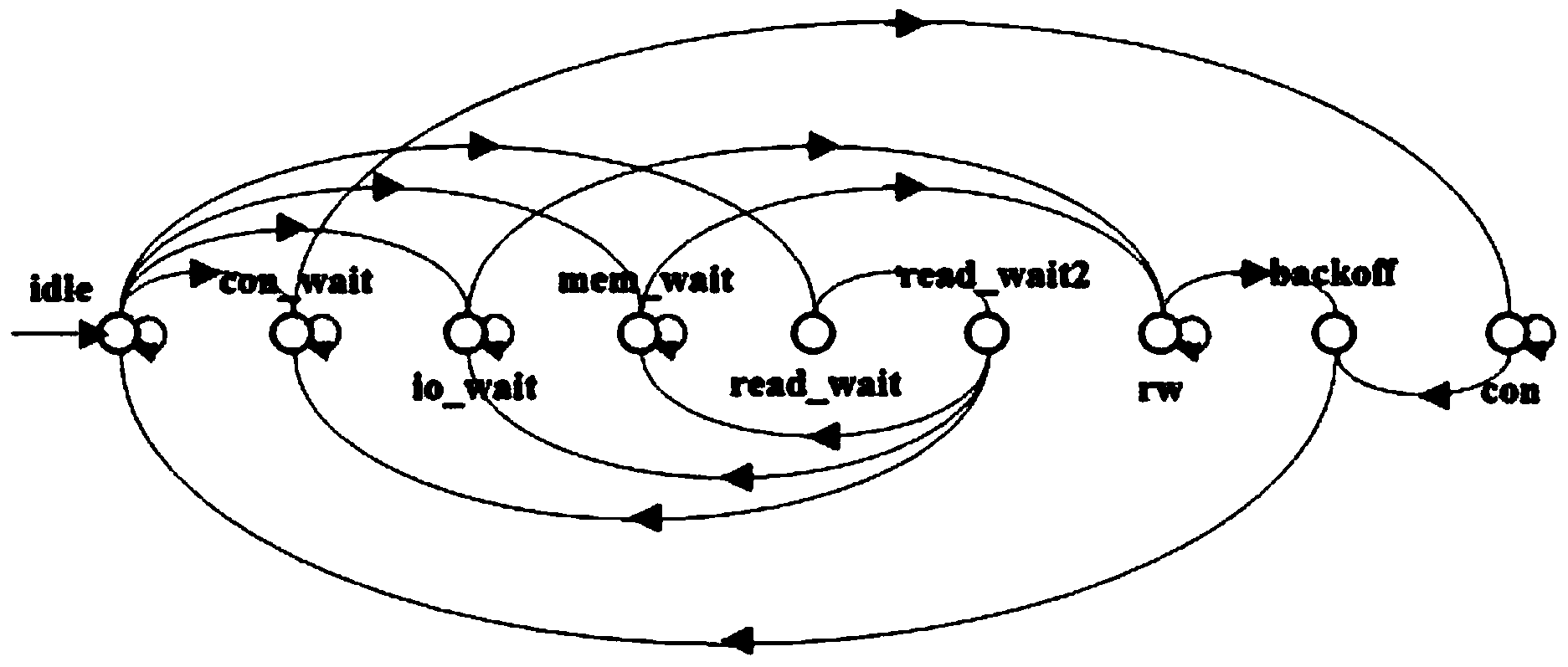

PCI (peripheral component interconnect) slave unit core control module applied to high-speed motion control system

The invention relates to a PCI (peripheral component interconnect) slave unit core control module applied to a high-speed motion control system, which relates to a PCI slave unit core control module, and solves the problem that an existing PCI slave unit occupies a large space, the function cannot be customized, the cost is high, and the design of an embedded system is limited. The PCI slave unit core control module comprises a core state machine, a configuration unit, an input-output controller, a verifying block, an RAM (random access memory) reading-writing controller and an interruption controller, wherein the core state machine comprises an idle state idle, a configuration operation waiting state con_wait, a port operation waiting state io_wait, a storage operation waiting state mem_wait, a reading-writing state read-wait, a configuration reading-writing state con, a port or storage reading-writing state rw and an ending state backoff. The PCI slave unit core control module is applied to the development of the PCI slave unit.

Owner:HARBIN INST OF TECH

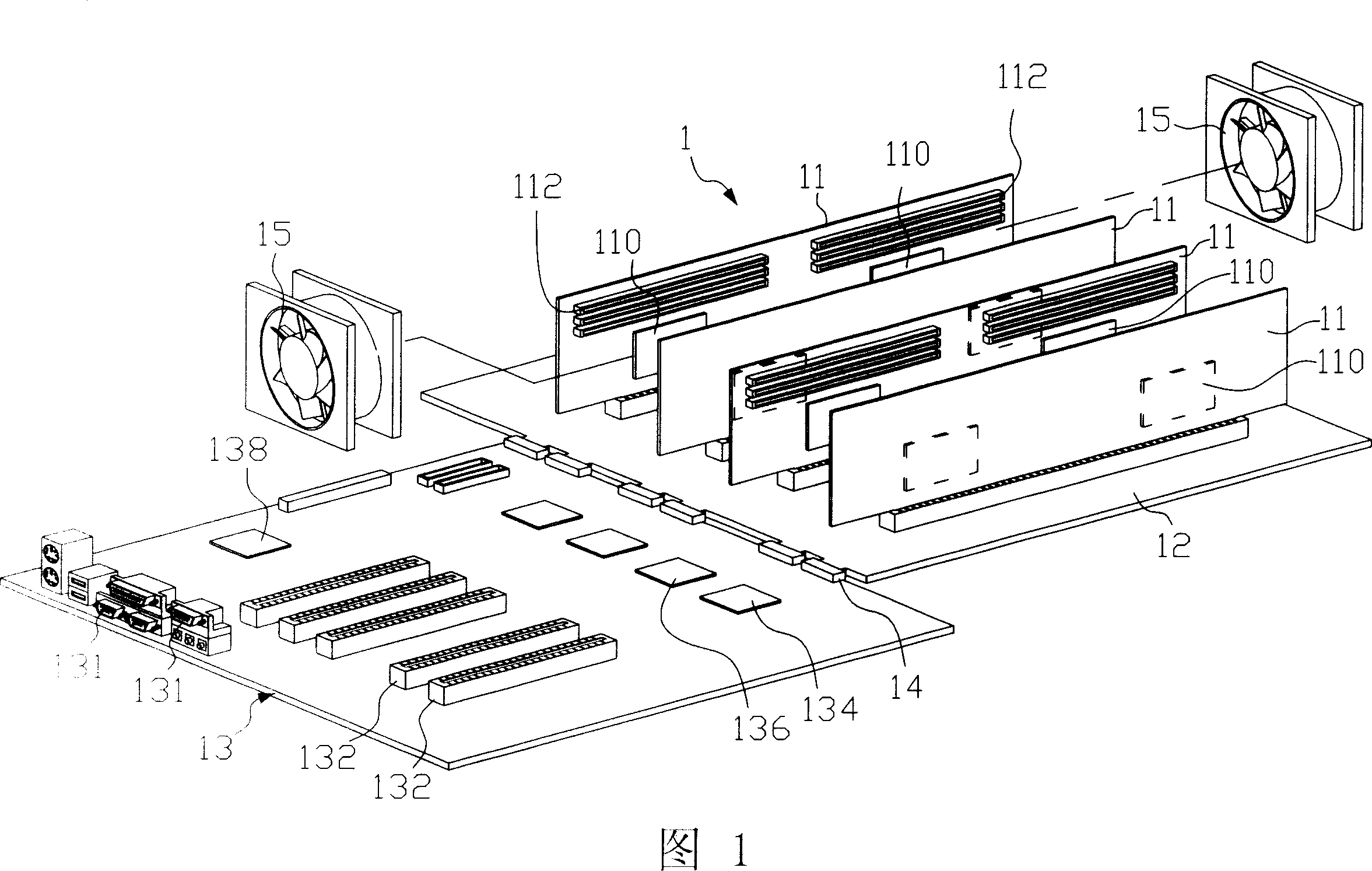

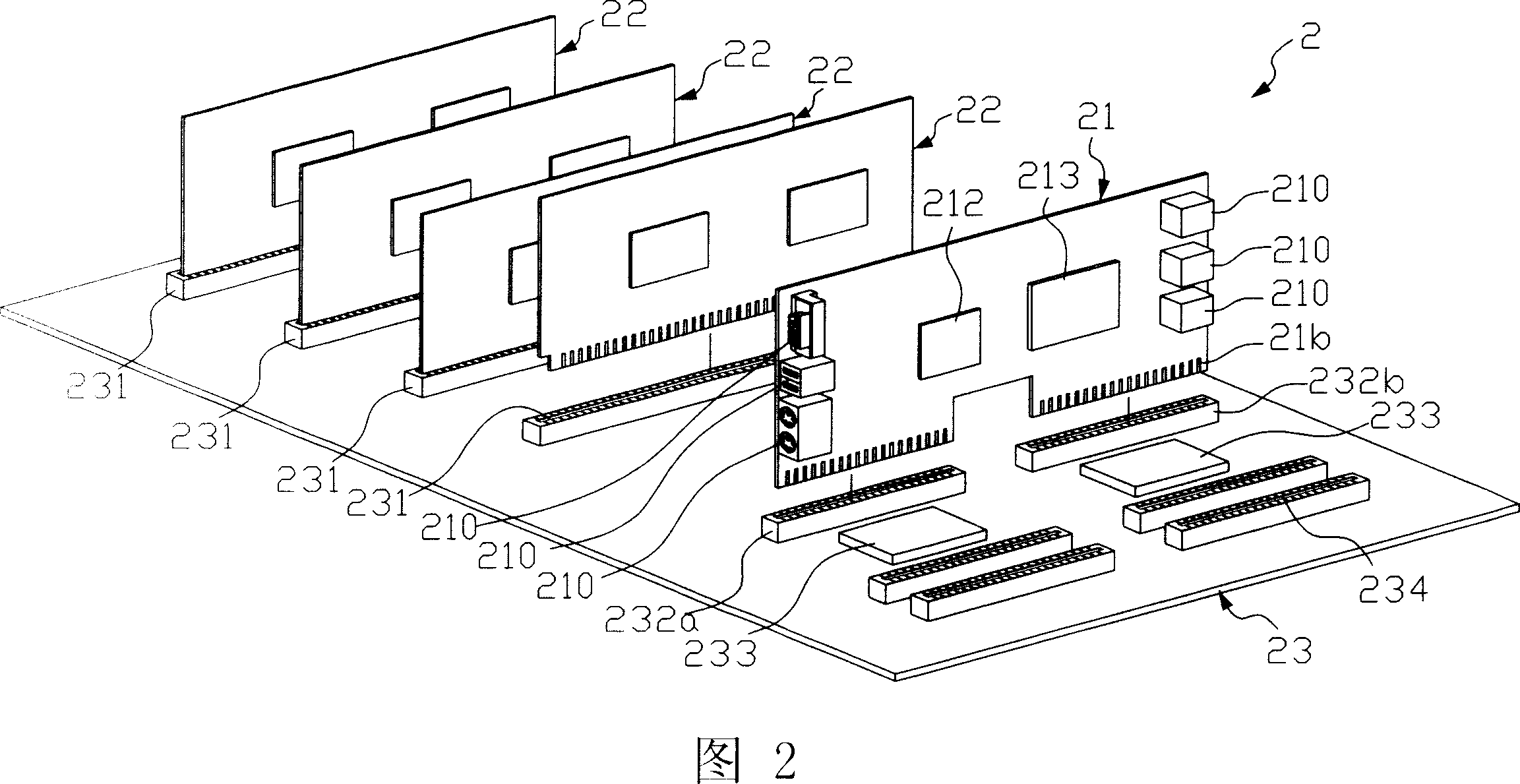

Computer system and input/output plate

InactiveCN101046780AGood cooling channelImprove cooling effectElectric digital data processingComputerized systemEngineering

The present invention discloses a computer system and its input / output machine plate. Said computer system includes at least a processor card, an expansion plate and input / output machine plate, in which the processor card has at least one processor, the expansion plate includes at least one expansion slot, and the input / output machine plate includes south bridge chip, input / output controller and several input / output ports. Said invention utilizes at least one processor bus connector and several interconnected bus connectors to make south bridge chip, processor and expansion slot form communication.

Owner:HUANDA COMPUTER (SHANGHAI) CO LTD

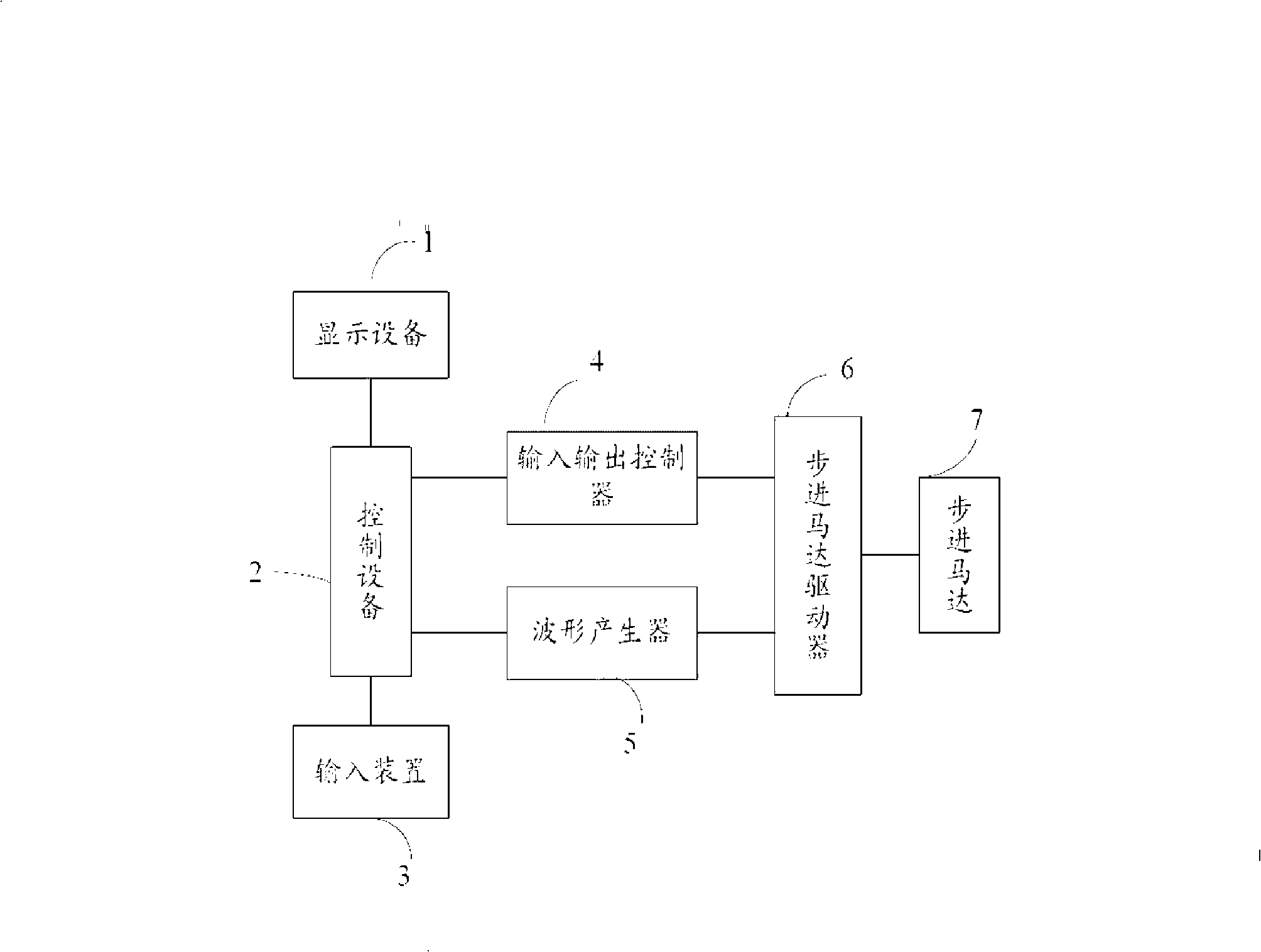

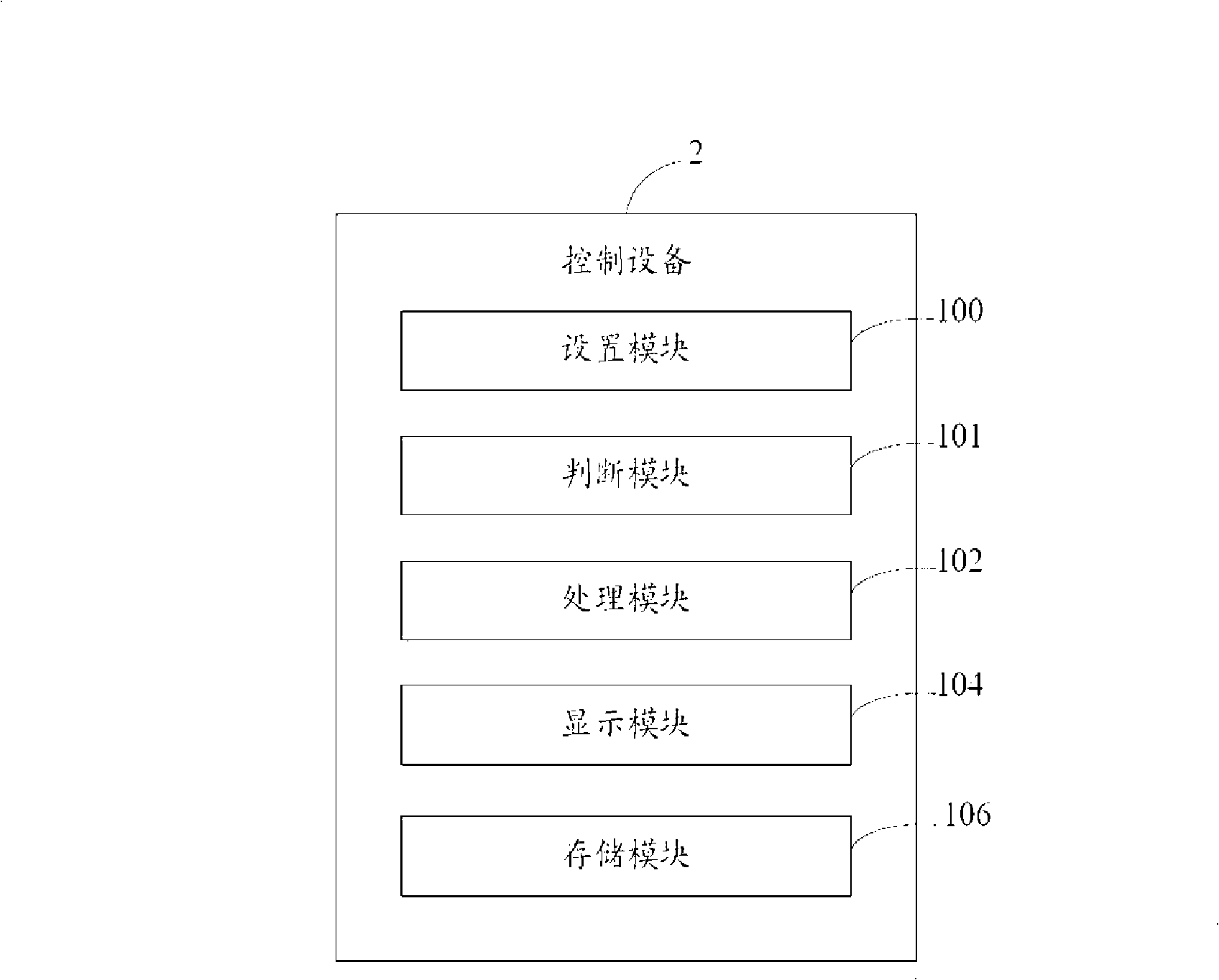

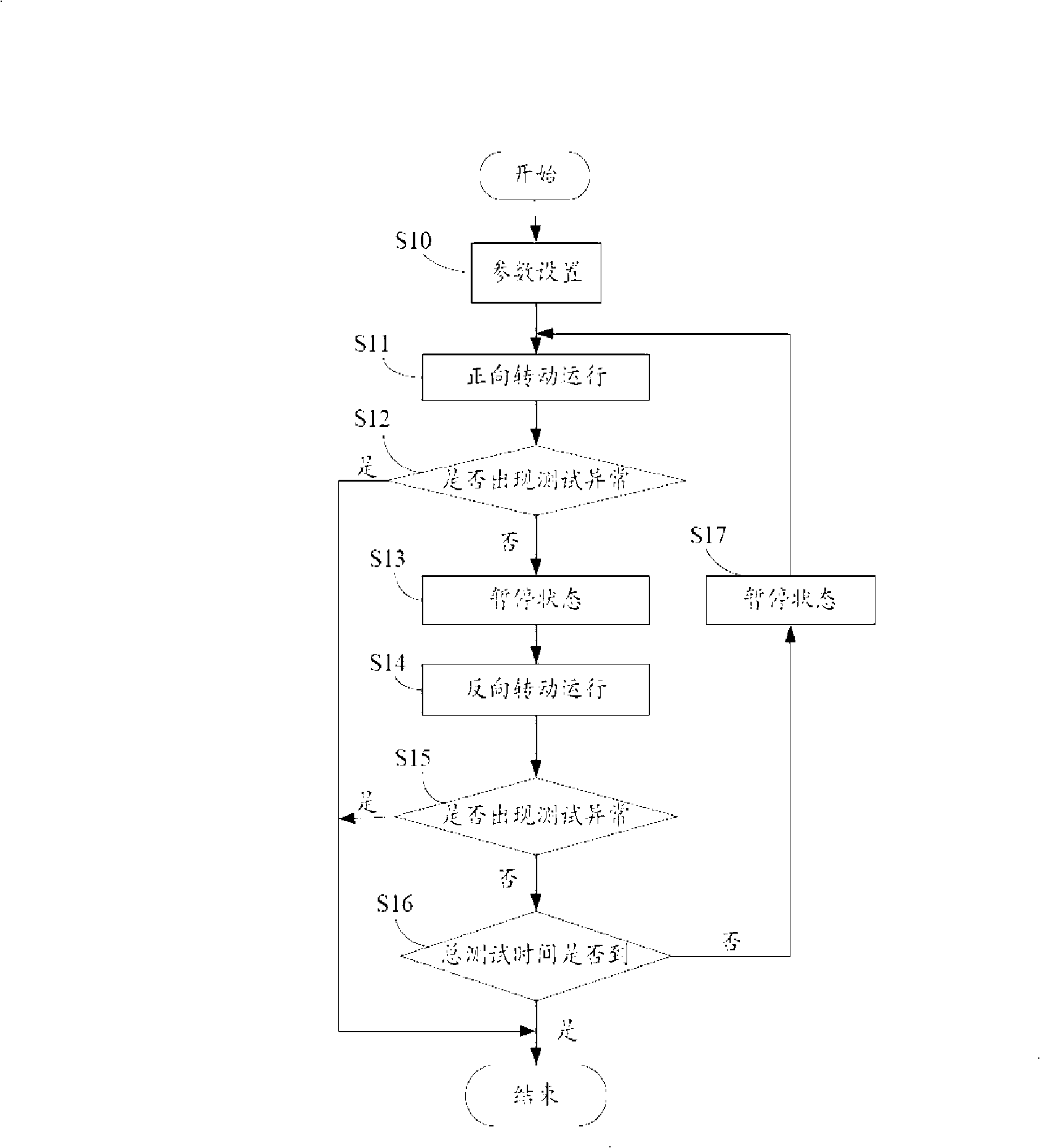

Step motor test system and method

InactiveCN101344577AStructural/machines measurementDynamo-electric machine testingControl theoryControl equipment

The invention provides a step motor test method adopting an input device, a control device, an input-output controller and a step motor driver which are sequentially connected to test whether the step motor can be qualified; wherein, a waveform generator is connected between the control device and the step motor driver. The method includes the following steps: parameters containing the running direction and test time of the step motor which are needed to be tested for the step motor are set through the input device; the input-output controller is controlled by the control device to send out control instructions and the wave generator is also controlled by the control device to send out impulse signals so as to drive the step motor to run according to the set running direction; the control device judges whether the step motor runs normally in the test time. The invention also provides a step motor test system. Adopting the test system and method can quickly and accurately complete the test to the step motor.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

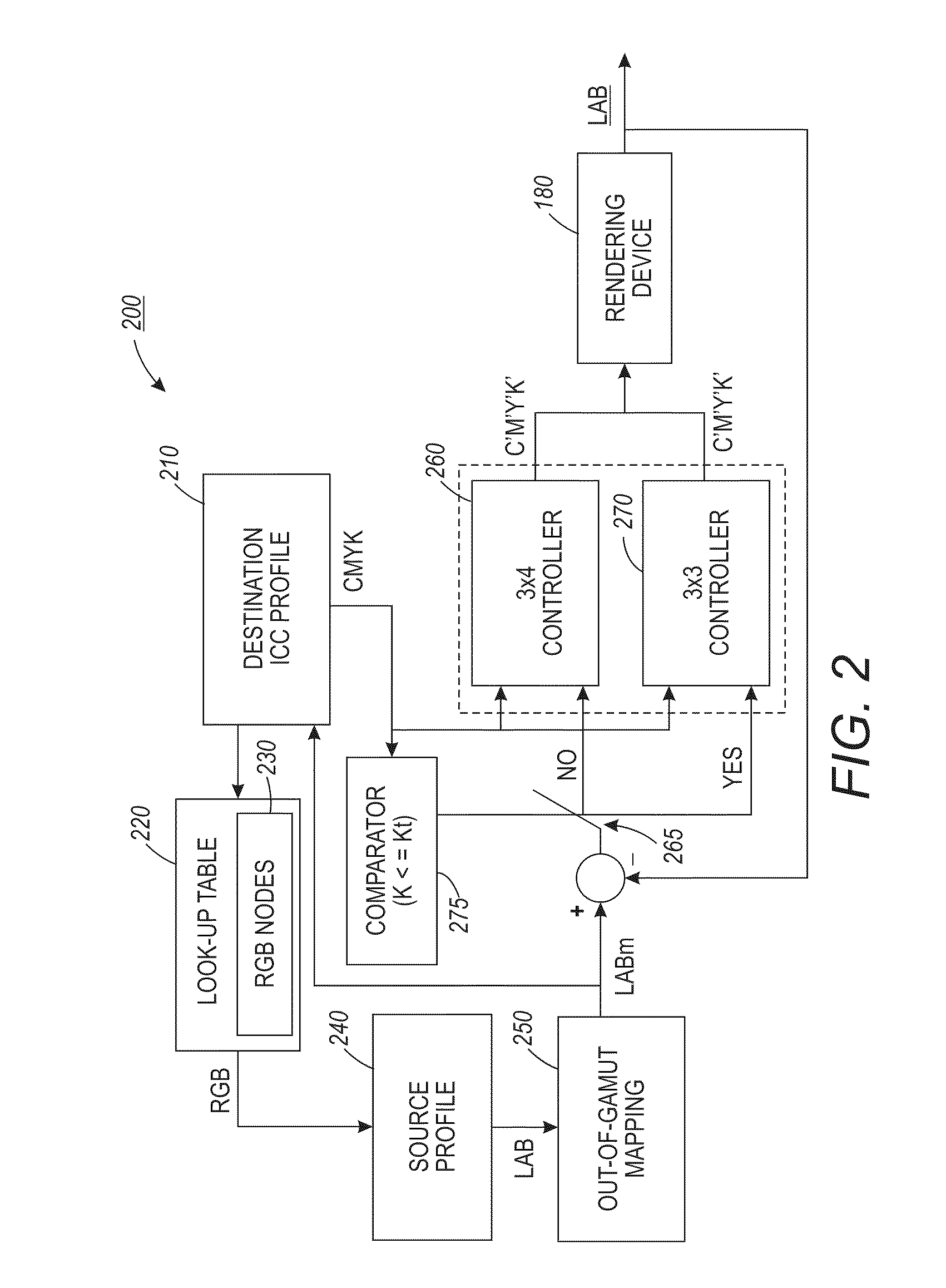

Switching controller system and method for improving image graininess during color management profile construction

InactiveUS20110317915A1Minimizes graininessReduce graininessDigitally marking record carriersDigital computer detailsICC profileControl theory

A switching controller system and method for improving graininess in an image during a profile construction. A switching control strategy can be employed to construct an ICC destination profile by switching between a first controller (e.g., a 3-input 4-output controller) and a second controller (e.g., a 3-input 3-output controller) based on a color space region that requires a graininess minimization. The first controller dynamically modifies the CMYK values until reaching a subset of LAB values contained in the ICC profile. The second controller varies three colorants and holds a remaining colorant of the CMYK values until reaching the remaining LAB values in the ICC profile. Such an approach reduces the graininess and provides an improved smoothness with respect to the image during the ICC profile construction.

Owner:XEROX CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com