Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

76 results about "Elementary circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

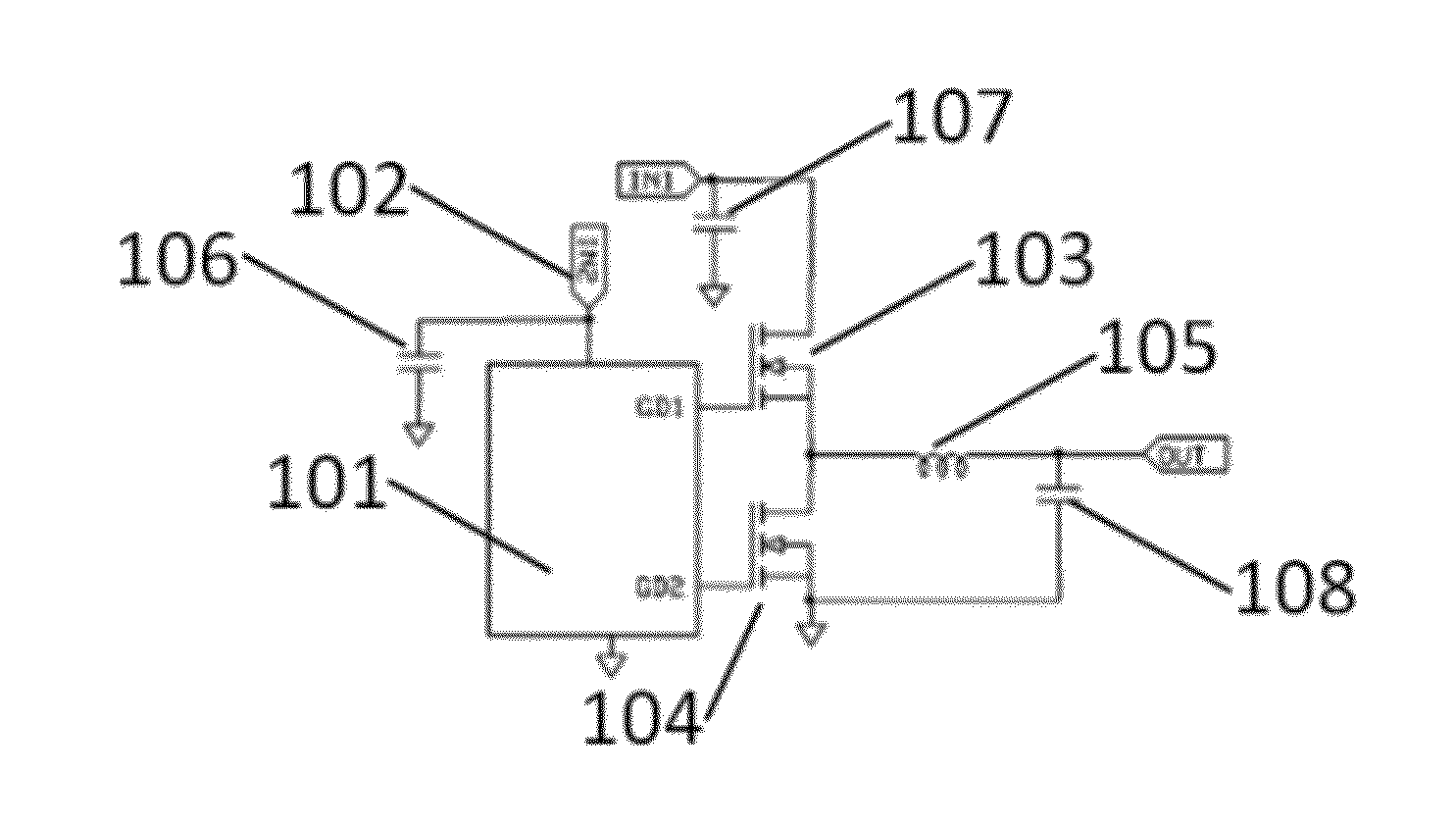

Temperature sensor circuit for microdisplays

InactiveUS20050052437A1Conveniently and flexibly determiningReduce the possibilityThermometers using electric/magnetic elementsUsing electrical meansElectrical resistance and conductanceFrequency measurements

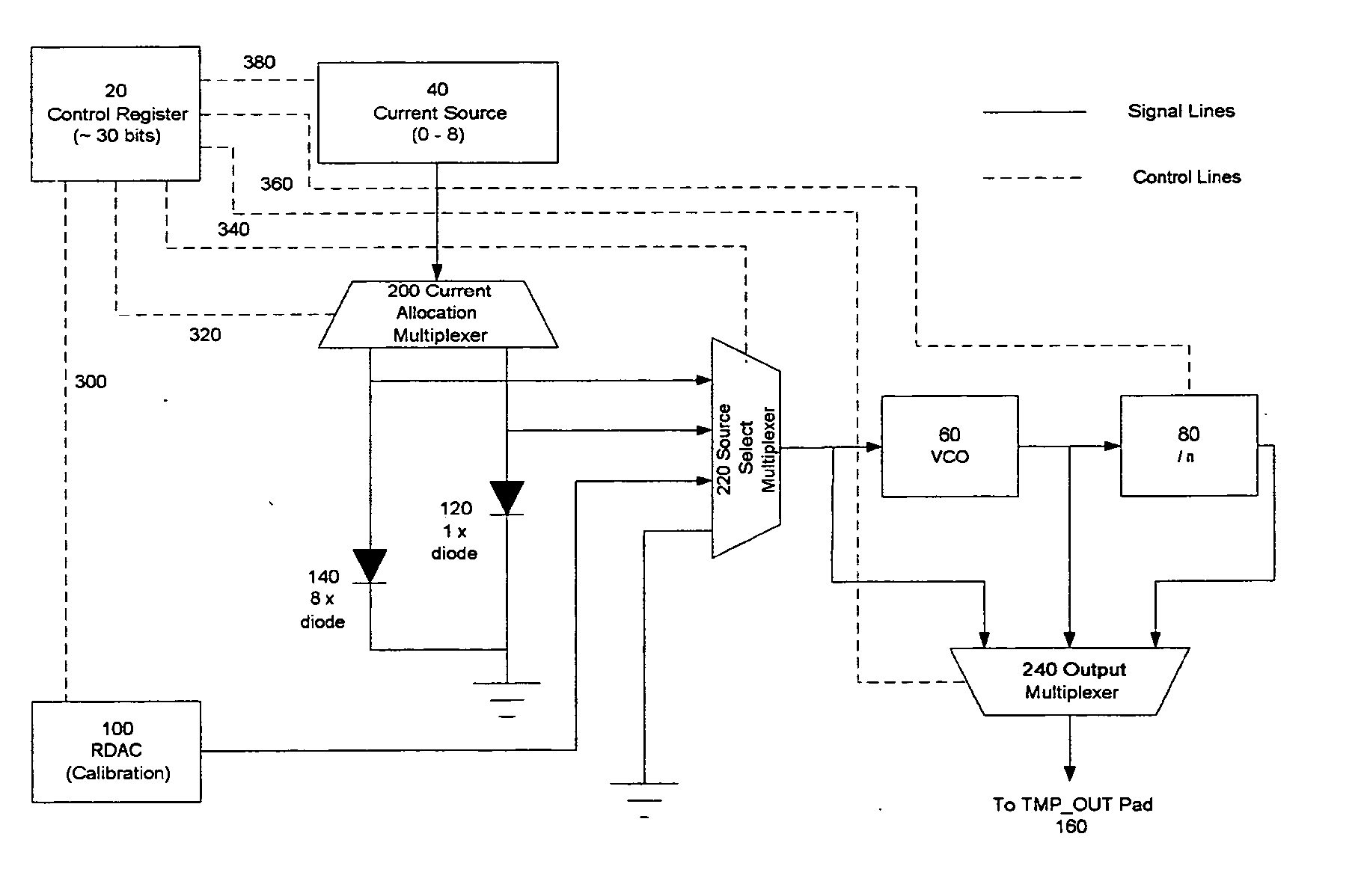

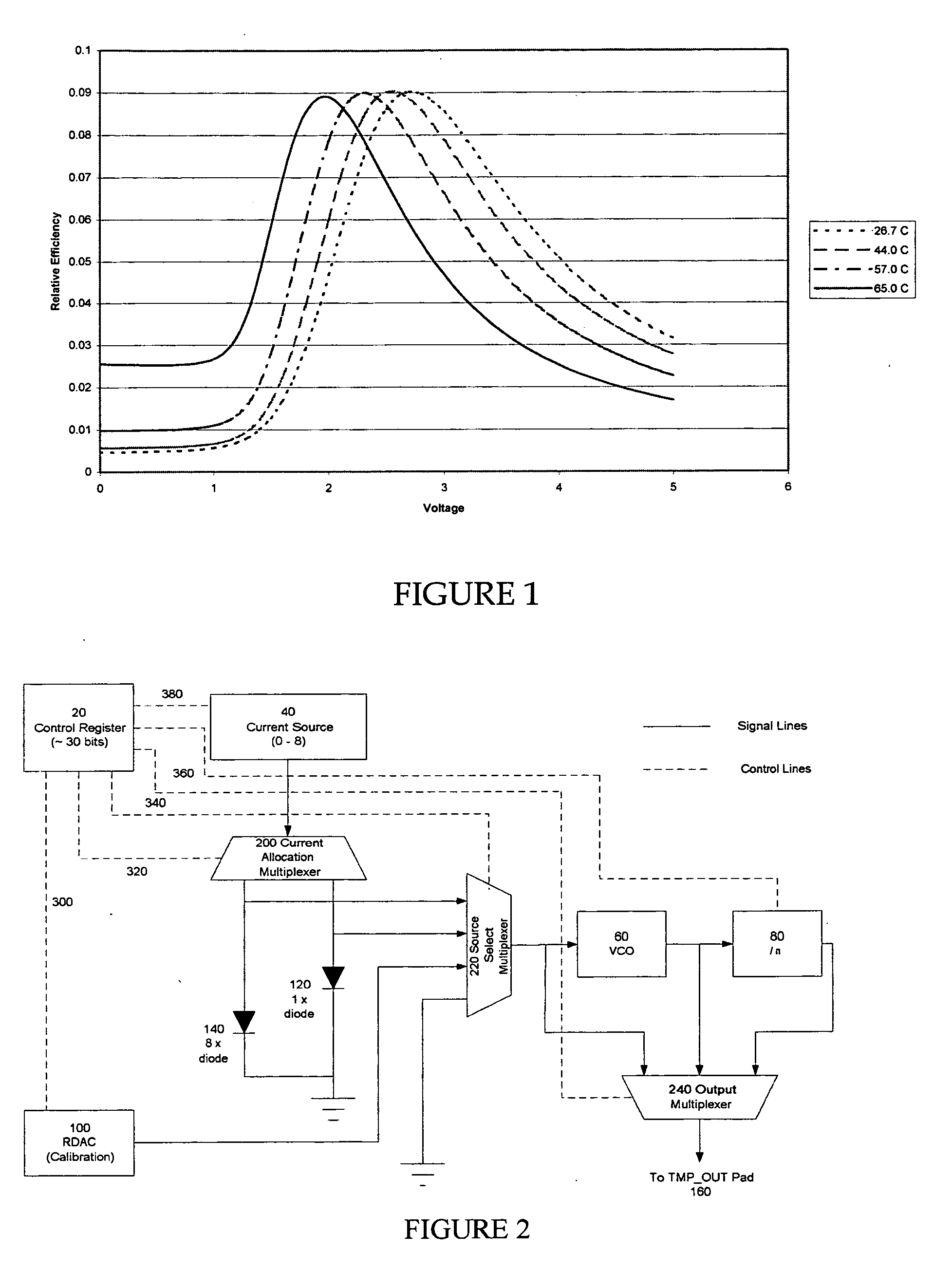

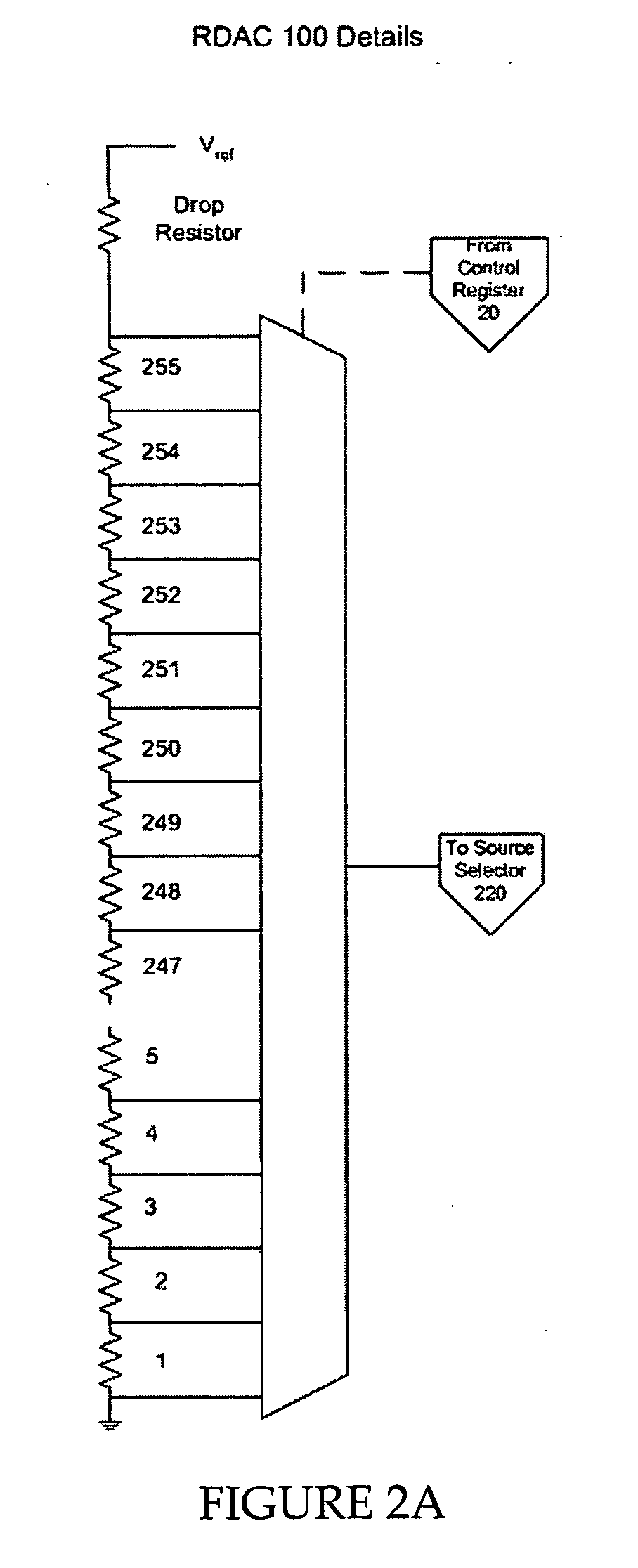

This invention discloses a proportional to absolute temperature (PTAT) type of temperature measurement to improve the accuracy of temperature measurements. Instead of measuring resistance variations across a distance of diode, a technique of temperature determination using frequency measurements is performed in this invention through a voltage control oscillator. The measurement circuits are more compatible with the use of a flexible PCA connection to the microdisplay to a board. The basic circuit of this invention achieved an improved resistance noise and provides additional operation modes with added benefits of more conveniently and flexibly determining an operation mode to overcome the measurement noises. Furthermore, measurement of frequency as carried out by this invention improves the measurement accuracy and reduces the likelihood of false temperature readings.

Owner:JASPER DISPLAY

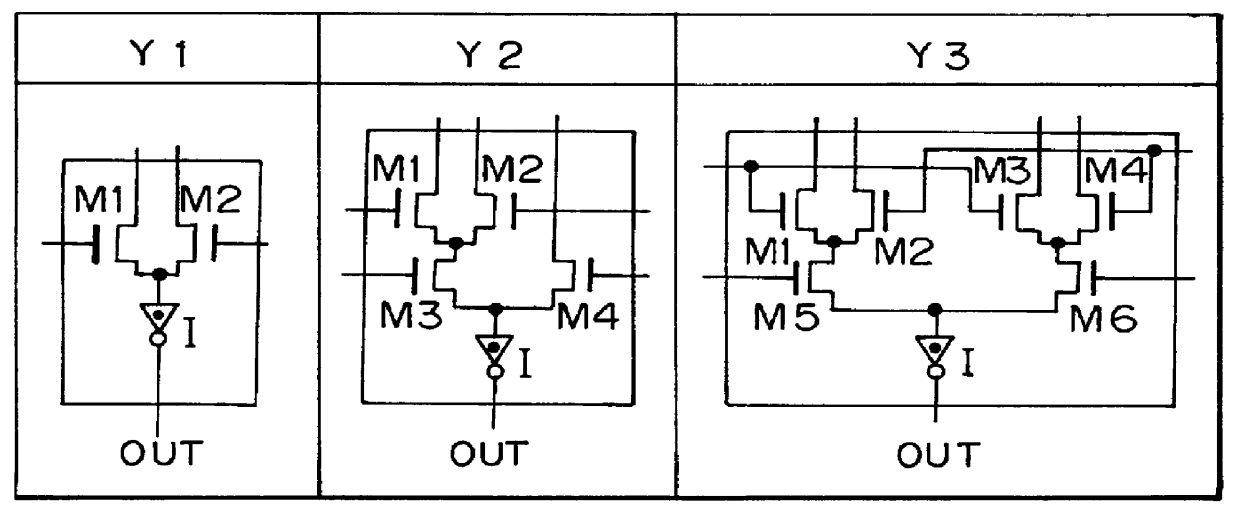

Semiconductor integrated circuit capable of realizing logic functions

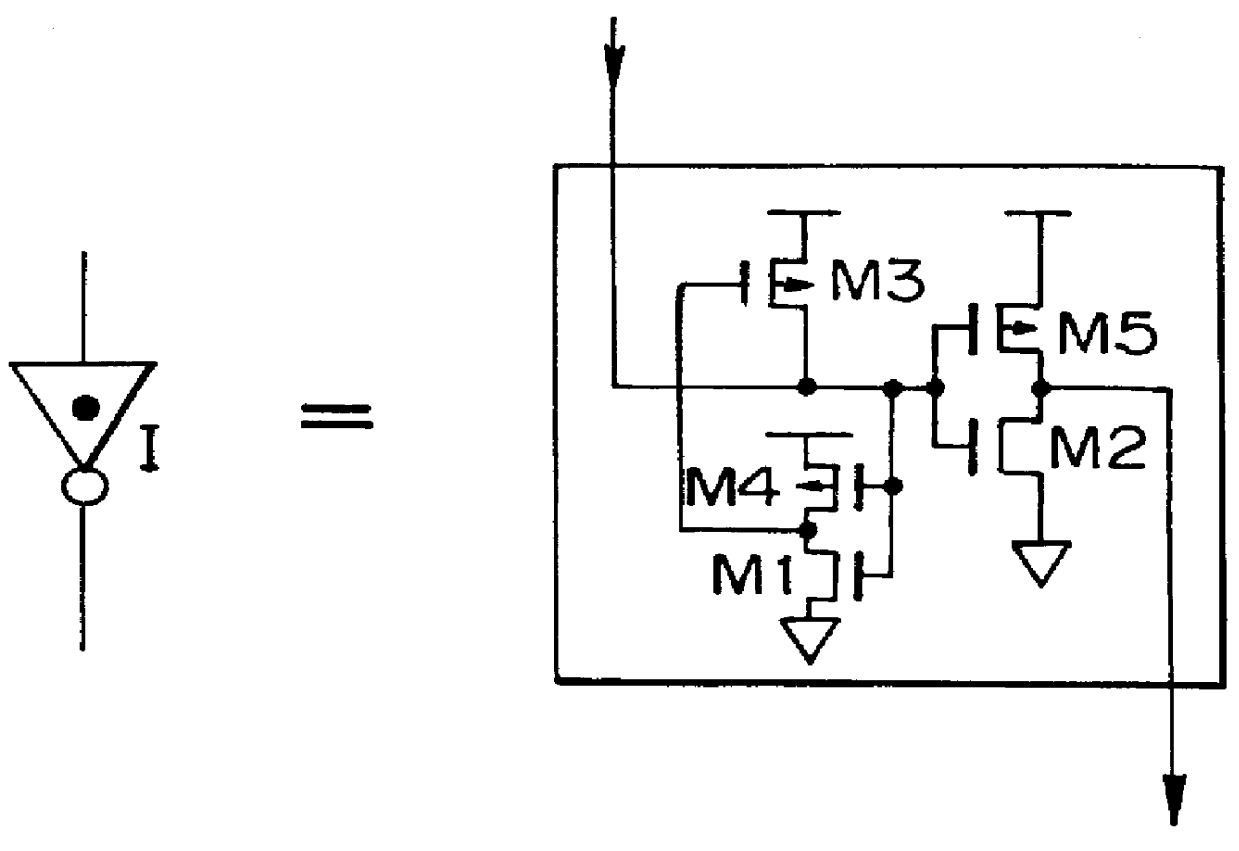

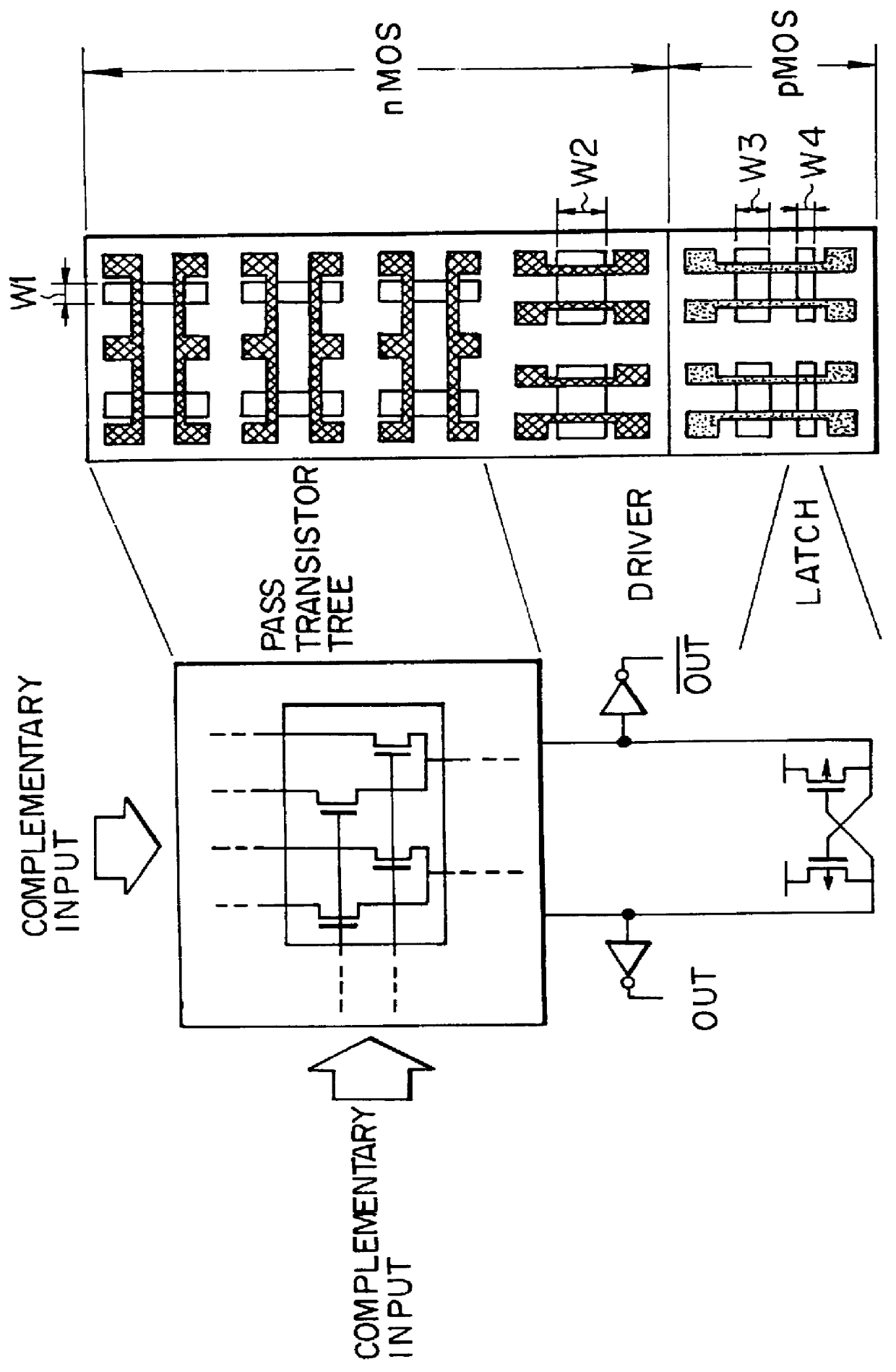

InactiveUS6194914B1Switching accelaration modificationsLogic circuits characterised by logic functionGate arrayEngineering

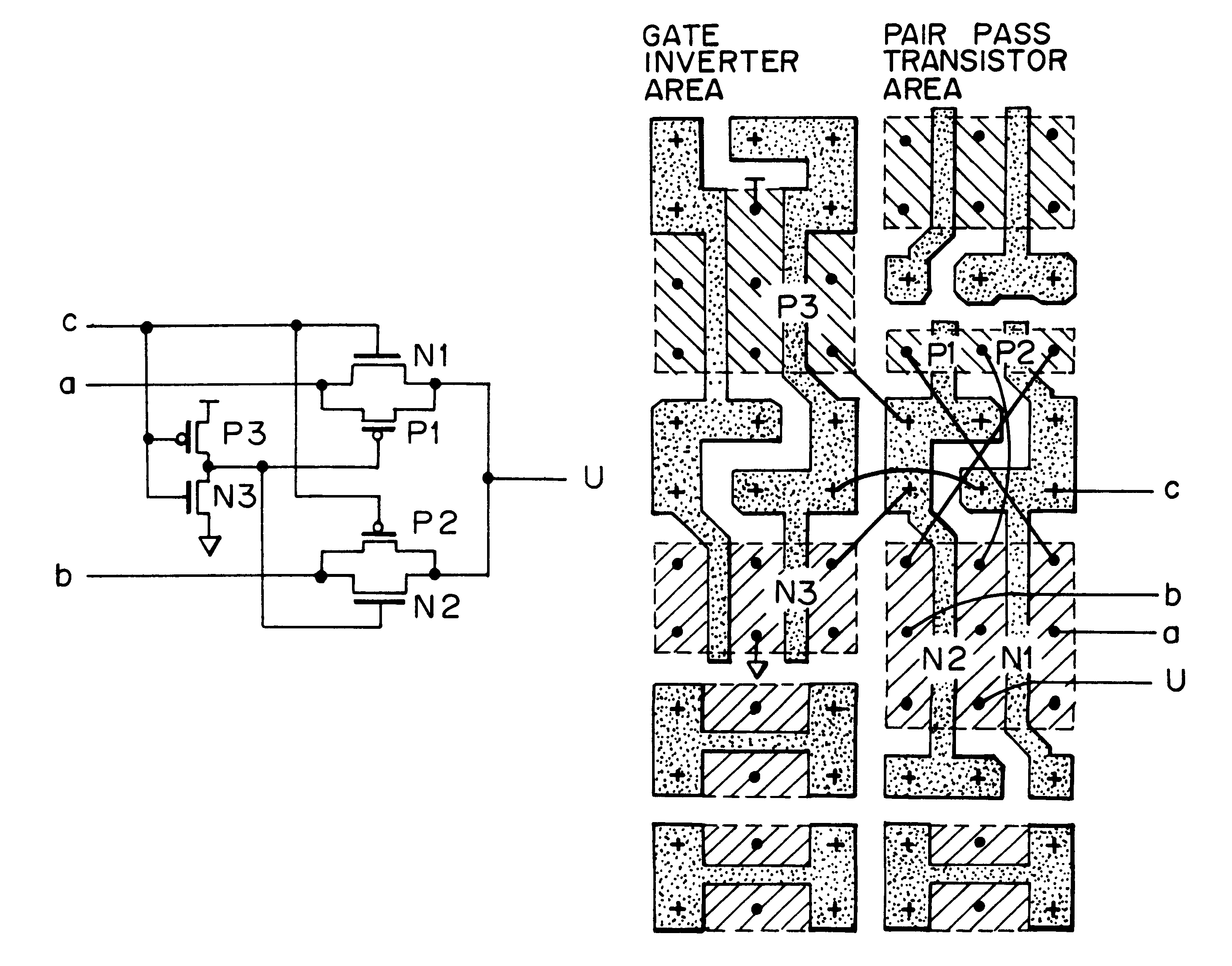

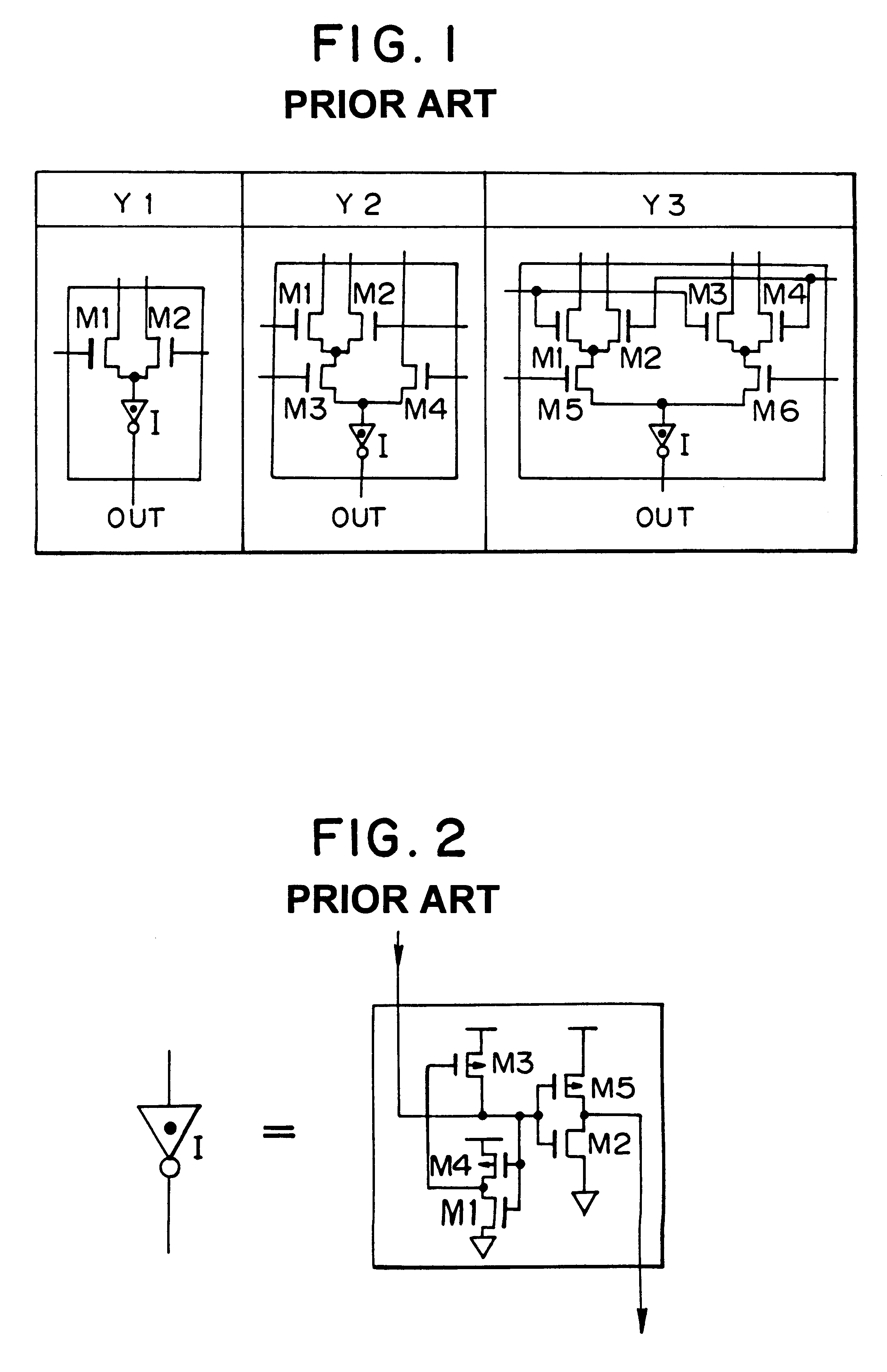

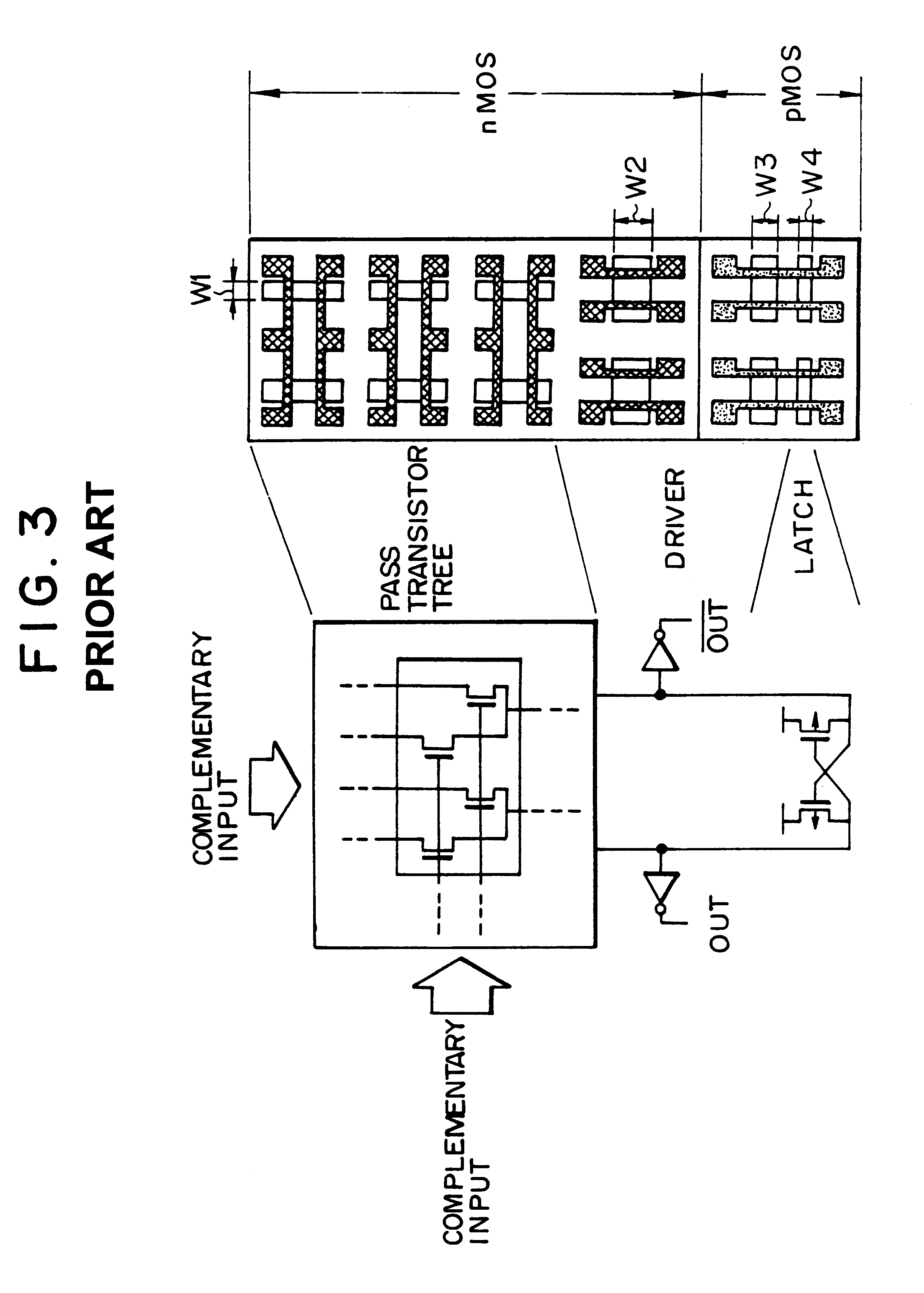

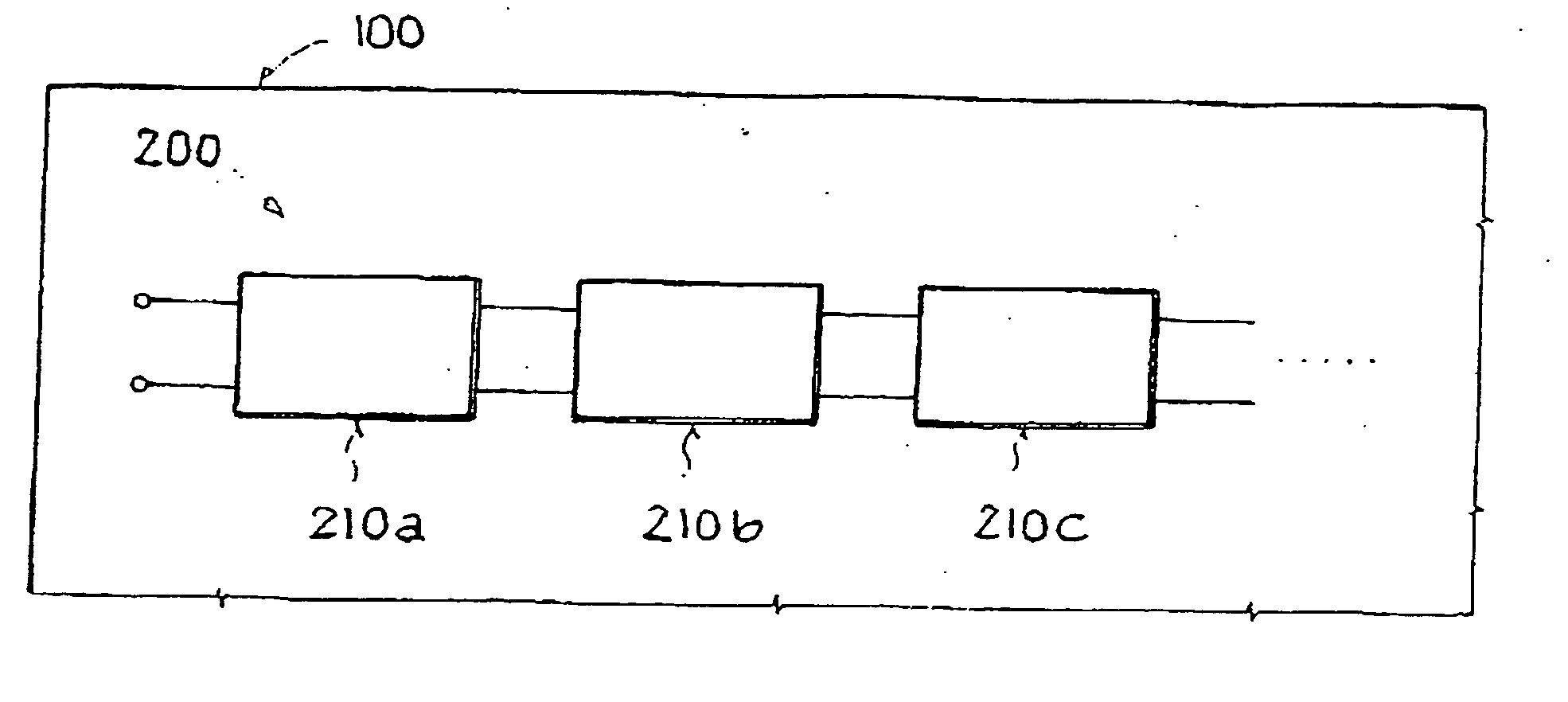

A semiconductor integrated circuit is constructed with composite pass-transistor logic circuits serving as elementary circuit units each including a plurality of pass-transistor logic trees and a multiple-input logic gate. A wide variety of logical operations, even complex opearations, can be efficiently expressed using the composite pass-transistor logic circuit, and the resultant logic circuit can operate at a high speed. Thus, the semiconductor integrated circuit of the present invention can realize various logic functions required for various users in an efficient fashion. The present invention is particularly useful when applied to a field-programmable gate array integrated circuit, since complex logical operations can be expressed in a simple and efficient fashion by the composite pass-transistor logic circuits. The gate array integrated circuit obtained in accordance with the present invention can operate at a high speed with low power consumption. The present invention also discloses a basic cell suitable for use in an integrated circuit in the form of a gate array, and more particularly, a programmable logic block for use in a field programmable gate array integrated circuit.

Owner:KAWASAKI MICROELECTRONICS

Storage circuit with layered structure element

InactiveUS6473333B1Reduce power consumptionIncrease speedSolid-state devicesDigital storageLow leakageElectrical resistivity and conductivity

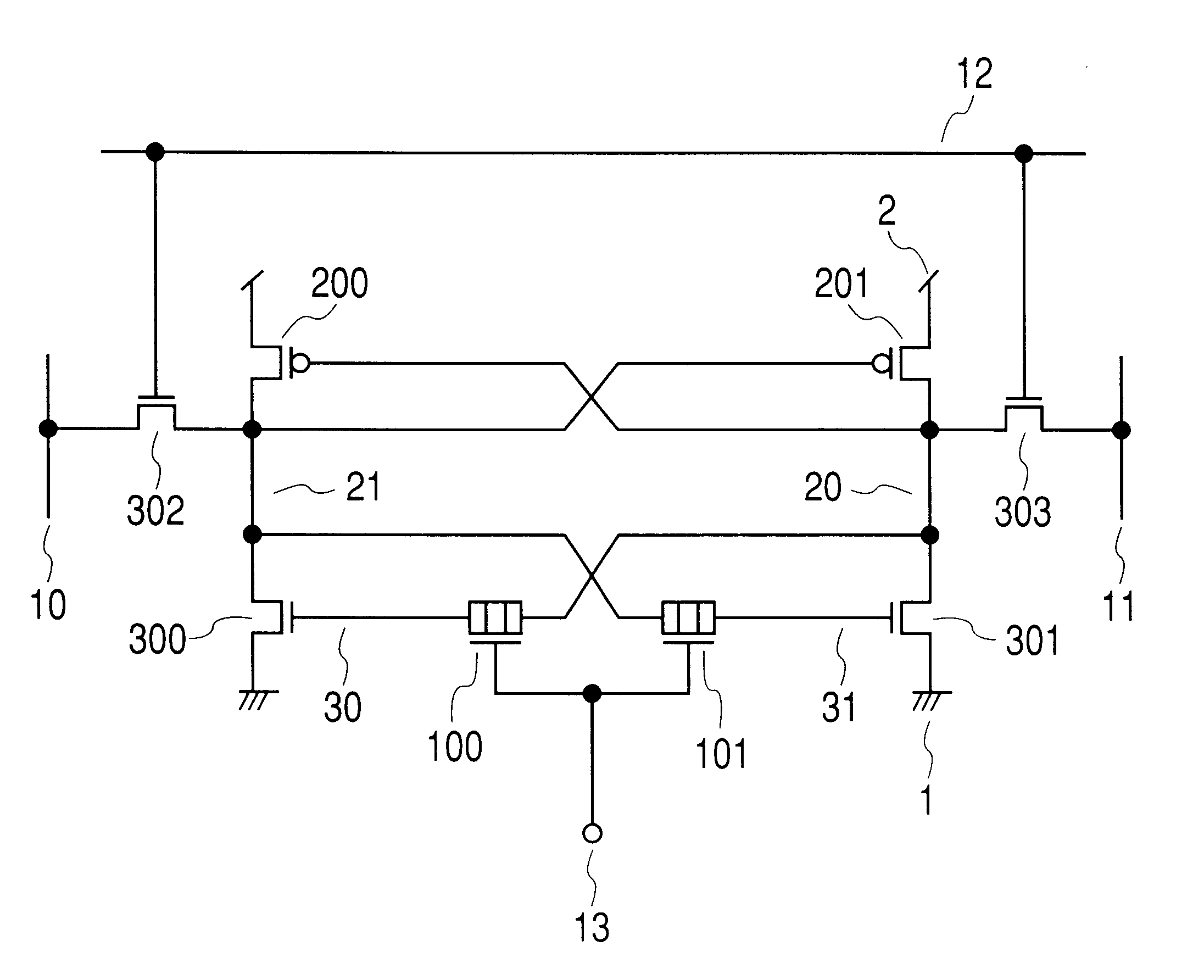

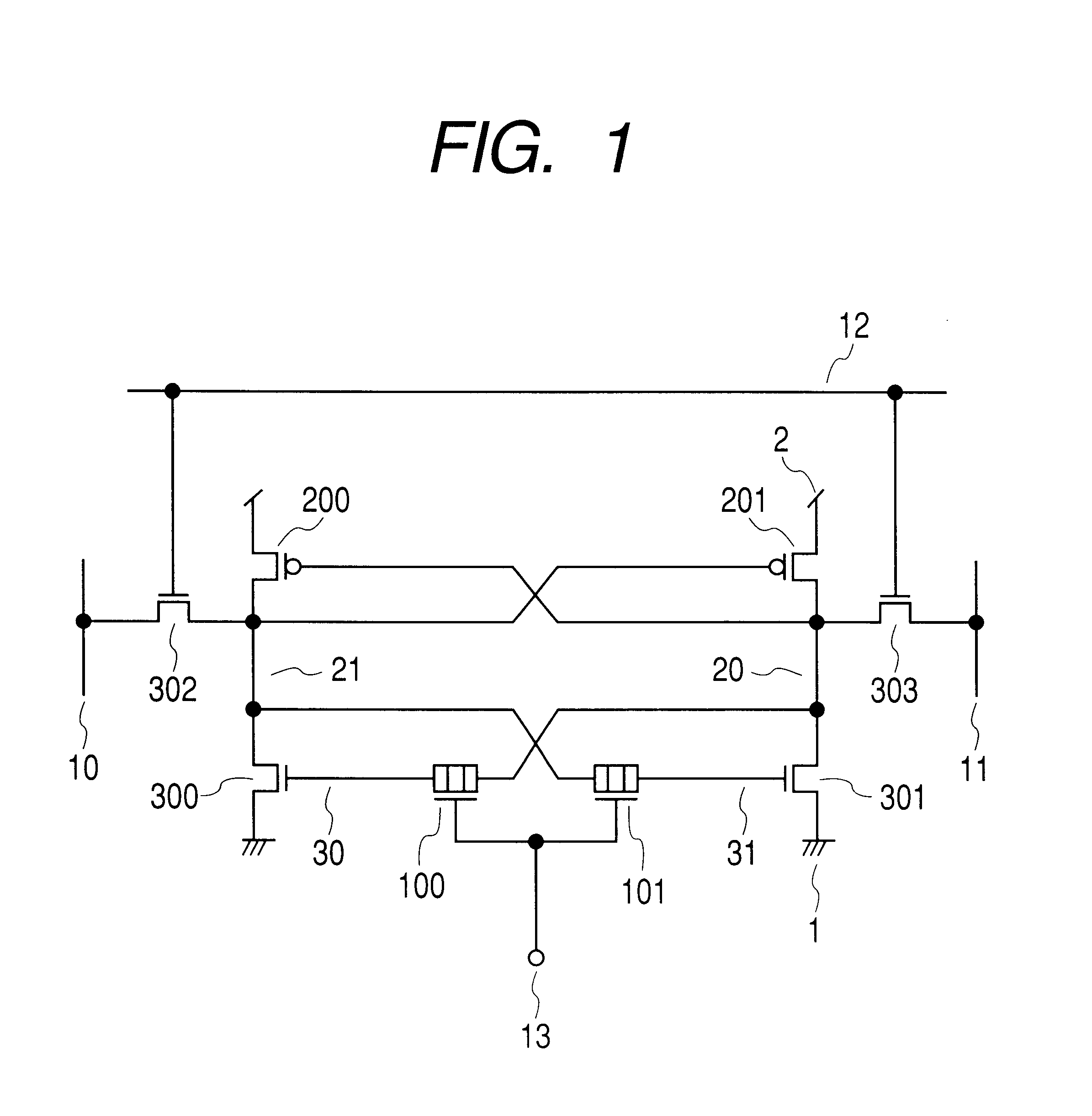

The present invention provides a circuit, in which a device typified by a PLED element is built into a flip-flop. In this case, a storage node of the device is low leakage. According to the present invention, it is possible to realize a SRAM that has nonvolatility while achieving high-speed operation. It is also possible to realize a flip-flop having the same characteristics. An example of a typical mode of the present invention is a storage circuit characterized by the following: a storage element is a device incorporating: a first path for a carrier; a first mode for storing a charge that generates an electric field where conductivity of the first path is changed; and a barrier structure through which a second carrier moves in response to given voltage so that the second carrier is stored in the first node; and the storage circuit includes a second node, to which information stored in the first node is outputted steadily in a state in which power is supplied. The flip-flop and the SRAM are realized using such a basic circuit.

Owner:HITACHI LTD

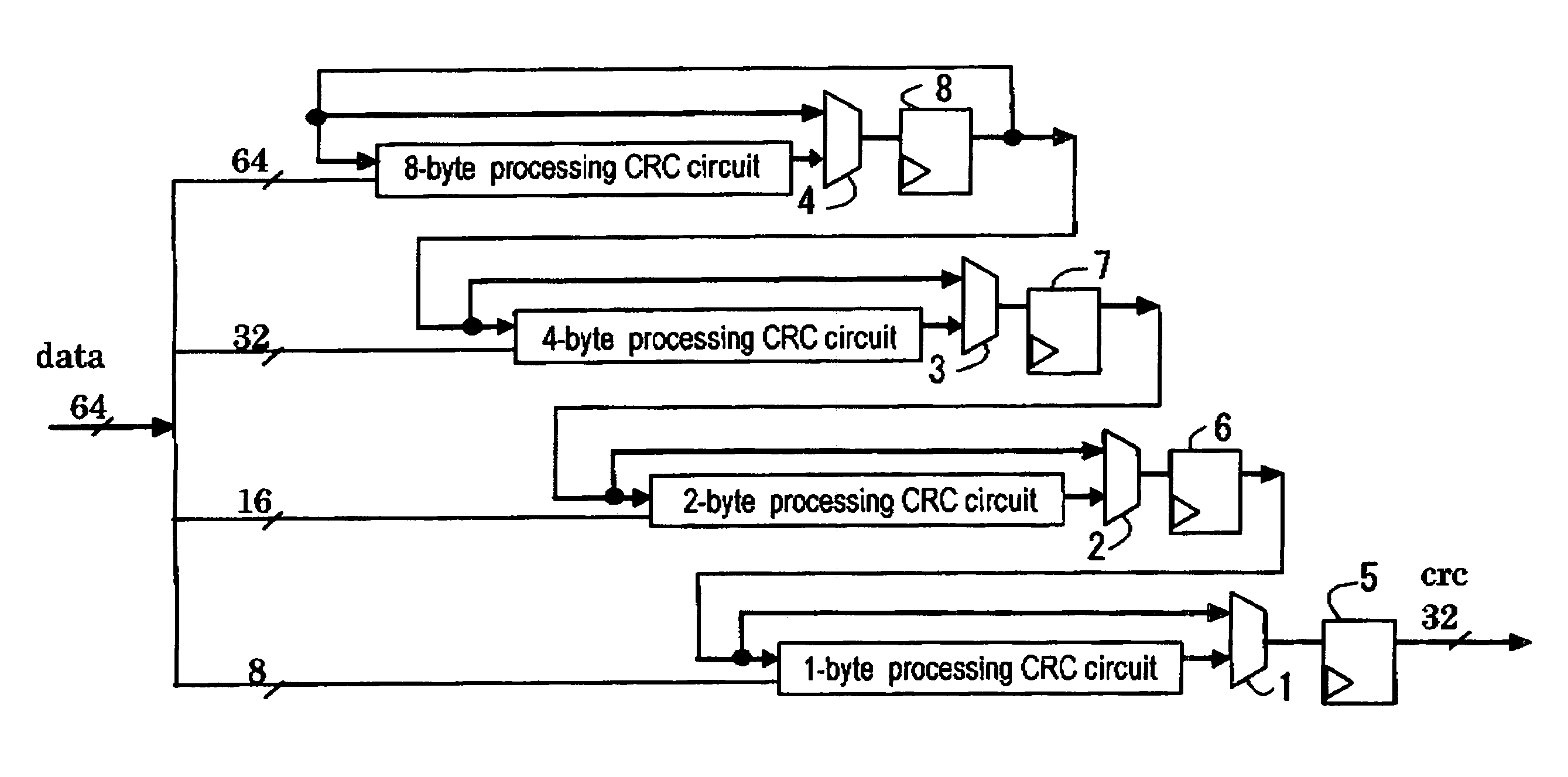

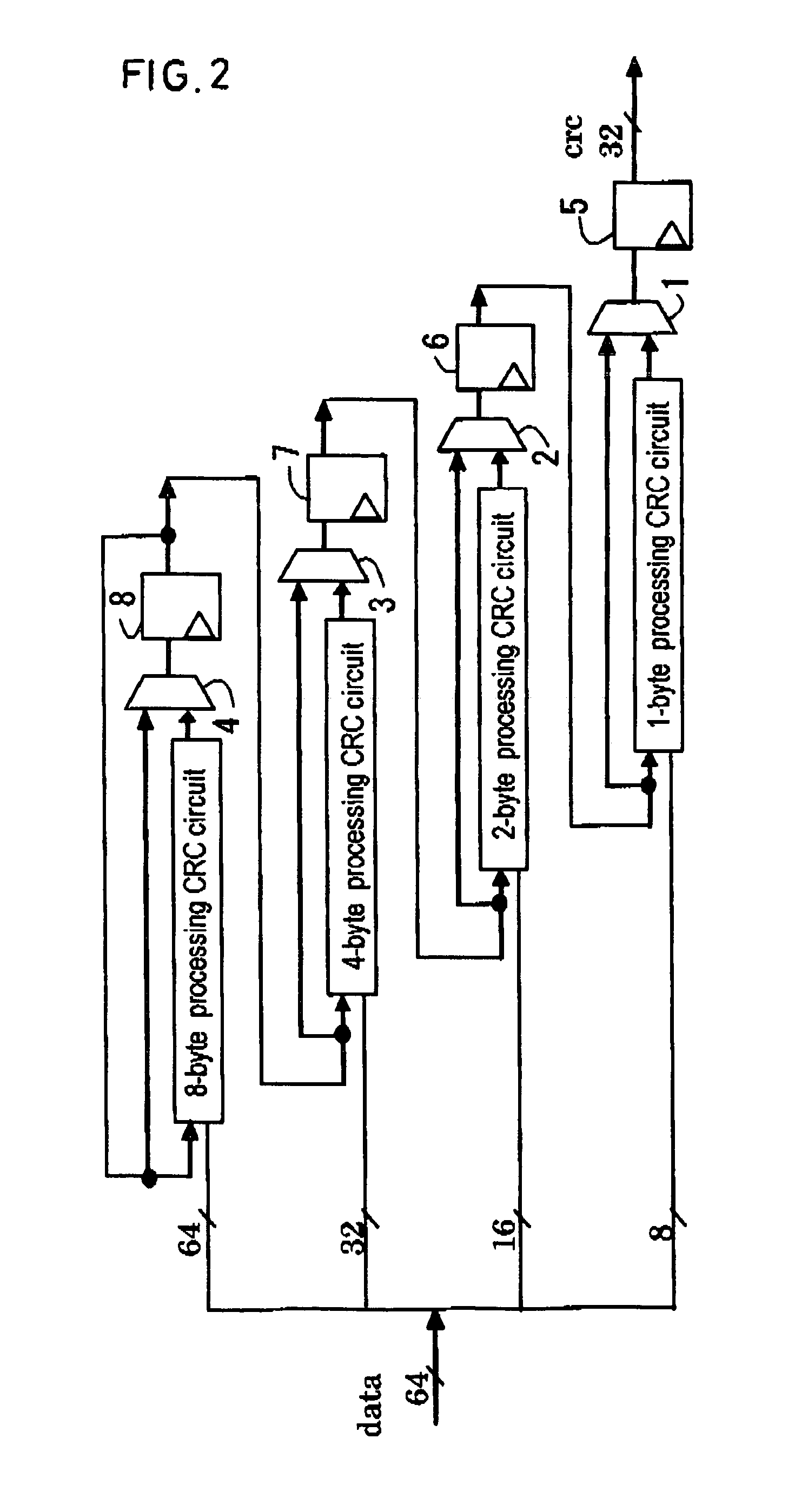

Cyclic redundancy checking value calculator

InactiveUS7590916B2Reduce circuit sizeSwelling in increase of scale of circuitryCode conversionError detection onlyProcessor registerComputer science

A CRC value calculator enables throughput to be improved while keeping down the increase in the size of the circuitry. This is achieved by using (n+1) basic CRC circuits to configure a CRC value calculator in which the width of the data processed during one clock cycle is m2n bits. For example, when m2n bits is the data width processed per calculator cycle, the CRC value calculator of this invention is configured by using selectors to serially connect a CRC circuit that processes every m2n bits, a CRC circuit that processes every m2(n−1) bits, . . . , and a CRC circuit that processes every m20 bits. This configuration makes it possible to calculate a correct CRC value even when the remainder of an input network frame is not a multiple of m2n bits. Selectors are used to select CRC circuit output according to process data width. Reduction of the operating frequency is avoided by using registers to form a pipeline between CRC circuits.

Owner:BITS CO LTD

Semiconductor integrated circuit capable of realizing logic functions

InactiveUS6097221AReliability increasing modificationsLogic circuits characterised by logic functionGate arrayEngineering

A semiconductor integrated circuit is constructed with composite pass-transistor logic circuits serving as elementary circuit units each including a plurality of pass-transistor logic trees and a multiple-input logic gate. A wide variety of logical operations, even complex opearations, can be efficiently expressed using the composite pass-transistor logic circuit, and the resultant logic circuit can operate at a high speed. Thus, the semiconductor integrated circuit of the present invention can realize various logic functions required for various users in an efficient fashion. The present invention is particularly useful when applied to a field-programmable gate array integrated circuit, since complex logical operations can be expressed in a simple and efficient fashion by the composite pass-transistor logic circuits. The gate array integrated circuit obtained in accordance with the present invention can operate at a high speed with low power consumption. The present invention also discloses a basic cell suitable for use in an integrated circuit in the form of a gate array, and more particularly, a programmable logic block for use in a field programmable gate array integrated circuit.

Owner:KAWASAKI MICROELECTRONICS

Intelligent vibration monitor system

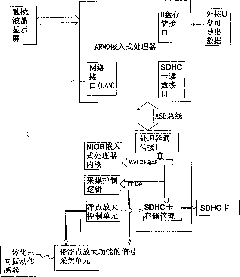

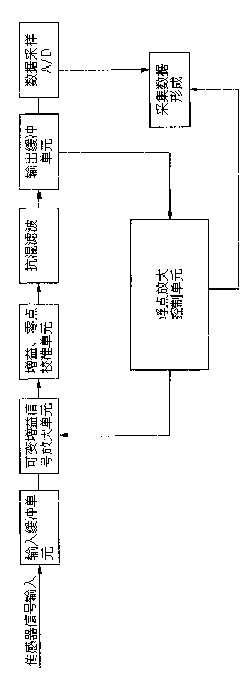

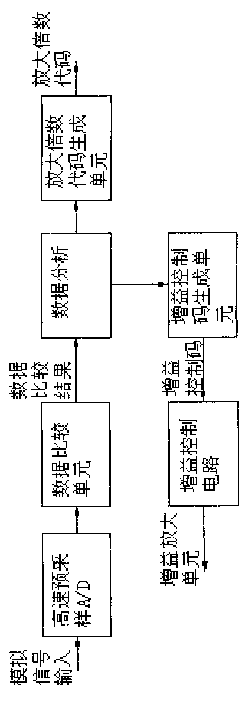

InactiveCN101799321AEasy to useSolve complex operationsSubsonic/sonic/ultrasonic wave measurementAnalog signalFloating point

An intelligent vibration monitor system relates to the field test, record and analysis system of vibration signals. The whole collecting function from analog signal input, floating point amplification and A / D quantization to data storage is realized through the following processes that: (1) the vibration signals generated in the test field are collected, (2) a signal collecting unit design realizes the basic circuit with the floating point amplification function, in the process, floating point amplification control logic carries out comparative analysis on signals and continuously emits gain control codes to a signal collecting unit so that the signal collecting unit amplifies the signals and completes digital quantization at the optimal amplification times, (3) after the signal collection with the floating point amplification function is realized, the data after the digital quantization is stored effectively and an FPGA embedded NIOS processor and an SDHC storage management logic designed in a FPGA are adopted to finish the read and write operation of an SDHC card together. The invention is an advanced device, with which self-adaption floating point amplification technology is applied to the vibration tester field.

Owner:四川拓普测控科技有限公司

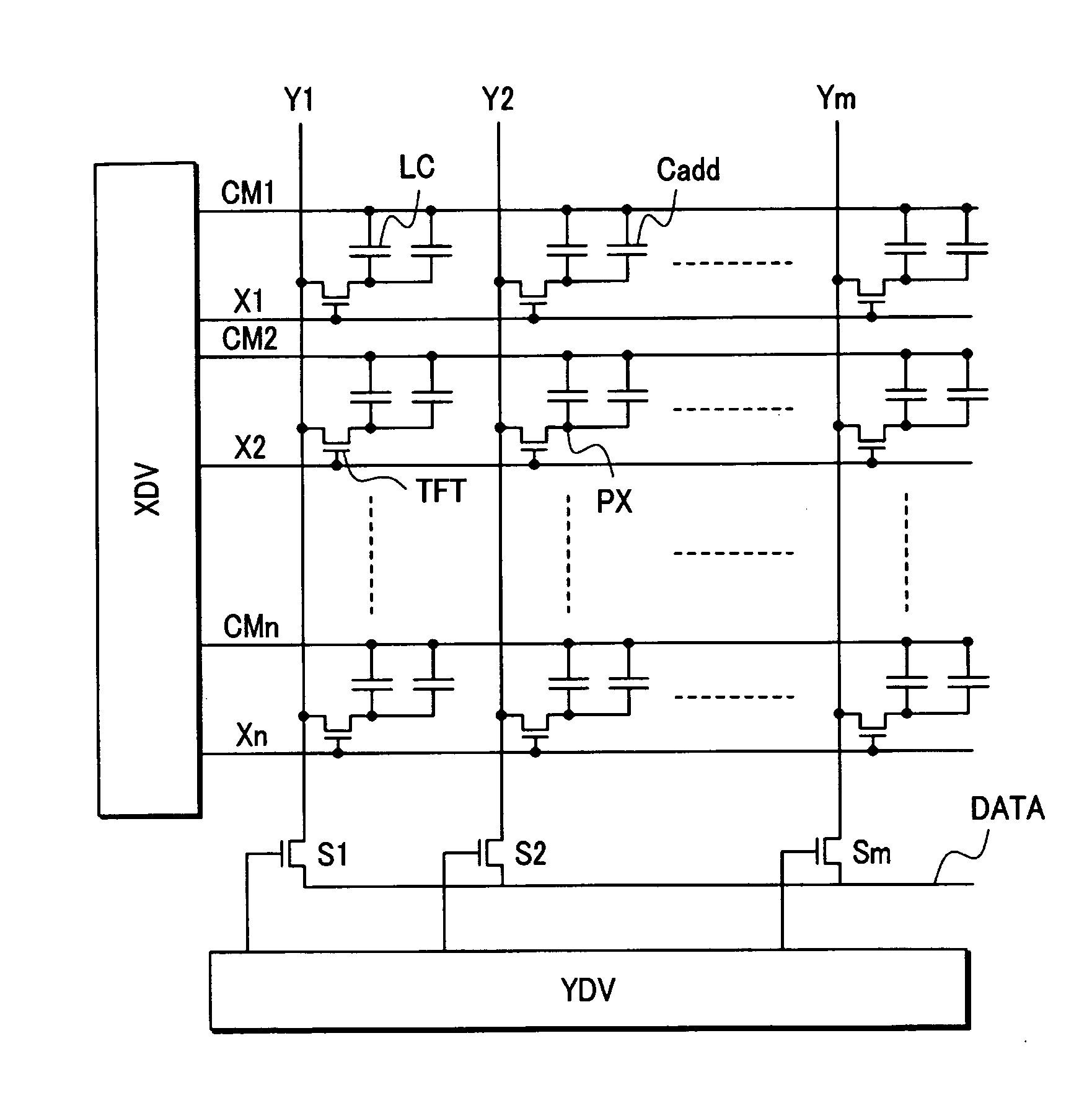

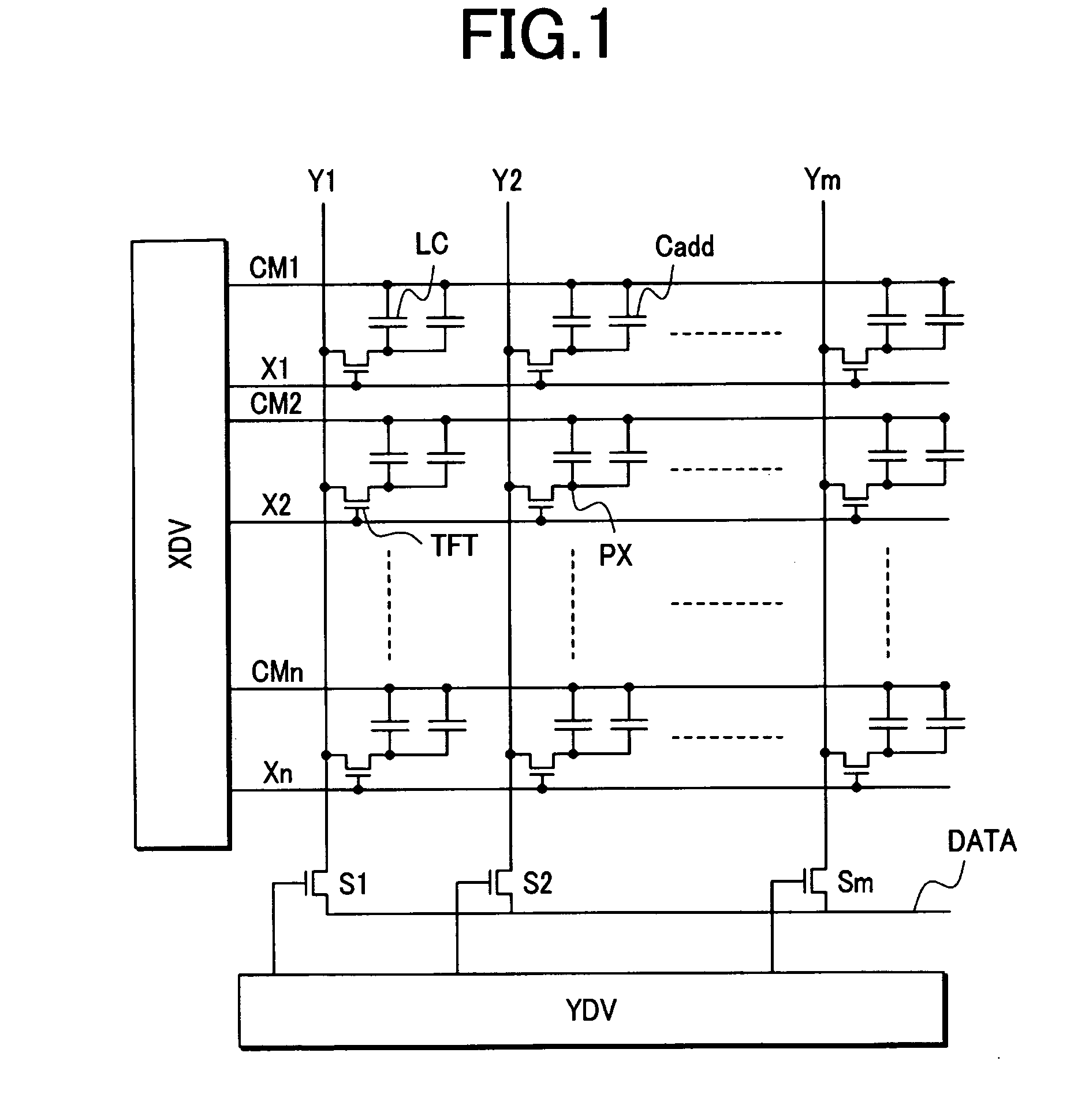

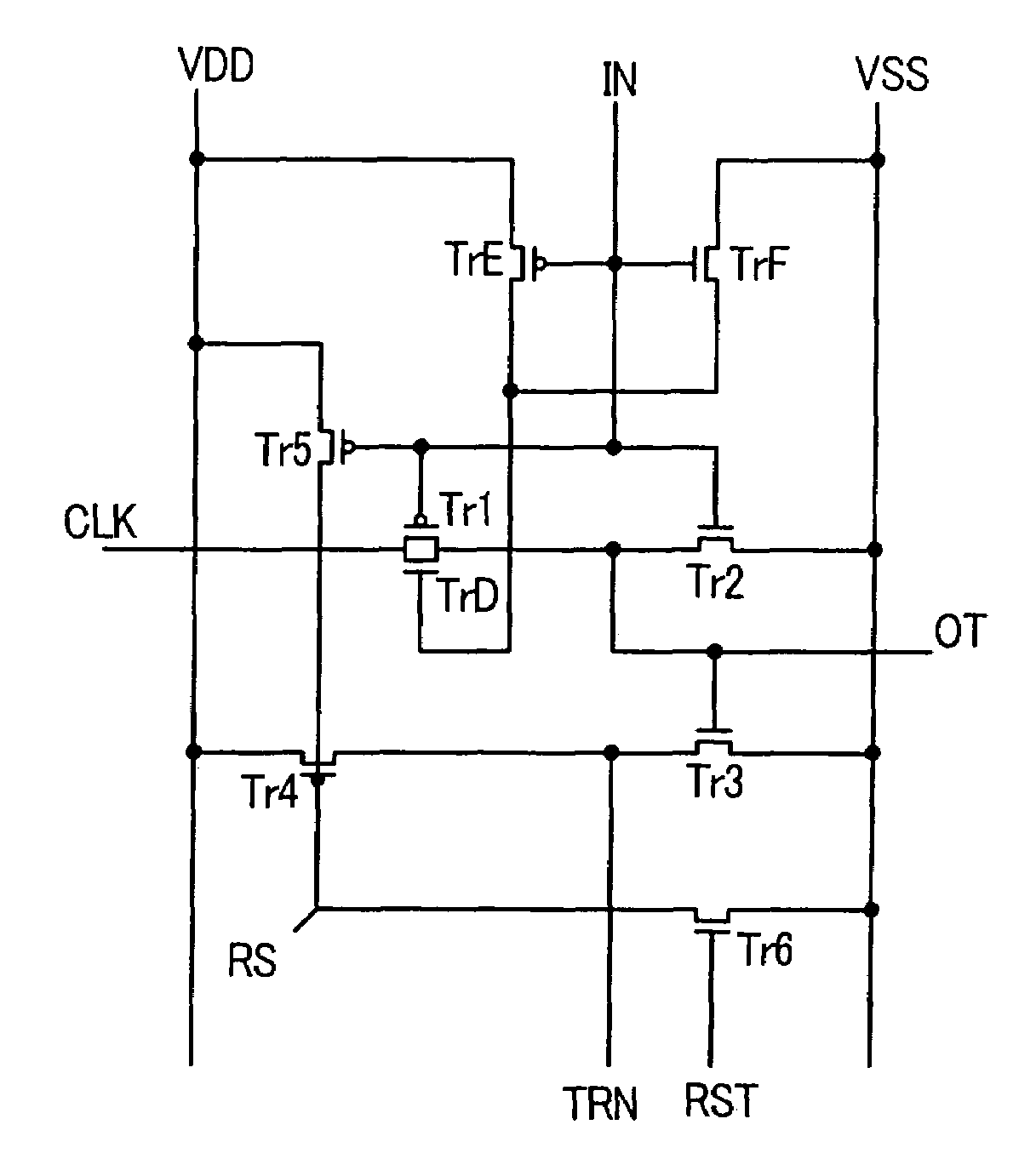

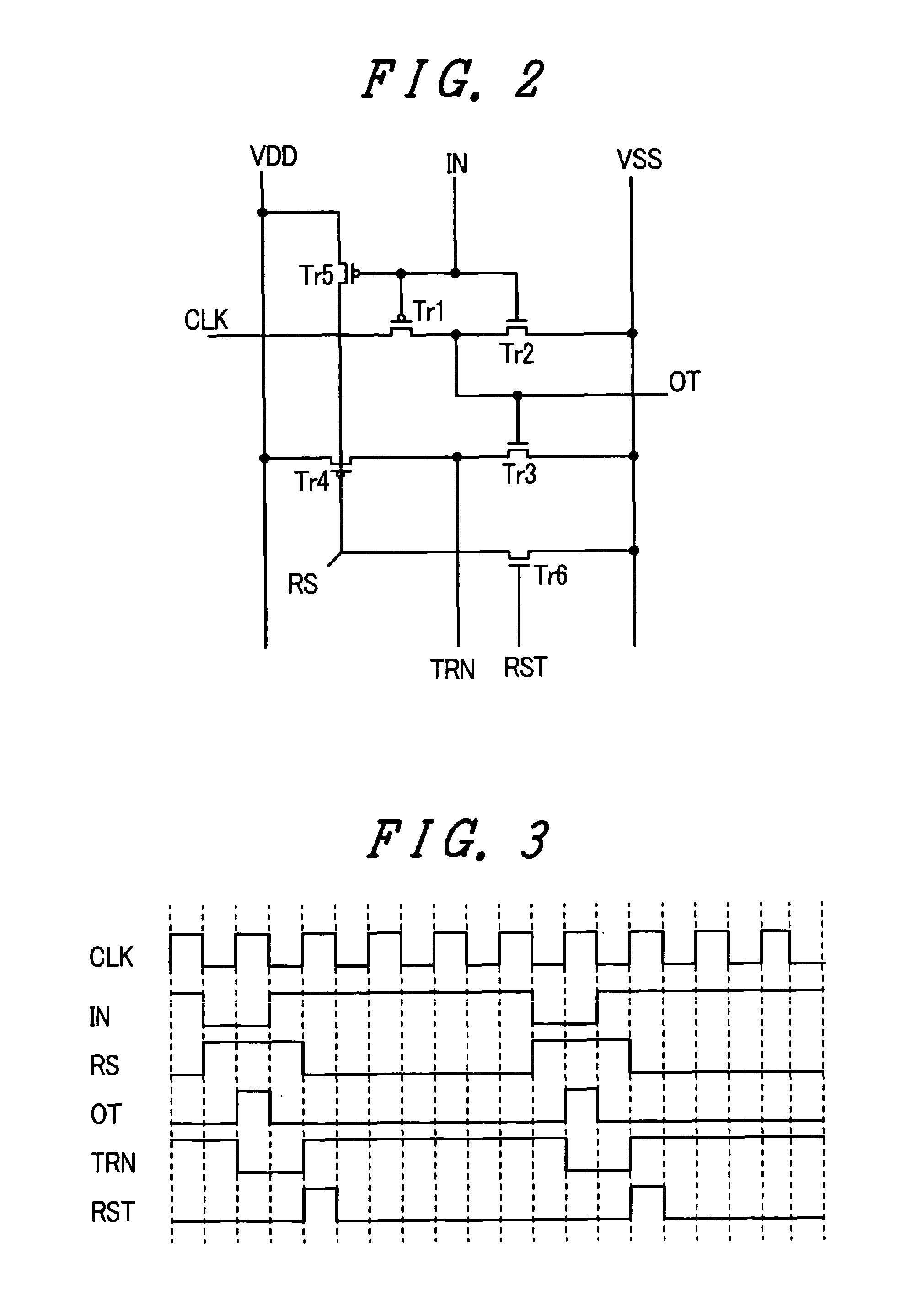

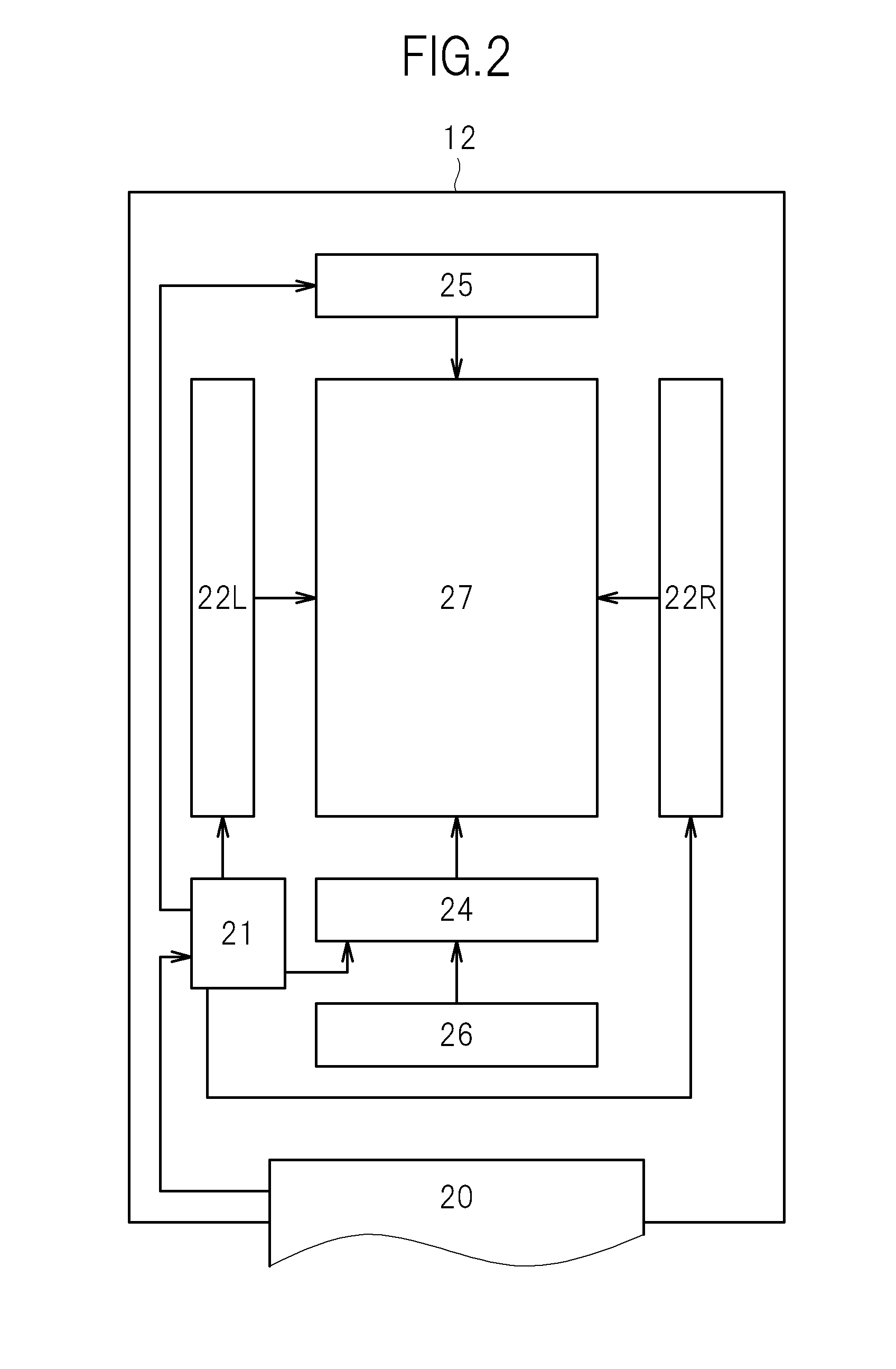

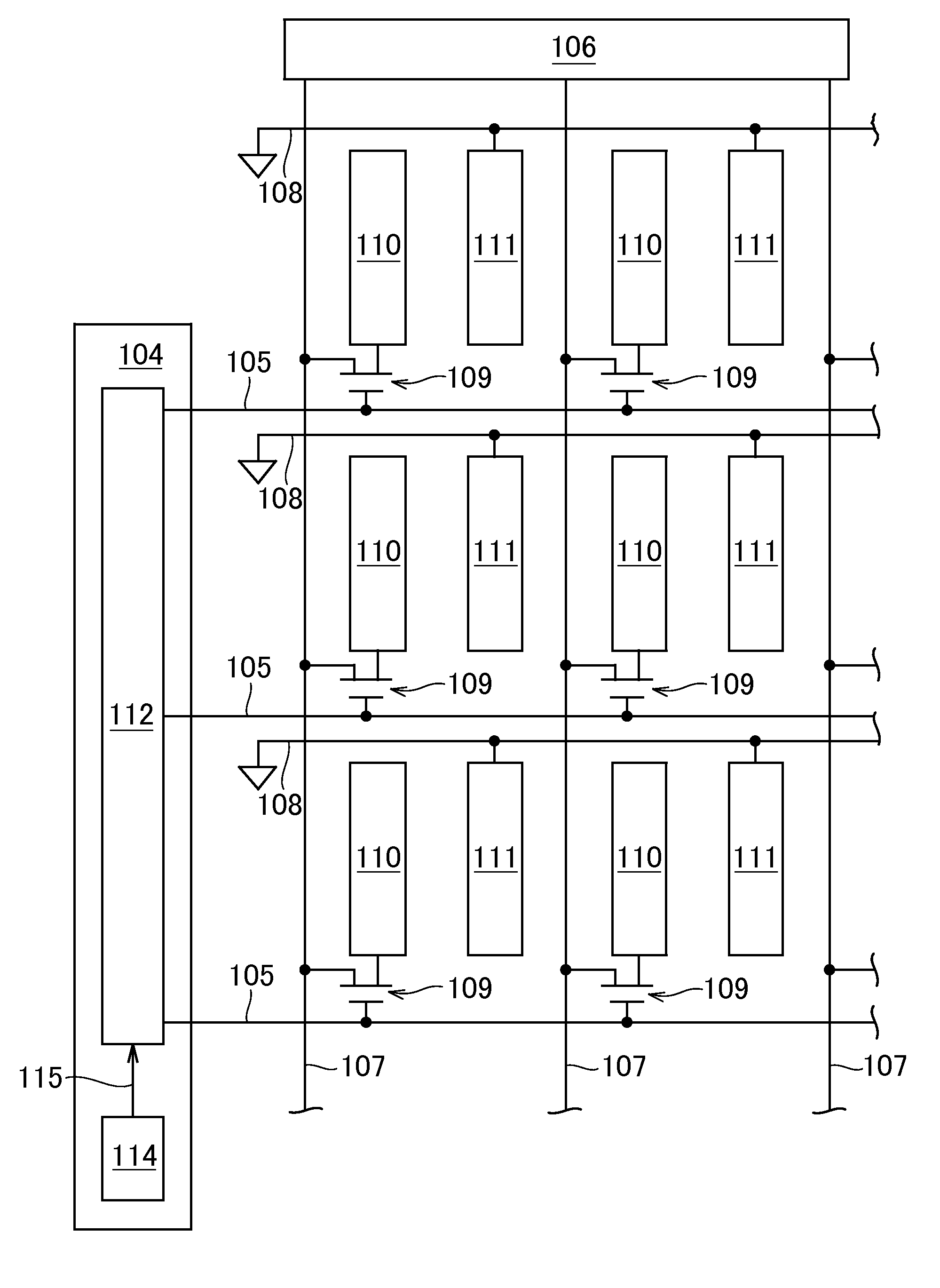

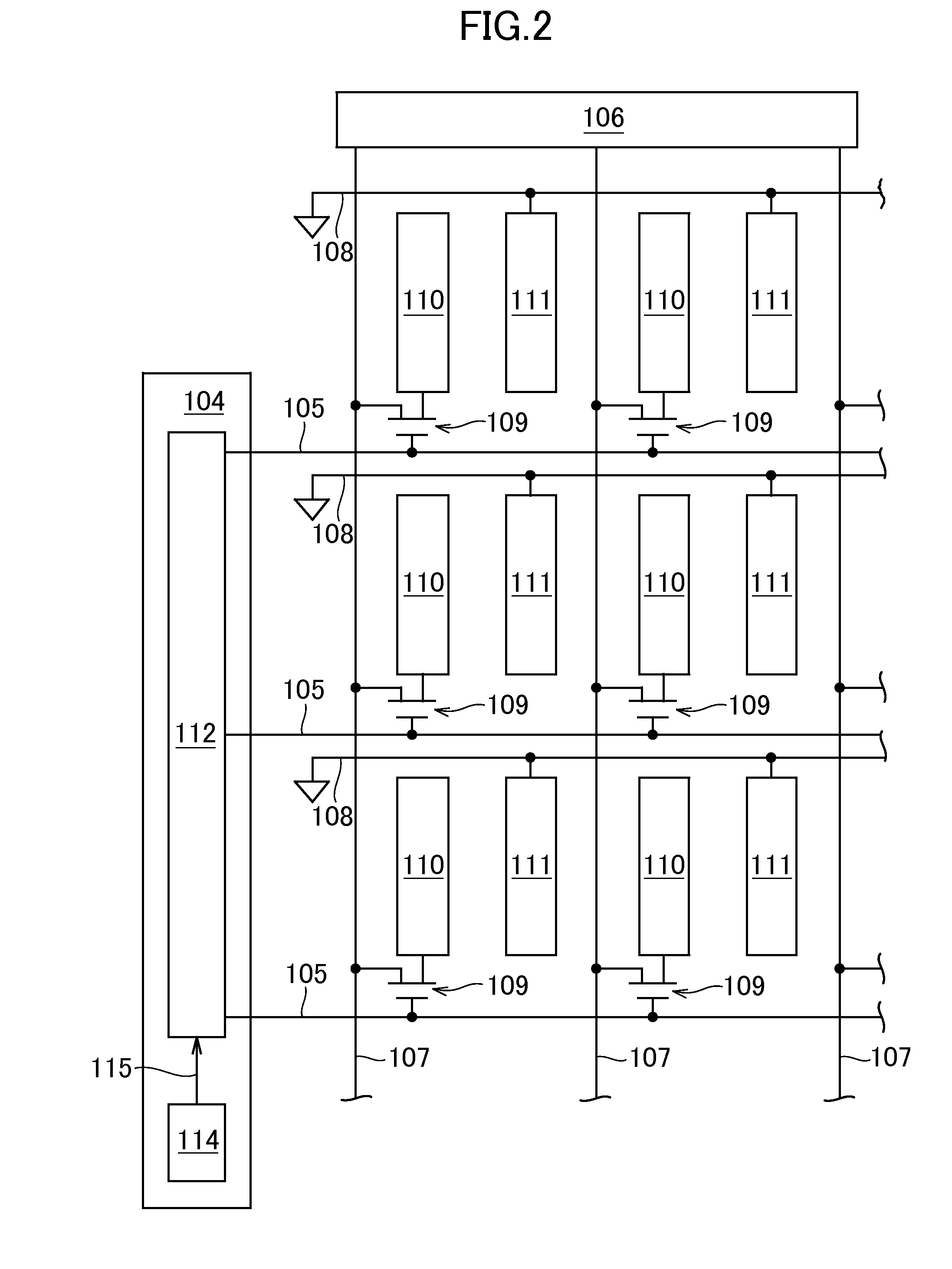

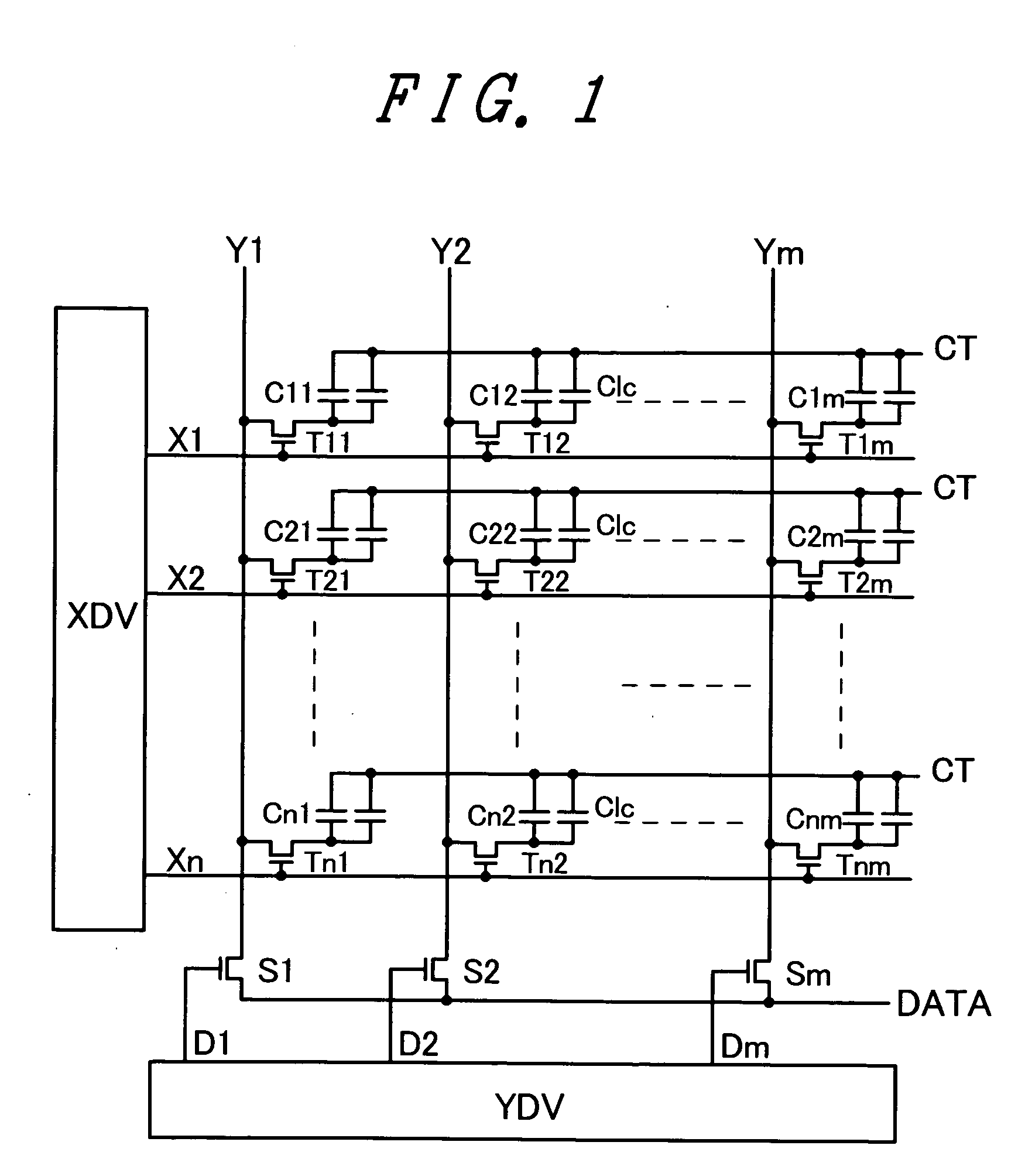

Display device

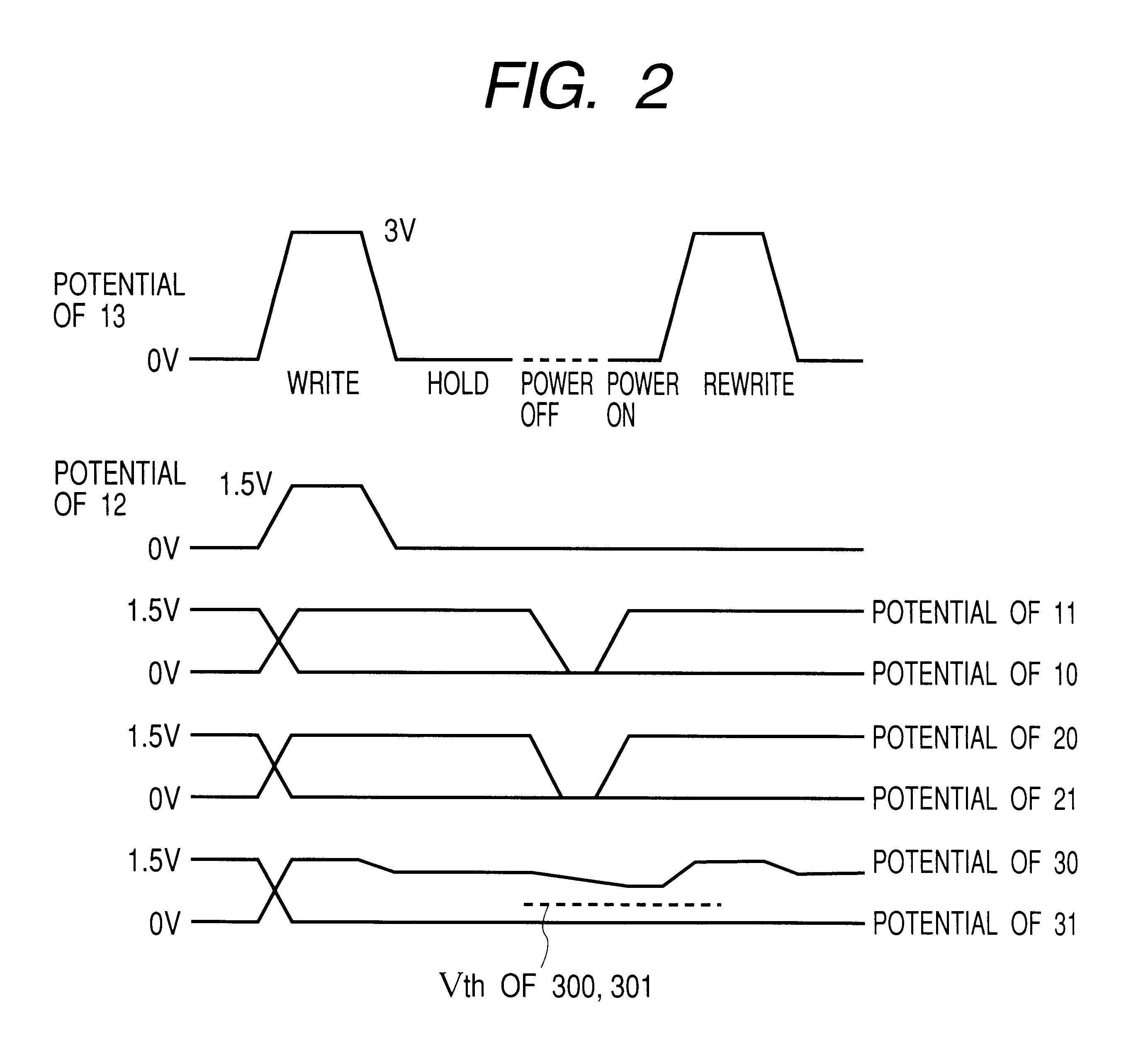

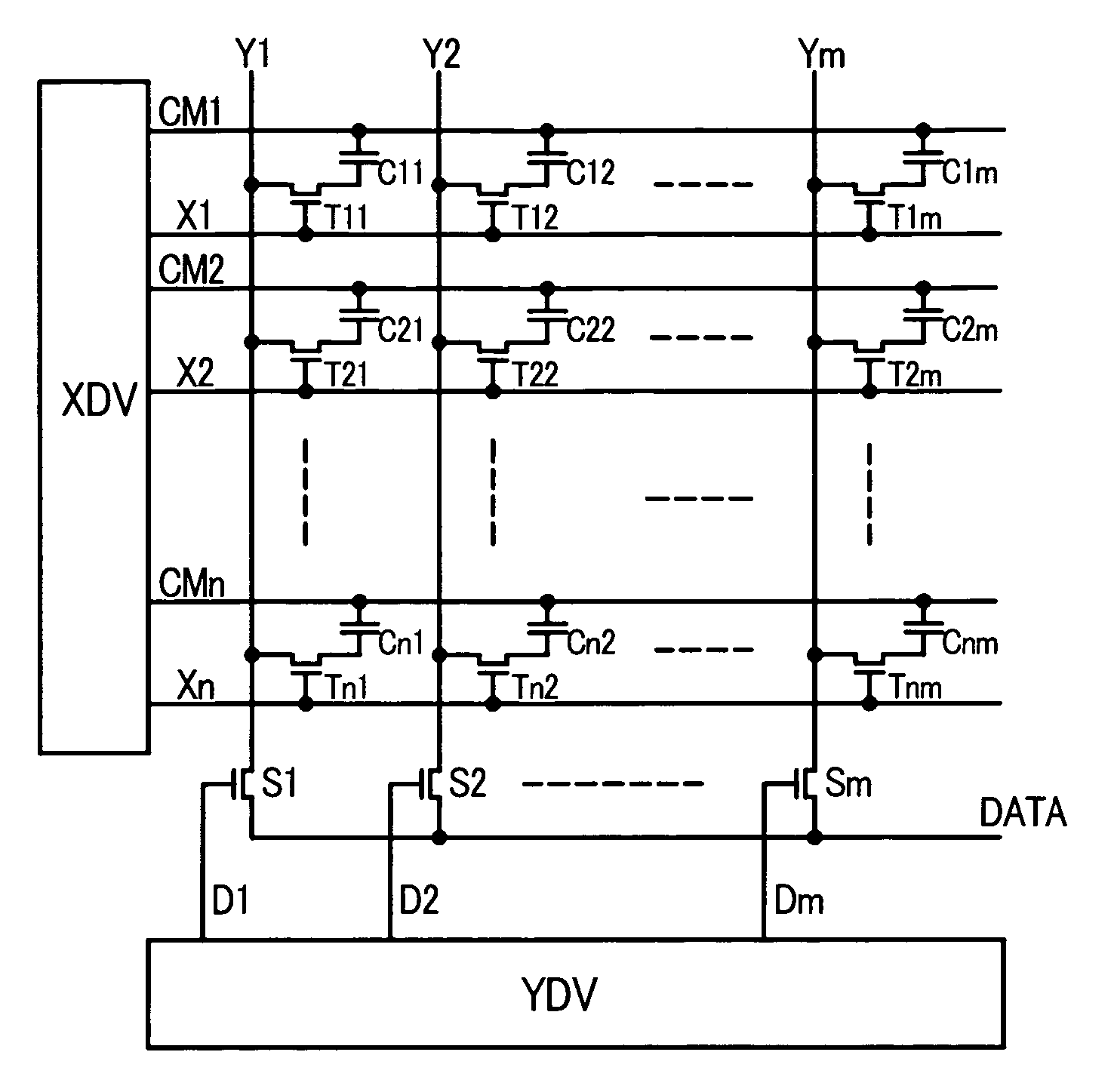

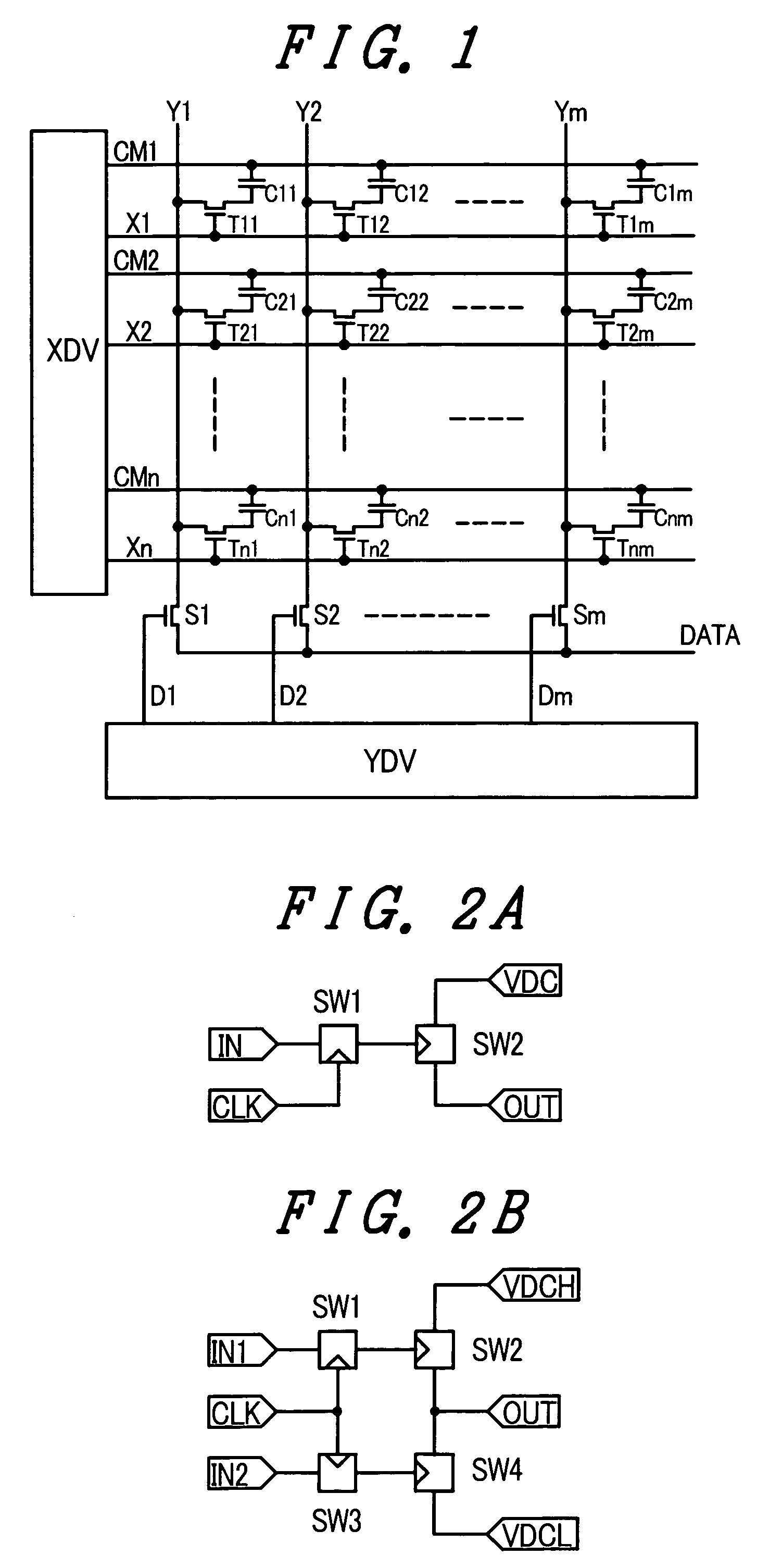

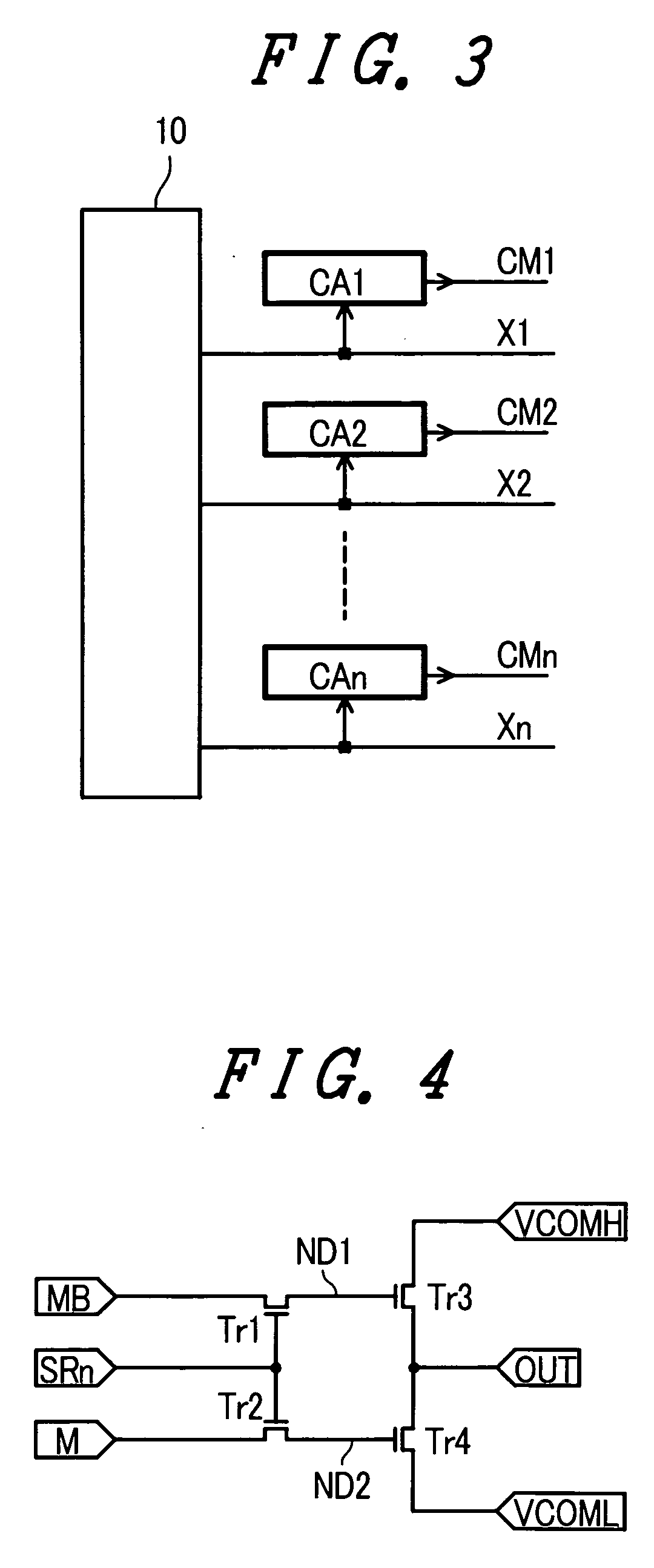

ActiveUS20060221034A1Reduce the numberReduce circuit sizeStatic indicating devicesRoad vehicle drive control systemsElectricityDisplay device

The present invention provides a display device which includes a common electrode drive circuit having the single channel constitution which can miniaturize a circuit scale without increasing elements compared to a conventional display device. A display device includes a plurality of pixels and a common electrode drive circuit. The common electrode drive circuit includes a plurality of basic circuits, wherein the basic circuit includes a first circuit which latches a first input signal at a point of time that a clock signal is changed to a first voltage level from a second voltage level; a second circuit which latches a second input signal at the point of time that the clock signal is changed to the first voltage level from the second voltage level; a first switching circuit which is turned on based on the voltage latched by the first circuit and outputs a first power source voltage to an output terminal in an ON state; and a second switching circuit which is turned on based on the voltage which is latched by the second circuit and outputs a second power source voltage to an output terminal in an ON state, wherein when the first input signal assumes the second voltage level, the second input signal assumes the first voltage level, and when the second input signal assumes the second voltage level, the first input signal assumes the first voltage level, and after the clock signal is changed to the second voltage level from the first voltage level and before the clock signal returns to the first voltage level from the second voltage level, either one of the first input signal and the second input signal is changed to the second voltage level form the first voltage level.

Owner:JAPAN DISPLAY INC +1

Display device

A shift register circuit has a plurality of shift pulse generation circuits, and a scanning voltage generation circuit has a plurality of base circuits. The base circuits are presented with a first shift pulse generated by a shift pulse generation circuit, and a scanning line clock. The base circuits have a first transistor in which the first shift pulse is input to a first electrode, and a first power supply voltage is input to a control electrode; and a second transistor in which a control electrode is connected to a second electrode in the first transistor, a scanning line clock is input to the first electrode, and the second electrode is connected to a scanning voltage output terminal. The base circuits output a selected scanning voltage synchronized with the scanning line clock from the scanning voltage output terminal when the first shift pulse is at a first voltage level.

Owner:JAPAN DISPLAY INC

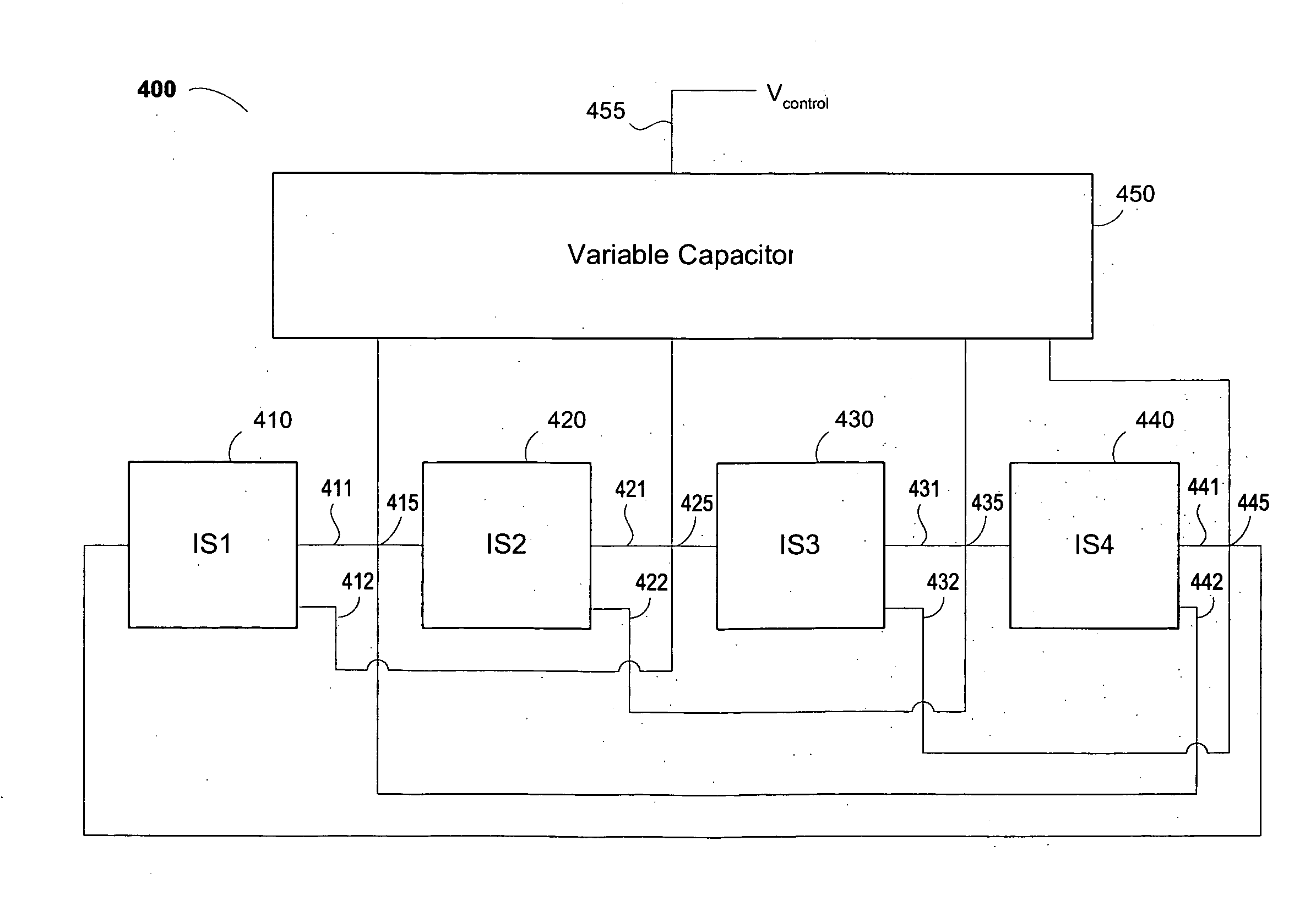

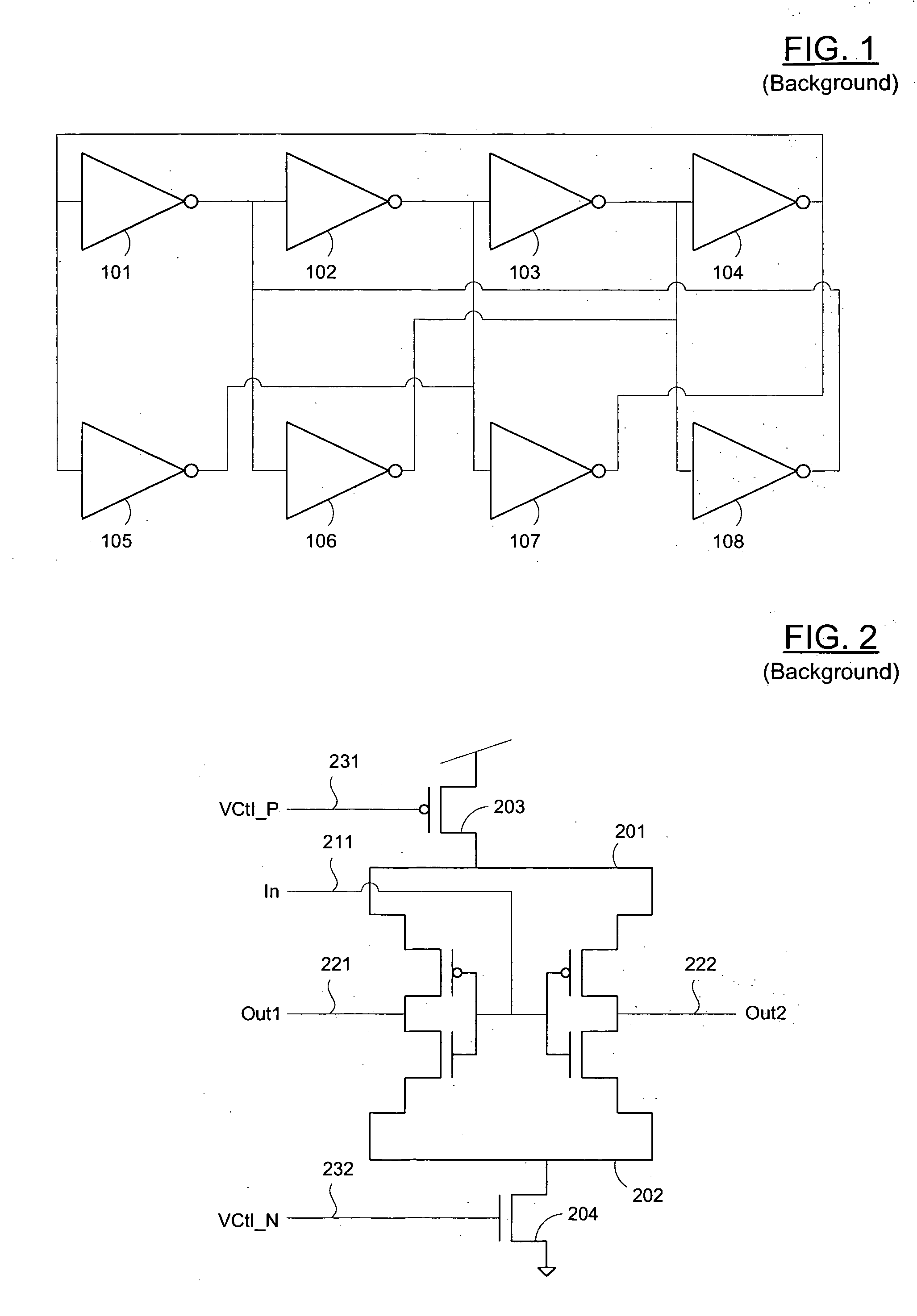

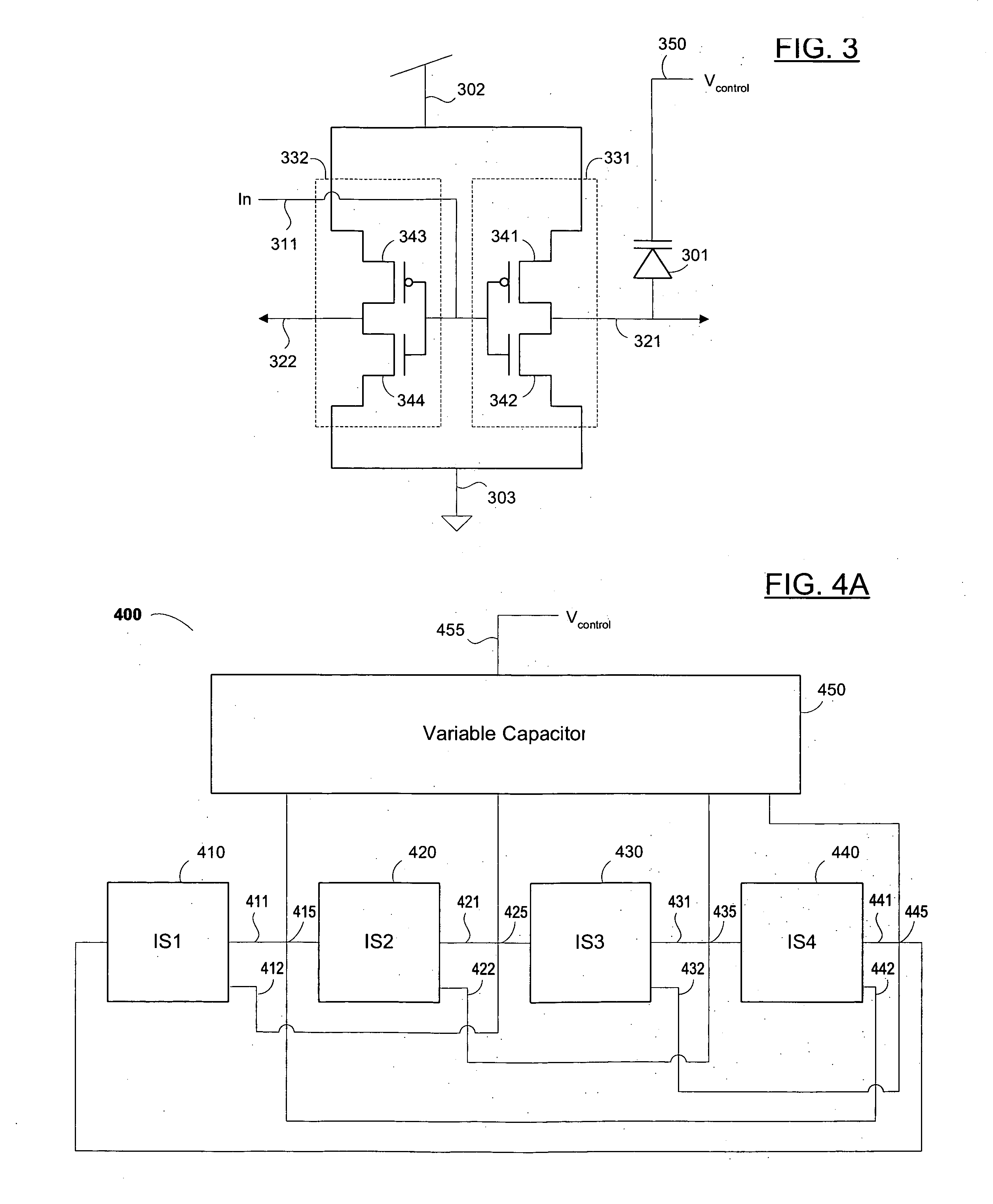

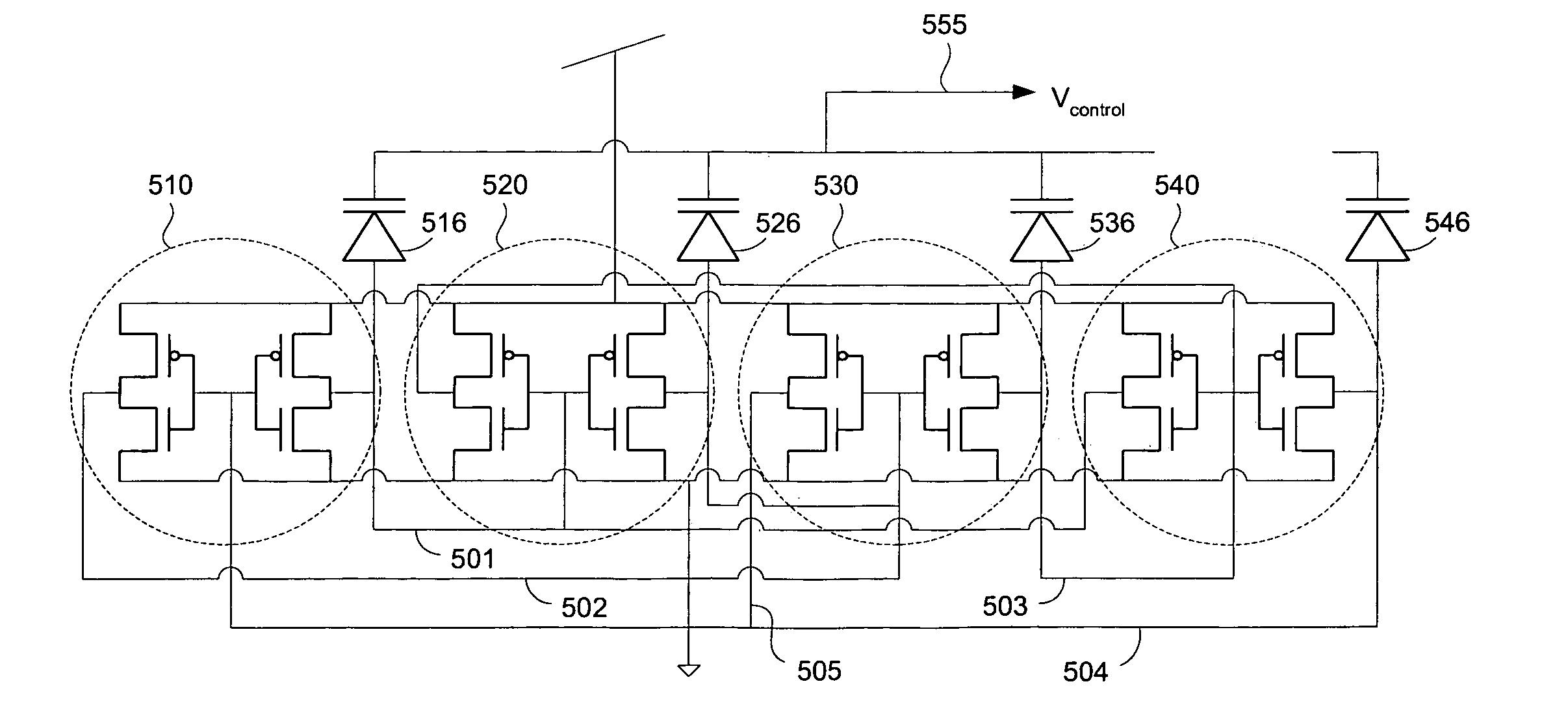

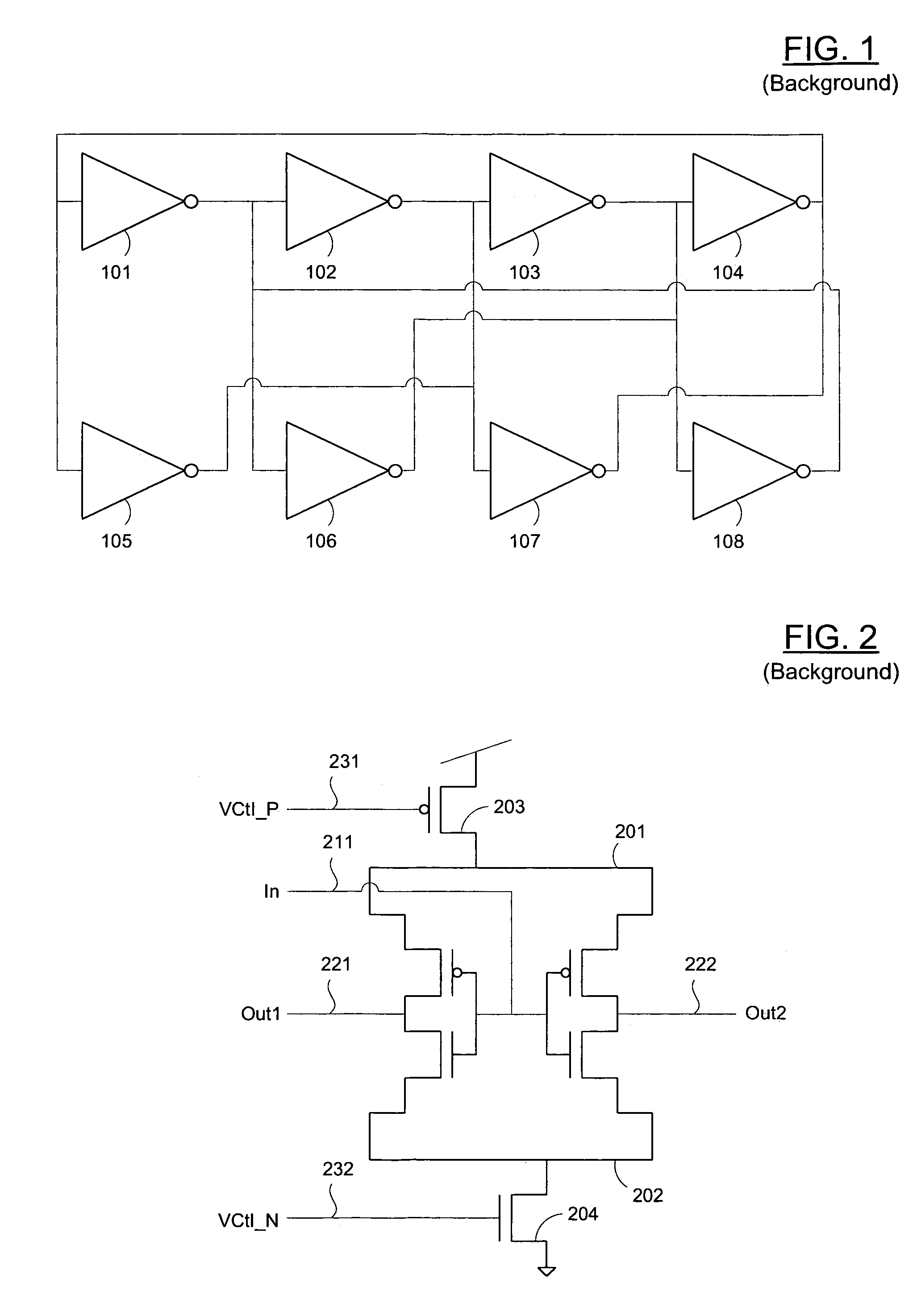

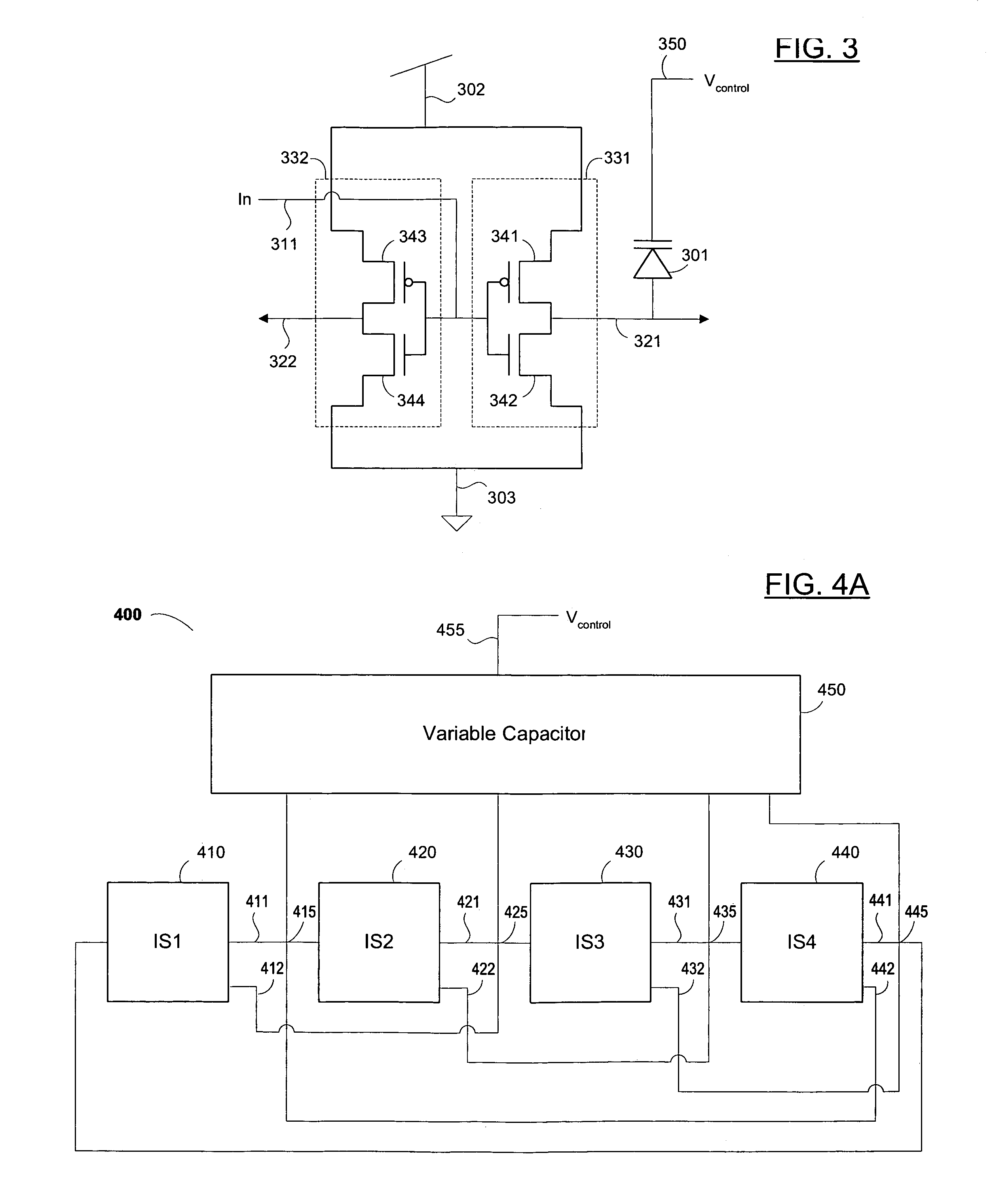

Circuits for voltage-controlled ring oscillators and method of generating a periodic signal

InactiveUS20060244543A1Easy to implementPulse generation by logic circuitsQuadrature oscillatorSoi cmos technology

Circuits and methods and for generating oscillator outputs using standard integrated circuit components. The basic circuit generally includes two inverters and a variable capacitor to configure a delay of the circuit input and / or output. The oscillator circuit generally includes a plurality of inverter circuits, at least one of which uses a variable capacitor to adjust a delay between stages, and thereby adjust a frequency of oscillation. Thus, the oscillator outputs may be tuned using a single control voltage. The method generally includes the steps of (1) applying an operating voltage to a ring oscillator comprising a plurality of stages; and (2) applying a control voltage to a variable capacitor coupled to a node between at least two of those stages. The circuits have particular advantage in quadrature oscillators, and may be easily implemented using widely available CMOS technology.

Owner:SEIKO EPSON CORP

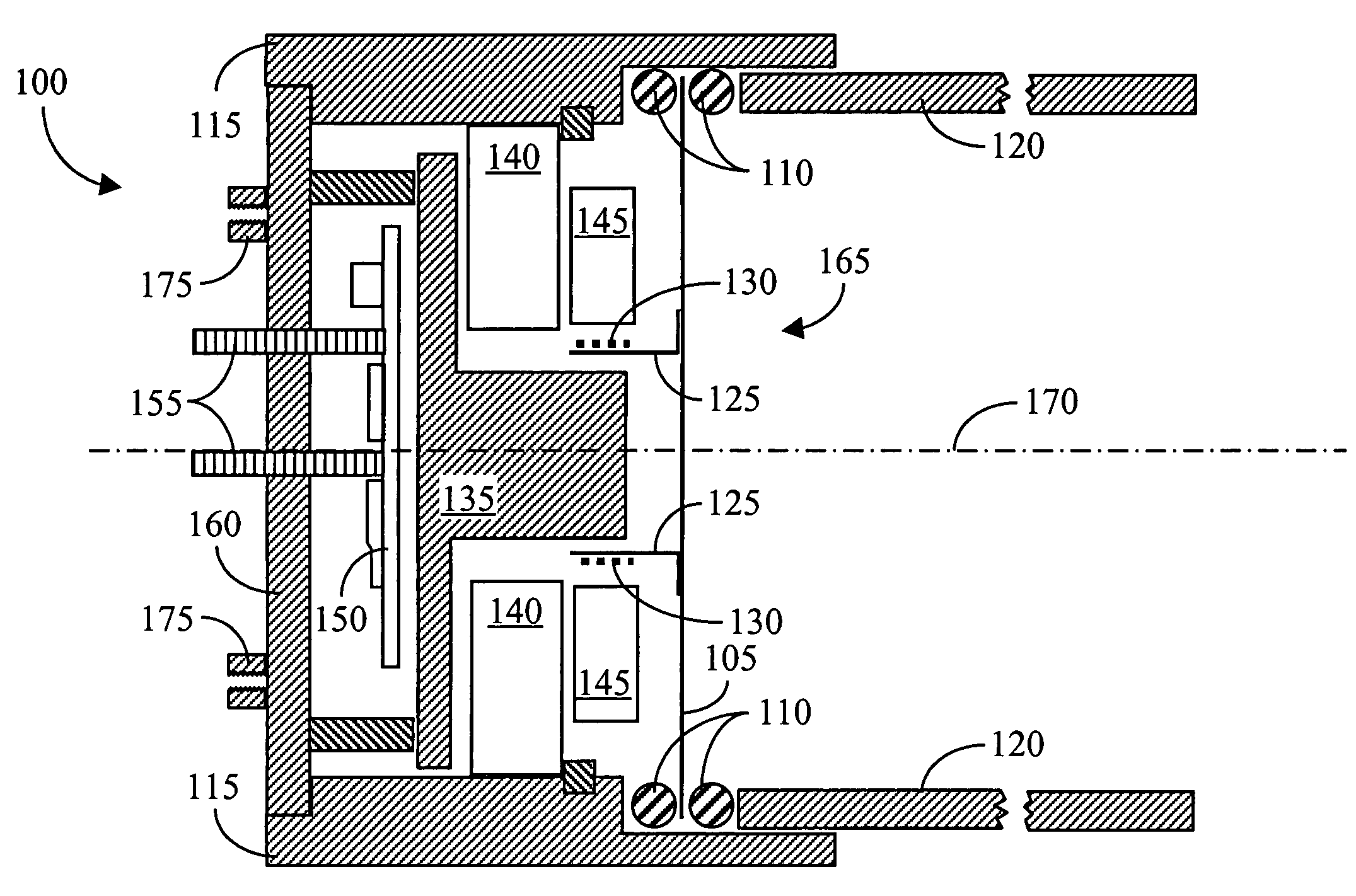

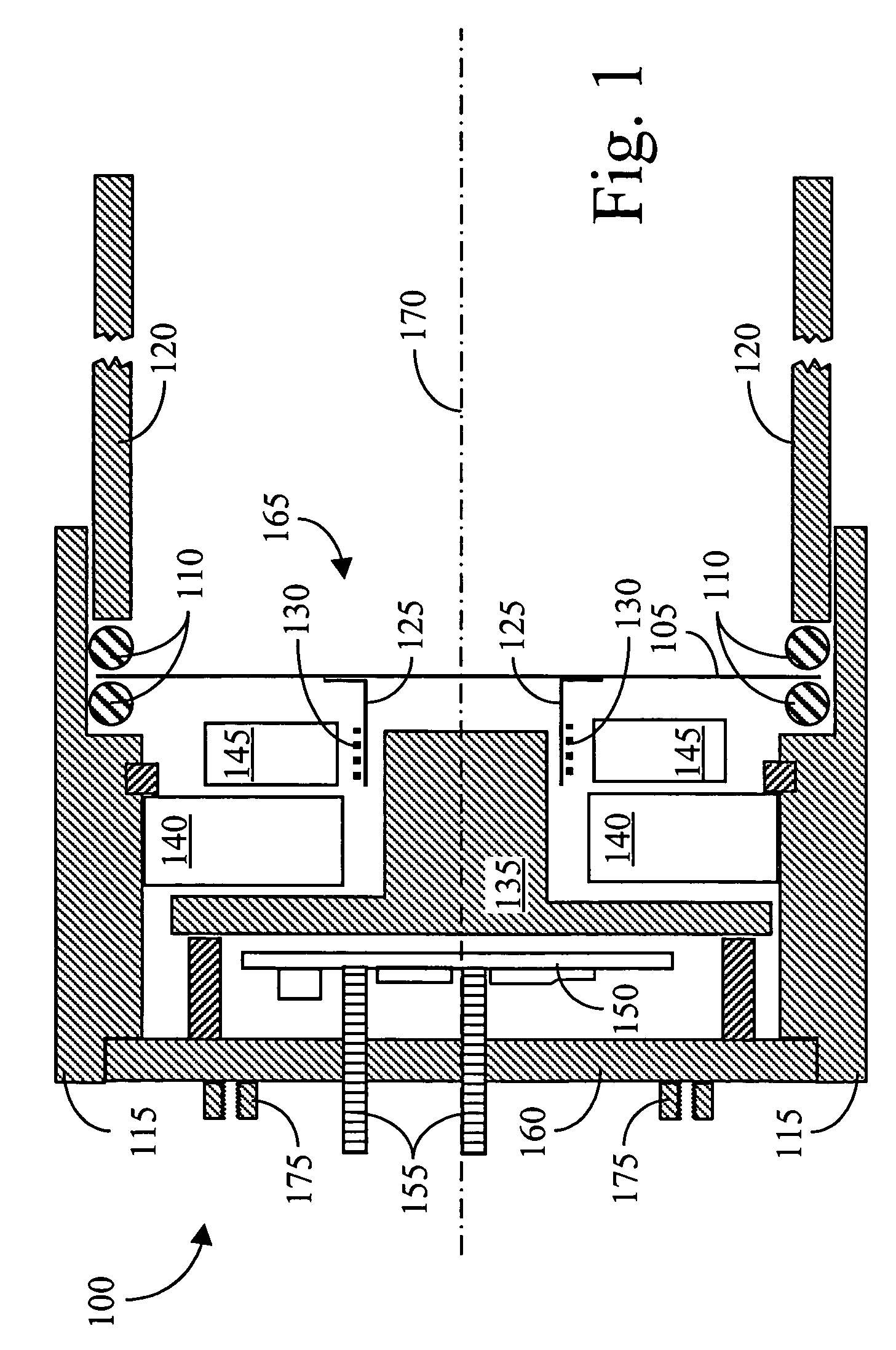

Integrated microprocessor controlled alarm

InactiveUS7245226B1Improve sealingImprove heat transfer performanceGain controlElectric lighting sourcesEnvironmental noiseDriver/operator

Alarms are often required on various vehicles and equipment such as fork lifts, dump trucks, bulldozers, etc. An alarm is disclosed controlled by a microprocessor, which is an integral part of the basic circuit. The alarm has a flat diaphragm, and a novel acoustic lens. The acoustic lens is constructed such that sound emanating from the center of the diaphragm has a direct path to the outside of the alarm. Sound produced around the periphery of the diaphragm must pass through a path containing switchbacks, that serve as an acoustic delay line, so this sound is delayed in exiting the alarm. The result is an alarm that with full sound in the important regions such as behind and to the side rear of the vehicle, but is very quiet for the operator or driver of the vehicle. The microprocessor is relied upon for adjusting alarm output based on source voltage and varying the signal based on ambient noise, as well as specific signals for particular applications.

Owner:LONGWOOD CORP

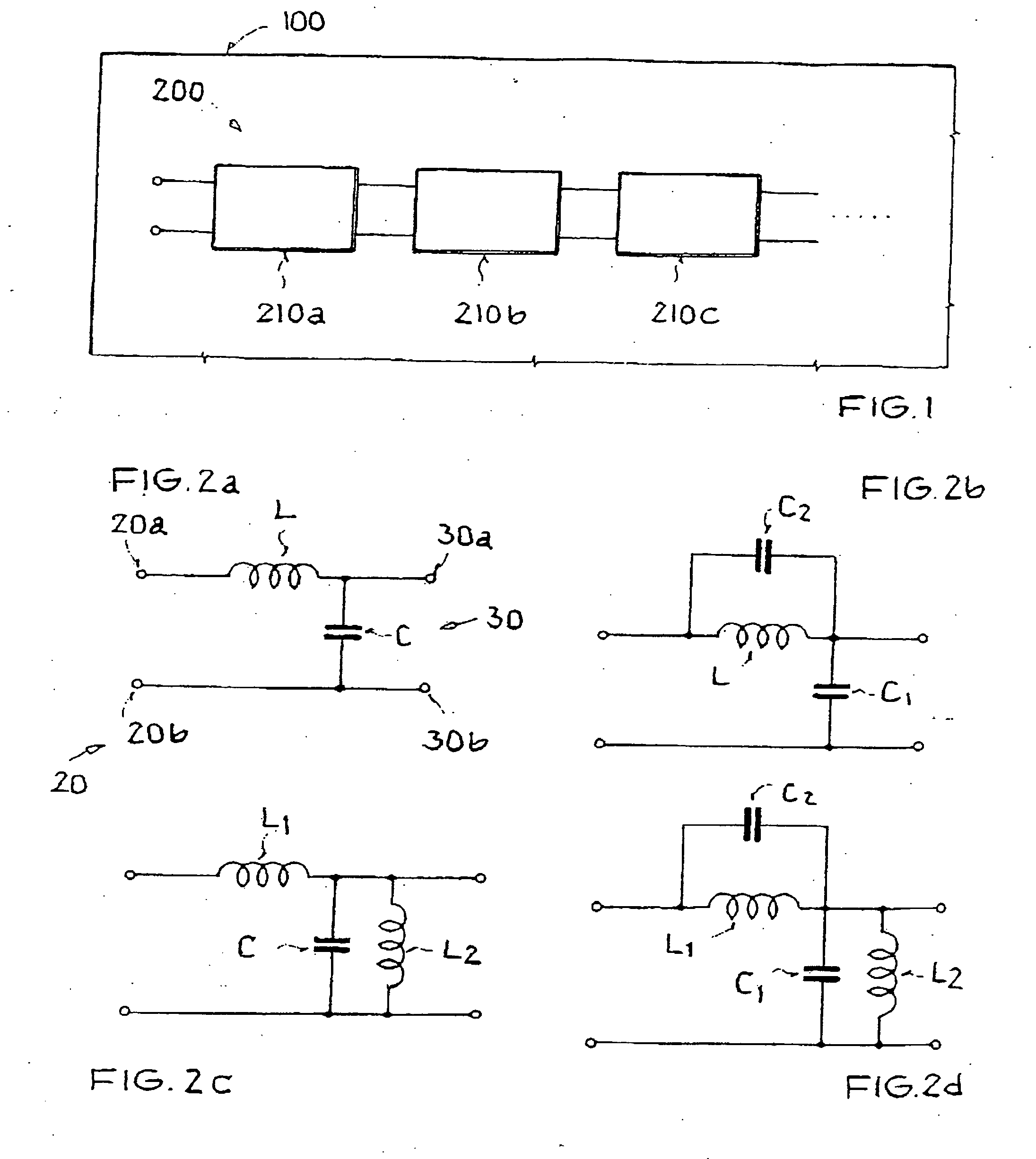

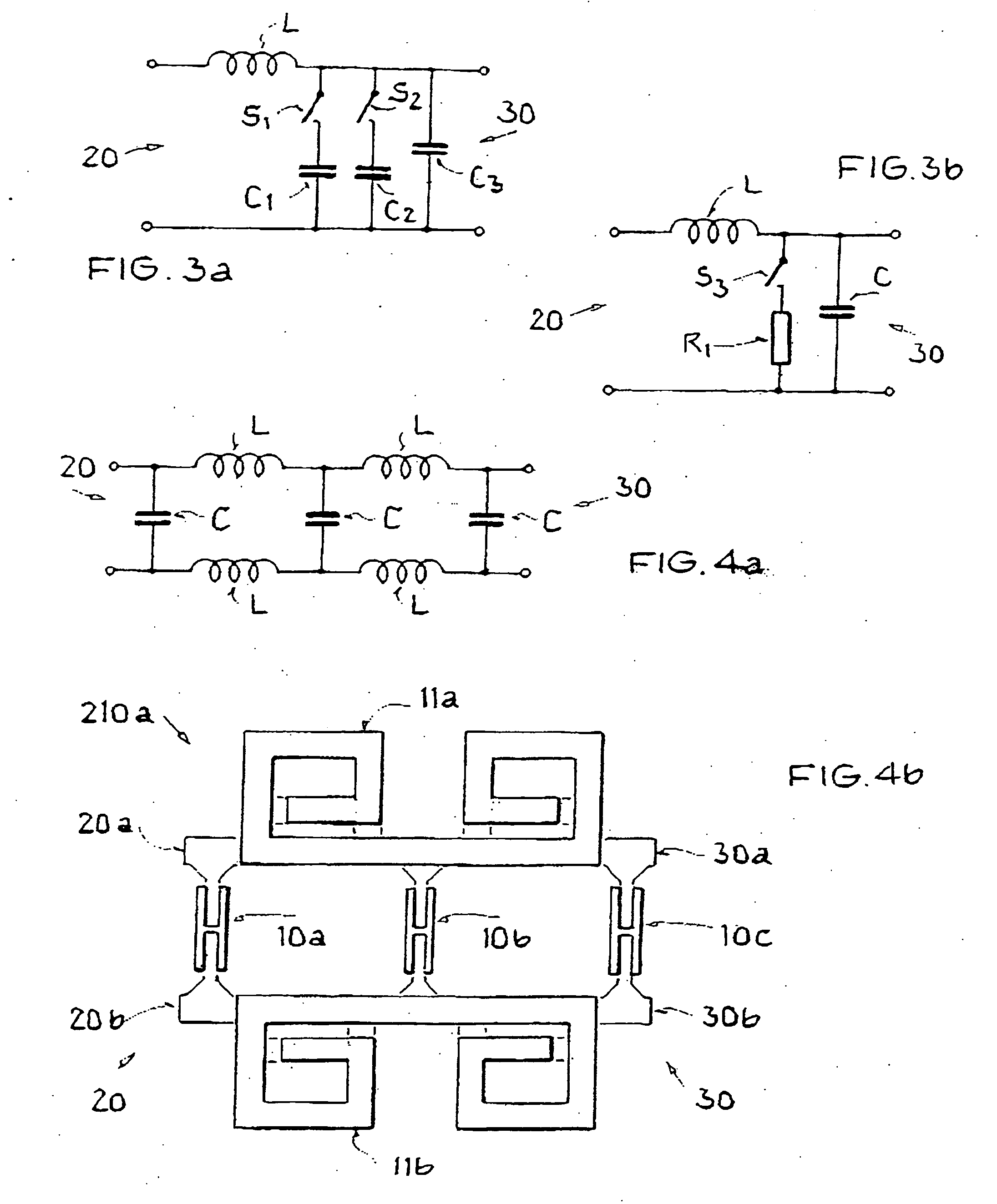

Monolithic integrated circuit

InactiveUS20070187804A1Multiple-port networksSemiconductor/solid-state device detailsCapacitanceInductor

A monolithic integrated circuit is provided that includes at least one transmission line integrated into the circuit. The transmission line includes a series circuit of at least two elementary circuits, wherein each elementary circuit has at least one lumped inductive element (L) and / or at least one lumped capacitive element (C).

Owner:ATMEL DUISBURG

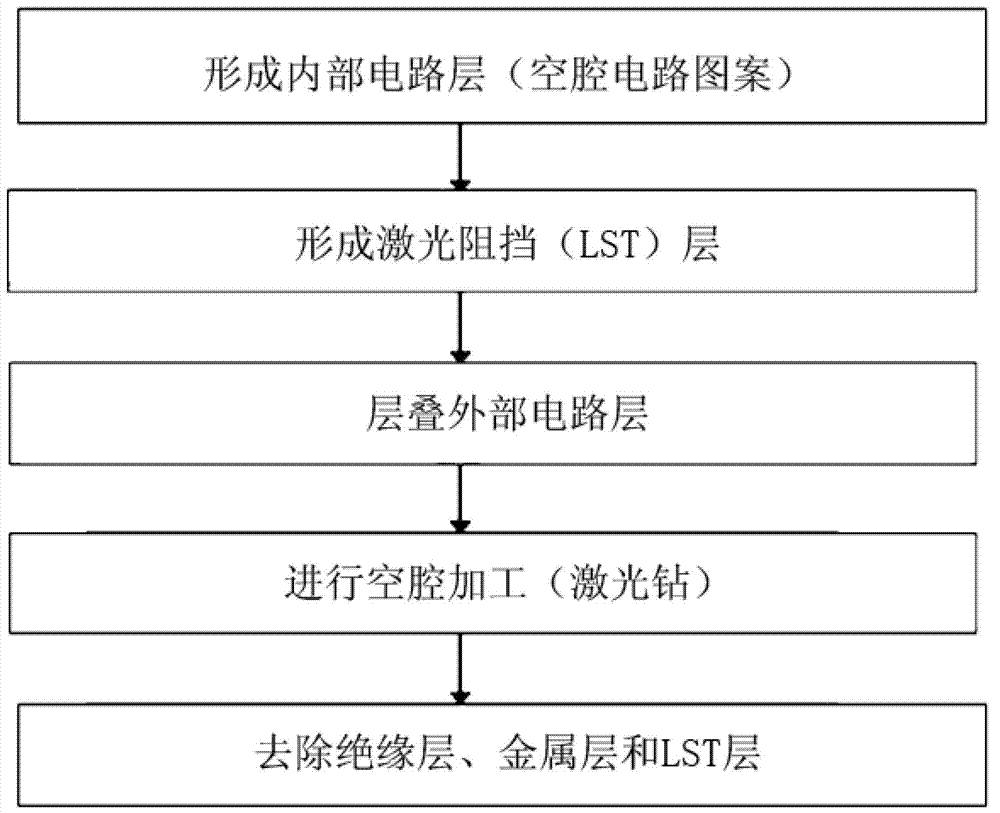

Pcb with cavity and fabricating method thereof

ActiveCN102860144APromote rapid formationForming accuratelyConductive material mechanical removalMultilayer circuit manufactureEngineeringPrinted circuit board

A fabricating method of a printed circuit board (PCB) with a cavity and a structure of the PCB fabricated by the method are provided. The method includes a first step of forming a base circuit board provided with an internal circuit layer having cavity circuit patterns on a surface of a substrate, a second step of forming a laser stopper layer on upper portions of the cavity circuit patterns, a third step of forming at least one external circuit layer on the base circuit board, and a fourth step of forming a cavity region by removing the external circuit layer on an upper portion of the laser stopper layer. Accordingly, in a fabricating method of a multi-layered PCB with a cavity, a laser stopper layer is formed on upper surfaces of cavity circuit patterns, so that it is possible to rapidly and precisely form the cavity, to precisely control the depth of the cavity and to have no influence on a circuit previously formed in the interior of the cavity.

Owner:LG INNOTEK CO LTD

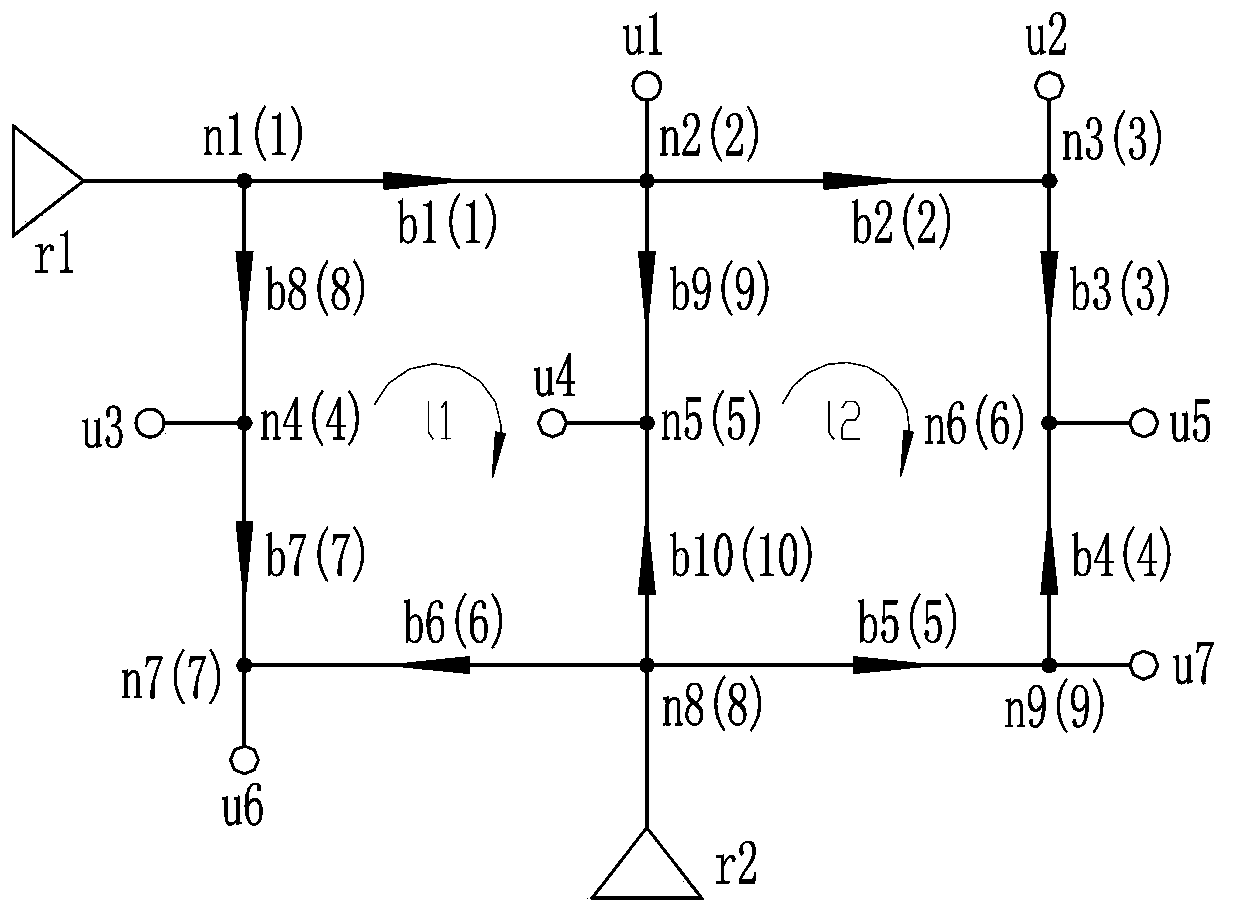

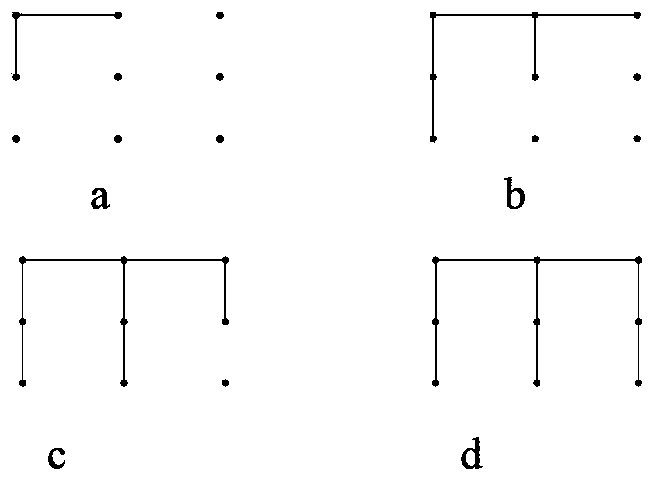

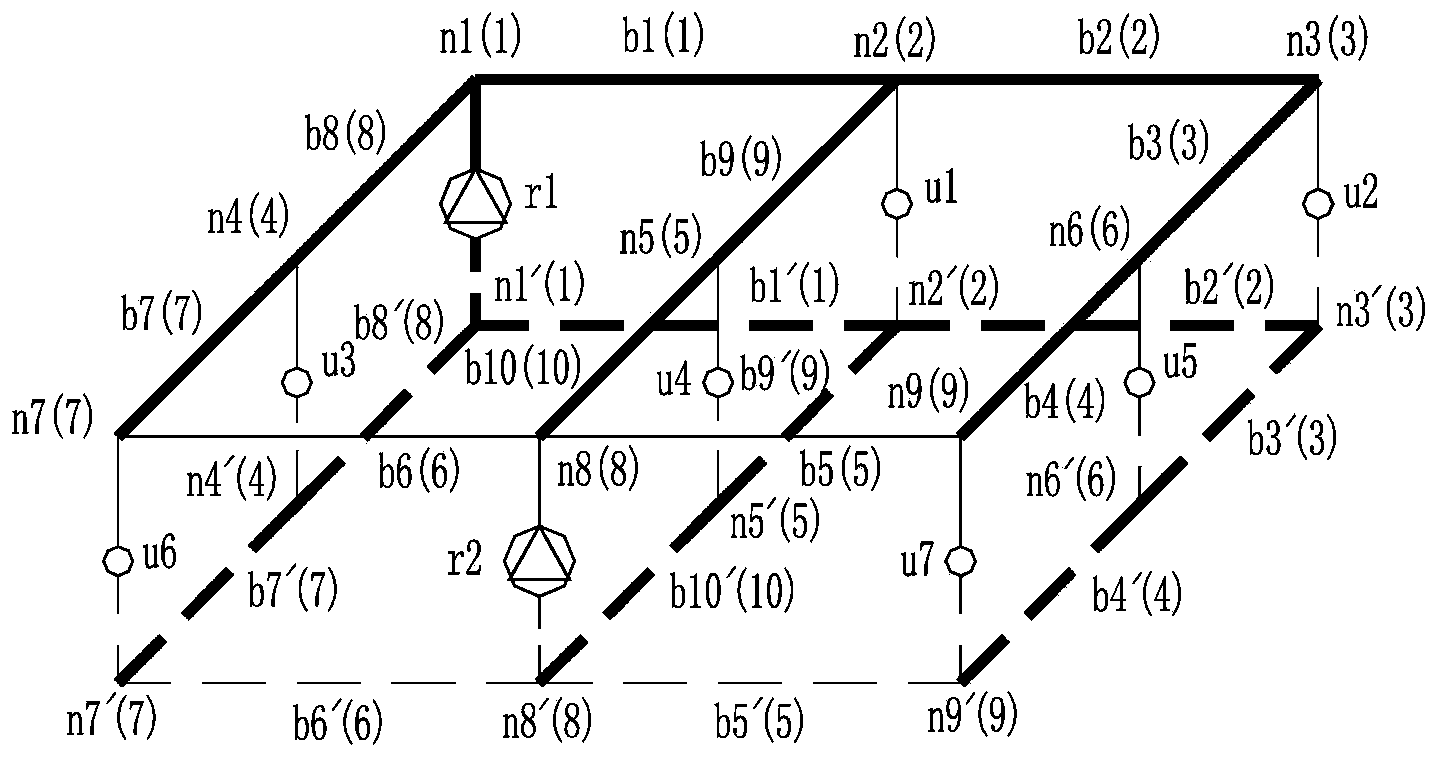

Construction method of heating ventilation air conditioning hot and cold water pipe network space topological structure

The invention discloses a construction method of a heating ventilation air conditioning hot and cold water pipe network space topological structure, which comprises the following steps: 1) recording pipe section information of a water supplying pipe network and a water return pipe network and cold and heat source and user's information respectively; 2) building incidence matrix and elementary circuit matrix of the water supplying pipe network and the water return pipe network respectively; 3) building incidence matrix and elementary circuit matrix of the cold and heat source and the user respectively; 4) combining the incidence matrix of the water supplying pipe network and the water return pipe network and the incidence matrix of the cold and heat source and the user into a space pipe network incidence matrix; combining the elementary circuit matrix of the water supplying pipe network and the water return pipe network the elementary circuit matrix the cold and heat source and the user into a space pipe network elementary circuit matrix. Through the building of the heating ventilation air conditioning hot and cold water pipe network space topological structure, the topological structure of pipe network with arbitrary shape is built, and a traditional plane pipe network method is broken through, so as to realize hydraulic working condition simulation and analysis of multiple source multiple loop pipe network, asymmetrical pipe network and the like.

Owner:GUANGDONG UNIV OF TECH

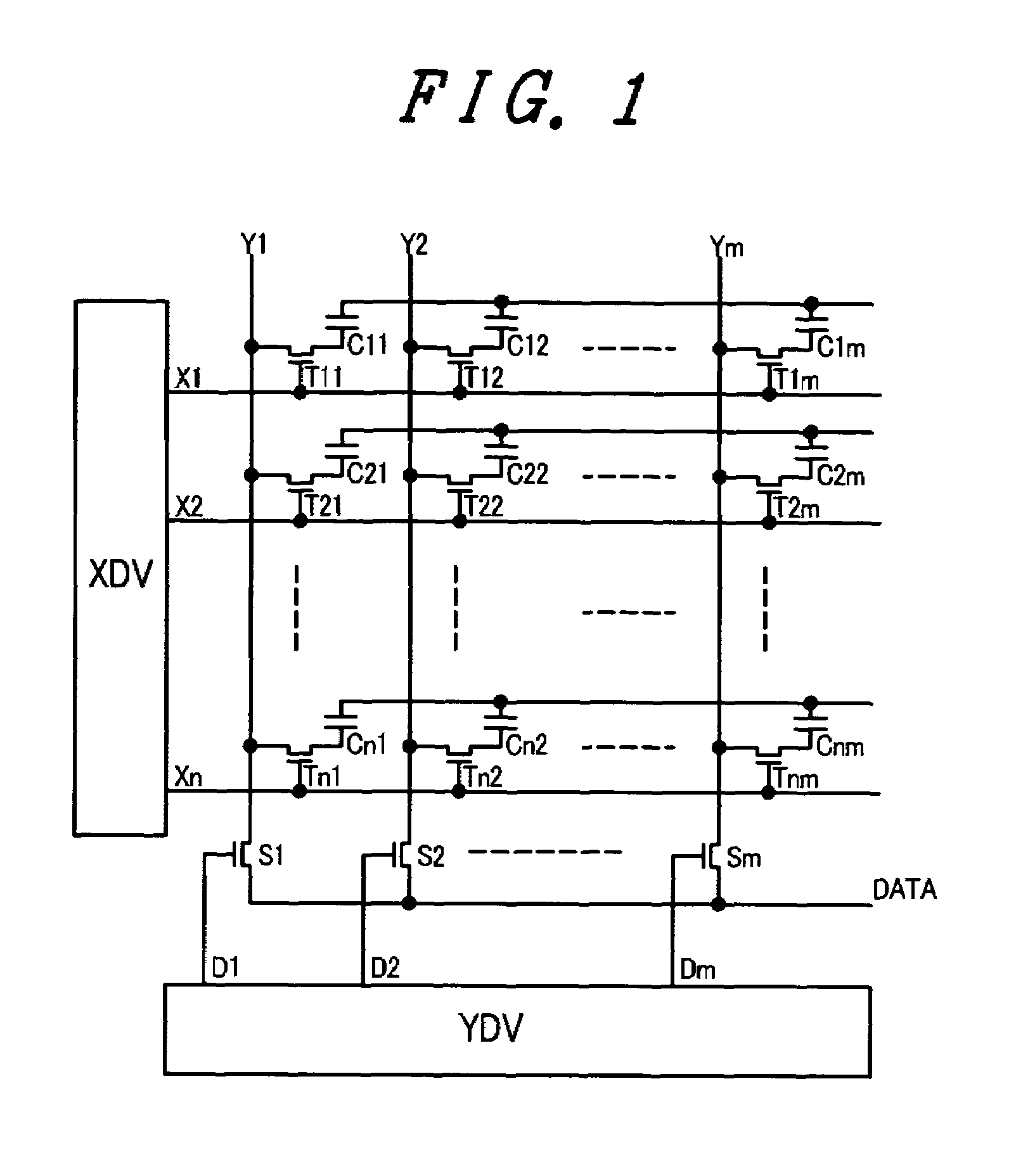

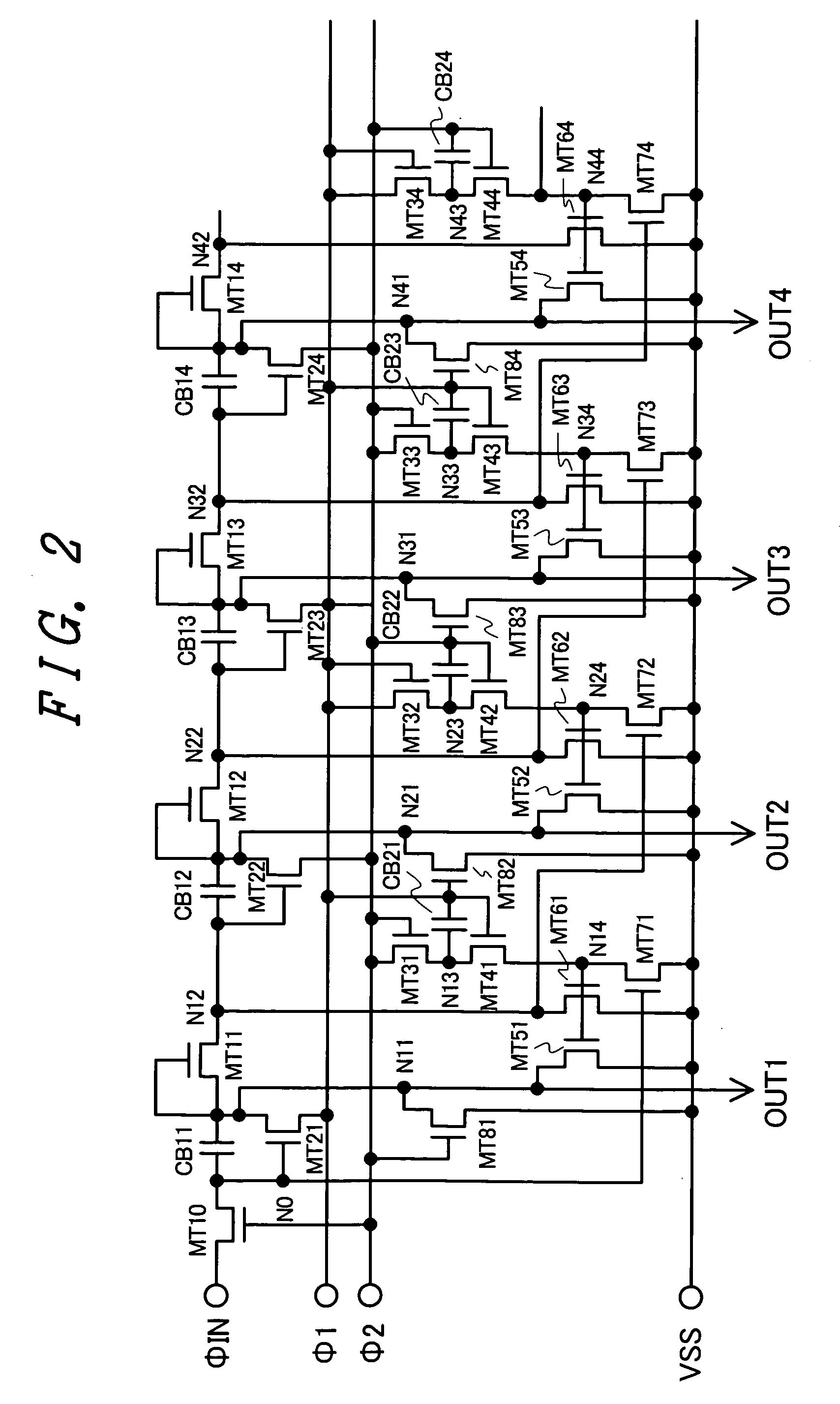

Scanning-line selecting circuit and display device using the same

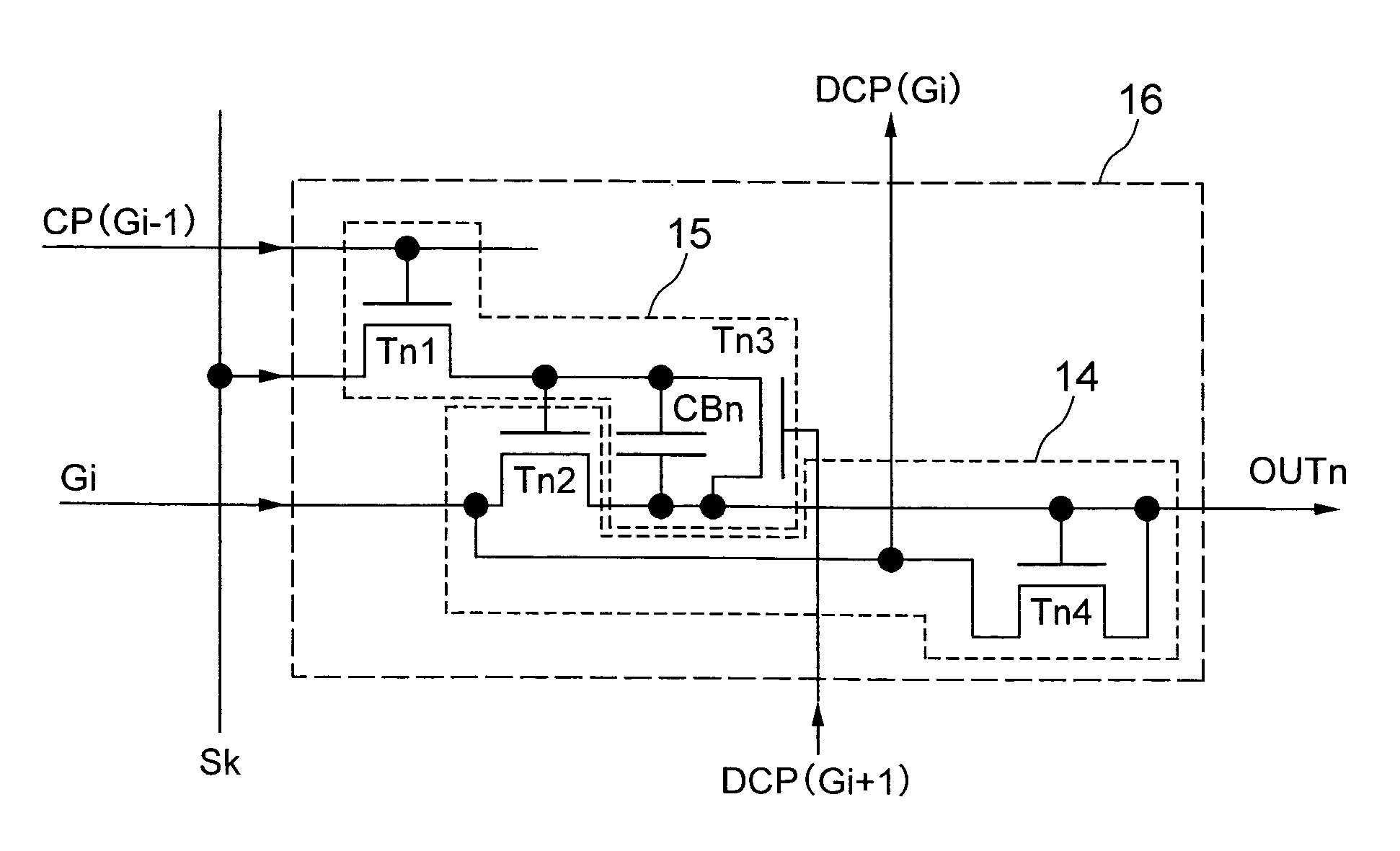

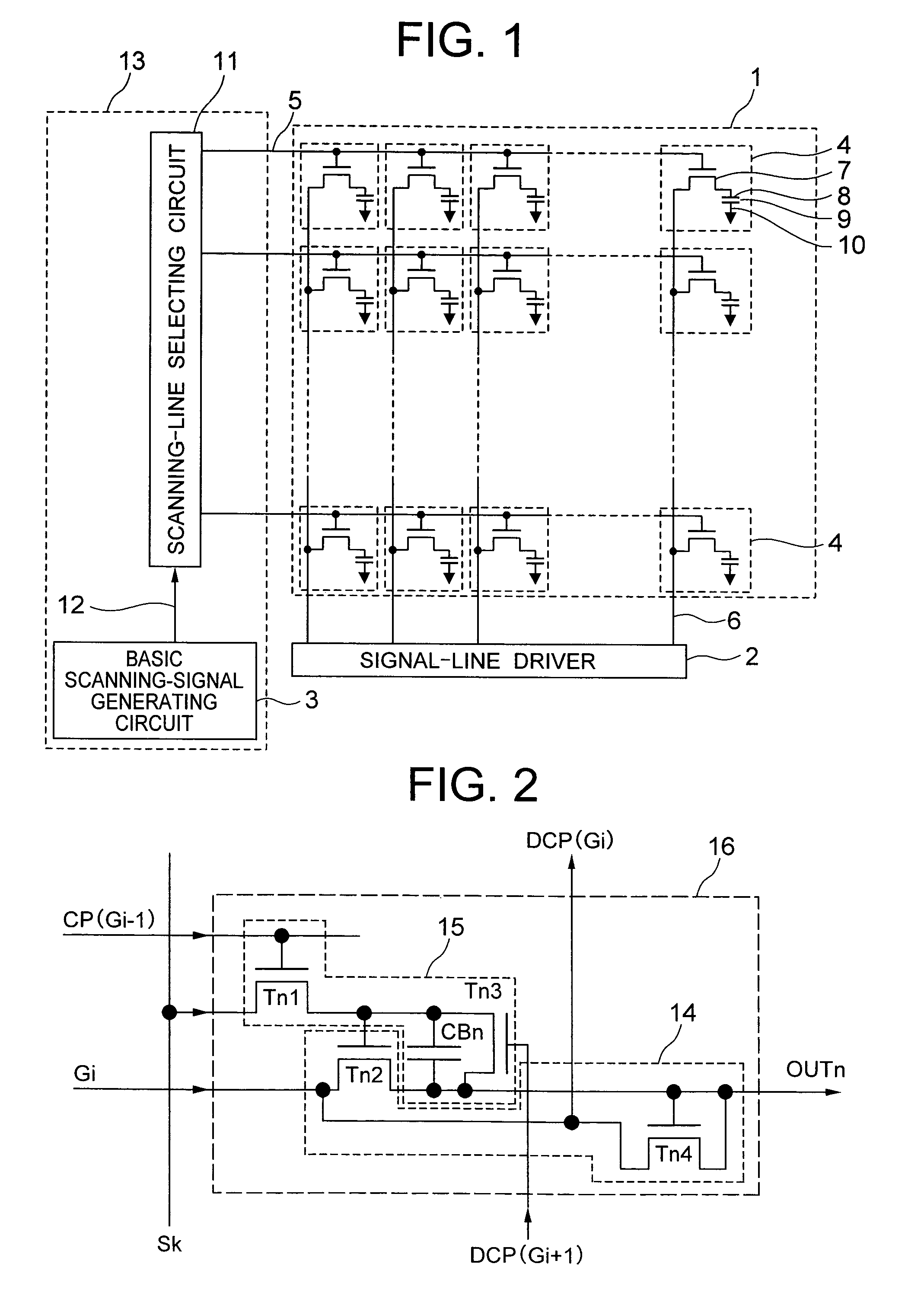

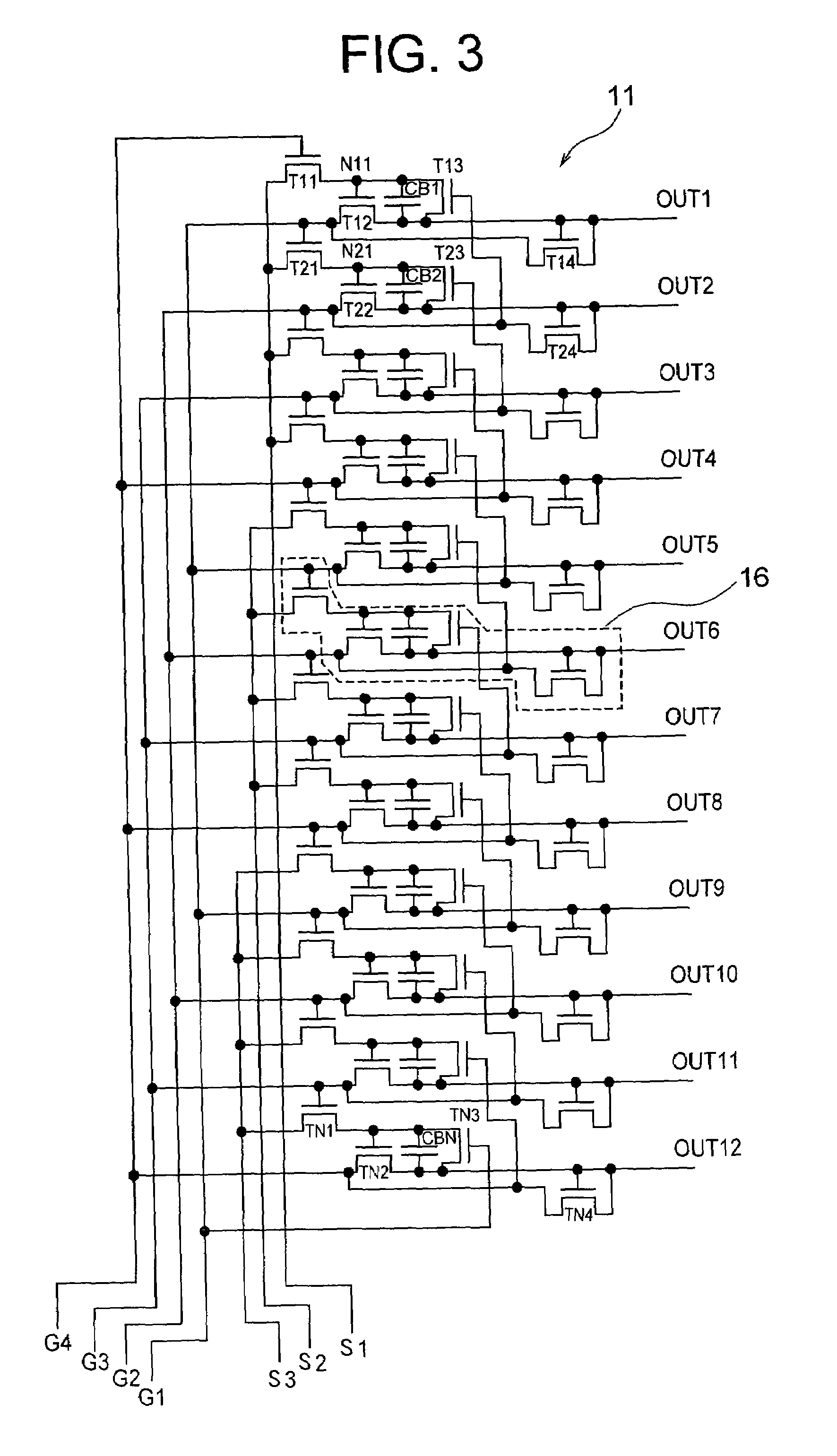

ActiveUS7522146B2Variation can be suppressedExcellent in economy and stabilityStatic indicating devicesDigital storageDisplay deviceEngineering

A scanning-line selecting circuit is configured by connecting basic circuits with each other over plural stages. Each of the basic circuits includes a basic scanning-line driving circuit and a voltage raising circuit. A basic scanning signal is inputted into the basic scanning-line driving circuit, which, then, outputs a scanning signal. A charge pulse, a selecting signal, and a discharge pulse are inputted into the voltage raising circuit, which, then, drives the basic scanning-line driving circuit. Accordingly, in the basic circuits, there exists none of the problems of threshold-value shift and voltage lowering. This characteristic makes it possible to implement high efficiency and stable operation.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

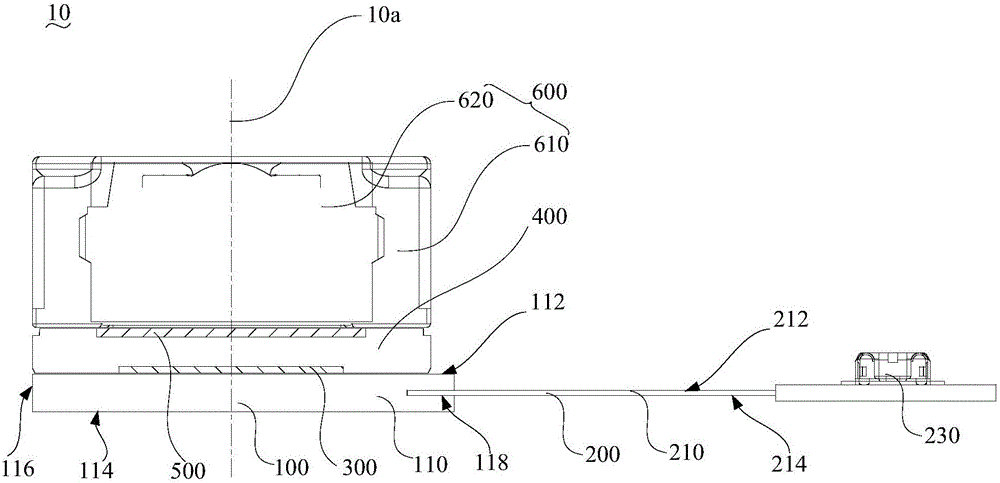

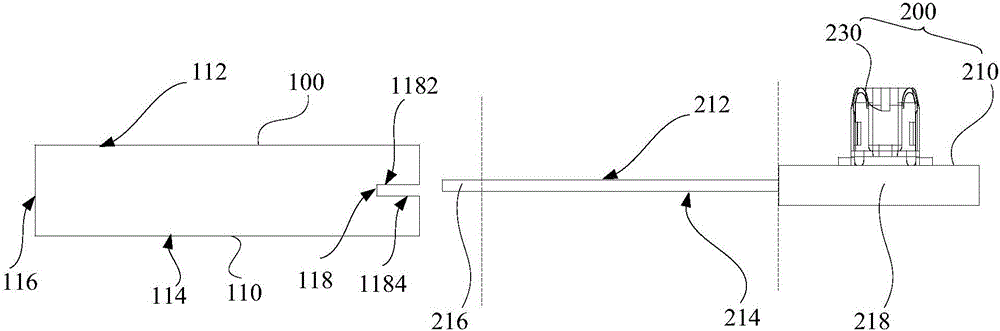

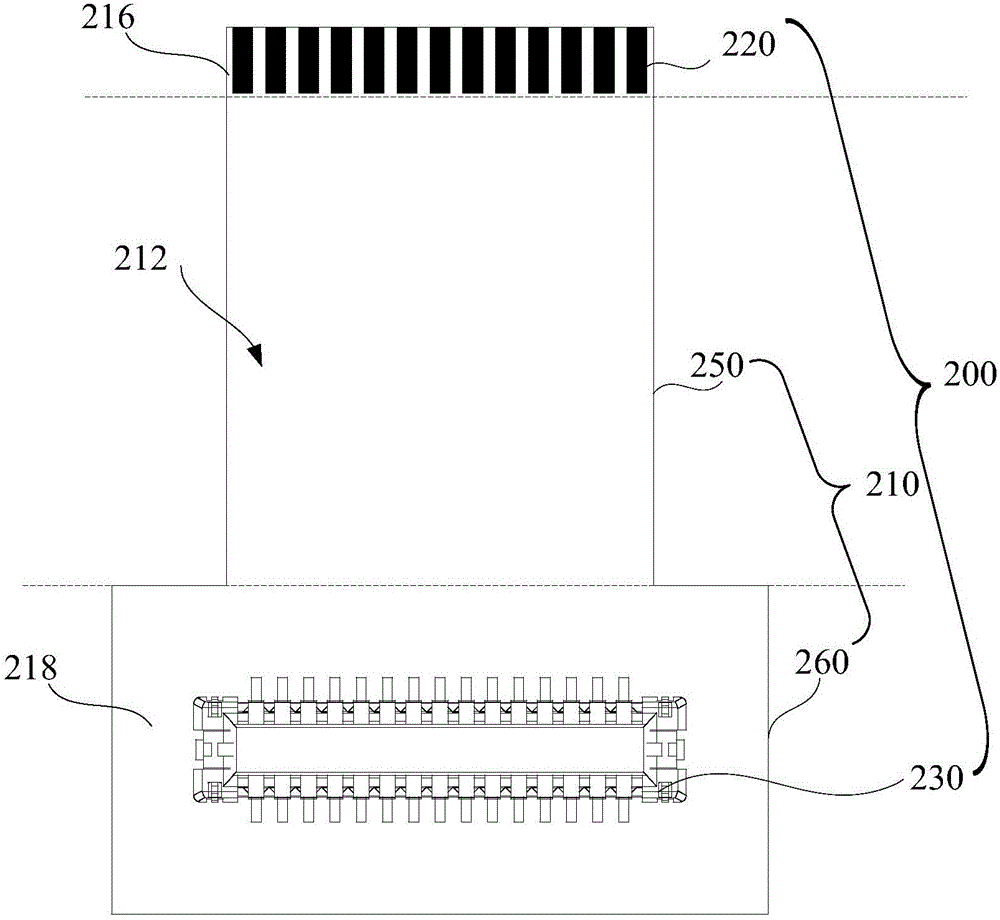

Camera module group and first and second circuit boards thereof

The invention relates to a camera module and first and second circuit boards thereof. The first circuit board comprises a ceramic substrate and a basic circuit which is integrated in the ceramic substrate, wherein the ceramic substrate is provided with an installation surface, a connection surface, and a side surface which is used for connecting the installation surface and the connection surface. The installation surface is used for installing an image sensing chip of the camera module group, and the side surface is recessed to form a card slot. The card slot is provided with a first inner wall and a second inner wall, wherein the first inner wall is close to the installation surface. The first circuit board also comprises two groups of first golden fingers which are respectively disposed on the first and second inner walls and are respectively connected with the basic circuit in an electrical manner. The card slot is in pluggable connection with the second circuit board of the camera module group, so as to enable the circuit board to be electrically connected with an external circuit board through the two groups of first golden fingers and the second circuit board of the camera module group. The first circuit board is used in the camera module group, thereby effectively shortening the manufacturing period of a sample.

Owner:NANCHANG O FILM OPTICAL ELECTRONICS TECH CO LTD +3

Circuits for voltage-controlled ring oscillators and method of generating a periodic signal

InactiveUS7268635B2Easy to implementAngle modulation by variable impedencePulse generation by logic circuitsSoftware engineeringQuadrature oscillator

Owner:SEIKO EPSON CORP

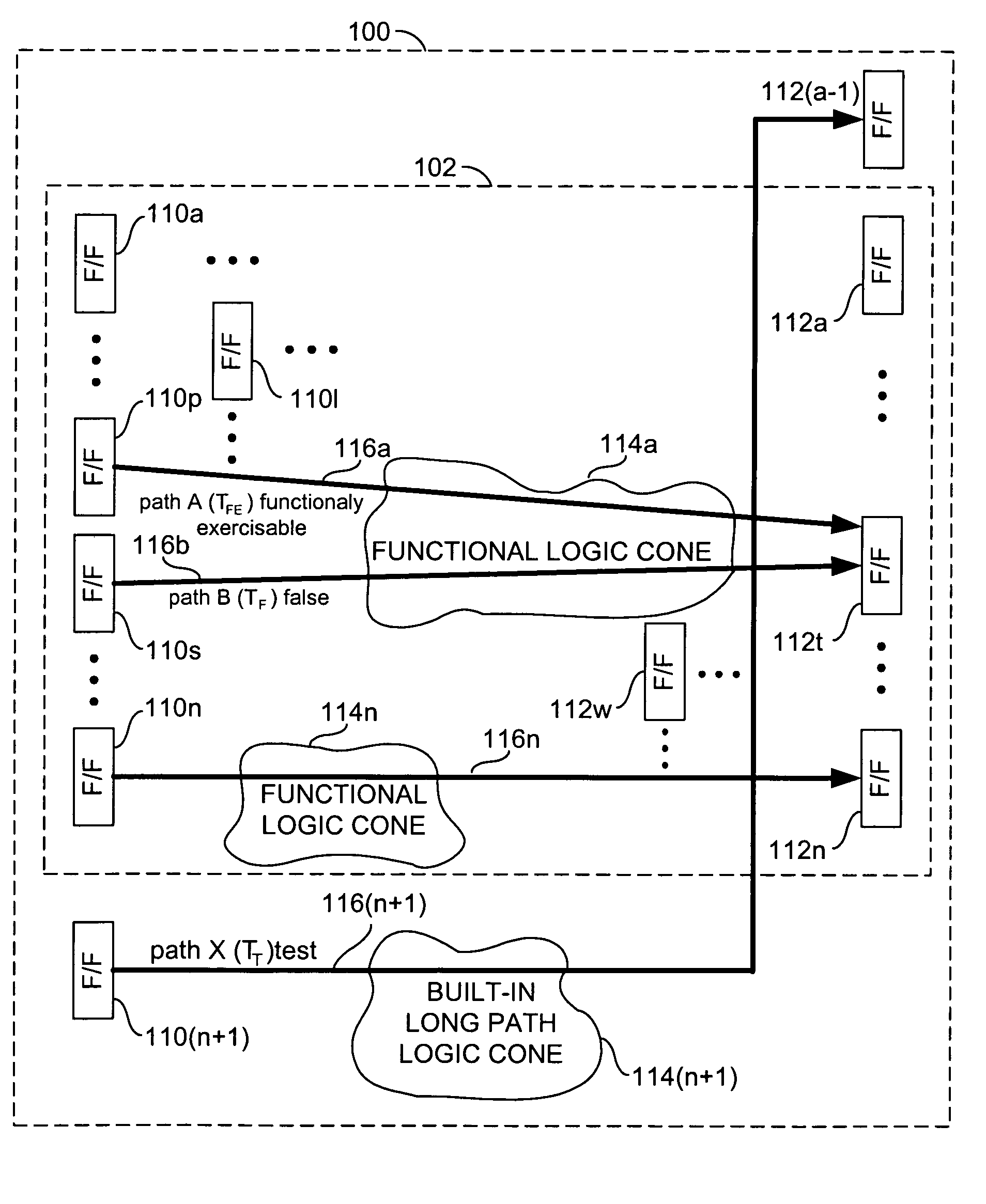

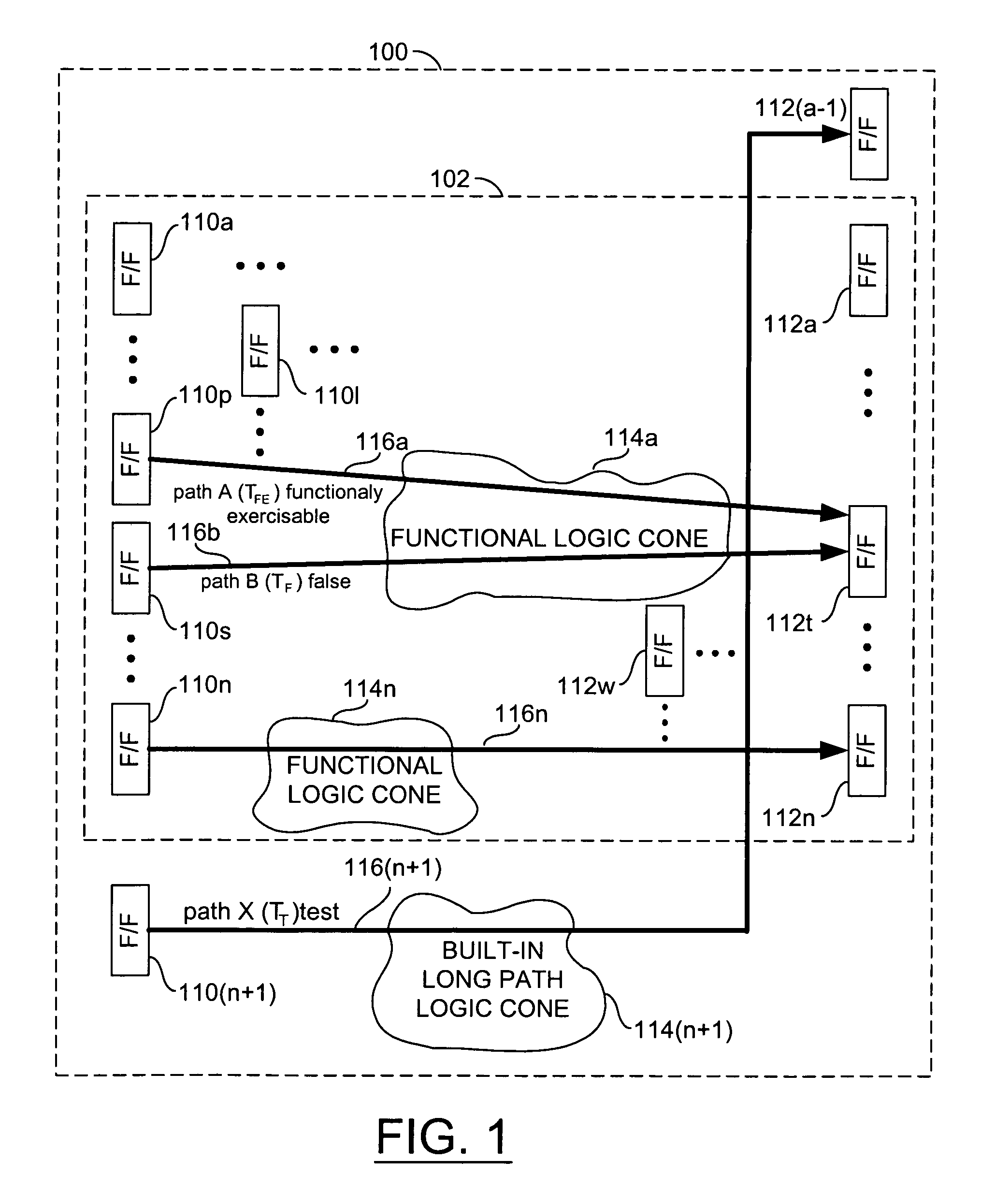

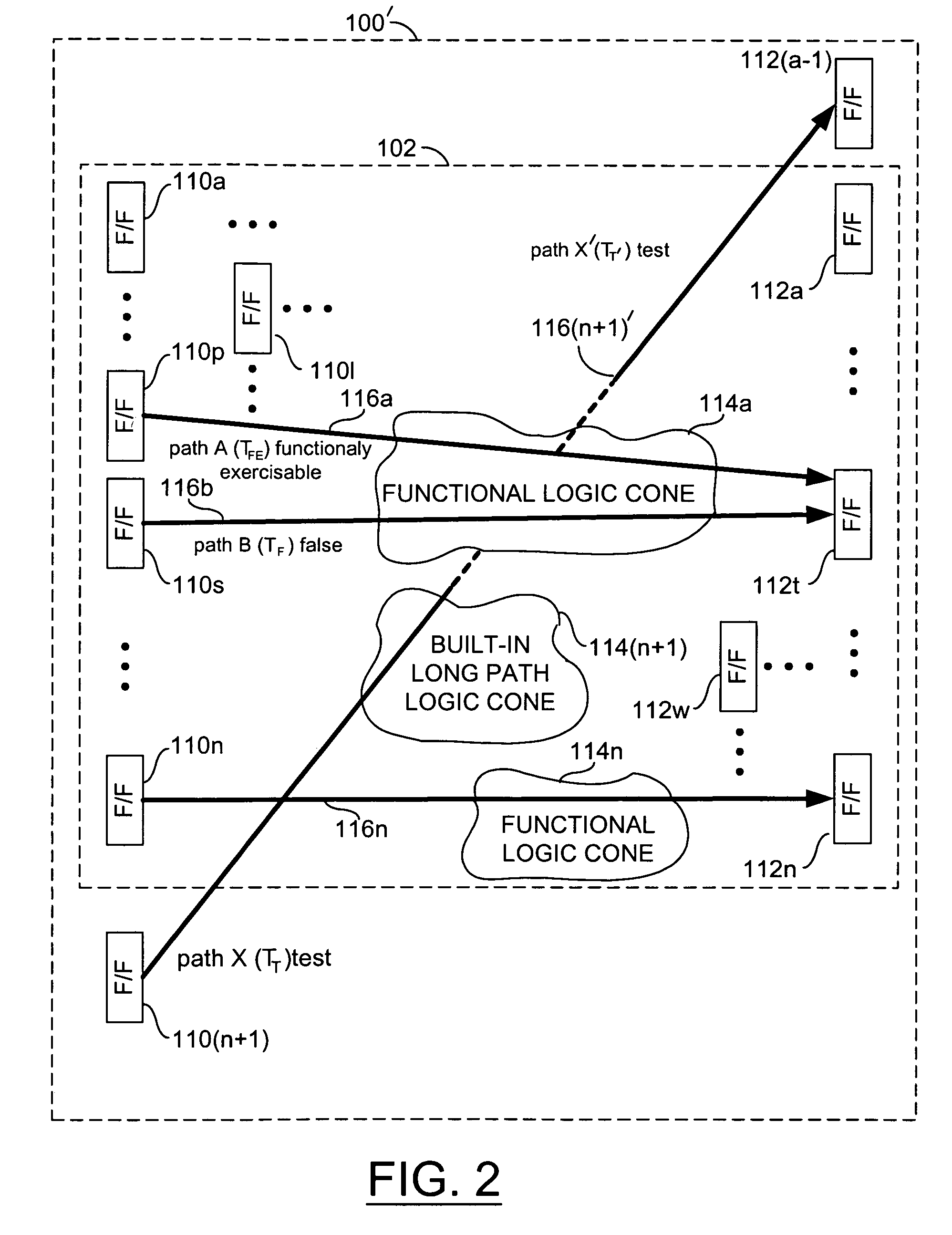

Long path at-speed testing

InactiveUS7065683B1Reduce chip development costShorten the timeElectronic circuit testingError detection/correctionTime delaysTested time

An apparatus including a plurality of first base circuits, a plurality of second base circuits, a first test circuit, a second test circuit, and a test path. The plurality of first base circuits may be coupled to the plurality of second base circuits via one or more base circuit paths on a layout. The first test circuit may be disposed in a first distal location of the layout. The second test circuit may be disposed in a second distal location of the layout. The test path may be configured to (i) couple the first test circuit to the second test circuit and (ii) generate a test time delay from the first test circuit to the second test circuit incrementally longer than a maximum time delay generated by any of the base circuit paths.

Owner:BELL SEMICON LLC

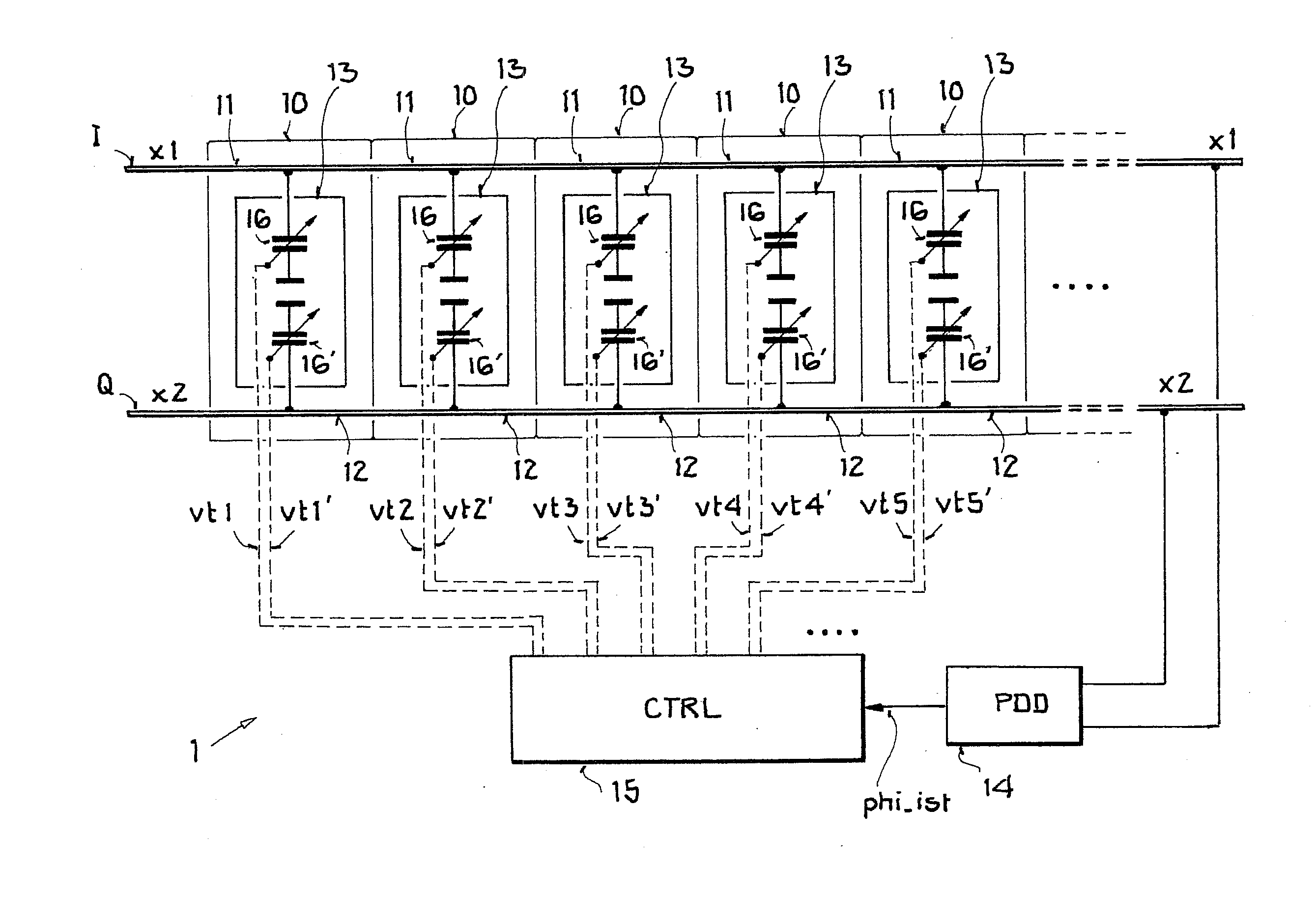

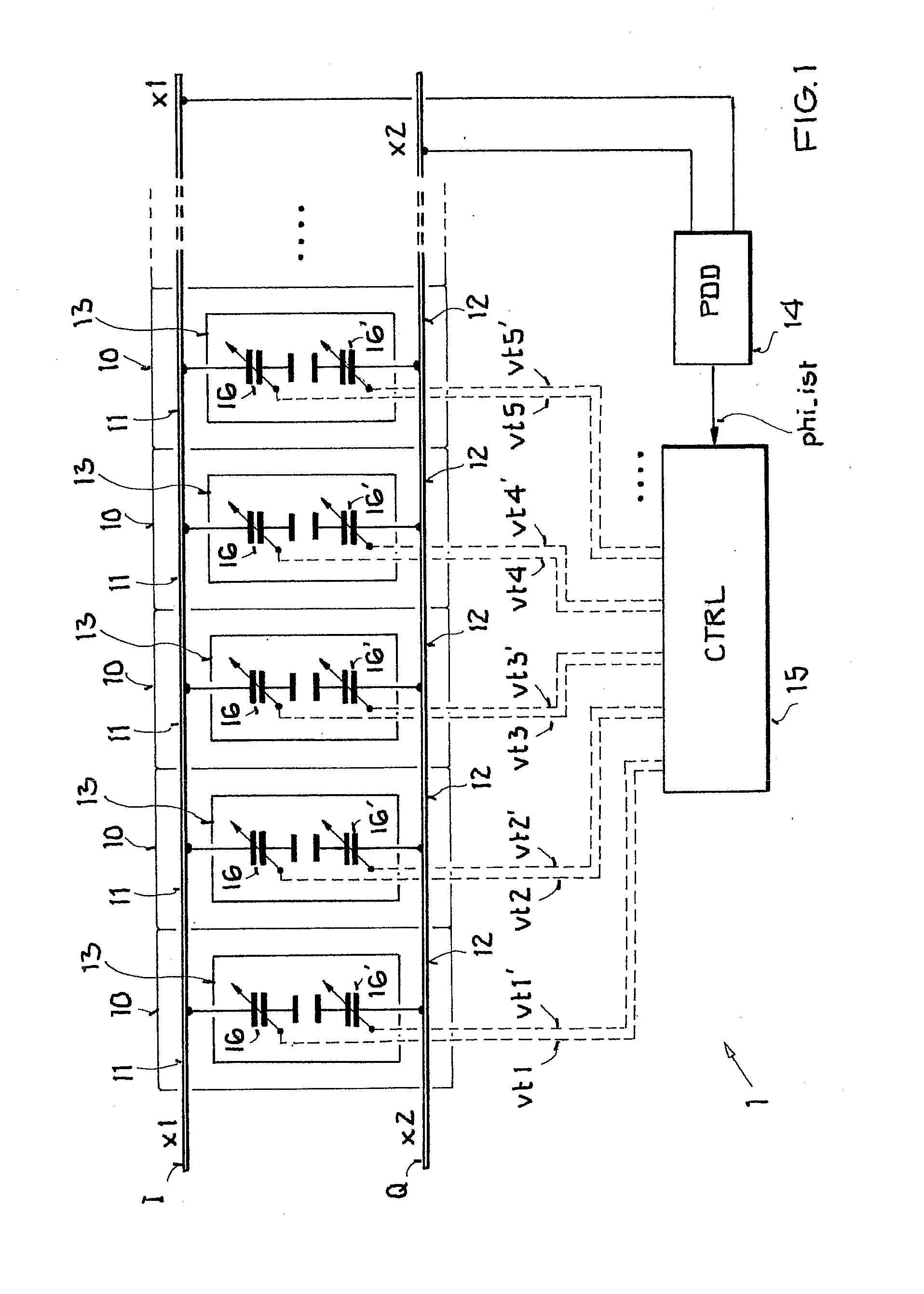

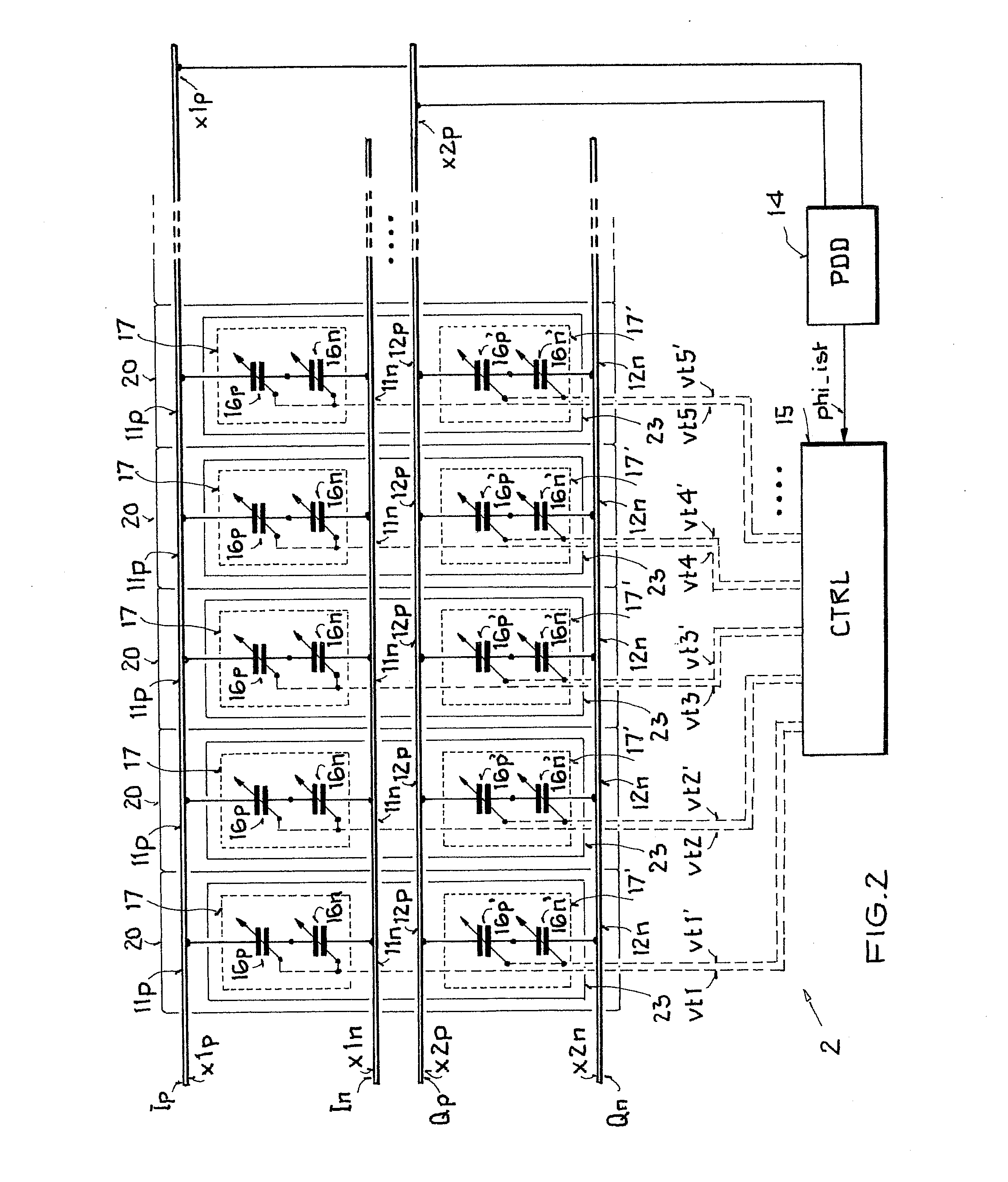

Integrated circuit arrangement to set a phase difference

ActiveUS20080157900A1Advantageously long electrical lengthAdvantageously long phase shiftMultiple-port networksTransmission control/equlisationCapacitanceControl signal

An integrated circuit arrangement (1; 2; 3; 4) for setting a predefined phase difference (phi_target) between a first high-frequency signal (x1; x1p, x1n) and a second high-frequency signal (x2; x2p, x2n), comprising:e) a chain connection of a plurality (N) of basic circuits (10; 20; 30; 40), whereby each basic circuit has a first transmission line (11; 11p, 11n) for transmitting the first signal (x1; x1p, x1n), a second transmission line (12; 12p, 12n) for transmitting the second signal (x2; x2p, x2n), and a controllable phase-influencing means (13; 23; 33; 43), connected to the first transmission line, for controllably influencing the phase of the first signal,f) a phase difference detector (14; 34), which is connected to the output-side basic circuit and is formed to detect a current phase difference (phi_actual) between the first and second signal,g) a control unit (15; 35), which is connected to the phase difference detector and each controllable phase-influencing means (13; 23; 33; 43) and is formed to generate first digital control voltages, dependent on the current phase difference (phi_actual), as control signals (vt1, vt2, . . . ) for each phase-influencing means (13; 23; 33; 43), whereby the digital control voltage can assume only two different voltage values, andh) whereby each controllable phase-influencing means (13; 23; 33; 43;) has at least one first tunable capacitive unit (16; 16p, 16n; 46p, 46n), which is connected to the first transmission line and the control unit and is designed to delay the first signal depending on one of the first control signals.

Owner:ATMEL CORP

Display device

Owner:JAPAN DISPLAY INC +1

Equivalence checking method, equivalence checking program, and generating method for equivalence checking program

ActiveUS8122402B2Computer aided designSoftware simulation/interpretation/emulationAlgorithmModel testing

Owner:RENESAS ELECTRONICS CORP

Gate signal line drive circuit and display device

ActiveUS20120188220A1Improve voltage qualityIncrease in displayCathode-ray tube indicatorsInput/output processes for data processingLow voltageDisplay device

A gate signal line driving circuit includes plural basic circuits, each outputting to a gate signal line a gate signal which is high during a high signal period and low during a low signal period. Each of the basic circuits includes: agate line high voltage application circuit which is turned on in accordance with the high signal period to apply the high voltage to the gate signal line; a gate line low voltage application circuit which is turned on in accordance with the low signal period to apply the low voltage to the gate signal line; and a second gate line low voltage application circuit which is turned on to apply the low voltage to the gate signal line in at least a part of a period between turning off the gate line high voltage application circuit and turning on the gate line low voltage application circuit.

Owner:JAPAN DISPLAY INC

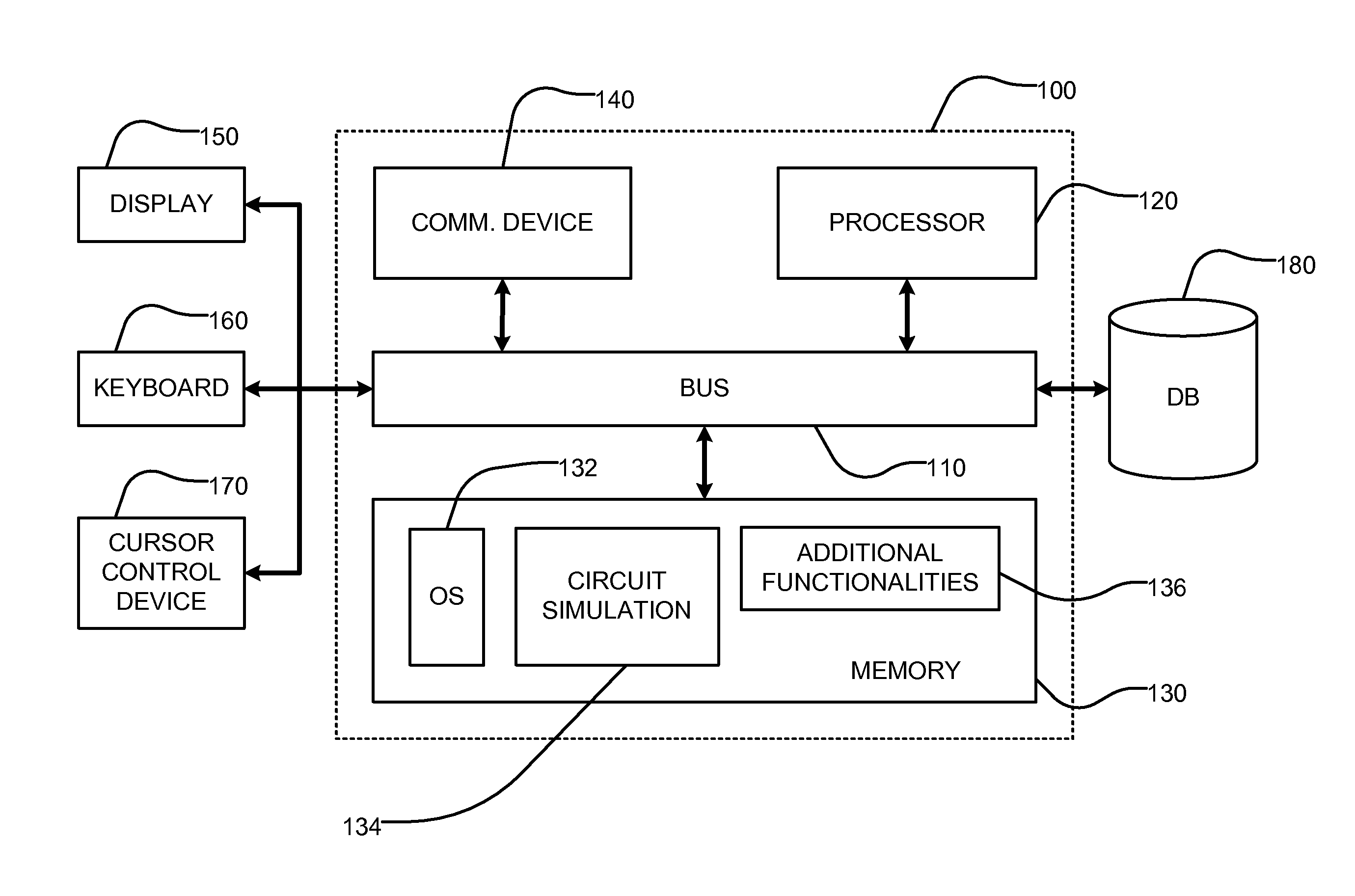

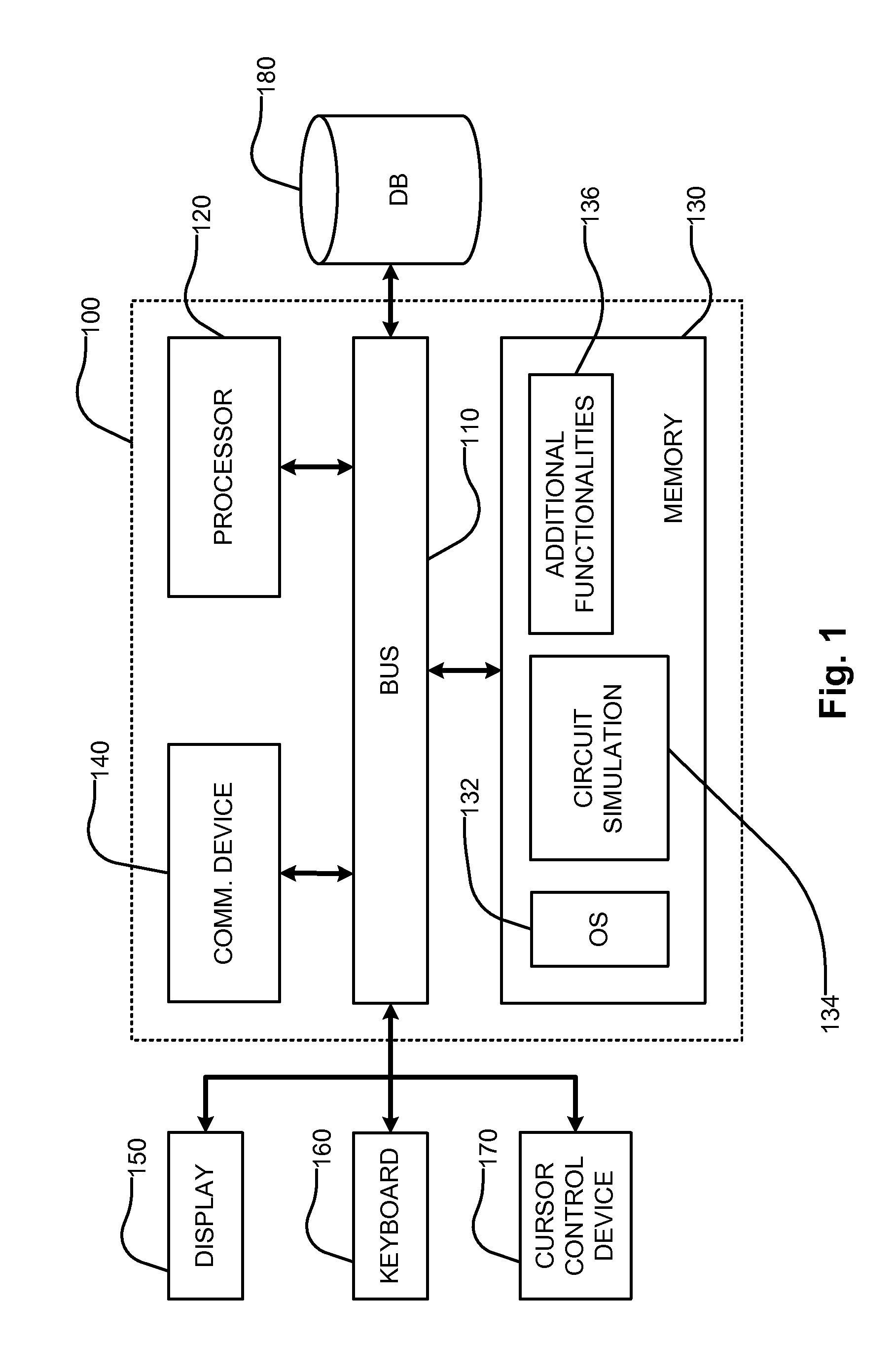

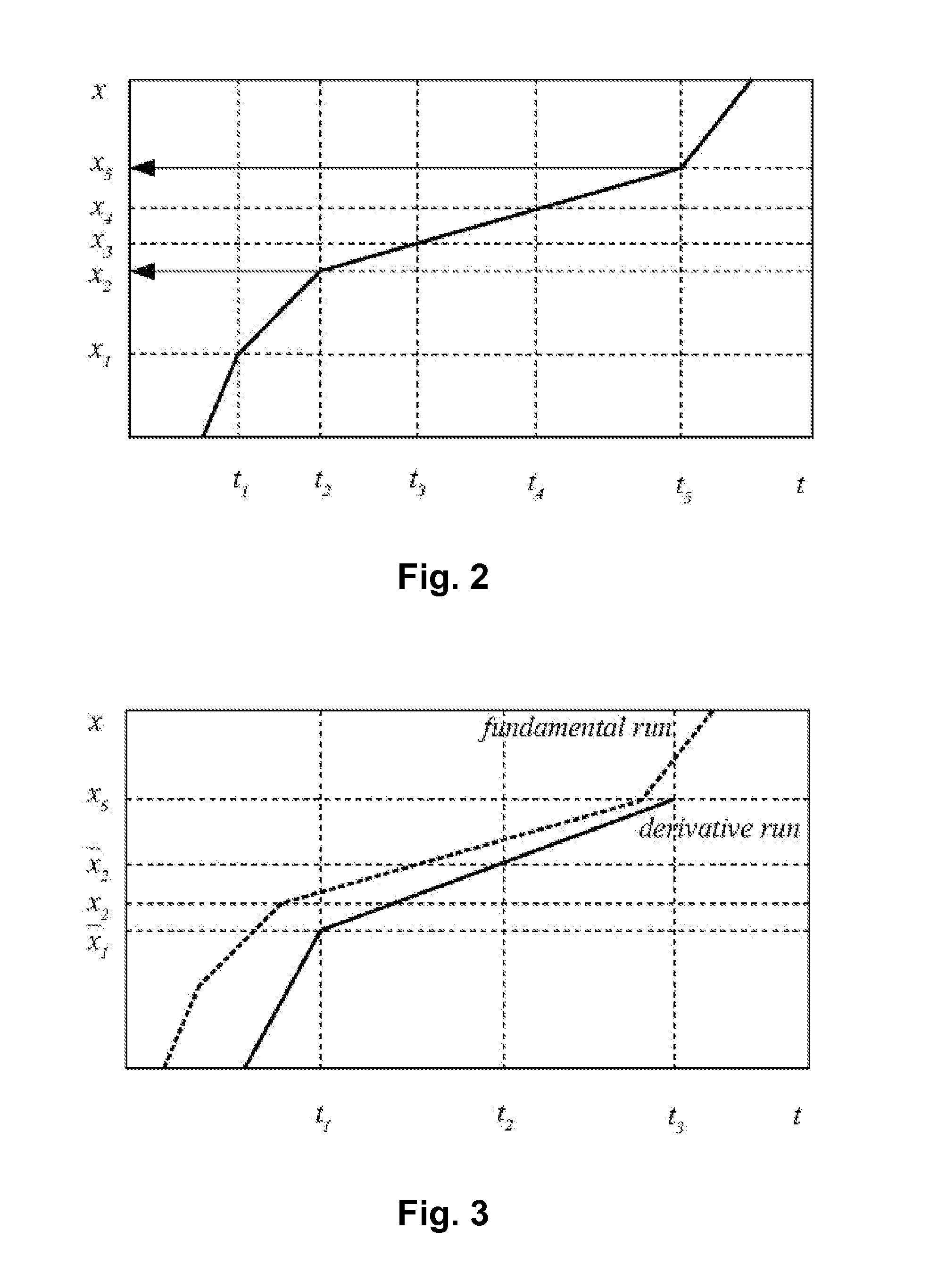

Integrated circuit simulation using fundamental and derivative circuit runs

ActiveUS20130305201A1Software simulation/interpretation/emulationSpecial data processing applicationsSystem usageEvent queue

A system that simulates an integrated circuit is formed of a plurality of devices. The system initially performs a fundamental circuit simulation run using original parameters for the plurality of devices and an initial time step. The system generates one or more fundamental time steps from the fundamental circuit simulation run. The fundamental time steps are generated when changes that indicate state time derivatives during two or more successive integration steps are within a predetermined range. The system stores the one or more fundamental time steps as fundamental circuit events in an events queue, and updates the parameters for the plurality of devices based on the fundamental circuit events to generate one or more derivative circuits. The system then performs one or more derivative circuit simulation runs using the derivative circuits.

Owner:ORACLE INT CORP

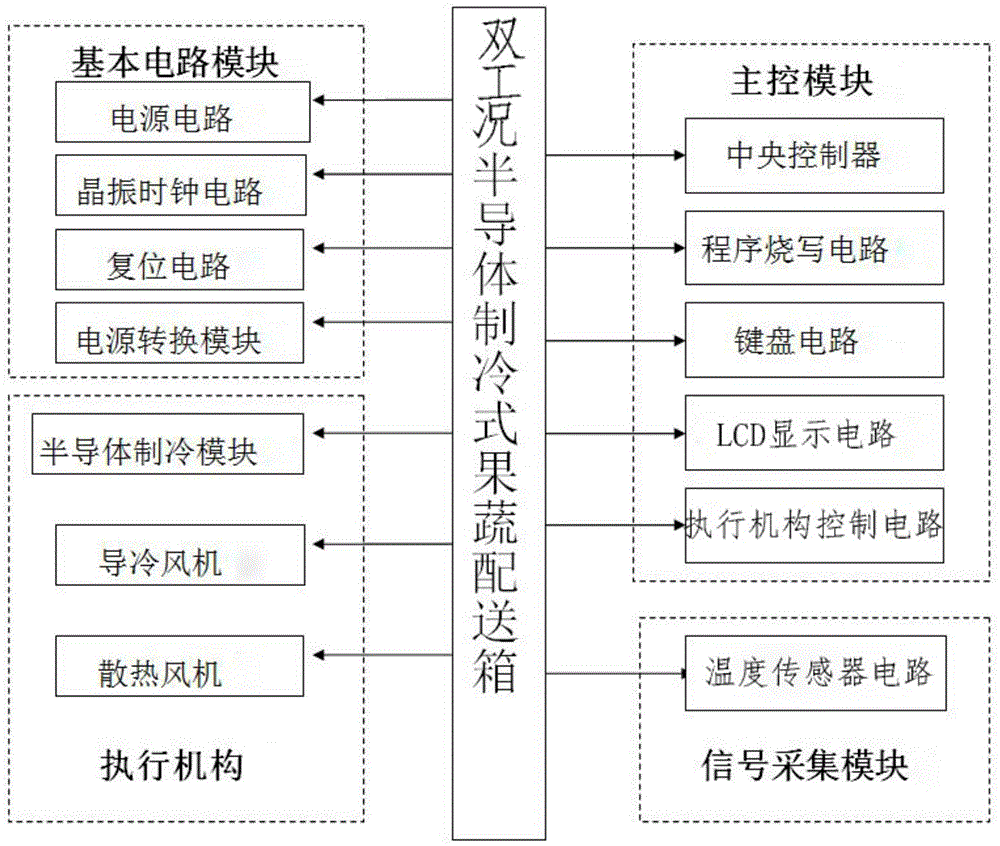

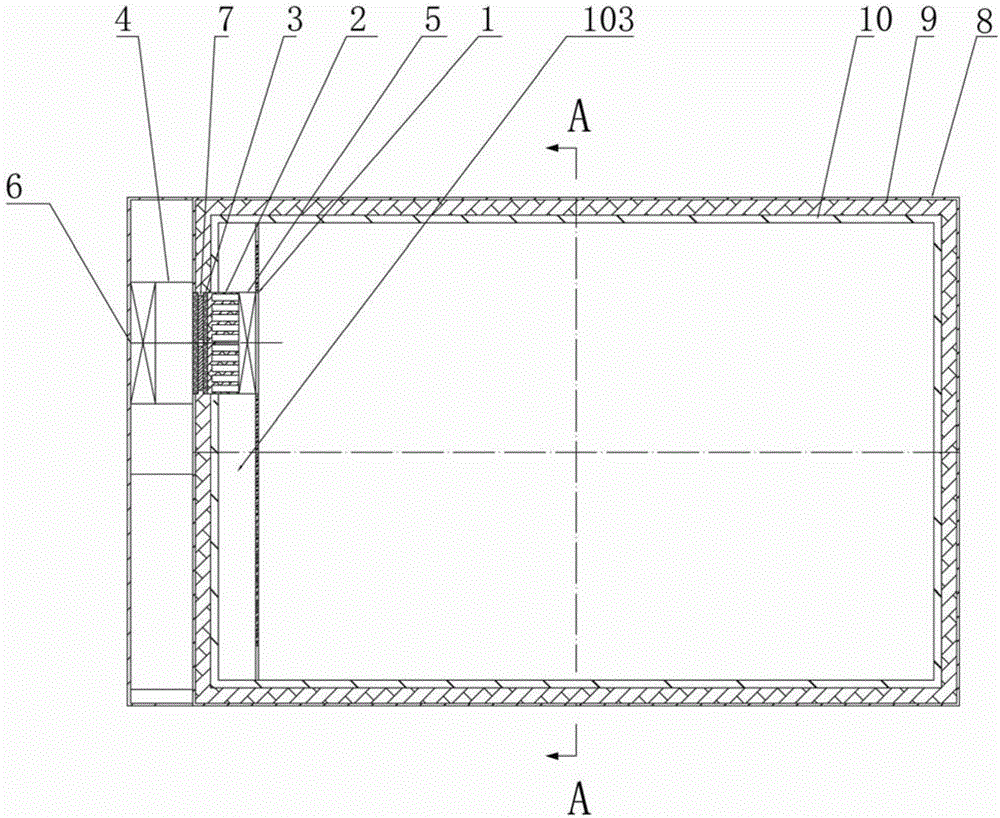

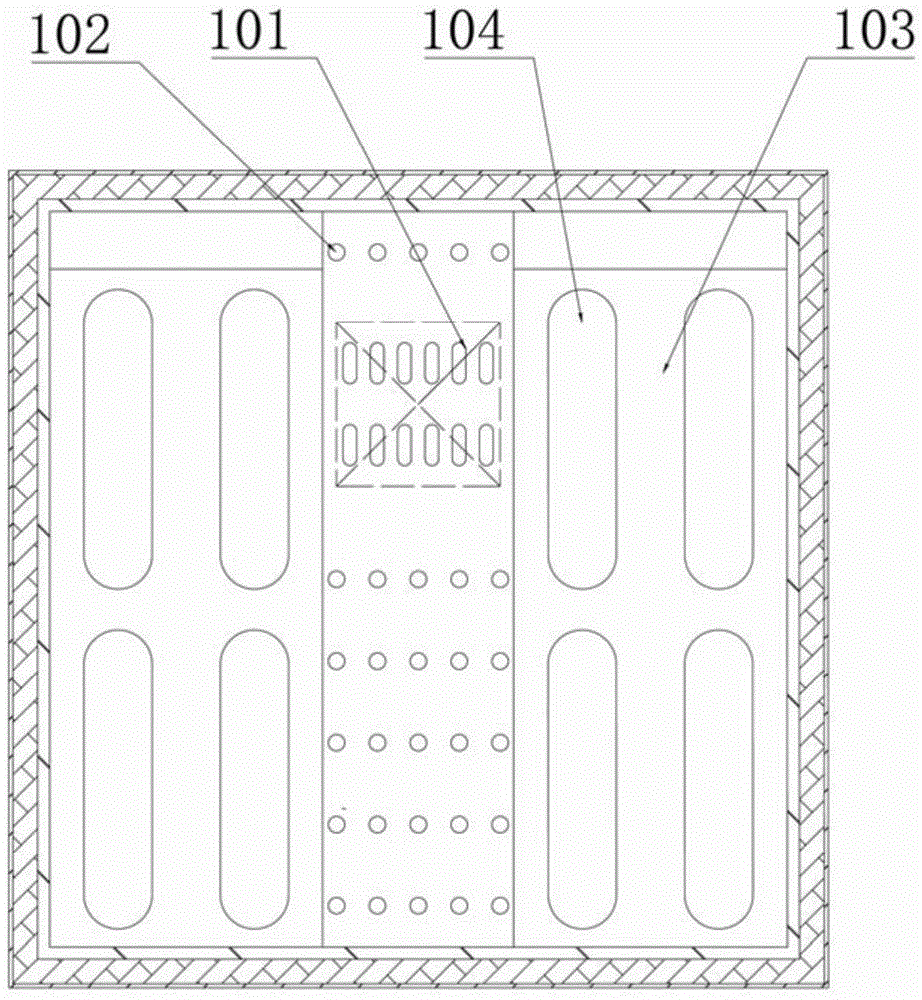

Double-working-condition semiconductor refrigeration type fruit and vegetable distribution box and control method thereof

ActiveCN104859958ASmall temperature fluctuationsStable jobShock-sensitive articlesCold airRefrigeration

The invention discloses a double-working-condition semiconductor refrigeration type fruit and vegetable distribution box and a control method thereof. The distribution box includes a distribution box body provided with an air guide baffle, a cold guide aluminium plate, a cold equalizing plate and a heat dissipation aluminium plate, as well as a basic circuit module, a master control module, an executing mechanism and a signal acquisition module, wherein the basic circuit module includes a power source circuit, a crystal oscillation clock circuit, a reset circuit and a power source conversion module; the master control module includes a central controller, a program writing circuit, a keyboard circuit, an LCD display circuit and an executing mechanism control circuit; the executing mechanism includes a cold guiding blower, a heat dissipation blower and a semiconductor refrigeration module; the signal acquisition module includes a temperature sensor circuit. During working, the cold guiding blower drives air flow to circulate in a forced manner, so that air flow absorbs cold energy at the cold guide aluminium plate, cold air flow passing through the air guide baffle is guided to the fruit and vegetable fresh-keeping environment and transfers heat with fruits and vegetables and then reflows to the cold guide aluminium plate, as a result, the refrigeration and cooling are realized. According to the invention, the distribution box has the advantages that the temperature is adjustable, the temperature reduction is uniform, the control is flexible, energy is saved, and the environment is protected, and the like.

Owner:SOUTH CHINA AGRI UNIV

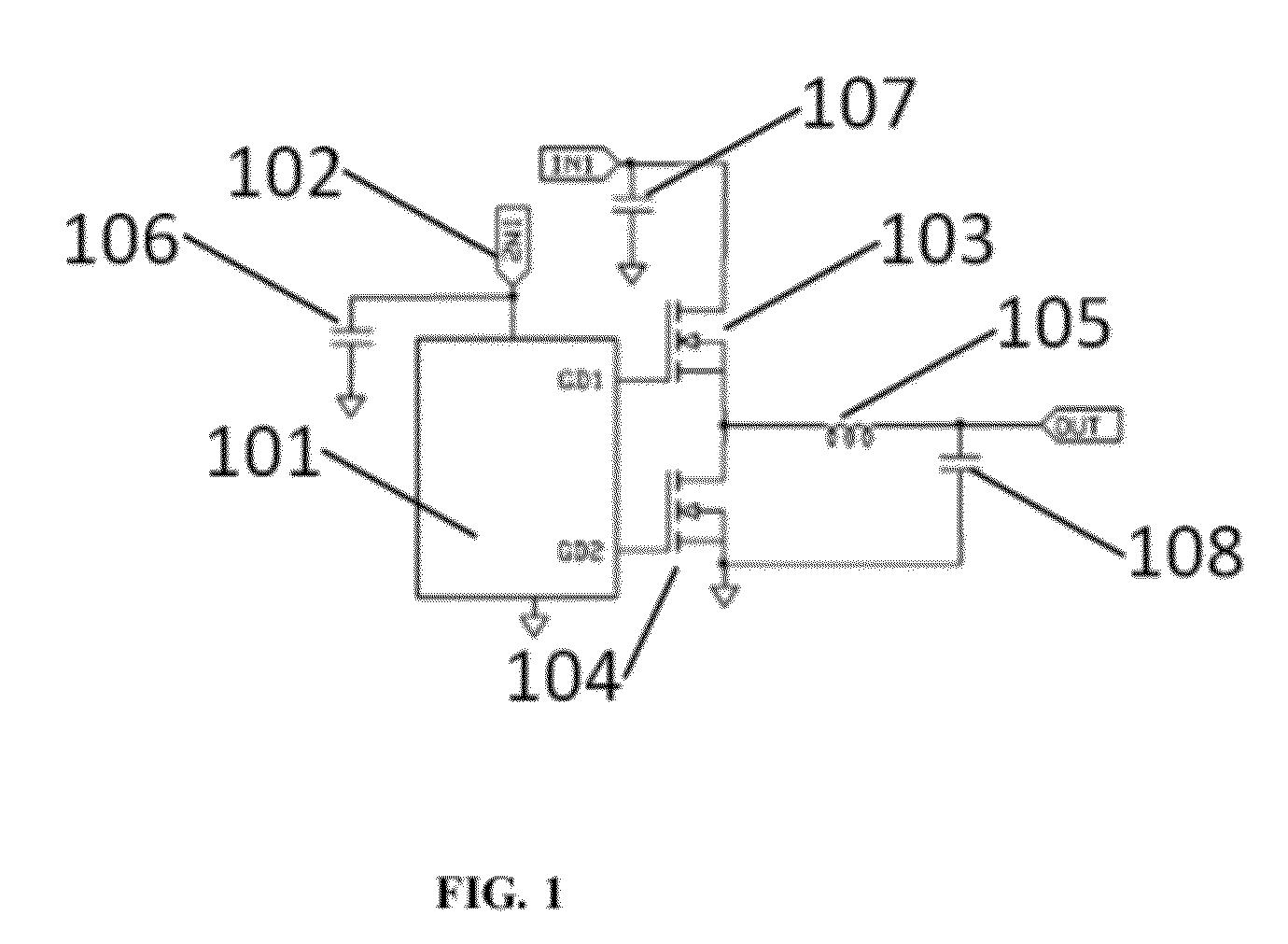

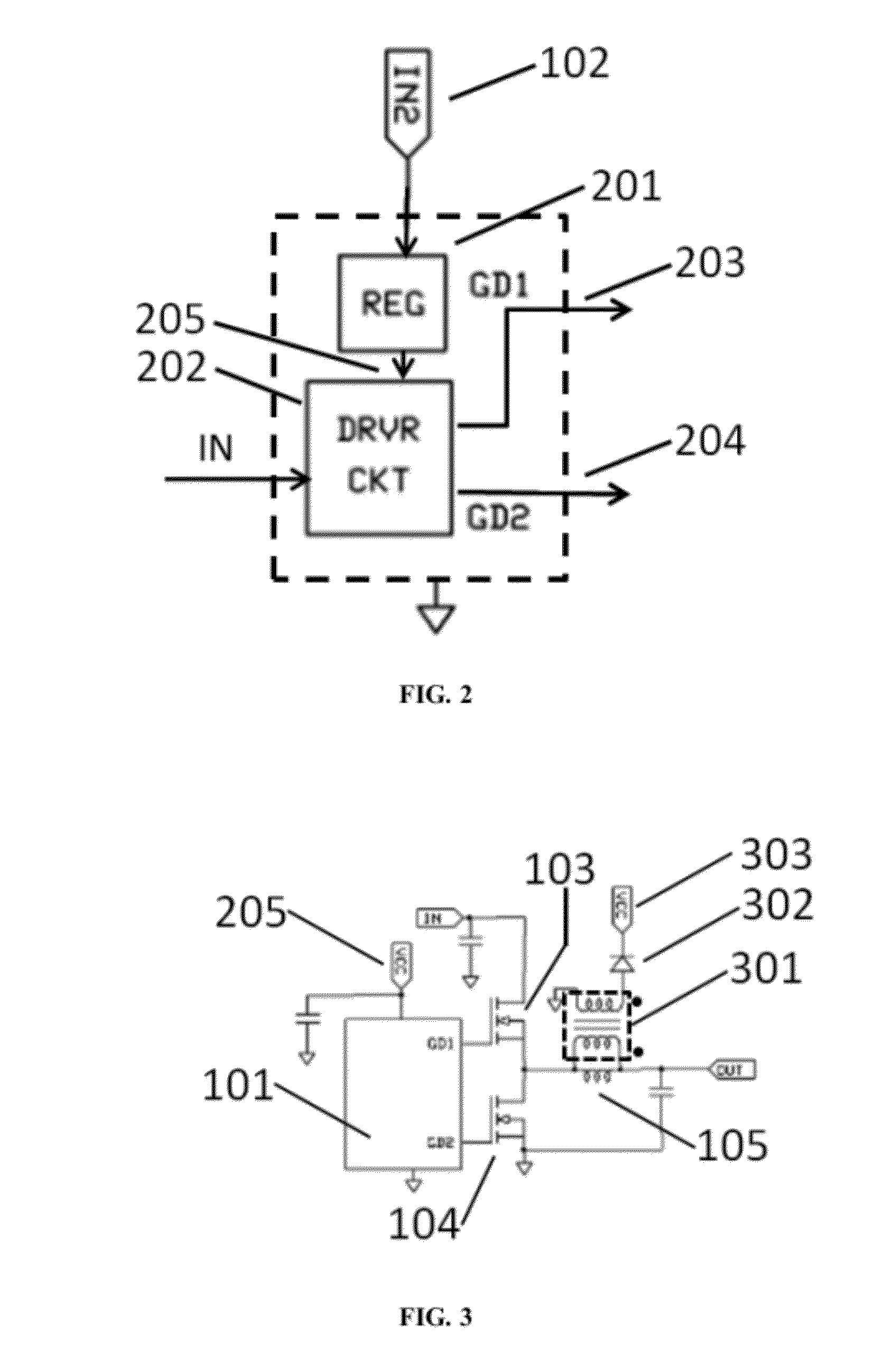

Efficient bias power supply for non-isolated dc/dc power conversion applications

InactiveUS20120313604A1Efficient power electronics conversionDc-dc conversionPower switchingTransformer

Unique methods are disclosed to construct an efficient bias supply for a main non-isolated DC / DC power conversion system. Additional bias supplies developed by employing an arbitrary number of transformers and / or an arbitrary number of secondary windings can be used to provide bias power to other isolated and non-isolated power conversion systems. By employing a transformer in forward conversion mode the basic circuit of the efficient bias supply is built without using any extra switching controllers and power switches. Furthermore a new architecture for monitoring and selecting the bias power source to ensure smooth start-up and operation during abnormal conditions and / or maintaining optimum and efficient steady state operation of a power conversion system is disclosed.

Owner:HUDA MUZAHID BIN

Gate signal line drive circuit and display device

ActiveUS20150091887A1Reduce power consumptionCathode-ray tube indicatorsDigital storageLow voltageDisplay device

A gate signal line drive circuit whose power consumption is reduced, is provided. In the gate signal line drive circuit having plural basic circuits outputting respective gate signals, each basic circuit includes a high voltage application switching element to which a first basic clock signal having high voltage in a signal high period is input, a low voltage application switching element that turns on at timing starting a signal low period, and outputs a low voltage, and a first low voltage application on control element having an input terminal to which a second basic clock signal subsequent to the first basic clock signal is input, and which turns on according to the signal high period, and outputs the voltage of the second basic clock signal to the control terminal of the low voltage application switching element.

Owner:JAPAN DISPLAY INC

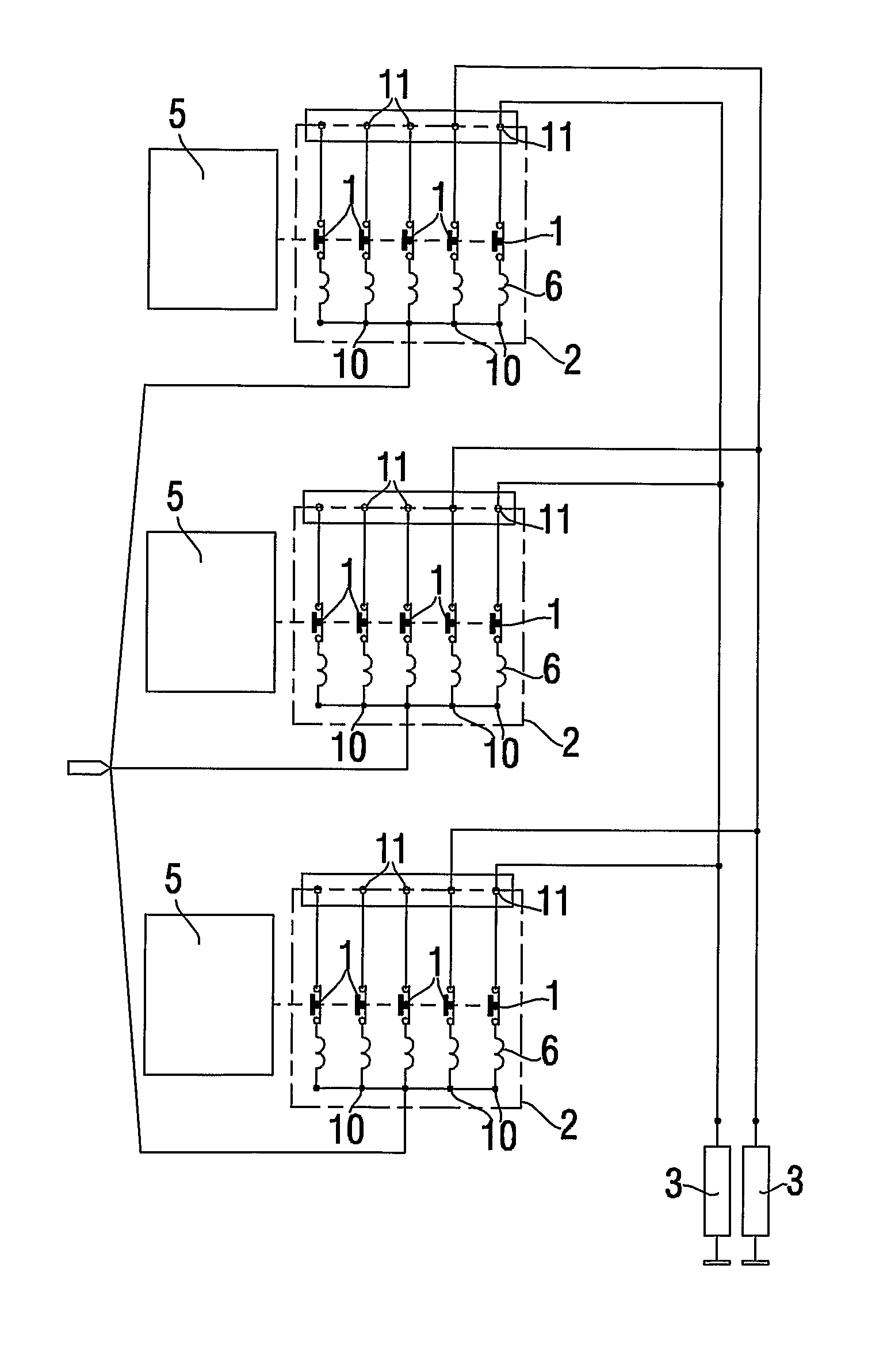

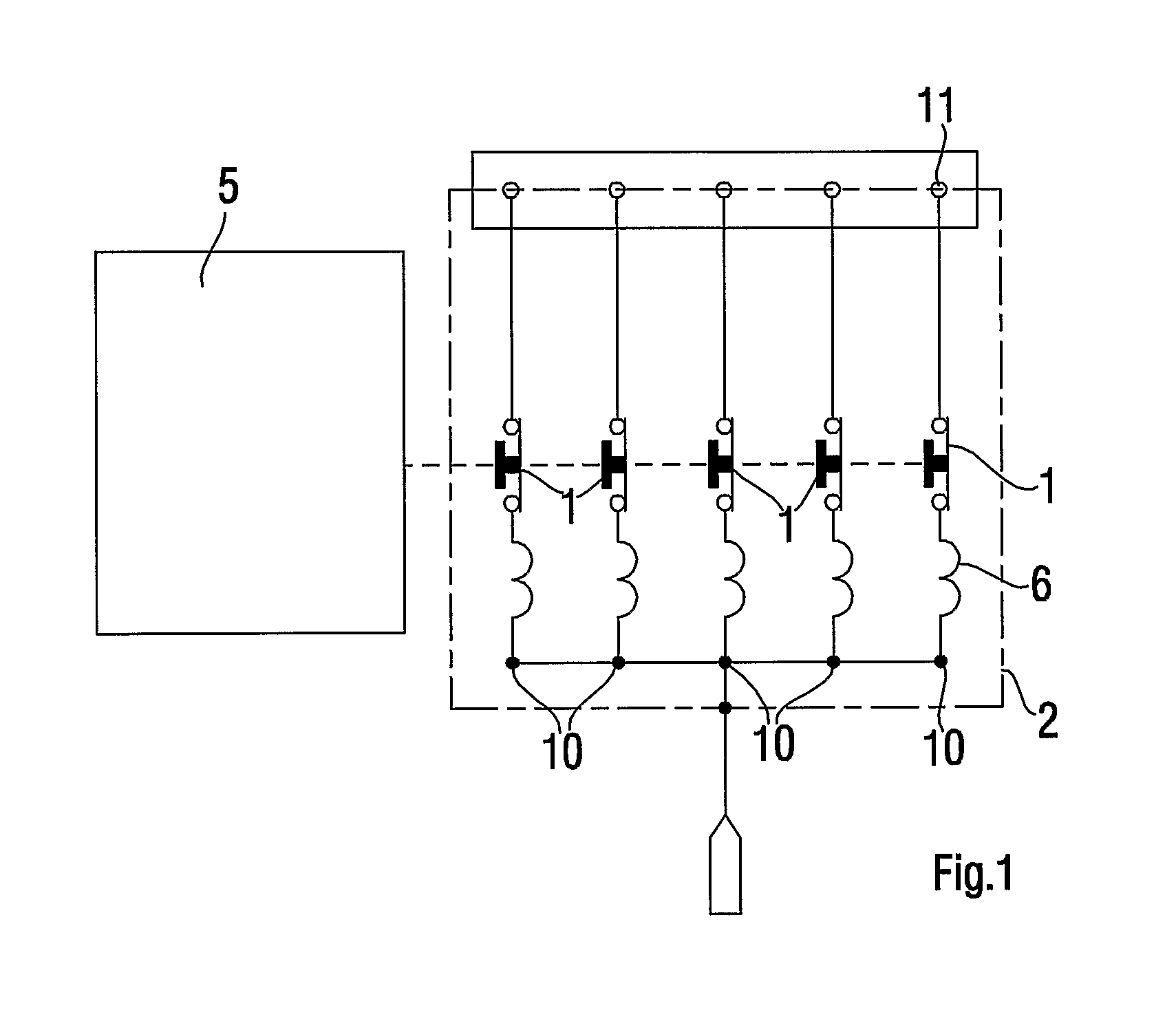

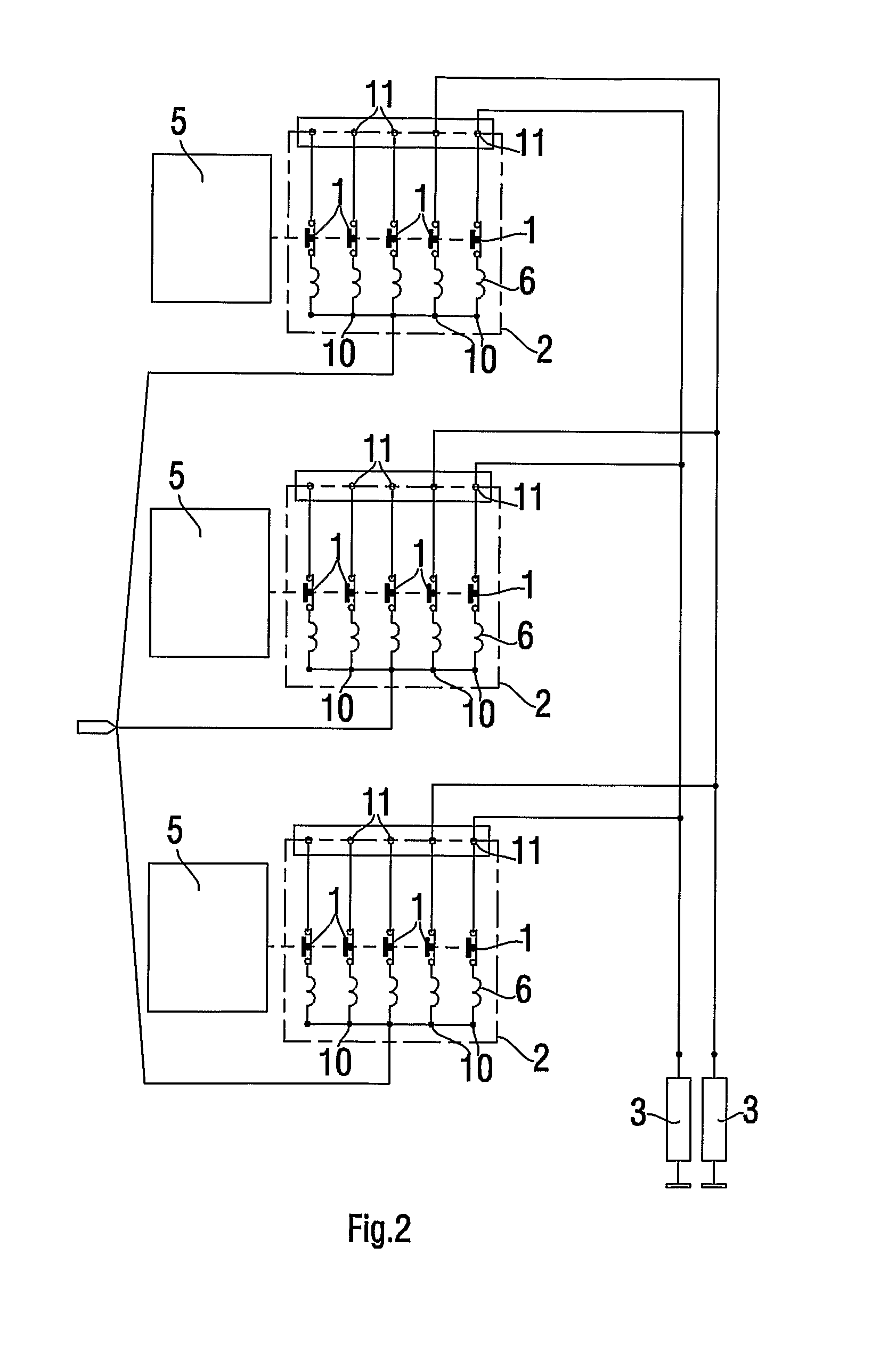

Segmental electronic circuit breaker and installation comprising same

Owner:NOVATEC 45 PARTIAL INTEREST +2

Display device

ActiveUS20090225019A1Raise the possibilityHigh voltageStatic indicating devicesDigital storageDriver circuitShift register

In a display device which includes a driver circuit having a shift register circuit, the shift register circuit is constituted of basic circuits in plural stages. Each basic circuit is constituted of a circuit A, a circuit B and a circuit C. The circuit A fetches a first drive clock (or a second drive clock) inputted from the outside when transfer data is inputted to the circuit A from a circuit of preceding stage, outputs the transfer data as a shift output of own stage, and transfers the transfer data to the circuit B. The circuit B transfers the transfer data to the circuit A of the basic circuit of the succeeding stage, and resets the circuit C. The circuit C resets the circuit A and the circuit B in synchronism with the first drive clock (or the second drive clock) generated at next timing or succeeding timing of the first drive clock.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

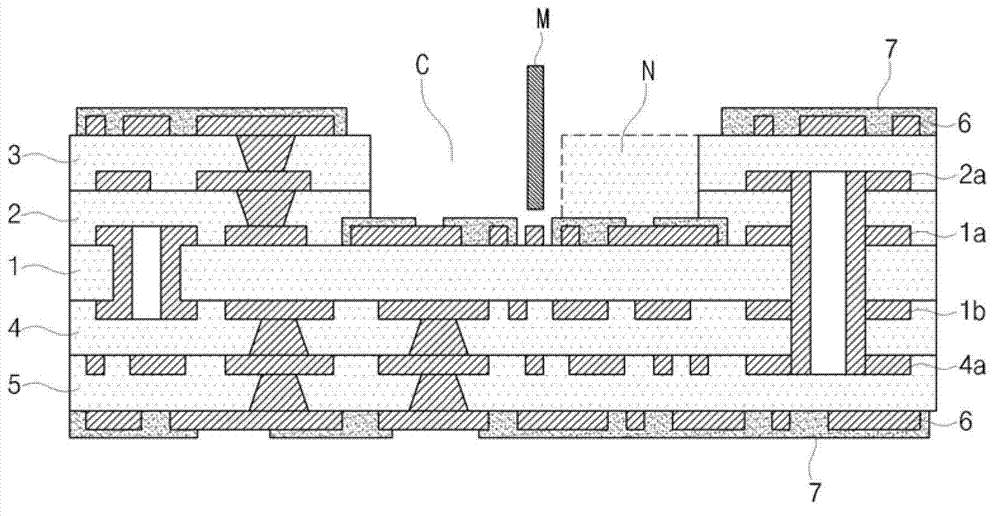

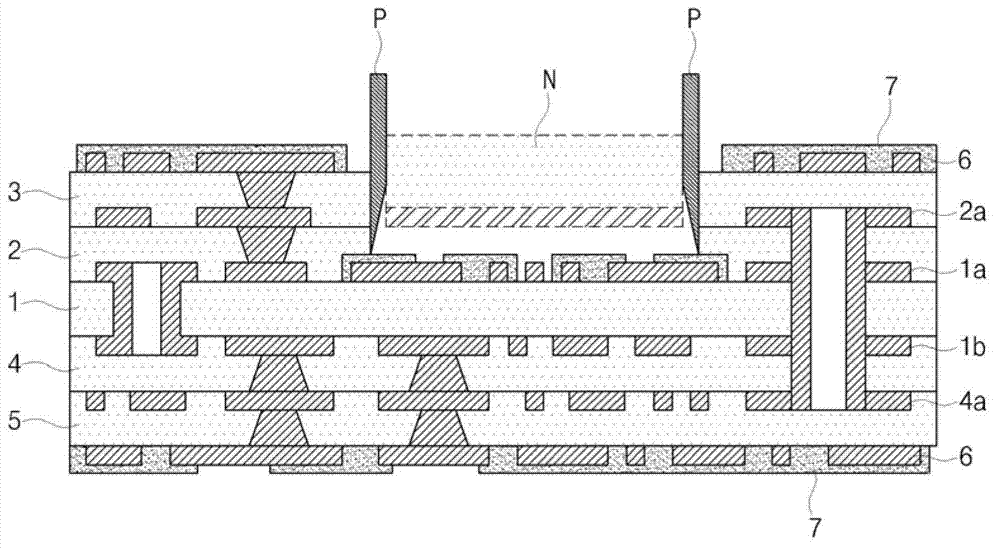

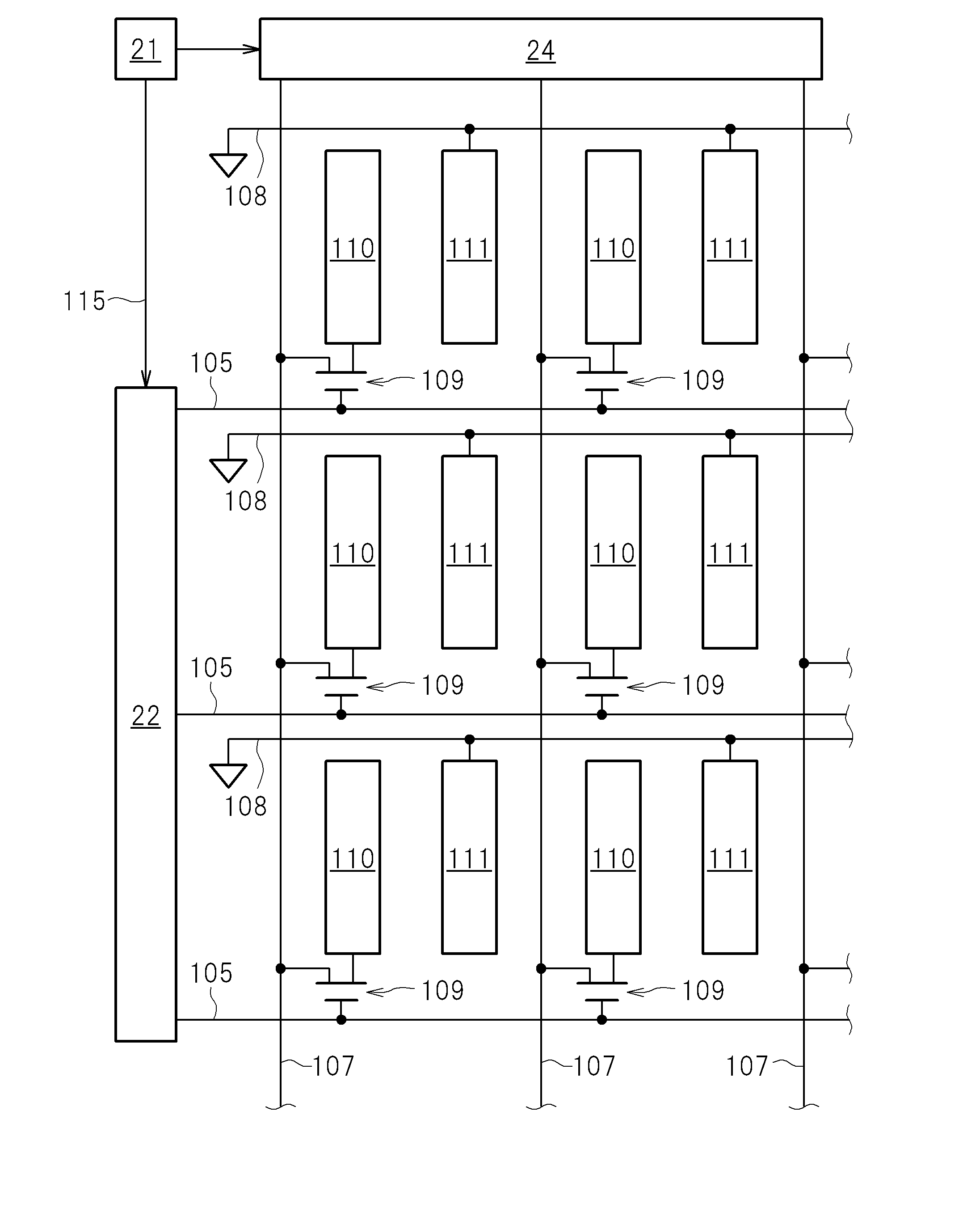

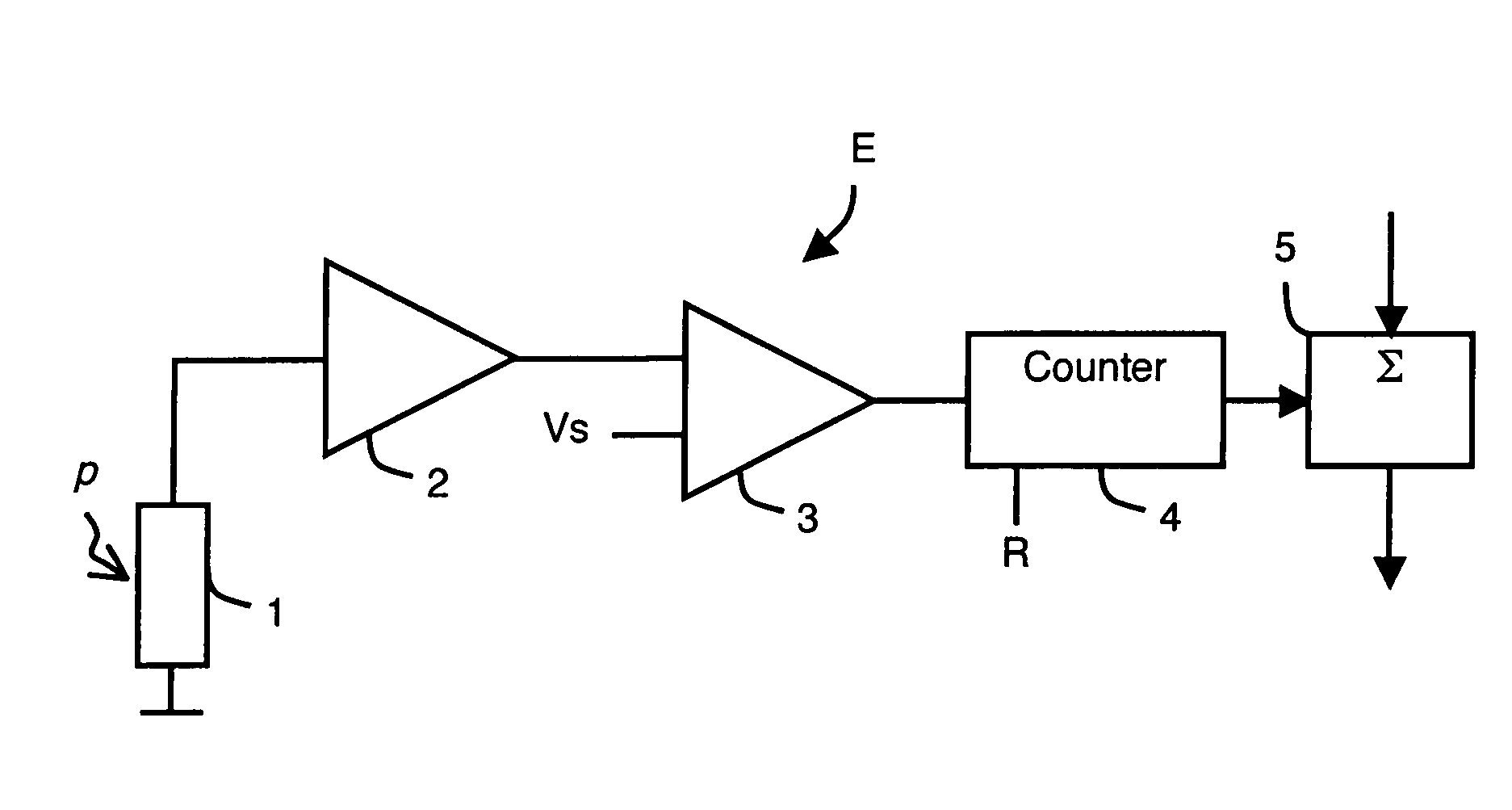

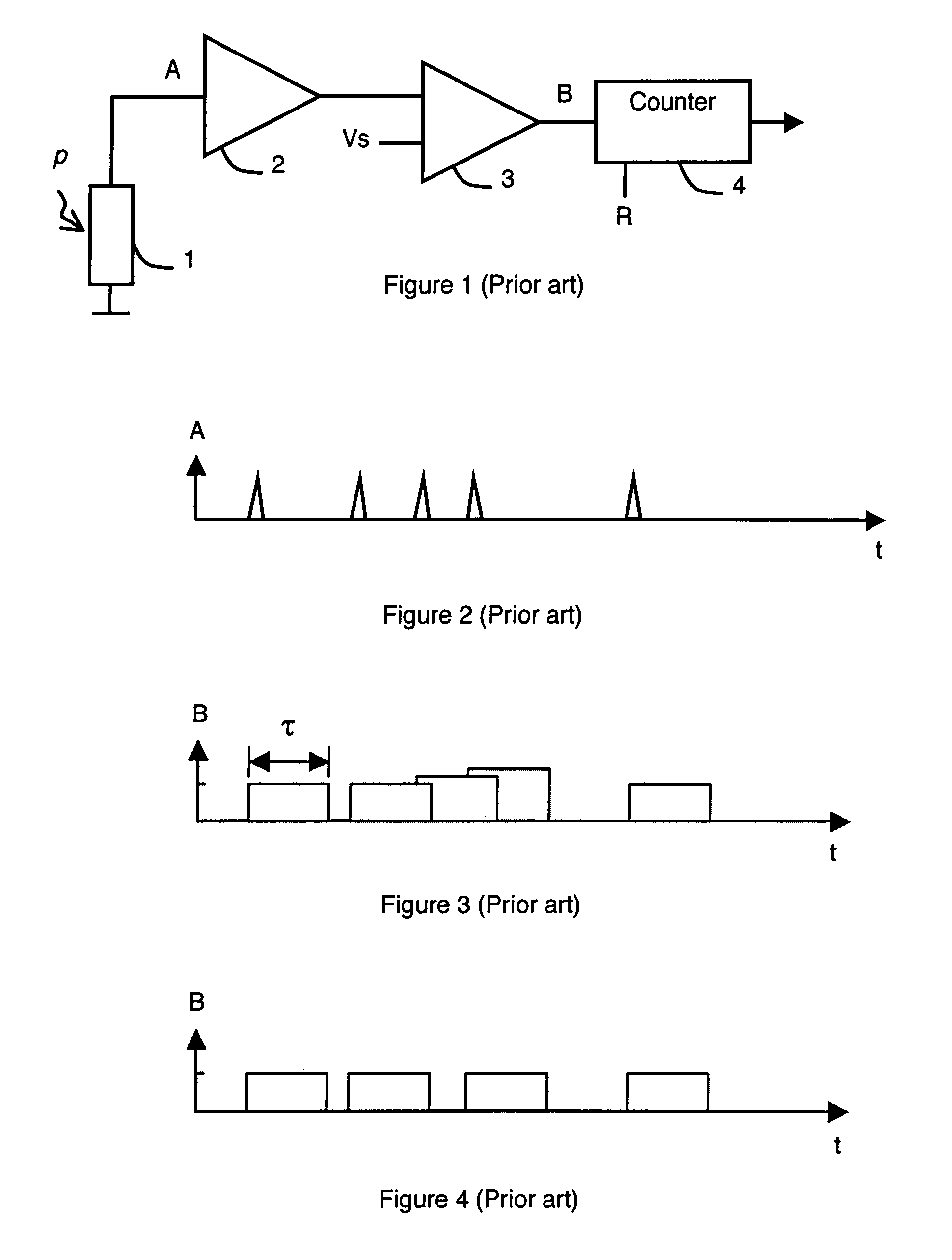

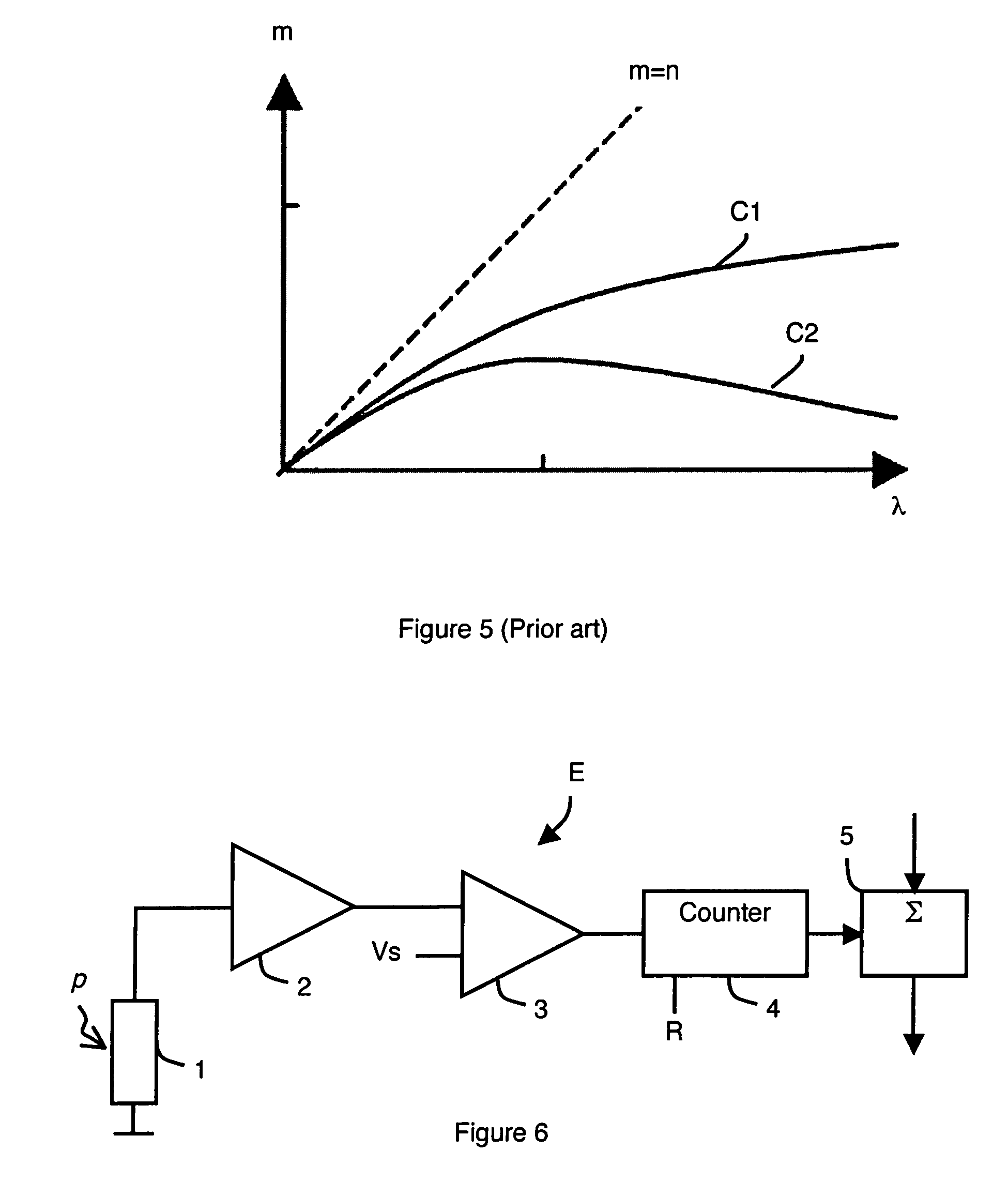

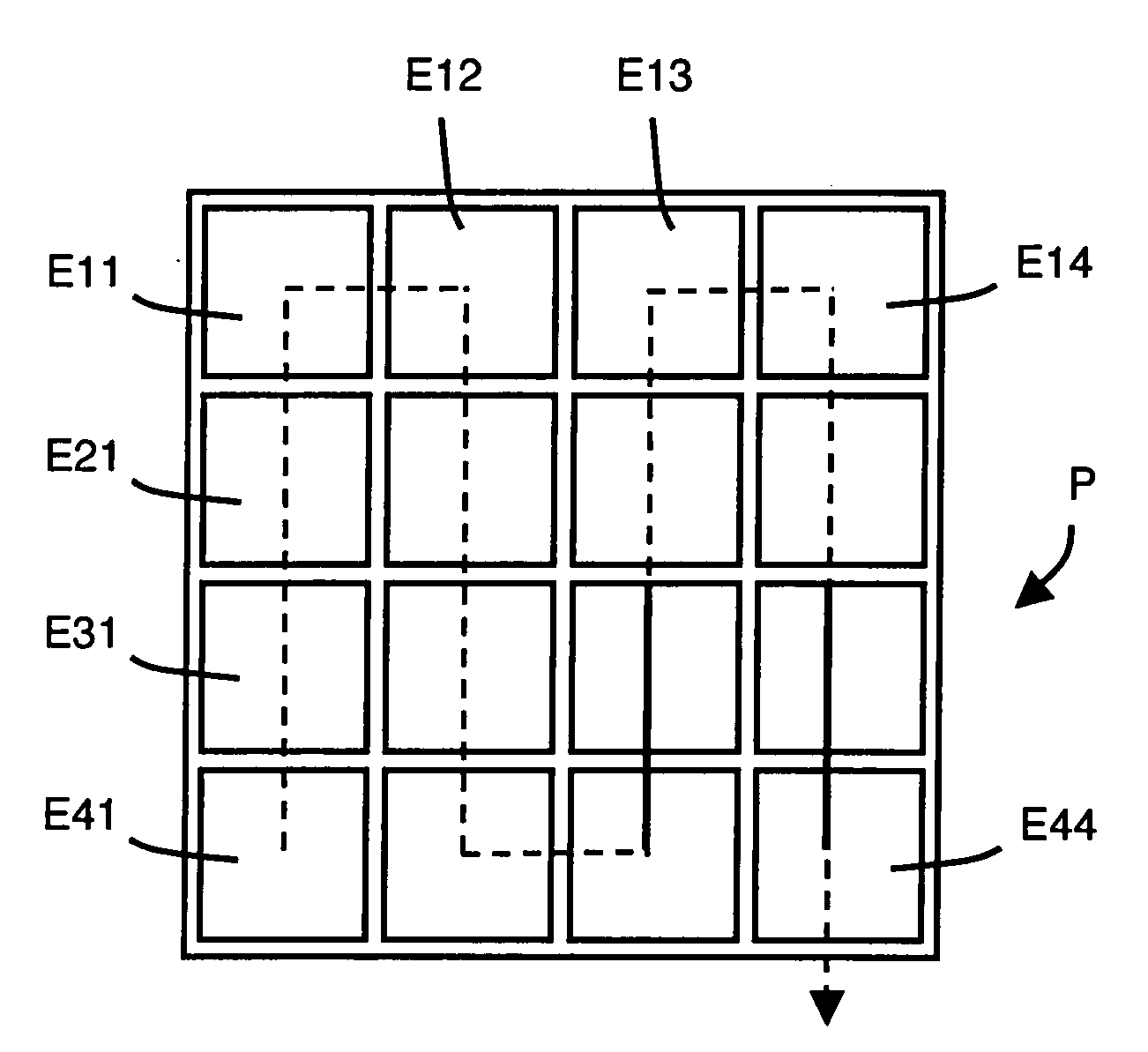

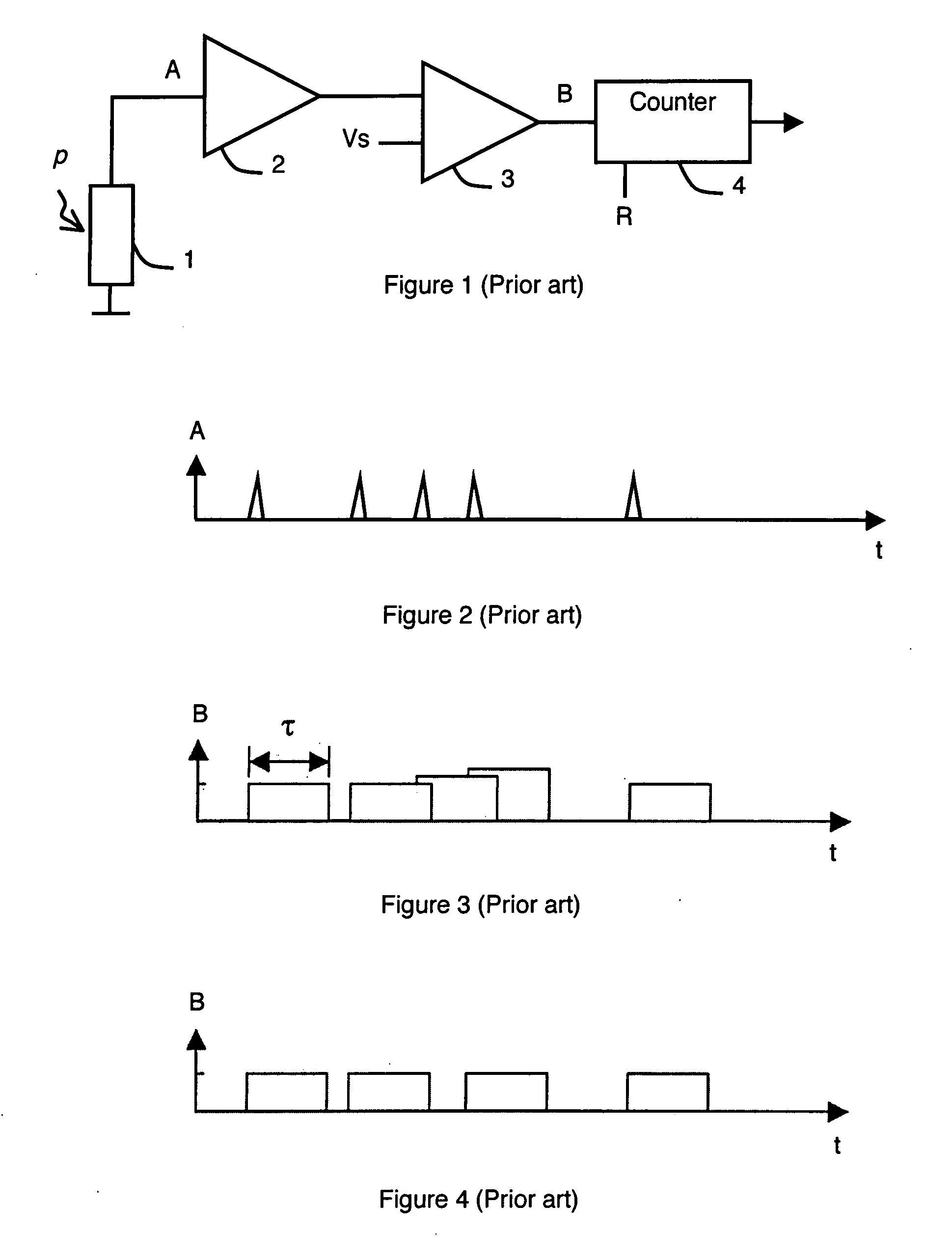

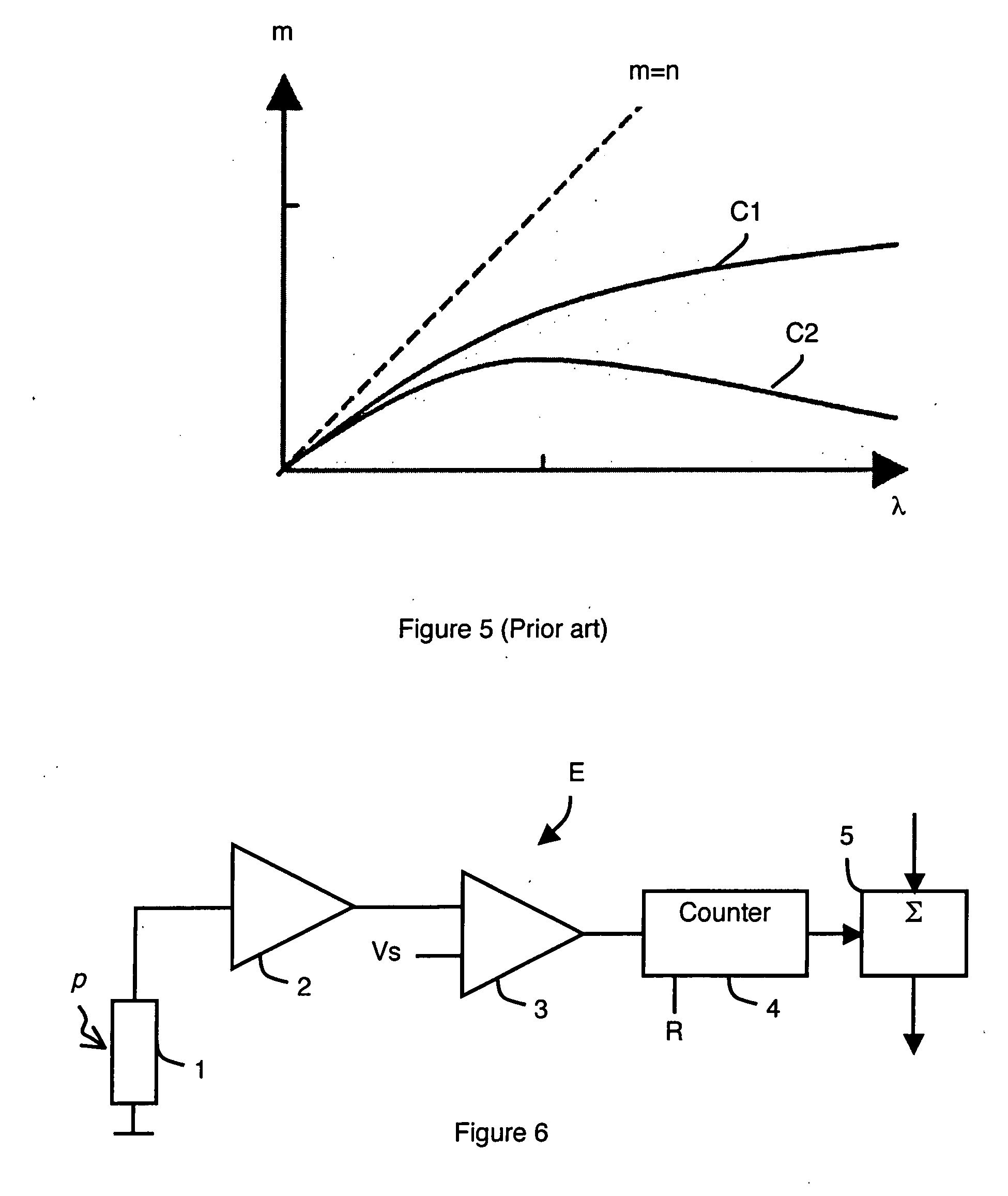

Particle detection circuit comprising basic circuits forming subpixels

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

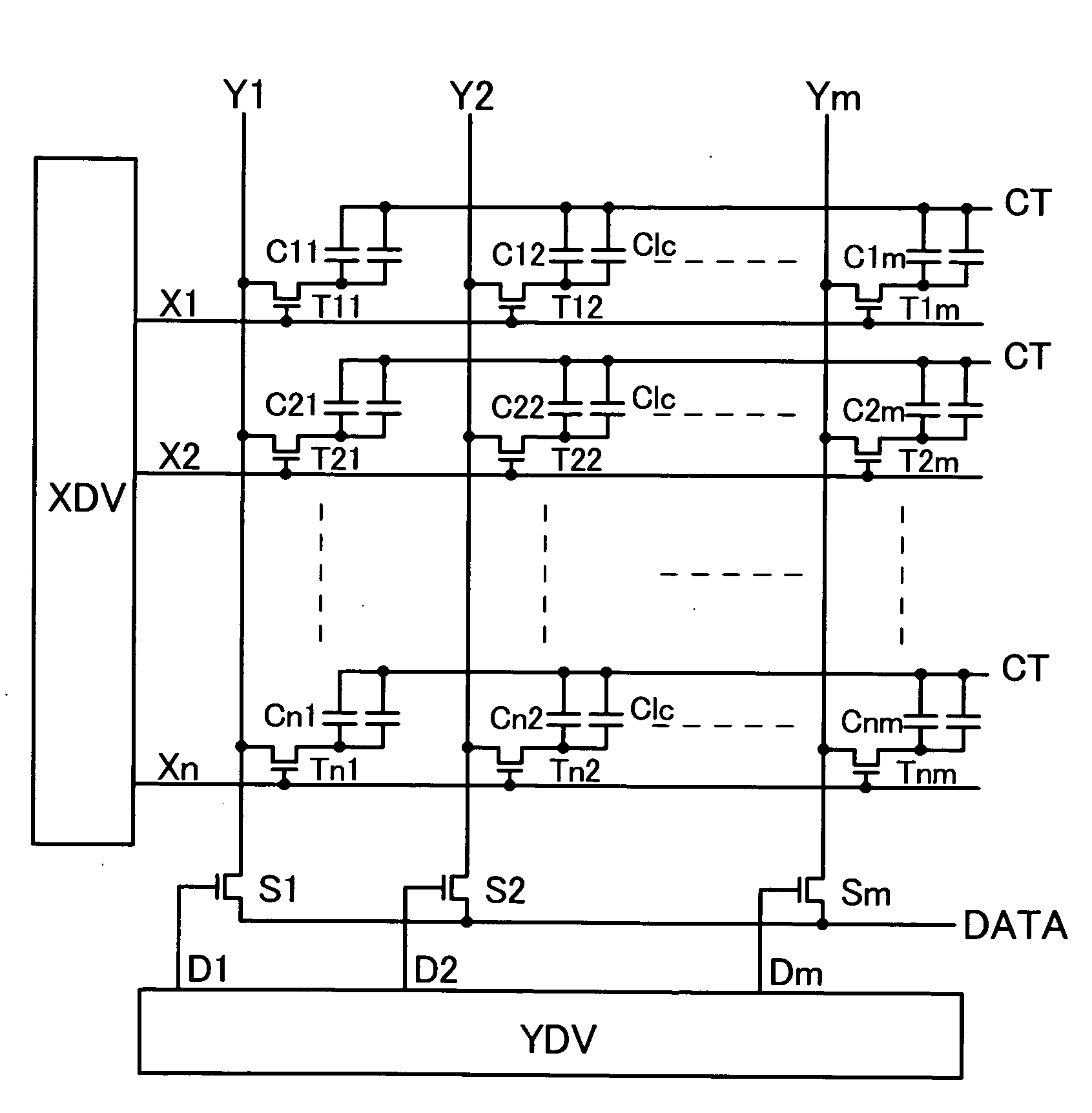

Particle detection circuit comprising basic circuits forming subpixels

ActiveUS20090121145A1Improve spatial resolutionTelevision system detailsSolid-state devicesRegion detectionPhysics

The particle detection circuit comprises a plurality of basic circuits. Each basic circuit comprises a particle detector element connected to an associated counter and a summing circuit having a first input connected to the output of the counter. Basic circuits, each forming a subpixel, are grouped together by series connection of their summing circuits to form a pixel. The output of the pixel, formed by the output of the summing circuit of a last basic circuit of the pixel, supplies counting signals representative of the number of particles detected by the set of basic circuits of the pixel. Disabling certain basic circuits of the pixel, by selective zero resetting of the first input of their summing circuit, can enable only the particles detected by certain zones of the pixel to be counted.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

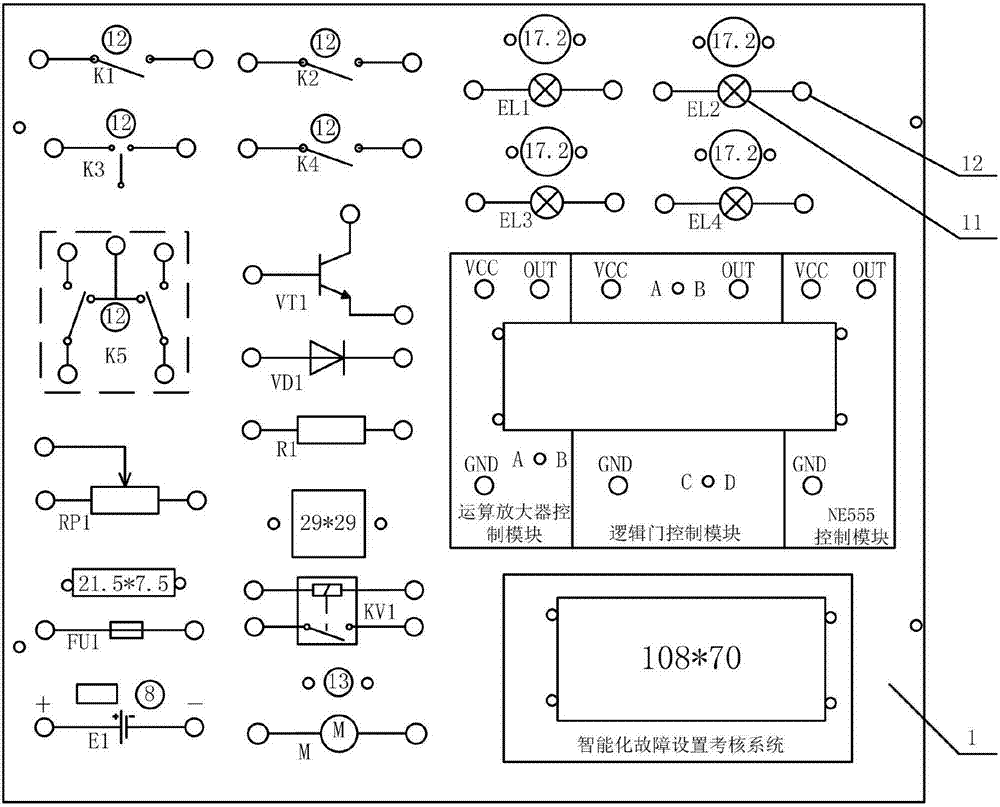

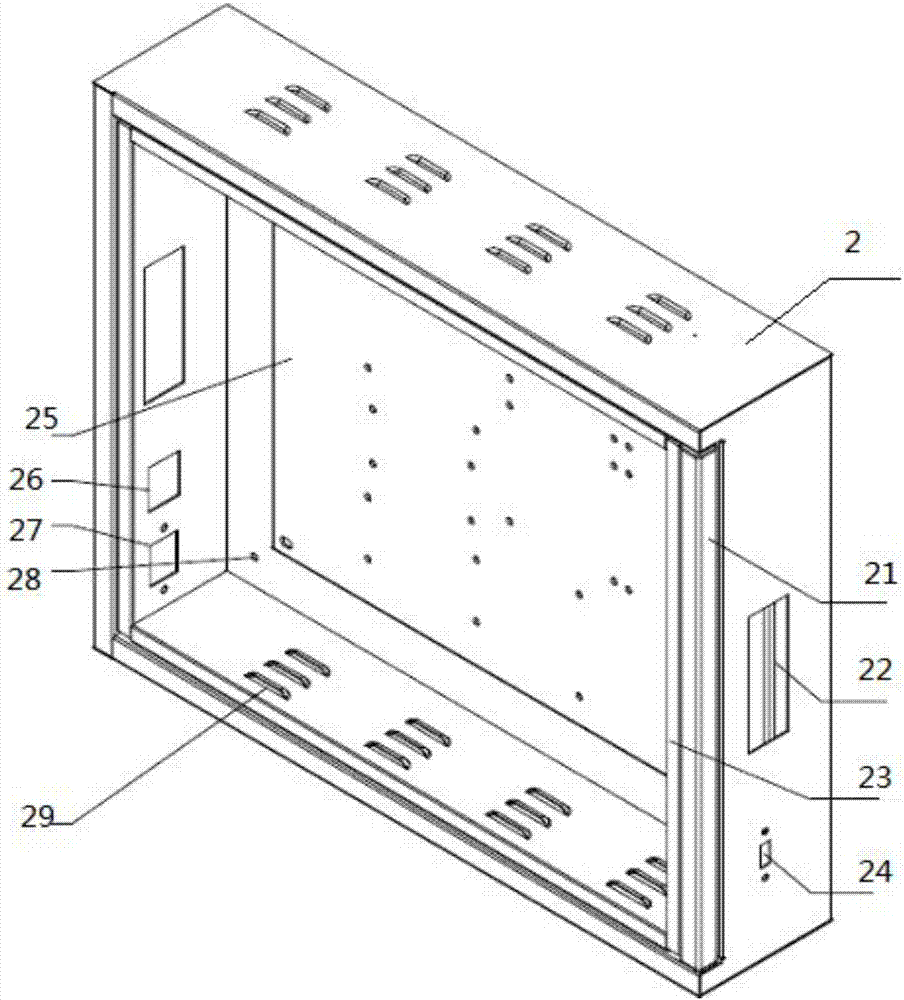

Automobile electronic appliance experiment box used for teaching and system thereof

The invention provides an automobile electronic appliance experiment box used for teaching and a system thereof. The electronic appliance experiment box used for teaching comprises a shell, a panel, an automobile electronic appliance component, a direct current voltage stabilization power supply, a modularization circuit, a matched lead and an intelligent fault setting examination system. The modularization circuit comprises an automobile light basic circuit, an automobile light parallel circuit, an automobile light series circuit, an automobile light series and parallel circuit and other automobile typical circuits. The intelligent fault setting examination system is provided with a typical fault and comprises three modes of exercise, examination and management. And under the different management modes, examination is performed and grading is automatically completed. The automobile electronic appliance experiment box used for teaching is suitable for automobile electronic appliance practice teaching learnt by automobile application and maintenance majors of a secondary vocational school. The typical circuit fault can be set and a skill examination requirement is satisfied. Simultaneously, the direct current voltage stabilization power supply is configured with various kinds of protection functions so that safe and reliable performance is achieved.

Owner:HANGZHOU CHUANGGUAN TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com