Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

48 results about "ECC memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Error-correcting code memory (ECC memory) is a type of computer data storage that can detect and correct the most-common kinds of internal data corruption. ECC memory is used in most computers where data corruption cannot be tolerated under any circumstances, such as for scientific or financial computing.

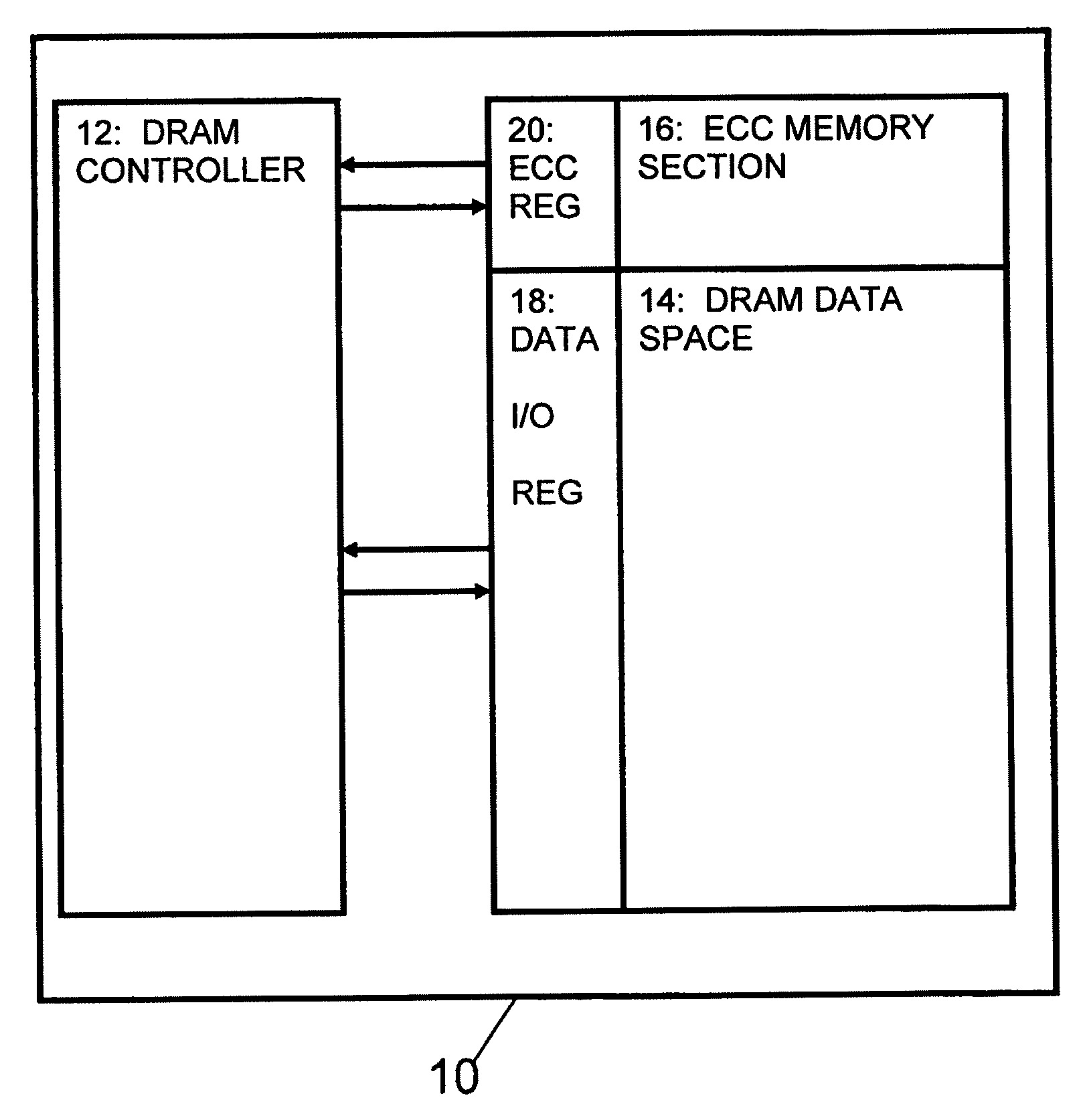

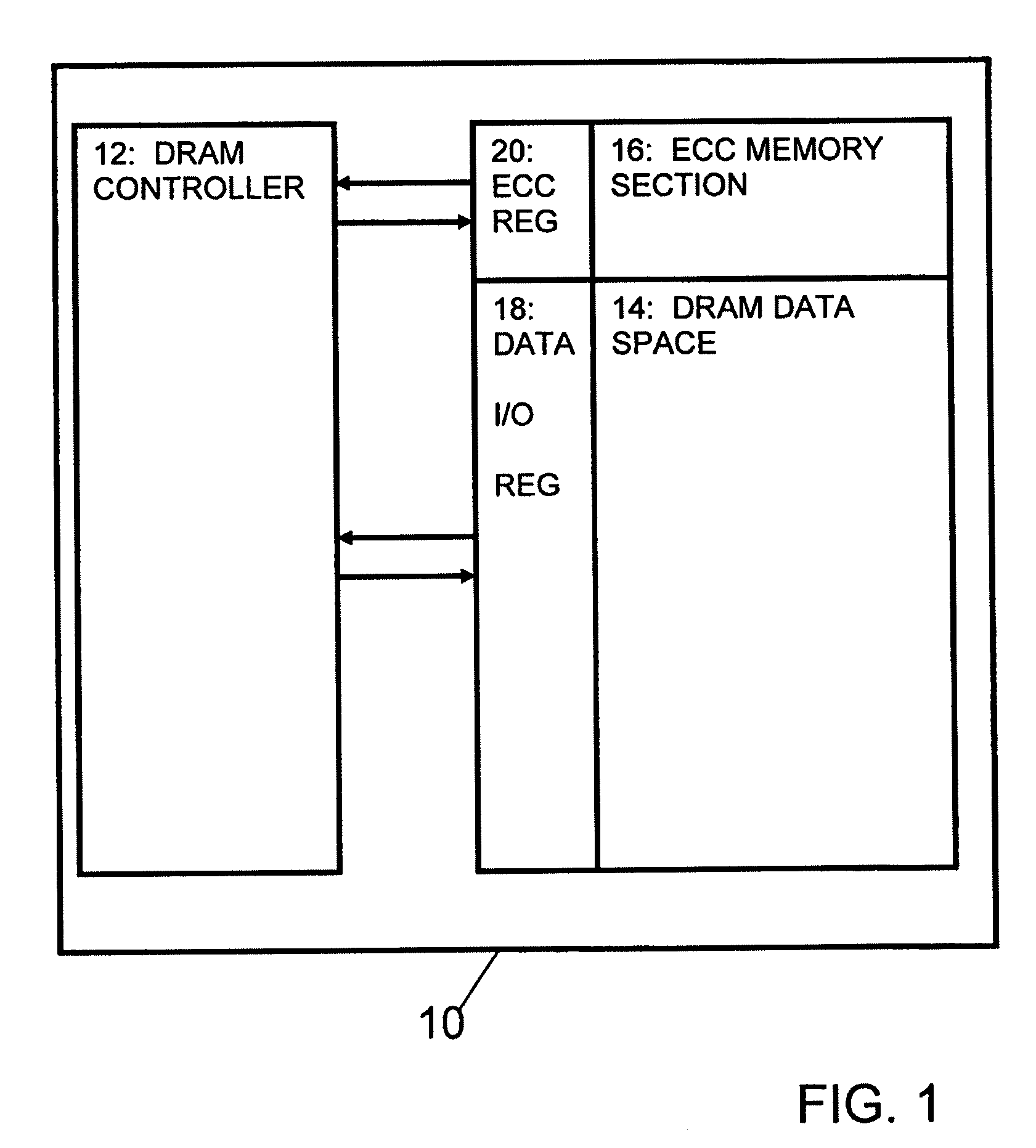

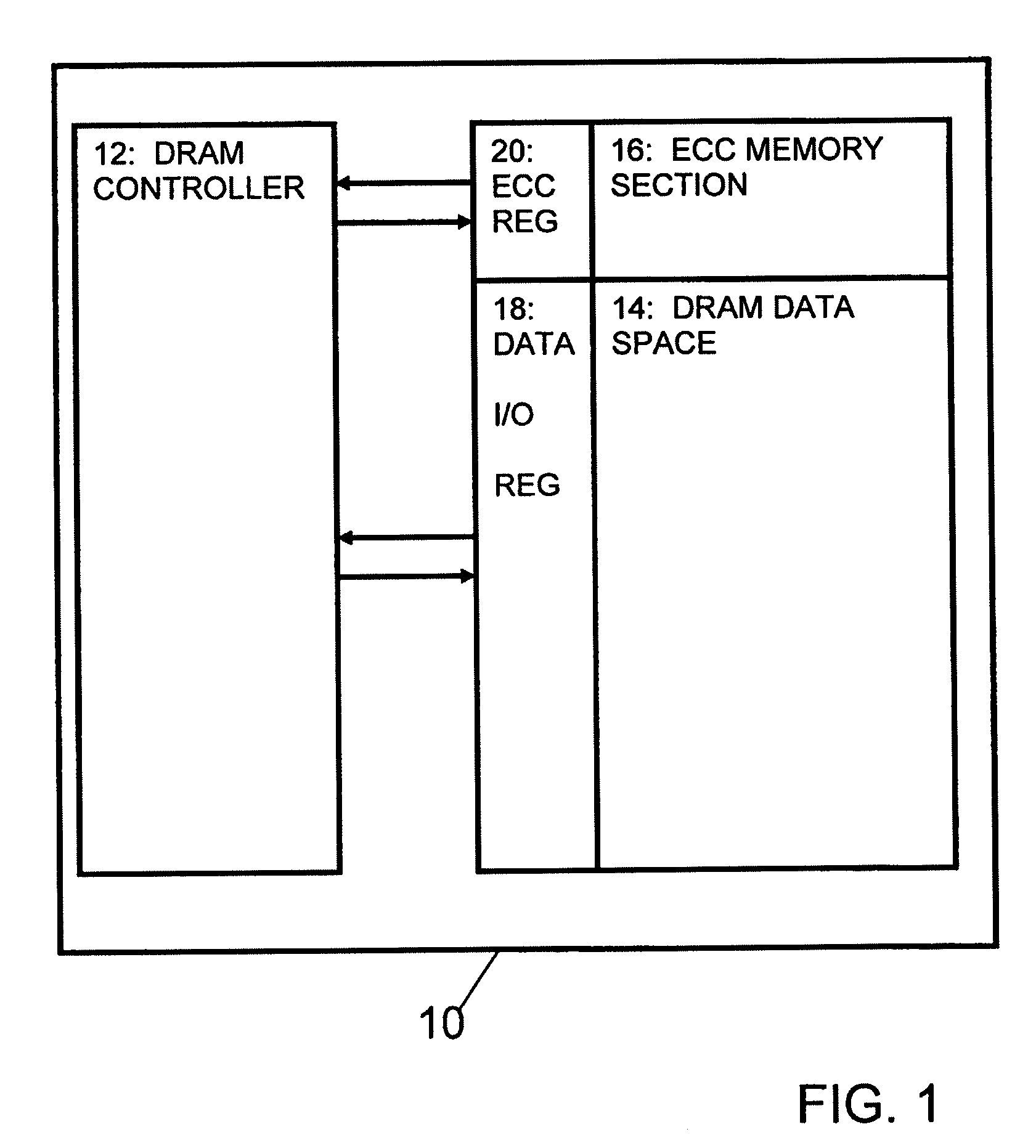

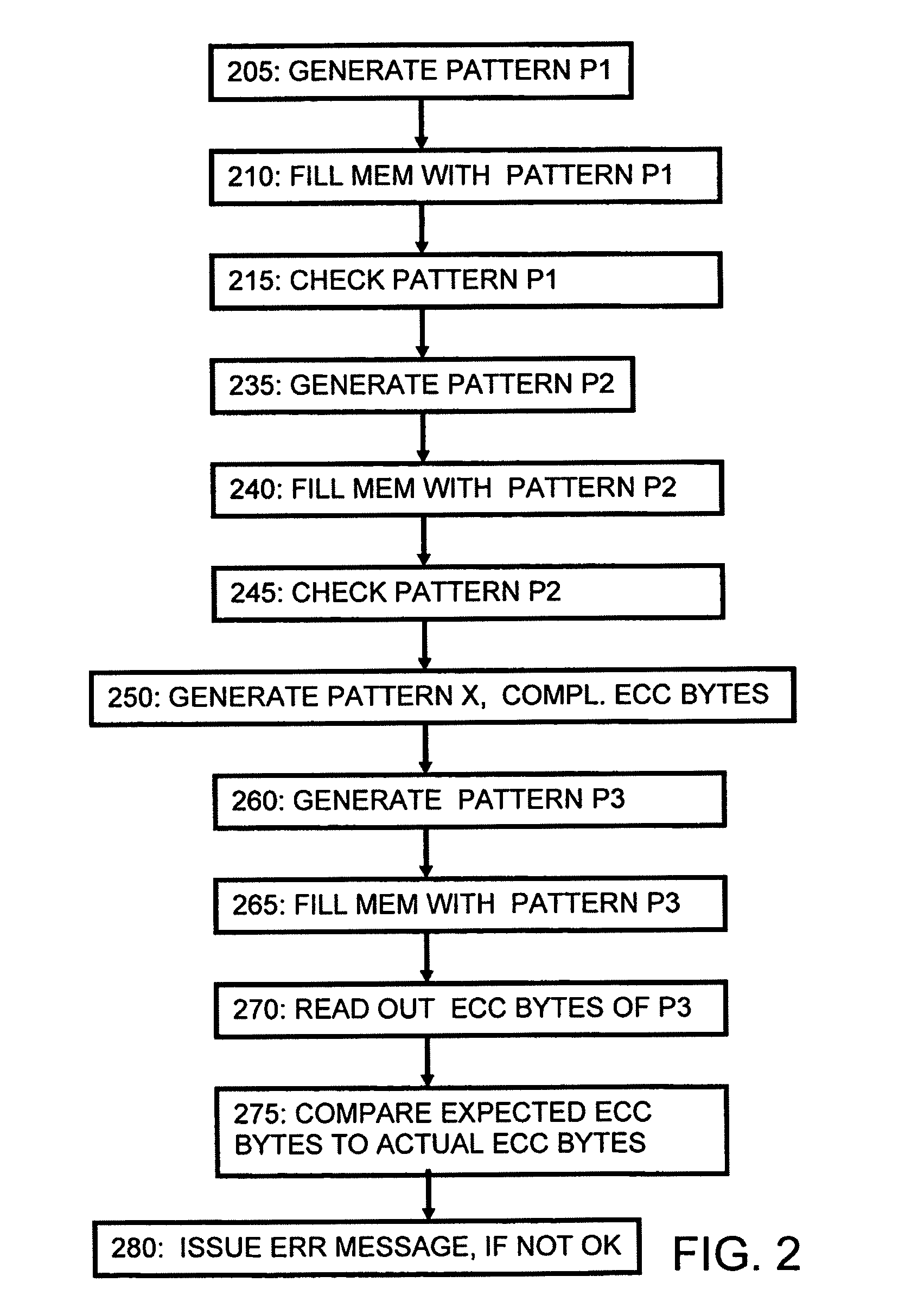

Method for fast ecc memory testing by software including ecc check byte

ActiveUS20080229176A1Accurate operationCorrection errorFault responseElectronic circuit testingECC memoryByte

The present invention relates to the architecture and operation of computer hardware memory logic, and in particular to a method and respective system for verifying hardware memory logic, wherein an Error Correction Code (ECC) is used for correcting single-bit or multi-bit errors when the ECC-bits cannot be accessed directly for a read or write process. The system and process employs the selection of data patterns that produce check bits that are all ones to ferret out errors in the ECC circuitry.

Owner:META PLATFORMS INC

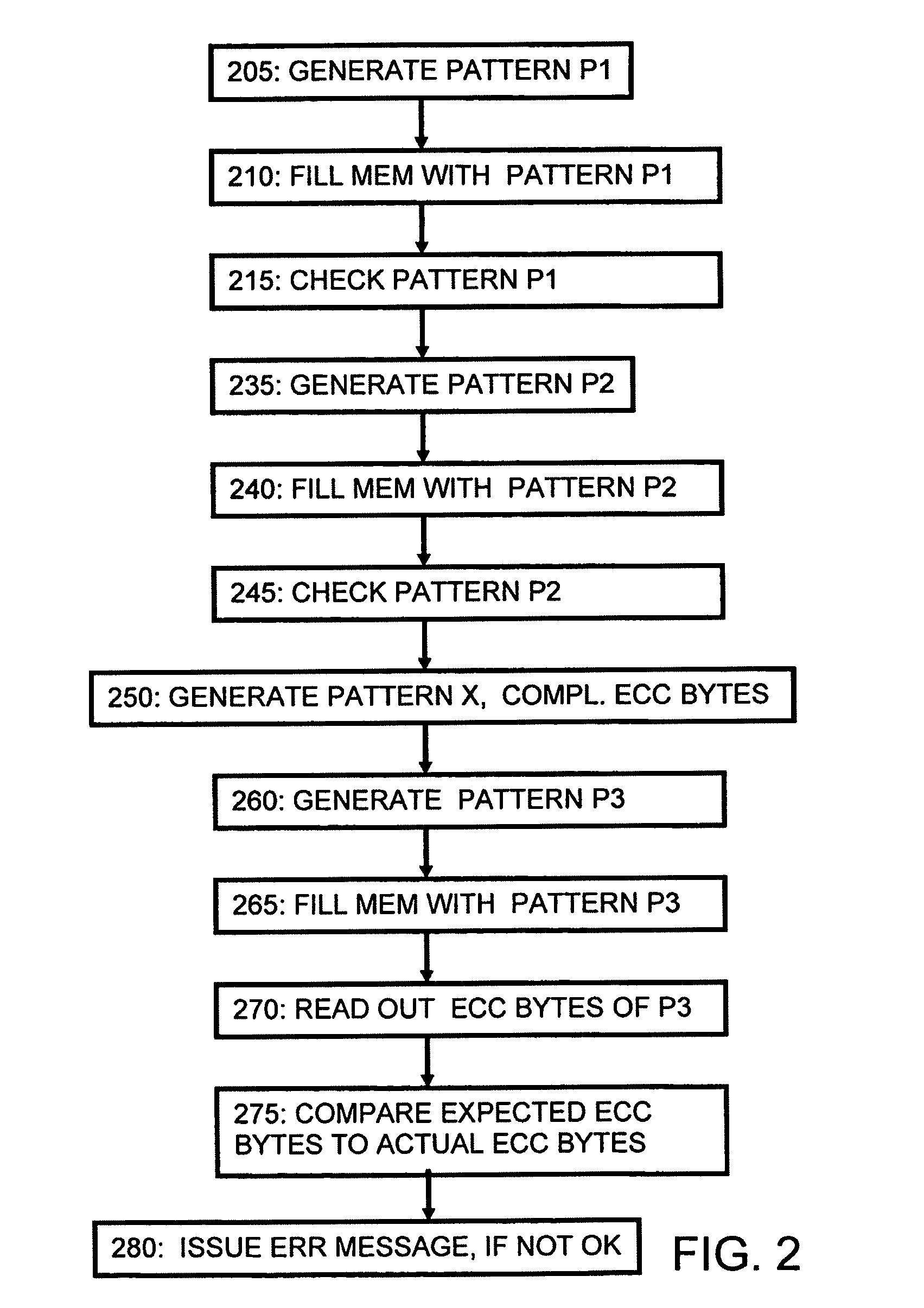

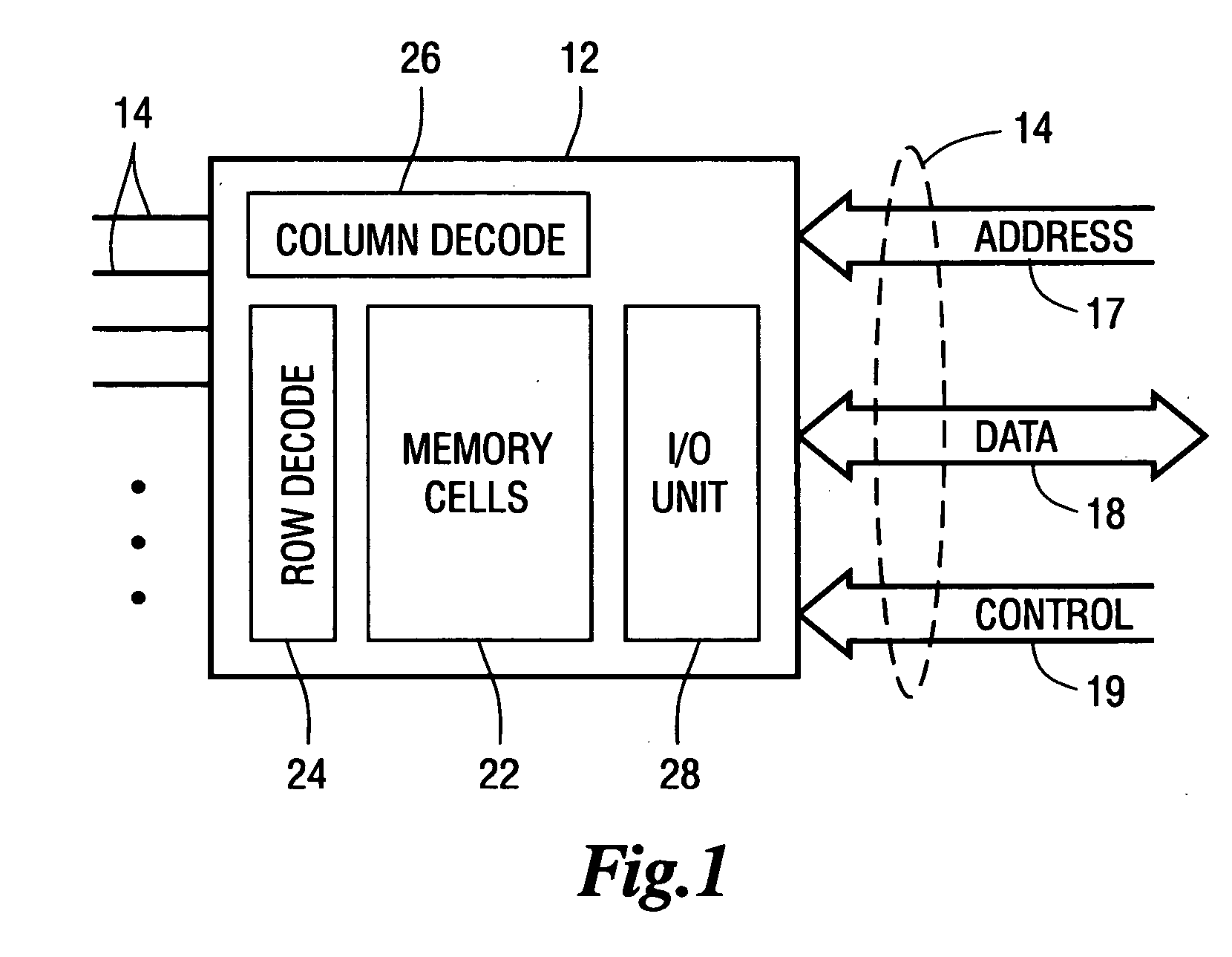

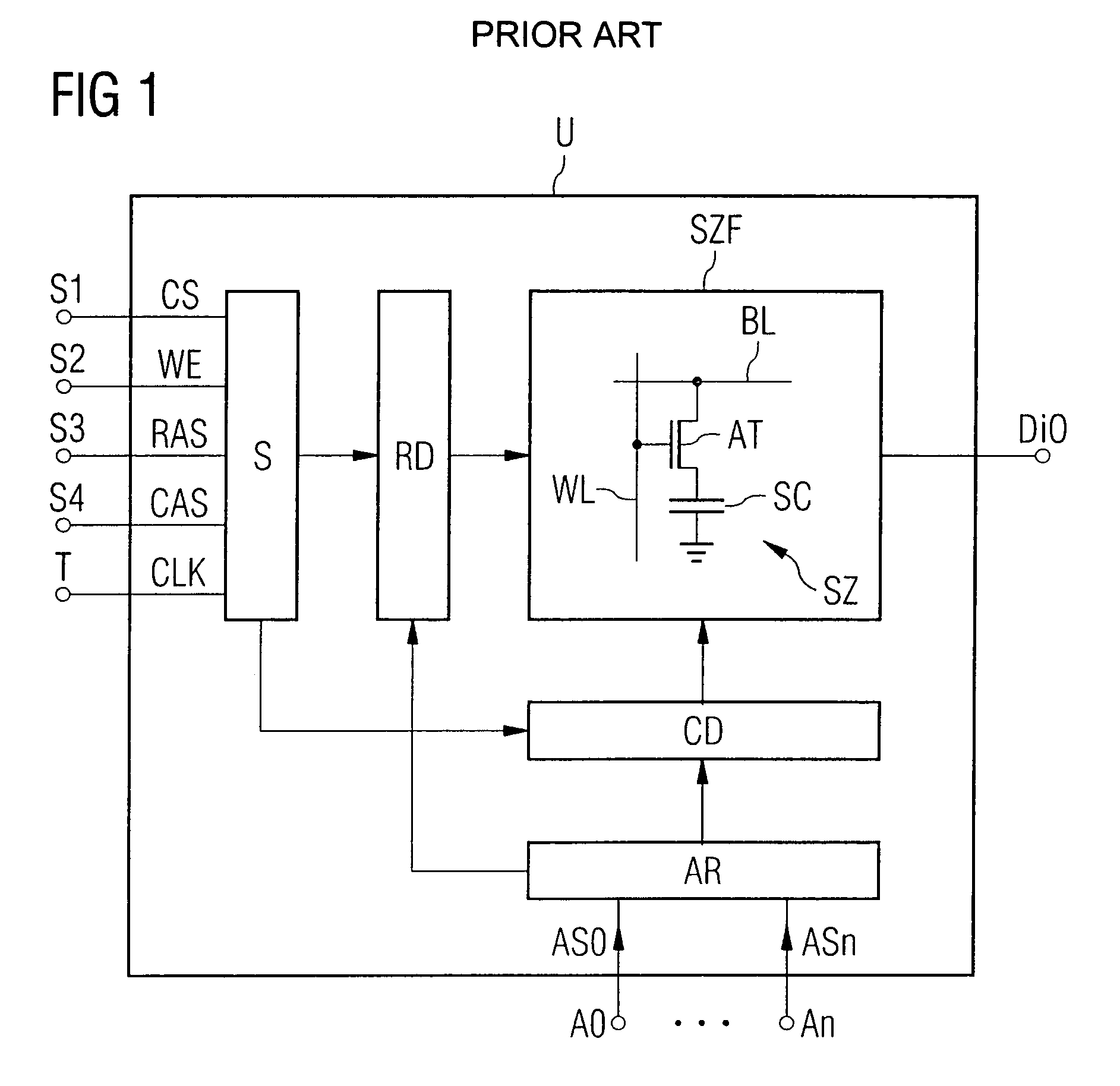

Semiconductor memory device having ECC type error recovery circuit

InactiveUS6851081B2Easy to measureEasy to readMemory loss protectionEmergency protective arrangements for automatic disconnectionType errorError check

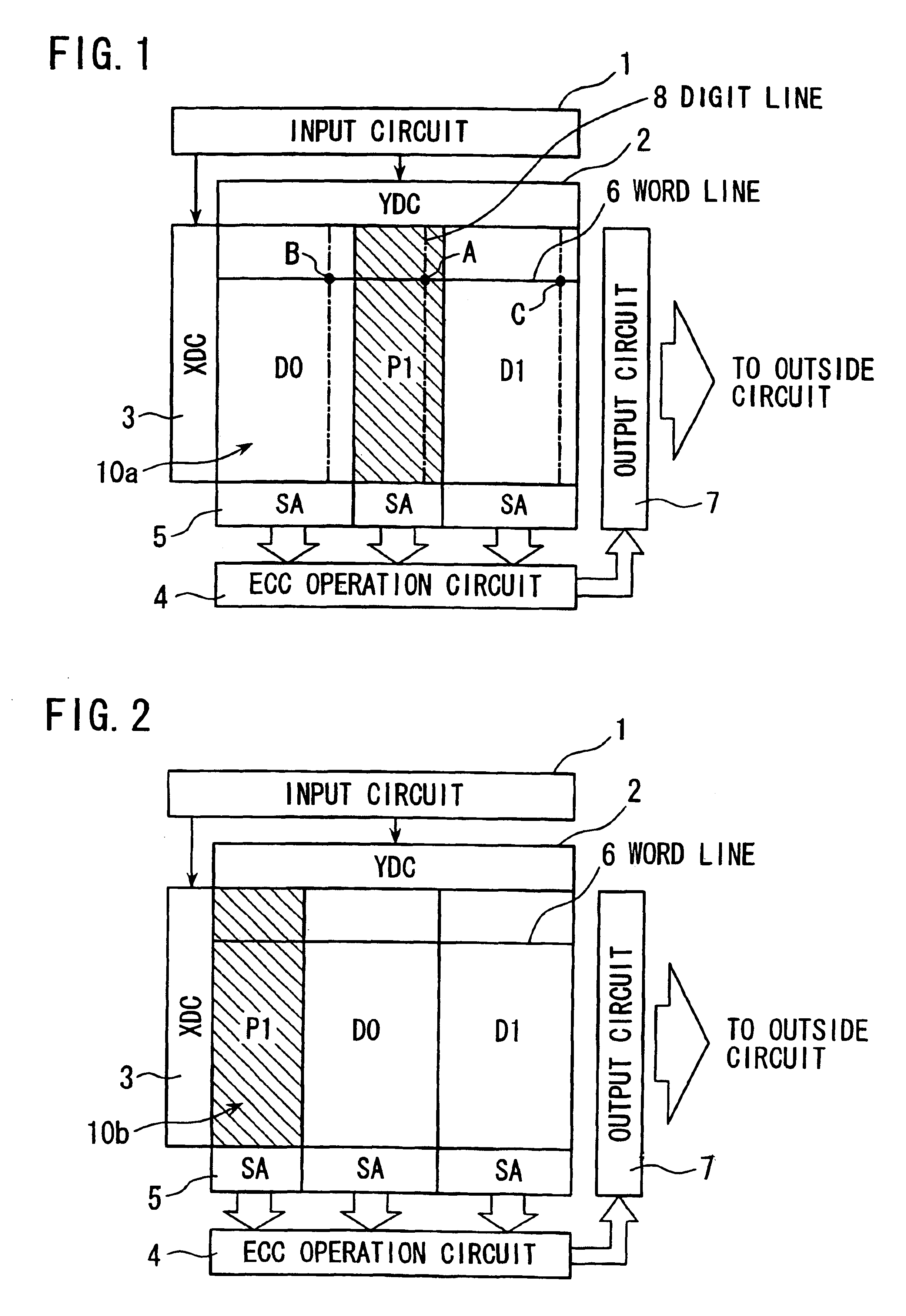

A semiconductor memory device having an error check and correction (ECC) type error recovery circuit in which disposition of ECC cells is improved. The memory device comprises: a memory cell array including a plurality of normal cell array portions and an ECC cell array portion; an X decoder for selecting one of word lines in the memory cell array, the word lines extending from the X decoder to the memory cell array; an ECC operation circuit for performing error check and correction based on cell data read out from a selected word line, the cell data including data from normal cells and ECC cells of the selected word line. The ECC memory cell array portion is disposed at a location other than the far end of the word lines from the X decoder, that is, the ECC cell array portion is disposed at a location in which read out speed of data from ECC cell or cells does not become the worst speed in the memory device. Therefore, the worst data read out speed can be measured from outside.

Owner:RENESAS ELECTRONICS CORP

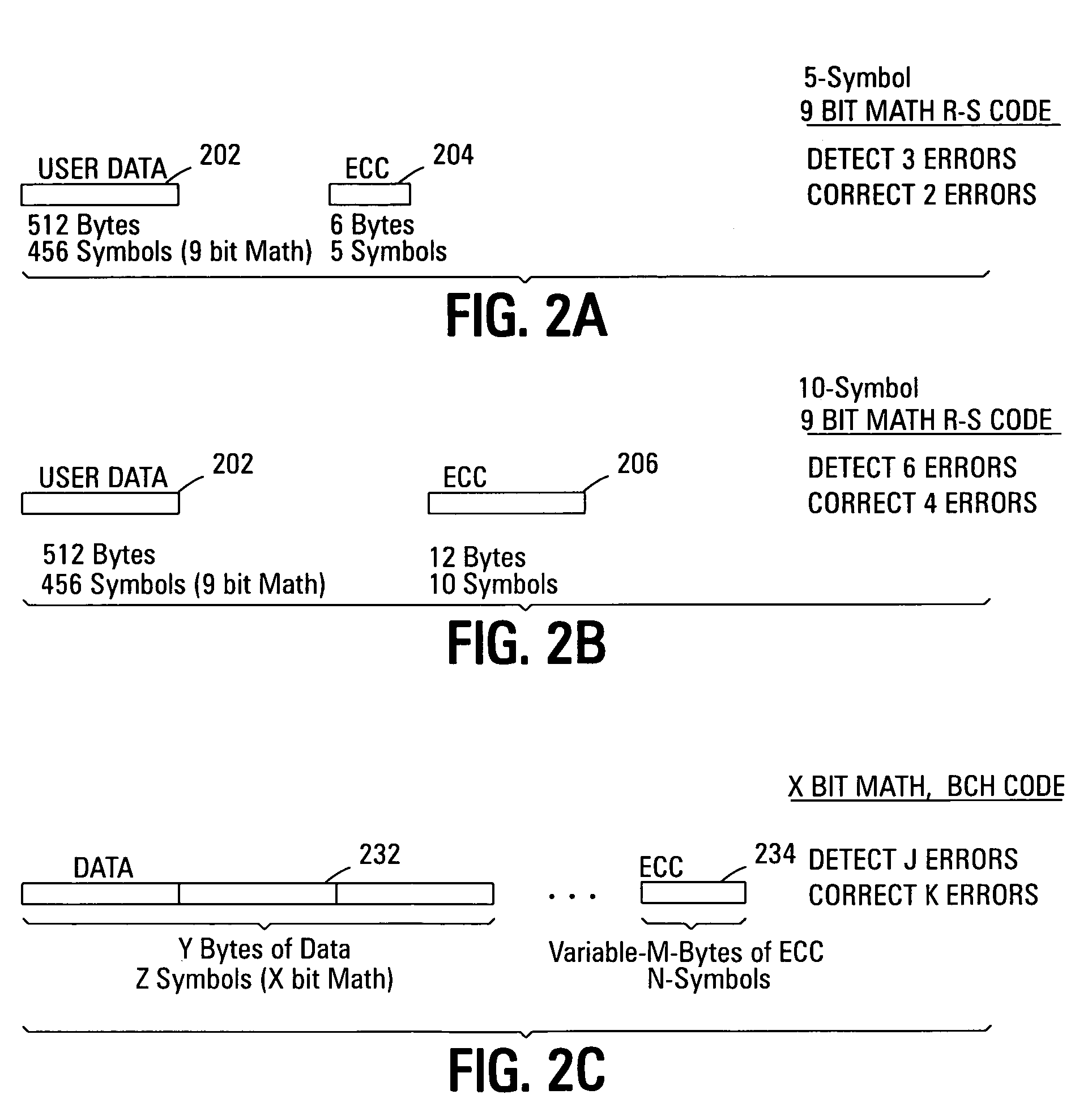

Variable strength ECC

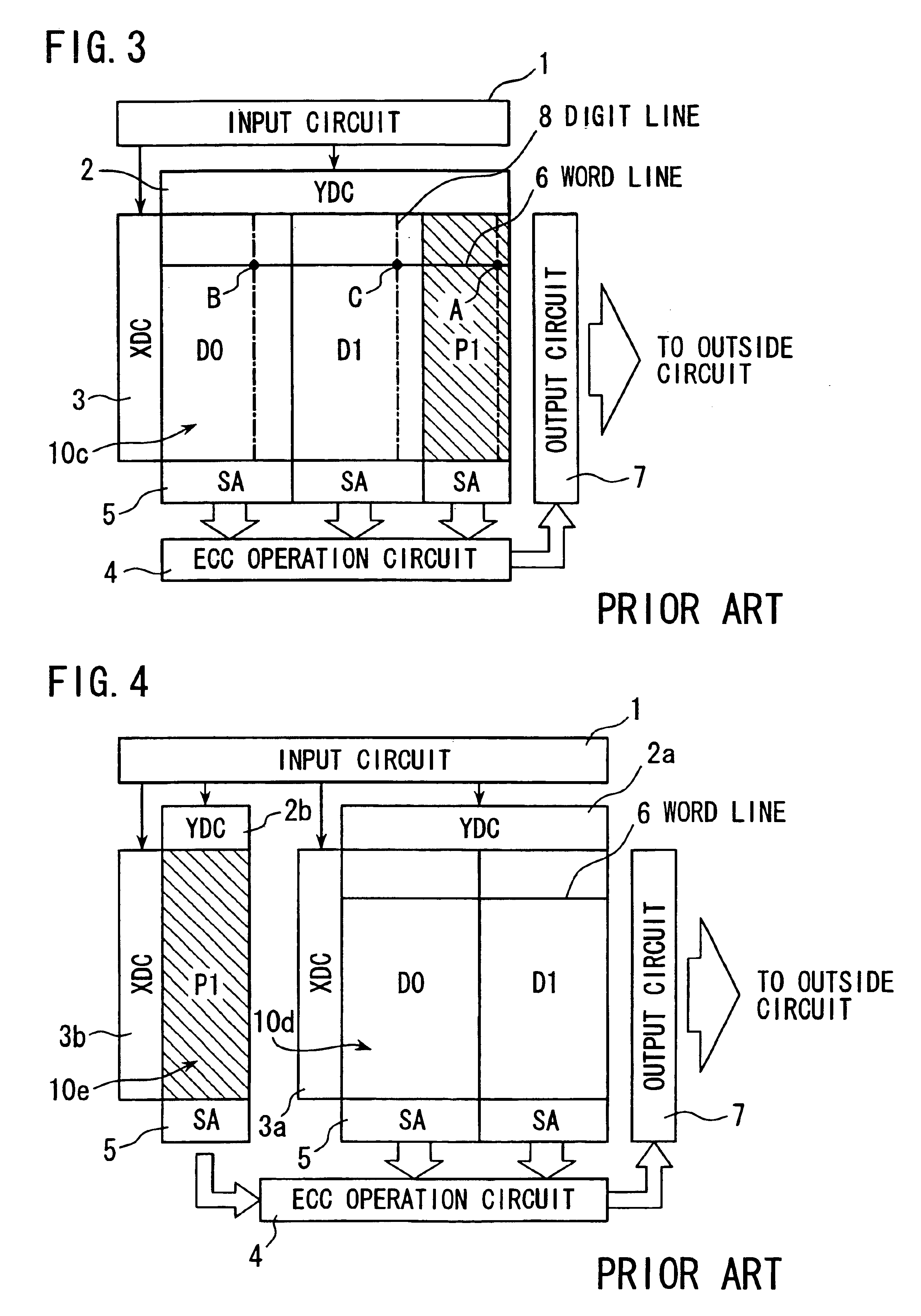

Memory devices, circuitry, and data methods are described that facilitate the detection and correction of data in memory controllers, memory systems, and / or non-volatile memory devices by allowing the number of ECC check bytes being utilized to be varied to increase or decrease the ECC check depth. This allows the depth of the ECC coverage (the overall number of bit errors detectable and / or correctable in each sector by the stored ECC check bytes) to be selected based on the application, the amount of available data storage for ECC check bytes in the overhead / spare area associated with the sector, the version of memory device or controller being utilized, or the number of errors being seen in the memory system, device, bank, erase block, or sector (the error incidence rate), while the base data size of the area (sector) covered by the ECC check bytes stays the same.

Owner:MICRON TECH INC

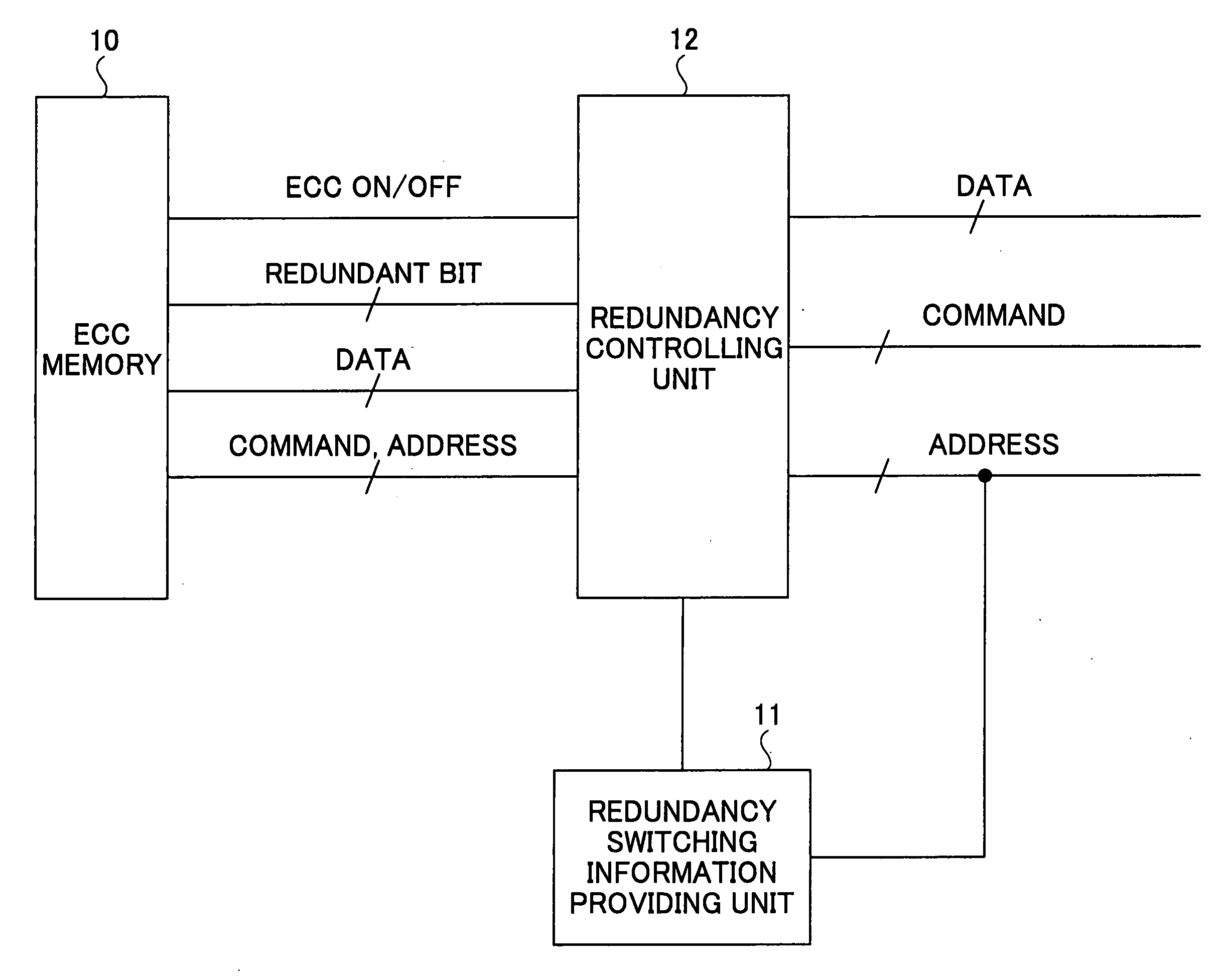

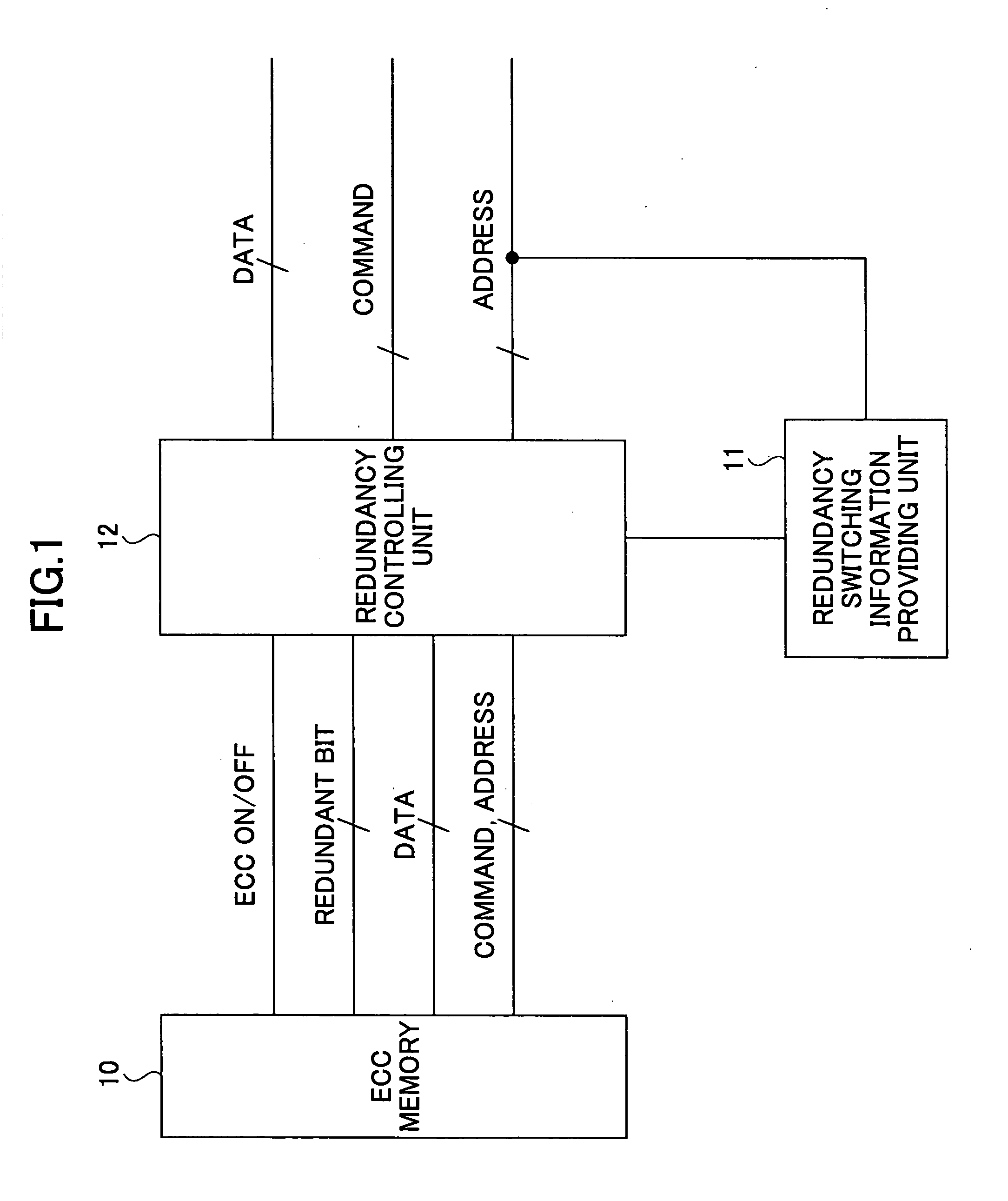

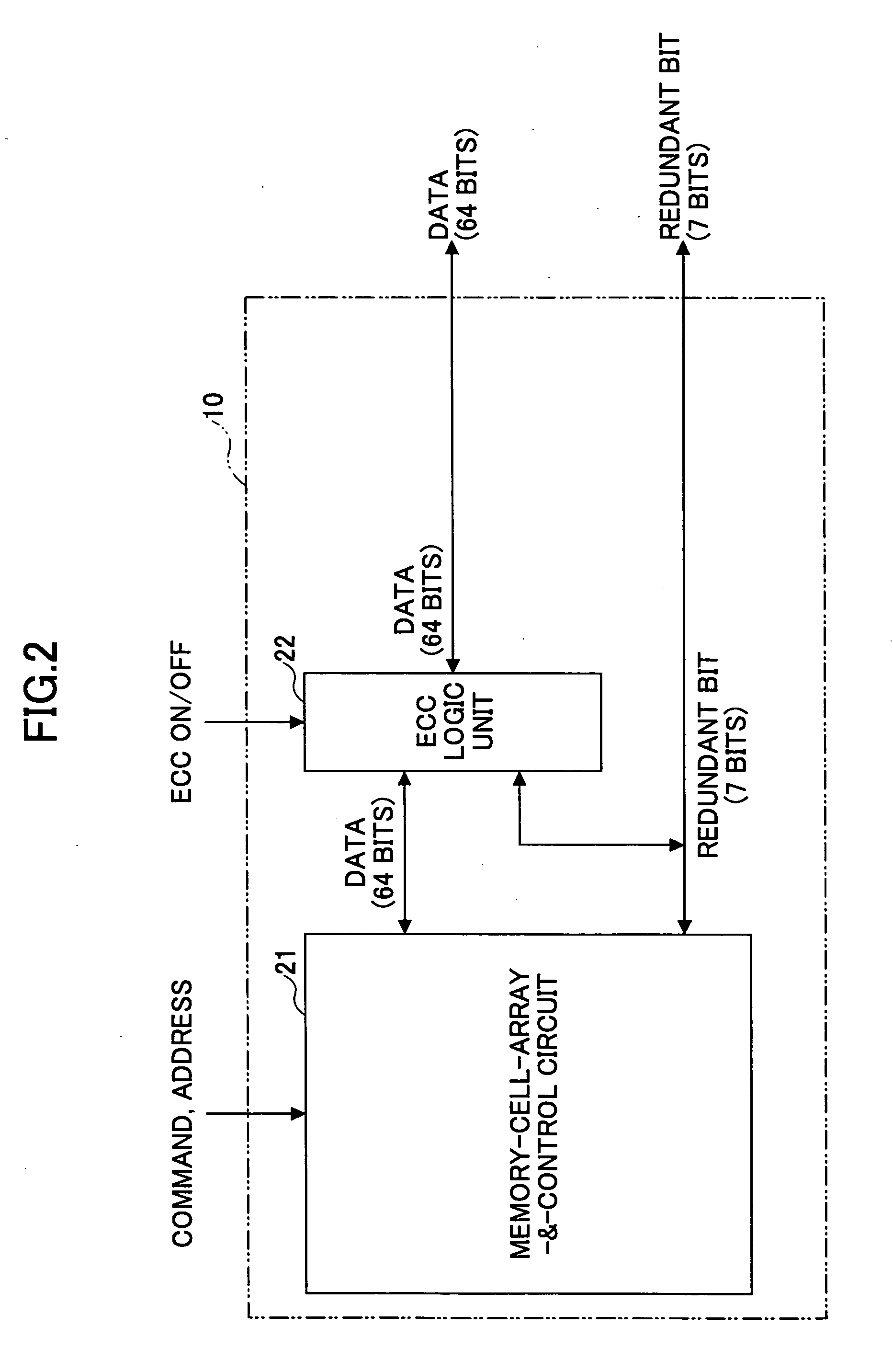

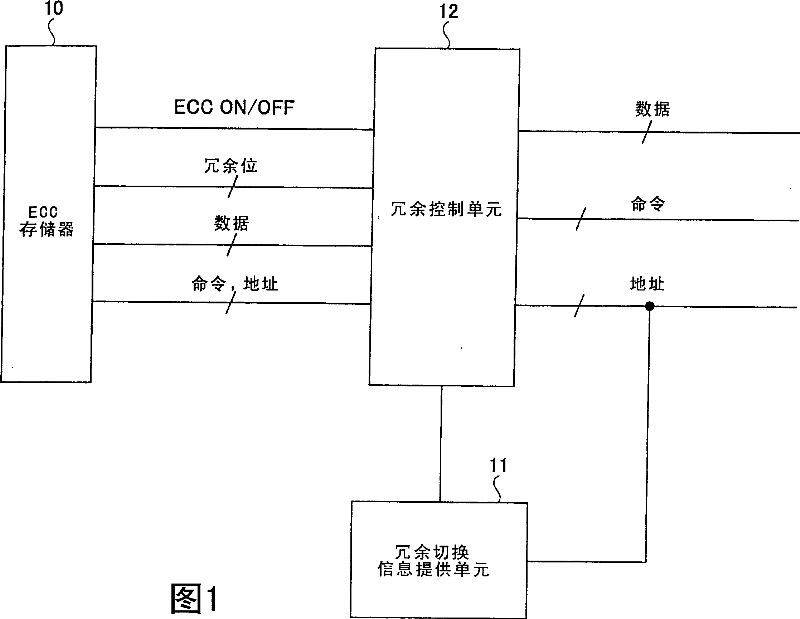

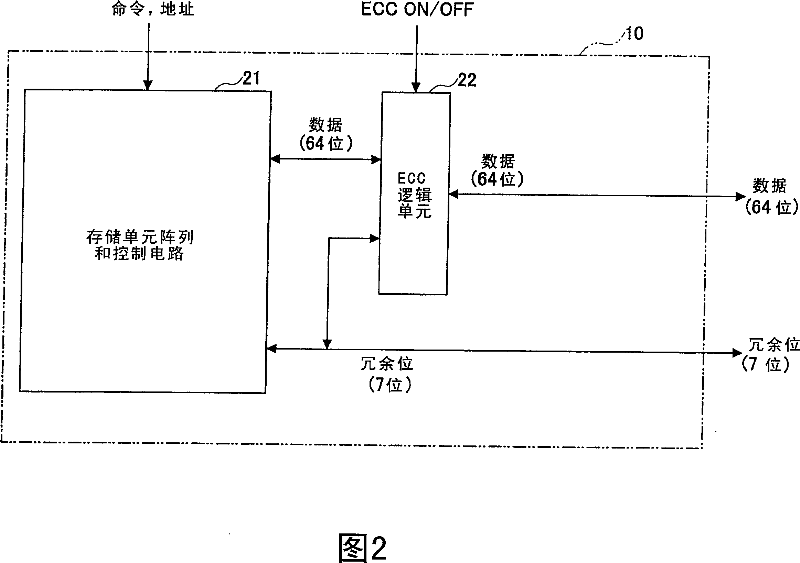

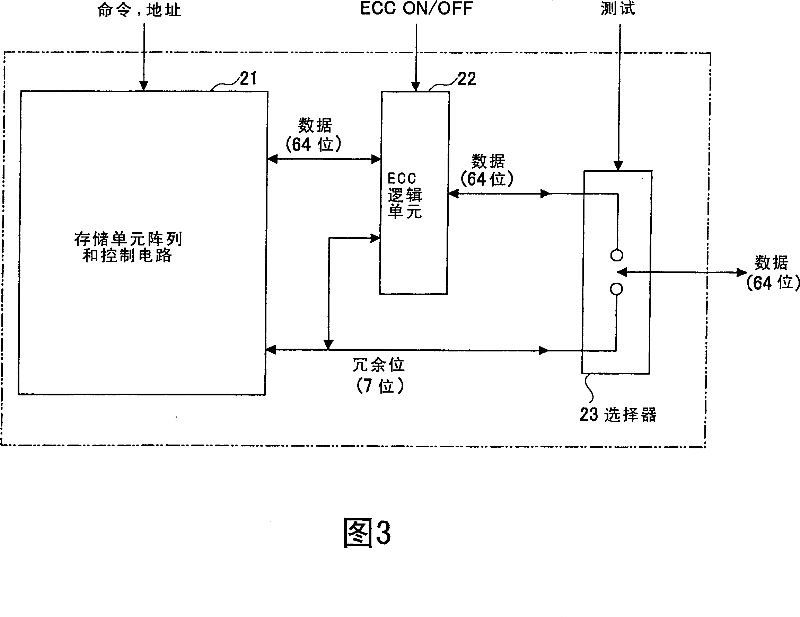

Redundancy-function-equipped semiconductor memory device made from ECC memory

InactiveUS20070255981A1Data recoveryMinimal modificationError detection/correctionStatic storageECC memorySemiconductor

A semiconductor memory device includes a memory configured to input / output first data and second data in parallel, the first data being all or part of a predetermined number of bits, and the second data being comprised of a number of bits necessary to correct error of the predetermined number of bits, a unit configured to supply redundancy switching information in response to an address signal supplied to the memory, and a controlling unit situated between the memory and input / output nodes, having a first path that couples a given bit of the input / output nodes to a corresponding bit of the first data of the memory and a second path that couples the given bit of the input / output nodes to a predetermined bit of the second data of the memory, and configured to select and enable one of the first path and the second path in response to the redundancy switching information.

Owner:FUJITSU MICROELECTRONICS LTD

Redundancy-function-equipped semiconductor memory device made from ecc memory

InactiveCN101042938AThe error correction function hasError detection/correctionStatic storageECC memorySemiconductor

A semiconductor memory device includes a memory configured to input / output first data and second data in parallel, the first data being all or part of a predetermined number of bits, and the second data being comprised of a number of bits necessary to correct error of the predetermined number of bits, a unit configured to supply redundancy switching information in response to an address signal supplied to the memory, and a controlling unit situated between the memory and input / output nodes, having a first path that couples a given bit of the input / output nodes to a corresponding bit of the first data of the memory and a second path that couples the given bit of the input / output nodes to a predetermined bit of the second data of the memory, and configured to select and enable one of the first path and the second path in response to the redundancy switching information.

Owner:FUJITSU MICROELECTRONICS LTD

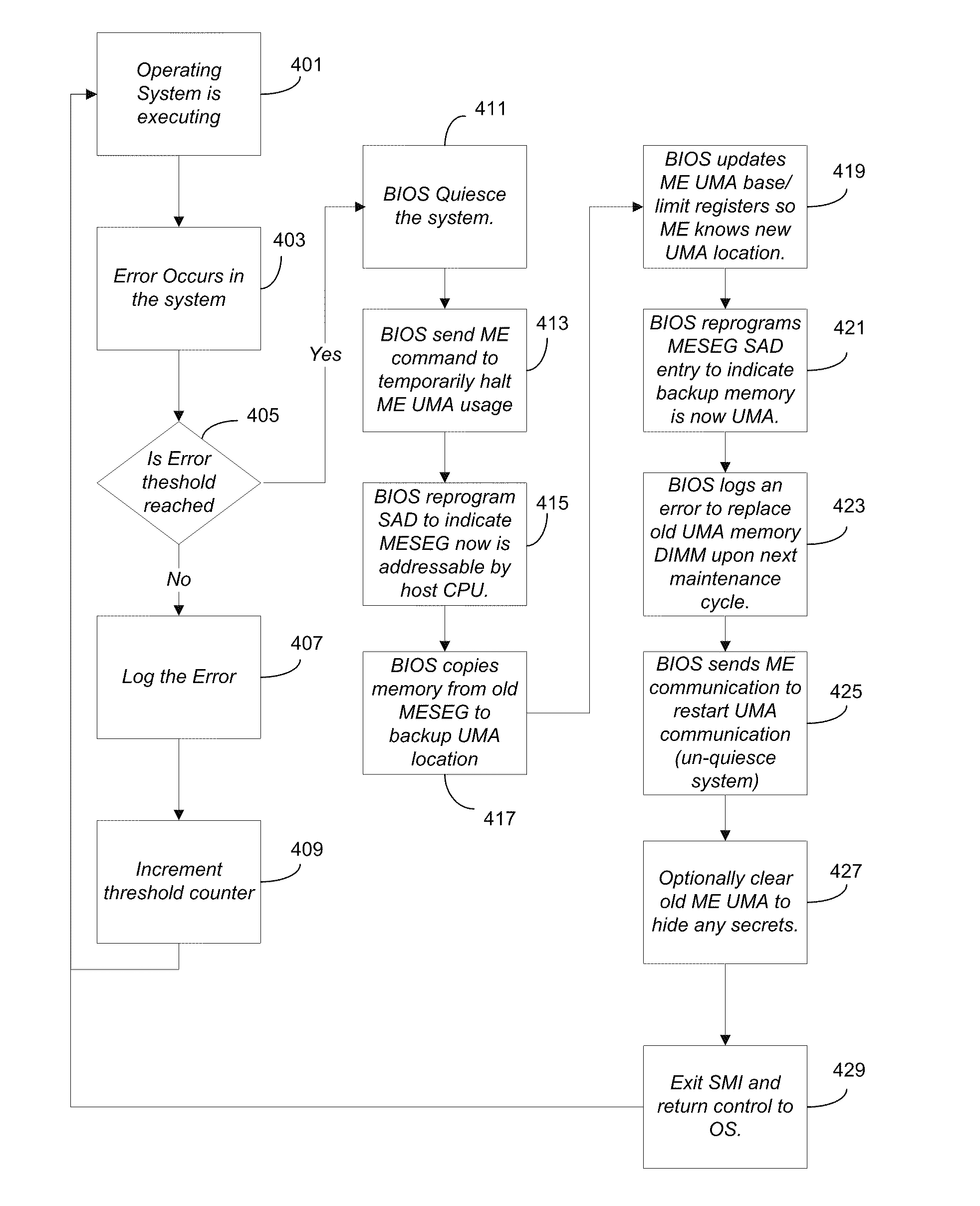

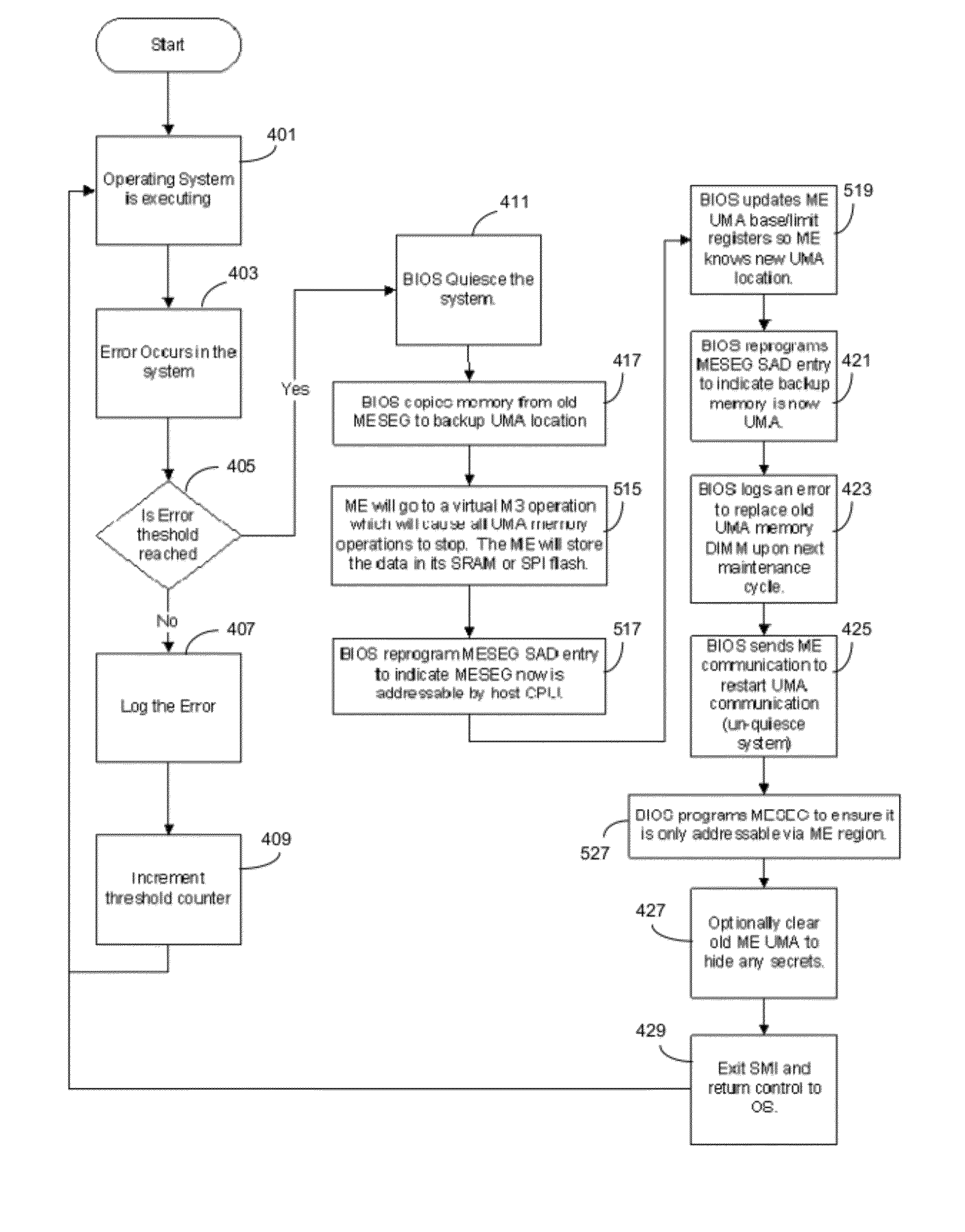

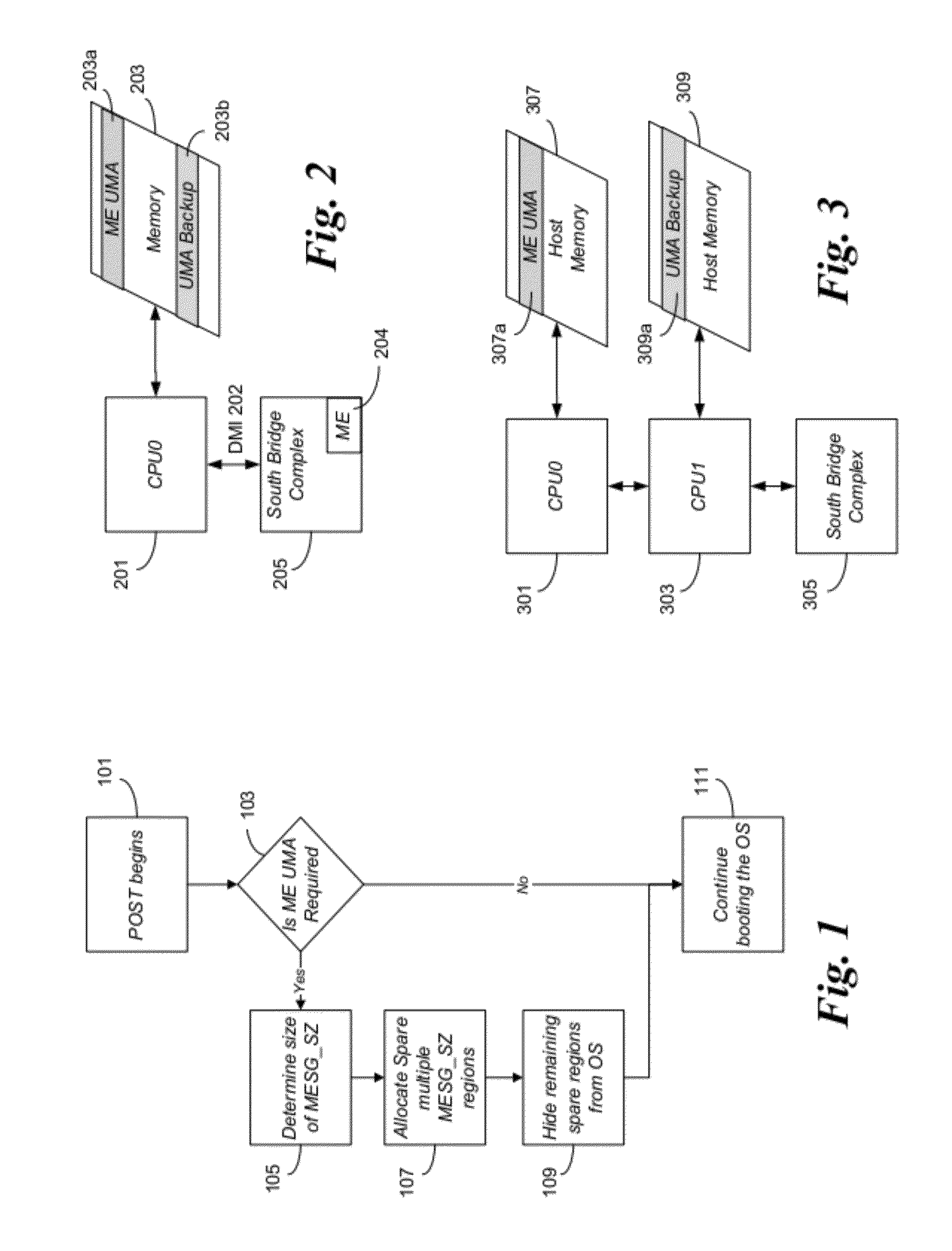

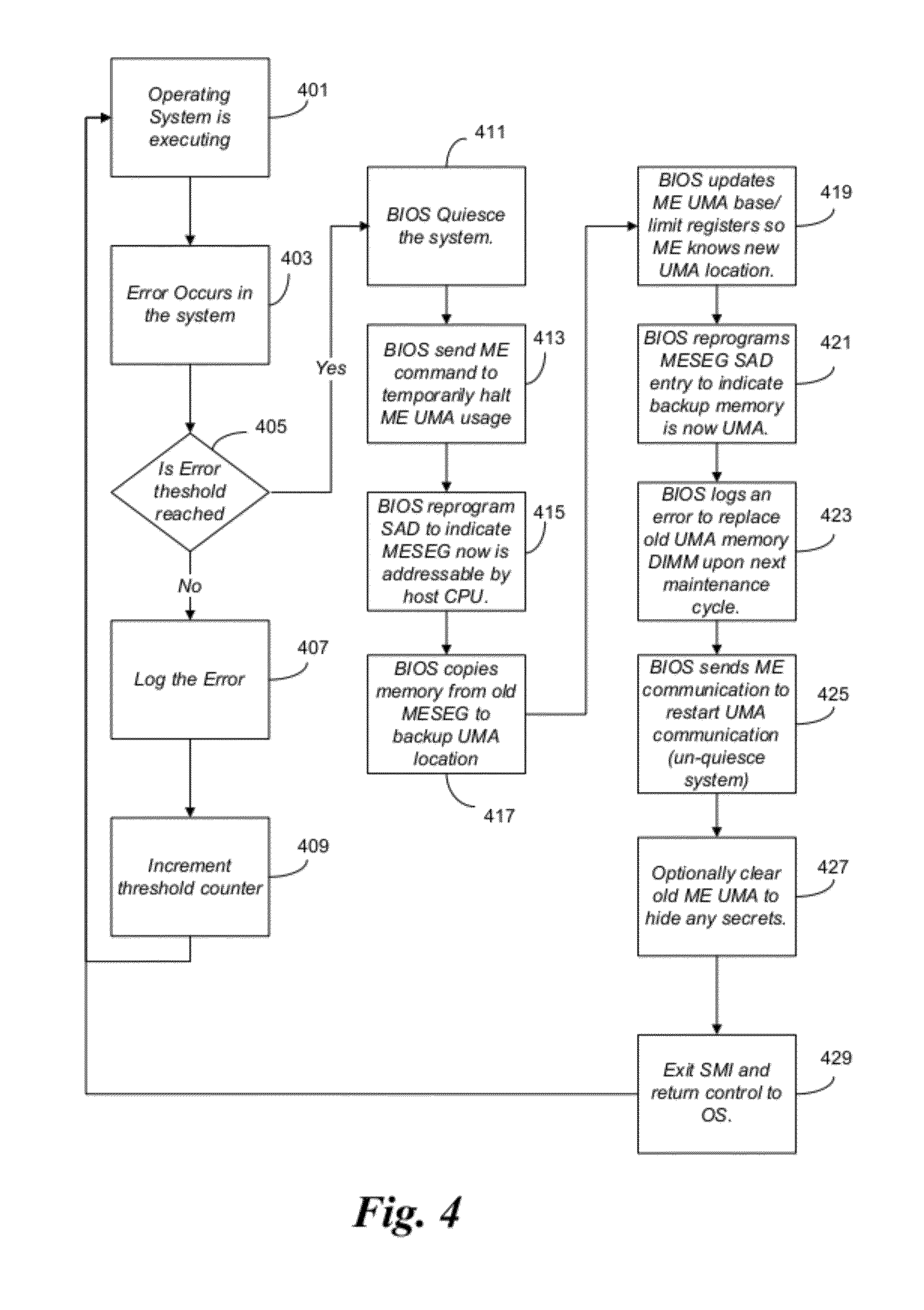

System ras protection for uma style memory

InactiveUS20110161726A1Digital computer detailsNon-redundant fault processingSystem recoveryECC memory

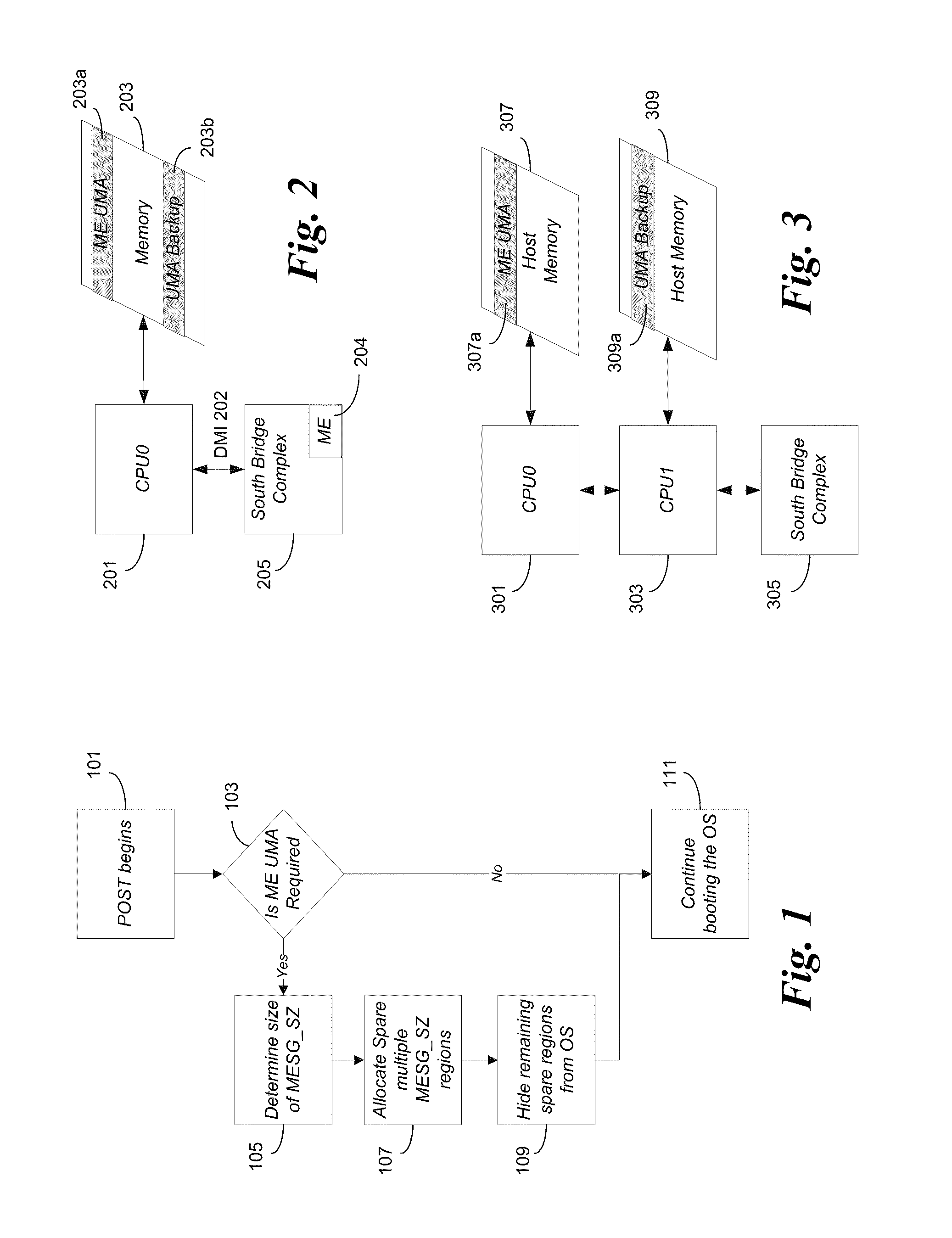

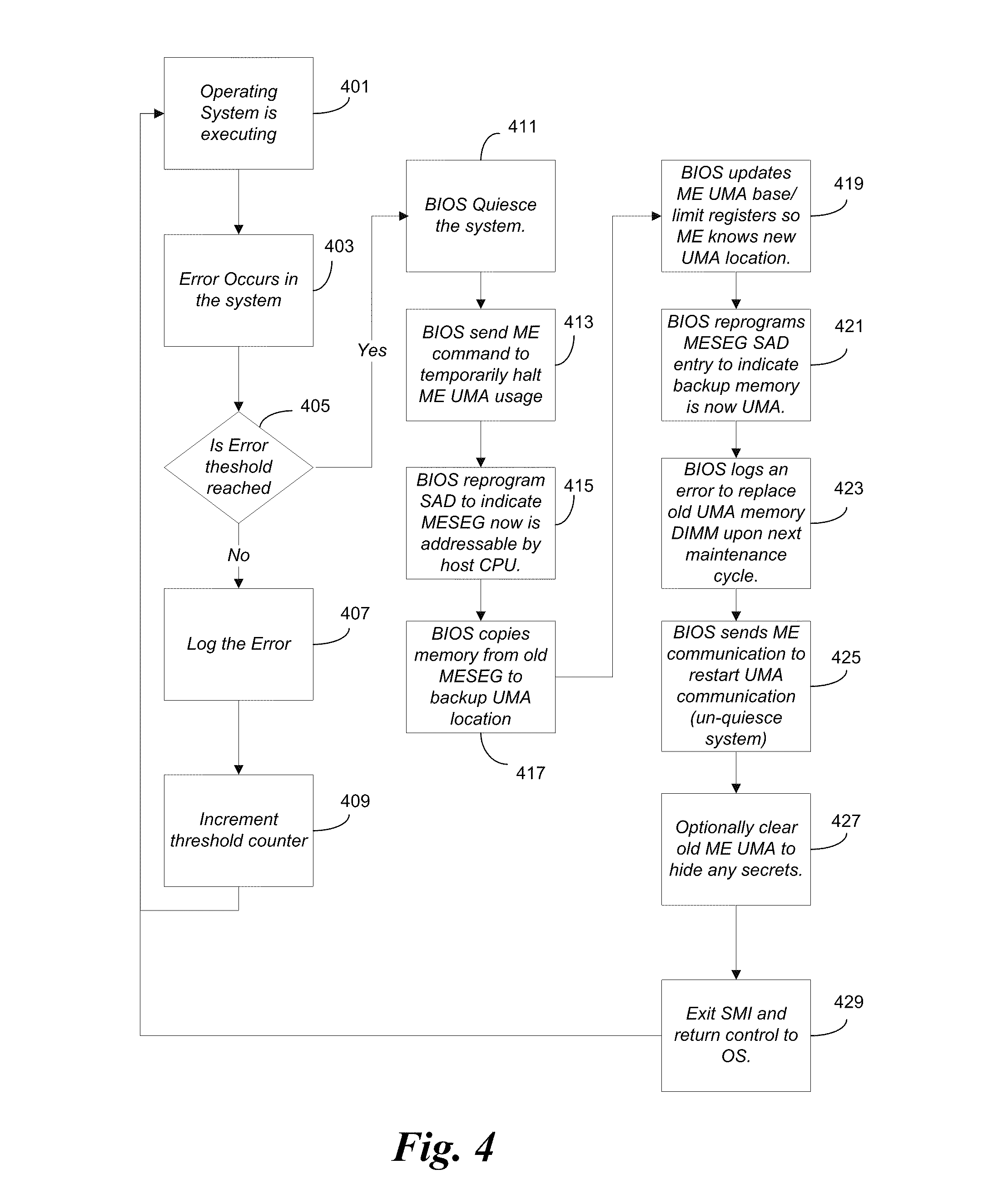

In some embodiments, the invention involves a system and method relating to system recovery in a fault resilient manner by isolating errors associated with the management engine (ME) UMA memory. BIOS logs errors occurring on memory within the system. The ME UMA is invisible to the host OS, so the OS will not be notified about the errors occurring in the ME UMA range. When an error threshold has been reached for a memory unit in which ME UMA resides, ME UMA data is migrated to a previously reserved backup region of memory and the ME is notified of the new ME UMA location. The faulty memory is flagged for replacement at a next maintenance cycle. Embodiments may be applied to workstations that utilize ECC memory protection which utilize AMT (Active Management Technology) and ME UMA. Other embodiments are described and claimed.

Owner:INTEL CORP

Low power cost-effective ECC memory system and method

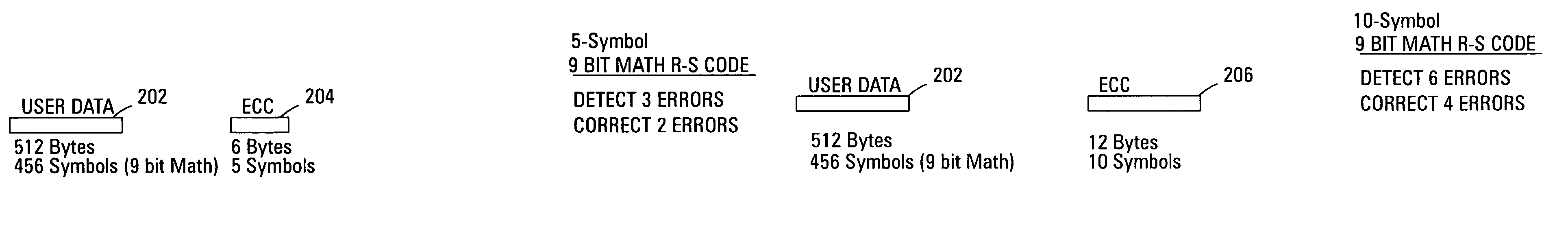

ActiveUS20060218469A1Reduce overheadData representation error detection/correctionMemory loss protectionError checkingMemory controller

Owner:MICRON TECH INC

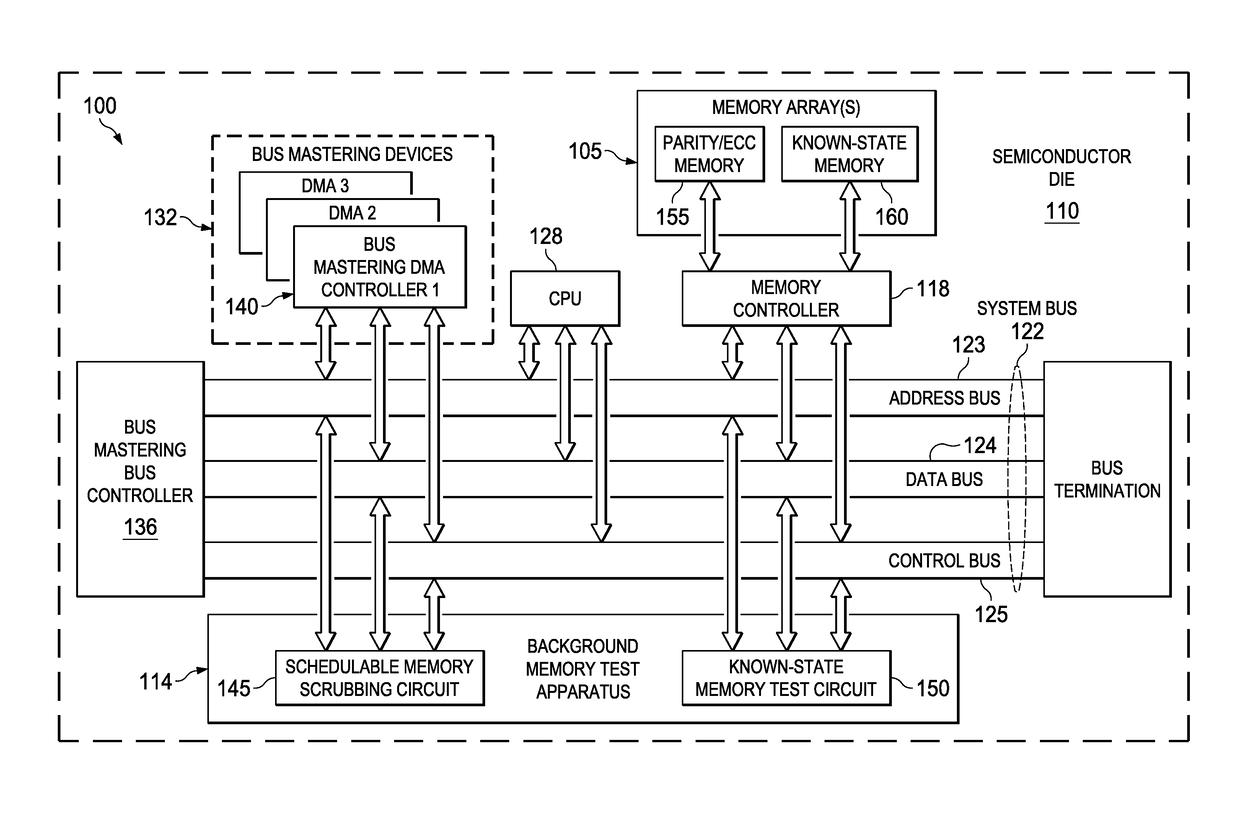

Background memory test apparatus and methods

ActiveUS20170133106A1Increase probabilityImpact system throughputCode conversionStatic storageError processingMemory scrubbing

A schedulable memory scrubbing circuit and / or a known-state memory test circuit (collectively, background memory test apparatus (“BGMTA”)) are located on-chip with an integrated computing system. The BGMTA operates in parallel with a system CPU but shares a system bus with the CPU. The BGMTA sequentially reads one word at a time from a block of memory to be tested during system bus idle cycles. The schedulable memory scrubbing circuit embodiment tests on-chip parity / ECC memory arrays using memory controller-implemented parity or ECC error detection to trigger error handling interrupts. The known-state memory test circuit embodiment performs CRC calculations on known-state memory arrays as each data word is read sequentially. A final resulting CRC calculation value is compared to a known CRC value for the block, sometimes referred to as a “golden CRC.” If the two CRC values differ, a CRC error interrupt is triggered for servicing by the CPU.

Owner:TEXAS INSTR INC

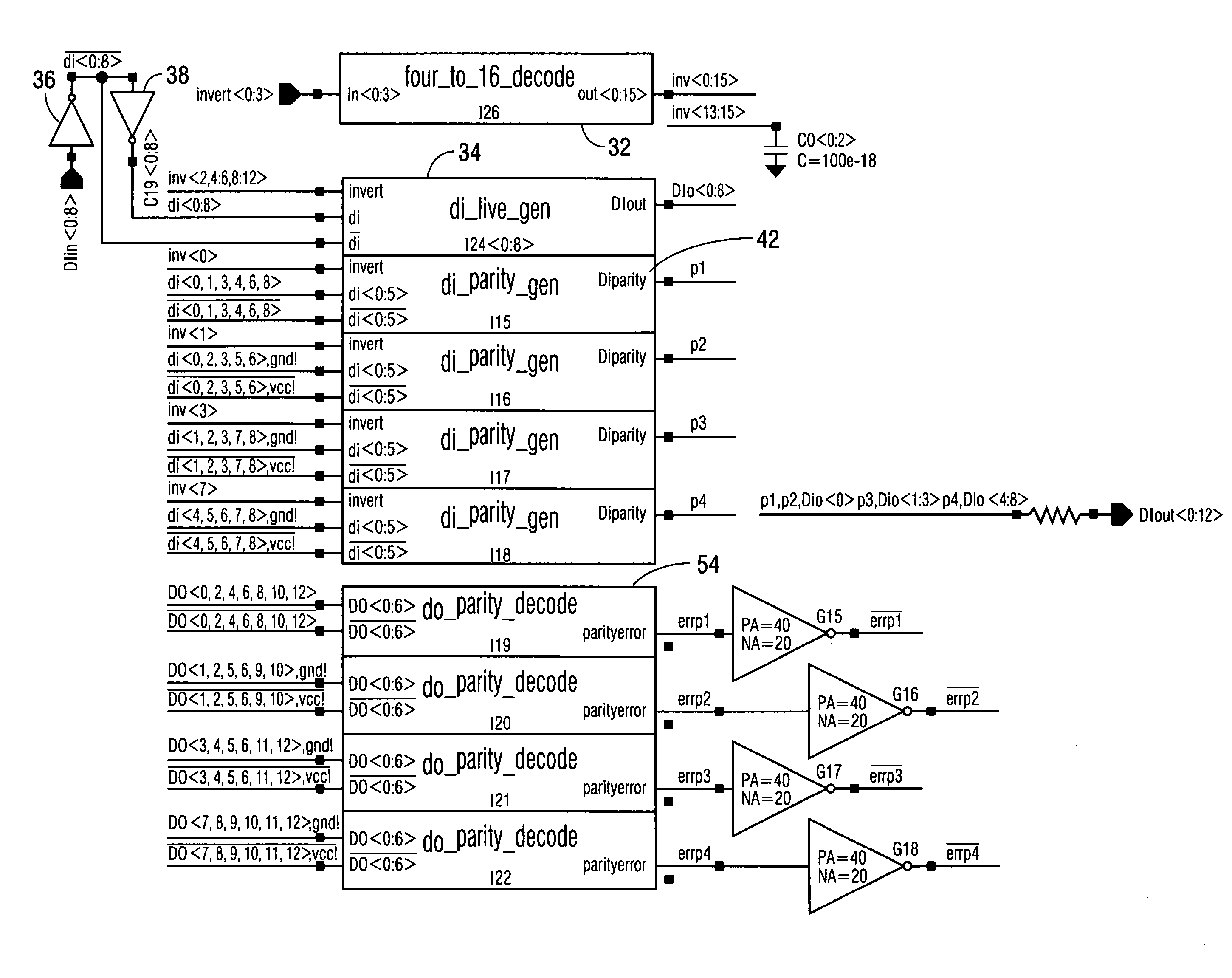

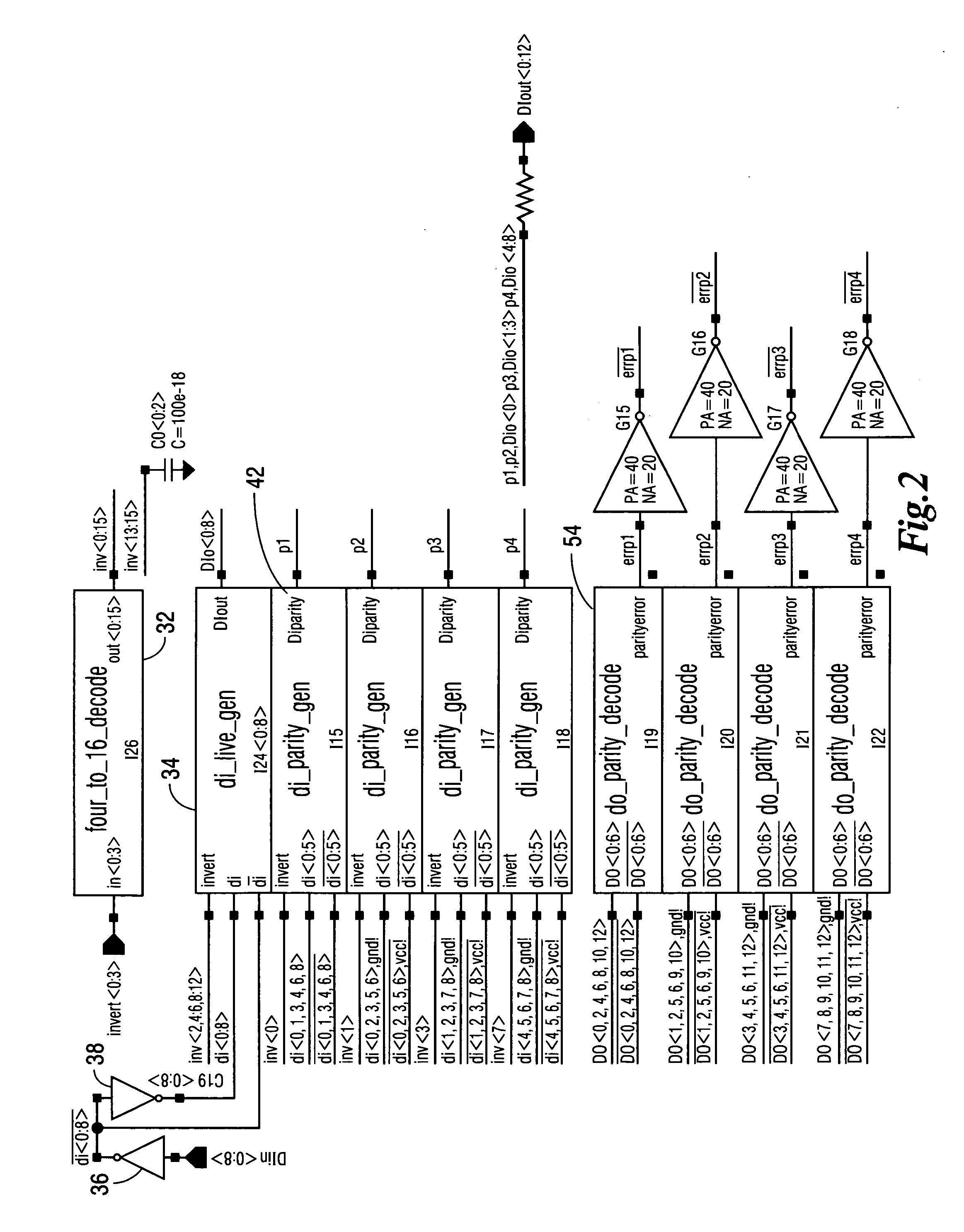

Test mode to force generation of all possible correction codes in an ECC memory

The present disclosure enables individual bits of a data signal to be flipped (their state changed from logic one to logic zero or vice versa) to mimic an error. By flipping various bits or combinations of bits, various predetermined errors can be forced. By measuring the time delay between when uncorrected data is output from the memory device and when corrected data is output, the time the error correction circuitry takes to correct each of the forced errors can be measured and the part characterized according to the various measurements. Because of the rules governing abstracts, this abstract should not be used to construe the claims.

Owner:MICRON TECH INC

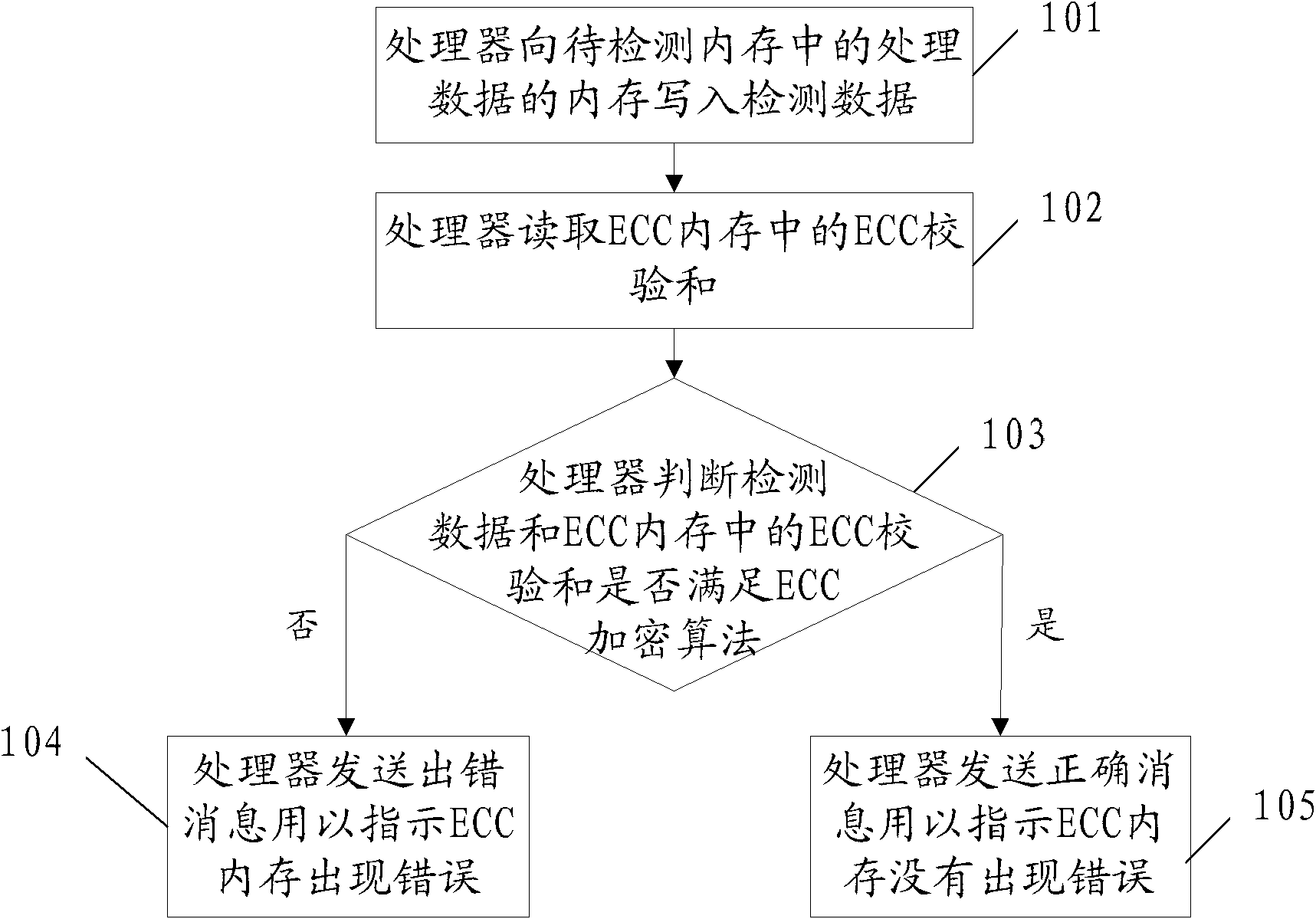

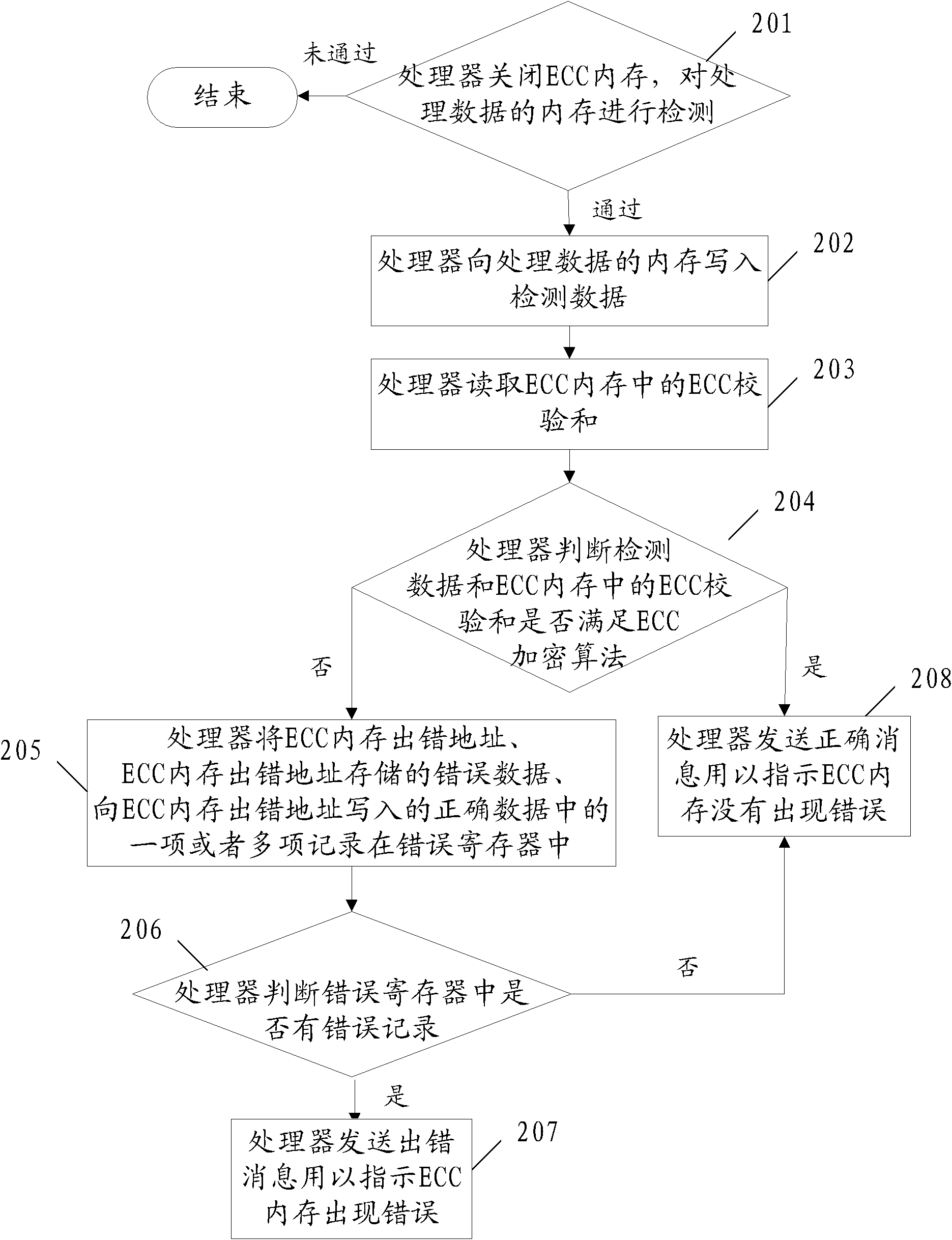

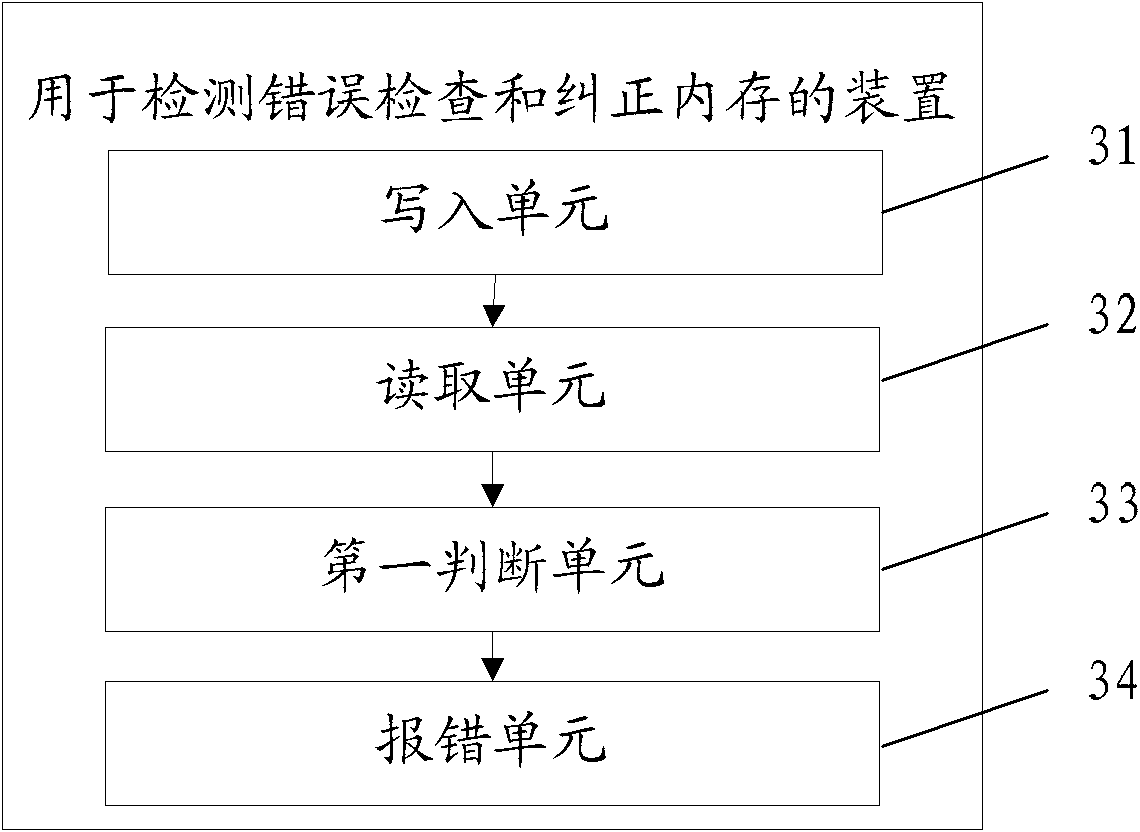

Method and device for detecting error check and correcting memory

InactiveCN102135925ARealize detectionBugchecking implementationRedundant data error correctionEncryptionECC memory

The embodiment of the invention discloses a method and a device for detecting error check and correcting memory, which relate to the technology of memory and can detect whether the ECC (Error Correction Code) function in the memory is in failure. The method comprises the following steps: writing detection data to the memory of processing data; reading the error check and correcting the error check in the memory and corrected check sum; judging whether the relationship between the detected data with the error check and corrected check sum satisfies the error check and corrected encryption algorithm; and if the relationship between the detected data with the error check and corrected check sum does not satisfy the error check and the corrected encryption algorithm, sending an error message for indicating the error check and correcting the error in the memory. The method and the device are mainly applied to detecting an ECC memory.

Owner:XIAN RUIXIN TECH CO LTD

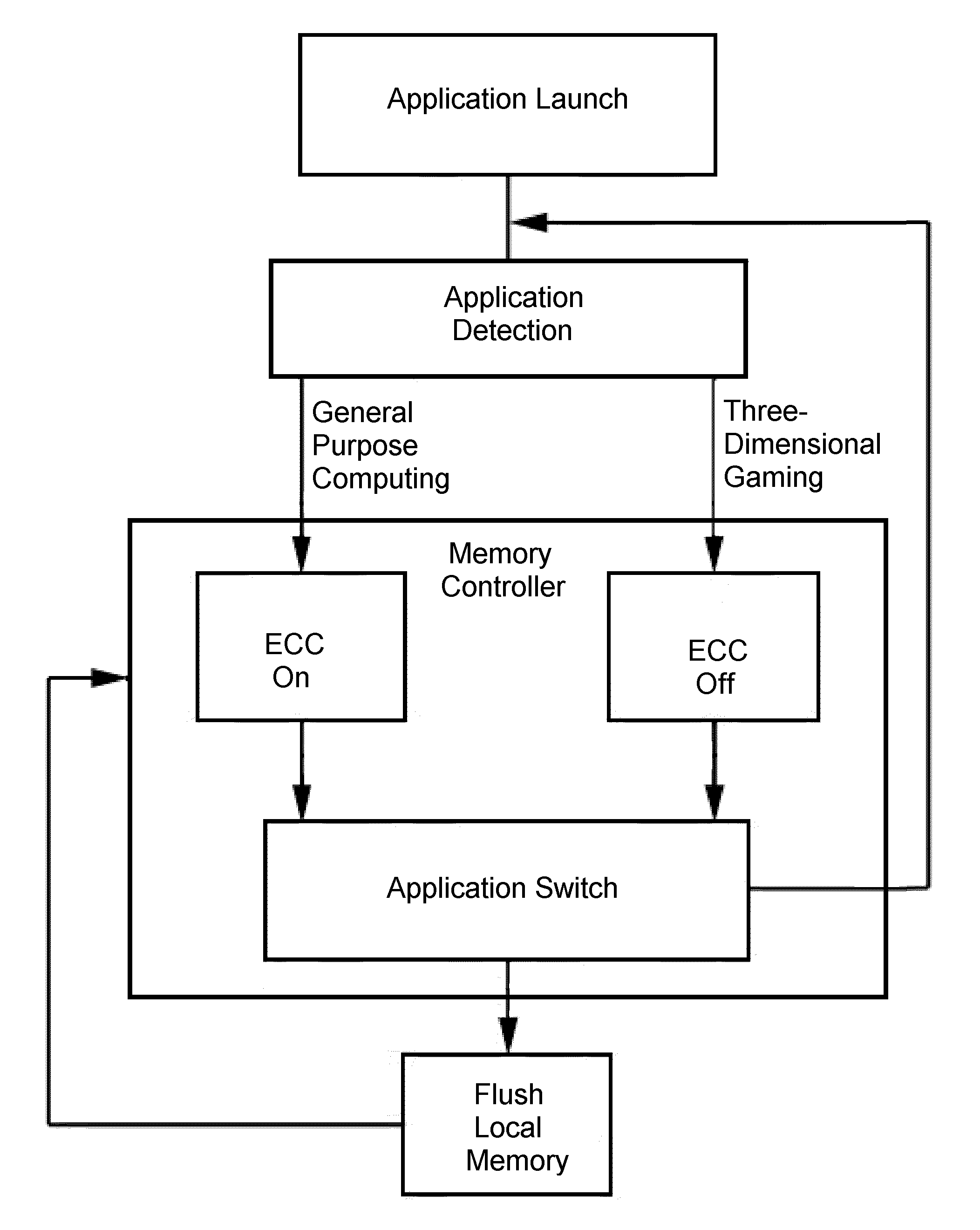

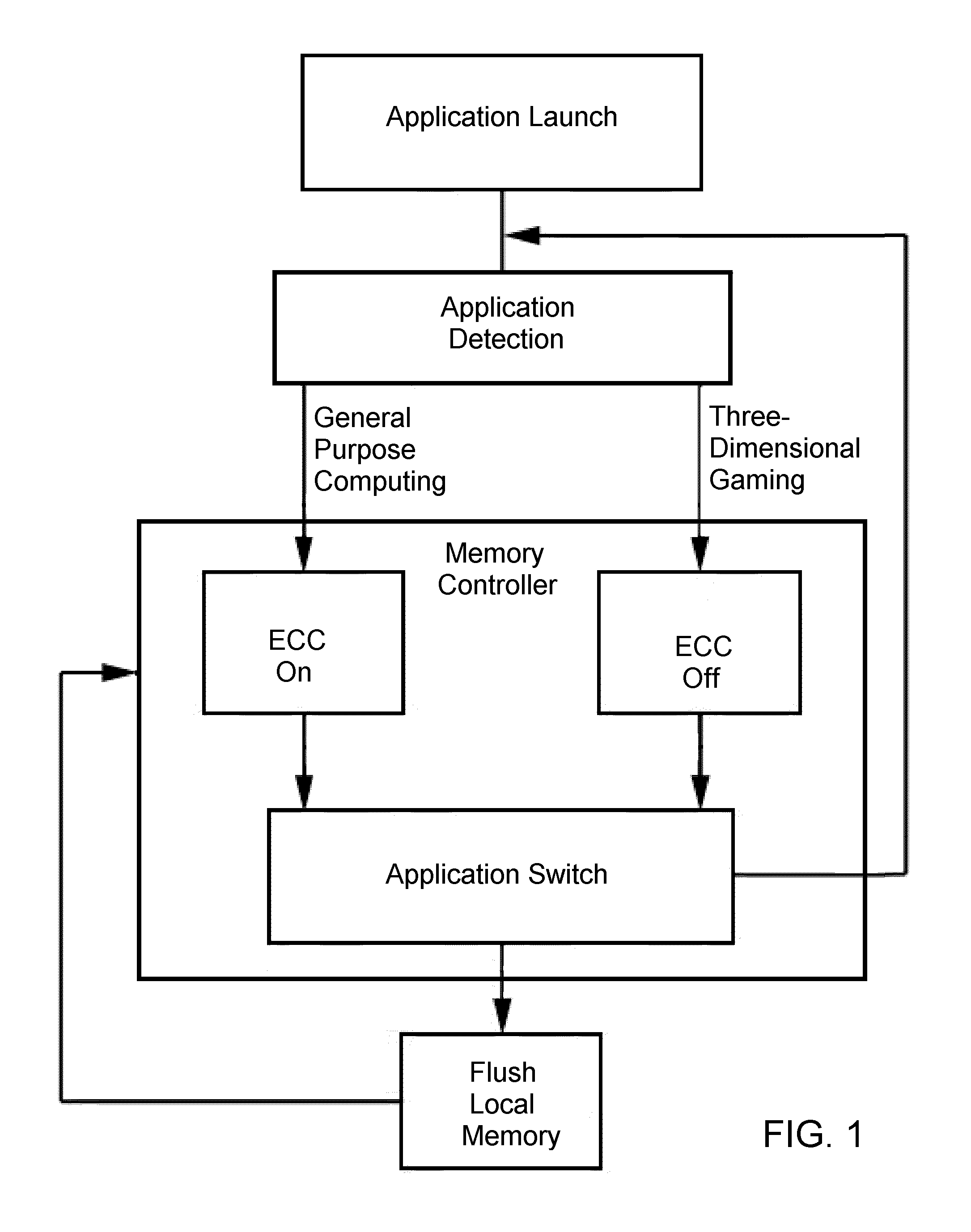

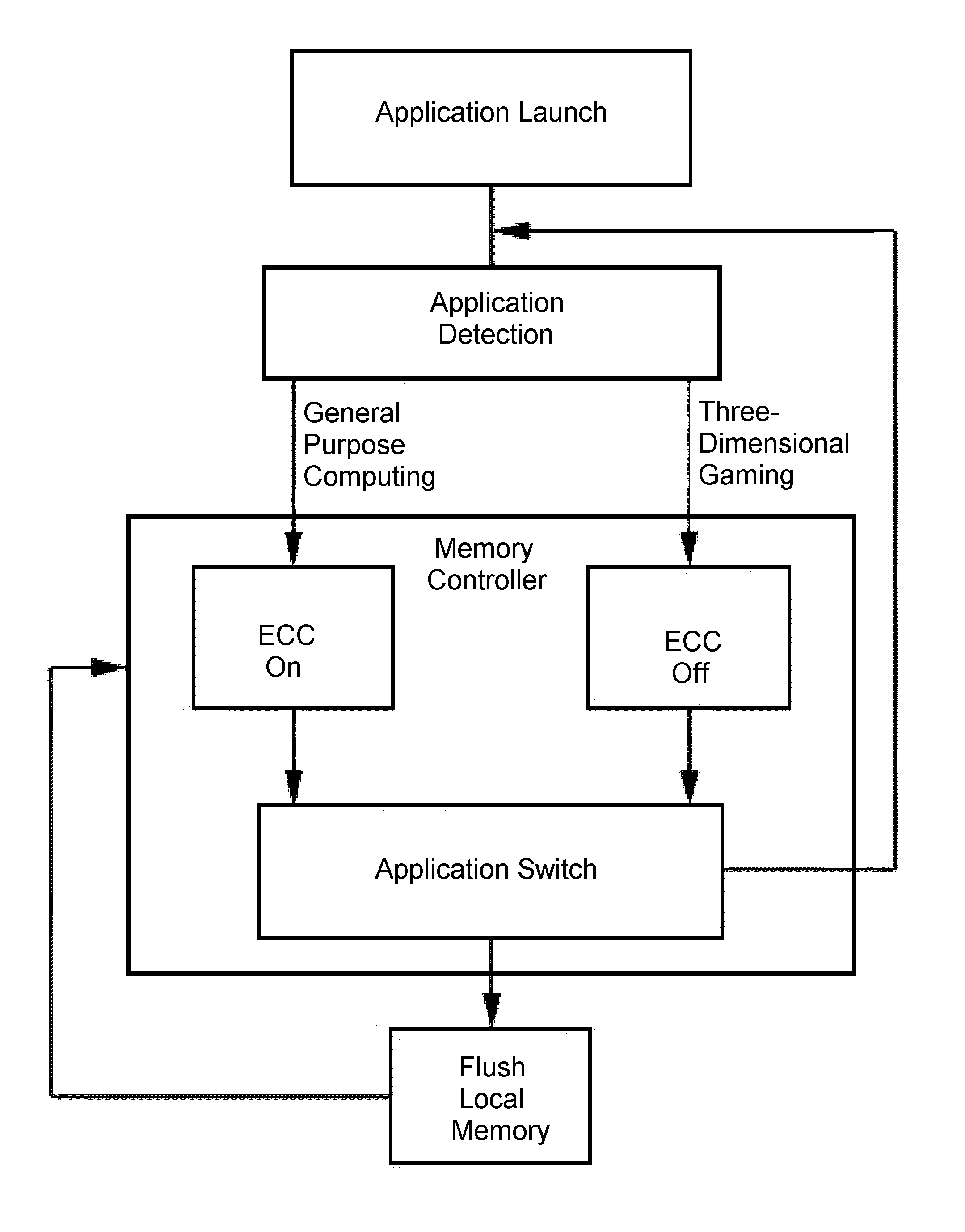

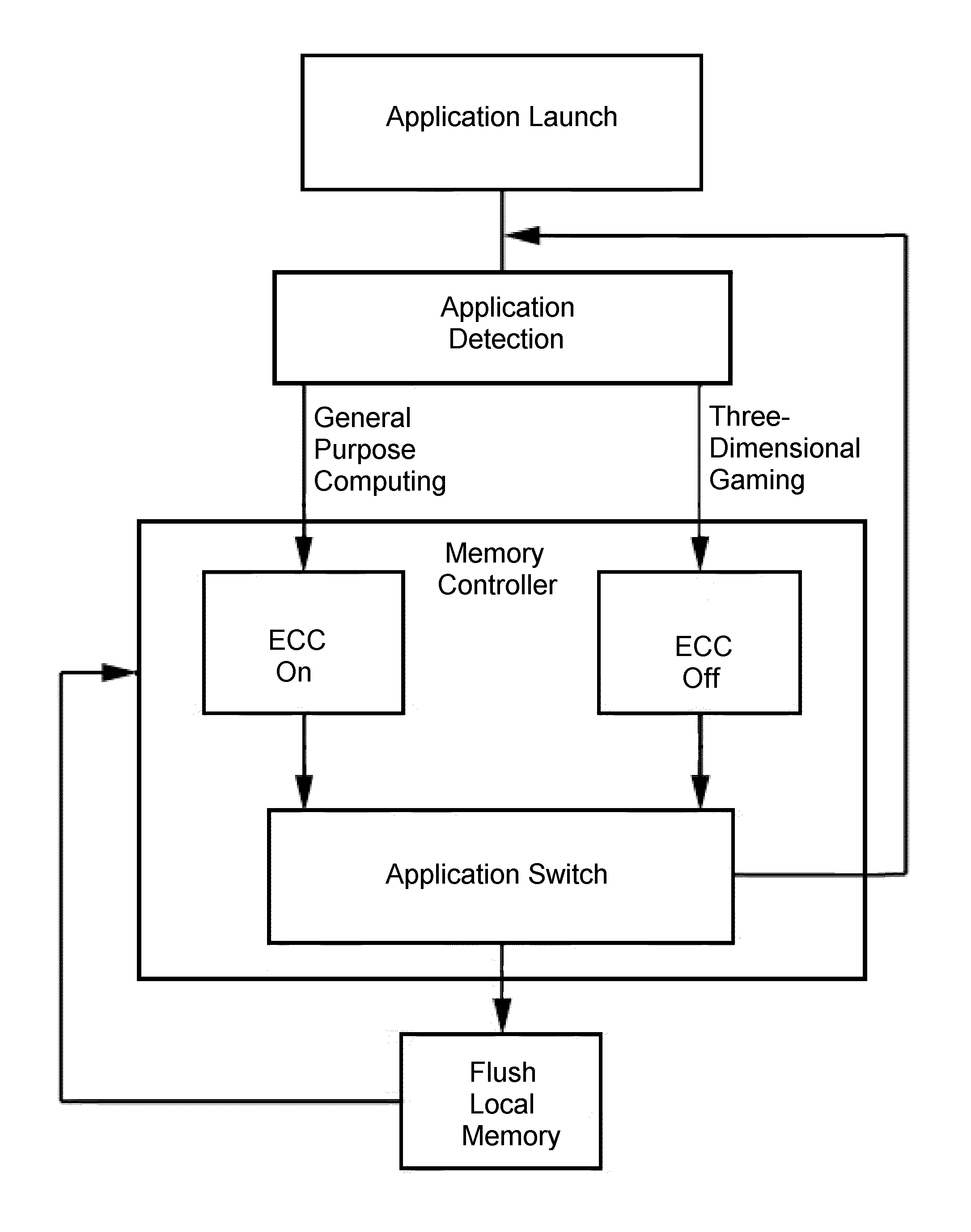

Computer system and processing method utilizing graphics processing unit with ecc and non-ecc memory switching capability

Computer systems and methods that utilize a GPU whose operation is able to switch between ECC and non-ECC memory operations on demand. The computer system includes a graphics processing unit and a memory controller and local memory that are functionally integrated with the graphics processing unit. The memory controller has at least two operating modes comprising a first memory access mode that uses error checking and correction when accessing the local memory, and a second memory access mode that does not use error checking and correction when accessing the local memory. The memory controller is further operable to switch the operation of the memory controller between the first and second memory access modes without rebooting the computer system.

Owner:KIOXIA CORP

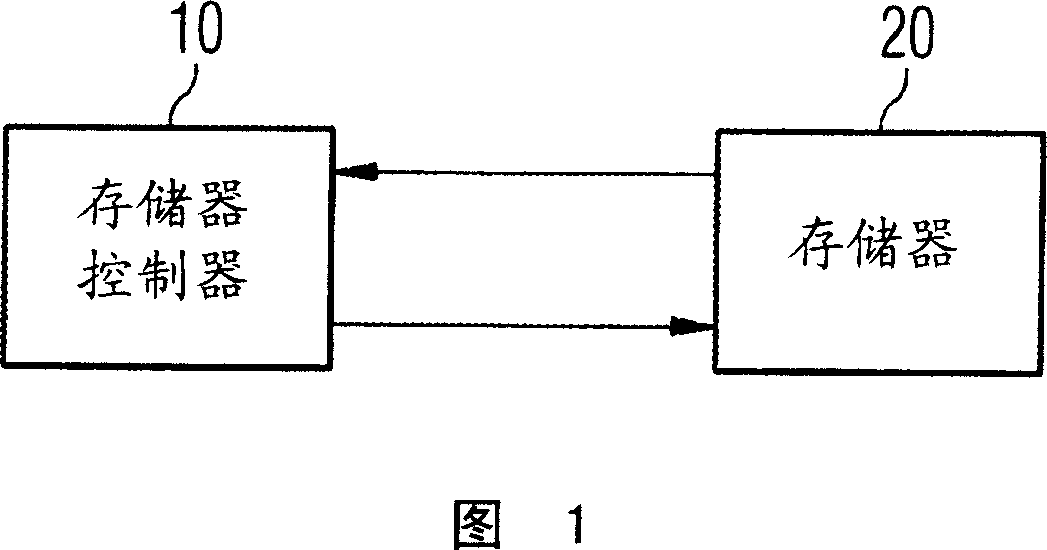

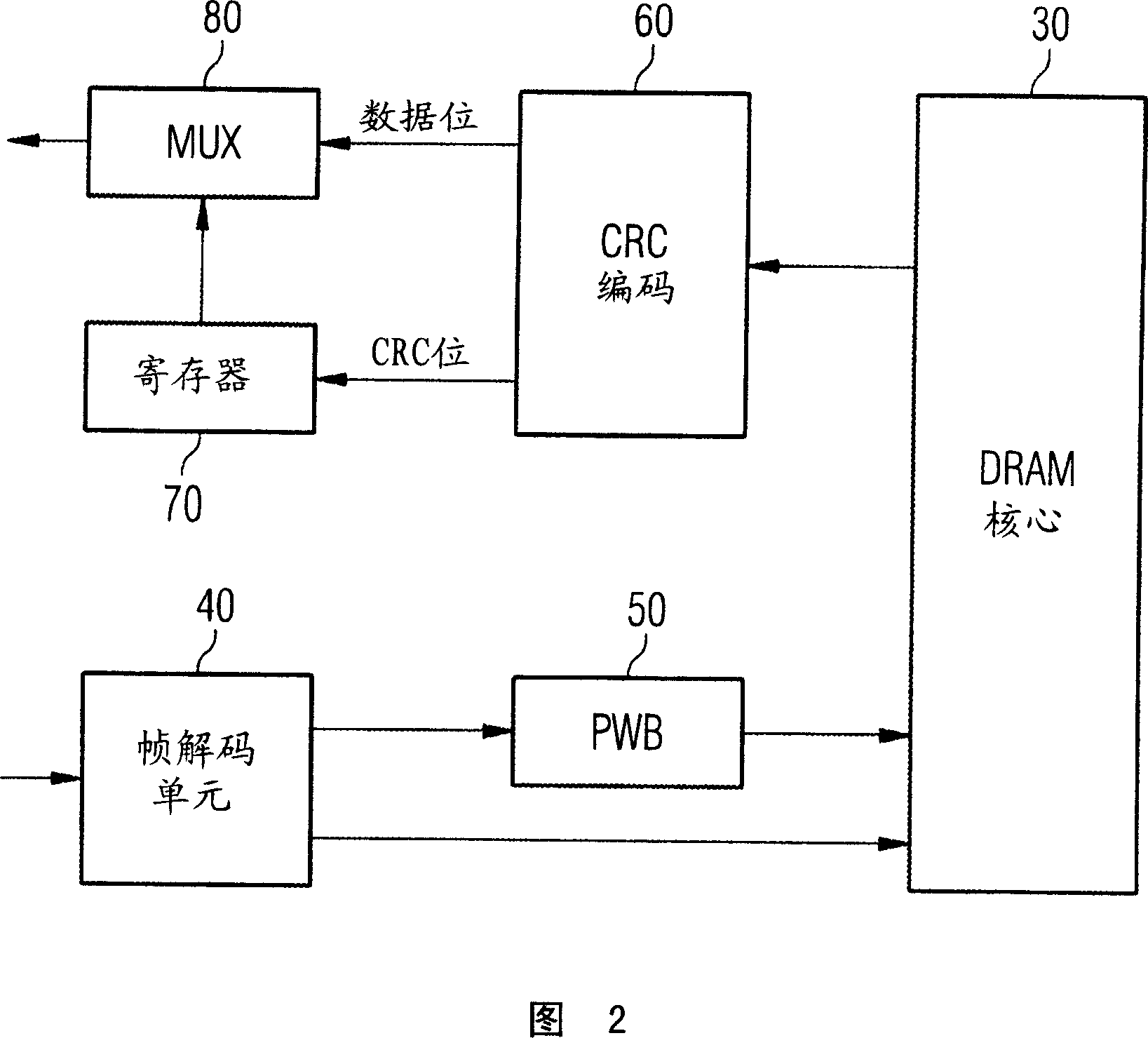

Data memory system and method for transferring data into a data memory

InactiveCN1924820AThe protocol format remains unchangedRedundant data error correctionData memoryData shipping

A method for transferring data into a data memory using a data protocol is presented. The data memory is an error correction code (ECC) memory or a non-error correction code memory. The data protocol has different frames. When data are written into an ECC memory, the protocol includes a data mask frame in which the data mask bits are replaced by ECC bits. The method is designed such that ECC and non-ECC DRAMs can be established with the same protocol and at least a similar architecture.

Owner:QIMONDA

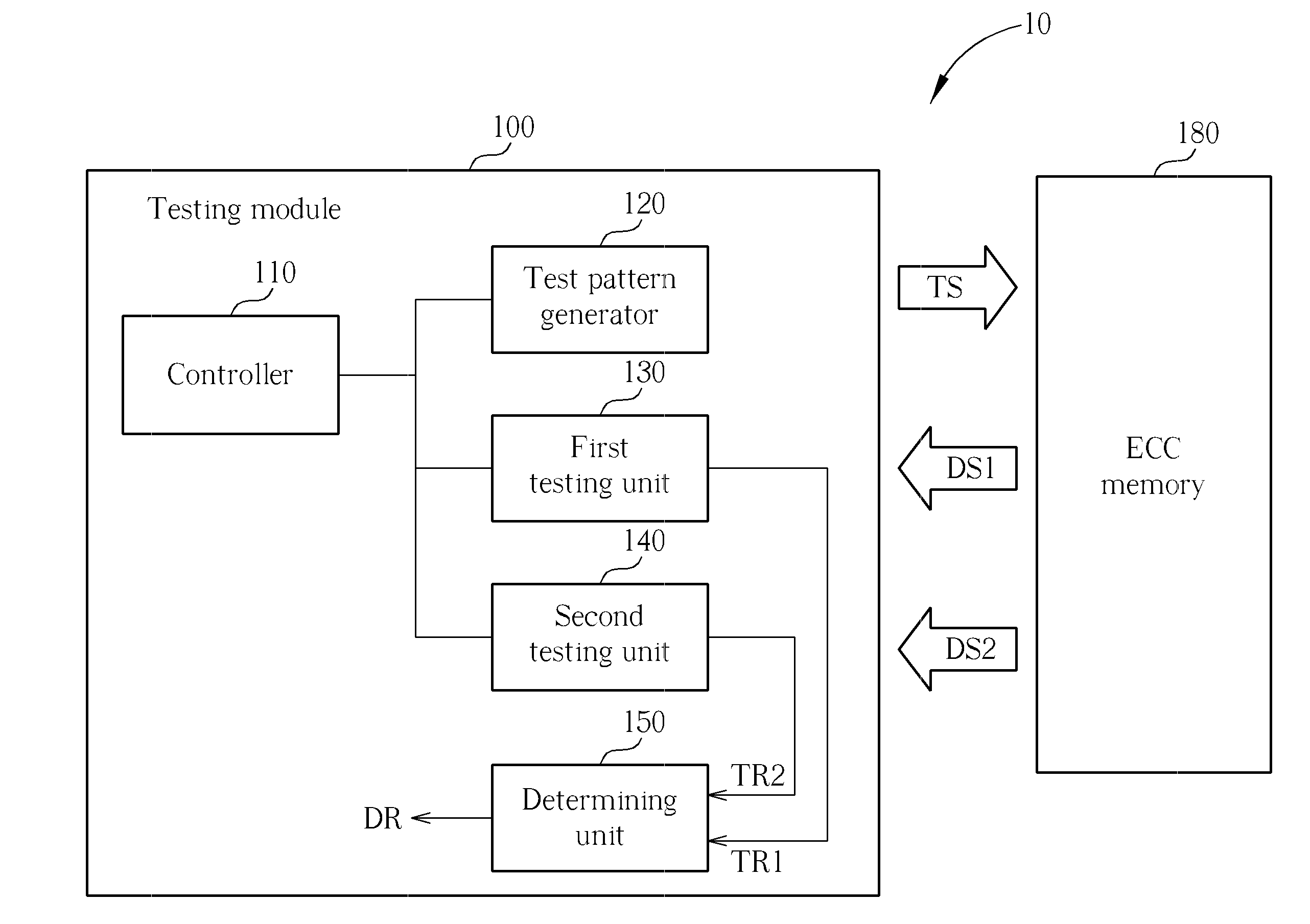

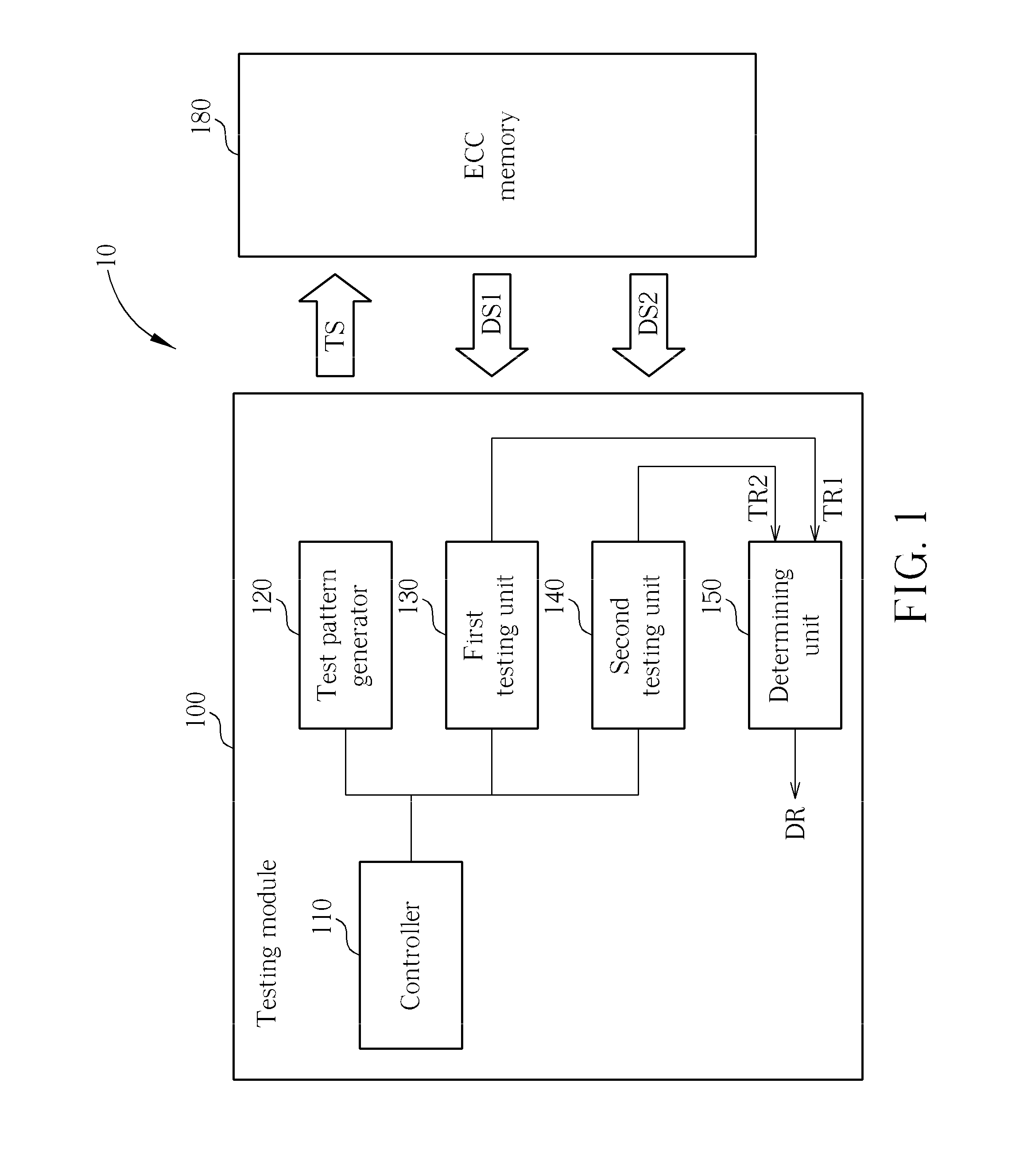

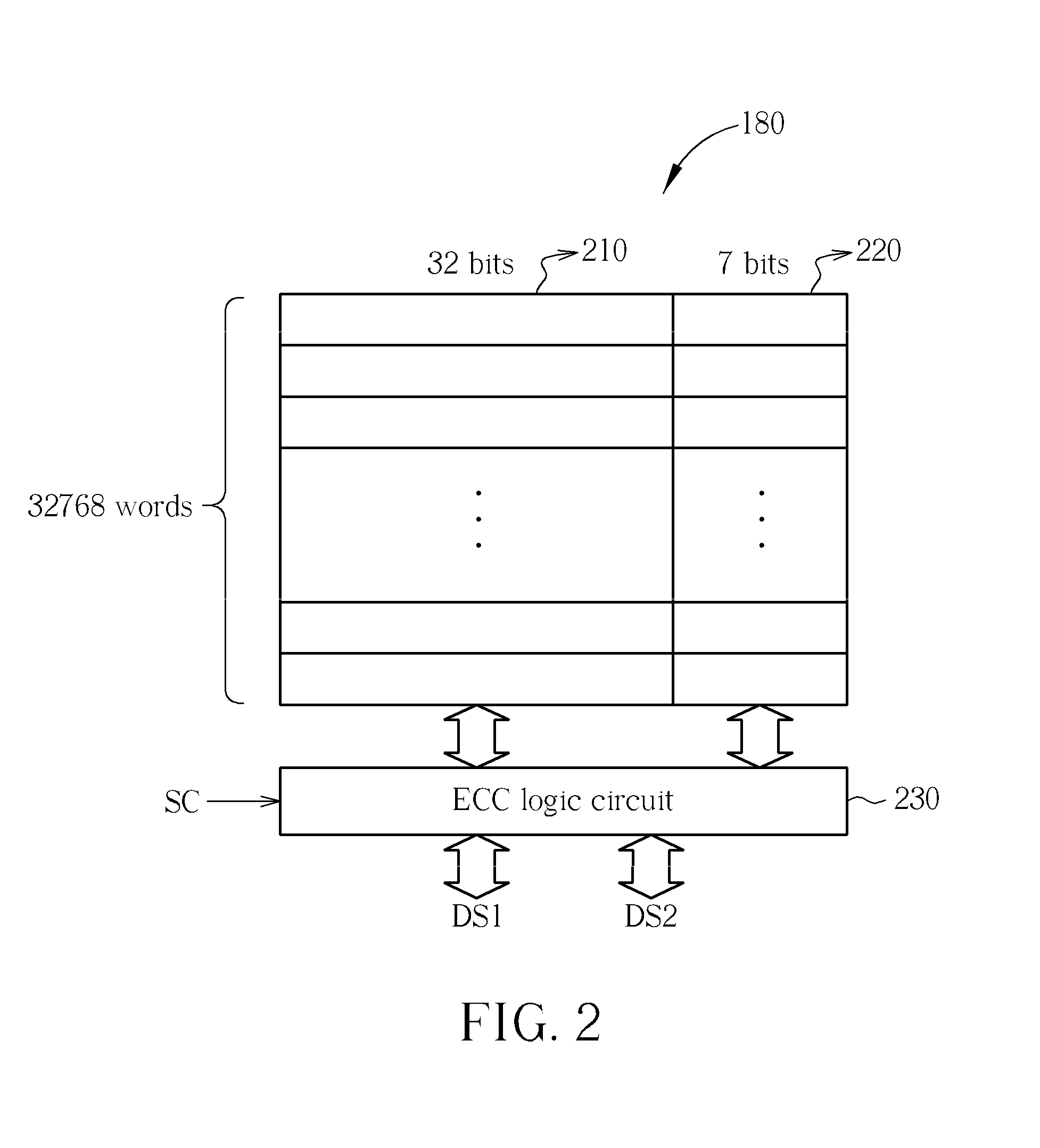

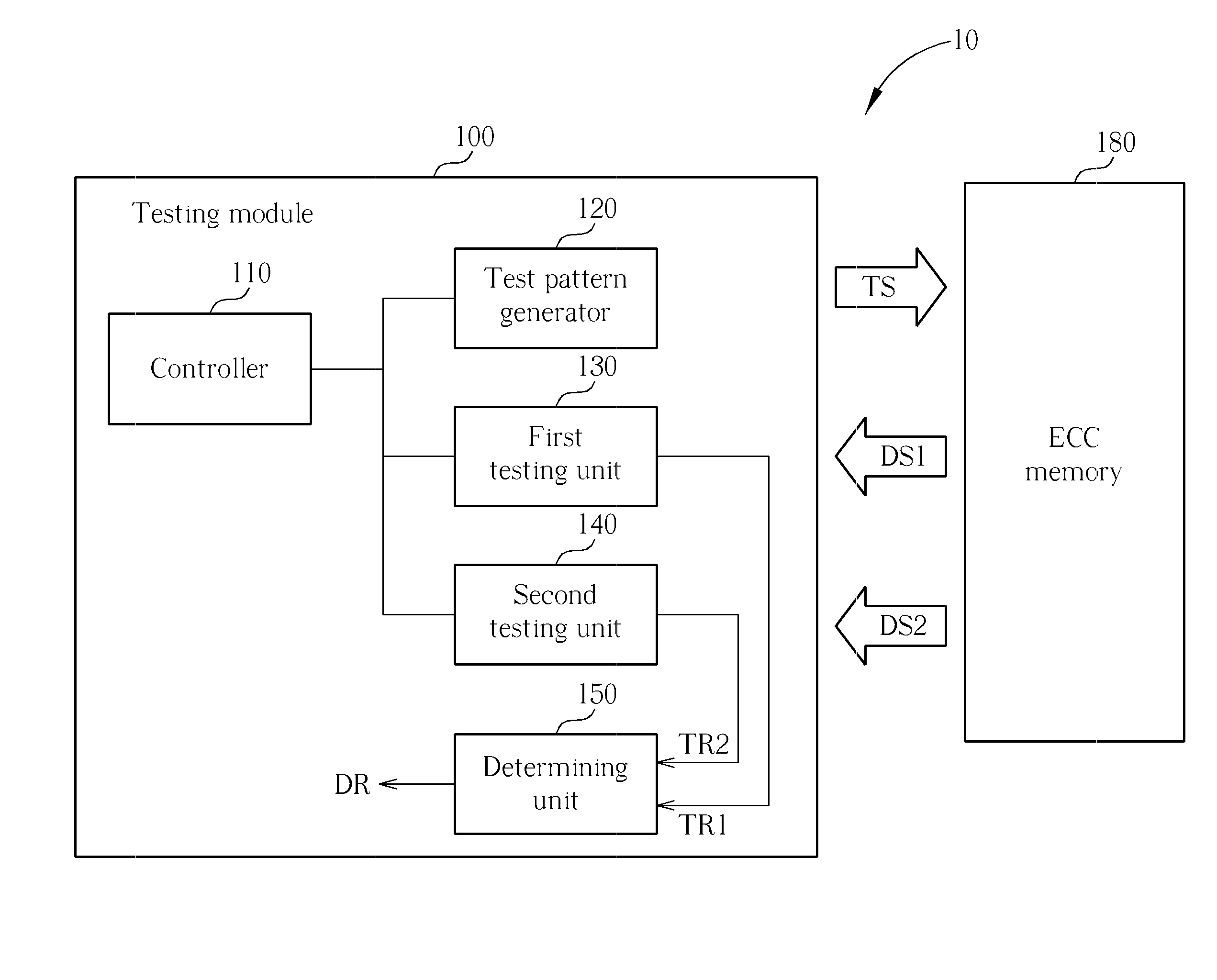

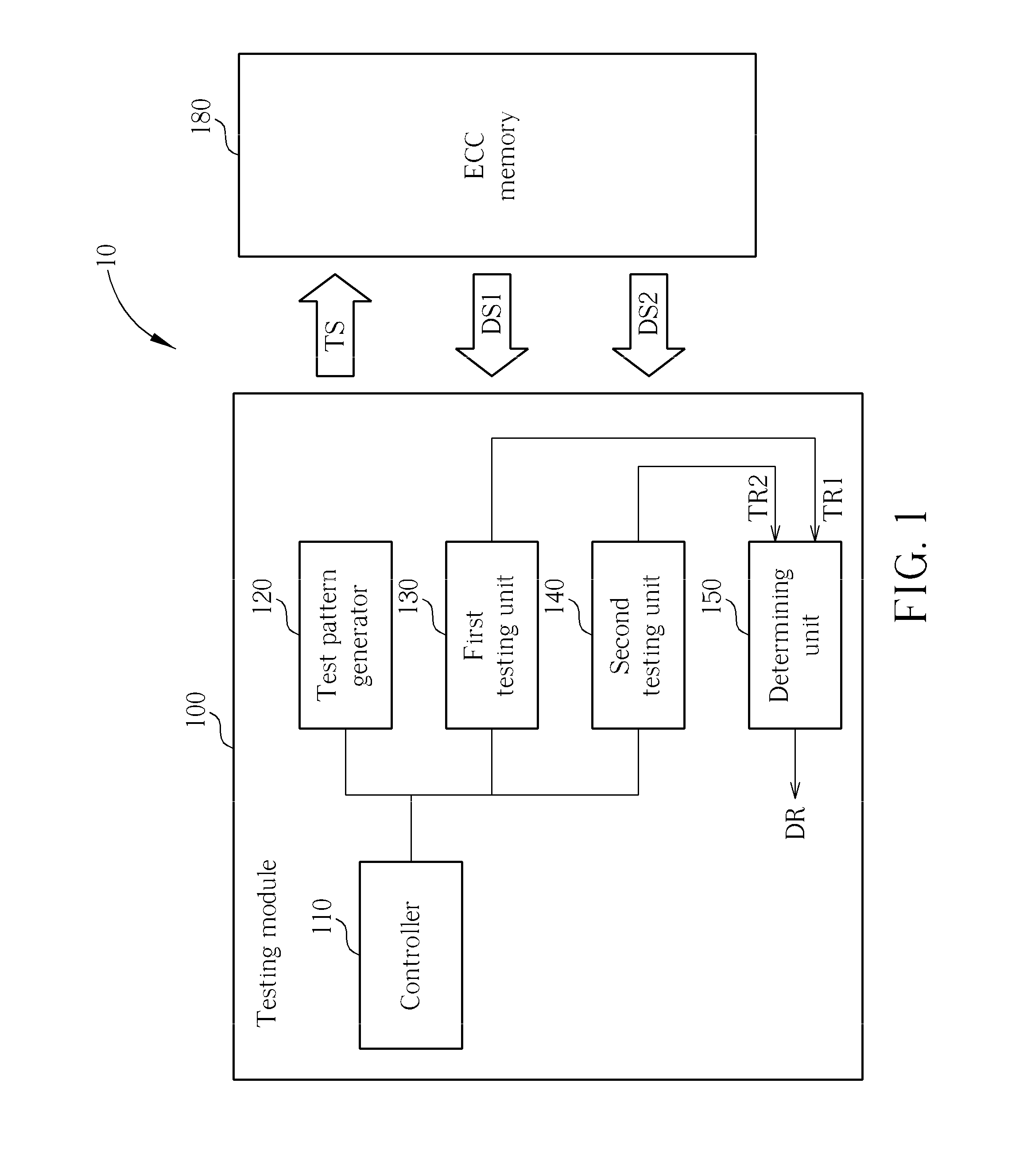

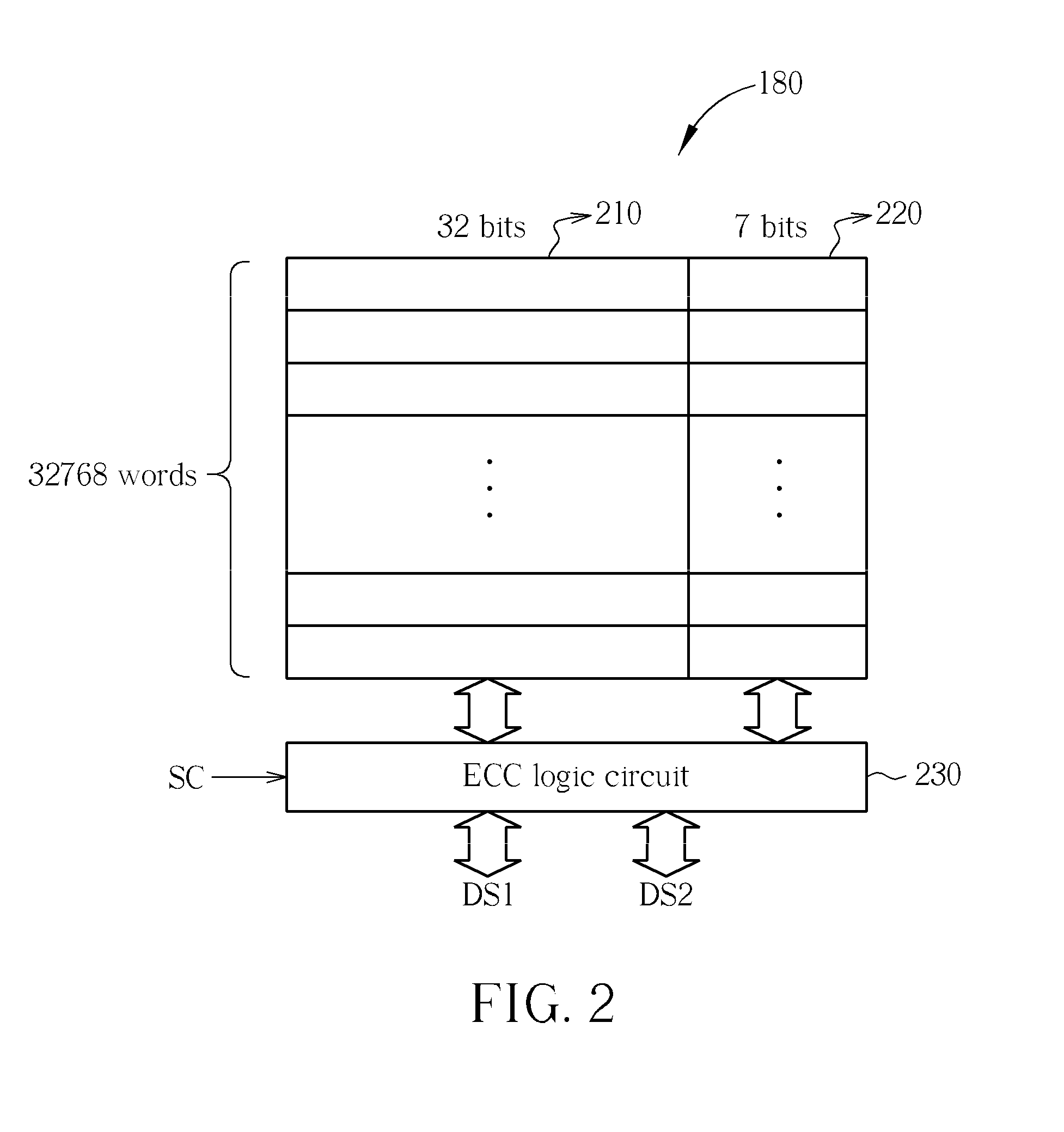

Memory apparatus and testing method thereof

ActiveUS20100235695A1Memory adressing/allocation/relocationError correction/detection using block codesComputer moduleECC memory

A memory apparatus and a related testing method are provided in the present invention. The memory apparatus includes a memory and a testing module. The testing module includes an error recording unit for recording corresponding addresses of bit errors occurred in the memory. The testing module determines whether the memory has multi-bit error according to the addresses recorded in the error recording unit. The memory is an ECC memory.

Owner:REALTEK SEMICON CORP

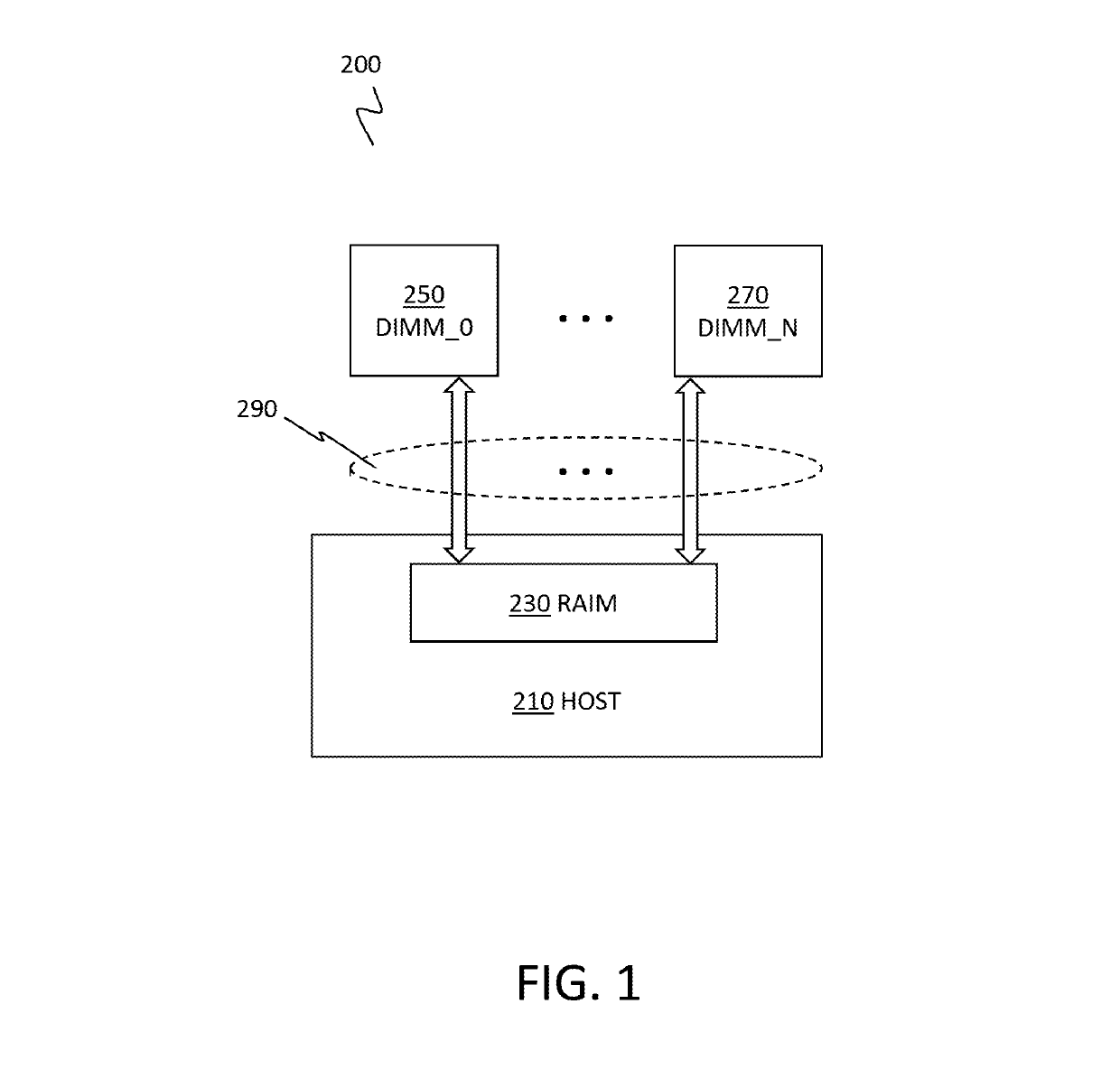

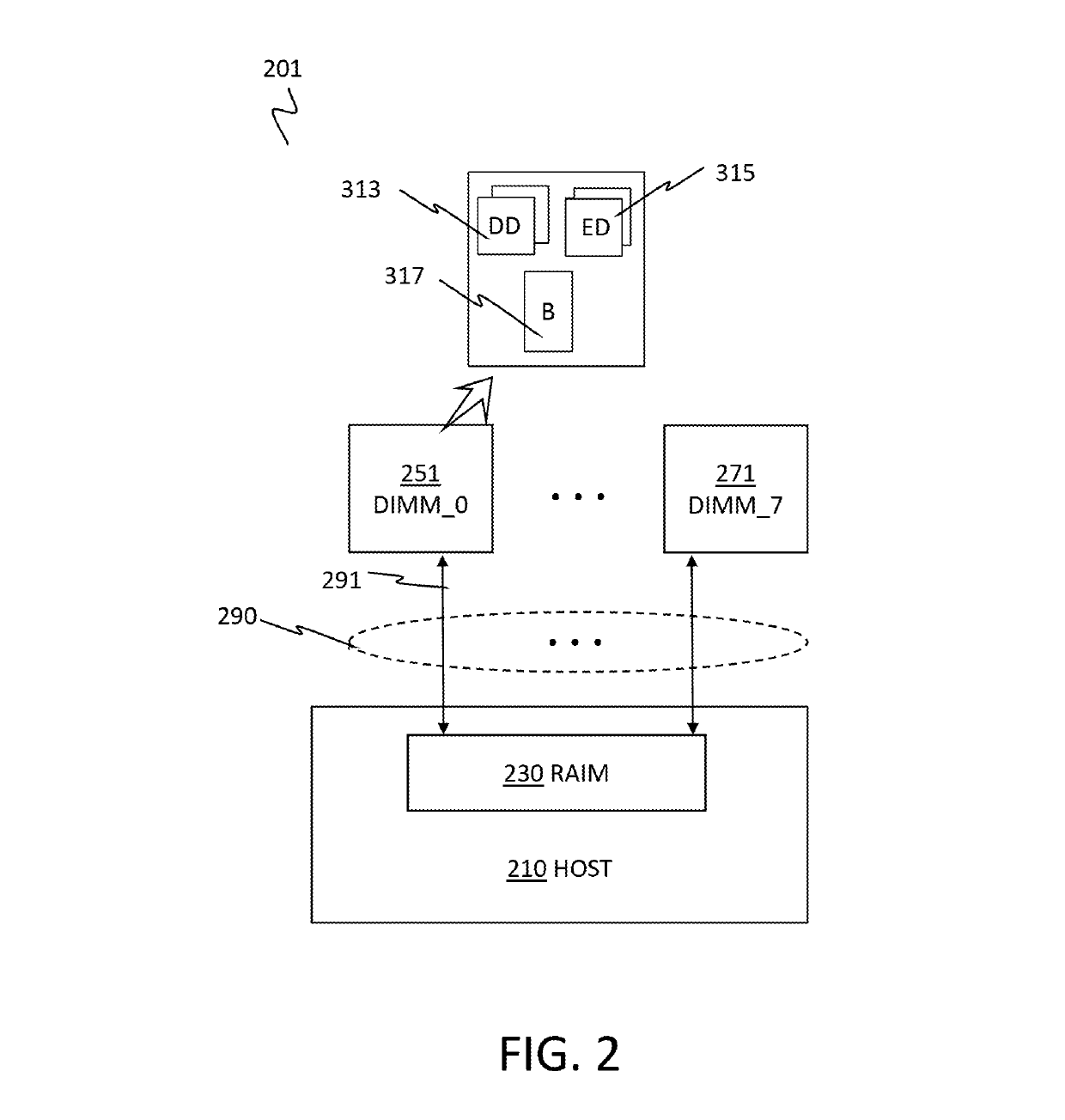

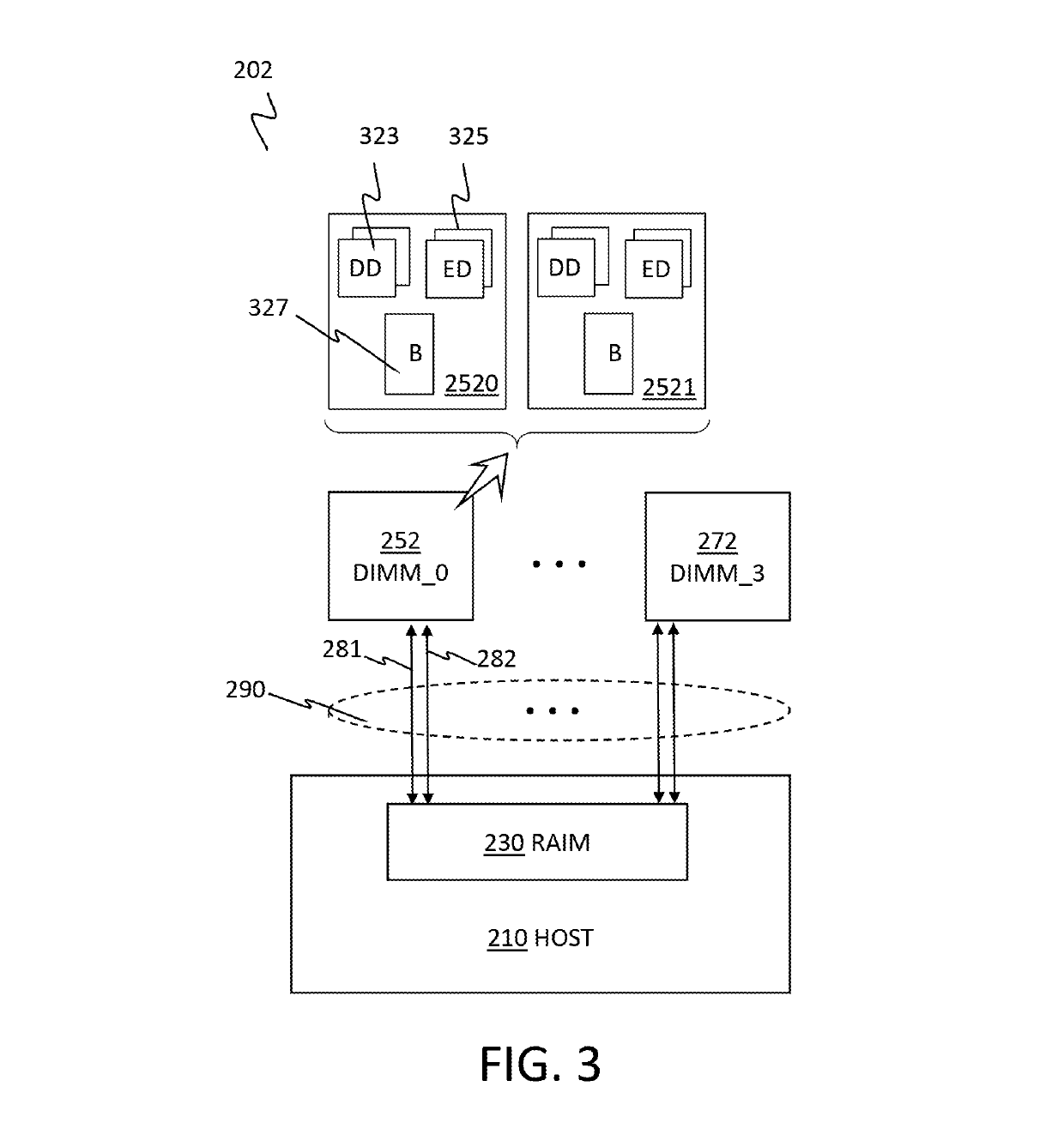

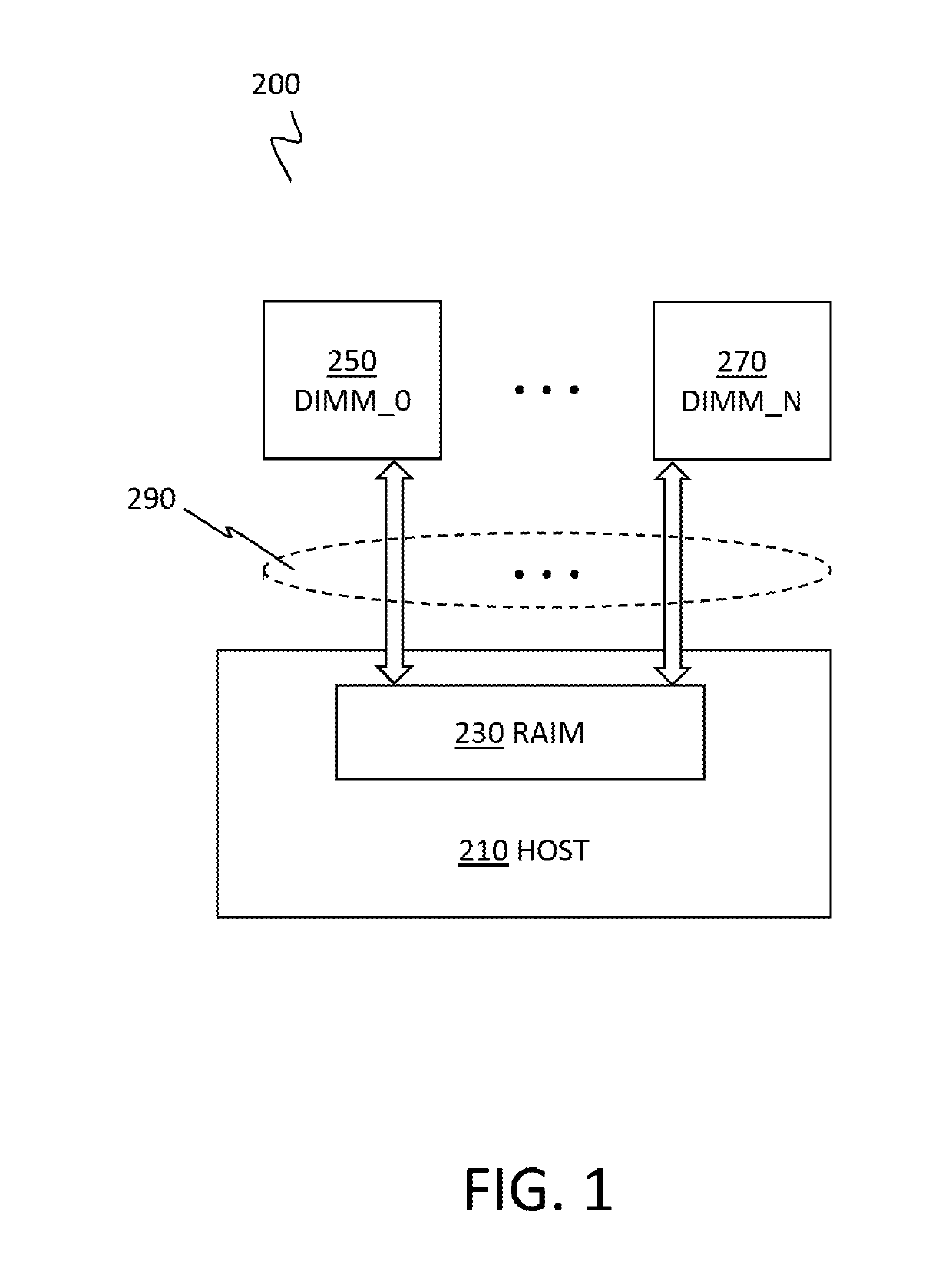

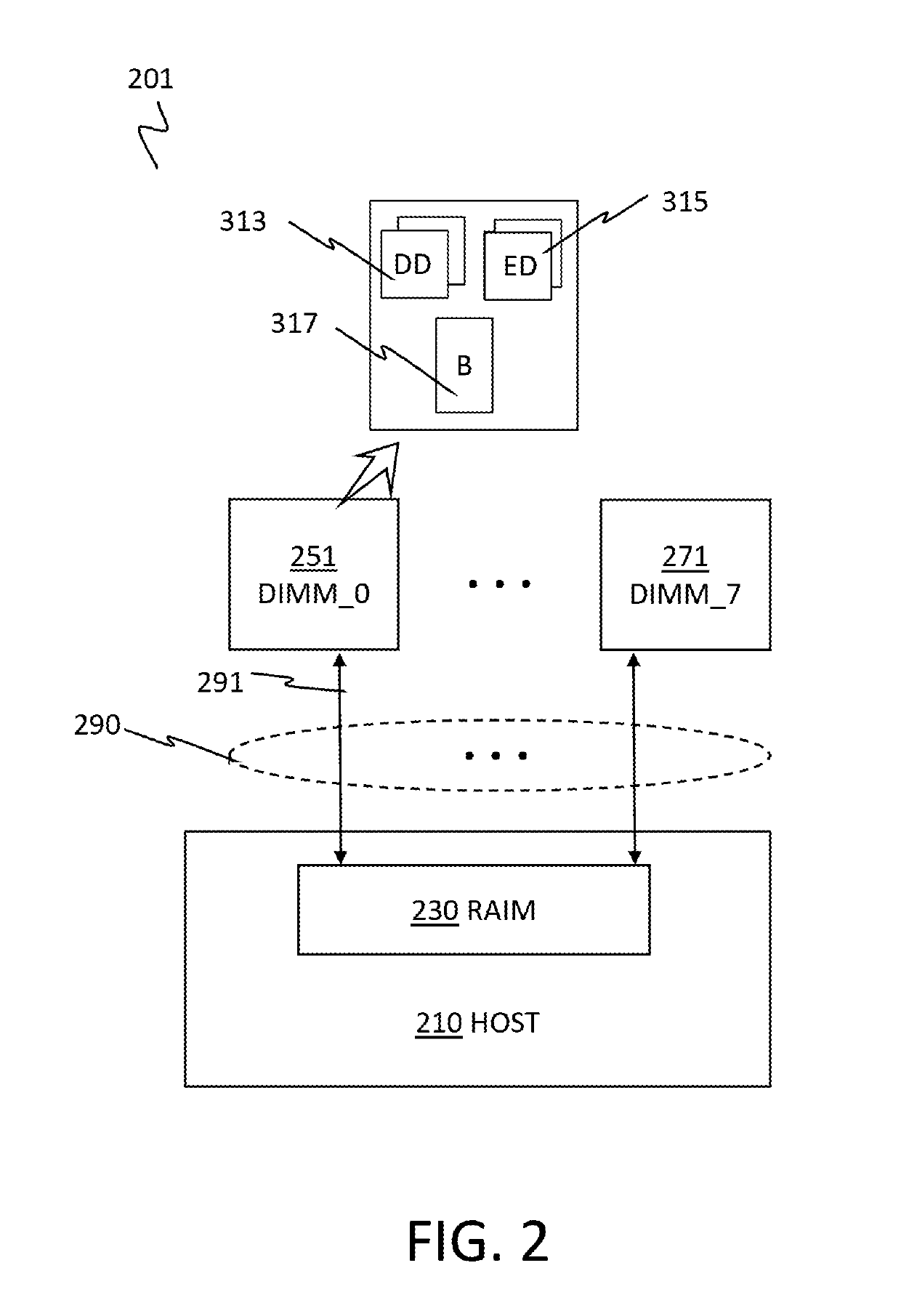

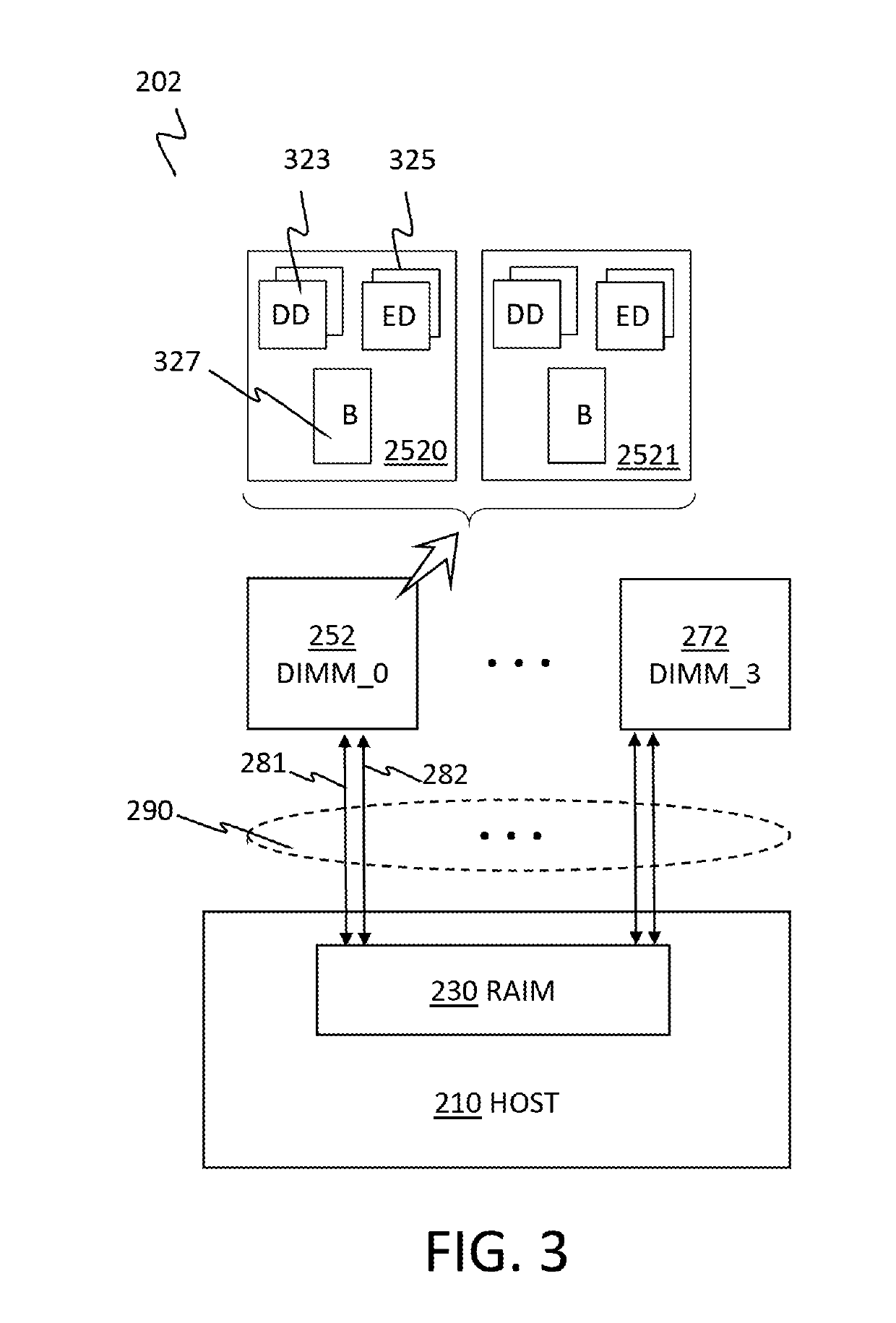

High efficiency redundant array of independent memory

A memory system includes memory modules having a number of sets of memory devices including data memory devices for data and error correction code (ECC). The ECC memory devices carry ECC symbols in order to facilitate Redundant Array of Independent Memory (RAIM) functionalities for the memory modules. A host receives and decodes the ECC symbols and executes RAIM operations. The host and the memory modules are coupled by a number of channels, one channel per each set of the memory devices.

Owner:IBM CORP

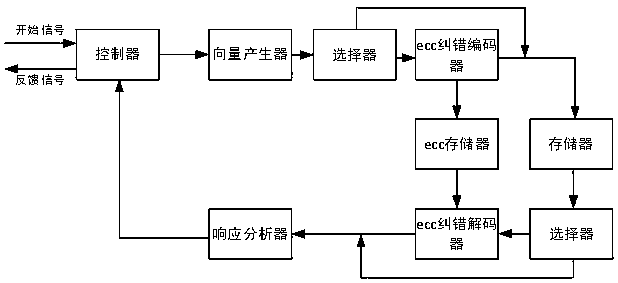

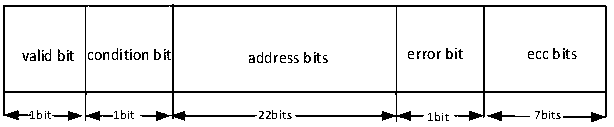

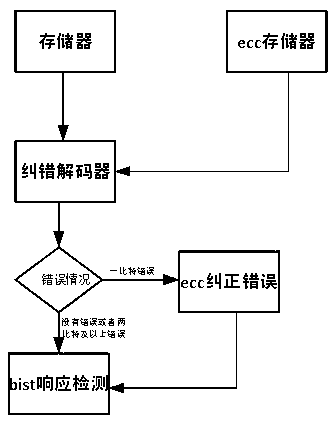

BIST and ECC combined memory detection device in system chip

The invention provides a memory detection device for an ECC module in a BIST multiplexing system chip, and belongs to the field of memory detection. The device comprises a BIST circuit module, an ECC memory, a memory, an error correction encoder and an error correction decoder. When the ECC module has no error, the BIST may select to multiplex the ECC module. According to the device provided by the invention, the data is detected in a manner of reading and writing the data into the memory. In the process, when an error of one bit occurs, the error can be corrected by the ECC error correction decoder module, the error cannot be detected at the BIST detection end, a given detection result signal is pass, and it is considered that the area is still available. And when more than two bits of errors exist, it is considered that the errors are true errors, and a fail signal is reported. The device improves the yield of the memory during detection.

Owner:ZHEJIANG UNIV +1

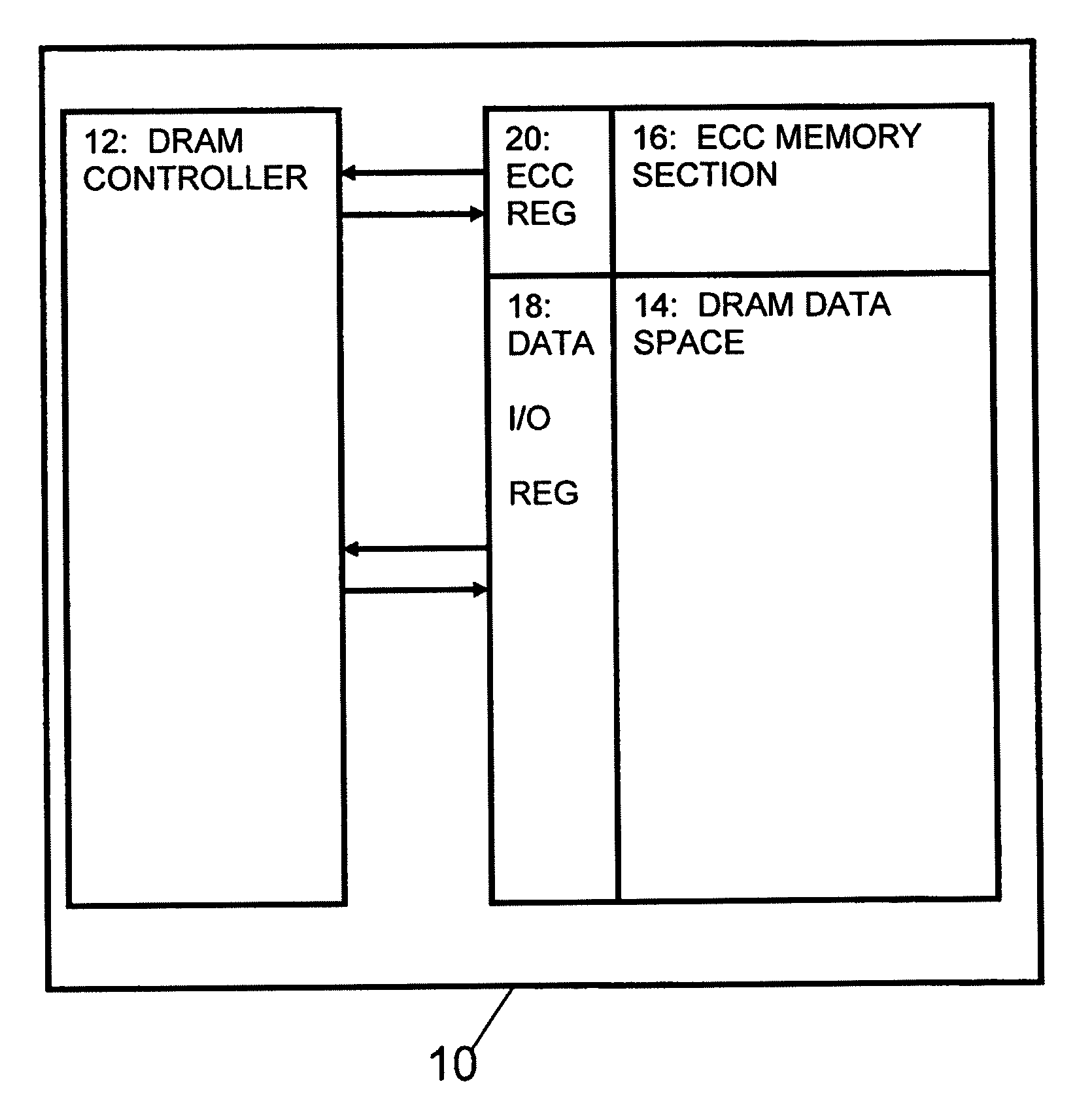

Error code management in systems permitting partial writes

ActiveUS20150039968A1Reduce overheadIncreased riskStatic storageRedundant data error correctionECC memoryControl circuit

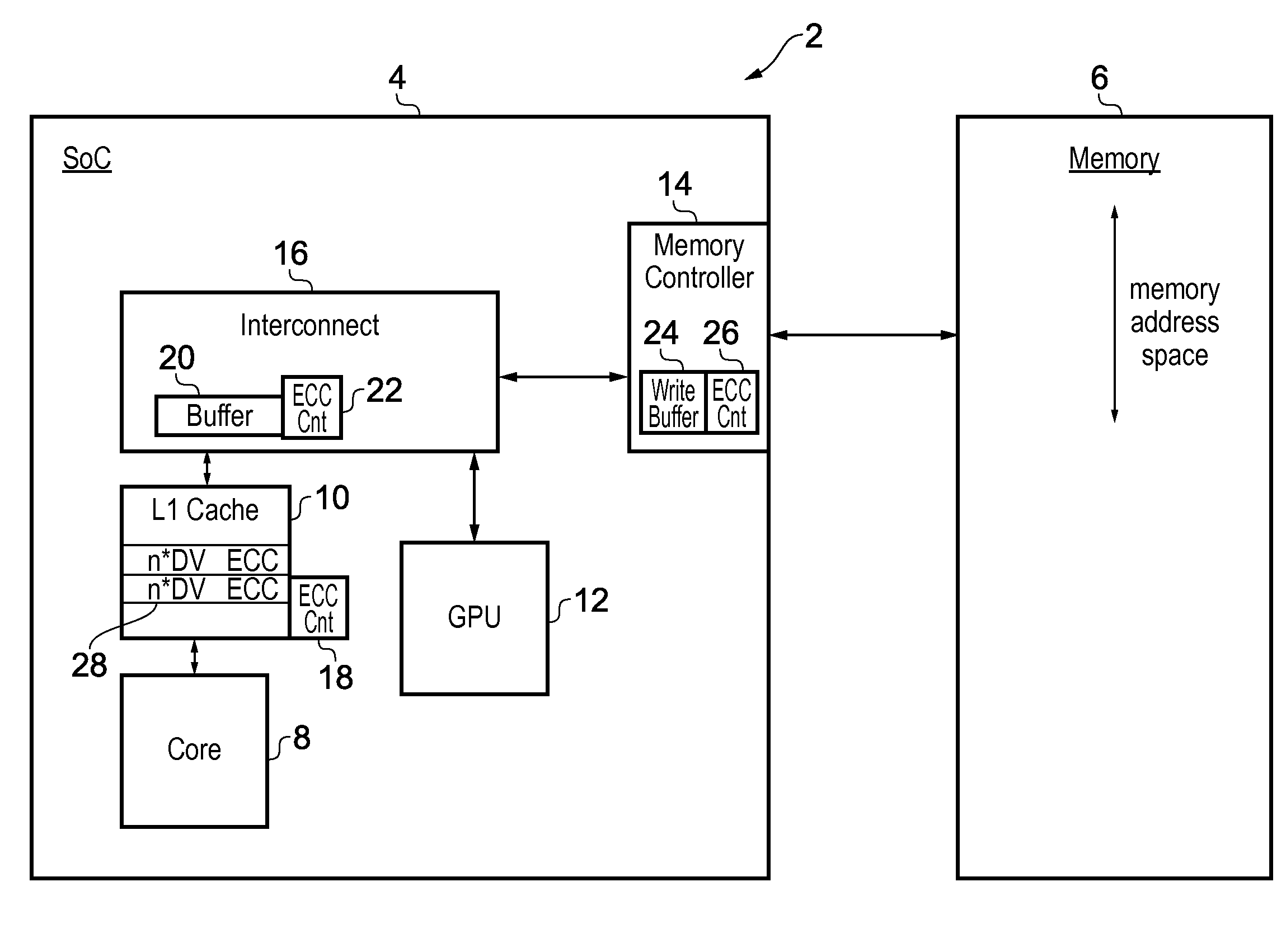

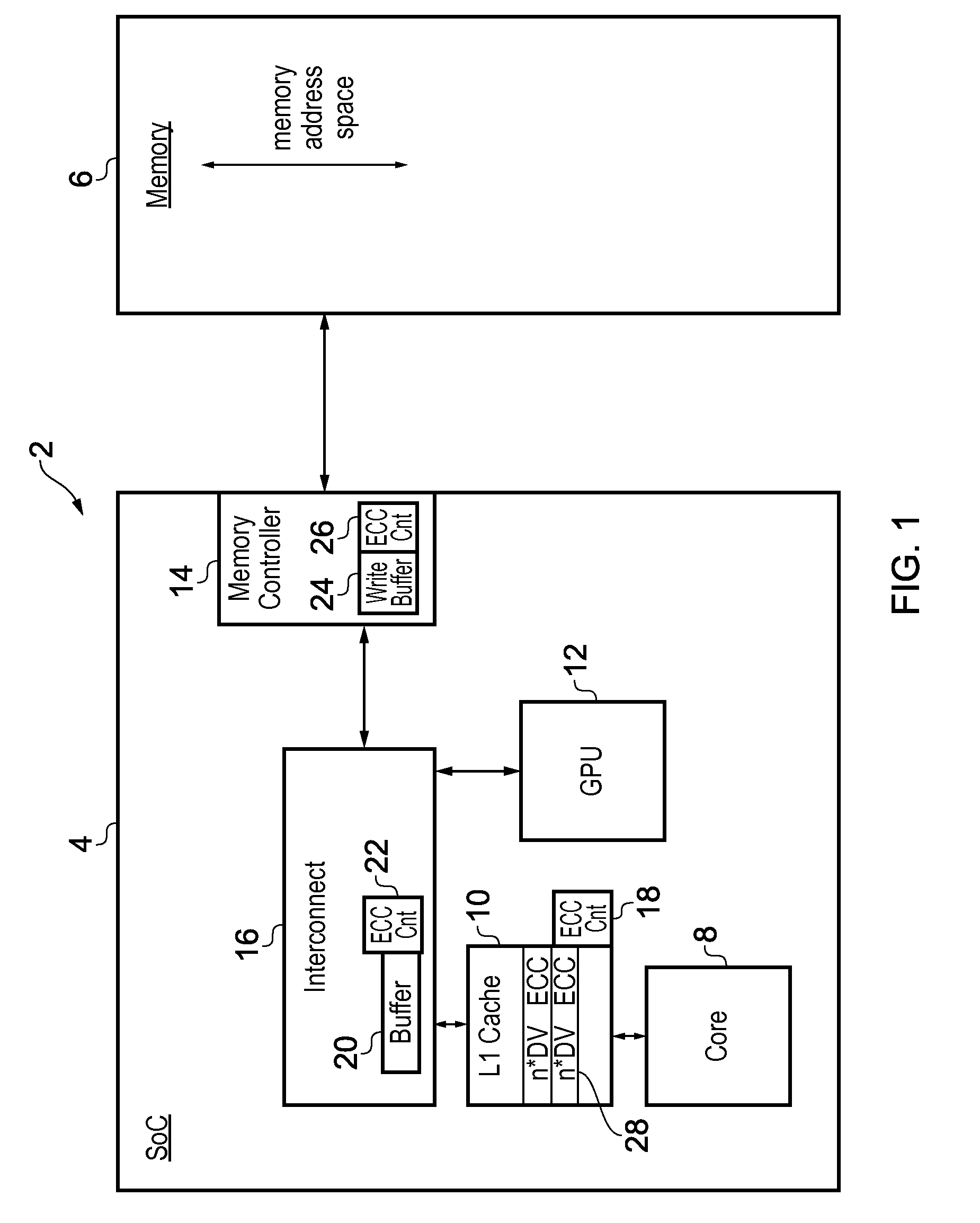

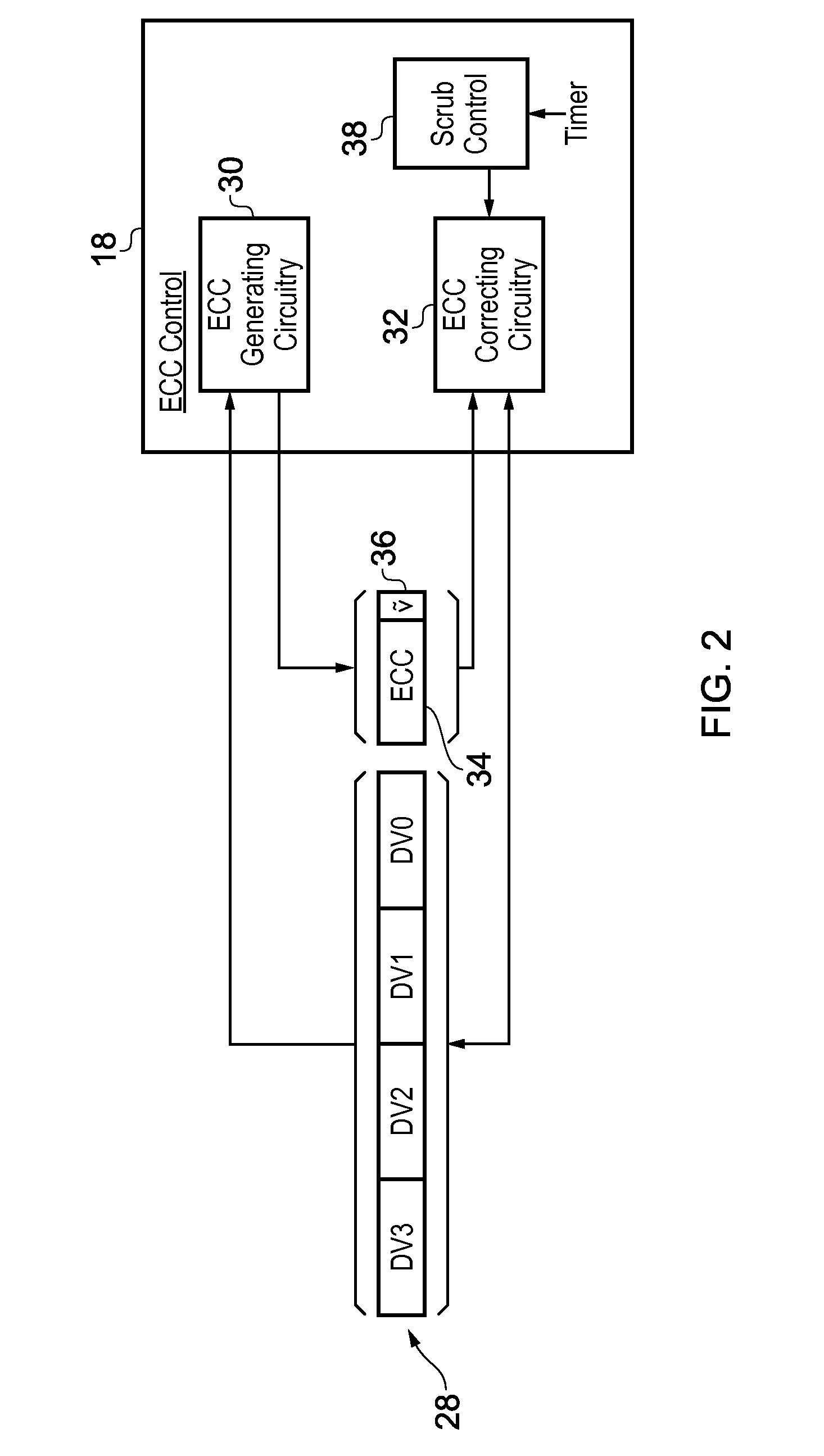

A memory 10 stores a data block comprising a plurality of data values DV. An error code, such as an error correction code ECC, is associated with the memory and has a value dependent upon the plurality of data values which form the data block stored within the memory. If a partial write is performed on a data block, then the ECC information becomes invalid and is marked with an ECC_invalid flag. The intent is avoiding the need to read all data values to compute the ECC and thus save time and energy. The memory may be a cache line 28 within a level 1 cache memory 10. Memory scrub control circuitry 38 performs periodic memory scrub operations which trigger flushing of partially written cache lines back to main memory.

Owner:ARM LTD

Memory apparatus and testing method thereof

Owner:REALTEK SEMICON CORP

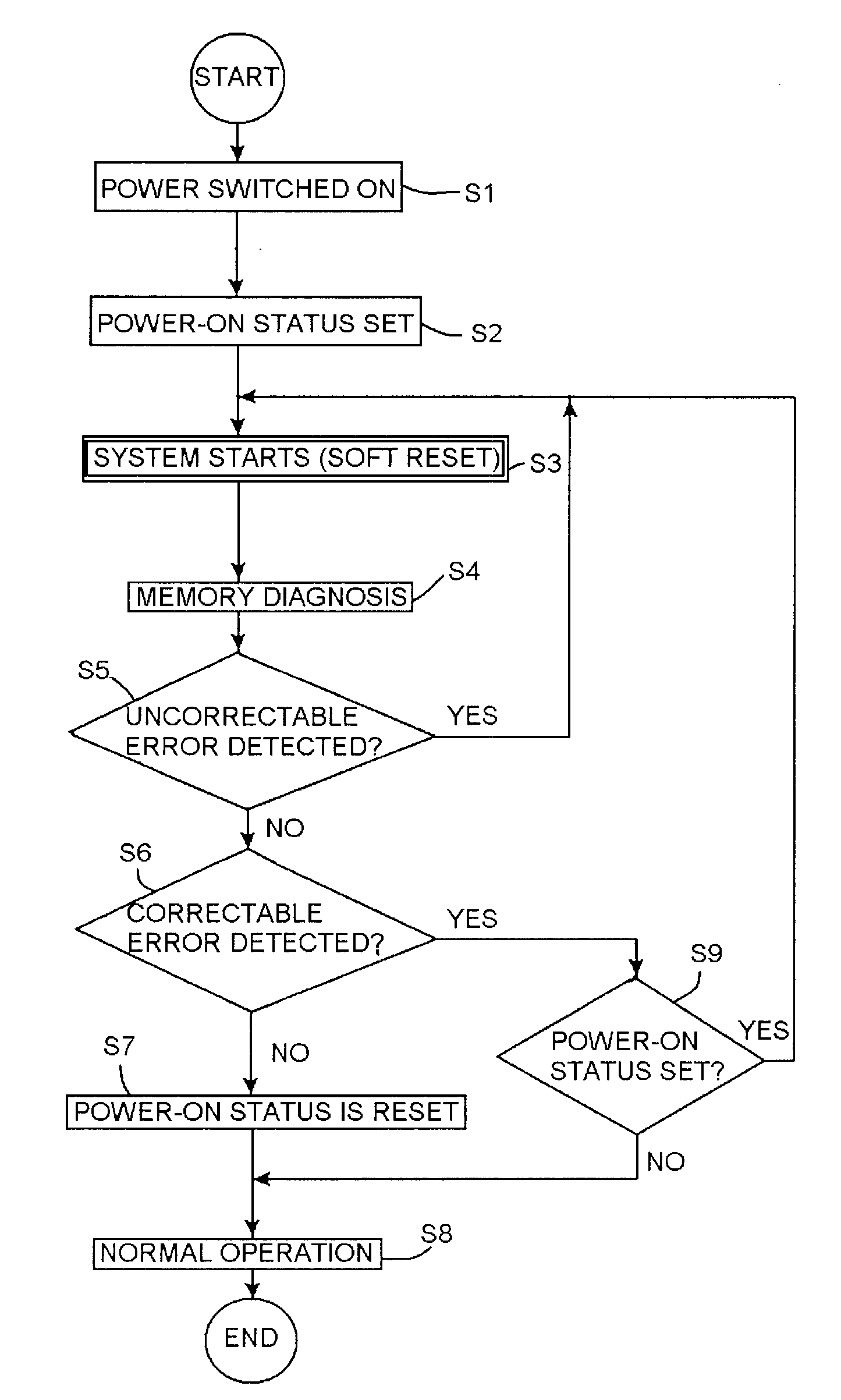

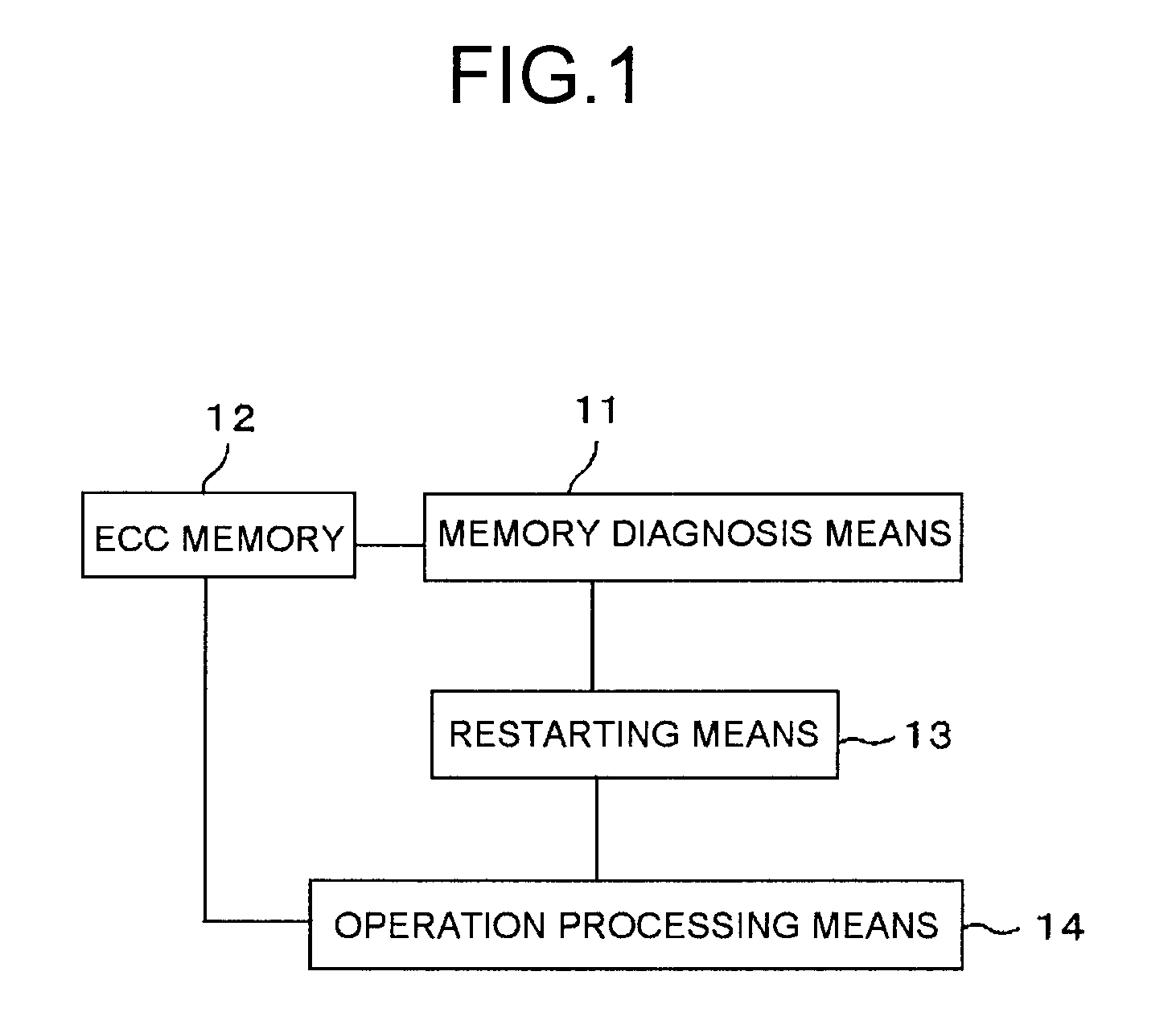

Control device

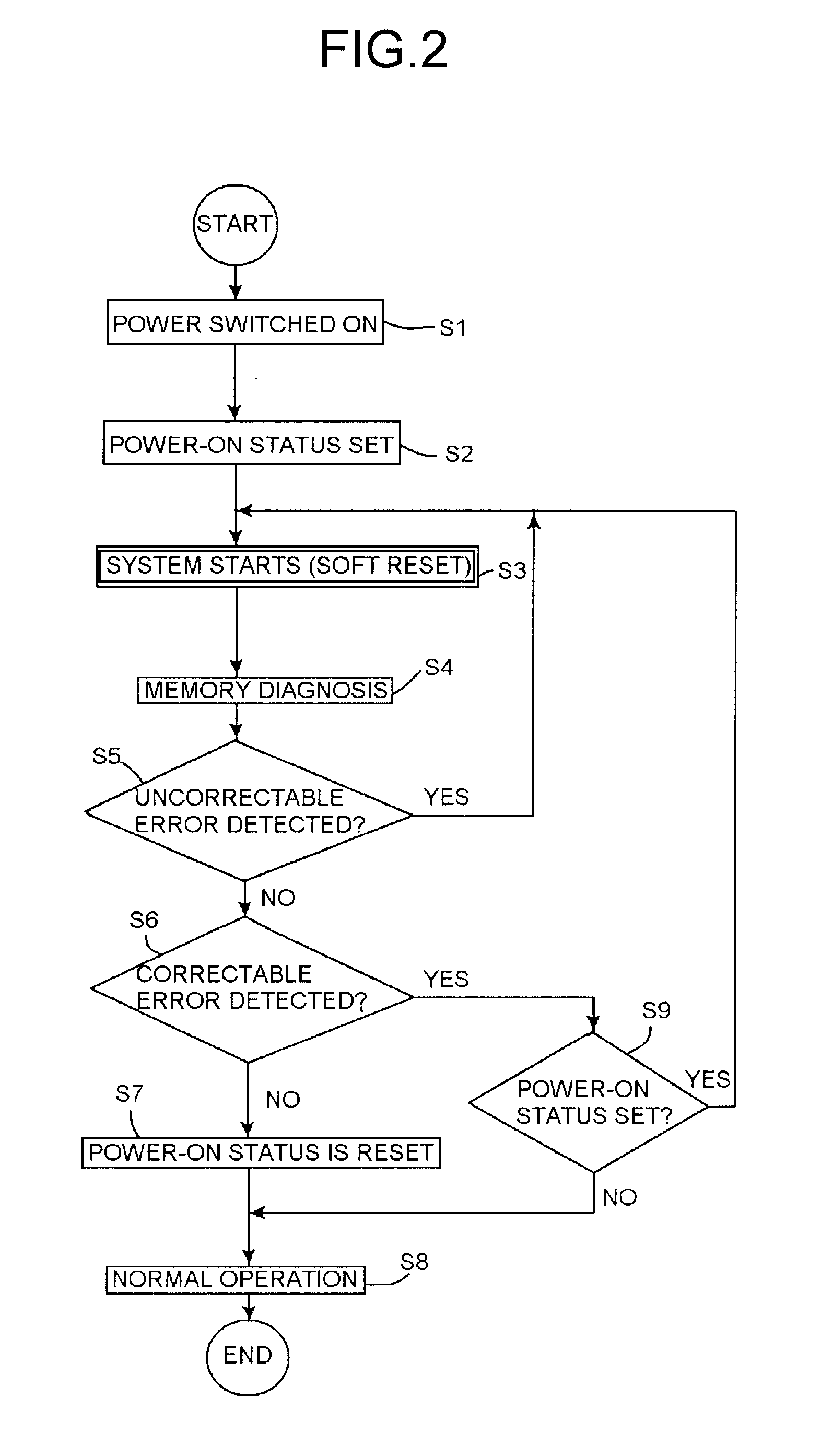

ActiveUS20100251019A1Detecting faulty hardware by power-on testFault responseComputer hardwareECC memory

A control device includes: memory diagnosis means for setting a power-on status when an electric power is turned on and diagnosing an ECC memory; restarting means for restarting the control device when the memory diagnosis means detects a correctable error of the ECC memory during the power-on status of the ECC memory; and operation processing means for resetting the power-on status and performing a normal operation when the memory diagnosis means does not detect a correctable error of the ECC memory, while performing the normal operation when a correctable error of the ECC memory is detected because of the restart of the control device by soft reset after the reset of the power-on status but when the control device is not in the power-on status.

Owner:KK TOSHIBA

High efficiency redundant array of independent memory

Owner:INT BUSINESS MASCH CORP

System RAS protection for UMA style memory

In some embodiments, the invention involves a system and method relating to system recovery in a fault resilient manner by isolating errors associated with the management engine (ME) UMA memory. BIOS logs errors occurring on memory within the system. The ME UMA is invisible to the host OS, so the OS will not be notified about the errors occurring in the ME UMA range. When an error threshold has been reached for a memory unit in which ME UMA resides, ME UMA data is migrated to a previously reserved backup region of memory and the ME is notified of the new ME UMA location. The faulty memory is flagged for replacement at a next maintenance cycle. Embodiments may be applied to workstations that utilize ECC memory protection which utilize AMT (Active Management Technology) and ME UMA. Other embodiments are described and claimed.

Owner:INTEL CORP

Fast ECC memory testing by software including ECC check byte

The present invention relates to the architecture and operation of computer hardware memory logic, and in particular to a method and respective system for verifying hardware memory logic, wherein an Error Correction Code (ECC) is used for correcting single-bit or multi-bit errors when the ECC-bits cannot be accessed directly for a read or write process. The system and process employs the selection of data patterns that produce check bits that are all ones to ferret out errors in the ECC circuitry.

Owner:META PLATFORMS INC

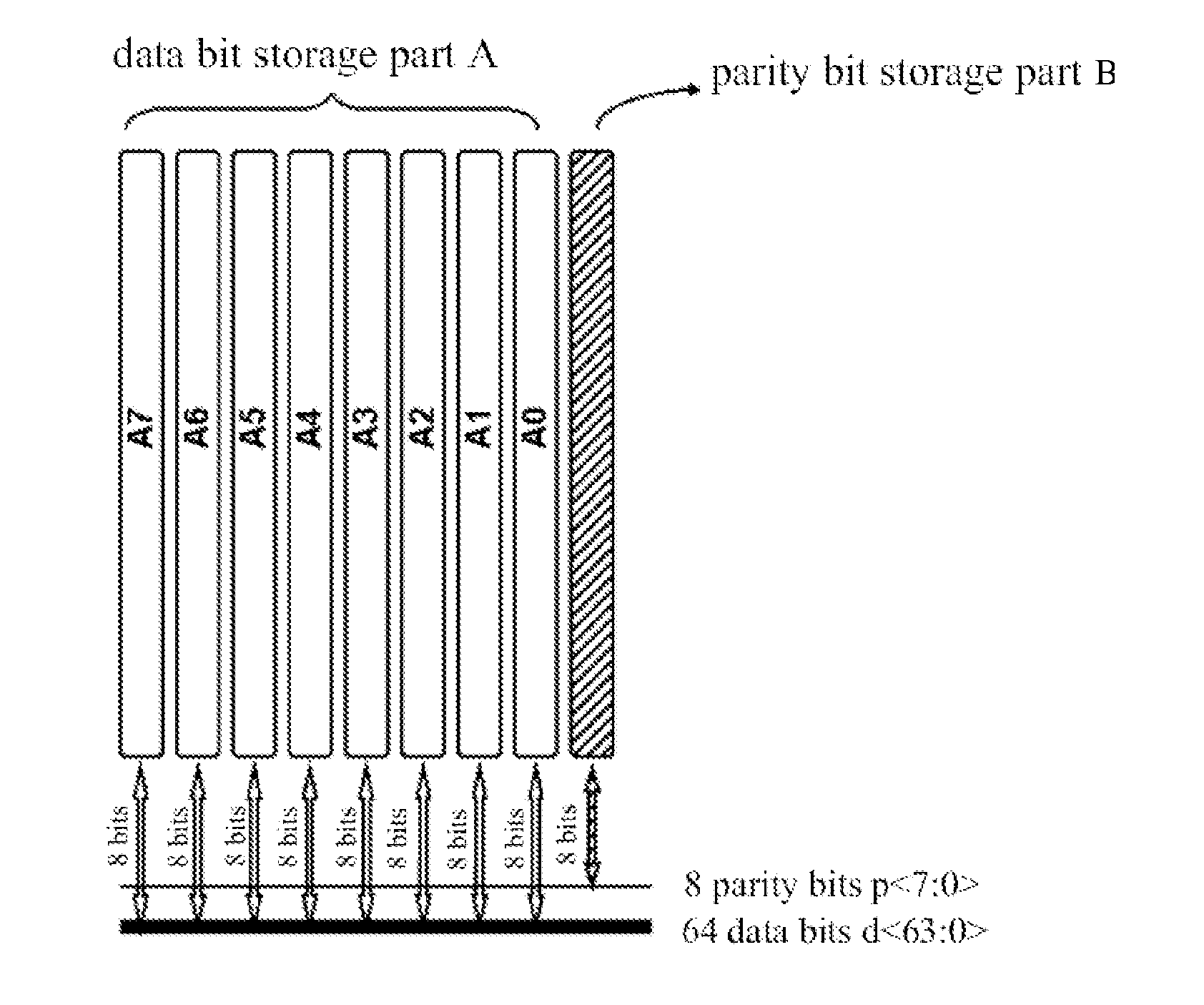

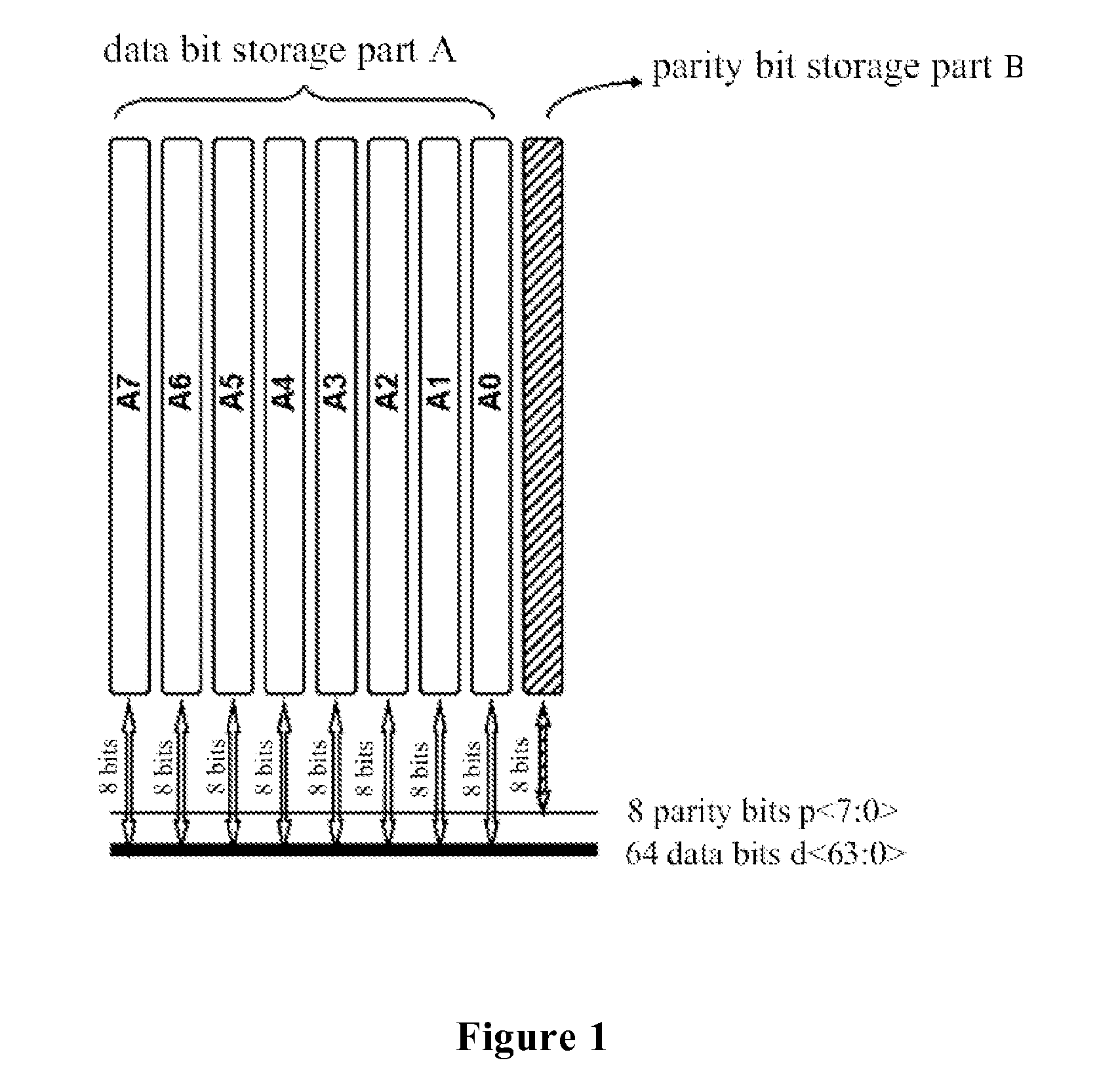

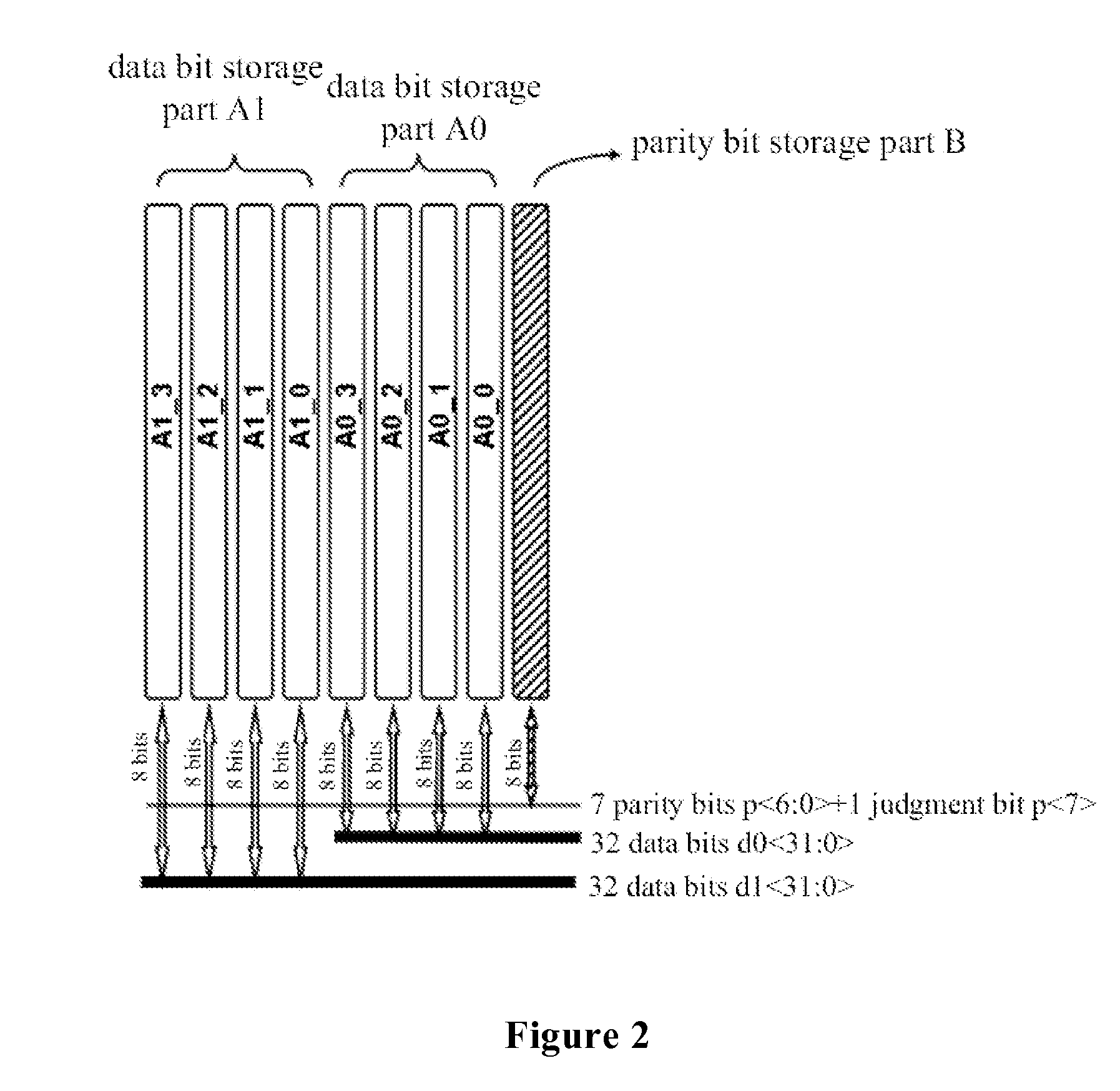

Storing Data by an ECC Memory

ActiveUS20150121170A1Data representation error detection/correctionStatic storageECC memoryParity bit

Methods, systems and apparatus for storing data by an ECC memory are provided. In one aspect, when an ECC memory configured to be used for data blocks with a first data length is used for data blocks with a reduced second data length, a method includes storing at least one data block with the second data length in a data bit storage part of a storage array and storing parity bits generated for only one data block of the at least one data block according to a relevant encoding rule in a parity bit storage part of the storage array. When the at least one data block is two or more data blocks, one or more judgment bits, which indicate that the stored parity bits correspond to the only one data block, are stored in one or more storage bits of the parity bit storage part that are not occupied.

Owner:XI AN UNIIC SEMICON CO LTD

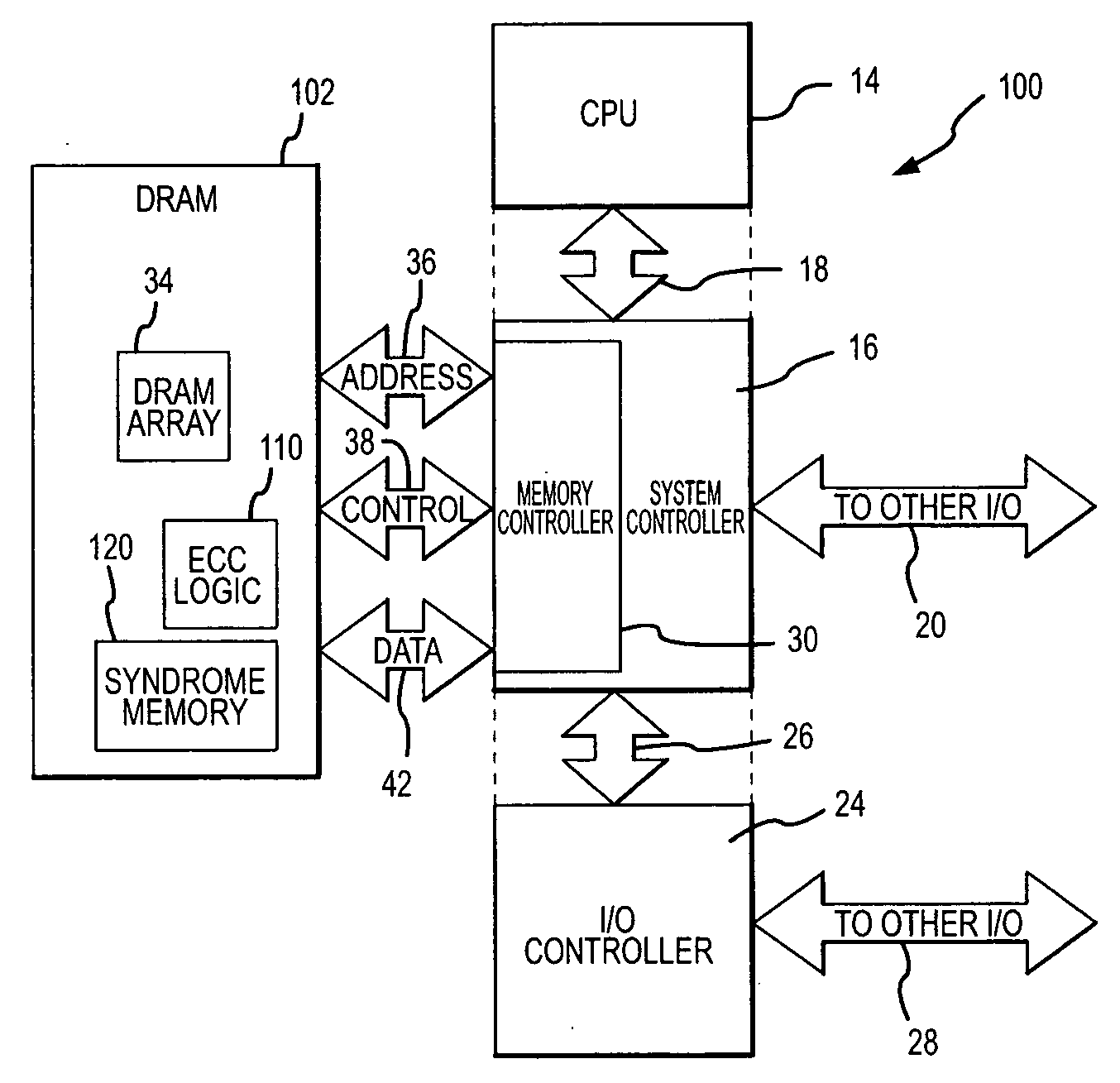

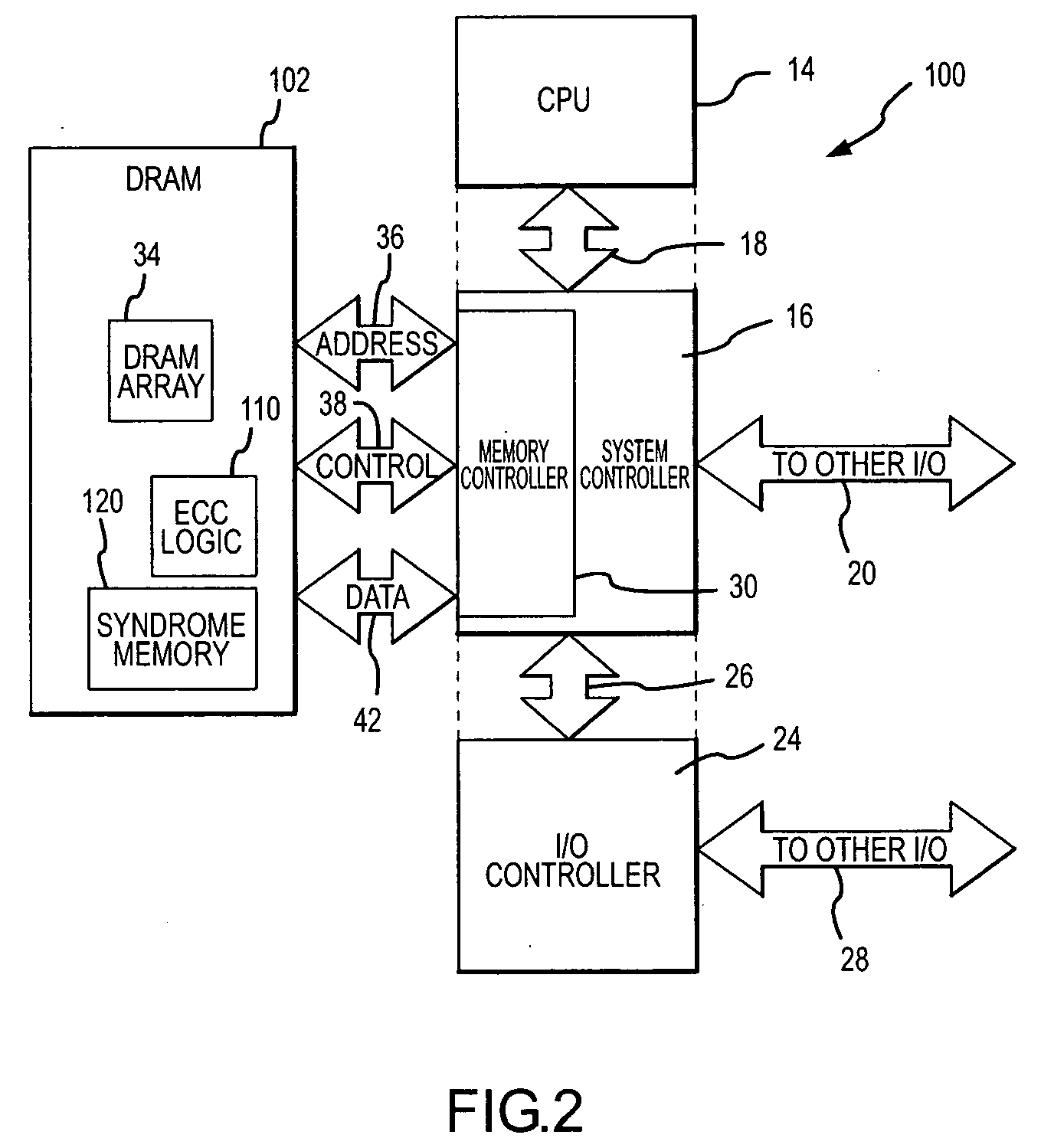

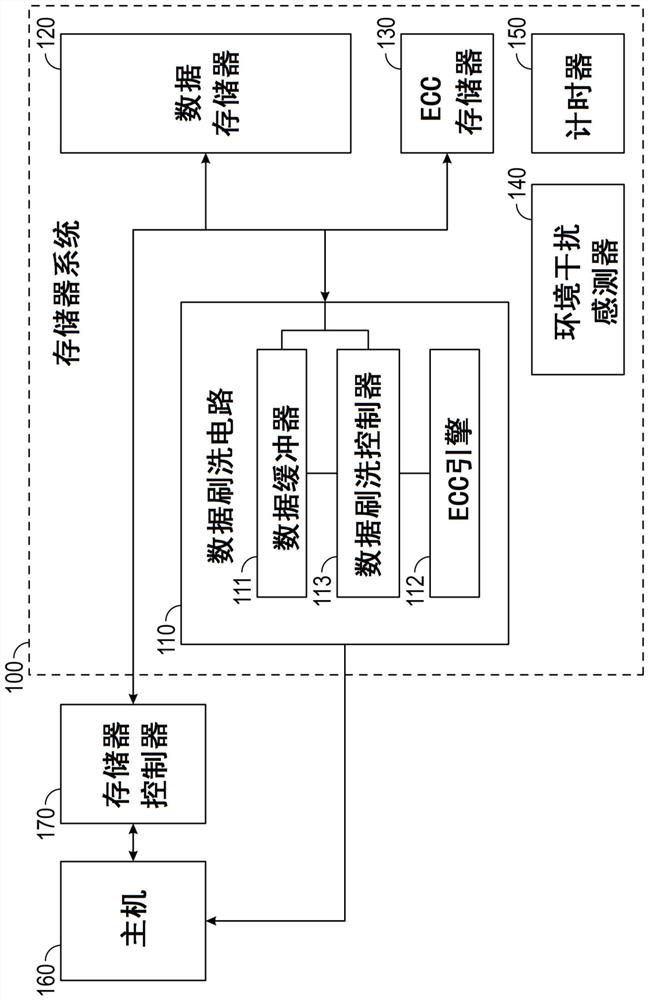

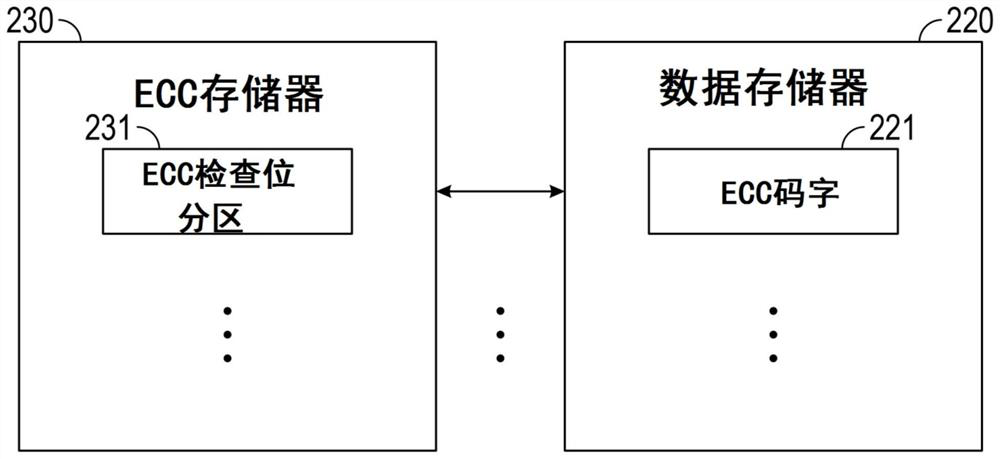

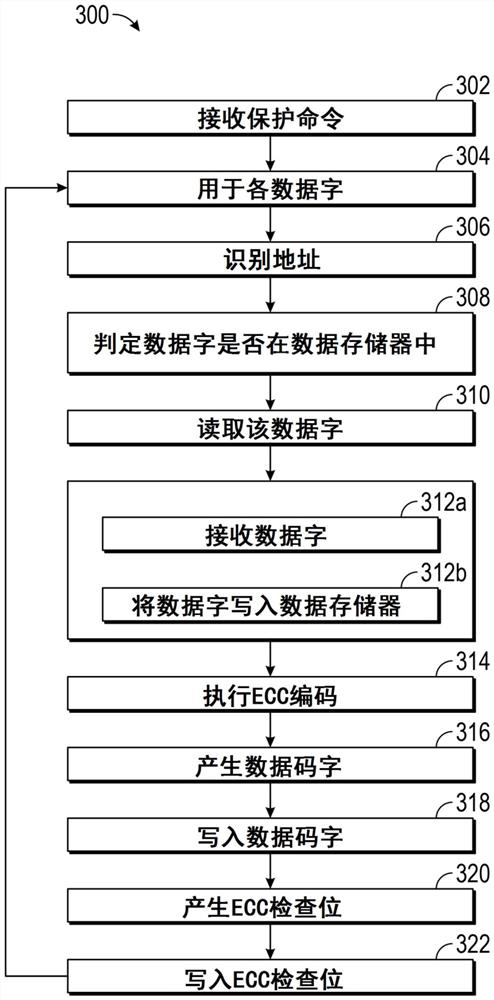

Error correcting memory systems

Error correcting memory systems and methods of operating the memory systems are disclosed. In some embodiments, a memory system includes: a data memory; an ECC memory; and a data scrubbing circuit electrically coupled to the ECC memory and the data memory. The data scrubbing circuit may be configured to, in response to receiving a scrub data command, correct an error in the data memory. A code word length used to correct the error may be longer than a word length used during normal access of the data memory. In some embodiments, a memory system includes a first memory circuit associated with a first bit error rate and a second memory circuit associated with a second bit error rate. In some embodiments, a memory system includes an error correctable multi-level cell (MLC) array.

Owner:SUPERMEM INC

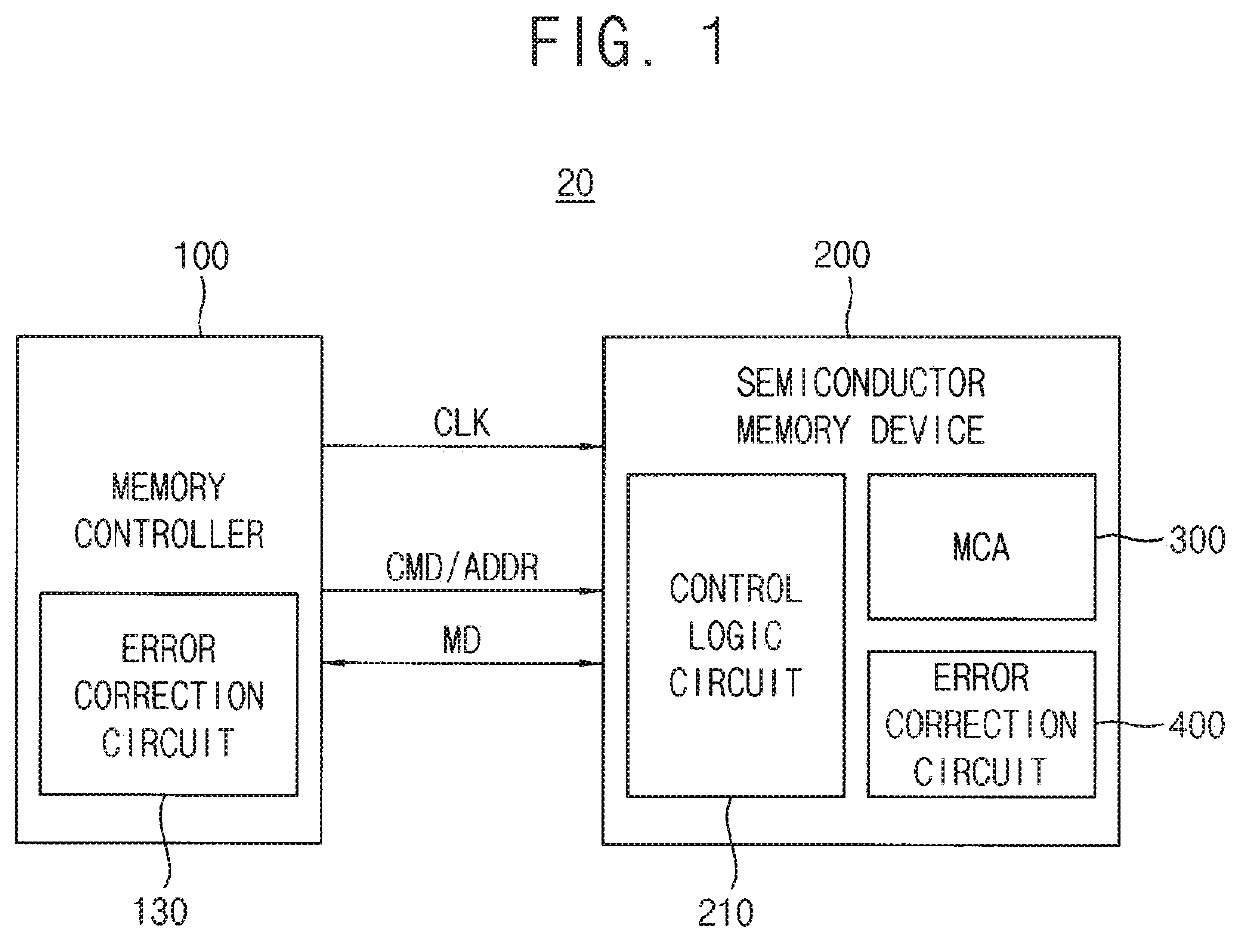

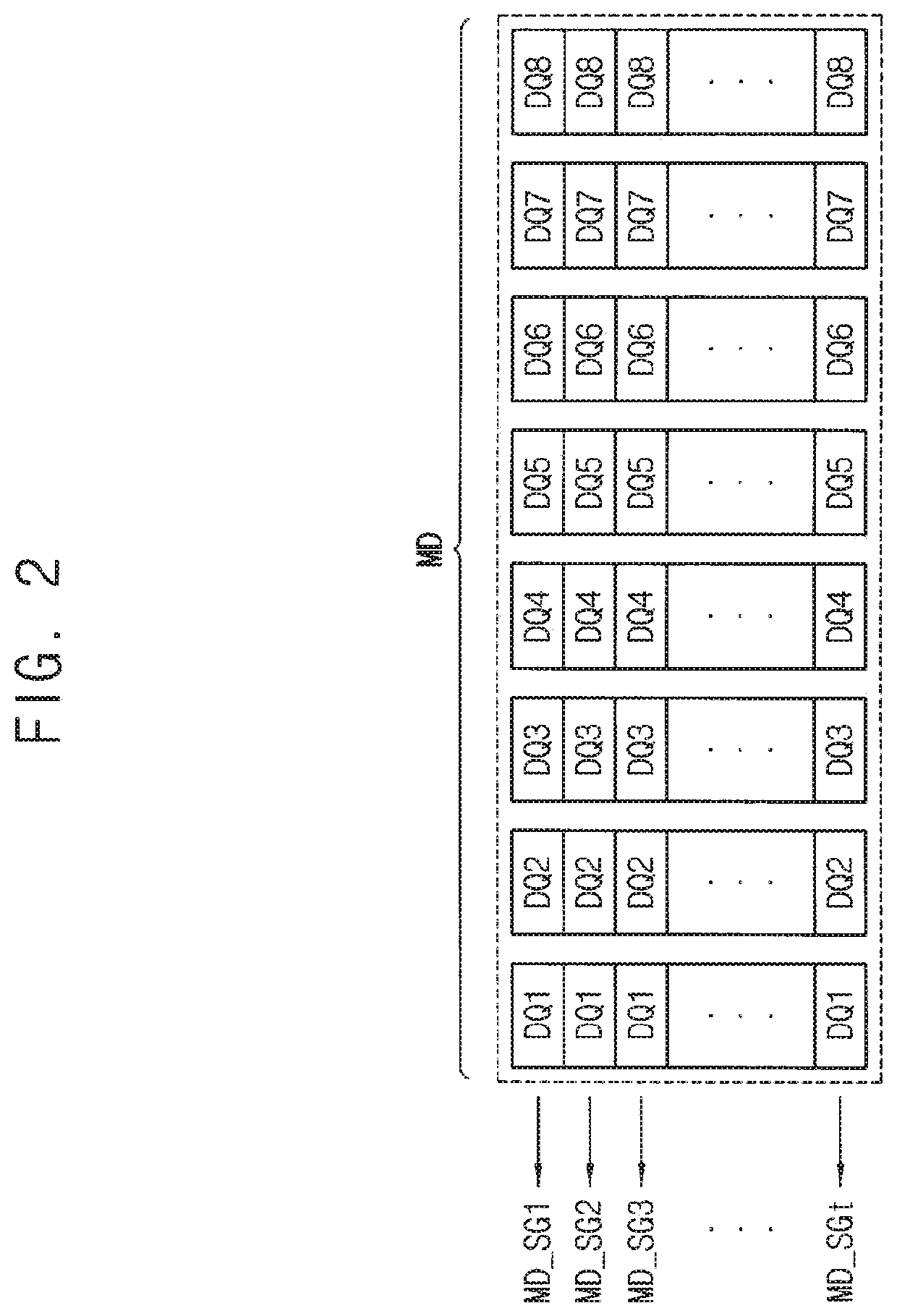

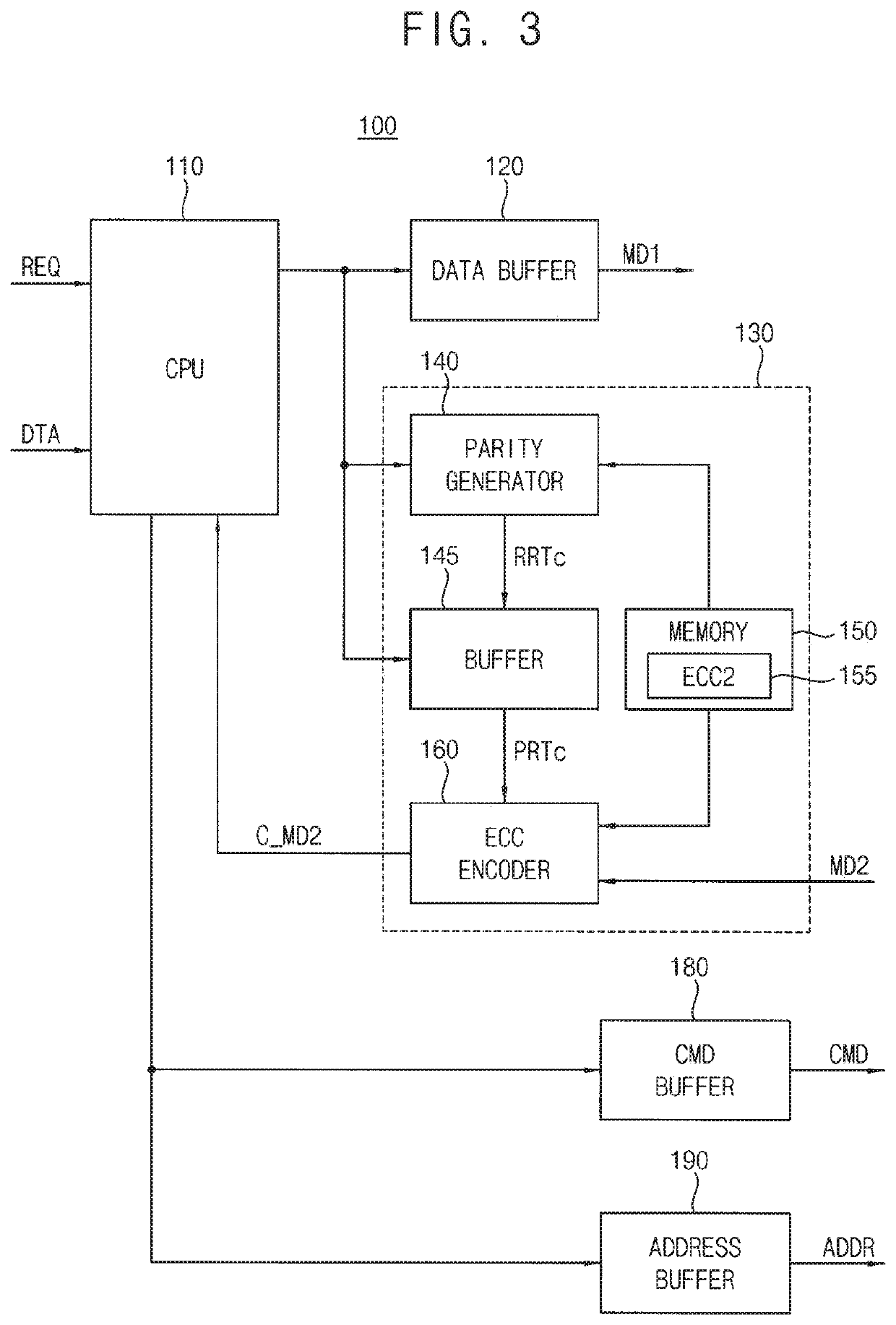

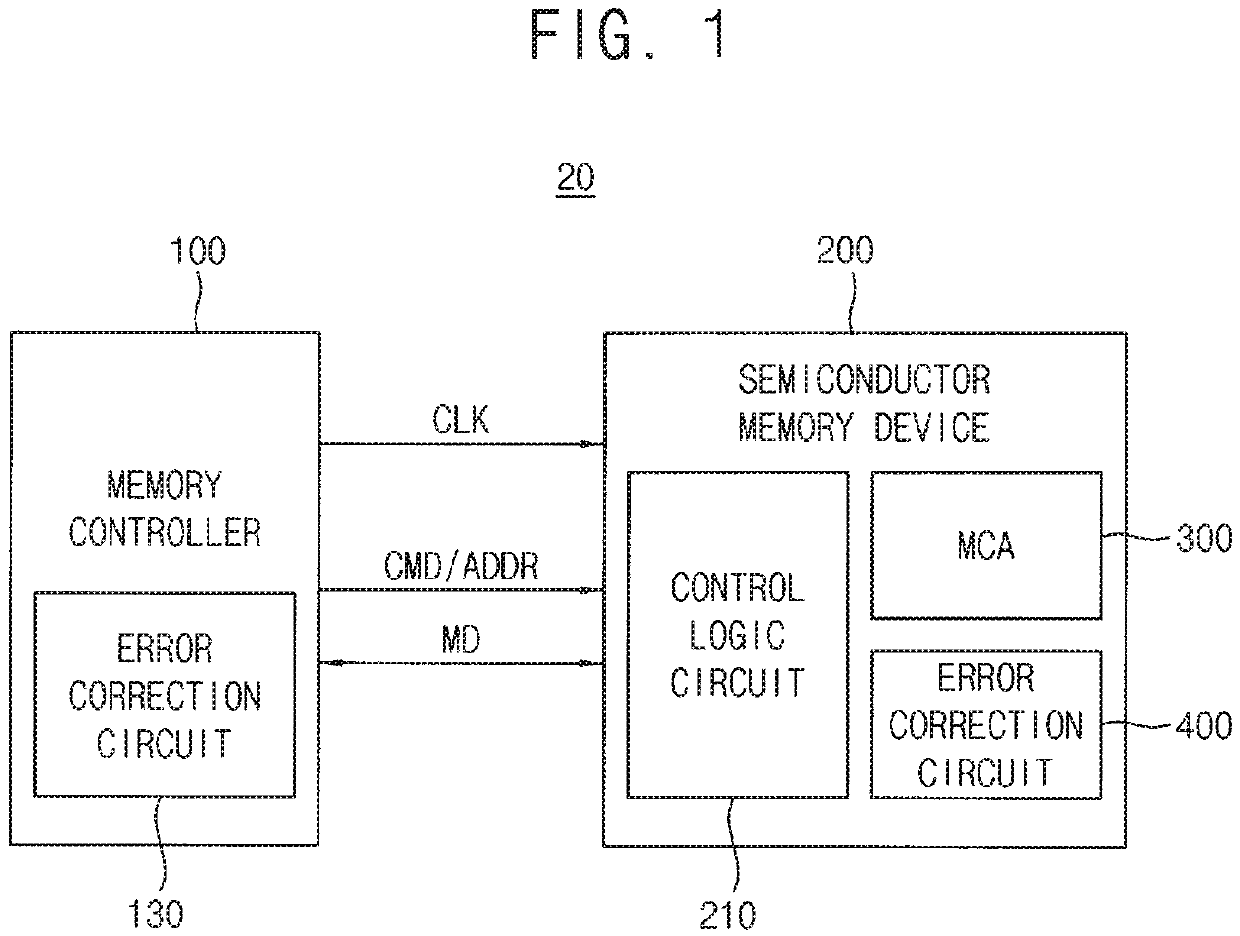

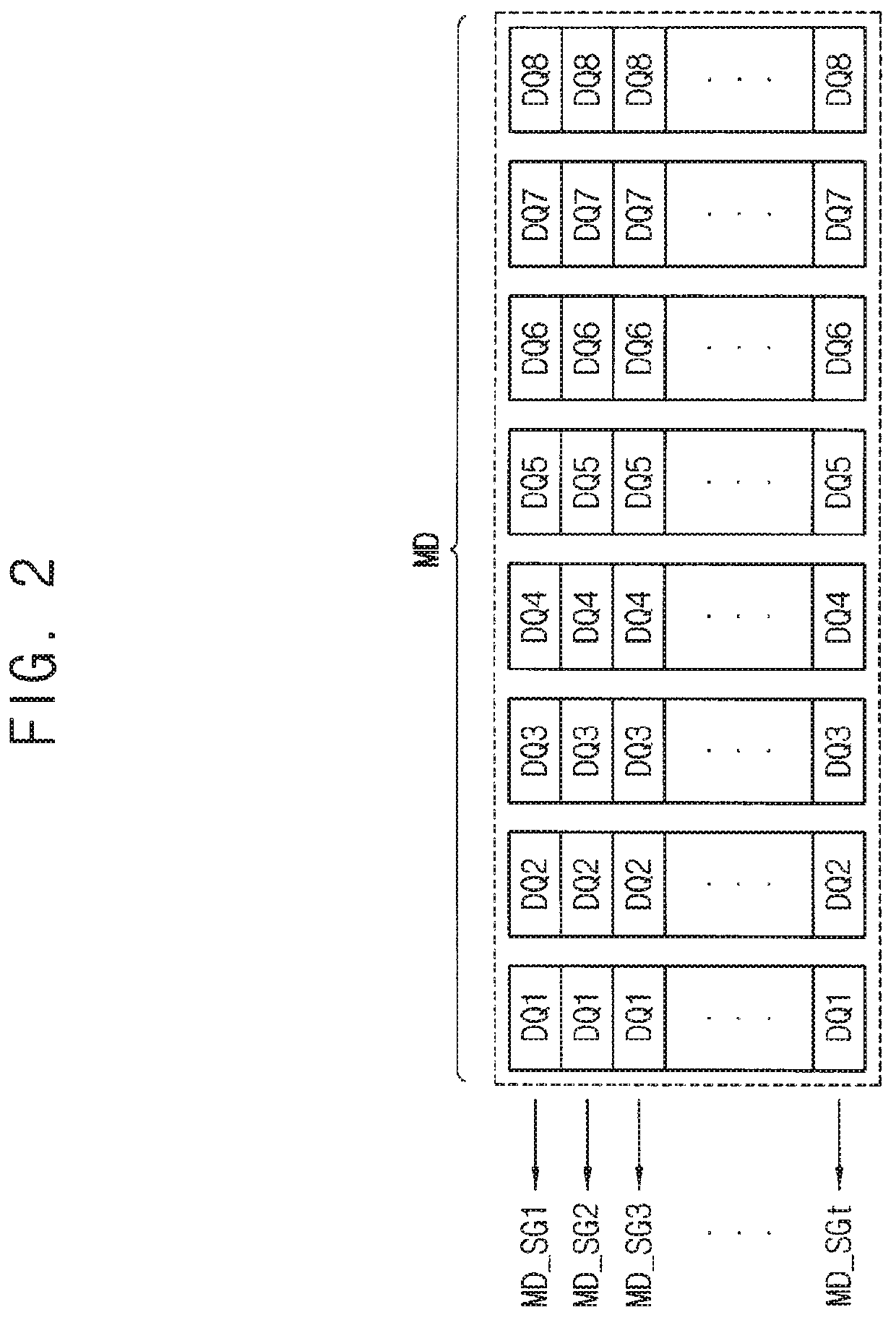

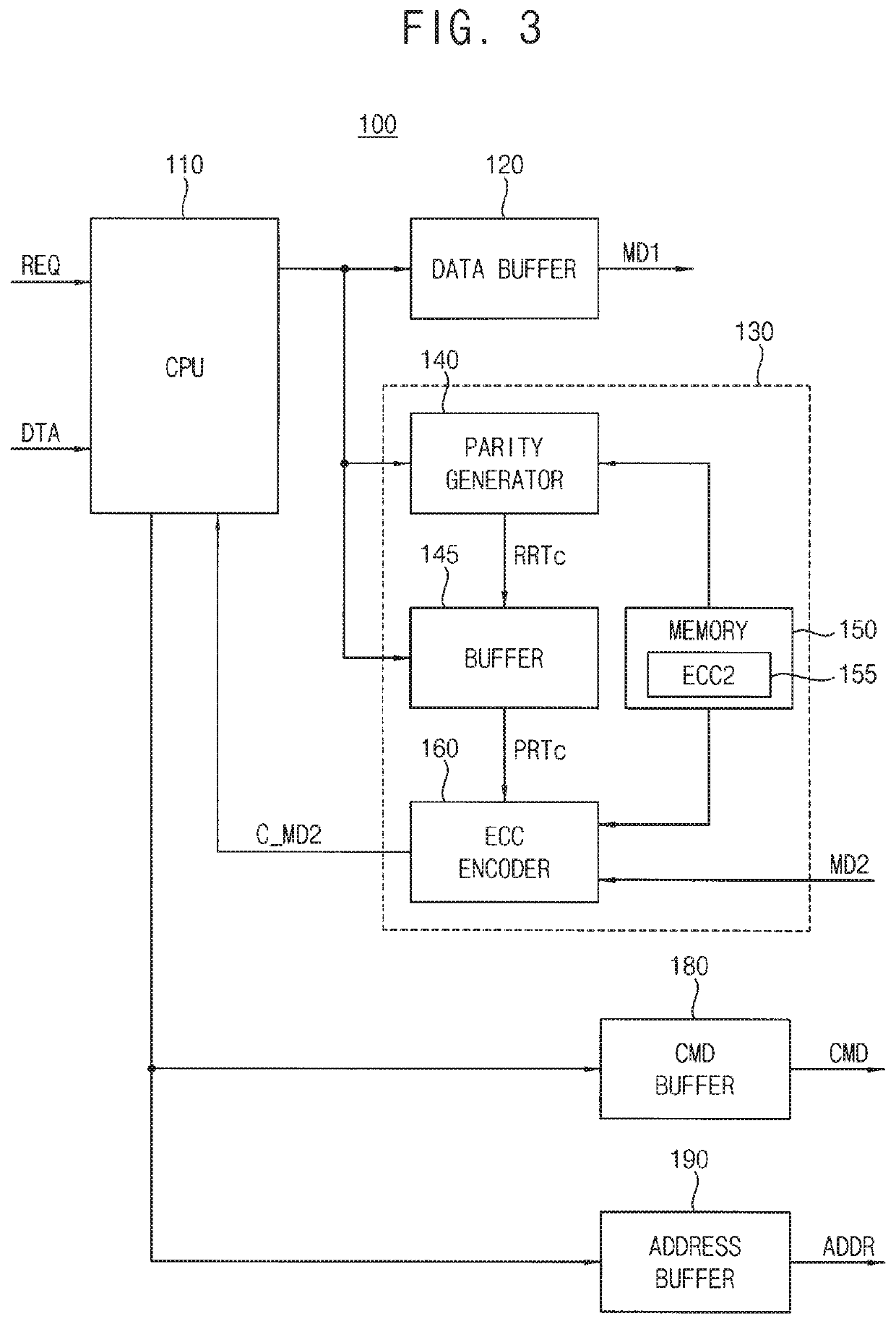

Semiconductor memory devices having enhanced error correction circuits therein

ActiveUS20200394102A1Improve reliability and performanceSolid-state devicesCode conversionMemory cellHemt circuits

An error correction circuit includes an error correction code (ECC) memory and an ECC engine. The ECC memory stores an ECC, which is at least partially represented by a generation matrix. The ECC engine generates parity data based on main data using the ECC, and detects and / or corrects at least one error bit in the main data read from the memory cell array using the parity data. The main data includes a plurality of data bits divided into a plurality of sub data units. The ECC includes a plurality of column vectors divided into a plurality of code groups corresponding to the sub data units. The column vectors have elements configured to gather a mis-corrected bit and multiple error bits in one symbol and the mis-corrected bit is generated due to the multiple error bits in the main data.

Owner:SAMSUNG ELECTRONICS CO LTD

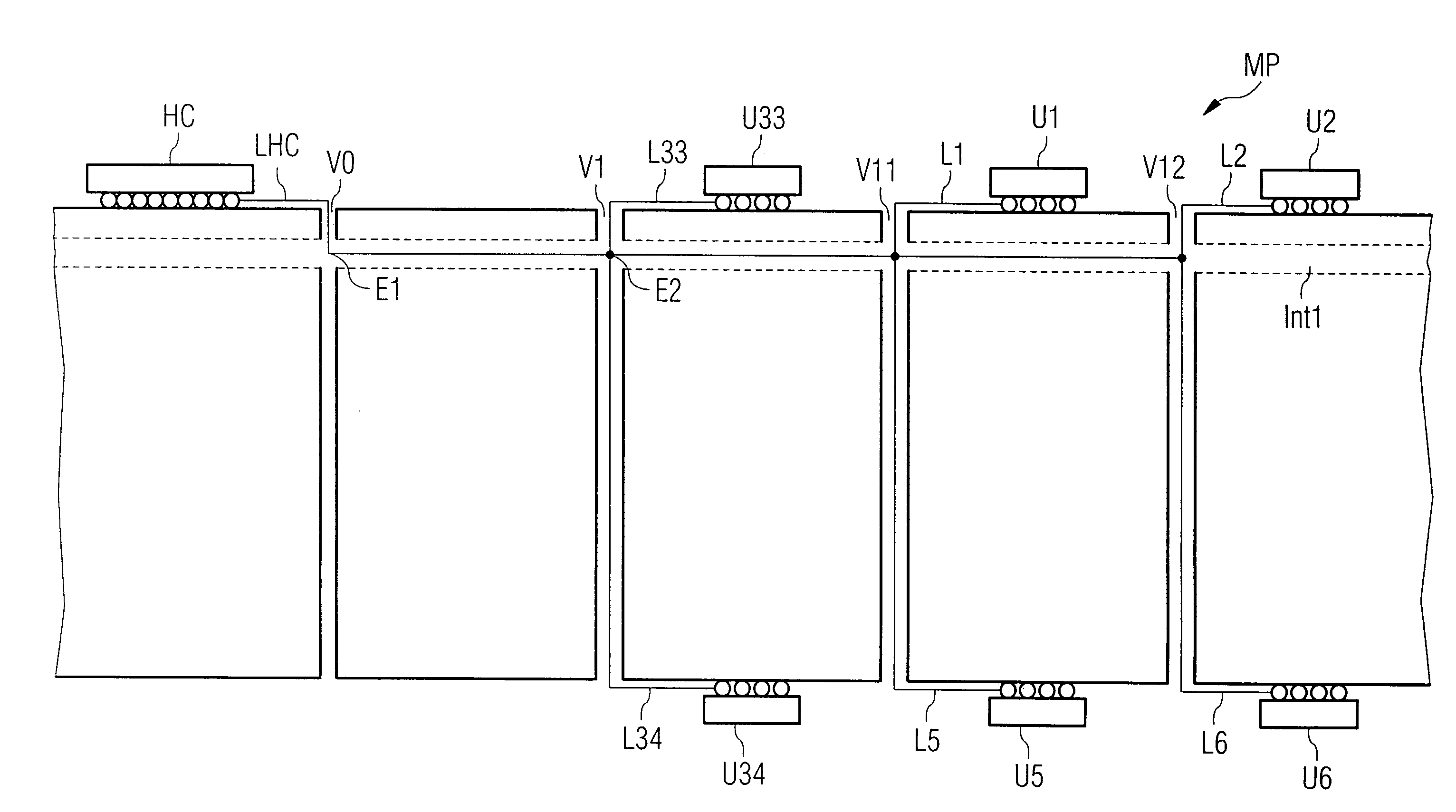

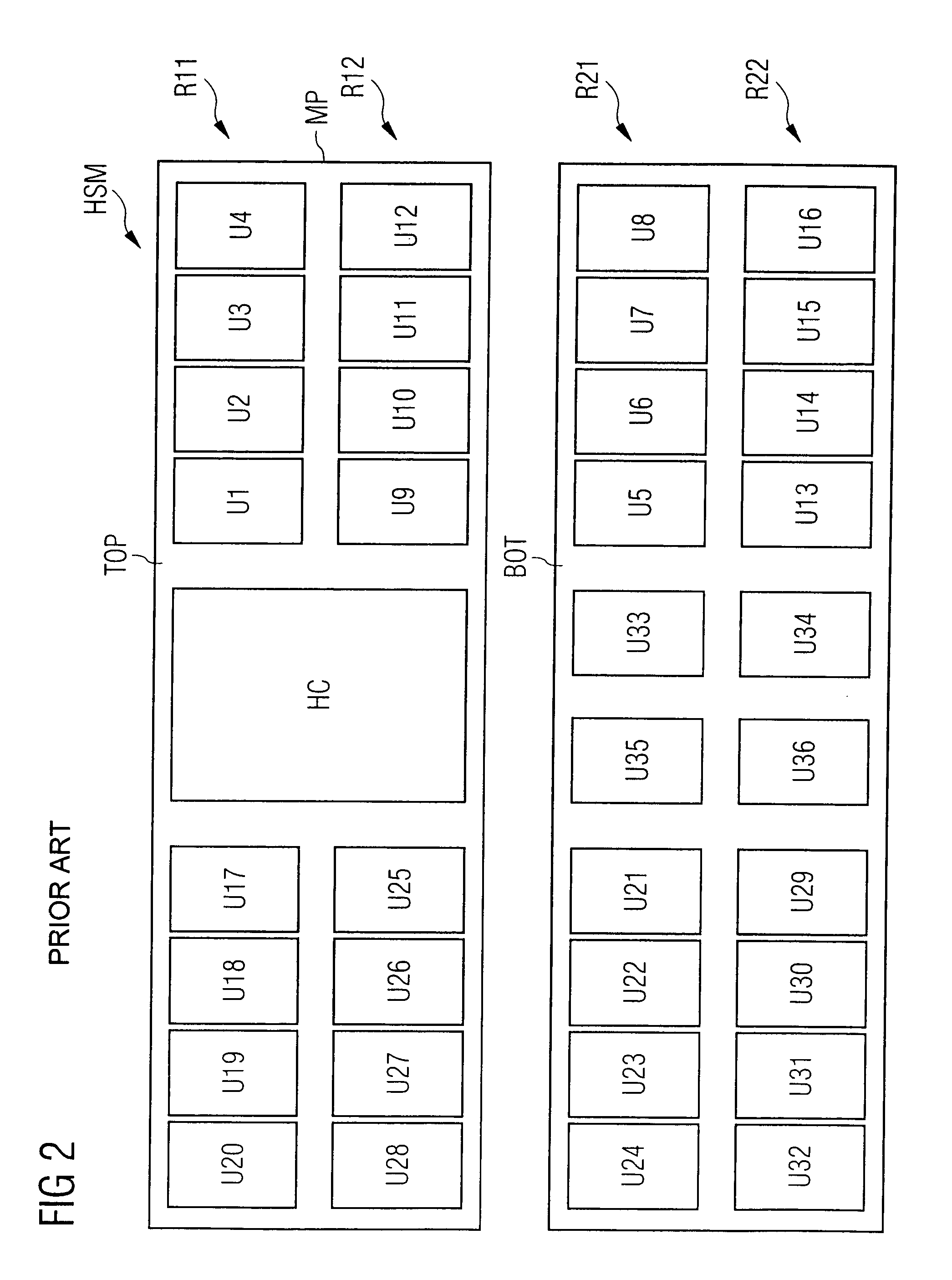

Semiconductor memory module with error correction

InactiveUS7681108B2Simple and space-savingFinal product manufacturePrinted circuit aspectsMemory chipEngineering

A semiconductor memory module comprises a control chip for driving ECC memory chips and further memory chips. The memory chips are arranged in two rows on a top side and a bottom side of the module circuit board. The ECC memory chips are arranged centrally on the module circuit board alongside the rows of the memory chips. A control bus connects the ECC memory chips and also the memory chips to the control chip. In a region remote from the control chip, the control bus branches in a contact-making hole into a first partial bus, to which a first group of memory chips are connected, and a second partial bus, to which a second group of memory chips are connected. The ECC memory chips are likewise connected to the control bus via the contact-making hole. Since the ECC memory chips are not arranged directly under the control chip, a bus branch directed backward is not required. As a result, space considerations on the module circuit board are eased and signal integrity on the control buses is improved.

Owner:POLARIS INNOVATIONS LTD

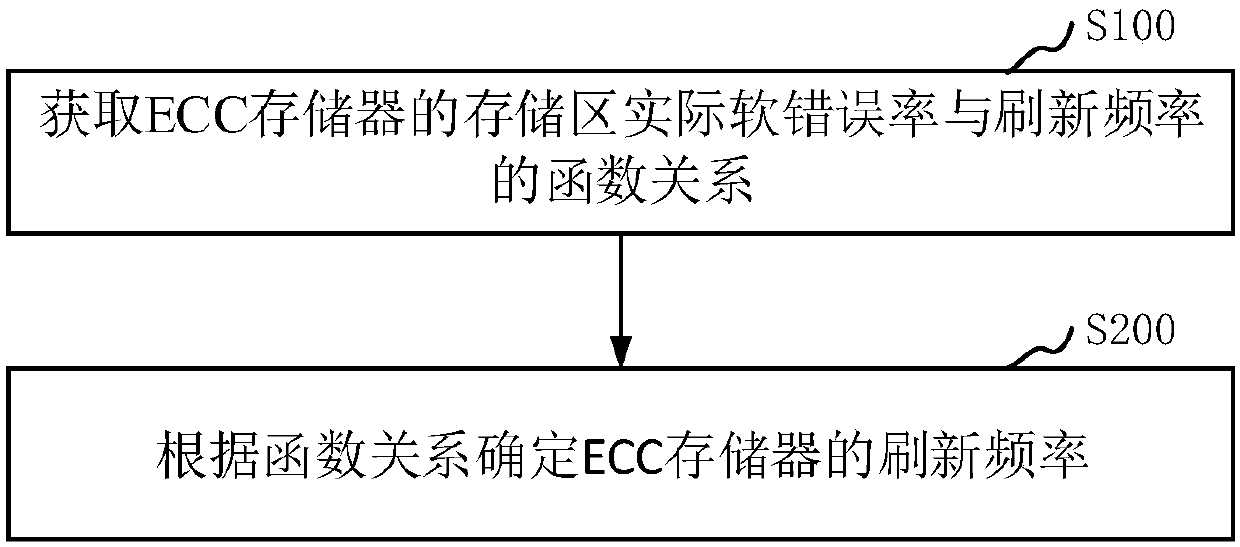

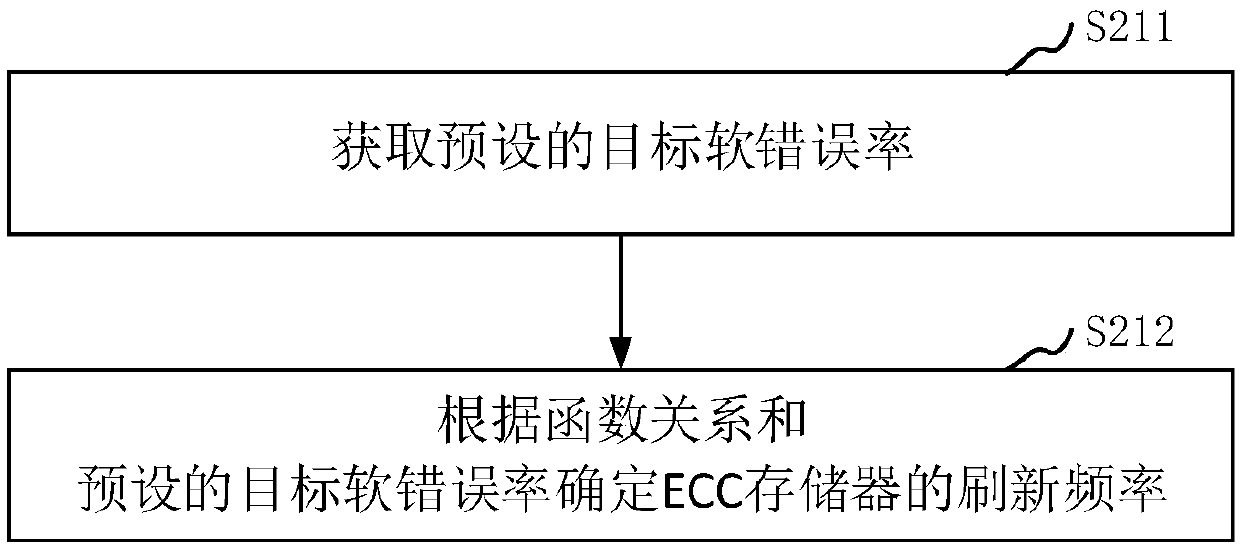

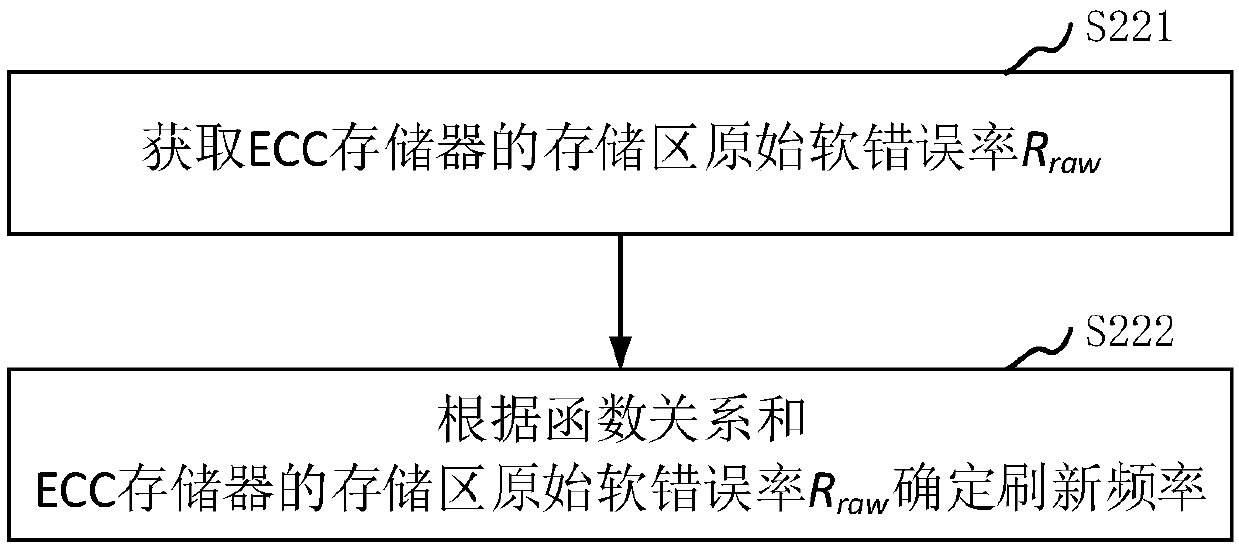

A method and apparatus for determining a refresh frequency of an ECC memory

PendingCN109656746AReduce soft error rateImprove resistance to soft errorsRedundant data error correctionECC memoryDependability

The invention relates to a method and an apparatus for determining a refresh frequency of an ECC memory. The invention provides a method for determining the refresh frequency of an ECC (Error Correction Code) memory. The method comprises the following steps of: obtaining a function relationship between an actual soft error rate and the refresh frequency of a storage region of the ECC memory; And determining the refresh frequency of the ECC memory according to the function relationship. According to the method, the optimal design of the refresh frequency is realized by obtaining the function relationship between the actual soft error rate and the refresh frequency of the storage area of the ECC memory and determining the refresh frequency of the ECC memory according to the function relationship; The soft error rate of the ECC memory can be reduced without occupying system resources excessively, it is guaranteed that the soft error rate of the ECC memory meets the actual engineering requirement, the soft error resistance of a storage area of the ECC memory is effectively improved, and the reliability of the ECC memory and a system applying the ECC memory is enhanced. The invention also provides a device for determining the refresh frequency of the ECC memory and a computer readable storage medium.

Owner:CHINA ELECTRONICS PROD RELIABILITY & ENVIRONMENTAL TESTING RES INST THE FIFTH ELECTRONICS RES INST OF MIITCEPREI LAB

Semiconductor memory devices having enhanced error correction circuits therein

ActiveUS11436079B2Improve reliability and performanceSolid-state devicesCode conversionMemory cellHemt circuits

An error correction circuit includes an error correction code (ECC) memory and an ECC engine. The ECC memory stores an ECC, which is at least partially represented by a generation matrix. The ECC engine generates parity data based on main data using the ECC, and detects and / or corrects at least one error bit in the main data read from the memory cell array using the parity data. The main data includes a plurality of data bits divided into a plurality of sub data units. The ECC includes a plurality of column vectors divided into a plurality of code groups corresponding to the sub data units. The column vectors have elements configured to gather a mis-corrected bit and multiple error bits in one symbol and the mis-corrected bit is generated due to the multiple error bits in the main data.

Owner:SAMSUNG ELECTRONICS CO LTD

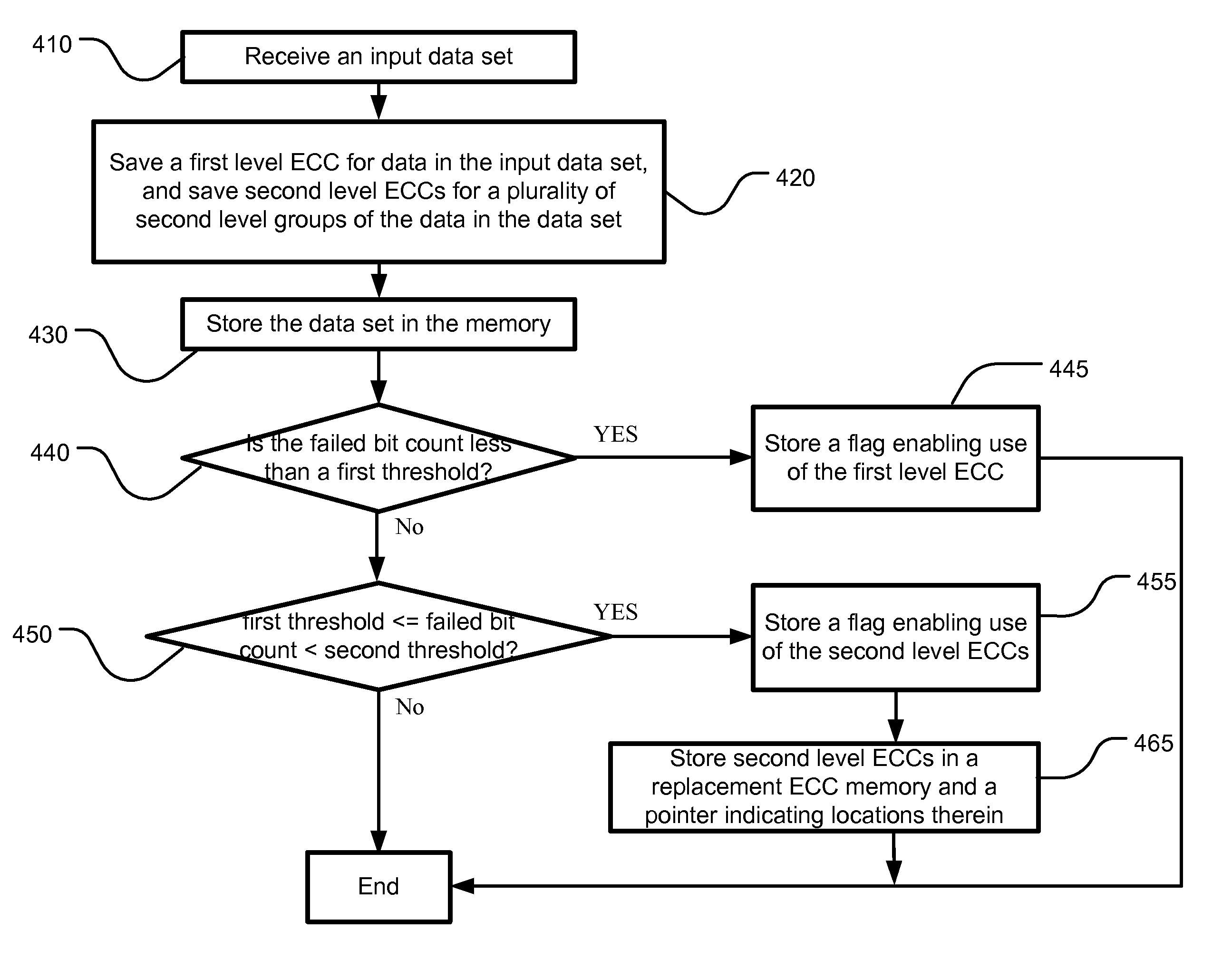

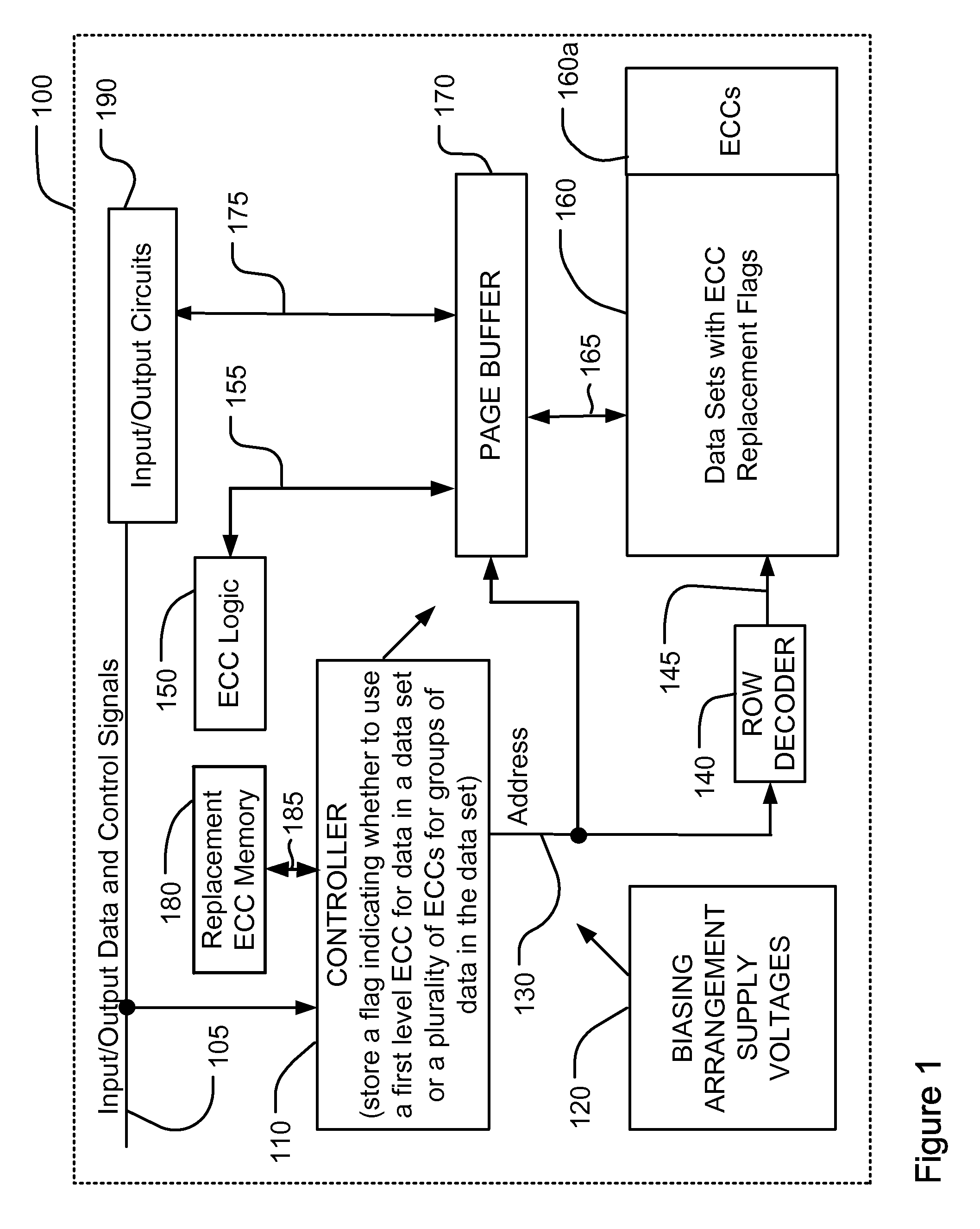

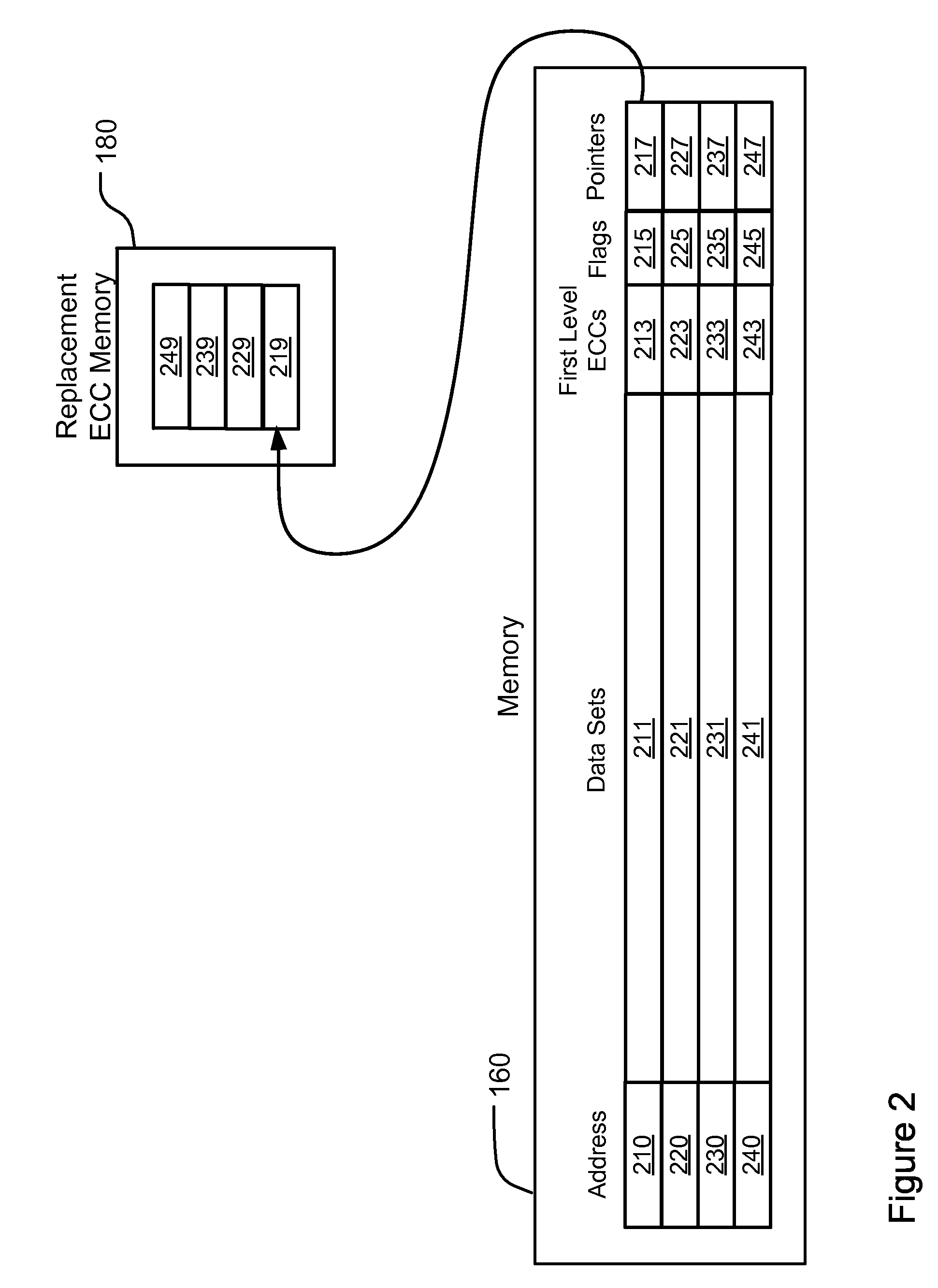

Dynamic data density ECC

ActiveUS9542268B2Error correction/detection using multiple parity bitsCode conversionData setParallel computing

Owner:MACRONIX INT CO LTD

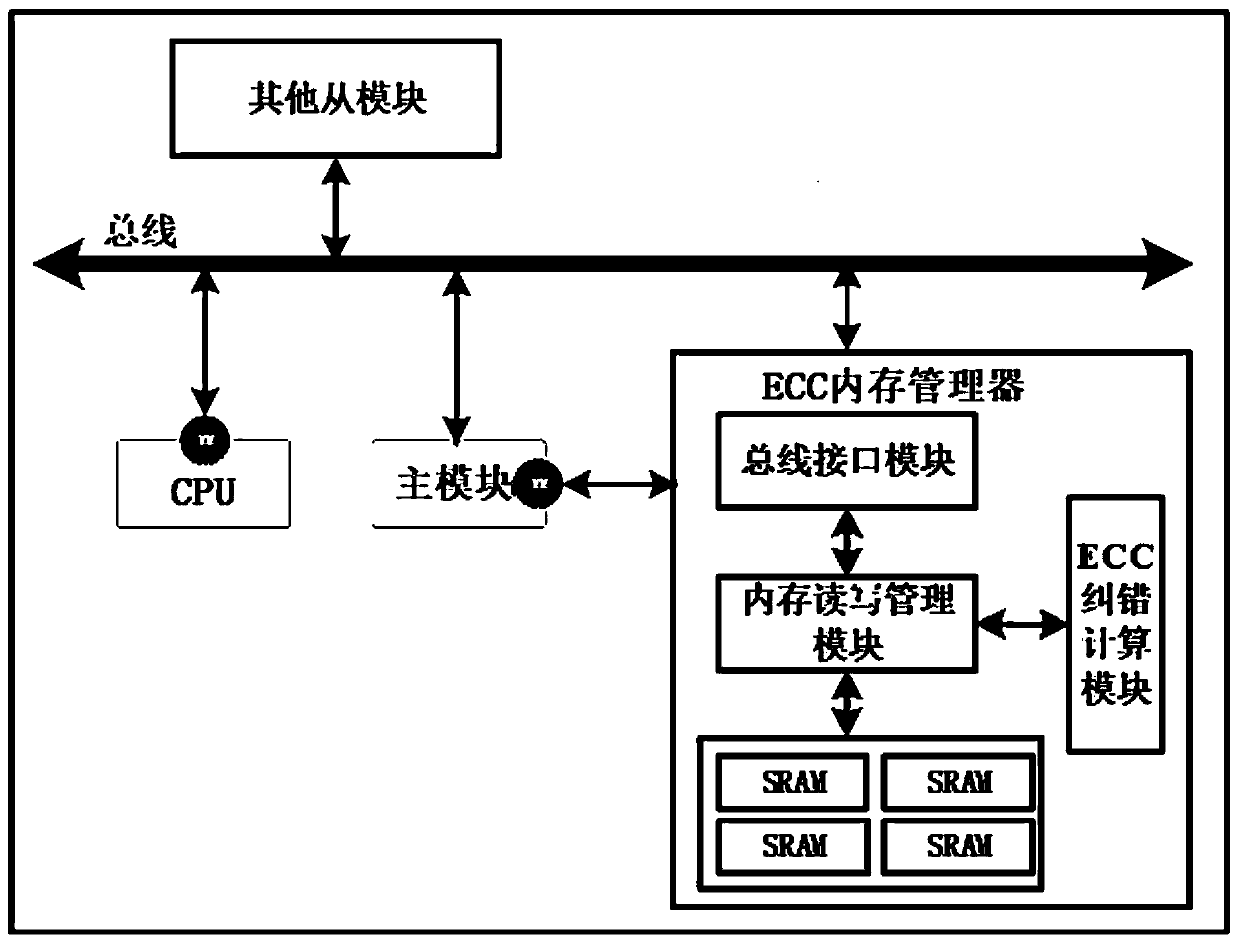

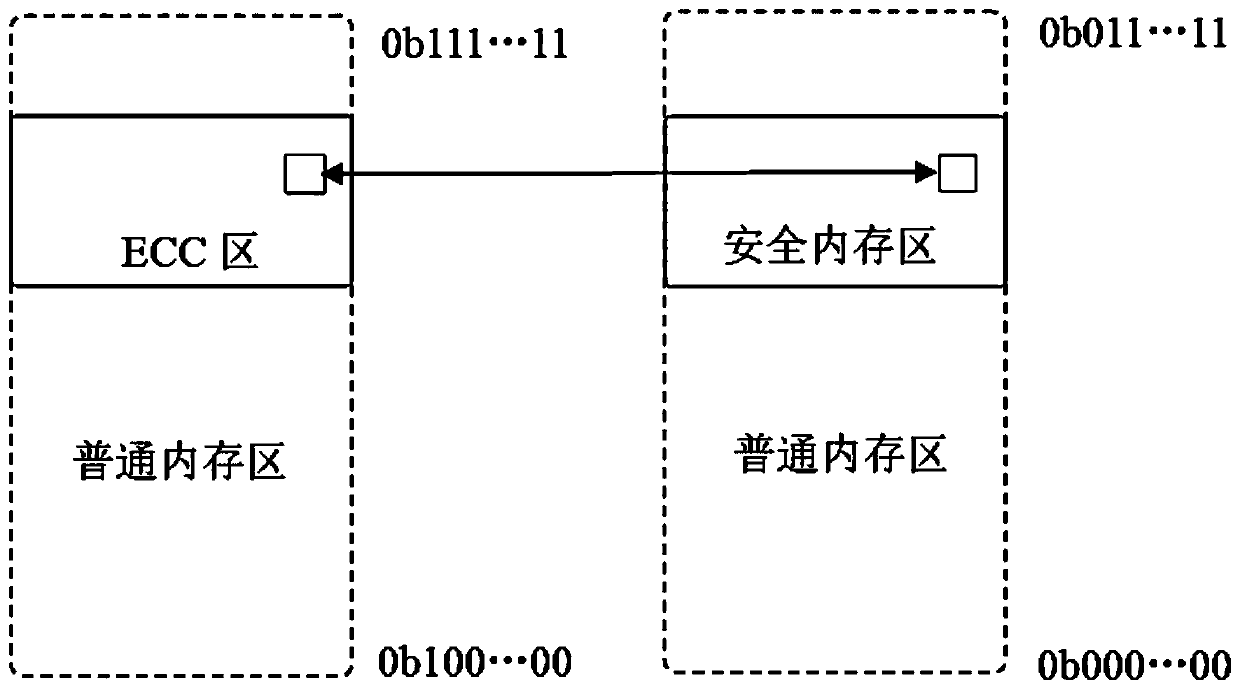

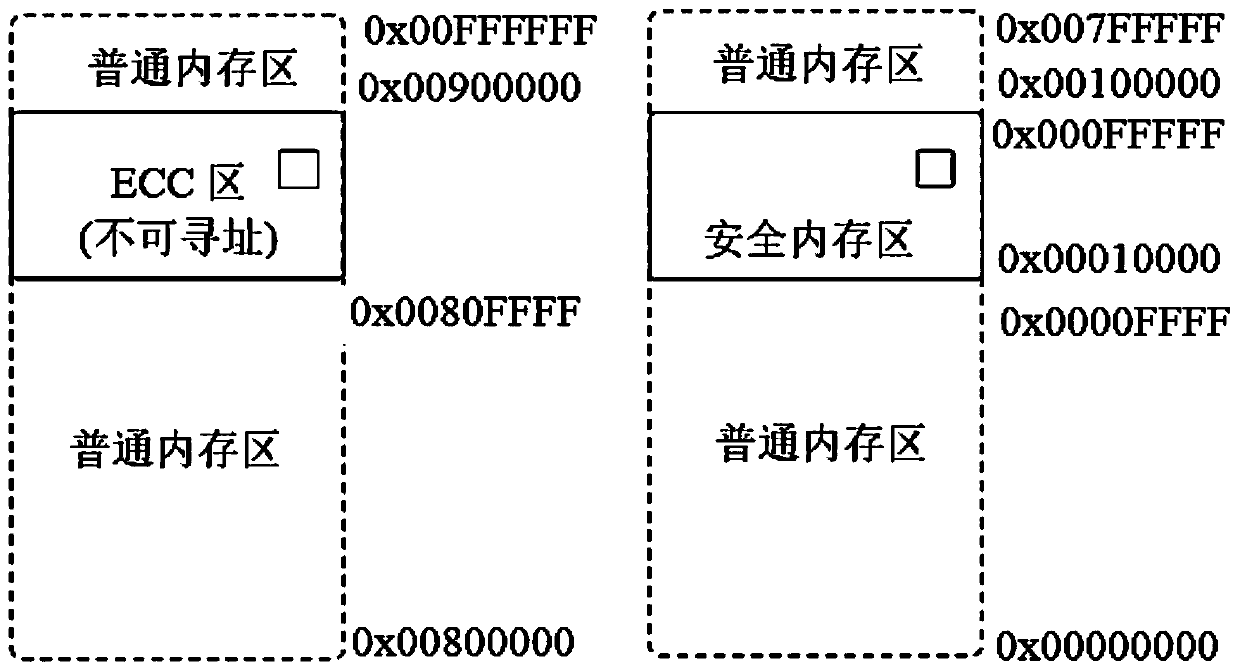

ECC memory manager, ECC memory management method and electronic equipment

The invention discloses an ECC memory manager, an ECC memory management method and electronic equipment. A bus interface module is provided with a register group and is used for configuring configuration information of an ECC memory manager. The memory can be freely divided into an ECC memory area and a common memory area according to an address space; the ECC error correction function of the memory is freely switched; when the ECC memory area is configured to be 0, namely an ECC closed state, the two memory areas are consistent with a conventional use mode; and when the ECC is in an open state and an effective memory area range is configured, an ECC check value is generated at the corresponding ECC area address for all byte data written into the ECC memory area through the ECC error correction calculation module, and errors of the read data are carefully detected and corrected through the ECC error correction calculation module. Therefore, the invention has the technical characteristics that the memory utilization rate is high, the ECC function can be freely switched on and off, the size of the ECC memory is adjustable, and the read-write speed is high.

Owner:ZHEJIANG UNIV +1

Computer system and processing method utilizing graphics processing unit with ECC and non-ECC memory switching capability

Computer systems and methods that utilize a GPU whose operation is able to switch between ECC and non-ECC memory operations on demand. The computer system includes a graphics processing unit and a memory controller and local memory that are functionally integrated with the graphics processing unit. The memory controller has at least two operating modes comprising a first memory access mode that uses error checking and correction when accessing the local memory, and a second memory access mode that does not use error checking and correction when accessing the local memory. The memory controller is further operable to switch the operation of the memory controller between the first and second memory access modes without rebooting the computer system.

Owner:KIOXIA CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com