Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

63results about How to "Sufficient gain" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

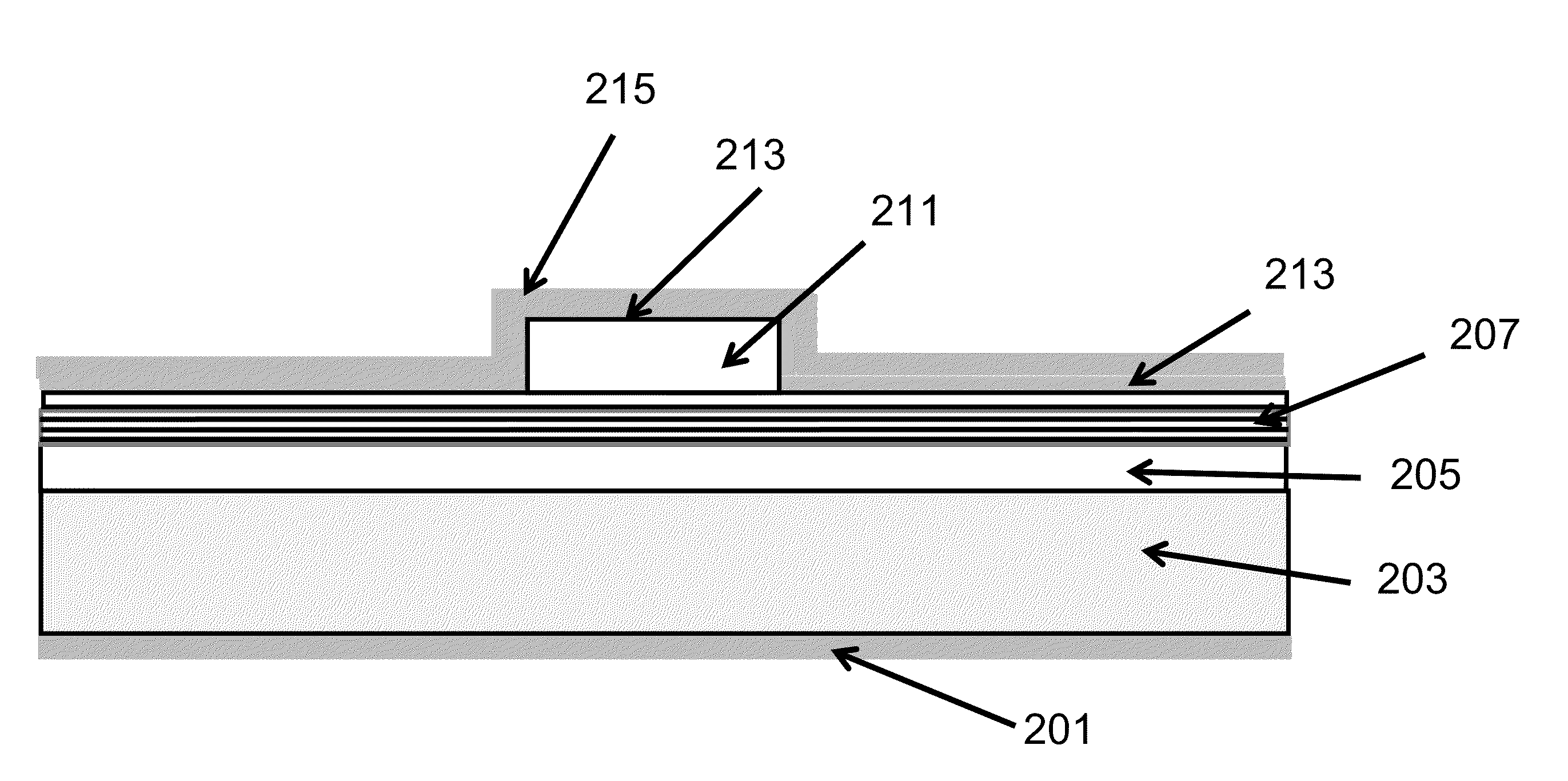

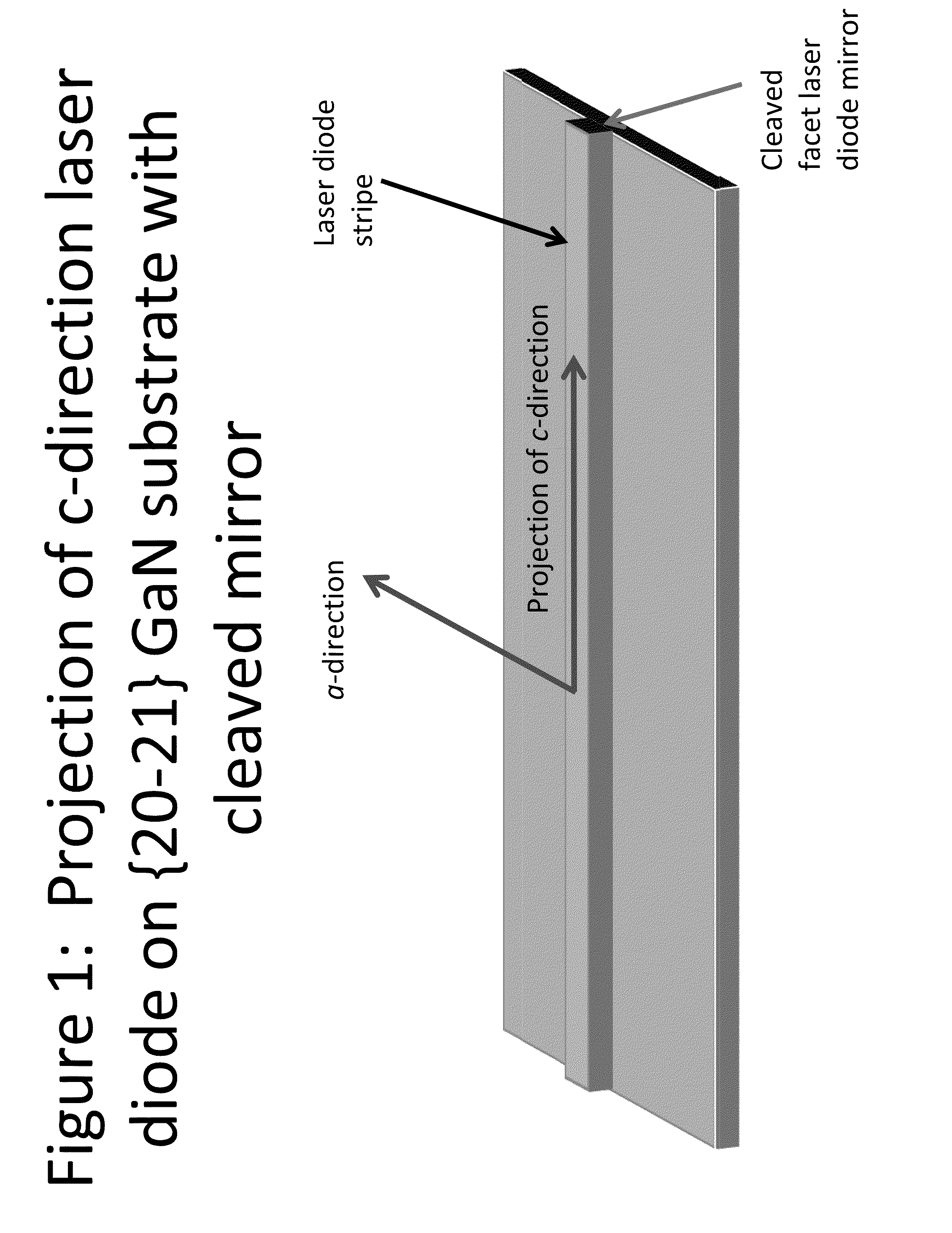

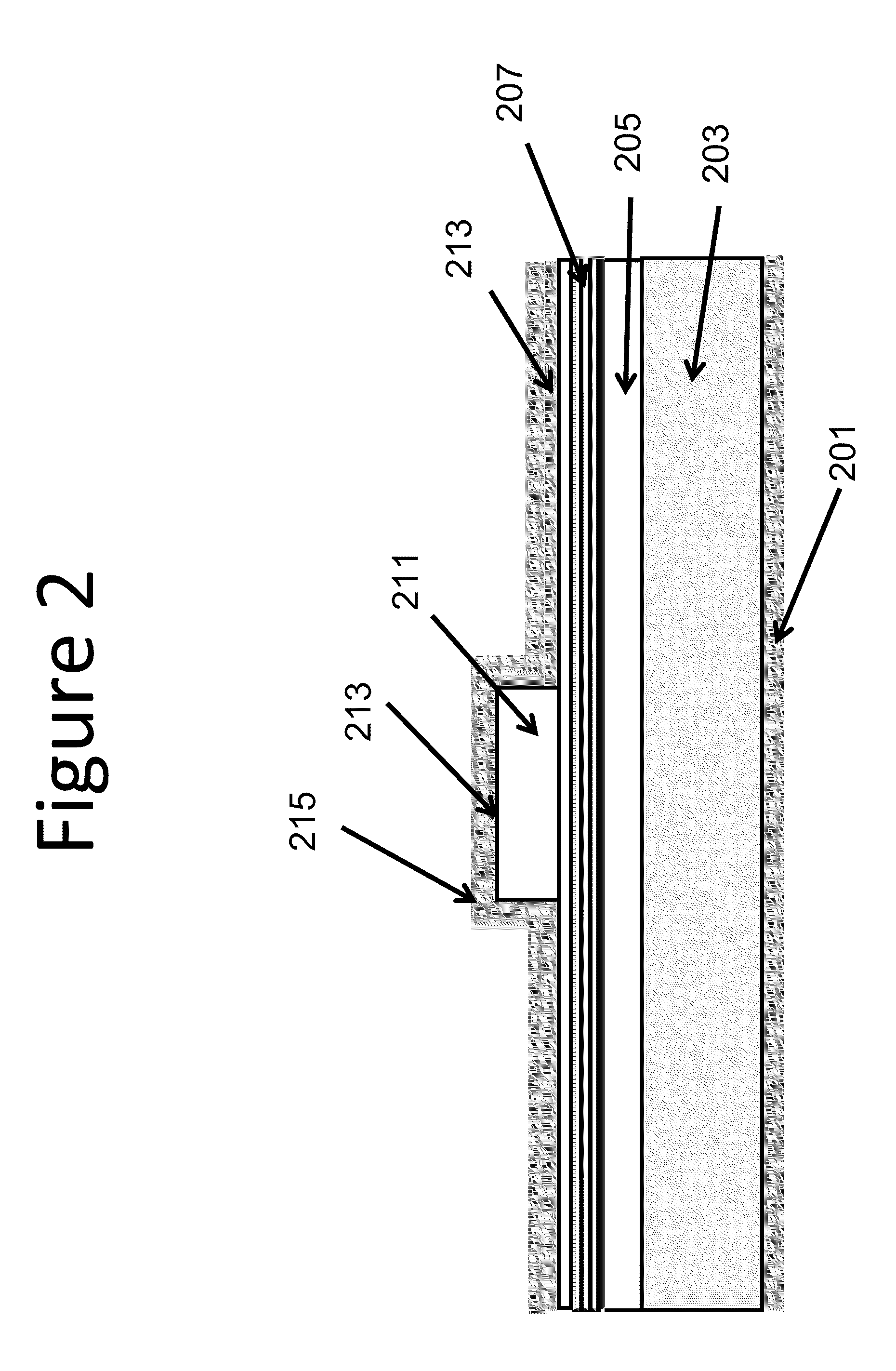

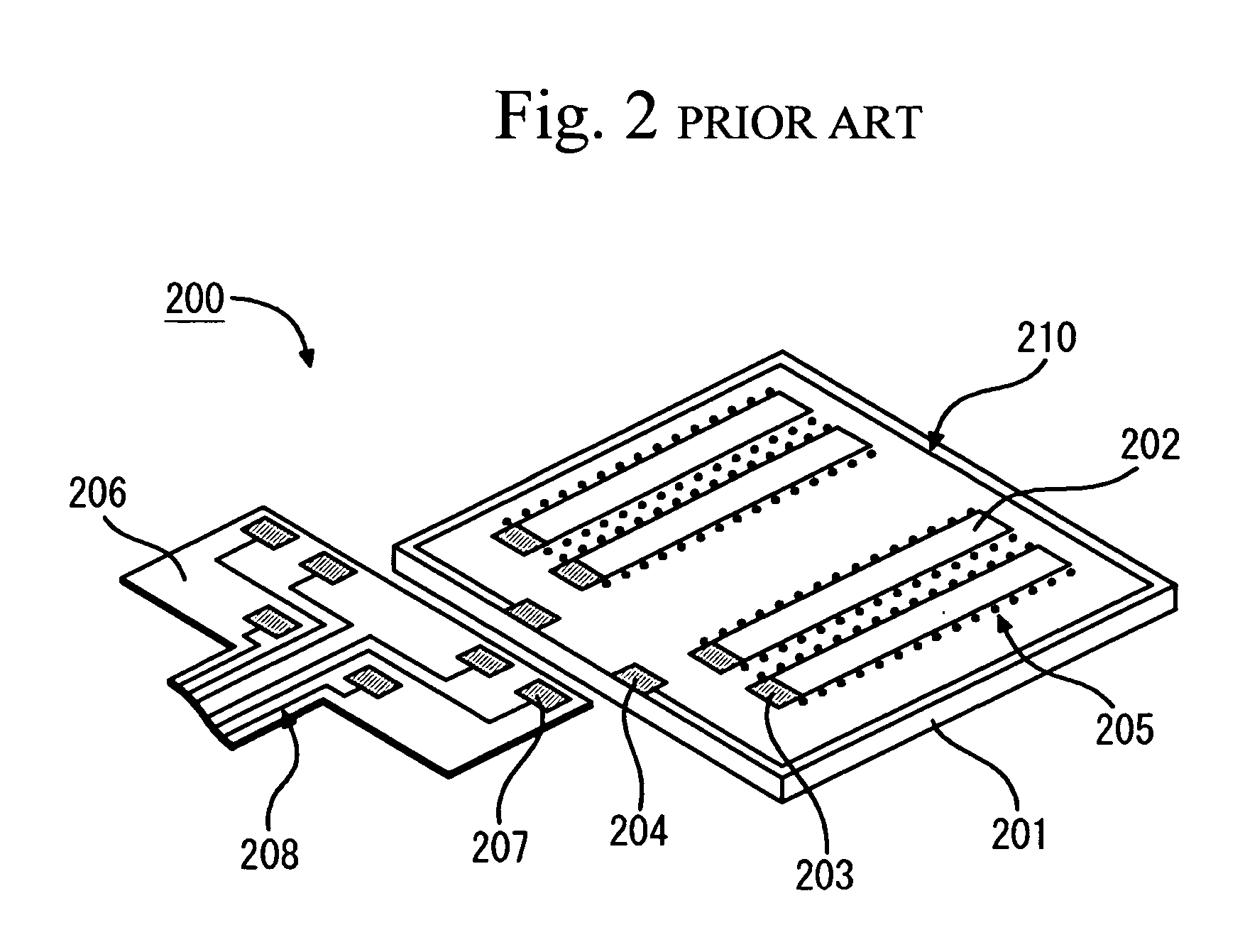

Low Voltage Laser Diodes on Gallium and Nitrogen Containing Substrates

ActiveUS20110064101A1Improved cleavesSimple and cost-effectiveOptical wave guidanceLaser detailsLow voltageNitrogen

A low voltage laser device having an active region configured for one or more selected wavelengths of light emissions.

Owner:KYOCERA SLD LASER INC

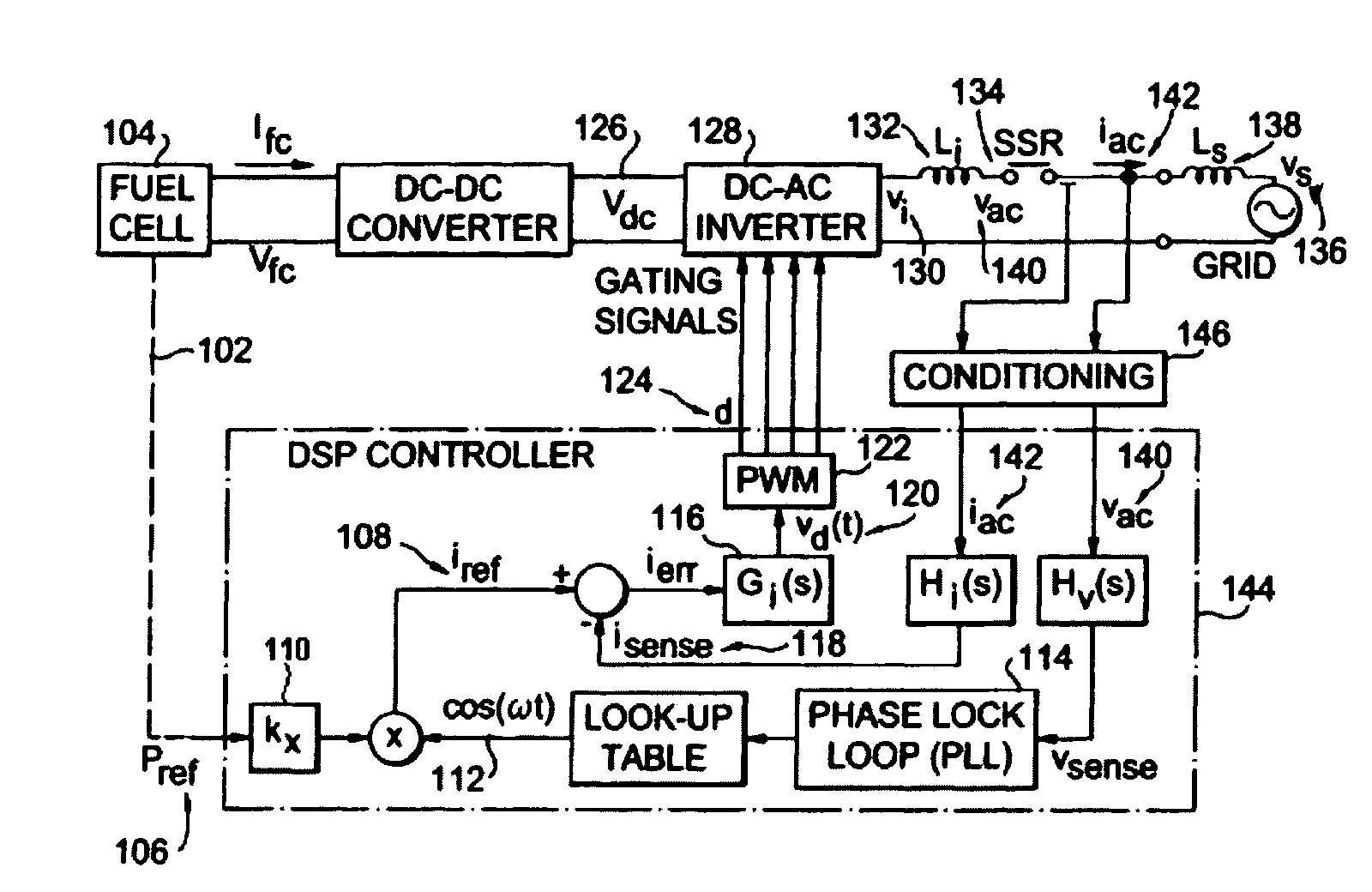

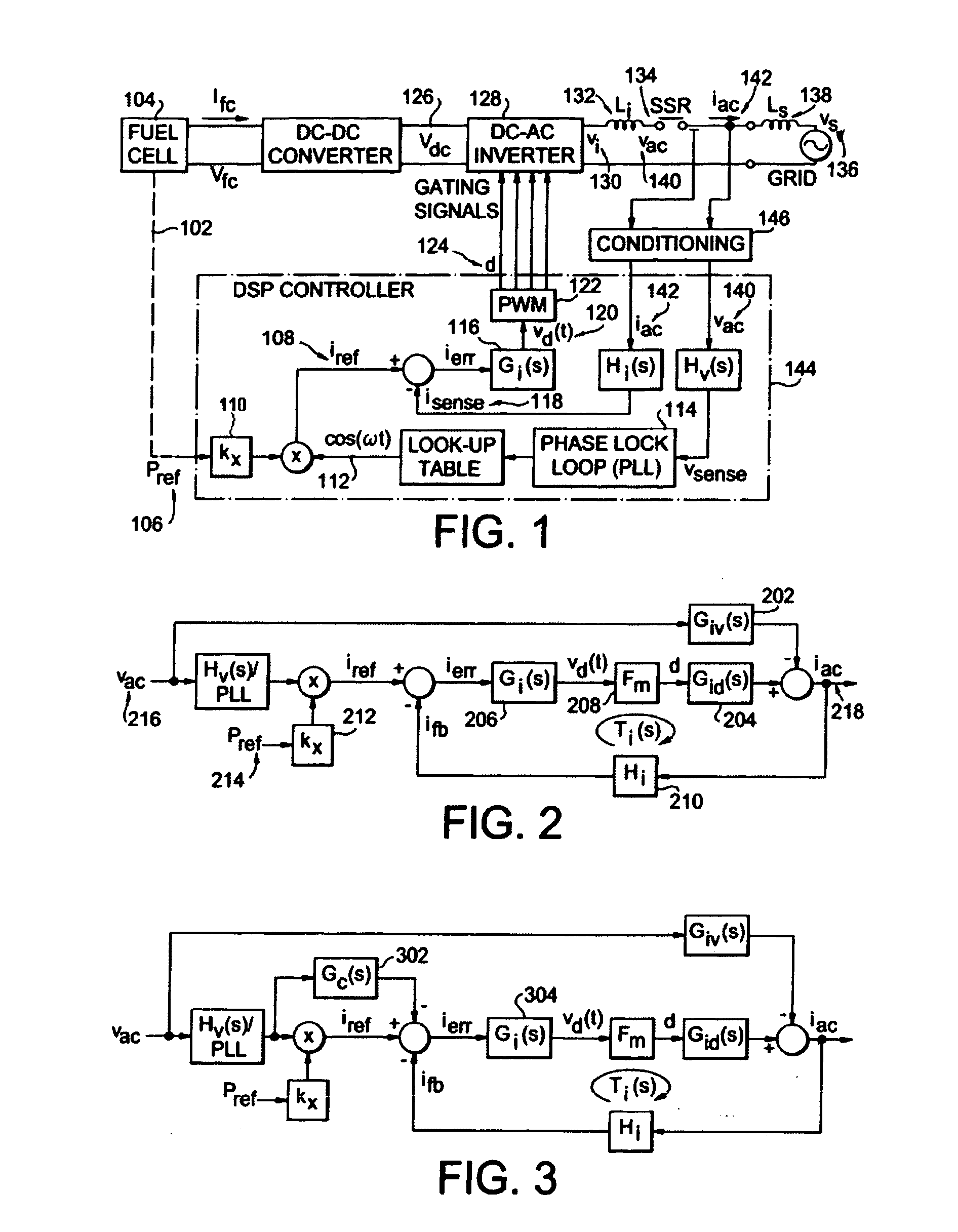

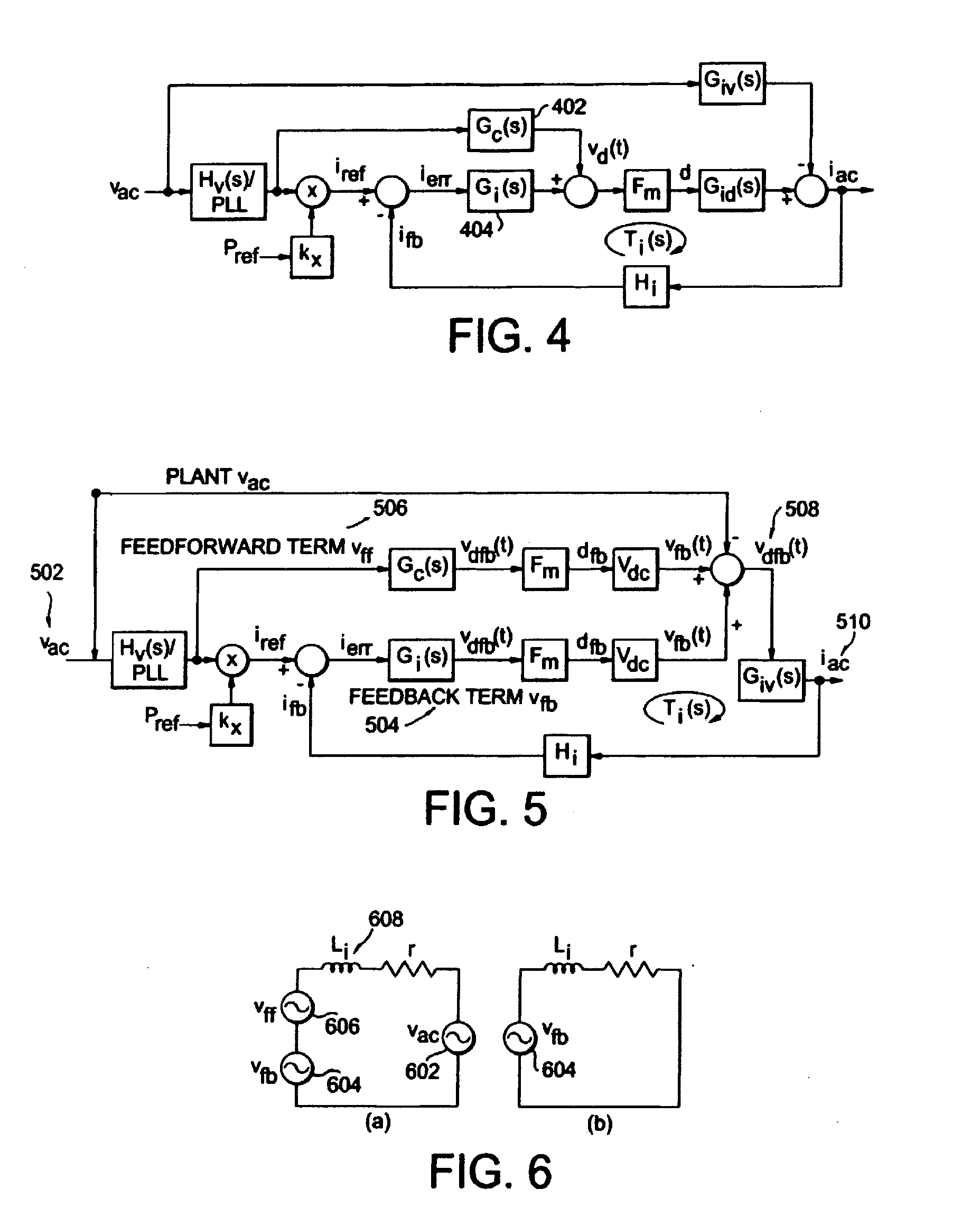

Control system and method for a universal power conditioning system

ActiveUS20080205096A1Avoid precision problemsSolve the stability is not highEfficient power electronics conversionAc-dc conversionFundamental frequencyCatastrophic failure

A new current loop control system method is proposed for a single-phase grid-tie power conditioning system that can be used under a standalone or a grid-tie mode. This type of inverter utilizes an inductor-capacitor-inductor (LCL) filter as the interface in between inverter and the utility grid. The first set of inductor-capacitor (LC) can be used in the standalone mode, and the complete LCL can be used for the grid-tie mode. A new admittance compensation technique is proposed for the controller design to avoid low stability margin while maintaining sufficient gain at the fundamental frequency. The proposed current loop controller system and admittance compensation technique have been simulated and tested. Simulation results indicate that without the admittance path compensation, the current loop controller output duty cycle is largely offset by an undesired admittance path. At the initial simulation cycle, the power flow may be erratically fed back to the inverter causing catastrophic failure. With admittance path compensation, the output power shows a steady-state offset that matches the design value. Experimental results show that the inverter is capable of both a standalone and a grid-tie connection mode using the LCL filter configuration.

Owner:VIRGINIA TECH INTPROP INC

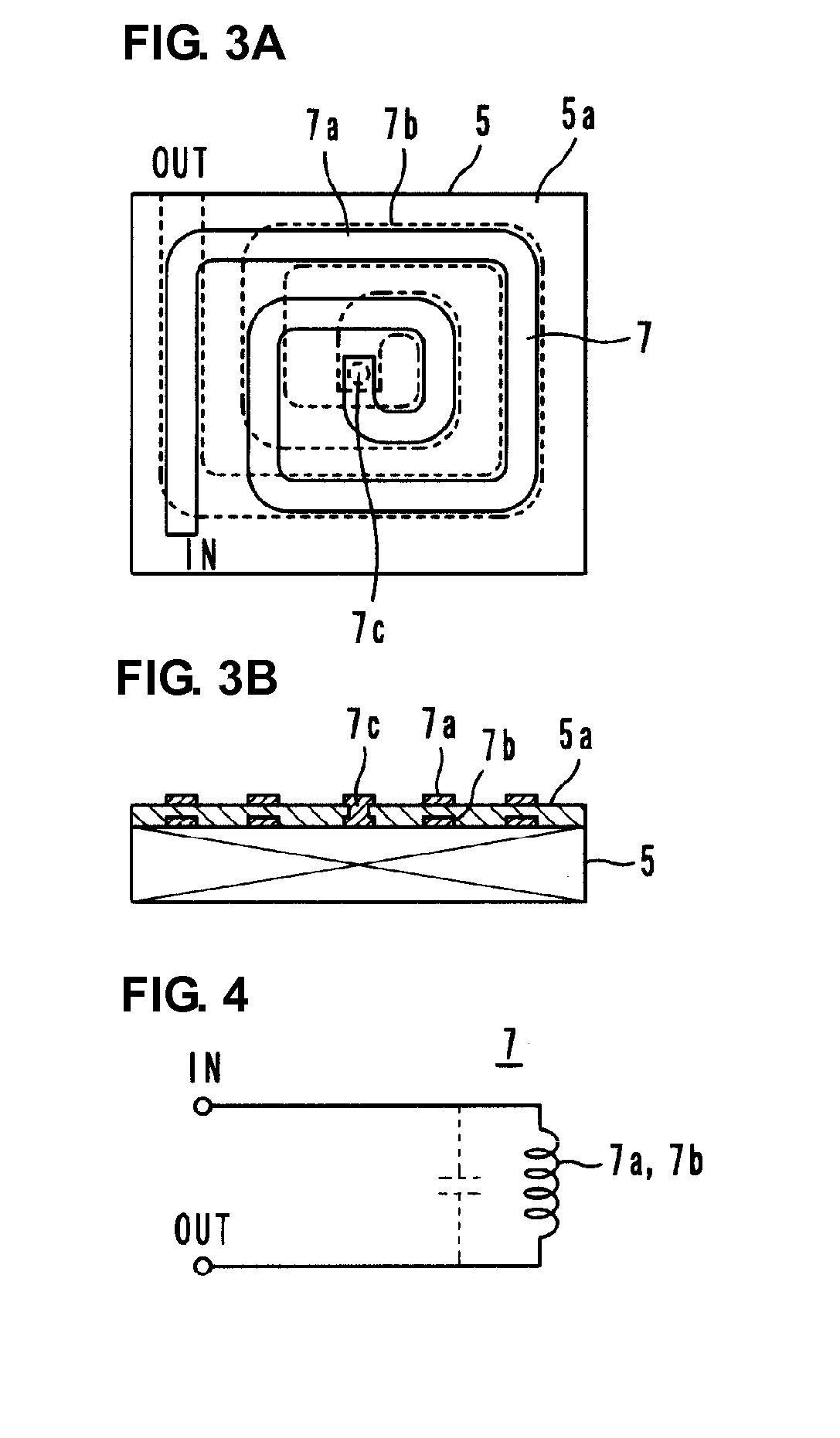

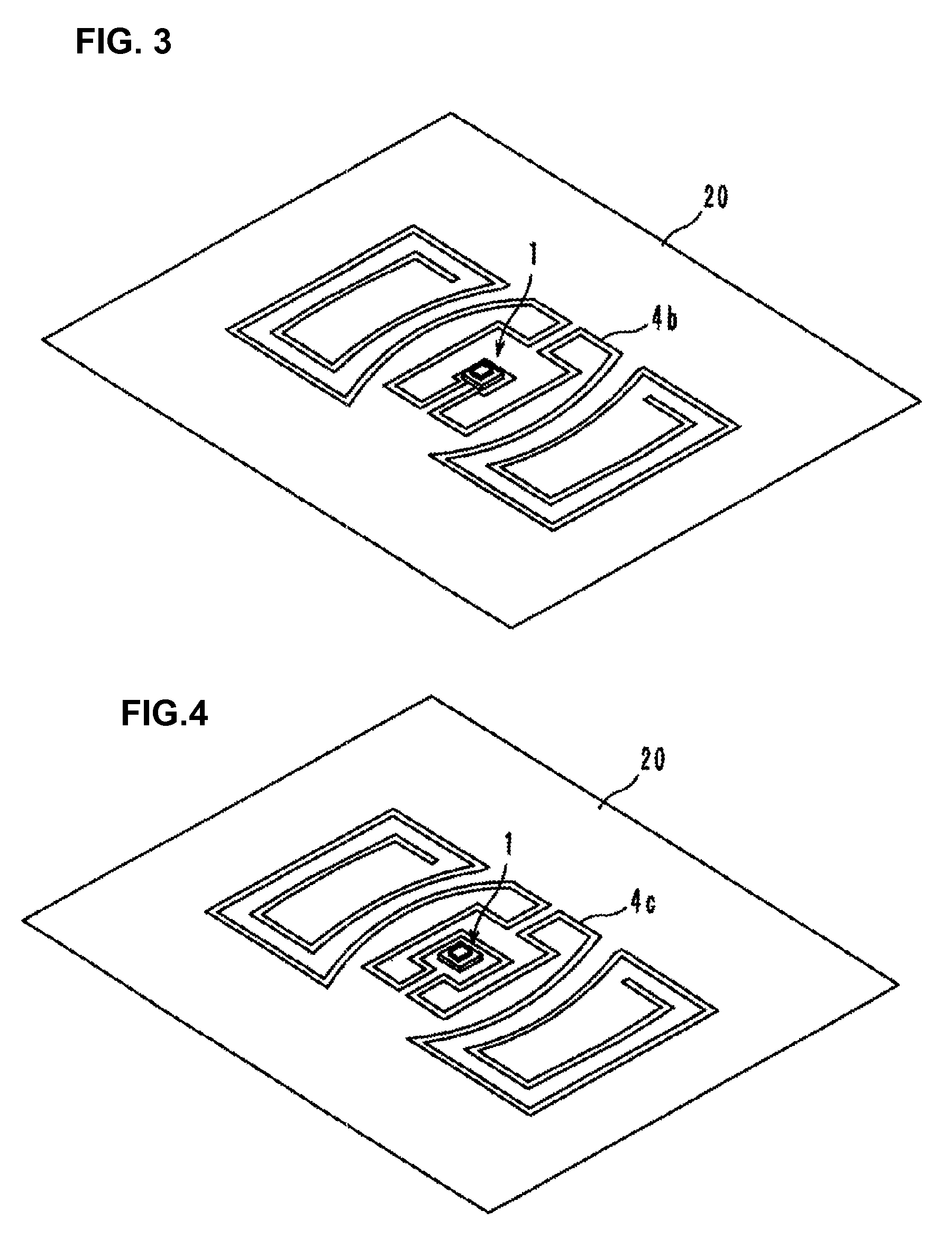

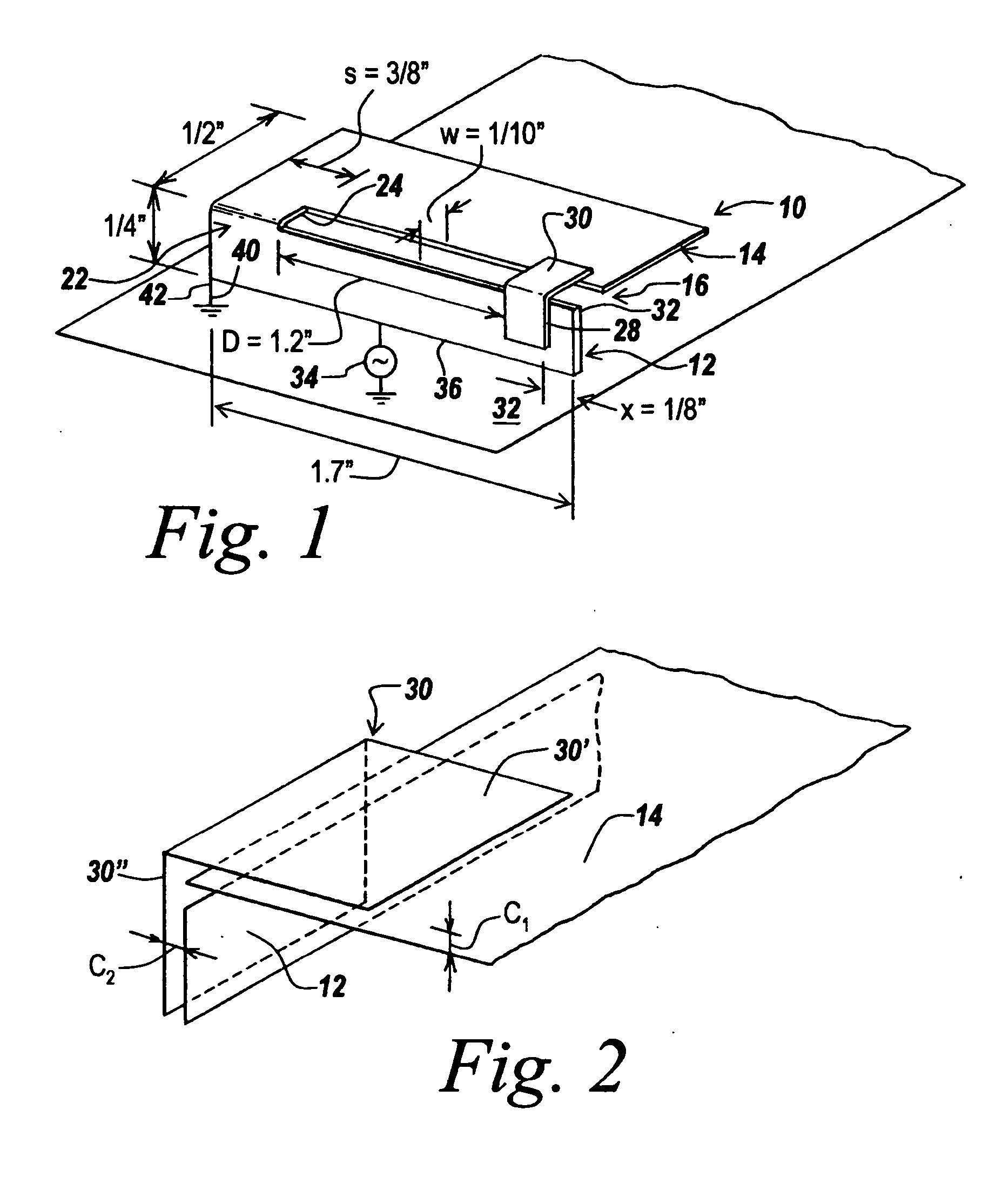

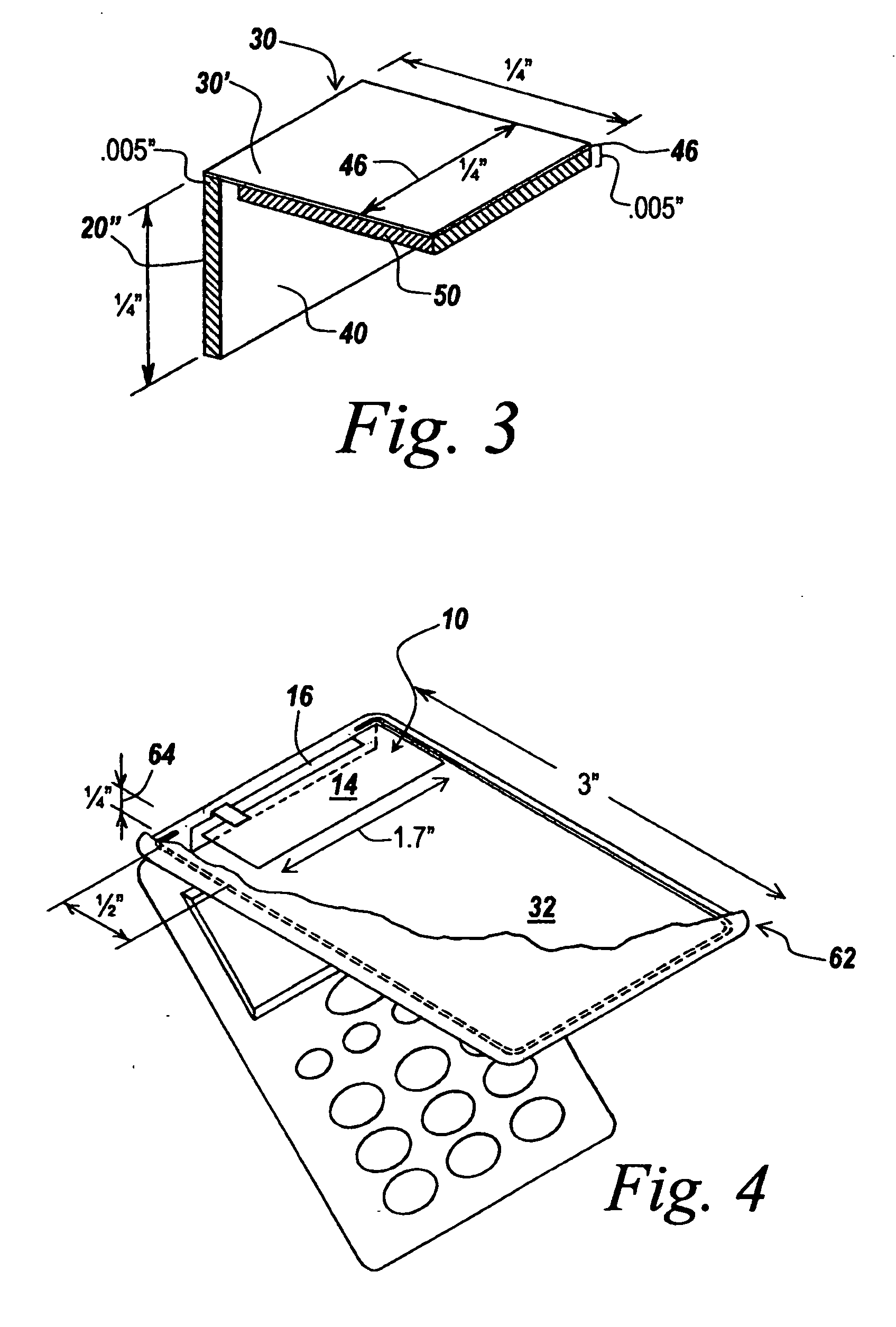

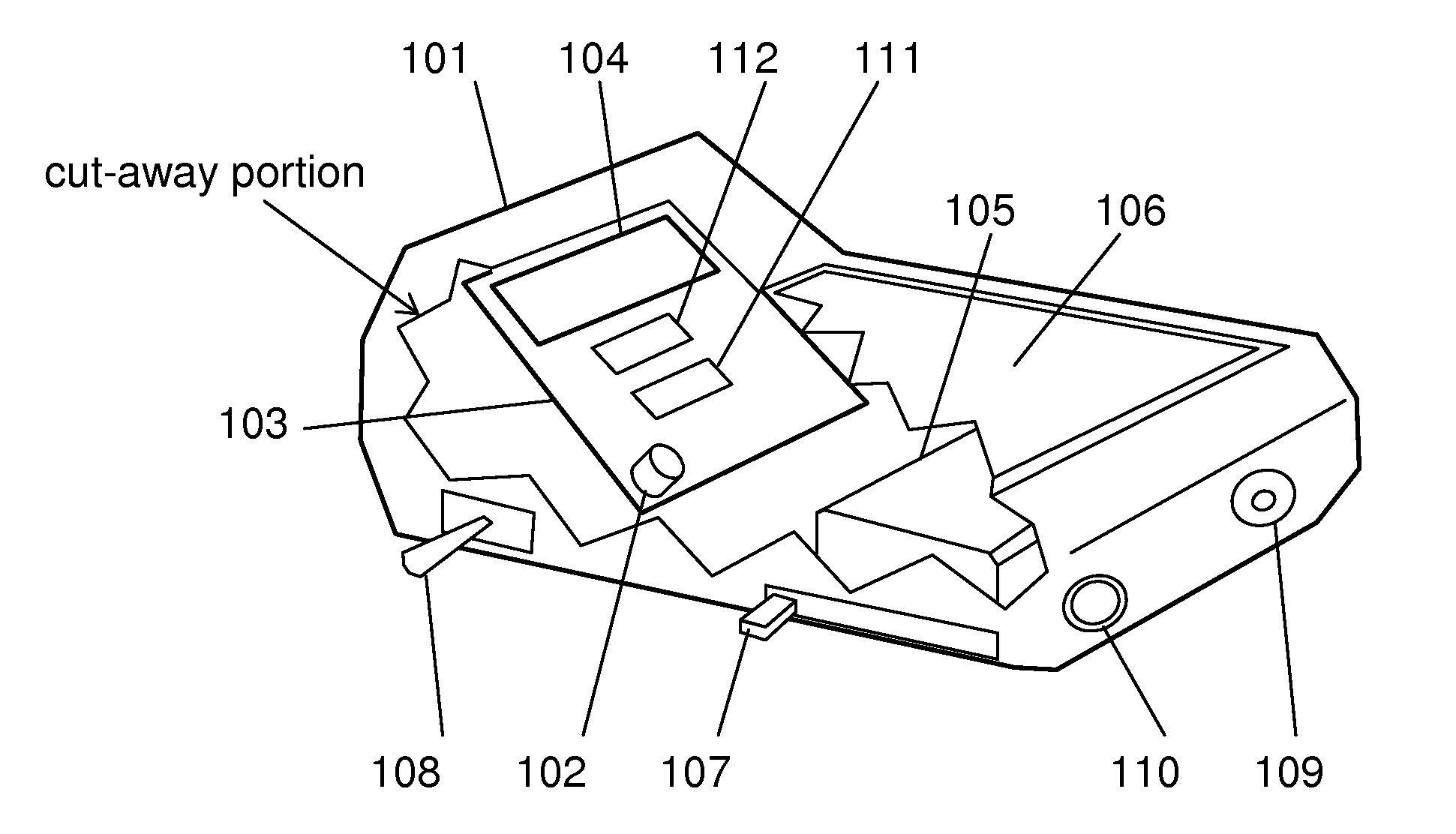

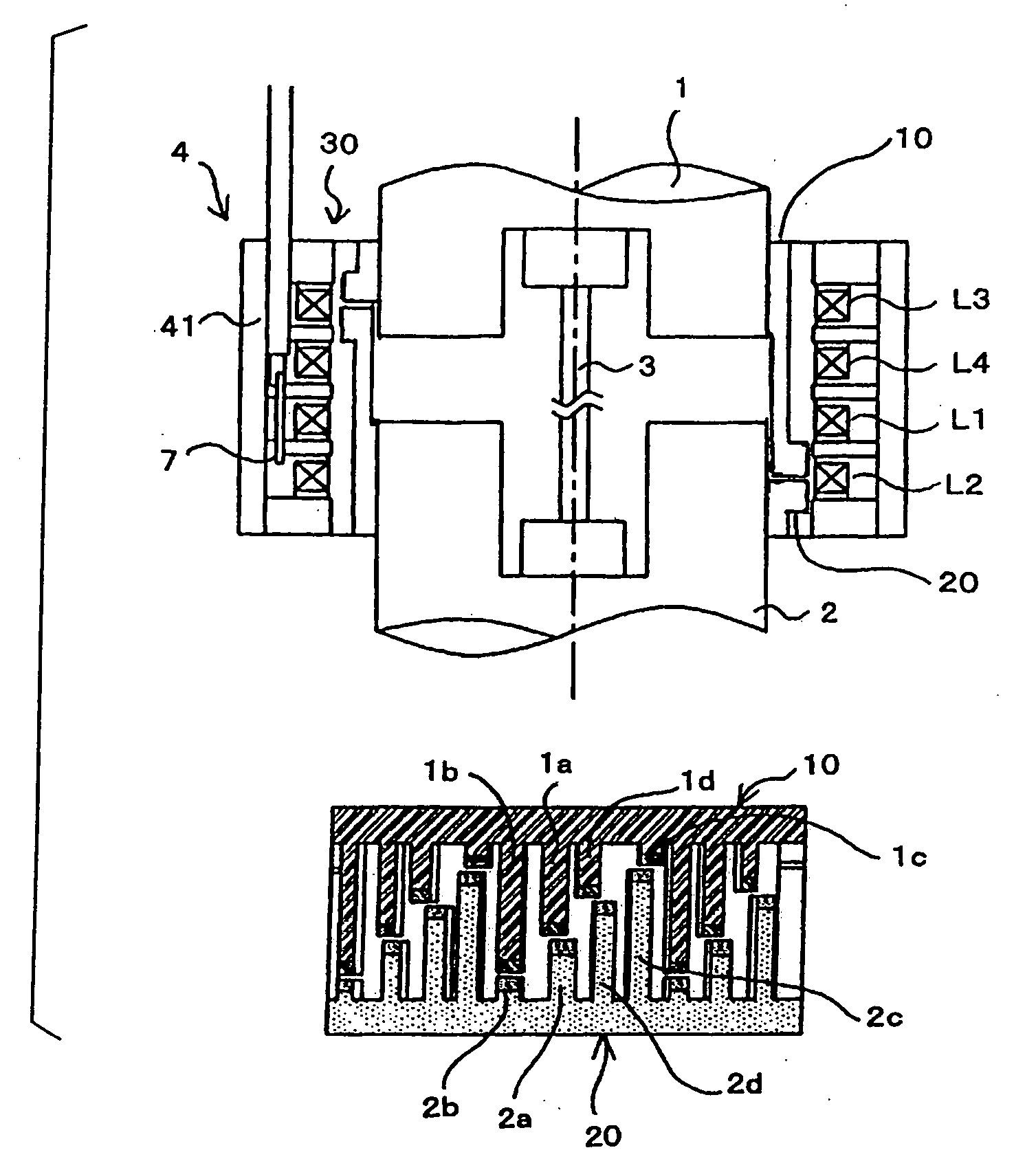

Wireless IC device

ActiveUS20090002130A1Increased antenna gainSufficient distanceRadiating elements structural formsRadio transmissionEngineeringIc devices

A wireless IC device includes a wireless IC chip having a power supply circuit including a resonant circuit having a predetermined resonant frequency and a radiation plate that externally radiates a transmission signal supplied from the power supply circuit and that supplies a reception signal externally transmitted to the power supply circuit. The radiation plate is connected to the power supply circuit via an electric field or the radiation plate is coupled to the power supply circuit via a magnetic field. The radiation plate is a two-surface-open type radiation plate including at least one radiation portion arranged to externally exchange a transmission-reception signal and a power supply portion arranged to exchange a transmission-reception signal with the power supply circuit.

Owner:MURATA MFG CO LTD

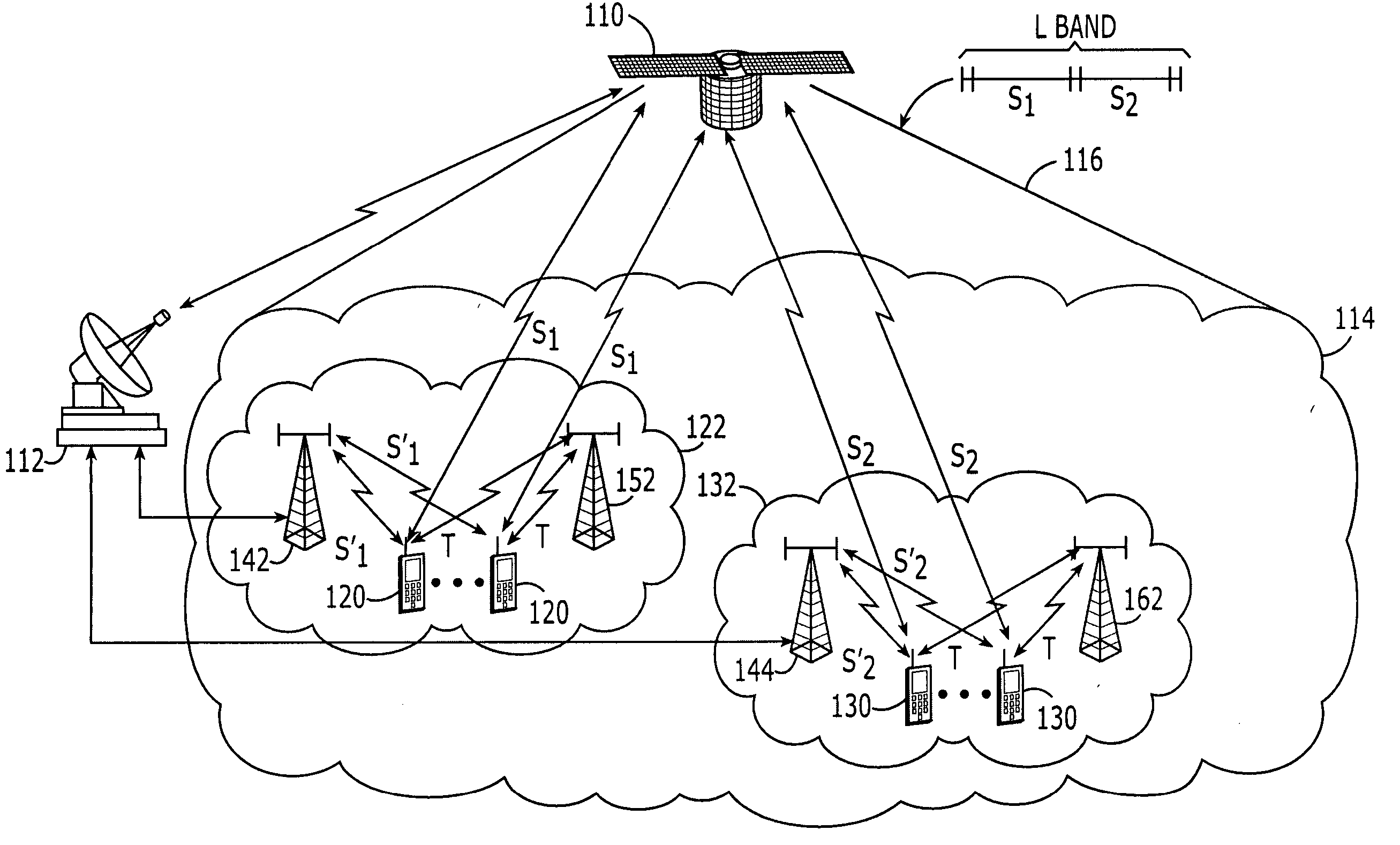

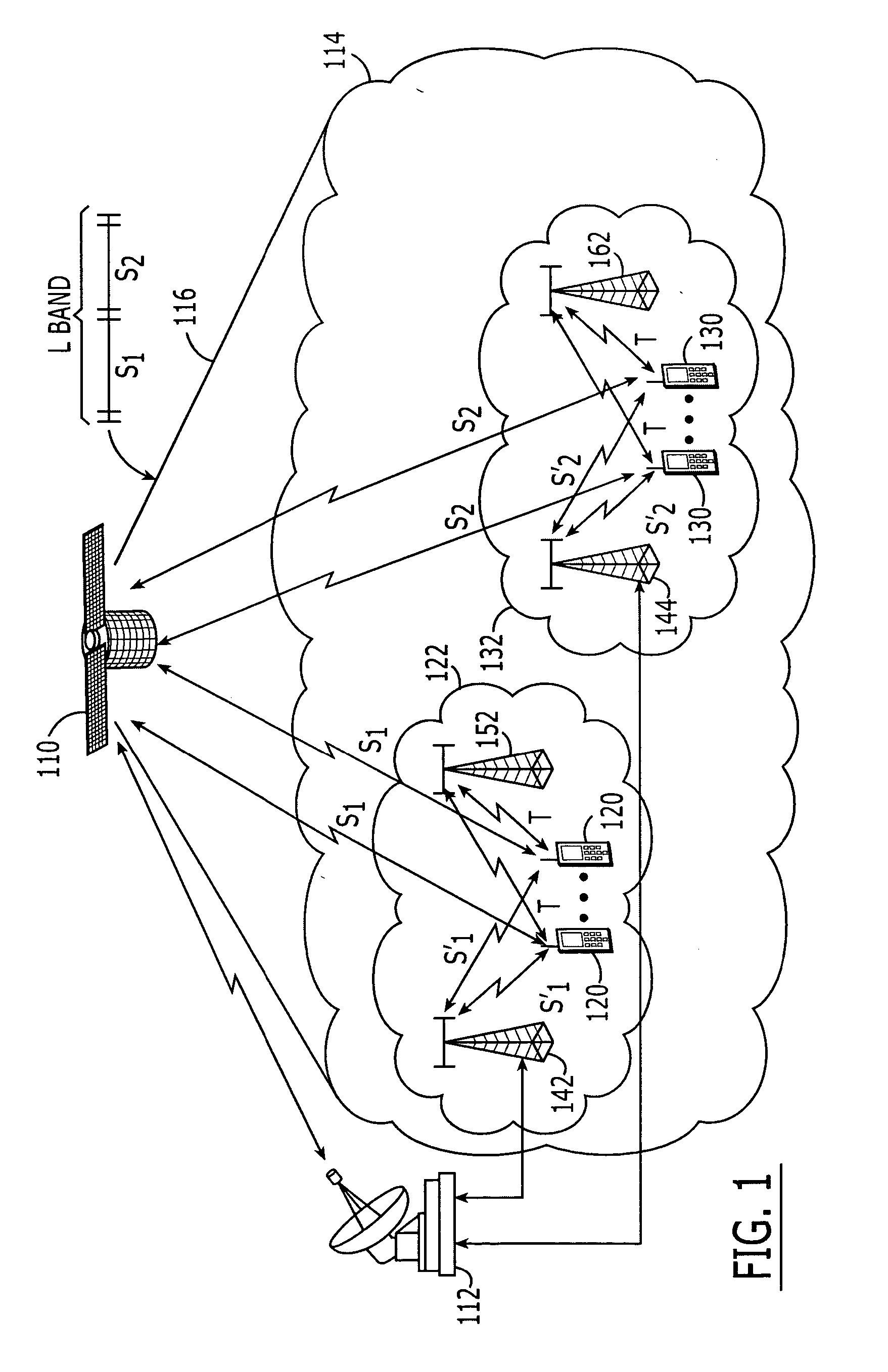

Multi frequency band/multi air interface/multi spectrum reuse cluster size/multi cell size satellite radioterminal communicaitons systems and methods

InactiveUS20060094420A1Enhance effective gain and selectivityReduce fadingRadio/inductive link selection arrangementsRadio transmissionCommunications systemFrequency spectrum

Satellite radioterminal communications systems, methods and components thereof, can use multiple frequency segments of at least one satellite frequency band, multiple air interfaces, multiple spectrum reuse cluster sizes and / or multiple geographic cell sizes. For example, a space-based component is configured to communicate with first radioterminals in first satellite cells over a first frequency segment of a satellite frequency band, such as a first frequency segment of a satellite L-band, and to communicate with second radioterminals in second satellite cells over a second frequency segment of the same or different satellite frequency band. The space-based component also may be configured to communicate with a first radioterminal over a first air interface and to communicate with the second radioterminals over a second air interface.

Owner:ATC TECH LLC

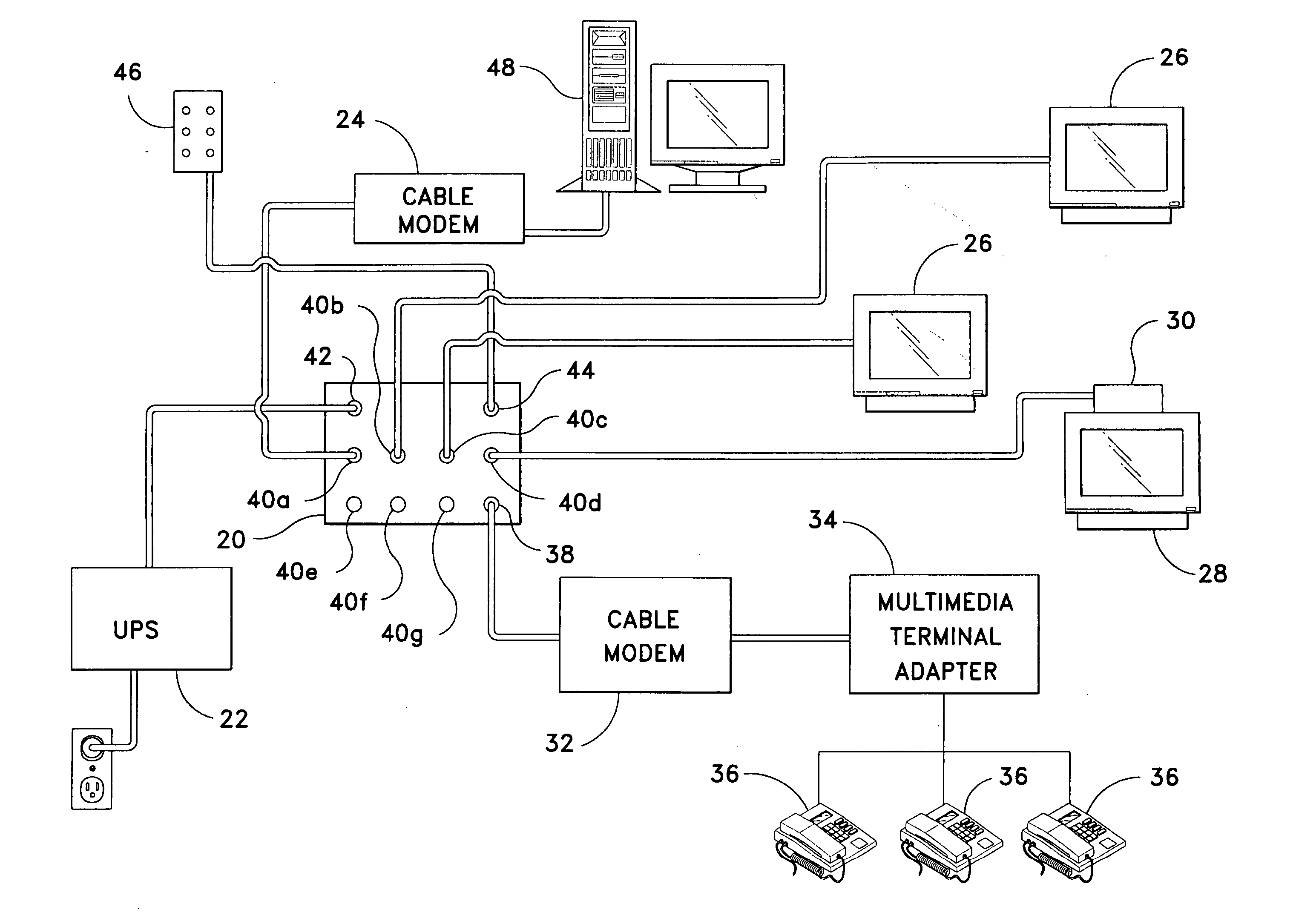

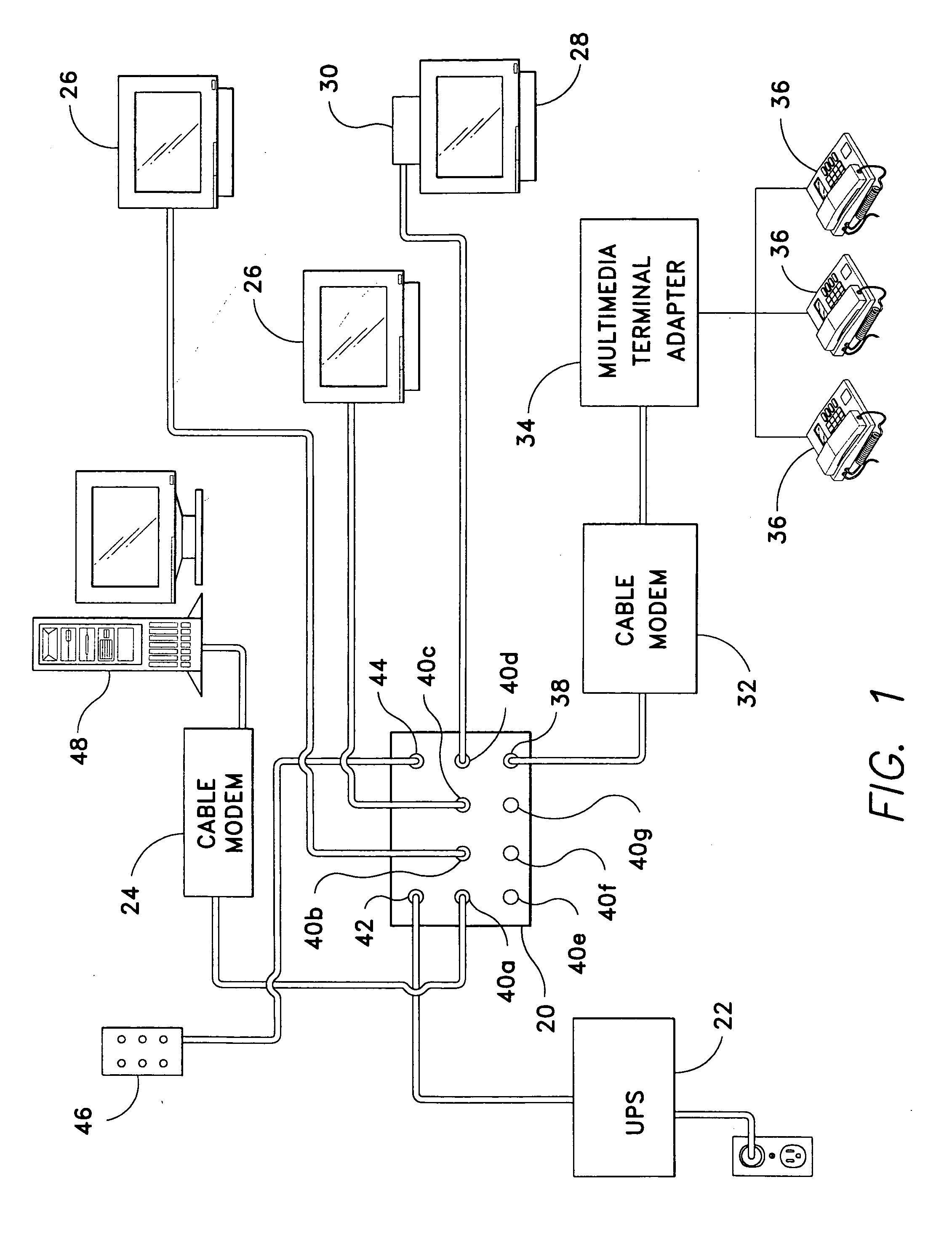

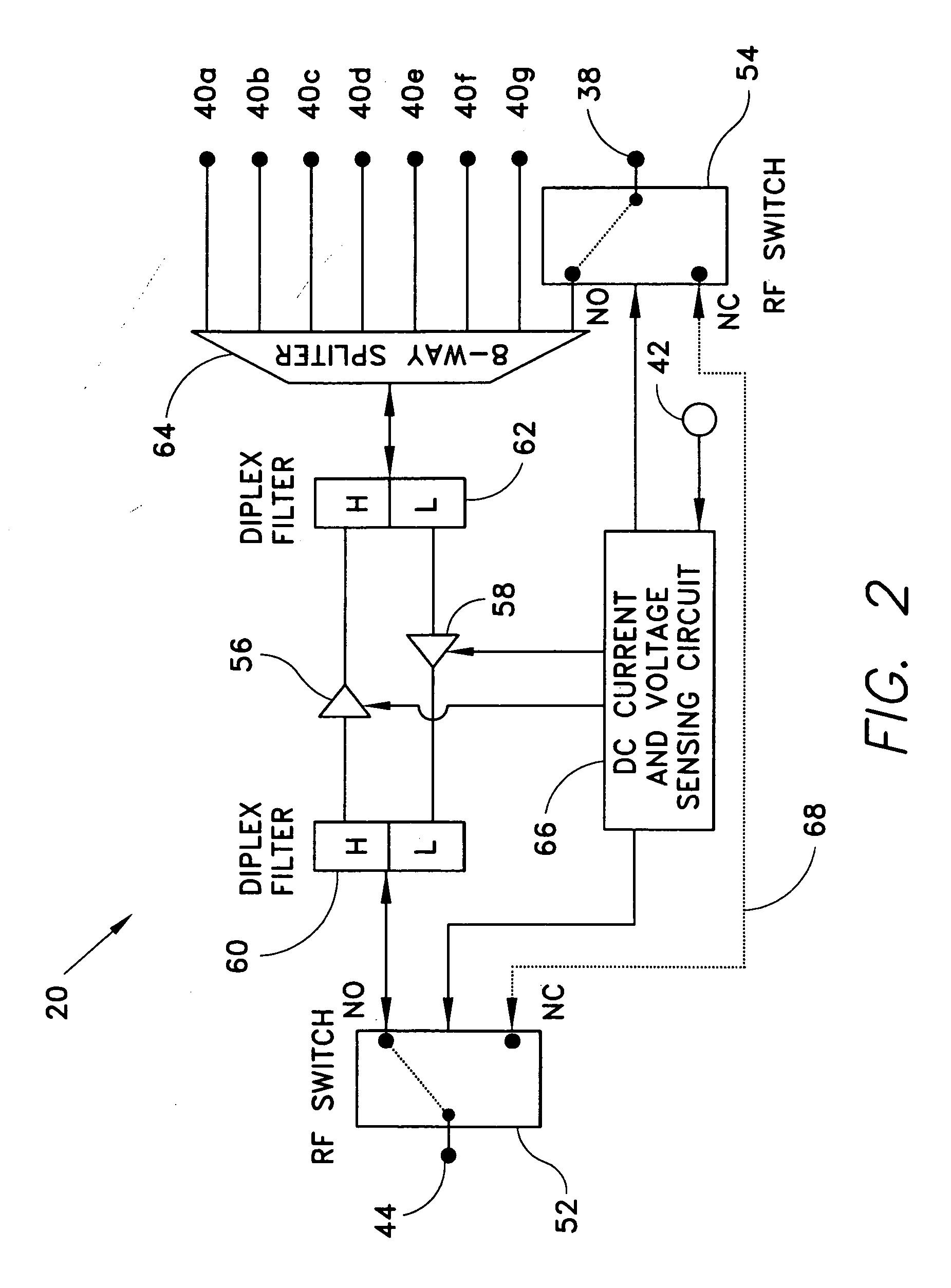

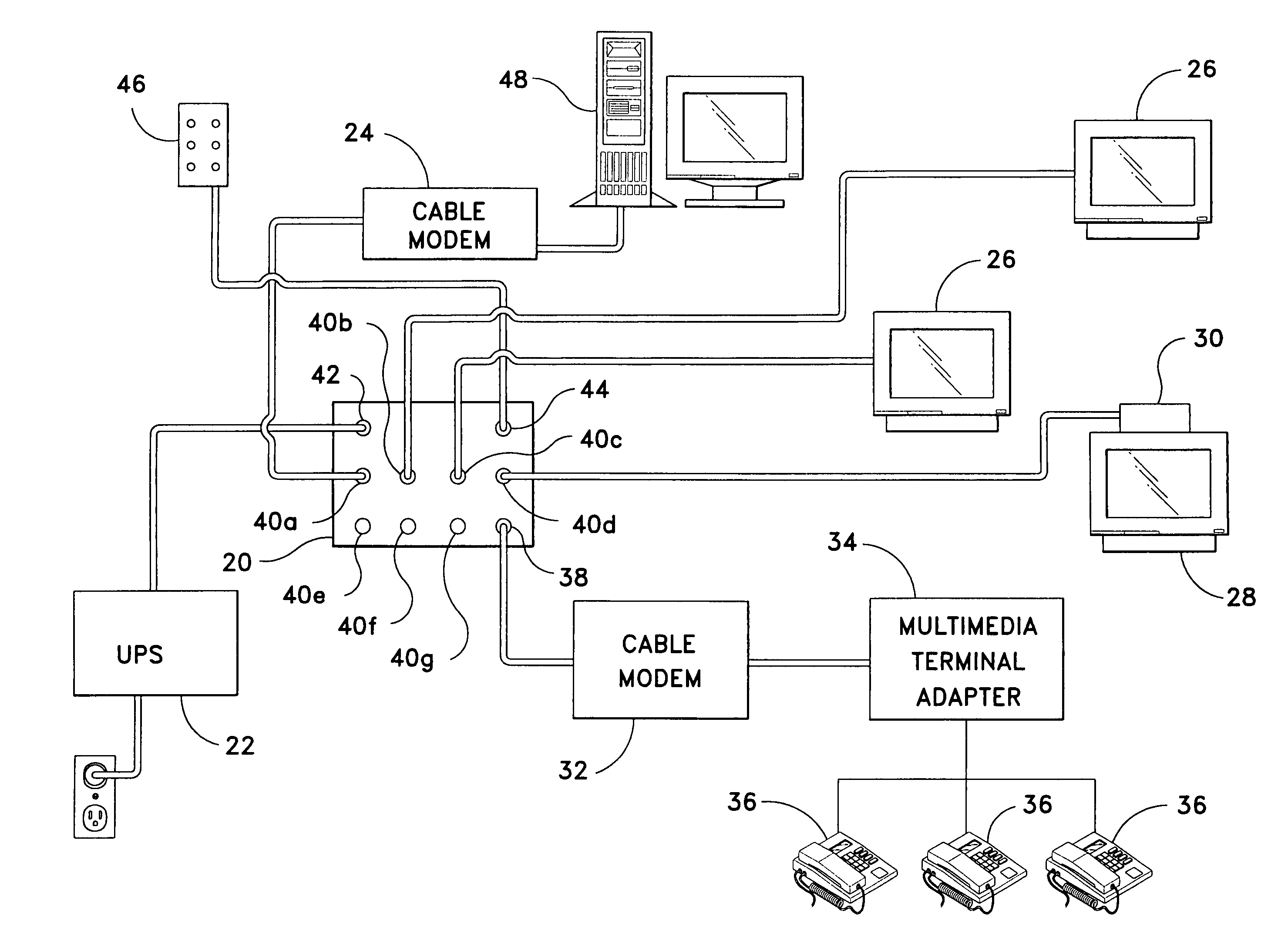

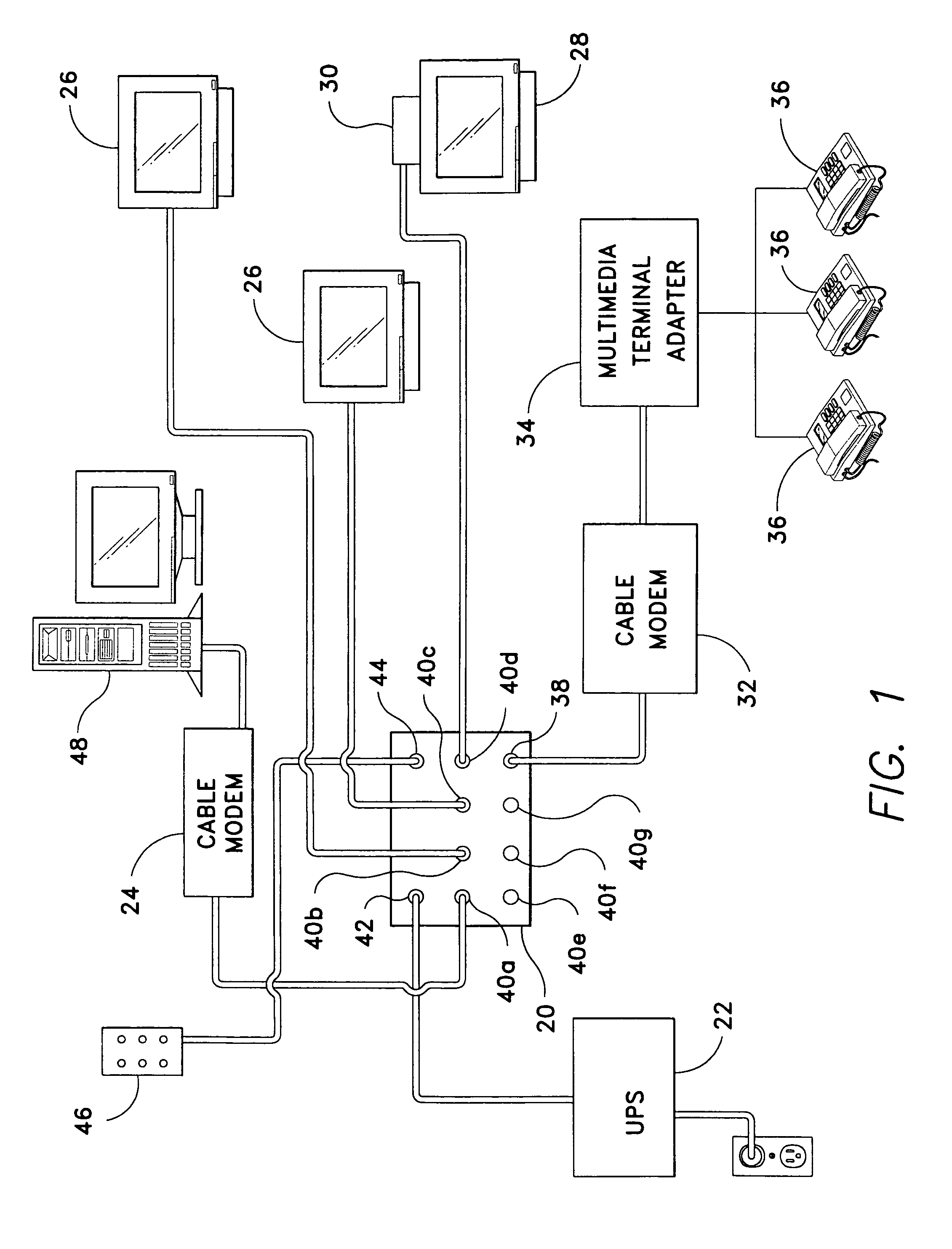

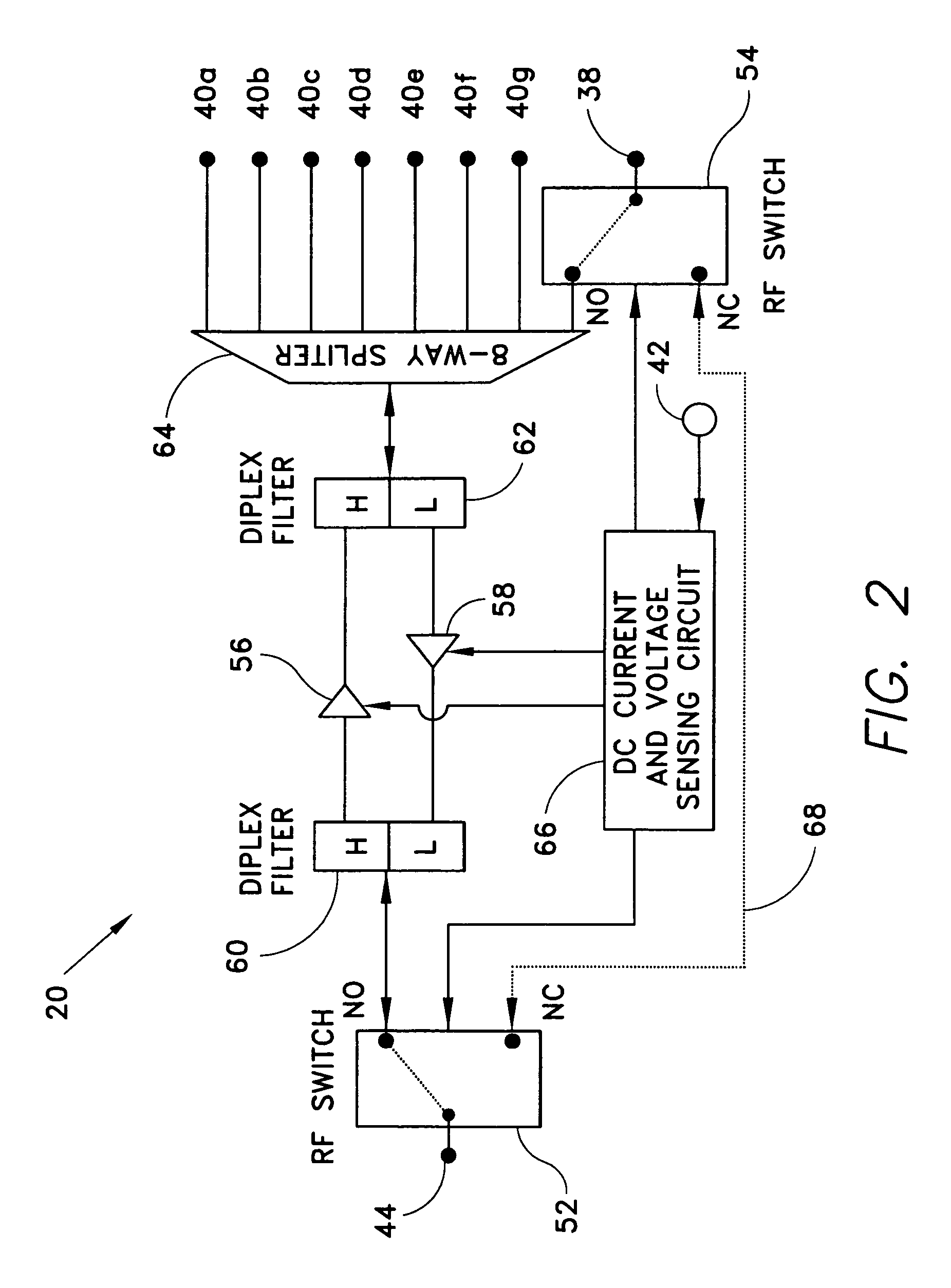

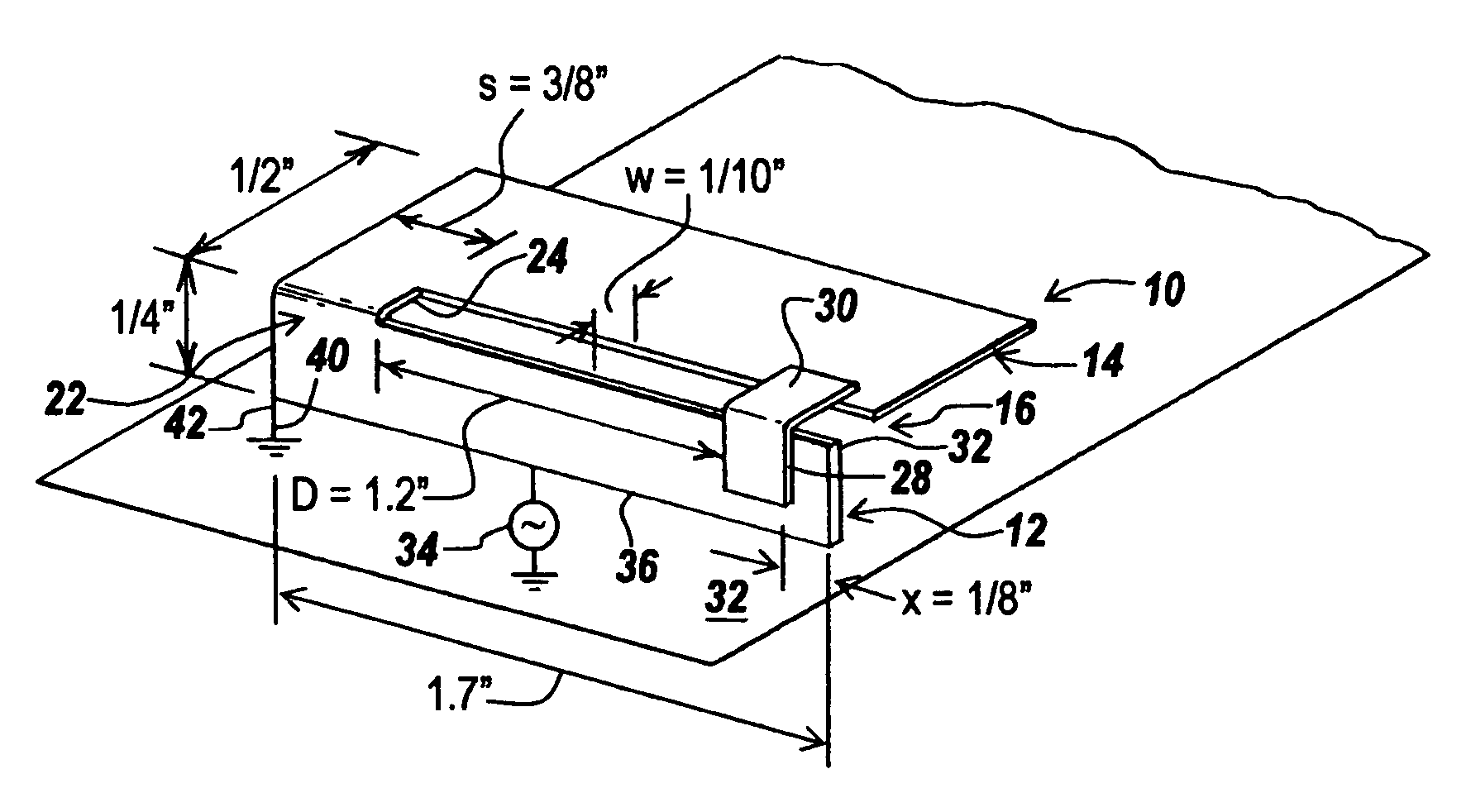

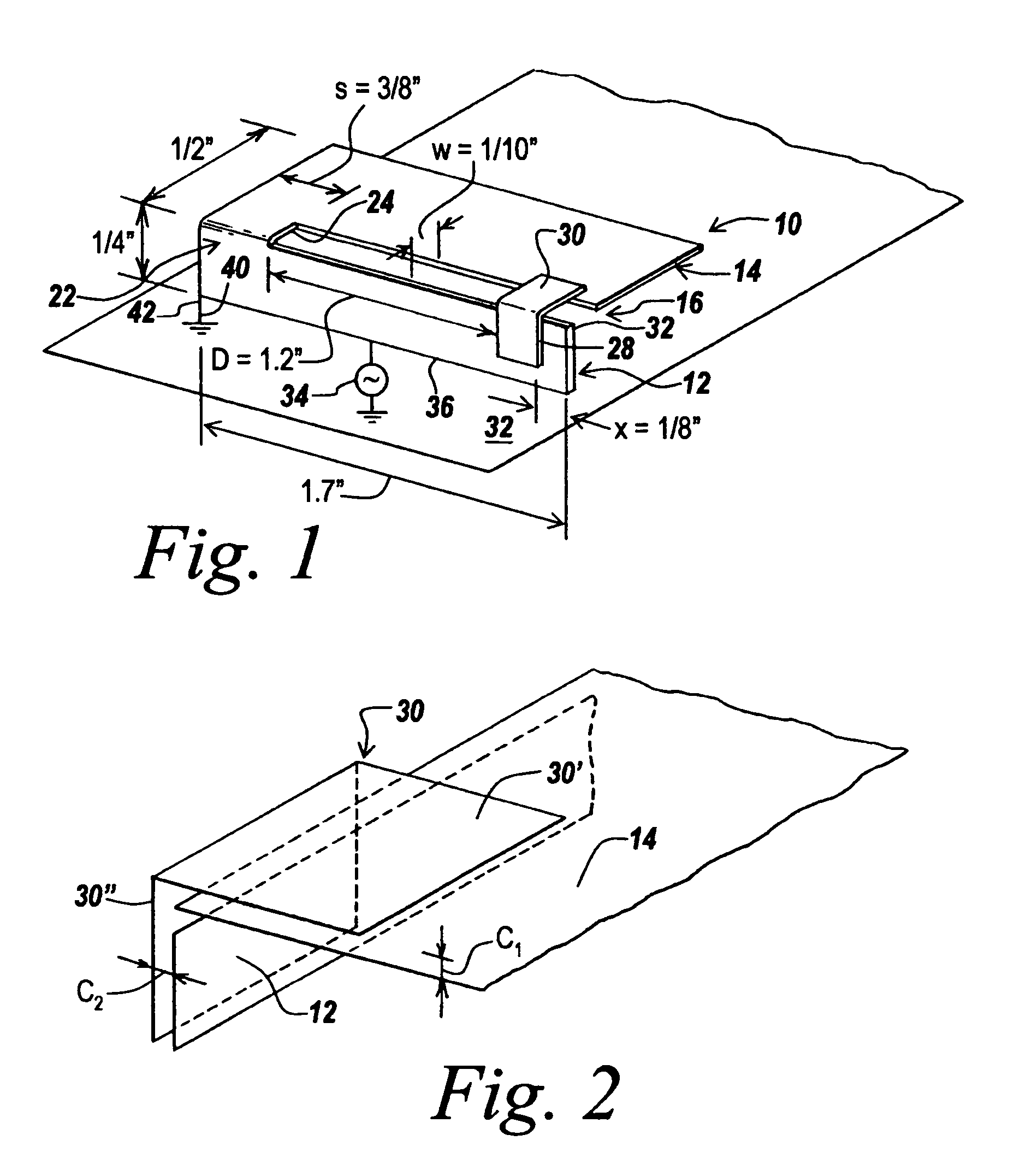

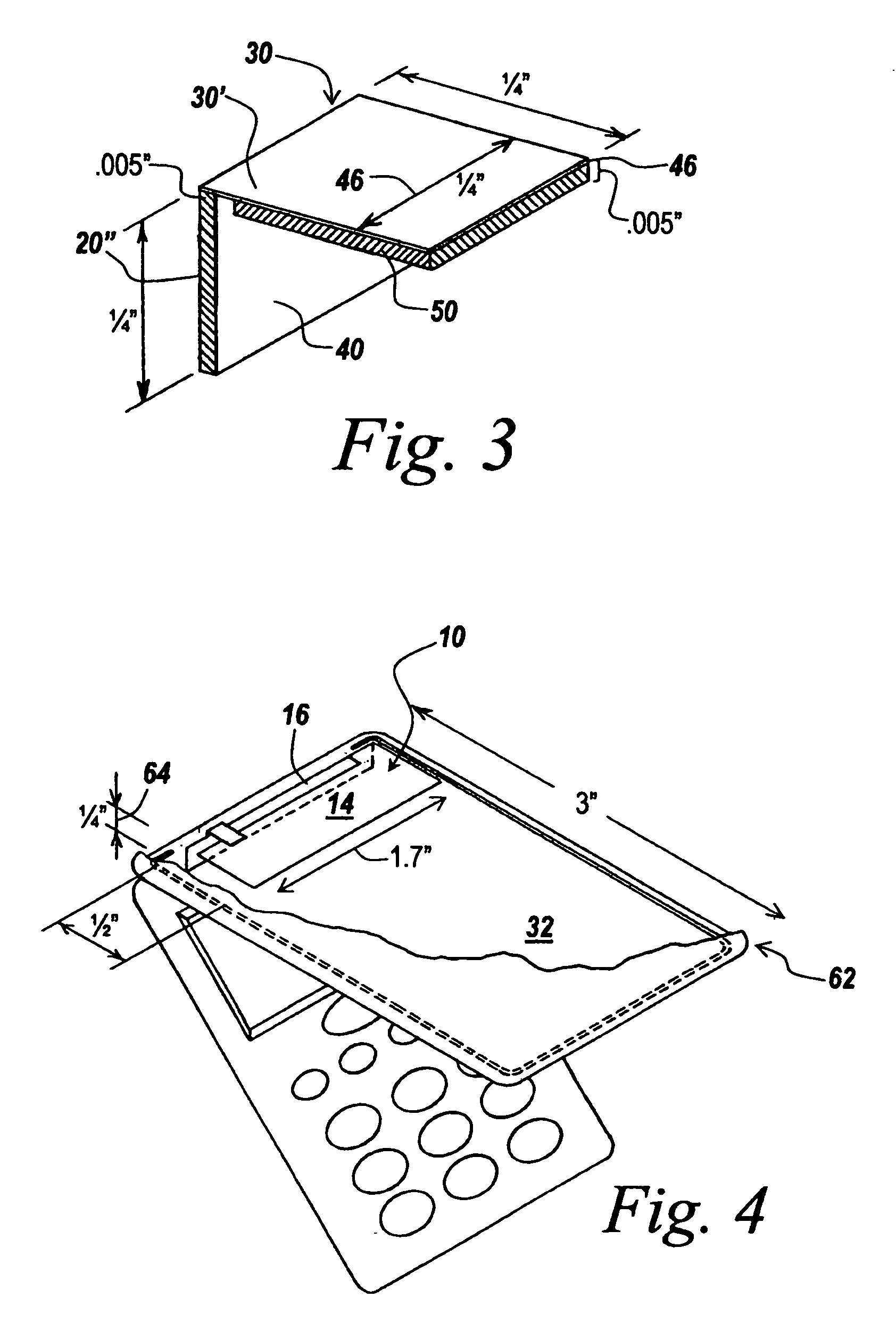

VoIP drop amplifier

InactiveUS20060015921A1Sufficient gainLoss can be compensatedFrequency-division multiplex detailsTwo-way working systemsAudio power amplifierBroadband

The VOIP drop amplifier connects end user equipment to a broadband system, such as that provided by a cable provider. The amplifier includes a splitter for connecting the cable signal to multiple output connectors, and RF amplifiers compensating for losses in the splitter and other passive components in the amplifier. The drop amplifier includes an input connection for accepting a broadband cable signal from a cable system and returning broadband signals to the cable system. The drop amplifier includes an amplification path connecting the input connection to the plurality of output connections through RF amplifiers and a splitter, and a bypass path that bypass the splitter and forward and reverse amplifiers in the amplification path to connect the input connection directly to the output connection for the essential circuits. A sensing circuit monitors the amplifiers and the supply voltages, and selects the bypass path when a failure is detected.

Owner:PCT INT

VOIP drop amplifier

InactiveUS7530091B2Sufficient gainLoss can be compensatedFrequency-division multiplex detailsTwo-way working systemsAudio power amplifierBroadband

Owner:PCT INT

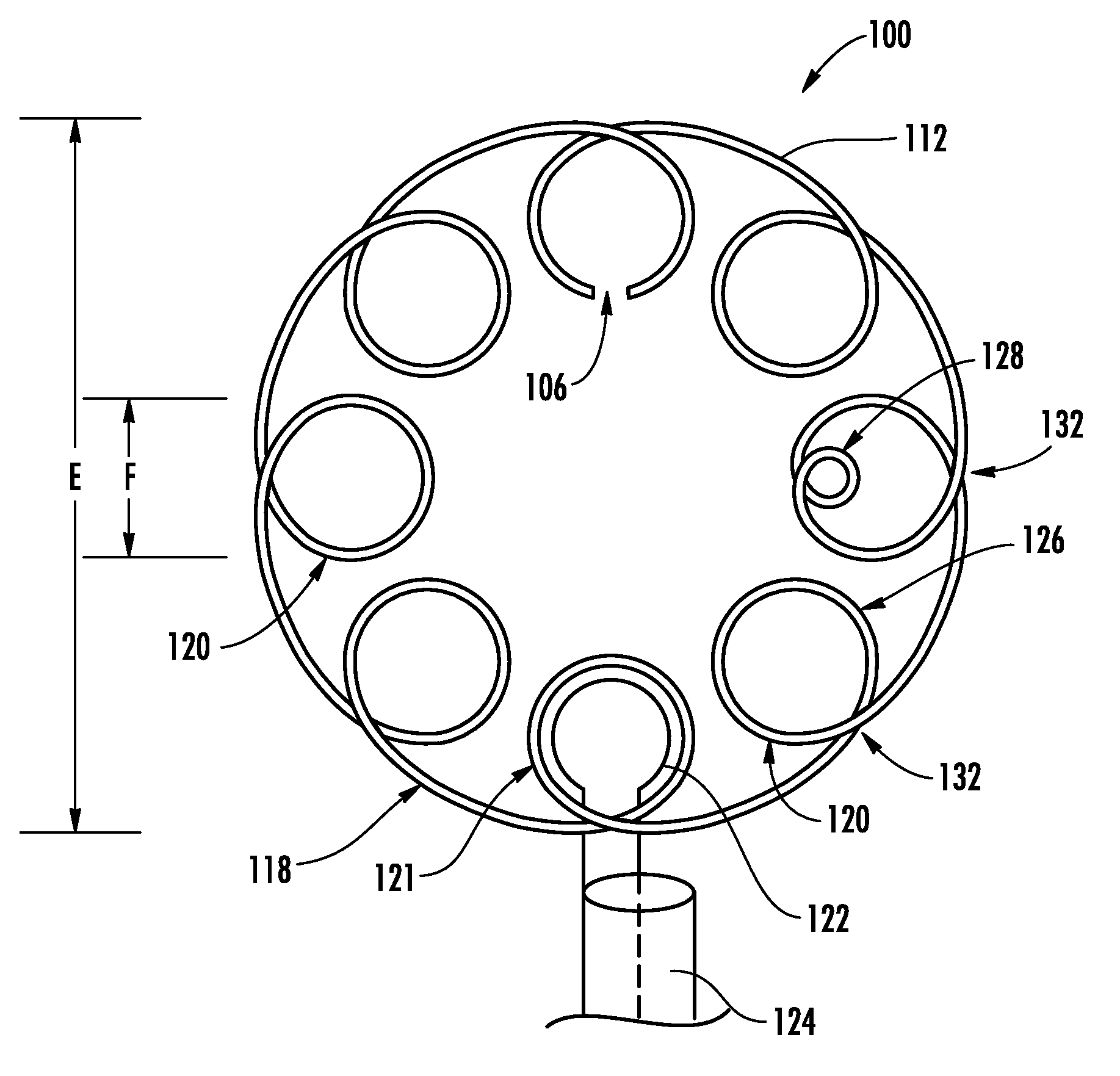

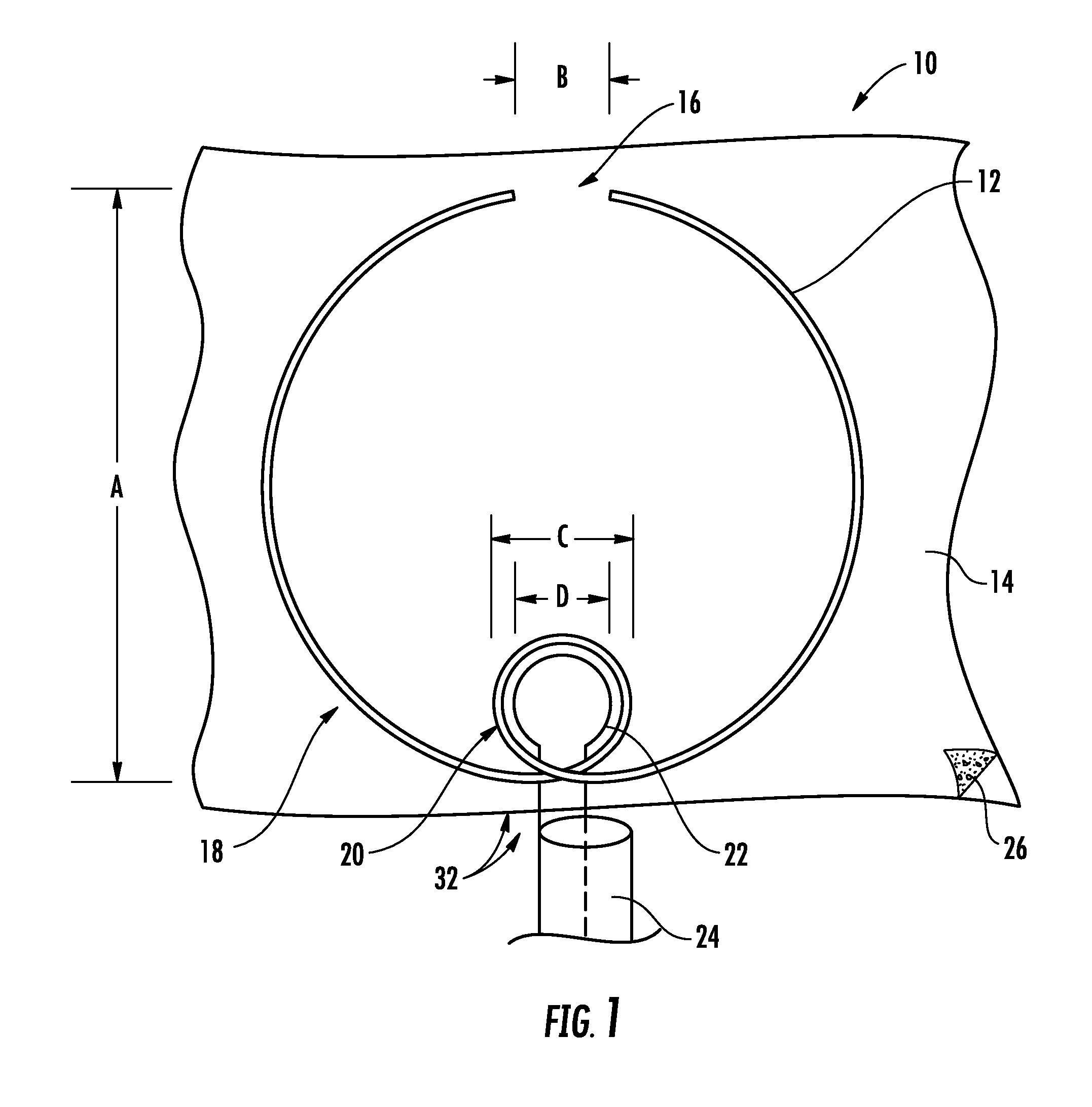

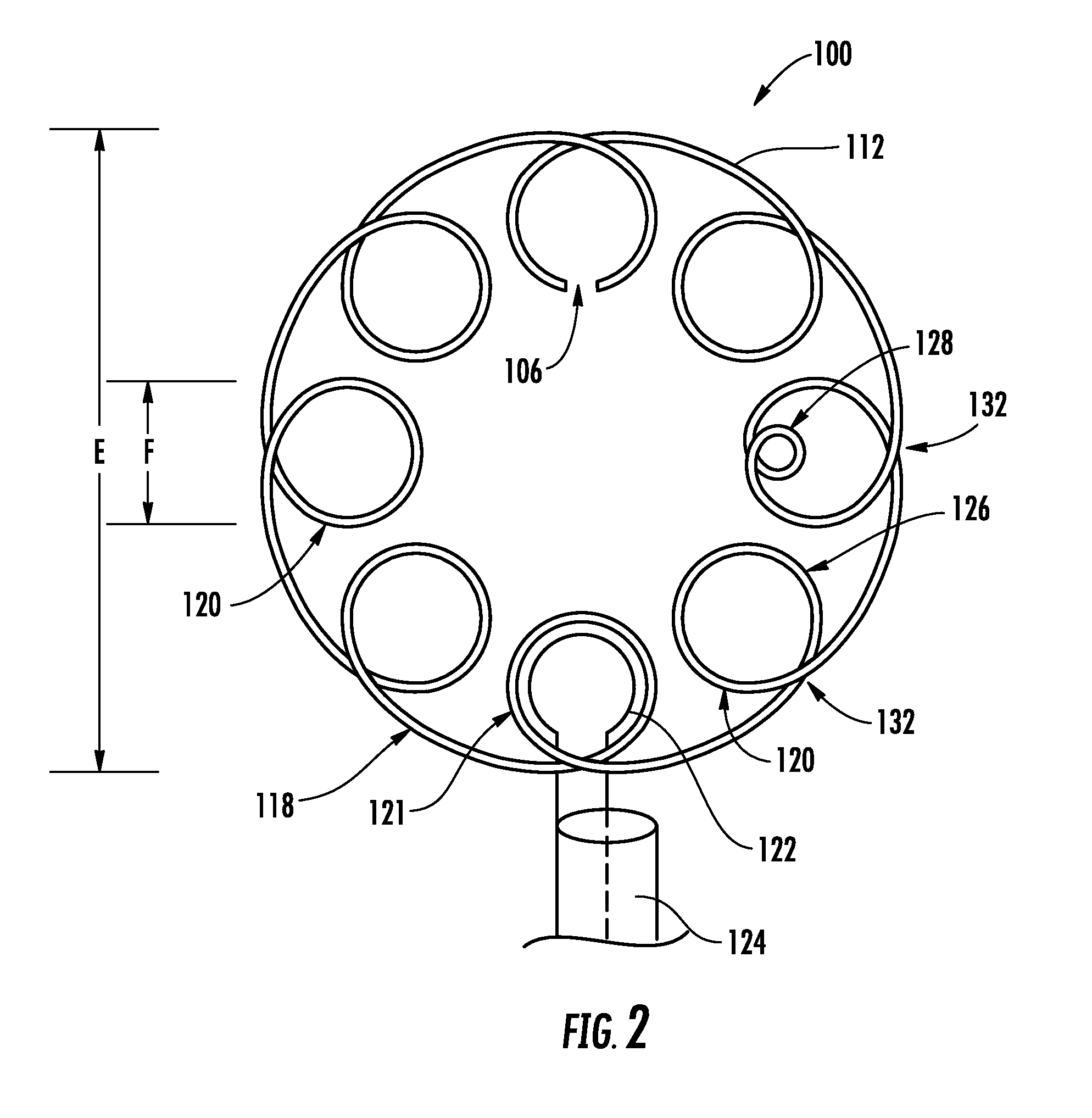

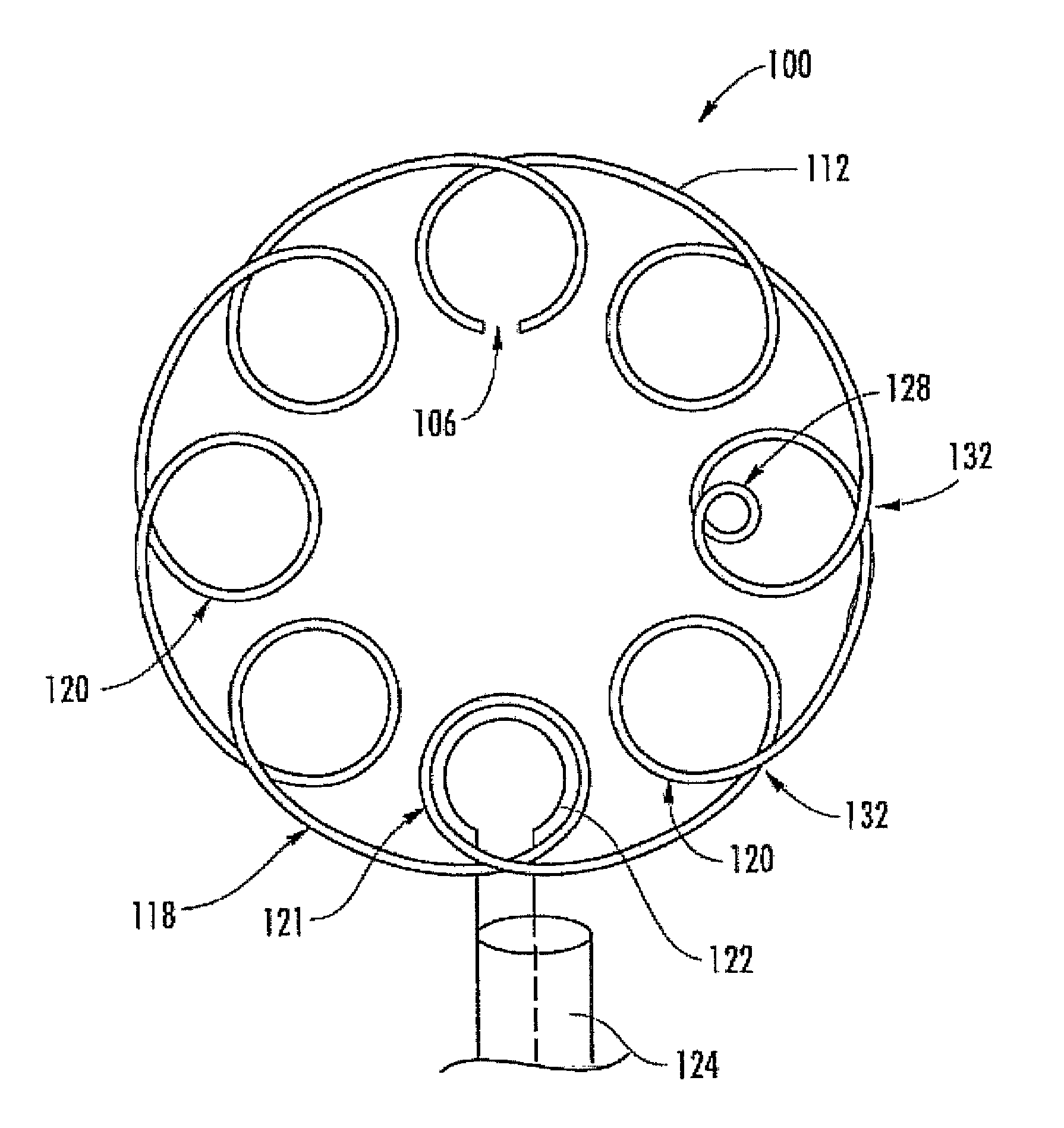

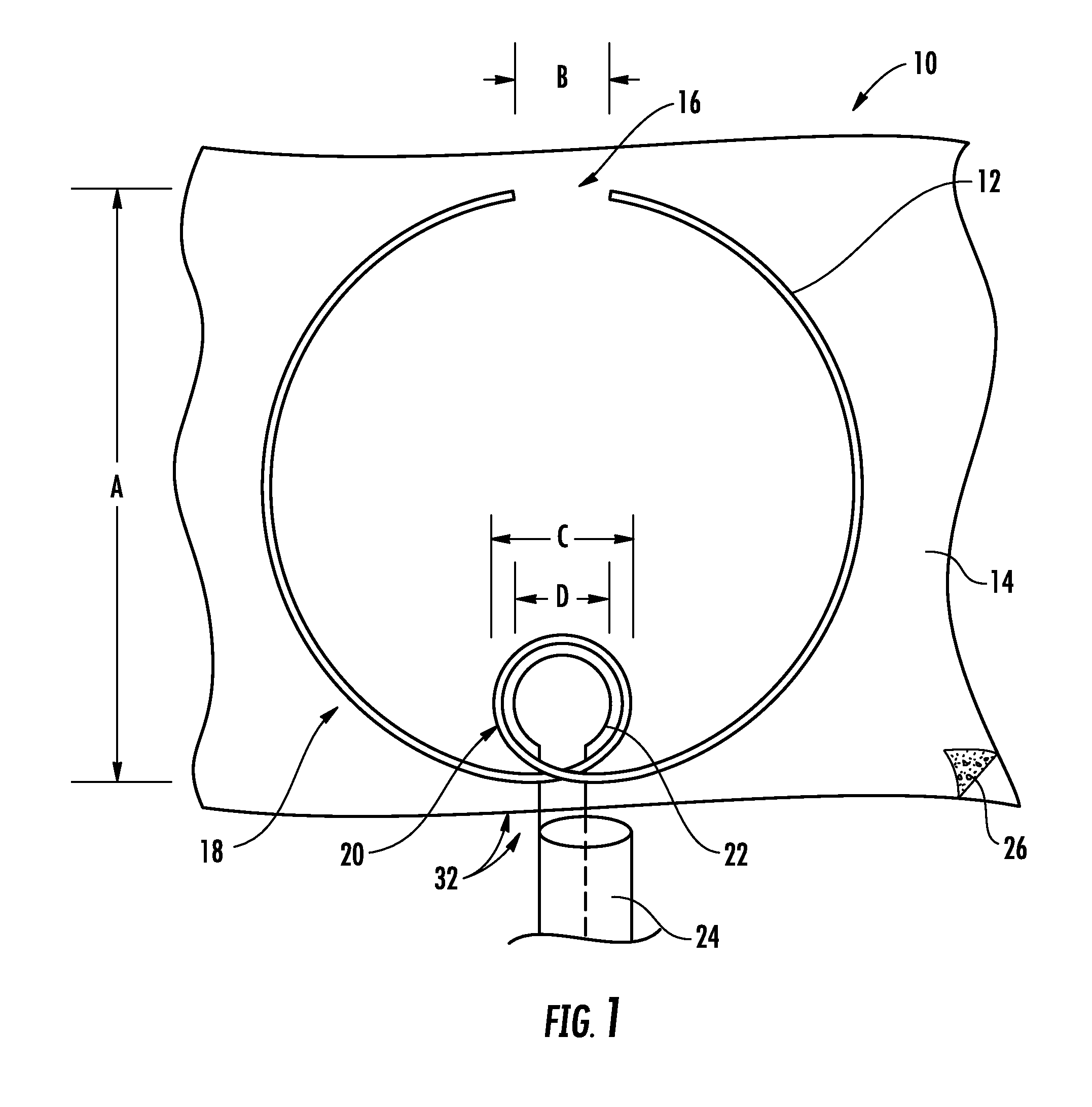

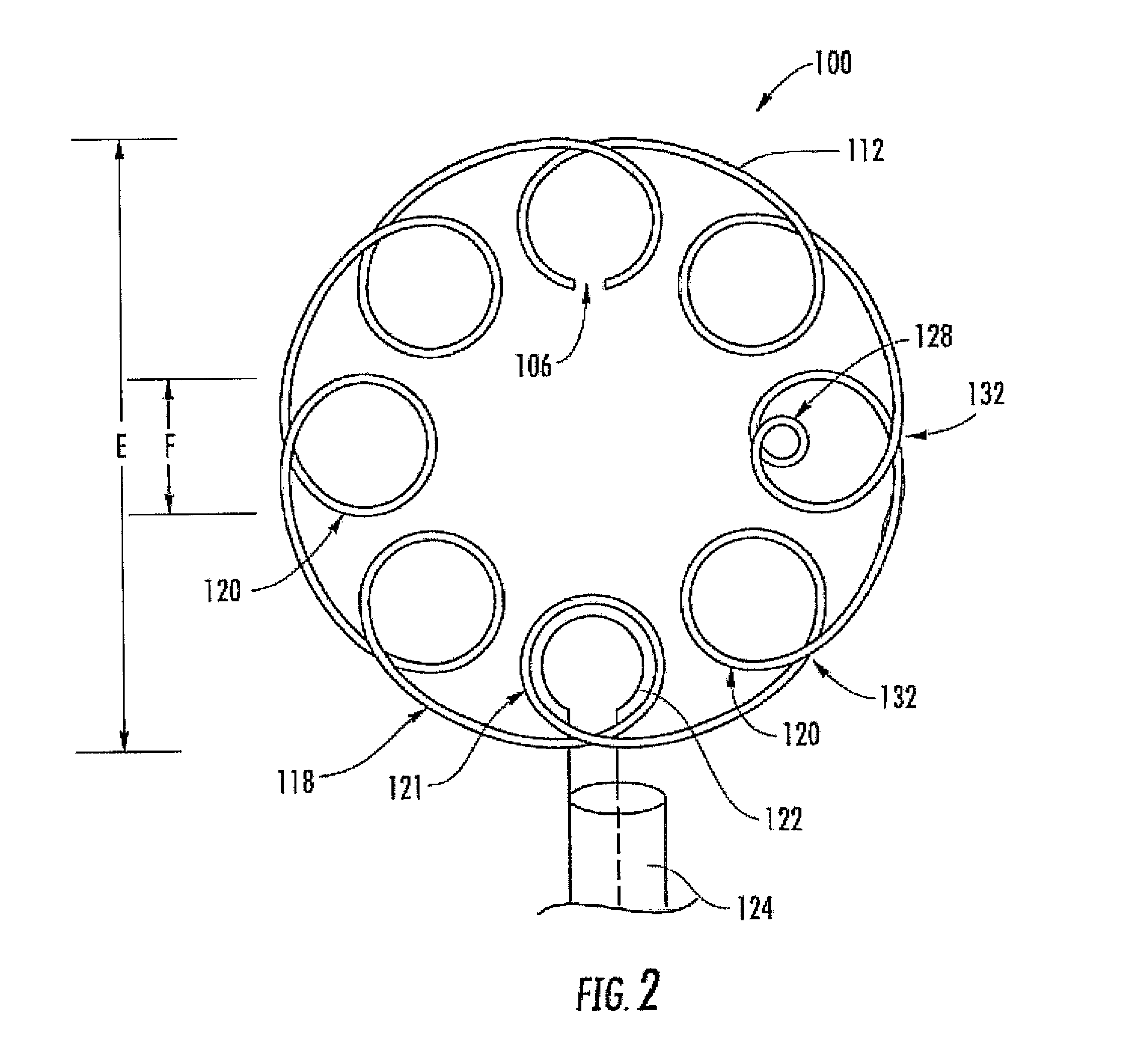

Planar communications antenna having an epicyclic structure and isotropic radiation, and associated methods

ActiveUS20110121822A1Frequency stabilitySufficient gainLoop antennas with ferromagnetic coreSimultaneous aerial operationsAntenna designElectrical conductor

The antenna device includes an electrical conductor extending on a substrate and having at least one gap therein, and with an outer ring portion to define a radiating antenna element, and at least one inner ring portion to define a feed coupler and connected in series with the outer ring portion and extending within the outer ring portion. A coupling feed element is adjacent the at least one inner ring portion, and a feed structure is connected to the coupling feed element to feed the outer ring portion. A plurality of inner ring portions may be provided with the coupling feed element being adjacent a selected one of the plurality of inner ring portions. The plurality of inner ring portions may have a common size and be symmetrically spaced within the outer ring portion. The radiation pattern may be sufficiently isotropic to eliminate the need for antenna aiming. An epicyclic geometry radiating element provides for a compound antenna design.

Owner:HARRIS CORP

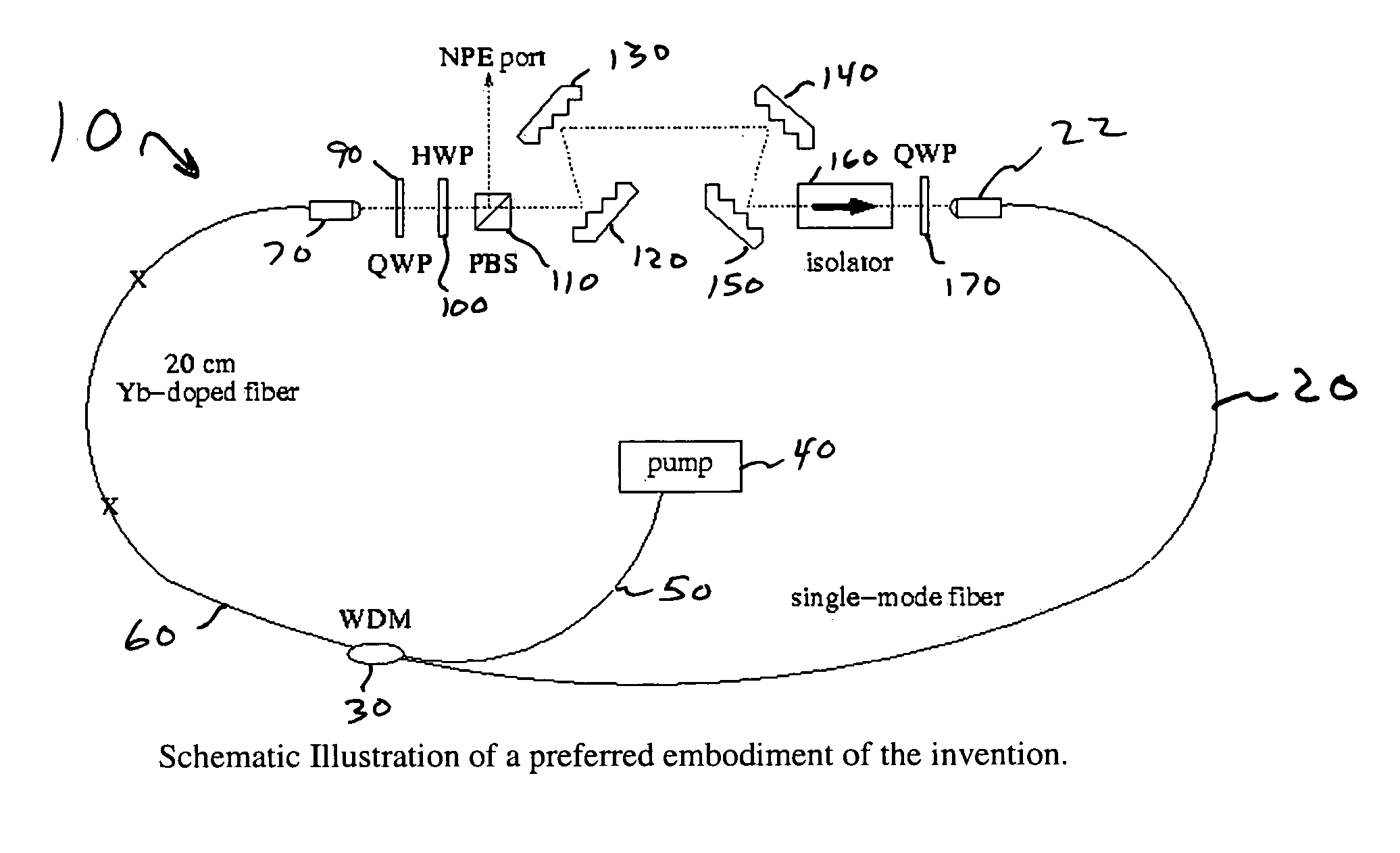

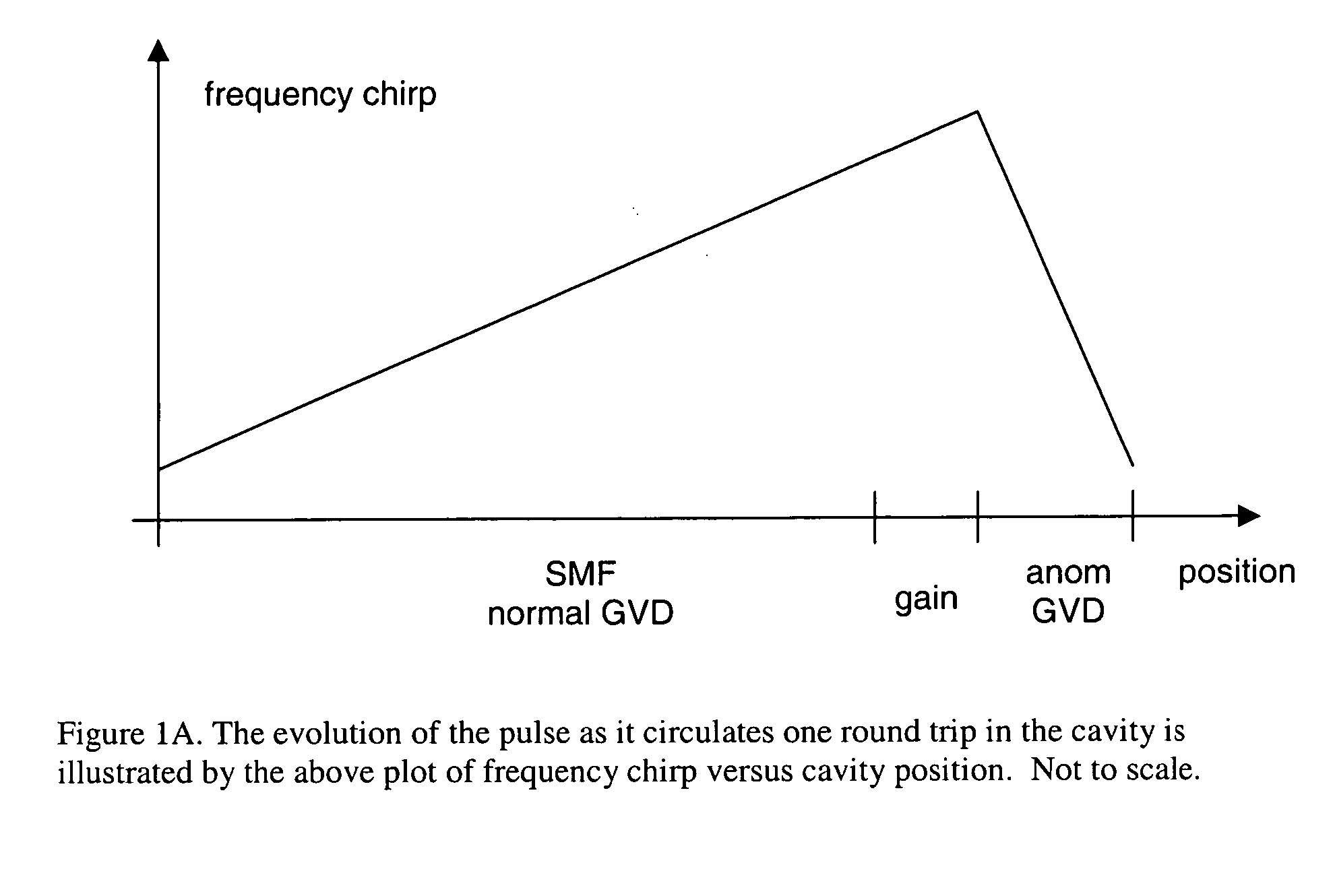

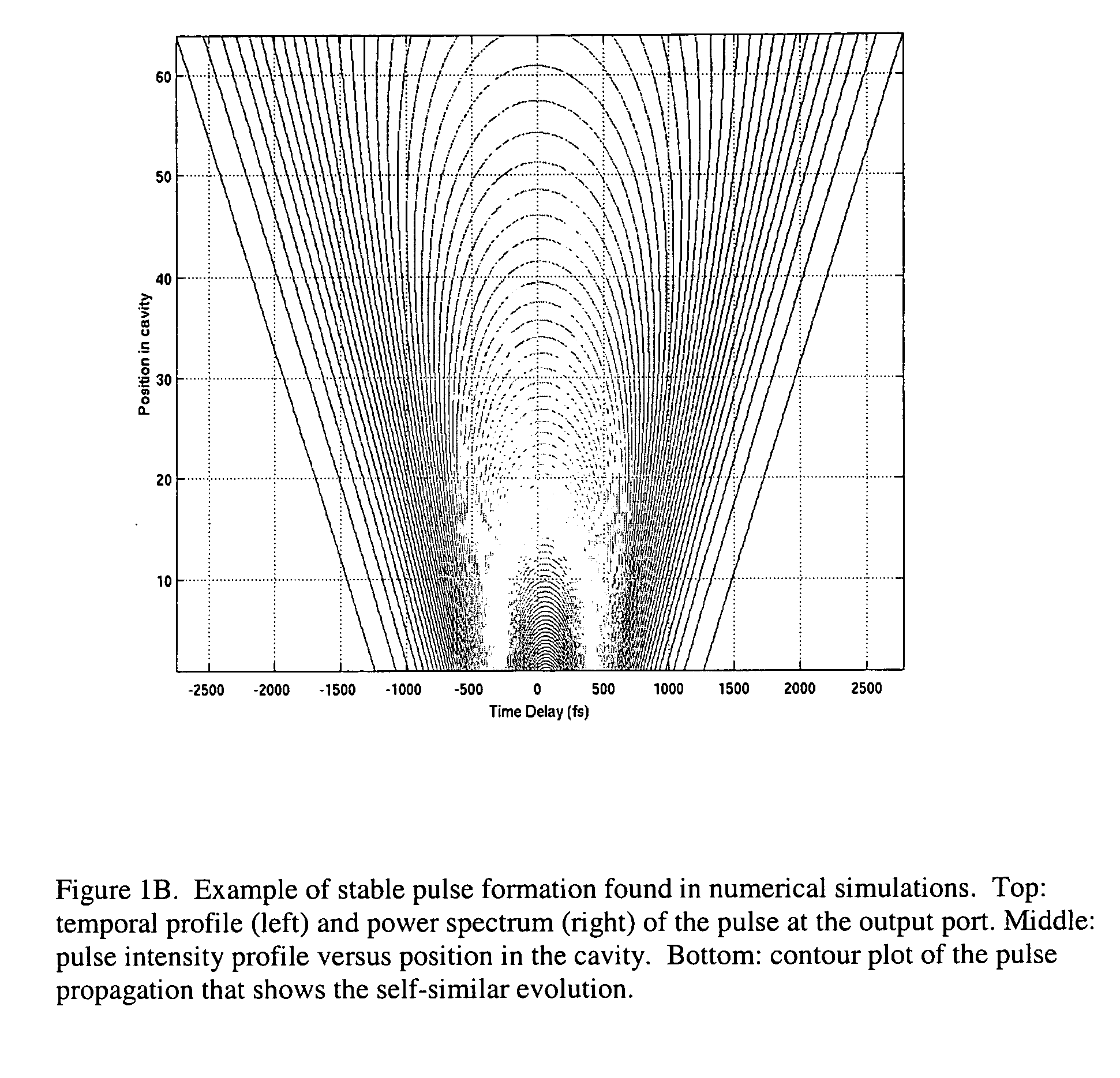

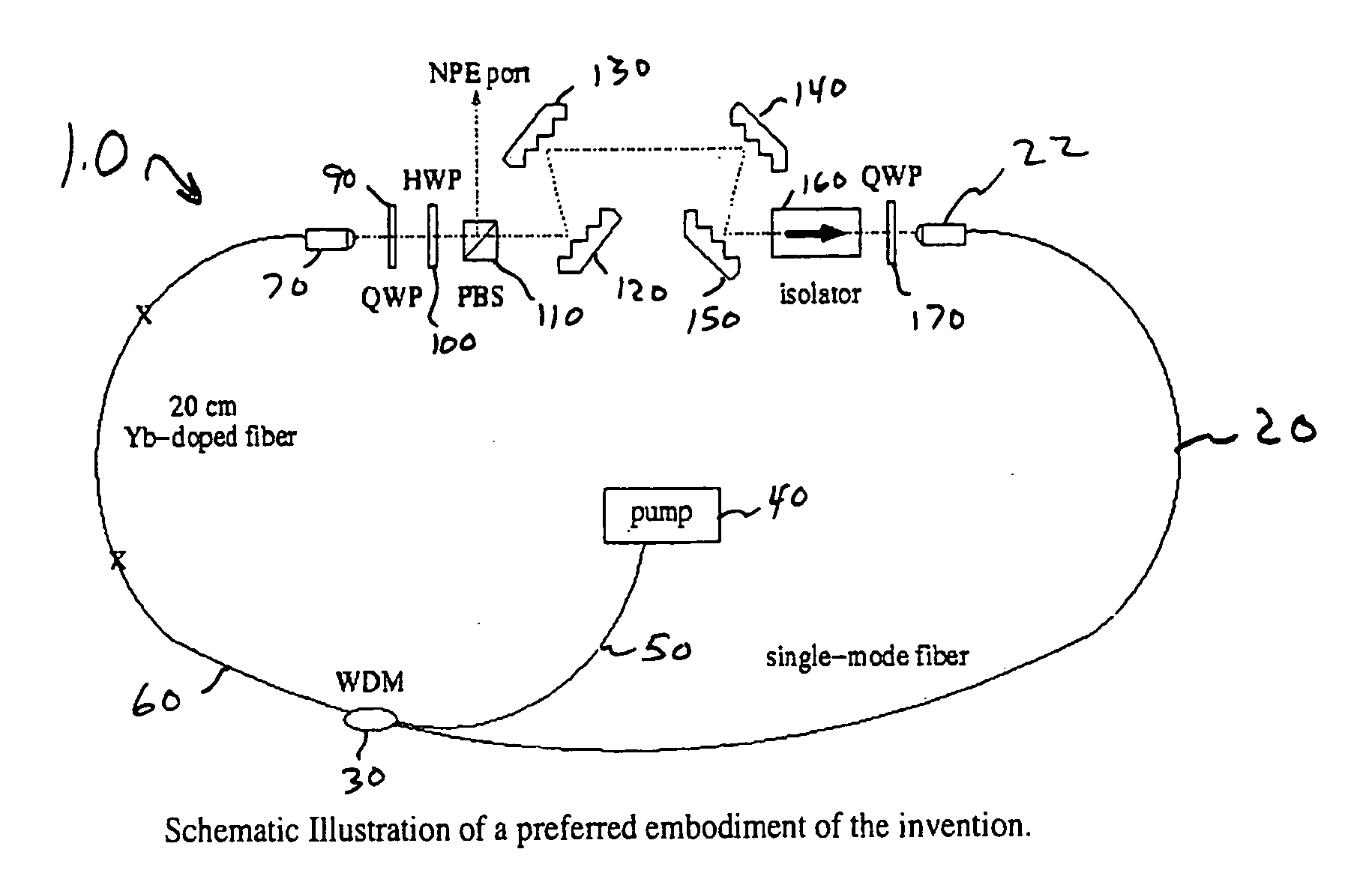

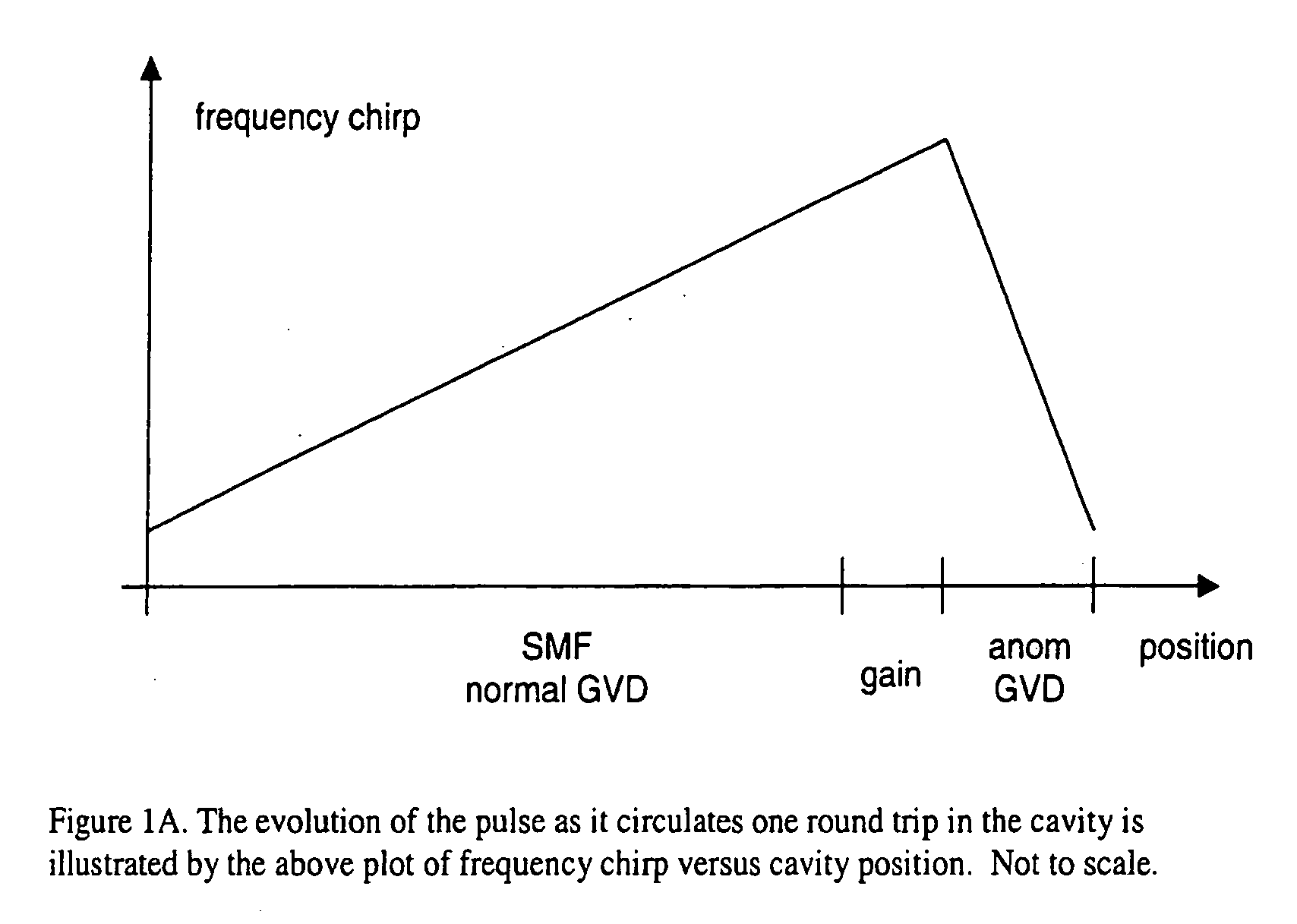

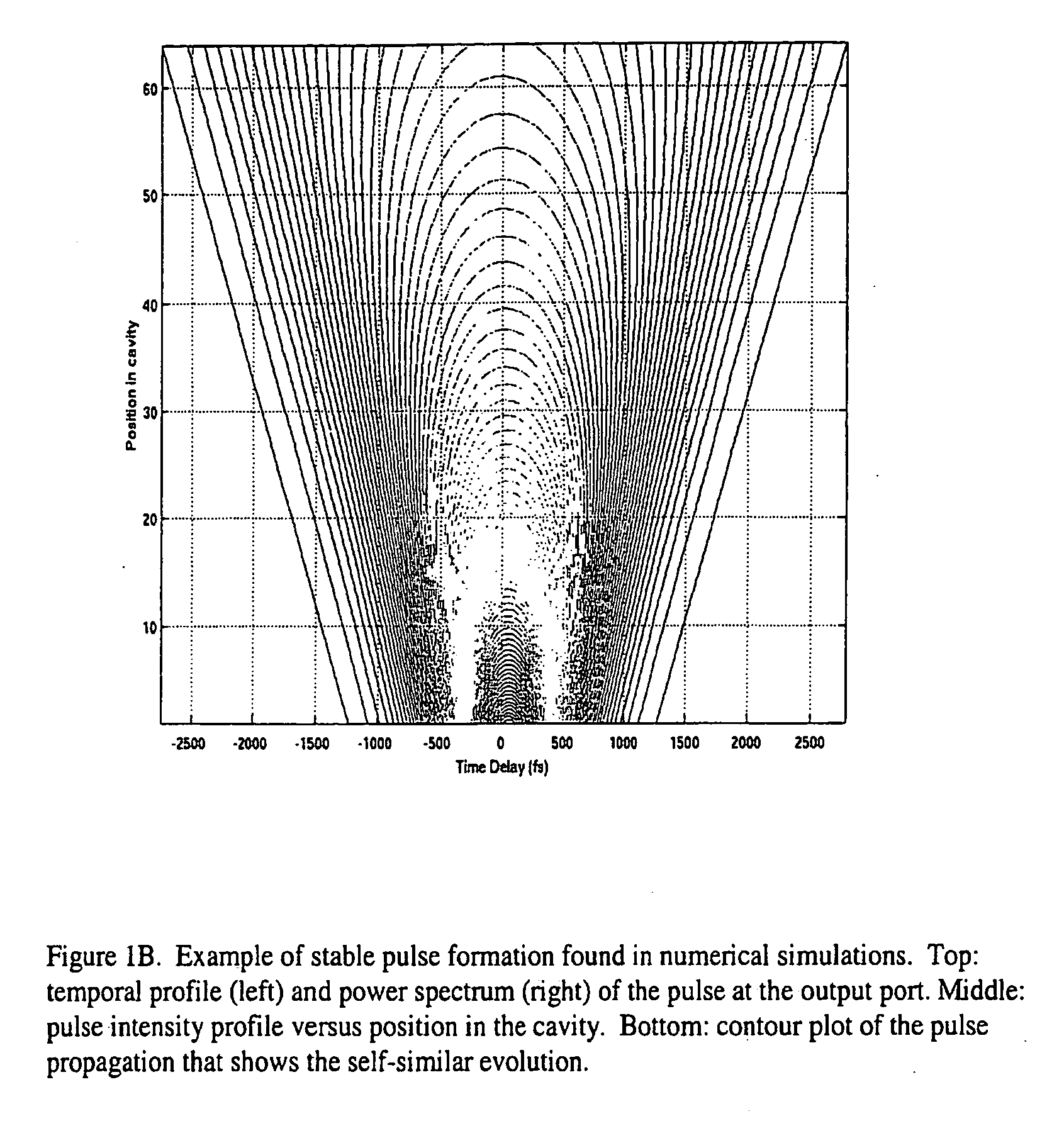

Self-similar laser oscillator

InactiveUS20050169324A1Stable operation of laserHigh bandwidthLaser using scattering effectsActive medium materialState of artHigh energy

A laser producing high energy ultrashort laser pulses comprises a normal dispersion segment, a gain segment, an anomalous dispersion segment with negligible nonlinearity and an effective saturable absorber arranged to form a laser cavity. Each segment is optically interconnected so that a laser pulse will propagate self-similarly therein. (A pulse that propagates in a self-similar manner is sometimes referred to as a “similariton.”) With this laser the limitations of prior art laser oscillators are avoided. Also provided are means for pumping the gain medium in the laser cavity, and means for extracting laser pulses from the laser cavity. The laser cavity is preferably a ring cavity. Preferably the laser is configured to achieve unidirectional circulation of laser pulses therein. This configuration is scalable to much higher pulse energy than lasers based on soliton-like pulse shaping.

Owner:CORNELL RES FOUNDATION INC

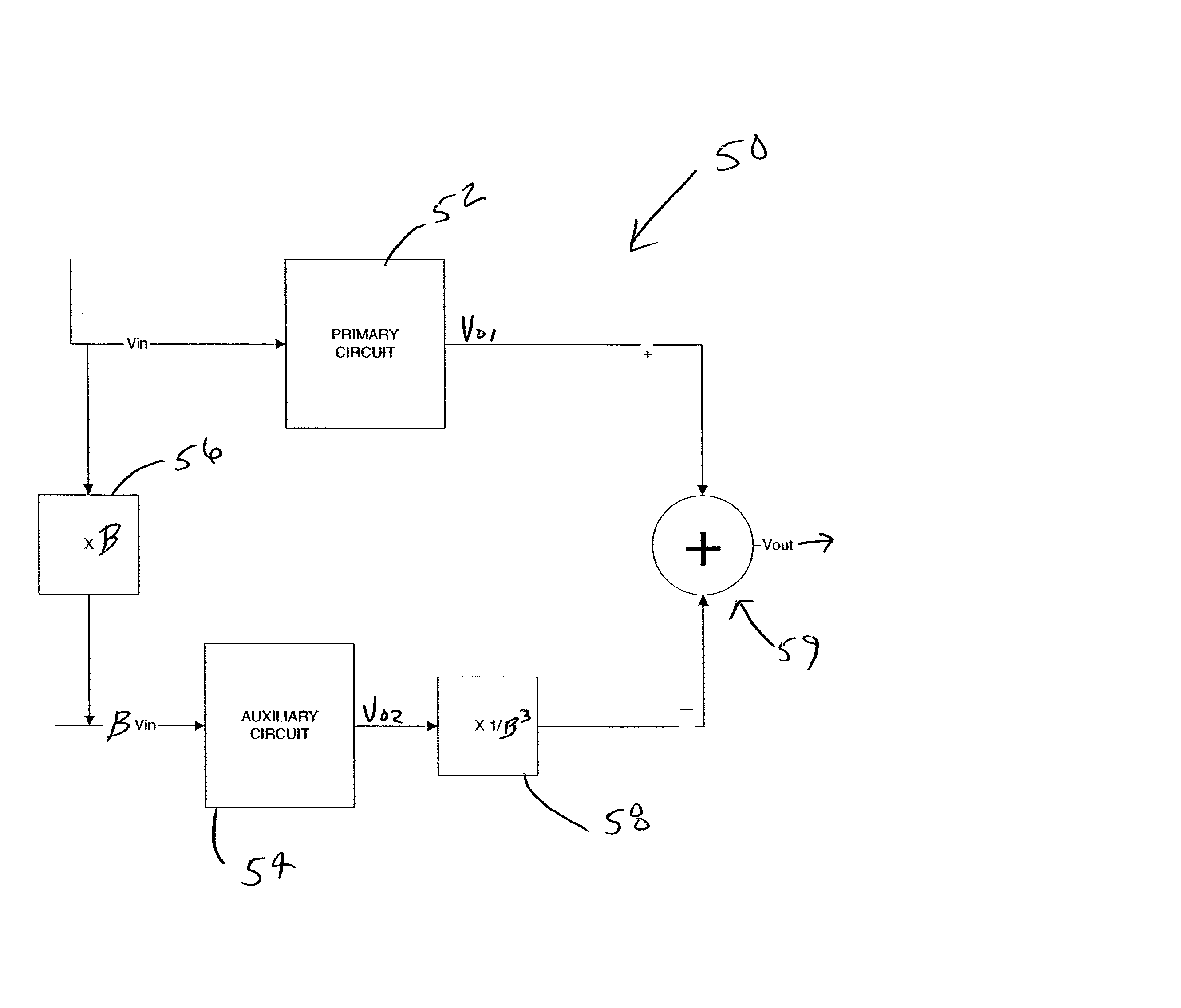

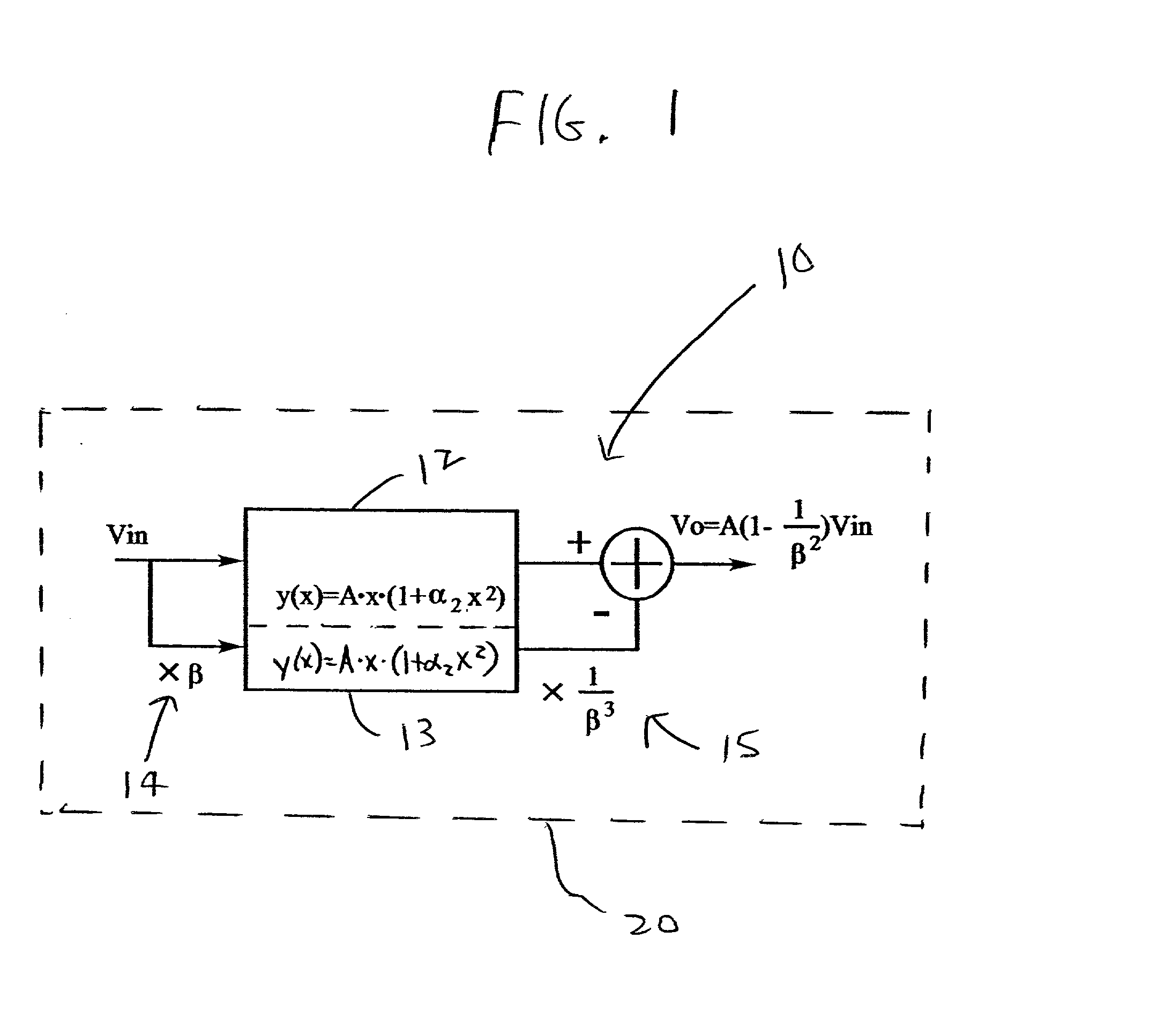

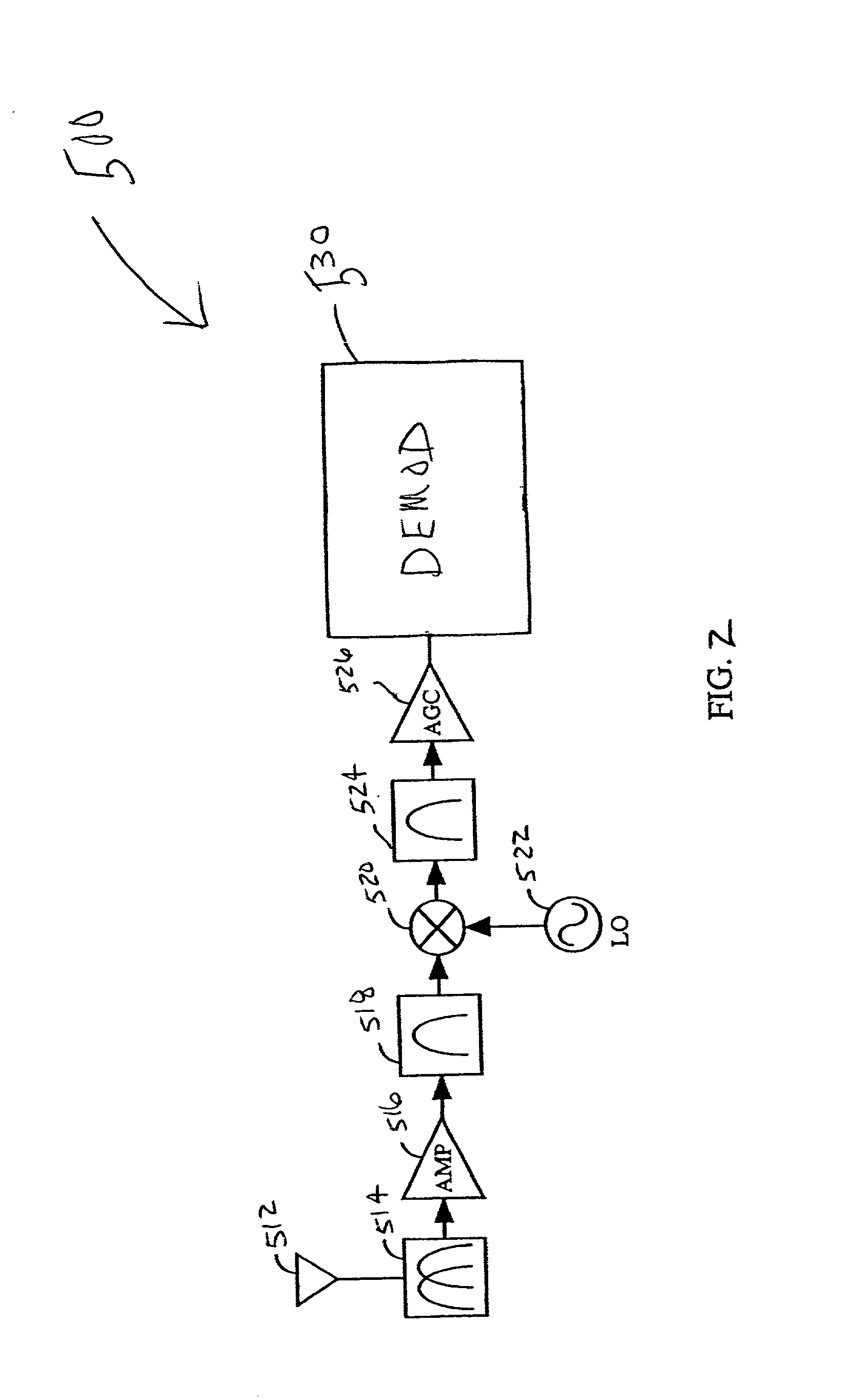

High linearity circuits and methods regarding same

InactiveUS20020126767A1Improve linearitySufficient gainAmplifier modifications to reduce non-linear distortionComputations using contact-making devicesHarmonicLinearity

Circuits and methods that improve linearity with use of cancellation of at least a portion, and preferably, substantially all of, at least one significant harmonic from the output of a primary circuit, e.g., the 3.sup.rd harmonic, using the output of a substantially functionally identical auxiliary circuit.

Owner:RGT UNIV OF MINNESOTA

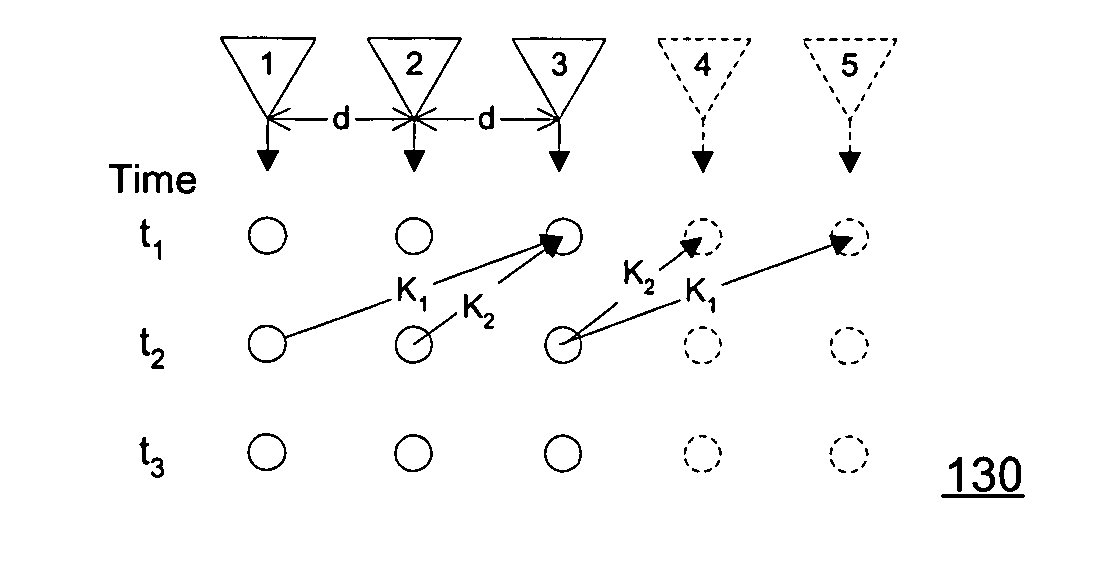

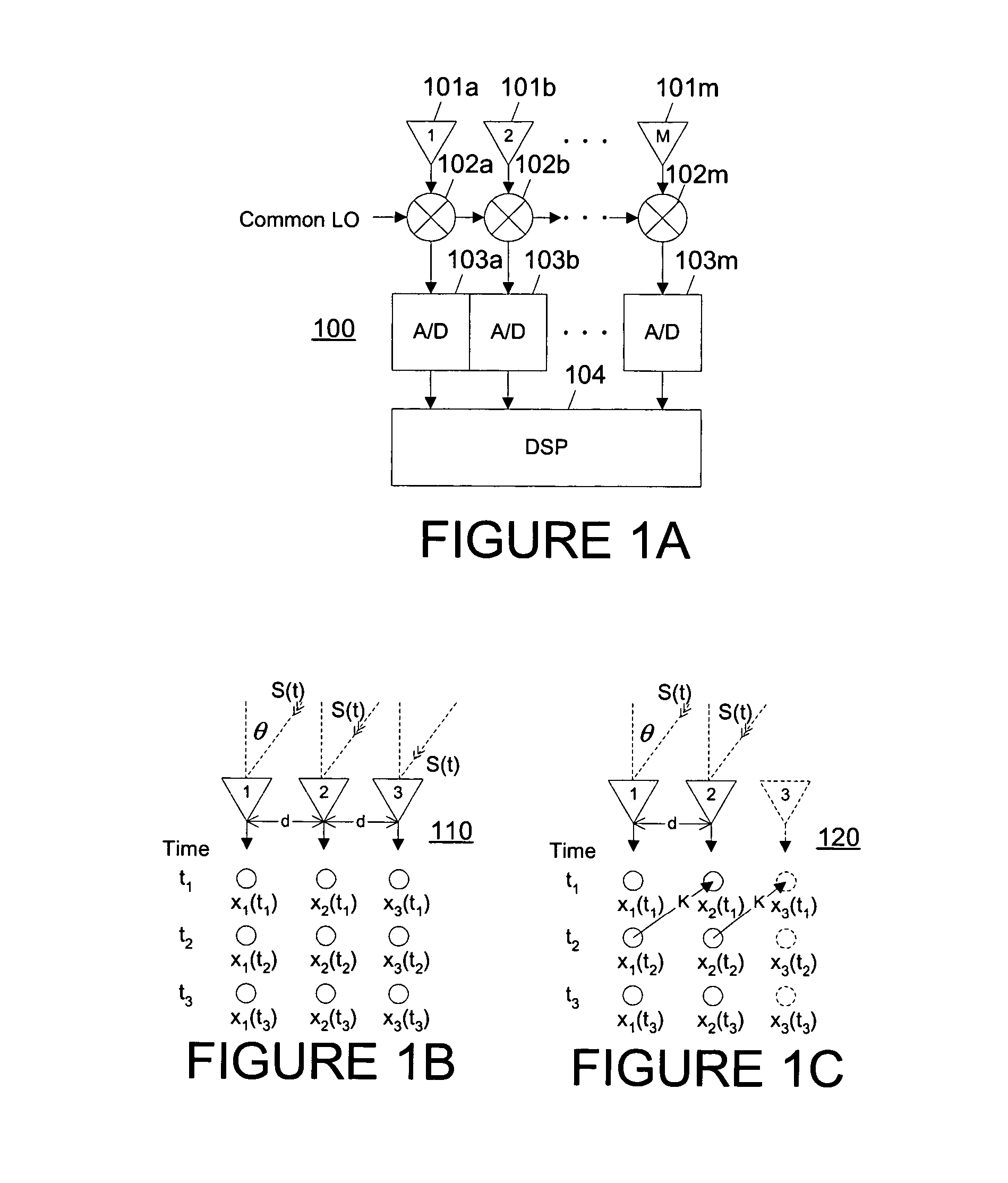

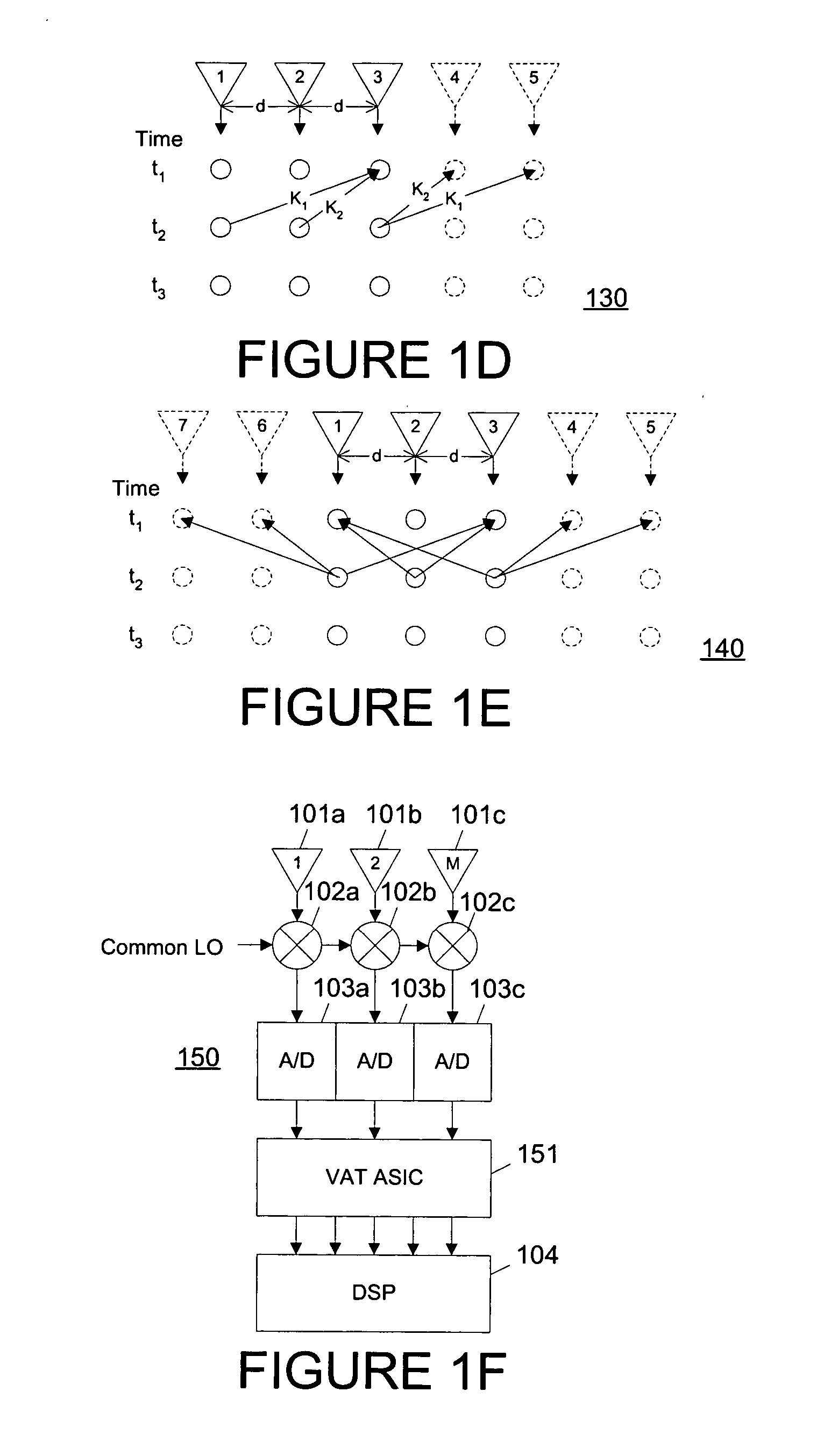

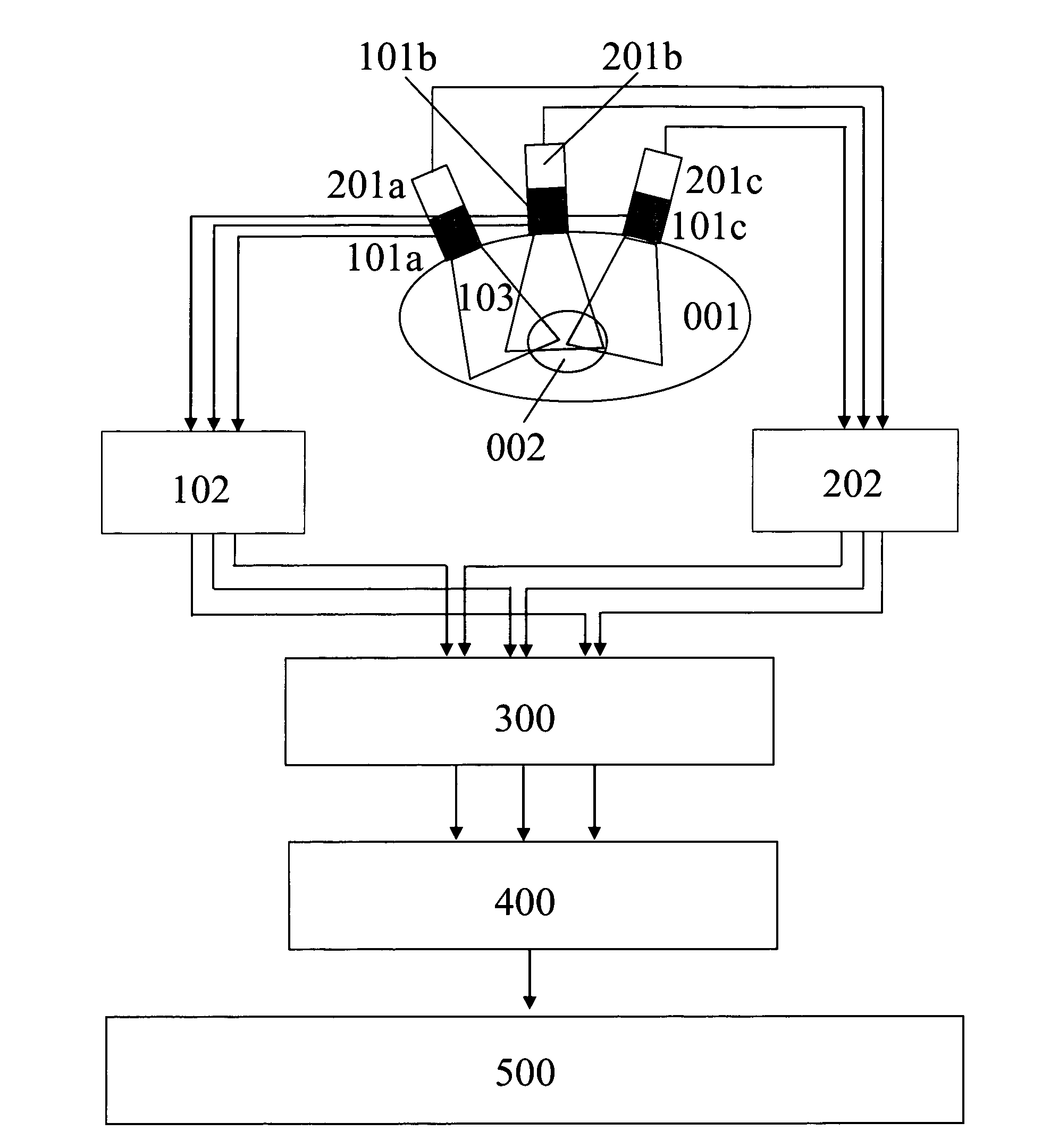

Virtual antenna technology (VAT) and applications

InactiveUS20050030228A1Sufficient gainLow noiseRadio wave direction/deviation determination systemsIndividually energised antenna arraysPhysicsRadio frequency

Within an antenna array 120, the magnitude and phase of a relationship resulting from propagation delay between a sample taken at a first antenna 1 to a sample taken at a second antenna 2 at a different time is employed to derive a data value for a virtual antenna 3. Sub-patch antennas 203 perturbed in elevation are employed to expand the elevation range of acceptable gain. Multiple arrays each providing a separate radio frequency output are employed with digital beamform steering to a single point, together with low noise amplification at the feed point, to achieve sufficient gain with an acceptable total array size. A modular implementation with fiber transport is preferably used.

Owner:DAVIS MUNCK P C

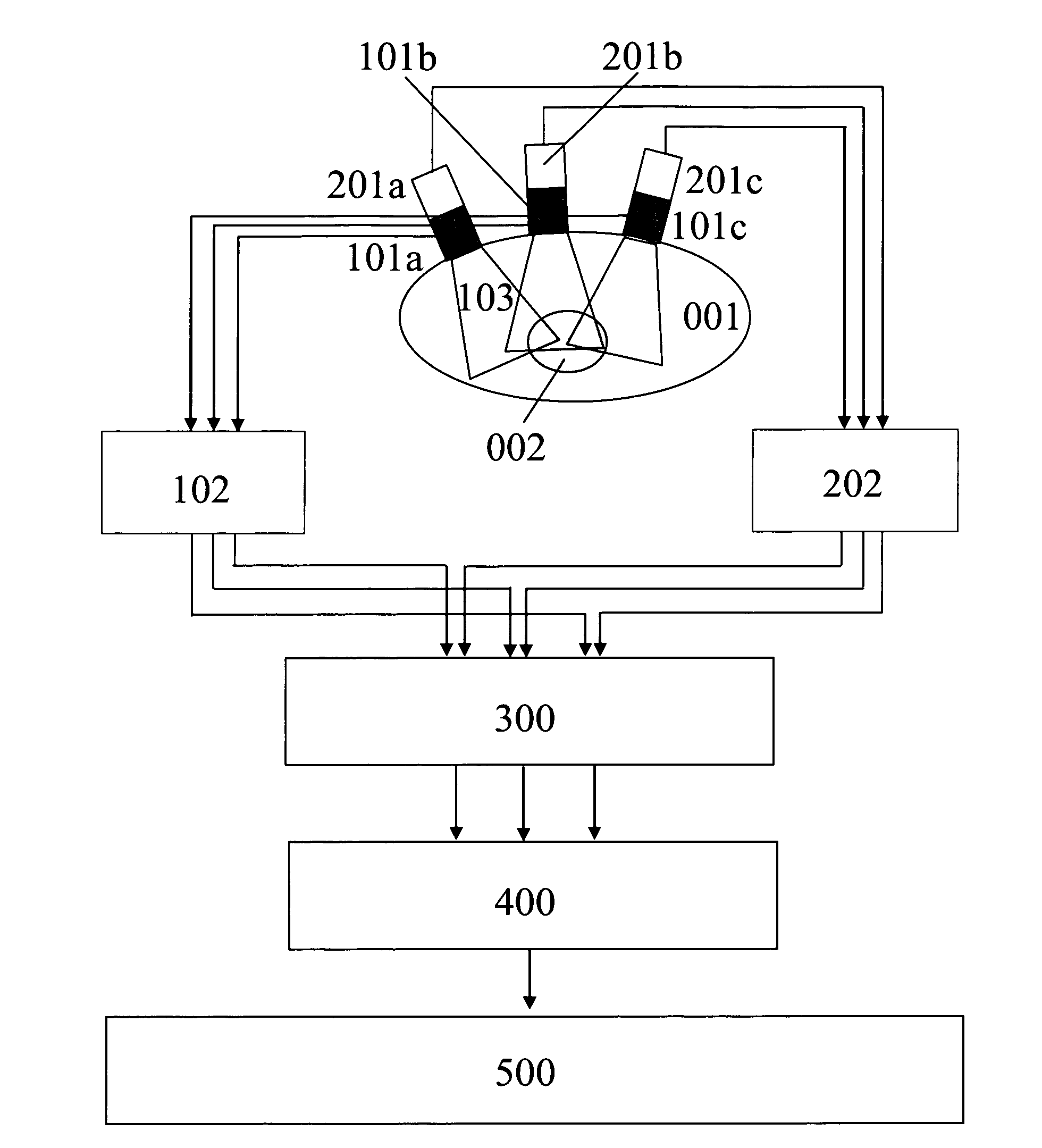

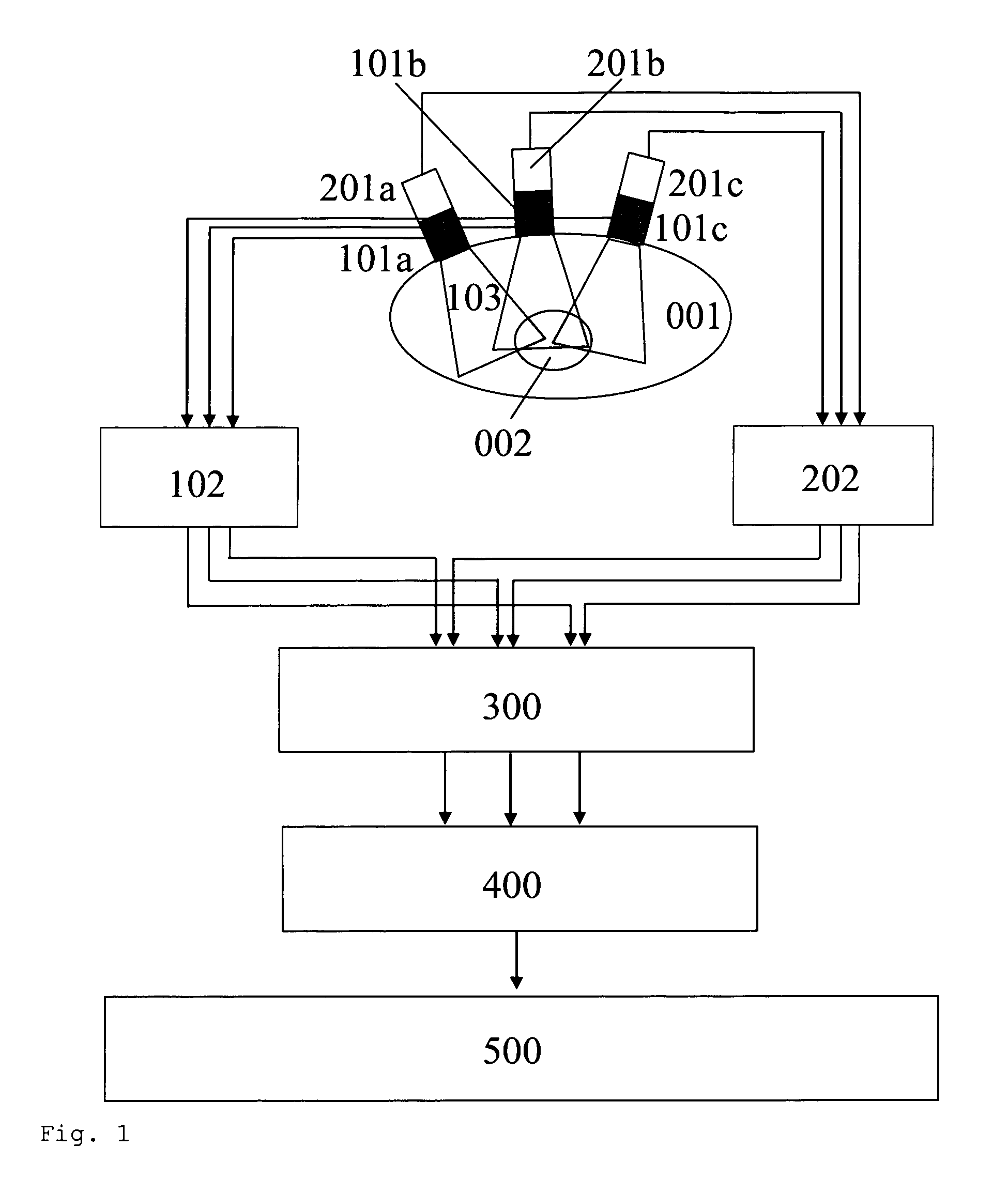

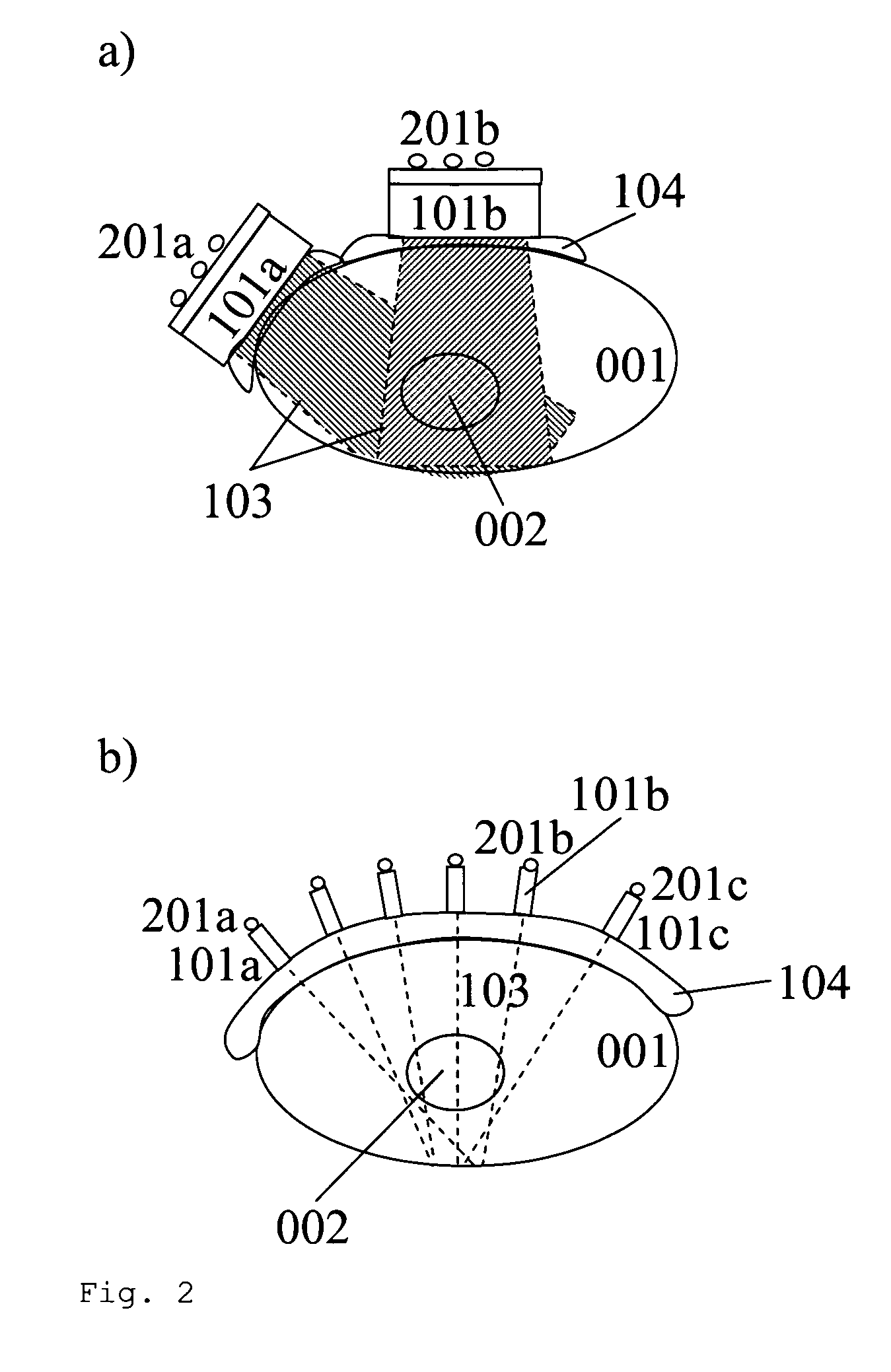

3D Motion Detection and Correction By Object Tracking in Ultrasound Images

InactiveUS20110190629A1Simple processShorten the timeOrgan movement/changes detectionSurgical navigation systemsNumerical controlSonification

An arrangement to determine physiologic data, position, orientation and / or geometry of an object of interest includes an ultrasound unit with a multiplicity of ultrasound transducers to monitor physiologic parameters, especially motion and deformation, of an object of interest encapsulated by a body in real-time in three dimensions of space and to generate numerical control or trigger information for other medical devices.

Owner:MEDIRI

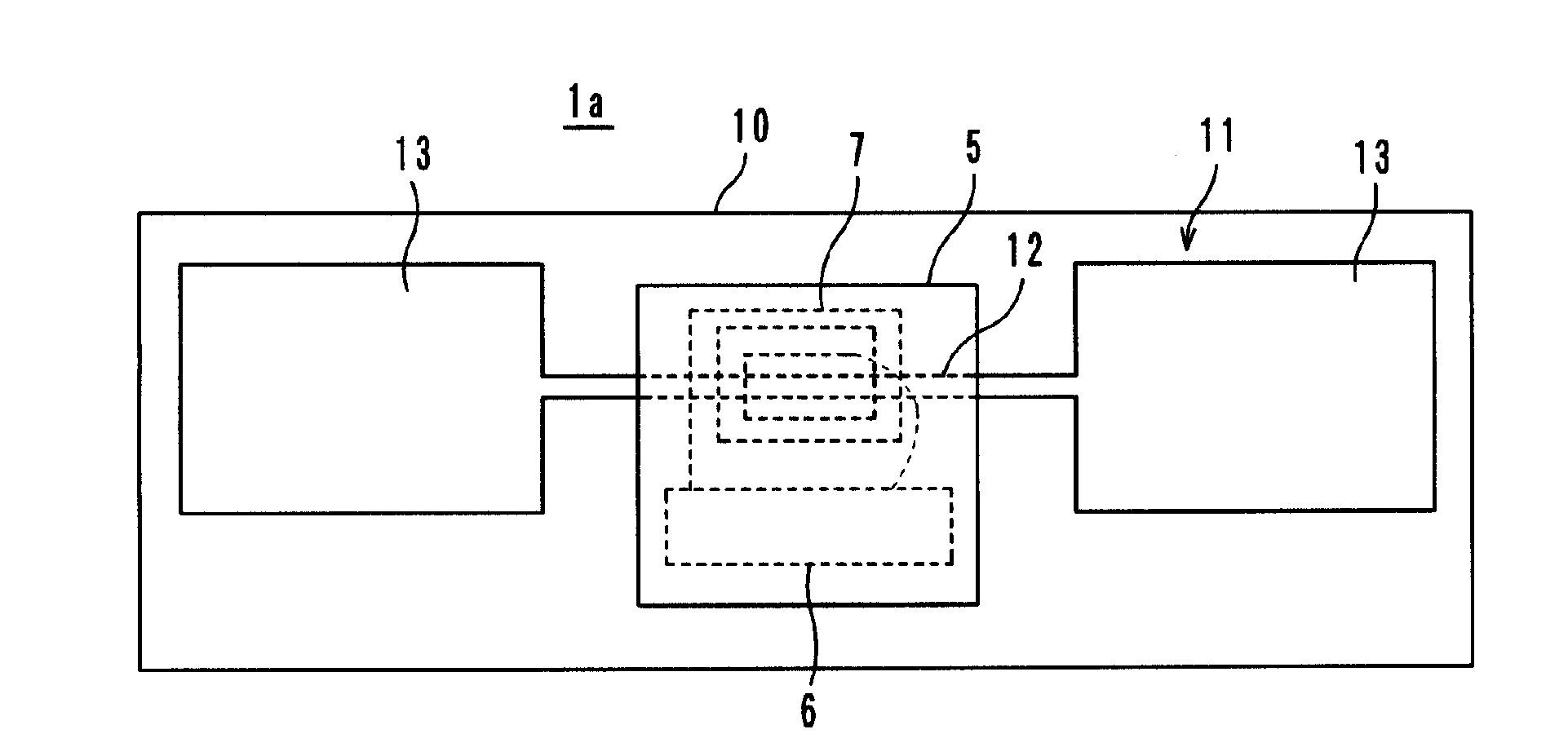

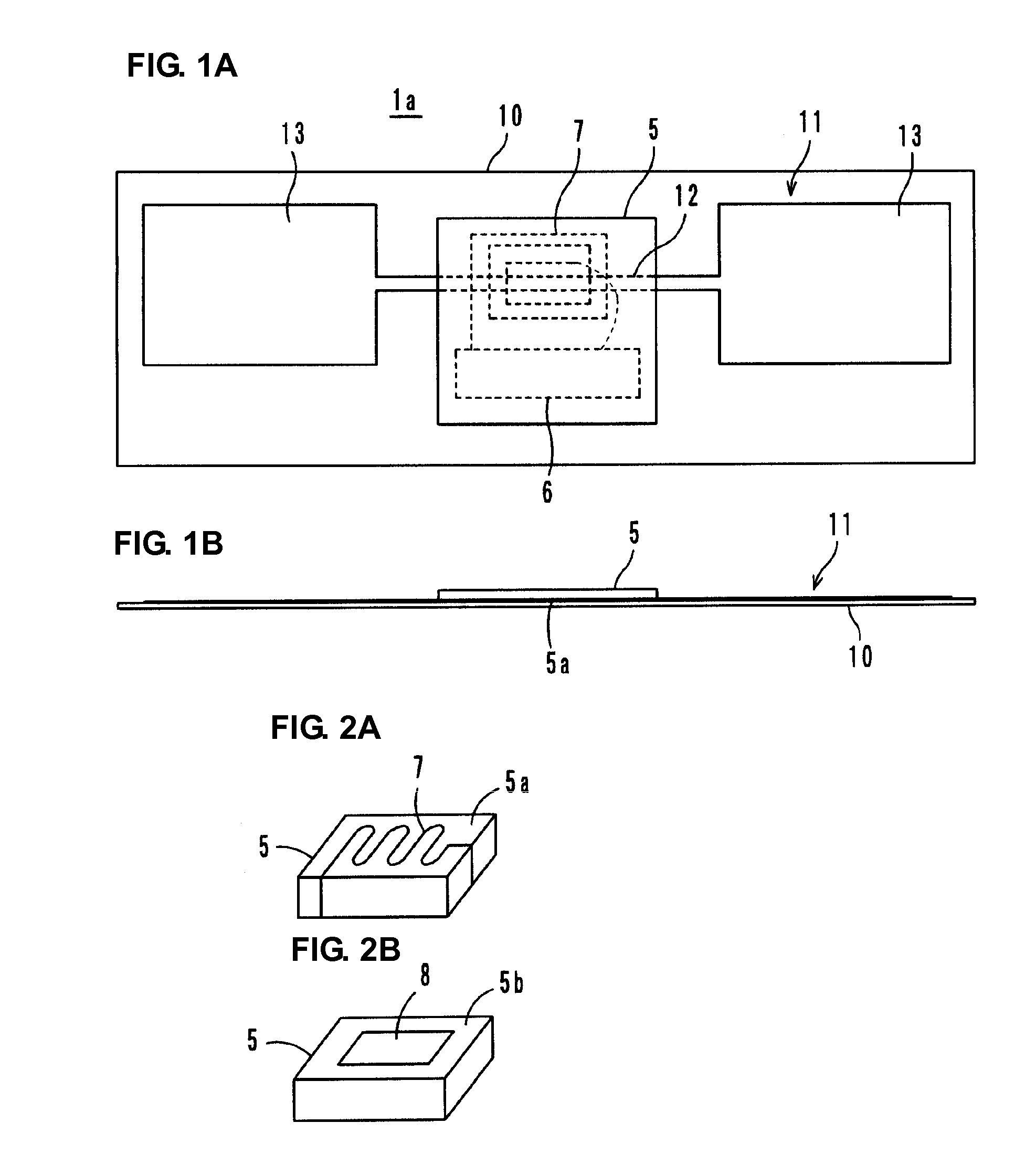

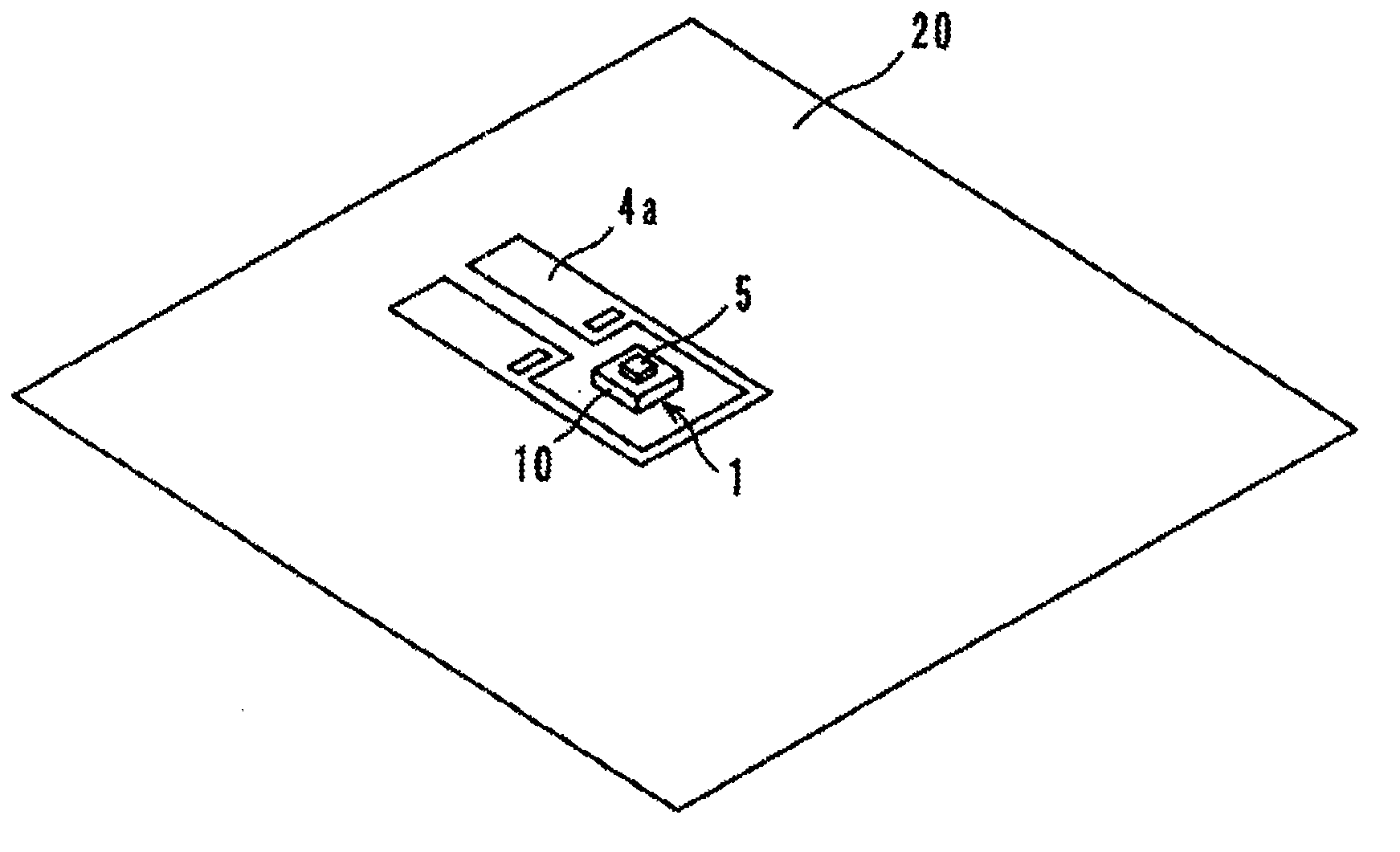

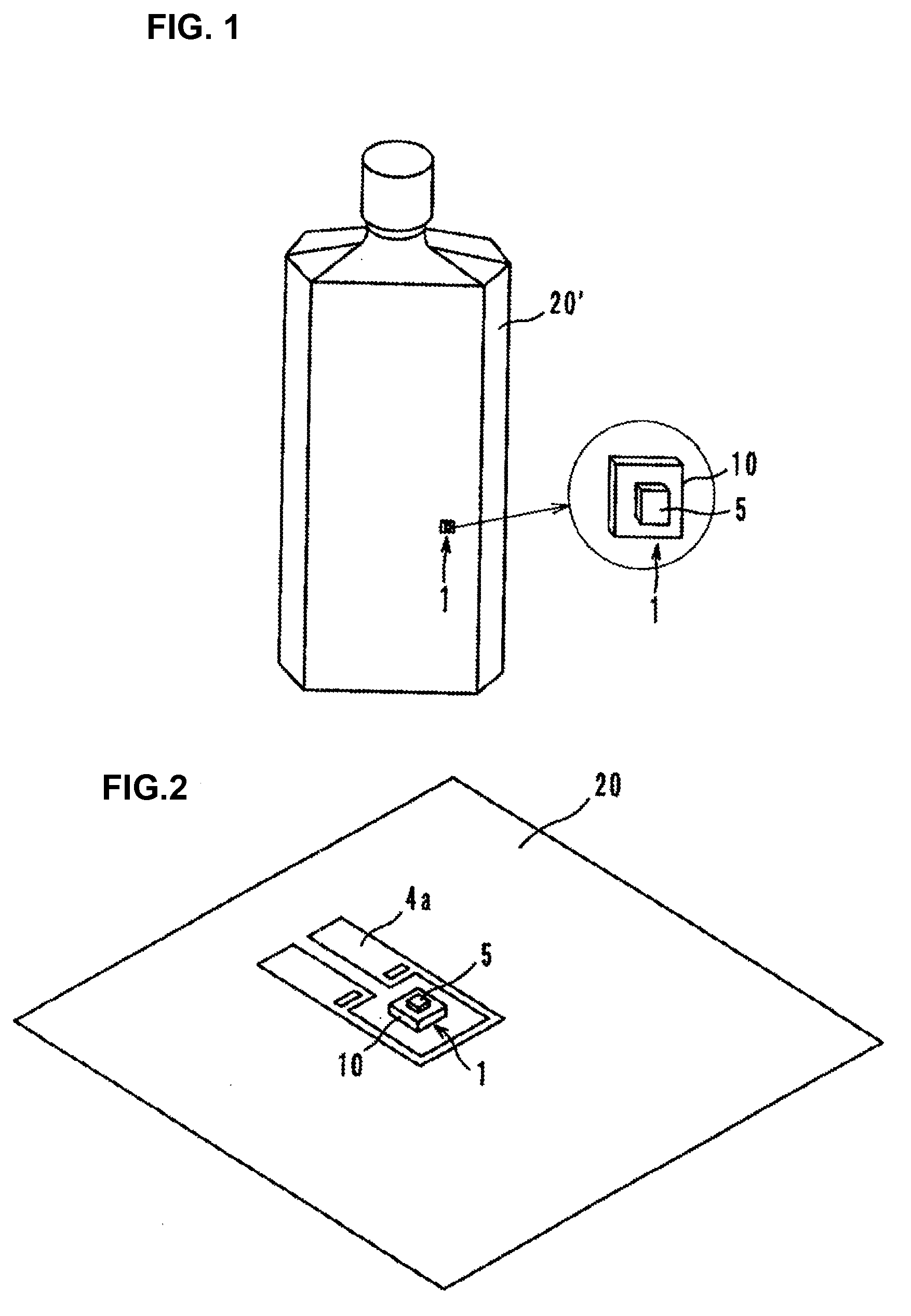

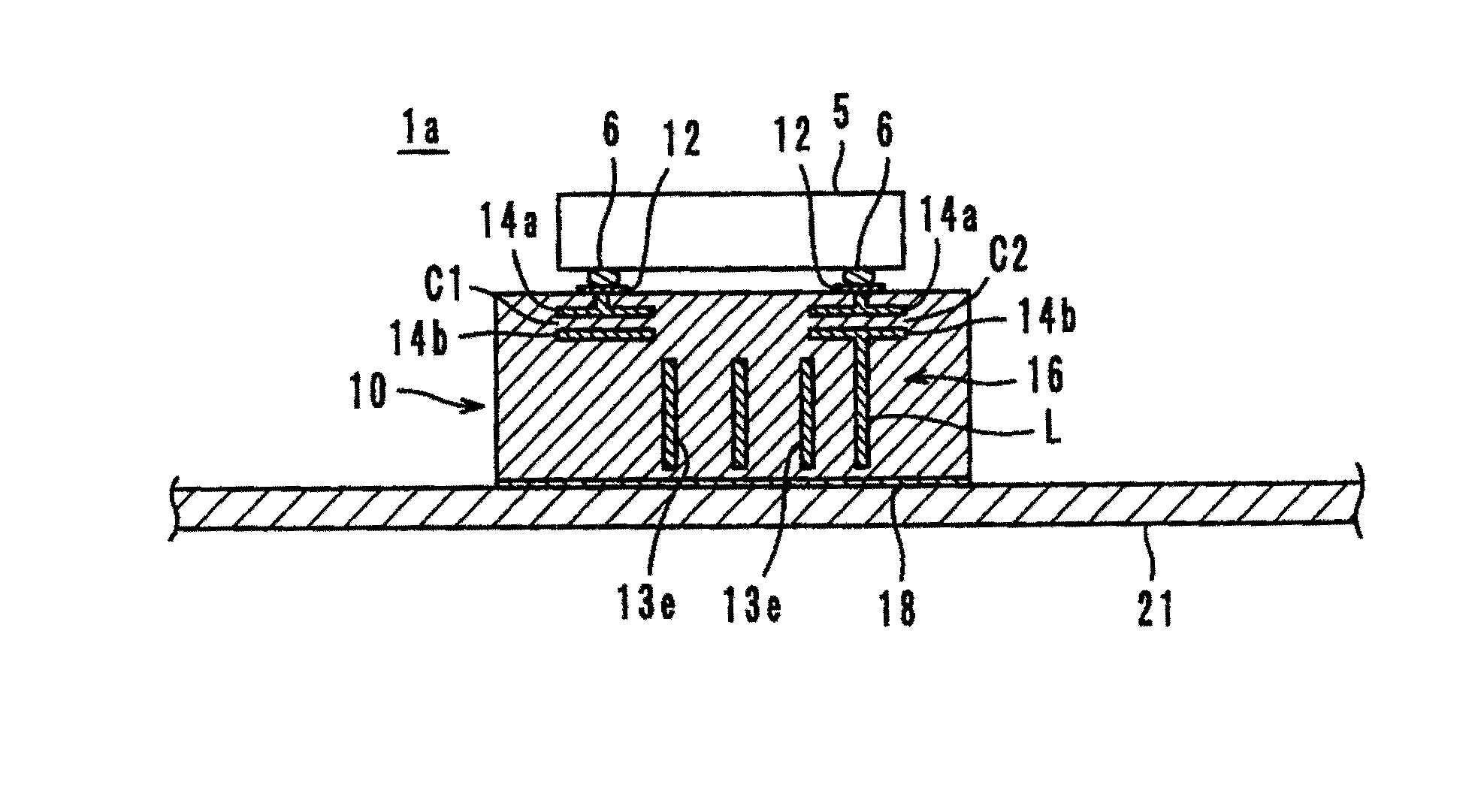

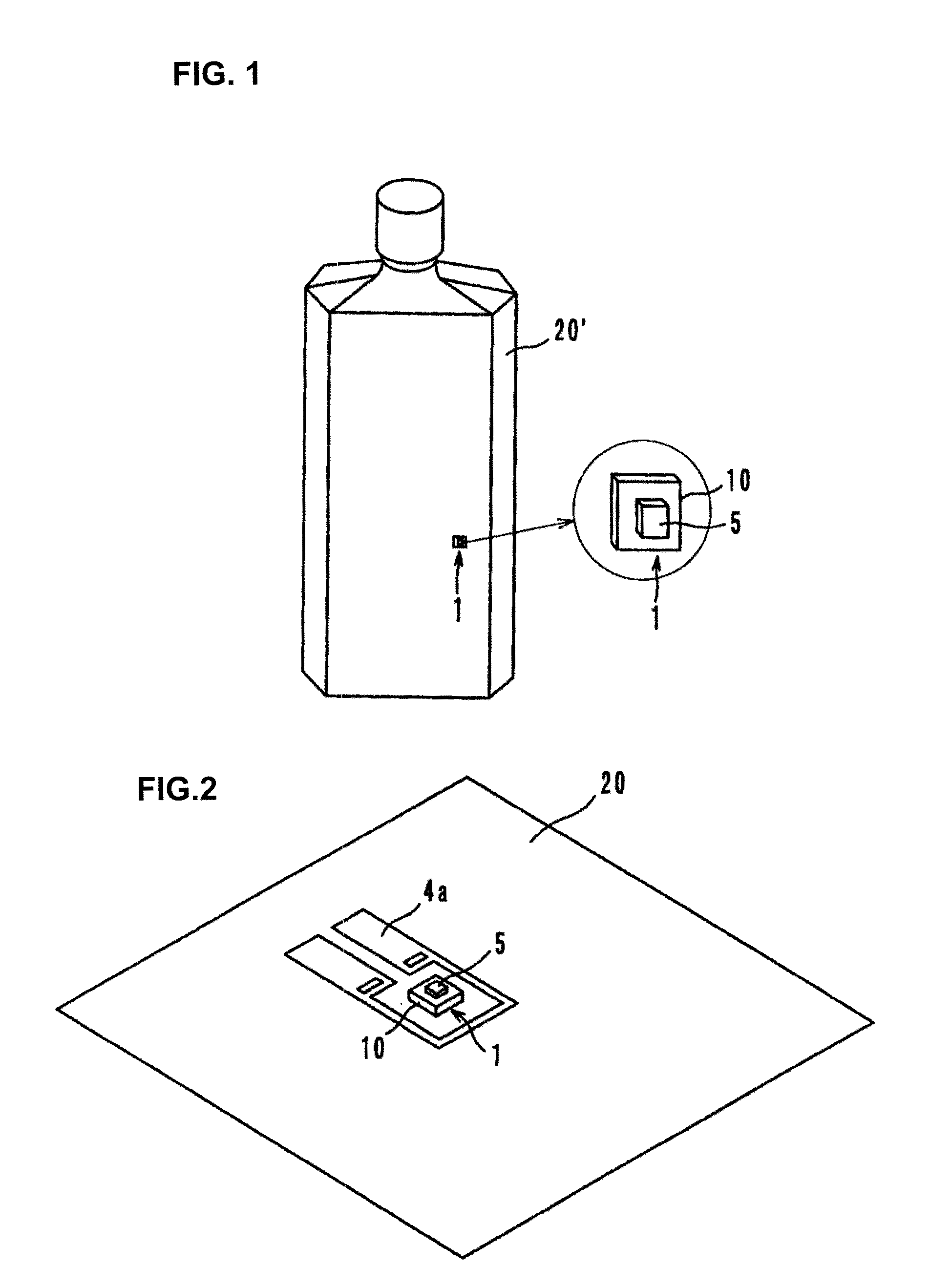

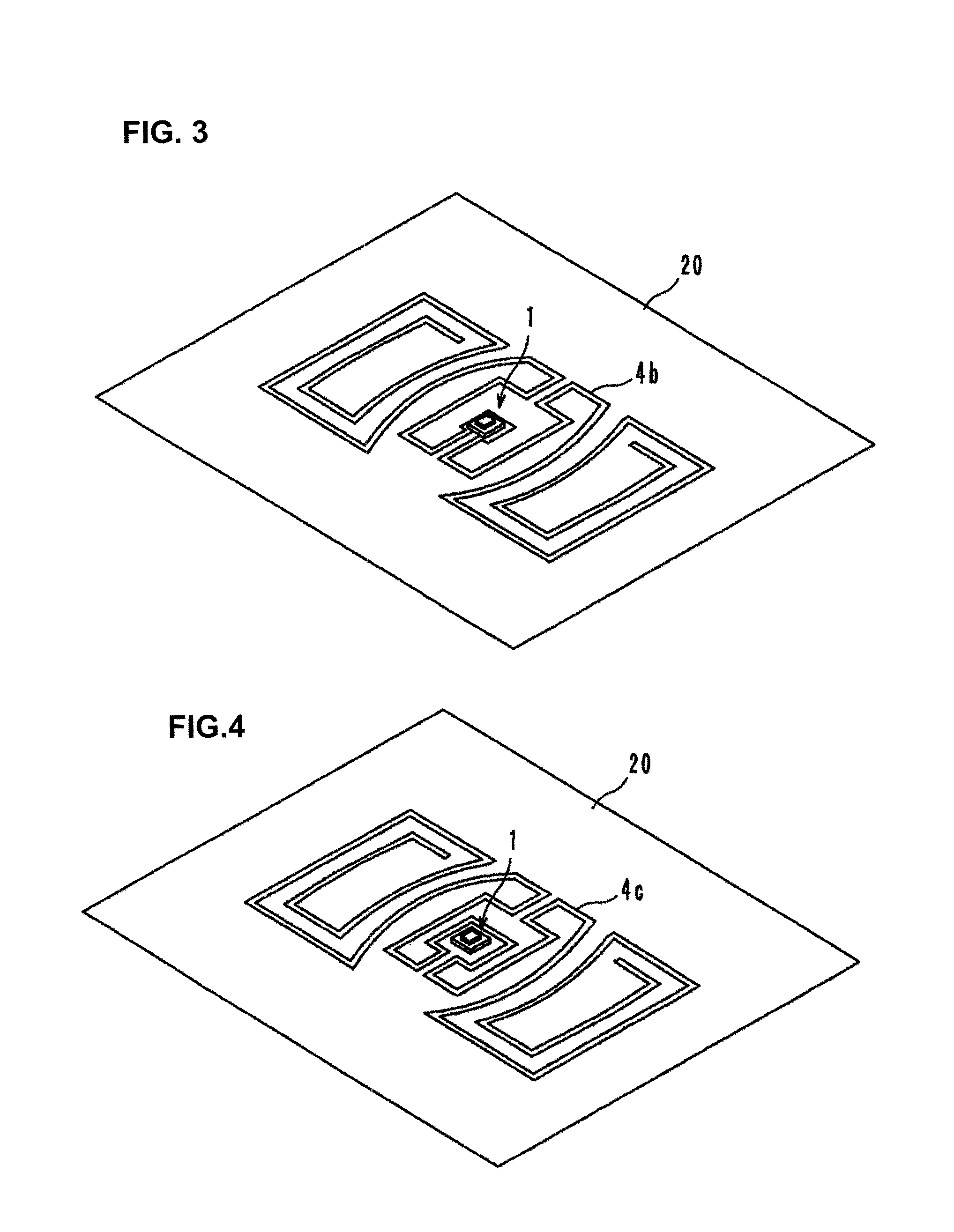

Article having electromagnetic coupling module attached thereto

ActiveUS20090179810A1Negligible negative effectReduce sizeSolid-state devicesSensing record carriersElectromagnetic couplingElectromagnetic field coupling

An article having an electromagnetic coupling module attached thereto includes an electromagnetic coupling module and a PET bottle having the electromagnetic coupling module bonded thereto. The electromagnetic coupling module includes a wireless IC chip arranged to process transmission and reception signals and the feed circuit board having the wireless IC chip mounted thereon. The feed circuit board includes a feed circuit including a resonant circuit having a predetermined resonant frequency. The feed circuit performs characteristic impedance matching between the PET bottle and the wireless IC chip. The PET bottle functions as a radiator arranged to radiate a transmission signal supplied from the feed circuit using electromagnetic field coupling and to supply a received reception signal to the feed circuit using electromagnetic field coupling.

Owner:MURATA MFG CO LTD

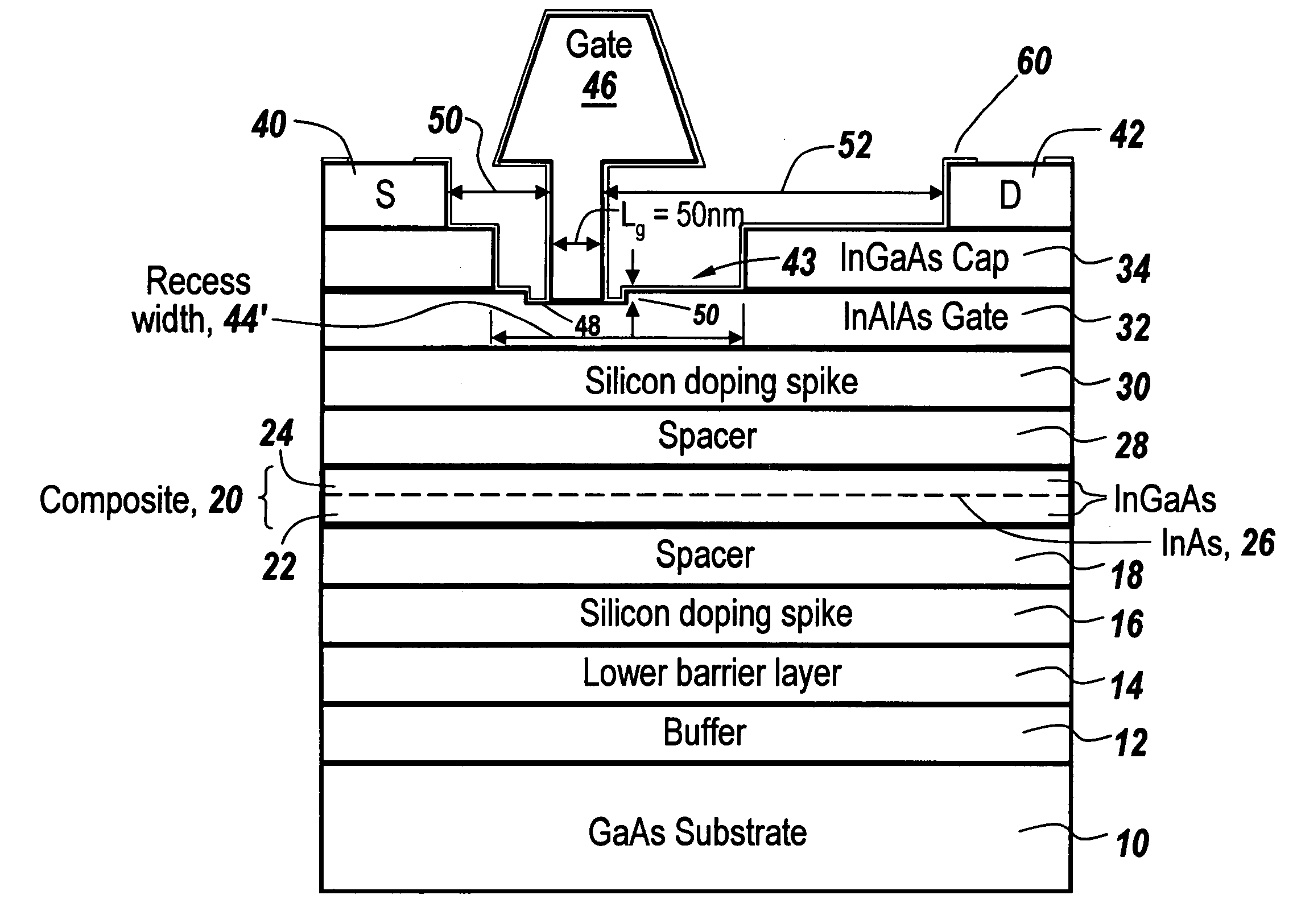

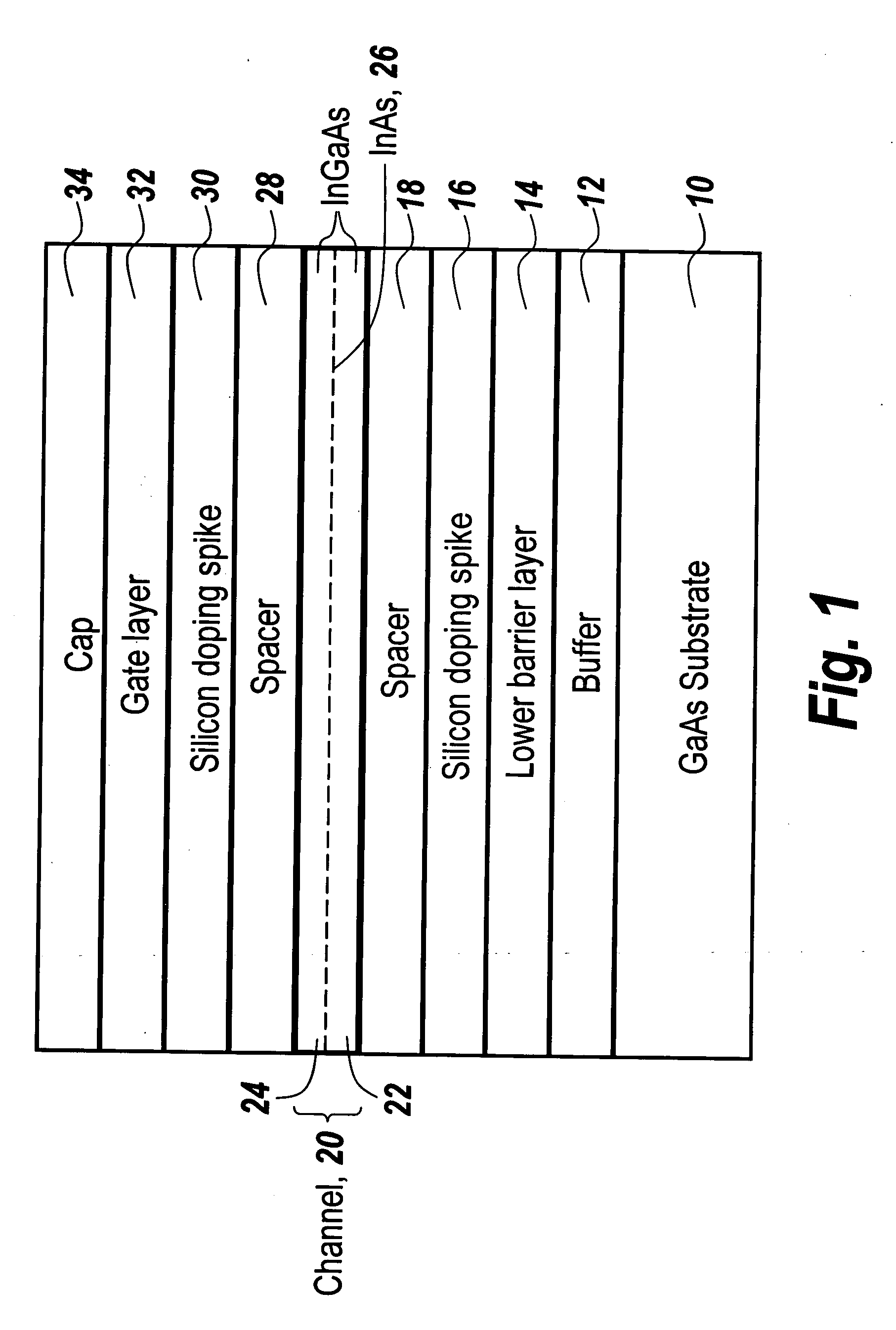

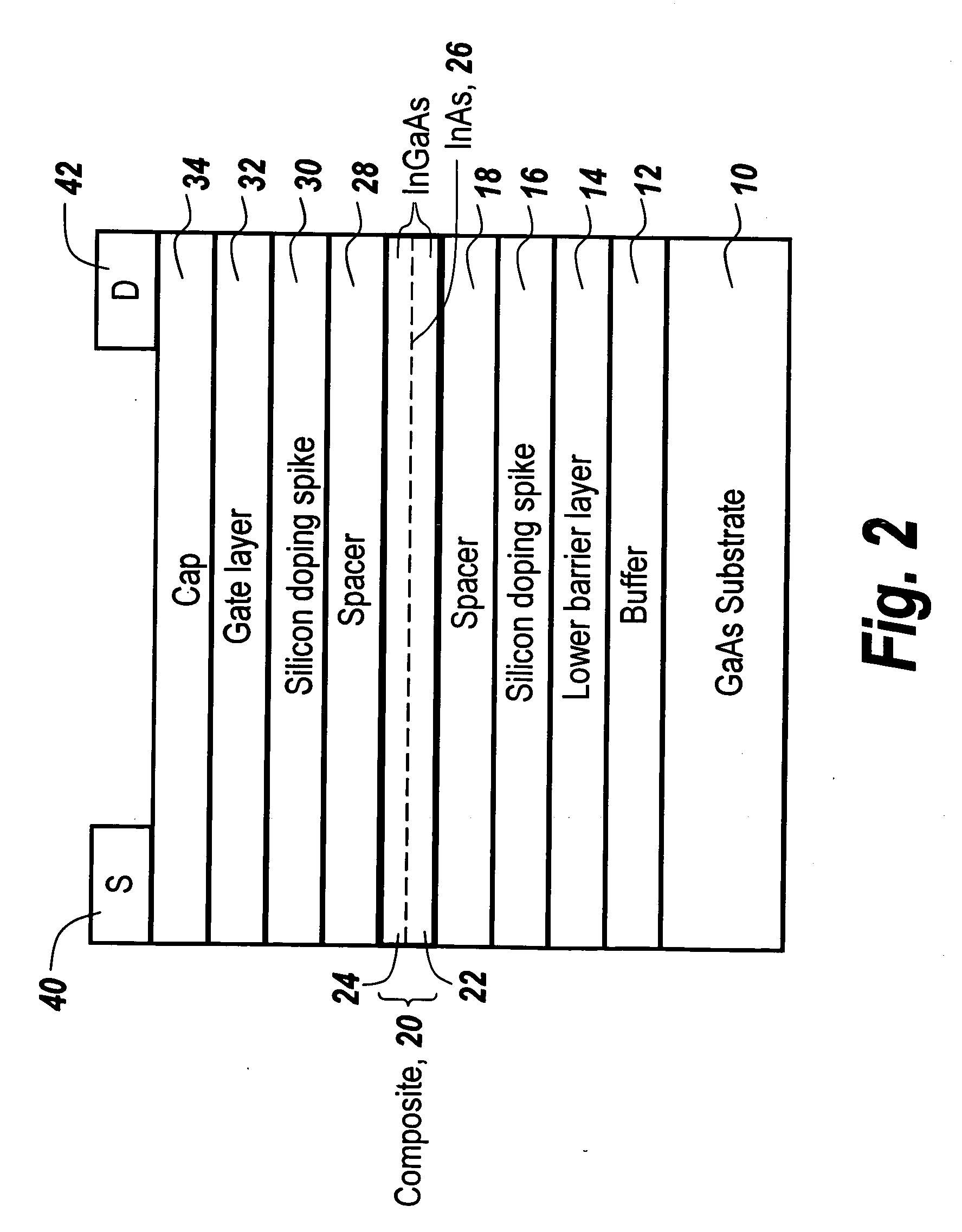

Asymmetrically recessed high-power and high-gain ultra-short gate HEMT device

ActiveUS20100301395A1Improve performanceEnhanced breakdown performanceSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsIndium

A high-power and high-gain ultra-short gate HEMT device has exceptional gain and an exceptionally high breakdown voltage provided by an increased width asymmetric recess for the gate electrode, by a composite channel layer including a thin indium arsenide layer embedded in the indium gallium arsenide channel layer and by double doping through the use of an additional silicon doping spike. The improved transistor has an exceptional 14 dB gain at 110 GHz and exhibits an exceptionally high 3.5-4 V breakdown voltage, thus to provide high gain, high-power and ultra-high frequency in an ultra-short gate device.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

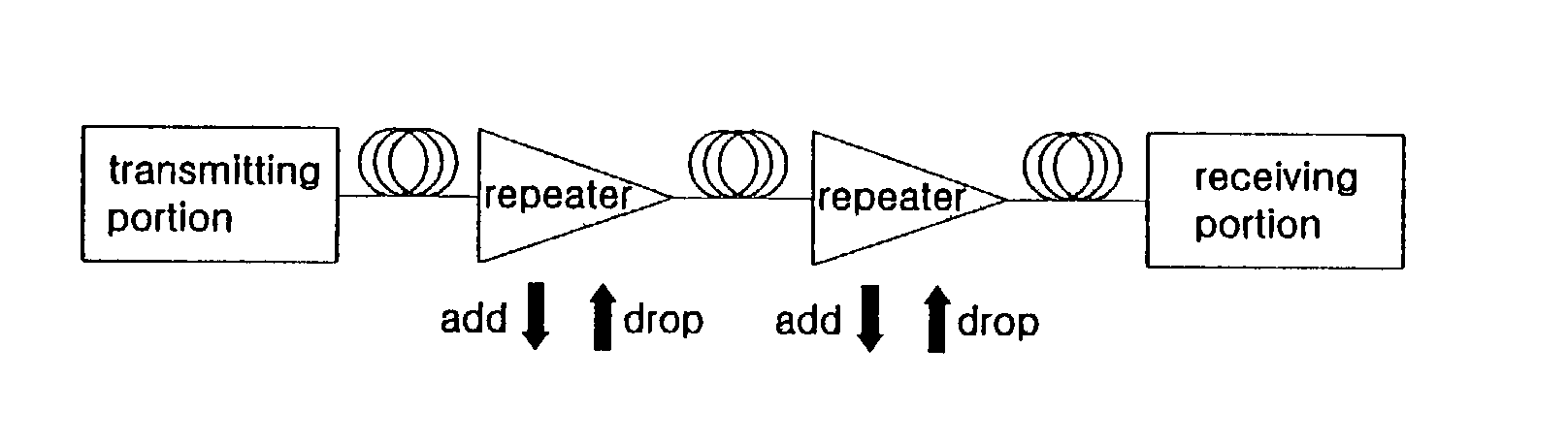

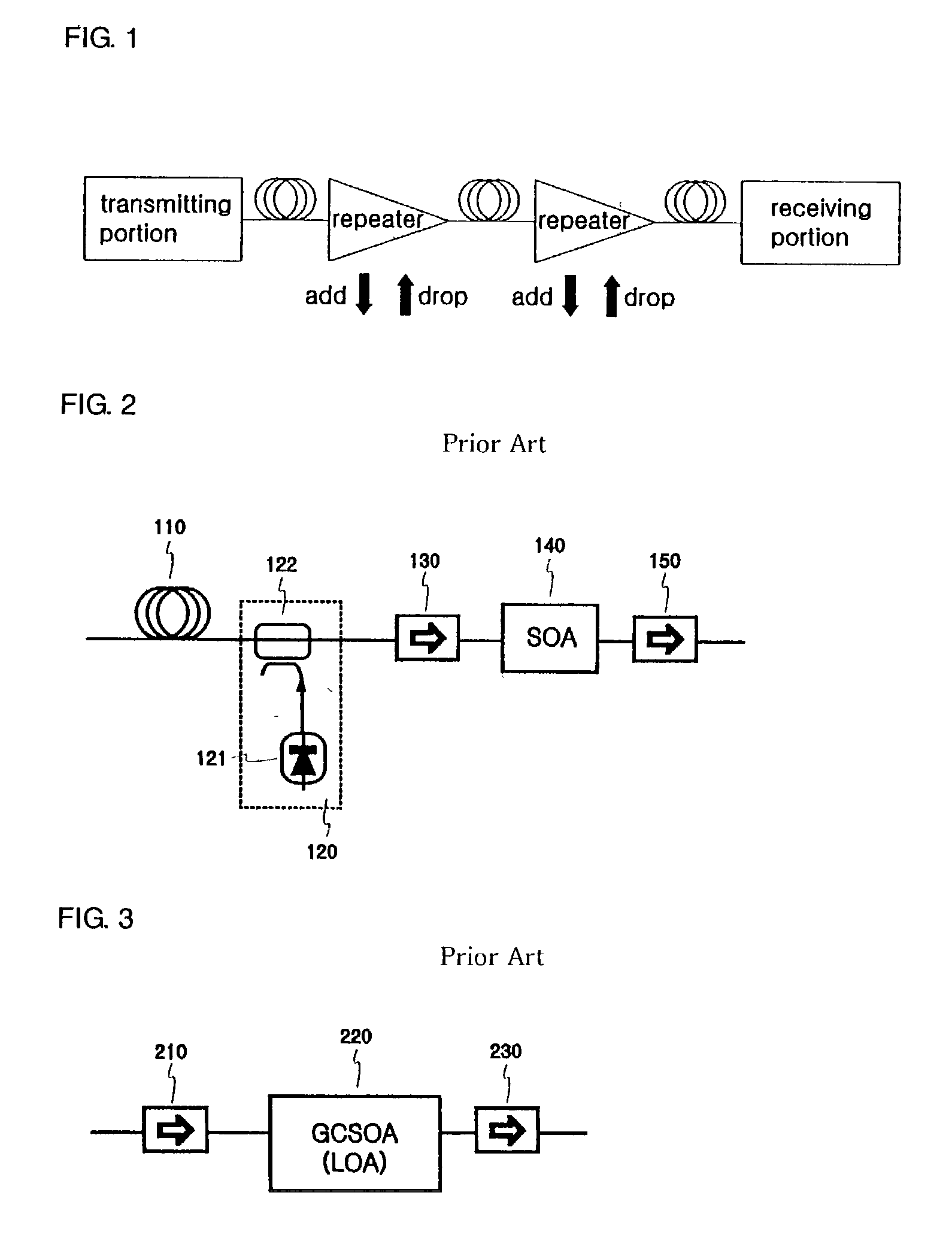

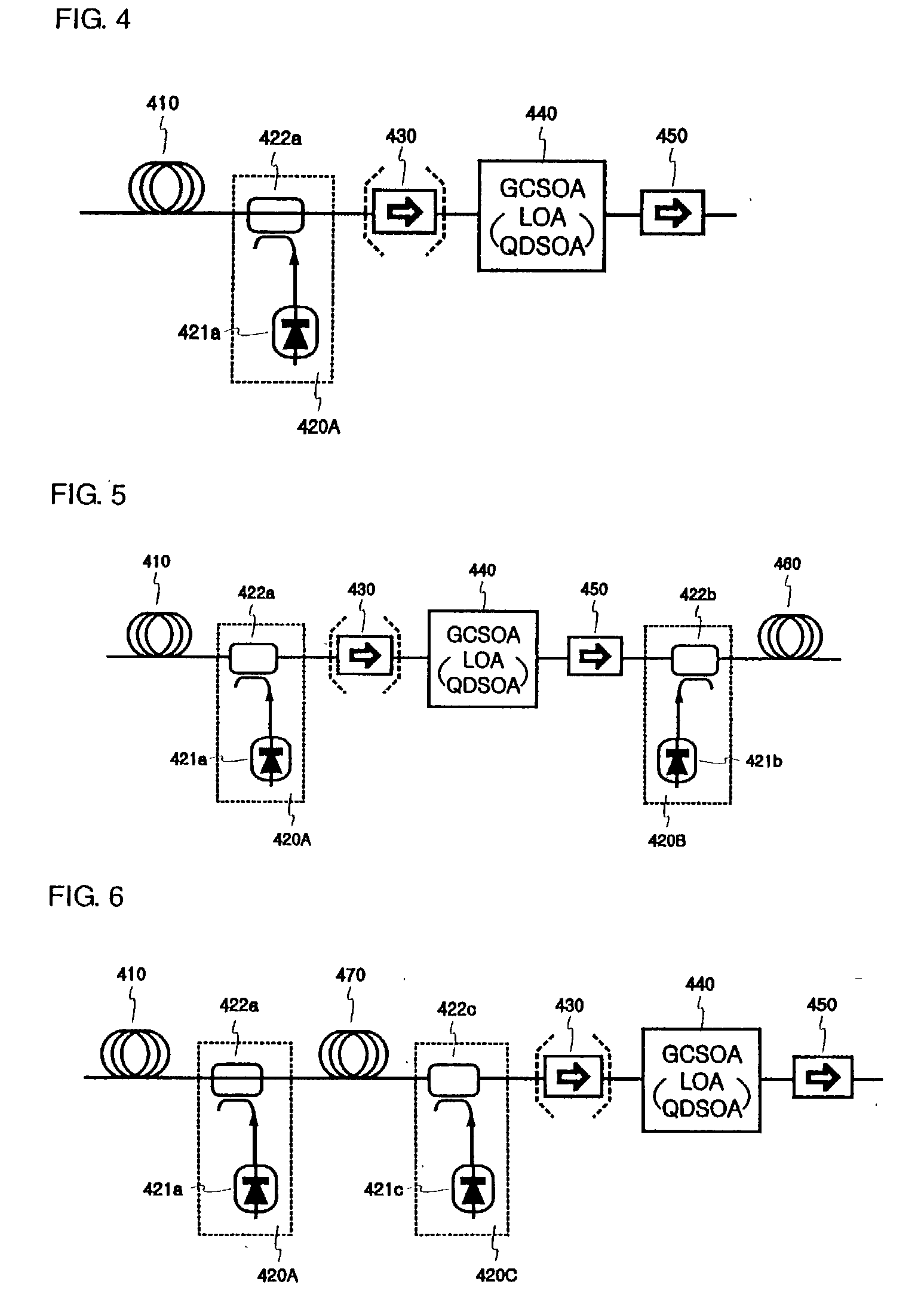

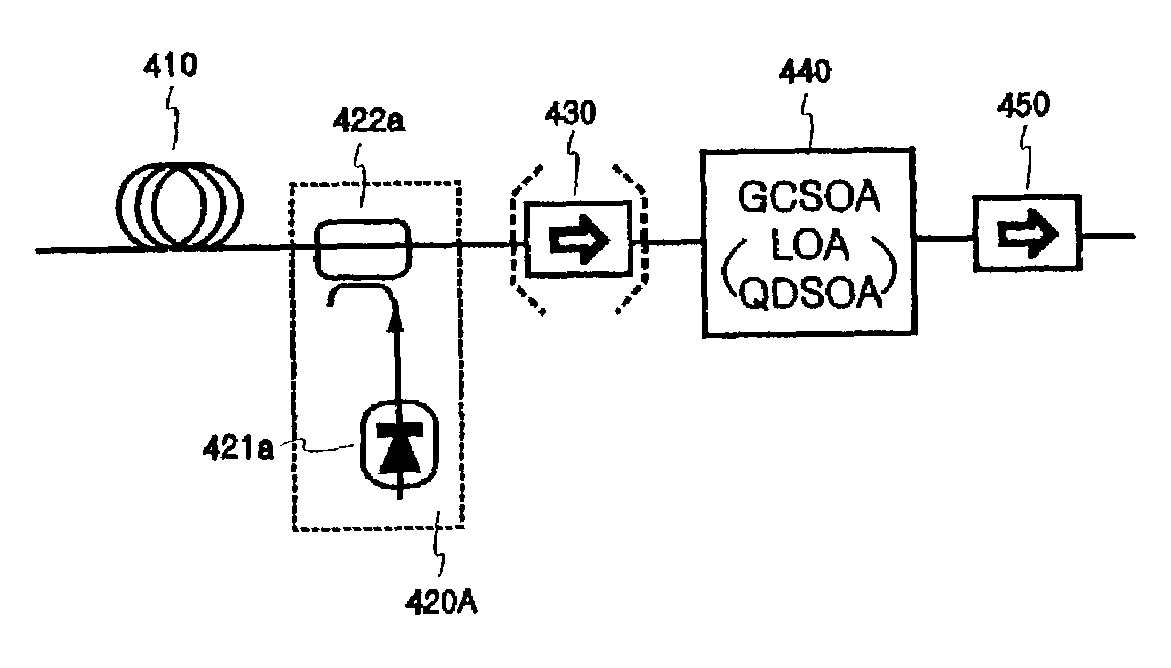

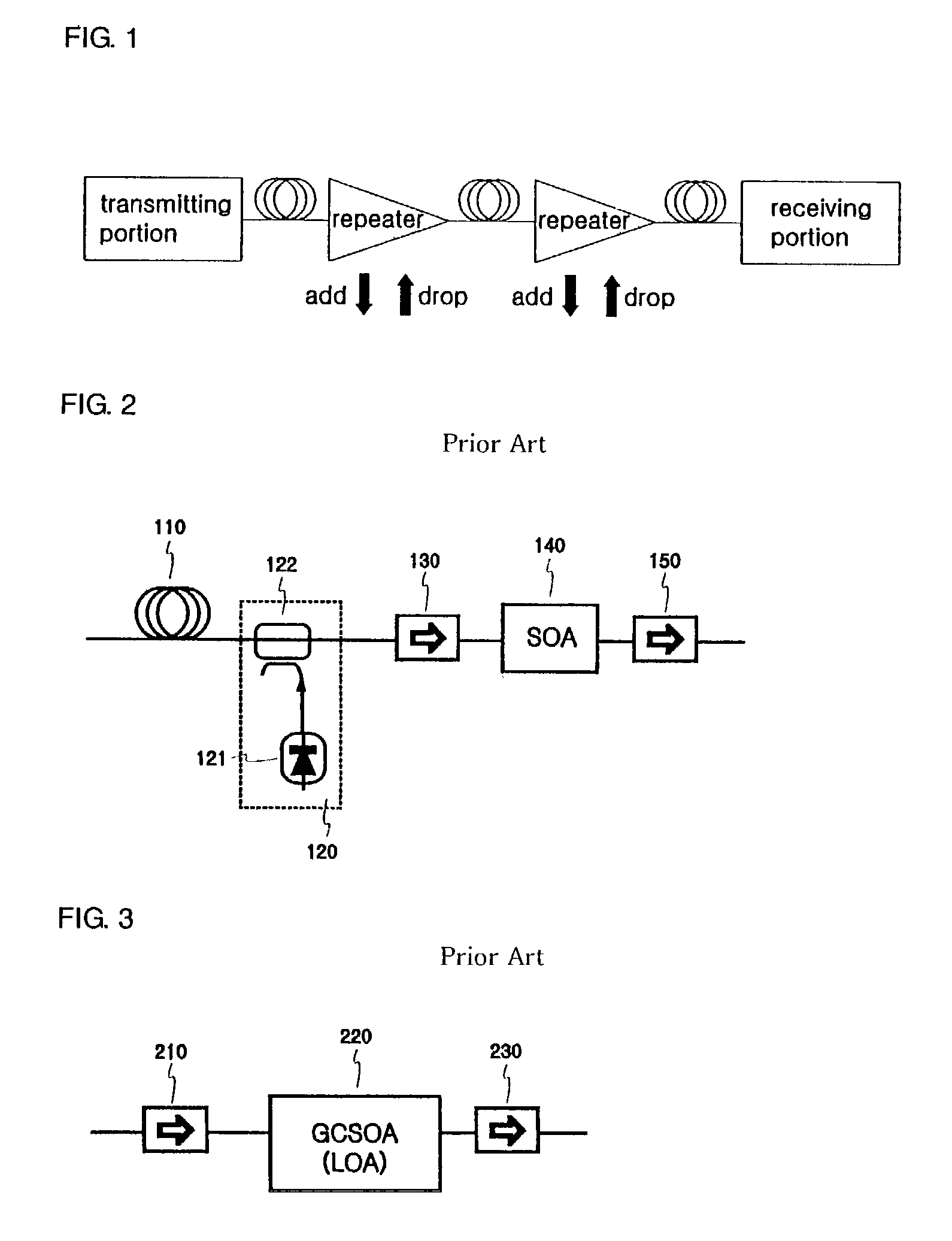

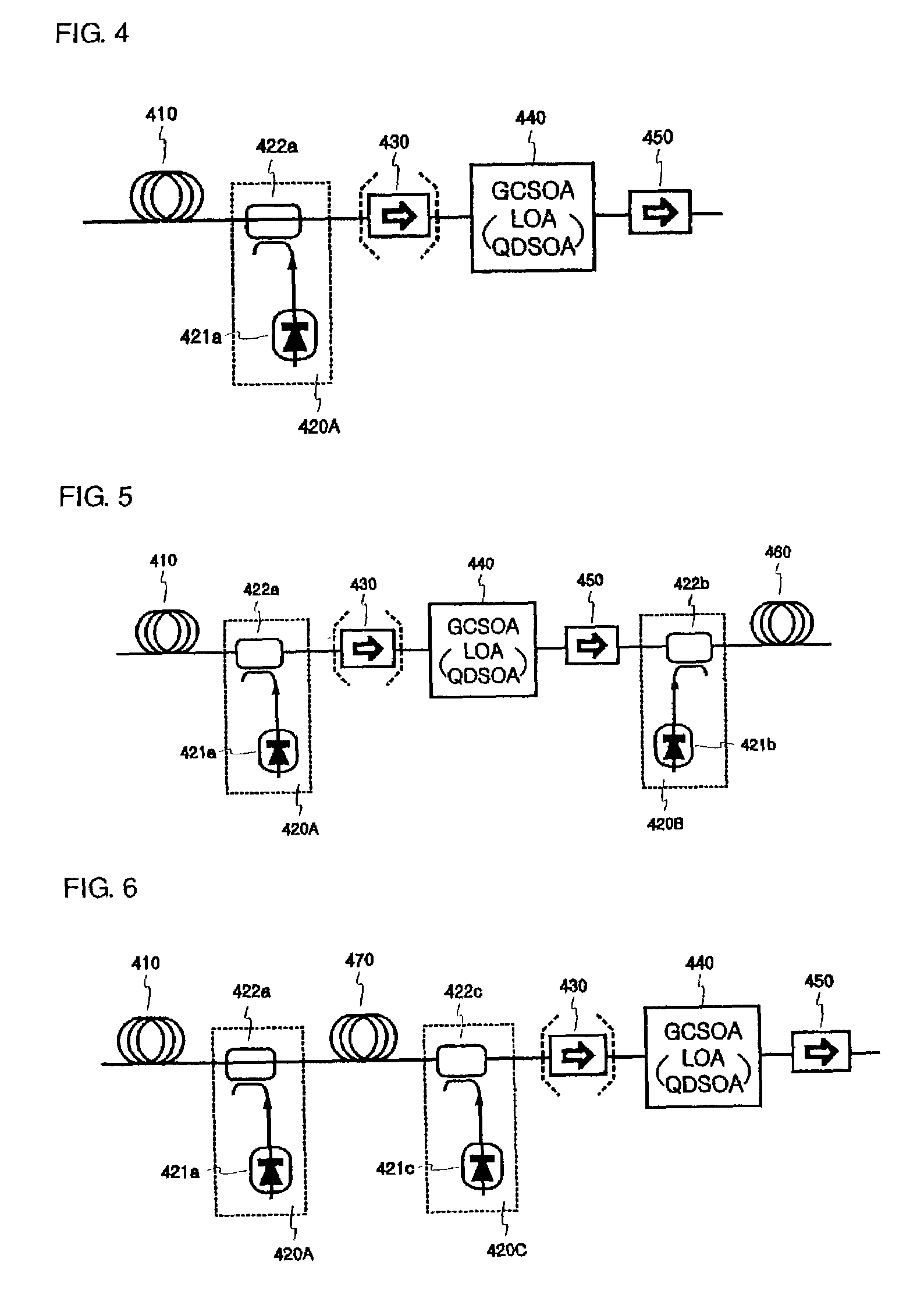

Hybrid optical amplifier coupling raman fiber amplifier semiconductor optical amplifier

ActiveUS20030090779A1Sufficient gainReduce noiseLaser using scattering effectsActive medium shape and constructionWavelength-division multiplexingLaser light

The present invention discloses a hybrid optical amplifier coupling a Raman fiber amplifier and a semiconductor optical amplifier, comprising: a laser diode generating and irradiating a laser light for a Raman optical amplification; a wavelength division multiplexer passing an incident signal light and irradiating a laser light irradiated from the laser diode in a reverse direction of the incident signal light; and a gain clamped semiconductor optical amplifier amplifying an optical signal irradiated from the wavelength division multiplexer.

Owner:THE IND & ACADEMIC COOPERATION & CHUNGNAM NAT UNIV

Self-similar laser oscillator

InactiveUS20060291521A1Guaranteed uptimeHigh bandwidthLaser using scattering effectsOptical resonator shape and constructionState of artHigh energy

A laser producing high energy ultrashort laser pulses comprises a normal dispersion segment, a gain segment, an anomalous dispersion segment with negligible nonlinearity and an effective saturable absorber arranged to form a laser cavity. Each segment is optically interconnected so that a laser pulse will propagate self-similarly therein. (A pulse that propagates in a self-similar manner is sometimes referred to as a “similariton.”) With this laser the limitations of prior art laser oscillators are avoided. Also provided are means for pumping the gain medium in the laser cavity, and means for extracting laser pulses from the laser cavity. The laser cavity is preferably a ring cavity. Preferably the laser is configured to achieve unidirectional circulation of laser pulses therein. This configuration is scalable to much higher pulse energy than lasers based on soliton-like pulse shaping.

Owner:CORNELL RES FOUNDATION INC

Meander-lineless wide bandwidth L-shaped slot line antenna

InactiveUS6999037B2Limit the VSWR of the antenna across the entire bandwidthSufficient gainResonant long antennasAntenna supports/mountingsCapacitanceNon symmetric

An asymmetric slotted L-shaped antenna is provided with a wide bandwidth in an exceedingly small size with good gain across the entire bandwidth by shorting out one end of the slot and by providing a capacitor at the other end of the slot, with the result that with appropriate capacitance, spacings and dimensions, the impedance of the slotted transmission line cancels the reactance of the antenna such that the gain of the antenna can be made to match a similar sized meander line loaded antenna.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

Planar communications antenna having an epicyclic structure and isotropic radiation, and associated methods

ActiveUS8390516B2Frequency stabilitySufficient gainLoop antennas with ferromagnetic coreSimultaneous aerial operationsElectrical conductorCoupling

Owner:HARRIS CORP

Hybrid optical amplifier coupling Raman fiber amplifier and semiconductor optical amplifier

InactiveUS7126747B2Sufficient gainReduce noiseLaser using scattering effectsActive medium shape and constructionMultiplexerCoupling

The present invention discloses a hybrid optical amplifier coupling a Raman fiber amplifier and a semiconductor optical amplifier, comprising: a laser diode generating and radiating a laser light for a Raman optical amplification; a wavelength division multiplexer passing an incident signal light and radiating a laser light radiated from the laser diode in a reverse direction of the incident signal light; and a gain clamped semiconductor optical amplifier amplifying an optical signal light radiated from the wavelength division multiplexer.

Owner:THE IND & ACADEMIC COOP IN CHUNGNAM NAT UNIV (IAC)

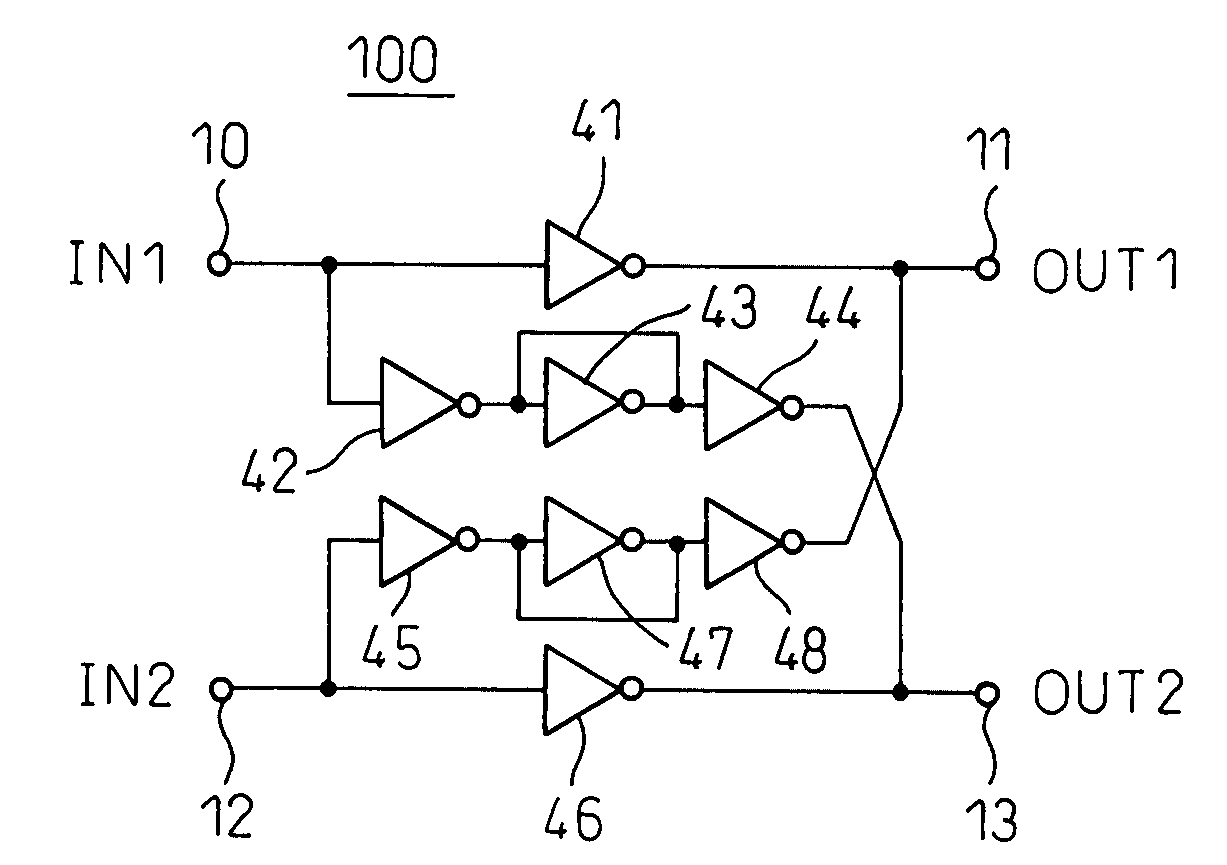

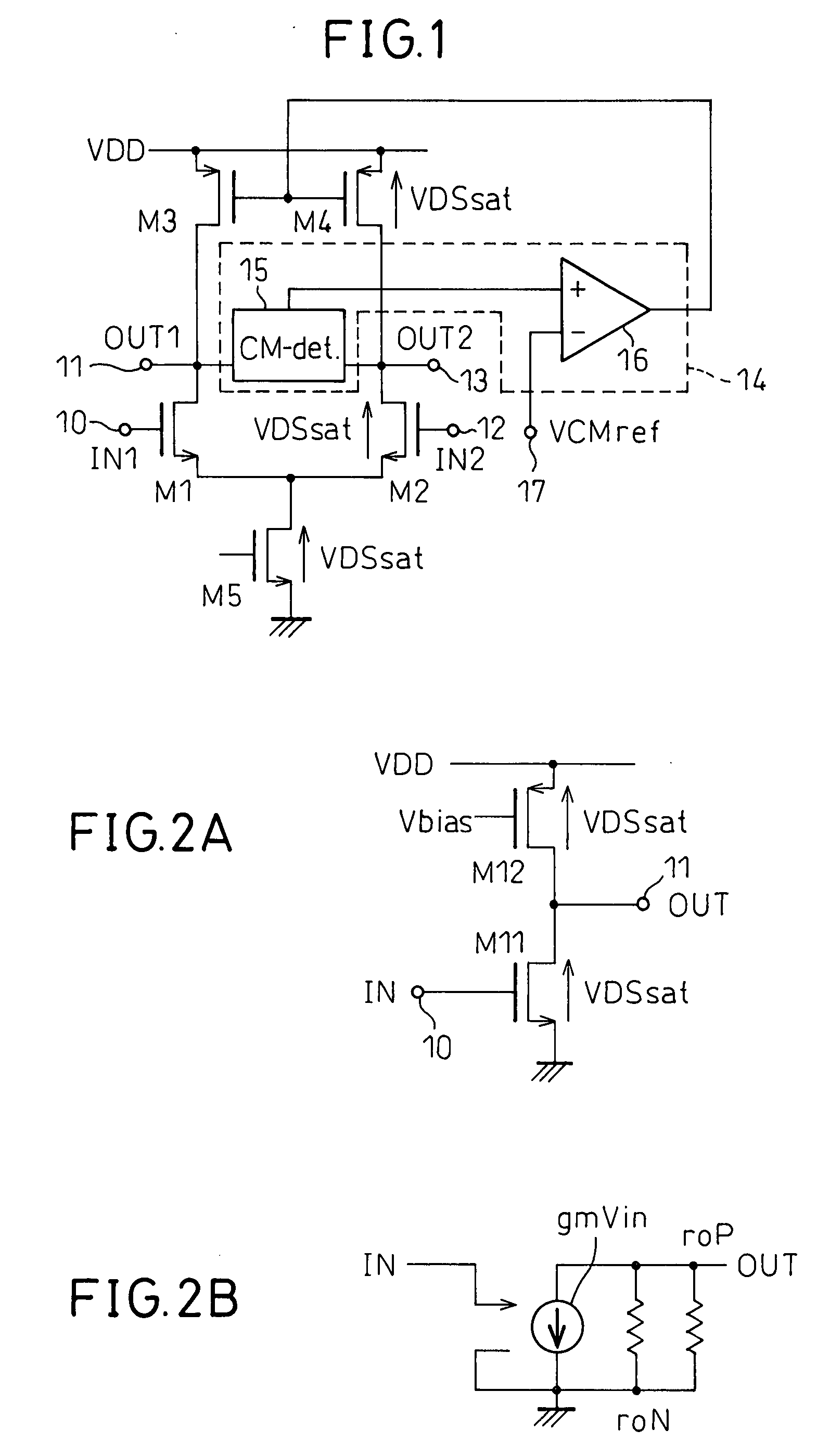

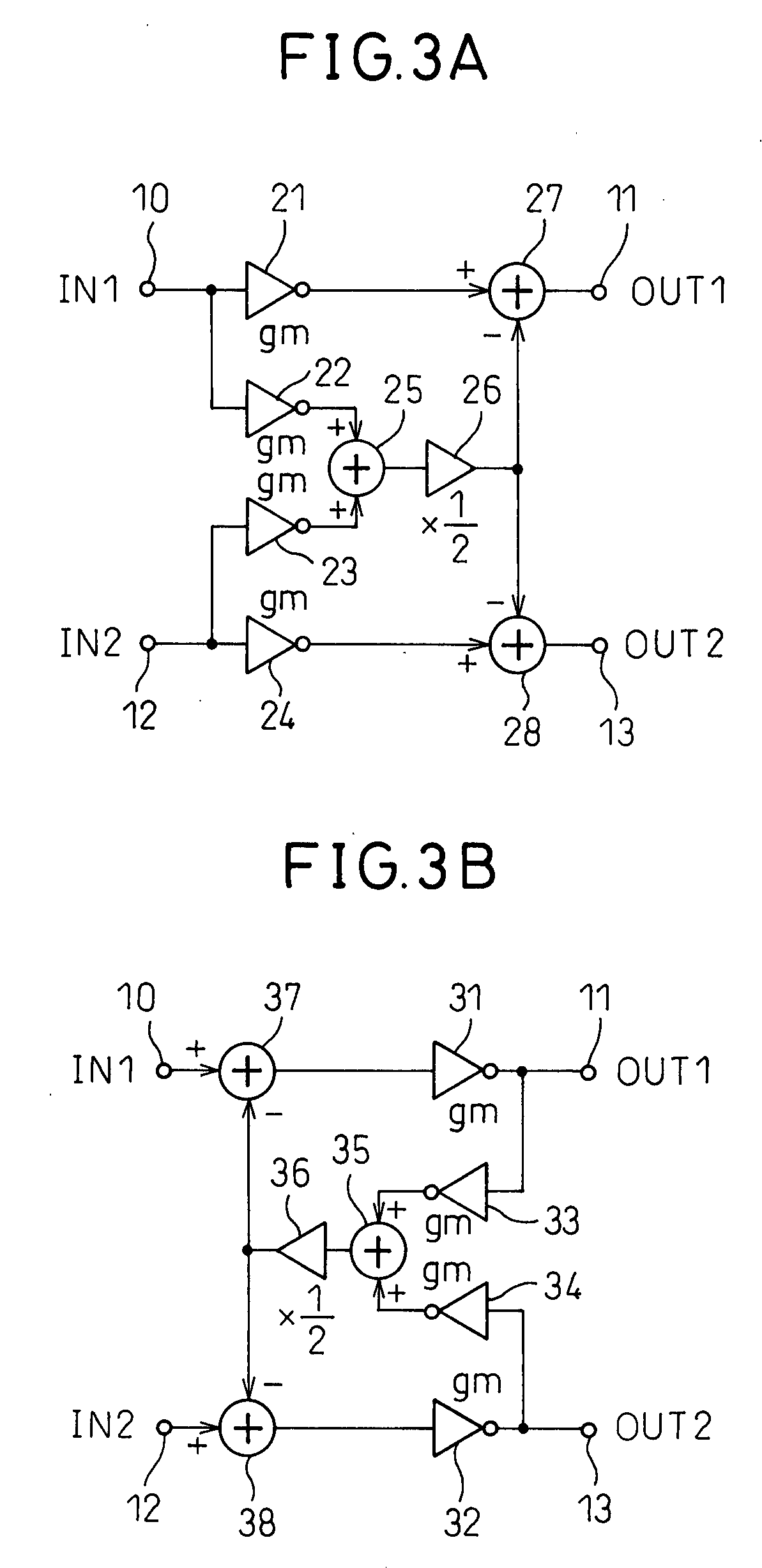

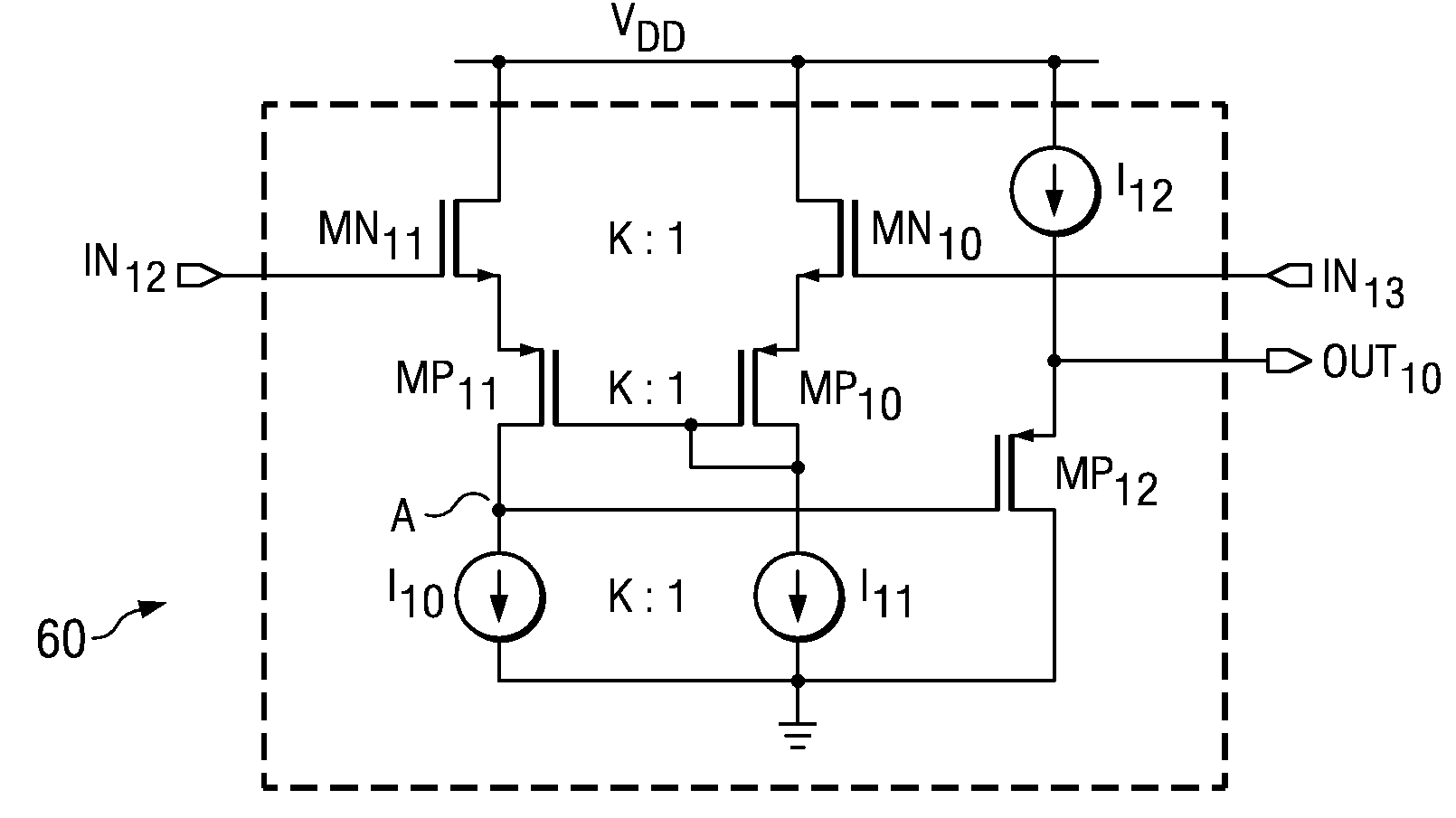

Fully-differential amplifier

ActiveUS20080143439A1Sufficient gainSolve the large power consumptionDifferential amplifiersDc-amplifiers with dc-coupled stagesSingle stageDifferential amplifier

Owner:ROHM CO LTD

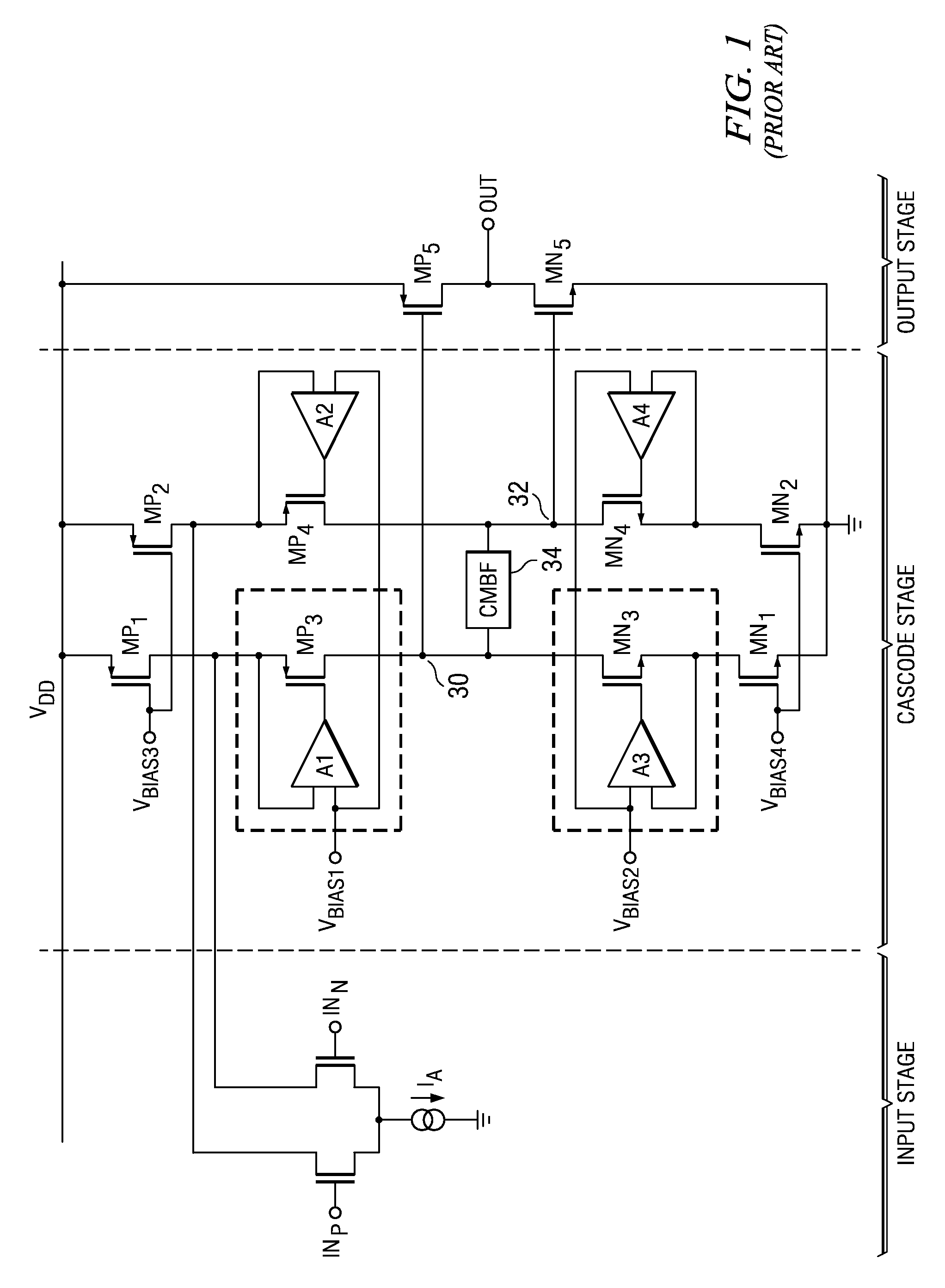

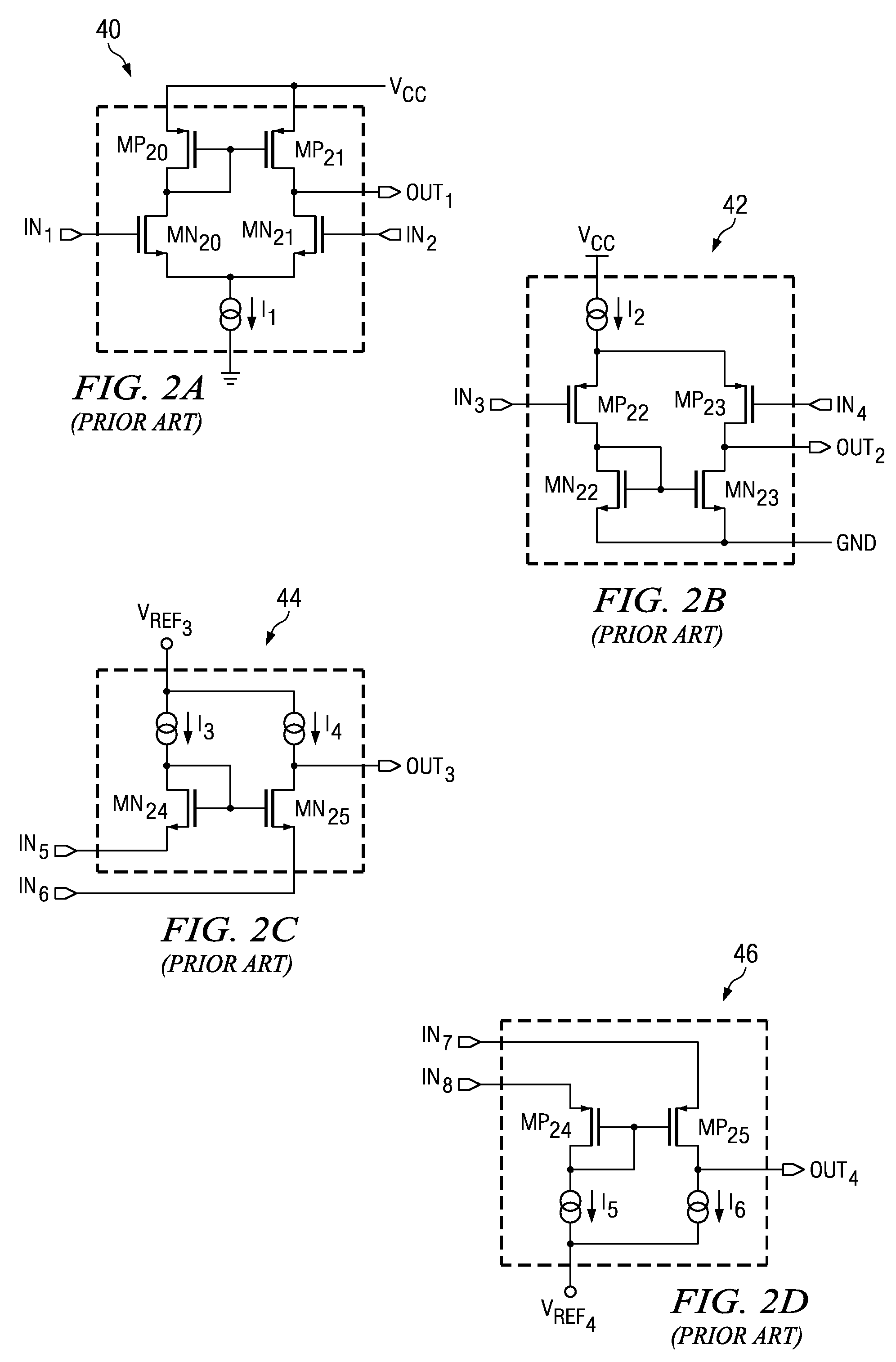

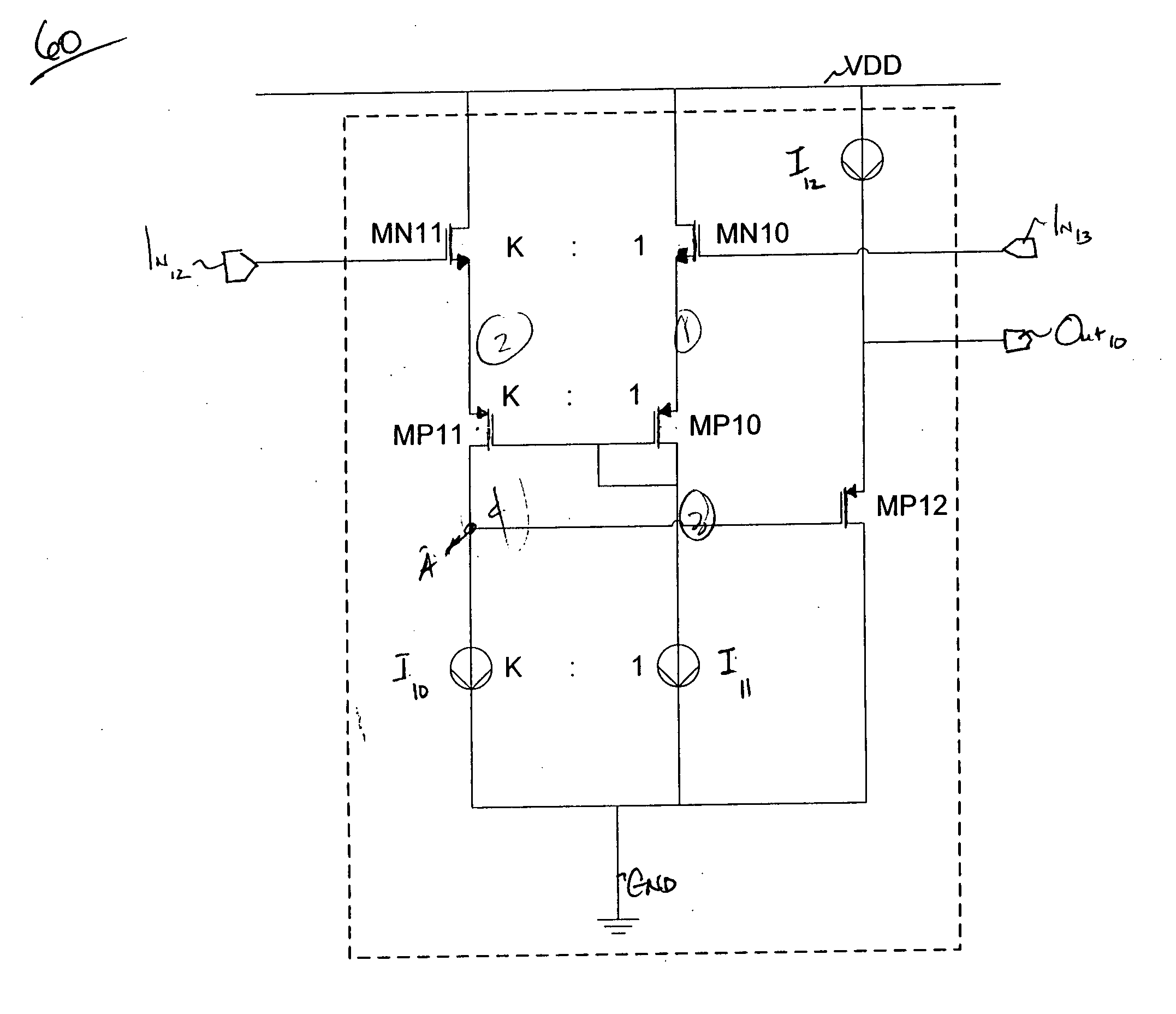

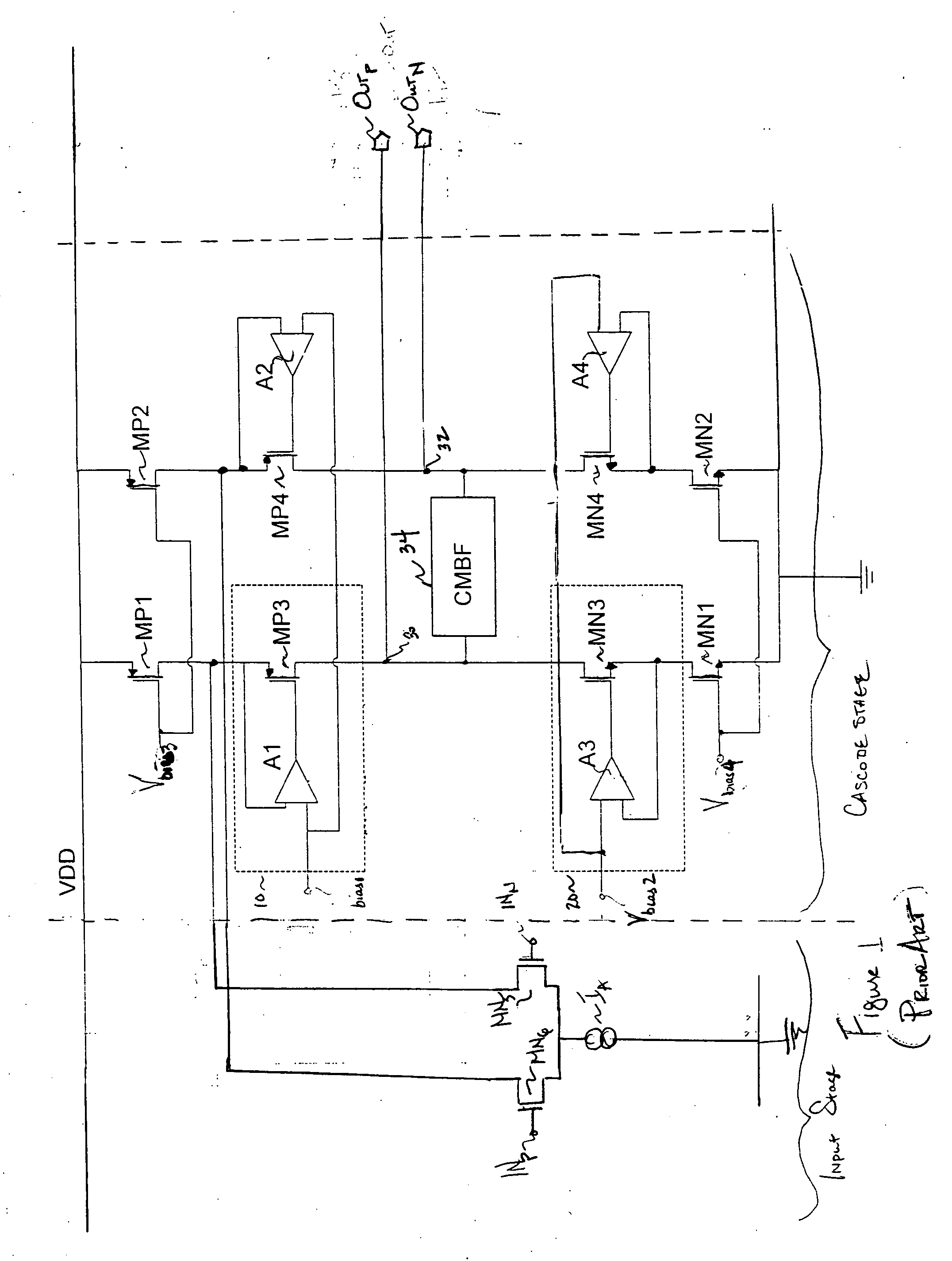

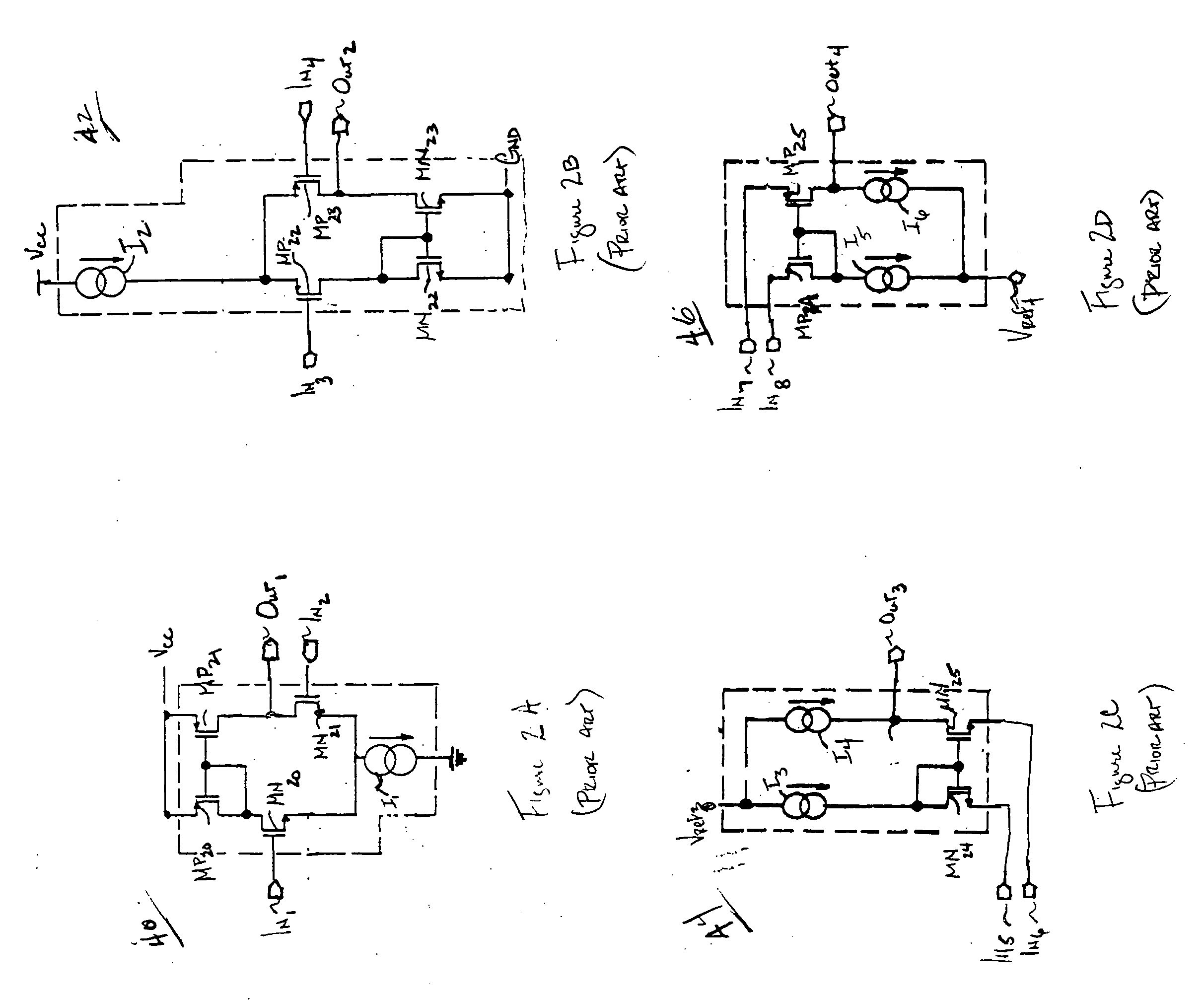

High-swing folded cascode having a novel gain-boost amplifier

ActiveUS7116172B2High voltageMaximizes available dynamic rangeDifferential amplifiersDc-amplifiers with dc-coupled stagesAudio power amplifierCoupling

A circuit topology for gain boosted high-swing folded cascode has been improved to maximize the available dynamic range in applications having low supply voltage requirements. The circuit includes an improved gain boost amplifier that maximizes the available dynamic range for applications having low supply voltage requirements. The improved gain boosting amplifier includes a differential pair of input transistors connected to a current mirror, wherein a pair of current sources supply current to each lead of the current mirror. One lead of the current mirror is level-shifted by a transistor coupled to another current source, wherein the coupling of the transistor and the current source form the output of the amplifier. Effectively, the amplifier consists of a level shifter and a series common-drain, common-gate amplifier. A reduction in transconductance gm from the series combination is compensated by a current mirror ratio (K:1) between the level shift and the common-drain, common-gate amplifier.

Owner:TEXAS INSTR INC

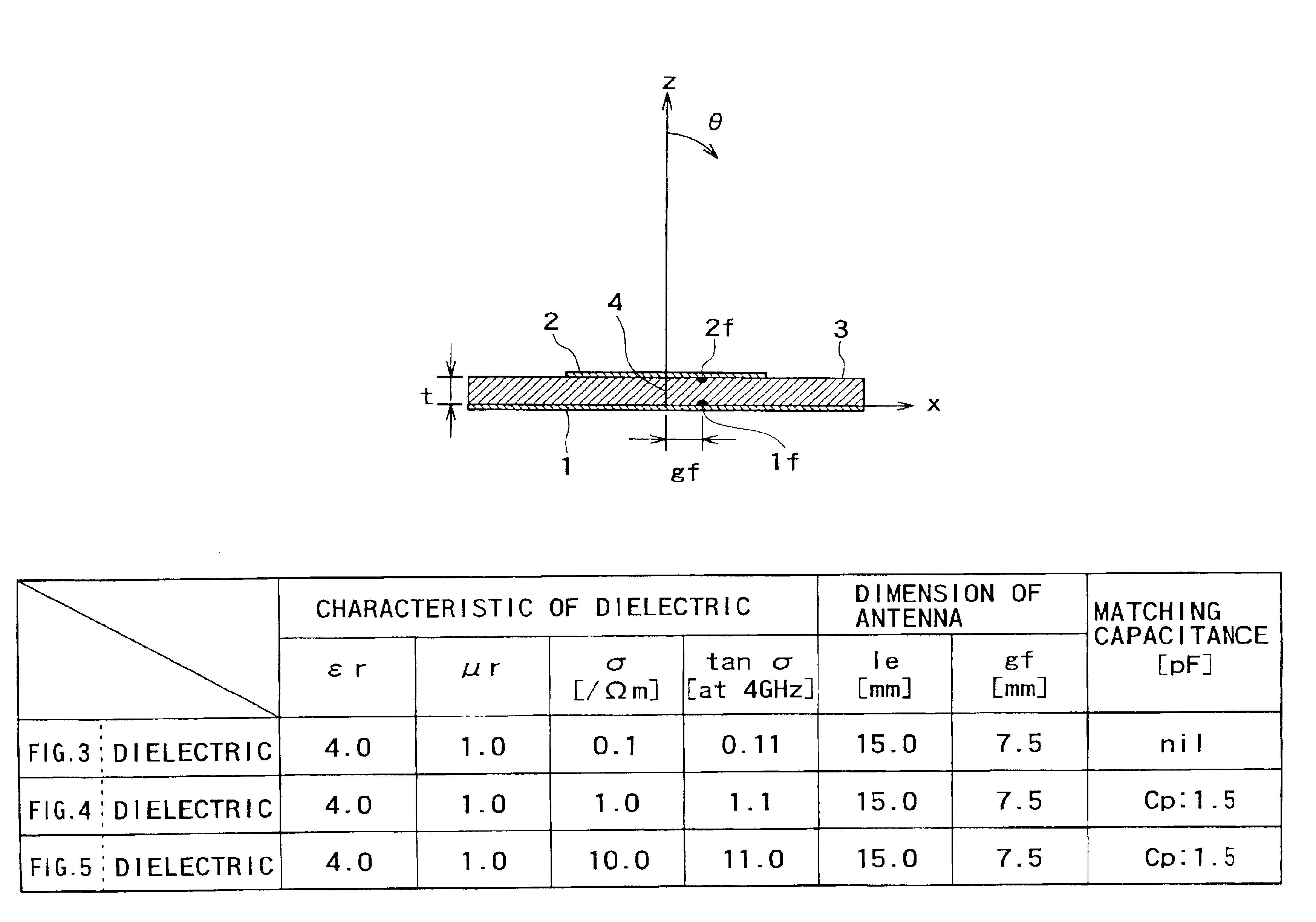

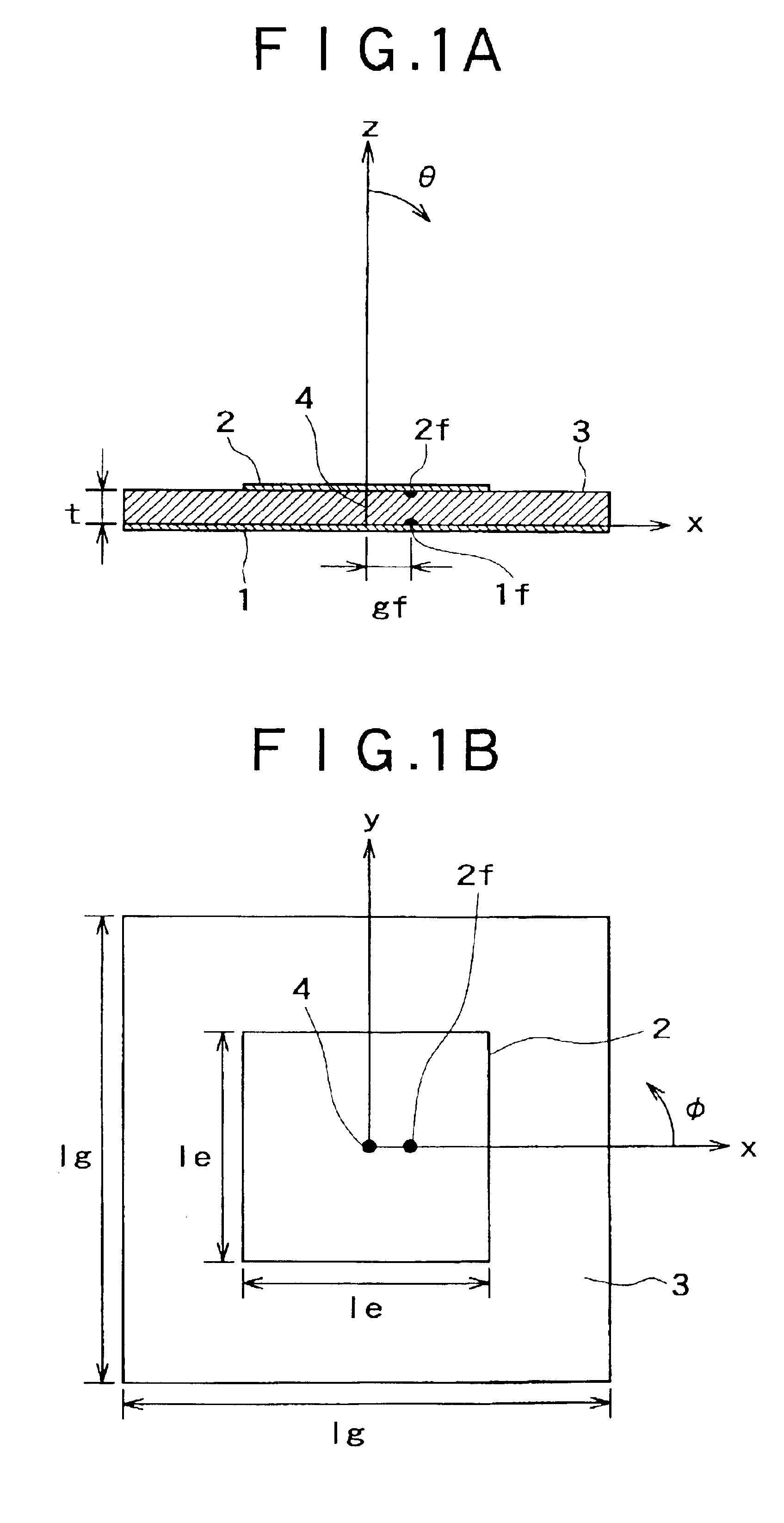

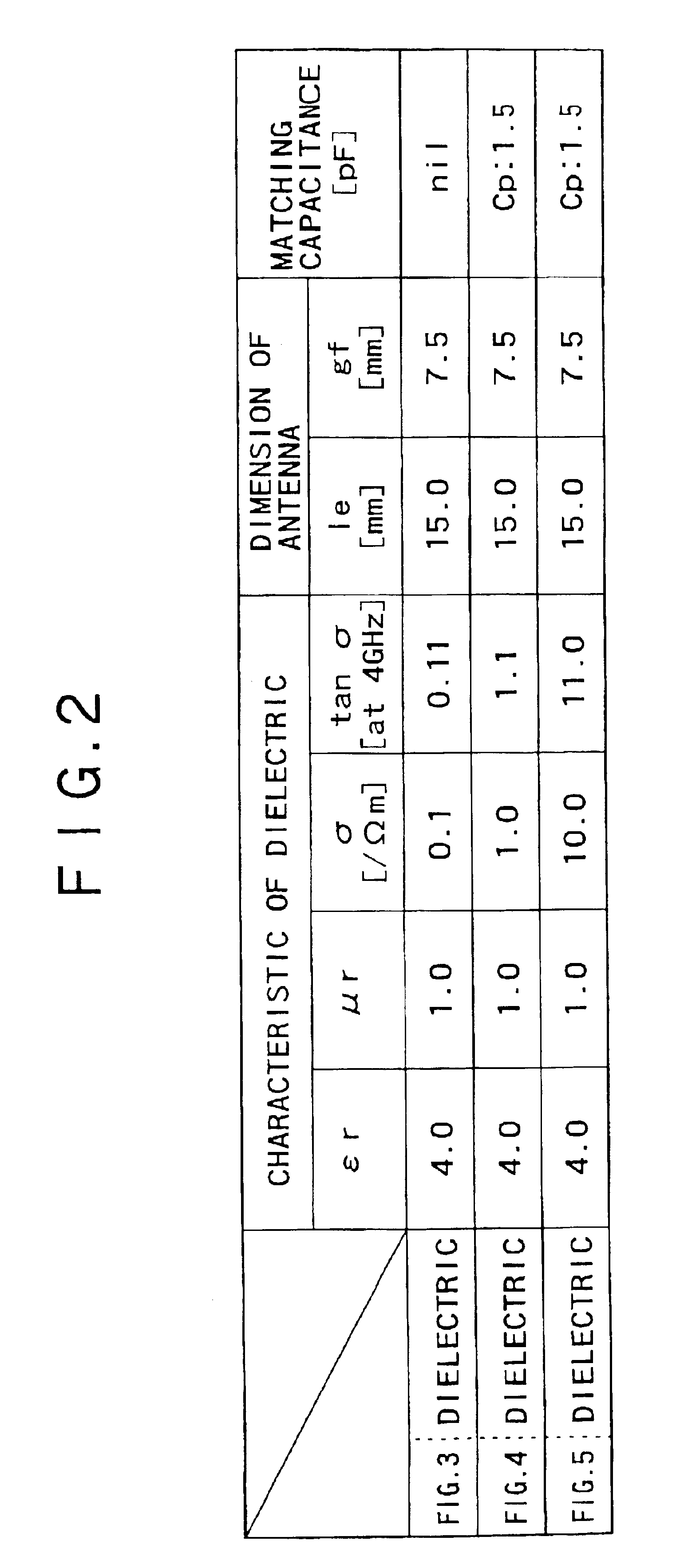

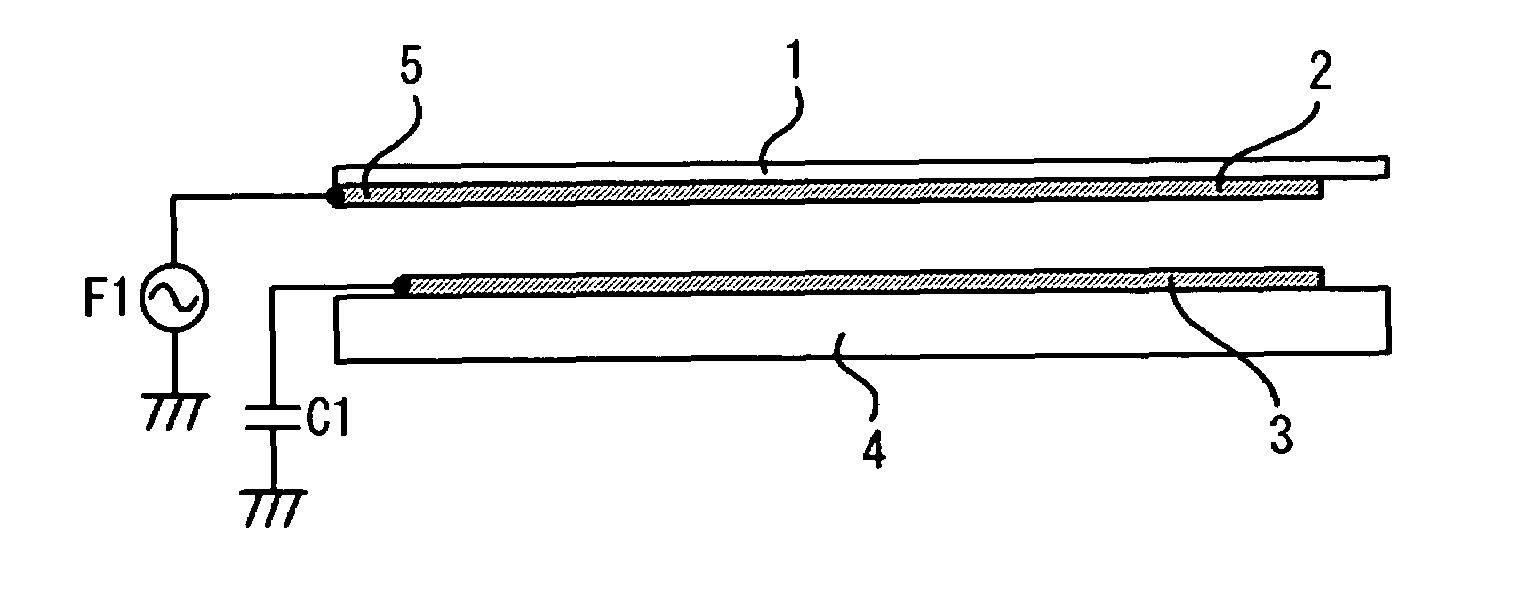

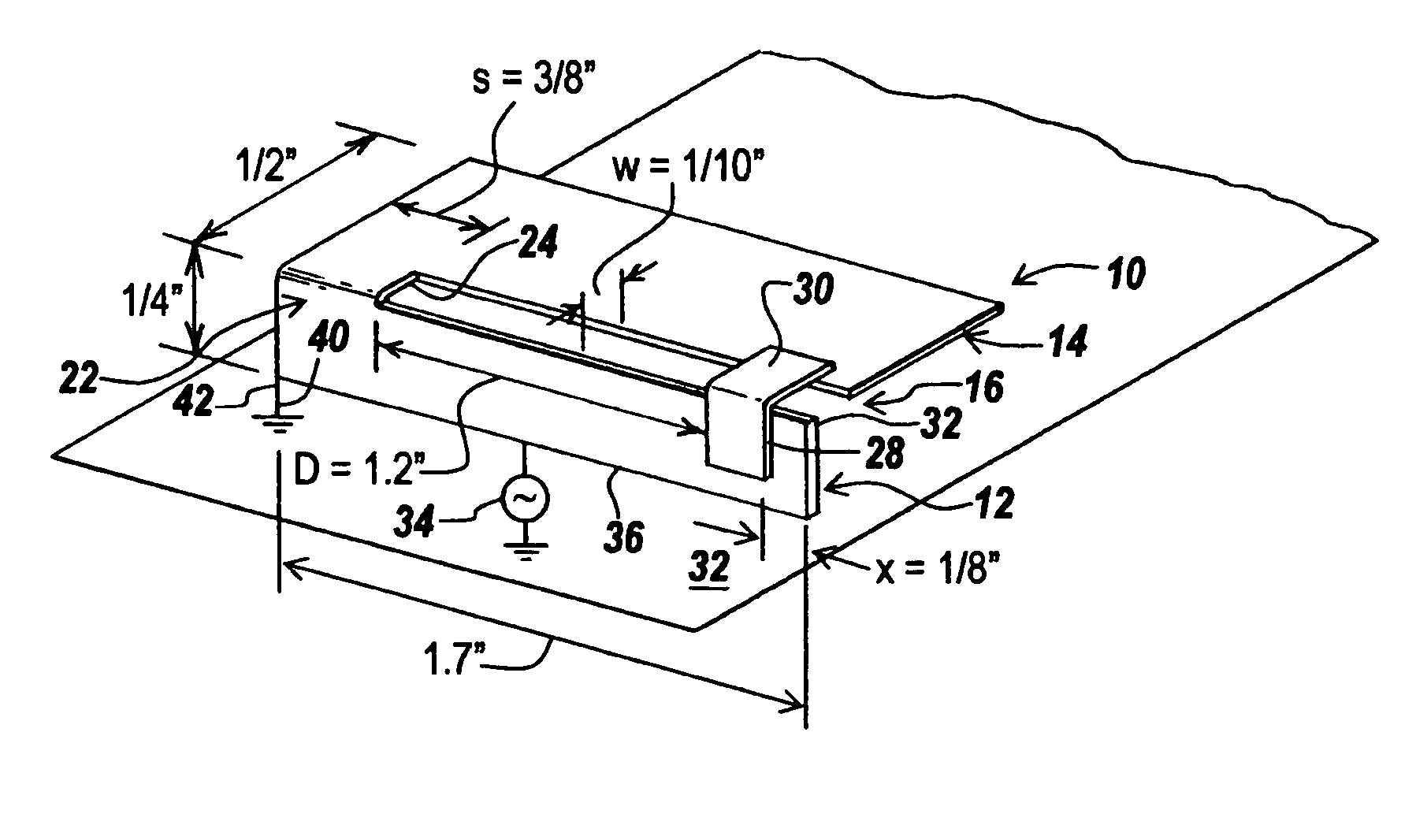

Wide band antenna

InactiveUS6914561B2Sufficient gainReduce the ratioSimultaneous aerial operationsRadiating elements structural formsElectrical conductorWide band

Disclosed is a wideband antenna with a lowered standing wave ratio. The wideband antenna interposes a substance whose conductivity is about 0.1 through 10.0 as an interposition between a conductive plate and a radiation conductor; and thereby, the antenna reduces reflections of signals, and achieves a wider bandwidth as well as a sufficient gain with a lowered standing wave ratio. Also, the invention realizes a thin-type wideband antenna with a wider bandwidth and a sufficient gain, by interposing a magnetic substance whose relative permeability is more than 1 through about 8 as the interposition between the conductive plate and the radiation conductor.

Owner:TESSERA ADVANCED TECH

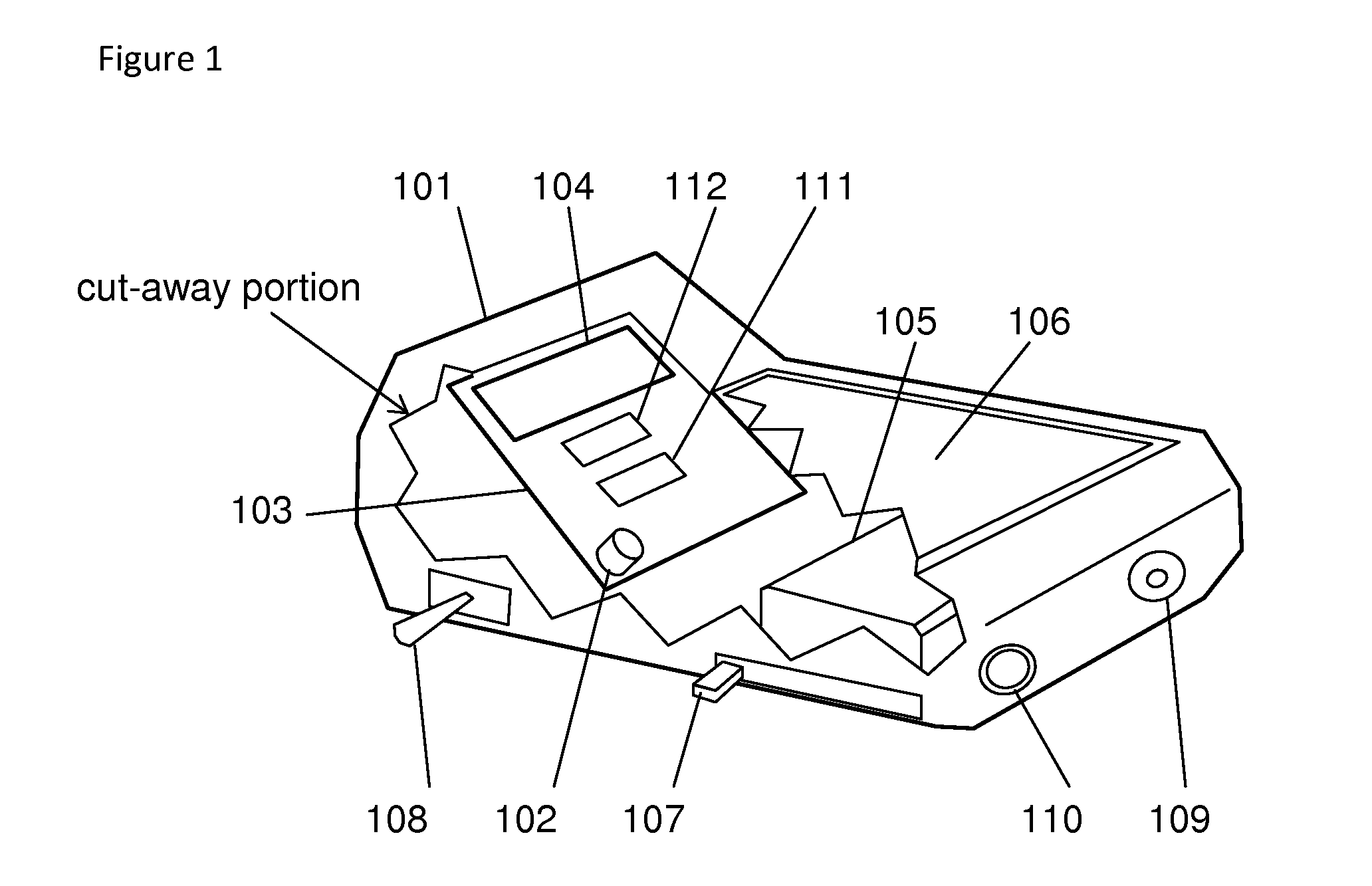

Touch panel, and input device and electronic apparatus each equipped with the touch panel

InactiveUS7307625B2Sufficient gainDigital data processing detailsRadiating elements structural formsTouch panelSurface plate

A touch panel includes: a first layer and a second layer that are arranged to face each other, with a predetermined gap being formed between the first layer and the second layer; a first resistance film that is formed on a surface of the first layer, the surface facing the second layer; a second resistance film that is formed on a surface of the second layer, the surface facing the first layer; and a power supply unit that is provided on the first resistance film. In this touch panel, the first resistance film and the second resistance film form an antenna.

Owner:FUJITSU COMPONENENT LTD

High-swing folded cascode having a novel gain-boost amplifier

ActiveUS20060091952A1Increase voltage headroomMaximizes available dynamic rangeDifferential amplifiersDc-amplifiers with dc-coupled stagesCascodeEngineering

A circuit topology for gain boosted high-swing folded cascode has been improved to maximize the available dynamic range in applications having low supply voltage requirements. The circuit includes an improved gain boost amplifier that maximizes the available dynamic range for applications having low supply voltage requirements. The improved gain boosting amplifier includes a differential pair of input transistors connected to a current mirror, wherein a pair of current sources supply current to each lead of the current mirror. One lead of the current mirror is level-shifted by a transistor coupled to another current source, wherein the coupling of the transistor and the current source form the output of the amplifier. Effectively, the amplifier consists of an effective level shift and a series common-drain, common-gate amplifier. A reduction in transconductance gm from the series combination is compensated by a current mirror ratio (K:1) between the level shift and the common-drain, common-gate amplifier. Specifically, the size of one of the transistors in the differential pair is a multiple integer (K) times the size of the other transistor in the differential pair. In addition, the size of one of the transistors in the current mirror is a multiple integer (K) times the size of the other transistor in the current mirror. Moreover the amount of current supplied by the second current source is a multiple integer (K) times the amount of current provided by the first current source.

Owner:TEXAS INSTR INC

3D motion detection and correction by object tracking in ultrasound images

InactiveUS8348846B2Simple processShorten the timeOrgan movement/changes detectionSurgical navigation systemsNumerical controlSonification

Owner:MEDIRI

Meander-lineless wide bandwidth l-shaped slot line antenna

InactiveUS20050206572A1Convenient to accommodateKeep sizeResonant long antennasAntenna supports/mountingsCapacitanceNon symmetric

An asymmetric slotted L-shaped antenna is provided with a wide bandwidth in an exceedingly small size with good gain across the entire bandwidth by shorting out one end of the slot and by providing a capacitor at the other end of the slot, with the result that with appropriate capacitance, spacings and dimensions, the impedance of the slotted transmission line cancels the reactance of the antenna such that the gain of the antenna can be made to match a similar sized meander line loaded antenna.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

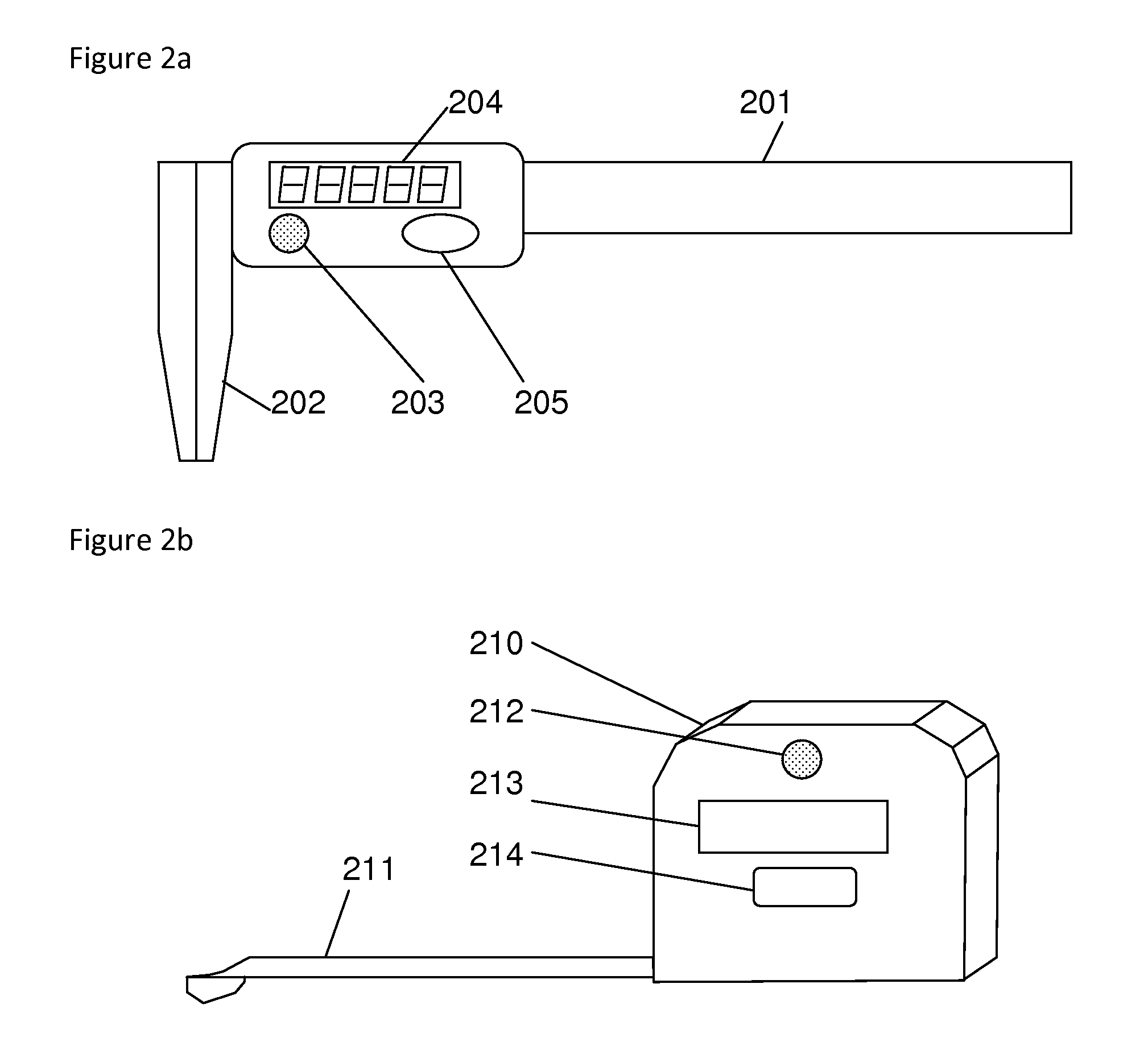

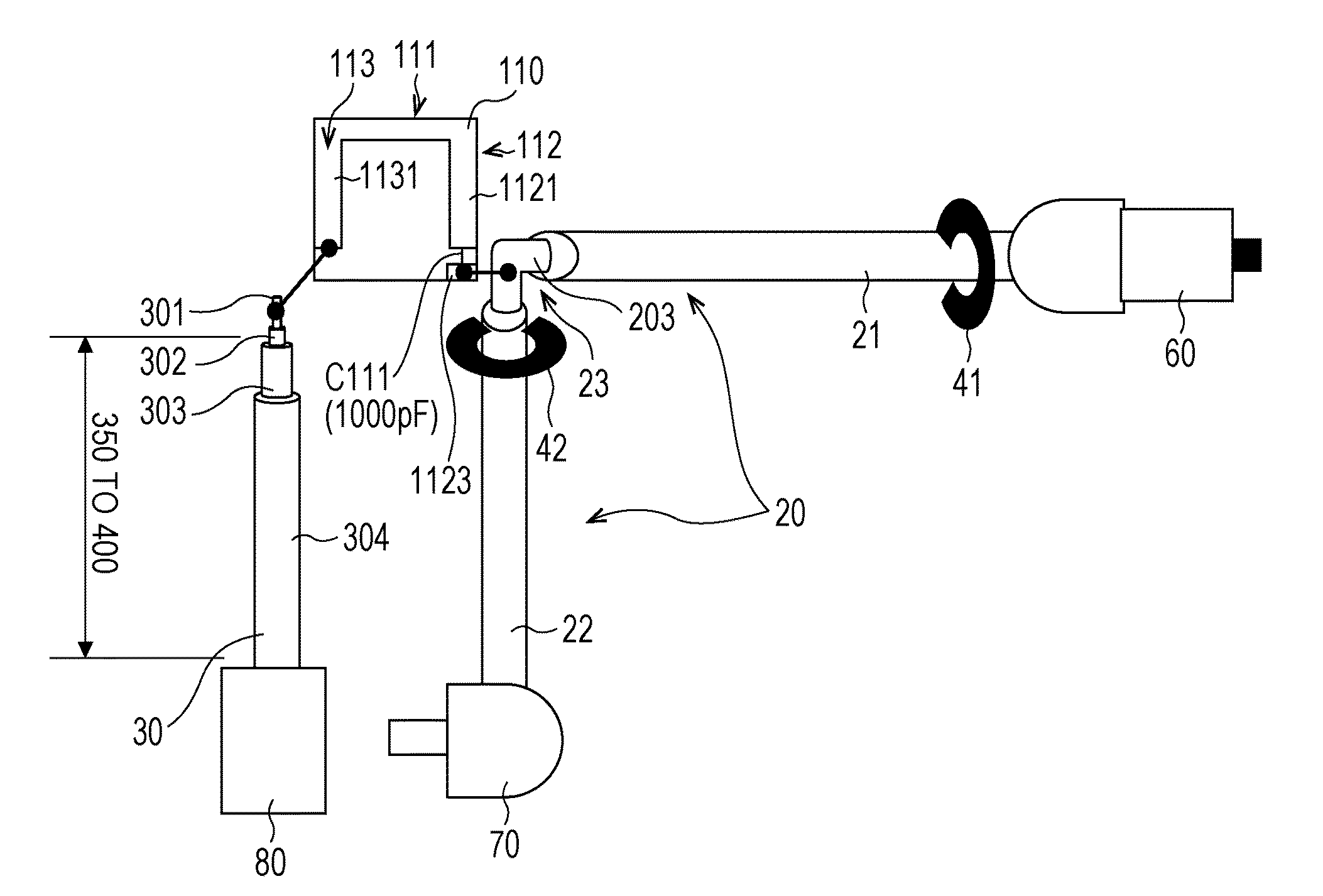

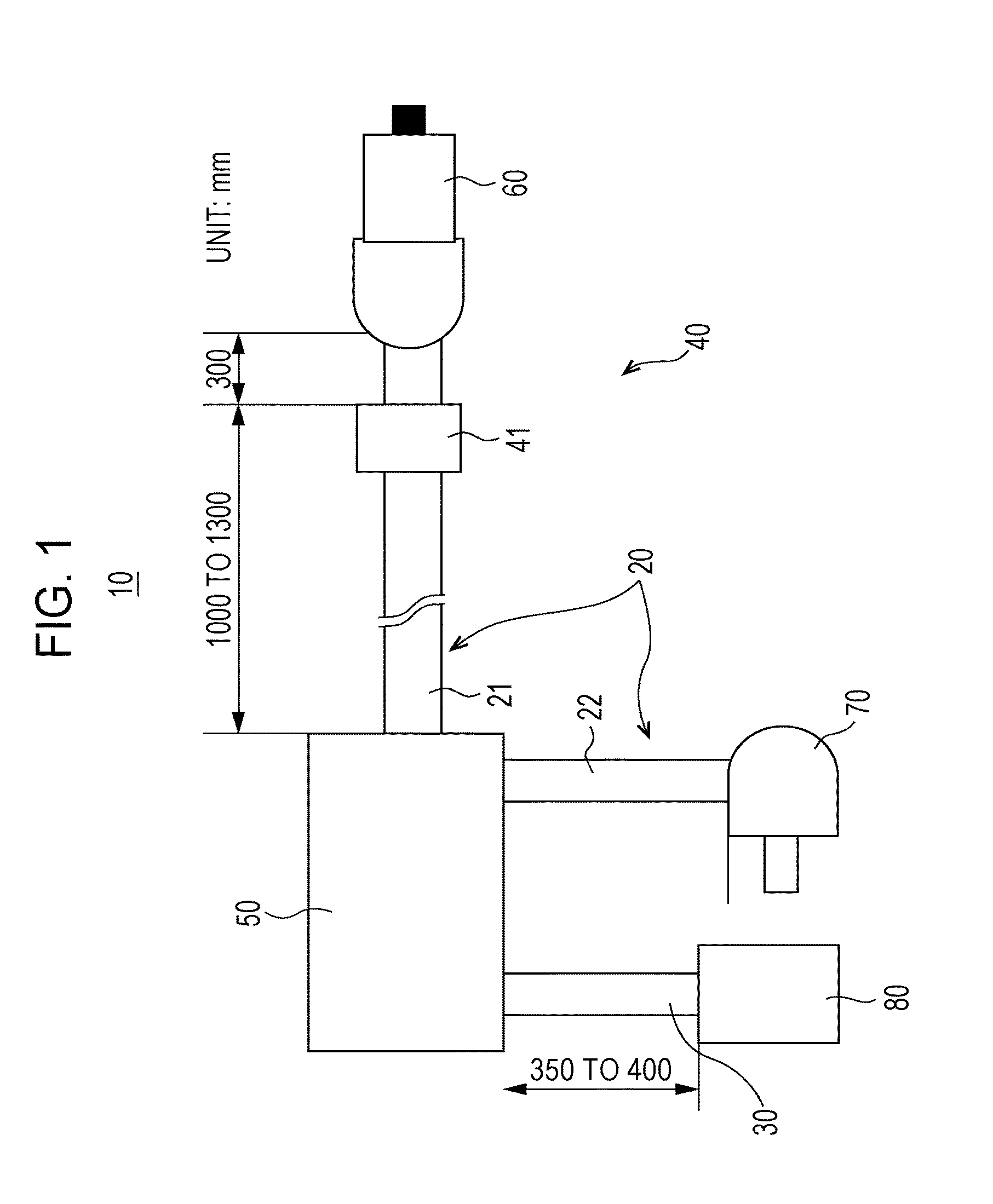

Voice-Activated Measurement System

InactiveUS20130054246A1Read more difficultEasy to readElectrical measurement instrument detailsUsing mechanical meansMeasurement deviceEngineering

A voice-activated instrument performs a measurement and displays the measured value when commanded by voice. The system also resets under voice control. The measurement trigger is any single-syllable command such as “Count” or “Go”. The reset trigger is any two-syllable command such as “Reset”. Any type of momentary measurement device may be controlled in this way, including time interval measurements, event counting, length measuring, weighing, and electronic metering measurements, and many others.

Owner:ELOQUI VOICE SYST LLC

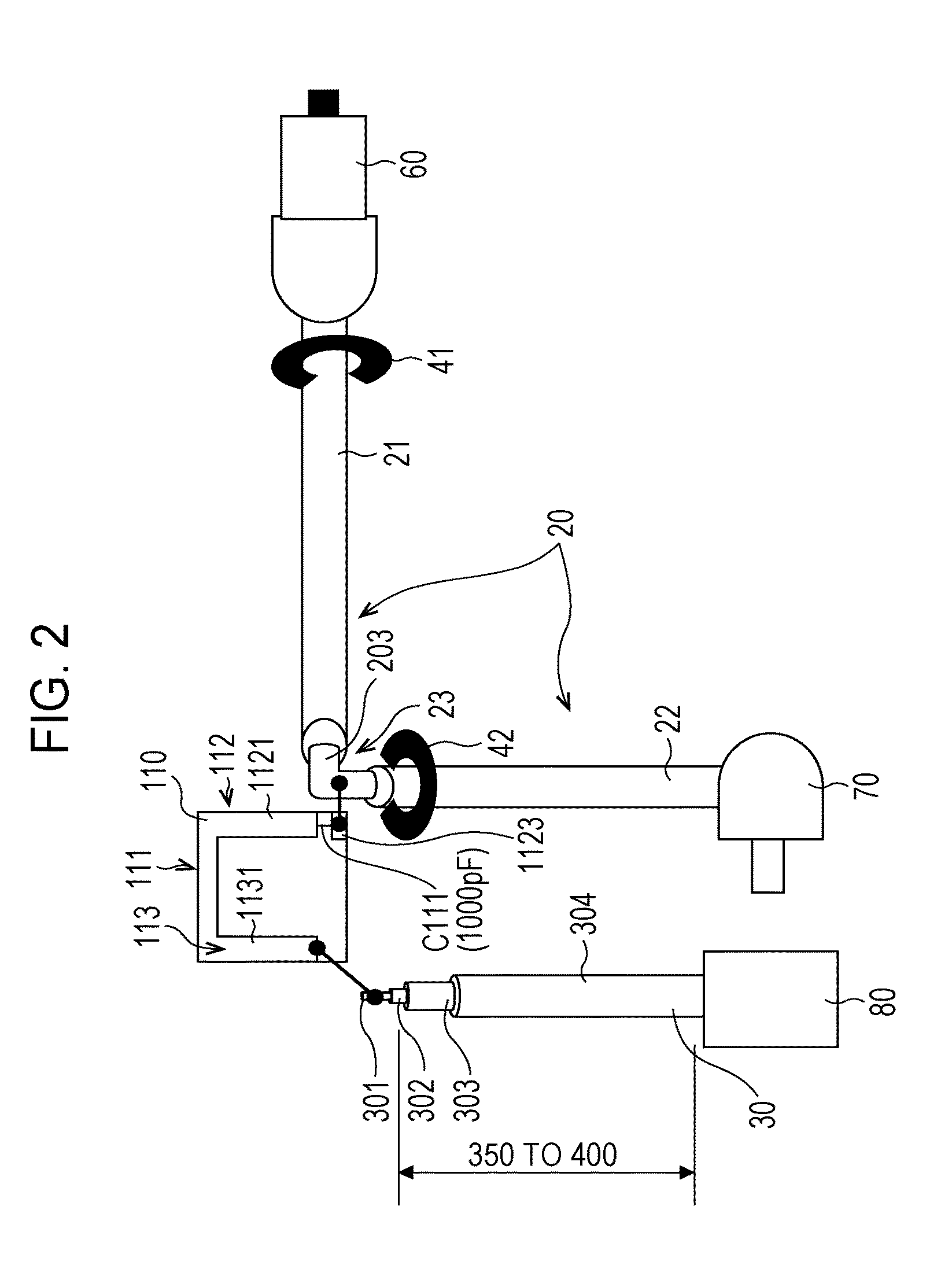

Antenna device

ActiveUS20120050133A1Sufficient gainSuitable reception sensitivitySimultaneous aerial operationsAntenna supports/mountingsTransmitted powerElectric power

The present invention relates to an antenna device whereby there can be provided an antenna device which can receive broadcast waves with a sufficiently wide frequency band and sufficient gain just by connecting wire material even if used bundled without complicated efforts, and can obtain suitable reception sensitivity.This antenna device includes a power supply cord 20 which can transmit power, a connecting portion 50, a high-frequency signal cable 30 for extracting a high-frequency signal from the connecting portion 50, and a high-frequency blocking portion 40 disposed in two places in the length direction of the power supply cord 20, and with the power supply cord 20, a portion between the two high-frequency blocking portions is connected to the connecting portion 50 to form an antenna, and the high-frequency signal cable 30 is connected to a portion of the power supply cord 20 at the connecting portion 50.

Owner:SONY CORP

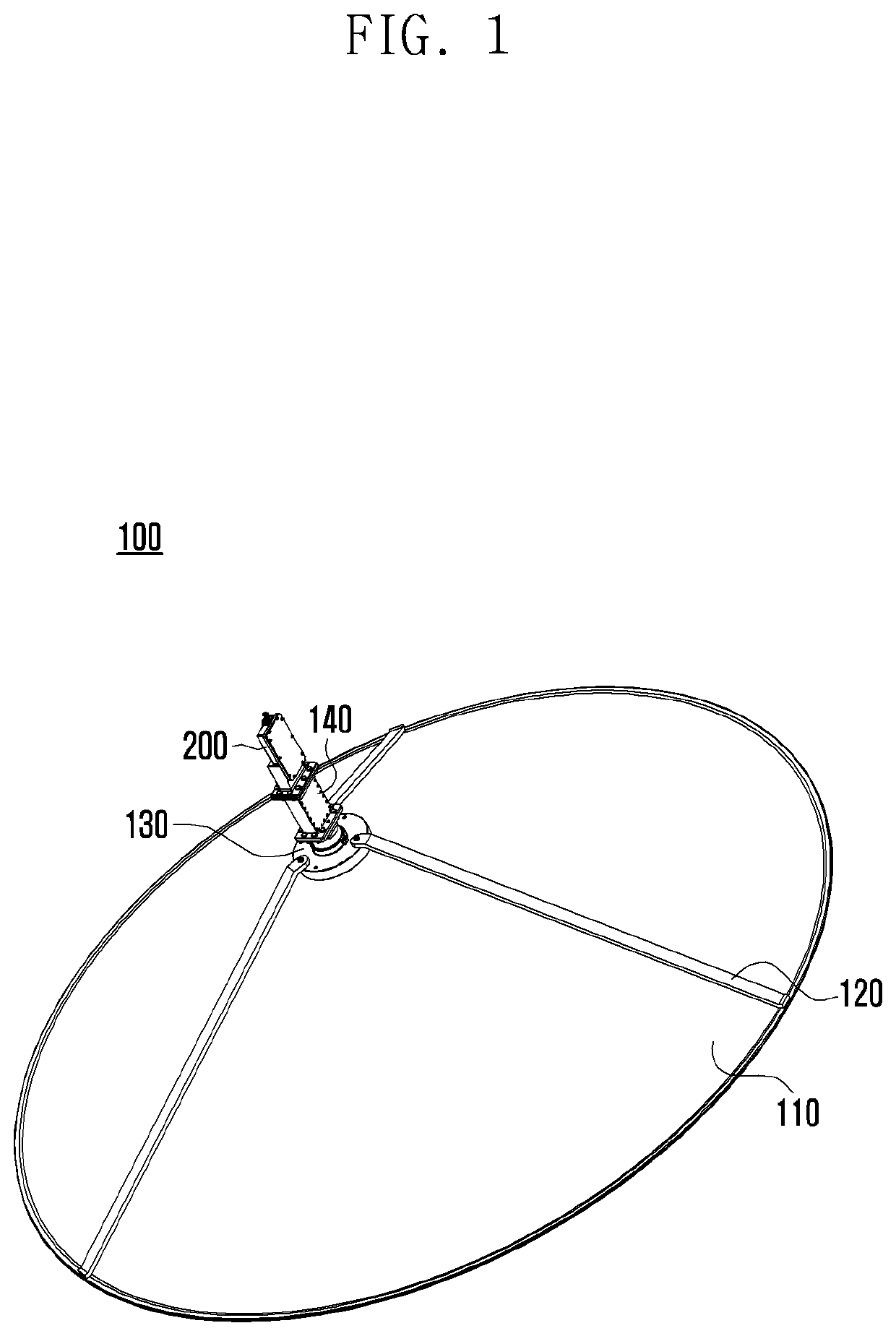

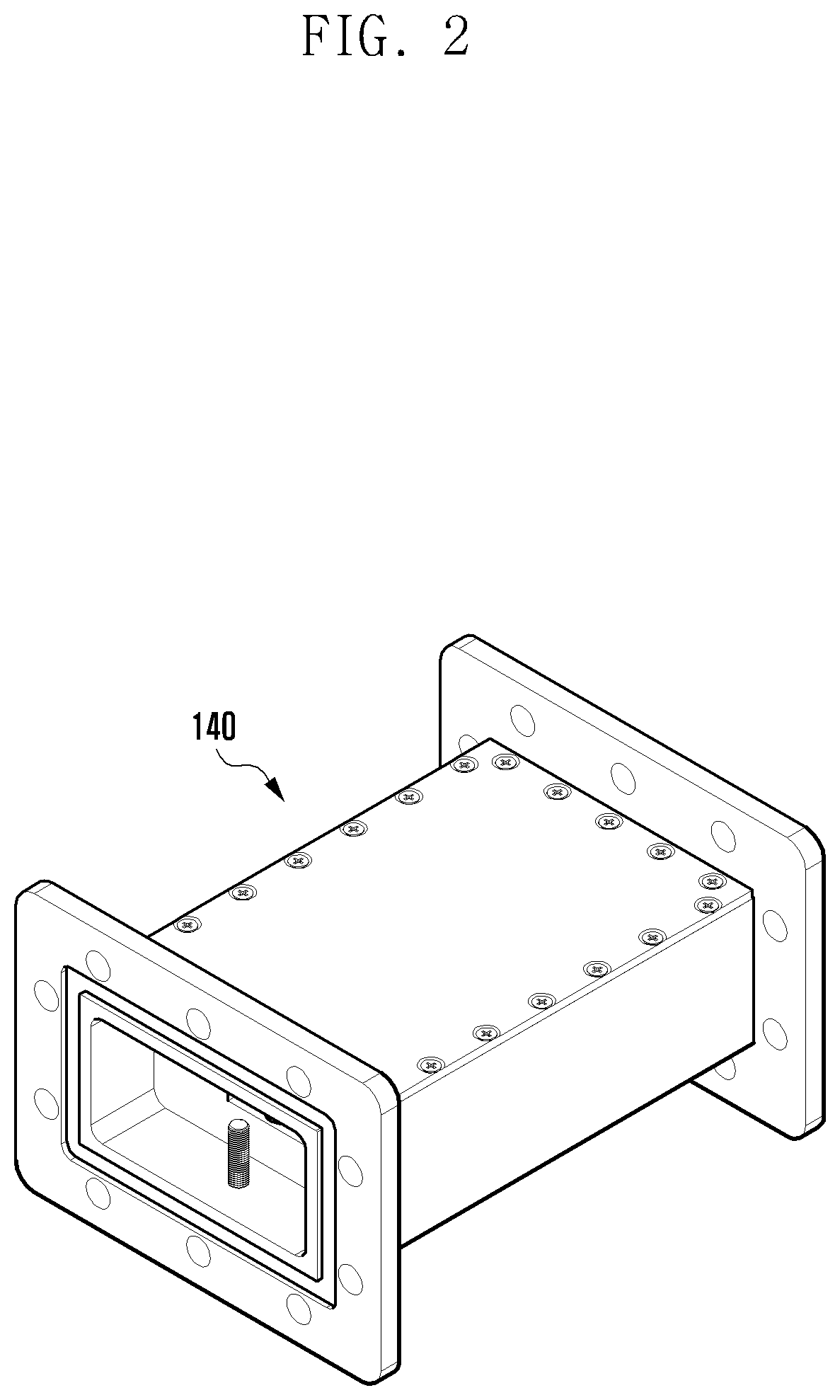

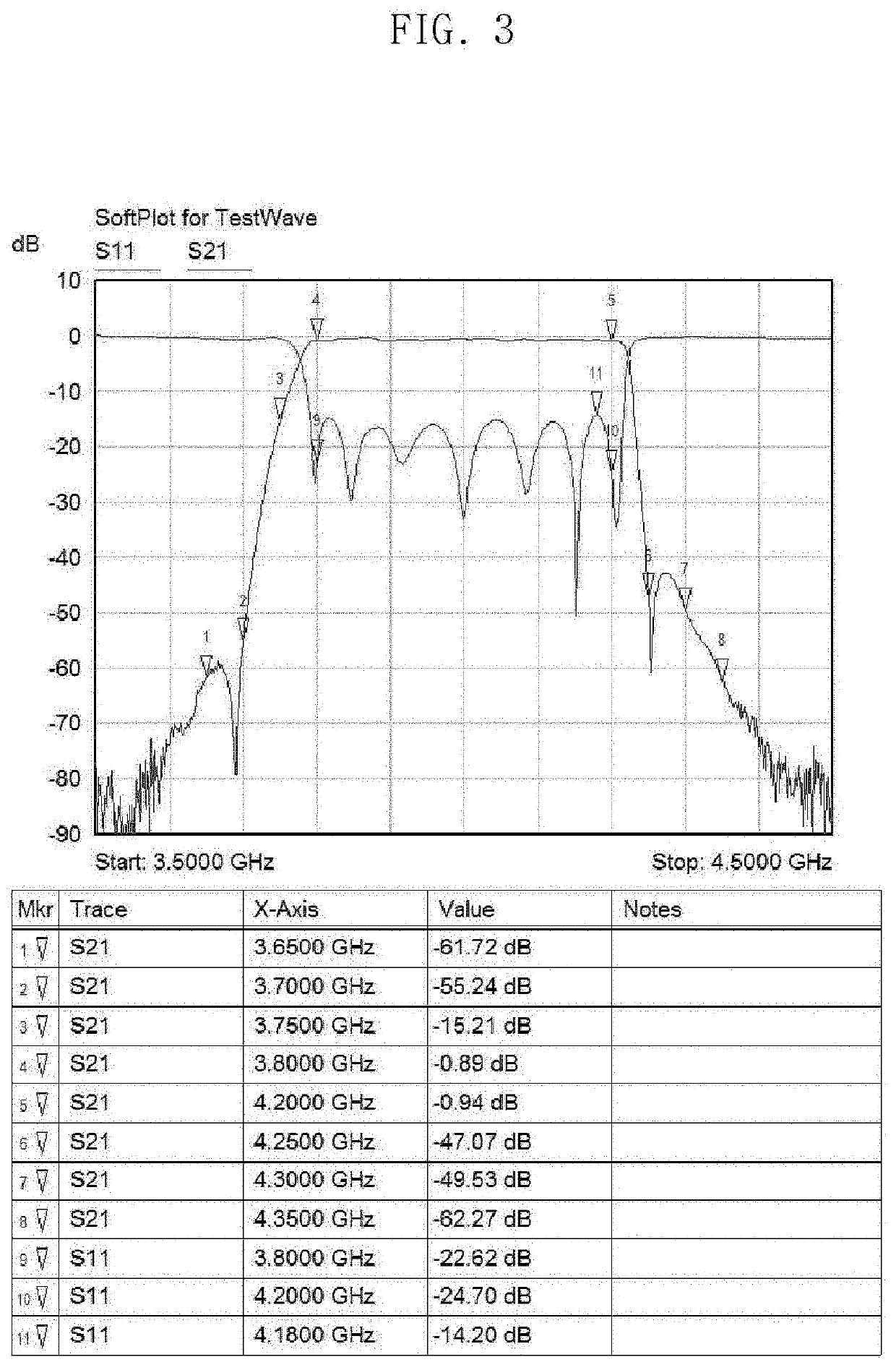

Low noise block down converter for receiving satellite broadcasting and antenna apparatus including the same

ActiveUS20210135696A1Quality improvementEliminate distractionsAntenna supports/mountingsTransmissionLow noiseIntermediate frequency

A low noise block down converter for receiving satellite broadcasting comprises an input terminal; a low noise amplifying unit including one or more low noise amplifiers configured to amplify a signal received from the input terminal, and a built-in cavity waveguide band pass filter configured to pass a frequency band being higher or lower than a frequency band of a predetermined terrestrial transmission signal among satellite broadcasting frequency bands of signals amplified by the one or more low noise amplifiers; and a mixer configured to convert the signal output from the low noise amplifying unit into an intermediate frequency signal by mixing the signal output from the low noise amplifying unit with a local oscillation signal.

Owner:ATRON

Article having electromagnetic coupling module attached thereto

ActiveUS8081121B2Precise positioningImprove adhesionSimultaneous aerial operationsSolid-state devicesElectromagnetic couplingElectromagnetic field coupling

An article having an electromagnetic coupling module attached thereto includes an electromagnetic coupling module and a PET bottle having the electromagnetic coupling module bonded thereto. The electromagnetic coupling module includes a wireless IC chip arranged to process transmission and reception signals and the feed circuit board having the wireless IC chip mounted thereon. The feed circuit board includes a feed circuit including a resonant circuit having a predetermined resonant frequency. The feed circuit performs characteristic impedance matching between the PET bottle and the wireless IC chip. The PET bottle functions as a radiator arranged to radiate a transmission signal supplied from the feed circuit using electromagnetic field coupling and to supply a received reception signal to the feed circuit using electromagnetic field coupling.

Owner:MURATA MFG CO LTD

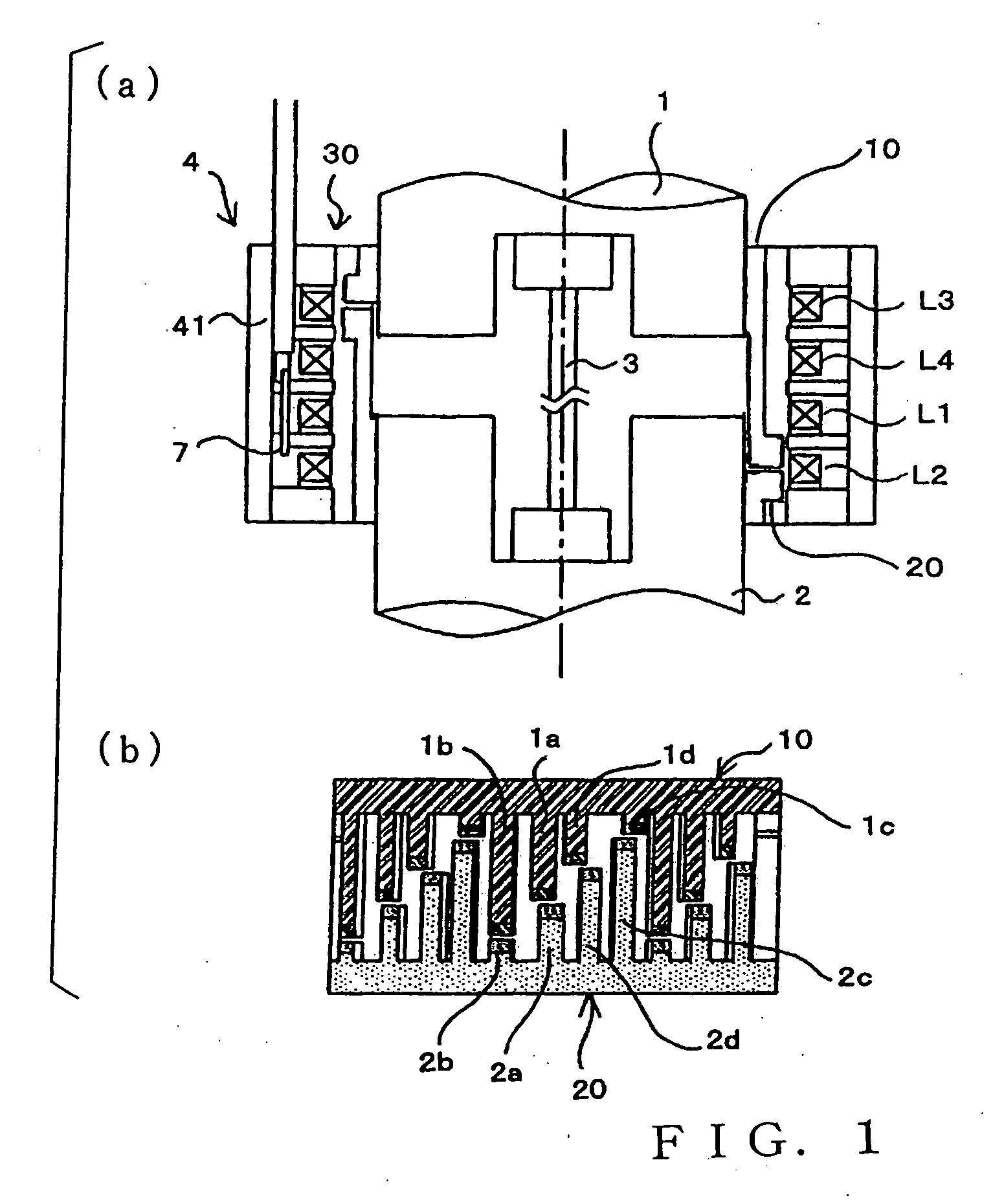

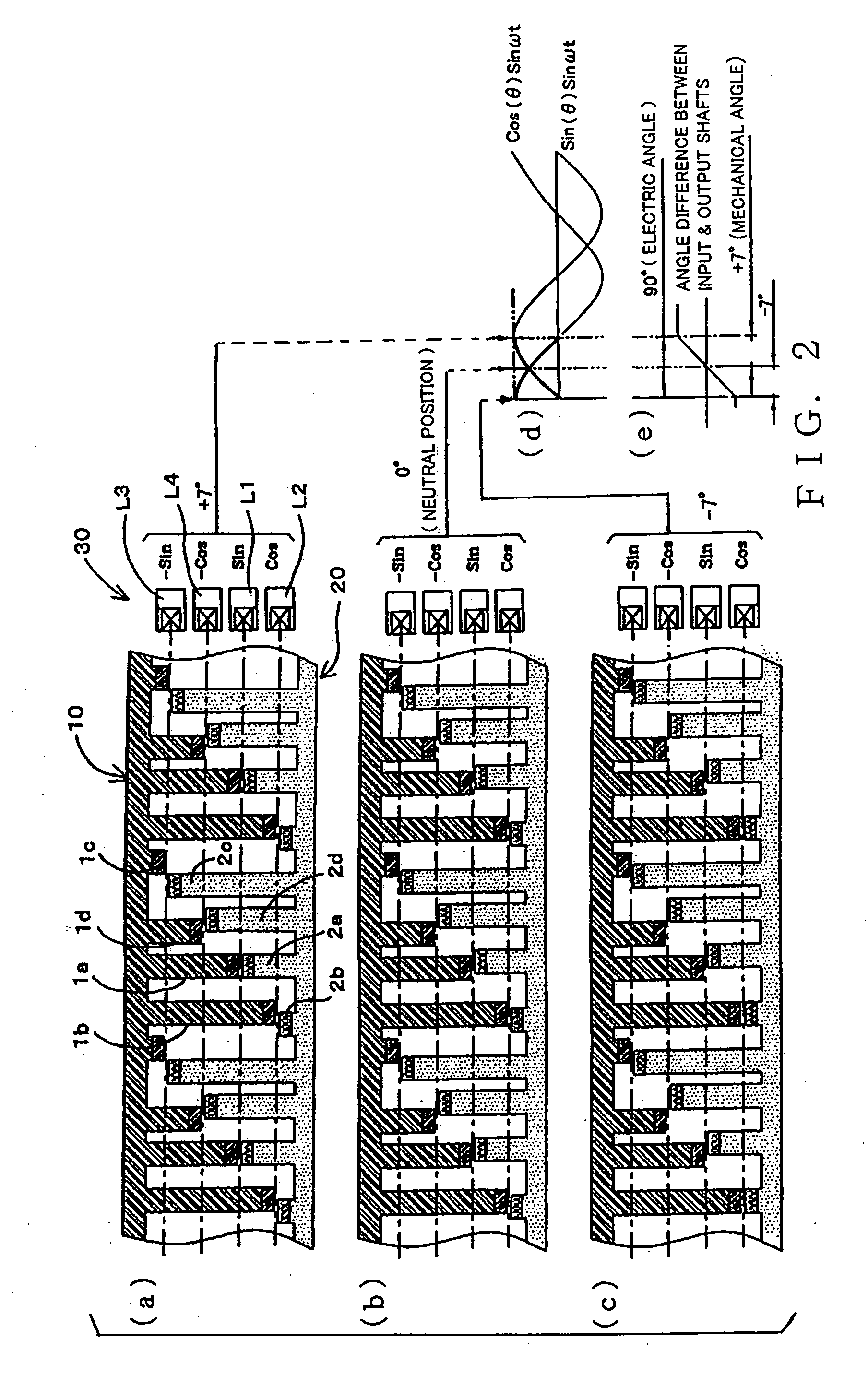

Relative rotational position-detection device

ActiveUS20070007950A1Sufficient gainImprove accuracySteering linkagesWork measurementCouplingEngineering

First and second shafts (1, 2) are interconnected via a torsion bar (3) for torsional (or rotational) movement relative to each other, and first and second magnetic body sections (10, 20) are provided to rotate in interlocked relation to the rotation of the first and second shafts, respectively. The first and second magnetic body sections form at least two ring-shaped variable magnetic coupling sections opposed to each other via a gap, magnetic coupling in each of the boundary sections varies in response to variation of a relative rotational position between the first and second shafts, and variation of the magnetic coupling differs in phase between the boundary sections. Coil section (30) includes magnetic-coupling detecting coils (L1-L4) provided in corresponding relation to the boundary sections. Each of the first and second magnetic body sections is of a cylindrical shape and has a plurality of magnetic teeth formed at unequal pitches along the circumferential direction thereof, and the magnetic teeth differ in axial length among tooth groups corresponding to the boundary sections.

Owner:AMITEQ

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com