Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

65results about How to "Simplify Design Requirements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

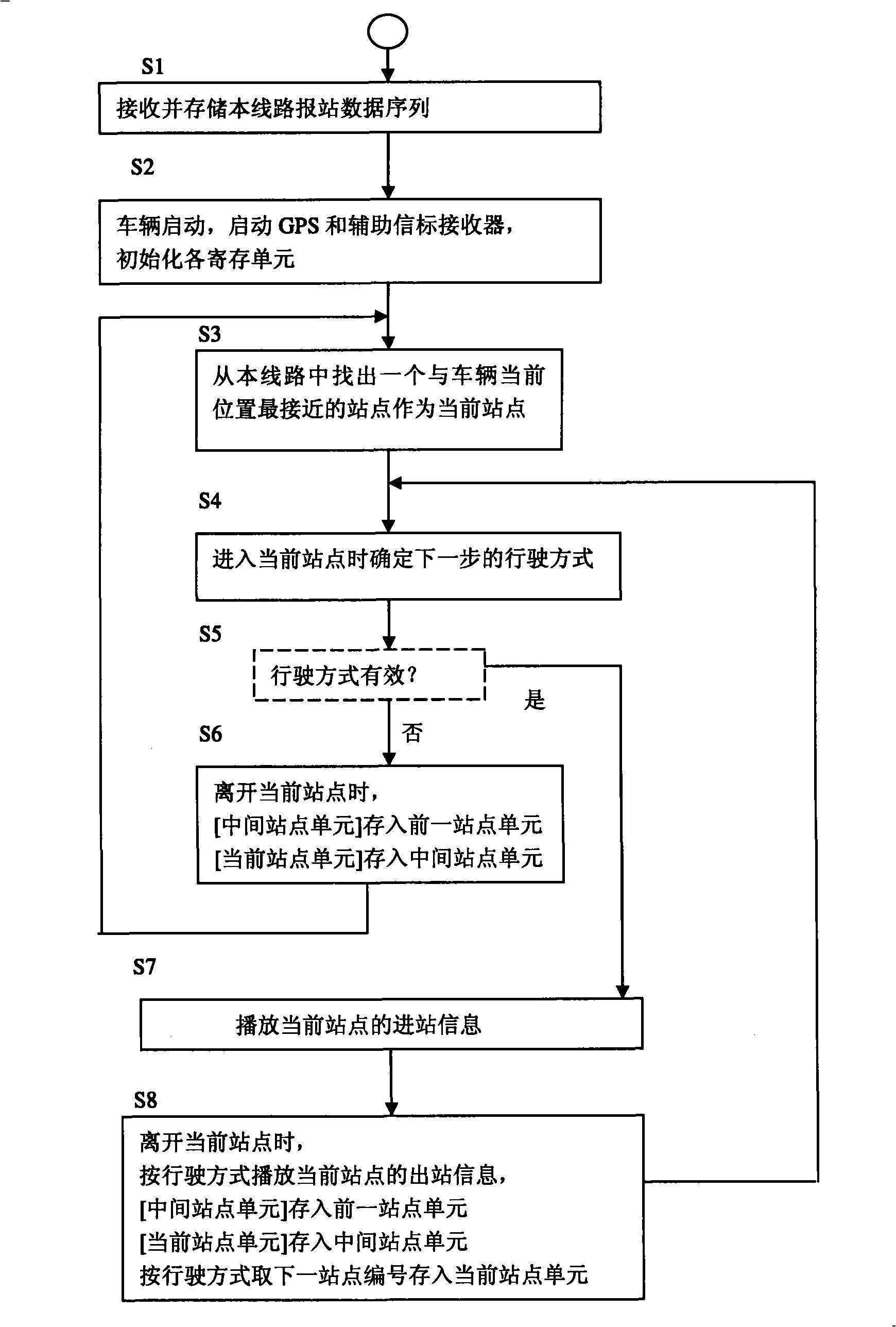

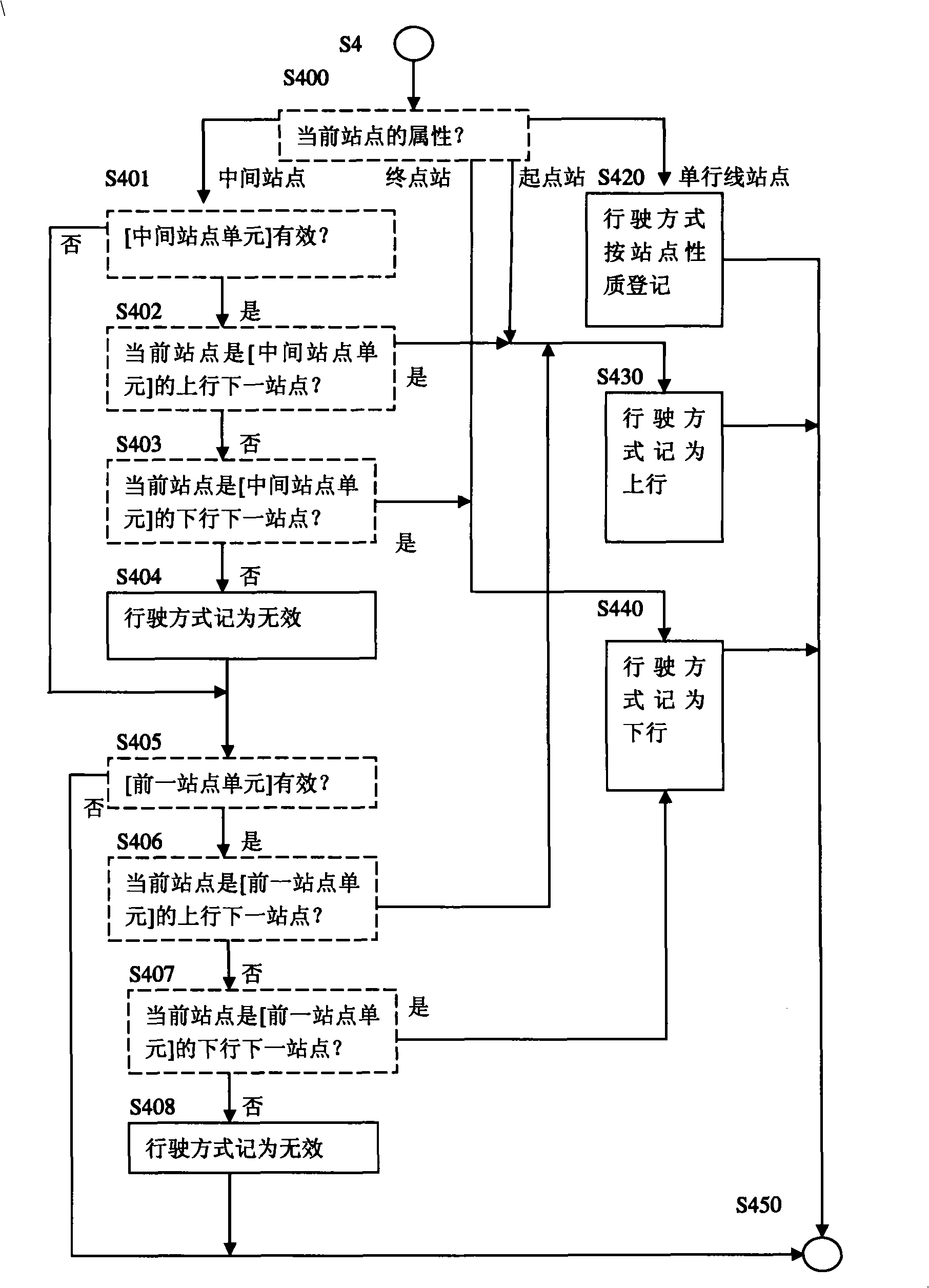

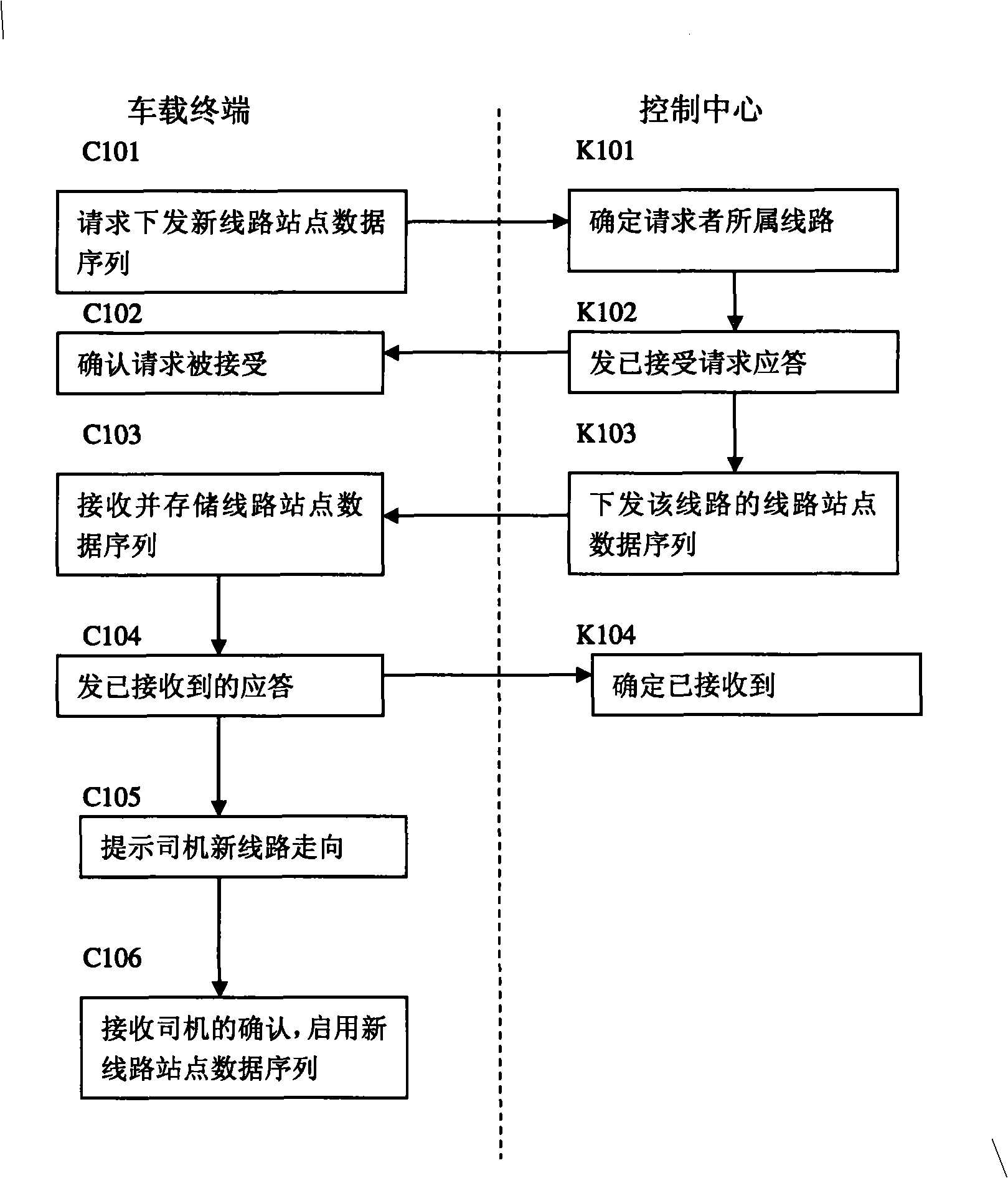

Method for automatically reporting station of public transport vehicle

ActiveCN101493990AAccurate and timely station announcementEasy to schedule and manageRoad vehicles traffic controlBroadcastingData sequences

The invention relates to an automatic stop announcement method of a bus, pertaining to a bus information-releasing method. The method solves the problems of difficult data adjustment and low accuracy of stop announcement under a complicated situation, and comprises the following steps: a bus terminal receives and stores a data sequence of stop announcement in a running route, sent out by a control center through mobile communication. When the bus is in running, the bus terminal first combines current GPS location information with stop location information of auxiliary beacons to periodically find out the nearest stop as a current stop in the running route from the data sequence of the stop announcement. The running modes, namely, the uplink or the downlink, is determined when the bus runs into the current stop. And then the bus terminal adjusts the running mode according to the data sequence, controls the broadcasting and displays the information of the current stop; when the bus leaves the stop, the bus terminal, combining the running mode and in accordance with the data sequence, controls the broadcasting and displays leaving information consisting of the name of the next stop, and sets the next stop in the running route as the current stop.

Owner:XIAMEN YAXON NETWORKS CO LTD

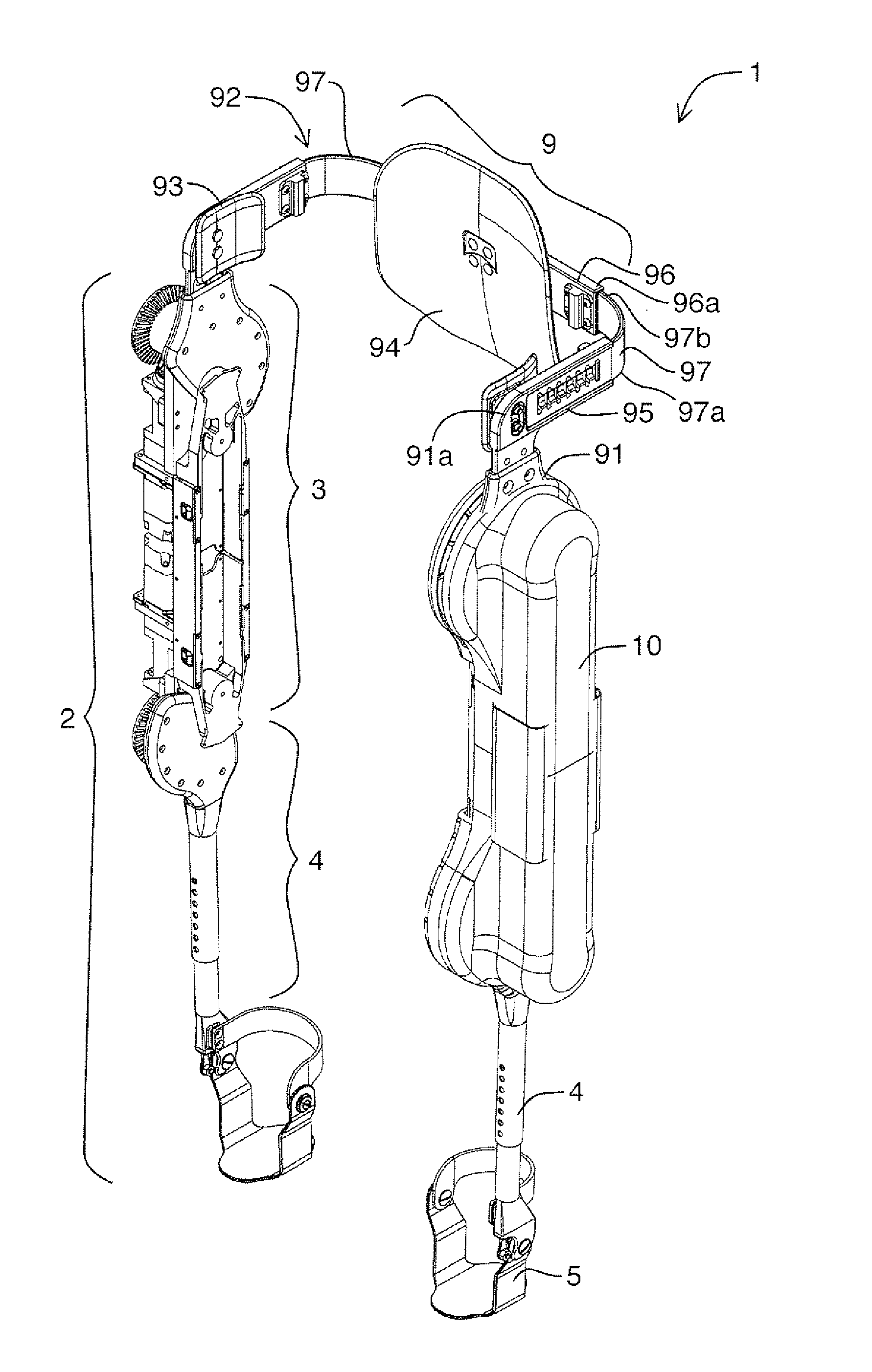

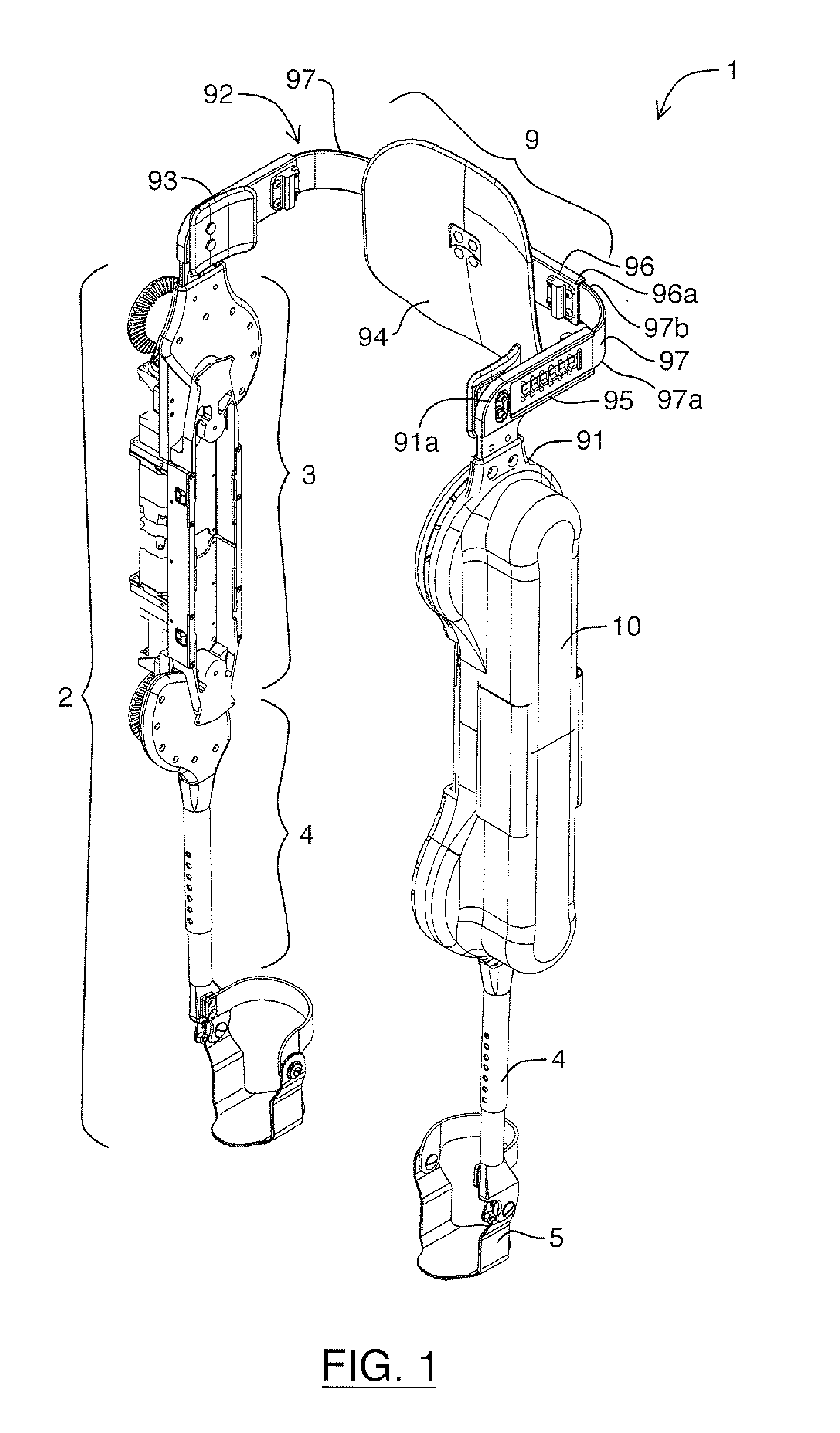

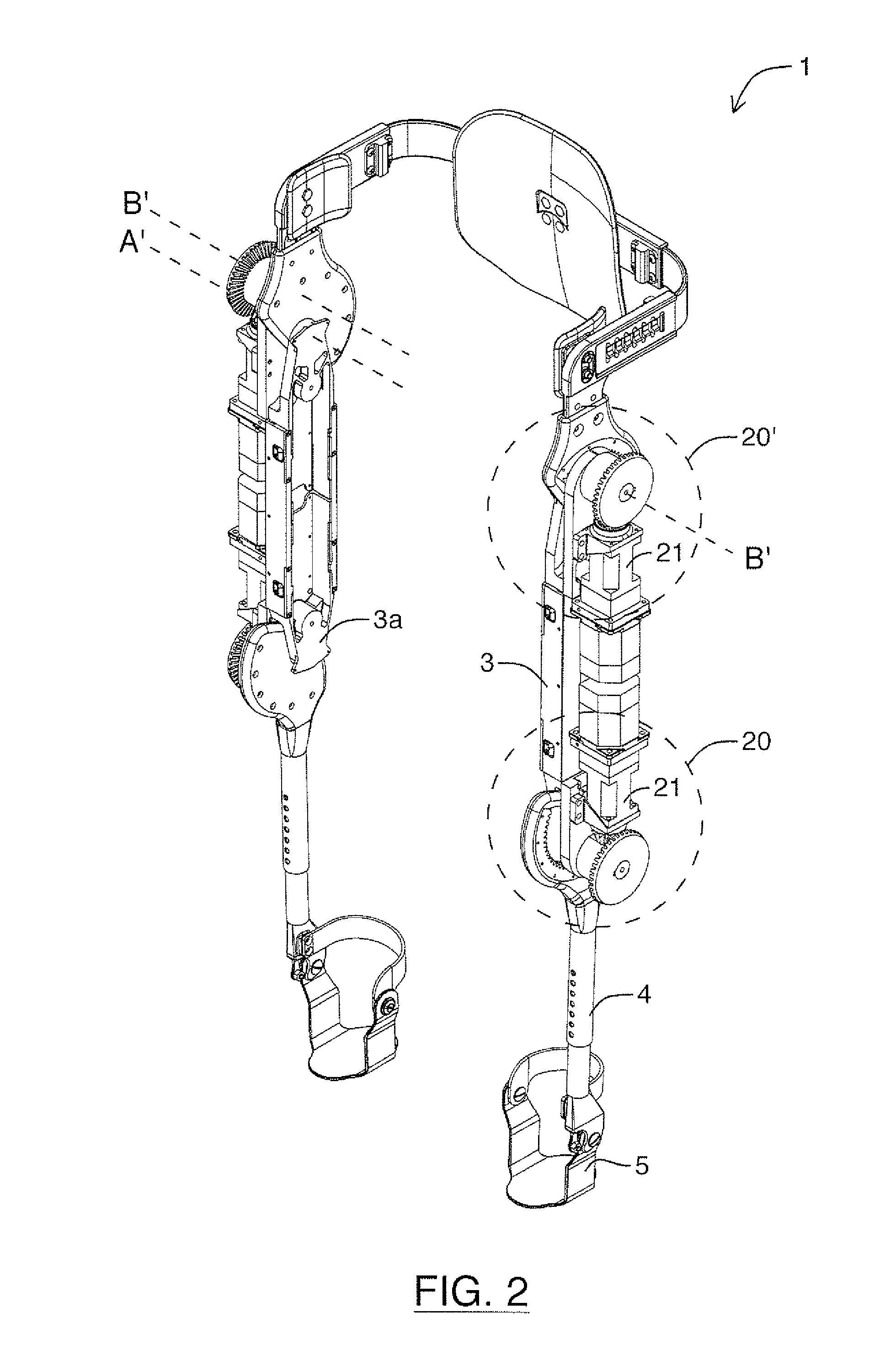

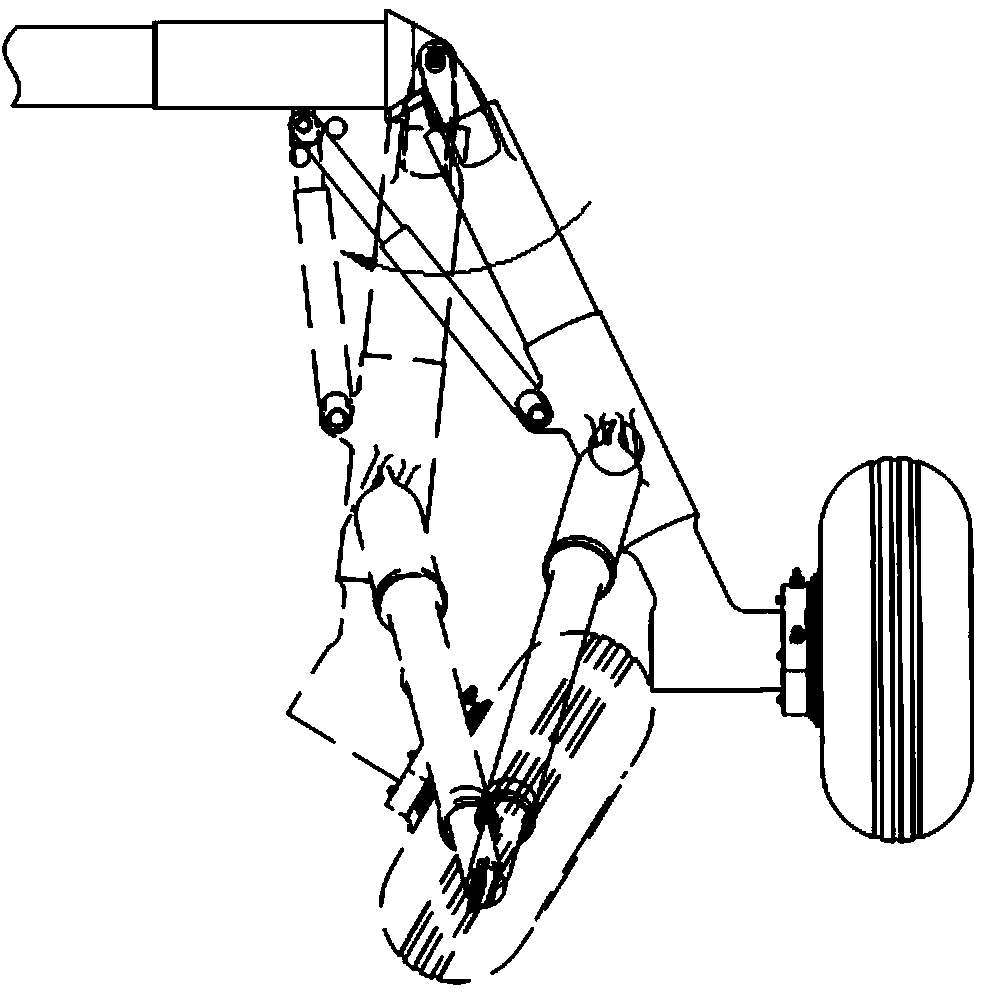

Transmission assembly for use in an exoskeleton apparatus

ActiveUS20140276261A1High mass moment of inertiaRelieve pressureChiropractic devicesWalking aidsEngineeringExoskeleton Device

An exoskeleton for a limb of a user wherein the limb has an upper portion that is pivotally mounted to another part of the exoskeleton about a pivot axis and the upper portion is drivingly connected to the exoskeleton by a force applied via a drive force transmission axis that is vertically offset from the pivot axis.

Owner:BIONIK LAB

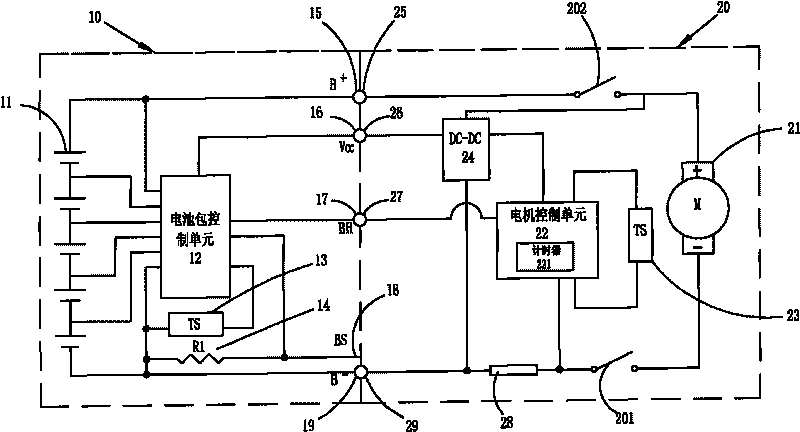

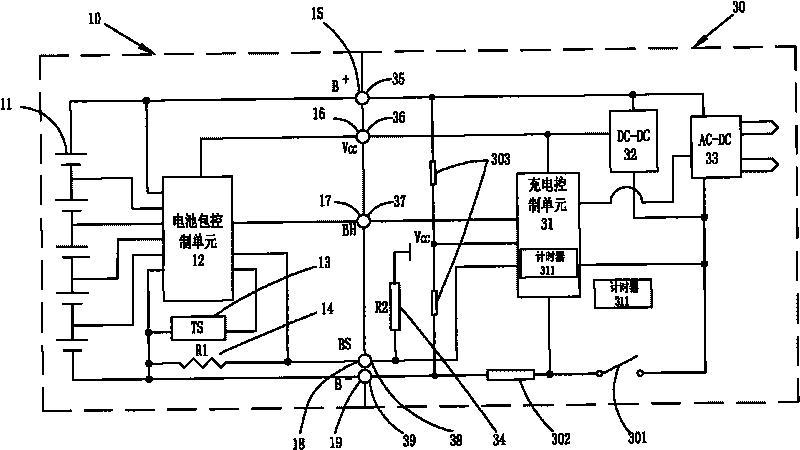

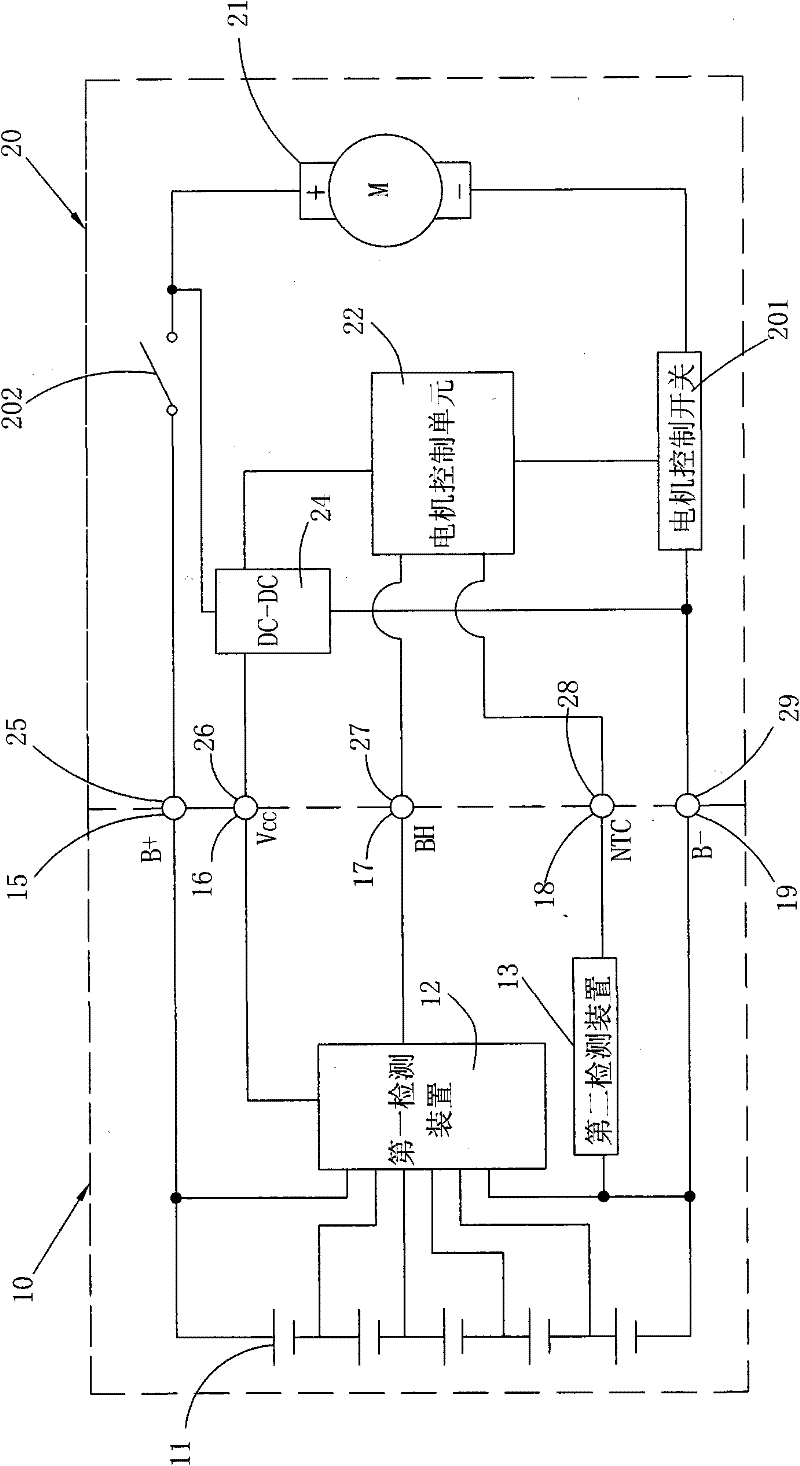

Electric tool and combination of electric tool and battery pack

ActiveCN101758488ASimple requirementsLow costSecondary cellsPortable power-driven toolsPower toolElectrical battery

The invention relates to a combination of an electric tool and a battery pack, wherein the battery pack comprises a plurality of batteries, a circuit board and an electronic control assembly; the circuit board is connected with the batteries; the electronic control assembly is arranged on the circuit board; the electric tool also comprises a circuit board and an electronic control assembly; and the electronic control assembly is arranged on the circuit board. The electronic control assemblies in the battery pack and the electric tool can be respectively used for monitoring the states of the battery pack and performing protection control on the battery pack. With the design, the integral design requirements of the battery pack and the electric tool can be greatly simplified, and the design cost is correspondingly reduced.

Owner:POSITEC POWER TOOLS (SUZHOU) CO LTD

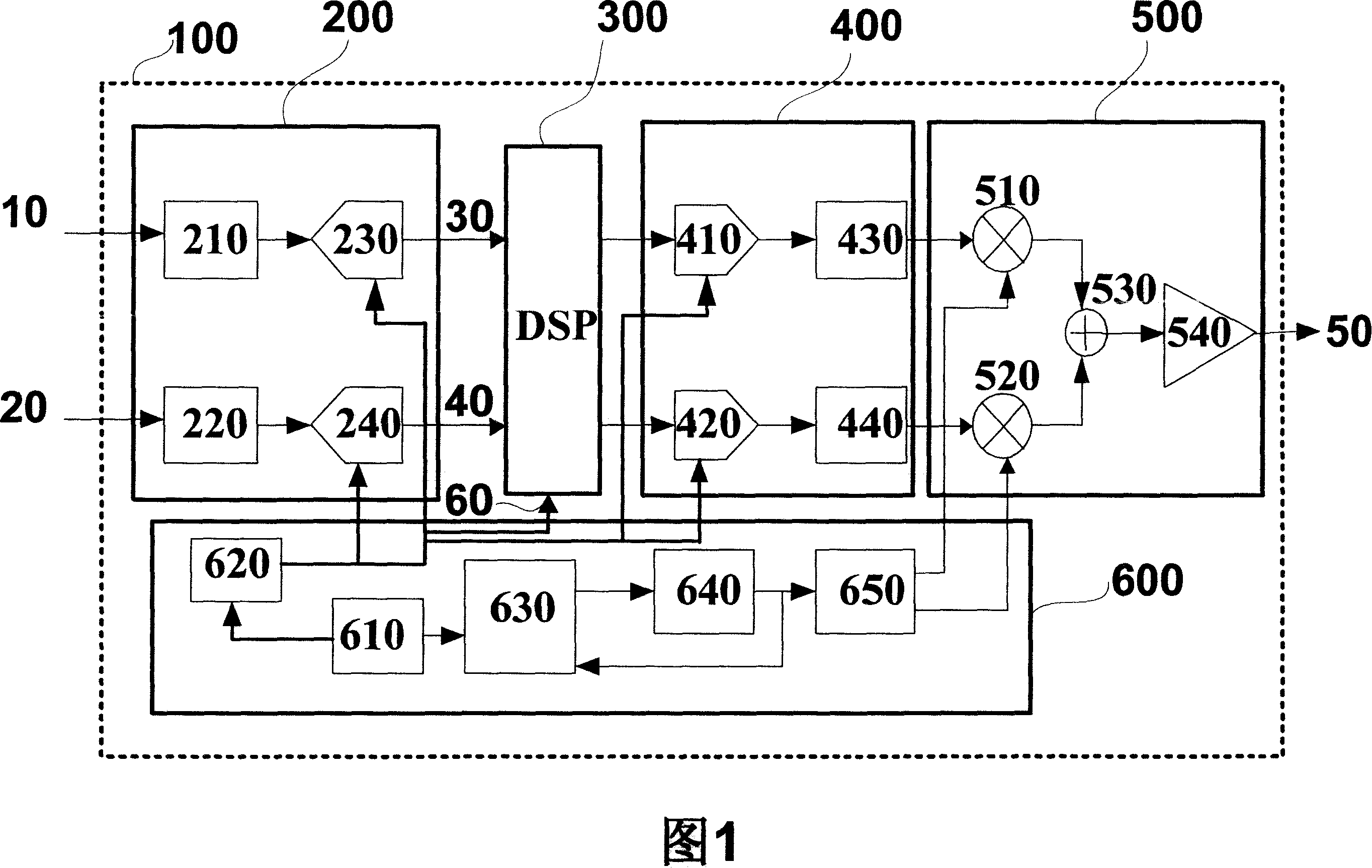

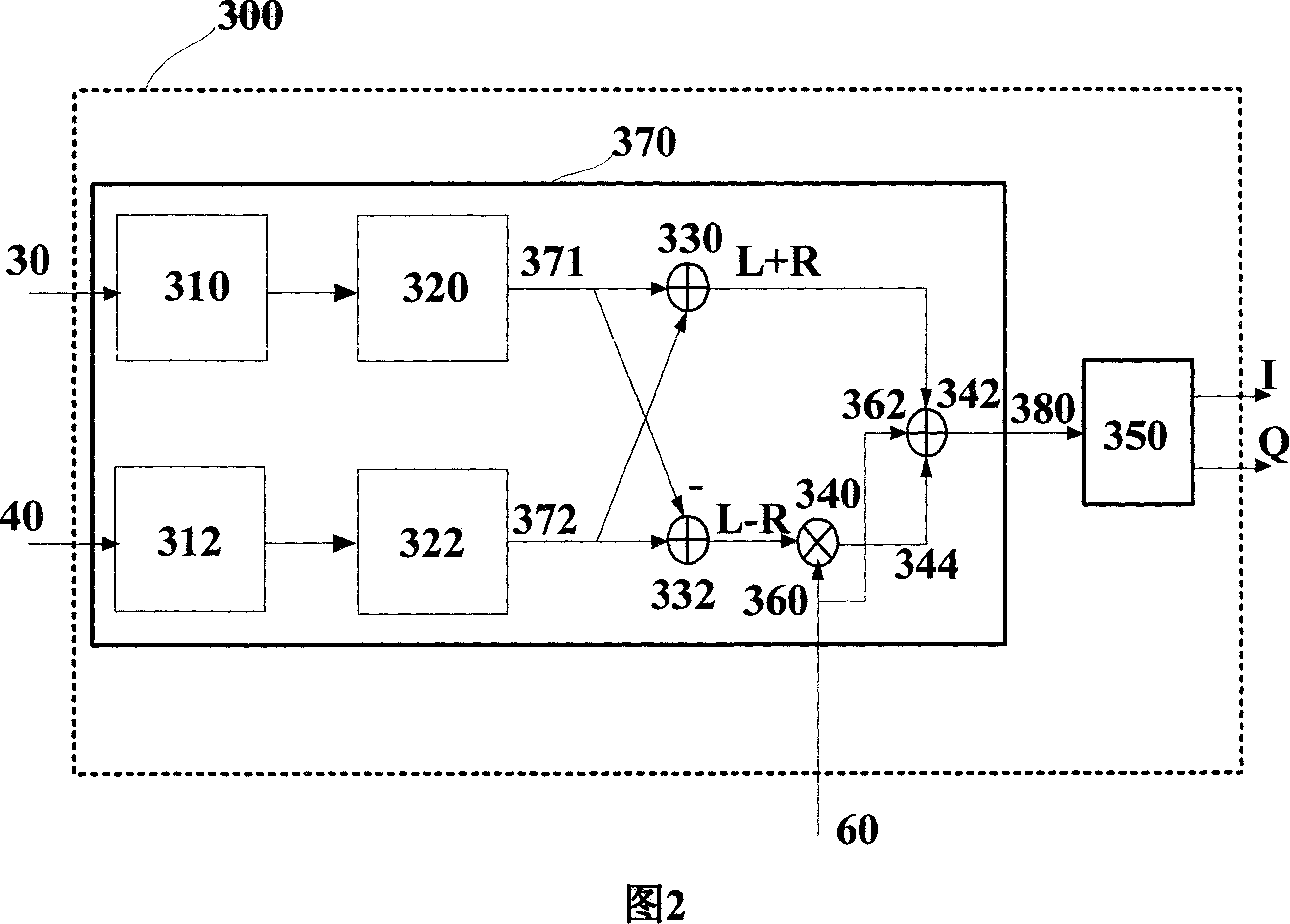

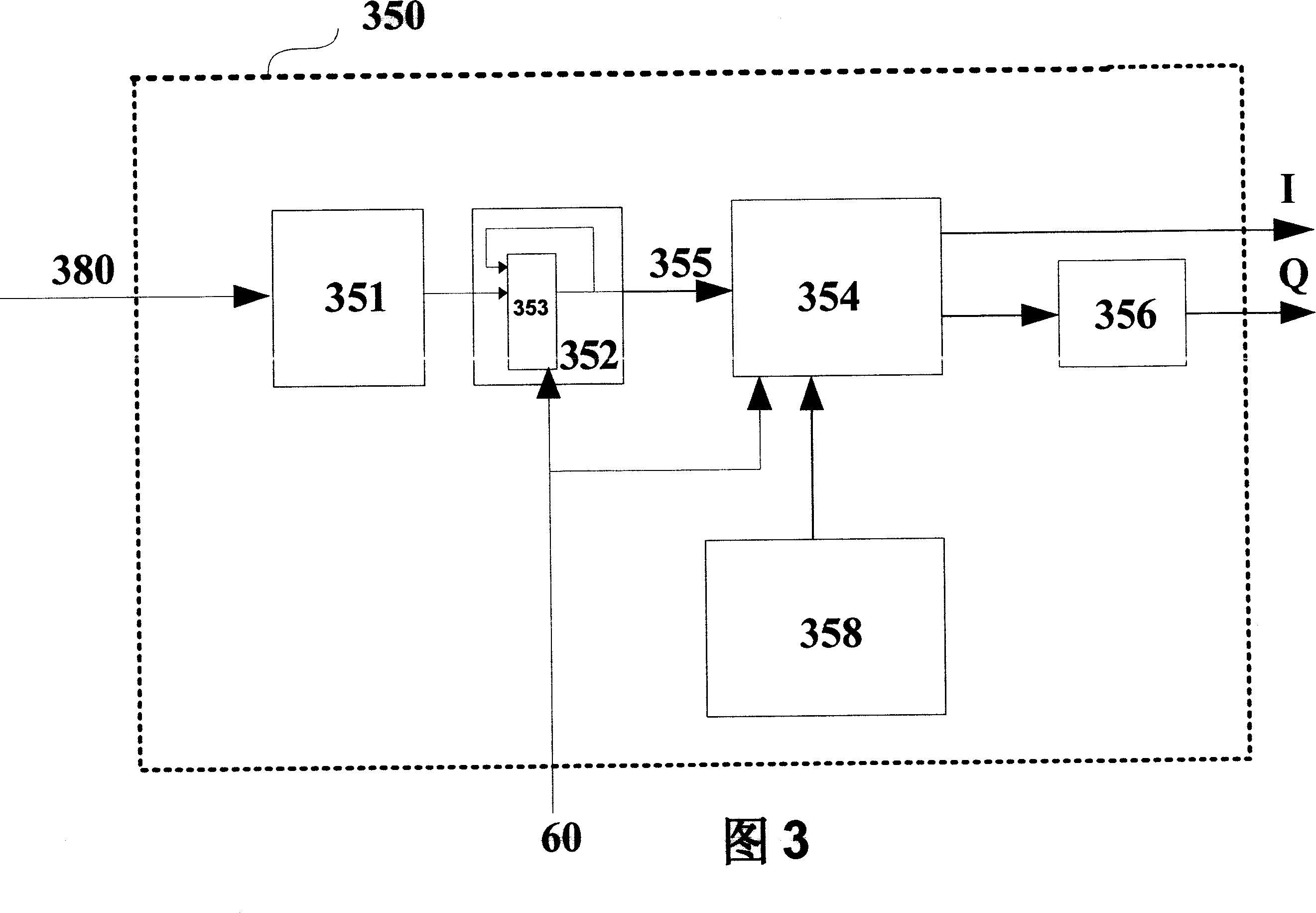

Frequency modulation transmitter

ActiveCN101132382ASimplify Design RequirementsImprove anti-jammingFrequency-modulated carrier systemsDigital signal processingCarrier signal

This invention provides a FM emitter including an audio signal input end and a RF signal input end, a signal input processor, a digital signal process unit used in carrying out audio code and frequency modulation to signals output by the signal input processor, a signal output processor used in carrying out filter and D / A conversion to signals output by the digital signal process unit, a FM signal process part used in carrying out up frequency conversion and D / A conversion and emitting them to signals output by the unit and a frequency integrating module providing stable carrier signals, which not only simplifies design requirement to VCO and PLL of synthesizers, but also can integrate it in a chip by putting the frequency modulation part on a digital baseband.

Owner:豪威国际控股有限公司

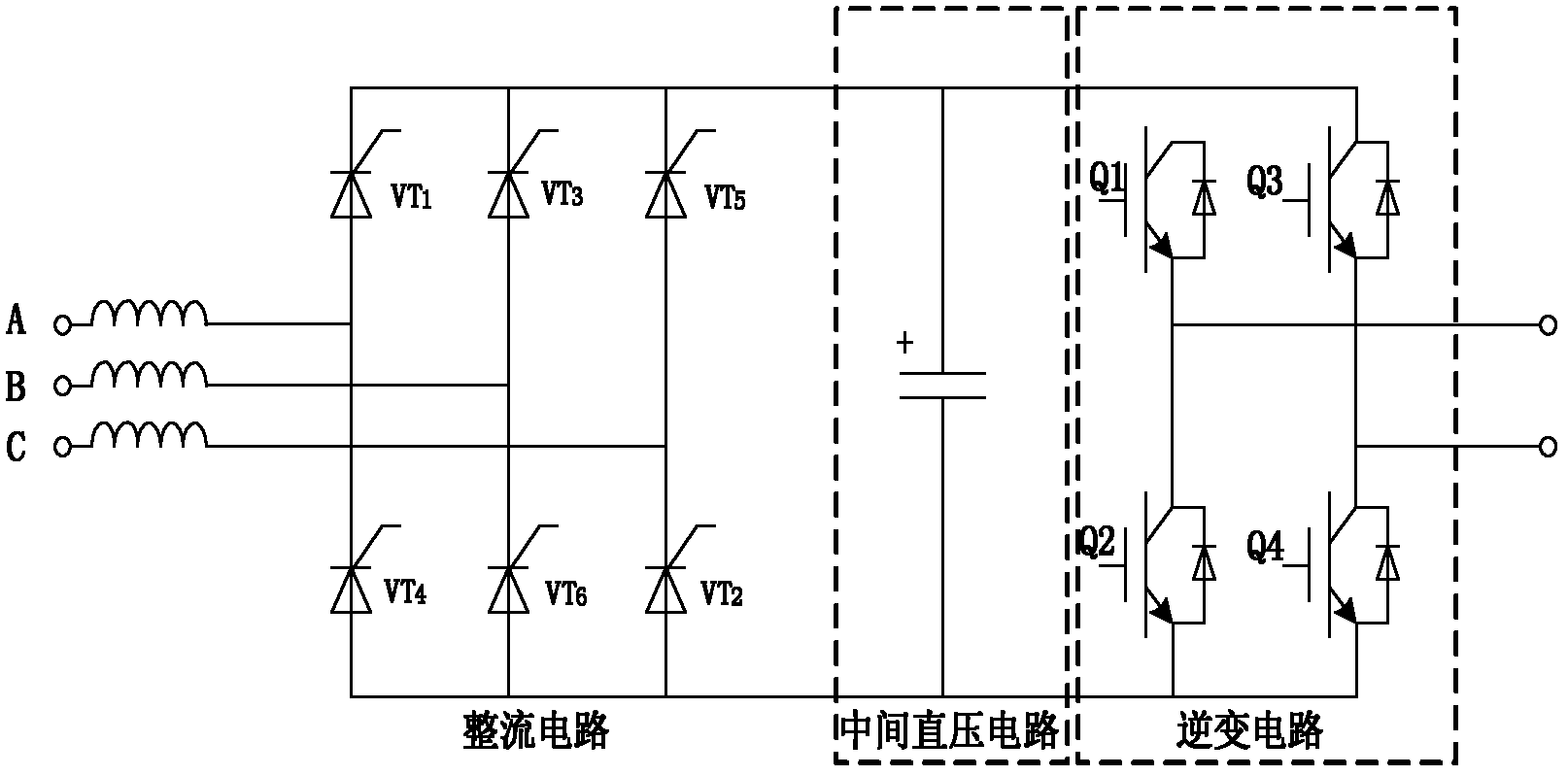

Energy feedback device with composite unit cascade multi-level inverter circuit and control method of energy feedback device

InactiveCN102624025AMeet the requirements of four-quadrant operationSimplify Design RequirementsClimate change adaptationAc-dc conversionClosed loopPower grid

The invention relates to an energy feedback device with a composite unit cascade multi-level inverter circuit and a control method of the energy feedback device. The energy feedback device consists of a power unit based on a three-phase control rectifying circuit and a power unit based on a three-phase PWM (pulse width modulation) rectifying circuit, wherein the two power units are in cascade connection. Direct-current voltage of an intermediate direct-voltage circuit of the power unit based on the three-phase control rectifying circuit is stabilized within a safety range by controlling a closed loop of the direct-current voltage of the intermediate direct-voltage circuit of the power unit based on the three-phase control rectifying circuit in a feedback manner, while load feedback energy mainly flows into the intermediate direct-voltage circuit in the power unit based on the three-phase PWM rectifying circuit and is fed into the power grid in a grid integration inverter mode by the three-phase PWM rectifying circuit. The energy feedback device is capable of realizing feedback of load energy to the power grid, so that energy-saving effect is achieved, output voltage is stabilized, and meanwhile, the topological structure of the power units and complexity of control links are simplified to some extent. Further, usage number of insulated gate bi-polar transistors is reduced, manufacturing cost is reduced as well, and the energy feedback device has high economic value.

Owner:WUHAN UNIV

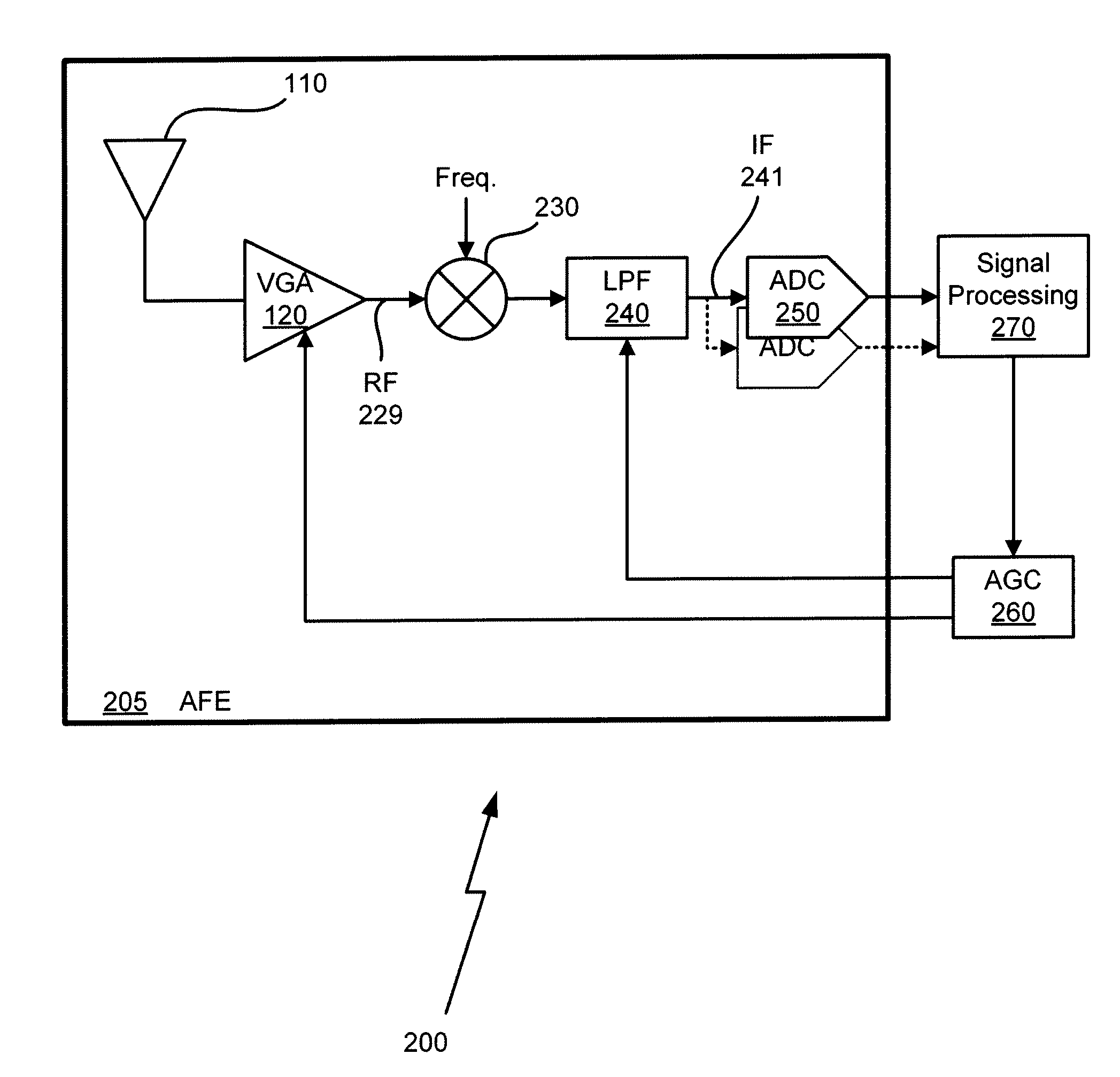

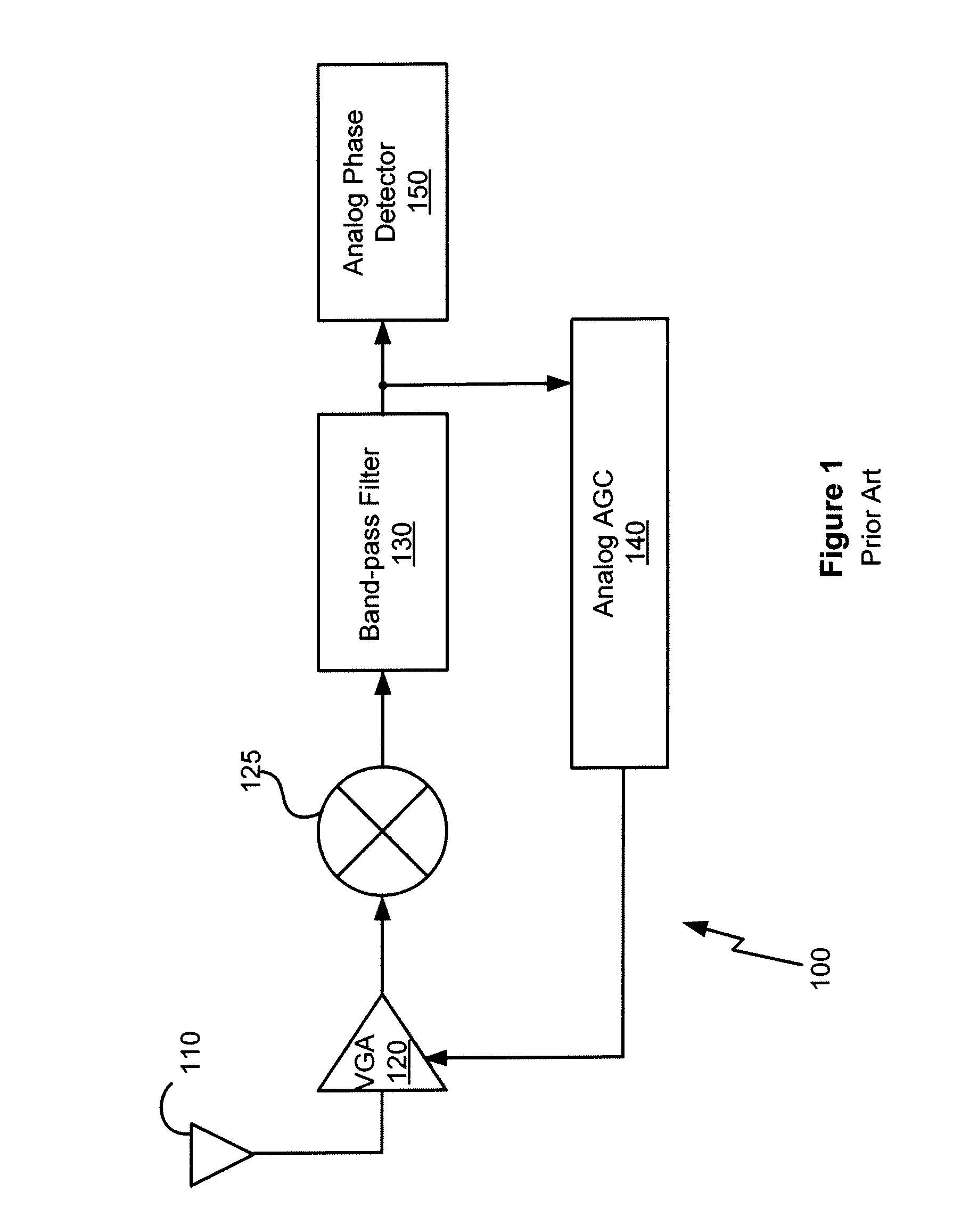

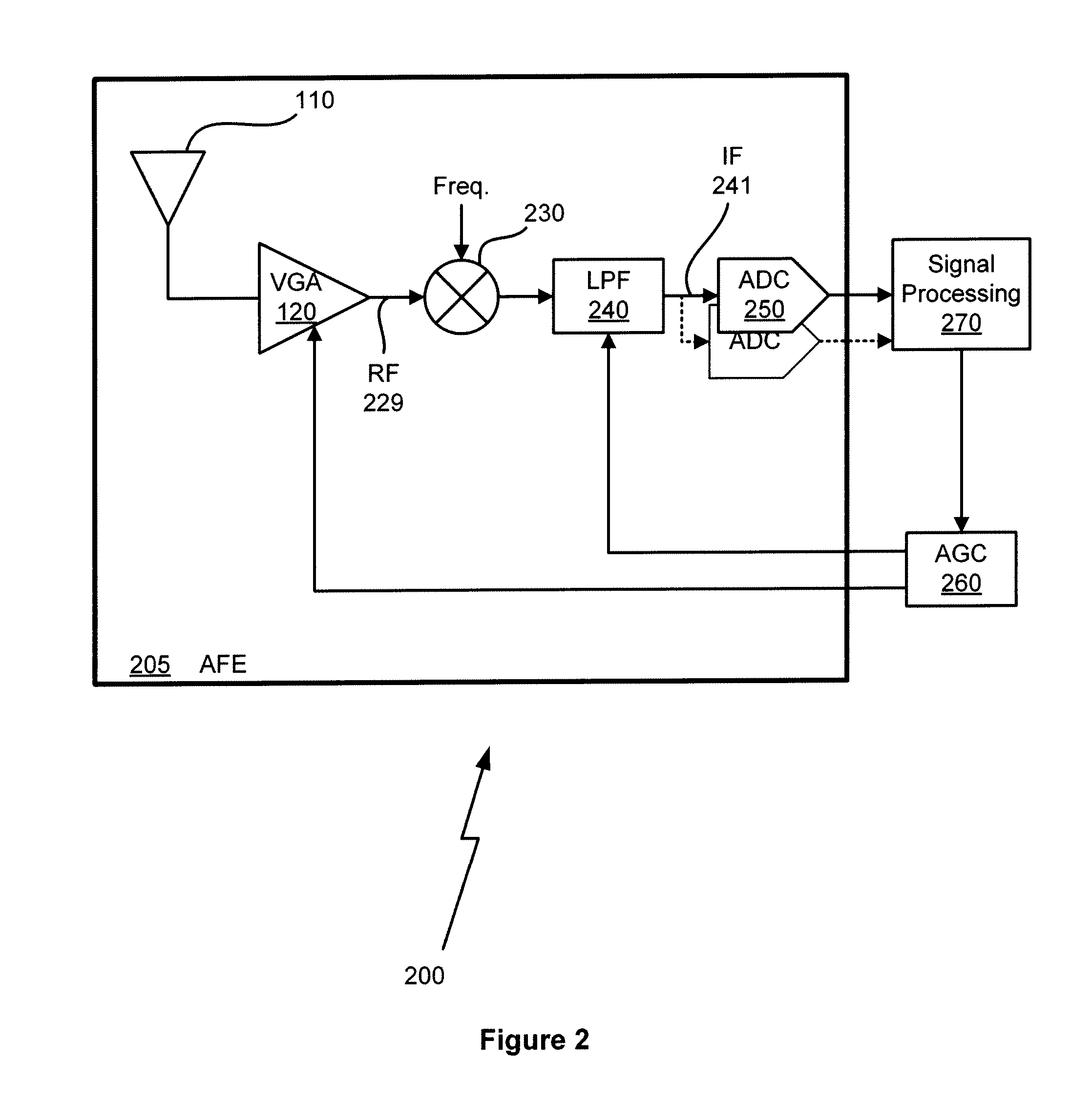

Hybrid Zero-IF Receiver

InactiveUS20080181284A1Less-proneEasy to implementError preventionDc level restoring means or bias distort correctionFrequency spectrumIntermediate frequency

An apparatus for processing a Bluetooth signal advantageously mixes down a received RF signal to an IF signal wherein one band-edge of the spectrum of the IF signal may be approximately 0 Hz. In one embodiment, the IF signal may be digitized, decimated and filtered before being processed into a baseband signal. The baseband signal may be processed by a cordic (COordinate Rotation DIgital Computer) processor to transform the baseband signal from rectangular to polar coordinates. A phase signal from the cordic processor may be used to determine transmitted Bluetooth data symbols. The apparatus may advantageously use less area than traditional Bluetooth receivers.

Owner:QUALCOMM INC

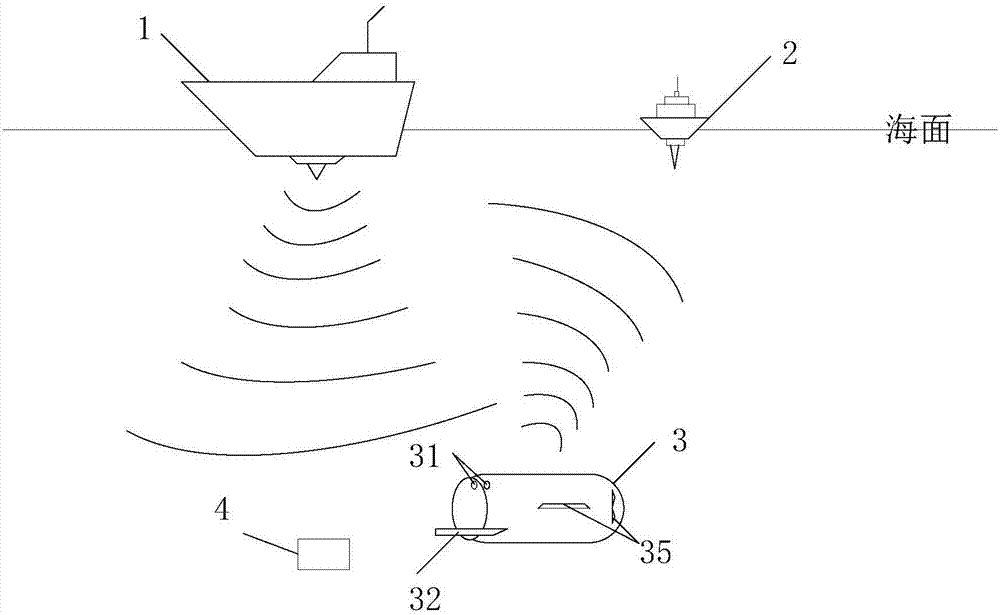

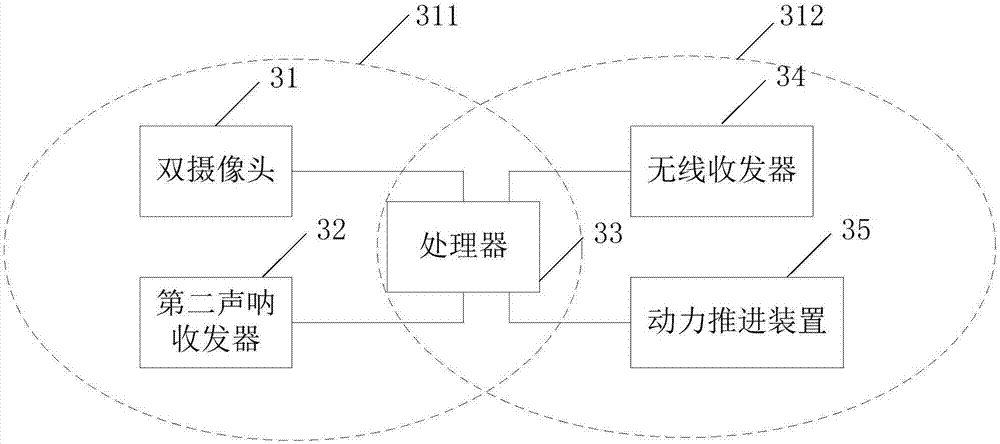

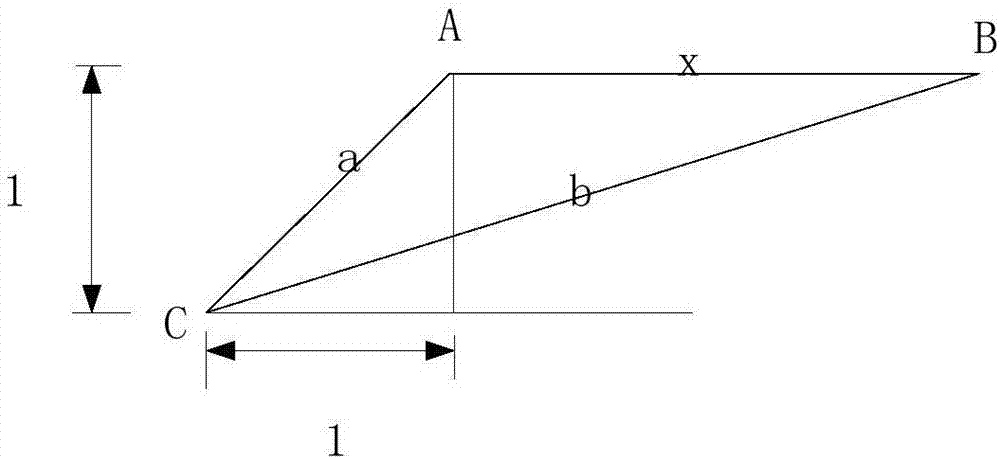

Target positioning and identifying method and system for underwater robot

ActiveCN107153192ASimplify Design RequirementsImprove battery lifeAcoustic wave reradiationMarine engineeringUnderwater robot

The invention that relates to the field of the underwater robot technology provides a target positioning and identifying method and system for an underwater robot. An underwater robot in the system is used for obtaining first position information of a target object relative to the underwater robot and transmitting the first position information to a mother ship; the mother ship is used for obtaining second position information of a miniature unmanned ship; and the miniature unmanned ship feeds back a collected sonar reflection signal from the underwater robot to the mother ship. The mother ship is also used for carrying out calculation based on third position information of the mother ship, the second position information of the miniature unmanned aerial vehicle, and sonar reflection signals collected by the mother ship and the miniature unmanned ship as well as the first position information of the target object relative to the underwater robot, thereby obtaining positioning information of the target. Compared with the prior art with the underwater robot as an active sonar source, the target positioning and identifying method and system have the following beneficial effects: the cruising power of the underwater robot can be enhanced on the premise that the target positioning and identifying accuracy of the underwater robot is guaranteed; and the operation efficiency of the underwater robot is reduced.

Owner:DAPENG GAOKE WUHAN INTELLIGENT EQUIP CO LTD

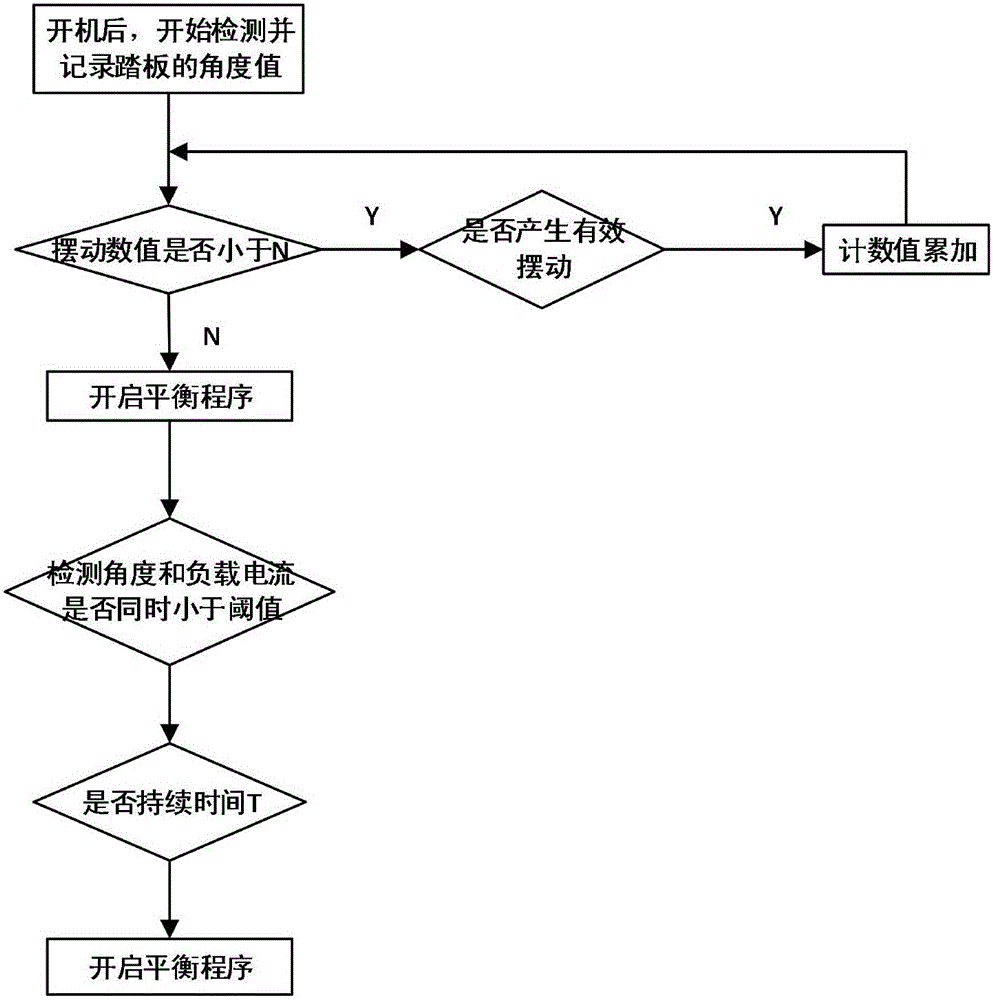

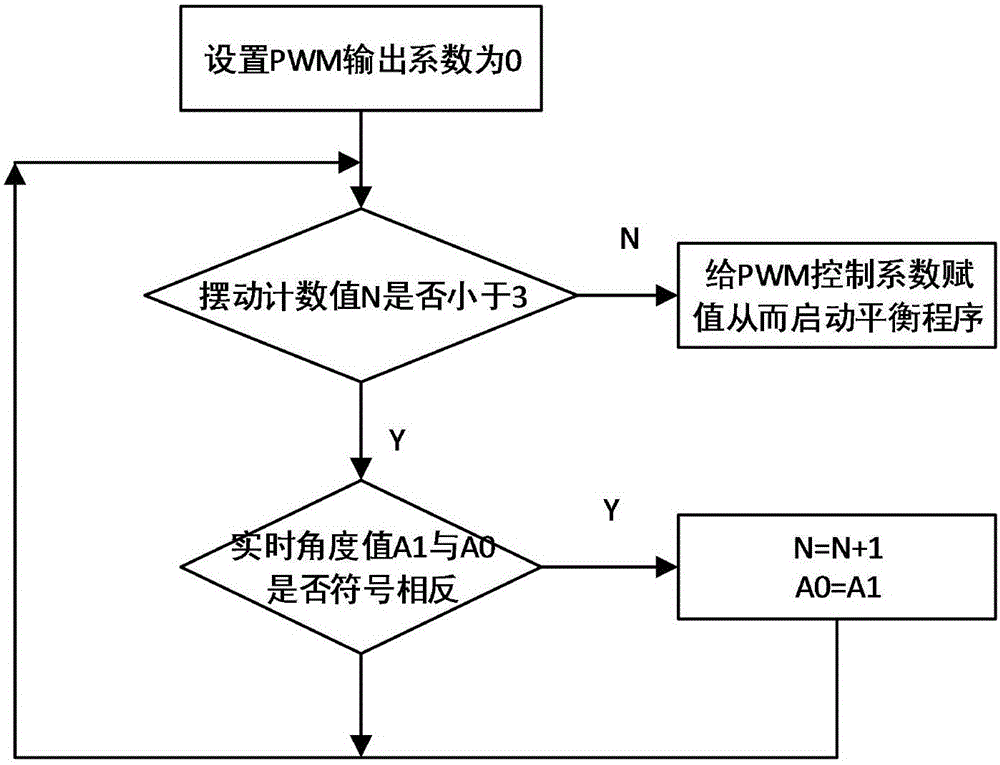

Starting and stopping method for two-wheel balanced electric swing car without optoelectronic switches

InactiveCN105966509AReduce weightReduce mechanical structureBicyclesPosition/course control in two dimensionsElectricityEngineering

The invention discloses a starting and stopping method for a self-balanced electric swing car. The starting and stopping method comprises the following steps that 1, after the self-balanced electric swing car is electrified, the angle value of pedals is detected through an attitude sensor on a control plate and is returned to controllers of the corresponding pedals; 2, when the positive-negative alternating times of the transmitted angle value are detected to exceed N through any controller, a balancing program is started through the corresponding controller; 3, the controllers controls the self-balanced electric swing car to go forward and backward; and 4, when the collected angle change value and a load current are smaller than the corresponding set threshold value within the time T, the self-balanced electric swing car is stopped normally. According to the starting and stopping method for the self-balanced electric swing car, the situation that a rider gets on or off can be judged through the method of software, accordingly, starting and stopping of the balancing program are controlled, and then dangerous situations are avoided, so that the driving safety is ensured.

Owner:INTELLIGENT MFG INST OF HFUT

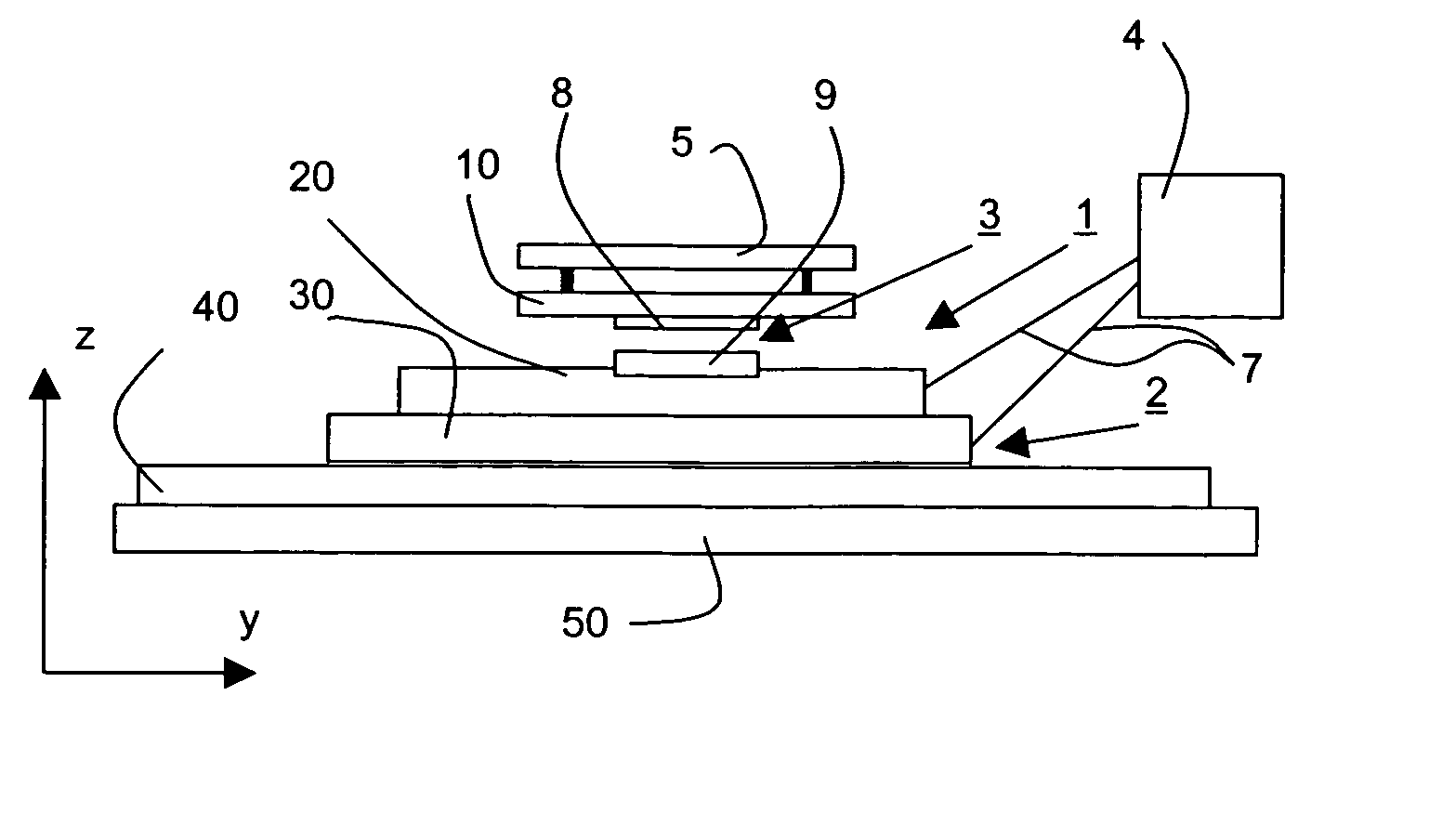

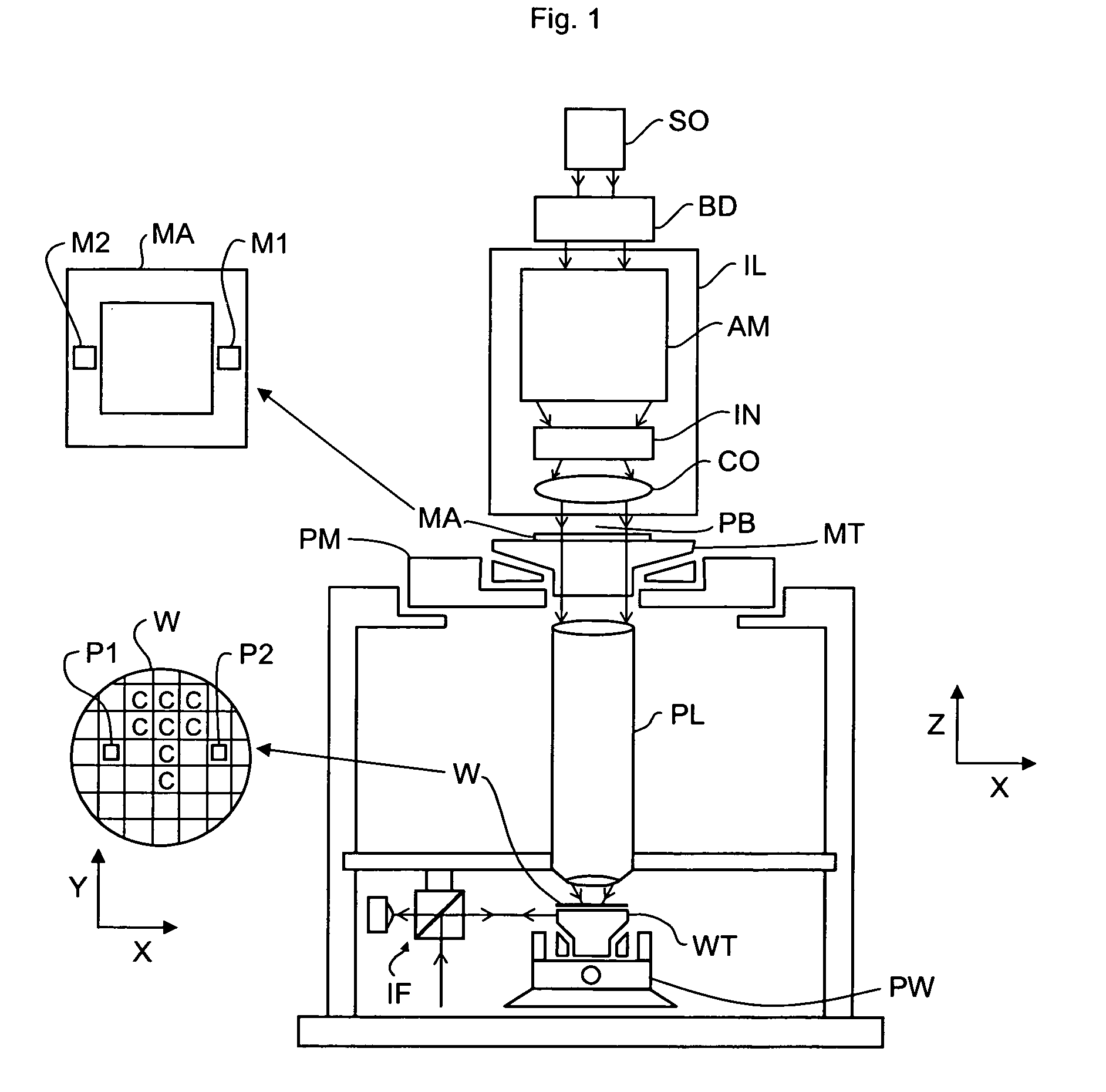

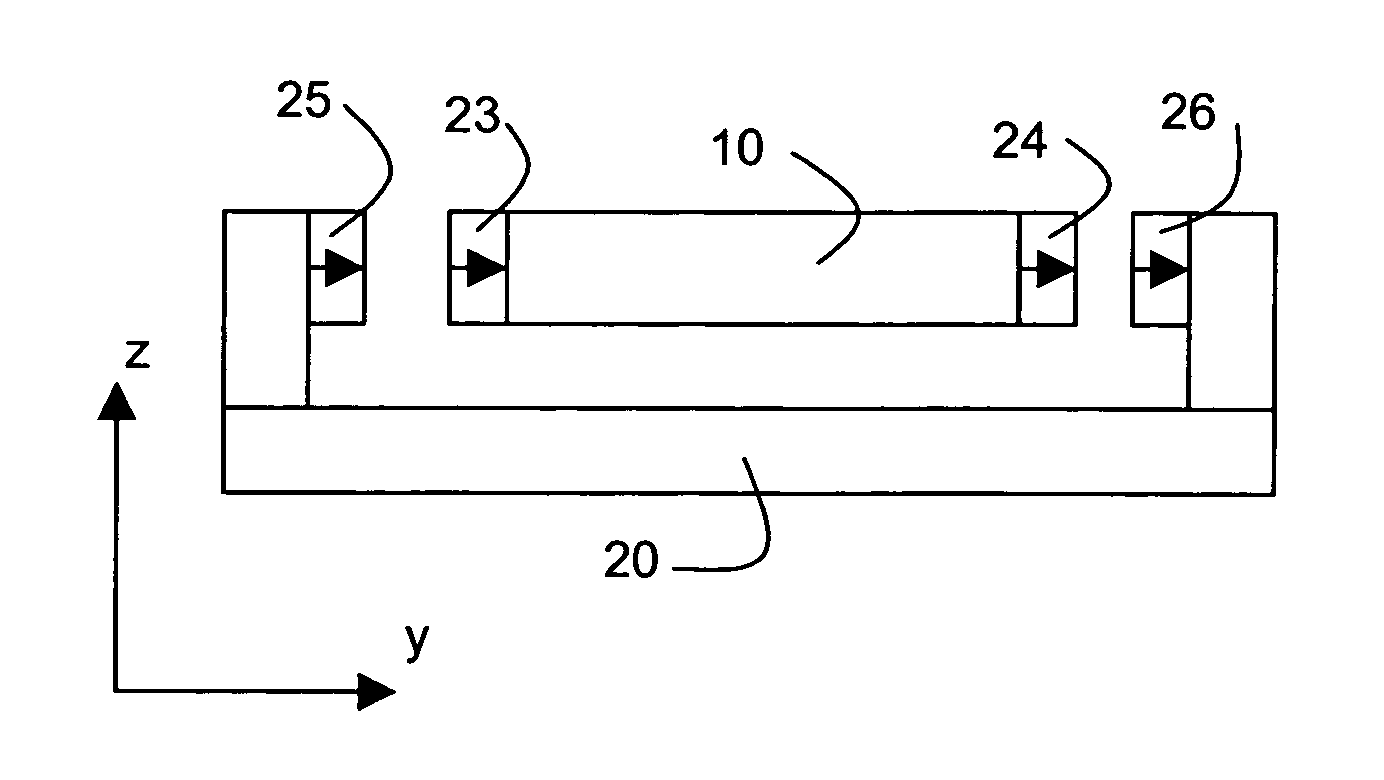

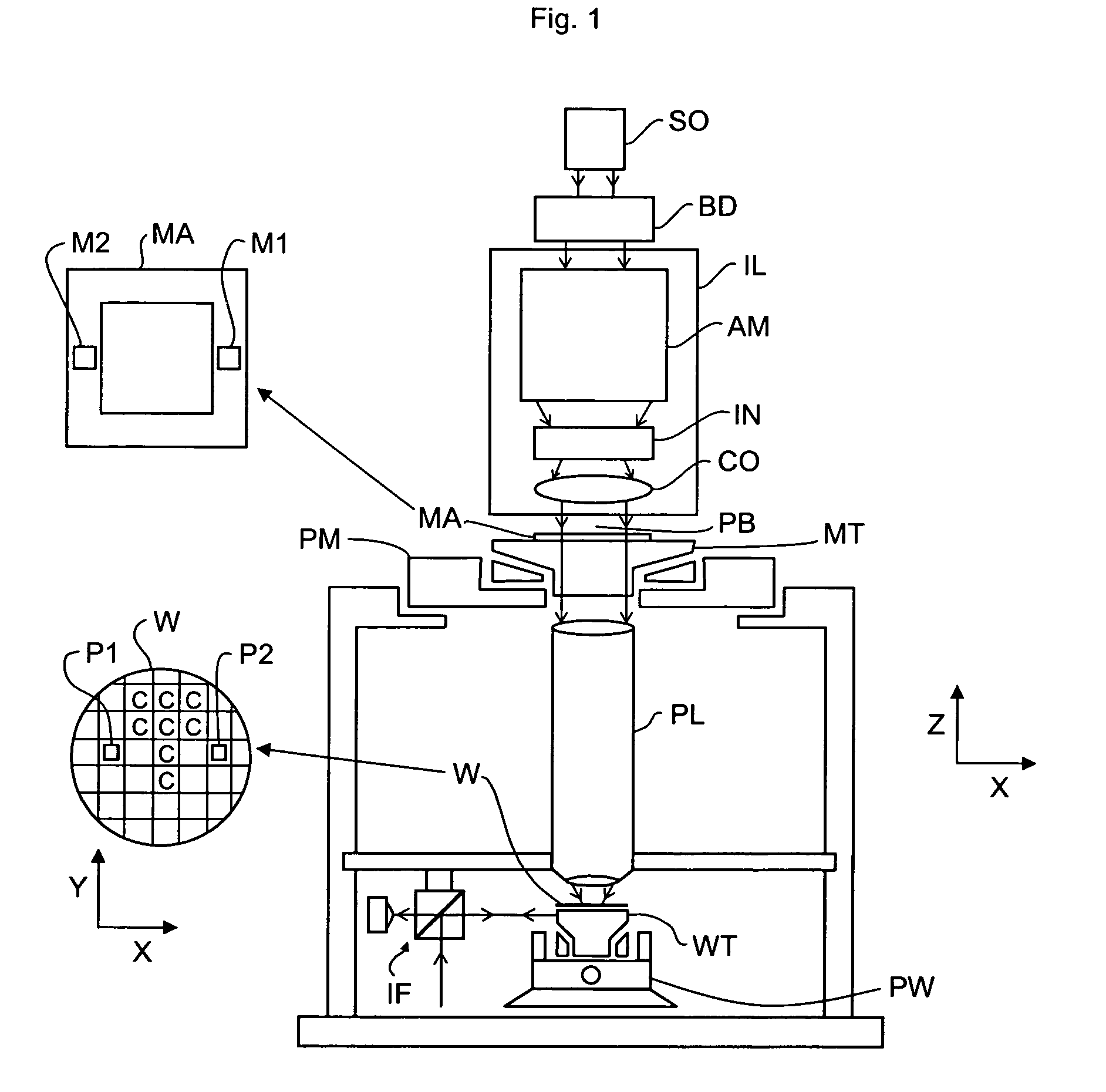

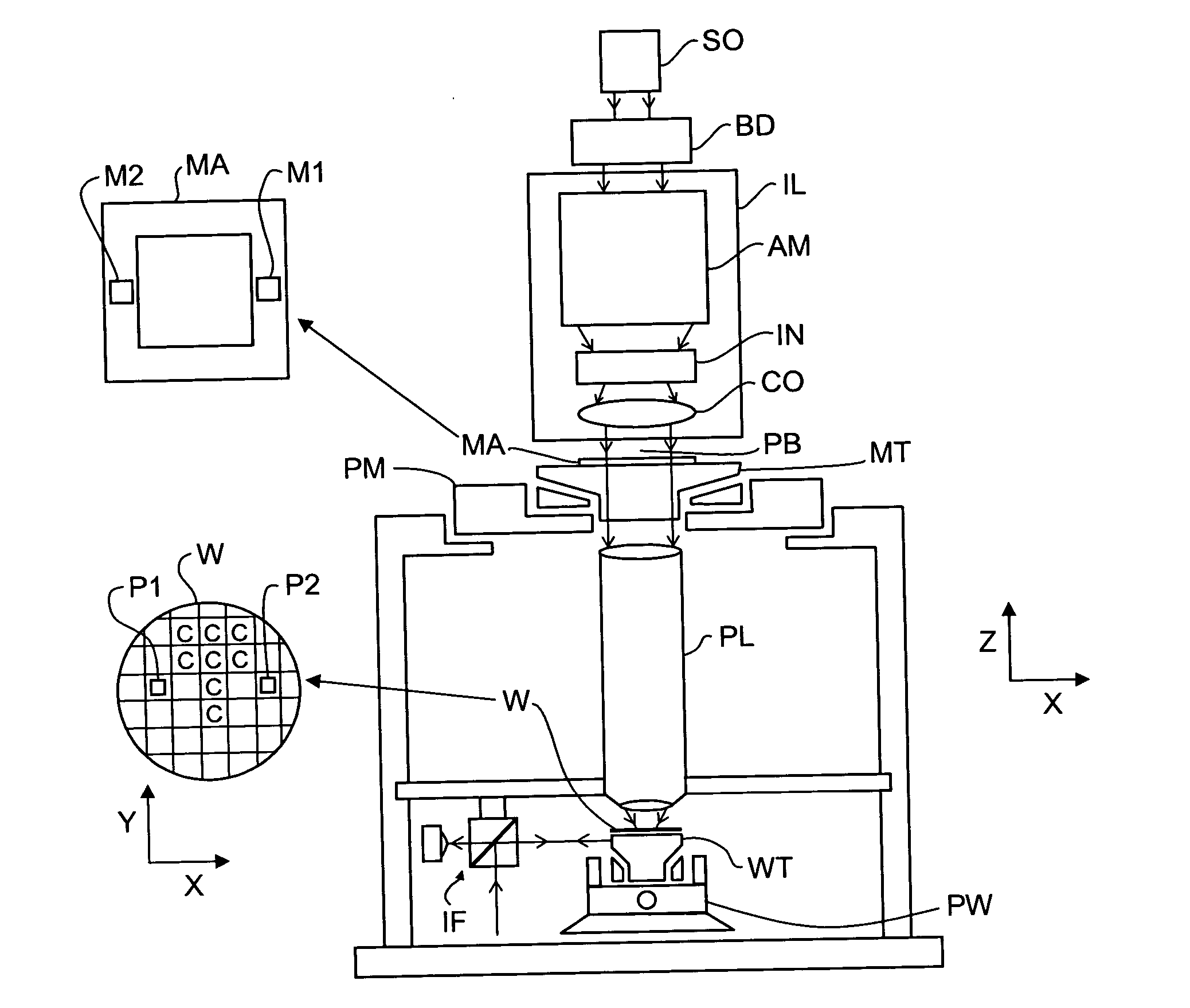

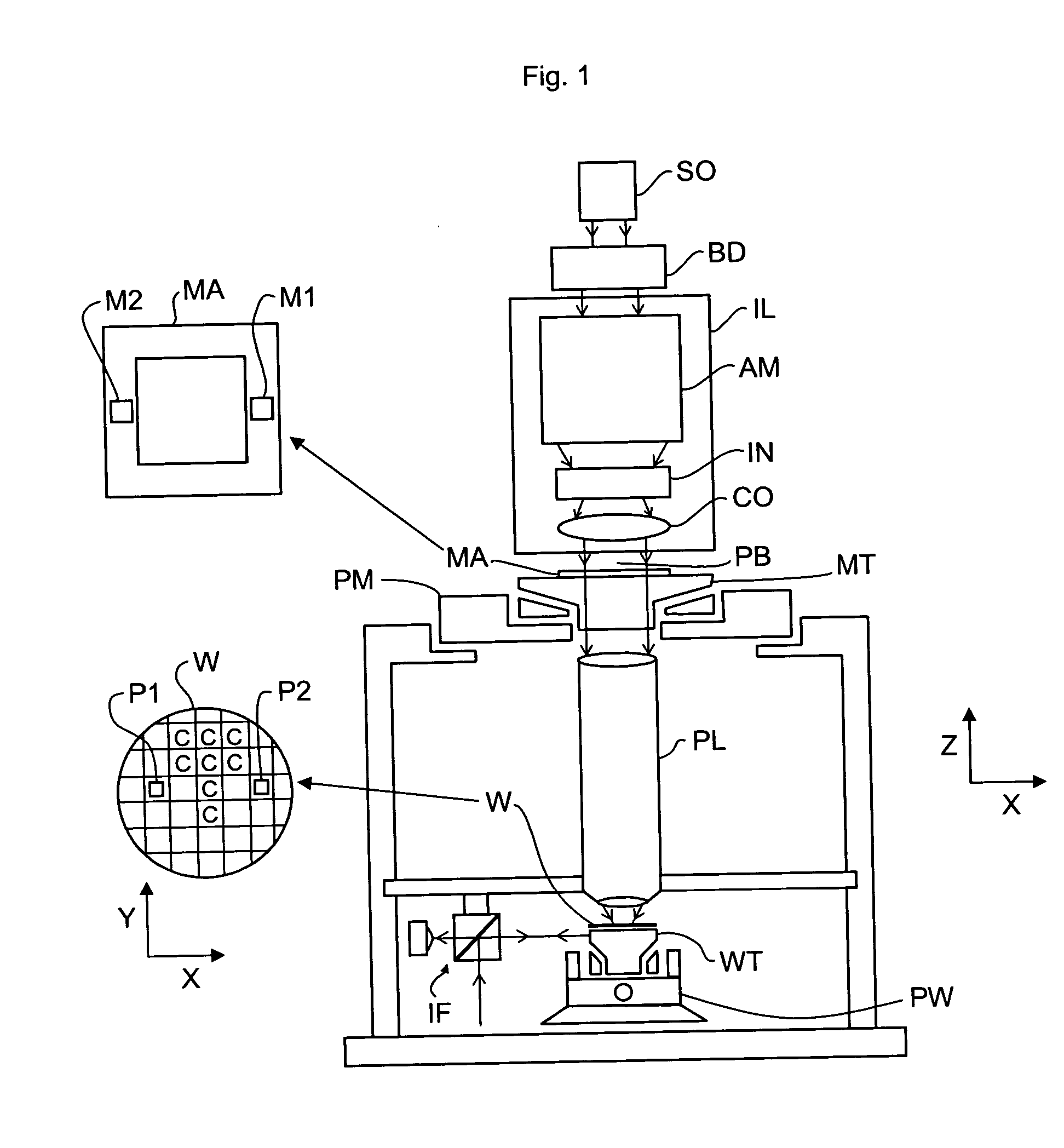

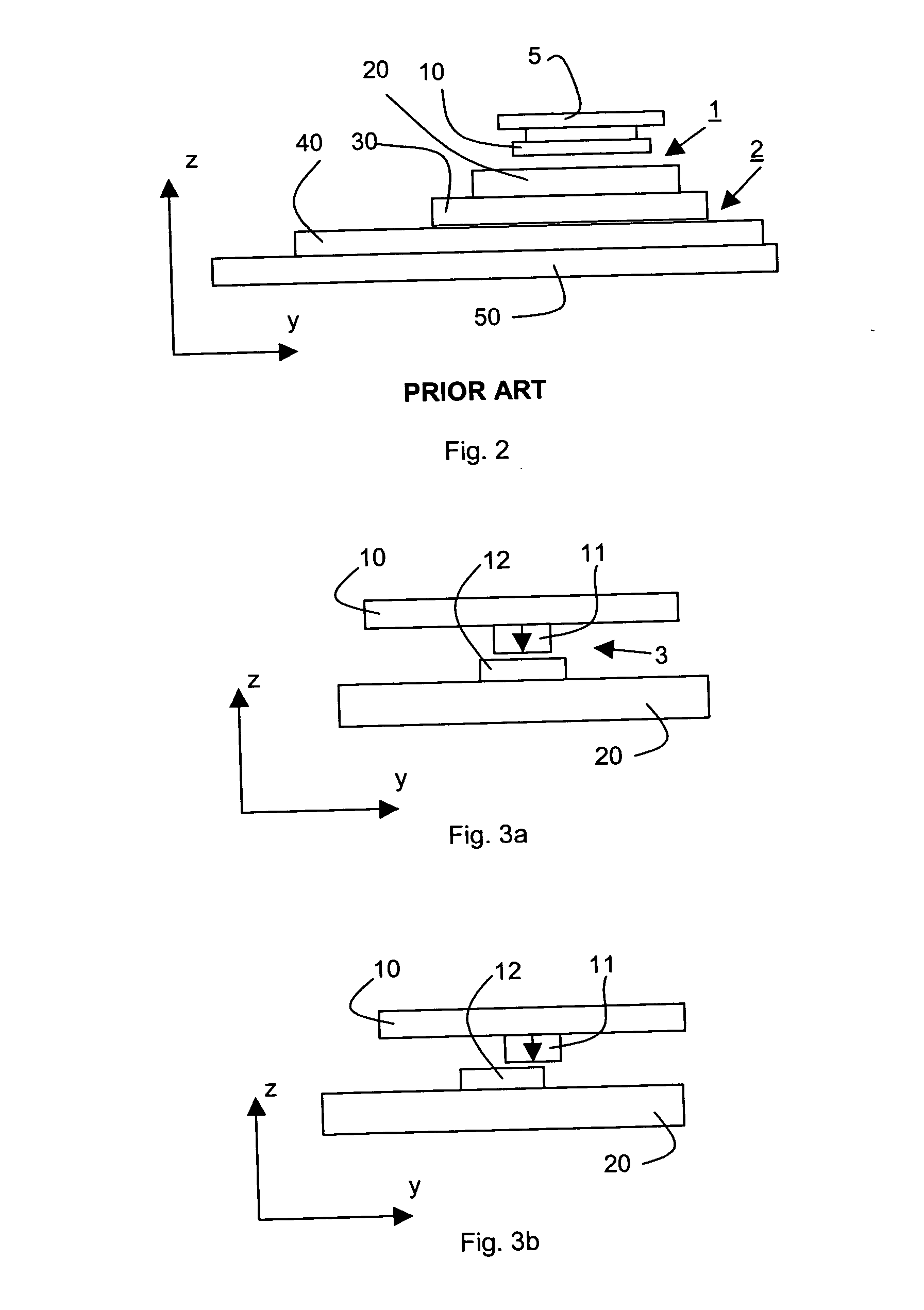

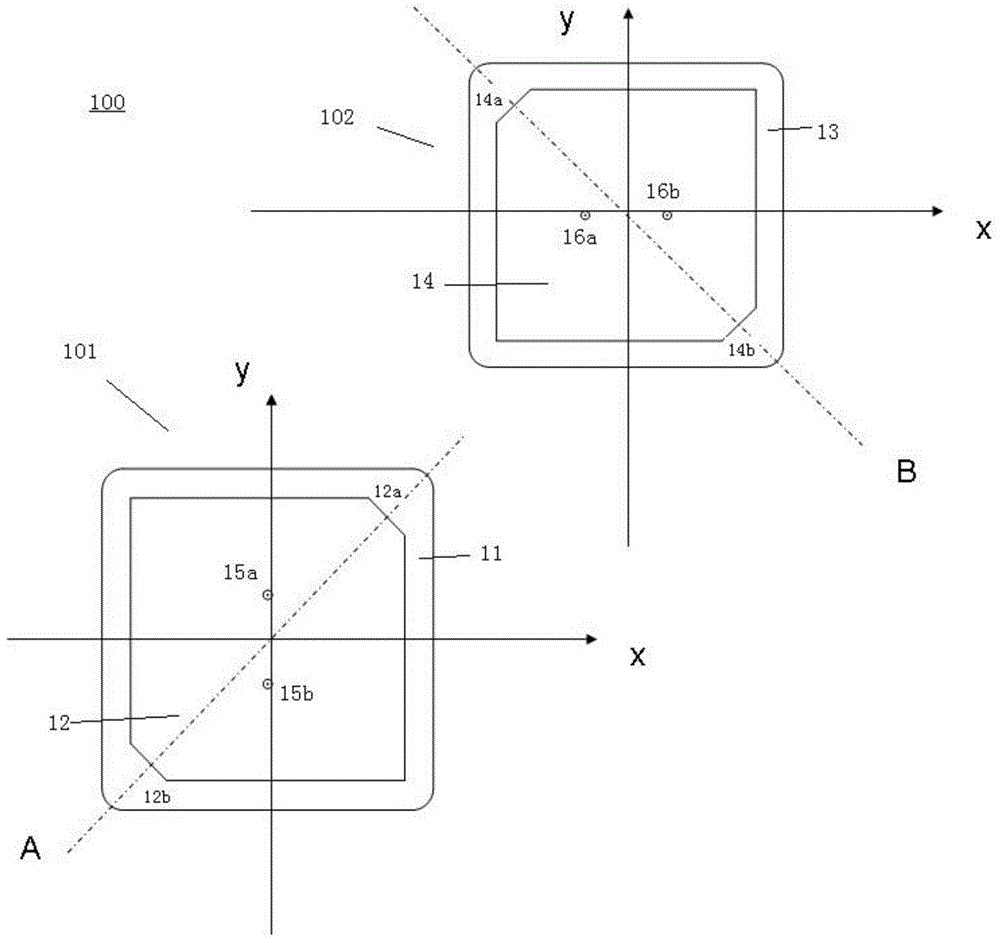

Lithographic positioning device and device manufacturing method

InactiveUS20050200826A1Precise positioningReduce dissipationMagnetic circuit rotating partsPhotomechanical apparatusEngineeringMagnet

A positioning device for positioning an object inside a lithographic apparatus is described. The positioning device comprises a first drive unit and a second drive unit for positioning the object. The first drive unit has a first part connected to the object and a second part connected to a first part of the second drive unit. The positioning device further comprises a permanent magnet system constructed and arranged to provide at least part of the force for accelerating or decelerating the object.

Owner:ASML NETHERLANDS BV

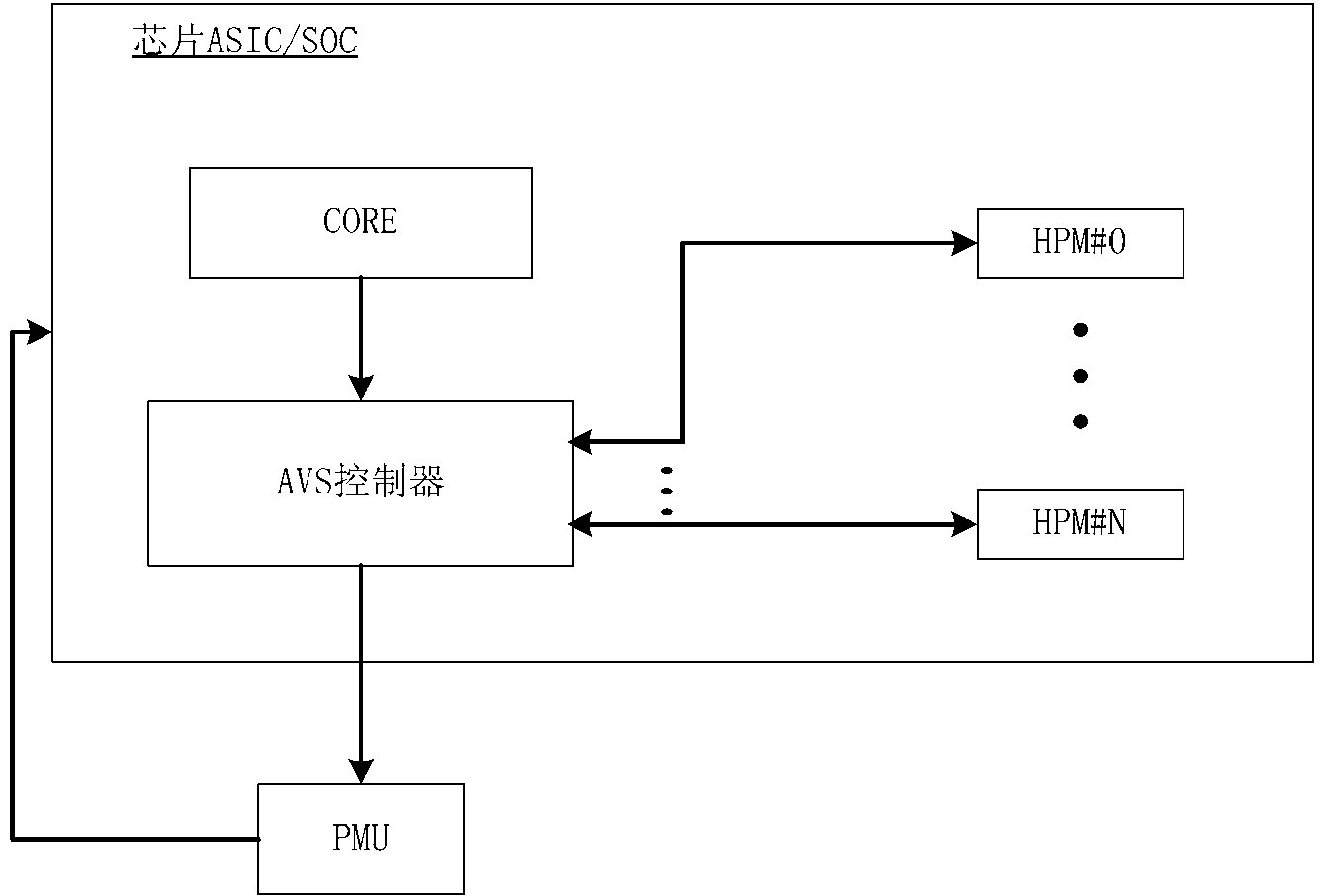

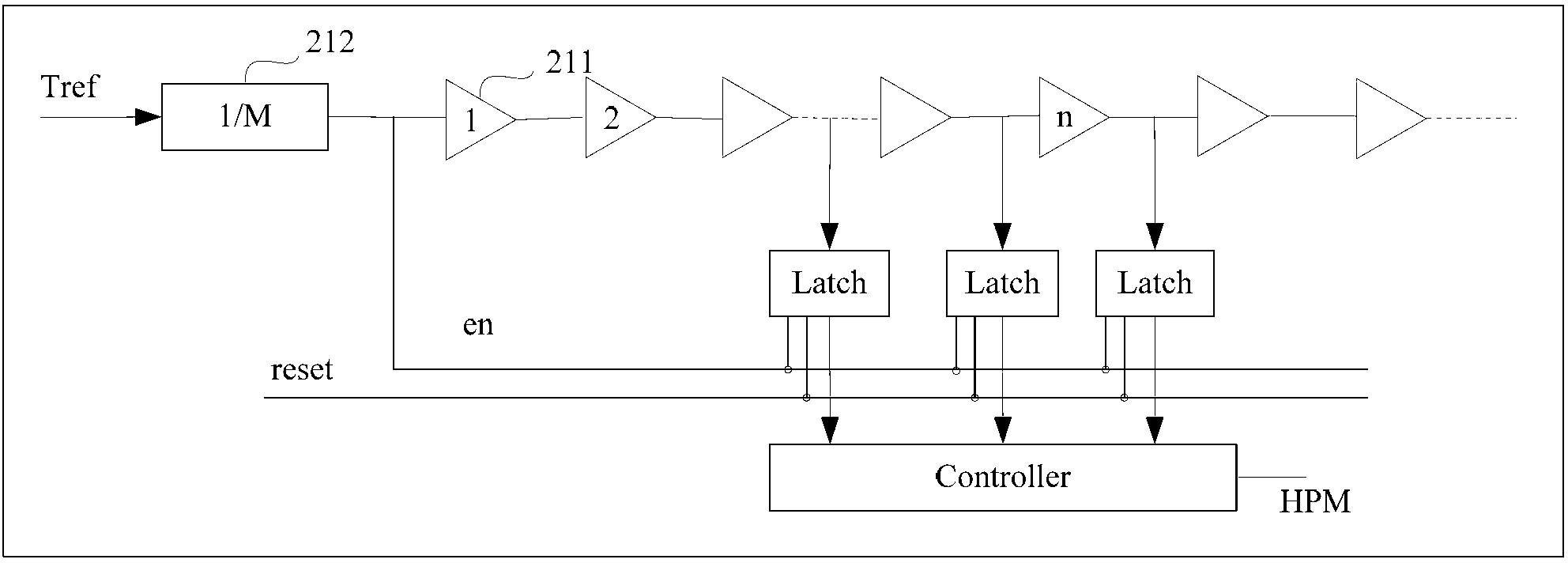

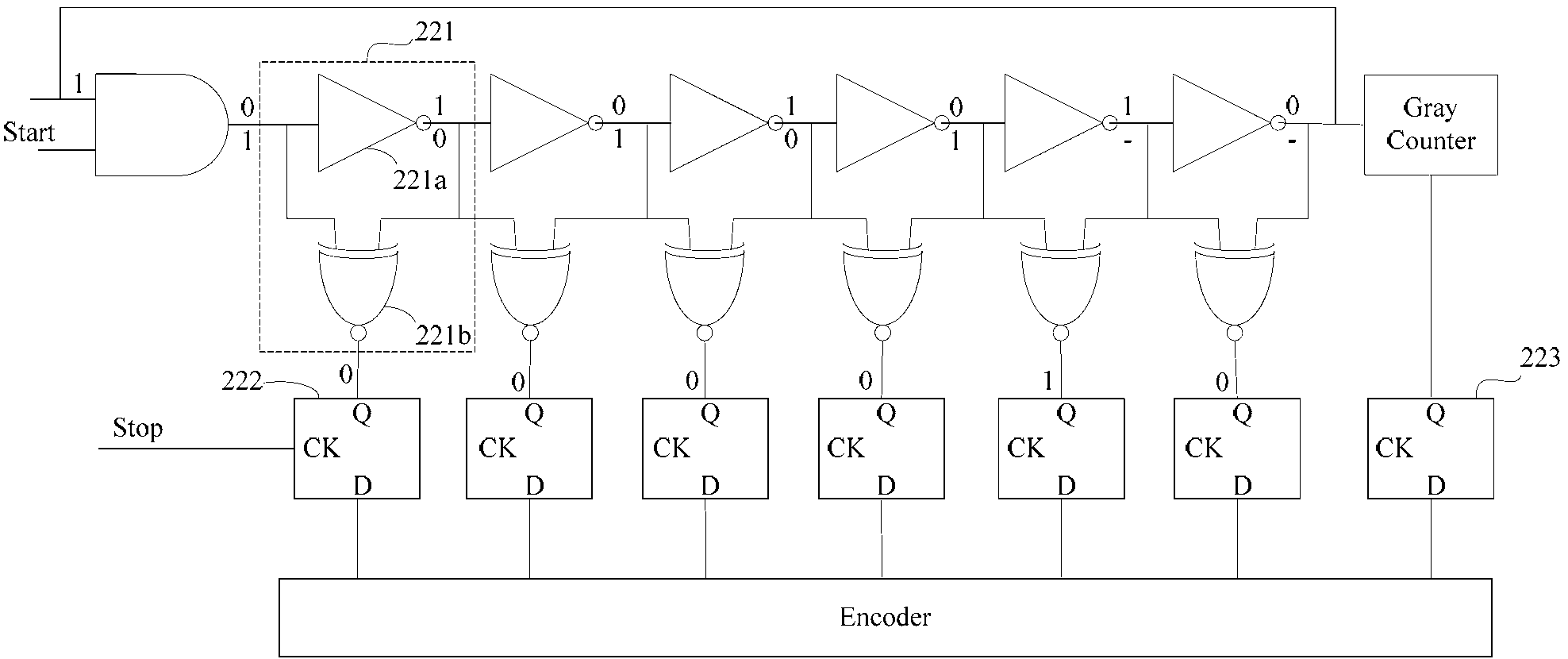

Digital control oscillator and method, system and detector for hardware performance detection

ActiveCN103326714AGuaranteed stabilitySimplify Design RequirementsPulse automatic controlDigital controlled oscillatorOperation mode

The invention discloses a digital control oscillator, a method, system and detector for hardware performance detection and belongs to the technical field of electron. The detector for hardware performance detection comprises the digital control oscillator, a first frequency divider, a second frequency divider, a first counter, a second counter and a control unit. The control unit is connected with the digital control oscillator, so that the digital control oscillator is controlled to output an oscillation clock. Frequency division is conducted on a reference clock and the oscillation clock through the first frequency divider and the second frequency divider respectively so that a first frequency dividing clock and a second frequency dividing clock can be obtained. The first counter and the second counter count for the first frequency dividing clock and the second frequency dividing clock respectively in a preset counting period. A difference obtained through counting is output by the control unit. A parameter signal is determined under a correction mode; under an operation mode, the parameter signal is received and a detection value is output; voltage is reduced appropriately according to the detection value so that the power consumption can be reduced, or voltage is increased appropriately so that the stability of a circuit can be guaranteed.

Owner:日照金慧科技信息咨询有限公司

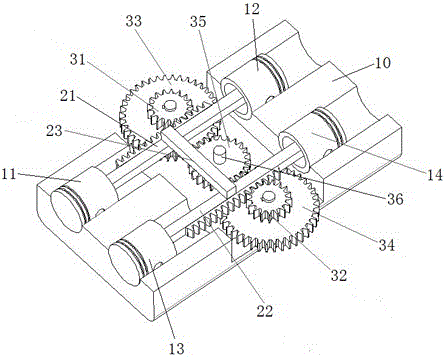

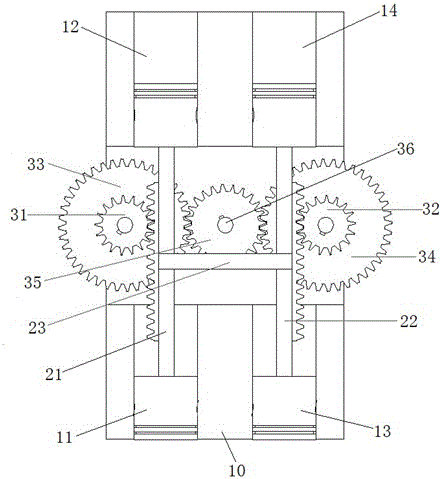

Horizontal opposed engine

The invention discloses a horizontal opposed engine. The horizontal opposed engine comprises four air cylinders arranged horizontally and oppositely, pistons arranged in the air cylinders, a connecting rod assembly and a gear transmission mechanism. The connecting rod assembly comprises a first connecting rod and a second connecting rod. The two ends of the first connecting rod are connected with the first piston and the second piston correspondingly, and the two ends of the second connecting rod are connected with the third piston and the fourth piston correspondingly. The gear transmission mechanism comprises a first ratchet wheel, a second ratchet wheel, a first gear, a second gear and a transmission gear. The first ratchet wheel and the first gear are arranged coaxially. The second ratchet wheel and the second gear are arranged coaxially, and the first ratchet wheel and the second ratchet wheel are same in direction. The transmission gear is arranged between the first gear and the second gear and engaged with the first gear and the second gear. The first connecting rod and the second connecting rod are provided with racks correspondingly. The racks on the connecting rods are engaged with the ratchet wheels. The transmission gear is connected with a power output shaft. Compared with traditional crank-connecting-rod structures, through the adopted connecting rod mechanism, the design requirements of the air cylinders is simplified, and the impact force of high-pressure gas on the pistons is offset to a certain degree.

Owner:ZHEJIANG UNIV

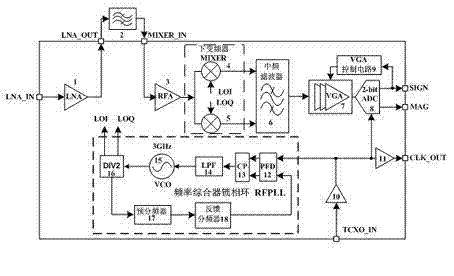

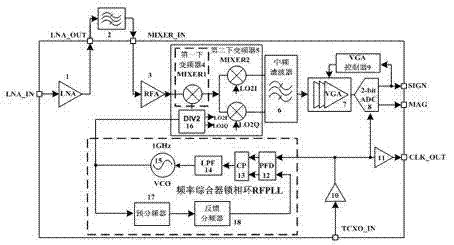

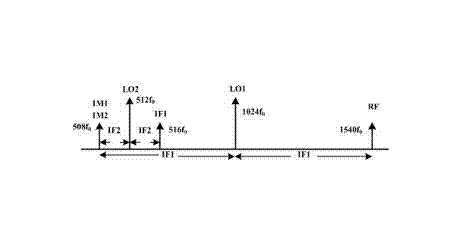

Novel system architecture of navigation radio frequency (RF) receiver with low power consumption

InactiveCN102253397AReduce power consumptionSimplify Design RequirementsSatellite radio beaconingFrequency changerIntermediate frequency

The invention provides novel system architecture of a navigation radio frequency (RF) receiver with low power consumption. The system architecture comprises a first down converter and two orthogonal second down converters and also comprises a divide-by-2 divider of a frequency synthesizer, wherein the first down converter and the two orthogonal second down converters are arranged in a signal channel in sequence and are used for carrying out twice down conversion on the RF signals received by the signal channel; and the divide-by-2 divider is arranged in a same sub-chip together with the first and second down converters, directly outputs the output frequency of a voltage-controlled oscillator to the first down converter and outputs the output frequency of the voltage-controlled oscillator to the second down converters after dividing the output frequency by 2. The system architecture has the following advantages: the system architecture is optimized and improved and the design requirements of a plurality of submodules such as an intermediate frequency (IF) filter, a prescaler and the like for subsequent signal processing are simplified through twice IF conversion, thus using a single submodule with lower power consumption to achieve the aim of reducing the power consumption of the whole navigation chip while realizing the receiving function of the navigation chip towards the RF signals.

Owner:上海迦美信芯通讯技术有限公司

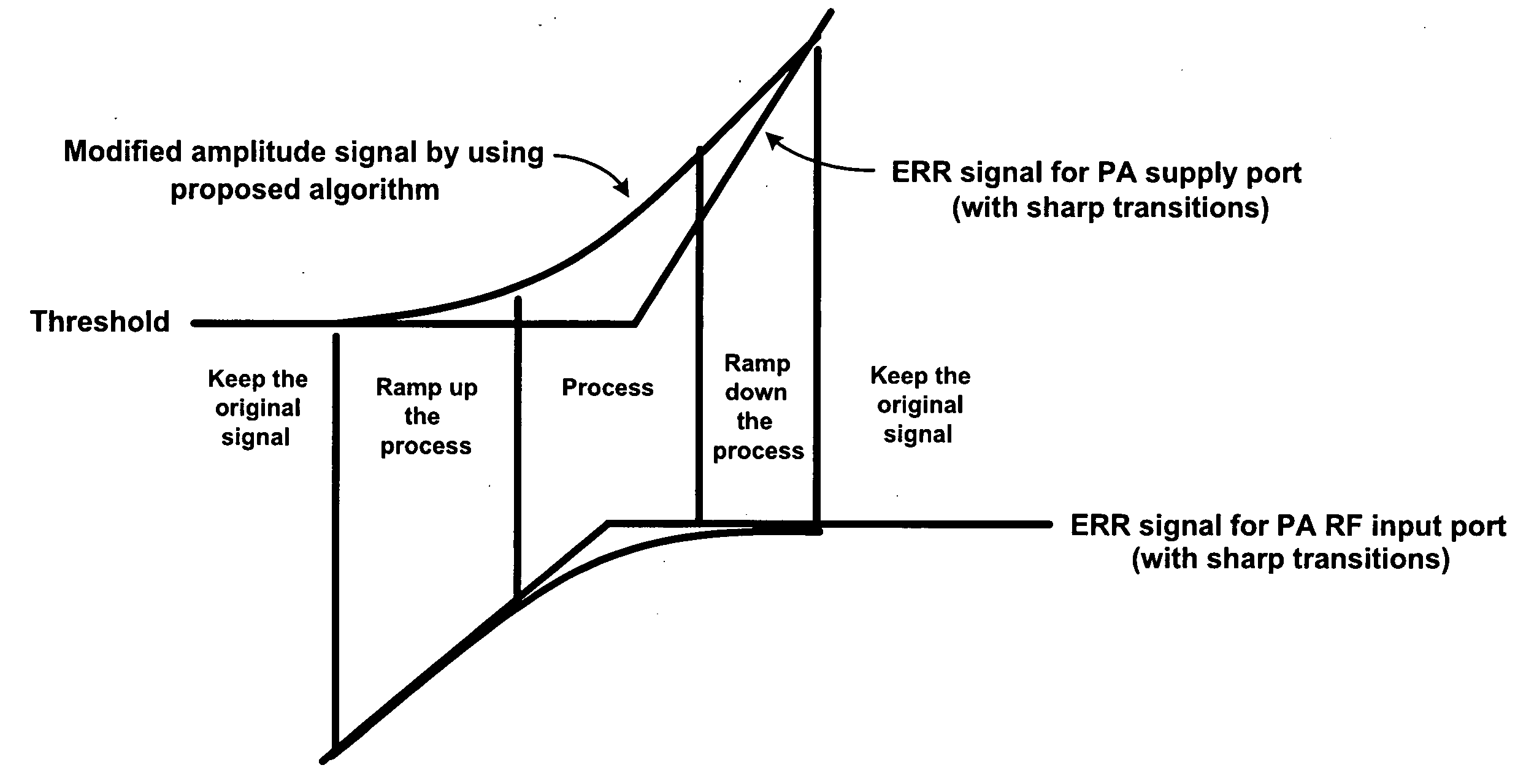

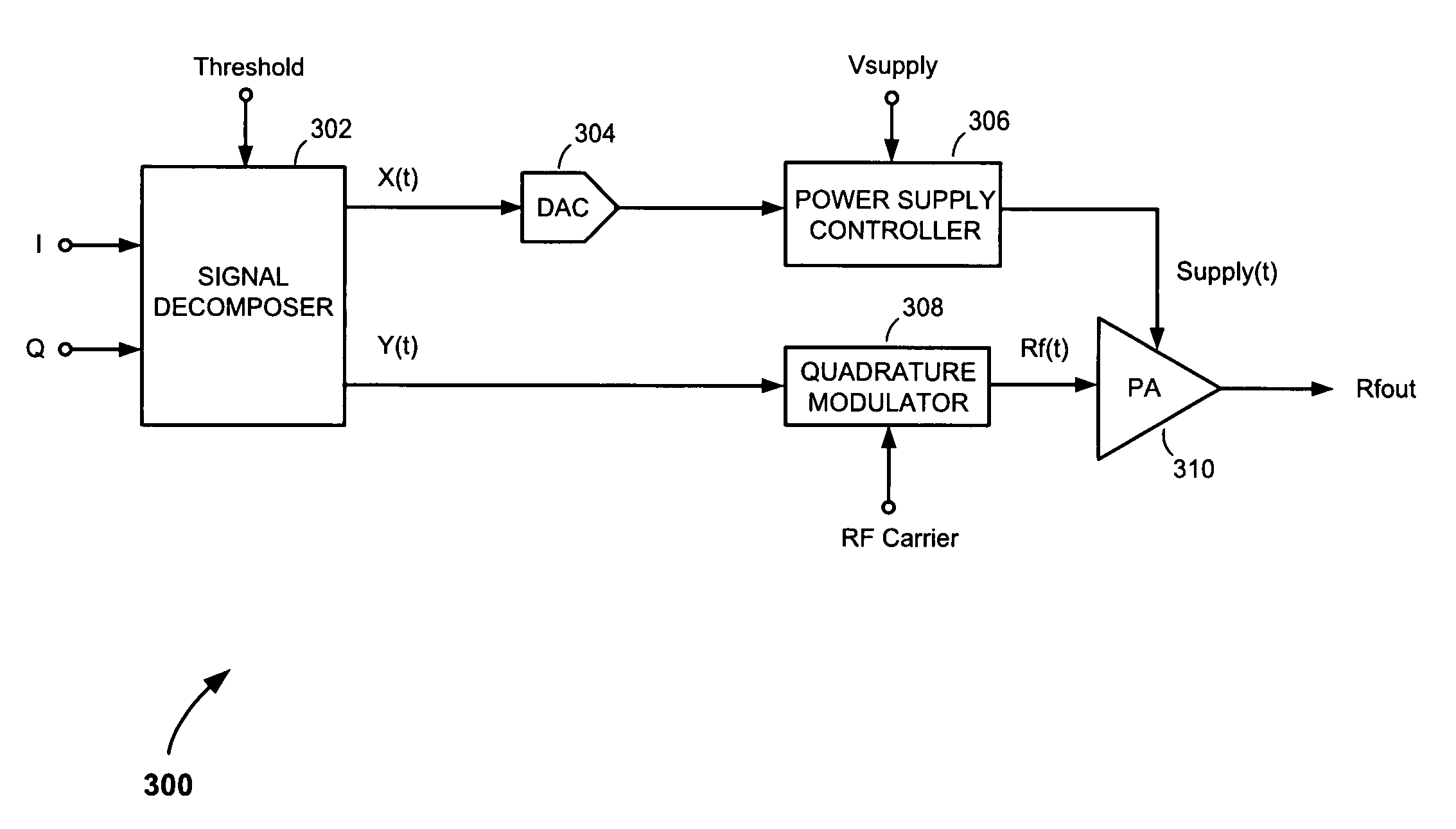

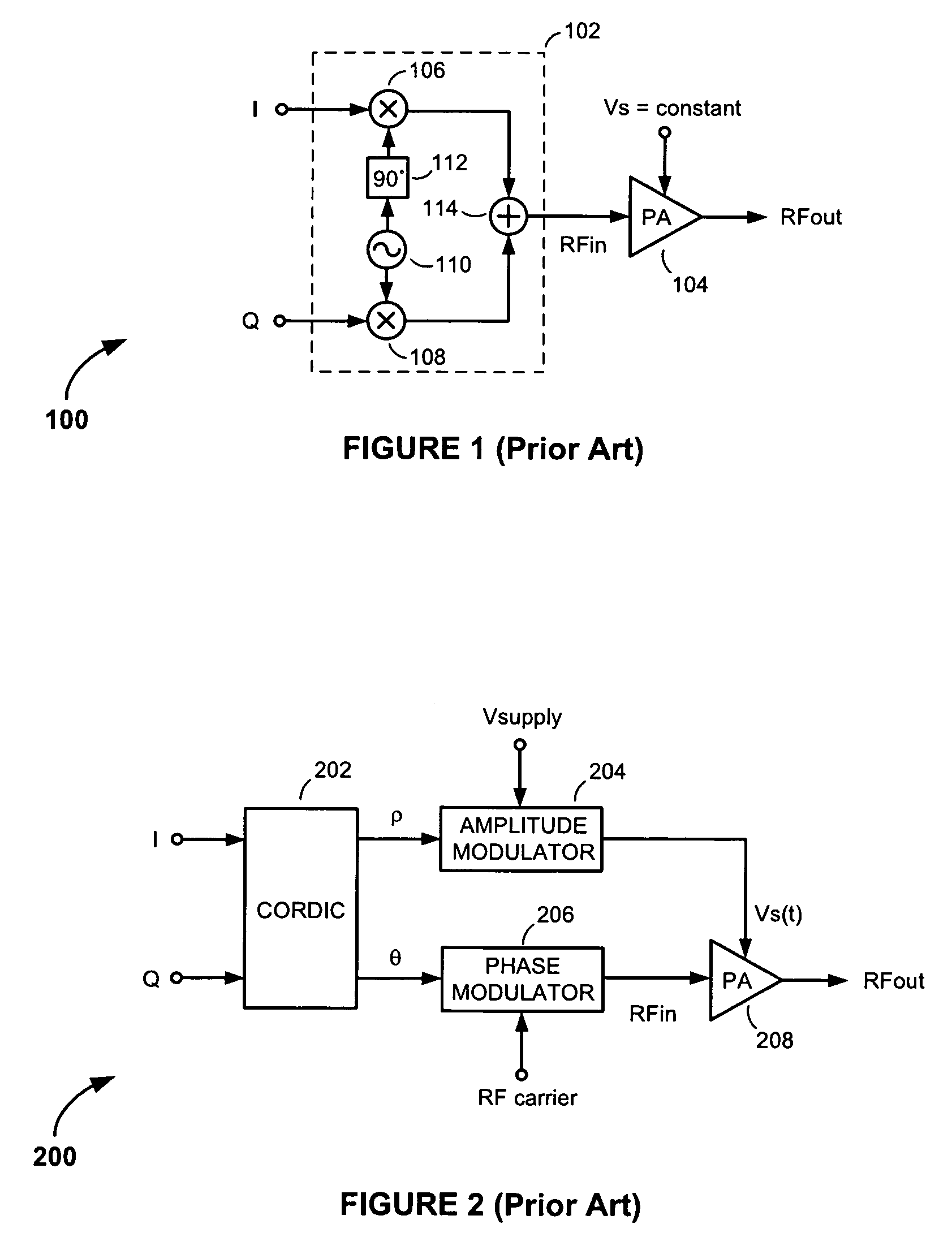

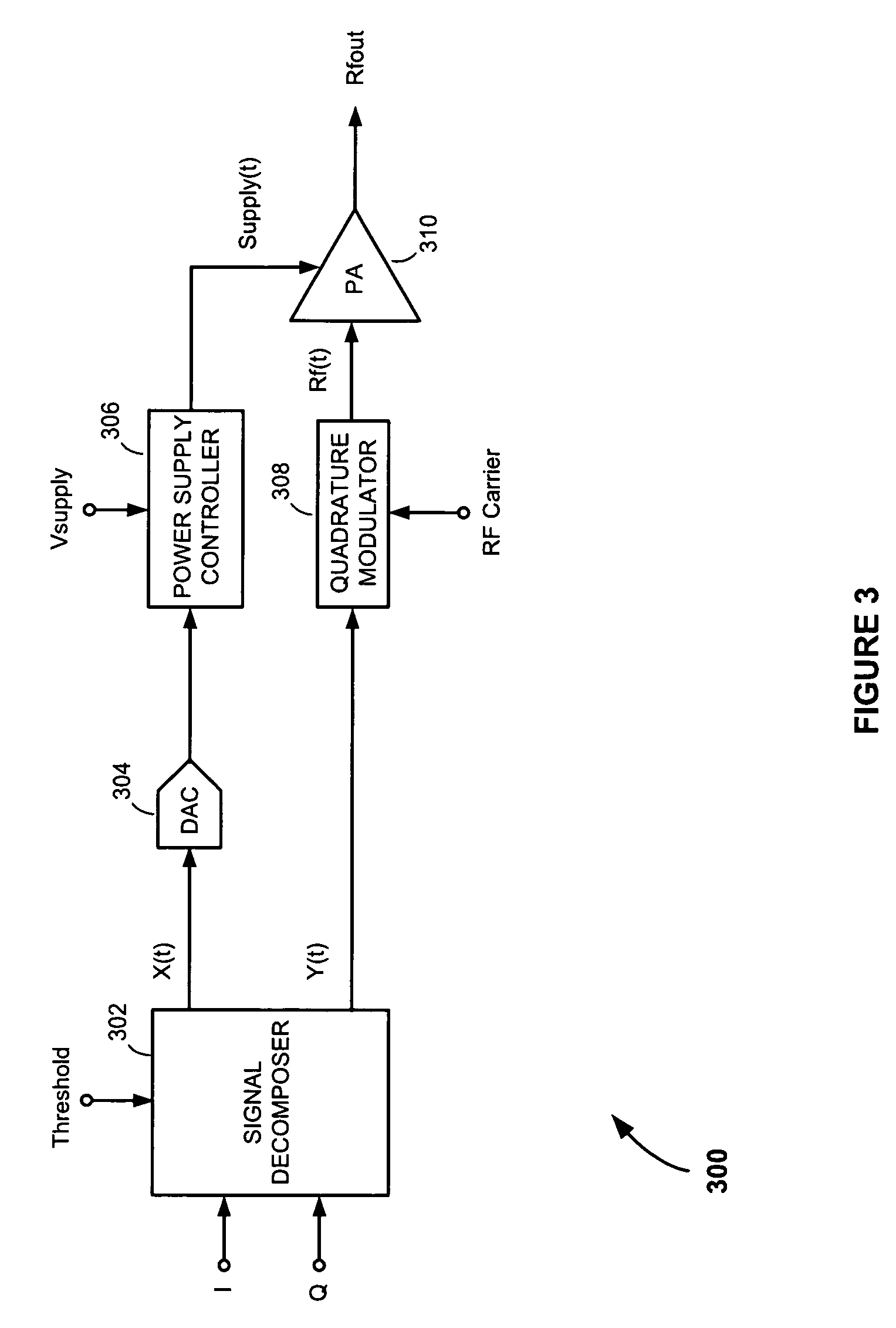

Signal decomposition methods and apparatus for multi-mode transmitters

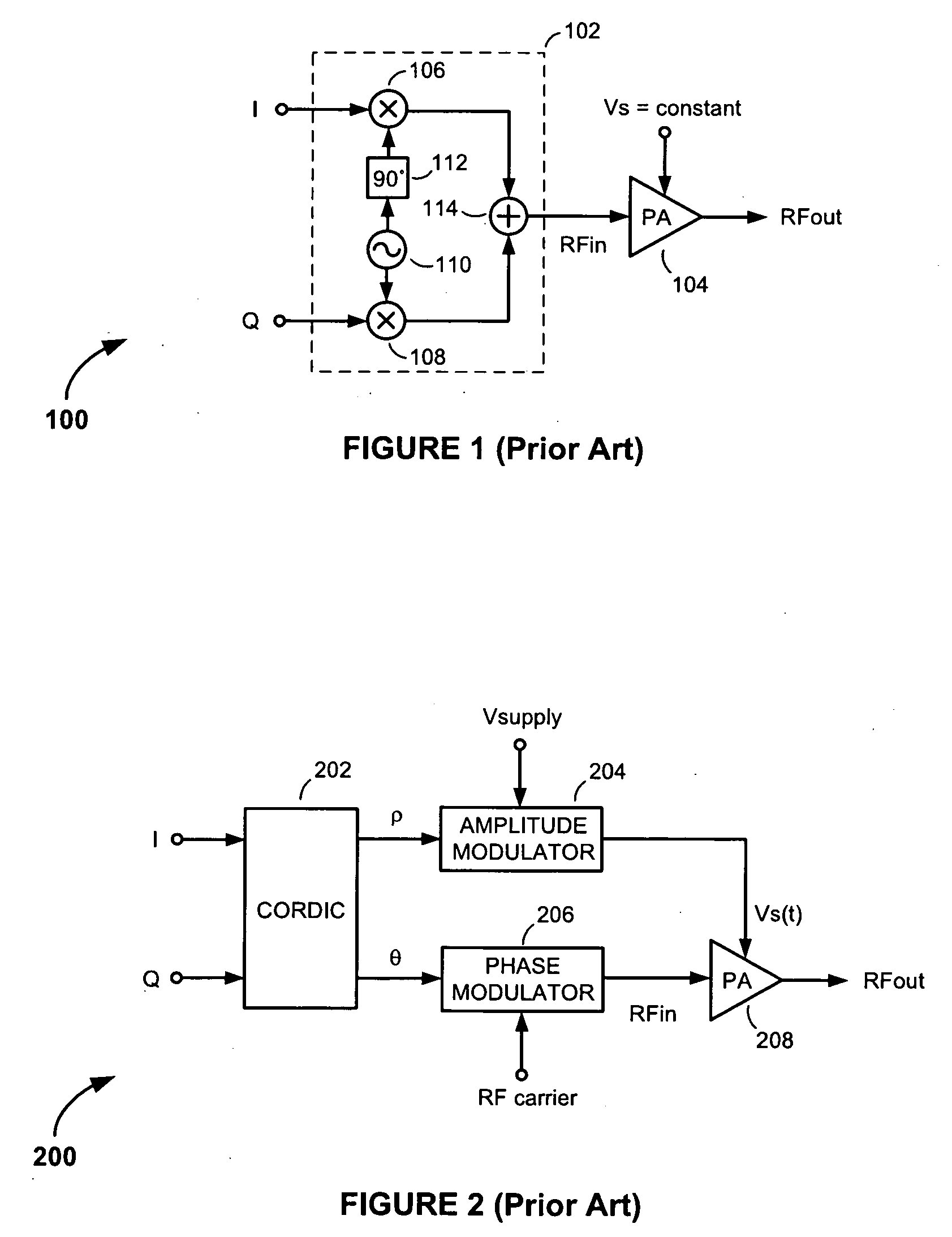

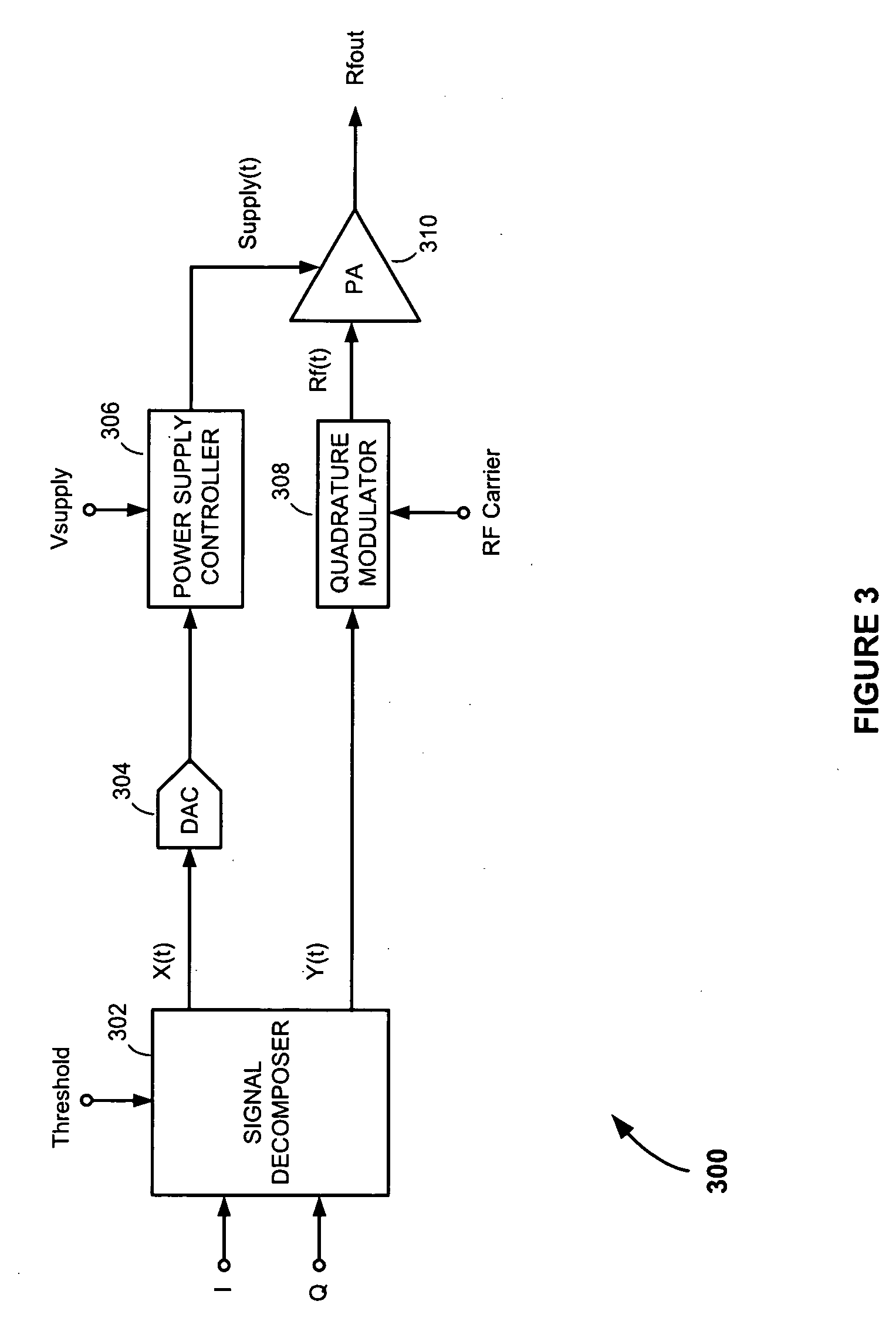

InactiveUS20100015932A1Reduced bandwidthSimplify Design RequirementsResonant long antennasModulation with suppressed carrierDecompositionRectangular coordinates

A multi-mode communications transmitter includes a signal decomposer that converts rectangular-coordinate in-channel and quadrature channel signals into polar-coordinate amplitude and angle component signals and form therefrom first and second modulation signals. The signal decomposition process performed by the signal decomposer combines envelope-reduction and restoration (ERR) with filtering to reduce the bandwidths of the first and second modulation signals compared to the bandwidths of the unmodified amplitude and angle component signals. The reduction in signal bandwidths eases the design requirements of the electrical components needed to process and generate the signals applied to the power supply and radio frequency (RF) input ports of the multi-mode communications transmitter's power amplifier (PA). It also makes the multi-mode communications transmitter more forgiving to gain and delay mismatches between the signals applied to the power supply and RF input ports of the PA, compared to conventional polar modulation transmitters.

Owner:PANASONIC CORP

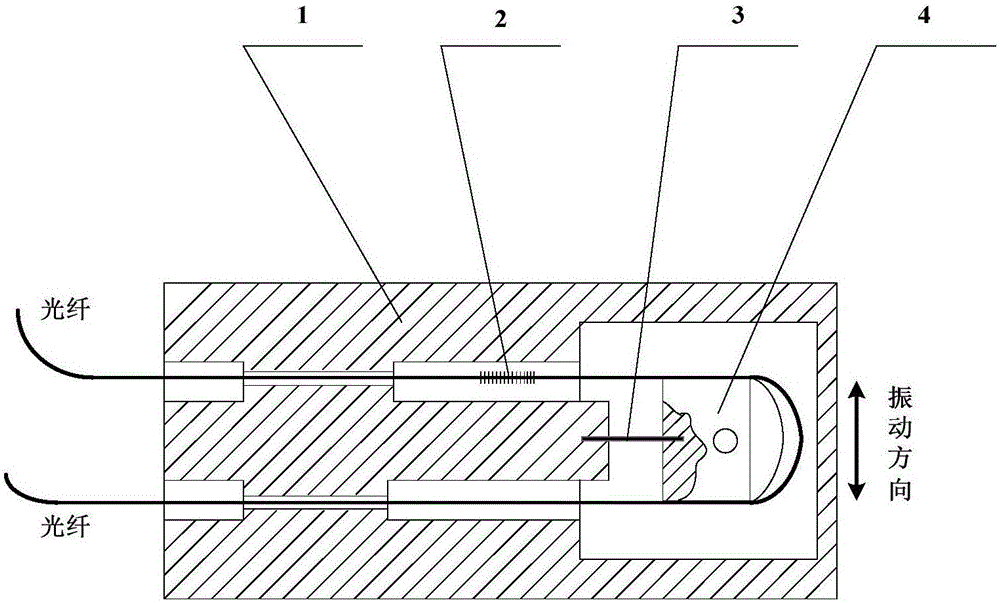

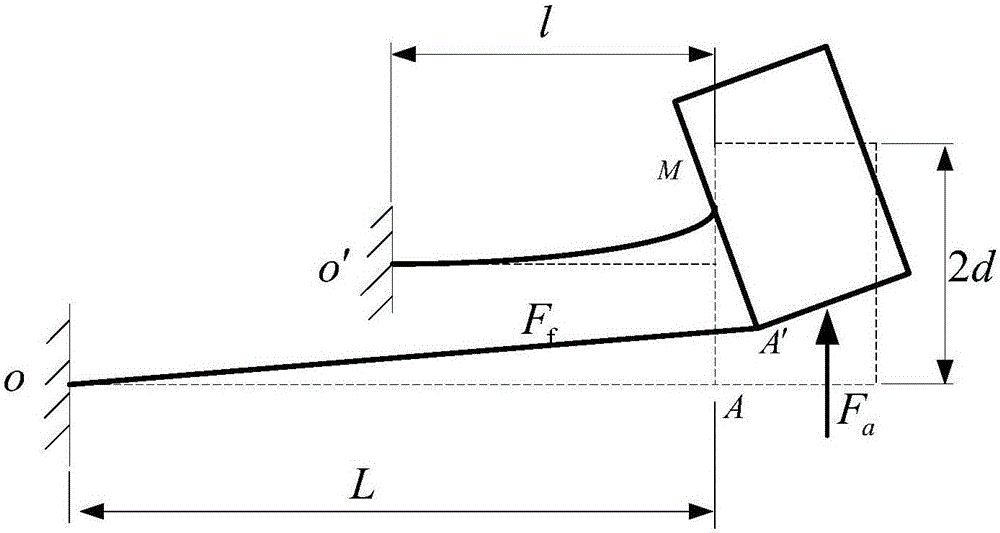

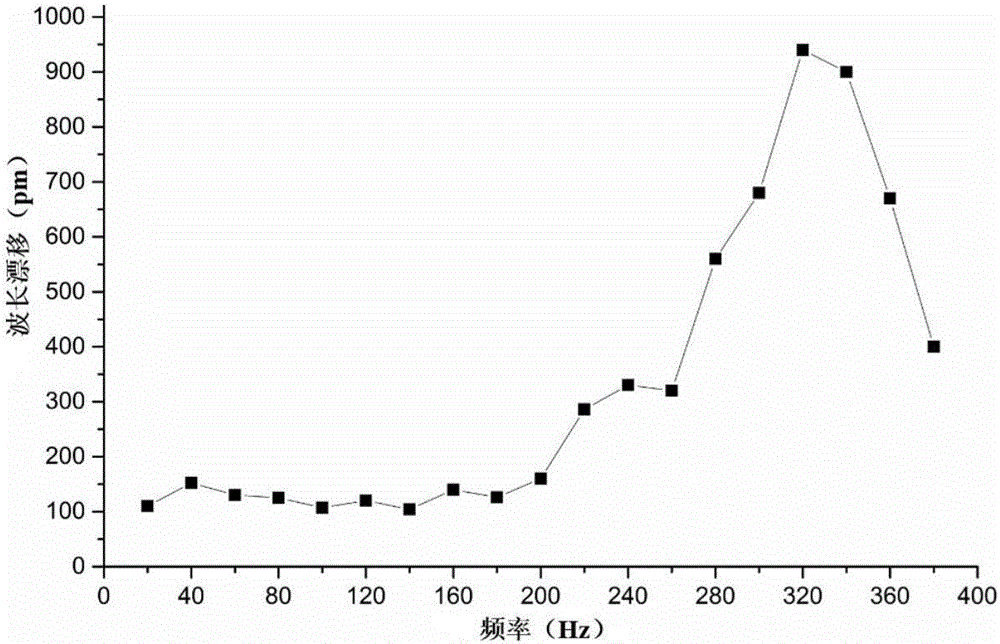

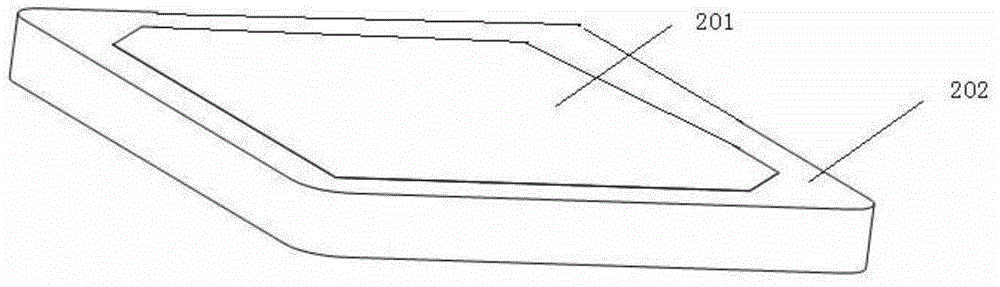

Manufacturing method of cantilever beam fiber grating accelerometer

The present invention provides a manufacturing method of a cantilever beam fiber grating accelerometer. The sensor comprises a substrate, a spring leaf, a quality block, a side cover and a fiber grating. The substrate, the spring leaf and the quality block are assembled through mechanical coordination and laser welding to form a cantilever structure. The fiber grating performs etching on the G.657 fiber, the fiber tension performance is improved through adoption of macromolecule ultrathin coating, and the epoxy resin dispensing is employed to fix the positions between the fiber grating and substrate and the quality block to assemble a fiber grating acceleration sensor. A balance weight hole is processed on the quality block in advance, the assembled sensor is calibrated, and the dispensing or machining is performed on the balance weight hole to flexibly regulate the sensitivity and the resonant frequency point of the sensor to optimize the performance index of the acceleration sensor. The manufacturing method of the cantilever beam fiber grating accelerometer simplifies the design and processing requirement of the acceleration sensor, simple in operation method and high in practicality, and the made sensor is high in sensitivity, small in insertion loss and excellent in performace.

Owner:湖北三峡物联网知识产权运营有限公司

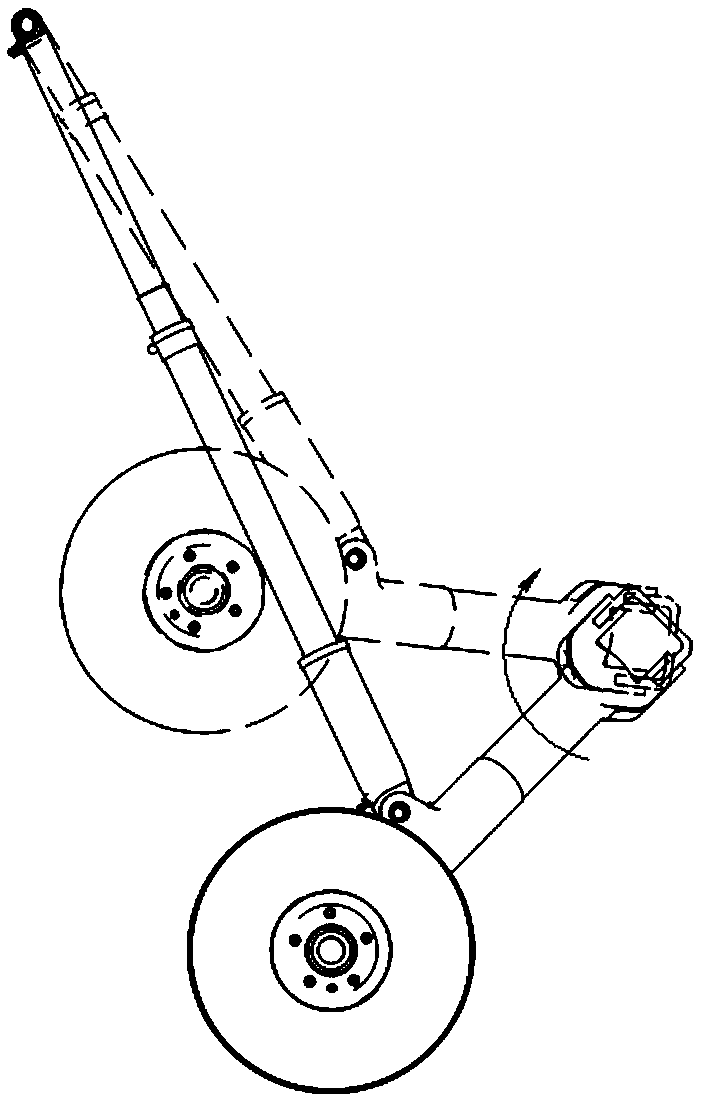

Rocker arm landing gear

InactiveCN104210653ASimplify Design RequirementsCompact structureWheel arrangementsAviationRocker arm

The invention discloses a rocker arm landing gear, belonging to the technical field of landing gears of aviation helicopters and airplanes. The rocker arm landing gear is characterized in that a rocker arm (1) is hinged with a circular tube joint (5) through a forked connector; the folding process is resolved into movement of the rocker arm in two directions. The movement in one direction is that the rocker arm and the circular tube joint are driven to rotate around a horizontal pipe by contraction of a buffer with an active stretching function, so that the landing gear contracts upwards, and the movement on the other direction is that the rocker arm is driven to rotate around the circular tube joint by movement of a contracting and releasing mechanism, so that the landing gear contract inwards, wherein the releasing process and the contracting process are opposite. The rocker landing gear is capable of achieving a contracting and releasing design of the rocker landing gear with a large outer splayed structure size within a small contracting and releasing space, and thus the rocker landing gear is compact in structure, low in demand on contracting and releasing space, and high in contracting and releasing efficiency, due to the design of the circular tube joint, rotation of the rocker arm around two directions is realized, and weight control is facilitated without the horizontal pipe.

Owner:CHINA HELICOPTER RES & DEV INST

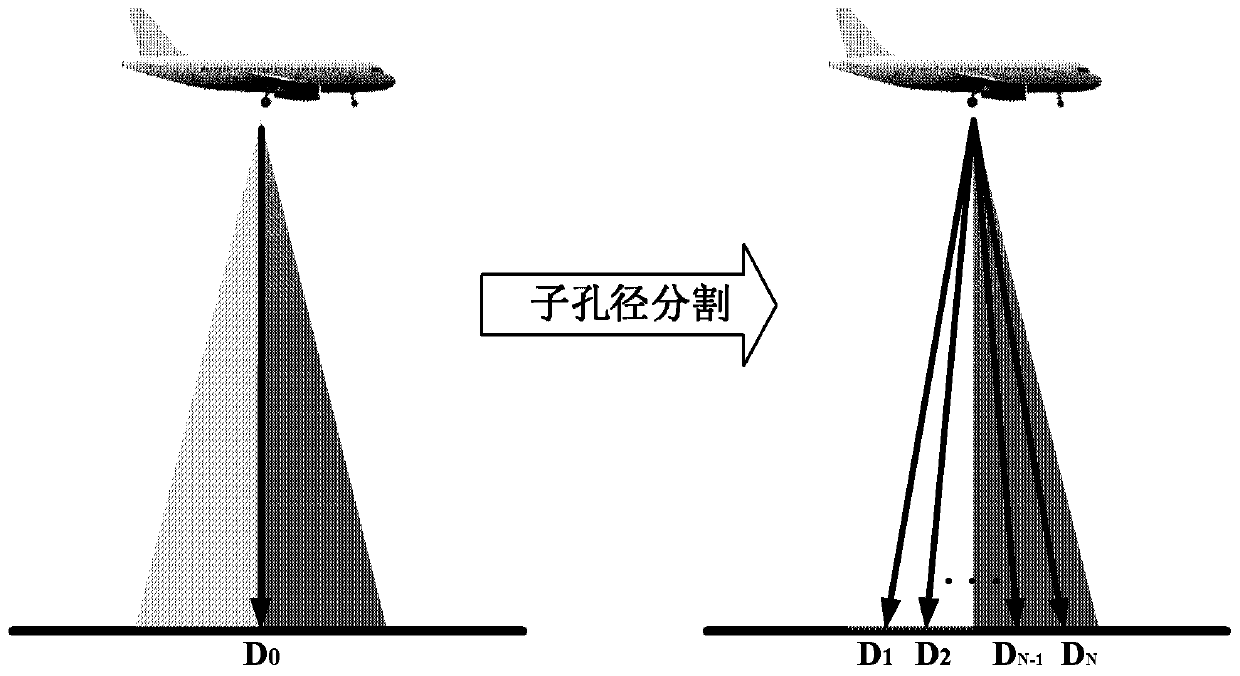

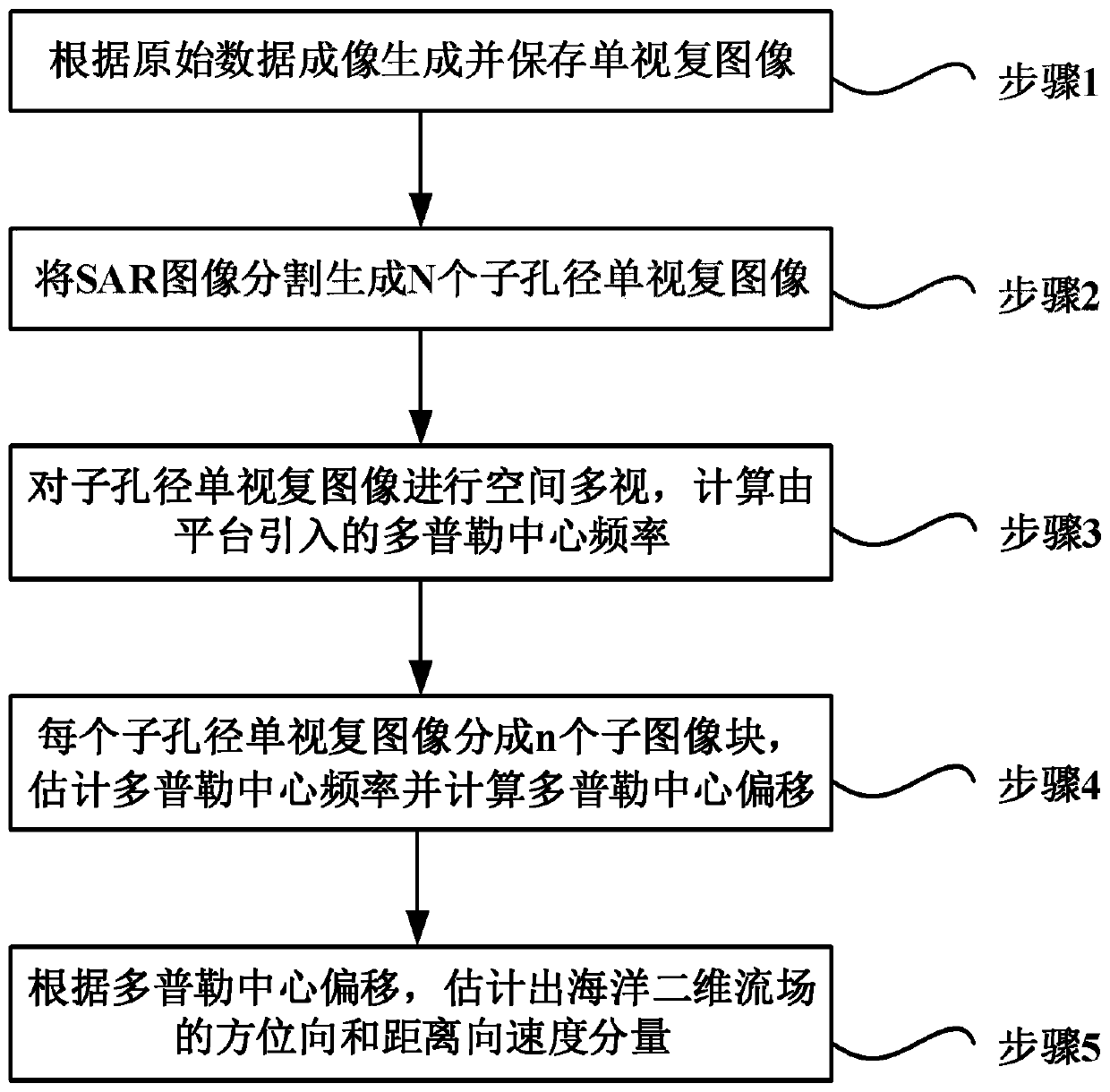

Single-channel SAR two-dimensional flow field inversion method and system based on Doppler center migration

ActiveCN110554377AIncrease profitSimplify Design RequirementsRadio wave reradiation/reflectionOriginal dataImage segmentation

The invention discloses a single-channel SAR two-dimensional flow field inversion method and system based on Doppler center migration. The method comprises the following steps: enabling a single-channel SAR to receive original data of a to-be-measured area and carry out imaging to generate a single-view complex image; segmenting the single-view complex image into N sub-aperture single-view complex images; performing spatial multi-view processing on each sub-aperture single-view complex image to obtain sub-aperture complex images; dividing each sub-aperture complex image into n sub-image blocks; and according to the Doppler center offset of each sub-image block, sequentially calculating the azimuth and distance velocity components of the two-dimensional flow field of each sub-image block region to obtain the two-dimensional flow field with the azimuth and distance velocity components in the to-be-measured region. According to the Doppler center migration-based single-channel SAR two-dimensional flow field inversion method and system provided by the invention, the influence of different motion components of the sea surface on Doppler center migration is fully considered, and the keyproblem that an existing single-channel SAR Doppler center migration method can only invert an ocean one-dimensional flow field is solved.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

Signal decomposition methods and apparatus for multi-mode transmitters

InactiveUS8489046B2Reduced bandwidthSimplify Design RequirementsResonant long antennasModulation with suppressed carrierRectangular coordinatesEngineering

A multi-mode communications transmitter includes a signal decomposer that converts rectangular-coordinate in-channel and quadrature channel signals into polar-coordinate amplitude and angle component signals and form therefrom first and second modulation signals. The signal decomposition process performed by the signal decomposer combines envelope-reduction and restoration (ERR) with filtering to reduce the bandwidths of the first and second modulation signals compared to the bandwidths of the unmodified amplitude and angle component signals. The reduction in signal bandwidths eases the design requirements of the electrical components needed to process and generate the signals applied to the power supply and radio frequency (RF) input ports of the multi-mode communications transmitter's power amplifier (PA). It also makes the multi-mode communications transmitter more forgiving to gain and delay mismatches between the signals applied to the power supply and RF input ports of the PA, compared to conventional polar modulation transmitters.

Owner:PANASONIC CORP

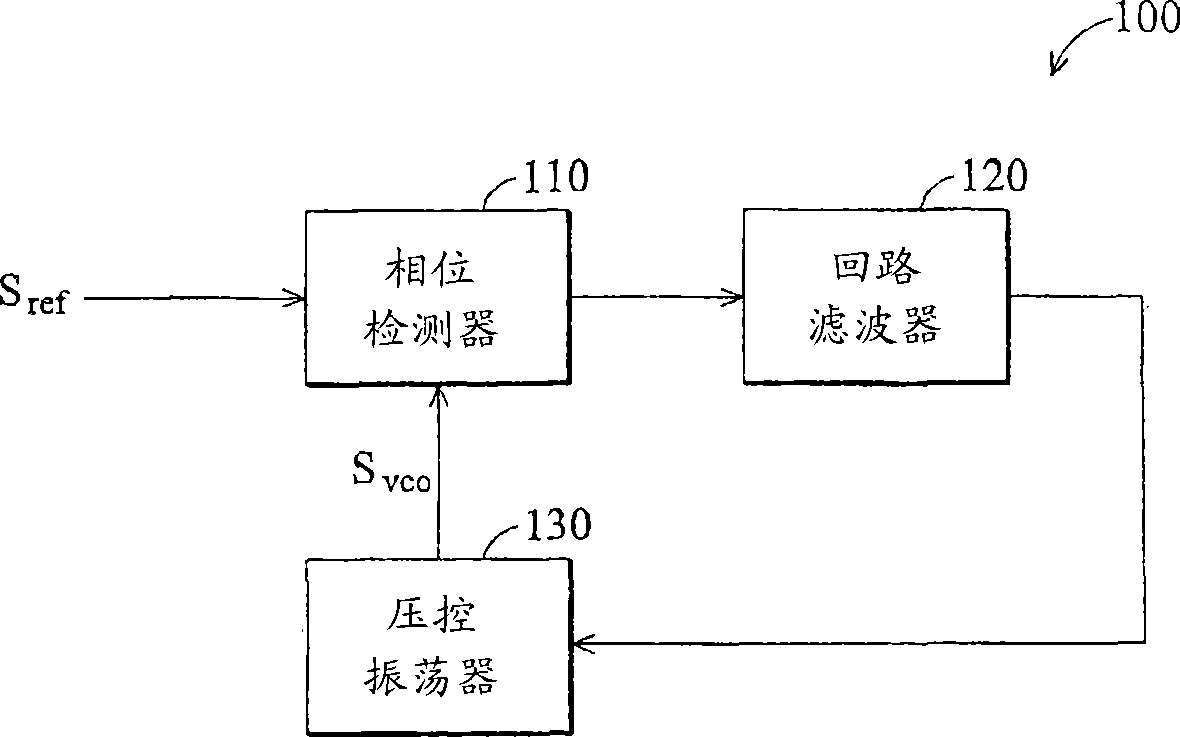

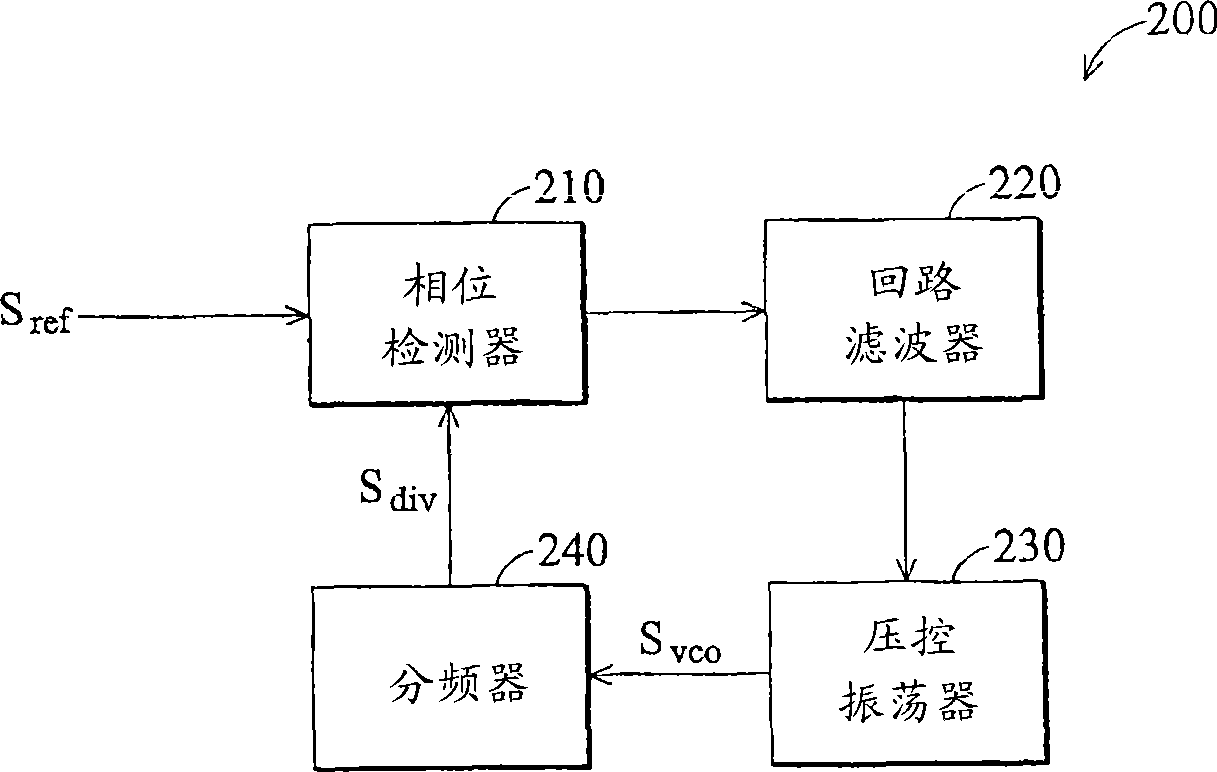

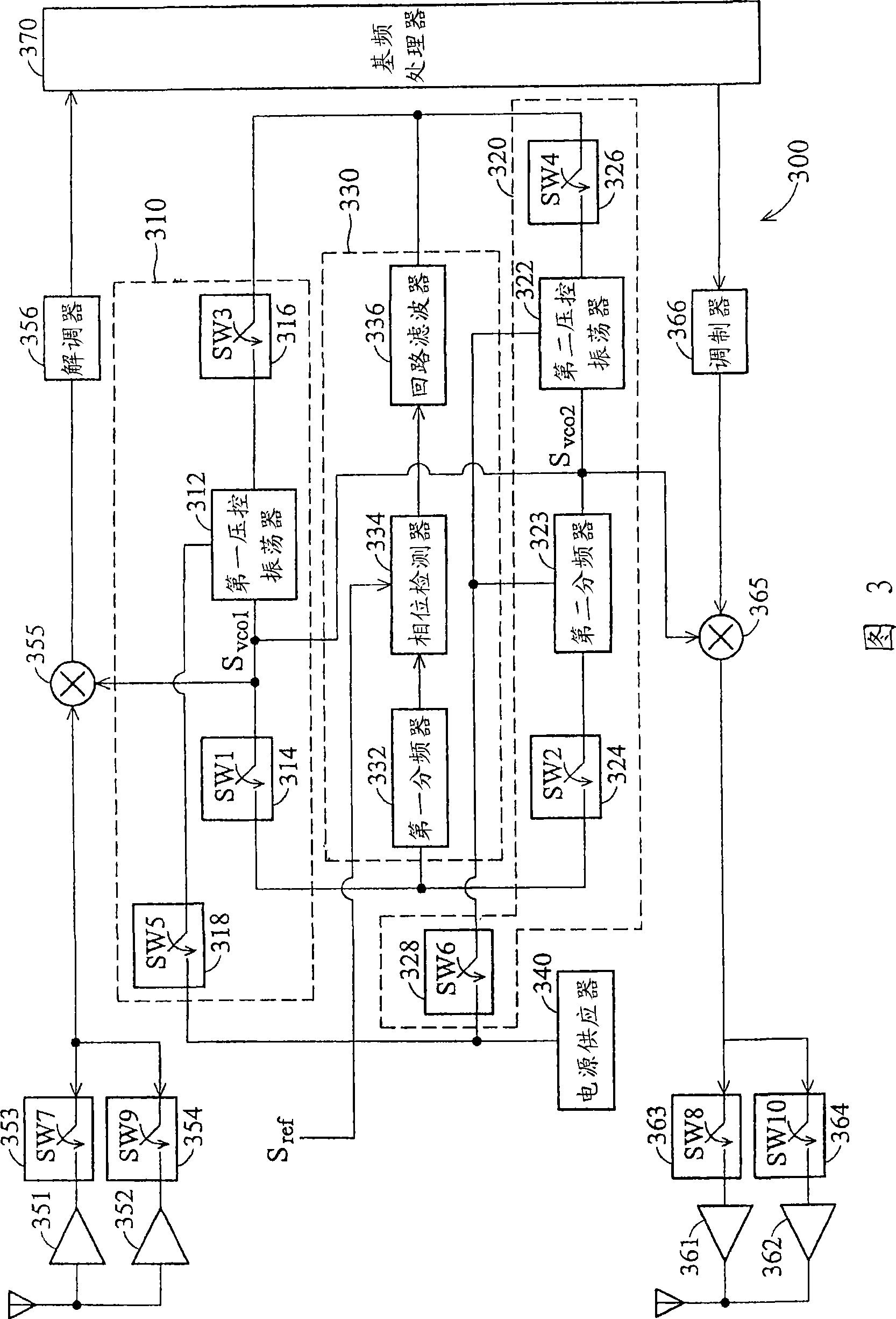

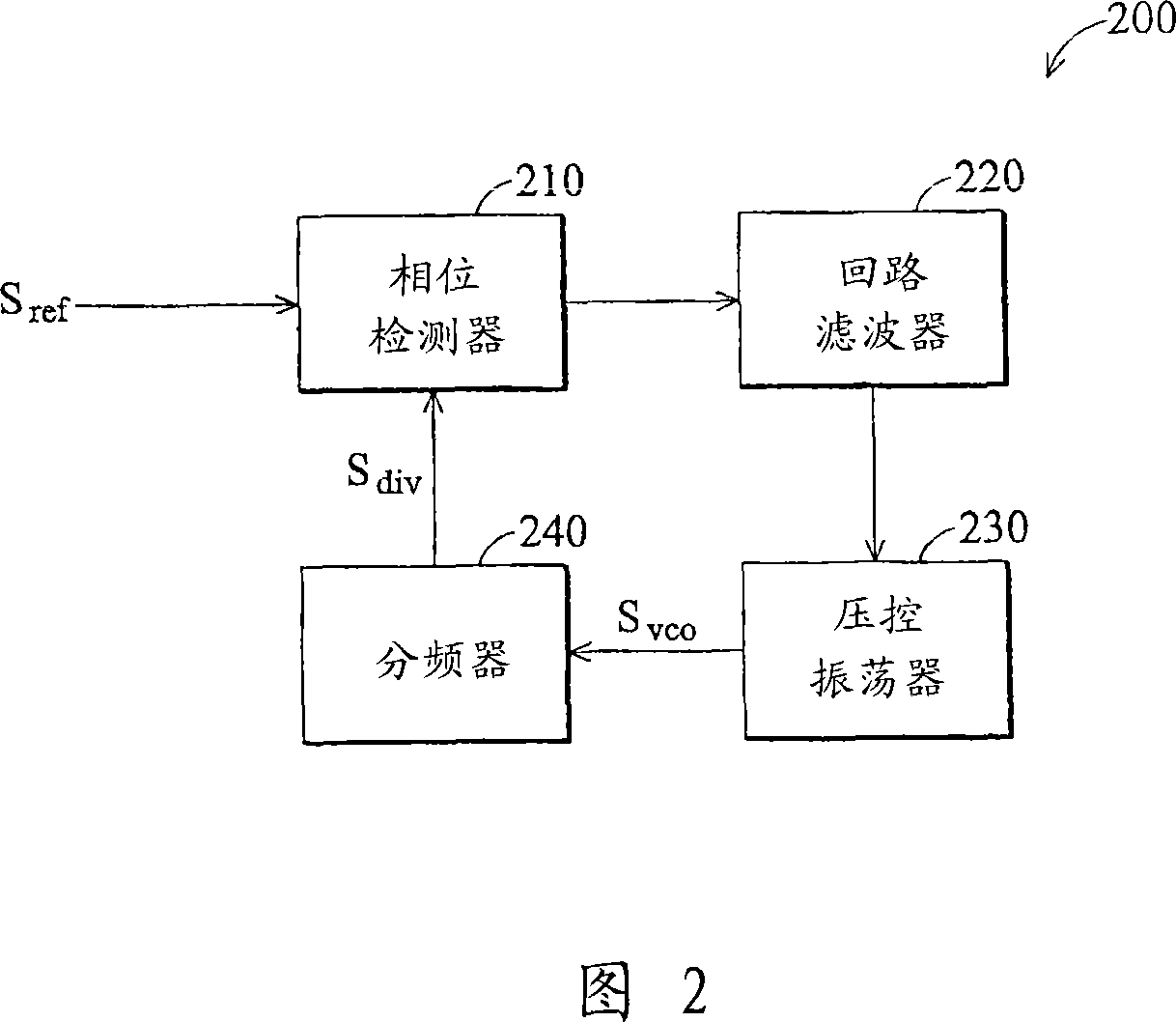

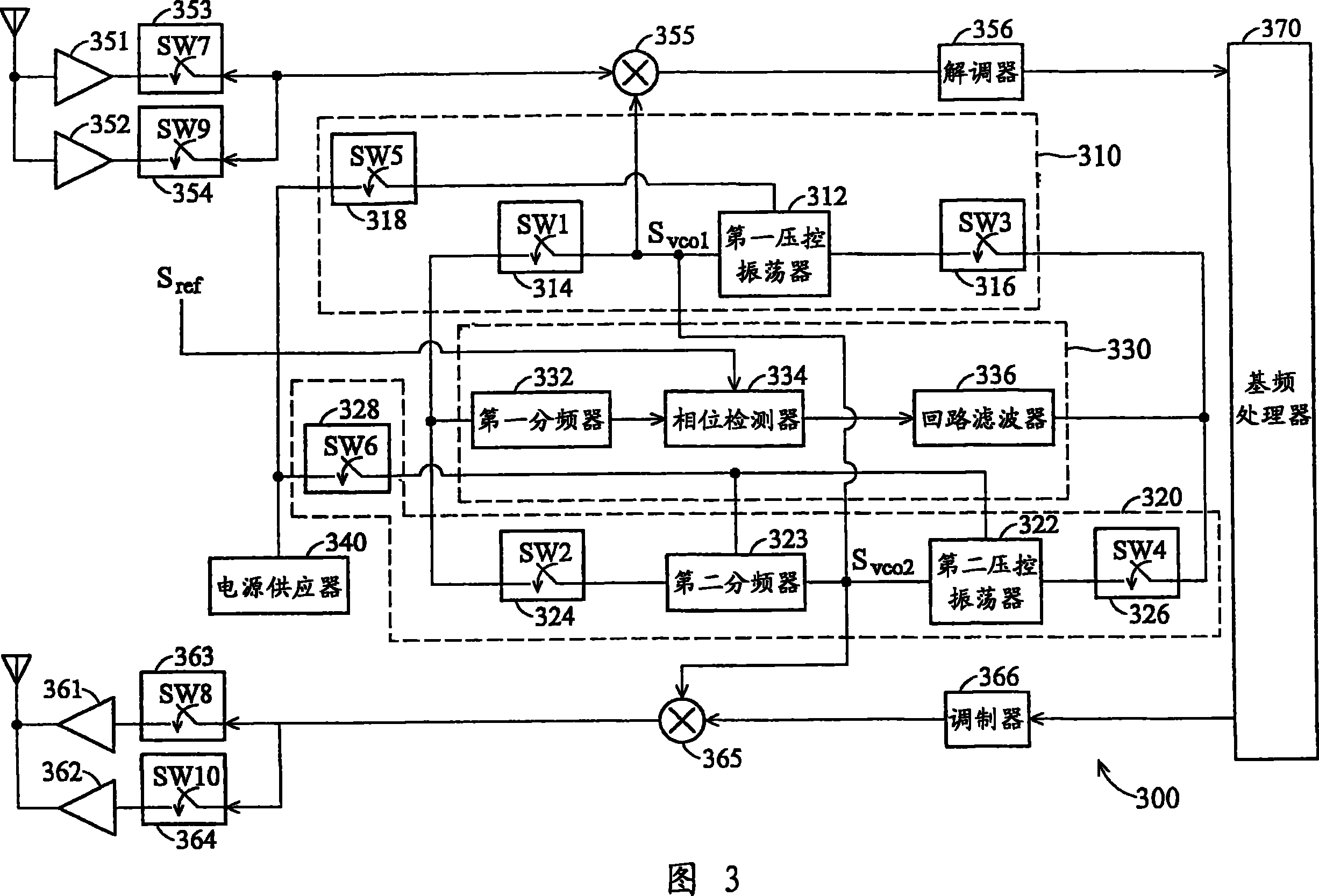

Multi-frequency band electronic device and multi-frequency band signal processing method

ActiveCN101431333ASimplify Design RequirementsReduce complexityPulse automatic controlFrequency synthesizerSwitching signal

The invention provides a multiband electronic device and a multiband signal processing method. The multiband electronic device comprises a first circuit part, a second circuit part and a third circuit part. According to a switching signal, the first circuit and the third circuit selectively form a first phase-locked loop frequency synthesizer, and at the same time the second circuit and the third circuit do not form a phase-locked loop, and the output range of the first phase-locked loop frequency synthesizer is in a first frequency band; or according to the switching signal, the second circuit and the third circuit selectively form a second phase-locked loop frequency synthesizer, and at the same time the first phase-locked loop frequency synthesizer forms a broken circuit, and the output range of the second phase-locked loop frequency synthesizer is in a second frequency band; and the first frequency band and the second frequency band are not completely overlapped.

Owner:RICHWAVE TECH CORP

Multi-frequency band electronic device and multi-frequency band signal processing method

ActiveCN101431333BSimplify Design RequirementsReduce complexityPulse automatic controlSwitching signalFrequency synthesizer

The invention provides a multiband electronic device and a multiband signal processing method. The multiband electronic device comprises a first circuit part, a second circuit part and a third circuit part. According to a switching signal, the first circuit and the third circuit selectively form a first phase-locked loop frequency synthesizer, and at the same time the second circuit and the thirdcircuit do not form a phase-locked loop, and the output range of the first phase-locked loop frequency synthesizer is in a first frequency band; or according to the switching signal, the second circuit and the third circuit selectively form a second phase-locked loop frequency synthesizer, and at the same time the first phase-locked loop frequency synthesizer forms a broken circuit, and the output range of the second phase-locked loop frequency synthesizer is in a second frequency band; and the first frequency band and the second frequency band are not completely overlapped.

Owner:RICHWAVE TECH CORP

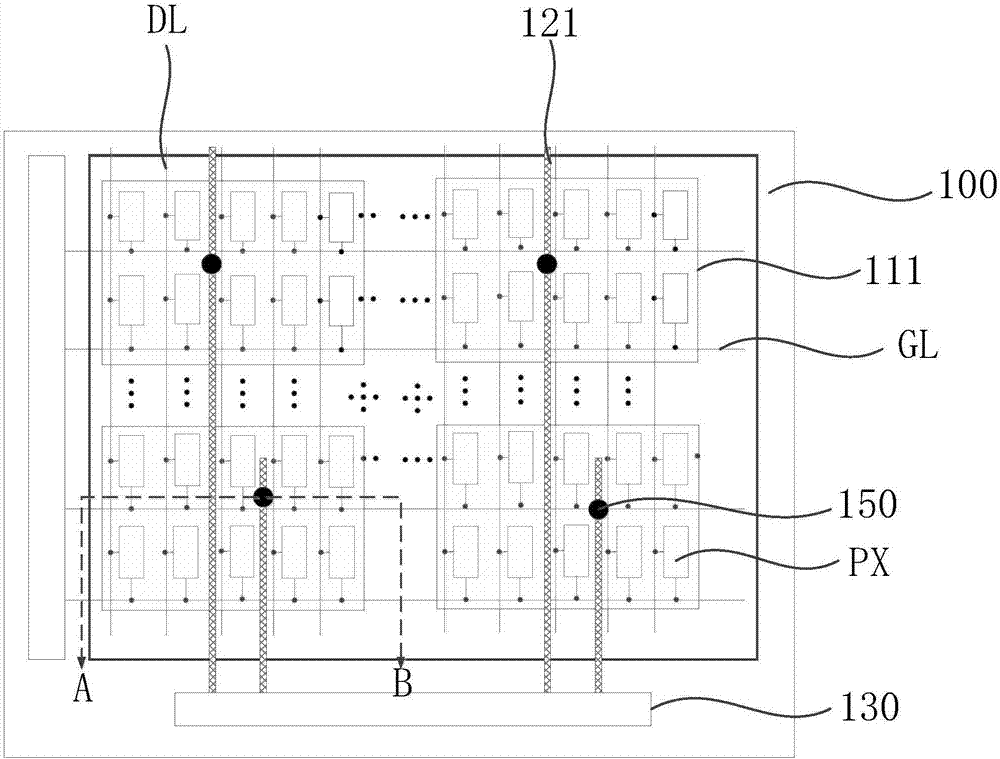

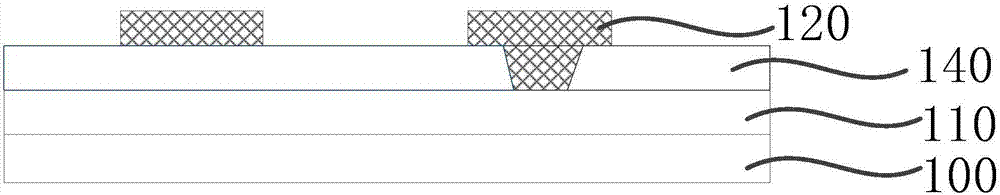

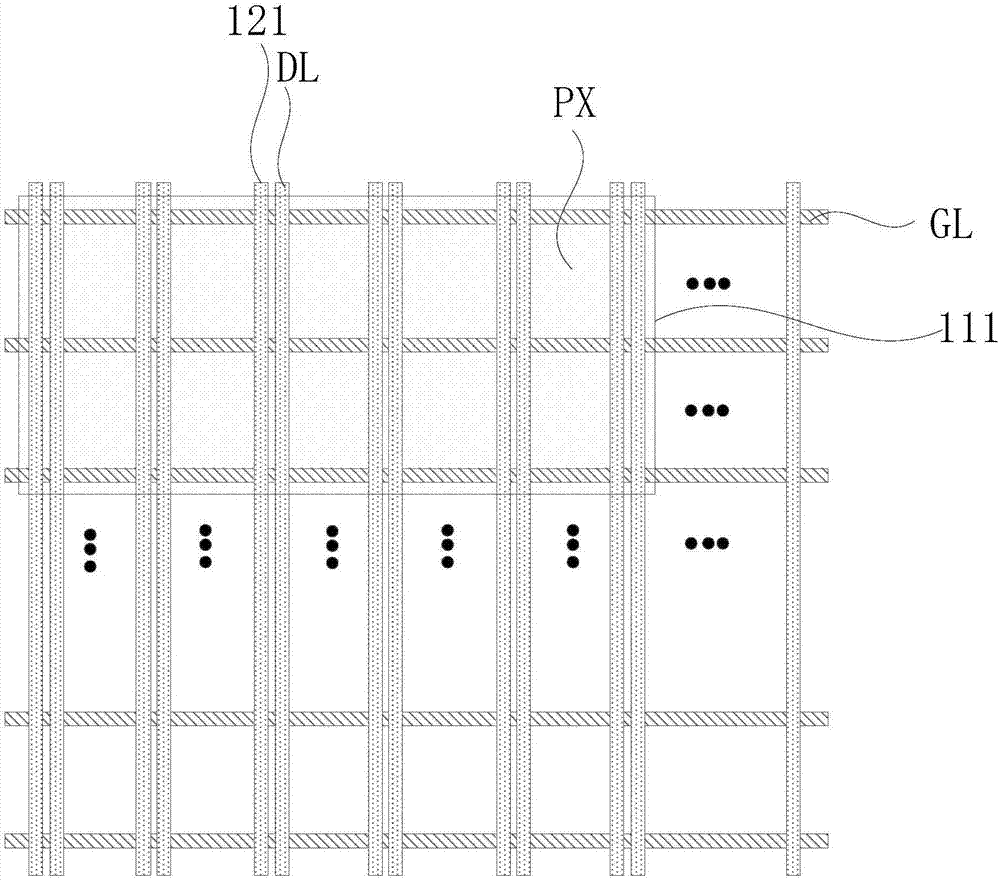

Touch display panel

ActiveCN107168582AGood displayPrevent display of muraNon-linear opticsInput/output processes for data processingElectricitySignal lines

The invention provides a touch display panel, comprising a first substrate, a plurality of pixel units arranged on the first substrate, the pixel units being arranged in an array manner, a touch electrode layer arranged on the first substrate, and an insulating layer between the touch electrode layer and a touch signal line layer. The touch electrode layer comprises a plurality of touch electrodes. The touch electrodes are arranged in an array manner and are insulated to each other. The insulating layer is provided with a plurality of via holes. The touch electrode and the touch signal line realize electric connection through the via holes. Value range of density of the via holes is smaller than or equal to 0.1. Definition of density of the via hole is ratio of number of via holes covered by a touch electrode to number of pixel units covered by a touch electrode. Through limiting density of the via hole to be smaller than or equal to 0.1, good display effect can be obtained, preventing display mura generated by visible via holes. Arranging methods of the via holes are not limited in uniform distribution in the prior art, so that process and design requirements of the touch display panel are greatly simplified.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

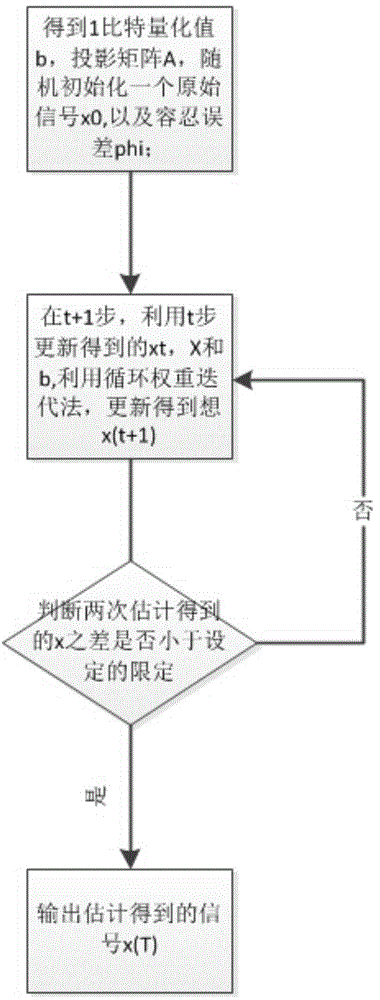

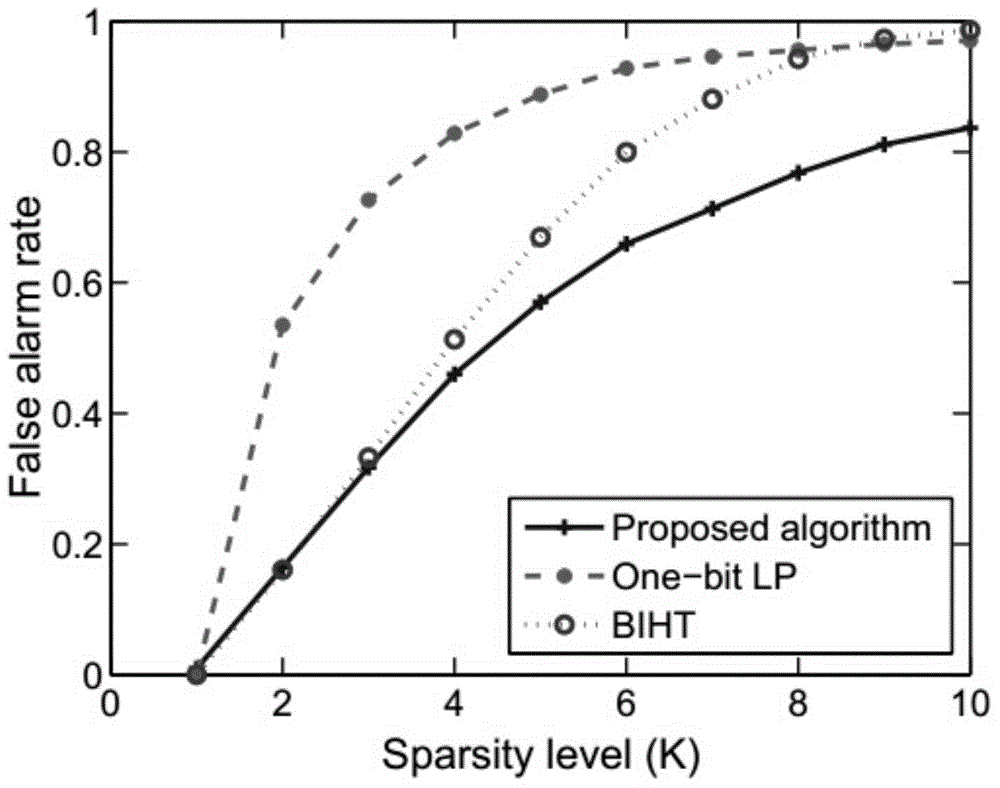

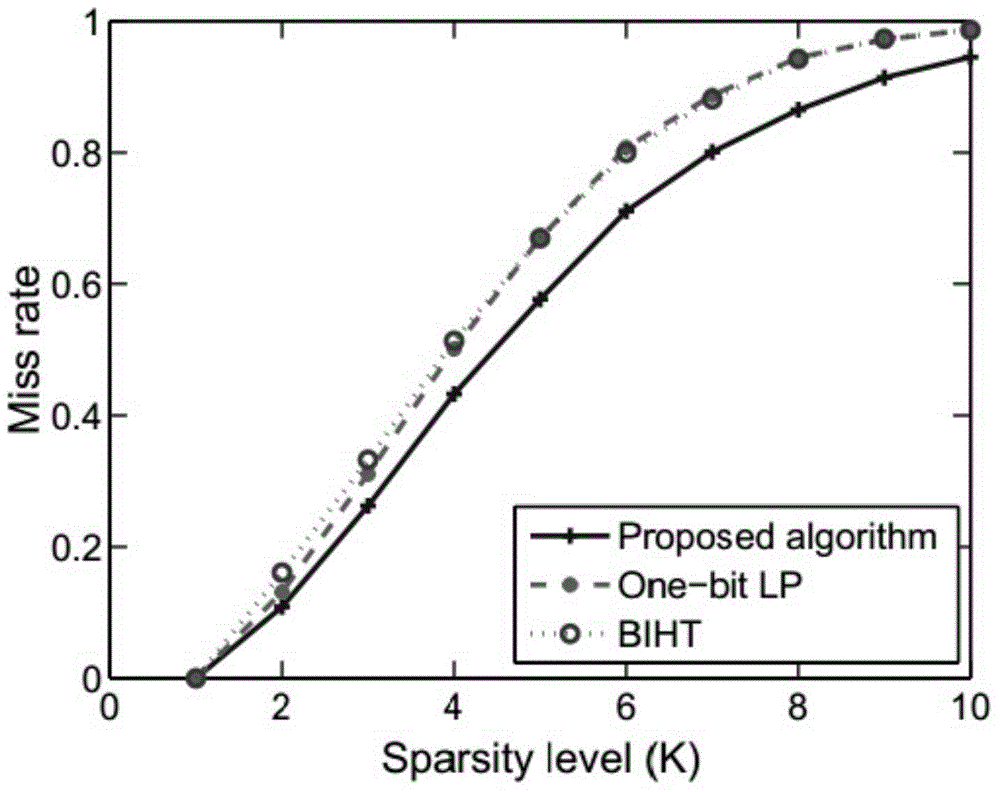

A method of low power consumption data acquisition and reconstruction based on 1-bit quantization compressed sensing

InactiveCN104135290ASimplify Design RequirementsAnalogue-digital convertersHypothesisData acquisition

The invention belongs to the technical field of signal reception quantization, and especially relates to a method of low power consumption data acquisition and reconstruction based on 1-bit quantization compressed sensing. According to the invention, 1-bit quantization of a signal to be measured is executed based on a compressed sensing theory to remove a hypothesis that energy of the signal measured previously is 1, and the signal to be measured is recovered finally by using a formula of loop iteration to minimize a convex replacement function, which enables recovery accuracy of the signal to be improved significantly compared with the previous related algorithm.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

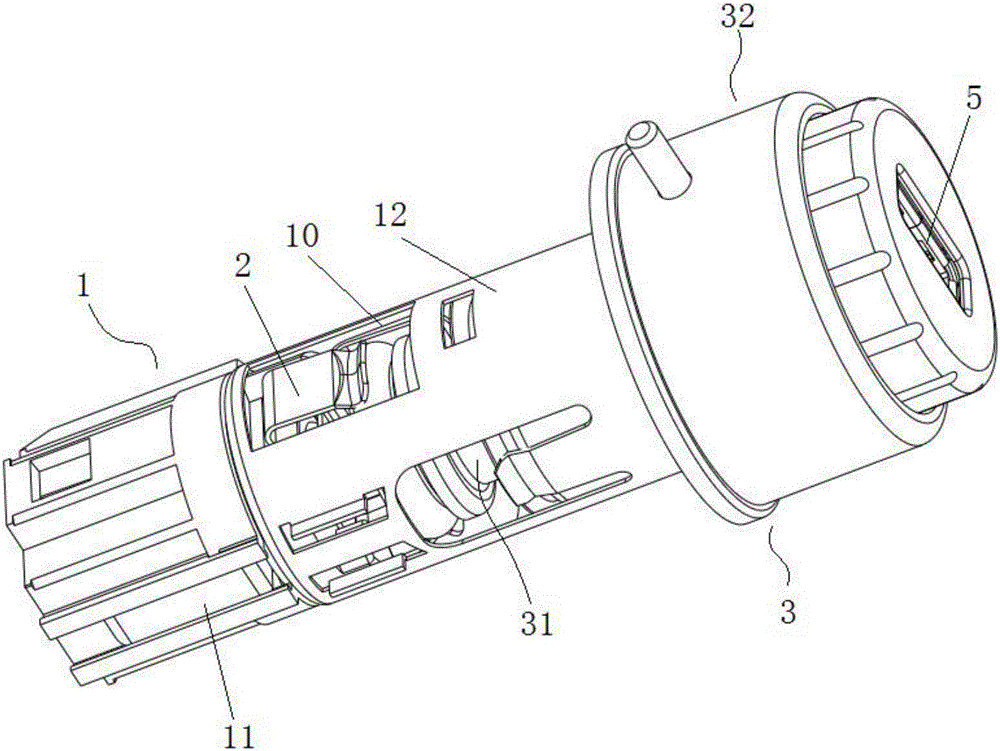

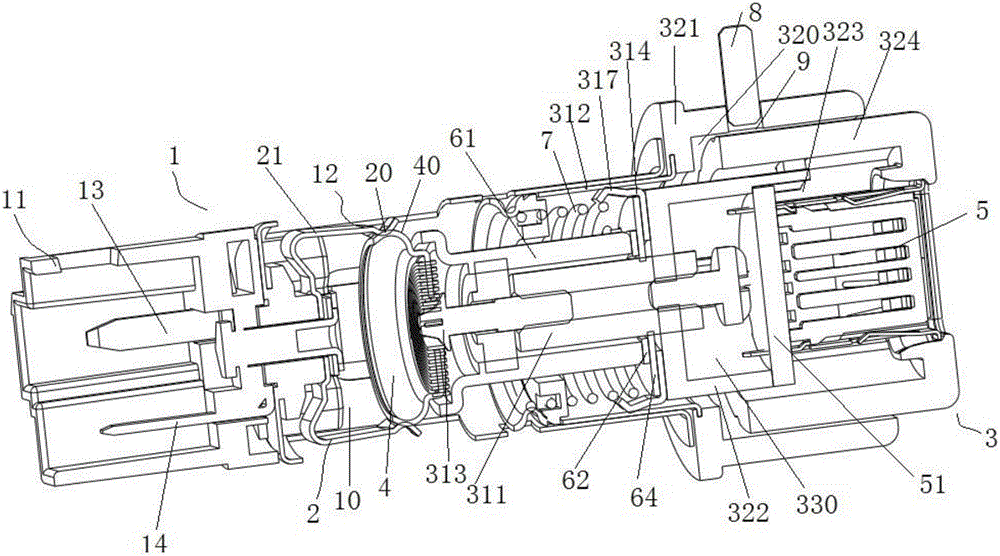

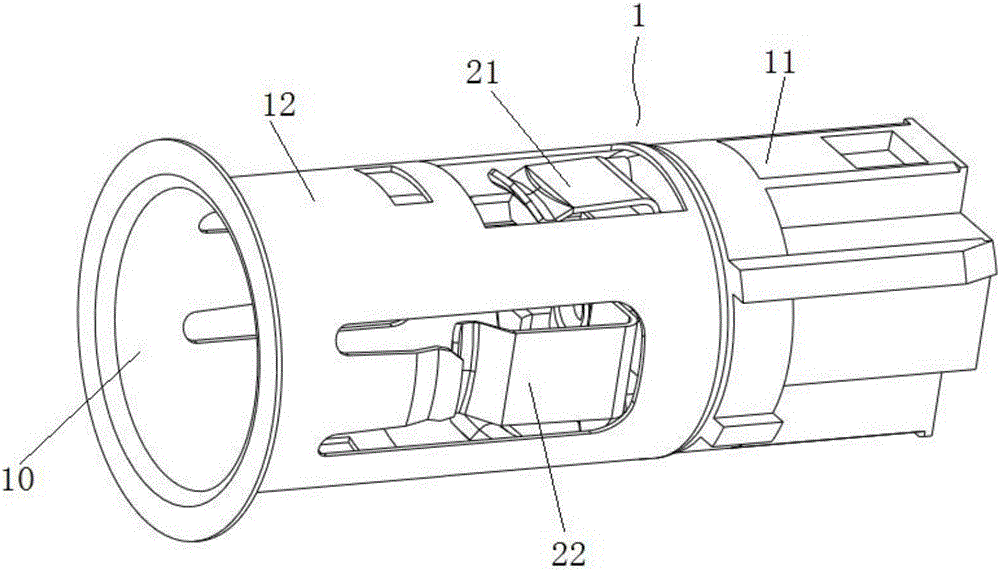

Cigarette lighter structure with charging function

ActiveCN106051818ANo collision damageEasy to useBatteries circuit arrangementsVehicle arrangementsElectricityElectrode

The invention provides a cigarette lighter structure with a charging function. The cigarette lighter structure comprises a base and a cigarette lighter, wherein a first electrode and a second electrode suitable for being electrically connected with a vehicle-mounted power supply are arranged on the base; an accommodating end is electrically connected with the first electrode; an electricity-taking sheet installed in an accommodating inner cavity of the accommodating end is electrically connected with the second electrode; the cigarette lighter is provided with a heating part, a charging part, a first electricity-taking structure and a second electricity-taking structure; one end of the first electricity-taking structure is electrically connected with a heating basin, the other end of the first electricity-taking structure is electrically connected with the accommodating end, one end of the second electricity-taking structure is electrically connected with the electricity-taking sheet, and the other end of the second electricity-taking structure is electrically connected with the accommodating end through a charging socket; when the heating part is located at a first plugging position, the electricity-taking sheet contacts with the heating basin, and at this moment, the cigarette lighter structure enters a cigarette lighting mode; and when the heating part is located at a second plugging position, the electricity-taking sheet contacts with the second electricity-taking structure, and at this moment, the cigarette lighter structure enters a charging mode. According to the cigarette lighter structure disclosed by the invention, the charging socket is integrated on the cigarette lighter; and the two working modes are provided, thus great convenience is brought to use of people.

Owner:浙江致威电子科技有限公司

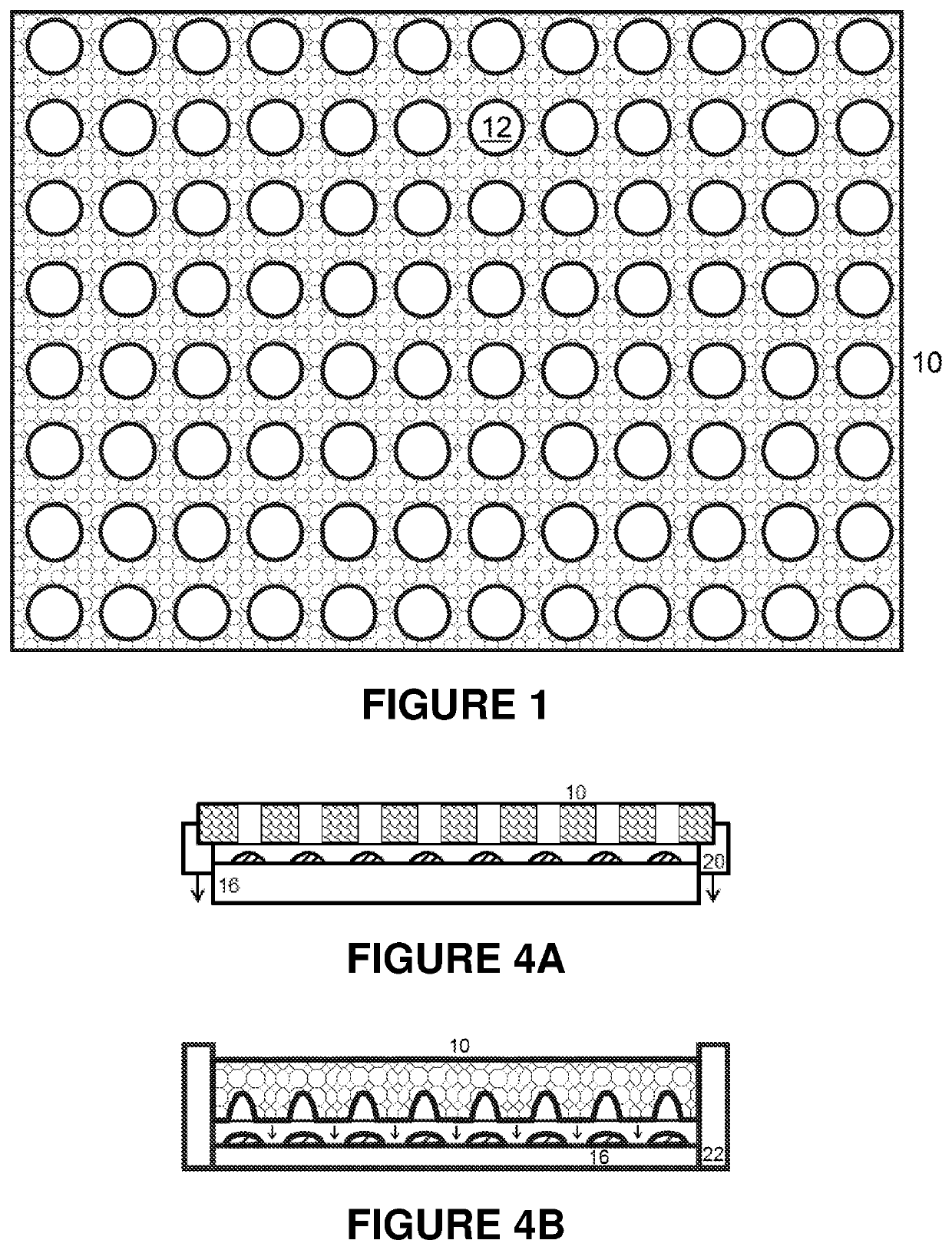

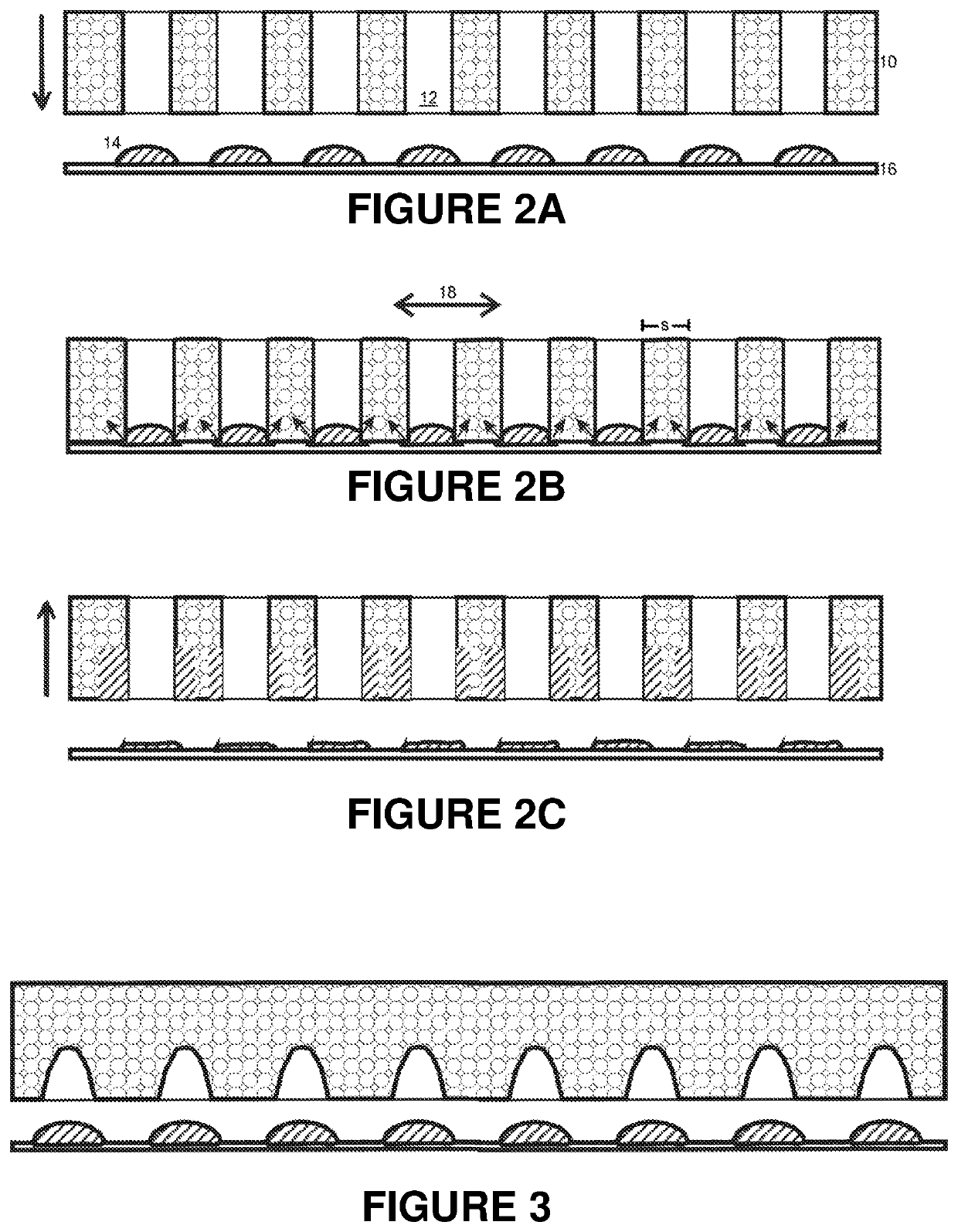

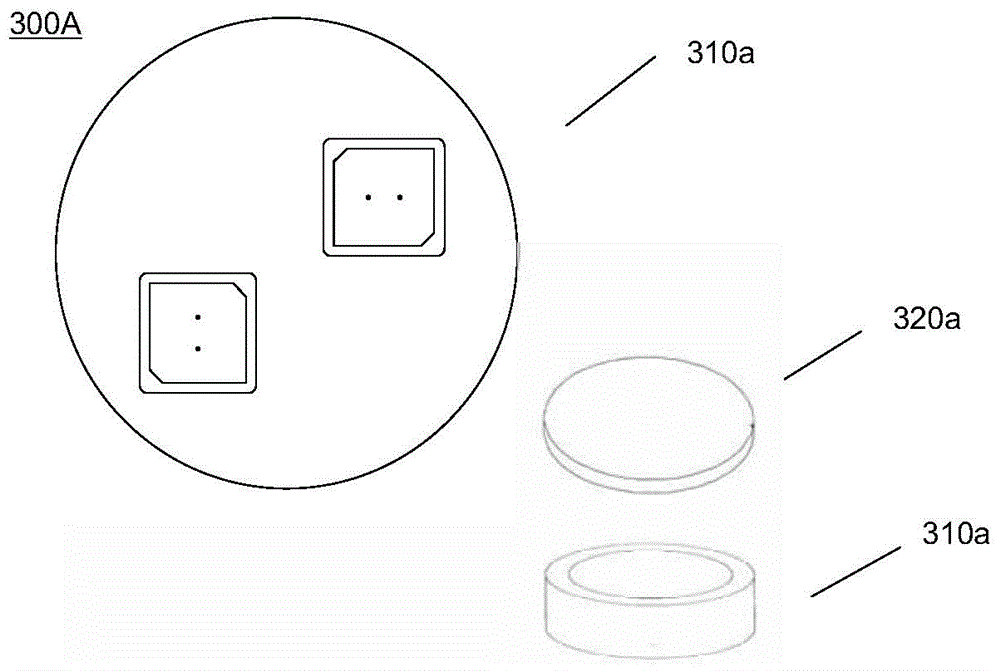

Separation of liquid in droplets and sedimented material enclosed therein

ActiveUS20180269050A1Easy to disassembleNo risk of contaminationSamplingSamples introduction/extractionAbsorbent materialBiomedical engineering

The invention relates to methods for drawing-off liquid from individual droplets which are in a predefined arrangement on a flat substrate and have sedimented material enclosed in them. A mask of an absorbent material comprising a pattern of indentations or holes which corresponds at least partially to the regular arrangement of the individual droplets, or a stiff, rigid plate of an absorbent material is positioned above the flat substrate in such a way that the droplets come into contact with the absorbent material peripherally so that liquid is drawn off there-into. The invention also relates to a mask of an absorbent material with a substantially rectangular shape which has a predefined pattern of indentations or holes for the purpose of separating liquid and sedimented material enclosed therein.

Owner:BRUKER DALTONIK GMBH & CO KG

Lithographic positioning device and device manufacturing method

InactiveUS7006199B2Improve machining accuracyPrecise positioningMagnetic circuit rotating partsPhotomechanical apparatusEngineeringMagnet

A positioning device for positioning an object inside a lithographic apparatus is described. The positioning device includes a first drive unit and a second drive unit for positioning the object. The first drive unit has a first part connected to the object and a second part connected to a first part of the second drive unit. The positioning device further includes a permanent magnet system constructed and arranged to provide at least part of the force for accelerating or decelerating the object.

Owner:ASML NETHERLANDS BV

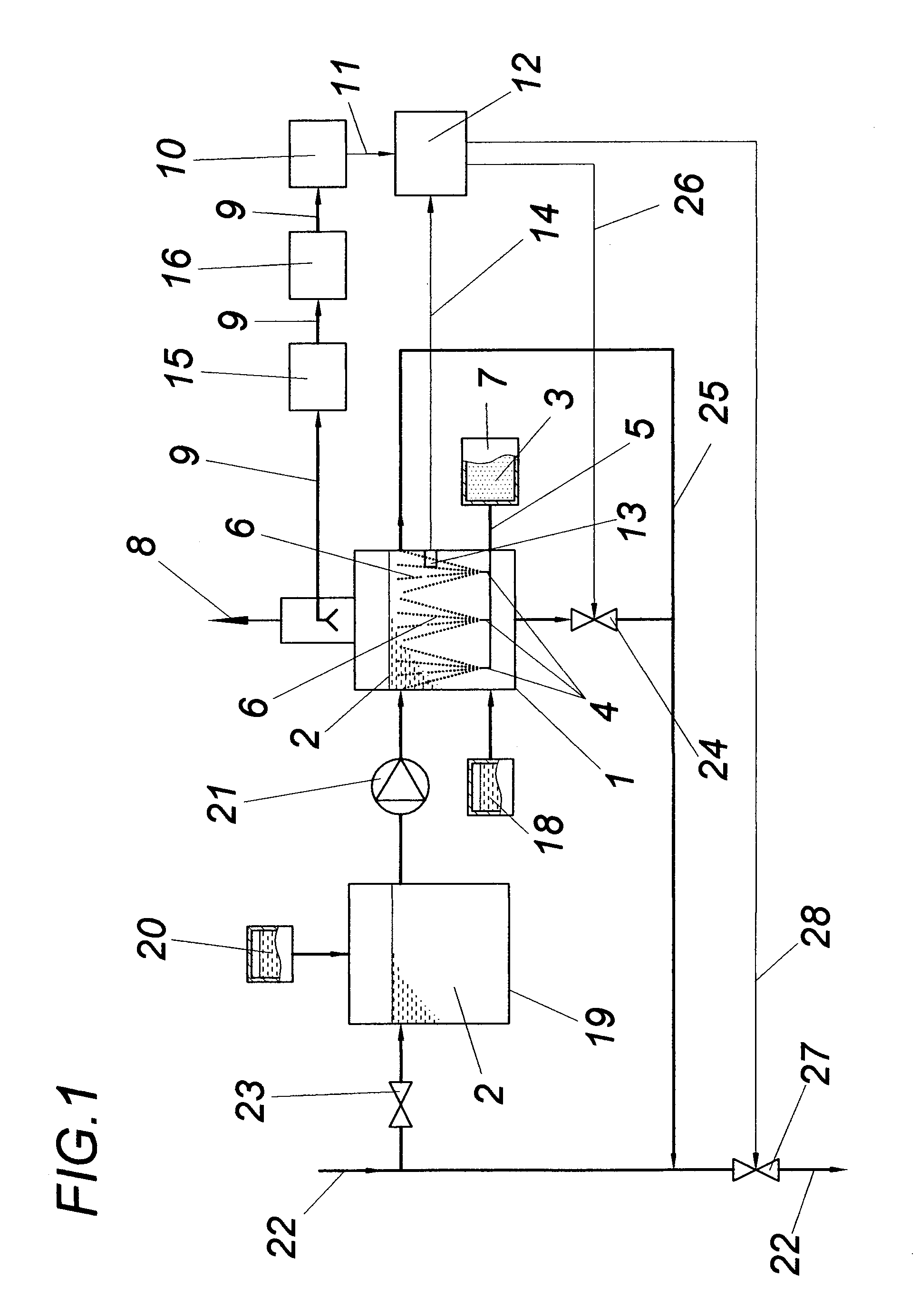

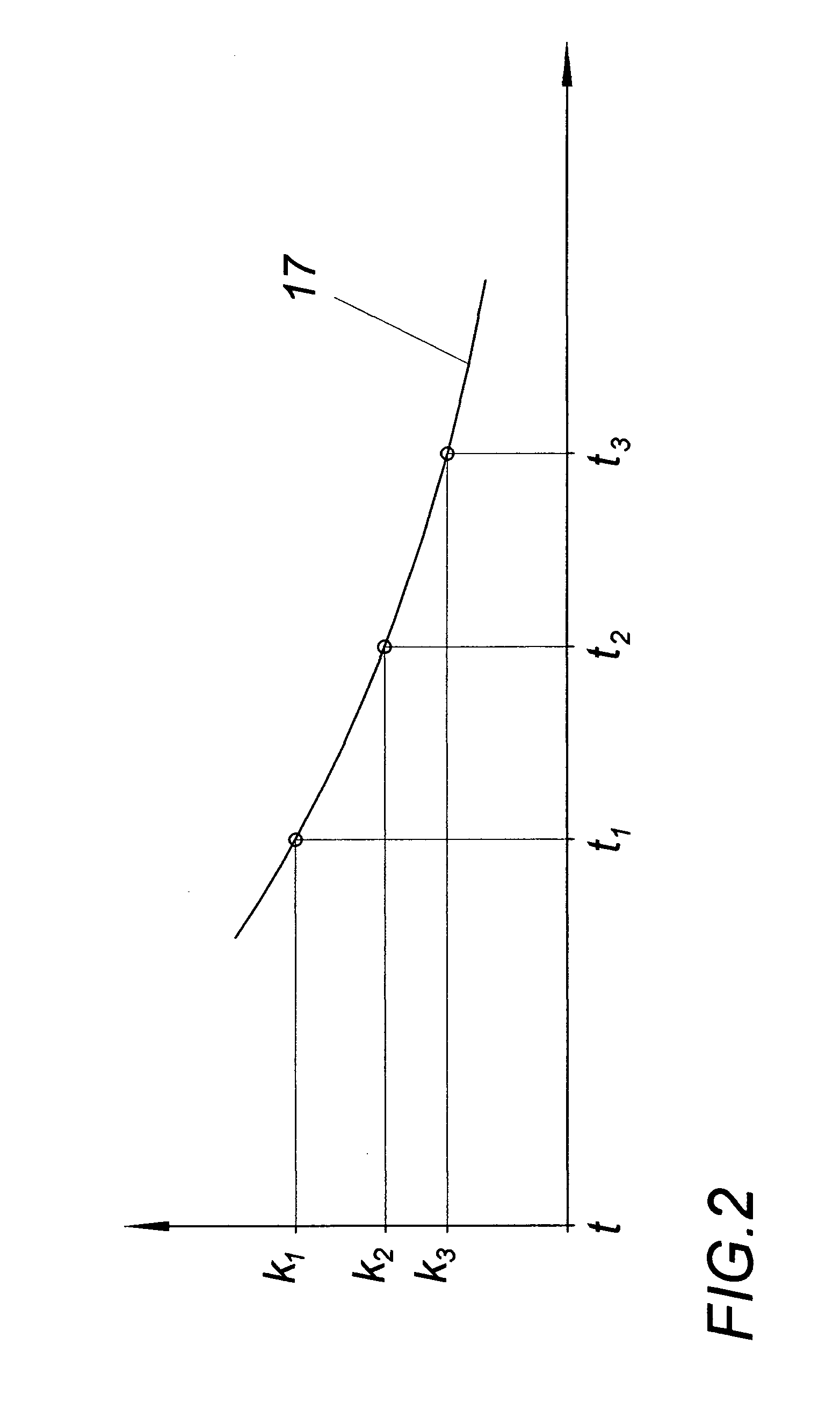

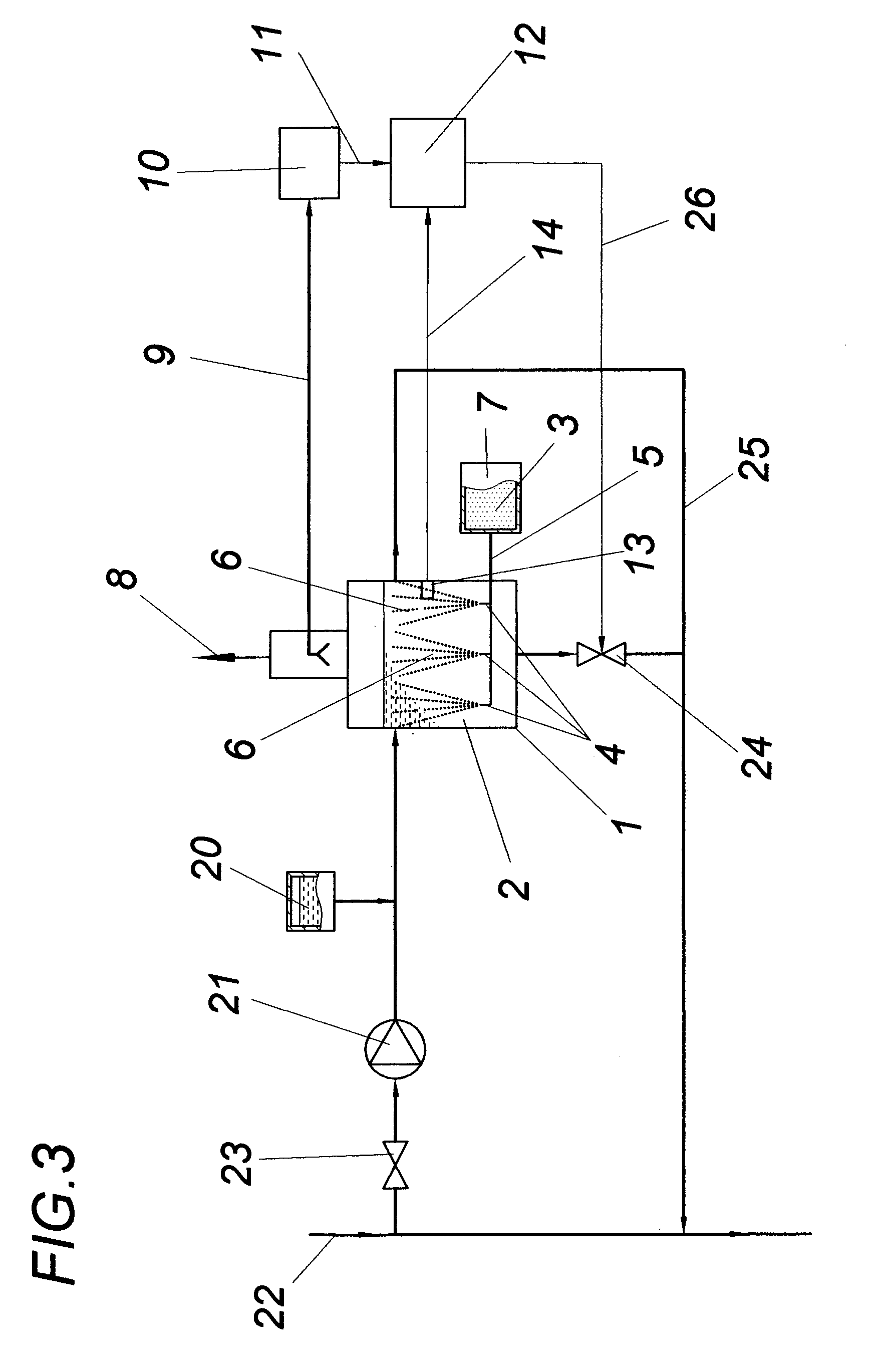

Method for continuously determining the concentration of at least one cn compound in an aqueous solution

InactiveUS20120195795A1Simple operationInexpensive deviceWithdrawing sample devicesDispersed particle separationAnalysis dataAqueous solution

The invention relates to a method for continuously determining the concentration of at least one CN compound in an aqueous solution, wherein a carrier gas, for example compressed air, is introduced into the aqueous solution and the introduced carrier gas is fed at least partially to a gas analyzer, for example an HCN gas analyzer, the analysis data of which are considered in the determination of the concentration of the CN compound in the aqueous solution. In order to create advantageous method conditions, the temperature of the aqueous solution exposed to carrier gas is considered in the determination of the concentration of the CN compound.

Owner:VOESTALPINE STAHL GMBH

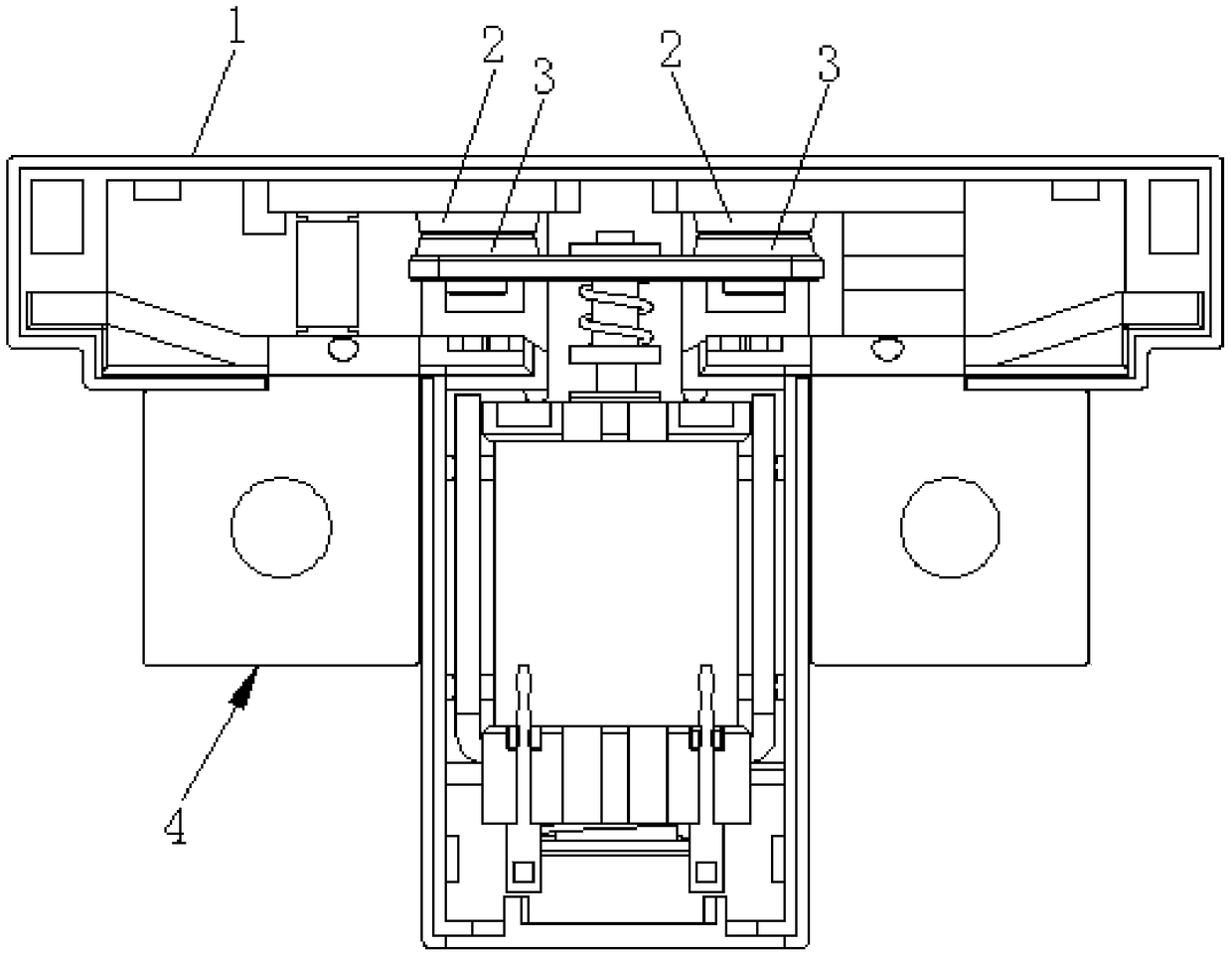

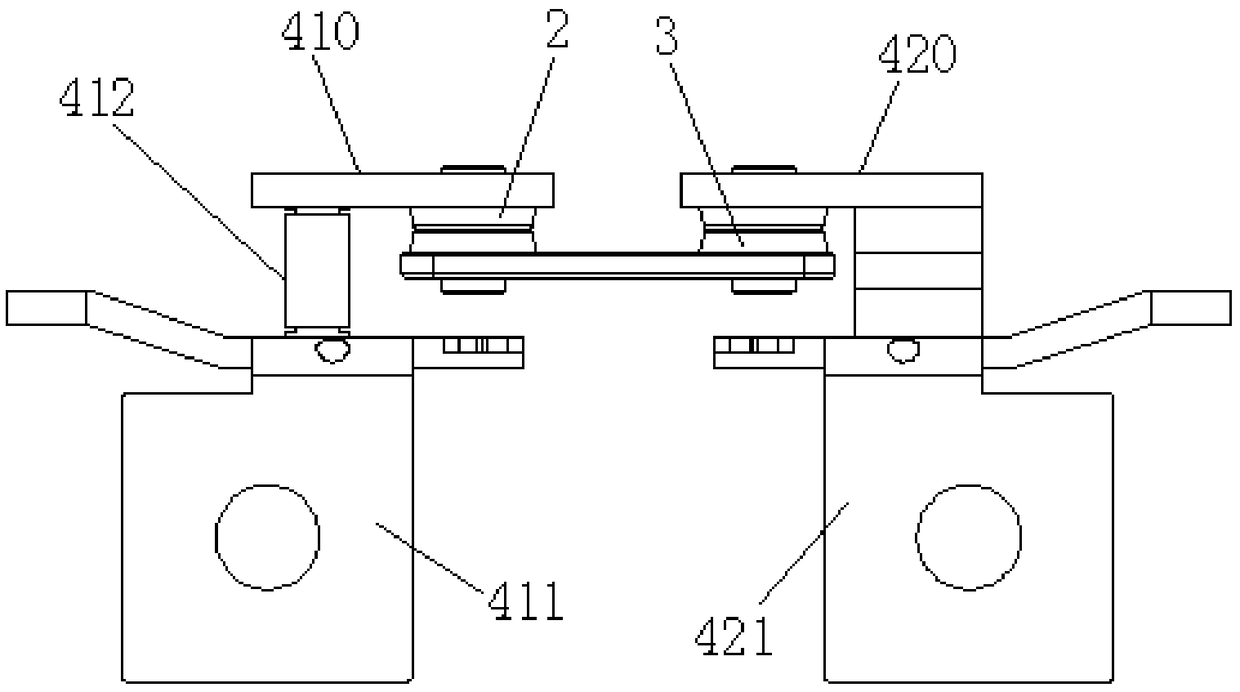

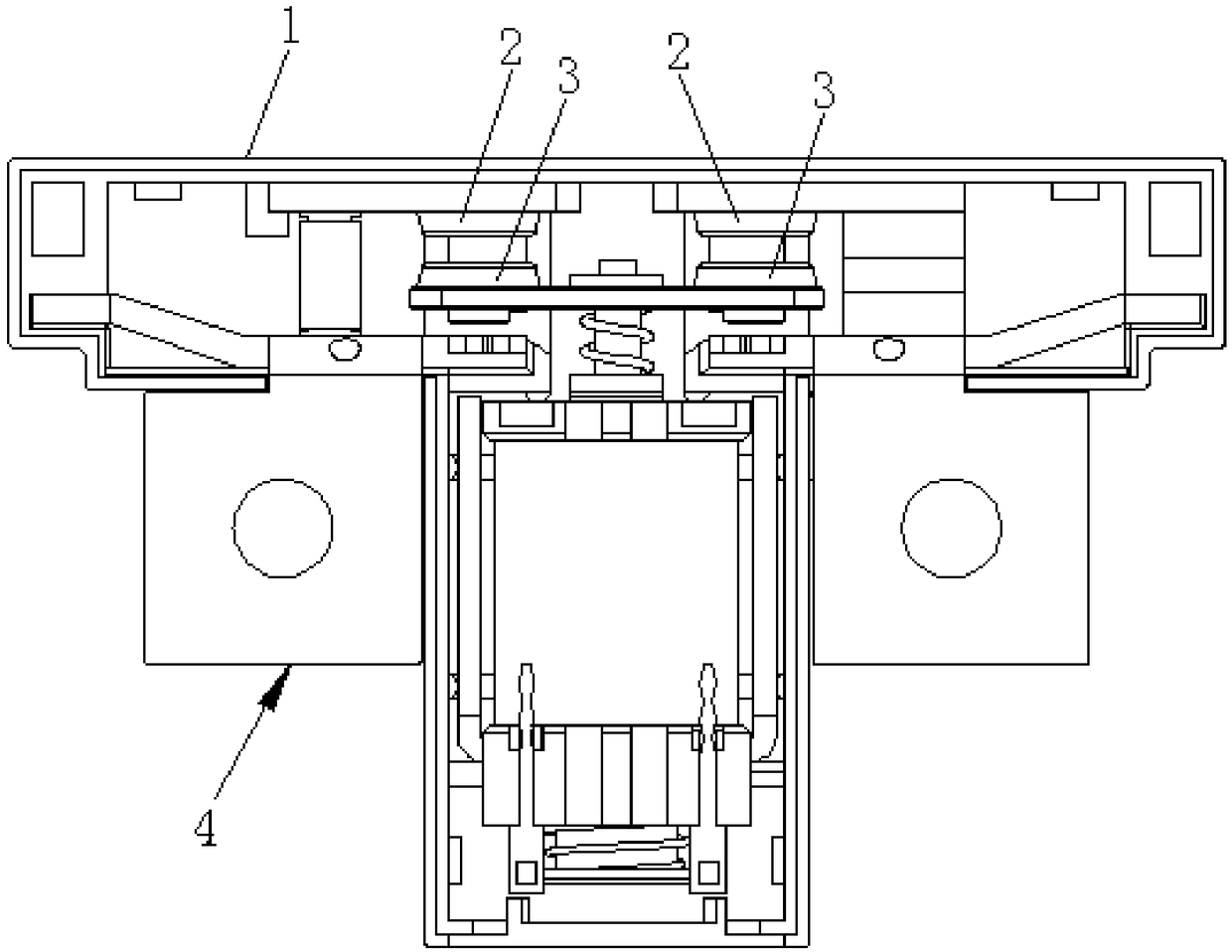

Direct-current contactor with fuse protection function

PendingCN108899234AImprove operational safetyGuaranteed uptimeElectric switchesEngineeringOperation safety

The invention discloses a direct-current contactor with a fuse protection function. The direct-current contactor comprises a shell, two fixed contacts and two movable contacts, wherein the two movablecontacts are electrically connected and are arranged correspondingly opposite to the two fixed contacts in a vertical direction respectively; the two movable contacts can also be correspondingly connected with or disconnected from the two fixed contacts respectively; a fuse protection component capable of protecting the direct-current contactor is also arranged in the shell; the fuse protection component comprises a first component and a second component; the first component is provided with a first conductive part positioned on a fixed contact and sleeves a fixed contact, a first wiring partserving as an electrical input end, and a fuse body connected between the first conductive part and the first wiring part; the second component is provided with a second conductive part which is positioned on the other fixed contact and sleeves the other fixed contact, and a second wiring part connected with the second conductive part and serving as an electrical output end. The direct-current contactor has the advantages of functional integration, high operation safety, saving of the mounting space and the like.

Owner:昆山国力源通新能源科技有限公司

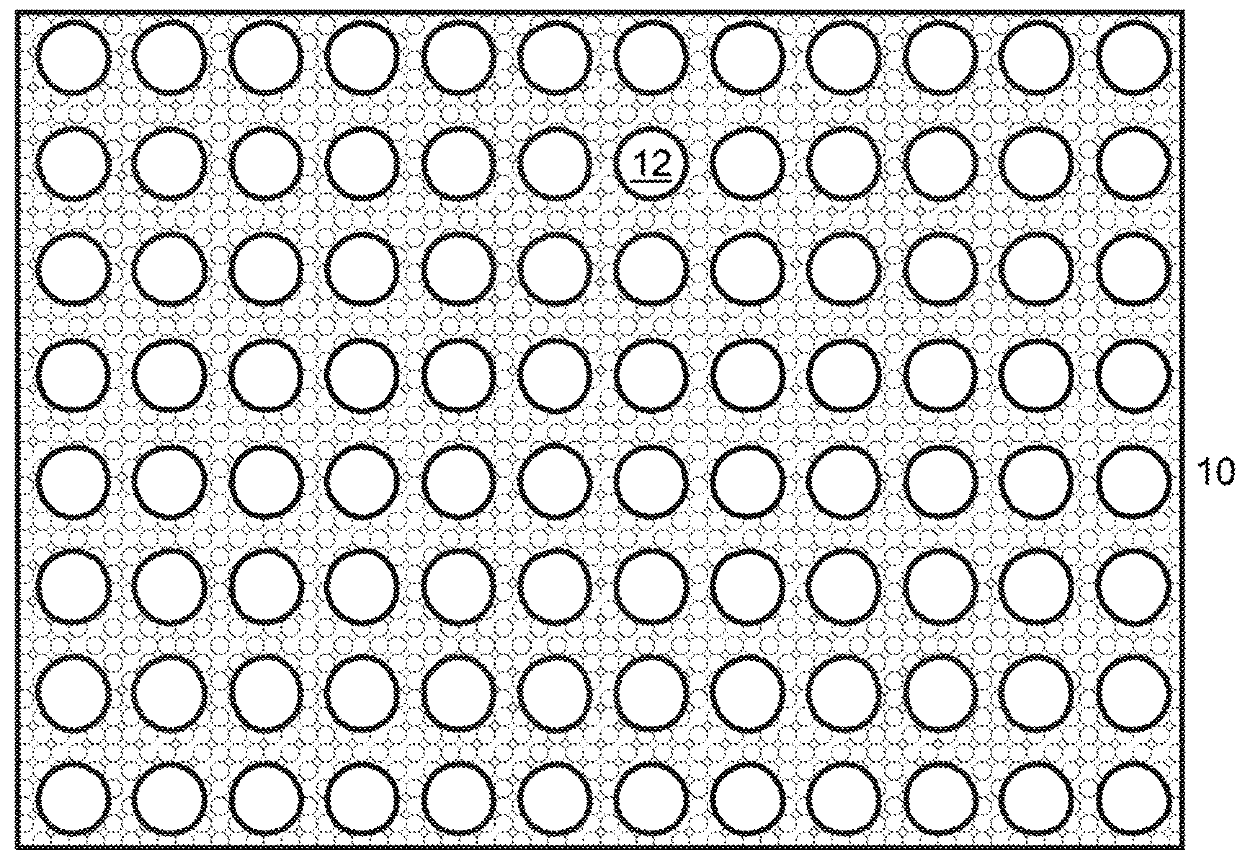

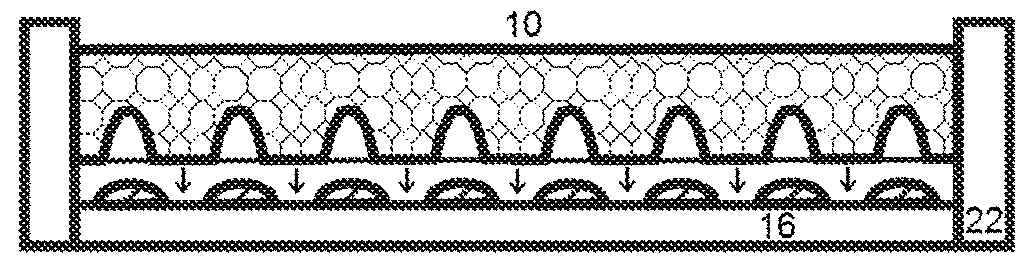

Separation of liquid in droplets and sedimented material enclosed therein

ActiveUS11017993B2Improve overall utilizationSimplify Design RequirementsSamples introduction/extractionMicrobiological testing/measurementPolymer scienceAbsorbent material

The invention relates to methods for drawing-off liquid from individual droplets which are in a predefined arrangement on a flat substrate and have sedimented material enclosed in them. A mask of an absorbent material comprising a pattern of indentations or holes which corresponds at least partially to the regular arrangement of the individual droplets, or a stiff, rigid plate of an absorbent material is positioned above the flat substrate in such a way that the droplets come into contact with the absorbent material peripherally so that liquid is drawn off there-into. The invention also relates to a mask of an absorbent material with a substantially rectangular shape which has a predefined pattern of indentations or holes for the purpose of separating liquid and sedimented material enclosed therein.

Owner:BRUKER DALTONIK GMBH & CO KG

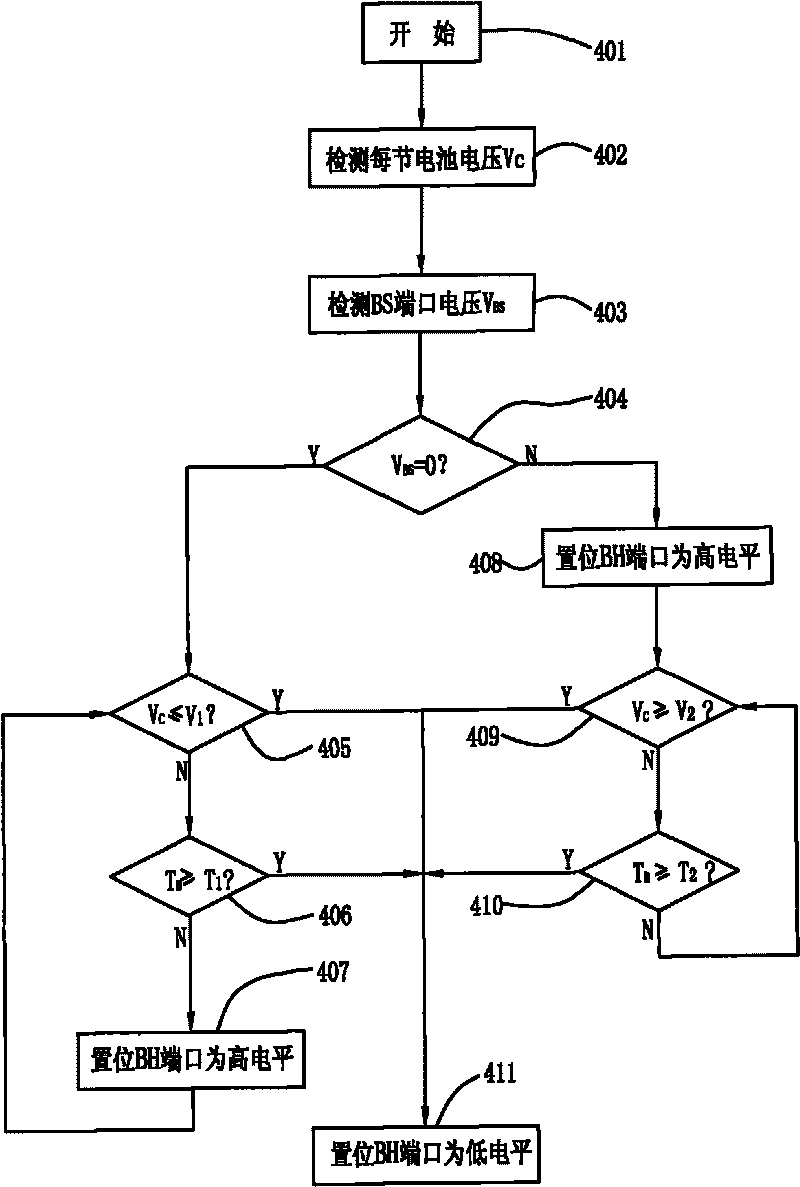

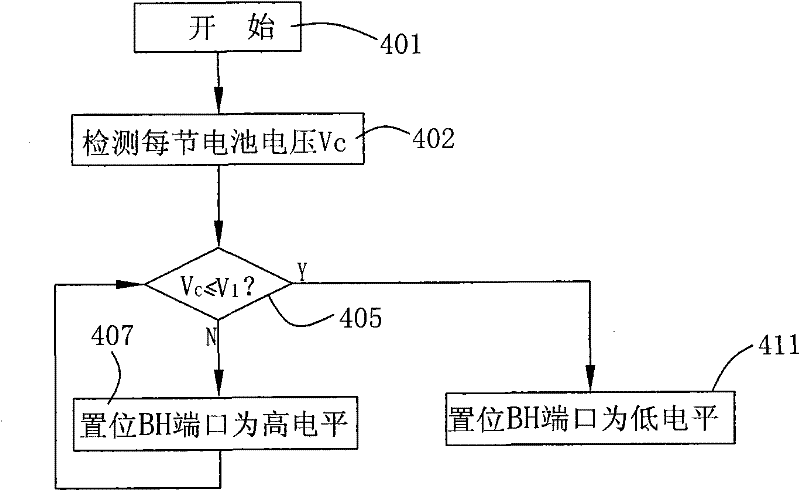

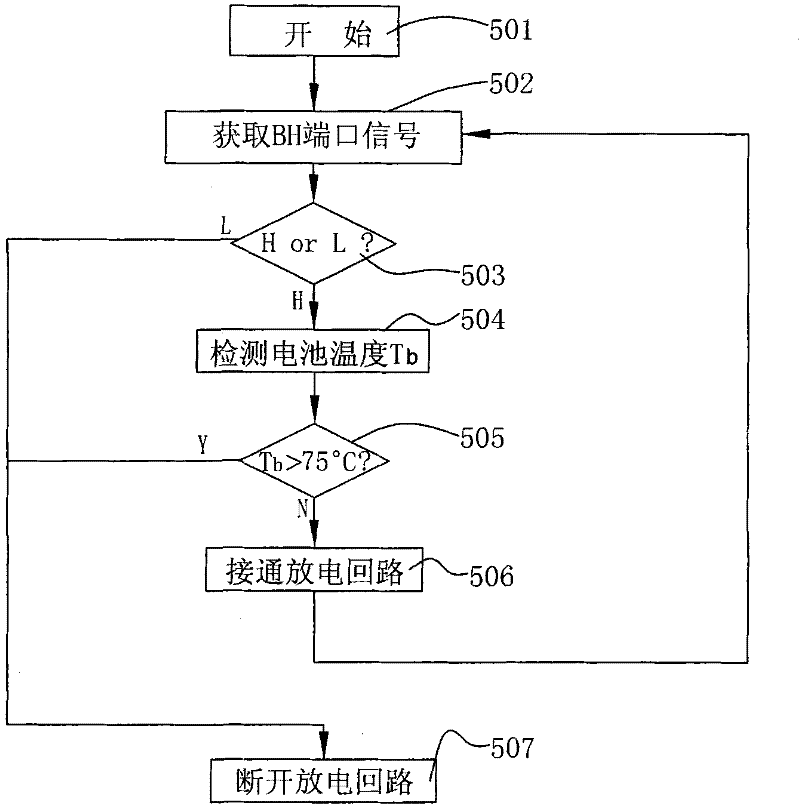

Combination of electric power tool and battery pack

InactiveCN102130471ASimplify Design RequirementsLow costBatteries circuit arrangementsElectric powerElectric power systemElectrical battery

The invention discloses a combination of an electric power tool and a battery pack, which comprises an electric power tool and a battery pack, wherein the battery pack comprises a first detection device and a second detection device; the electric power tool is internally provided with a control device, the first detection device and the second detection device are respectively used for detecting voltage of a single battery in the battery pack and temperature of the battery pack, the signal of the first detection device is primarily processed in the battery pack and then transmitted to the control device in the electric power tool through one conductive terminal; the signal of the second detection device is not pressed in the battery pack and directly transmitted to the control device in the electric power tool through another conductive terminal; and the control device is used for realizing over-discharge protection on the battery pack according to the signals of the first detection device and the second detection device. According to the design, the structure of the battery pack can be simplified and the design cost of the battery pack is lowered.

Owner:POSITEC POWER TOOLS (SUZHOU) CO LTD

Positioning device

InactiveUS20050200825A1Improve machining accuracyPrecise positioningMagnetic circuit rotating partsPhotomechanical apparatusEngineeringMagnet

A positioning device for positioning an object is presented. The positioning device comprises a first drive unit and a second drive unit for positioning the object. The first drive unit has a first part connected to the object and a second part connected to a first part of the second drive unit. The positioning device further comprises a permanent magnet system constructed and arranged to provide at least part of the force for accelerating or decelerating the object.

Owner:ASML NETHERLANDS BV

Communication antenna, antenna system and communication device

PendingCN105990640ALow profileRequirements for reduced installation heightRadiating elements structural formsAntennas earthing switches associationTelecommunicationsCommunication device

The present invention relates to a communication antenna. The communication antenna comprises a first radiator and a second radiator. The first radiator includes a first substrate and a first radiation fin arranged on the first substrate; the second radiator includes a second substrate and a second radiation fin arranged on the second substrate; the first radiator has a first feed portion and a second feed portion; the second radiator has a third feed portion and a fourth feed portion; and the first radiator and the second radiator are arranged at the same installation surface, and the radiation surfaces of the first radiation fin and the second radiation fin are planes.

Owner:KUANG CHI CUTTING EDGE TECH LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com