Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

70results about How to "Increase in consumption" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

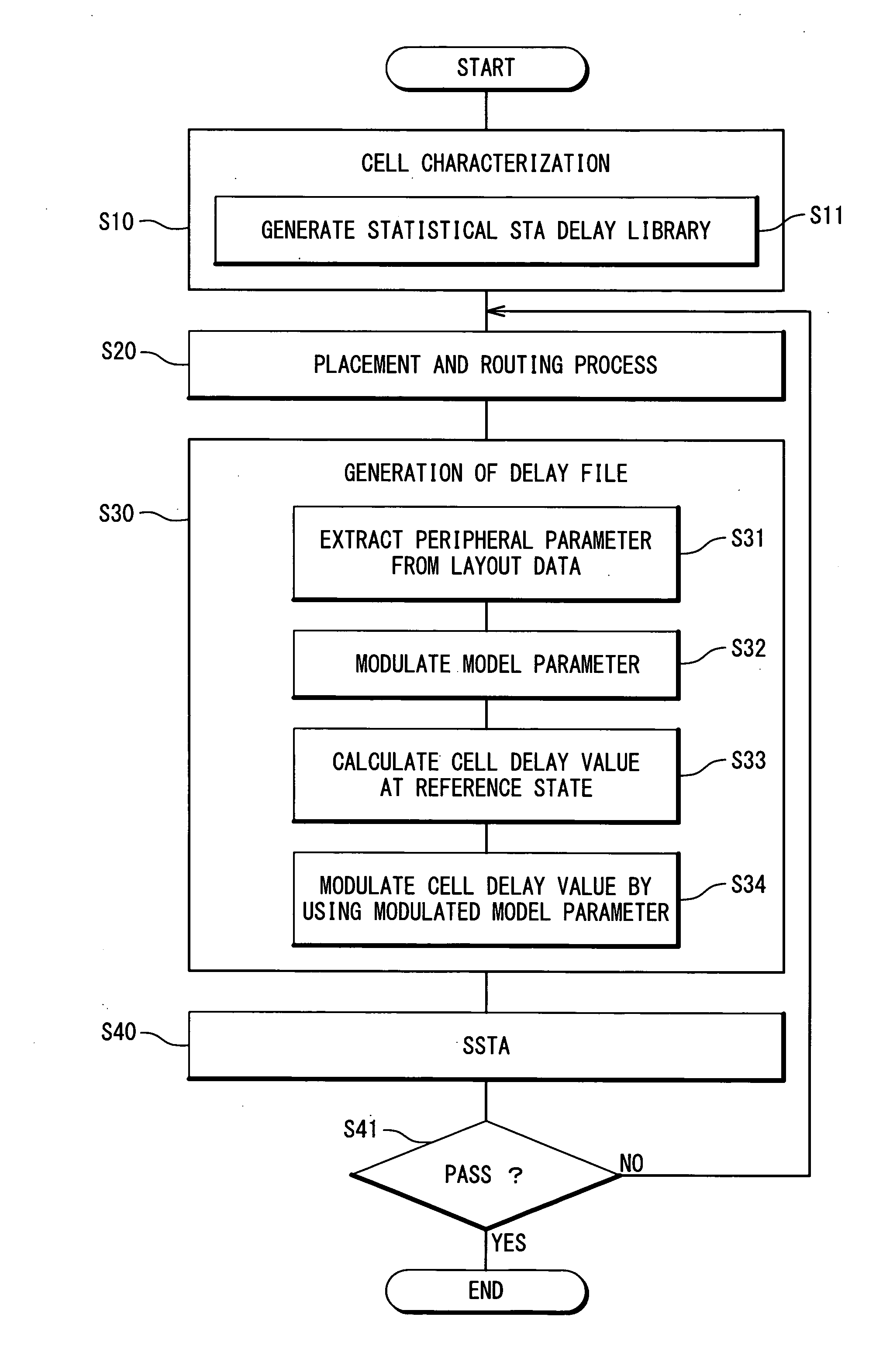

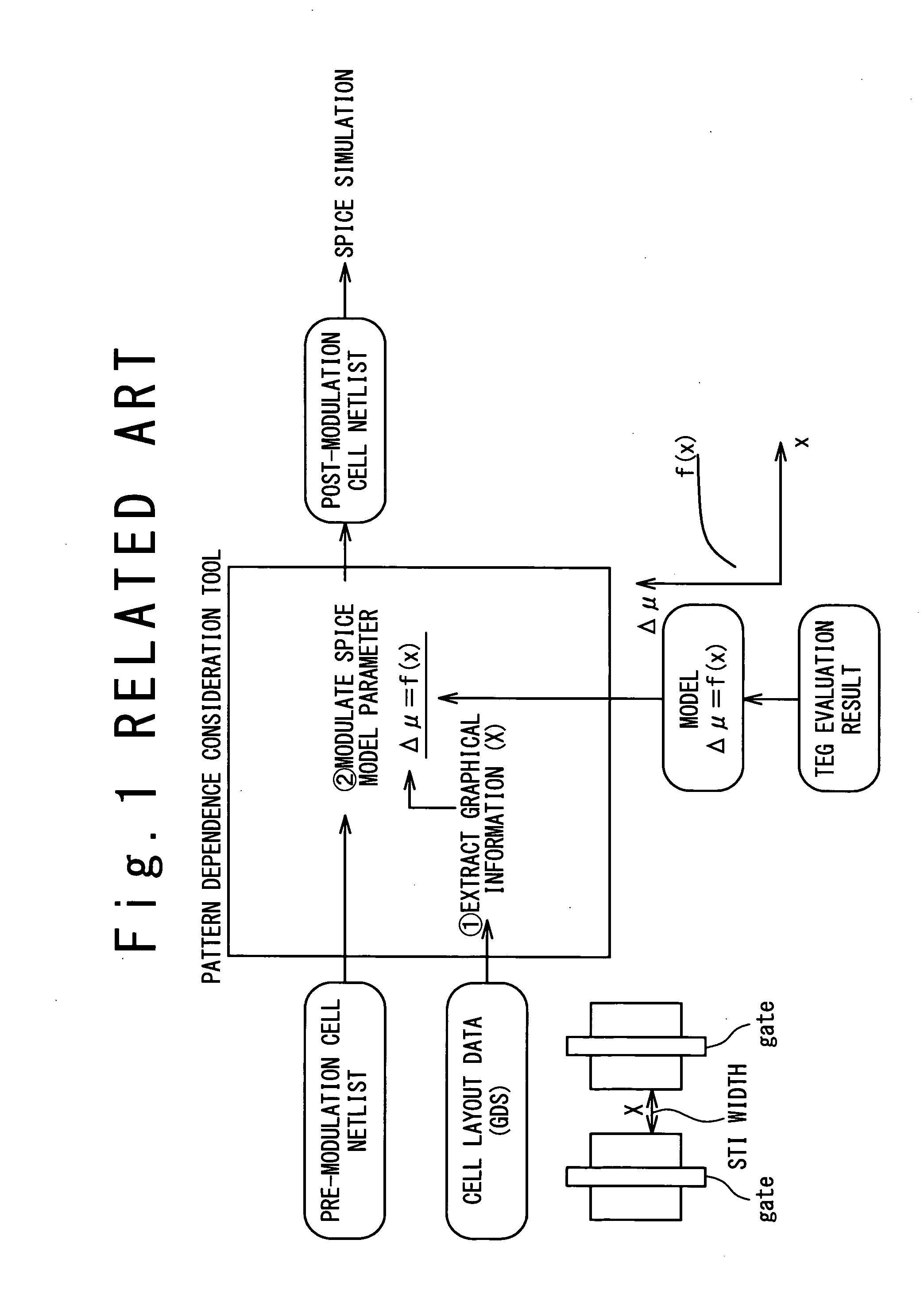

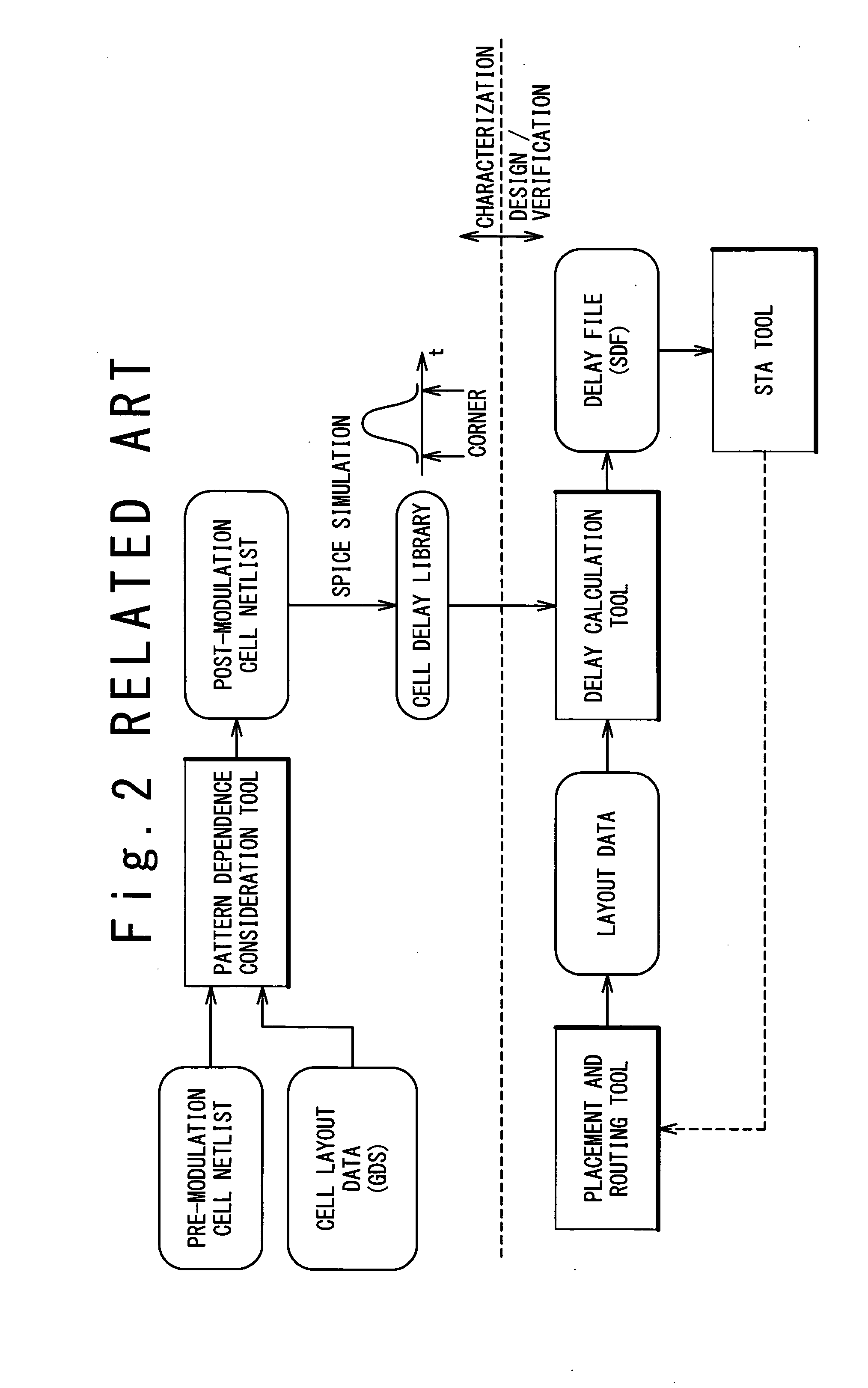

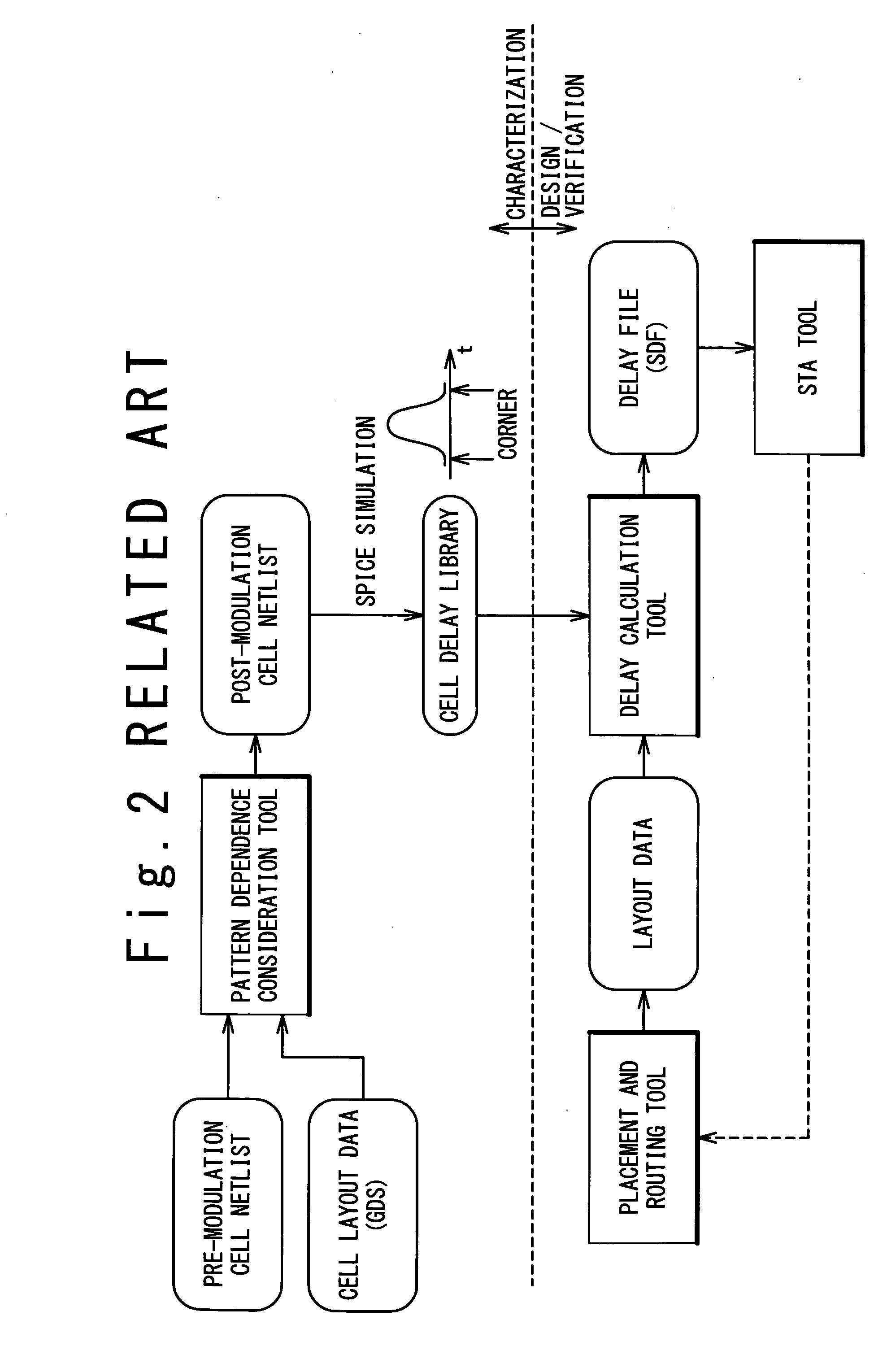

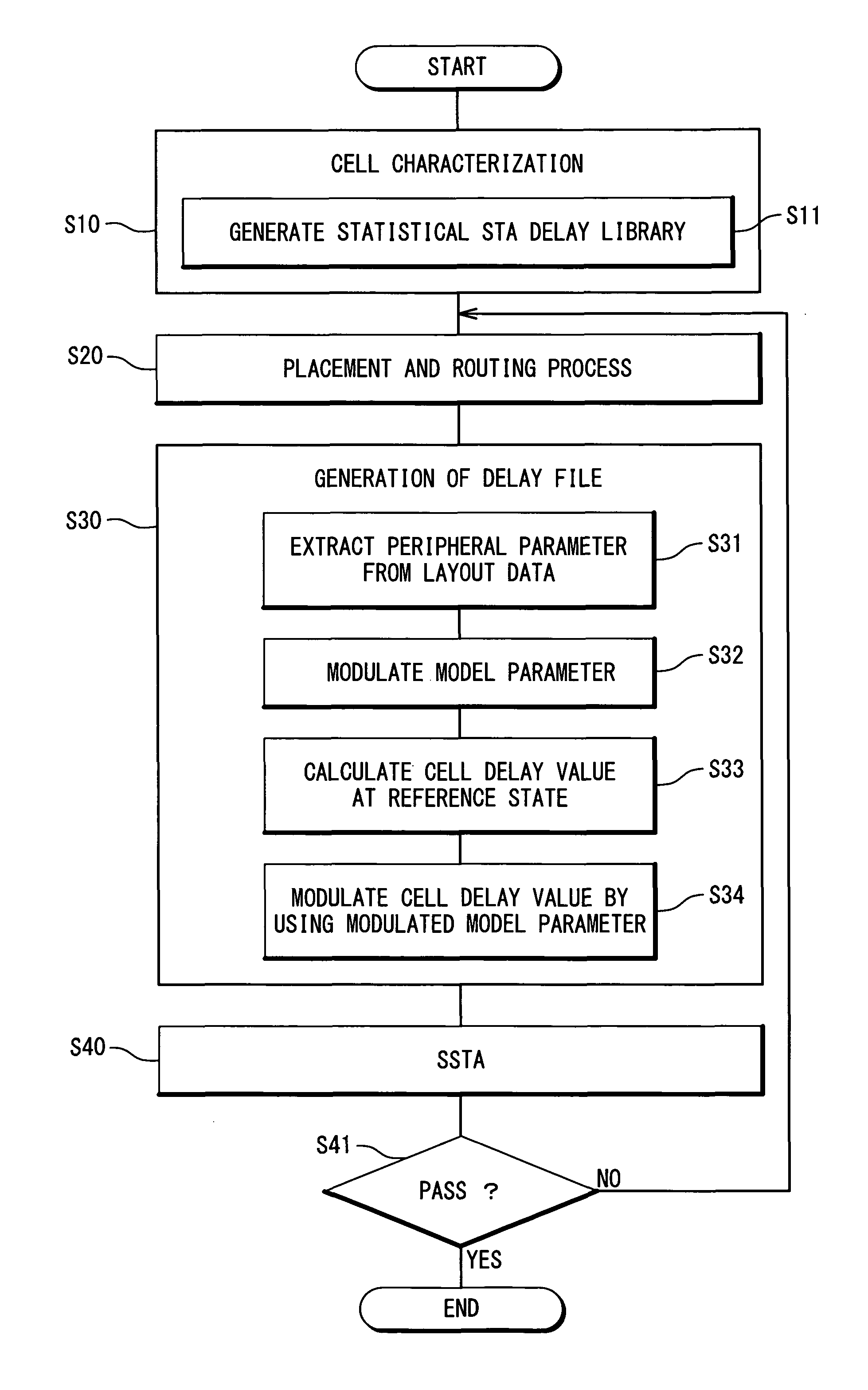

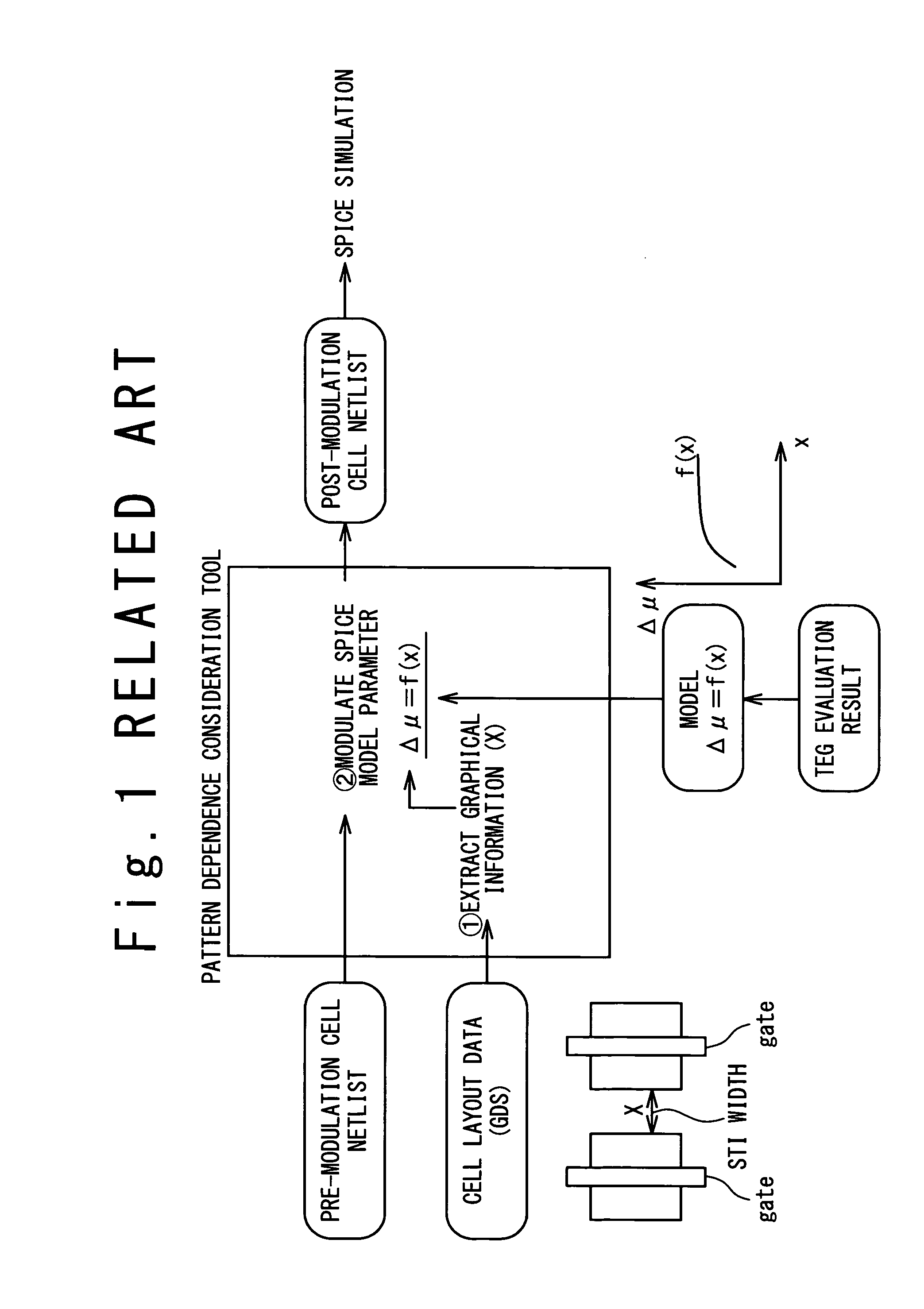

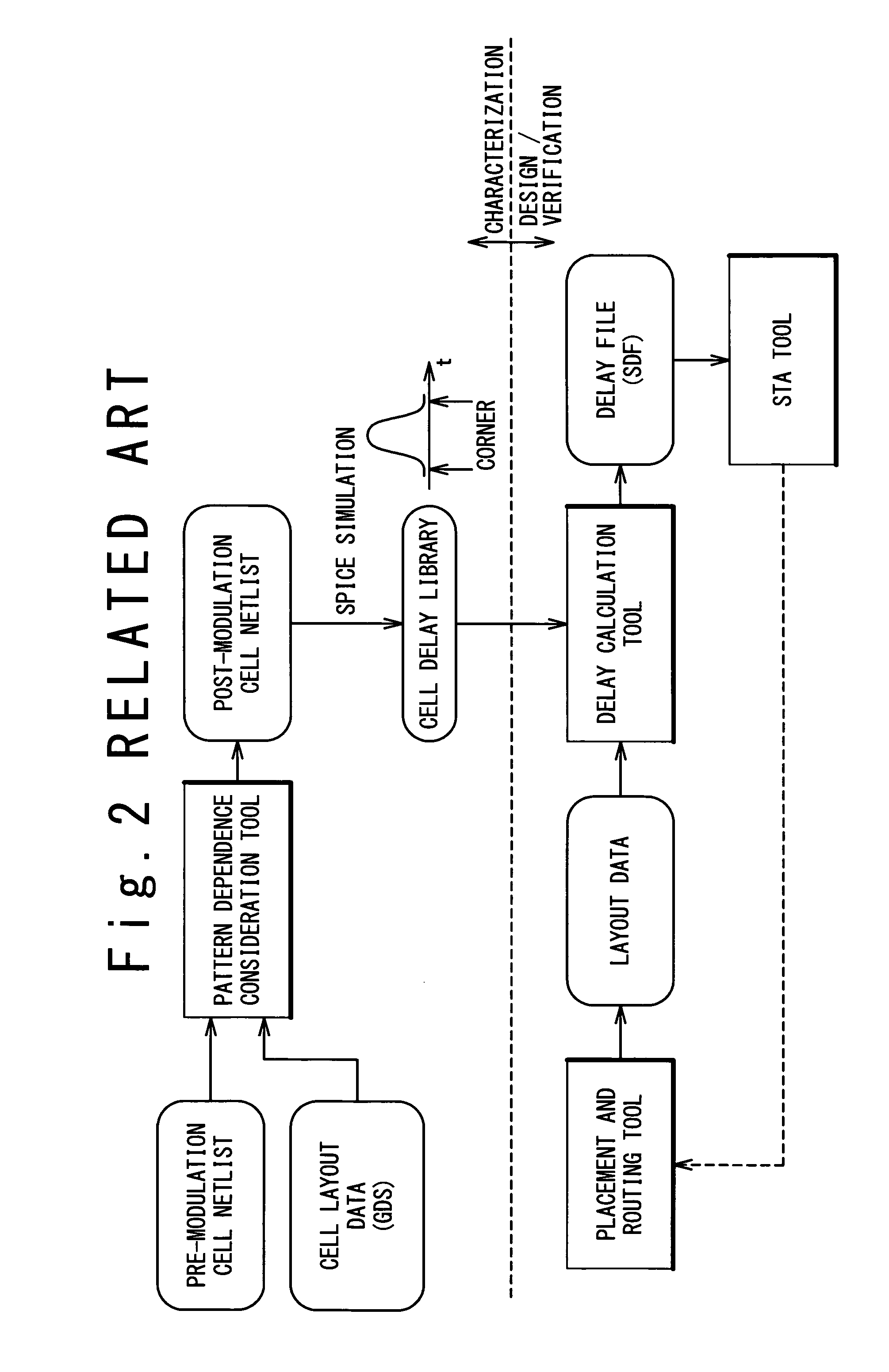

Method and program for designing semiconductor integrated circuit

InactiveUS20090024974A1Increase in design/verification TAT can be preventedHigh delay accuracyCAD circuit designSoftware simulation/interpretation/emulationModel parametersCell based

A design method for an LSI includes: generating a delay library for use in a statistical STA, wherein the delay library provides a delay function that expresses a cell delay value as a function of model parameters of a transistor; generating a layout data; and calculating a delay value of a target cell based on the delay library and the layout data. The calculating includes: referring to the layout data to extract a parameter specifying a layout pattern around a target transistor; modulating model parameters of the target transistor such that the characteristics corresponding to the extracted parameter is obtained in a circuit simulation; calculating, by using the delay function, a reference delay value of the target cell; and calculating, by using the delay function and the modulation amount of the model parameter, a delay variation from the reference delay value depending on the modulation amount.

Owner:RENESAS ELECTRONICS CORP

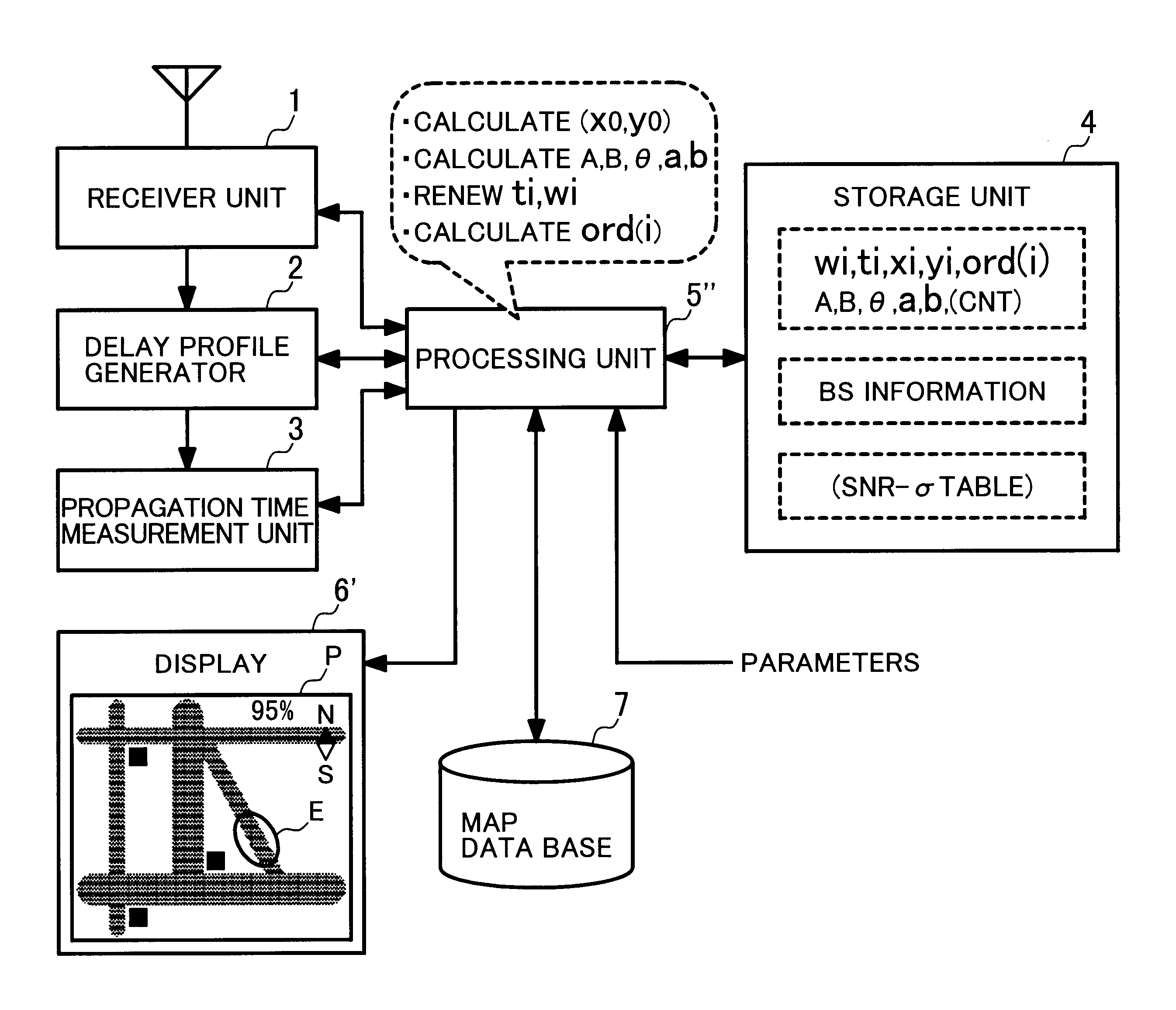

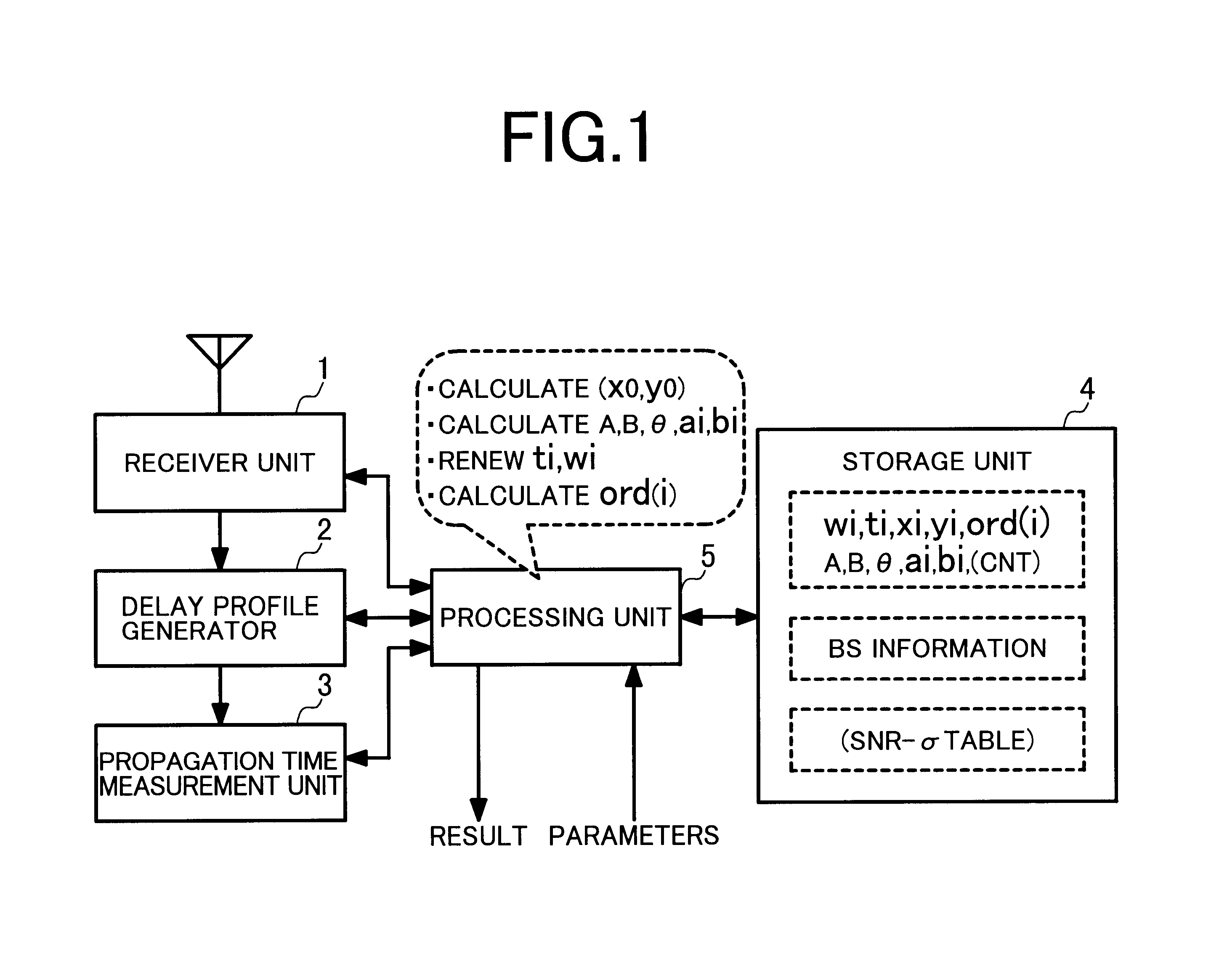

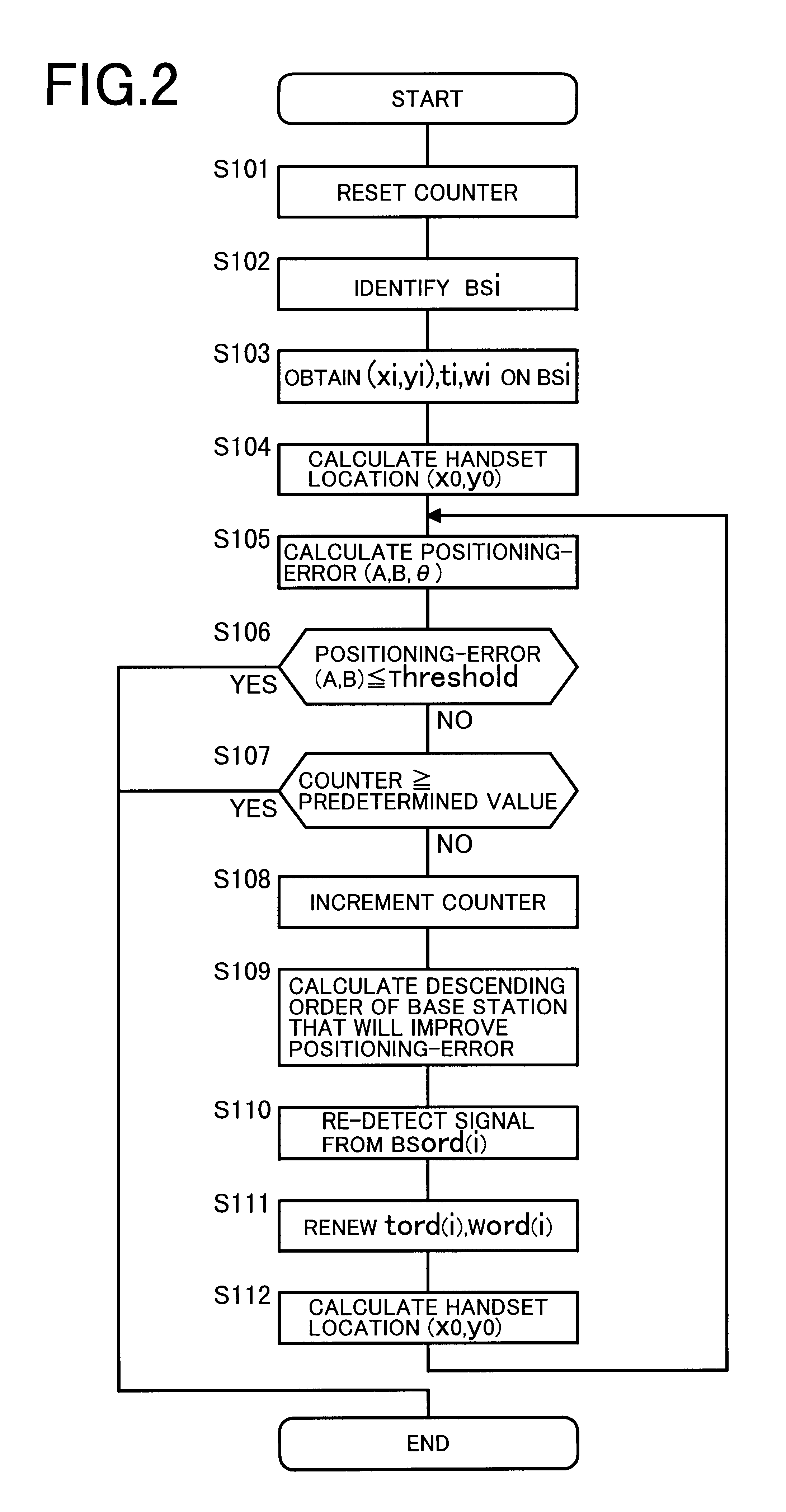

Location detection method, location detection system and location detection program

InactiveUS6865394B2Increase in powerIncrease in timeBeacon systems using radio wavesRoad vehicles traffic controlLocation detectionPropagation delay

A positioning method, which is related to a technique to measure a correct position of a terminal by preventing time required for the position measurement, of calculating a position of a receiver according to signals from a plurality of wireless transmitters includes a first step of measuring propagation delay time of the signal from each of the wireless transmitters and calculating a position of the receiver and a standard deviation about measuring distance error, a second step of calculating a positioning error of the receiver a third step of determining, according to the positioning error calculated by the second step, wireless transmitters in directions nearer to a direction in which the positioning error is large, and a fourth step of re-detecting signals from the wireless transmitters determined by the third step and thereby re-calculating the position of the receiver.

Owner:HITACHI LTD

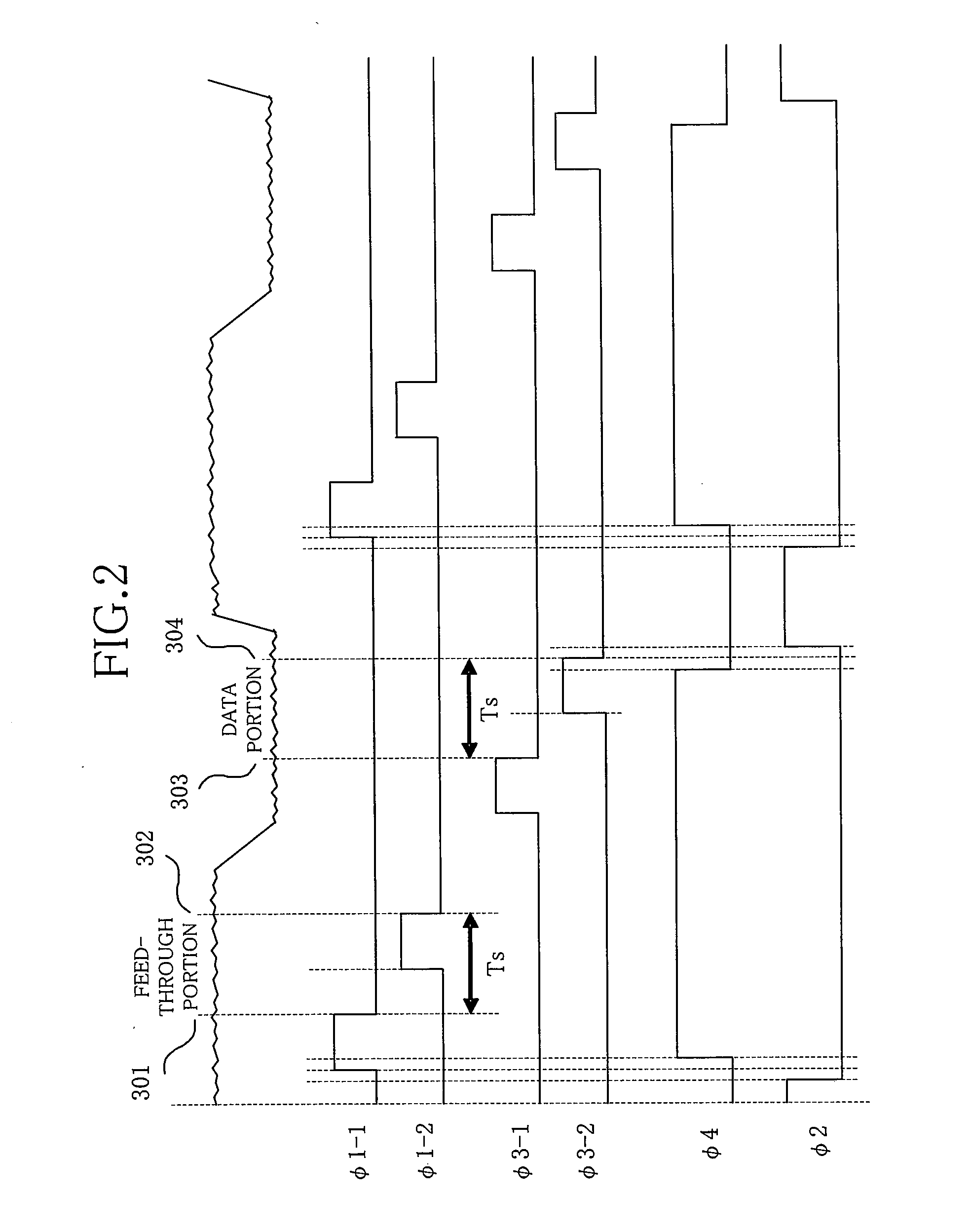

Synchronization timing detecting apparatus, receiving apparatus, and synchronization timing detecting method

InactiveUS20070211835A1Reduced sampling rate requirementsMaintain accuracySynchronisation error detectionTime-division multiplexSelf correlationComputer science

A synchronization timing detecting apparatus includes a correlation calculator configured to generate a first correlation value by calculating a cross-correlation between an input signal being sampled and a reference signal or an auto-correlation of the sampled input signal, an interpolation processor configured to generate a second correlation value interpolating a plurality of the first correlation values having a different combination of sampling points of the input signal, and a detector to detect a synchronization timing based on the first and the second correlation values.

Owner:RENESAS ELECTRONICS CORP

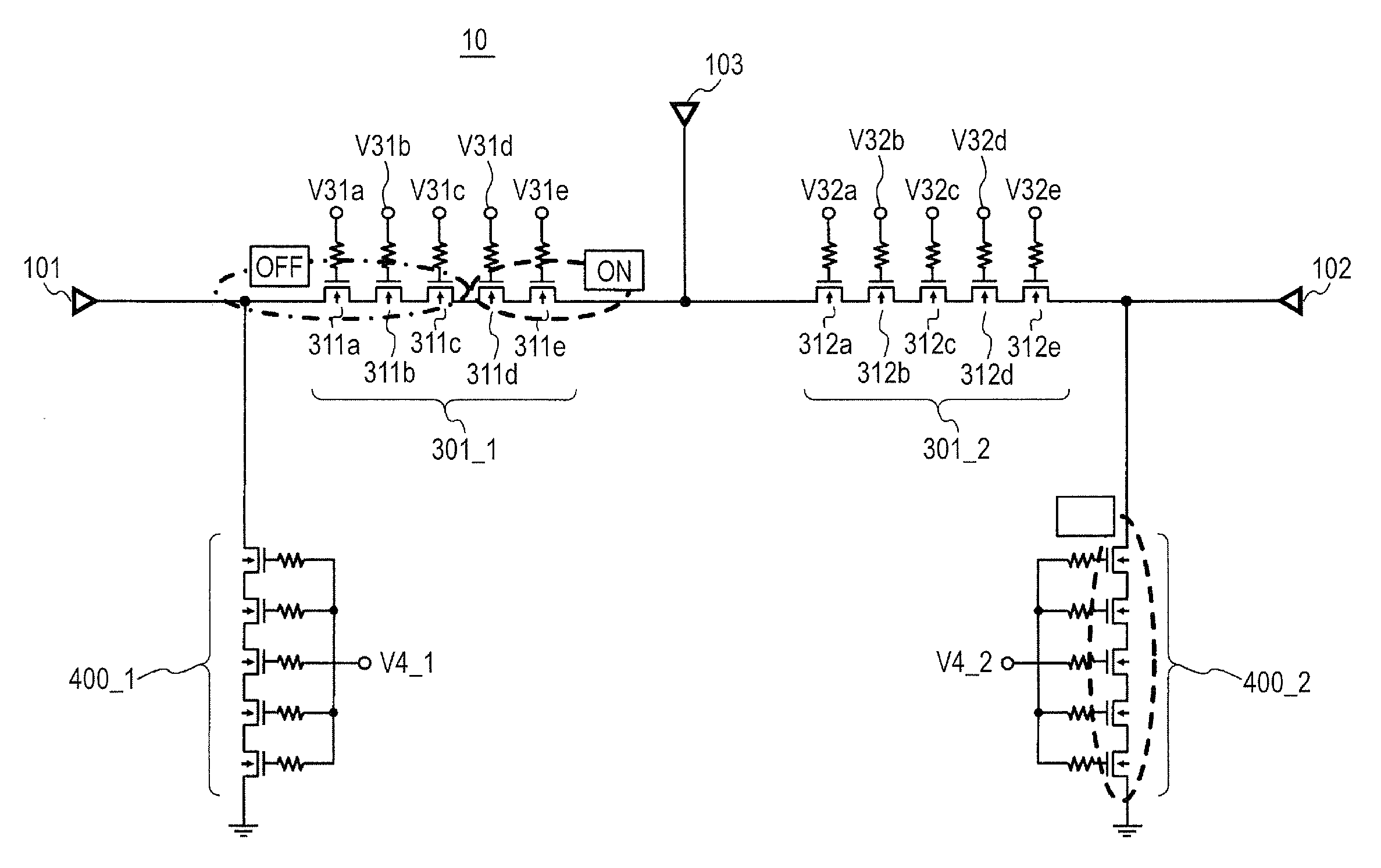

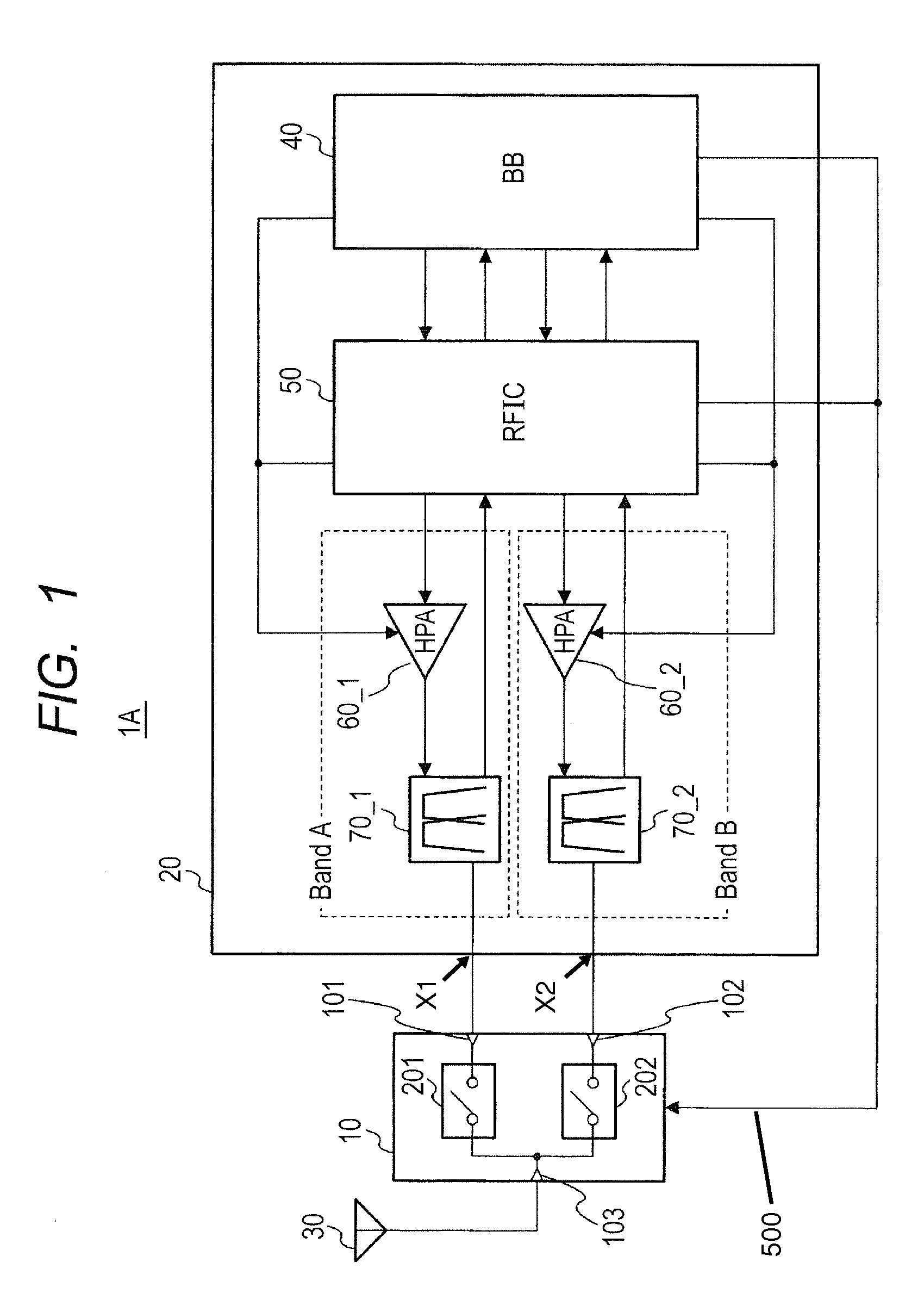

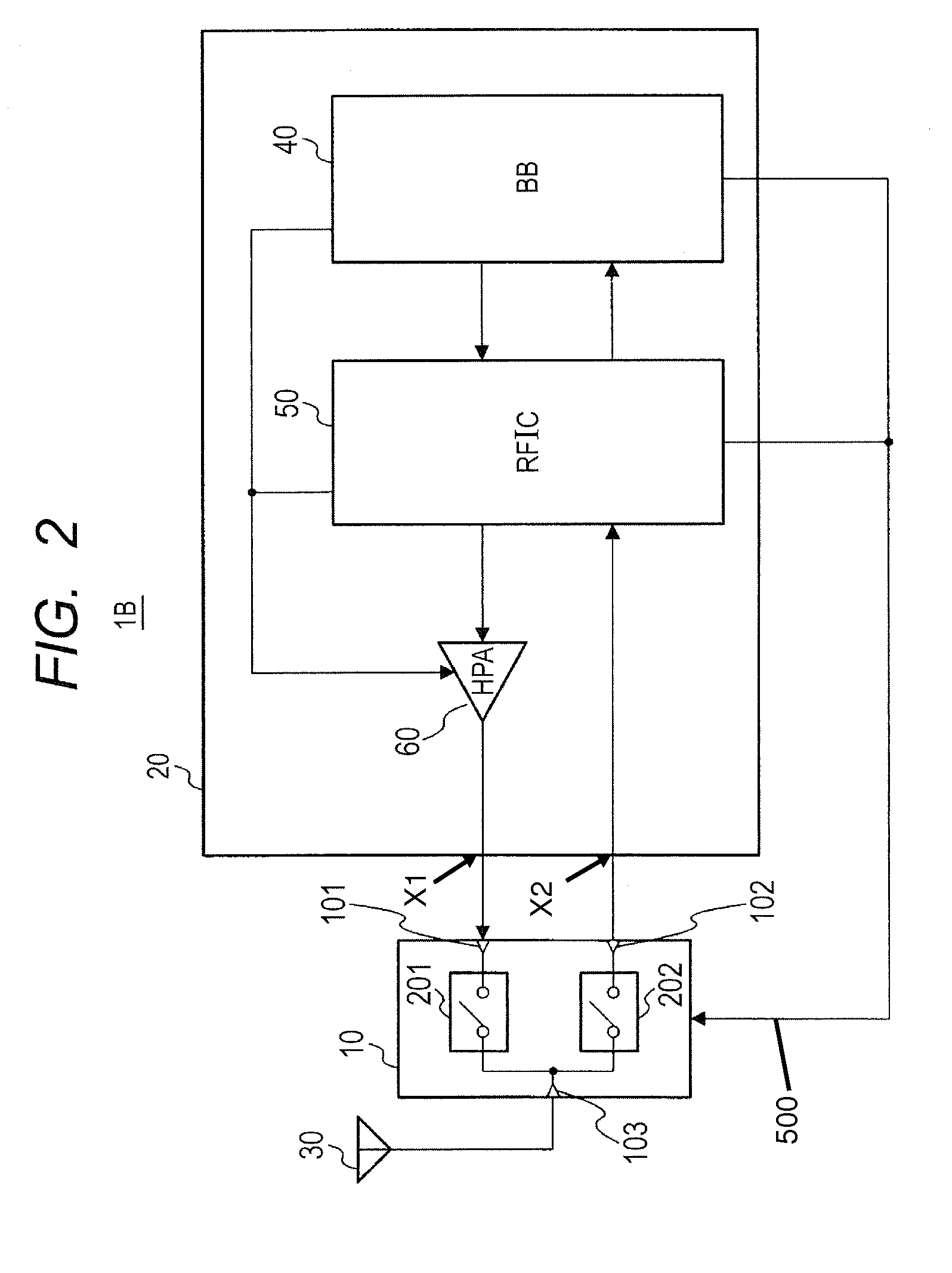

Attenuating antenna switch and communication device

ActiveUS20130072134A1Reduce signalingNarrow dynamic rangeEnergy efficient ICTTransmissionUltrasound attenuationRFIC

An attenuating antenna switch may be used to suppress increase in the scale and power consumption of an RFIC. The antenna switch has a first terminal, a second terminal, and an antenna terminal coupled to the first and second terminals and configured to be connected to an antenna. The first switch switches between a first state in which a high frequency signal is propagated between the first terminal and the antenna terminal, and a second state in which the high frequency signal is interrupted. A second switch switches between the first and second states between the second terminal and the antenna terminal. The first and second switches are controlled in a mutually exclusive manner such that only one of the two switches can be in the first state at any given time. When in the first state, each switch adjusts an attenuation amount of the high frequency signal.

Owner:RENESAS ELECTRONICS CORP

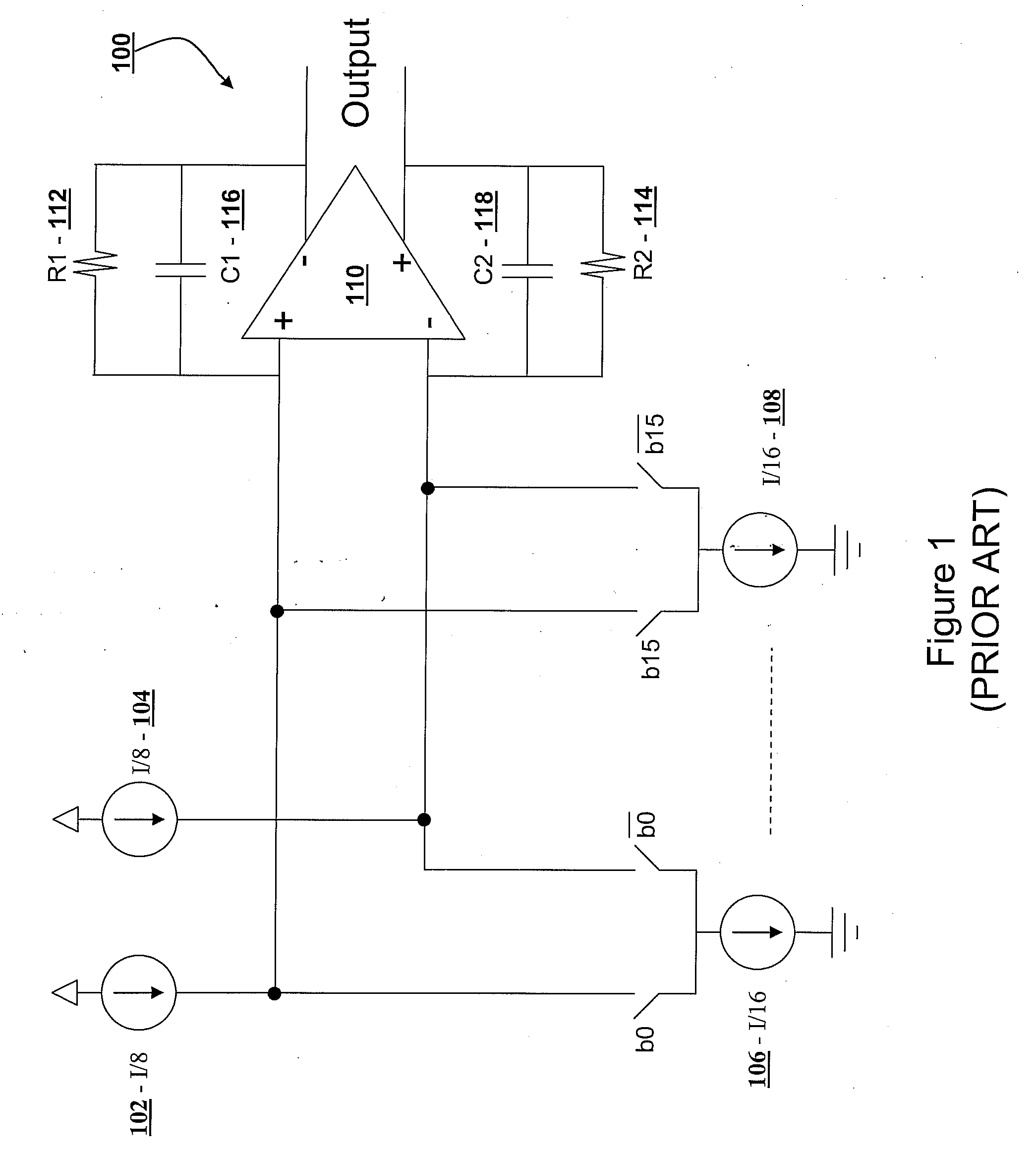

Return-to-hold switching scheme for dac output stage

ActiveUS20080001801A1Increase in areaIncrease in consumptionElectric signal transmission systemsDigital-analogue convertorsAudio power amplifierWave shape

A novel clock control circuit completely removes the inter-symbol interference (ISI) in the DAC output waveform without any significant increase in power consumption and silicon area of the DAC. The novel circuit does not increase the requirement for slew rate and bandwidth of the amplifier.

Owner:ANALOG DEVICES INC

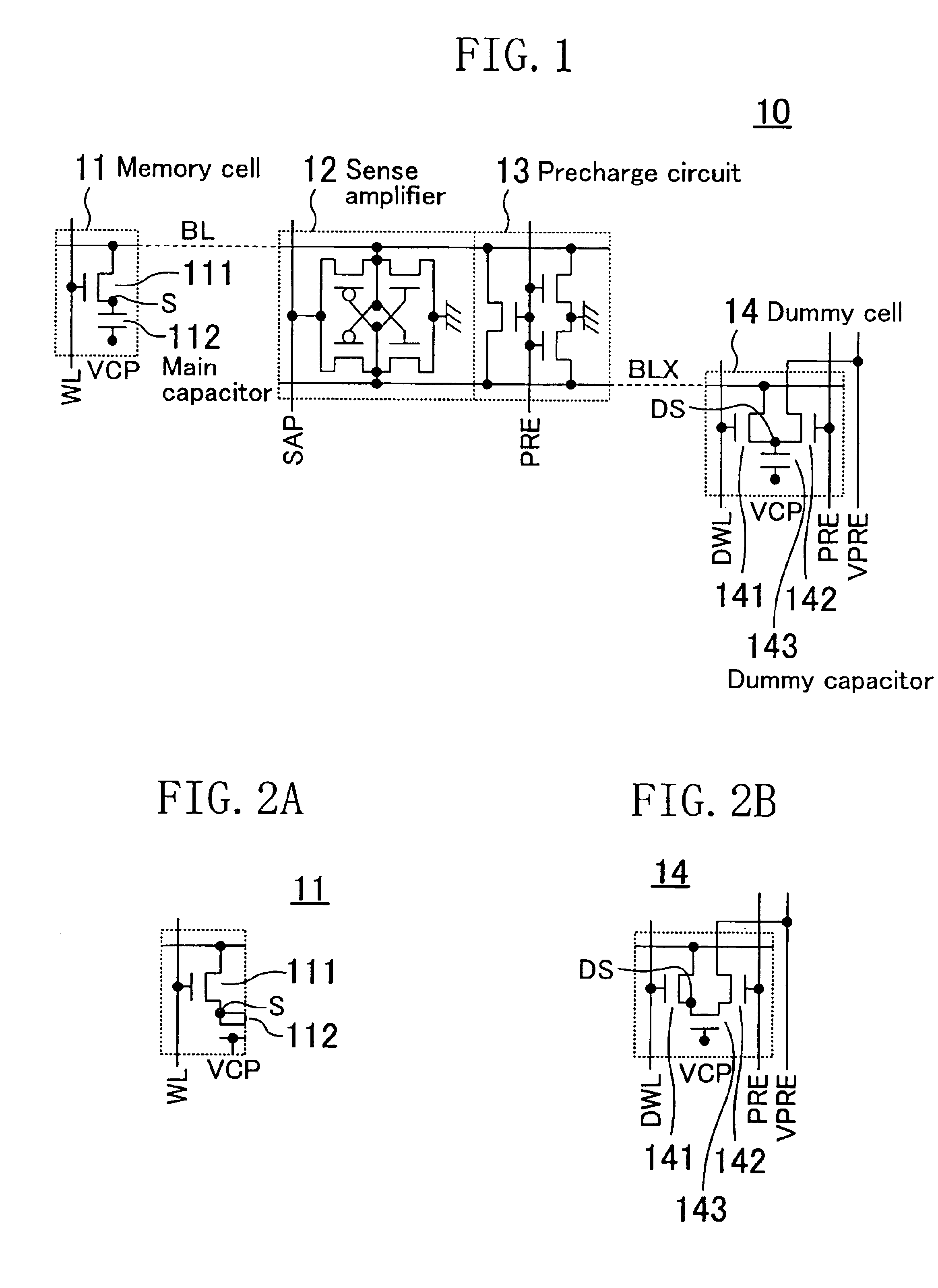

Semiconductor memory circuit

InactiveUS6914840B2Easy to optimizeIncrease in in areaTransistorSolid-state devicesCapacitanceElectricity

Data reading speed of a DRAM is enhanced without causing an increase in the power consumption and in the chip area. To that end, when data is read, a pair of bit lines is precharged to a GND level, while a dummy cell is charged at a power supply voltage. Immediately after a word line and a dummy word line are activated and their respective potentials are increased by the threshold voltage of an access transistor, a main capacitor and a dummy capacitor are electrically connected to the bit lines, thereby allowing the data to fade in. The resultant potential difference between the pair of bit lines is detected and amplified by a sense amplifier, thereby enabling the data to be read. The capacitance of the dummy capacitor is about half of that of the main capacitor, so that the dummy capacitor can be precharged at the power supply voltage.

Owner:PANASONIC CORP

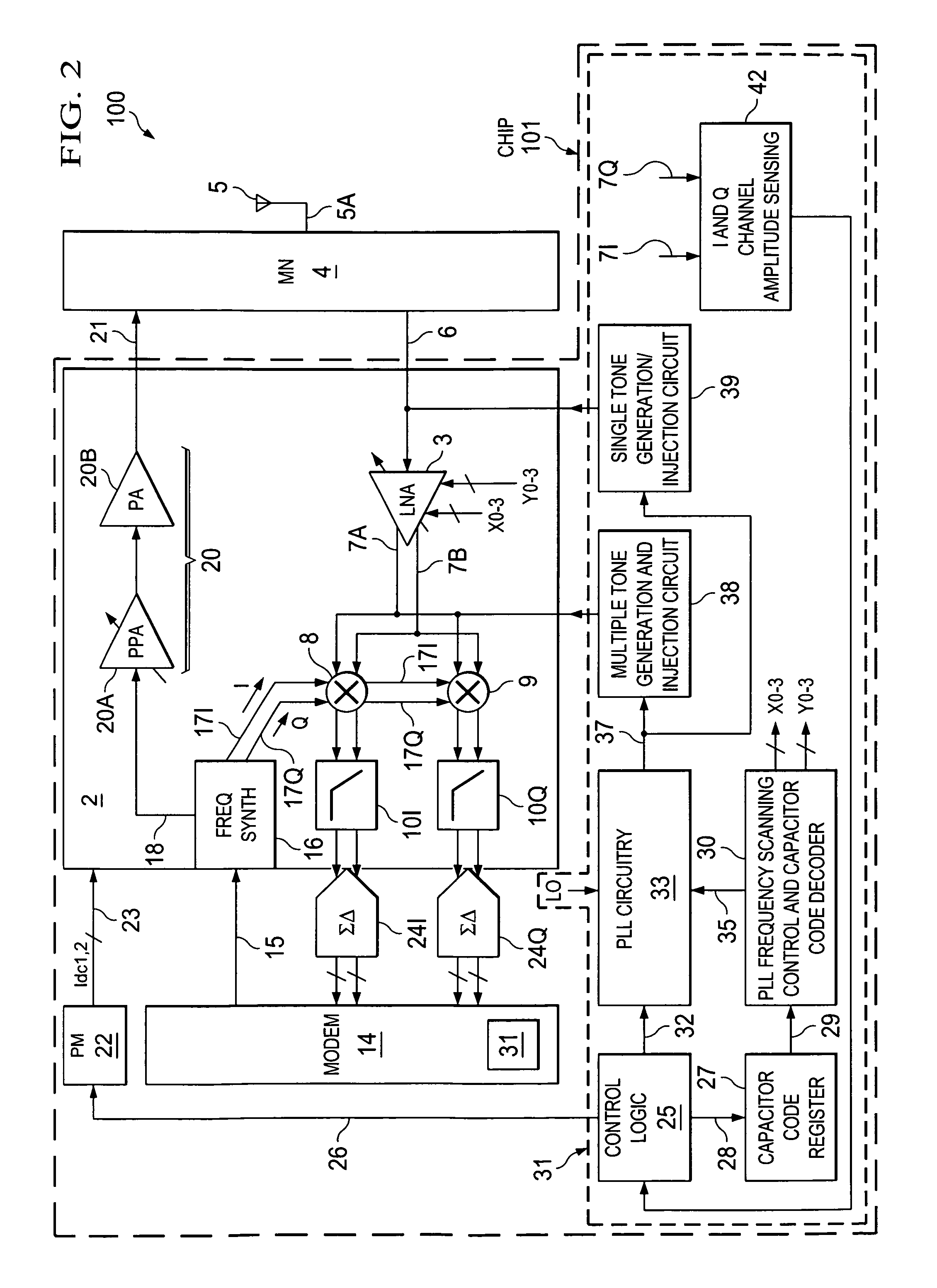

Built in self test and method for RF transceiver systems

ActiveUS20140355655A1Increase in consumptionIncrease in of rangePower managementTransmission monitoringAudio power amplifierTransceiver

Integrated circuit transceiver circuitry (2) includes a first resonant circuit (3A) coupled to a narrowband interface (6,7A,7B,21) between a first amplifier (3,20) and an interfacing circuit (4,8,9,44), including a programmable first reactive element (C) and a second reactive element (L). Amplitude sensing circuitry (42) senses a maximum amplitude of an in-phase signal (I) or a quadrature-phase signal (Q). An on-chip first tone generation circuit (38,38A,38B,38C) generates tones for injection into the in-phase signal and the quadrature-phase signal and operates in response to frequency scanning circuitry (30) and the amplitude sensing circuitry to adjust the first reactive element (C) to calibrate the first resonant circuit to a desired resonant frequency by selectively coupling reactive sub-elements (1,2,4,8 . . . ×Cv) into the first reactive element (C).

Owner:TEXAS INSTR INC

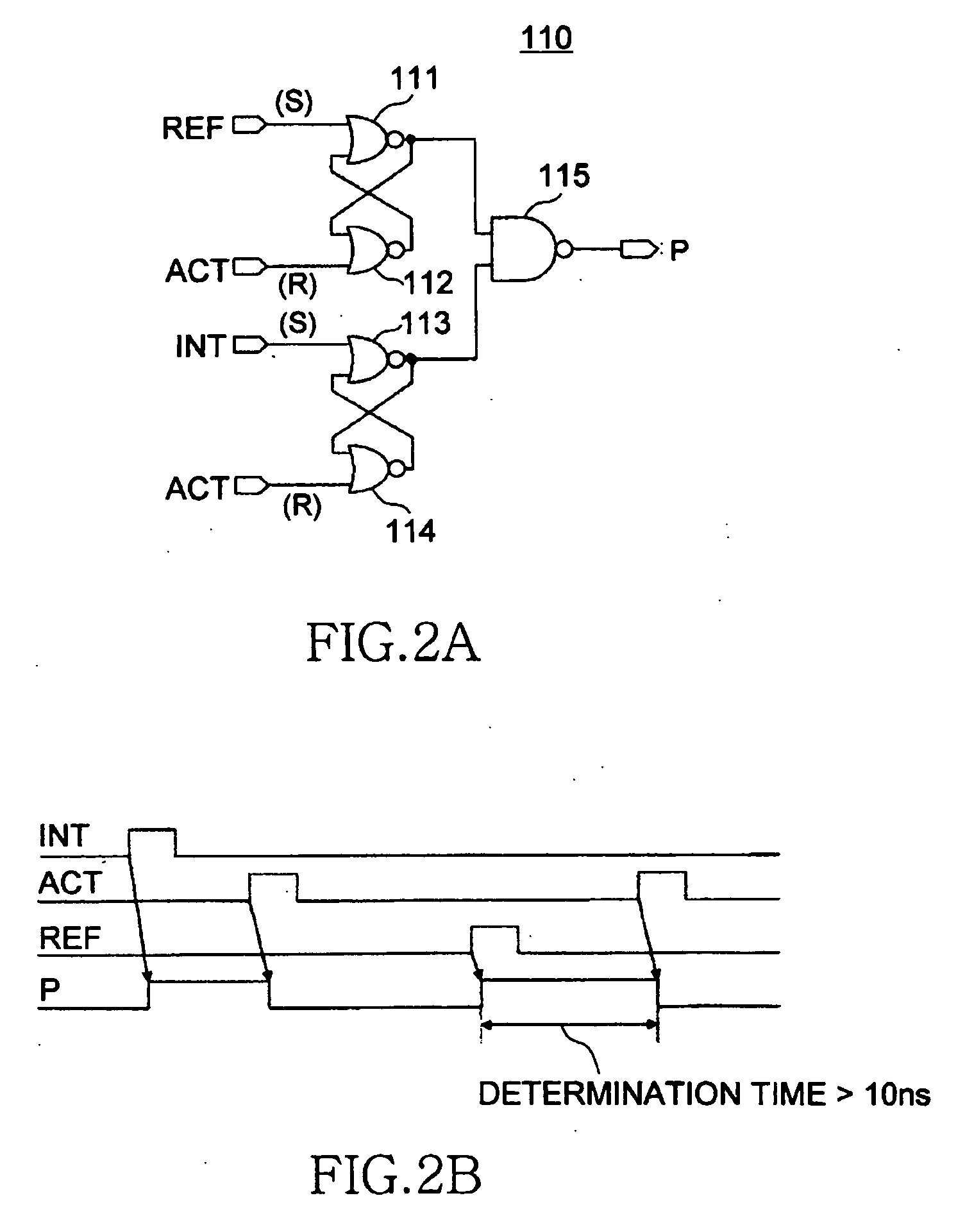

Semiconductor device having delay control circuit

InactiveUS20100085824A1Performance degradation can be preventedIncrease in circuit sizeMultiple input and output pulse circuitsPulse automatic controlEngineeringControl circuit

A first delay circuit and a second delay circuit having different operation conditions from each other, a detection circuit that detects a difference in propagation speed of a pulse signal, which is simultaneously input to the first and second delay circuits, and a setting circuit that generates a selection signal based on a detection result from the detection circuit are provided. The selection signal is supplied to a delay control circuit that generates an operation timing signal by delaying a reference signal, of which a delay amount is controlled by the selection signal. With this arrangement, a necessity to set the delay amount of the delay control circuit with a large design margin can be eliminated considering PVT variation, and as a result, performance degradation can be prevented.

Owner:LONGITUDE LICENSING LTD

Return-to-hold switching scheme for DAC output stage

ActiveUS7307568B1Eliminate inter-symbol interference errorMaintain standardElectric signal transmission systemsDigital-analogue convertorsAudio power amplifierWave shape

A novel clock control circuit completely removes the inter-symbol interference (ISI) in the DAC output waveform without any significant increase in power consumption and silicon area of the DAC. The novel circuit does not increase the requirement for slew rate and bandwidth of the amplifier.

Owner:ANALOG DEVICES INC

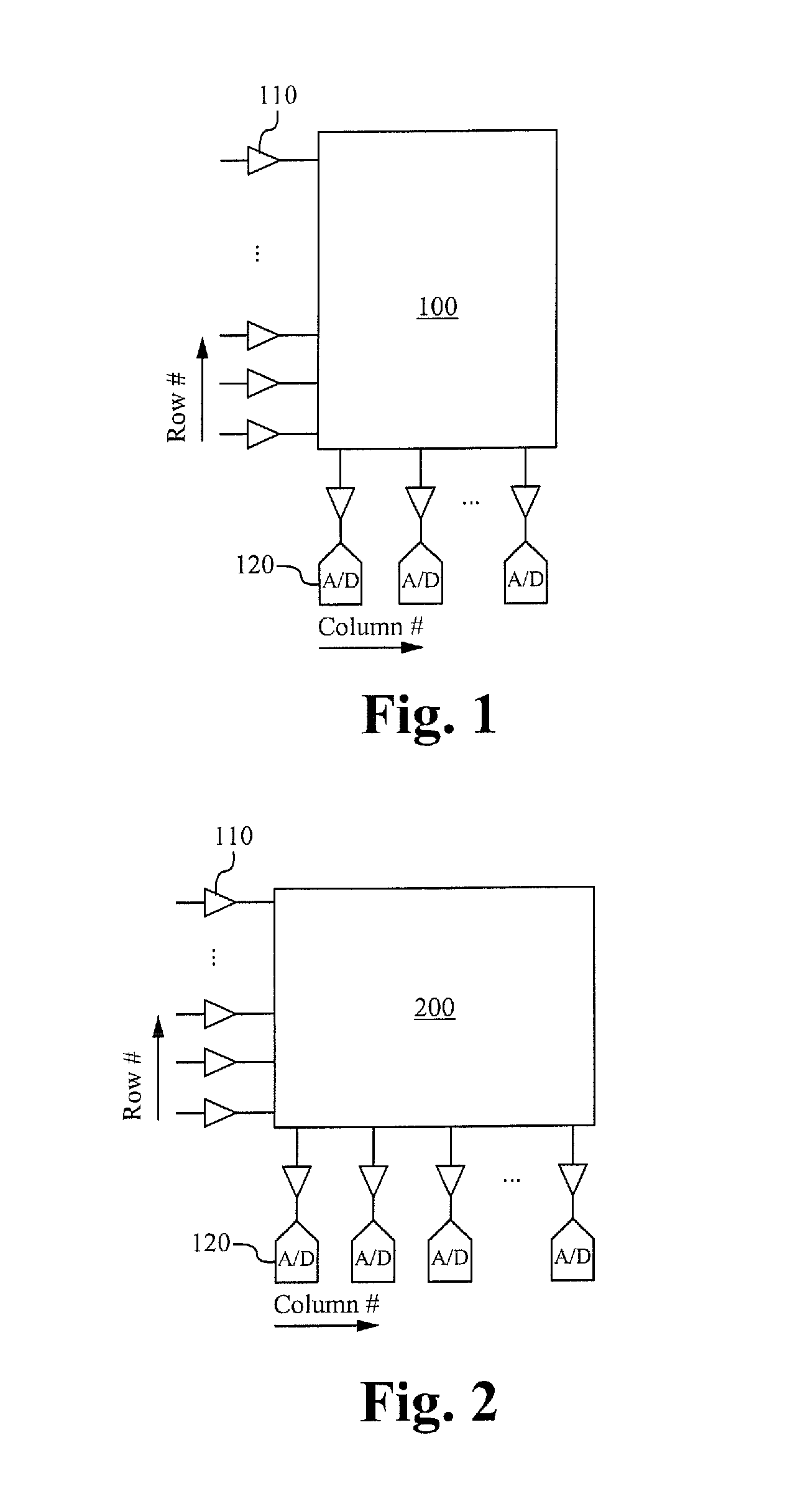

Correlated double sampling circuit and sample hold circuit

ActiveUS20090219058A1Reduce high frequency noiseReduce circuit sizeComputing operations for integral formationTelevision system detailsEngineeringElectrical and Electronics engineering

A correlated double sampling circuit has a sampling capacitor equally divided into a plurality of portions. In the correlated double sampling circuit, an input signal is sampled at a plurality of sampling points and an averaging switch is closed to obtain an average value of a plurality of sampling values obtained by sampling. High frequency noise superimposed on the input signal is thus reduced and a difference between the average values of the plurality of sampling values obtained by sampling is output.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

Mutual capacitance large panel phase shift mitigation

ActiveUS9235280B1Reduce areaReduce consumptionInput/output processes for data processingElectrical conductorPhase shifted

A method of mitigating a phase shift in a mutual capacitance touch screen panel having a plurality of row conductors intersecting with a plurality of column conductors to form a matrix of pixels, the method comprising: driving the row conductors with row drive signals formed from an excitation matrix, wherein each row in the excitation matrix is orthogonal to every other row in the excitation matrix, and the excitation matrix has a dimension larger than the matrix of pixels; sensing signals from the column conductors; and determining the mutual capacitance of the pixels using the sensed signals and an inverse of the excitation matrix. The excitation matrix can be a Hadamard matrix or a modified Hadamard matrix and can comprise a cyclic extension at the end of each row. A different region-specific phase shift can be applied to different clusters of signals.

Owner:QUALCOMM INC

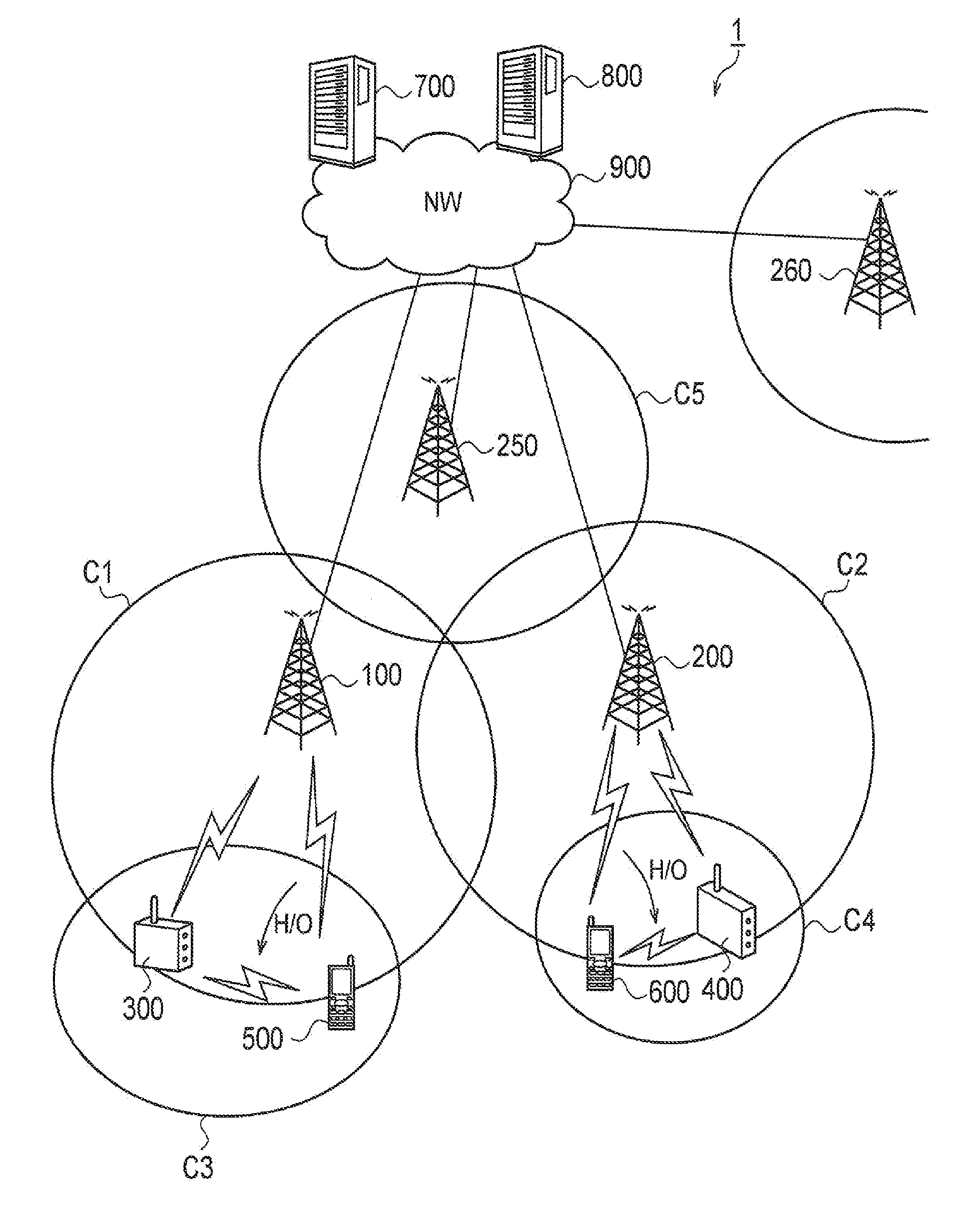

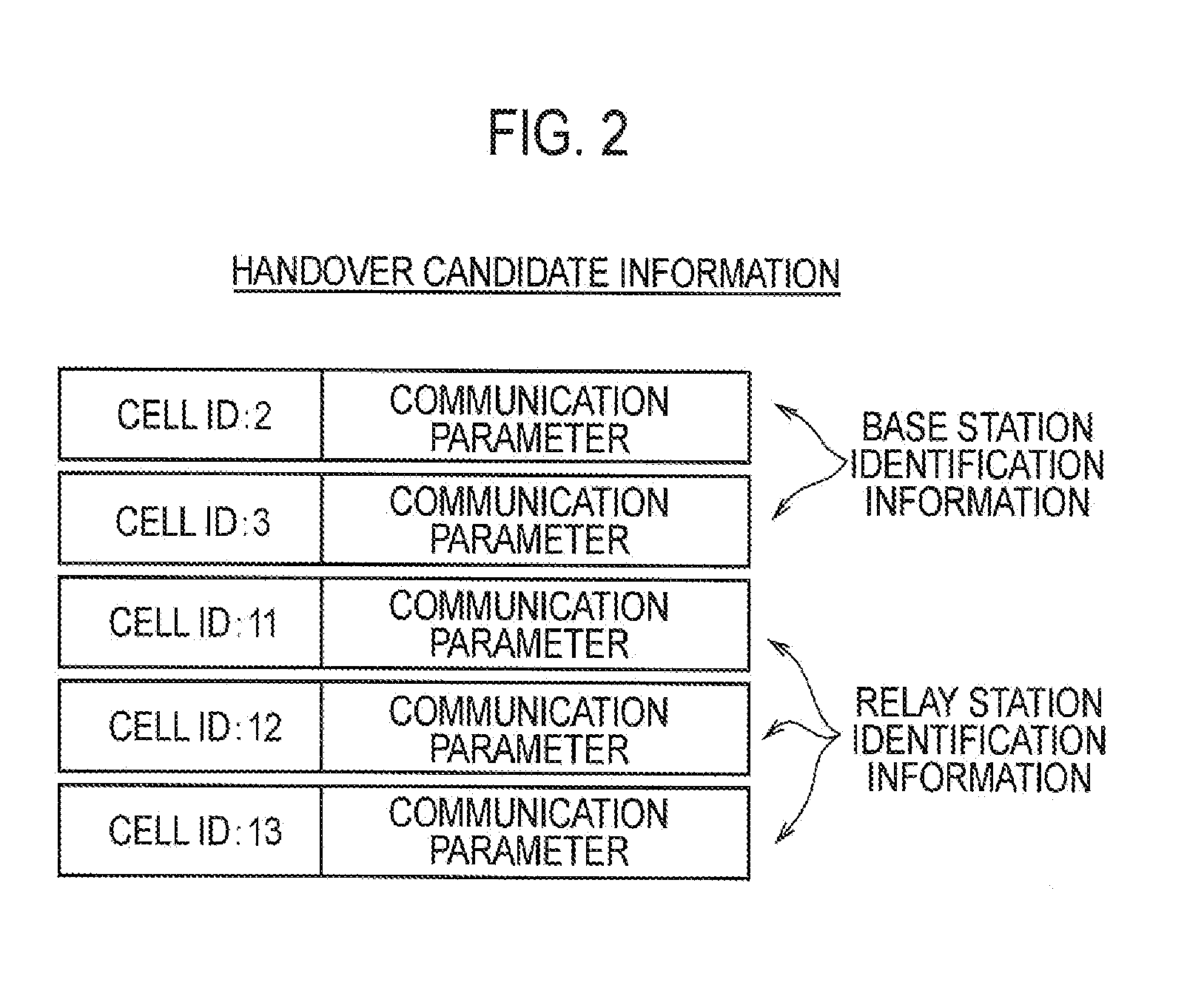

Radio communication system, radio base station, radio relay station and radio communication method

ActiveUS20110159874A1Increase consumptionIncrease loadAssess restrictionNetwork topologiesCommunications systemCell search

The radio communication system has a radio base station, a radio relay station connectable to the radio base station, and a radio terminal configured to connect to the radio base station. The radio base station notifies the radio terminal of identification information for a predetermined number of relay stations based on the number of radio relay stations that can be simultaneously connected to the radio base station. When the radio relay station is connected to the radio base station, identification information for any one of the relay stations is assigned to the radio relay station. The radio terminal performs a cell search based on the relay station identification information.

Owner:KYOCERA CORP

Multilevel amplitude modulated signaling in fibre channel

ActiveUS7477849B2Increase in consumptionIncrease in sizeAmplitude-modulated carrier systemsElectromagnetic transmittersCommunications systemFibre Channel

In a communication system comprising first and second nodes, a multilevel amplitude modulated signaling technique is utilized. The first and second nodes may communicate over a Fibre Channel link or other medium. The first and second nodes comprise respective transmitter and receiver pairs, with the transmitter of the first node configured for communication with the receiver of the second node and the receiver of the first node configured for communication with the transmitter of the second node. The first node is configured to generate a signal for transmission over a serial data channel to the second node, the signal having a multilevel amplitude modulated format in which, within a given clock cycle of the signal, multiple bits are represented by a given signal level.

Owner:AVAGO TECH INT SALES PTE LTD

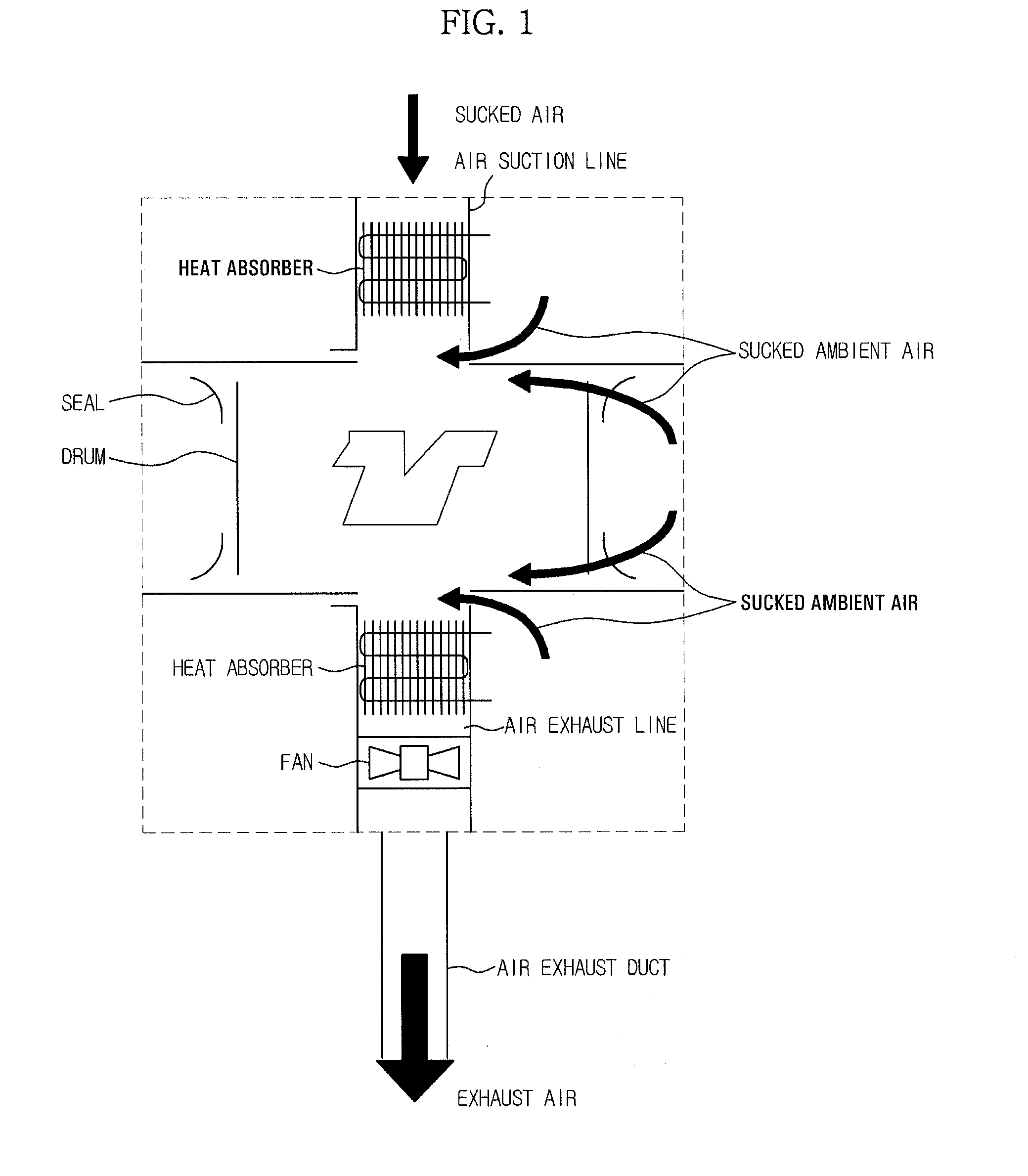

Heat pump type clothes dryer with secondary blowing mechanism

ActiveUS20120144693A1Reduce air volumeIncrease internal pressureDrying solid materials with heatDrying gas arrangementsLine tubingEngineering

A heat pump type clothes dryer compensates for pressure loss caused by a radiator to increase the flow rate of air passing around the radiator, and suppressing introduction of ambient air through gaps formed in air flow lines to avoid degradation in drying capacity, while avoiding an increase in the power consumption or noise of a fan. The clothes dryer includes a drum to accommodate clothes, an air suction or intake line to suck air into the drum, an air exhaust line to exhaust air from the drum, a heat pump circuit including a compressor, a radiator, a pressure reducer, and a heat absorber, where the heat absorber is provided in the air exhaust line, and the radiator is provided in the air suction or intake line, a first blowing mechanism provided in the air exhaust line, and a second blowing mechanism provided in the air suction or intake line.

Owner:SAMSUNG ELECTRONICS CO LTD

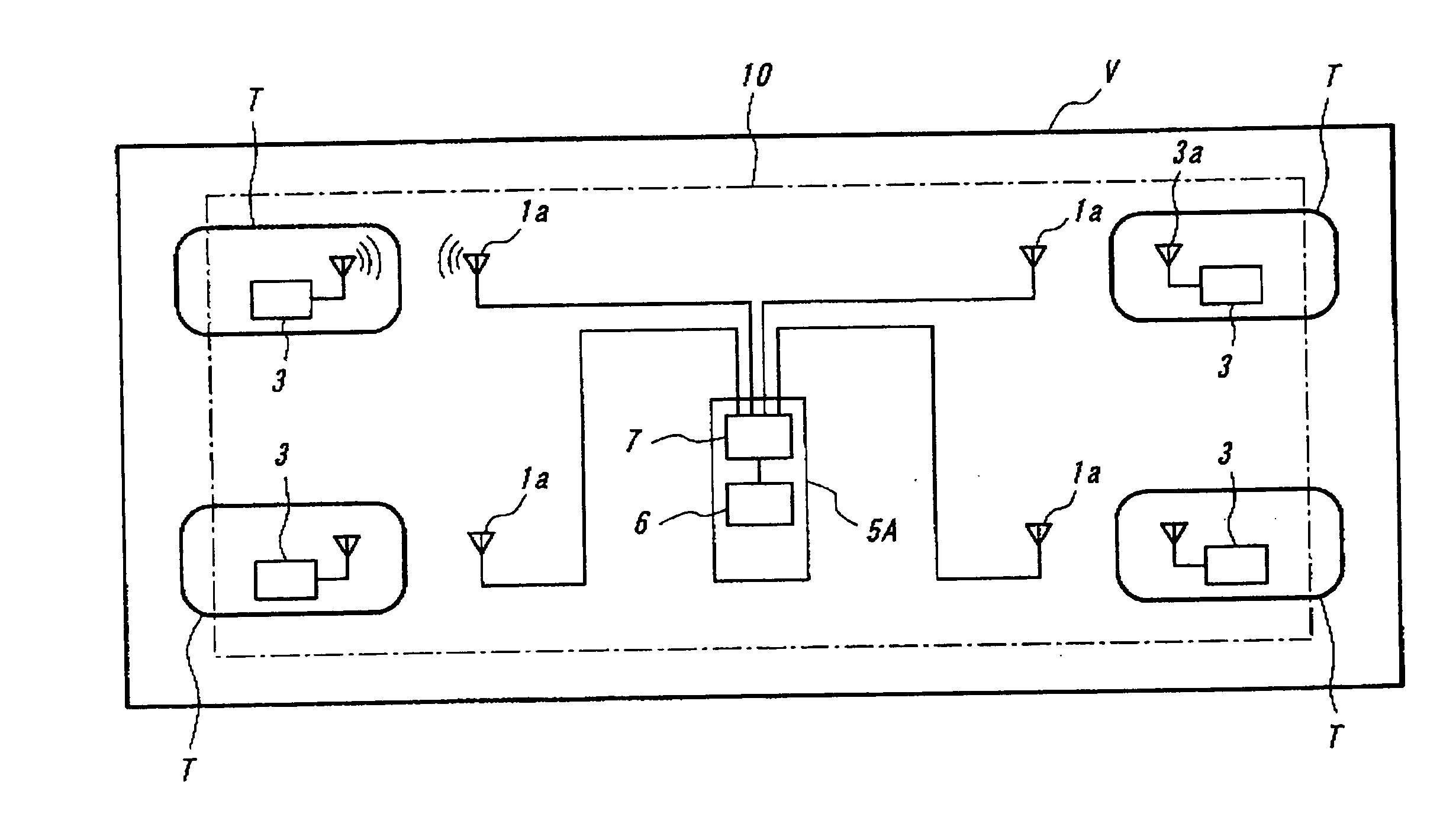

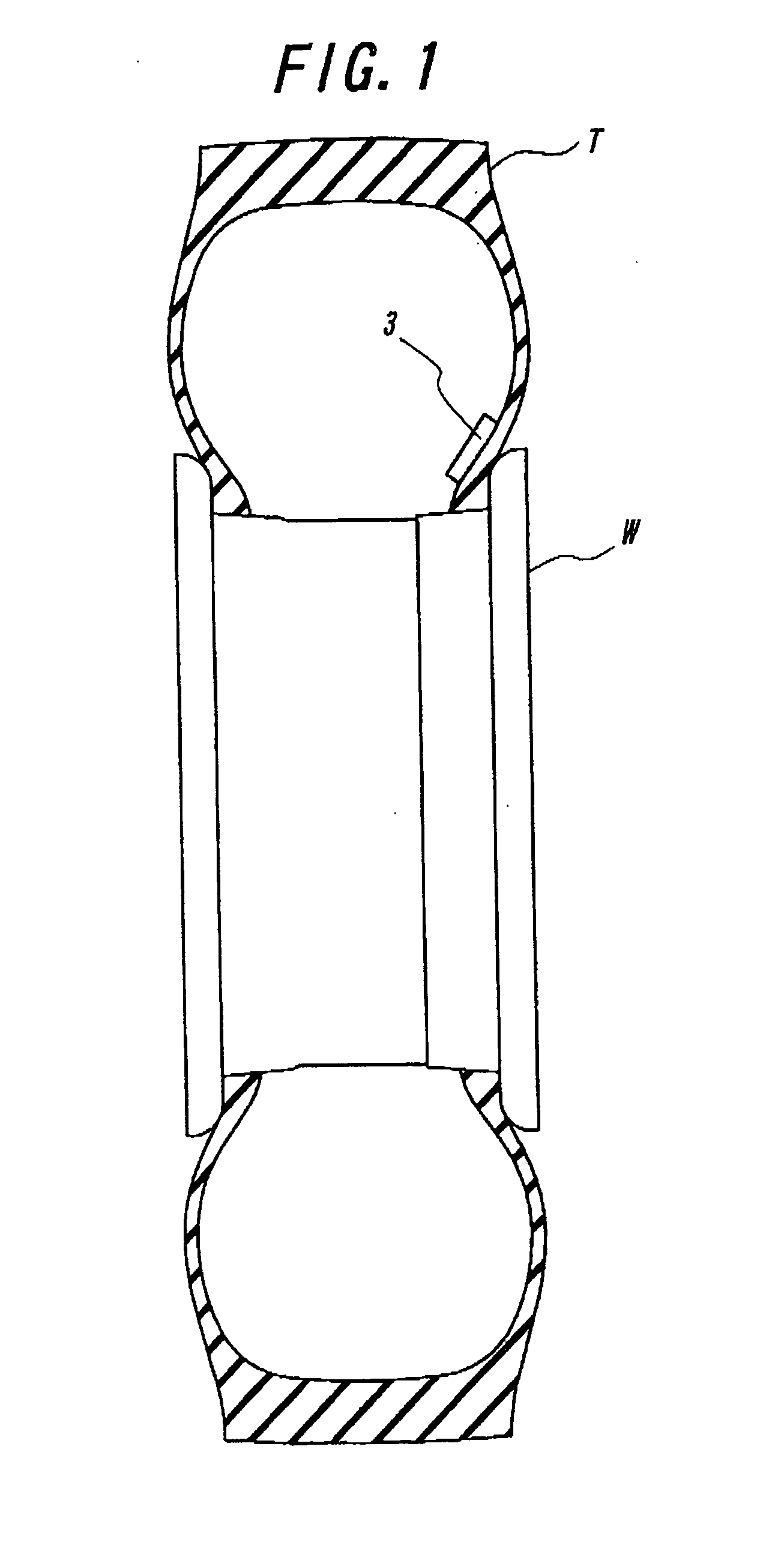

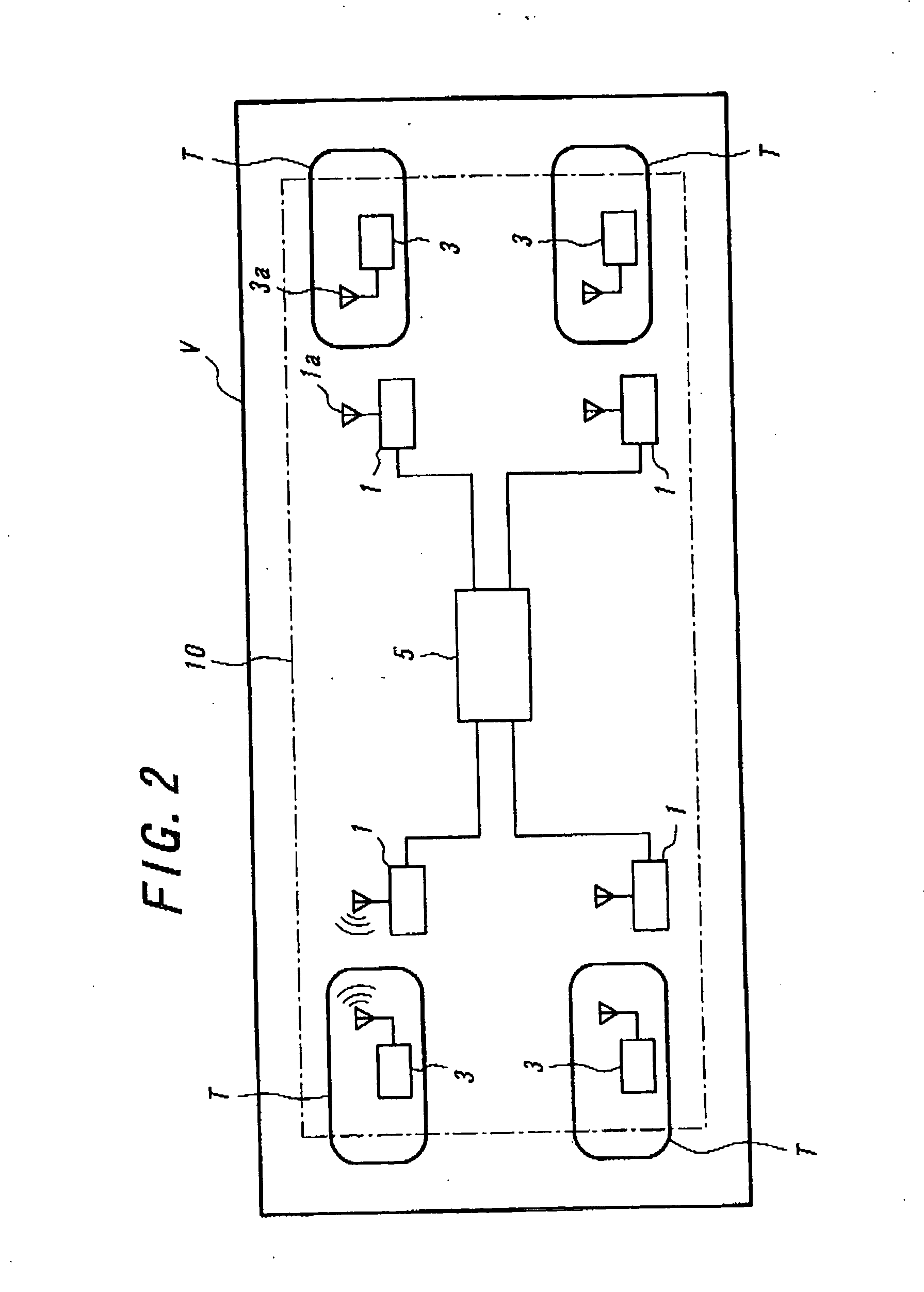

Tire Management System

InactiveUS20070252685A1Increase consumptionIncrease the probability of receivingTyre measurementsEngineeringManagement system

A tire management system includes a sensor module secured to inside of a tire that is mounted on a vehicle, for measuring a tire state value and transmitting the measured data to the vehicle side, and a receiver module secured to the vehicle side for transmitting a signal demanding the measured data to the sensor module at a predetermined cycle and receiving the measured data transmitted from the sensor module. The sensor module measures a tire status value at a predetermined cycle, judges whether the measured data is out of a predetermined normal range, and immediately transmits the measured data and an abnormal state data through a predetermined channel exclusively used for transmitting the abnormal state data to the receiver module, if the data is judged to be out of the normal range. With this structure, if an abnormal state occurs, the receiver module can receive the abnormality without any delay, while preventing shortening of the cell life.

Owner:BRIDGESTONE CORP

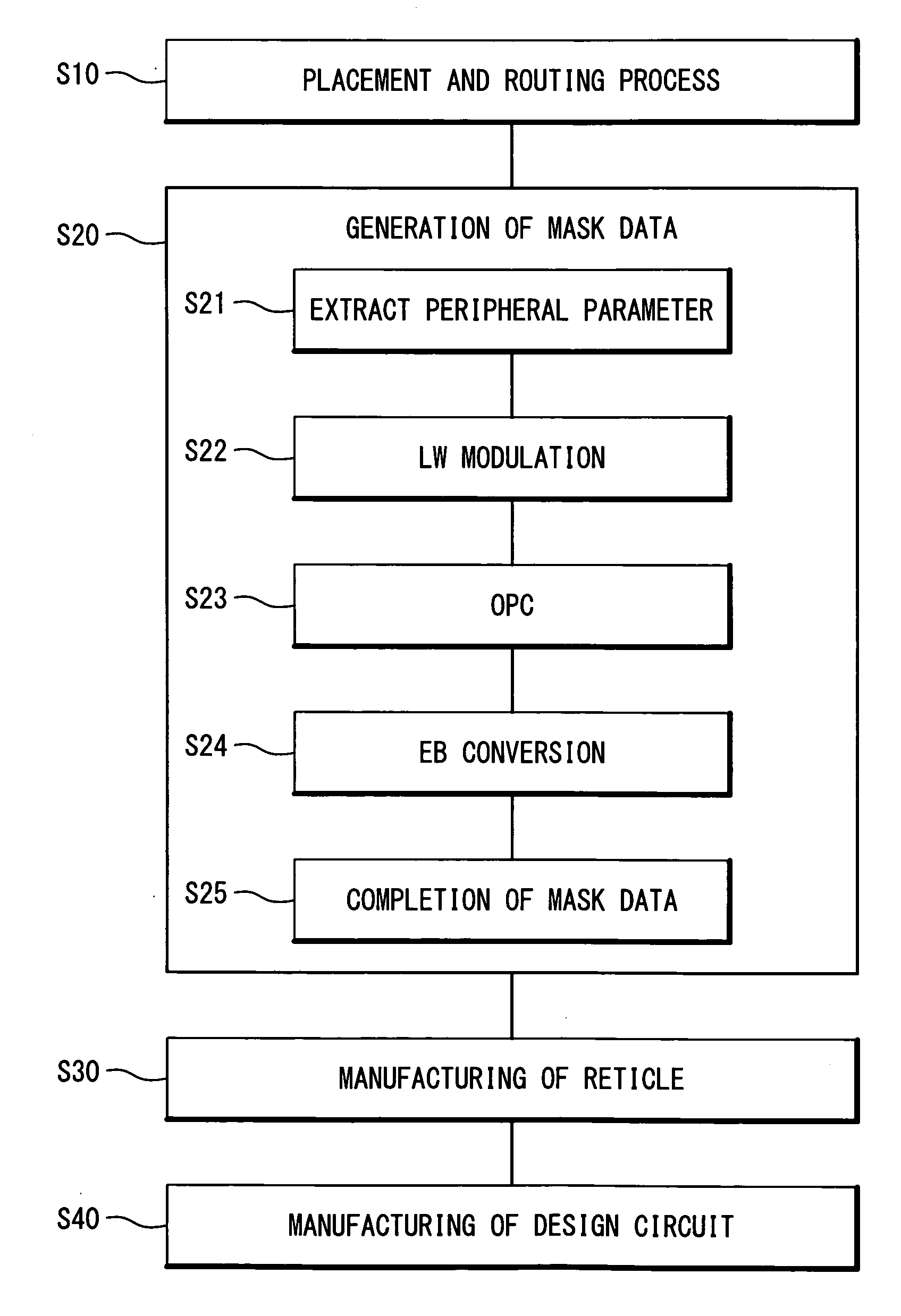

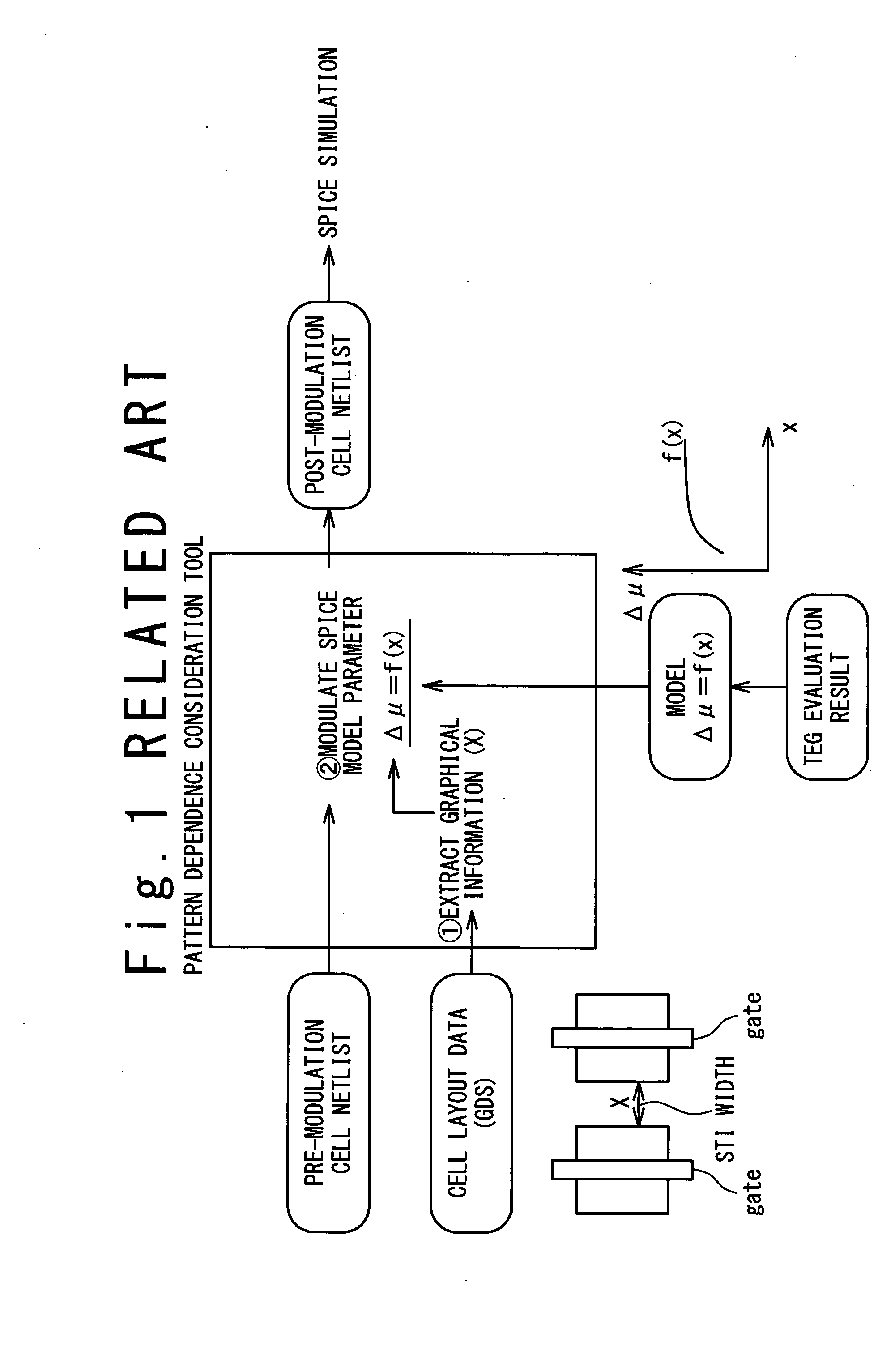

Method of designing semiconductor integrated circuit and mask data generation program

InactiveUS20090024968A1Prevent increase in design/verification TATImprove reliabilityDetecting faulty computer hardwareSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A method of designing a semiconductor integrated circuit includes: generating a layout data indicating a layout; and generating a mask data based on the layout data. The generating the mask data includes: referring to the layout data to extract a parameter that specifies a layout pattern around a target transistor included in the semiconductor integrated circuit, wherein the parameter includes at least a width of a device isolation structure around the target transistor; correcting a gate length and a gate width of the target transistor to offset a variation of a characteristic of the target transistor from a design value, the variation depending on the extracted parameter; and generating the mask data from the layout data in which the gate length and the gate width are corrected.

Owner:RENESAS ELECTRONICS CORP

Synchronization timing detecting apparatus, receiving apparatus, and synchronization timing detecting method

InactiveUS7778363B2Increase in consumptionSmall sizeSynchronisation error detectionSolid-state devicesSelf correlationComputer science

A synchronization timing detecting apparatus includes a correlation calculator configured to generate a first correlation value by calculating a cross-correlation between an input signal being sampled and a reference signal or an auto-correlation of the sampled input signal, an interpolation processor configured to generate a second correlation value interpolating a plurality of the first correlation values having a different combination of sampling points of the input signal, and a detector to detect a synchronization timing based on the first and the second correlation values.

Owner:RENESAS ELECTRONICS CORP

Method and program for designing semiconductor integrated circuit

InactiveUS7913214B2Increase in design/verification TAT can be preventedHigh delay accuracyCAD circuit designSoftware simulation/interpretation/emulationModel parametersCell based

Owner:RENESAS ELECTRONICS CORP

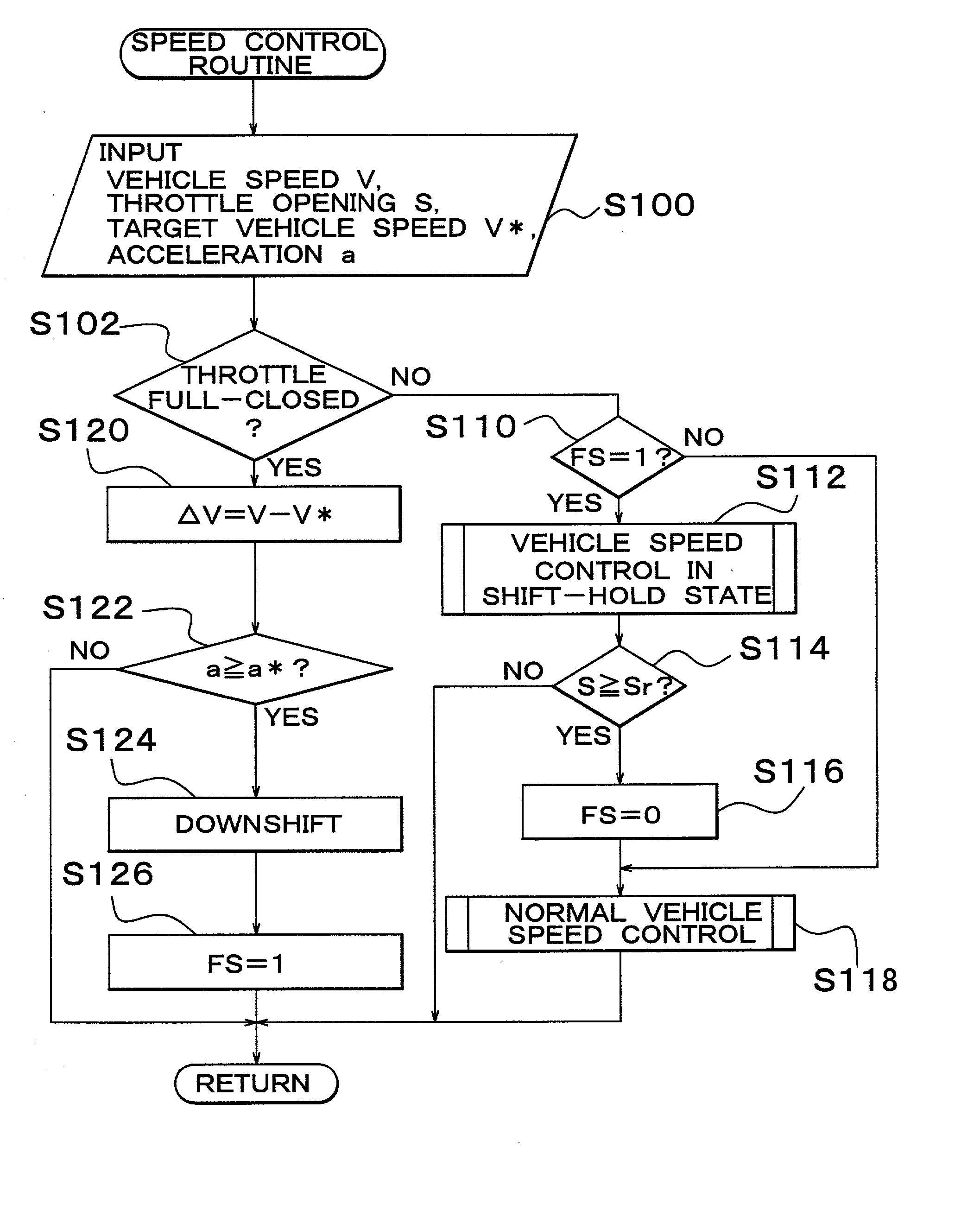

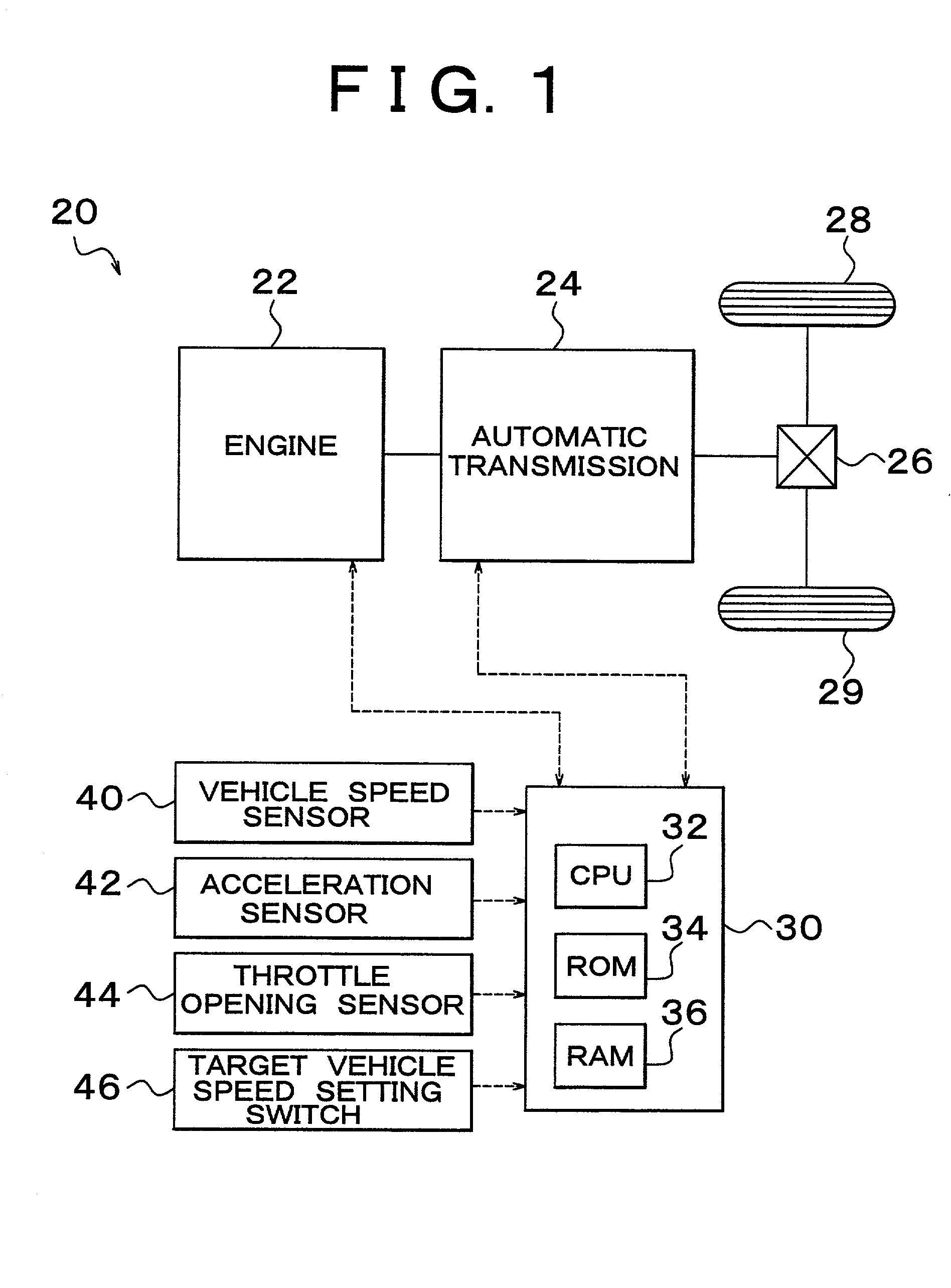

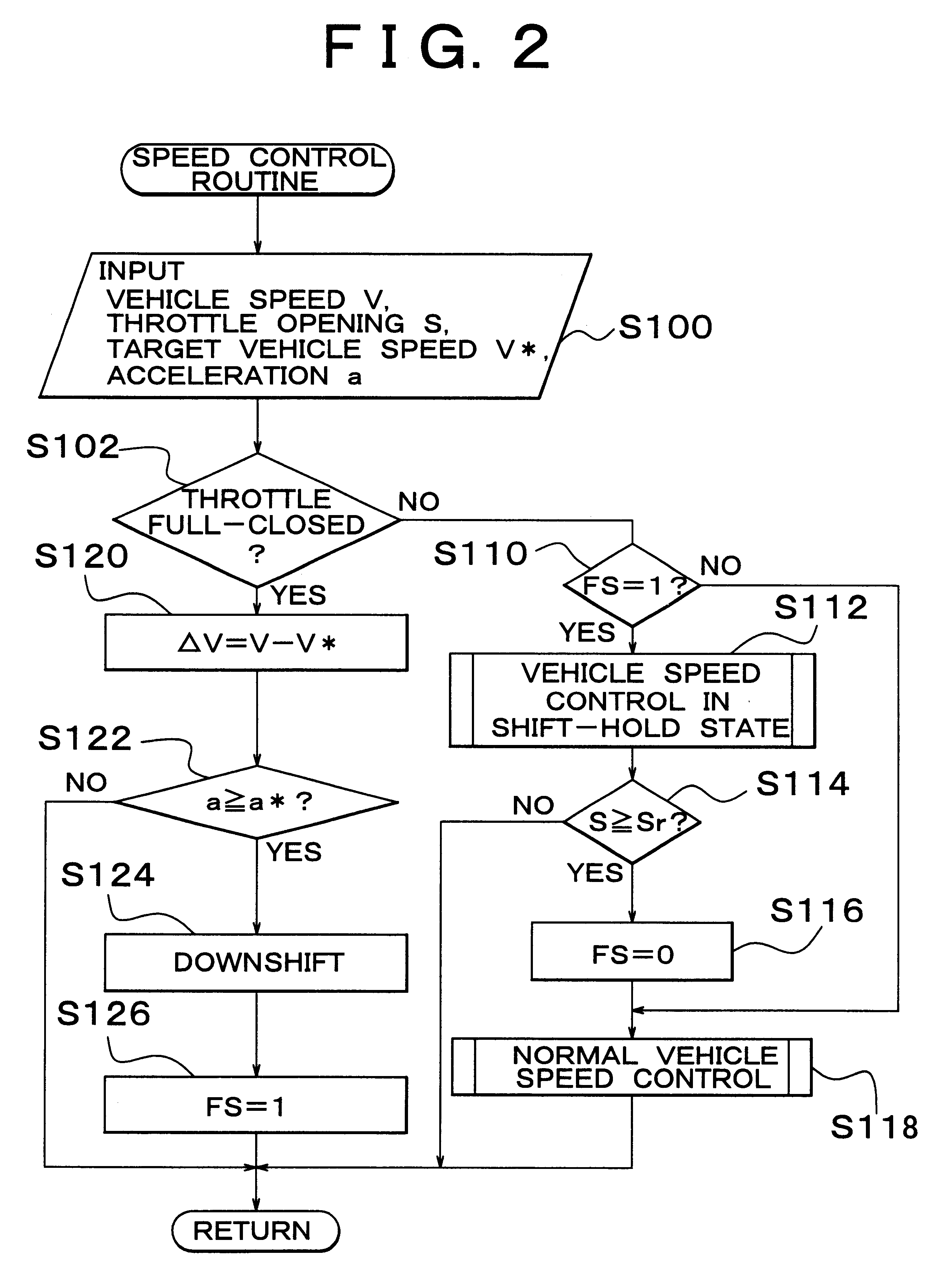

Vehicular constant-speed control apparatus and method of controlling vehicle speed

InactiveUS20020006850A1Acceleration of the vehicle is greatDownshiftVehicle fittingsGearing controlThrottleAcceleration Unit

If a throttle valve is fully-closed, it is determined whether or not a transmission is to be downshifted, by determining whether or not an acceleration of the vehicle is equal to or greater than a downshift criterion value. The downshift criterion value is set as a value that decreases as the vehicle speed deviation, which is a difference between a vehicle speed and a target vehicle speed, increases. By using the downshift criterion value, an increase in the vehicle speed deviation resulting from a quick downshift on a steep downhill can be restrained. On a gentle downhill, a downshift is not performed even if the vehicle speed deviation assumes a significant value. Thus, it becomes possible to inhibit the vehicle speed from becoming lower than the target vehicle speed during a short period after downshift. Accordingly, an increase in fuel consumption and deterioration of noise of the engine can be restrained.

Owner:TOYOTA JIDOSHA KK

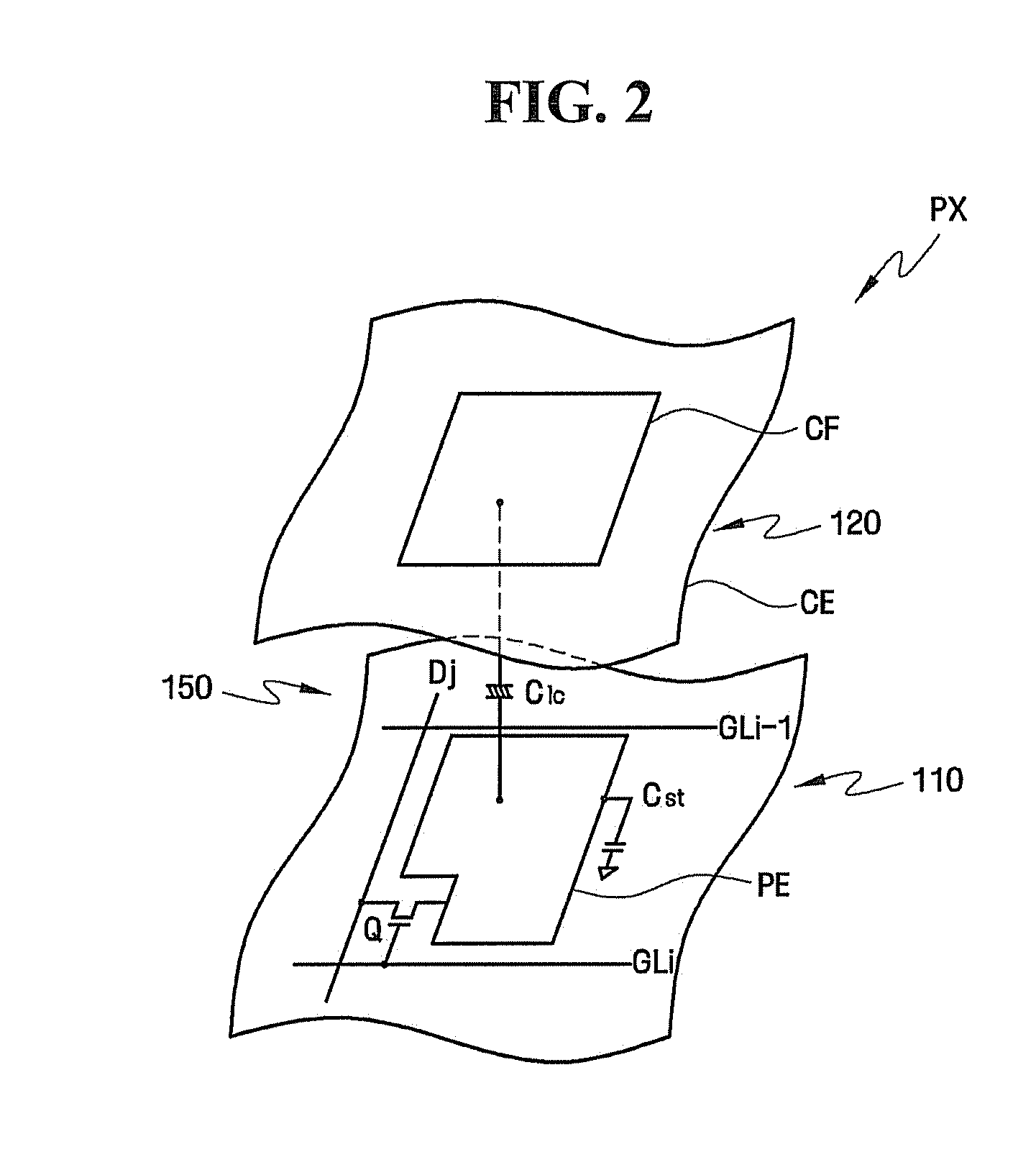

Liquid crystal display and method of driving the same

InactiveUS20100007597A1Minimized increaseIncrease in consumptionCathode-ray tube indicatorsNon-linear opticsLiquid-crystal displayComputer science

A liquid crystal display (“LCD”) includes: a liquid crystal panel, a timing controller which receives previous image data and current image data, corrects or does not correct the current image data according to a reference bit of conversion image data generated using the previous image data, and outputs a display image signal to the liquid crystal panel, and a data driver which receives the display image signal and applies a data voltage corresponding to the display image signal to the liquid crystal panel.

Owner:SAMSUNG DISPLAY CO LTD

Vehicular constant-speed control apparatus and method of controlling vehicle speed

InactiveUS6497637B2Acceleration of the vehicle is greatDownshiftVehicle fittingsGearing controlThrottleAcceleration Unit

Owner:TOYOTA JIDOSHA KK

Method of designing semiconductor integrated circuit and mask data generation program

InactiveUS8056020B2Improve reliabilityHigh yieldDetecting faulty computer hardwareSemiconductor/solid-state device manufacturingSemiconductorDesign values

A method of designing a semiconductor integrated circuit includes: generating a layout data indicating a layout; and generating a mask data based on the layout data. The generating the mask data includes: referring to the layout data to extract a parameter that specifies a layout pattern around a target transistor included in the semiconductor integrated circuit, wherein the parameter includes at least a width of a device isolation structure around the target transistor; correcting a gate length and a gate width of the target transistor to offset a variation of a characteristic of the target transistor from a design value, the variation depending on the extracted parameter; and generating the mask data from the layout data in which the gate length and the gate width are corrected.

Owner:RENESAS ELECTRONICS CORP

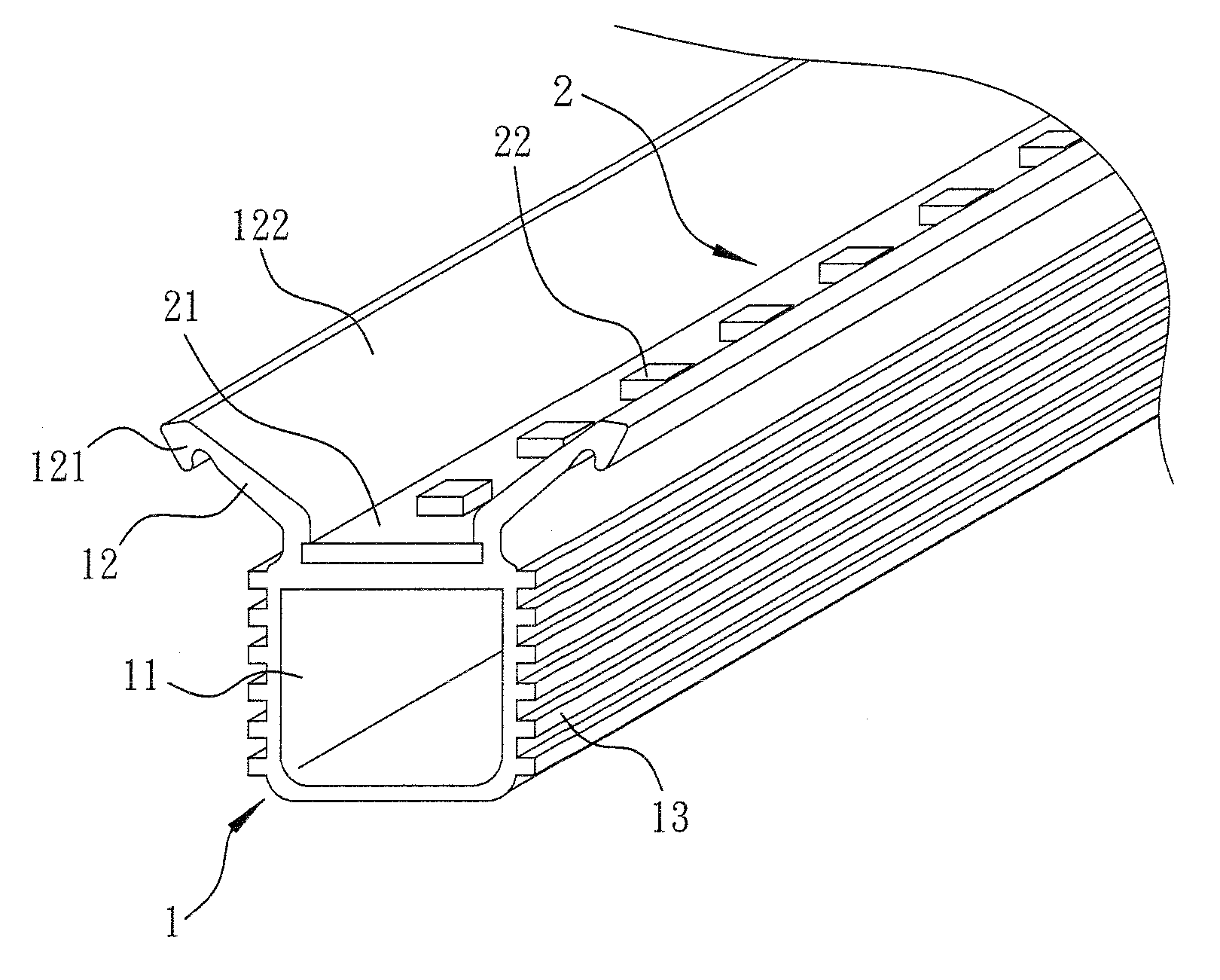

Optical cavity structure of LED lighting apparatus

InactiveUS8899778B2Convenient lightingIncrease in consumptionNon-electric lightingPoint-like light sourceOptical cavityEffect light

The present invention provides an optical cavity structure of an LED lighting apparatus comprising a base, a light reflector, LED module, and a light cover. The light reflector can be integrally formed with the base or an independent unit. An optical cavity is constructed by the base, light reflector and light cover altogether, and the LED module is attached to the base received within the optical cavity. The light reflector can be symmetrical with inclined angle or as a conical shape provided on two sides opposing to the direction of light from the LED module. The inner surface of the light reflector is a light reflecting surface. The light cover is attached to the light reflector. As a result, the light from the LED is gathered and reflected by the light reflecting surface via the angle and shape of the light reflector to achieve an enhanced luminance range and illumination.

Owner:YANG MEI LING +1

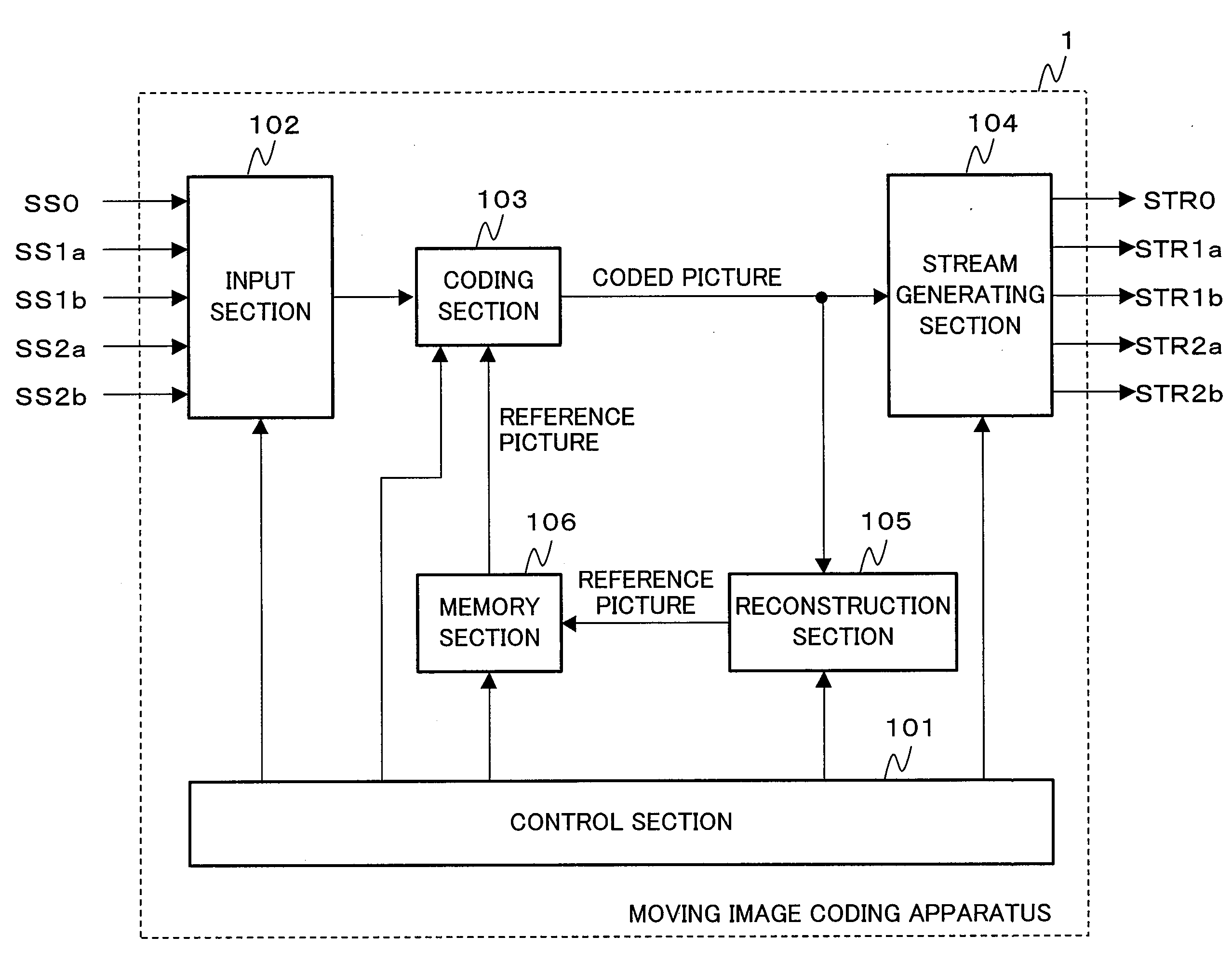

Method and apparatus for coding moving image and imaging system

InactiveUS20090052551A1Increase in circuit scale and power consumptionIncrease in consumptionPulse modulation television signal transmissionPicture reproducers using cathode ray tubesFrame rateImage signal

A moving image signal is coded so that a coded stream is generated. Coded pictures are periodically eliminated from the coded moving image signal so that another coded stream associated with another moving image signal having a frame rate different from the coded moving image signal is generated.

Owner:PANASONIC CORP

Built in self test and method for RF transceiver systems

ActiveUS9136899B2Increase in consumptionIncrease in of rangePower managementTransmission monitoringElectricityTransceiver

Integrated circuit transceiver circuitry (2) includes a first resonant circuit (3A) coupled to a narrowband interface (6,7A,7B,21) between a first amplifier (3,20) and an interfacing circuit (4,8,9,44), including a programmable first reactive element (C) and a second reactive element (L). Amplitude sensing circuitry (42) senses a maximum amplitude of an in-phase signal (I) or a quadrature-phase signal (Q). An on-chip first tone generation circuit (38,38A,38B,38C) generates tones for injection into the in-phase signal and the quadrature-phase signal and operates in response to frequency scanning circuitry (30) and the amplitude sensing circuitry to adjust the first reactive element (C) to calibrate the first resonant circuit to a desired resonant frequency by selectively coupling reactive sub-elements (1,2,4,8 . . . ×Cv) into the first reactive element (C).

Owner:TEXAS INSTR INC

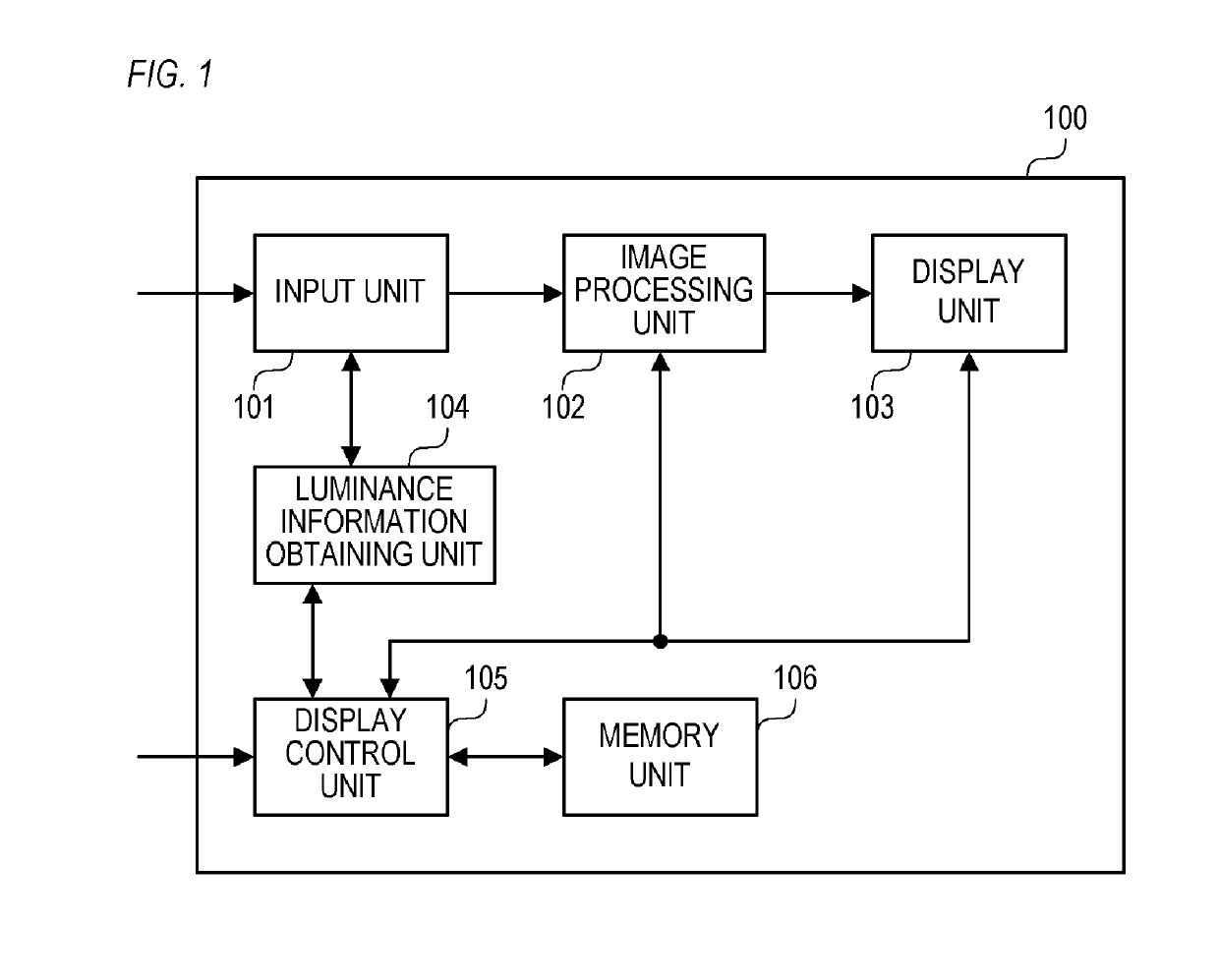

Display control apparatus and display control method

ActiveUS20190295454A1Increase in in display luminanceIncrease in power consumptionStatic indicating devicesMachine execution arrangementsPower limitsComputer science

A display control apparatus includes: an obtaining unit that obtains average luminance information representing a maximum period average luminance value which is a maximum value of average luminance in target image data for each frame in a first period; and a setting unit that sets one of a first control mode for displaying an image based on the target image data with carrying out power limiting processing for reducing display luminance of each frame so that power consumption by a display unit is equal to or less than a predetermined power threshold value and a second control mode for displaying the image without carrying out the power limiting processing, wherein the setting unit sets the second control mode in a case where the maximum period average luminance value is higher than a first threshold value on the basis of the average luminance information.

Owner:CANON KK

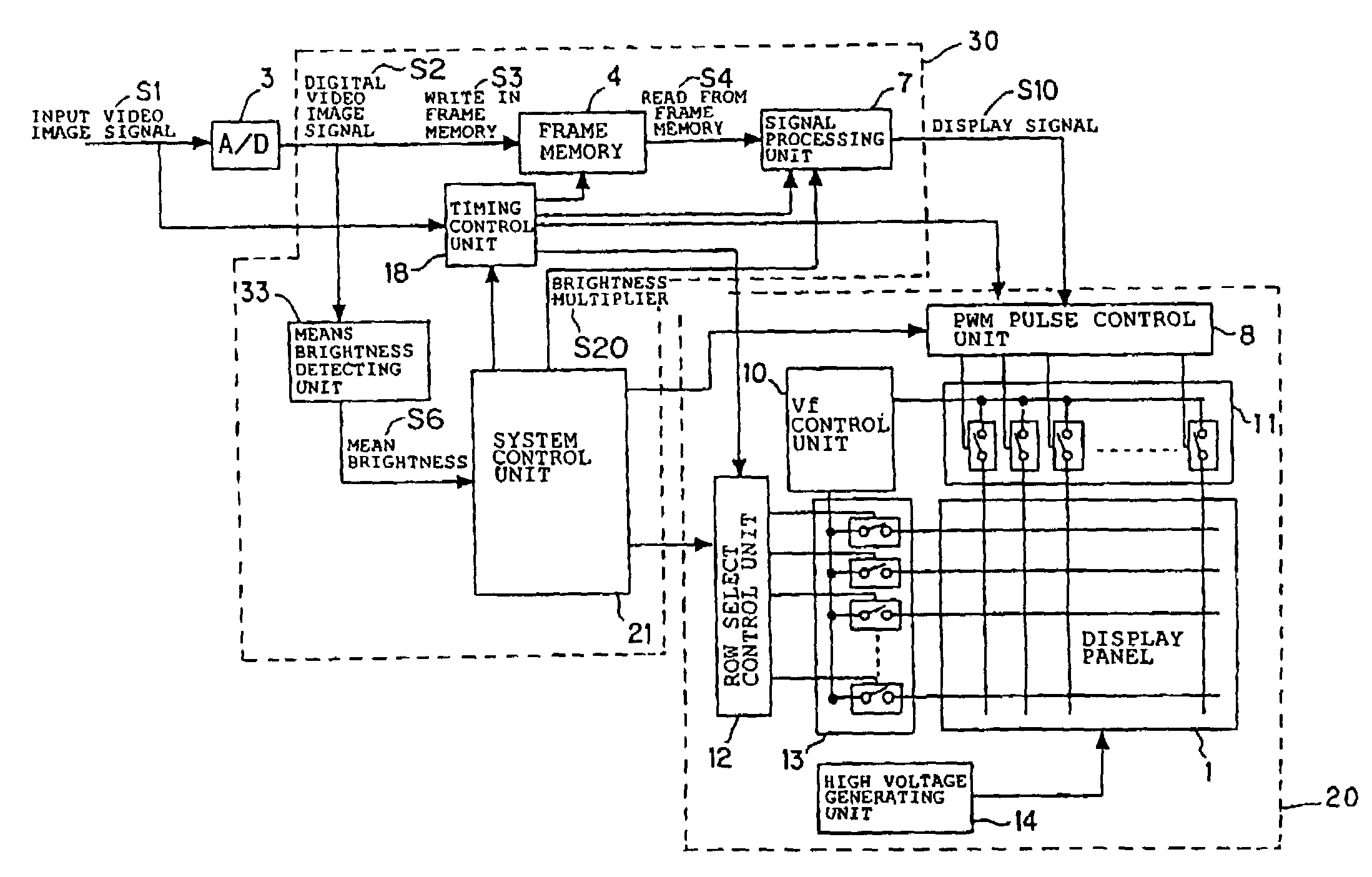

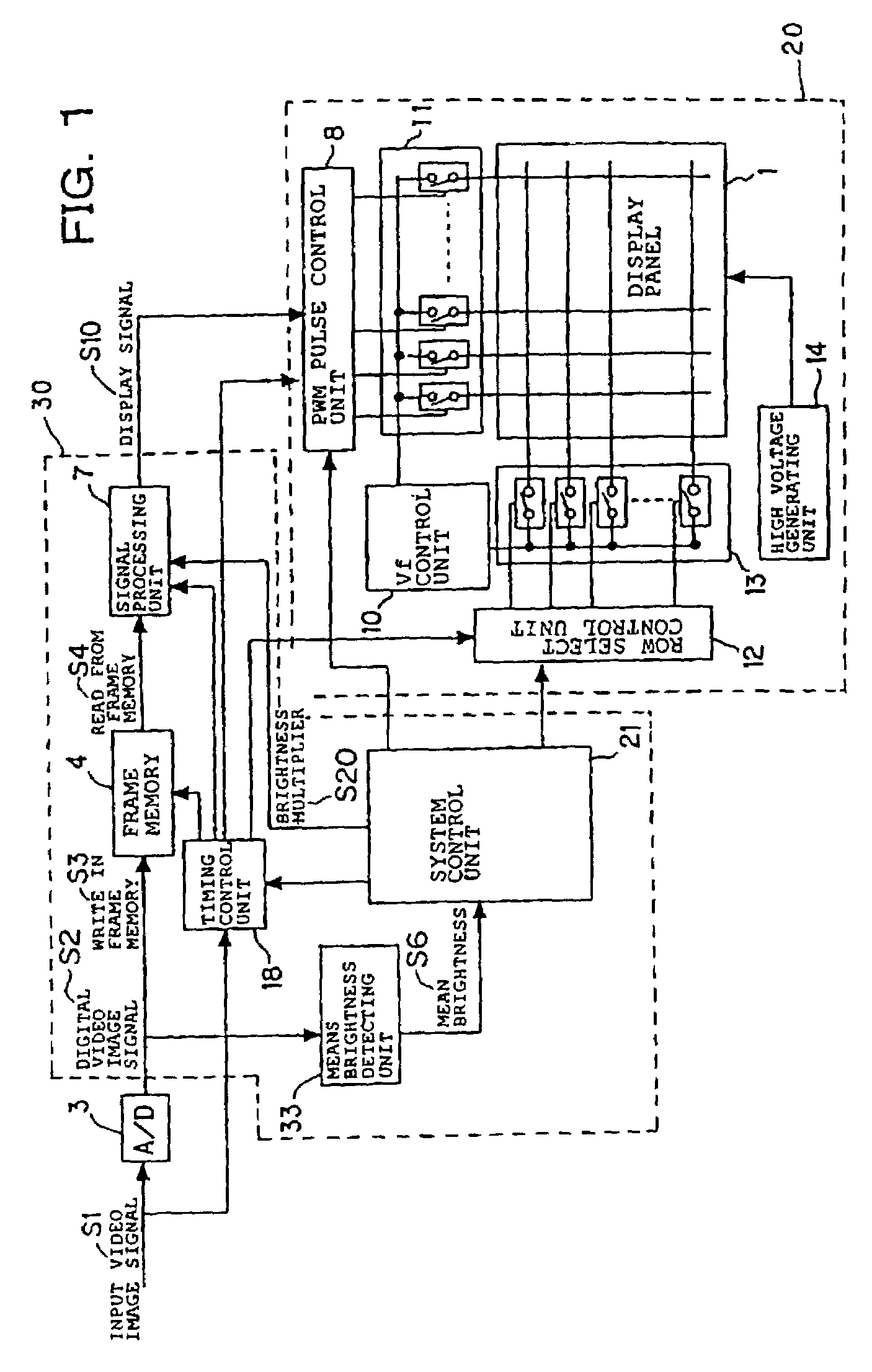

Drive control device for a display apparatus, video image display apparatus and method of controlling the driving of the video image display apparatus

InactiveUS7679626B2Increase in of display surfaceIncrease in power consumptionTelevision system detailsColor television detailsComputer graphics (images)Execution control

In a drive control device 30 for controlling the driving of a display apparatus 20 that displays a video image on the basis of an input video image signal S1 (or S2), there is provided brightness control means (33, 21, 7) for controlling a display brightness in the display apparatus 20 in accordance with brightness information S6 corresponding to the mean brightness of the video image, and the brightness control means (33, 21, 7) performs a control operation so that the display brightness of the video image display variably changes a plurality of times within respective one-frame scanning periods of the video image display.

Owner:CANON KK

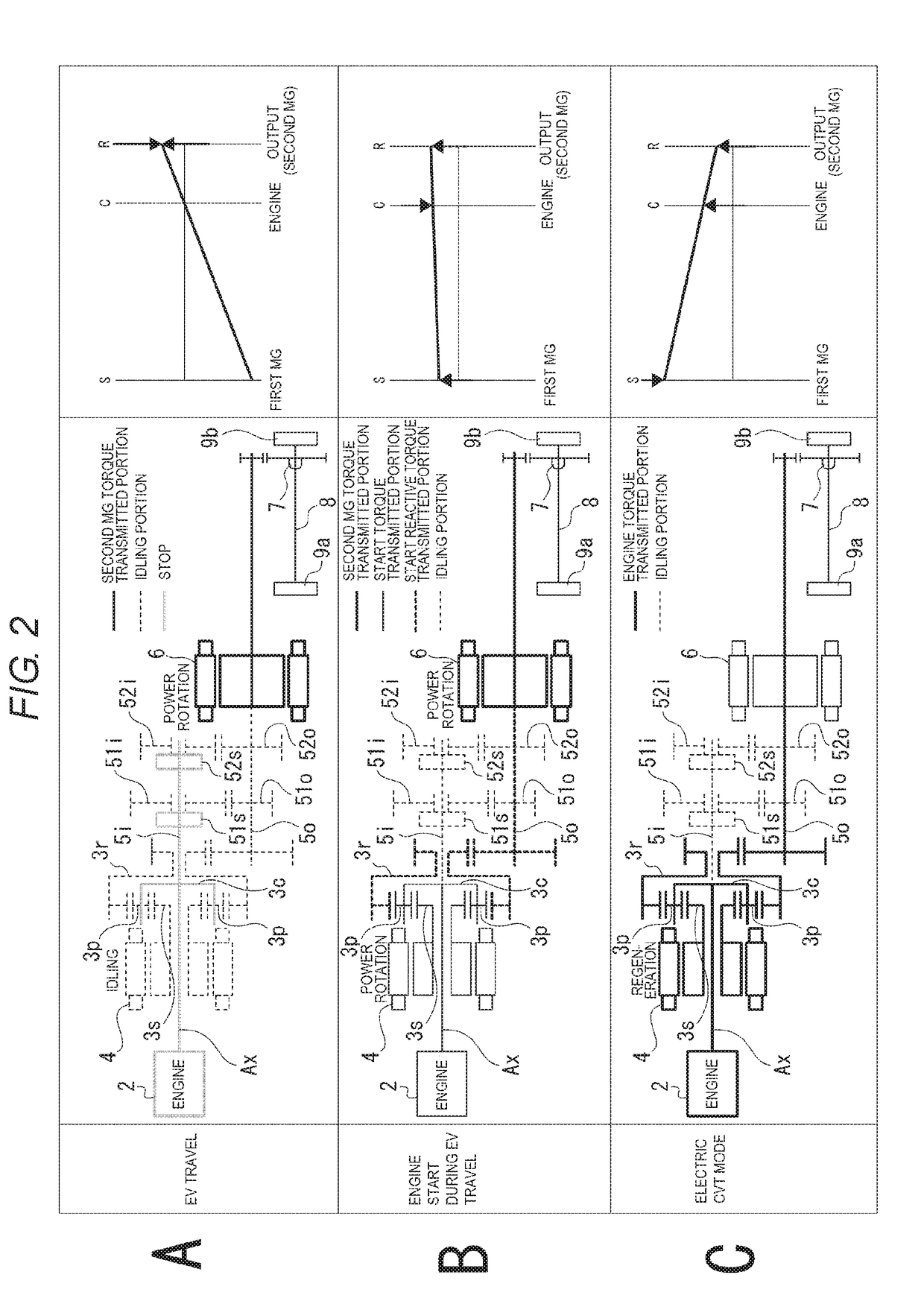

Power transmission apparatus

ActiveUS20180029584A1Increase power generationIncrease in consumptionHybrid vehiclesToothed gearingsElectric power transmissionAutomatic transmission

A power transmission apparatus that is mountable on a vehicle includes a planetary gear mechanism, a first motor generator, a second motor generator, and a stepped automatic transmission with parallel gears. The first motor generator and an output side shaft of the stepped automatic transmission are configured to be coupled to a power input shaft from an engine provided in the vehicle via the planetary gear mechanism. An input side shaft of the stepped automatic transmission is configured to be coupled to the power input shaft. The second motor generator is coupled to the output side shaft of the stepped automatic transmission.

Owner:SUBARU CORP

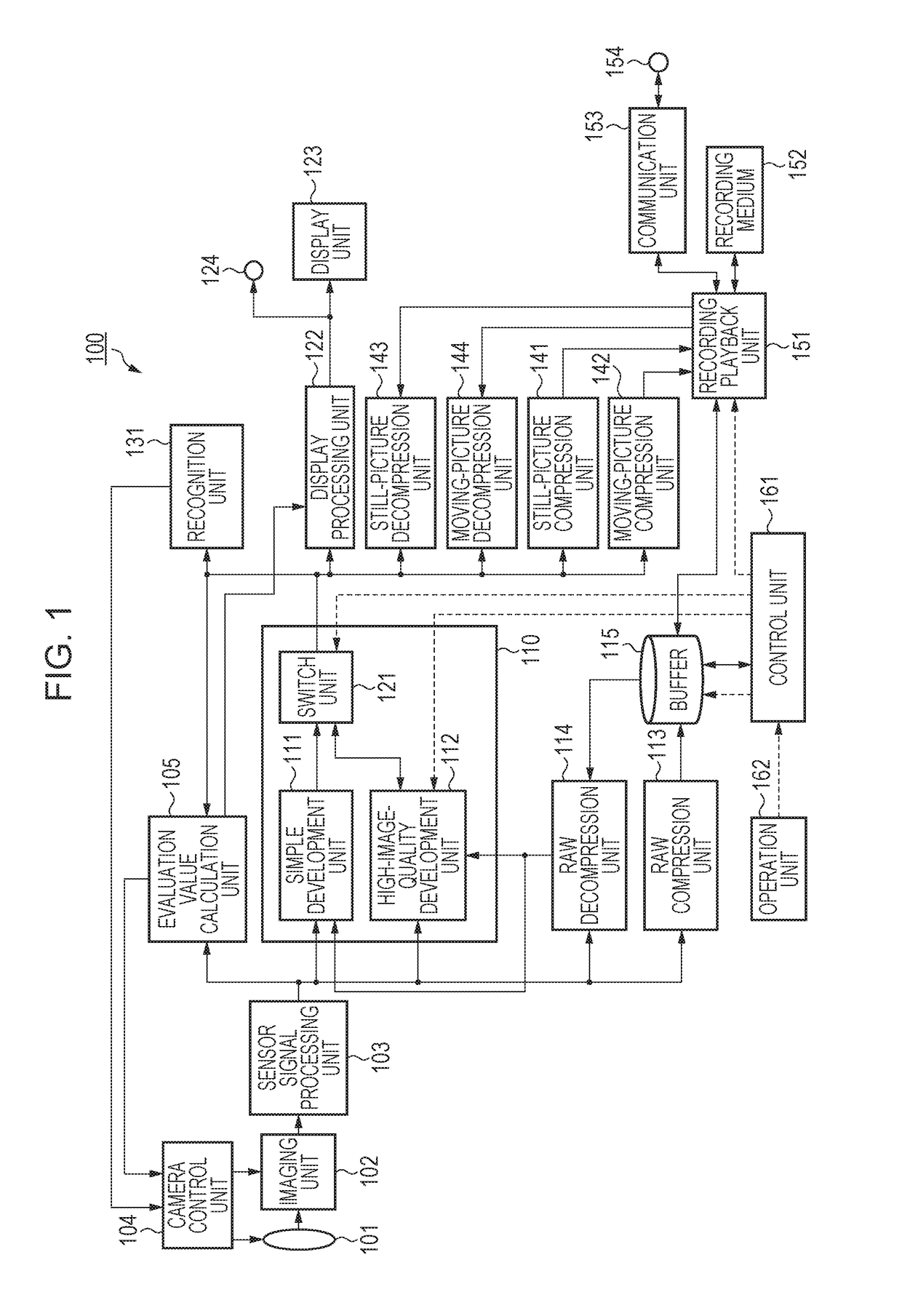

Imaging apparatus

ActiveUS20170150091A1Increase in circuit sizeIncrease power consumptionTelevision system detailsColor television detailsComputer hardwareImaging equipment

An imaging apparatus includes: a recording unit configured to record RAW image data into a recording medium in accordance with a recording instruction; a setting unit configured to control whether to set the RAW image data as a target of storage into the recording medium or not in accordance with a user instruction; a development unit configured to perform development processing on RAW image data; and a control unit configured to perform control to automatically develop the RAW image data recorded in the recording medium after recording of the RAW image data and to automatically record the developed image data into the recording medium. In a case where RAW image data not set as the target of storage has been developed by the development unit, the control unit performs control to automatically delete said RAW image data from the recording medium.

Owner:CANON KK

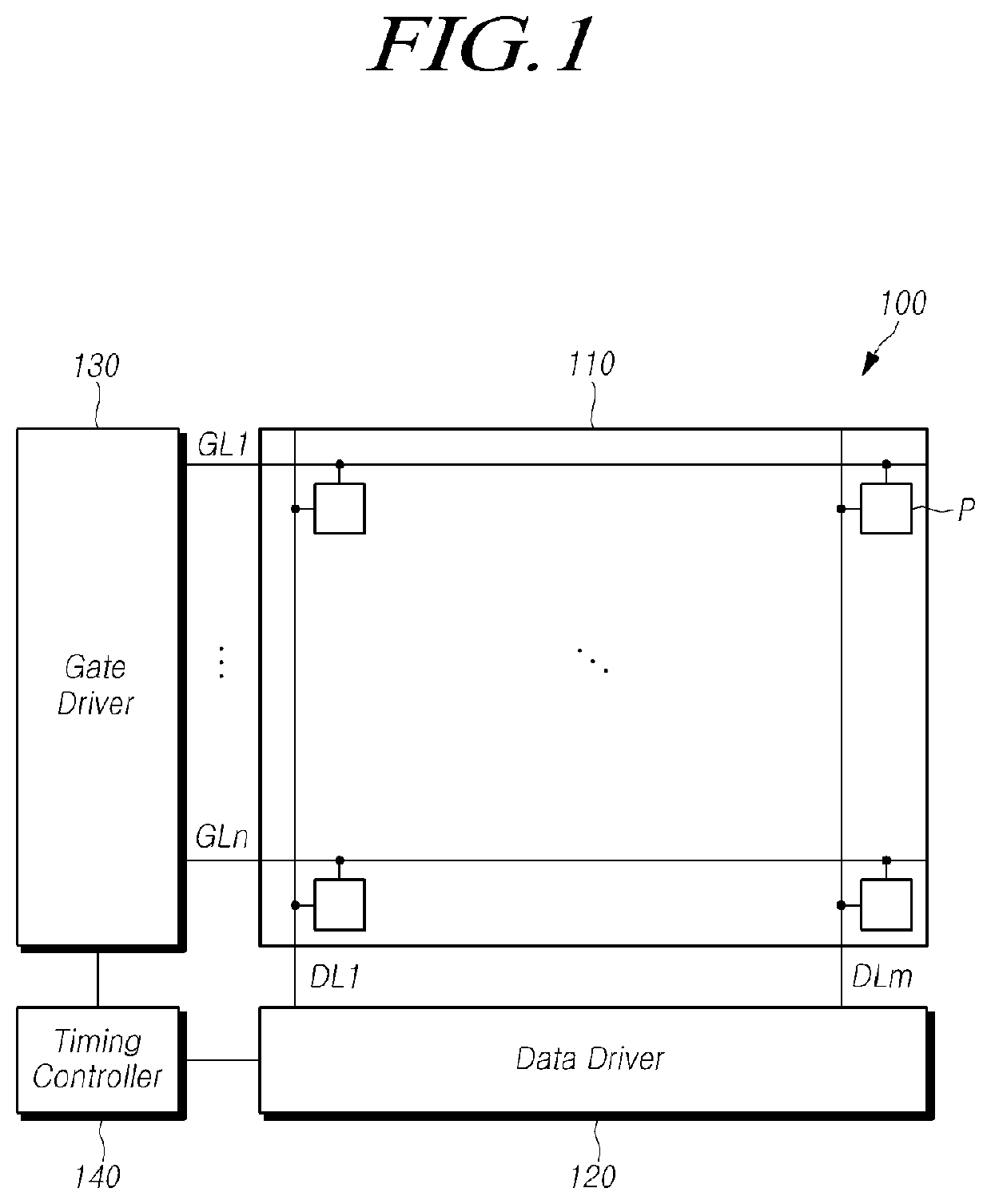

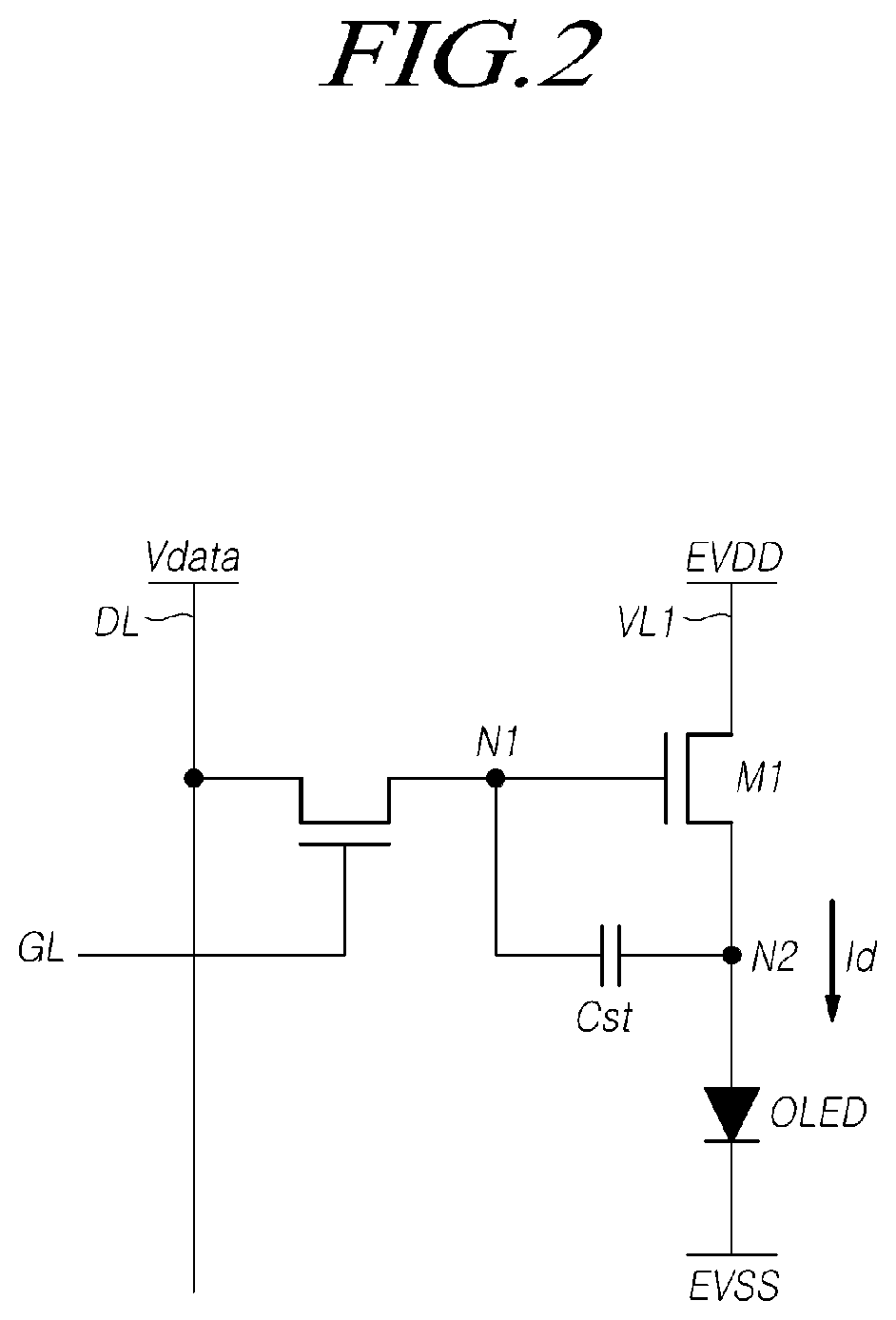

Sensor package module and organic light-emitting display having same

ActiveUS20200105194A1Increase in consumptionQuality improvementStatic indicating devicesDiodeDisplay deviceData signal

An organic light-emitting display device includes a display panel includes an active area in which a plurality of subpixels are arrayed, and a bezel area in which lines, through which a signal and a voltage to be supplied to the subpixels are transferred, are disposed, wherein each subpixels has a cathode and an anode; a data driver supplying a data signal to the subpixels; a gate driver supplying a data signal to the subpixels; a timing controller controlling the data driver and the gate driver; and a sensor package module having a portion that overlaps the active area.

Owner:LG DISPLAY CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com