Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

269results about How to "Increase image brightness" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

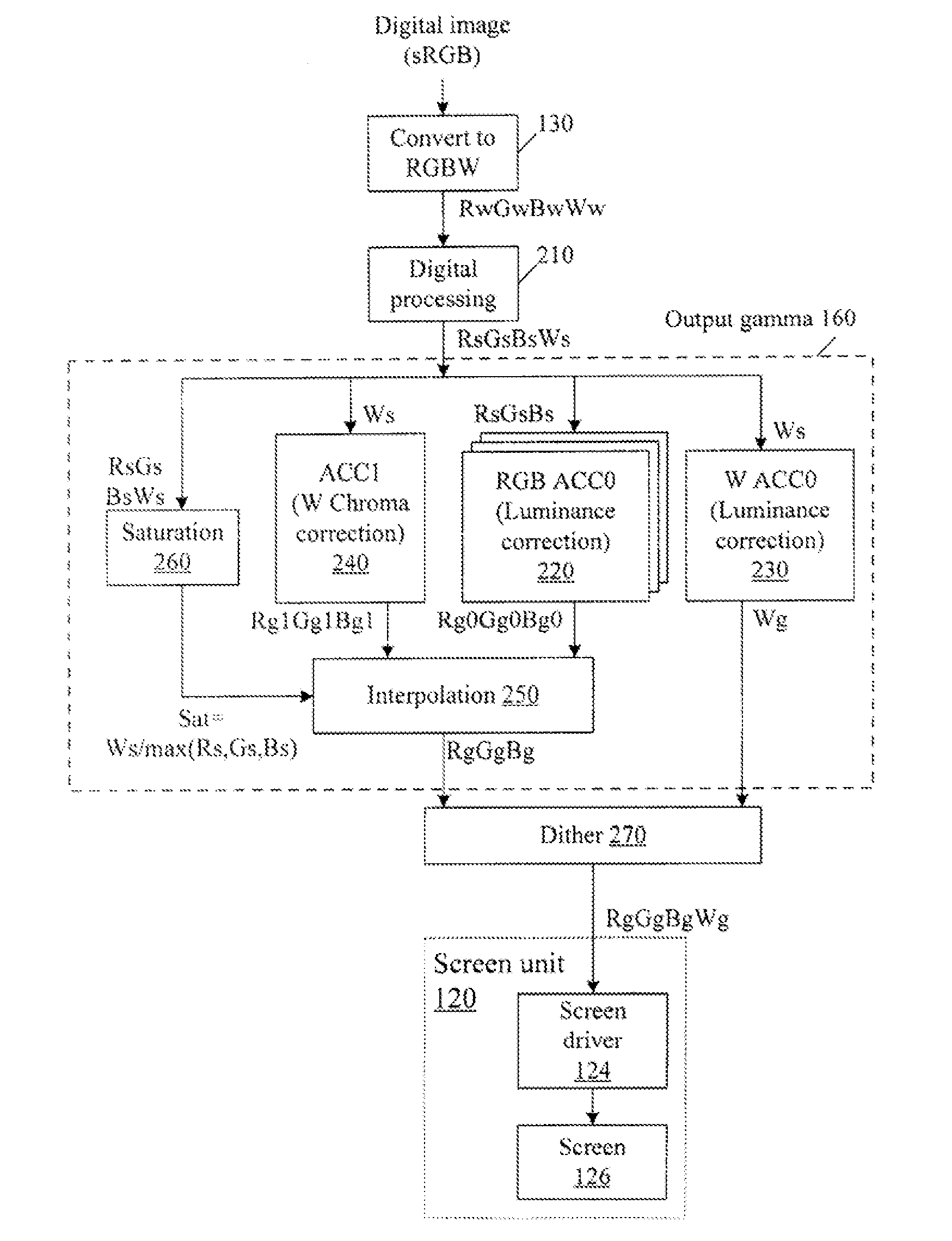

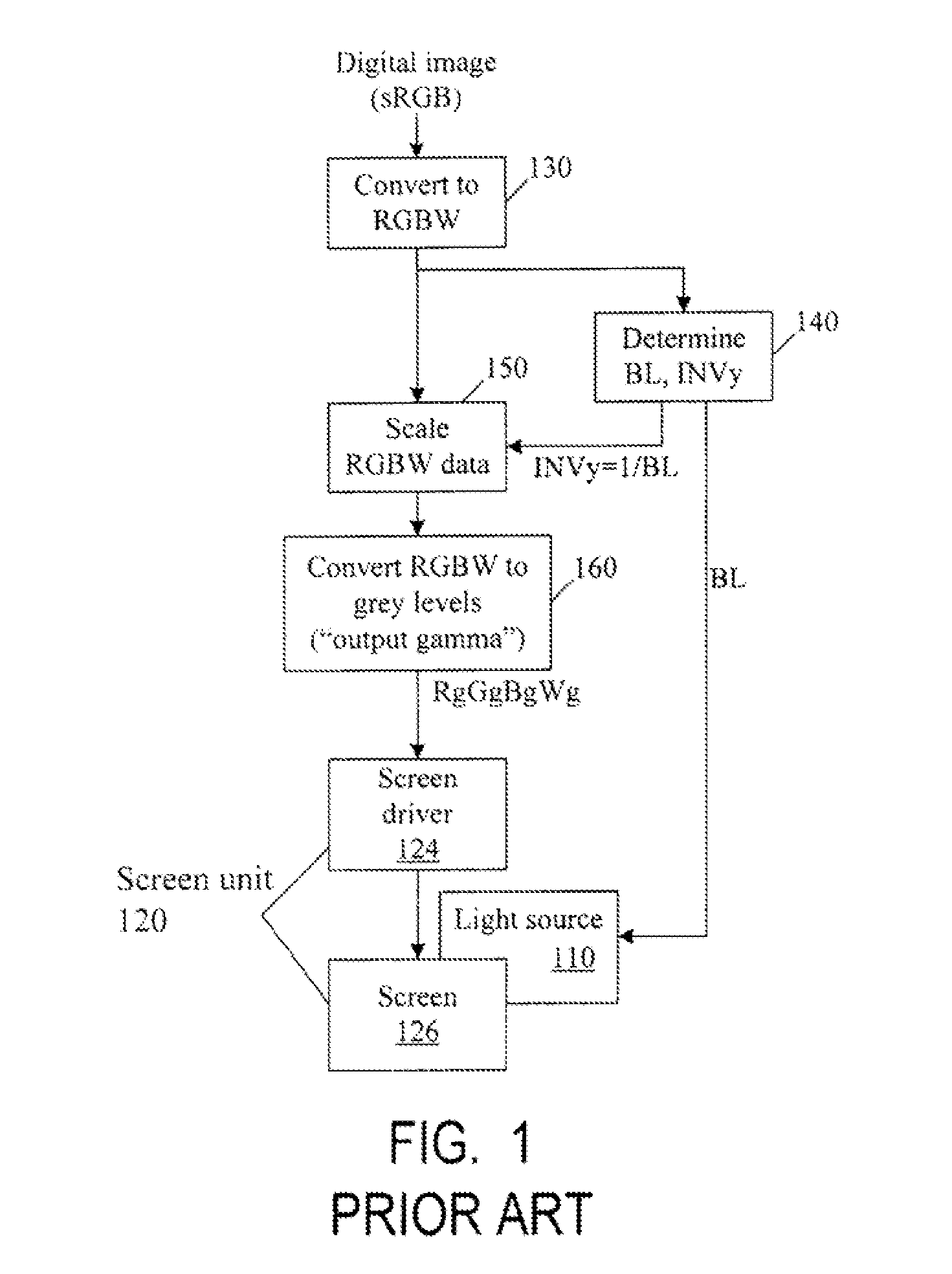

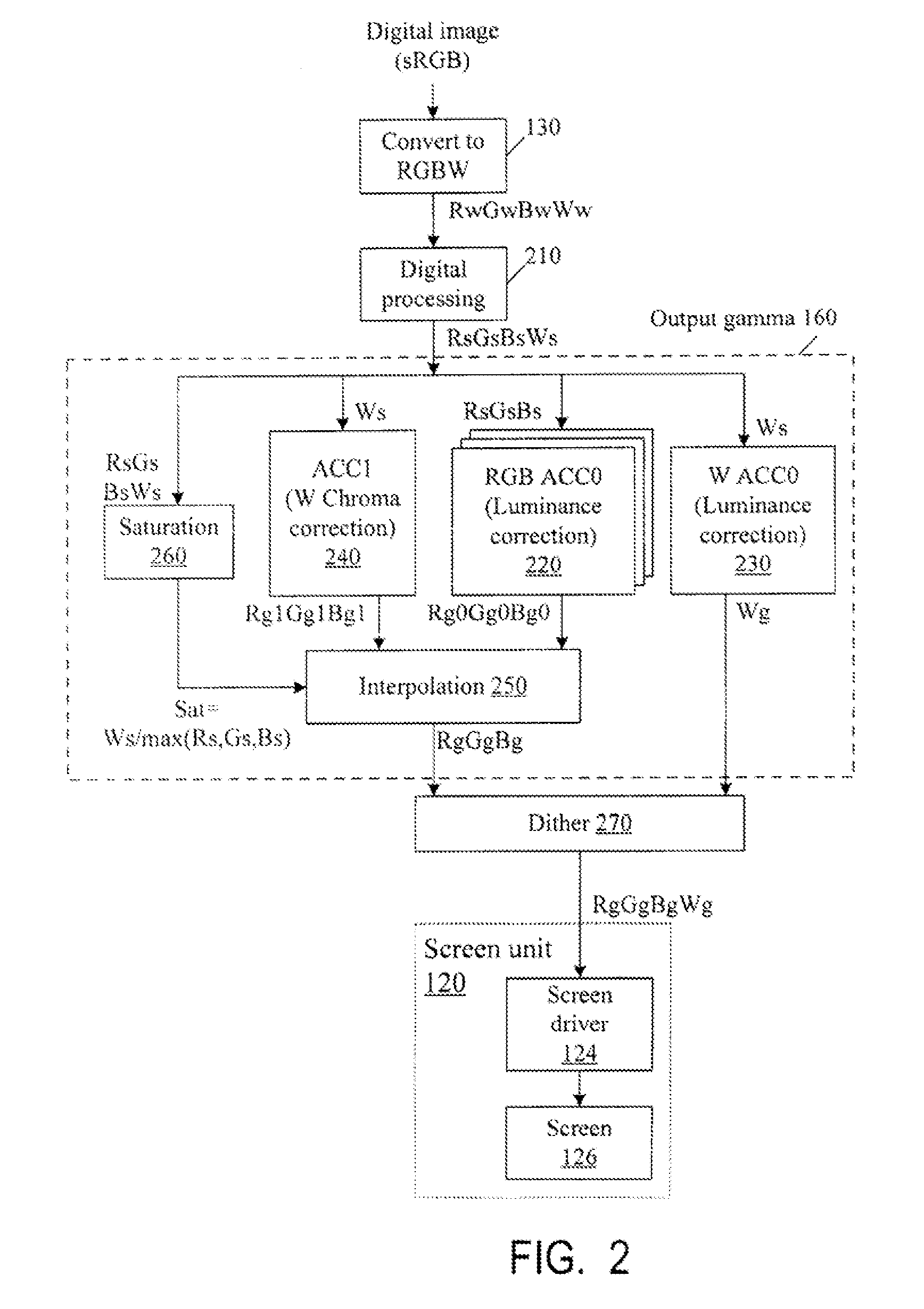

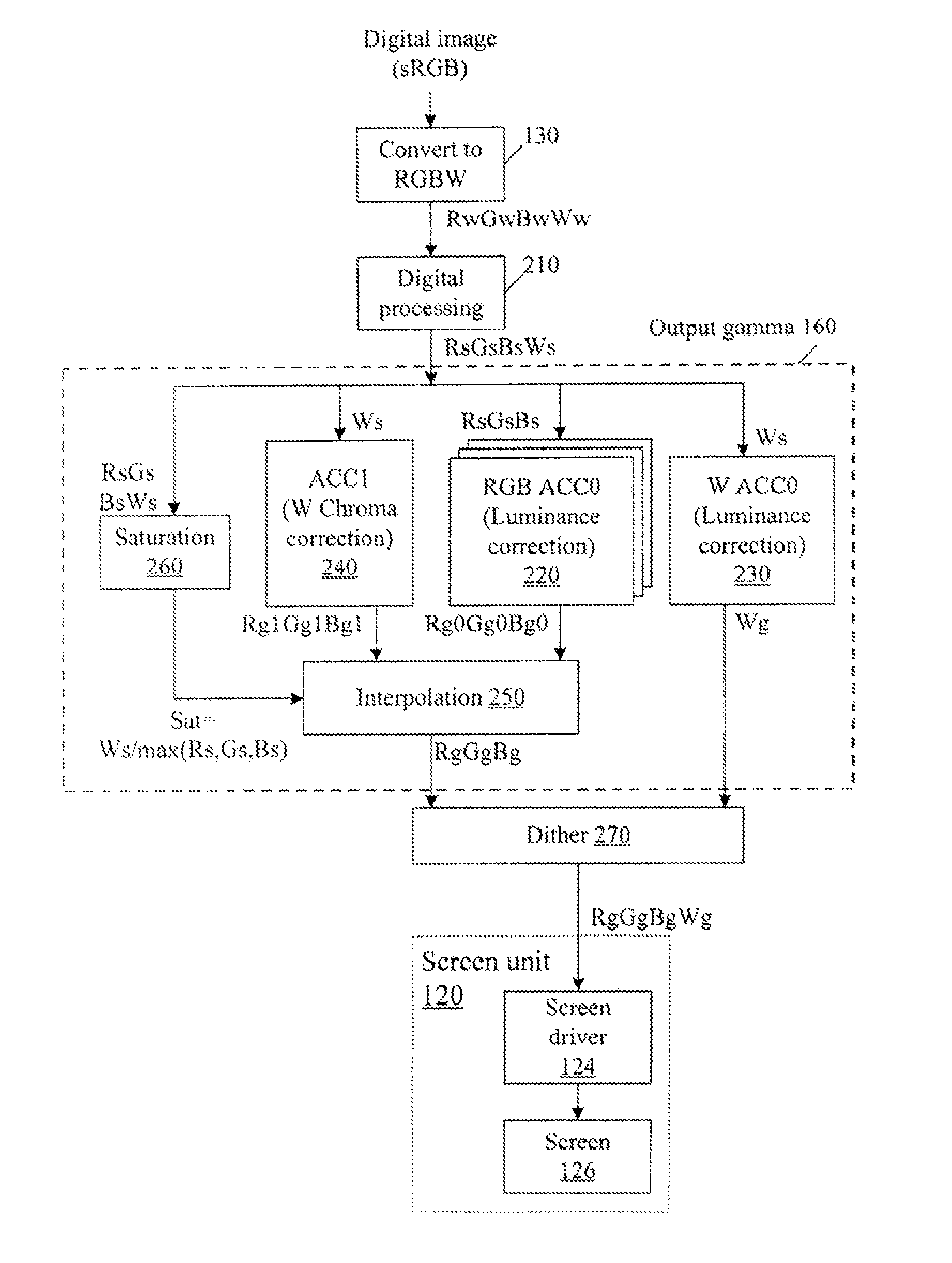

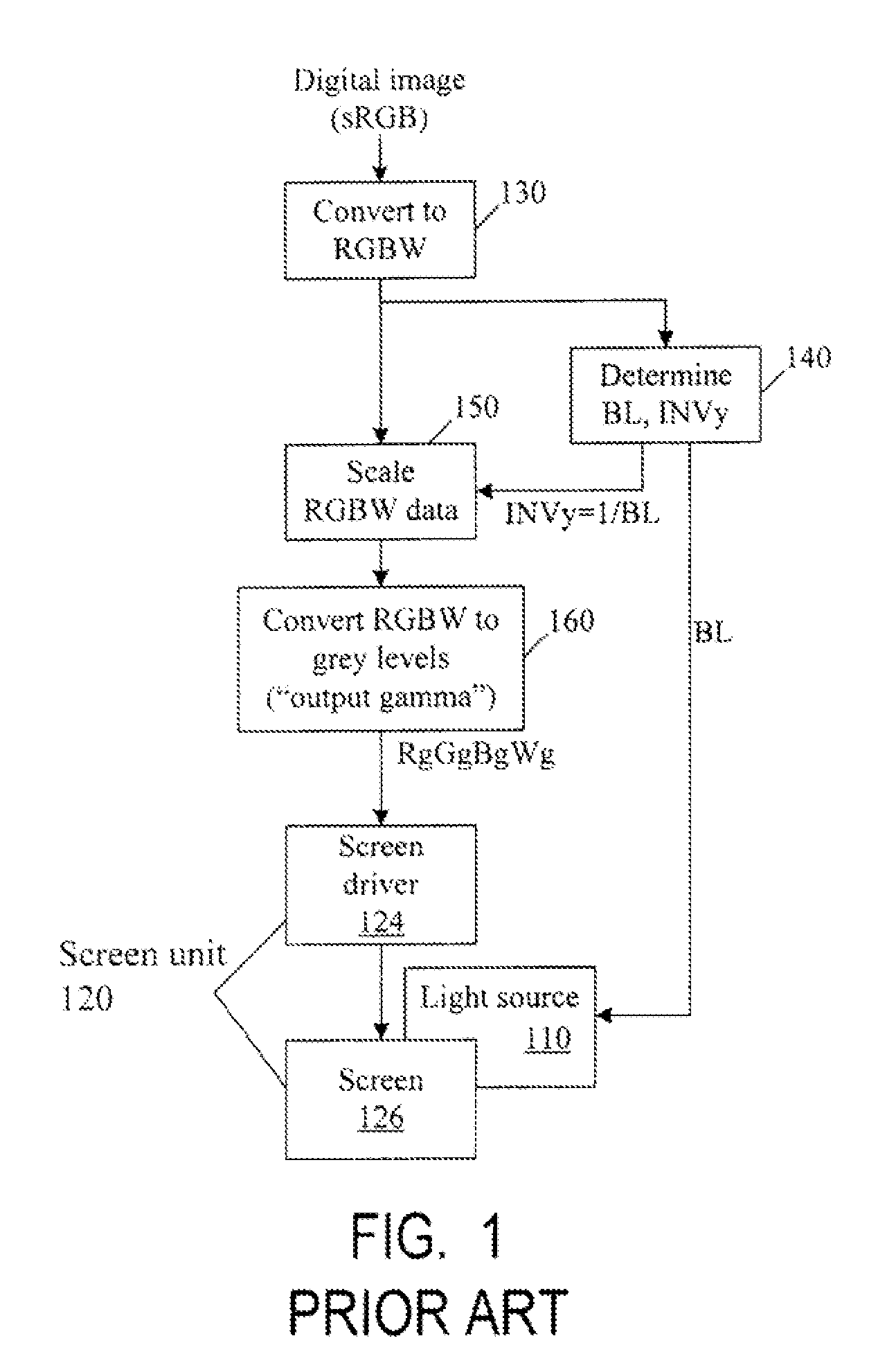

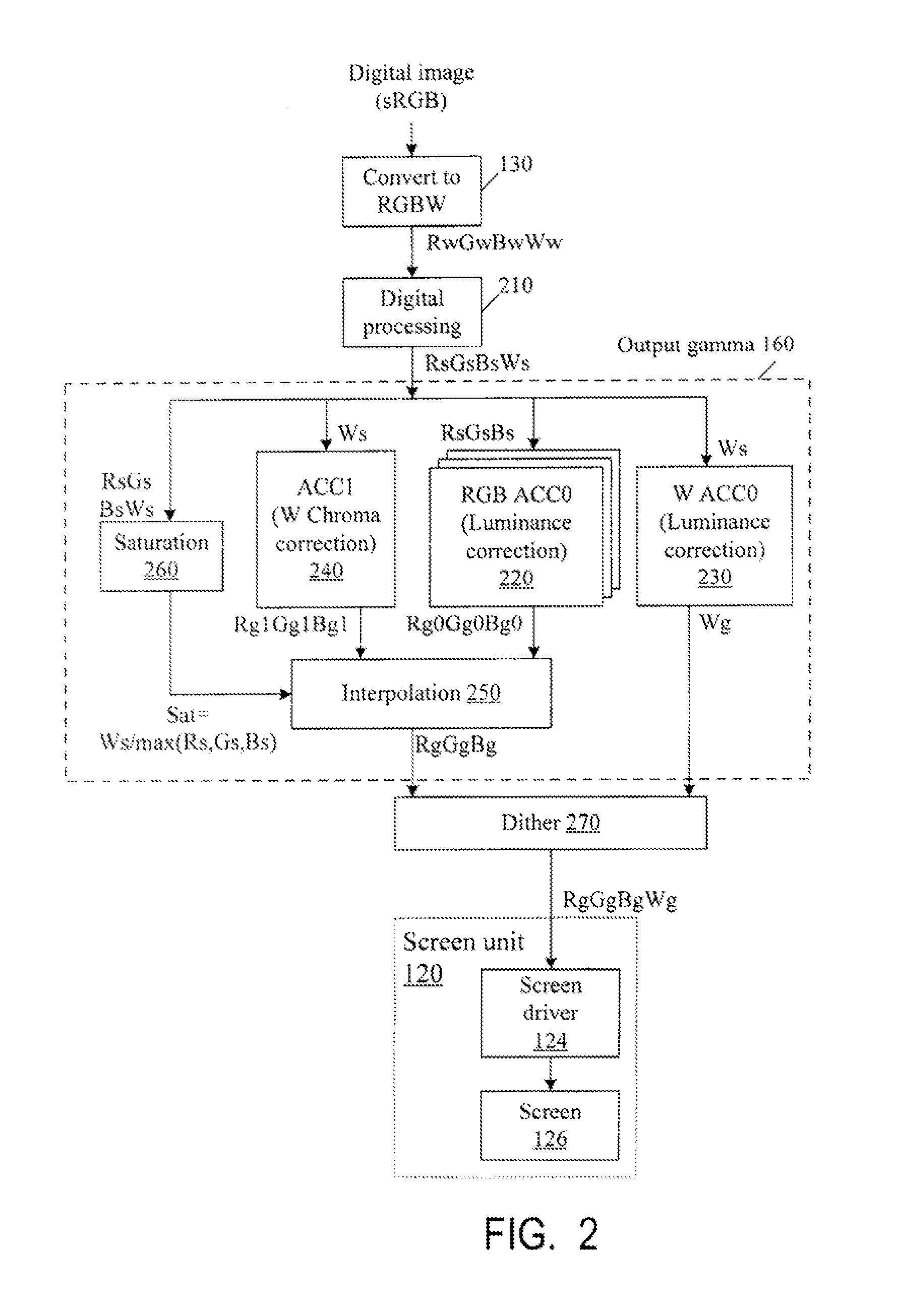

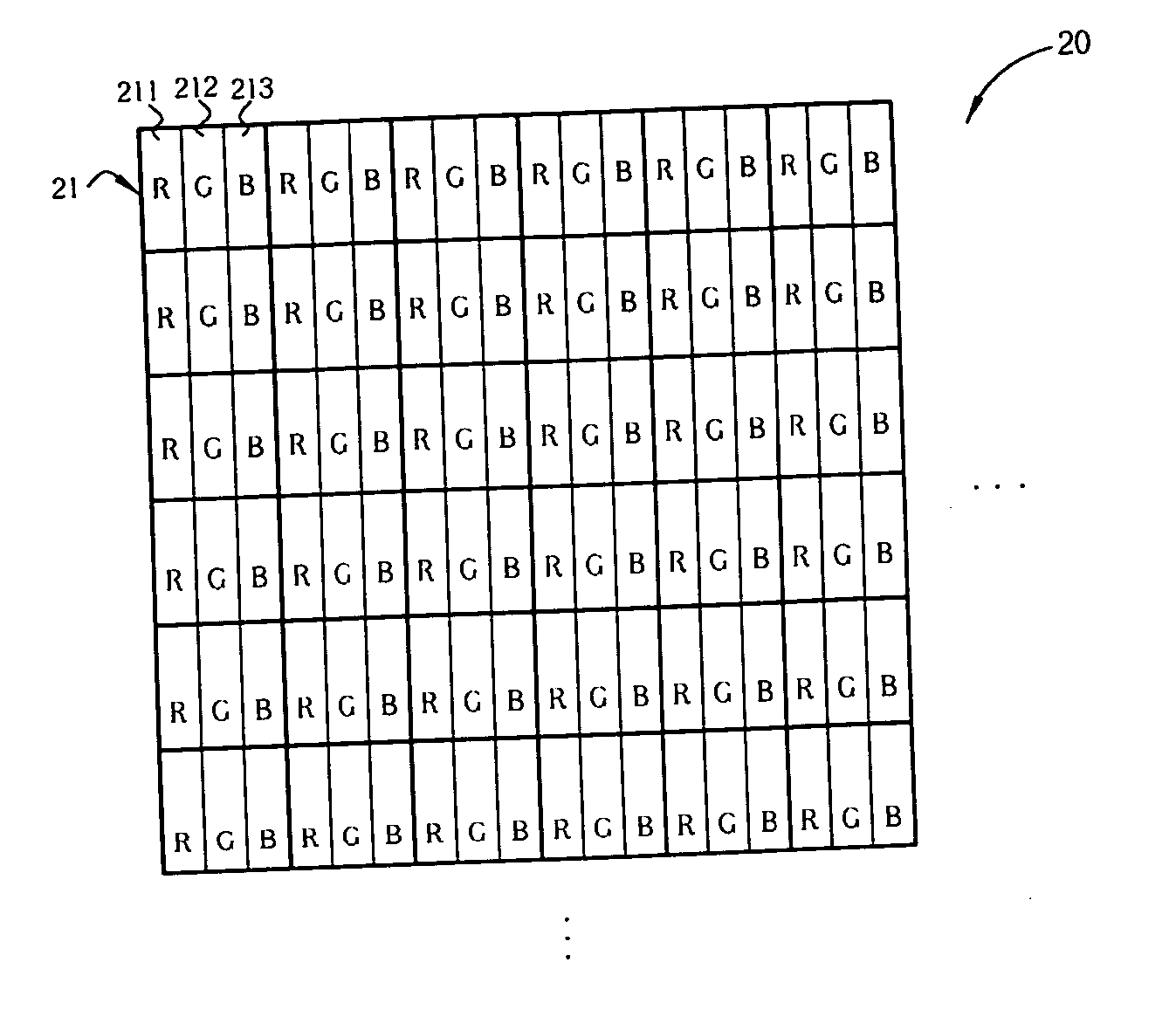

Color correction to compensate for displays' luminance and chrominance transfer characteristics

ActiveUS20110149166A1Image degradation can be highIncrease brightnessTelevision system detailsColor signal processing circuitsColor correctionDisplay device

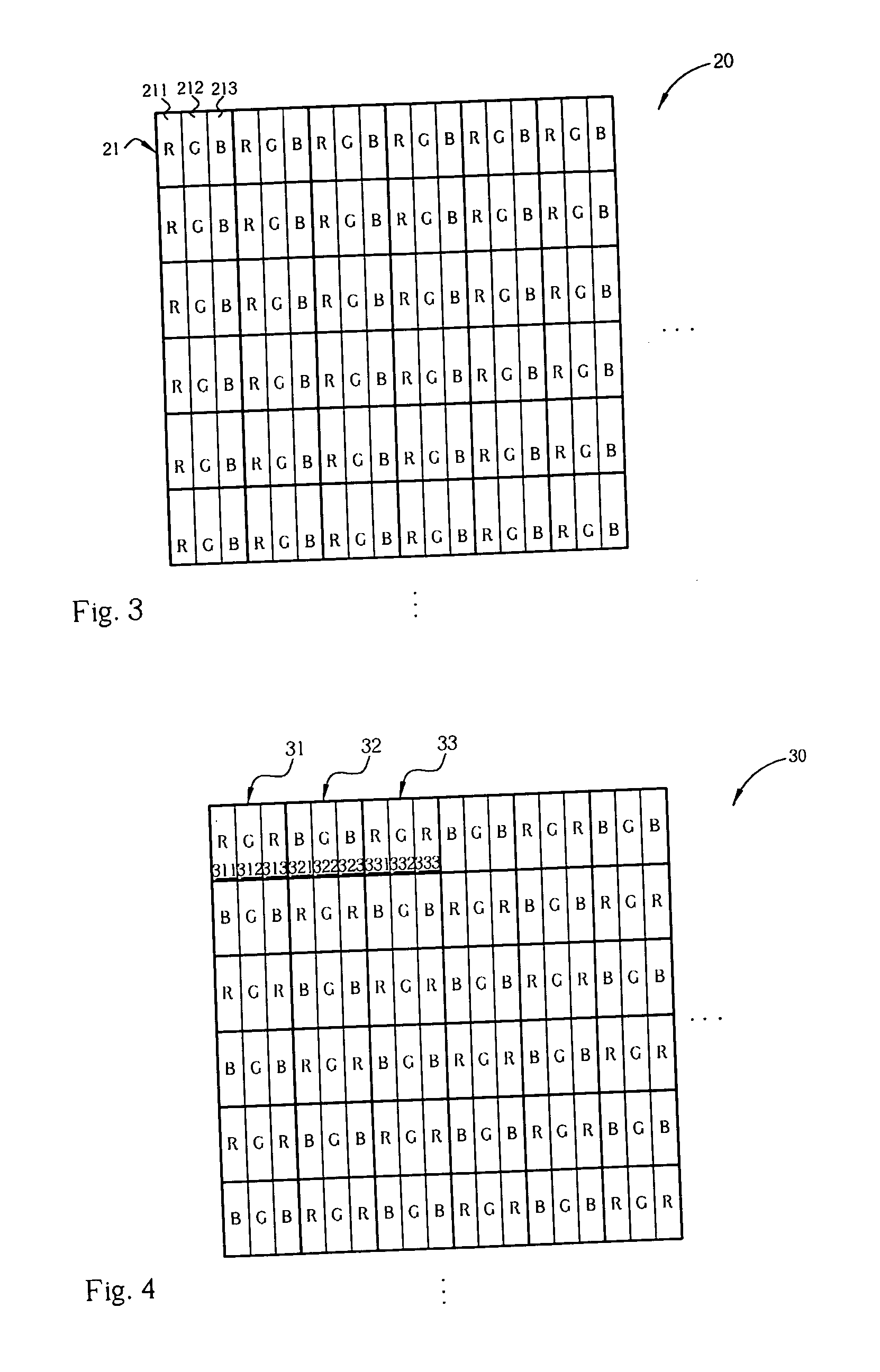

Displays are provided with circuitry performing color correction to compensate for the displays' luminance and chrominance transfer characteristics. Some techniques are suitable for RGBW displays and for subpixel-rendered displays. Some displays include an external light source (e.g. a backlight unit in LCDs), and the color correction is coordinated with dynamic control of the light source.

Owner:SAMSUNG DISPLAY CO LTD

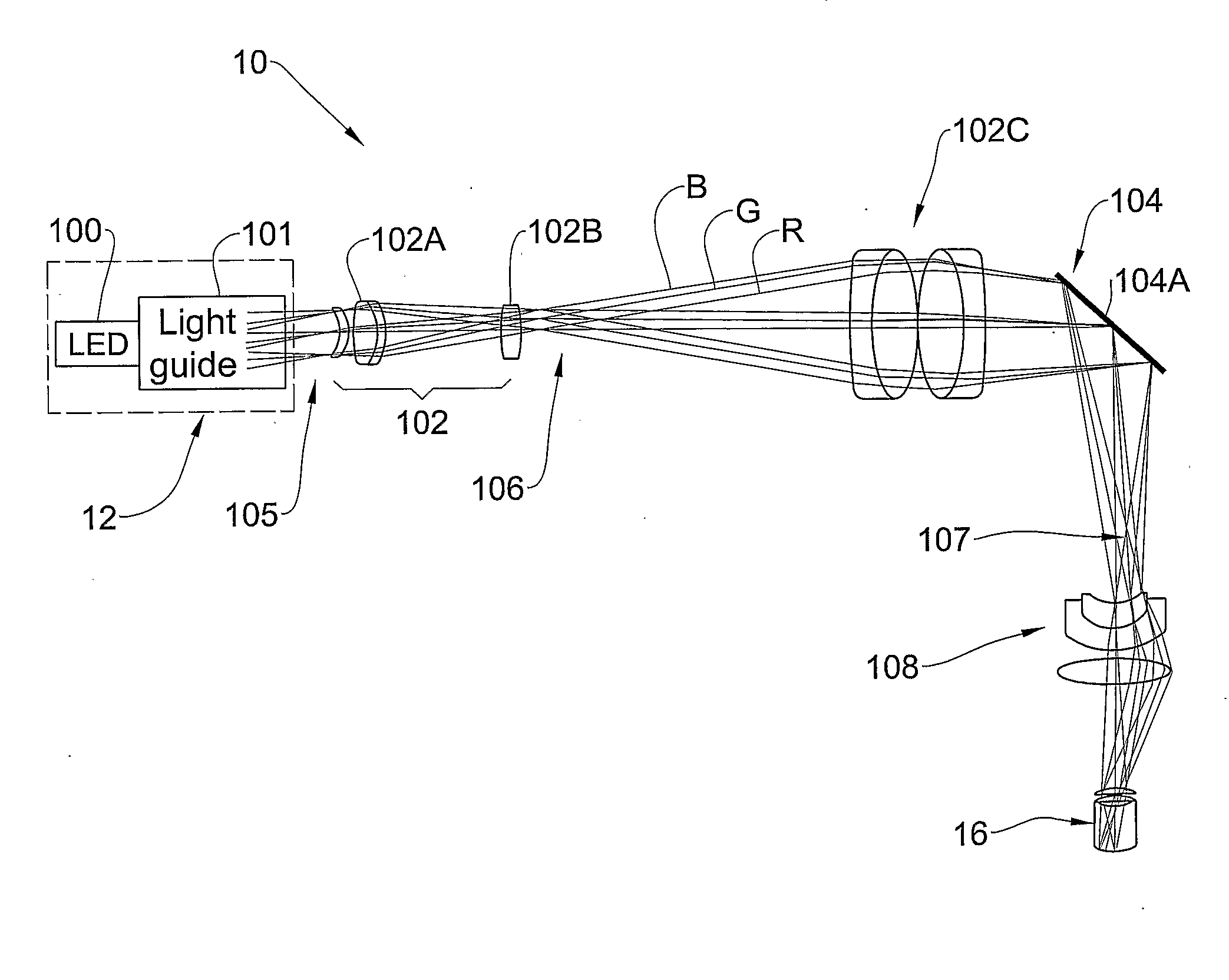

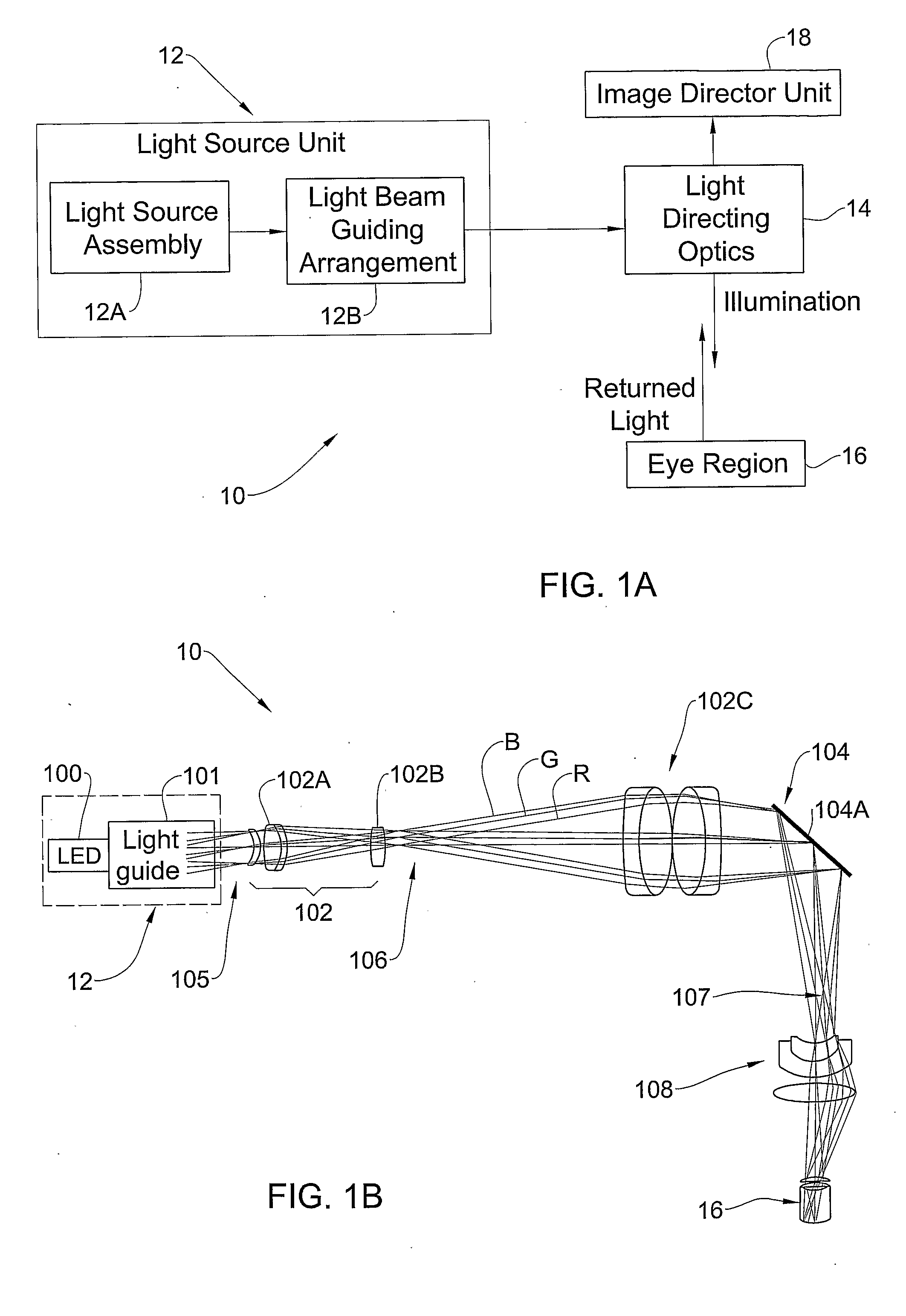

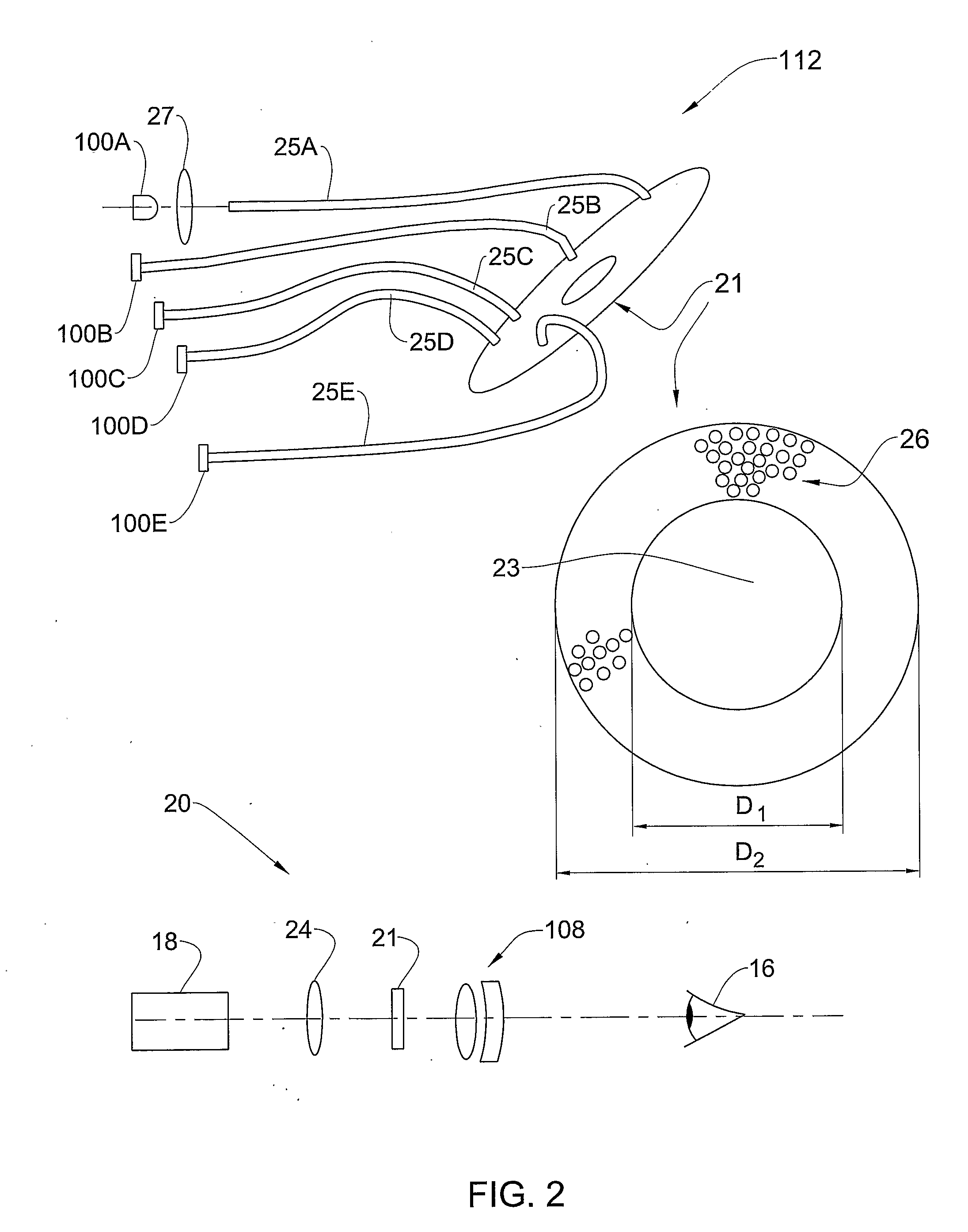

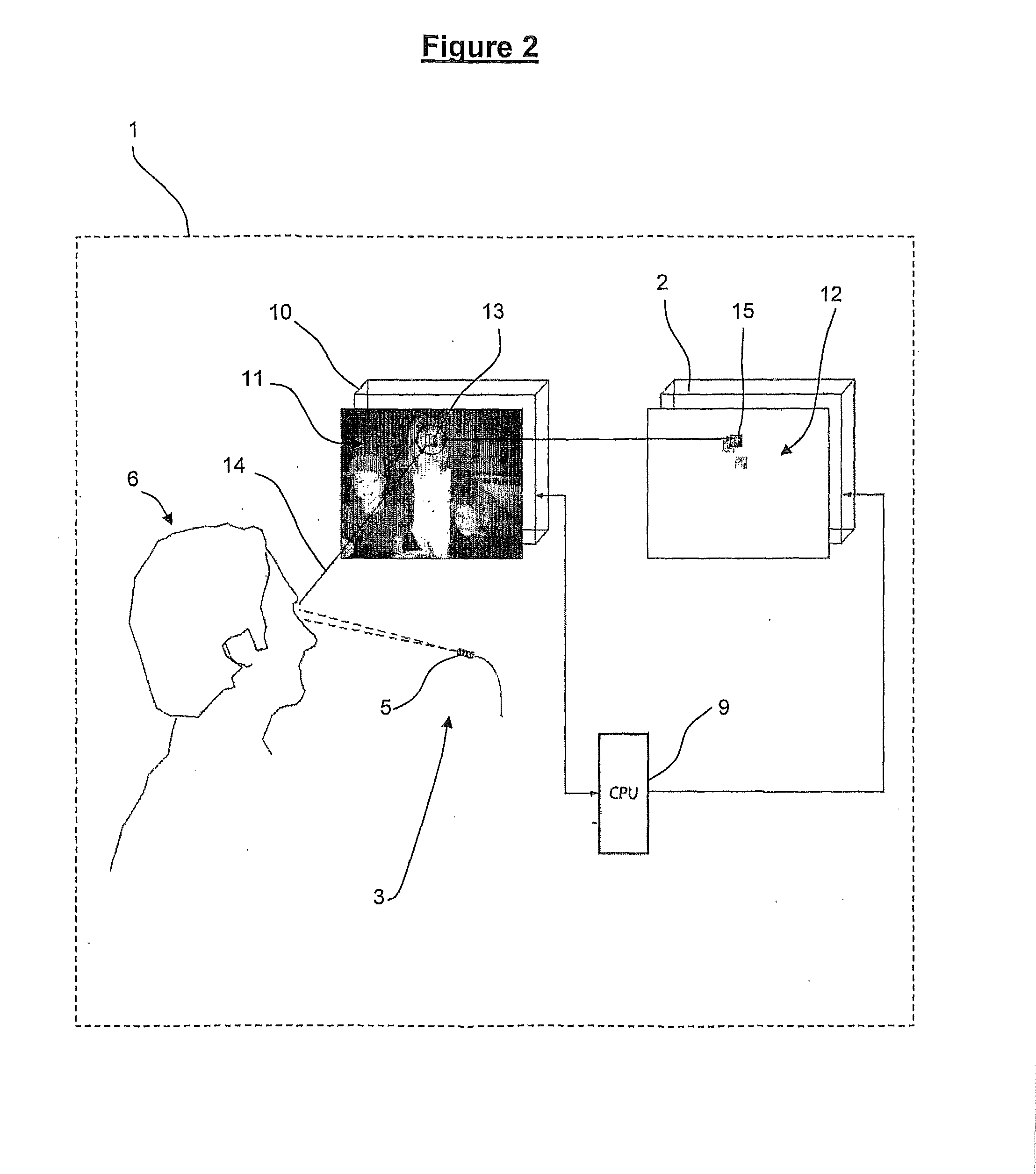

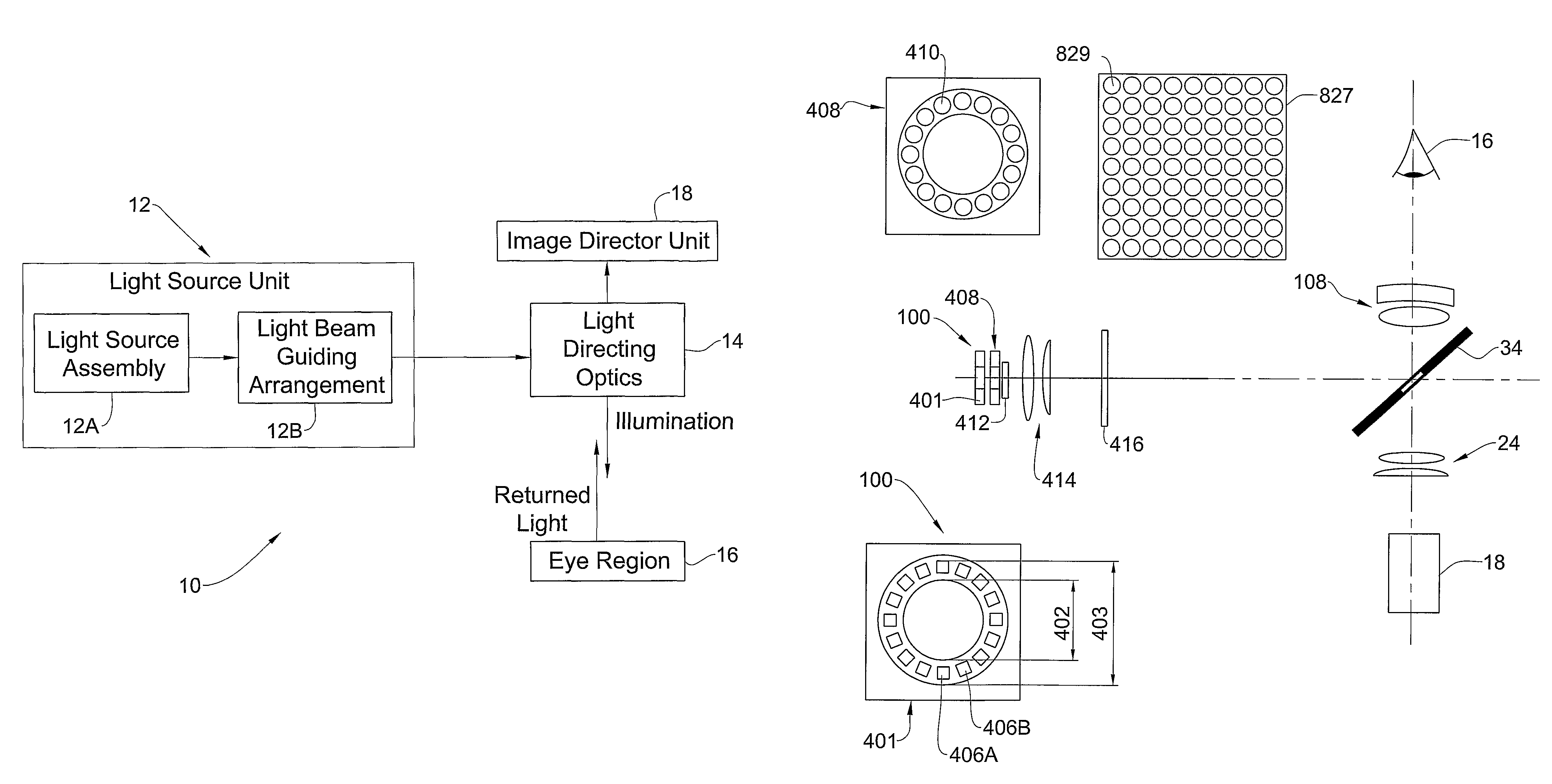

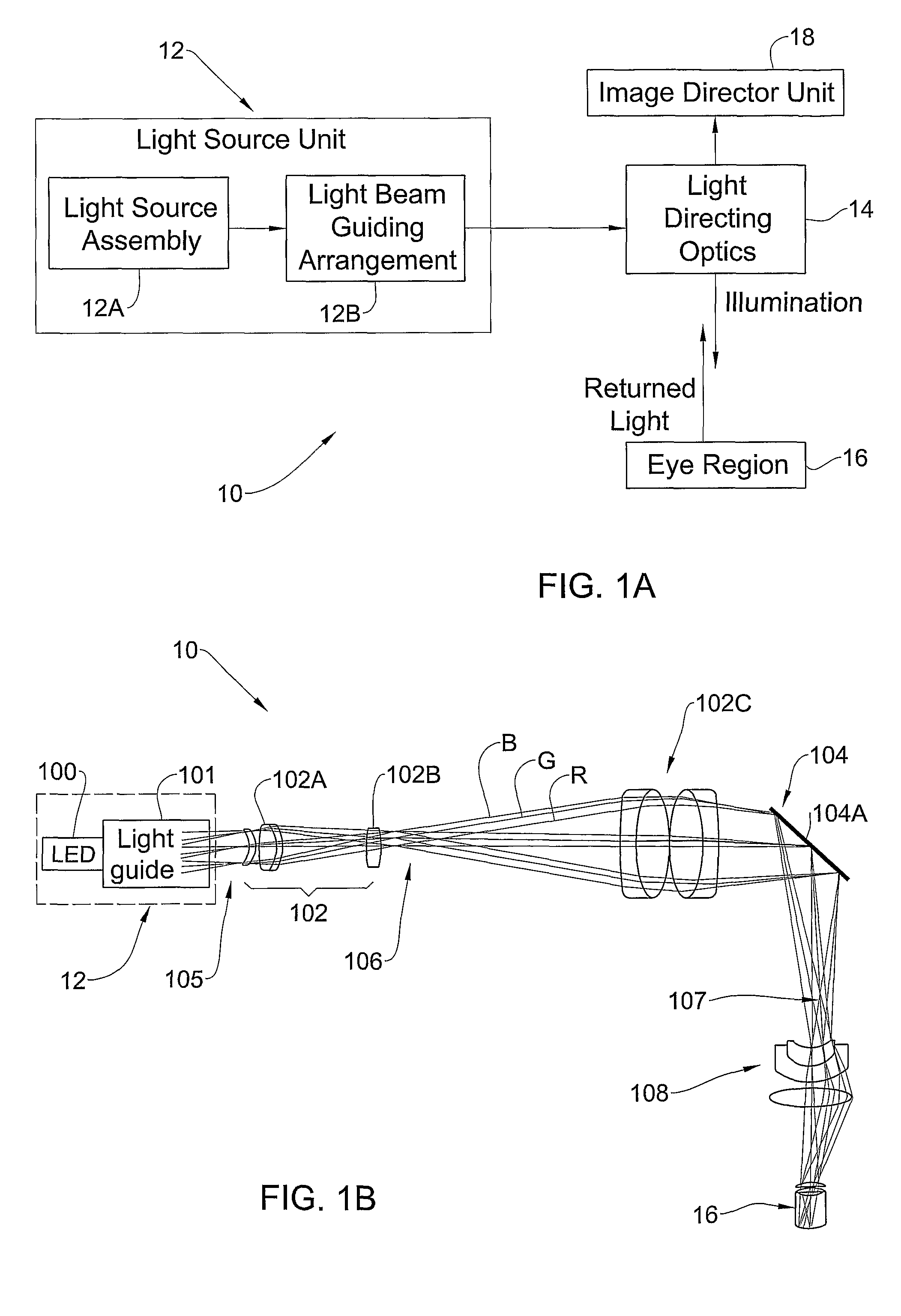

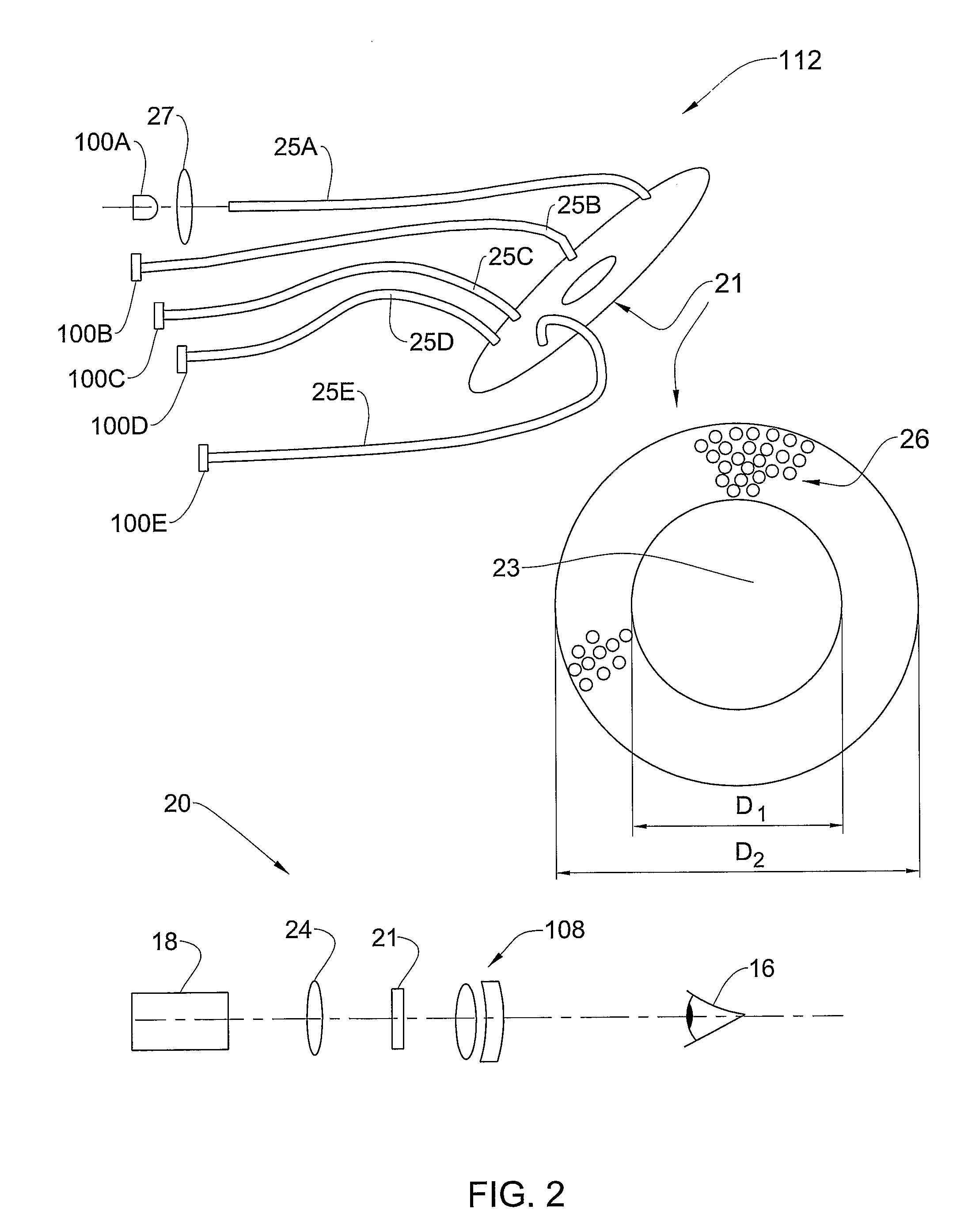

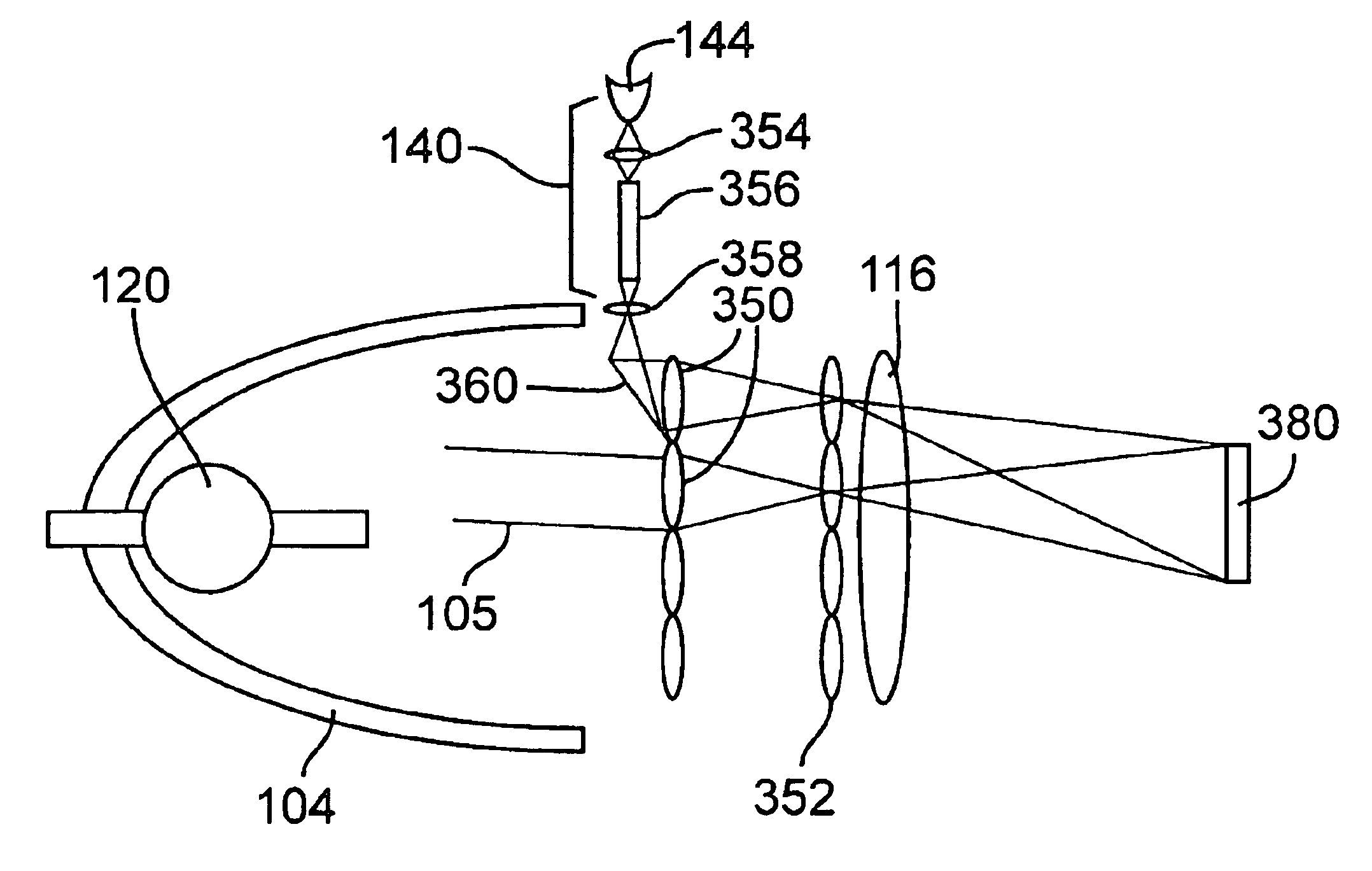

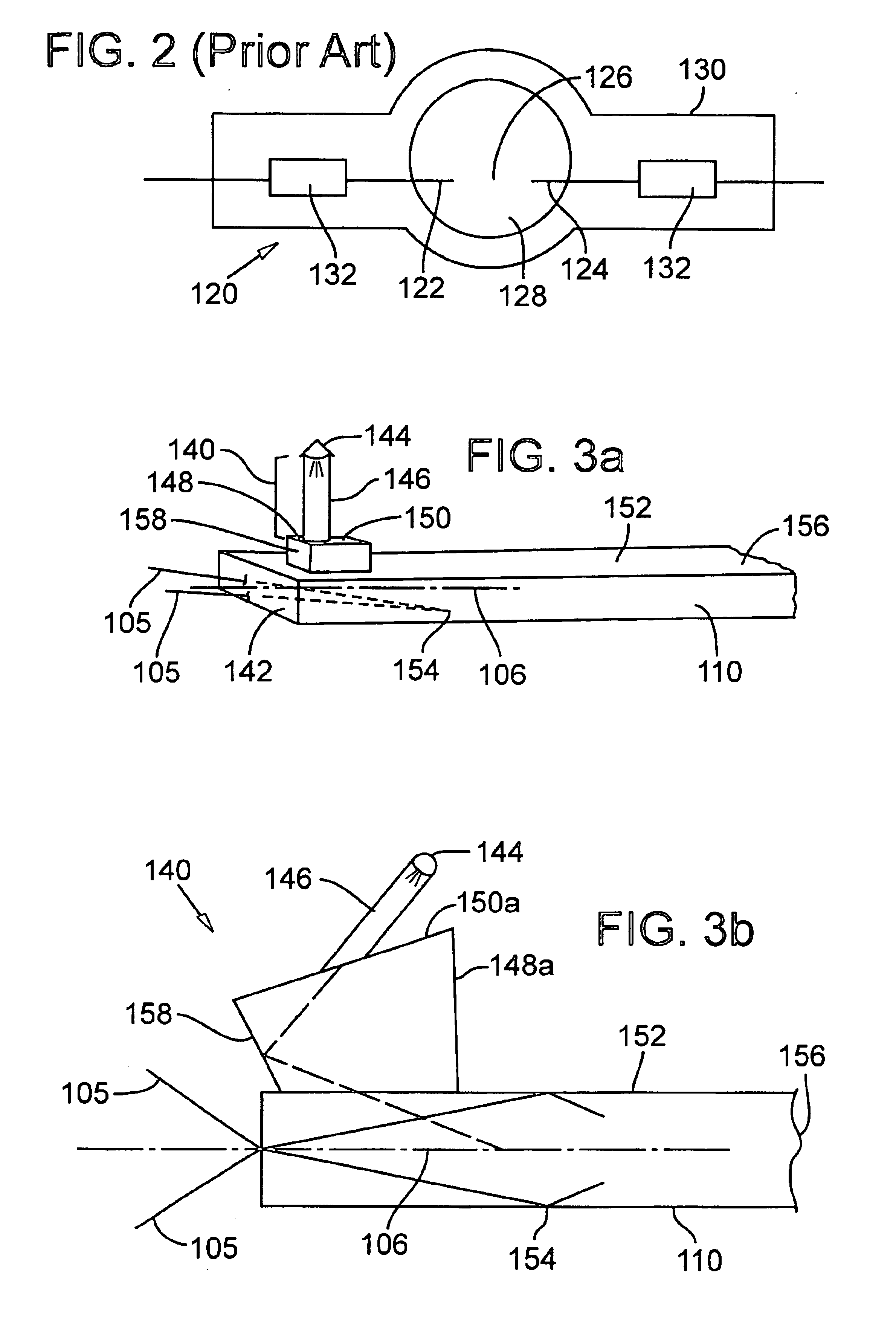

Integrated Retinal Imager And Method

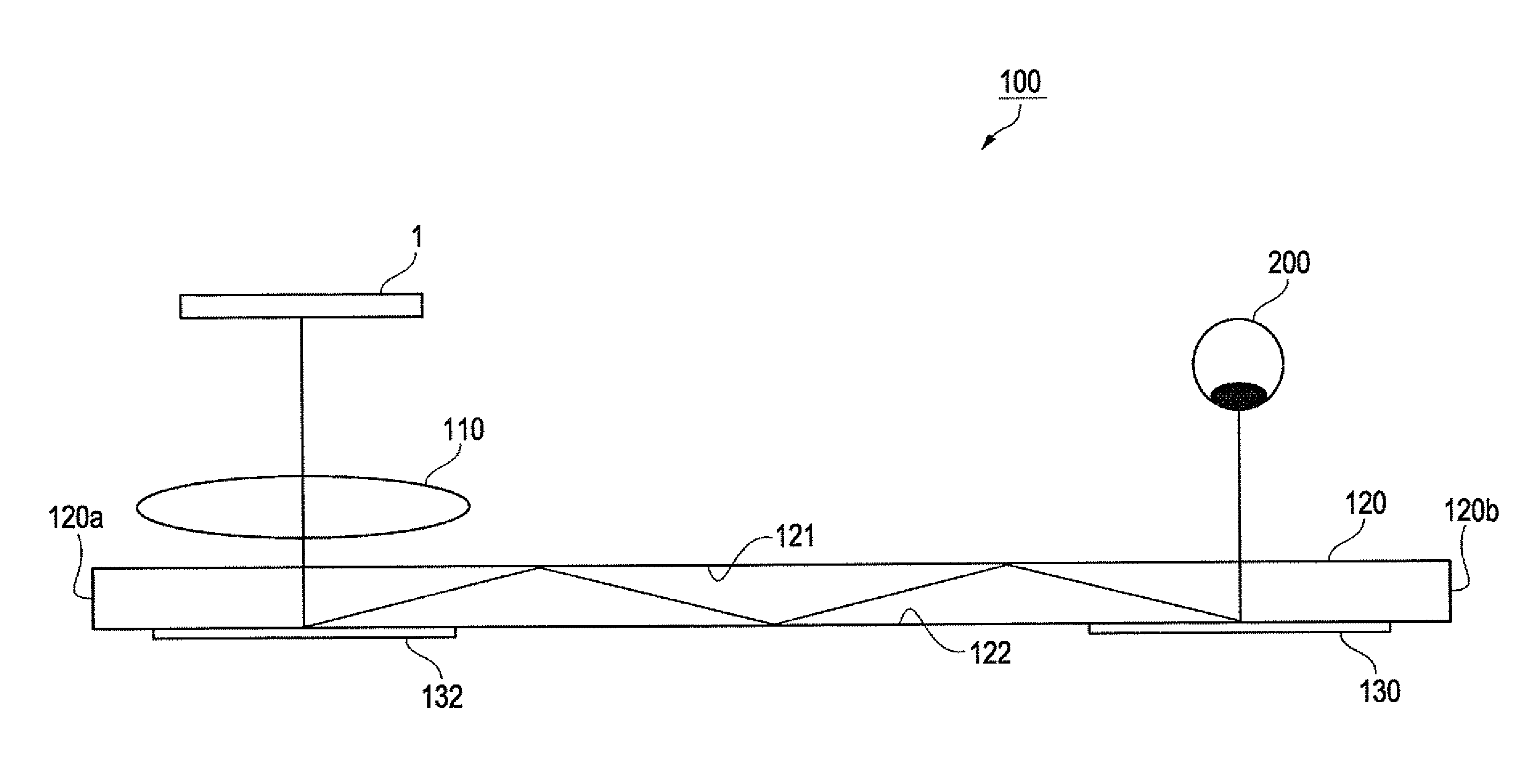

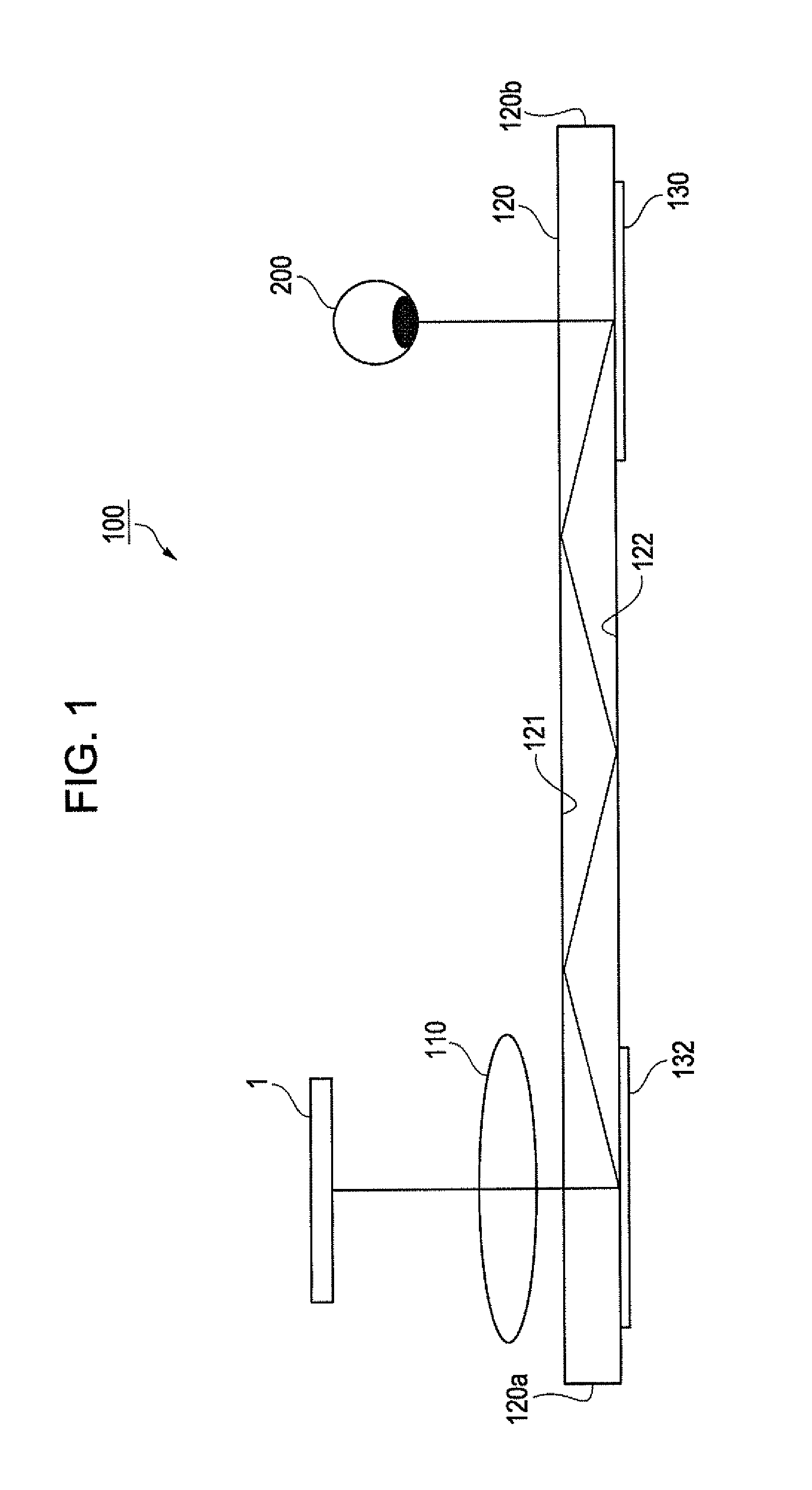

ActiveUS20090153797A1Enhance the imageEfficient couplingMechanical apparatusLight guides for lighting systemsImaging qualityExposure control

A system and method are presented for use in imaging the patient's retina. A light source unit is provided including a light emitting diode (LED) arrangement comprising multiple LEDs of different wavelength ranges. A light guide arrangement is used with the LEDs arrangement and is configured for coupling light from the LEDs and providing output light beams of a desired shape. The illuminating light is directed towards a region on the retina, and light returned from the illuminated region is collected and directed to an image detector unit. The invention enables the use of LED light at high intensity as required in the eye retina imaging, while maintaining the required high-quality imaging. Also, the invention provides for simultaneous or quasi-simultaneous as well as high-speed imaging in FA and ICG imaging procedures, thereby satisfying a long felt need in ophthalmology. Also, the invention provides for automated illumination or light exposure control to optimize overall light exposure to the patient eye and best acquired image quality in terms of brightness, contrast and image signal-to-noise ratio.

Owner:IBM CORP

Color correction to compensate for displays' luminance and chrominance transfer characteristics

ActiveUS20110148910A1Reducing table sizeIncrease image brightnessCathode-ray tube indicatorsInput/output processes for data processingColor correctionDisplay device

Displays are provided with circuitry performing color correction to compensate for the displays' luminance and chrominance transfer characteristics. Some techniques are suitable for RGBW displays and for subpixel-rendered displays. Some displays include an external light source (e.g. a backlight unit in LCDs), and the color correction is coordinated with dynamic control of the light source.

Owner:SAMSUNG DISPLAY CO LTD

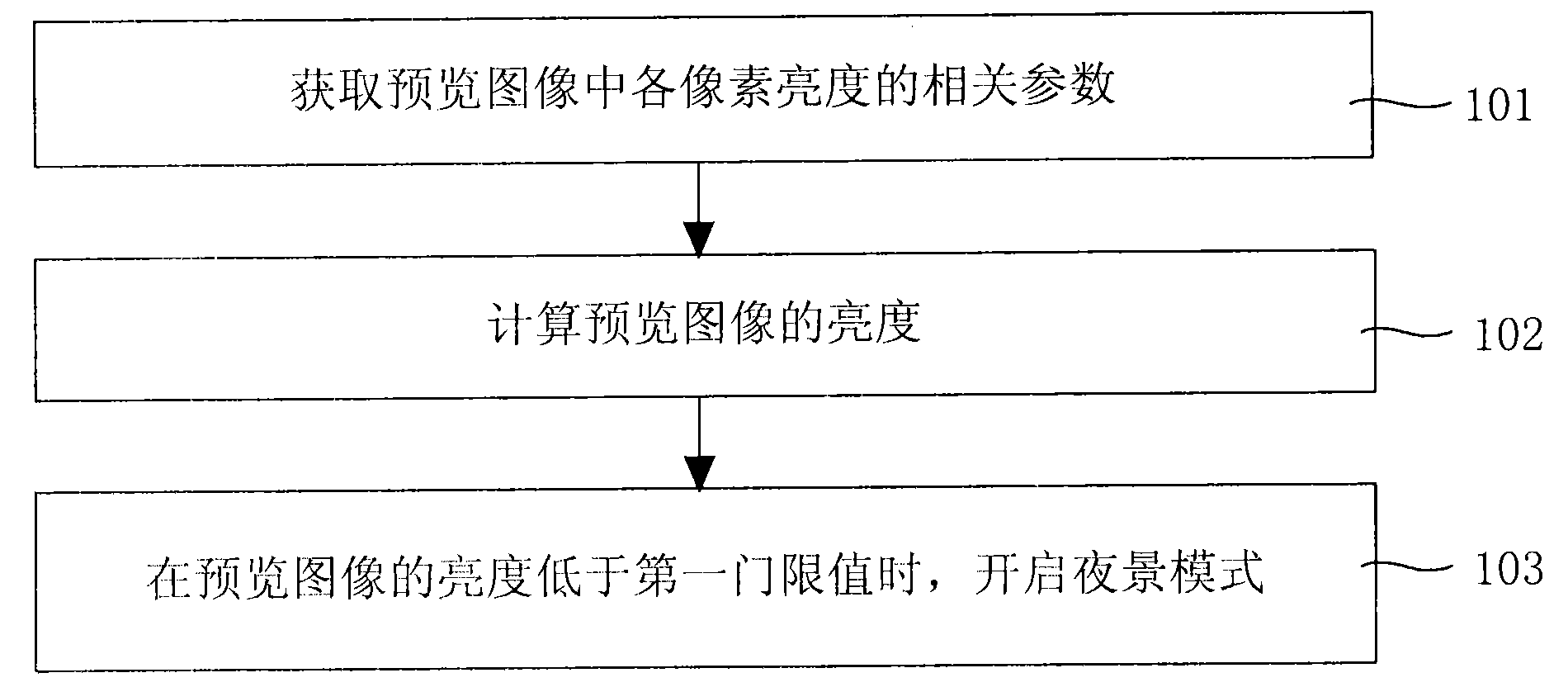

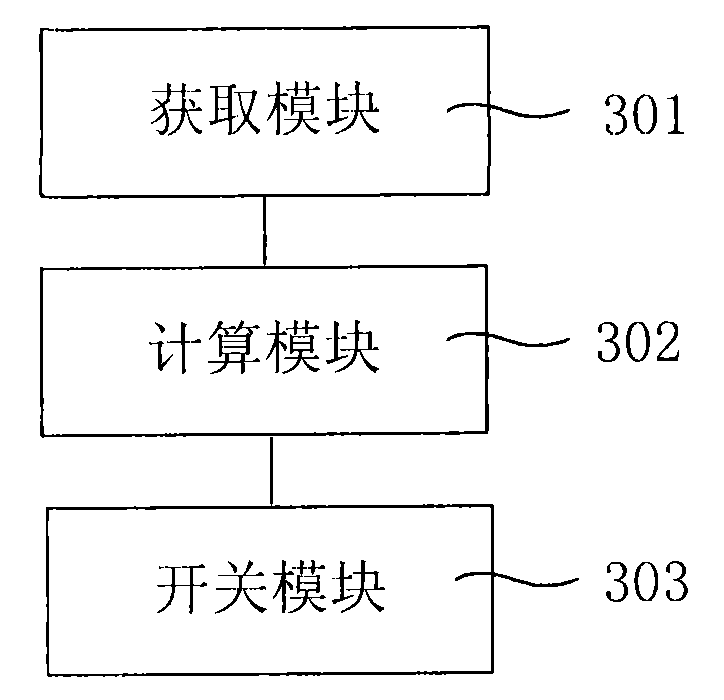

Method for automatically switching over night scene mode and image pickup device

InactiveCN101778220AIncrease exposure timeIncrease image brightnessTelevision system detailsColor television detailsComputer graphics (images)Brightness perception

The invention relates to a method for automatically switching over a night scene mode and an image pickup device, wherein the method for automatically switching over the night scene mode comprises the following steps: obtaining the relevant parameters of pixel brightness in a preview image, and calculating the brightness of the preview image; and opening the night scene mode when the brightness of the preview image is lower than a first threshold value. The embodiment of the invention obtains the brightness of the current ambient environment of the shot scenes by the preview image; when the brightness of the ambient environment is lower than the first threshold value, the night scene mode of the image pickup device is opened and the exposure time of a photoreceptor in the image pickup device is increased so as to increase the image brightness and cause that a user automatically obtains the image with the reasonable brightness.

Owner:HUAWEI DEVICE CO LTD

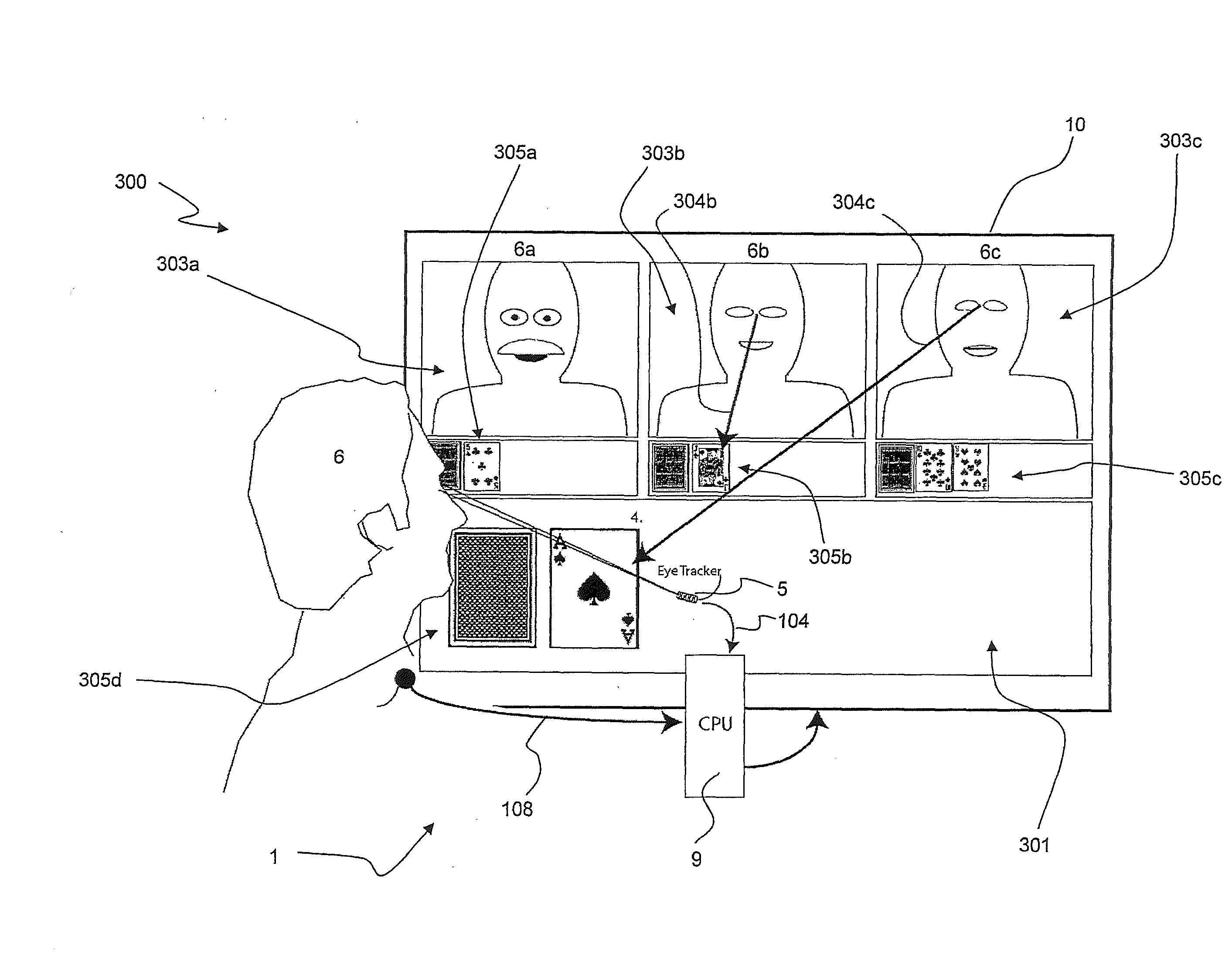

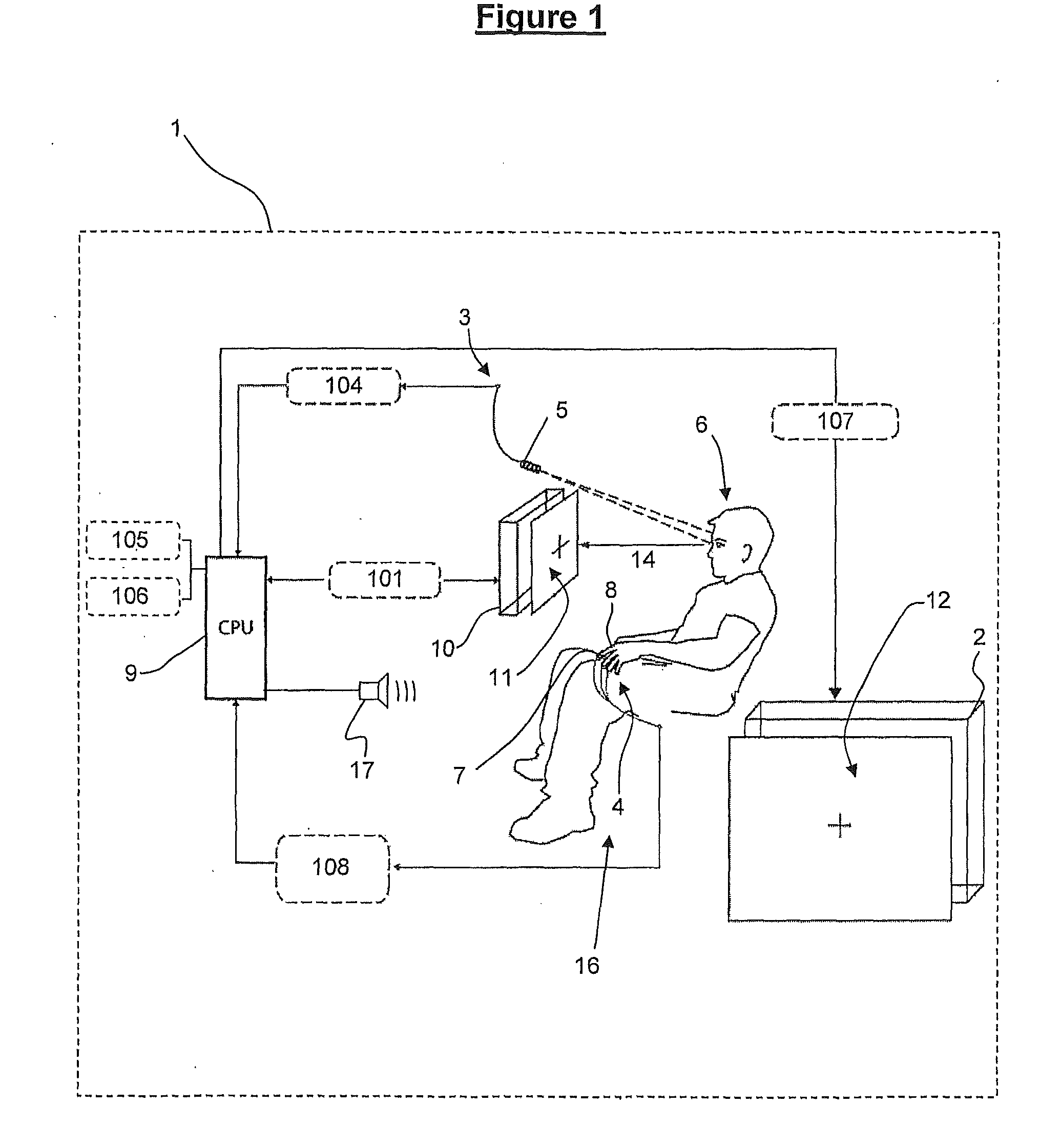

Image Generation System

InactiveUS20100207877A1Improve imaging clarityIncrease brightnessCathode-ray tube indicatorsColor television detailsPhysiological functionEye tracking system

An image generation system for generating an image on a display screen. The image generation system includes an eye-tracking system capable of determining a user's eye orientation and outputting a signal indicative of same. The image generation system also includes a bio-feedback sensor capable of detecting activity of one or more physiological functions of the user and outputting a signal indicative of the level of activity. A processor is included and is adapted to receive and process the output signals from the eye-tracking system and bio-feedback sensor. The processor determines an image to be generated on the display screen indicative of the signals from the eye-tracking system and bio-feedback sensor.

Owner:WOODARD WILLIAM BRYAN

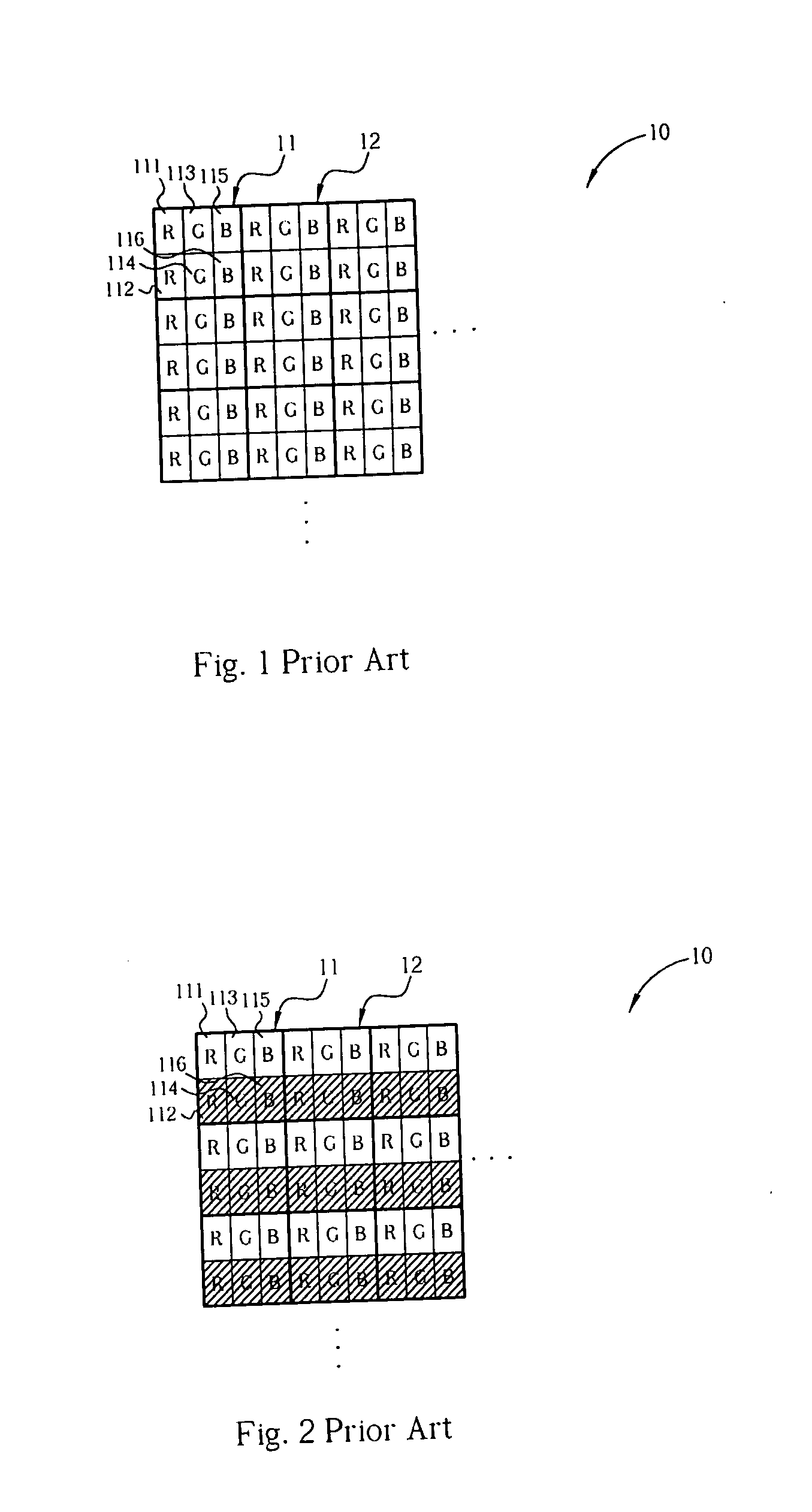

Displaying method and image display device

ActiveUS20060221030A1Reduce color castUniform color distributionCharacter and pattern recognitionCathode-ray tube indicatorsPattern recognitionColor shift

In a displaying method for use in an image display, an original gray scale is divided into a higher gray scale and a lower gray scale. Further, the color subpixels are divided into two groups corresponding to the higher and lower gray scales, respectively. The gray scale to be expressed by each subpixel is calibrated by weighing the original higher or lower gray scale for the pixel and the adjacent pixels and summing up the results. The color shift problem due to different visual angles can therefore be solved.

Owner:INNOLUX CORP

Virtual image display apparatus

InactiveUS20130250380A1Increase image brightnessImprove lighting efficiencySolid-state devicesSemiconductor/solid-state device manufacturingLight guideOptical resonance

A virtual image display apparatus includes an organic EL device that outputs light having one kind of wavelength band, a light guide member, and a reflection-type volume hologram that is disposed on a first face of the light guide member and diffracts and reflects light of a predetermined wavelength band of the light that has entered. The organic EL device includes an optical resonance structure that causes the above-mentioned light of one-kind wavelength band to resonate.

Owner:SEIKO EPSON CORP

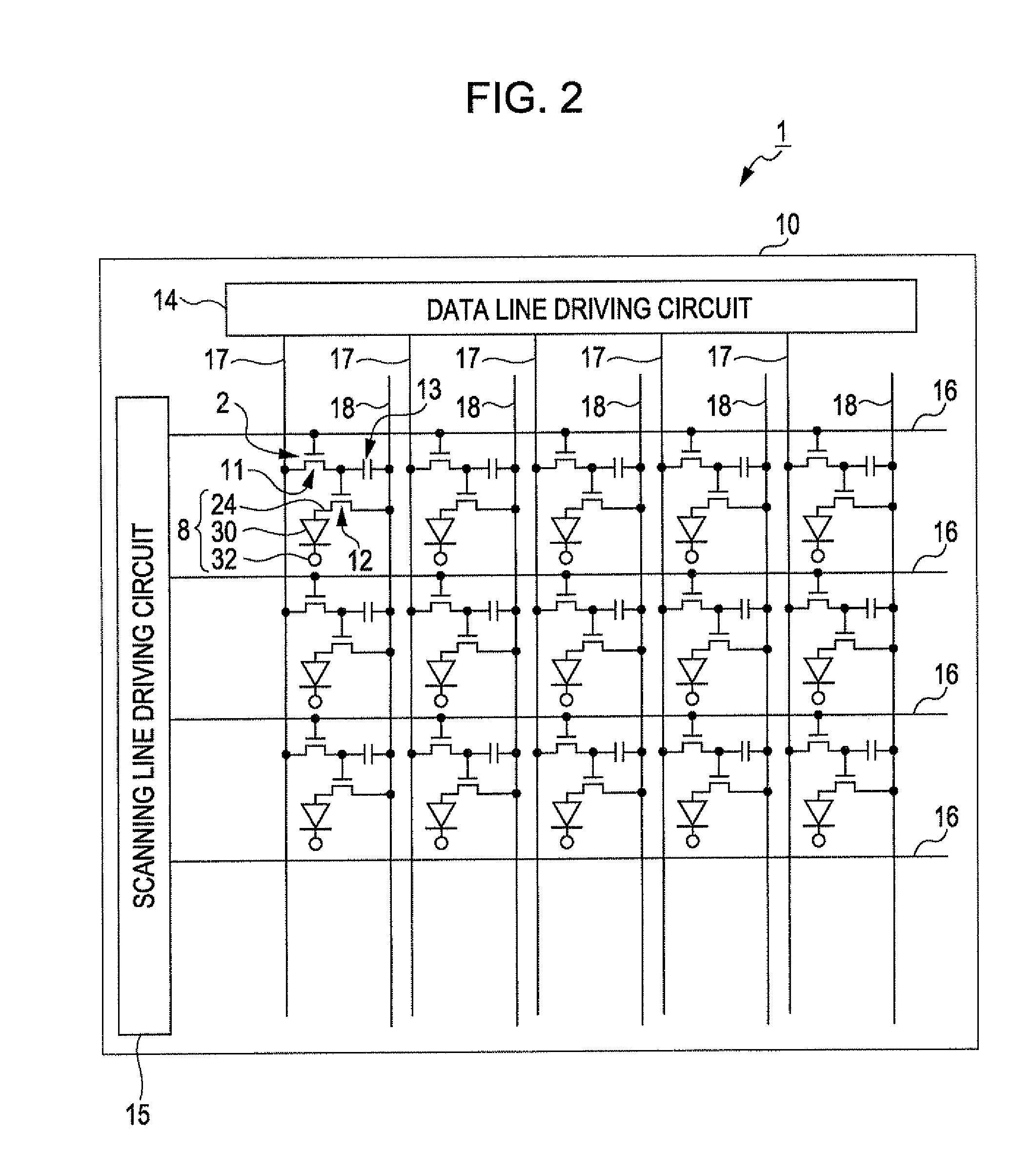

Display device, apparatus for driving the same and method of driving the same

ActiveUS20060038837A1Improve display qualityRemove motion blurCathode-ray tube indicatorsNon-linear opticsDisplay deviceComputer science

A display device has a display panel and a driver. The display panel displays an image signal. The driver provides the display panel with a frame data in a first sub frame using a first gamma curve that has a first gamma value, and provides the display panel with the frame data in a second sub frame using a second gamma curve that has a second gamma value, wherein the second gamma value is greater than the first gamma value. Therefore, the display device may have an improved brightness and display moving pictures in a high display quality.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

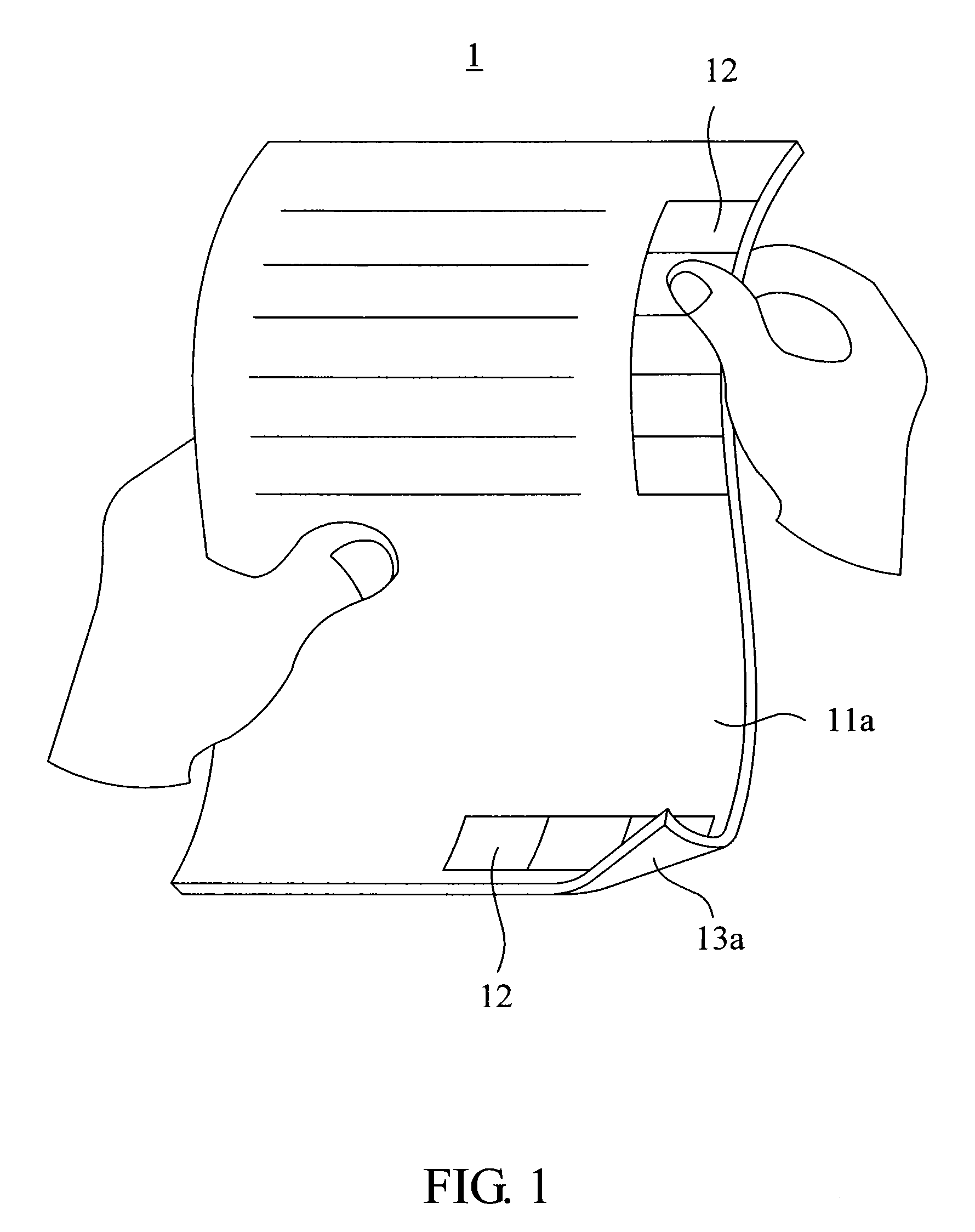

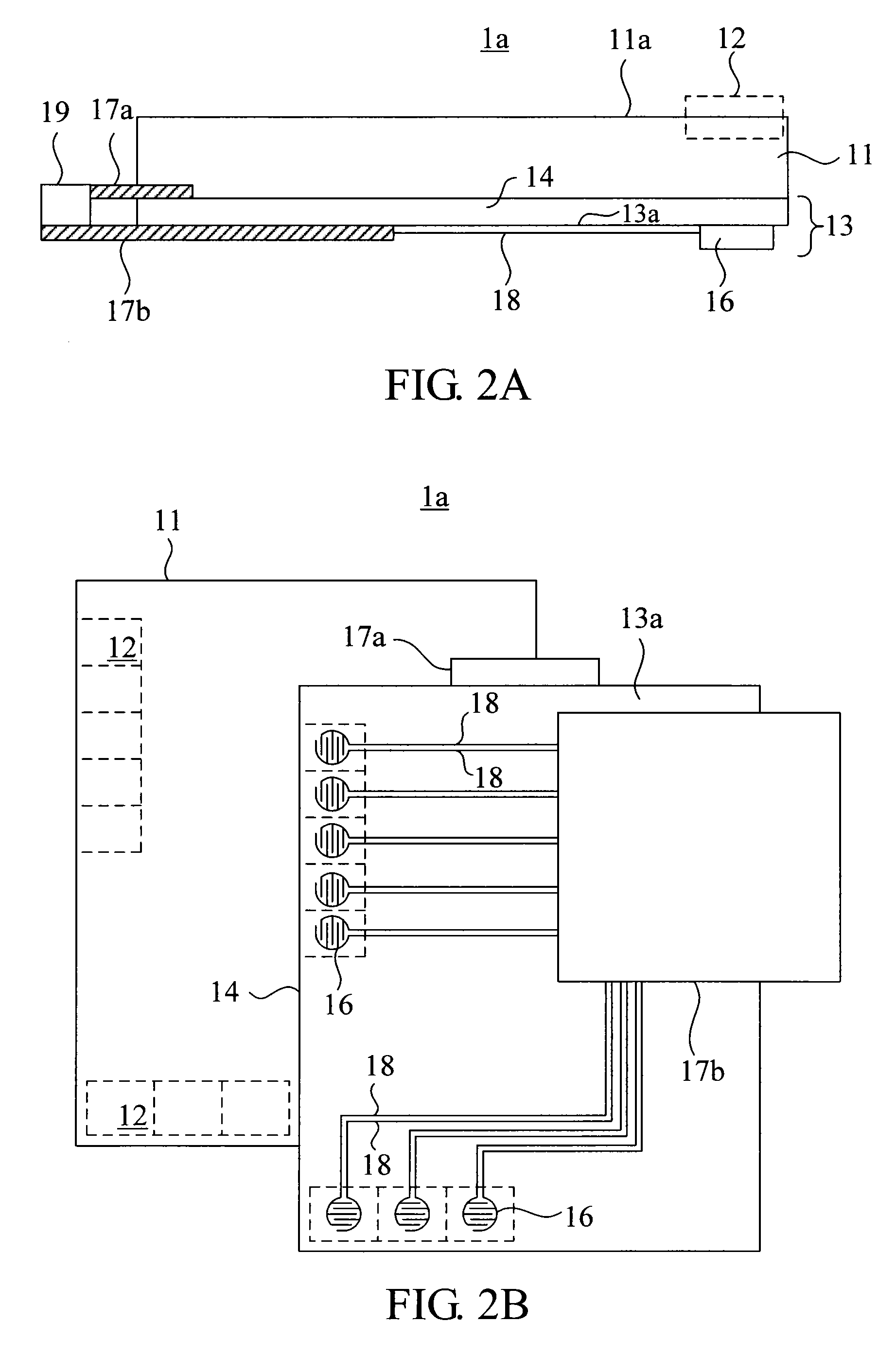

Touch-control structure for a flexible display device

ActiveUS20100171708A1Simple structureSimple manufacturing processDigital data processing detailsInput/output processes for data processingEngineeringFlexible display

A touch-control structure for a flexible display device is provided. The touch-control structure comprises a flexible display panel, at least one menu display area, a touch film and at least one sensing element. The flexible display panel comprises a visible surface. The menu display area is located on at least one side of the visible surface. The touch film comprises a first flexible substrate and an operating contact surface. The visible surface and the operating contact surface are disposed on the two opposite ends of the touch structure respectively. The sensing element is disposed on at least one side of the first flexible substrate corresponding to the menu display area.

Owner:E INK HLDG INC

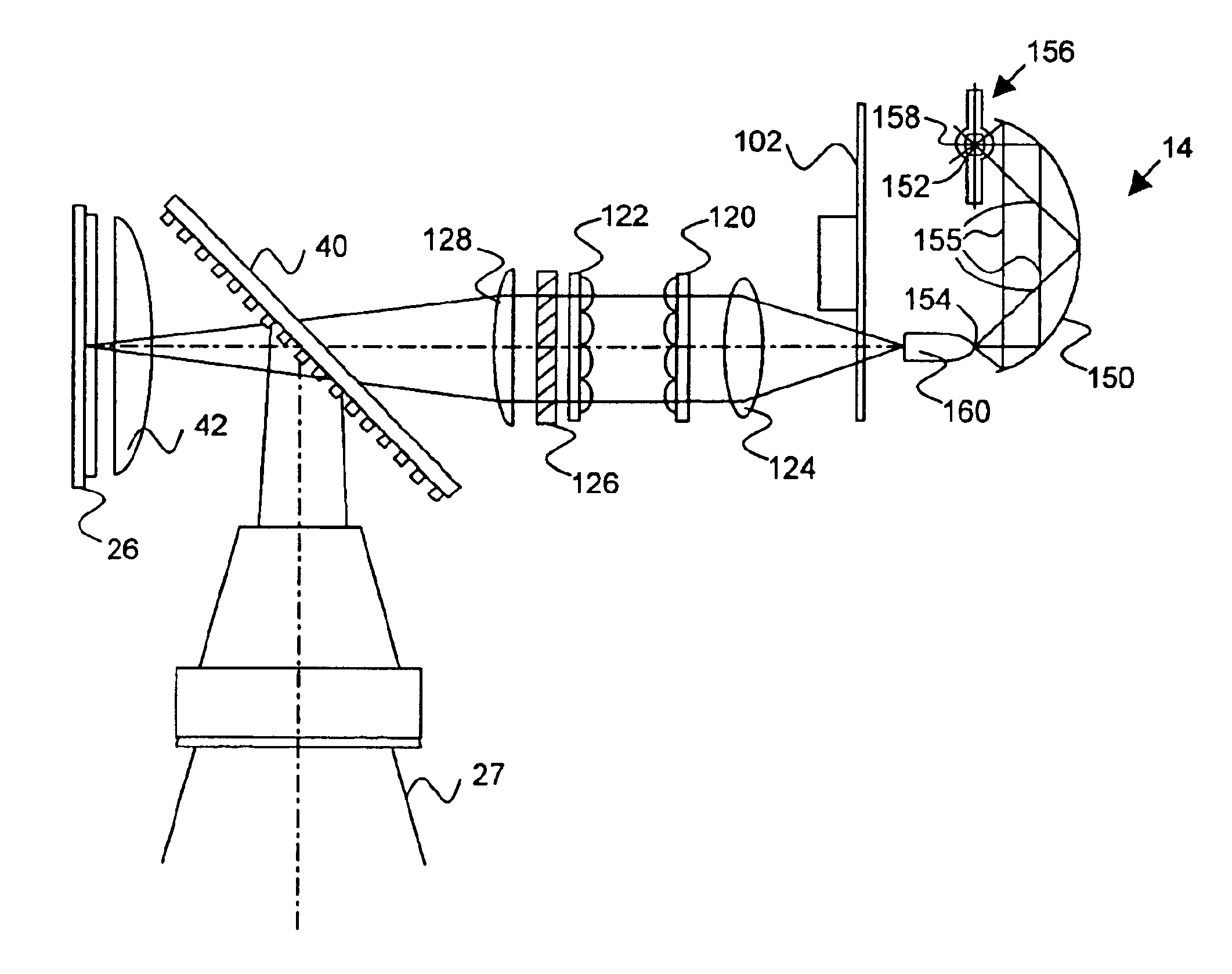

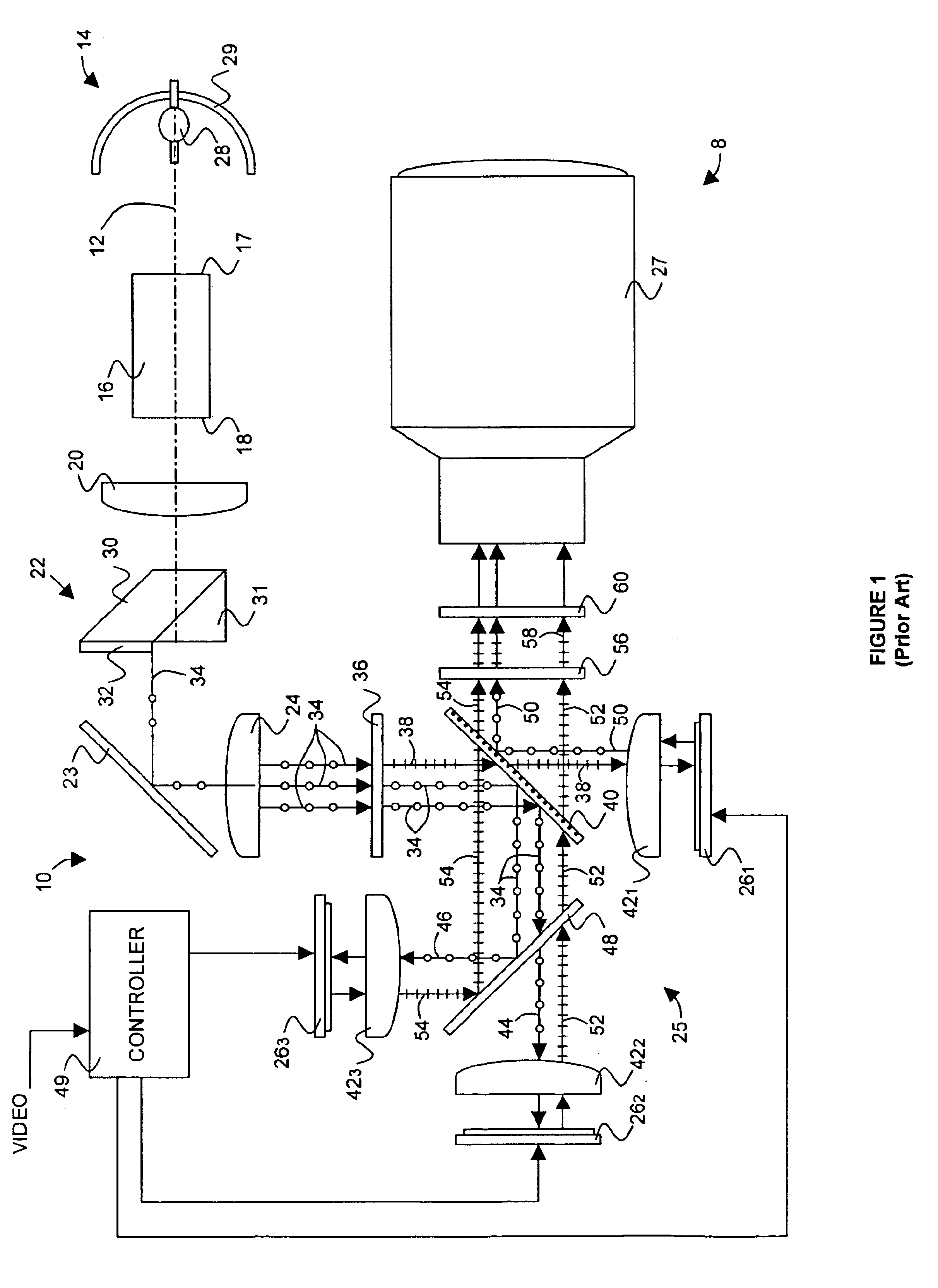

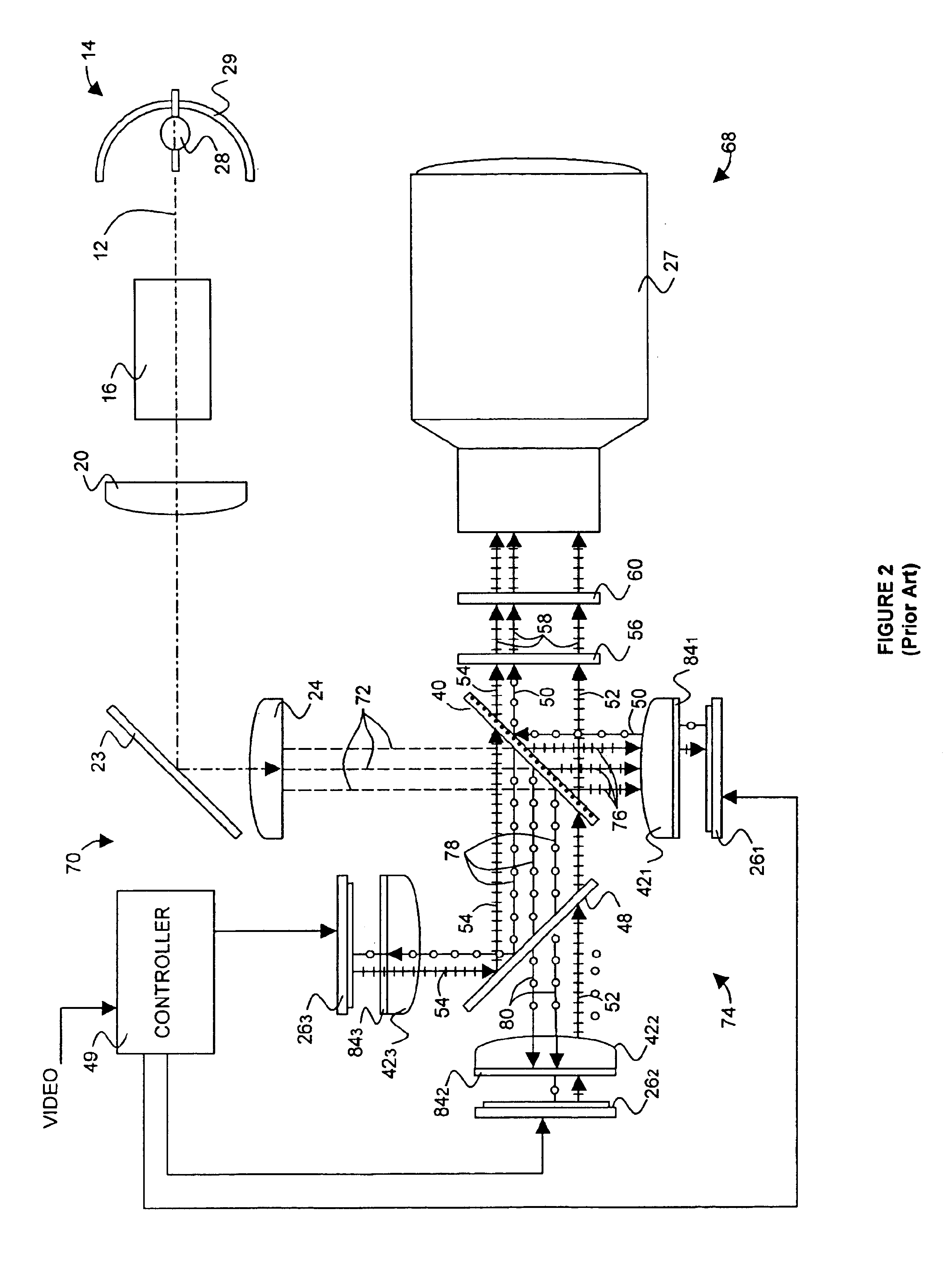

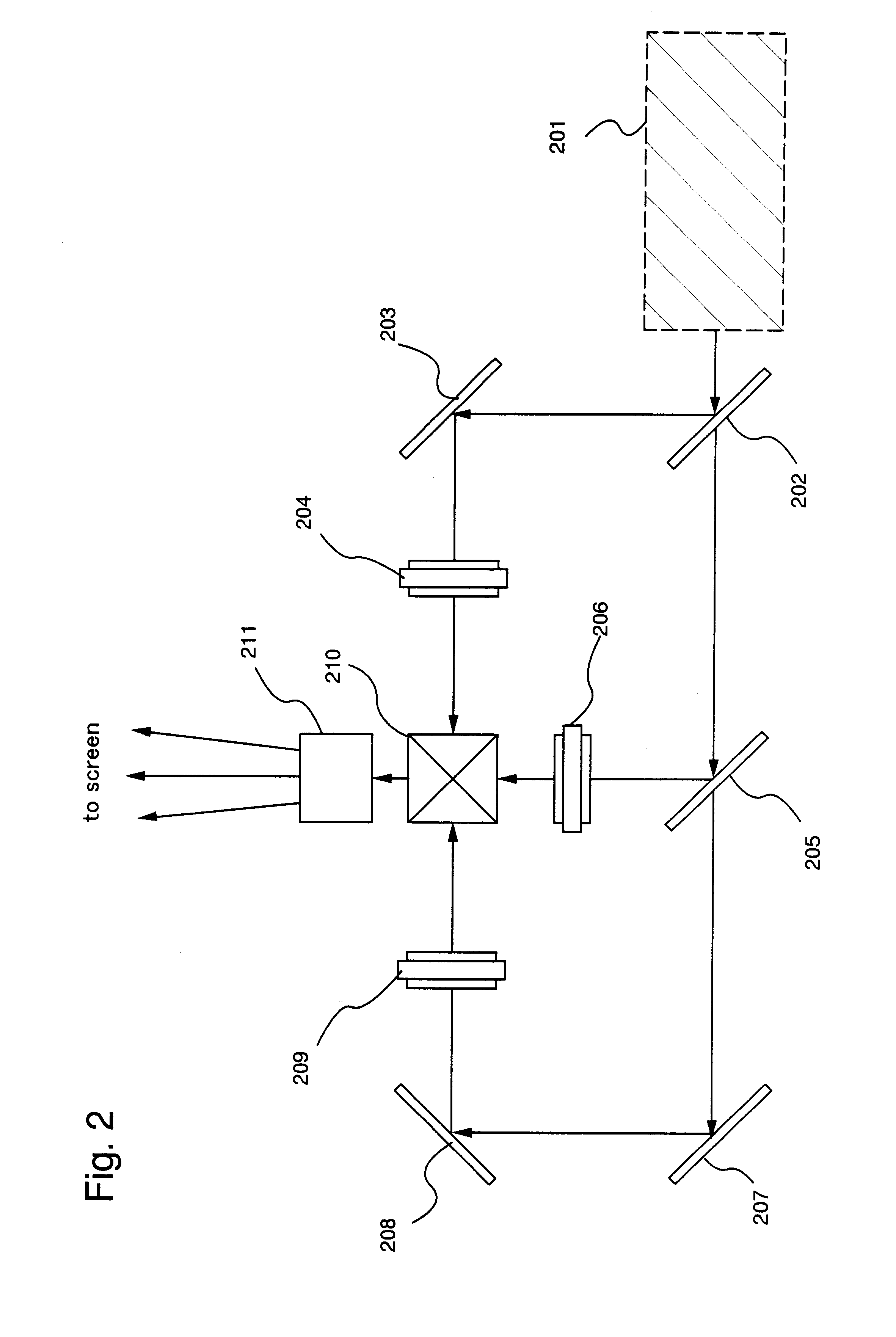

Single-path color video projection systems employing reflective liquid crystal display devices

InactiveUS6839095B2Light collection efficiency be improveMinimize étendueMirrorsStatic indicating devicesIntegratorProjection system

A multimedia projector (100) includes a single-path frame-sequential color optical system in which light rays emitted by a light source (14) propagate through a color wheel (102) and an optical integrator (16, 120, 122), and are directed toward a transflective polarizing beam splitter (40) that separates them into P-polarized components (76) and S-polarized components (78). The P-polarized components are transmitted toward a reflective LCD (26) in which pixels in a dark state reflect the light rays without a polarization change and return them through the transflective polarizing beam splitter, whereas pixels in a bright state reflect the light rays with a 90° polarization change as S-polarized light rays (112), which are reflected by the transflective polarizing beam splitter toward a projection lens (27).

Owner:STRAIGHT SIGNALS

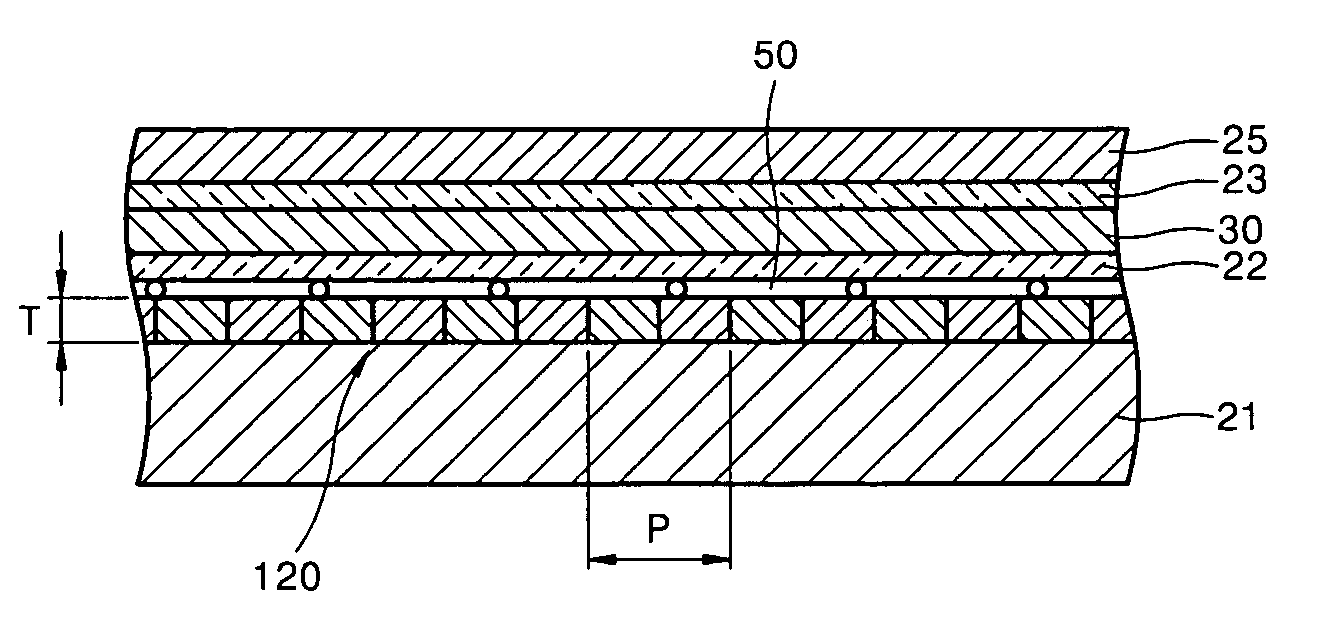

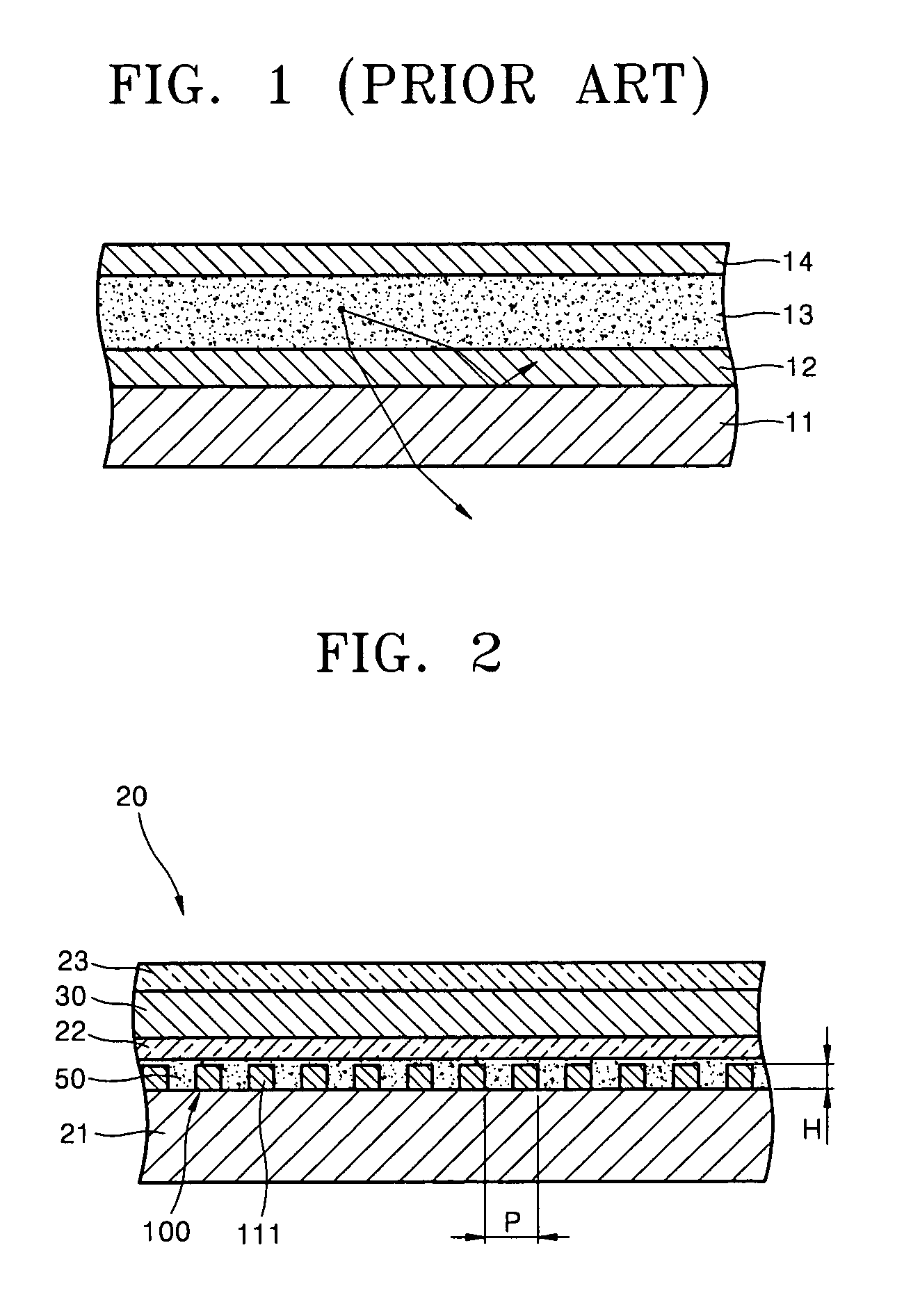

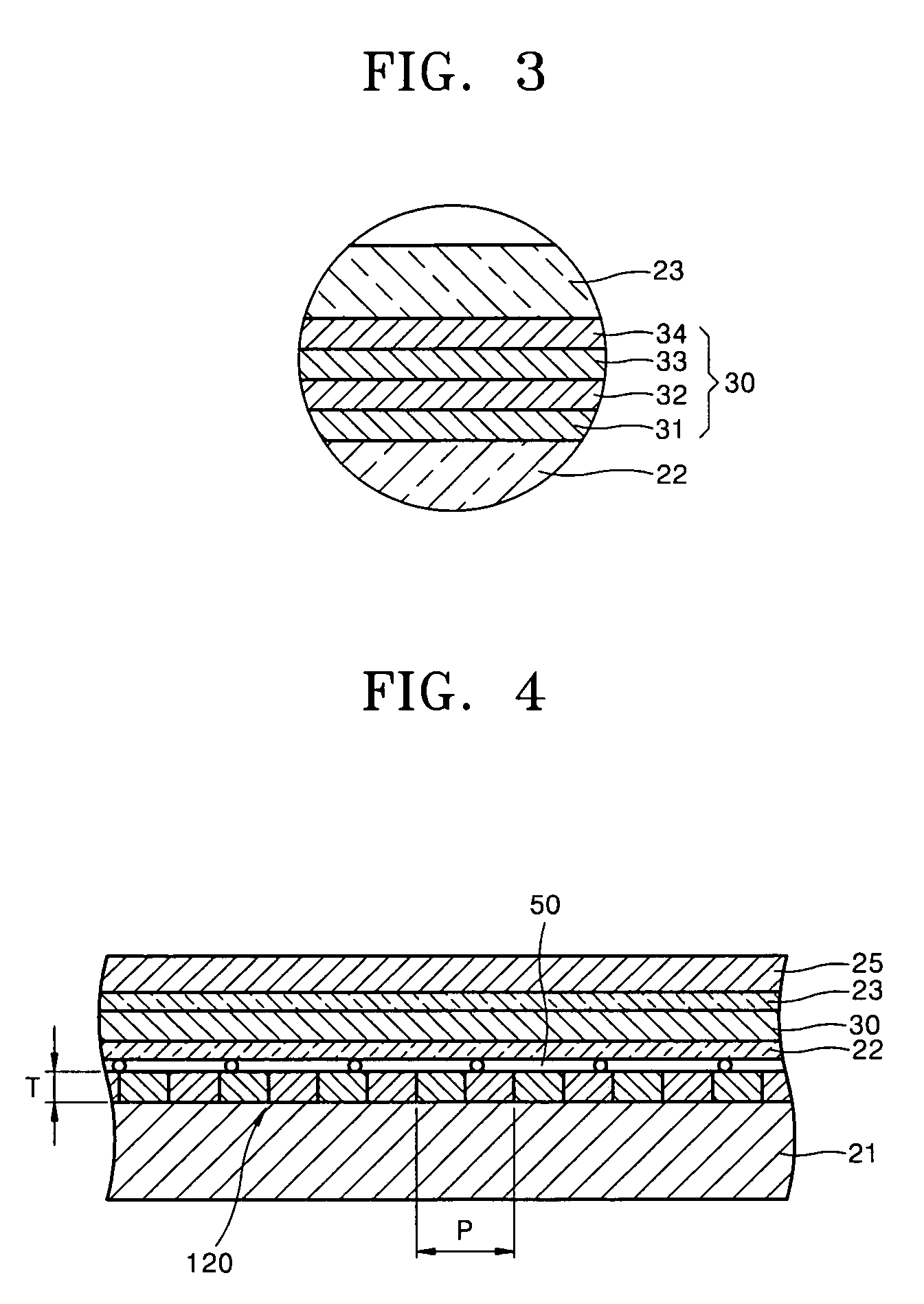

Assembly of organic electroluminescence display device

ActiveUS7084565B2Convenient lightingReduces internal optical lossDischarge tube luminescnet screensStatic indicating devicesDisplay deviceOptoelectronics

An organic electroluminescence (EL) display device assembly includes a substrate, an organic EL portion, an optical loss prevention layer, and a fine space layer. The organic EL portion has a first electrode layer, an organic luminescent layer, and a second electrode layer which are each patterned and stacked on the upper surface of the substrate. The optical loss prevention layer is used to increase light bleeding efficiency. The fine space layer is formed between the optical loss prevention layer and a layer facing the optical loss prevention layer and is filled with a gas or evacuated.

Owner:SAMSUNG DISPLAY CO LTD

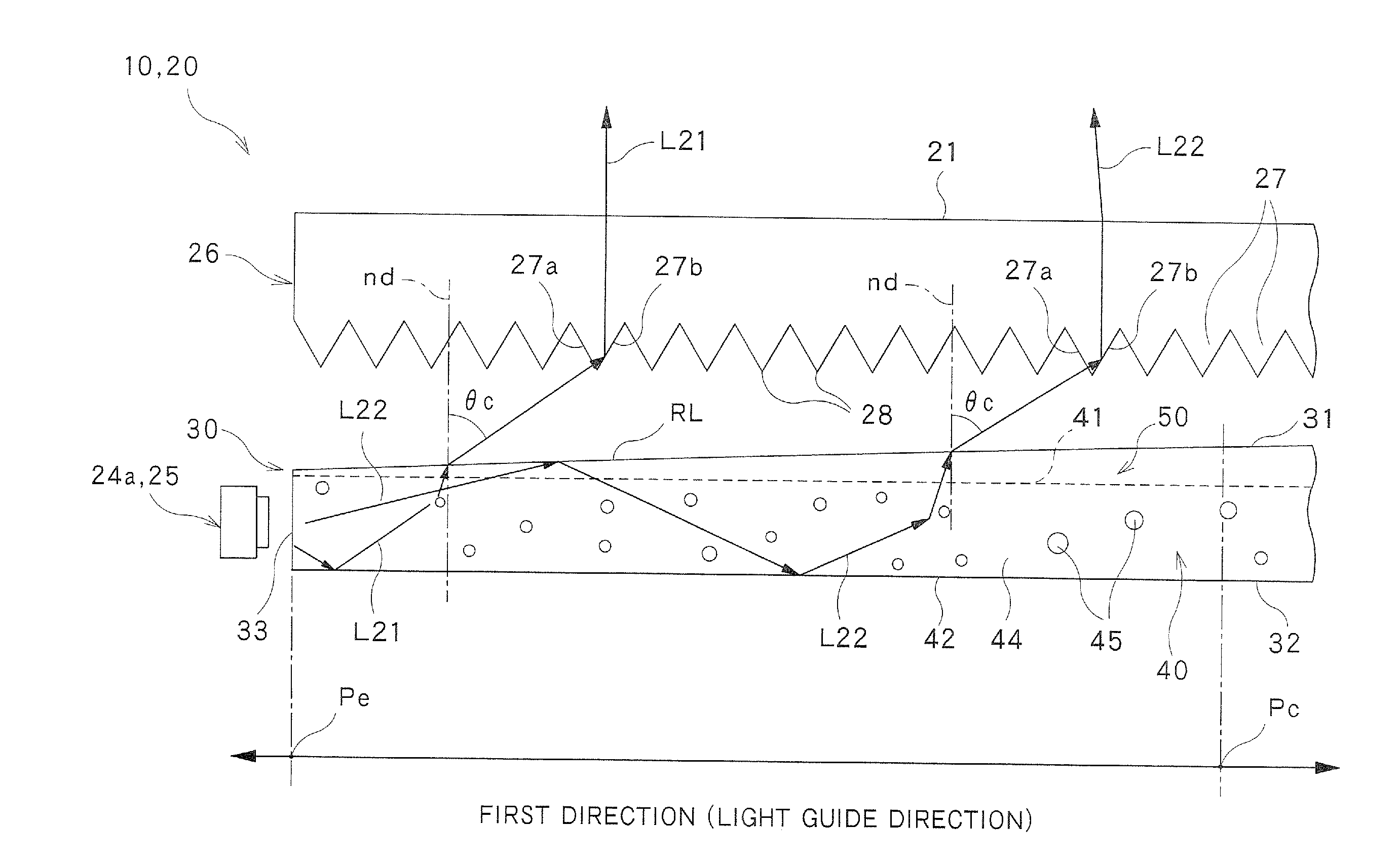

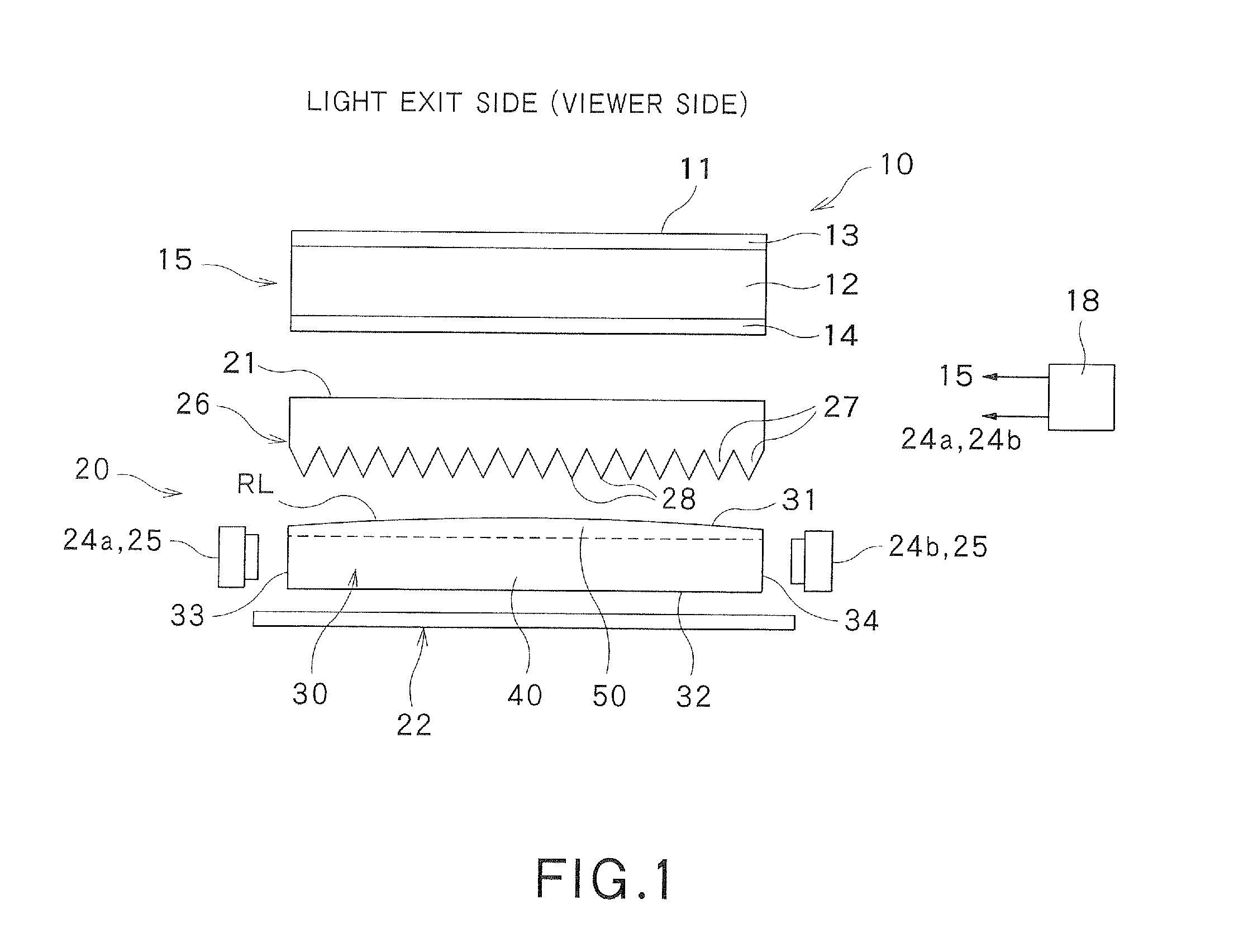

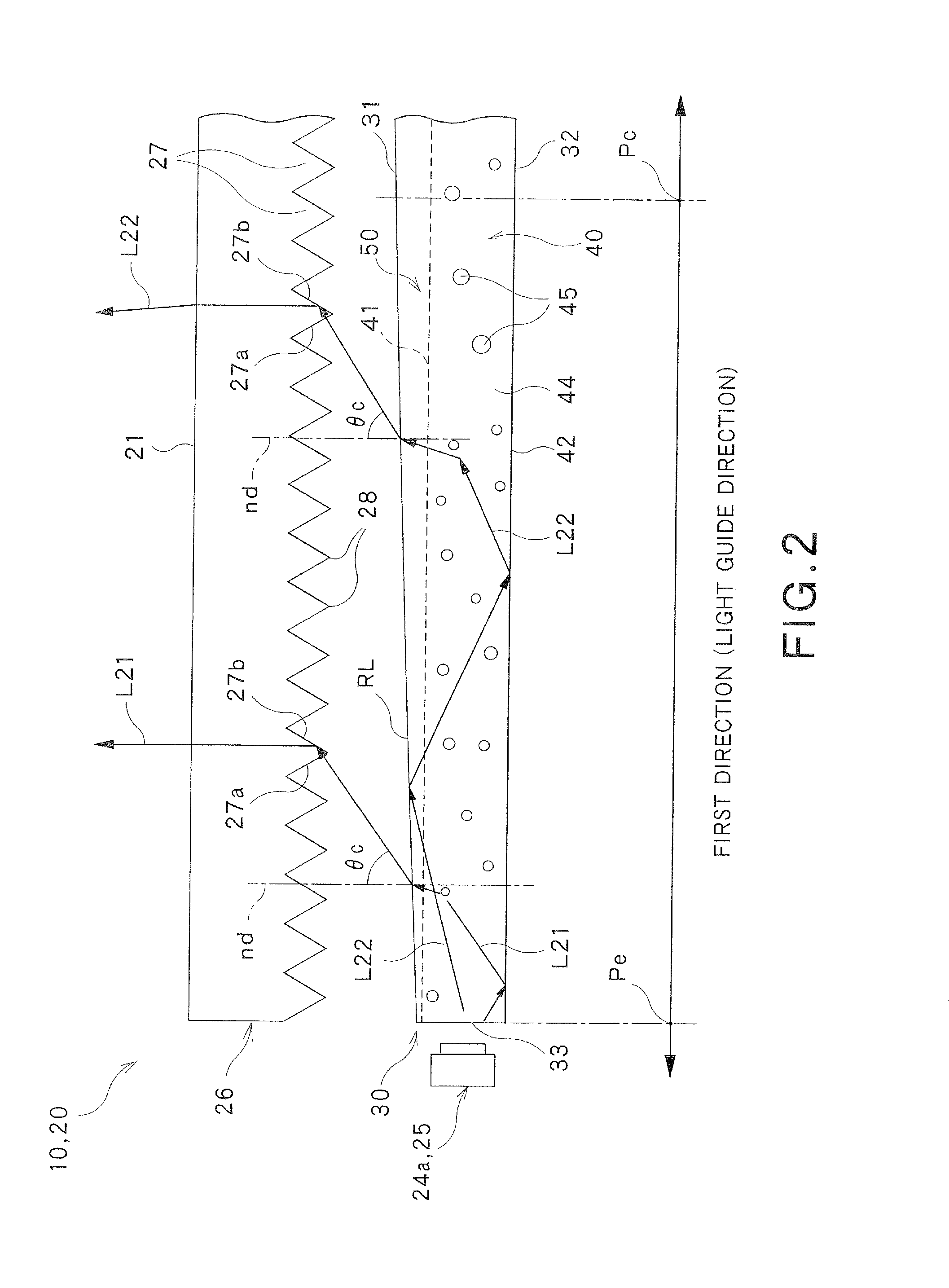

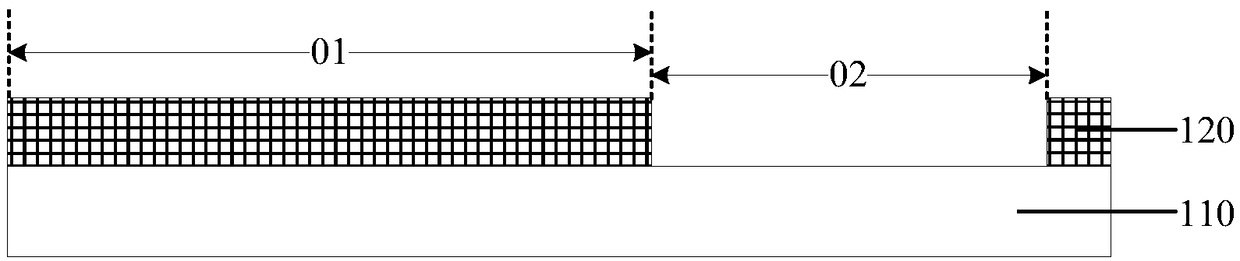

Light guide plate, sufrace light source device, and display device

ActiveUS20130057807A1Increase image brightnessSufficient amountMechanical apparatusLight guides for lighting systemsOptoelectronicsLight guide

A light guide plate includes a body portion, first unit optical elements extending on the body portion in the light guide direction, and second unit optical elements disposed in between the first unit optical elements on the body portion. The width of each first unit optical element gradually decreases from that at the center to that at each end in the light guide direction. The ratio of the height to the width in each first unit optical element at the center is higher than the ratio of the height to the width in each second unit optical element.

Owner:DAI NIPPON PRINTING CO LTD

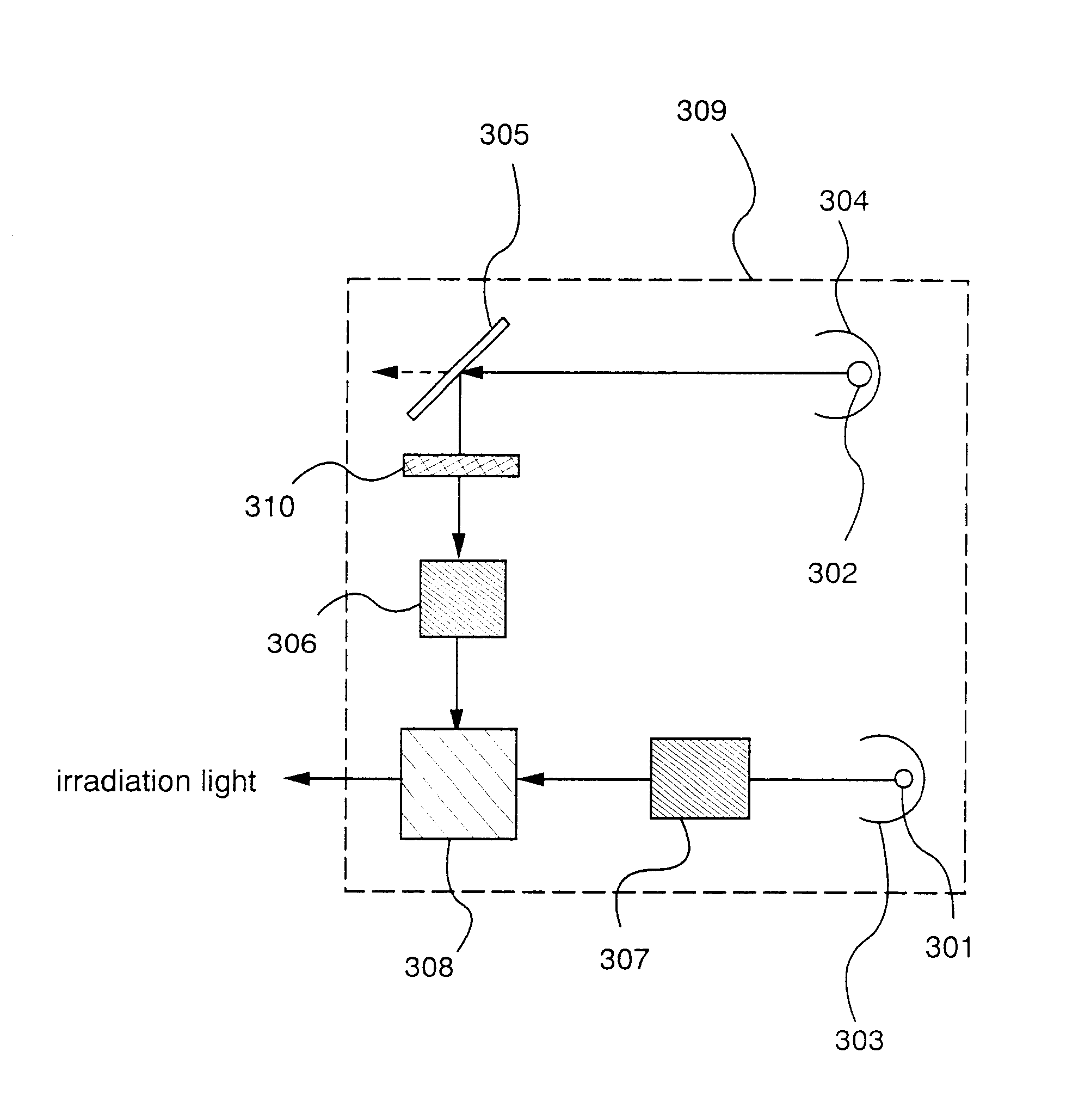

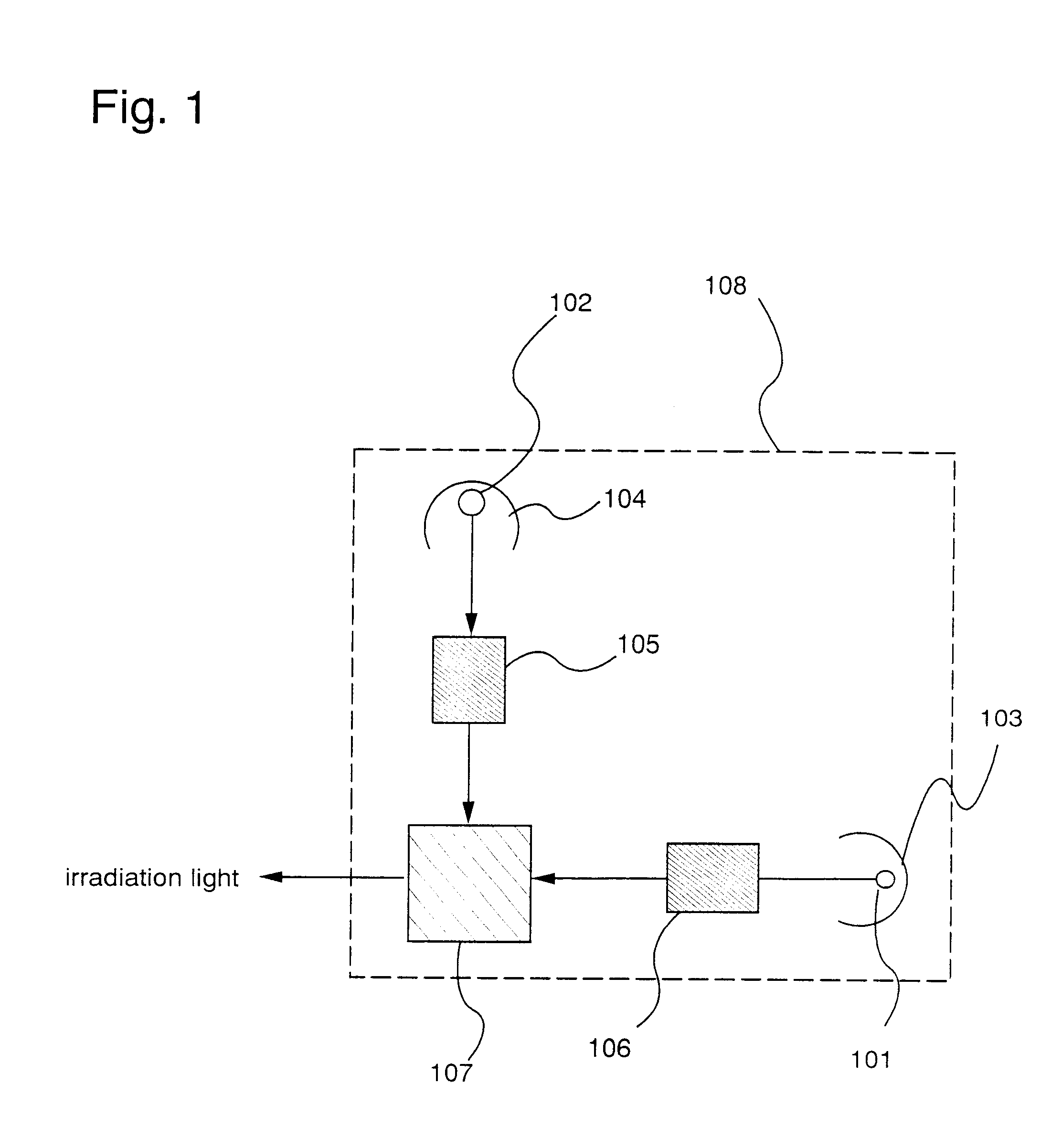

Light source optical system and projector having first and second lamps of different spectral distributions

InactiveUS6623122B1Good balance in brightnessHigh color purityTelevision system detailsPoint-like light sourceOptoelectronicsOptic system

A light source optical system capable of forming an image having good balance in brightness of red, blue, and green color light, having high overall brightness, and having good color reproducibility, on a screen is provided. The light source optical system has a first lamp, a second lamp, and a condensing optical system for synthesizing a first light emitted from the first lamp and a second light emitted from the second lamp to form irradiation light. The light source optical system is characterized in that the first light and the second light have mutually differing spectral distributions.

Owner:SEMICON ENERGY LAB CO LTD

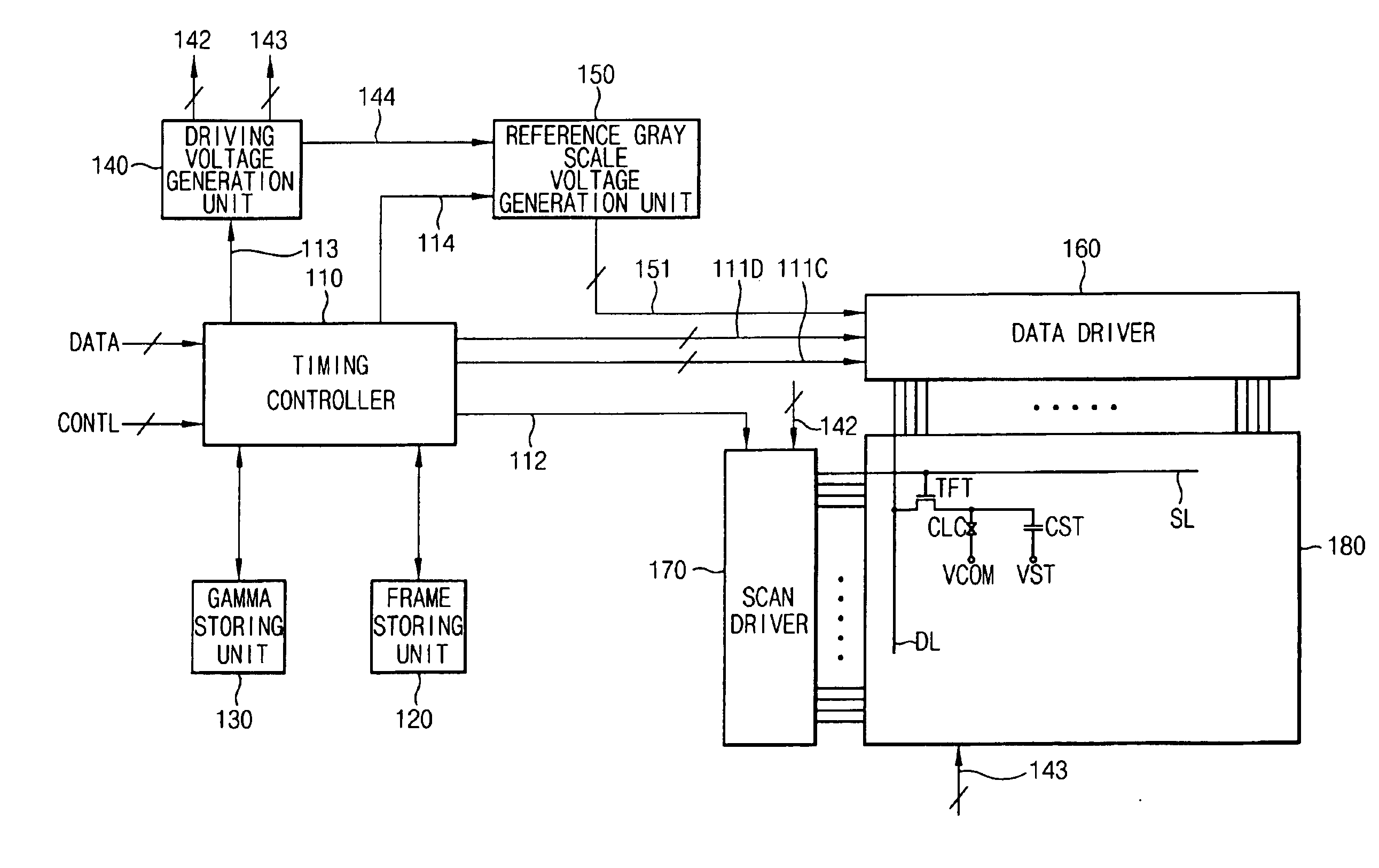

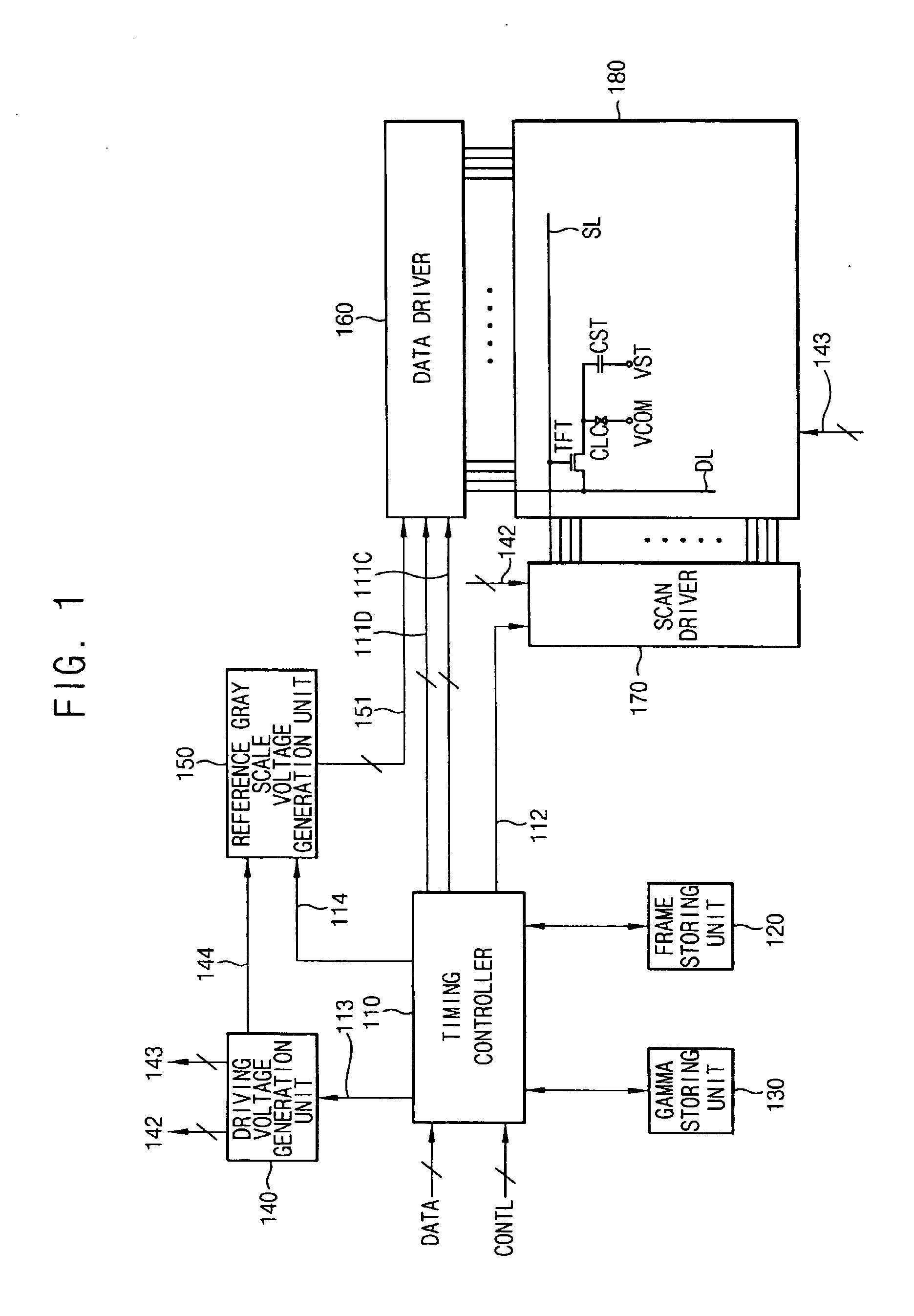

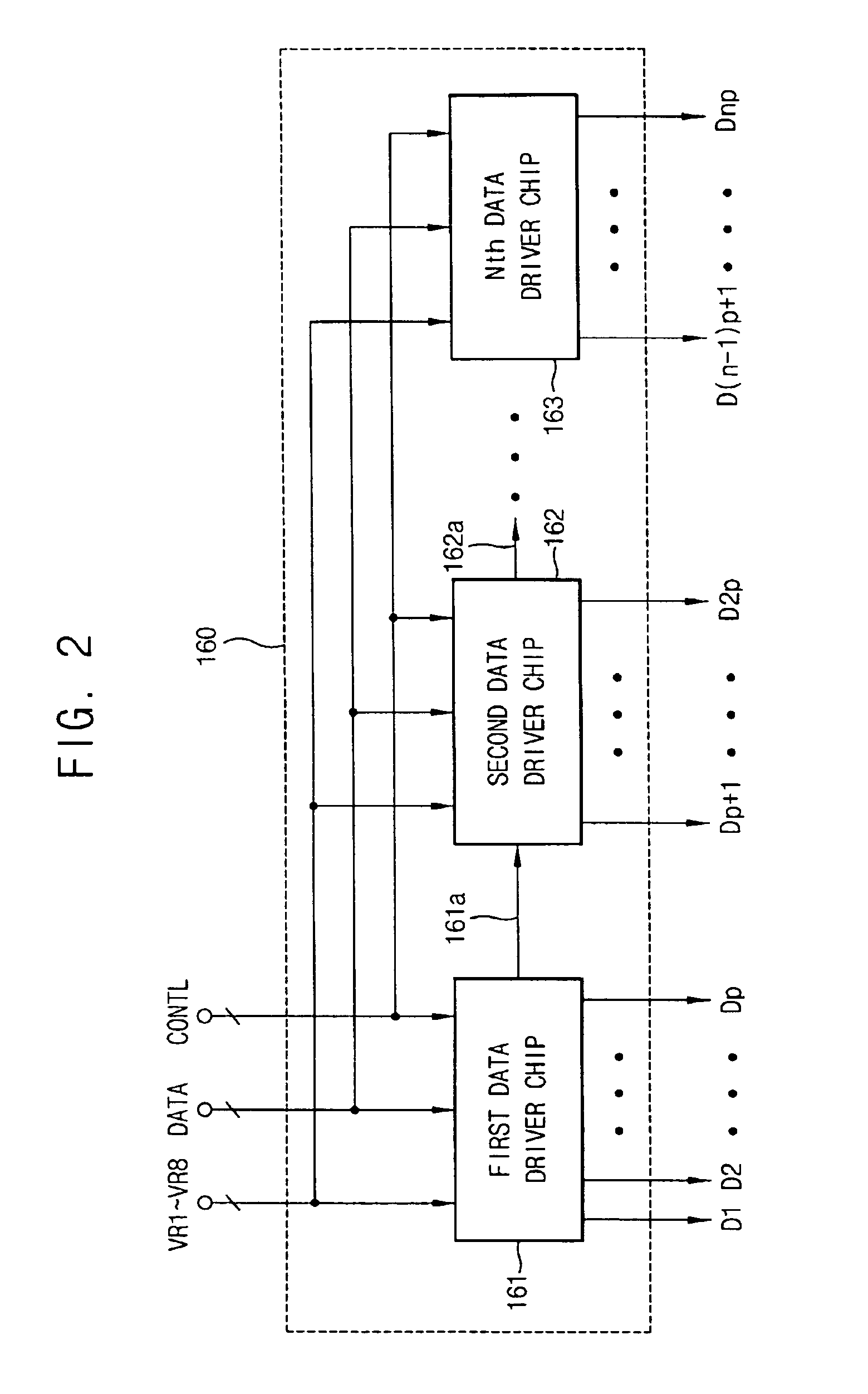

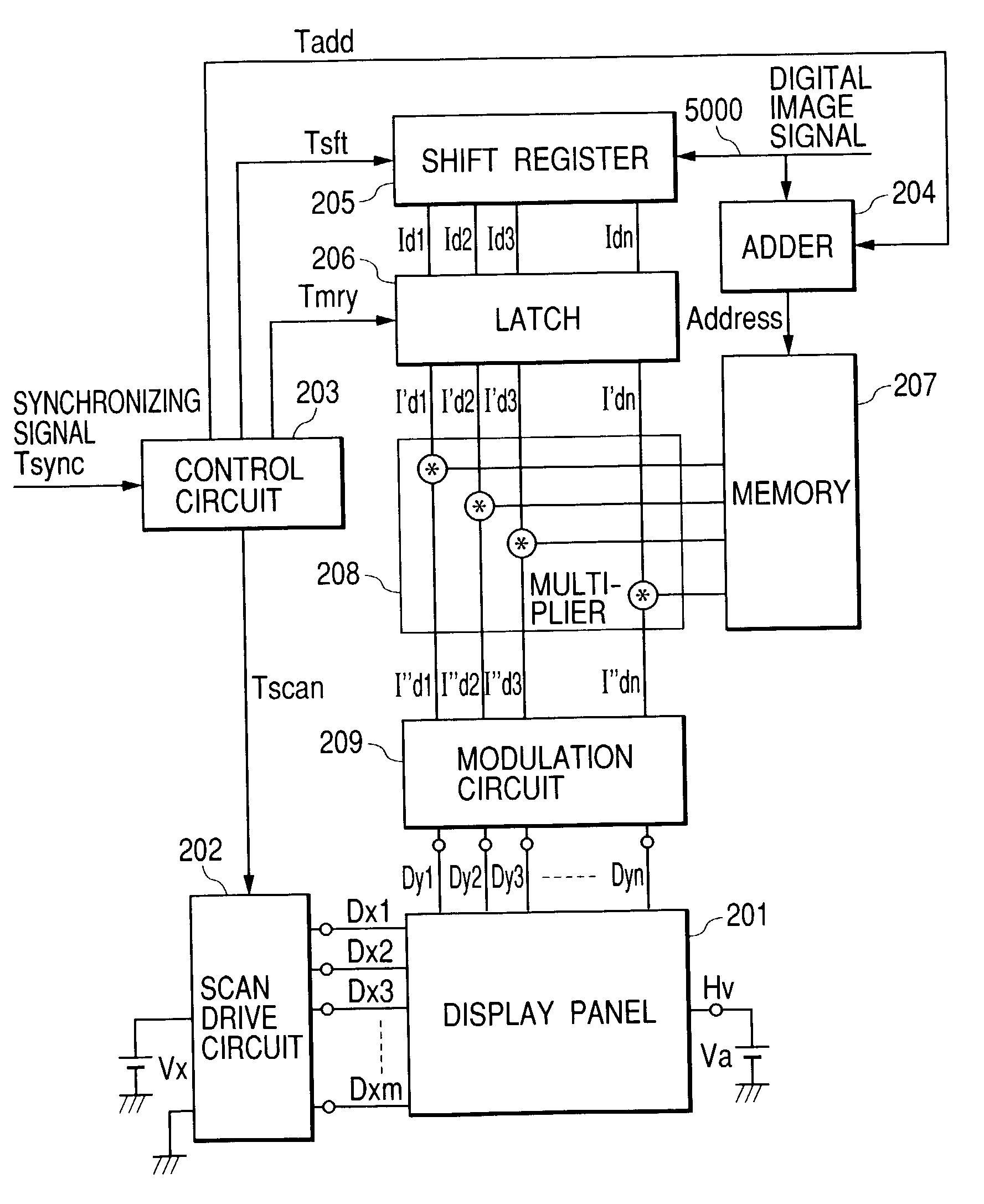

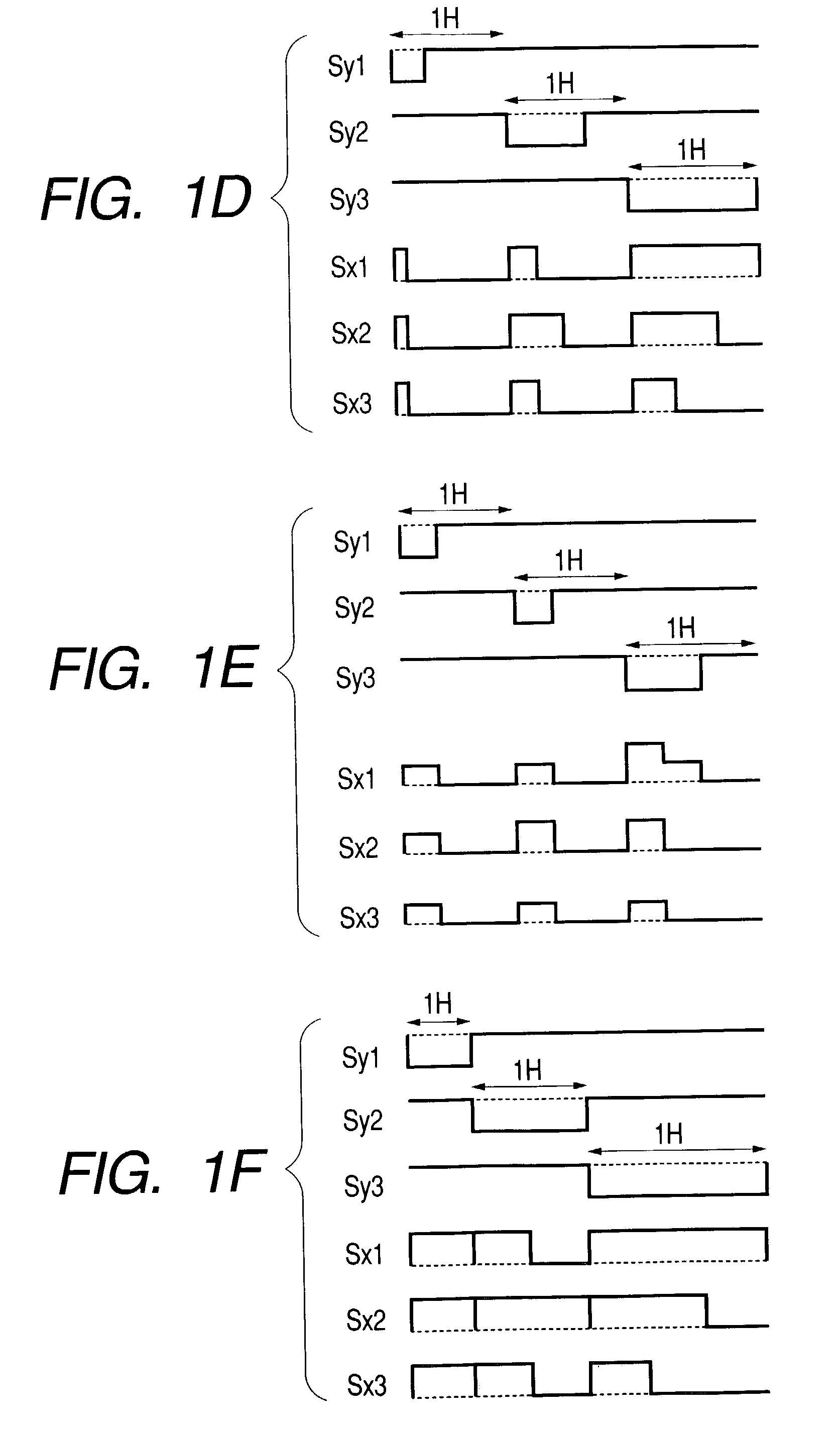

Display driving method and display apparatus utilizing the same

InactiveUS6985141B2Increase image brightnessAvoid wasting timeCathode-ray tube indicatorsInput/output processes for data processingDisplay deviceComputer science

Owner:CANON KK

Integrated retinal imager and method

ActiveUS8109635B2Enhance the imageEfficient couplingOthalmoscopesPhotographyImaging qualityExposure control

A system and method are presented for use in imaging the patient's retina. A light source unit is provided including a light emitting diode (LED) arrangement comprising multiple LEDs of different wavelength ranges. A light guide arrangement is used with the LEDs arrangement and is configured for coupling light from the LEDs and providing output light beams of a desired shape. The illuminating light is directed towards a region on the retina, and light returned from the illuminated region is collected and directed to an image detector unit. The invention enables the use of LED light at high intensity as required in the eye retina imaging, while maintaining the required high-quality imaging. Also, the invention provides for simultaneous or quasi-simultaneous as well as high-speed imaging in FA and ICG imaging procedures, thereby satisfying a long felt need in ophthalmology. Also, the invention provides for automated illumination or light exposure control to optimize overall light exposure to the patient eye and best acquired image quality in terms of brightness, contrast and image signal-to-noise ratio.

Owner:INT BUSINESS MASCH CORP

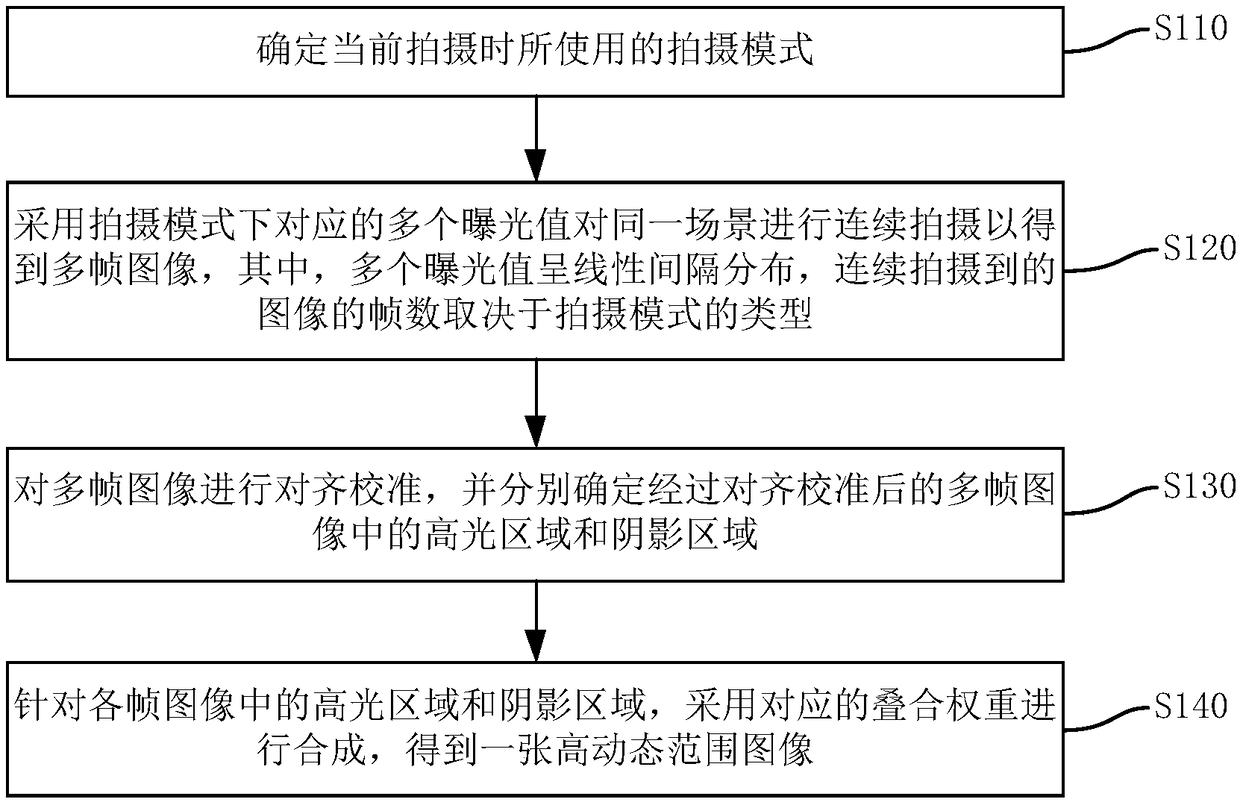

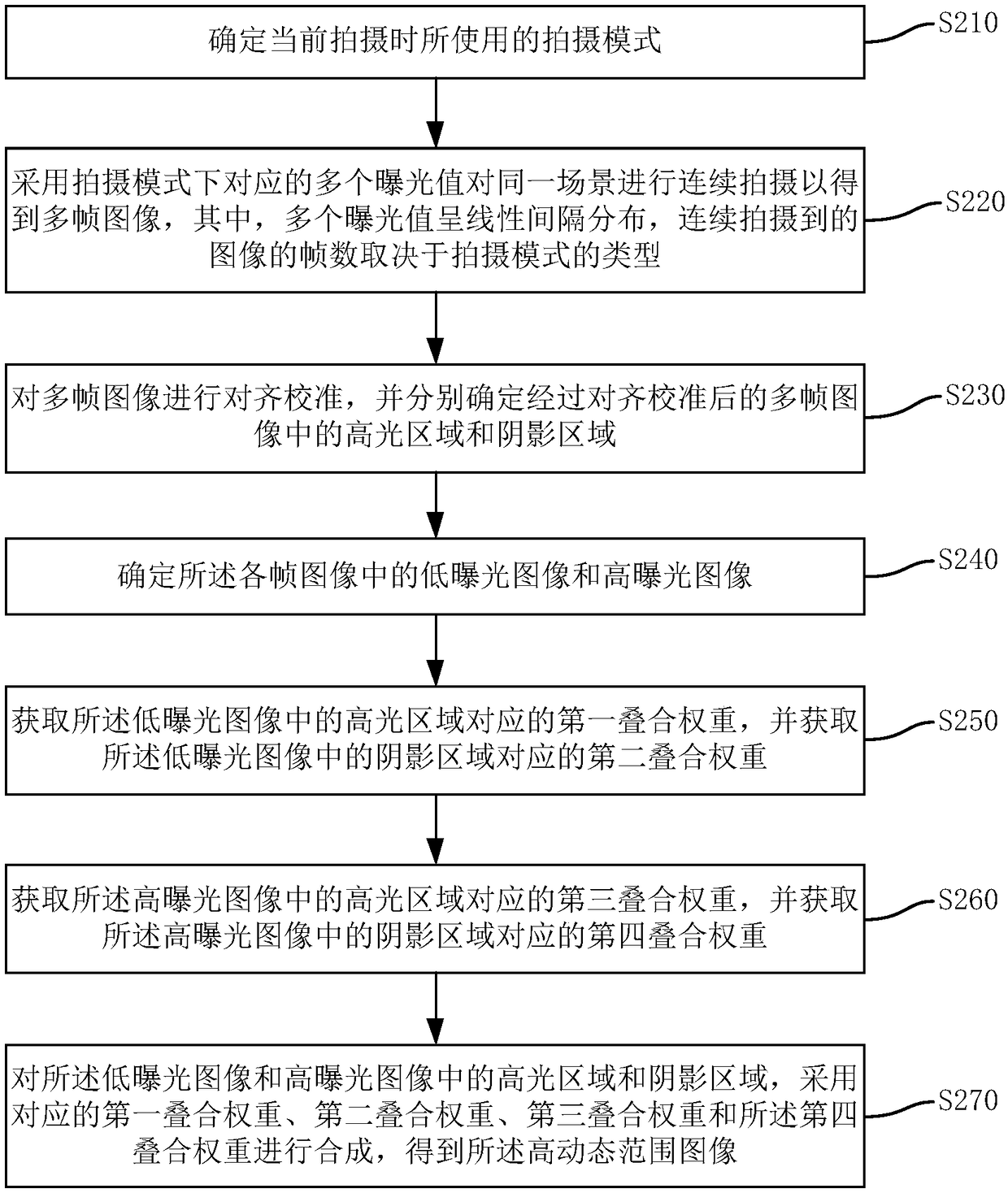

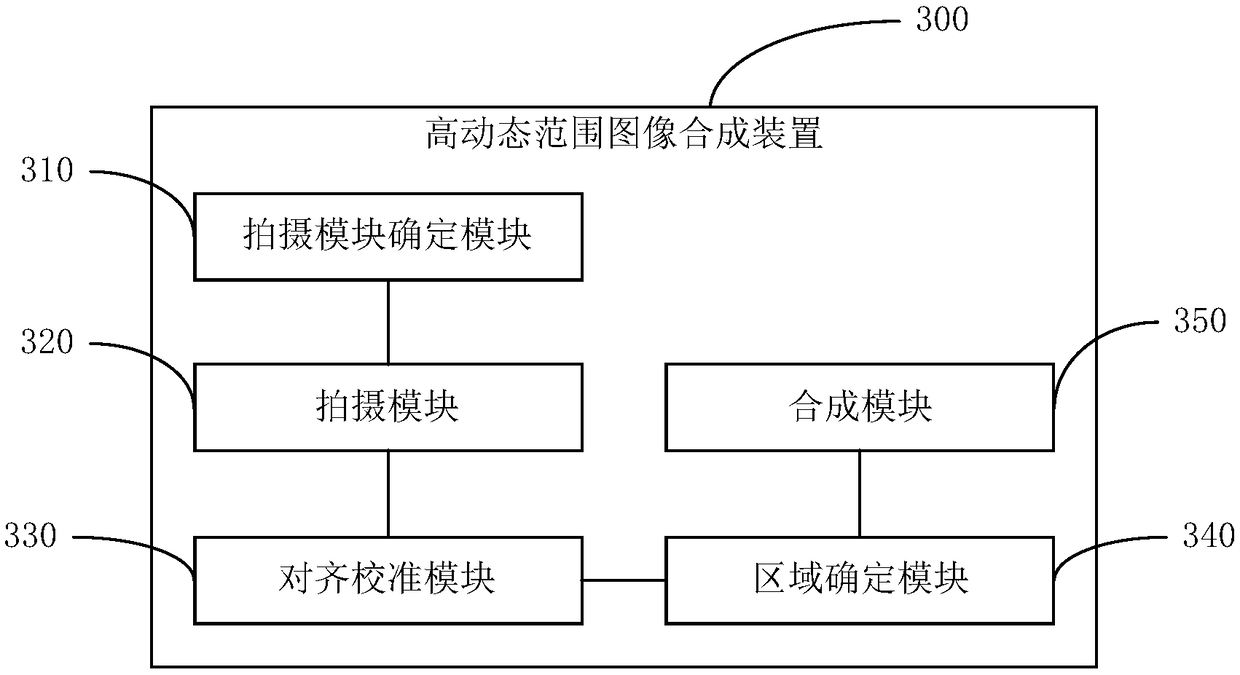

High-dynamic-range image synthesis method, apparatus, terminal device, and storage medium

ActiveCN109218613AIncrease image brightnessIncrease brightnessTelevision system detailsColor television detailsImage synthesisHigh dynamic range

Embodiments of the present application disclose a high-dynamic-range image synthesis method, an apparatus, a terminal device, and a storage medium. The method comprises the following steps of: determining a shooting mode used in the current shooting; A plurality of exposure values corresponding to the shooting mode are used to continuously shoot the same scene to obtain a plurality of frames of images, wherein the plurality of exposure values are distributed at linear intervals, and the number of frames of the continuously shot images depends on the type of the shooting mode; Aligning and calibrating the multi-frame images, and respectively determining highlight regions and shadow regions in the aligned and calibrated multi-frame images; A high dynamic range image is obtained by synthesizing the highlight region and the shadow region of each frame image with corresponding overlapping weights. This method can improve the brightness, restrain the over-exposure area, increase the dynamicrange and reduce the noise of the image.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

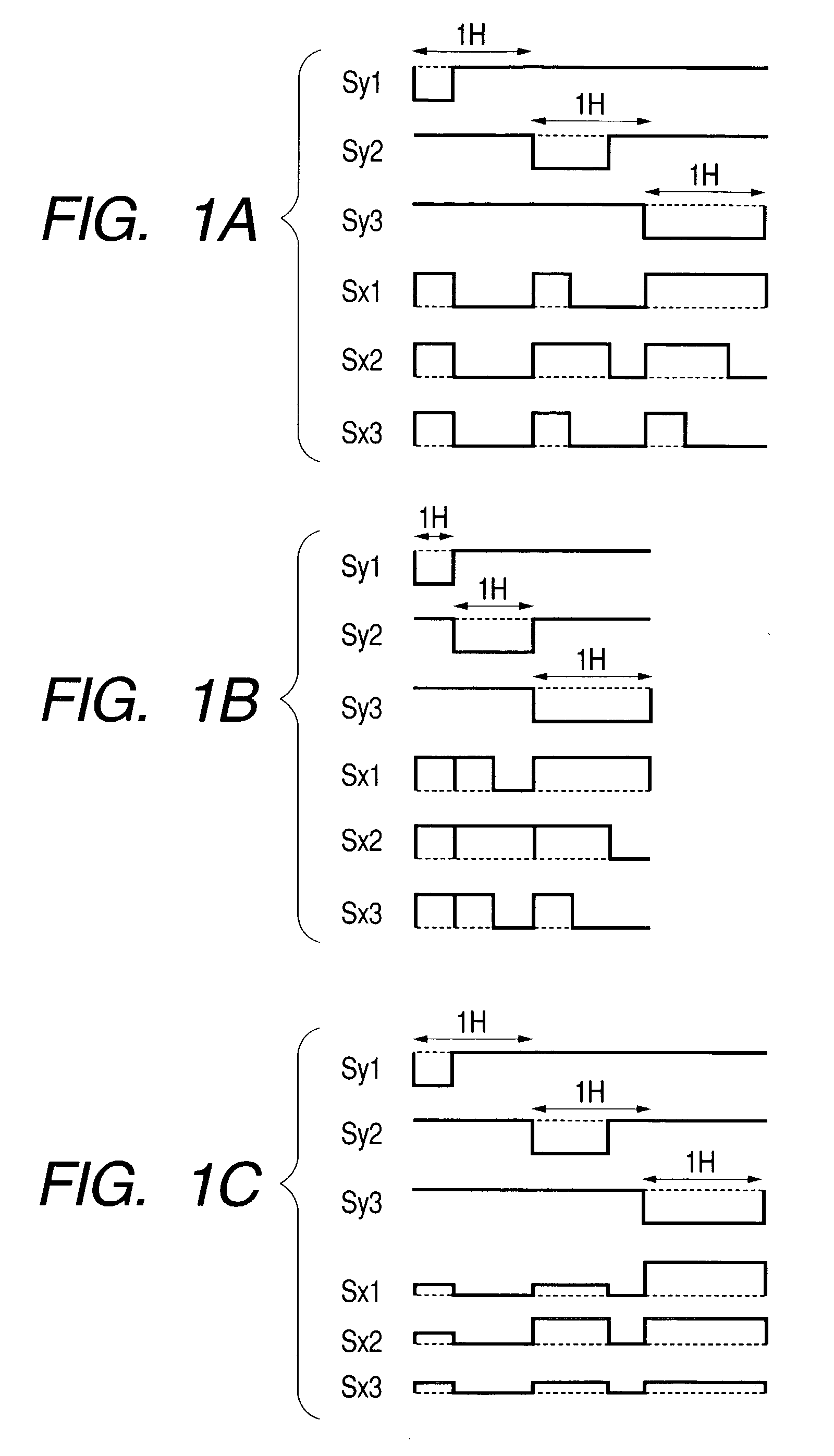

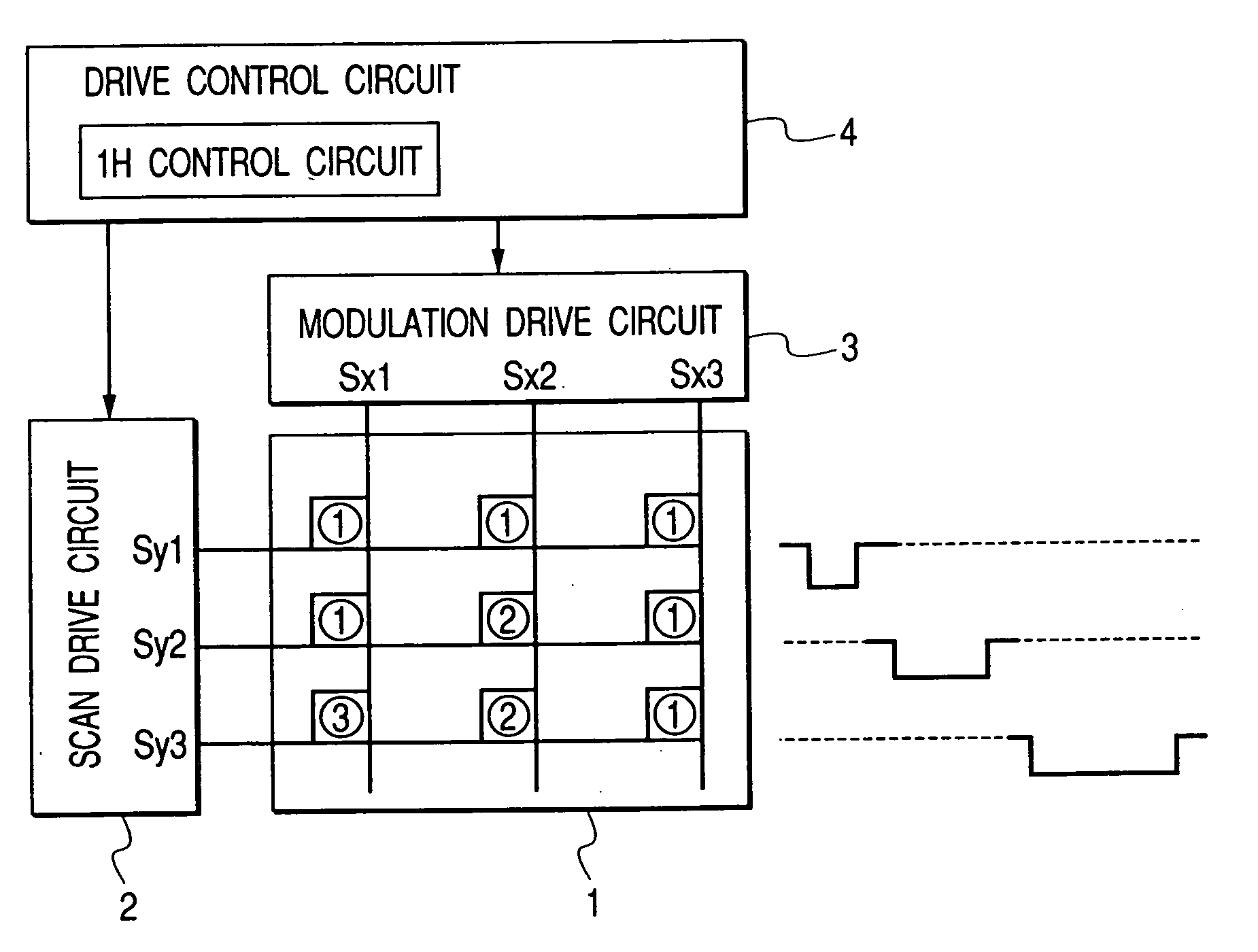

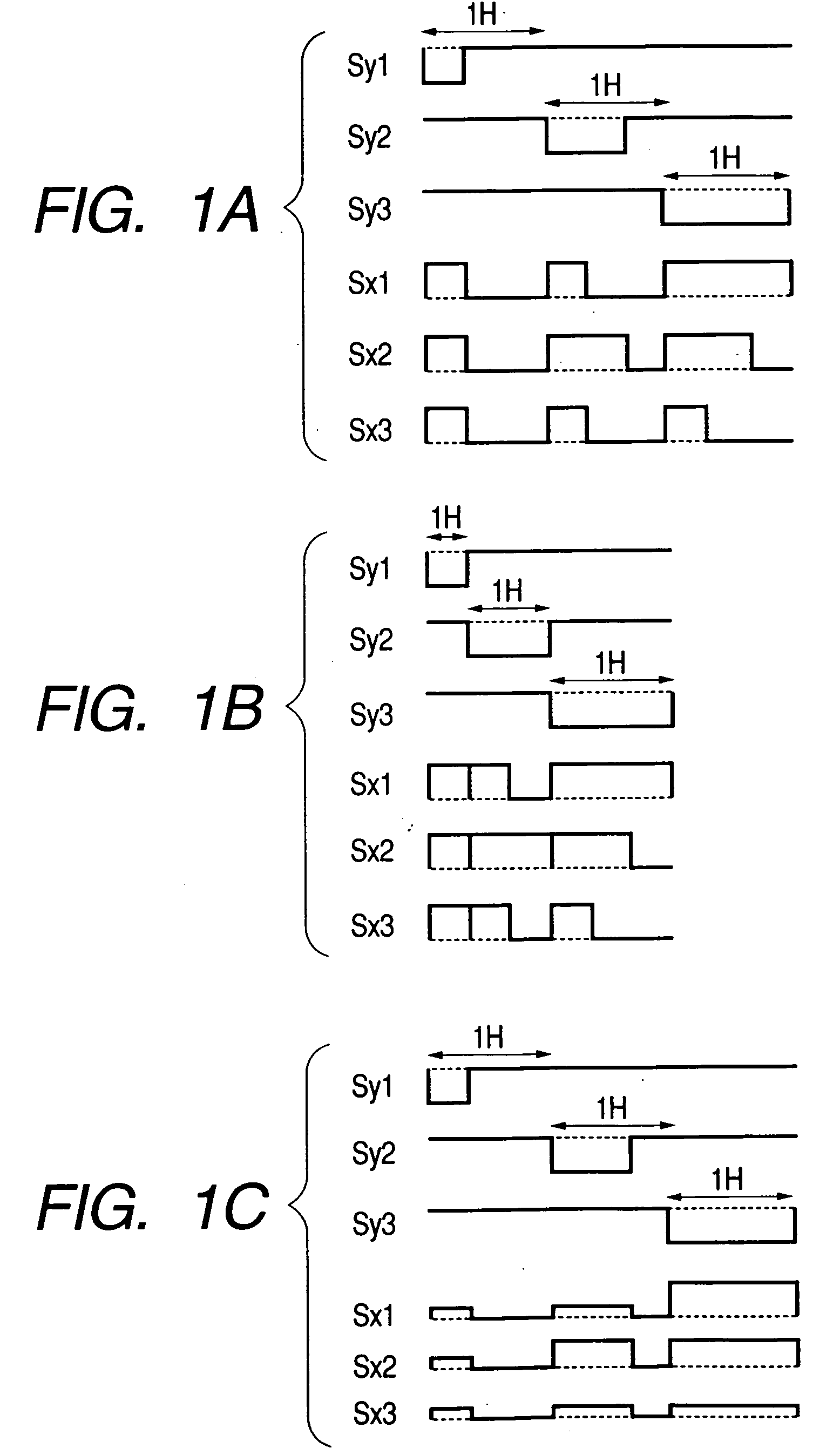

Display driving method and display apparatus utilizing the same

InactiveUS20050231498A1Increase luminance of imageIncrease image brightnessCathode-ray tube indicatorsInput/output processes for data processingDisplay deviceImaging data

In order to obtain a satisfactory image by making a peak luminance of an image to be displayed large and suppressing an occurrence of unnecessary period, there is provided a display driving method for driving a display with a plurality of scanning wirings and a plurality of modulation wirings, comprising: a step of supplying a scan selection signal to a scanning wiring selected out of the plural scanning wirings for each horizontal scanning period; and a step of supplying a modulation signal modulated in accordance with image data to the plural modulation wirings for each horizontal scanning period, in which the selection period of the scan selection signal varies between at least two horizontal scanning periods in a vertical scanning period.

Owner:CANON KK

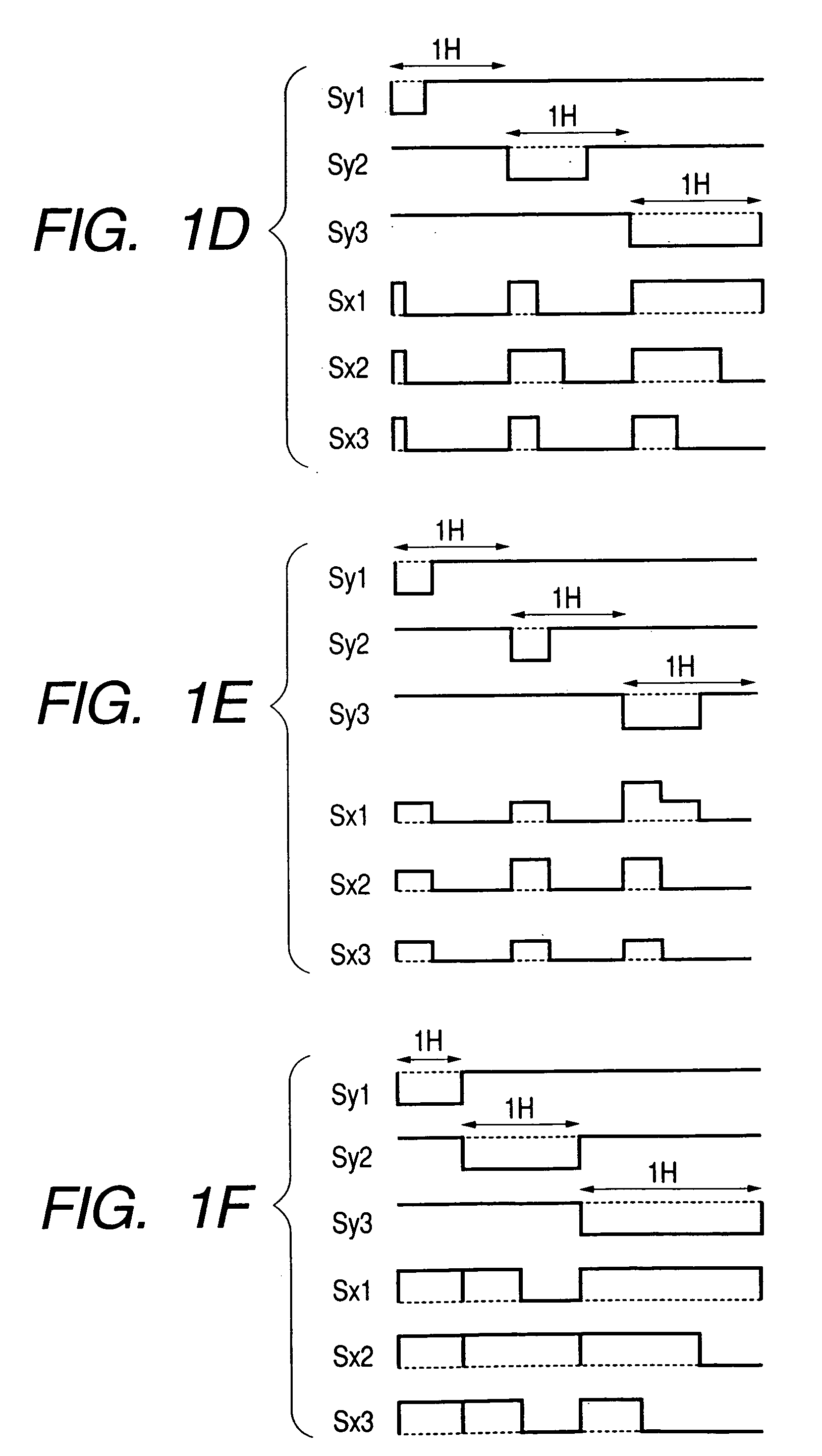

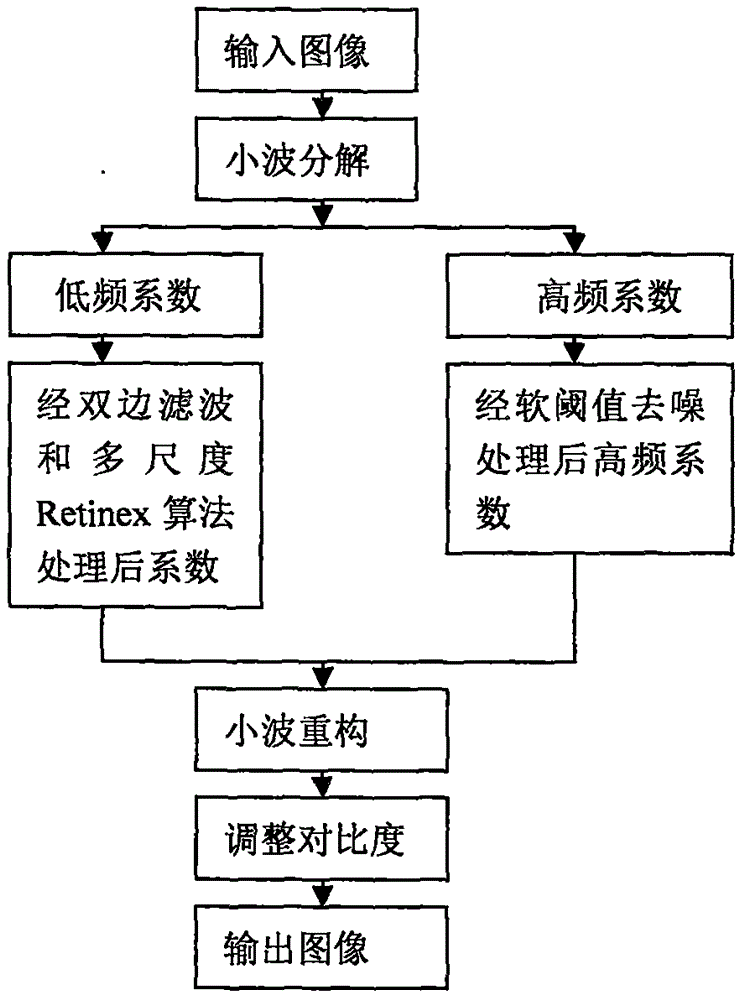

Mine image enhancement method based on bilateral filtering and multi-scale Retinex algorithm

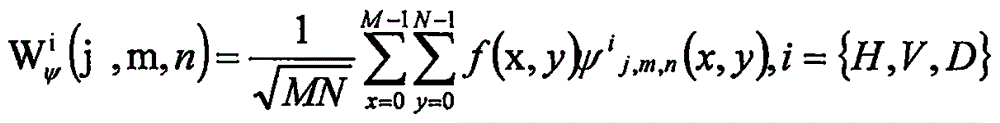

InactiveCN105844601AEliminate halo phenomenonEnhance image details and edge characteristicsImage enhancementWavelet decompositionRetinex algorithm

The invention discloses a mine image enhancement method based on bilateral filtering and a multi-scale Retinex algorithm. The method comprises the steps that 1 image wavelet decomposition is carried out to acquire high frequency and low frequency coefficients of an image; 2 the multi-scale Retinex algorithm and bilateral filtering are carried out on the low frequency coefficient of the image; 3 a soft threshold filtering algorithm is carried out on the high frequency coefficient of the image; 4 a discrete wavelet inverse transform formula is used to acquire an enhanced spatial domain image; and 5 local self-adaptive contrast enhancing is carried out on the enhanced spatial domain image. Compared with the existing enhancement method, the enhancement method provided by the invention has the advantage that based on wavelet transformation, the multi-scale Retinex algorithm and bilateral filtering are combined for processing; self-adaptive contrast enhancing is finally carried out; a processed picture has the advantages of rich detail, being structured and easy identification; and the shortcomings of halo, blurry detail and poor contrast of a result processed by a traditional scheme are overcome.

Owner:CHINA UNIV OF MINING & TECH (BEIJING)

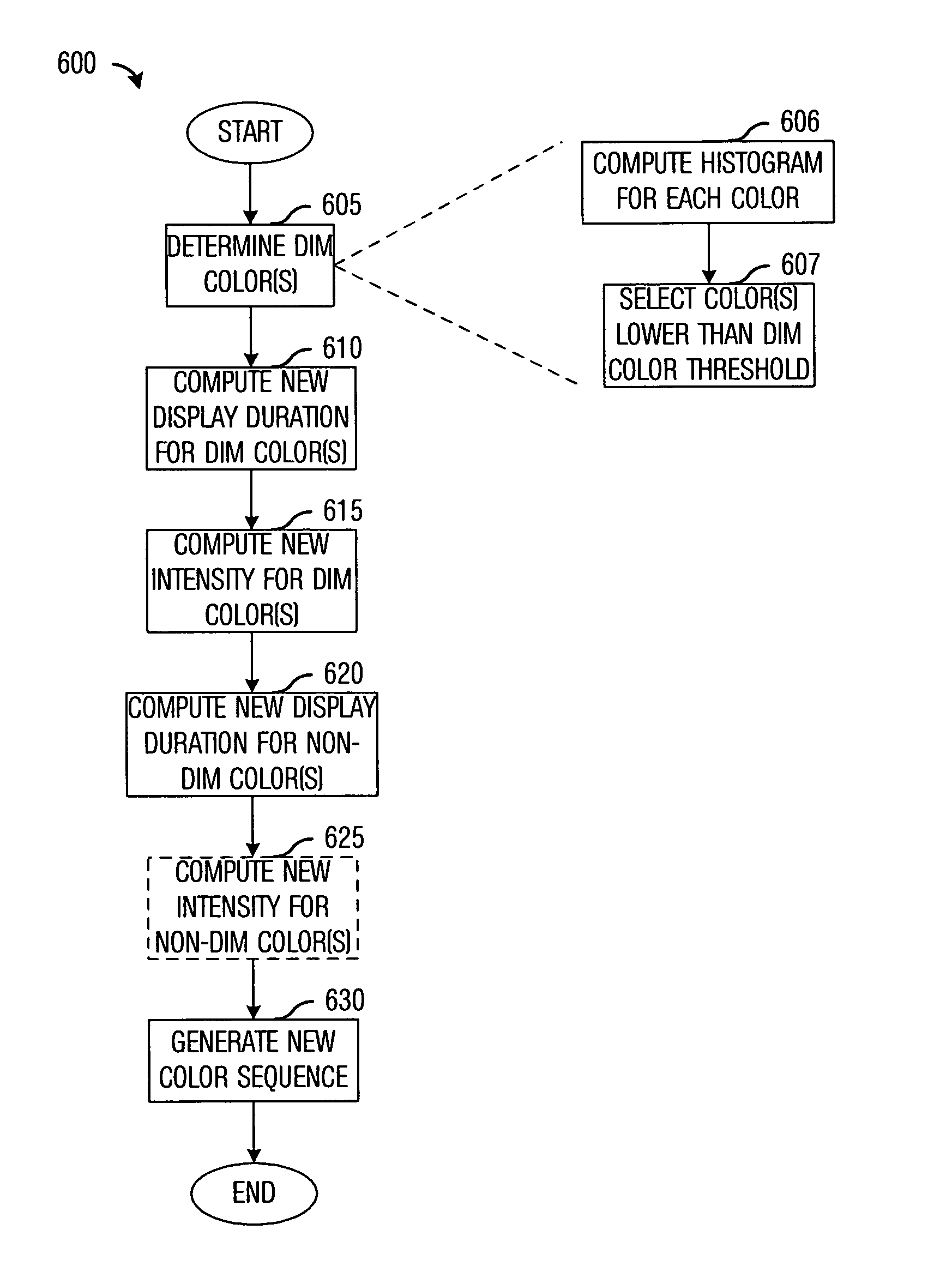

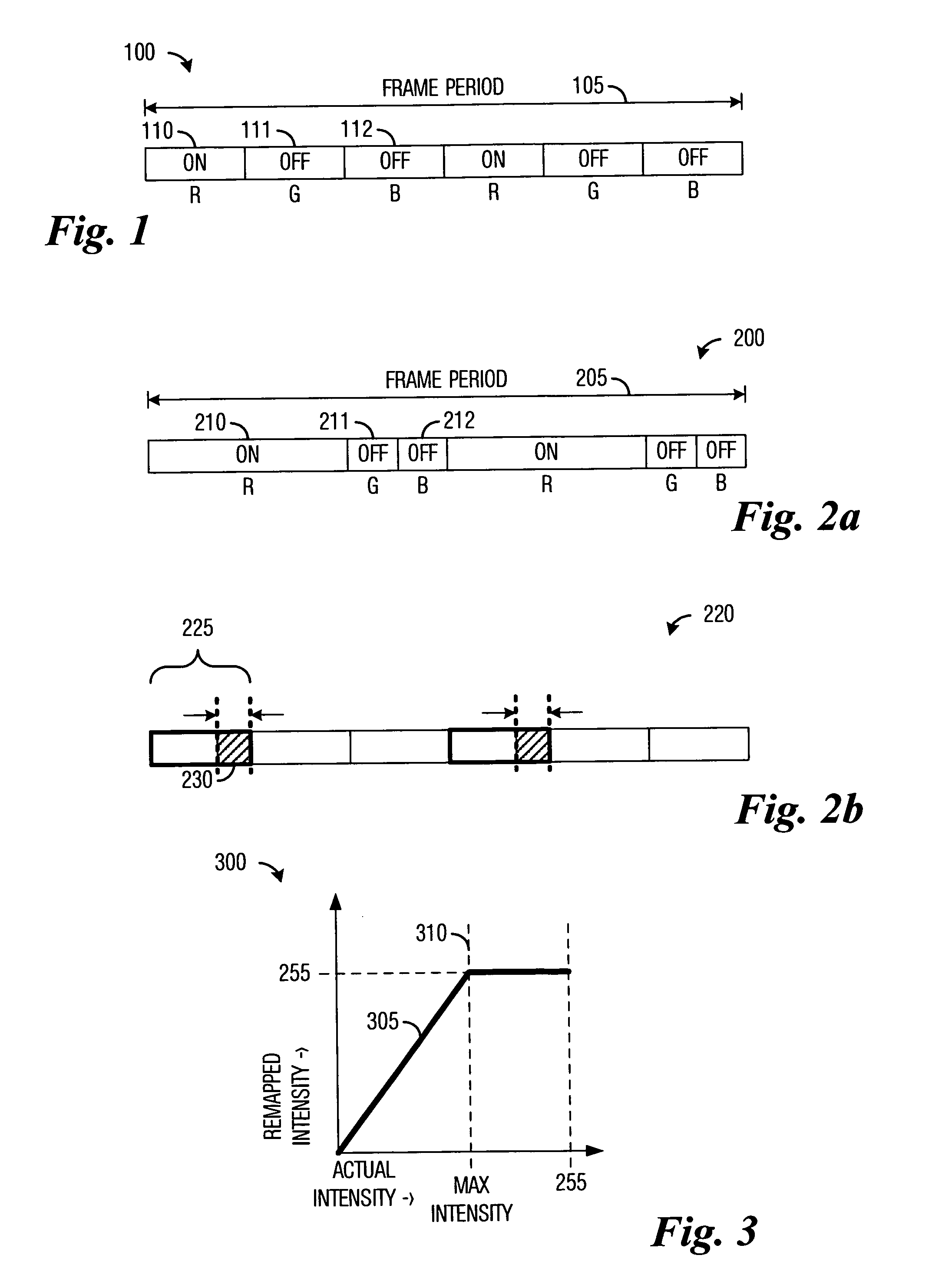

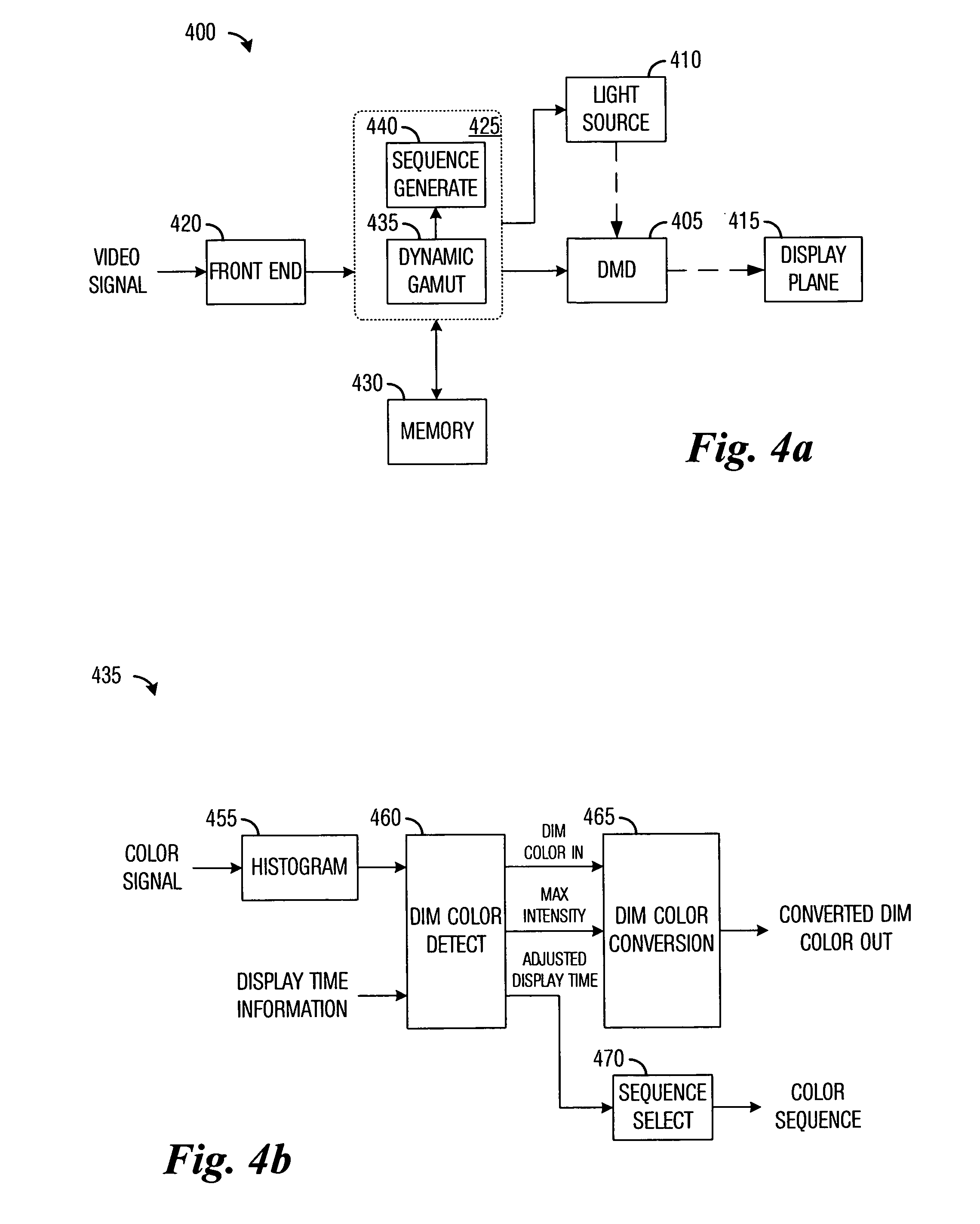

System and method for dynamically altering a color gamut

ActiveUS20080143736A1Increase image brightnessImprove color brightnessCathode-ray tube indicatorsNon-linear opticsGamutComputer graphics (images)

System and method for dynamically altering a color gamut used in projection display systems. An embodiment comprises determining a dim color from colors used in representing an image, adjusting the dim color to increase an available display time for a non-dim color used to represent the image, adjusting the non-dim color using the available display time, and generating a color sequence based on the adjusted dim color and the adjusted non-dim color. The pixel intensities of a dim color are increased, permitting a shortening of the display time of the dim color. The newly freed display time can be reallocated to all colors to increase the amount of light used to display the image, thereby increasing image brightness or altering color point.

Owner:TEXAS INSTR INC

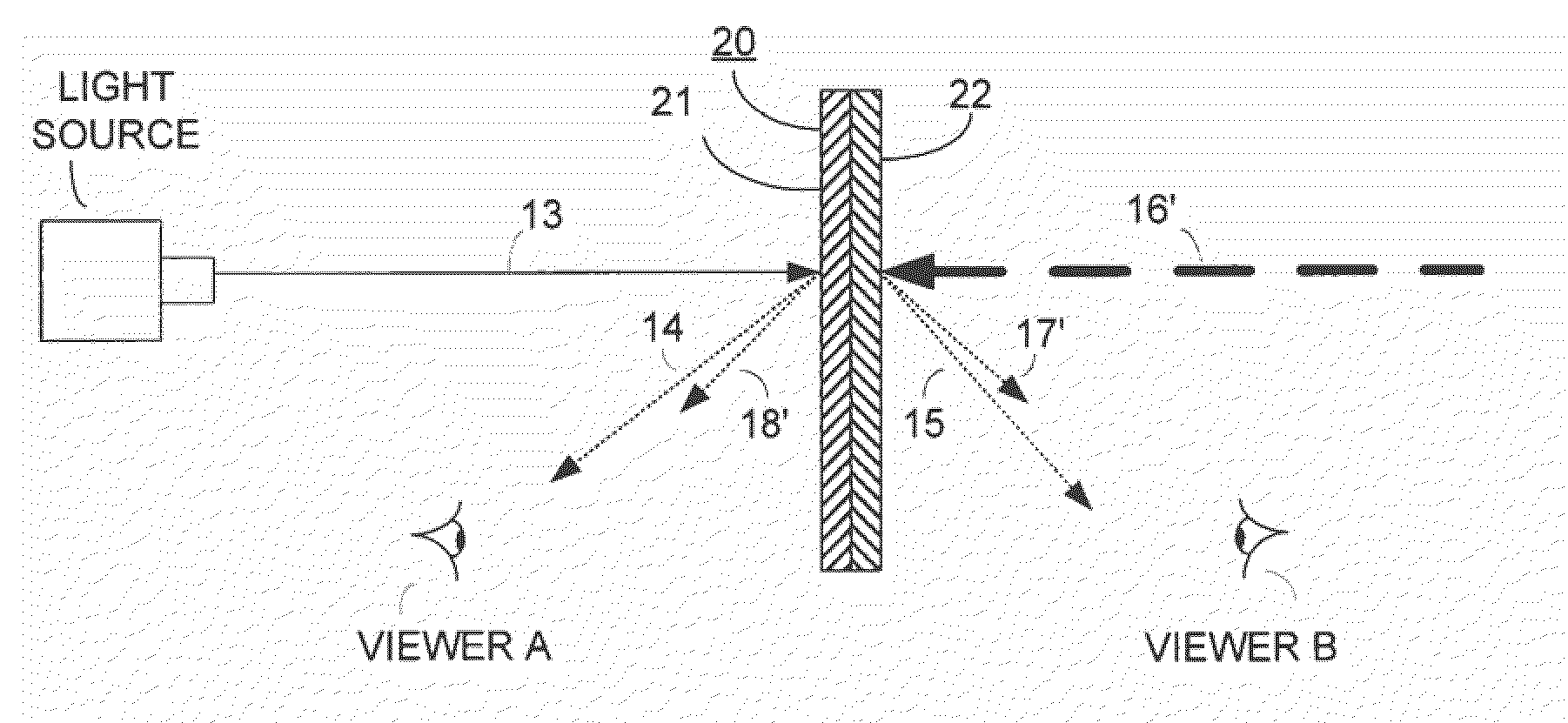

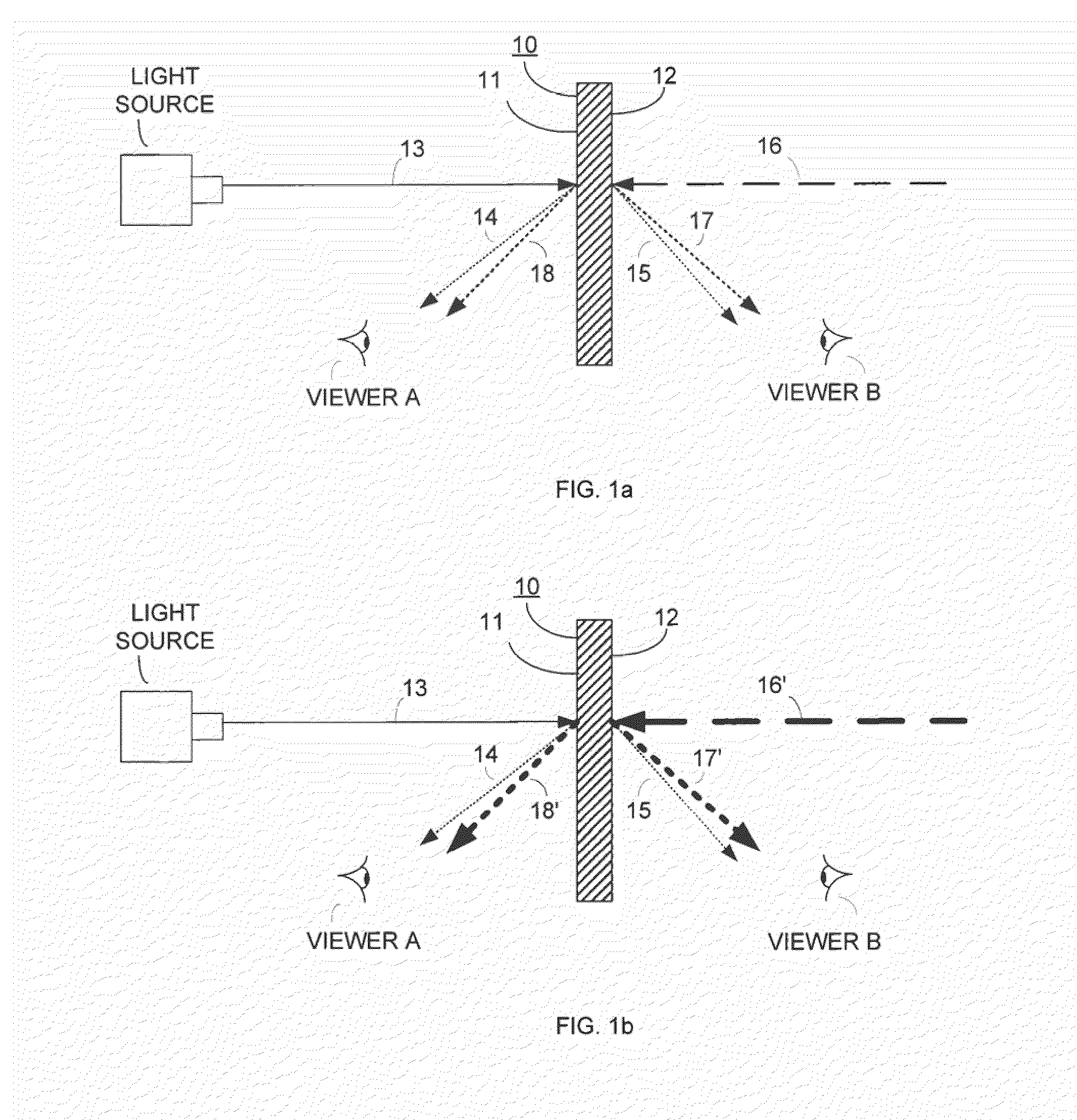

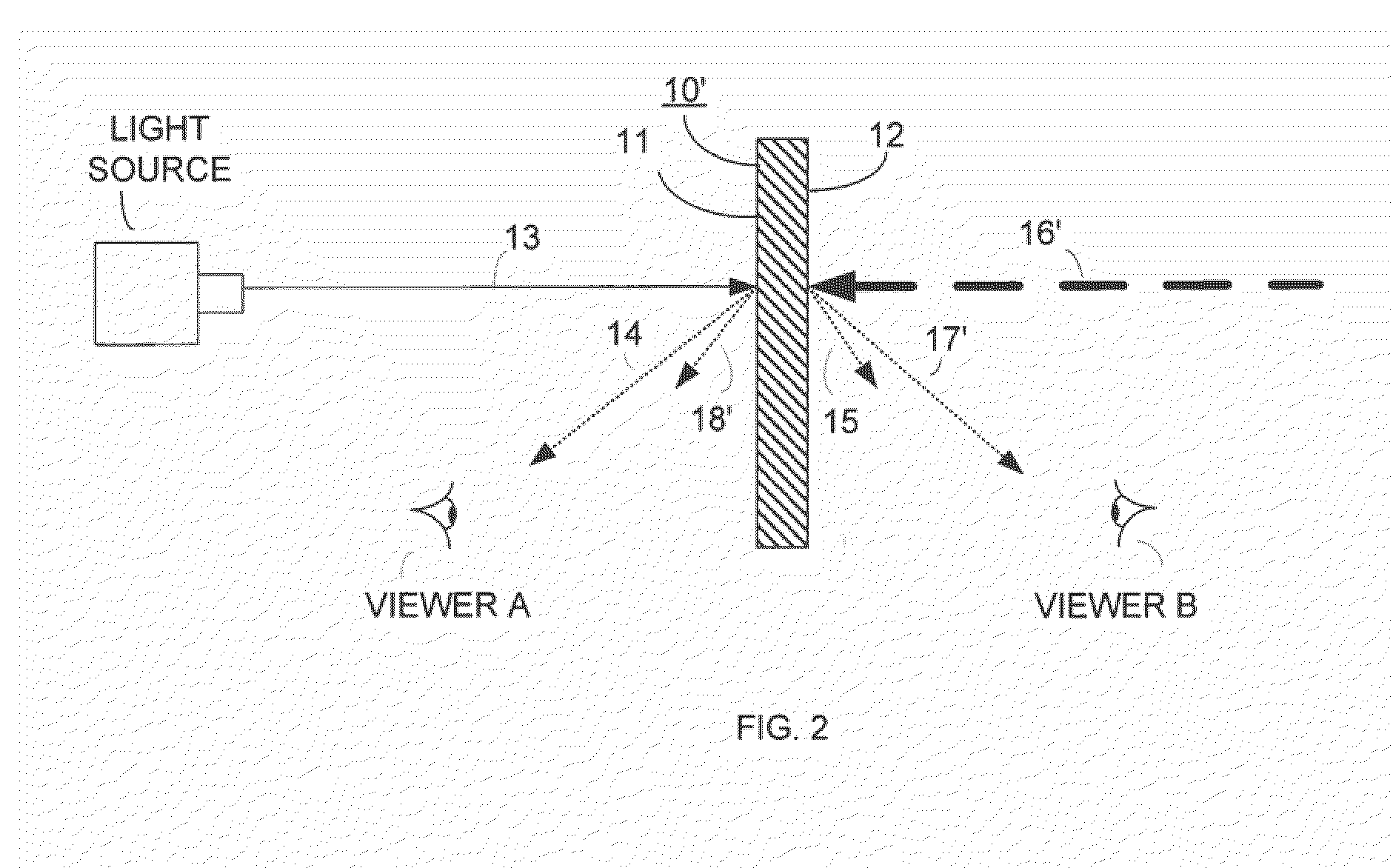

Rear-Projection Screen

The present invention is directed to a rear-projection screen which encompasses 1) a flexible light-diffusive first film having a substantially smooth first surface and an opposing substantially smooth second surface, and comprising a wax-free amorphous thermoplastic matrix having a plurality of light-diffusing particles dispersed therein and which is lens-free; and 2) an opposing flexible light-absorption second film having a first surface and an opposing second surface, and comprising a thermoplastic matrix having a plurality of light-absorbing particles dispersed therein, wherein the first and second films are adapted to be 3) bonded together in direct contact with each other and then, affixed as a laminate to one or more transparent rigid substrates or 4) affixed individually to a transparent rigid substrate.

Owner:AVERY DENNISON CORP

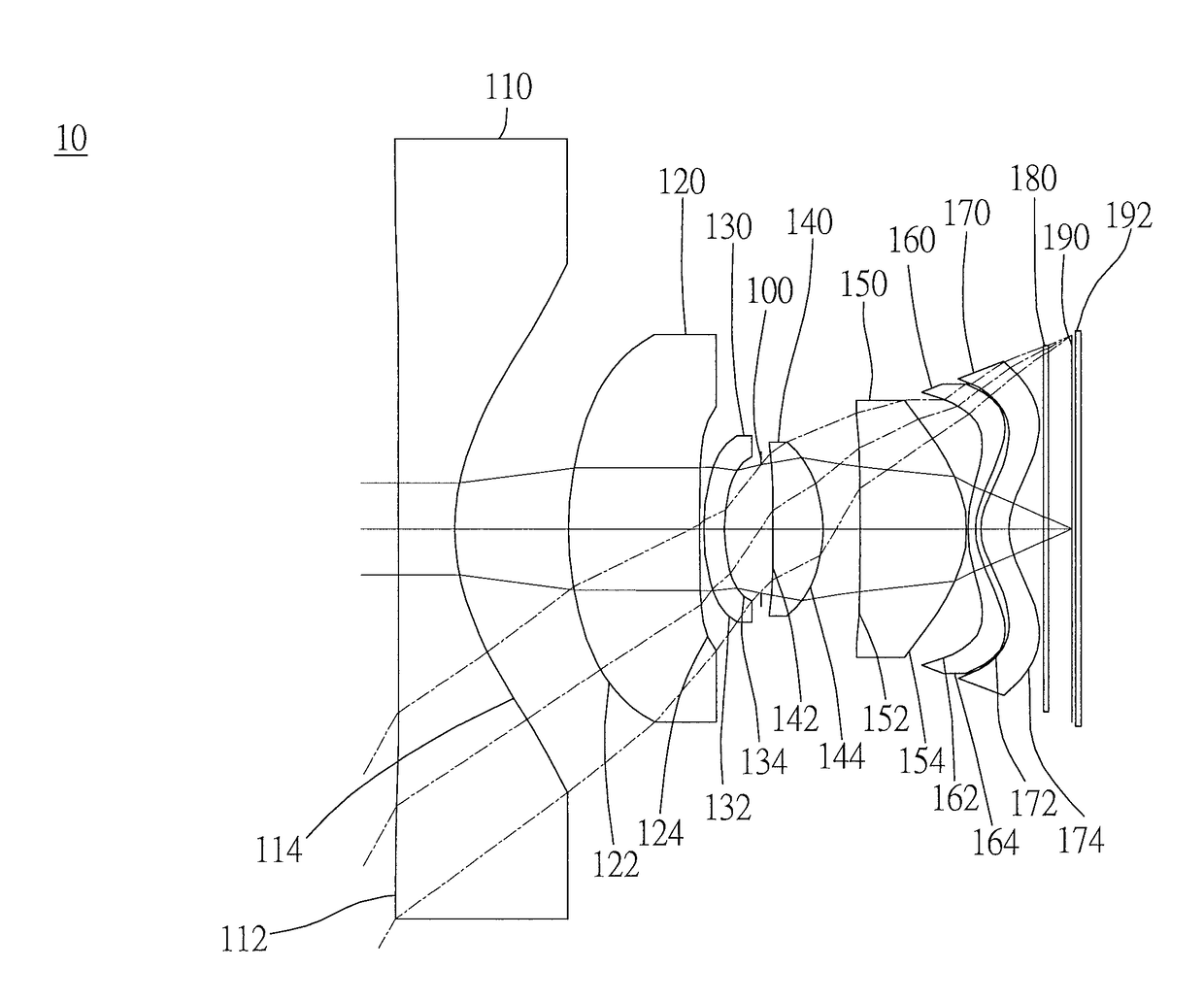

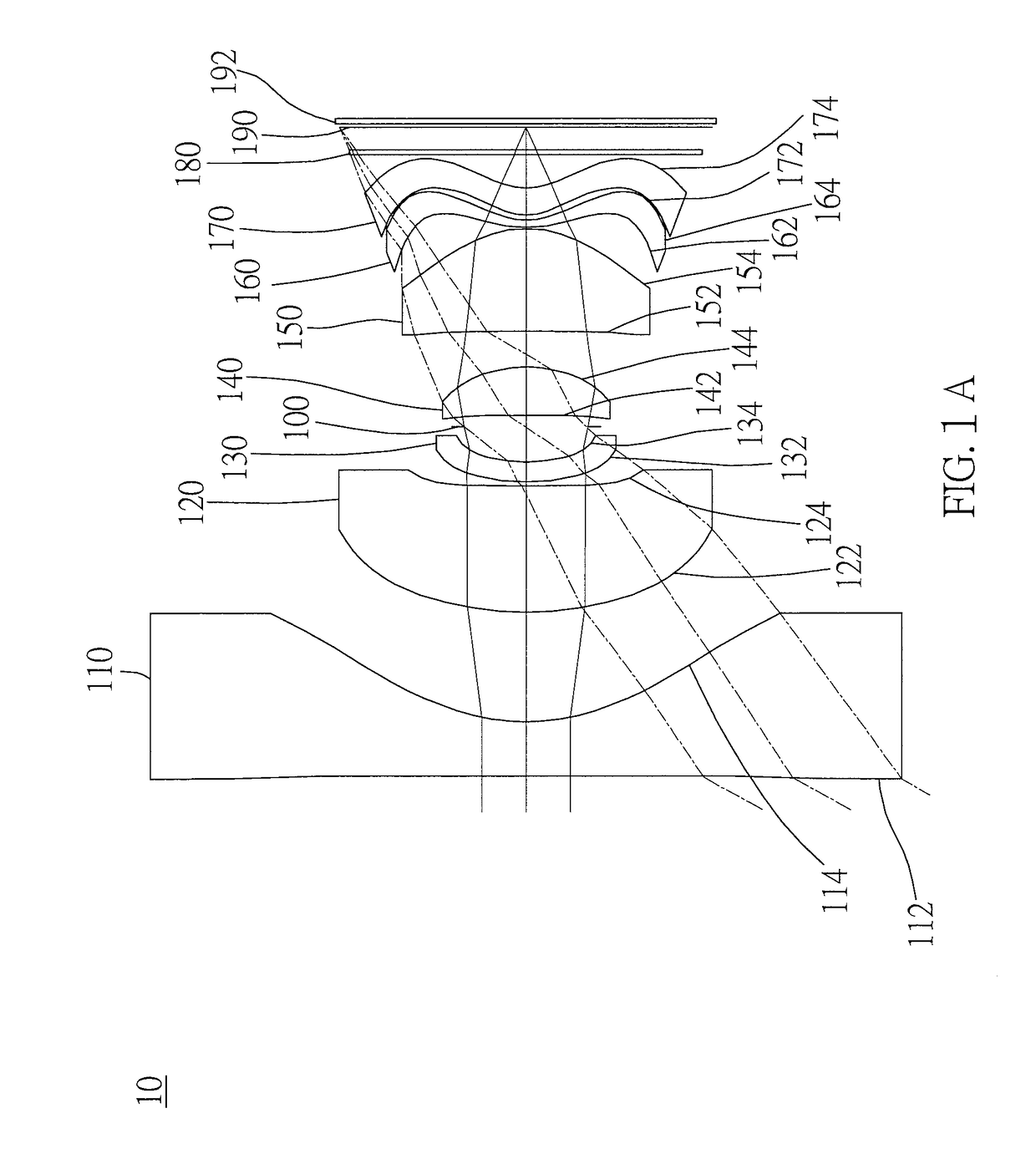

Optical image capturing system

ActiveUS20180196239A1Increase the amount of incident lightImprove image qualityOptical elementsImaging qualityOptical axis

An optical image capturing system includes, along the optical axis in order from an object side to an image side, a first lens, a second lens, a third lens, a fourth lens, a fifth lens, a sixth lens, and a seventh lens. At least one lens among the first to the sixth lenses has positive refractive force. The seventh lens can have negative refractive force, and both surfaces thereof are aspheric. At least a surface of the seventh lens has an inflection point. The lenses in the optical image capturing system which have refractive power include the first to the seventh lenses. The optical image capturing system can increase aperture value and improve the imaging quality for use in compact cameras.

Owner:ABILITY OPTO ELECTRONICS TECH

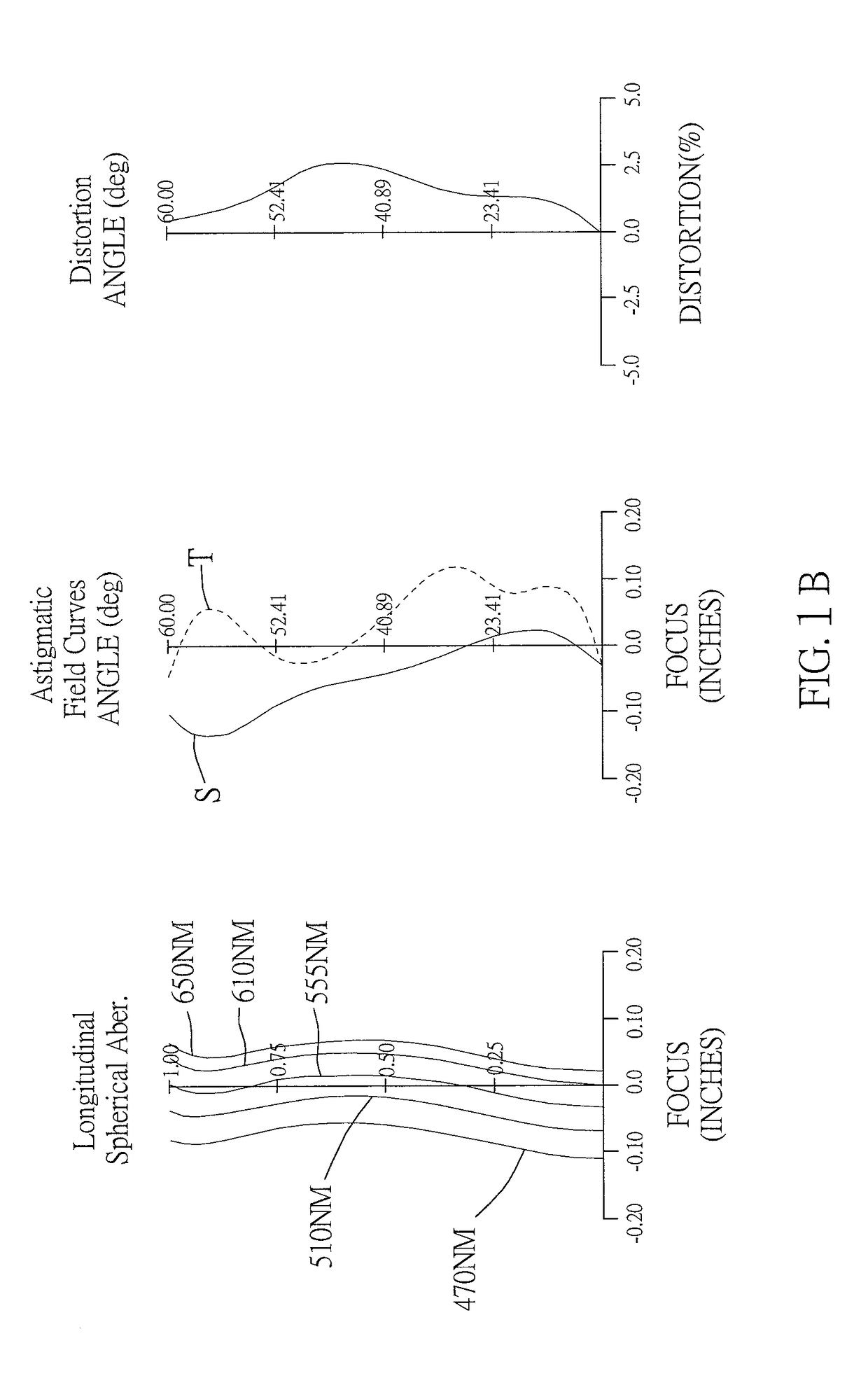

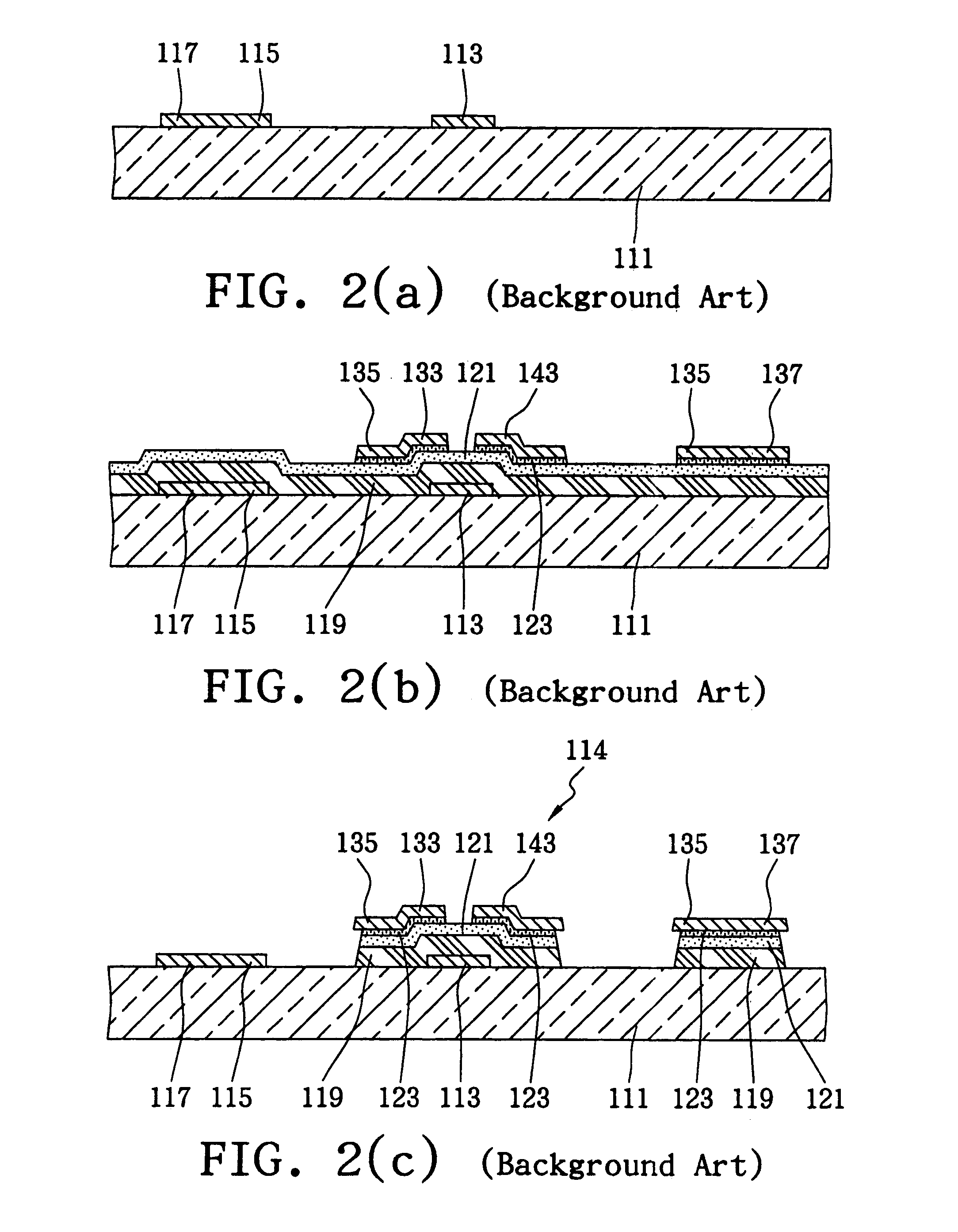

Method of manufacturing liquid crystal display

ActiveUS7112512B2Increase opening ratioIncrease image brightnessSolid-state devicesSemiconductor/solid-state device manufacturingResistLiquid-crystal display

On a substrate, the pattern of the first conductive layer is defined, that is, a gate line combination including gate pads, scanning lines and gate electrodes. A gate insulating layer, a semiconductor layer, a doped semiconductor layer and a second conductive layer are deposited on the substrate and the above-mentioned gate line combination in sequence. A photoresist layer is overlaid on the second conductive layer. The photoresist layer within the aperture areas is fully exposed. Using a half-tone mask or a slit pattern to make parts of the photoresist layer lying on the gate pads and the gate electrodes are not exposed to its full depth. As a result, the photoresist pattern formed varies in thickness. After being processed with drying etching and wet etching for several times, all the layers previously deposited within the aperture areas can be totally etched and removed. However, as regards the layers deposited on the gate pads and the gate electrodes, etching only takes place in those layers above the semiconductor layer. Then, an organic protection layer is laid on the substrate and the above-mentioned structure, and the holes, which are to function as the passageways for the transparent conductive layer to contact the metallic layer, are defined on the organic protection layer. Then, the gate pads are exposed out of holes above them, using dry etching again. Lastly, the pattern of the transparent conductive layer is defined on the organic protection layer and in the plurality of holes.

Owner:HANNSTAR DISPLAY CORPORATION

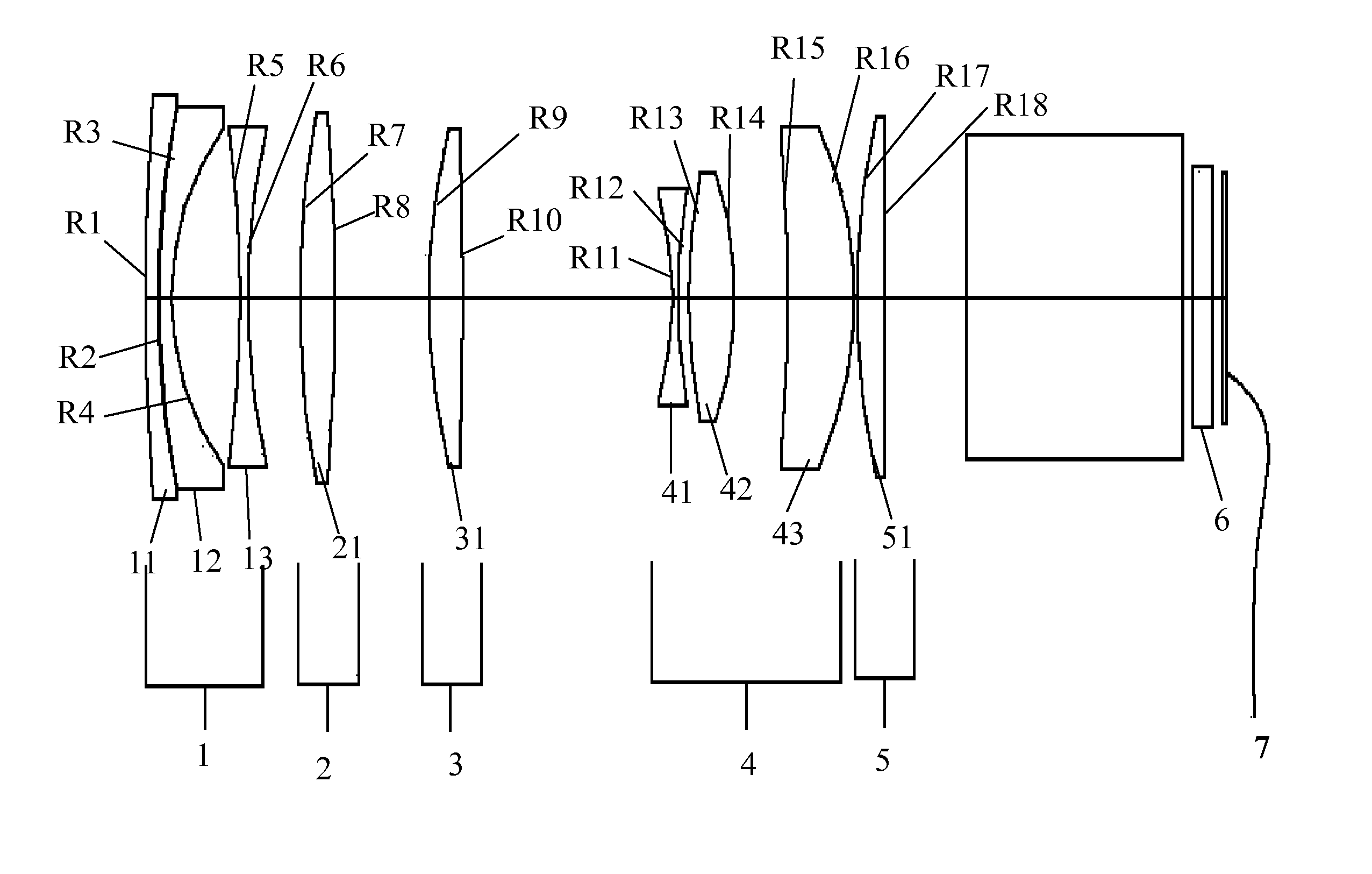

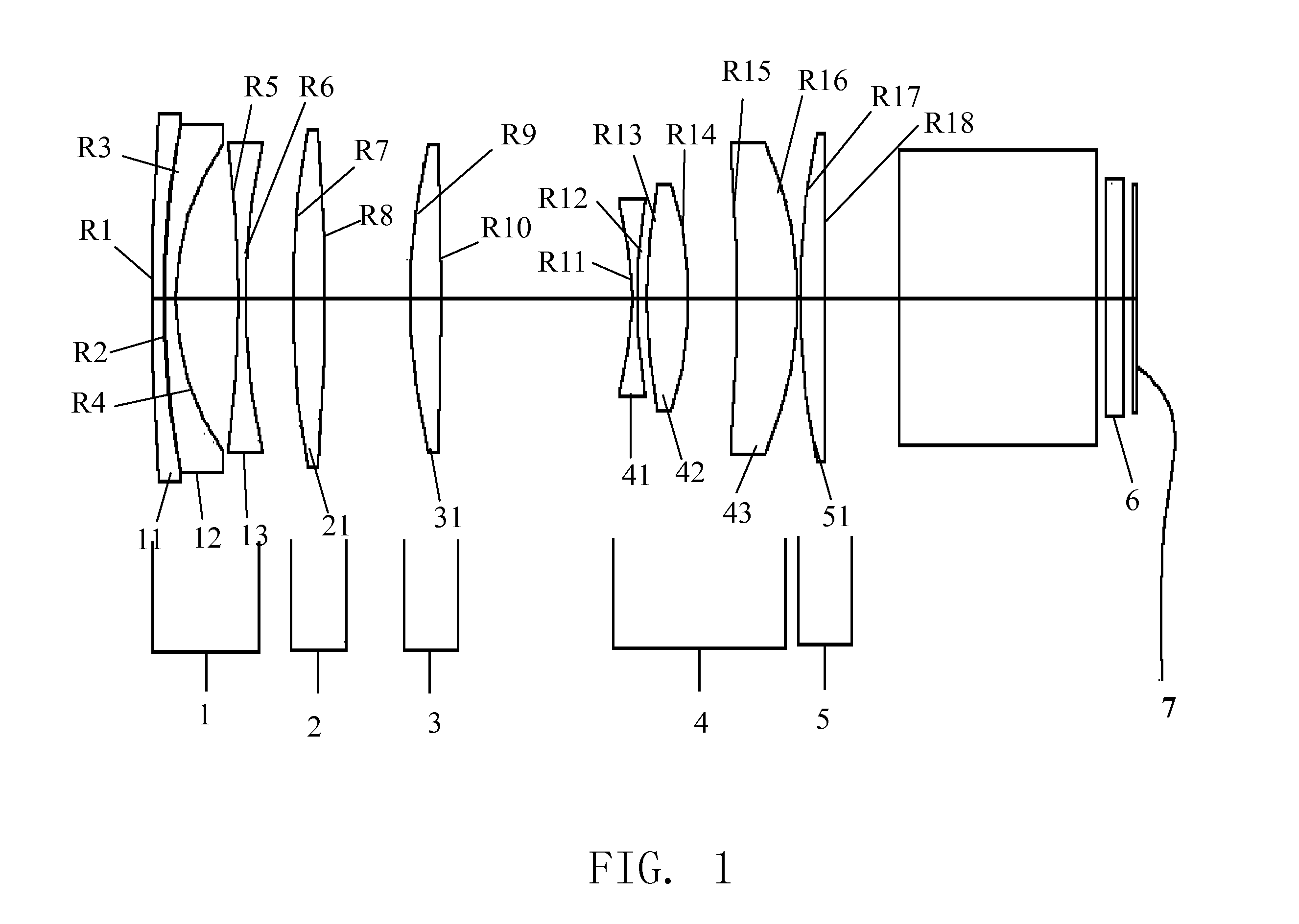

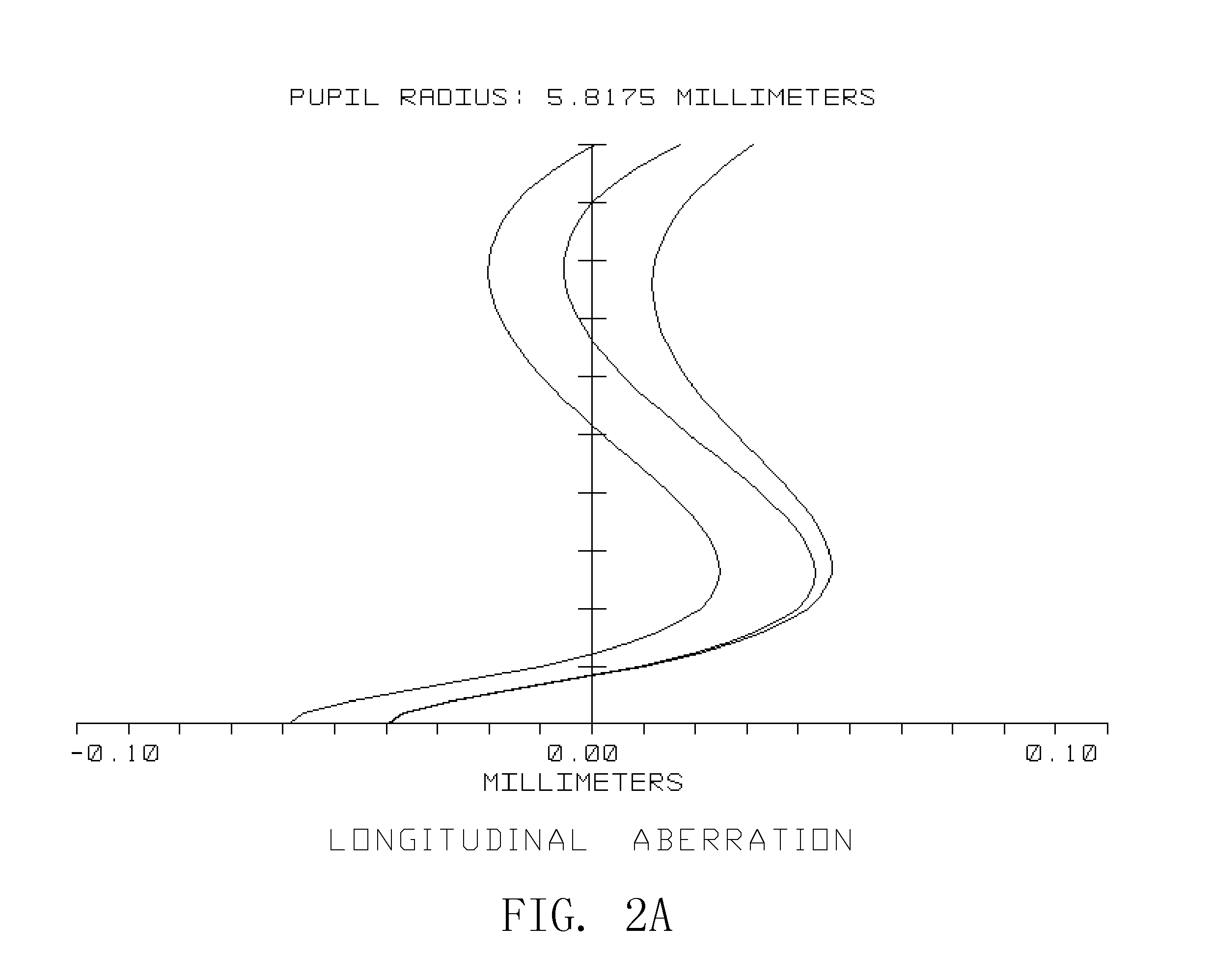

Compact zoom lens

InactiveUS20070121214A1Compact structureGood optical performanceOptical elementsOphthalmologyZoom lens

A compact zoom lens includes, in order from an object side to an image side, a first lens group (1) of negative refractive power, and second, third, fourth and fifth lens groups (2, 3, 4, 5) of positive refractive power. The second, third and fourth lens groups are movable to effect zooming and focusing. During zooming from the telephoto end to the wide-angle end, the fourth lens group moves from the object side to the image side. The compact zoom lens has a long back focal length with various aberrations satisfactorily corrected, and a small F-number for enhanced image brightness.

Owner:ASIA OPTICAL INT LTD

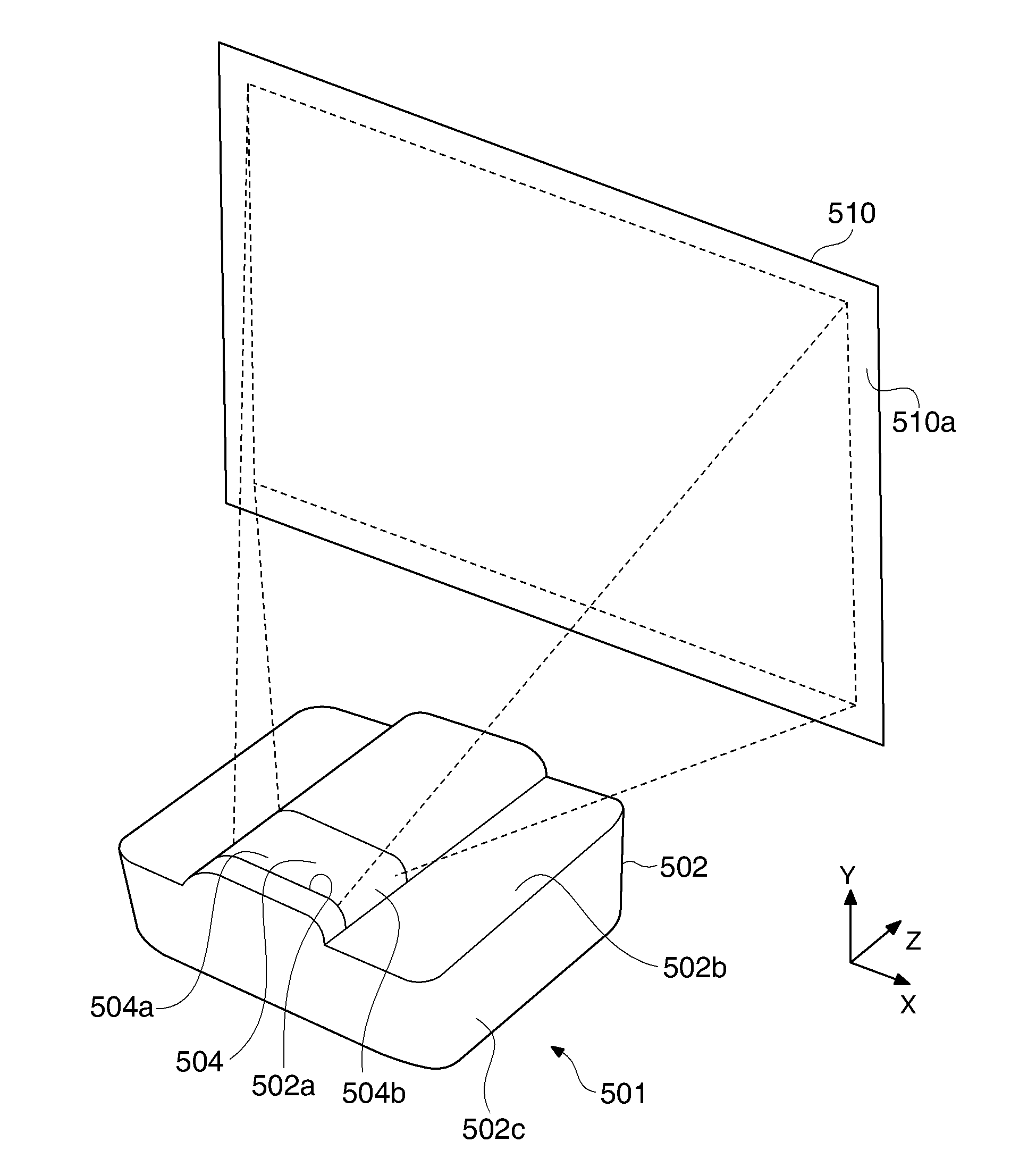

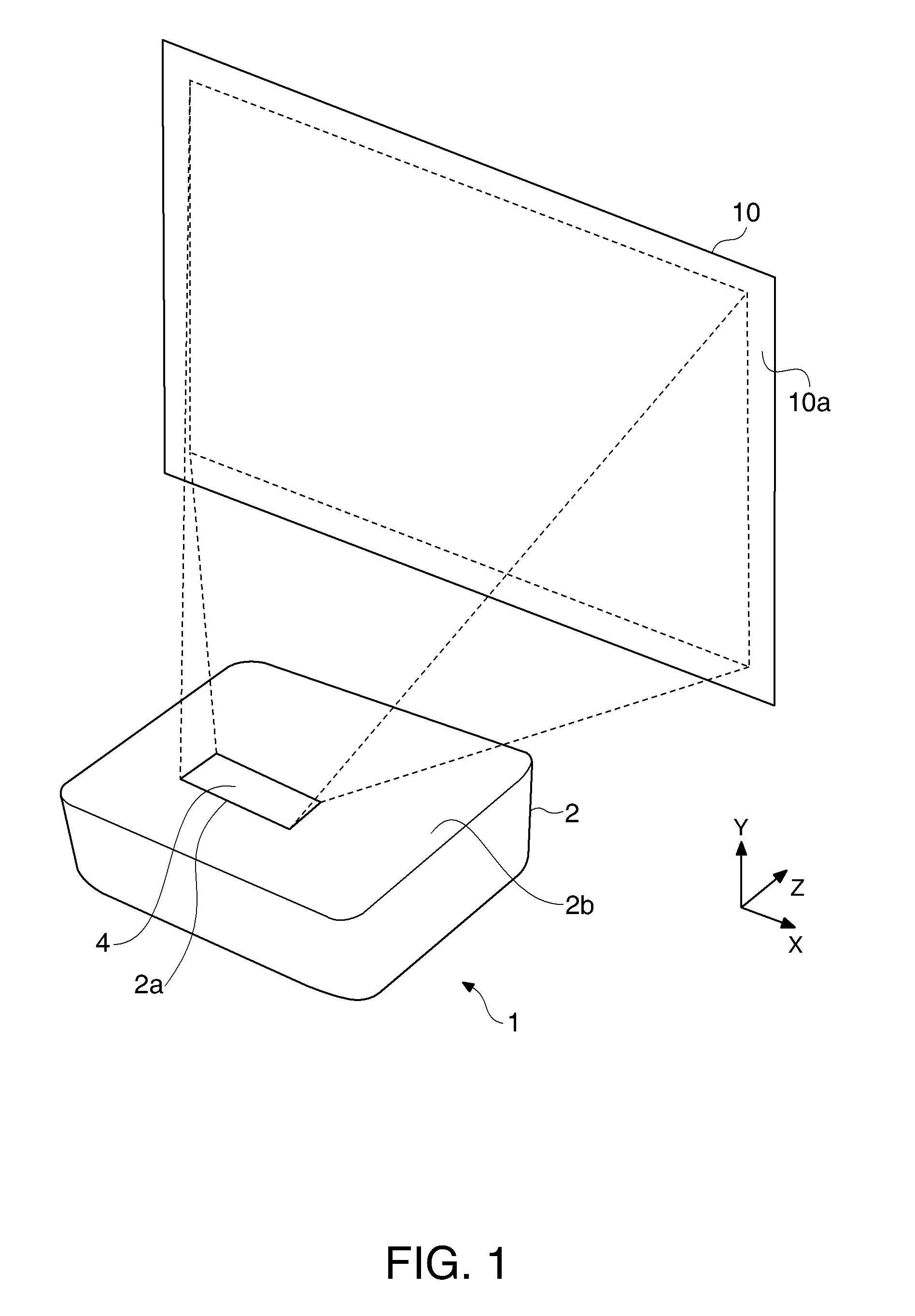

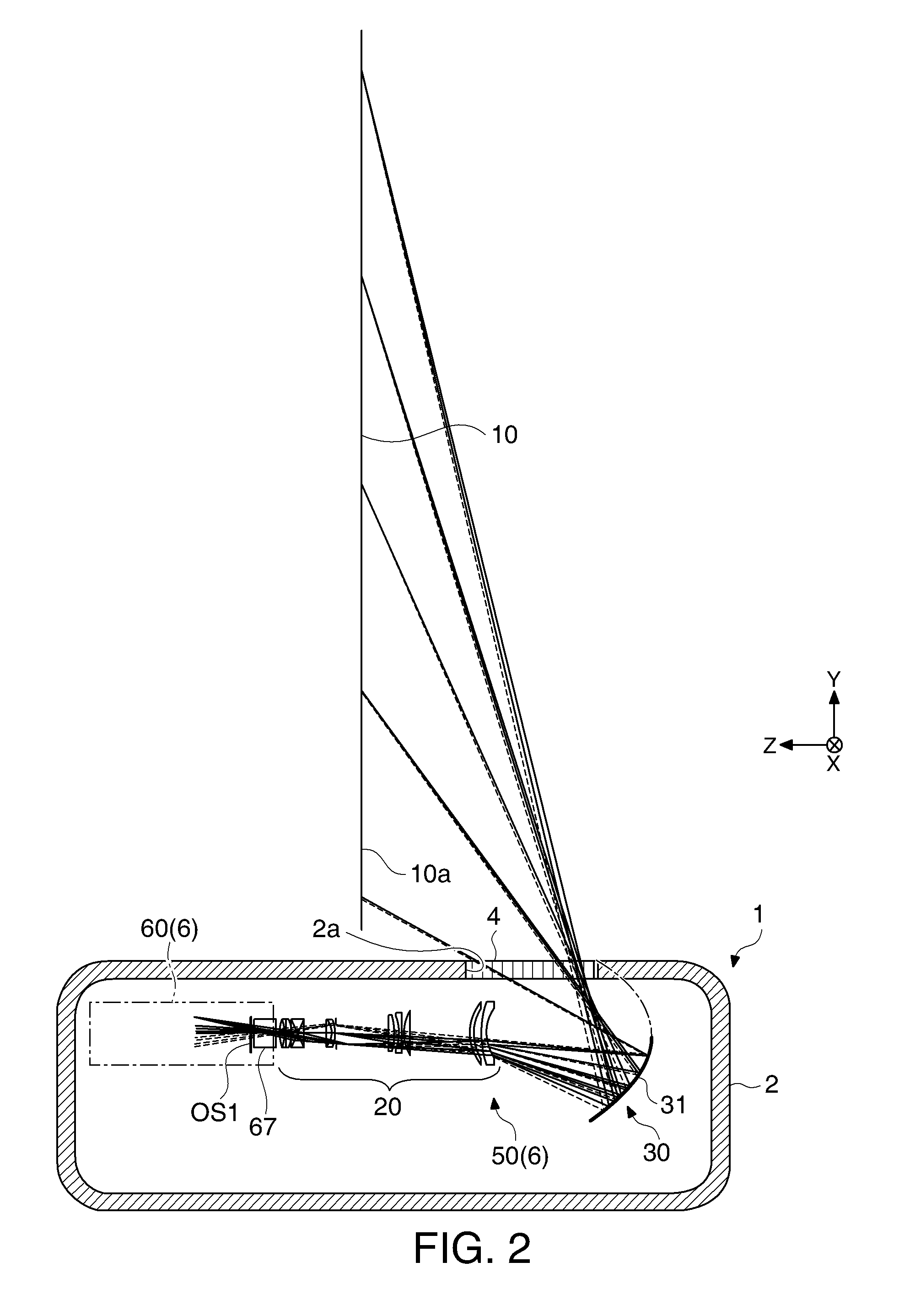

Projector

ActiveUS20100165308A1Reduce manufacturing costDegree of design can be increasedProjectorsReflectivityProcesses of change

A projector includes: a projection unit that projects projection light toward an illuminated surface; a housing that houses the projection unit and has an opening that allows the projection light to exit outward; and a cover portion that blocks the opening and transmits the projection light, wherein a plurality of areas is set in the cover portion relative to the projection unit, and a process of changing the reflectance of the light-incident surface of the cover portion at which the projection light is reflected is performed on each of the areas.

Owner:SEIKO EPSON CORP

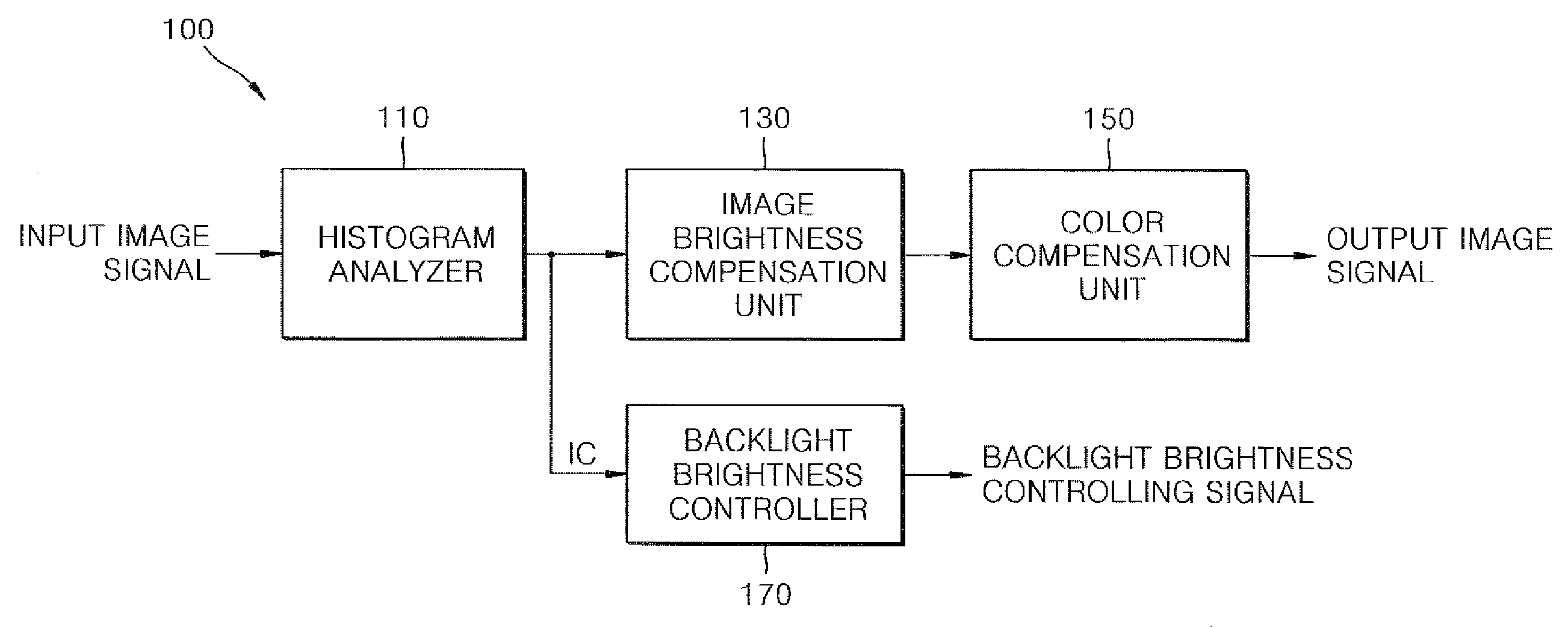

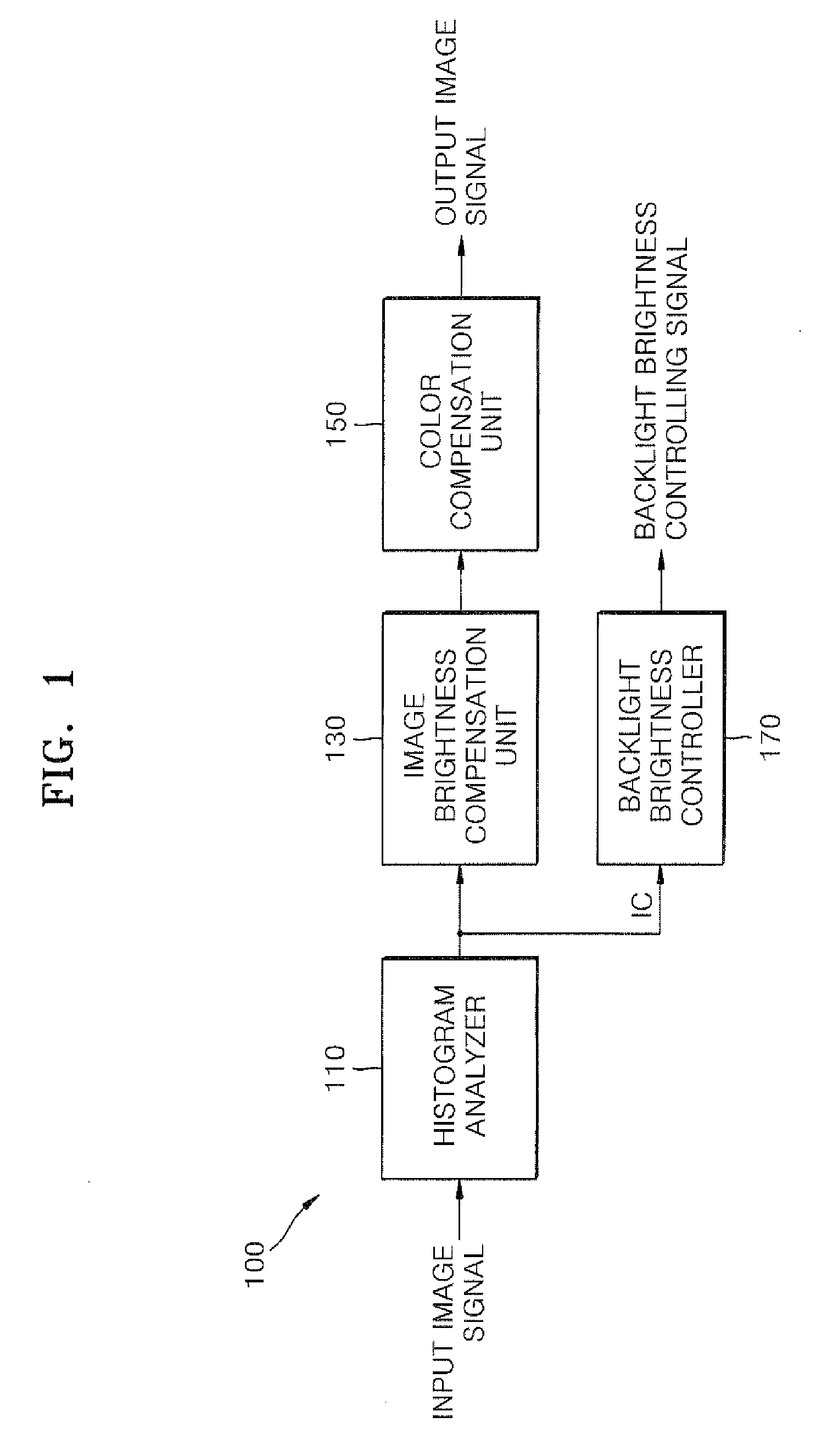

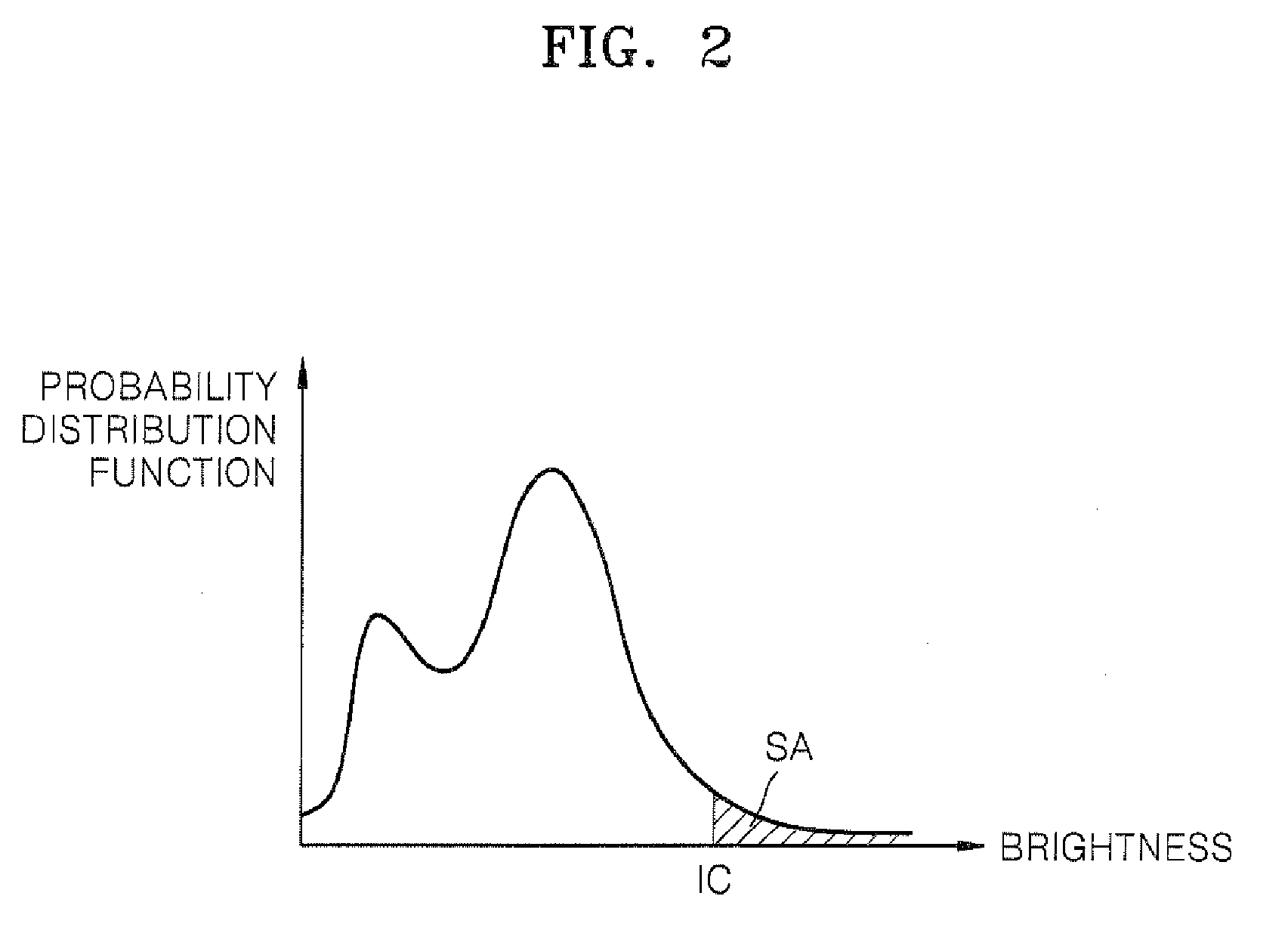

Method and apparatus for controlling power of display device based on histogram of input image and display device including the apparatus

InactiveUS20080218468A1Reduce backlight brightnessIncrease image brightnessTelevision system detailsStatic indicating devicesDisplay deviceImage signal

A method and an apparatus for controlling a power of a display device including a backlight, and a display device having a power controlling function are provided. The apparatus includes: a histogram analyzer that analyzes a histogram of an input image signal including one or more color components, and determines an intensity clipping based on the analyzed histogram; an image brightness compensation unit that calculates an intensity increasing ratio of the input image signal using the intensity clipping, and applies the intensity increasing ratio to each of the color components to generate an output image signal, an intensity of which is increased; and a backlight brightness controller that controls a brightness of the backlight based on the intensity increasing ratio.

Owner:SAMSUNG ELECTRONICS CO LTD

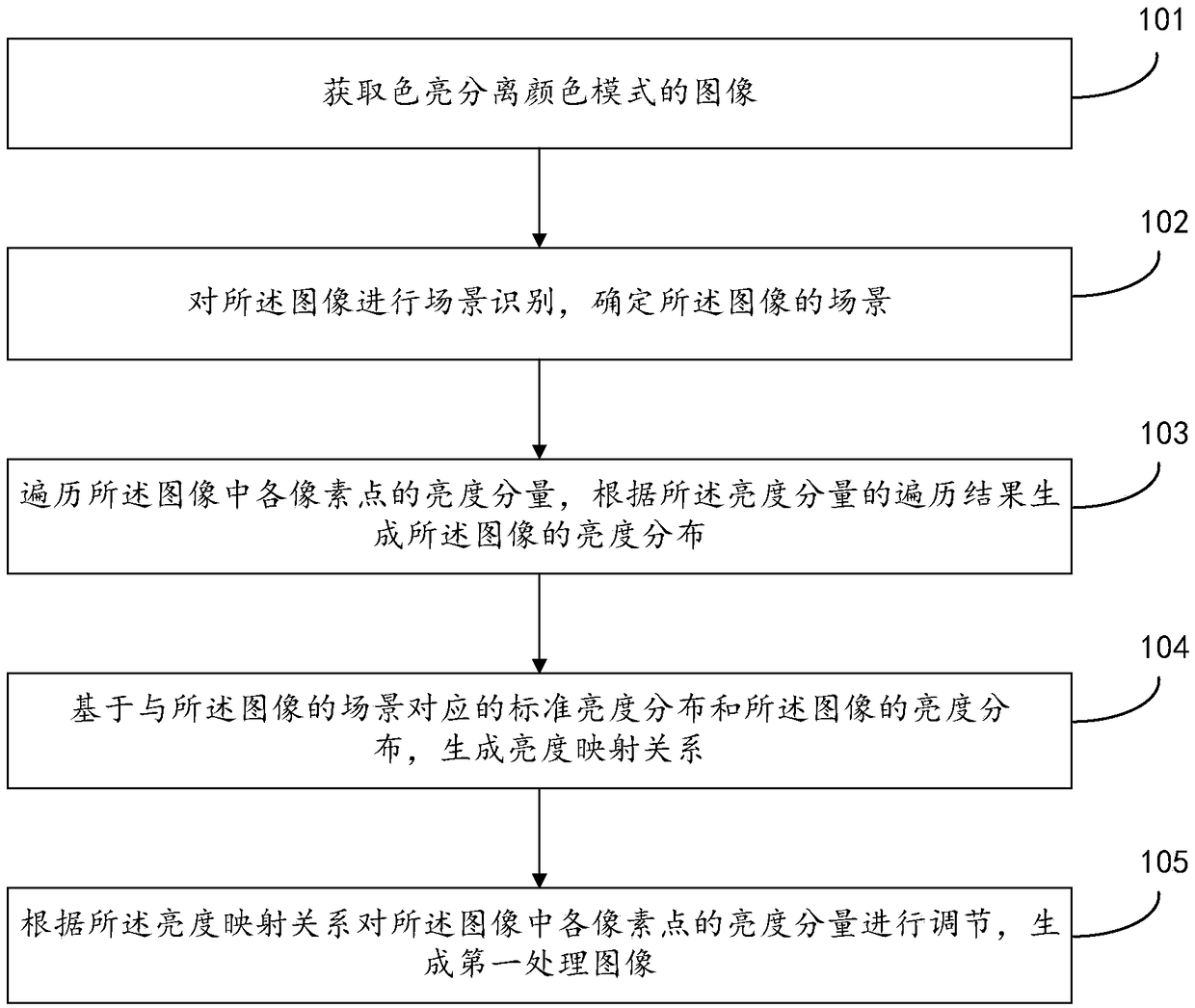

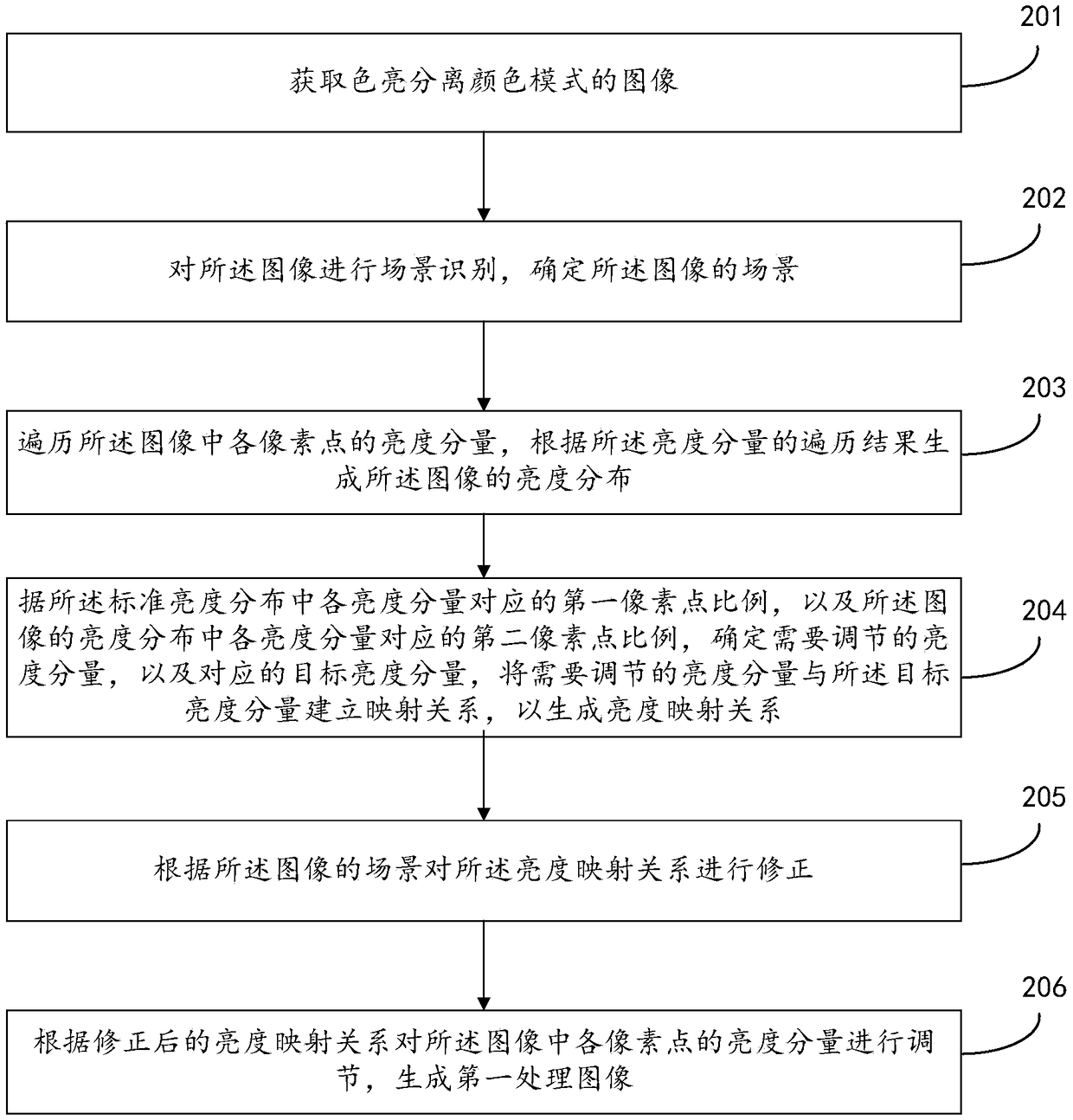

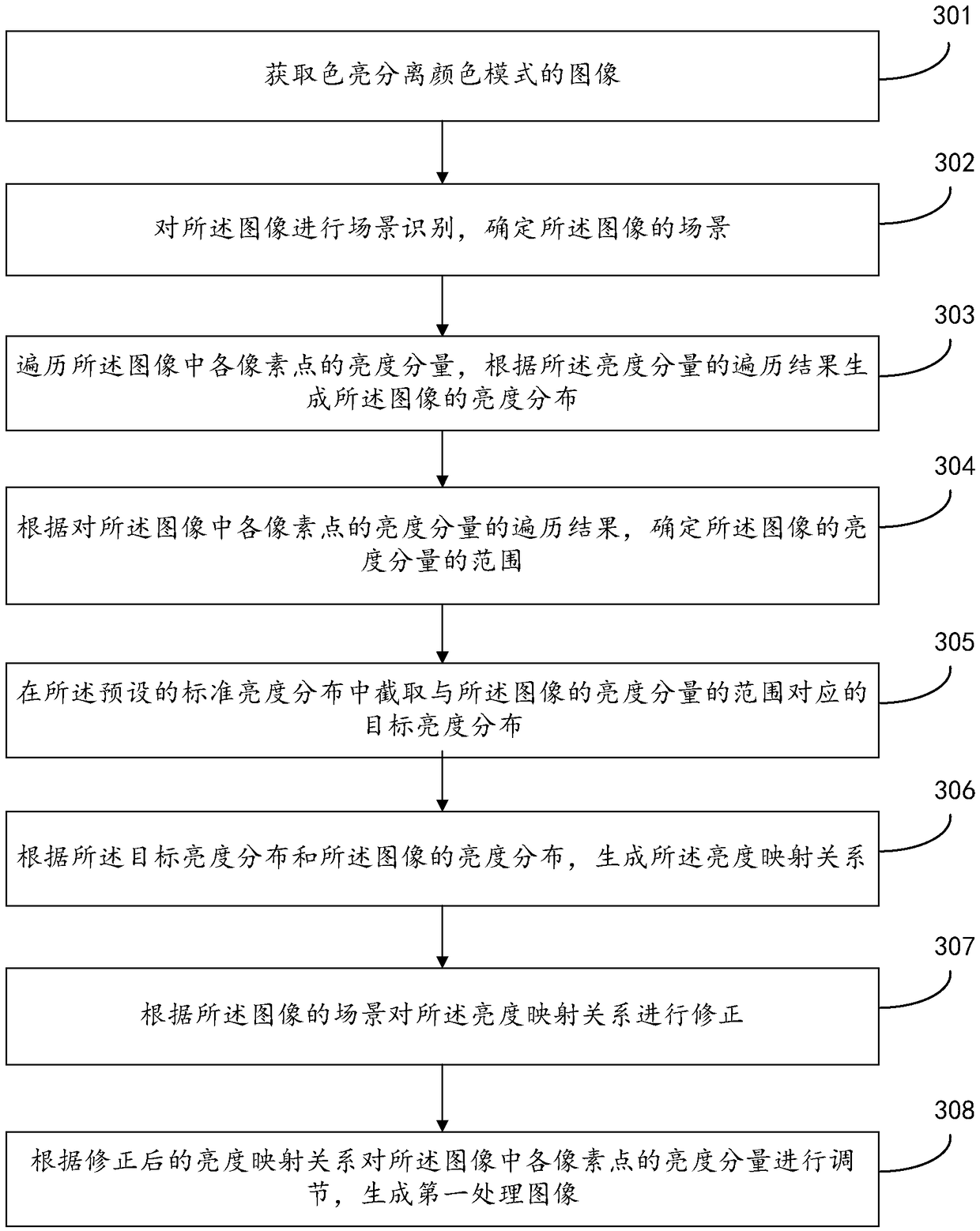

Image processing method, device, storage medium, and electronic device

ActiveCN109272459AIncrease image brightnessImprove applicabilityImage enhancementImage analysisImaging processingBrightness perception

An embodiment of the present application discloses an image processing method, a device, a storage medium, and an electronic device. The method comprises the following steps of: acquiring an image ofa color mode of color brightness separation; performing scene recognition on the image to determine a scene of the image; traversing a luminance component of each pixel point in the image, and generating a luminance distribution of the image according to a traversal result of the luminance component; generating a brightness mapping relationship based on a standard brightness distribution corresponding to a scene of the image and a brightness distribution of the image; adjusting a luminance component of each pixel point in that image according to the luminance map relationship to generate a first processed image. By adopting the technical proposal, the embodiment of the present application can achieve the best effect for images of different scenes on the basis of ensuring that the images are not distorted, and the applicability of the image processing method is improved.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

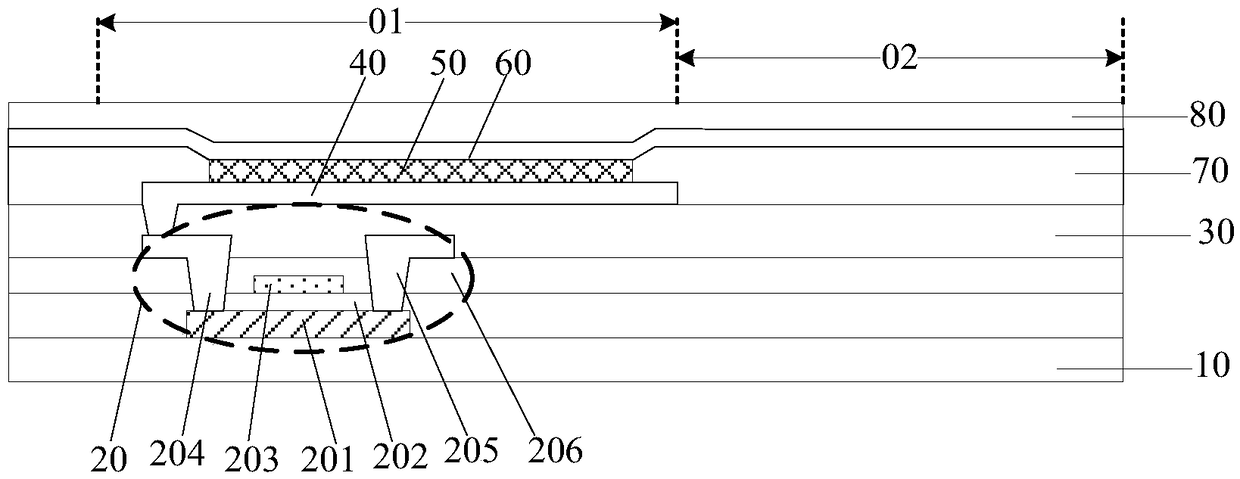

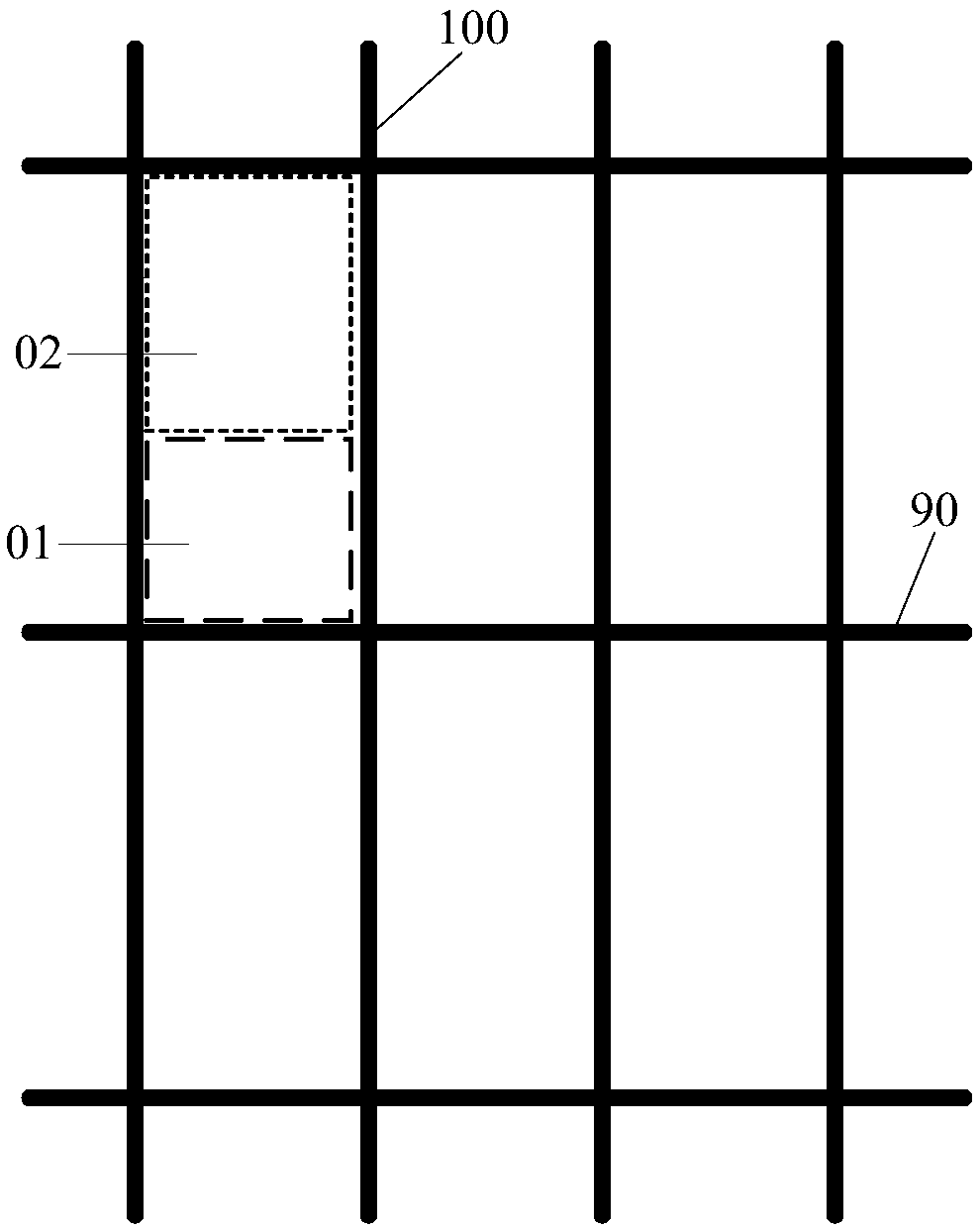

OLED substrate and transparent display

ActiveCN109300957AAvoid lossImprove experienceSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceLight transmission

The embodiment of the invention provides an OLED substrate and a transparent display, and relates to the technical field of display. The problem can be solved that the light transmission of the display is low. The OLED substrate comprises a luminous area and a transparent area. The OLED substrate comprises a substrate and a display layer arranged on the substrate, wherein the portion of the display layer is located on the transmission area has a first hollow area. The OLED substrate and the transparent display are configured to improve the light transmission of the transparent display.

Owner:BOE TECH GRP CO LTD

Instant-on projector

InactiveUS6988806B2Increase image brightnessAdjust balanceProjectorsPicture reproducers using projection devicesEnergy deficiencyProjection system

A projection system is provided with a primary light source and an auxiliary light source to compensate the primary light source for at least white light during an initial period to provide a user with an instant-on experience. In various embodiments, the auxiliary light source further compensates the primary light source for energy deficiencies for the red spectrum to achieve more balance in color.

Owner:SEIKO EPSON CORP

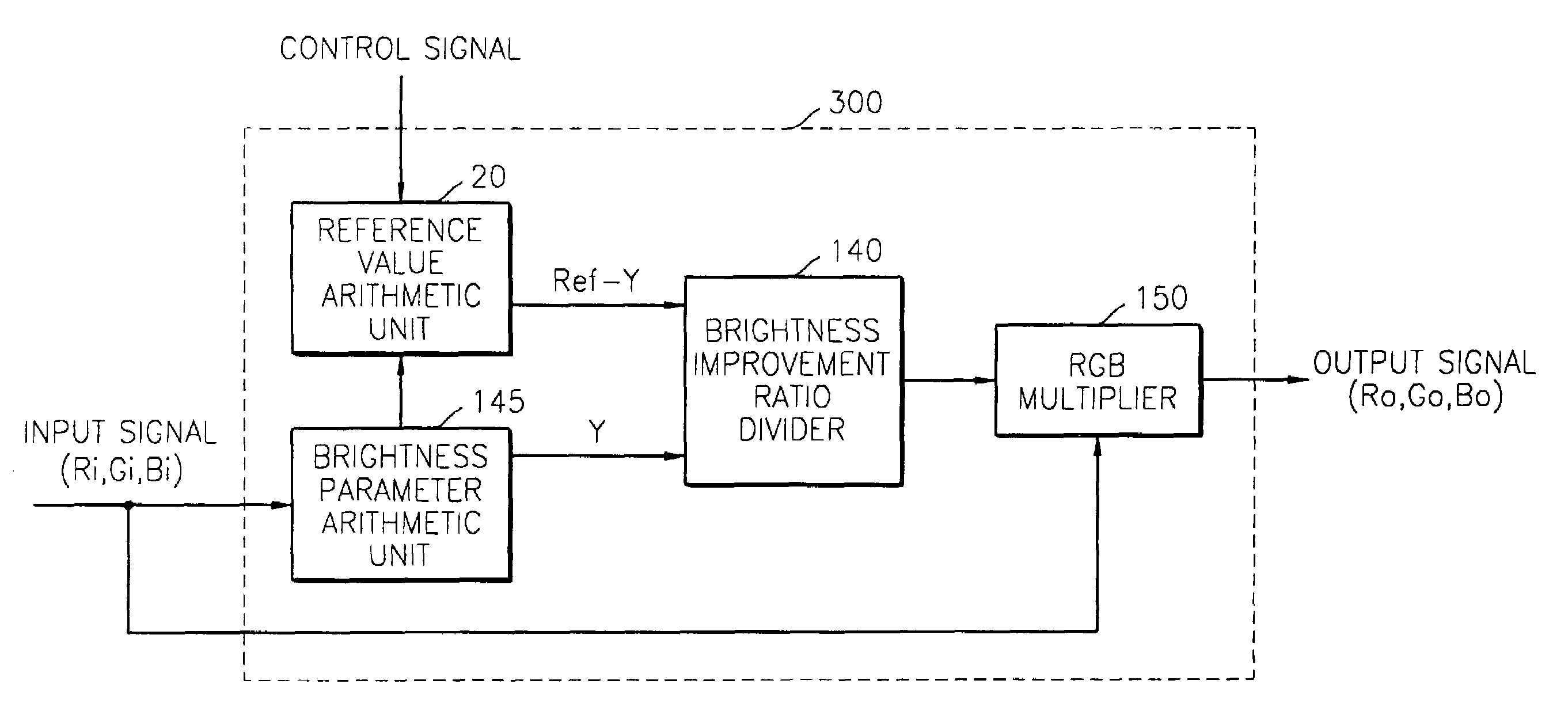

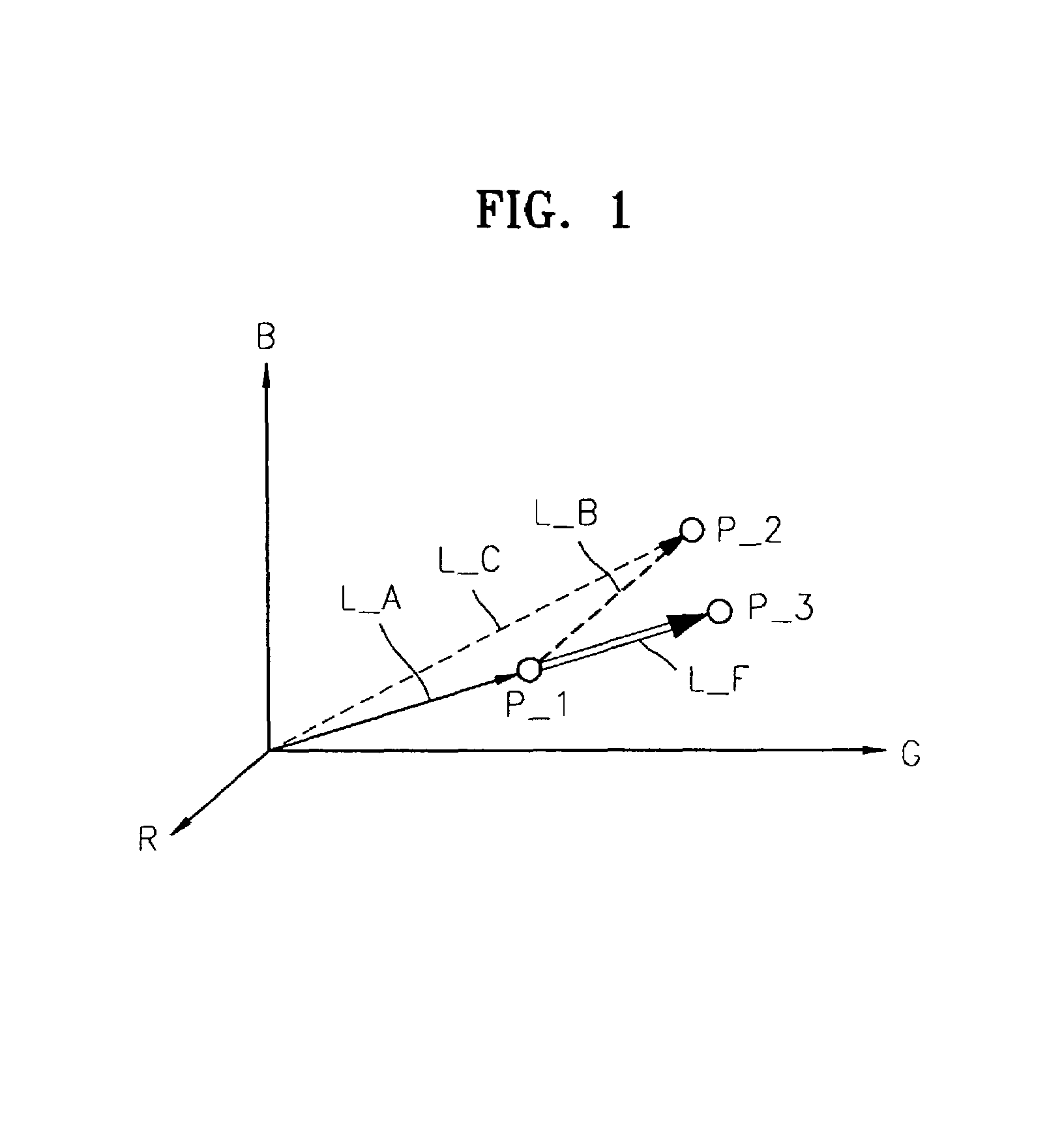

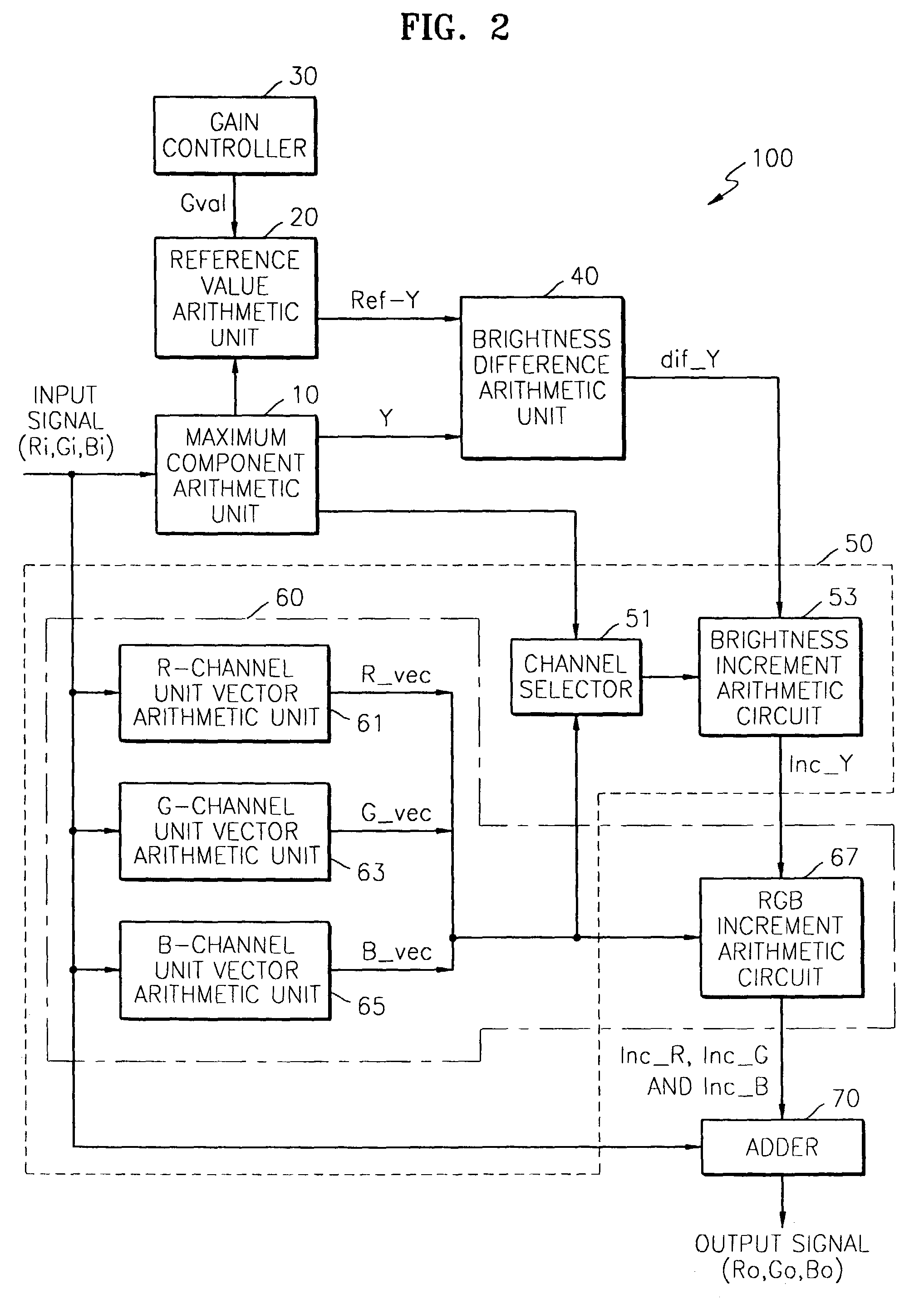

Apparatus and method of controlling brightness of image

InactiveUS7268753B2Increase image brightnessTelevision system detailsColor signal processing circuitsComputer graphics (images)Hue

Provided are an image brightness controlling apparatus and method, and an adaptive brightness controlling apparatus and method based on the brightness degree and / or brightness range of an image. The image brightness controlling apparatus includes a brightness increment arithmetic unit for outputting a brightness increment for a pixel, and an individual component brightness increment arithmetic unit for outputting the brightness increments of individual components constituting the pixel in response to the brightness increment for a pixel. The individual component brightness increment arithmetic unit multiplies the brightness increment of the pixel by each of the unit vectors of the components constituting the pixel to obtain the brightness increments of the individual components. The image brightness controlling apparatus further includes an adder for adding the components constituting the pixel to the brightness increments of the components. The image brightness controlling apparatus and the adaptive image brightness controlling apparatus can maintain the sense of color of an image (e.g., the hue or chroma of an image) while increasing the brightness degree and brightness range of an image.

Owner:SAMSUNG ELECTRONICS CO LTD

Low illumination level video image enhancement method

ActiveCN103455979AEnsure balanceIncrease image brightnessImage enhancementImaging processingIlluminance

The invention discloses a low illumination level video image enhancement method, and belongs to the technical field of image processing. The method includes a white balance processing module, an image de-noising module, an image enhancement module, an edge compensation module and an interframe compensation module, video image information sequentially passes through the white balance processing module, the image de-noising module, the image enhancement module, the edge compensation module and the interframe compensation module, and finally enhanced video images are obtained.

Owner:DALIAN UNIV OF TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com