Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

63results about How to "Improve electromigration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Selective deposition of metal-containing cap layers for semiconductor devices

ActiveUS20100248473A1Improve electromigrationImprove stress migrationSemiconductor/solid-state device manufacturingDevice materialSelective deposition

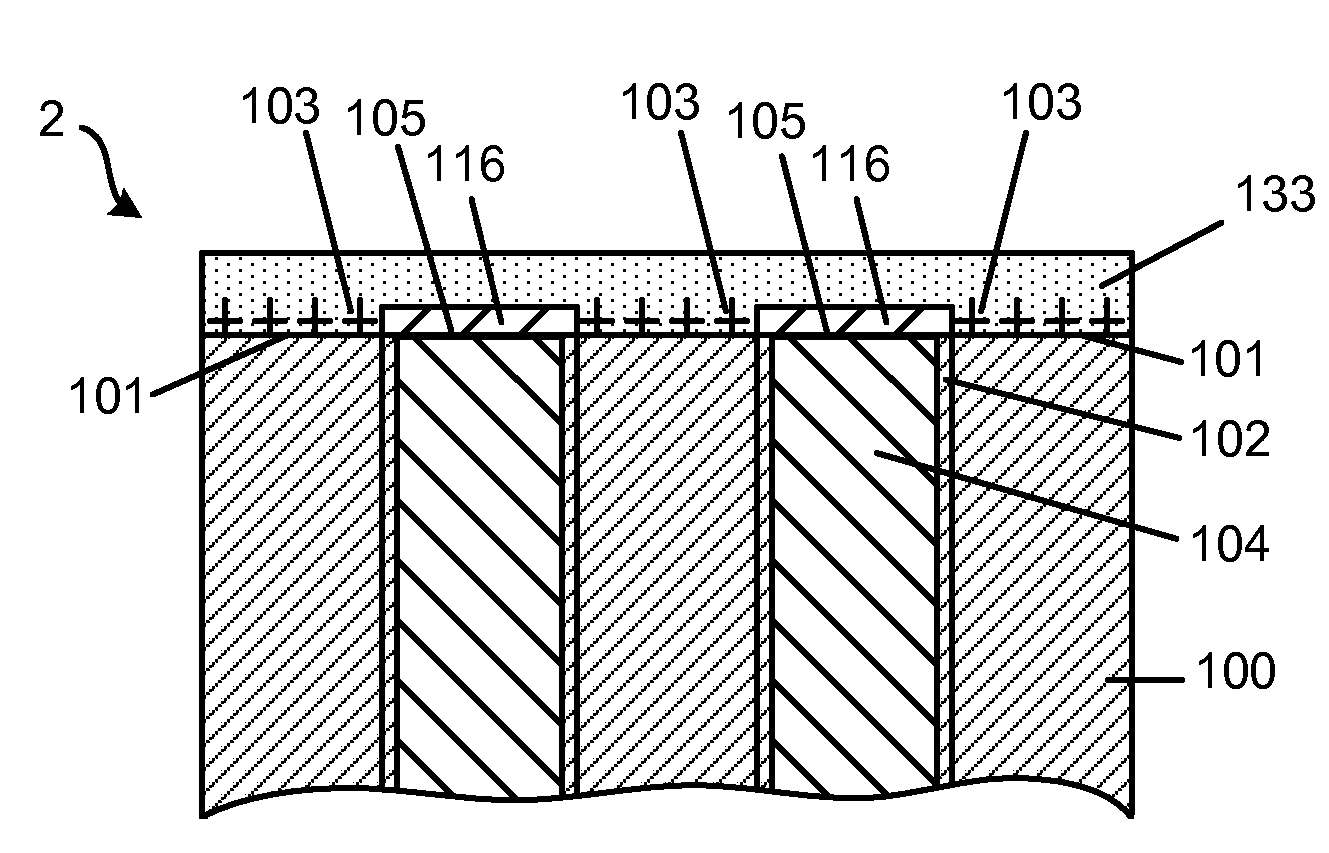

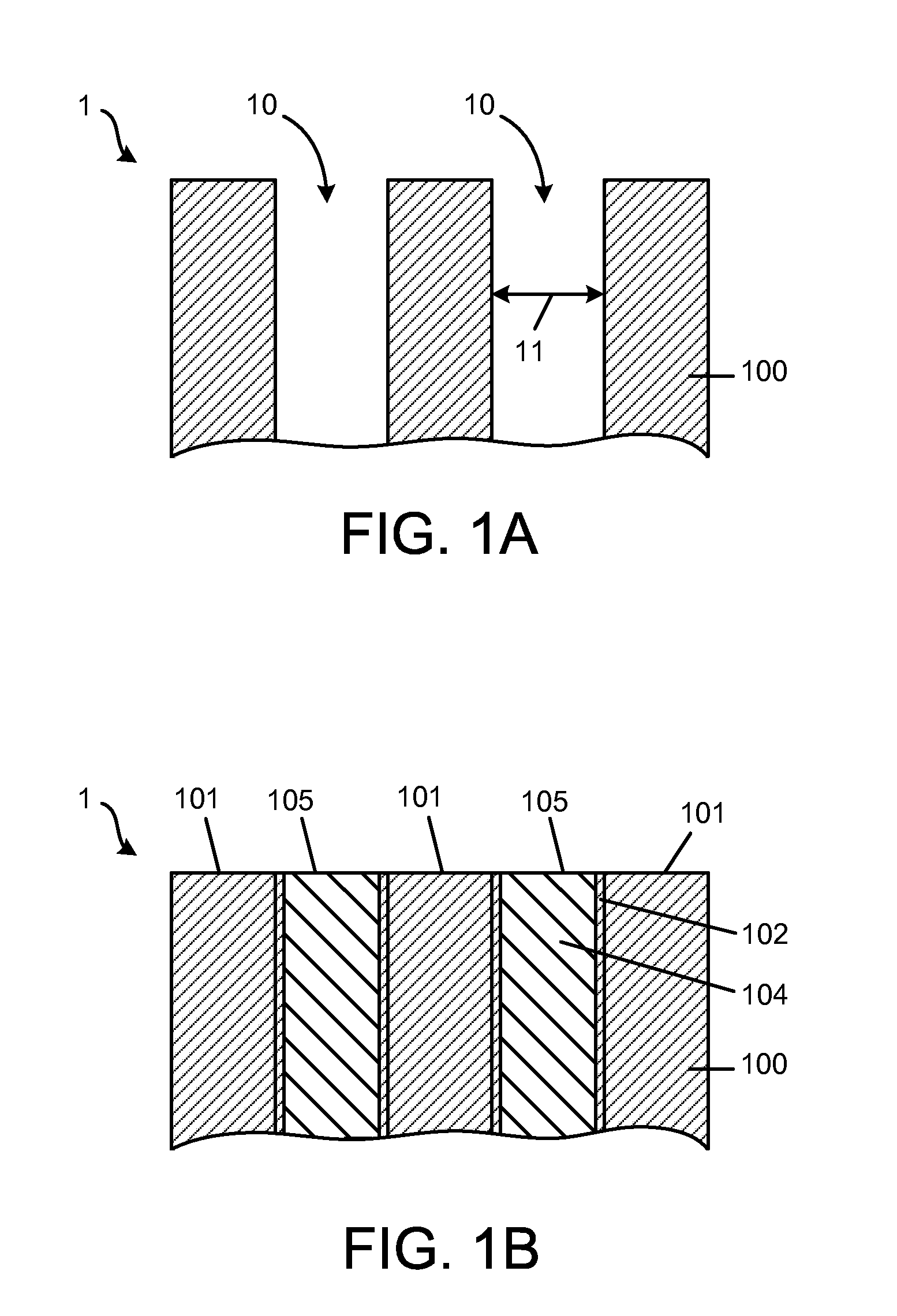

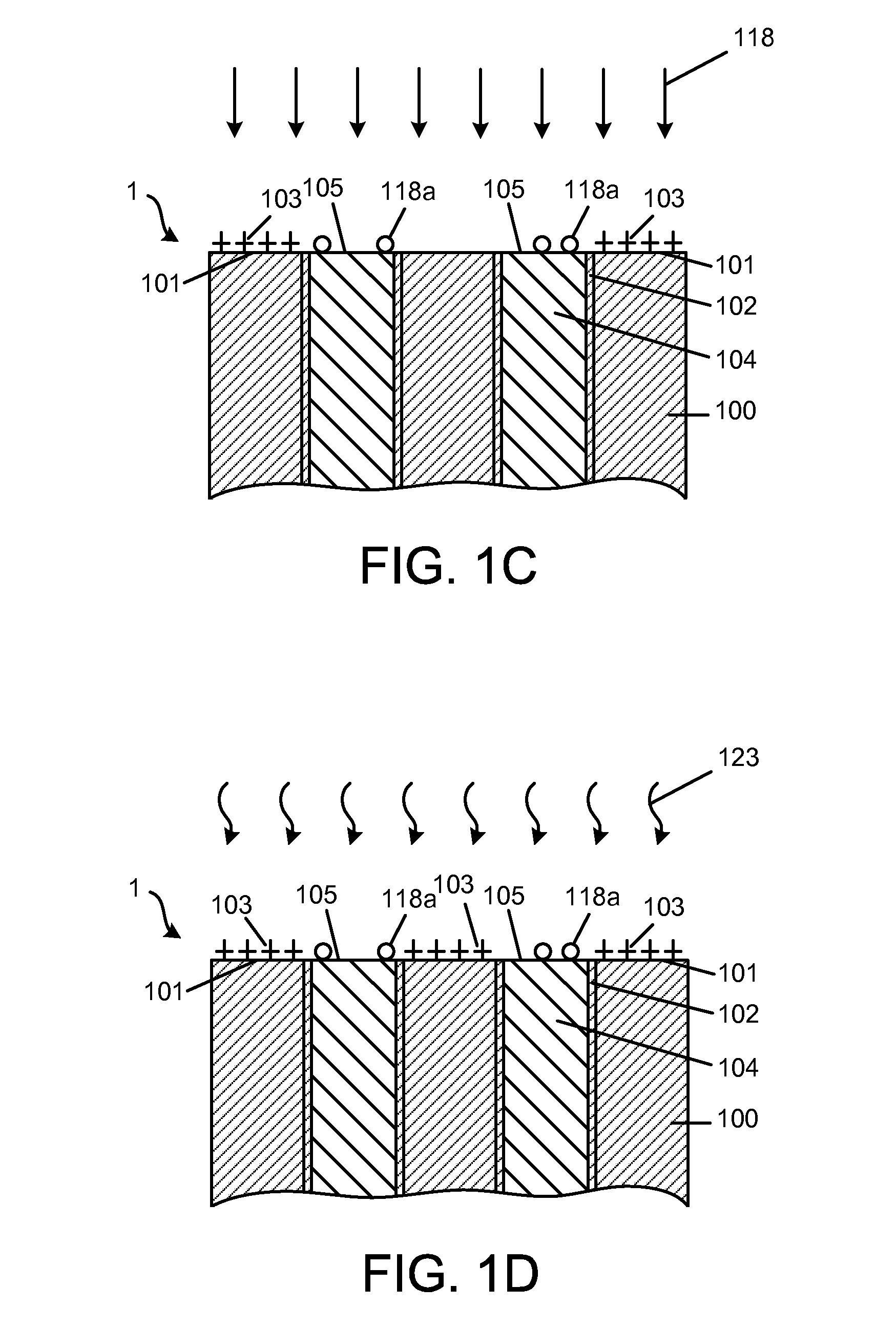

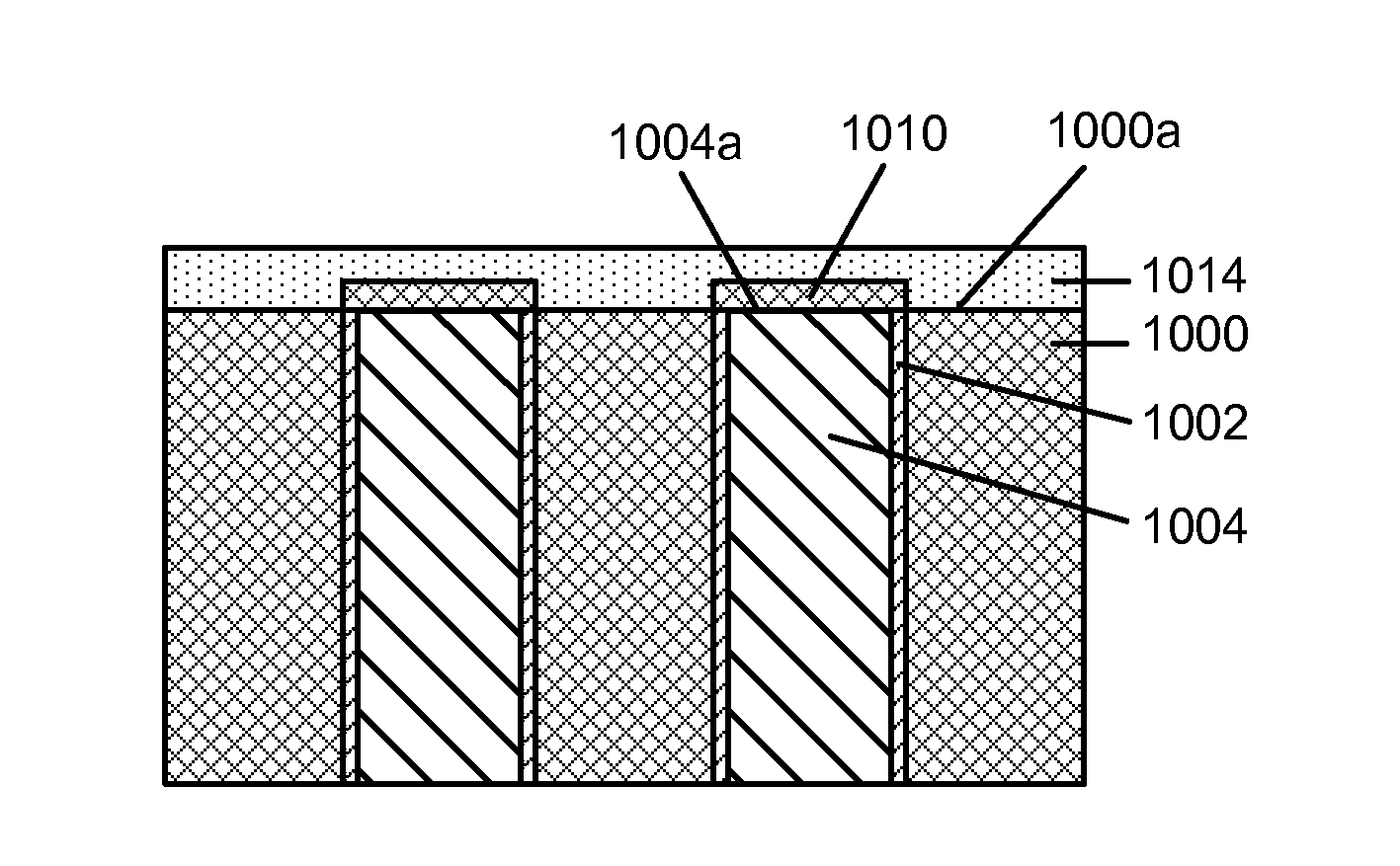

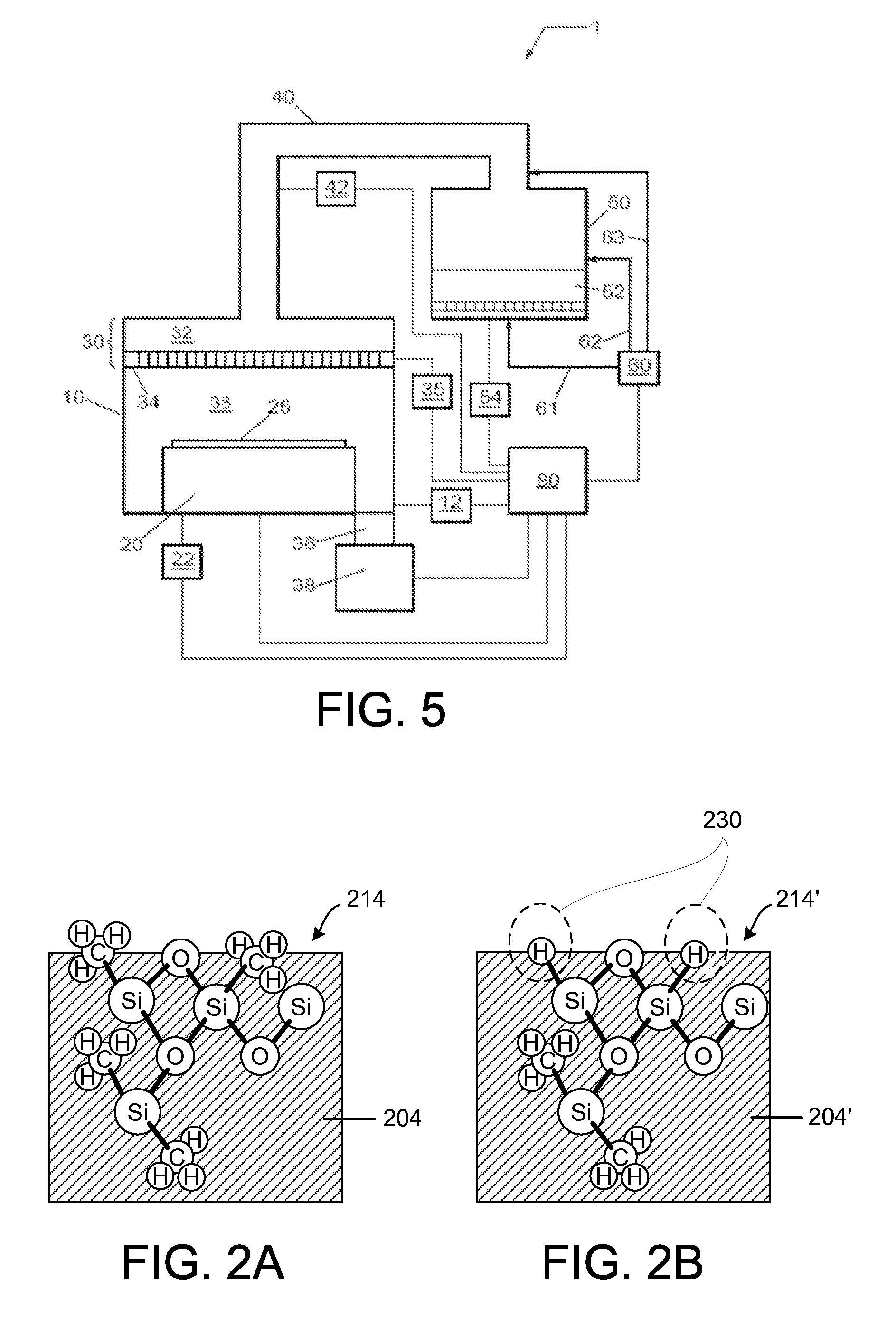

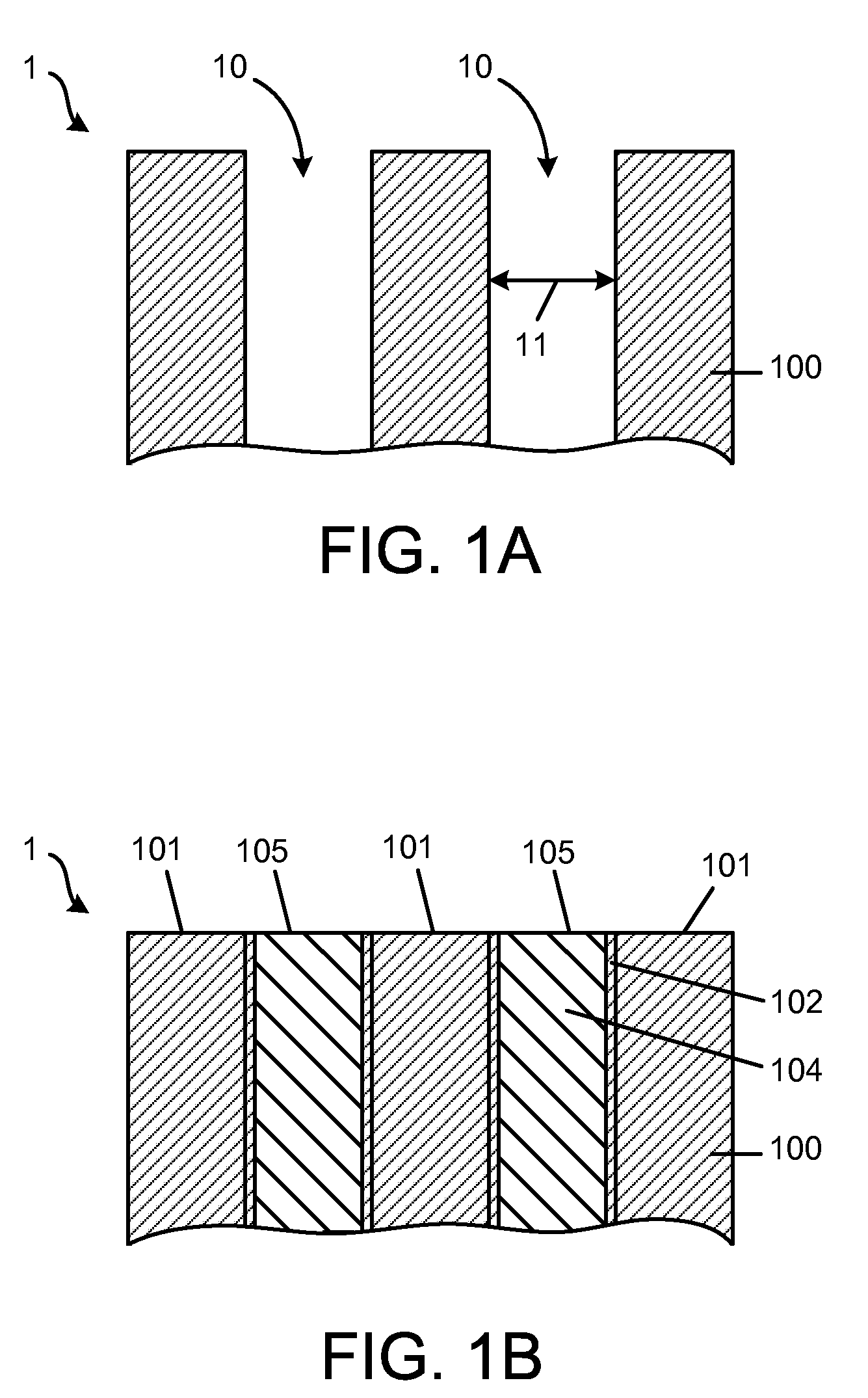

A method for integrating metal-containing cap layers into copper (Cu) metallization of semiconductor devices. In one embodiment, the method includes providing a patterned substrate containing metal surfaces and dielectric layer surfaces, and modifying the dielectric layer surfaces by exposure to a reactant gas containing a hydrophobic functional group, where the modifying substitutes a hydrophilic functional group in the dielectric layer surfaces with a hydrophobic functional group. The method further includes depositing metal-containing cap layers selectively on the metal surfaces by exposing the modified dielectric layer surfaces and the metal surfaces to a deposition gas containing metal-containing precursor vapor.

Owner:TOKYO ELECTRON LTD

Method for integrating selective low-temperature ruthenium deposition into copper metallization of a semiconductor device

InactiveUS20090186481A1Improve electromigrationImprove stress migrationSemiconductor/solid-state device detailsSolid-state devicesDevice materialRuthenium

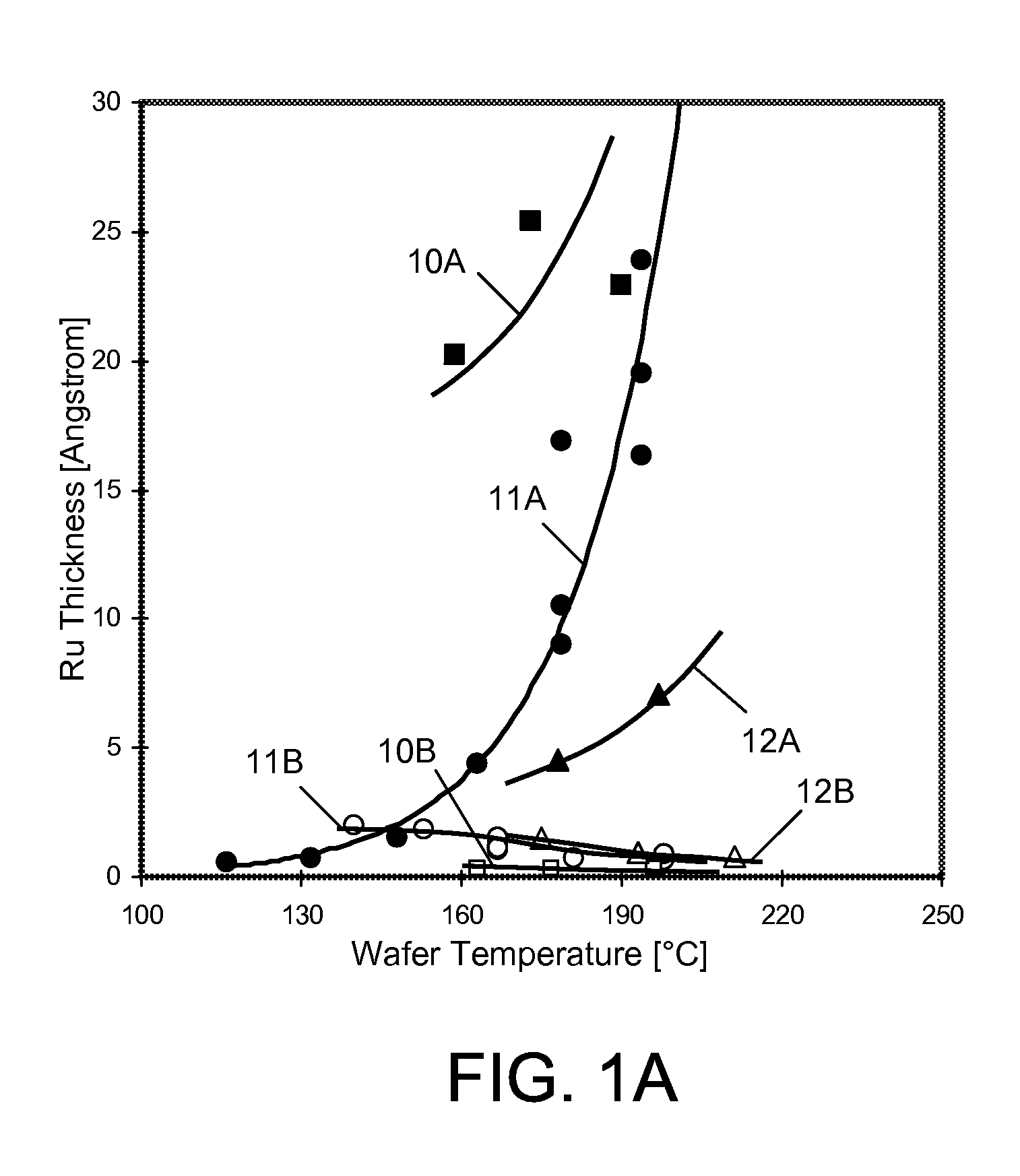

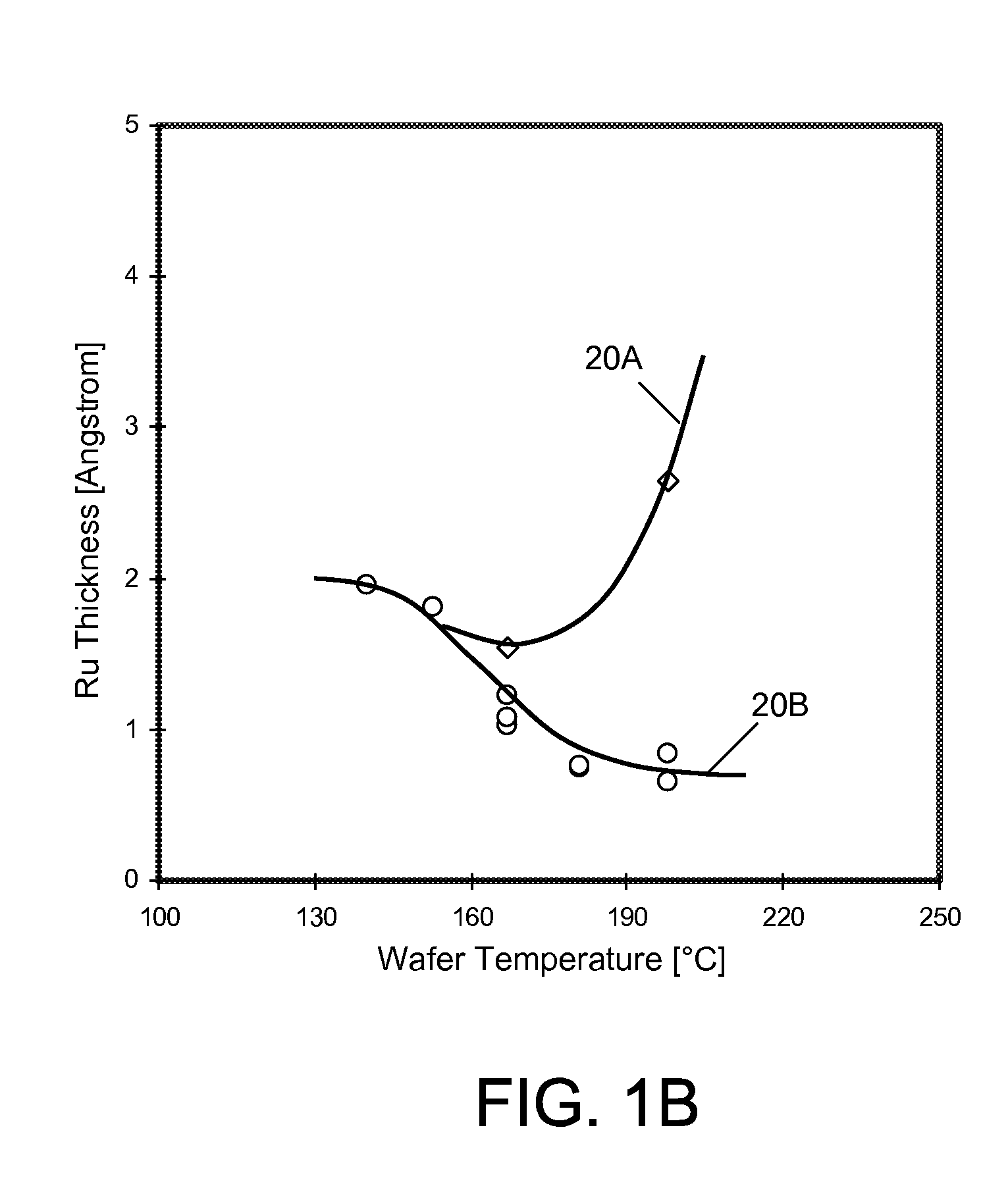

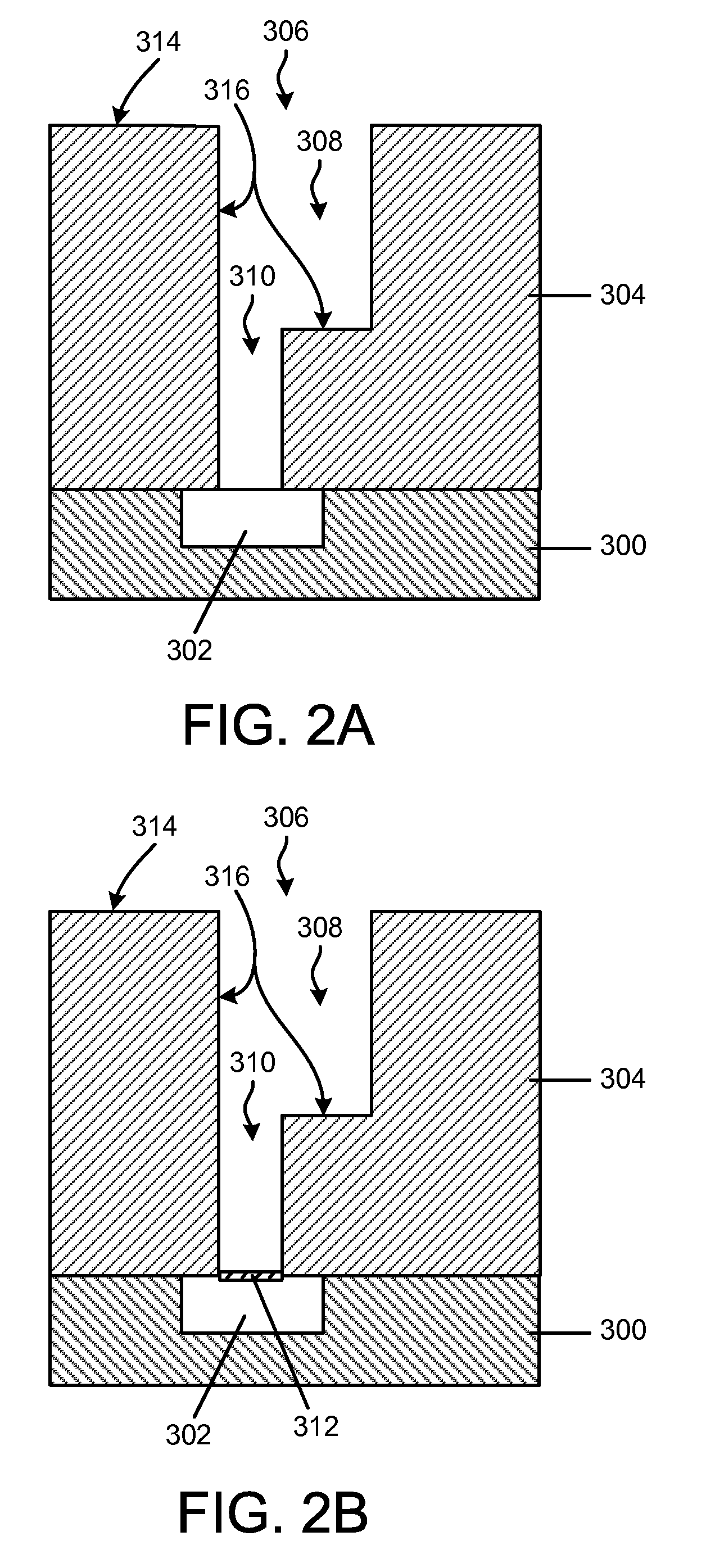

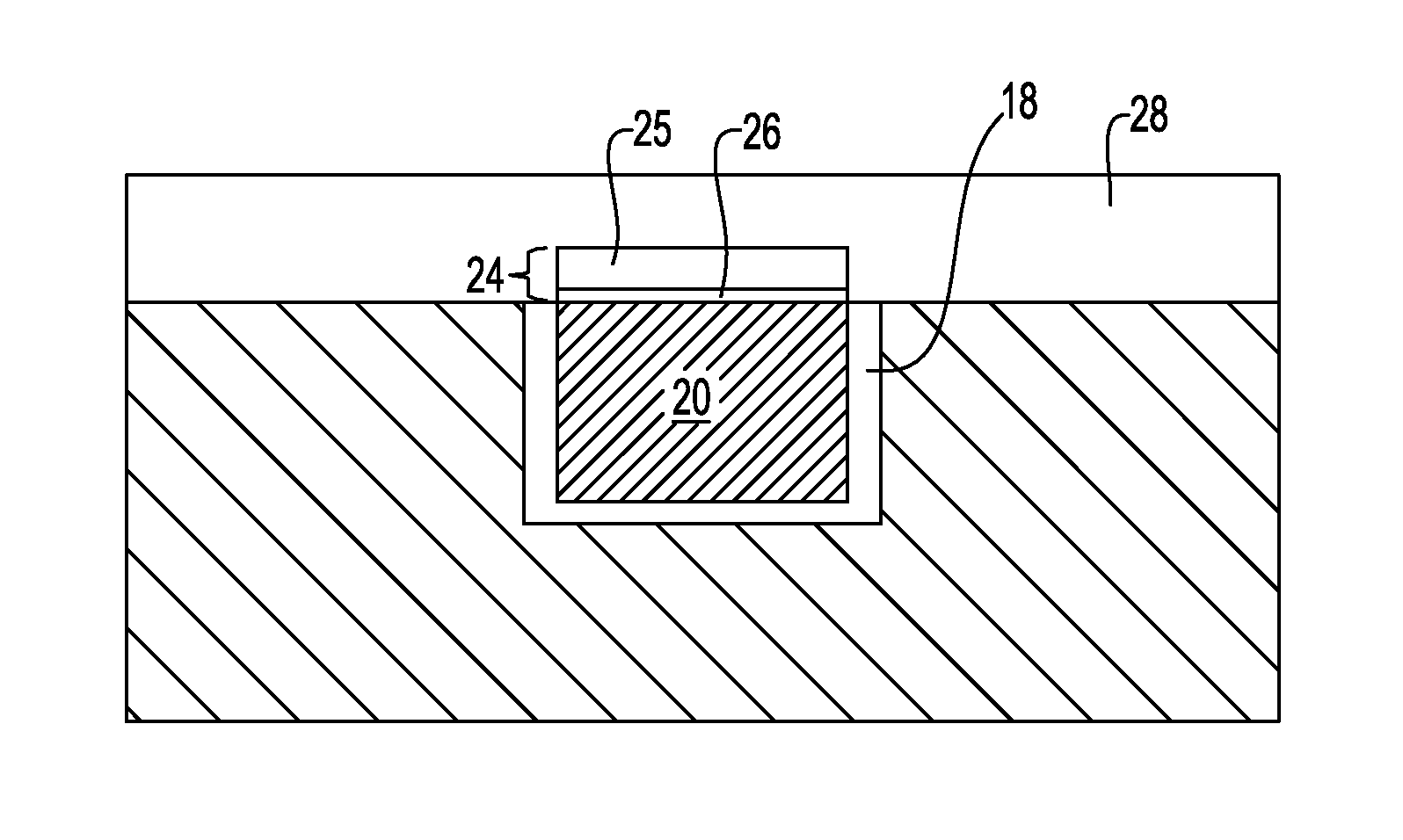

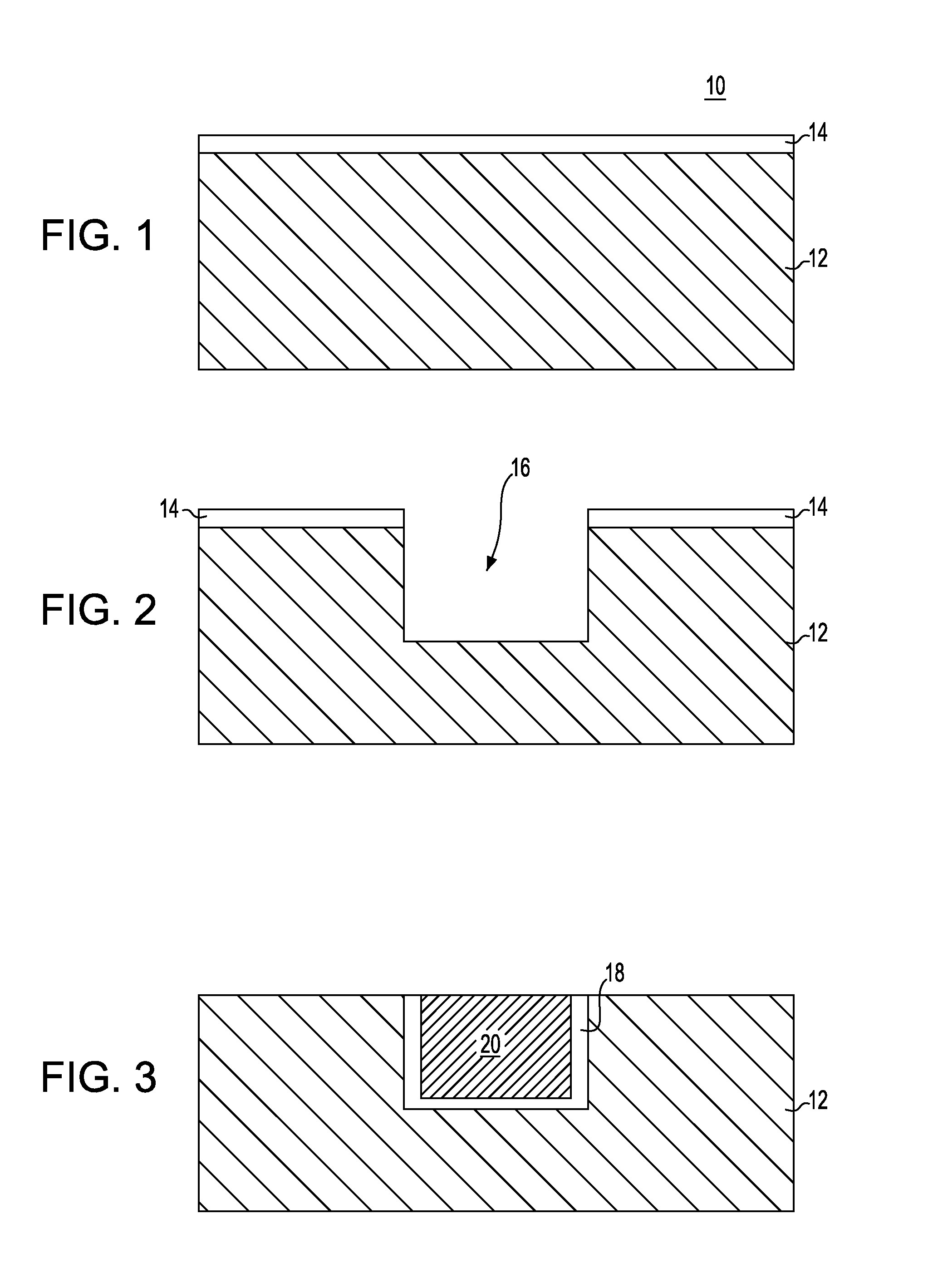

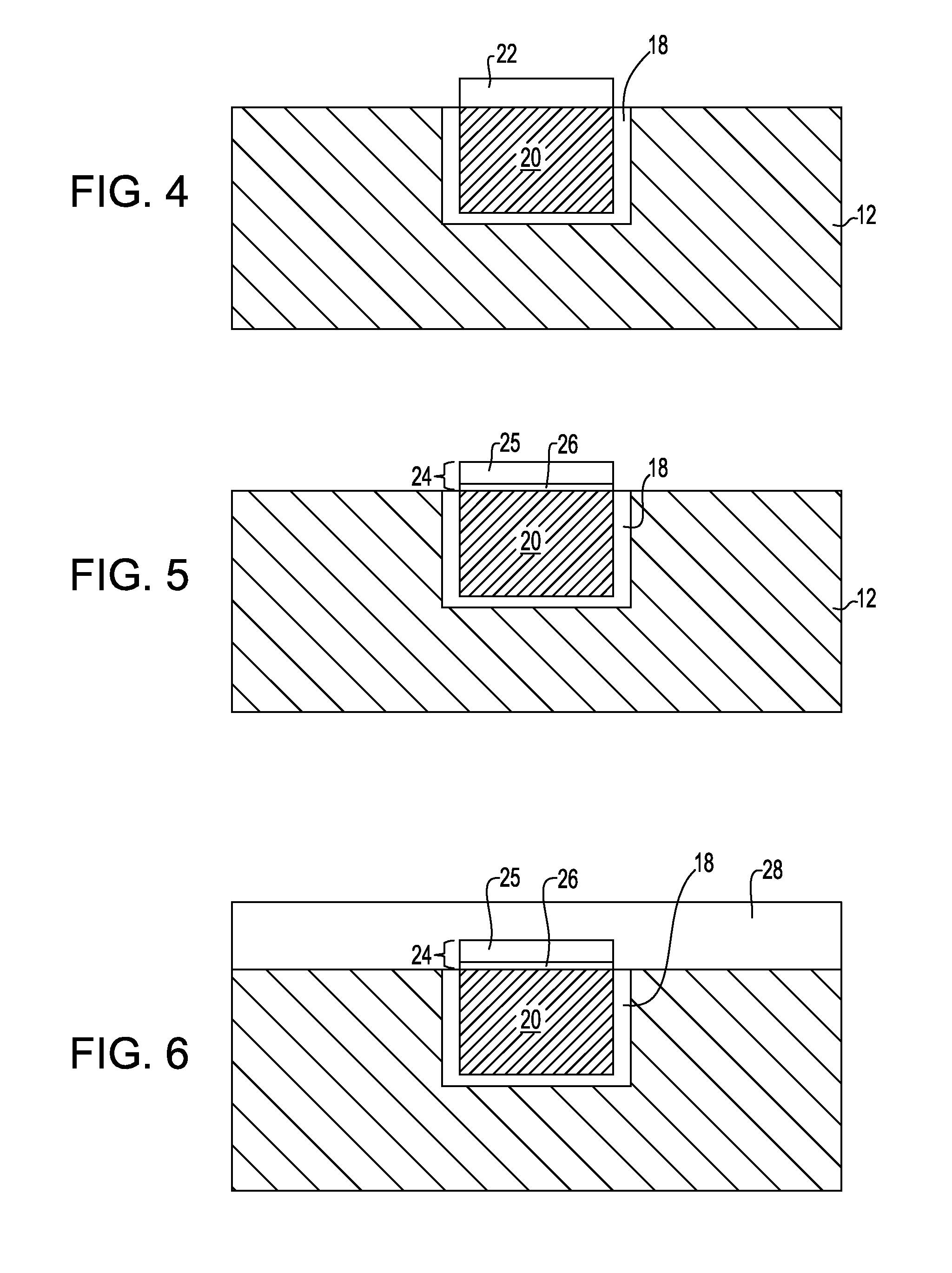

A method for integrating low-temperature selective Ru metal deposition into manufacturing of semiconductor devices to improve electromigration and stress migration in bulk Cu metal. The method includes providing a patterned substrate containing a recessed feature in a dielectric layer, where the recessed feature is at least substantially filled with planarized bulk Cu metal, heat-treating the bulk Cu metal and the dielectric layer in the presence of H2, N2, or NH3, or a combination thereof, and selectively depositing a Ru metal film on the heat-treated planarized bulk Cu metal.

Owner:TOKYO ELECTRON LTD

Method for modifying metal cap layers in semiconductor devices

InactiveUS20120252210A1Improve electromigrationImprove stress migrationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingPatterned substrateAmmonia

A method for forming a semiconductor device with improved electromigration (EM) and stress migration (SM) properties. The method includes providing a planarized patterned substrate containing a copper (Cu) metal surface and a low-k dielectric layer surface, selectively depositing a metal cap layer on the Cu metal surface, and modifying the metal cap layer by exposing the metal cap layer to a process gas containing ammonia (NH3) gas without plasma excitation. The method further includes forming a dielectric barrier film on the modified metal cap layer and on the dielectric layer surface, and exposing the dielectric barrier film to a gaseous oxidizing environment, where the dielectric barrier film and the modified metal cap layer prevent oxidation of the Cu metal surface when the dielectric barrier film is exposed to the gaseous oxidizing environment.

Owner:TOKYO ELECTRON LTD

On-chip Cu interconnection using 1 to 5 nm thick metal cap

ActiveUS7247946B2Improve electromigrationIncrease resistanceSemiconductor/solid-state device detailsSolid-state devicesDielectricSolubility

Disclosed is a procedure to coat the free surface of Cu damascene lines by a 1-5 nm thick element prior to deposition of the inter-level dielectric or dielectric diffusion barrier layer. The coating provides protection against oxidation, increases the adhesion strength between the Cu and dielectric, and reduces interface diffusion of Cu. In addition, the thin cap layer further increases electromigration Cu lifetime and reduces the stress induced voiding. The selective elements can be directly deposited onto the Cu embedded within the under layer dielectric without causing an electric short circuit between the Cu lines. These chosen elements are based on their high negative reduction potentials with oxygen and water, and a low solubility in and formation of compounds with Cu.

Owner:GLOBALFOUNDRIES US INC

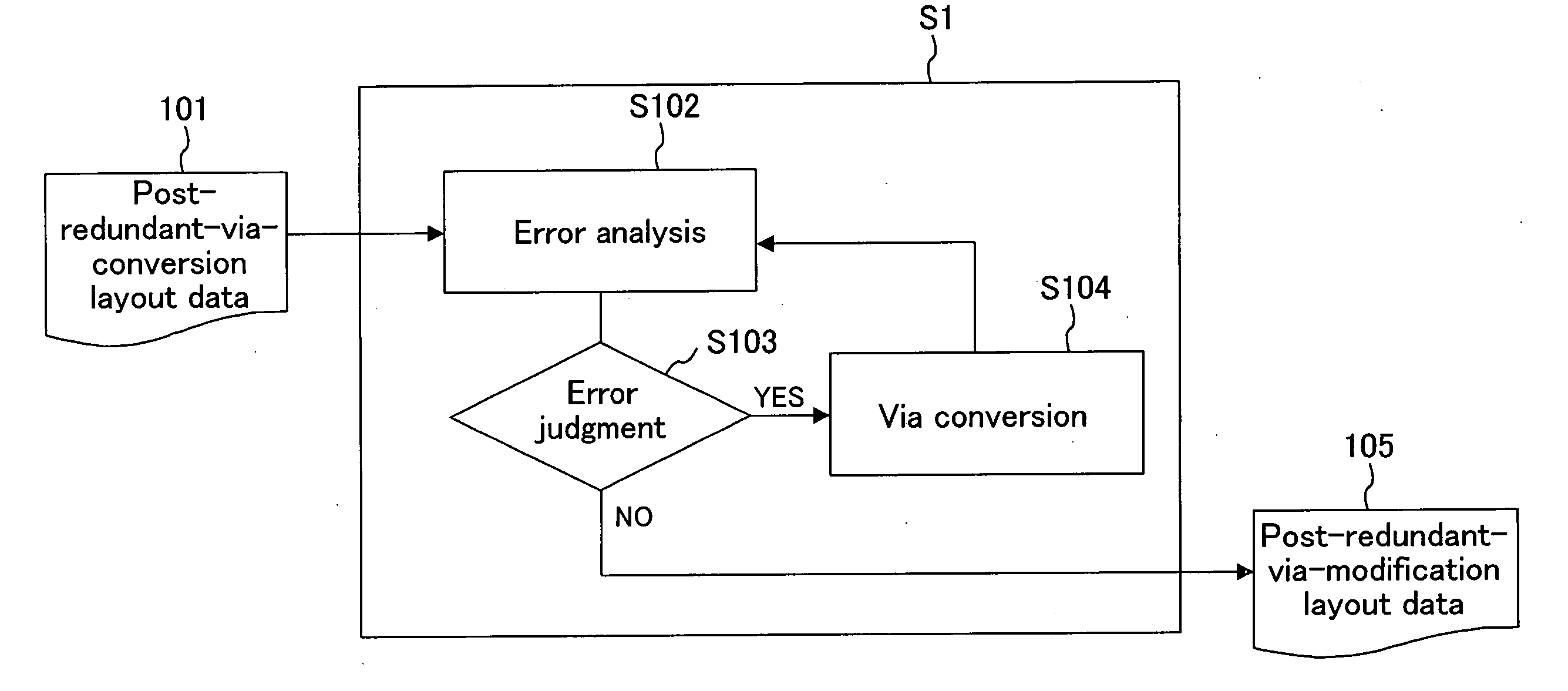

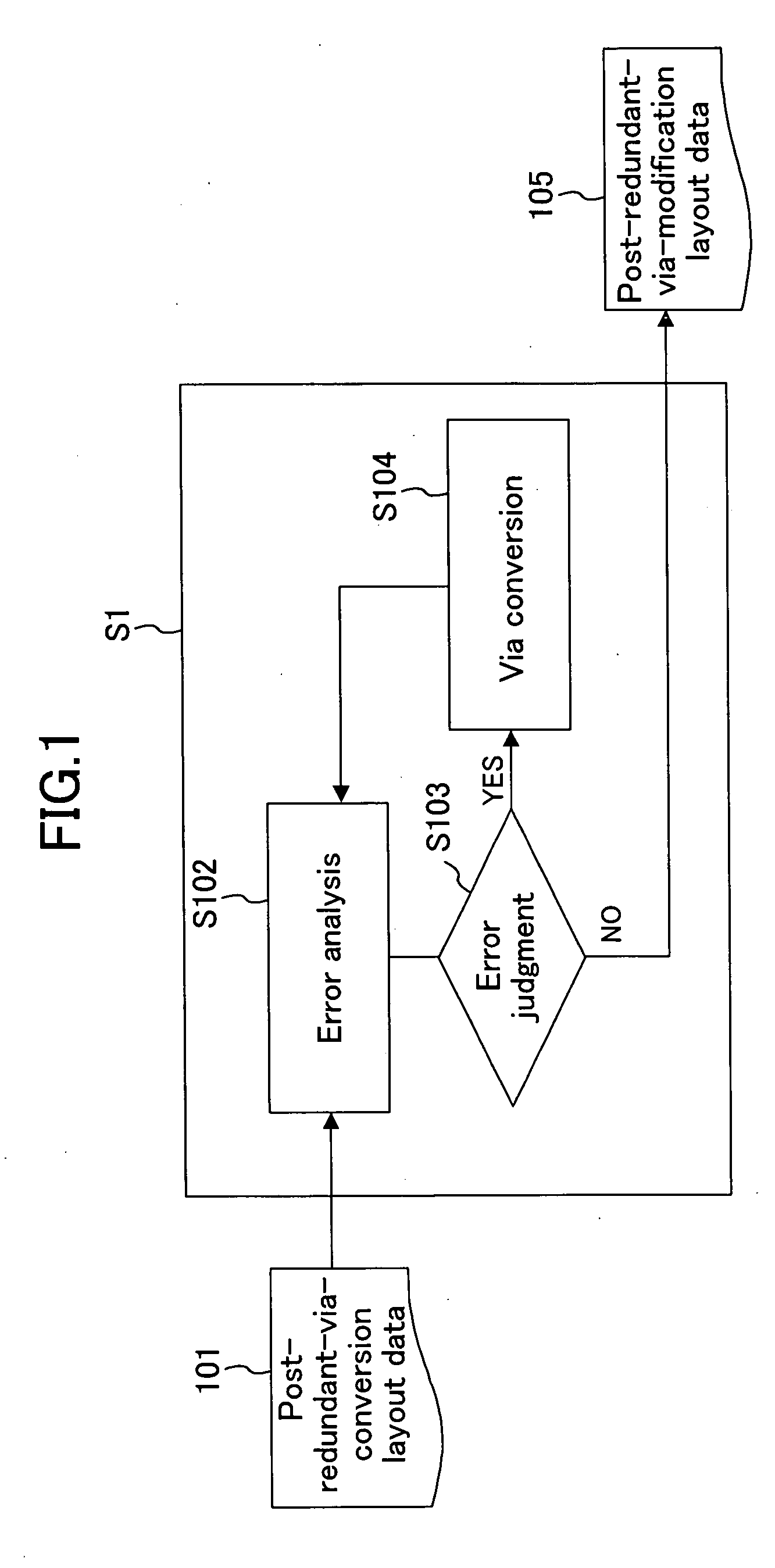

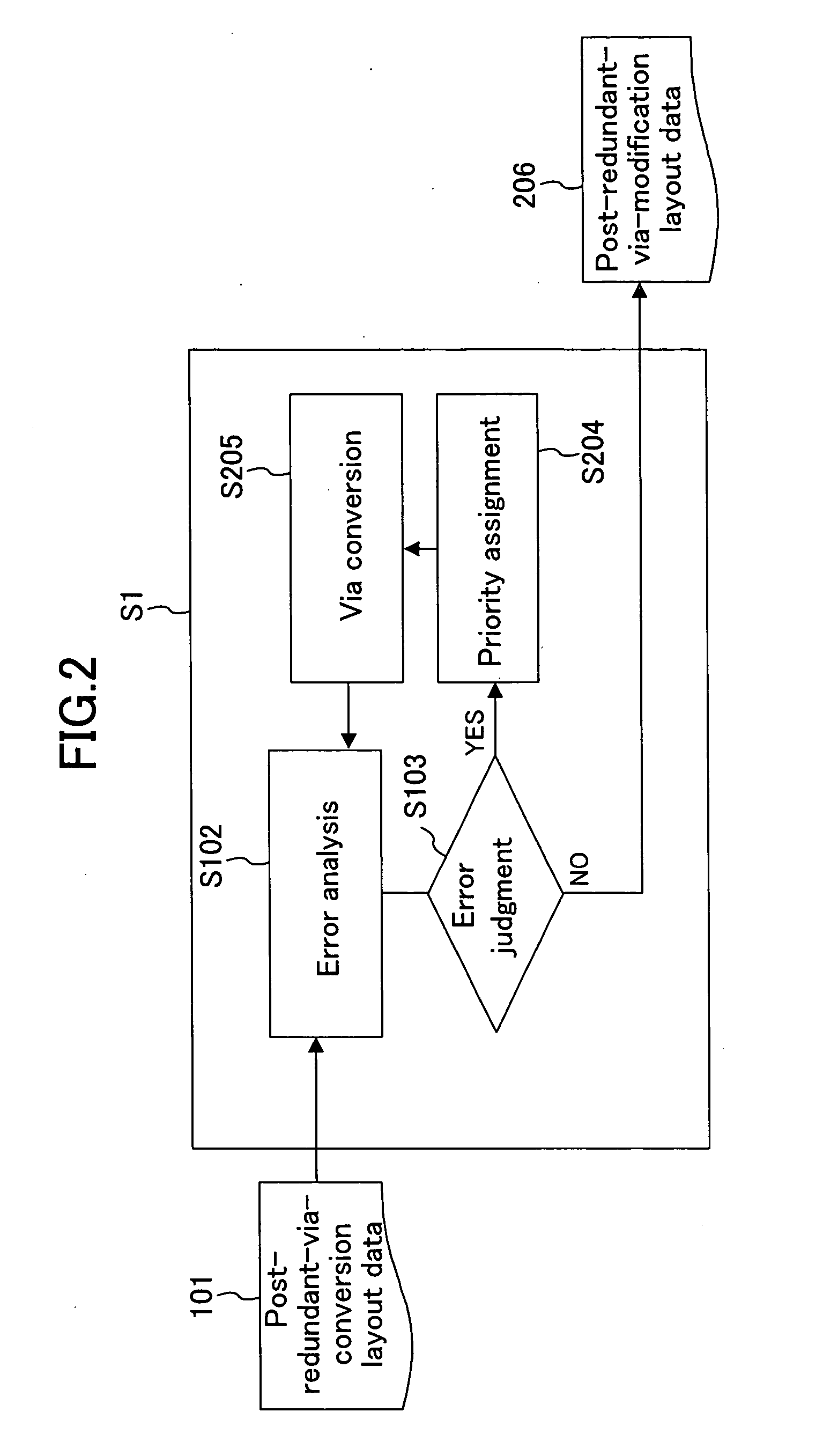

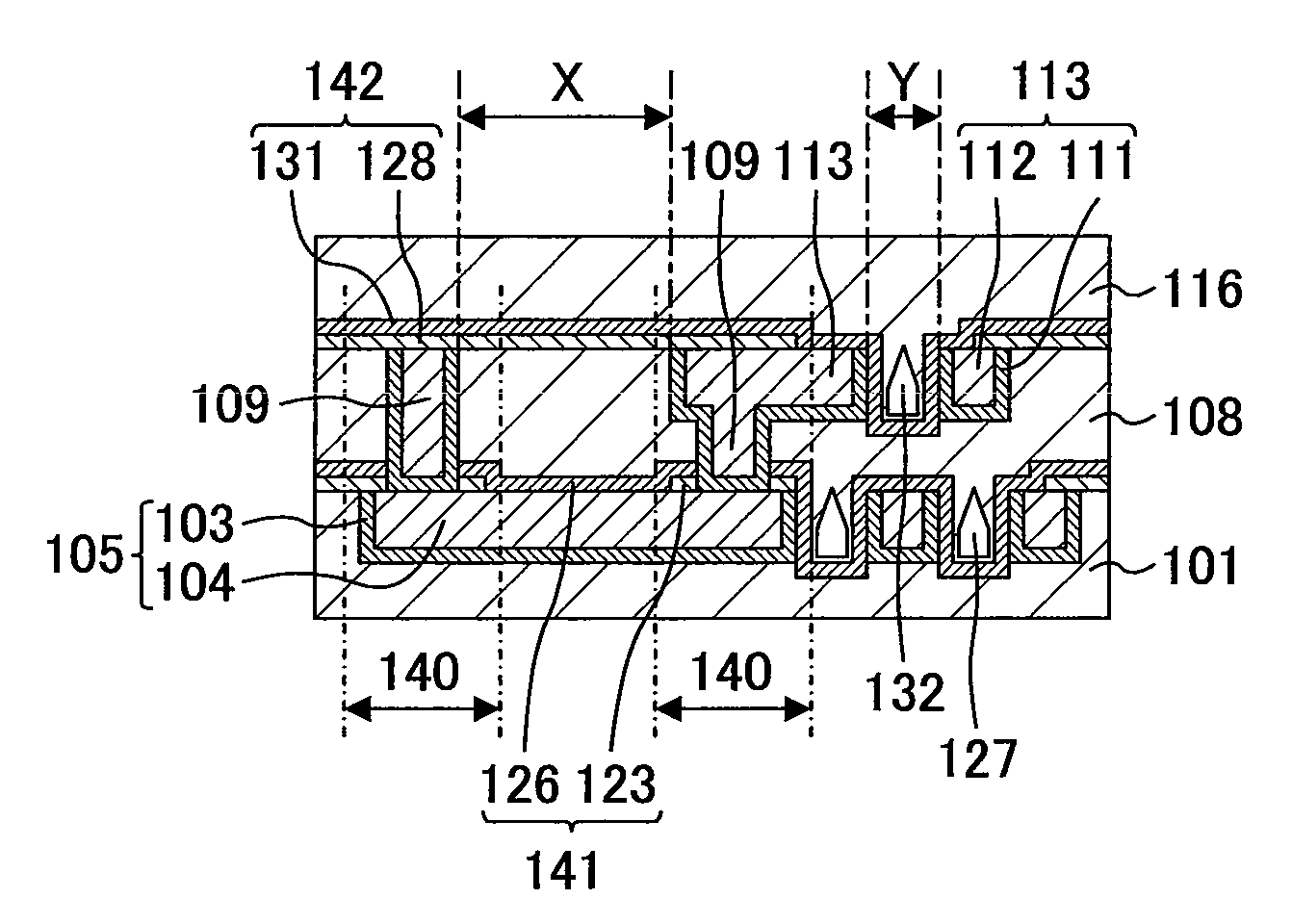

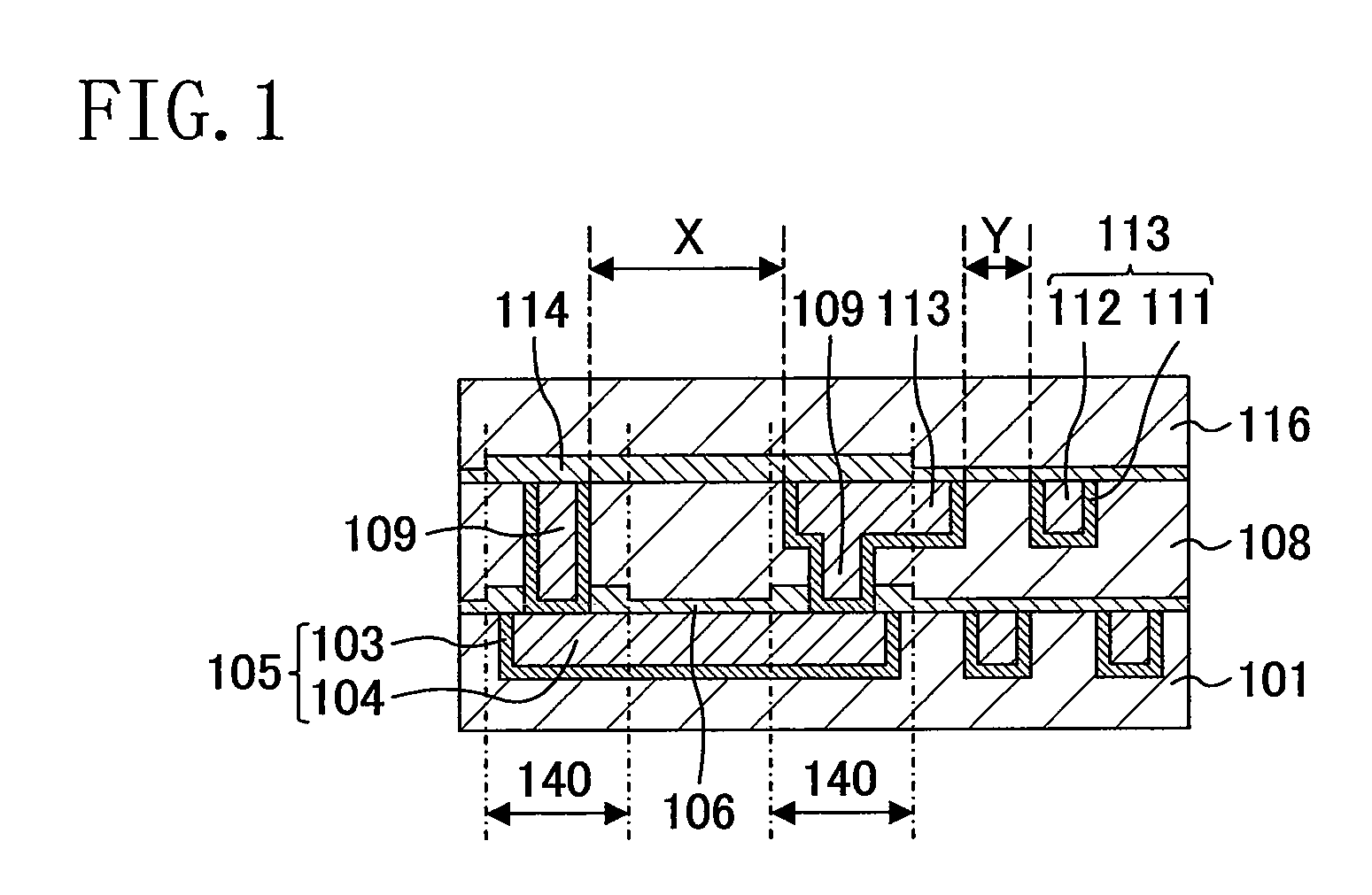

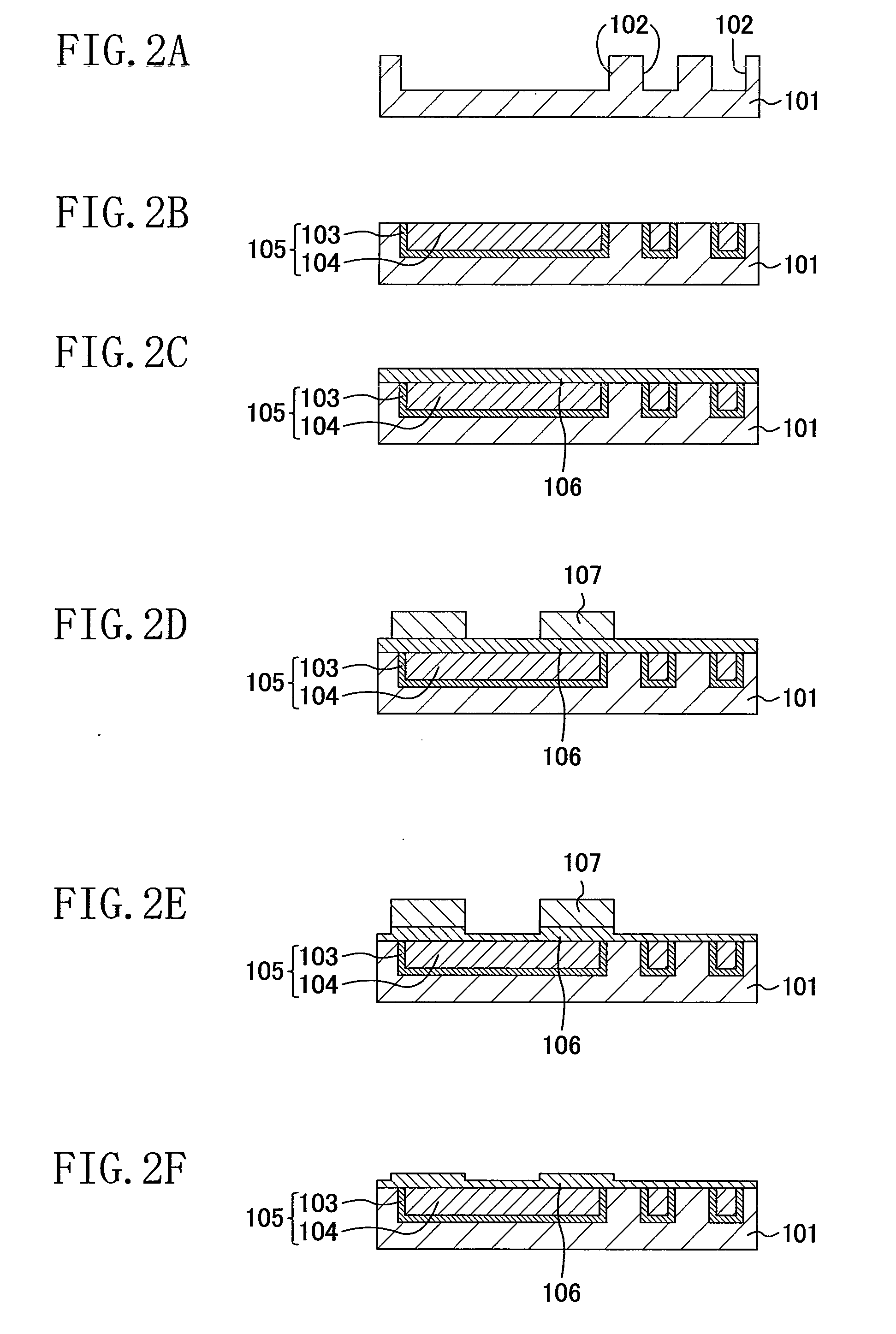

Design method of semiconductor device and semiconductor device

InactiveUS20060101367A1Improve electromigrationHigh yieldSemiconductor/solid-state device detailsSolid-state devicesAntenna effectDevice material

In an error analysis step, analysis of an antenna effect error, a timing constraint violation and the like is performed for layout data in which redundant via conversion has been performed. Then, whether or not an error exists is judged and, among redundant vias located on a signal line in which a design constraint violation has occurred, how many vias have to be converted to single vias, respectively, to avoid the design constraint violation is calculated. In a via conversion step, a redundant via which has caused an error is converted to a single via, based on a result of the calculation. Thus, a design constraint violation regarding an error such as an antenna effect error and a timing constraint violation caused by a redundant via obtained by converting a single via for improving yield hardly occurs.

Owner:PANASONIC CORP

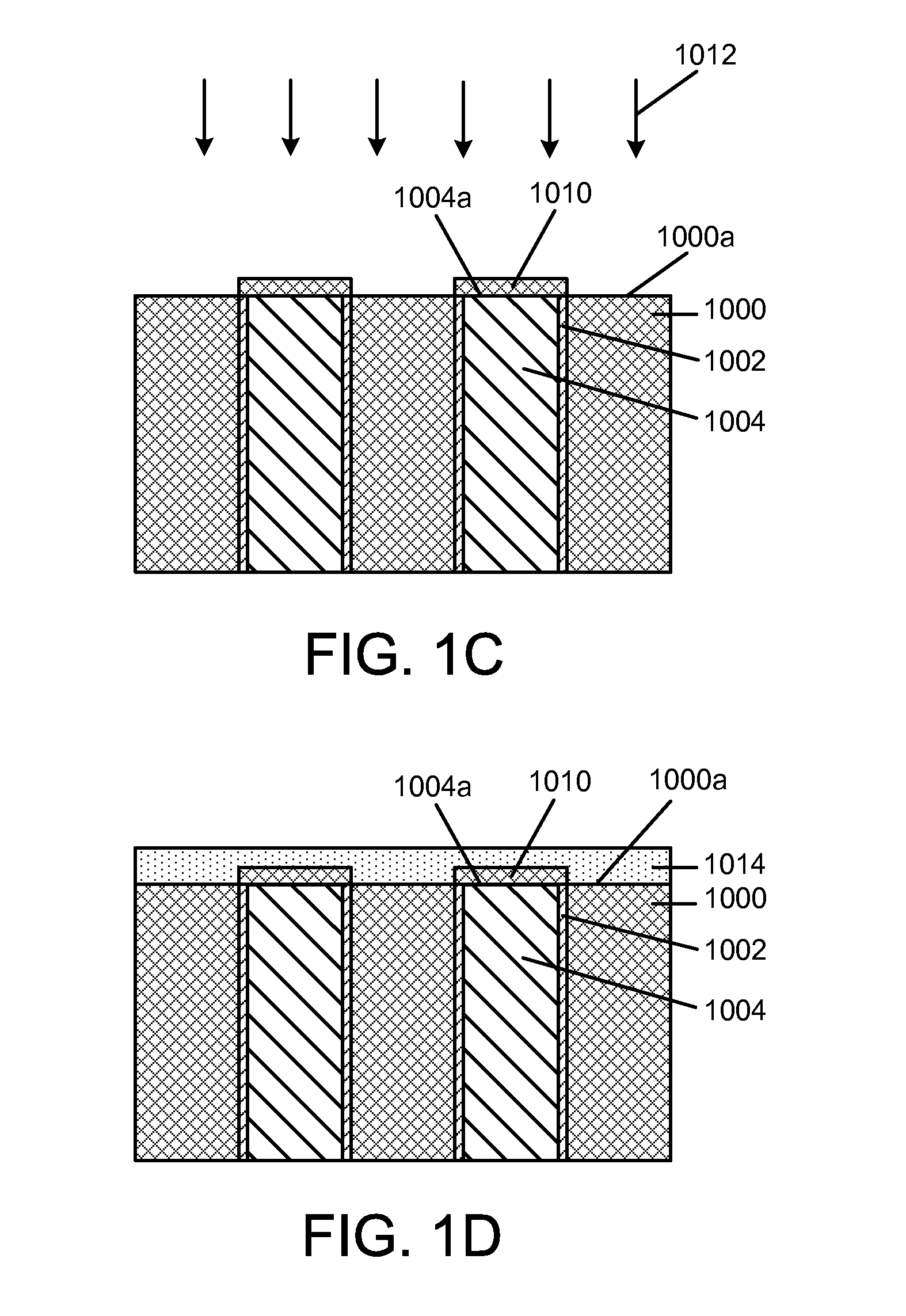

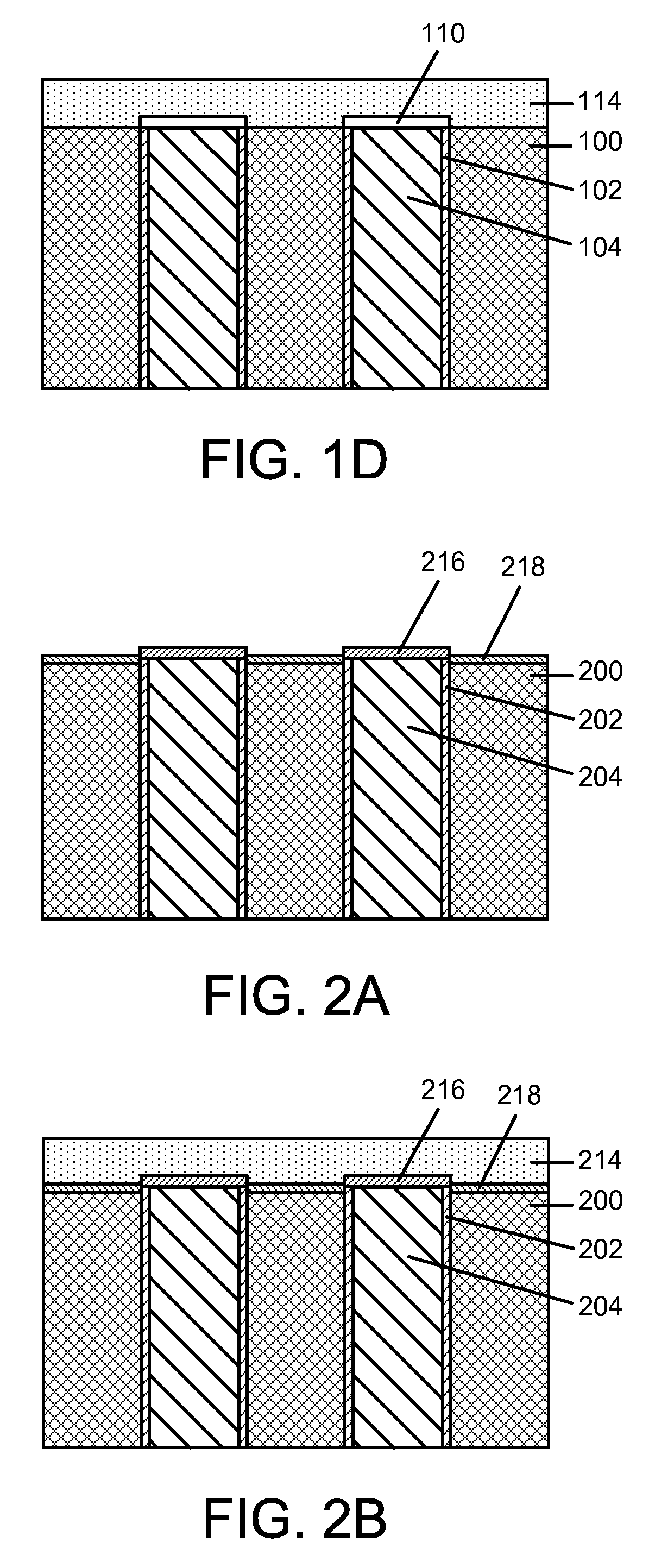

Method for manufacturing a semiconductor device with metal-containing cap layers

InactiveUS20100197135A1Improve electromigrationPromote migrationSemiconductor/solid-state device detailsSolid-state devicesDevice materialCopper

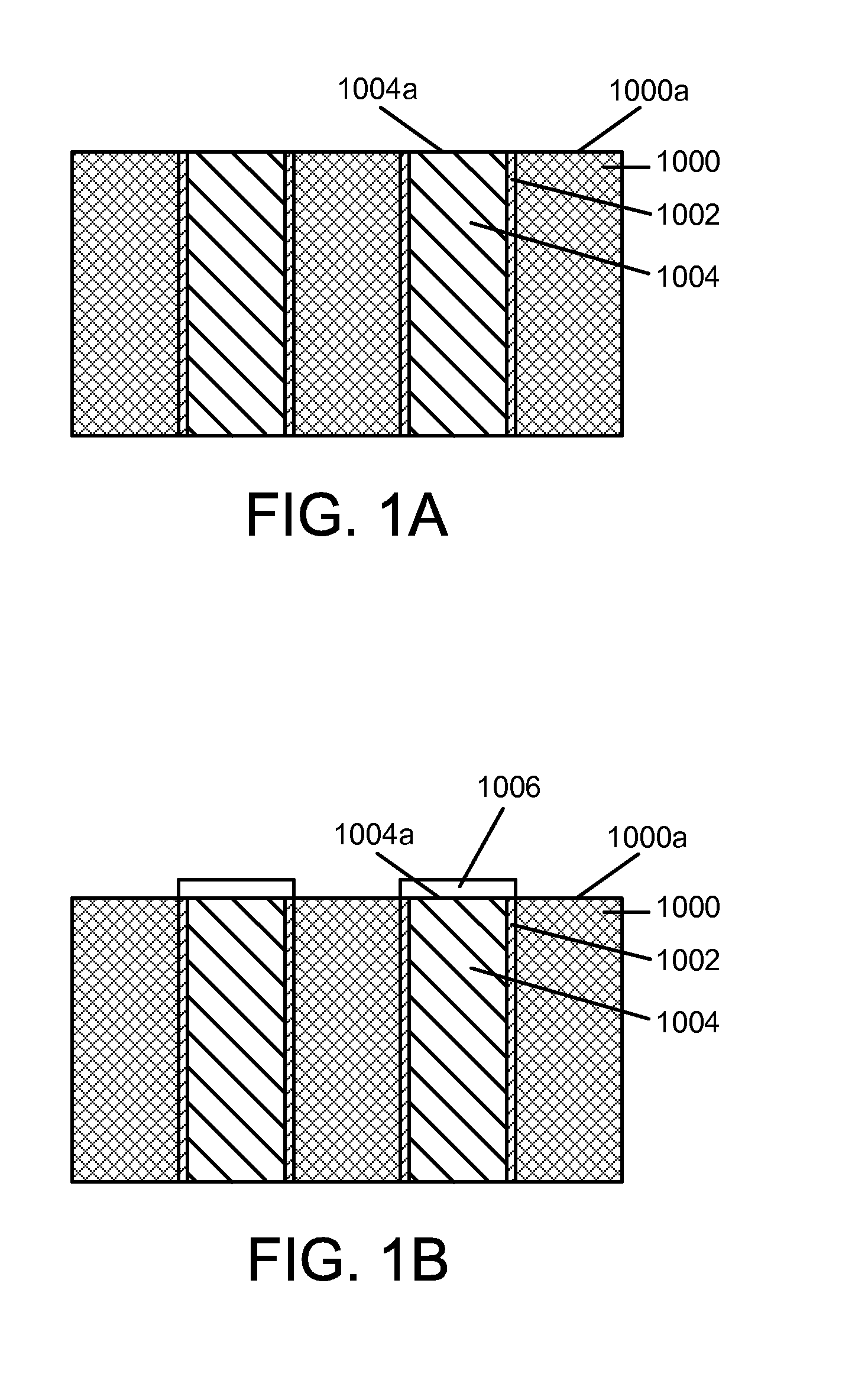

A method for integrating metal-containing cap layers into copper (Cu) metallization of semiconductor devices. In one embodiment, the method includes providing a patterned substrate containing Cu metal surfaces and dielectric layer surfaces, forming a patterned mask layer on the patterned substrate, where the patterned mask layer contains openings that expose the Cu metal surfaces. The method further includes depositing a metal-containing layer on the Cu metal surfaces, depositing an additional metal-containing layer on the patterned mask layer, and removing the patterned mask layer and the additional metal-containing layer from the patterned substrate to selectively form metal-containing cap layers on the Cu metal surfaces.

Owner:TOKYO ELECTRON LTD

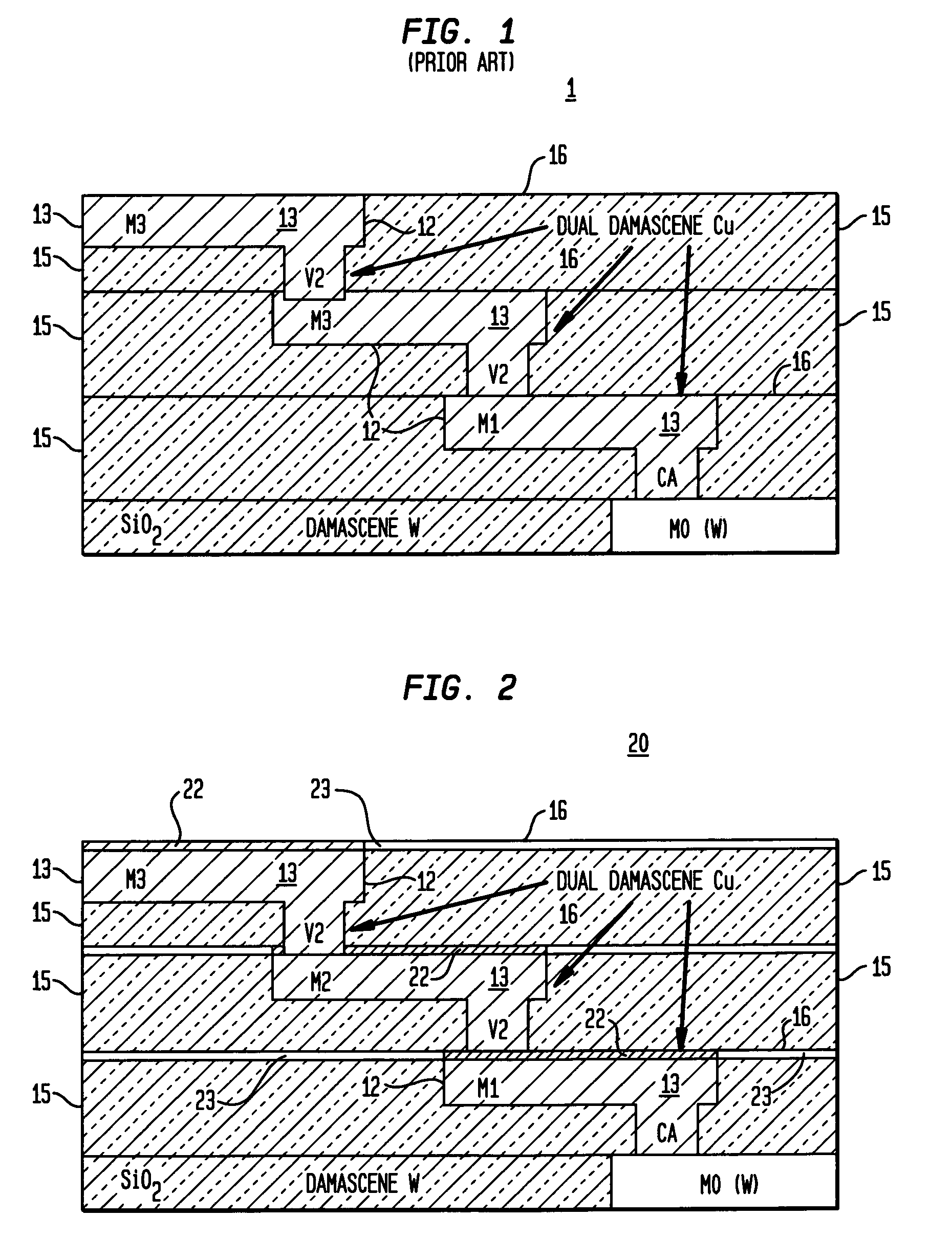

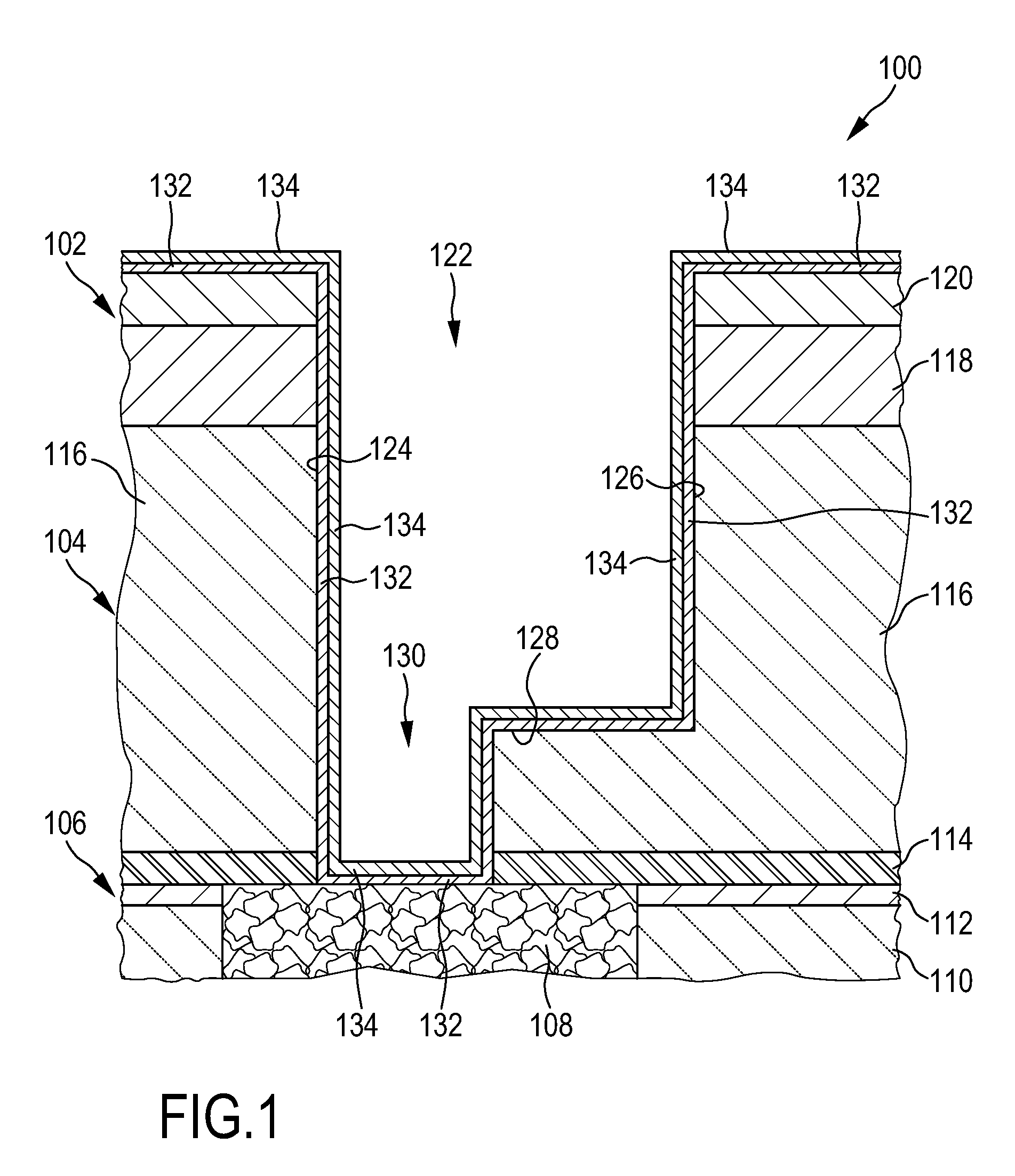

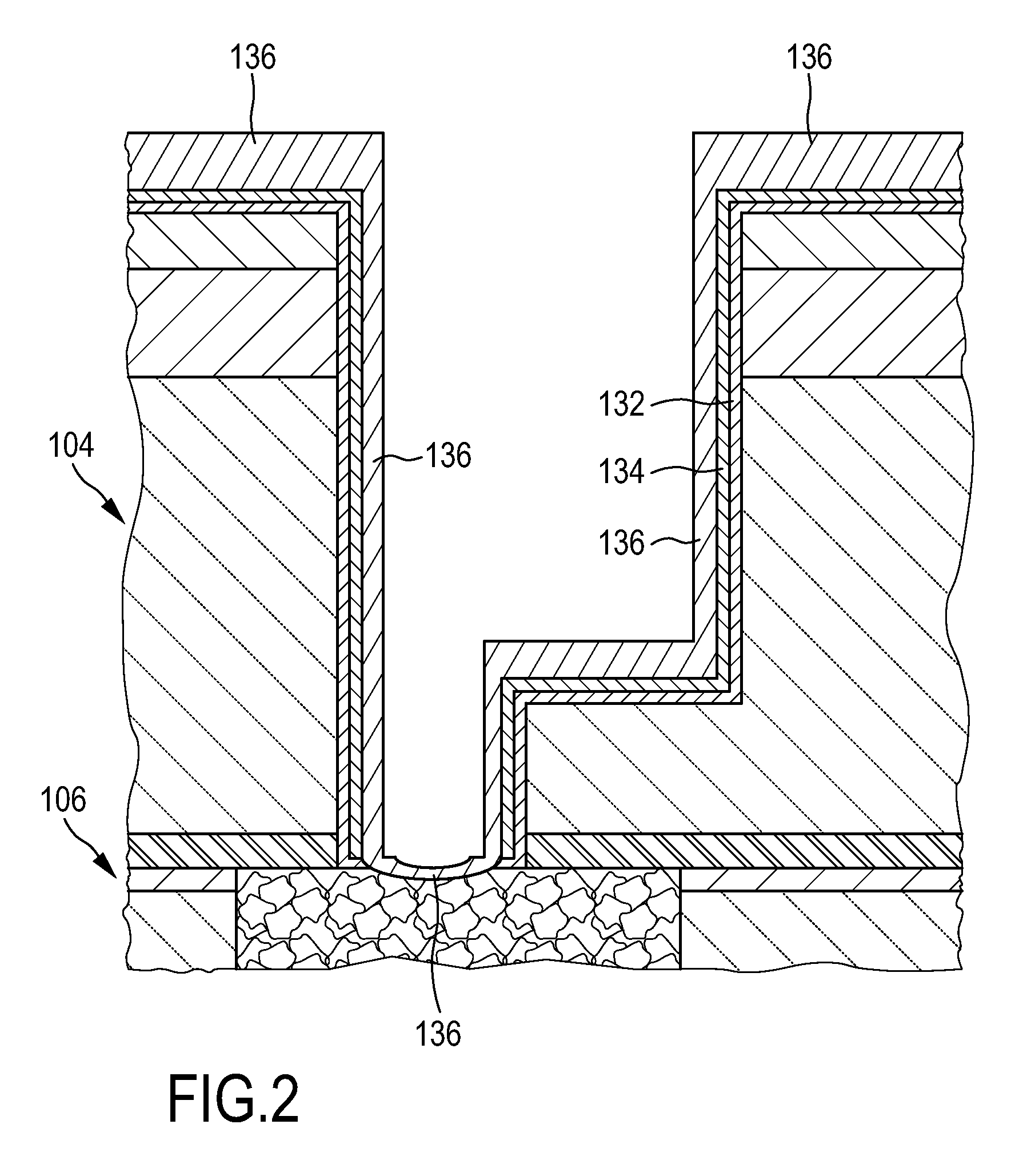

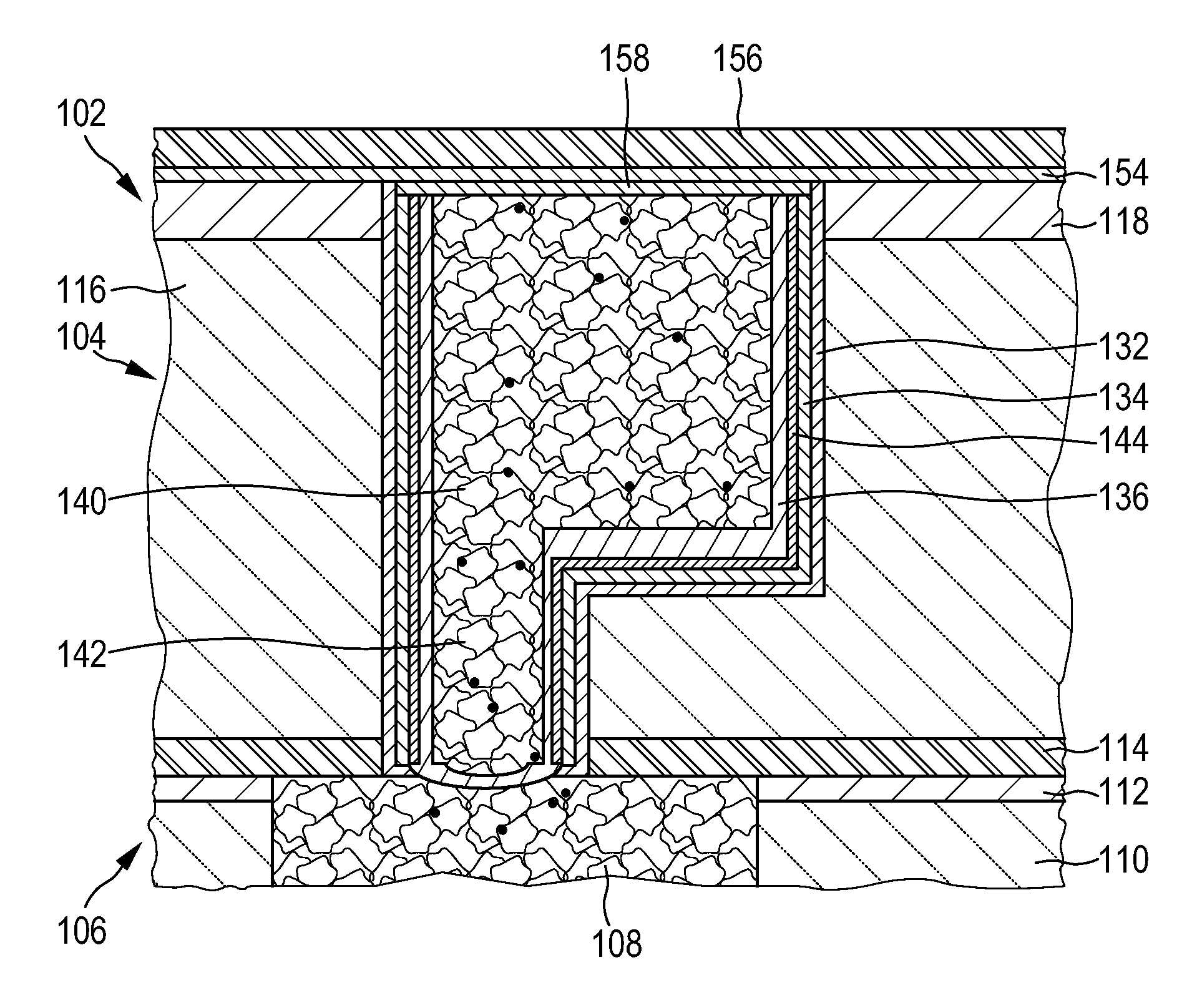

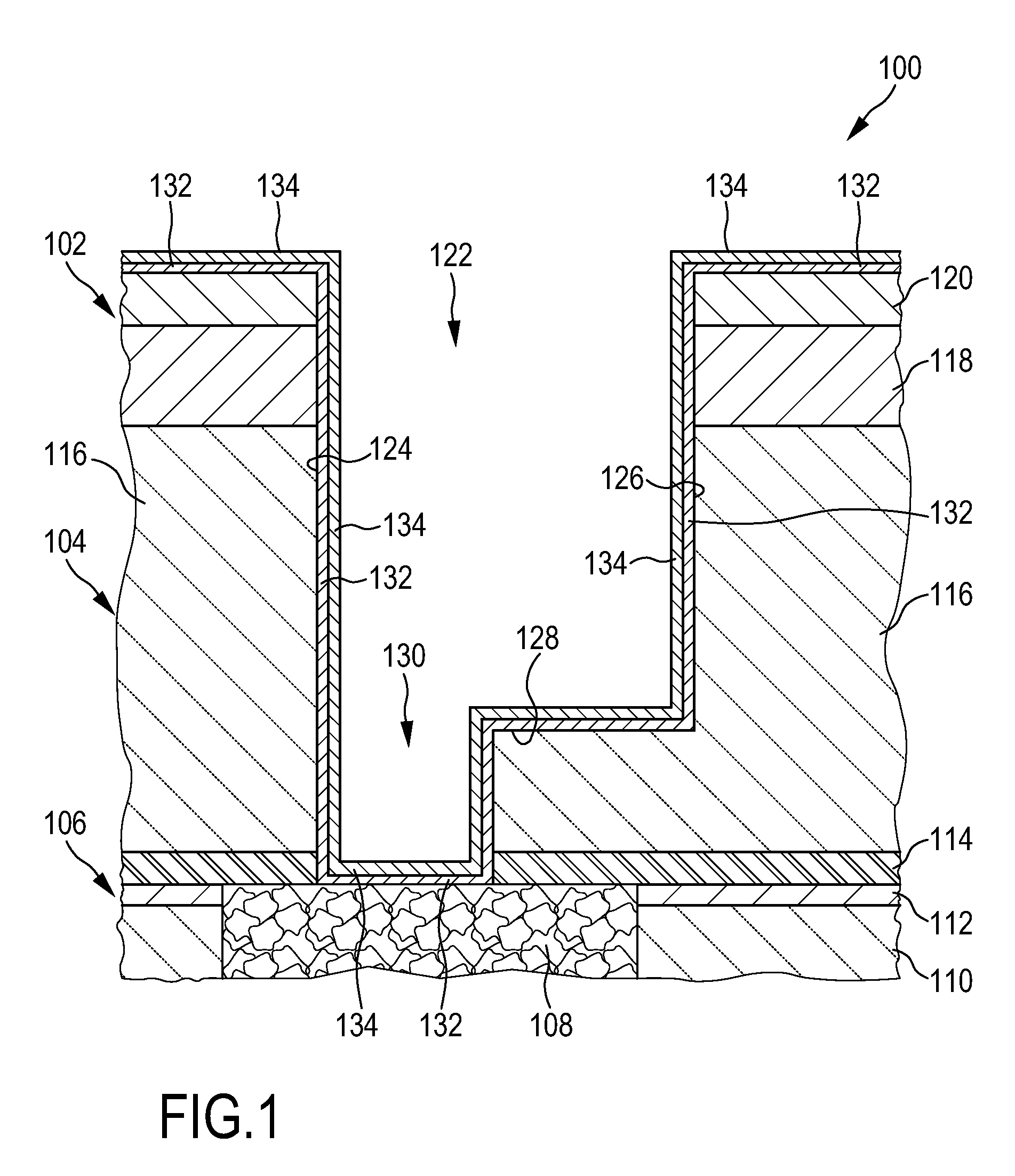

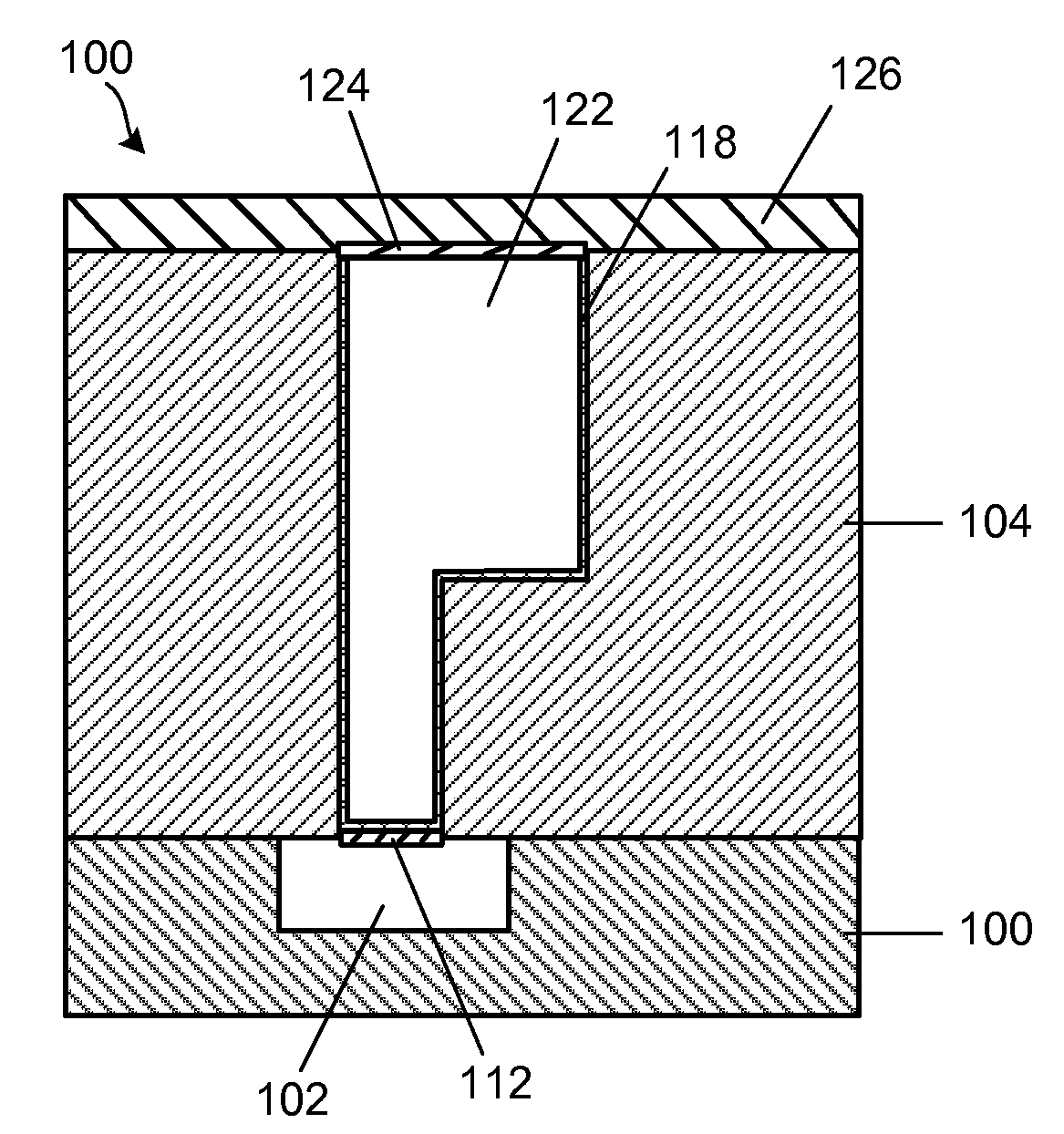

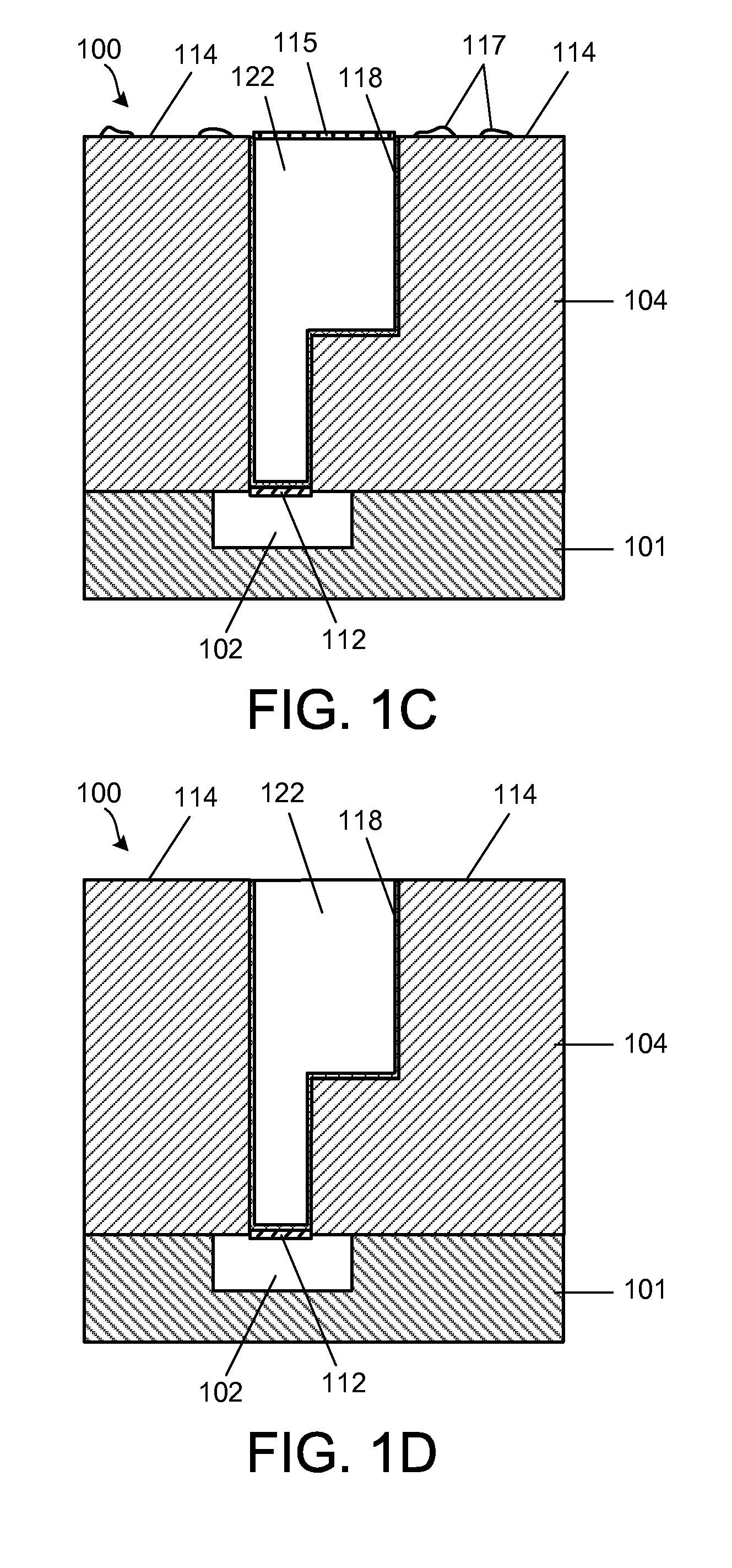

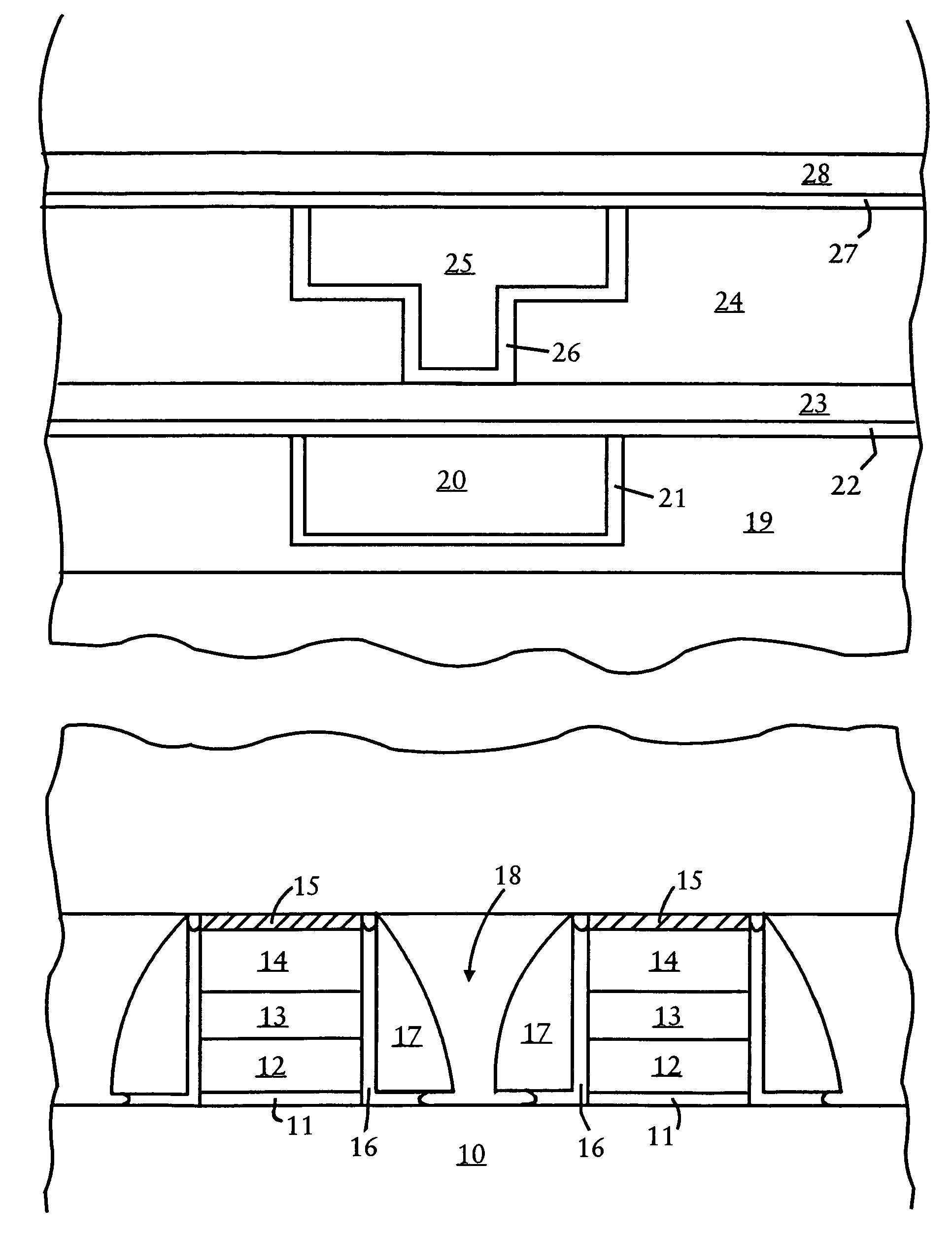

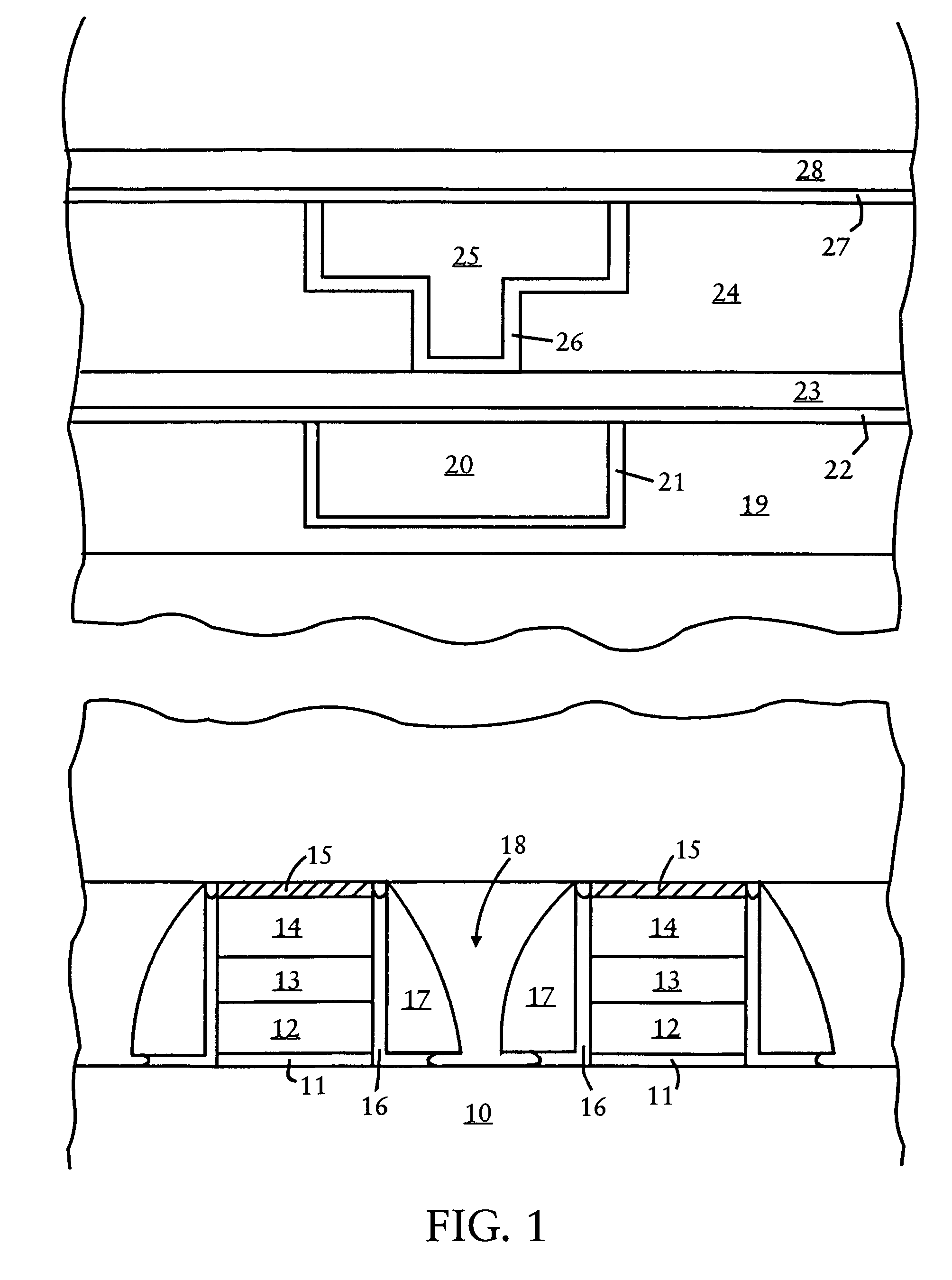

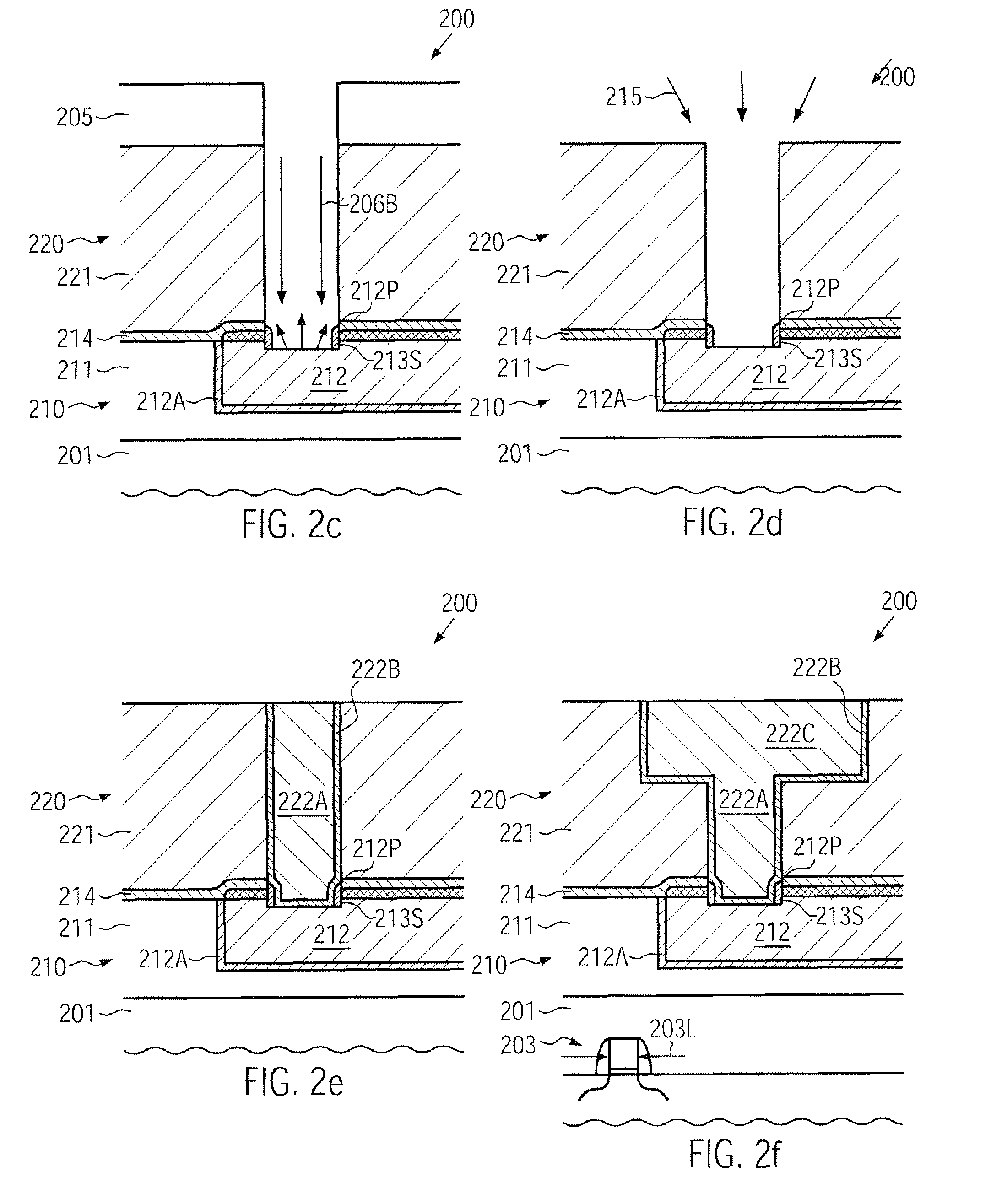

Composite tantalum capped inlaid copper with reduced electromigration and reduced stress migration

ActiveUS7071564B1Reduced via resistanceImprove electromigrationSemiconductor/solid-state device detailsSolid-state devicesTantalum nitrideDielectric layer

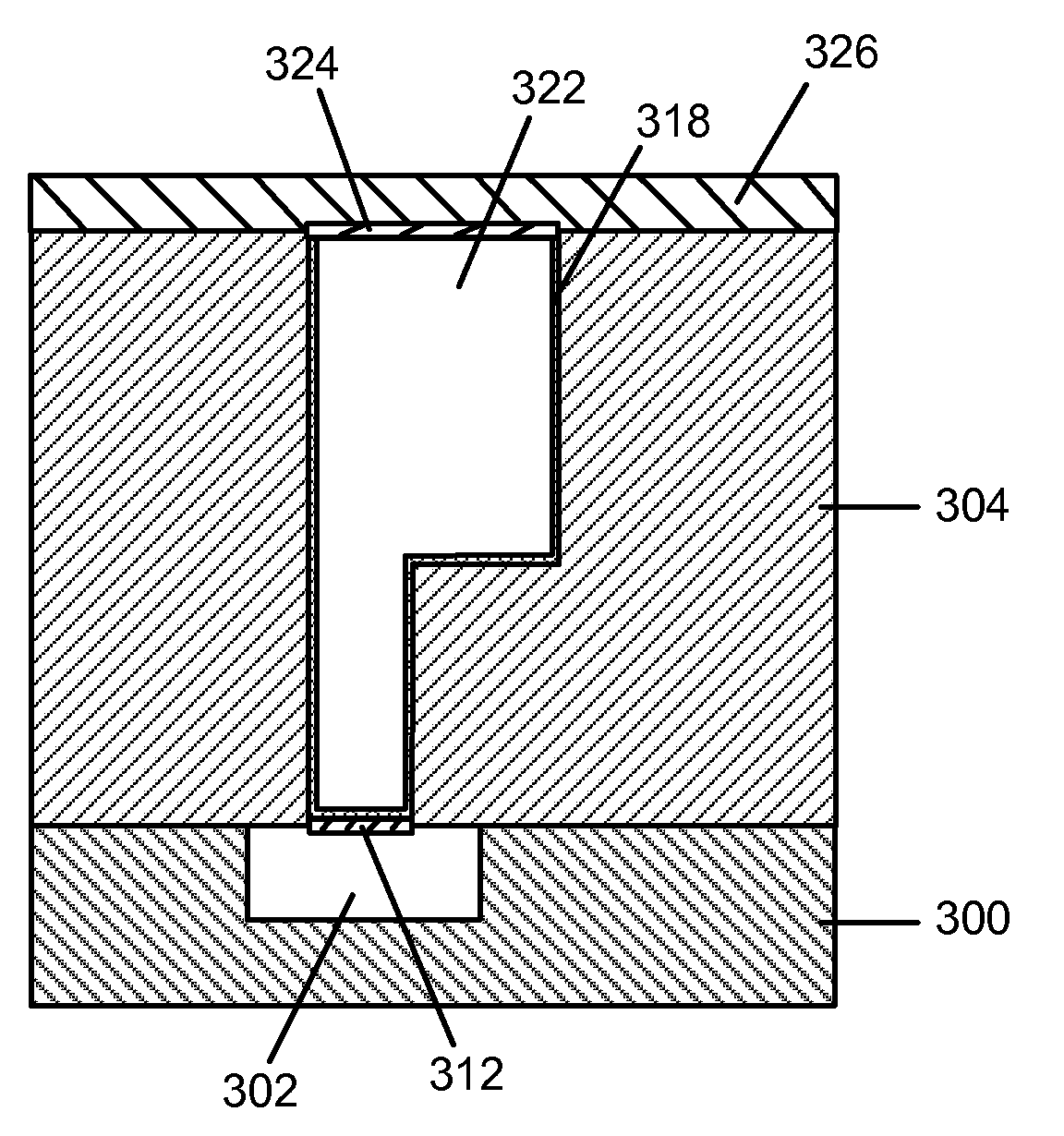

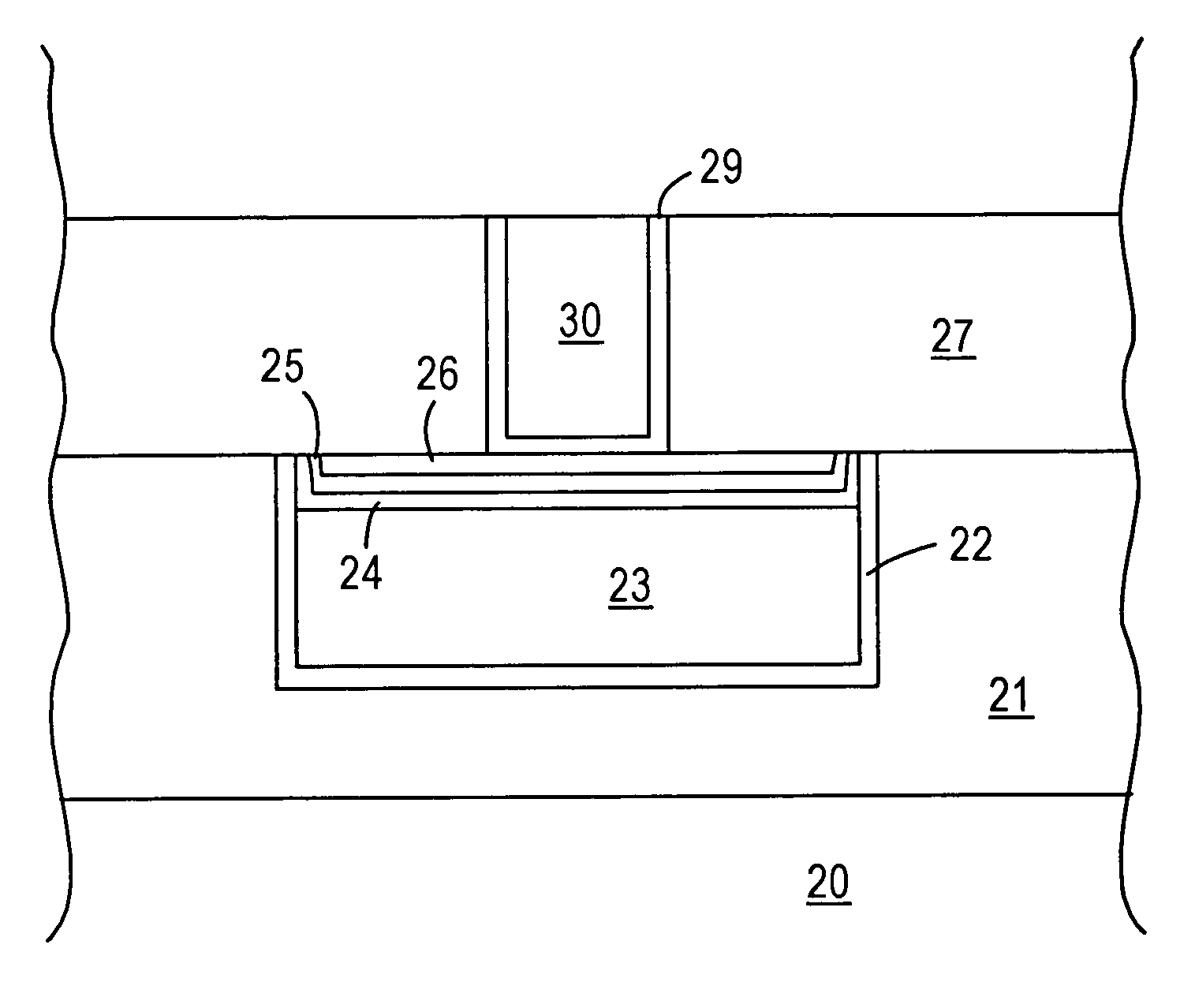

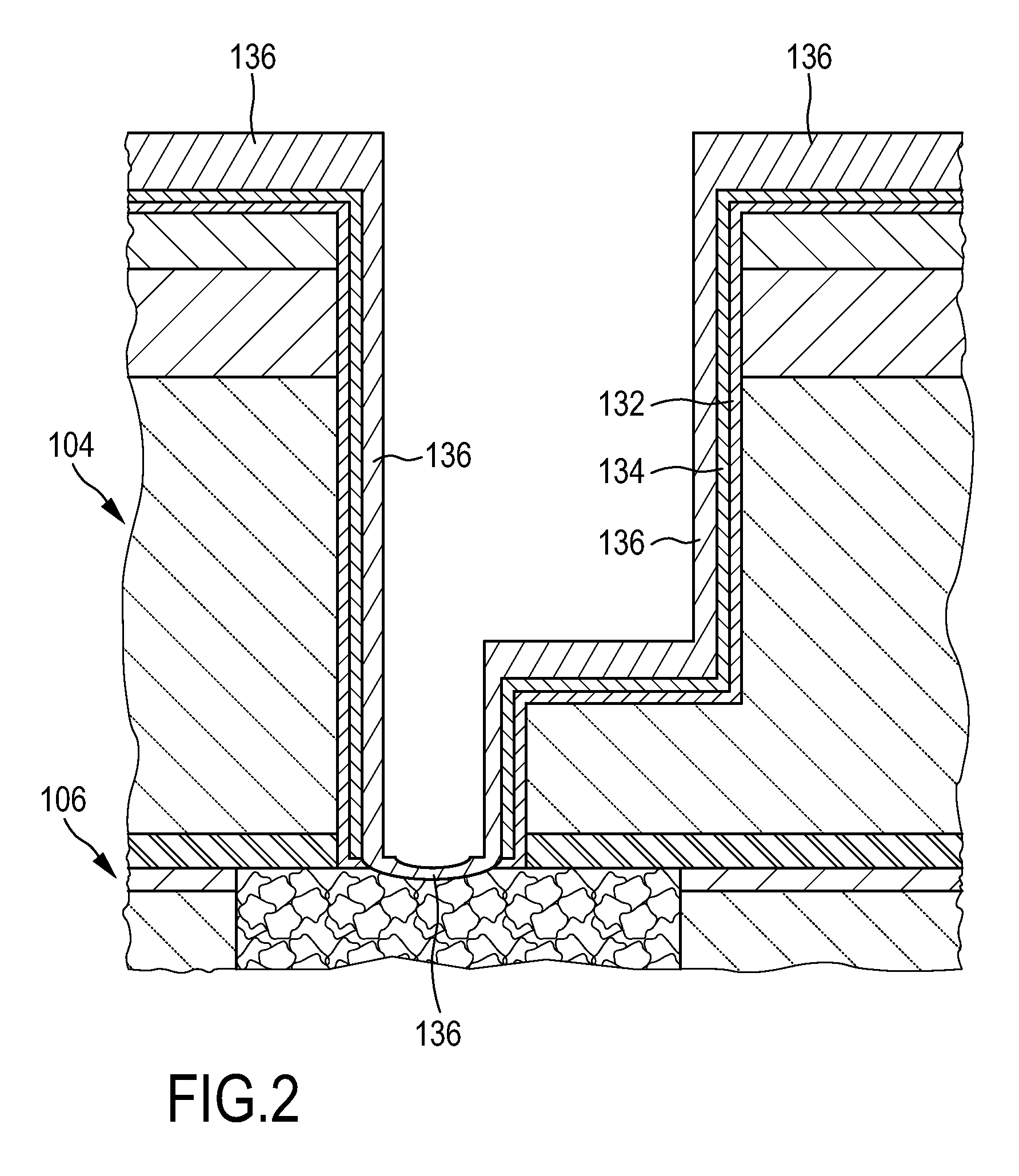

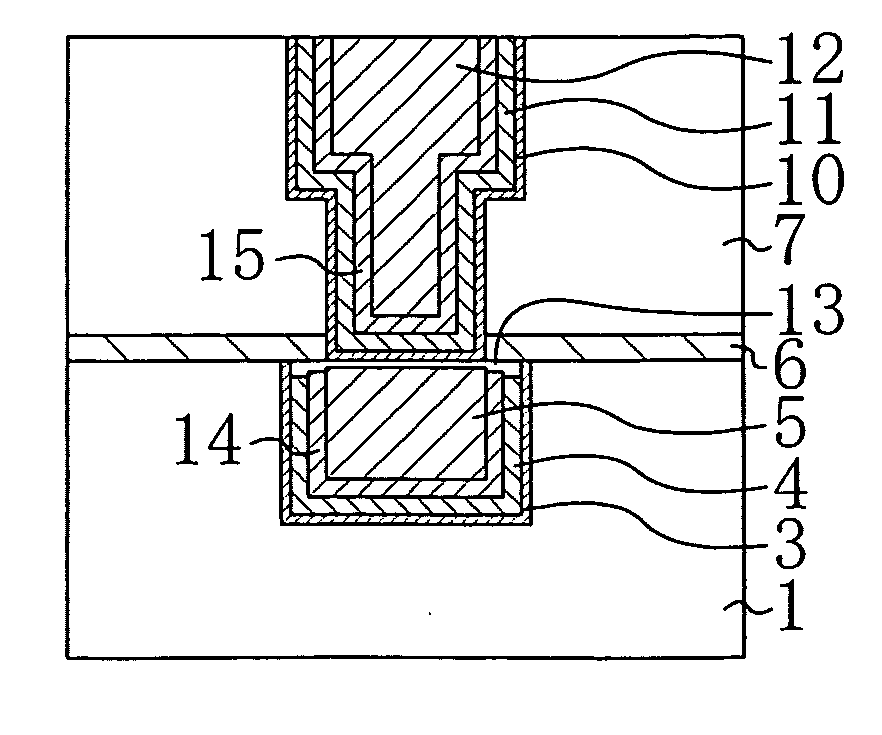

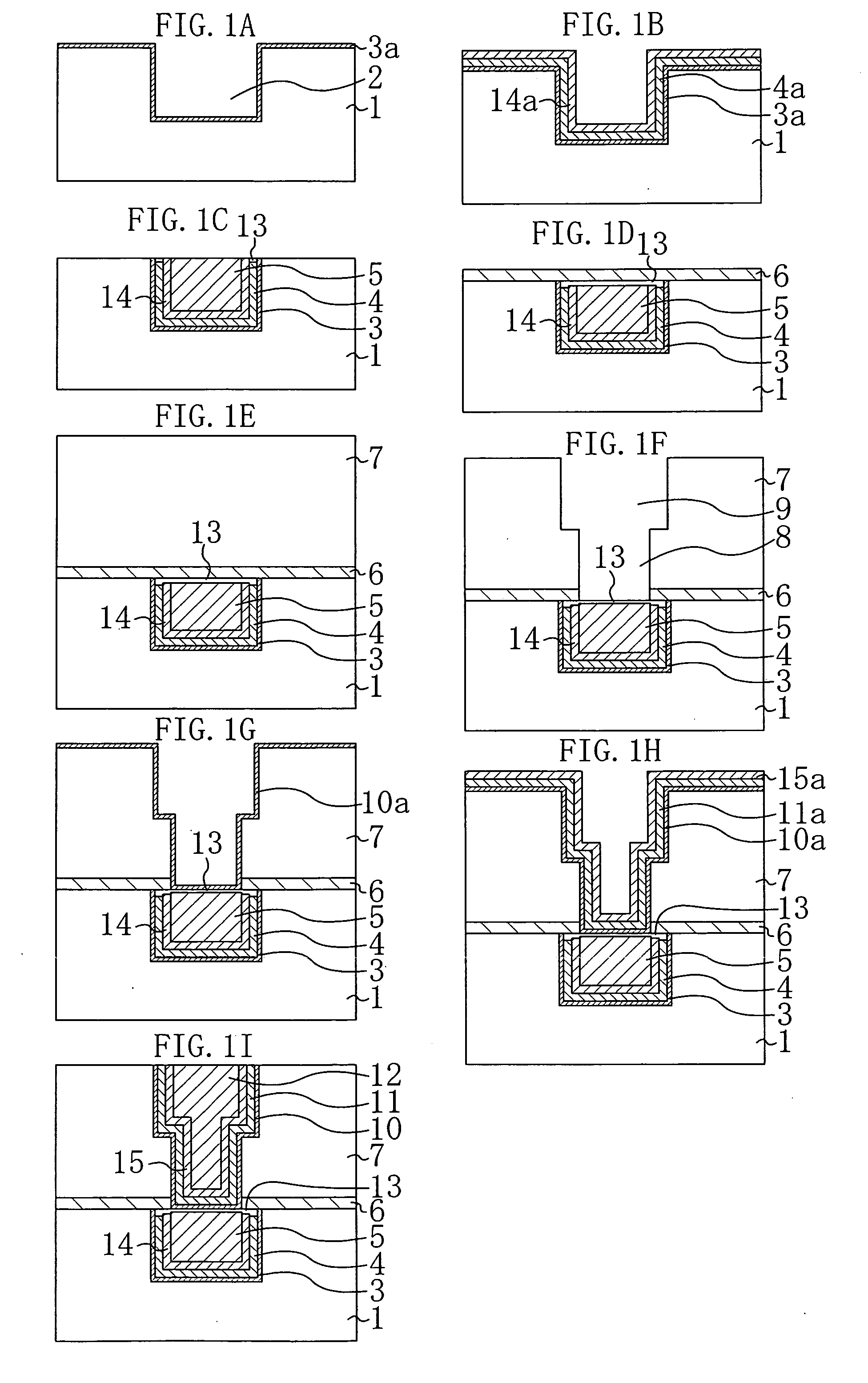

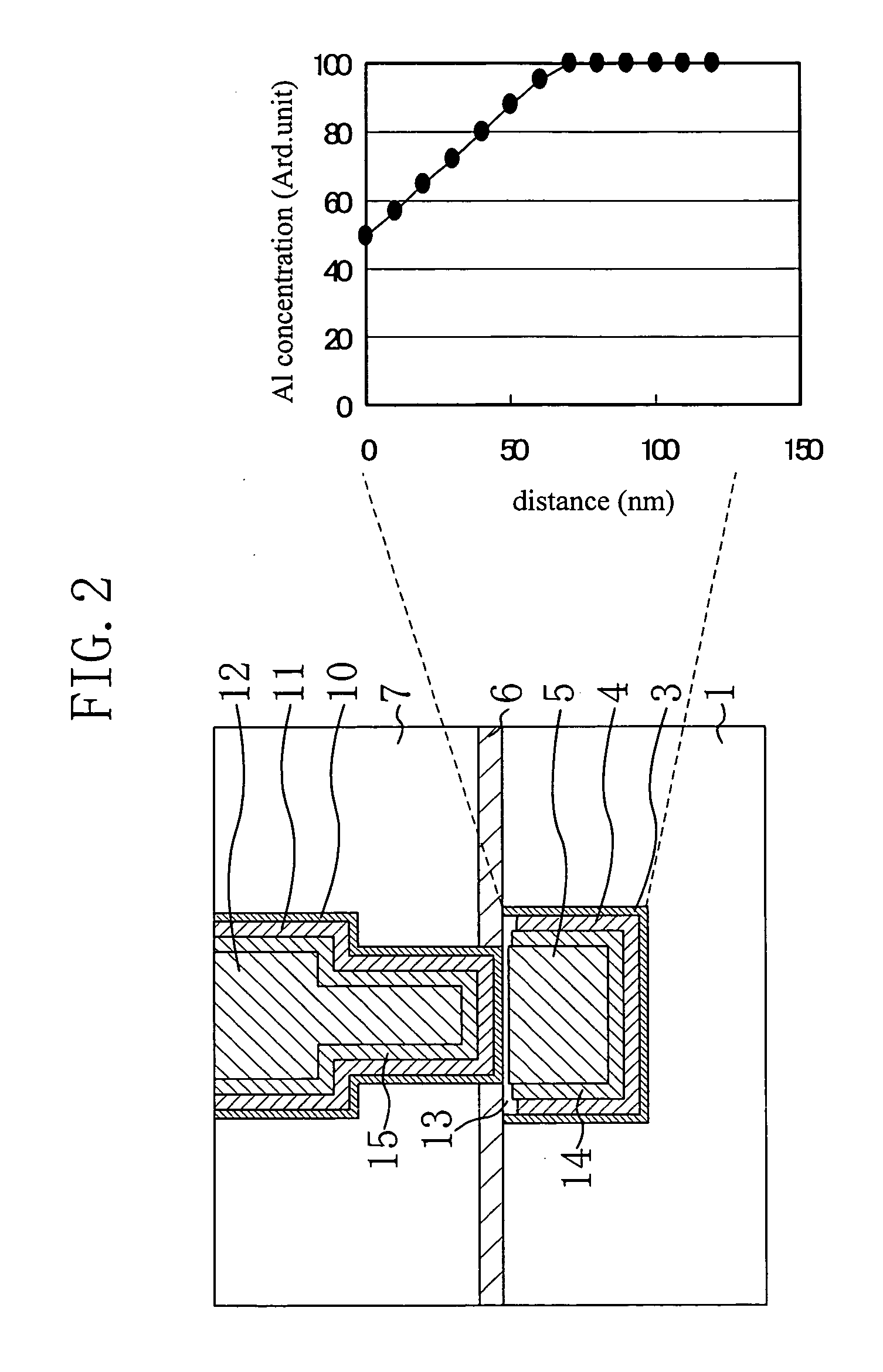

The electromigration and stress migration of Cu interconnects is significantly reduced by forming a composite capping layer comprising a layer of β-Ta on the upper surface of the inlaid Cu, a layer of tantalum nitride on the β-Ta layer and a layer of α-Ta on the tantalum nitride layer. Embodiments include forming a recess in an upper surface of Cu inlaid in a dielectric layer, depositing a layer of β-Ta at a thickness of 25 Å to 40 Å, depositing a layer of tantalum nitride at a thickness of 20 Å to 100 Å and then depositing a layer of α-Ta at a thickness of 200 Å to 500 Å. Embodiments further include forming an overlying dielectric layer, forming an opening therein, e.g., a via opening or a dual damascene opening, lining the opening with α-Ta, and filling the opening with Cu in electrical contact with the underlying inlaid Cu.

Owner:GLOBALFOUNDRIES US INC

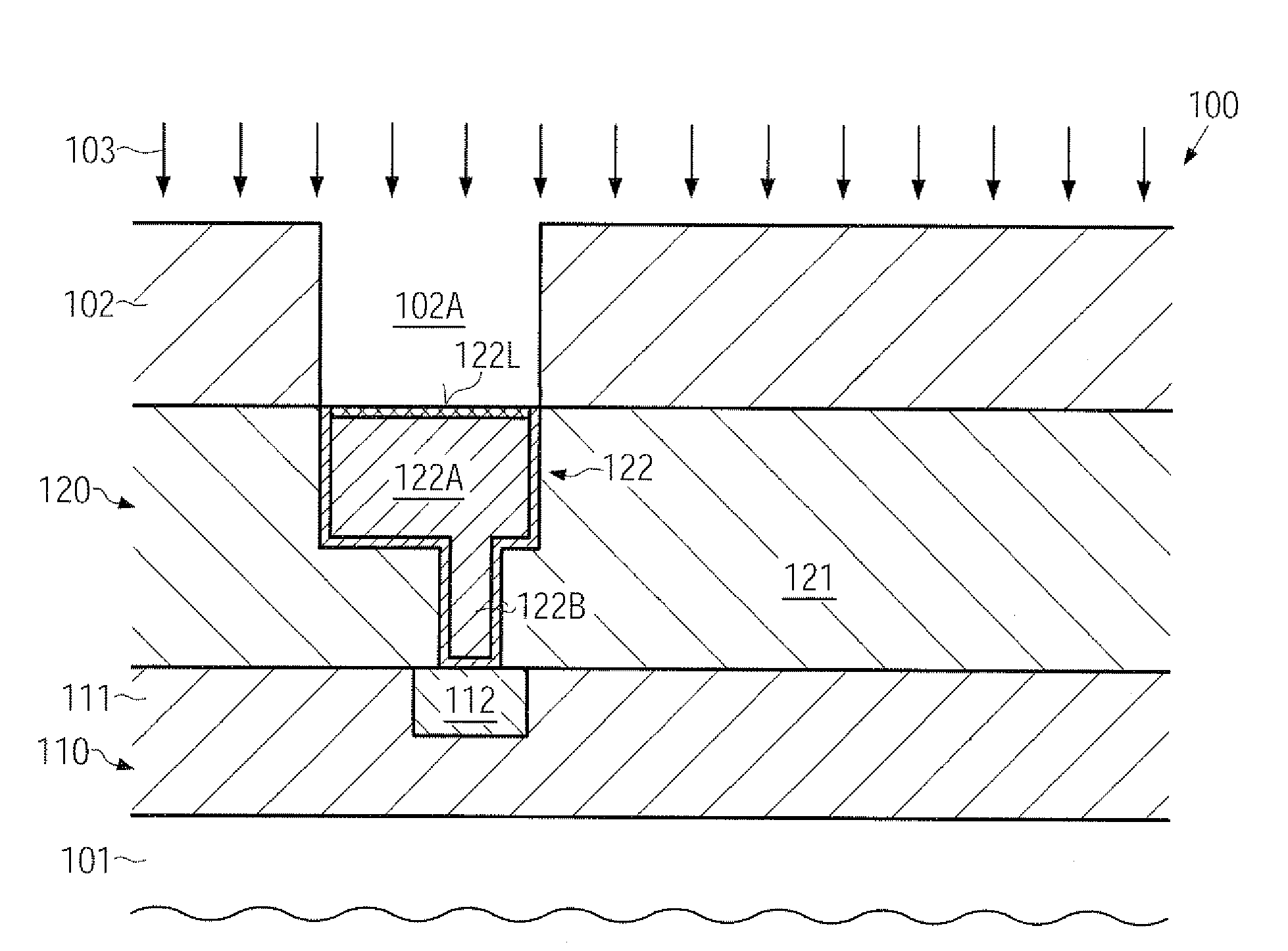

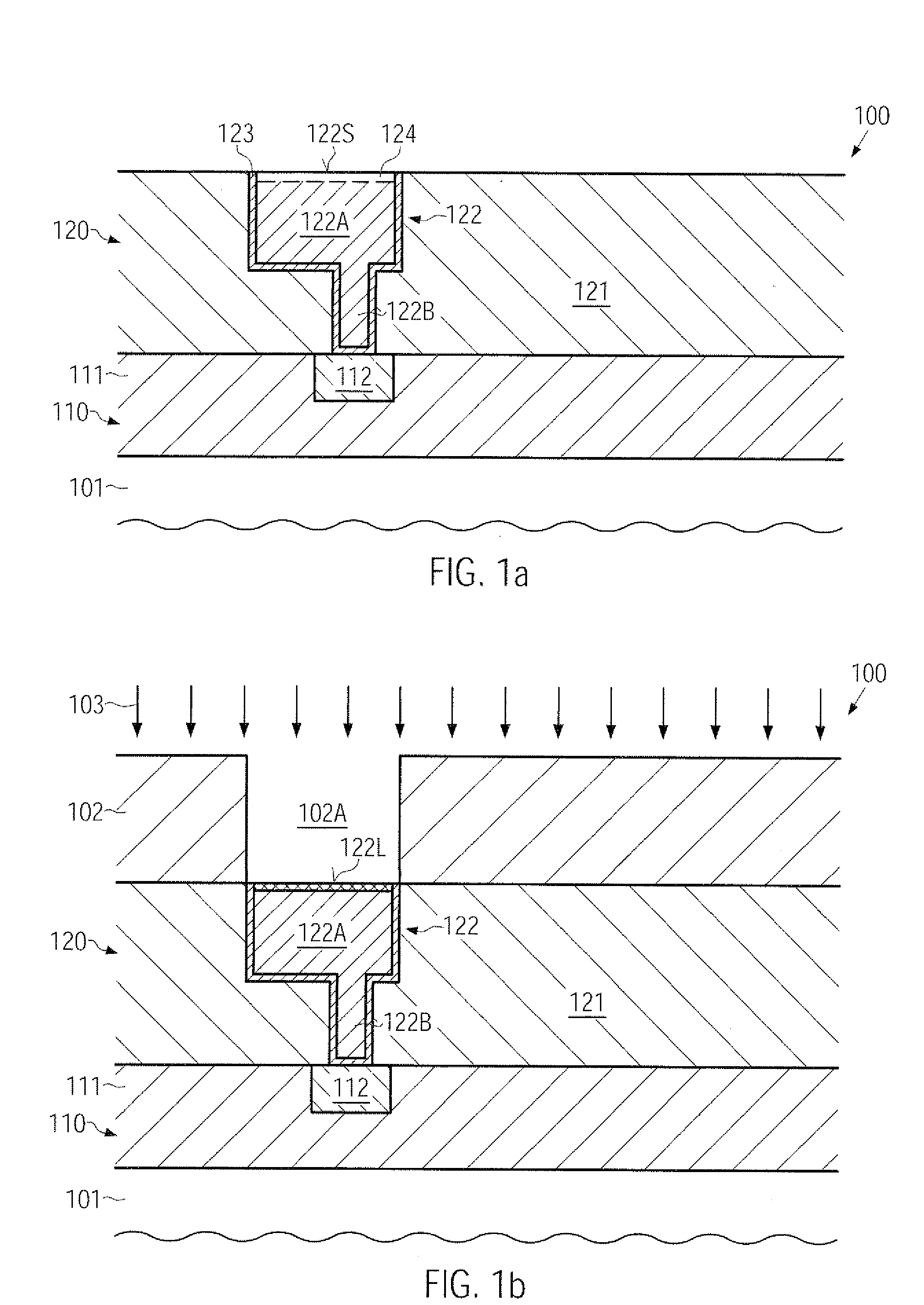

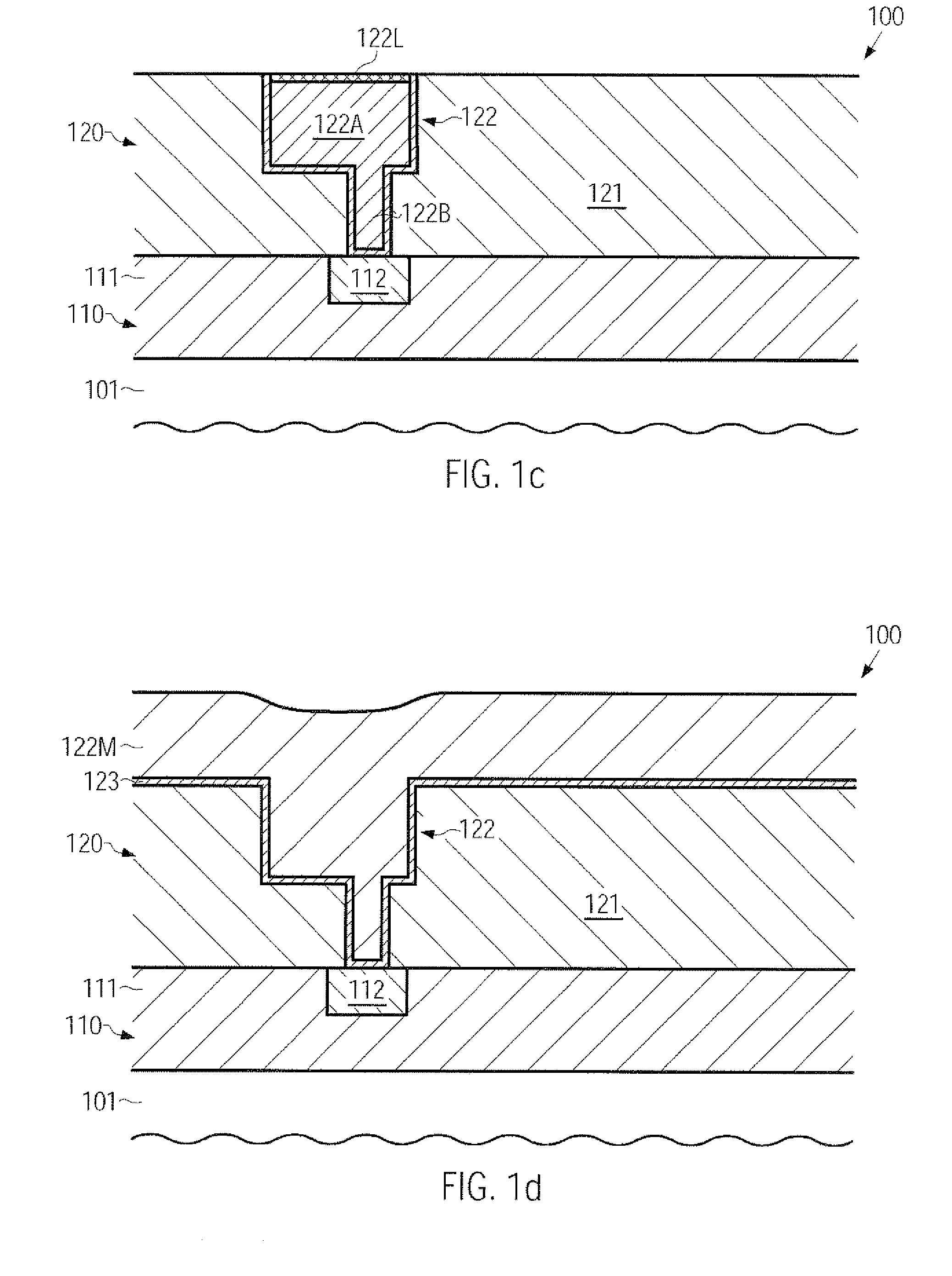

Method for integrating selective ruthenium deposition into manufacturing of a semiconductior device

ActiveUS20090065939A1Improve electromigrationImprove stress migrationSemiconductor/solid-state device detailsSolid-state devicesMetal depositionSemiconductor

Owner:TOKYO ELECTRON LTD

Method for forming ruthenium metal cap layers

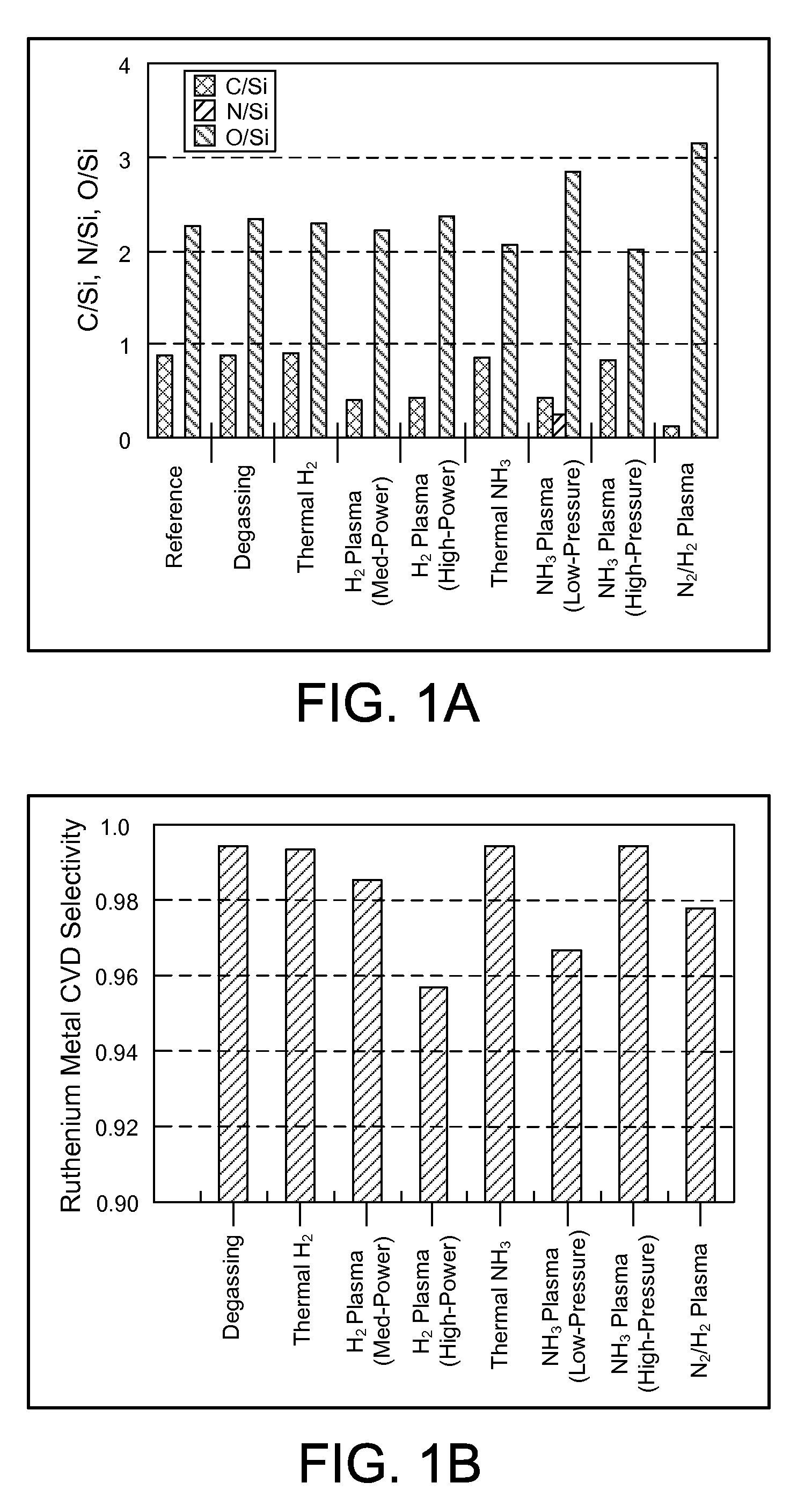

InactiveUS20100081274A1Improve electromigrationImprove stress migrationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingMetallurgyRuthenium

A method is provided for integrating ruthenium (Ru) metal deposition into manufacturing of semiconductor devices to improve electromigration and stress migration in copper (Cu) metal. Embodiments of the invention include treating patterned substrates containing metal layers and low-k dielectric materials with NHx (x≦3) radicals and H radicals to improve selective formation of ruthenium (Ru) metal cap layers on the metal layers relative to the low-k dielectric materials.

Owner:TOKYO ELECTRON LTD

Increasing electromigration resistance in an interconnect structure of a semiconductor device by forming an alloy

InactiveUS20090197408A1Improve electromigrationReduce riskSemiconductor/solid-state device manufacturingAlloyCopper

By introducing a metallic species into an exposed surface area of a copper region, the electromigration behavior of this surface area may be significantly enhanced. The incorporation of the metallic species may be accomplished in a highly selective manner so as to not unduly affect dielectric material positioned adjacent to the metal region, thereby essentially avoiding undue increase of leakage currents.

Owner:GLOBALFOUNDRIES INC

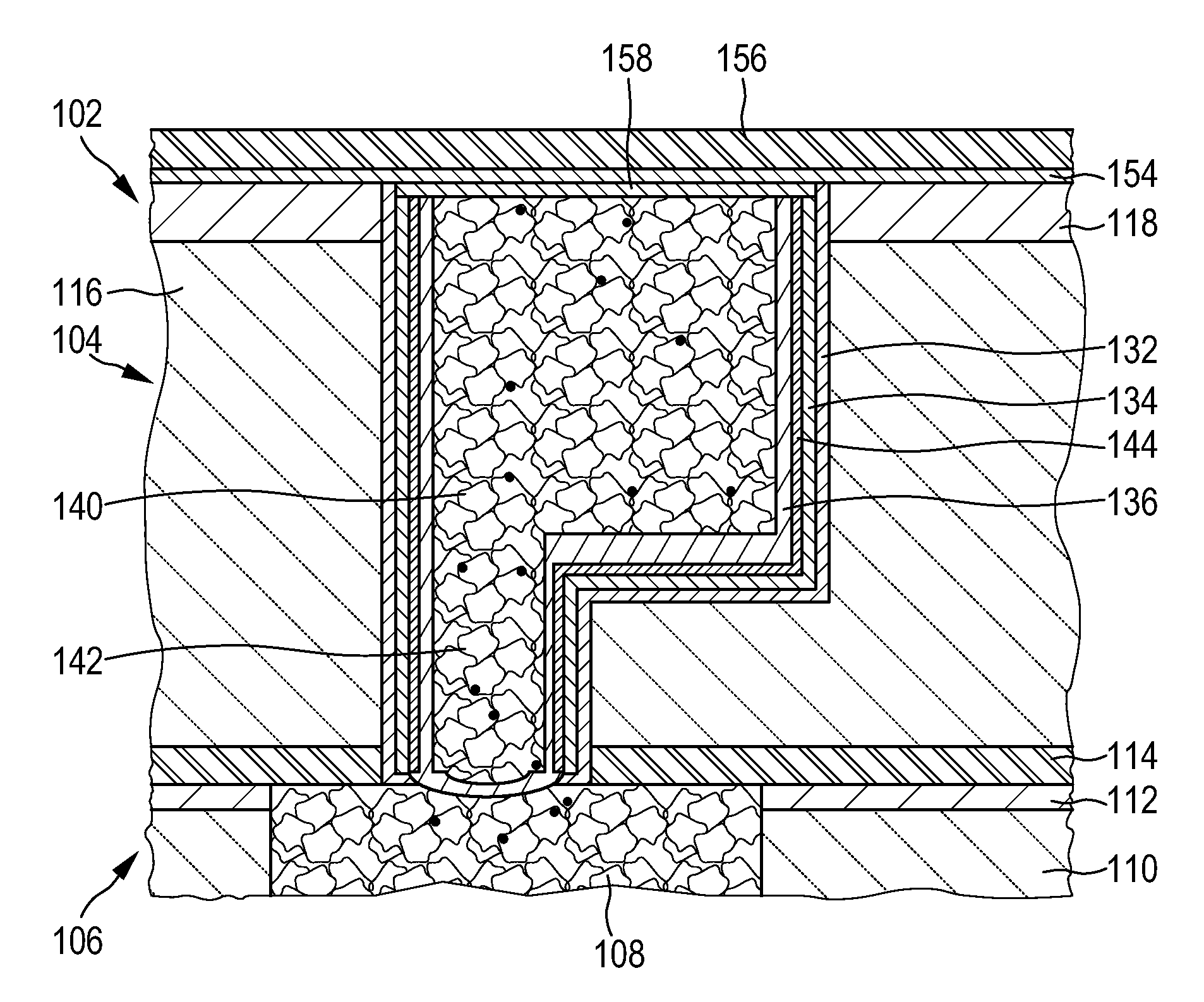

CuSiN/SiN DIFFUSION BARRIER FOR COPPER IN INTEGRATED-CIRCUIT DEVICES

ActiveUS20090273085A1High CMP-selectivityReduce surface roughnessSemiconductor/solid-state device detailsSolid-state devicesState of artCopper

The present invention relates to an integrated-circuit device that has at least one Copper-containing feature in a dielectric layer, and a diffusion-barrier layer stack arranged between the feature and the dielectric layer. The integrated-circuit device of the invention has a diffusion-barrier layer stack, which comprises, in a direction from the Copper-containing feature to the dielectric layer, a CuSiN layer and a SiN layer. This layer combination provides an efficient barrier for suppressing Copper diffusion from the feature into the dielectric layer. Furthermore, a CuSiN / SiN layer sequence provides an improved adhesion between the layers of the diffusion-barrier layer stack and the dielectric layer, and thus improves the electromigration performance of the integrated-circuit device during operation. Therefore, the reliability of device operation and the lifetime of the integrate-circuit device are improved in comparison with prior-art devices. The invention further relates to a method for fabricating such an integrated-circuit device.

Owner:NXP BV

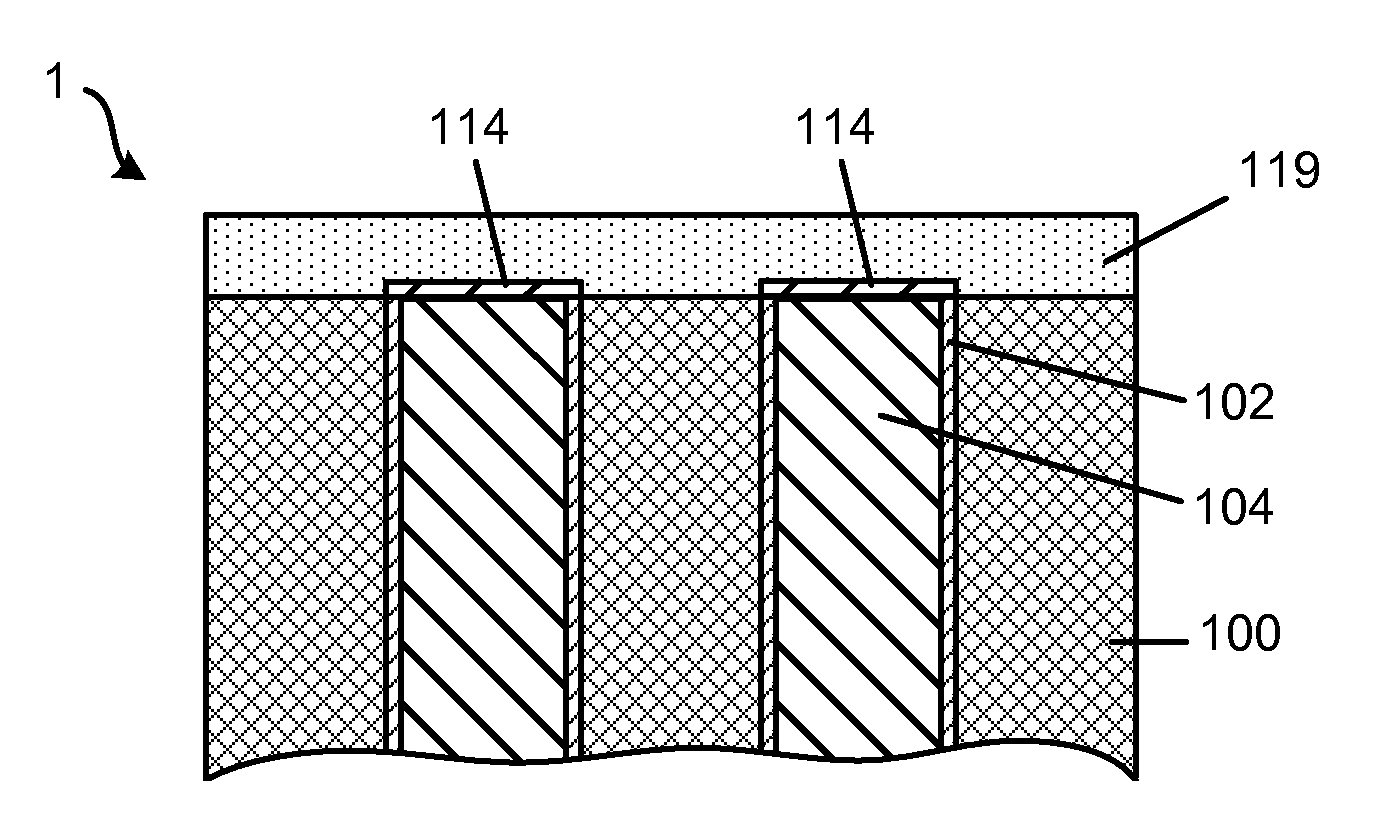

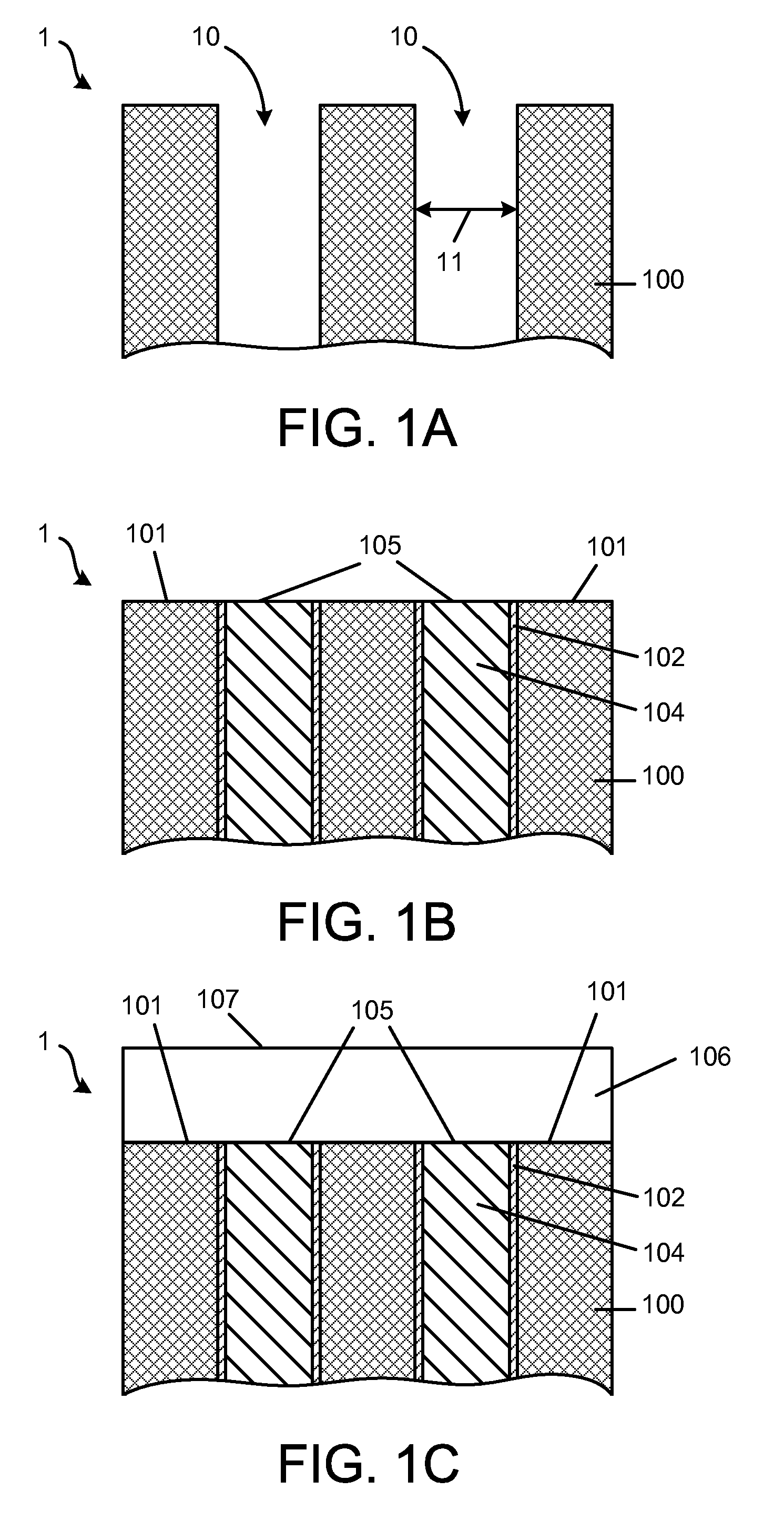

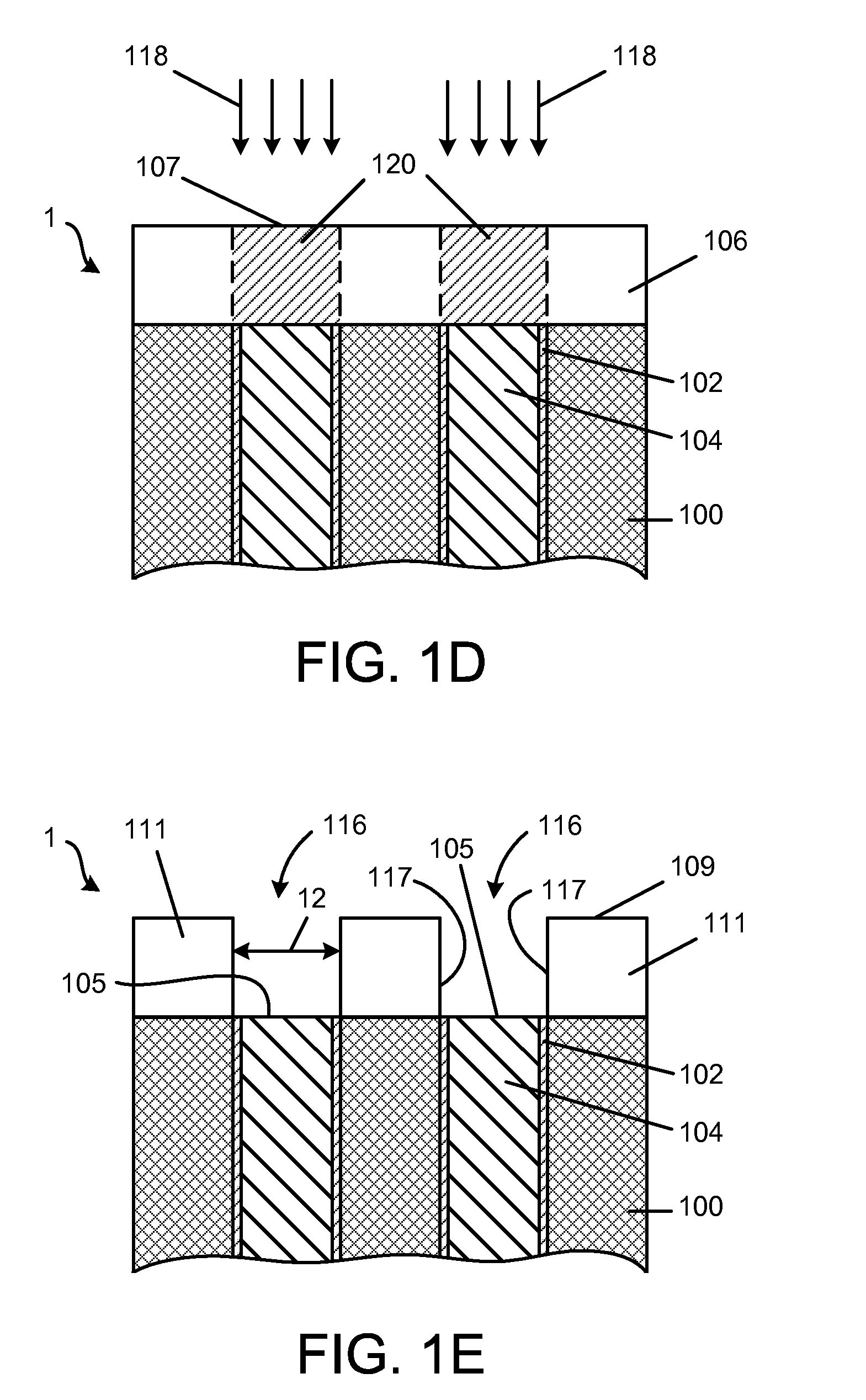

Selective thin metal cap process

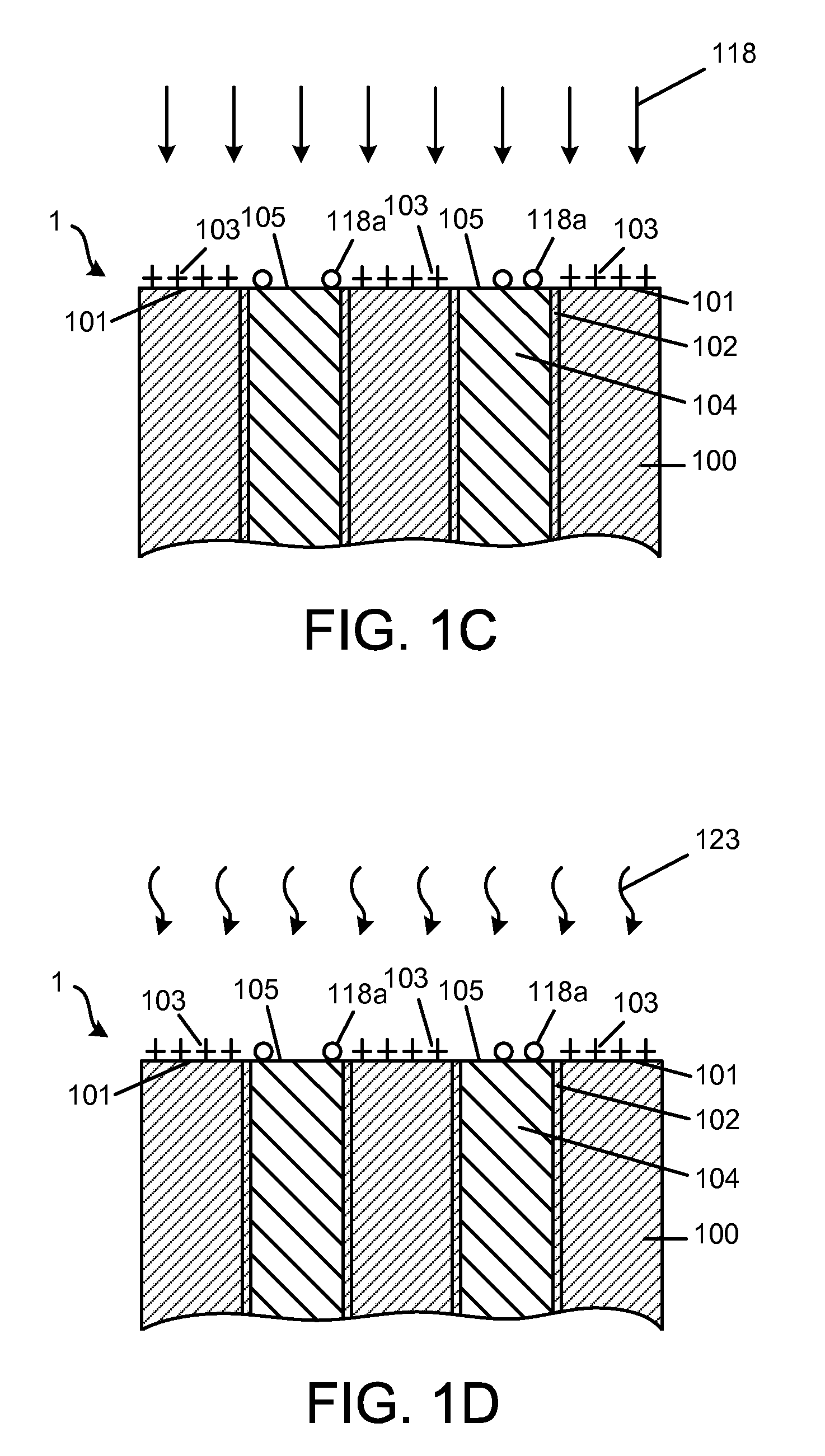

ActiveUS20090053890A1Electrical conductivity of the wiring material becomes increasingly more importantGood conductorSemiconductor/solid-state device manufacturingThin metalResist

A method of creating metal caps on copper lines within an inter-line dielectric (ILD) deposits a thin (e.g., 5 nm) metal blanket film (e.g., Ta / TaN) on top the copper lines and dielectric, after the wafer has been planarized. Further a thin dielectric cap is formed over the metal blanket film. A photoresist coating is deposited over the thin dielectric cap and a lithographic exposure process is performed, but without a lithographic mask. A mask is not needed in this situation, because due to the reflectivity difference between copper and the ILD lying under the two thin layers, a mask pattern is automatically formed for etching away the Ta / TaN metal cap between copper lines. Thus, this mask pattern is self-aligned above the copper lines.

Owner:TAIWAN SEMICON MFG CO LTD

CuSiN/SiN diffusion barrier for copper in integrated-circuit devices

ActiveUS8072075B2Strong interfaceImprove adhesionSemiconductor/solid-state device detailsSolid-state devicesDiffusion barrierMaterials science

The present invention relates to an integrated-circuit device that has at least one Copper-containing feature in a dielectric layer, and a diffusion-barrier layer stack arranged between the feature and the dielectric layer. The integrated-circuit device of the invention has a diffusion-barrier layer stack, which comprises, in a direction from the Copper-containing feature to the dielectric layer, a CuSiN layer and a SiN layer. This layer combination provides an efficient barrier for suppressing Copper diffusion from the feature into the dielectric layer. Furthermore, a CuSiN / SiN layer sequence provides an improved adhesion between the layers of the diffusion-barrier layer stack and the dielectric layer, and thus improves the electromigration performance of the integrated-circuit device during operation. Therefore, the reliability of device operation and the lifetime of the integrate-circuit device are improved in comparison with prior-art devices. The invention further relates to a method for fabricating such an integrated-circuit device.

Owner:NXP BV

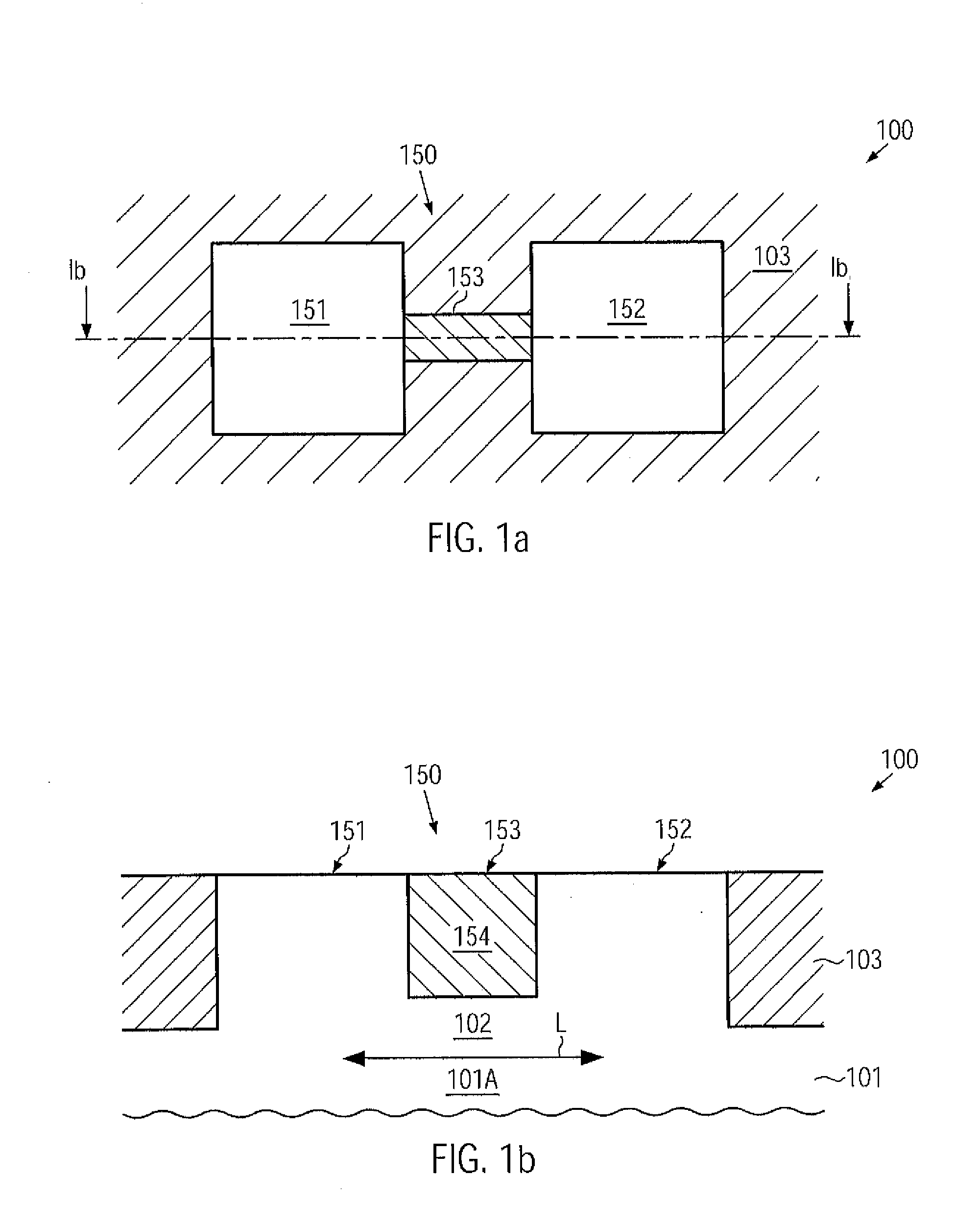

SELF-ALIGNED COMPOSITE M-MOx/DIELECTRIC CAP FOR Cu INTERCONNECT STRUCTURES

ActiveUS20110162874A1Improve electromigrationReducing metal cap thicknessSemiconductor/solid-state device detailsSolid-state devicesDielectricCopper oxide

An interconnect structure is provided that has improved electromigration resistance as well as methods of forming such an interconnect structure. The interconnect structure includes an interconnect dielectric material having a dielectric constant of about 4.0 or less. The interconnect dielectric material has at least one opening therein that is filled with a Cu-containing material. The Cu-containing material within the at least one opening has an exposed upper surface that is co-planar with an upper surface of the interconnect dielectric material. The interconnect structure further includes a composite M-MOx cap located at least on the upper surface of the Cu-containing material within the at least one opening. The composite M-MOx cap includes an upper region that is composed of the metal having a higher affinity for oxygen than copper and copper oxide and a lower region that is composed of a non-stoichiometric oxide of said metal. The interconnect structure further includes a dielectric cap located on at least an upper surface of the composite M-MOx cap.

Owner:AURIGA INNOVATIONS INC

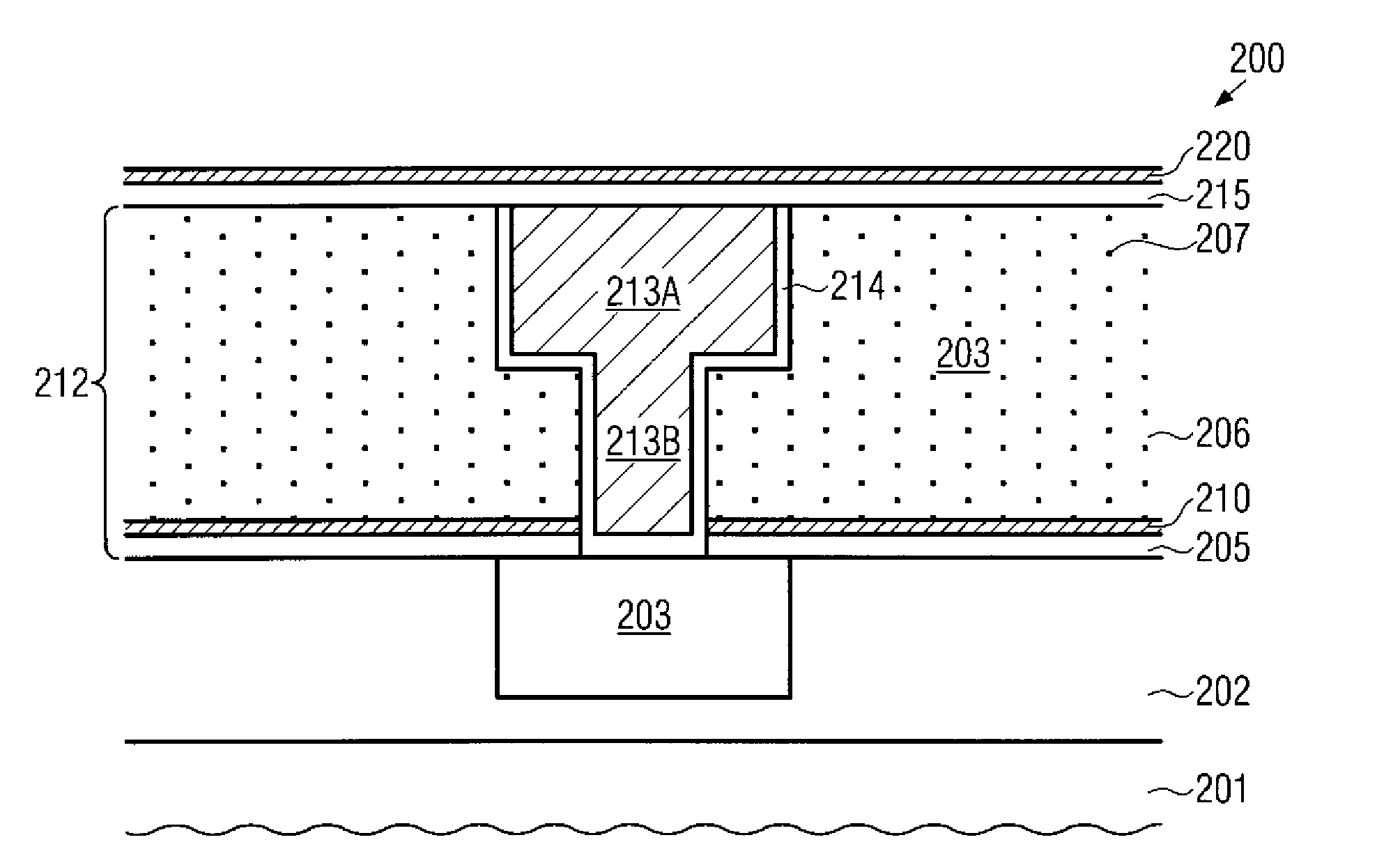

Semiconductor device including a porous low-k material layer stack with reduced UV sensitivity

InactiveUS20080099918A1High porosityImprove mechanical stabilitySemiconductor/solid-state device detailsSolid-state devicesLayer thicknessVanadium oxide

By forming a cap layer on a dielectric barrier layer of a low-k dielectric material stack, the interaction of UV radiation during the generation of pores in the low-k dielectric material may be significantly reduced. In some illustrative embodiments, the cap layer may comprise titanium oxide and / or vanadium oxide which may provide a high degree of reflectivity and absorption, respectively. The layer thickness of the cap layer may be 10 nm or significantly less, thereby reducing any adverse influence on the overall performance of the resulting layer stack.

Owner:GLOBALFOUNDRIES INC

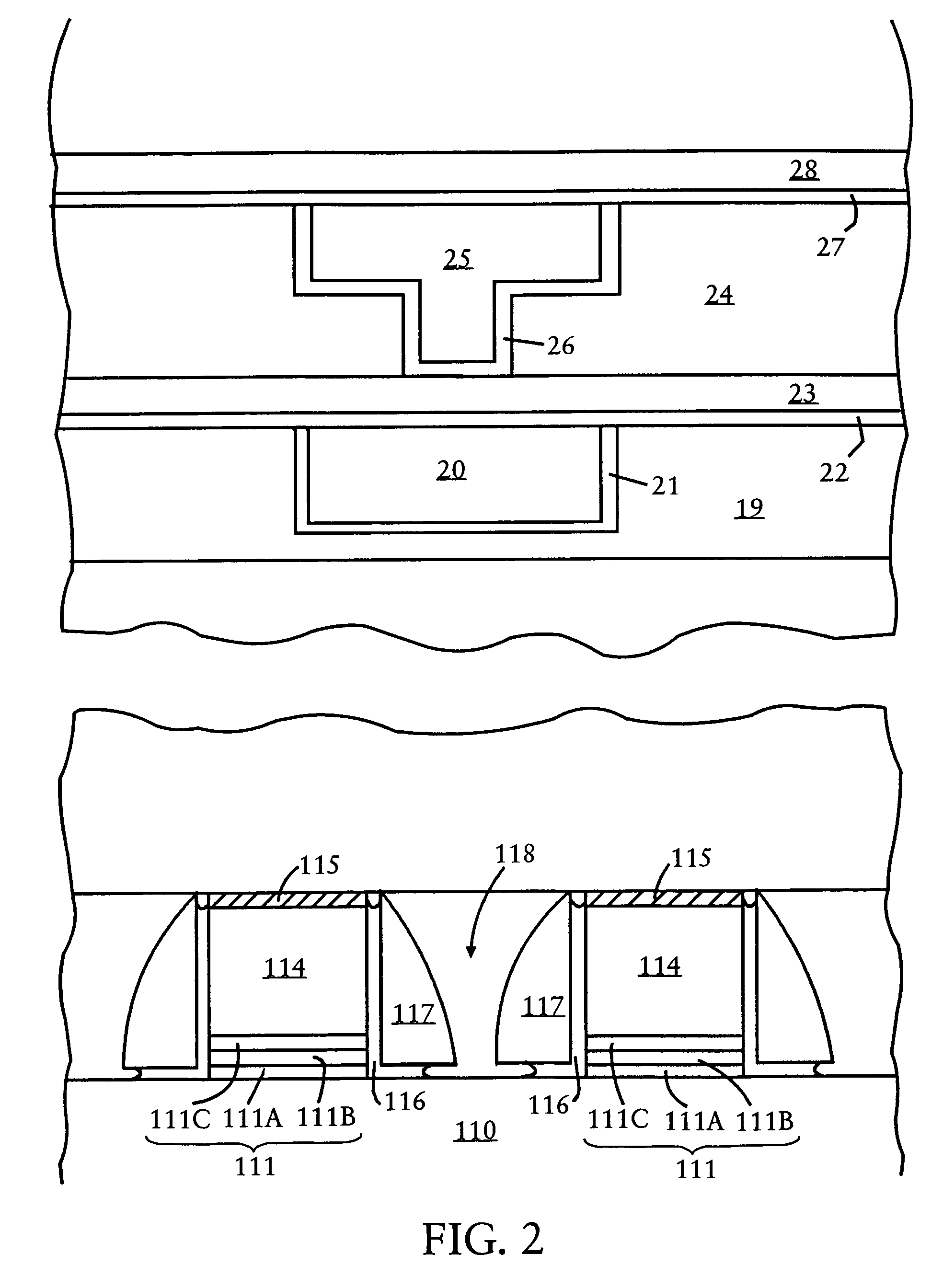

Method for forming cobalt nitride cap layers

ActiveUS20100081275A1Improve electromigrationImprove stress migrationSemiconductor/solid-state device detailsSolid-state devicesCobalt metalDevice material

A method is provided for integrating cobalt nitride cap layers into manufacturing of semiconductor devices to improve electromigration and stress migration in copper (Cu) metal. One embodiment includes providing a patterned substrate containing a recessed feature formed in a low-k material and a first metallization layer at the bottom of the feature, forming a cobalt nitride cap layer on the first metallization layer, depositing a barrier layer in the recessed feature, including on the low-k dielectric material and on the first cobalt metal cap layer, and filling the recessed feature with Cu metal. Another embodiment includes providing a patterned substrate having a substantially planar surface with Cu paths and low-k dielectric regions, and selectively forming a cobalt nitride cap layer on the Cu paths relative to the low-k dielectric regions.

Owner:TOKYO ELECTRON LTD

Device interconnection

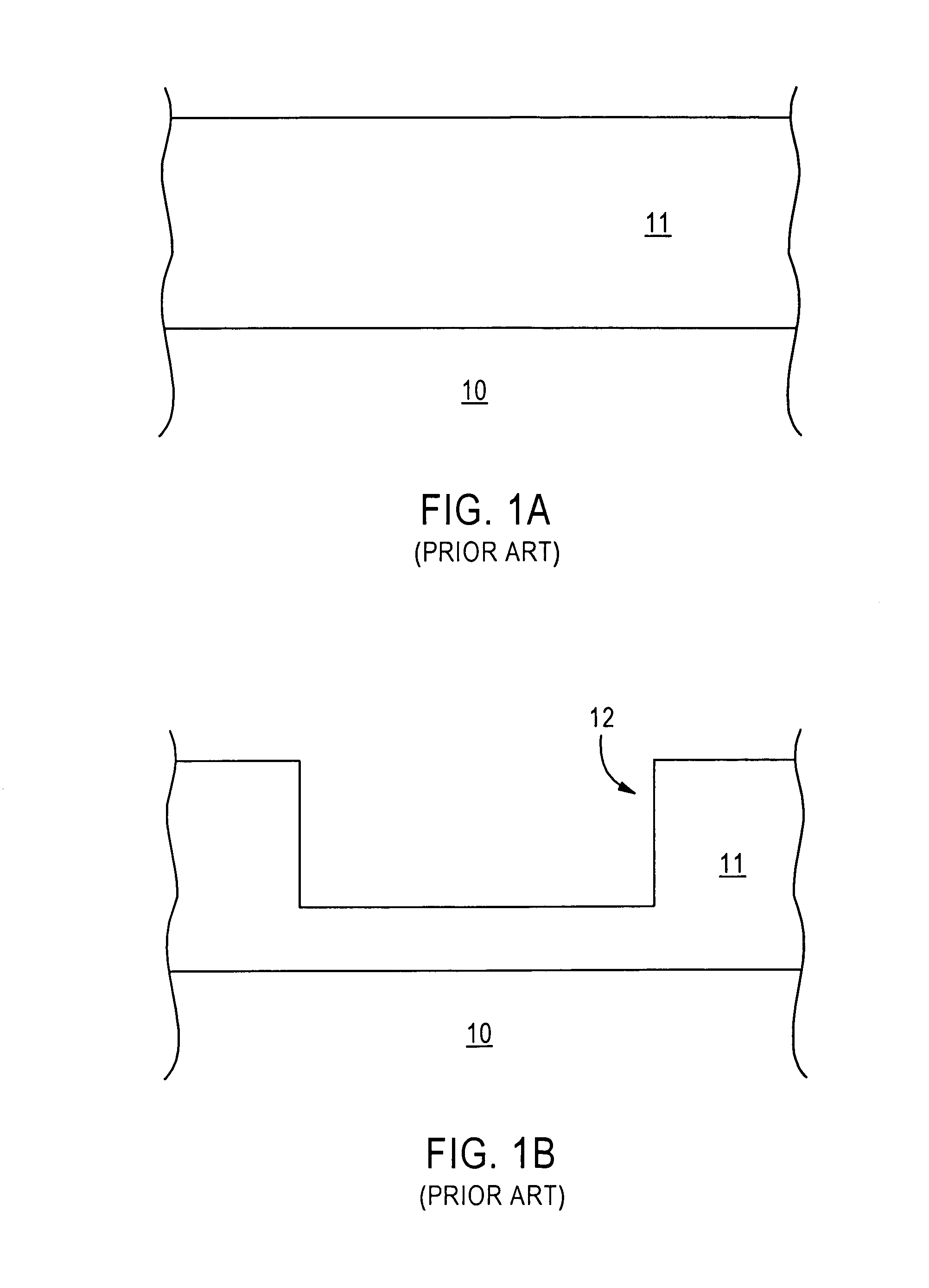

InactiveUS6870263B1Improve reliabilityImprove electromigrationSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorInterconnection

A conductor for interconnecting integrated circuit components having improved reliability. The conductor includes a liner surrounding at least three surfaces of the conductor, producing a low textured conductor. It has been found that low textured conductor results in improved electromigration lifetime.

Owner:IBM CORP +1

Copper Sputtering Target With Fine Grain Size And High Electromigration Resistance And Methods Of Making the Same

InactiveUS20100000860A1Increase thermal stability and electromigration resistanceImprove adhesive capabilityCellsVacuum evaporation coatingAlloy elementCrystallite

The present invention generally provides a sputtering target comprising copper and a total of 0.001 wt %˜10 wt % alloying element or elements chosen from the group consisting of Al, Ag, Co, Cr, Ir, Fe, Mo, Ti, Pd, Ru, Ta, Sc, Hf, Zr, V, Nb, Y, and rare earth metals. An exemplary copper sputtering containing 0.5 wt % aluminum has superfine grain size, high thermal stability, and high electromigration resistance, and is able to form films with desired film uniformity, excellent resistance to electromigration and oxidation, and high adhesion to dielectric interlayer. An exemplary copper sputtering containing 12 ppm silver has superfine grain size. This invention also provides methods of manufacturing copper sputtering targets.

Owner:TOSOH SMD

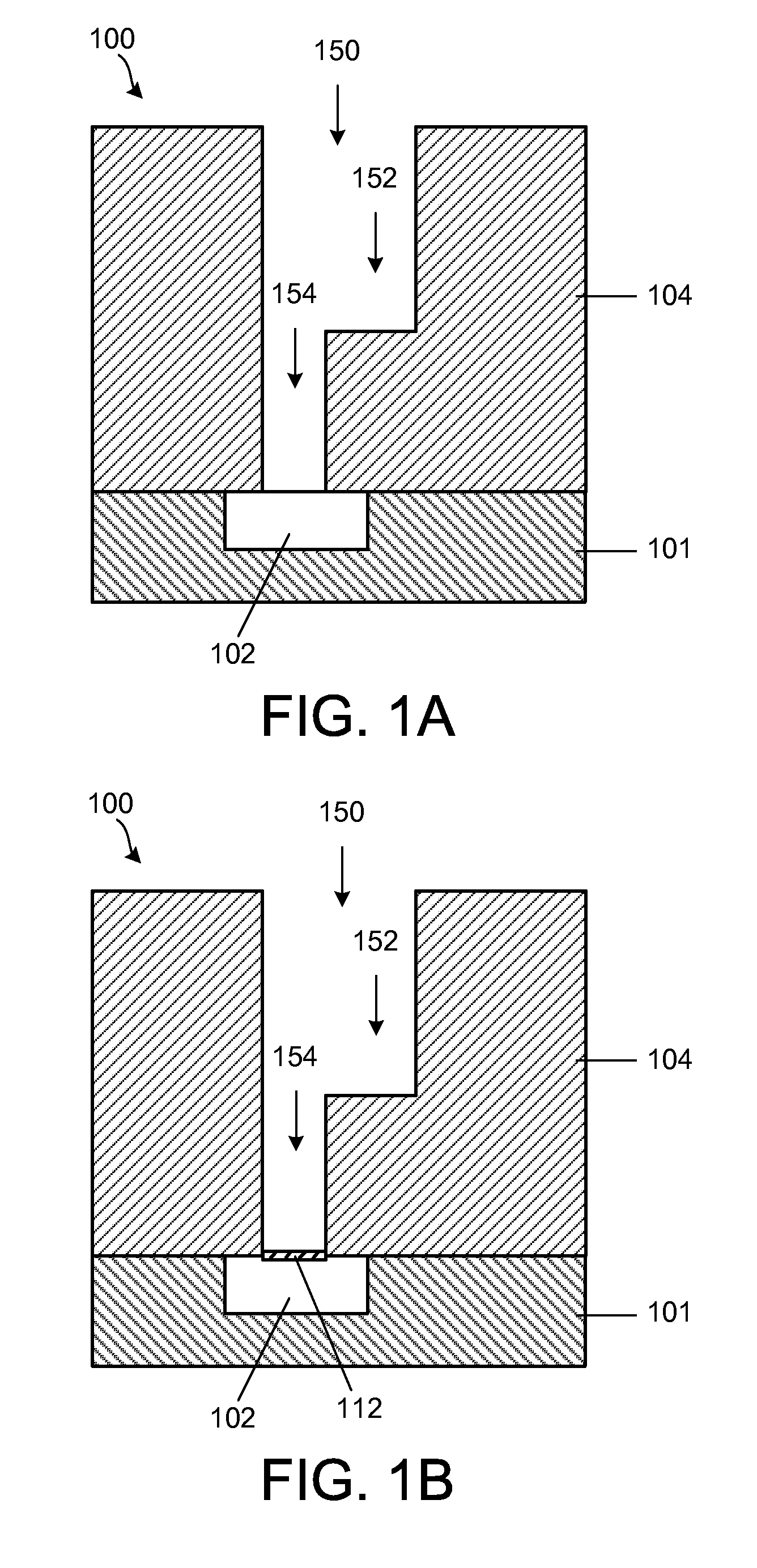

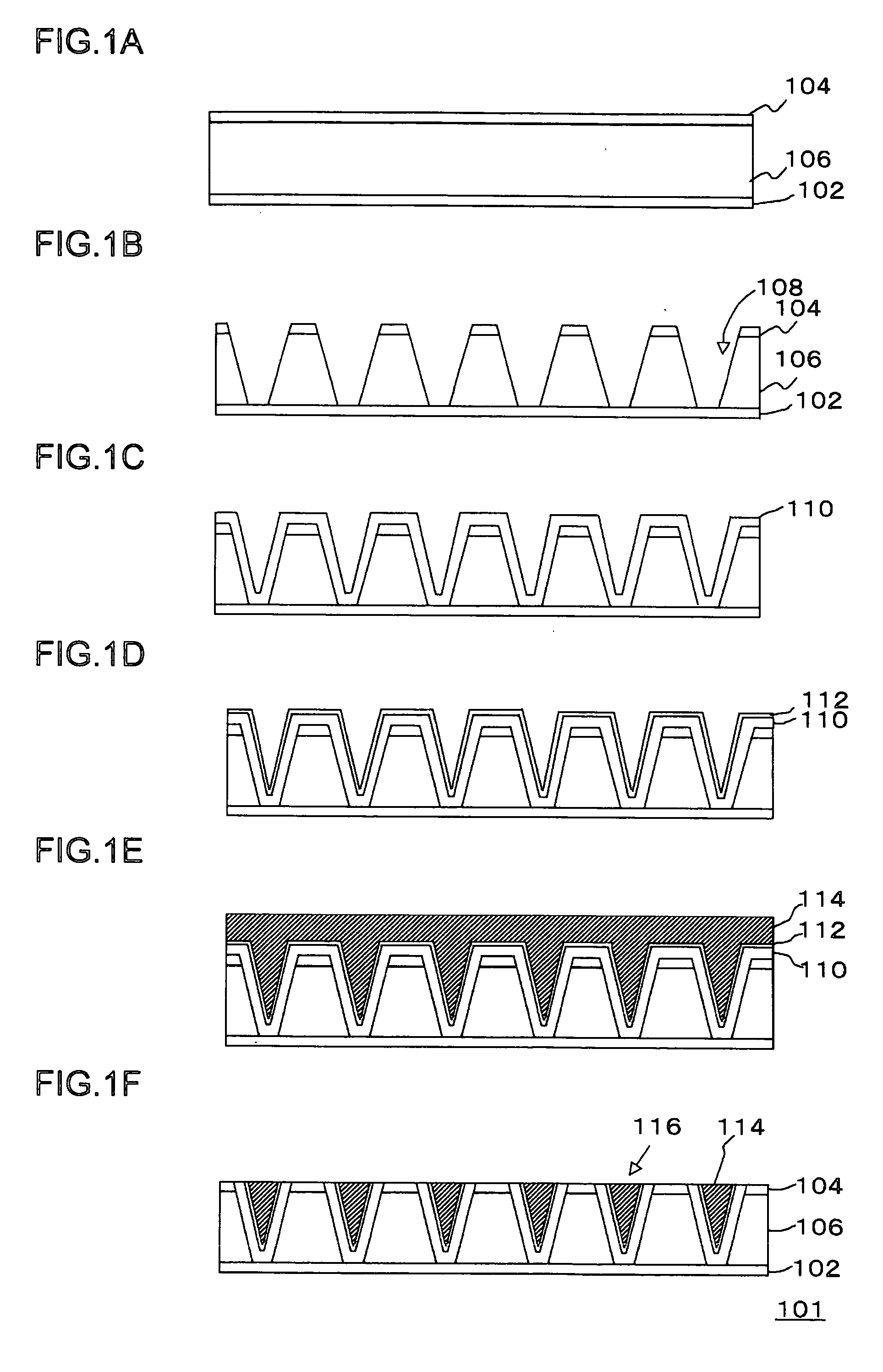

Wiring substrate and method of fabricating the same

InactiveUS20050266214A1Improve wiring reliabilityMetal materialSemiconductor/solid-state device detailsPrinted circuit aspectsEngineeringMetal

A wiring substrate is provided with an insulating resin film; and first and second conductive films provided on the back side and top side of the insulating resin film, respectively. The wiring substrate includes a via formed to fill a recess provided in the insulating resin film and electrically connecting the top side and back side of the insulating resin film. The via includes a first metal film formed to cover the side wall of the recess, an oxide film formed to cover the first meal film, and a second metal film formed on the metal oxide film.

Owner:SANYO ELECTRIC CO LTD

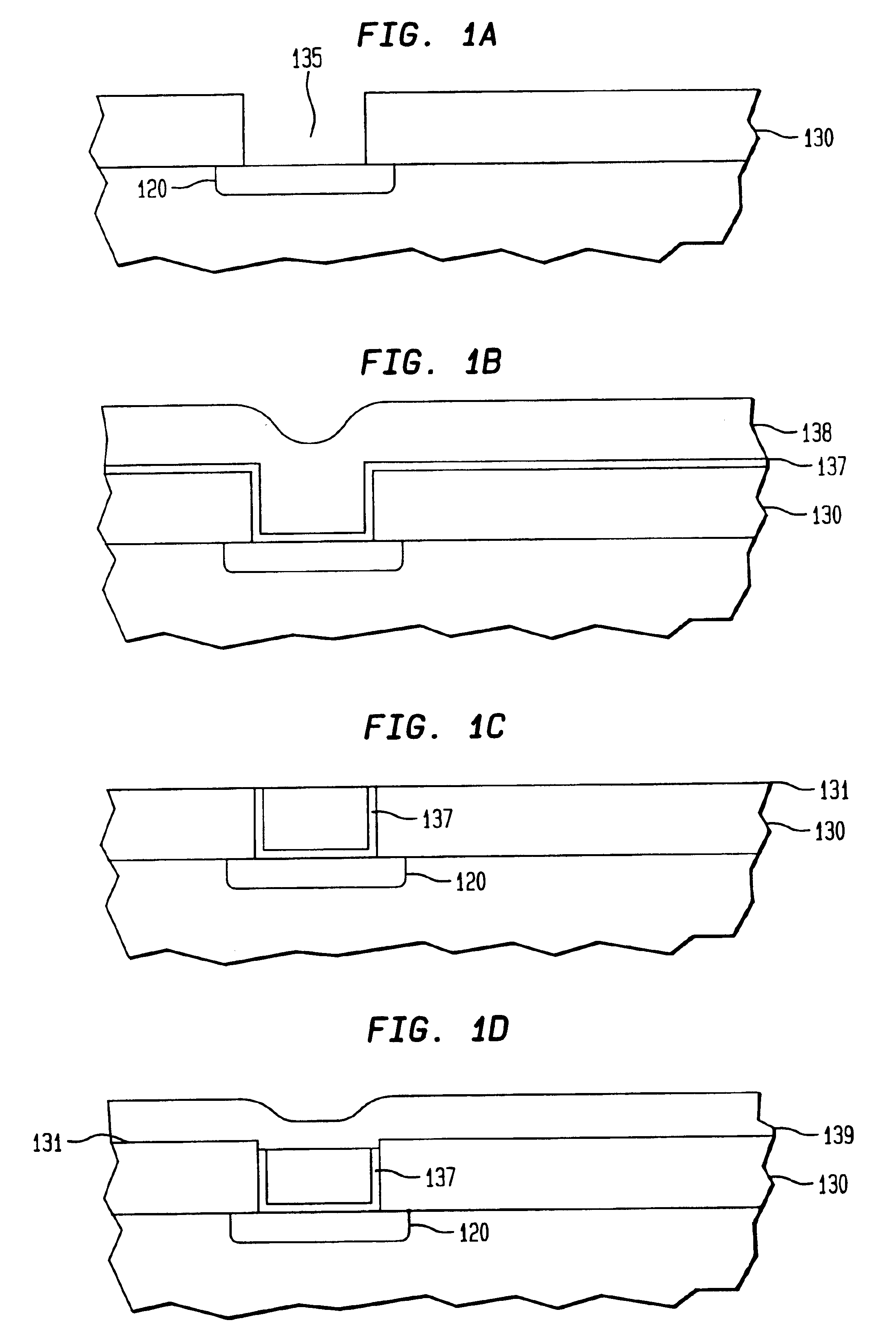

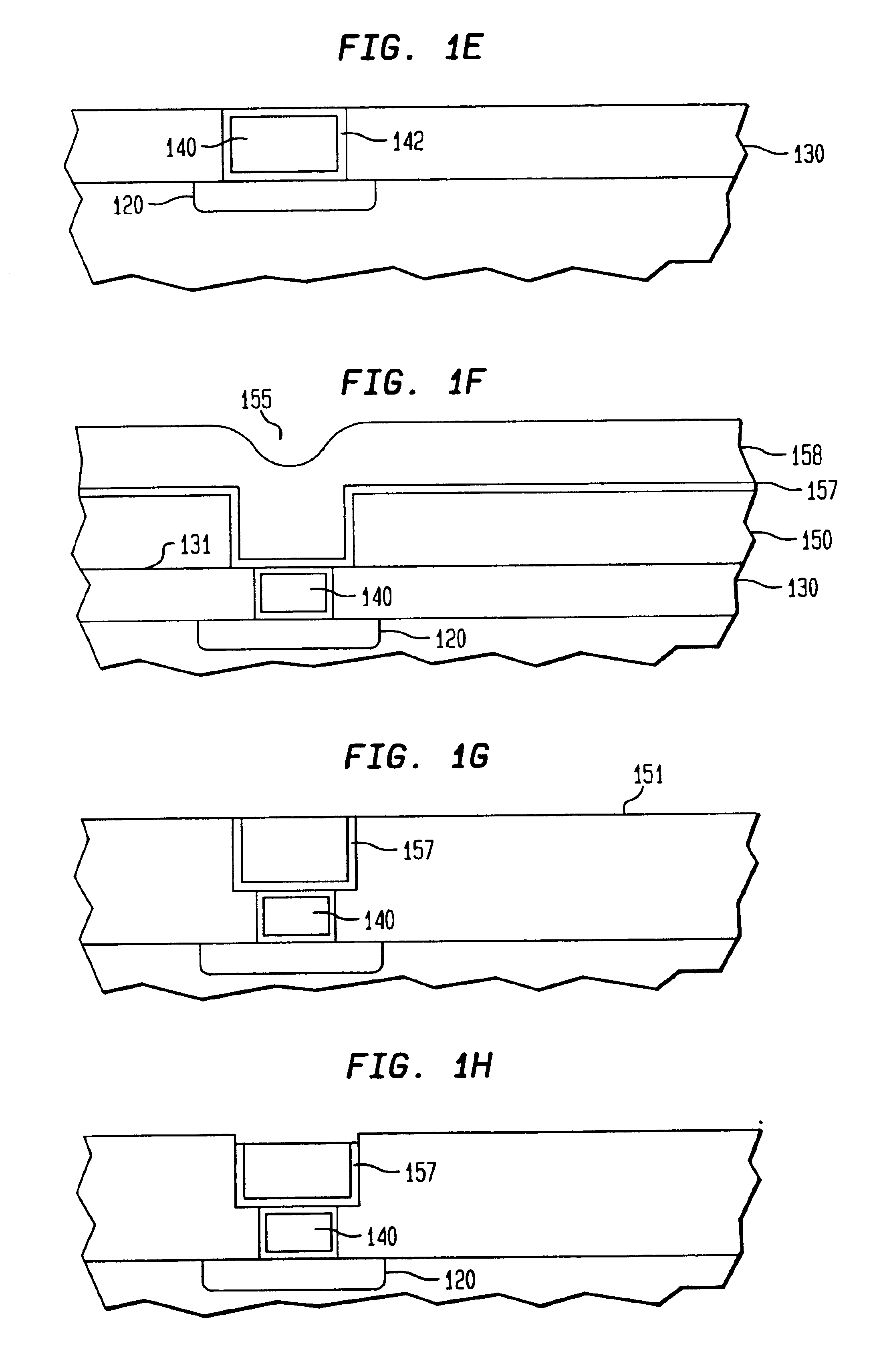

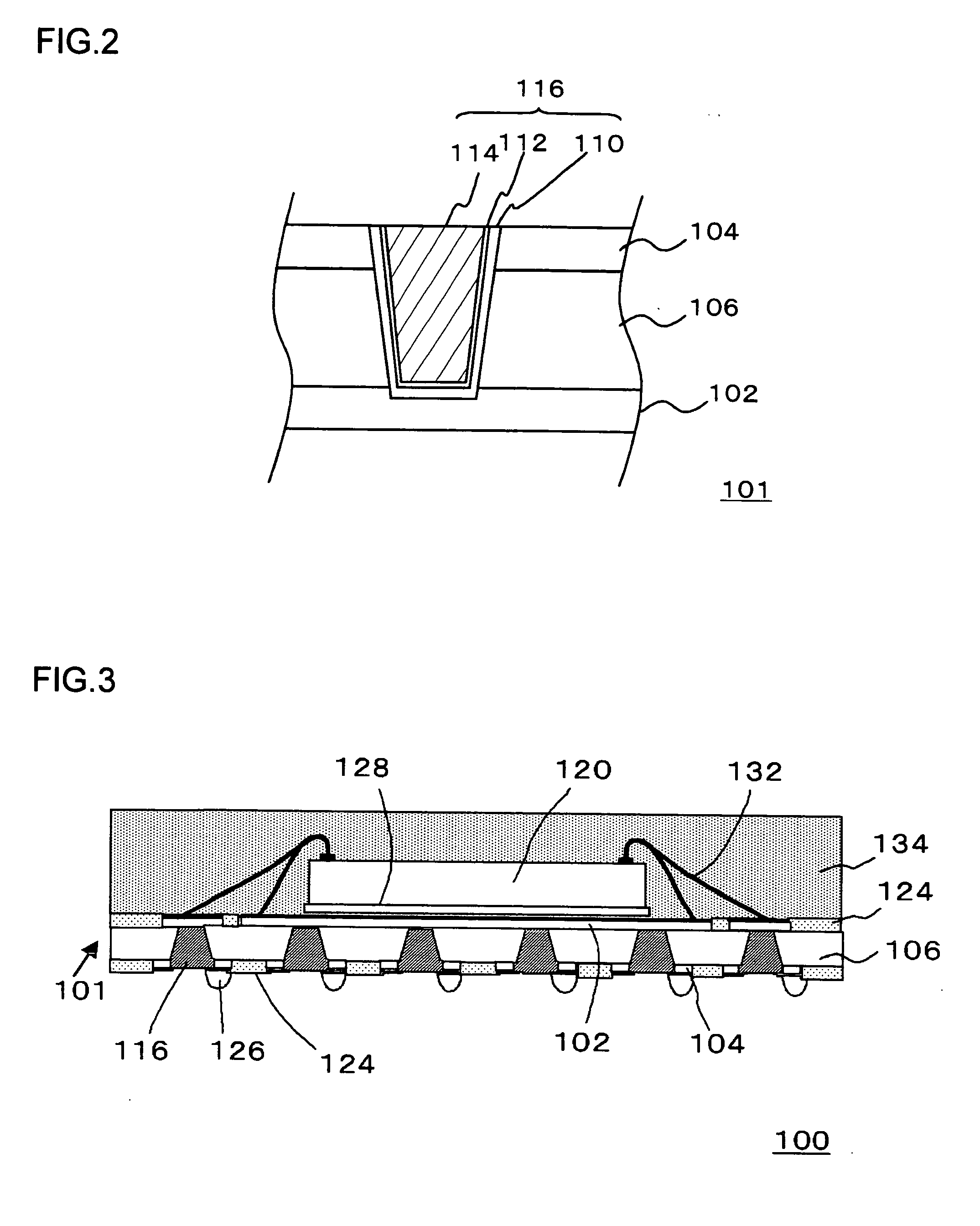

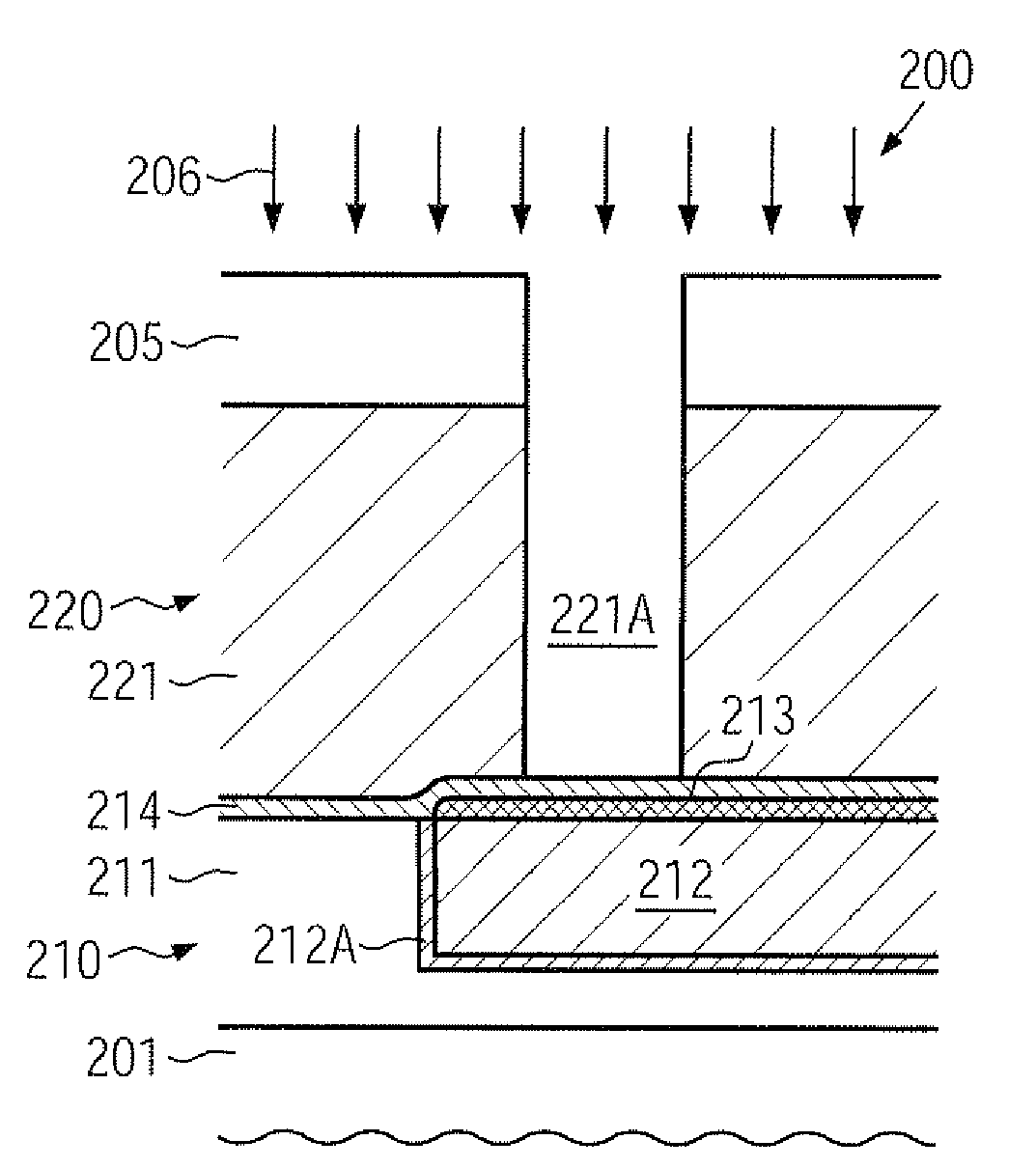

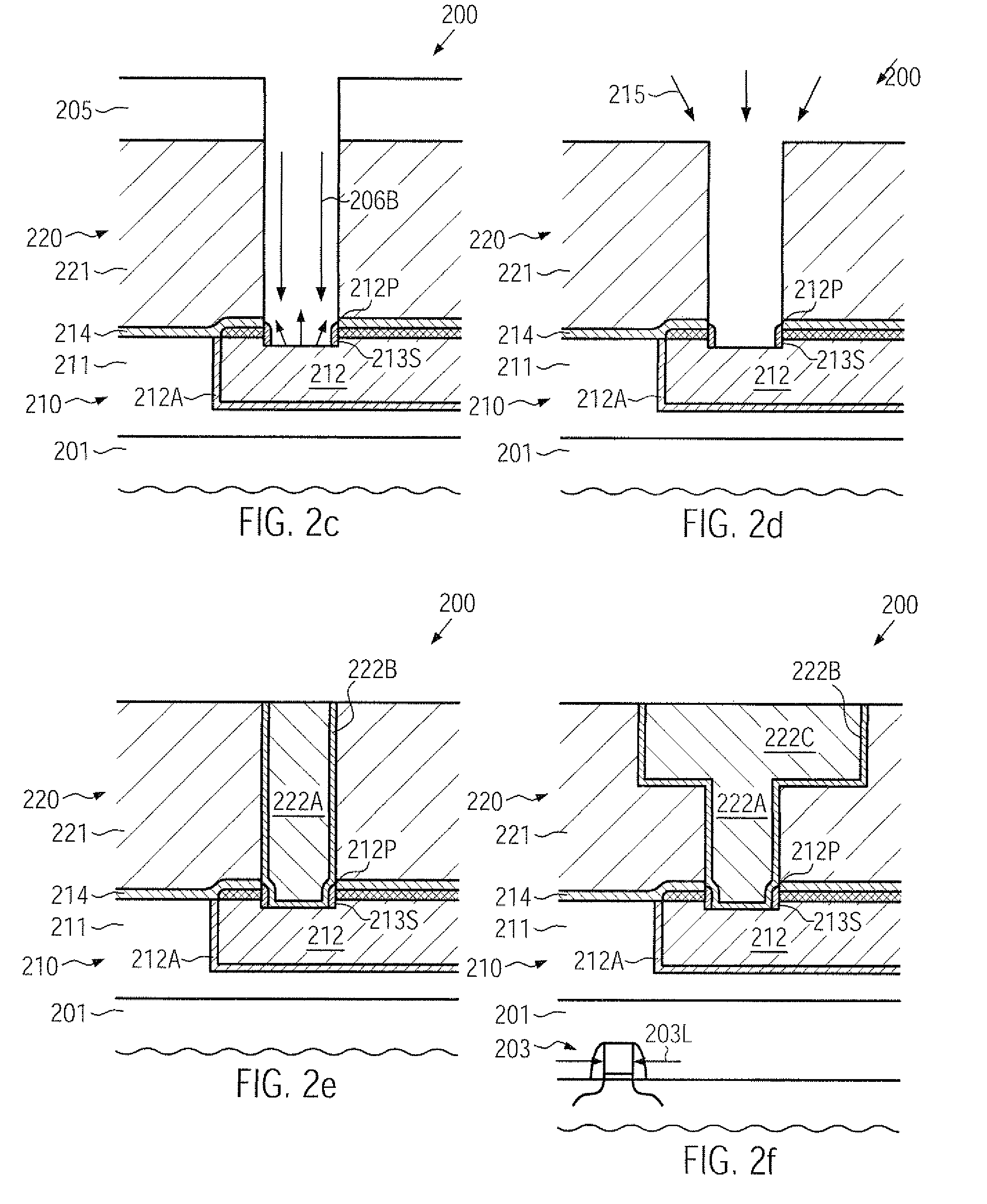

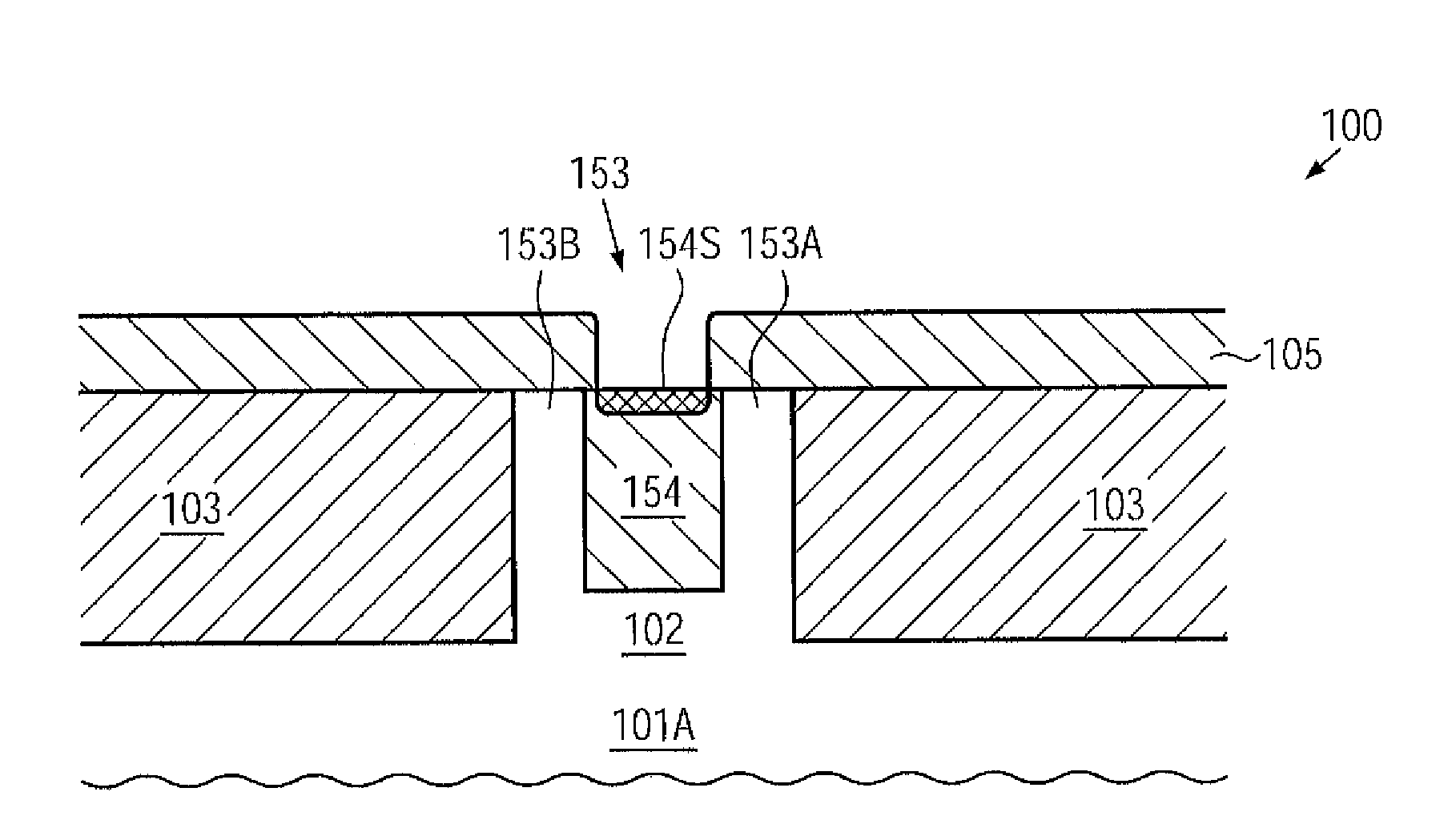

Method of reducing erosion of a metal cap layer during via patterning in semiconductor devices

ActiveUS20090273086A1Efficient overall manufacturing flowEnhancing electromigration behaviorSemiconductor/solid-state device detailsSolid-state devicesIon bombardmentMaterial removal

During the patterning of via openings in sophisticated metallization systems of semi-conductor devices, the opening may extend through a conductive cap layer and an appropriate ion bombardment may be established to redistribute material of the underlying metal region to exposed sidewall portions of the conductive cap layer, thereby establishing a protective material. Consequently, in a subsequent wet chemical etch process, the probability for undue material removal of the conductive cap layer may be greatly reduced.

Owner:ADVANCED MICRO DEVICES INC

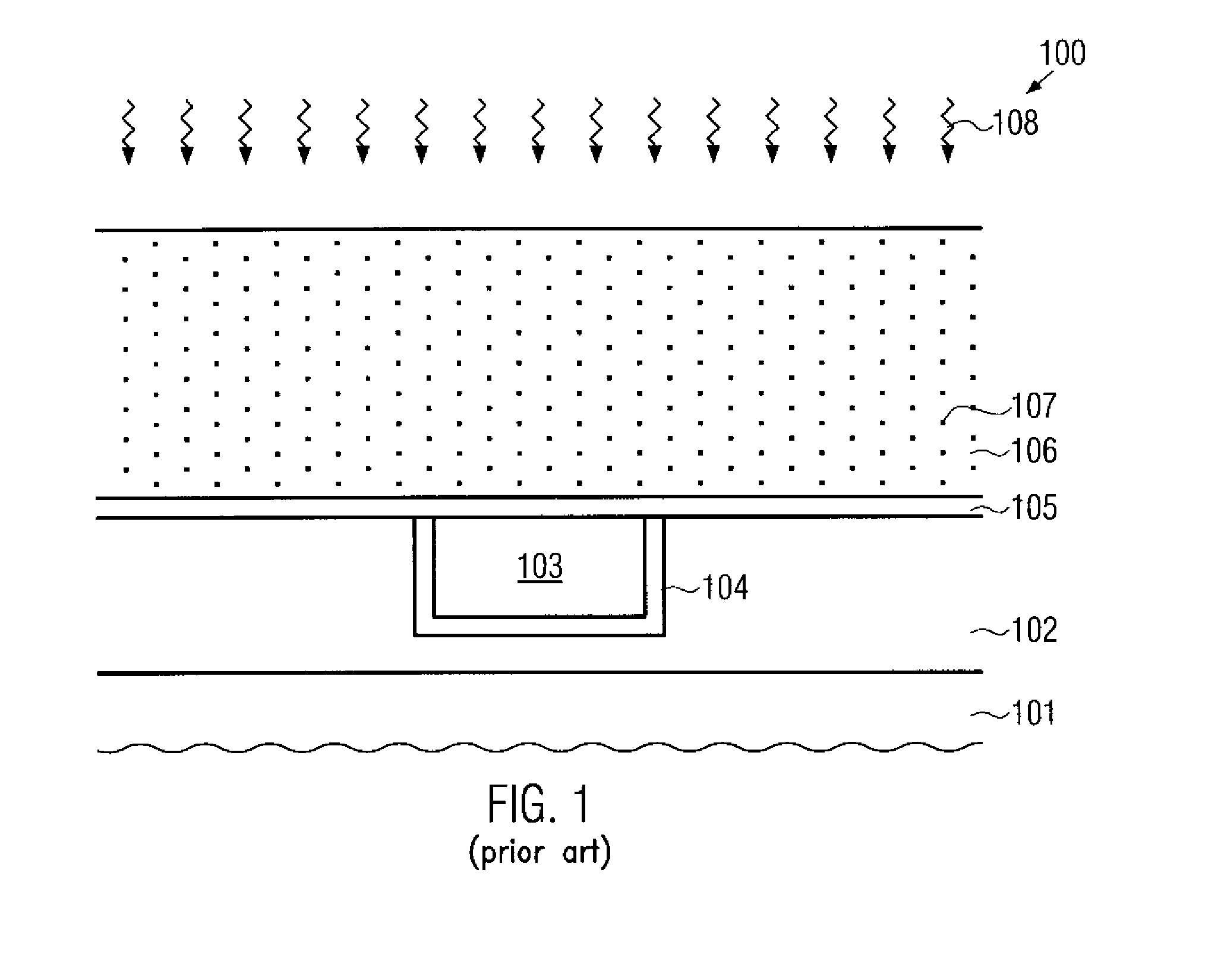

Semiconductor device and method for fabricating the same

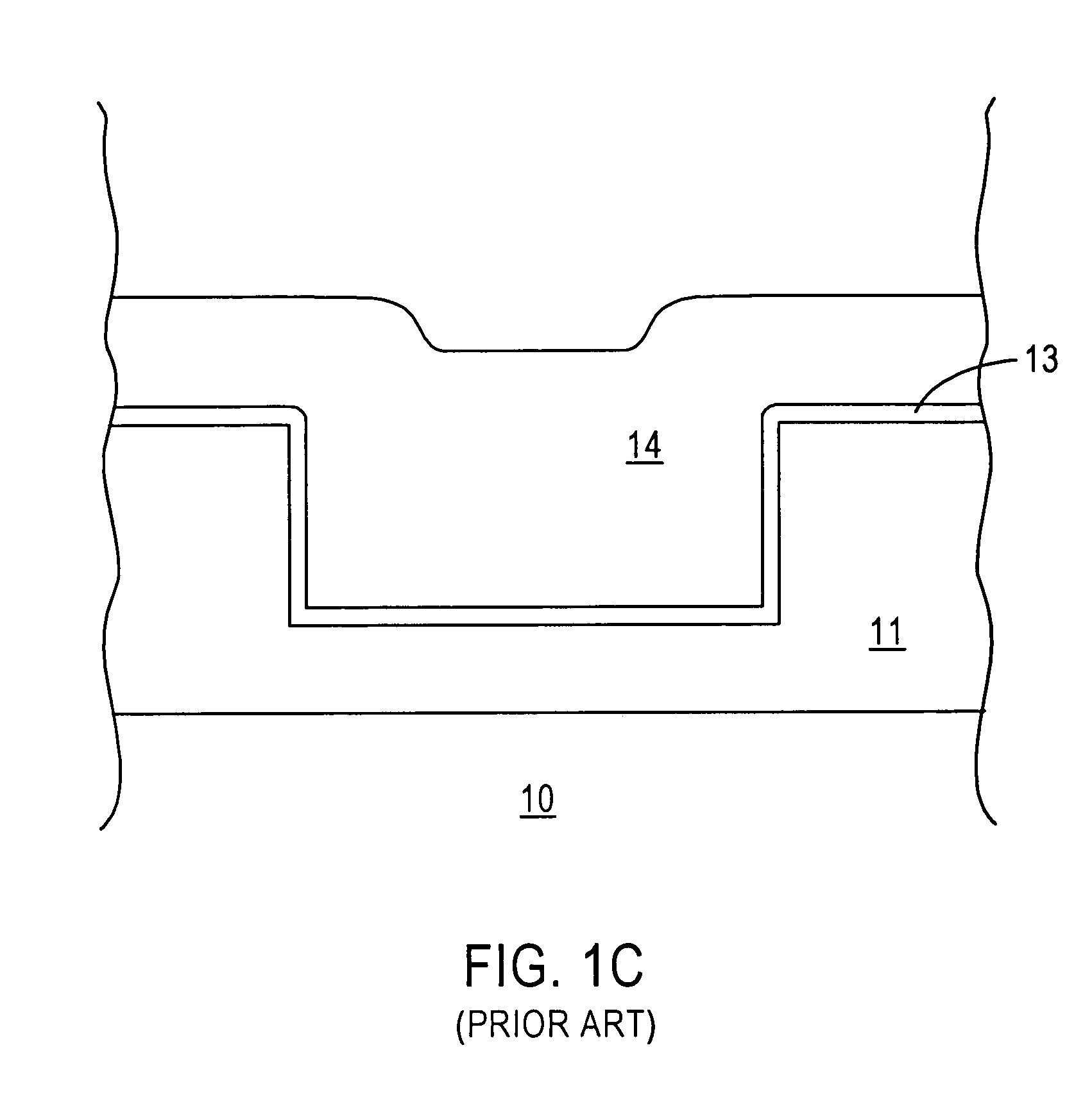

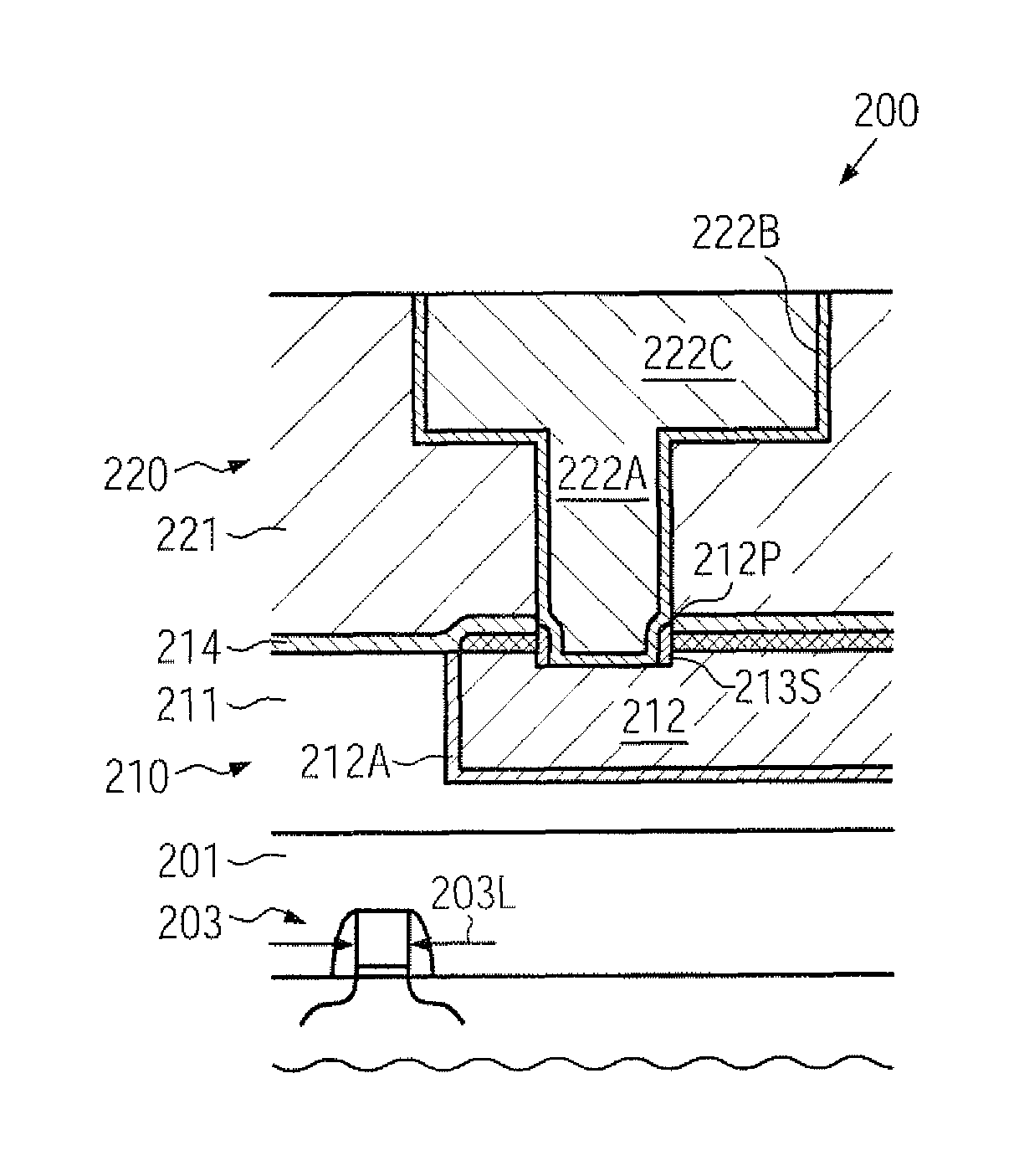

ActiveUS20090278261A1Effective mechanical strengthImprove electromigrationSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

An interlayer insulating film is formed on the upper surface of a semiconductor substrate, and lower-level interconnects are formed in the interlayer insulating film. A liner insulating film is formed on the upper surfaces of the interlayer insulating film and lower-level interconnects. An interlayer insulating film is formed on the upper surface of the liner insulating film. Upper-level interconnects are formed in the interlayer insulating film. The lower-level interconnects and the upper-level interconnects are connected with each other through vias. Parts of the liner insulating film formed in via-adjacent regions have a greater thickness than a part thereof formed outside the via-adjacent regions.

Owner:PANNOVA SEMIC

Method for integrating selective ruthenium deposition into manufacturing of a semiconductior device

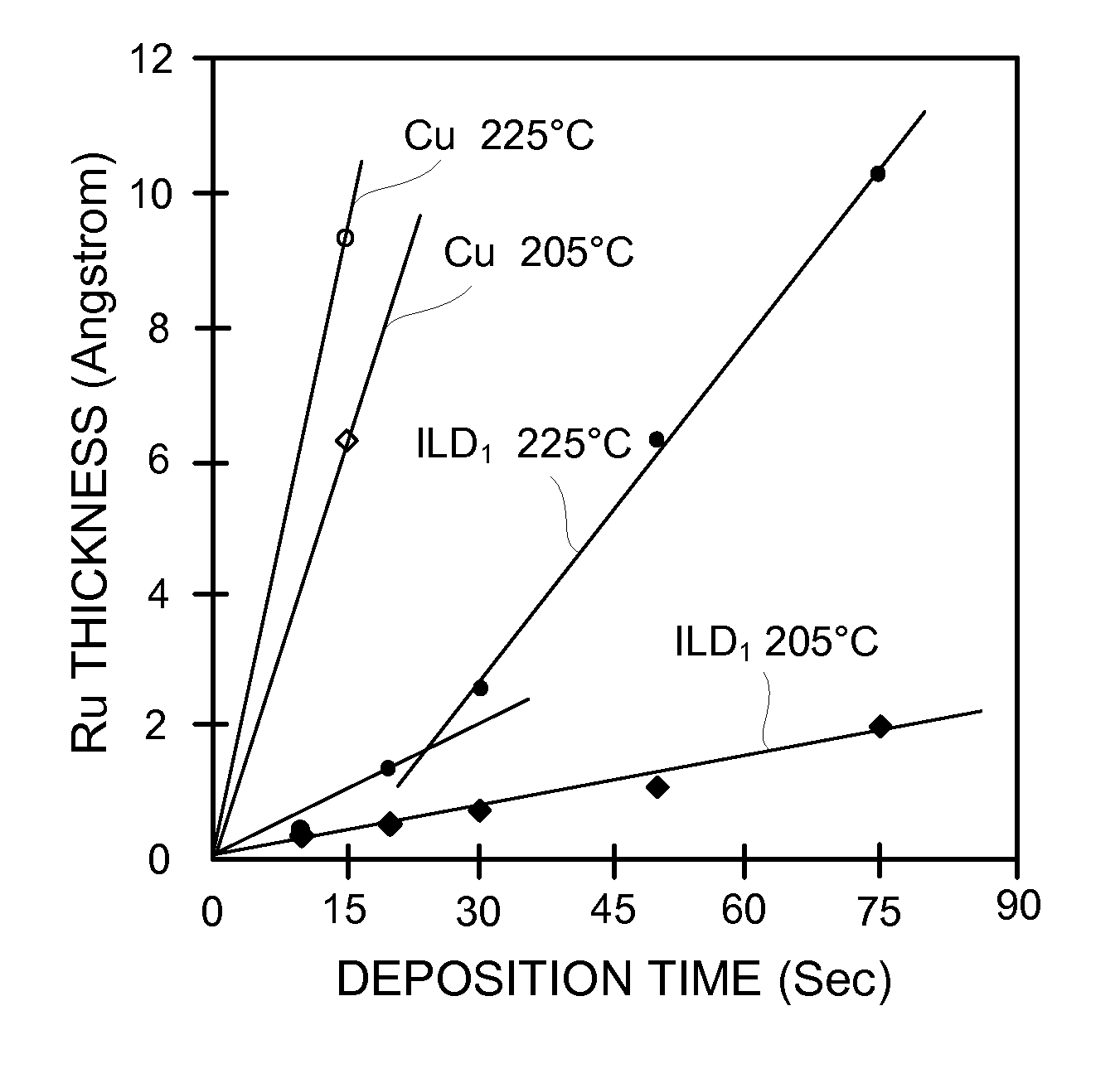

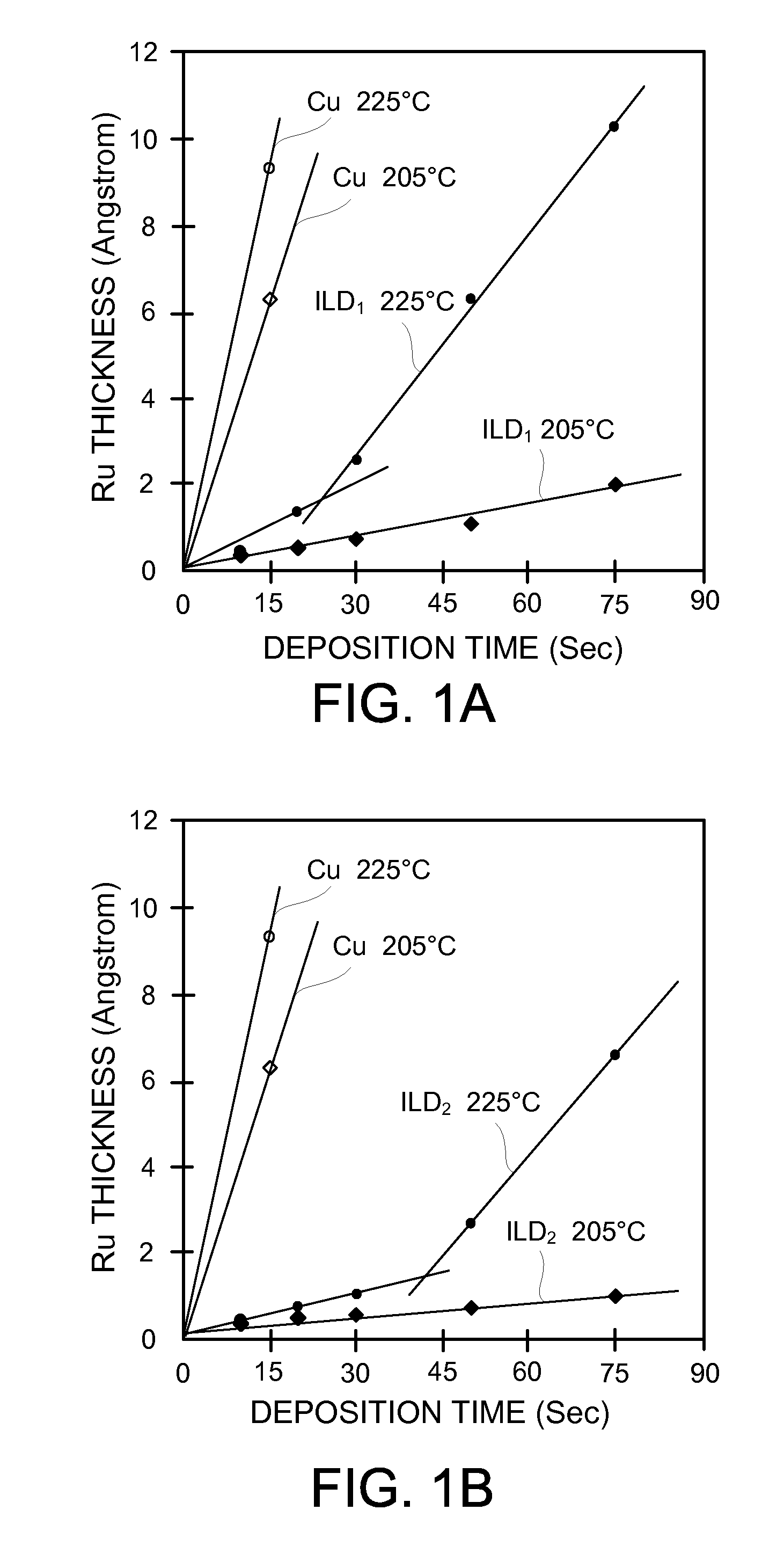

ActiveUS7829454B2Improve electromigrationImprove stress conditionSemiconductor/solid-state device detailsSolid-state devicesGas phaseThermal chemical vapor deposition

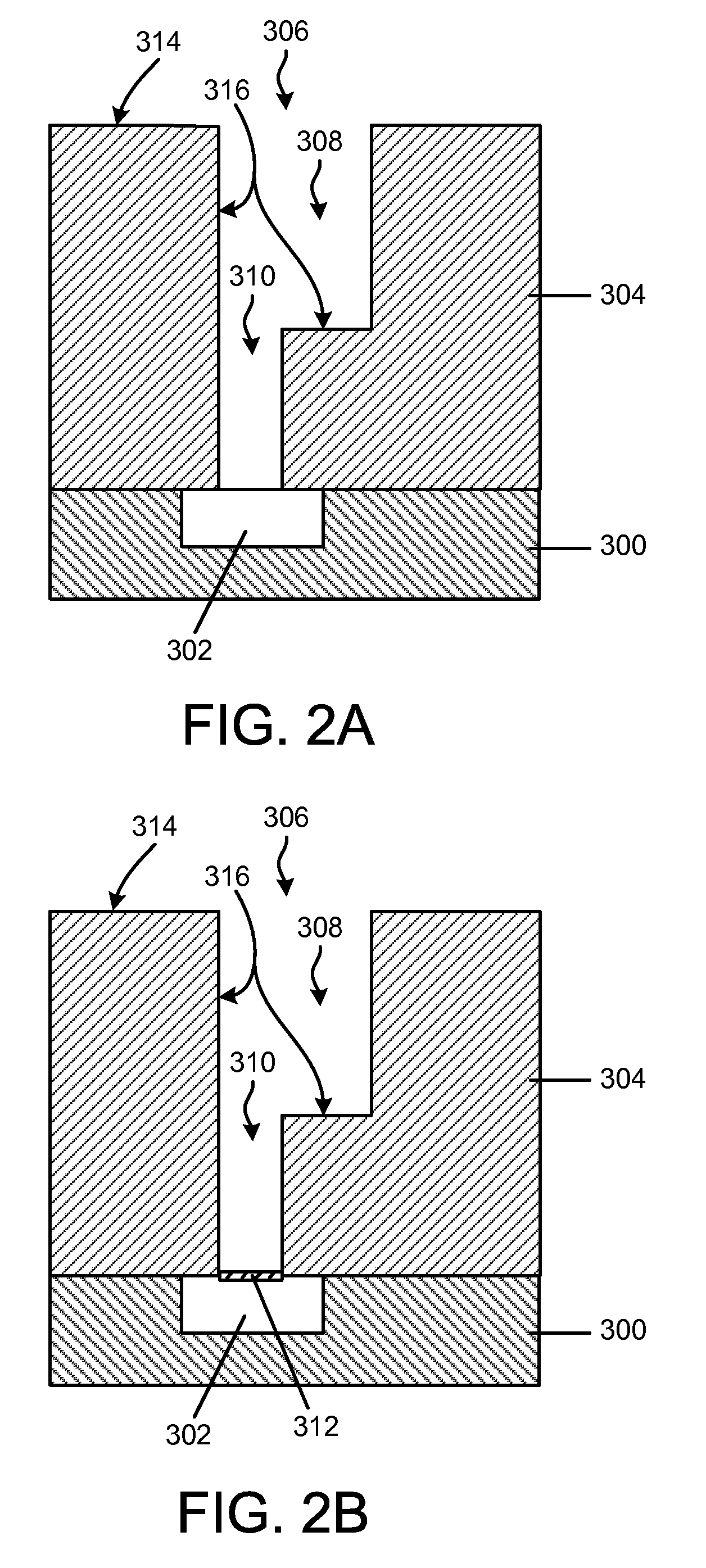

A method for integrating selective Ru metal deposition into manufacturing of semiconductor devices to improve electromigration and stress migration in bulk Cu. The method includes selectively depositing a Ru metal film on a metallization layer or on bulk Cu using a process gas containing Ru3(CO)12 precursor vapor and a CO gas in a thermal chemical vapor deposition process. A semiconductor device containing one or more selectively deposited Ru metal films is described.

Owner:TOKYO ELECTRON LTD

Selective deposition of metal-containing cap layers for semiconductor devices

ActiveUS8242019B2Improve electromigrationPromote migrationSemiconductor/solid-state device manufacturingSelective depositionCopper

A method for integrating metal-containing cap layers into copper (Cu) metallization of semiconductor devices. In one embodiment, the method includes providing a patterned substrate containing metal surfaces and dielectric layer surfaces, and modifying the dielectric layer surfaces by exposure to a reactant gas containing a hydrophobic functional group, where the modifying substitutes a hydrophilic functional group in the dielectric layer surfaces with a hydrophobic functional group. The method further includes depositing metal-containing cap layers selectively on the metal surfaces by exposing the modified dielectric layer surfaces and the metal surfaces to a deposition gas containing metal-containing precursor vapor.

Owner:TOKYO ELECTRON LTD

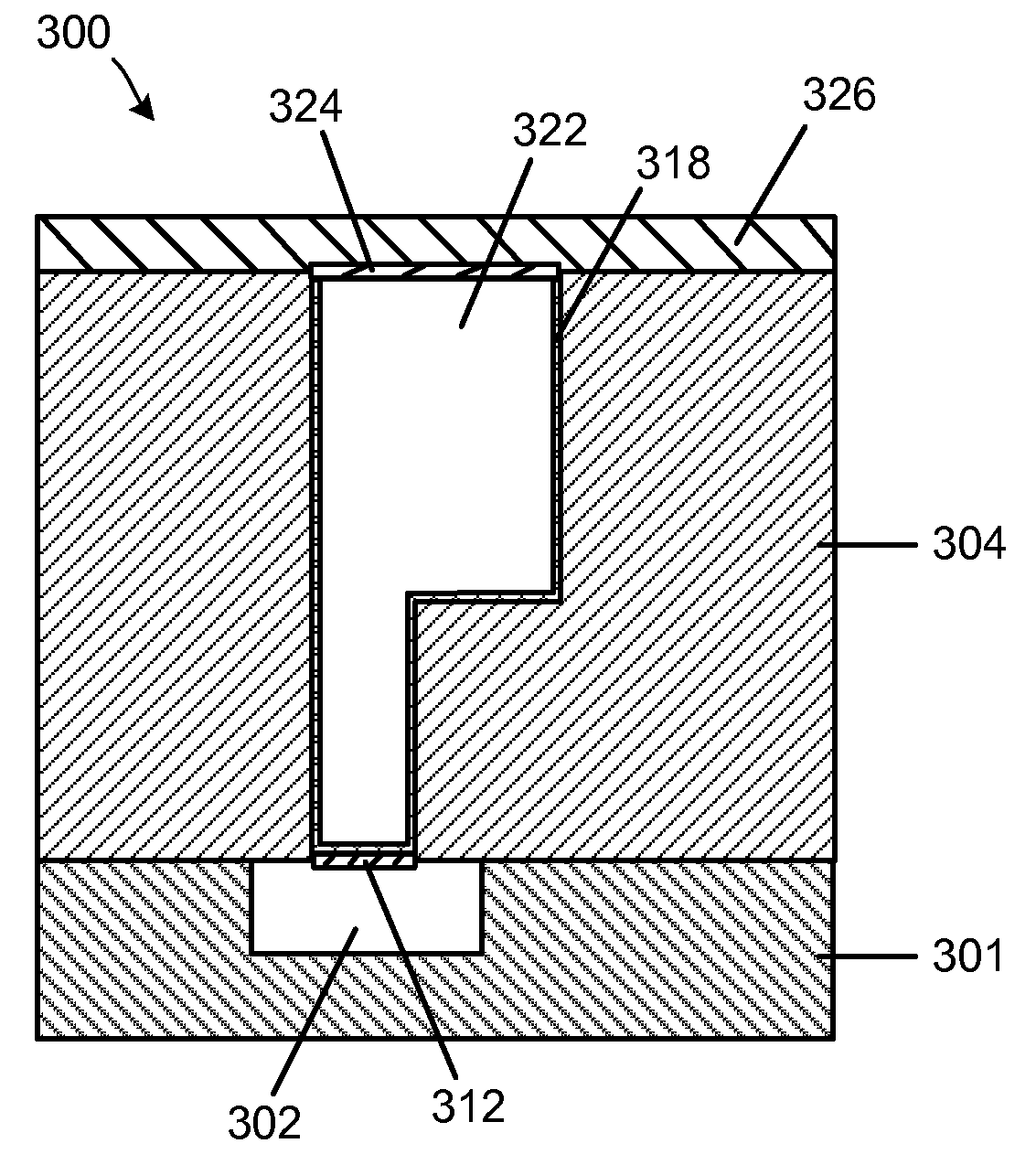

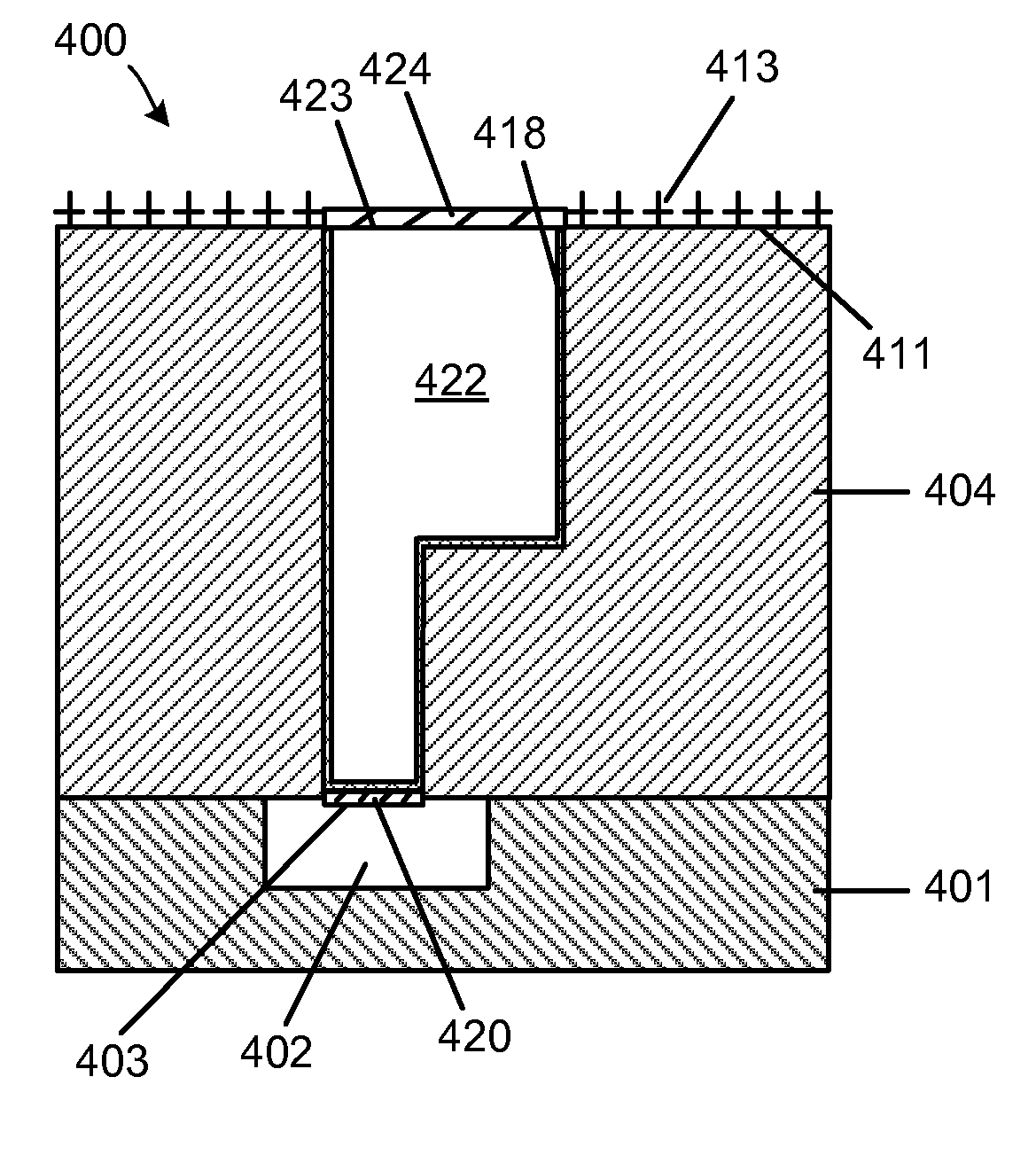

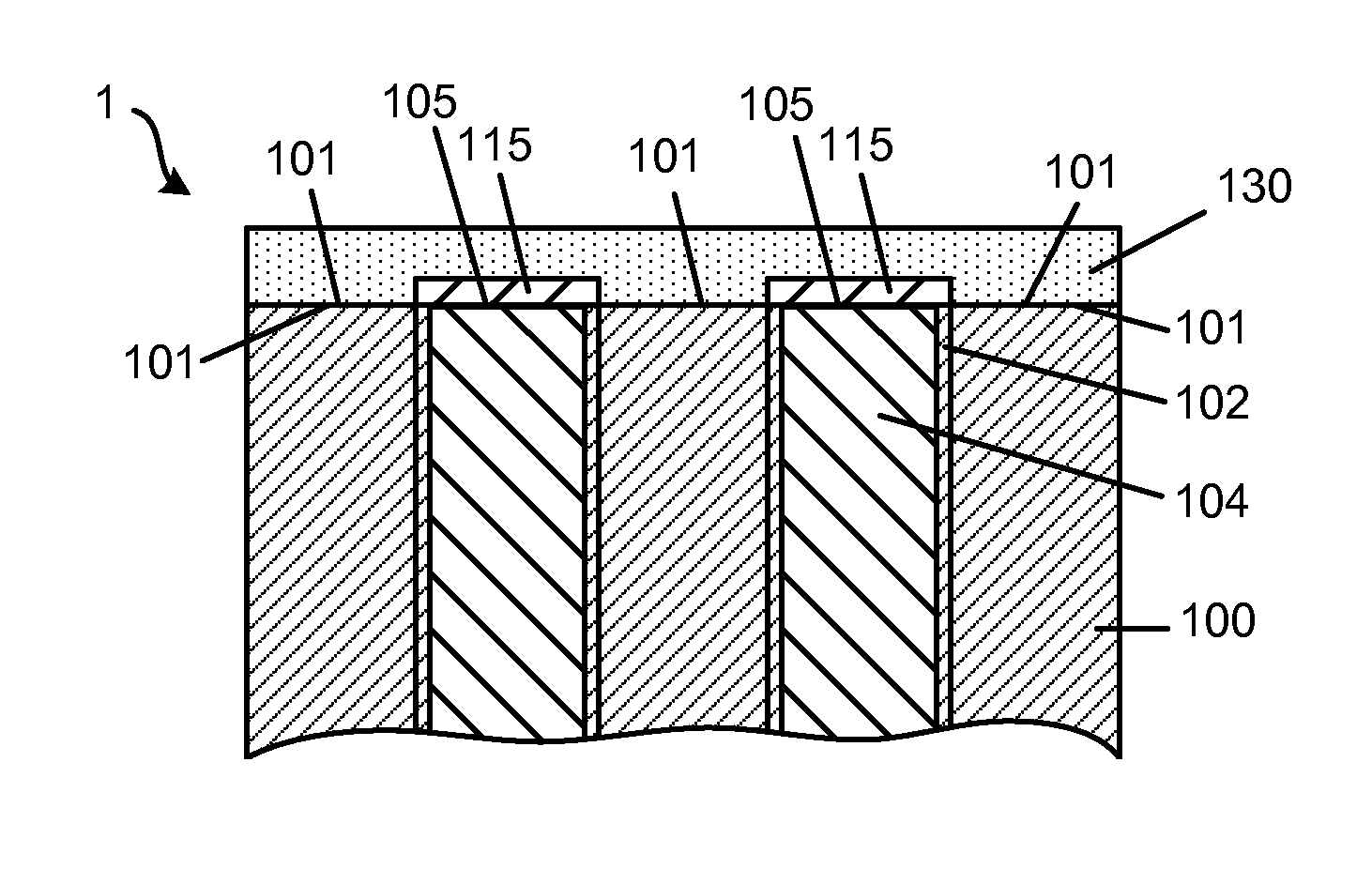

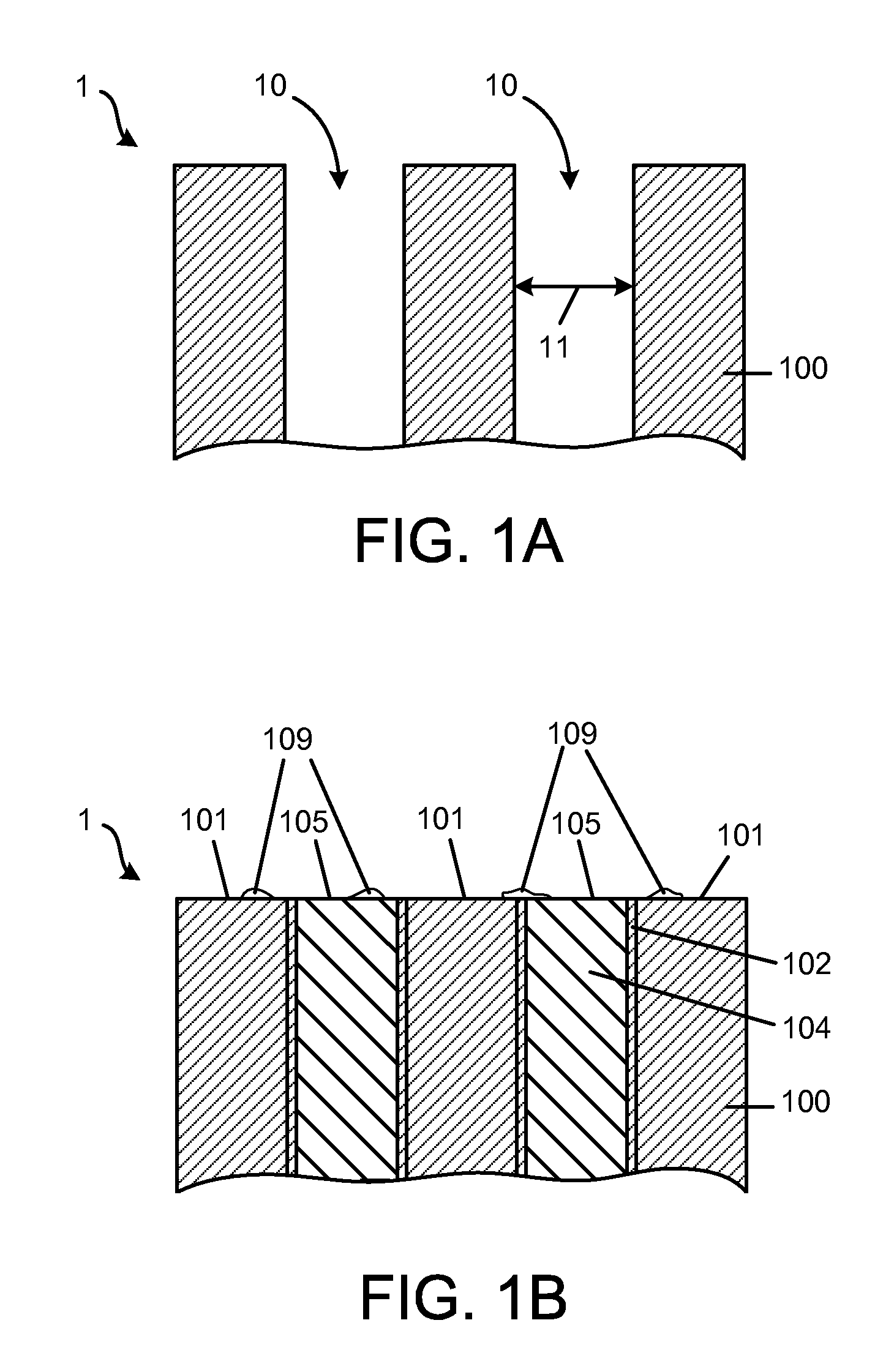

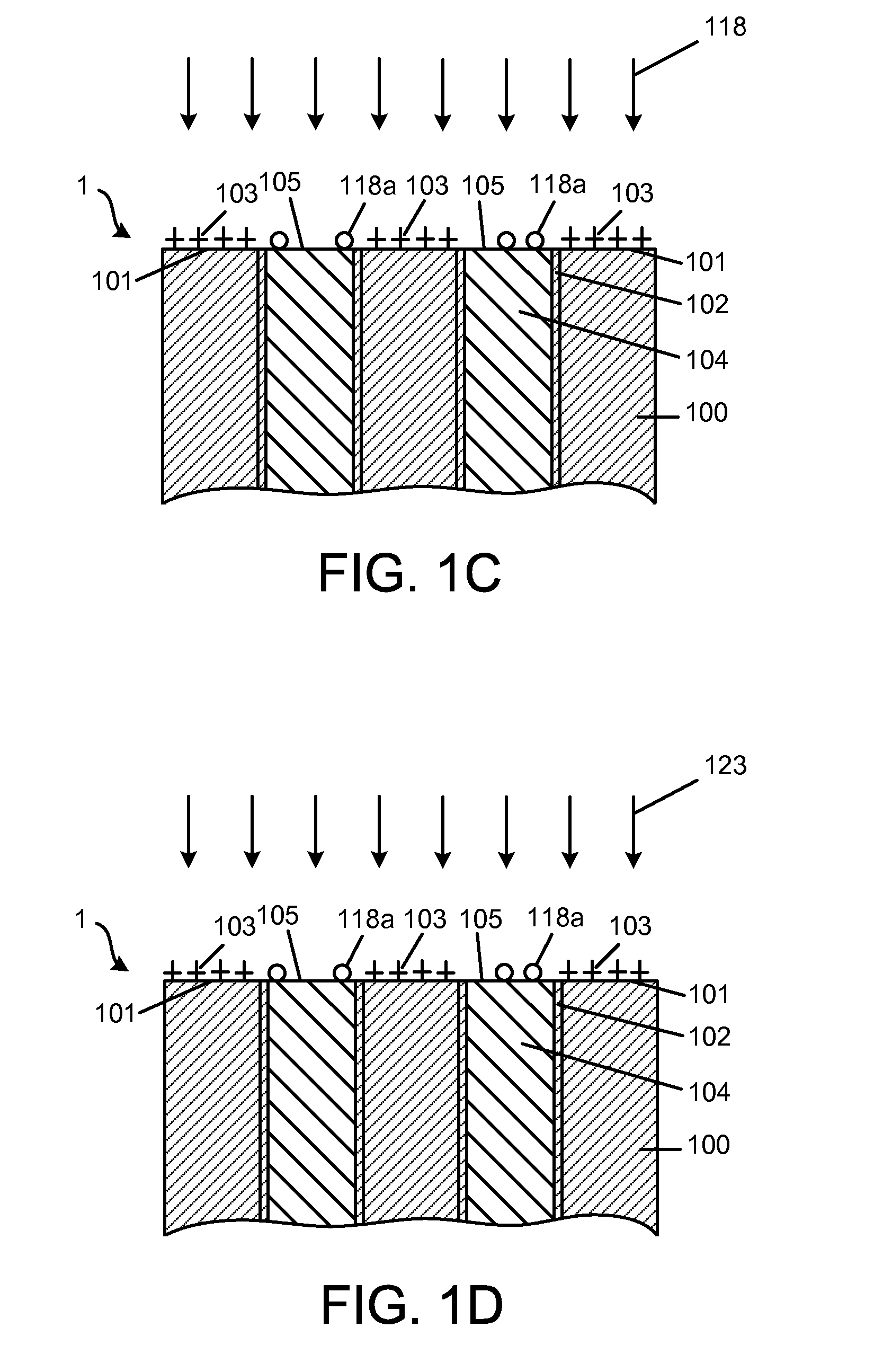

Method for forming a ruthenium metal cap layer

ActiveUS7799681B2Improve electromigrationPromote migrationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingRutheniumPatterned substrate

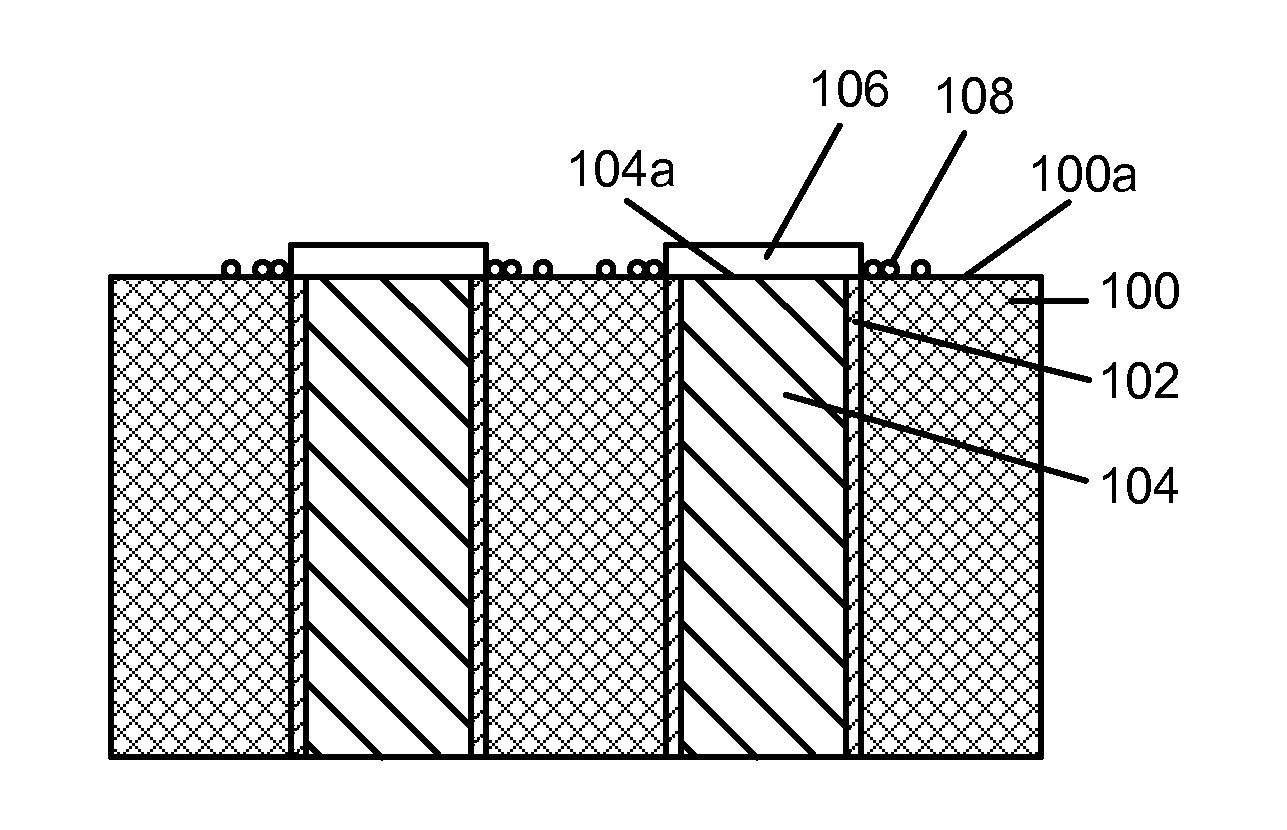

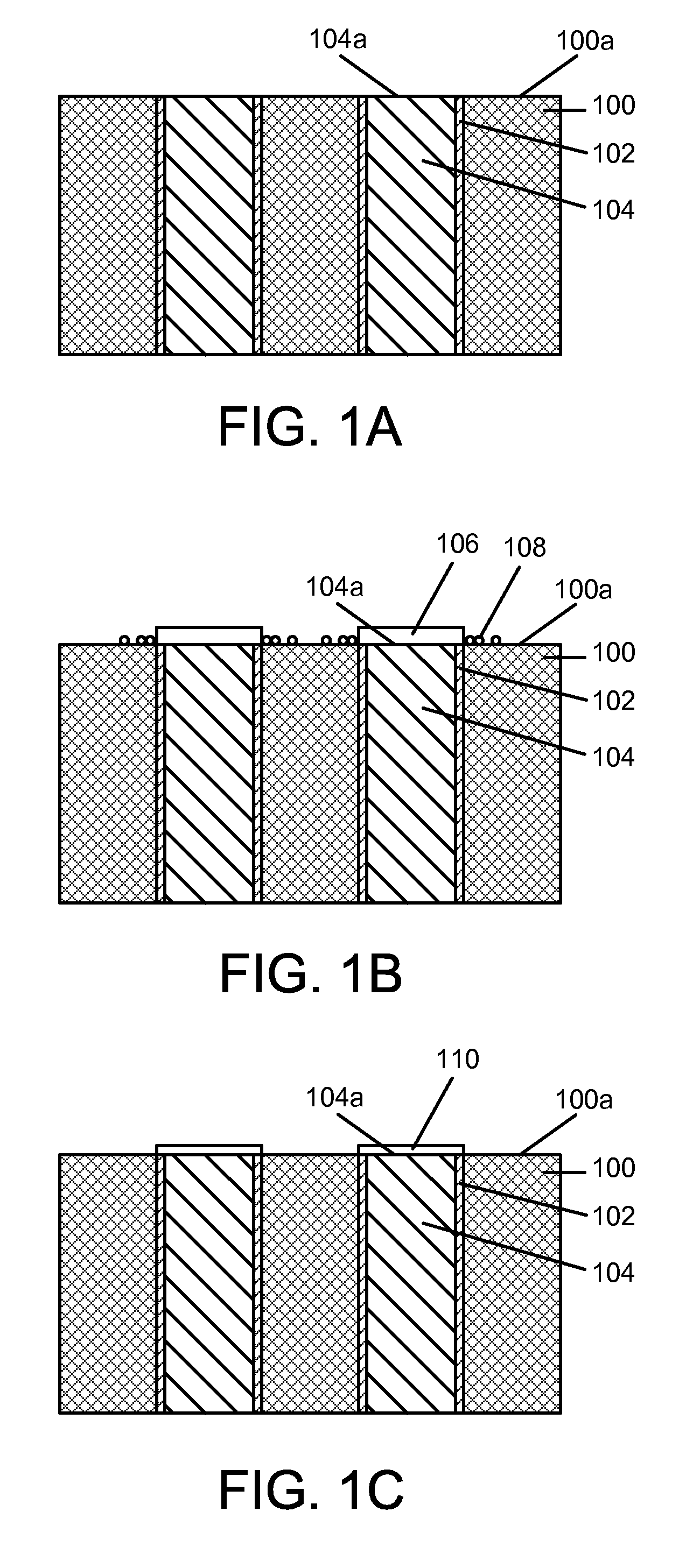

A method for integrating ruthenium (Ru) metal cap layers and modified Ru metal cap layers into copper (Cu) metallization of semiconductor devices to improve electromigration (EM) and stress migration (SM) in bulk Cu metal. In one embodiment, the method includes providing a planarized patterned substrate containing a Cu metal surface and a dielectric layer surface, depositing first Ru metal on the Cu metal surface, and depositing additional Ru metal on the dielectric layer surface, where the amount of the additional Ru metal is less than the amount of the first Ru metal. The method further includes at least substantially removing the additional Ru metal from the dielectric layer surface to improve the selective formation of a Ru metal cap layer on the Cu metal surface. Other embodiments further include incorporating one or more types of modifier elements into the dielectric layer surface, the Cu metal surface, the Ru metal cap layer, or a combination thereof.

Owner:TOKYO ELECTRON LTD

Surface cleaning and selective deposition of metal-containing cap layers for semiconductor devices

ActiveUS8178439B2Improve electromigrationPromote migrationSemiconductor/solid-state device manufacturingSurface cleaningSelective deposition

Owner:TOKYO ELECTRON LTD

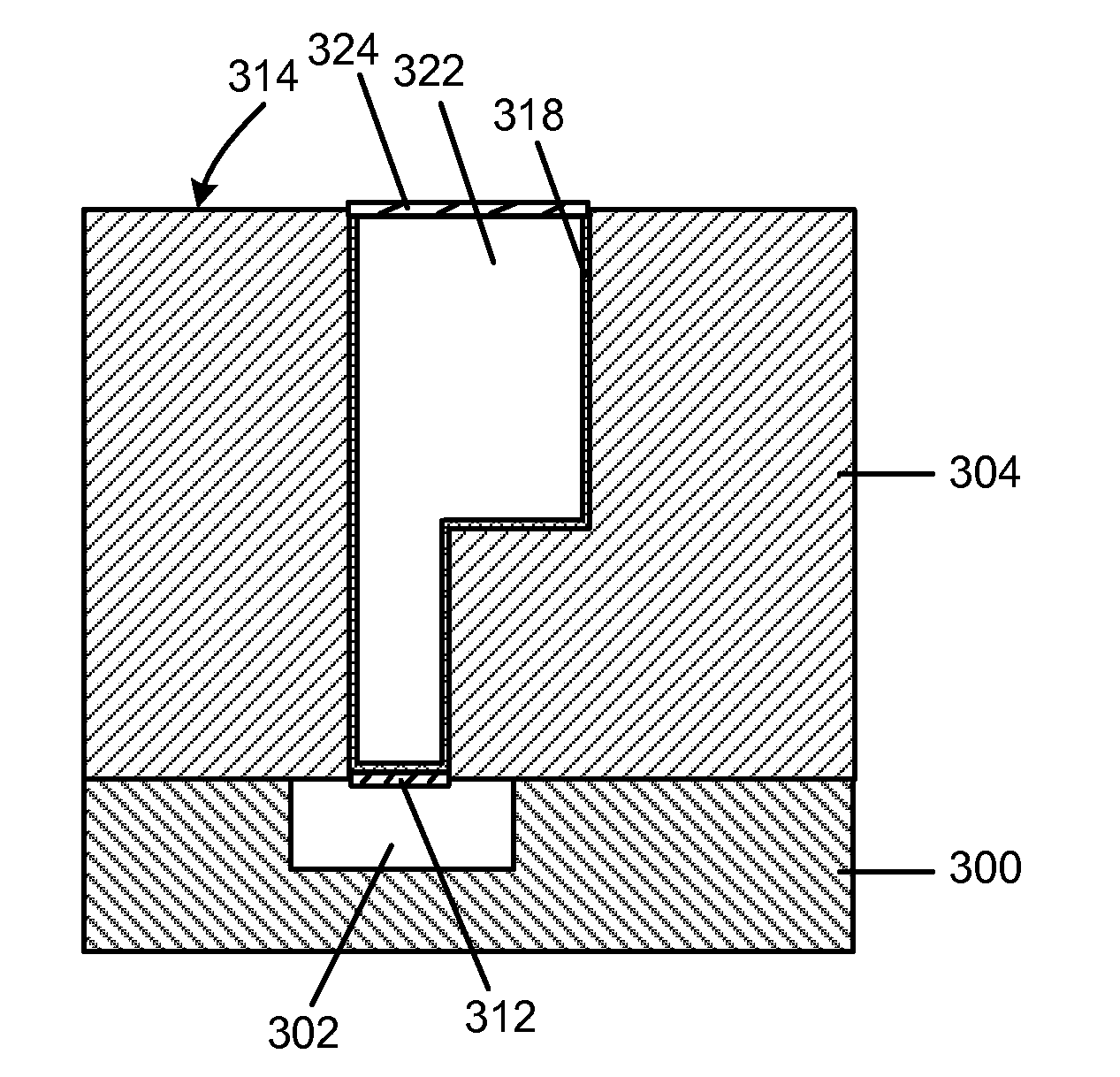

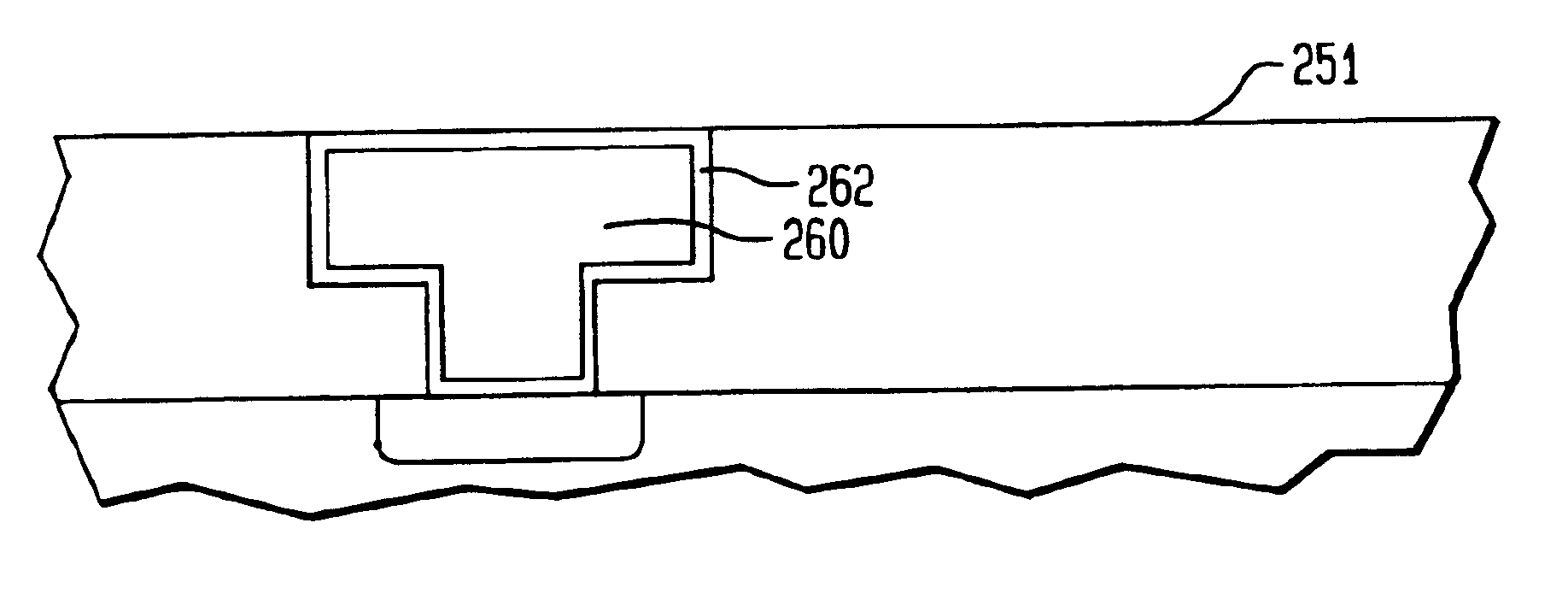

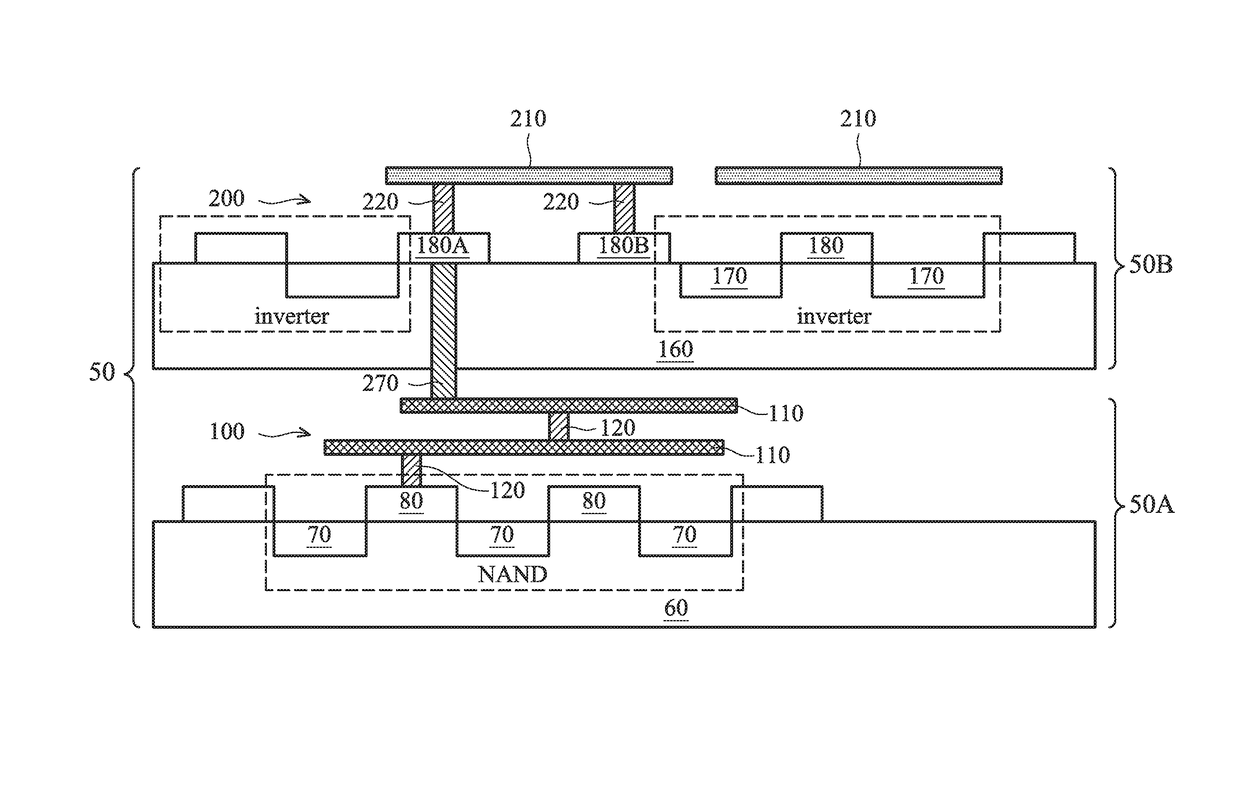

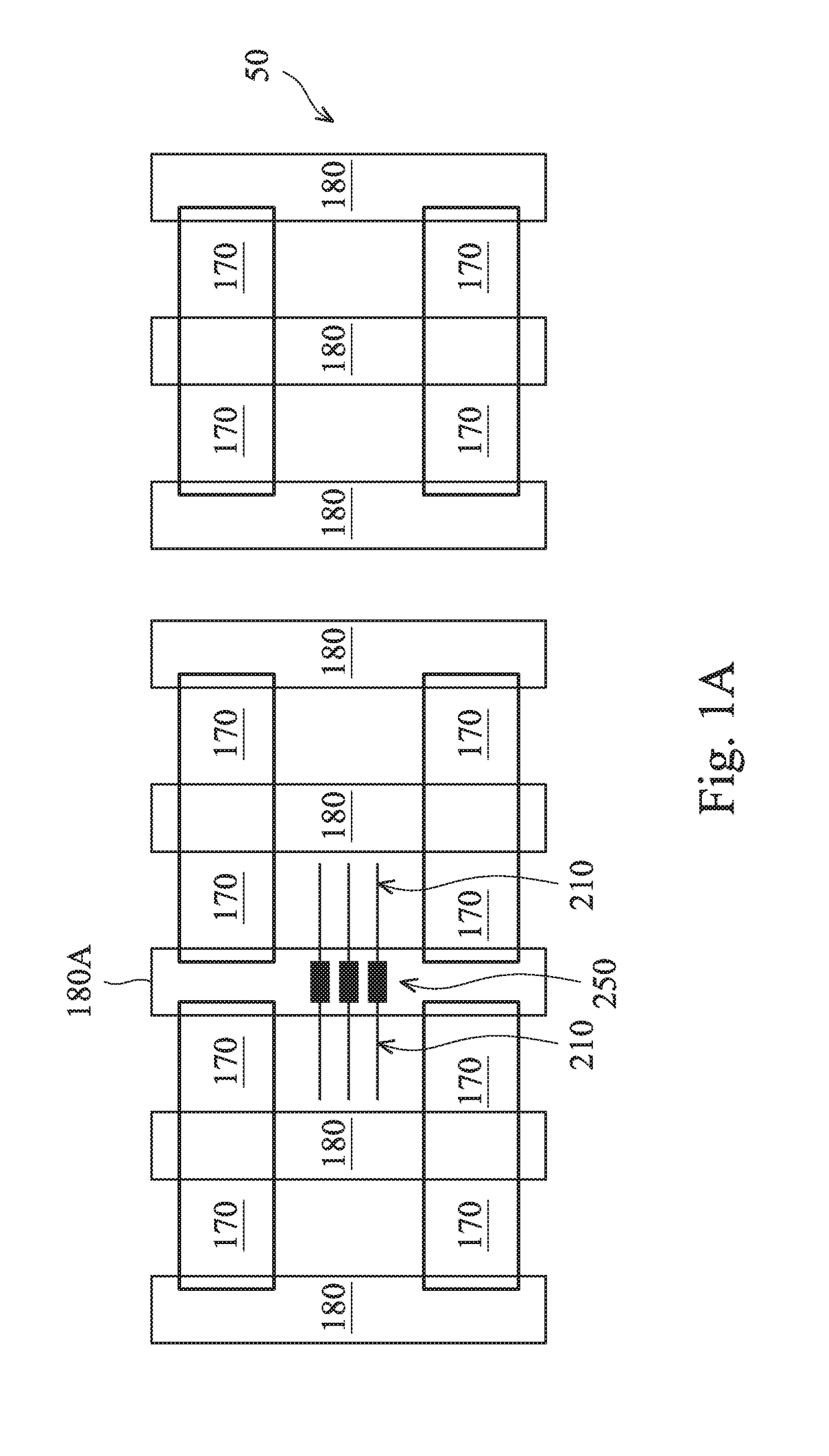

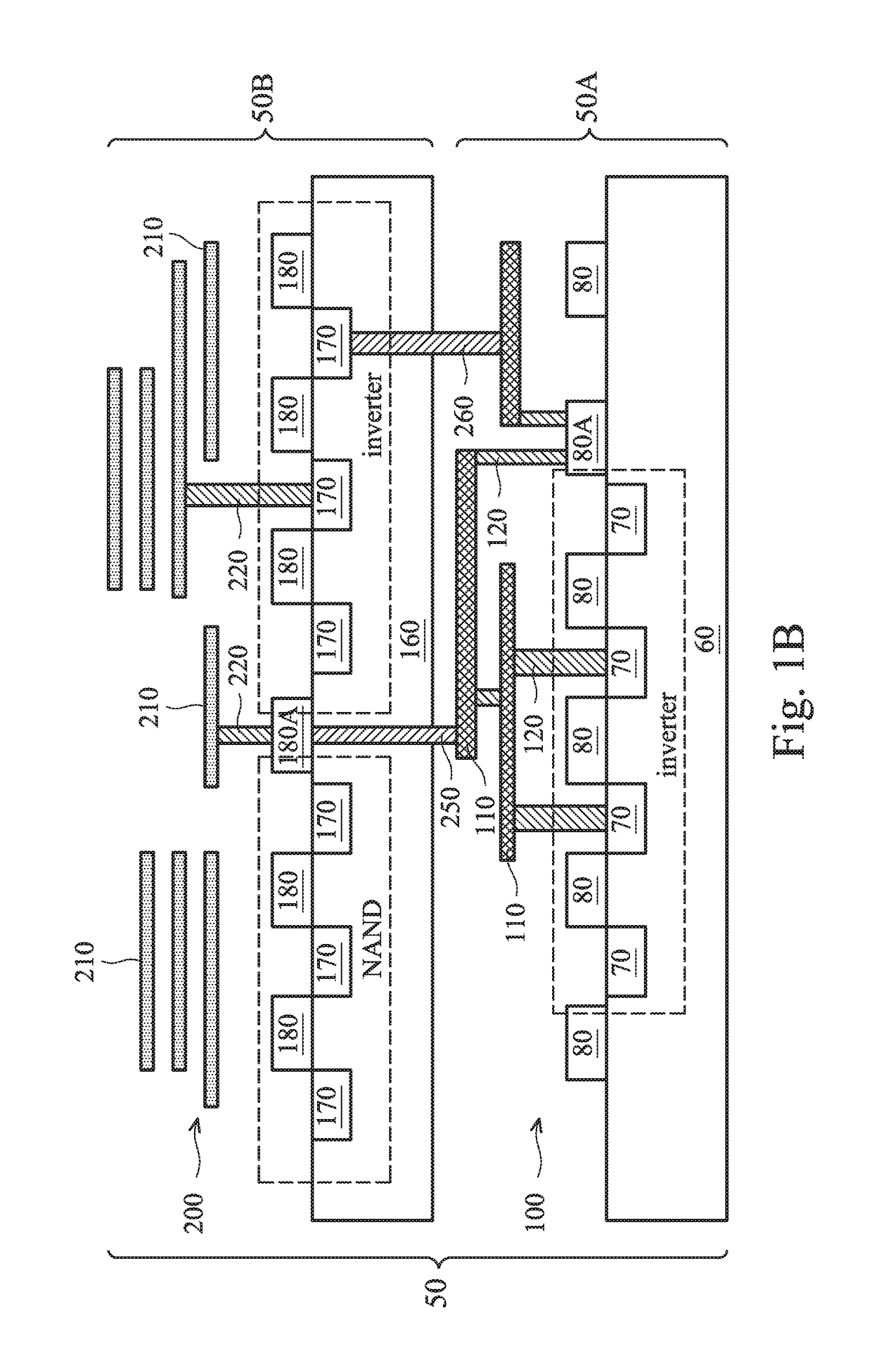

Monolithic 3D integration inter-tier vias insertion scheme and associated layout structure

ActiveUS20170287826A1Improve overall utilizationReduce areaTransistorSemiconductor/solid-state device detailsElectrical and Electronics engineeringEngineering

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor devices with copper interconnects and composite silicon nitride capping layers

ActiveUS7534732B1Improve data retentionReducing interconnect capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingElectromigrationSilicon nitride

Cu interconnects are formed with composite capping layers for reduced electromigration, improved adhesion between Cu and the capping layer, and reduced charge loss in associated non-volatile transistors. Embodiments include depositing a first relatively thin silicon nitride layer having a relatively high concentration of Si—H bonds on the upper surface of a layer of Cu for improved adhesion and reduced electromigration, and depositing a second relatively thick silicon nitride layer having a relatively low concentration of Si—H bonds on the first silicon nitride layer for reduced charge loss.

Owner:ADVANCED MICRO DEVICES INC

Semiconductor Device Comprising High-K Metal Gate Electrode Structures and Precision eFuses Formed in the Active Semiconductor Material

ActiveUS20120001295A1Low thermal conductivitySuperior heat conductivitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsEngineering

In a complex semiconductor device, electronic fuses may be formed in the active semiconductor material by using a semiconductor material of reduced heat conductivity selectively in the fuse body, wherein, in some illustrative embodiments, the fuse body may be delineated by a non-silicided semiconductor base material.

Owner:GLOBALFOUNDRIES US INC

Semiconductor device and manufacturing method thereof

InactiveUS20070145600A1High yieldImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesDielectricCopper

A semiconductor device includes an embedded wire in a first wire trench formed in a first interlayer dielectric film, the embedded wire having a barrier metal, a first seed film, a second seed film, and a copper film. The first seed film is formed by a copper film containing metal, and the second film is formed by a copper film. The second seed film suppresses that the metal contained in the first seed film diffuses into a wiring material film in a manufacturing process.

Owner:PANASONIC CORP +1

Method of reducing erosion of a metal cap layer during via patterning in semiconductor devices

ActiveUS7986040B2Avoiding undue material removalImprove electromigrationSemiconductor/solid-state device detailsSolid-state devicesIon bombardmentMaterial removal

Owner:ADVANCED MICRO DEVICES INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com