Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

33results about How to "Competitive advantage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

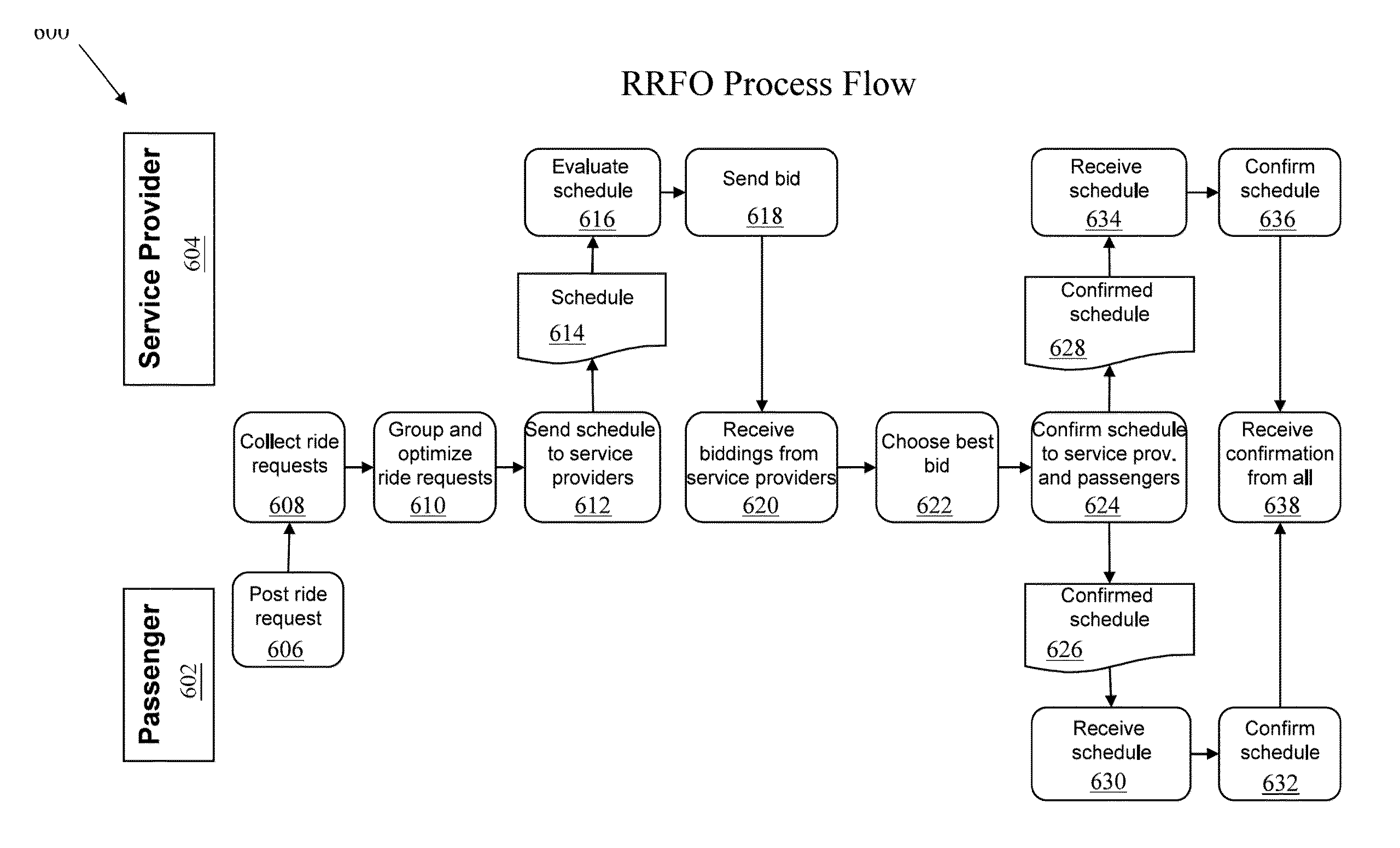

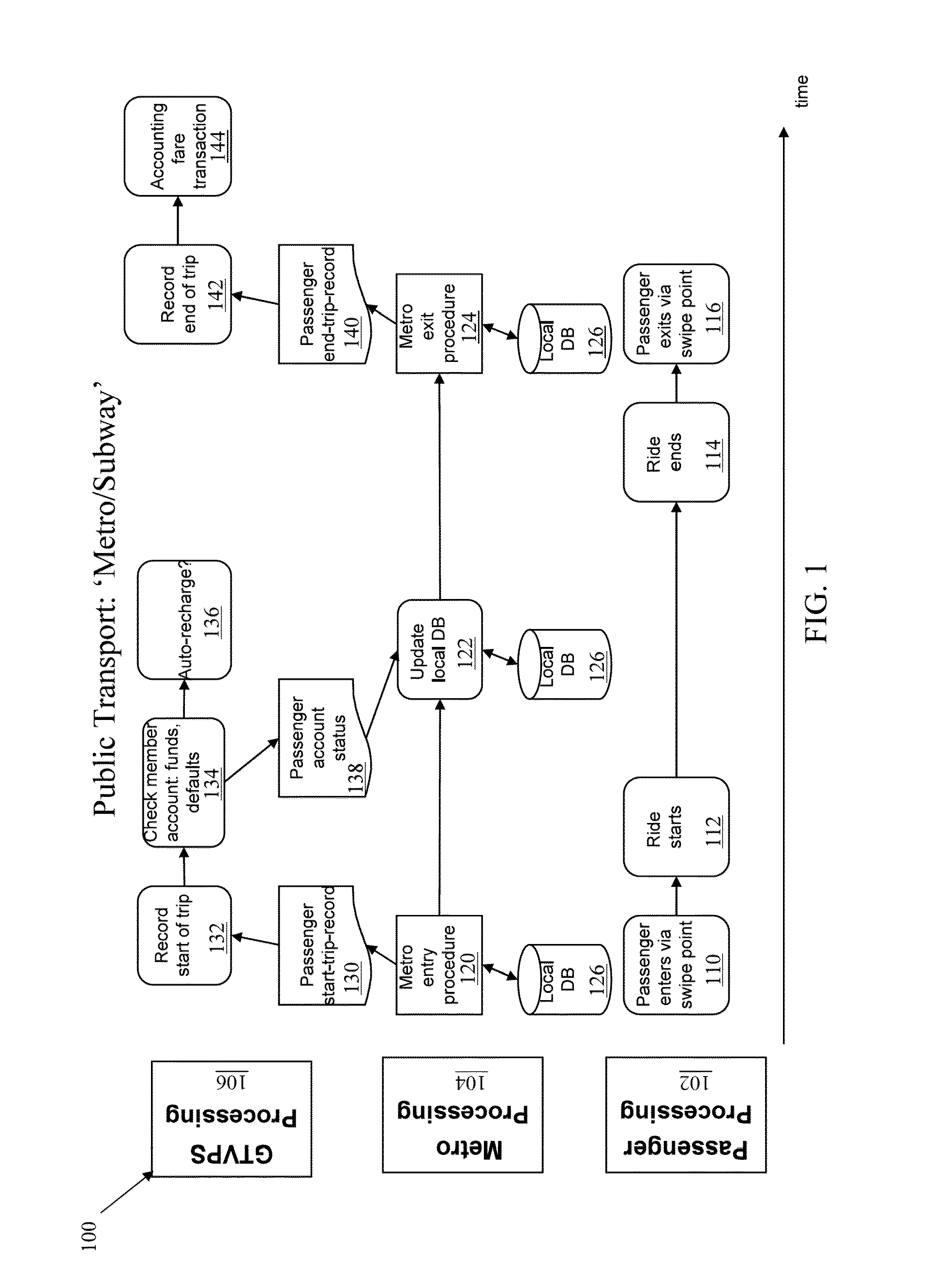

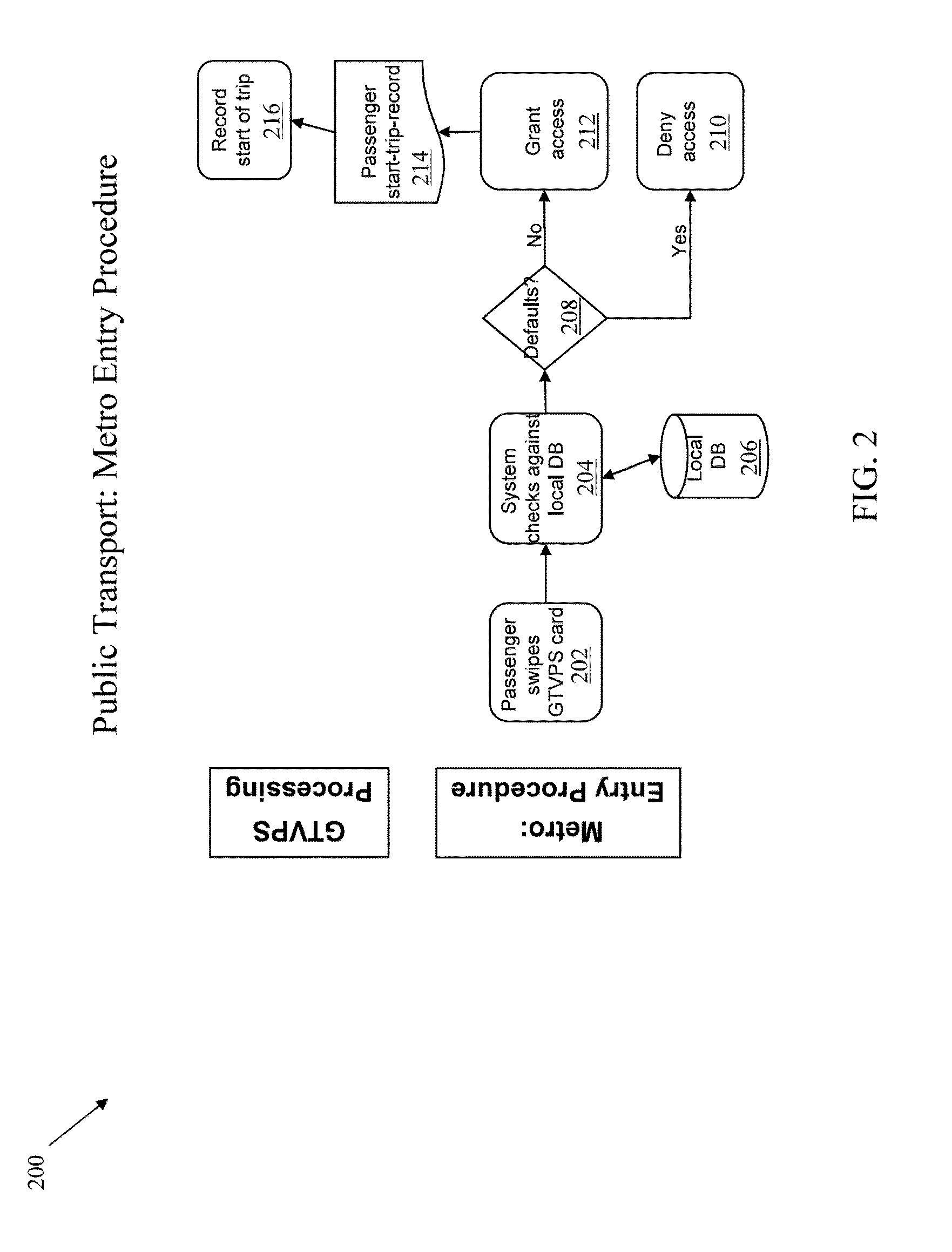

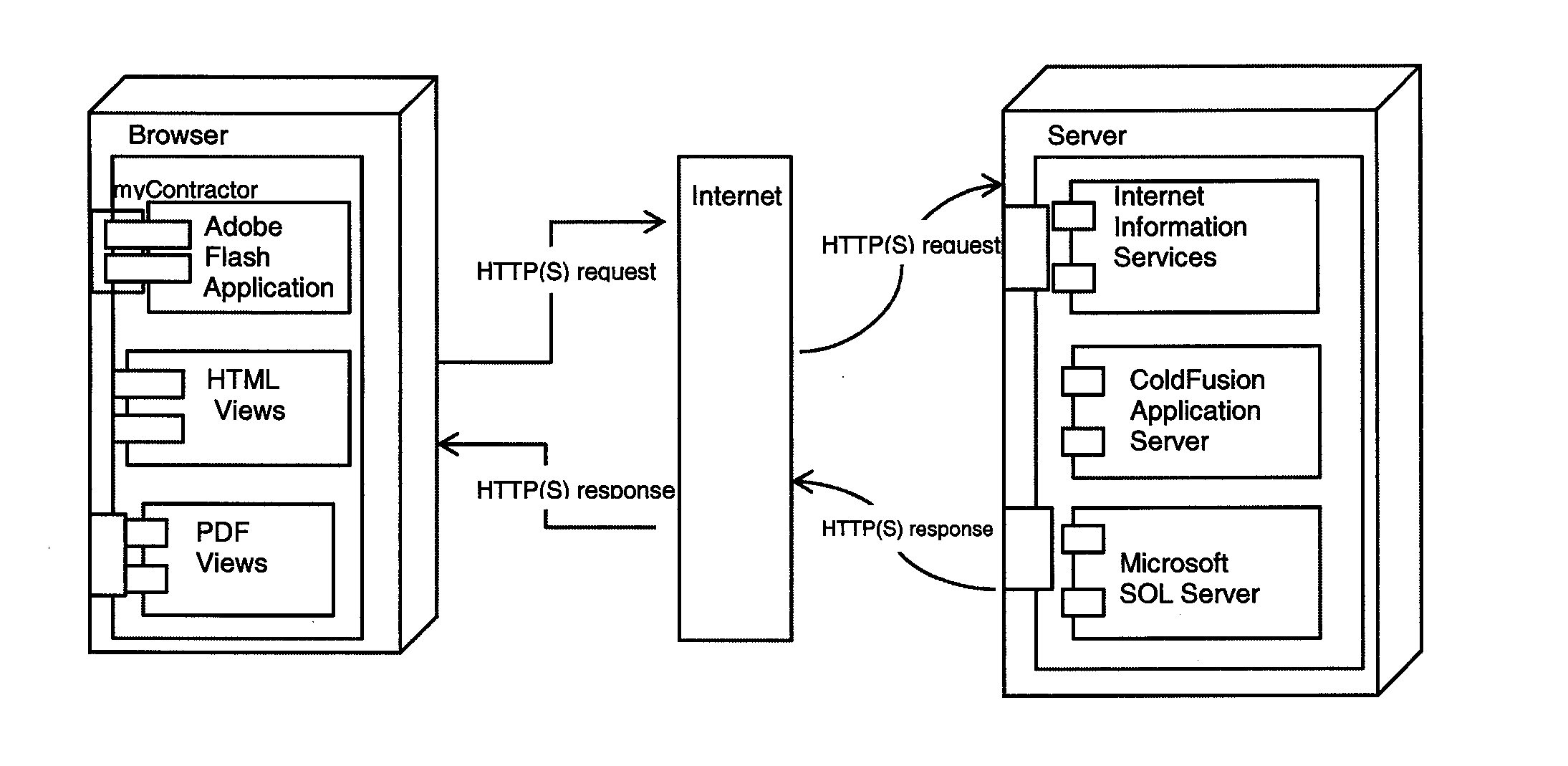

Systems and methods for global transportation,vetting, and payment

Described are computer-based methods and apparatuses, including computer program products, for use and payment of global transportation and vetting systems and methods.

Owner:ZAHN WALTER

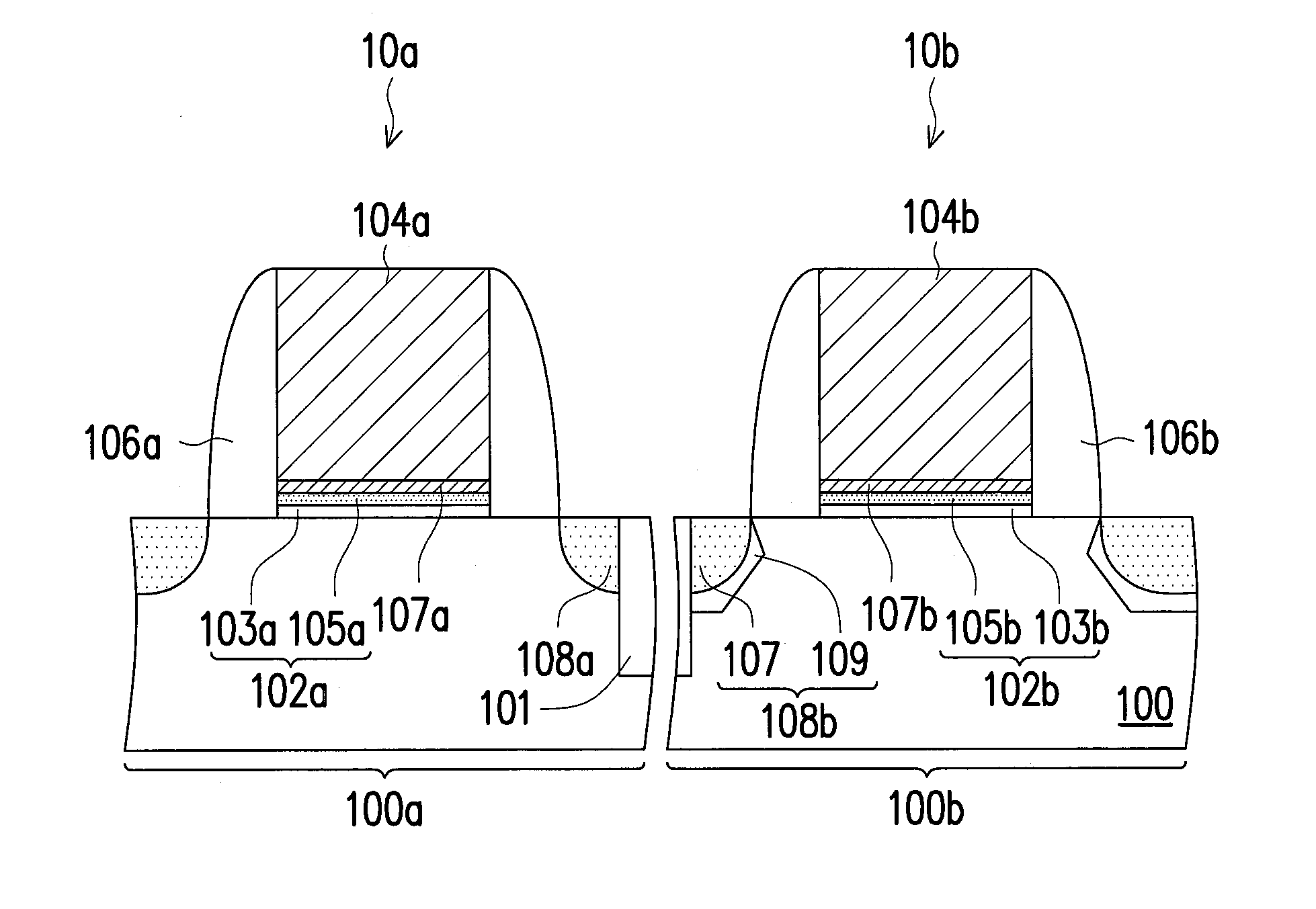

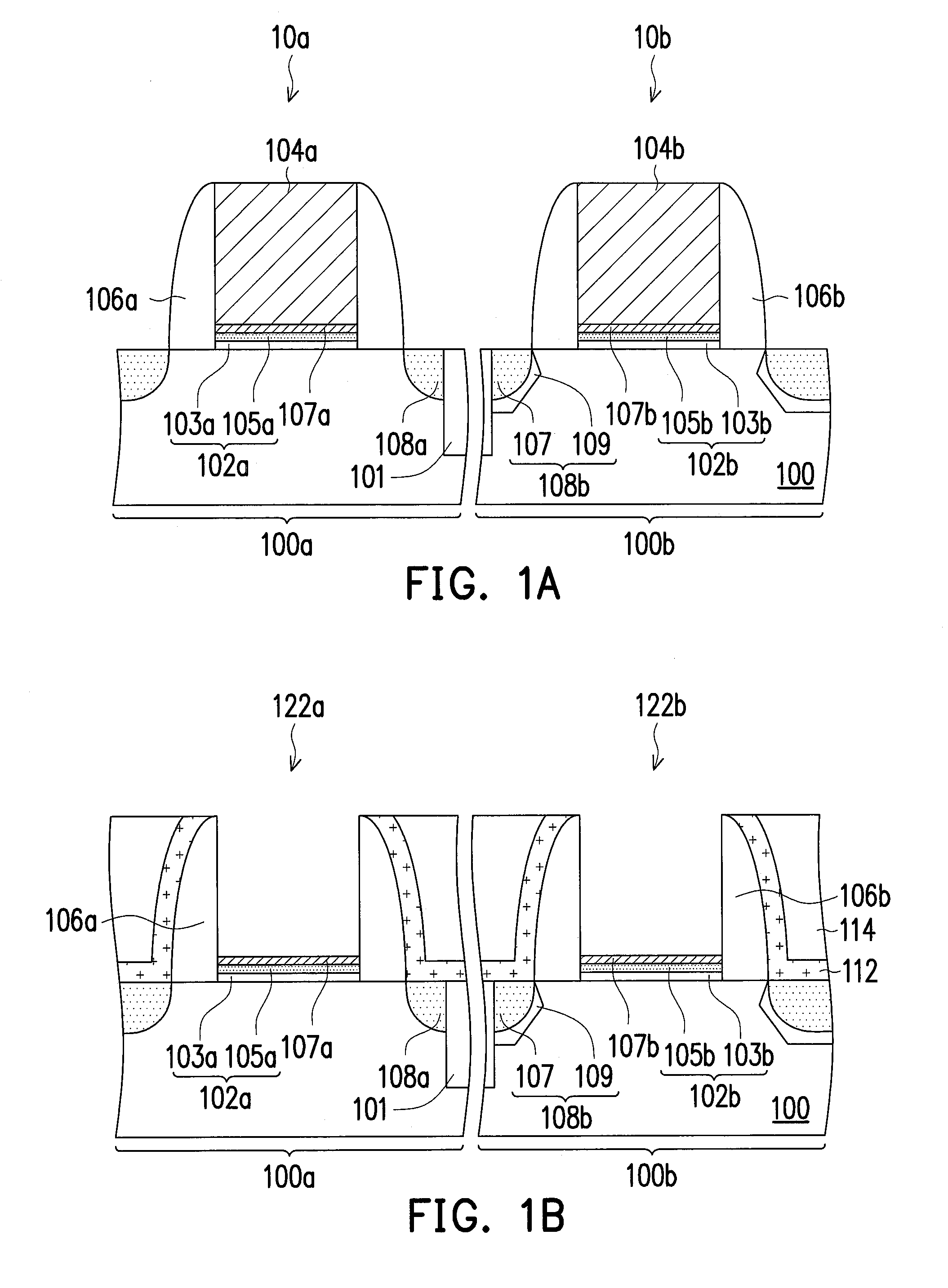

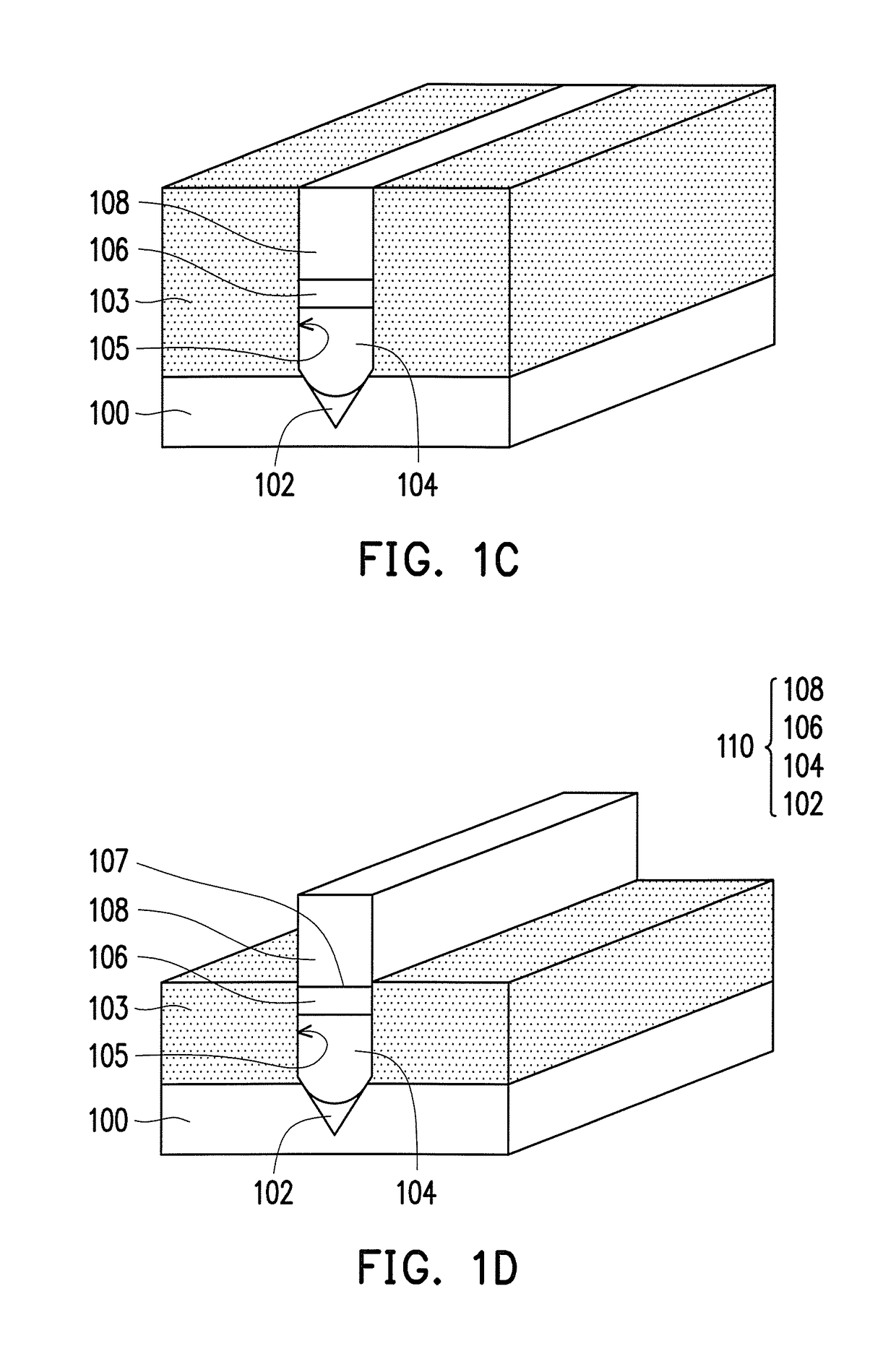

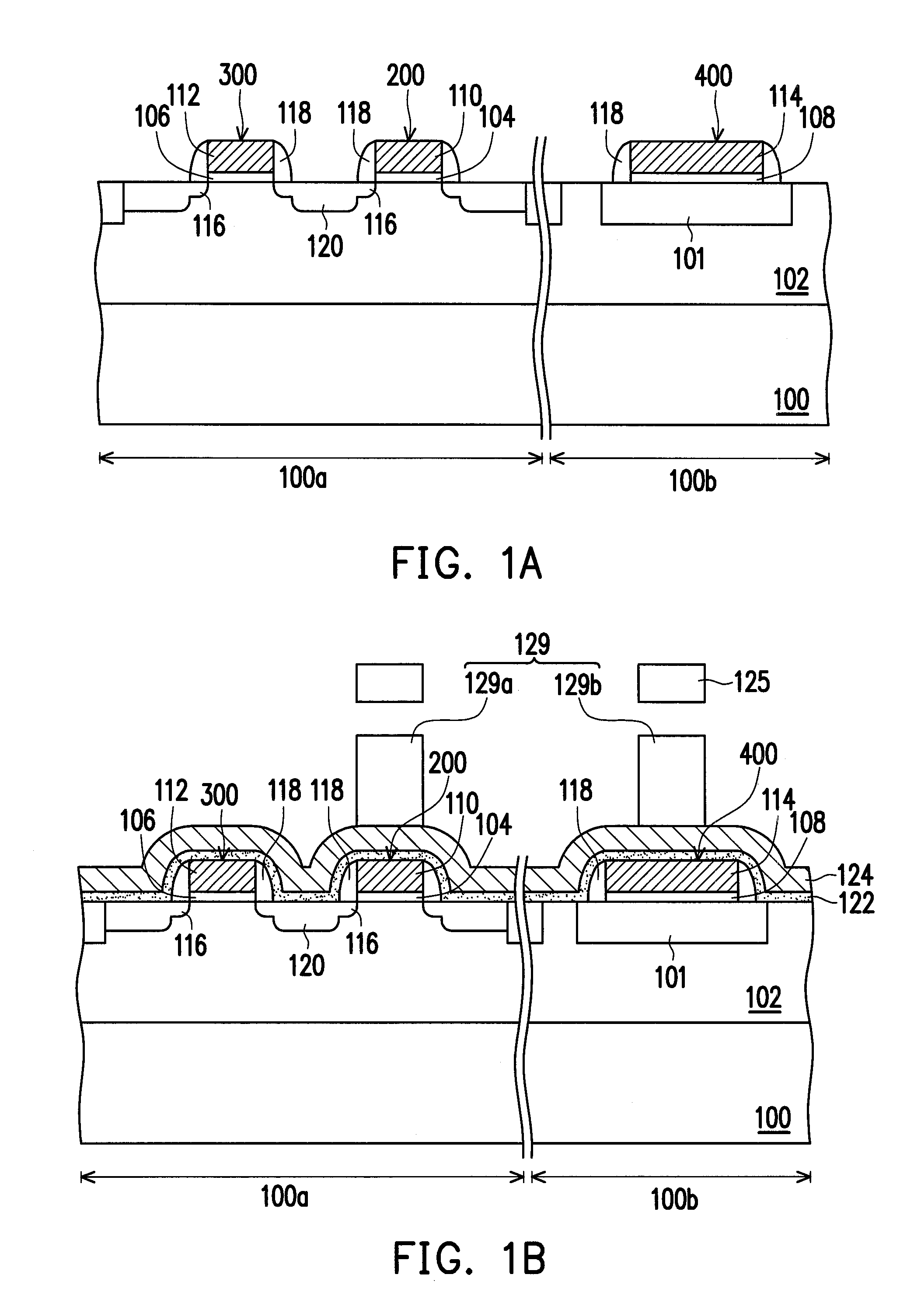

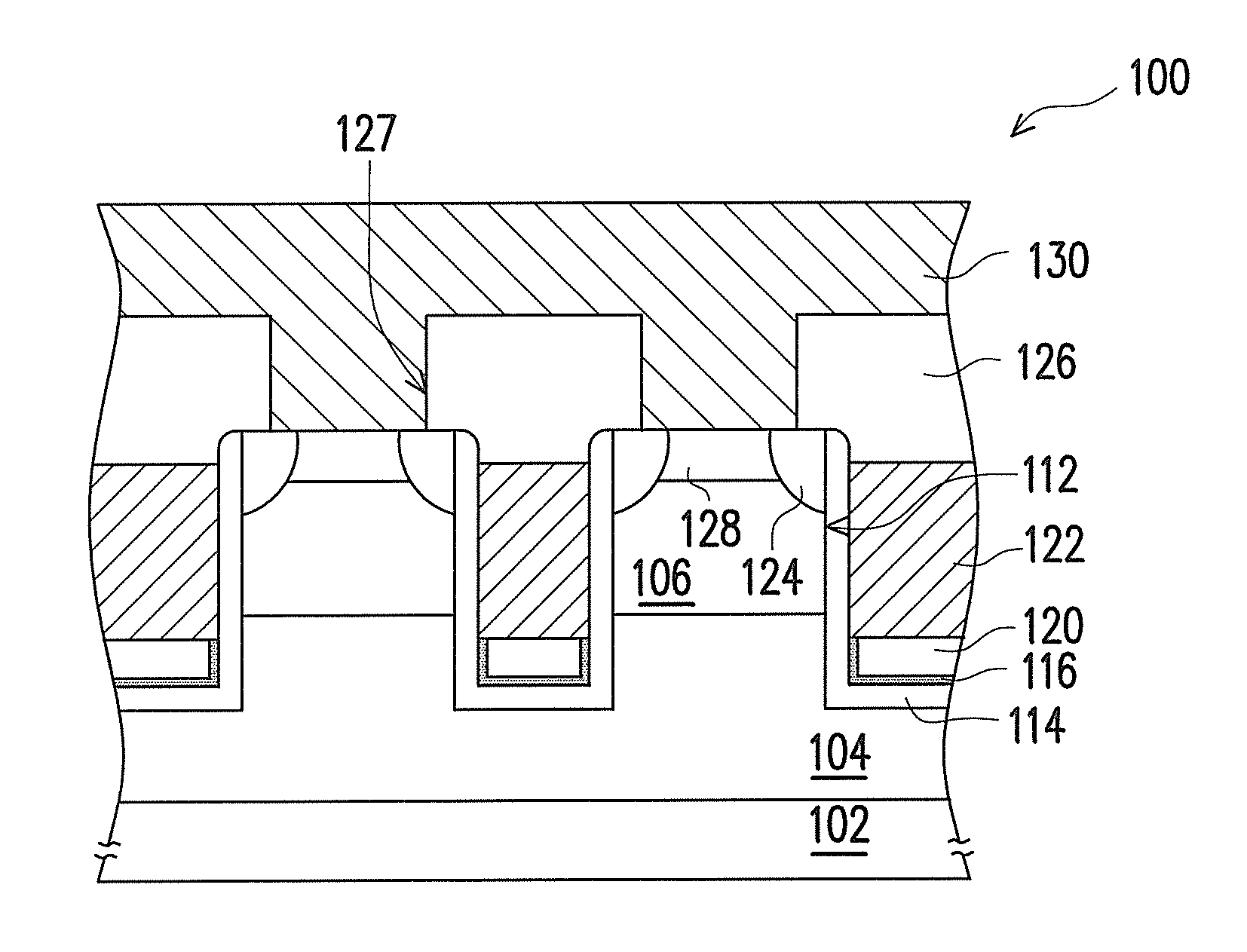

Semiconductor structure and method of forming the same

ActiveUS20150061041A1Effective blockingImprove device performanceSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor structure

A method of forming a semiconductor device is disclosed. A substrate having a dielectric layer thereon is provided. The dielectric layer has a gate trench therein and a gate dielectric layer is formed on a bottom of the gate trench. A work function metal layer and a top barrier layer are sequentially formed in the gate trench. A treatment is performed to the top barrier layer so as to form a silicon-containing top barrier layer. A low-resistivity metal layer is formed in the gate trench.

Owner:UNITED MICROELECTRONICS CORP

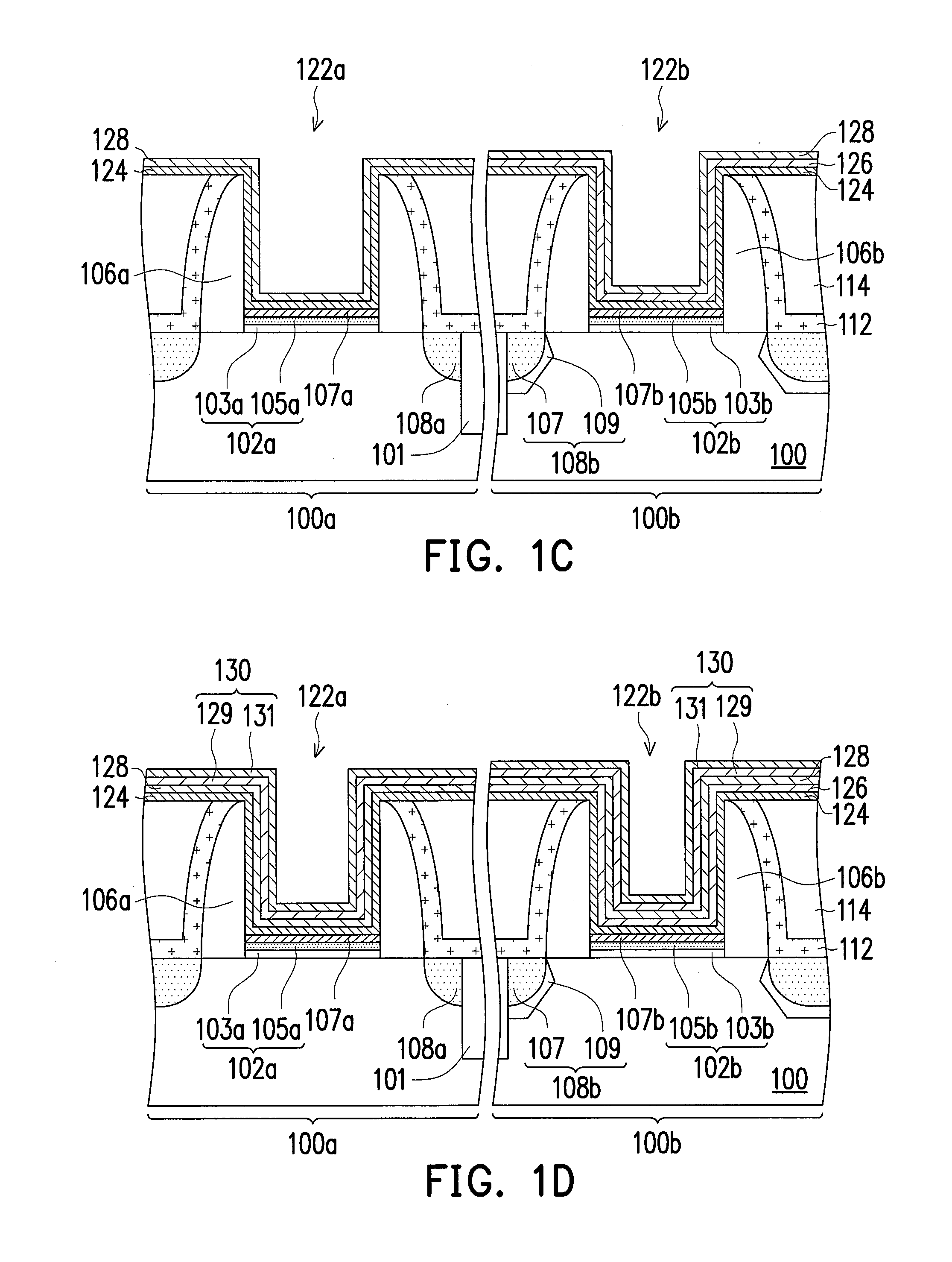

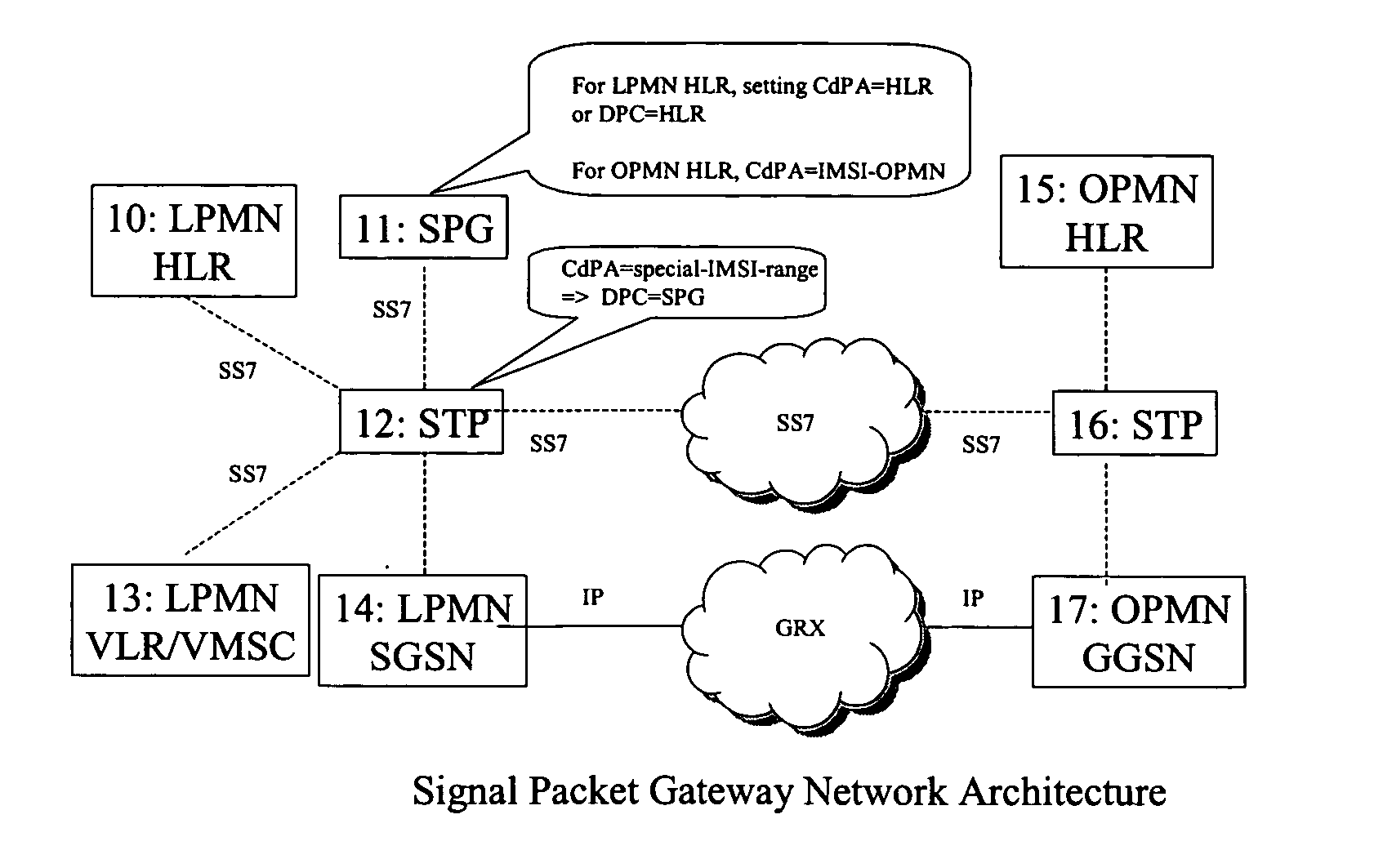

Method and apparatus for subscribers to use a proprietary wireless e-mail and personal information service within a public mobile network not otherwise configured to enable that use

Methods and systems are described herein enabling a local public mobile network that is not configured to offer a certain type proprietary wireless e-mail and personal information service (such as a Blackberry service) to one of its subscribers that otherwise subscribes to such a proprietary service via non-local public network.

Owner:ROAMWARE

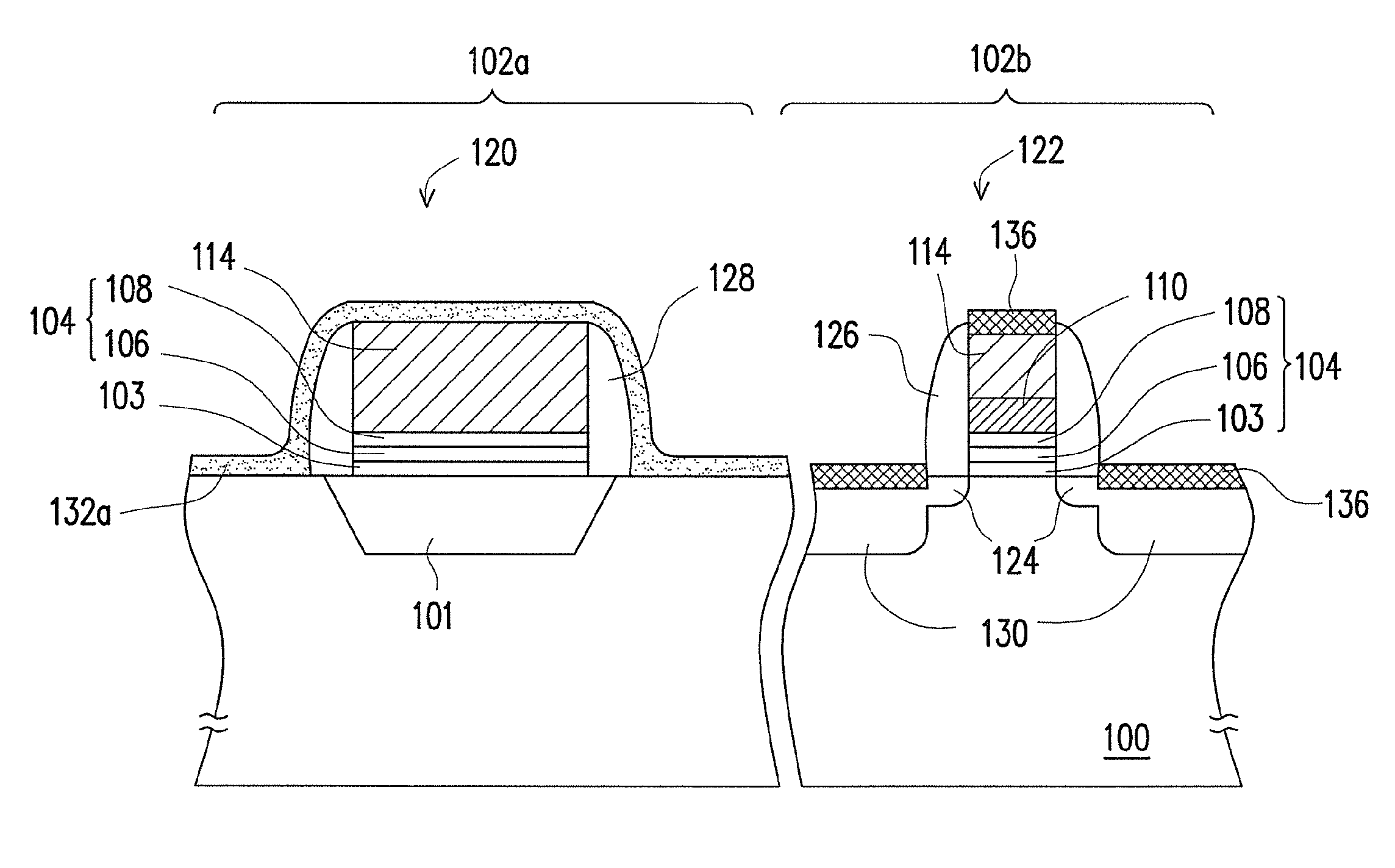

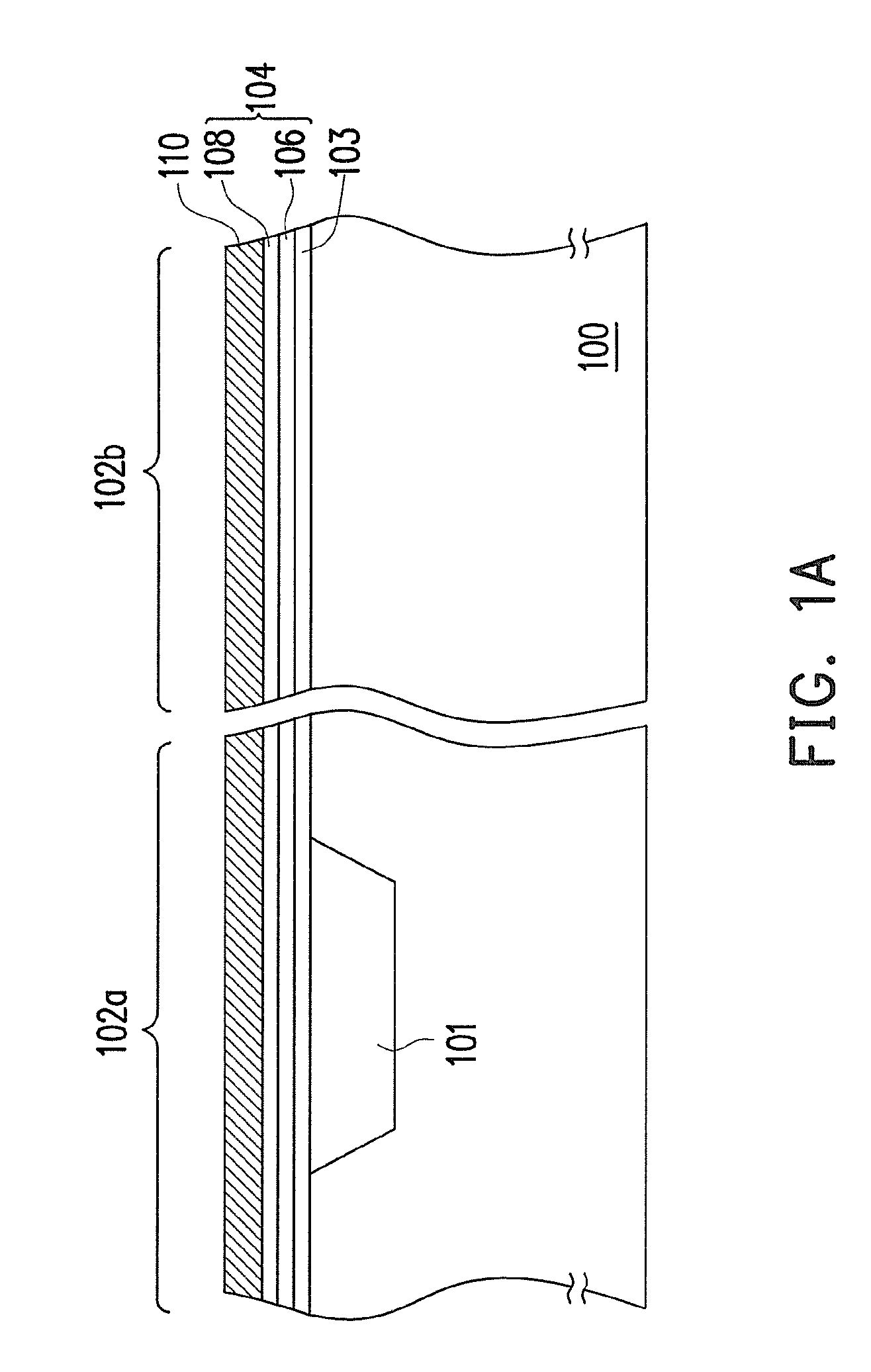

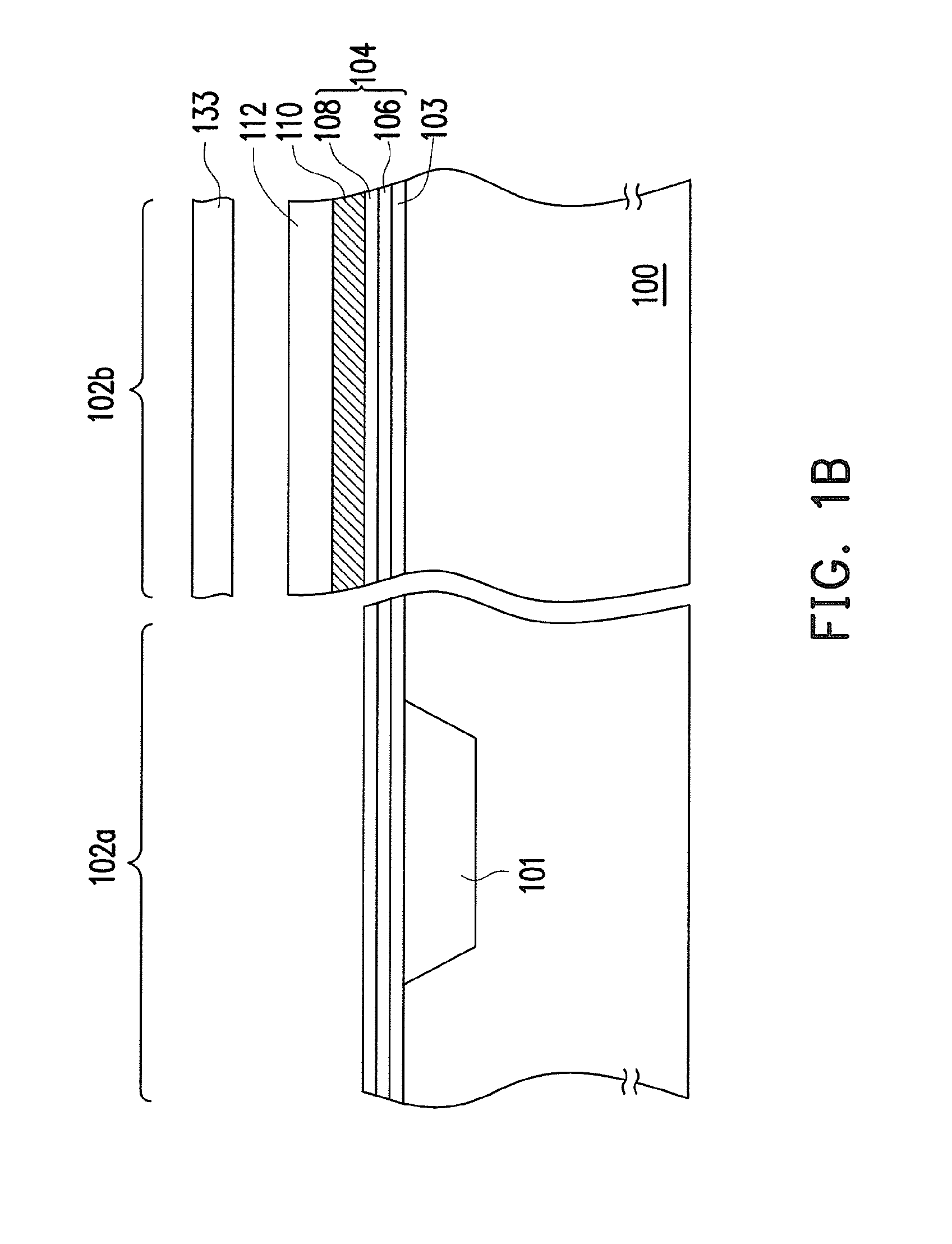

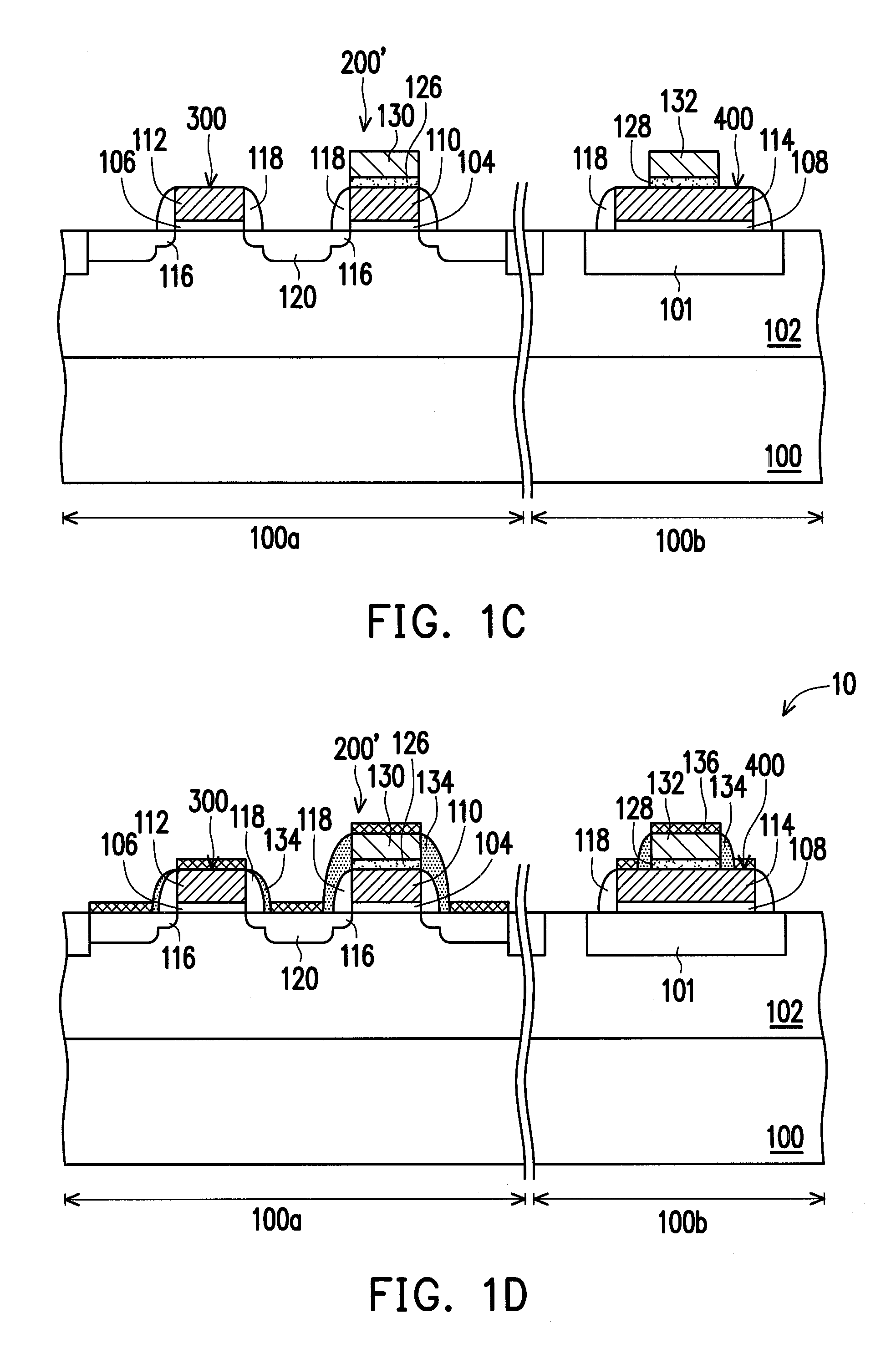

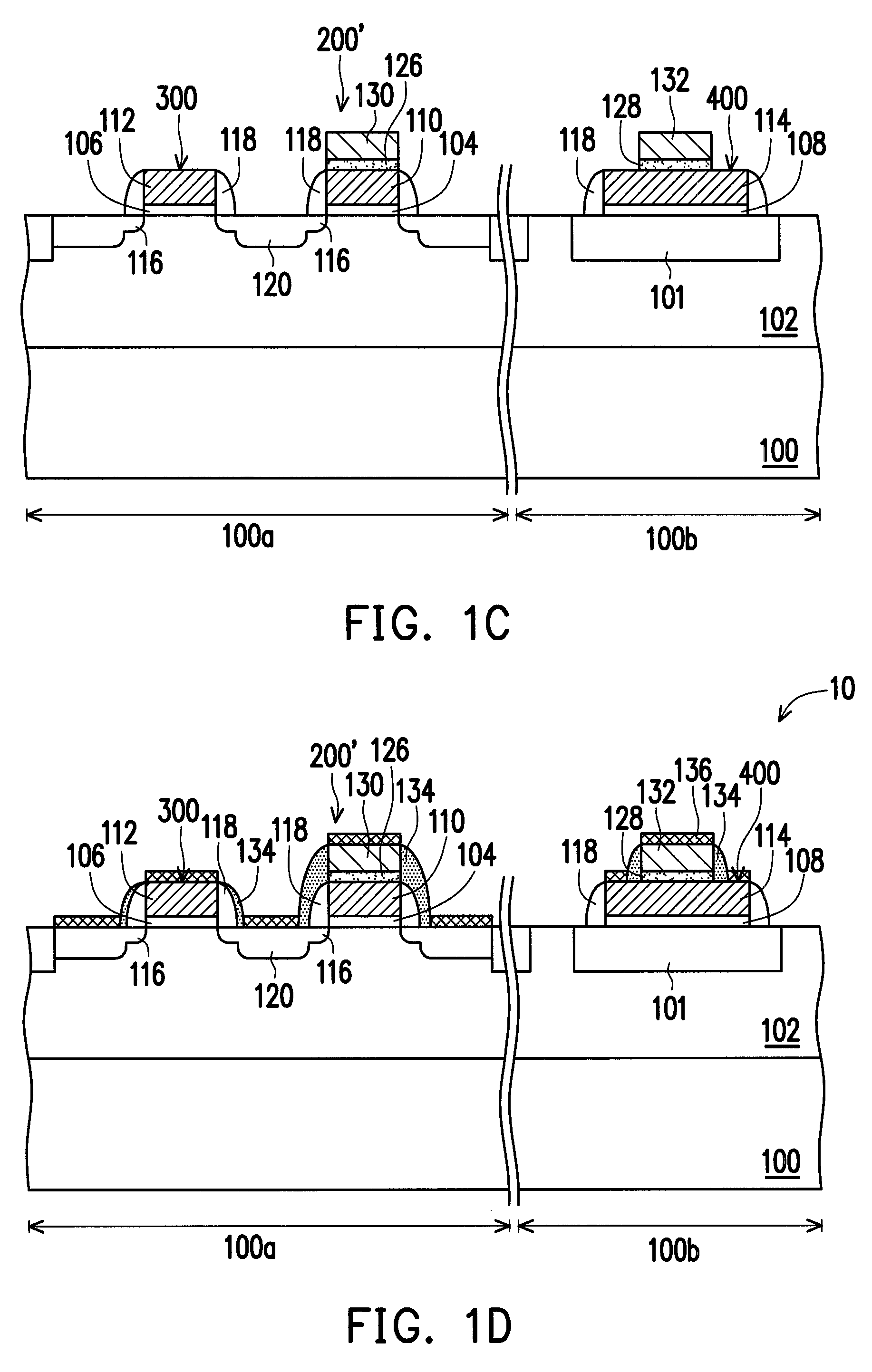

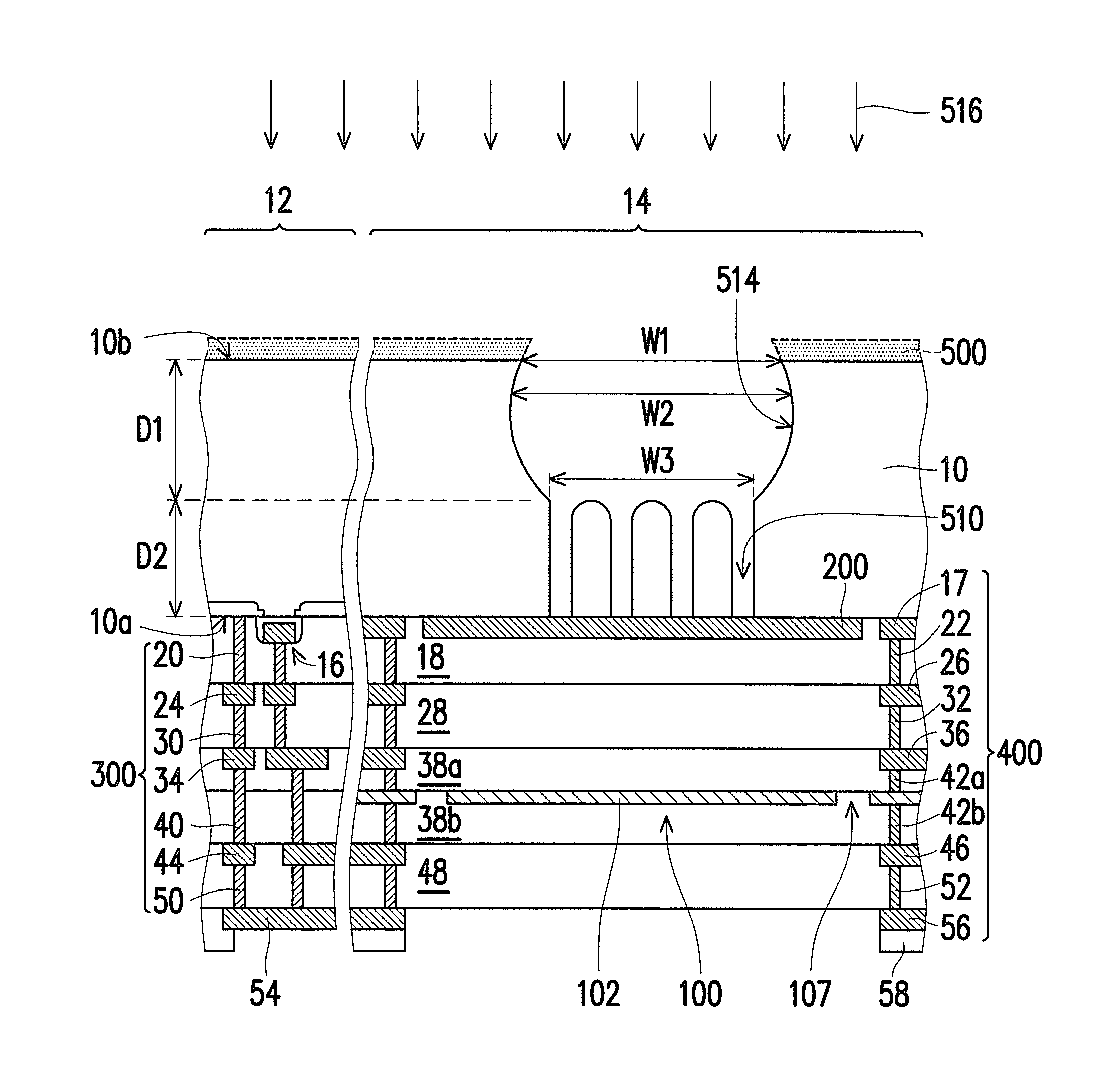

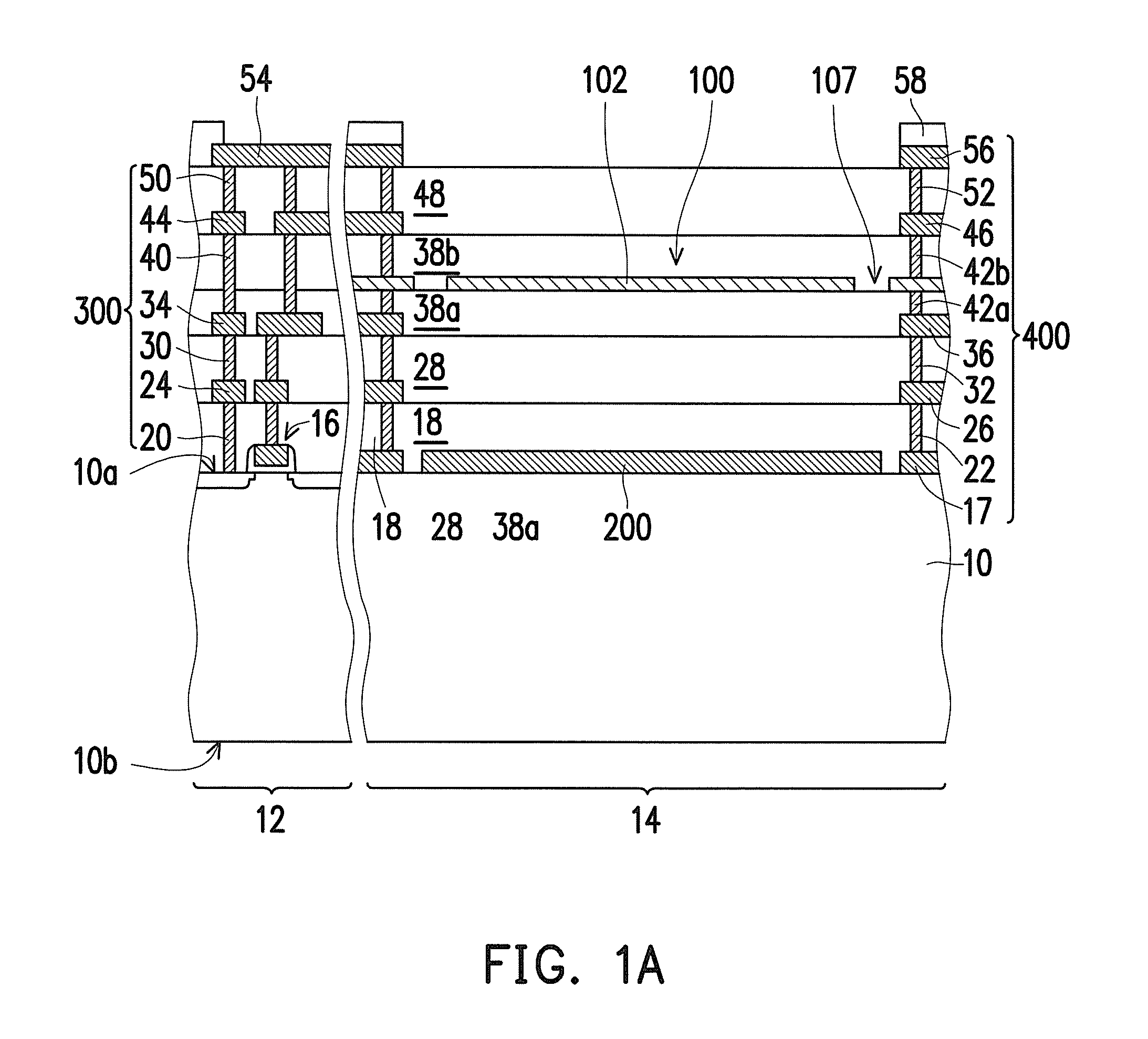

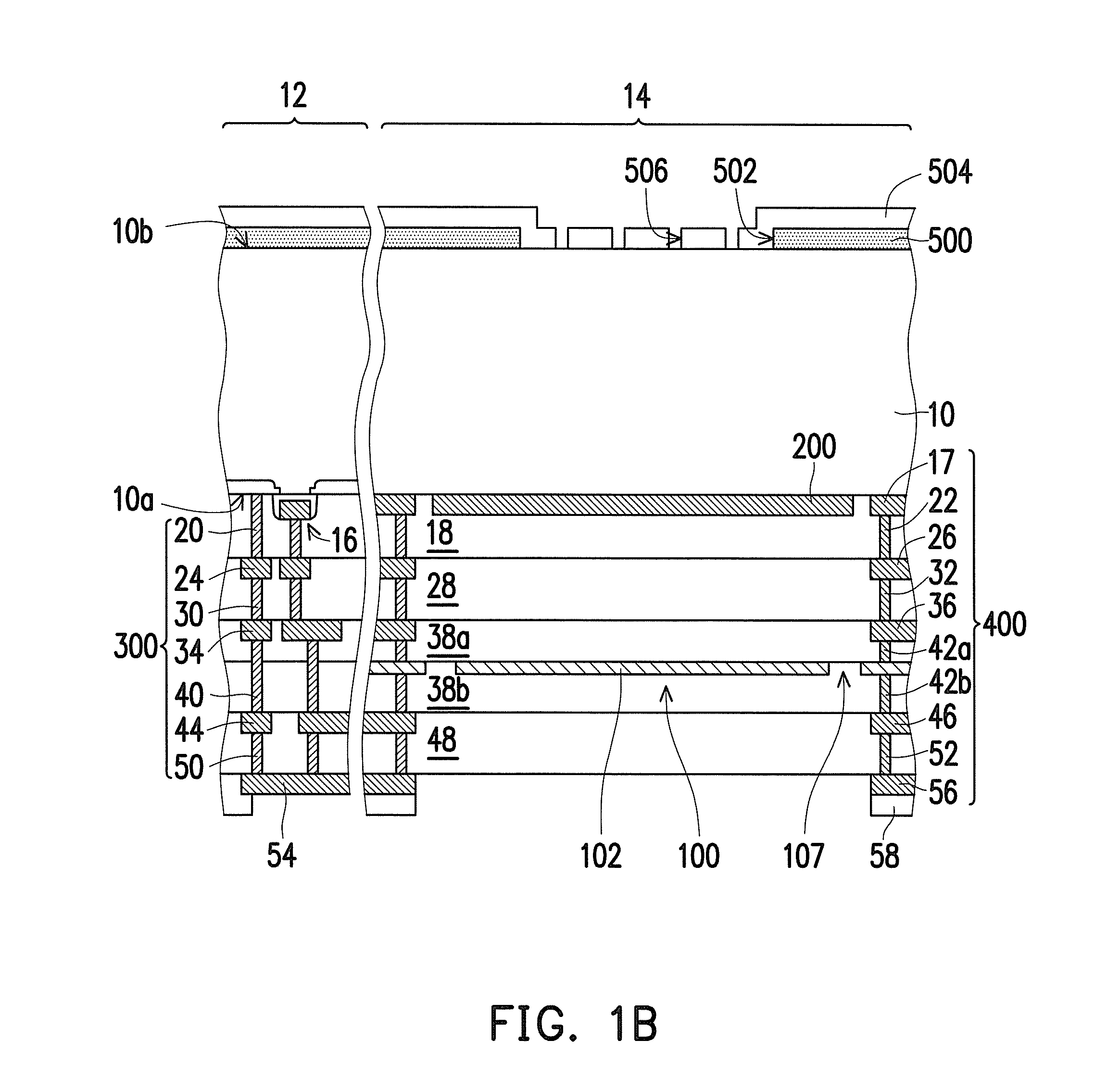

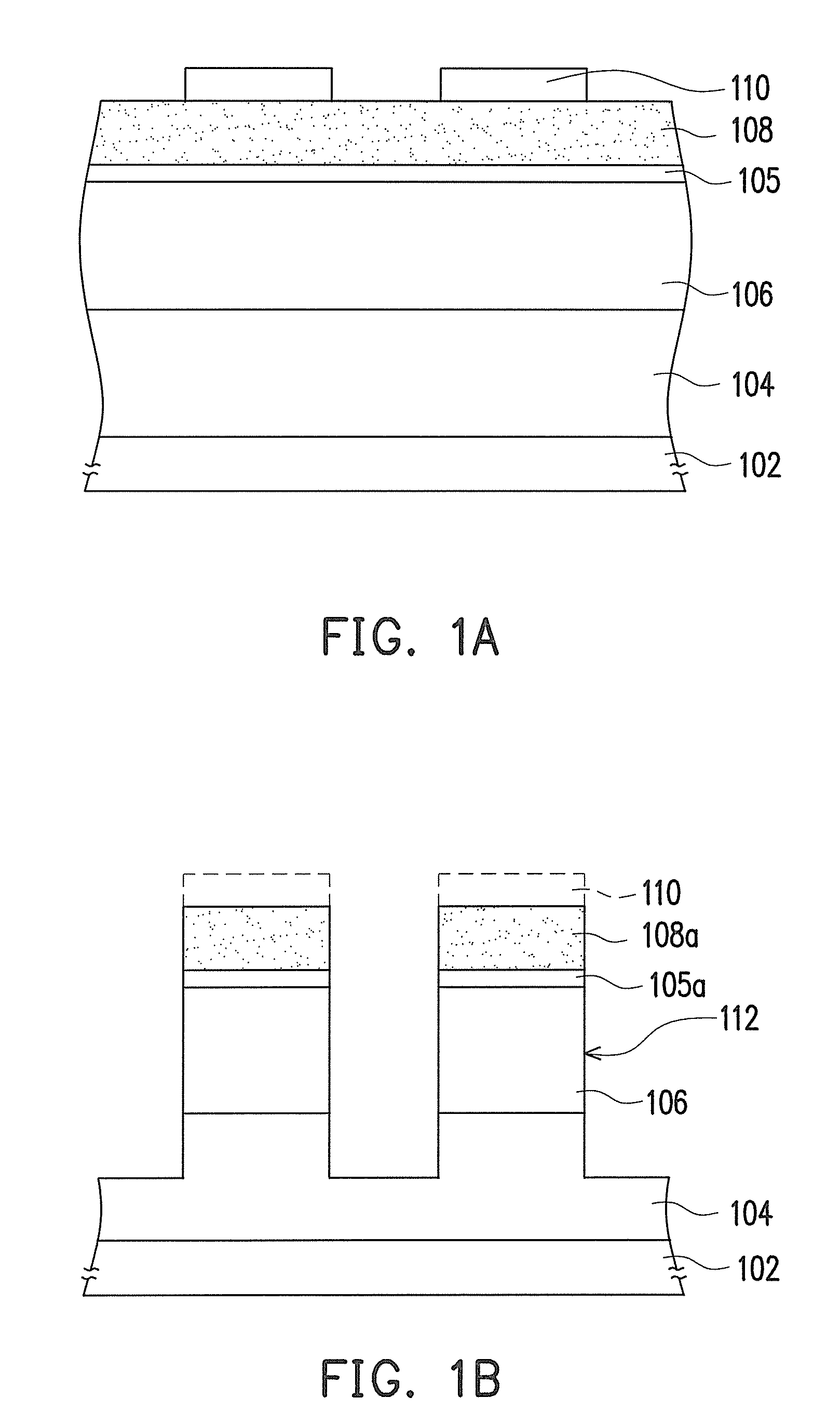

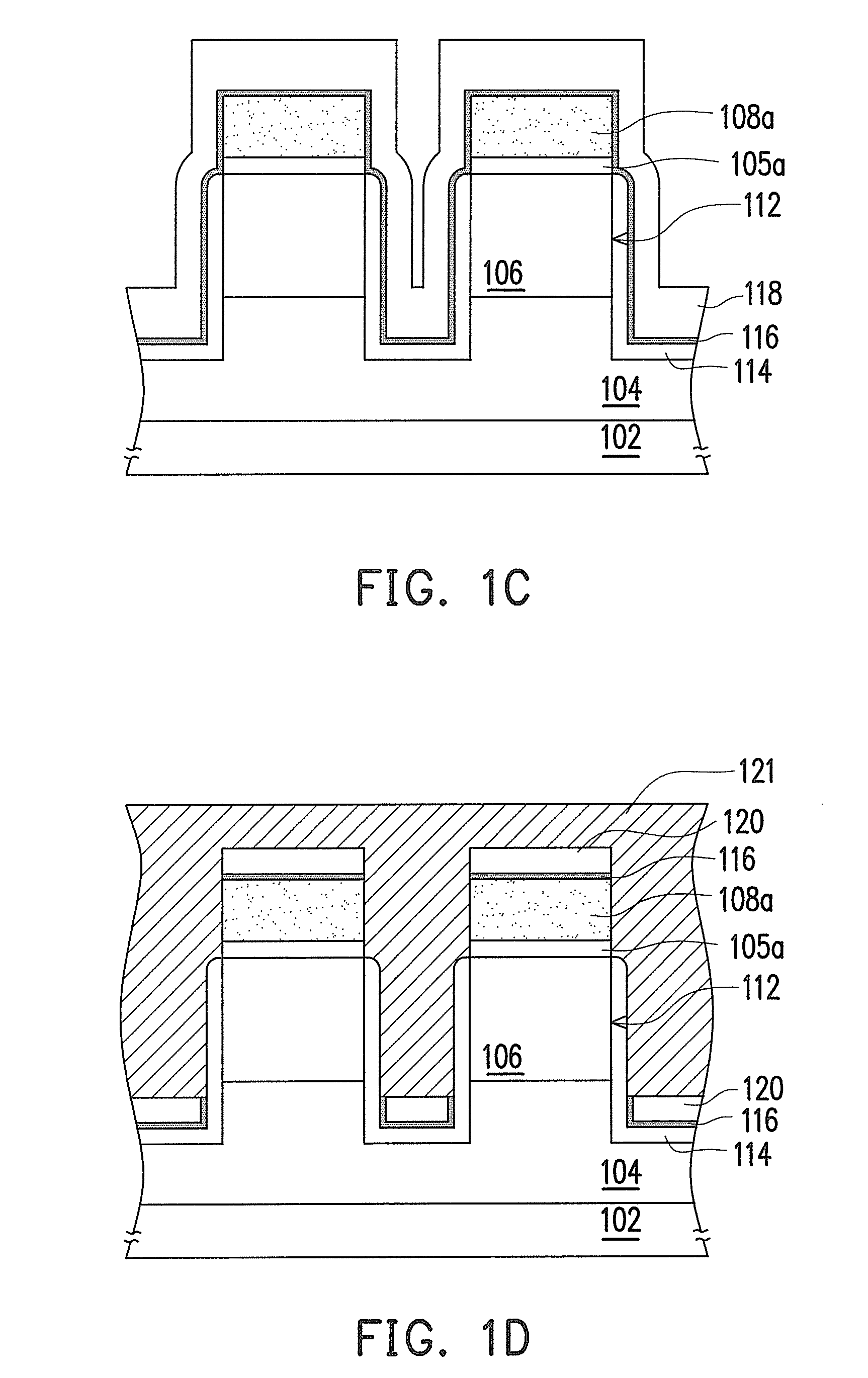

Method of forming semiconductor structure

InactiveUS20150079780A1Improve device performanceImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureDevice material

A method of forming a semiconductor device is disclosed. A gate structure is formed on a substrate. The gate structure includes a dummy gate and a spacer at a sidewall of the dummy gate. A dielectric layer is formed on the substrate outside of the gate structure. A metal hard mask layer is formed to cover tops of the dielectric layer and the spacer and to expose a surface of the gate structure. The dummy gate is removed to form a gate trench. A low-resistivity metal layer is formed on the metal hard mask layer filling in the gate trench. The low-resistivity metal layer outside of the gate trench is removed. The metal hard mask layer is removed.

Owner:UNITED MICROELECTRONICS CORP

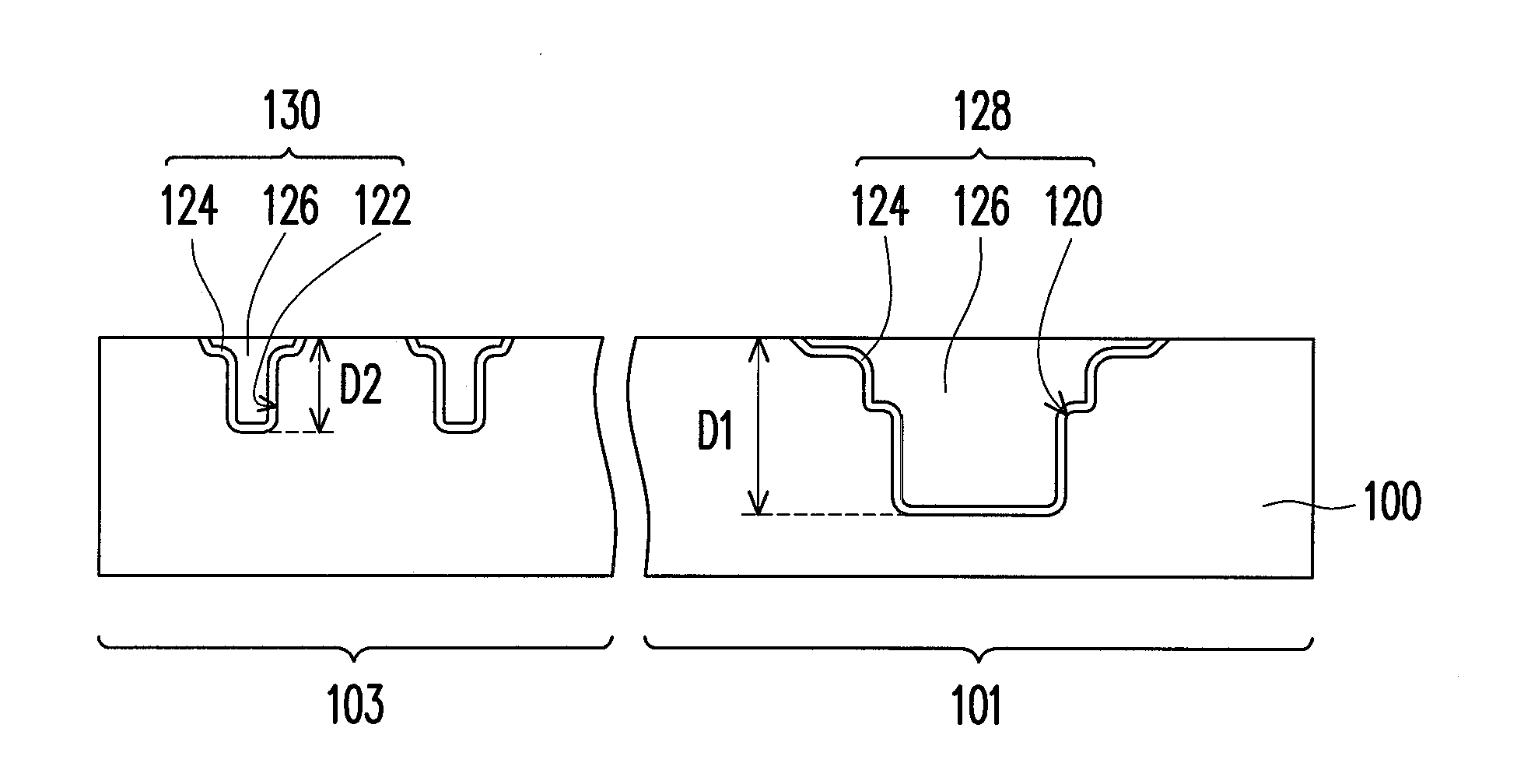

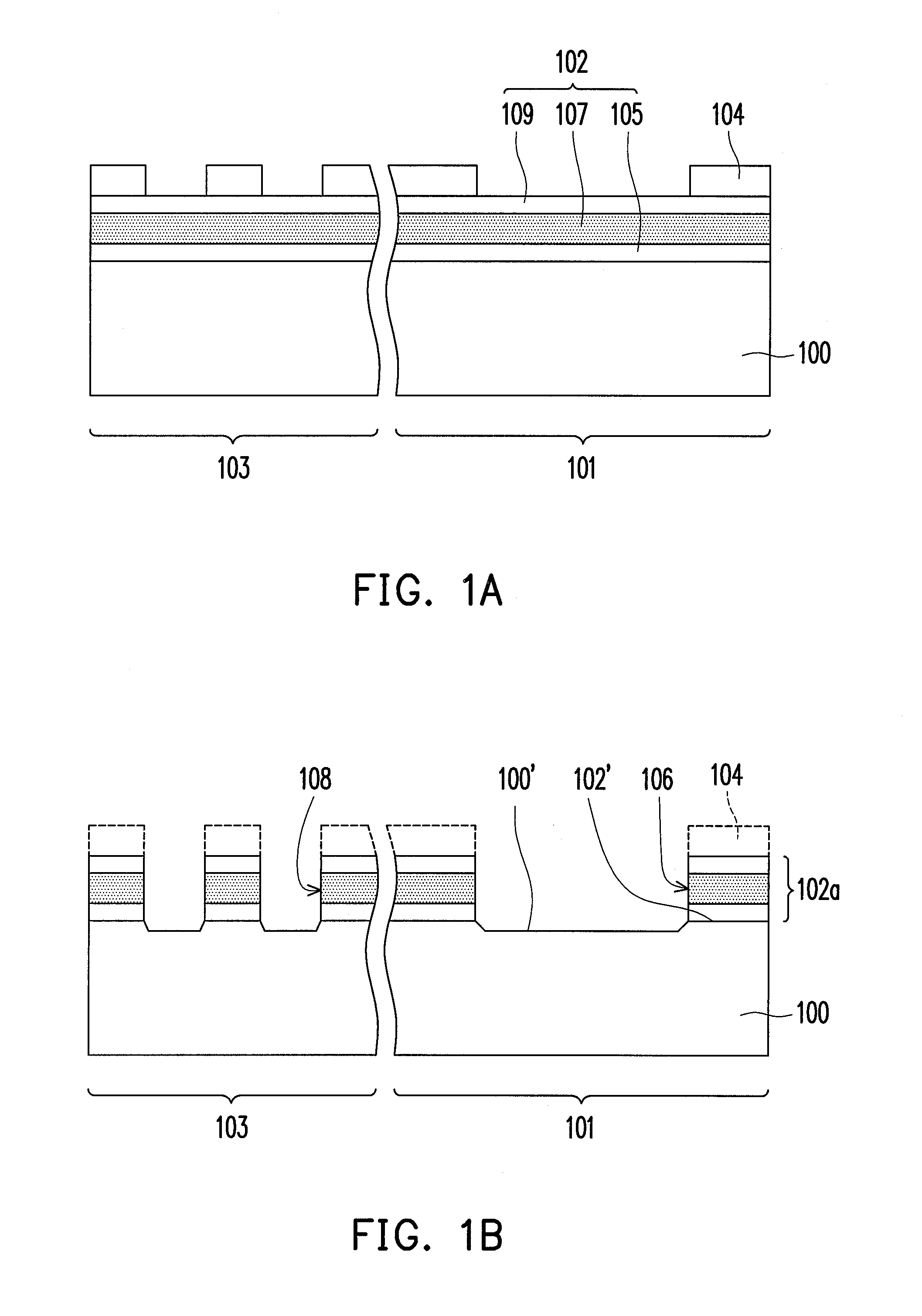

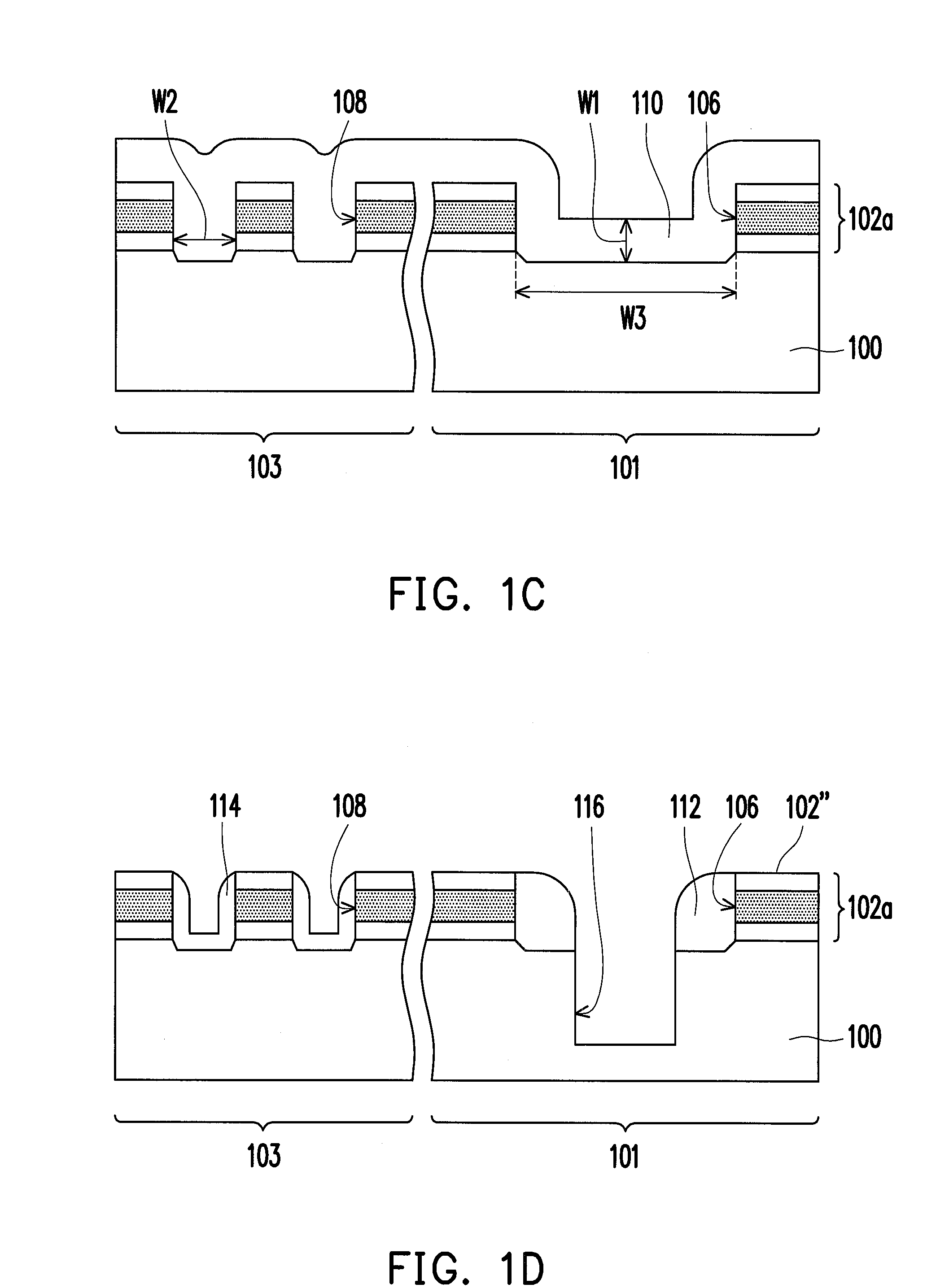

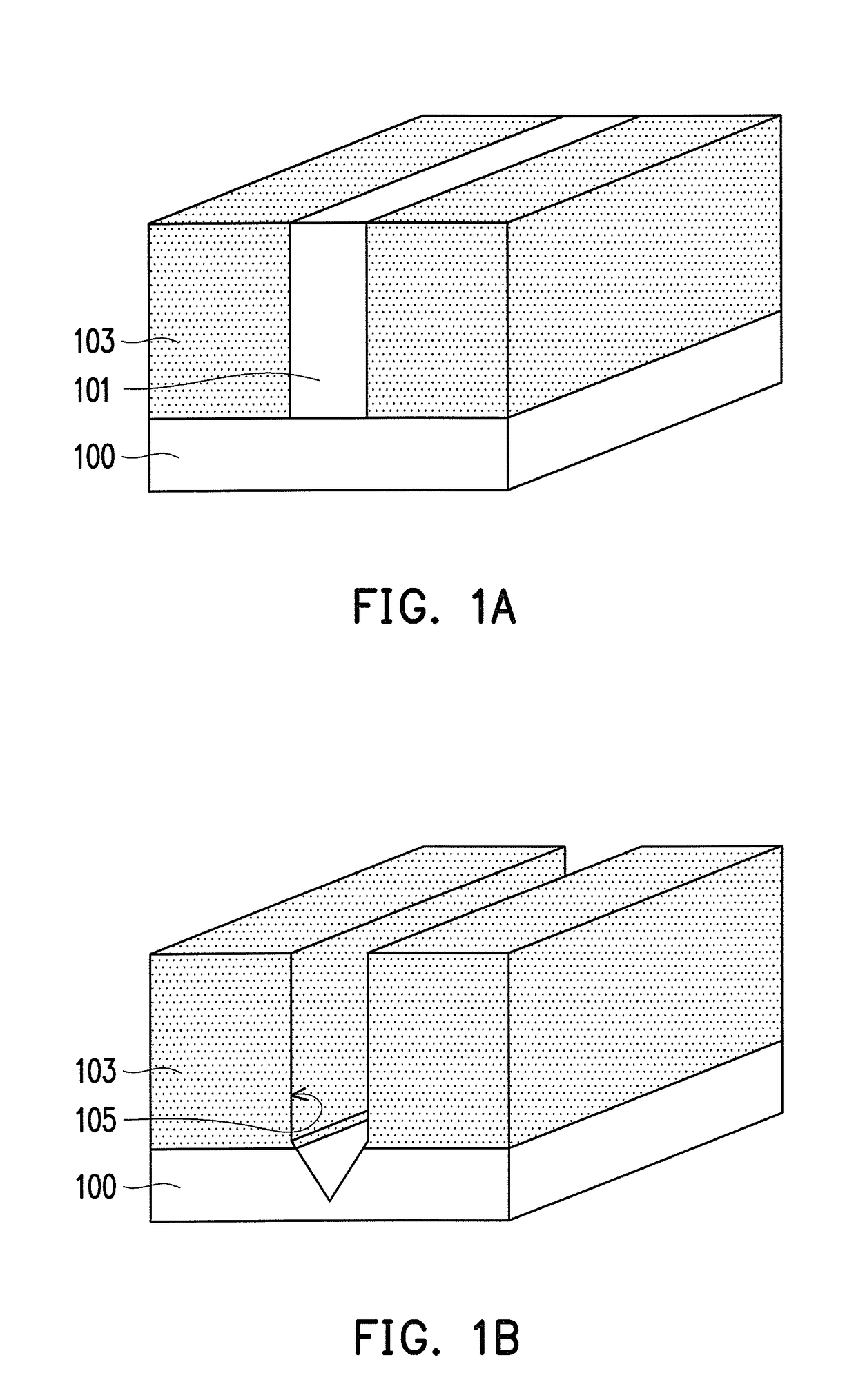

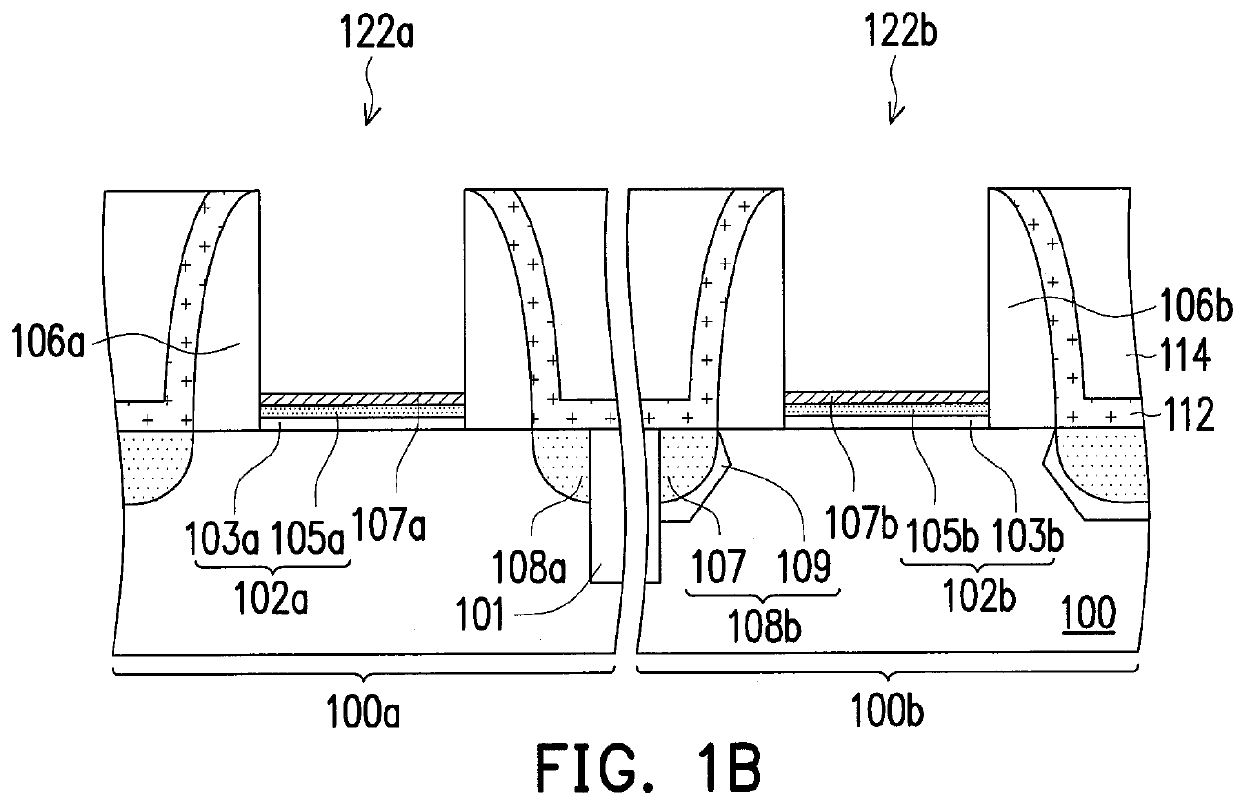

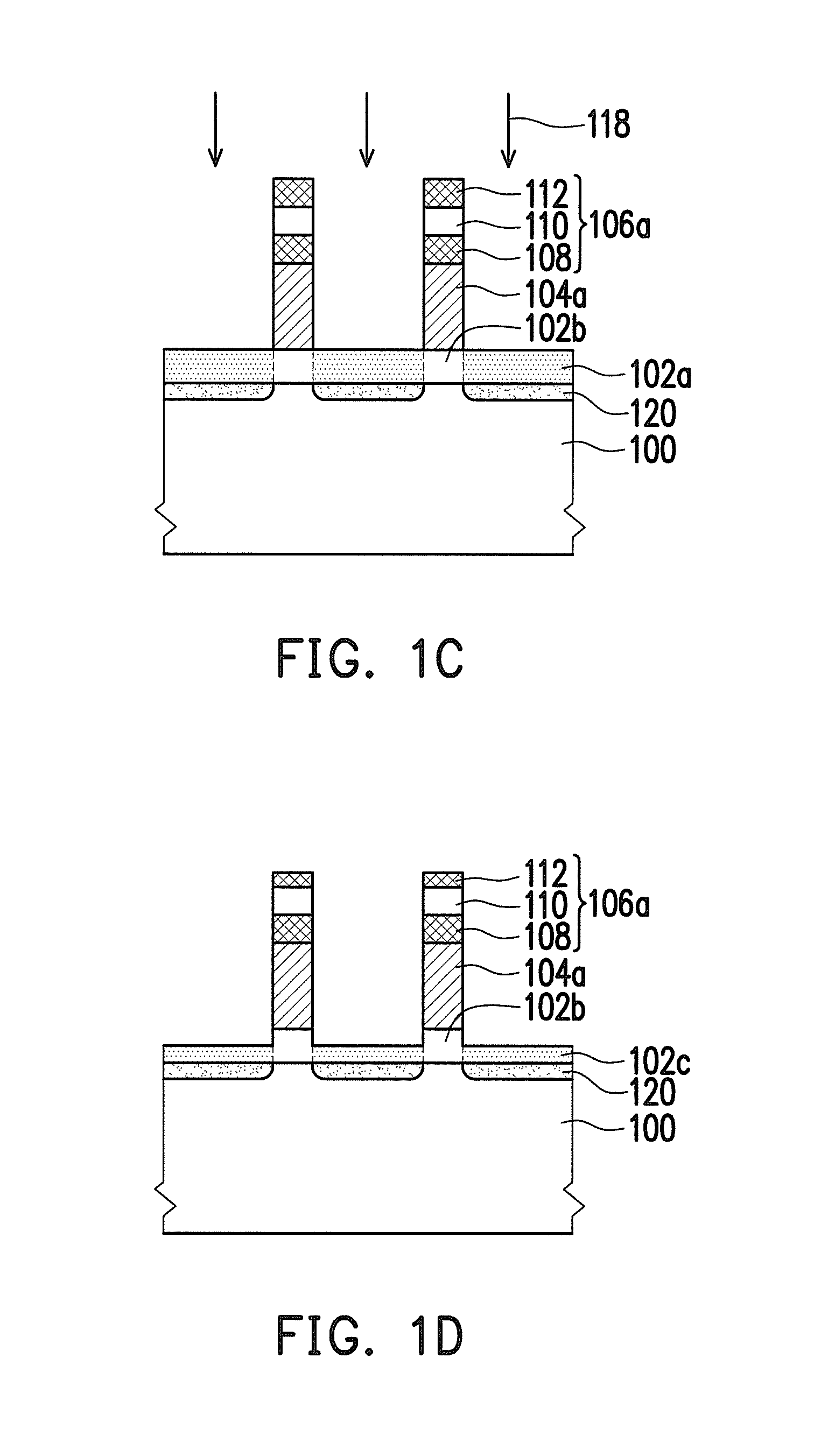

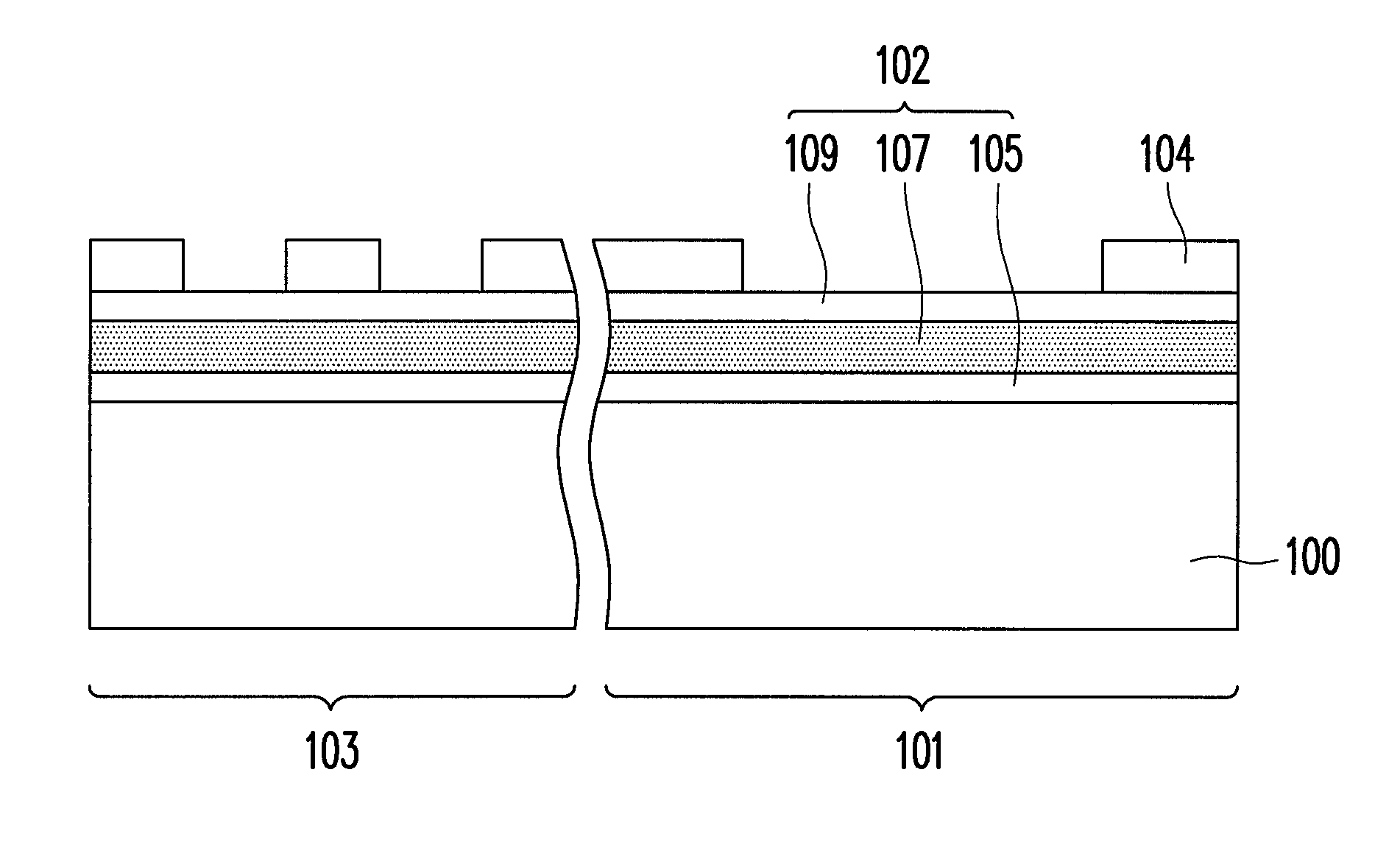

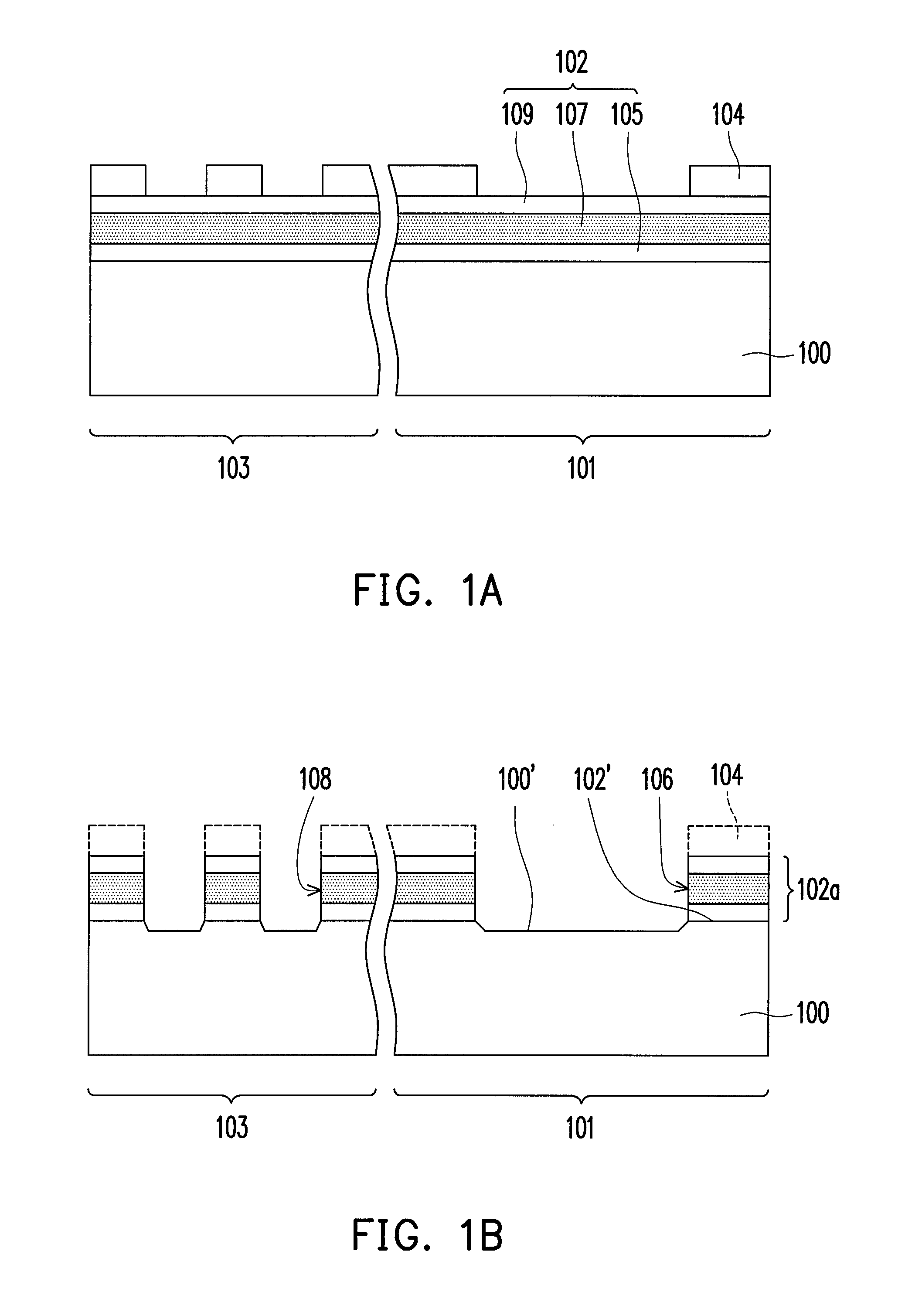

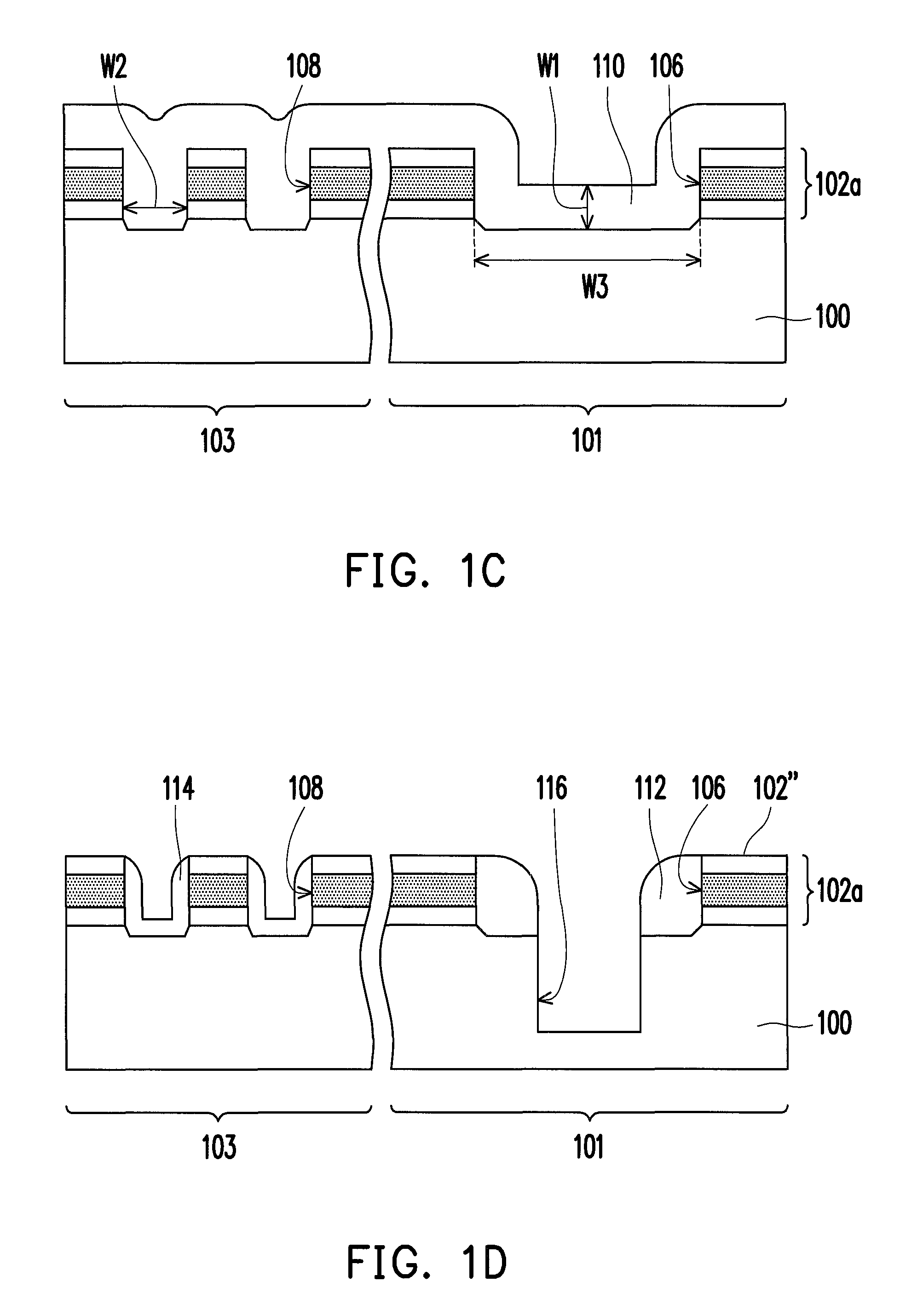

Methods of forming semiconductor trench and forming dual trenches, and structure for isolating devices

ActiveUS20120168897A1Simple processLow costSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

Methods of forming a semiconductor trench and forming dual trenches and a structure for isolating devices are provided. The structure for isolating devices is disposed in a substrate having a periphery area and an array area. The structure for isolating devices includes a first isolation structure and a second isolation structure. The first isolation structure has a profile with at least three steps and is disposed in the substrate in the periphery area. The second isolation structure has a profile with at least two steps and is disposed in the substrate in the array area.

Owner:MACRONIX INT CO LTD

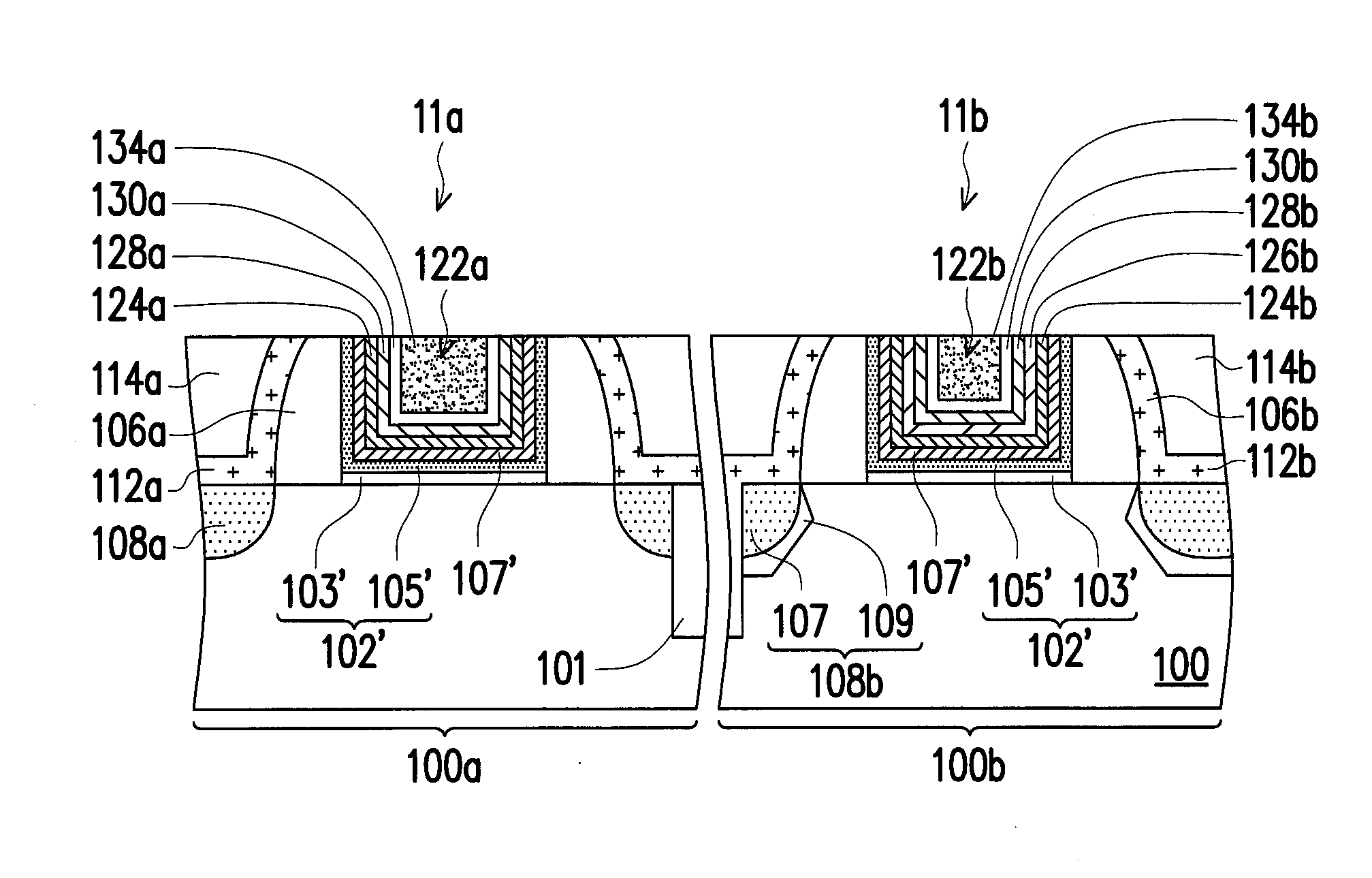

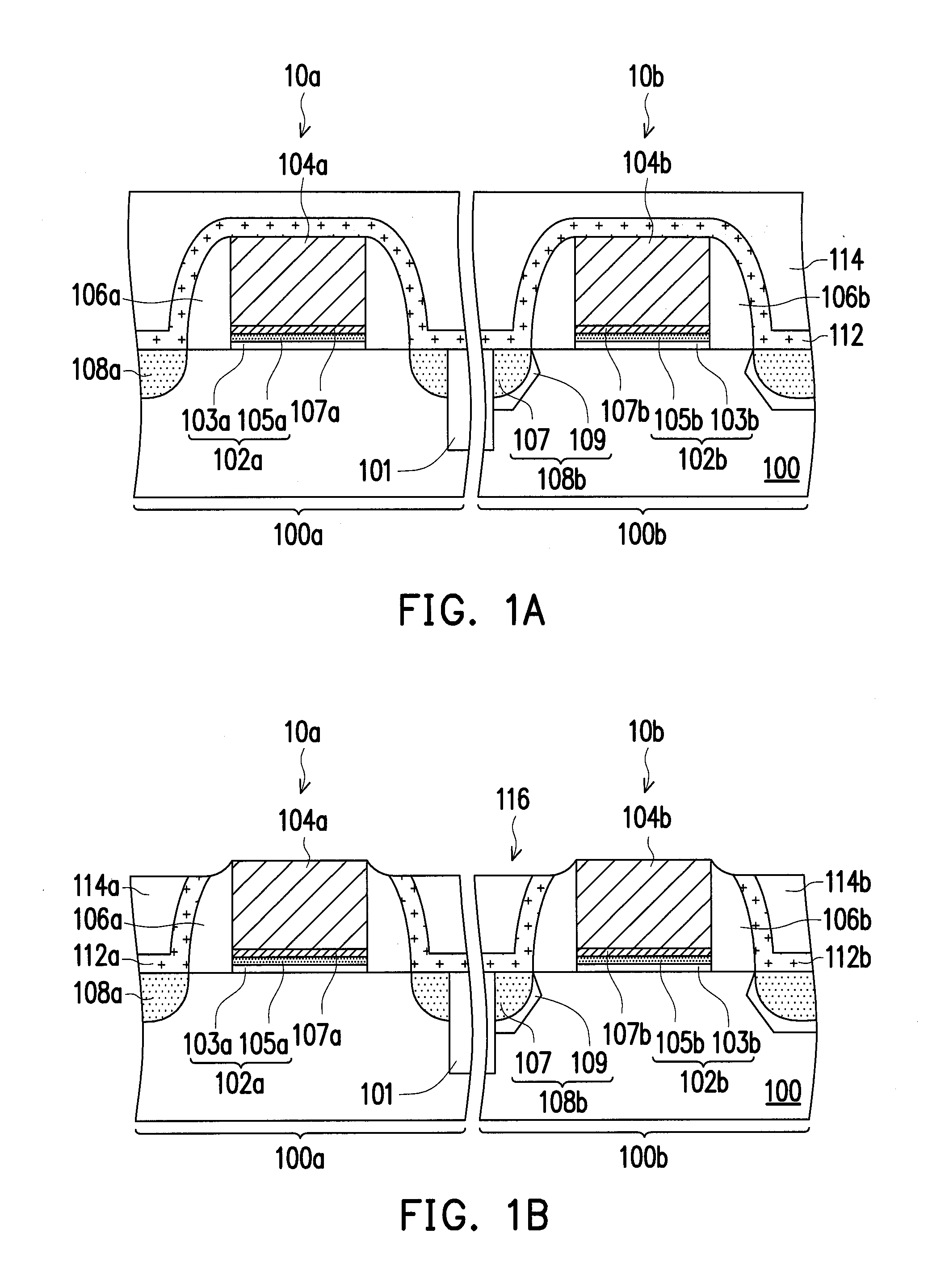

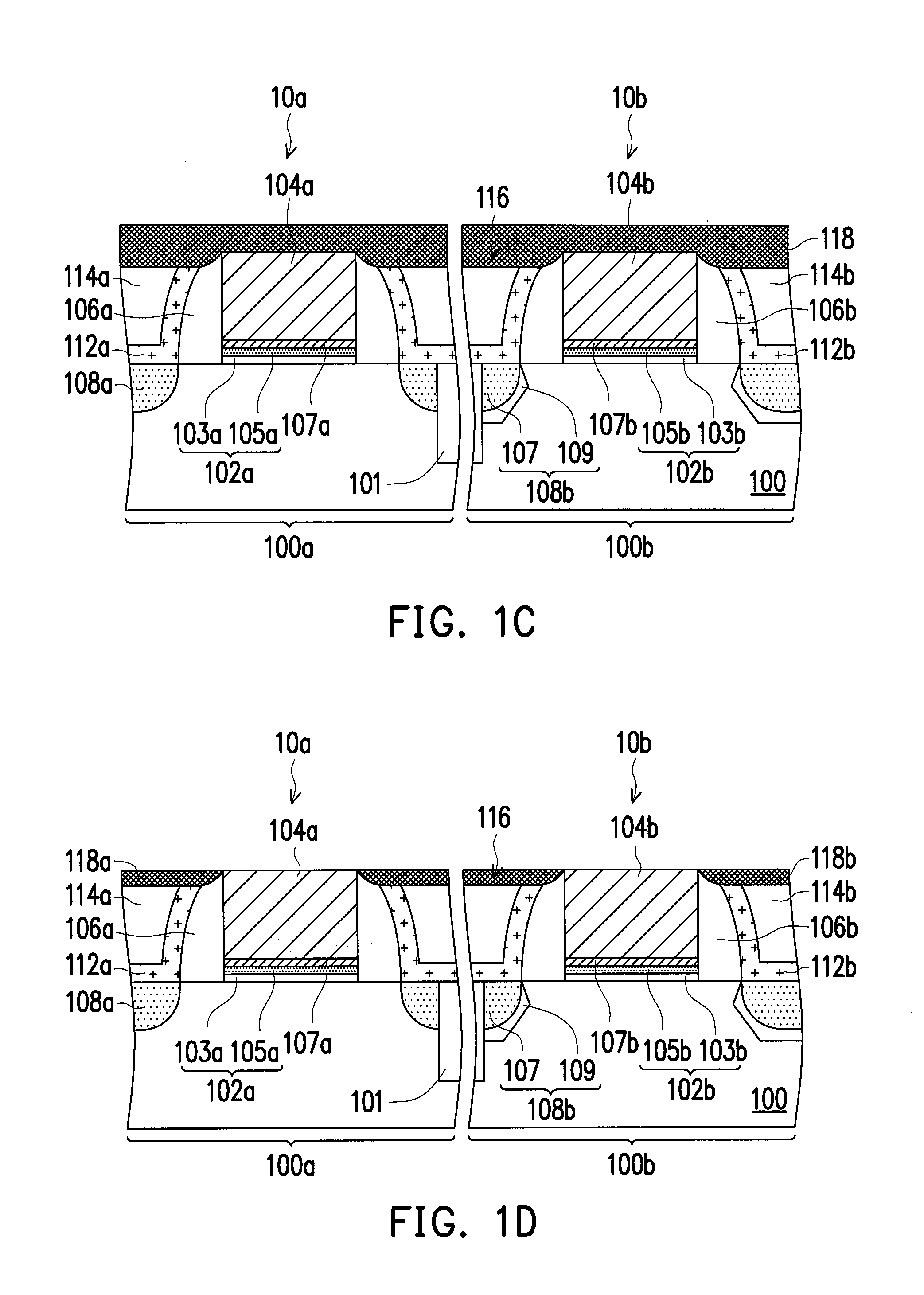

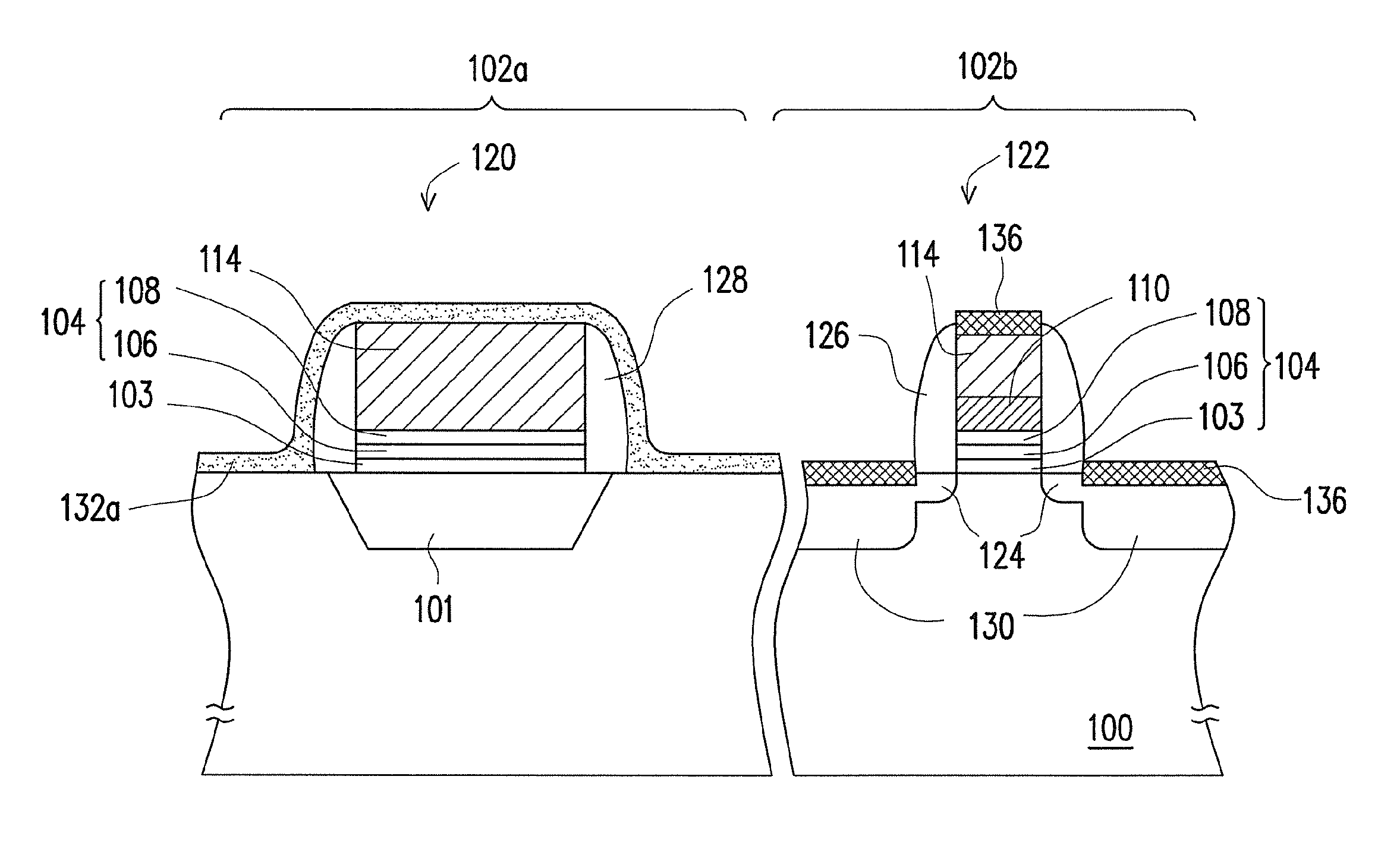

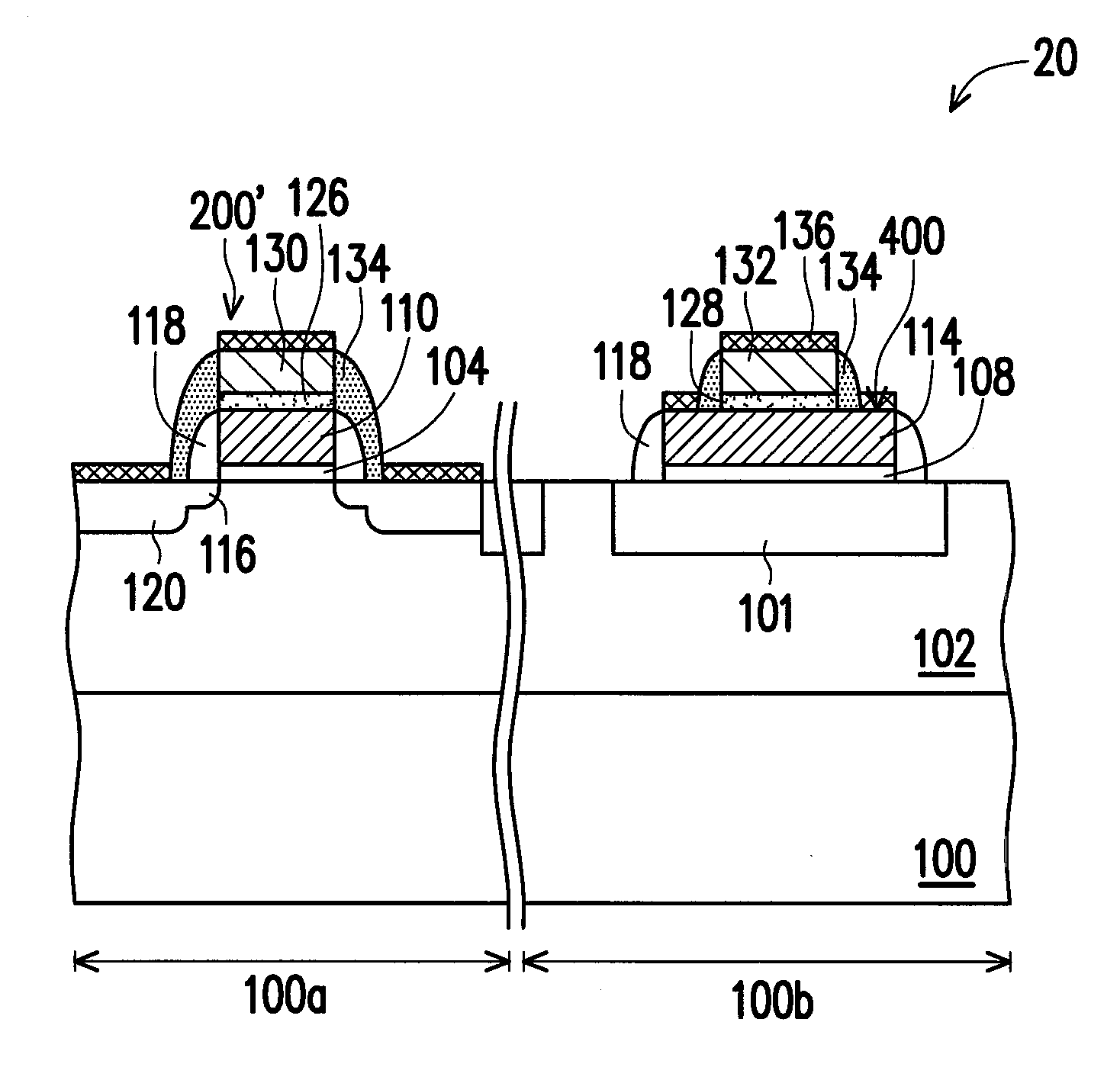

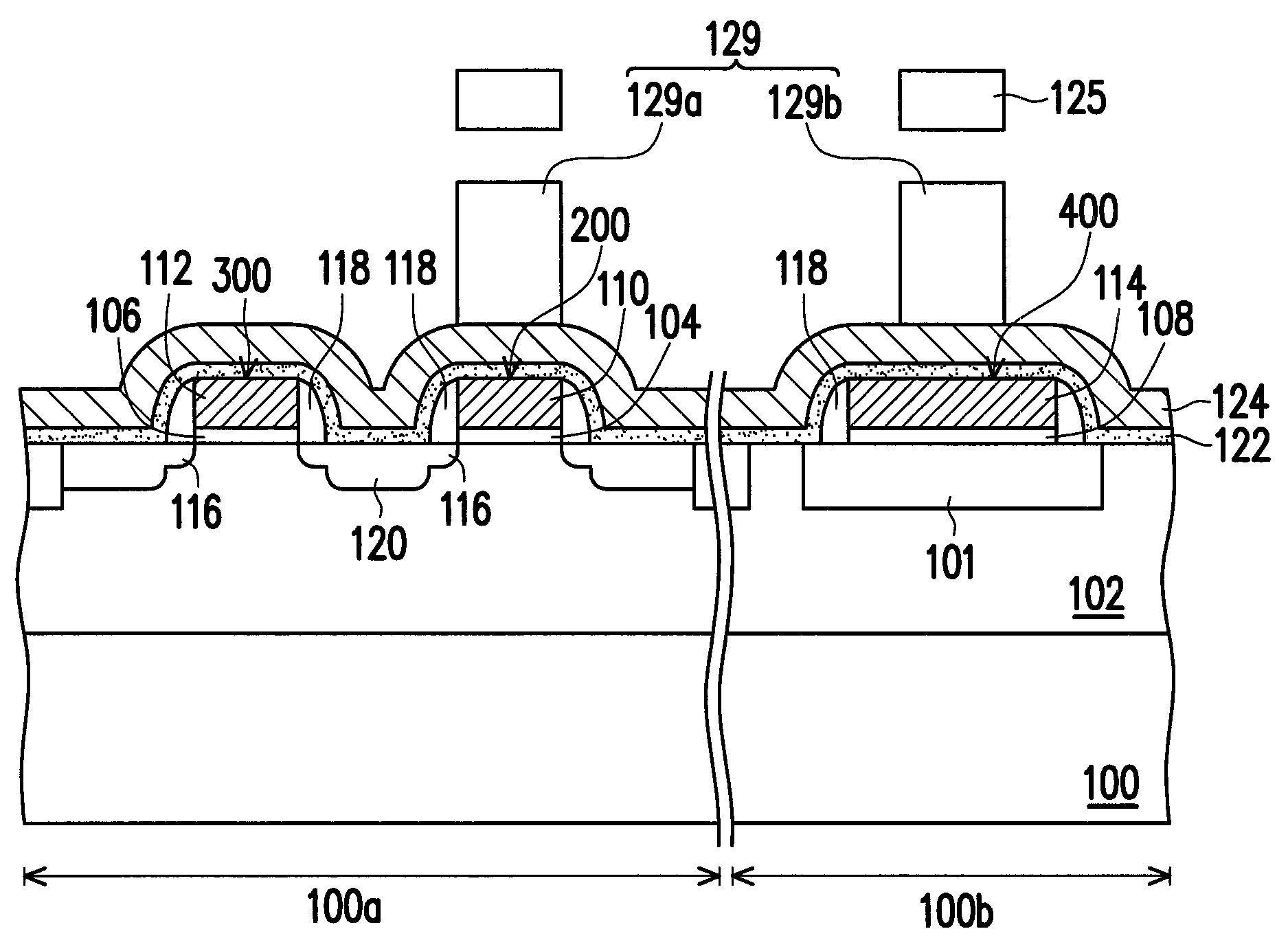

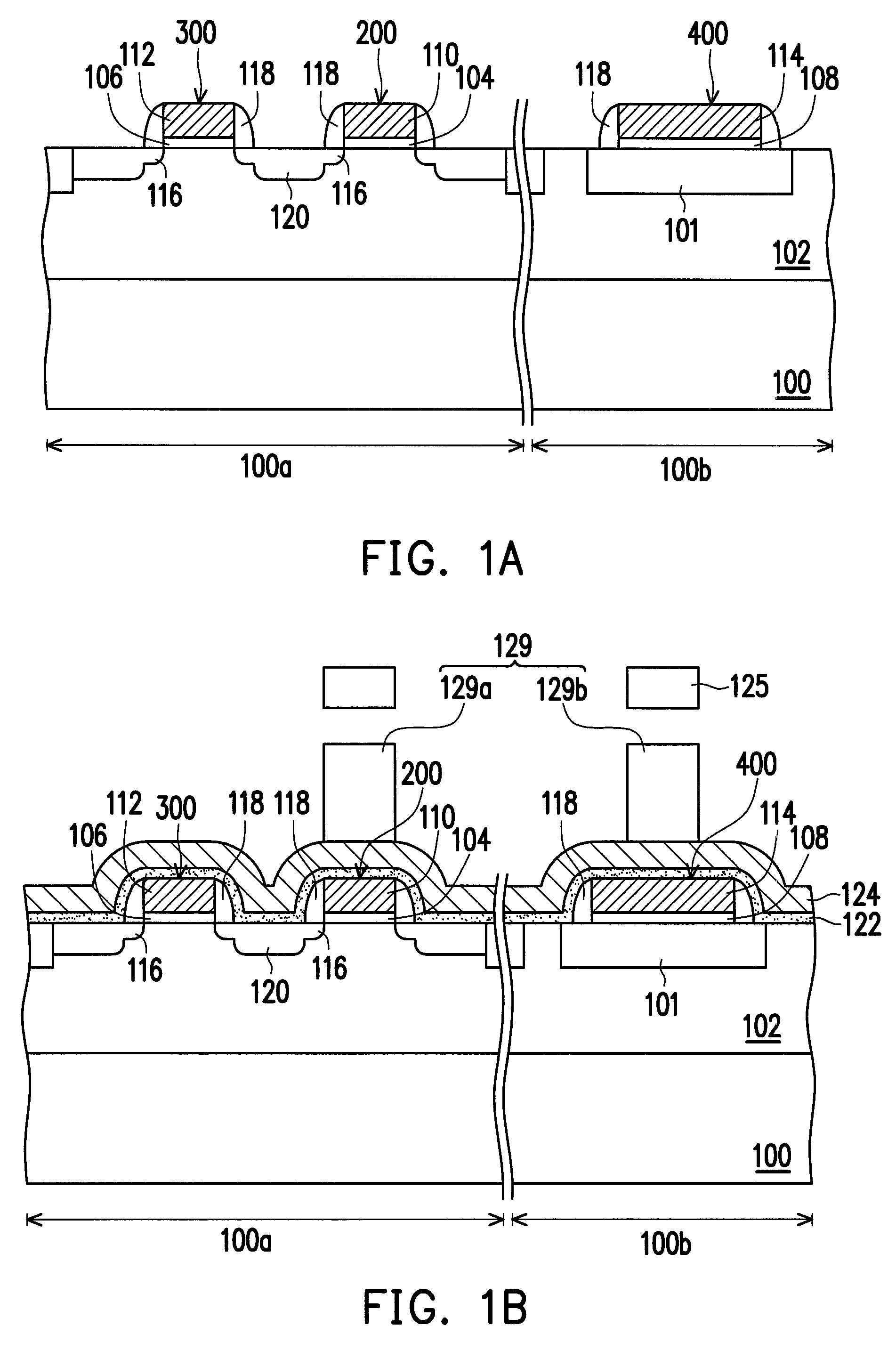

Semiconductor structure and method of forming the same

ActiveUS8093118B2Simple forming methodIncrease resistanceTransistorSolid-state devicesSemiconductor structureEngineering

A semiconductor structure and a method of forming the same are provided. The semiconductor structure includes a substrate, a resistor and a metal gate structure. The substrate has a first area and a second area. The resistor is disposed in the first area, wherein the resistor does not include any metal layer. The metal gate structure is disposed in the second area.

Owner:UNITED MICROELECTRONICS CORP

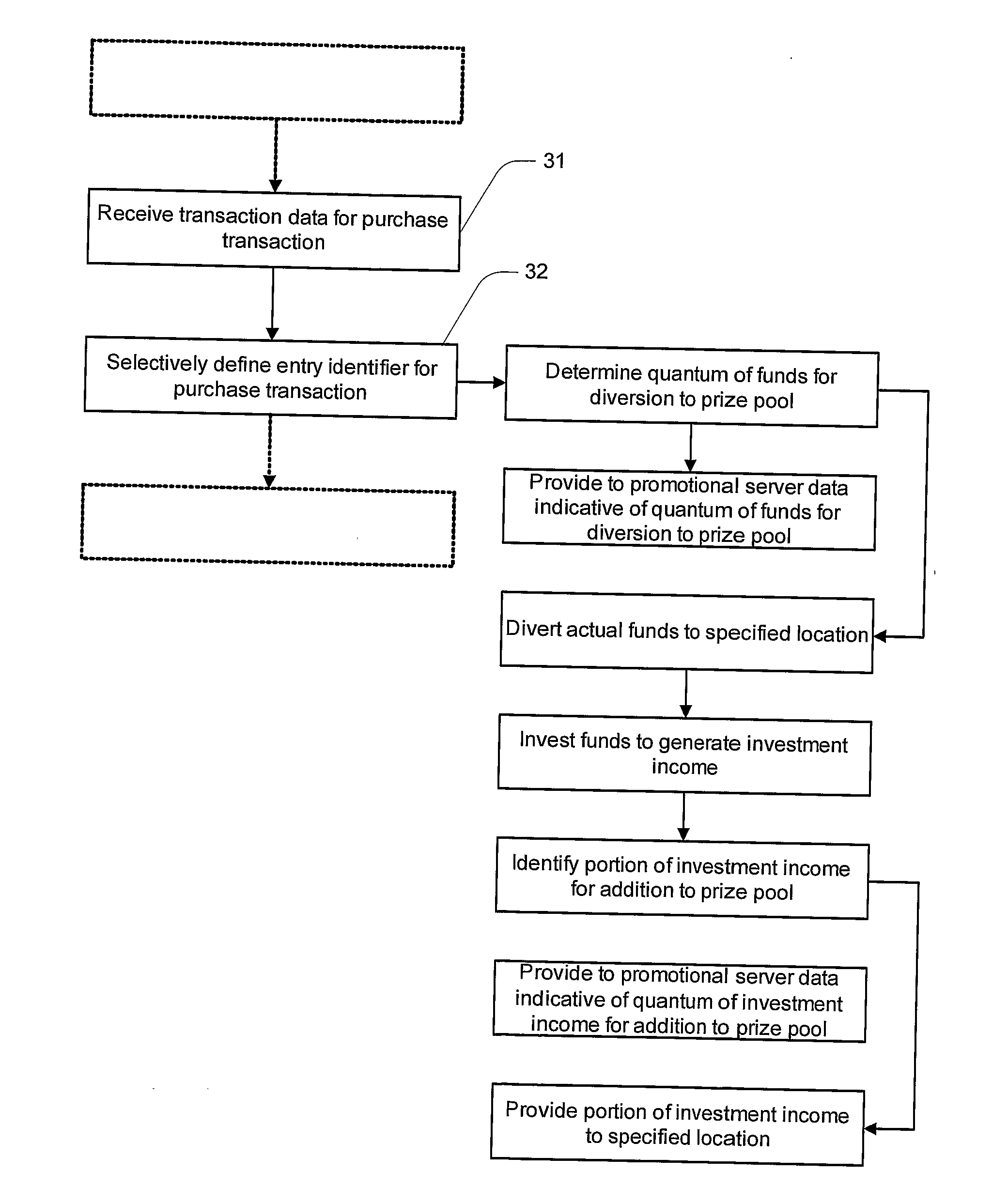

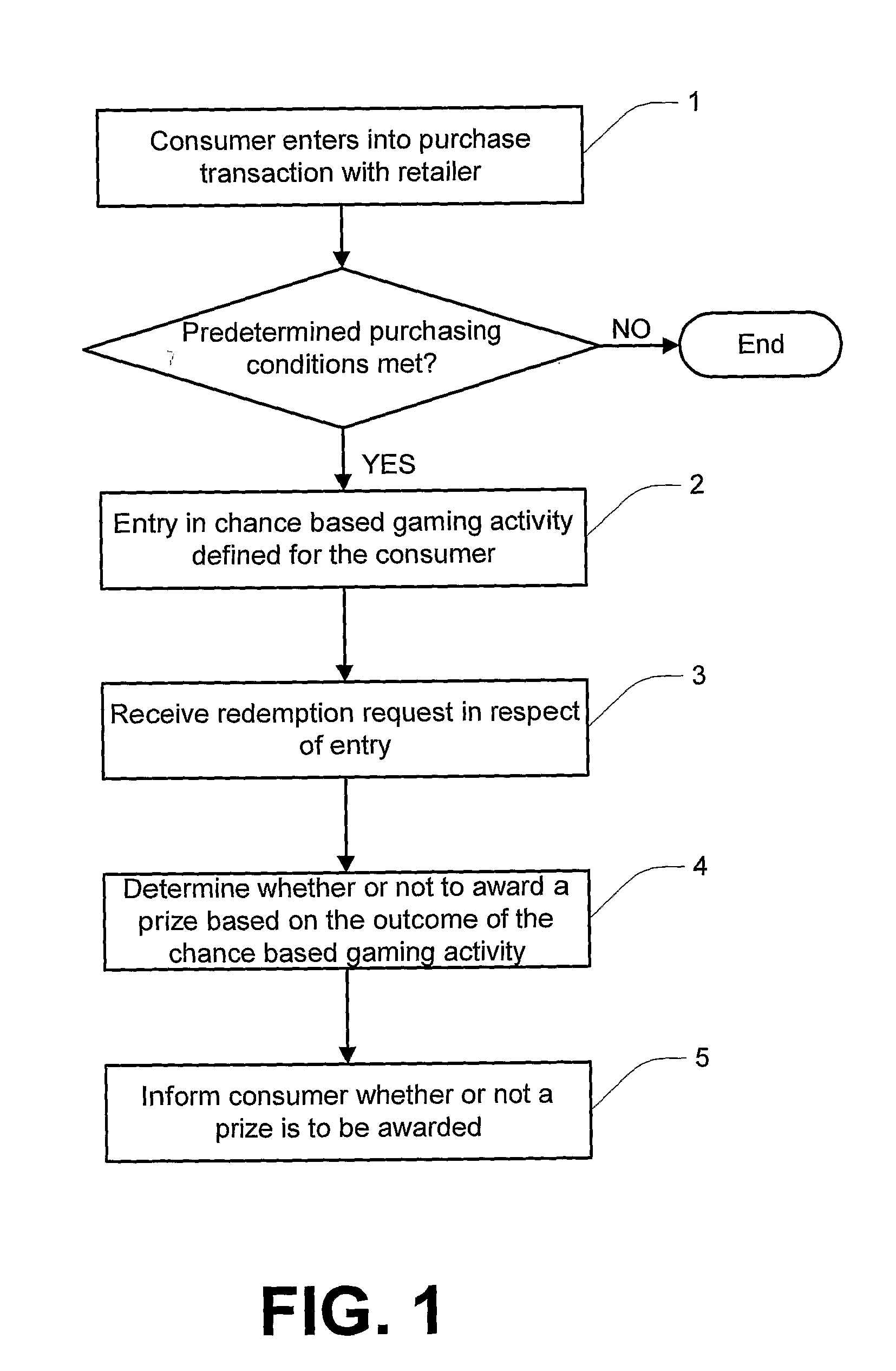

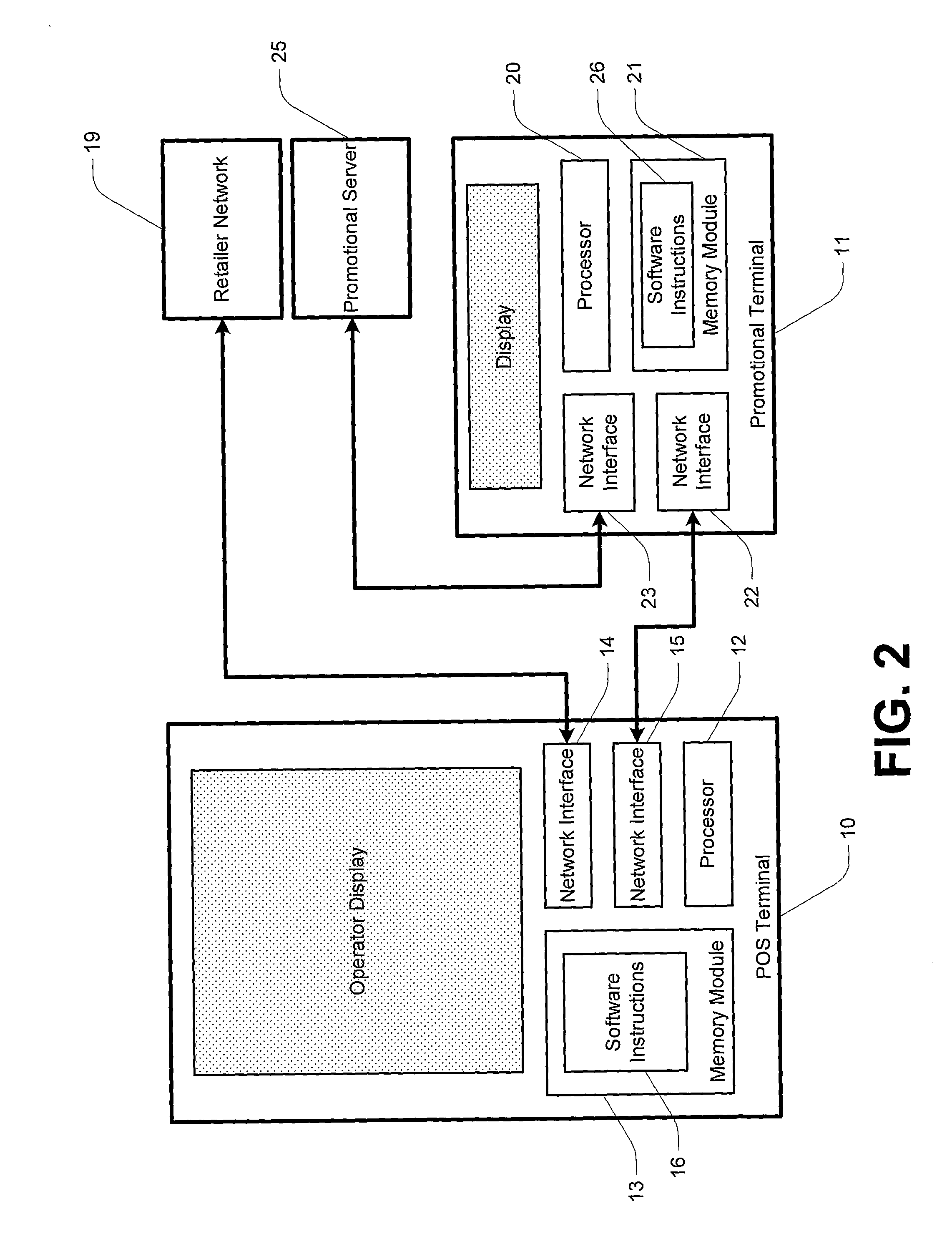

Methods and systems for sales promotion

InactiveUS20100262476A1Increase probabilityGood chancePayment architectureApparatus for meter-controlled dispensingPurchasingFinancial transaction

Described herein are methods and systems for conducting sales promotions in accordance with embodiments of the present invention. In some embodiments a retailer offers to consumers an opportunity to win a prize according to predetermined purchasing criteria, this offer being provided as an incentive for the consumers to purchase goods and or services. In overview, and as shown in FIG. (1), a consumer enters into a purchase transaction with a retailer at step (1). In the case that this purchase transaction satisfies predetermined purchasing criteria, an entry in a chance-based gaming activity is defined for the consumer at step (2). This entry is provided to the consumer free of charge. A redemption request is subsequently allowed to be placed in respect of the entry, such a request being received at step (3). Responsive to the redemption request, it is substantially immediately determined whether or not to award a prize to the consumer based on the outcome of the chance-based gaming activity at step (4). The consumer is then substantially immediately informed as to whether or not a prize is to be awarded at step (5).

Owner:SRG ENTERPRIZES

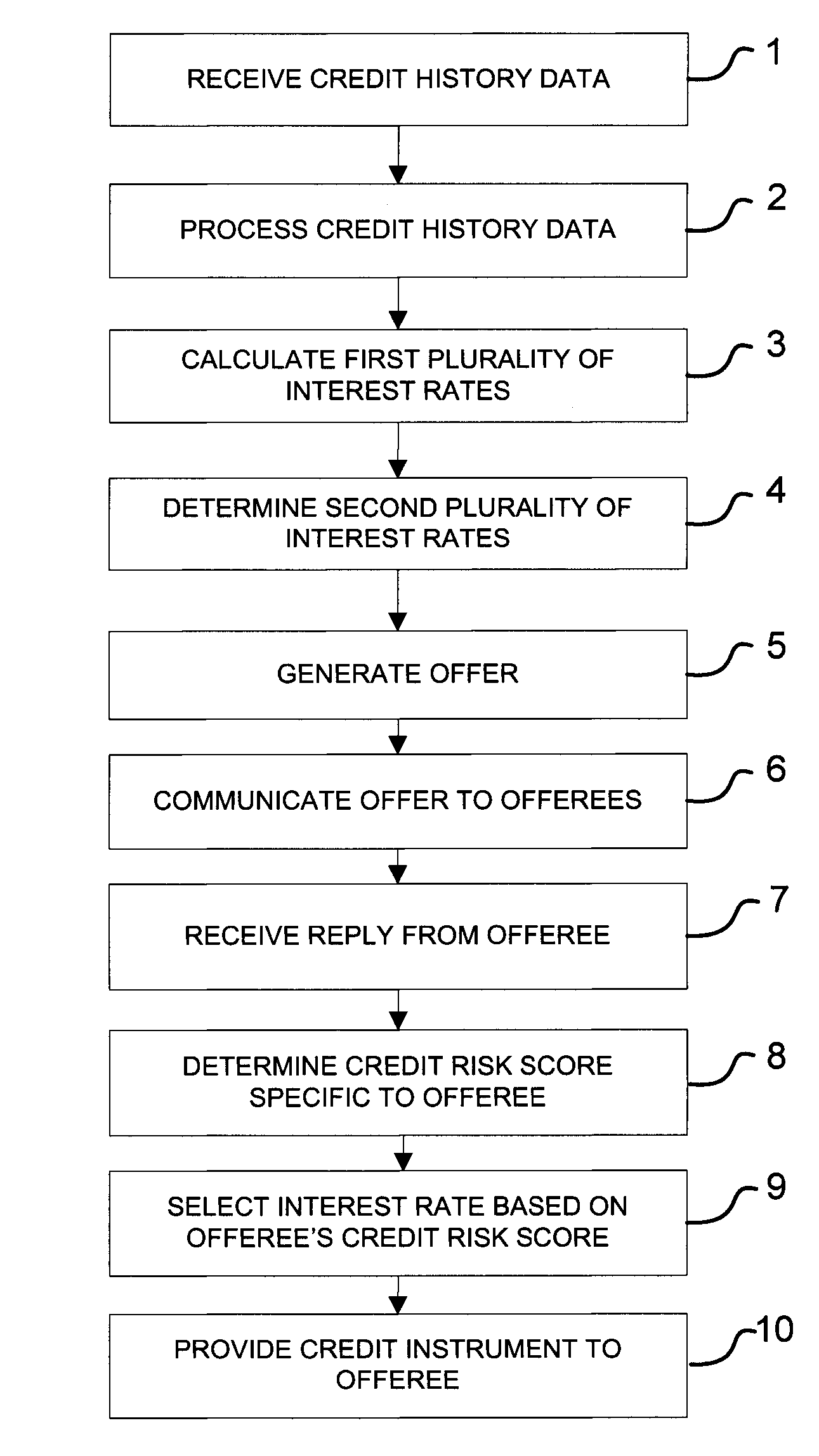

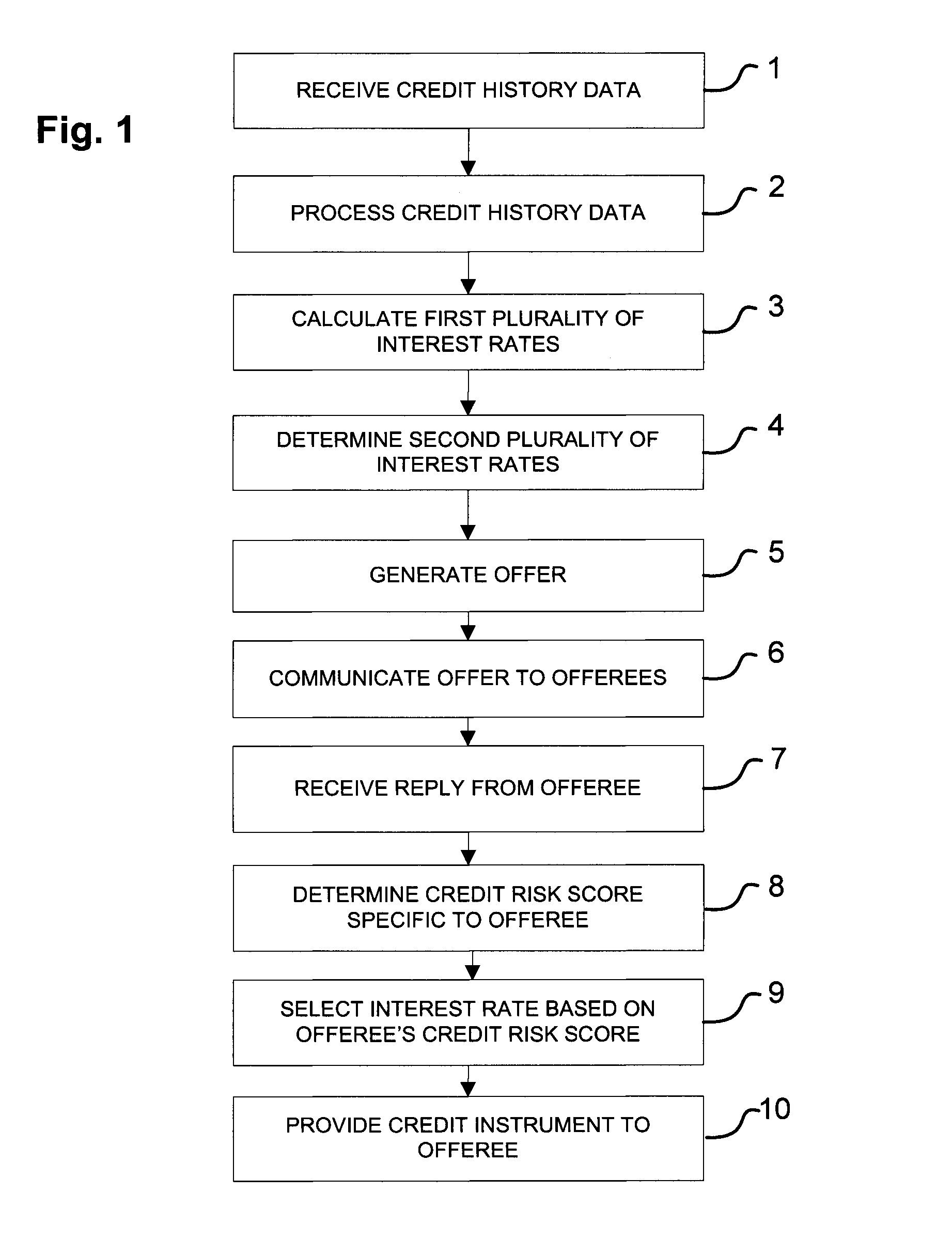

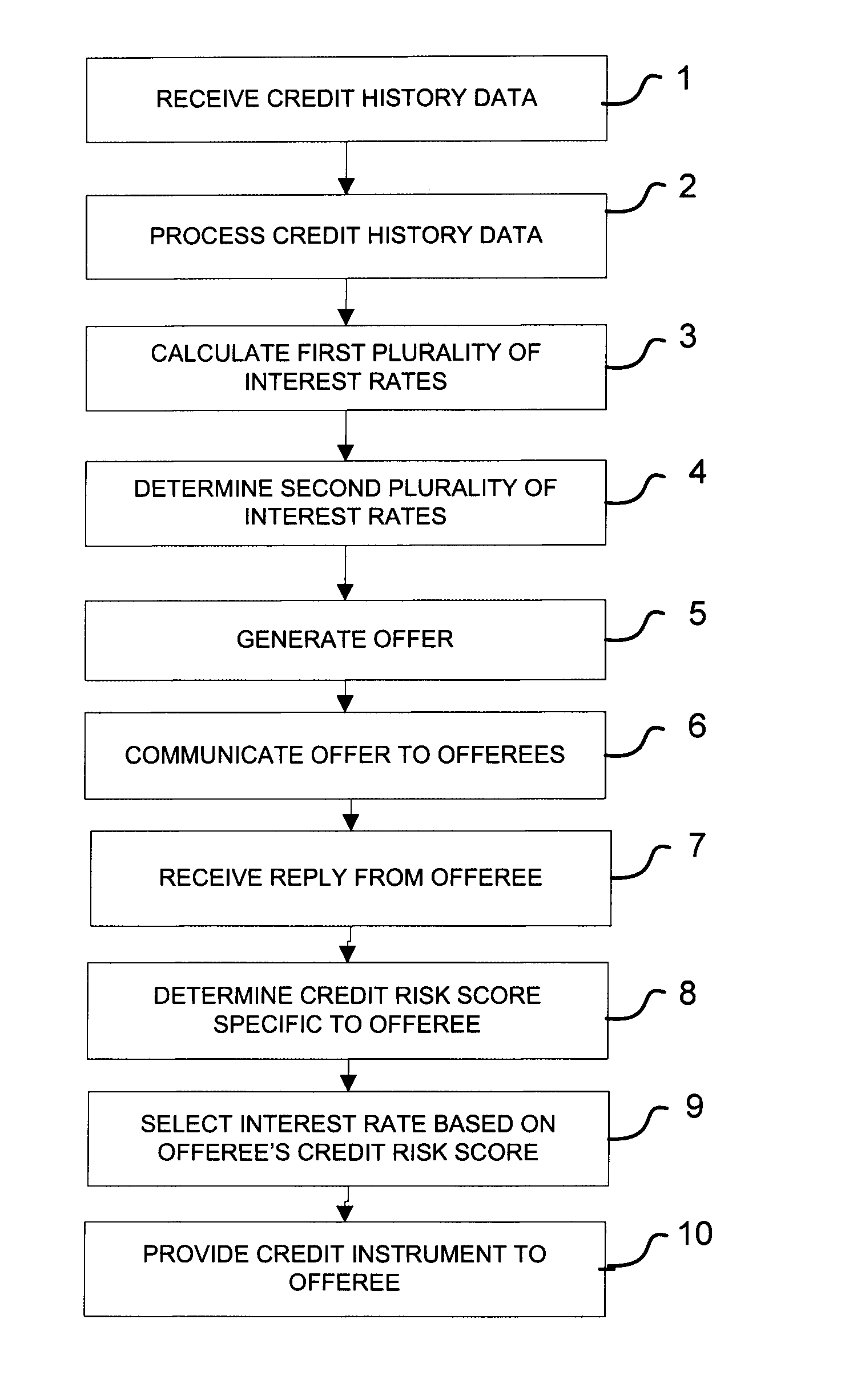

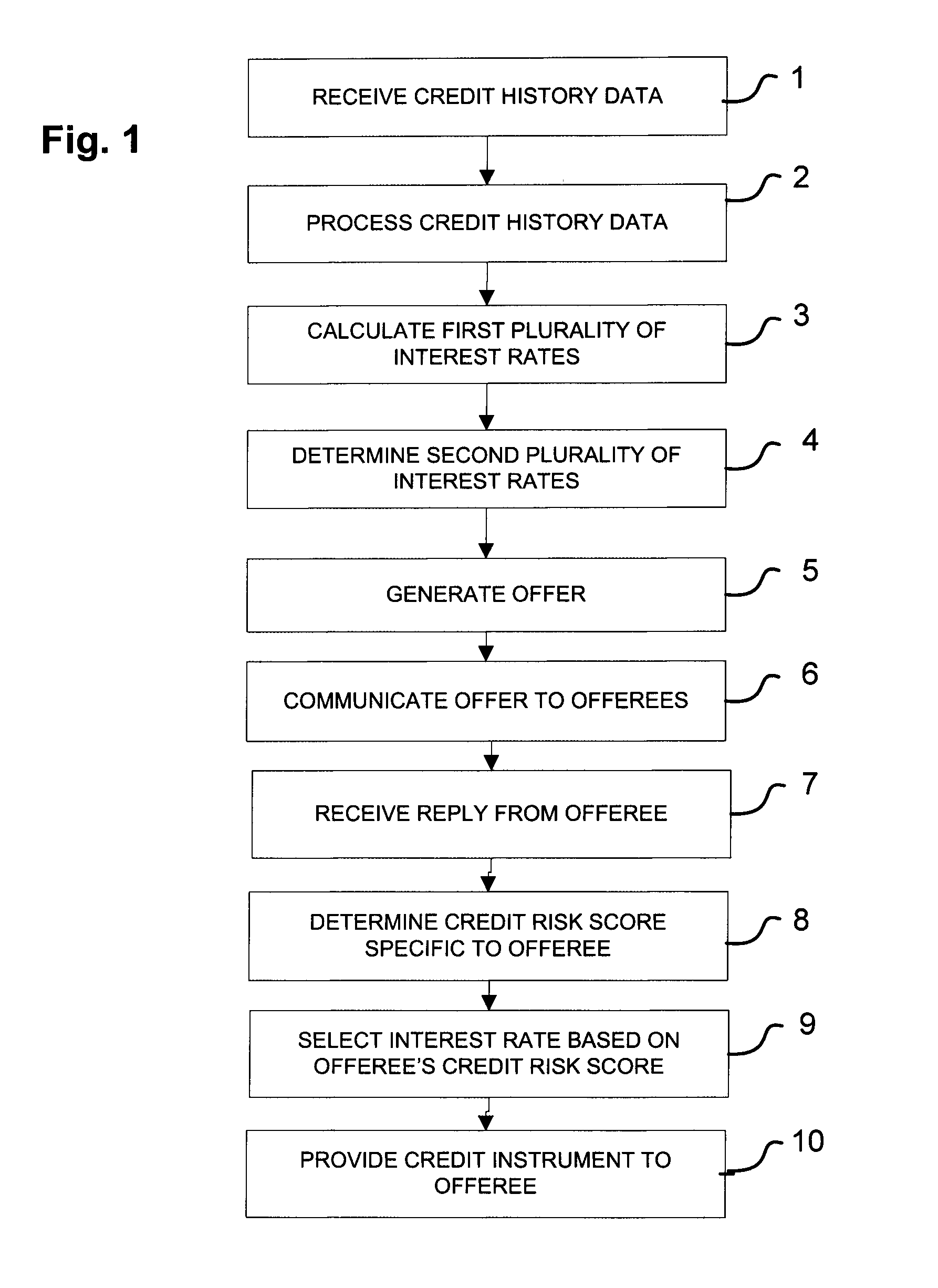

System and method for offering risk-based interest rates in a credit instutment

A system and method for communicating an offer to apply for a credit instrument is provided. A processing allows for processing credit history data. A calculating step allows for calculating a first plurality of interest rates based on the credit history data. A determining step allows for determining a second plurality of interest rates based on the first plurality of interest rates, wherein the second plurality of interest rates corresponds to a plurality of credit risk scores. Finally, a communicating step allows for communicating the offer to apply for a credit instrument in an initial communication with an offeree, the offer disclosing the second plurality of interest rates. An apparatus that calculates the interest rates used in the offer is also provided.

Owner:JPMORGAN CHASE BANK NA

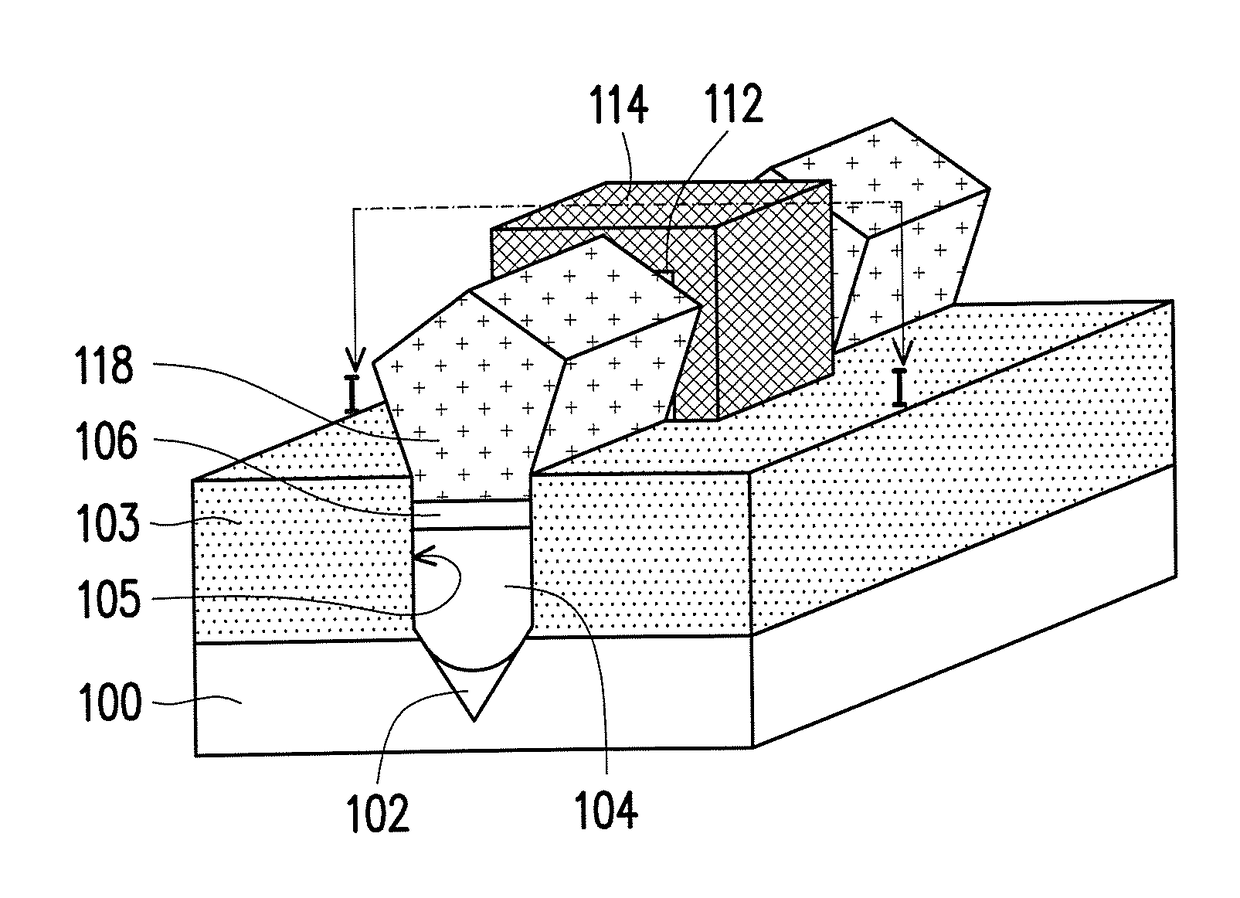

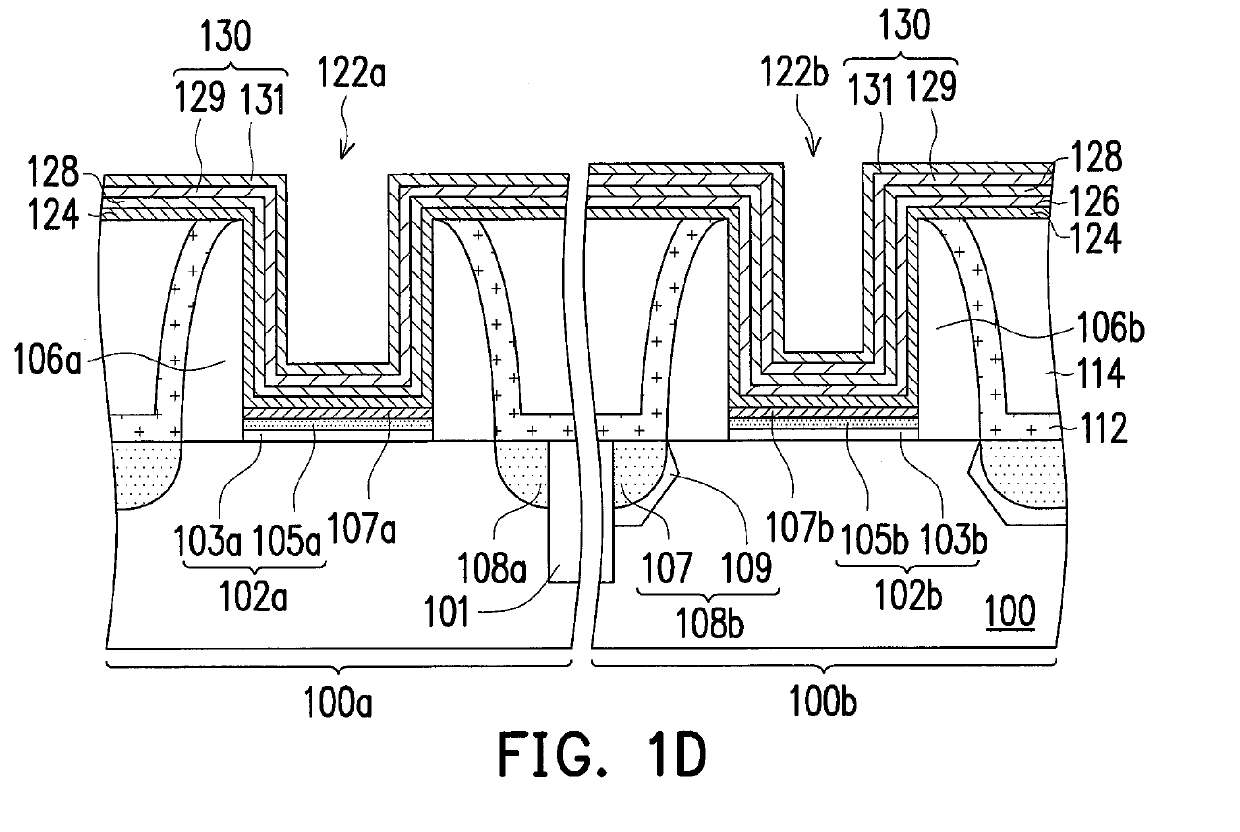

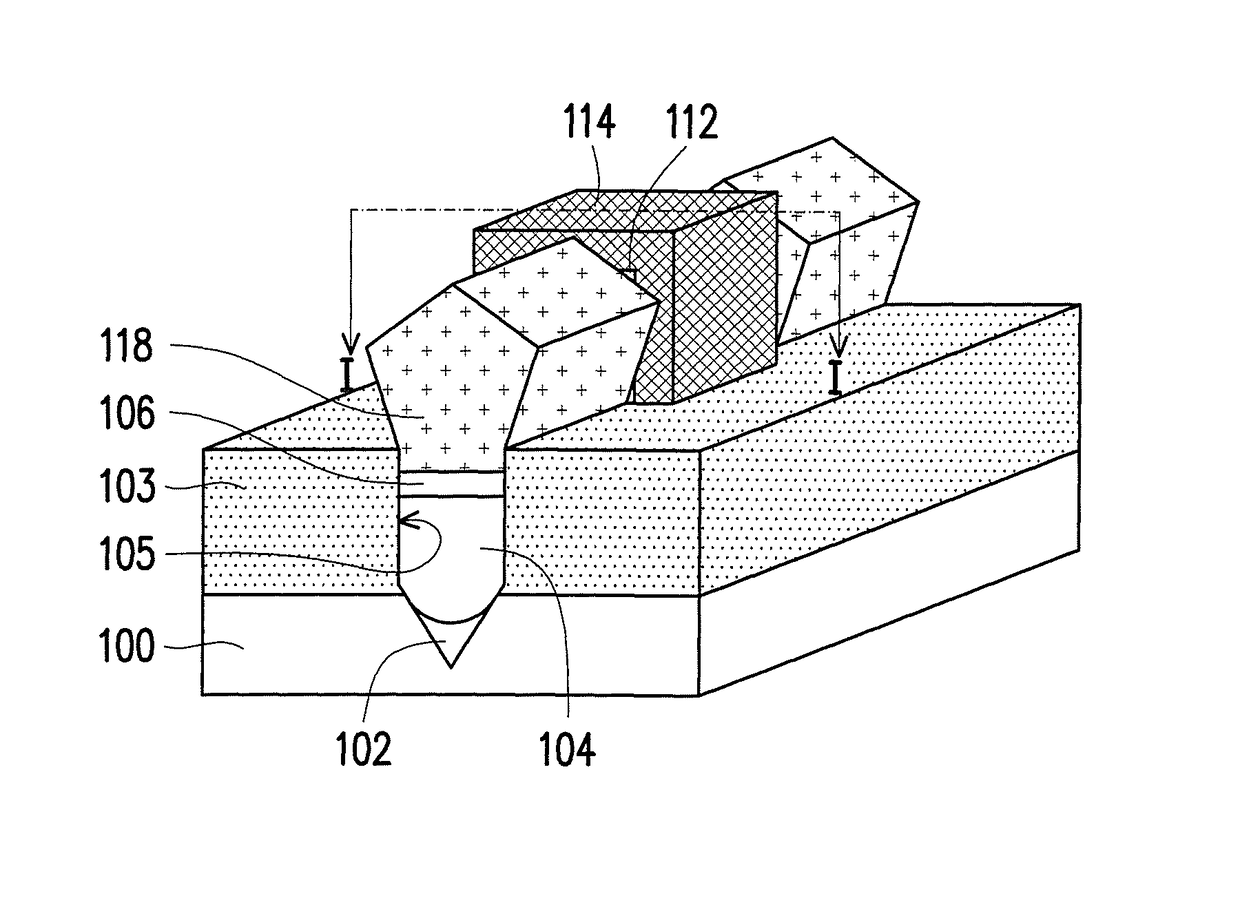

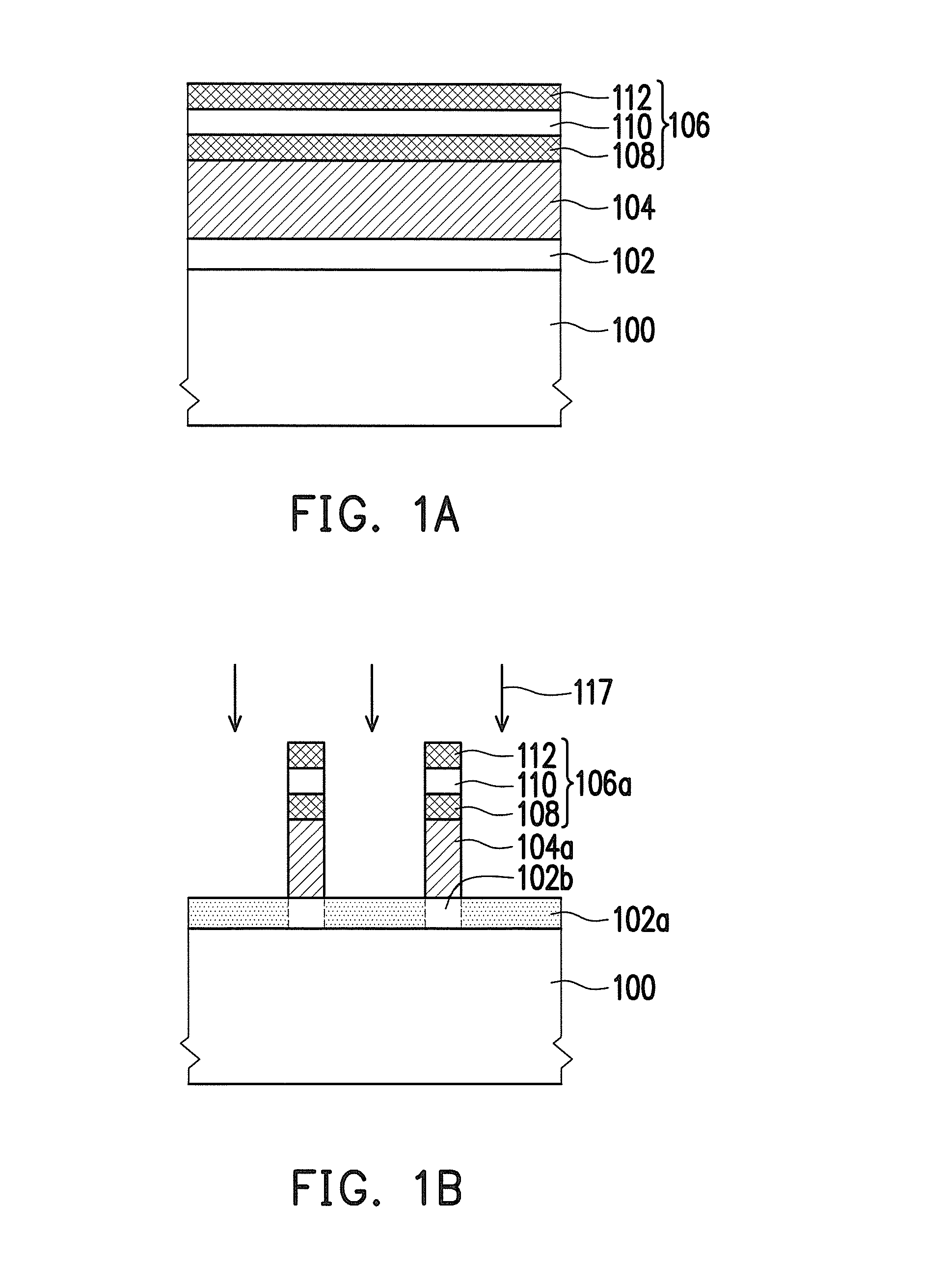

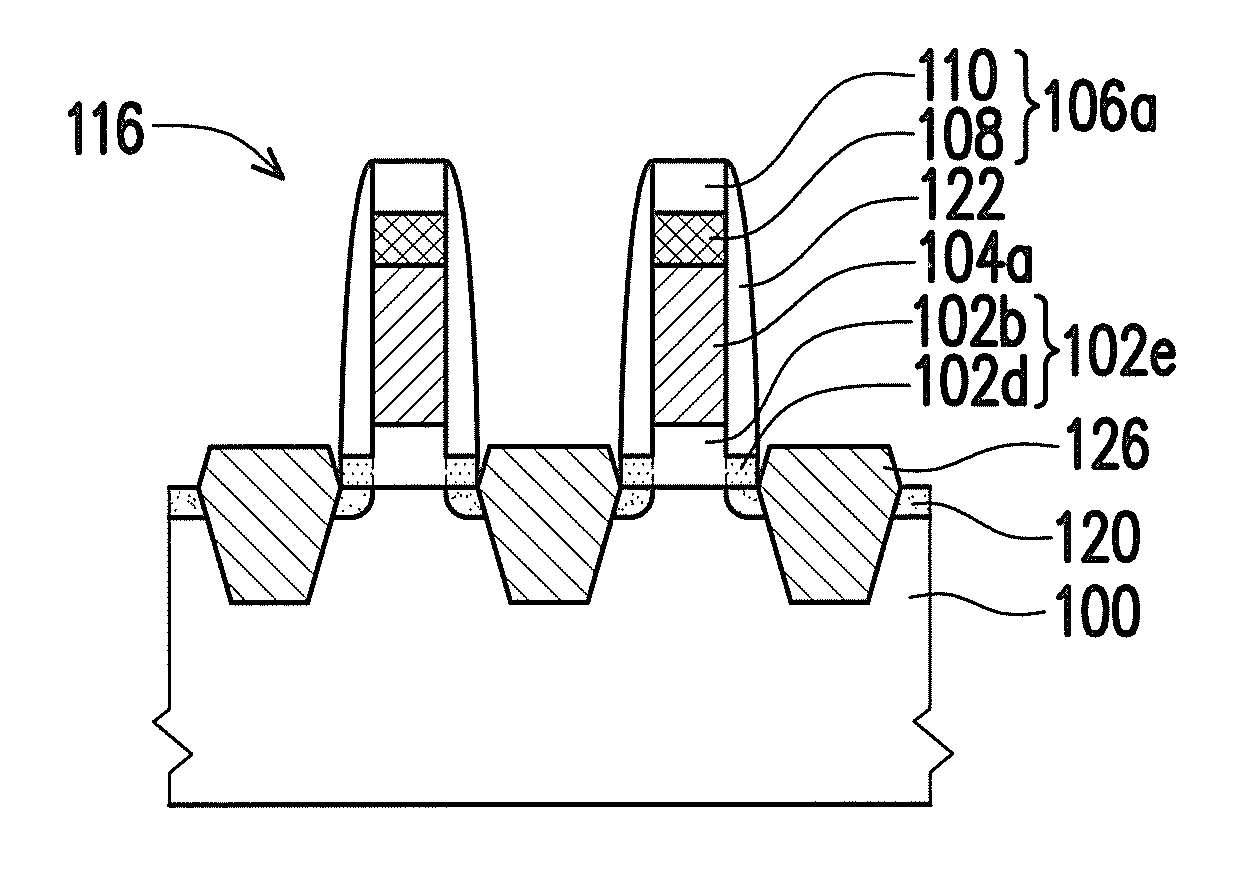

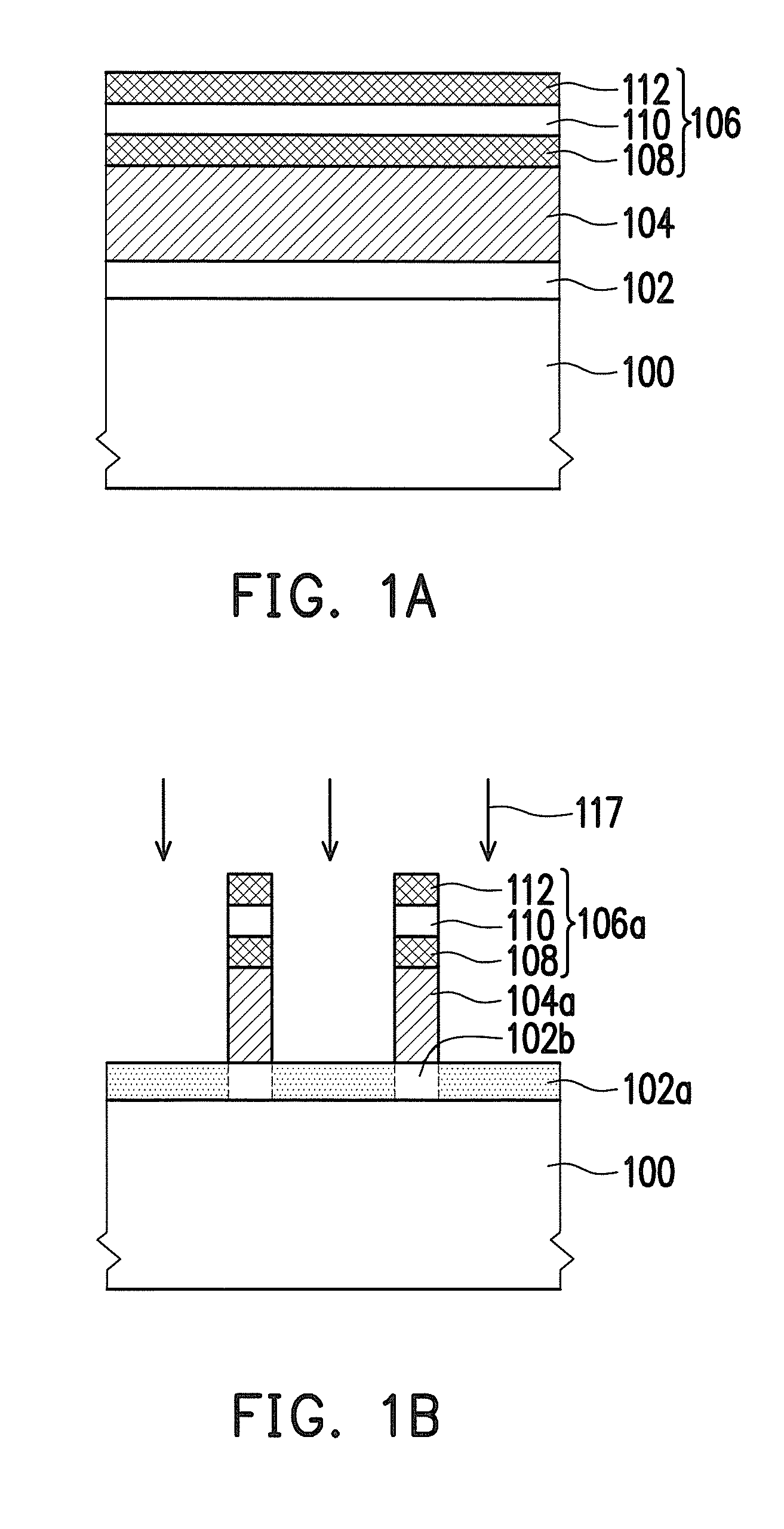

Fin-type field effect transistor and method of forming the same

ActiveUS20170098692A1Mismatch dislocationInhibitionSemiconductor/solid-state device manufacturingSemiconductor devicesStress relaxationEngineering

Provided is a FinFET including a substrate, at least one fin and at least one gate. A portion of the at least one fin is embedded in the substrate. The at least one fin includes, from bottom to top, a seed layer, a stress relaxation layer and a channel layer. The at least one gate is across the at least one fin. A method of forming a FinFET is further provided.

Owner:UNITED MICROELECTRONICS CORP

System and method for lawn care

InactiveUS20110289832A1Simple processImprove usabilityHops/wine cultivationTurf growingSpecific functionMedicine

The present invention features a multi-step organic lawn care program that comprises four or more specified treatments that are applied at specific times throughout the year. Each step serves specific functions that assist in the maintenance and improvement of turf. Each treatment is intended to be applied at a prescribed time to ensure maximum benefits to the turf. The treatments are preferably applied in a liquid format are generally effective at detoxifying a surface that has been treated with chemical fertilizers. The treatments may be applied in conjunction with other products.

Owner:NATURAL TECH

Semiconductor structure and method of forming the same

ActiveUS9384984B2Effective blockingImprove device performanceSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor structure

A method of forming a semiconductor device is disclosed. A substrate having a dielectric layer thereon is provided. The dielectric layer has a gate trench therein and a gate dielectric layer is formed on a bottom of the gate trench. A work function metal layer and a top barrier layer are sequentially formed in the gate trench. A treatment is performed to the top barrier layer so as to form a silicon-containing top barrier layer. A low-resistivity metal layer is formed in the gate trench.

Owner:UNITED MICROELECTRONICS CORP

Fin-type field effect transistor and method of forming the same

ActiveUS10068963B2Mismatch dislocationInhibitionSemiconductor/solid-state device manufacturingSemiconductor devicesStress relaxationEngineering

Provided is a FinFET including a substrate, at least one fin and at least one gate. A portion of the at least one fin is embedded in the substrate. The at least one fin includes, from bottom to top, a seed layer, a stress relaxation layer and a channel layer. The at least one gate is across the at least one fin. A method of forming a FinFET is further provided.

Owner:UNITED MICROELECTRONICS CORP

Semiconductor structure and method of forming the same

ActiveUS20100327378A1Simple forming methodIncrease resistanceTransistorSolid-state devicesSemiconductor structureEngineering

A semiconductor structure and a method of forming the same are provided. The semiconductor structure includes a substrate, a resistor and a metal gate structure. The substrate has a first area and a second area. The resistor is disposed in the first area, wherein the resistor does not include any metal layer. The metal gate structure is disposed in the second area.

Owner:UNITED MICROELECTRONICS CORP

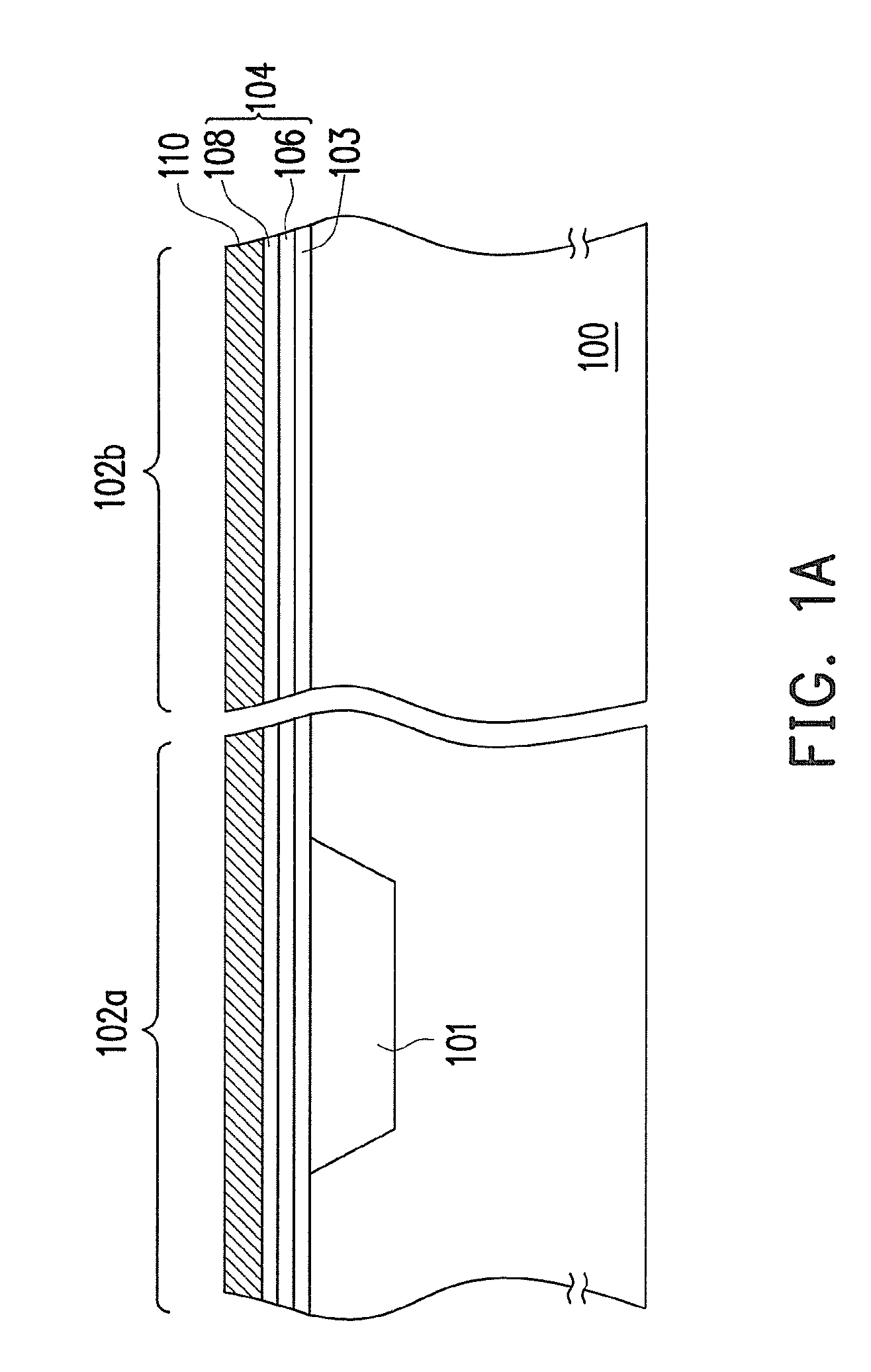

Semiconductor structure and method of forming the same

ActiveUS20130043522A1Well formedEasy to integrateTransistorSolid-state devicesGate dielectricSemiconductor structure

A method of forming a semiconductor structure is provided. A substrate having a cell area and a periphery area is provided. A stacked structure including a gate oxide layer, a floating gate and a first spacer is formed on the substrate in the cell area and a resistor is formed on the substrate in the periphery area. At least two doped regions are formed in the substrate beside the stacked structure. A dielectric material layer and a conductive material layer are sequentially formed on the substrate. A patterned photoresist layer is formed on the substrate to cover the stacked structure and a portion of the resistor. The dielectric material layer and the conductive material layer not covered by the patterned photoresist layer are removed, so as to form an inter-gate dielectric layer and a control gate on the stacked structure, and simultaneously form a salicide block layer on the resistor.

Owner:POWERCHIP SEMICON MFG CORP

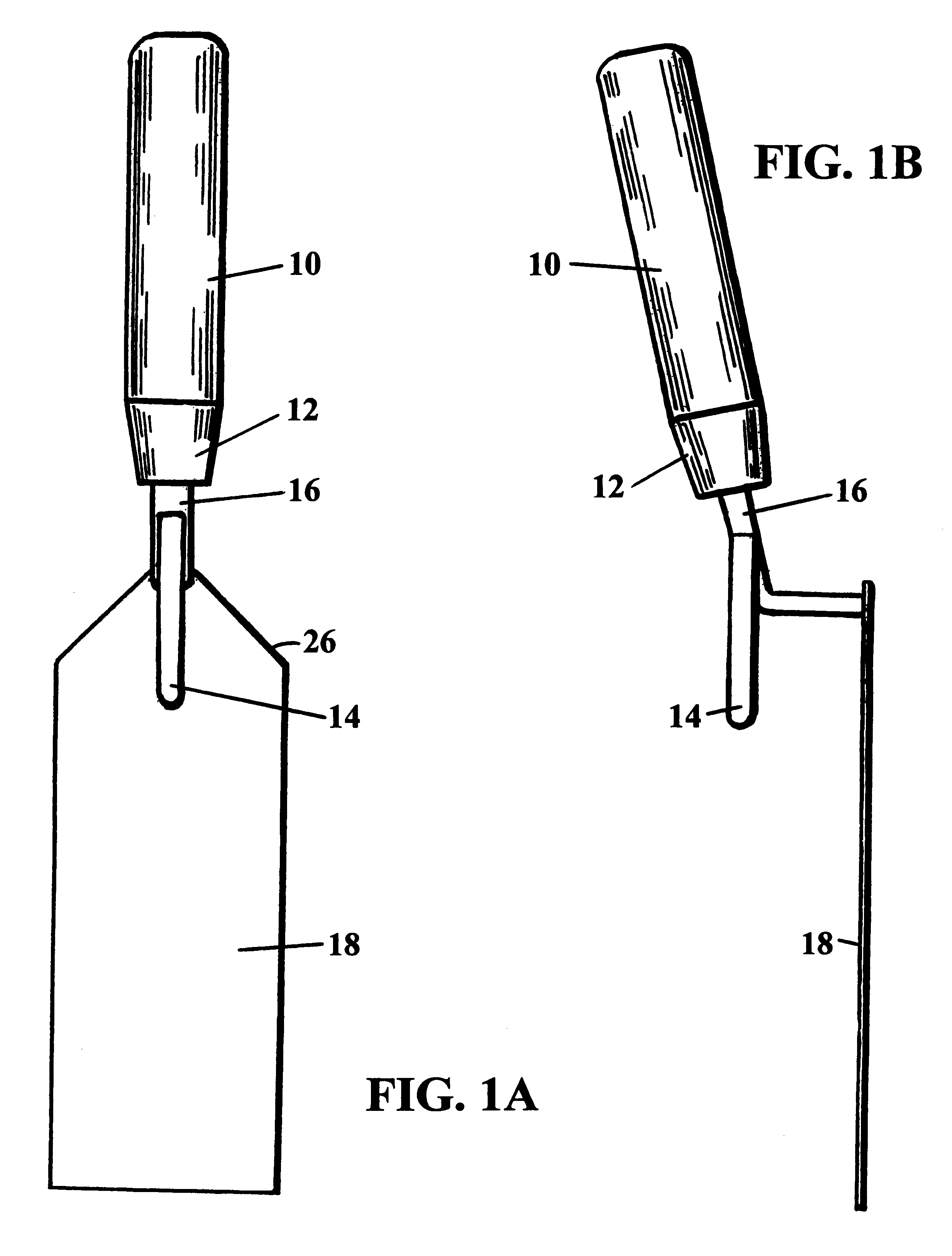

Margin trowel with bucket hook

InactiveUS6393650B1Easy to cleanNot to clutterLiquid surface applicatorsCarpet cleanersEngineeringFixed position

A hand trowel having a flat blade, a handle, an angled stem, and a bucket hook which has a length dimension of approximately one-and-one-half inches and extends beyond the attachment point of one end of the stem to the blade. Thus, the trowel can be stored in a substantially vertical, secure and fixed position on the lip of a bucket, preventing the handle from coming into contact with the contents of the bucket, or the contents being inadvertently spilled onto the work area. It also has a larger blade than is typically used for semi-fluid masonry products, to carry more product at a time to the working area, as well as act as a counterweight for the handle to keep the tool from falling out of bucket when it is moved. Thus, the present invention allows the operator to work more efficiently, and maintain a cleaner, less cluttered working area.

Owner:NORTHWESTERN UNIV

Semiconductor structure

ActiveUS8907395B2Well formedEasy to integrateTransistorSolid-state devicesGate dielectricSemiconductor structure

A method of forming a semiconductor structure is provided. A substrate having a cell area and a periphery area is provided. A stacked structure including a gate oxide layer, a floating gate and a first spacer is formed on the substrate in the cell area and a resistor is formed on the substrate in the periphery area. At least two doped regions are formed in the substrate beside the stacked structure. A dielectric material layer and a conductive material layer are sequentially formed on the substrate. A patterned photoresist layer is formed on the substrate to cover the stacked structure and a portion of the resistor. The dielectric material layer and the conductive material layer not covered by the patterned photoresist layer are removed, so as to form an inter-gate dielectric layer and a control gate on the stacked structure, and simultaneously form a salicide block layer on the resistor.

Owner:POWERCHIP SEMICON MFG CORP

Method of fabricating semiconductor device structure

ActiveUS20150093870A1Avoid undercutSimple and easyTransistorSemiconductor/solid-state device manufacturingGate dielectricSemiconductor

A method of fabricating a semiconductor device structure is provided. The method includes the following step. A gate dielectric layer is formed on a substrate. A gate electrode is on the gate dielectric layer. The gate dielectric layer exposed by the gate electrode is treated. A first etching process is performed to remove at least a portion of the gate dielectric layer exposed by the gate electrode. A spacer is formed on the sidewall of the gate electrode. A second etching process is performed to form recesses in the substrate beside the gate electrode. Besides, during the first etching process and the second etching process, an etching rate of the treated gate dielectric layer is greater than an etching rate of the untreated gate dielectric layer.

Owner:UNITED MICROELECTRONICS CORP

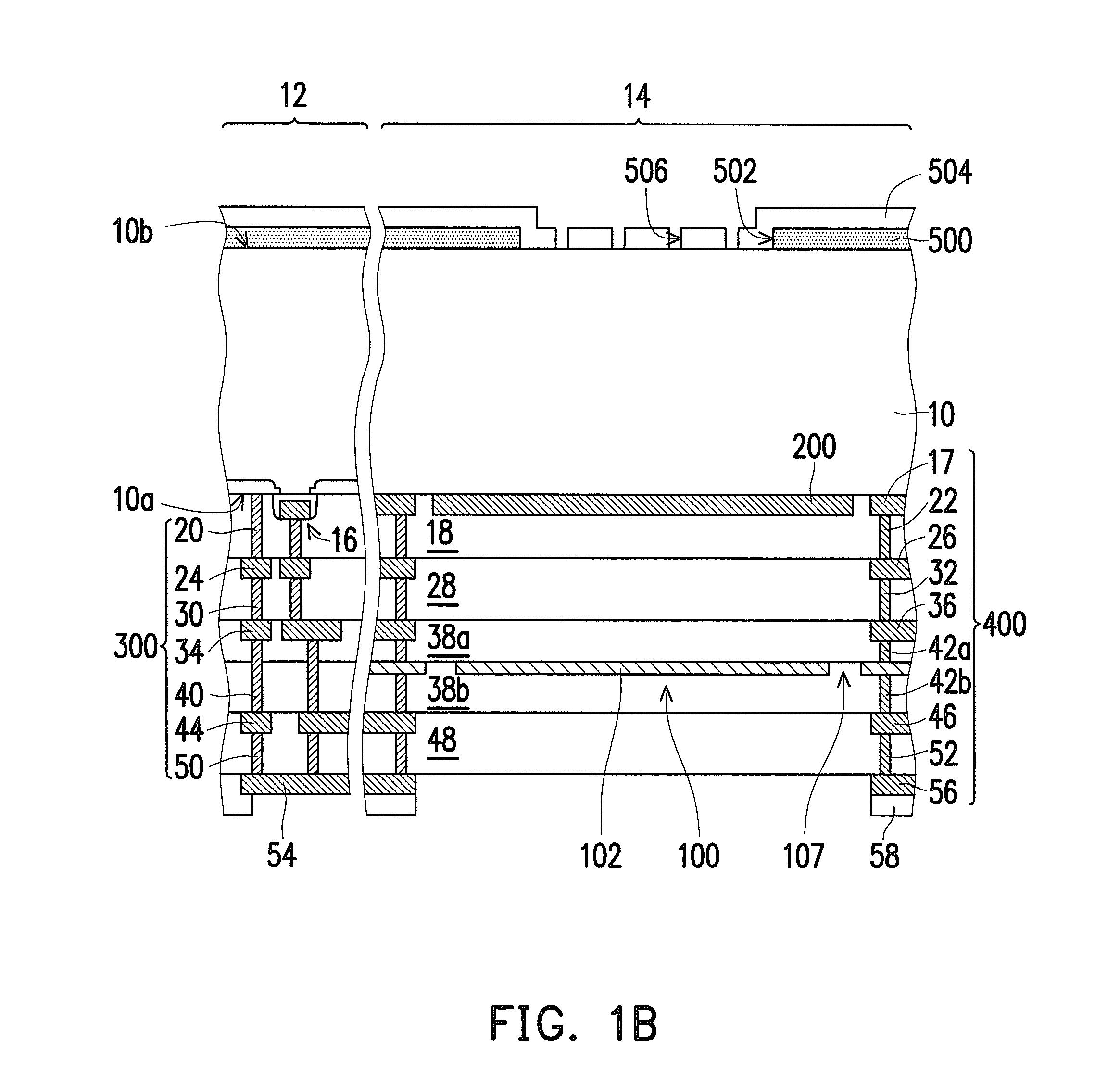

Semiconductor device and method of forming the same

ActiveUS20140319693A1MEMS performanceImprove performanceMicrophonesElectrical transducersDevice formInterconnection

A method of forming a semiconductor device is disclosed. Provided is a substrate having at least one MOS device, at least one metal interconnection and at least one MOS device formed on a first surface thereof. A first anisotropic etching process is performed to remove a portion of the substrate from a second surface of the substrate and thereby form a plurality of vias in the substrate, wherein the second surface is opposite to the first surface. A second anisotropic etching process is performed to remove another portion of the substrate from the second surface of the substrate and thereby form a cavity in the substrate, wherein the remaining vias are located below the cavity. An isotropic etching process is performed to the cavity and the remaining vias.

Owner:UNITED MICROELECTRONICS CORP

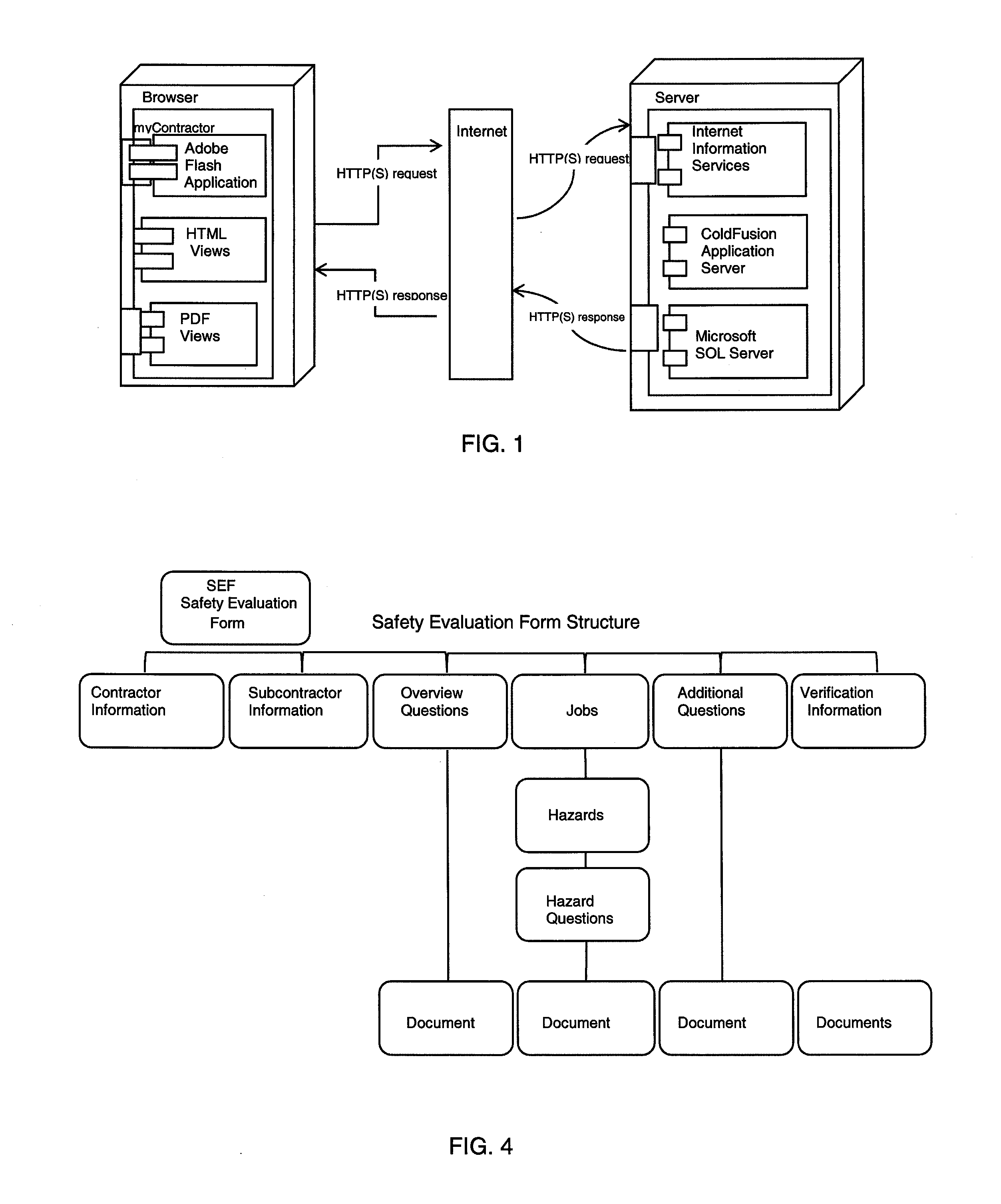

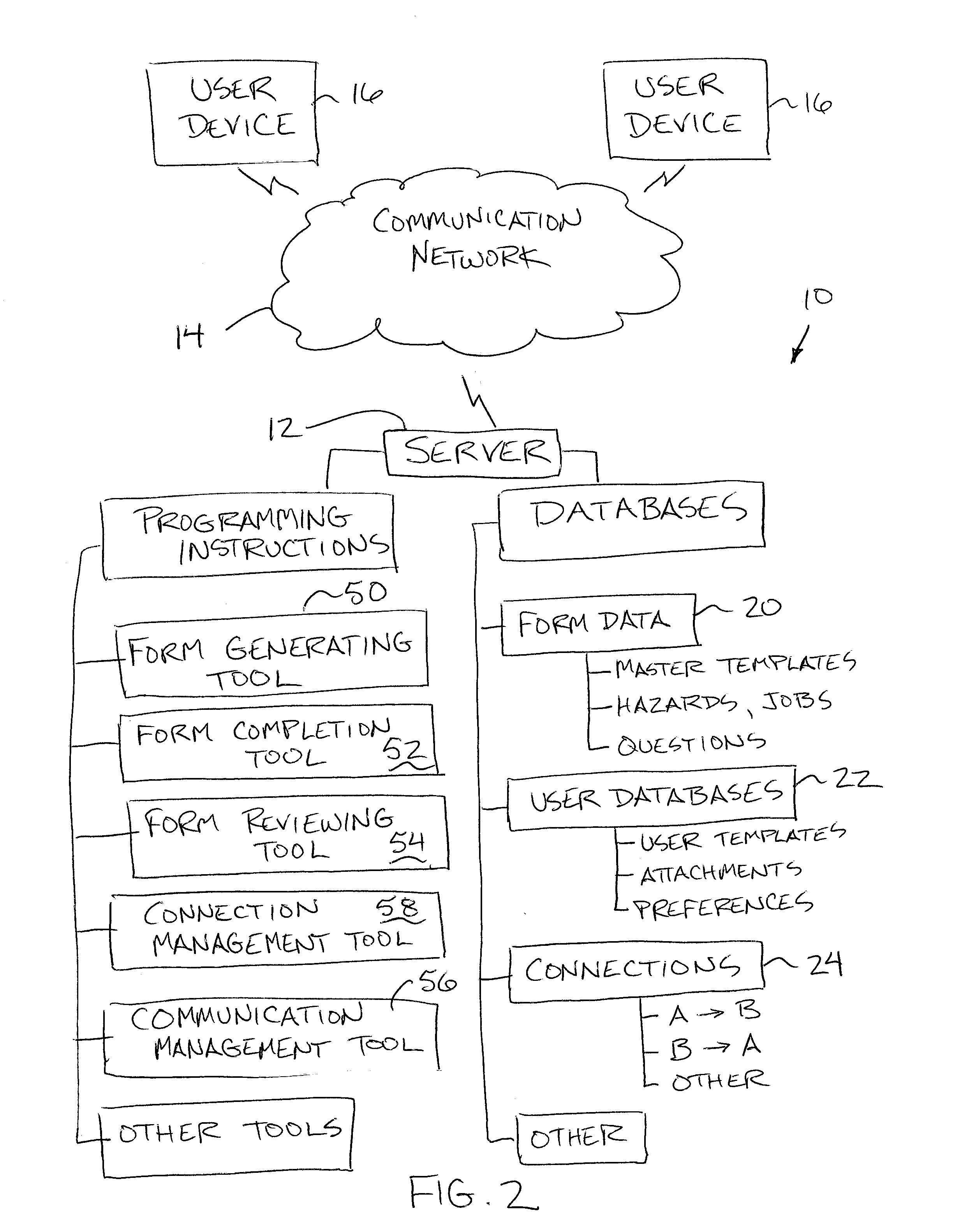

System for Generating and Completing Safety Evaluation Forms

InactiveUS20150370773A1Ensure continuityReduce riskNatural language data processingSpecial data processing applicationsDatabaseUser interface

A computer implemented system for exchanging safety information between a primary user and a secondary user, makes use of a server including a system memory storing programming instructions thereon, a form data database storing safety evaluation form data thereon in the form of safety questions relating to safety information, and a user interface arranged to receive input from the primary user and the secondary user. The programming instructions on the system memory include a form generating tool arranged to generate a prescribed safety evaluation form using the safety evaluation form data from the form data database according to input received from the primary user, a form completion tool arranged to append response data to the prescribed safety evaluation form according to input received from the secondary user to generate a completed form, and a form reviewing tool arranged to provide access to the completed form by the primary user.

Owner:1LIFE WORKPLACE SAFETY & HEALTH

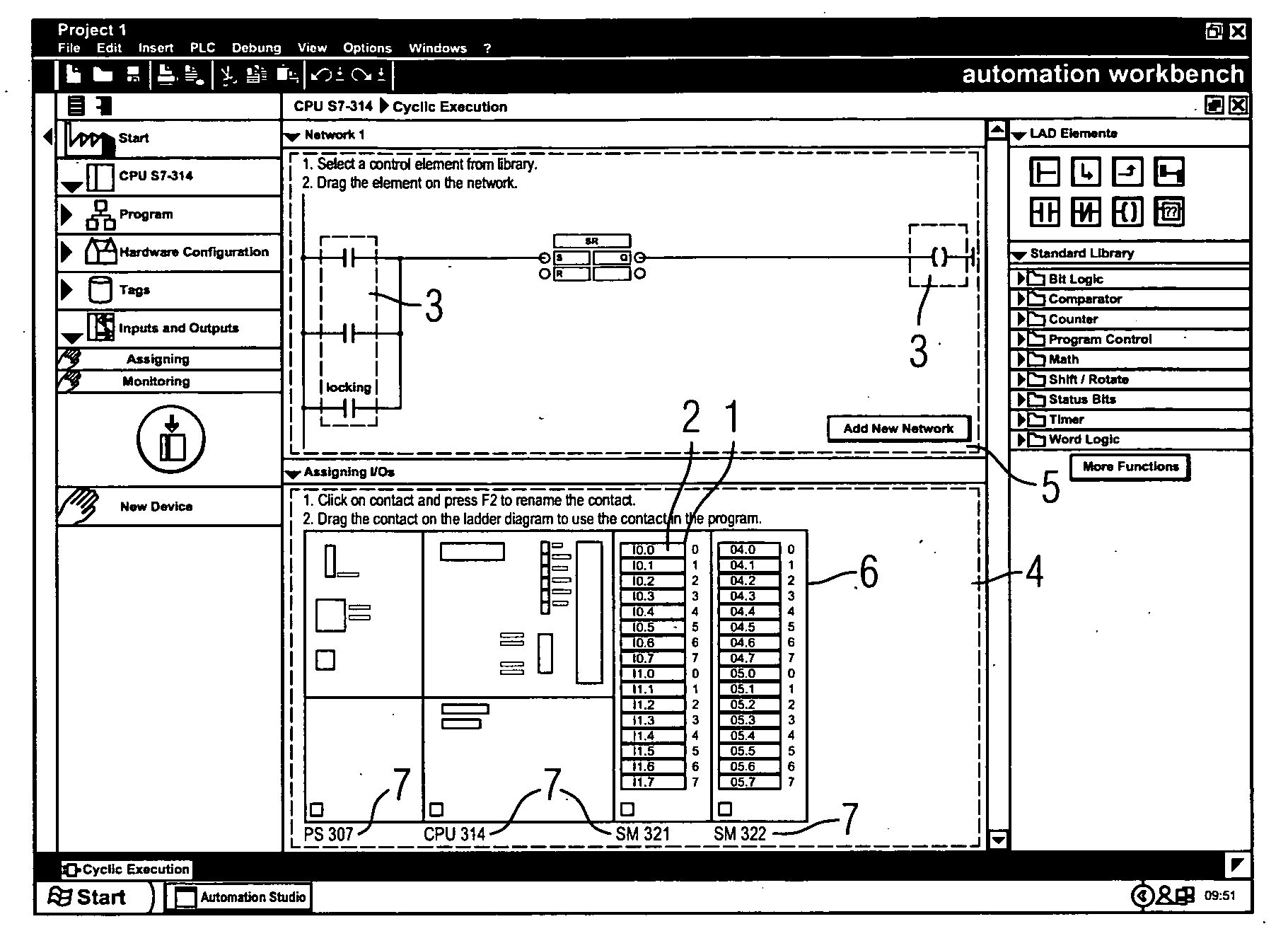

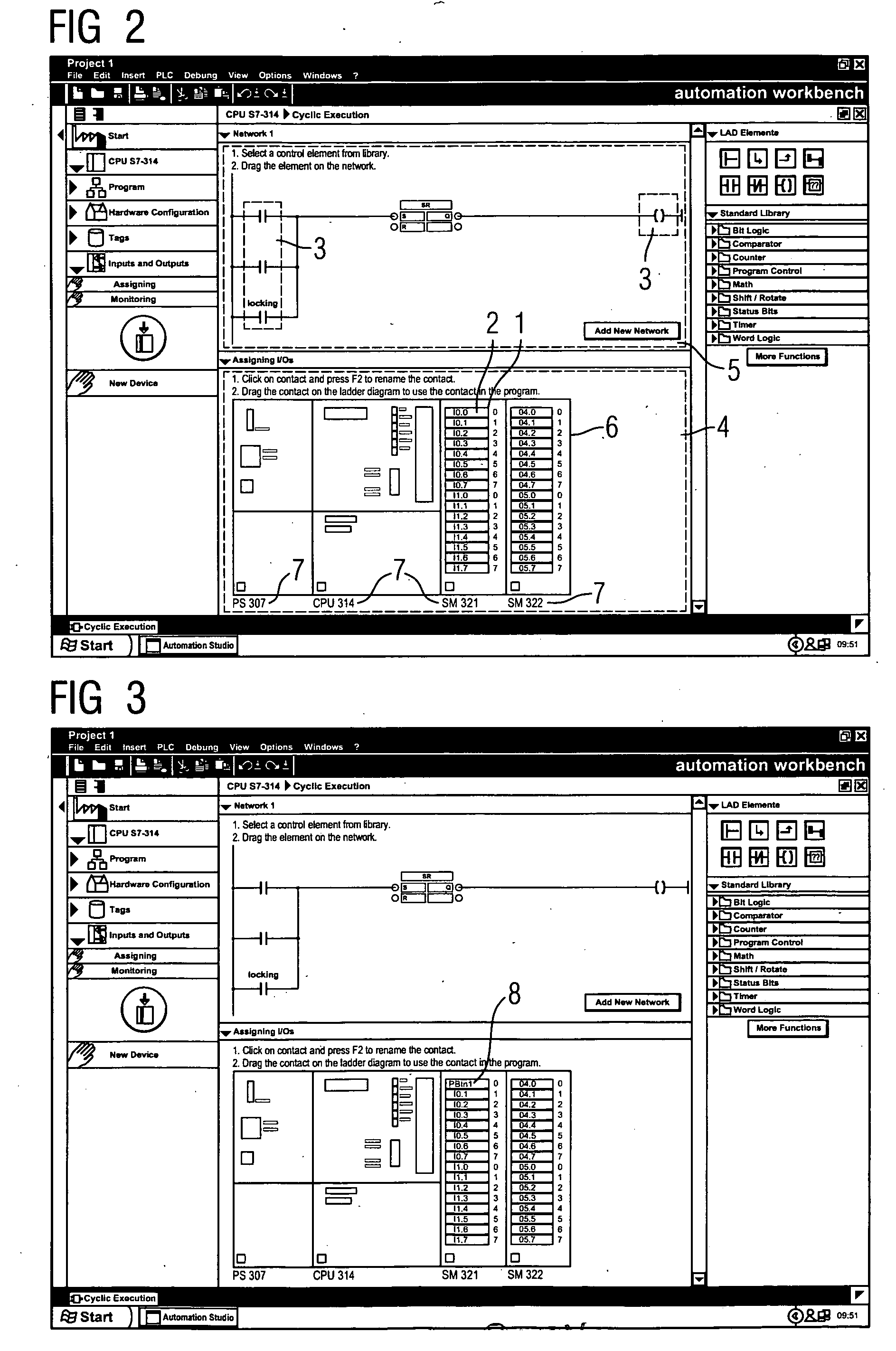

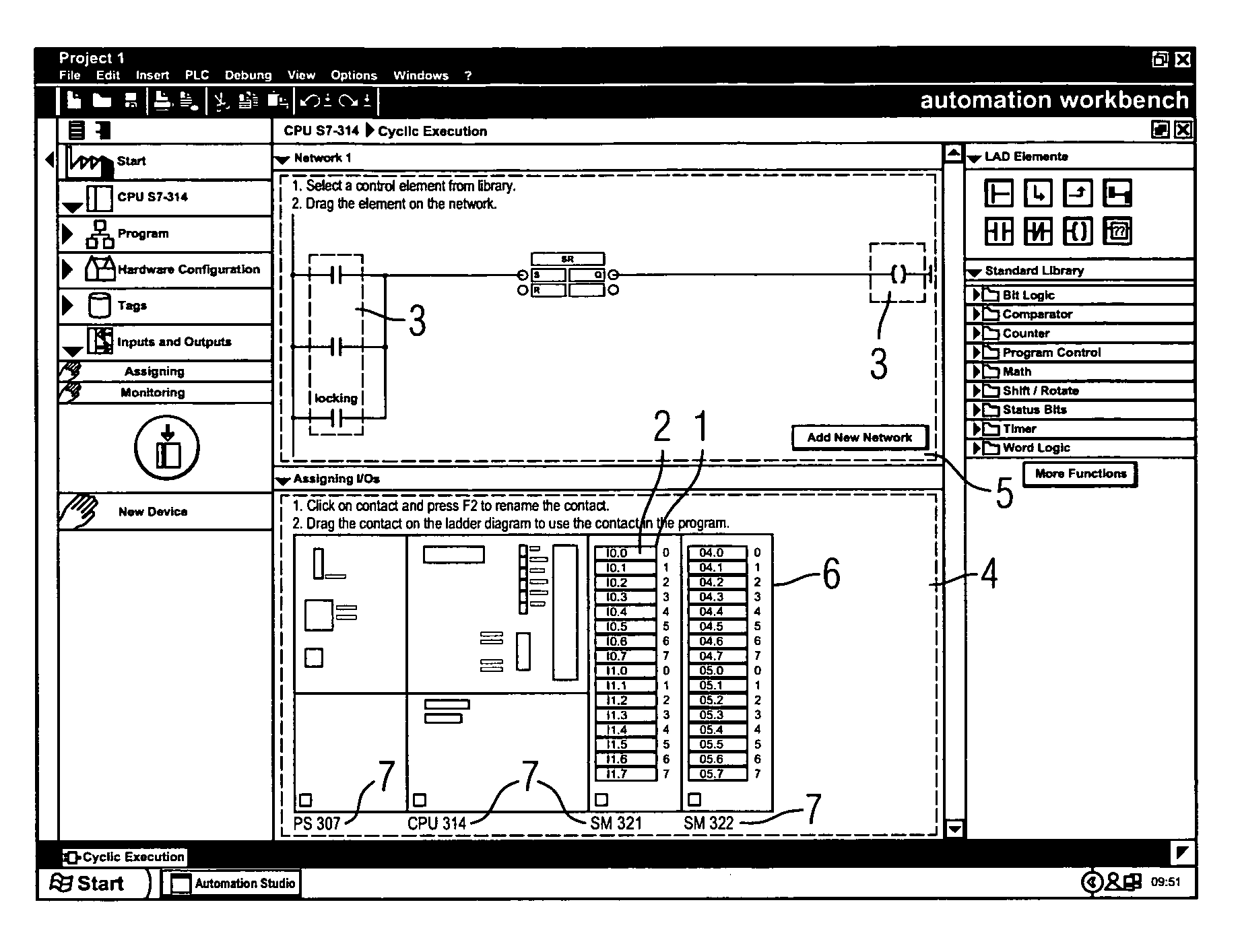

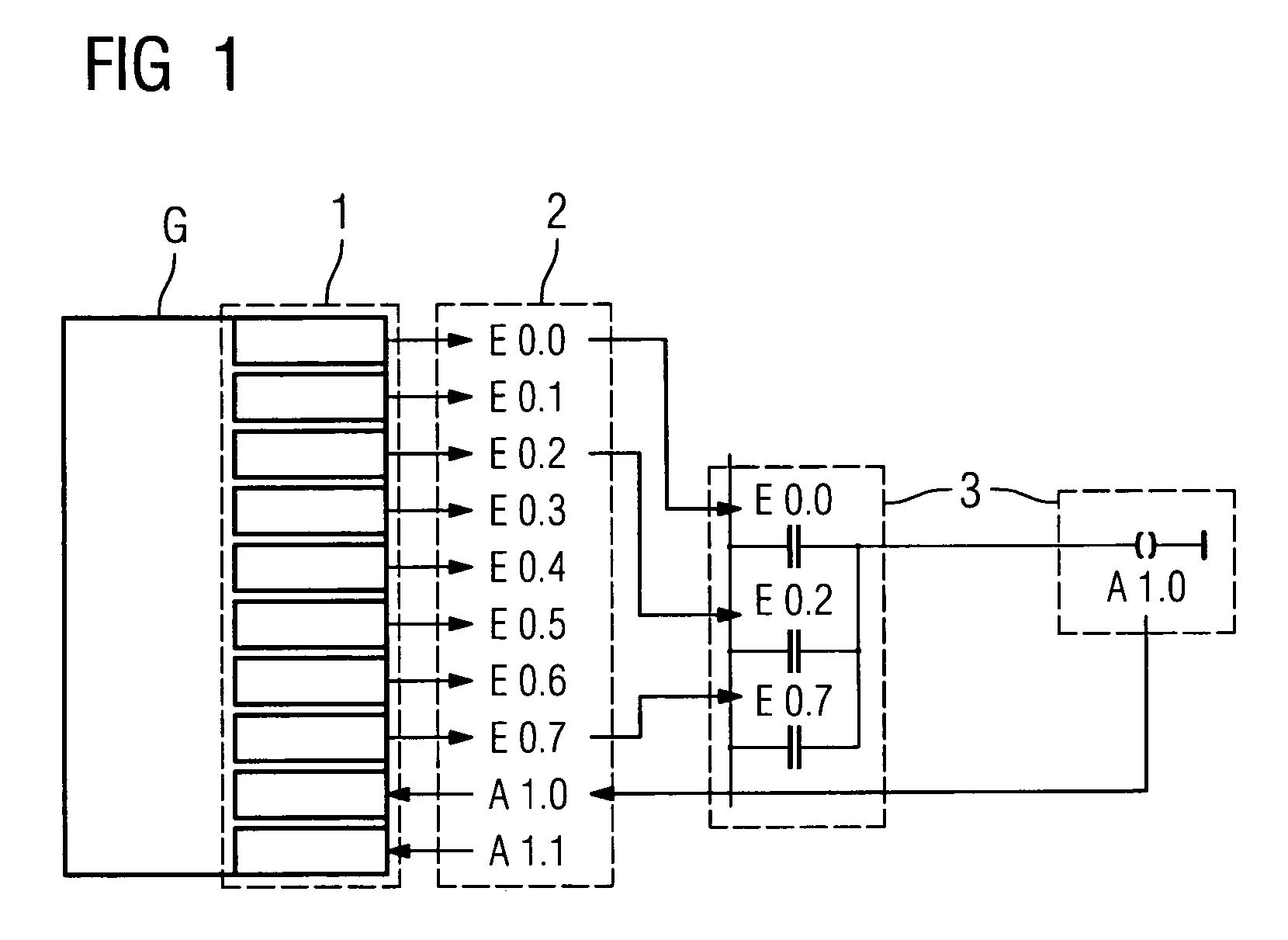

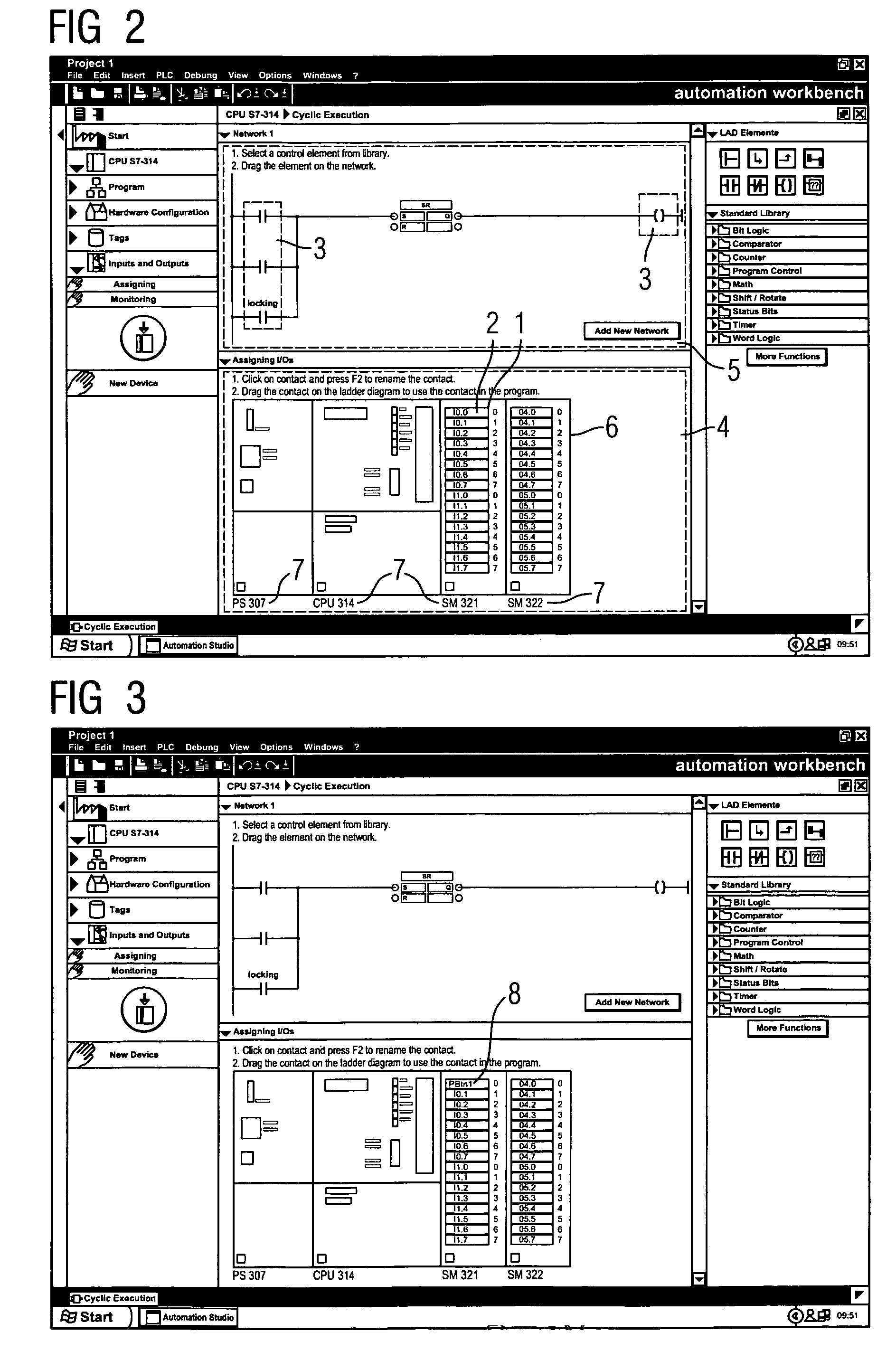

Graphical interconnection of hardware signals

ActiveUS20070067053A1Short timeCompetitive advantageComputer controlSimulator controlComputer hardwareGraphics

In one aspect, a system and a method for graphical interconnection of hardware signals of a device, especially of a controller device are provided. The object of the invention is to design the graphical interconnection in a simple manner so that a user can perform this function intuitively and without knowledge of the address convention used in the engineering system. This object is achieved by the inventive system and by the inventive method by the hardware signals being interconnected graphically with program elements of a programming environment using drag & drop. A clean copy of the Abstract that incorporates the above amendments is provided herewith on a separate page.

Owner:SIEMENS AG

Method of forming power mosfet

ActiveUS20110171799A1Reduce gate-to-drain capacitanceDeterioration of device performanceSemiconductor/solid-state device manufacturingSemiconductor devicesLine widthOptoelectronics

A method of forming a power MOSFET is described. An epitaxial layer of first conductivity type is formed on a substrate of first conductivity type. A body layer of second conductivity type is formed in the epitaxial layer. A plurality of mask patterns are formed on the substrate. A plurality of trenches are formed in the body layer and the epitaxial layer between the mask patterns. An oxide layer is formed on surfaces of the trenches. A conductive layer is formed in the trenches. A trimming process is performed to the mask patterns to reduce the line width of each mask pattern. Two source regions of first conductivity type are formed in the body layer beside each trench by using the trimmed mask patterns as a mask. A plurality of dielectric patterns are formed on the conductive layer and between the trimmed mask patterns. The trimmed mask patterns are removed.

Owner:EXCELLIANCE MOS

Graphical interconnection of hardware signals

ActiveUS8683364B2Short timeCompetitive advantageComputer controlSimulator controlGraphicsComputer hardware

A system and a method for graphical interconnection of hardware signals of a device, (e.g., a controller device) are provided. The graphical interconnection can now be implemented in a simple manner so that a user can perform this function intuitively and without knowledge of the address convention used in the engineering system. This may be achieved by the inventive system and by the inventive method by the hardware signals being interconnected graphically with program elements of a programming environment using drag & drop features in a graphical user interface.

Owner:SIEMENS AG

Semiconductor device and method of forming the same

ActiveUS8981501B2Improve performanceCompetitive advantageMicrophonesElectrical transducersMetal interconnectDevice form

A method of forming a semiconductor device is disclosed. Provided is a substrate having at least one MOS device, at least one metal interconnection and at least one MOS device formed on a first surface thereof. A first anisotropic etching process is performed to remove a portion of the substrate from a second surface of the substrate and thereby form a plurality of vias in the substrate, wherein the second surface is opposite to the first surface. A second anisotropic etching process is performed to remove another portion of the substrate from the second surface of the substrate and thereby form a cavity in the substrate, wherein the remaining vias are located below the cavity. An isotropic etching process is performed to the cavity and the remaining vias.

Owner:UNITED MICROELECTRONICS CORP

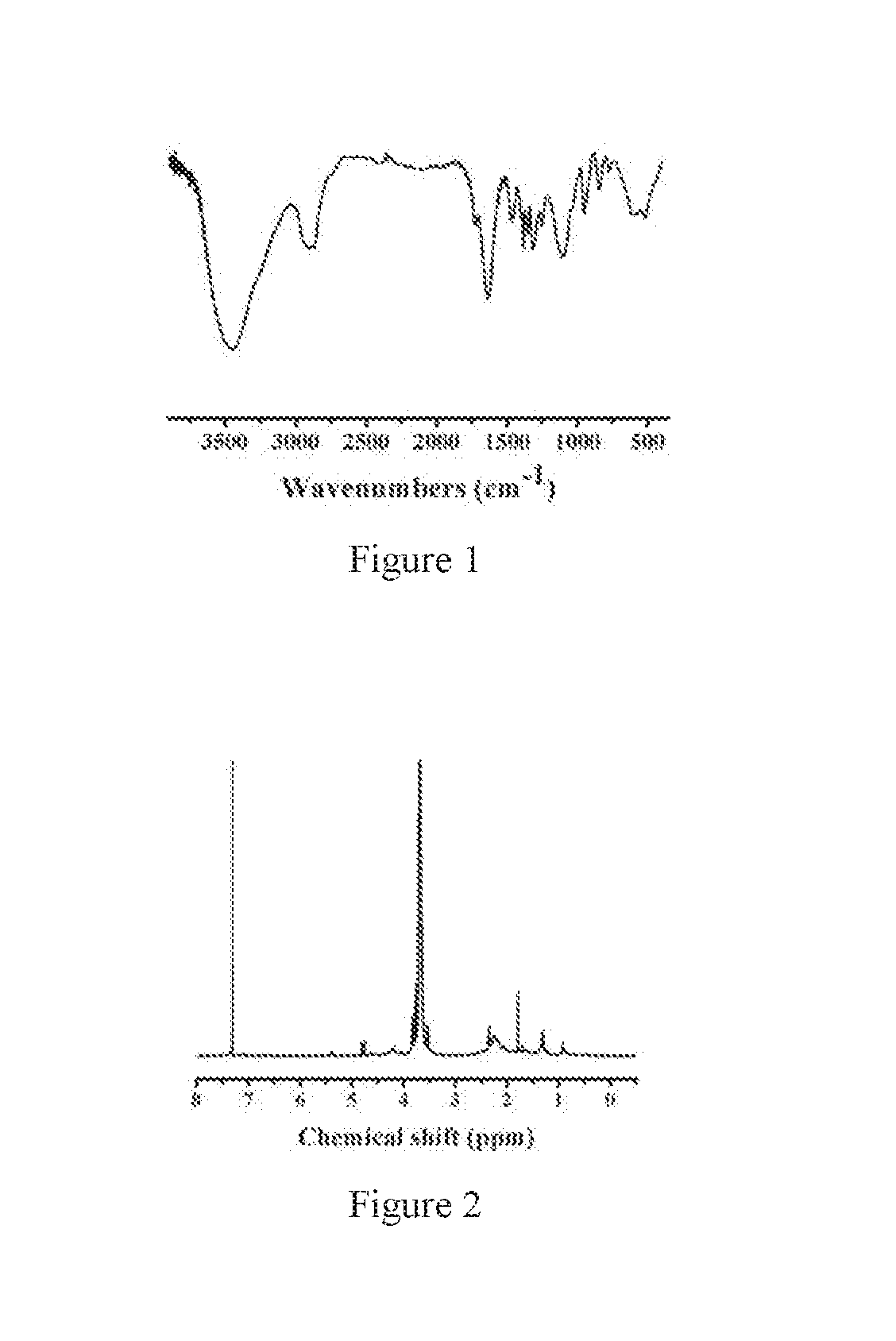

Preparation Method of Polycarboxylate Superplasticizer with Carbon Dioxide

ActiveUS20180155244A1Super cost-effectiveGood competitive advantageNitrogen atmosphereSuperplasticizer

The present invention discloses a preparation method of a polycarboxylate superplasticizer with carbon dioxide, comprising the following steps: (1) preparing a polycarboxylate superplasticizer prepolymer: performing an oxidation-reduction radical polymerization of an unsaturated macromonomer, an unsaturated phenol derivative, a reducing agent, an initiator and a chain transfer agent with different proportions under a nitrogen atmosphere to obtain a novel polycarboxylate superplasticizer prepolymer with different molecular weight; adjusting the pH by adding an alkali; (2) preparing a polycarboxylate superplasticizer: performing a Koble-Schmitt reaction between the polycarboxylate superplasticizer prepolymer and a carbon dioxide for a certain time to obtain the polycarboxylate superplasticizer. The polycarboxylate superplasticizer prepared by the method of the present invention retains the advantages of the existing water-reducing admixture of the polyether monomer compounds, and the production process is simple, safe, controllable, less side effect and has a better cost effective and competitive advantage.

Owner:JIANGSU CHINA RAILWAY ARIT NEW MATEIRALS CO LTD

Method of fabricating semiconductor device structure

ActiveUS9018066B2Simple and easyCompetitive advantageTransistorSemiconductor/solid-state device manufacturingGate dielectricSemiconductor

A method of fabricating a semiconductor device structure is provided. The method includes the following step. A gate dielectric layer is formed on a substrate. A gate electrode is on the gate dielectric layer. The gate dielectric layer exposed by the gate electrode is treated. A first etching process is performed to remove at least a portion of the gate dielectric layer exposed by the gate electrode. A spacer is formed on the sidewall of the gate electrode. A second etching process is performed to form recesses in the substrate beside the gate electrode. Besides, during the first etching process and the second etching process, an etching rate of the treated gate dielectric layer is greater than an etching rate of the untreated gate dielectric layer.

Owner:UNITED MICROELECTRONICS CORP

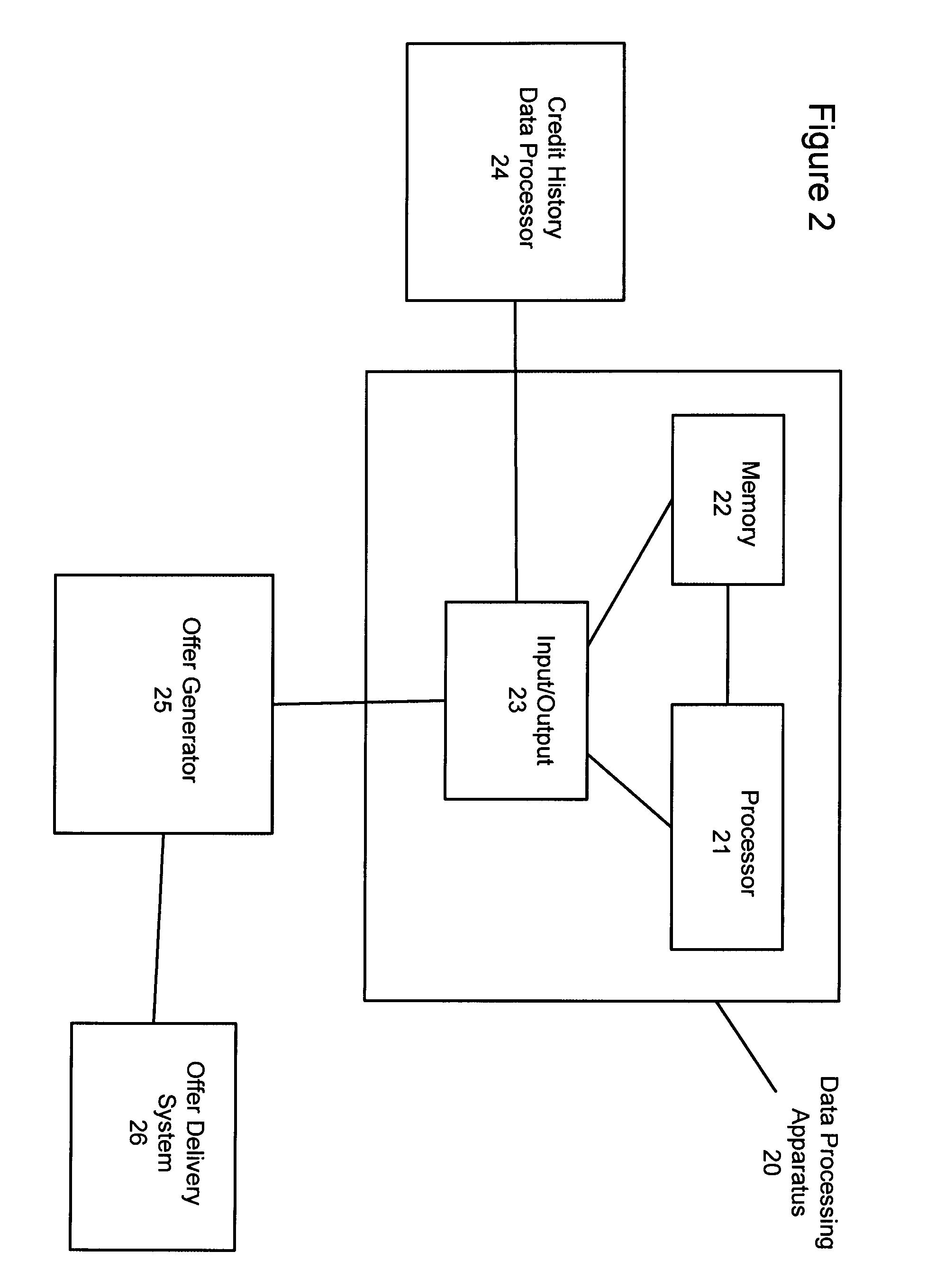

System and method for offering risk-based interest rates in a credit instrument

InactiveUS20110004545A1Competitive advantageReduced interest rateFinancePayment architectureData scienceCredit history

A system and method for communicating an offer to apply for a credit instrument is provided. A processing allows for processing credit history data. A calculating step allows for calculating a first plurality of interest rates based on the credit history data. A determining step allows for determining a second plurality of interest rates based on the first plurality of interest rates, wherein the second plurality of interest rates corresponds to a plurality of credit risk scores. Finally, a communicating step allows for communicating the offer to apply for a credit instrument in an initial communication with an offeree, the offer disclosing the second plurality of interest rates. An apparatus that calculates the interest rates used in the offer is also provided.

Owner:JPMORGAN CHASE BANK NA

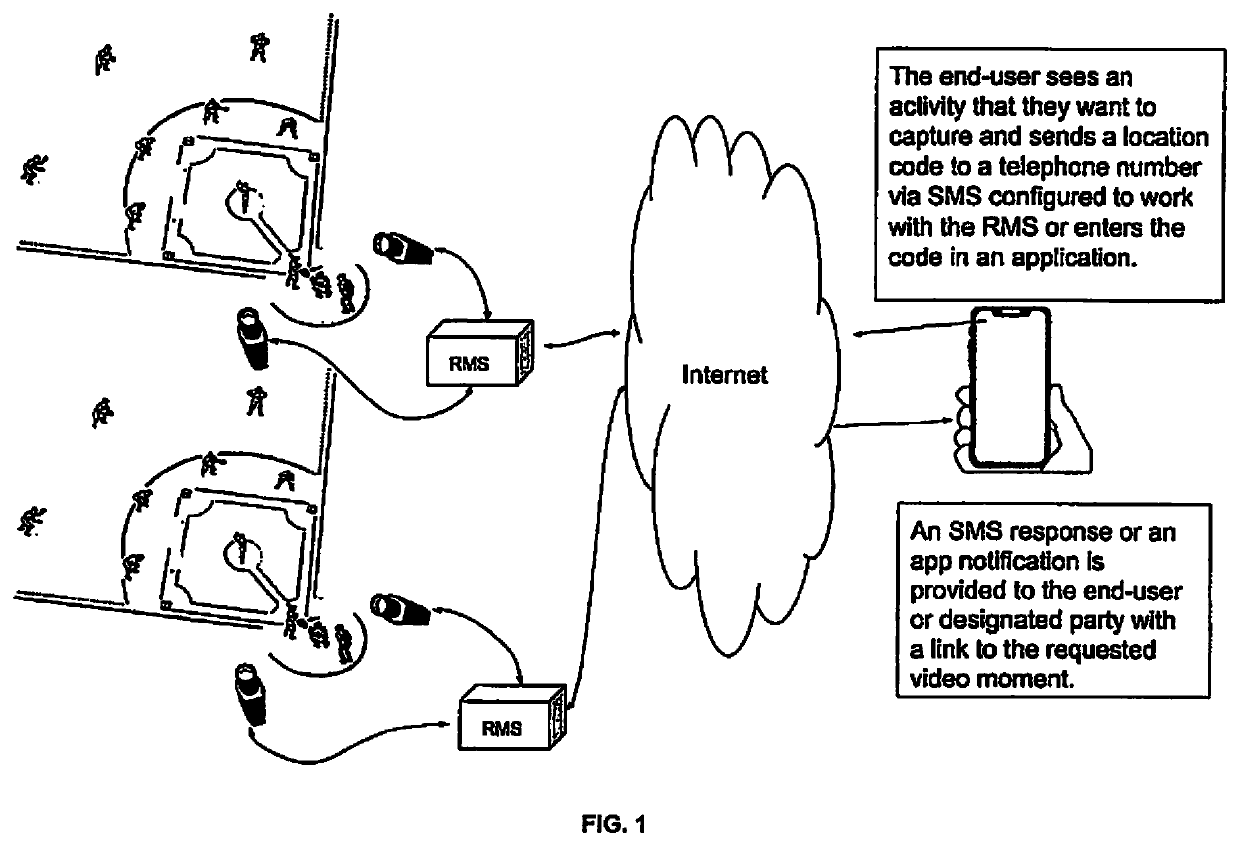

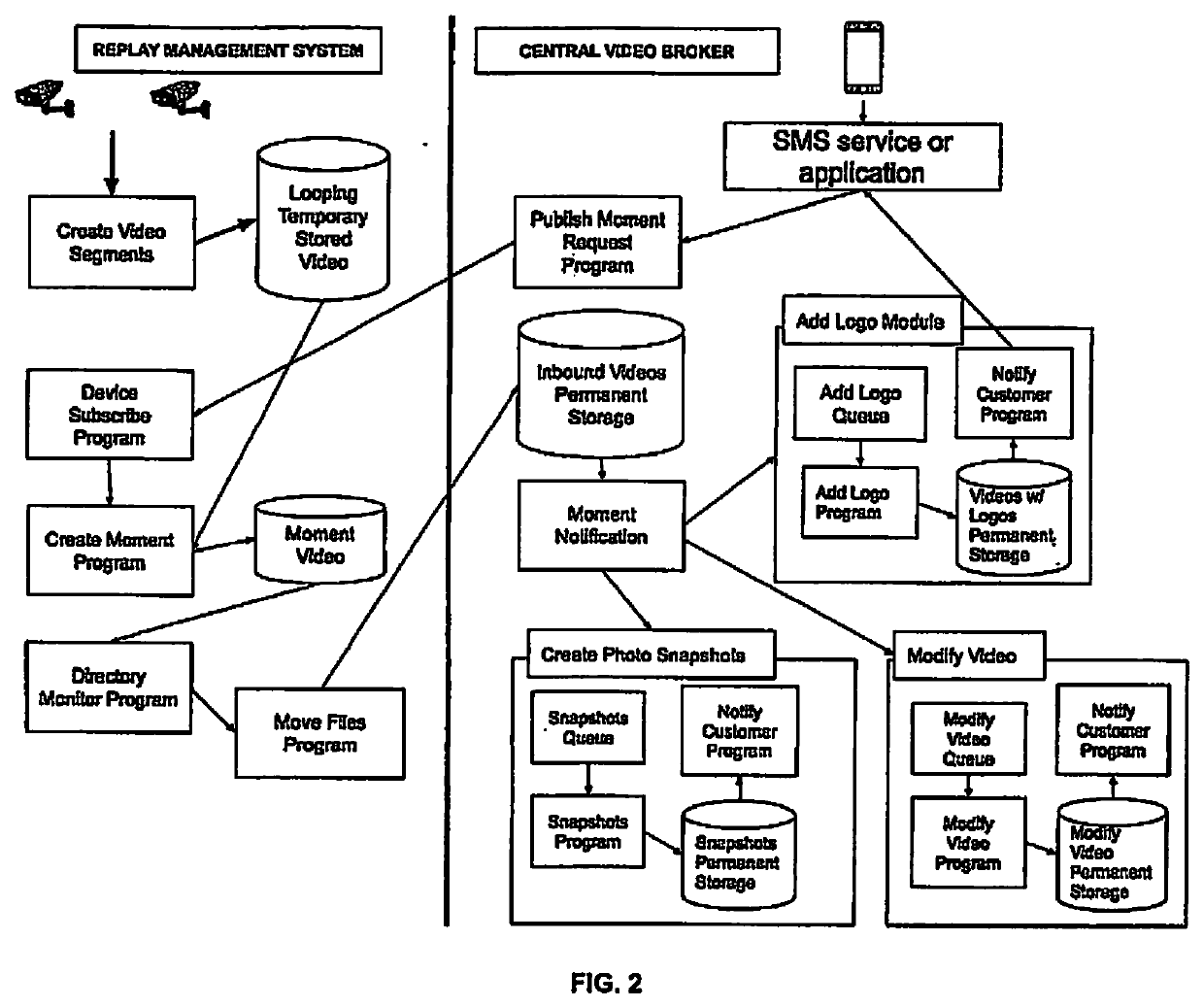

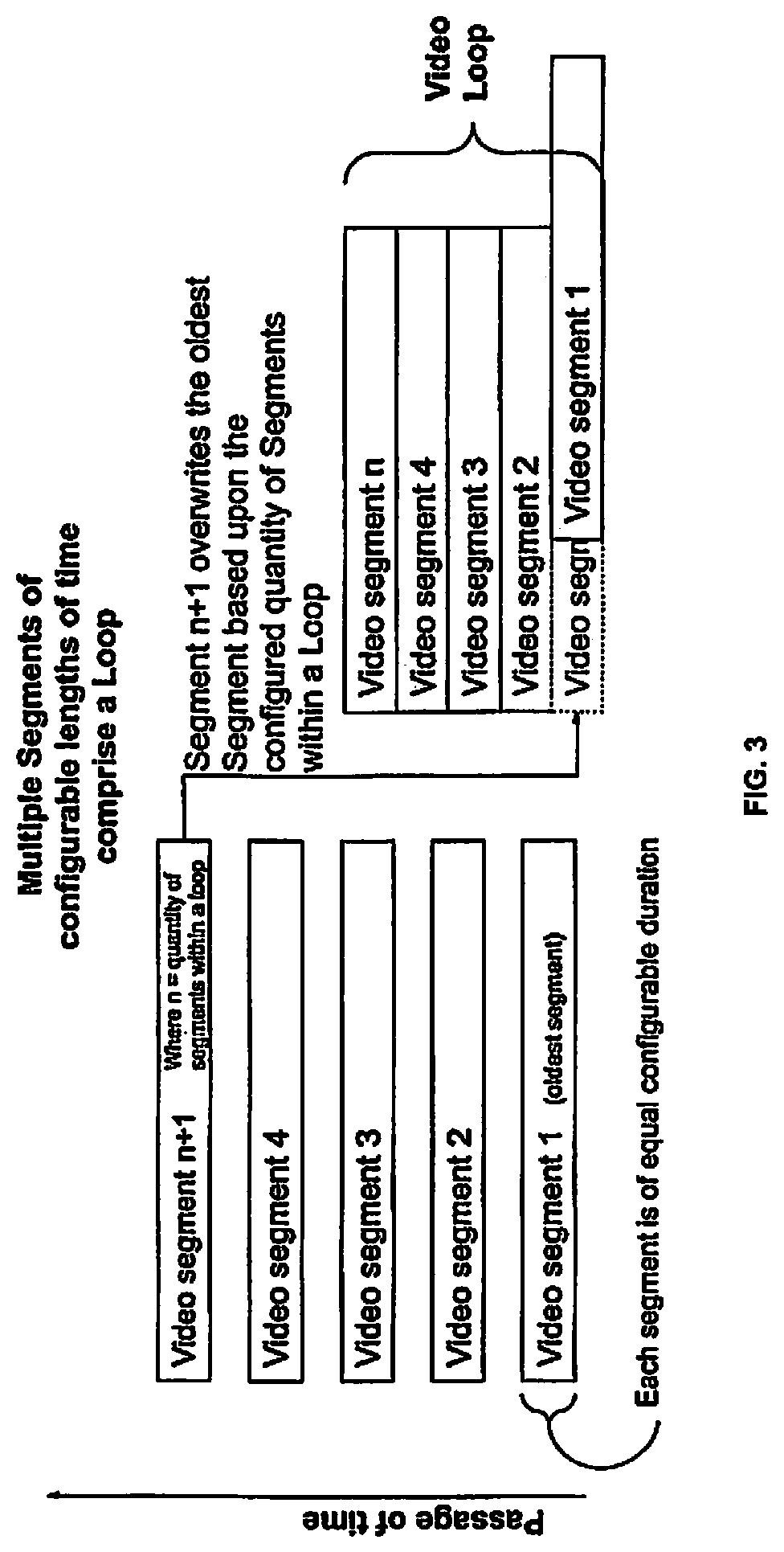

Systems and Methods for Capturing and Distributing Specified Moments of Activity

InactiveUS20220060788A1Easy to createCompetitive advantageMessaging/mailboxes/announcementsTransmissionAlgorithmEngineering

Owner:HARLING DOUGLAS C +2

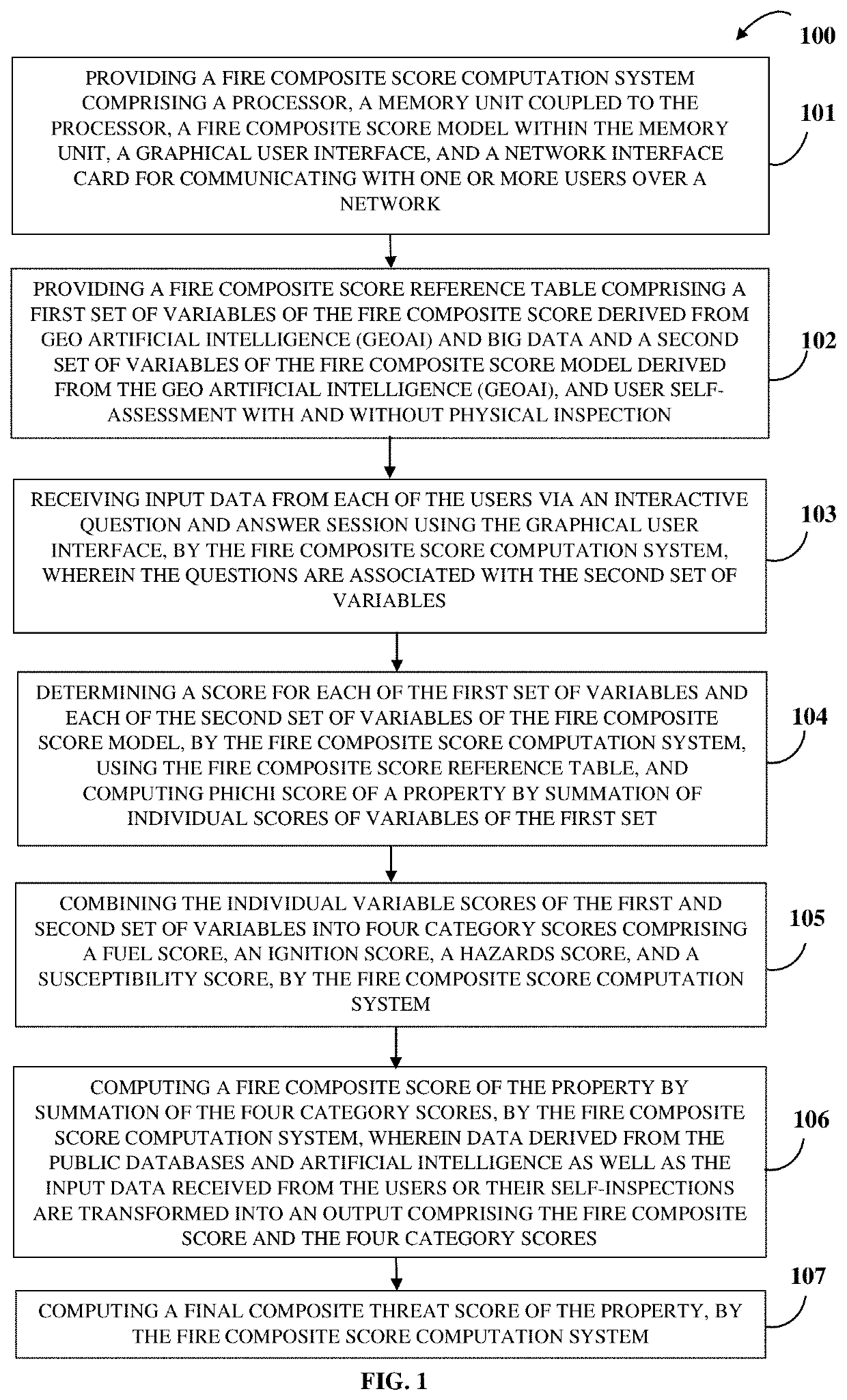

Method and system for computing a phichi score, four category scores, a 4score, and a final composite threat (FCT) score for a property

InactiveUS20210358049A1End lack of transparencyReduce exposureFinanceFire rescueGraphicsGraphical user interface

A method for computing a PhiChi score, four category scores, 4score and a Fire Composite Threat (FCT) score for a property comprises providing a fire composite score computation system comprising a processor, a memory unit, a fire composite score model, a graphical user interface (GUI), and a network interface card. A fire composite score reference table is stored within the memory unit comprising a first and a second set of variables. The first set of variables are derived from geospatial artificial intelligence (GEOAI) and wildfire data available in public databases. The second set of variables are derived from user feedback. Individual variable scores for the variables in the first and second set, the PhiChi score, the 4score comprising a Fuel score, an Ignitions score, a Susceptibility score and a Hazards score, and the FCT score are computed using the fire composite score model and the fire composite score reference table.

Owner:SCHWARTZ TAMMY NICHOLS

Methods of forming semiconductor trench and forming dual trenches, and structure for isolating devices

ActiveUS8450180B2Simple processLow costSemiconductor/solid-state device manufacturingEngineeringSemiconductor

Methods of forming a semiconductor trench and forming dual trenches and a structure for isolating devices are provided. The structure for isolating devices is disposed in a substrate having a periphery area and an array area. The structure for isolating devices includes a first isolation structure and a second isolation structure. The first isolation structure has a profile with at least three steps and is disposed in the substrate in the periphery area. The second isolation structure has a profile with at least two steps and is disposed in the substrate in the array area.

Owner:MACRONIX INT CO LTD

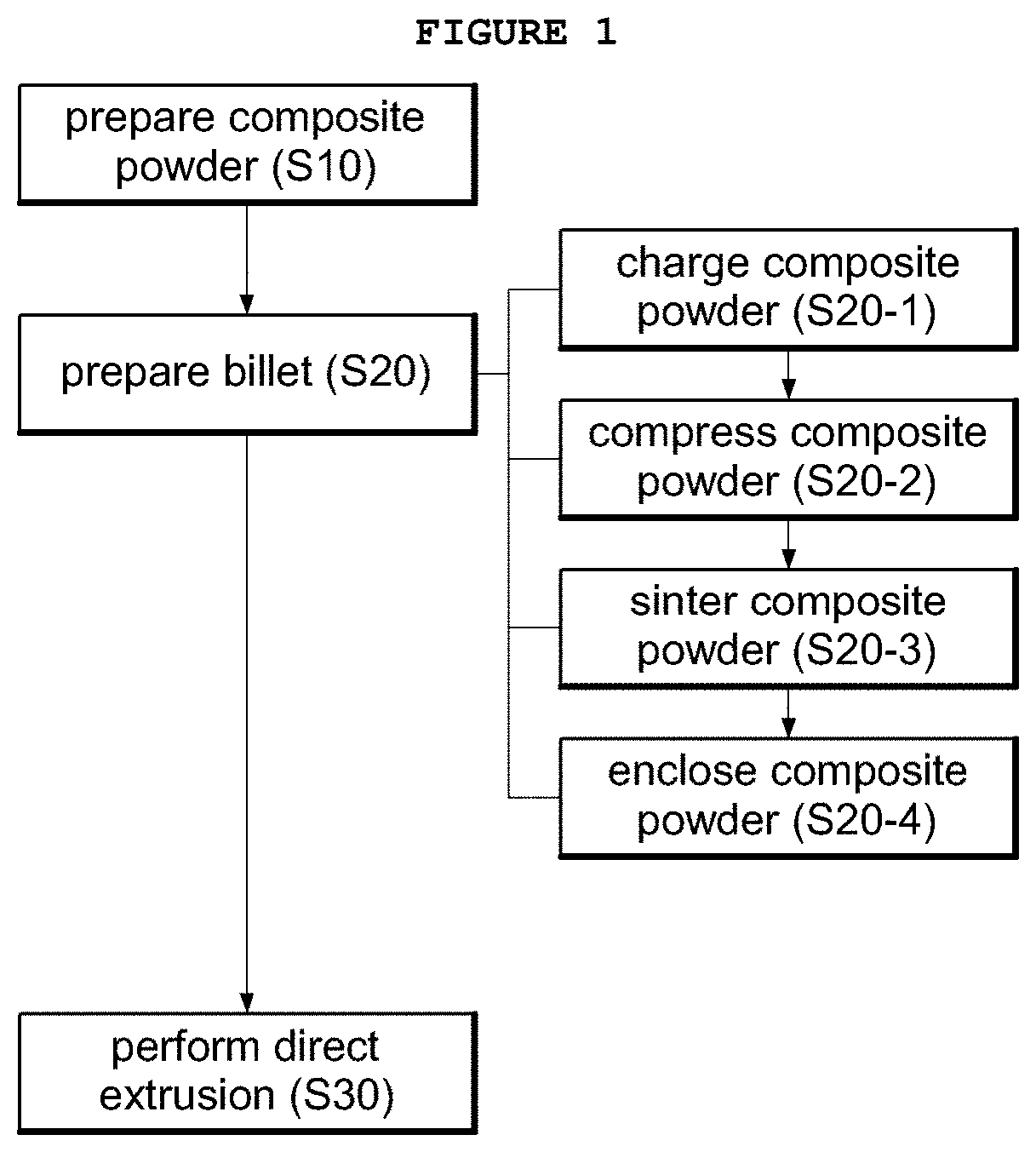

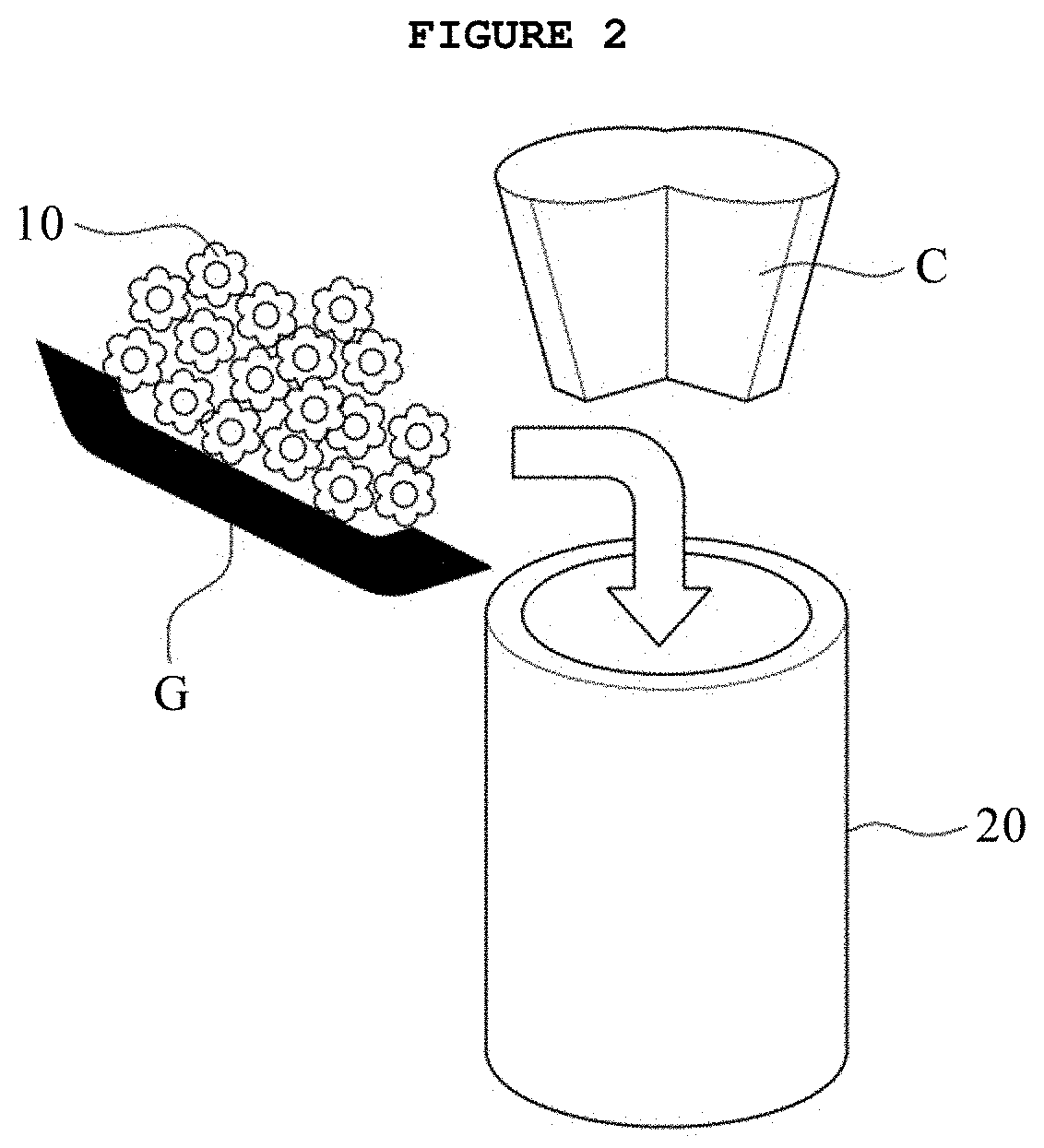

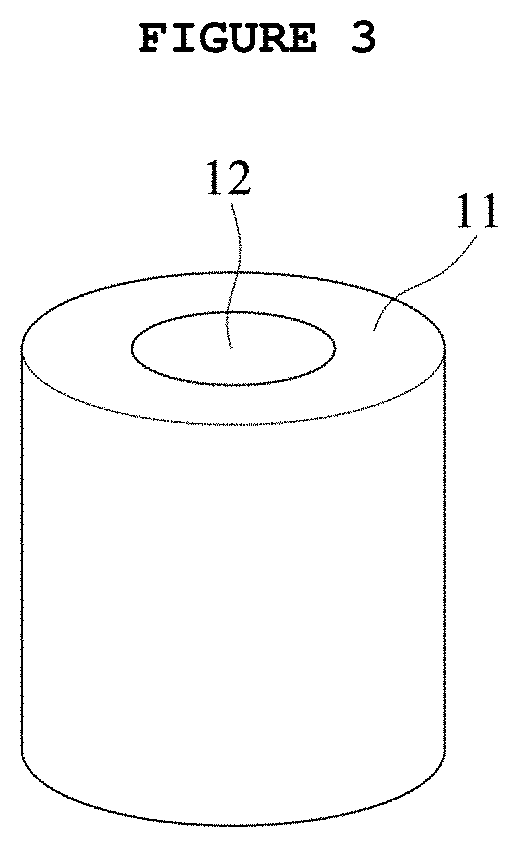

Method of manufacturing aluminum-based clad heat sink, and aluminum-based clad heat sink manufactured thereby

ActiveUS20200331066A1Competitive advantageSimple equipmentSemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingHigh volume manufacturingCarbon nanotube

Disclosed are a method of manufacturing an aluminum-based clad heat sink, and an aluminum-based clad heat sink manufactured by the method. The method includes ball-milling (i) aluminum or aluminum alloy powder and (ii) carbon nanotubes (CNT) to prepare a composite powder, preparing a multi-layered billet using the composite billet, and directly extruding the multi-layered billet using an extrusion die to produce a heat sink. The method has an advantage of producing a light high-strength high-conductivity aluminum-based clad heat sink having an competitive advantage in terms of price by using direct extrusion that is suitable for mass production due to its simplicity in process procedure and equipment required.

Owner:PUKYONG NAT UNIV IND ACADEMIC COOPERATION FOUND

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com