Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

78results about How to "Avoid excessive width" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

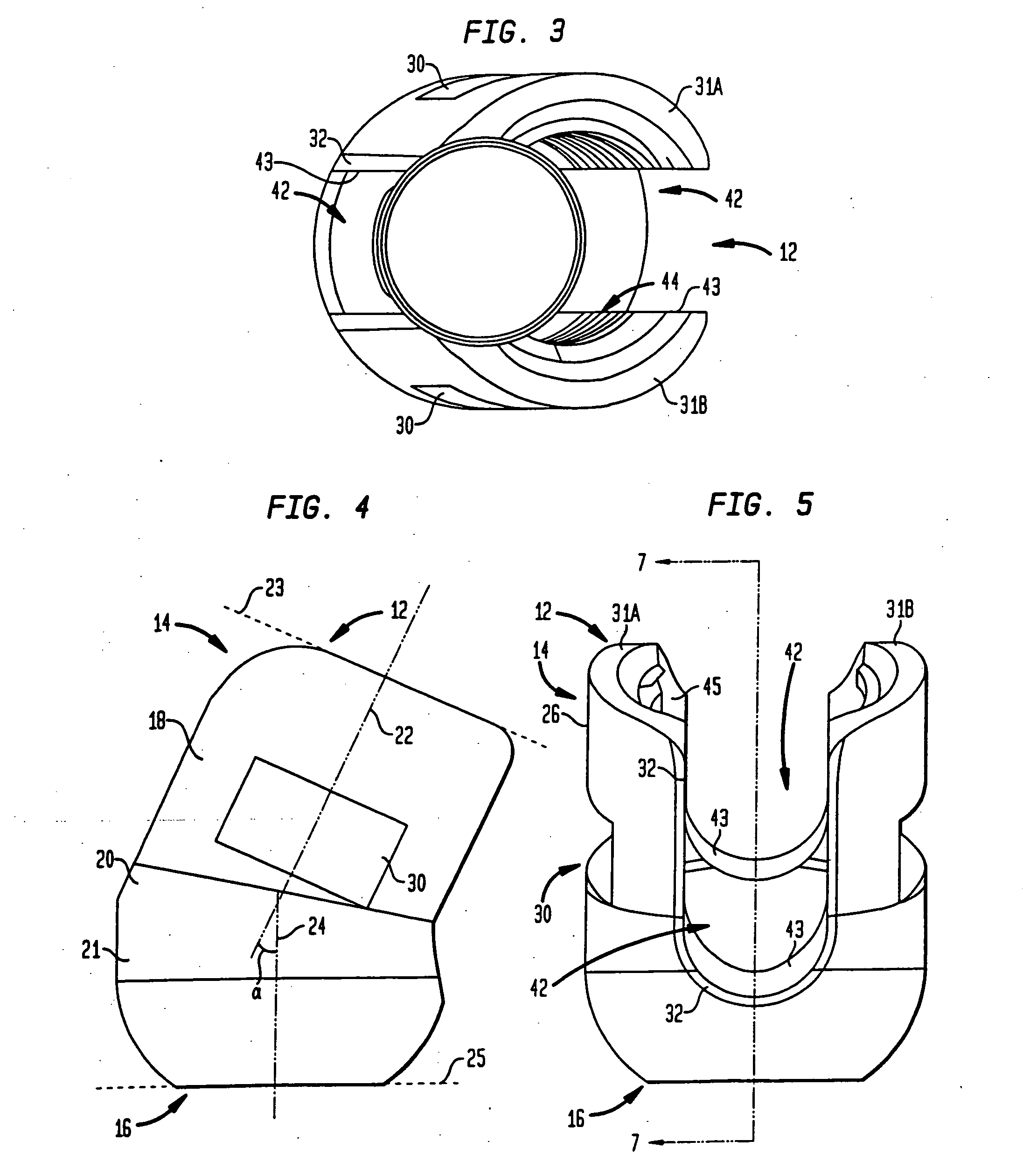

Suture anchor

Owner:BONUTTI 2003 TRUST A THE +1

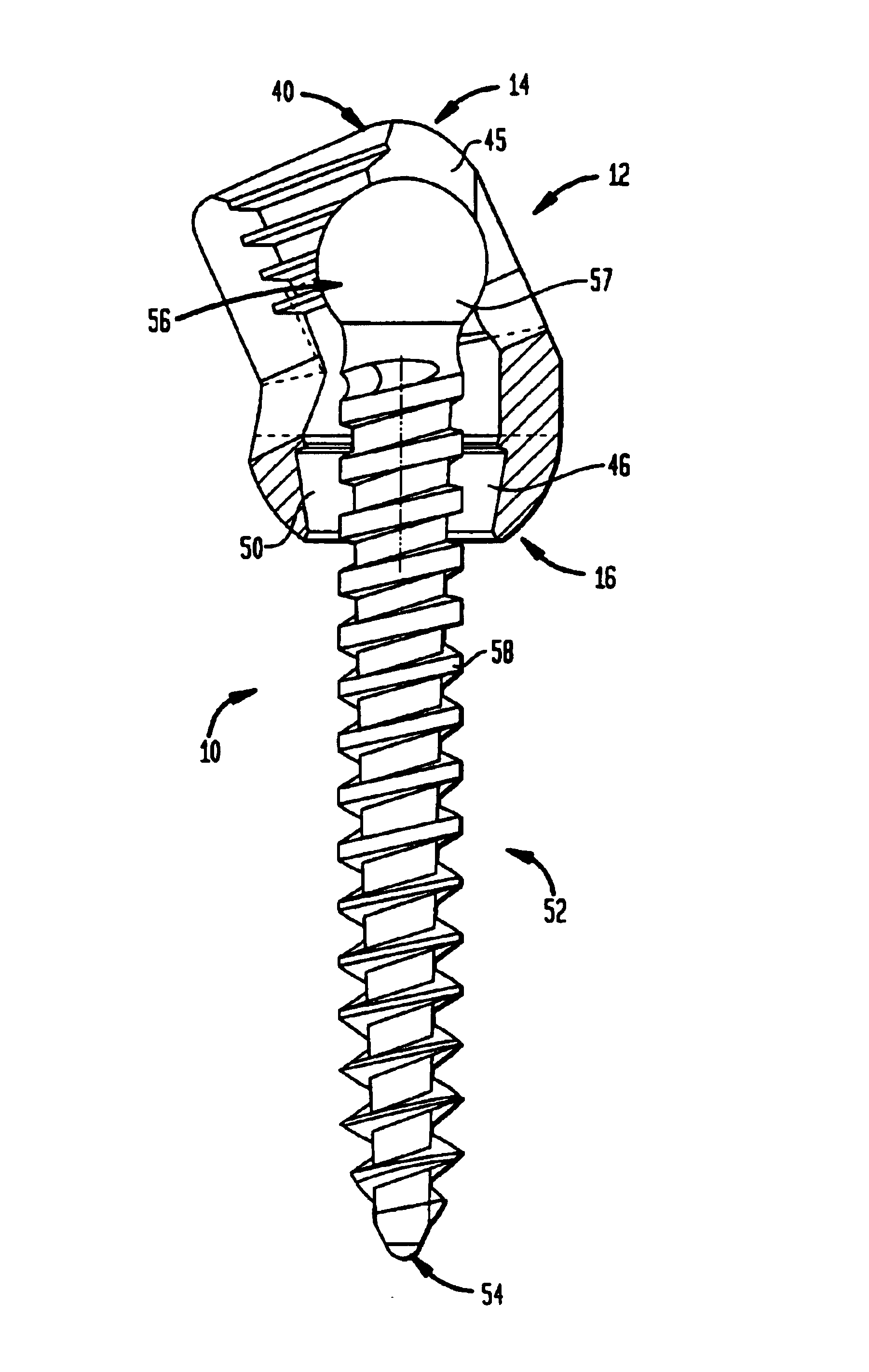

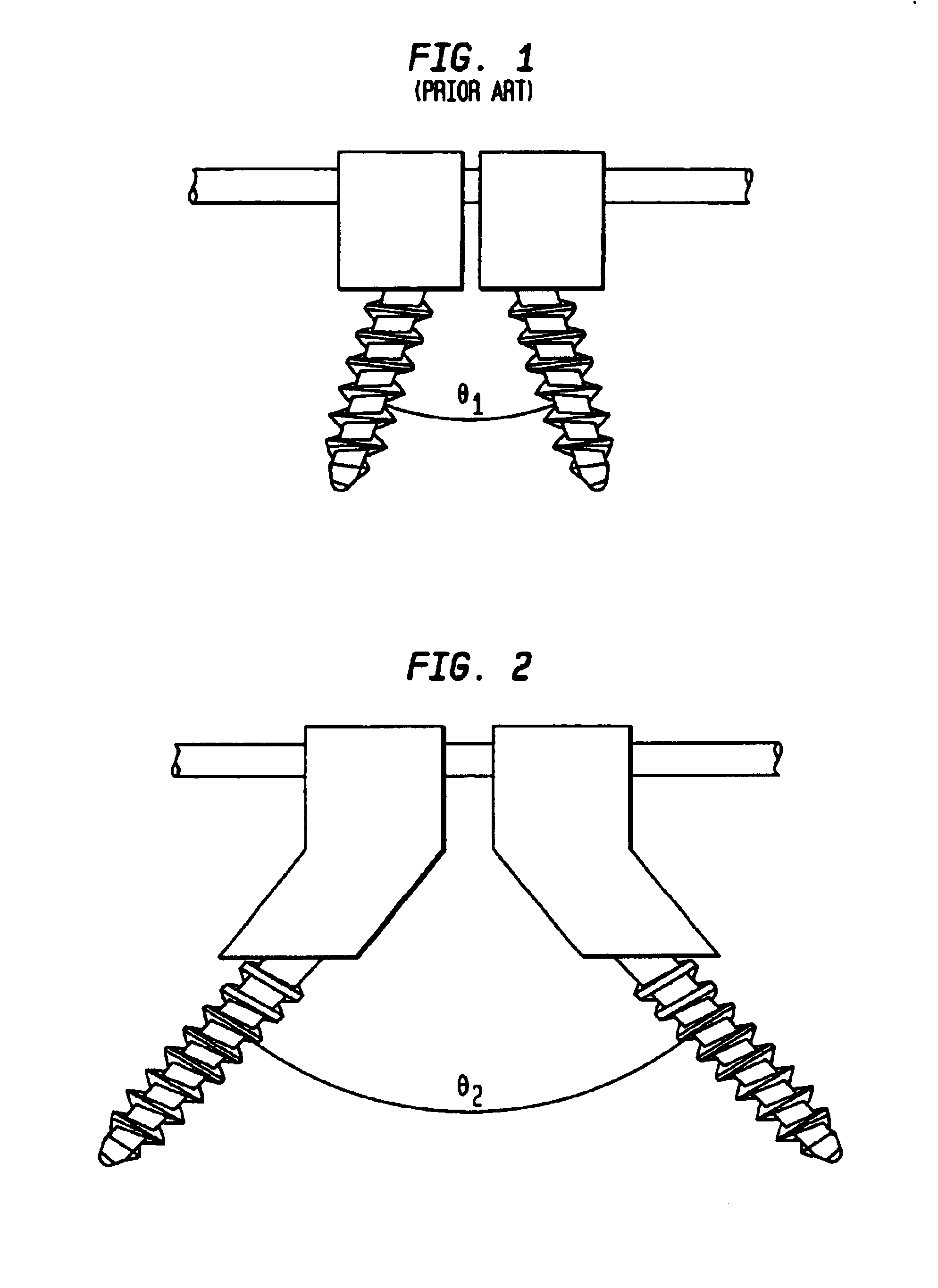

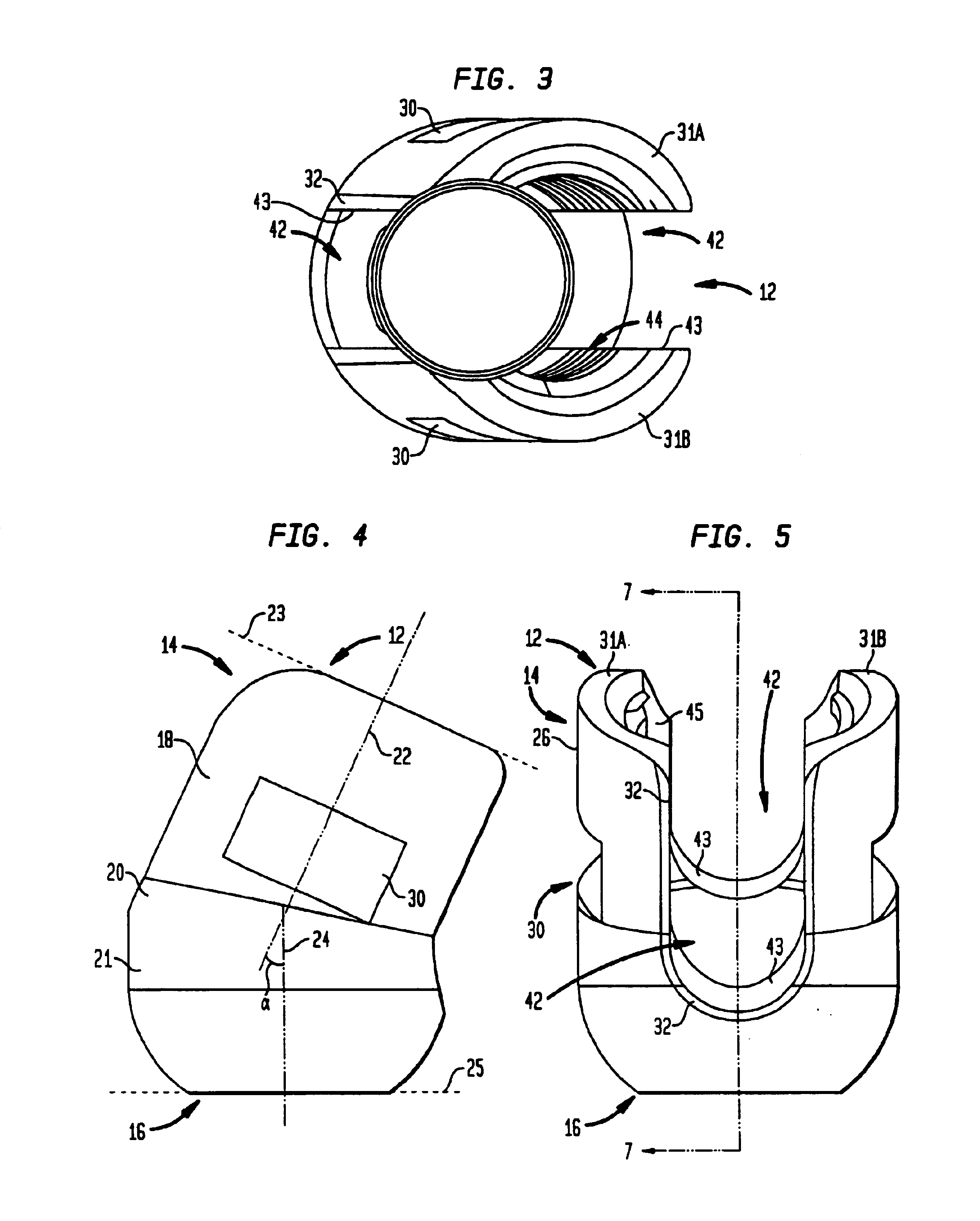

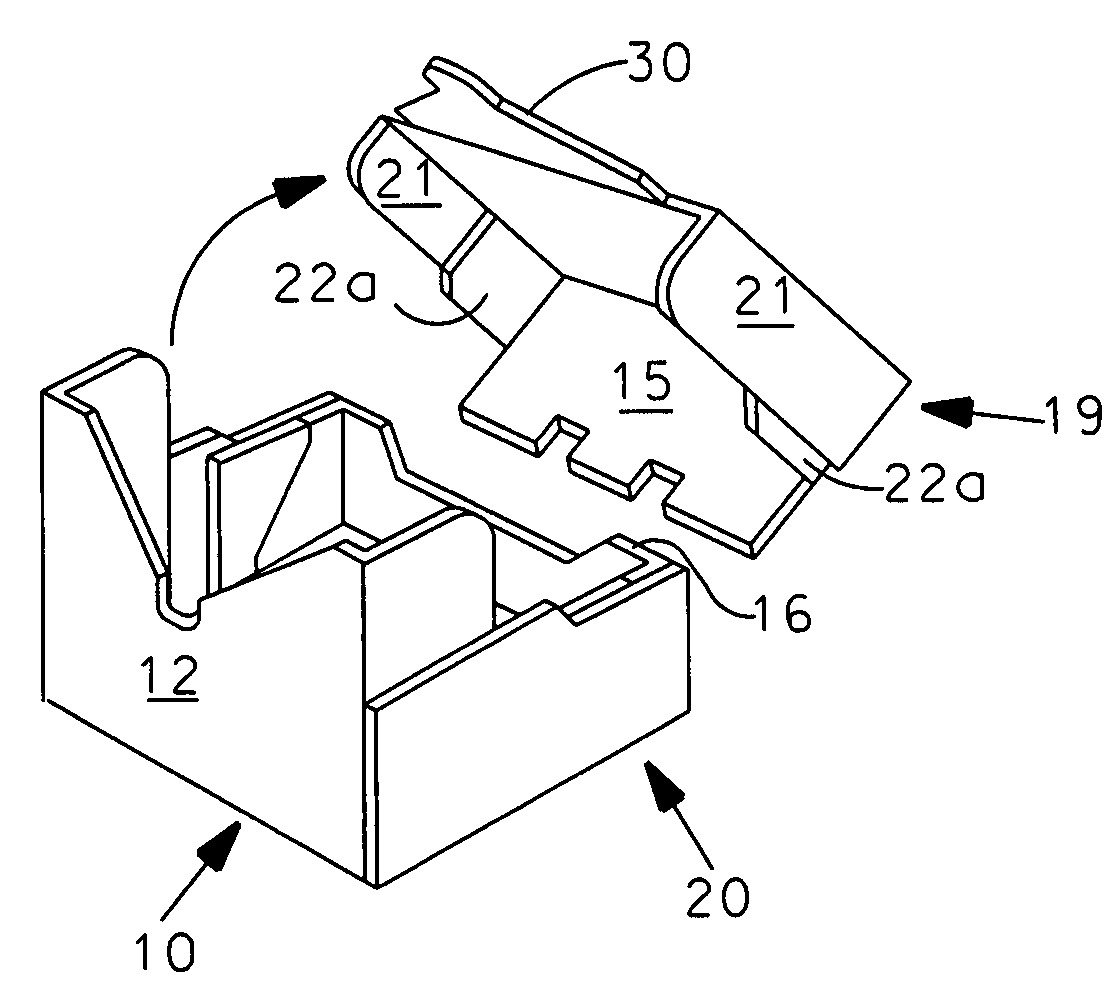

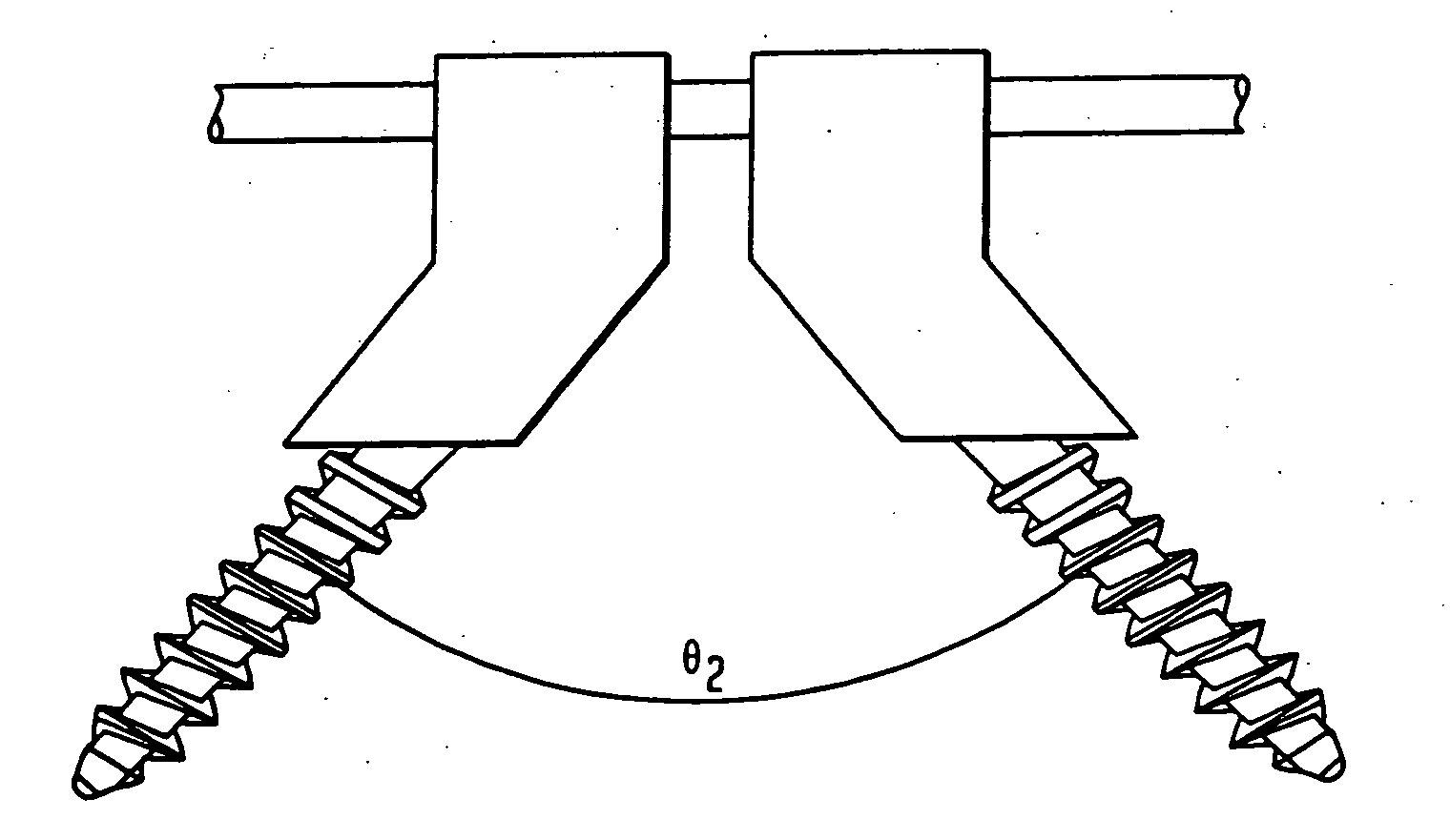

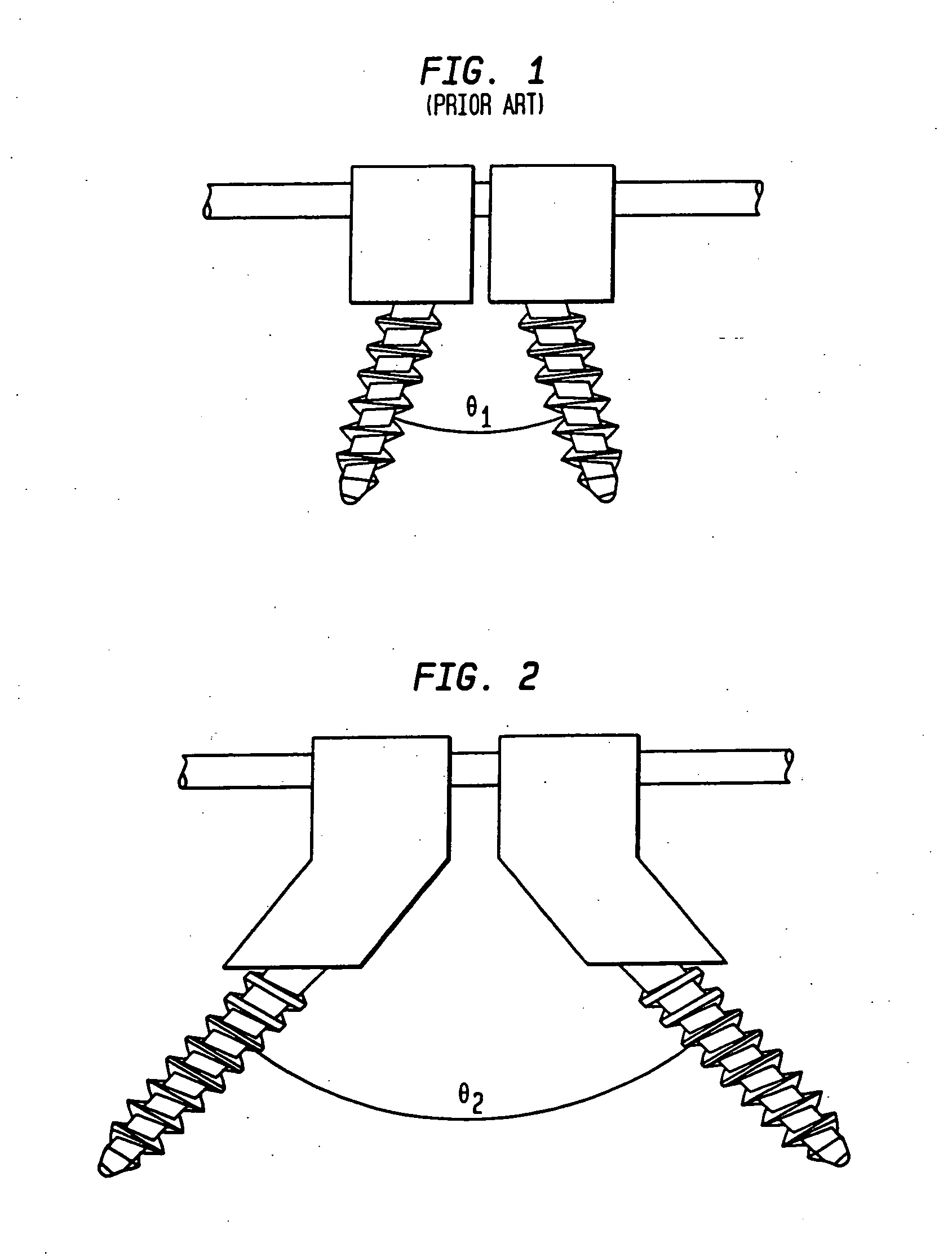

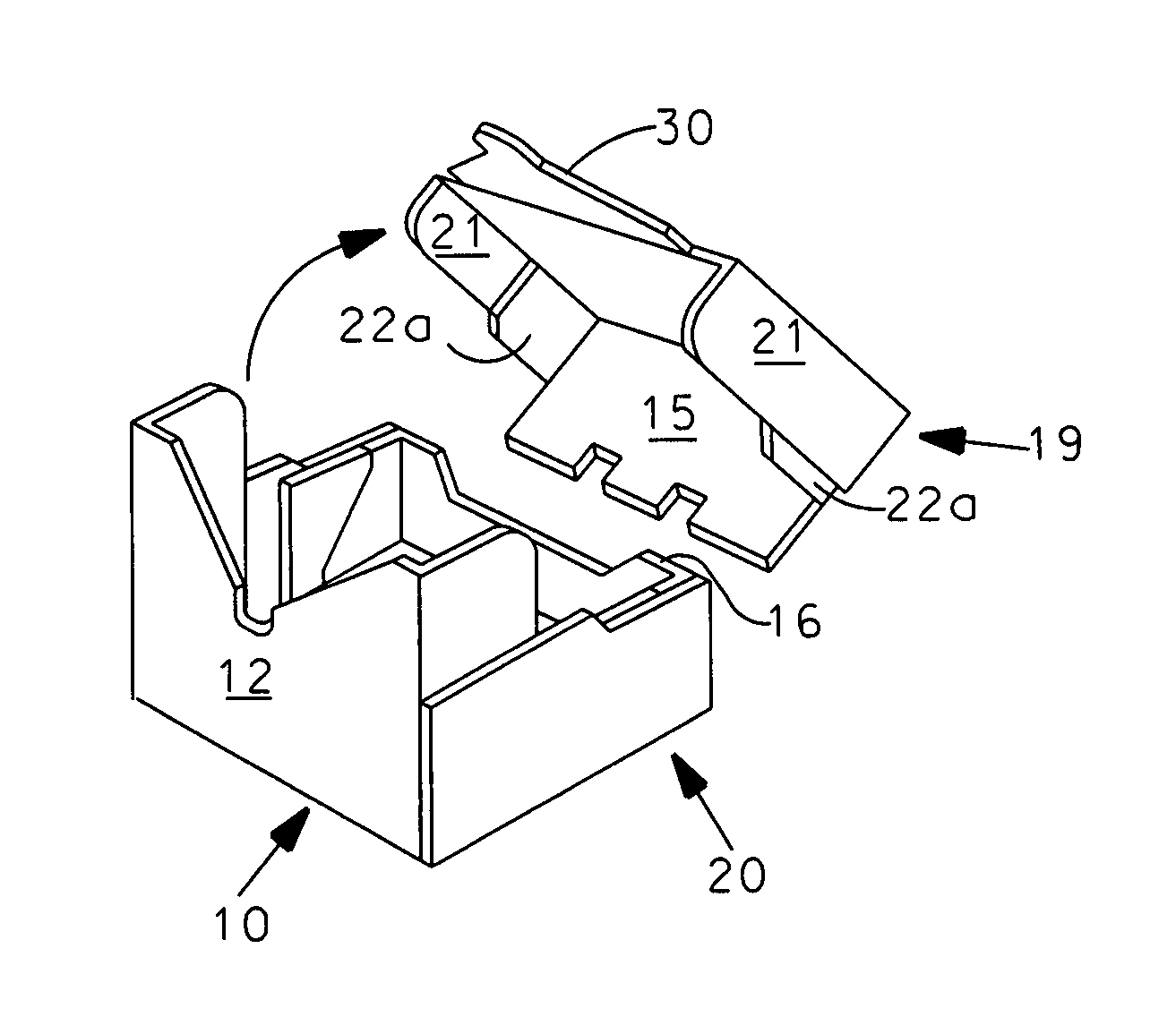

Biased angulation bone fixation assembly

InactiveUS6974460B2Reduce the overall diameterFacilitate pivotal movementSuture equipmentsInternal osteosythesisCouplingPlastic surgery

A bone fixation assembly including a coupling element having an inner surface defining a first bore coaxial with a first longitudinal axis, and a second bore coaxial with a second longitudinal axis, whereby the second longitudinal axis intersects the first longitudinal axis. The coupling element has a seat adjacent the lower end of the coupling element, the seat being defined by the inner surface of the coupling element. The assembly includes an anchoring element assembled with the coupling element, the anchoring element having a first end for insertion into bone and a head spaced from the first end, the head being in contact with the seat of the coupling element. The assembly provides sufficient angulation between adjacent anchoring elements securing a common orthopedic rod, and is particularly useful for assemblies mounted in spines having abnormal curvatures and in the cervicothoracic region of the spine.

Owner:STRYKER EURO OPERATIONS HLDG LLC

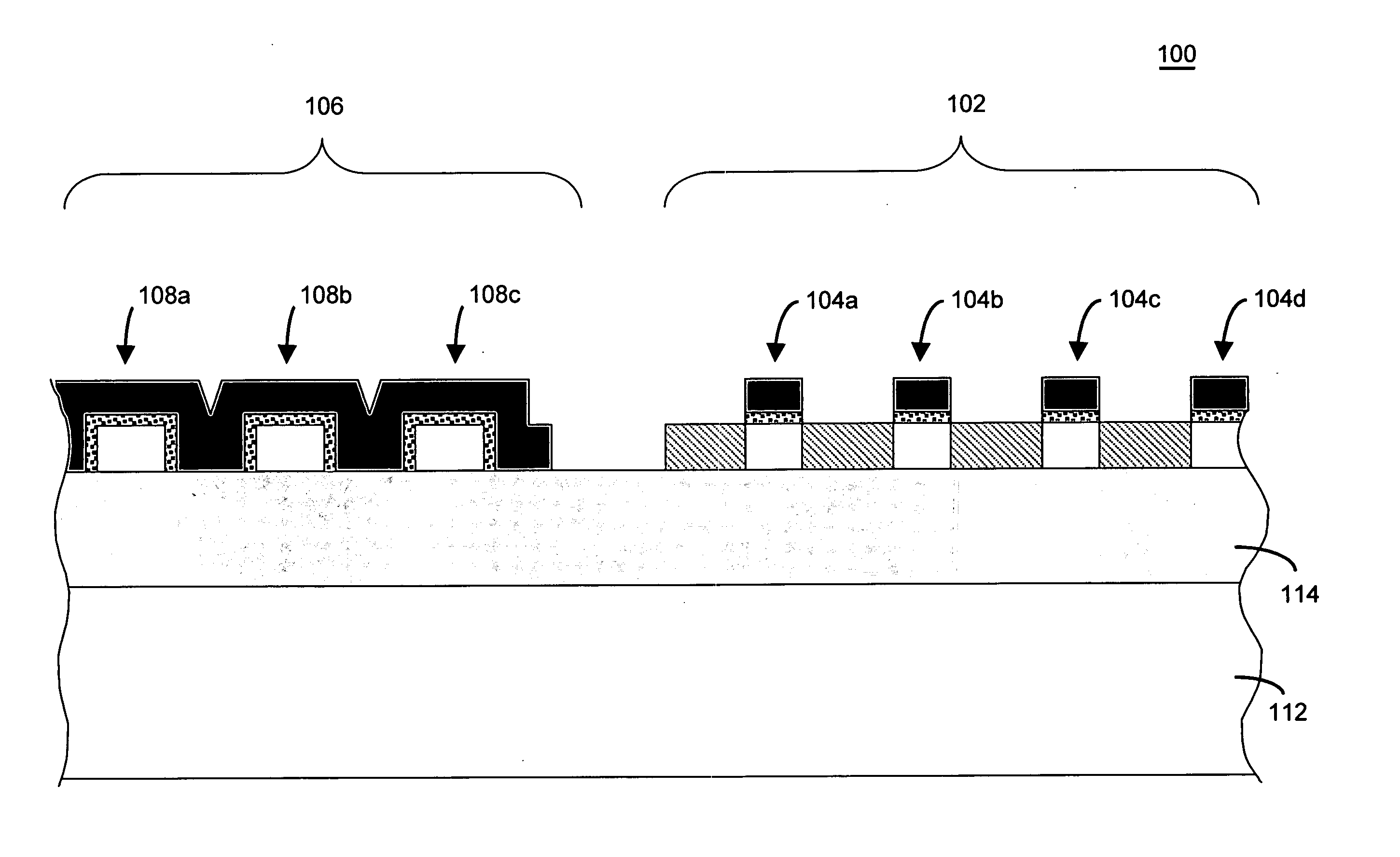

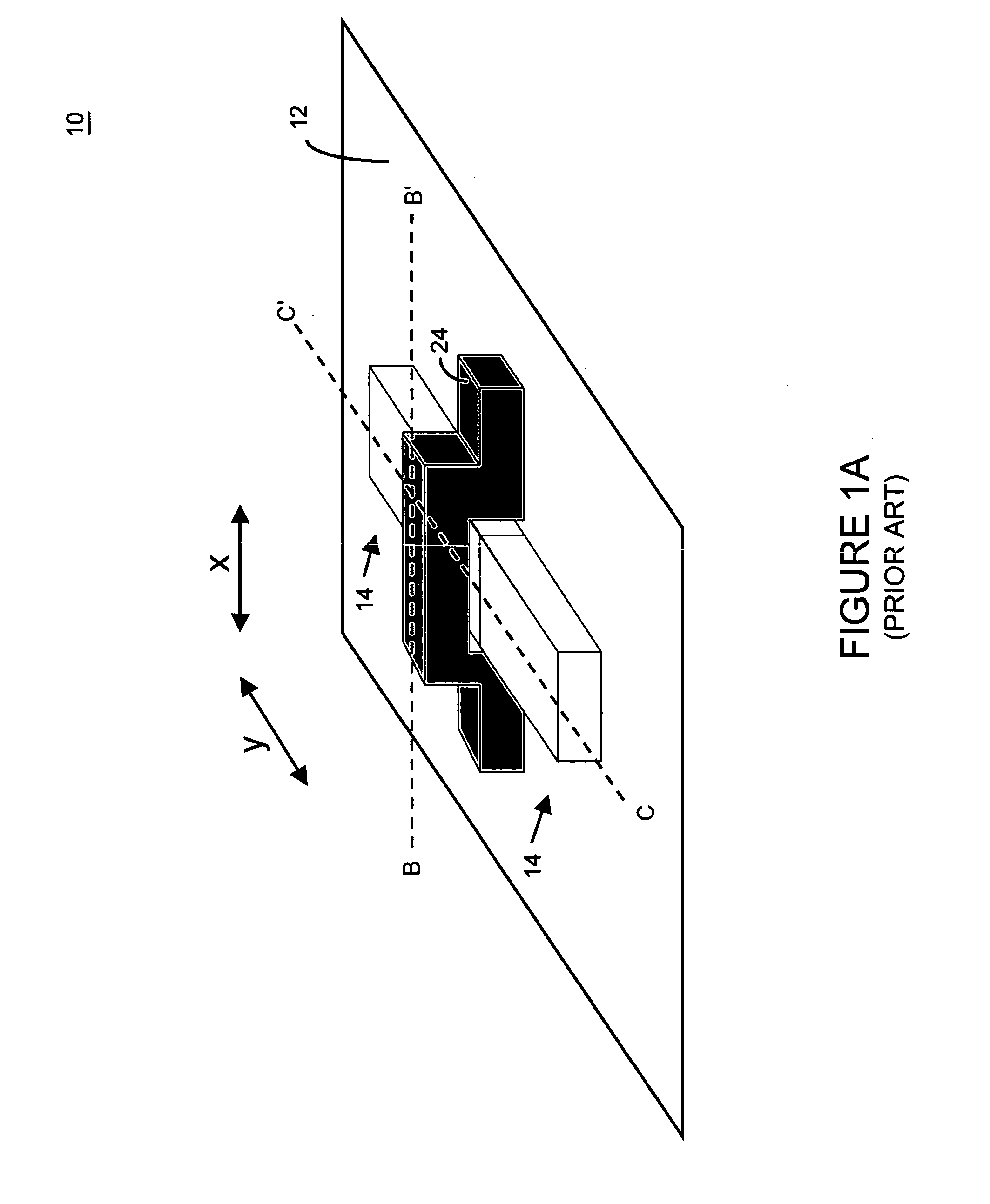

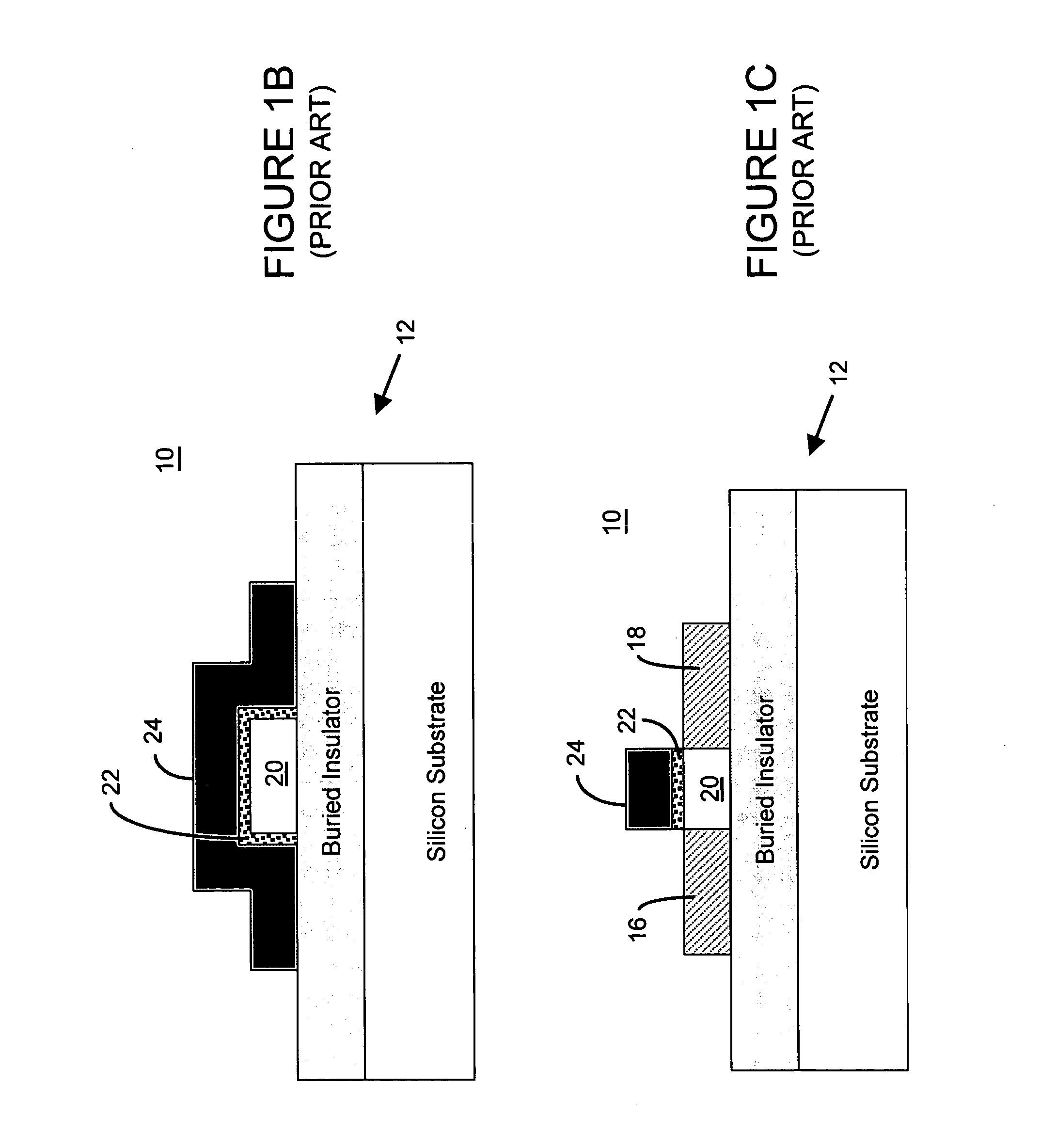

Integrated circuit device, and method of fabricating same

There are many inventions described and illustrated herein. In a first aspect, the present invention is directed to integrated circuit device including SOI logic transistors and SOI memory transistors, and method for fabricating such a device. In one embodiment, integrated circuit device includes memory portion having, for example, PD or FD SOI memory cells, and logic portion having, for example, high performance transistors, such as Fin-FET, multiple gate transistors, and / or non-high performance transistors (such as single gate transistors that do not possess the performance characteristics of the high performance transistors).

Owner:MICRON TECH INC

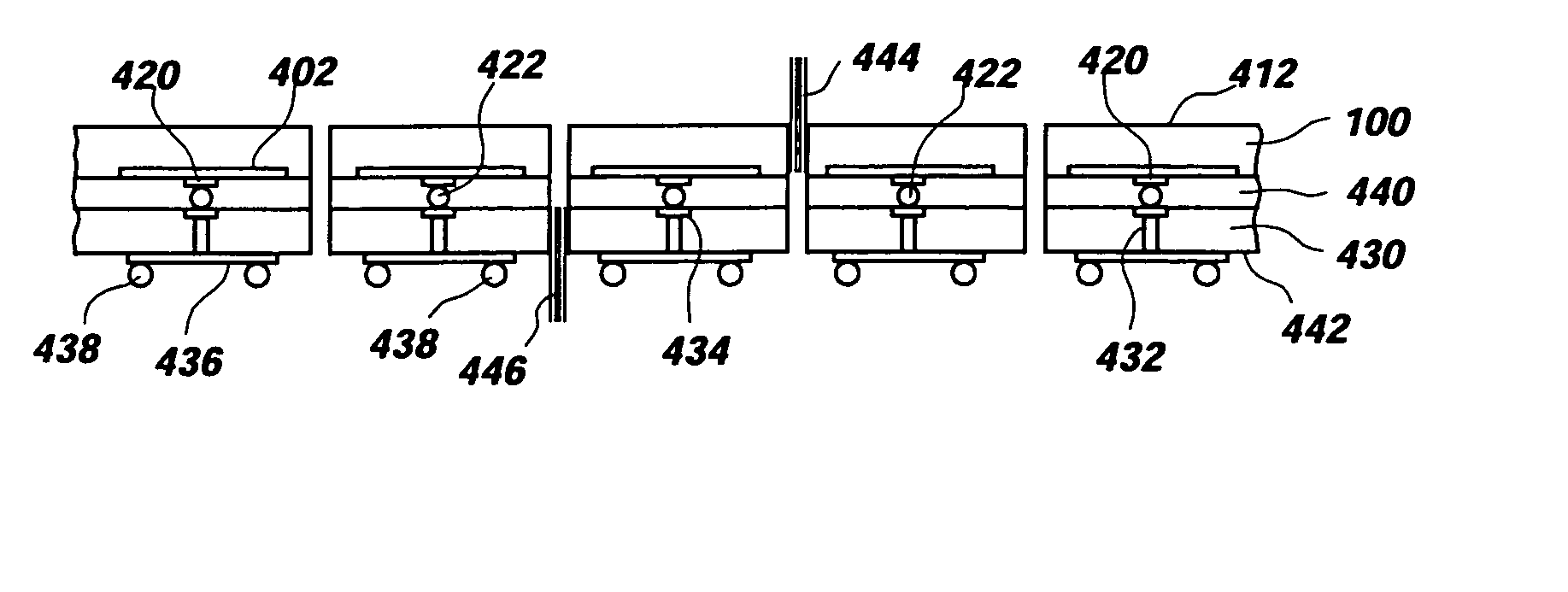

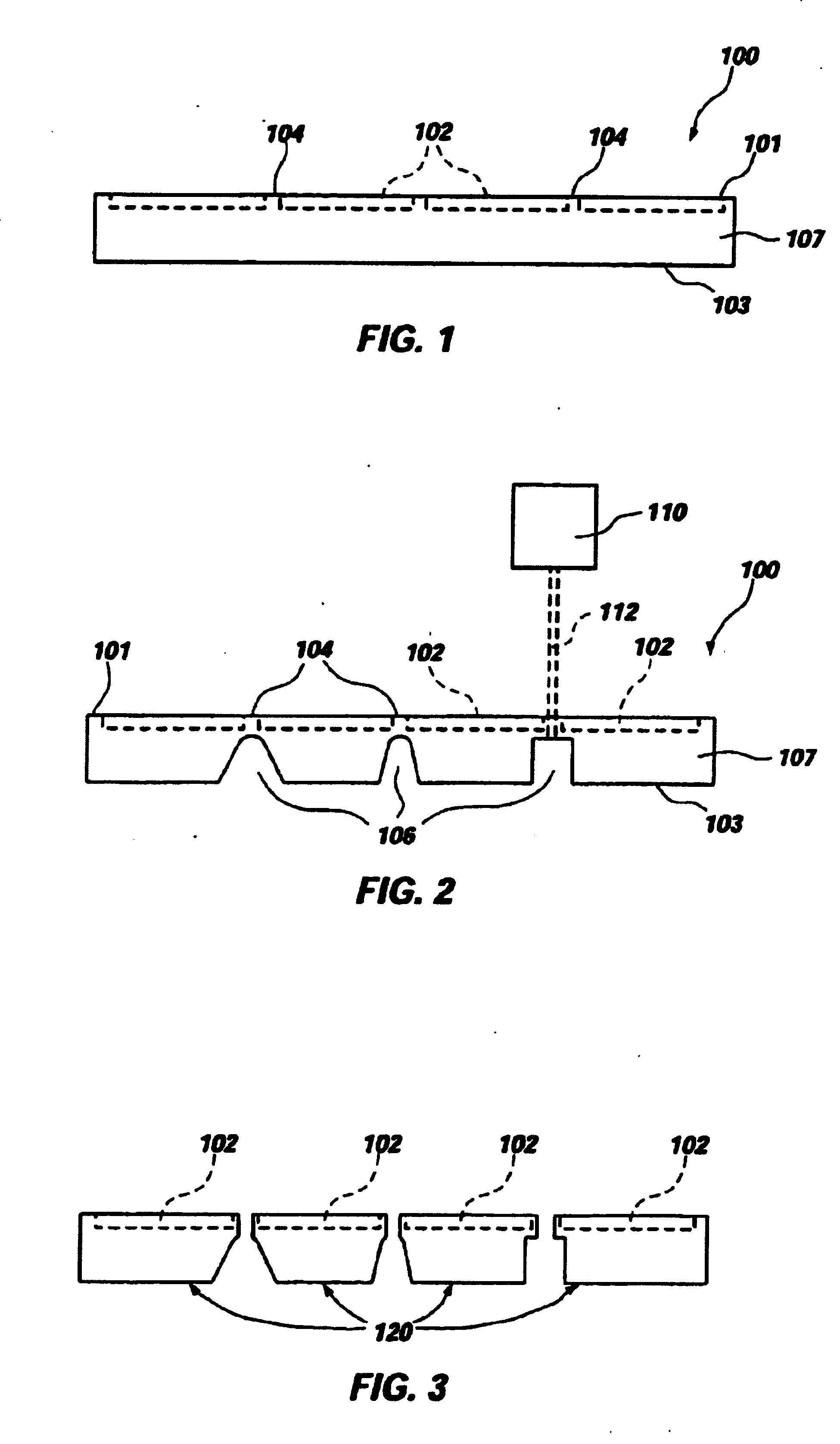

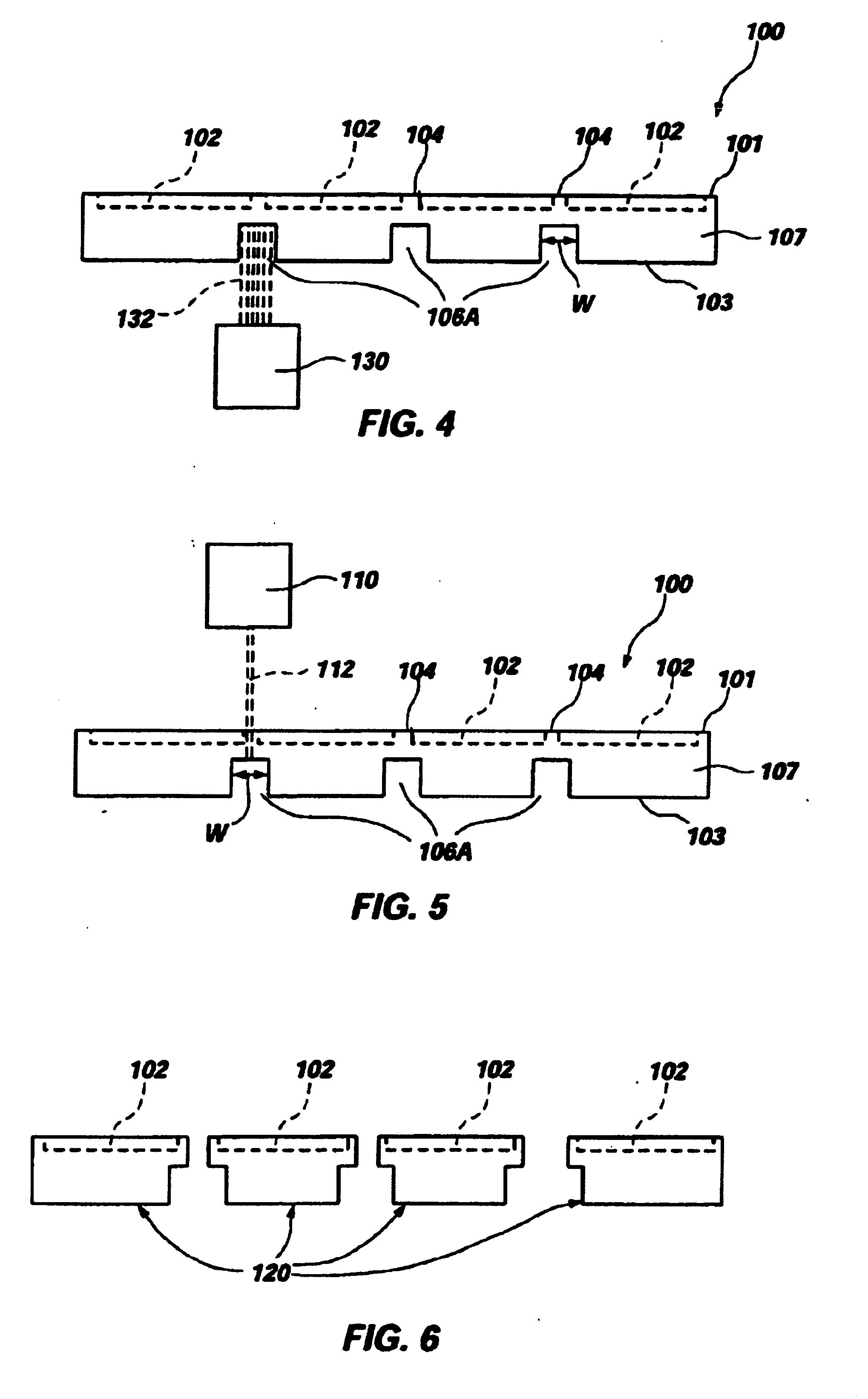

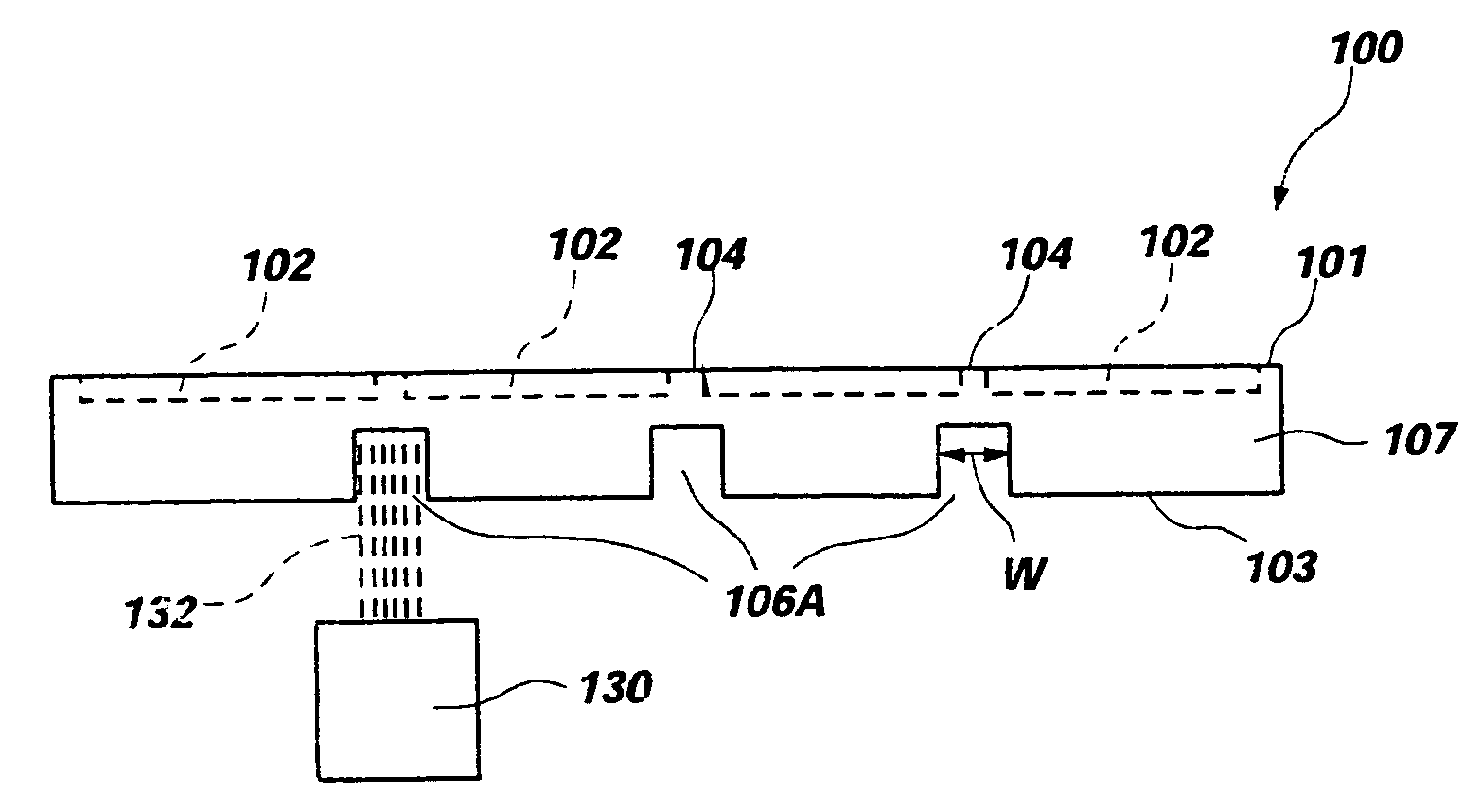

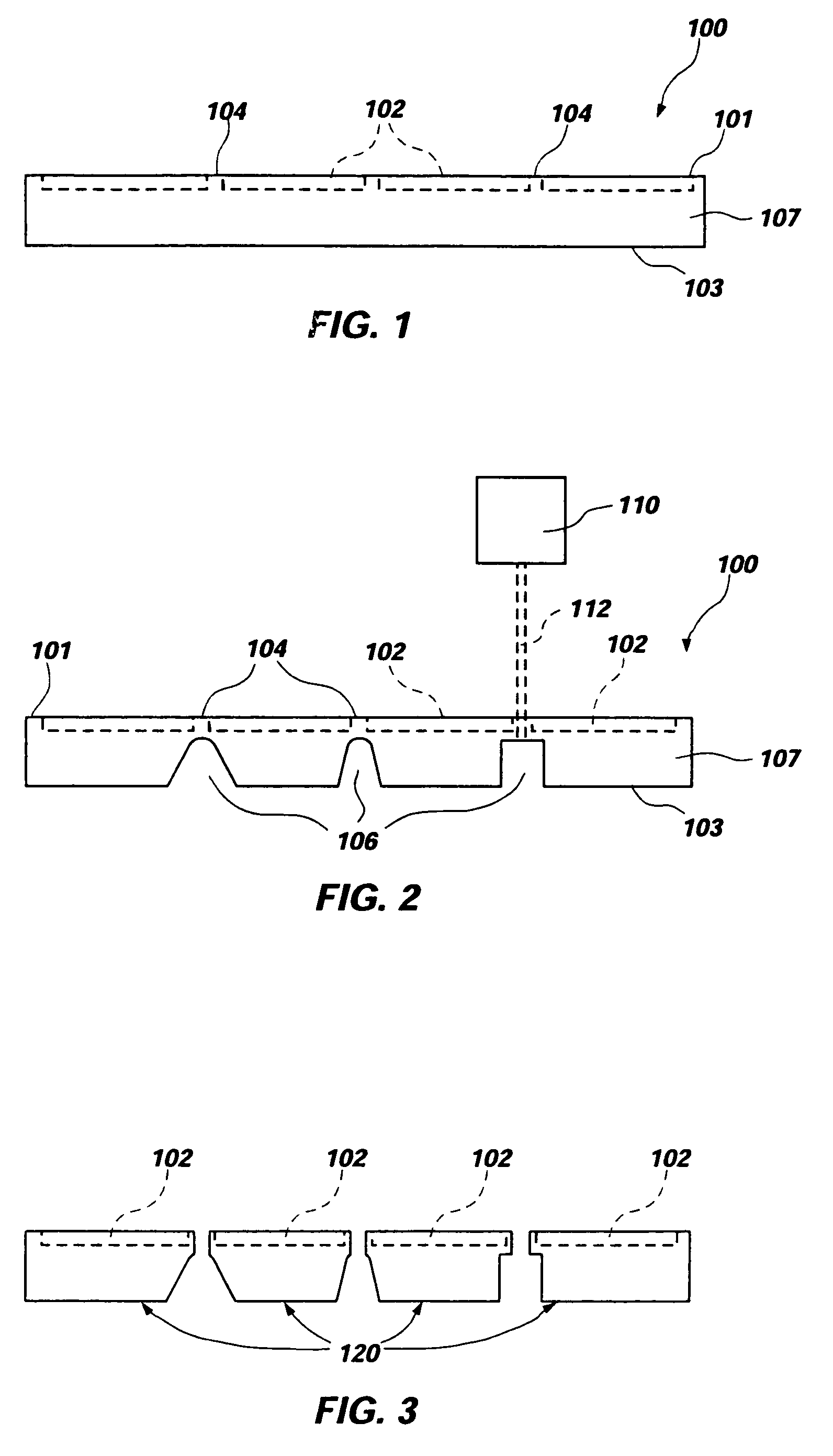

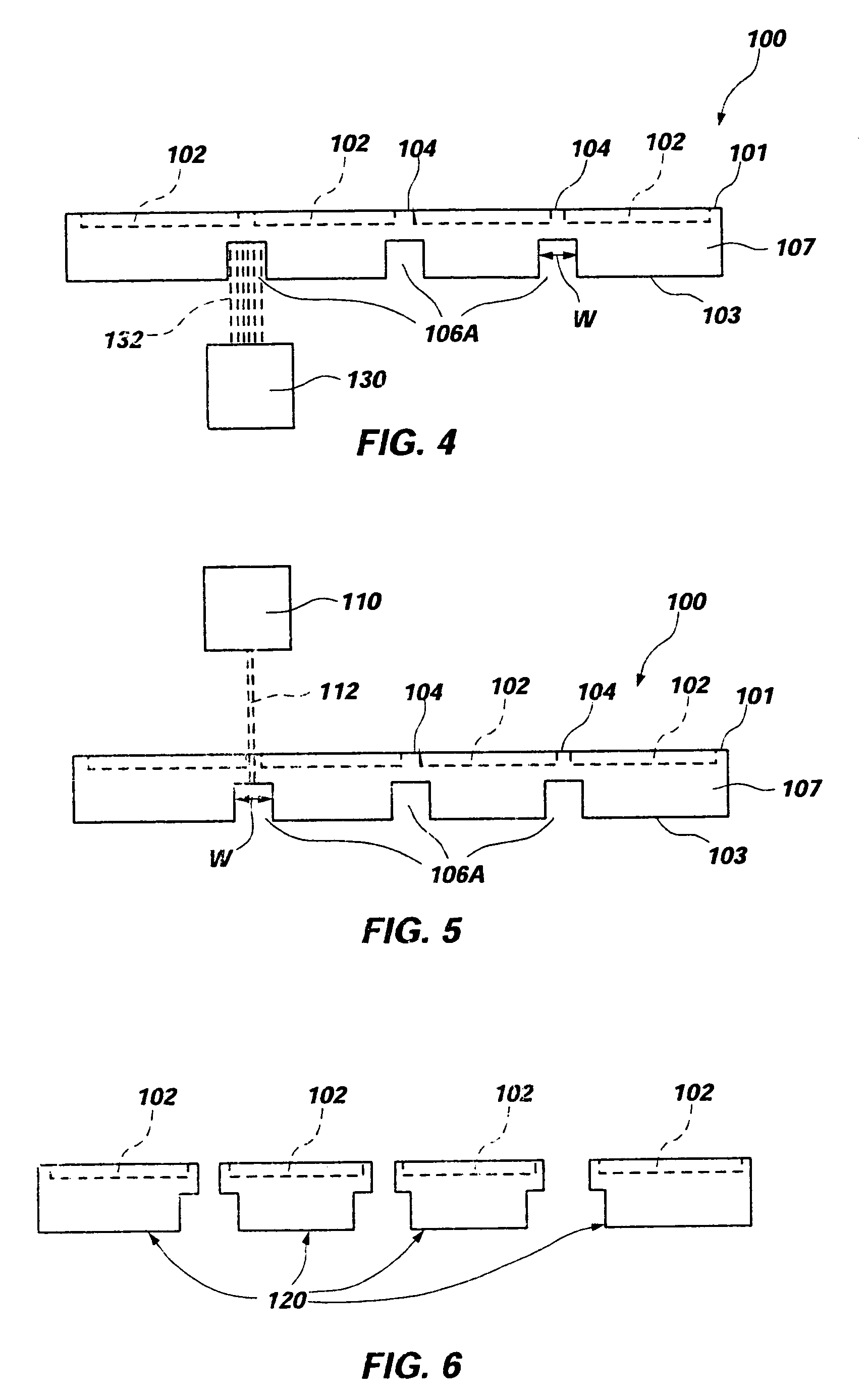

Methods and apparatus relating to singulating semiconductor wafers and wafer scale assemblies

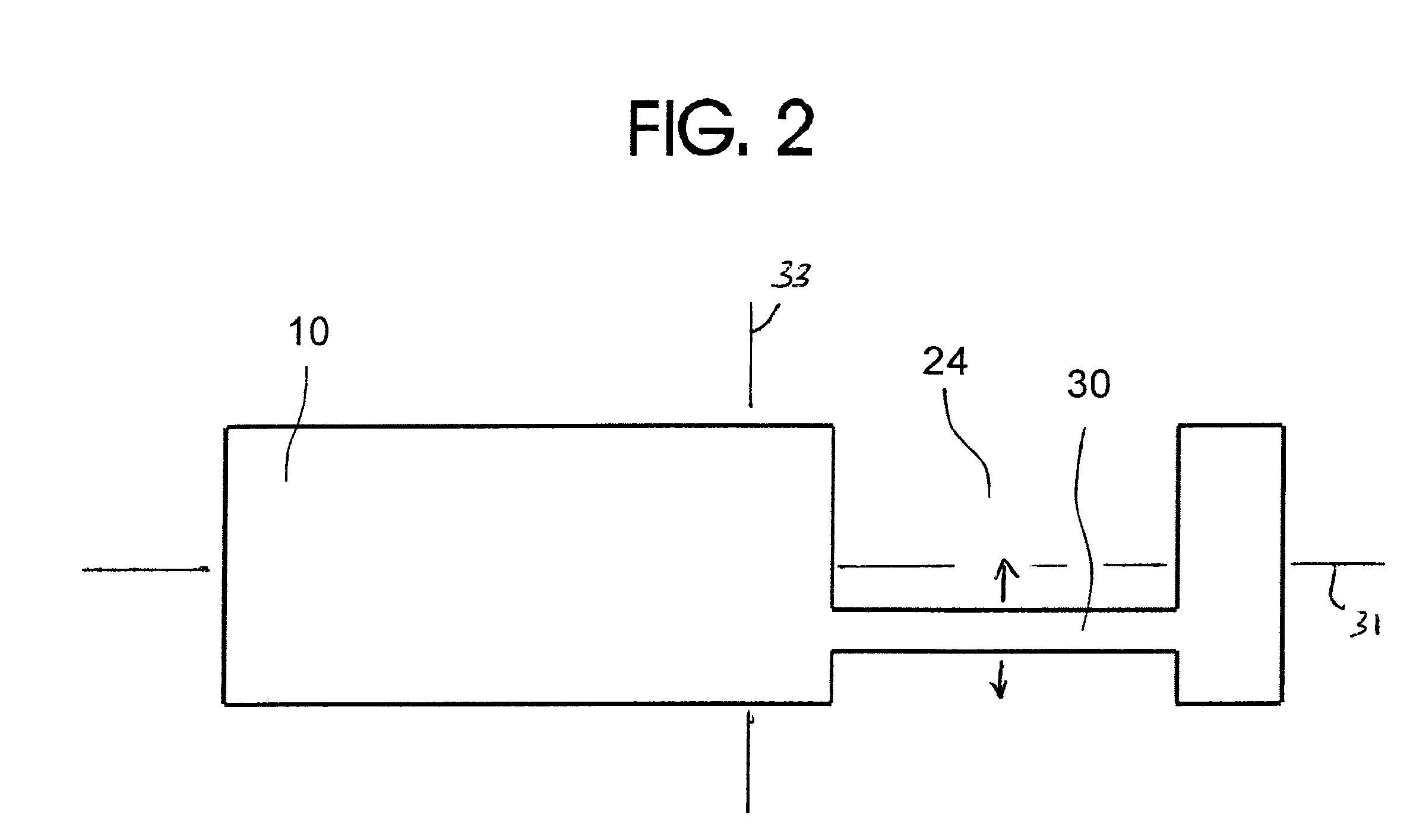

ActiveUS20050202651A1Increase distanceAvoid excessive widthSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

Methods relating to the singulation of dice from semiconductor wafers. Trenches or channels are formed in the bottom surface of a semiconductor wafer, corresponding in location to the wafer streets. The trenches may be formed by etching or through an initial laser cut. The wafer is then singulated along the streets with a laser preferably having a beam narrower than the trenches. Multiple, laterally spaced lasers may be used in combination during a single pass to perform simultaneous singulating cuts. Additional edge protection for integrated circuitry on the active surface of the semiconductor dice may be provided by forming trenches or channels along the streets in the active surface instead of the bottom surface, disposing protective material along the streets and within the trenches prior to singulation and cutting through the wafer, leaving protective material on the sidewalls of the channels.

Owner:MICRON TECH INC

Methods relating to singulating semiconductor wafers and wafer scale assemblies

ActiveUS20060079024A1Increase distanceAvoid excessive widthSolid-state devicesSemiconductor/solid-state device manufacturingWaferingEngineering

Methods relating to the singulation of dice from semiconductor wafers. Trenches or channels are formed in the bottom surface of a semiconductor wafer, corresponding in location to the wafer streets. The trenches may be formed by etching or through an initial laser cut. The wafer is then singulated along the streets with a laser preferably having a beam narrower than the trenches. Multiple, laterally spaced lasers may be used in combination during a single pass to perform simultaneous singulating cuts. Additional edge protection for integrated circuitry on the active surface of the semiconductor dice may be provided by forming trenches or channels along the streets in the active surface instead of the bottom surface, disposing protective material along the streets and within the trenches prior to singulation and cutting through the wafer, leaving protective material on the sidewalls of the channels.

Owner:MICRON TECH INC

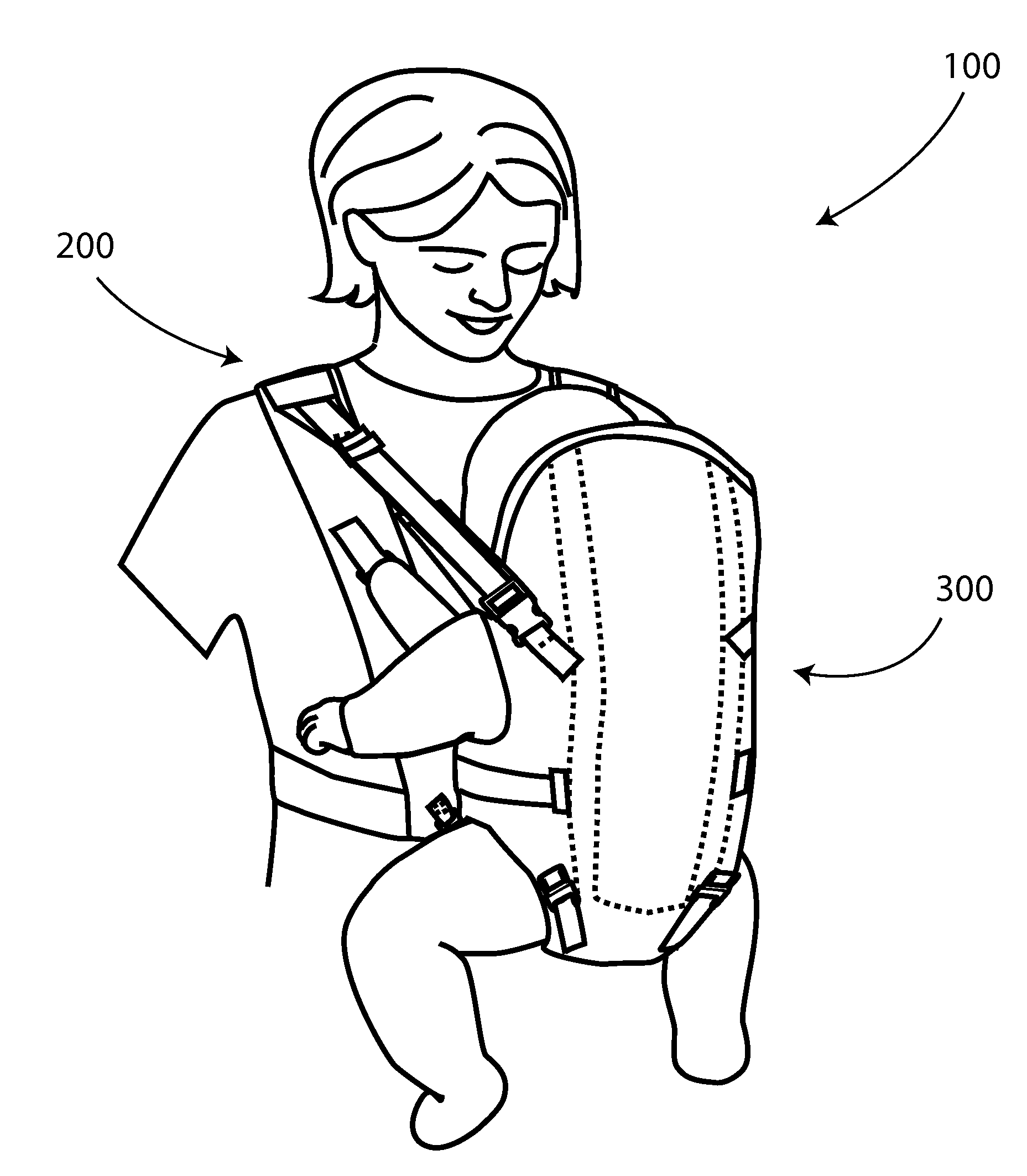

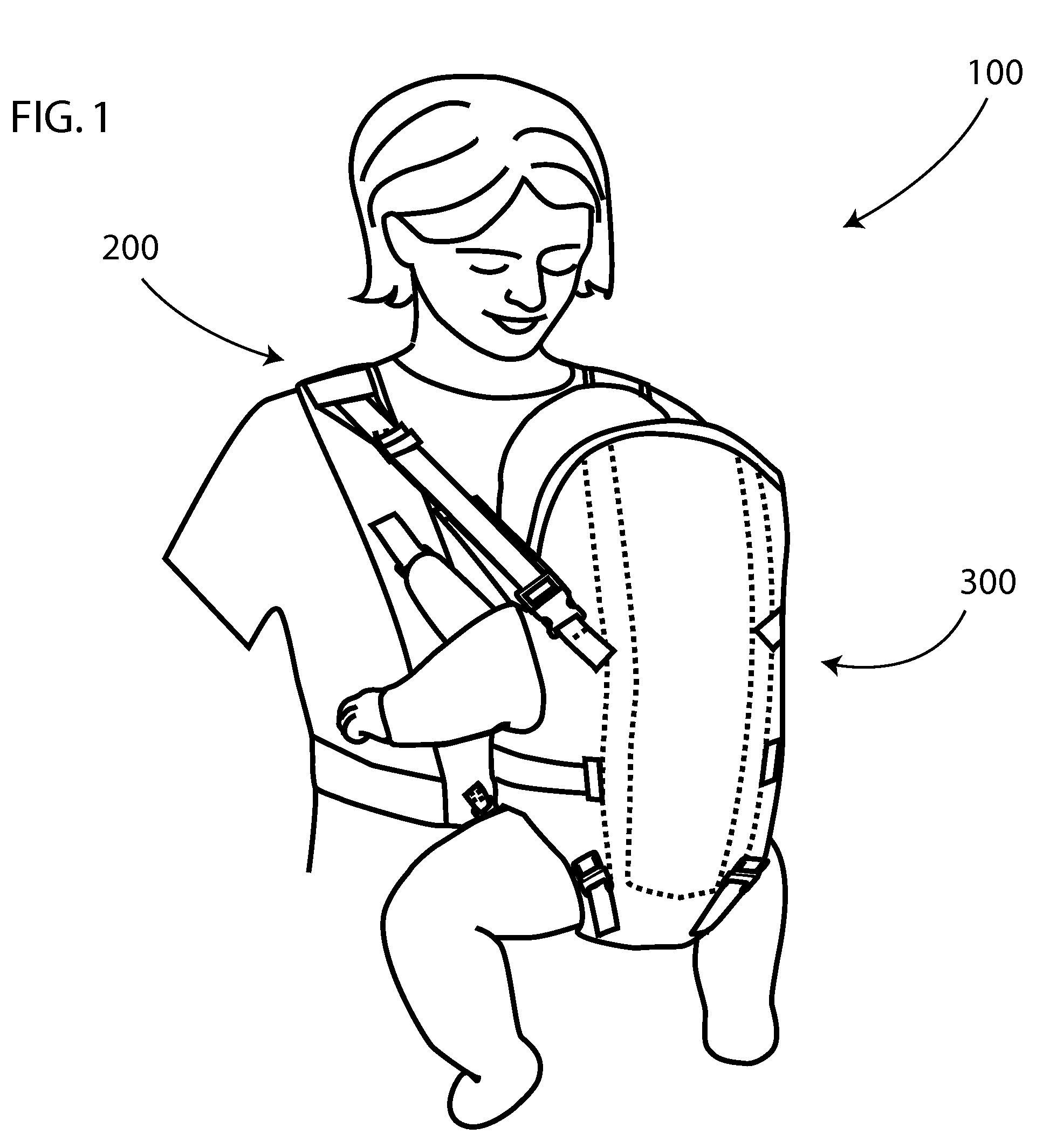

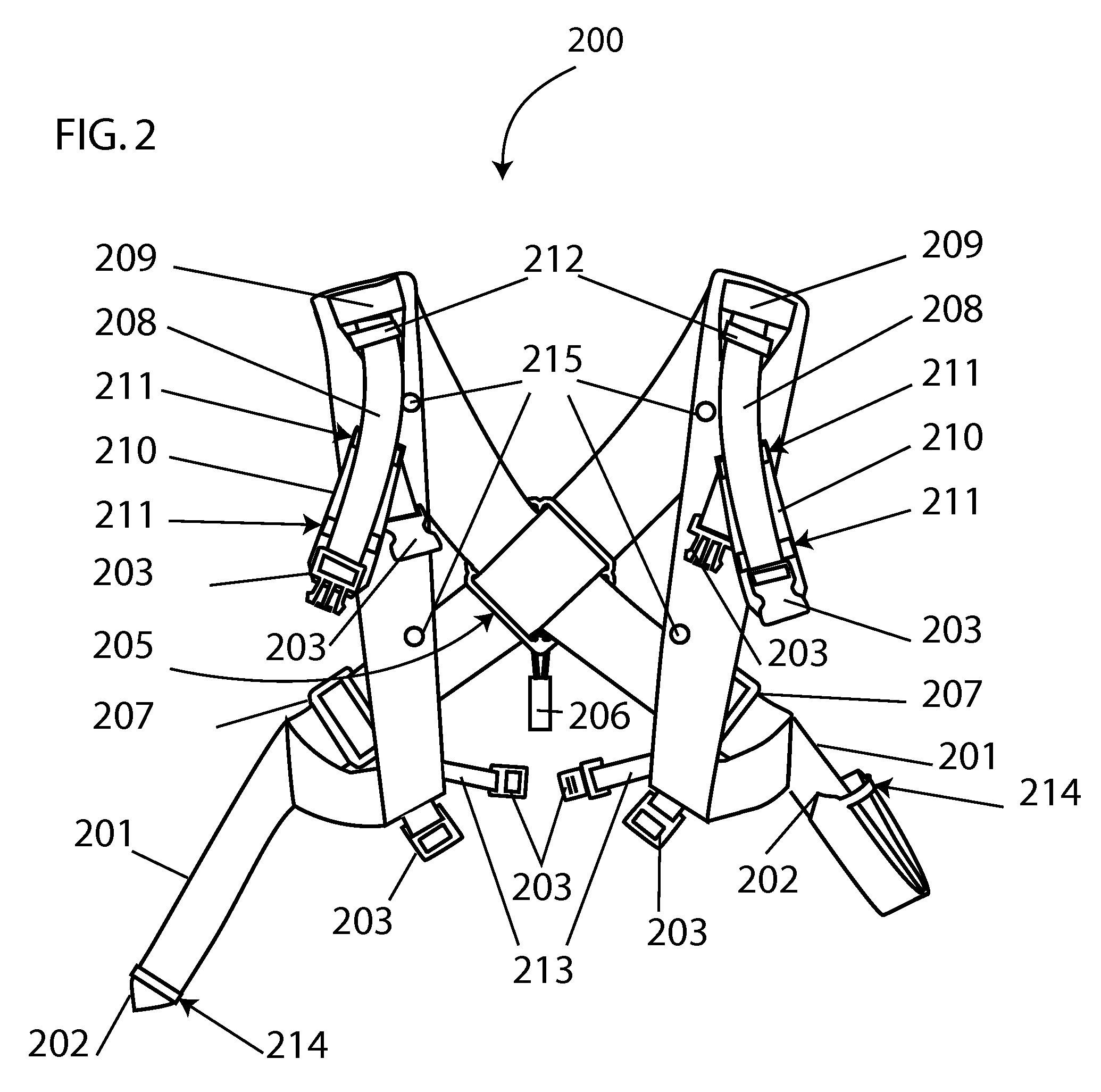

Baby carrier

InactiveUS8028871B2Safely and securely extend the pouch system away from the wearerQuickly and conveniently extendedTravelling sacksStretcherMechanical engineeringEngineering

A baby carrier comprising a shoulder harness featuring a detachable adjustable pouch system that may be worn or alternatively fastened to a secured object for supporting an infant. The shoulder harness features retractable shoulder straps that may be used to securely extend the detachable adjustable pouch system away from wearer without having to detach the pouch or remove the infant while simultaneously allowing the wearer face to face access with the infant. The detachable adjustable pouch system may encapsulate and support an infant in a substantially upright sitting position. The detachable adjustable pouch system may be adjusted to accommodate infants of varying sizes. The weight of the infant may be incorporated as a design component of the seat portion of the pouch system.

Owner:GRAY JEANETTE EDITH

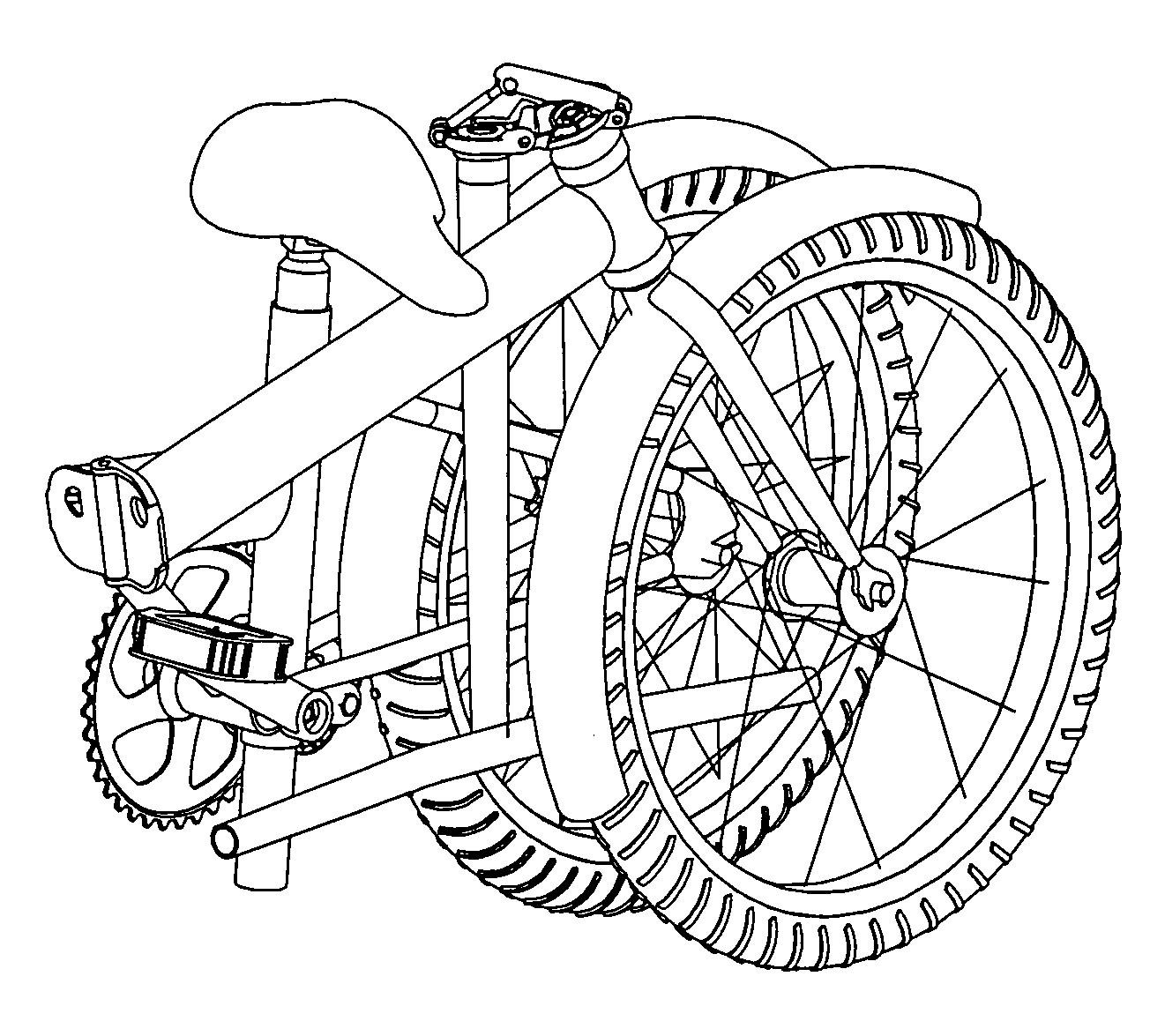

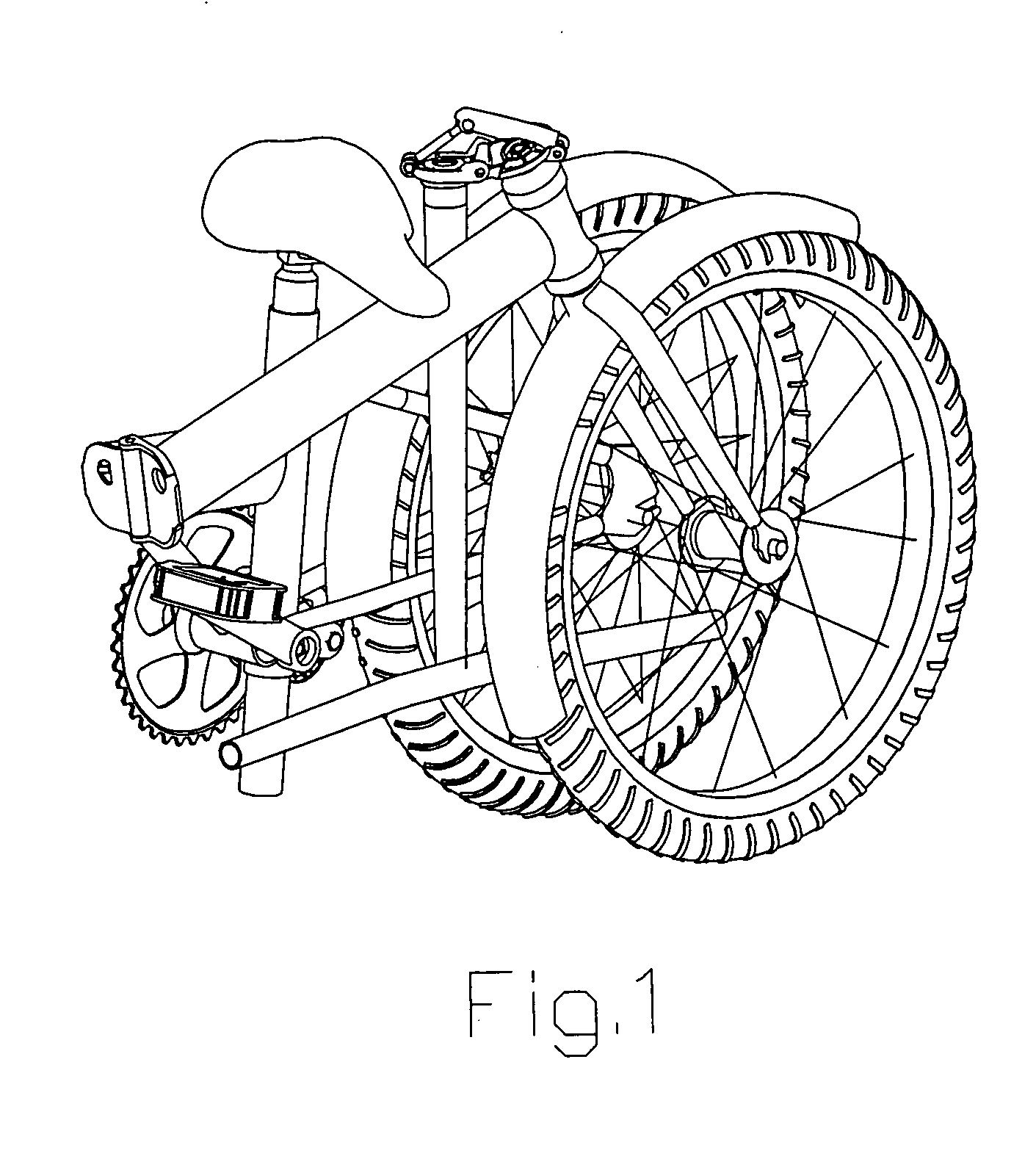

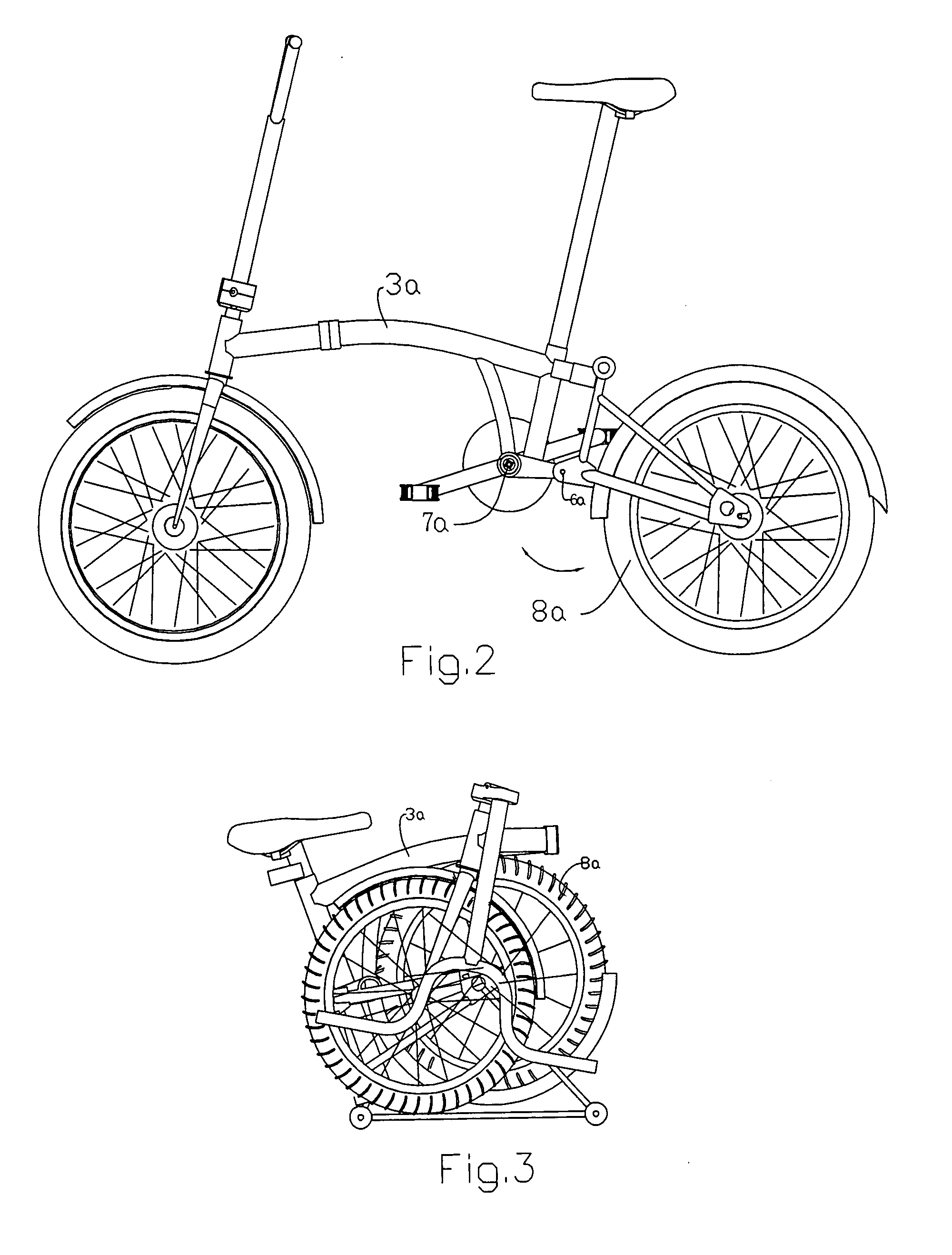

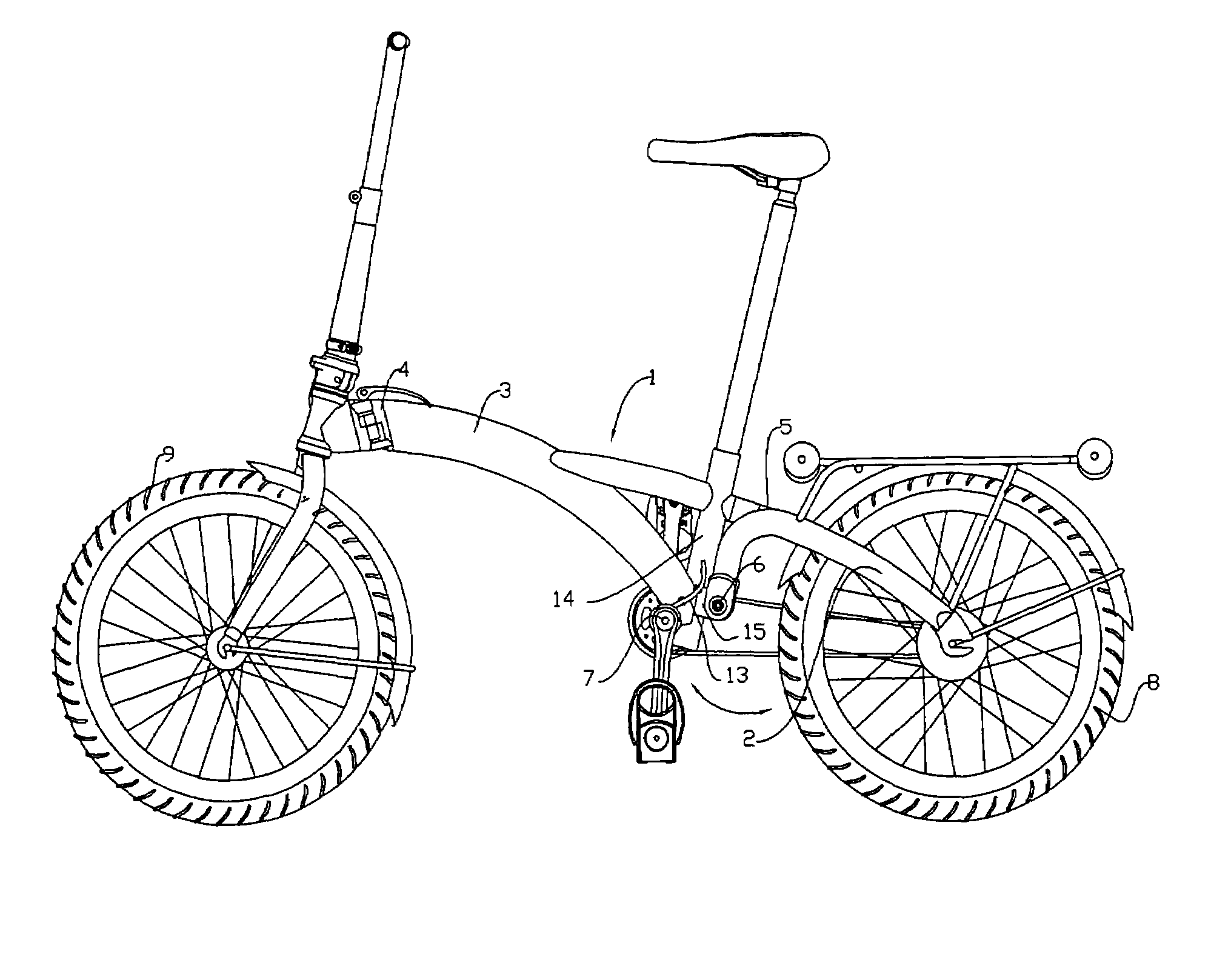

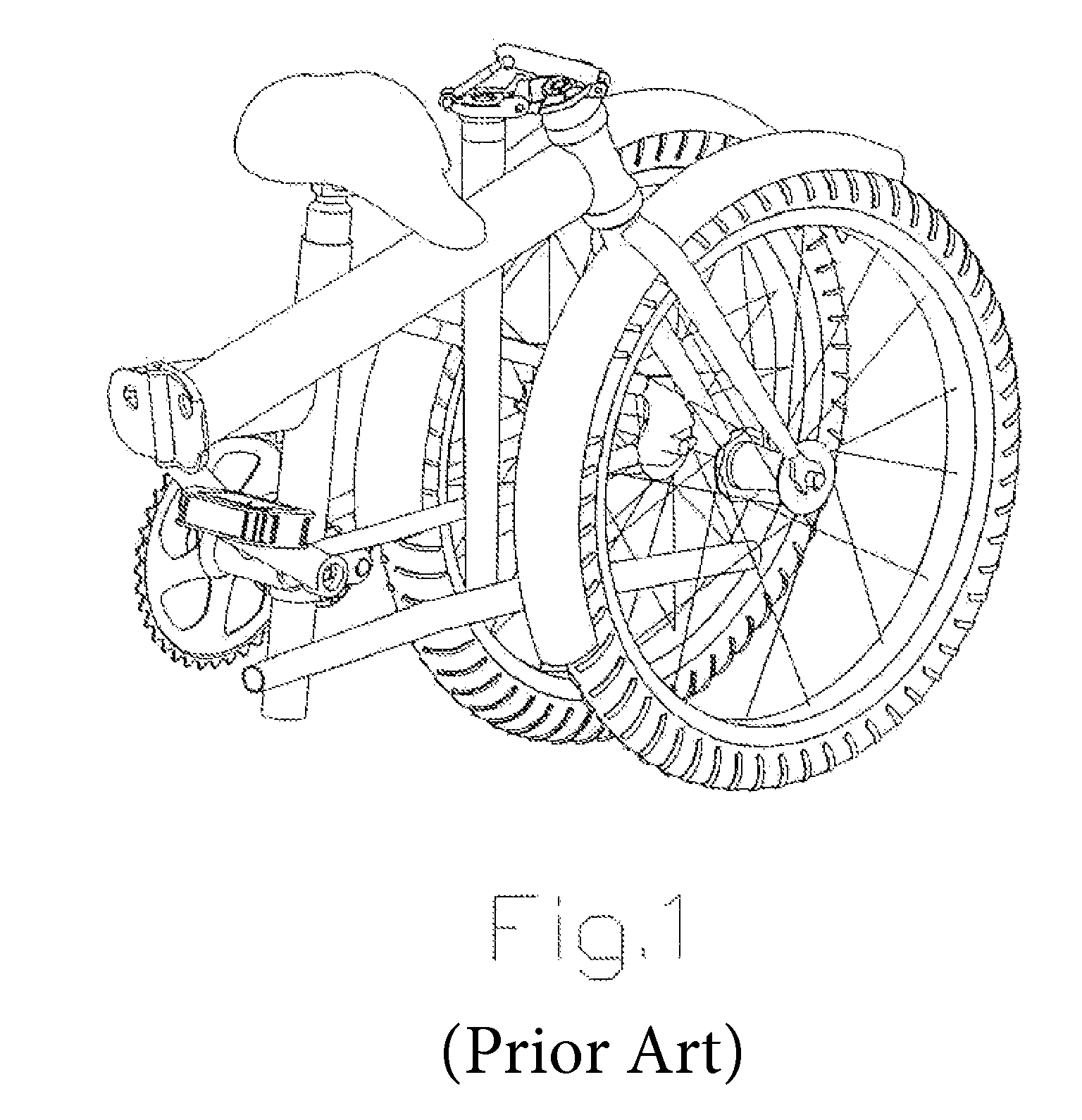

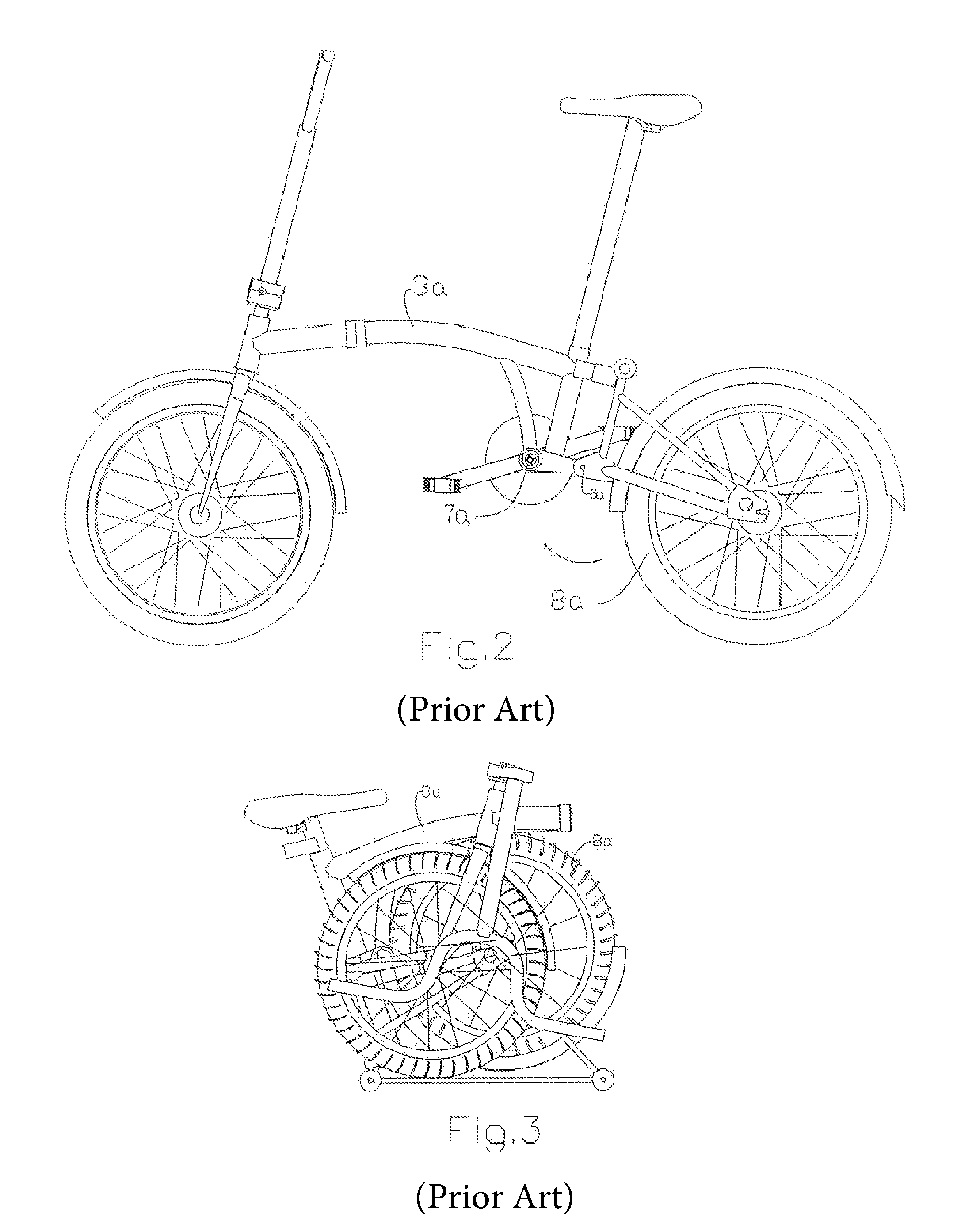

Folding bicycle

InactiveUS20070210556A1Avoid excessive widthAvoid excessive heightPassenger cyclesWheel based transmissionShaped beamAcute angle

The present invention discloses a folding bicycle, wherein a folding joint is installed on the beam, and the rear fork is hinged with the frame via a hinge axle, on the rear fork is installed a support bar which rests against the frame; and wherein the beam is S-shaped, and the hinge axle is tilted by an acute angle with respect to the central axle of the frame. When the bicycle is folded, the front and rear wheels are located separately, each at one side of the beam and within the concave section of the S-shaped beam, so that the bicycle is more compact and has a less width after being folded.

Owner:TAK WEI HON DAVID

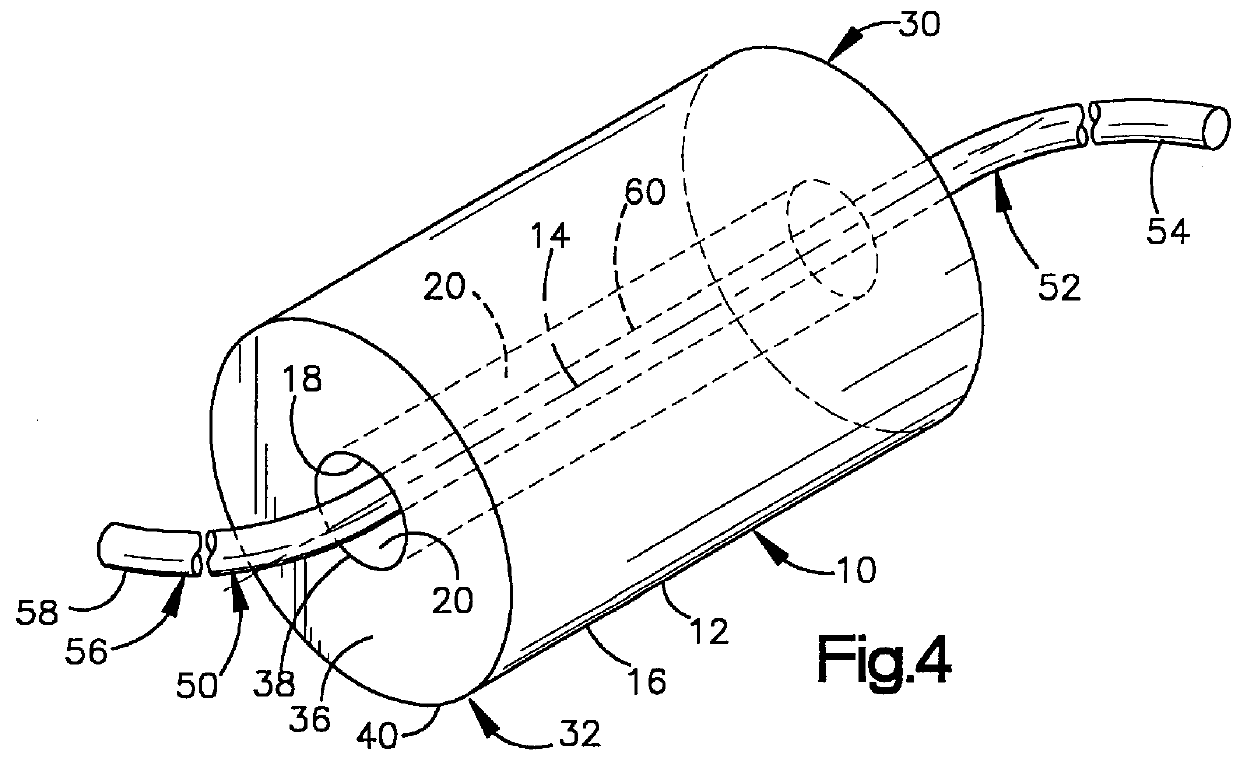

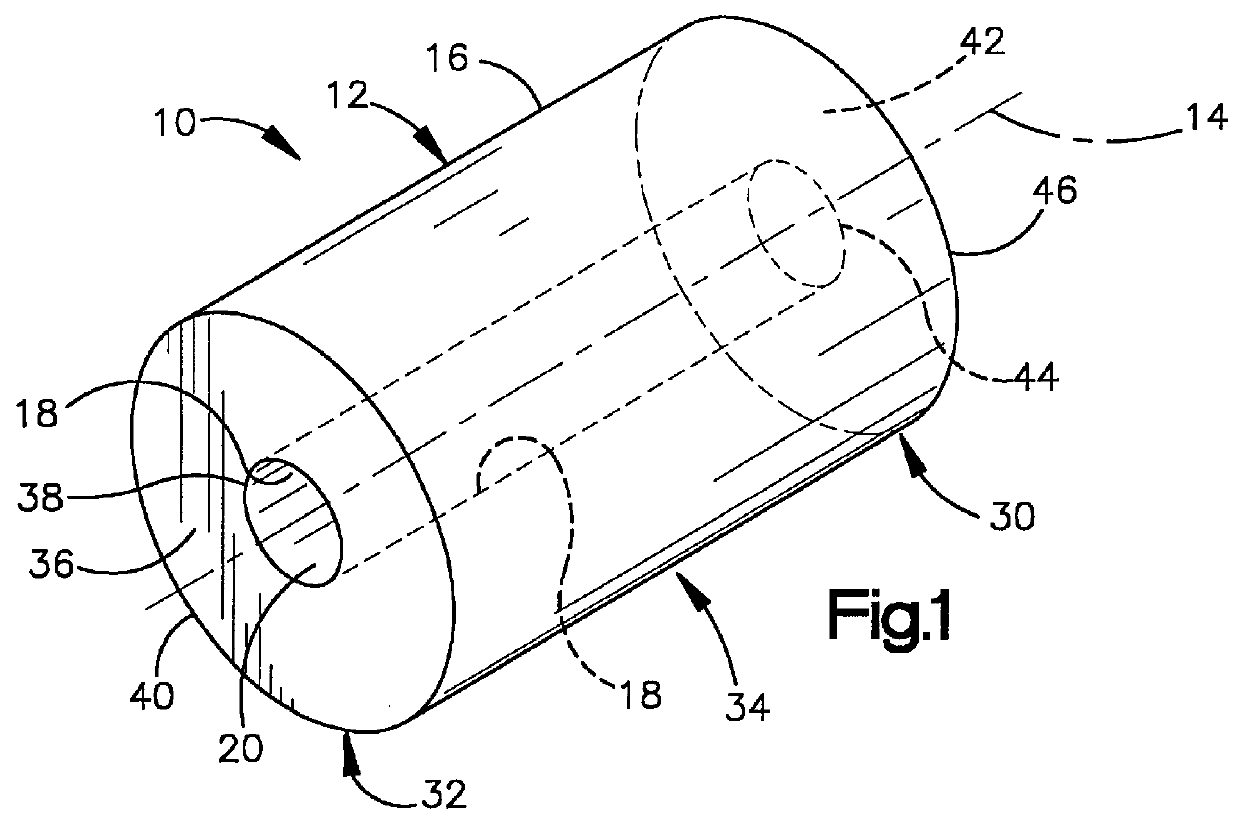

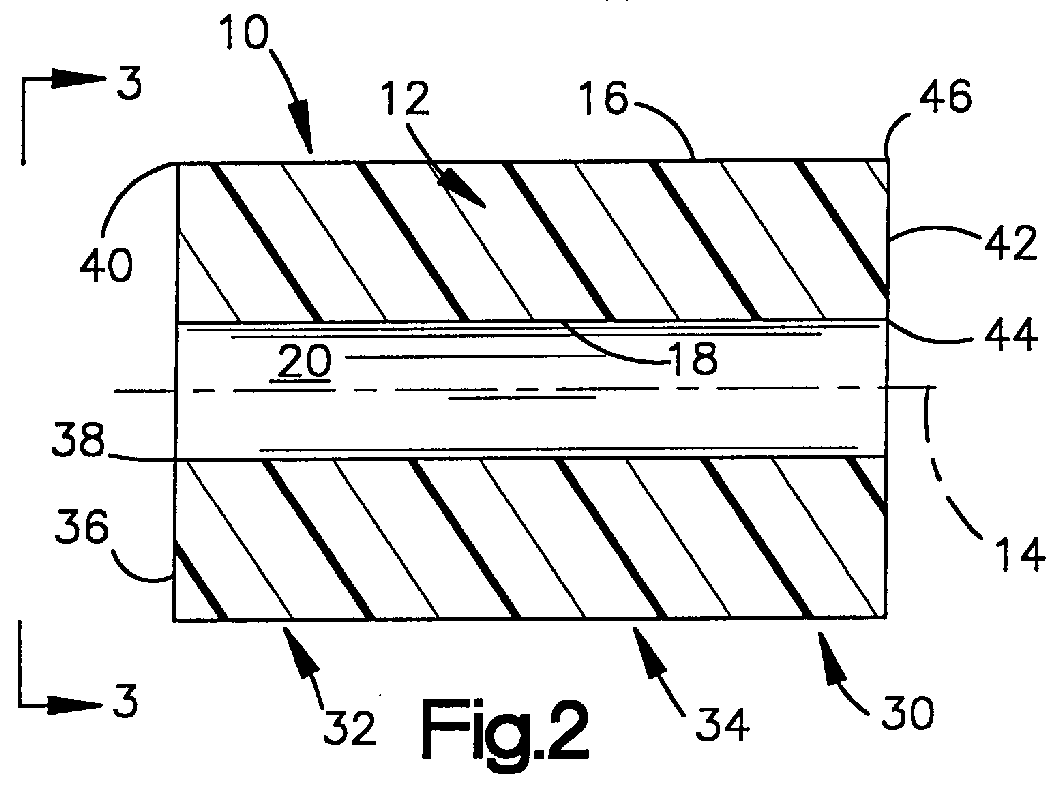

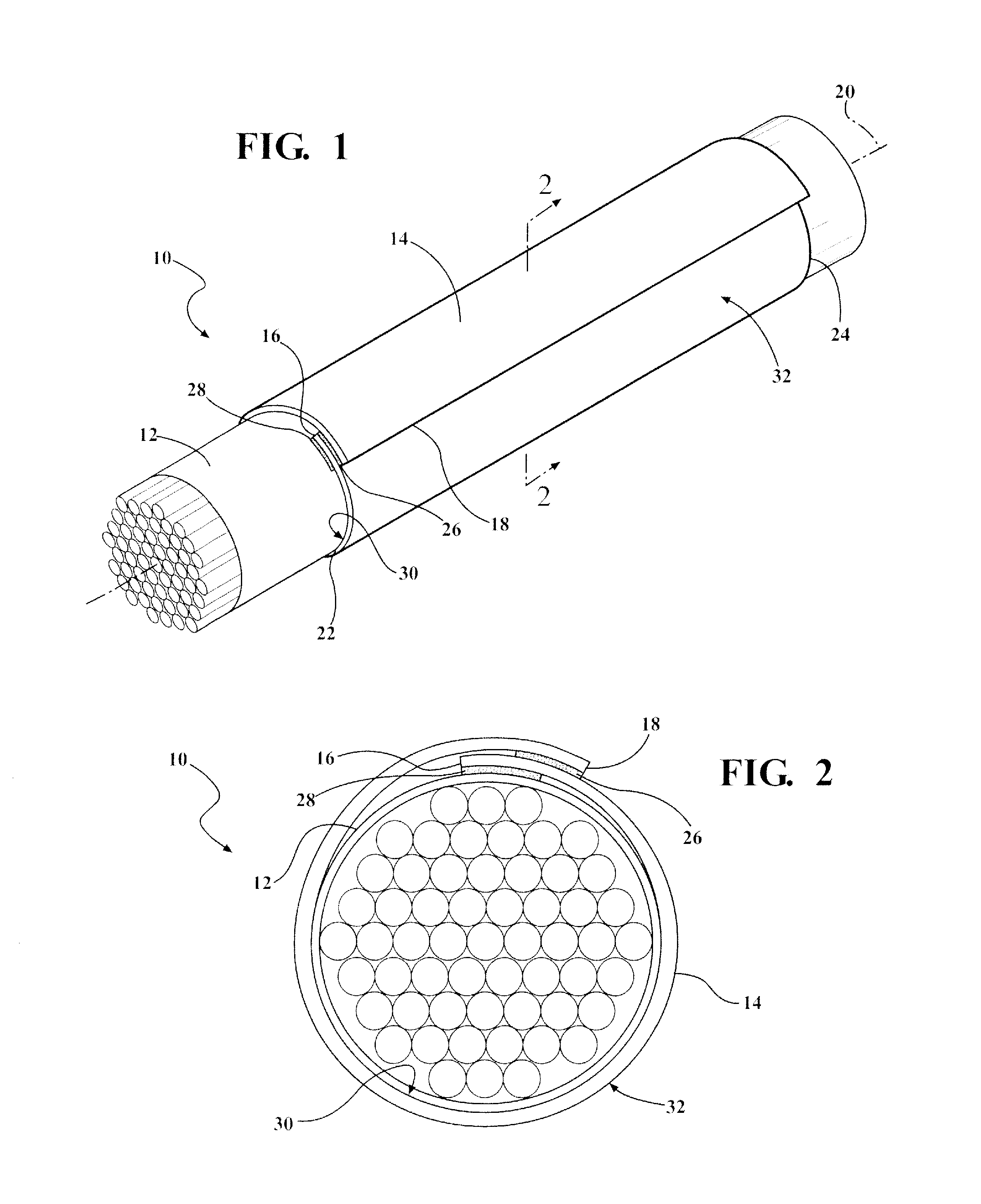

Catheter-stent device

A graftless prosthetic stent for treatment of vascular lesions such as aneurysms and arterio-venous fistulas, especially in neurovascular vessels, comprises a continuous helical ribbon formed of a shape-retaining metal having a transition temperature at which the stent expands from its contracted condition to a radially expanded condition, the stent remaining substantially cylindrical in its contracted and expanded conditions. The helical windings have variable width, thickness, number or size of openings, or combinations of these features, which affect the stiffness, rate of expansion at the transition temperature, and the area of vessel wall covered by the stent. A catheter device which includes the stent, and a method of treatment using the stent are also provided.

Owner:STRYKER EURO OPERATIONS HLDG LLC +1

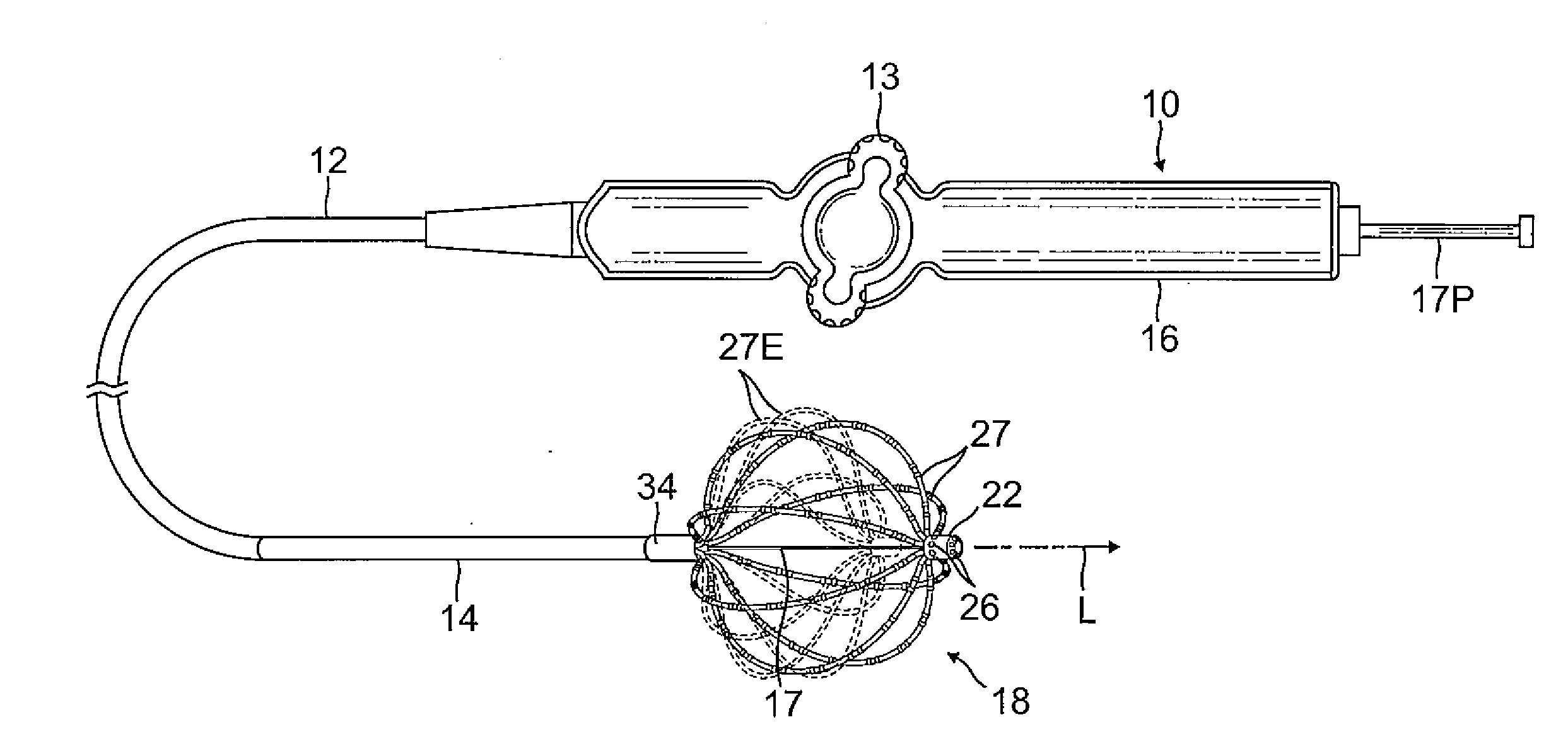

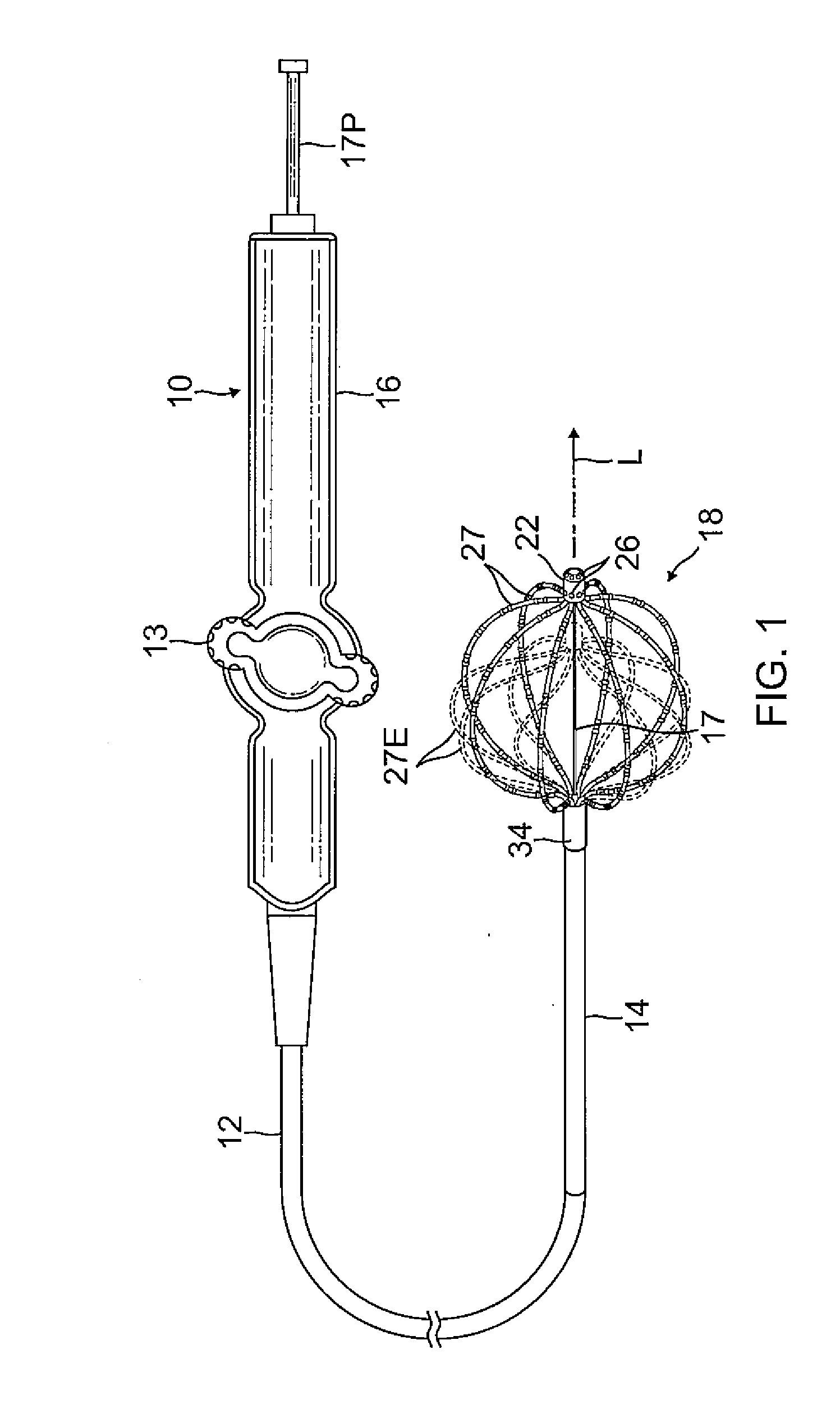

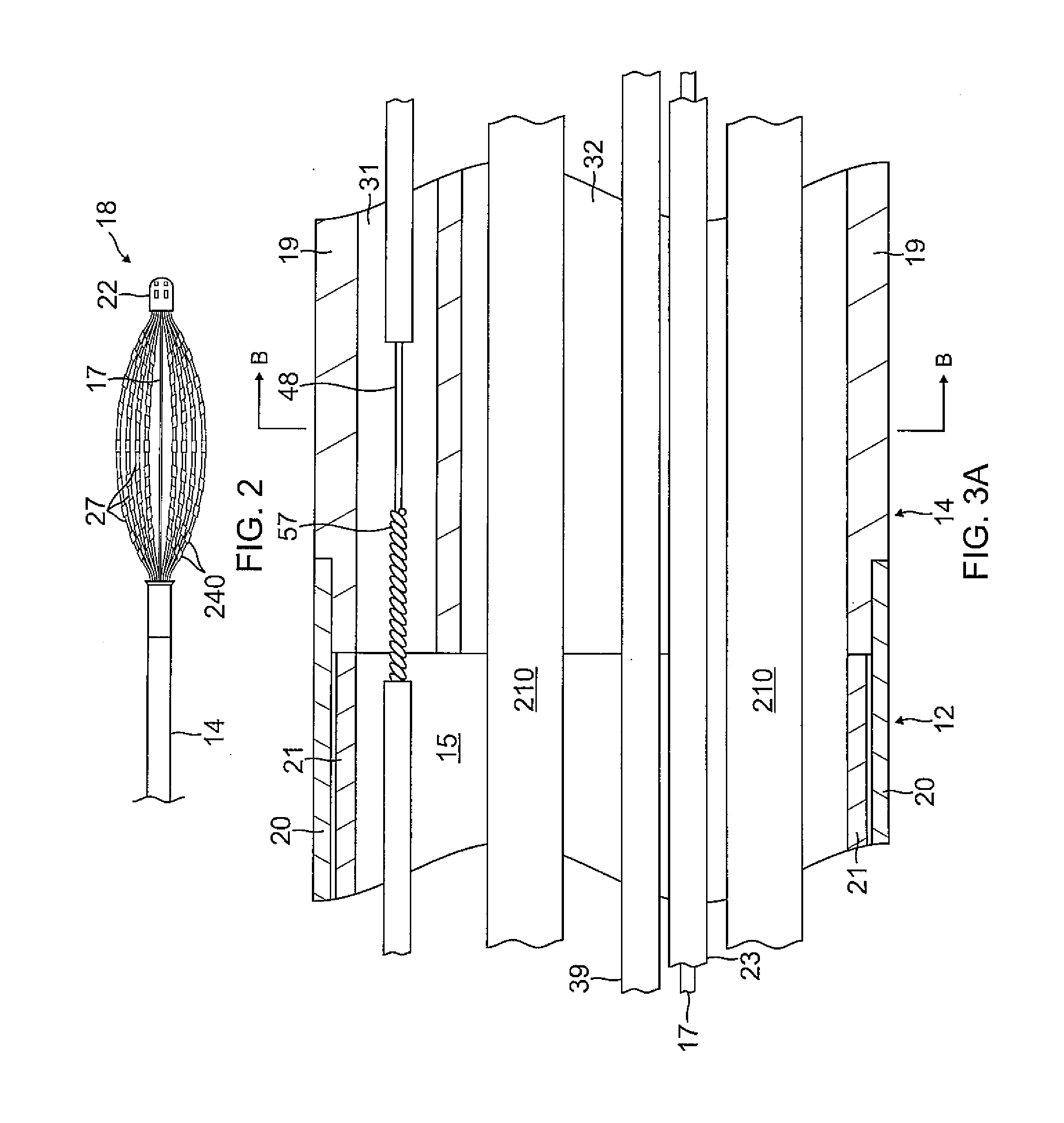

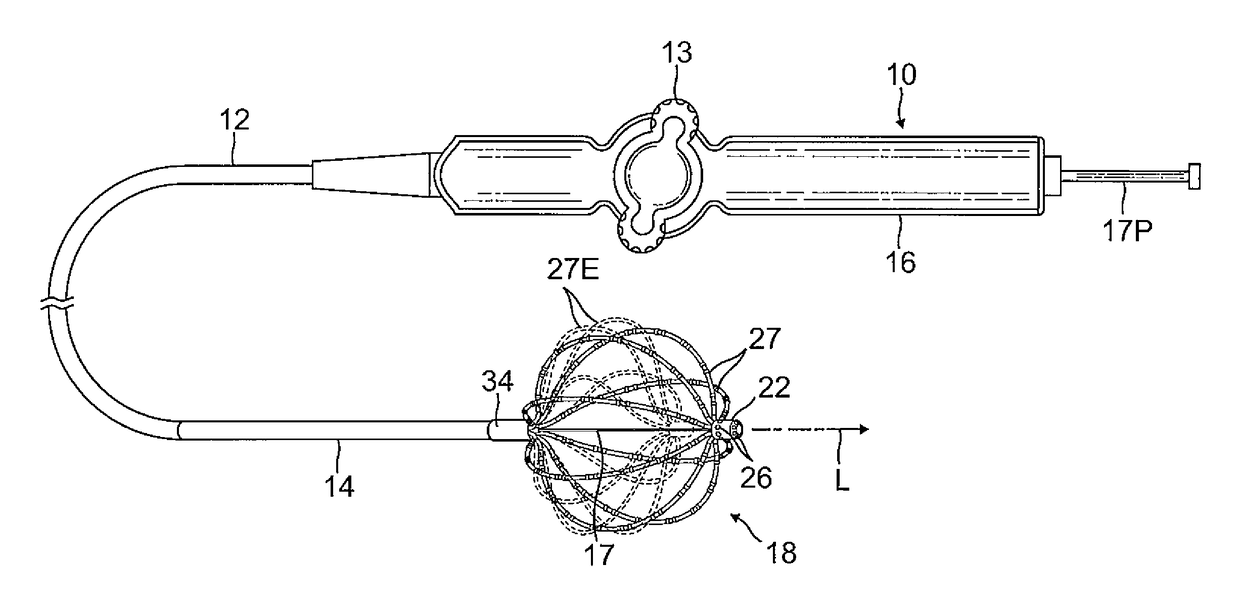

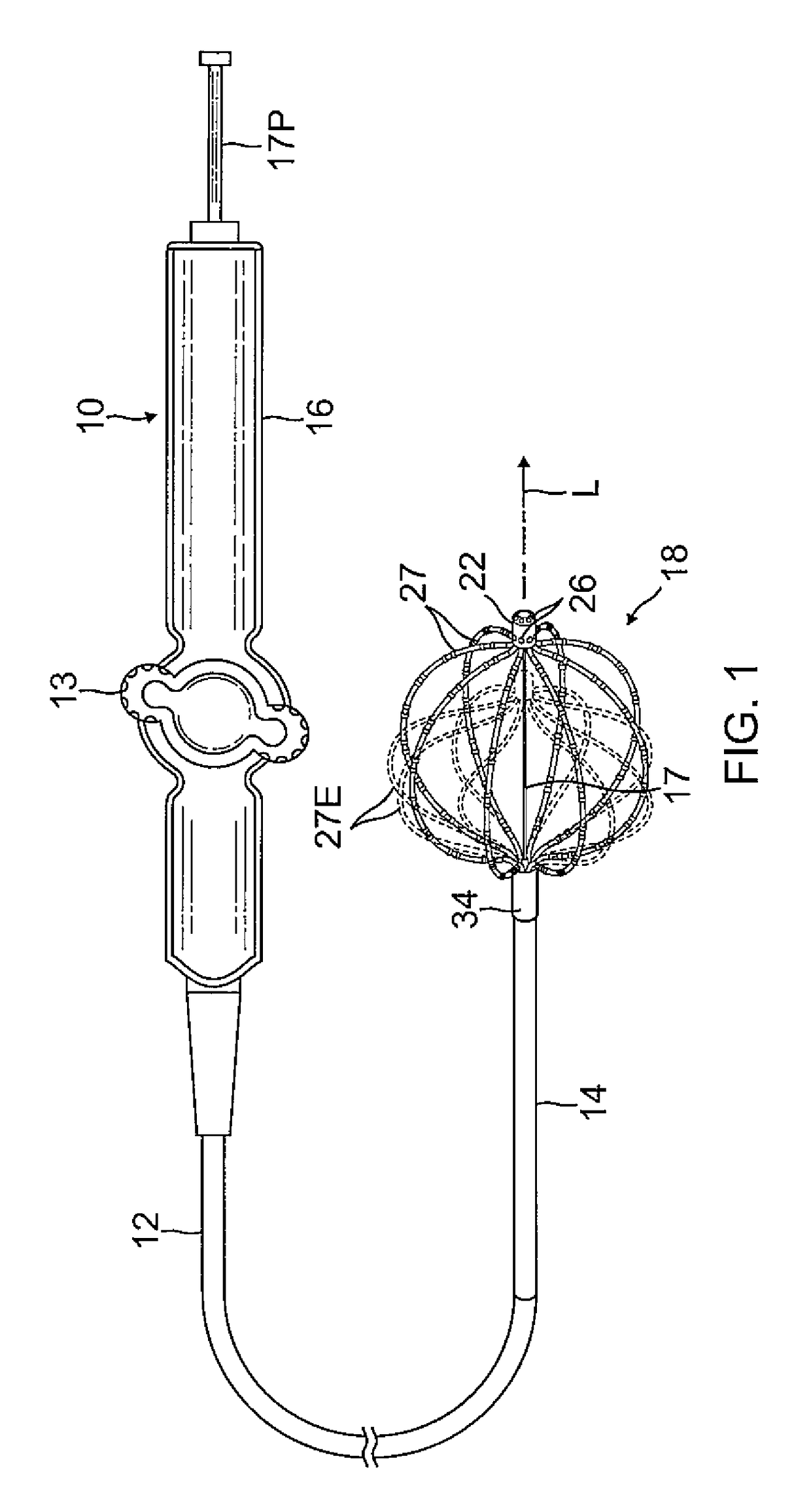

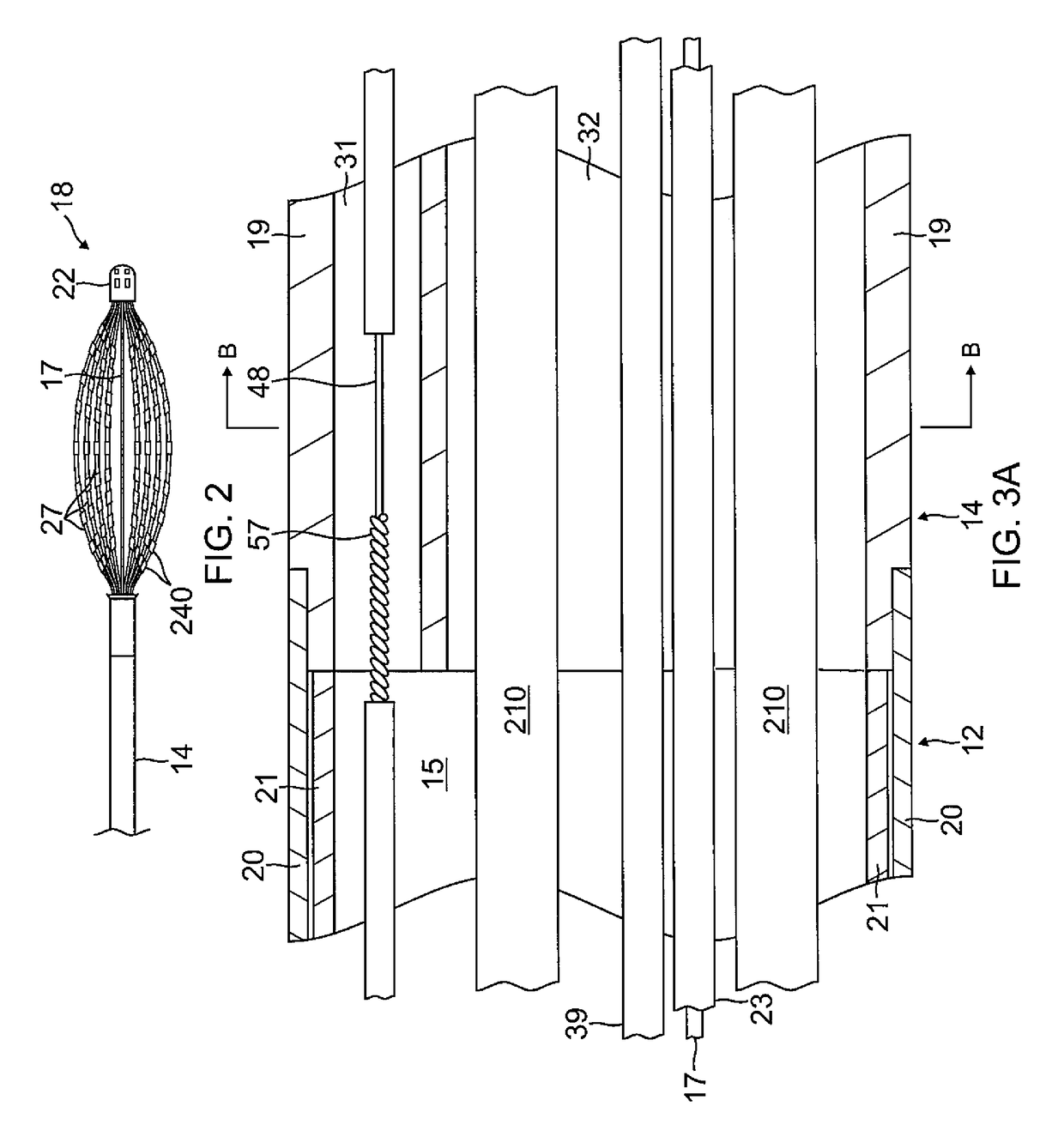

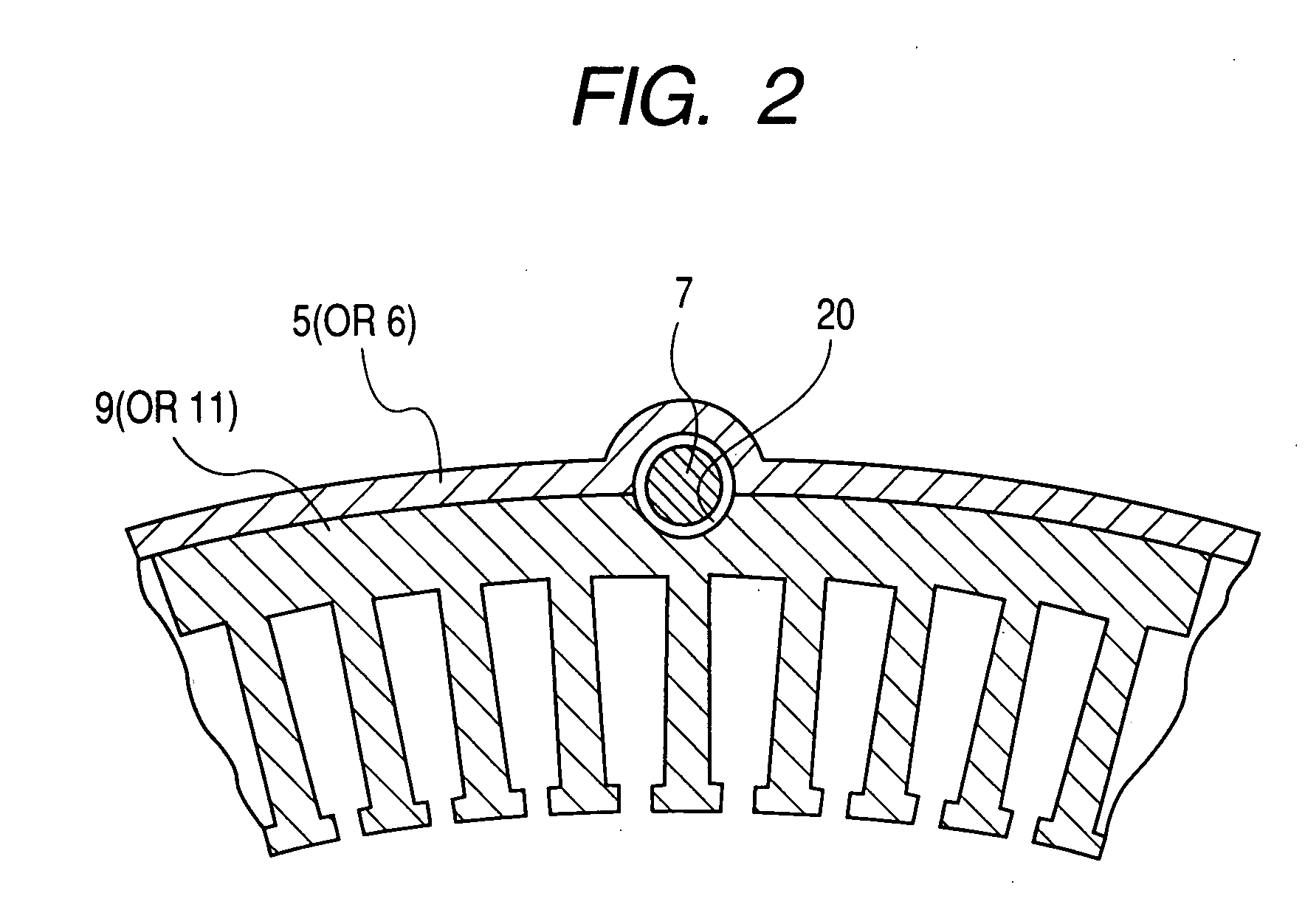

Basket catheter with improved spine flexibility

ActiveUS20160183877A1Reduce riskEasy to bendElectrocardiographyMedical devicesBasket catheterGuide tube

A catheter with basket-shaped electrode assembly with spines configured for hyper-flexing in a predetermined, predictable manner when a compressive force acts on the assembly from either its distal end or its proximal end. At least one spine has at least one region of greater (or hyper) flexibility that allows the electrode assembly to deform, for example, compress, for absorbing and dampening excessive force that may otherwise cause damage or injury to tissue wall in contact with the assembly, without compromising the structure and stiffness of the remaining regions of the spine, including its distal and proximal regions. The one or more regions of greater flexibility in the spine allow the spine to flex into a generally V-shape configuration or a generally U-shape configuration.

Owner:BIOSENSE WEBSTER (ISRAEL) LTD

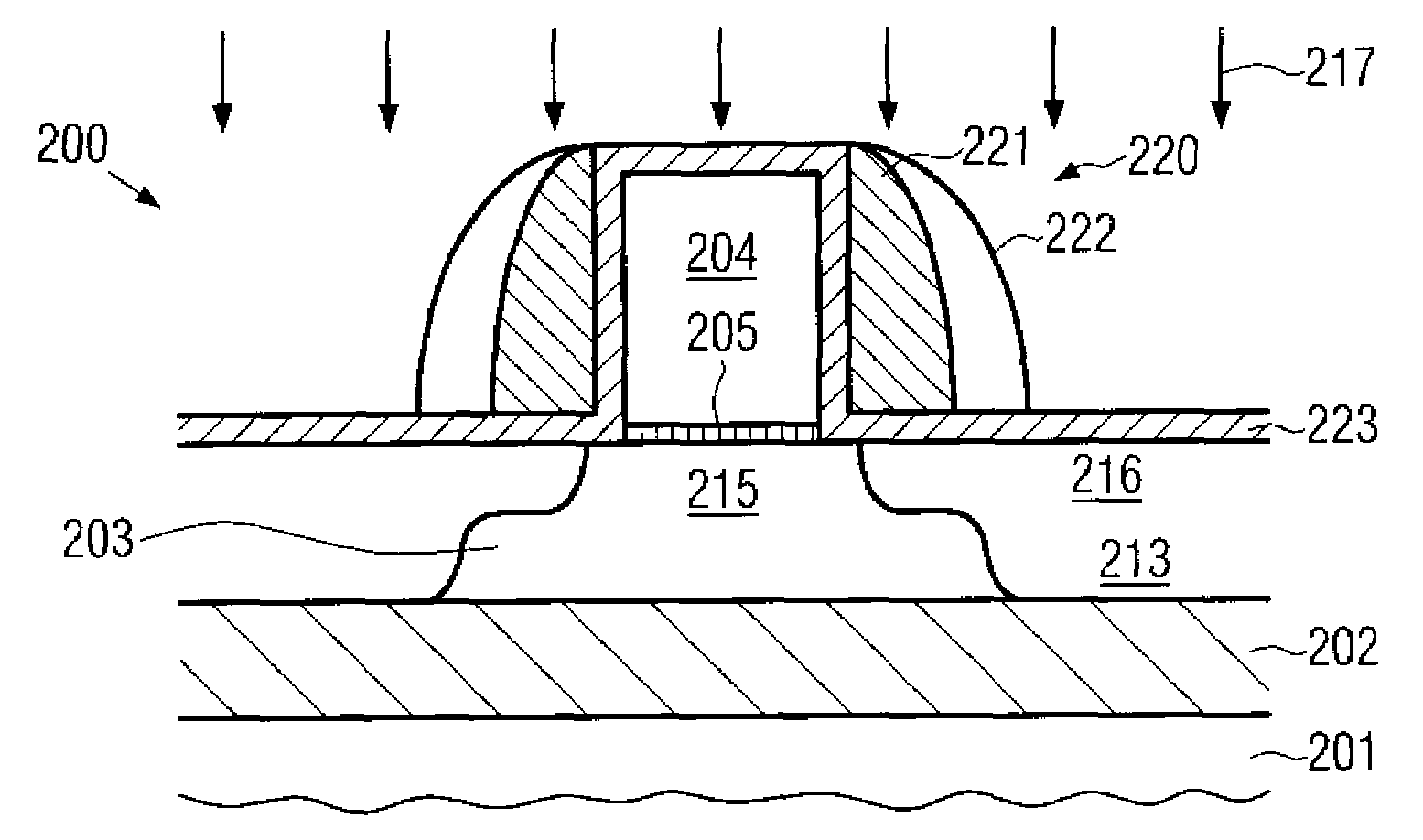

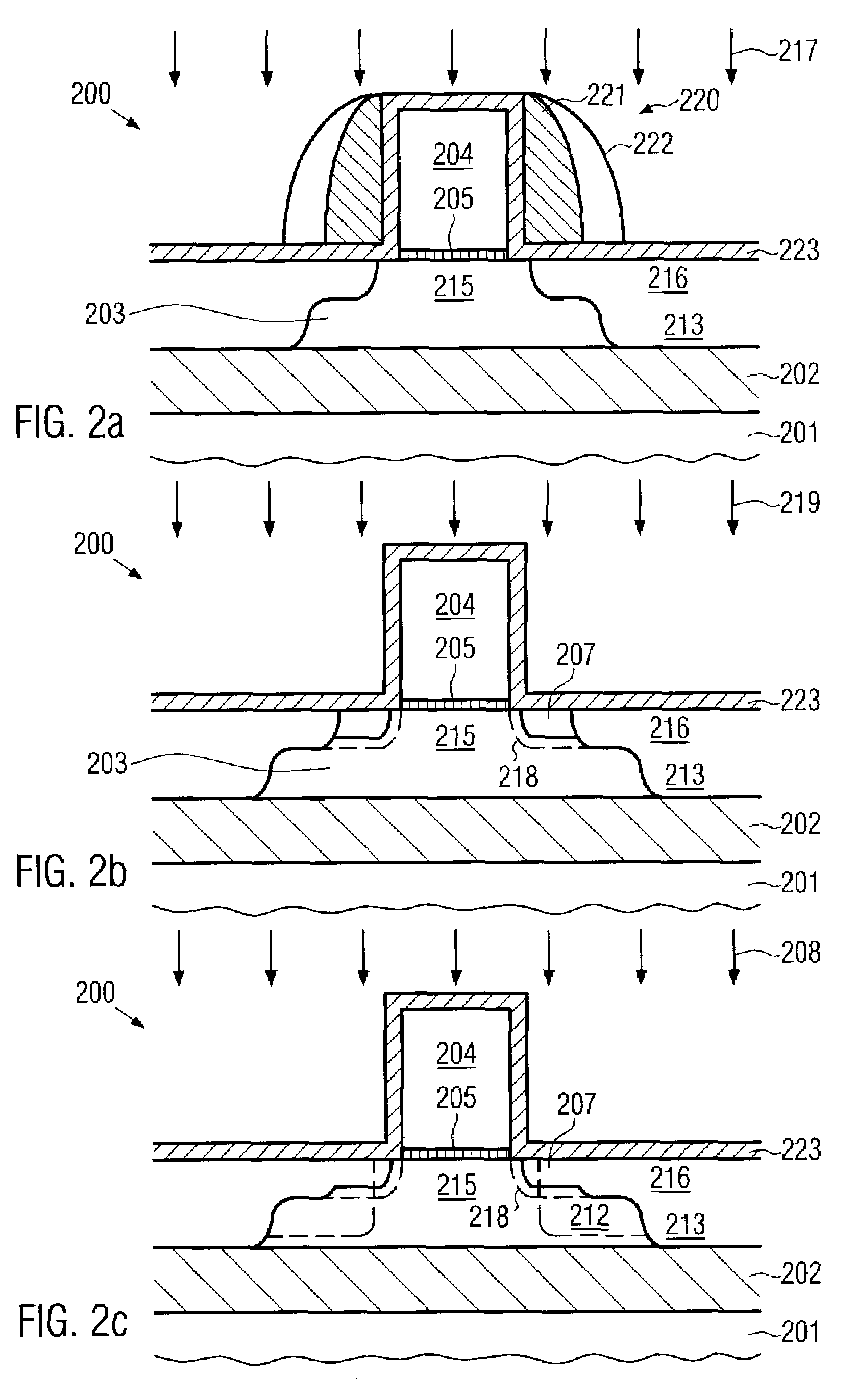

Technique for forming a strained transistor by a late amorphization and disposable spacers

ActiveUS20070202653A1Enhanced capabilityEnhance strain inducing mechanismSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsMetal silicide

By using a disposable spacer approach for forming drain and source regions prior to an amorphization process for re-crystallizing a semiconductor region in the presence of a stressed spacer layer, possibly in combination with enhanced anneal techniques, such as laser and flash anneal processes, a more efficient strain-generating mechanism may be provided. Furthermore, the spacer for forming the metal silicide may be provided with reduced width, thereby positioning the respective metal silicide regions more closely to the channel region. Consequently, an overall enhanced performance may be obtained on the basis of the above-described techniques.

Owner:GLOBALFOUNDRIES US INC

Basket catheter with improved spine flexibility

ActiveUS9782099B2Reduce riskEasy to bendElectrocardiographyMedical devicesProximal pointBasket catheter

A catheter with basket-shaped electrode assembly with spines configured for hyper-flexing in a predetermined, predictable manner when a compressive force acts on the assembly from either its distal end or its proximal end. At least one spine has at least one region of greater (or hyper) flexibility that allows the electrode assembly to deform, for example, compress, for absorbing and dampening excessive force that may otherwise cause damage or injury to tissue wall in contact with the assembly, without compromising the structure and stiffness of the remaining regions of the spine, including its distal and proximal regions. The one or more regions of greater flexibility in the spine allow the spine to flex into a generally V-shape configuration or a generally U-shape configuration.

Owner:BIOSENSE WEBSTER (ISRAEL) LTD

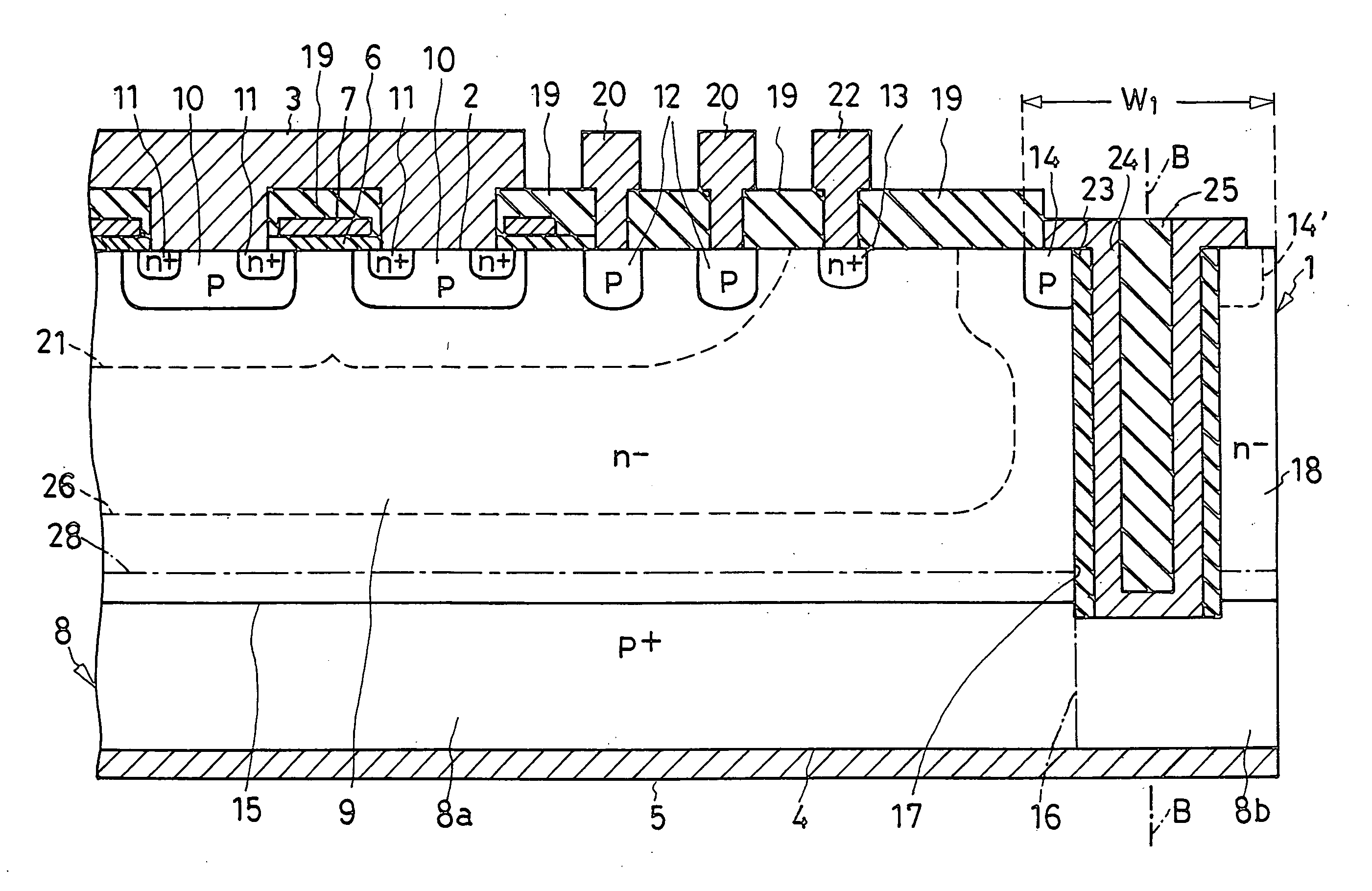

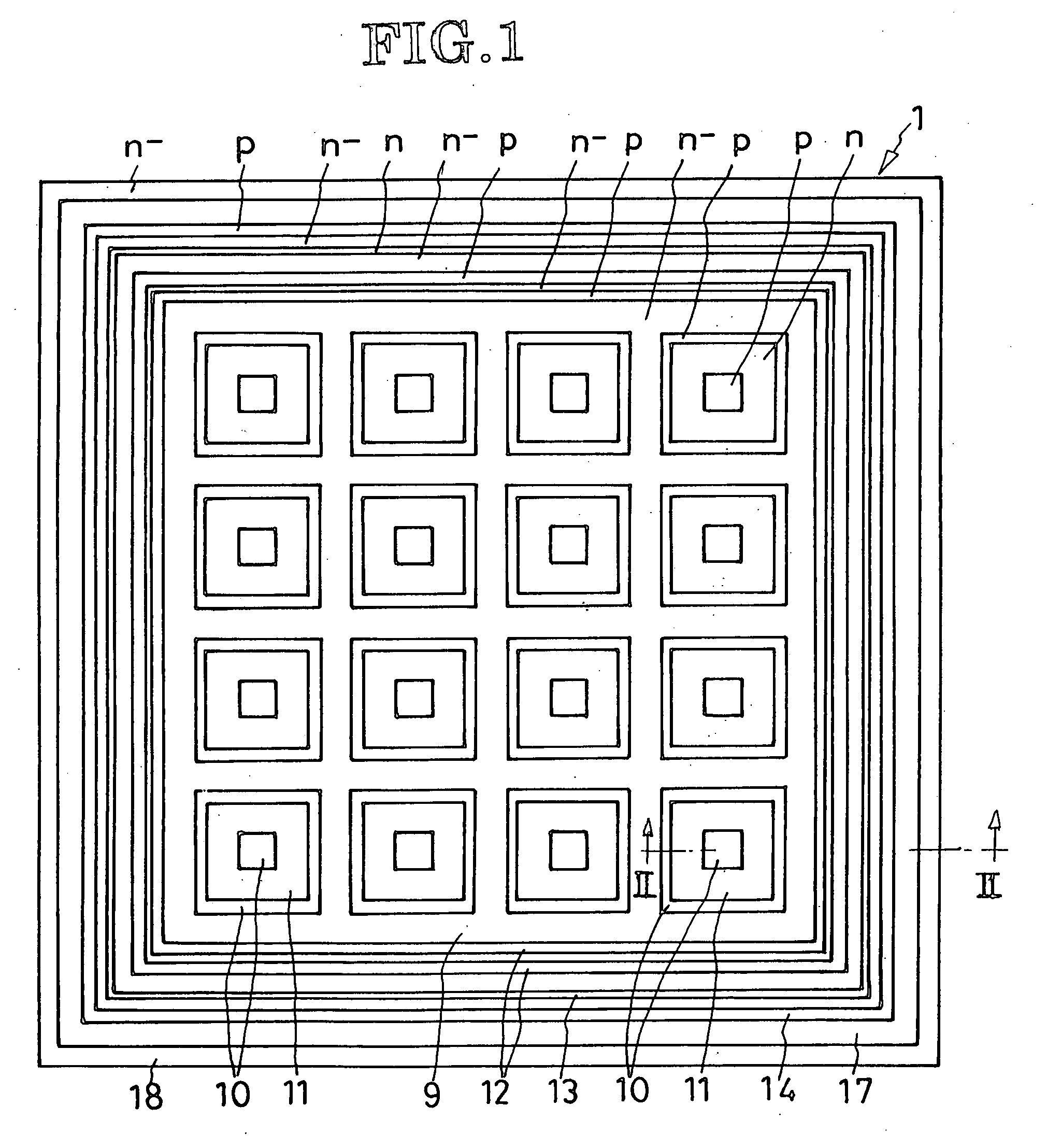

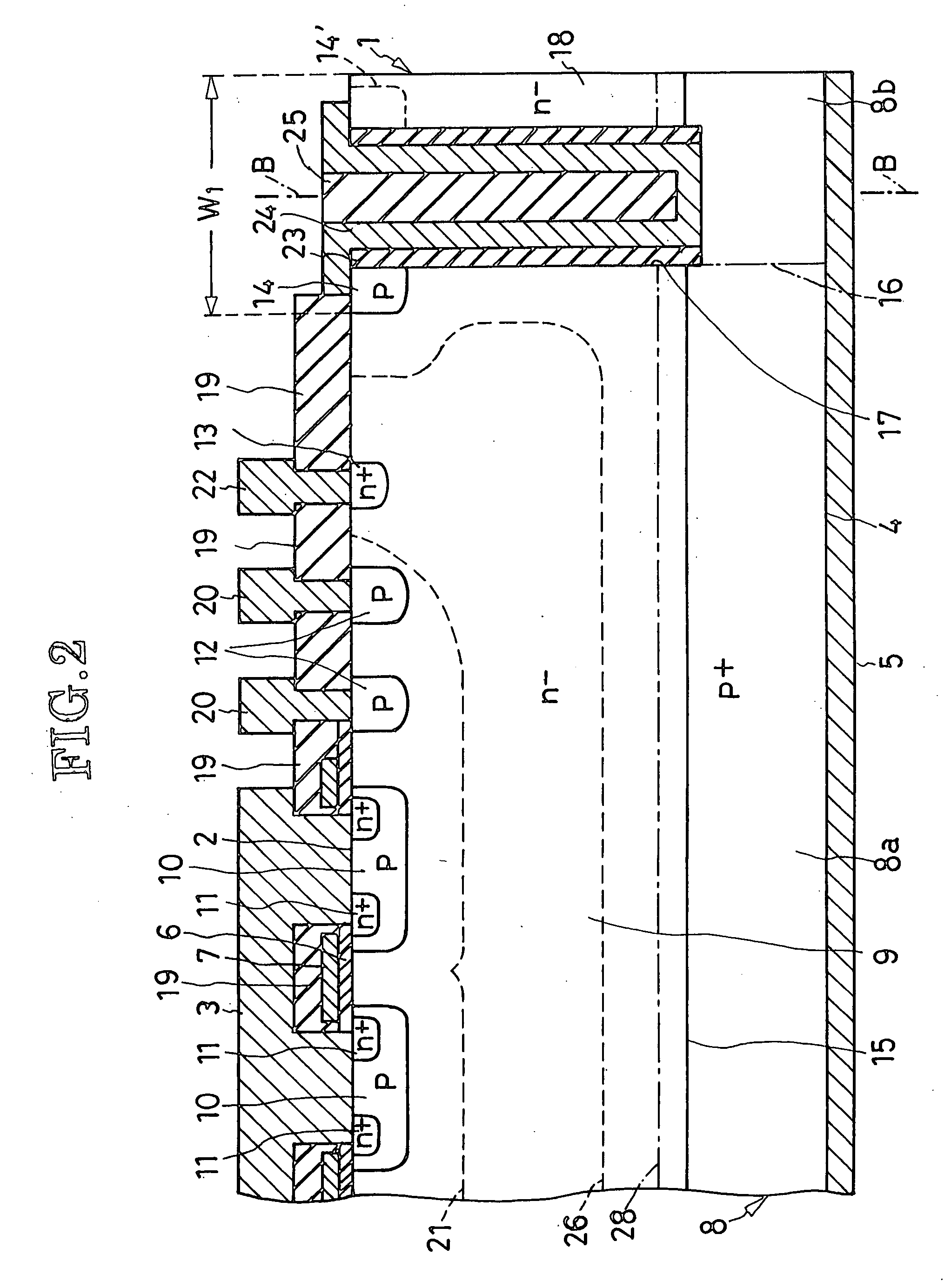

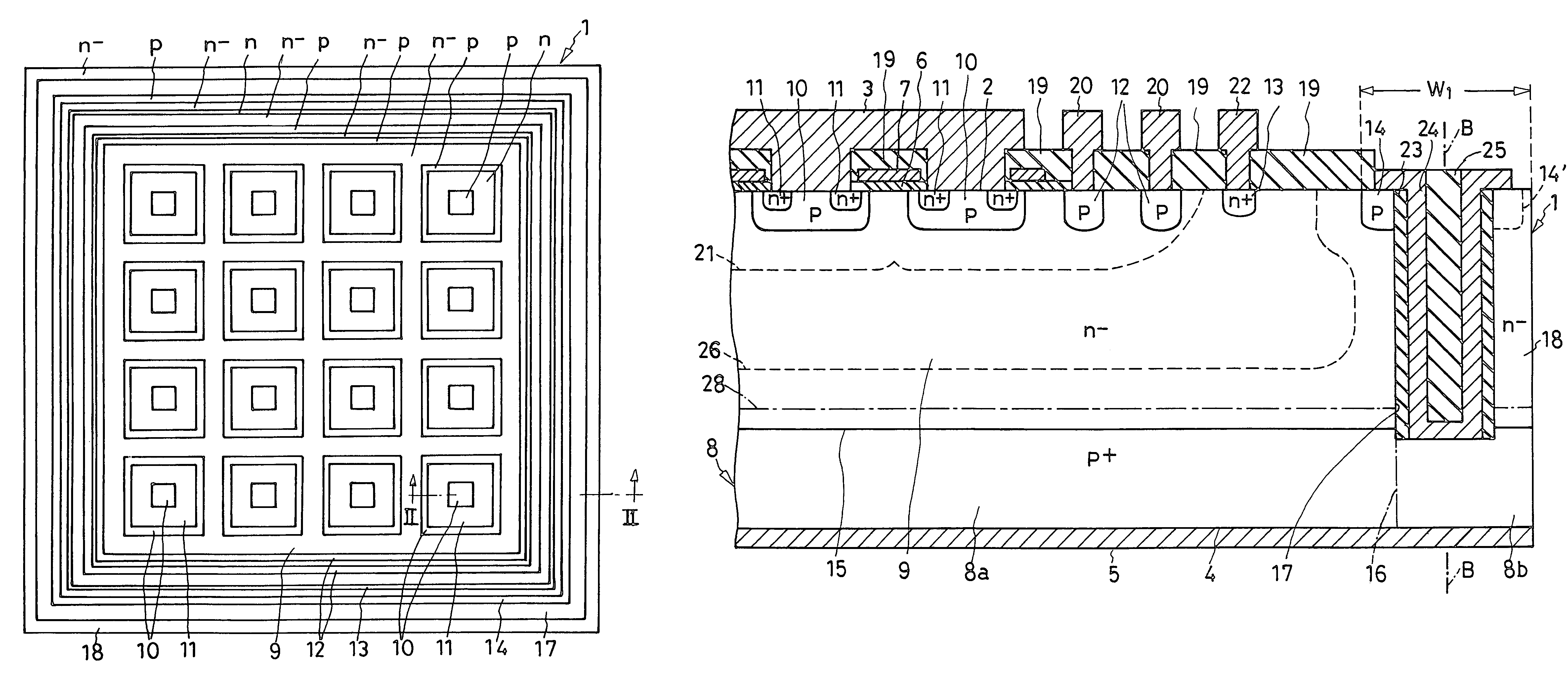

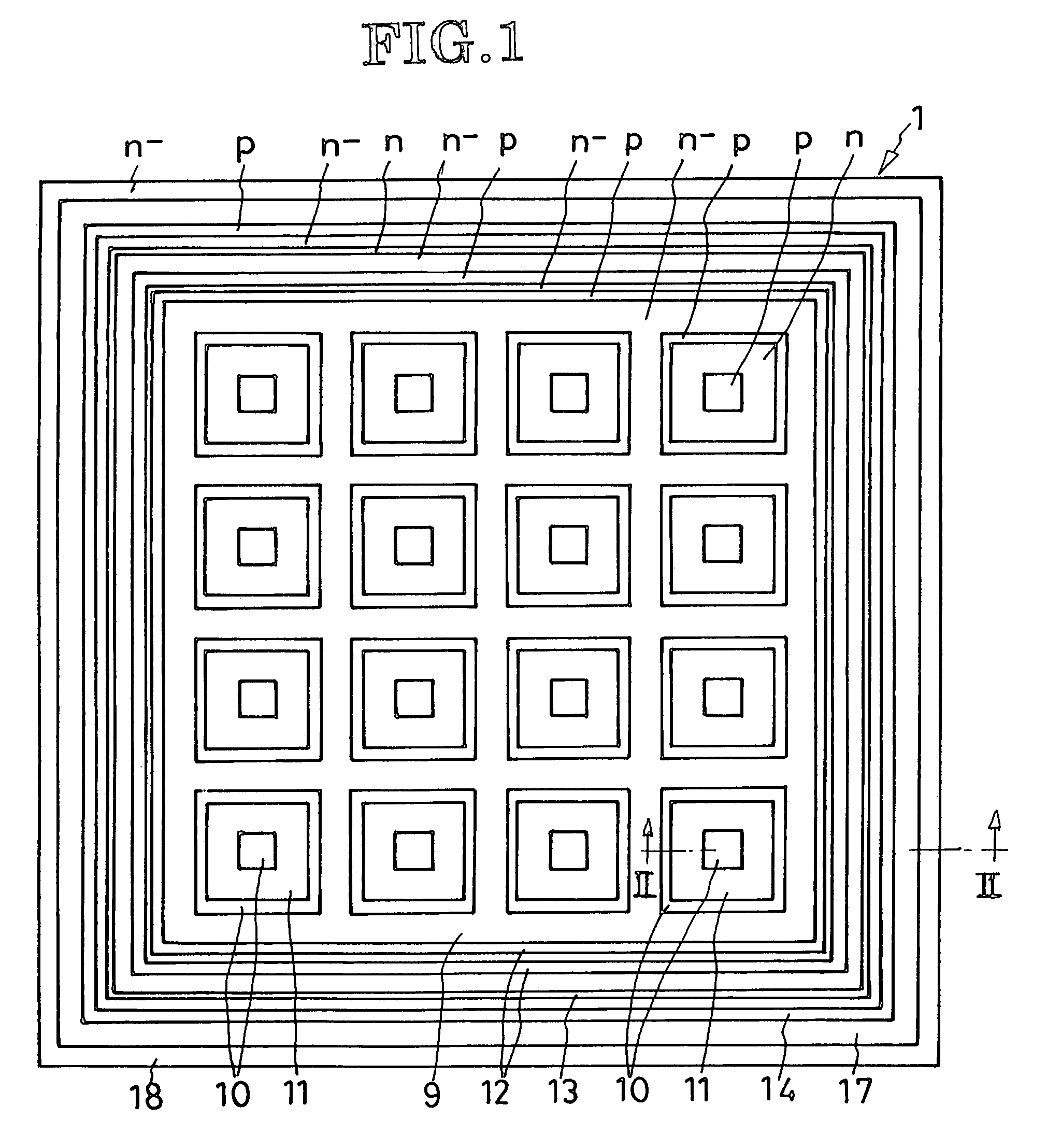

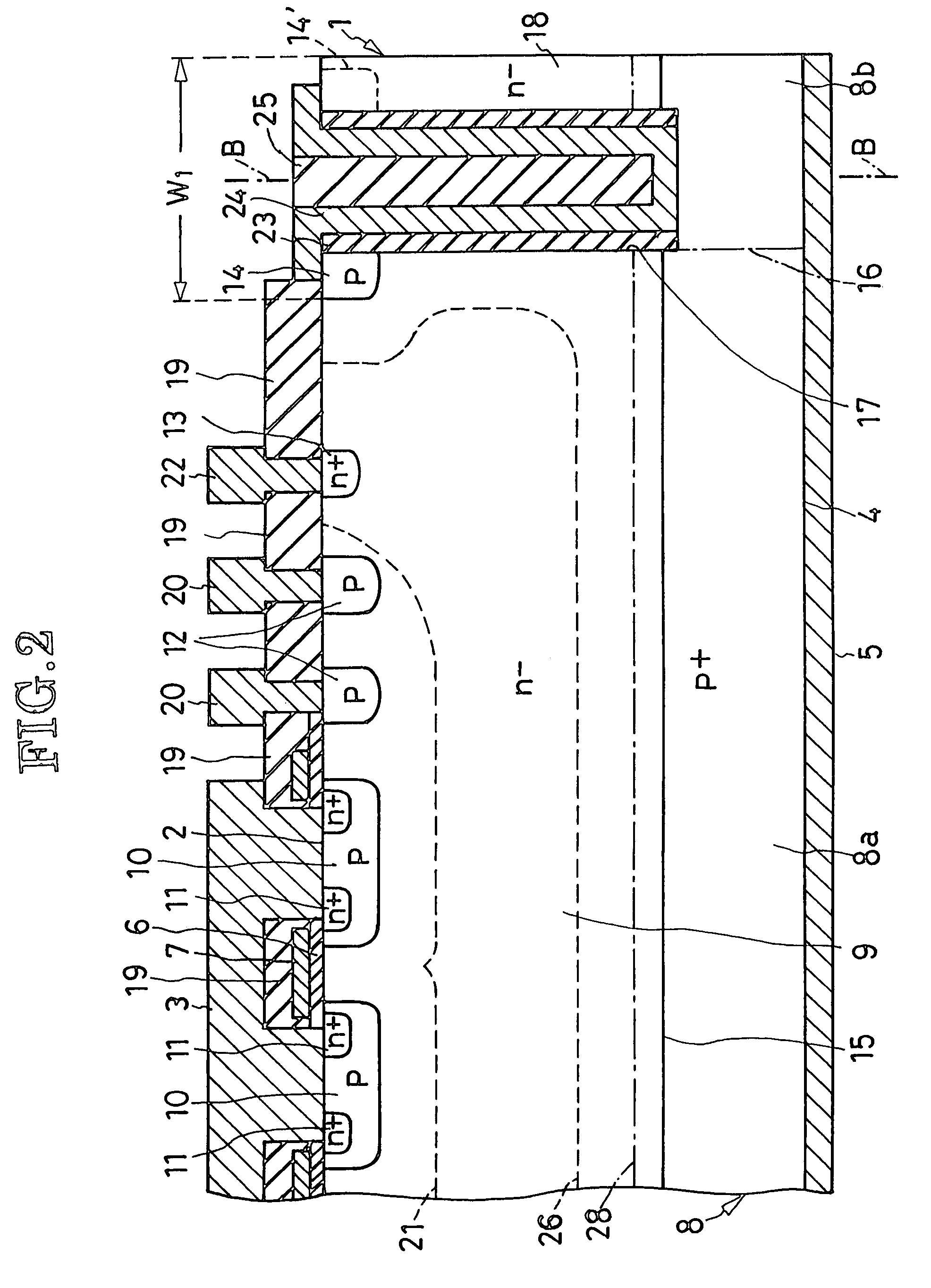

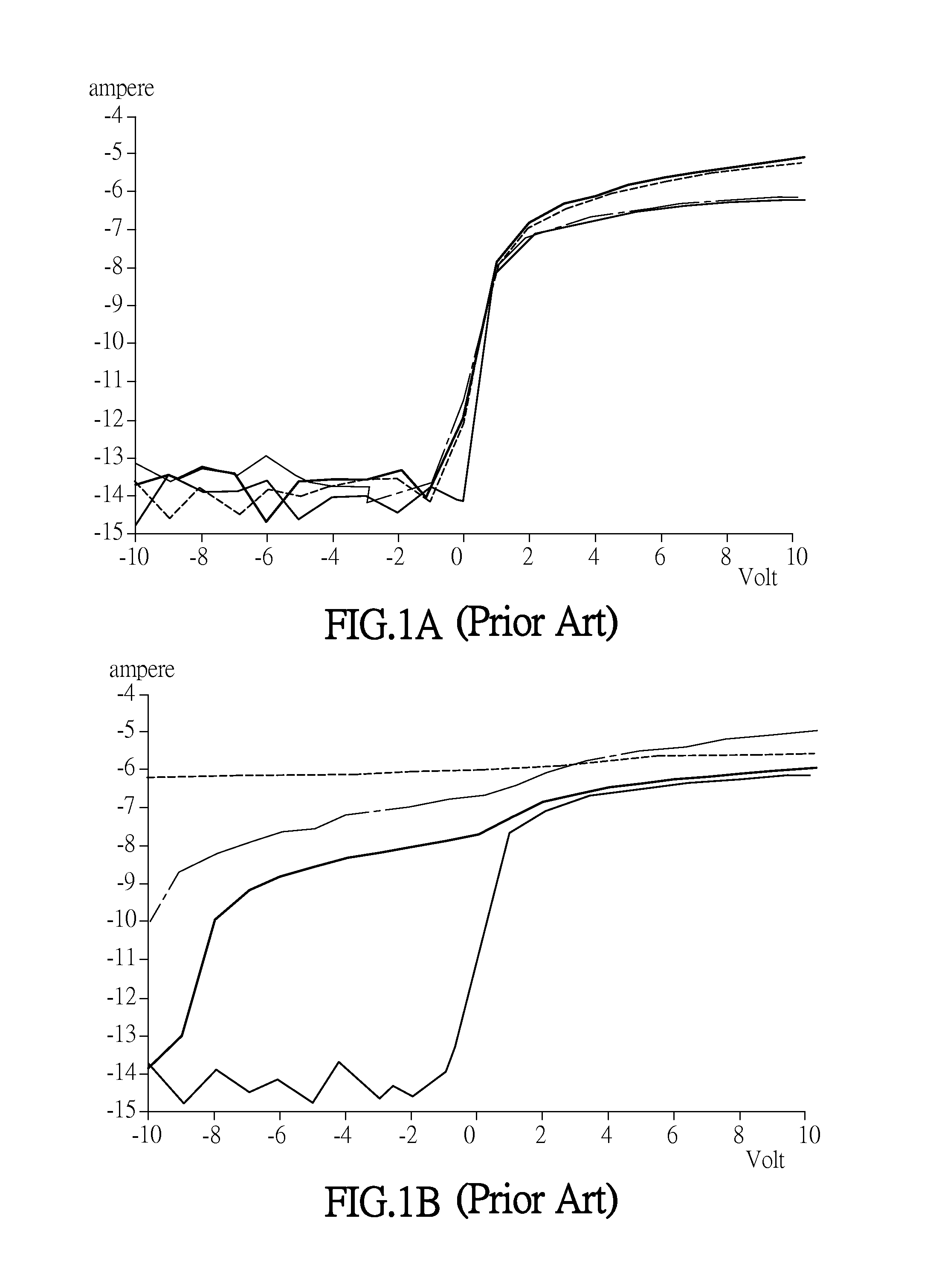

IGBT or like semiconductor device of high voltage-withstanding capability

ActiveUS20060267091A1High voltageLeakage currentTransistorSolid-state devicesInsulated-gate bipolar transistorSemiconductor

A multiple-cell insulated-gate-bipolar-transistor chip is disclosed which includes a semiconductor substrate having formed therein a p+-type collector region and an n−-type base region, with a pn junction therebetween. An annular trench is etched in the substrate so as to surround the array of IGBT cells. Received in the trench are a dielectric layer which is held against the base region, and an electroconductive layer which is held against the base region via the dielectric layer and which is electrically coupled to the collector region. When the pn junction between the collector and base regions is reverse biased, the electroconductive layer creates at the annular periphery of the base region a depletion layer which is joined to a depletion layer created in the base region by the pn junction, thereby preventing current leakage from the side surfaces of the IGBT chip.

Owner:SANKEN ELECTRIC CO LTD

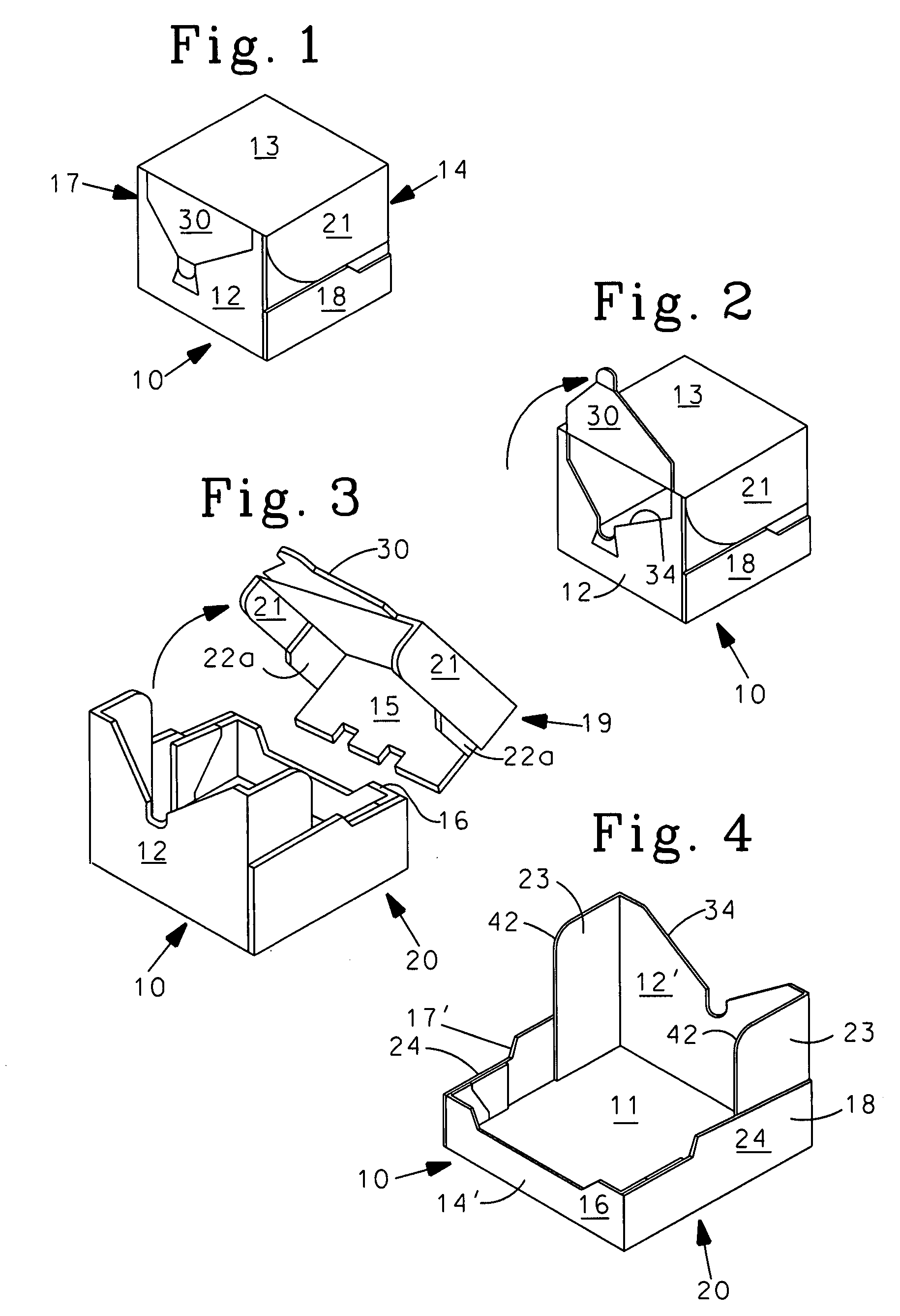

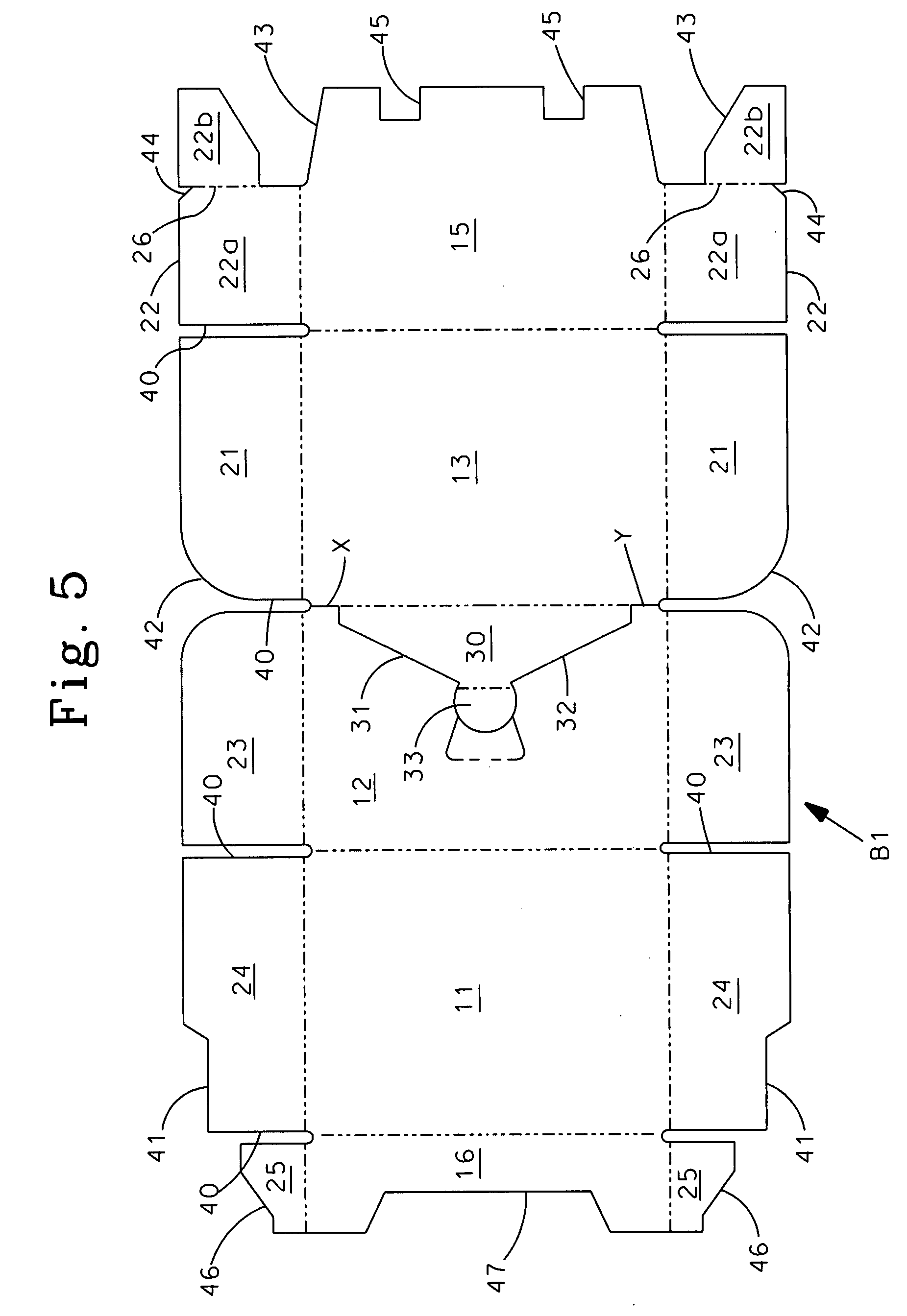

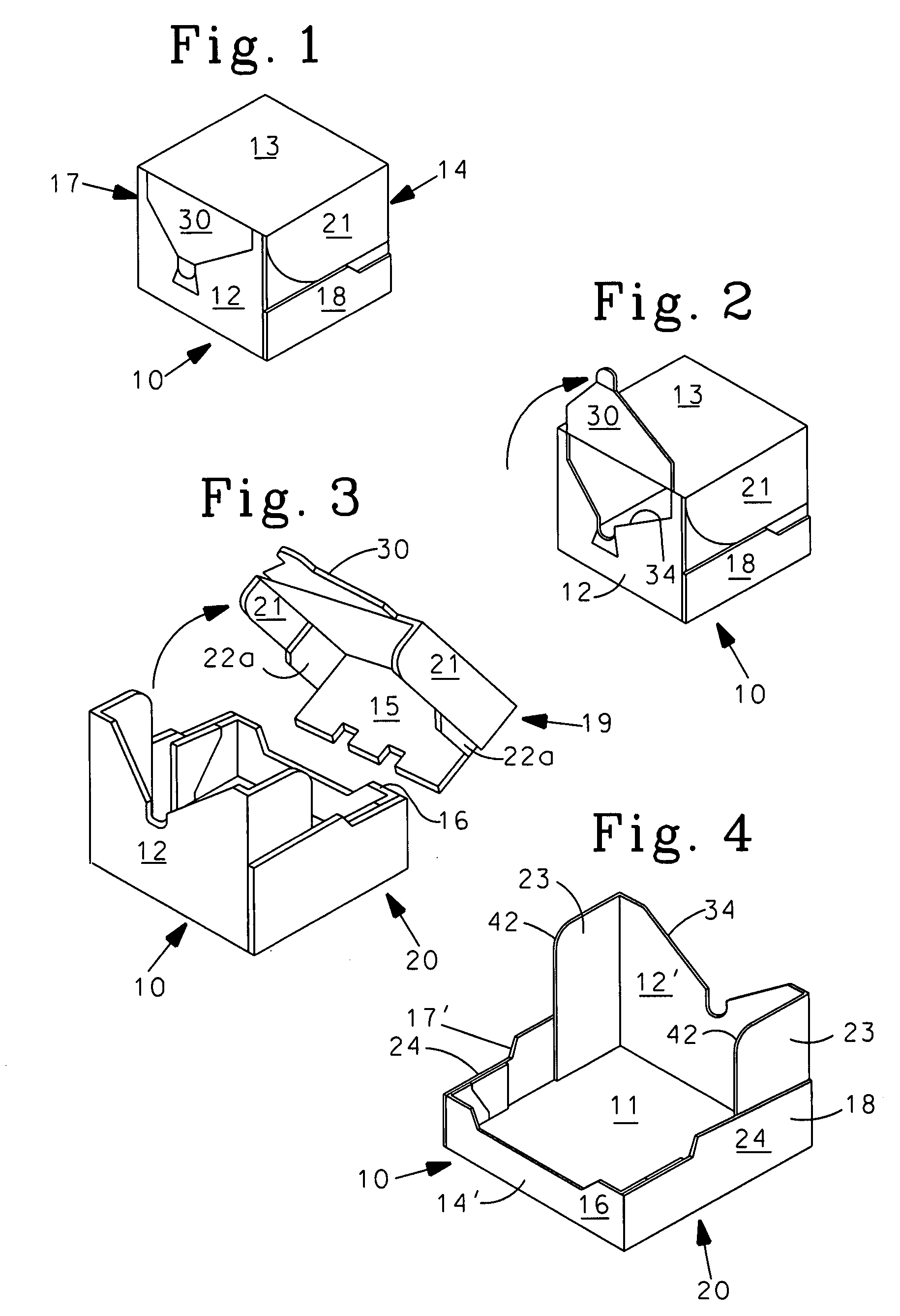

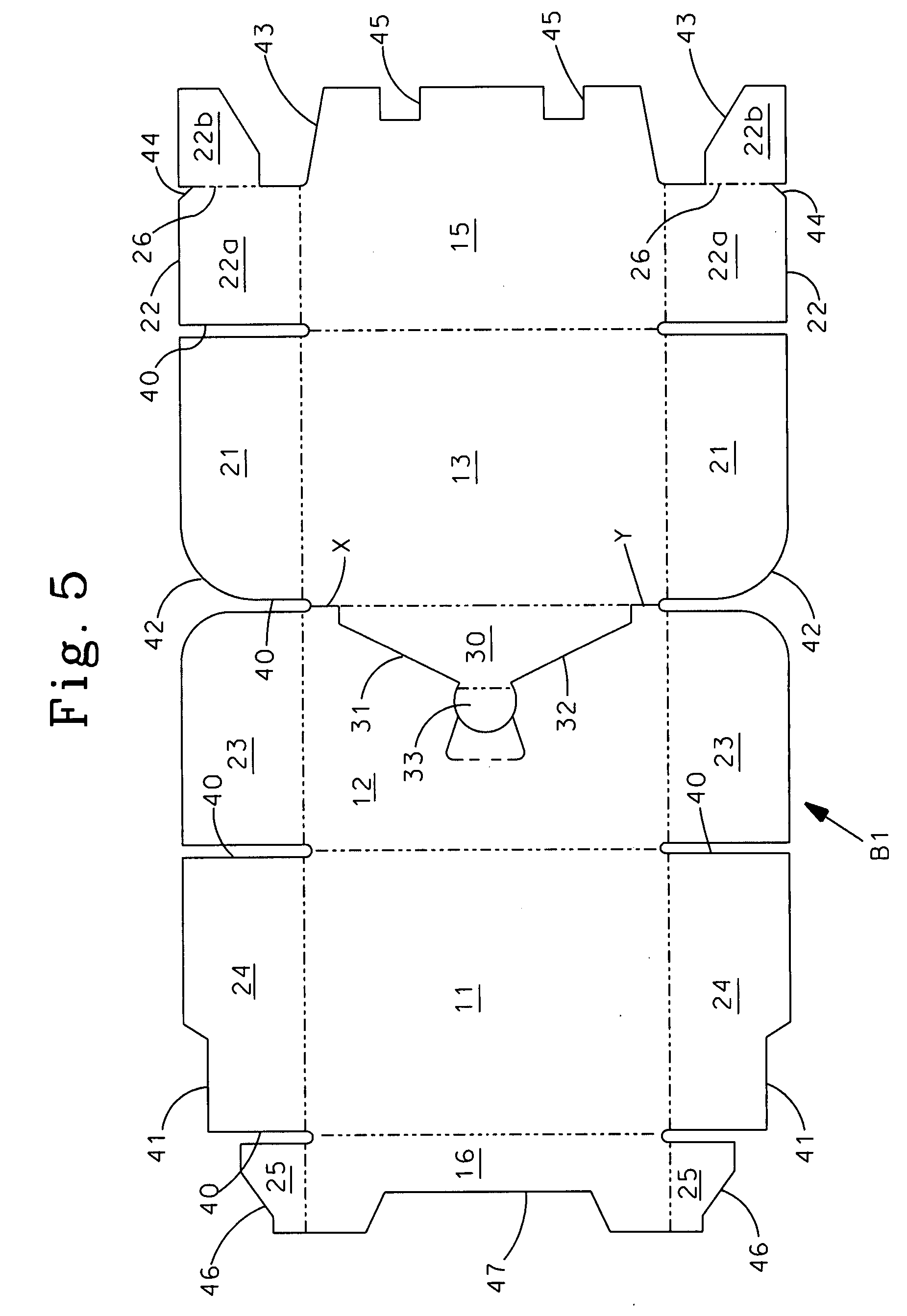

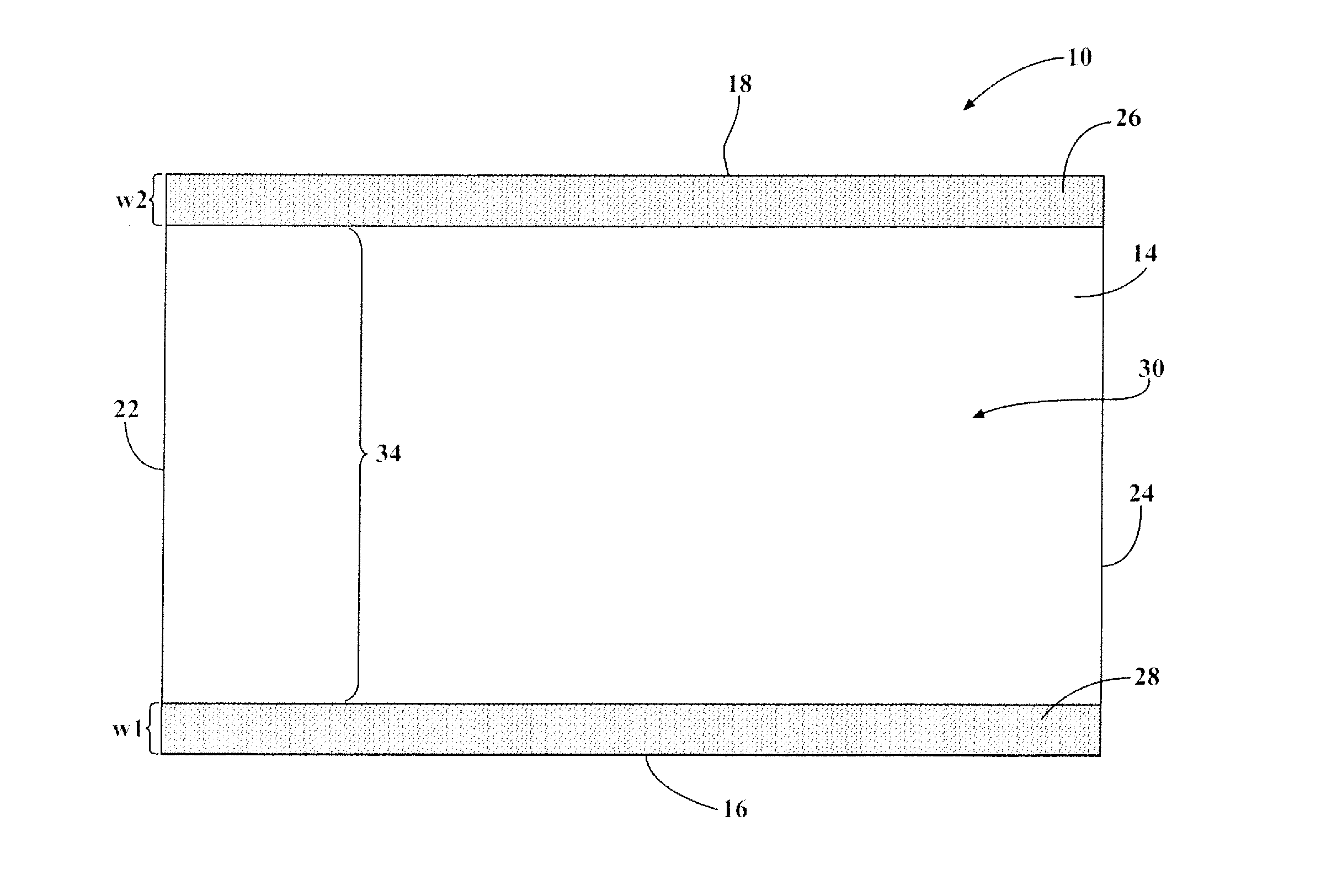

Shipping and display container

A container and a blank for making it. The container is constructed from a single sheet of foldable material and has a bottom wall, a top wall, first and second front wall panels, a back wall, and side flaps extending from opposite ends of the bottom, top, and back walls, and from the first and second front wall panels. The top wall is secured to the container by a tear-out panel extending from the top wall into the back wall and by frangible side flap portions in the side walls, whereby the tear-out panel may be grasped and lifted to lift the top wall and break the frangible side flap portions, completely freeing the top wall from the container by the single step of grasping and tearing out and lifting the tear-out panel to pivot the top upwardly. A blank and method of assembling and erecting the blank to form the container also are disclosed.

Owner:INT PAPER CO

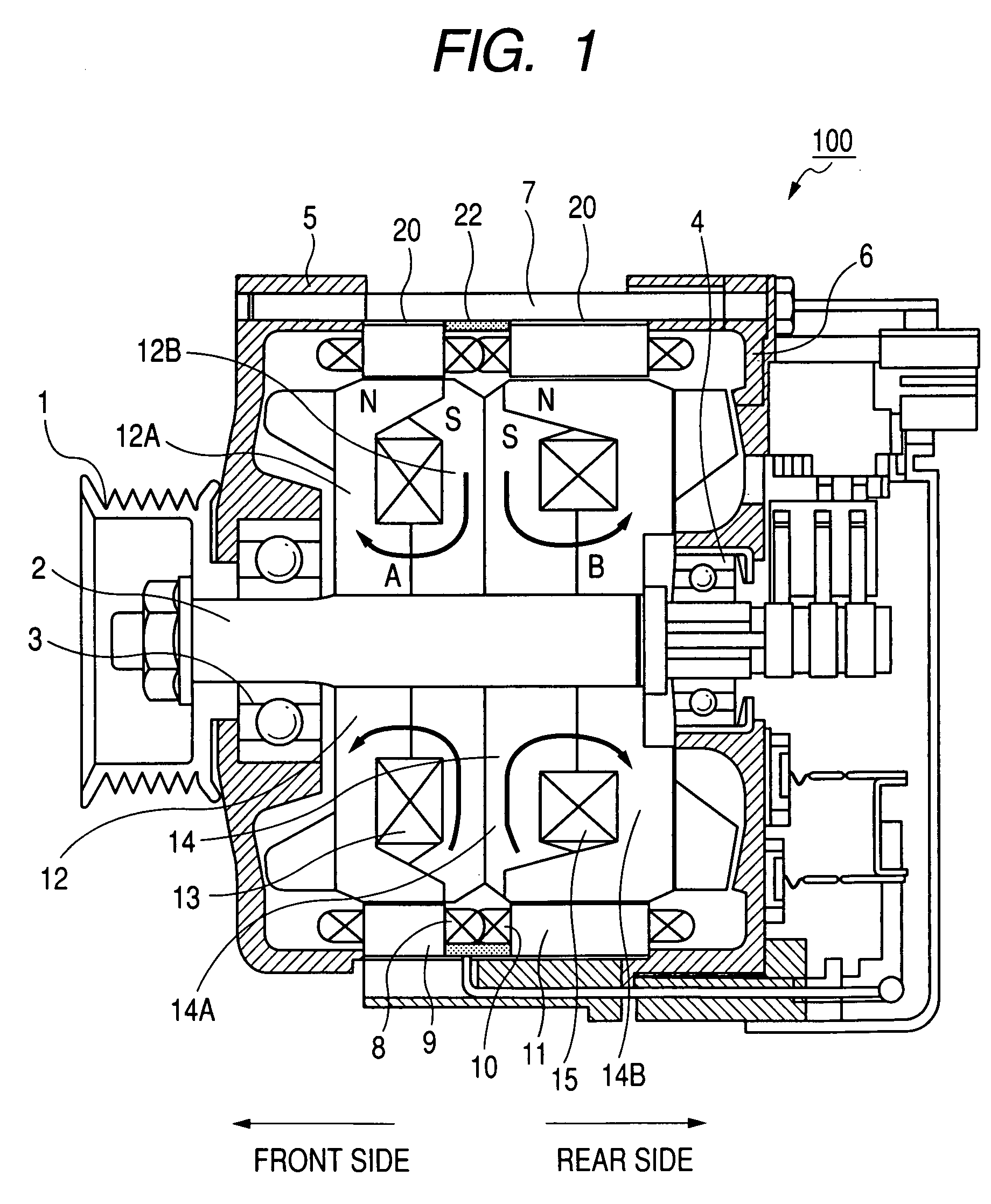

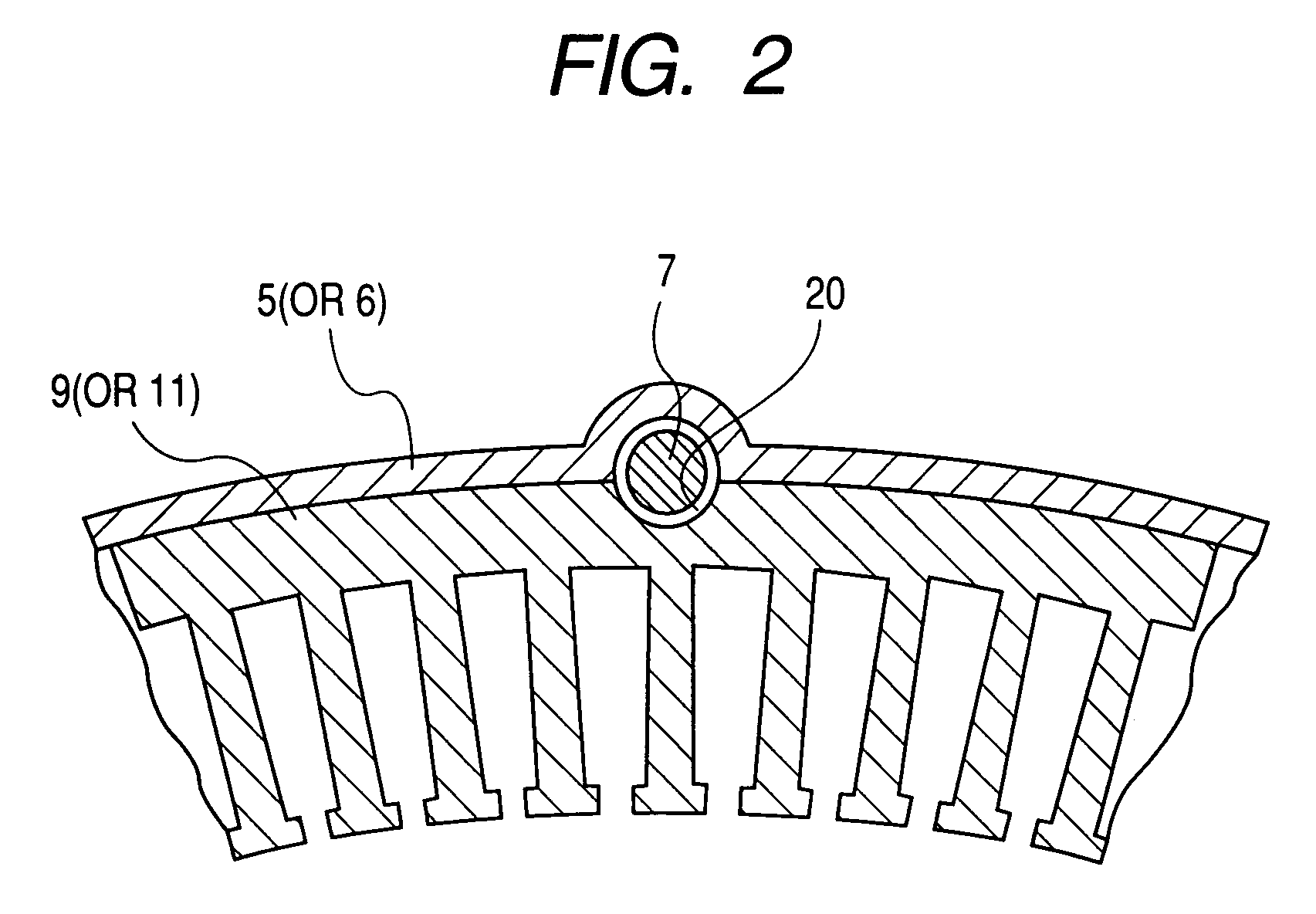

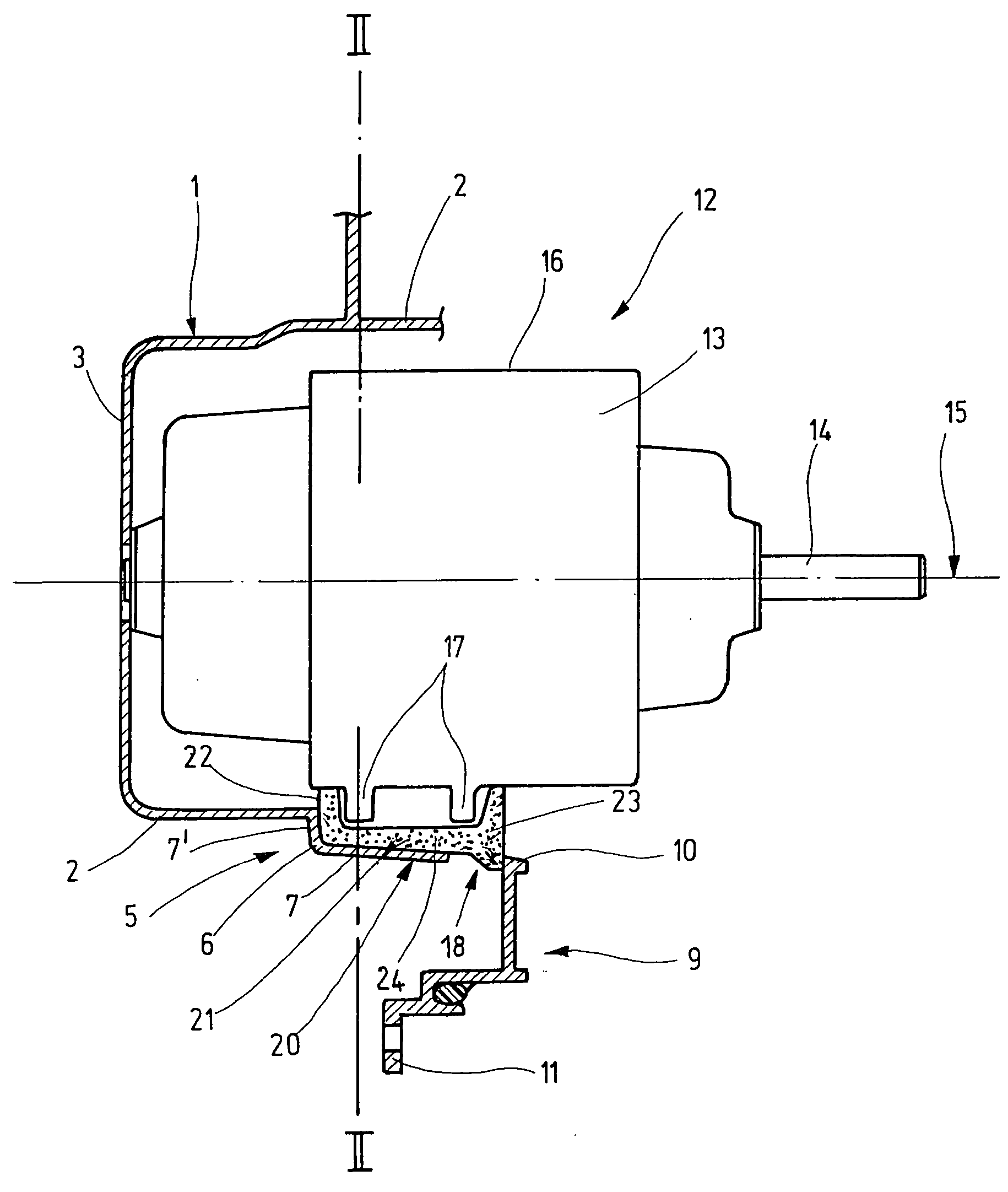

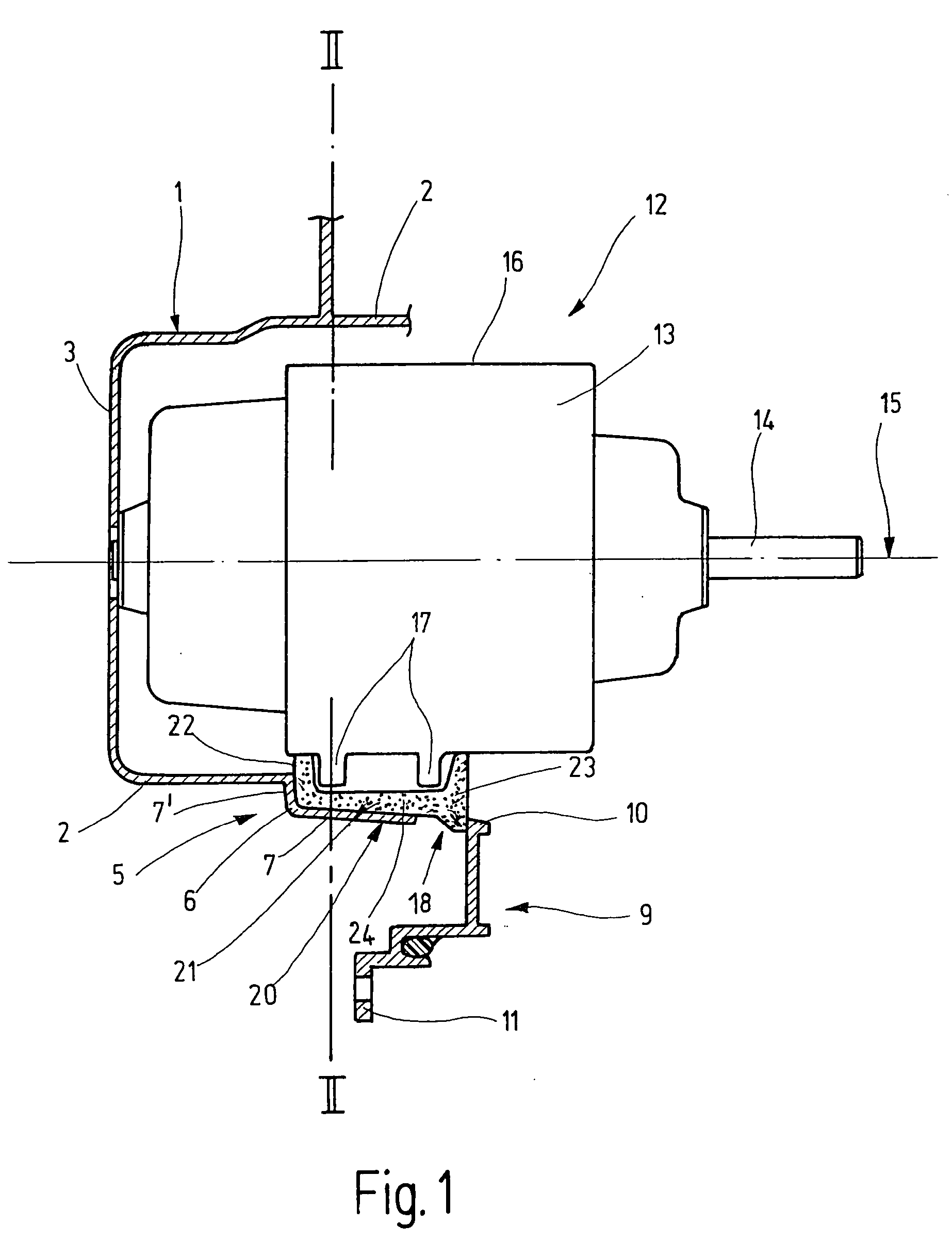

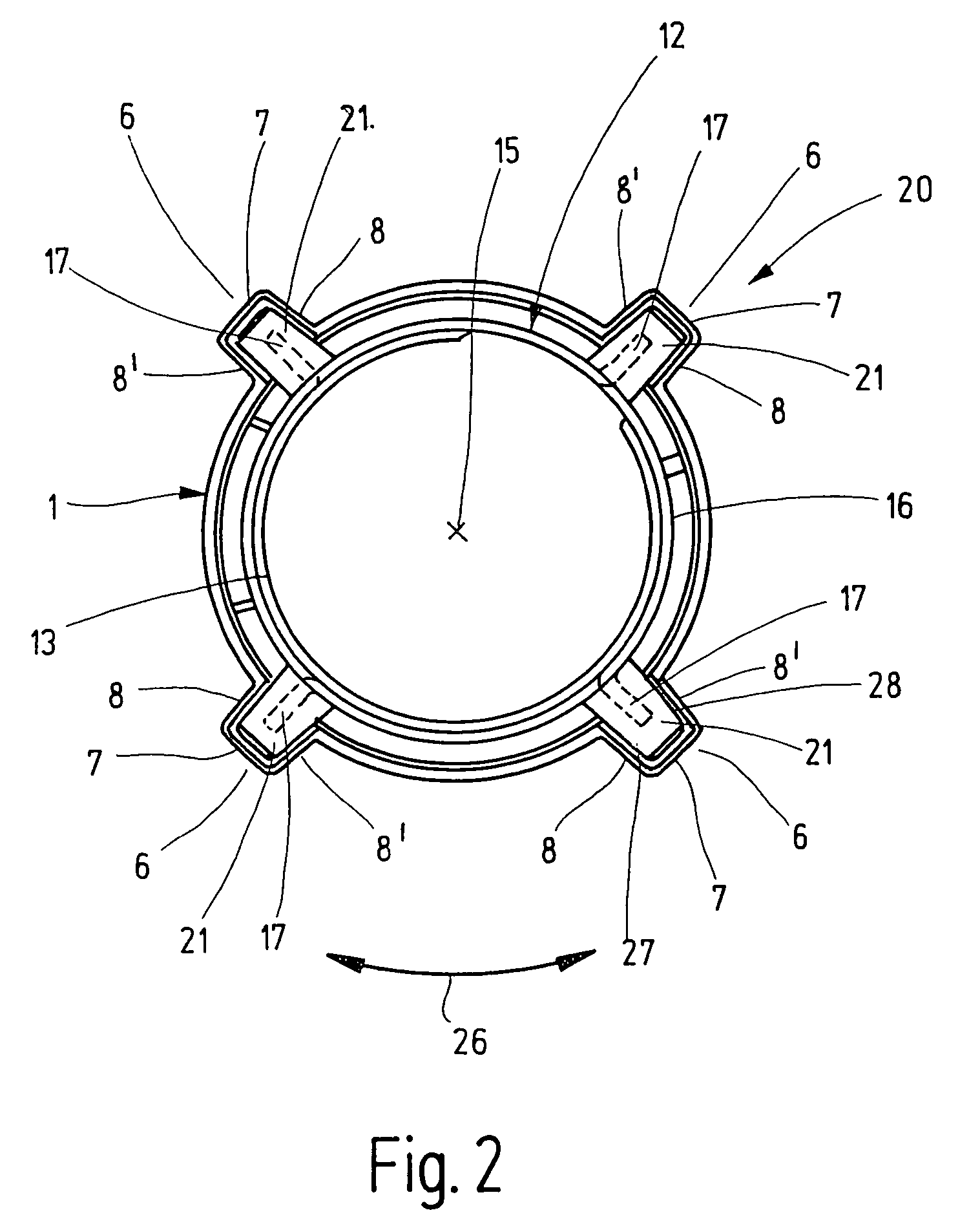

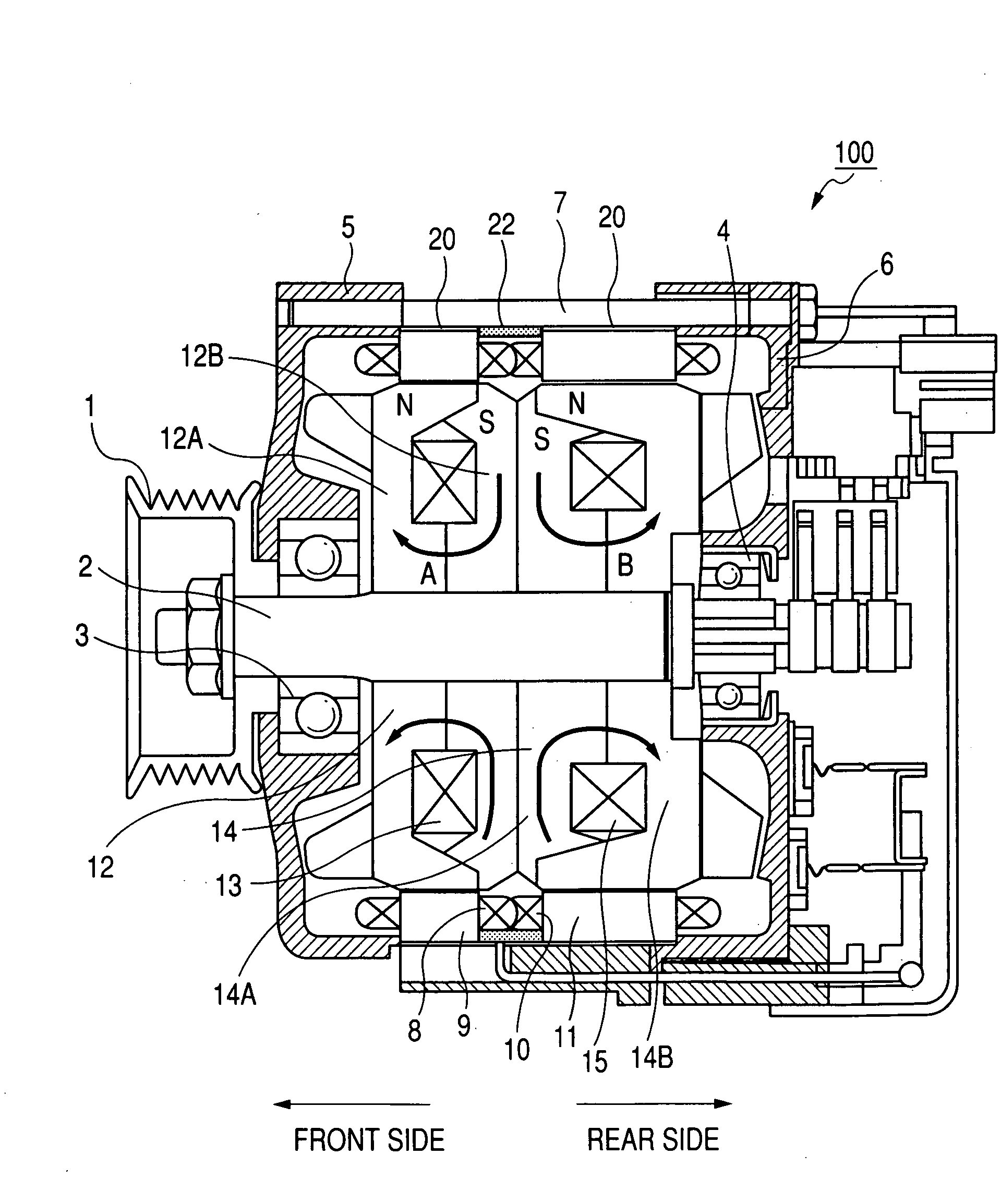

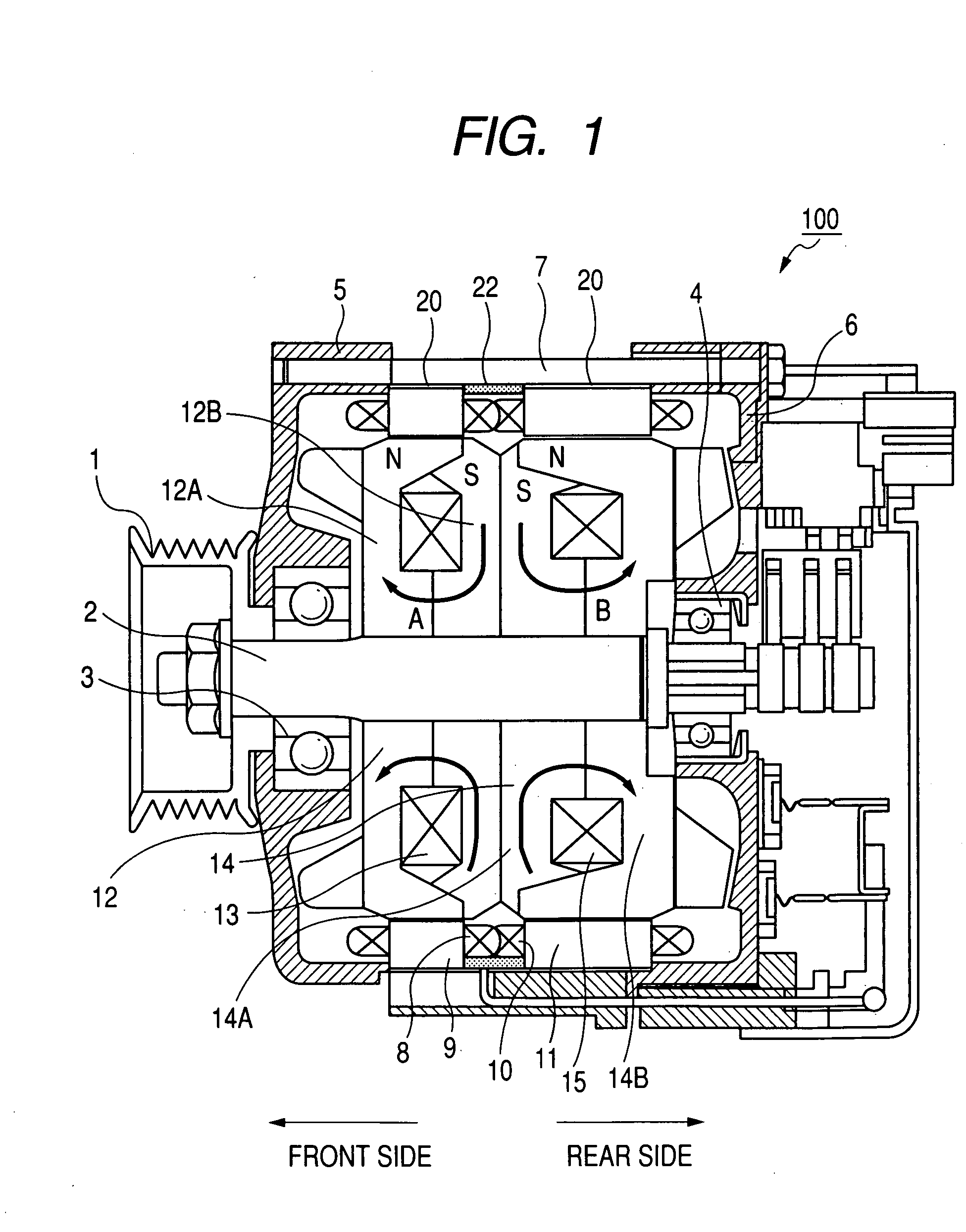

Automotive tandem alternator having reduced axial length and capable of effectively suppressing magnetic leakage

InactiveUS7602095B2Shorten the lengthSuppressing Flux LeakageSynchronous generatorsMagnetic circuit rotating partsMagnetomotive forceAlternator

According to the invention, a tandem alternator includes a rotary shaft, a first and a second field arranged in tandem on the rotary shaft, and a first and a second armature arranged in tandem in the axial direction of the rotary shaft. The first armature is provided on an outer periphery of the first field to constitute a first power generation unit. The second armature is provided on an outer periphery of the second field to constitute a second power generation unit. The first and second fields are arranged to abut each other in the axial direction of the rotary shaft, so as to minimize the axial length of the alternator. The first and second fields are configured to respectively create a first and a second magnetomotive force whose directions are opposite to each other, so as to minimize magnetic leakage between the first and second power generation units.

Owner:DENSO CORP

Methods for stabilizing bone using spinal fixation devices

InactiveUS20080132953A1Width minimizedAvoid excessive widthSuture equipmentsInternal osteosythesisCouplingBiomedical engineering

A method of stabilizing bone, such as a spine, includes providing a coupling element having first and second sections that are angled relative to one another, the coupling element having rod receiving openings for securing an elongated member such as an orthopedic rod, and assembling the coupling element with an anchoring element. The method includes securing the anchoring element in bone, moving the coupling element relative to the anchoring element to align the rod receiving openings with the orthopedic rod, securing the orthopedic rod in the rod receiving openings, and after the securing step, locking the coupling element from further movement relative to the anchoring element.

Owner:STRYKER EURO OPERATIONS HLDG LLC

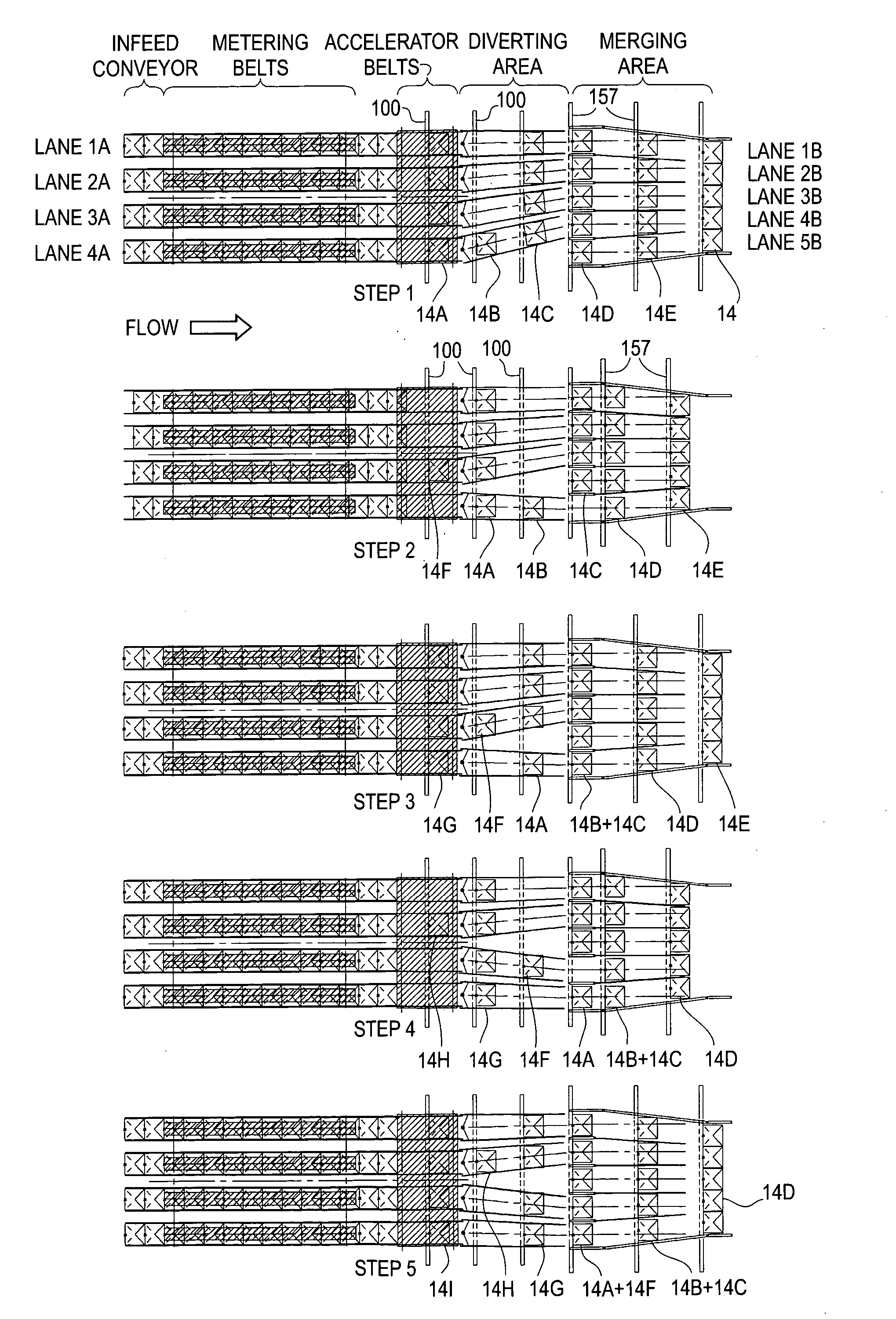

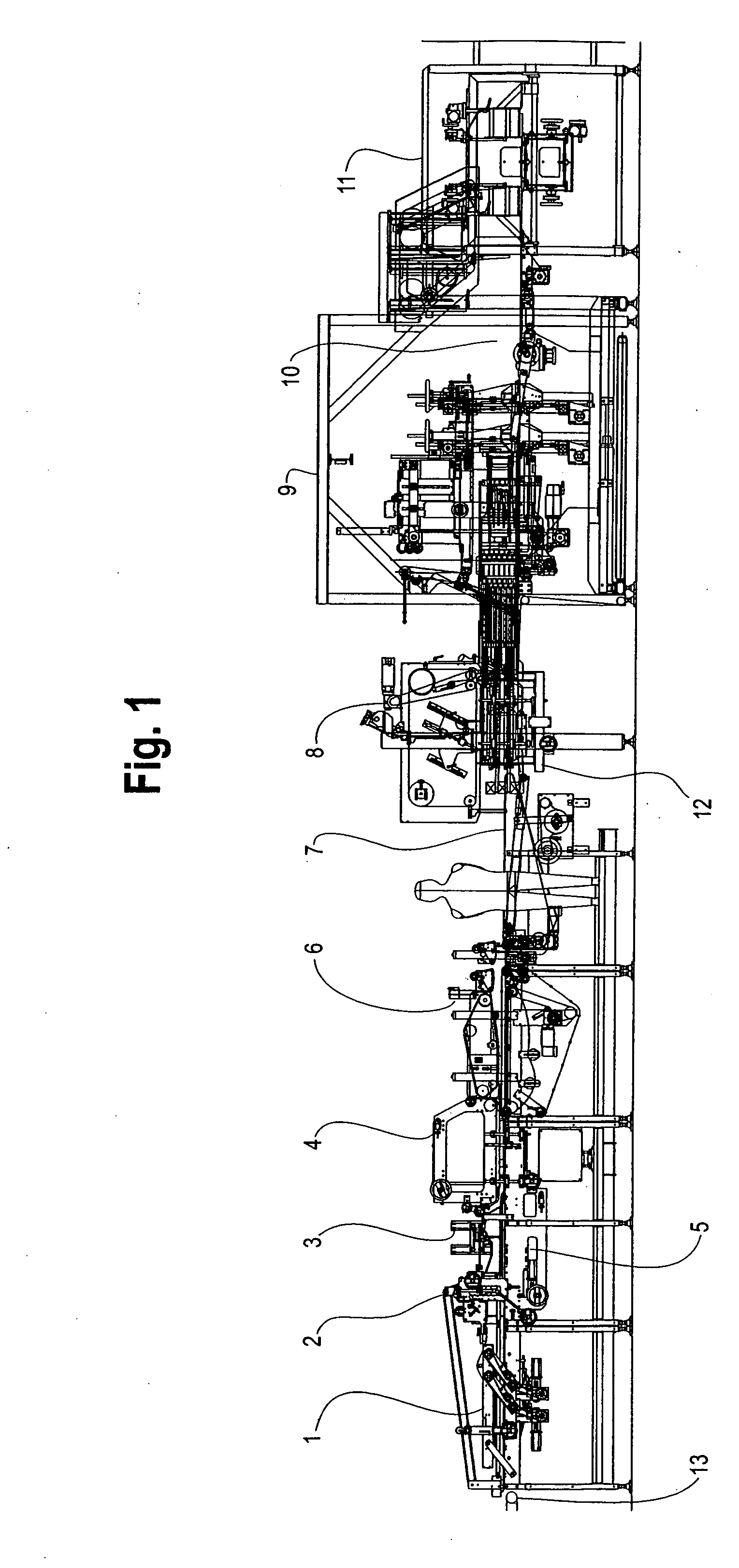

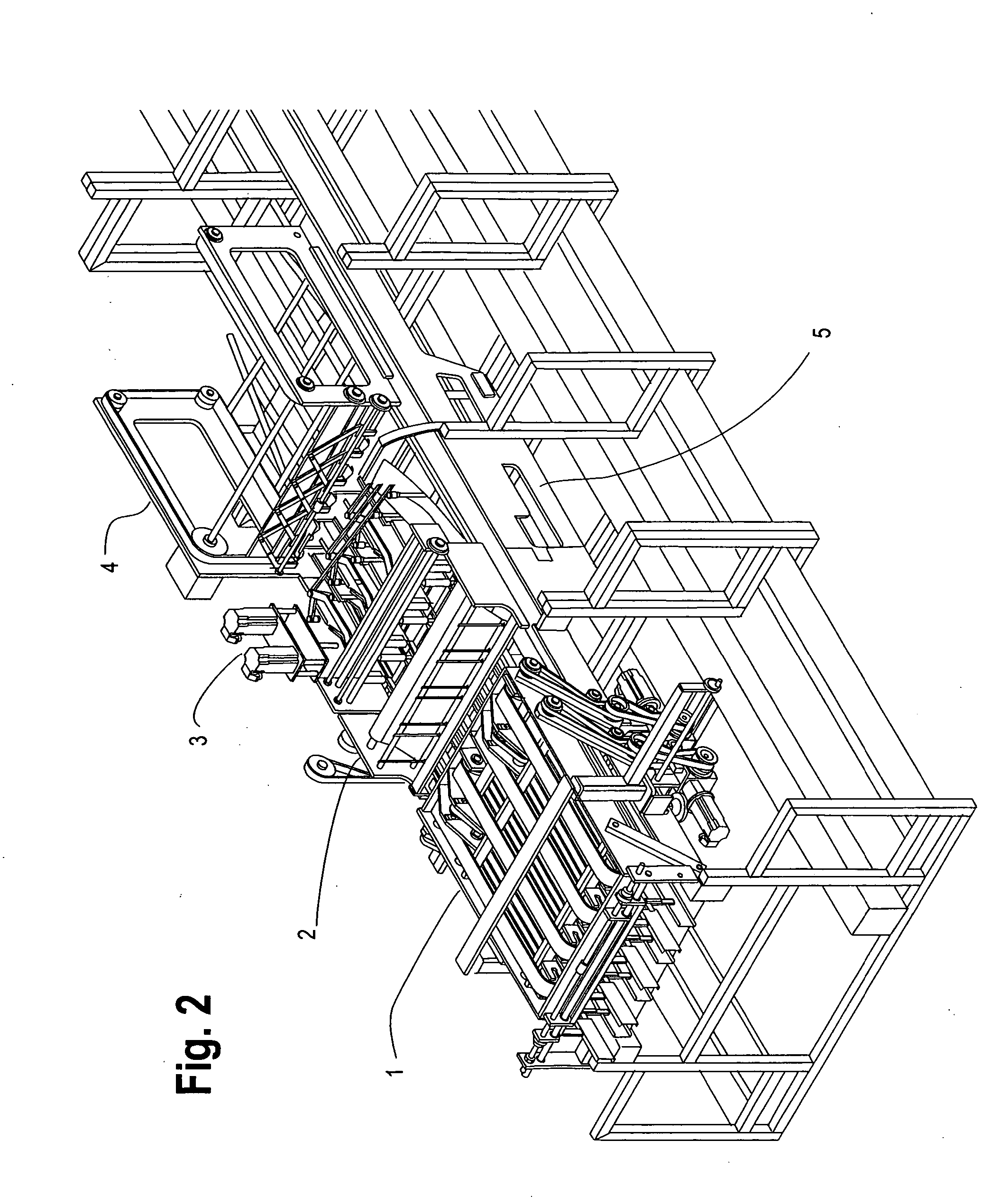

Product diverter and method

A wrapping machine for wrapping products is provided with a product diverter for producing package formats which are greater in width than the number of lanes which deliver product to the wrapper machine. A plurality of metering belts advance product from an infeed conveyor along a plurality of infeed lanes. The metering belts are independently driven so that product can be advanced in each lane independently of the product in the other lanes. The metering belts deliver product to accelerator belts which speed up the product to create a gap between successive products in a lane. A first flighted conveyor advances product from the accelerator belts to a plurality of pivotally mounted diverting gates, corresponding in number to the number of infeed lanes. Each of the diverting gates direct the product to one of a plurality of output lanes. The number of output lanes is equal to, less than, or greater than the number of infeed lanes. The diverting gates are independently controlled so that each diverting gate can be pivoted independently of the other gates. A second flighted conveyor advances product from the discharge end of the diverter gates along the output lanes.

Owner:PAPER CONVERTING MASCH CO INC

Folding bicycle

InactiveUS7591473B2Avoid excessive widthAvoid excessive heightFoot-driven leversWheel based transmissionShaped beamAcute angle

The present invention discloses a folding bicycle, wherein a folding joint is installed on the beam, and the rear fork is hinged with the frame via a hinge axle, on the rear fork is installed a support bar which rests against the frame; and wherein the beam is S-shaped, and the hinge axle is tilted by an acute angle with respect to the central axle of the frame. When the bicycle is folded, the front and rear wheels are located separately, each at one side of the beam and within the concave section of the S-shaped beam, so that the bicycle is more compact and has a less width after being folded.

Owner:TAK WEI HON DAVID

Vibration-damping receiving element

InactiveUS20070001522A1Large freedom of motionIncrease dampingPortable framesNon-rotating vibration suppressionEngineeringSupport surface

The present invention relates to a device for the elastic, vibration-damping accommodation of an assembly with respect to a mounting fixed to a frame, having at least one elastic element that is situated between the assembly and the mounting that is fixed to the frame, the assembly having at least one first support surface, and the mounting having at least one second support surface, and the two support surfaces face each other and run transversely, especially at right angles, to the vibrational plane of the vibration and, as seen in the direction of vibration, the elastic element lies in an overlapping position to the support surfaces. It is provided that the two support surfaces have a lateral clearance from each other, and that the first elastic element bridges the clearance in the form of a first free bridge.

Owner:NITZSCHE HARTMUT

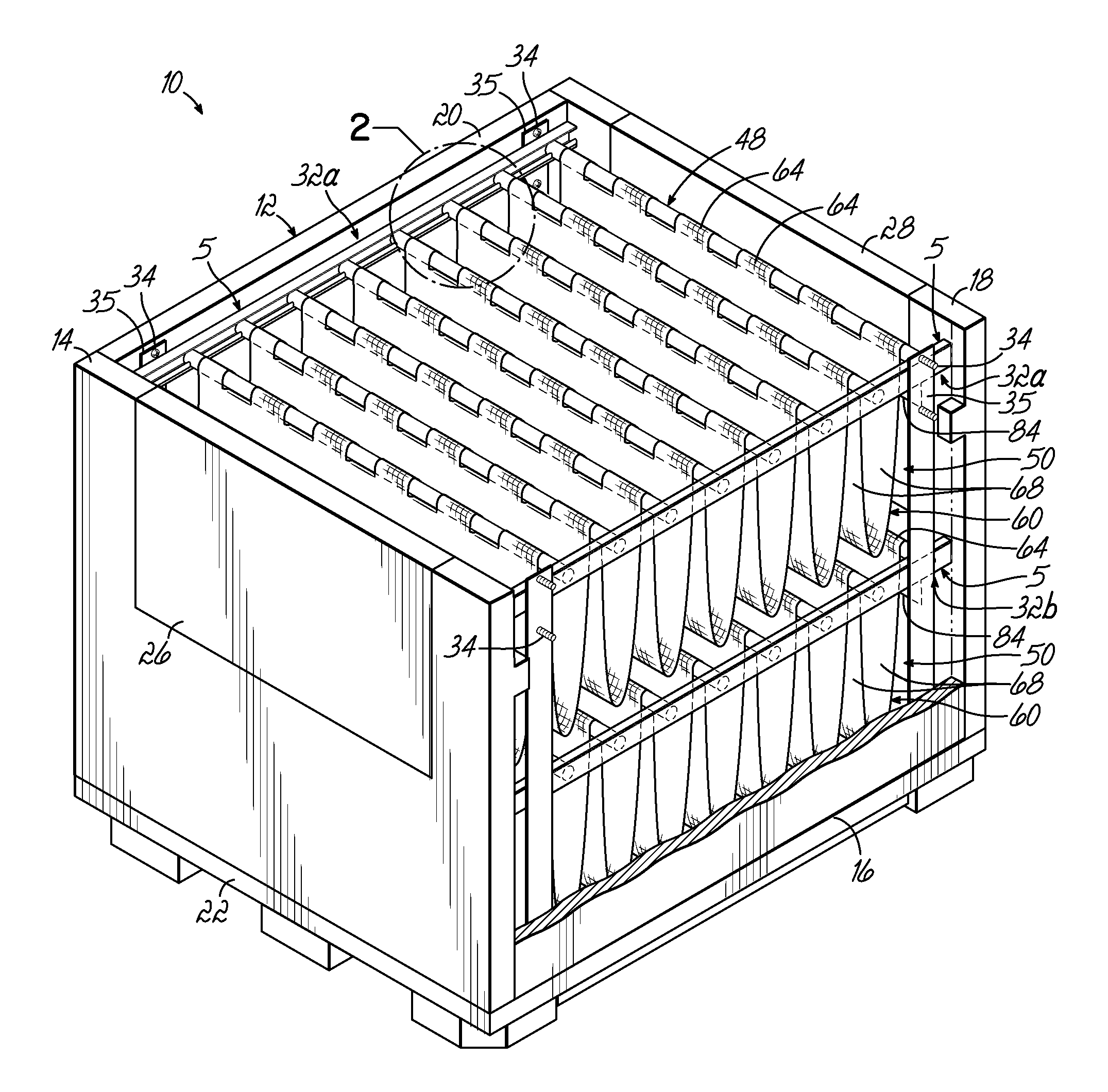

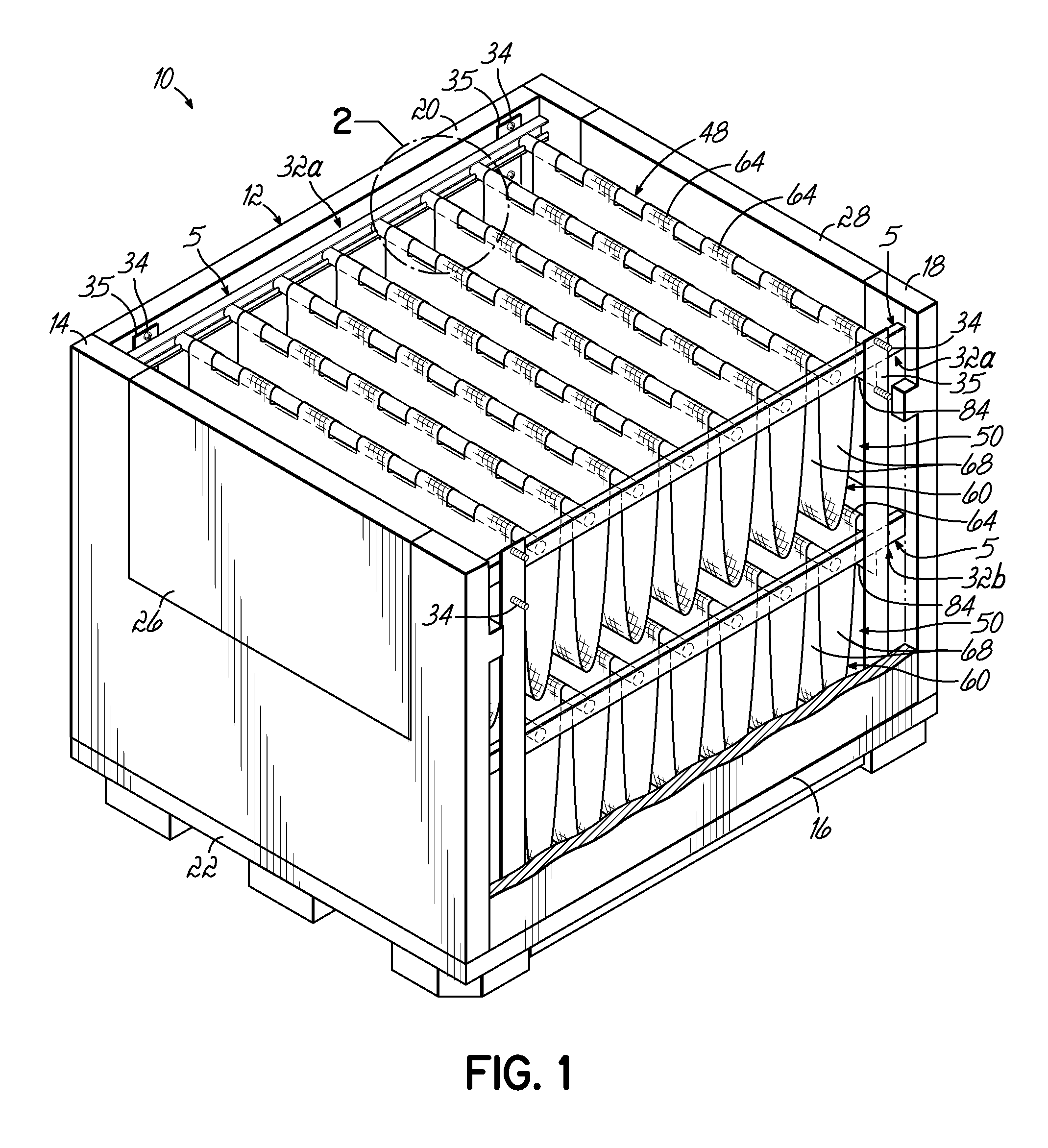

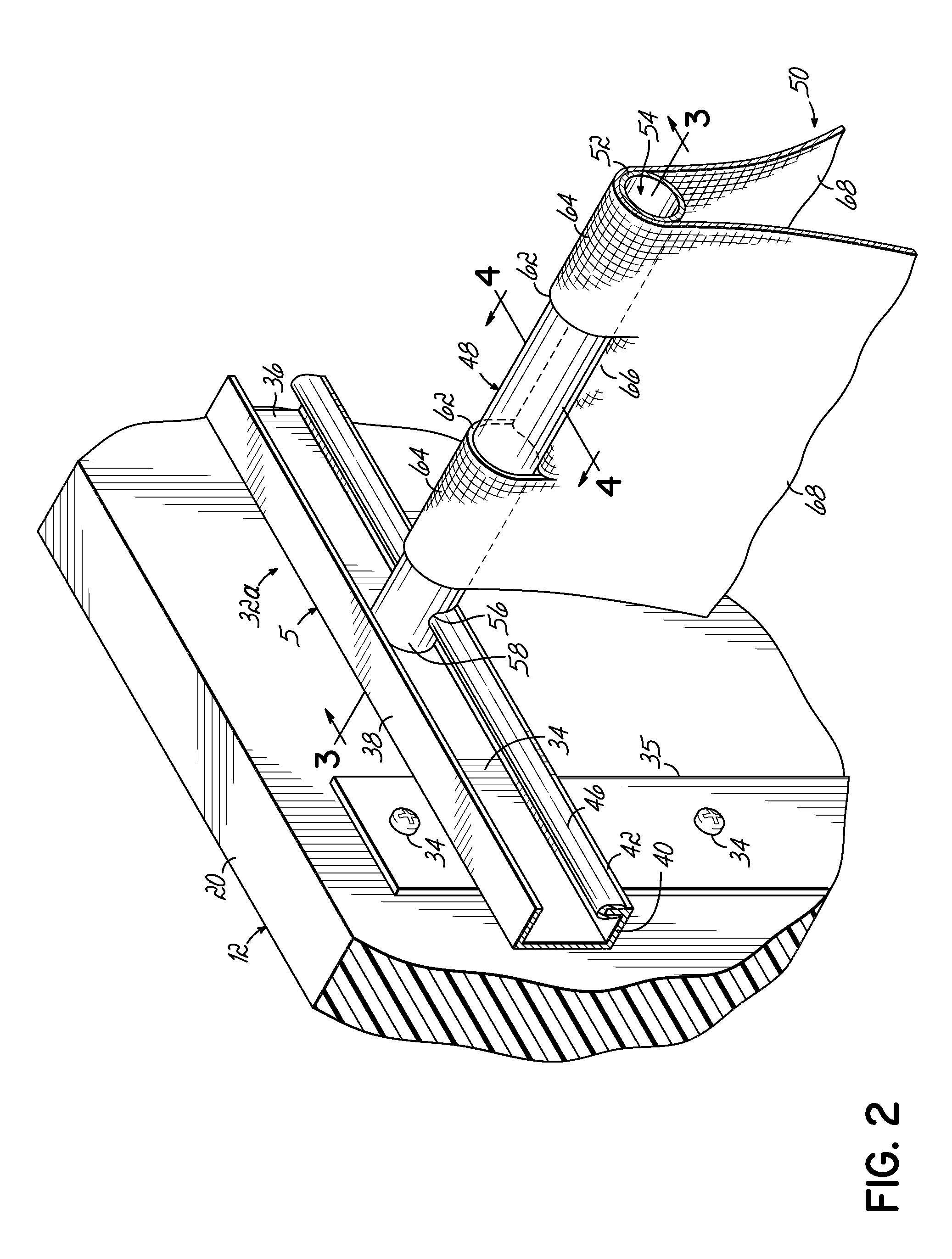

Container Having Sliding Support Assemblies For Supporting Dunnage

ActiveUS20130175912A1Avoid excessive widthIncrease the number ofPackaging vehiclesContainers for machinesMoving partsEngineering

A container for holding product therein during shipment and being returned for reuse has a body, track assemblies attached to opposite sides of the body, and a plurality of support assemblies extending between the track assemblies. Outer members of the support assemblies have notches which enable the support assemblies to slide along the track assemblies to move parts supported by dunnage suspended by the support assemblies.

Owner:BRADFORD CO

IGBT or like semiconductor device of high voltage-withstanding capability

ActiveUS7304356B2High voltageLeakage currentTransistorSolid-state devicesP–n junctionDielectric layer

A multiple-cell insulated-gate-bipolar-transistor chip is disclosed which includes a semiconductor substrate having formed therein a p+-type collector region and an n−-type base region, with a pn junction therebetween. An annular trench is etched in the substrate so as to surround the array of IGBT cells. Received in the trench are a dielectric layer which is held against the base region, and an electroconductive layer which is held against the base region via the dielectric layer and which is electrically coupled to the collector region. When the pn junction between the collector and base regions is reverse biased, the electroconductive layer creates at the annular periphery of the base region a depletion layer which is joined to a depletion layer created in the base region by the pn junction, thereby preventing current leakage from the side surfaces of the IGBT chip.

Owner:SANKEN ELECTRIC CO LTD

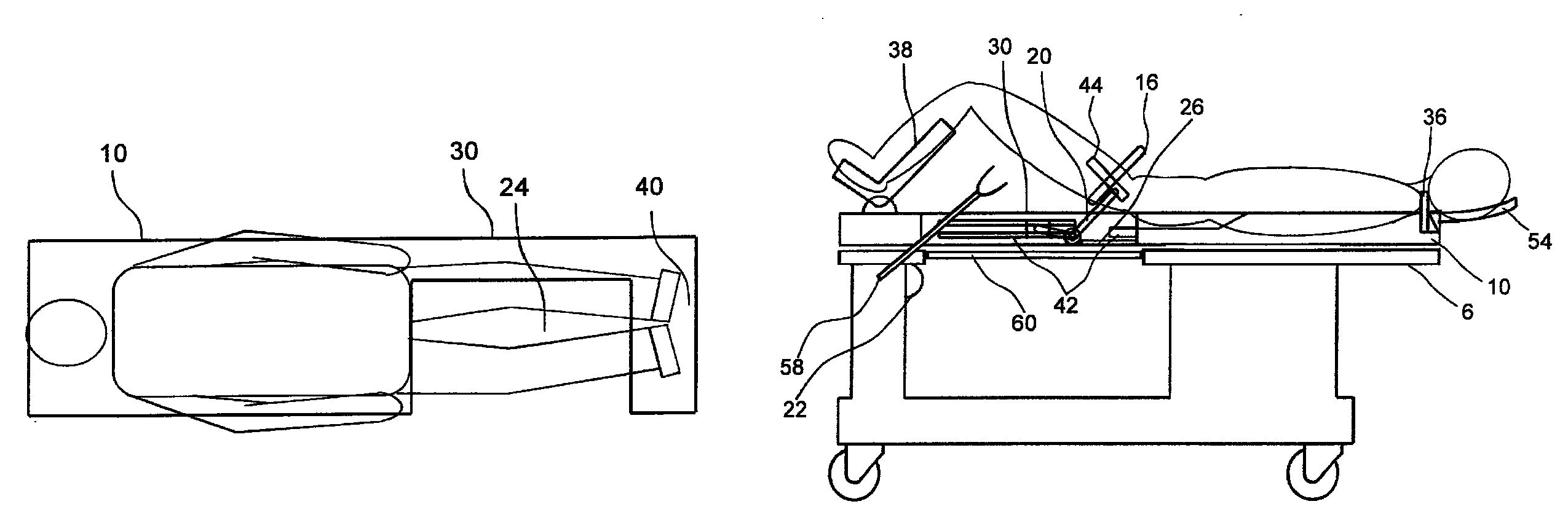

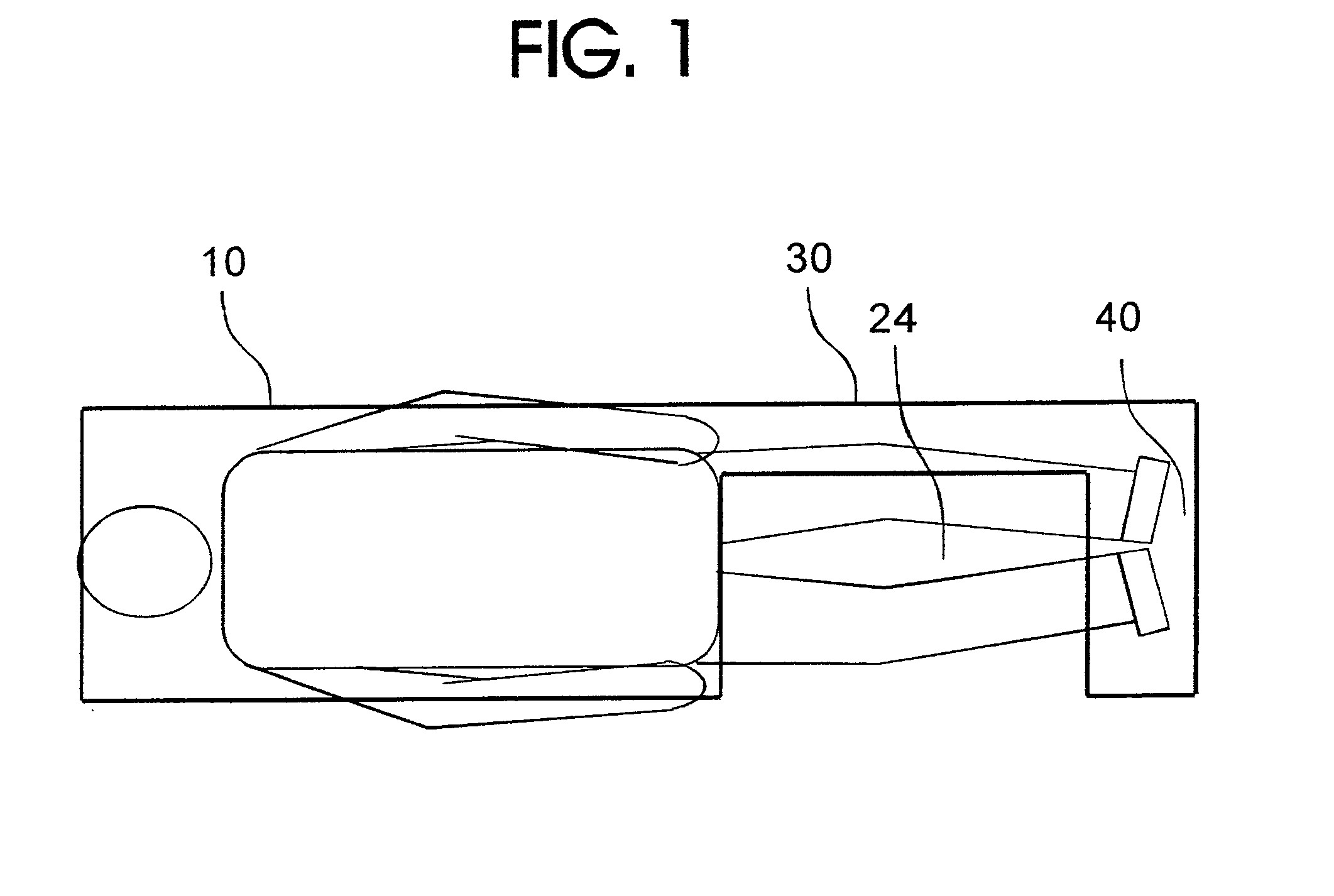

Supine patient support for medical imaging

ActiveUS7908690B2Reduce riskExpand accessMagnetic measurementsSurgical needlesPelvisMedical imaging technology

Owner:INVIVO CORP

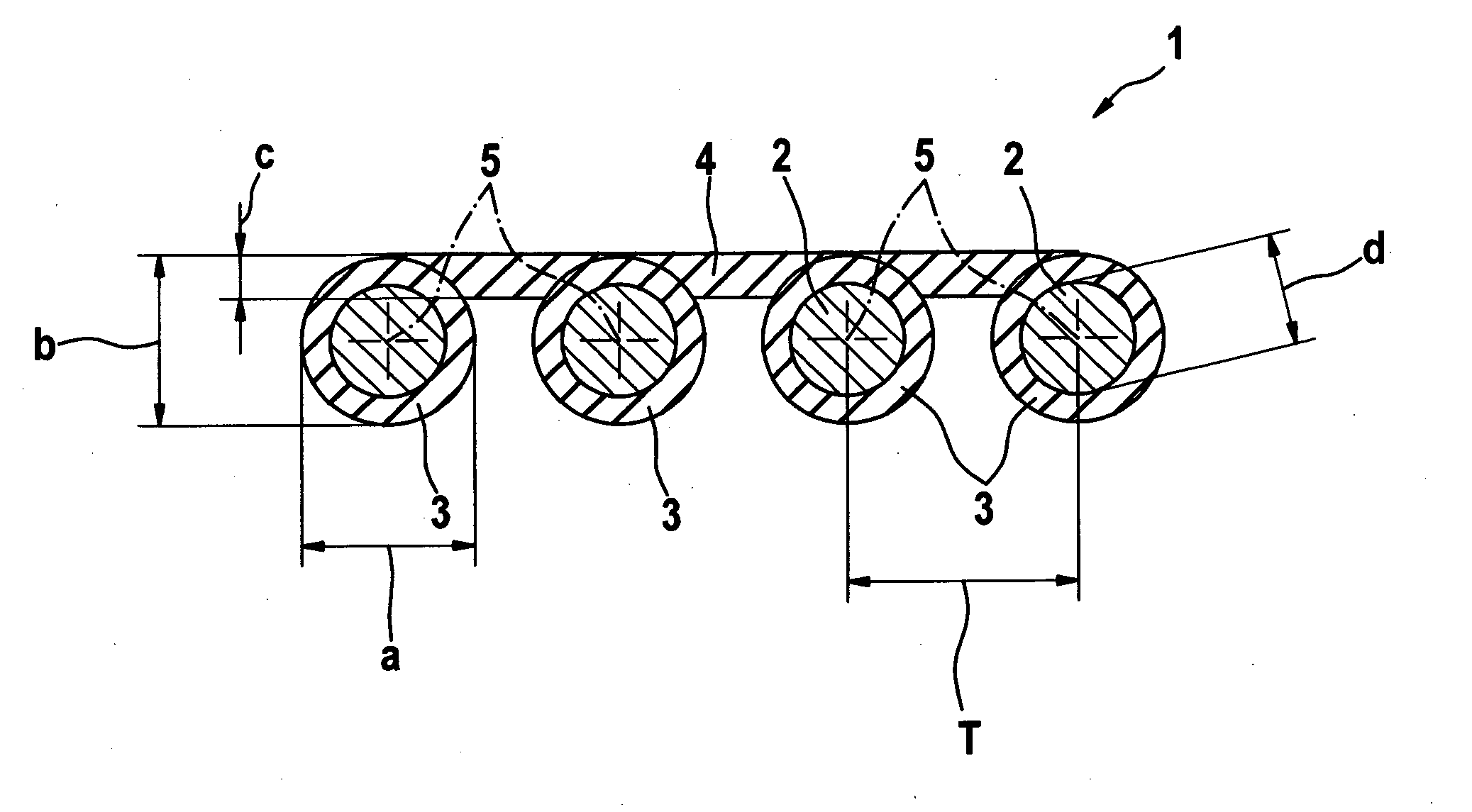

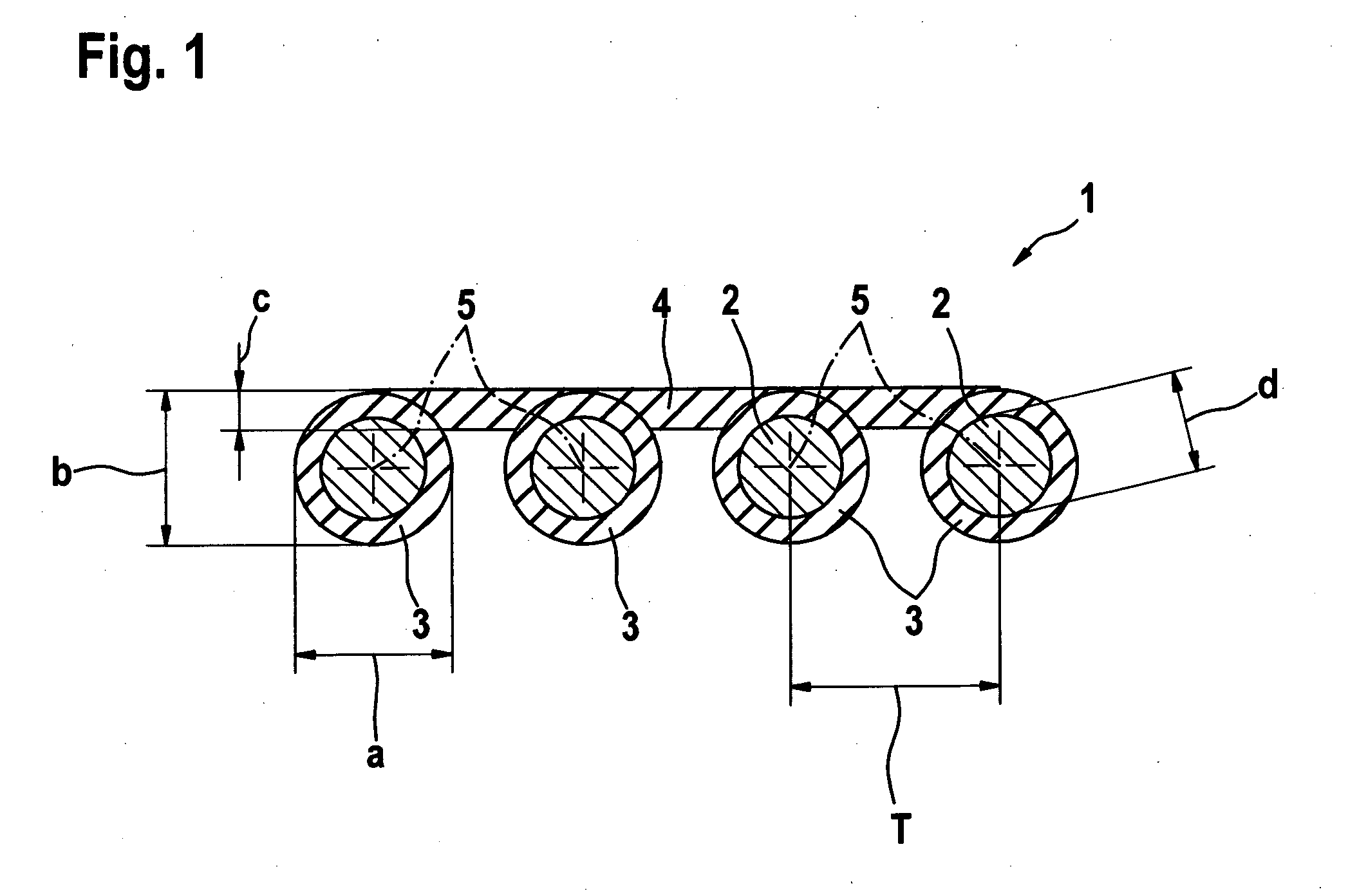

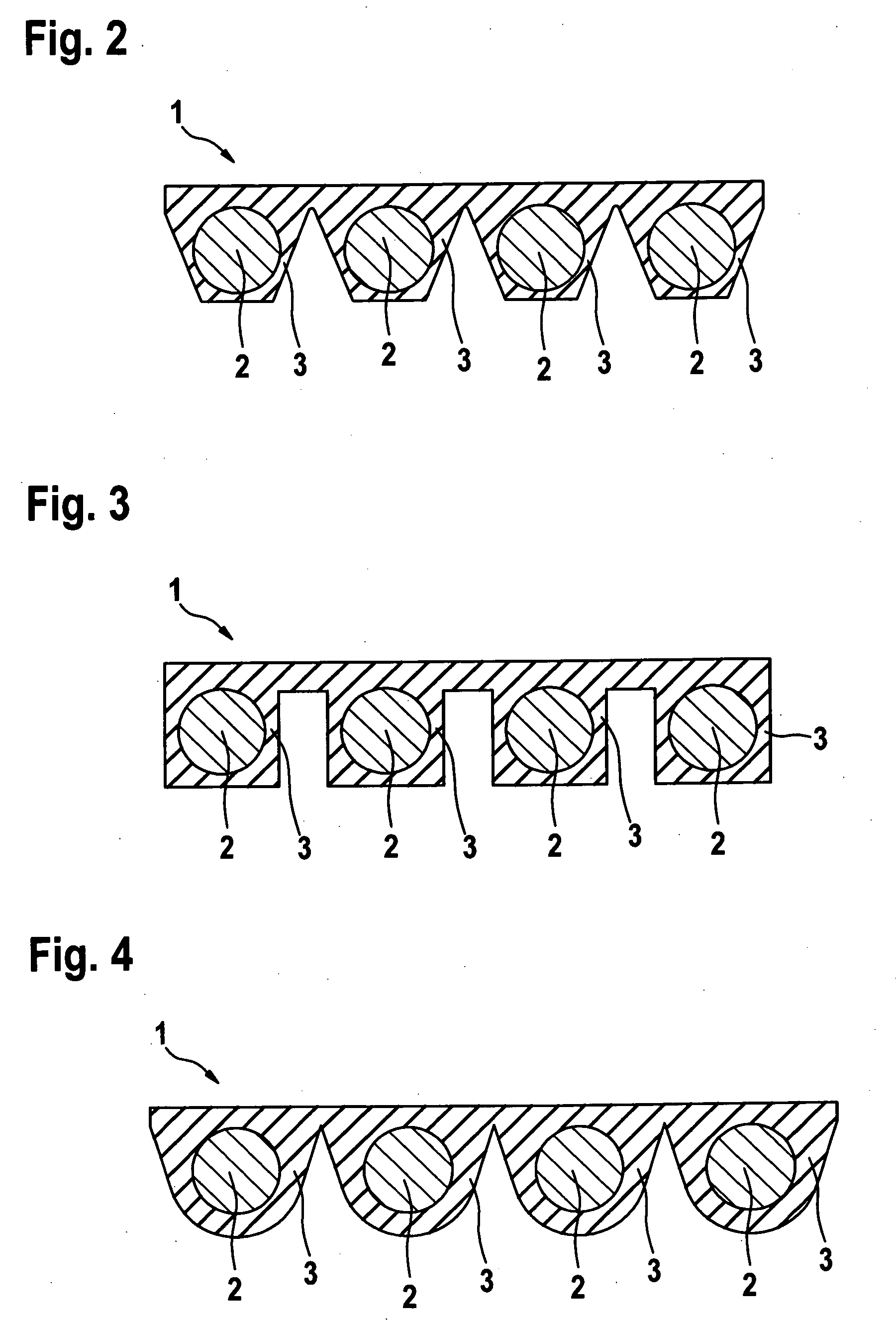

Traction device

ActiveUS20100044158A1Easy to operateAvoid excessive widthV-beltsRopes and cables for vehicles/pulleyElastomerElevator system

The invention relates to a traction device (1), especially for an elevator system. The traction device (1) is driveable by a traction sheave. The task which is the basis of the invention is to provide a traction device which is simple to manipulate. High tension forces are transferable and the traction device makes possible a drive unit of lesser width compared to the known belt technology. For this purpose, the traction device is configured as a composite rope (1) wherein individual tension carriers (2, 3) are connected to each other via a one-sided elastomer connecting layer (4). The individual tension carriers (2, 3) lie in parallel and are jacketed with elastomeric material. The tension carriers (2, 3) engage in corresponding grooves (13) of the traction sheave (10). The tension carriers (2, 3) engage in the grooves (13) of the traction sheave (10) with at least 25% of their total diameter.

Owner:CONTITECH ANTRIEBSSYST

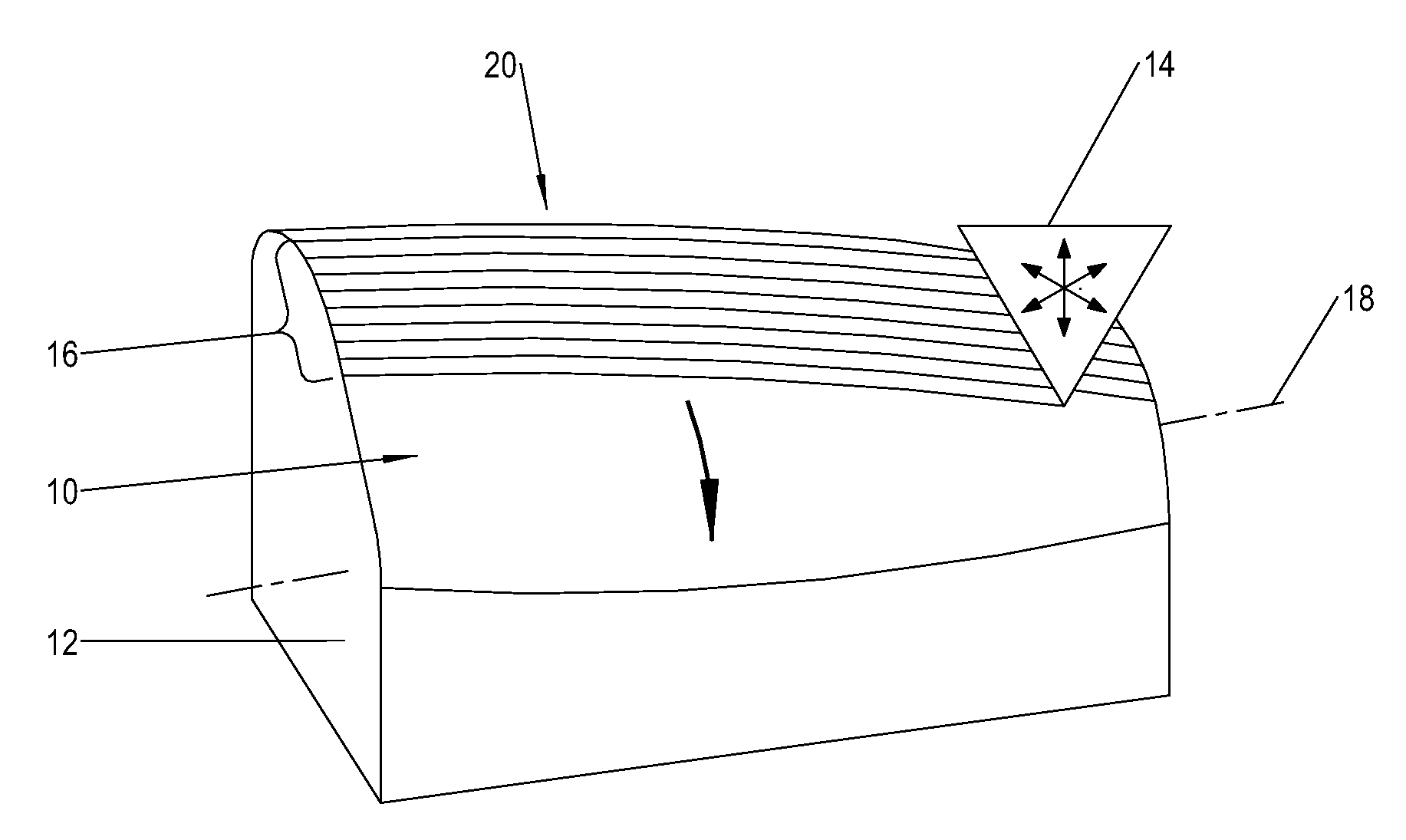

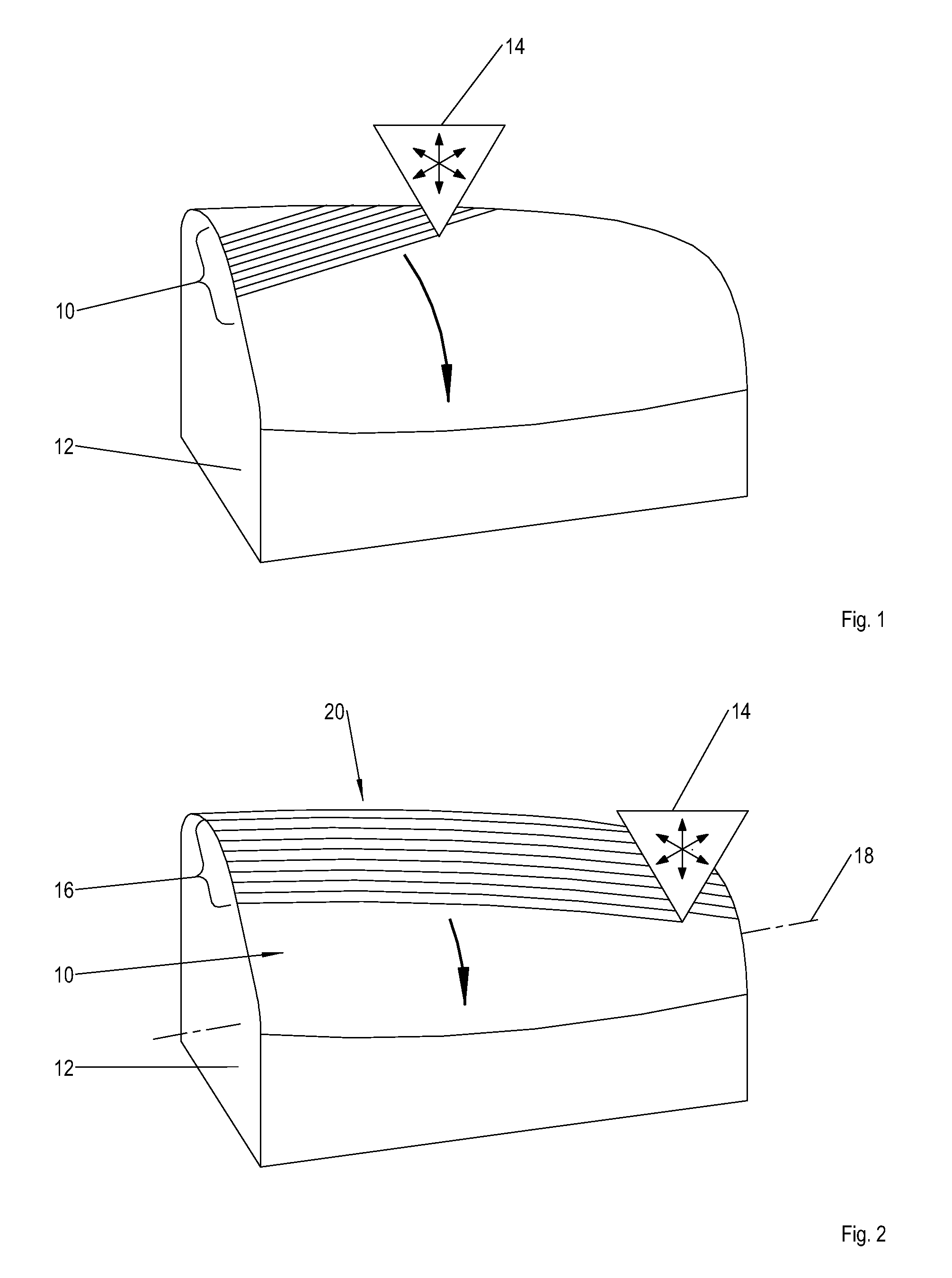

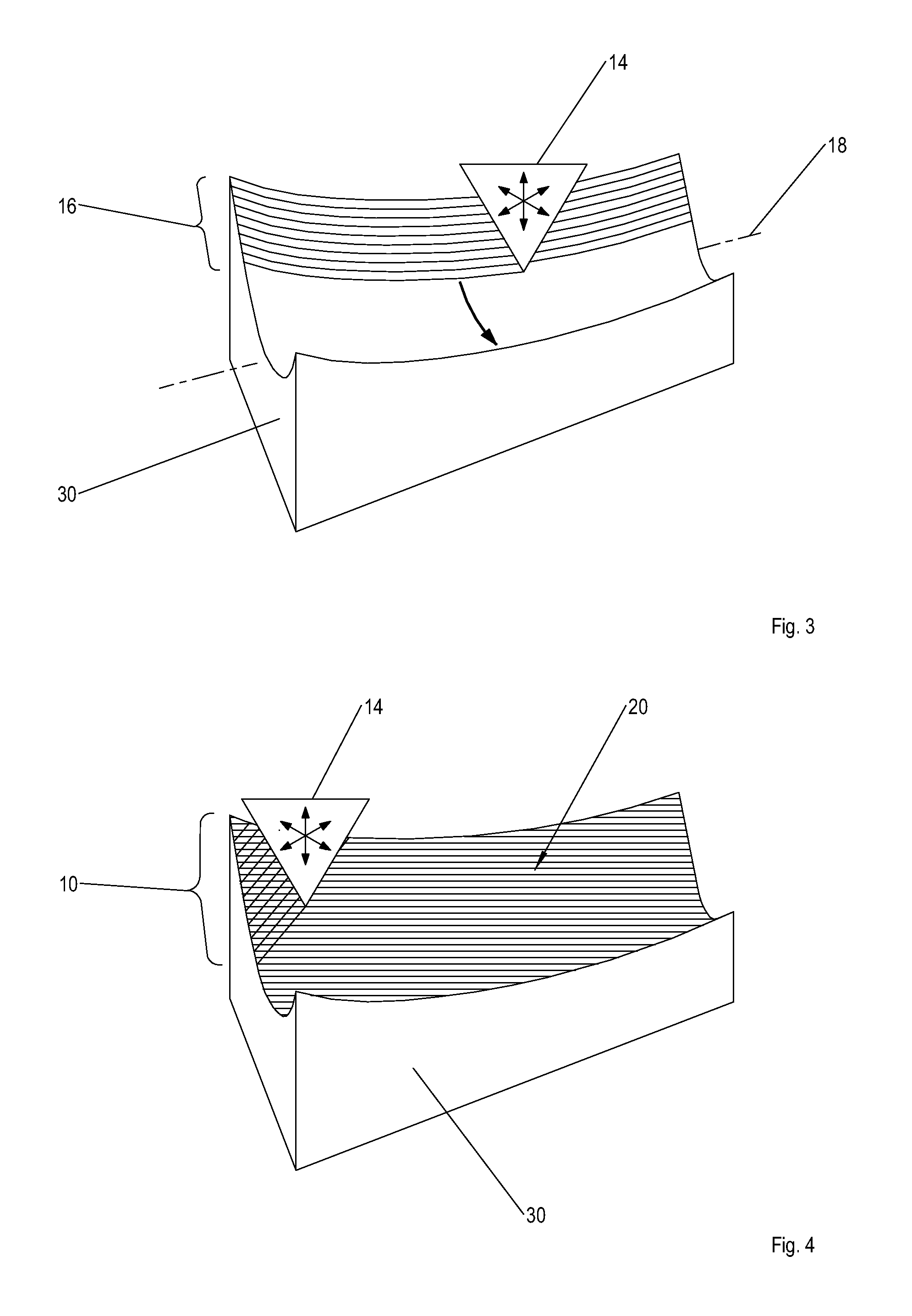

Method for the automated manufacture of a fibre composite component with integrated lightning protection, and also a fibre composite component

InactiveUS20130118770A1Highly effectiveLarge widthInstallation of lighting conductorsEfficient propulsion technologiesBand shapeFibrous composites

A method for manufacturing a fiber composite plastic component with integrated lightning protection. The steps include, for a positive mold, automatically laying down a ribbon-form pre-preg material or dry ribbon-form reinforcing fiber strands onto the mold. Then, automatically laying down a ribbon-form lightning protection material onto the pre-preg material or the reinforcing fiber strands. For a negative mold, the steps include automatically laying down the lightning protection material on the negative mold, then automatically laying down the pre-preg material or the dry reinforcing fiber strands onto the positioned lightning protection material. The method also includes curing the laminate construction formed with the pre-preg material and the lightning protection material to form the fiber composite component, or infiltrating the dry reinforcing fiber strands with a plastic, and subsequently curing the laminate construction formed with the infiltrated reinforcing fiber strands and the lightning protection material to form the fiber composite component.

Owner:AIRBUS OPERATIONS GMBH

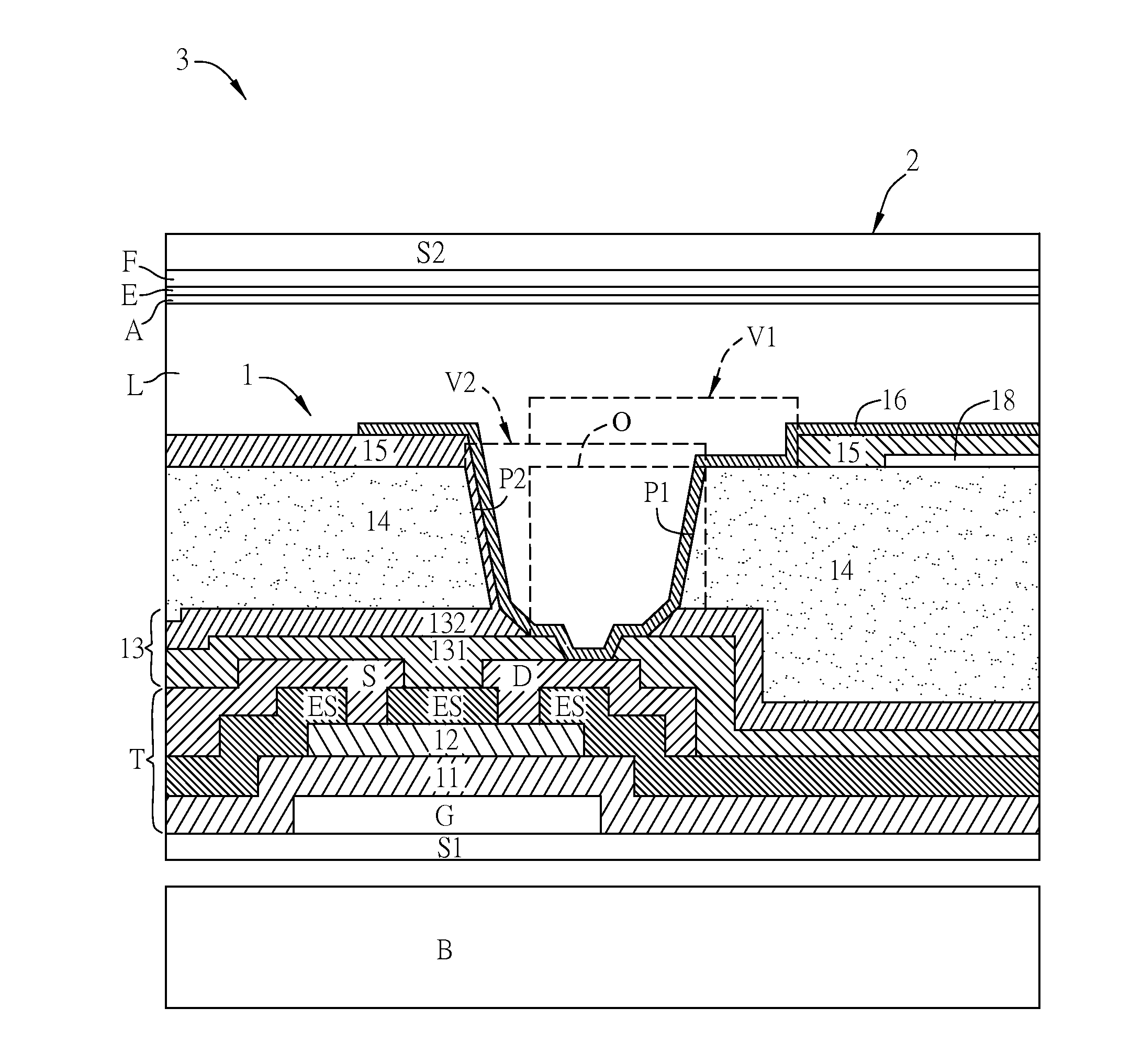

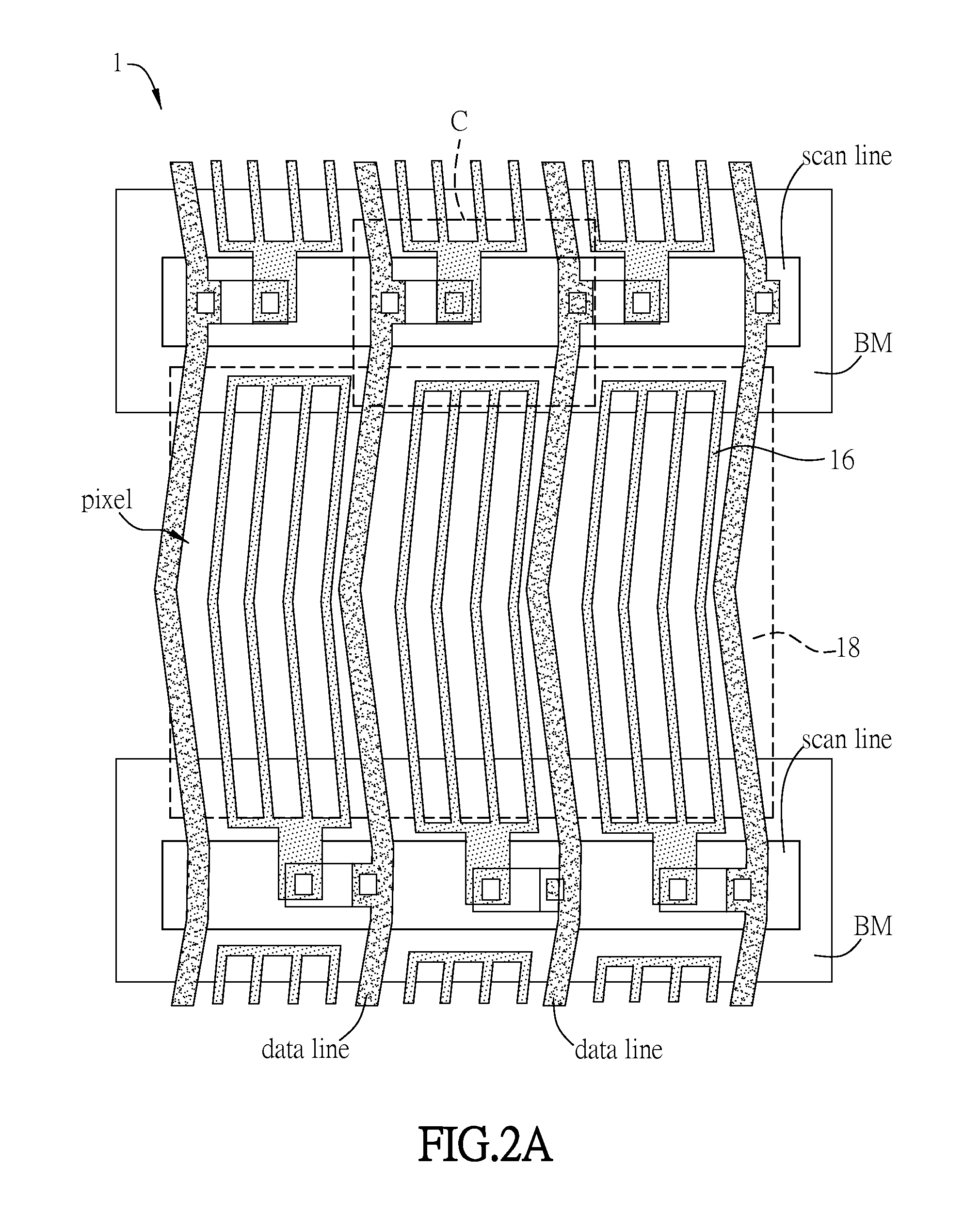

Display panel and display device

ActiveUS20150243684A1Improve efficiencyAffects display qualityTransistorSolid-state devicesDisplay deviceMaterials science

A display panel includes a TFT substrate, an opposite substrate and a display layer. A TFT of the TFT substrate has a drain. A first insulating layer has a first sub-layer and a second sub-layer disposed on the drain sequentially. The first sub-layer has a first opening with a first width. The second sub-layer has a second opening with a second width on the first opening. The first and second openings form a first via, and the second width is greater than the first width. A passivation layer is disposed on the first insulating layer. A second insulating layer is disposed on the passivation layer. A pixel electrode layer is disposed on the second insulating layer and disposed in the first via to connect the drain. The display layer is disposed between the TFT substrate and the opposite substrate.

Owner:INNOLUX CORP

Automotive tandem alternator having reduced axial length and capable of effectively suppressing magnetic leakage

InactiveUS20070241633A1Reduce widthShorten lengthSynchronous generatorsMagnetic circuit rotating partsMagnetomotive forceAxial length

According to the invention, a tandem alternator includes a rotary shaft, a first and a second field arranged in tandem on the rotary shaft, and a first and a second armature arranged in tandem in the axial direction of the rotary shaft. The first armature is provided on an outer periphery of the first field to constitute a first power generation unit. The second armature is provided on an outer periphery of the second field to constitute a second power generation unit. The first and second fields are arranged to abut each other in the axial direction of the rotary shaft, so as to minimize the axial length of the alternator. The first and second fields are configured to respectively create a first and a second magnetomotive force whose directions are opposite to each other, so as to minimize magnetic leakage between the first and second power generation units.

Owner:DENSO CORP

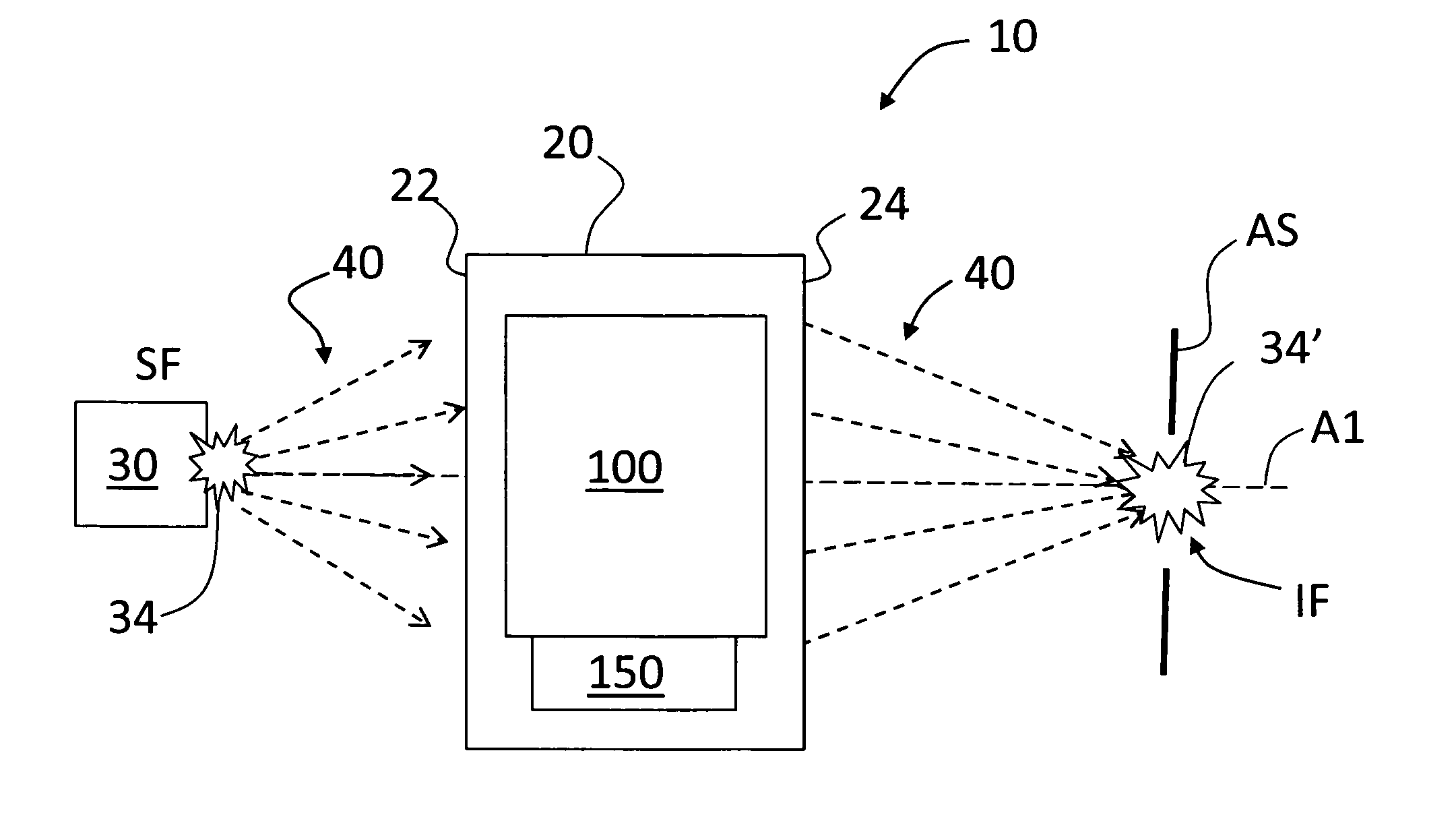

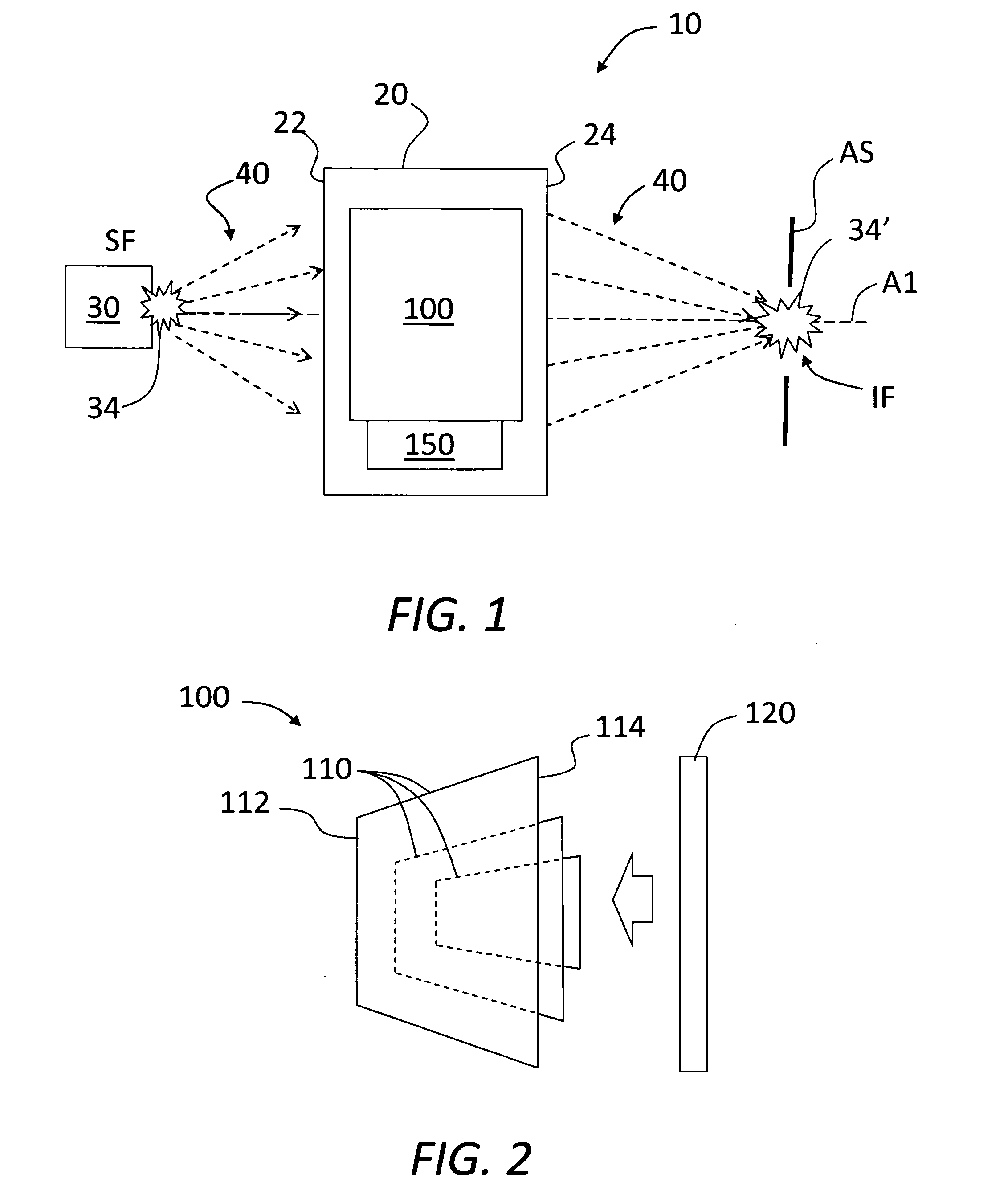

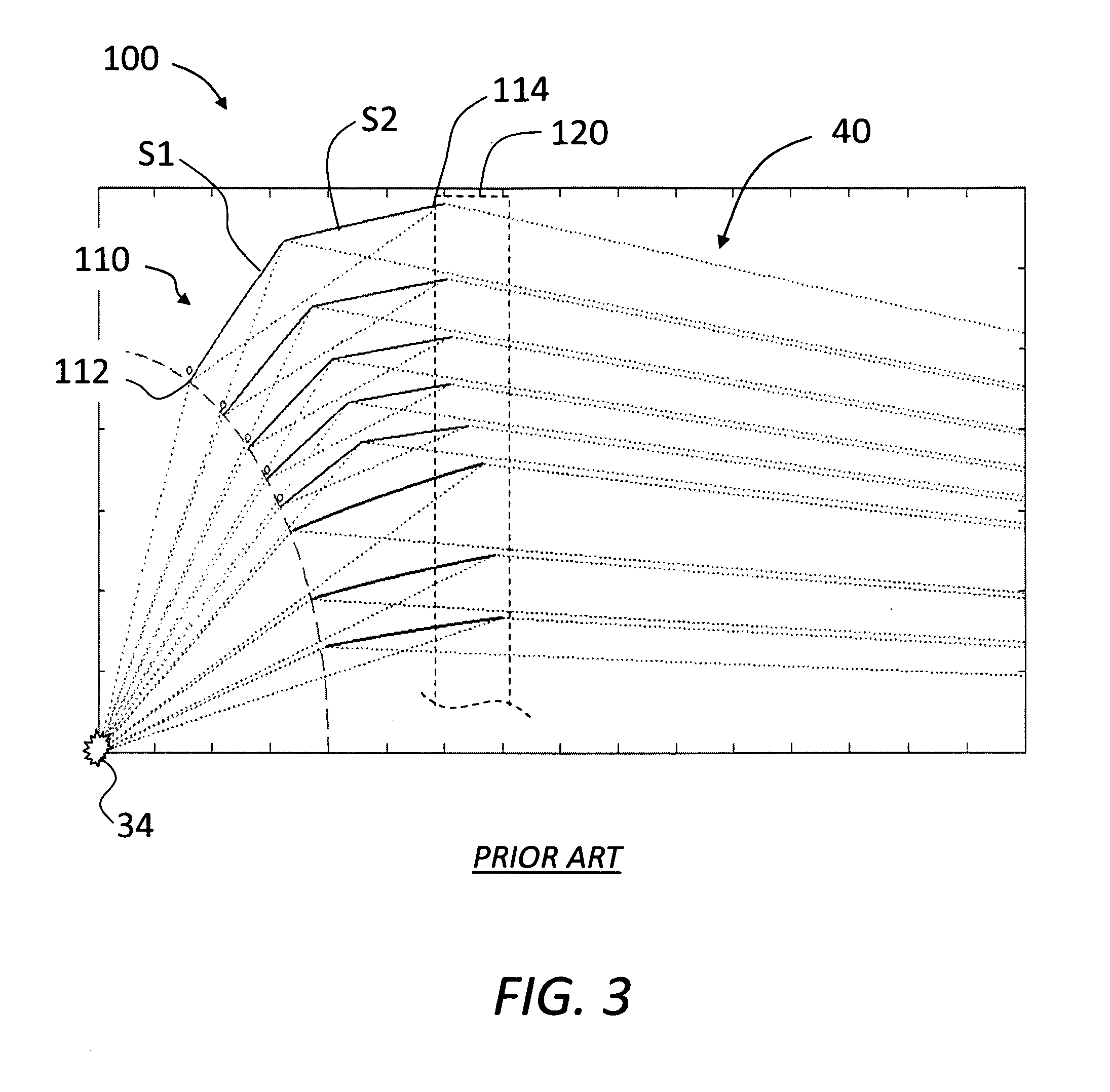

Evaporative thermal management of grazing incidence collectors for EUV lithography

ActiveUS20120281189A1Minimize thermal distortionUniform temperature distributionRadiation/particle handlingPhotomechanical apparatusThermal management systemEngineering

Evaporate thermal management systems for and methods of grazing incidence collectors (GICs) for extreme ultraviolet (EUV) lithography include a GIC shell interfaced with a jacket to form a structure having a leading end and that defines a chamber. The chamber operably supports at least one wicking layer. A conduit connects the wicking layer to a condenser system that support cooling fluid in a reservoir. When heat is applied to the leading end, the cooling fluid is drawn into the chamber from the condenser unit via capillary action in the wicking layer and an optional gravity assist, while vapor is drawn in the opposite direction from the chamber to the condenser unit. Heat is removed from the condensed vapor at the condenser unit, thereby cooling the GIC mirror shell.

Owner:MEDIA LARIO SRL

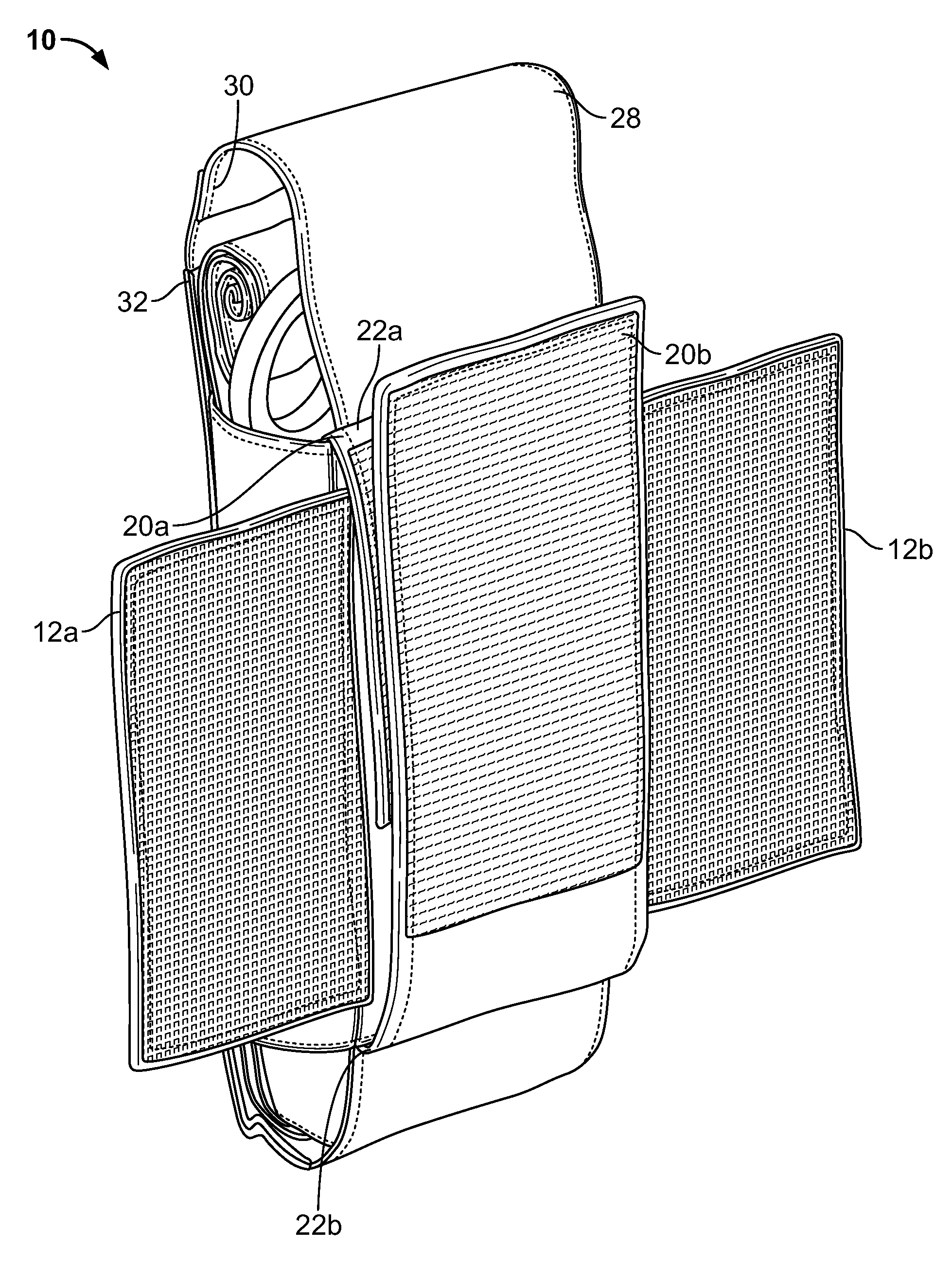

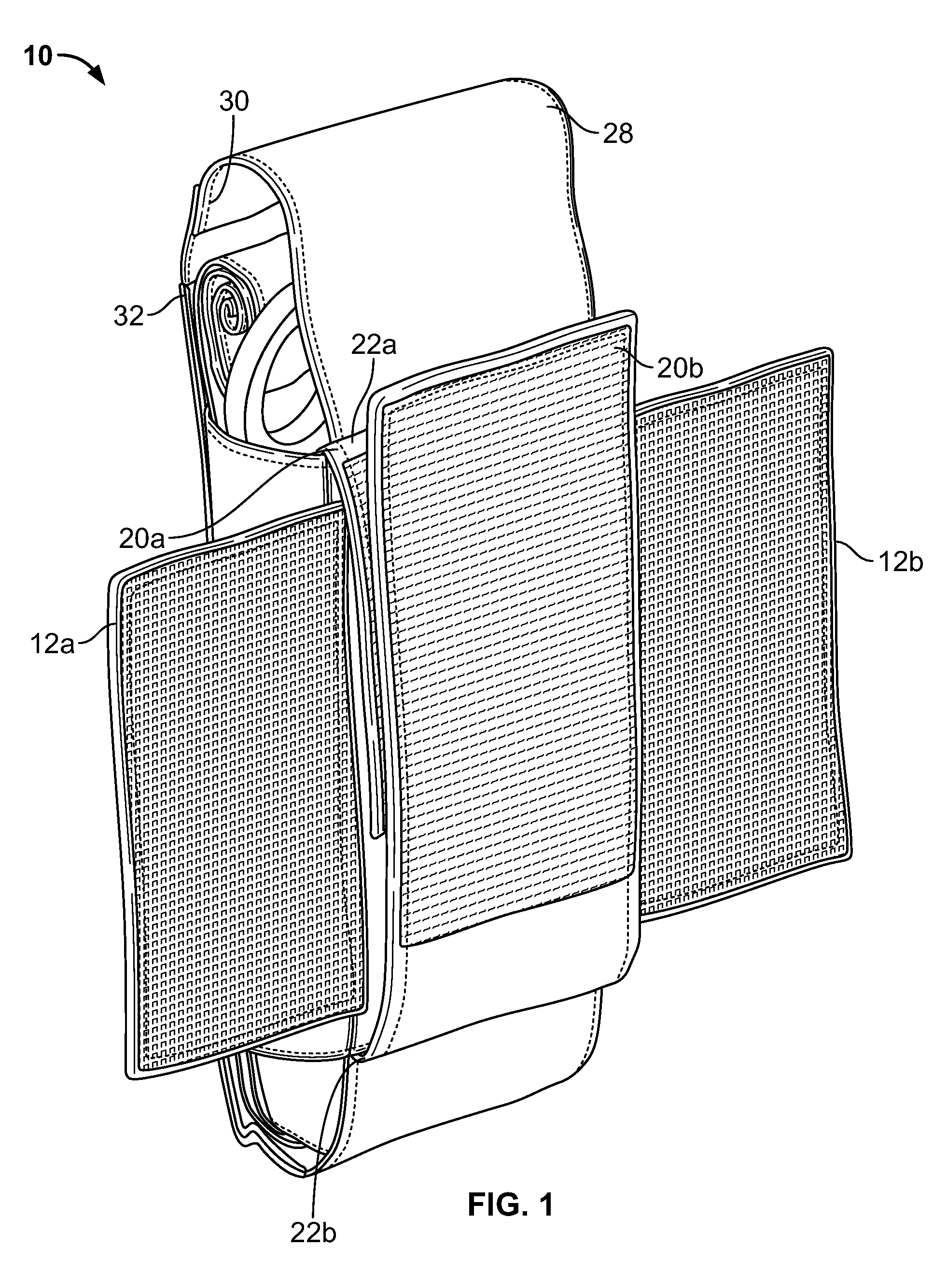

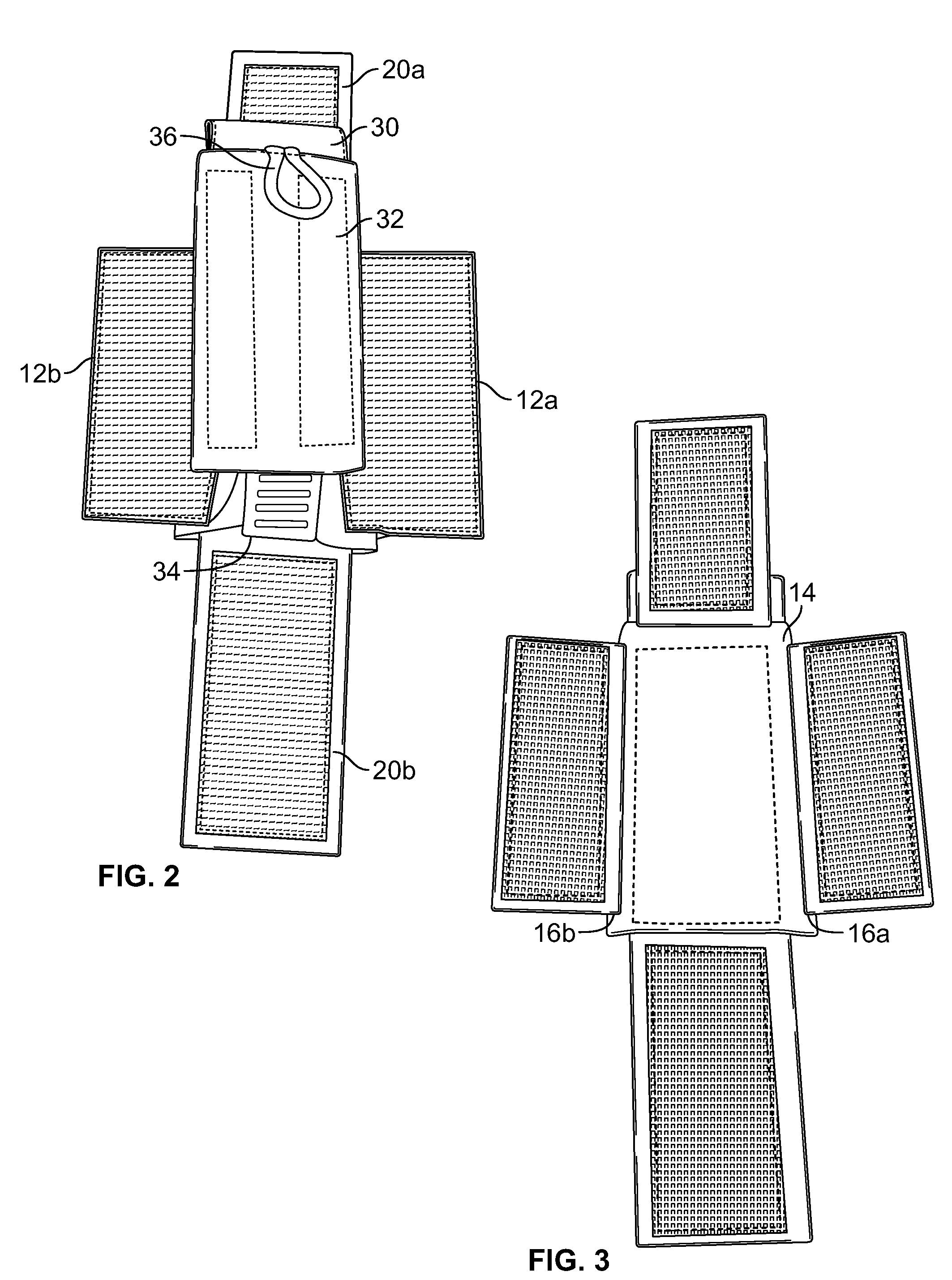

Tourniquet Holster

The present invention is related to a removably attachable tourniquet holster comprising: wings hingeably attached to a back panel wherein the wings can be folded inward and removably attached to each other to define a slot for receiving a strap attached to an article; side support wings hingeably attached to the back panel; and, a front panel removably attached to the side support wings to define a tourniquet compartment for receiving a tourniquet. The tourniquet allows for a single handed opening of the tourniquet to reveal the tourniquet compartment allowing one handed retrieval of a tourniquet form the tourniquet holster. The tourniquet can be attached in a manner so as to reduce the impact on the existing fasteners of the article for which tourniquet holster is attached.

Owner:NORTH AMERICAN RESCUE PRODS

Shipping and display container

A container and a blank for making it. The container is constructed from a single sheet of foldable material and has a bottom wall, a top wall, first and second front wall panels, a back wall, and side flaps extending from opposite ends of the bottom, top, and back walls, and from the first and second front wall panels. The top wall is secured to the container by a tear-out panel extending from the top wall into the back wall and by frangible side flap portions in the side walls, whereby the tear-out panel may be grasped and lifted to lift the top wall and break the frangible side flap portions, completely freeing the top wall from the container by the single step of grasping and tearing out and lifting the tear-out panel to pivot the top upwardly. A blank and method of assembling and erecting the blank to form the container also are disclosed.

Owner:INT PAPER CO

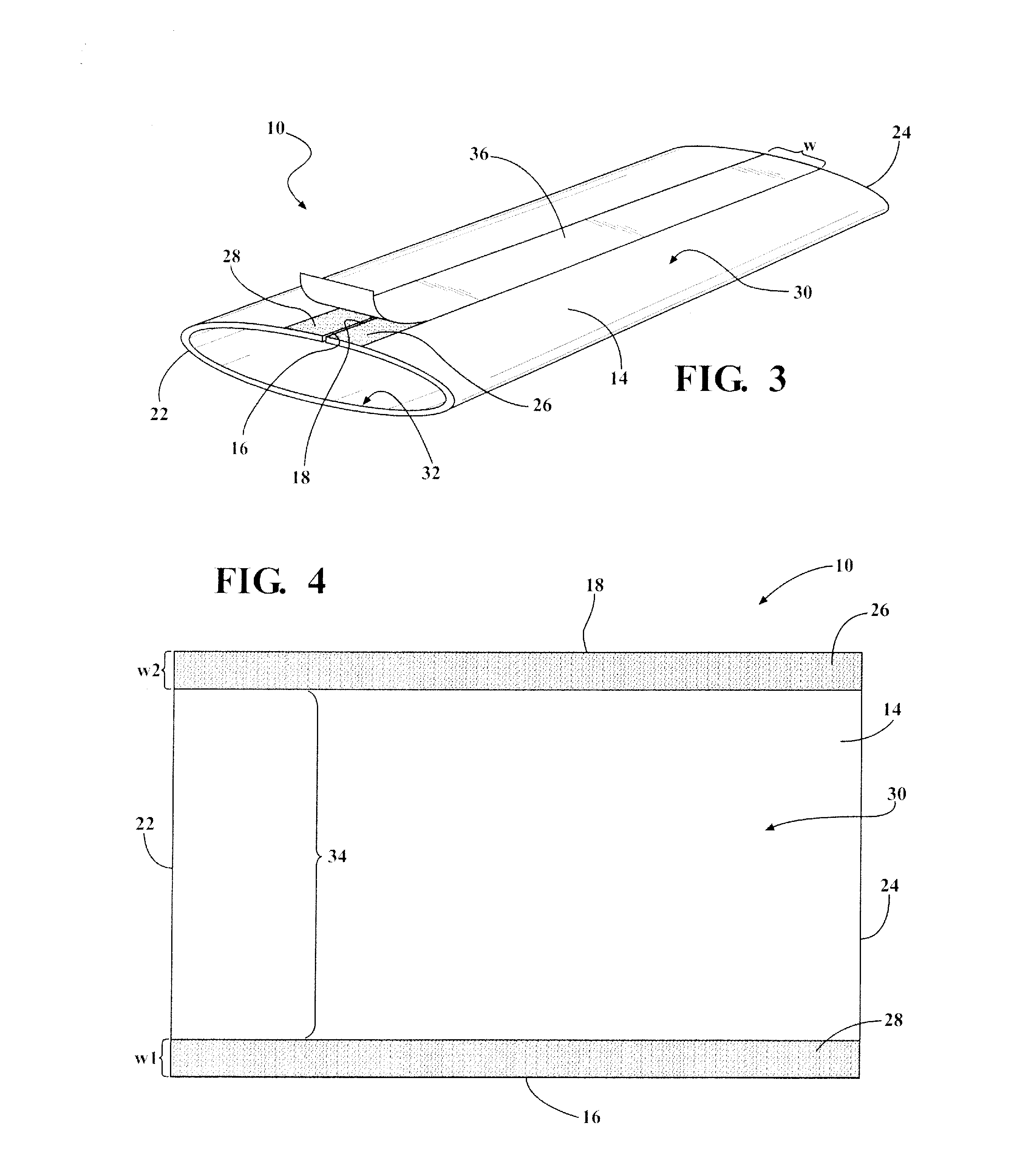

Wrappable Protective Sleeve With Closure And Locating Feature And Methods Of Construction And Use Thereof

ActiveUS20150027623A1Avoid excessive widthElectrical apparatusProtective equipmentEngineeringBuilding construction

A wrappable protective sleeve for providing protection to at least one elongate member contained therein and methods of construction and use thereof are provided. The sleeve includes a flexible textile wall having opposite inner and outer faces bounded by opposite edges and opposite ends. The opposite edges extend generally parallel to one another between the opposite ends. A pair of adhesive layers is bonded to the inner face, with each of the adhesive layers being spaced from one another. The adhesive layers extend between the opposite ends adjacent the opposite edges. Further, a release paper is releasably adhered to the pair of adhesive layers for subsequent removal and use of the sleeve.

Owner:FEDERAL MOGUL POWERTAIN LLC

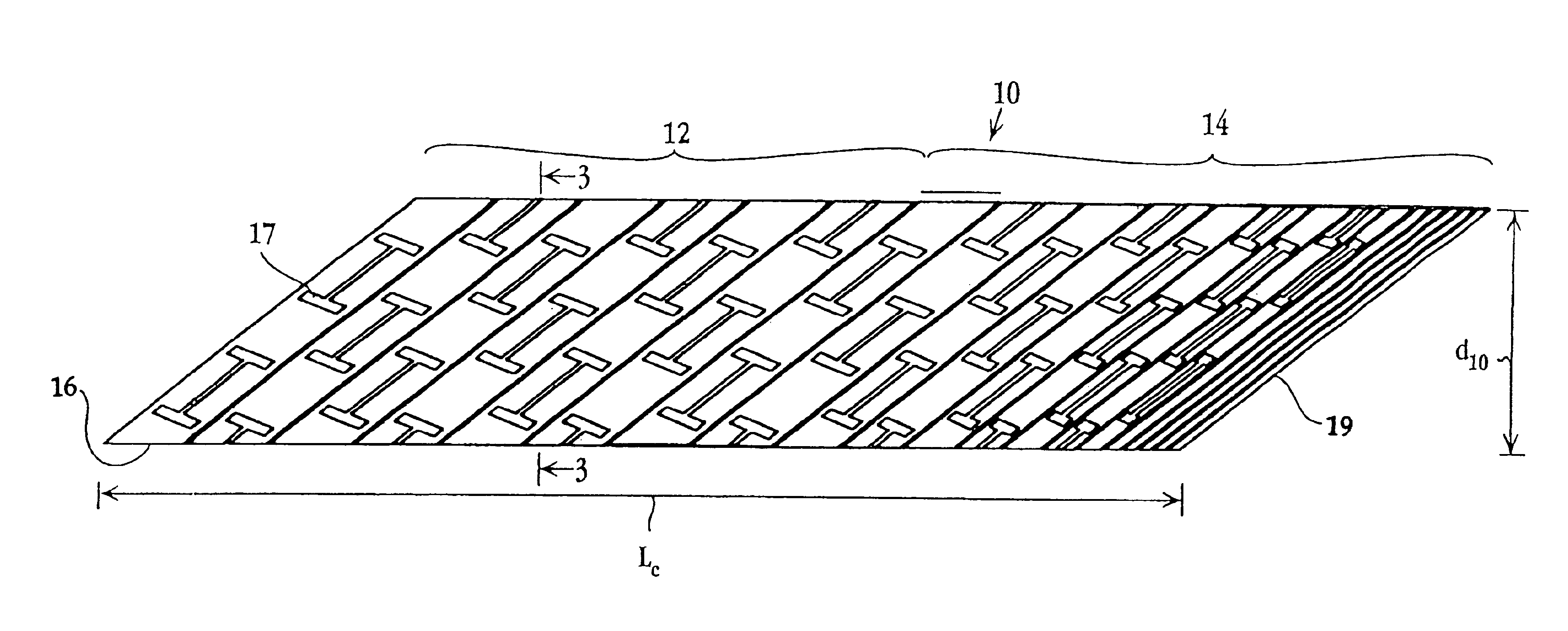

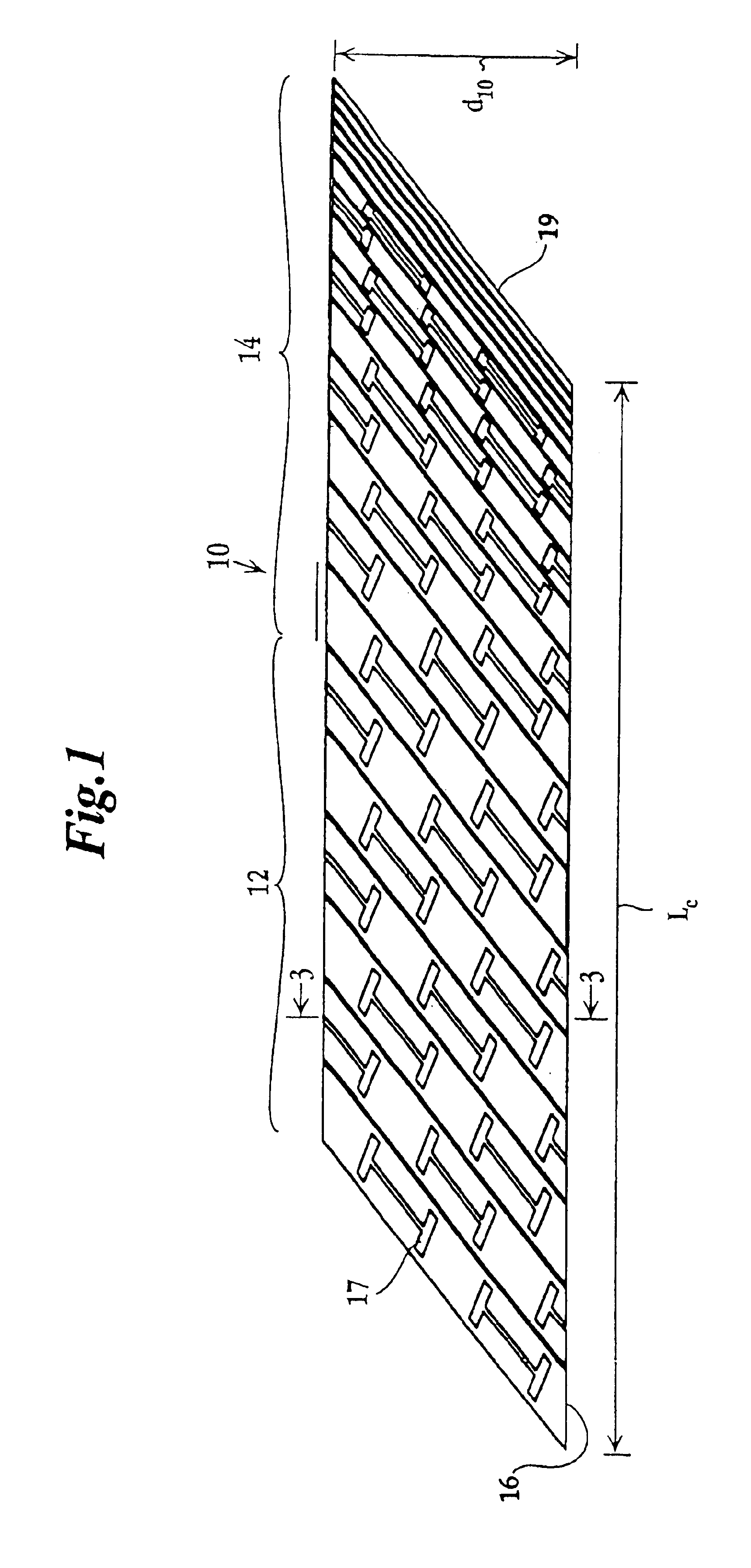

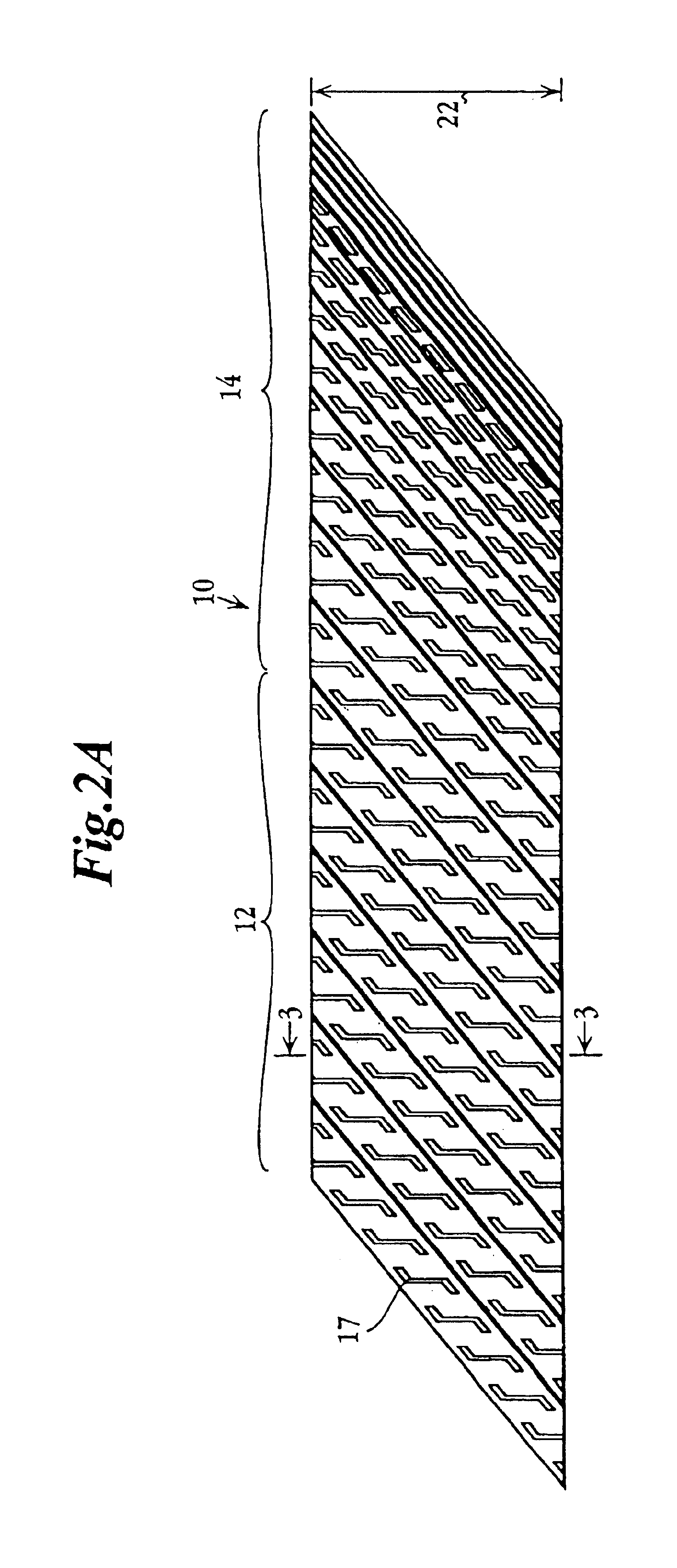

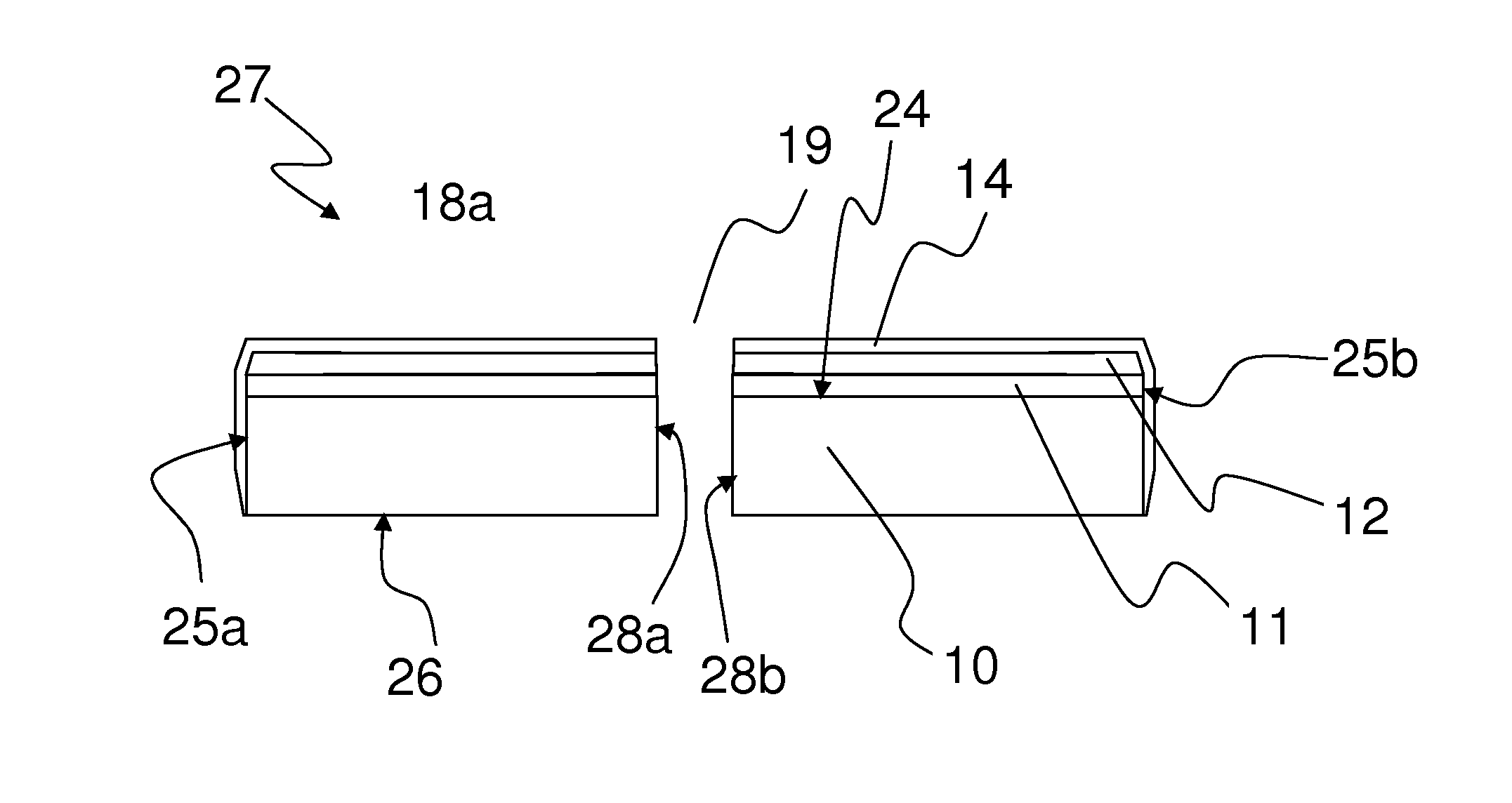

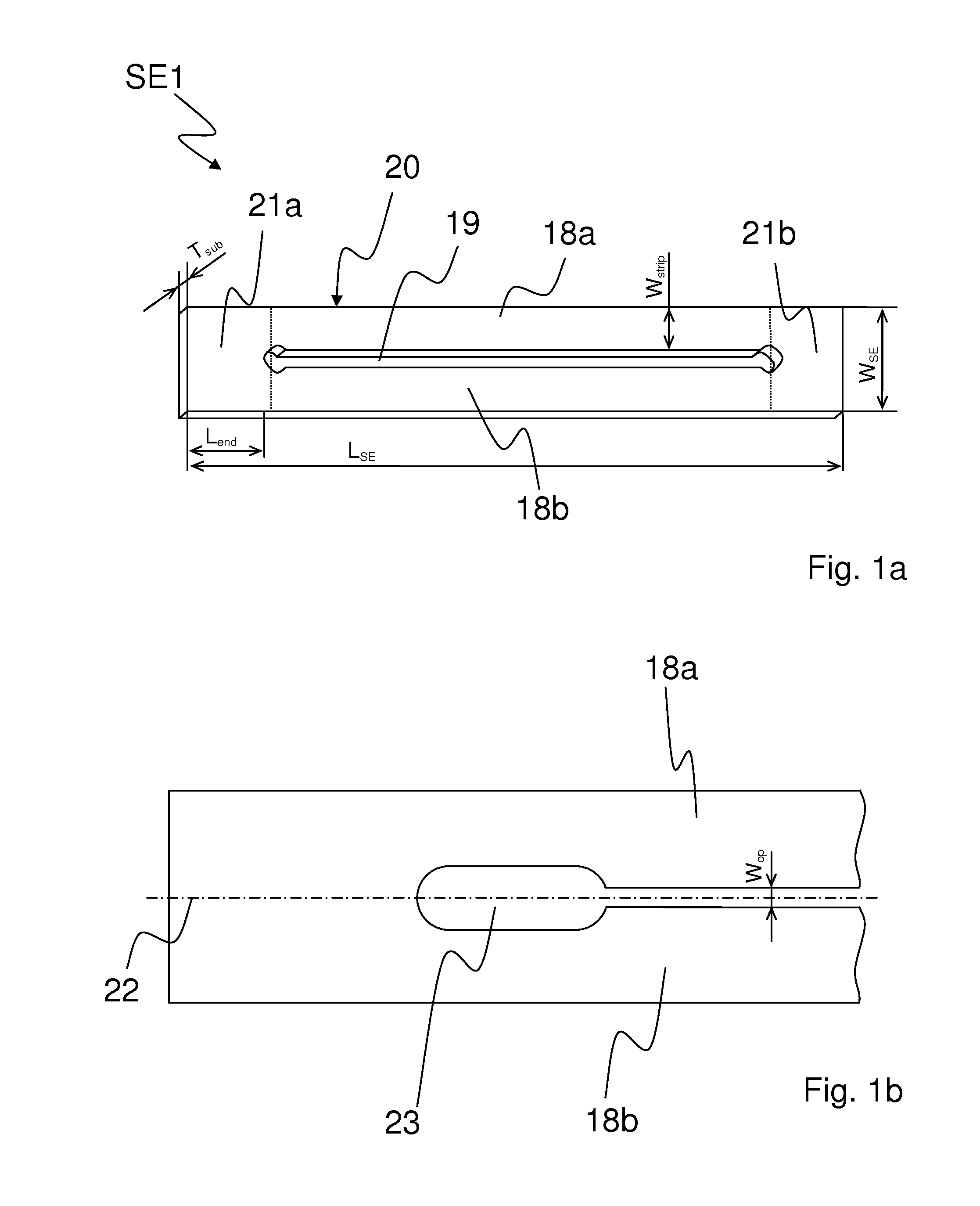

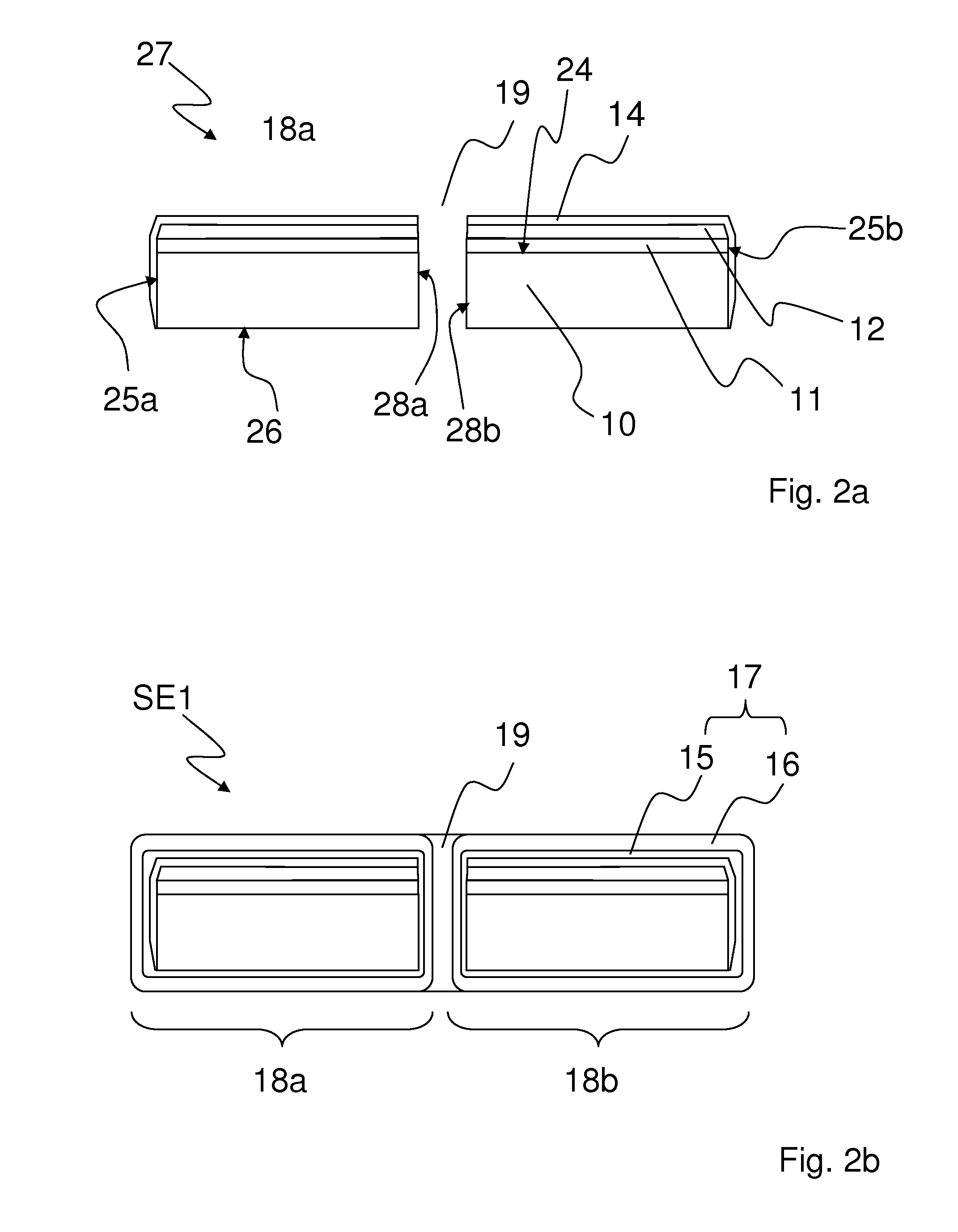

Superconducting element with elongated opening and method for manufacturing a superconducting element

InactiveUS20120214673A1Improve electrical performanceGood time stabilitySuperconductors/hyperconductorsLayered productsHigh temperature superconductingEngineering

A superconducting element (SE1-SE5) with a central section (20) located between two end sections (21a, 21b) of the superconducting element (SE1-SE5), the superconducting element (SE1-SE5) has a substrate tape (10), a buffer layer (11), a high temperature superconducting (HTS) layer (12), a first protection layer (14), and a shunt layer (17), The superconducting element (SE1-SE5) has at least one elongated opening (19) in the central section (20) elongated between the two end sections (21a, 21b), whereby the at least one elongated opening (19) divides the central section (20) of the superconducting element (SE1-SE5) into at least two HTS strips (18a, 18b, 18c), whereby the shunt layer (17) envelops the surface of each of the HTS strips (18a, 18b, 18c). The superconducting element shows improved electrical stabilization and time stability.

Owner:BRUKER HTS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com