Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

123results about "Error correction/detection using arithmatic codes" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

System And Method For Camera Imaging Data Channel

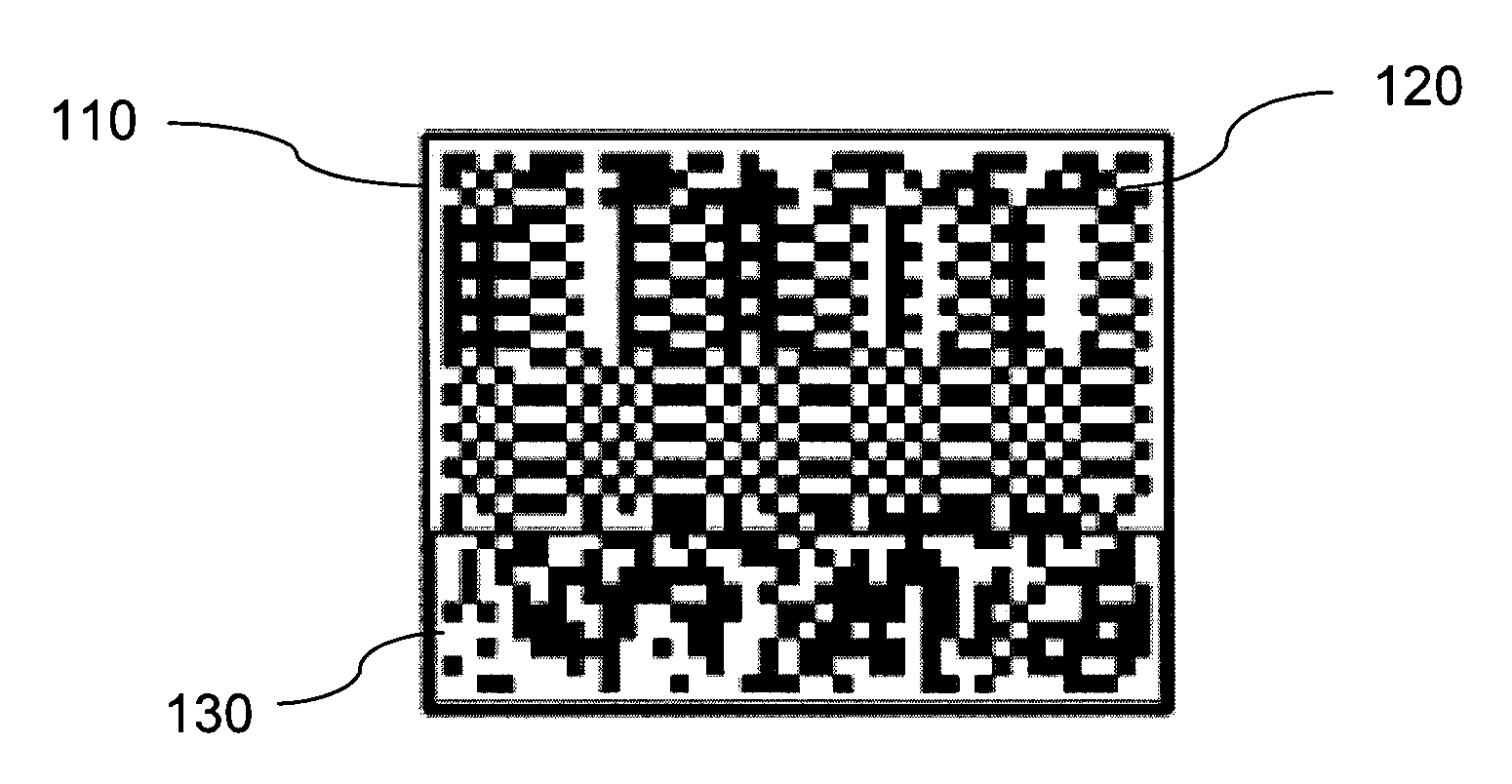

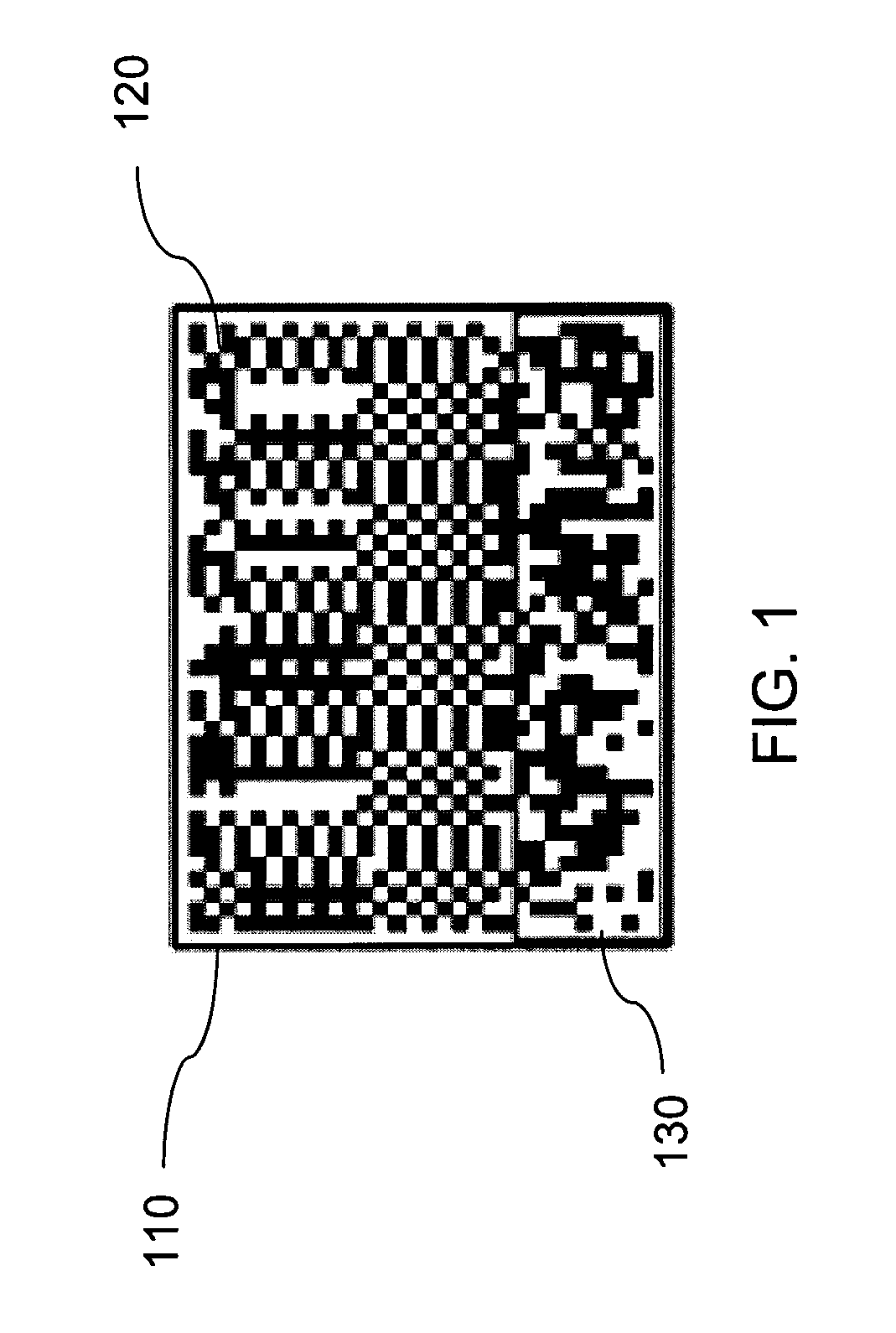

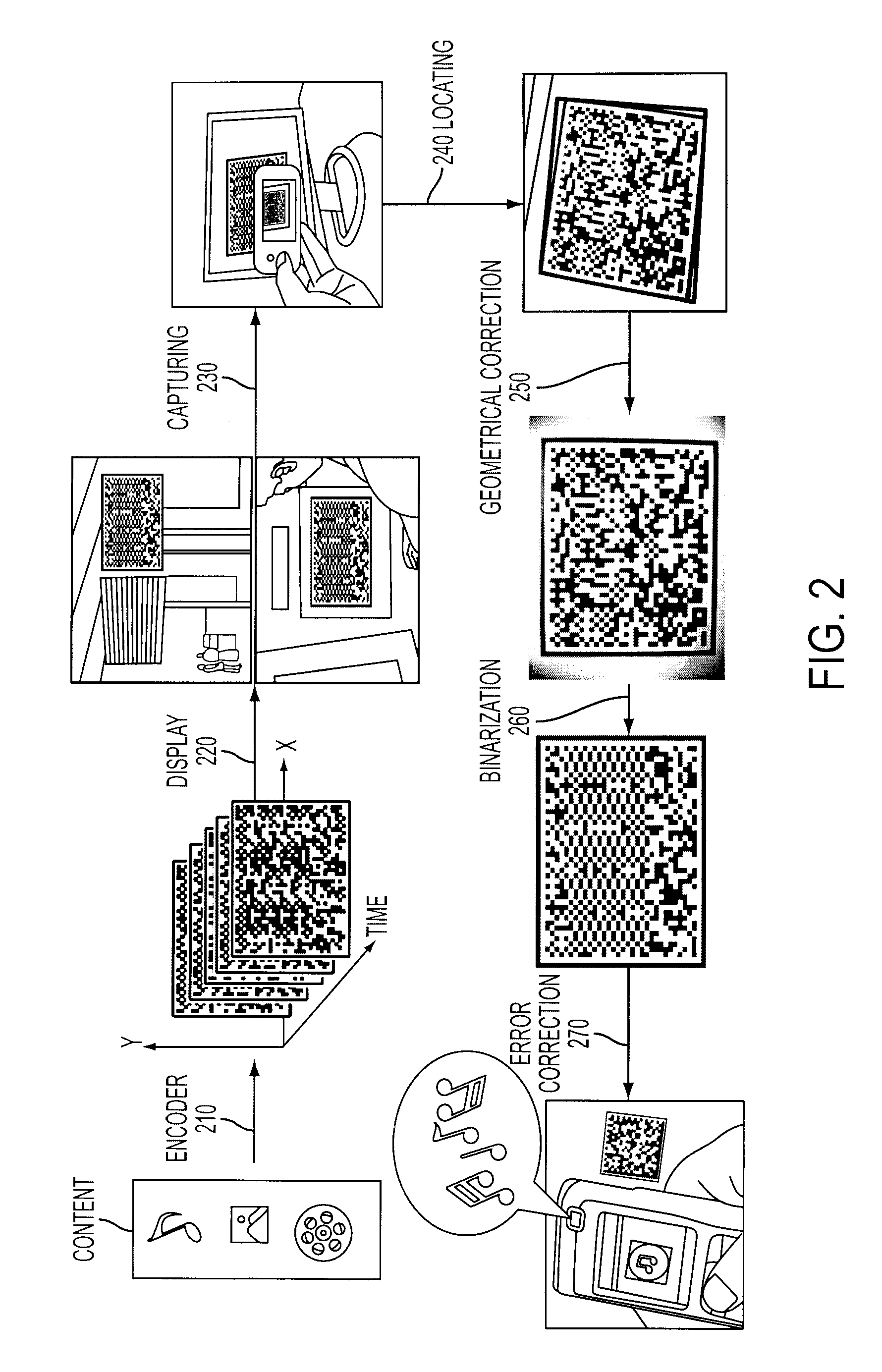

InactiveUS20100020970A1Low data costLow costCode conversionSecret communicationBarcodeDisplay device

A system and method for using cameras to download data to cell phones or other devices as an alternative to CDMA / GPRS, BlueTooth, Infrared or cable connections. The data is encoded as a sequence of images such as 2D bar codes, which can be displayed in any flat panel display, acquired by a camera, and decoded by software embedded in the device. The decoded data is written to a file. The system and method meet the following challenges: (1) To encode arbitrary data as a sequence of images. (2) To process captured images under various lighting variations and perspective distortions while maintaining real time performance. (3) To decode the processed images robustly even when partial data is lost.

Owner:LIU XU +2

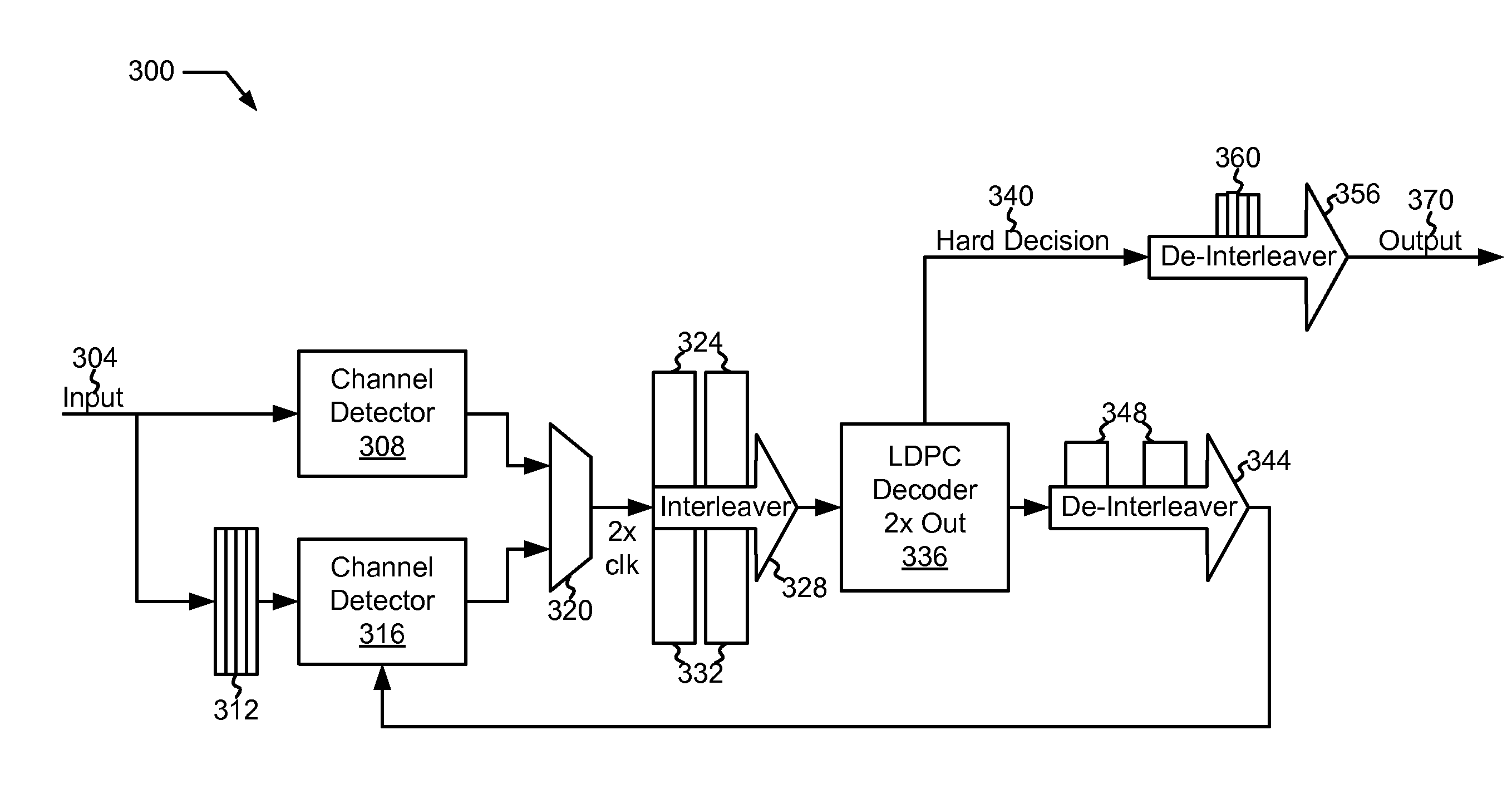

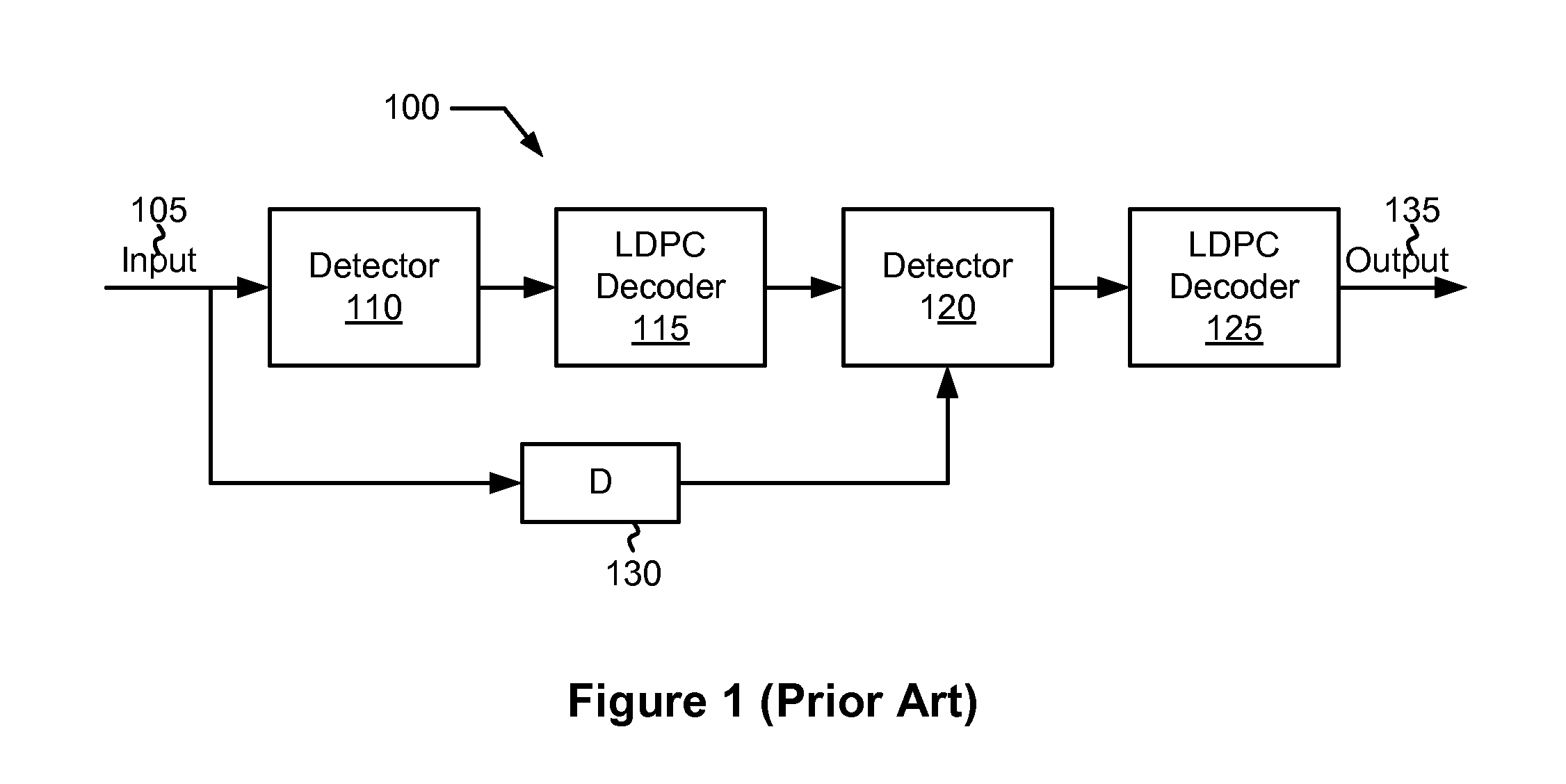

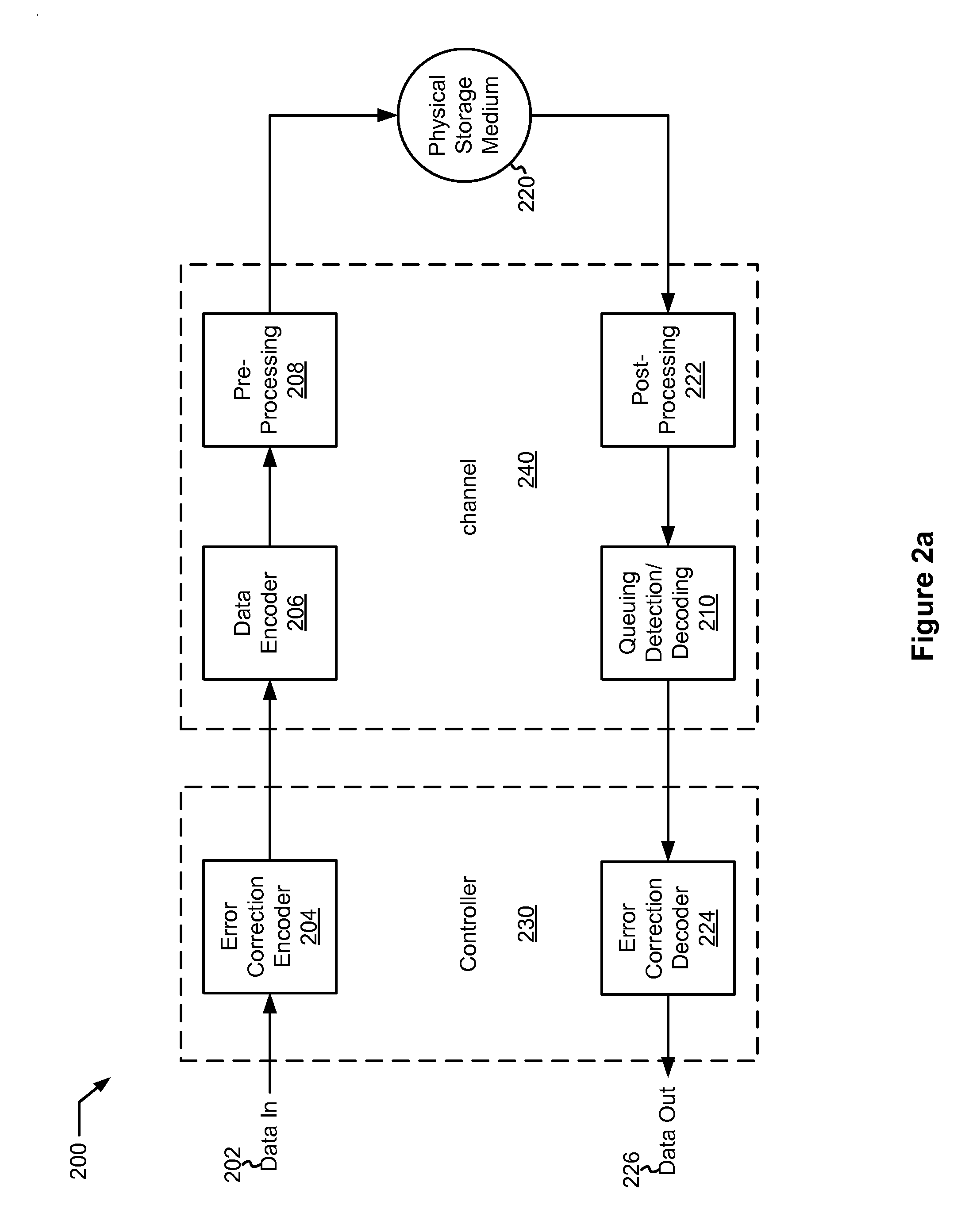

Systems and Methods for Queue Based Data Detection and Decoding

Various embodiments of the present invention provide systems and methods for data processing. For example, a variable iteration data processing system is disclosed that includes at least a first detector, a second detector, a decoder, and a queuing buffer. The first detector is operable to perform a data detection on an input data set at a first time. The decoder receives a derivation of an output from the first detector and performs a decoding process. Where the decoding process fails to converge, the decoder output is passed to the second detector for a subsequent detection and decoding process at a second time.

Owner:AVAGO TECH INT SALES PTE LTD

Method of Error Correction Code on Solid State Disk to Gain Data Security and Higher Performance

An electronic data storage device having a Reed Solomon (RS) decoder including a syndrome calculator block responsive to information including data and overhead and operative to generate a syndrome, in accordance with an embodiment of the present invention. The electronic data storage device further includes a root finder block coupled to receive said syndrome and operative to generate at least two roots, said RS decoder for processing said two roots to generate at least one error address identifying a location in said data wherein said error lies; and an erasure syndrome calculator block responsive to said information and operative to generate an erasure syndrome, said RS decoder responsive to said information identifying a disk crash, said RS decoder for processing said erasure syndrome to generate an erasure error to recover the data in said disk crash.

Owner:SUPER TALENT ELECTRONICS

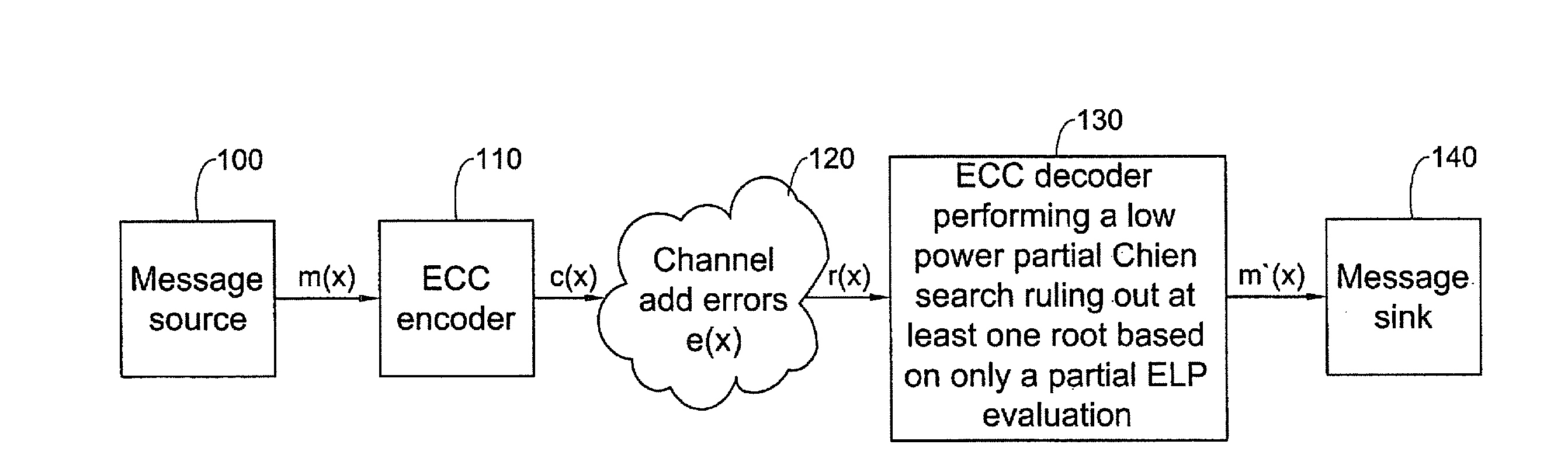

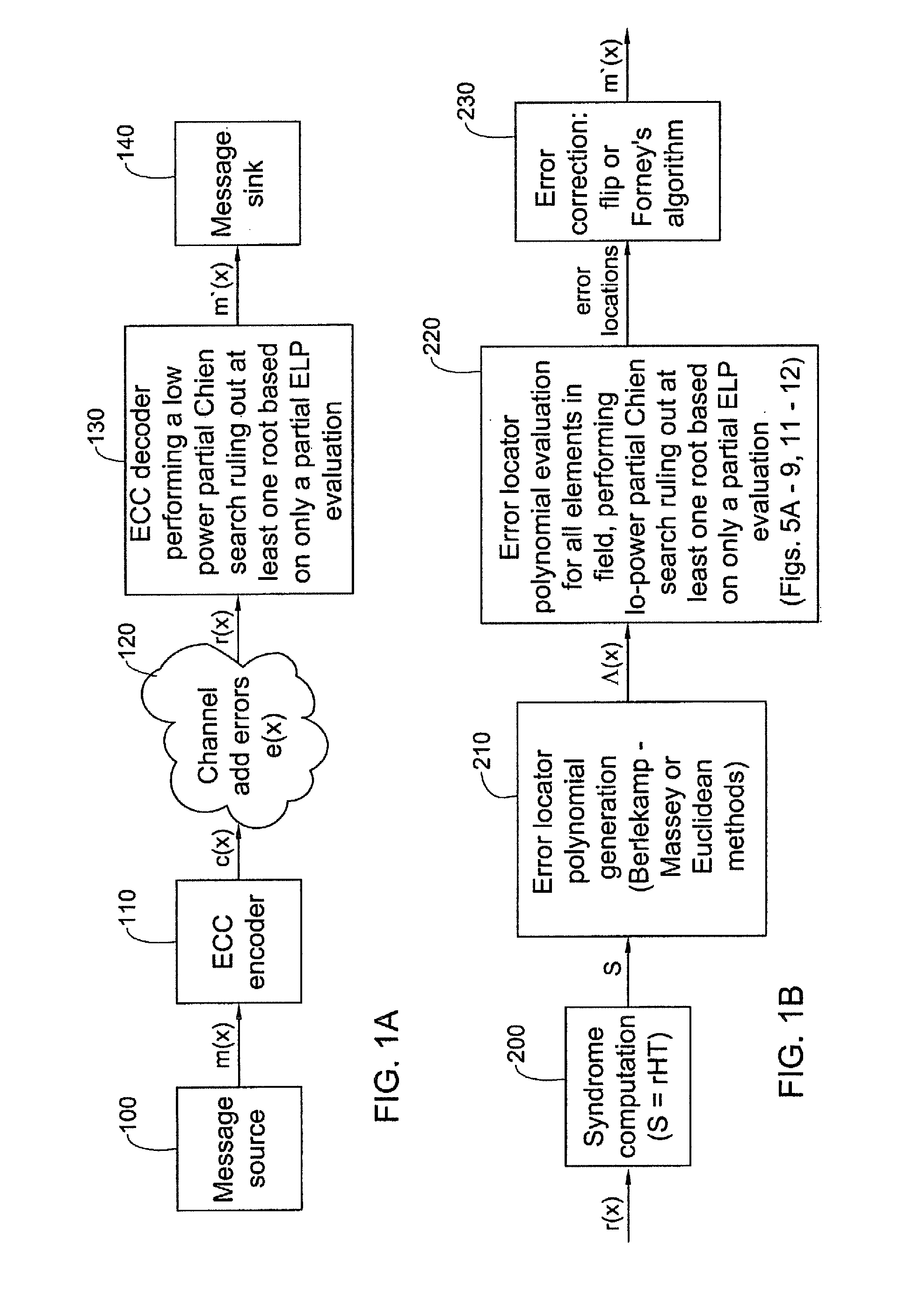

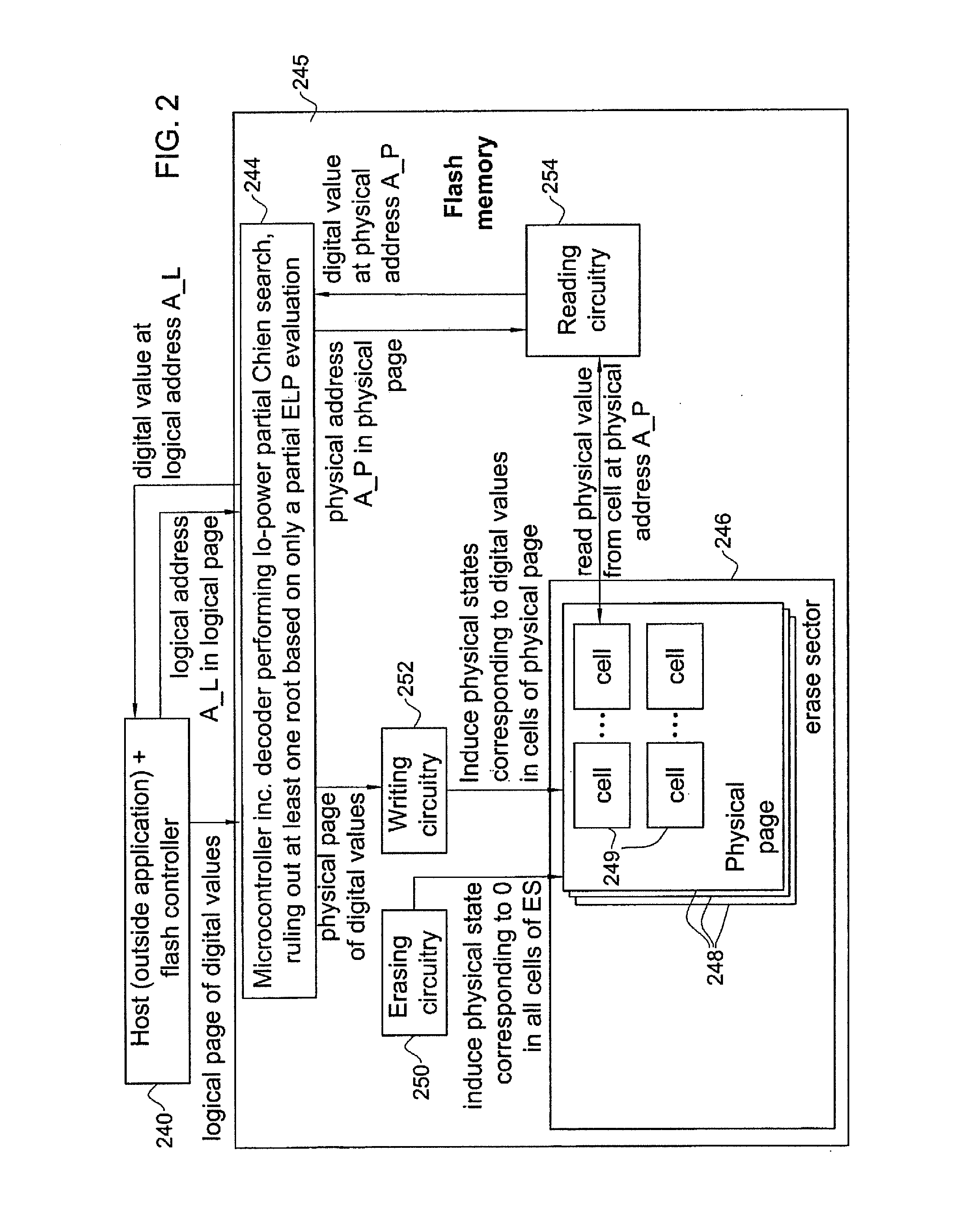

Low power chien-search based bch/rs decoding system for flash memory, mobile communications devices and other applications

ActiveUS20100131831A1Minimizing power useSaving in power consumptionCode conversionStatic storageCommunication deviceChien search

A low power Chien searching method employing Chien search circuitry comprising at least two hardware components that compute at least two corresponding bits comprising a Chien search output, the method comprising activating only a subset of the hardware components thereby to compute only a subset of the bits of the Chien search output; and activating hardware components other than those in the subset of hardware components, to compute additional bits of the Chien search output other than the bits in the subset of bits, only if a criterion on the subset of the bits of the Chien search output is satisfied.

Owner:AVAGO TECH INT SALES PTE LTD

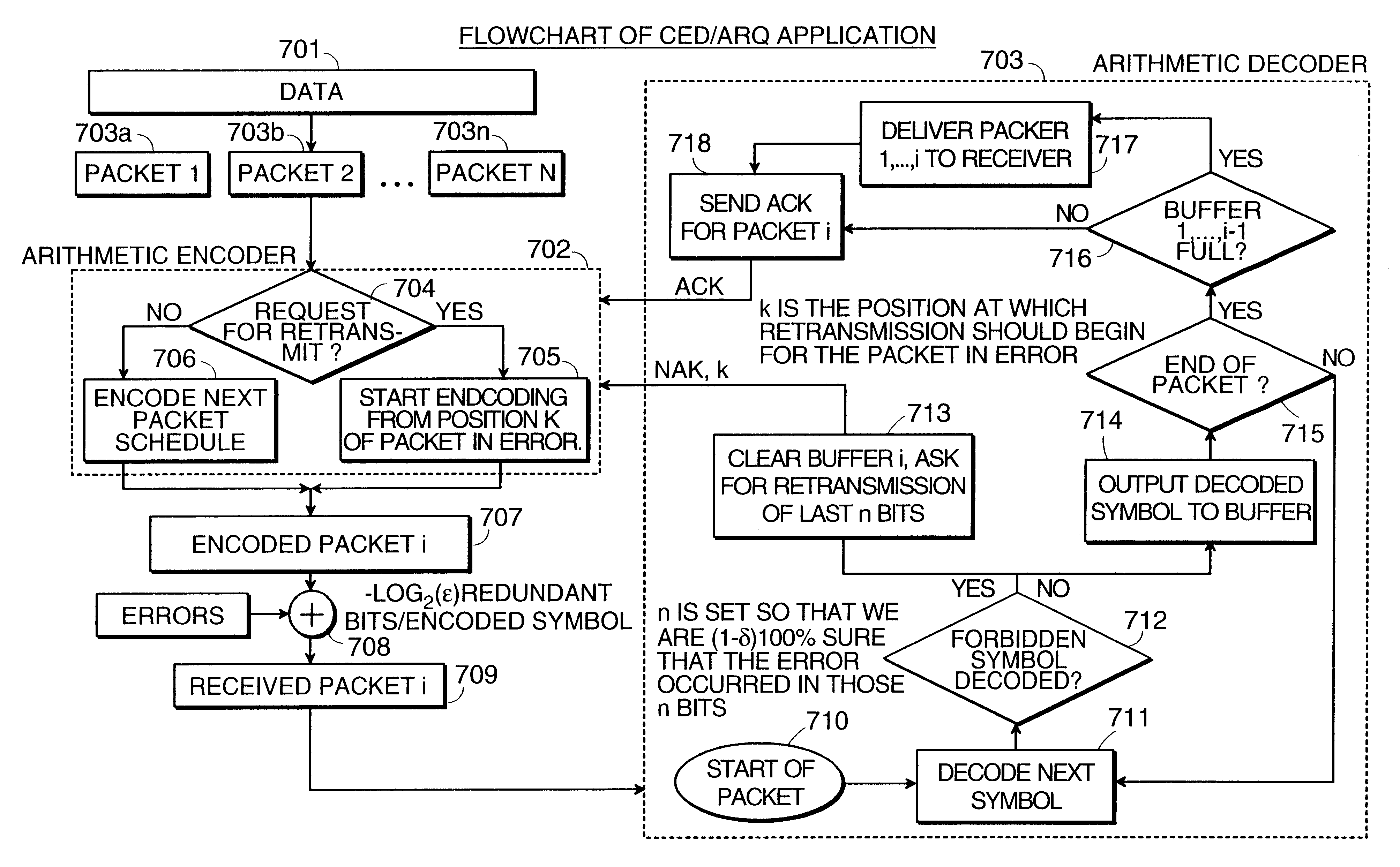

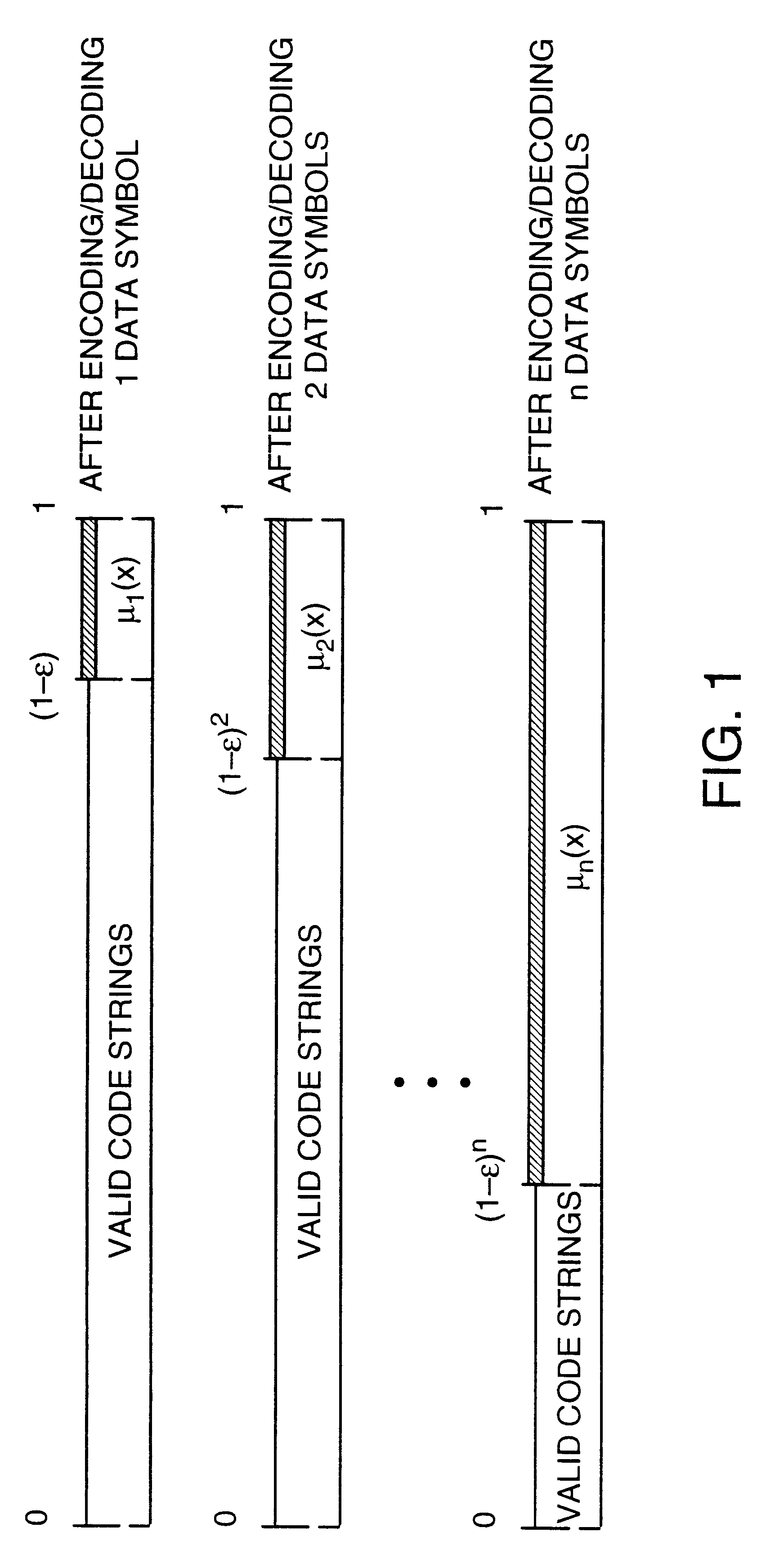

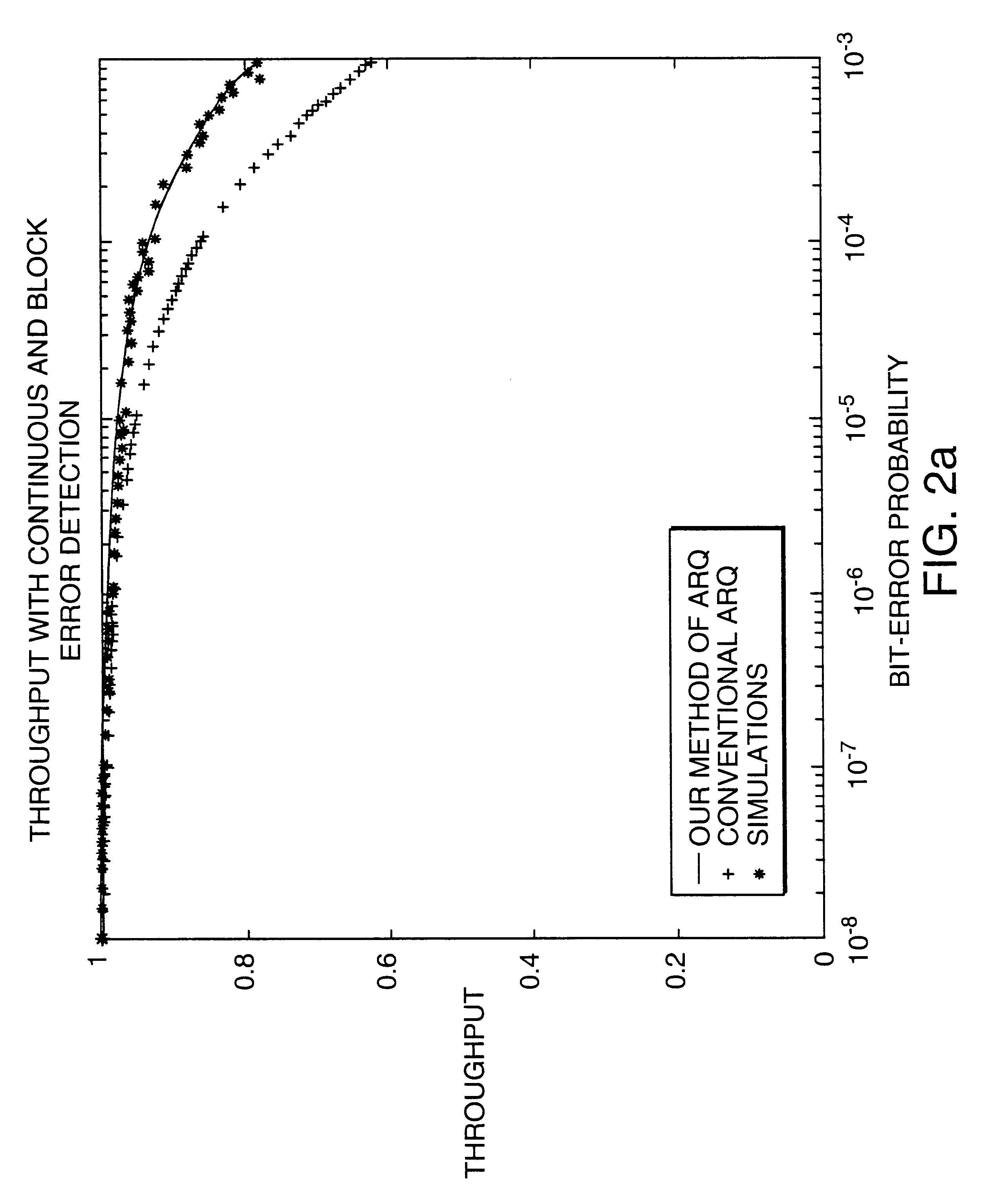

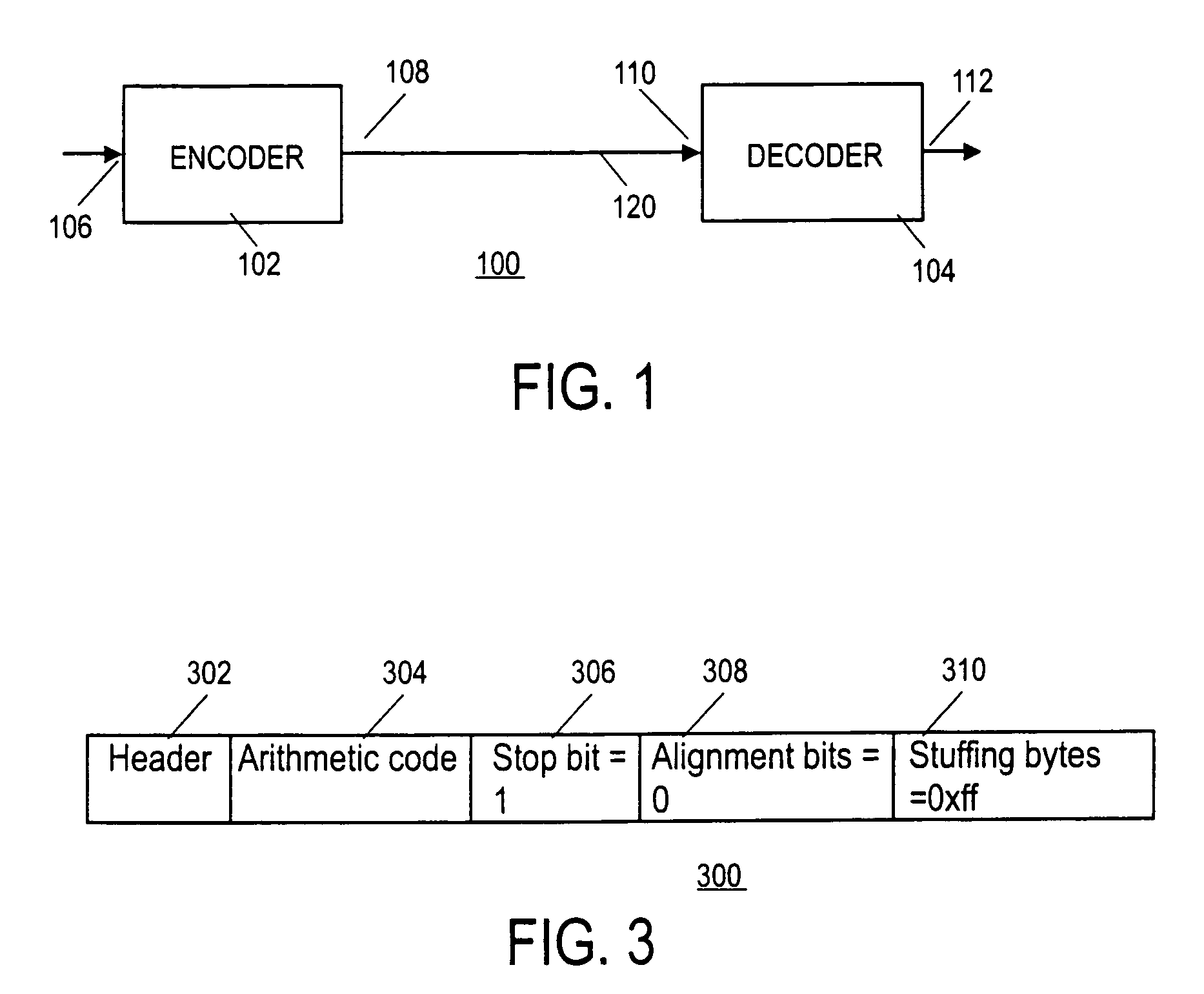

Data transmission using arithmetic coding based continuous error detection

InactiveUS6418549B1Error prevention/detection by using return channelTransmission systemsAutomatic repeat requestTrade offs

Method and apparatus for image transmission using arithmetic coding, based on continuous error detection uses a controlled amount of added redundancy. A continuous error detection scheme is provided, wherein there is a trade-off between the amount of added redundancy and the time needed to detect an error once it occurs. Herein, there is no need for the cyclic redundancy check (CRC) to wait until an entire block of data has been received and processed before an error can be detected. The invention can be used to great advantage both in the automatic repeat request (ARQ) and other concatenated coding schemes. Errors in the received bit stream are detected by introducing added redundancy, e.g., a forbidden symbol, in the arithmetic coding operation. The forbidden symbol is never intended to be encoded. The redundancy error causes loss of synchronization, which is used to detect errors. If a forbidden symbol gets decoded, it means that an error has occurred. In this invention, there is direct control over the amount of redundancy added vs. the amount of time it takes to detect an error. For image compression systems, by using the invention and ARQ, only one device would suffice both for source compression and channel coding.

Owner:MERU NETWORKS

Error correction by symbol reconstruction in binary and multi-valued cyclic codes

InactiveUS20080016431A1Rapidly detect and correct errorCode conversionCyclic codesAlgorithmSymbol of a differential operator

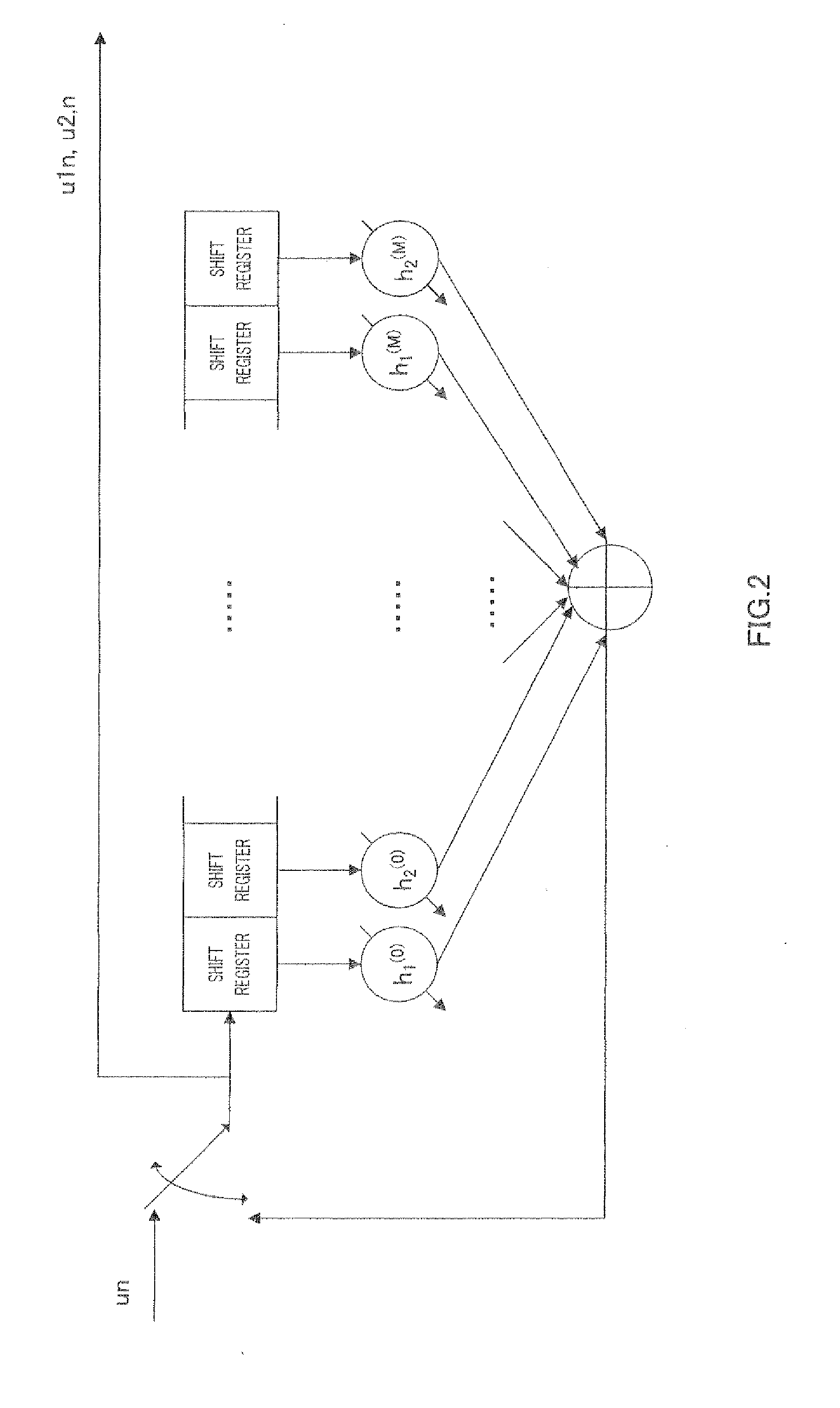

Methods, apparatus and systems for error correction of n-valued symbols in codewords of p n-valued symbols with n>2 and for n=2 and k information symbols have been disclosed. Coders and decoders using a Linear Feedback Shift Registers (LFSR) are applied to generate codewords and detect the presence of errors. An LFSR can be in Fibonacci or Galois configuration. Errors can be corrected by execution of an n-valued expression in a deterministic non-iterative way. Deterministic error correction methods based on known symbols in error are provided. Corrected codewords can be identified by comparison with received codewords in error. N-valued LFSR based pseudo-noise generators and methods to determine if an LFSR is appropriate for generating error correcting codes are also disclosed. Methods and apparatus applying error free assumed windows and error assumed windows are disclosed. Systems using the error correcting methods, including communication systems and data storage systems are also provided.

Owner:TERNARYLOGIC

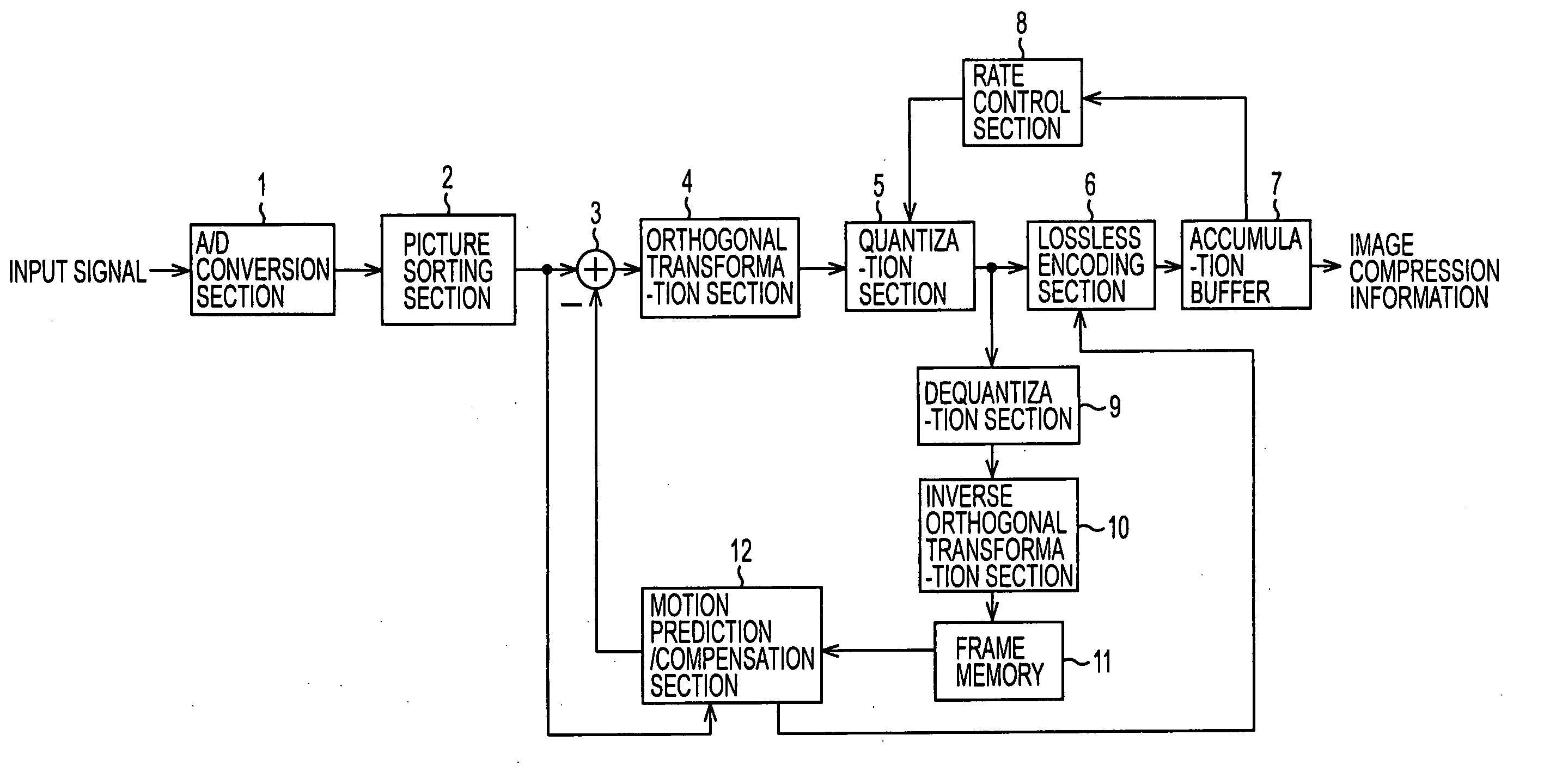

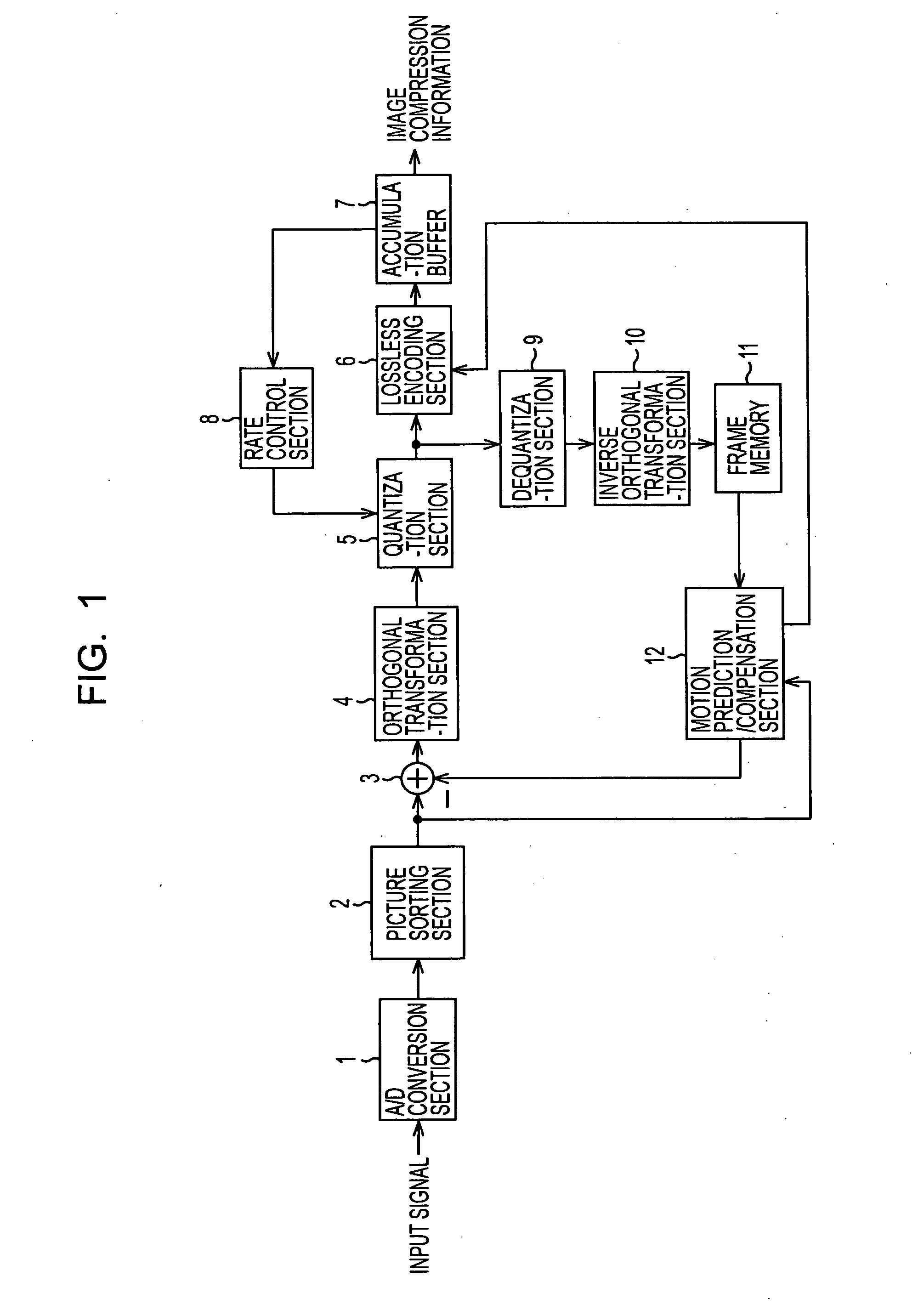

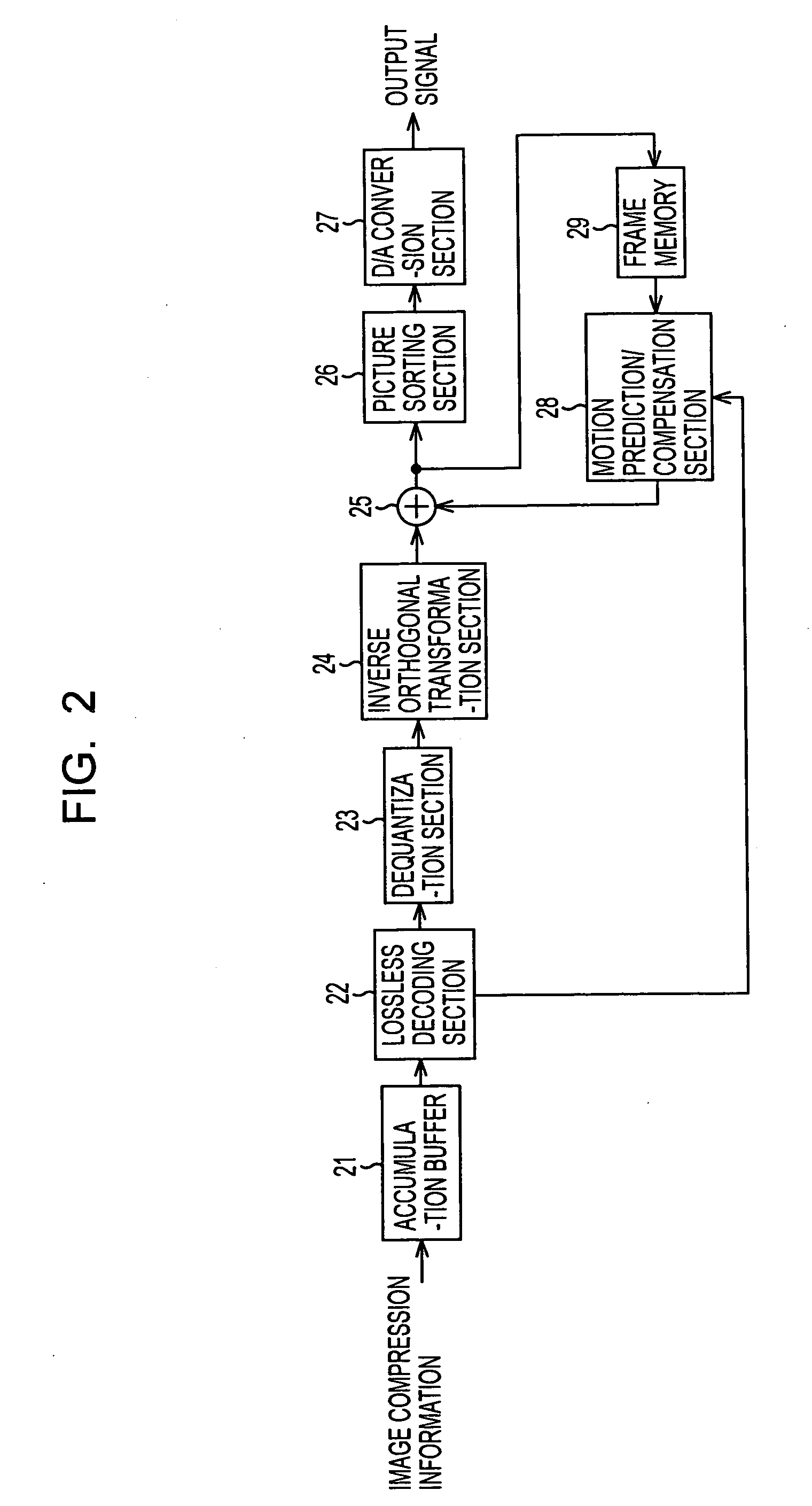

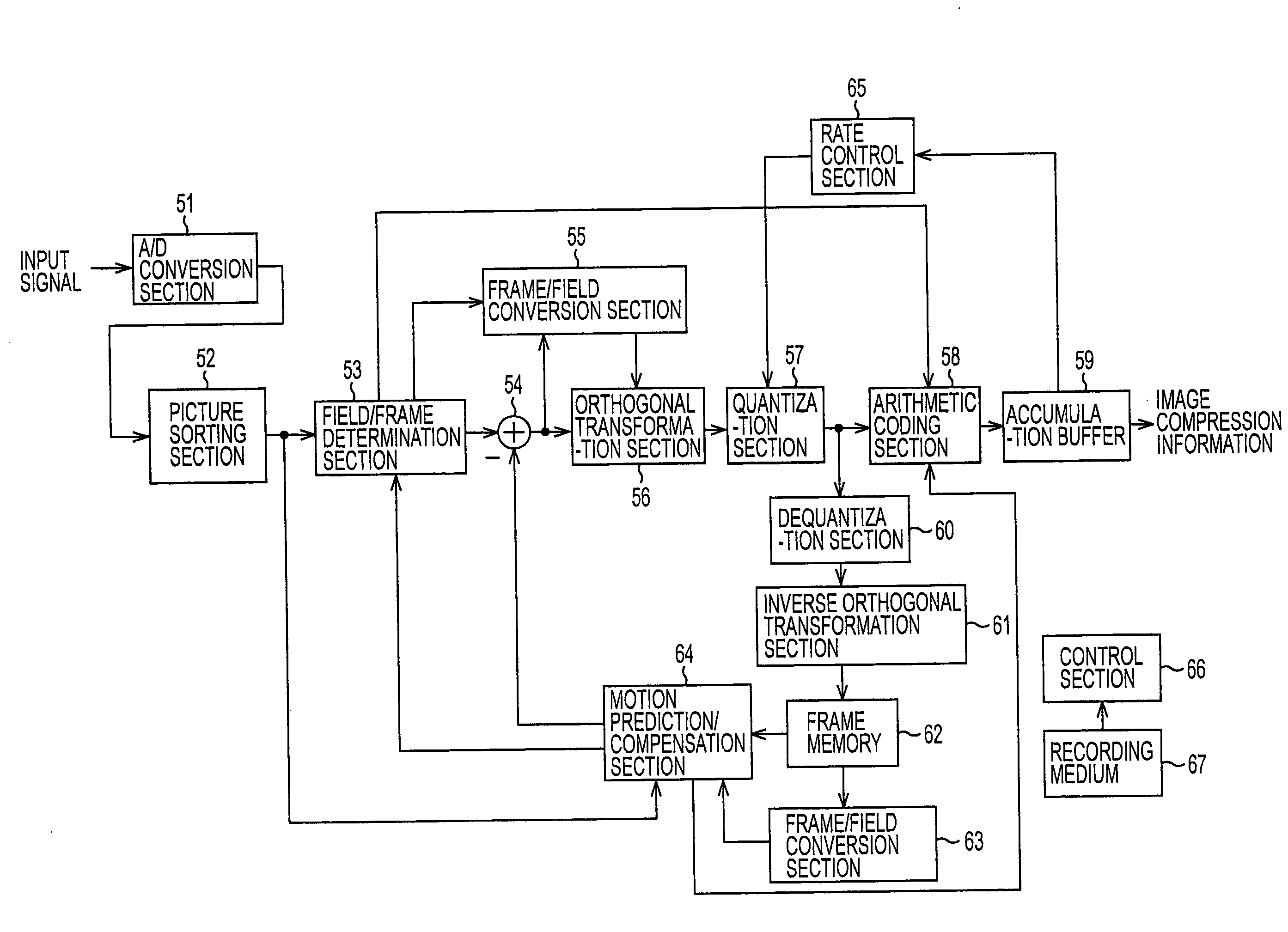

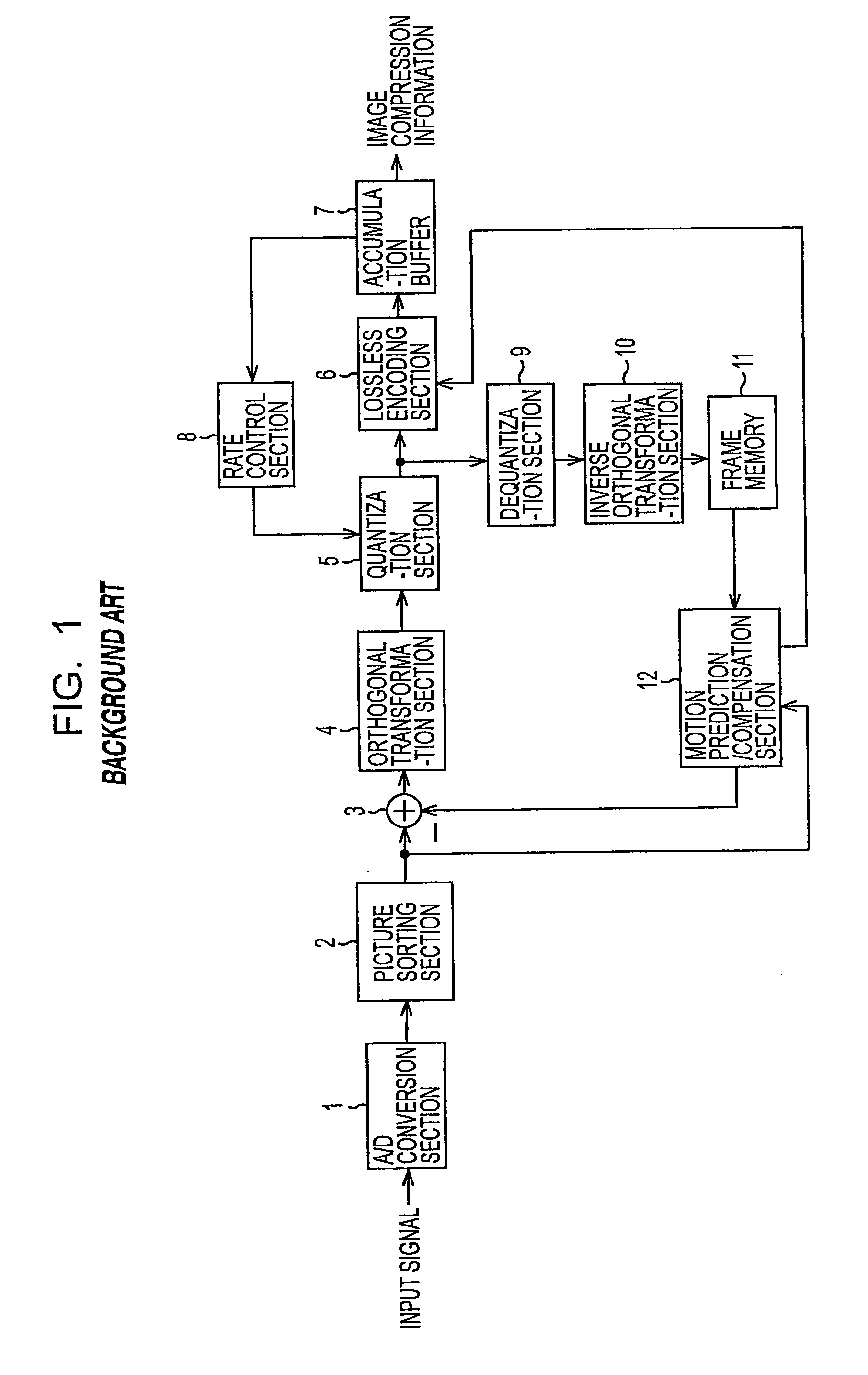

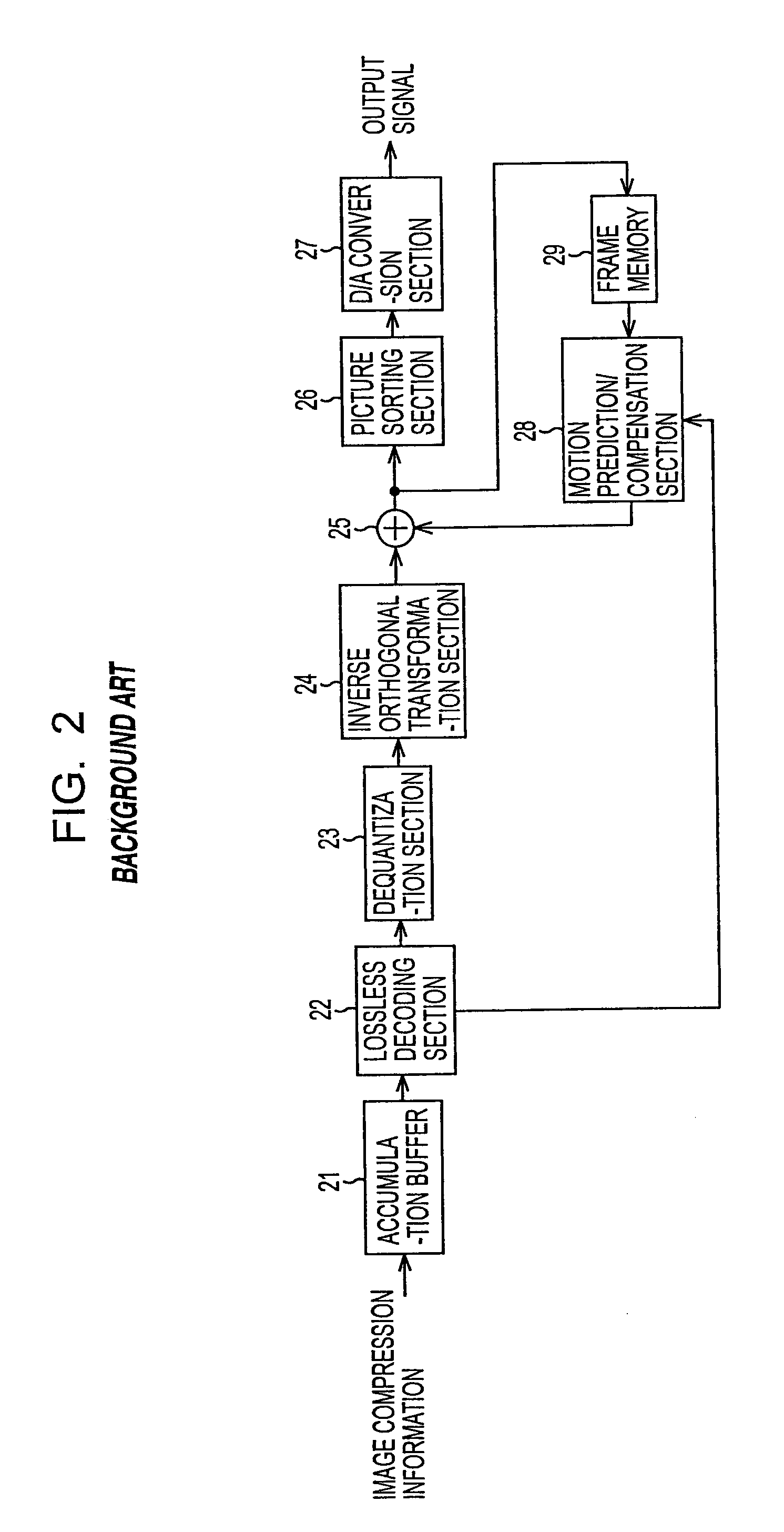

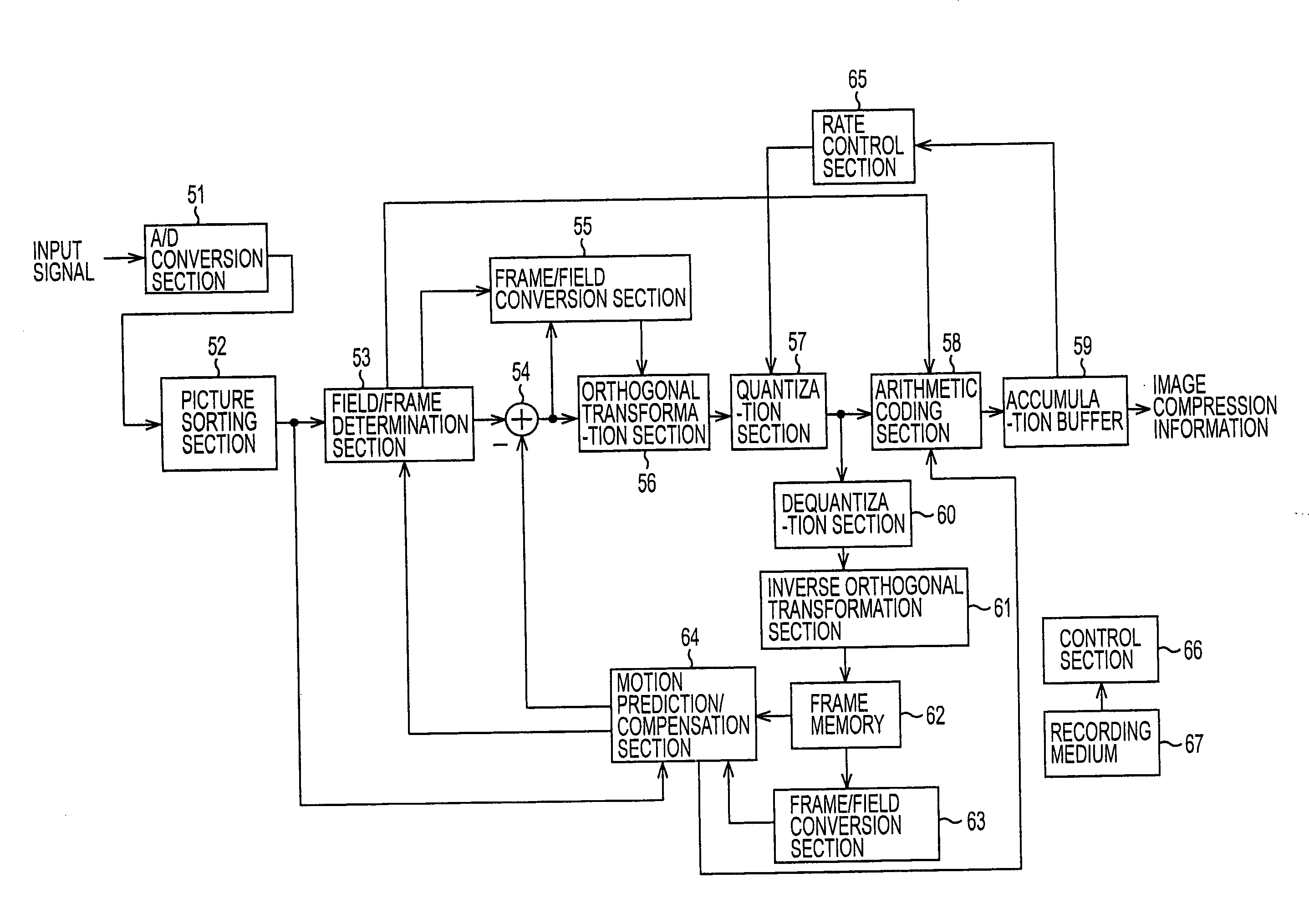

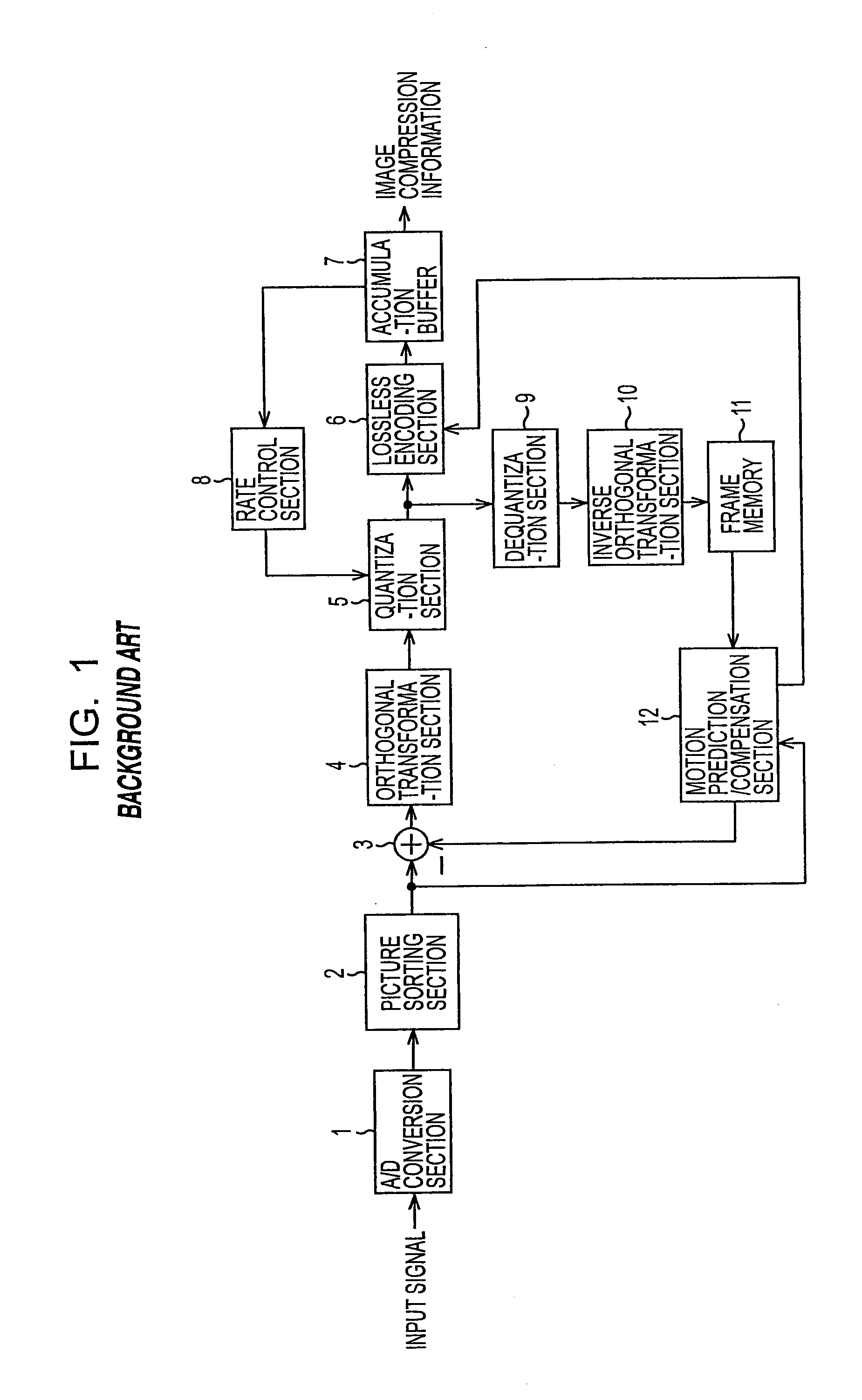

Coding device and method, decoding device and method, recording medium, and program

ActiveUS20050219069A1Picture reproducers using cathode ray tubesCode conversionFrame basedImage compression

The present invention relates to, for example, an encoding apparatus and an encoding method, a decoding apparatus and a decoding method, a recording medium, and a program suitable for encoding image signals with a higher compression ratio for transmission or accumulation. In an arithmetic coding section (58), from among the syntax elements of input image compression information, the frame / field flag is first encoded by a frame / field flag context model (91). When the macroblock to be processed is subjected to frame-based encoding, a frame-based context model (92), specified in the current H.26L standard, is applied. On the other hand, when the macroblock to be processed is subjected to field-based encoding, a field-based context model (94) is applied for the syntax elements described below. The present invention is applied to an encoder for encoding image information and a decoder for decoding image information.

Owner:SONY CORP

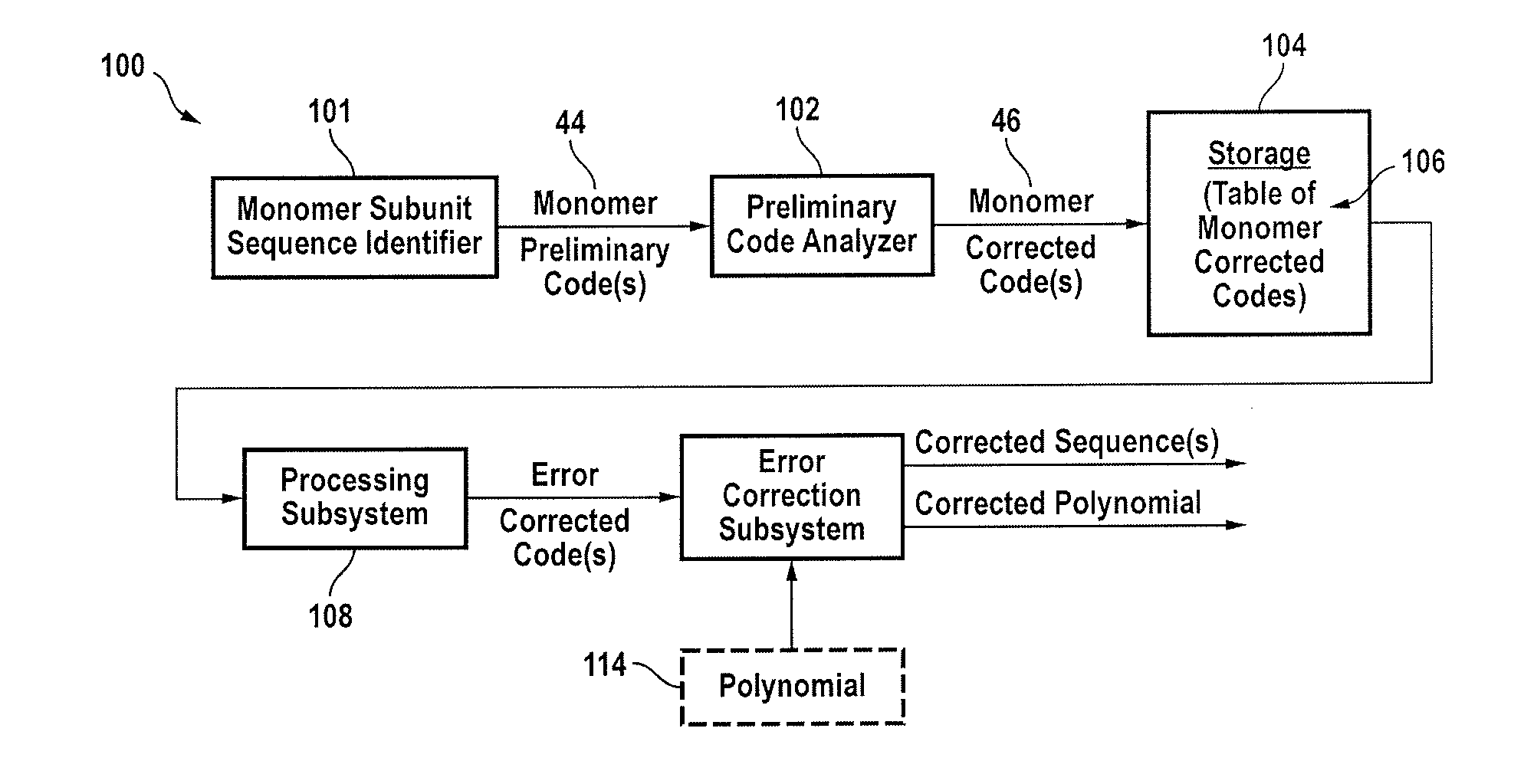

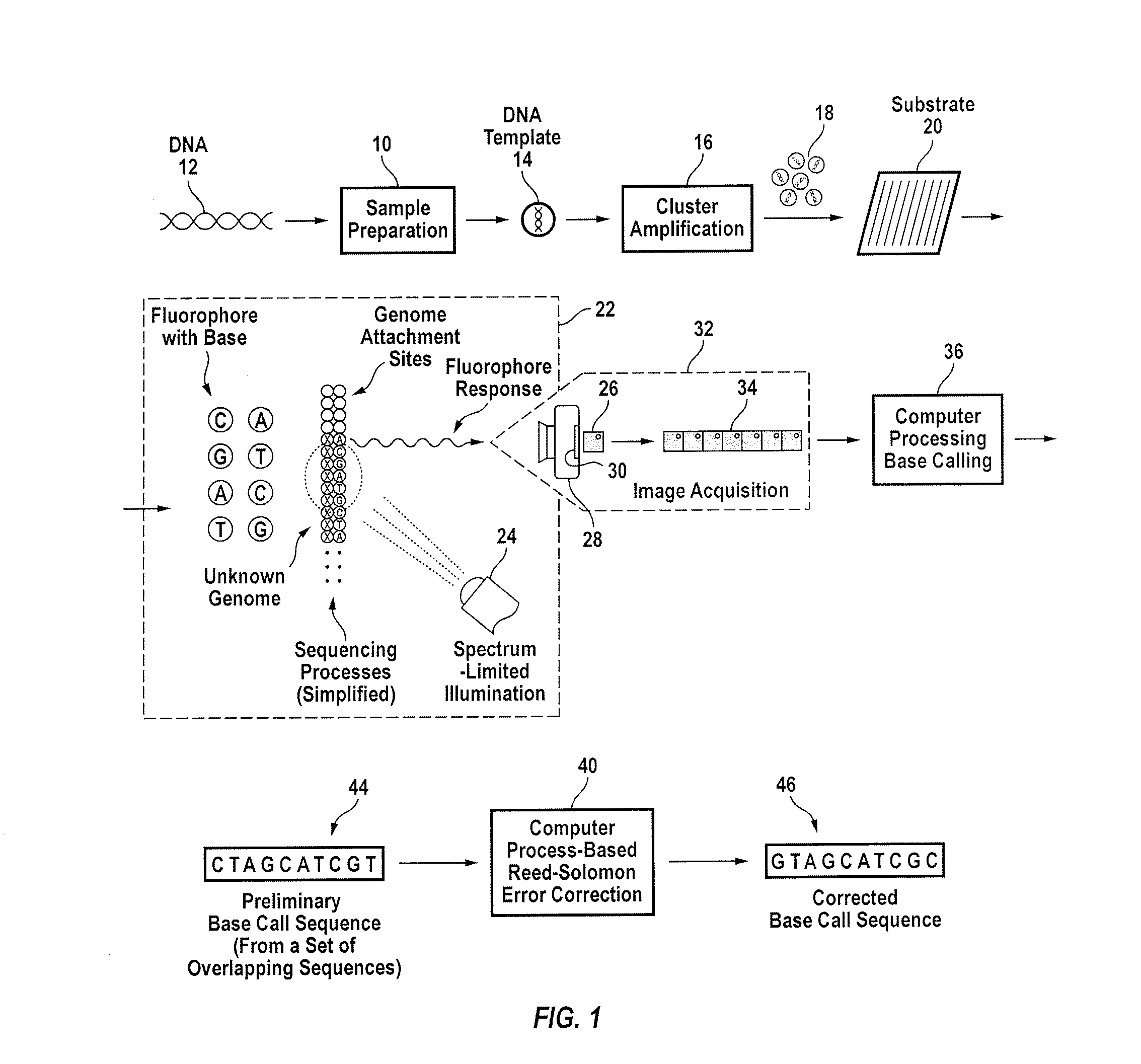

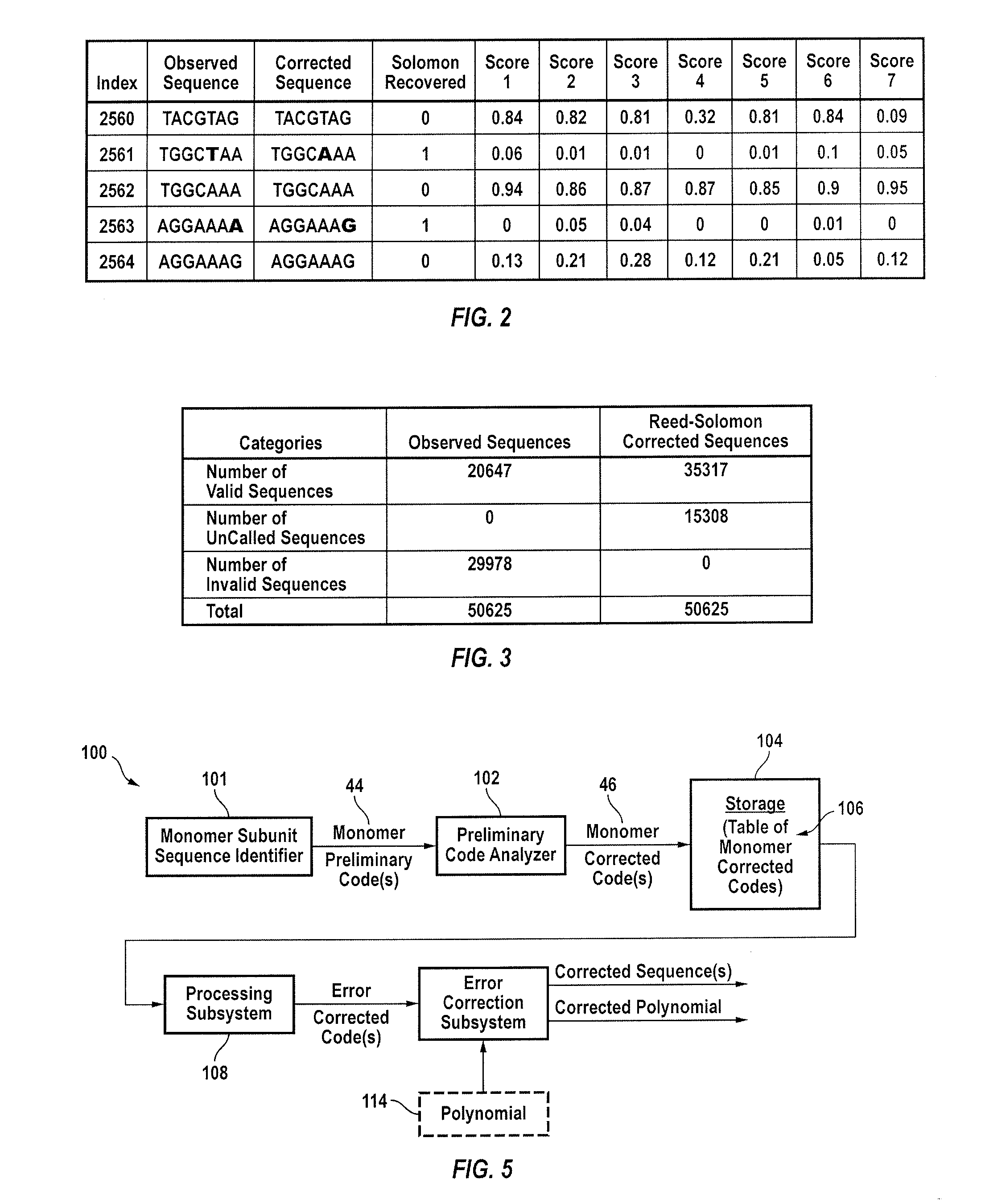

Method and apparatus for quantification of DNA sequencing quality and construction of a characterizable model system using reed-solomon codes

Data extracted from fluorosphore responses of fluorophore labeled bases in genetic material used in sequencing of unknown fragments from a defined set of for example a model system are converted into a class of block codes that are then employed in a computer-based process to compare and correct preliminary calls of calls of the categorically known genetic material. In a specific embodiment, the Reed-Solomon codes are employed to identify one or more errors as may occur in a finite block of codes. The methodology is also useful to identify elements of a real system containing known elements in the form of a tag. Reed-Solomon sensors may be employed with and in addition to other types of genome sensors.

Owner:COMPLETE GENOMICS INC

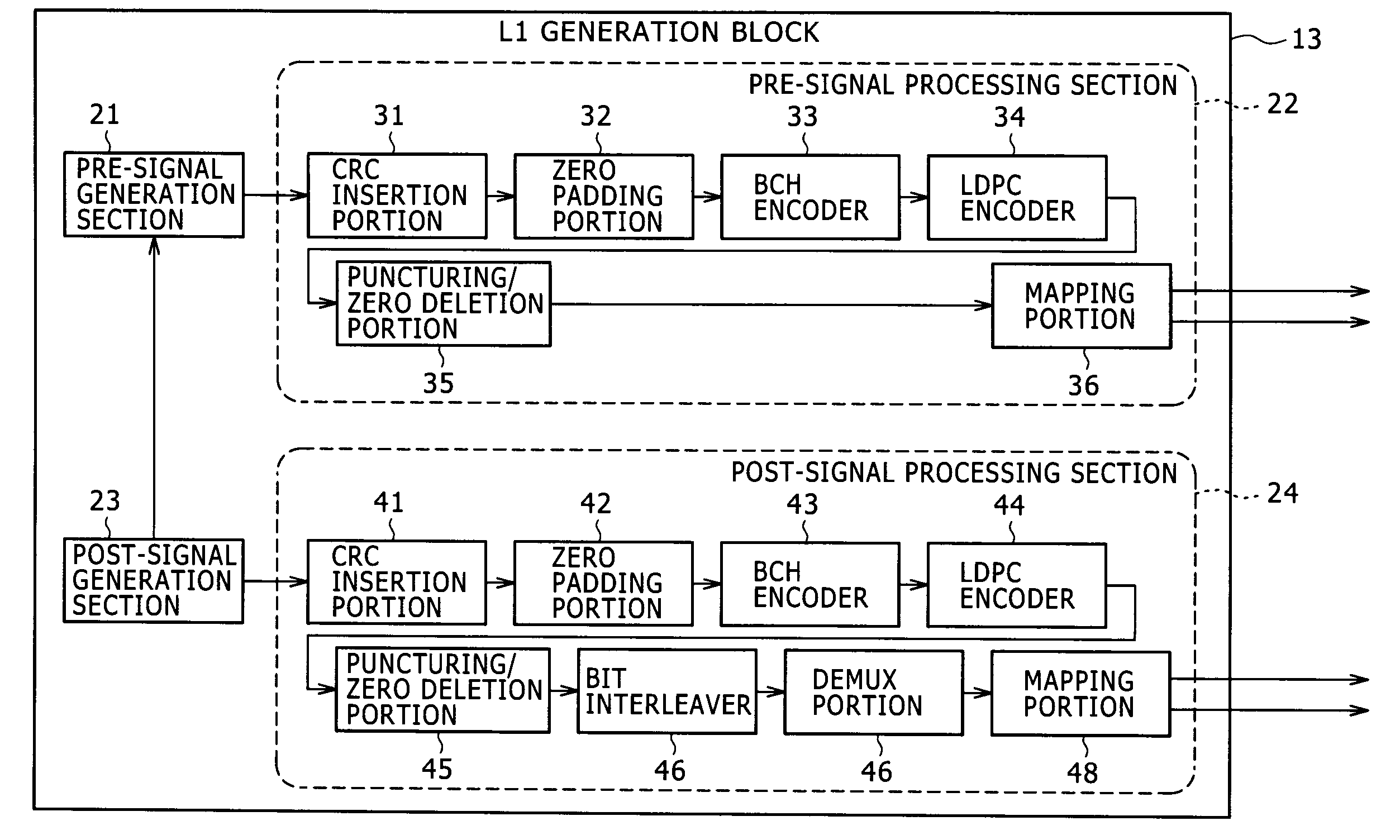

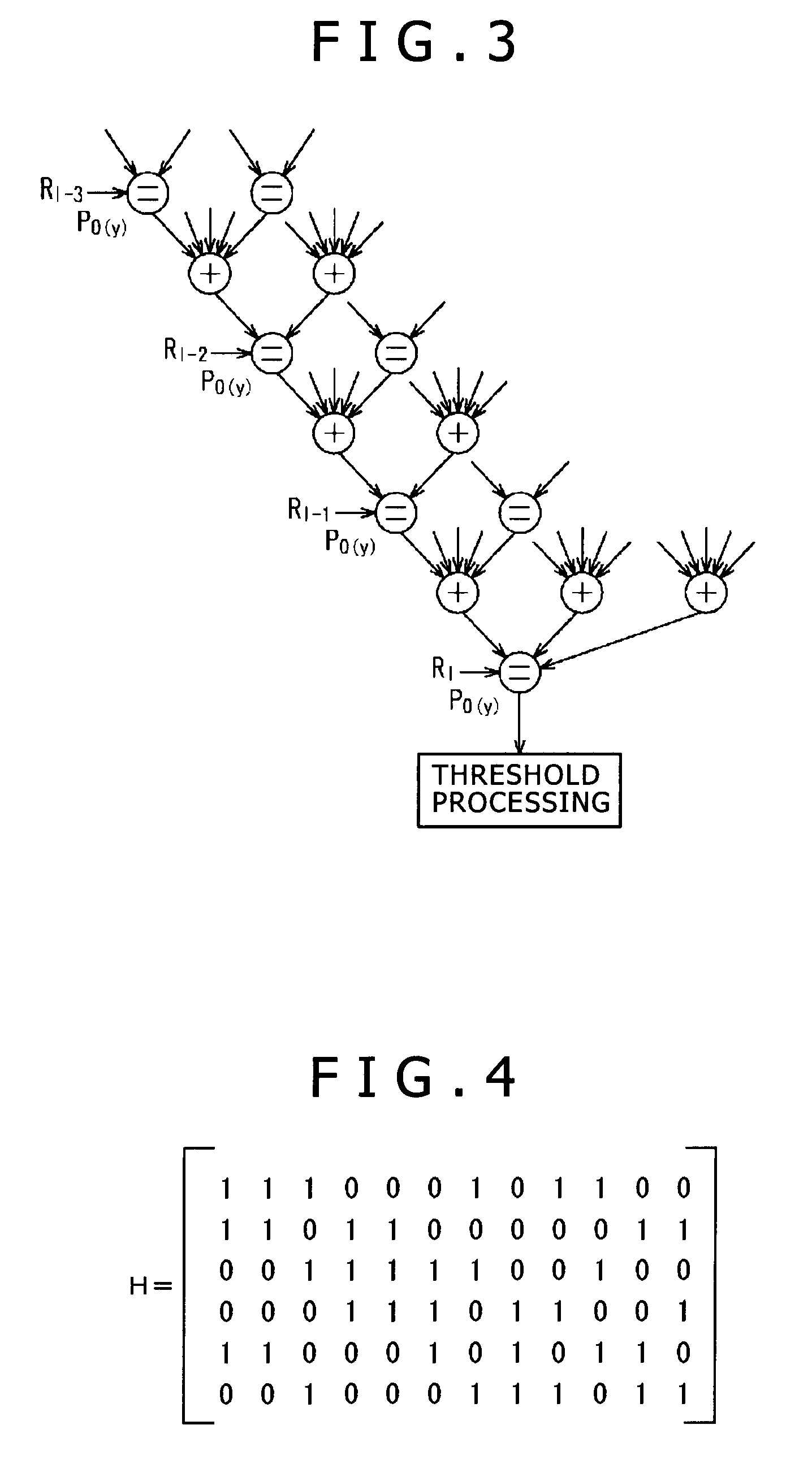

Receiving apparatus, receiving method, program, and receiving system

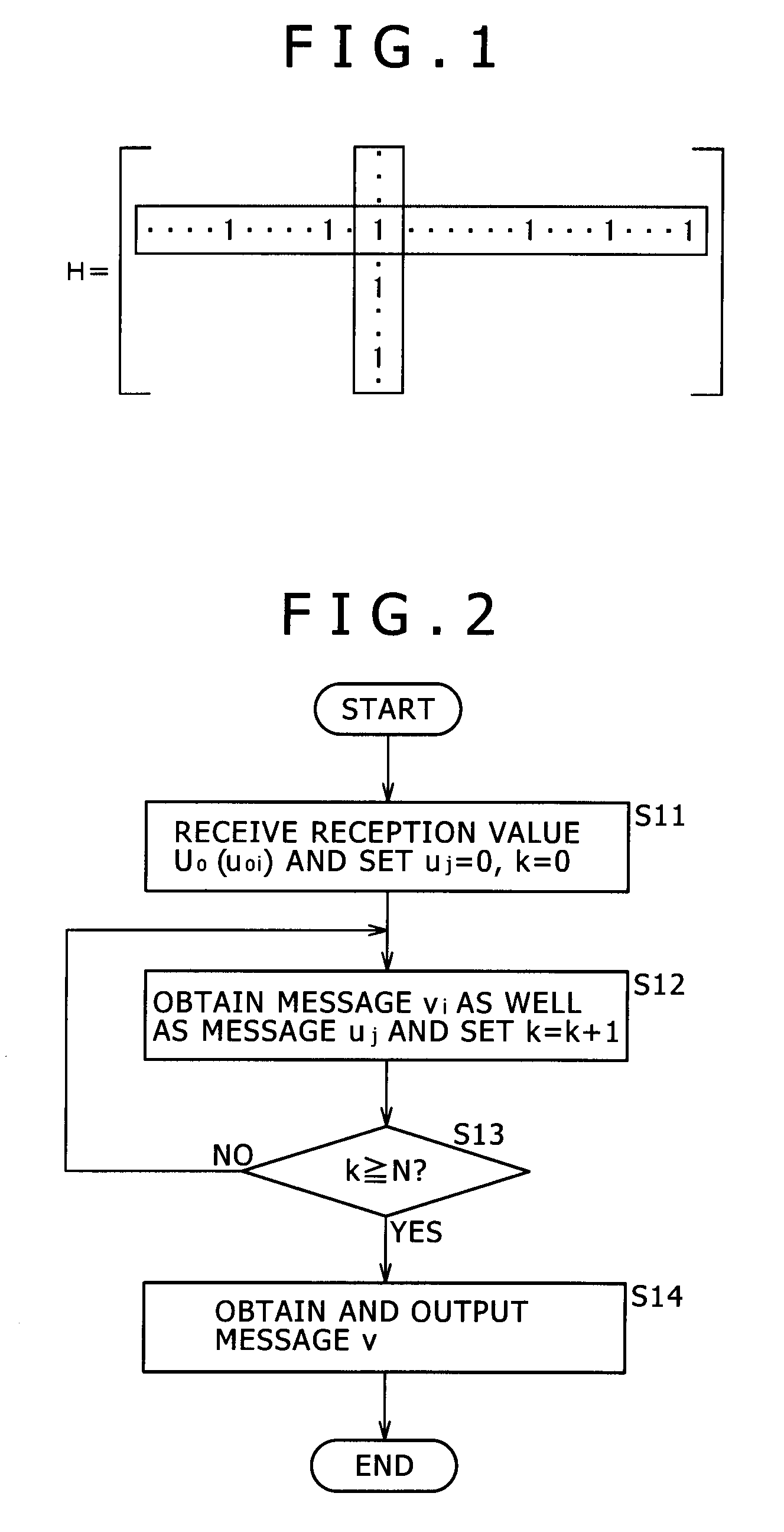

ActiveUS20100306627A1Fast convergenceModulated-carrier systemsCode conversionParity-check matrixLow density

Disclosed herein is a receiving apparatus including a reception device configured to receive a code sequence coded in LDPC (Low Density Parity Check) and punctured at least partially as a target to be decoded; and an LDPC decoding device configured to perform a punctured matrix transform process including a first and a second process on an original parity check matrix noted to have punctured bits or symbols and used in the LDPC coding. The LDPC decoding device further performs the first process to carry out Galois field addition operations on those rows of the original parity check matrix to set the non-zero elements to zero. The LDPC decoding device further performs the second process to delete the columns rid of the non-zero elements. The LDPC decoding device uses the matrix resulting from the process as the parity check matrix for performing an LDPC decoding process on the code sequence.

Owner:SATURN LICENSING LLC

Coding device and method, decoding device and method, recording medium, and program

ActiveUS20090225861A1Picture reproducers using cathode ray tubesCode conversionFrame basedContext model

An encoding apparatus and an encoding method, a decoding apparatus and a decoding method, a recording medium, and a program suitable for encoding image signals with a higher compression ratio for transmission or accumulation. In an arithmetic coding section, from among the syntax elements of input image compression information, the frame / field flag is first encoded by a frame / field flag context model. When the macroblock to be processed is subjected to frame-based encoding, a frame-based context model, specified in the current H.26L standard, is applied. On the other hand, when the macroblock to be processed is subjected to field-based encoding, a field-based context model is applied for the syntax elements described below. The present invention is applied to an encoder for encoding image information and a decoder for decoding image information.

Owner:SONY CORP

Coding device and method, decoding device and method, recording medium, and program

ActiveUS20090225862A1Picture reproducers using cathode ray tubesCode conversionAlgorithmContext model

An encoding apparatus and an encoding method, a decoding apparatus and a decoding method, a recording medium, and a program suitable for encoding image signals with a higher compression ratio for transmission or accumulation. In an arithmetic coding section, from among the syntax elements of input image compression information, the frame / field flag is first encoded by a frame / field flag context model. When the macroblock to be processed is subjected to frame-based encoding, a frame-based context model, specified in the current H.26L standard, is applied. On the other hand, when the macroblock to be processed is subjected to field-based encoding, a field-based context model is applied for the syntax elements described below. The present invention is applied to an encoder for encoding image information and a decoder for decoding image information.

Owner:SONY CORP

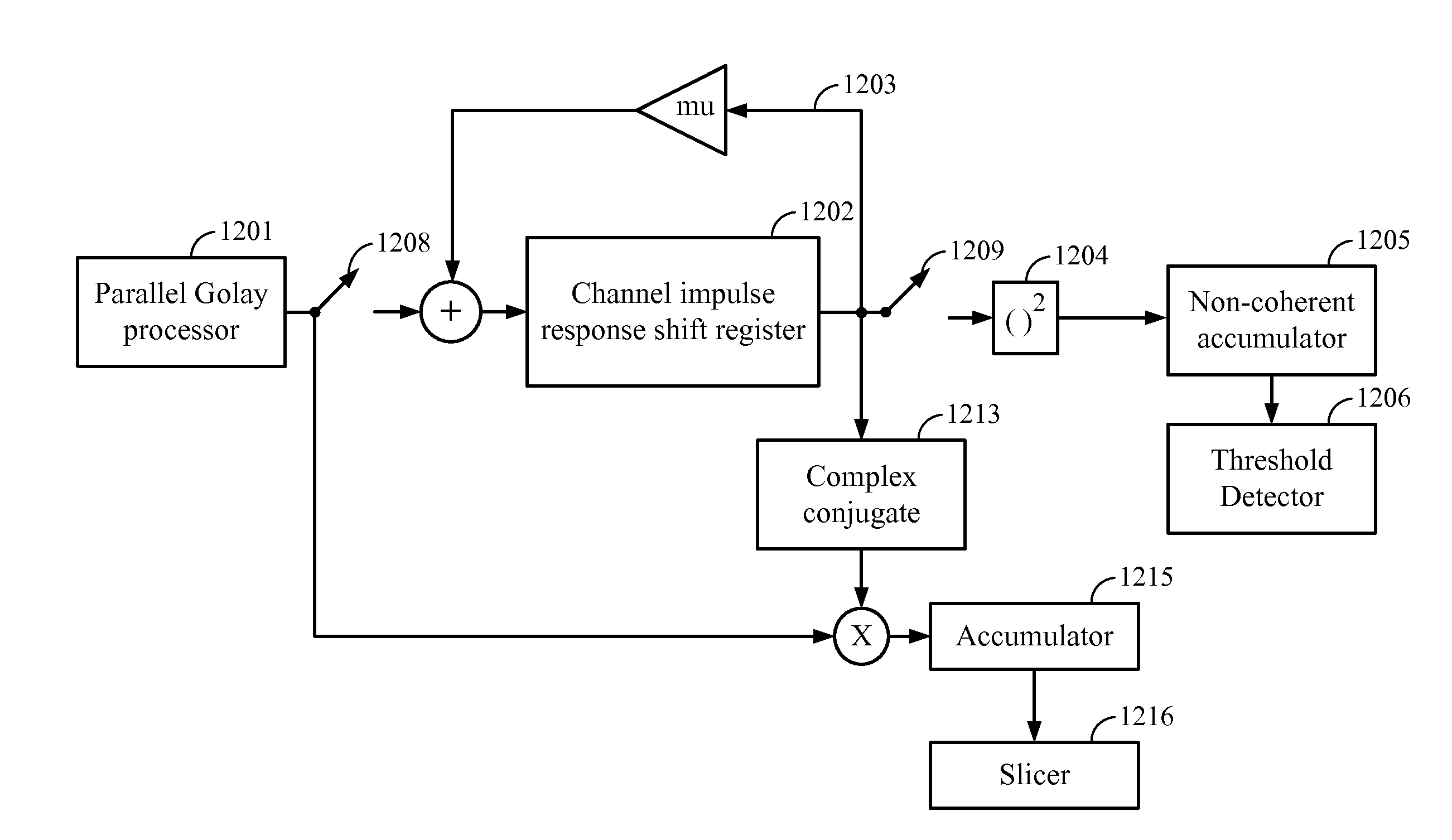

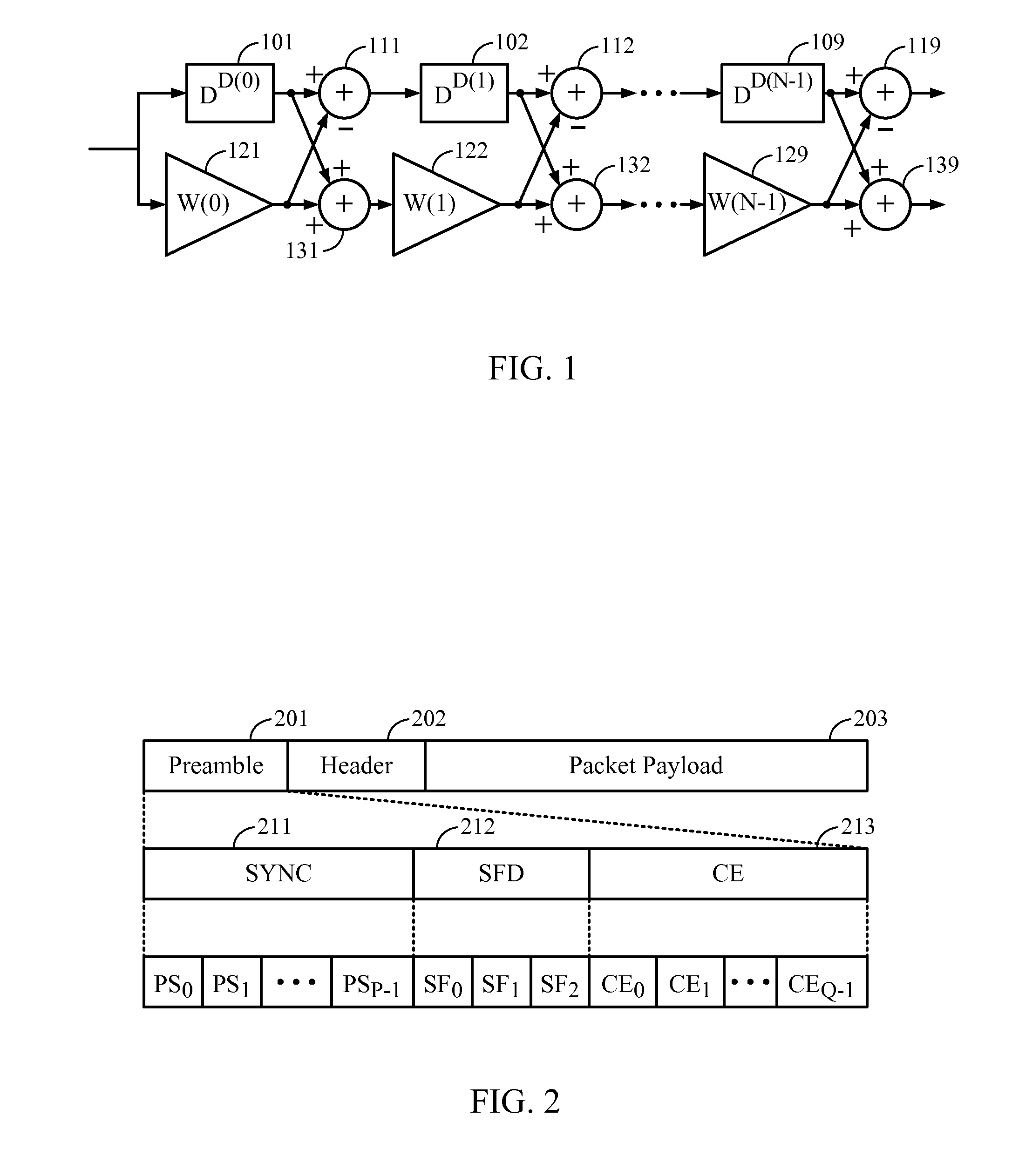

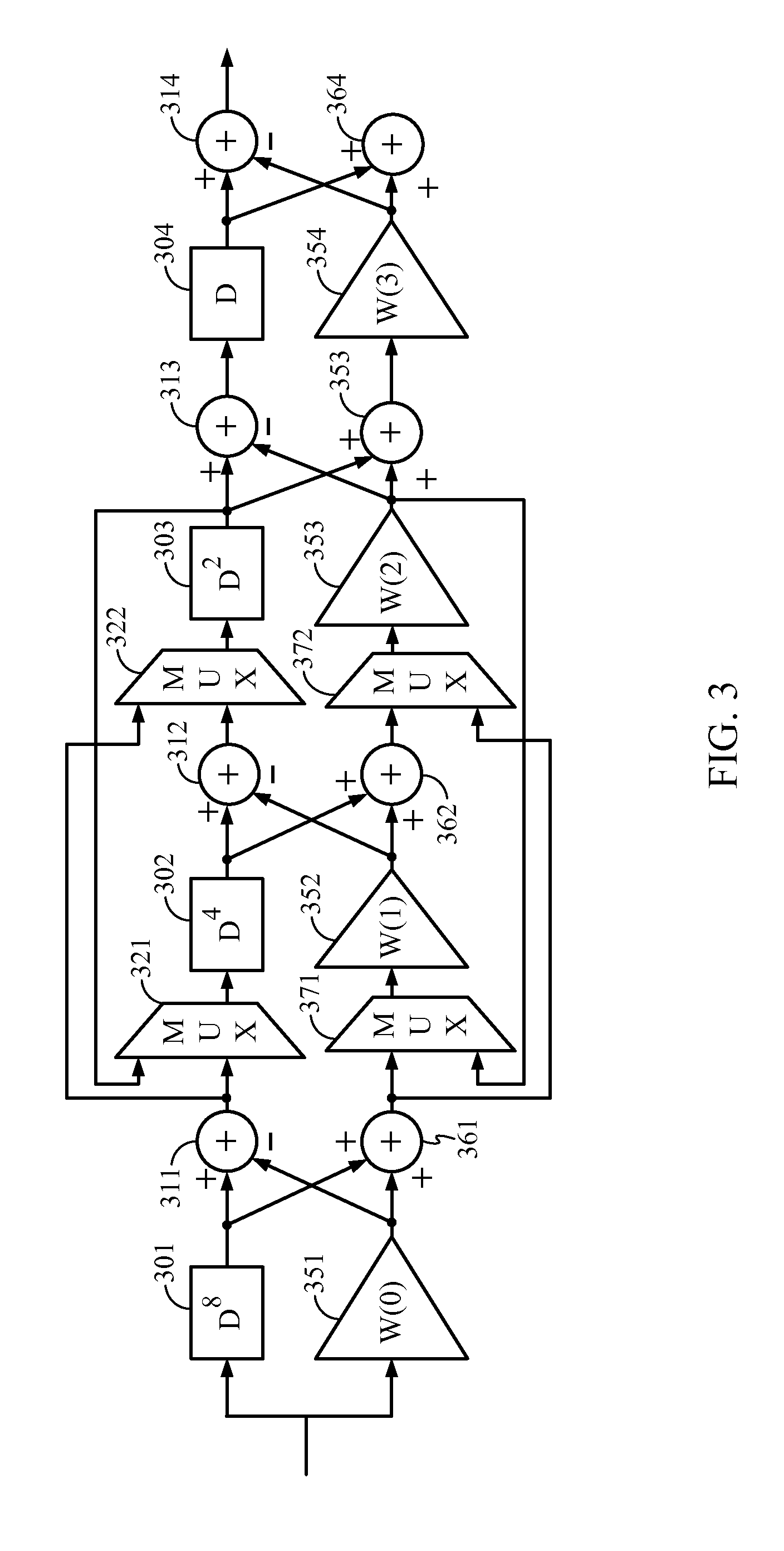

Golay-code generation

ActiveUS20110209035A1Solve complex processQuick updateCode conversionRedundant data error correctionMultiplexerComputer module

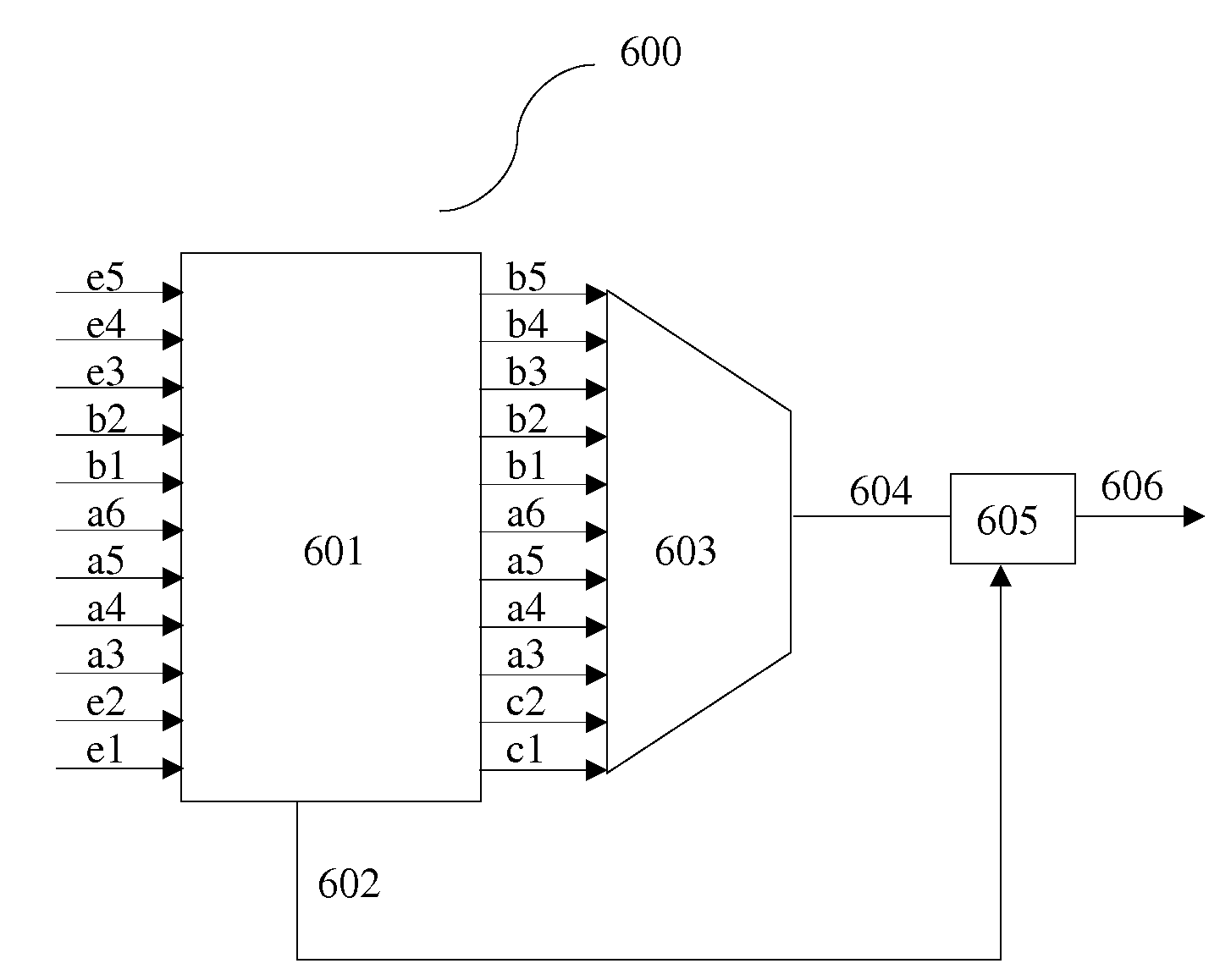

A Golay-code generator configured for generating Golay complementary code pairs comprises a sequence of delay elements configured for providing a predetermined set of fixed delays to at least a first input signal and a sequence of adaptable seed vector insertion elements configured for multiplying at least a second input signal by a variable seed vector, wherein each of a plurality of seed vectors corresponds to at least one predetermined piconet. The Golay-code generator may further comprise multiplexers configured for switching inputs and outputs of at least two delay elements in the sequence of delay elements to produce a plurality of compatible delay vectors. The Golay-code generator may further comprise a code-truncation module configured to shorten the Golay complementary code pairs for producing a plurality of daughter codes. This Abstract is provided for the sole purpose of complying with the Abstract requirement rules that allow a reader to quickly ascertain the subject matter of the disclosure contained herein. This Abstract is submitted with the explicit understanding that it will not be used to interpret or to limit the scope or the meaning of the claims.

Owner:QUALCOMM INC

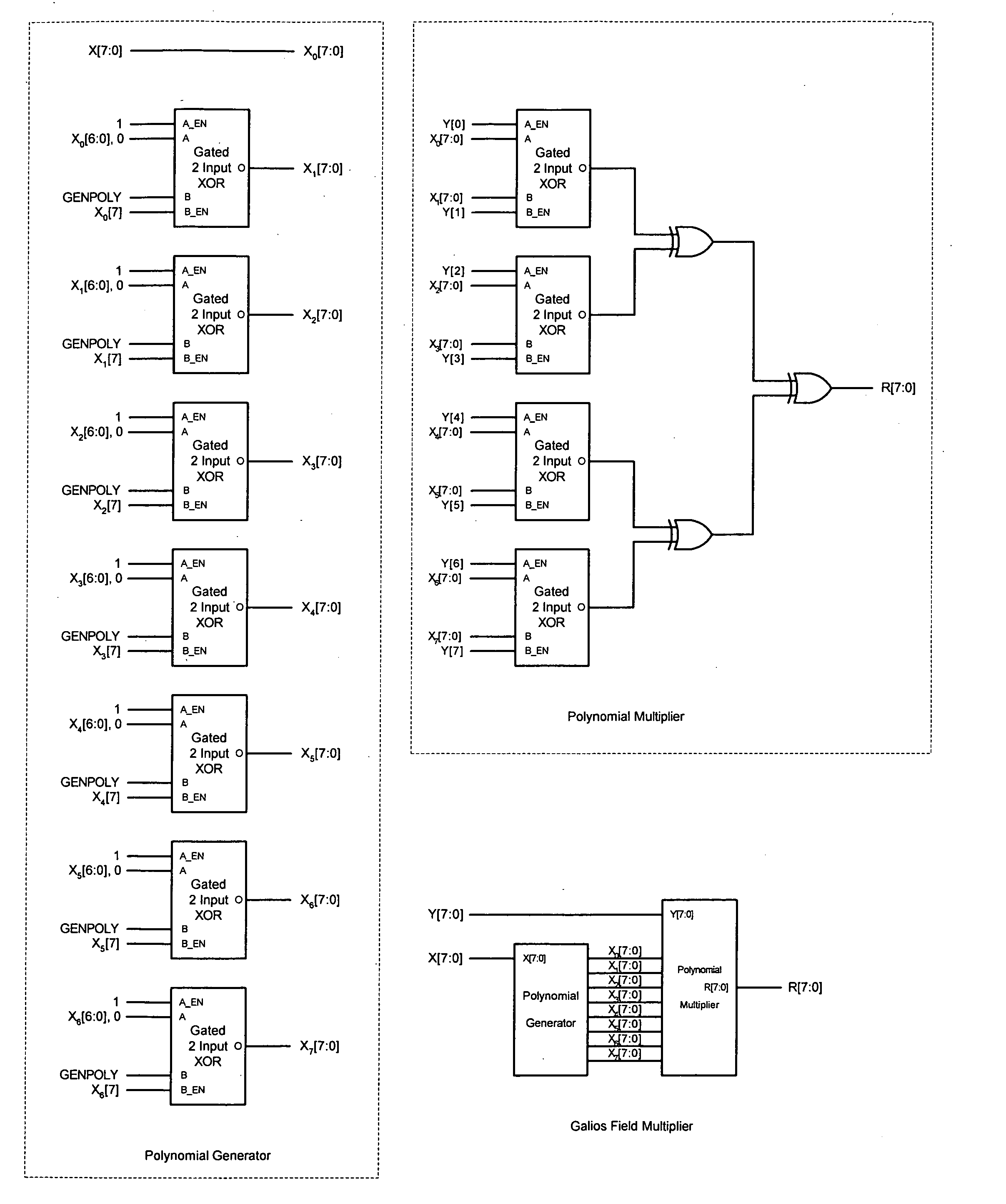

Array form reed-solomon implementation as an instruction set extension

InactiveUS20090199075A1Code conversionRedundant data error correctionRandom access memoryTheoretical computer science

A parallelized or array method is developed for the generation of Reed Solomon parity bytes which utilizes multiple digital logic operations or computer instructions implemented using digital logic. At least one of the operations or instructions used performs the following combinations of steps: a) provide an operand representing N feedback terms where N is greater than one, b) computation of N by M Galios Field polynomial multiplications where M is greater than one, and c) computation of (N−1) by M Galios Field additions producing M result bytes. In this case the result bytes are used to modify the Reed Solomon parity bytes in either a separate operation or instruction or as part of the same operation.A parallelized or array method is also developed for the generation of Reed Solomon syndrome bytes which utilizes multiple digital logic operations or computer instructions implemented using digital logic. At least one of the operations or instructions performs the following combinations of steps: a) provide an operand representing N data terms where N is one or greater, b) provide an operand representing M incoming Reed Solomon syndrome bytes where M is greater than one, c) computation of N by M Galios Field polynomial multiplications, d) computation of N by M Galios Field additions producing M modified Reed Solomon syndrome bytes.The values of N and M may be selected to match the word width of the candidate MIPS microprocessor which is 32 bits or four bytes. When N and M are both have the value of four, sixteen Galios Field polynomial multiplications may be computed concurrently or sequentially in a pipeline. Each Galios Field polynomial multiplication utilizes a coefficient delivered from a memory device, which in a preferred embodiment, would be implemented either by a read only memory (ROM), random access memory (RAM) or a register file. The generation of Reed Solomon parity bytes requires several iterations each time using previous modified Reed Solomon parity bytes as incoming Reed Solomon parity bytes. Similarly, the generation of Reed Solomon syndrome bytes requires several iterations each time using previous modified Reed Solomon syndrome bytes as incoming Reed Solomon syndrome bytes.

Owner:DEMJANENKO VICTOR +1

SDRAM convolutional interleaver with two paths

ActiveUS20080256417A1Simple technologyEfficient implementationCode conversionCyclic codesAccess timeComputer science

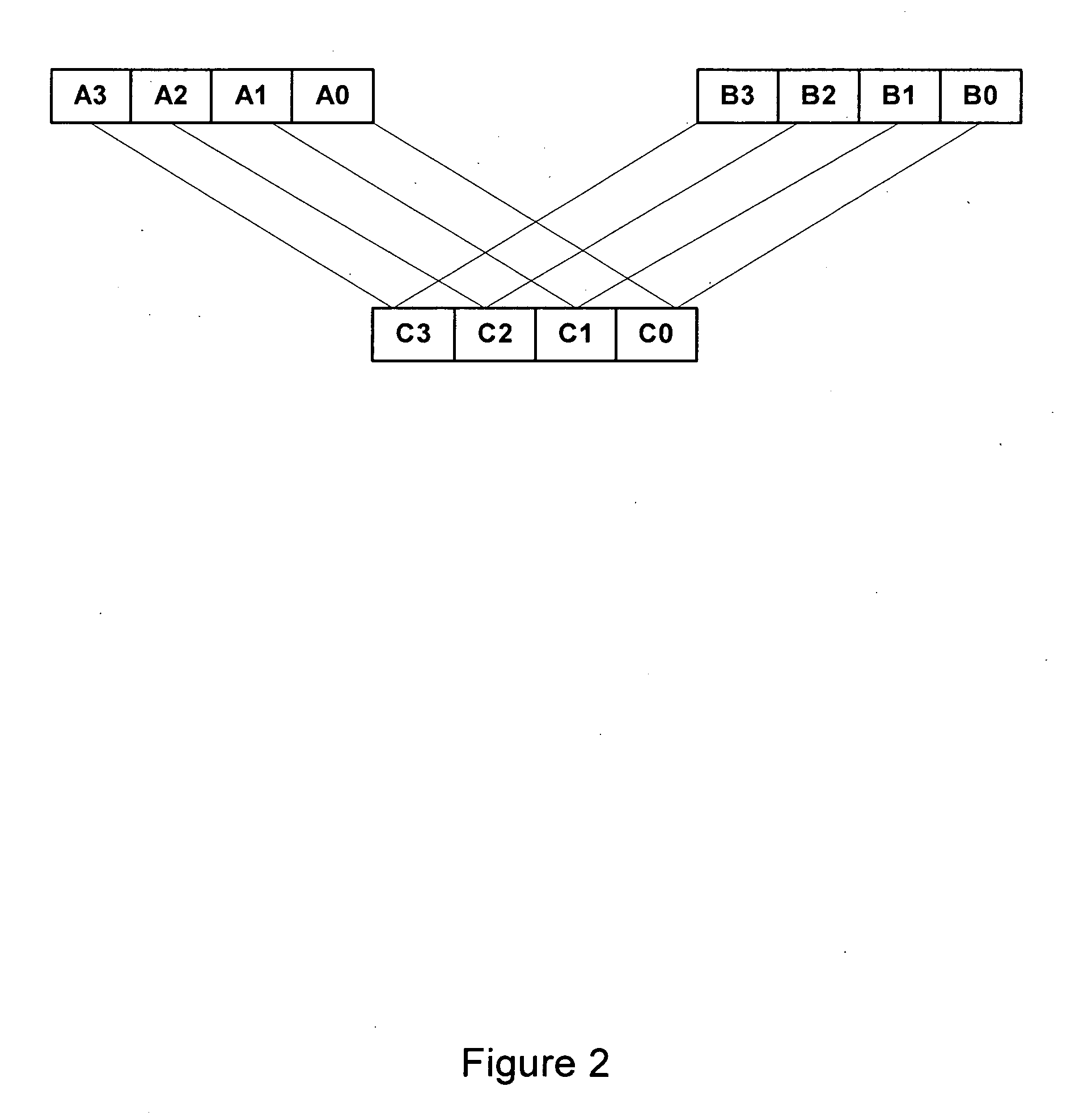

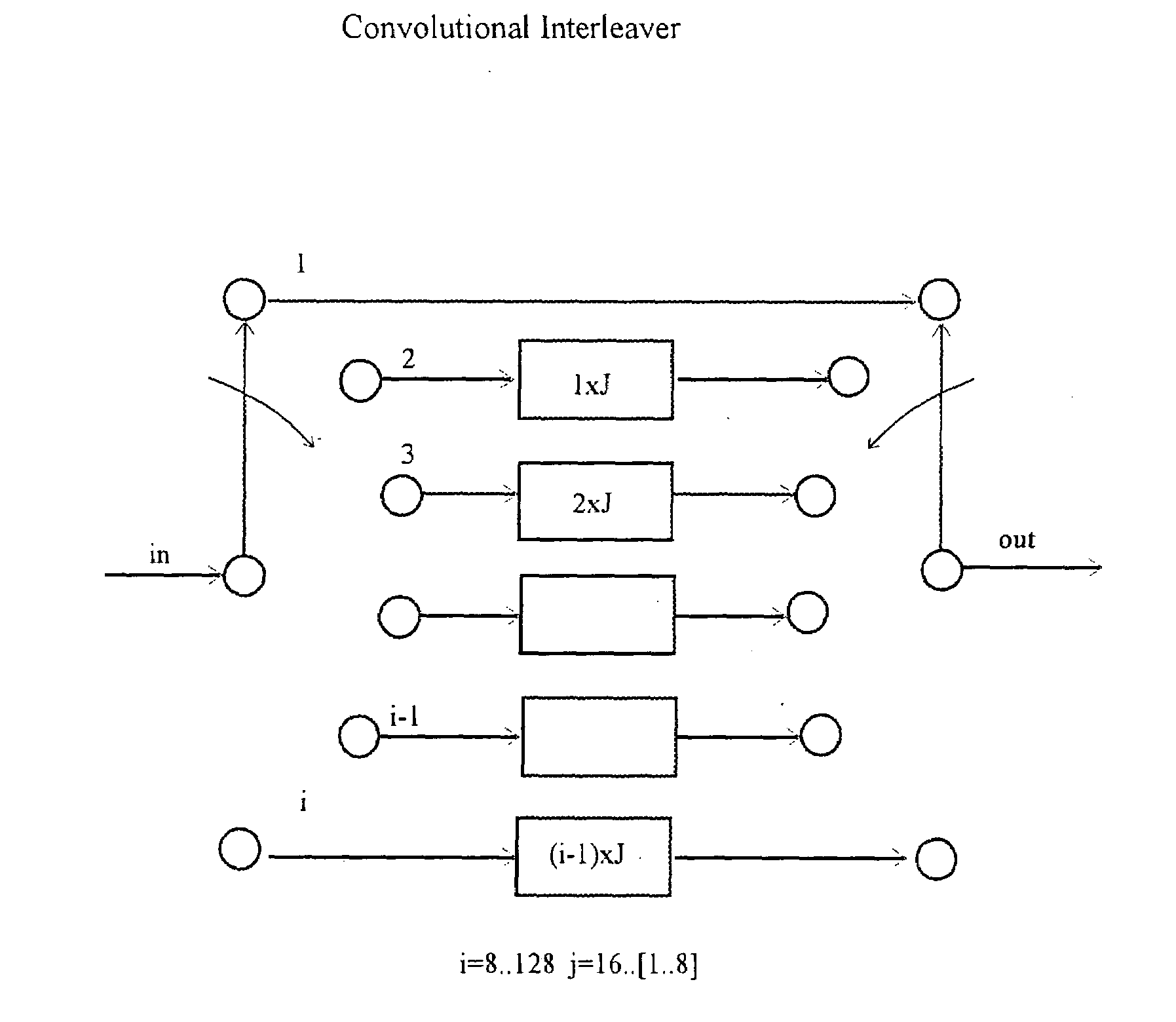

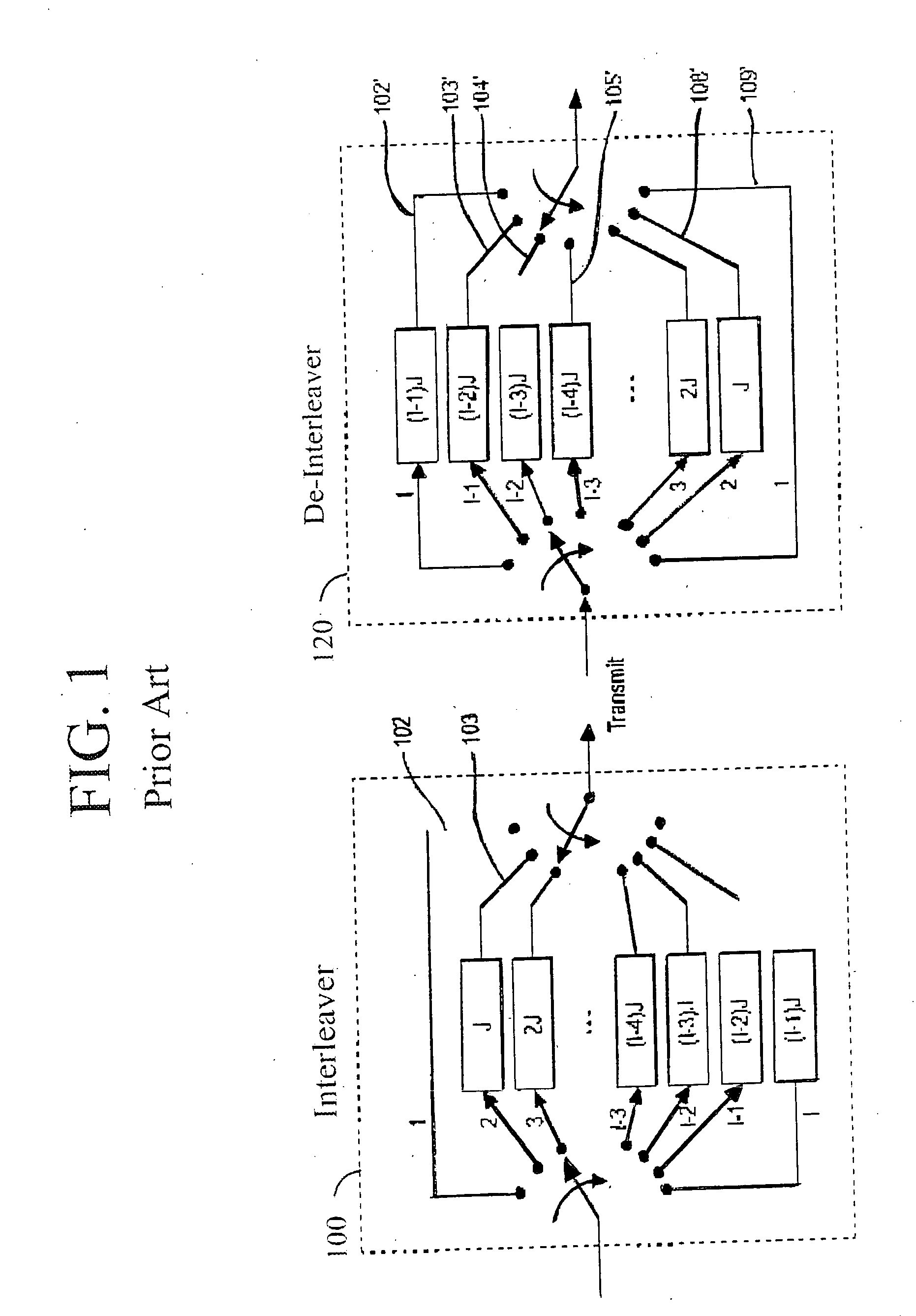

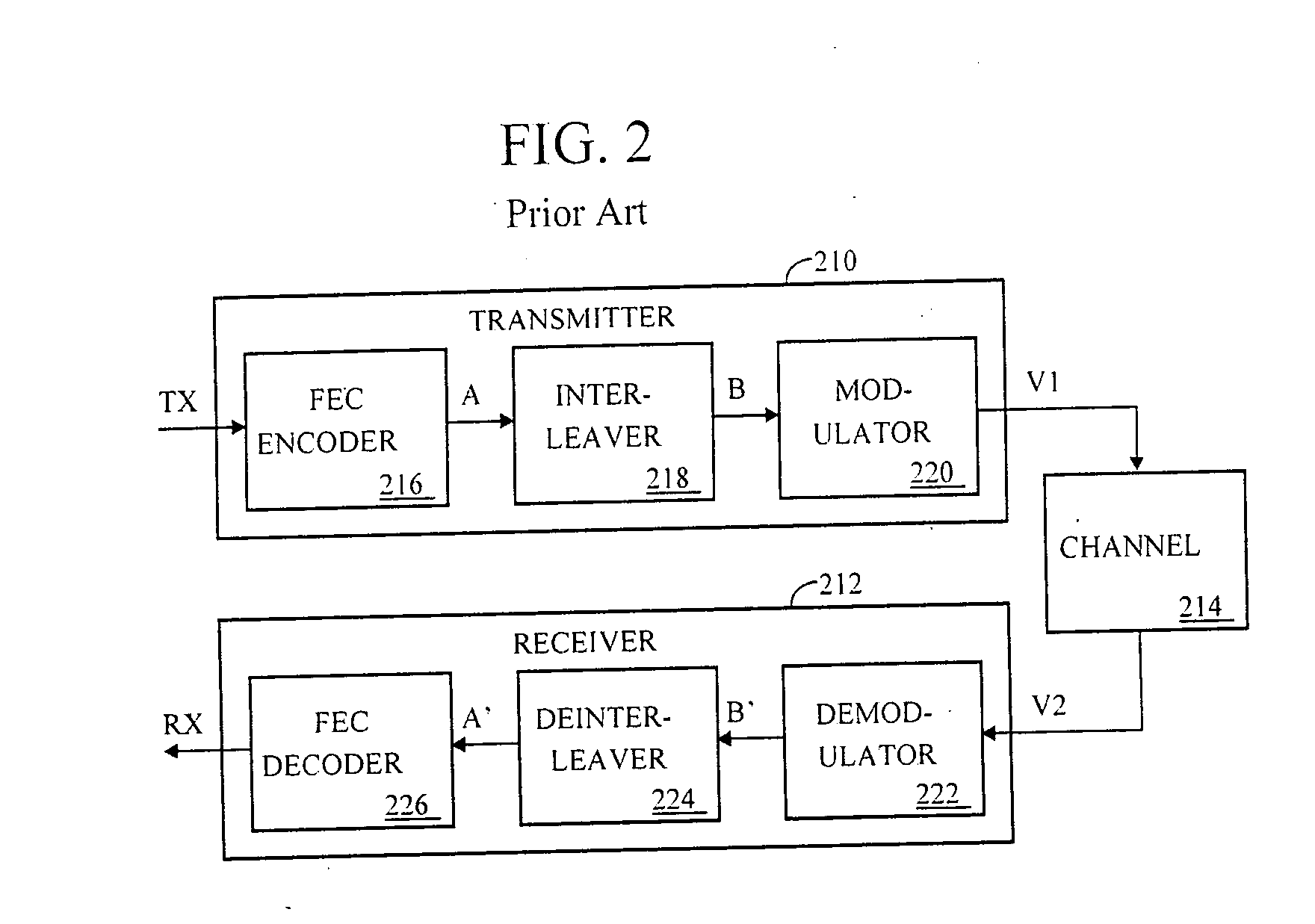

An SDRAM convolutional interleaver with two paths. Symbols are assigned to a given one of the two paths, then are sorted to minimize (to one) a number of breaks in a sequential Interleaver write address. After sorting, the symbols are stored staggered in SRAM and burst written to SDRAM. Before writing to SDRAM, data is accumulated for four symbols at a time, and the data is written four symbols wide to optimize SDRAM access time. 8 bit symbols are written 32 bits at a time to SDRAM.

Owner:IMAGINE COMM

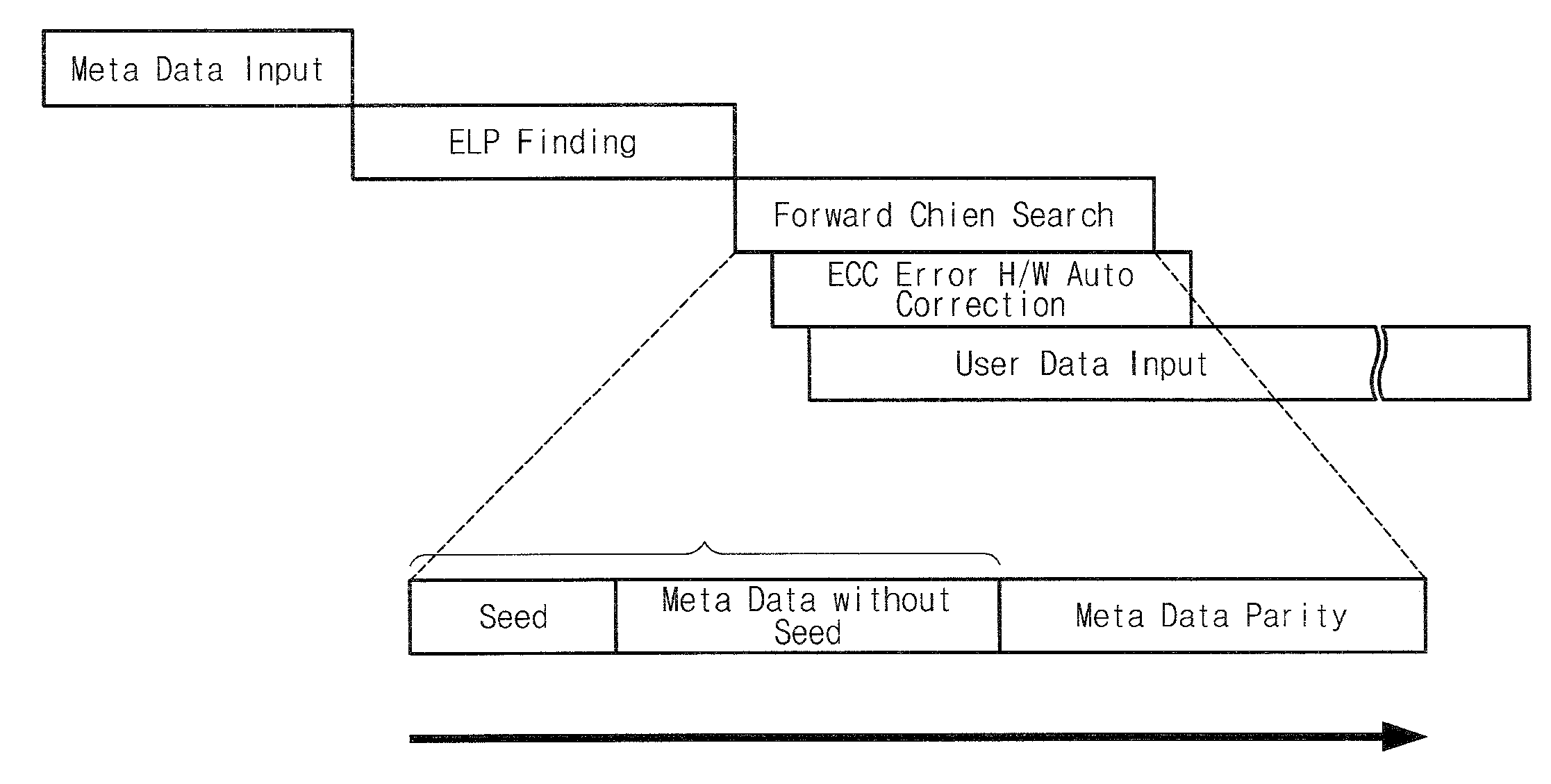

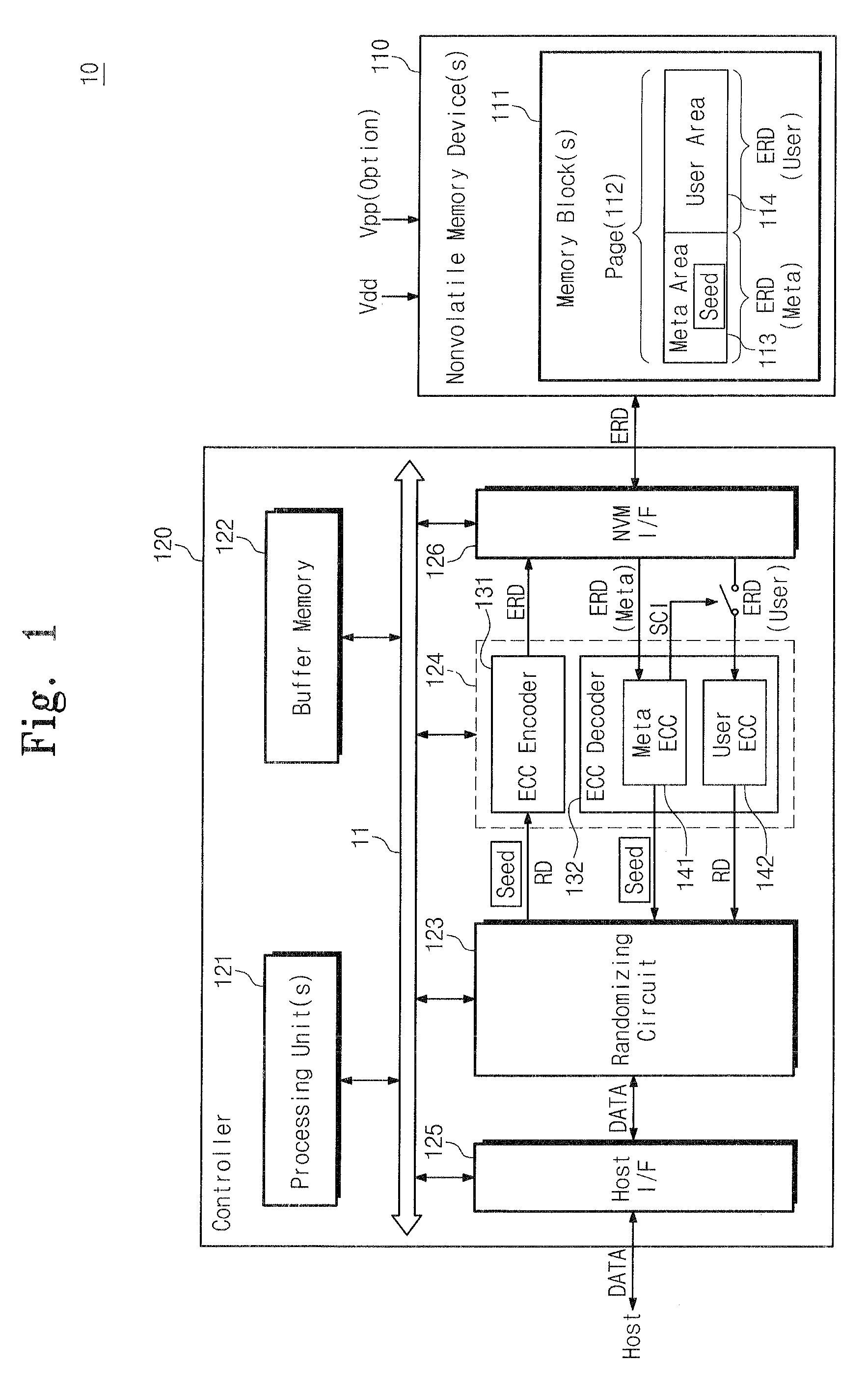

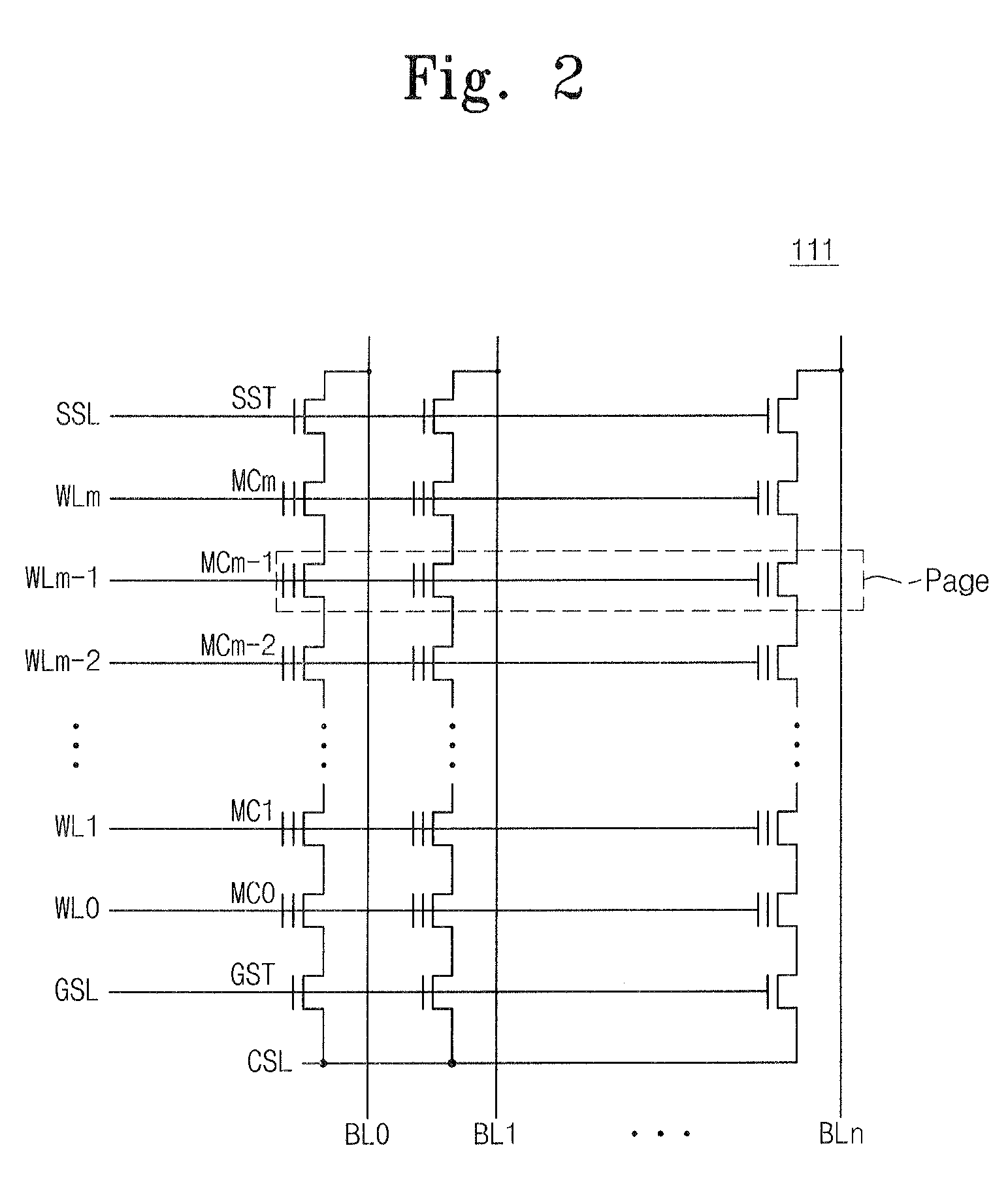

Memory system and error correction method

ActiveUS20120284589A1Described being slowCode conversionSingle error correctionCorrection methodError correcting

Disclosed is an error correcting method which includes detecting an error of meta data having a seed used to randomize user data; correcting the error of the meta data when the error is detected from the meta data; receiving the user data based upon seed confirmation information associated with an error existence of the seed or an error correction result of the seed; detecting an error of the user data; and correcting the error of the user data when the error is detected from the user data.

Owner:SAMSUNG ELECTRONICS CO LTD

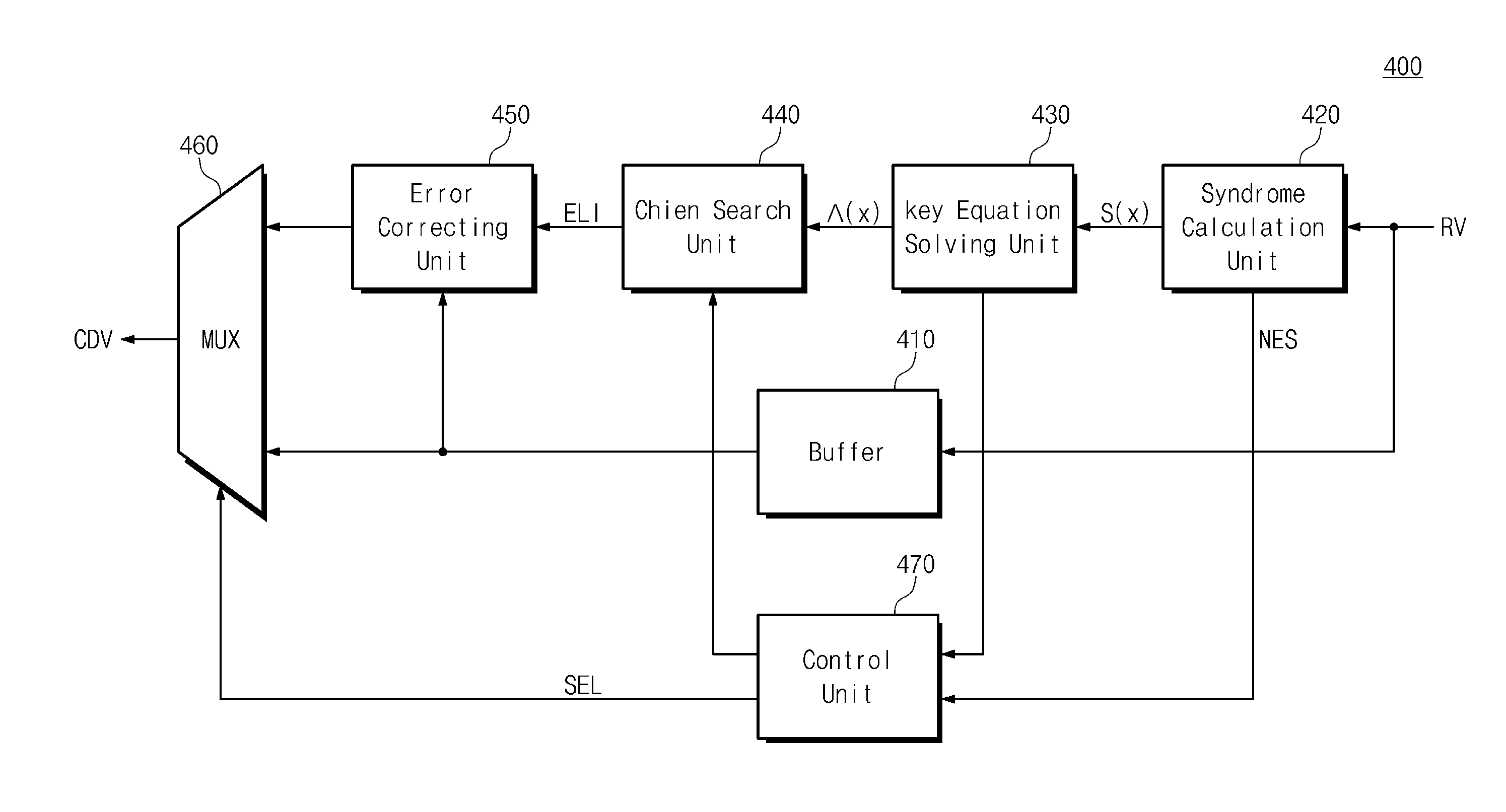

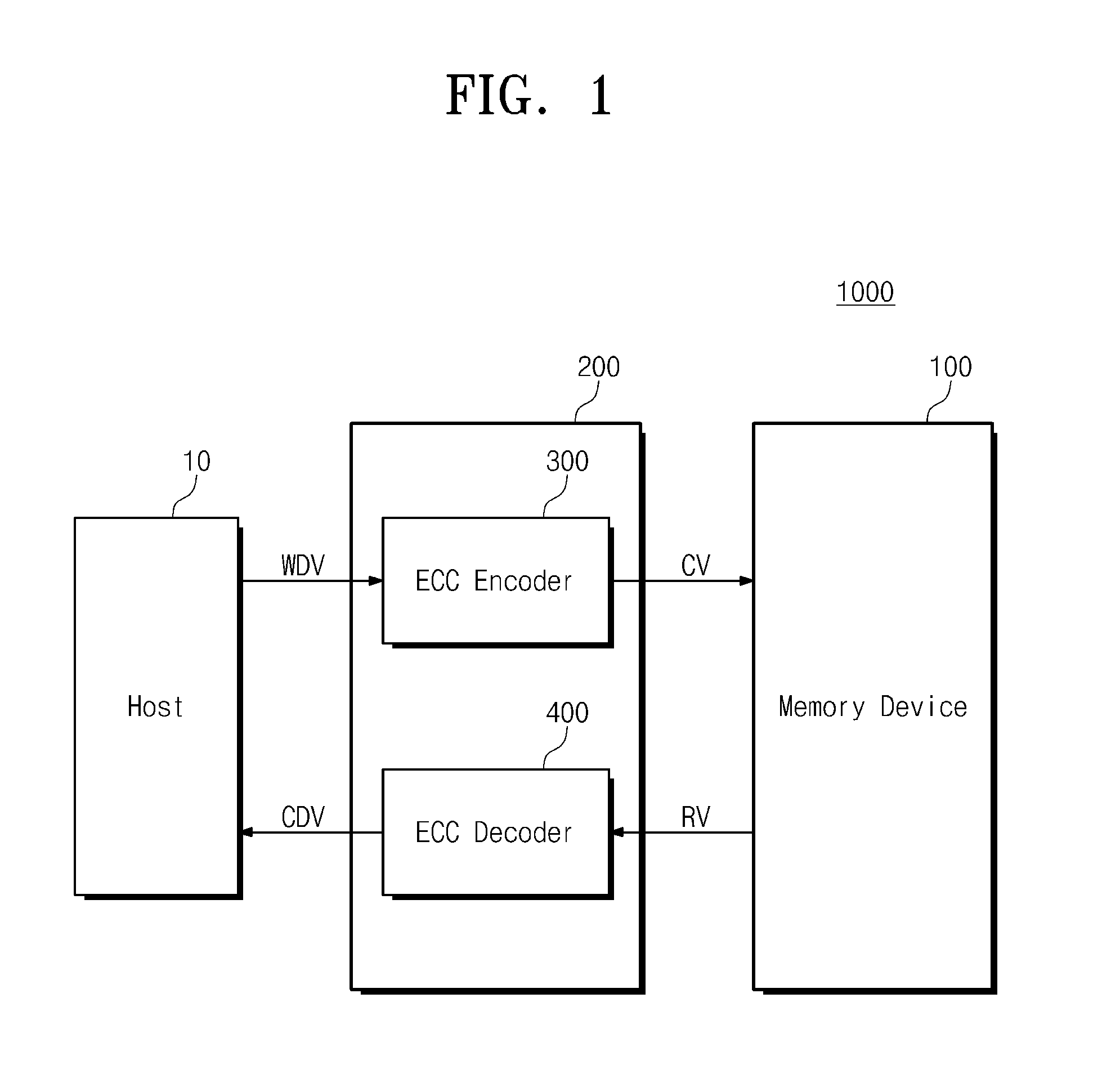

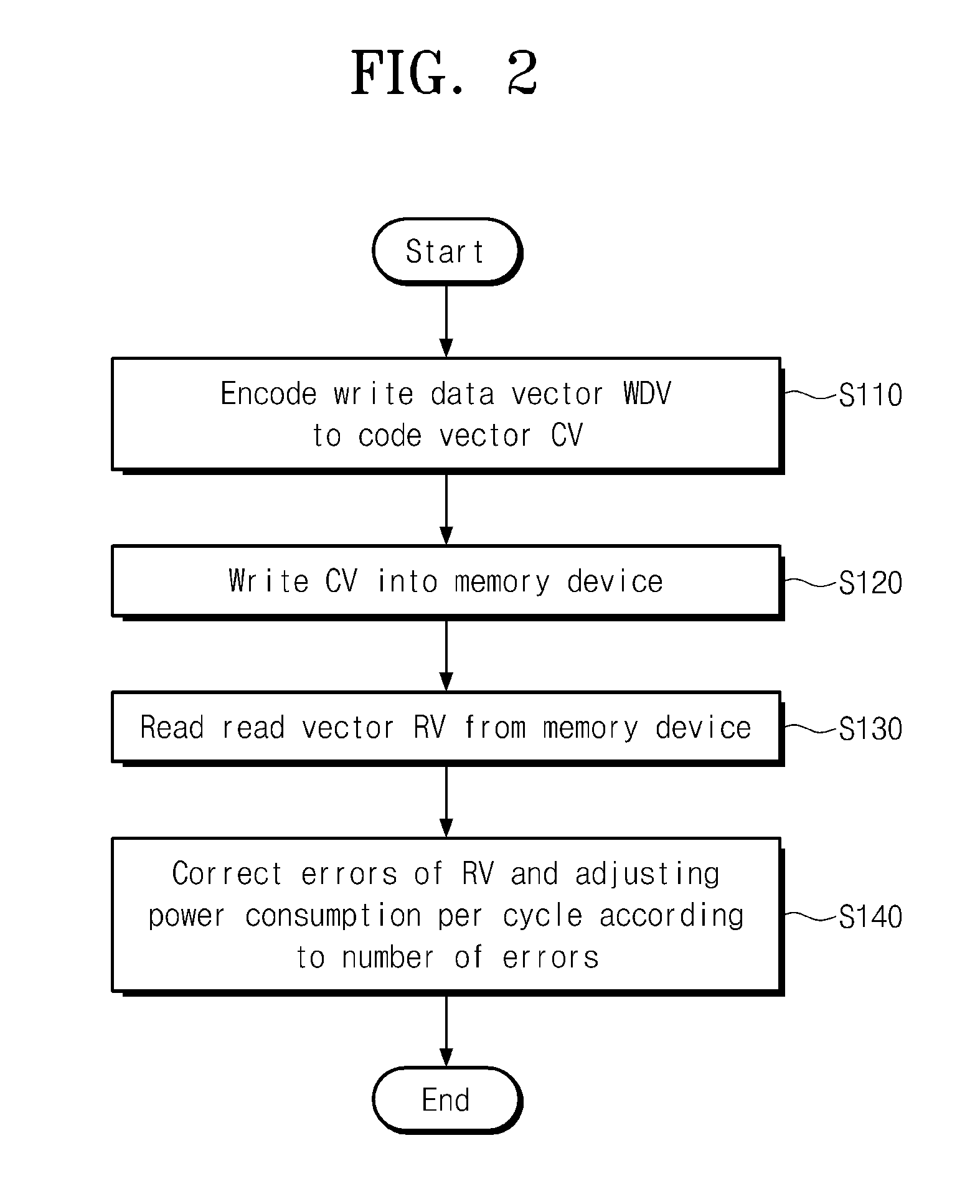

Memory controller and operating method of memory controller

ActiveUS20120290901A1Reduce consumptionEnergy efficient ICTDigital data processing detailsError locationControl memory

A controller to control a memory system including a memory device. The controlling the memory system may include calculating an error location polynomial in a received read vector with a key equation solving unit of the memory system to read data from the memory device, estimating the number of errors in the received read vector with a control unit of the memory system according to at least one of the calculated error location polynomial and information on the error location polynomial, searching error locations of the received read vector according to the calculated error location polynomial with a chien search unit of the memory system with the control unit. A cycle-per power consumption of the chien search unit may be adjusted with the control unit. A maximum correction time may be adjusted according to the number of errors of the read vector.

Owner:SAMSUNG ELECTRONICS CO LTD

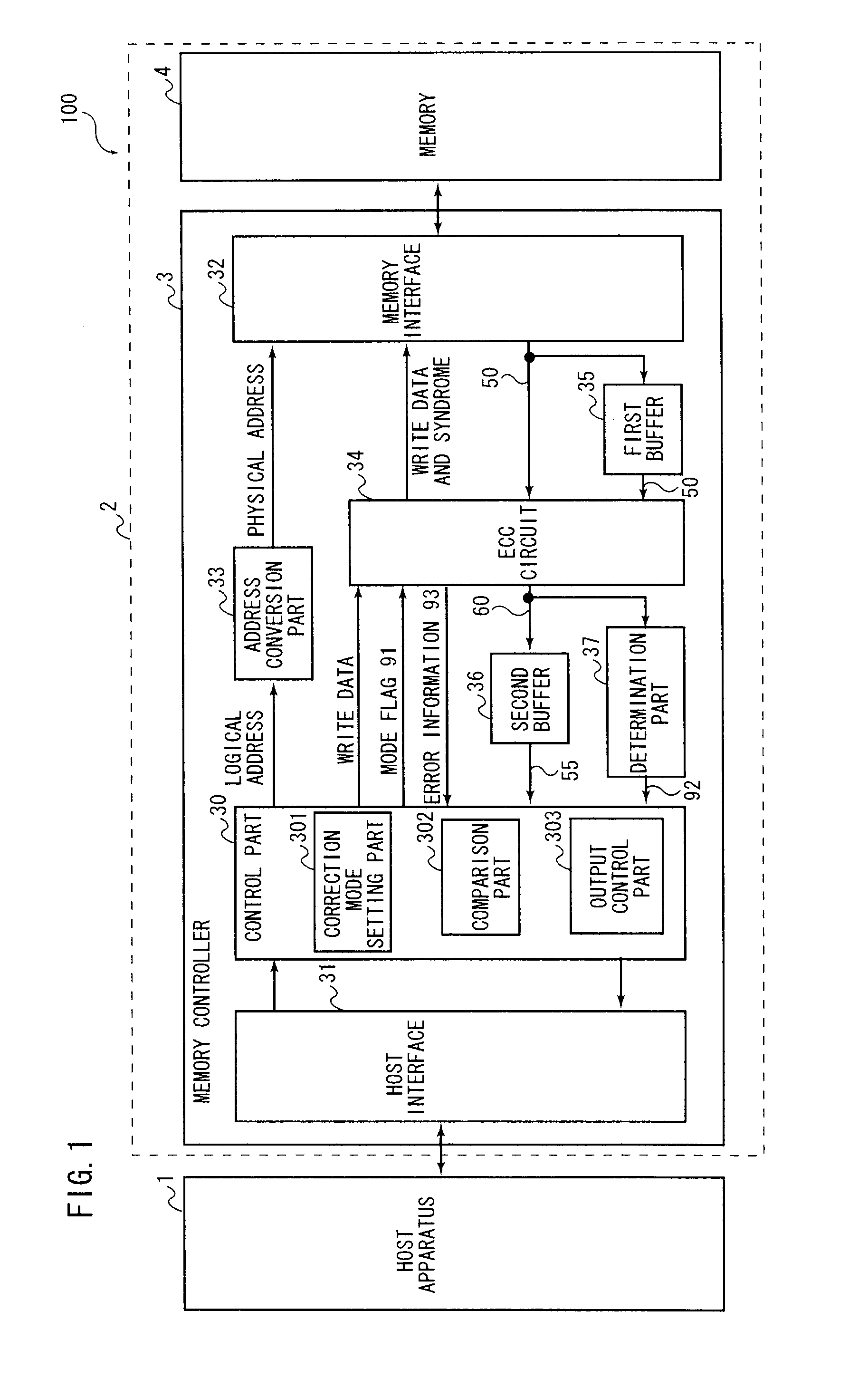

Memory controller

InactiveUS20120317463A1Improve reliabilityComplicated data managementCode conversionStatic storageSoftware engineeringTerm memory

An ECC circuit can operate in a plurality of error correction modes with different correcting capabilities for data stored in a memory. The ECC circuit calculates a syndrome with respect to information data in accordance with an error correction mode set by a control part and adds a syndrome of a fixed length in which dummy bits are added to the calculated syndrome, to the information data. When code data is read out, the ECC circuit performs a correction process on the code data by using the syndrome included in the code data.

Owner:MEGACHIPS

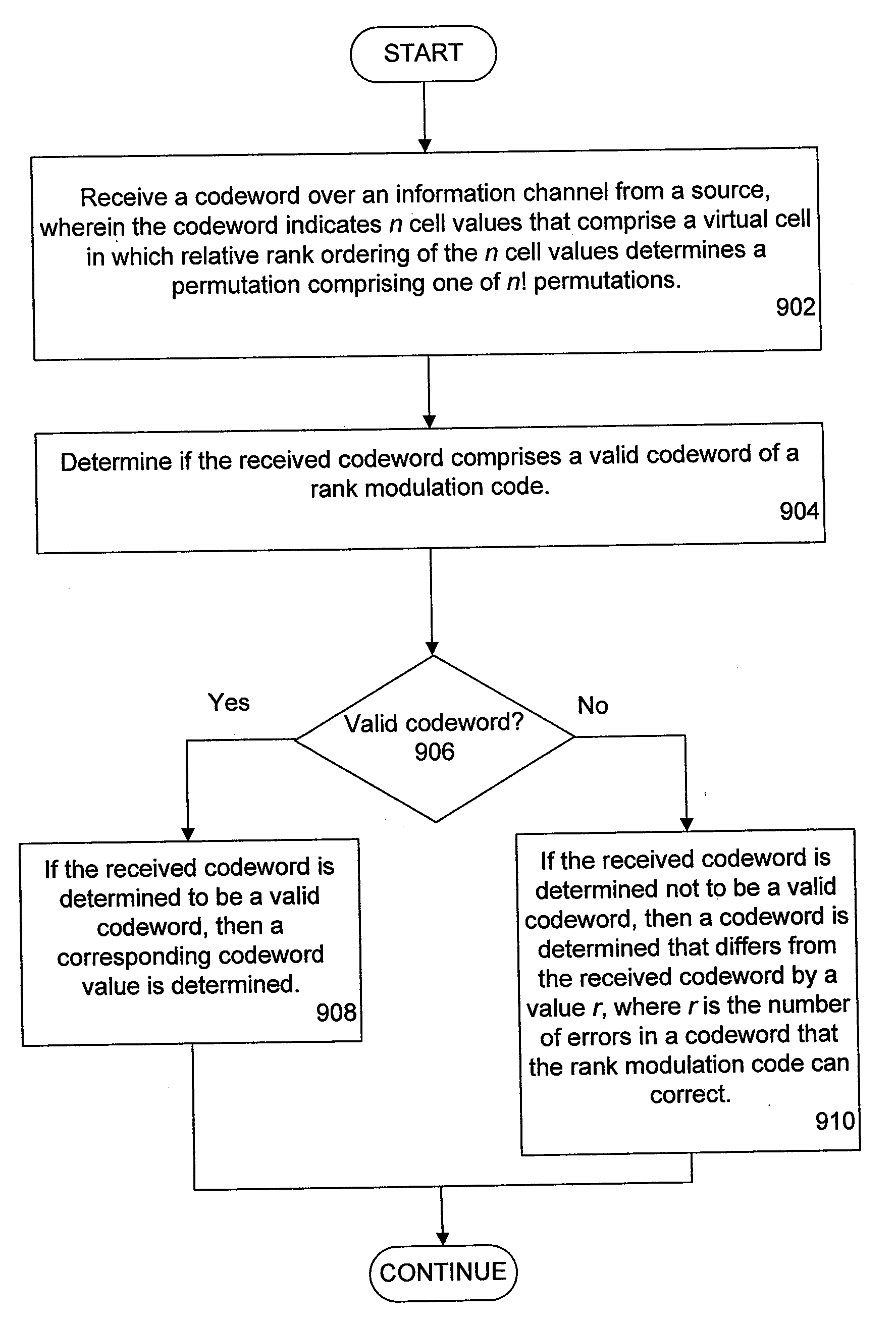

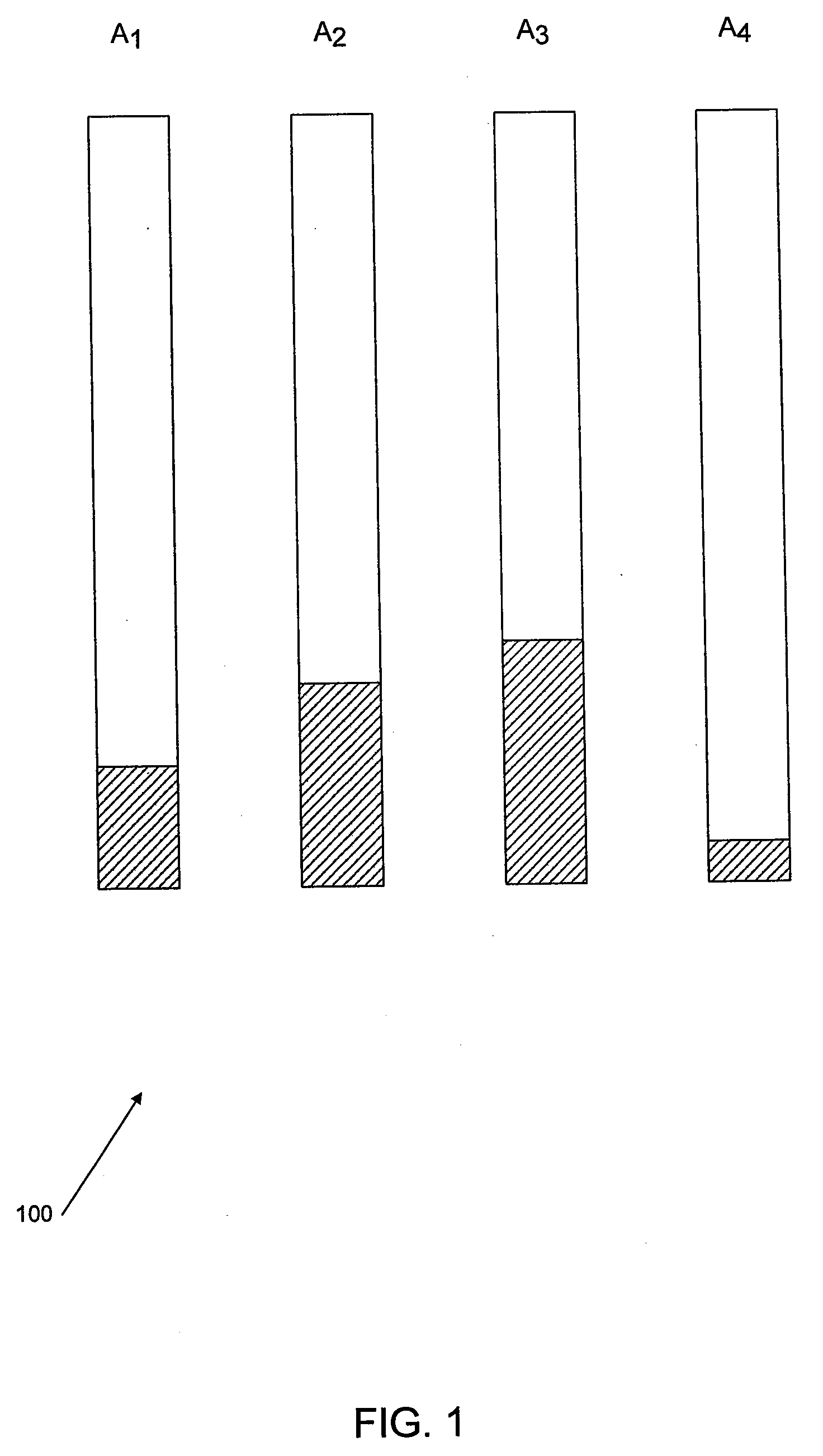

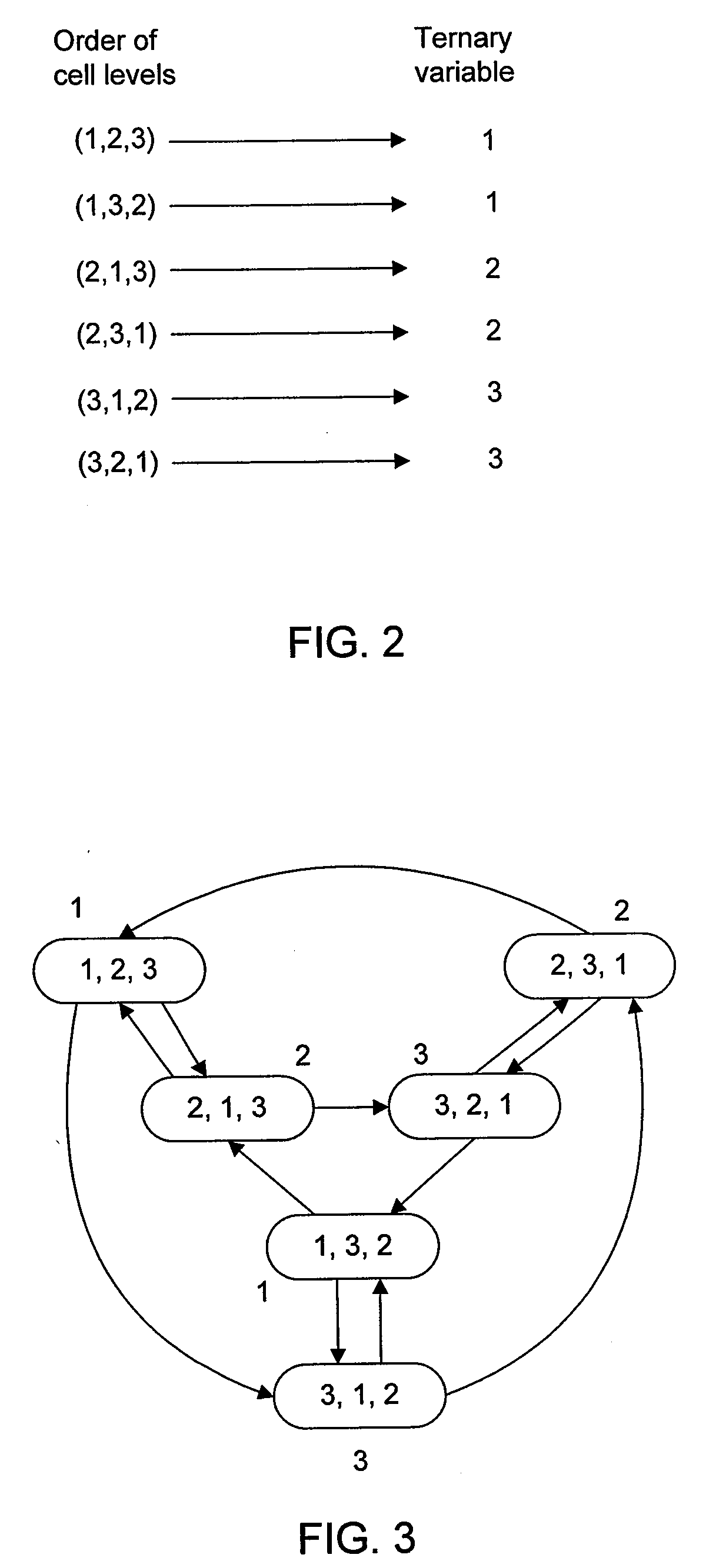

Error correcting codes for rank modulation

ActiveUS20090132895A1Eliminate riskReduce the impactError preventionRead-only memoriesArray data structureTheoretical computer science

We investigate error-correcting codes for a novel storage technology, which we call the rank-modulation scheme. In this scheme, a set of n cells stores information in the permutation induced by the different levels of the individual cells. The resulting scheme eliminates the need for discrete cell levels, and overshoot errors when programming cells (a serious problem that reduces the writing speed), as well as mitigates the problem of asymmetric errors. In this discussion, the properties of error correction in rank modulation codes are studied. We show that the adjacency graph of permutations is a subgraph of a multi-dimensional array of a special size, a property that enables code designs based on Lee-metric codes and L1-metric codes. We present a one-error-correcting code whose size is at least half of the optimal size. We also present additional error-correcting codes and some related bounds.

Owner:TEXAS A&M UNIVERSITY

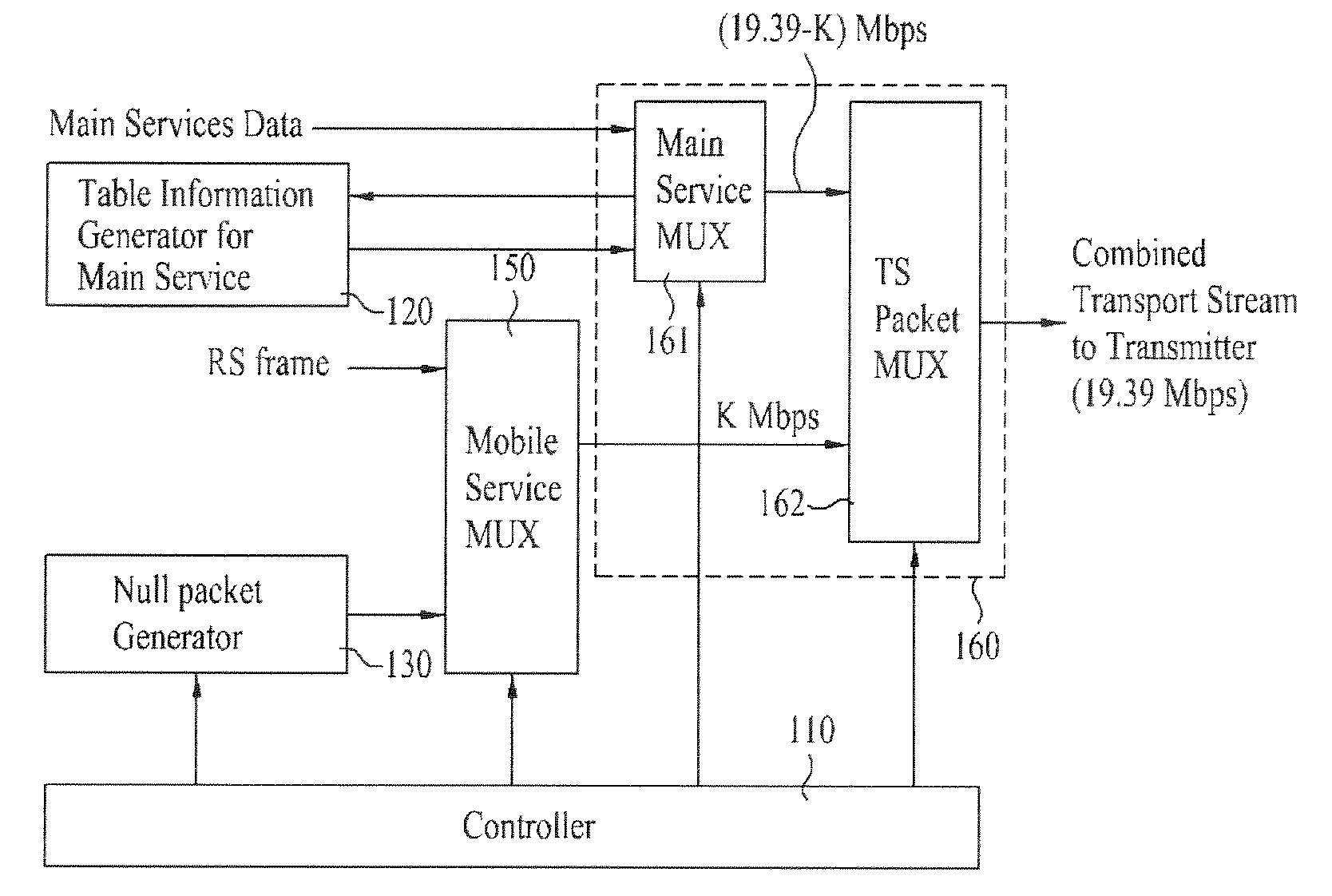

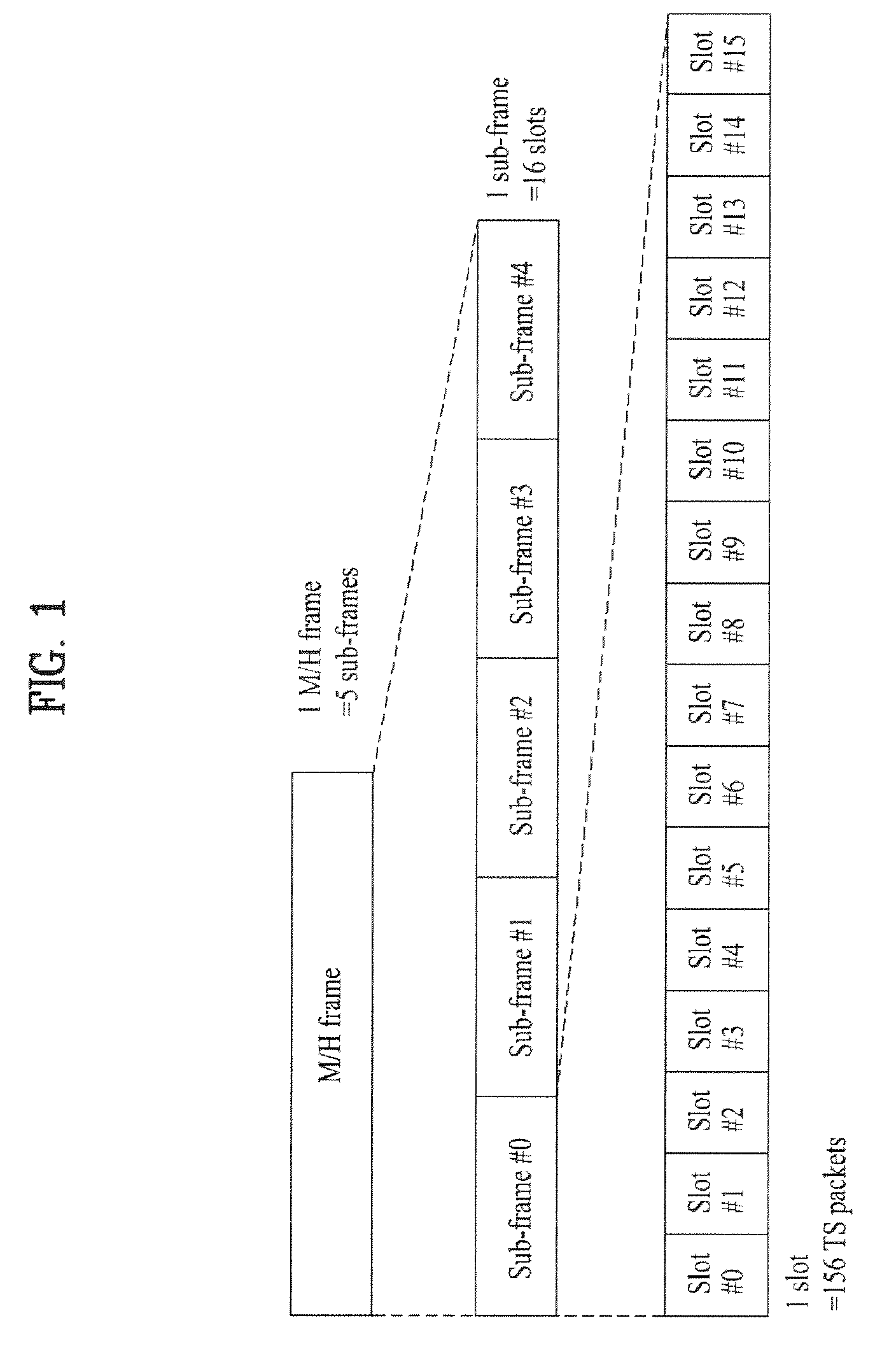

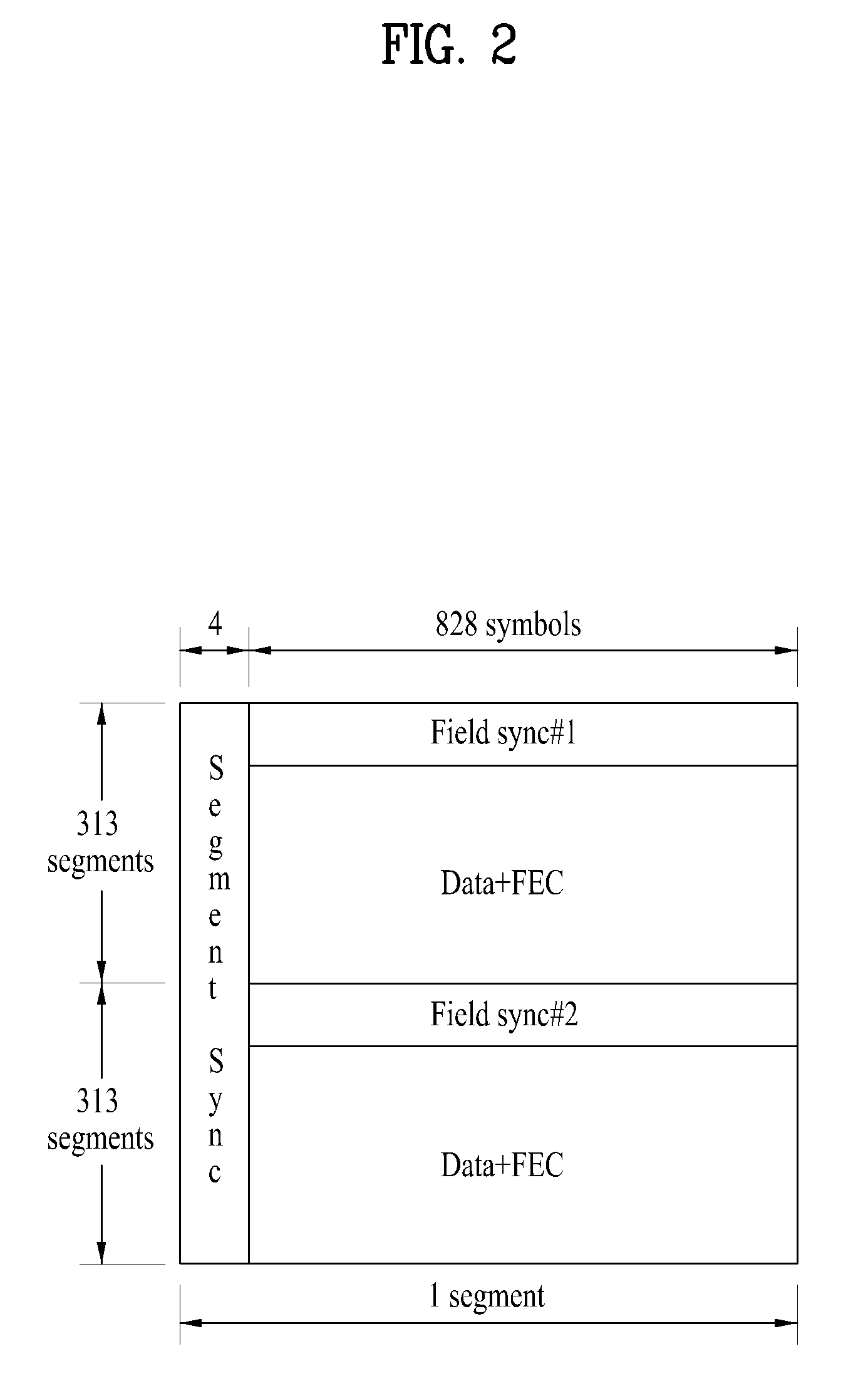

Transmitting/receiving system and method of processing broadcasting signal in transmitting/receiving system

ActiveUS20100306618A1Improve reception performanceBroadcast-related systemsCode conversionComputer hardwareBroadcasting

A transmitting system, a receiving system, and a method of processing broadcast signals are disclosed. Herein, the transmitting system includes an RS frame encoder, a block processor, a group formatter, and a trellis encoding module. The RS frame encoder performs error correction encoding on an RS frame payload including mobile service data so as to form an RS frame, divides the RS frame into a plurality of portions, and outputs the divided RS frame portions. The block processor performs one of ½-rate encoding and ¼-rate encoding on each bit of the mobile service data included in each portion. The group formatter maps a portion including symbols of the ¼-rate encoded mobile service data and symbols of the ½-rate encoded mobile service data to a corresponding region of a data group. And, the trellis encoding module performs trellis encoding on the symbols of the ¼-rate encoded mobile service data and the symbols of the ½-rate encoded mobile service data of the data group.

Owner:LG ELECTRONICS INC

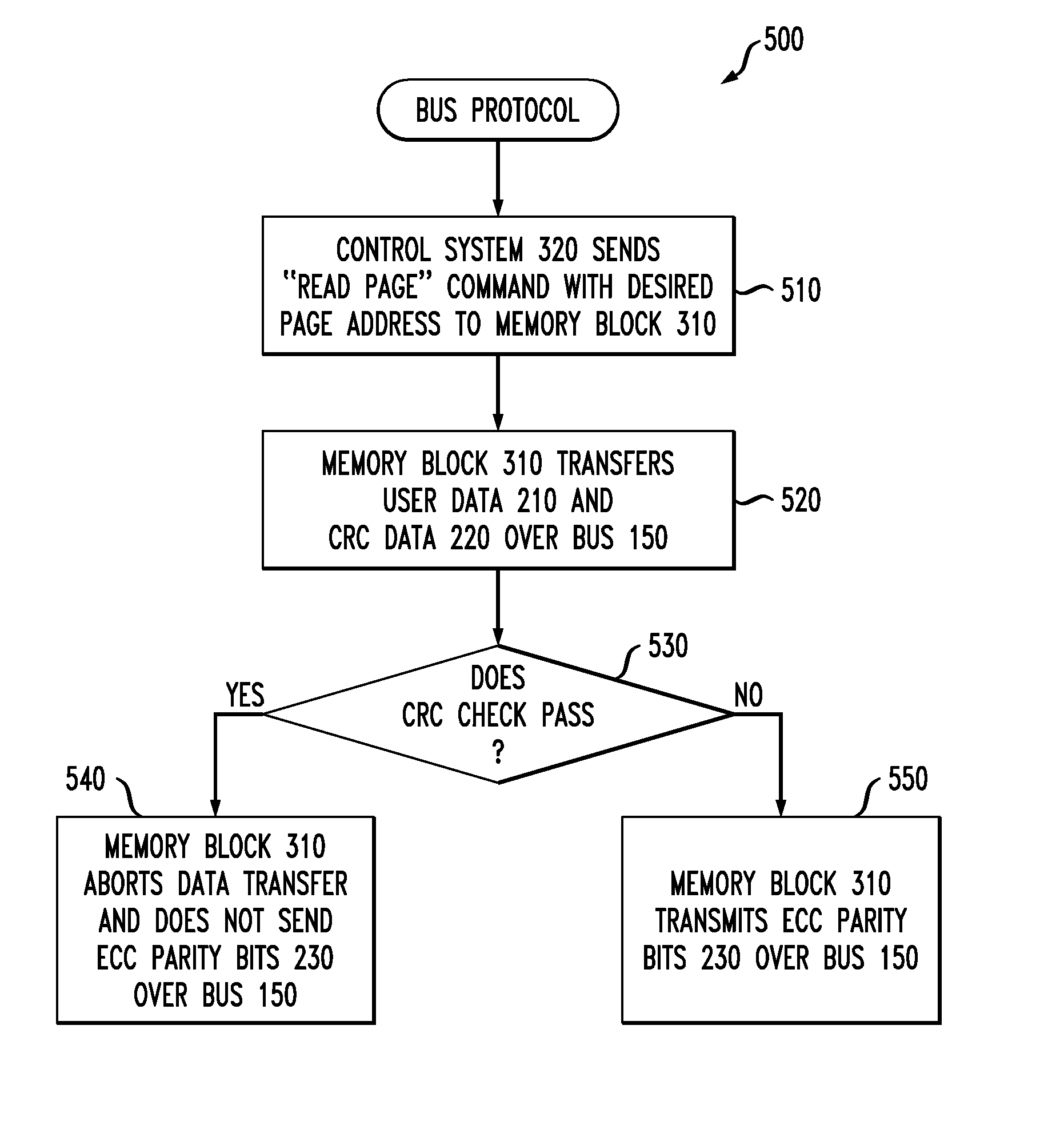

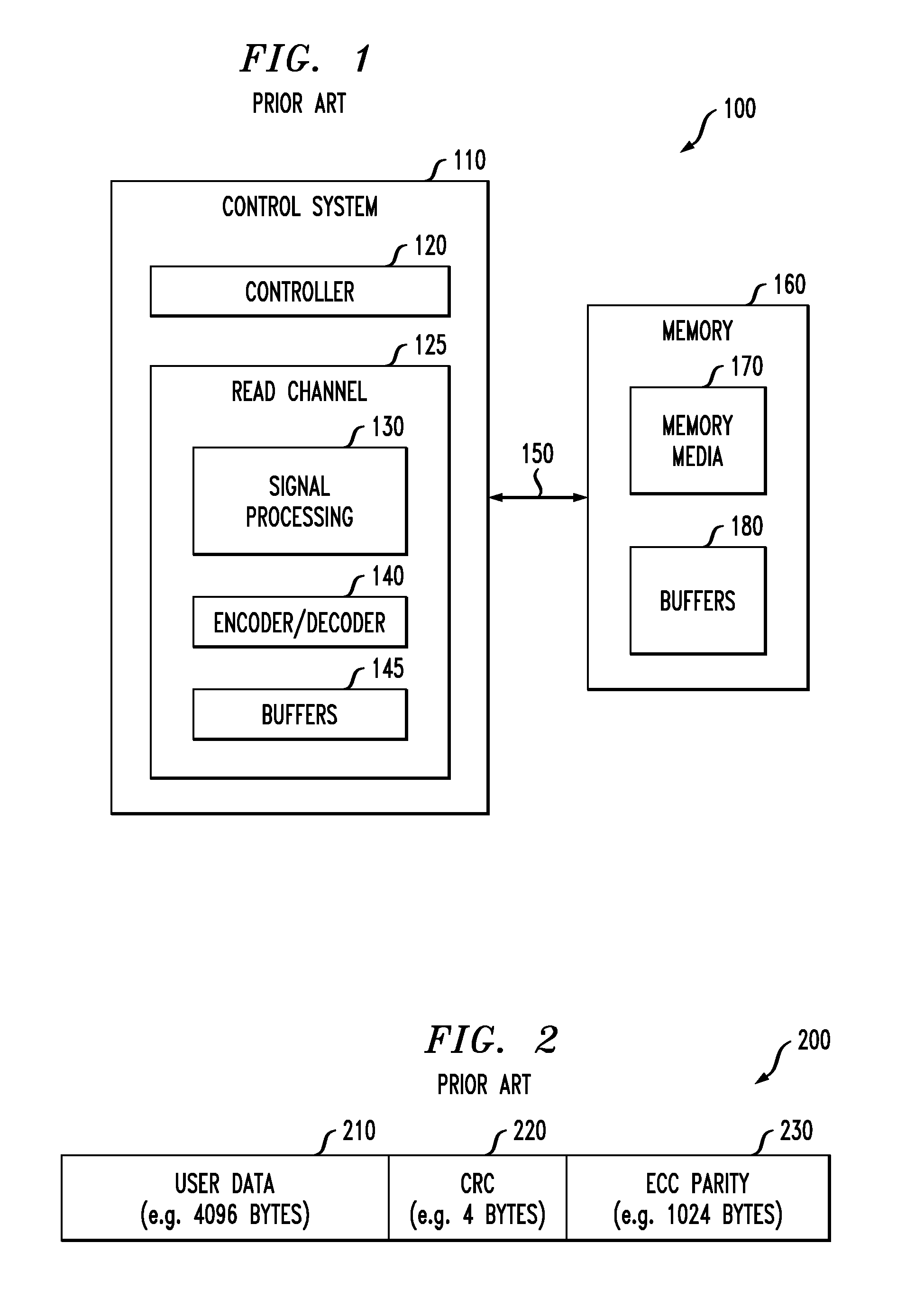

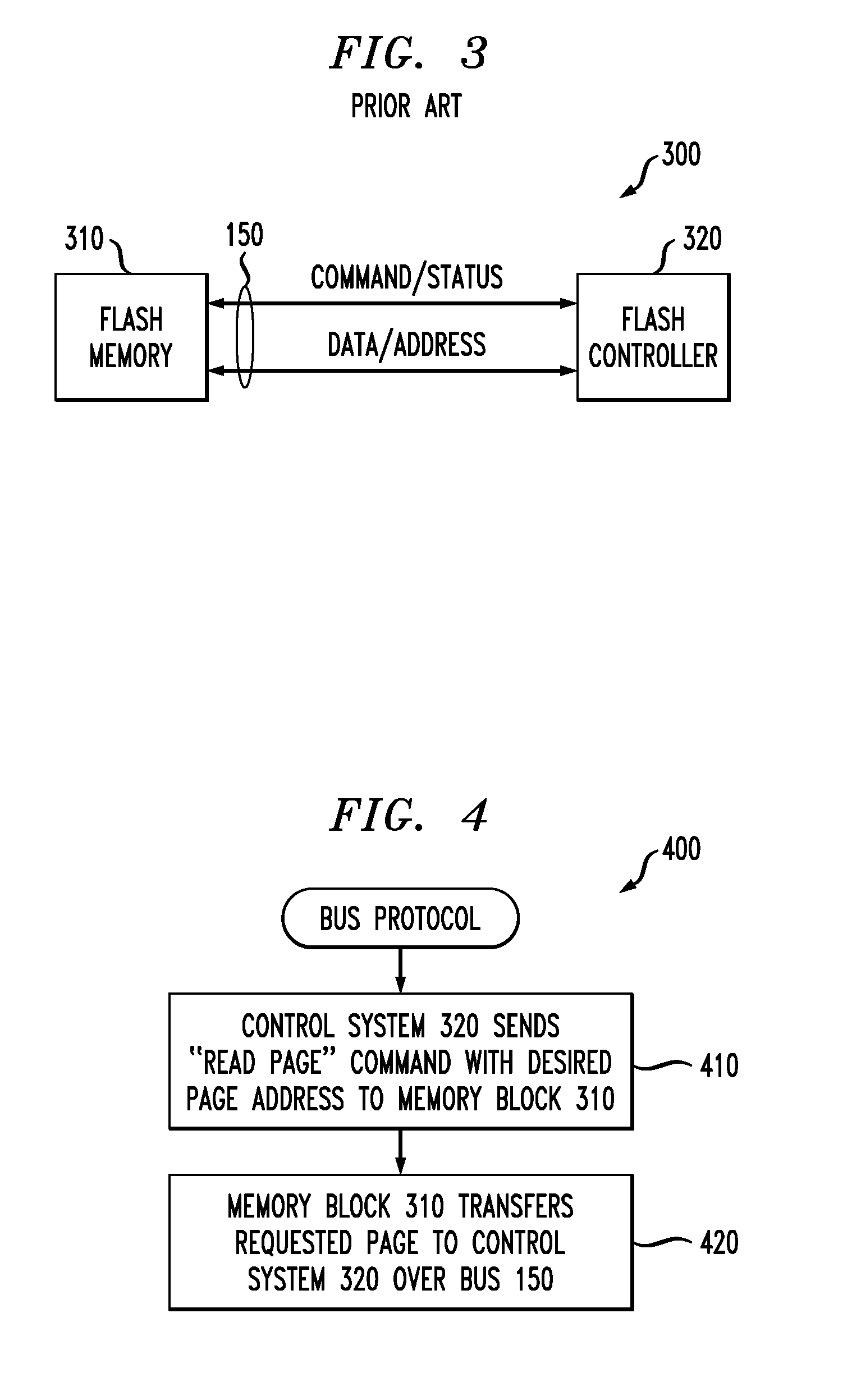

Memory read-channel with selective transmission of error correction data

InactiveUS20110191652A1Improve throughputReduce power consumptionCode conversionError correction/detection by combining multiple code structuresData errorData transmission

A memory read-channel is provided with selective transmission of error correction data. The disclosed read-channel improves throughput and reduces power consumption when error correction codes are unnecessary. The data read from a memory device comprises user data, error detection data and error correction data. In one embodiment, the error detection data is evaluated to determine if there is a data error; and the error correction data is transmitted only if a data error is detected. In another variation, the error detection data is evaluated during data transmission to determine if there is a data error and the transmission is suspended if a data error is detected. Typically, the error detection data comprises a cyclic redundancy check and the error correction data comprises parity check data.

Owner:AVAGO TECH INT SALES PTE LTD

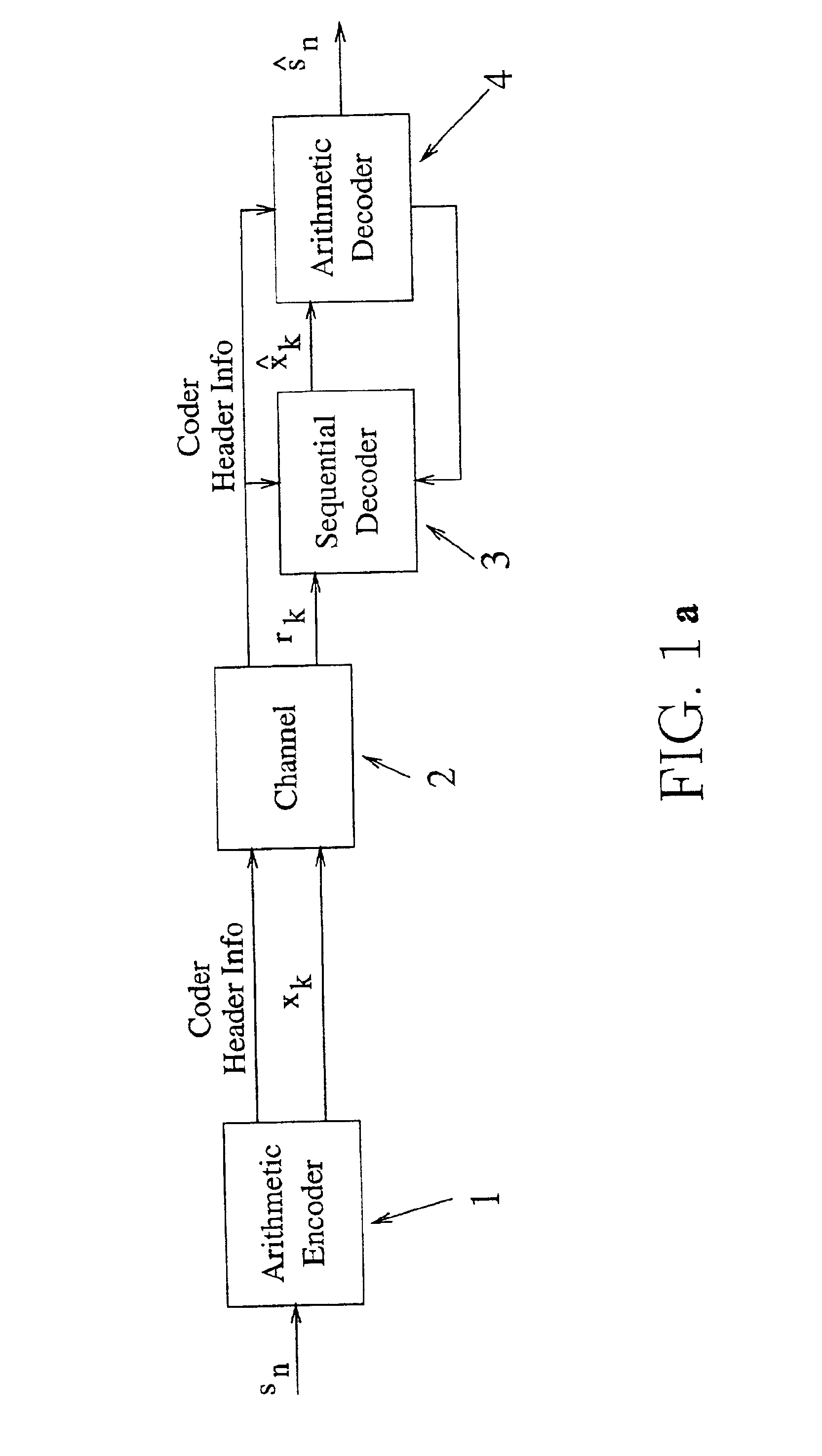

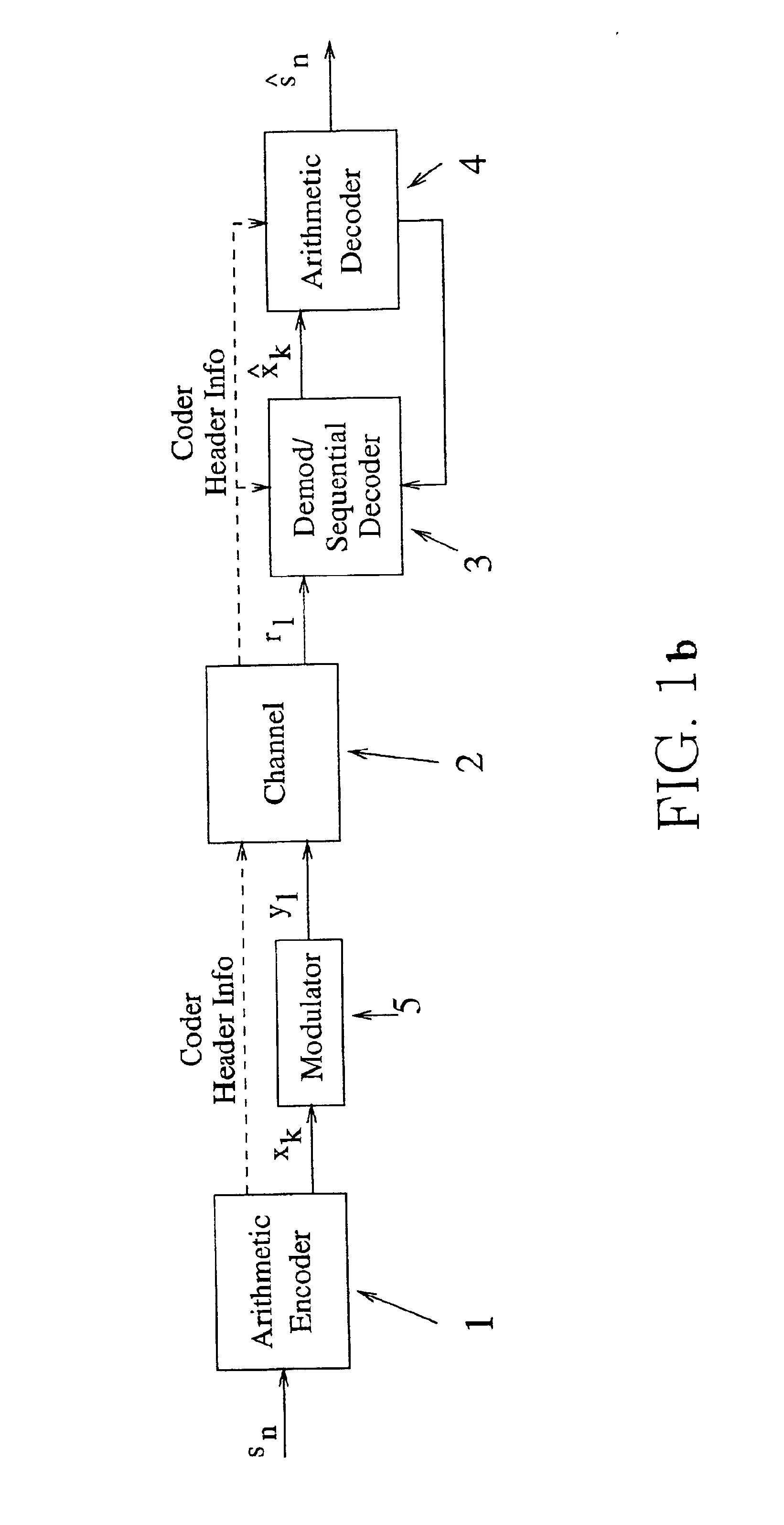

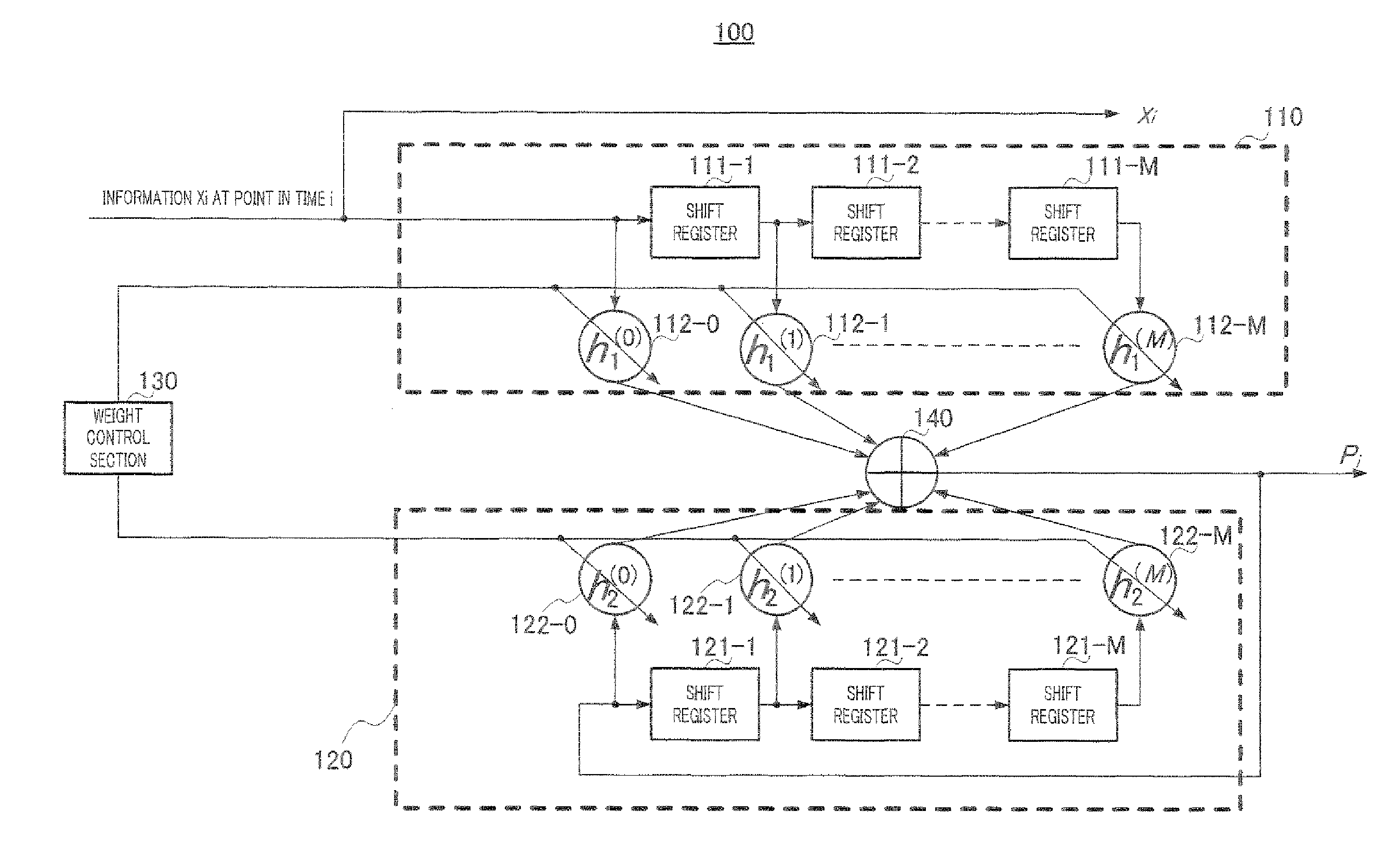

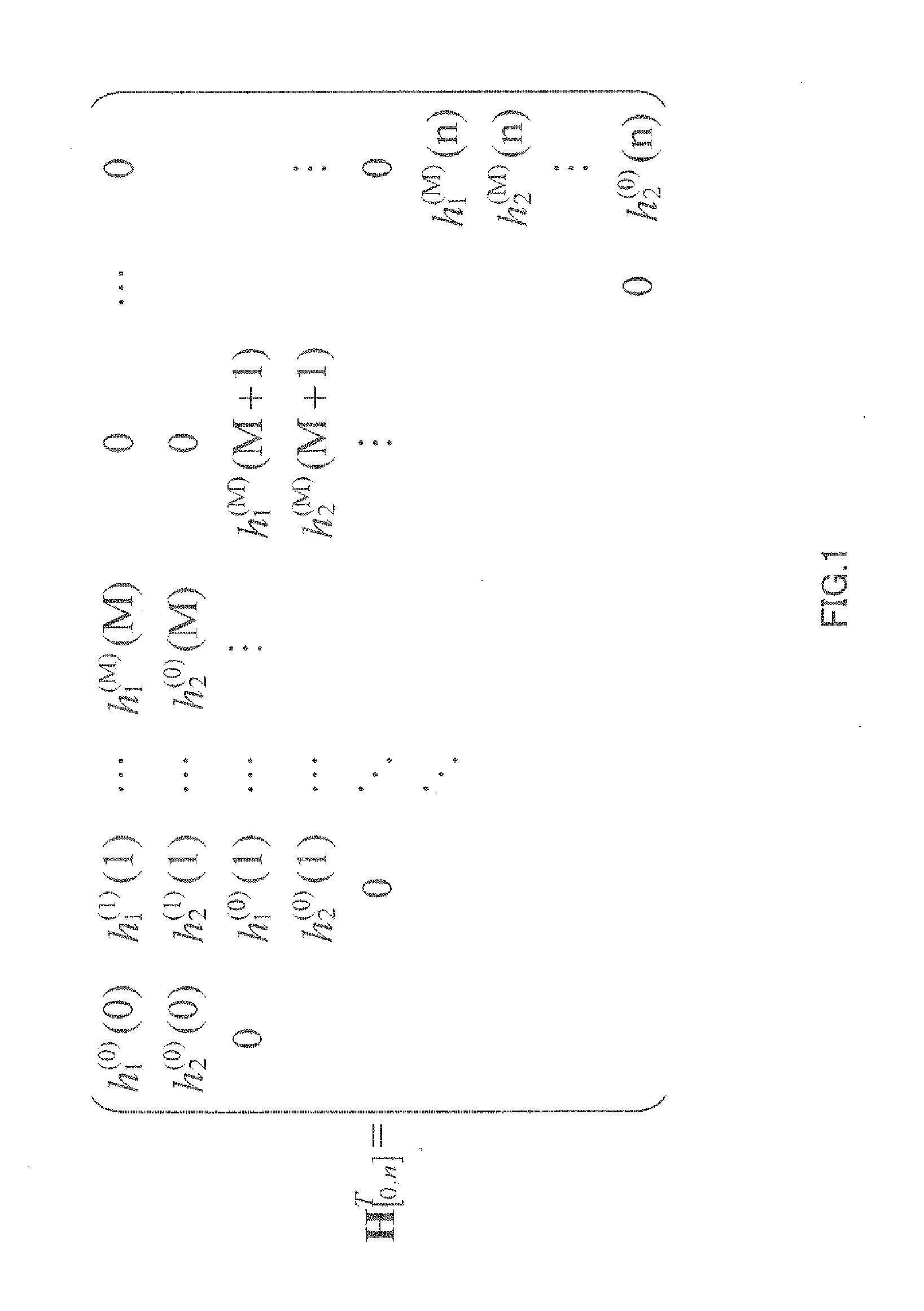

System and method for joint source-channel encoding, with symbol decoding and error correction

InactiveUS6892343B2Easy to operateError preventionOther error detection/correction/protectionComputer hardwareSymbol decoding

Disclosed is a system and method for joint source-channel encoding, symbol decoding and error correction, preferably utilizing an arithmetic encoder with operational error detection space; and a combination sequential, and arithmetic, encoded symbol decoder structure.

Owner:NEBRASKA BOARD OF RGT UNIV OF

Encoding method, decoding method, coder and decoder

ActiveUS20110283162A1Correction capabilityImprove data qualityError correction/detection using convolutional codesError preventionTheoretical computer scienceDecodes

An encoding method and encoder of a time-varying LDPC-CC with high error correction performance are provided. In an encoding method of performing low density parity check convolutional coding (LDPC-CC) of a time varying period of q using a parity check polynomial of a coding rate of (n−1) / n (where n is an integer equal to or greater than 2), the time varying period of q is a prime number greater than 3, the method receiving an information sequence as input and encoding the information sequence using equation 1 as a g-th (g=0, 1, . . . q−1) parity check polynomial to satisfy 0:(Da#g,1,1+Da#g,1,2+Da#g,1,3)X1(D)+(Da#g,2,1+Da#g,2,1+Da#g,2,2+Da#g,2,3)X2(D)+ . . . +(Da#g,n−1,1+Da#g,n−1,2+Da#g,n−1,3)Xn−1(D)+(Db#g,1+Db#g,2+1)P(D)=0 (Equation 1)where, in equation 1:“%” represents a modulo and each coefficient satisfies the following with respect to k=1, 2, . . . , n−1:a#0,k,1%q=a#1,k,1%q=a#2,k,1%q=a#3,k,1%q= . . . =a#g,k,1%q= . . . =a#q−2,k,1%q=a#q−1,k,1%q=vp=k (vp=k: fixed value);b#0,1%q=b#1,1%q=b#2,1%q=b#3,1%q= . . . =b#g,1%q= . . . =b#q−2,1%q=b#q−1,1%q=w (w: fixed value);a#0,k,2%q=a#1,k,2%q=a#2,k,2%q=a#3,k,2%q= . . . =a#g,k,2%q= . . . =a#q−2,k,2%q=a#q−1,k,2%q=yp=k (yp=k: fixed value);b#0,2%q=b#1,2%q=b#2,2%q=b#3,2%q= . . . =b#g,2%q= . . . =b#q−2,2%q=b#q−1,2%q=z (z: fixed value); anda#0,k,3%q=a#1,k,3%q=a#2,k,3%q=a#3,k,3%q= . . . =a#g,k,3%q= . . . =a#q−2,k,3%q=a#q−1,k,3%q=sp=k (sp=k: fixed value);a#g,k,1, a#g,k,2 and a#g,k,3 are natural numbers equal to or greater than 1 and a#g,k,1≠a#g,k,2, a#g,k,1≠a#g,k,3 and a#g,k,2≠a#g,k,3 hold true;b#g,1 and b#g,2 are natural numbers equal to or greater than 1 and b#g,1≠b#g,2 holds true; andvp=k and yp=k are natural numbers equal to or greater than 1.

Owner:PANASONIC INTELLECTUAL PROPERTY CORP OF AMERICA

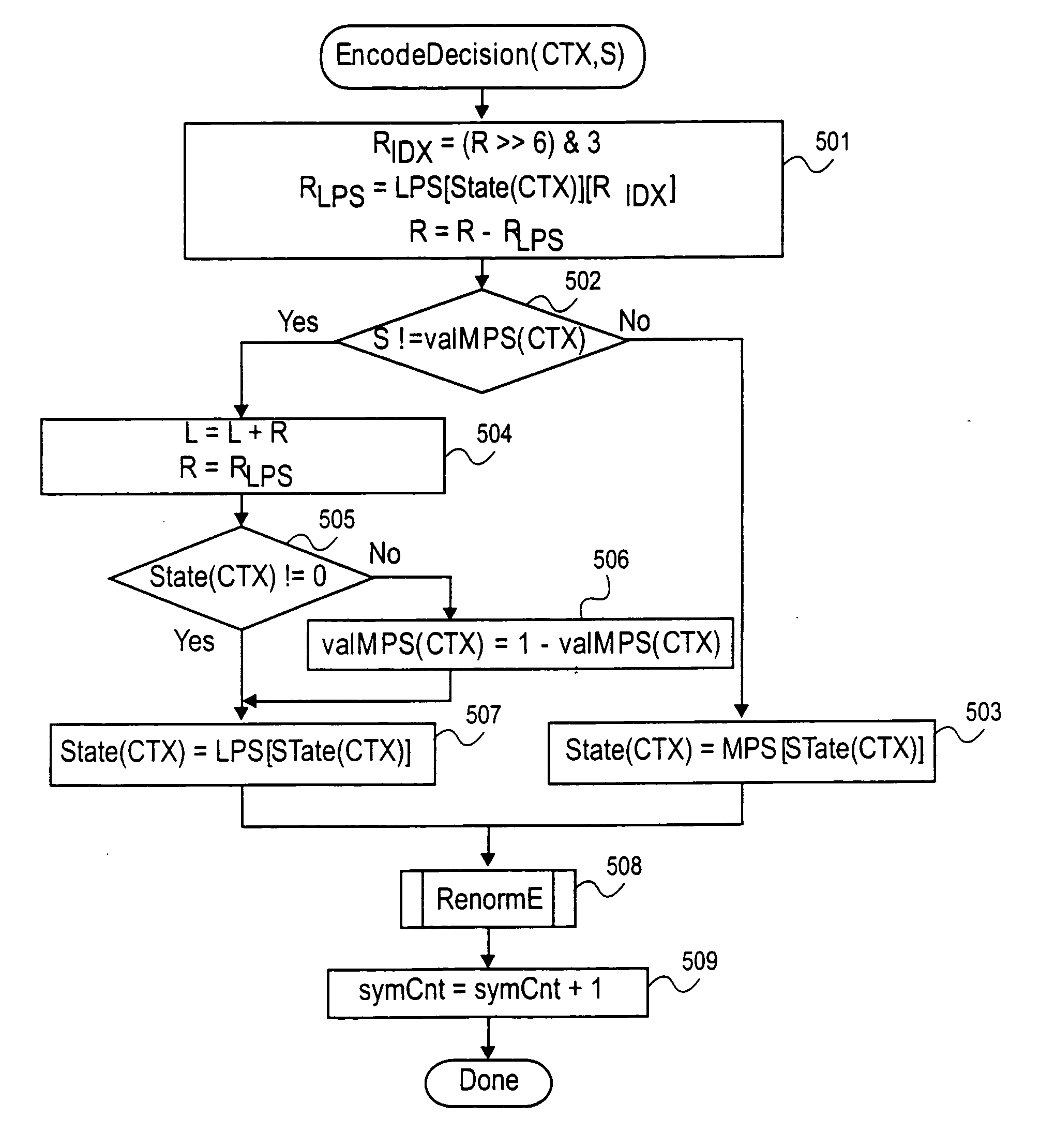

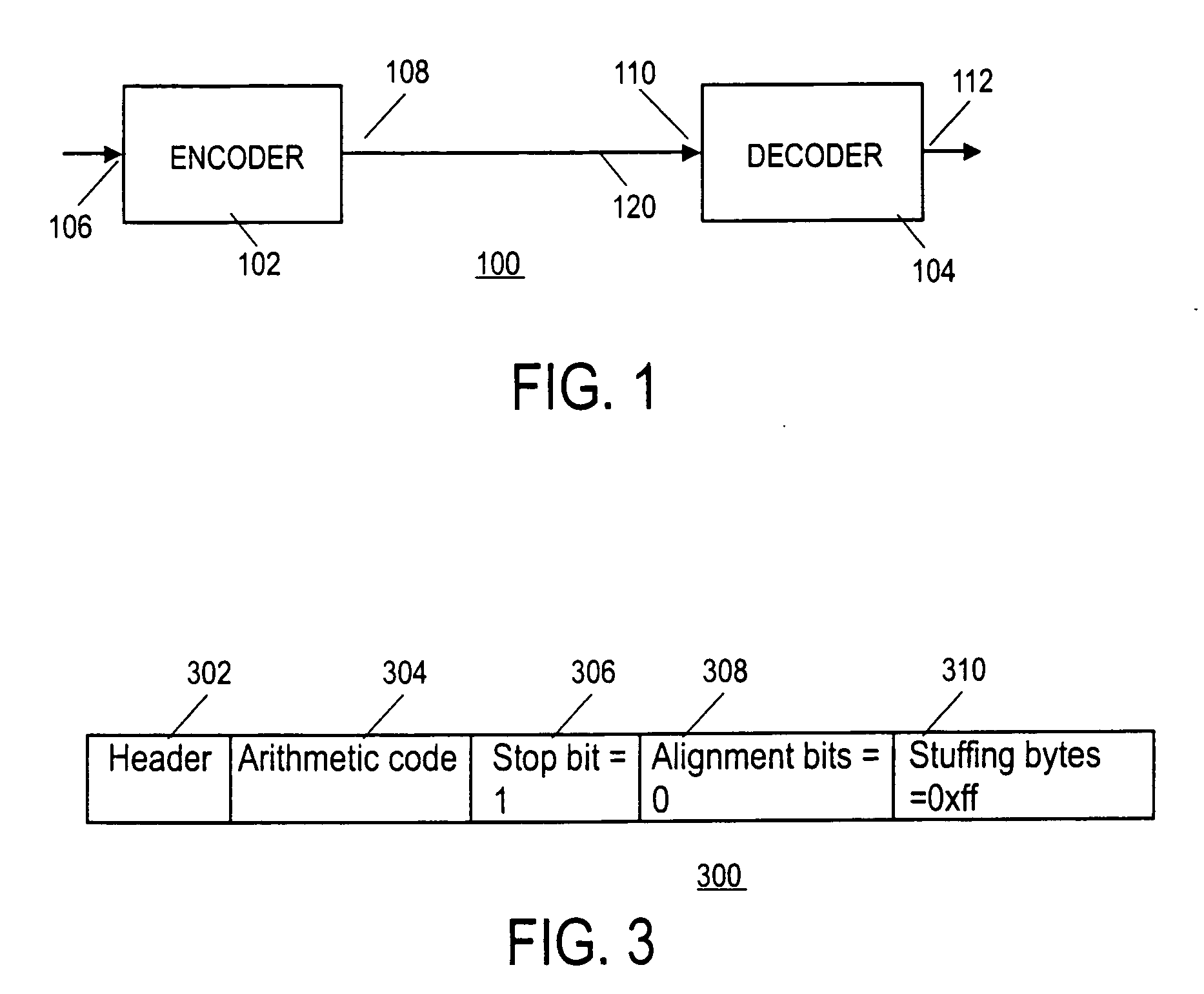

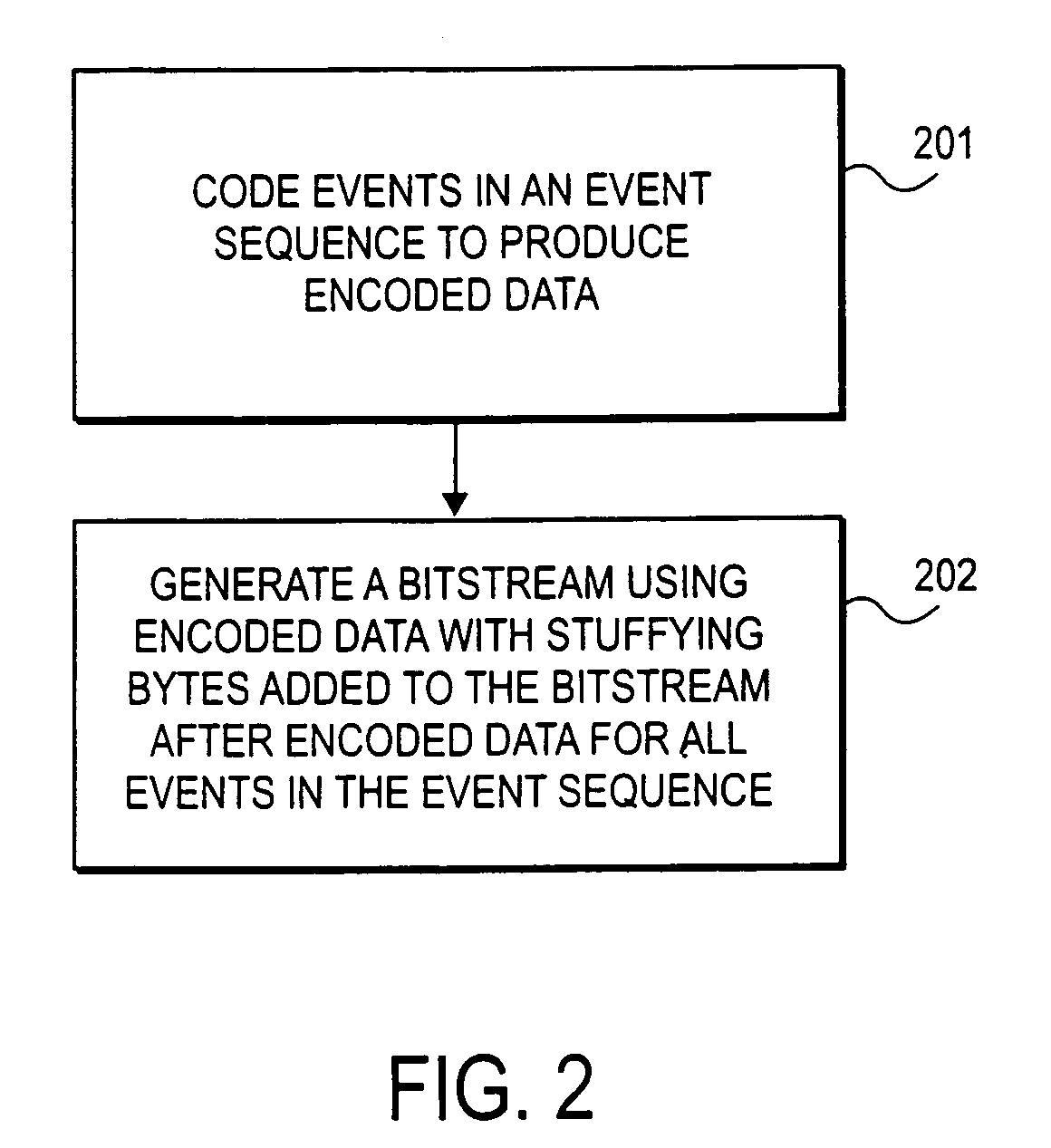

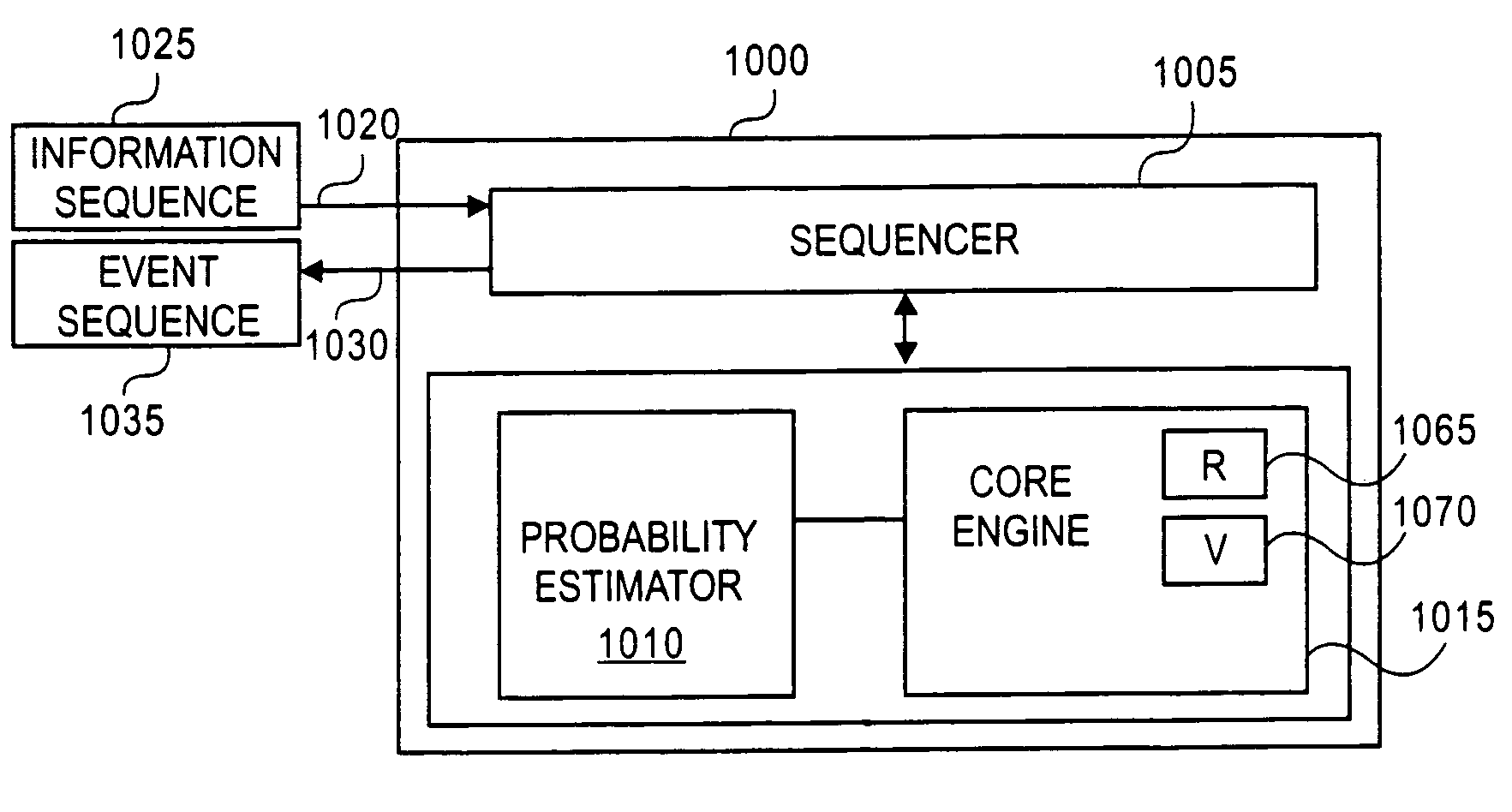

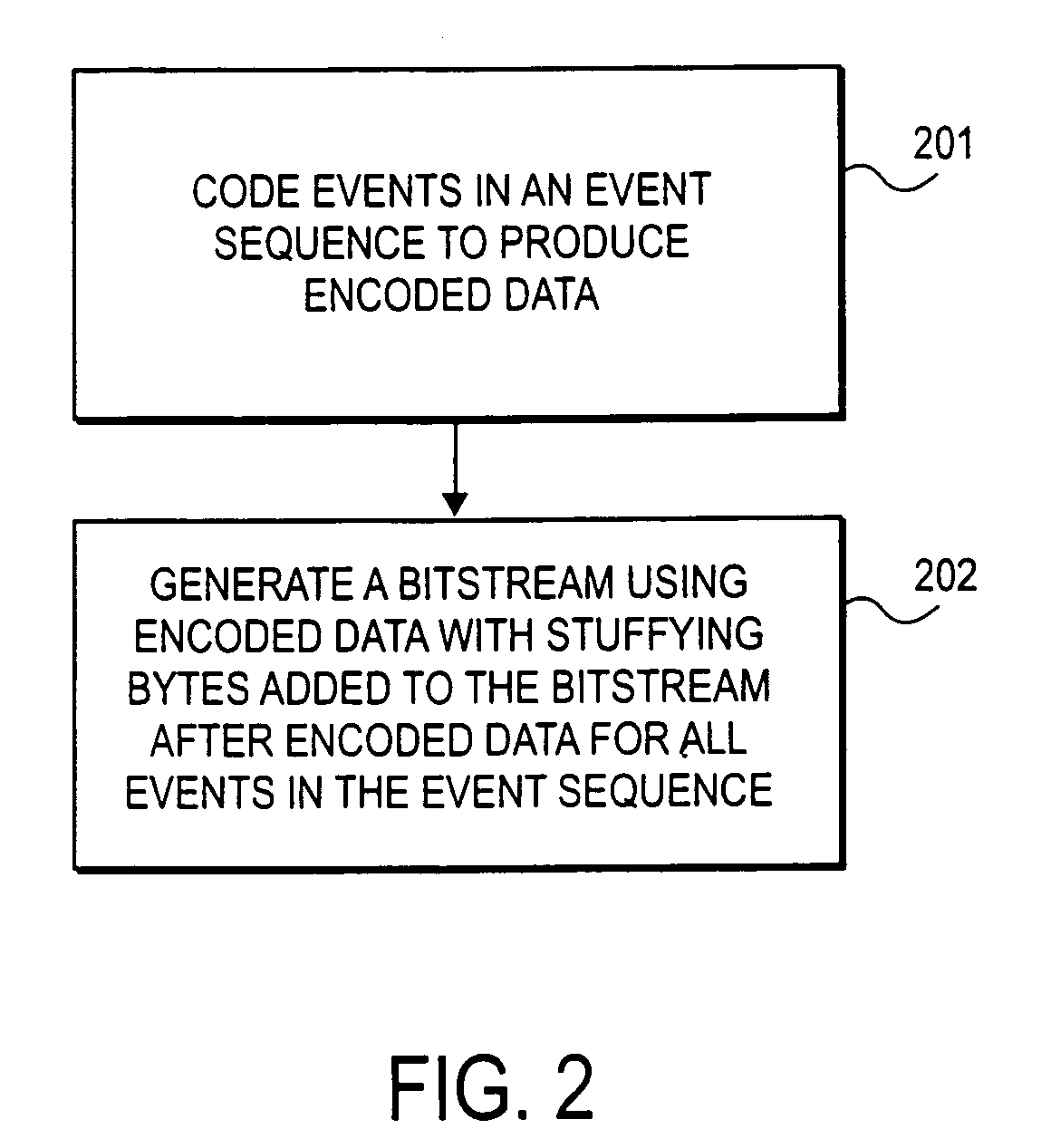

Method and apparatus for arithmetic coding and termination

InactiveUS20060017591A1Code conversionError correction/detection using arithmatic codesArithmetic codingComputer science

Methods and apparatuses for performing arithmetic encoding and / or decoding are disclosed. In one embodiment, an arithmetic decoder comprises a sequencer to generate a context identifier for an event of an event sequence, a probability estimator to determine a value for a LPS and a probability estimate for the LPS, and a decoding engine that includes a range register to assign a value to a range for the LPS. The value is based on the probability estimate, a value stored in the range register and the context identifier to a range for the LPS if the context identifier is not equal to an index and the value is not based on the value stored in range register if the context identifier is equal to the index. The decoding engine further determines a value of a binary event based on the value of the range for the LPS and bits from an information sequence.

Owner:NTT DOCOMO INC

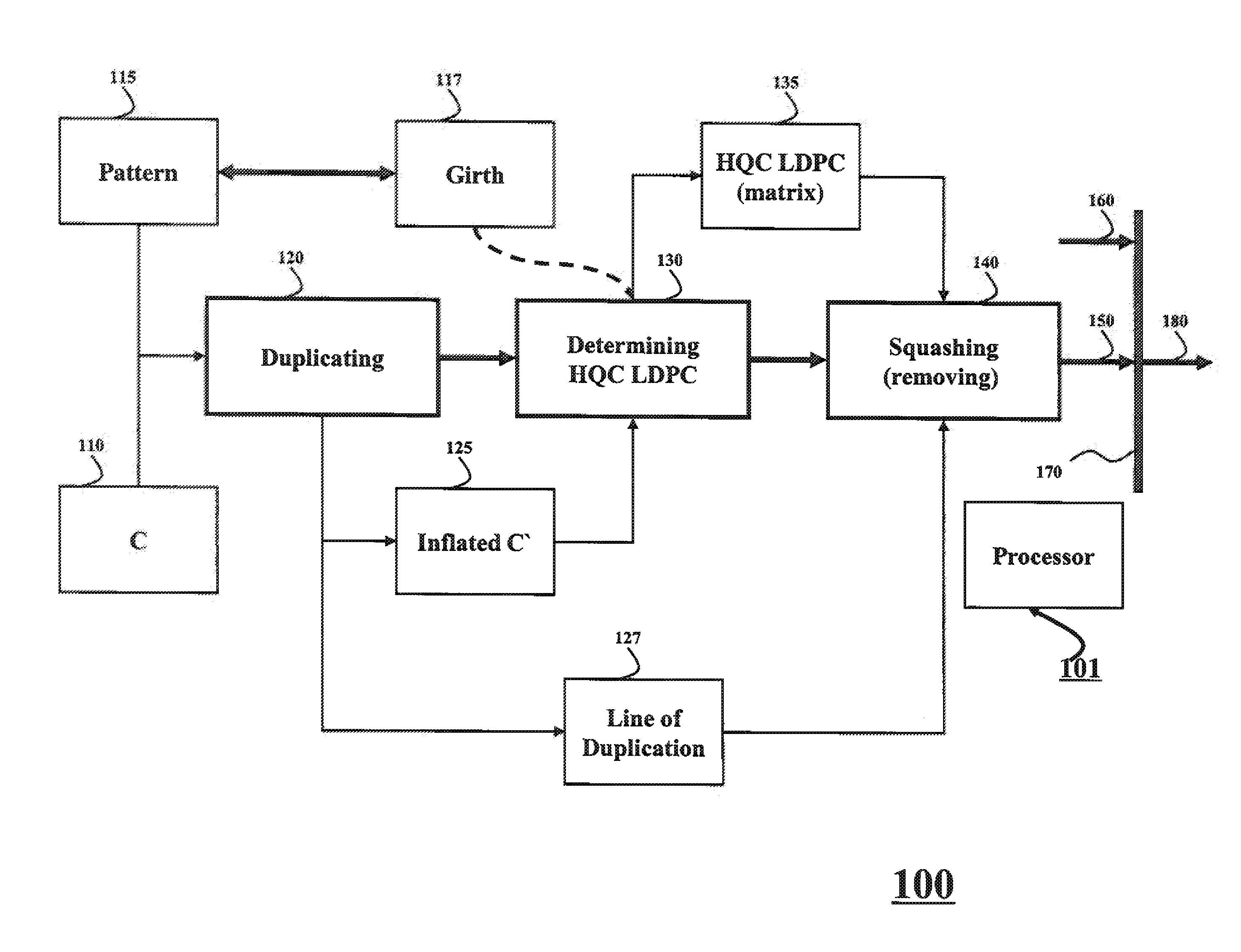

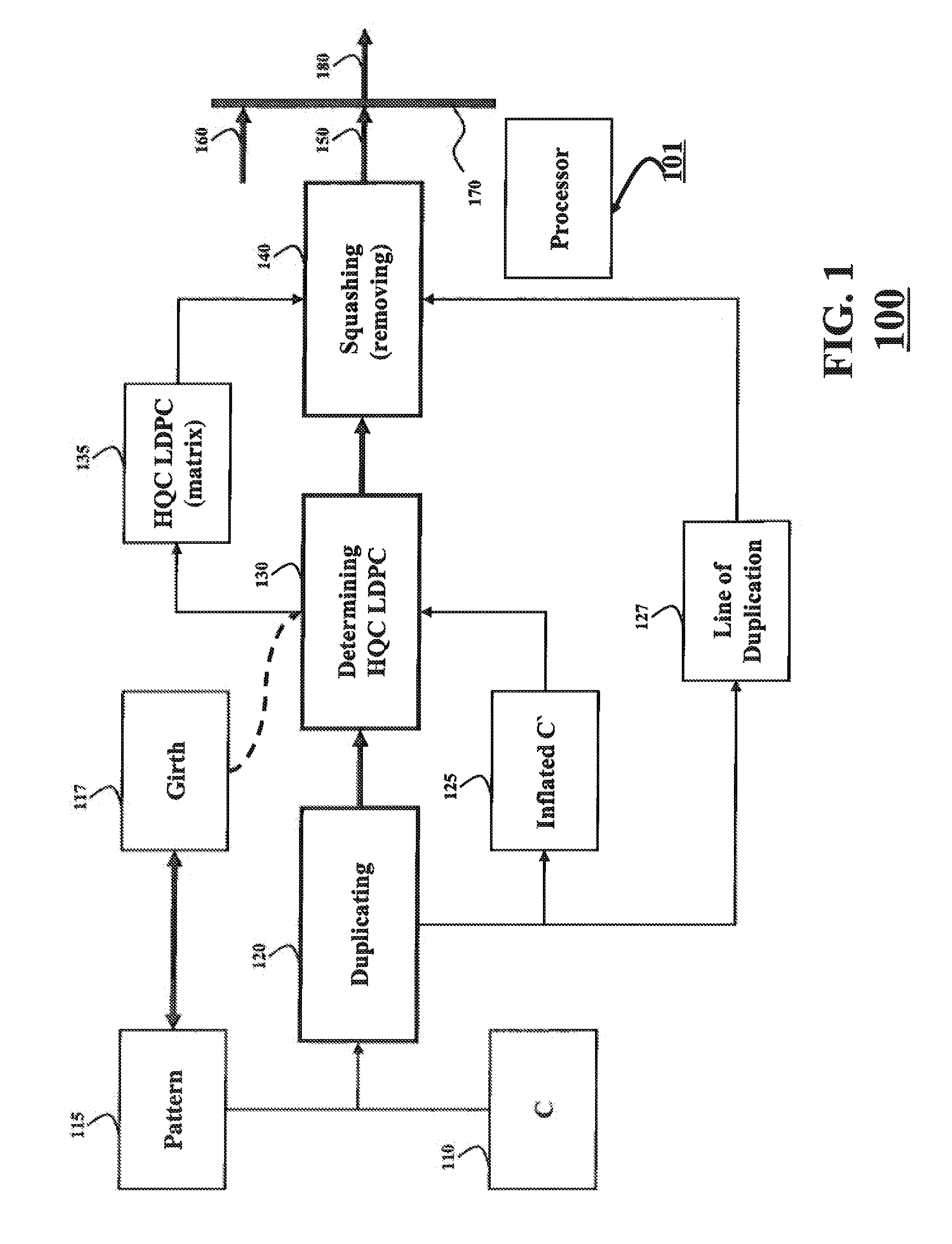

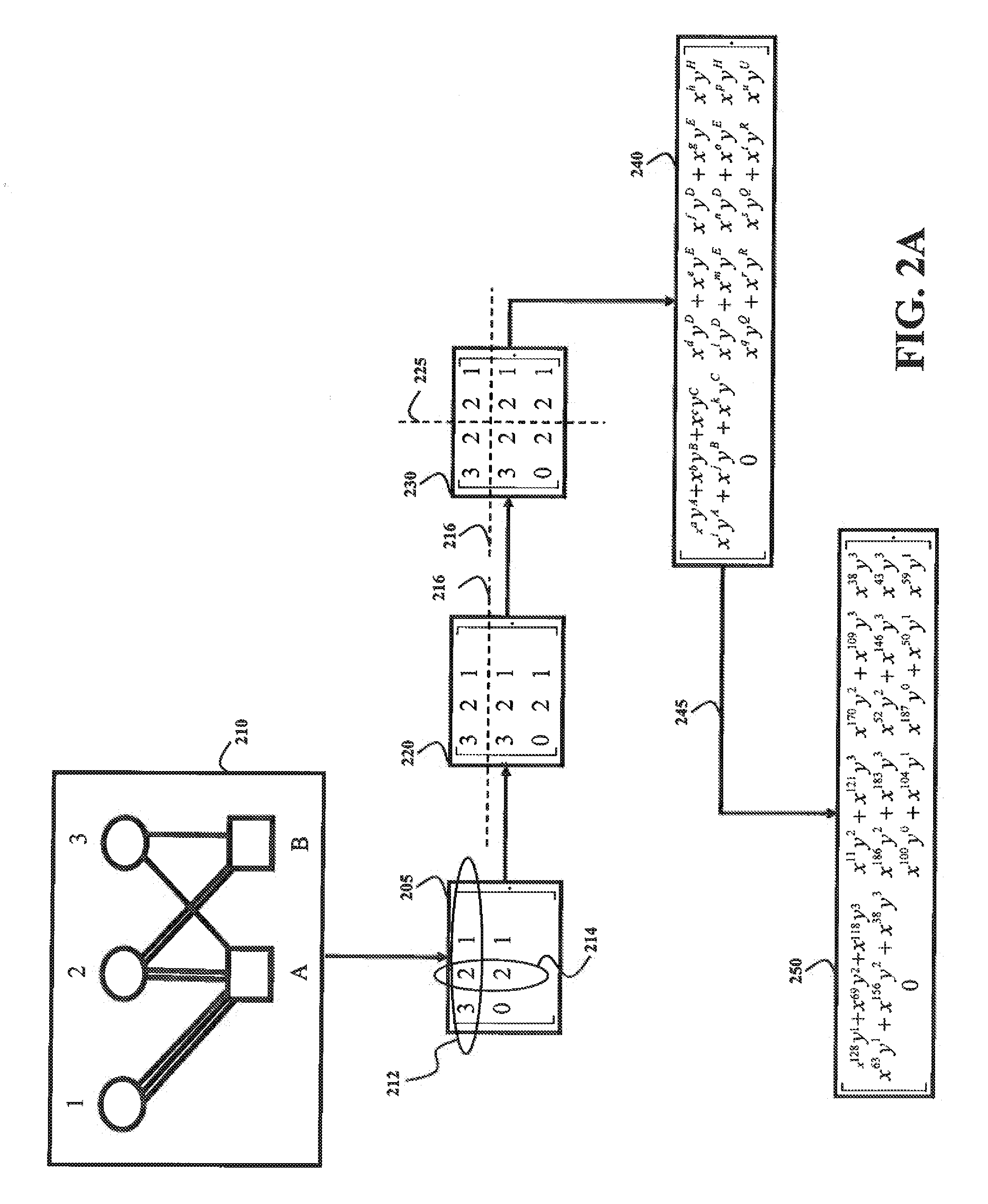

System and Method for Determining Quasi-Cyclic Low-Density Parity-Check Codes Having High Girth

A system and a method determine a quasi-cyclic (QC) low-density parity-check (LDPC) code corresponding to a protograph and having a predetermined girth. At least several elements of the connectivity matrix representing the protograph are duplicated along at least one line of duplication to produce an inflated connectivity matrix, wherein values of at least several elements in the connectivity matrix form a pattern indicated by the predetermined girth. A hierarchical quasi-cyclic (HQC) LDPC code corresponding to the inflated connectivity matrix is determined and at least several elements of a matrix representing the HQC LDPC code are removed, such that the matrix is squashed along the line of duplication to produce the QC LDPC code.

Owner:MITSUBISHI ELECTRIC RES LAB INC

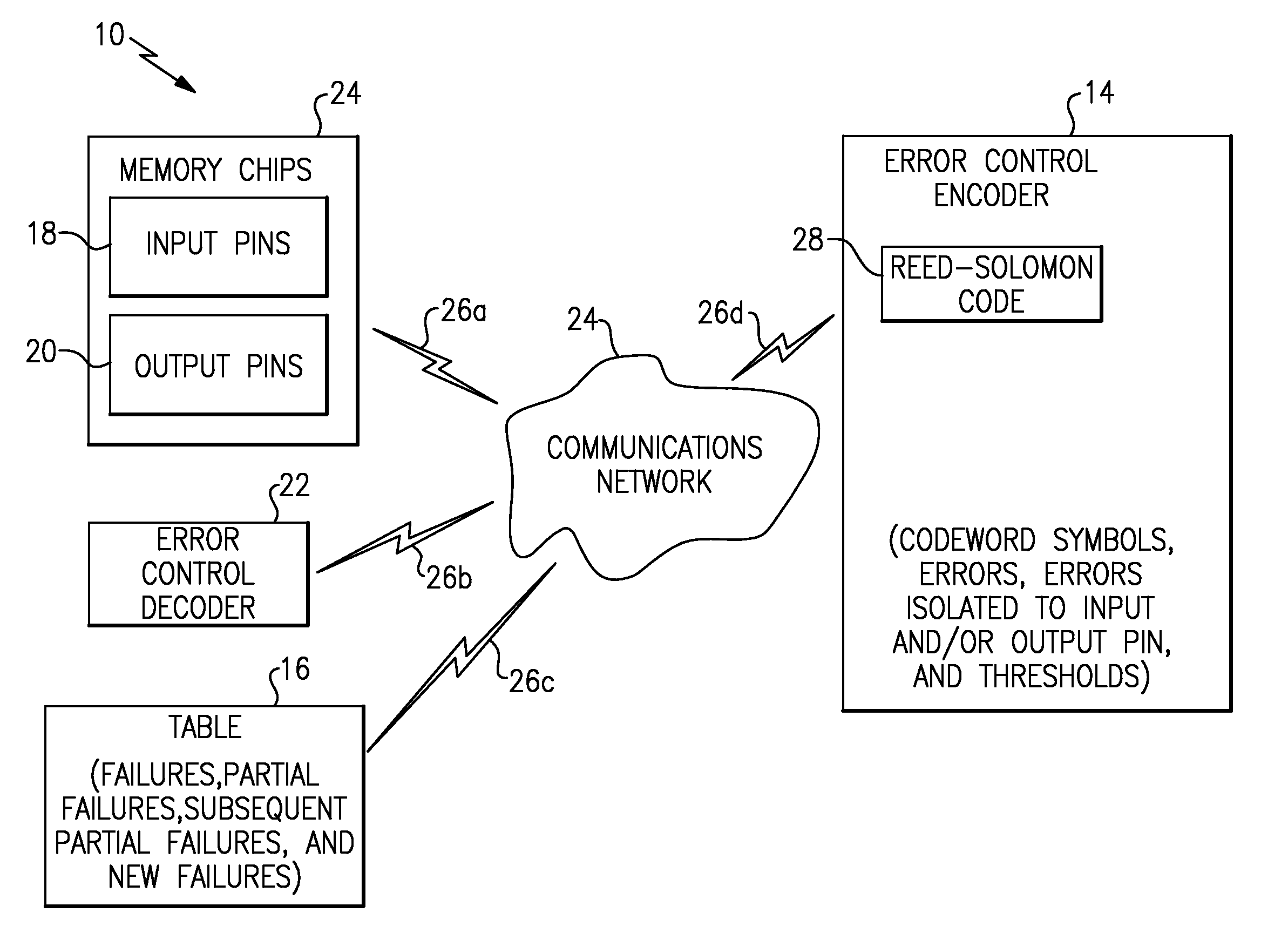

System to Improve Memory Reliability and Associated Methods

ActiveUS20100287445A1Improves memory reliabilityImprove memory reliabilityCode conversionStatic storageMemory chipComputerized system

A system to improve memory reliability in computer systems that may include memory chips, and may rely on a error control encoder to send codeword symbols for storage in each of the memory chips. At least two symbols from a codeword are assigned to each memory chip and therefore failure of any of the memory chips could affect two symbols or more. The system may also include a table to record failures and partial failures of the codeword symbols for each of the memory chips so the error control encoder can correct subsequent partial failures based upon the previous partial failures. The error control coder is capable of correcting and / or detecting more errors if only a fraction of a chip is noted in the table as having a failure as opposed to a full chip noted as having a failure.

Owner:IBM CORP

Method and apparatus for arithmetic coding and termination

InactiveUS7183951B2Code conversionError correction/detection using arithmatic codesProcessor registerArithmetic coding

Methods and apparatuses for performing arithmetic encoding and / or decoding are disclosed. In one embodiment, an arithmetic decoder comprises a sequencer to generate a context identifier for an event of an event sequence, a probability estimator to determine a value for a LPS and a probability estimate for the LPS, and a decoding engine that includes a range register to assign a value to a range for the LPS. The value is based on the probability estimate, a value stored in the range register and the context identifier to a range for the LPS if the context identifier is not equal to an index and the value is not based on the value stored in range register if the context identifier is equal to the index. The decoding engine further determines a value of a binary event based on the value of the range for the LPS and bits from an information sequence.

Owner:NTT DOCOMO INC

High structural LDPC coding and decoding method and coder and decoder

InactiveCN1625057AError correction/detection using multiple parity bitsError correction/detection using arithmatic codesDecoding methodsRound complexity

This invention discloses a highly structured LDPC coding and decoding methods. The code is through the checking matrix production unit of the encoder based on the pre-set code rate, column weight and row weight of HS-LDPC code to produce an odd-even checking matrix, and input the result into a compounding code unit of a coder, the compounding code unit calculates the input data information and the odd-even checking matrix, output the data information united by the odd-even checking information bit and input data information. The decoding method is according the need of the matrix odd-even checking code, pre-set the changeable node units, checks the number of the node units and the connecting units and the connecting structure, the changeable node units and the checking node units together complete the iterative decoding process of HS-LDPC code. This method can greatly reduce the complication of the hardware implementation of the entire decoder, compromises easily of the complicated degree and the speed of the hardware realization process.

Owner:TIMI TECH

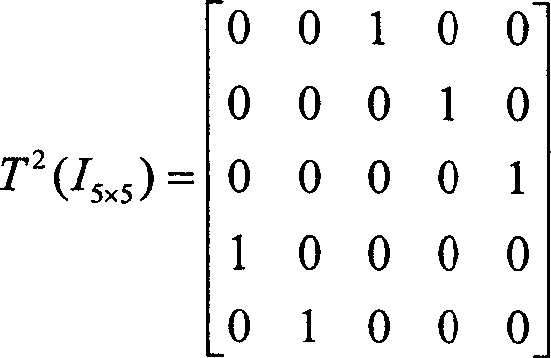

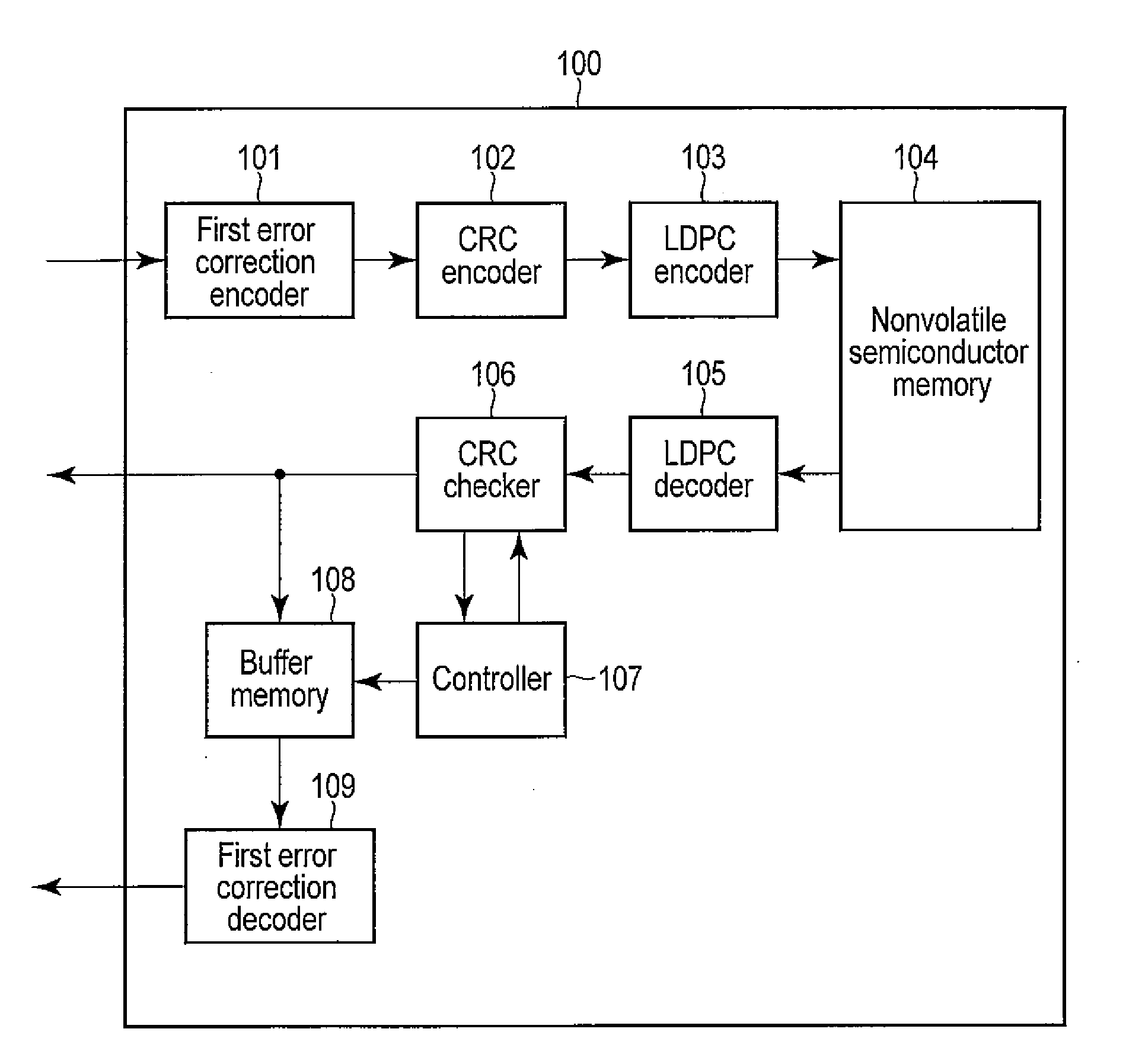

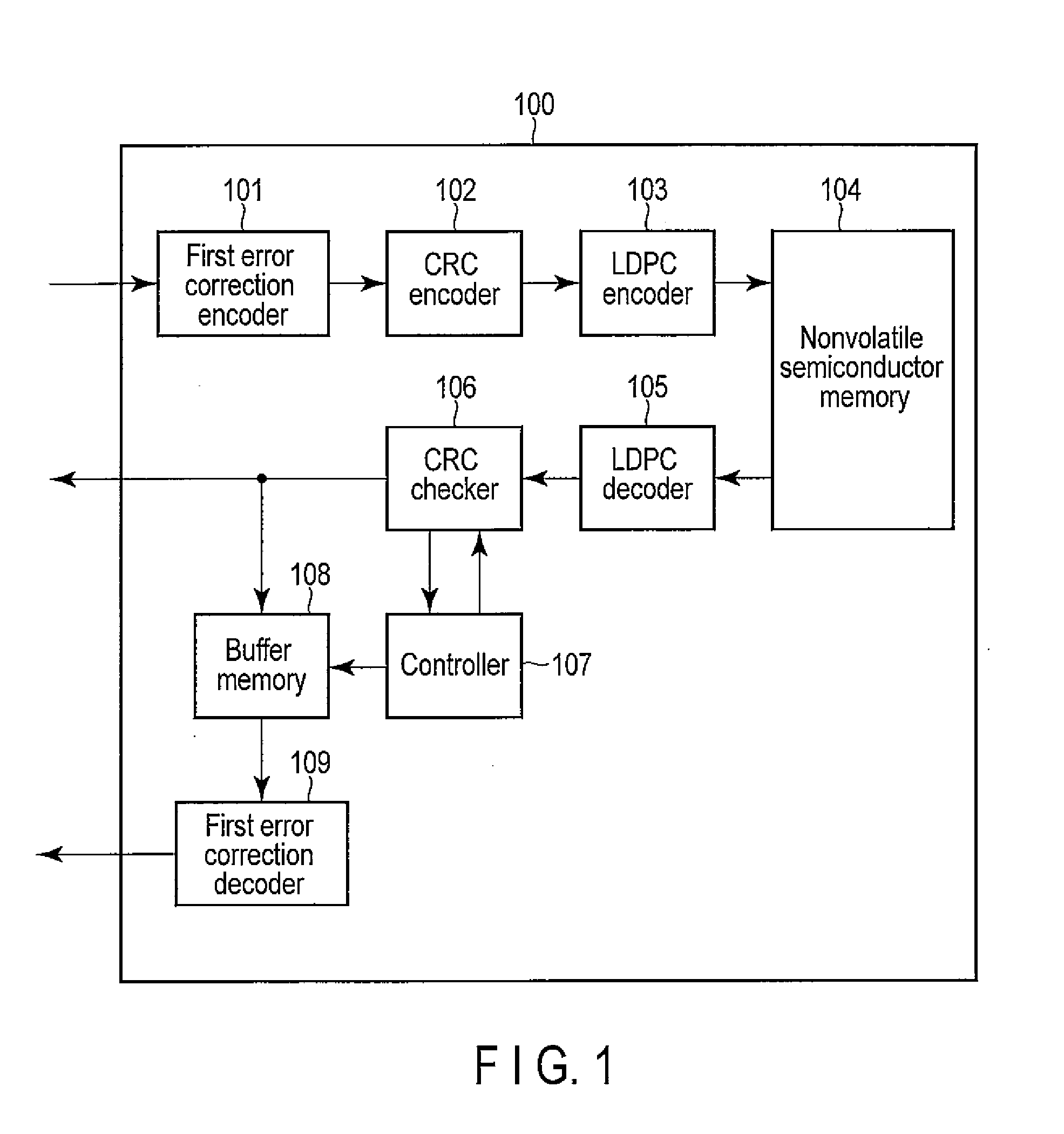

Error correction encoding apparatus, error correction decoding apparatus, nonvolatile semiconductor memory system, and parity check matrix generation method

ActiveUS20130055050A1Code conversionChecking code calculationsLinear codingTheoretical computer science

According to one embodiment, an error correction encoding apparatus includes a linear encoder and a low-density parity check (LDPC) encoder. The linear encoder supports a linear coding scheme enabling a parity check to be carried out by a division using a generating polynomial and applies the generating polynomial to input data to obtain linear coded data. The LDPC encoder applies a generator matrix corresponding to a parity check matrix for an LDPC code to the linear coded data to obtain output data. The parity check matrix satisfies Expression (1) shown in the specification.

Owner:KIOXIA CORP

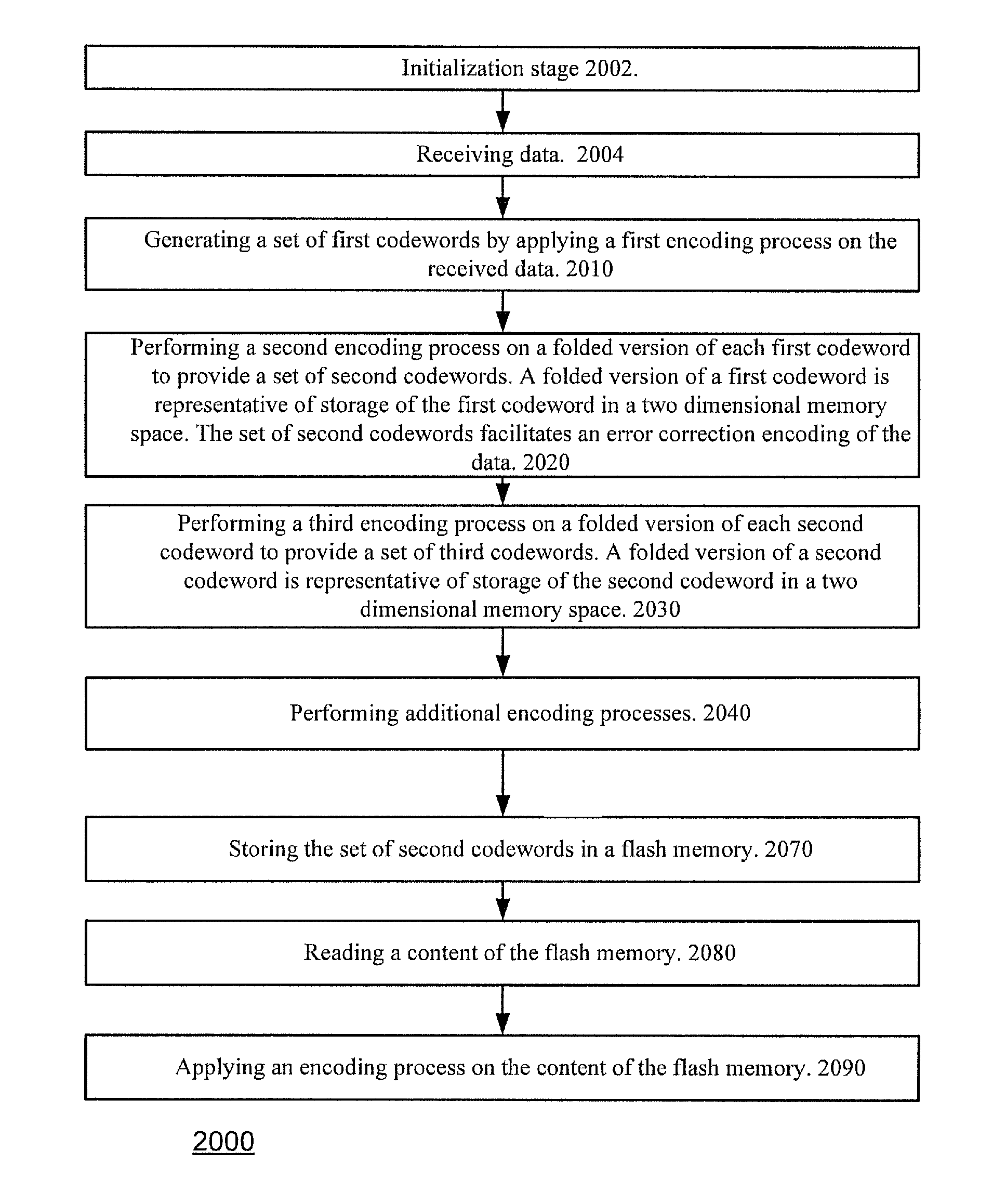

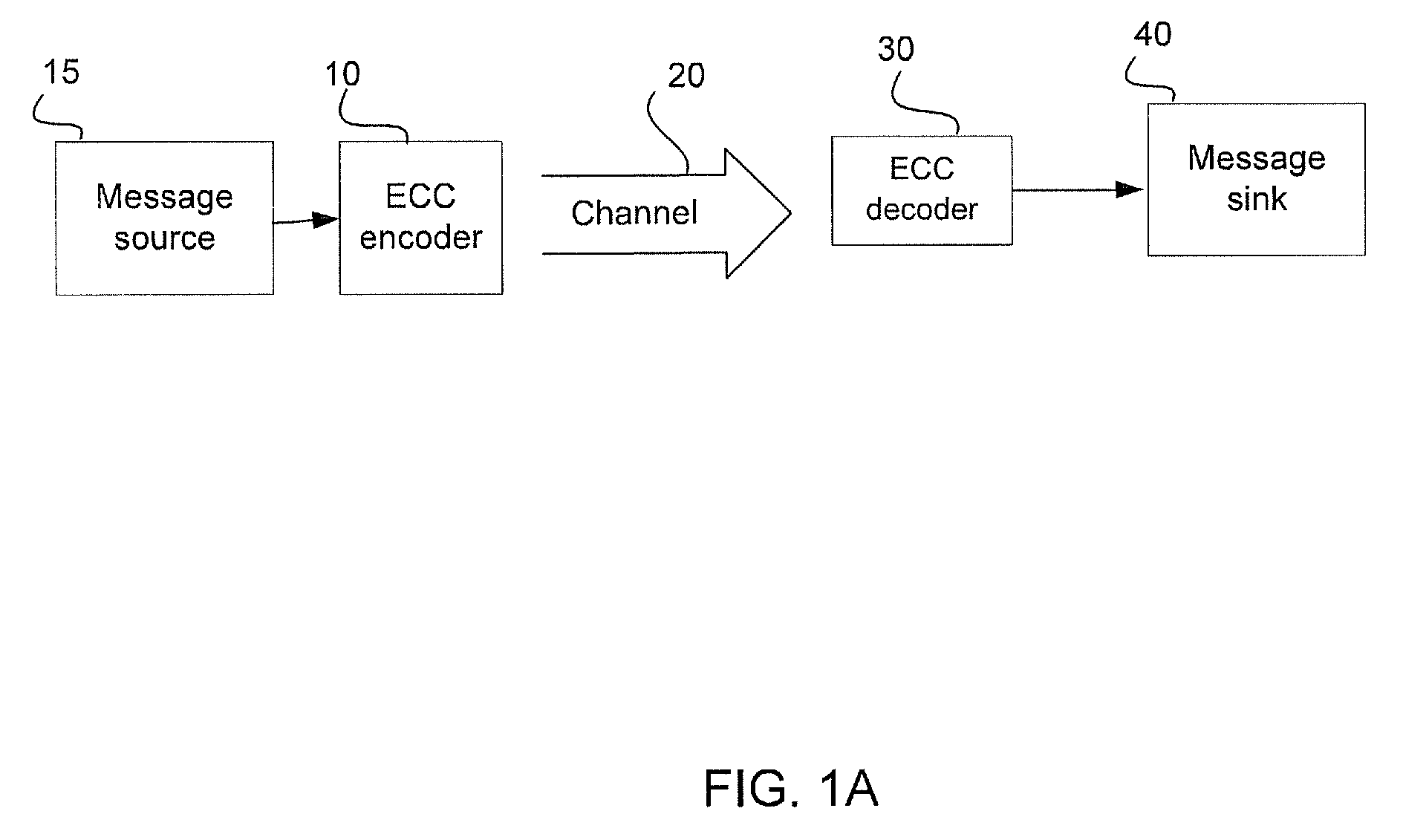

Encoding method and system, decoding method and system

ActiveUS8850296B2Correction errorAvoid modificationCode conversionError correction/detection by combining multiple code structuresDecoding methodsComputer architecture

A decoder, an encoder, a decoding method and an encoding method are provided. The encoding method includes receiving data; generating a set of first codewords by applying a first encoding process on the received data; and performing a second encoding process on a folded version of each first codeword to provide a set of second codewords, wherein a folded version of a first codeword is representative of a storage of the first codeword in a two dimensional memory space, wherein the second codeword comprises redundancy bits.

Owner:AVAGO TECH INT SALES PTE LTD

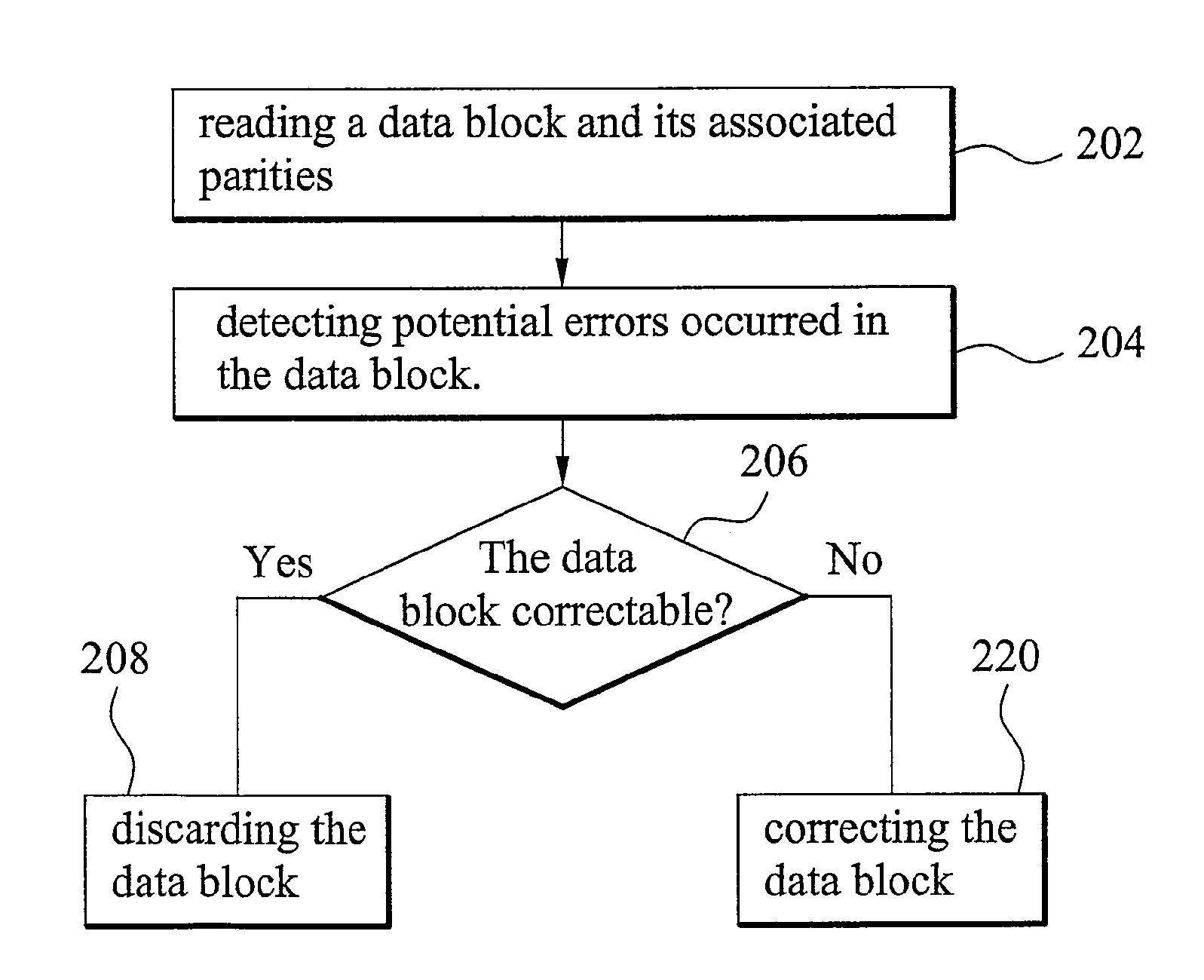

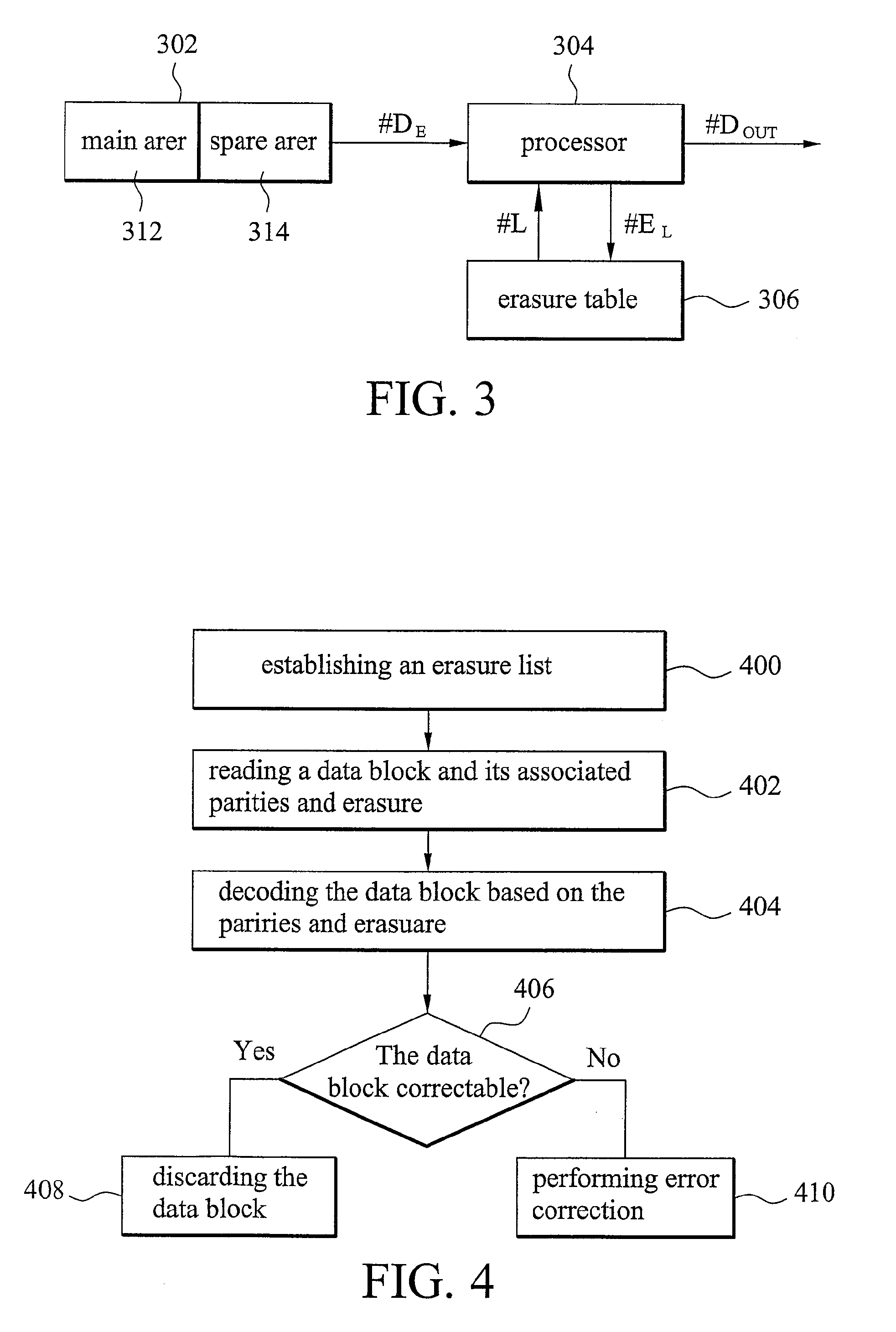

Method and apparatus for flash memory error correction

Error correction method and a flash memory device are provided. In the flash memory device, a memory array comprises a main area for data storage, and a spare area for storage of parities associated with the stored data. An erasure table maintains an erasure list indicating addresses of defects in the memory array where data storage is unavailable. A processor performs error correction on the stored data based on the parities and the erasure list to output a corrected output.

Owner:MEDIATEK INC

Popular searches

Coding/ciphering apparatus Securing communication Sensing by electromagnetic radiation Record carrier types Error correction/detection using interleaving techniques Error detection only Digital signal error detection/correction Forward error control use Error correction/detection using non-linear codes Picture reproducers with optical-mechanical scanning

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com