Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

233 results about "Program compilation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Reconfigurable test system

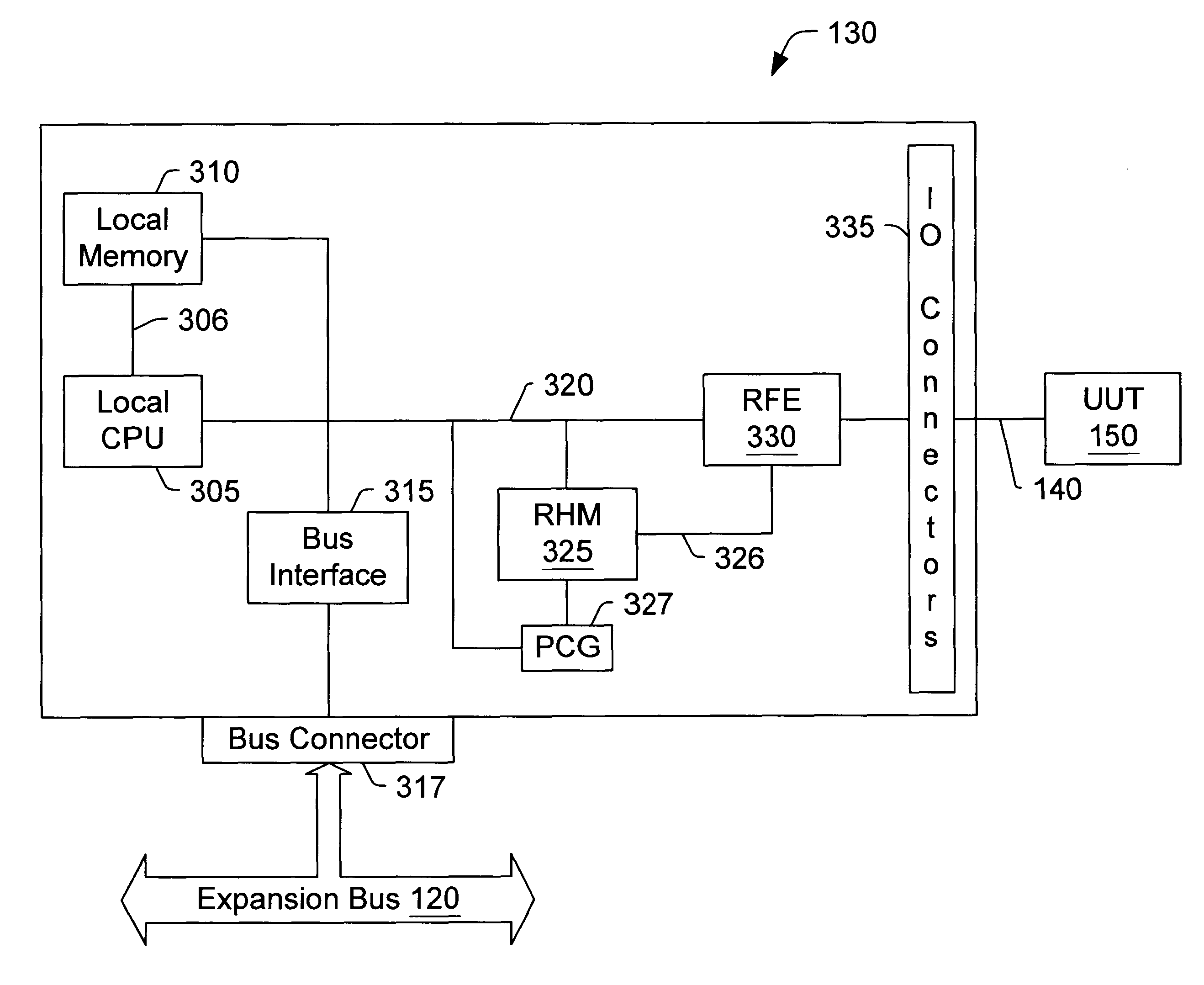

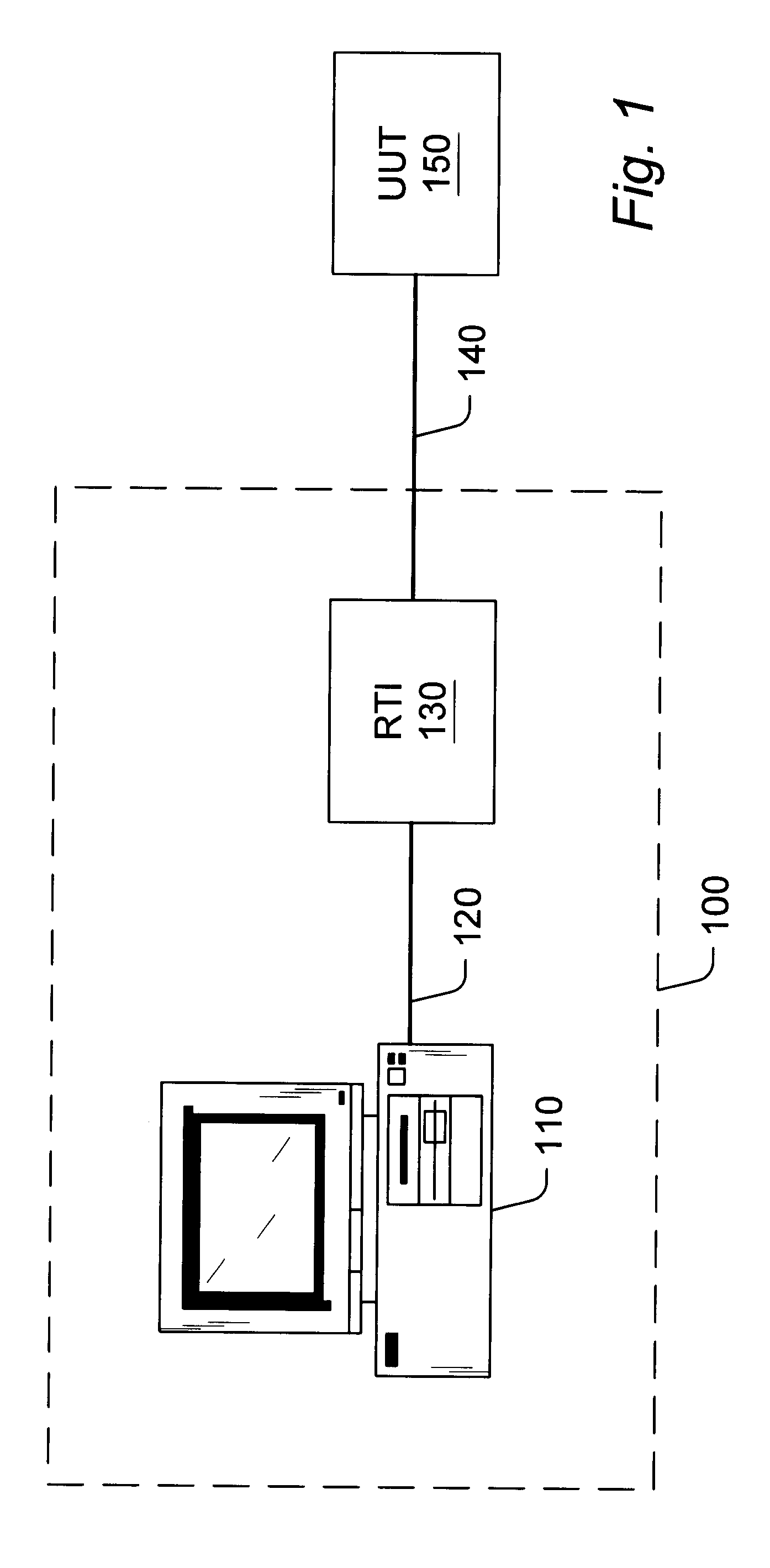

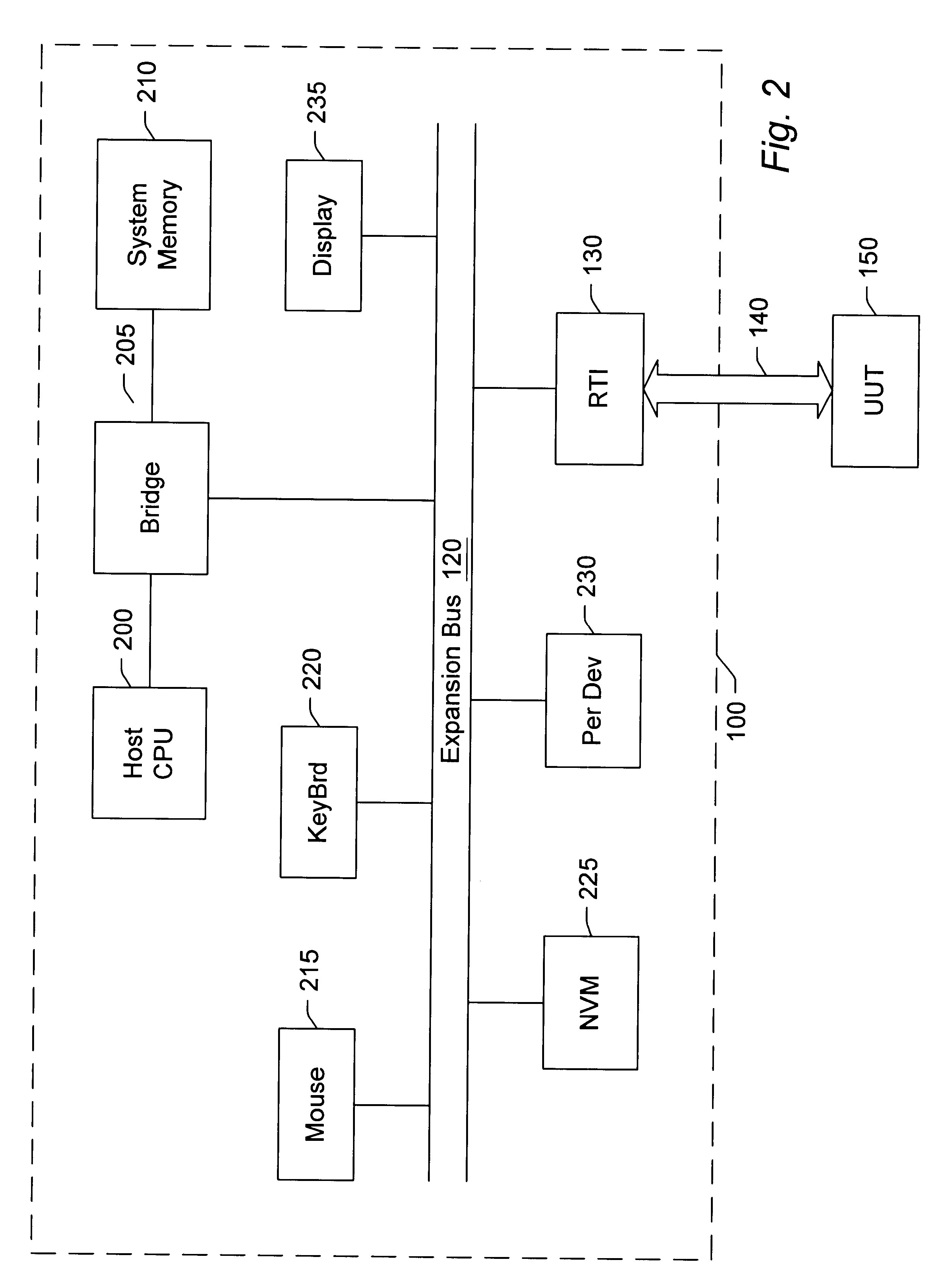

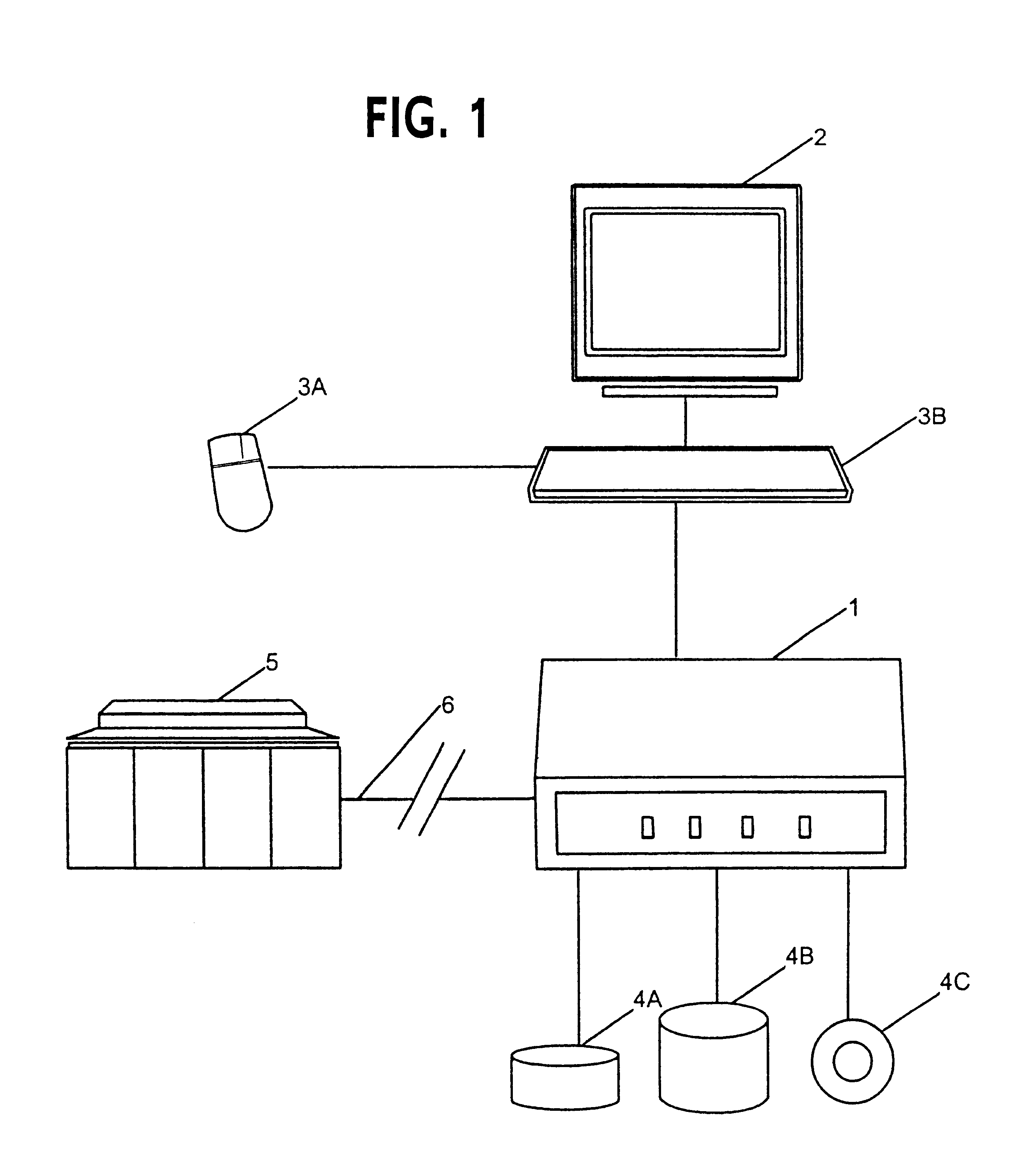

A reconfigurable test system including a host computer coupled to a reconfigurable test instrument. The reconfigurable test instrument includes reconfigurable hardware-i.e. a reconfigurable hardware module with one or more programmable elements such as Field Programmable Gate Arrays for realizing an arbitrary hardware architecture and a reconfigurable front end with programmable transceivers for interfacing with any desired physical medium-and optionally, an embedded processor. A user specifies system features with a software configuration utility which directs a component selector to select a set of software modules and hardware configuration files from a series of libraries. The modules are embedded in a host software driver or downloaded for execution on the embedded CPU. The configuration files are downloaded to the reconfigurable hardware. The entire selection process is performed in real-time and can be changed whenever the user deems necessary. Alternatively, the user may create a graphical program in a graphical programming environment and compile the program into various software modules and configuration files for host execution, embedded processor execution, or programming the reconfigurable hardware.

Owner:NATIONAL INSTRUMENTS

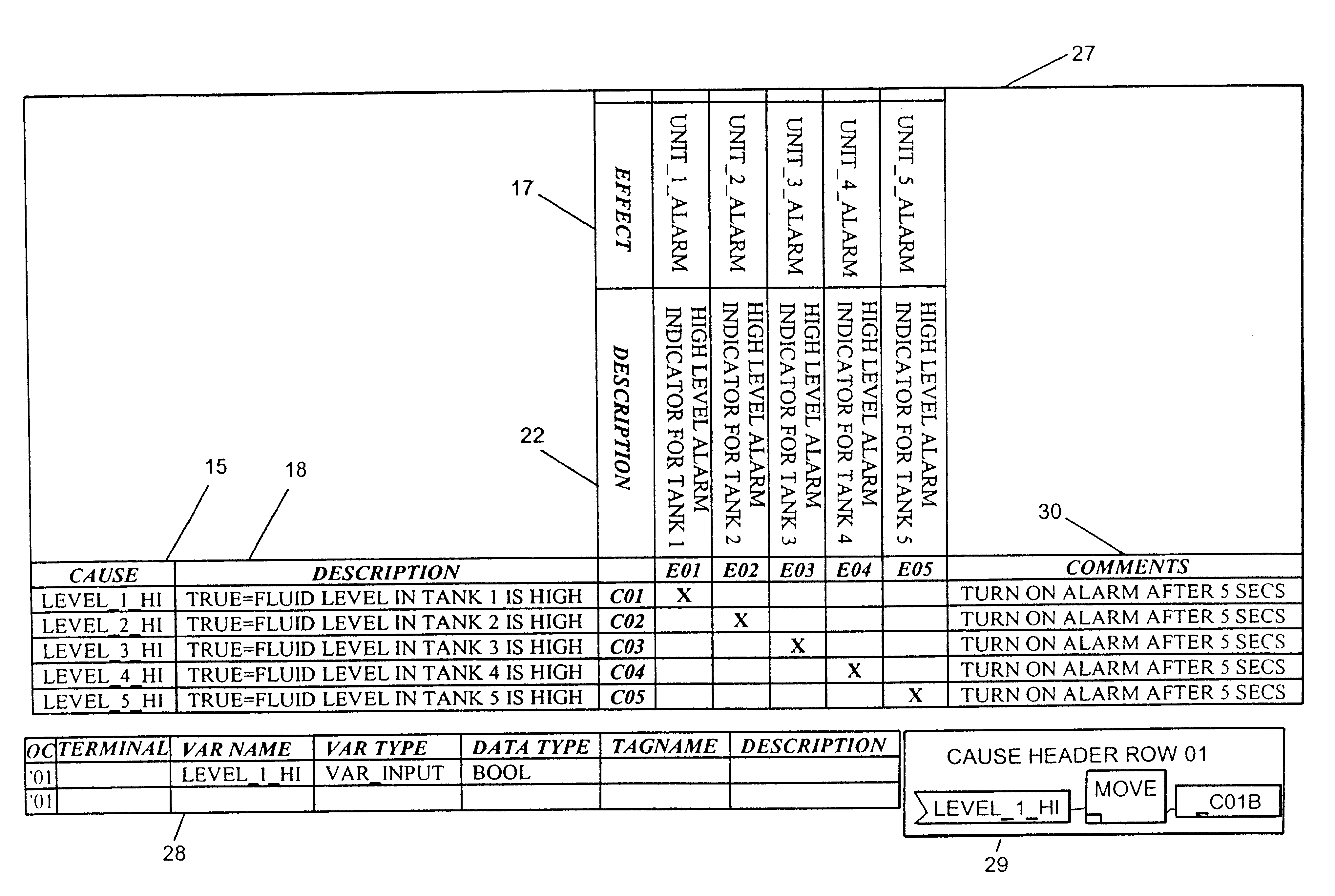

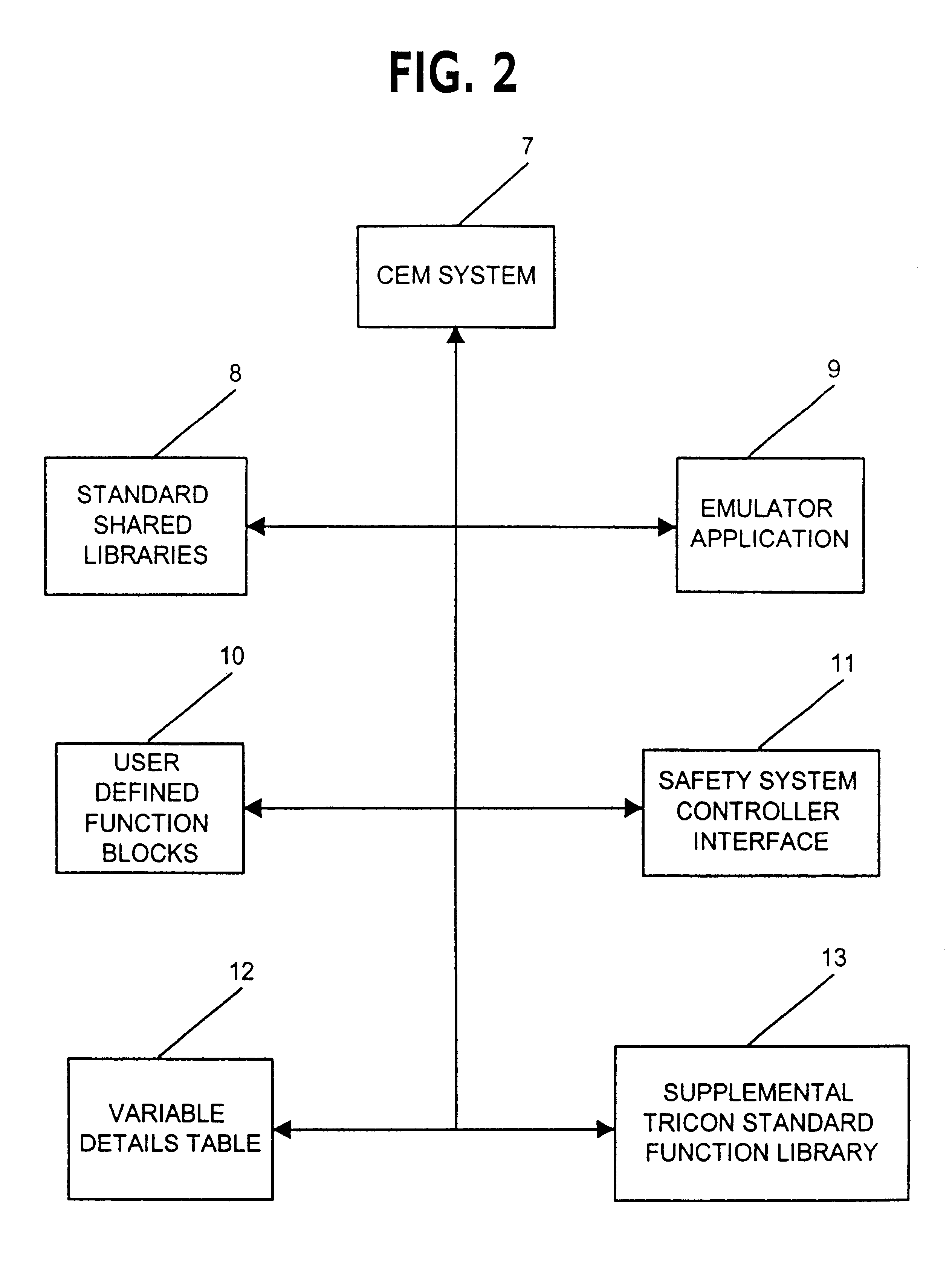

Cause effect diagram program

A computer system for generating a cause effect matrix as a user interface to develop a control program based on the cause effect matrix and to compile and download the resulting program into a programmable controller. A cause effect matrix diagram is used to develop a function block diagram program which is a standard IEC 1131-3 language. The function block diagram is translated into structured text which is compiled into intermediate code. The intermediate code is translated into the native code for the micro-processor of the target control system, including but not necessarily limited to the Motorola processor MPC-860. The automation of a cause effect matrix diagram to generate a function block diagram permits additional capability by allowing functions for causes, intersections, and effects. Because special functions may be included, the results of a cause generate timing functions or other computations before initiating the effect.

Owner:SCHNEIDER ELECTRIC SYST USA INC

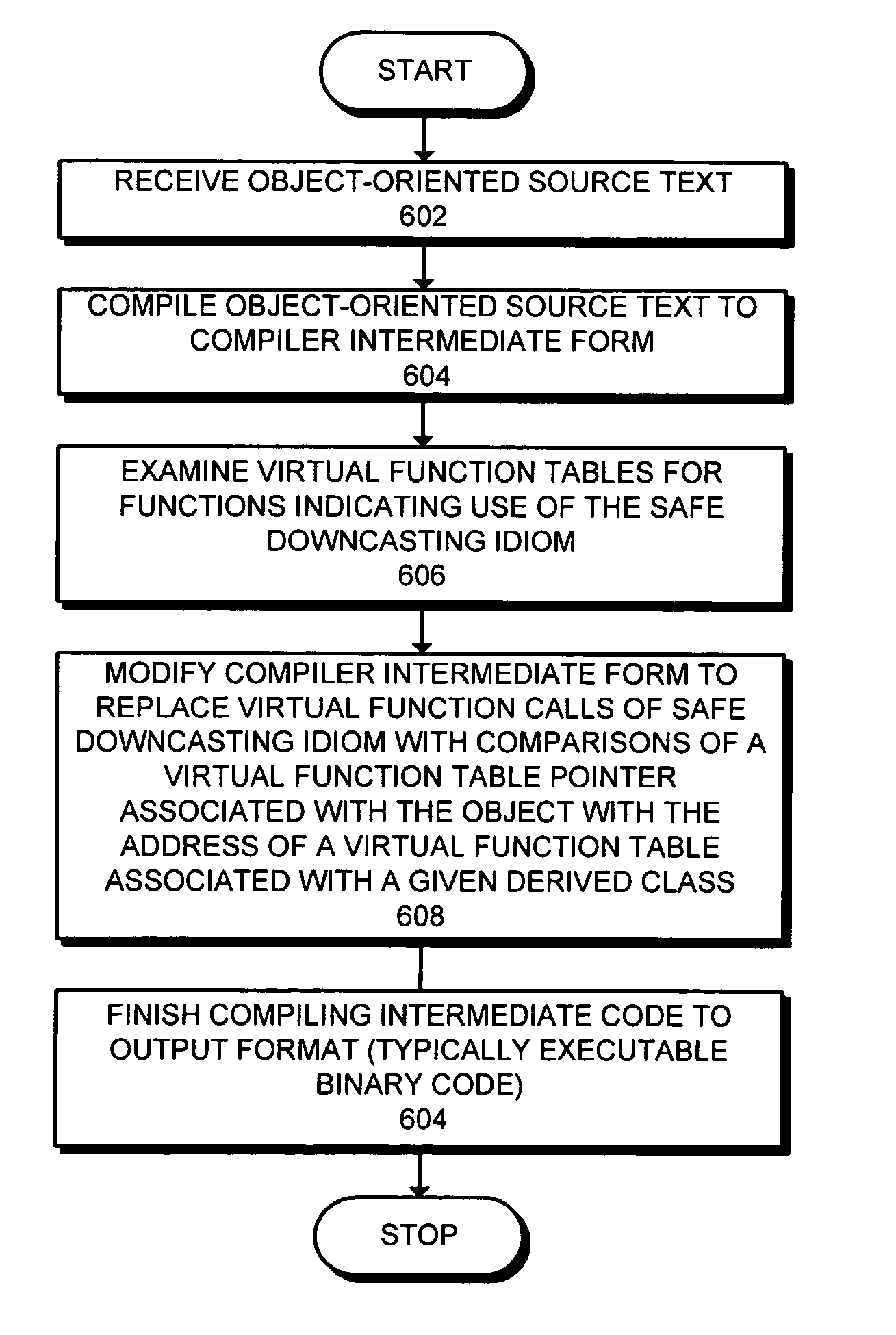

Optimizing safe downcasting in an object-oriented programming language

ActiveUS7171649B1Facilitates safe downcastingOptimizing safe downcasting and similar programming idiomsSpecific program execution arrangementsMemory systemsBase classProgramming idiom

A system is presented for optimizing safe downcasting and similar programming idioms in an object-oriented programming language. The system operates by receiving a source program written in the object-oriented programming language. The system compiles this source program into an intermediate representation. Next, the system examines the intermediate representation to identify the use of a virtual function call to determine if an object of a given base class is a member of a given derived class. Such usage facilitates safe downcasting of the object from the given base class to the given derived class. If the intermediate representation uses the virtual function call in this manner, the system replaces the virtual function call with a comparison of a virtual function table pointer associated with the object to an address of a virtual function table associated with the given derived class. The compiler finishes compiling the intermediate representation into executable binary code.

Owner:ORACLE INT CORP

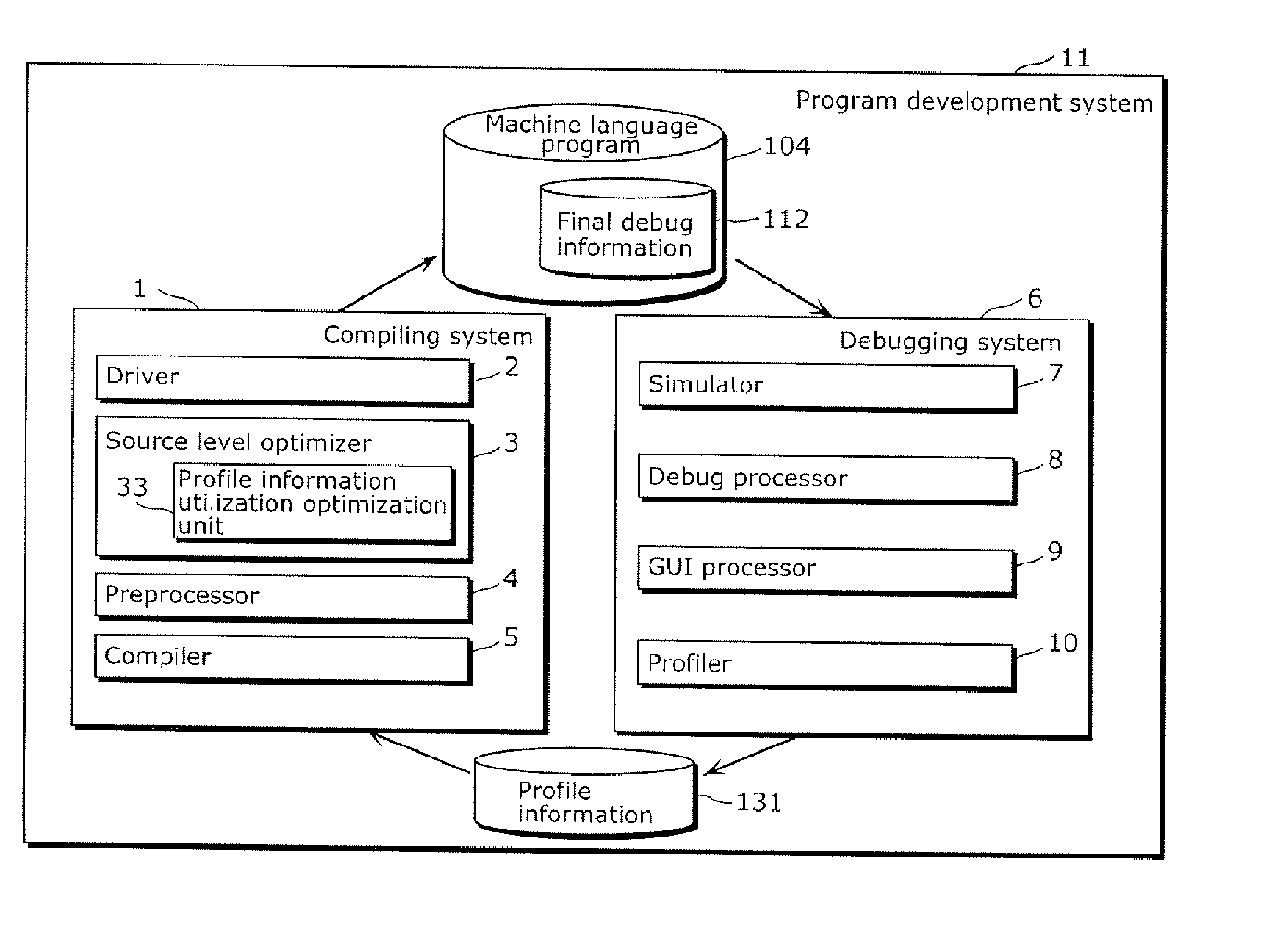

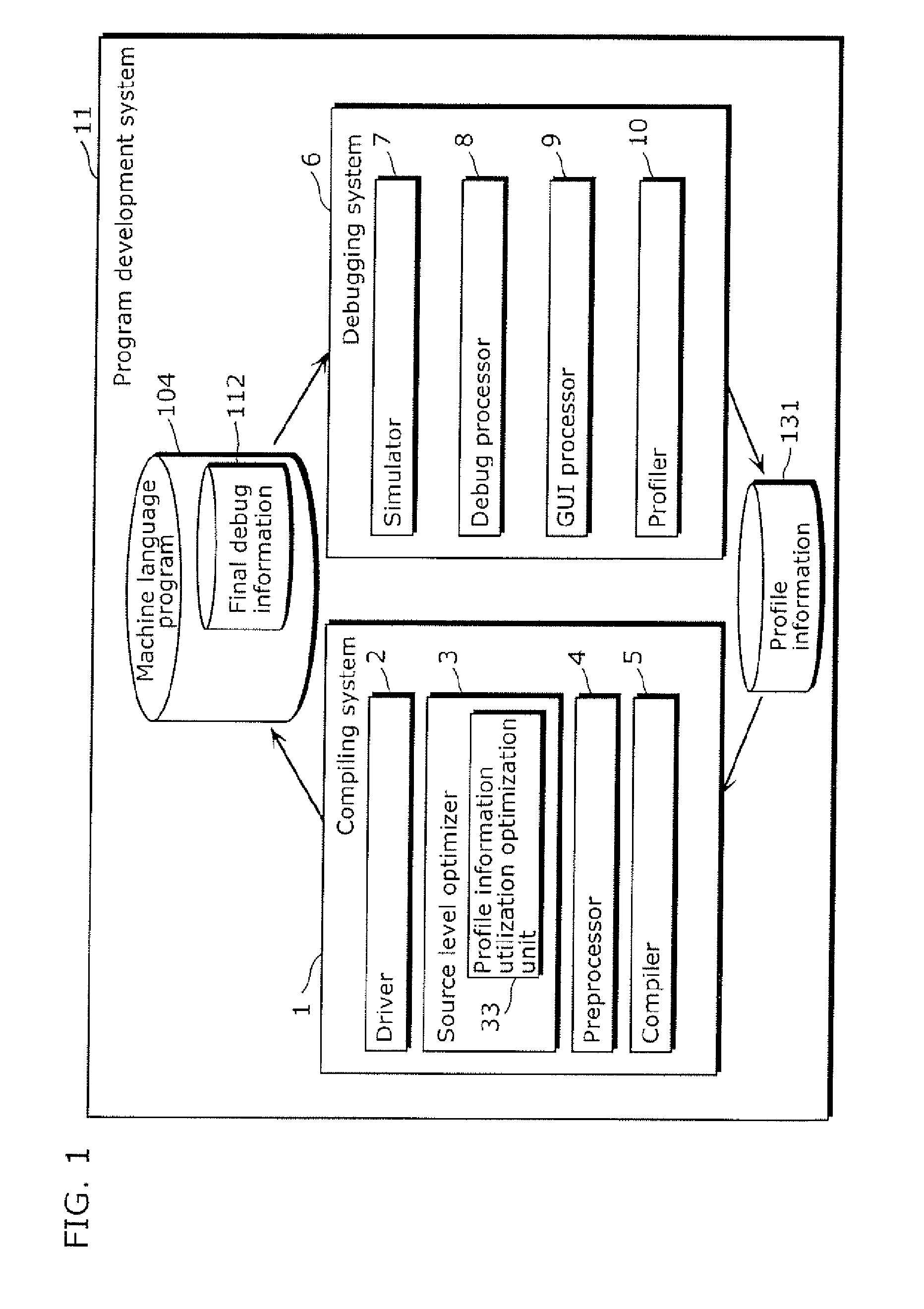

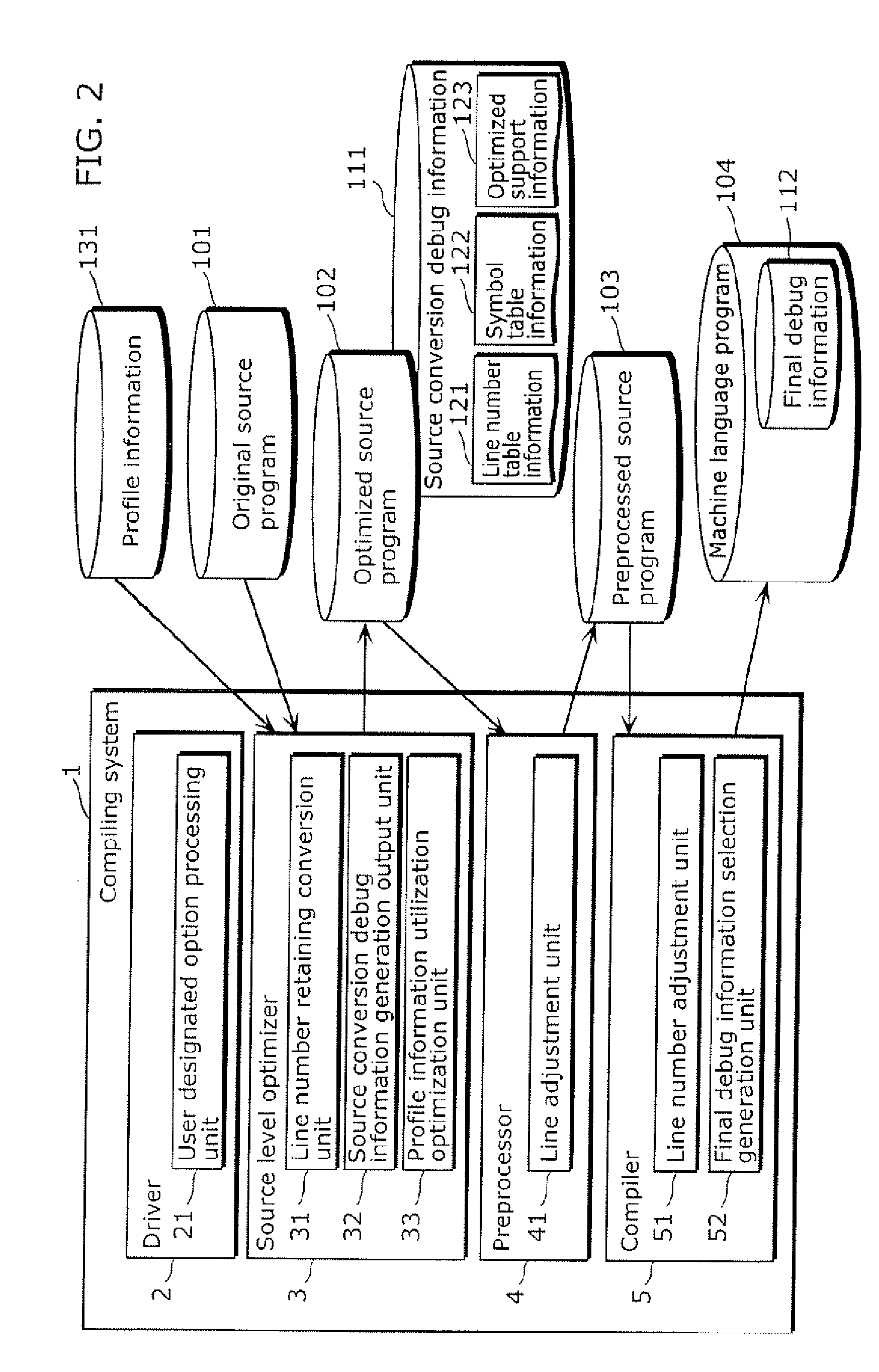

Compiling system, debugging system and program development system

InactiveUS20070168984A1Maintain easeImprove convenienceError detection/correctionSpecific program execution arrangementsSource levelProgram compilation

A compiling system which translates a source program written in a high-level language into a machine language program, and includes a source level optimizer which converts an original source S program into an optimized source program by optimizing the original source program at the source program level, a compiler which converts the optimized source program into the machine language program, and a final debug information selection generation unit which generates final debug information which indicates a corresponding relationship between the original source program and the machine language program.

Owner:PANASONIC CORP

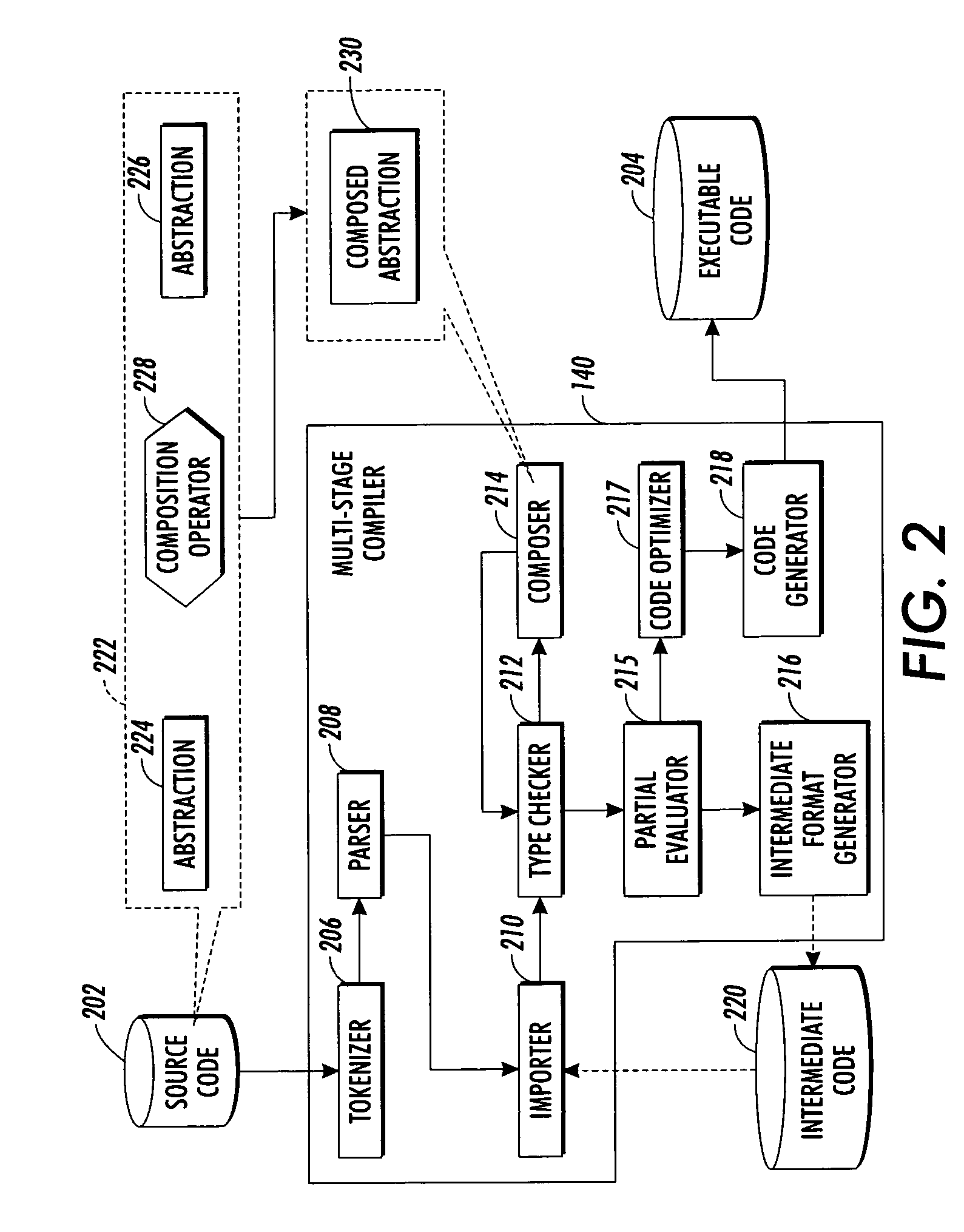

Program compiler with abstraction composer

InactiveUS20040148592A1Simplifying program maintenanceImprove legibilitySoftware engineeringSpecific program execution arrangementsTheoretical computer scienceSource code

Source code is compiled using a multi-stage compiler that includes a tokenizer, a type checker, and a composer. The tokenizer segments source code into a sequence of tagged segments. The source code includes at least one instruction that composes a first abstraction and a second abstraction with a selected composition operator. The parser builds a tree using the sequence of tagged segments. The type checker performs a first pass of the tree to determine whether abstractions on the tree are well typed. The composer reduces the at least one instruction composing the first and the second abstractions on the tree to a third abstraction. The composer substitutes the first and the second abstractions on the tree with the third abstraction, wherein the type checker performs a second pass of the tree to determine whether the third abstraction is well typed.

Owner:XEROX CORP

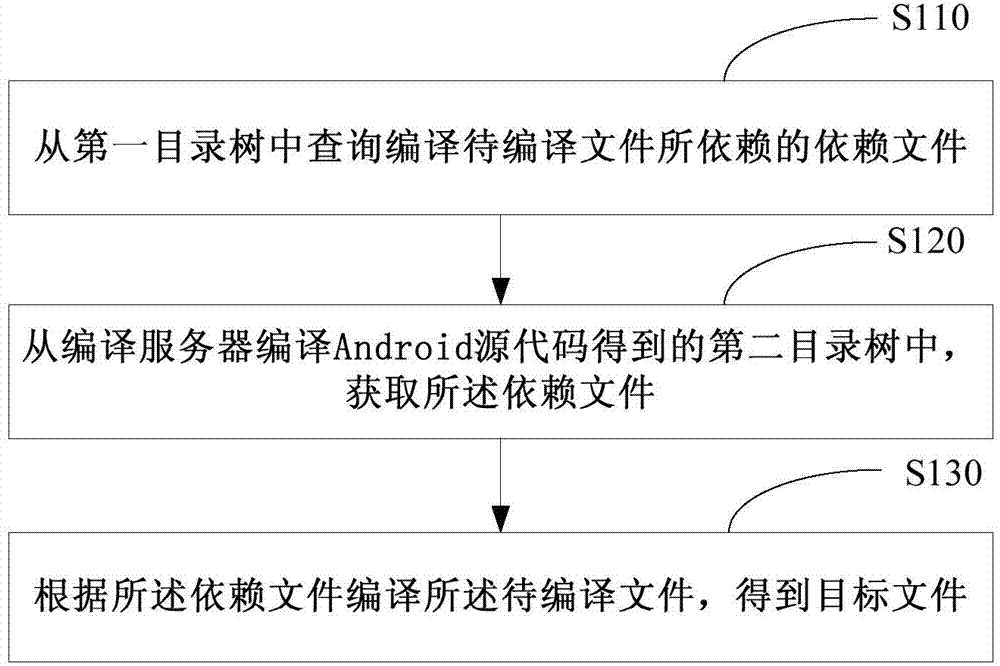

Program compilation method and relevant device

ActiveCN103870310AReduce occupancyShorten the timeProgram controlMemory systemsSystem developmentSource code

The invention relates to a program compilation method and a relevant device. The method comprises the steps of querying a dependent file depended by a selected file to be compiled from a first directory tree stored on a compilation host; then obtaining the dependent file from a second directory tree stored on a compilation server; using the dependent file for compiling the file to be compiled to obtain an object file. The effect of depending on the other directory tree (the second directory tree) in addition to the directory tree of the file to be compiled during compilation of Android source codes is realized, a set of complete Android source codes is not required to be downloaded and maintained by research and development personnel, source codes corresponding to a module are only required to be downloaded and the occupied space of a hard disk is reduced. Moreover, the dependent file required by the object file can be directly obtained from the second directory tree, the dependent file can be obtained without performing compilation and the time and resources for compiling the dependent file are saved. Accordingly, the required hard disk space and the compilation time are greatly reduced and the system development efficiency is improved.

Owner:XIAOMI INC

Cull before vertex attribute fetch and vertex lighting

ActiveUS8542247B1Save memory bandwidthReduce loadCathode-ray tube indicators3D-image renderingComputational scienceProgram compilation

One embodiment of the invention sets forth a mechanism for compiling a vertex shader program into two portions, a culling portion and a shading portion. The culling portion of the compiled vertex shader program specifies vertex attributes and instructions of the vertex shader program needed to determine whether early vertex culling operations should be performed on a batch of vertices associated with one or more primitives of a graphics scene. The shading portion of the compiled vertex shader program specifies the remaining vertex attributes and instructions of the vertex shader program for performing vertex lighting and performing other operations on the vertices in the batch of vertices. When the compiled vertex shader program is executed by graphics processing hardware, the shading portion of the compiled vertex shader is executed only when early vertex culling operations are not performed on the batch of vertices.

Owner:NVIDIA CORP

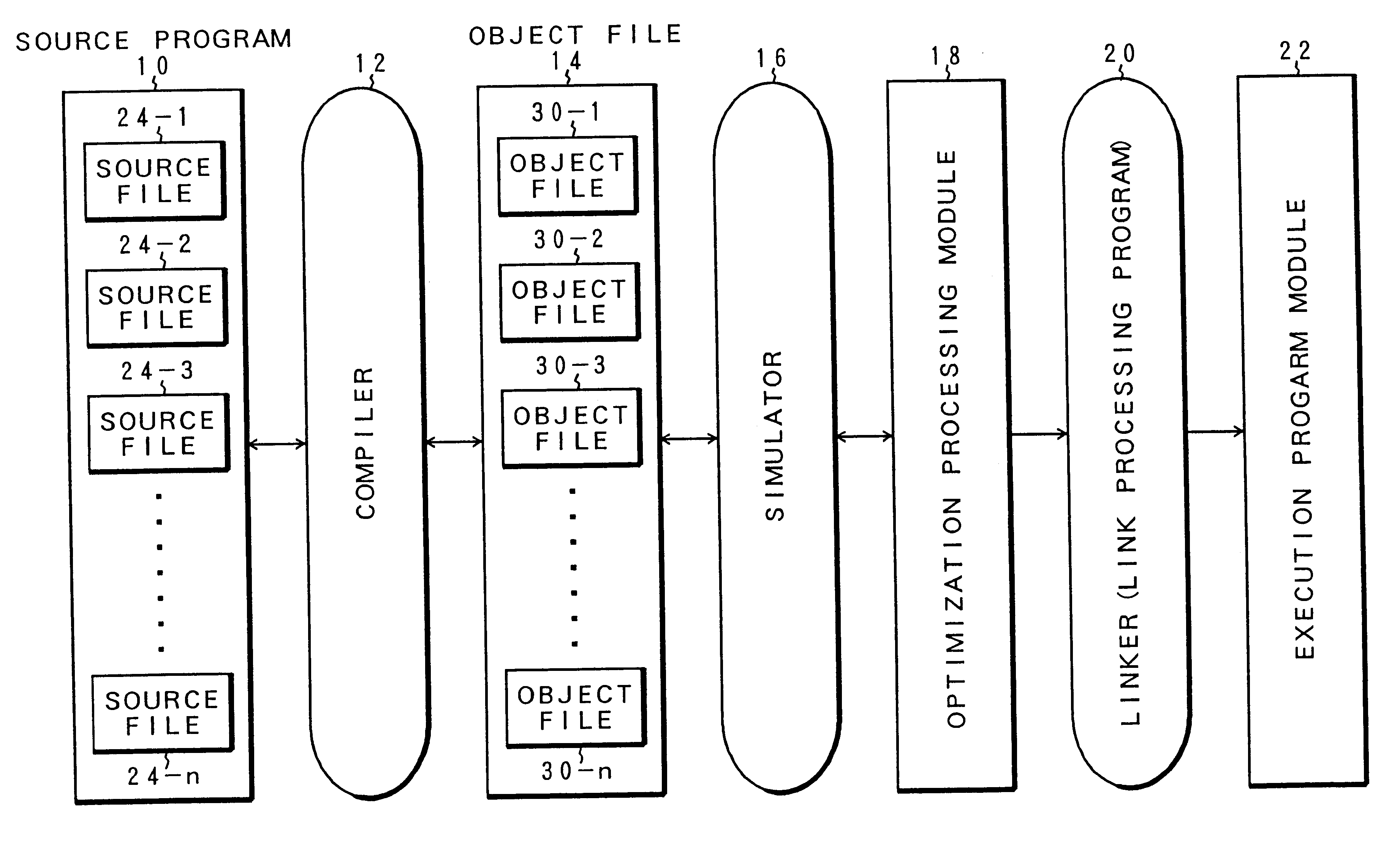

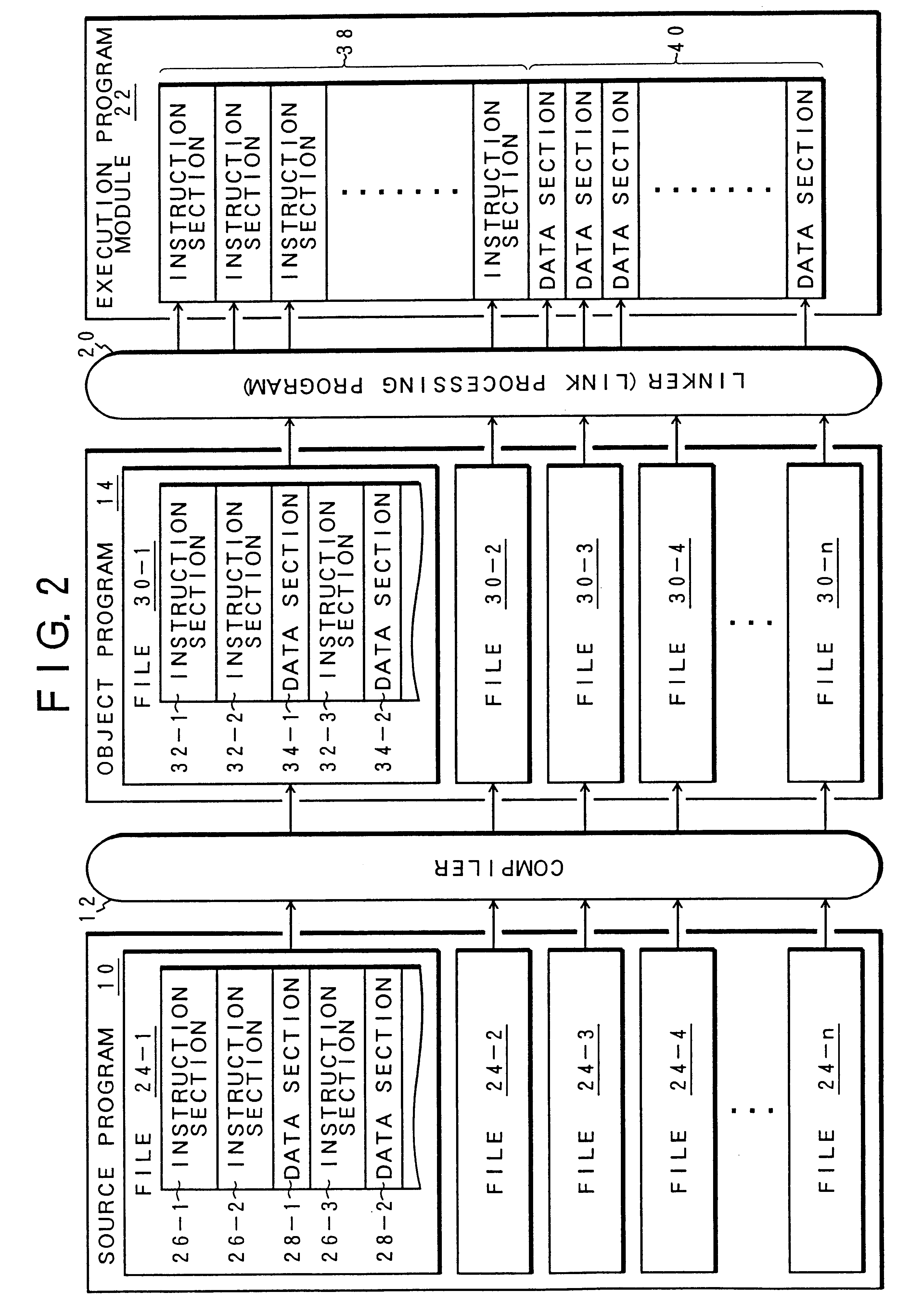

Apparatus and method for generating optimization objects

InactiveUS6678886B2Reduce frequencySpeed up executionSoftware engineeringSpecific program execution arrangementsBatch processingProgram compilation

A system and method enable appropriately concentrating instruction strings or data pieces sporadically present in a plurality of regions over more than one compilation unit and adjusting the front-and-rear relationship of executed instruction strings without changing the program compilation unit such as a file, subroutine, or function and also without creating a link processing program for batch processing of the system as a whole. Different section names are given to the executed instruction strings and the unexecuted instruction strings and the referenced data and the unreferenced data of an object program respectively. When an execution module is generated from the object program by linking, the sections having an executed section name and the sections having an unexecuted section name in a plurality of files may be aggregated respectively to divide the instructions into an execution portion and an unexecution portion.

Owner:FUJITSU LTD

Revalidation of a compiler for safety control

ActiveUS20060101433A1Improve reliabilityFaulty detectionSoftware testing/debuggingSpecific program execution arrangementsParallel computingComputer science

A method to revalidate a compiler intended for compilation of a user-written program for safety control in an industrial control system after it has been used. A test program is compiled a first time which test program is defined in a control language. The compiler is validated by verifying that the test program executes correctly. A first software is generated derived from the compiled test program intended for later comparison purposes. The test program is compiled a second time after the compilation of a user-written program. A second software is generated intended for a comparison based on the second compilation of the test program. The first software is compared with the second software, wherein the compiler is revalidated for any errors introduced between the first and the second compilation. Provided that the revalidation indicates no errors in the compiler, the user-written program is enabled to execute in a device with safety features for control of real world entities.

Owner:ABB (SCHWEIZ) AG

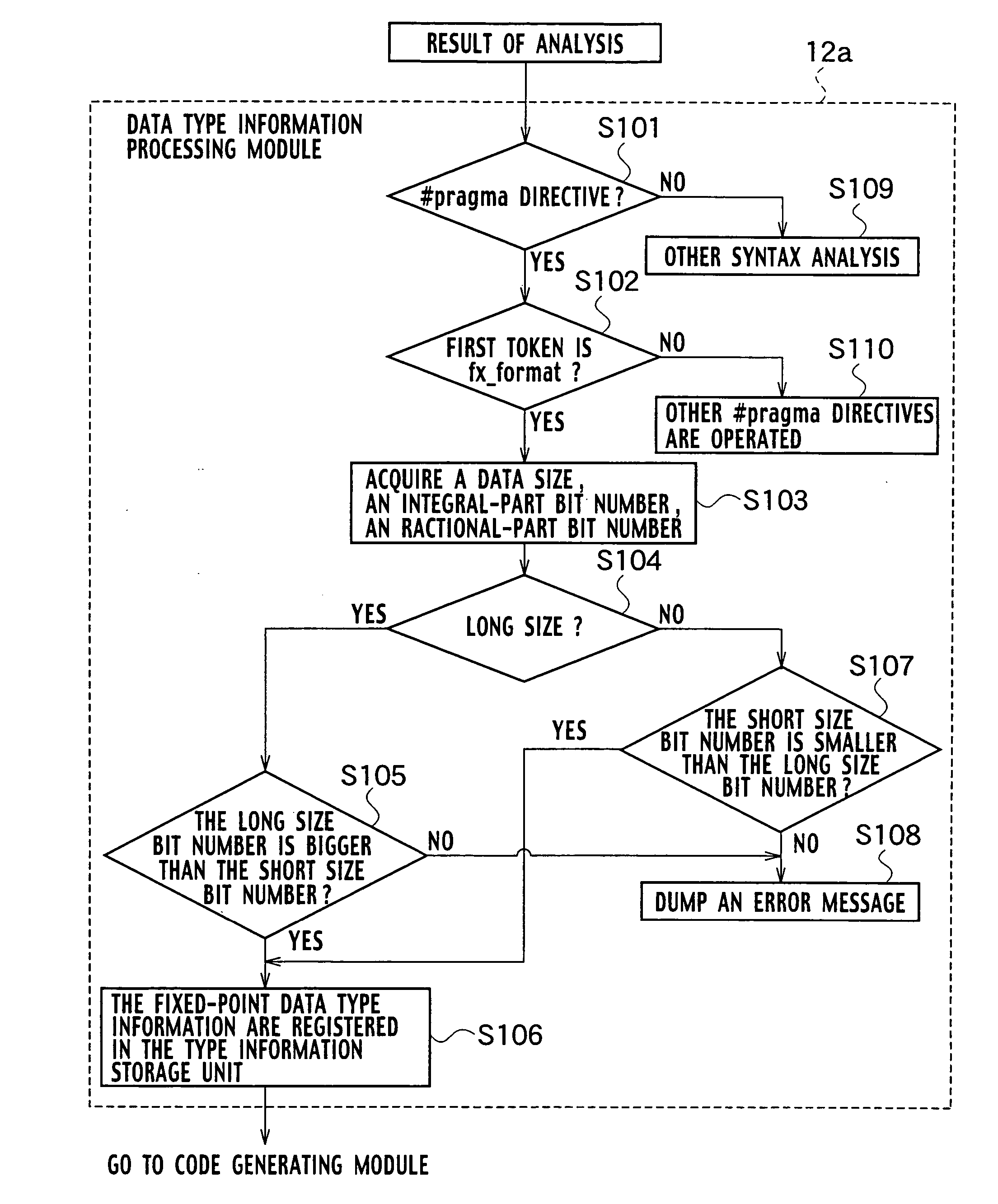

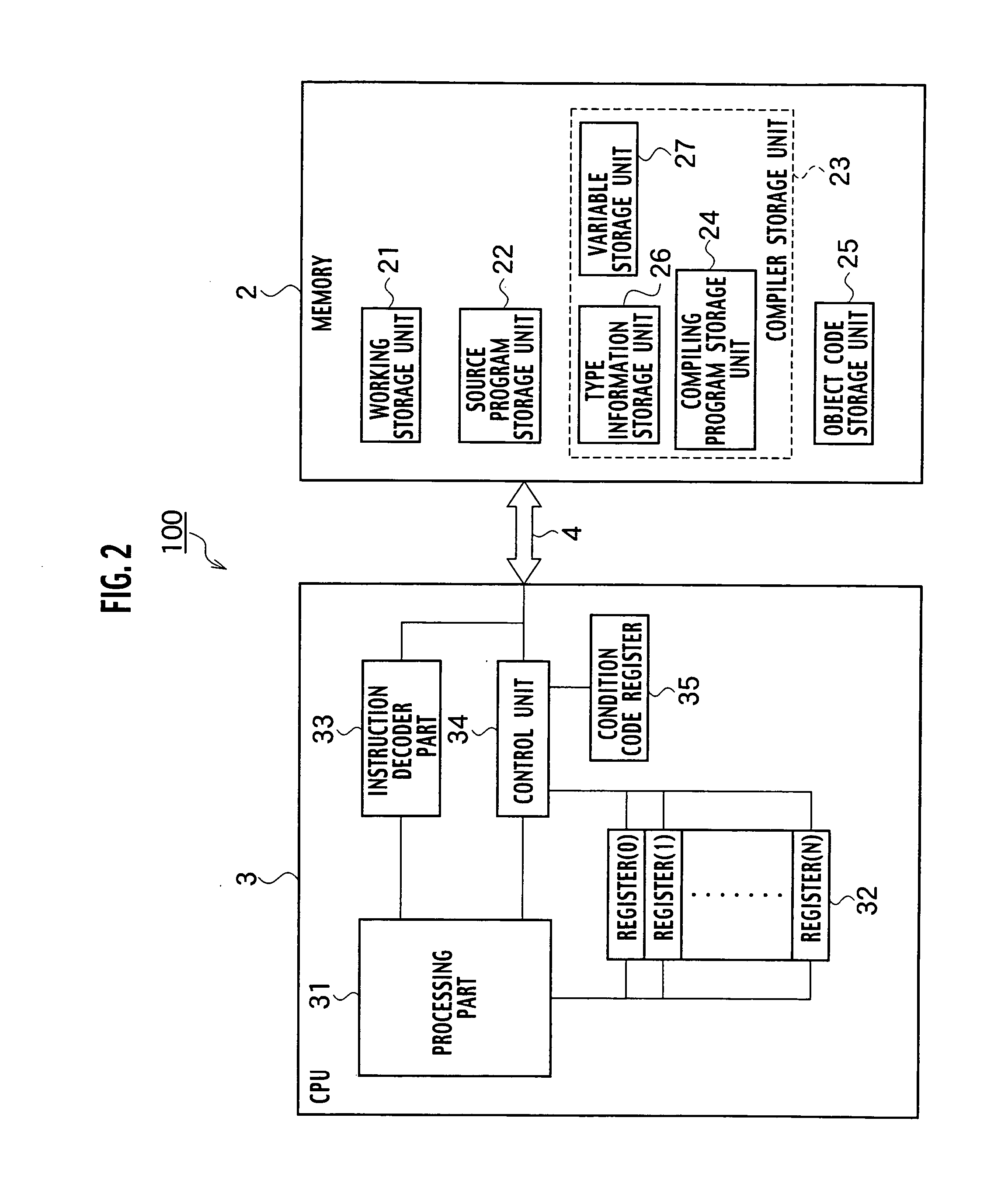

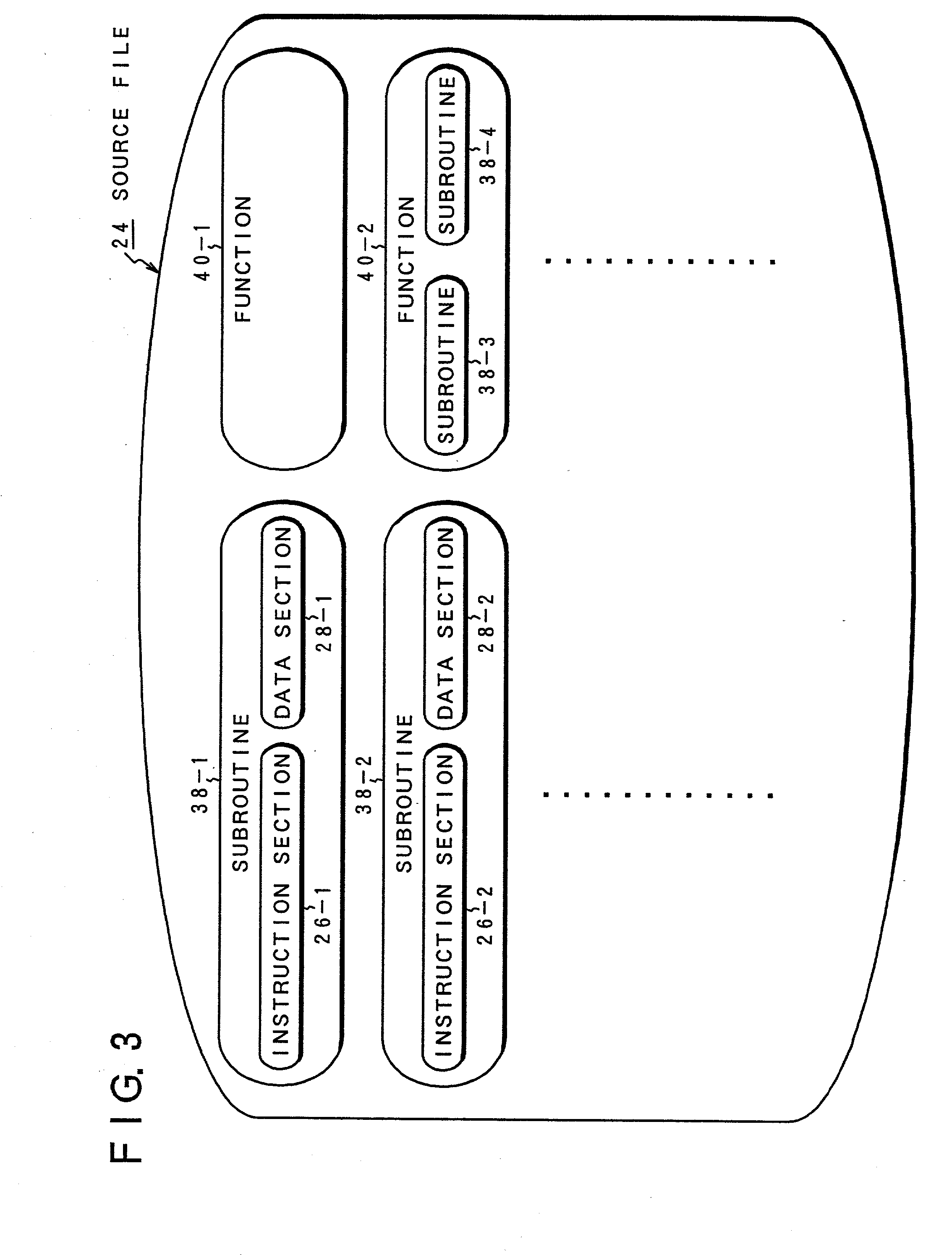

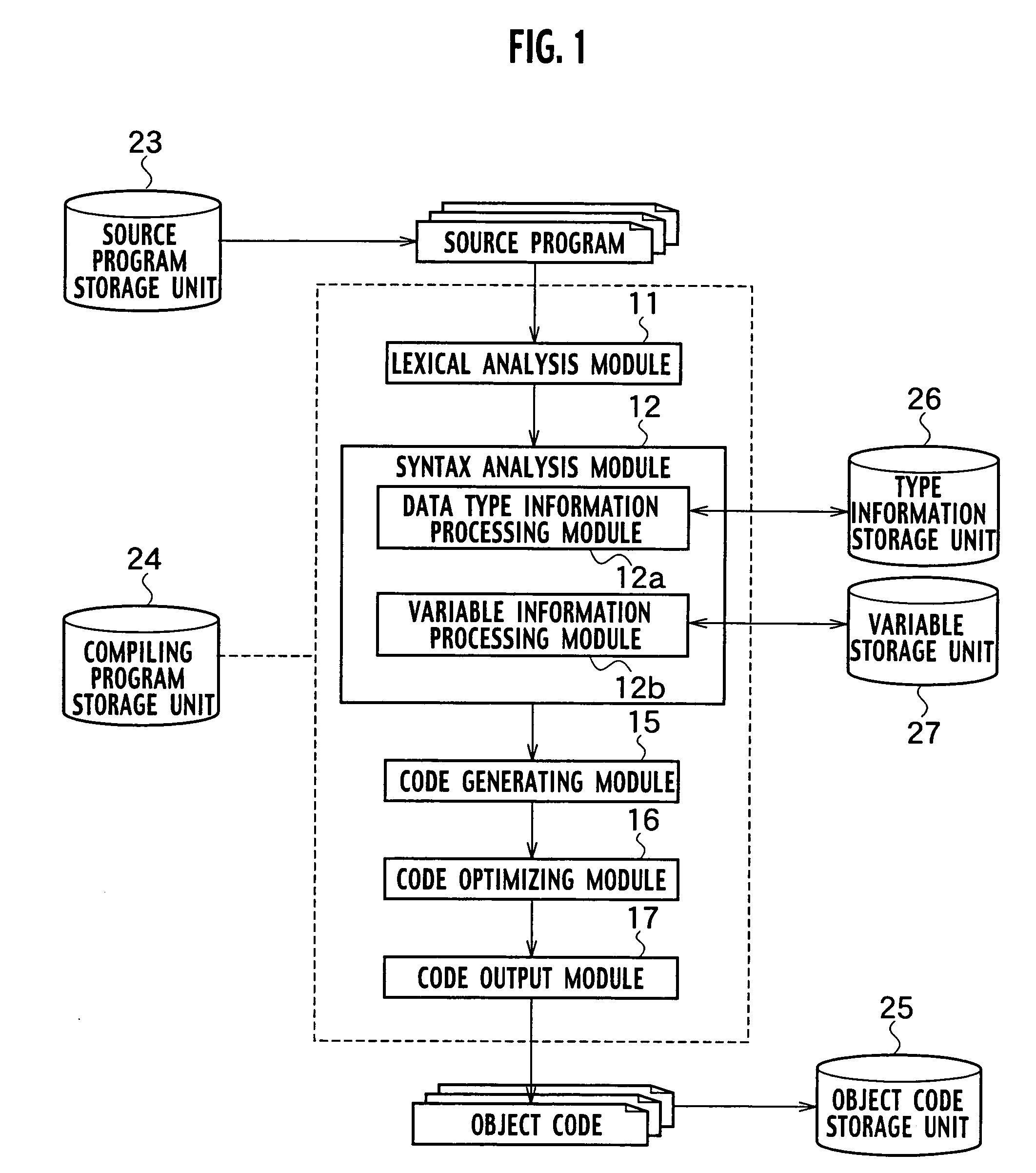

System for compiling source programs into machine language programs, a computer implemented method for the compiling and a computer program product for the compiling within the computer system

InactiveUS20050097523A1Specific program execution arrangementsMemory systemsInformation processingPoint data

A system for compiling source programs into machine language programs, comprising: a data type information processing module configured to analyze a definition statement of a fixed-point data type in a source program, acquire data type information of the fixed-point data type; a type-information storage; a variable information processing module configured to analyze a variable declaration statement of the fixed-point data type, acquire variable information; a variable storage; and a code generating module configured to read arithmetic expression data, acquire the type number, acquire the data type information, convert the arithmetic expression data.

Owner:KK TOSHIBA

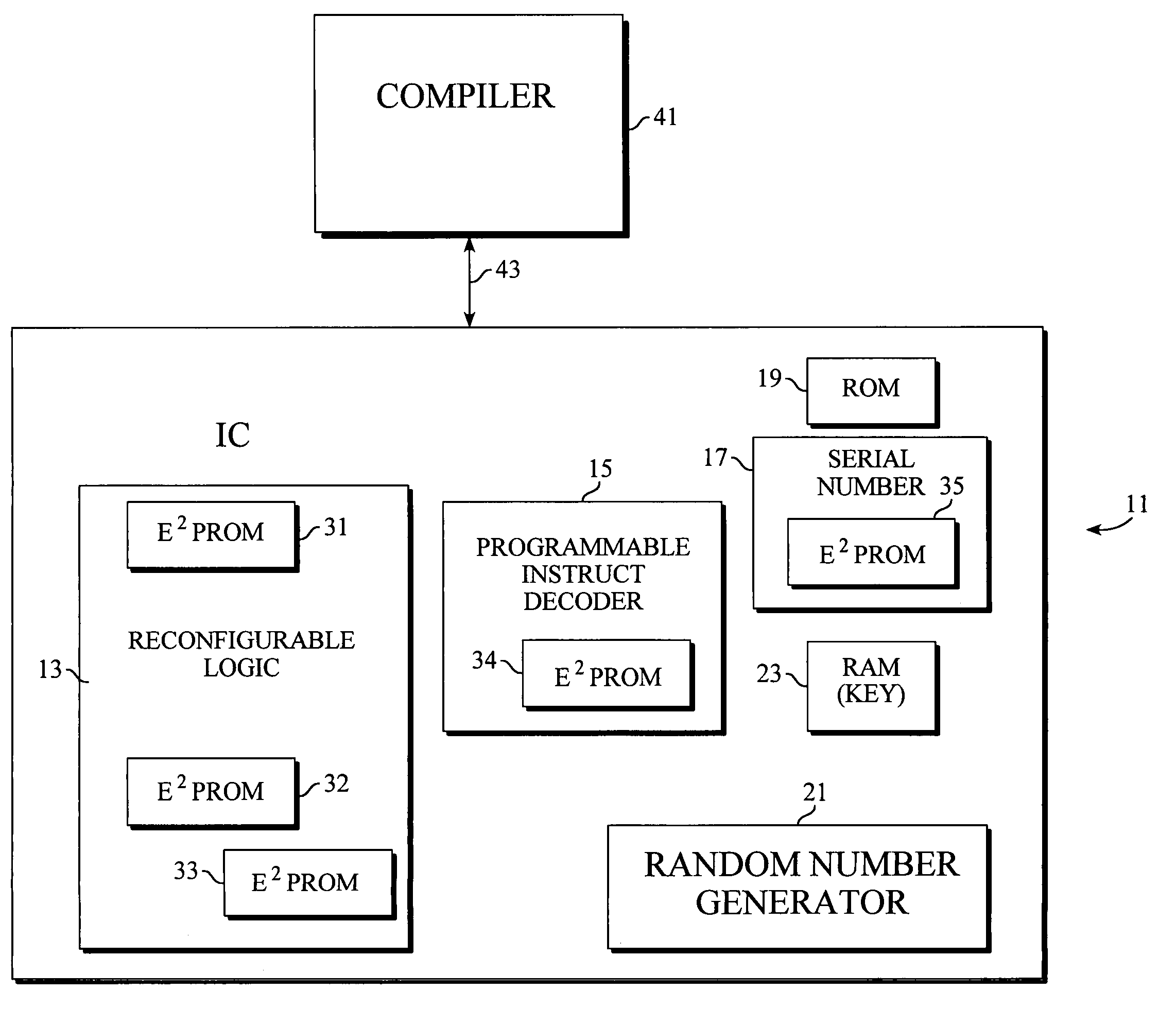

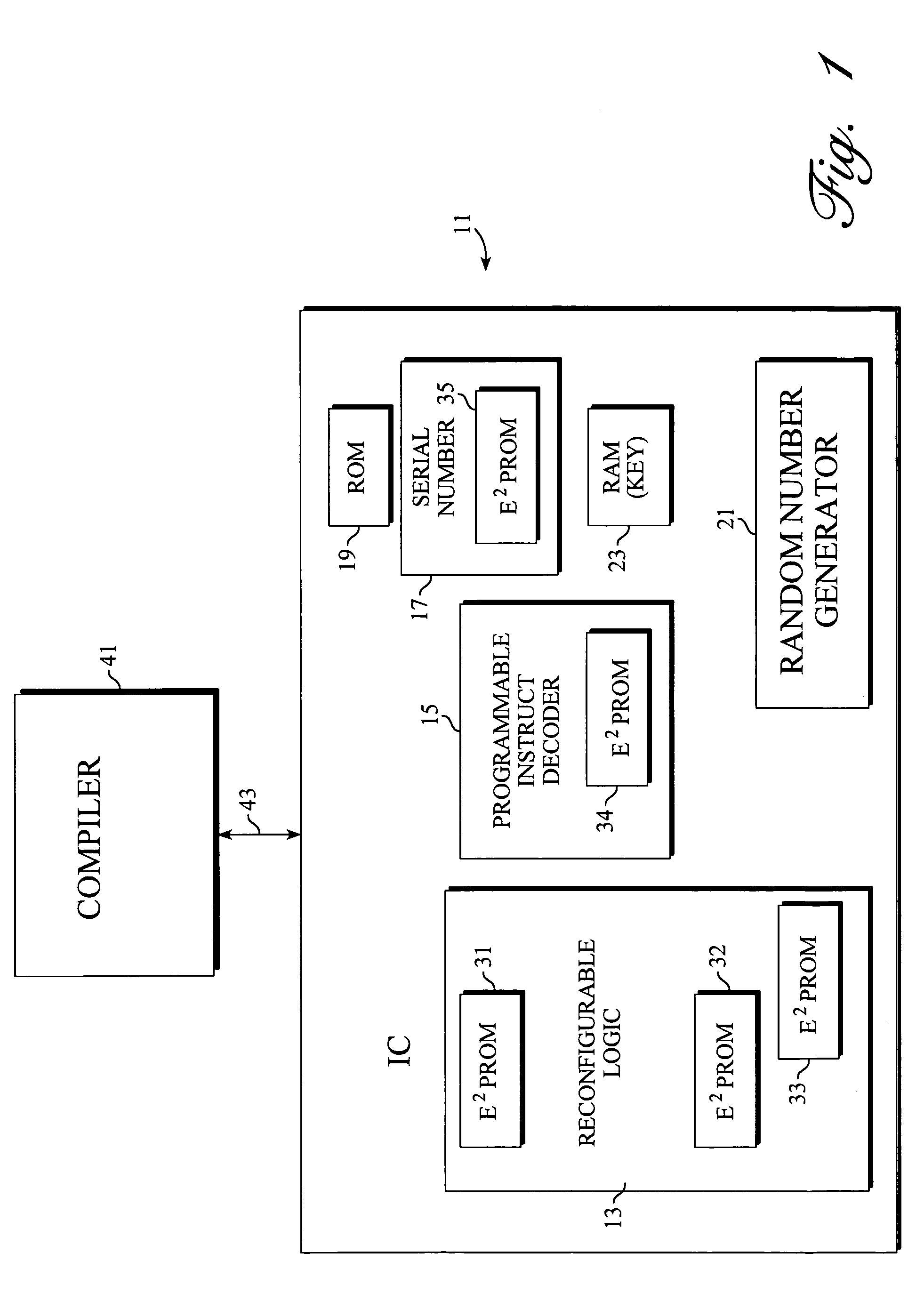

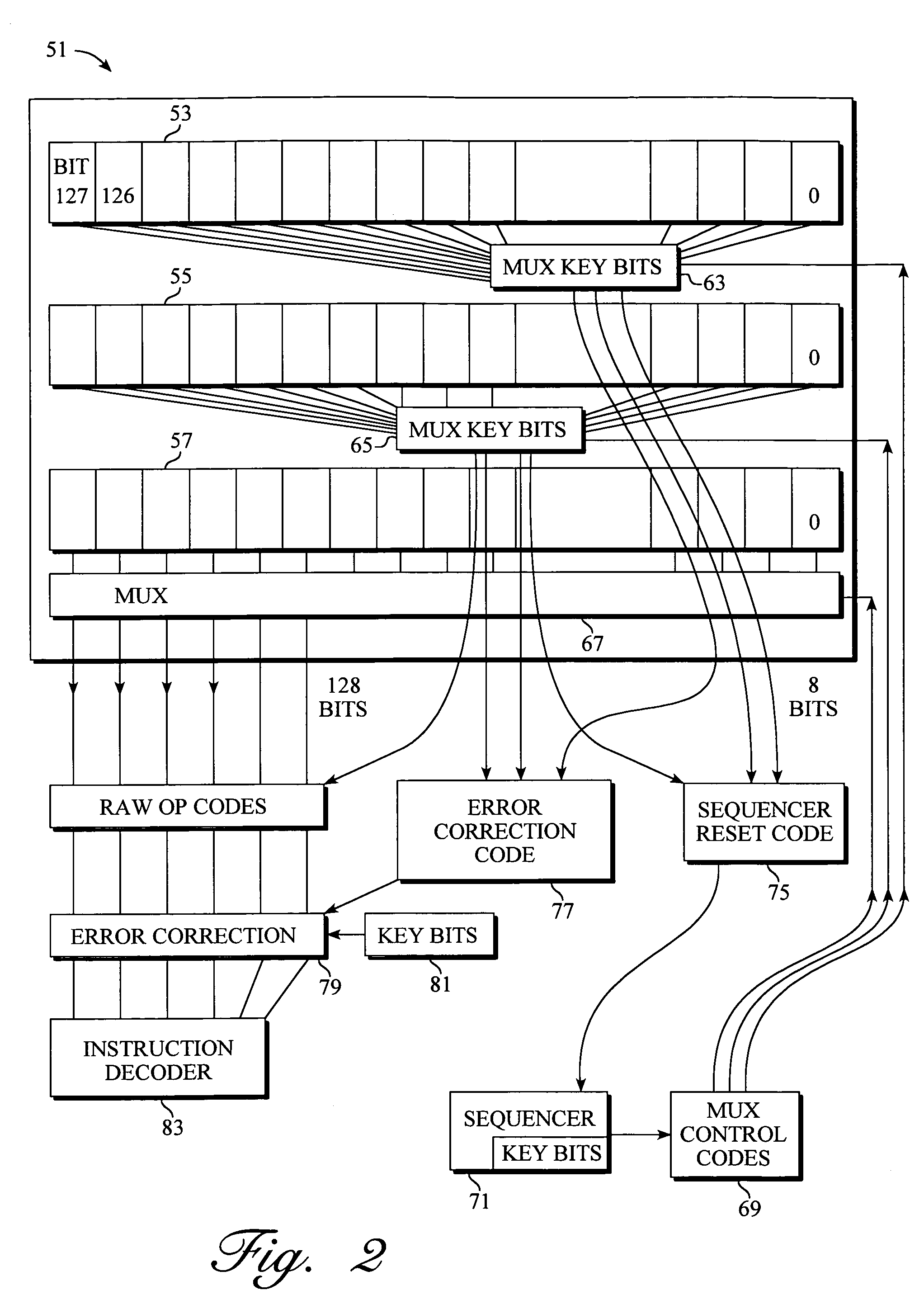

Secure program execution depending on predictable error correction

InactiveUS7353400B1ConfigurableUser identity/authority verificationUnauthorized memory use protectionTreatment errorComputer science

A CPU is provided with an ability to modify its operation, with respect to error correction, as a programmable feature. An error correction scheme is selected to be performed by the error correcting circuit. The compiled program may have intentionally introduced errors which are predictably corrected by the selected error correction scheme. When a program is compiled, the program is modified by the intentional insertion of errors which would result from the execution of the program. By providing error correction schema selected during program compilation, errors can be inserted in the program code, but are handled in a predictable manner by the error correction.

Owner:ORACLE INT CORP

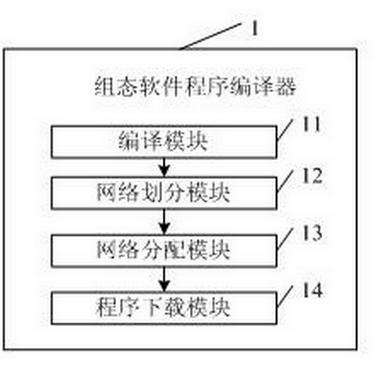

Programmable logic controller, program compiler, compiling system and method

ActiveCN102096390AImprove processing efficiencyReduce processing timeResource allocationProgramme control in sequence/logic controllersProgrammable logic controllerComputer science

The embodiment of the invention discloses a programmable logic controller, a configuration software program compiler, a compiling system and a compiling method. The programmable logic controller comprises a multi-core microprocessor and a storage module, wherein the multi-core microprocessor further comprises a main core processing module and at least one acceleration core processing module; the main core processing module is used for executing program network segments distributed to the main core processing module; the program network segments are formed by segmenting a compiling program required to be run by the programmable logic controller by using the configuration software program compiler which is connected with the programmable logic controller; and the acceleration core processing module is used for executing program network segments distributed to the acceleration core processing module; and the storage module is used for storing program network segments distributed to the main core processing module and at least one acceleration core processing module respectively through a plurality of data partitions. Through the programmable logic controller, the configuration software program compiler, the compiling system and the compiling method, programming languages compiled on the programmable logic controller can be executed in parallel.

Owner:深圳市合信自动化技术有限公司

Dynamic compiler program, dynamic compiling method and dynamic compiling device

InactiveUS20110246974A1Low reusabilitySoftware engineeringProgram controlDynamic compilationSoftware engineering

A dynamic compiler program product, method, and device for sequentially compiling a partial computer program in a computer. The program product causes the computer to function as: an execution status acquisition unit for acquiring respective values of one or more pieces of current execution status information; a determination unit for reading, from the shared pool, the second list of the conditions associated with an executable instruction stream generated by compiling a partial program that is the same as a partial program to be compiled and determining whether respective values of corresponding pieces of current execution status information satisfy the conditions; and a dynamic compilation unit for generating an executable instruction stream by compiling the partial program to be compiled on the condition that a result of determination made by the determination unit is negative.

Owner:IBM CORP

Program compiler with abstraction composer

InactiveUS7284242B2Easy maintenanceImprove legibilitySoftware engineeringSpecific program execution arrangementsSource codeProgram compilation

Source code is compiled using a multi-stage compiler that includes a tokenizer, a type checker, and a composer. The tokenizer segments source code into a sequence of tagged segments. The source code includes at least one instruction that composes a first abstraction and a second abstraction with a selected composition operator. The parser builds a tree using the sequence of tagged segments. The type checker performs a first pass of the tree to determine whether abstractions on the tree are well typed. The composer reduces the at least one instruction composing the first and the second abstractions on the tree to a third abstraction. The composer substitutes the first and the second abstractions on the tree with the third abstraction, wherein the type checker performs a second pass of the tree to determine whether the third abstraction is well typed.

Owner:XEROX CORP

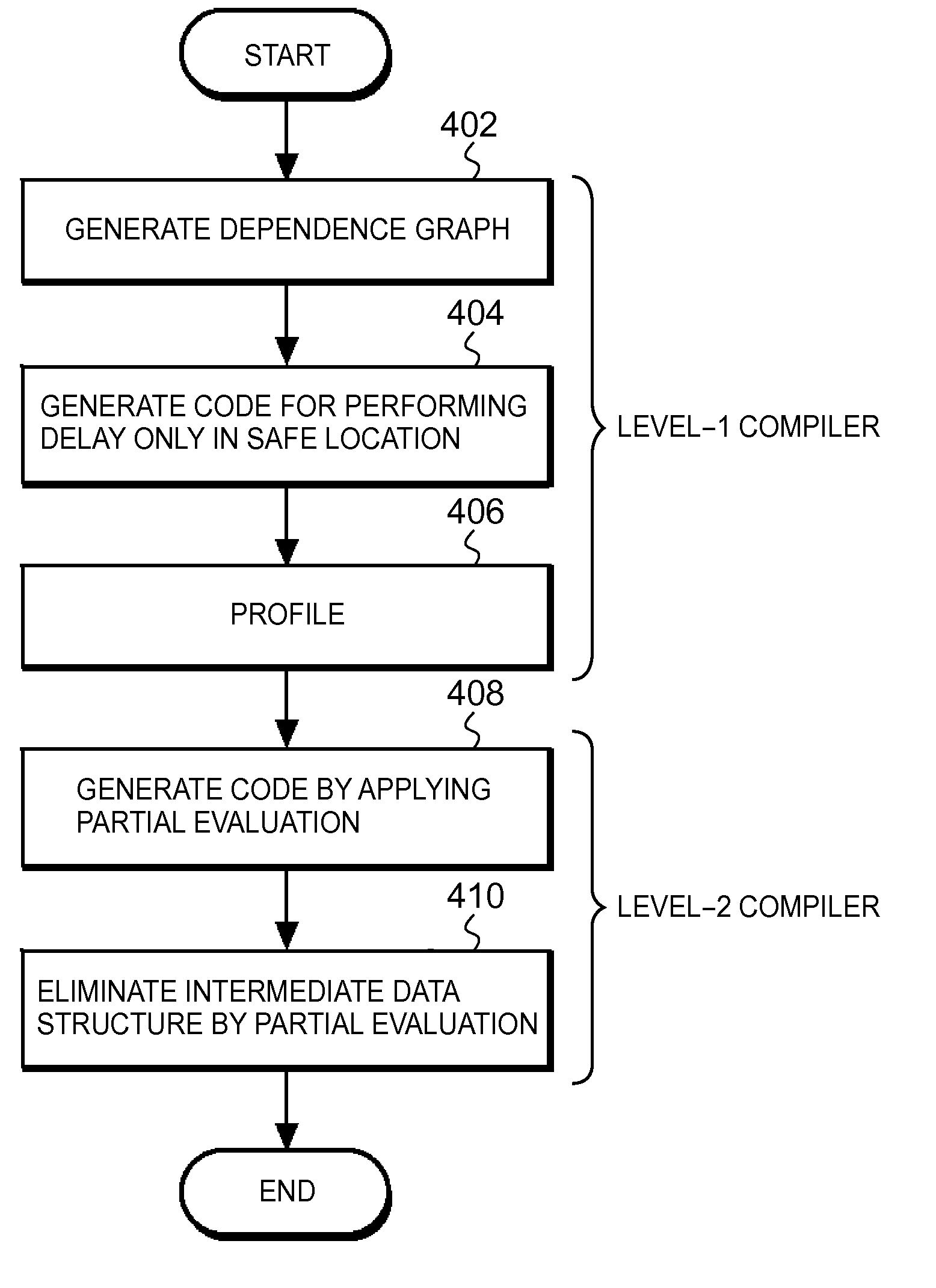

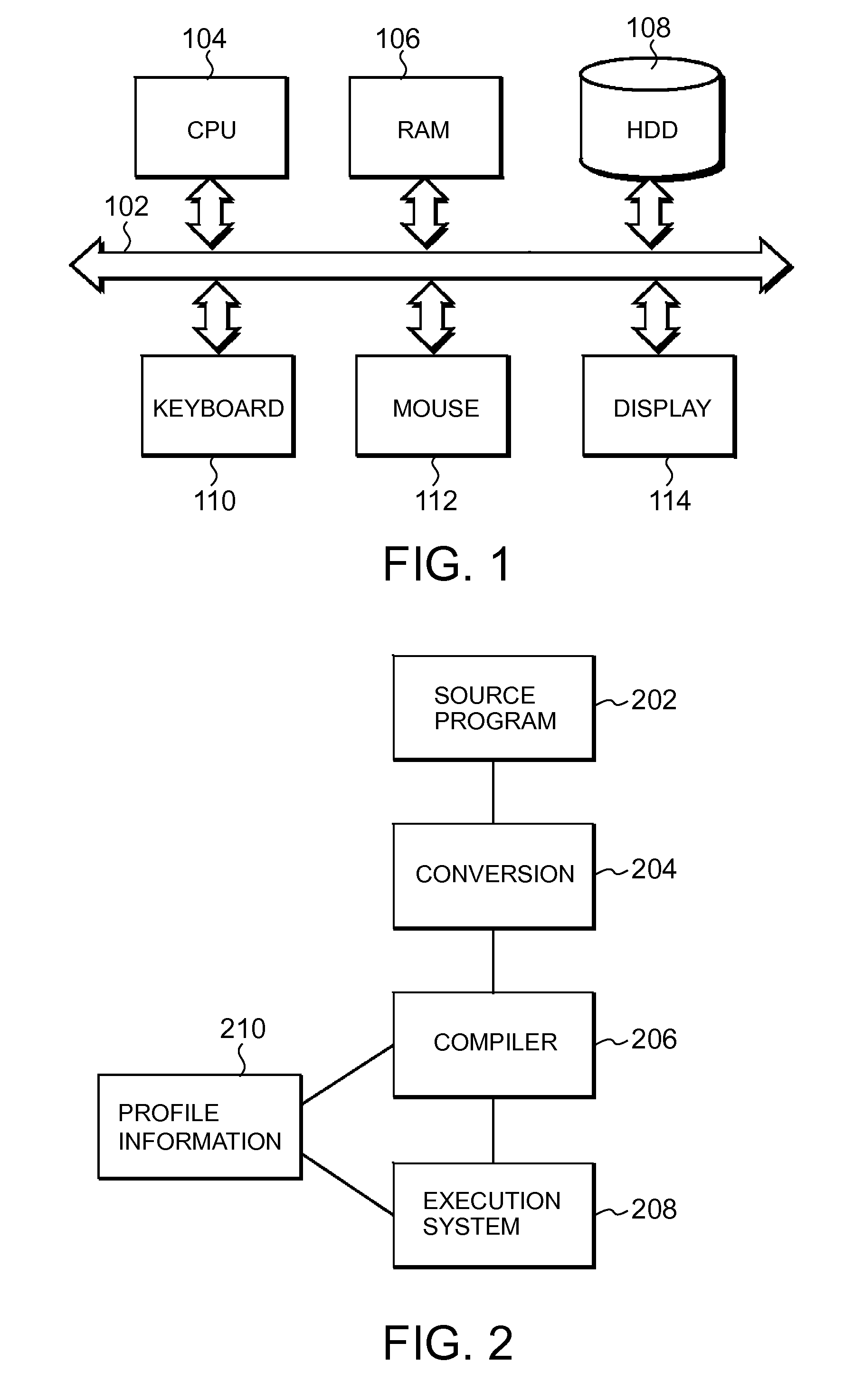

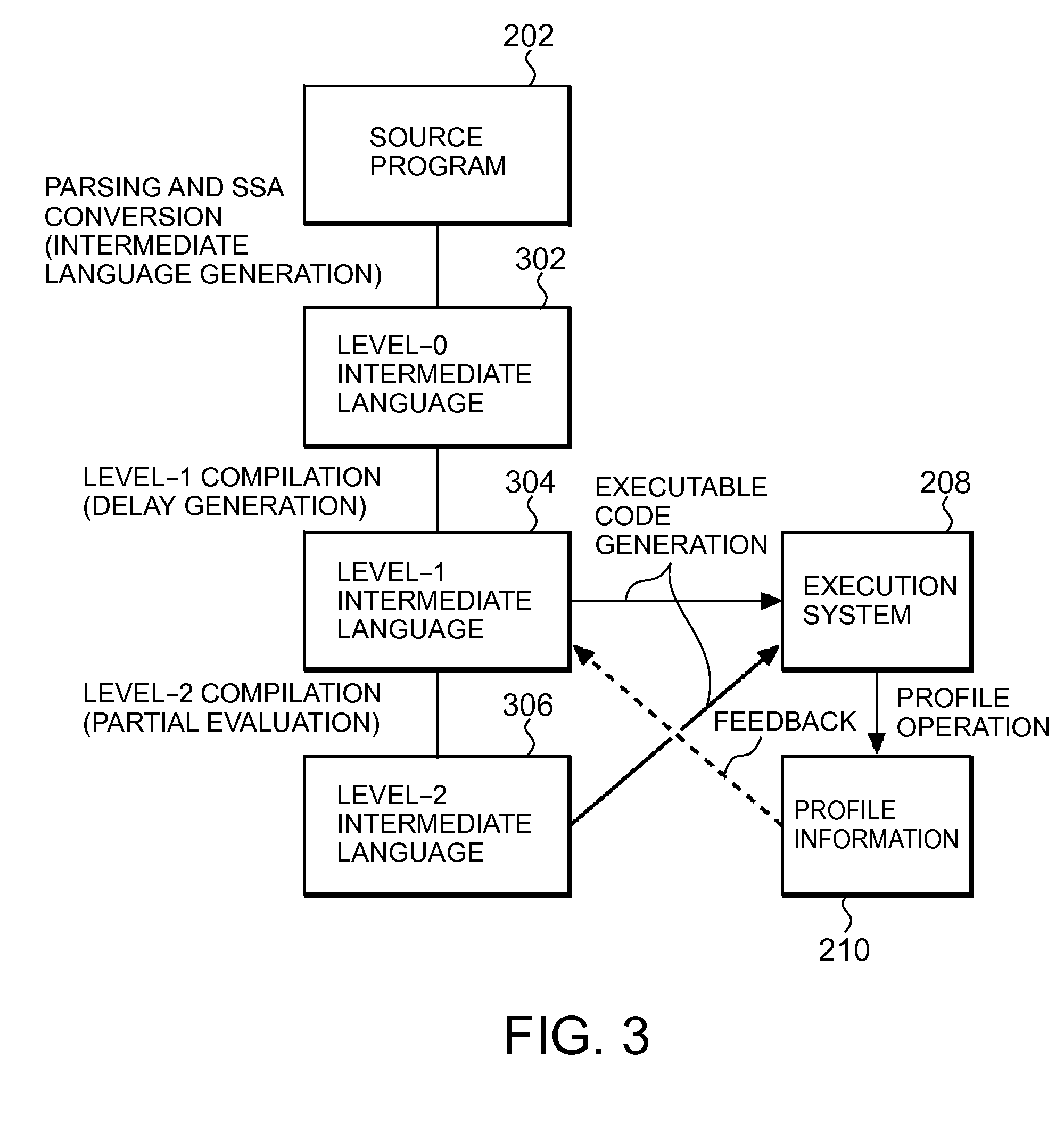

Compiler program, compilation method, and computer system

InactiveUS20110067018A1Improve programming performanceHigh frequencySoftware engineeringProgram controlCompilation errorCompiler

A method, computer program product and system for improving performance of a program during runtime. The method includes reading source code; generating a dependence graph with a dependency for (1) data or (2) side effects; generating a postdominator tree based on the dependence graph; identifying a portion of the program able to be delayed using the postdominator tree; generating delay closure code; profiling a location where the location is where the delay closure code is forced; inlining the delay closure code into a frequent location in which the delay closure code has been forced with high frequency; partially evaluating the program; and generating fast code which eliminates an intermediate data structure within the program, where at least one of the steps is carried out using a computer device so that performance of the program during runtime is improved.

Owner:IBM CORP

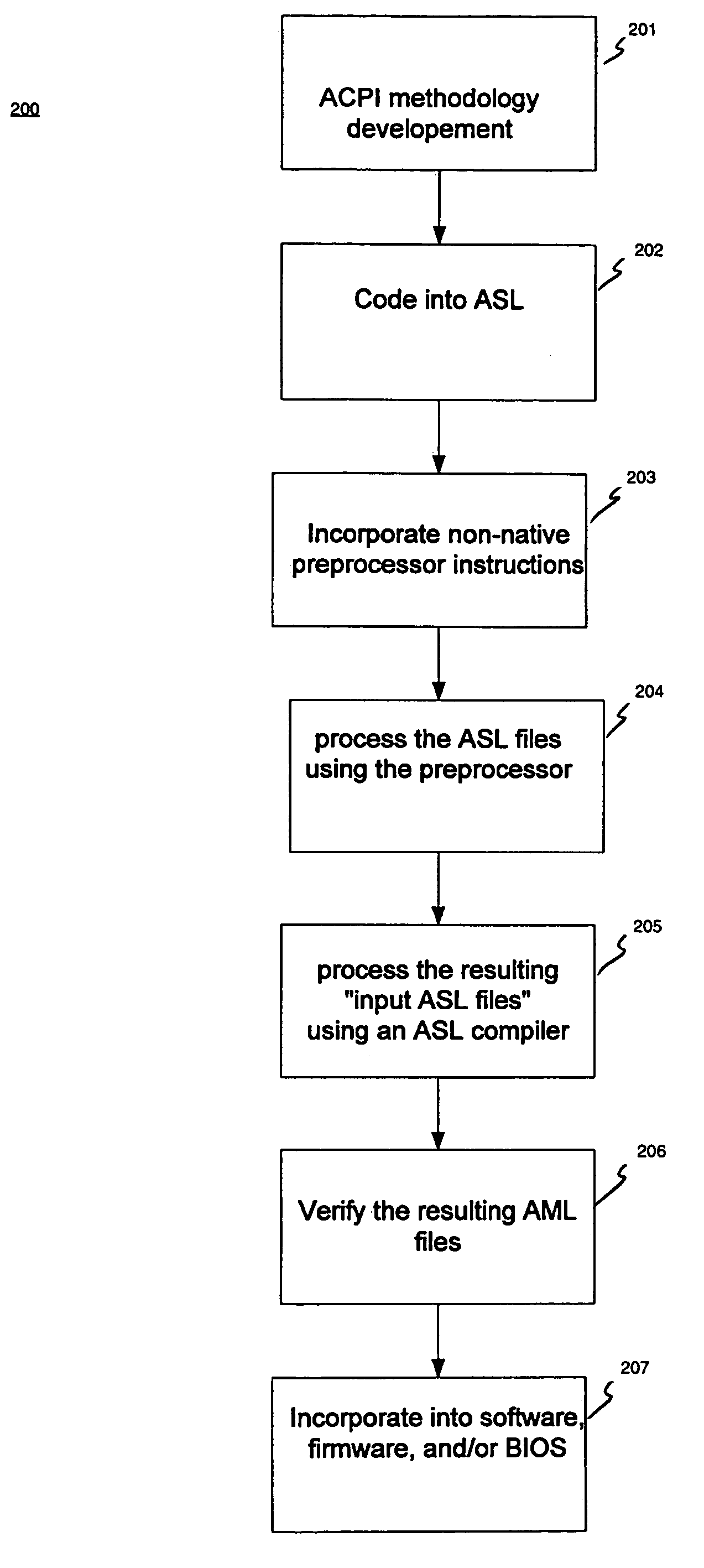

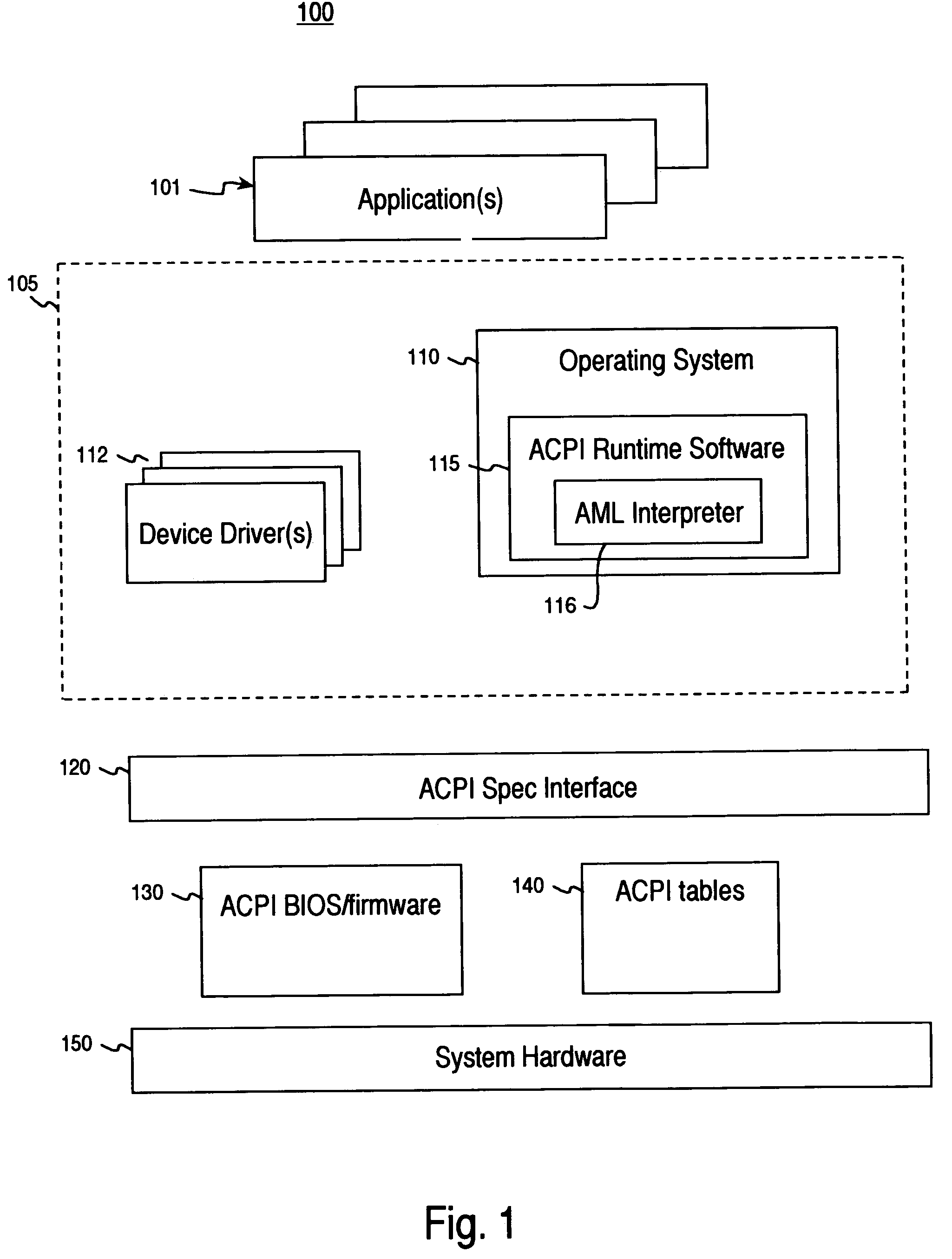

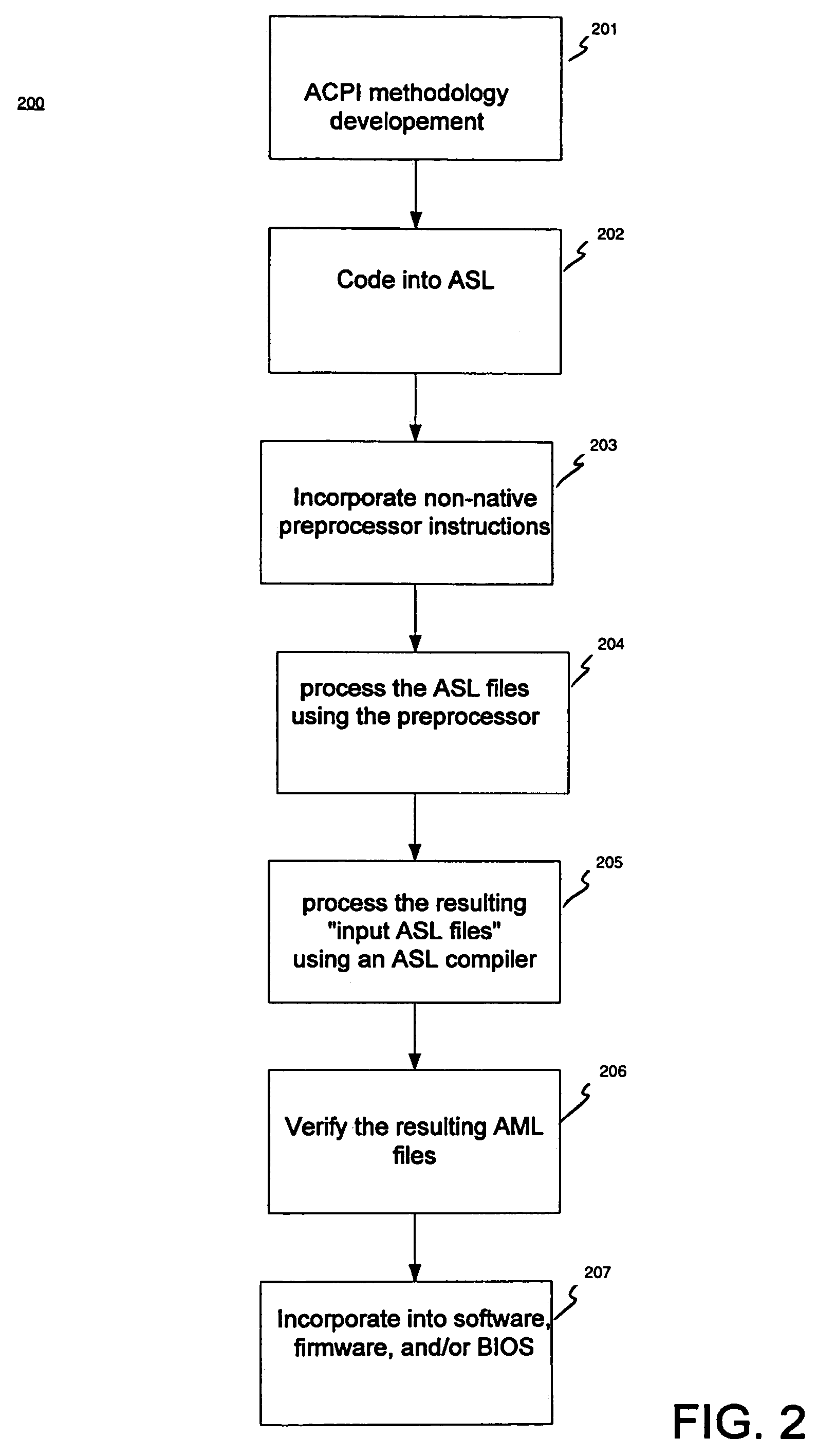

ACPI preprocessor

InactiveUS7188339B2Volume/mass flow measurementPower supply for data processingProgramming constructsHuman language

A computer-implemented method for compiling ASL (ACPI Source Language) code into AML (ACPI machine language) code. The method includes accessing an ASL program. A preprocessor is executed to process the ASL program and to insert support for at least one non-native programming construct. The ASL program is then processed using an ASL compiler to compile the ASL program into a resulting AML program.

Owner:HEWLETT PACKARD DEV CO LP

Development document generation method and device

InactiveCN107239271ANo need to manually writeReduce labor costsProgram documentationSpecific program execution arrangementsManagement toolSoftware engineering

The invention provides a development document generation method and device. The method comprises the following steps of: importing a control parameter in a preset program development management tool, wherein the control parameter is used for compiling parameter names of parameters appearing in each method in an API program into a class file corresponding to each method during program compilation; injecting a RequestMappingHandlerMapping to obtain related parameter information of each method in the API program, wherein the related parameter information comprises a URL, a Controller, a request parameter and a returned Header type; analyzing the request parameter to obtain a parameter name, a parameter type and parameter annotation content by using a reflective analysis technology; and packaging the related parameter information of each method in the API program and various analyzed contents to obtain an API development document. According to the method and device, development documents can be automatically generated, so that the problem that development document needs manual programming is solved.

Owner:BEIJING DIDI INFINITY TECH & DEV

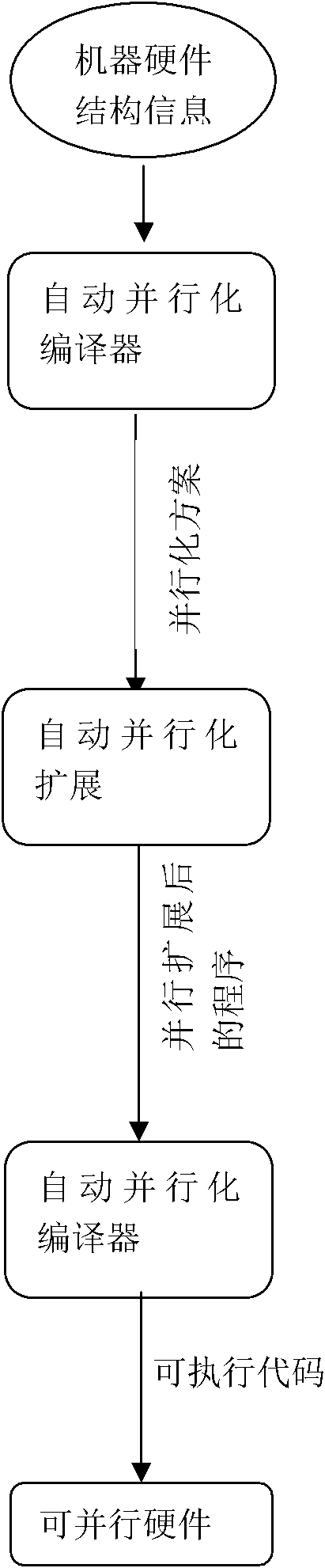

Method for automatically parallelizing program

InactiveCN101989192AImprove portabilityReduce development costsConcurrent instruction executionSpecific program execution arrangementsParallel ExtensionsParallel computing

The invention discloses a method for automatically parallelizing a program. The method comprises the following steps of: (1) acquiring a source program and acquiring a parallel part comprising a cyclic part and a branch part by analyzing the source program; (2) dividing the parallel part in the source program into a plurality of parallel modules, wherein the parallel modules are allocated to different processors for processing through threads; and (3) compiling the source program subjected to parallel extension into an executable code. The method has the advantages of providing a simple program parallelizing environment, fully designing the unique advantages in aspects of simplicity, safety and portability, achieving extremely high operating safety and reusability during development, greatly reducing multi-platform development cost, fully utilizing hardware resource, improving program performance and quickening a computation process.

Owner:ZHEJIANG UNIV

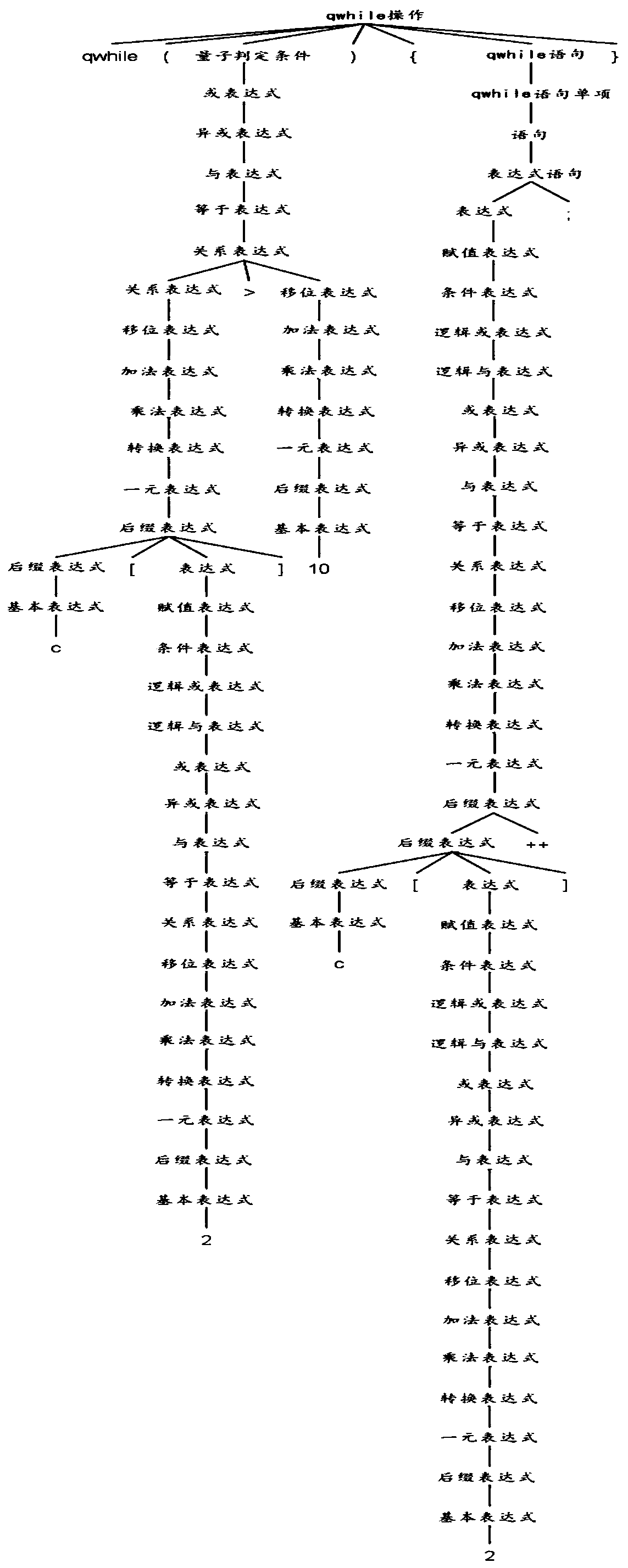

Intermediate code generation method and device for quantum program compilation

ActiveCN110187885AReduce duplicationReduce resource requirementsEnergy efficient computingCode compilationLexical analysisTheoretical computer science

The invention discloses an intermediate code generation method and device for quantum program compiling. The method comprises the steps of obtaining that a source code of a quantum program is obtained;, wherein the logic structure of the source code at least comprises a quantum branch structure, a quantum circulation structure and a quantum logic gate; carrying out lexical analysis on the source code, and segmenting the source code into a plurality of grammatical unit tokens; performing grammatical analysis on all tokens, and constructing an abstract syntax tree AST; wherein the AST comprisesa root node, a plurality of sub-tree nodes and a plurality of leaf nodes, the root node and the sub-tree nodes comprise grammar rule information, and the leaf nodes comprise token information; and according to the node information of the AST and a preset construction rule, constructing an intermediate code corresponding to the source code. By utilizing the embodiment of the invention, repeated labor can be avoided, and resource occupation is reduced.

Owner:ORIGIN QUANTUM COMPUTING TECH (HEFEI) CO LTD

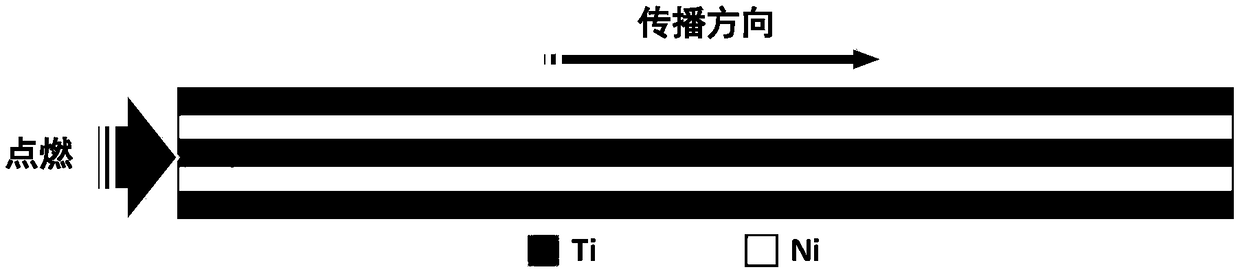

Molecular-dynamics simulation method of predicting diffusion coefficient of combustion process of nano-multilayer film

InactiveCN108491569APlay a guiding roleDesign optimisation/simulationSpecial data processing applicationsDiffusionMean square

The invention provides a molecular-dynamics simulation method of predicting a diffusion coefficient of a combustion process of a nano-multilayer film. The method comprises the following steps: 1) constructing a nano-multilayer-film molecular-dynamics simulation model, and exporting a configuration file; 2) completing a control file; 3) using a molecular-dynamics method to calculate and output mean-square-displacement (MSD) data of each component; 4), drawing the MSD data as a curve of MSD versus step length; 5) calculating a slope of the MSD versus time; and 6), obtaining the diffusion coefficient by solving according to Einstein's law. According to the method, solving is carried out for the diffusion coefficient of each component of the nano-multilayer film, the problem that real-time atomic diffusion behaviors of the self-propagating reaction combustion process of the nano-multilayer film cannot be tested and analyzed by experiment means is solved, difficulty of program compilation is significantly reduced, atomic behaviors and processes of nano-connection are more accurately understood, and a reference is provided for structure design of nano-multilayer films through study on diffusion coefficients and diffusion behaviors of the multilayer films of different atomic proportions under different temperatures.

Owner:BEIJING UNIV OF TECH

Web browsing apparatus and method through storing and optimizing javascript® code

ActiveUS20120185822A1Software engineeringSpecific program execution arrangementsWeb applicationWeb page

A web browsing method and apparatus for enhancing a user's convenience in web browsing is provided in a system that uses a multi-core processor. The web browsing method and apparatus is applicable in a system, such as a smart phone that has a low computing power or that has a storage device like a flash memory operating in a rapid manner. Optimized machine codes are stored in files and incremental optimization is achieved, so the JAVASCRIPT® program of the web application has a small compilation overhead and achieves fast execution.

Owner:SAMSUNG ELECTRONICS CO LTD +1

Compile method for storing source code within object code

InactiveUS6983457B2Eliminate wasteProcess uneconomicalSpecific program execution arrangementsSpecial data processing applicationsObject codeProgram compilation

A compiler, that generates an object program file from a source program in which a plurality of procedures are written, compiles procedures, by regarding the procedures as source-program compile units, to generate corresponding object-program compile units. A plurality of object-program compile units generated are output to a memory together with the corresponding source-program compile units. When compiling a source program in which one procedure has been changed, the compiler compiles only the source-program compile unit corresponding to the changed procedure.

Owner:HITACHI LTD +1

Chip authentication method, system, printer, consumable chip and consumable box

ActiveCN106626792ATroubleshooting Security VulnerabilitiesAchieve authenticationPrintingProgram compilationVulnerability

The embodiment of the invention provides a chip authentication method, a system, a printer, a consumable chip and consumable box. On one hand, according to the embodiment of the invention, the printer sends an authentication instruction to the consumable chip; the authentication instruction includes a designation code which is compiled in accordance with a program compilation format of the authentication consumable chip; the consumable chip receives the instruction sent by the printer, and identifies whether the received instruction is an authentication instruction; if the received instruction is identified as the authentication instruction, the consumable chip runs a designation code and obtains the running results; and the consumable chip returns the running result to the printer, and the printer receives the running result and judges whether the consumable chip is an authentication consumable chip. Therefore, the technical scheme provided by the embodiment of the invention can solve the problem of security vulnerability of an authentication method for the consumable chip by the printer in the prior art.

Owner:APEX MICROELECTRONICS CO LTD

Apparatus and method for generating optimization objects

InactiveUS20010037497A1Appropriate concentrationWithout any changeSoftware engineeringSpecific program execution arrangementsBatch processingParallel computing

The invention enables appropriately concentrating instruction strings or data pieces sporadically present in a plurality of regions over more than one compilation unit and adjusting the front-and-rear relationship of executed instruction strings without changing the program compilation unit such as a file, subroutine, or function and also without creating a link processing program for batch processing of the system as a whole. Different section names are given to the executed instruction strings and the unexecuted instruction strings and the referenced data and the unreferenced data of an object program respectively, so that, when an execution module is generated from the object program by linking, the sections having an executed section name and the sections having an unexecuted section name in a plurality of files may be aggregated respectively to divide the instructions into an execution portion and an unexecution portion.

Owner:FUJITSU LTD

System for compiling source programs into machine language programs, a computer implemented method for the compiling and a computer program product for the compiling within the computer system

A system for compiling source programs into machine language programs, comprising: a data type information processing module configured to analyze a definition statement of a fixed-point data type in a source program, acquire data type information of the fixed-point data type; a type-information storage; a variable information processing module configured to analyze a variable declaration statement of the fixed-point data type, acquire variable information; a variable storage; and a code generating module configured to read arithmetic expression data, acquire the type number, acquire the data type information, convert the arithmetic expression data.

Owner:KK TOSHIBA

Method for realizing automatic pipeline parallelism

InactiveCN101944014ABalance workloadAdded optimization capabilities for automatic parallel optimizationConcurrent instruction executionArray data structureThread scheduling

The invention belongs to the technical field of program compilation and in particular relates to a method for realizing automatic pipeline parallelism. The method of the invention mainly comprises the following steps of: (1) identification of the pipeline parallelism, namely judging a loop structure which is provided with cross-loop iteration dependence and a dependence distance vector is a constant; (2) synchronization among threads, namely inserting the synchronization according to the dependence distance vector and deleting the redundant synchronization with the same distance vector; and (3) thread scheduling in a static step length, namely self-defining a thread scheduling strategy for balancing the workload of each thread and reducing the communication expense. The type identification of the loop structure is depended on the conventional array data stream analysis and dependence tests, while the pipeline parallelism only processes the regular loop structure with backward cross-loop iteration. The synchronization expense of the pipeline parallelism is high, so the pipeline parallelism is only performed on the outmost layer of a nested loop. Profit of the pipeline parallelism depends on programs, the number of the cyclic iteration is larger and the dependence distance is longer, the performance promotion is greater. The method for realizing the pipeline parallelism improvesthe capacity of automatic parallel optimization and contributes to further improving the performance of scientific calculation programs.

Owner:FUDAN UNIV

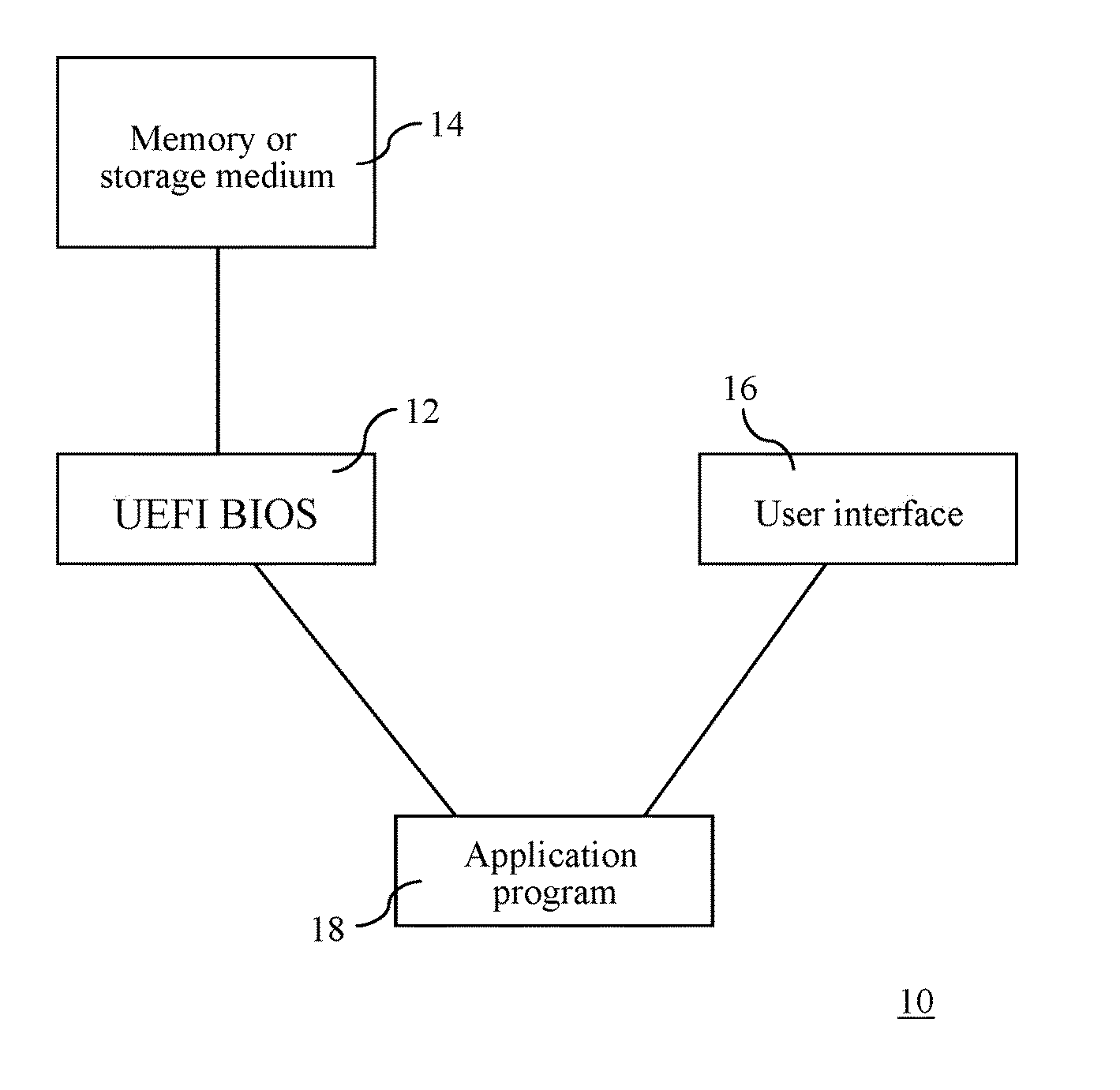

Platform system, method for changing support hardware configuration of universal extensible firmware interface basic input output system and computer program product

ActiveUS20150186161A1Avoid mistakesEasy to changeDigital computer detailsBootstrappingBIOSUser interface

A method for changing a support hardware configuration of a universal extensible firmware interface basic input output system (UEFI BIOS) is provided, and the change method is performed by a platform system. The method includes the following steps: in a boot stage, copying binary data of a setup menu in the UEFI BIOS to a memory or a storage medium, where a program of the setup menu to be displayed on a user interface is written in a visual forms representation (VFR) format, and a compiler compiles the program of the setup menu into the binary data of the setup menu in an internal forms representation (IFR) format; and writing a piece of address data to the UEFI BIOS, where the address data is used to query a location at which the binary data of the setup menu stored in the memory or the storage medium is located.

Owner:INSYDE SOFTWARE CORP

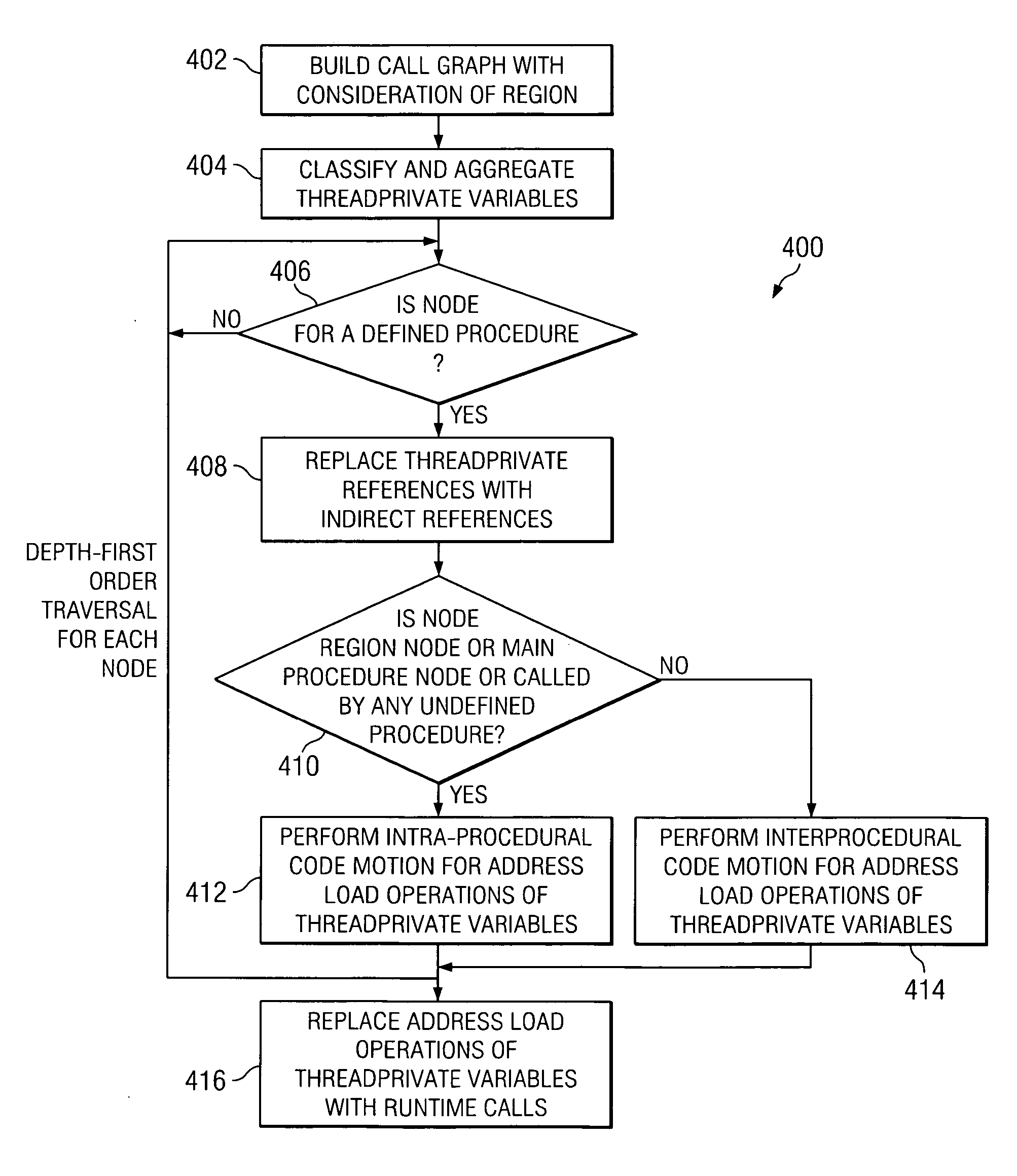

Method and system for reducing memory reference overhead associated with threadprivate variables in parallel programs

InactiveUS20070089105A1Improve programming performanceMinimize timeSoftware engineeringProgram controlParallel computingProgram compilation

A computer implemented method, system and computer program product for accessing threadprivate memory for threadprivate variables in a parallel program during program compilation. A computer implemented method for accessing threadprivate variables in a parallel program during program compilation includes aggregating threadprivate variables in the program, replacing references of the threadprivate variables by indirect references, moving address load operations of the threadprivate variables, and replacing the address load operations of the threadprivate variables by calls to runtime routines to access the threadprivate memory. The invention enables a compiler to minimize the runtime routines call times to access the threadprivate variables, thus improving program performance.

Owner:IBM CORP

Predicate-based automatic parallel optimizing method

InactiveCN101944040AEliminate data dependenciesAutomatic Parallel Optimization ImplementationProgram controlMemory systemsData streamArray data structure

Owner:FUDAN UNIV

Program compilation and optimization

InactiveUS7058935B2Improve efficiencySoftware engineeringError detection/correctionObject codePost processor

It is one object of the present invention to provide effective optimization for a program that includes commands that may cause exception processes. A novel compiler for converting source code for a program written in a programming language into object code in a machine language comprises: an optimization execution unit for performing an optimization process for an object program written in a machine language; and a pre-processor and a post-processor for modifying the object program in order to absorb a difference in content between the point of origin of an exception process, which occurs in response to the execution of a command in the object program, and a location whereat the exception process is performed.

Owner:TWITTER INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com