Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

155 results about "Operational transformation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Operational transformation (OT) is a technology for supporting a range of collaboration functionalities in advanced collaborative software systems. OT was originally invented for consistency maintenance and concurrency control in collaborative editing of plain text documents. Two decades of research have extended its capabilities and expanded its applications to include group undo, locking, conflict resolution, operation notification and compression, group-awareness, HTML/XML and tree-structured document editing, collaborative office productivity tools, application-sharing, and collaborative computer-aided media design tools (see OTFAQ). In 2009 OT was adopted as a core technique behind the collaboration features in Apache Wave and Google Docs.

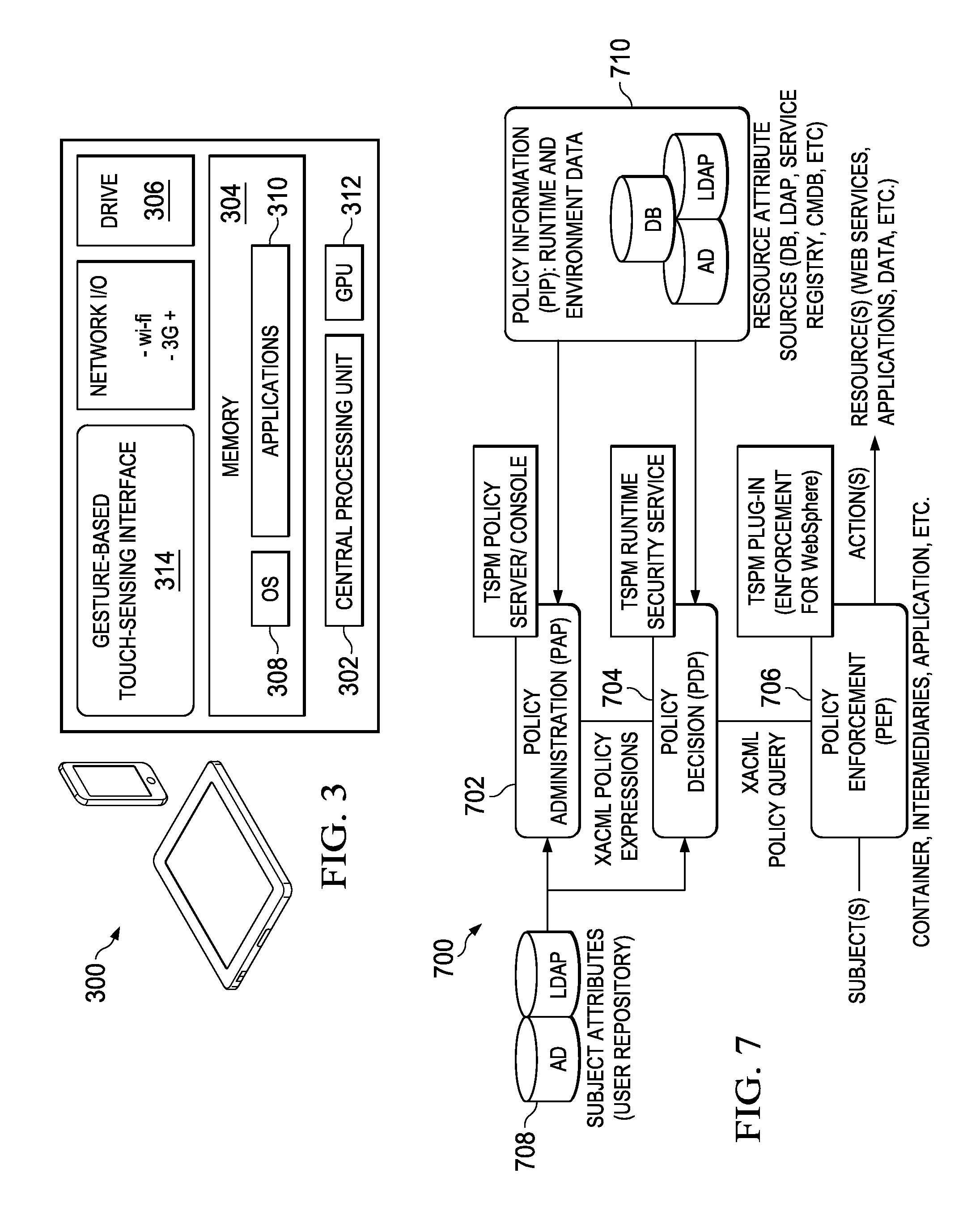

Policy enforcement using natural language processing

InactiveUS9369488B2TransmissionSpecial data processing applicationsState dependentOperational transformation

Owner:GLOBALFOUNDRIES INC

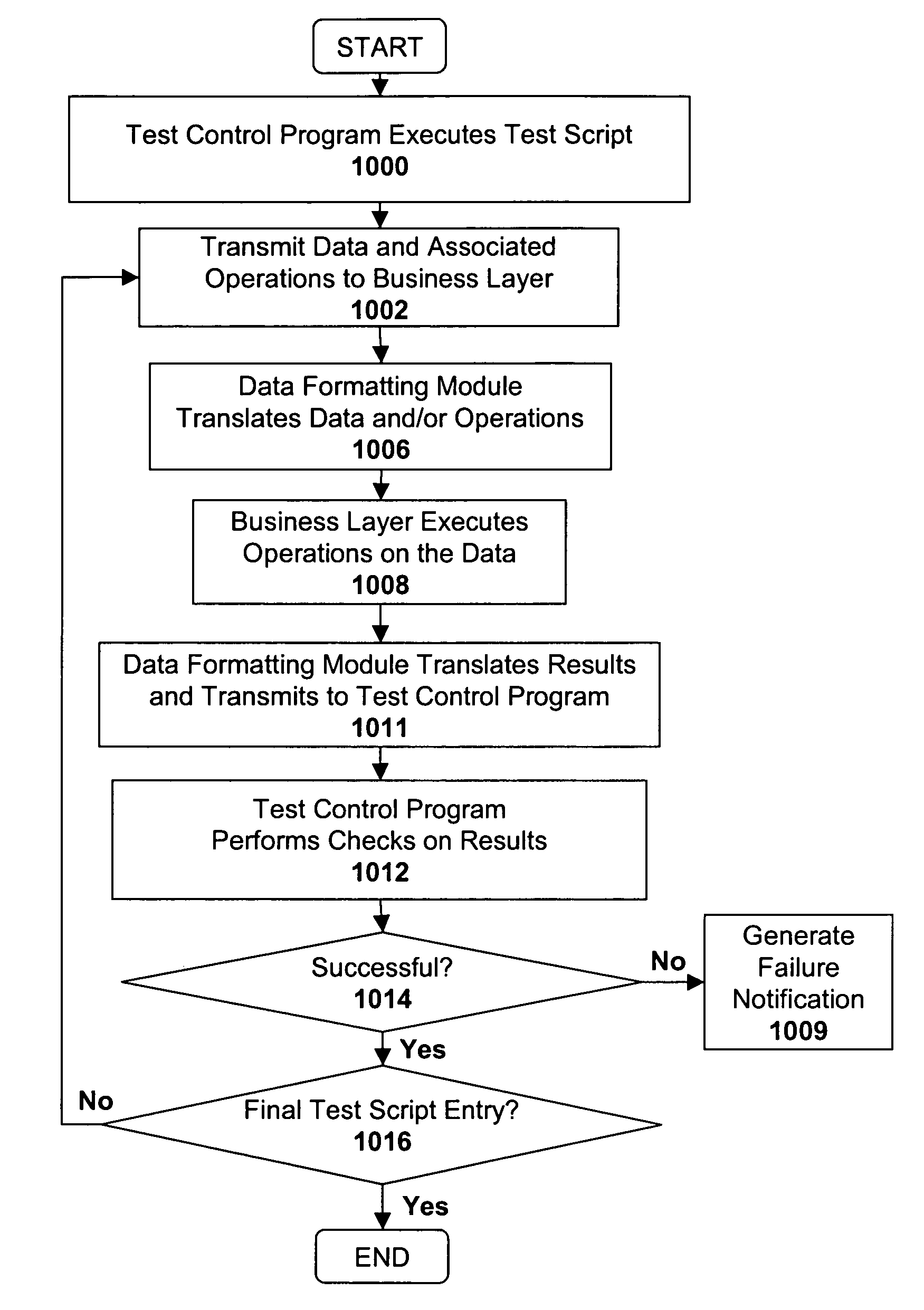

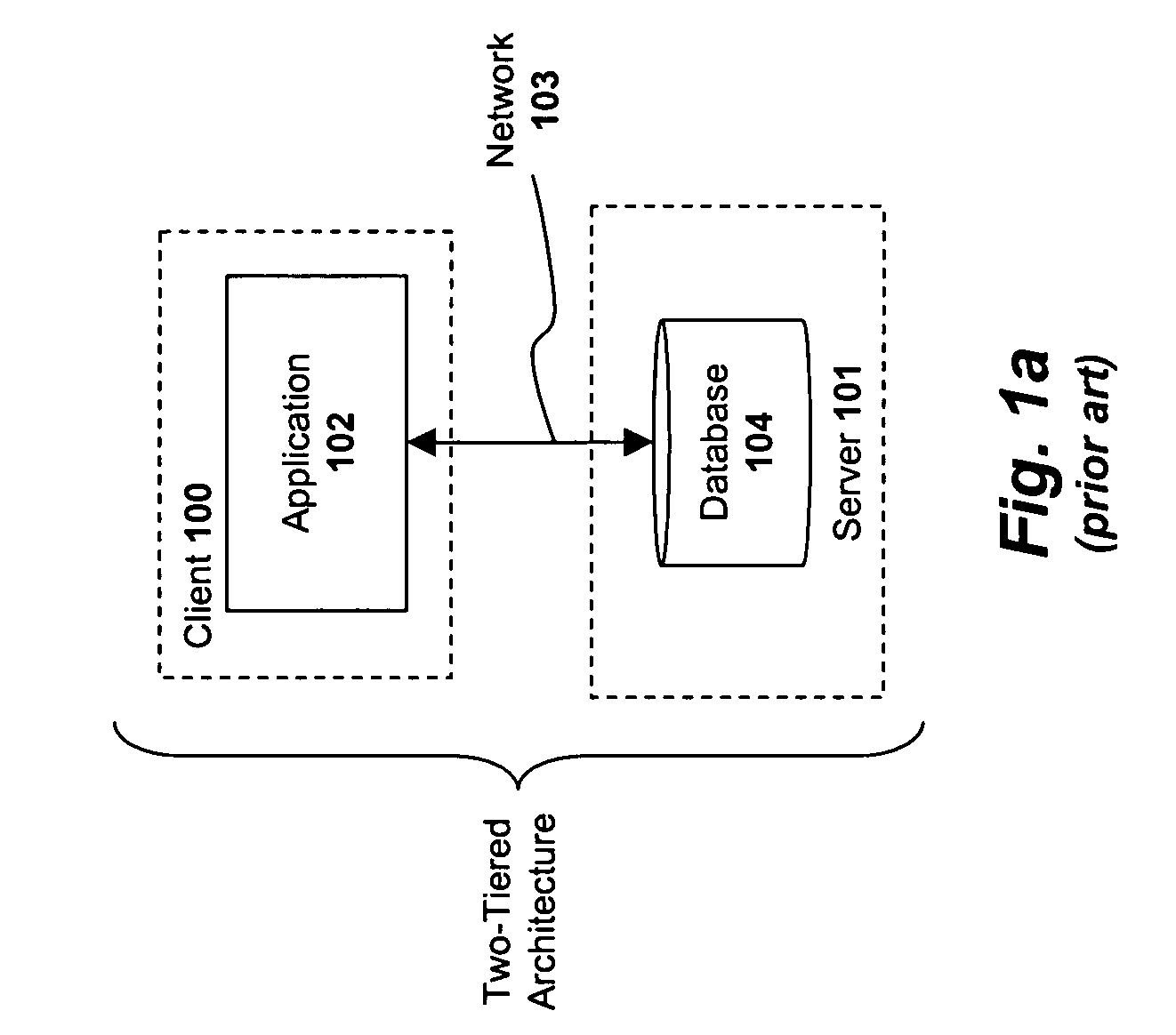

System and method for testing applications at the business layer

A method is described comprising: providing a user interface for entering data and triggering one or more operations to process the data; translating the data and / or operations to a business layer format; receiving results of the data and / or operations in a business layer format; and storing the entered data, operations and / or results in the business layer format within a test script, the test script usable to test an instance of an application at the business layer of the application.Also described is a method for testing an application comprising: transmitting a series of business layer data and associated operations to an instance of a business layer of an application, the application processing the test data and associated operations; receiving business layer results of the associated operations; and comparing the business layer results to recorded business layer results to ensure that the application is functioning properly.

Owner:SAP AG

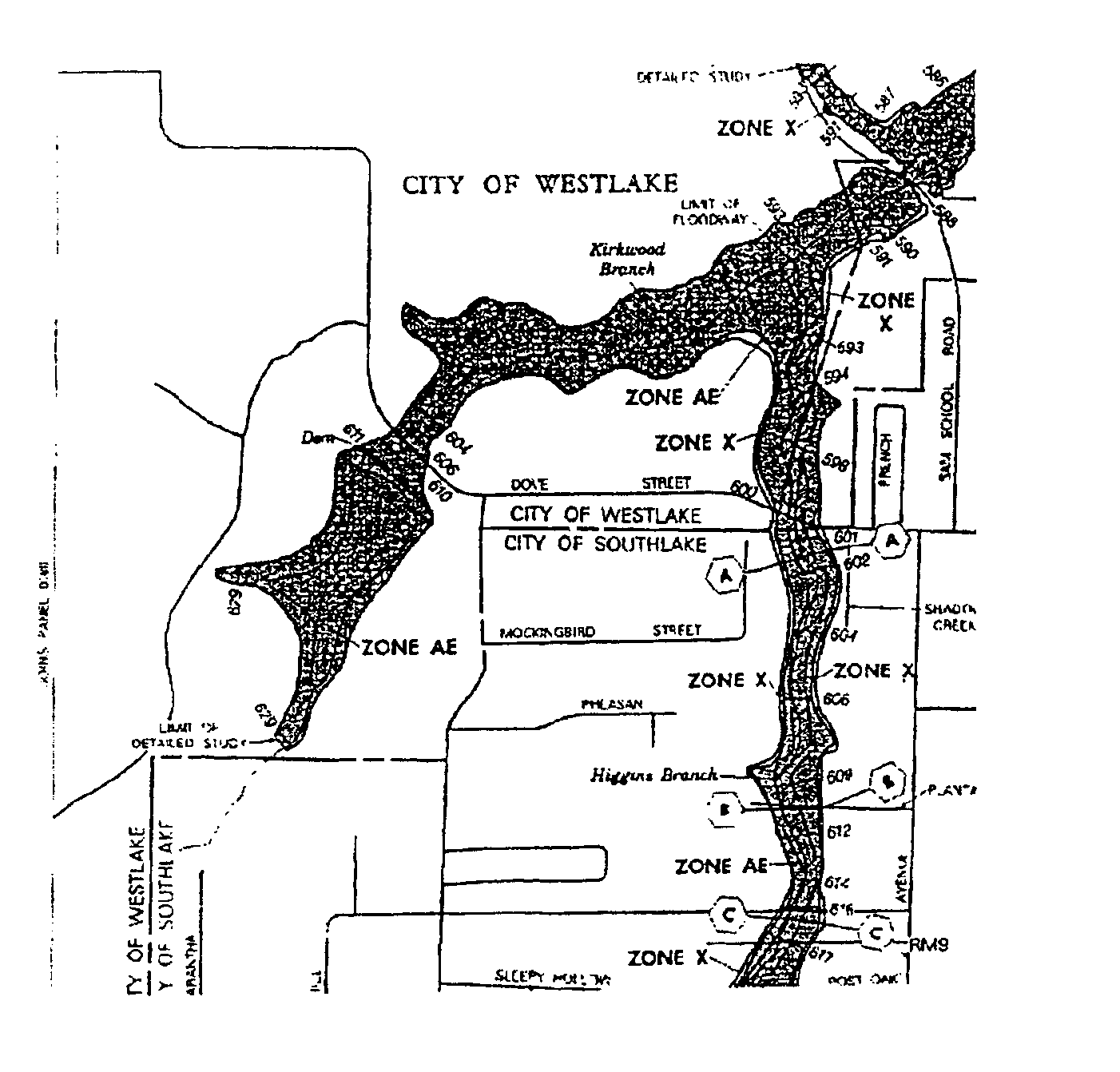

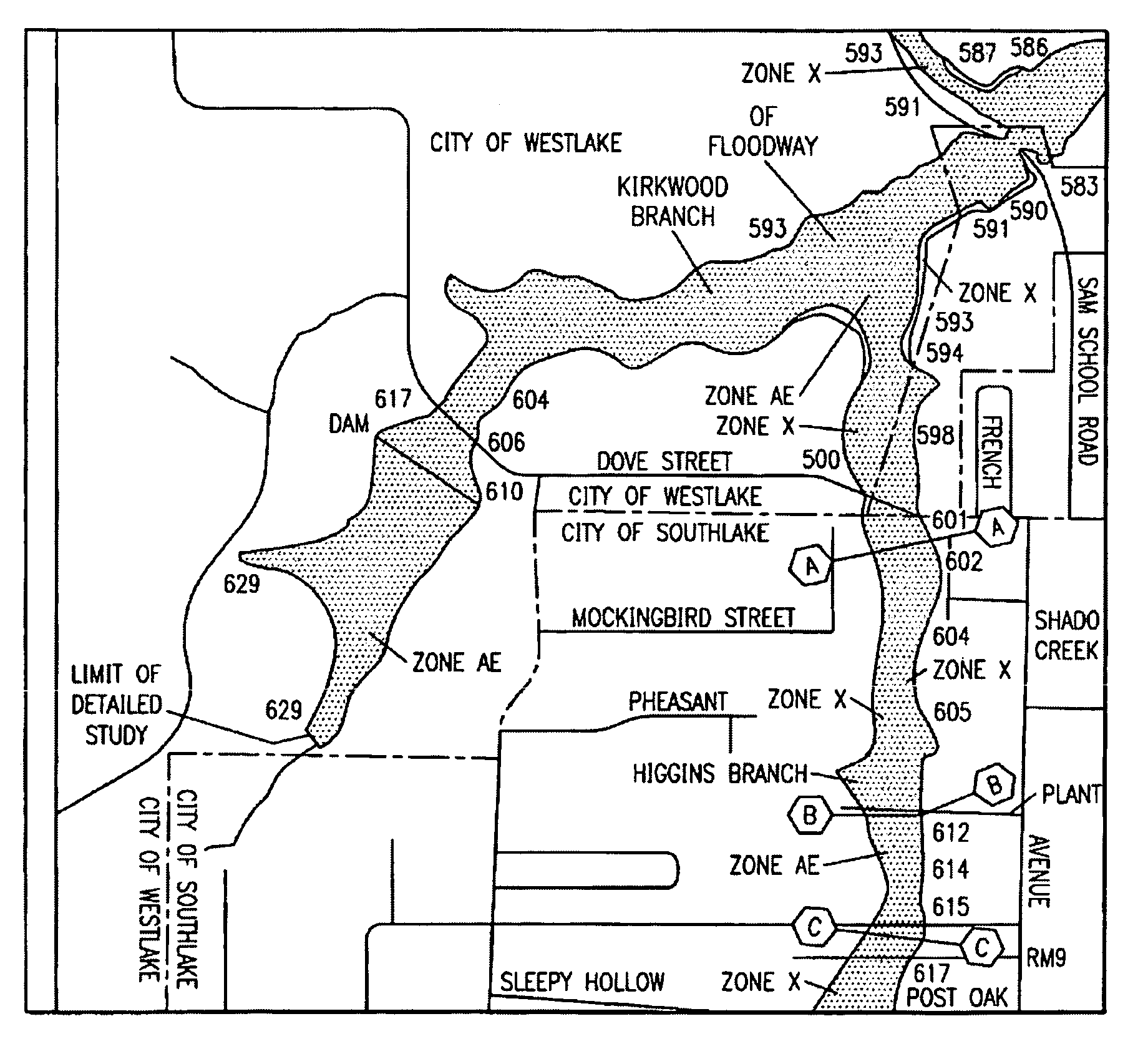

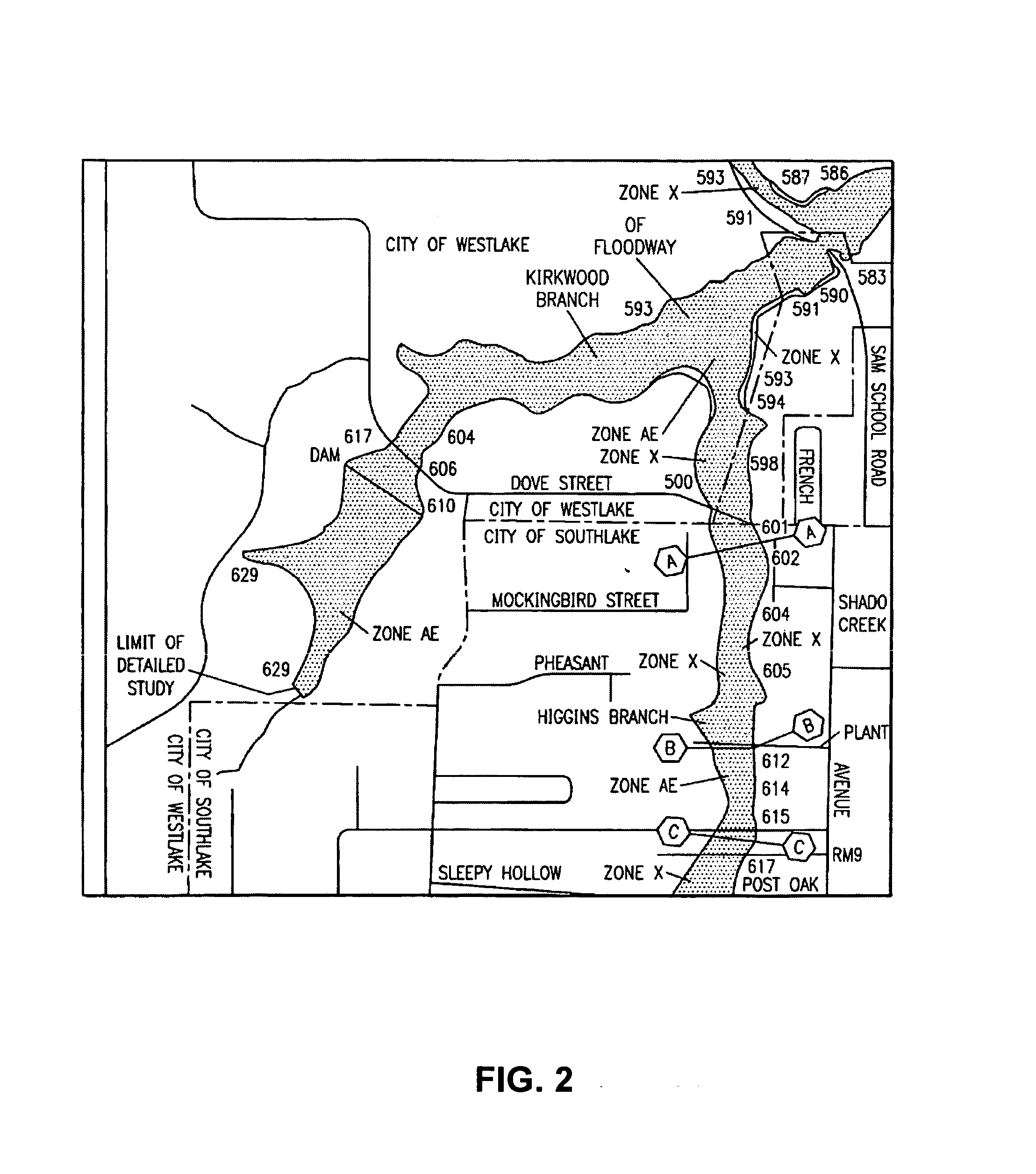

System and method for synchronizing raster and vector map images

InactiveUS7161604B2Enhance the imageEasy to operateCathode-ray tube indicatorsMaps/plans/chartsOperational transformationLongitude

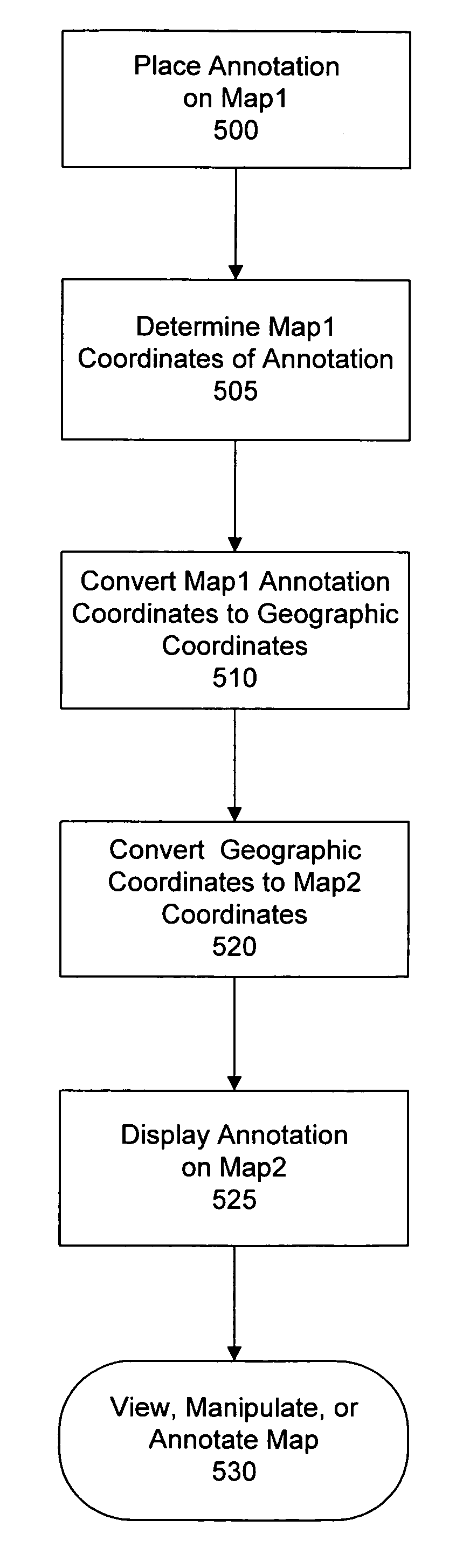

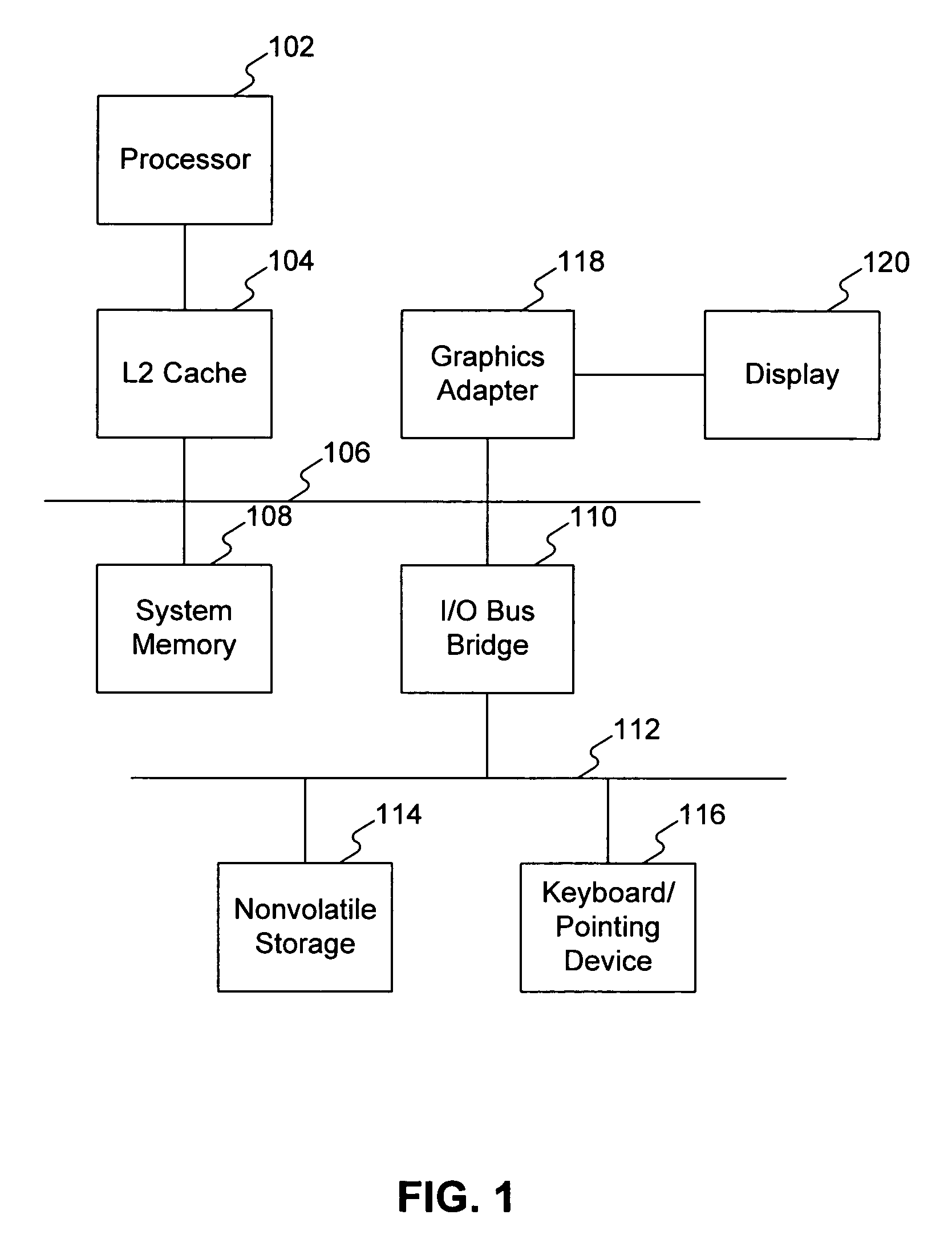

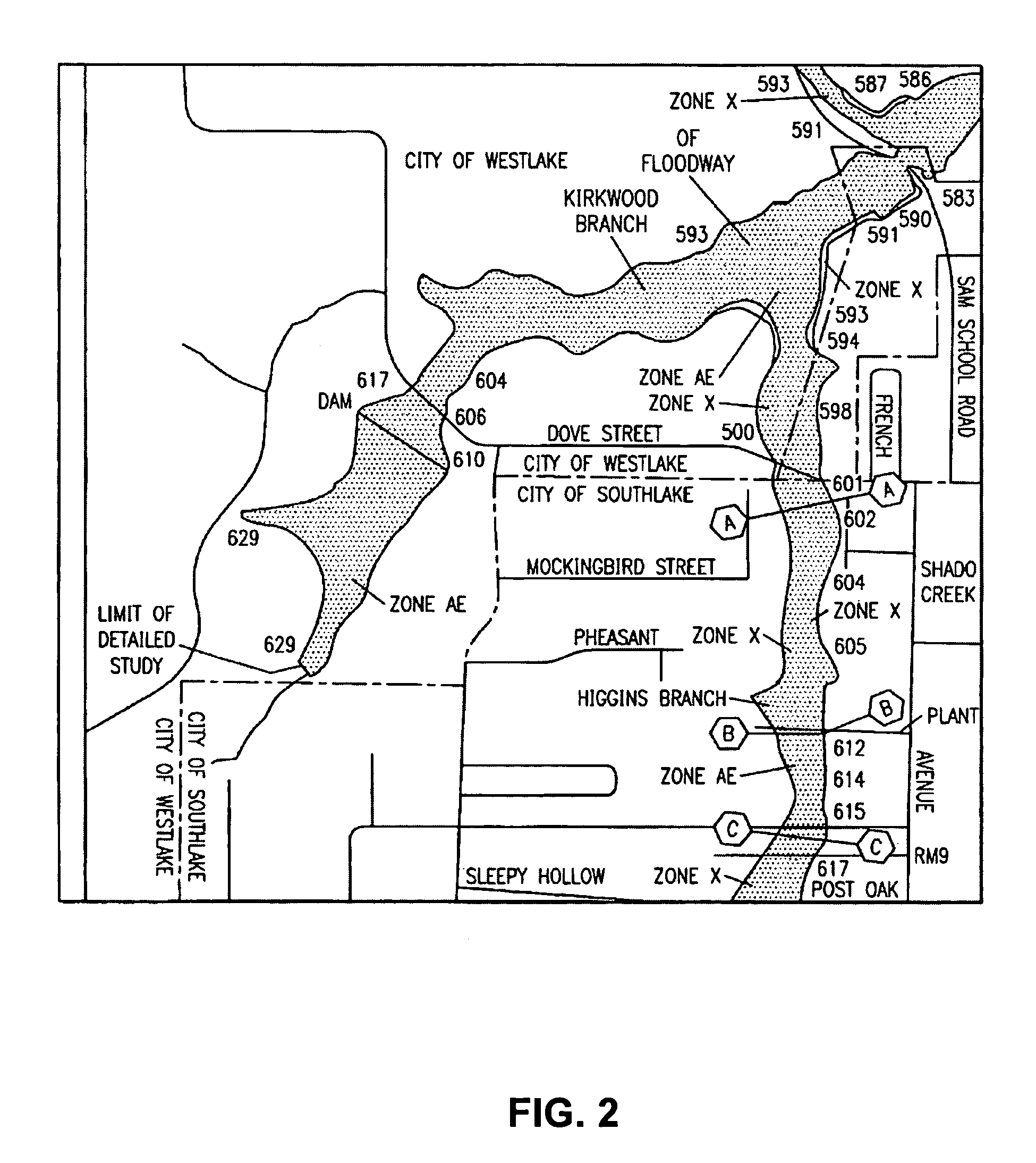

A system and method for coordinated manipulation of multiple displayed maps, even when the maps use different internal coordinate systems. According to this embodiment, each map image to be displayed is first georeferenced, to provide a set of conversion functions between each map's internal coordinate system and a geographic coordinate system, which is latitude / longitude in the preferred embodiment. After this is done, any point on each map can be referenced using the geographic coordinate set. Since this is the case, the maps can now be manipulated, edited, and annotated in a synchronized manner, by defining the manipulations in terms of the geographic coordinate system, and using the georeferencing functions to translate the manipulation to each map's internal coordinate system.

Owner:SOURCEPROSE CORP

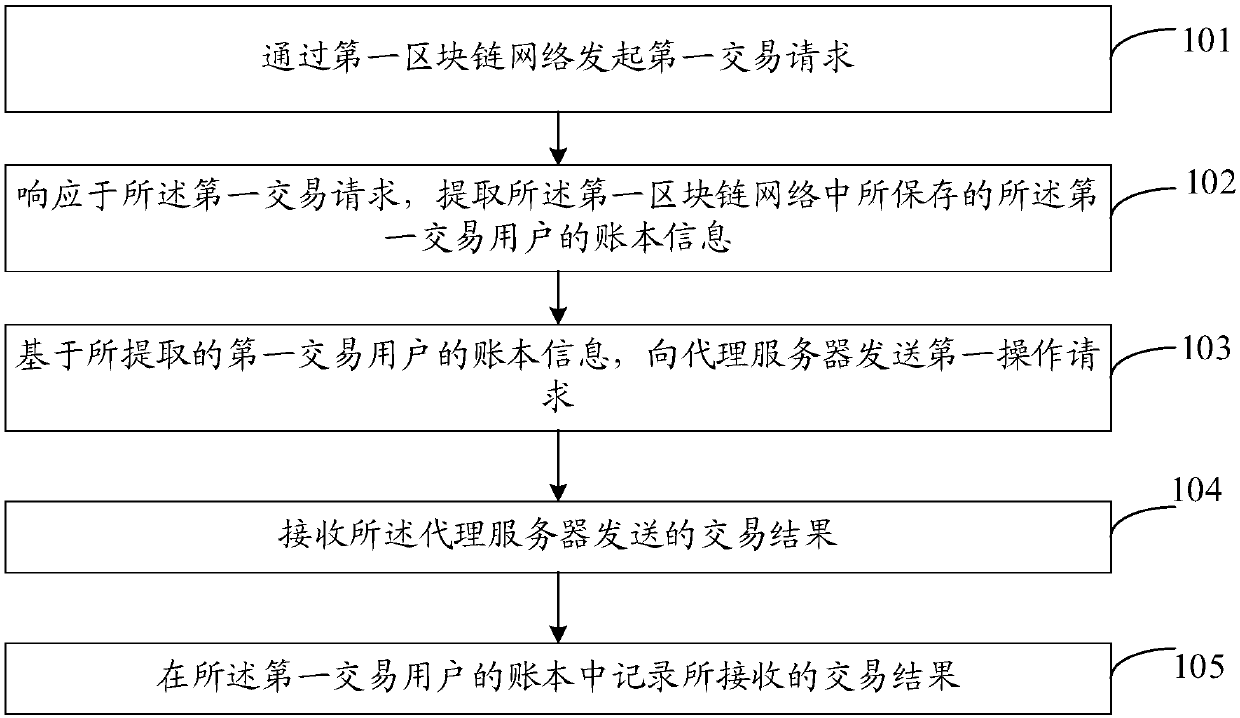

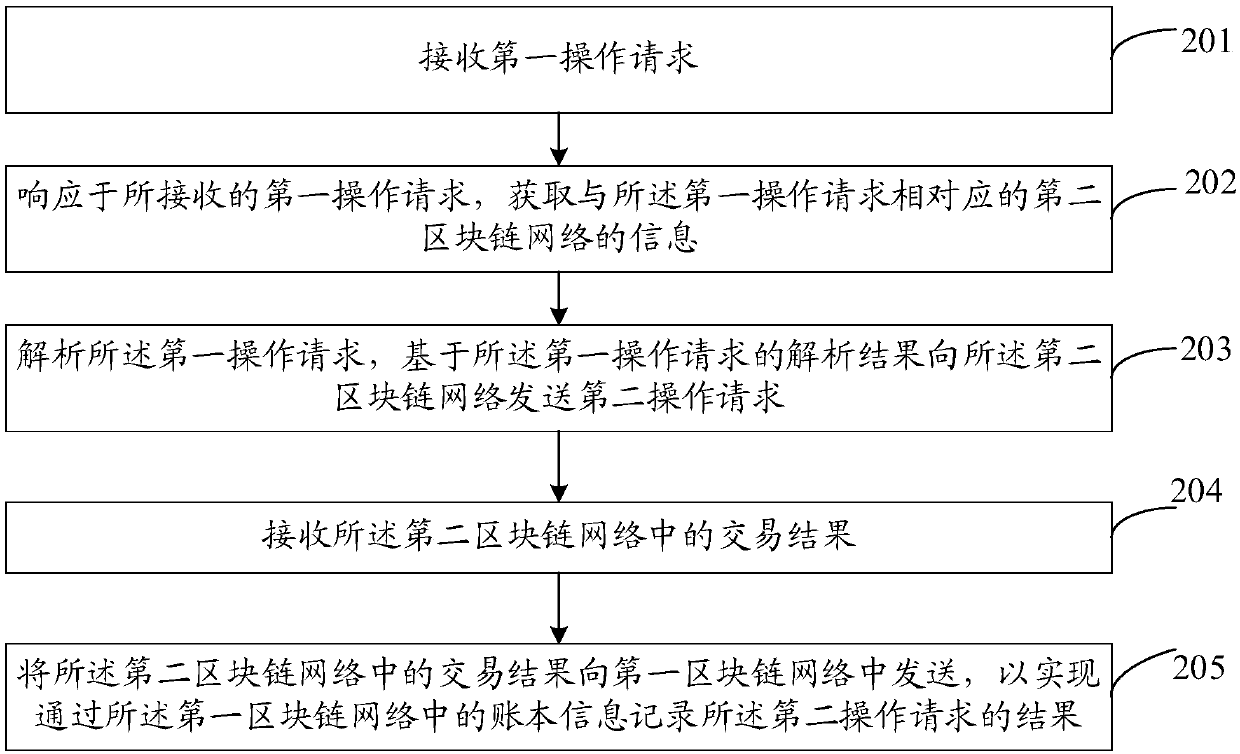

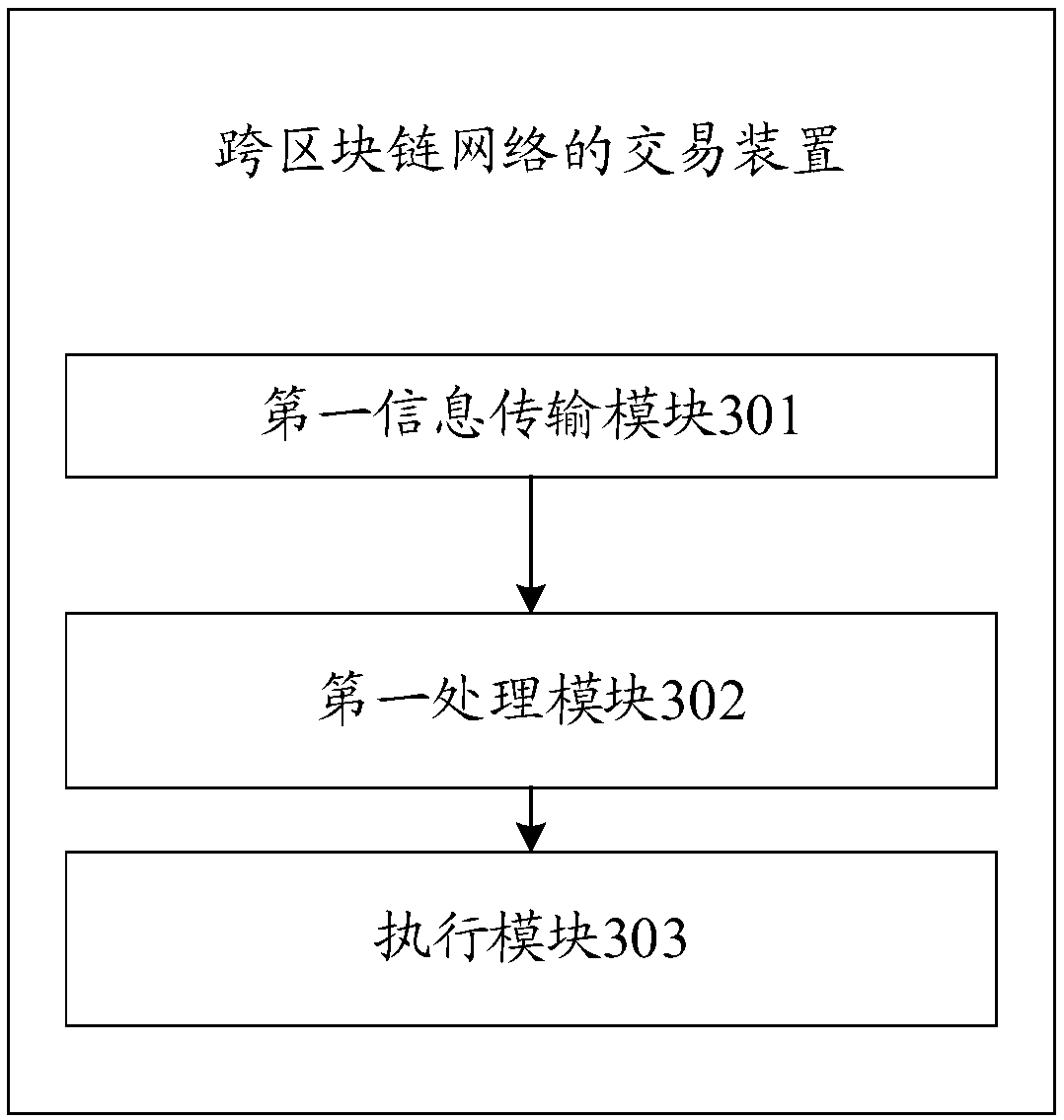

Transaction method and device of cross-block chain network and storage medium

InactiveCN109559227AImprove experienceEasy to implementFinanceDigital data protectionOperational transformationFinancial transaction

The invention discloses a transaction method of a cross-block chain network. The method comprises the steps that a first transaction request is initiated through a first block chain network, the firsttransaction request is used for representing that a first transaction user initiates a transaction request of a cross-block chain network to other block chain networks from the first block chain network, and the first transaction user is an initiator of the first transaction request; in response to the first transaction request, account book information, stored in the first block chain network, of the first transaction user is extracted; based on the extracted account book information of the first transaction user, sending a first operation request to a proxy server, so as to convert an operation corresponding to the first transaction request into an executable SQL statement of a corresponding type through the proxy server; receiving a transaction result sent by the proxy server; and recording the received transaction result in the account book of the first transaction user. The invention also discloses a cross-block chain network transaction device and a storage medium.

Owner:MIGU CO LTD

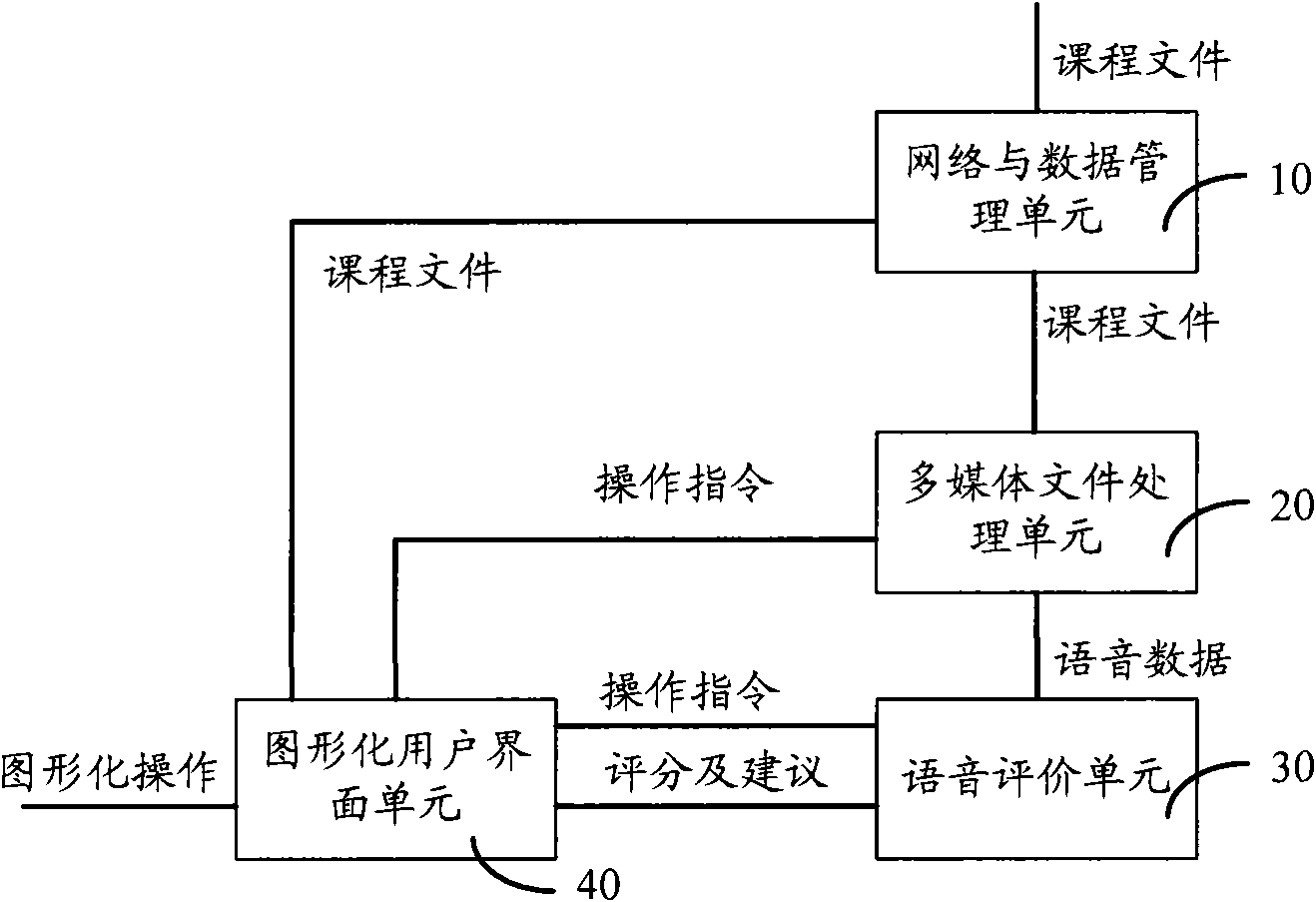

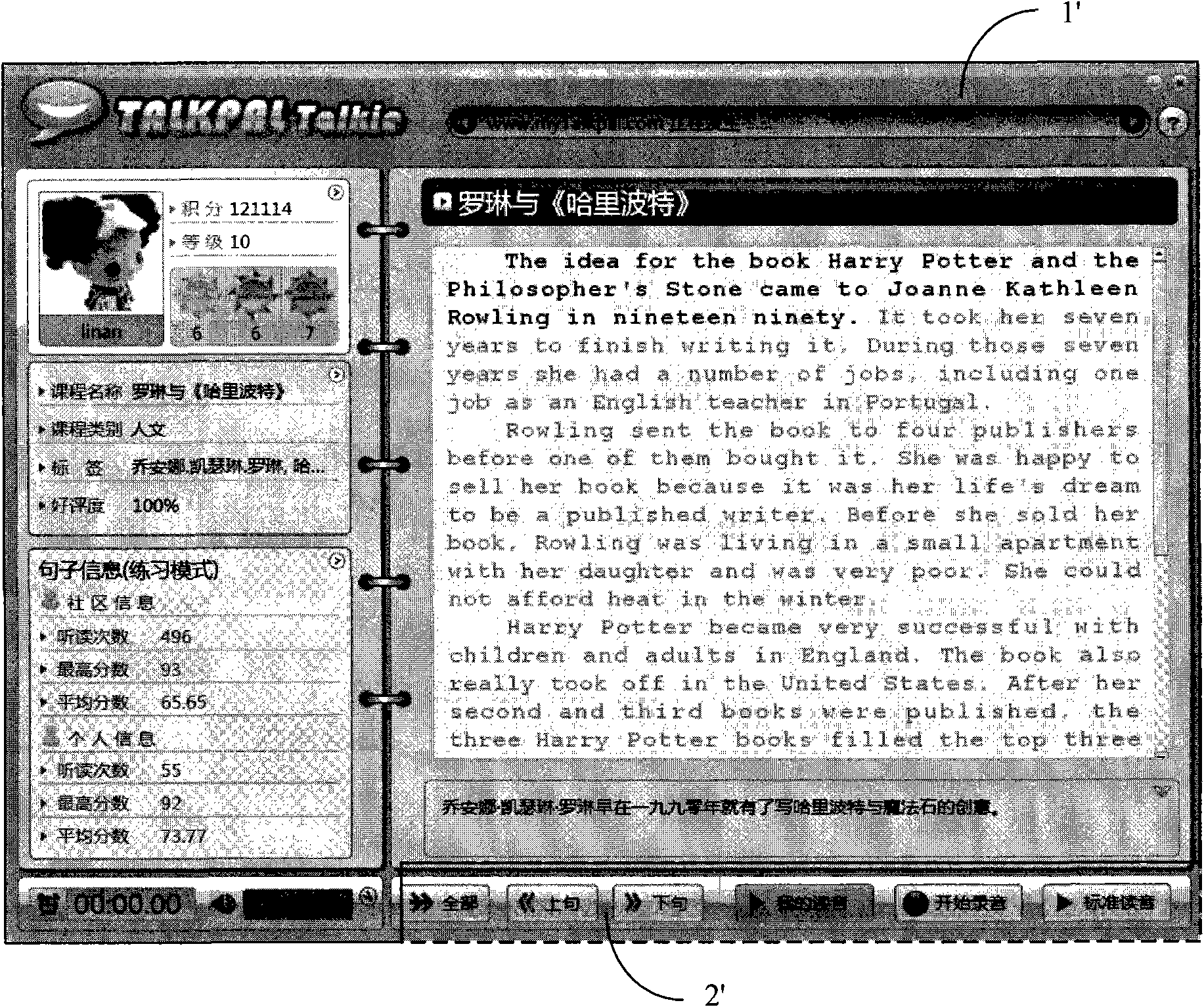

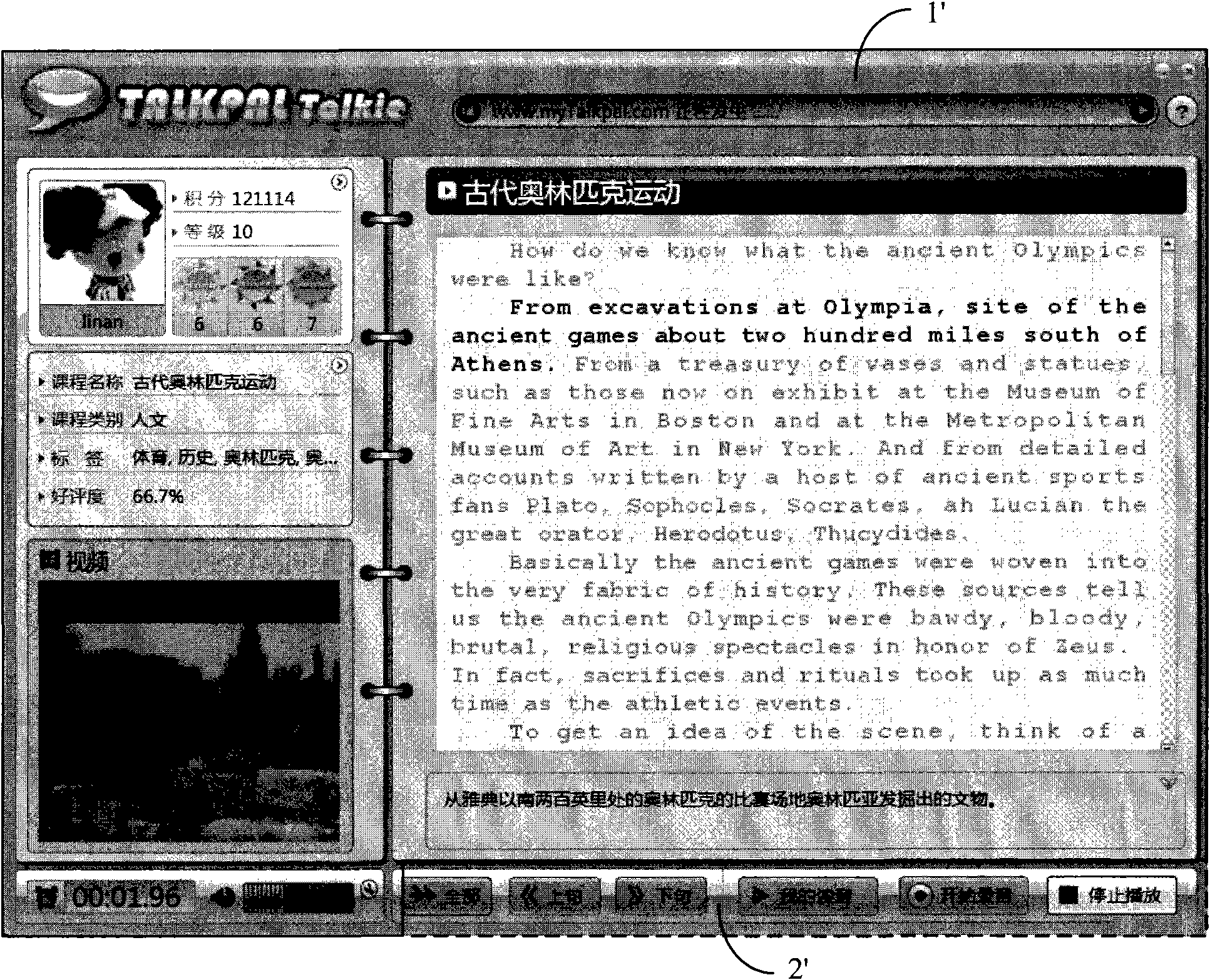

Language learning client and system

InactiveCN101630448AImprove the efficiency of secondary language learningSpeech recognitionElectrical appliancesVoice dataUser interface

The invention relates to a language learning client and a system. The language learning client comprises a network and data management unit, a graphical user interface unit, a multimedia file processing unit and a voice evaluation unit, wherein the network and data management unit is used for acquiring a course file which at least comprises audio frequency of standard voice and a text corresponding to the audio frequency; the graphical user interface unit is used for displaying a graphic operation interface, the course contents and course learning records, and converting graphic operations of users into operation instructions; the multimedia file processing unit is used for decoding and playing the course file provided by the network and data management unit, and also used for acquiring user voice data and converting the user voice data and the audio frequency of the standard voice into voice data; and the voice evaluation is used for comparing the voice data provided by the multimedia file processing unit and giving scores. The language learning client and the system improve the efficiency of assisting language learning.

Owner:上海启态软件科技有限公司

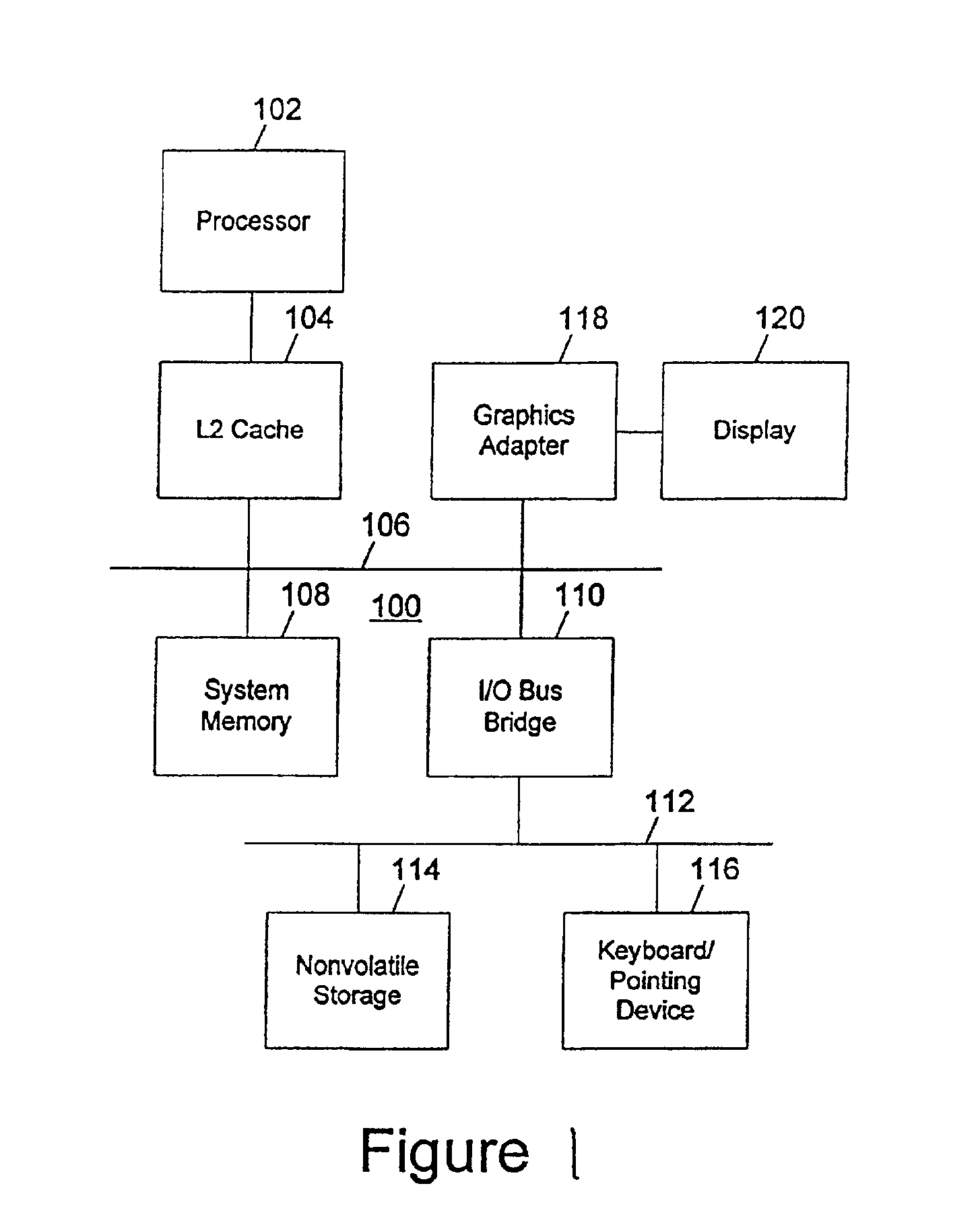

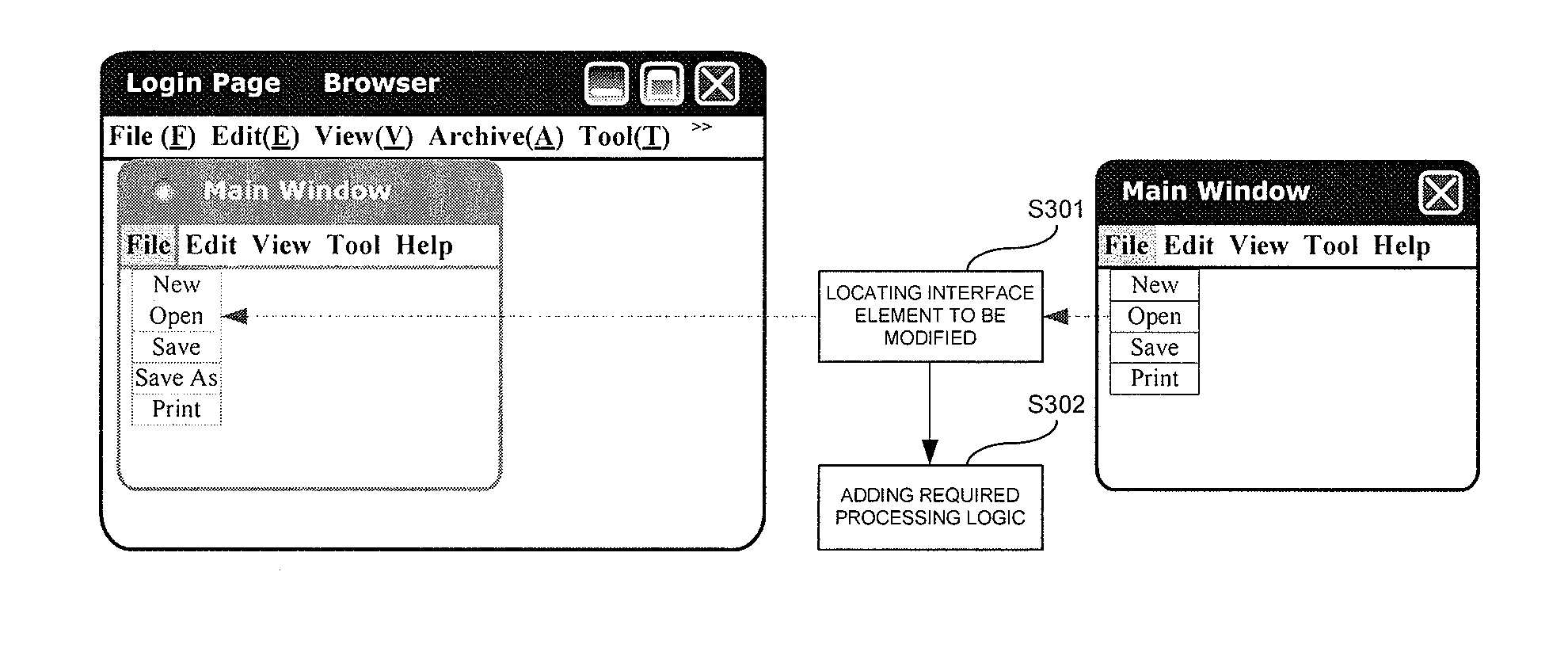

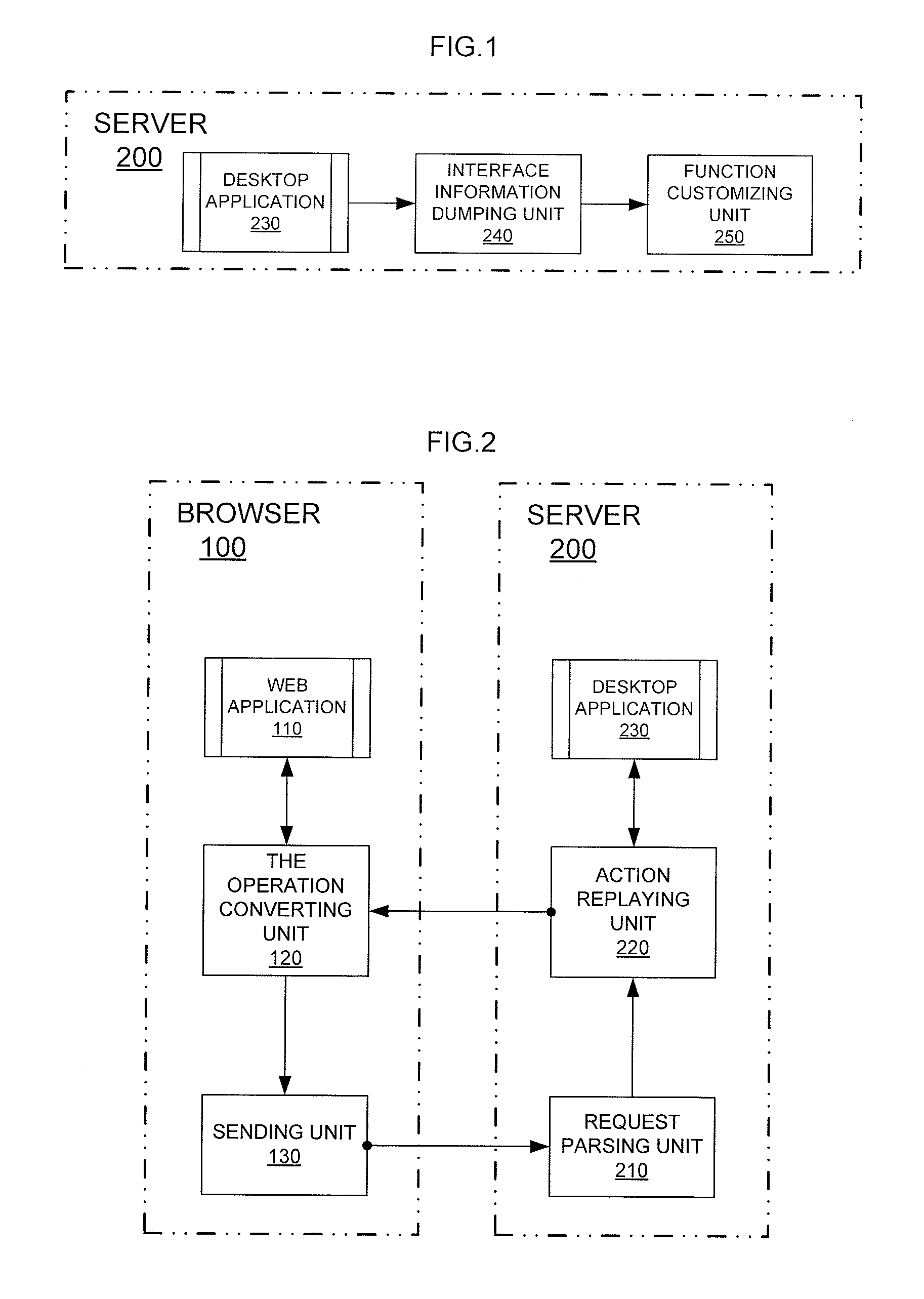

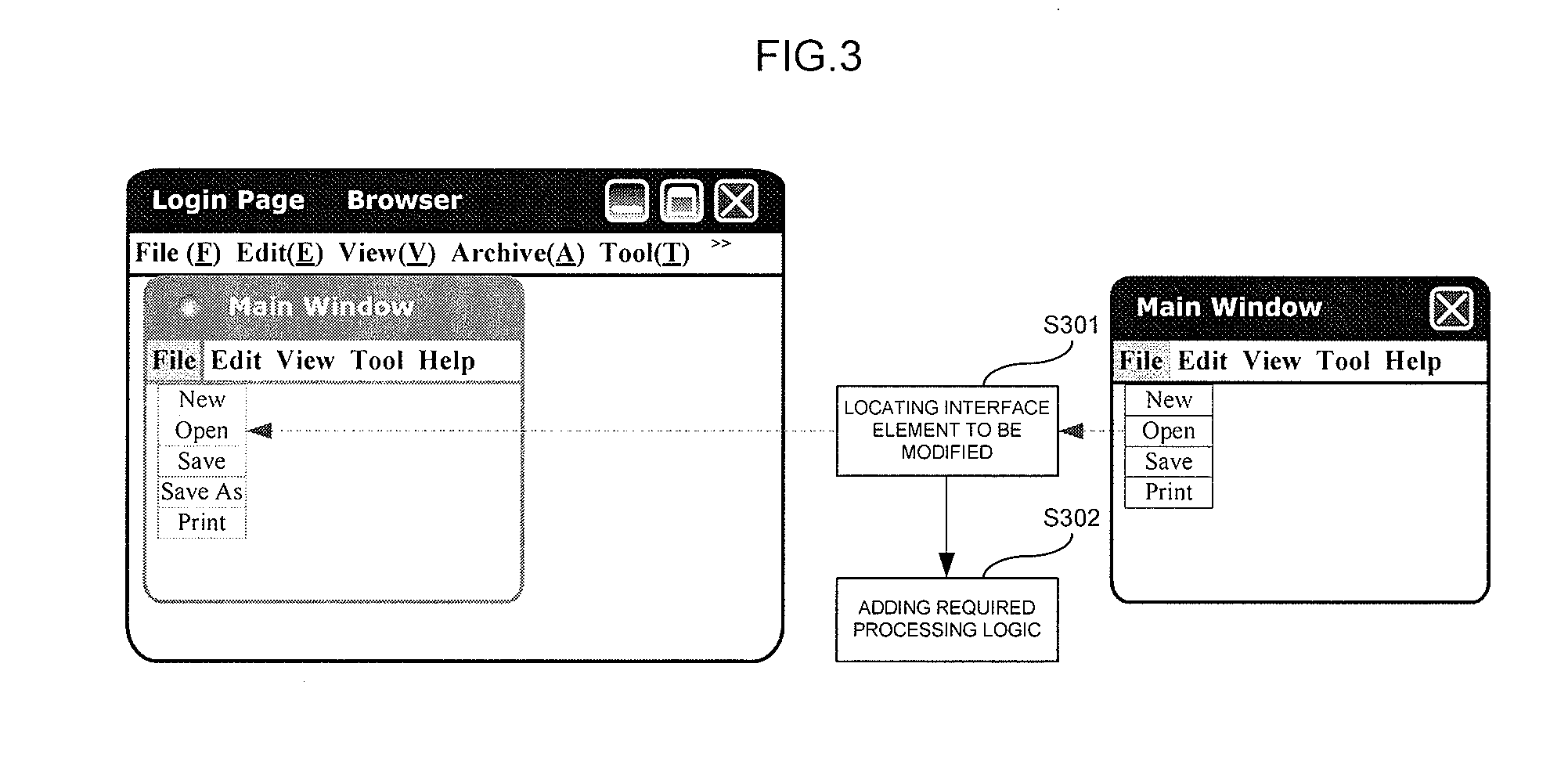

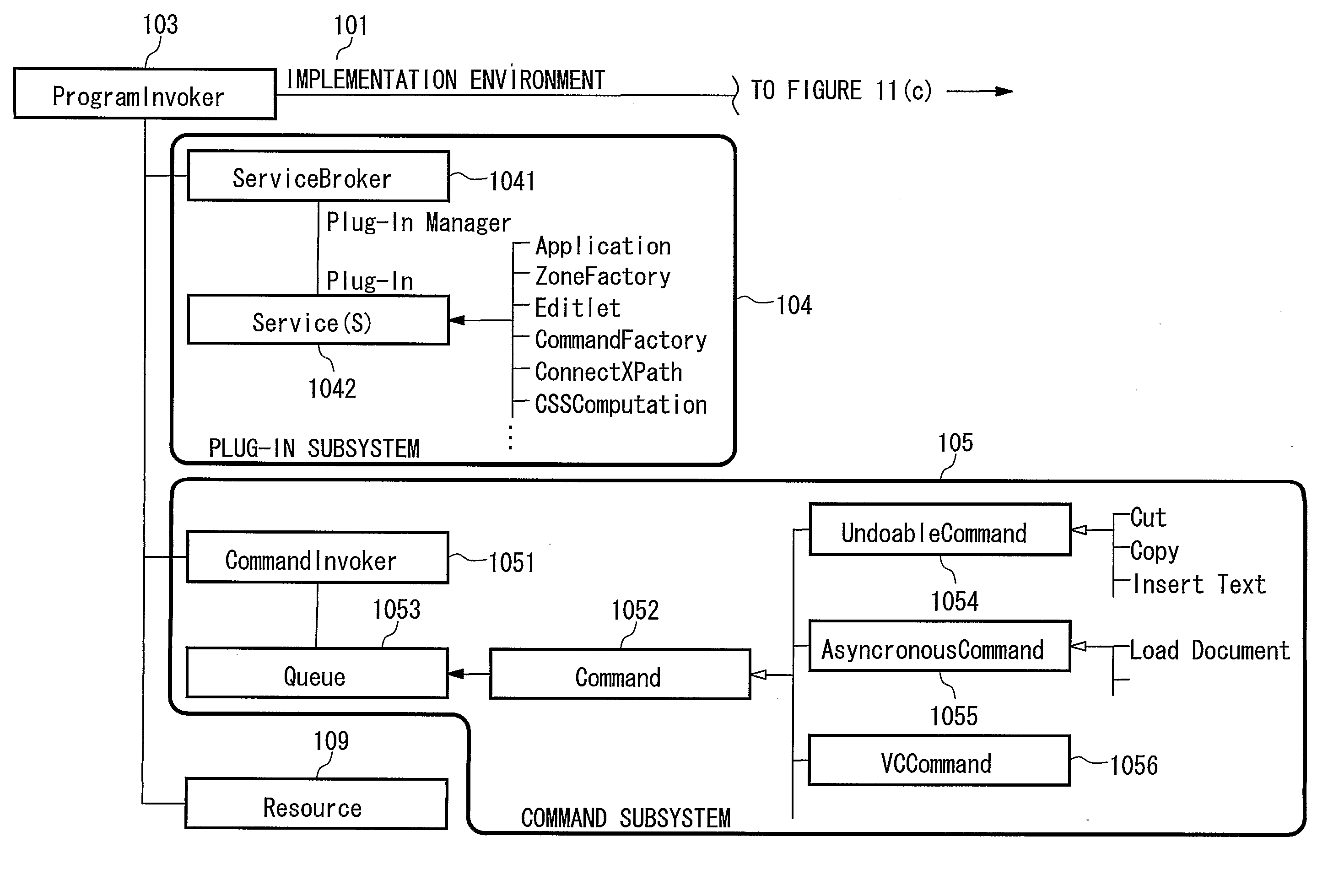

Customizing system and method for converting desktop application into web application

InactiveUS20110239127A1Software maintainance/managementInput/output processes for data processingWeb applicationOperational transformation

The present invention provides a customizing system and a customizing method for converting a desktop application into a web application. A required processing logic may be added by locating an interface element which is needed to be modified, and modifying a callback function of the interface element (interface description data), so as to implement user's operations on local data by a web application. When a user operates on the modified interface element at a browser side, the added processing logic automatically converts the user's operation to a plurality of operations, so that the user may feel that he is operating on a local file at the browser side, rather than a remote file at a server side. The present invention may implement complex webpage function customization, and thus may implement remote operations on local data.

Owner:NEC (CHINA) CO LTD

Methods of exposing a sequence of instructions into an object-oriented programming language

InactiveUS20060241999A1Digital computer detailsCode refactoringOperational transformationObject-oriented programming

Embodiments of methods and systems consistent with the invention transform business application operations, rules, and schemas into OOP constructs that represent the operation, rule, or schema, emulate its operation in terms of sequence with other operations, and represent its relationship(s) to the data it operates with and upon in the business application. An automated system determines each operation that makes up a schema or rule in the business application by analyzing the database table(s) that hold the schema or rule. The system may transform the business operation into part of an OOP model by declaring or creating an empty OOP language construct to represent the operation, such as a Java™ function or method. The transformation process may be controlled by a set of transformation rules.

Owner:SAP AG

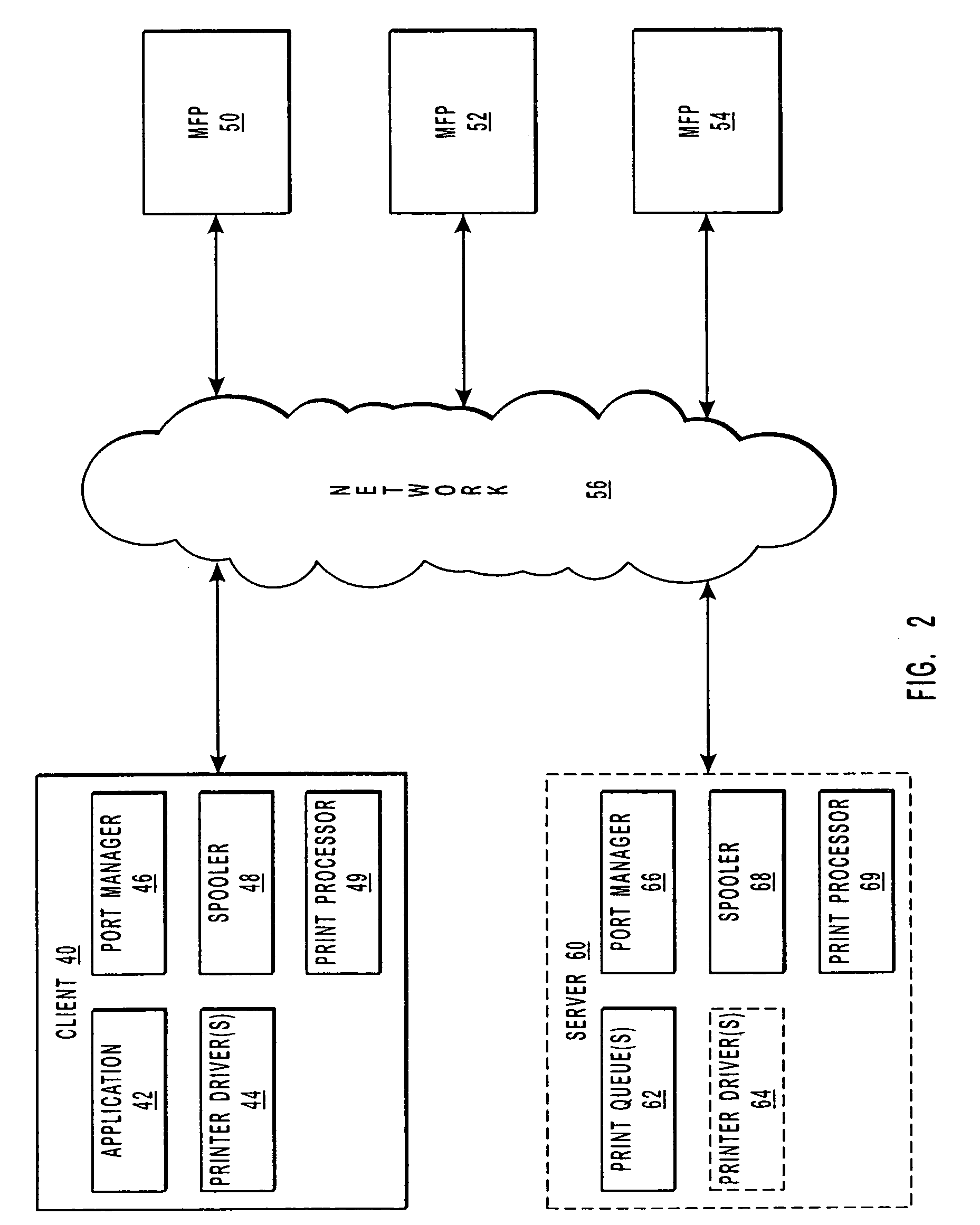

Systems and methods for providing imaging job control

ActiveUS20050052664A1Provide controlDigitally marking record carriersDigital computer detailsOperational transformationControl system

Systems and methods for describing imaging tasks across a distributed environment of imaging clients, servers and devices, wherein the tasks include complex imaging operations, and interchanging imaging data and operations. The imaging jobs include diverse imaging tasks that can be constructed in a single program unit. The imaging tasks are constructed using a single imaging job language and common interface across all imaging devices, clients and servers, or managers thereof. A manager communicates with the imaging components through the common interface and translates the operations into the communication methods that are compatible with the devices, clients and servers. Composite imaging jobs are selectively dispatched to diverse imaging components through a single imaging spooler subsystem. Further, distribution may occur across various imaging devices, clients and / or servers, such that a first imaging system performs some subset of steps, deletes the executed steps and makes the appropriate substitutions or interchanges and the portion is performed by a second and / or subsequent imaging system.

Owner:SHARP KK

System and method for synchronizing raster and vector map images

InactiveUS7148898B1Enhance the imageEasy to operateCathode-ray tube indicatorsMaps/plans/chartsOperational transformationGrating

A system and method for coordinated manipulation of multiple displayed maps, even when the maps use different internal coordinate systems. According to this embodiment, each map image to be displayed is first georeferenced, to provide a set of conversion functions between each map's internal coordinate system and a geographic coordinate system, which is latitude / longitude in the preferred embodiment. After this is done, any point on each map can be referenced using the geographic coordinate set. Since this is the case, the maps can now be manipulated, edited, and annotated in a synchronized manner, by defining the manipulations in terms of the geographic coordinate system, and using the georeferencing functions to translate the manipulation to each map's internal coordinate system.

Owner:SOURCEPROSE CORP

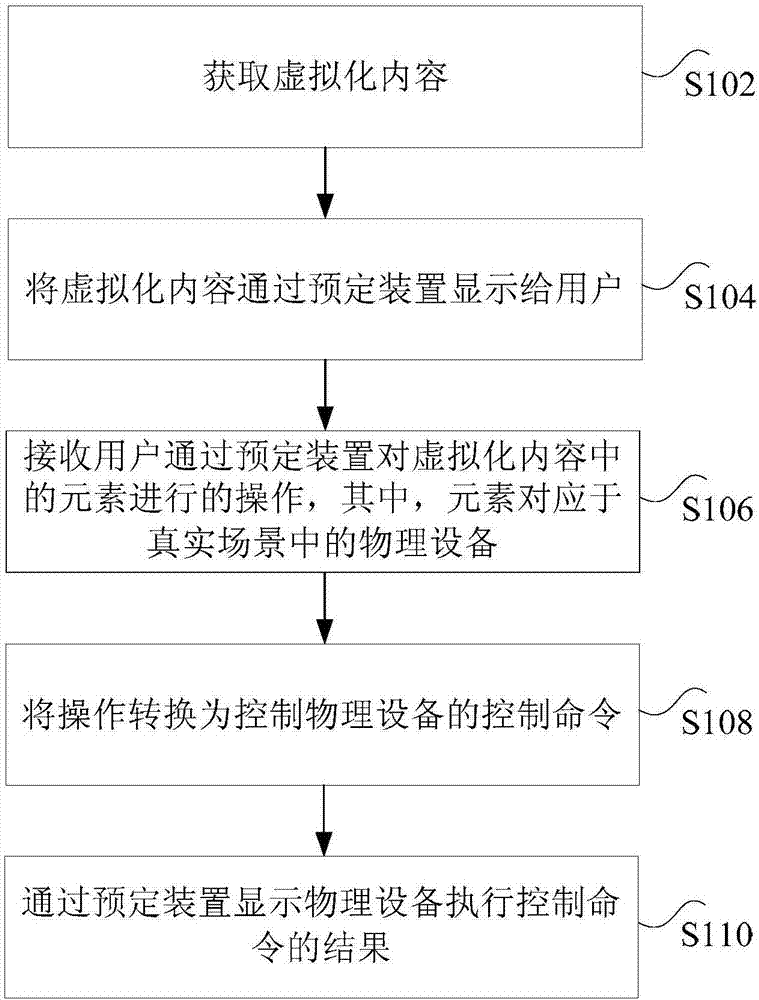

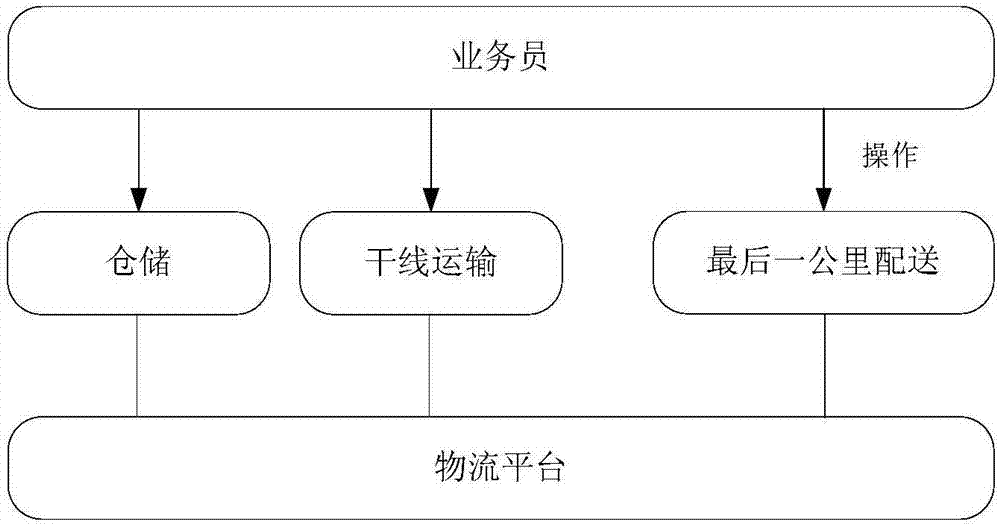

Logistics system processing method and device, and logistics system

InactiveCN107392519AImprove distribution efficiencySolve the technical problems of poor logistics timelinessInstruments for road network navigationLogisticsVirtualizationOperational transformation

The invention discloses a logistics system processing method and device, and a logistics system. The logistics system processing method comprises the following steps: obtaining the virtualization content, wherein the virtualization content comprises at least one of the following: the virtualization content obtained by performing virtualization on a part or all real scenes corresponding to at least one service link in the logistics system, and the virtualization content created by at least one service link in the logistics system; displaying the virtualization content to the user through a predetermined device; receiving the operations of users on the elements in the virtualization content through the predetermined device, wherein the elements correspond to the physical devices in the real scene; converting the operations to the control commands of physical devices; and displaying the results of the physical devices executing the control commands through the predetermined device.The invention solves the technical problem that the timeliness is bad because the logistics system depends on the manual operations in the prior art.

Owner:海航创新科技研究有限公司

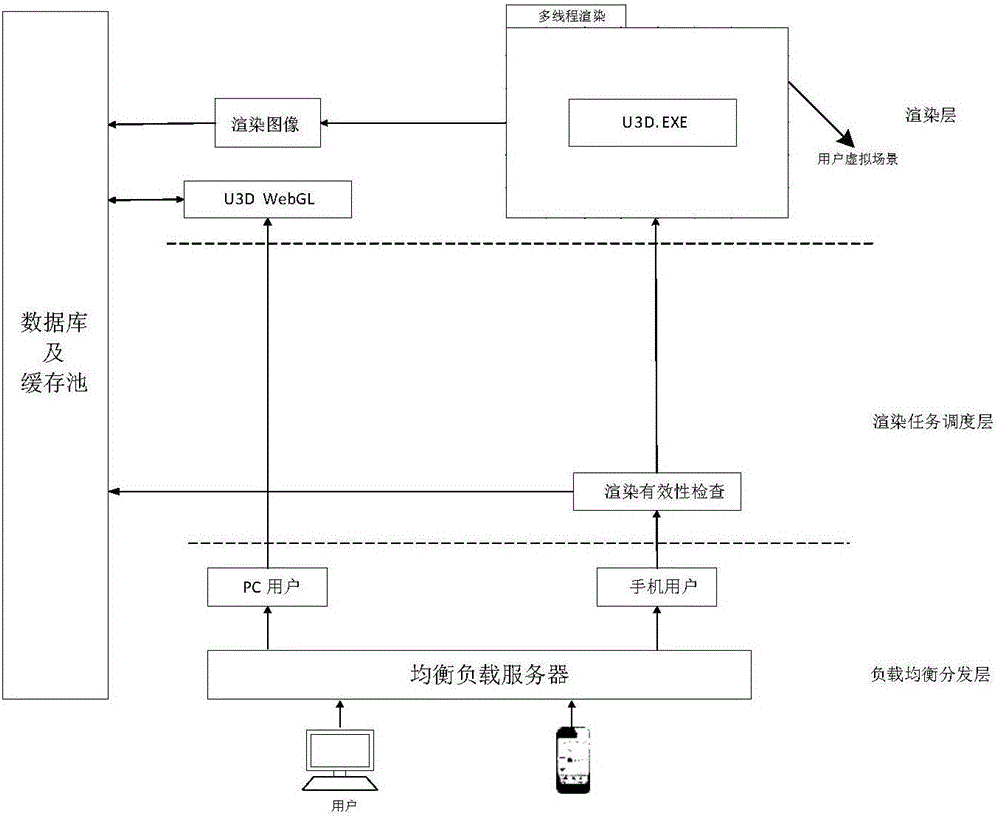

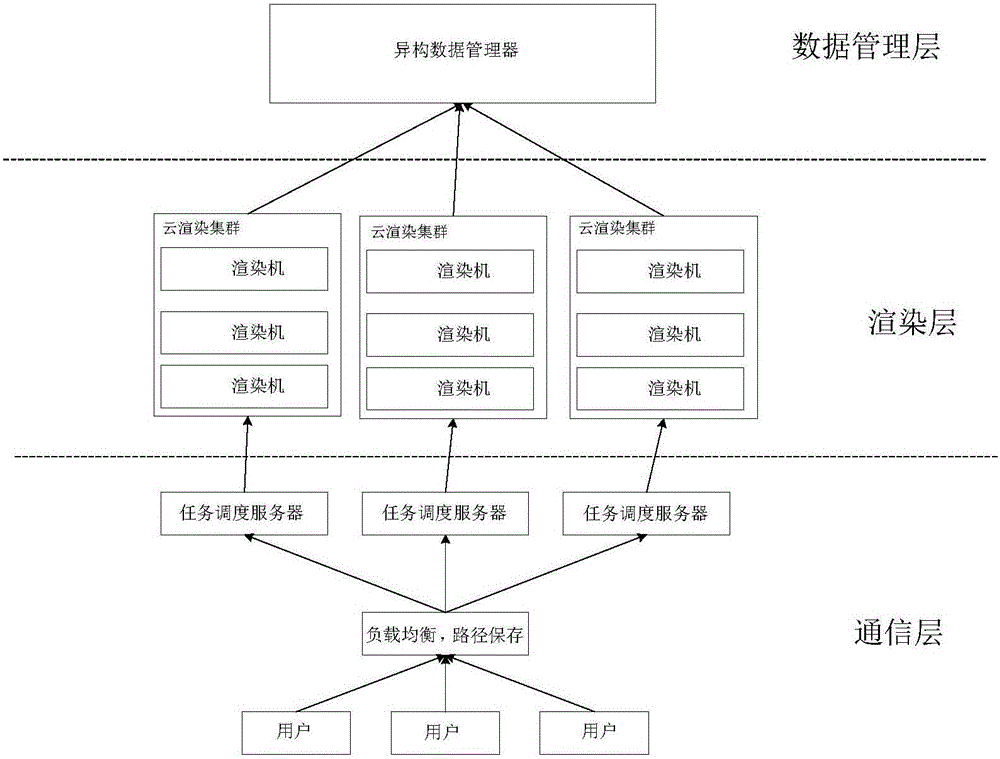

Rendering interaction method for real-time interactive access of remote 3D scene by mobile terminal user

InactiveCN106127844AImprove experienceAvoid differencesResource allocation3D-image renderingOperational transformationCloud rendering

The invention provides a rendering interaction method for a mobile terminal user to interactively access a remote 3D scene in real time, and belongs to the application of virtual reality in a mobile intelligent terminal. This method is implemented based on a three-layer rendering interaction framework. The communication channel between the mobile terminal and the cloud rendering cluster is established at the communication layer, the user access requests of the mobile terminal are distributed and sent to the cloud server, and the user operations are converted into corresponding operation instructions and transmitted to the cloud. Server: the rendering machine in the cloud rendering layer requests resource files from the resource management layer, constructs a virtual scene, adjusts the camera in the virtual scene for rendering according to the operation instructions, and sends the rendering results back to the file server in the form of pictures for storage, and transmitted to the user. The present invention realizes the fluency of playing dynamic scenes on the mobile terminal and good user experience by means of cloud service and continuous interval pictures, so that mobile terminal users can have user experience similar to that of PC terminal users when accessing remote 3D scenes.

Owner:民政部一零一研究所 +1

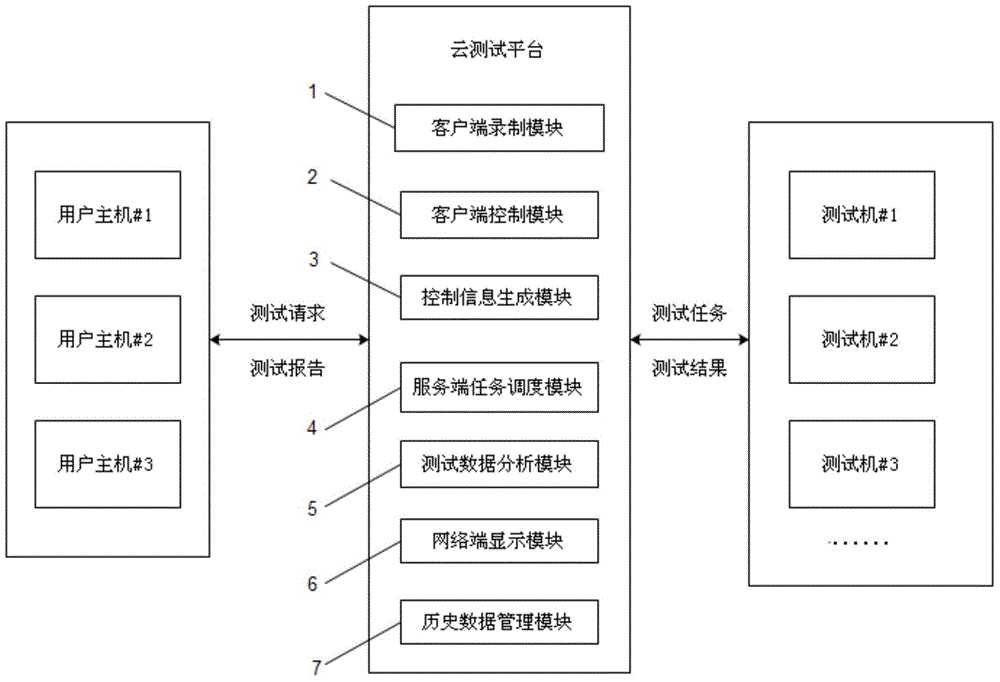

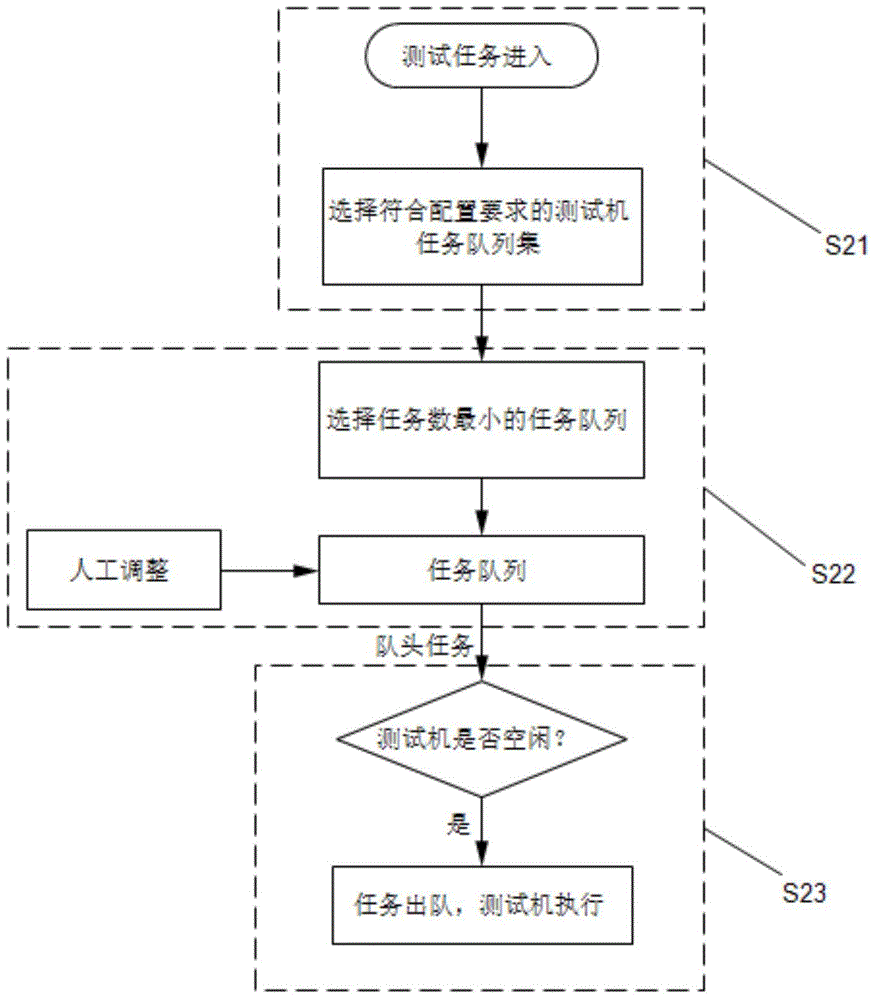

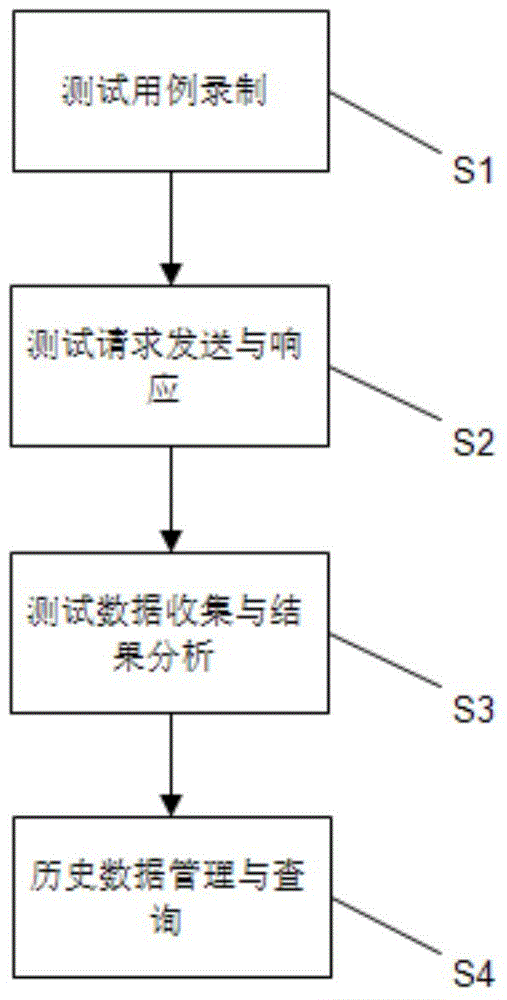

Cloud testing platform for game performance and testing method for cloud testing platform

ActiveCN104572444AIncrease profitImprove test efficiencySoftware testing/debuggingComputer hardwareOperational transformation

The invention relates to a cloud testing platform for game performance and a testing method for the cloud testing platform. The testing platform comprises a client recording module, a server task scheduling module, a control information generation module and a testing data analysis module, wherein the client recording module is used for converting manual setting and operation of a testing case into codes or data description to realize recording of the testing case; the server task scheduling module is connected with a plurality of testing machines, and is used for receiving a testing request and allocating and sending a testing task to one of the testing machines; the control information generation module is used for receiving a recording result of the client recording module, converting the recording result into corresponding operation and codes controlled by a game client, and sending the corresponding operation and codes to the testing machines for automatic testing; the testing data analysis module is used for analyzing testing data and generating a testing report. The invention also relates to the testing method applied to the testing platform.

Owner:NETEASE (HANGZHOU) NETWORK CO LTD

System and method for synchronizing raster and vector map images

InactiveUS7142217B2Improved graphic image manipulationEnhance the imageCathode-ray tube indicatorsMaps/plans/chartsOperational transformationLongitude

A system and method for coordinated manipulation of multiple displayed maps, even when the maps use different internal coordinate systems. According to this embodiment, each map image to be displayed is first georeferenced, to provide a set of conversion functions between each map's internal coordinate system and a geographic coordinate system, which is latitude / longitude in the preferred embodiment. After this is done, any point on each map can be referenced using the geographic coordinate set. Since this is the case, the maps can now be manipulated, edited, and annotated in a synchronized manner, by defining the manipulations in terms of the geographic coordinate system, and using the georeferencing functions to translate the manipulation to each map's internal coordinate system.

Owner:SOURCEPROSE CORP

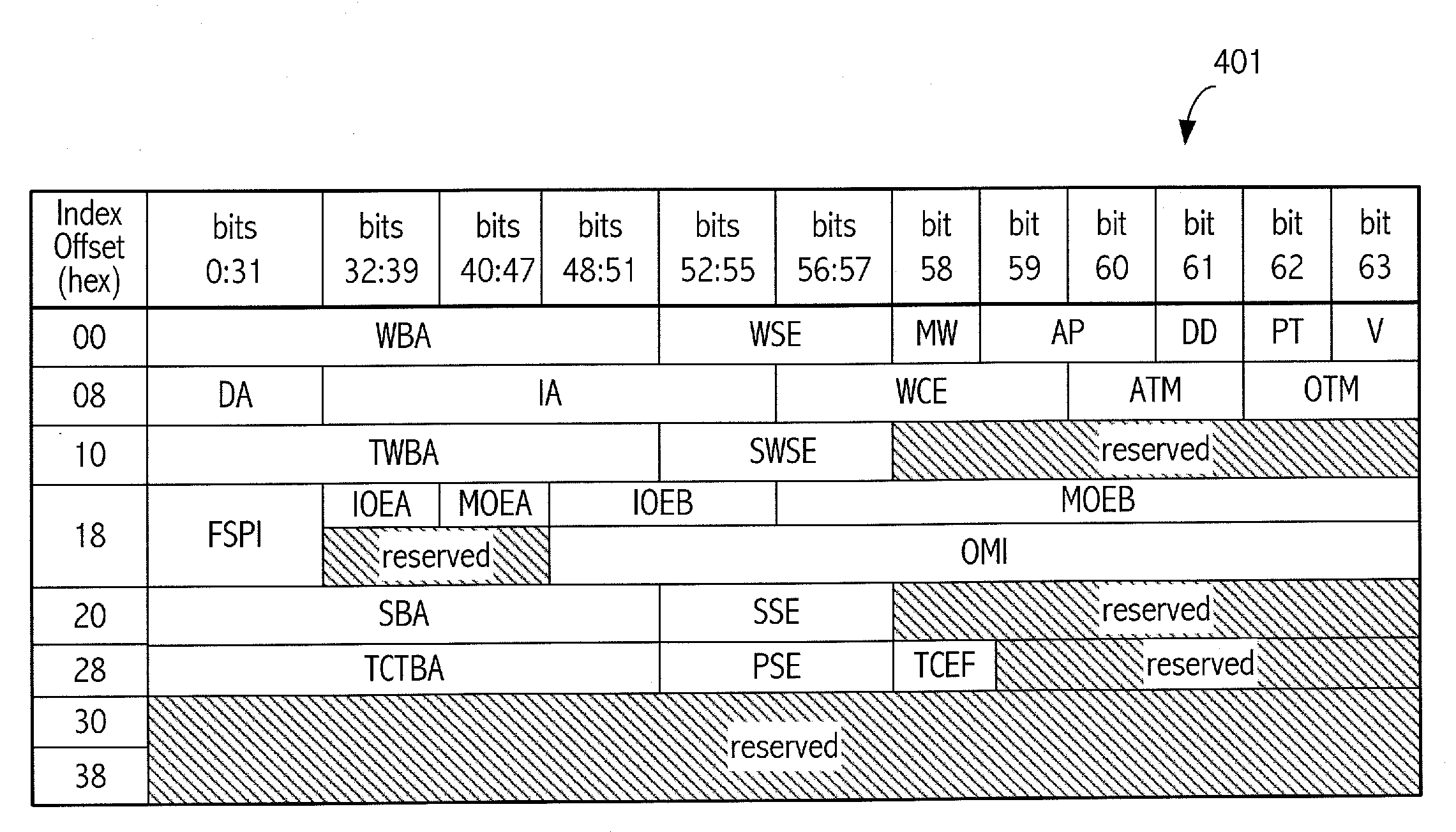

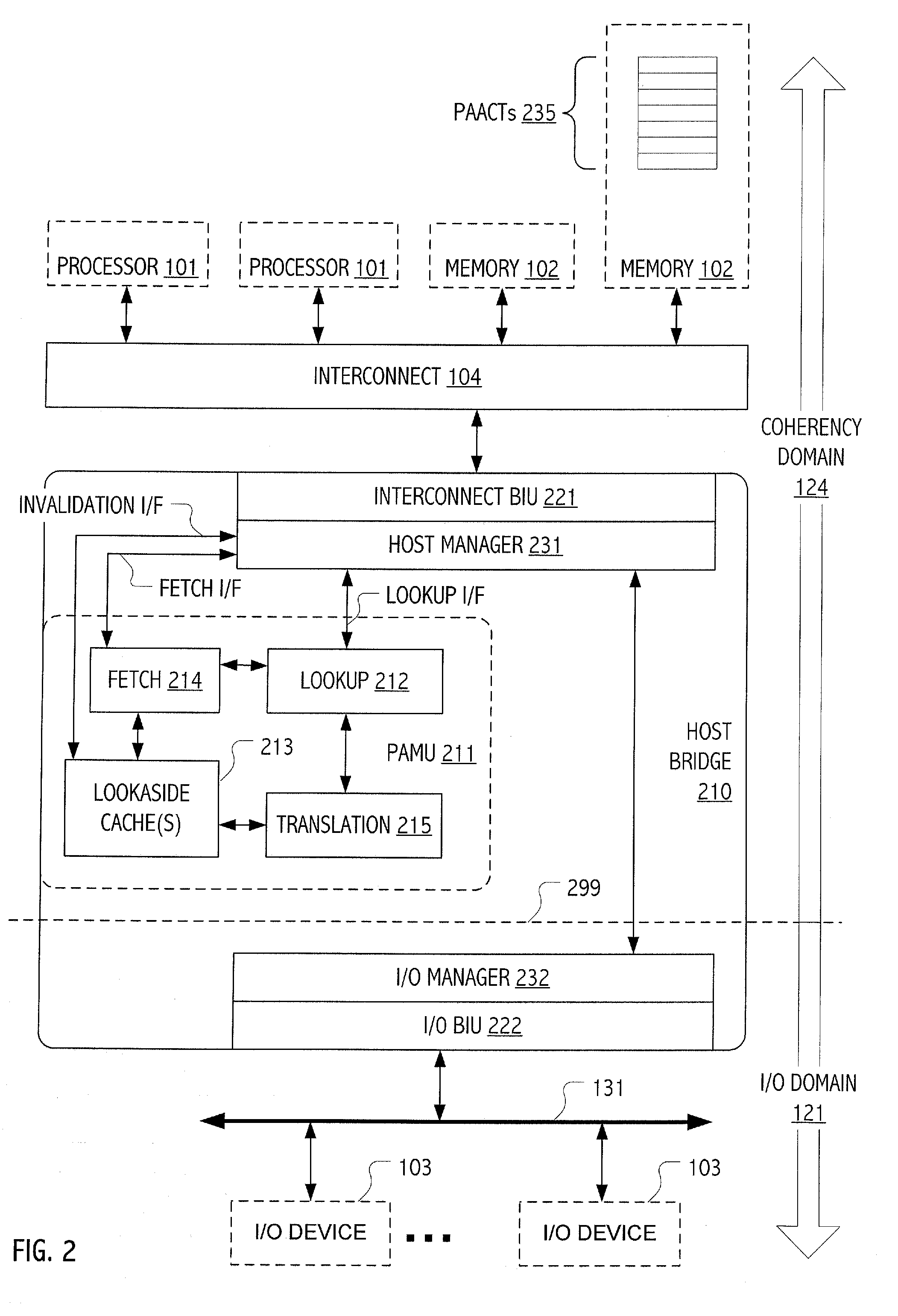

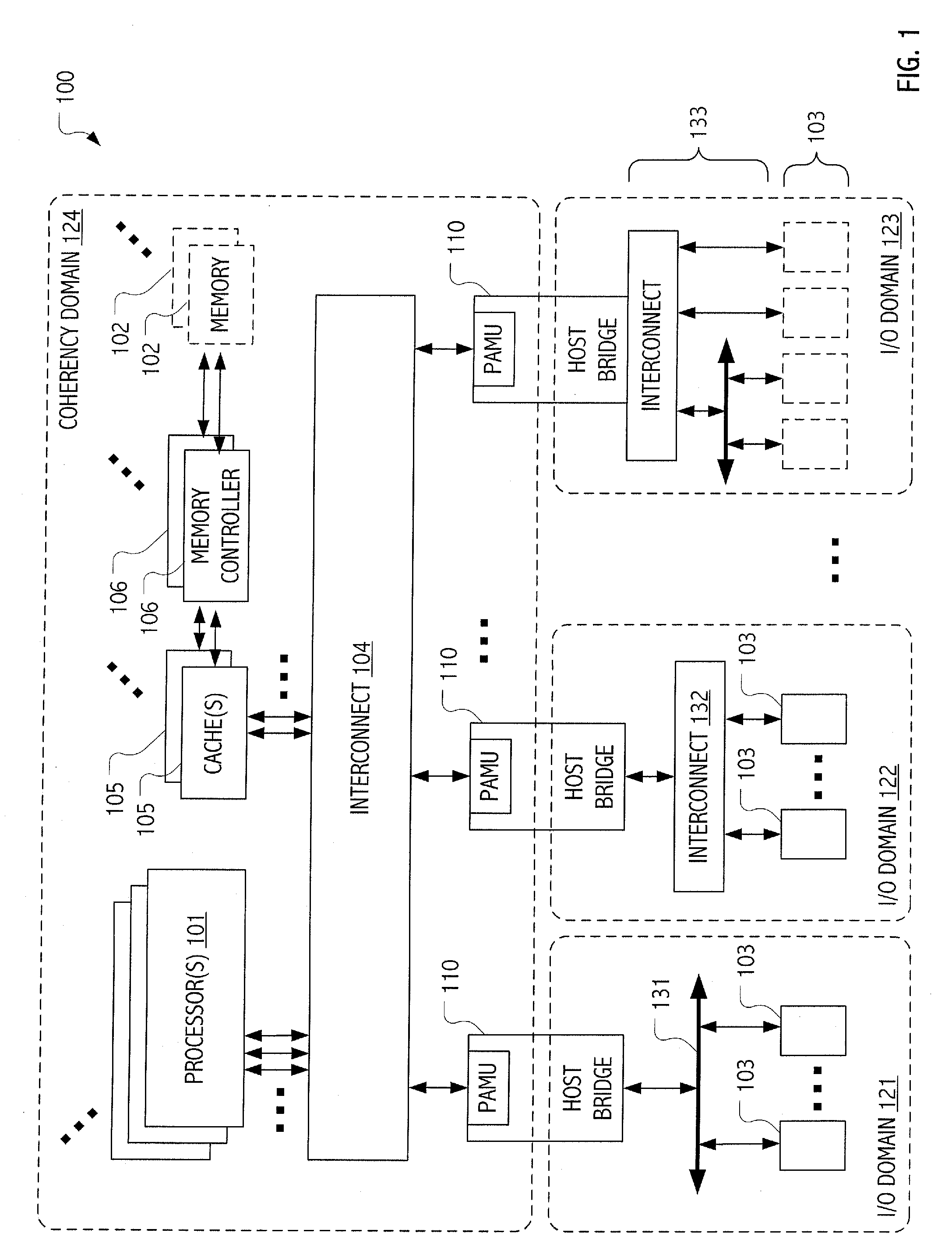

Access management technique with operation translation capability

InactiveUS20100228945A1Memory adressing/allocation/relocationInput/output processes for data processingVirtualizationDevice type

Access management techniques have been developed to specify and facilitate mappings between I / O and host domains in ways that provide flexibility in the form, granularity and / or extent of mappings, attributes and access controls coded relative to a particular I / O domain. In some embodiments of the present invention, operation translations coded relative to a particular logical I / O device, domain or sub-window seek to optimize functionality, isolation or some other figure of merit without regard to needs or limitations of another. In this way, operation translations need not be uniform and need not reduce supported operation semantics to correspond to that of a lowest common denominator I / O device. In some embodiments, the form of mappings (e.g., of operation translations) may be specialized on a per-logical-device basis (or even a per-sub-window basis), thereby offering individual logical I / O devices (or sub-windows thereof) immediate, indexed, and / or untranslated operation mapping frameworks appropriate to their individual requirements or needs. In general, flexibilities and efficiencies afforded in some embodiments of the present invention can be desirable, particularly as the diversity of I / O device types and richness of transaction semantics supported in interconnect fabrics increase. Some embodiments may be leveraged in support of sophisticated system partitions or I / O virtualizations.

Owner:NXP USA INC

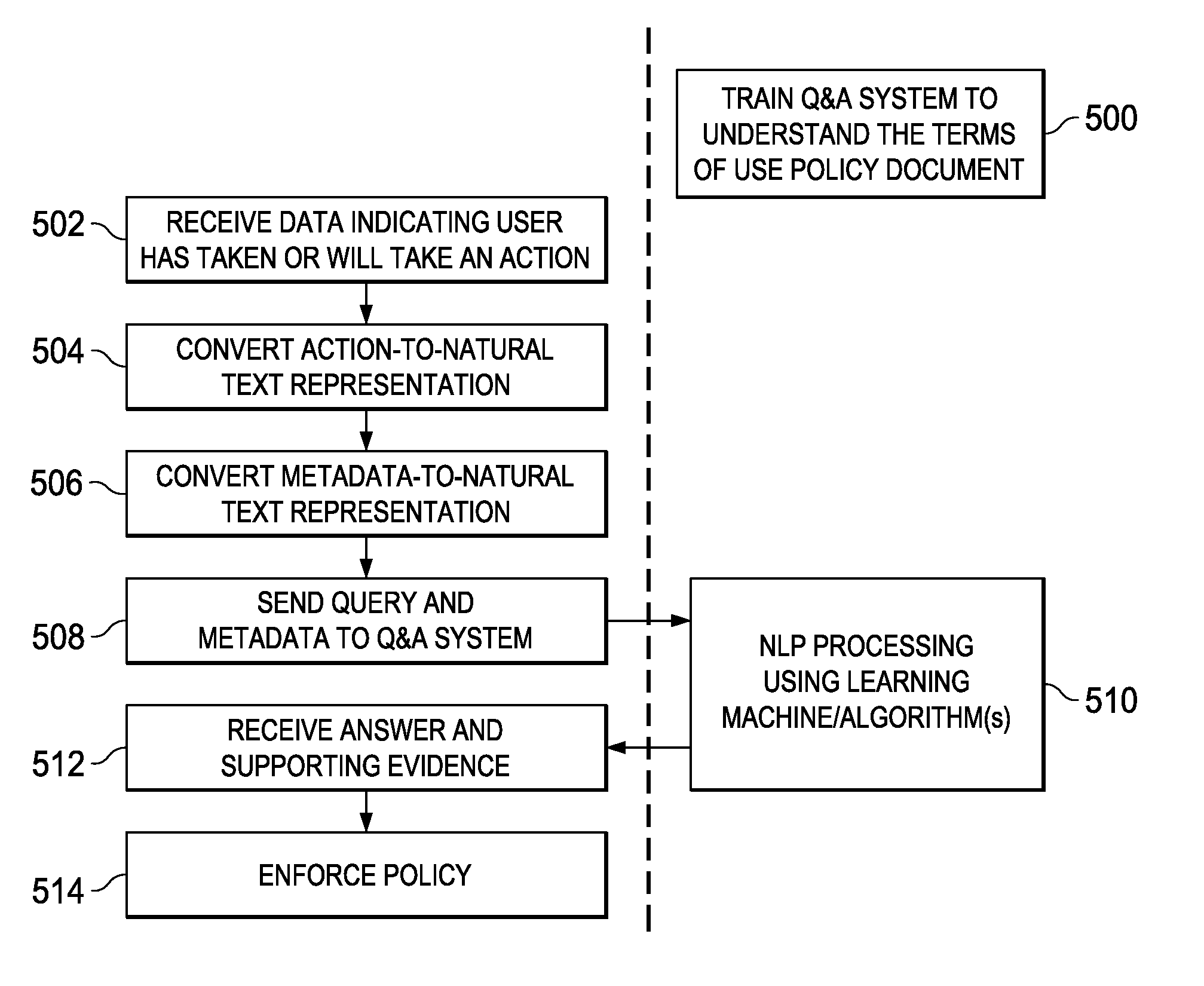

Policy enforcement using natural language processing

A term of use policy document defines permissible actions that may be implemented by a user using a computing device. A natural language processing (NLP)-based question and answer (Q&A) system is trained to understand the policy document. The device includes a management application that interacts with the Q&A system to identify a policy violation. When the user performs an action on the device, the application converts that action into an NLP query directed to the Q&A system to determine whether the action constitutes a violation. The query may be accompanied by metadata associated with the user, the device or its state. Upon receipt of the query and any associated metadata, the Q&A system determines if the user action is compliant with the policy and returns a response. Based on the response, the user's computing device may take an enforcement action, e.g., restricting or disabling functionality, or issuing a warning.

Owner:GLOBALFOUNDRIES INC

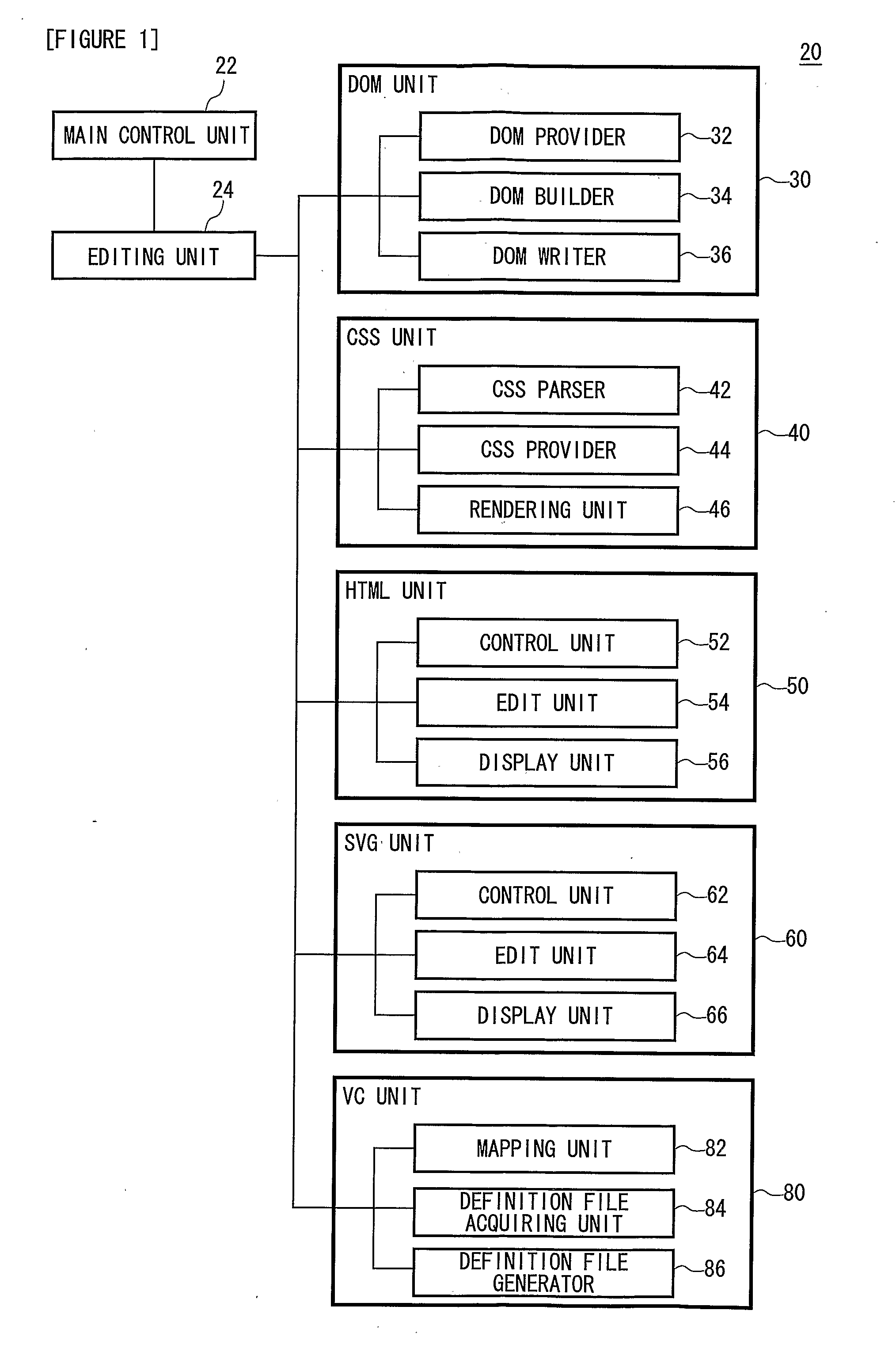

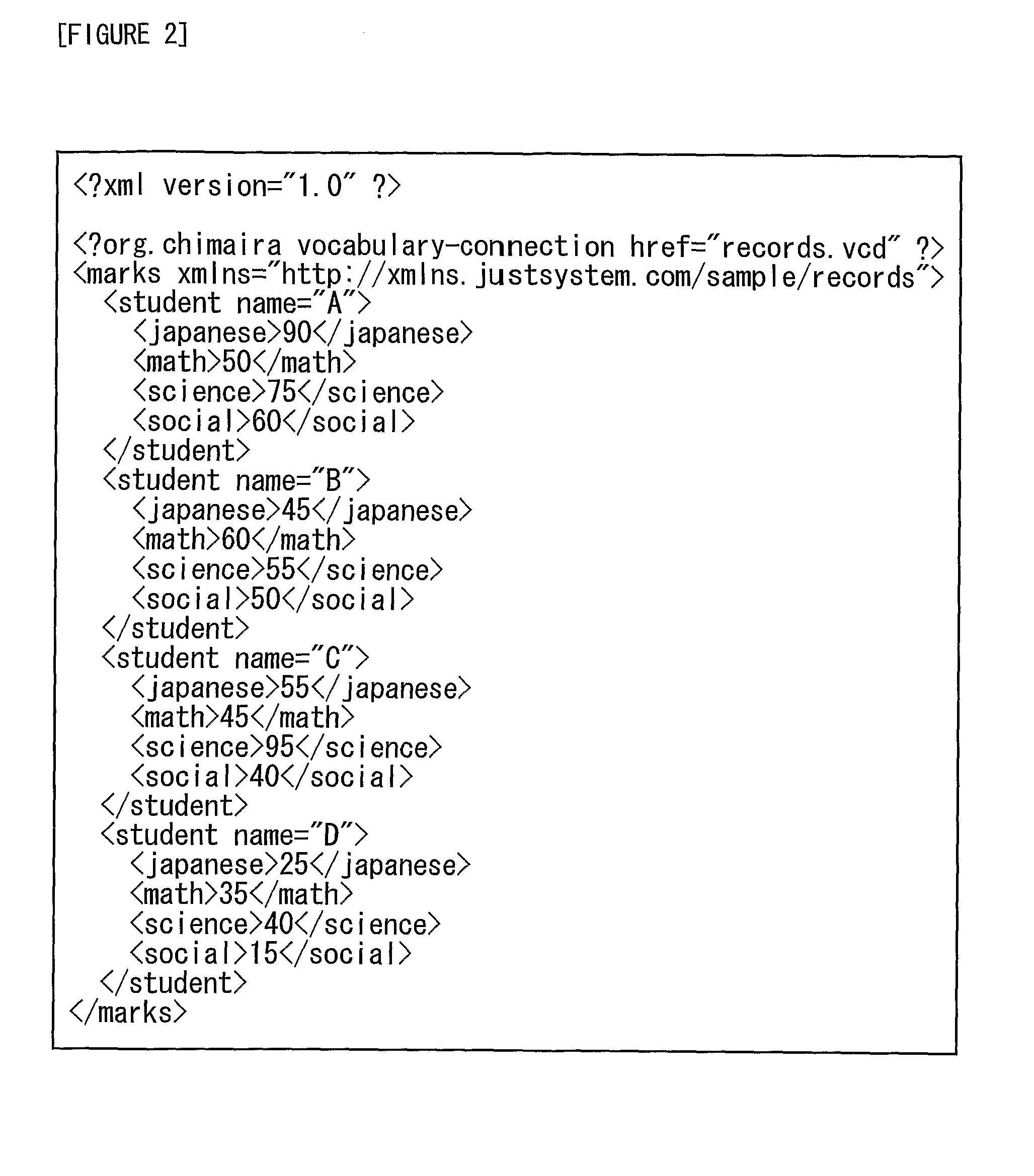

Processing Data And Documents That Use A Markup Language

InactiveUS20080134019A1Efficient processingNatural language data processingSpecial data processing applicationsOperational transformationDocumentation

A data processing apparatus that comprises a data acquisition unit operable to receive a document in a first markup language. A definition file comprising logic for processing data in said document, said logic including logic for converting a complex editing operation on the document in a second markup language to an equivalent operation in the first markup language is provided. A processing unit executes the logic.

Owner:JUSTSYSTEMS

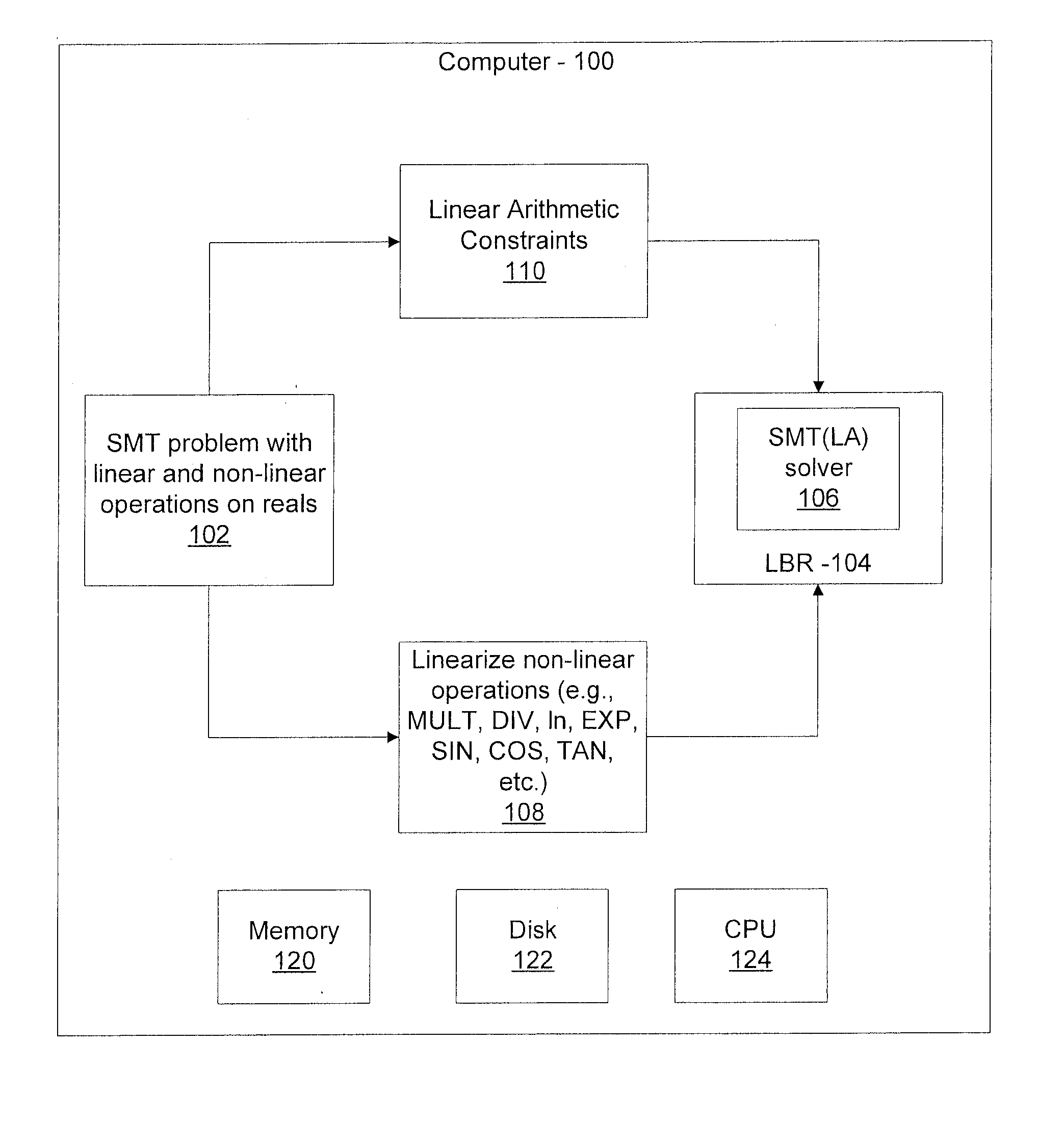

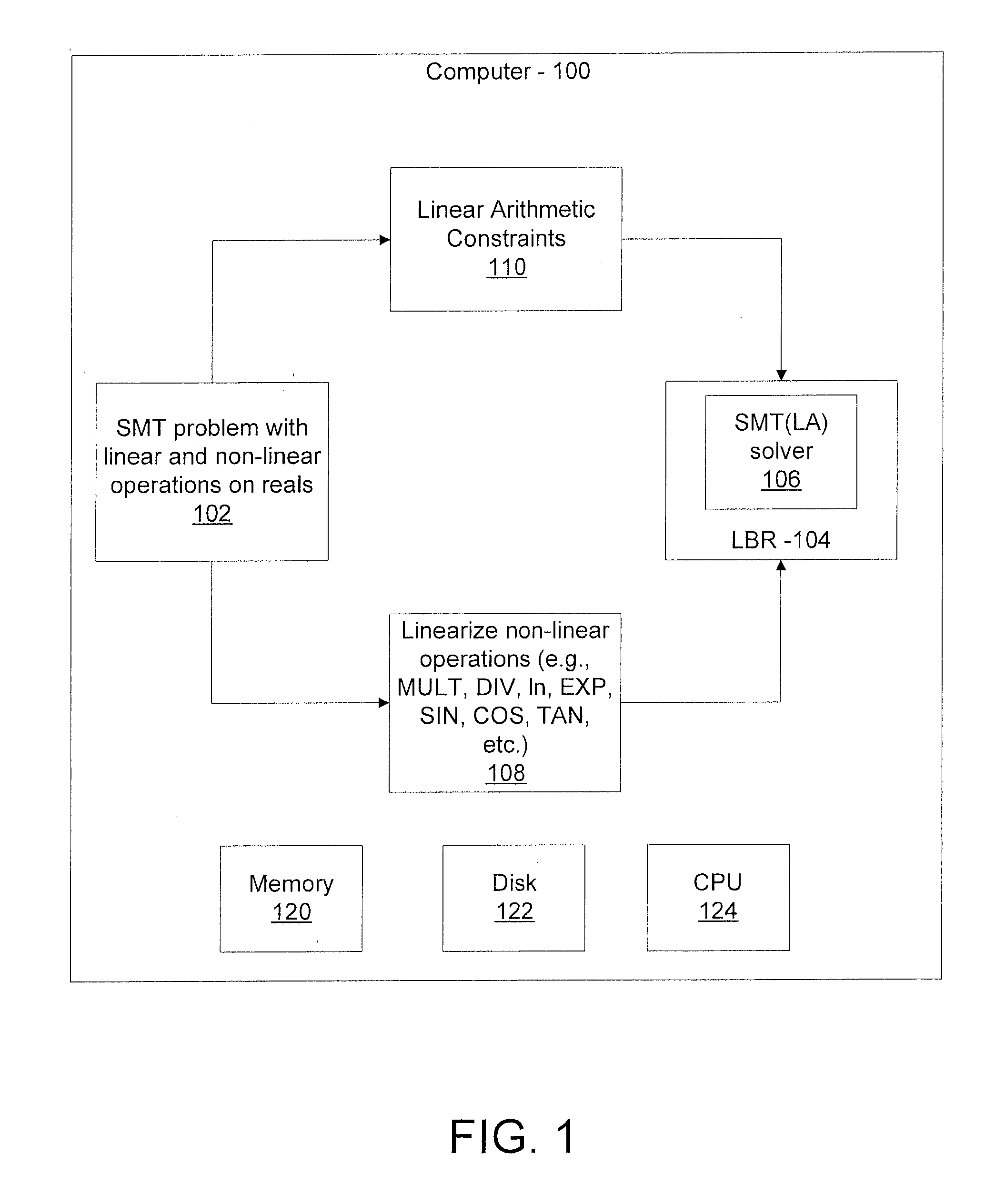

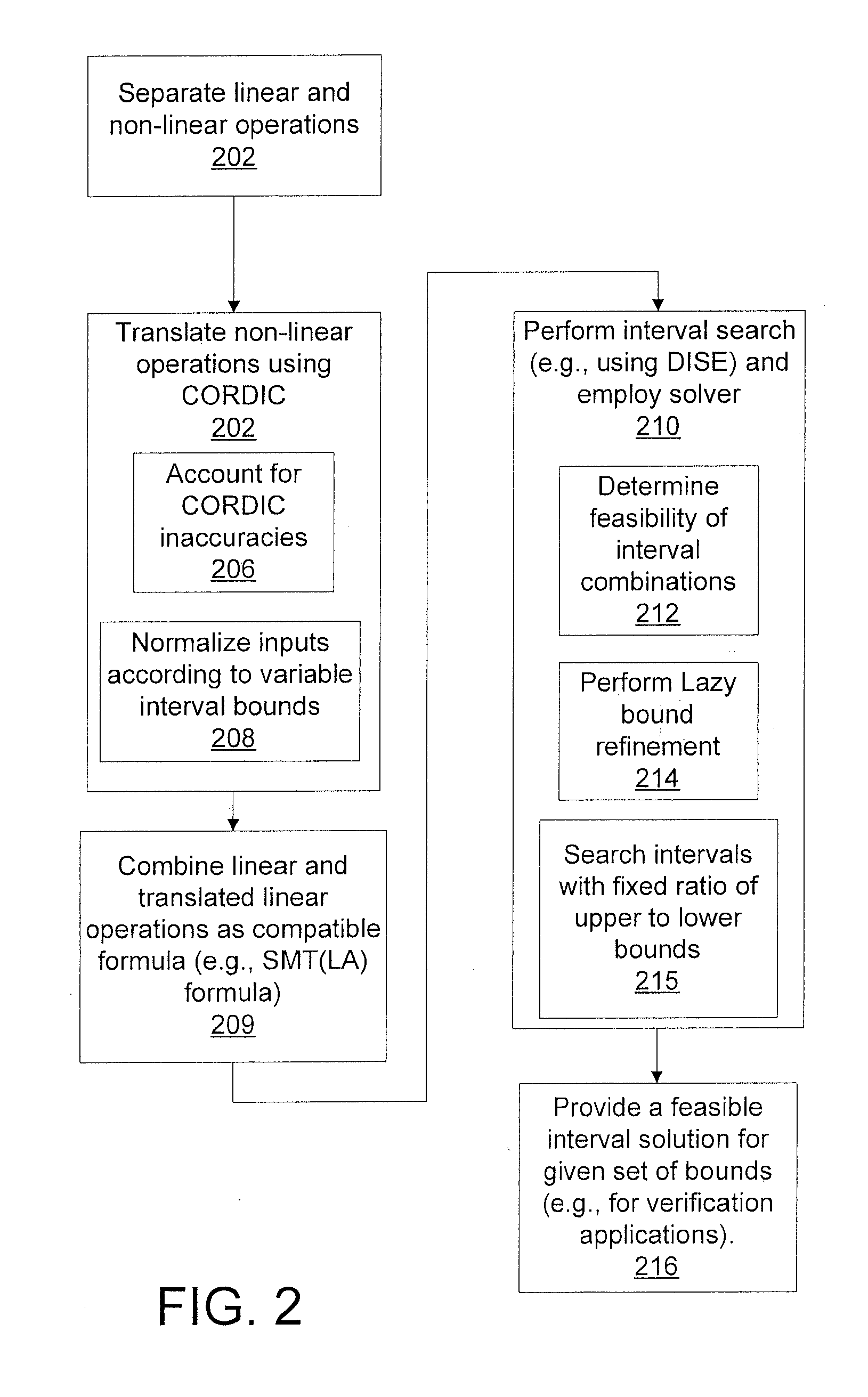

Efficient decision method for real non-linear arithmetic constraints

InactiveUS20100281086A1Digital computer detailsKnowledge representationReal arithmeticOperational transformation

A system and method for solving a decision problem having Boolean combinations of linear and non-linear operations includes translating the non-linear real operations using a COordinate Rotation DIgital Computer (CORDIC) method programmed on a computer device into linear operations maintaining a given accuracy. Linear and translated linear operations are combined into a formula. Satisfiablity of the formula is solved using a decision procedure for Boolean combinations of linear operations over integers and reals.

Owner:NEC CORP

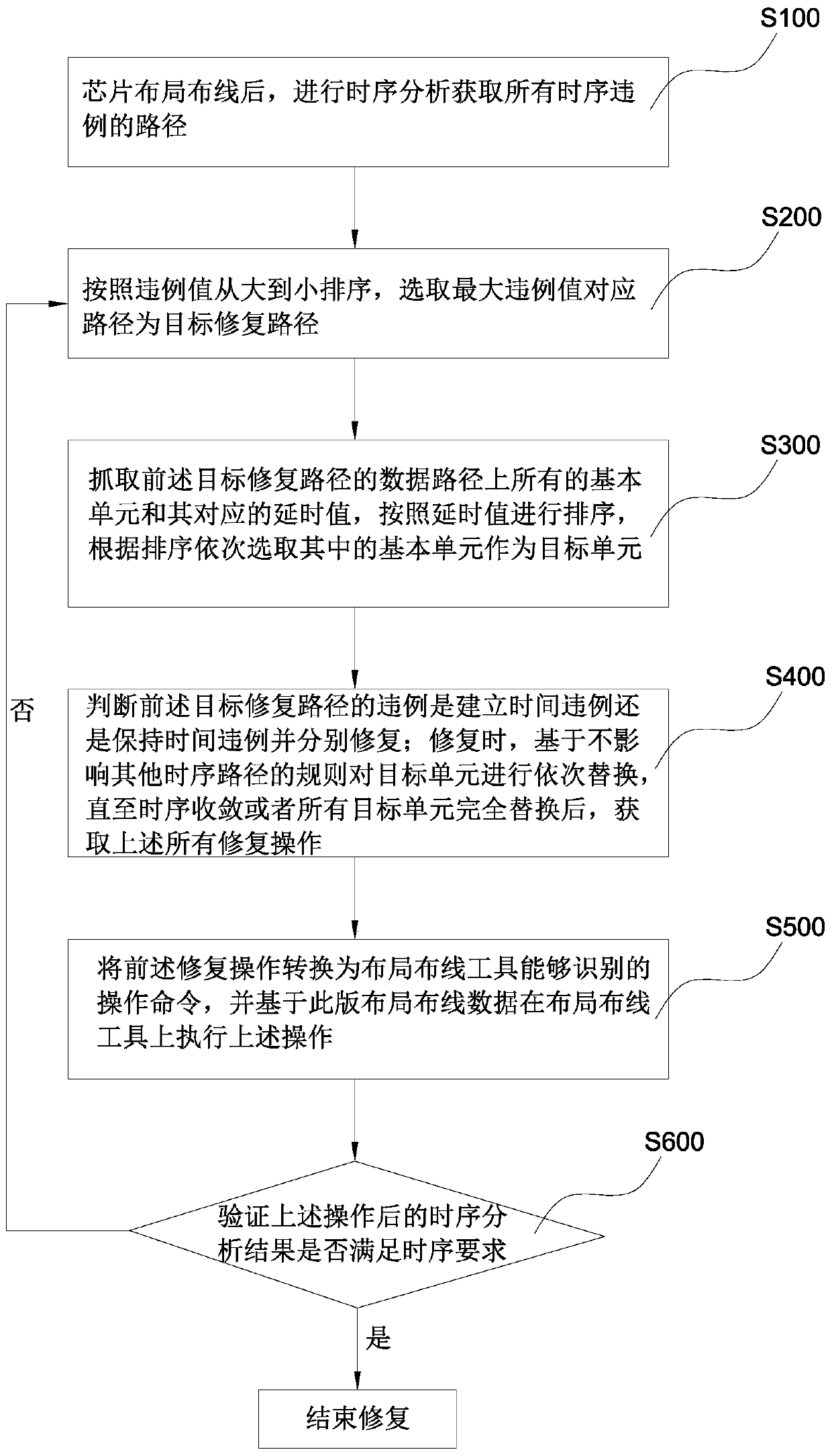

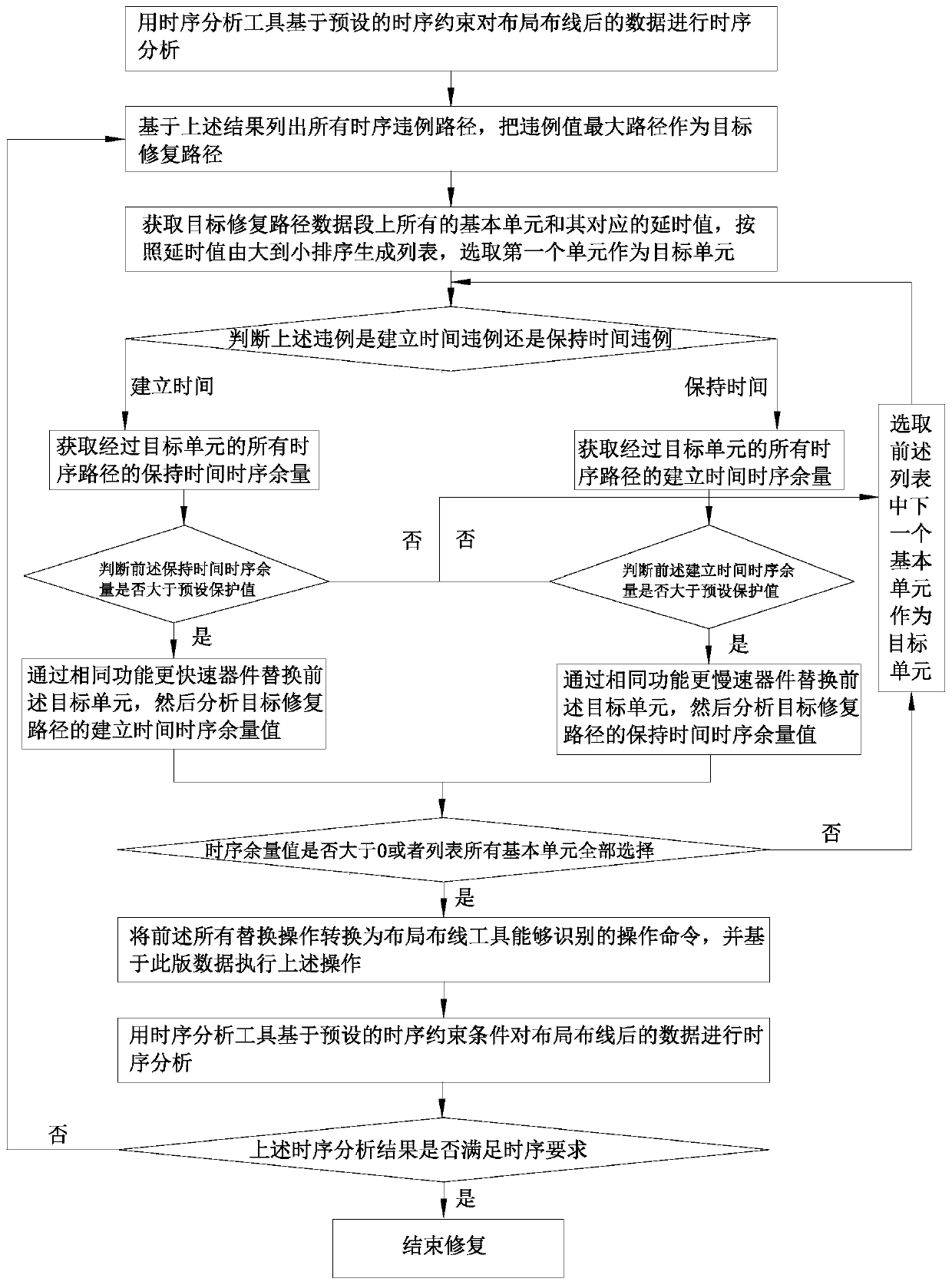

Method and system for repairing time sequence violations in chip design

ActiveCN110598235AReduce areaReduce design costSpecial data processing applicationsOperational transformationRepair time

The invention discloses a method and system for repairing time sequence violations in chip design, and relates to the technical field of integrated circuit design. The method comprises the following steps of selecting a target repair path from time sequence violation paths, grabbing all basic units and the delay values corresponding to the basic units in the target repair path and sorting, and sequentially selecting the basic units as the target units according to the sequence; judging whether the violation is an establishment time violation or a retention time violation, replacing the targetunits sequentially based on the rules which do not affect other time sequence paths, and obtaining the repair operation meeting requirements; and converting the repair operation into an operation command which can be identified by a layout wiring tool, executing the operation on the layout wiring tool, and ending the repair under the condition of verifying that the time sequence analysis result after the operation meets the time sequence requirement. According to the invention, when the time sequence violation repair is carried out, the re-layout and the re-wiring are not needed, and the timesequence convergence can be realized through the rapid iteration.

Owner:MOLCHIP TECH (SHANGHAI) CO LTD

Access management technique for storage-efficient mapping between identifier domains

InactiveUS20100228943A1Memory adressing/allocation/relocationMicro-instruction address formationVirtualizationOperational transformation

Access management techniques have been developed to specify and facilitate mappings between I / O and host domains in ways that are storage-efficient and which can provide flexibility in the form, granularity and / or extent of mappings, attributes and access controls coded relative to a particular I / O domain. Indeed, different identifier and / or operation translation models may be employed on a per logical device (or even a per sub-window) basis. In general, the flexibility and efficiency afforded using some embodiments of the present invention can be desirable, particularly as numbers of I / O domains increase, such as in the case of virtualization system implementations in which a multiplicity of logical I / O devices may be represented using underlying physical resources.

Owner:FREESCALE SEMICON INC

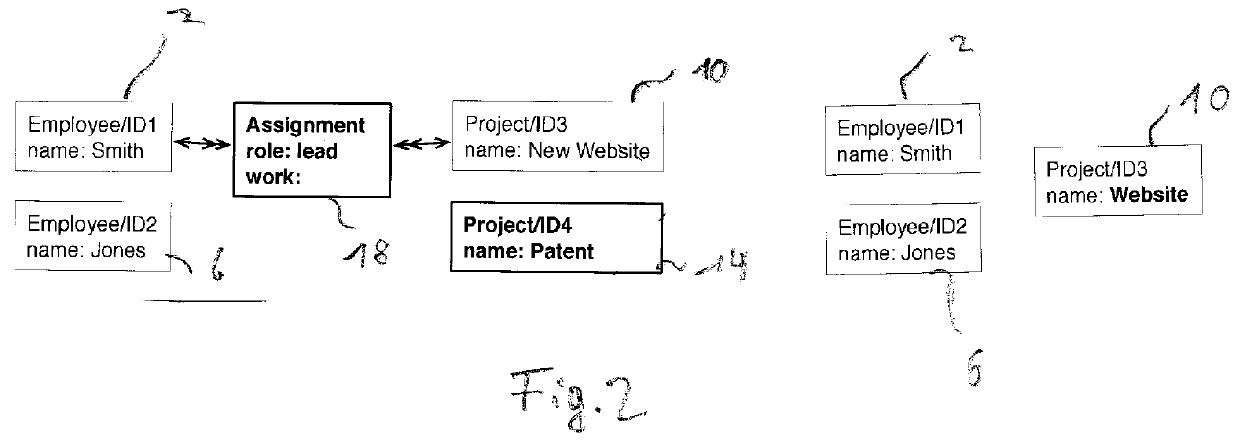

Method and system for syncing data structures

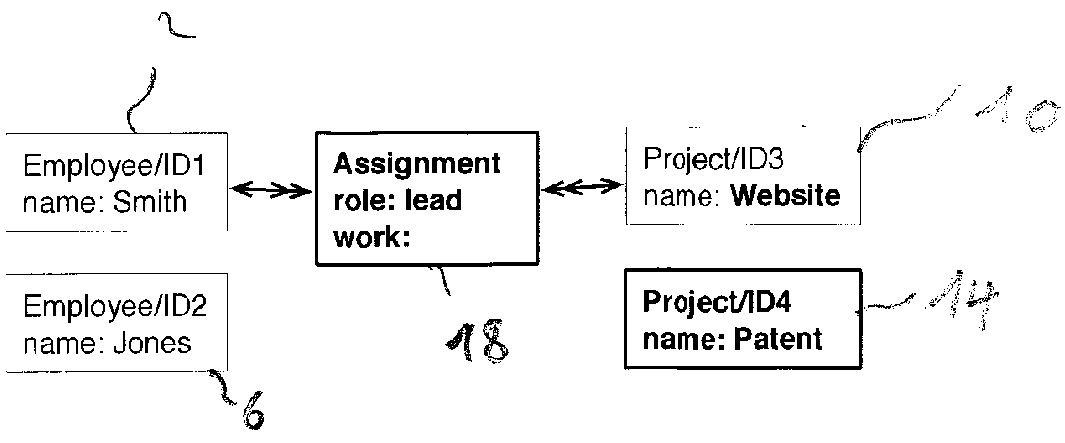

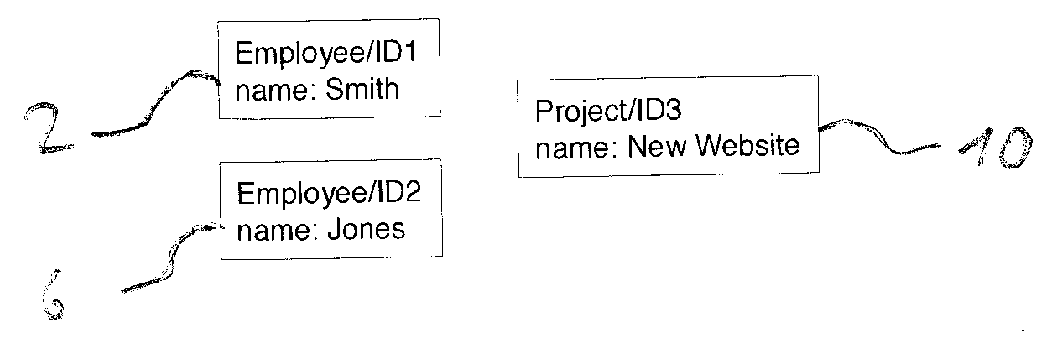

ActiveUS20160055226A1Powerful and versatile and flexible representation of dataLoss of resourceDigital data information retrievalDigital data processing detailsOperational transformationObject graph

The consistency of a data structure is maintained where changes in the form of atomic operations are requested by more than one user to an object graph containing a plurality of objects. Operational transformations specifying how one atomic operation is transformed against another one are accessed and the object graph is modified with the first and second set of changes by employing the operational transformations on the atomic operations and applying the resulting transformed operations to the object graph. The transformed operations are recorded in a history log. The atomic operations are object operations that create or delete an object of the object graph and / or property operations changing a property of an object. Each operation retains the identifier of the object it acts on and information on each change of the object resulting from the operation. Multi-operation conflicts are resolved by defined conflict resolution events.

Owner:PROJECTWIZARDS

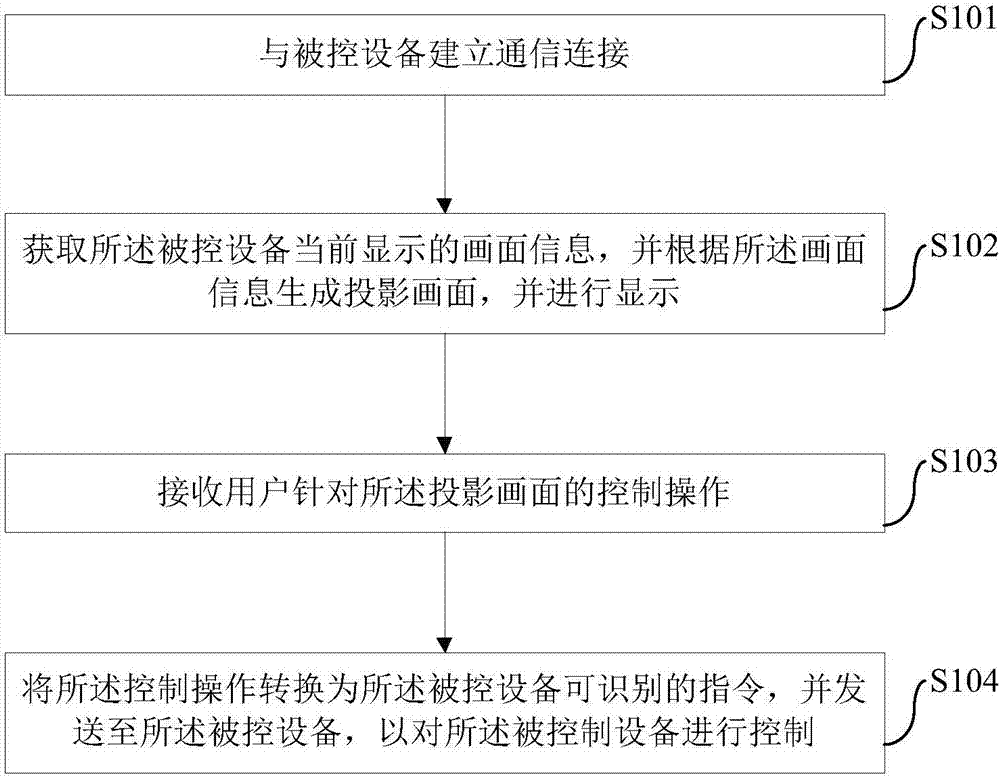

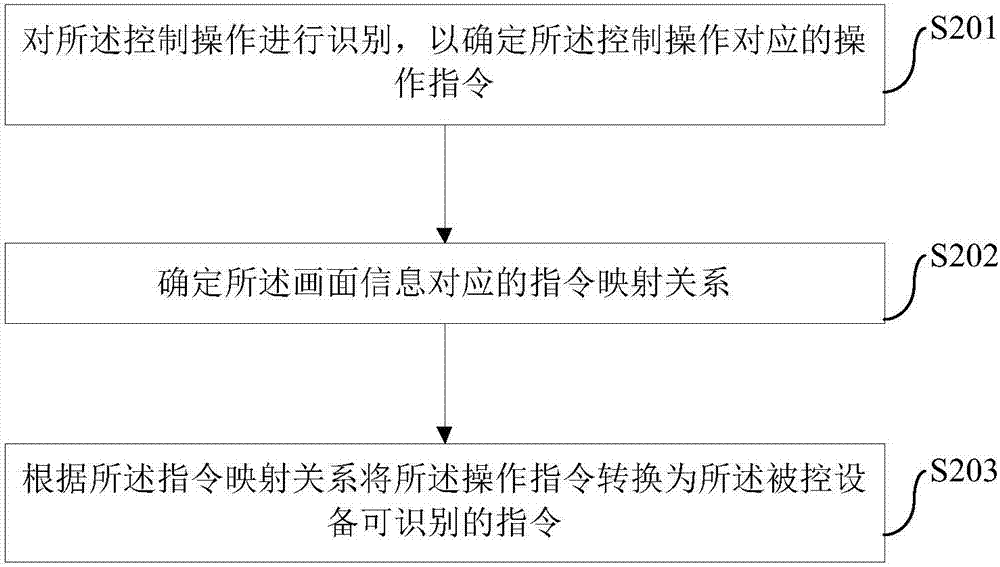

Mobile terminal-based device control method, equipment and mobile terminal

ActiveCN107147769AOperate naturallyEasy to operateTelevision system detailsTransmission systemsOperational transformationComputer terminal

The invention provides a mobile terminal-based device control method, equipment and a mobile terminal. The mobile terminal-based device control method comprises the steps of establishing the communication connection with a controlled device; acquiring the currently displayed picture information of the controlled device, generating a projection picture according to the picture information and displaying the projection picture; receiving the control operation of a user on the projection picture; converting the control operation into an instruction identified by the controlled device, sending the instruction to the controlled device and controlling the controlled device. By adopting the mobile terminal-based device control method, the advantage complementation between devices can be realized, and the freedom degree and the flexibility of user interaction are greatly improved.

Owner:ALIBABA GRP HLDG LTD

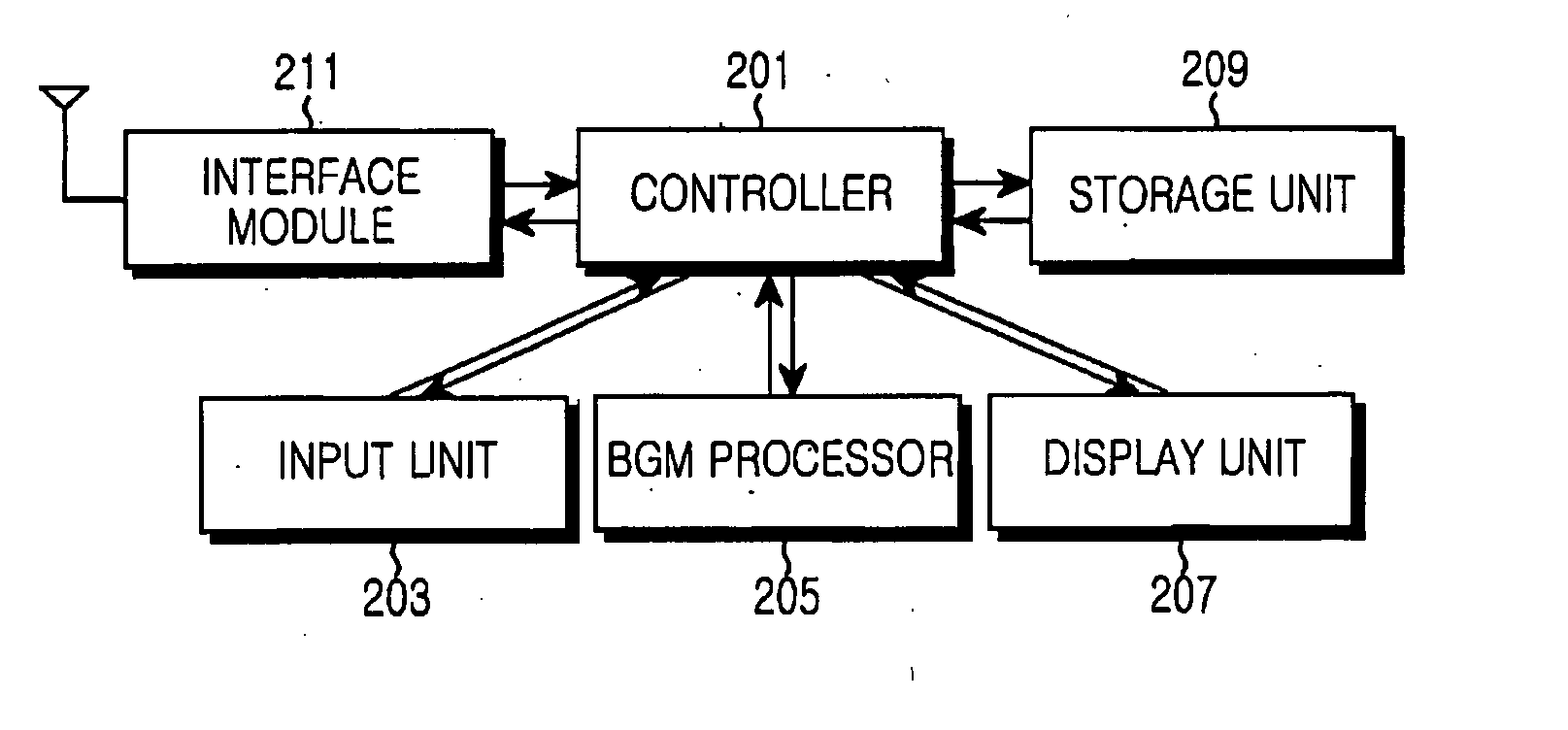

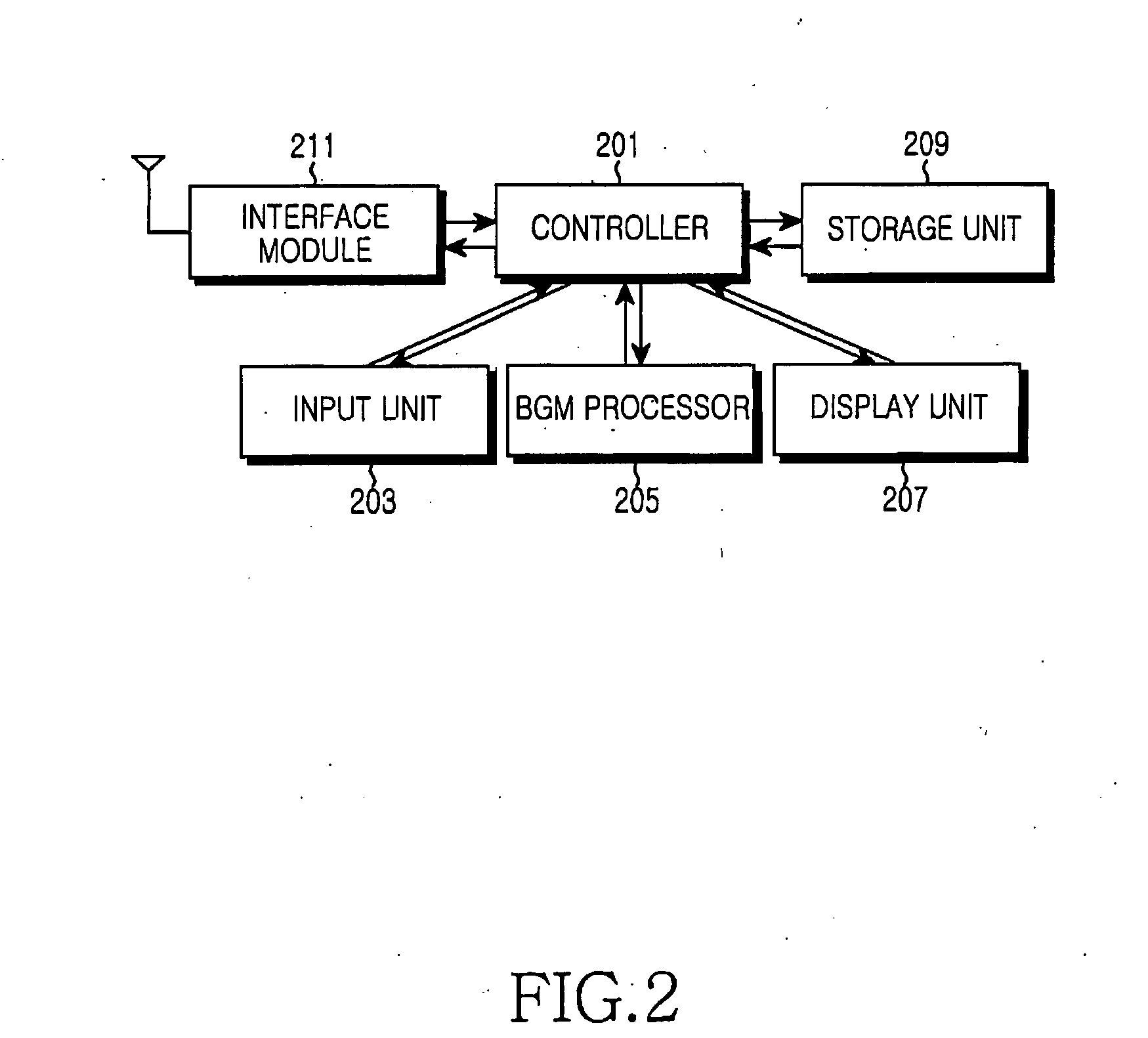

Apparatus and method for controlling backround music in mobile communication system

InactiveUS20070186758A1Electrophonic musical instrumentsSubstation equipmentOperational transformationFunction mapping

A method and apparatus for controlling a background music (BGM) play operation is disclosed. The method determines if a predetermined hotkey is pressed during the BGM play operation and, if pressed, a BGM play control box is displayed while maintaining the state of an ongoing main operation. Function mapping of a series of predetermined keys is then changed. If determined that the predetermined key is pressed for control of the BGM play operation, the BGM play operation is controlled according to the mapped function of the pressed key. The BGM play control operation can be adjusted using the predetermined hotkey without converting the BGM play operation into the main operation.

Owner:SAMSUNG ELECTRONICS CO LTD

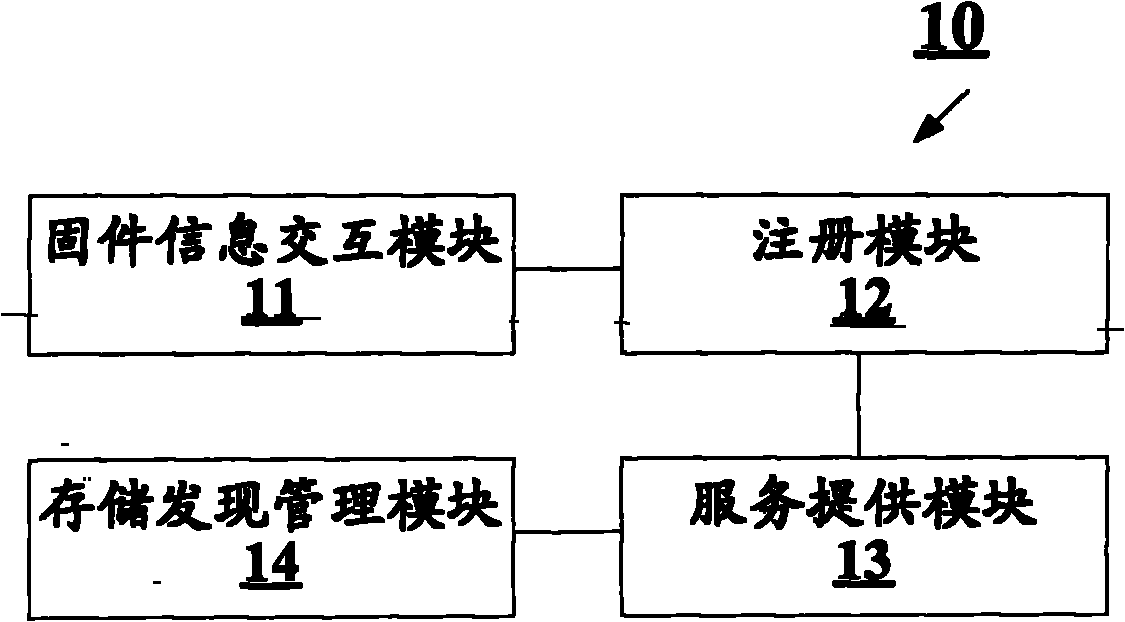

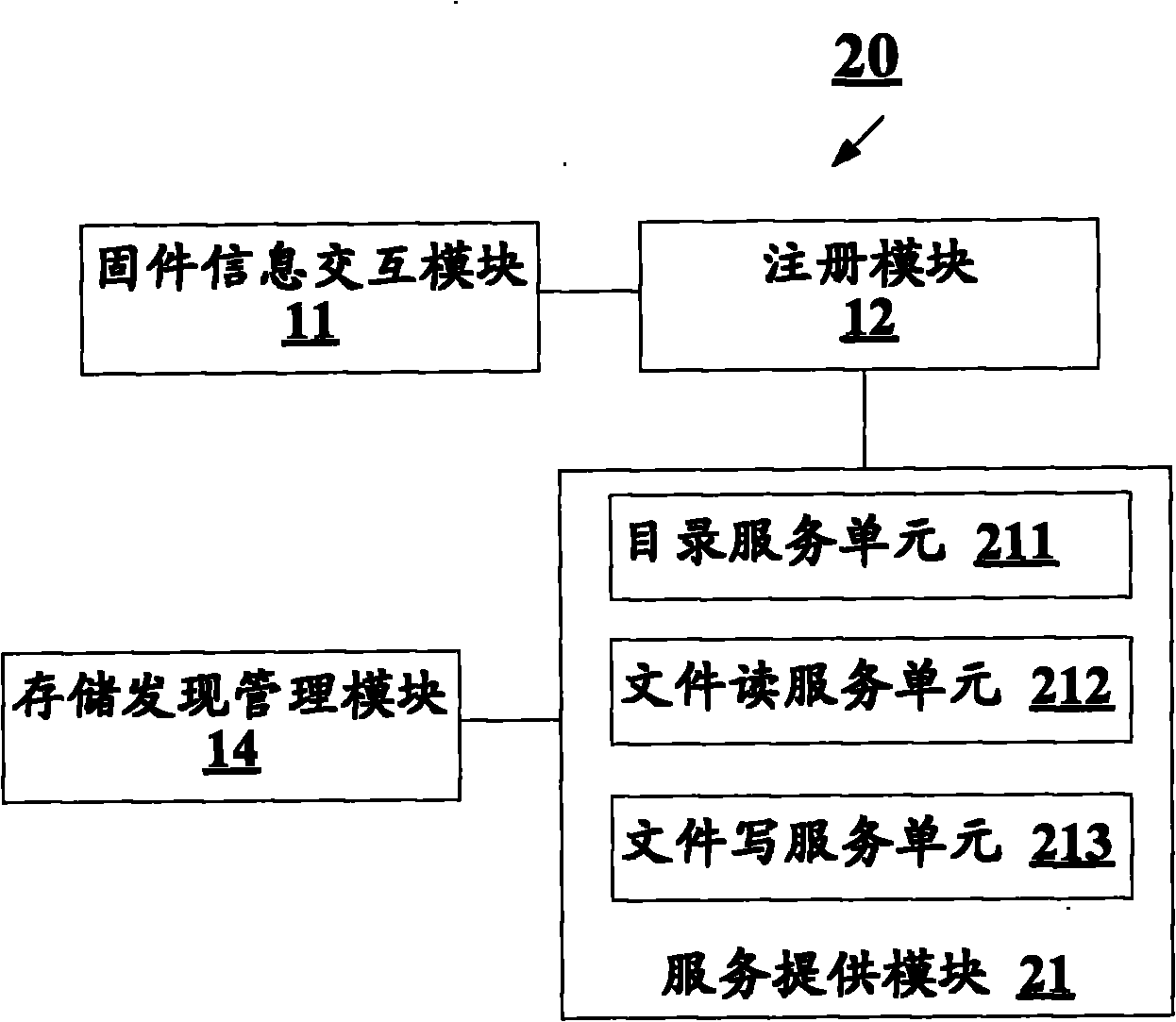

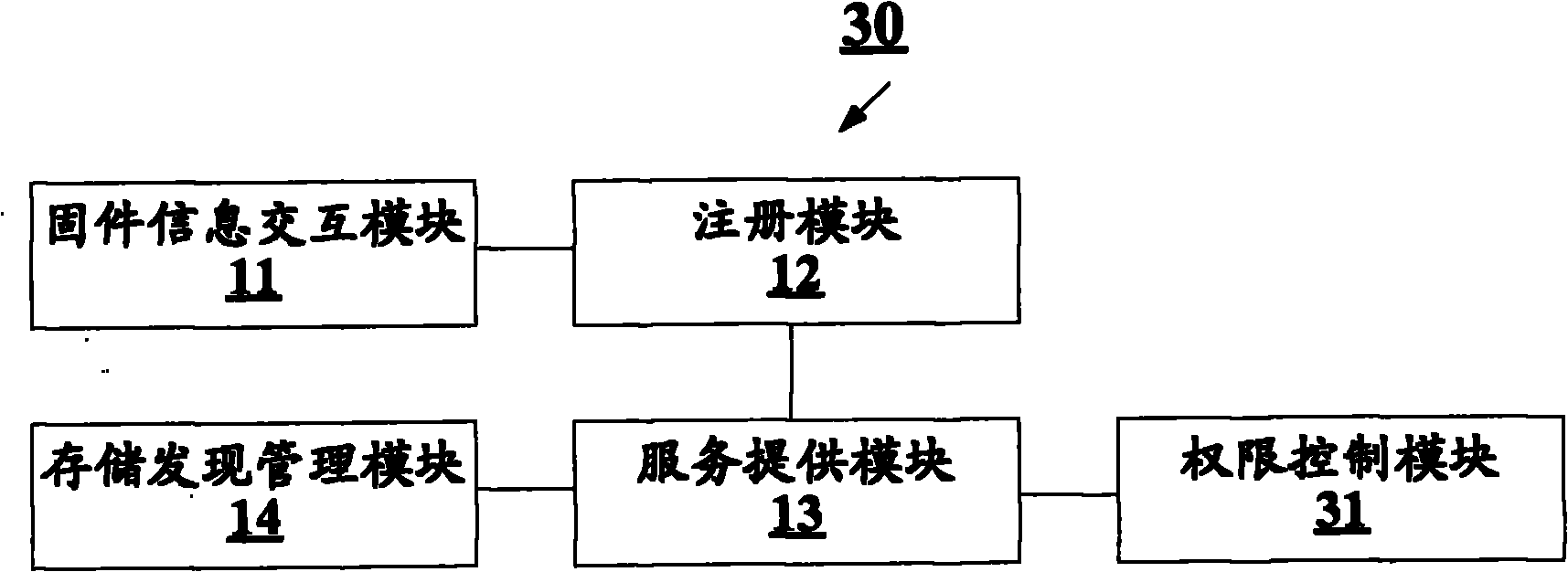

Home gateway based storage service method and storage service device

The invention discloses a home gateway based storage service method and storage service device. The device comprises a firmware information exchange module, a registration module, a service providing module and a storage discovery and management module, wherein the firmware information exchange module is connected with the registration module and used for transmitting registration information; the registration module is used for registering a storage service access address provided by a home gateway to a storage service platform in a public network by utilizing the registration information; the service providing module is connected with the storage discovery management module and used for processing a service request operation of a user, transferring the service request operation to the storage discovery management module, receiving a service request operation result returned by the storage discovery management module and returning the service request operation result to the user; and the storage discovery management module is used for receiving the service storage request operation, converting the service storage request operation into a service request command in an interactive protocol form used by a service request operation object and transferring the service request command to storage equipment in which the service request operation object is.

Owner:CHINA TELECOM CORP LTD

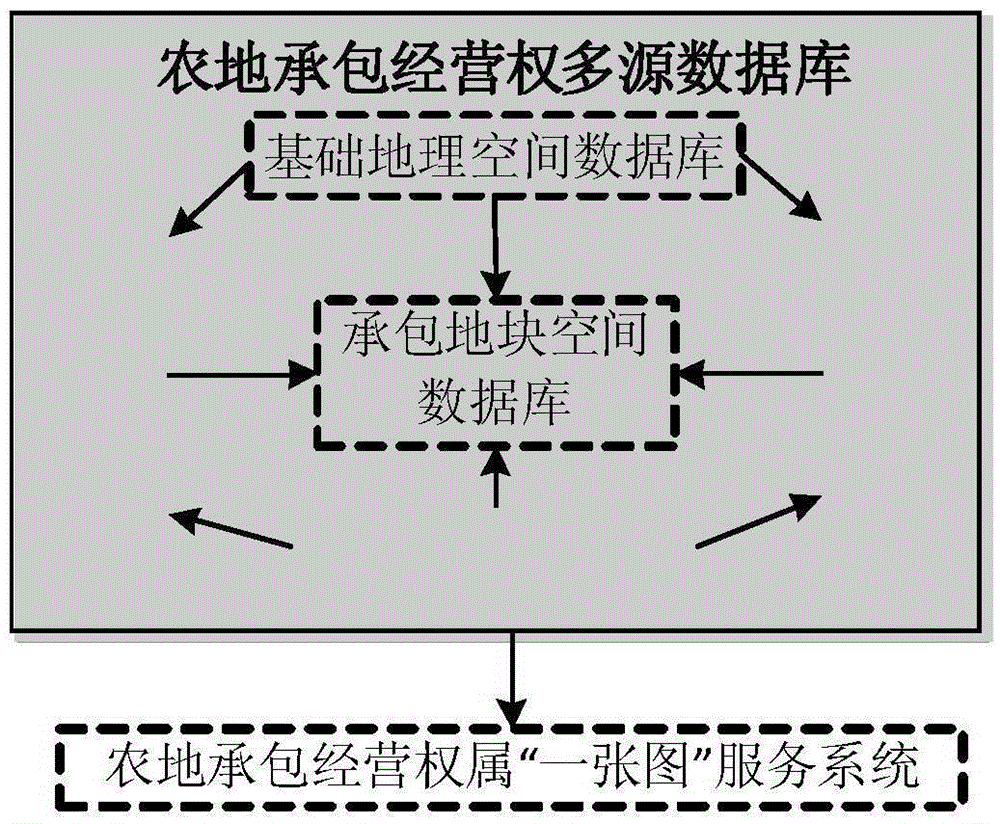

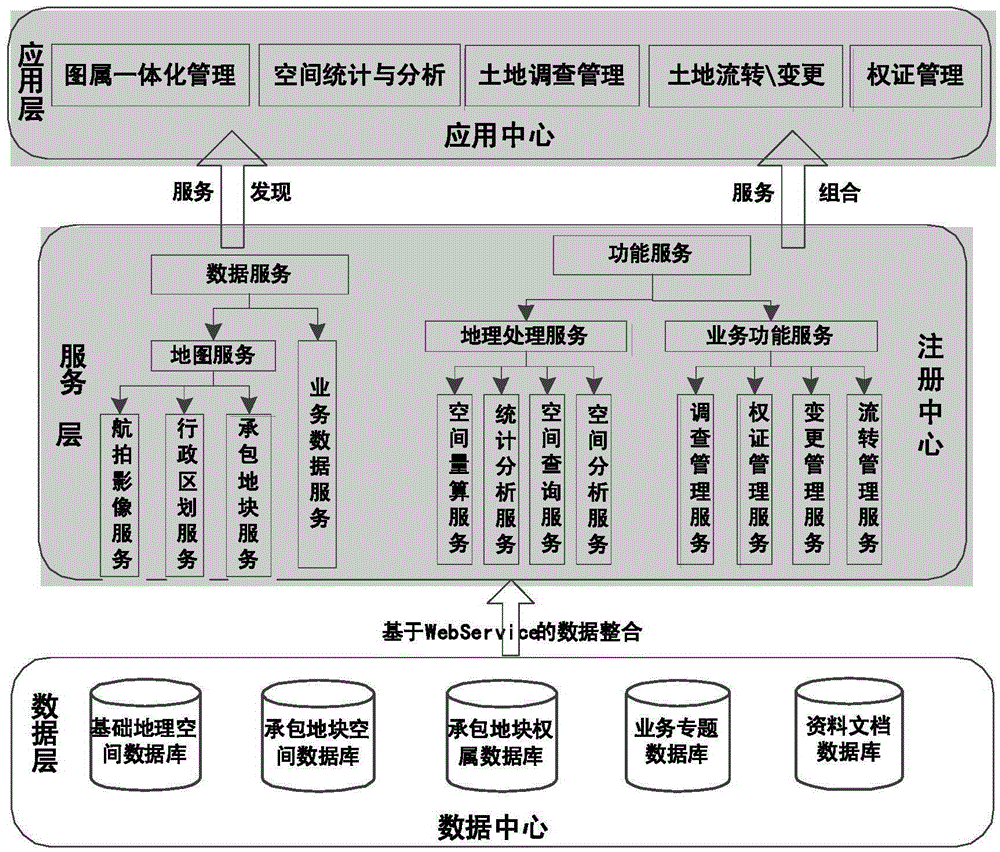

Farmland contract management ownership one-map service system and realization method thereof

ActiveCN105389753AAchieving processing powerAchieve integrated expressionData processing applicationsGeographical information databasesInformatizationAnalysis data

The invention discloses a farmland contract management ownership one-map service system and a realization method thereof, thereby realizing integrated processing and unified management on multisource heterogeneous data such as basic geographic data, contract block space data, contract block ownership data, service special data and file data. A Silverlight for ArcGIS API is used for realizing service integration on geoprocessing, map operation, service data management and service function operation, each type of operation is converted into a loose coupling request, needed service is queried and executed by a registration center, binding of the request operation and the service and calling of the data are realized, the contract block space positioning function is used for realizing one-map representation and analysis on the contract block ownership data, space statistics and analysis data, the service data and the like, and a new farmland contract management ownership management mode is realized. The informatization level for the rural land contract management integrated service can be enhanced, and technical supports are provided for rural land resource intelligent management and scientific decision making.

Owner:江苏金沙地理信息股份有限公司

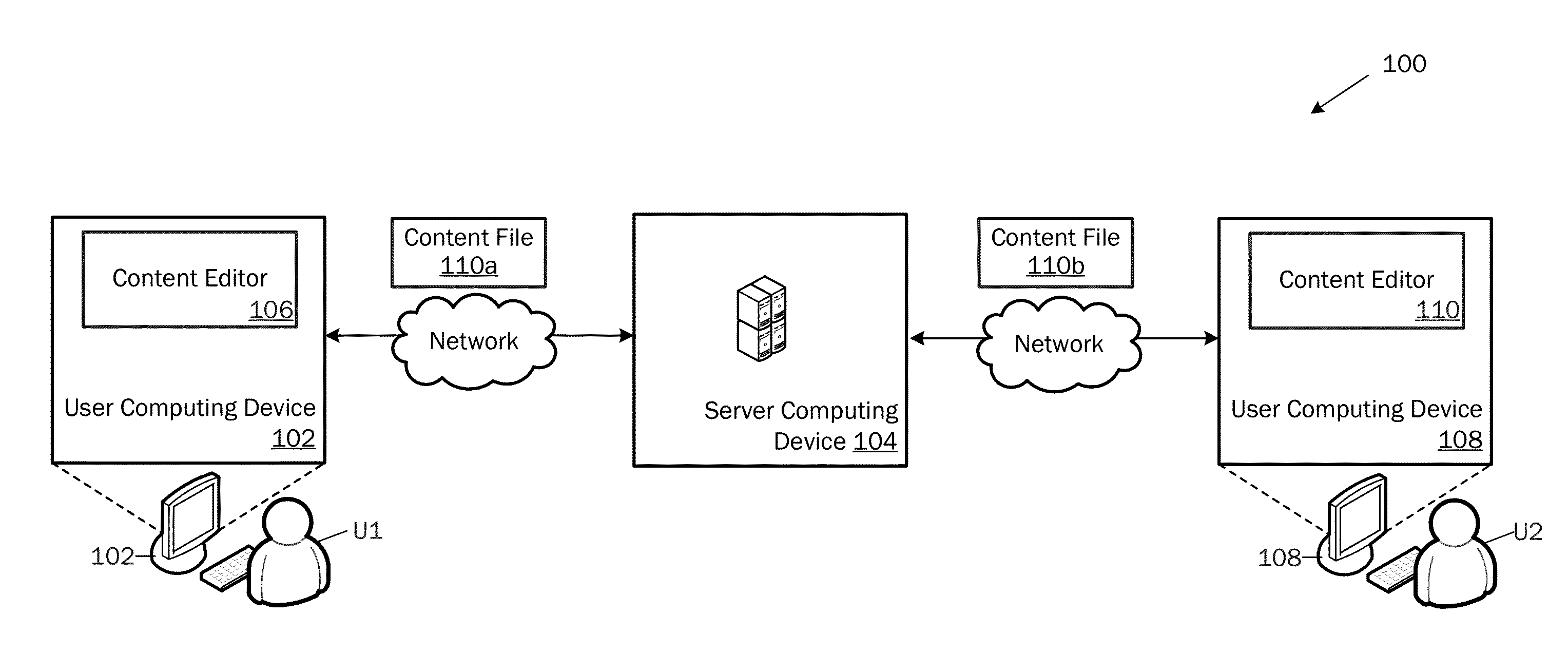

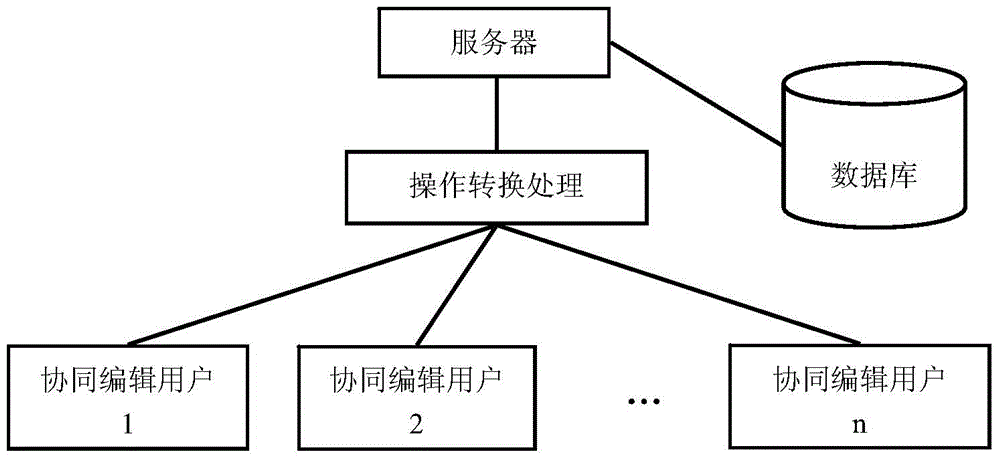

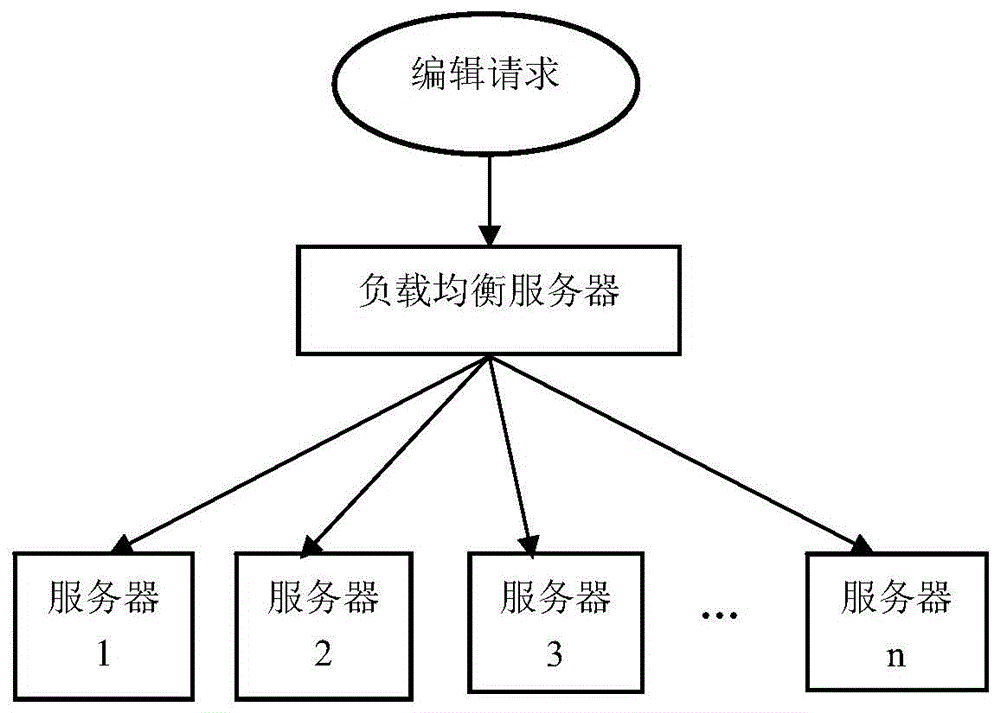

Blended operational transformation for multi-user collaborative applications

ActiveUS20160173594A1Well formedDigital data information retrievalNatural language data processingOperational transformationApplication software

Multi-user collaborative software applications may synchronize data between multiple users or multiple devices. There are multiple existing ways to synchronize data. Some of these synchronization methods, such as file locking, are easy to implement but have performance or functionality drawbacks. Operational transformation (OT) is a high performance synchronization method, but difficult and time-consuming to implement in many cases, and cannot be partially implemented throughout a system. Methods and systems provide for blending operational transformation with other synchronization methods in the same collaborative software application, allowing operational transformation to be used in situations where it cannot be implemented throughout a system.

Owner:MICROSOFT TECH LICENSING LLC

Cooperative plotting method based on internet

InactiveCN1658567AEnsure consistencyEnsure safetySpecial service provision for substationGraphicsOperational transformation

This invention relates to computer supporting coordinating work (CSCW) technology field, especially belongs to the new coordinating application environment of coordinating geographic information system, the communication, the architecture and the coordinating medicine. The device of this invention is composed of plot input and output, the processor, the coordinating processor and the internet. This invention solves the problem of coordinating plot of multi-users in the internet environment and it is completed by plot and edit; through the data communication of user terminal and server terminal adopt compressing and encrypting methods, and form a picture target sheet before the plot conclusion and send it out, and realize the response speed and data safety of the system. The advantages are maintaining the coherence of the user terminal video through conflict detection and operation switch, ensuring the response speed and data safety of the system, and also has high-relative response, highly efficient data transmission, good coordination and safety.

Owner:EAST CHINA NORMAL UNIV

Consistency maintaining method in document collaborative editing

ActiveCN104462037ABasic data consistency maintenance functionApplicable Consistency MaintenanceSpecial data processing applicationsOperational transformationDocumentation

The invention discloses a consistency maintaining method in document collaborative editing. The consistency maintaining method comprises the following steps that firstly, a support for consistency maintaining is provided through the operation conversion algorithm under the multi-user collaborative editing environment; secondly, the consistency maintaining method can meet the requirement under the heterogeneous environment based on the first step and the operation conversion algorithm under the mobile environment; thirdly, a support for concurrent operation is provided by the consistency maintaining method based on the second step and the characteristics of Node.js. The consistency maintaining method has the advantages that the resource of a server is effectively utilized and the utilization rate of the resource is increased.

Owner:SOUTH CHINA UNIV OF TECH

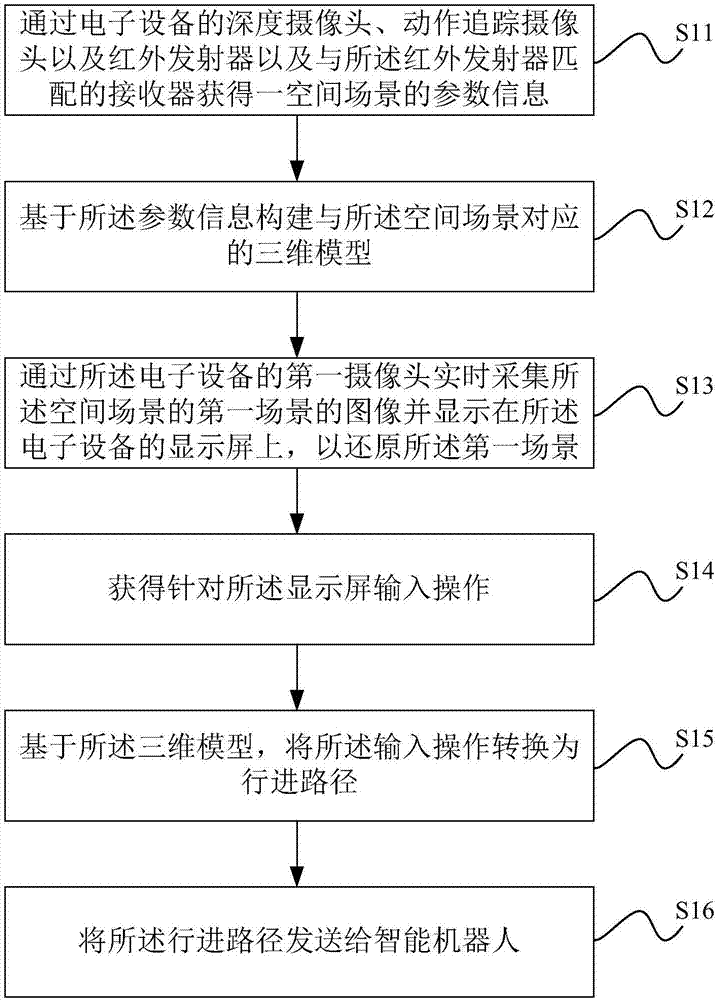

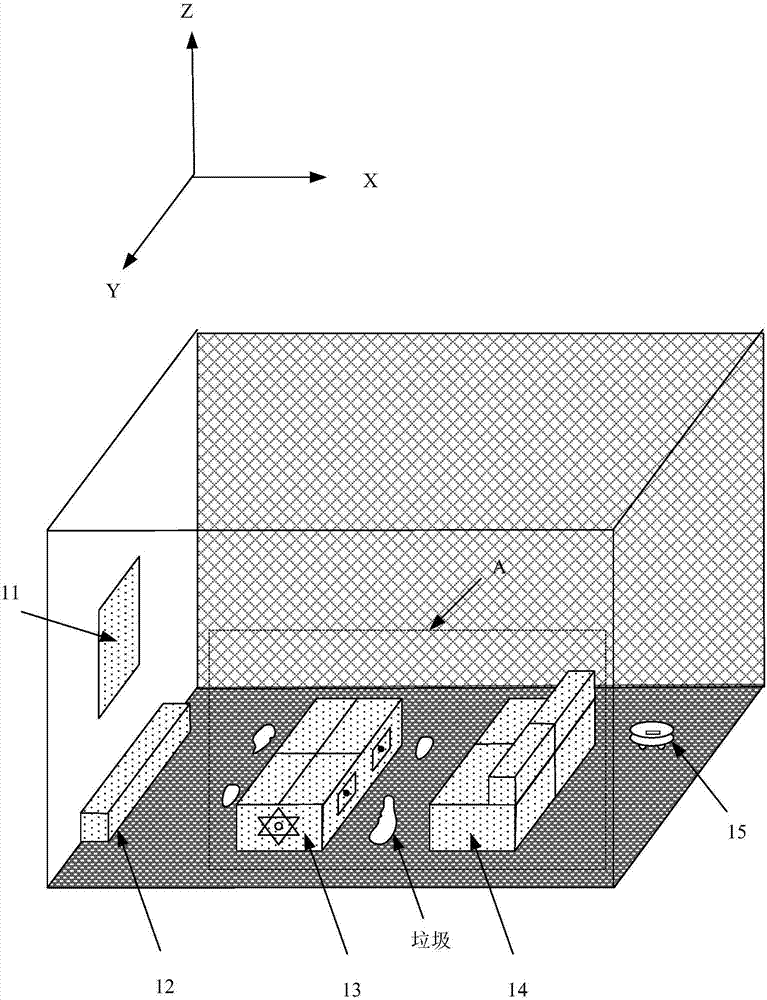

Method for guiding intelligent robot and electronic equipment

ActiveCN106933227AAccurately control the movement routePosition/course control in two dimensionsVehiclesOperational transformationSimulation

The invention discloses a method for guiding an intelligent robot and electronic equipment. The method comprises the steps that parameter information of a space scene is obtained through the depth camera, the motion tracking camera and the receiver of the electronic equipment; a three-dimensional model corresponding to the space scene is constructed based on the parameter information; the image of the first scene of the space scene is acquired in real time through the first camera of the electronic equipment and displayed on the display screen of the electronic equipment; input operation for the display screen is obtained; the input operation is converted into an advancing path based on the three-dimensional model; and the advancing path is transmitted to the intelligent robot. According to the technical scheme, the input operation on the display screen of the electronic equipment can be obtained according to the image of the first scene of the space scene acquired in real time, and the input operation can be converted into the movement advancing path of the intelligent robot based on the three-dimensional model so that the movement path of the intelligent robot can be accurately controlled.

Owner:LENOVO (BEIJING) CO LTD

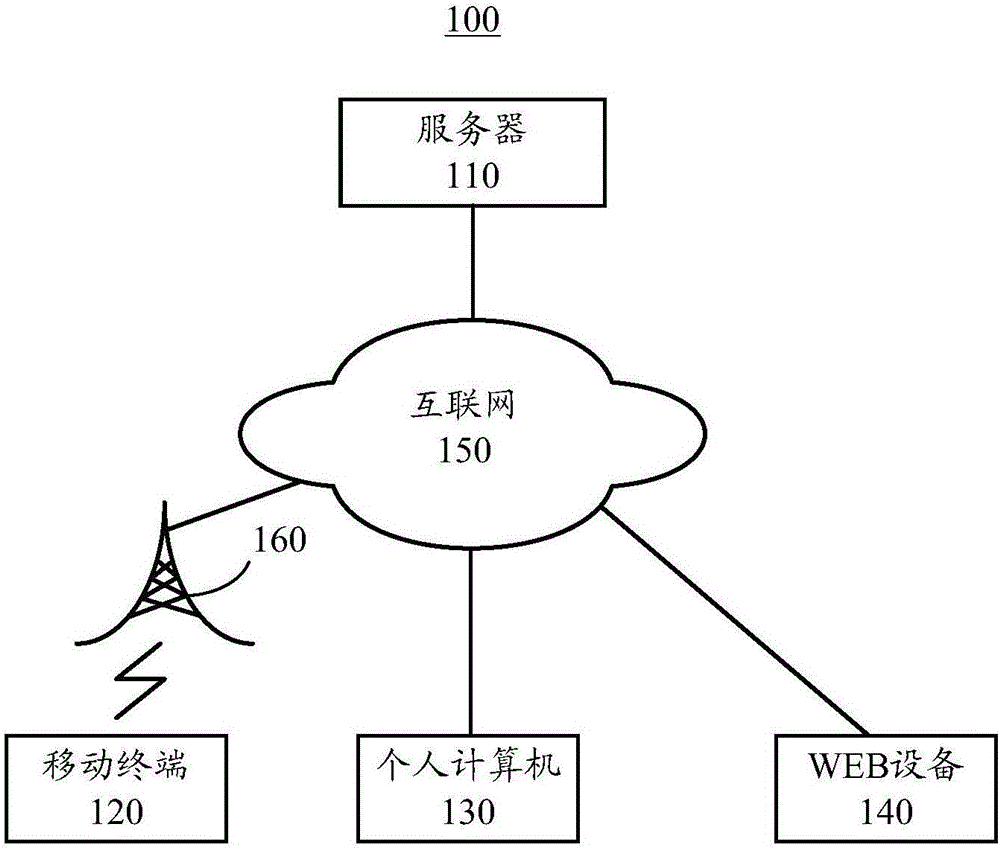

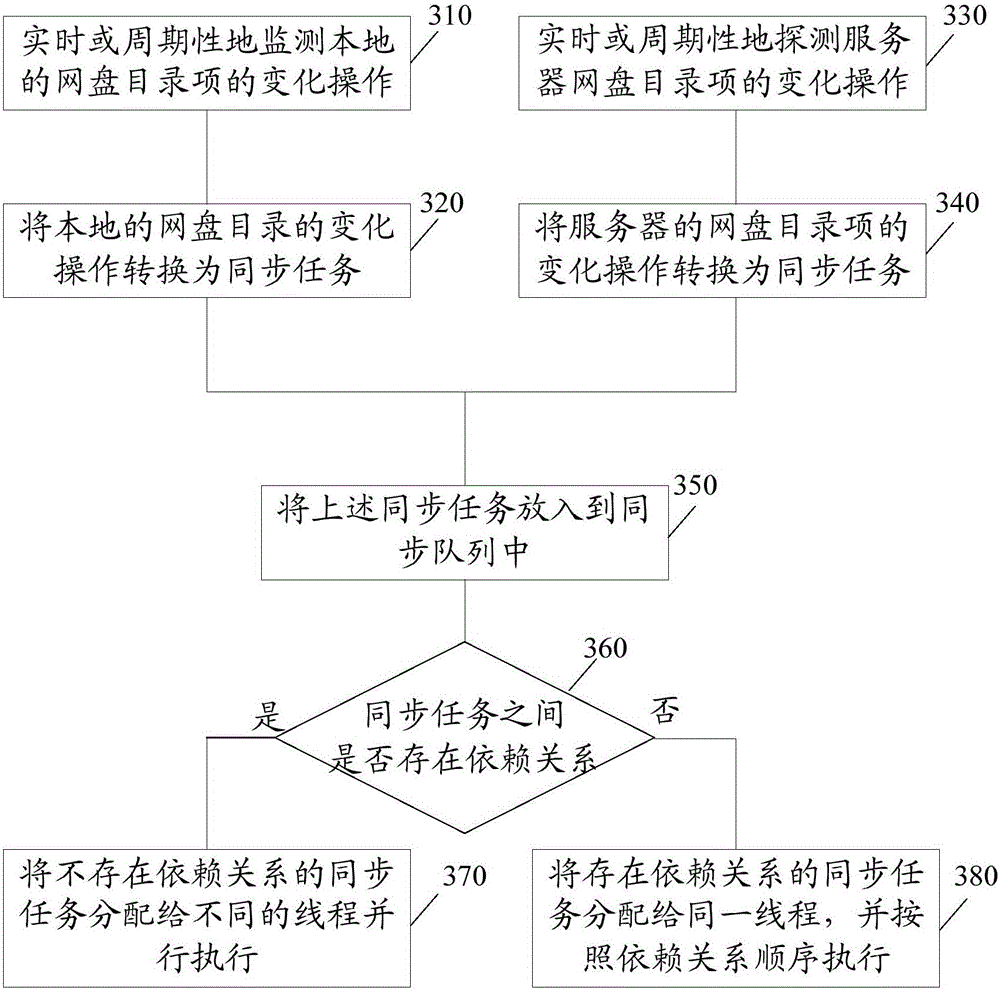

Synchronized method of network disk system, terminal equipment and network disk system

InactiveCN104994177AImprove synchronization efficiencyAvoid sync failuresTransmissionOperational transformationTerminal equipment

The invention discloses a synchronized method of a network disk system, terminal equipment and the network disk system. The synchronized method comprises the steps as follows: detecting a network disk directory entry of a client of the network disk system and / or a plurality of change operations of the network disk directory entry of a server of the network disk system; converting the plurality of change operations into a plurality of synchronization tasks, wherein the plurality of synchronization tasks are used for realizing synchronization between the disk directory entry of the client and the disk directory entry of the server; determining dependency relationship among the plurality of synchronization tasks; distributing the synchronization tasks which do not have the dependency relationship in the plurality of synchronization tasks to different threads to carry out parallel execution. According to the technical solution of the invention, the synchronized method could improve synchronizing efficiency of the network disk system and avoid synchronization failures brought by logical errors.

Owner:EISOO SOFTWARE

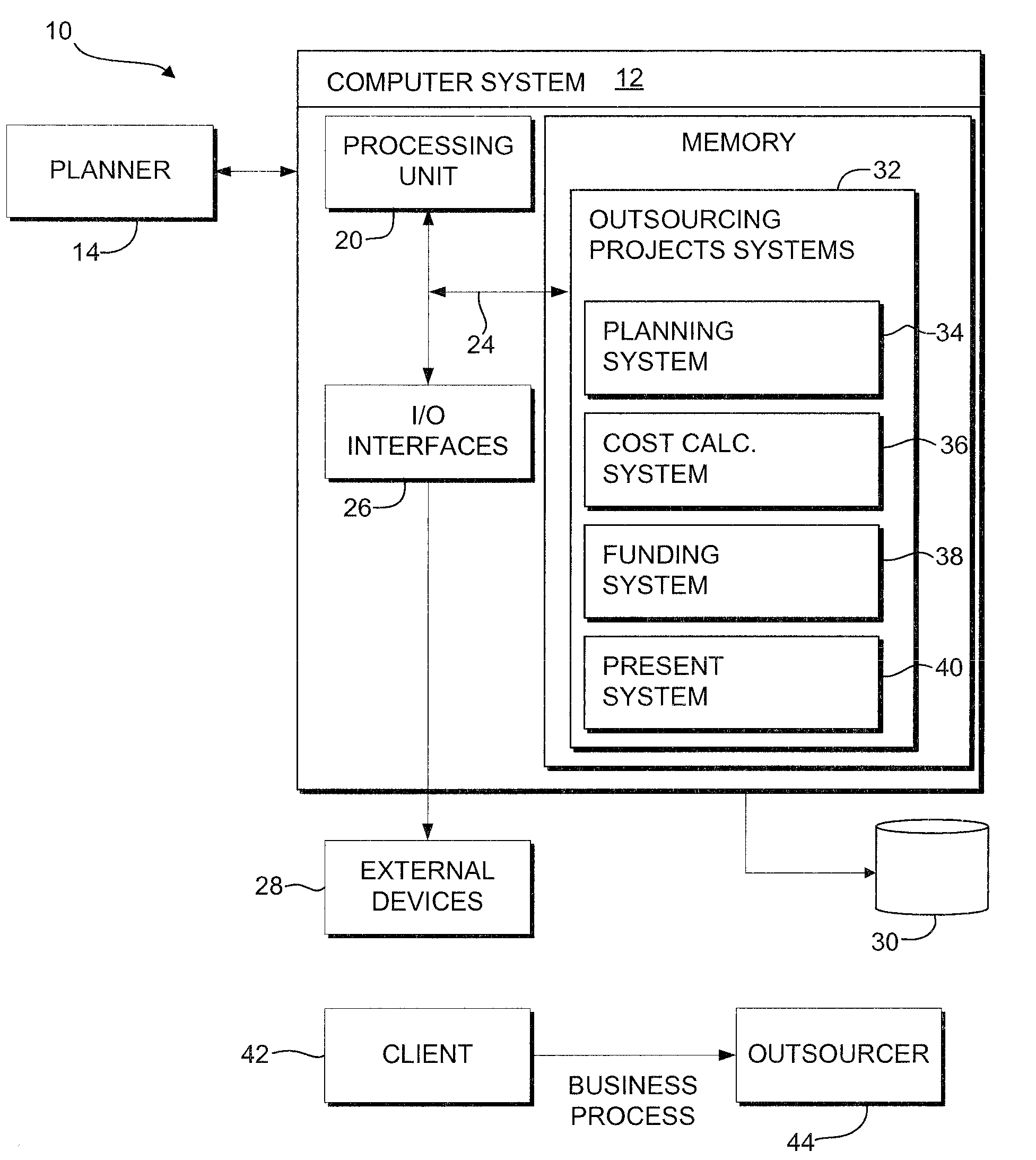

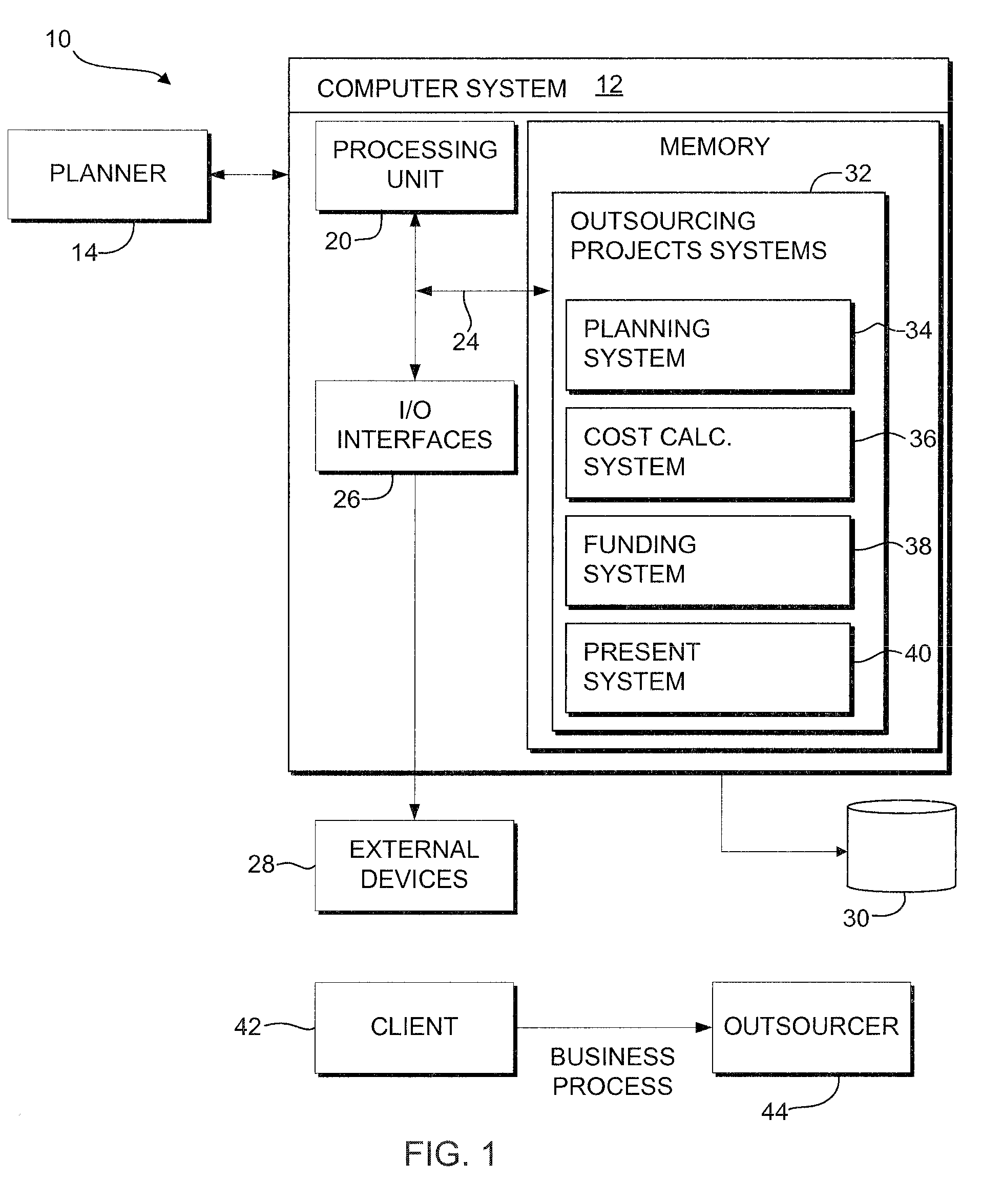

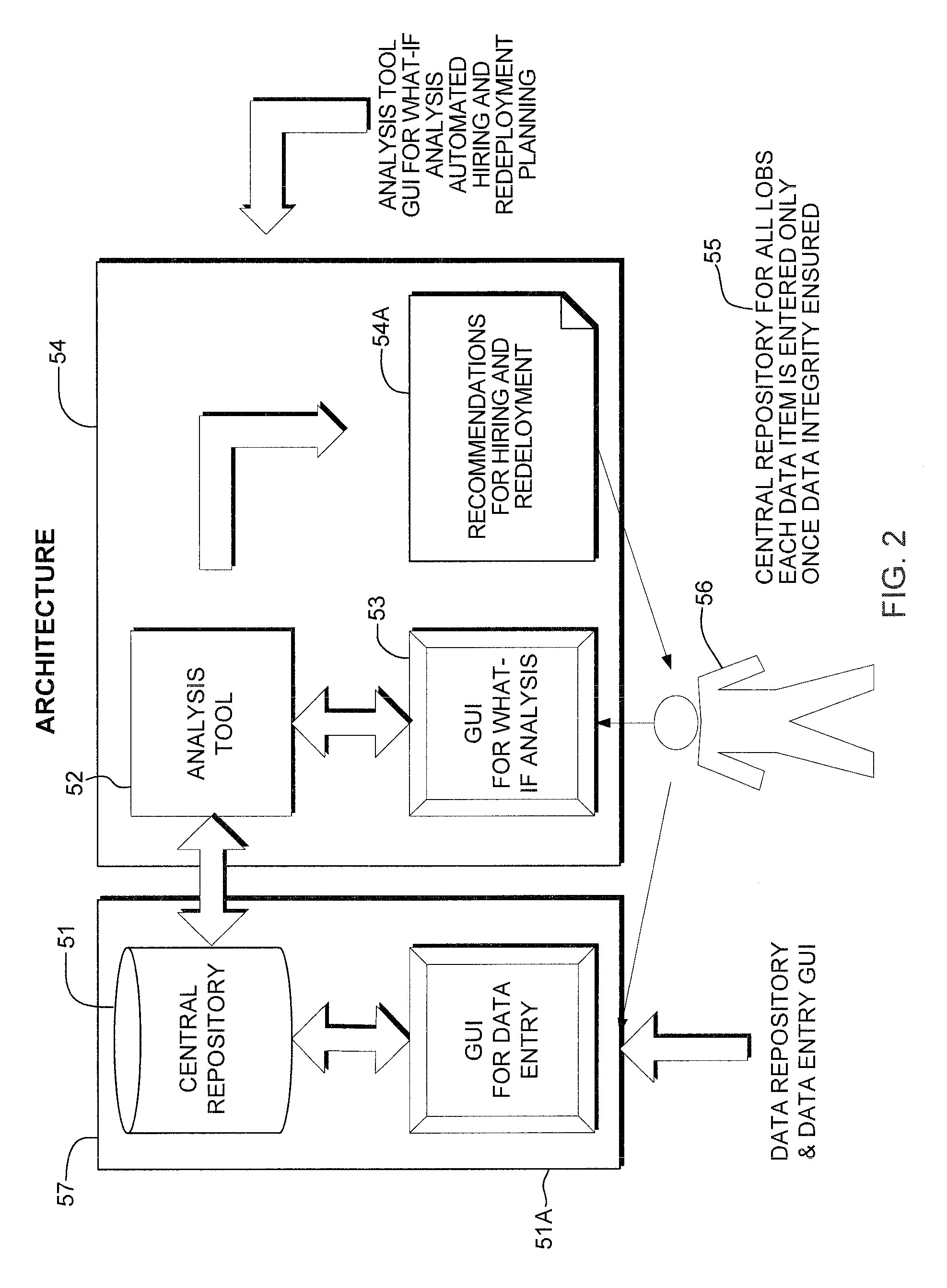

Method and system for strategic headcount planning with operational transition management of workforce

InactiveUS20090271240A1Effective headcount planningImprove performanceMultiprogramming arrangementsResourcesOperational transformationProgram planning

A method and system are disclosed for planning a workforce headcount for a given business process. The method comprises the steps of providing as inputs, i) productivity ramp-ups to model the level of experience and to measure the performance of both new hires and current employees, and ii) industry / market attrition rates for employees; and performing an evaluation, using said inputs, of at least one given management objective. On the basis of this evaluation, a future hiring and transition plan is provided for the given business process for a defined period of time. In the preferred embodiment of the invention, uncertainty is associated with one or more of the inputs, and the future hiring and transition plan is provided by using stochastic programming to model the uncertainty associated with at least one of said one or more of the inputs.

Owner:IBM CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com