Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

43 results about "Interconnection matrix" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and Apparatus for Self-Healing Symmetric Multi-Processor System Interconnects

InactiveUS20080168255A1Program control using stored programsGeneral purpose stored program computerSelf-healingComputer architecture

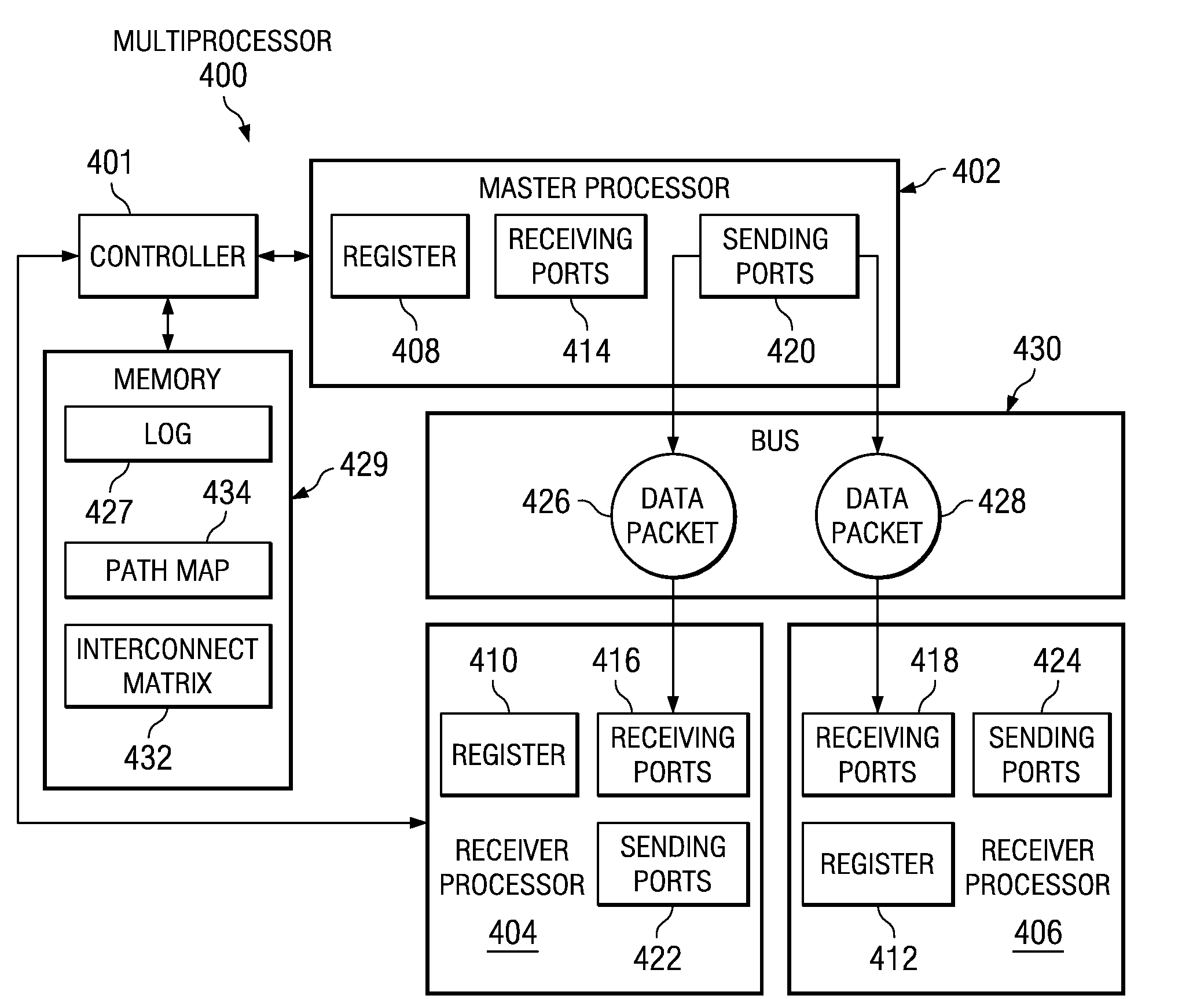

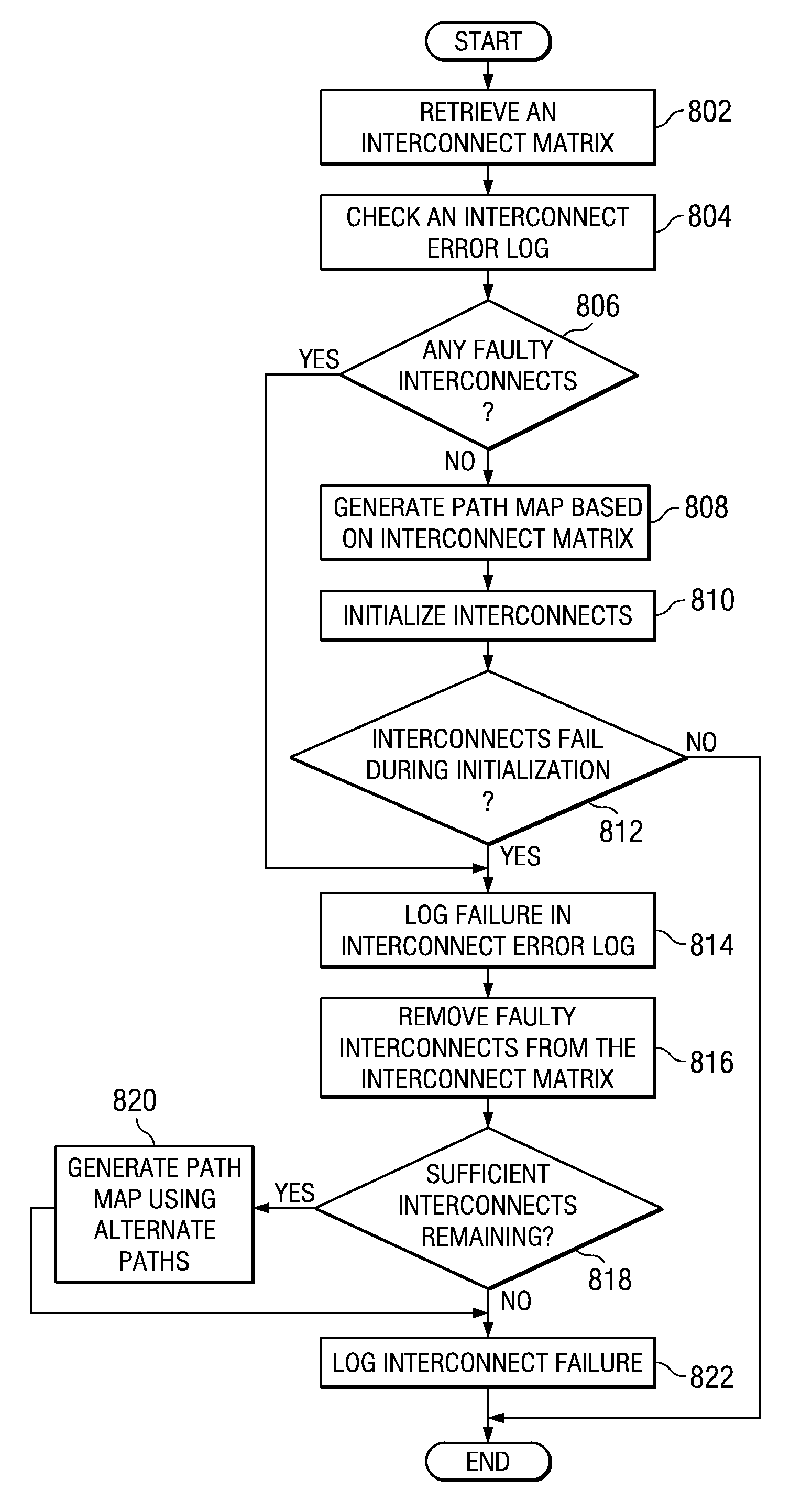

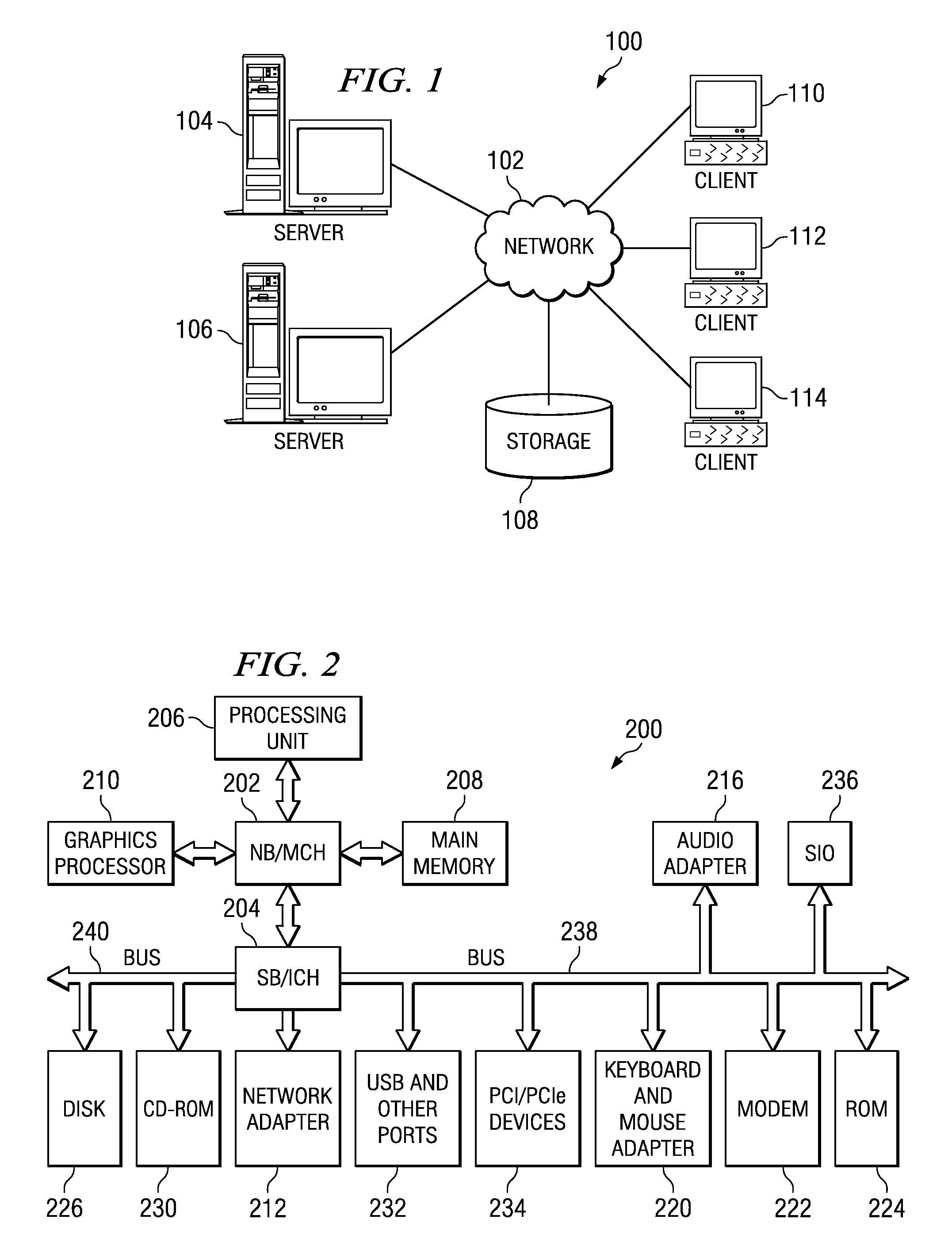

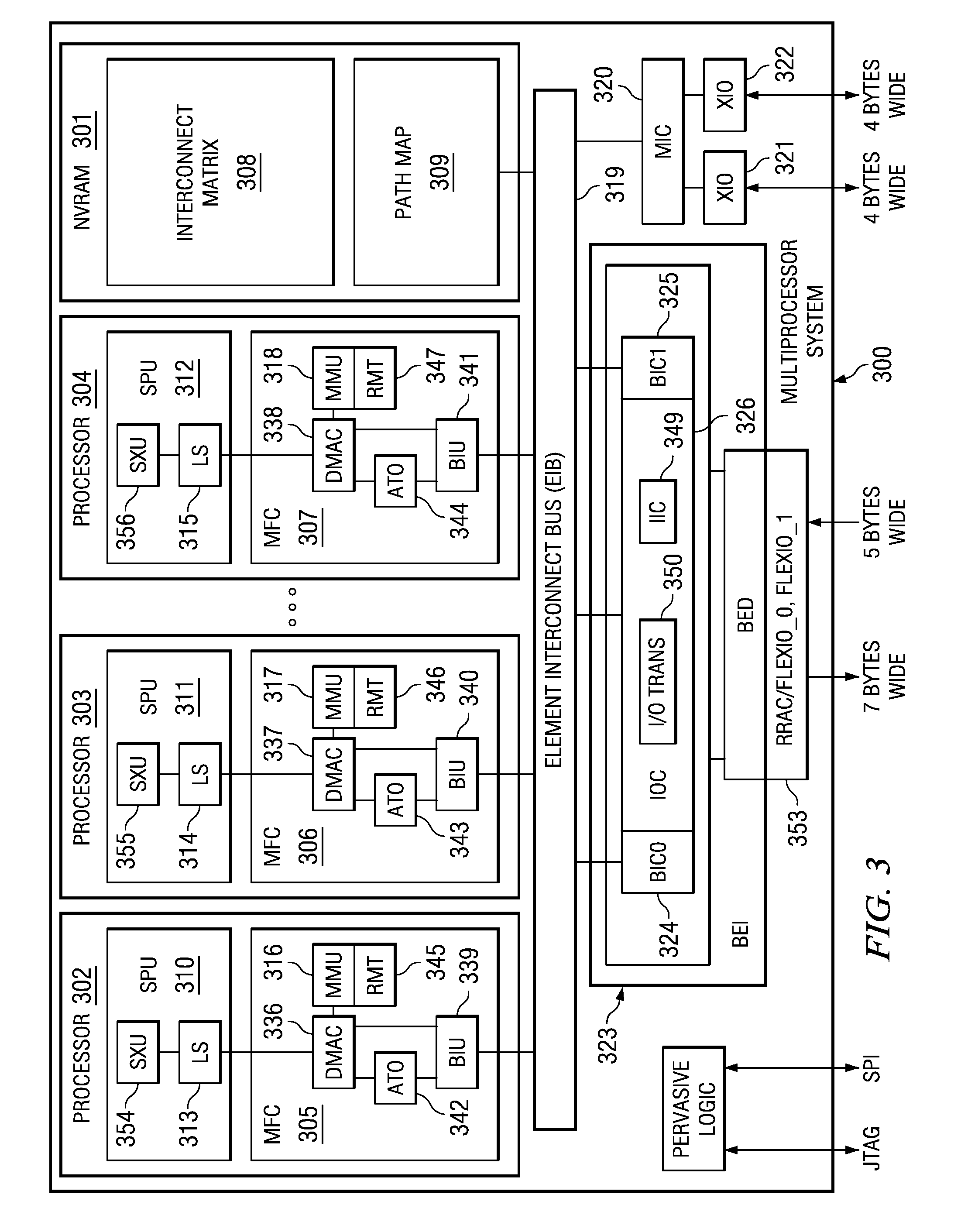

A computer implemented method, apparatus, and computer program product for managing symmetric multiprocessor interconnects. The process identifies functional communication connections between each processor in a plurality of processors on a multiprocessor to form identified functional communication connections. The process maps every functional communication connection between any two processors in the plurality of processors, based on the identified functional communication connections, to form an interconnect matrix. The process creates a path map using the interconnect matrix. The path map comprises a sequence of communication connections between the plurality of processors. The process initializes the plurality of processors using the path map.

Owner:IBM CORP

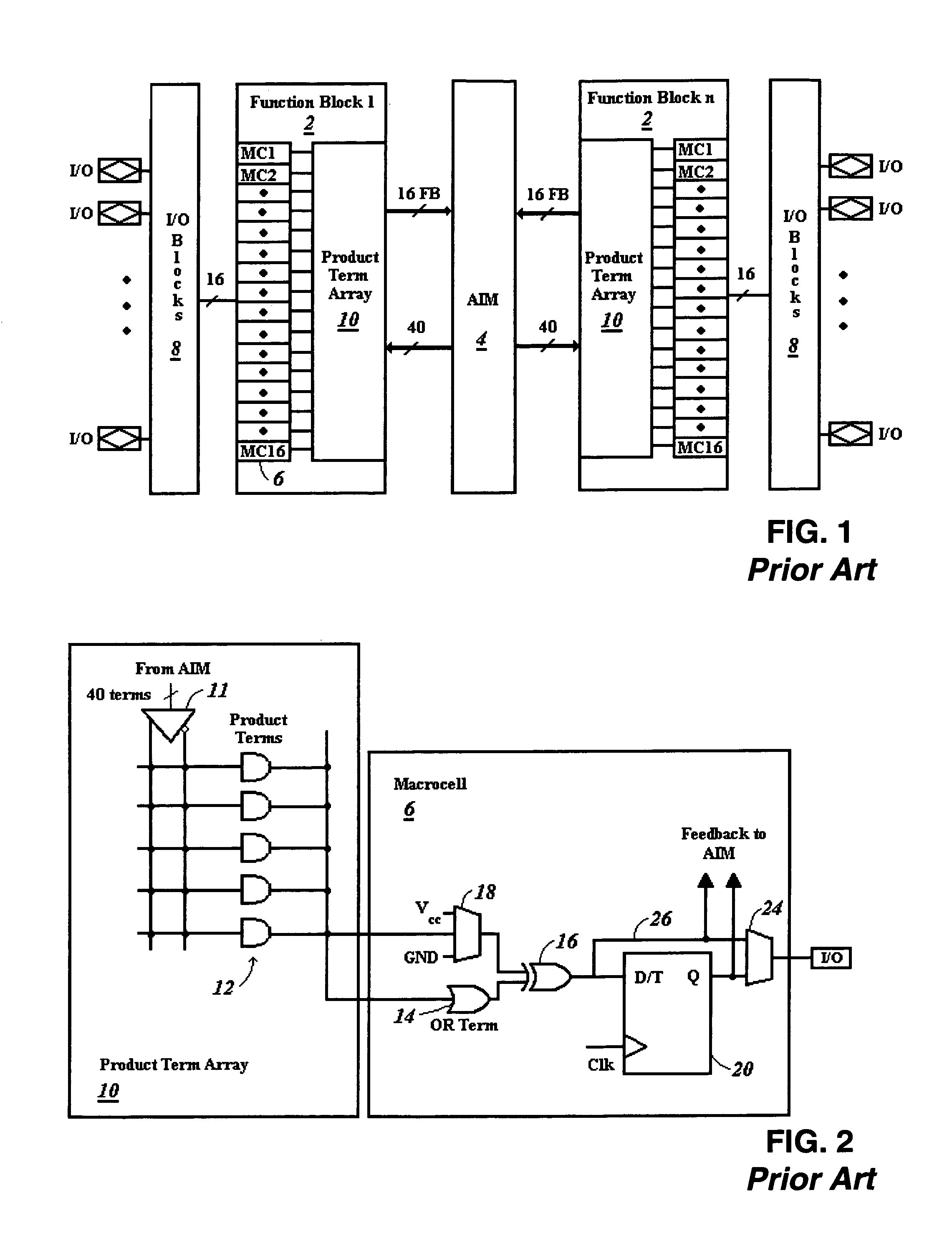

CPLD with fast logic sharing between function blocks

InactiveUS7129747B1OptimizationOperational shortcomings of conventional CPLDsSolid-state devicesSpecial data processing applicationsComputer architectureProcessor register

Fast logic sharing is created using a feedback path from the output logic macrocell of one functional block to the product term inputs of another function block without going through an advanced interconnect matrix (AIM). The fast feedback path may be provided from the macrocell after the product terms XOR gate without registering, and / or after the register in the macrocell. The fast logic sharing avoids the slow AIM for feedback logic, and allows additional resources to be borrowed from other function blocks with a limited delay penalty. In particular, delay penalties resulting from dividing wide operations requiring multiple product terms between the product terms of multiple functional blocks are significantly reduced.

Owner:XILINX INC

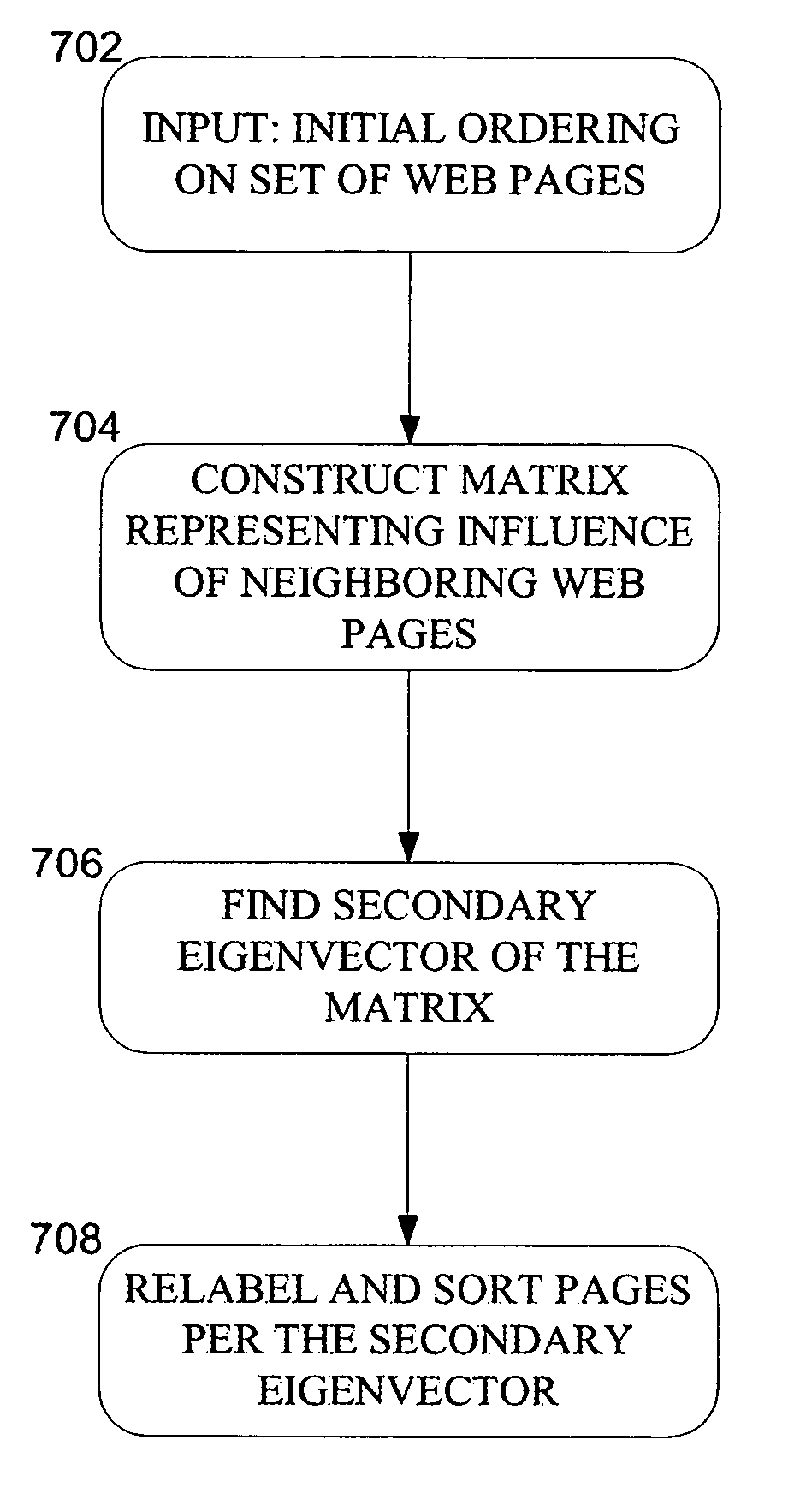

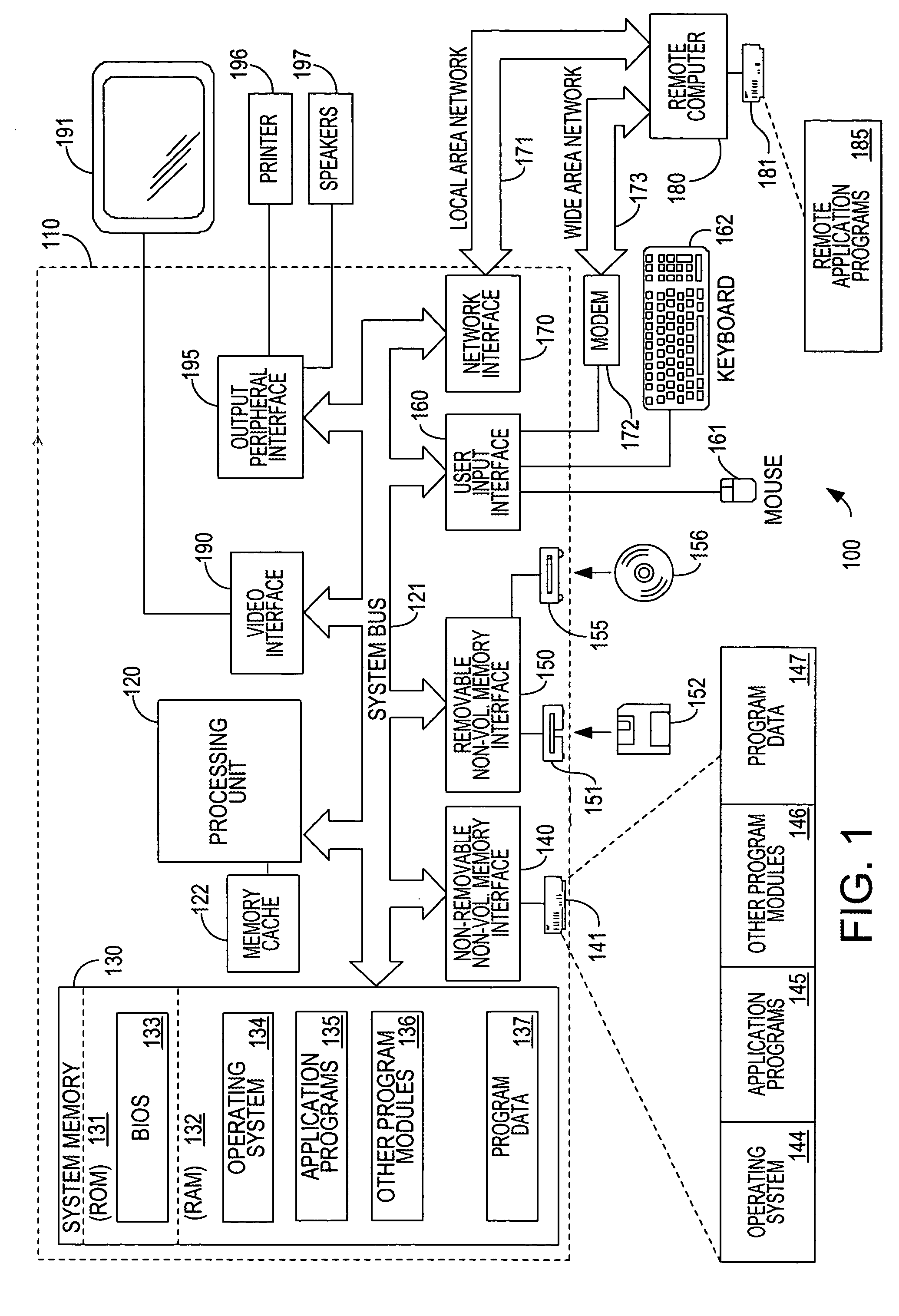

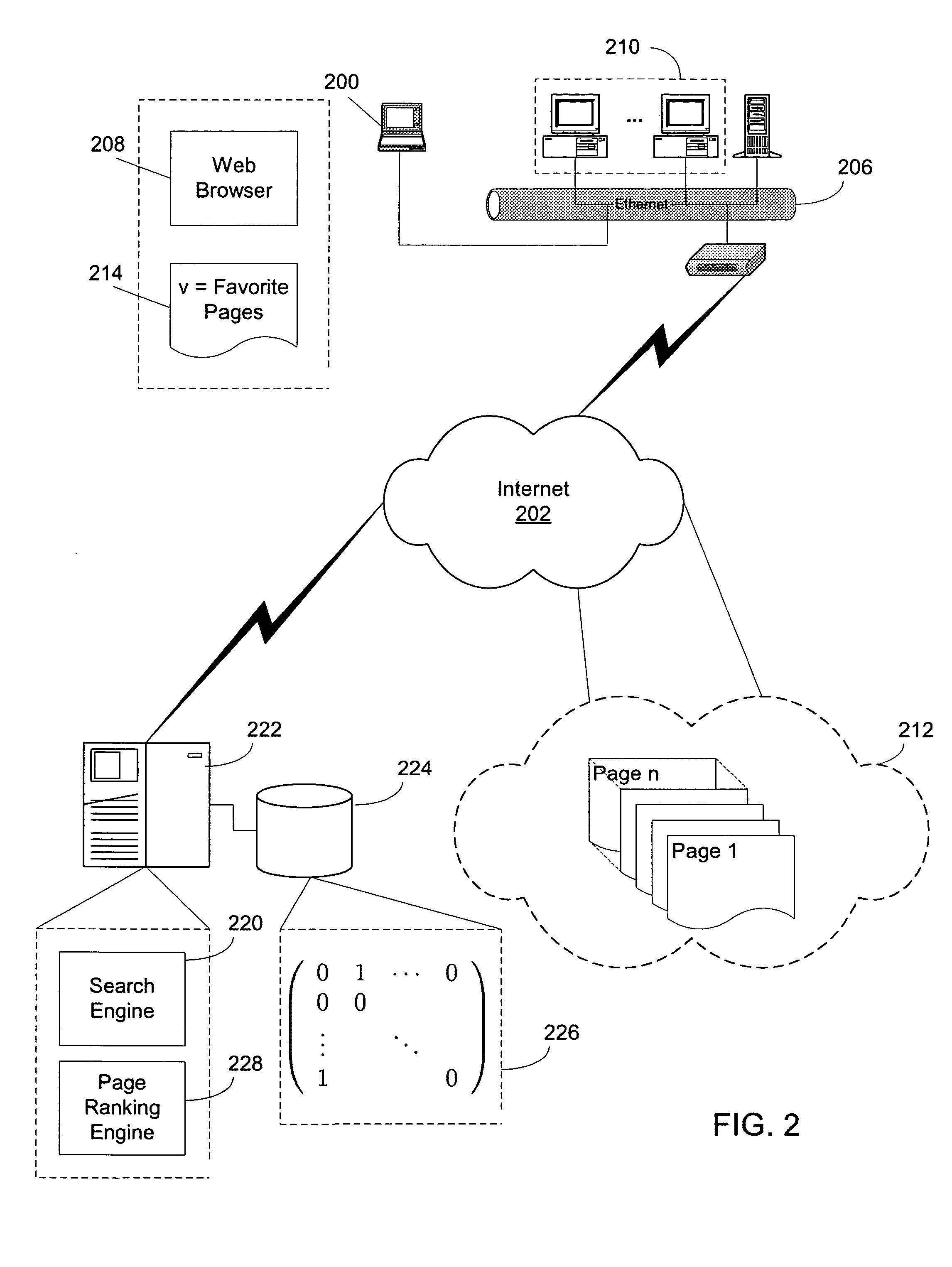

Efficiently ranking web pages via matrix index manipulation and improved caching

InactiveUS20060026191A1Computing page rankings more efficientlyEfficient executionData processing applicationsWeb data indexingInterconnectivityFeature vector

Methods and systems are described for computing page rankings more efficiently. Using an interconnectivity matrix describing the interconnection of web pages, a new matrix is computed. The new matrix is used to compute the average of values associated with each web page's neighboring web pages. The secondary eigenvector of this new matrix is computed, and indices for web pages are relabeled according to the eigenvector. The data structure storing the interconnectivity information is preferably also physically sorted according to the eigenvector. By reorganizing the matrix used in the web page ranking computations, caching is performed more efficiently, resulting in faster page ranking techniques. Methods for efficiently allocating the distribution of resources are also described.

Owner:MICROSOFT TECH LICENSING LLC

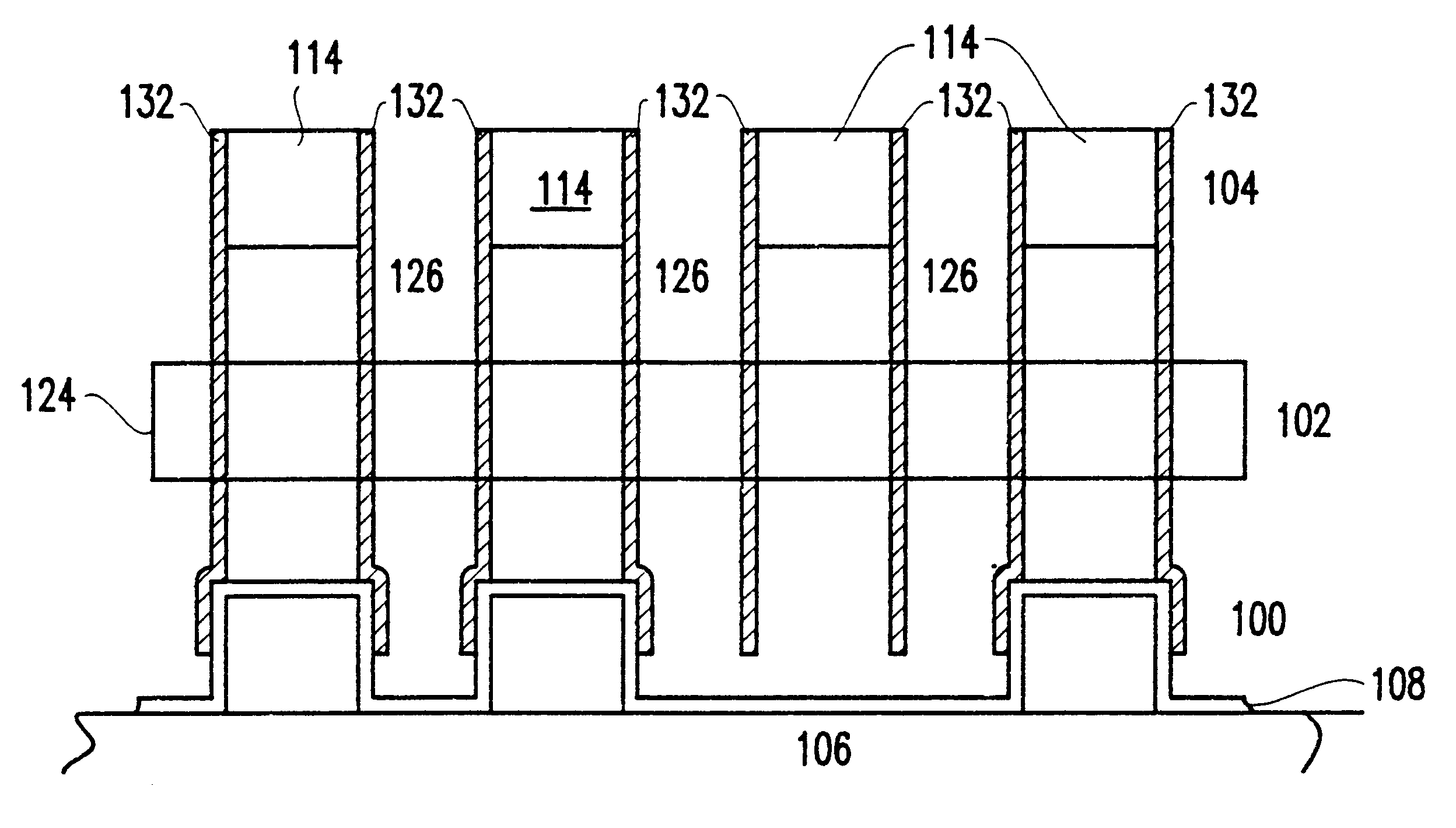

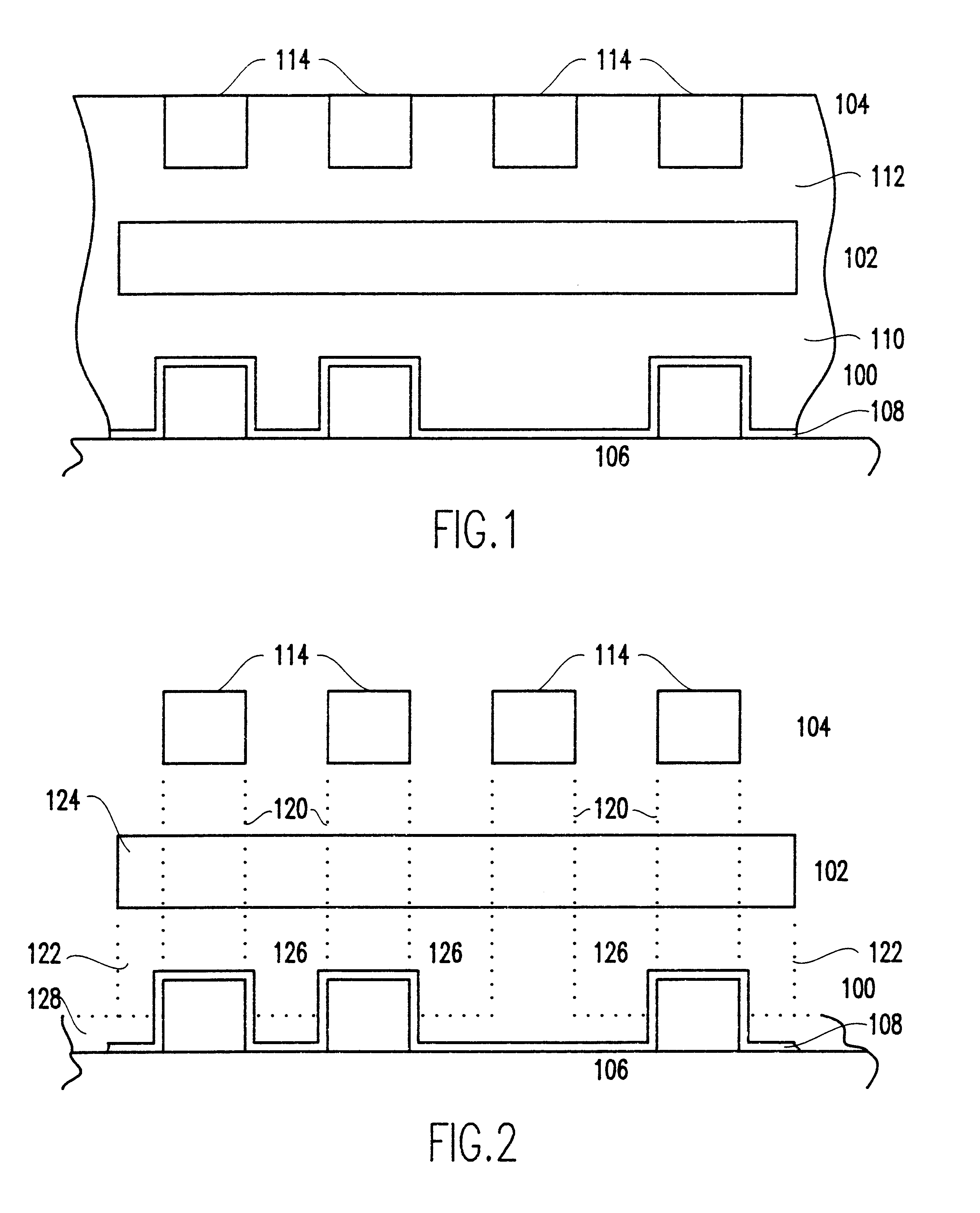

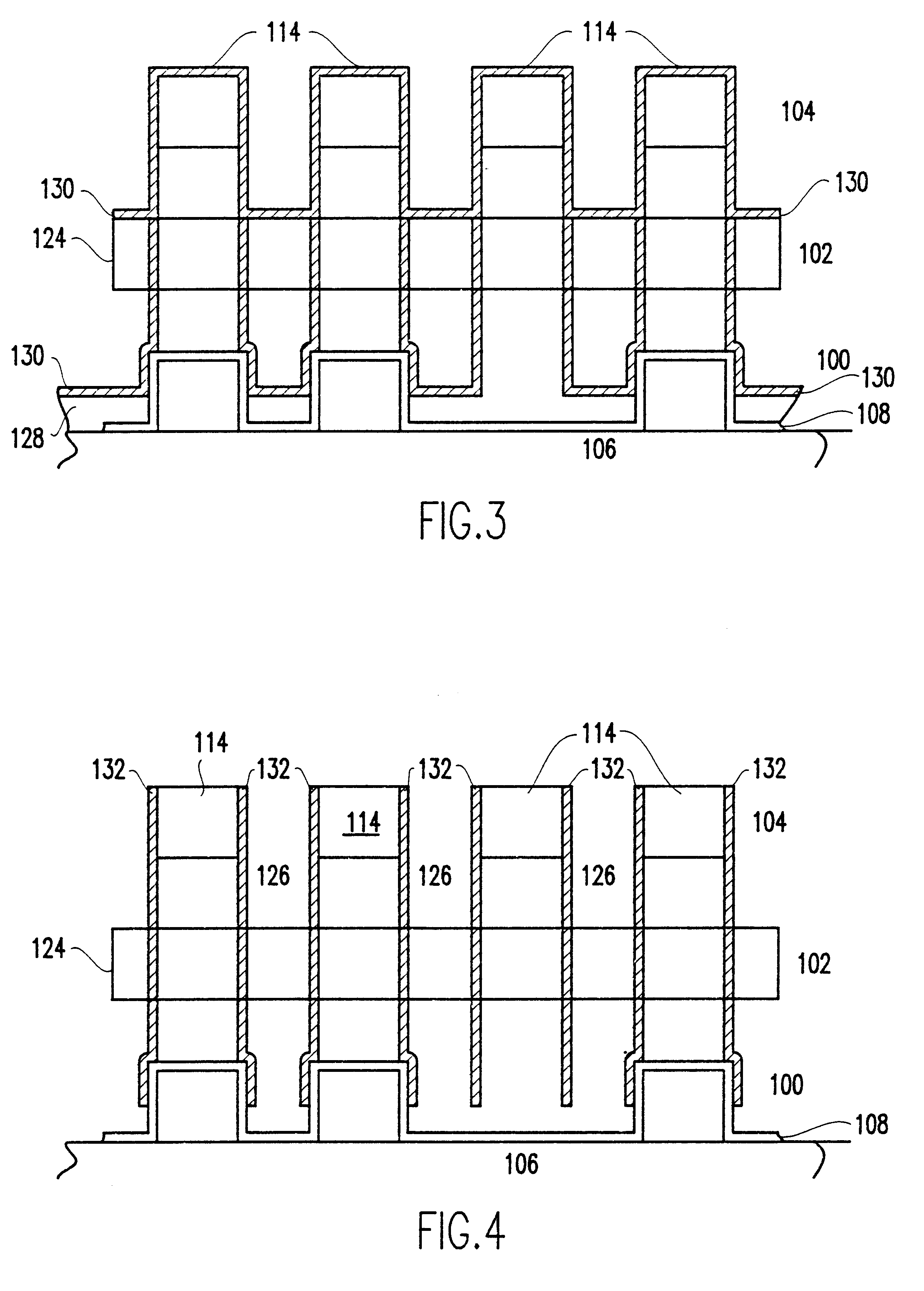

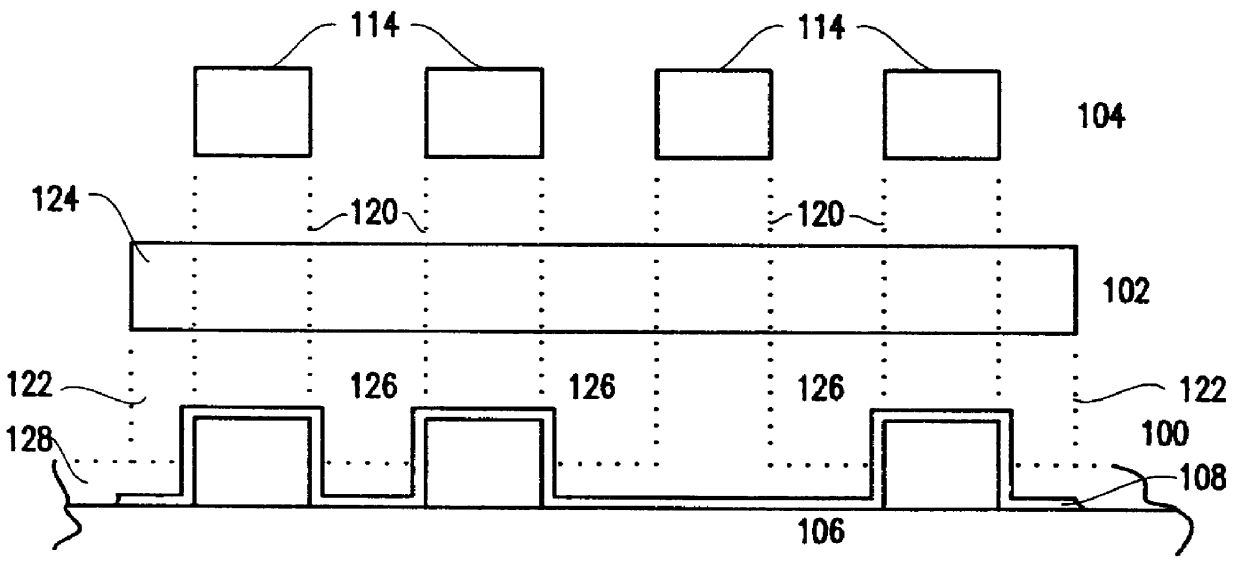

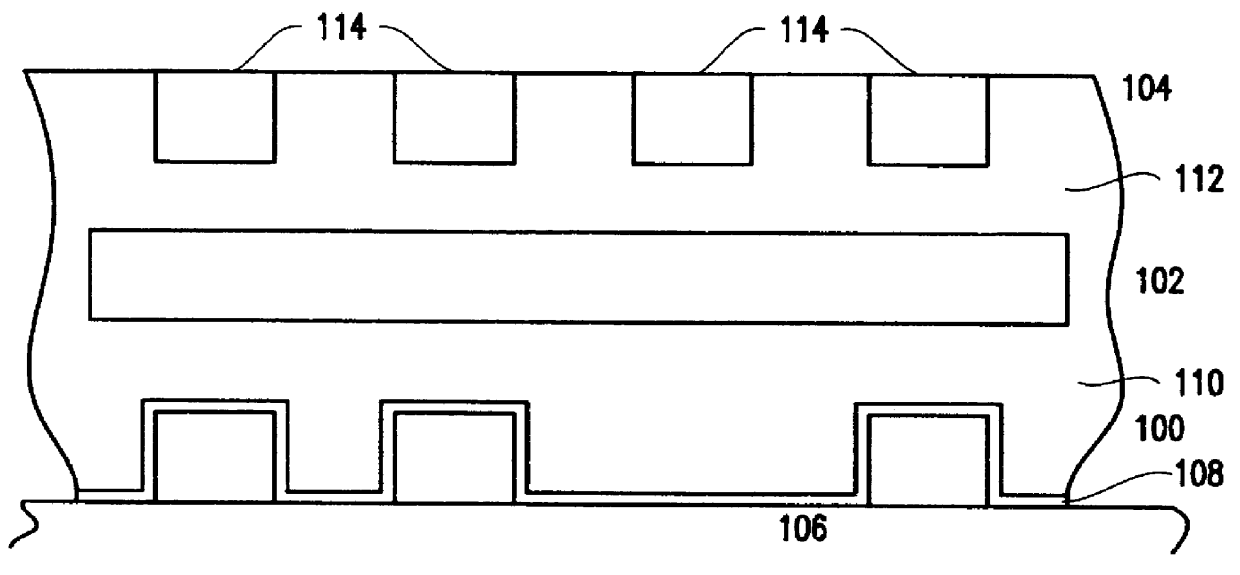

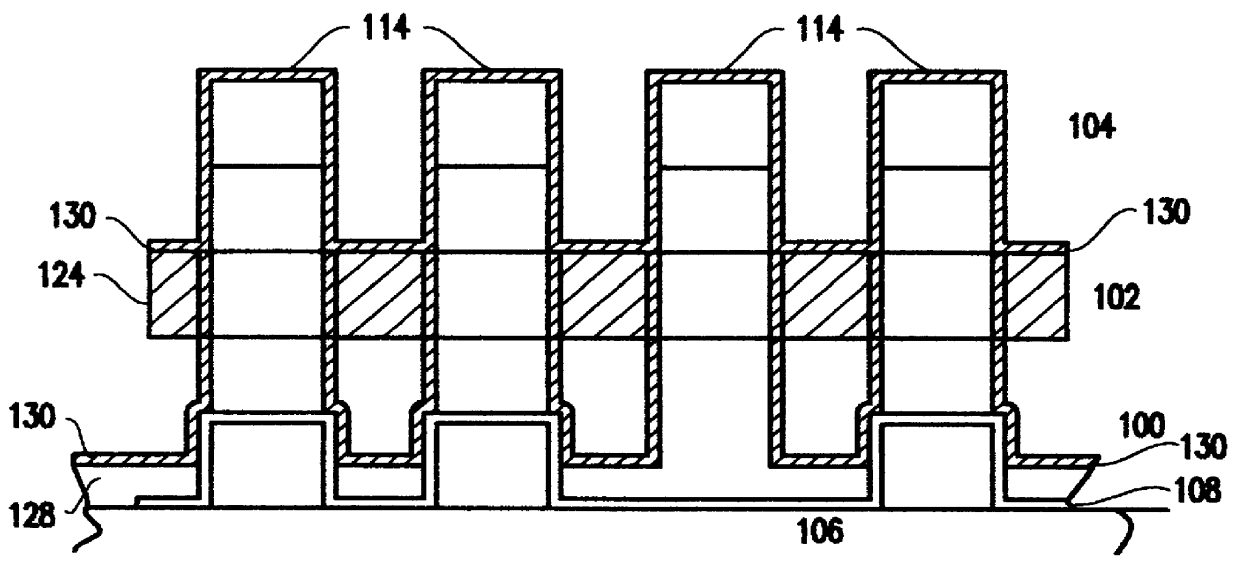

Freestanding multilayer wiring structure

A dielectric wiring structure and method of manufacture therefor. Successively formed wiring layers synergistically combine with subsequently formed sidewall supports spanning two or more layers to form a self supporting air dielectric interconnection matrix. Wires are supported by vertical nitride sidewalls which are, in turn, held in place and supported by the wires. After forming the complete wiring-sidewall structure, SiO2 between and under the wires is removed using gaseous HF at a partial pressure between 5 and 30 Torr. The metal wires may be clad with nitride for short and oxidation protection. Because sidewalls are formed after wiring, with the wiring at each level providing support definition, complex support alignment is unnecessary.

Owner:GLOBALFOUNDRIES INC

Freestanding multilayer IC wiring structure

A dielectric wiring structure and method of manufacture therefor. Successively formed wiring layers synergistically combine with subsequently formed sidewall supports spanning two or more layers to form a self supporting air dielectric interconnection matrix. Wires are supported by vertical nitride sidewalls which are, in turn, held in place and supported by the wires. After forming the complete wiring-sidewall structure, SiO2 between and under the wires is removed using gaseous HF at a partial pressure between 5 and 30 Torr. The metal wires may be clad with nitride for short and oxidation protection. Because sidewalls are formed after wiring, with the wiring at each level providing support definition, complex support alignment is unnecessary.

Owner:GLOBALFOUNDRIES INC

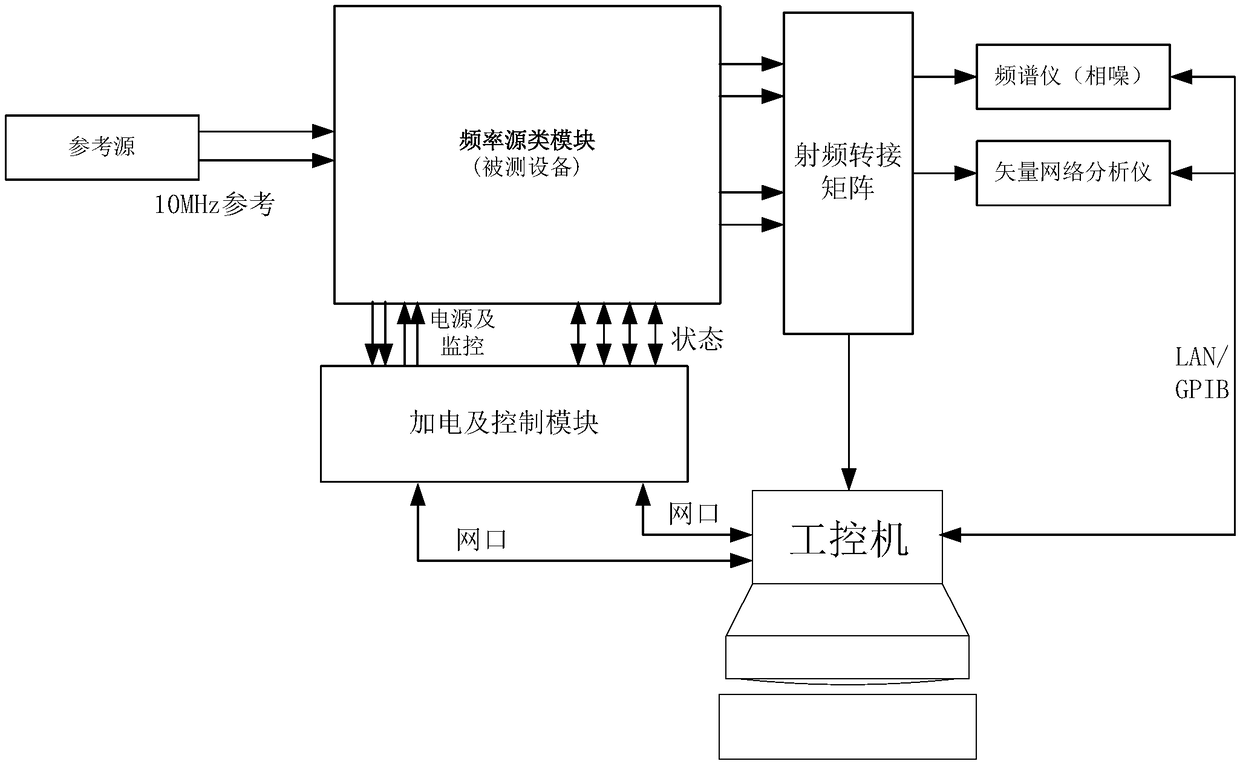

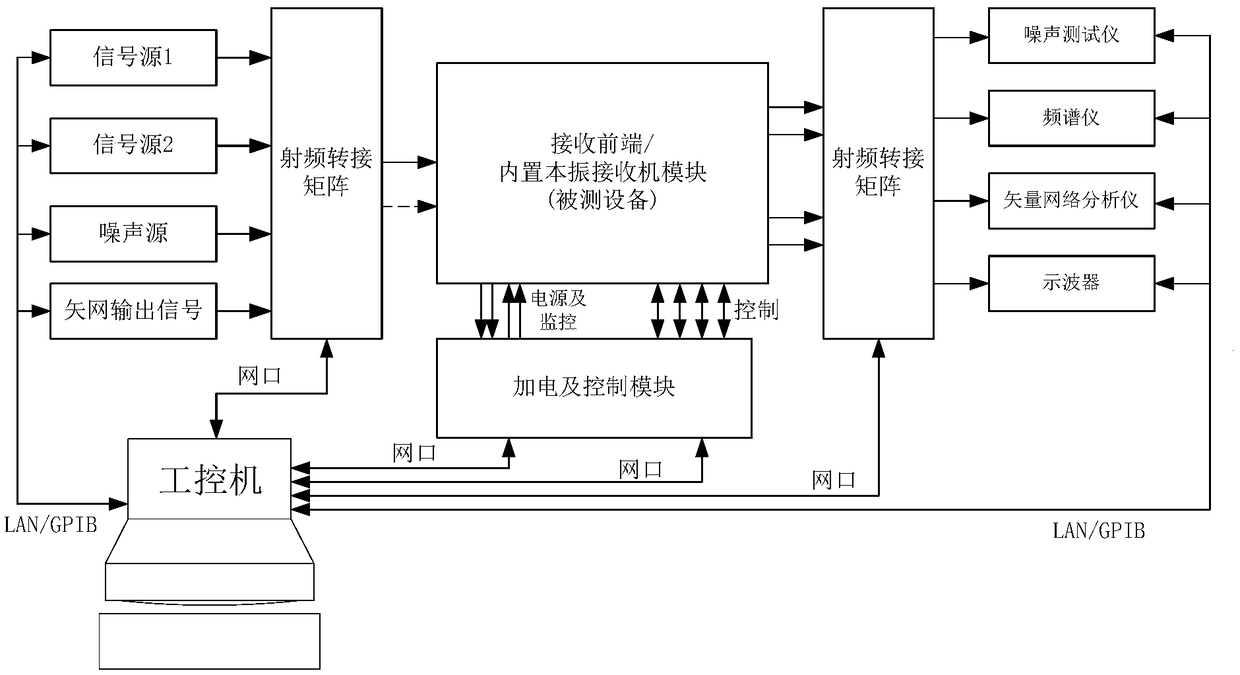

High-coverage automatic radio frequency index test device

InactiveCN109302713AQuick verificationReduce cost inputNetwork planningLocal oscillator signalPhase noise

The invention discloses a high-coverage automatic radio frequency index test device. By using the device provided by the invention, quick tests with high coverage can be performed on multi-channel radio frequency indexes of various types of equipment under test. The device provided by the invention is implemented via the technical scheme as follows: an input radio frequency interconnection matrixmodule receives multiple signal sources, a noise source and an output signal of a vector network, and provides source signals such as a microwave vector signal source, the noise source and the vectornetwork output signal to the equipment under test; the equipment under test receives a low-phase noise local oscillator signal and a reference clock signal from a multi-channel local oscillator sourcemodule; the equipment under test completes automatic switching of multiple channels via an output radio frequency interconnection matrix module, and transmits a test signal to an universal measurement instrument; an industrial control computer calls control parameters of the universal measurement instrument and the equipment under test to complete automatic test of the multiple indexes, reads a test result of the universal measurement instrument and automatically generates a test report in a standard format; the artificial configuration test and automatic test on the main indexes of the equipment under test are achieved by using a visual manual control interface.

Owner:10TH RES INST OF CETC

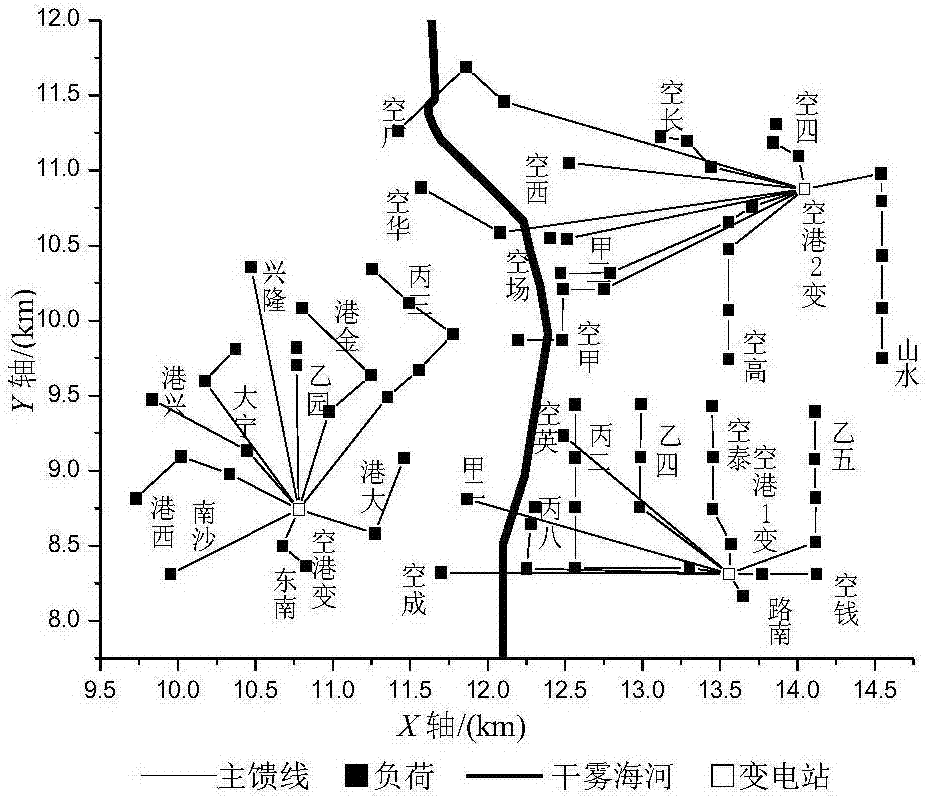

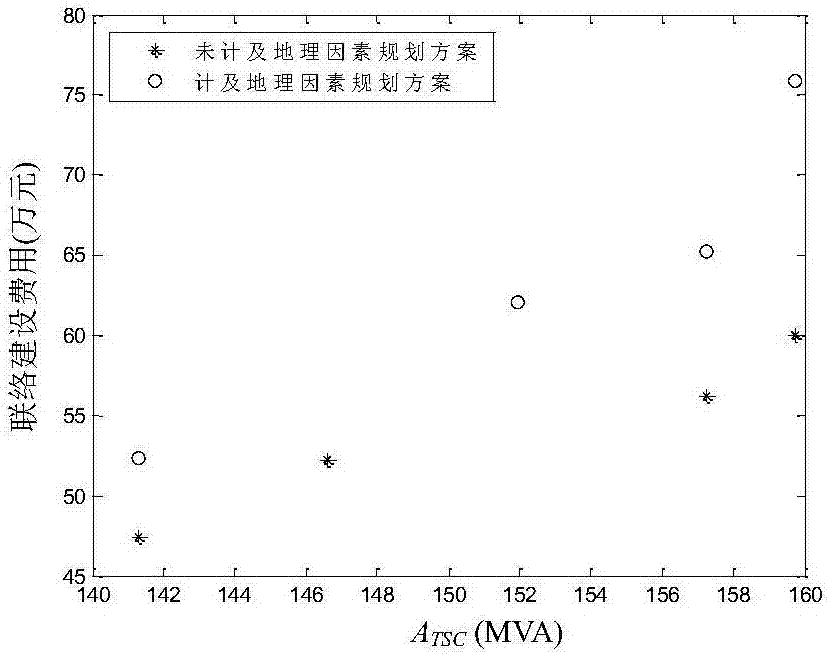

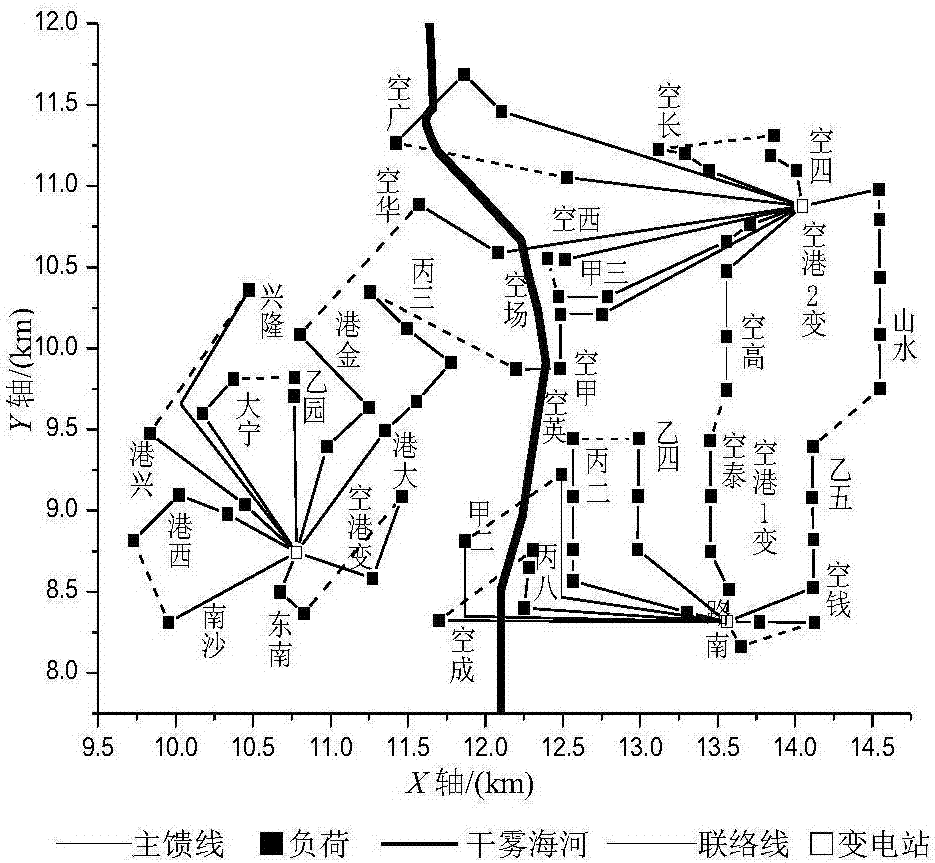

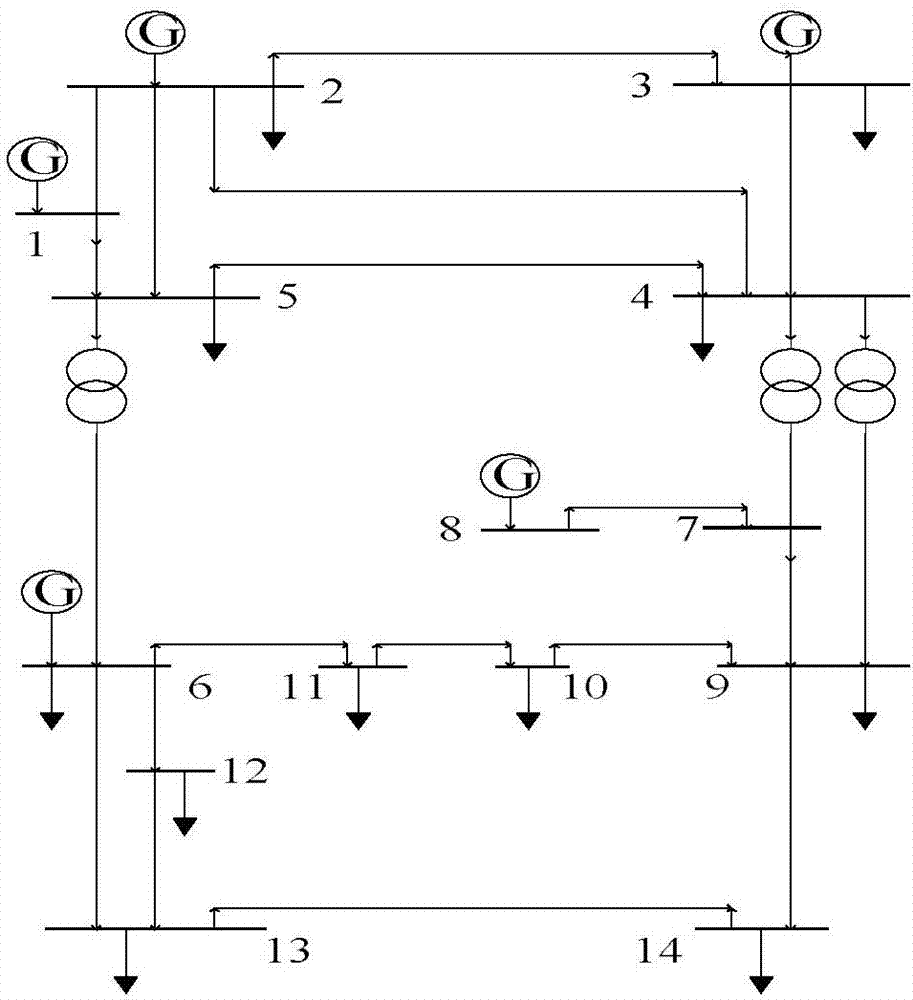

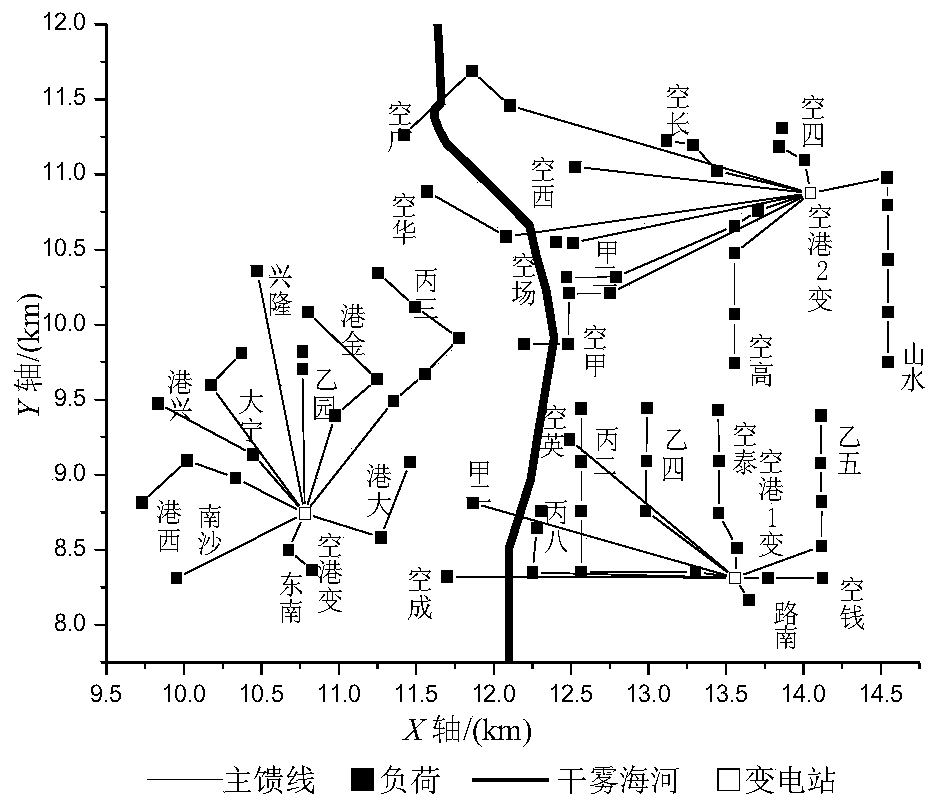

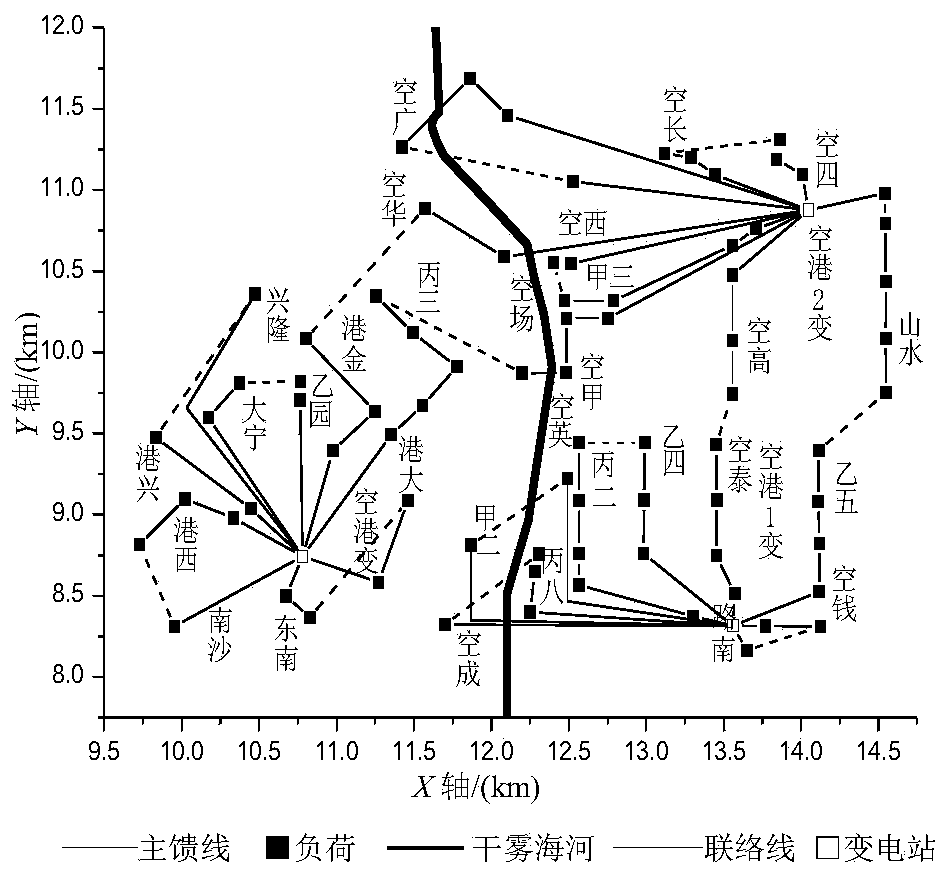

Power distribution network main transformer connection structure optimization planning method taking maximum power supply capability and minimum connection construction cost into account

The invention discloses a power distribution network main transformer connection structure optimization planning method taking maximum power supply capability and minimum connection construction cost into account. The method is characterized by comprising establishment of a connection structure optimization model, solving of the connection structure optimization model, section of an optimal solution and the like. According to the method, overall consideration is given to the maximum power supply capability and investment costs, a main transformer connection structure optimization model is built while a feed line interconnection matrix is used as decision variable, a medium voltage power distribution network connection structure optimization method taking geography factors into account is put forward, effects exerted on a connection structure by geographic environment is demonstrated, and connection relations among all feed lines are shown; the method is advantaged by scientific and reasonable properties, strong applicability, good effect and the like.

Owner:NORTHEAST DIANLI UNIVERSITY

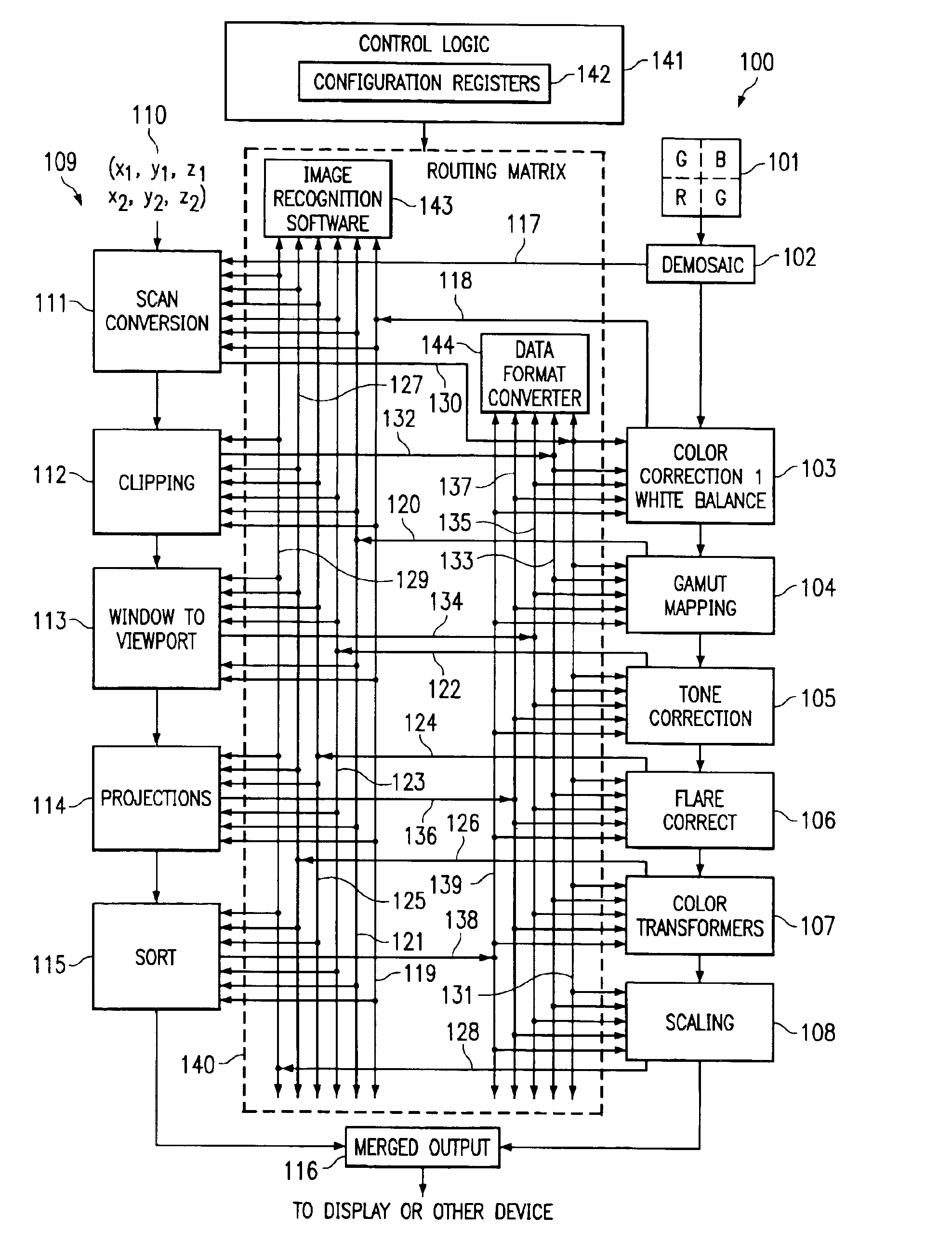

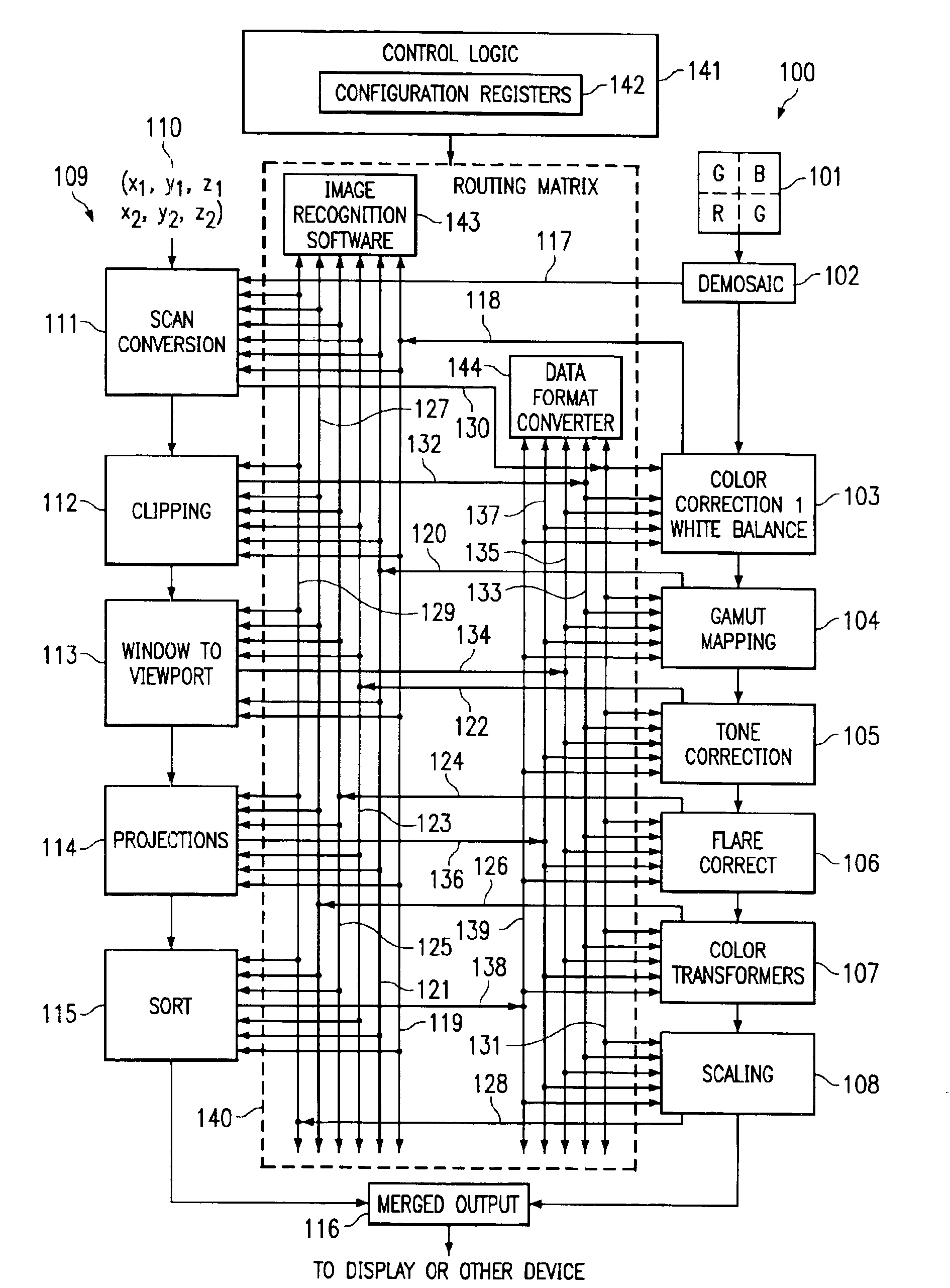

System and method for combining graphics formats in a digital video pipeline

Generally, graphics are displayed on a monitor or printed on an output device after a series of steps are performed, typically implemented in the form of a graphics pipeline, in the case of an object-oriented graphic image. Similarly, a digital picture or digital video image passes through a digital pipeline for the digital image or images to be displayed, printed, or otherwise processed. The present invention encompasses a system and method in which the stages of the graphics pipeline used to process a graphic object are interconnected to the stages of the digital pipeline used to process a bit-mapped image so that a single, interconnected pipeline can be used to process object-oriented graphic images, bit map images and / or images which contain graphics and bit map portions. This interconnected pipeline can be used to process images through various stages of the graphics pipeline followed by stages typically contained in the digital pipeline, or vice versa, to create desired effects. This interconnected pipeline includes a switch or a selectively configurable interconnection matrix which defines an image path which connects desired stages of the pipeline.

Owner:HEWLETT PACKARD DEV CO LP

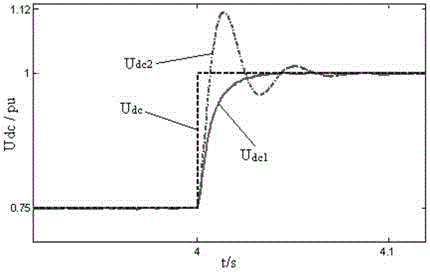

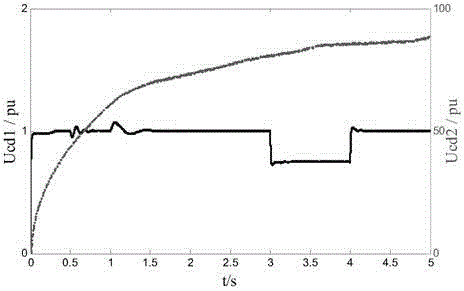

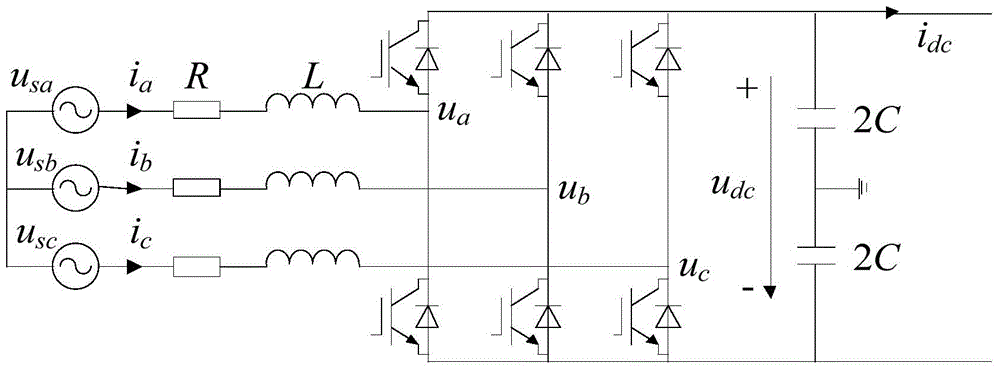

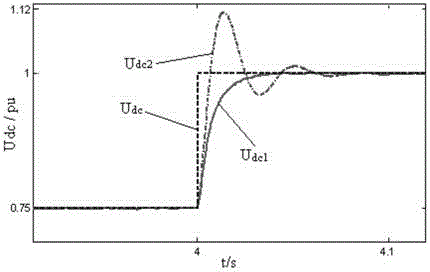

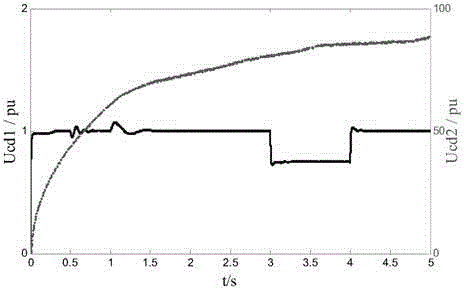

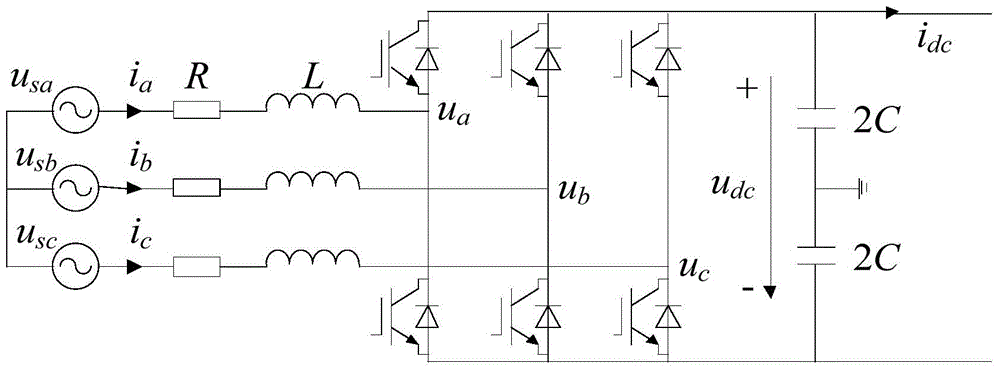

Exponential convergence control method for global stability of voltage source converter based high-voltage direct-current (VSC-HVDC) system

InactiveCN104319758AImprove stabilityImprove transient characteristicsDc circuit with intermediate acTransient stateHigh-voltage direct current

The invention discloses an exponential convergence control method for the global stability of a voltage source converter based high-voltage direct-current (VSC-HVDC) system, comprising the following steps: (1) obtaining a PCHD model of a VSC-HVDC system; (2) presetting an energy function of the VSC-HVDC system, and changing the original energy function of the system according to a preset interconnection matrix Jd and a damping matrix Ra(x) to obtain a new PCHD model when the VSC-HVDC system is passive; (3) selecting a steady-state equilibrium point needed by the VSC-HVDC system, constructing a needed closed-loop storage function Hd(x), and enabling the closed-loop storage function Hd(x) to meet the conditions of an IDA-PB theorem; and (4) obtaining an exponential stability IDA-PB controller of the VSC-HVDC system, and controlling the VSC-HVDC system according to the exponential stability IDAPB controller. By adopting the method, the VSC-HVDC system is enabled to have good steady-state and transient property when the system is under large disturbance or system parameters cannot be accurately predicted, and the global asymptotic stability is maintained.

Owner:CHINA EPRI ELECTRIC POWER ENG CO LTD +1

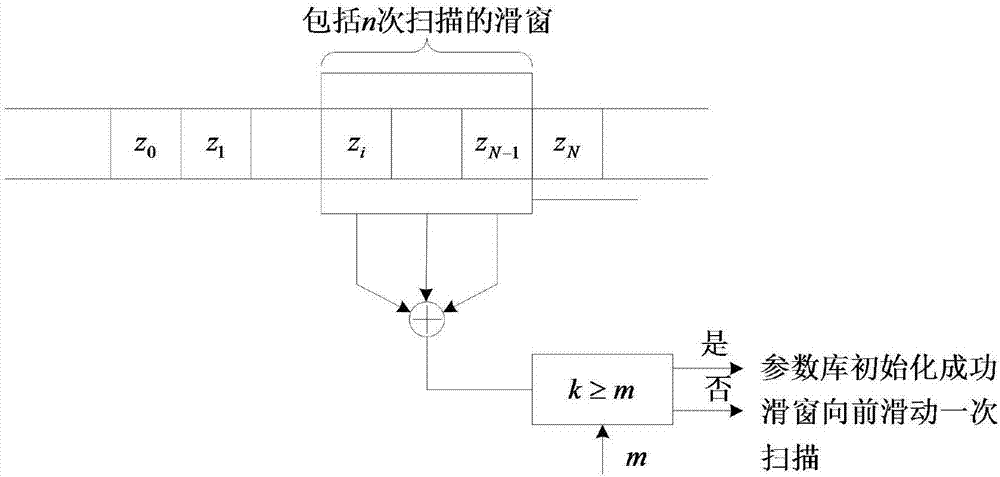

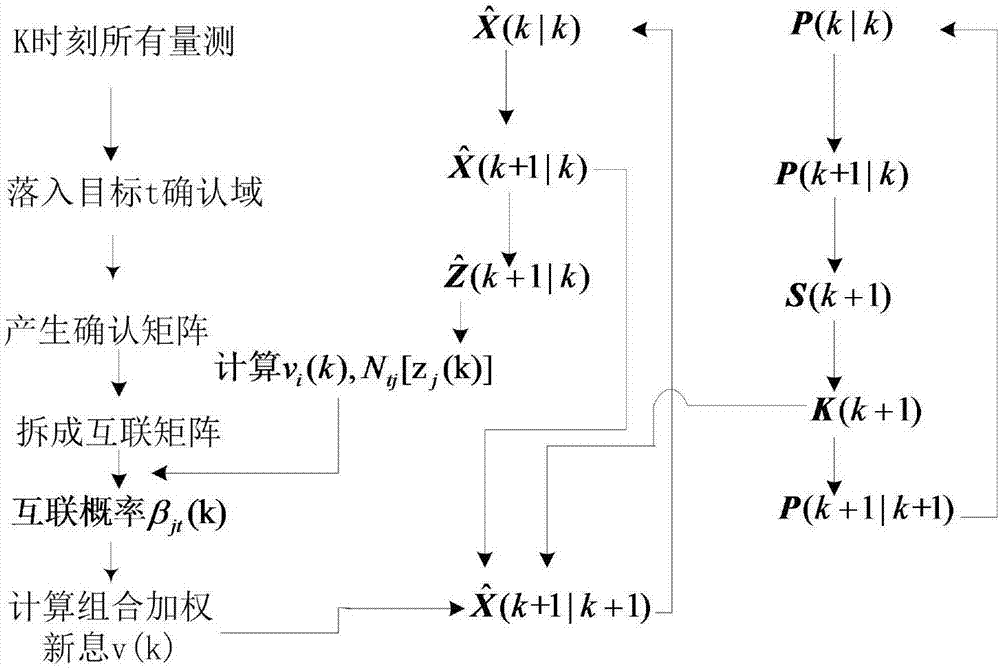

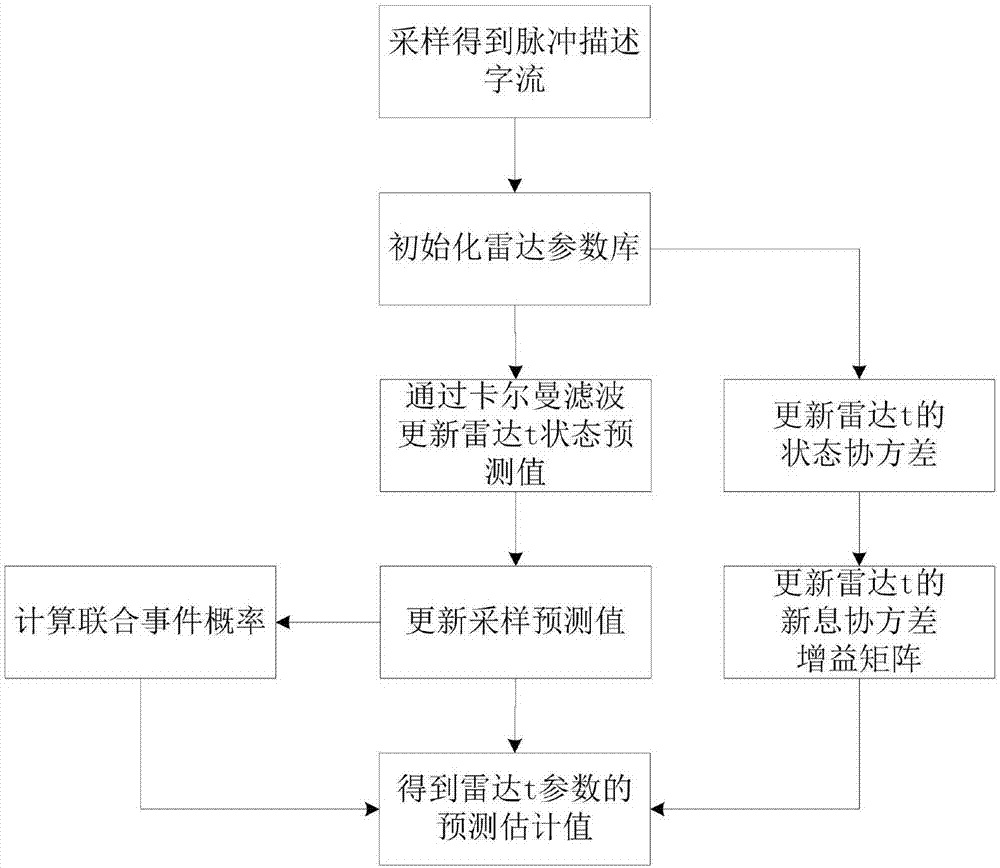

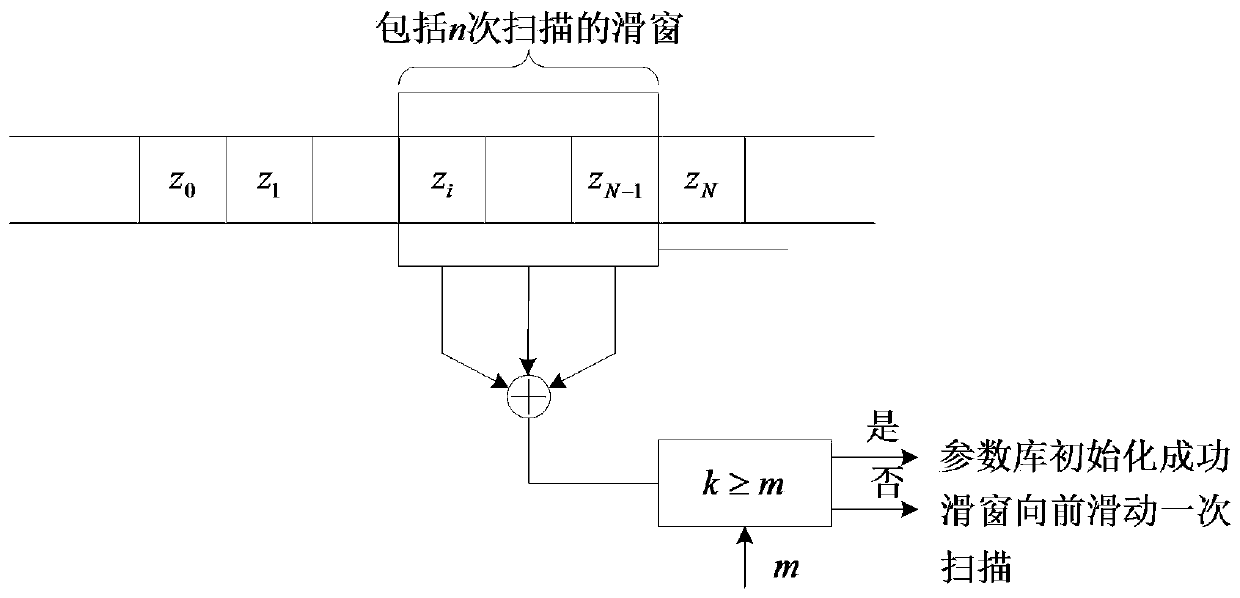

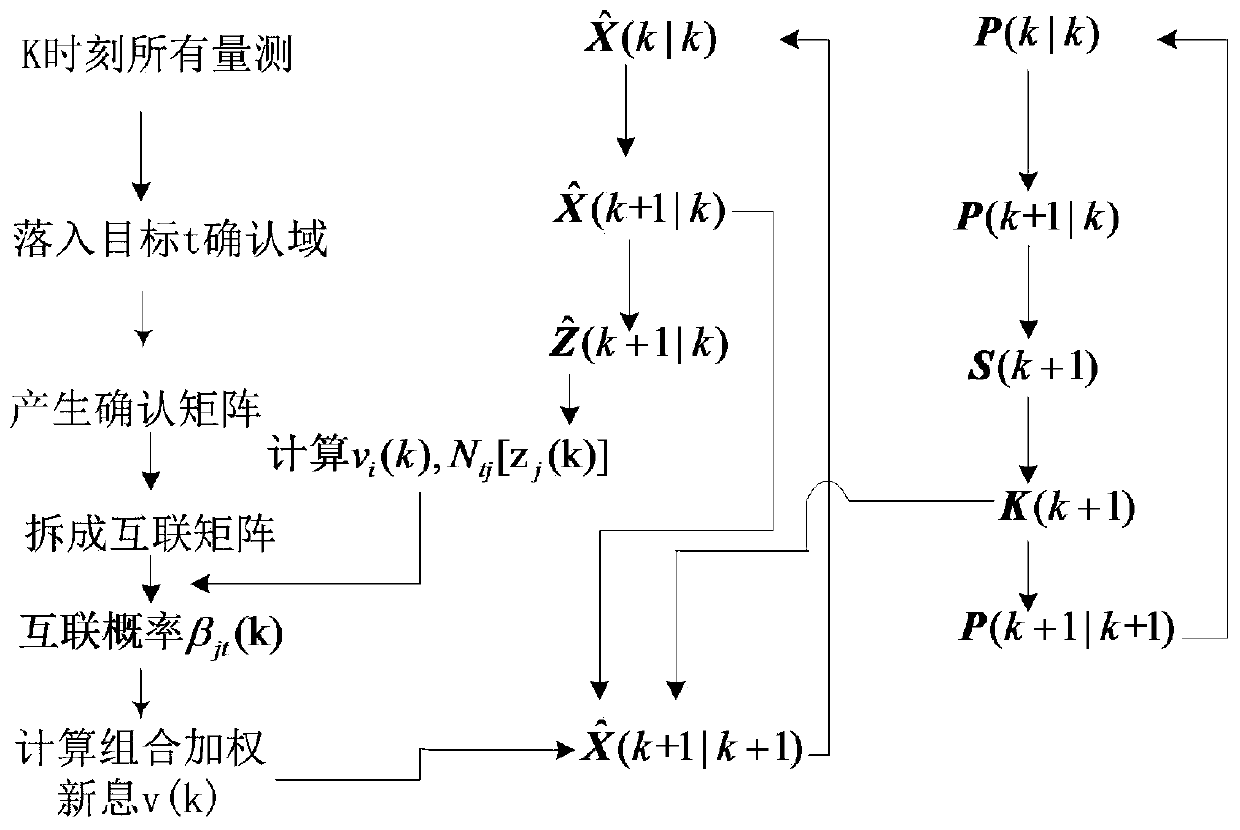

Radar signal sorting method based on probability data association

ActiveCN106896348AAccurate sortingWave based measurement systemsSignal-to-noise ratio (imaging)Interconnection matrix

The invention belongs to the radar signal sorting technology field and particularly relates to a radar signal sorting method based on probability data association. The method comprises steps that sampling data of one sampling period under the clutter environment is utilized to determine an initial radar parameter database through a logic method; combined probability data association is carried out for the sampling data, a confirmation matrix is split into interconnection matrixes, and combined event probability is calculated, including calculating an innovation covariance, a target gain matrix and a state estimation covariance; the radar parameter database is updated; steps are repeated till association of the sampling data is accomplished. The method is advantaged in that the stable radar signal parameters can be accurately and effectively acquired under conditions of relatively low signal to noise ratio and limited sampling data accuracy, probability interconnection of data of each sampling point at each moment in the sampling period and the radar database data is carried out, the radar database parameters are further predicted and updated, and thereby a purpose of sorting accurate radar signals under clutter and signal coexistence conditions can be realized.

Owner:HARBIN ENG UNIV

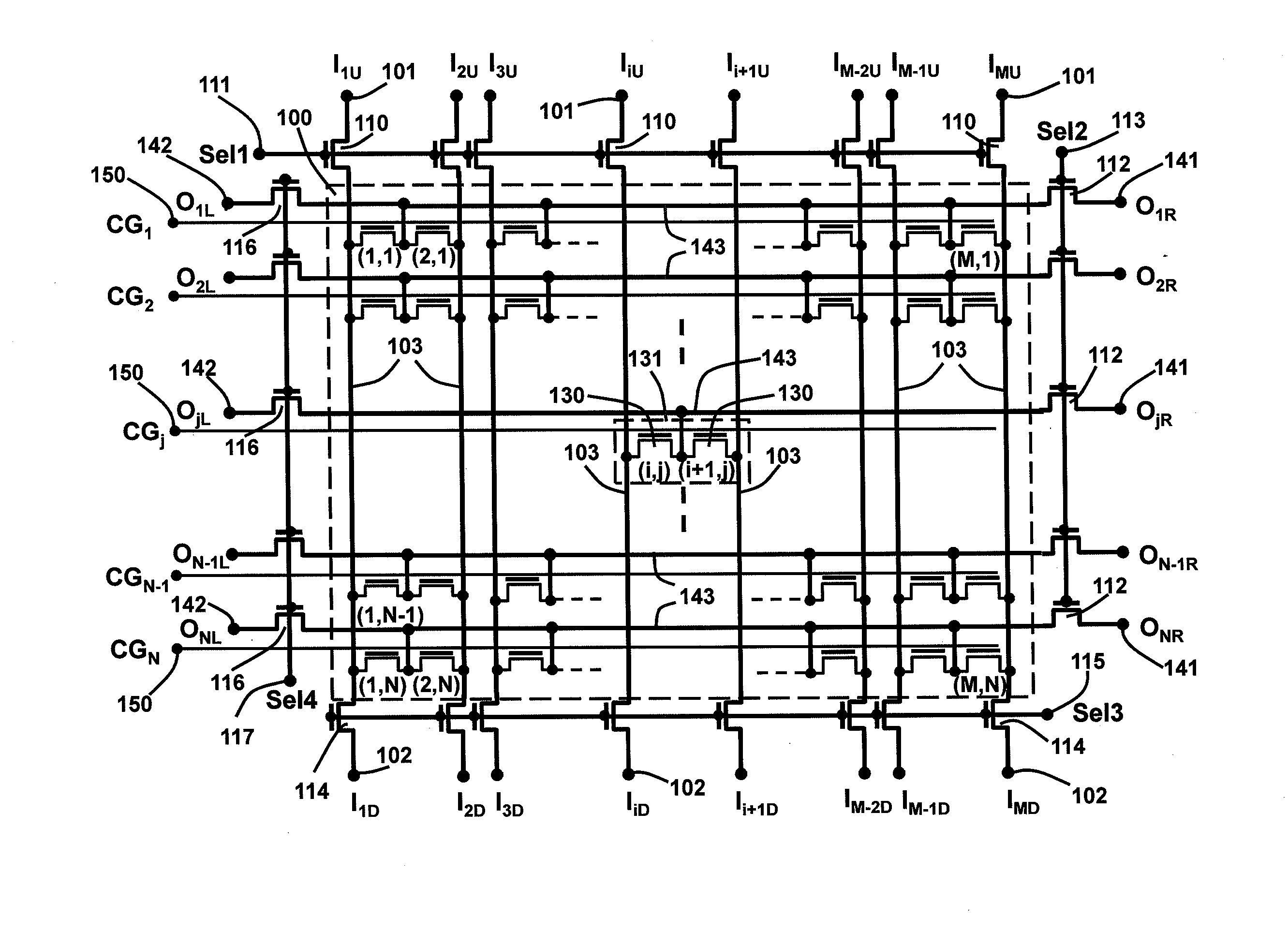

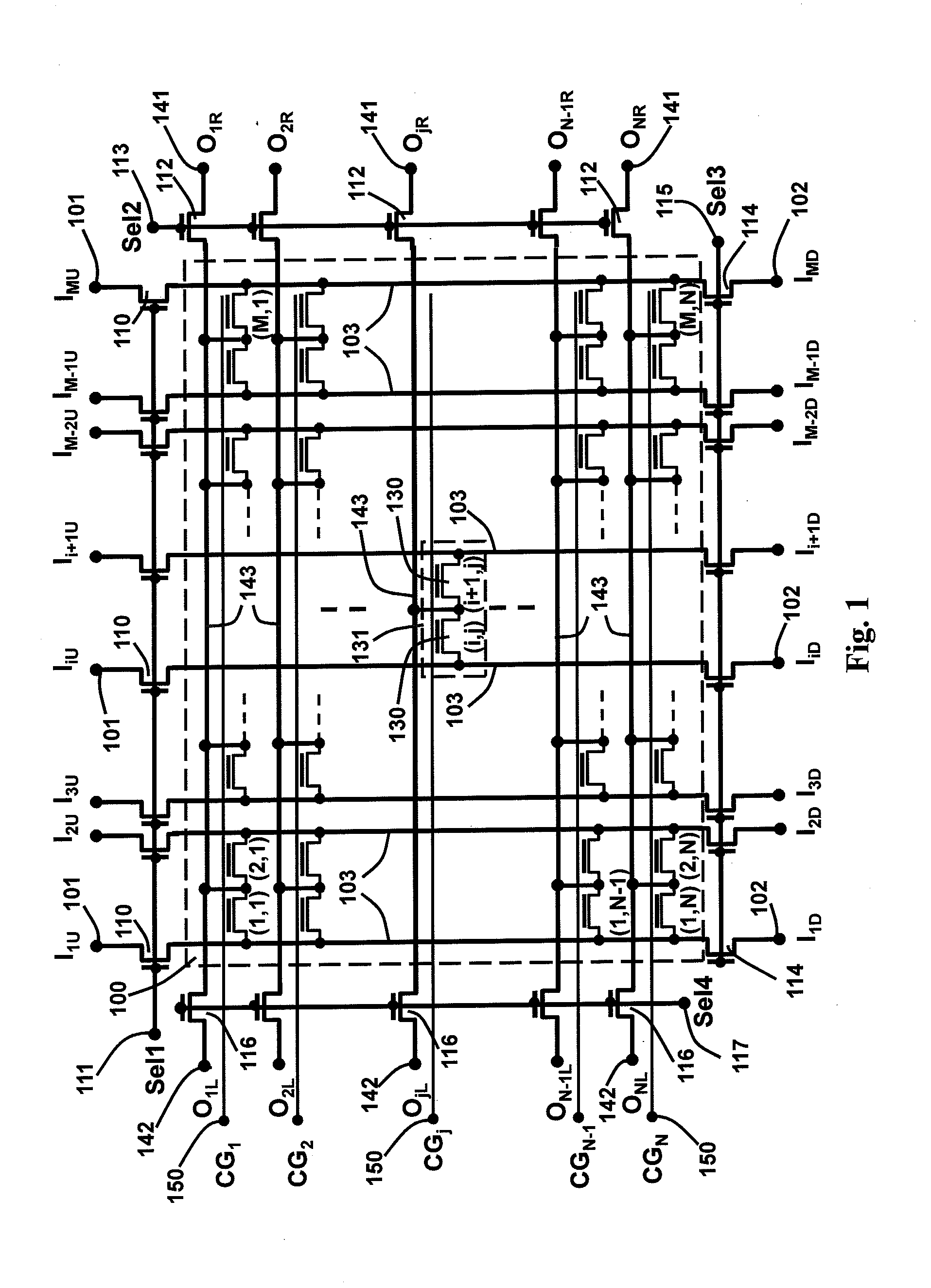

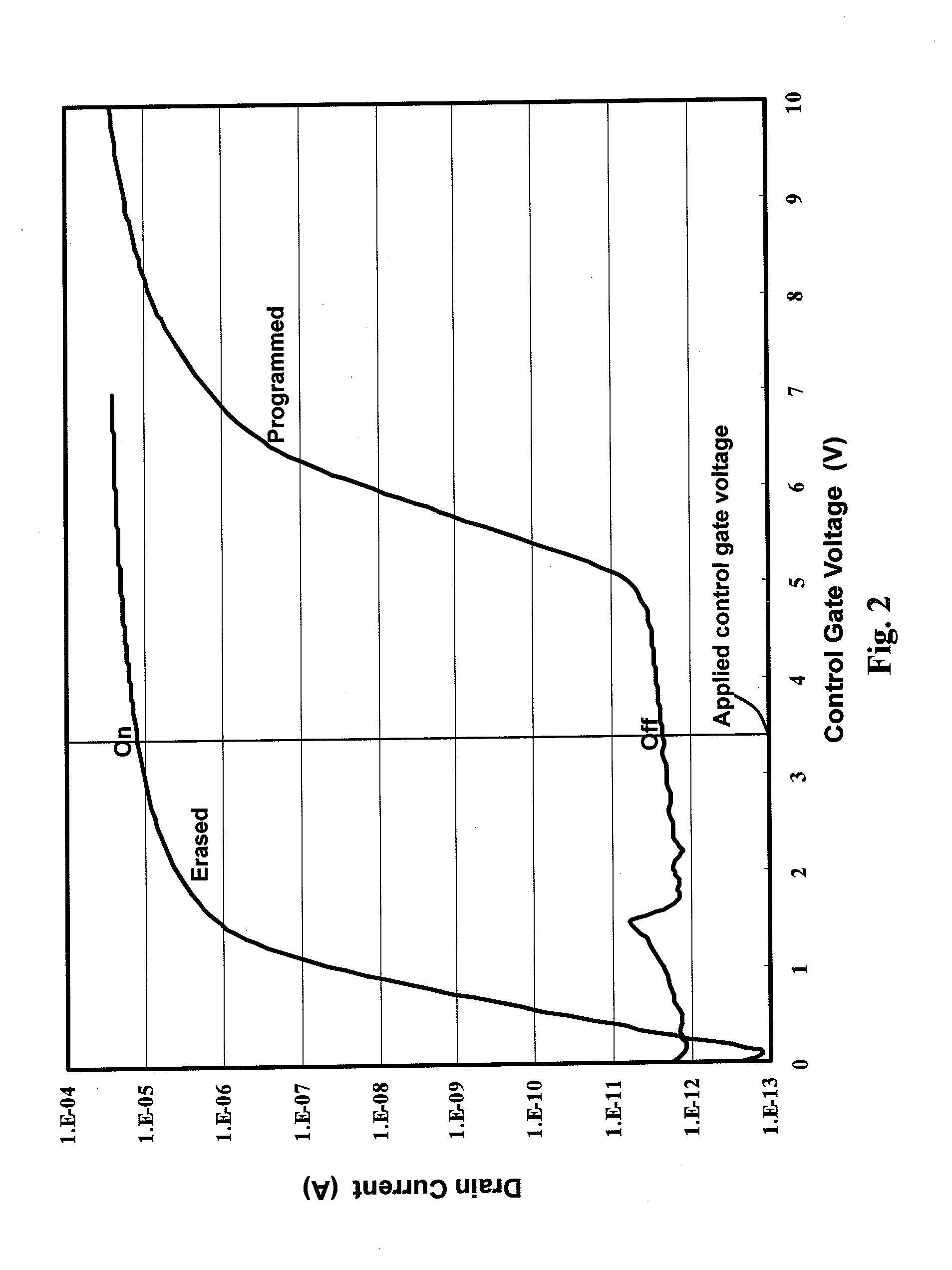

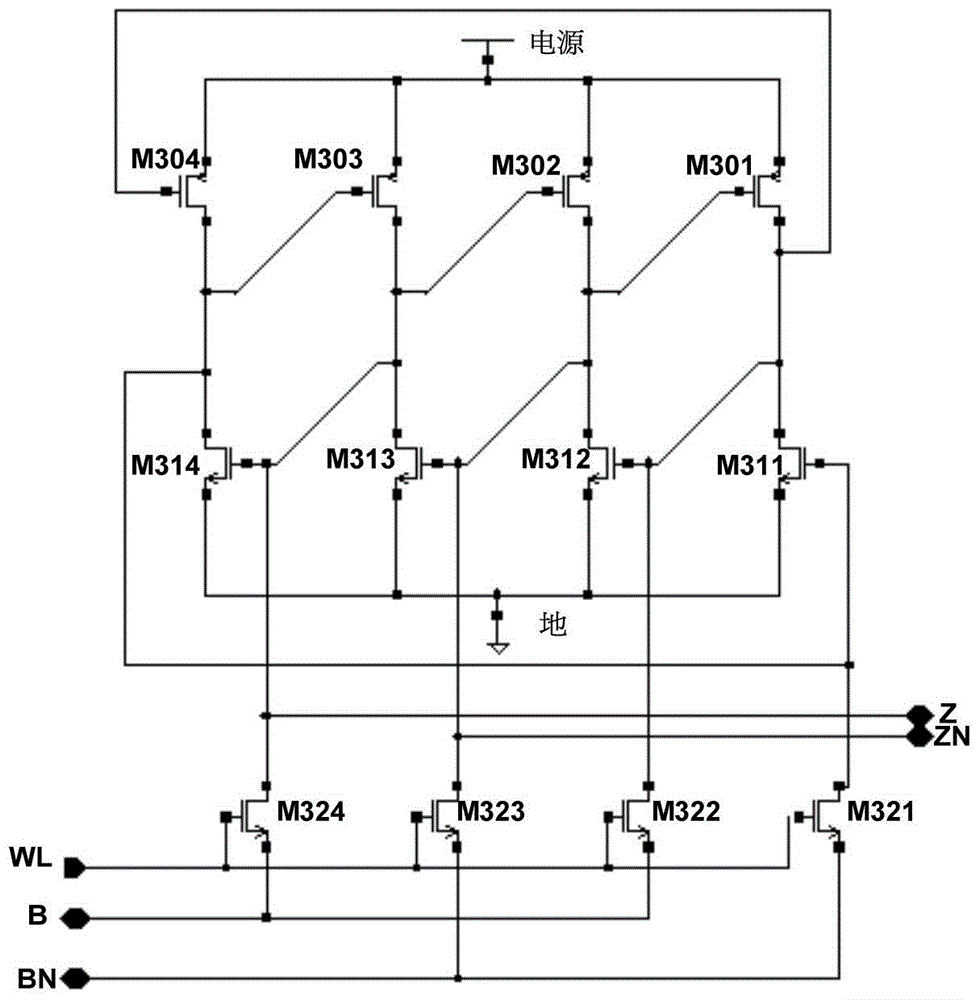

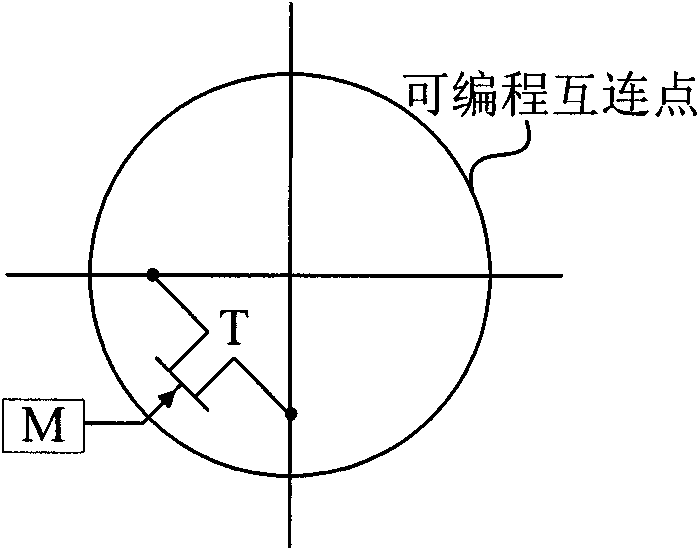

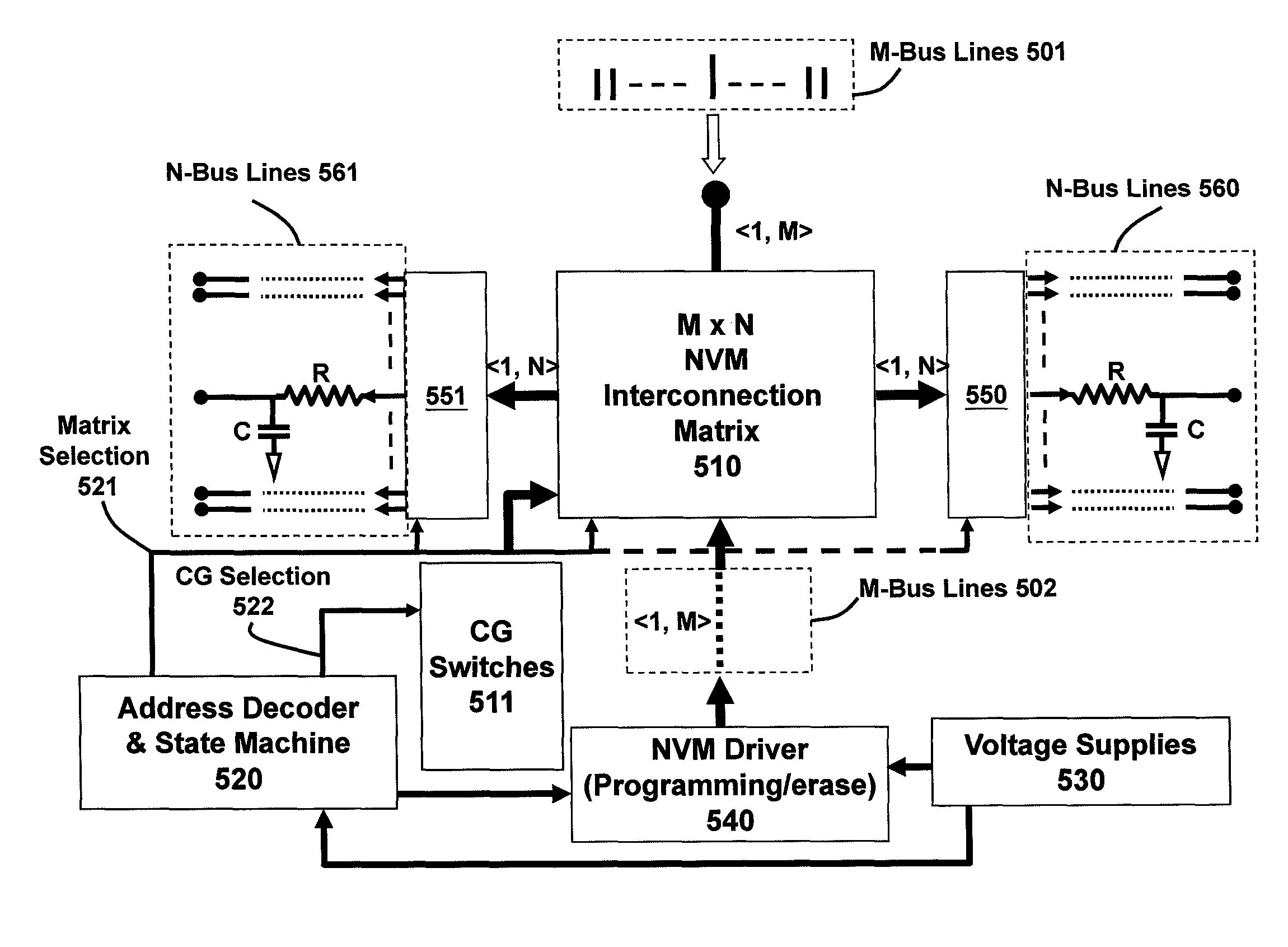

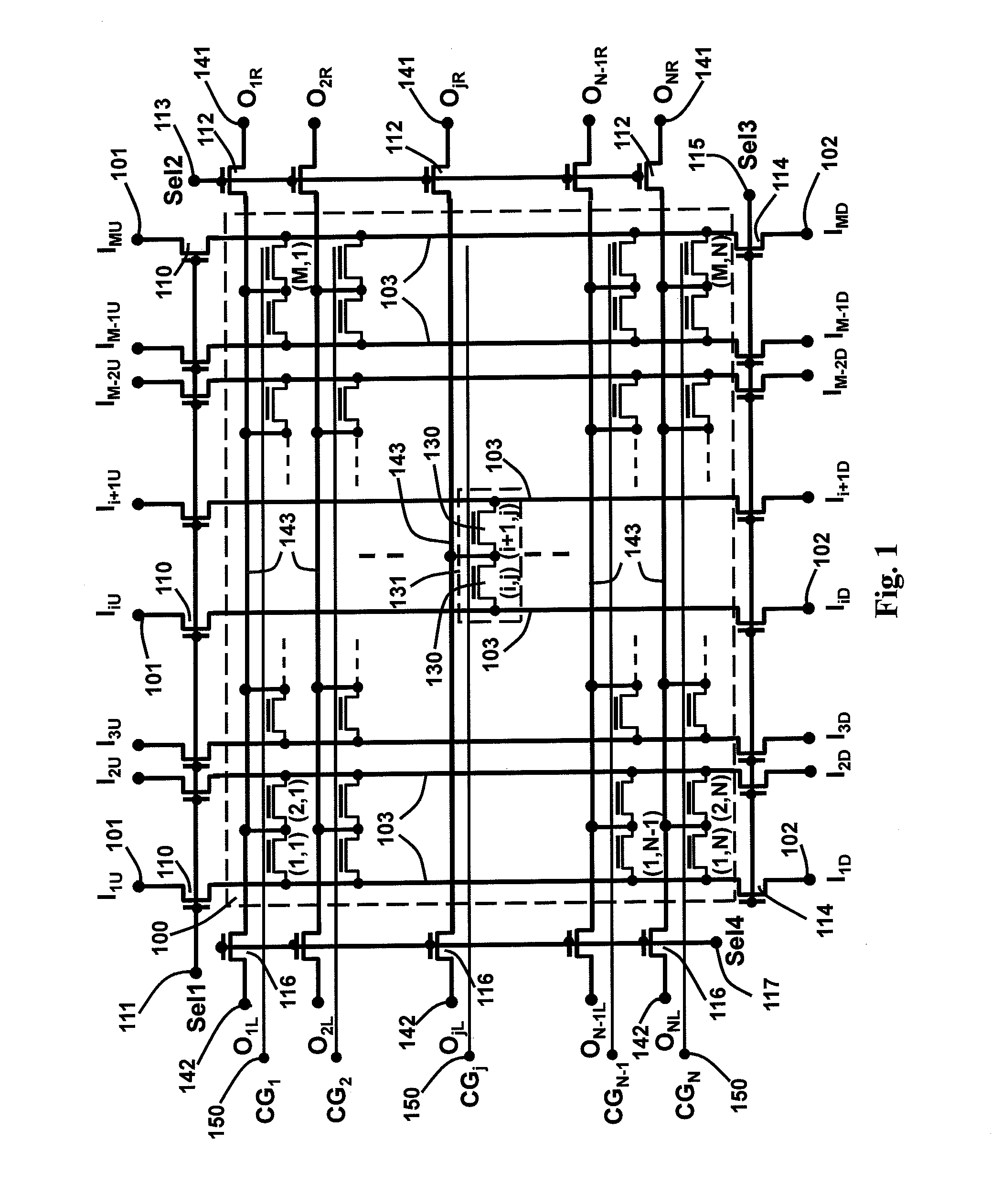

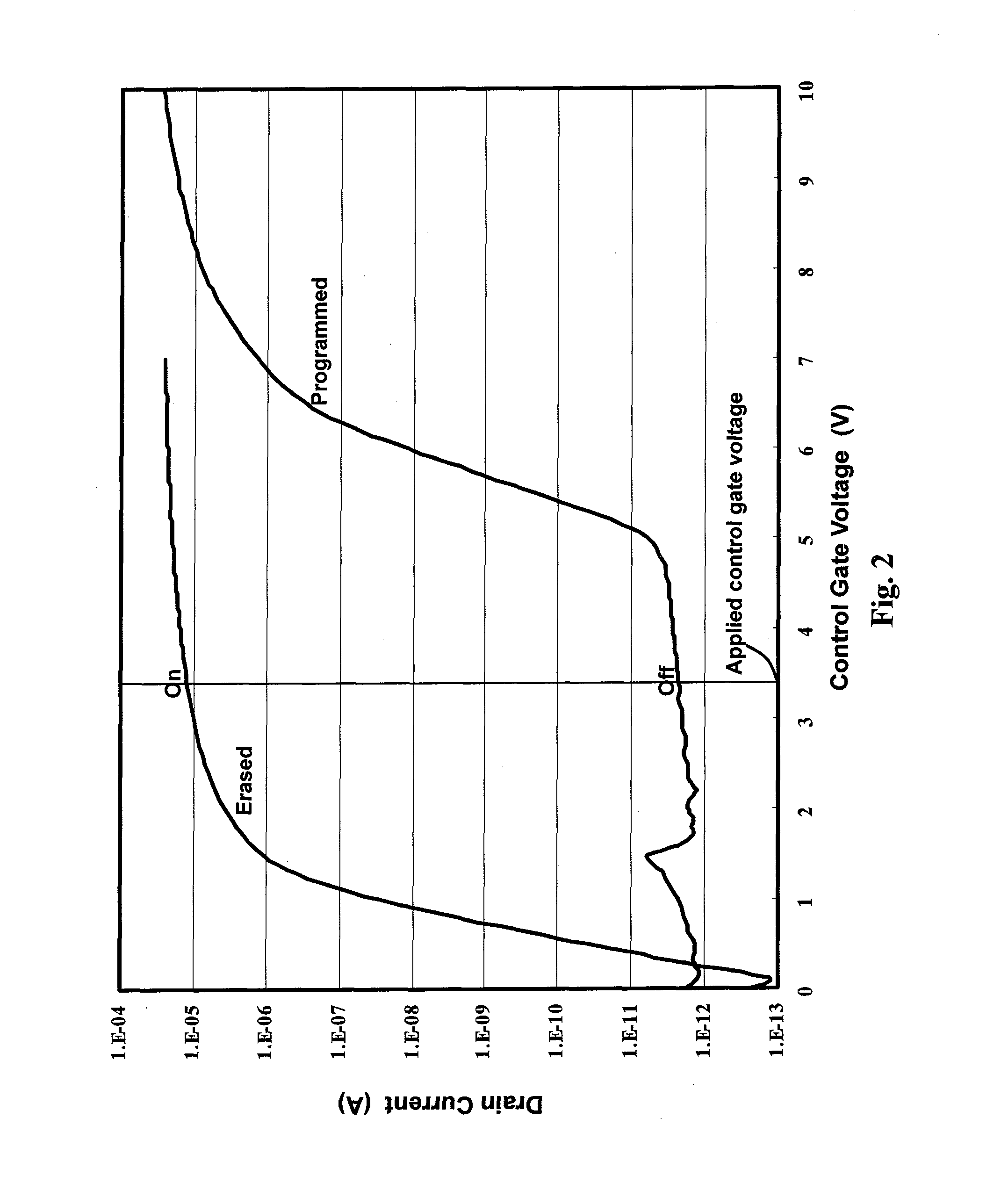

Interconnection matrix using semiconductor non-volatile memory

ActiveUS20140140139A1Quality improvementRead-only memoriesDigital storageHemt circuitsHigh Threshold Logic

An interconnection matrix consists of a plurality of semiconductor Non-Volatile Memory (NVM) forming an M×N array. Semiconductor NVM devices in the array are either programmed to a high threshold voltage state or erased to a low threshold voltage state according to a specific interconnection configuration. Applied with a gate voltage bias higher than the low threshold voltage and lower than the high threshold voltage to the control gates of the entire semiconductor NVM devices in the array, the configured interconnection network is formed. The disclosed interconnection matrix can be applied to configuring circuit routing in Integrated Circuit (IC).

Owner:FLASHSILICON

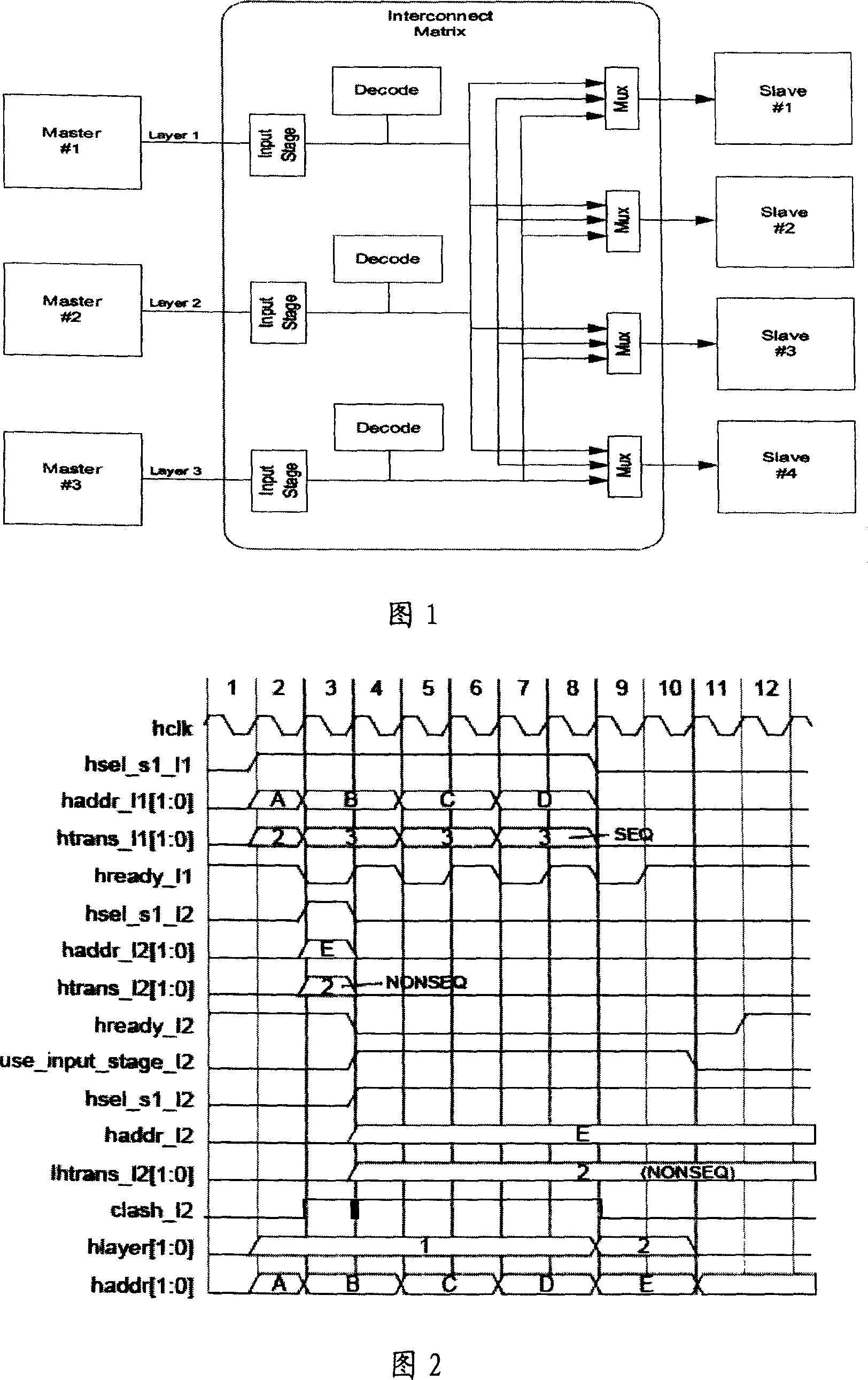

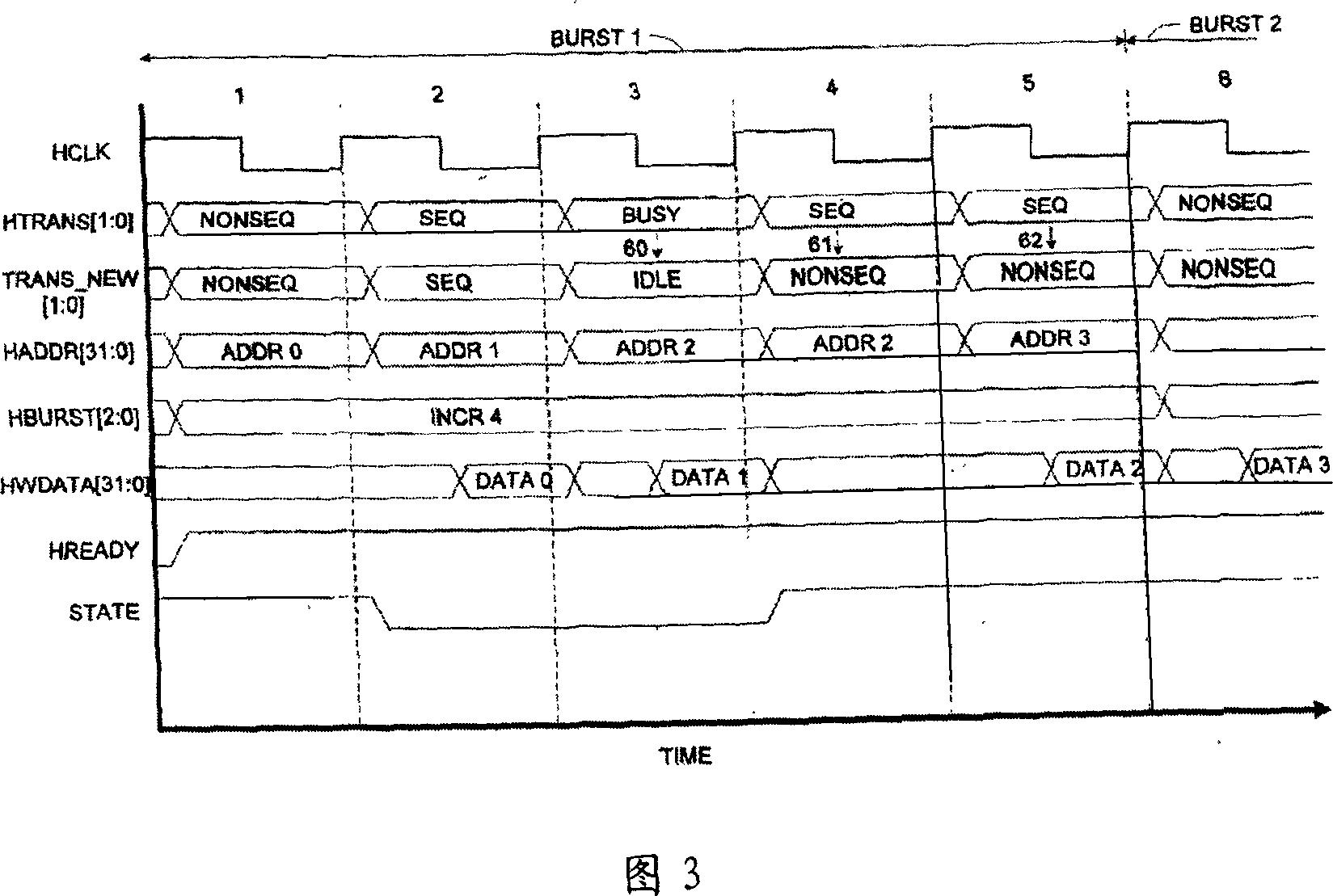

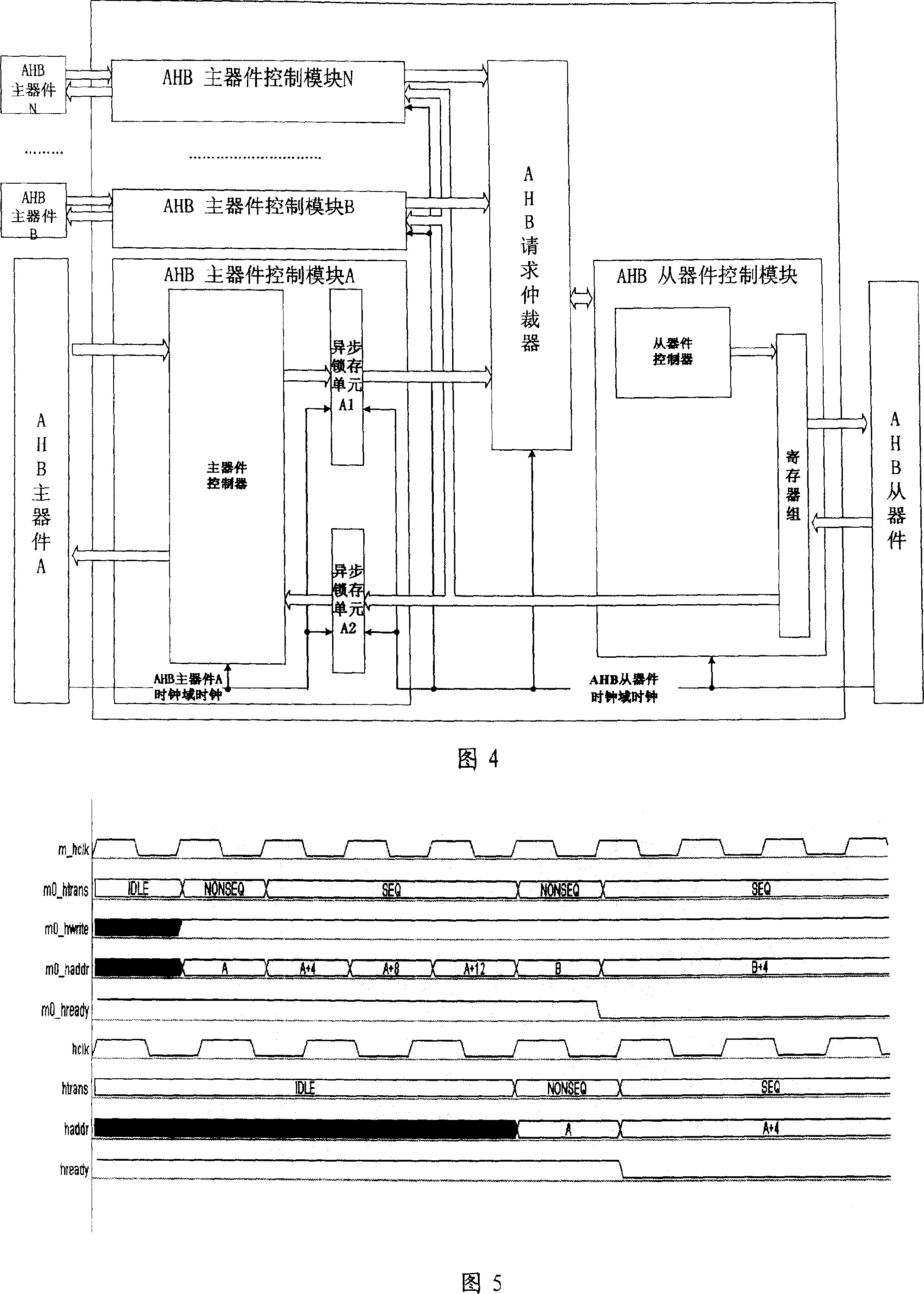

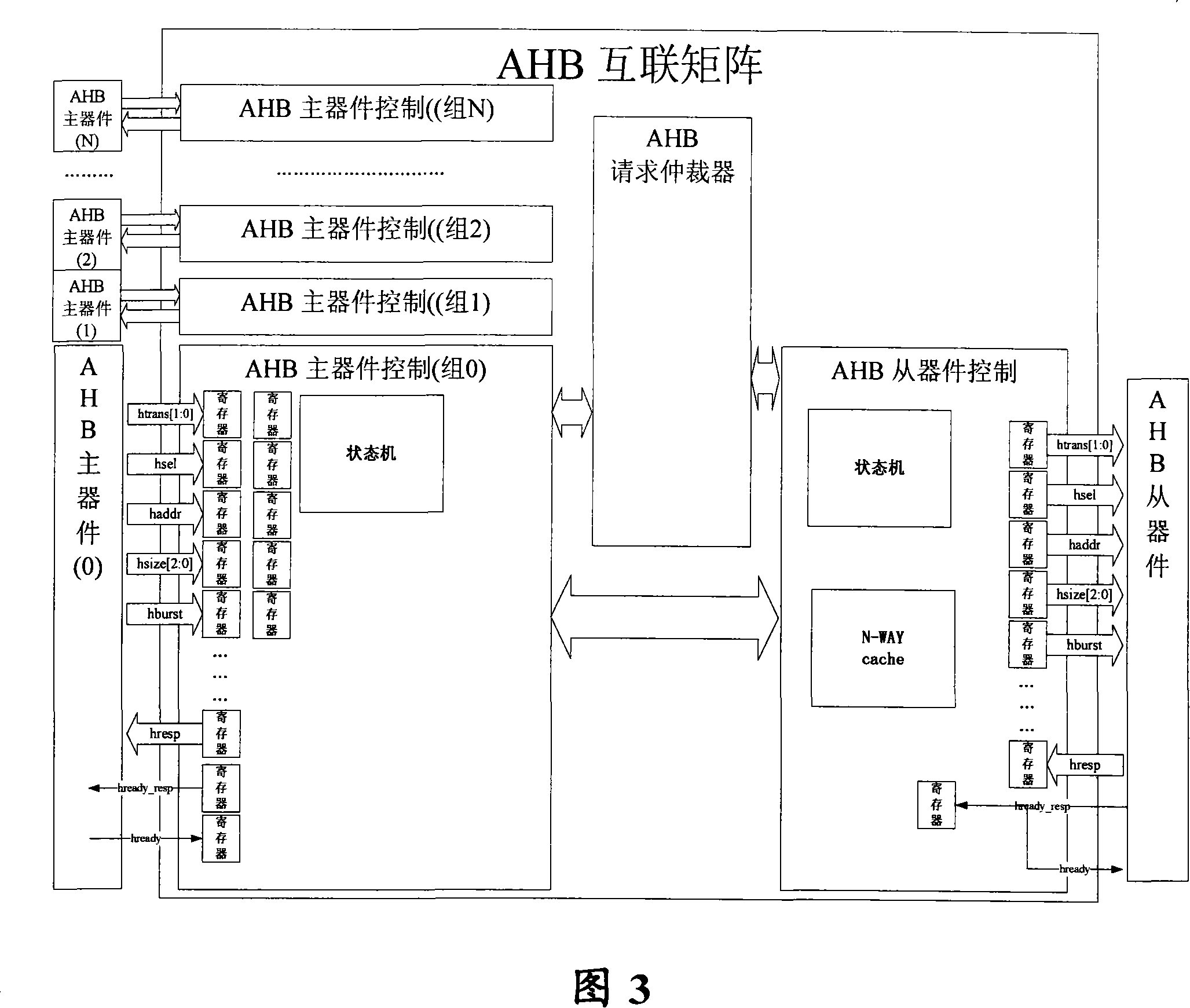

Asynchrous AHB interconnection matrix interface device

InactiveCN101071405AHigh speedImprove operational efficiencyElectric digital data processingInterconnection matrixData exchange

The invention discloses asynchronous AHB interconnect matrix interface devices. Including a number of AHB main device control module, a module AHB request for arbitration, at least from an AHB device control module; AHB Each module contains the main control device controller device. The first and second units asynchronous induction latches latch unit; period from AHB device control module contains the device controller, register; AHB referred to the main device to control module for asynchronous clock lock AHB main way of receiving an order from the device, its signal will be converted to AHB clock domain signal from the device and after docking with the AHB control modules from the device parameters and data asynchronous clock and data exchange. This invention enabled the AHB AHB from the devices and devices can be at different clock domains, AHB agreement correct signal transmission integrity and improve the speed of the system bus and operational efficiency.

Owner:ZTE CORP

Method and apparatus for self-healing symmetric multi-processor system interconnects

InactiveUS7661006B2Fault responseGeneral purpose stored program computerSelf-healingComputer architecture

A computer implemented method, apparatus, and computer program product for managing symmetric multiprocessor interconnects. The process identifies functional communication connections between each processor in a plurality of processors on a multiprocessor to form identified functional communication connections. The process maps every functional communication connection between any two processors in the plurality of processors, based on the identified functional communication connections, to form an interconnect matrix. The process creates a path map using the interconnect matrix. The path map comprises a sequence of communication connections between the plurality of processors. The process initializes the plurality of processors using the path map.

Owner:IBM CORP

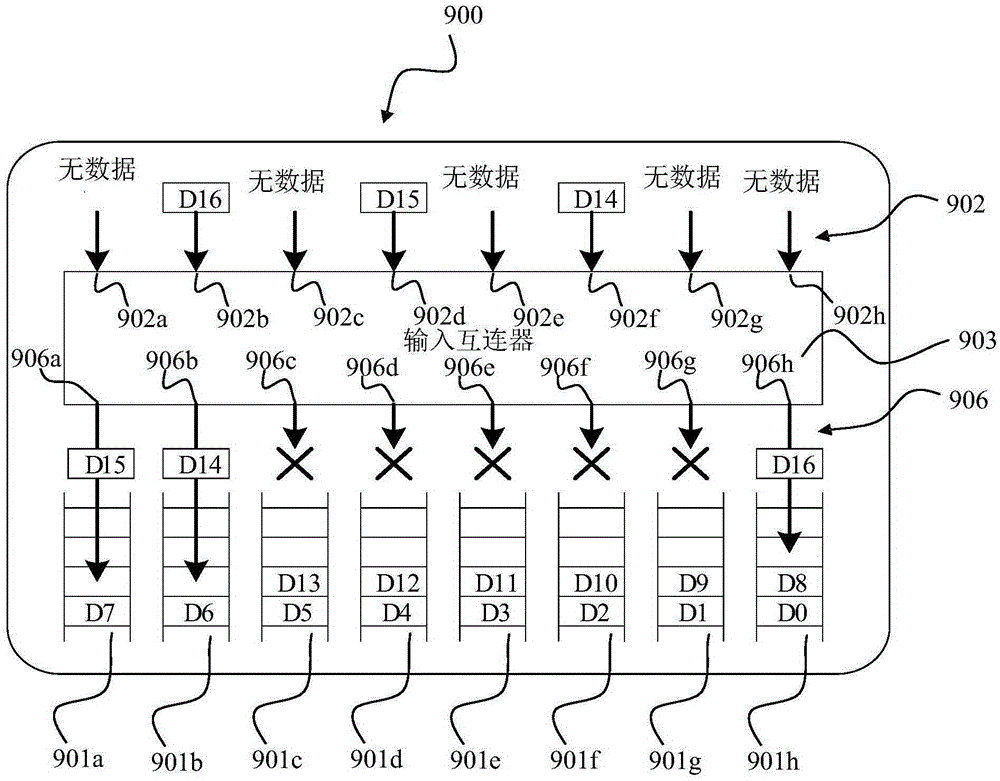

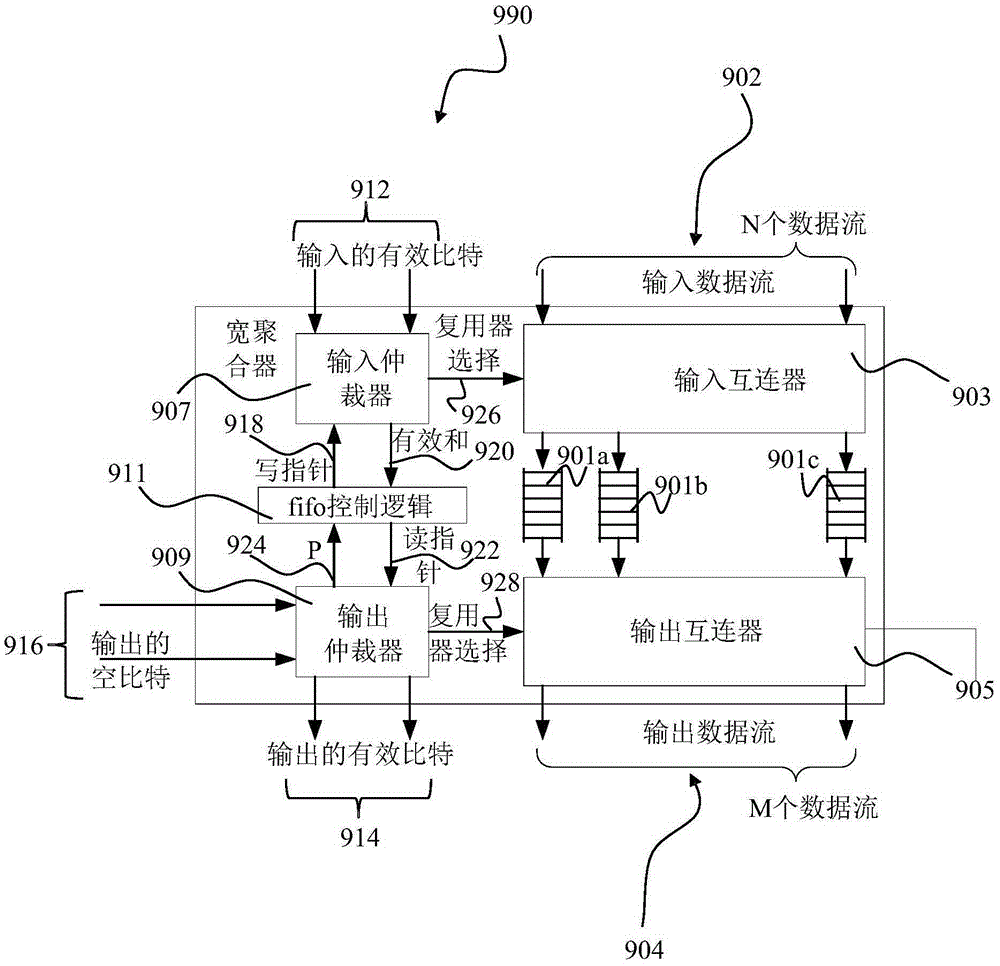

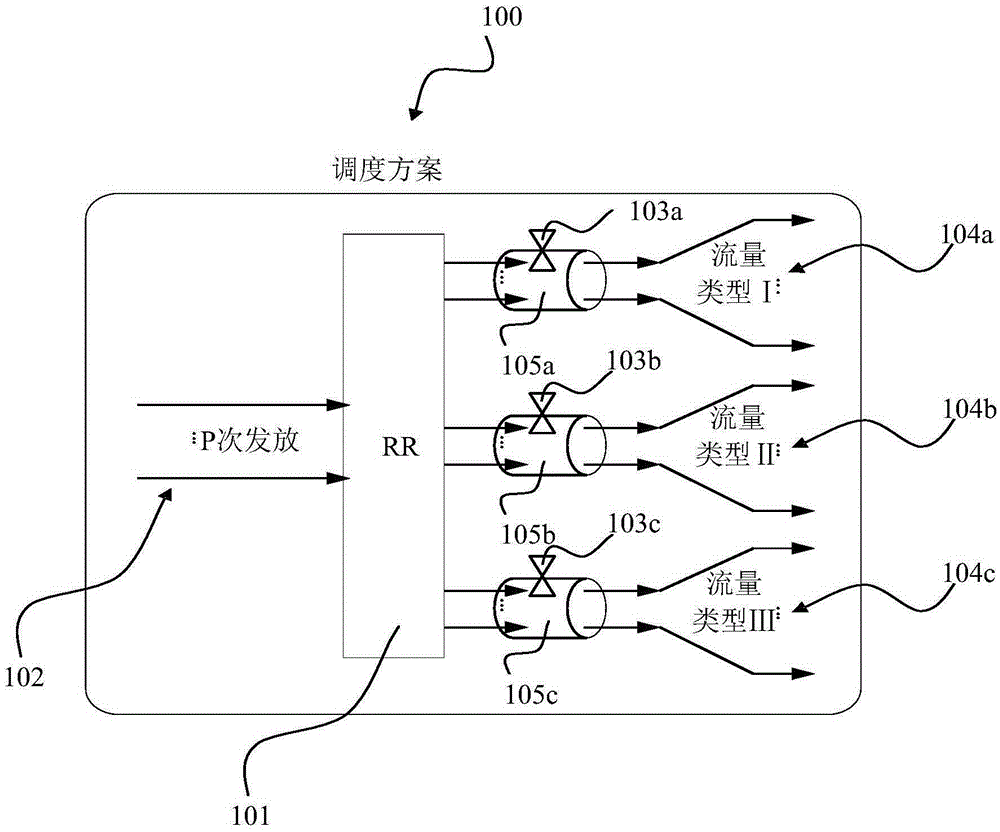

Memory aggregation device

The invention relates to a memory aggregation device (990) for storing a set of input data streams (902) and retrieving data to a set of output data streams (904), both the set of input data streams (902) and the set of output data streams (904) being operable to perform one of sending and stop sending new data in each clock cycle, the memory aggregation device (990) comprising: a set of FIFO memories (901a, 901b,..., 901c) each comprising an input and an output; an input interconnector (903) configured to interconnect each one of the set of input data streams (902) to each input of the set of FIFO memories (901a, 901b,..., 901c) according to an input interconnection matrix; an output interconnector (905) configured to interconnect each output of the set of FIFO memories (901a, 901b,..., 901c) to each one of the set of output data streams (904) according to an output interconnection matrix; an input selector (907) configured to select the input interconnection matrix according to an input data scheduling scheme; an output selector (909) configured to select the output interconnection matrix according to an output data scheduling scheme; and a memory controller (911) coupled to both, the input selector (907) and the output selector (909), wherein the memory controller (911) is configured to control the input data scheduling scheme such that data from the set of input data streams (902) is spread among the set of FIFO memories (901a, 901b,..., 901c) in a round-robin manner and to control the output data scheduling scheme such that data from the set of FIFO memories (901a, 901b,..., 901c) is retrieved to the set of output data streams (904) in a round-robin manner.

Owner:HUAWEI TECH CO LTD

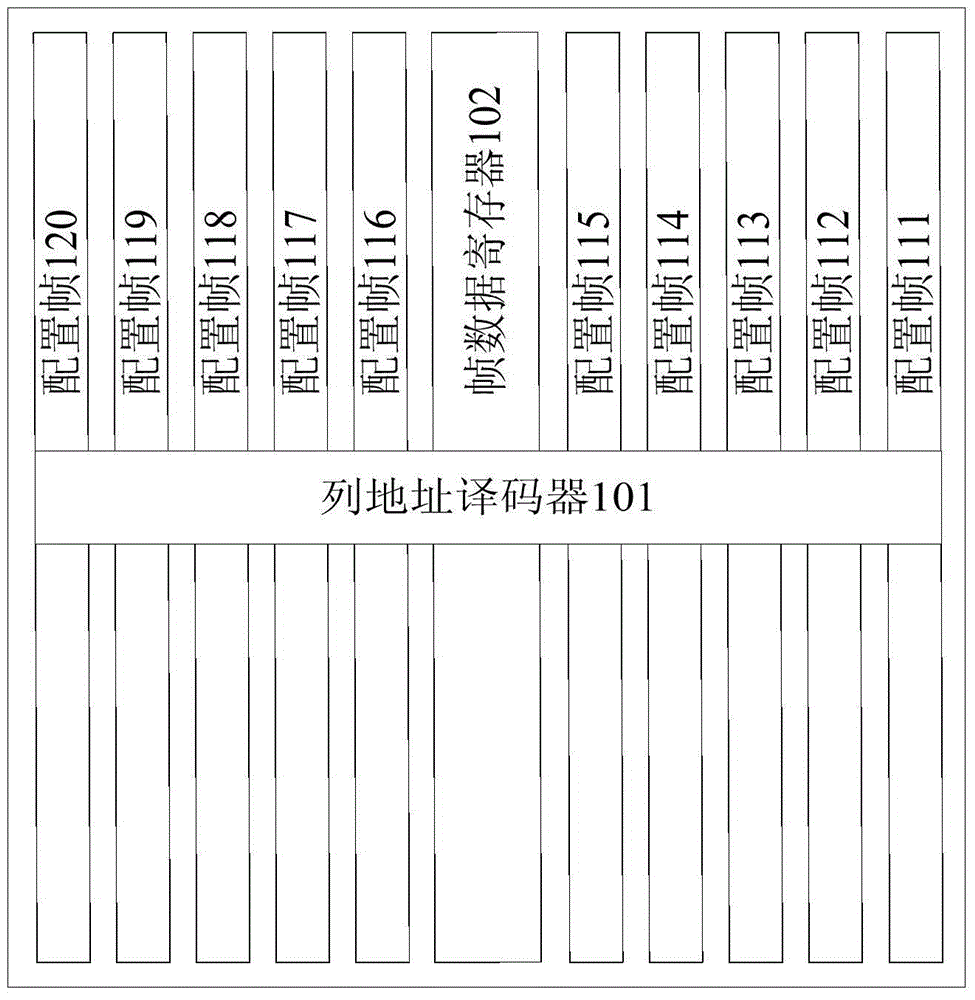

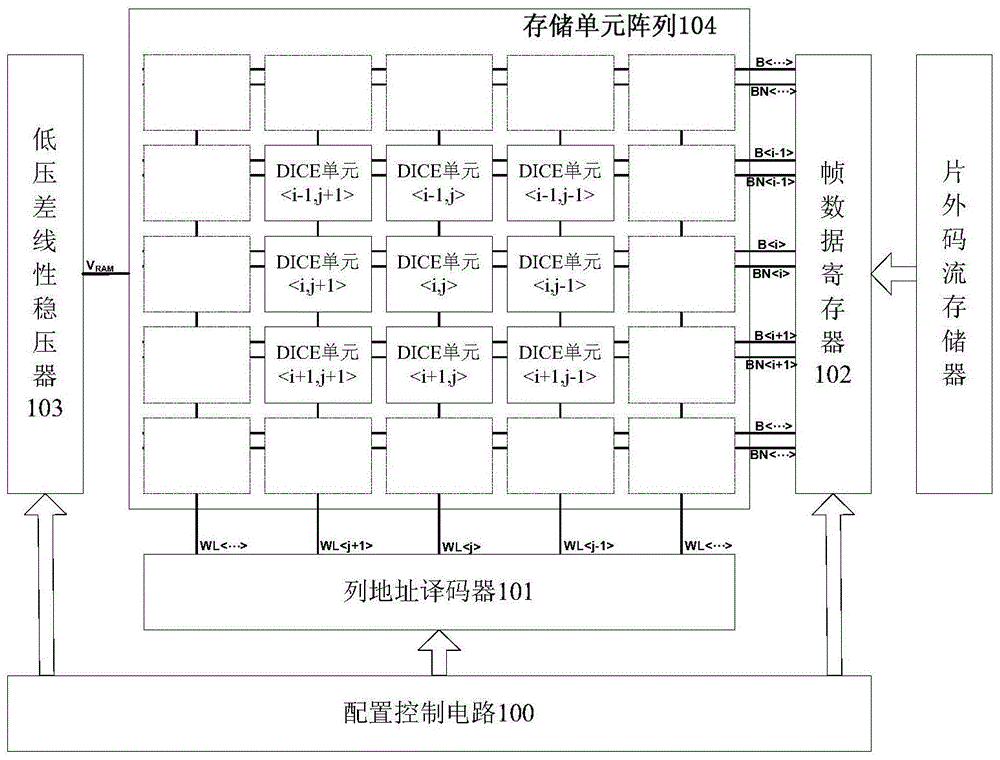

Reinforcement configuration memory array applicable to FPGA for space navigation and configuration method of reinforcement configuration memory array

ActiveCN105741872ASmall area consumptionAchieve radiation resistance hardeningRead-only memoriesElectricityComputer architecture

The invention relates to a reinforcement configuration memory array applicable to an FPGA (Field Programmable Gate Array) for space navigation and a configuration method of the reinforcement configuration memory array, wherein the configuration memory array uses DICEs (Double Interlocked Storage Cells) for realizing single particle reinforcement of the configuration memory array; and the influence of single particles on the configuration memory array is reduced. The configuration method is characterized in that before the configuration memory array is electrified, all configuration memory units are in a 0-write state through a column address decoding circuit and a frame data register; and during electrification, all initial states of all DICEs after the electrification are 0 due to the inductive effect of external work conditions. The logic conflict of an FPGA interconnection matrix after the electrification due to the non-determined state of the configuration memory units is avoided, so that the problem of electrification surge current of the FPGA is effectively solved; the design difficulty of a system using the FPGA is reduced; and the work reliability of the FPGA for space navigation is improved.

Owner:BEIJING MXTRONICS CORP +1

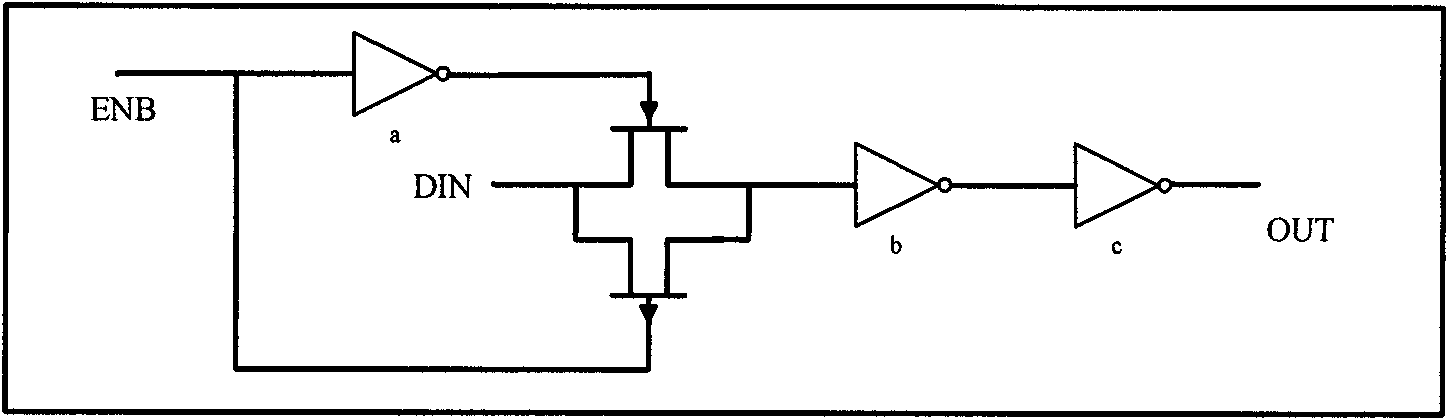

Interconnection matrix for uncompetitive electrification, configuration and reconfiguration of FPGA (Field Programmable Gate Array)

ActiveCN102324926ASolve the problem of high currentLower average currentLogic circuits using elementary logic circuit componentsInformation processingElectricity

The invention discloses an interconnection matrix for uncompetitive electrification, configuration and reconfiguration of an FPGA (Field Programmable Gate Array), comprising a PIPS (Patterned Information Processing System) input point, a PIPS output point, a PIPS two-way point, a logic input controller and a three-state input controller. The input port of the PIPS input point is connected with the output end of a logic module through the logic input controller or directly connected with a power supply or the ground through the three-state input controller, wherein the logic module is connected to the interconnection matrix. The output port of the PIPS output point is connected with the input end of the logic module connected to the interconnection matrix. The outputs of the logic input controller and the three-state input controller are opened or closed under the control of an enable signal. By adopting the interconnection matrix, the problem of heavy current caused by inside signal competition in the processes of electrification, configuration and reconfiguration of an SRAM (System Random Access Memory) type FPGA is solved, and the load of a power supply system during electrification is reduced.

Owner:BEIJING MXTRONICS CORP +1

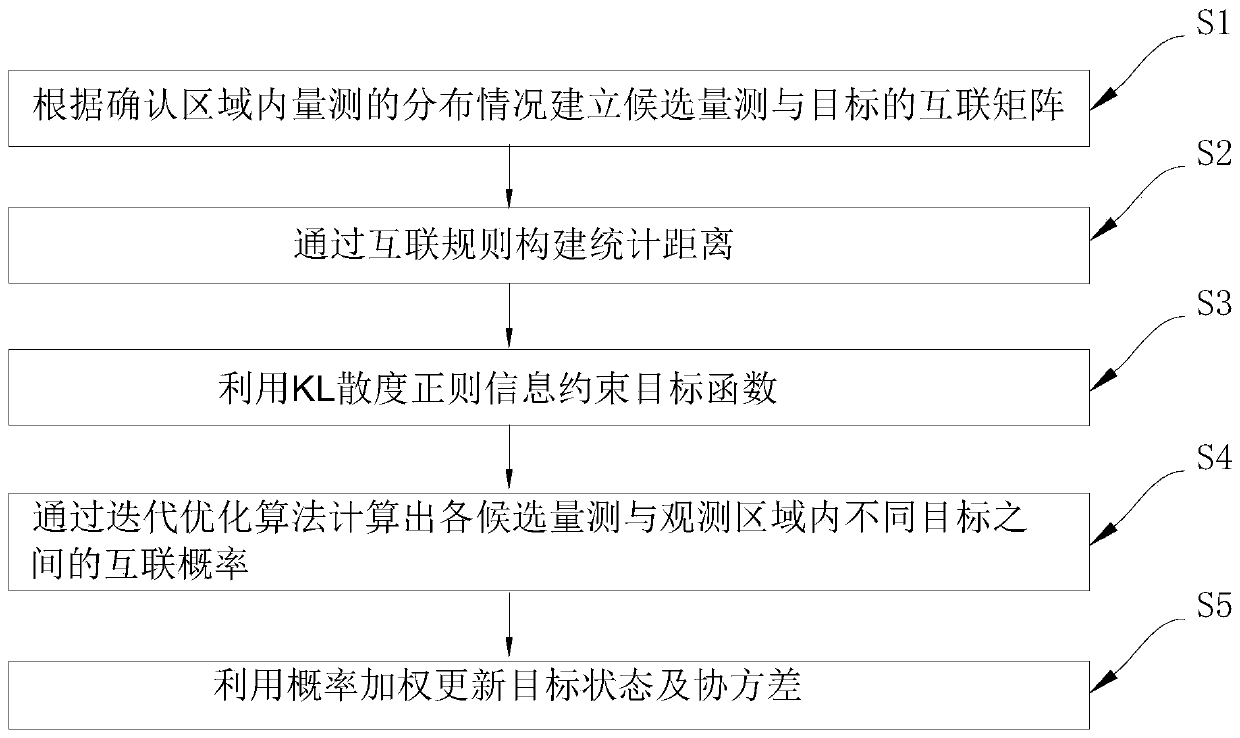

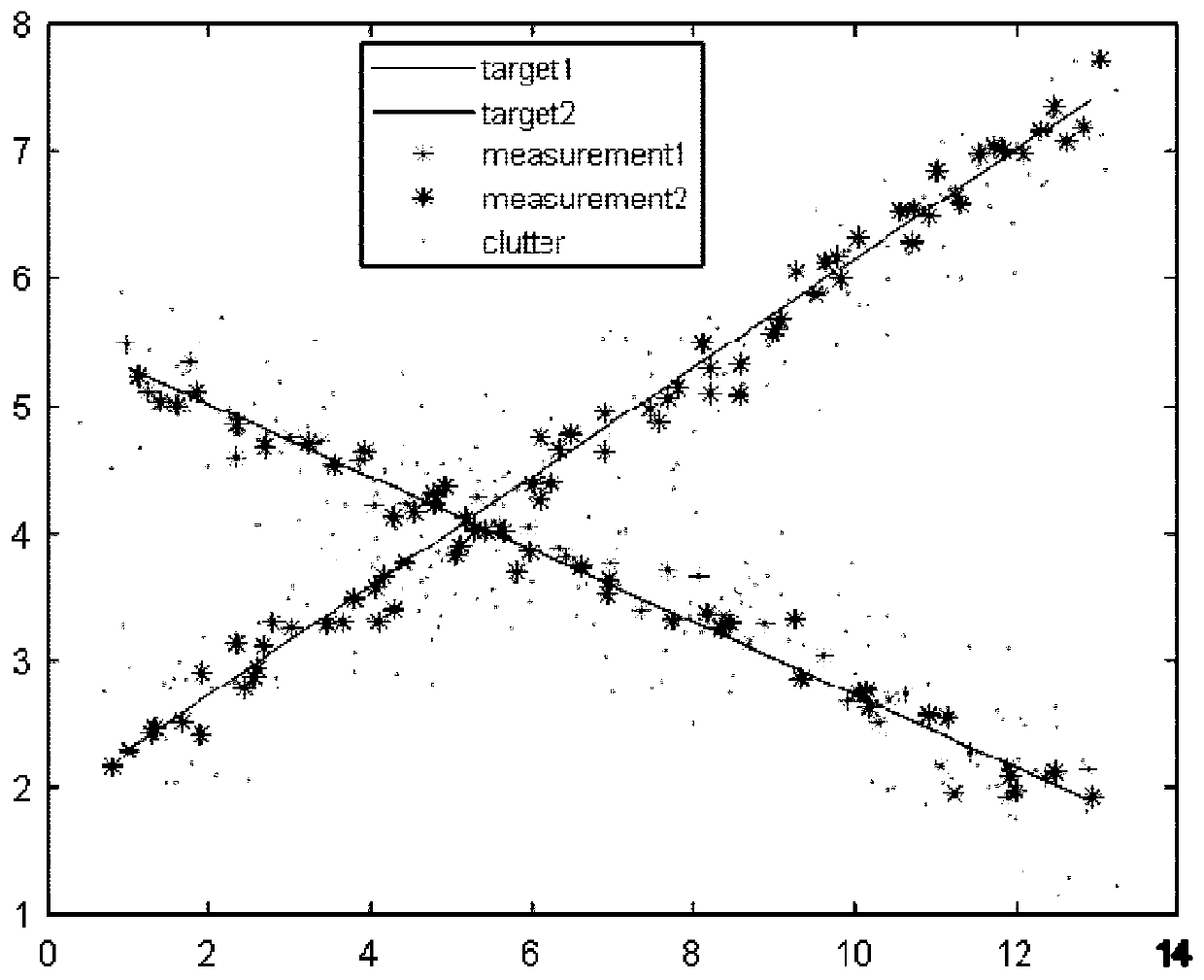

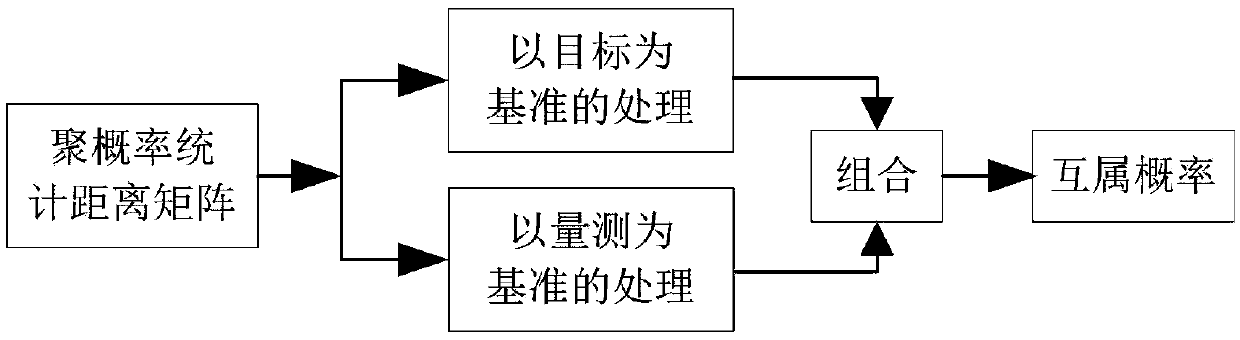

Fuzzy data association method in clutter environment and multi-target tracking method

ActiveCN111259332AImproved real-time performance of multi-target trackingRequirements to meet effective tracking goalsComplex mathematical operationsICT adaptationMulti target trackingEngineering

The invention provides a fuzzy data association method in a clutter environment. The fuzzy data association method comprises the following steps: step 1, establishing an interconnection matrix of candidate measurement and targets according to the distribution condition of measurement in a confirmation area; step 2, constructing a statistical distance through an interconnection rule; step 3, constraining the target function by utilizing KL divergence regular information; step 4, calculating the interconnection probability between each candidate measurement and different targets in the observation area through an iterative optimization algorithm; and step 5, updating the target state and the covariance by using probability weighting. The real-time performance of multi-target tracking is greatly improved, the multi-target tracking precision and the effective tracking rate of the method are similar to those of a classical joint probability data association algorithm, and the requirement for effective target tracking can be met. Correspondingly, the invention further provides a multi-target tracking method.

Owner:SUN YAT SEN UNIV

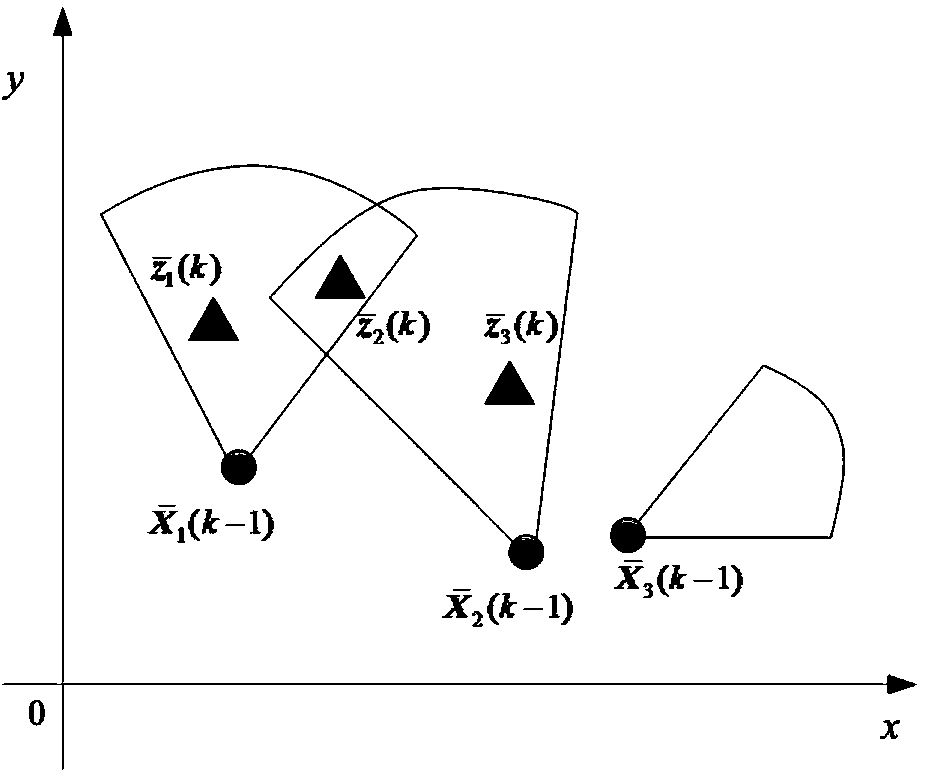

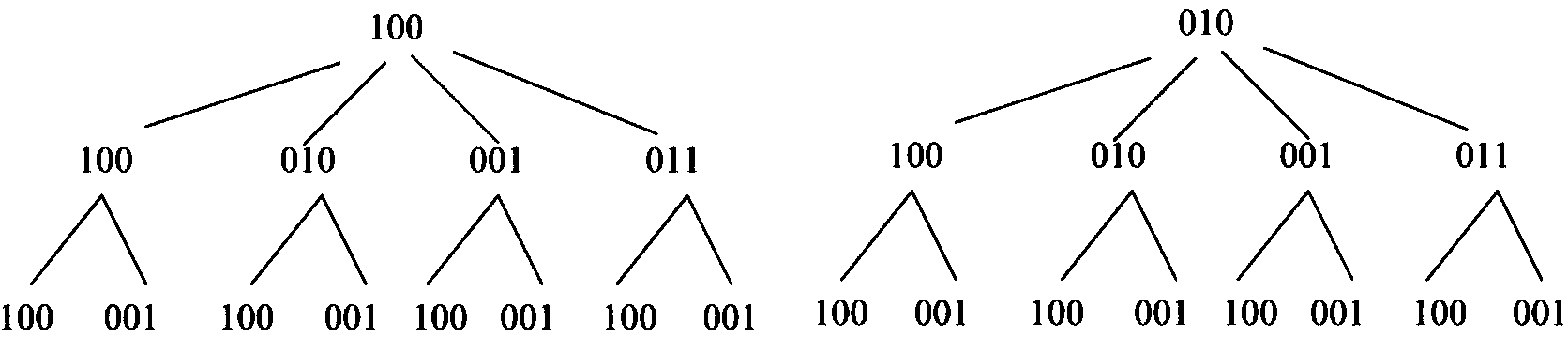

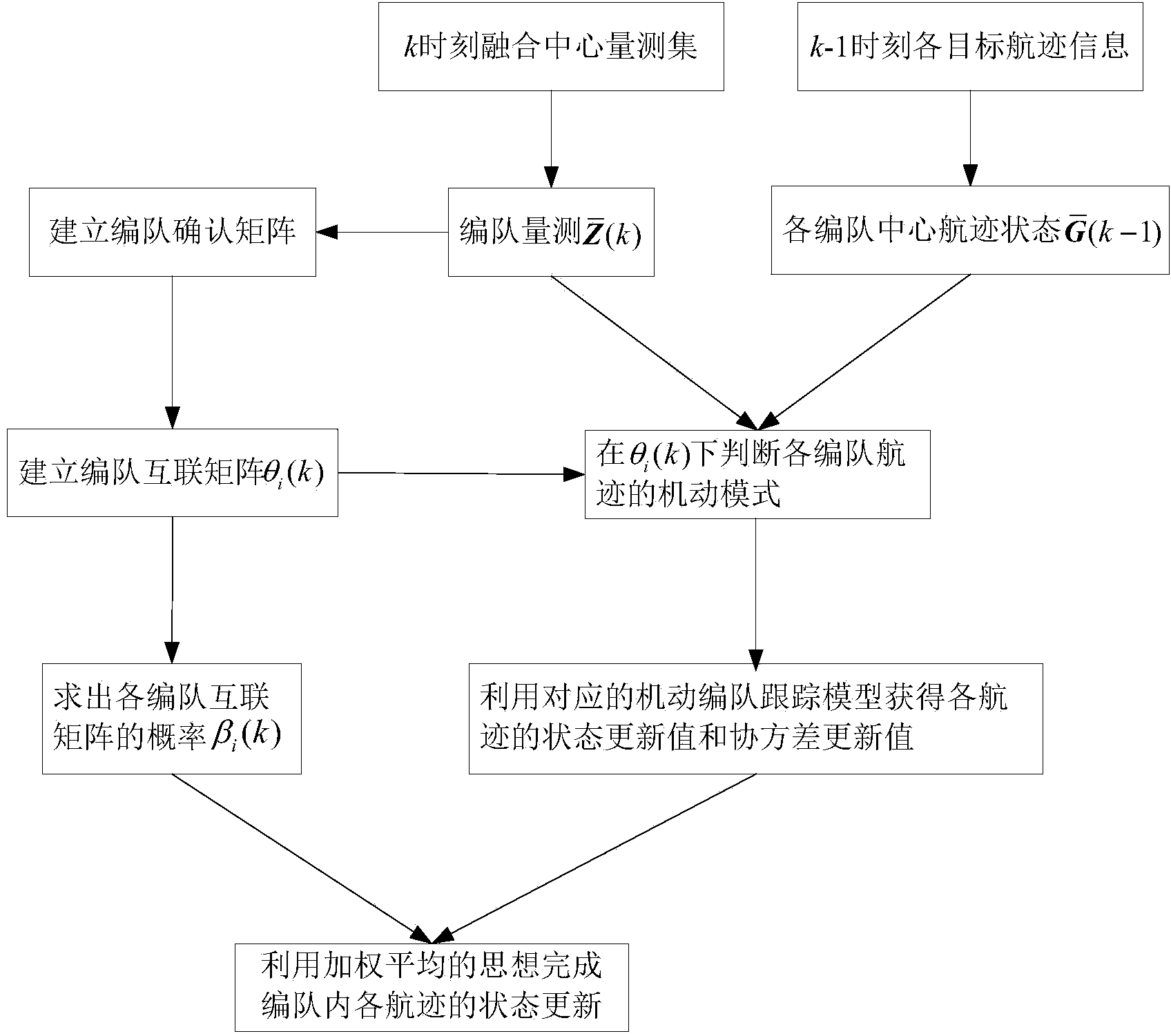

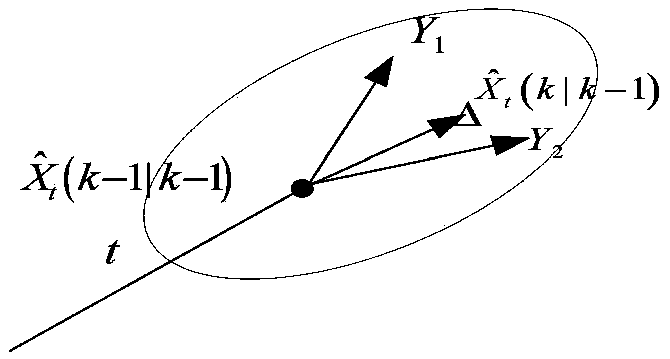

Variable structure joint probability data interconnection formation target tracking method

ActiveCN104237880AImprove tracking accuracyHigh effective tracking rateRadio wave reradiation/reflectionTracking modelMultiple sensor

The invention discloses a variable structure joint probability data interconnection formation target tracking method, and belongs to the field of radar data processing. According to the tracking method, the measurement characteristic of a target in formation when formation maneuvers under detection of multiple sensors is deeply analyzed, a formation confirmation matrix is built based on the central point of formation measurement and a central track of a formation track, a plurality of formation interconnection matrixes are obtained by splitting the formation confirmation matrix, the probability that the interconnection matrixes are true is derived, state update of the target in the formation is completed by judging the maneuvering mode of the target in the formation based on the formation interconnection matrixes and through a corresponding maneuvering formation target tracking model, and accurate tracking of the target in the maneuvering formation under detection of the centralized multiple sensors is achieved according to the probability that the interconnection matrixes are true on the basis of weighted average idea. Compared with the prior tracking technique, the tracking method has the advantages that the tracking accuracy is higher, the effective tracking efficiency is higher, the algorithm time consumption is small, and the application and popularization value is high.

Owner:NAVAL AERONAUTICAL & ASTRONAUTICAL UNIV PLA

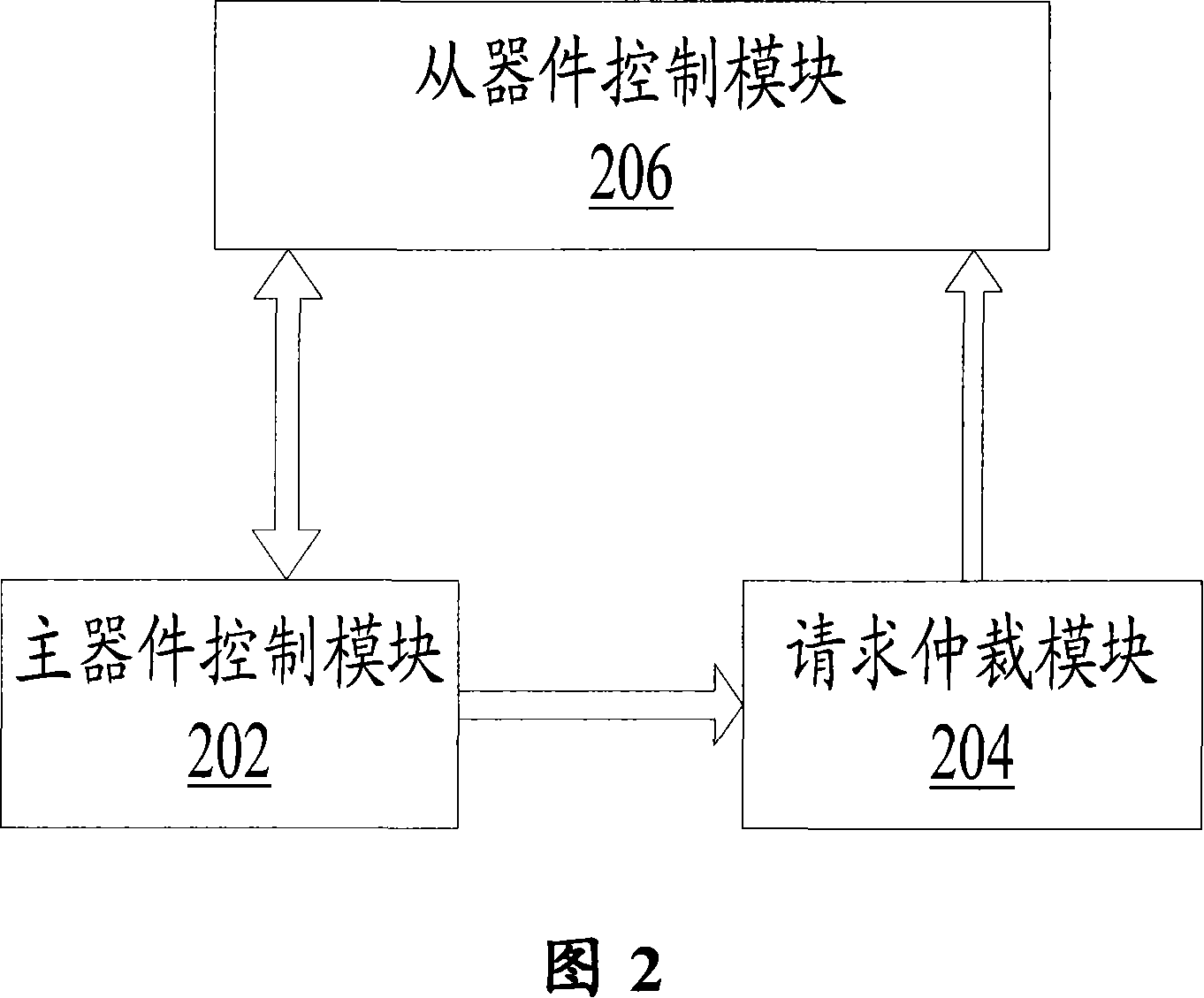

AHB interconnection matrix interface

InactiveCN101141486AImprove operational efficiencyData switching networksElectric digital data processingComputer moduleInterconnection matrix

The present invention discloses an AHB interconnection matrix interface, which comprises a main device control module, which is used to receive the information from the main device and to latch the information, and to send an application for a request arbitration module in a pipeline way; the request arbitration module, which is used to arbitrate the application sent by the main device control module, and to generate the arbitration information; and a sub-device control module, which is used to get the arbitration information from the request arbitration module, and the internal cache or the sub-device performs an information interaction with the main device control module according to the content of the arbitration information and the information. Through the present invention, the pipeline and a high-speed buffer are added on the interconnection matrix through the AHB interconnection matrix with the high-speed buffer, to enable the operating efficiency of the matrix to be increased greatly, simultaneously, due to the high-speed buffer being taken as a sharing high-speed buffer, the integrated operating efficiency of a multi-kernel system can be improved.

Owner:ZTE CORP

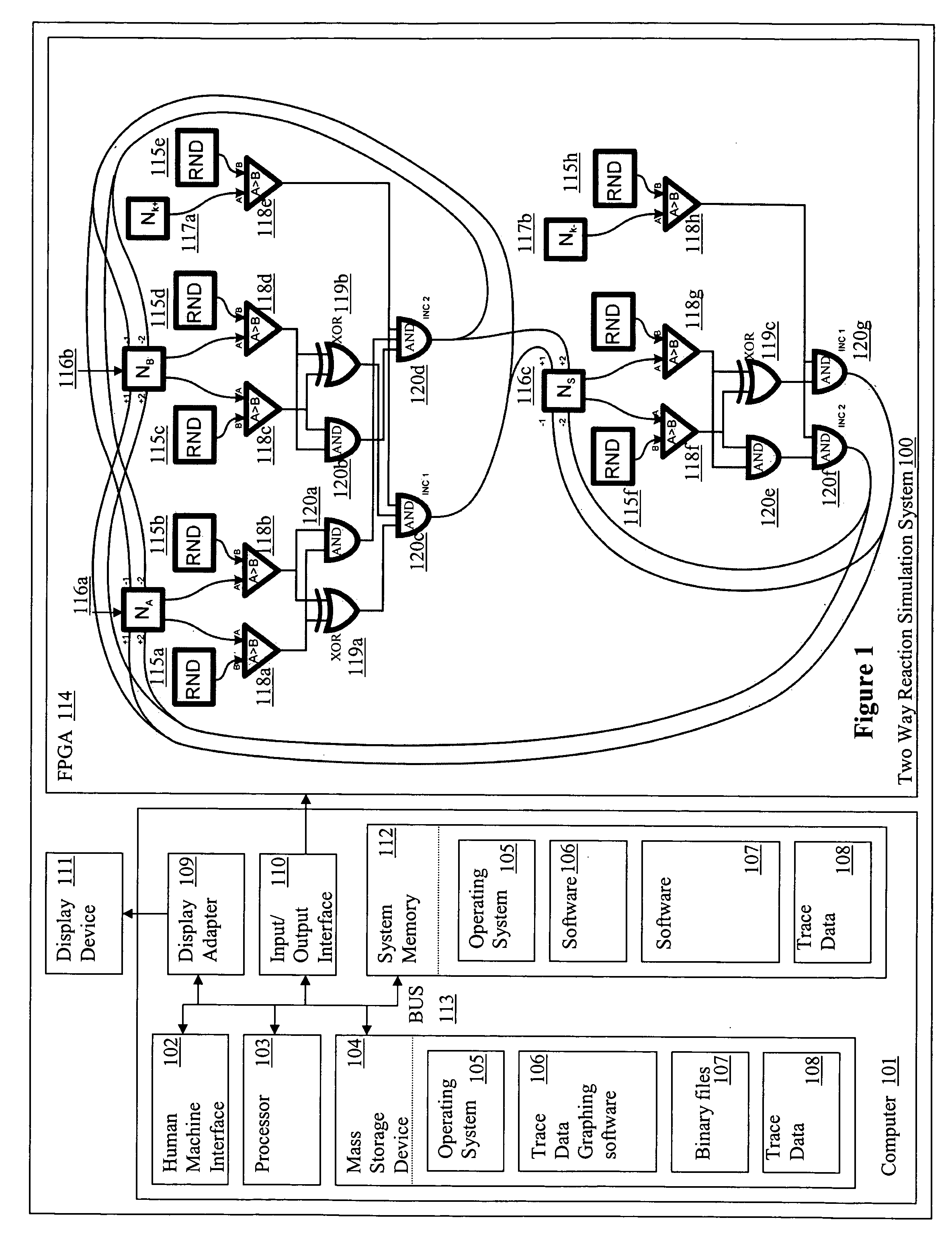

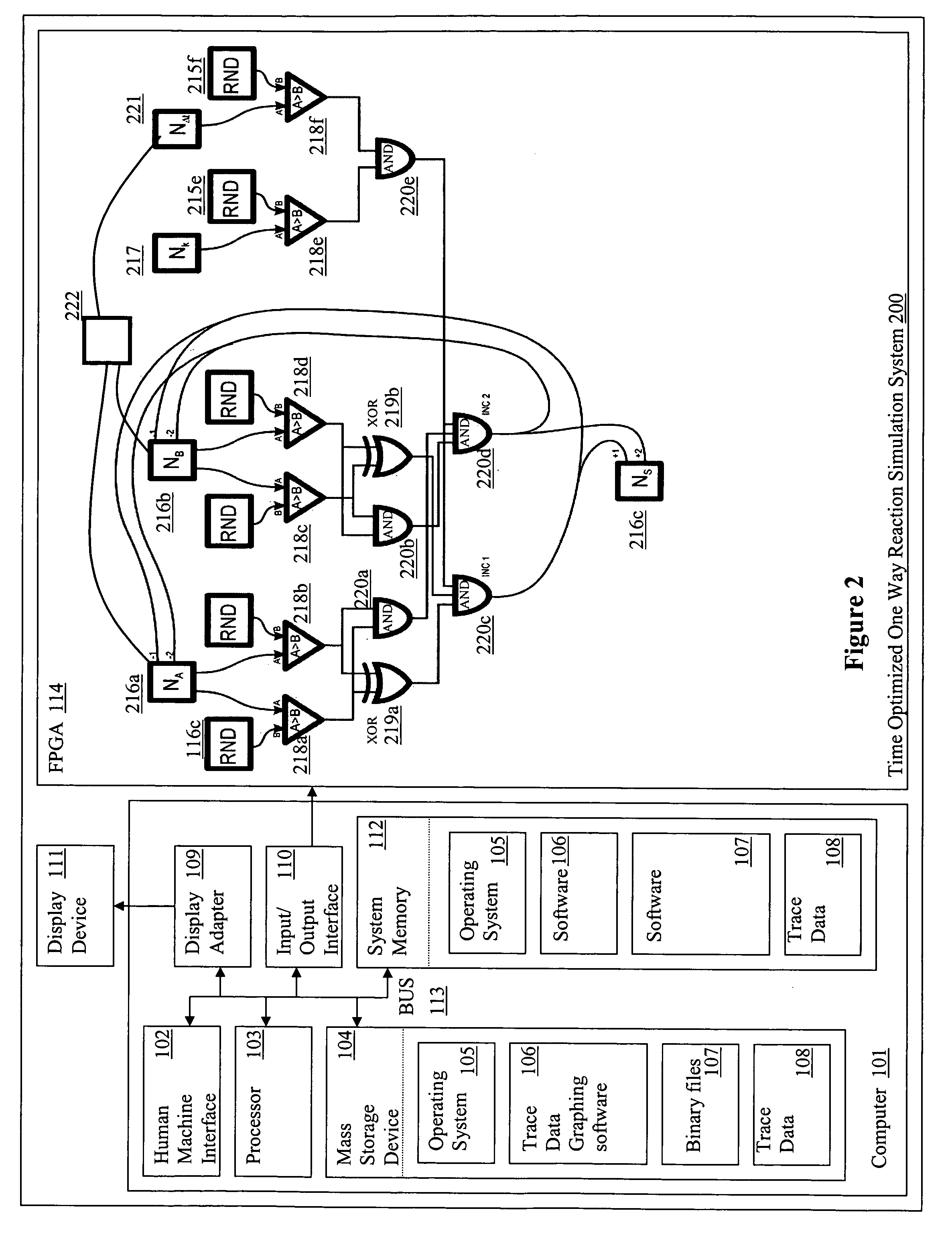

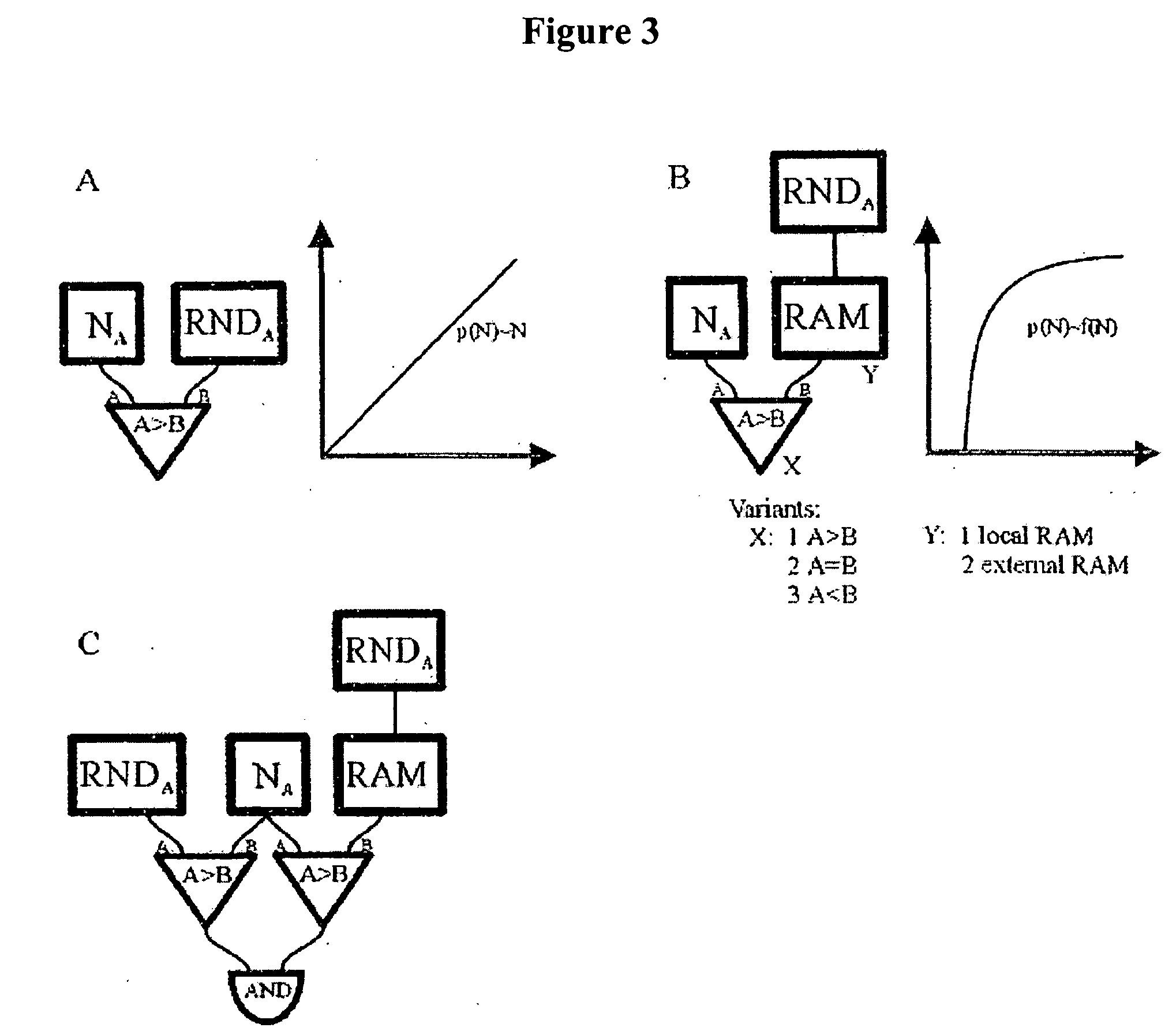

Method for simulating the dynamics of biological networks in silico

InactiveUS20050251375A1NanoinformaticsAnalogue computers for chemical processesAnalog computerChemical network

A stochastic simulation method for simulating the kinetics of chemical networks implemented using reprogrammable Field Programmable Gate Array (FPGA) devices. Such devices, built as an array of simple configurable logic blocks embedded in a programmable interconnection matrix, implement highly parallel architectures comparable in complexity to biochemical networks. Circuits based on FPGAs scale efficiently so that simulations of realistic biological systems are possible.

Owner:RGT UNIV OF CALIFORNIA

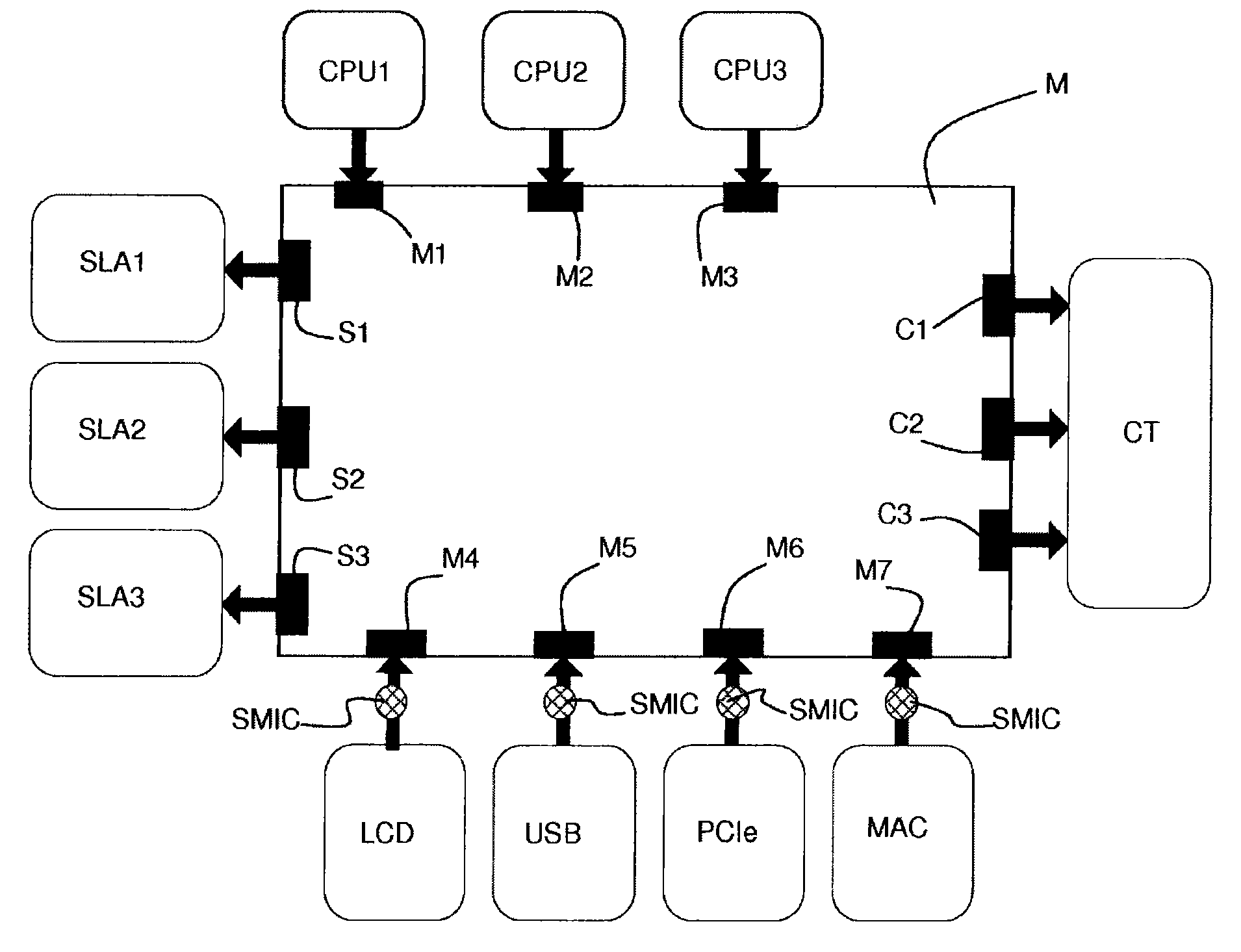

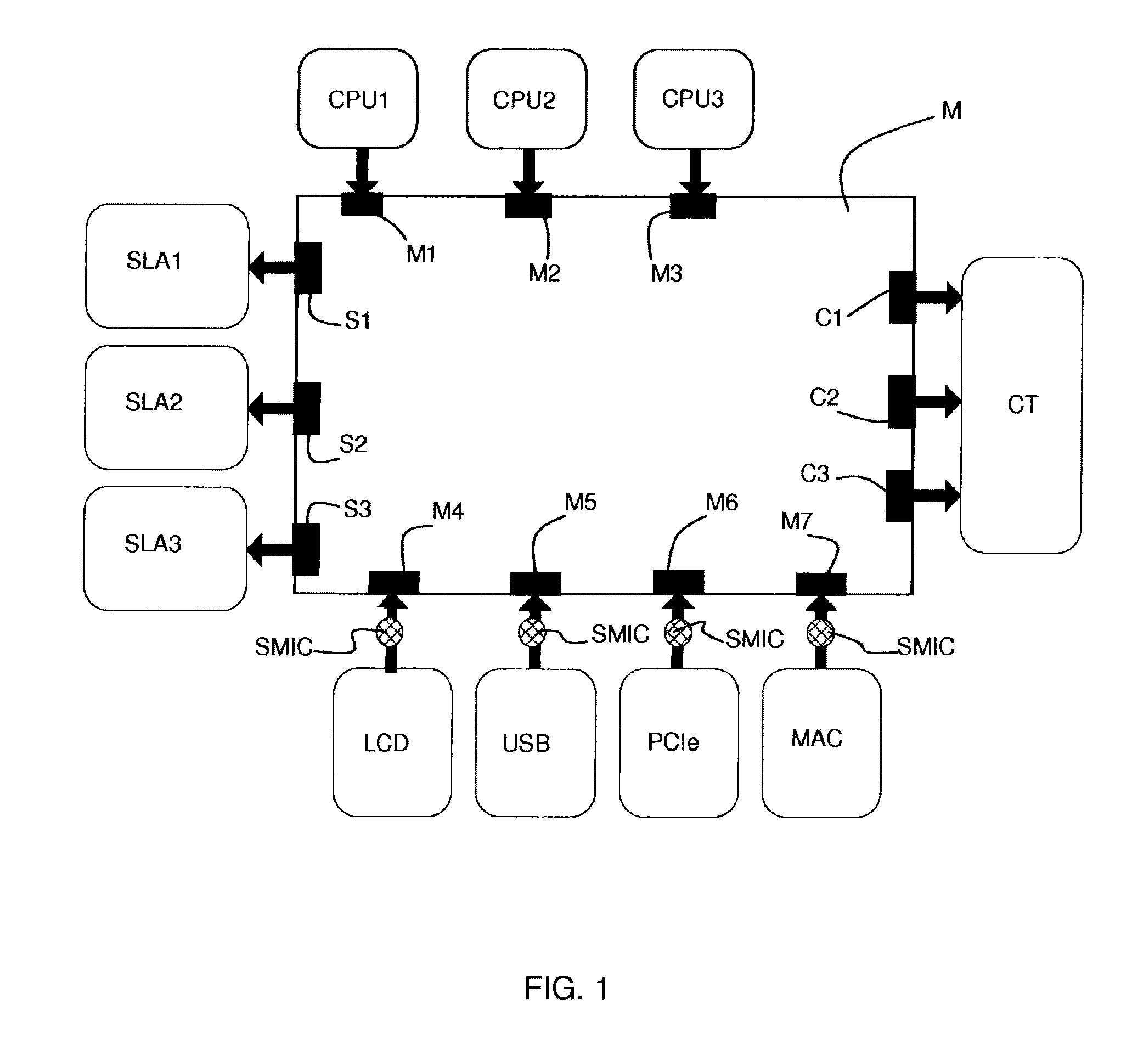

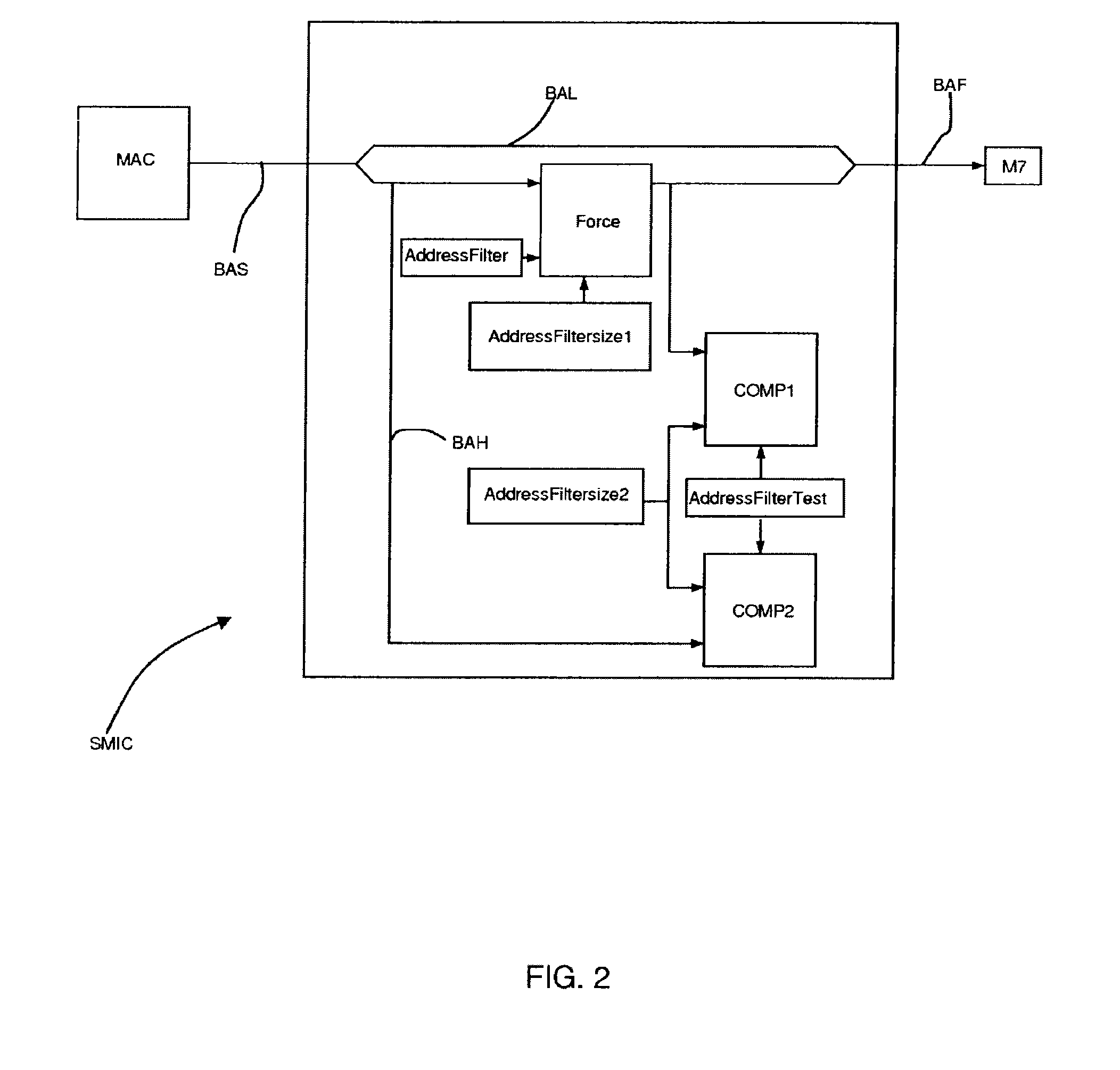

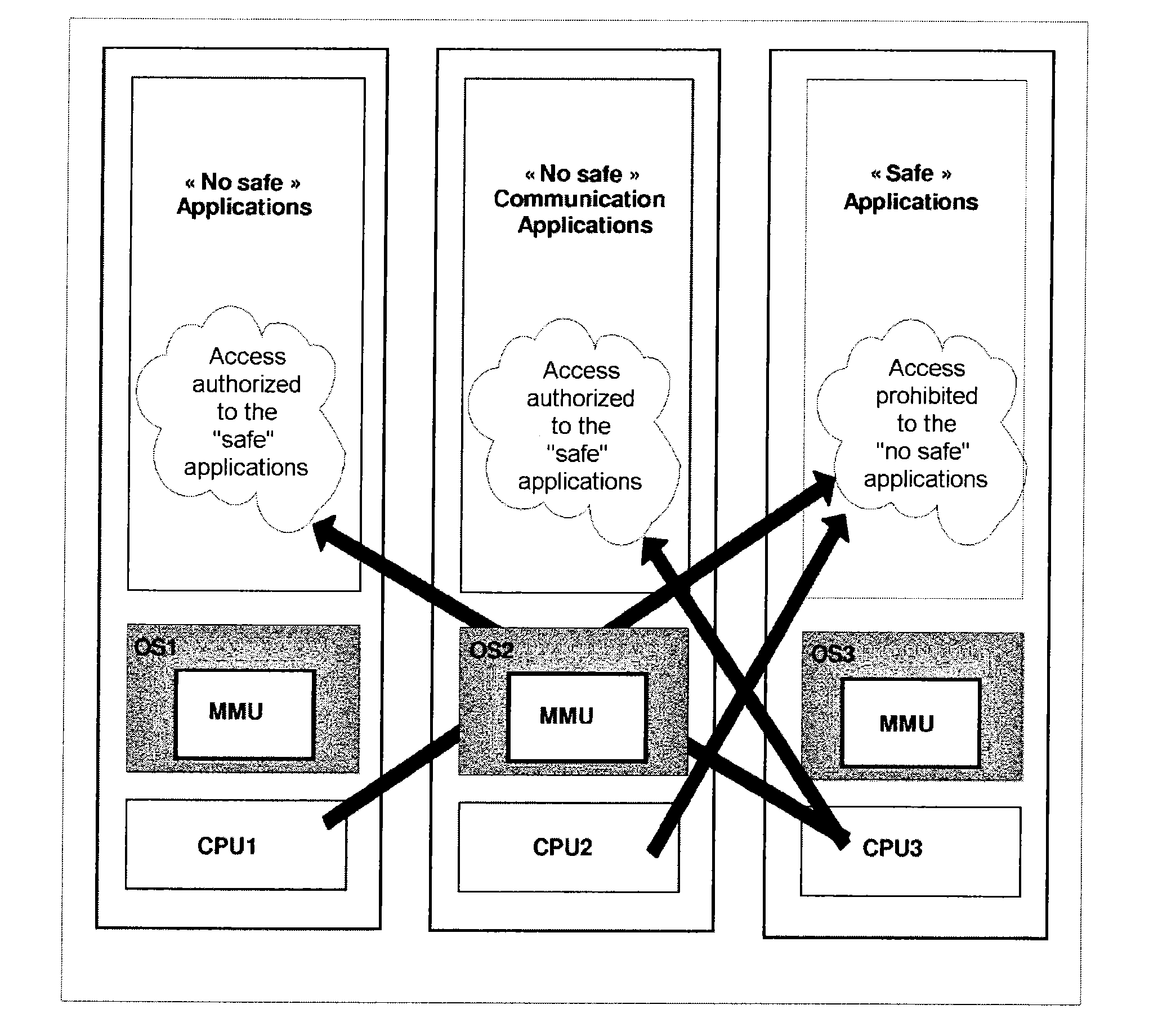

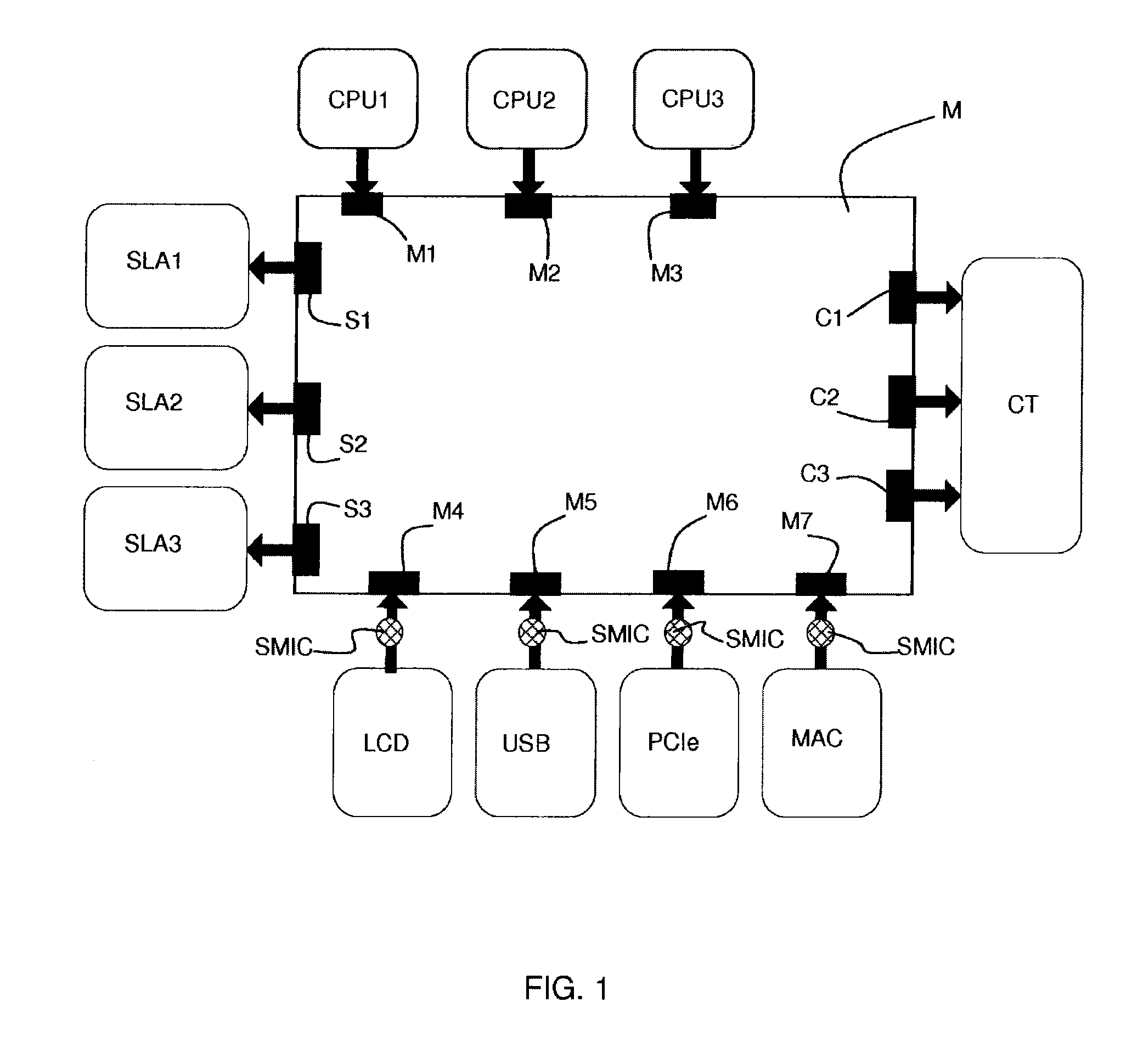

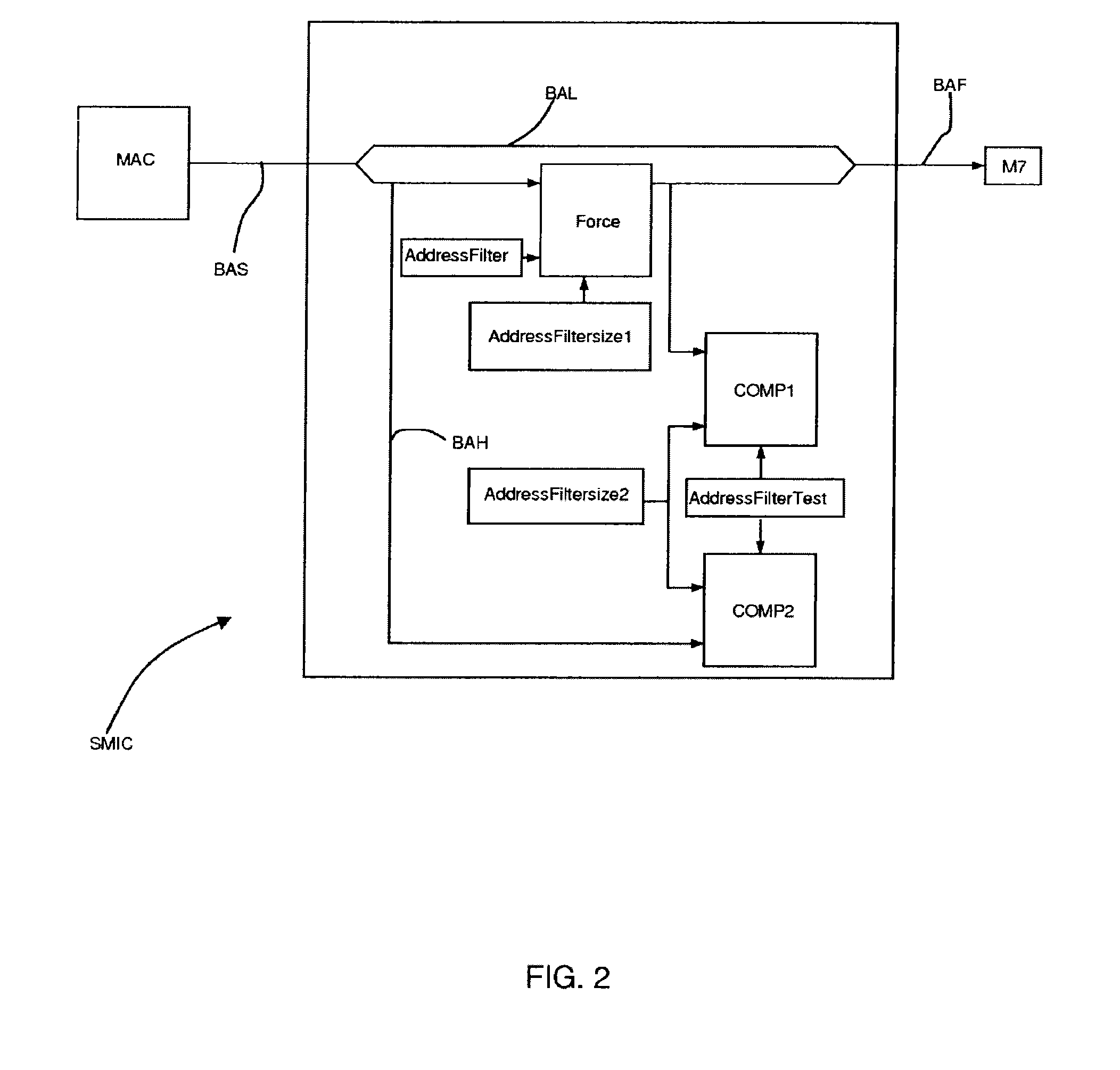

System for managing secure and nonsecure applications on one and the same microcontroller

ActiveUS9323953B2Unauthorized memory use protectionInternal/peripheral component protectionMicrocontrollerInterconnection matrix

An electronic microcontroller system including: plural processors; at least one interface for exchange with at least one peripheral, the peripheral being user master of the electronic microcontroller system; a mechanism for access to a shared memory space; an interconnection matrix for interconnecting the exchange interface, the processors and the mechanism for access to a shared memory space; a mechanism managing applications involving a guaranteed level of security and integrity and of applications exhibiting a nonguaranteed level of security and integrity. The exchange interface cooperates with a secure isolation cell of the memory situated between the user master peripheral and the interconnection matrix.

Owner:SCHNEIDER ELECTRIC IND SAS

System for managing secure and nonsecure applications on one and the same microcontroller

ActiveUS20150067773A1Digital data processing detailsUnauthorized memory use protectionMicrocontrollerInterconnection matrix

An electronic microcontroller system including: plural processors; at least one interface for exchange with at least one peripheral, the peripheral being user master of the electronic microcontroller system; a mechanism for access to a shared memory space; an interconnection matrix for interconnecting the exchange interface, the processors and the mechanism for access to a shared memory space; a mechanism managing applications involving a guaranteed level of security and integrity and of applications exhibiting a nonguaranteed level of security and integrity. The exchange interface cooperates with a secure isolation cell of the memory situated between the user master peripheral and the interconnection matrix.

Owner:SCHNEIDER ELECTRIC IND SAS

Interconnection matrix using semiconductor non-volatile memory

An interconnection matrix consists of a plurality of semiconductor Non-Volatile Memory (NVM) forming an M×N array. Semiconductor NVM devices in the array are either programmed to a high threshold voltage state or erased to a low threshold voltage state according to a specific interconnection configuration. Applied with a gate voltage bias higher than the low threshold voltage and lower than the high threshold voltage to the control gates of the entire semiconductor NVM devices in the array, the configured interconnection network is formed. The disclosed interconnection matrix can be applied to configuring circuit routing in Integrated Circuit (IC).

Owner:FLASHSILICON

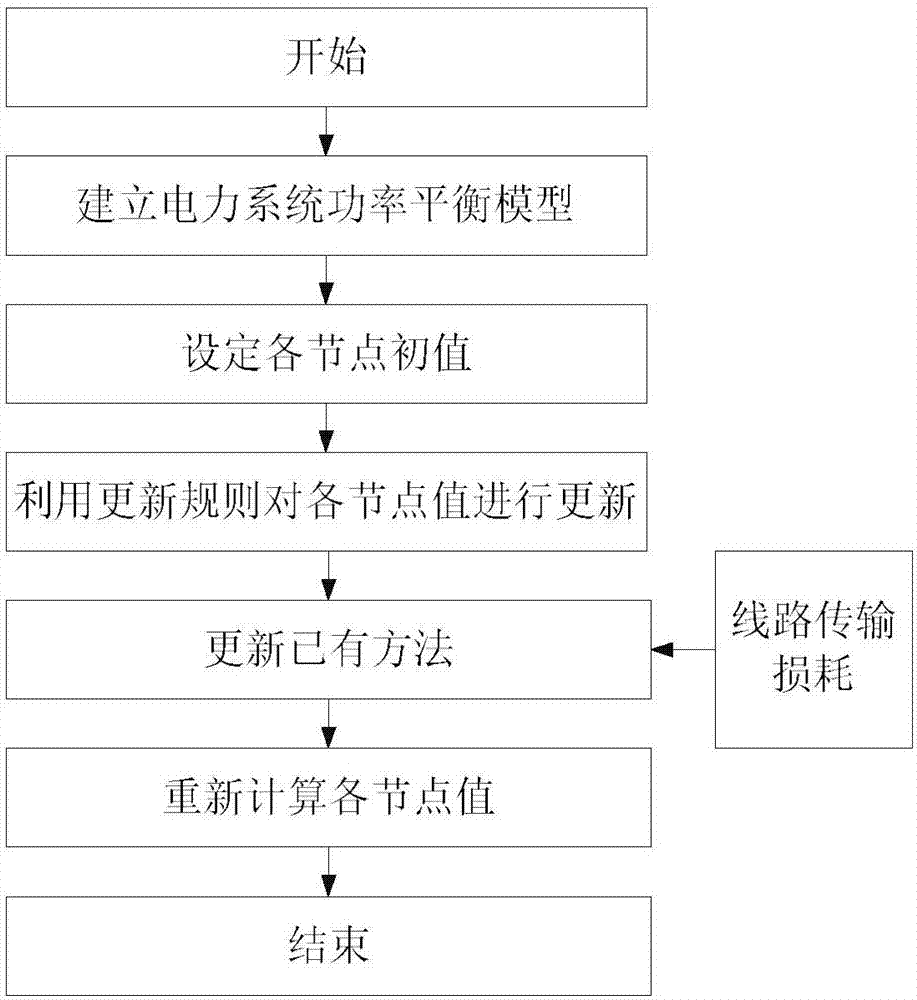

Power system load scheduling method considering line transmission loss

The invention provides a power system load scheduling method considering line transmission loss. The method comprises the following steps: firstly, establishing a power system power balance model based on the distributed control principle, then setting initial power values of nodes, and establishing a node interconnection matrix according to the constraint conditions of the nodes; then, updating the power values of the nodes by using the node interconnection matrix and the initial power values to obtain stable power values of the nodes; and finally updating the method by considering the line transmission loss condition to obtain a new method satisfying the constraint conditions and considering the line transmission loss at the same time, and calculating the power values of the nodes again. And example analysis is provided to test the correctness of the provided method.

Owner:HOHAI UNIV

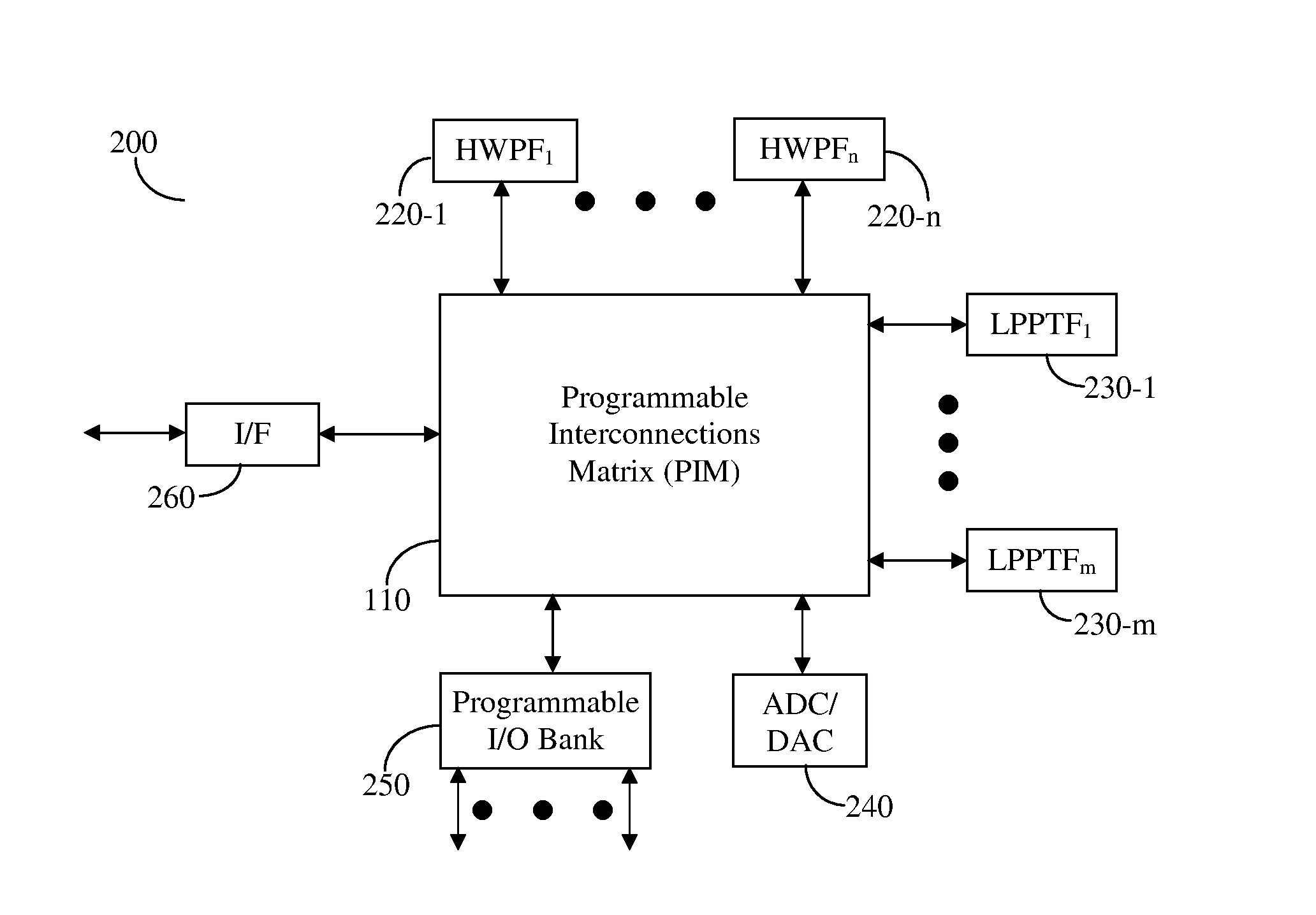

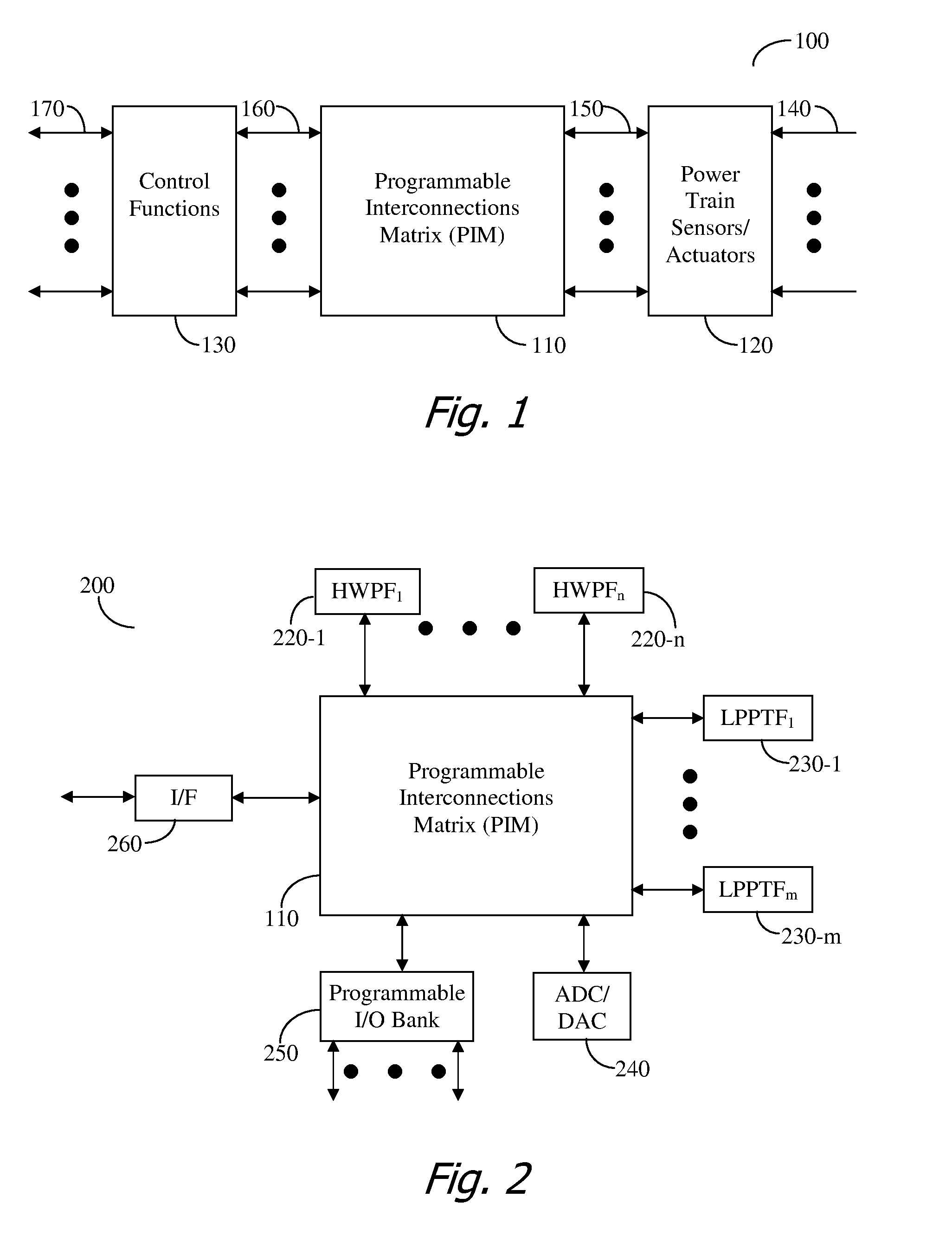

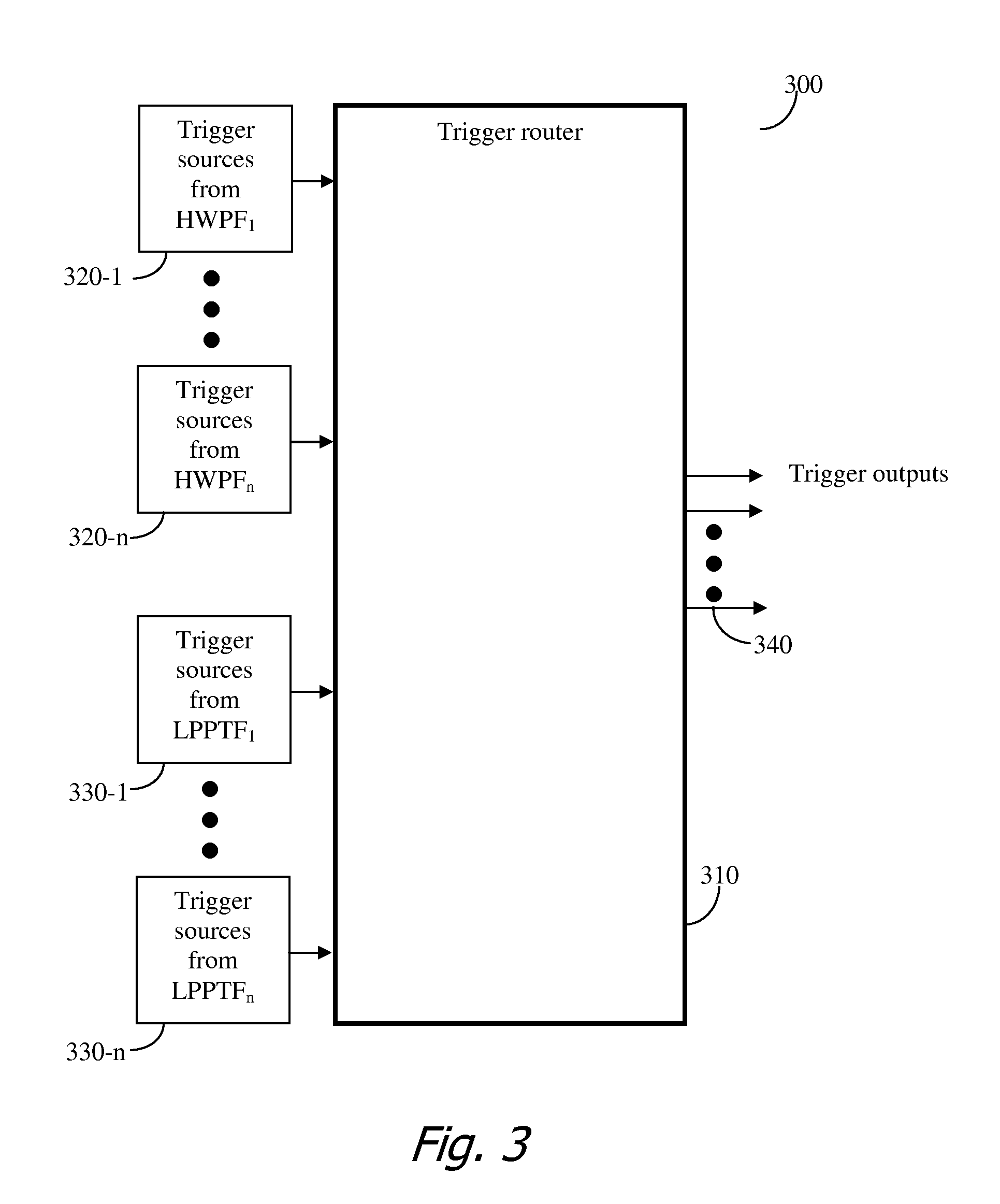

Real-Time Flexible Vehicle Control Apparatus

ActiveUS20130138263A1Electrical controlDigital data processing detailsInterconnection matrixEmbedded system

An apparatus on an integrated circuit provides a real-time flexible interface between inputs from a vehicle components and outputs to the vehicle control components. The functions comprises of a programmable interconnection matrix, engine sensors and a control interface. Both engine sensors and control functions comprise of fixed hardwired functions and a customization hardware area. The apparatus therefore provides means for flexible powertrain events control target for the next generation of low-polluting power trains of vehicles.

Owner:SILICON MOBILITY

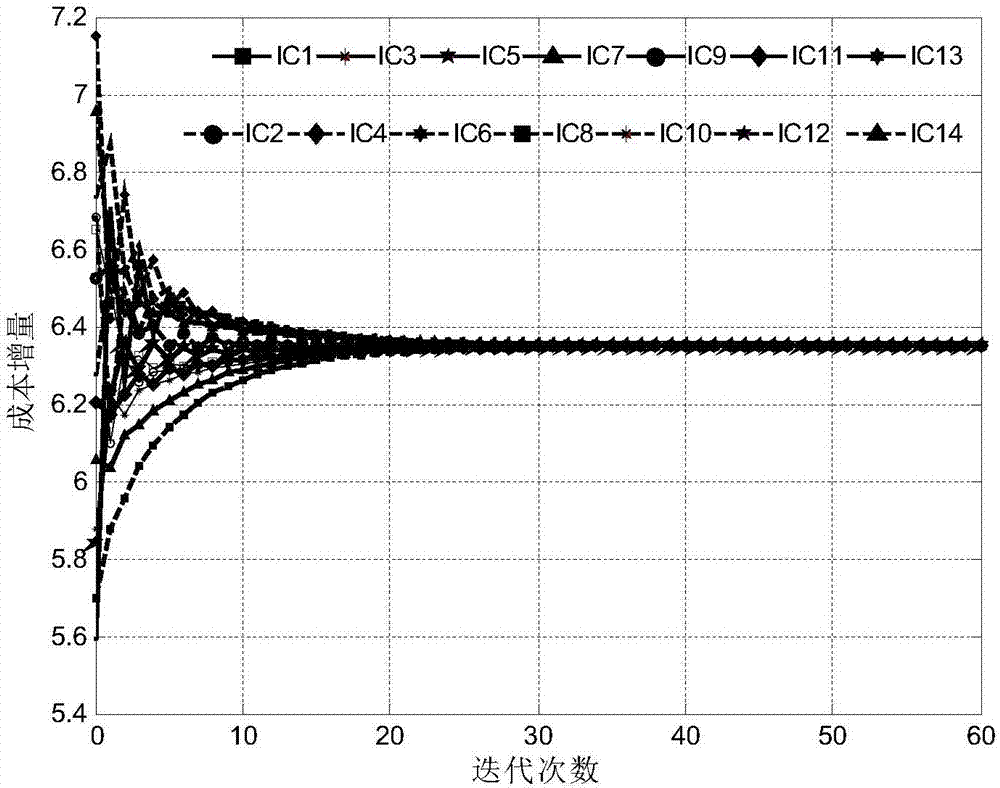

An Optimal Planning Method for Main Transformer Connection Structure of Distribution Network Considering mpsc and MCCC

The invention discloses a power distribution network main transformer connection structure optimization planning method taking maximum power supply capability and minimum connection construction cost into account. The method is characterized by comprising establishment of a connection structure optimization model, solving of the connection structure optimization model, section of an optimal solution and the like. According to the method, overall consideration is given to the maximum power supply capability and investment costs, a main transformer connection structure optimization model is built while a feed line interconnection matrix is used as decision variable, a medium voltage power distribution network connection structure optimization method taking geography factors into account is put forward, effects exerted on a connection structure by geographic environment is demonstrated, and connection relations among all feed lines are shown; the method is advantaged by scientific and reasonable properties, strong applicability, good effect and the like.

Owner:NORTHEAST DIANLI UNIVERSITY

A Radar Signal Sorting Method Based on Probabilistic Data Association

The invention belongs to the radar signal sorting technology field and particularly relates to a radar signal sorting method based on probability data association. The method comprises steps that sampling data of one sampling period under the clutter environment is utilized to determine an initial radar parameter database through a logic method; combined probability data association is carried out for the sampling data, a confirmation matrix is split into interconnection matrixes, and combined event probability is calculated, including calculating an innovation covariance, a target gain matrix and a state estimation covariance; the radar parameter database is updated; steps are repeated till association of the sampling data is accomplished. The method is advantaged in that the stable radar signal parameters can be accurately and effectively acquired under conditions of relatively low signal to noise ratio and limited sampling data accuracy, probability interconnection of data of each sampling point at each moment in the sampling period and the radar database data is carried out, the radar database parameters are further predicted and updated, and thereby a purpose of sorting accurate radar signals under clutter and signal coexistence conditions can be realized.

Owner:HARBIN ENG UNIV

An Exponential Convergence Control Method for Global Stability of Flexible HVDC Transmission System

InactiveCN104319758BImprove stabilityImprove transient characteristicsDc circuit with intermediate acTransient stateHigh-voltage direct current

The invention discloses an exponential convergence control method for the global stability of a voltage source converter based high-voltage direct-current (VSC-HVDC) system, comprising the following steps: (1) obtaining a PCHD model of a VSC-HVDC system; (2) presetting an energy function of the VSC-HVDC system, and changing the original energy function of the system according to a preset interconnection matrix Jd and a damping matrix Ra(x) to obtain a new PCHD model when the VSC-HVDC system is passive; (3) selecting a steady-state equilibrium point needed by the VSC-HVDC system, constructing a needed closed-loop storage function Hd(x), and enabling the closed-loop storage function Hd(x) to meet the conditions of an IDA-PB theorem; and (4) obtaining an exponential stability IDA-PB controller of the VSC-HVDC system, and controlling the VSC-HVDC system according to the exponential stability IDAPB controller. By adopting the method, the VSC-HVDC system is enabled to have good steady-state and transient property when the system is under large disturbance or system parameters cannot be accurately predicted, and the global asymptotic stability is maintained.

Owner:CHINA EPRI ELECTRIC POWER ENG CO LTD +1

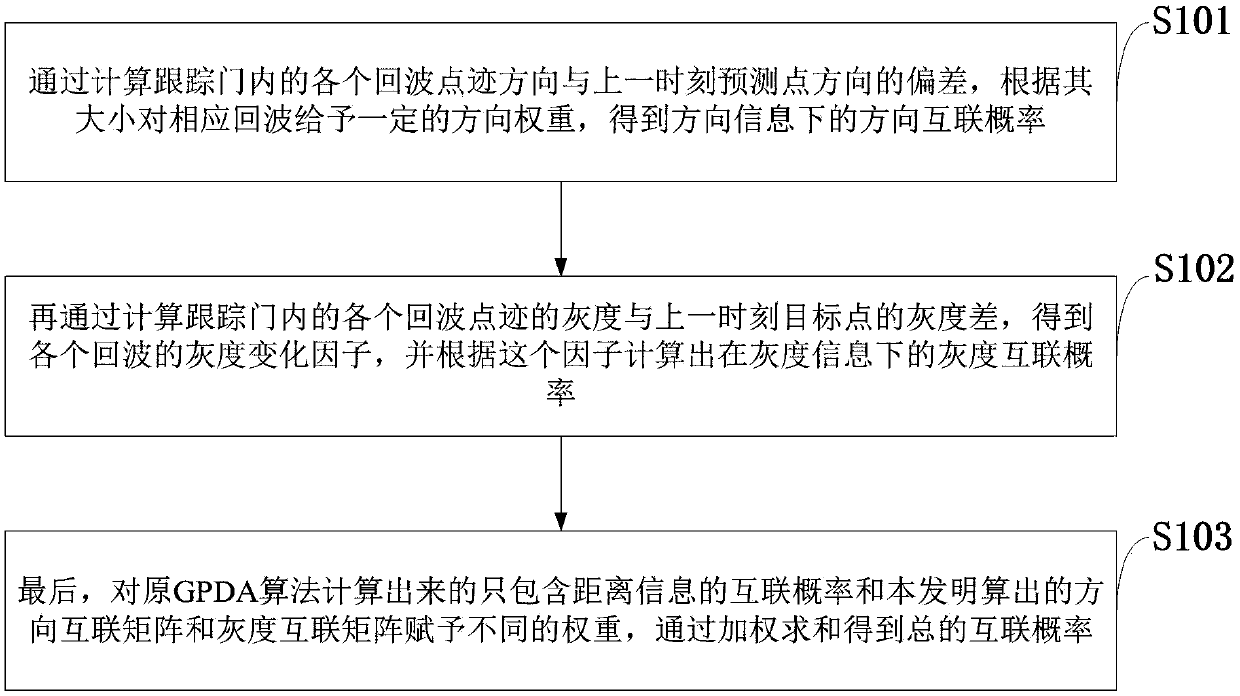

Data correlation problem processing method in large-view field photoelectric imaging multi-weak and small target tracking

InactiveCN109633677ALost follow rate reductionImproved precision impactElectromagnetic wave reradiationGray levelImaging analysis

The invention belongs to the technical field of image analysis, and discloses a data correlation problem processing method in large-view field photoelectric imaging multi-weak and small target tracking. The processing method comprises the following steps that deviation between the direction of each echo point trace in a tracking door and the direction of a prediction point at the previous moment is calculated, a certain direction weight is given to corresponding echoes according to the size of the deviation, and the direction interconnection probability under the direction information is obtained; then a gray level difference between each echo point trace in the tracking door and a target point at the previous moment is calculated, a gray scale change factor of each echo is obtained, and the grey level interconnection probability under the gray level information is obtain through calculation according to the factor; and finally, different weights are given to the interconnection probability which only contains the distance information calculated through an original GPDA algorithm and the calculated direction interconnection matrix and the gray level interconnection matrix, and thetotal interconnection probability is obtained through weighted summation. The processing method has the advantage that on the basis of inheriting the original GPDA algorithm, the tracking performanceis greatly improved at a small calculation amount cost.

Owner:ARMOR ACADEMY OF CHINESE PEOPLES LIBERATION ARMY

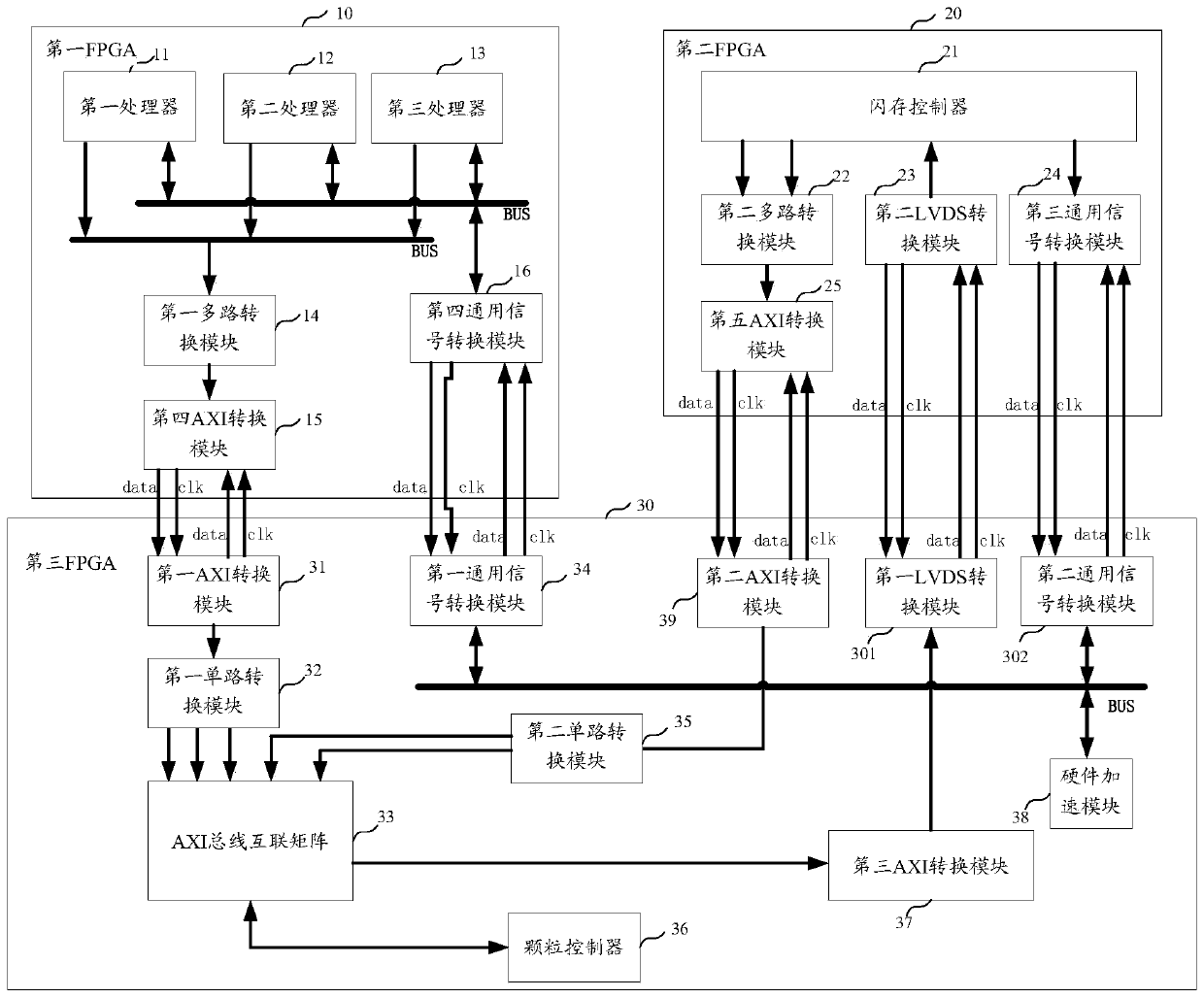

A multi-fpga interconnection device

ActiveCN109144927BHigh speedTiming easyElectric digital data processingComputer architectureFlash memory controller

Owner:SHENZHEN YILIAN INFORMATION SYST CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com