Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

254 results about "Image reduction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and apparatus for contactless hand recognition

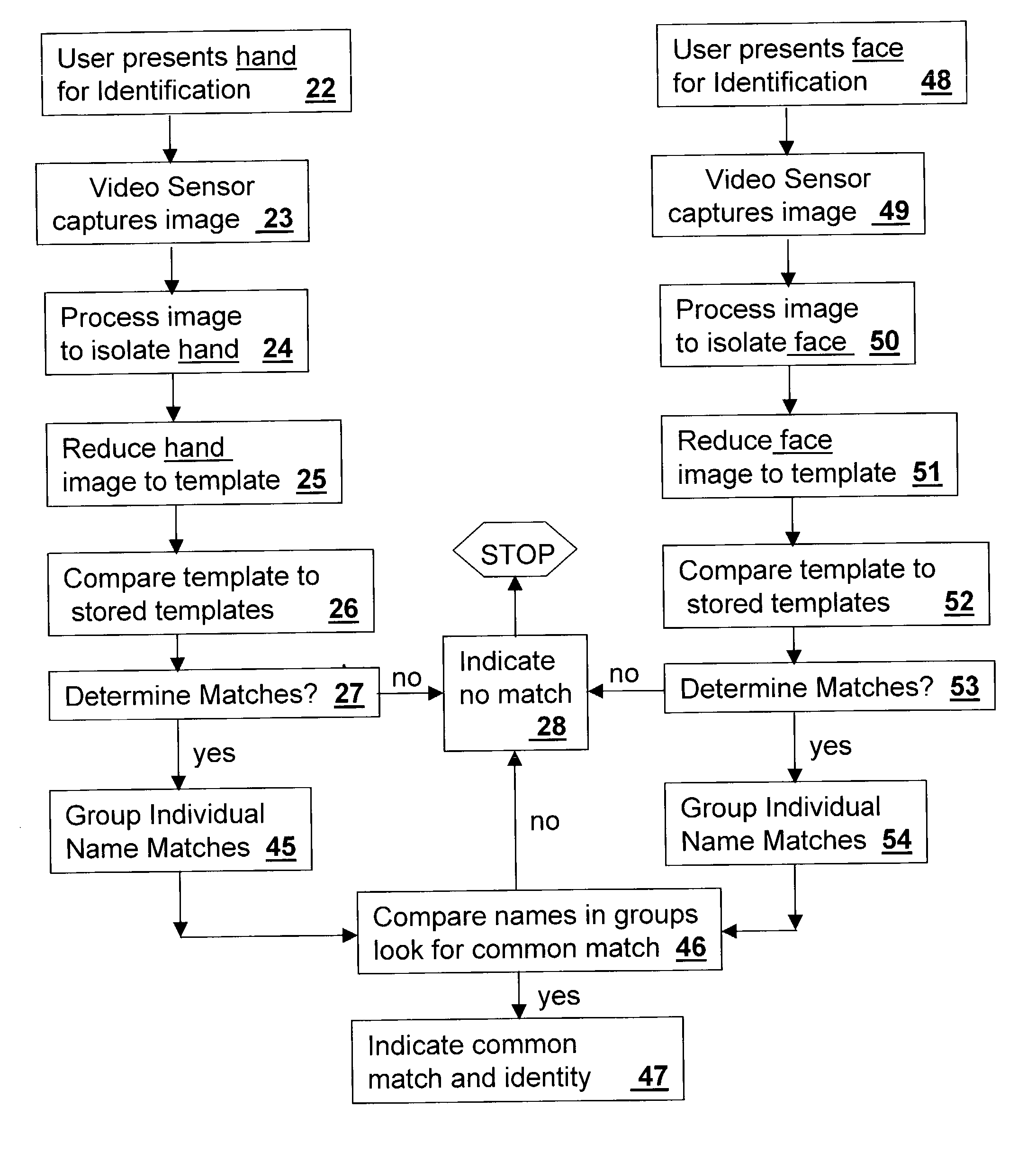

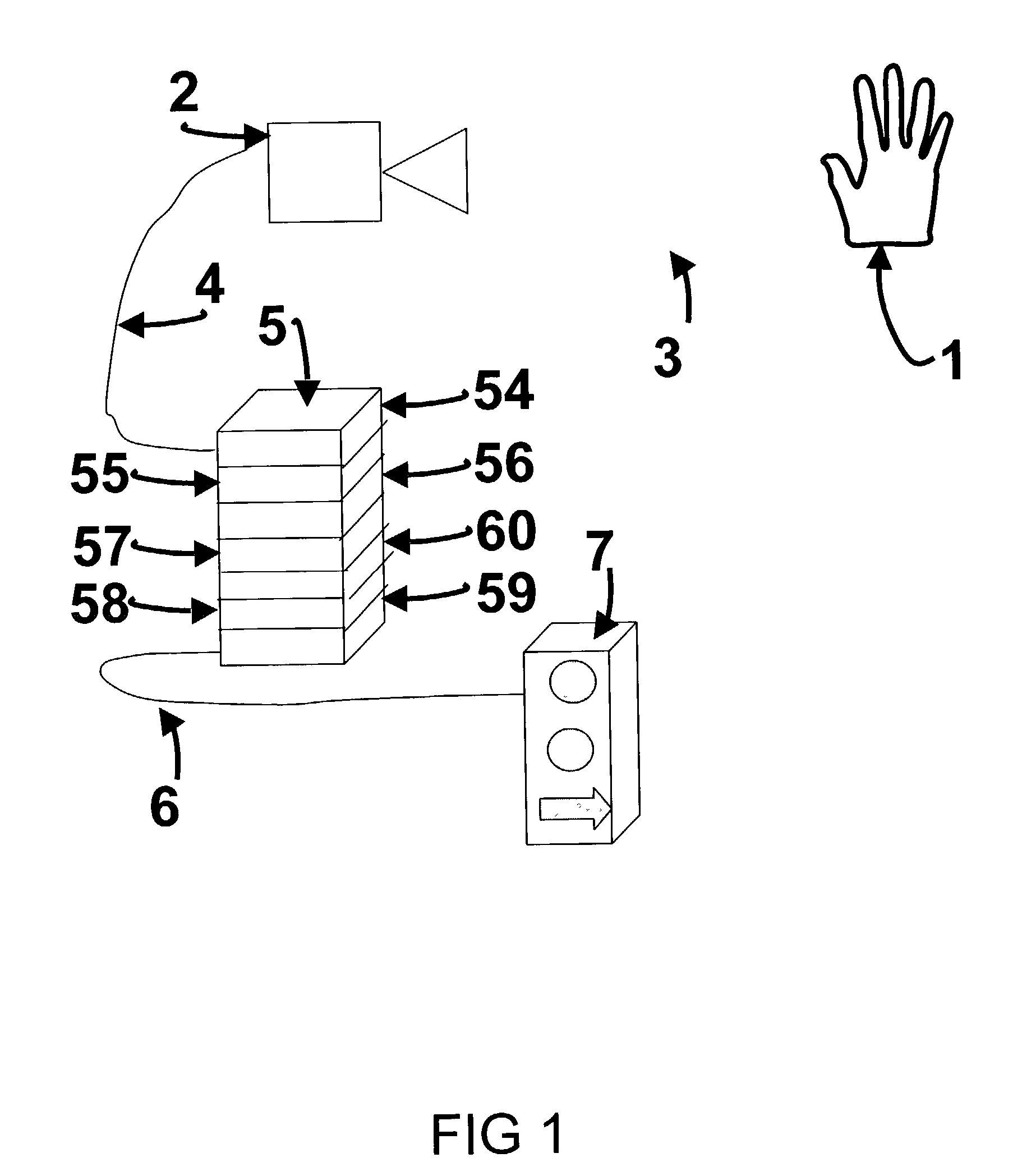

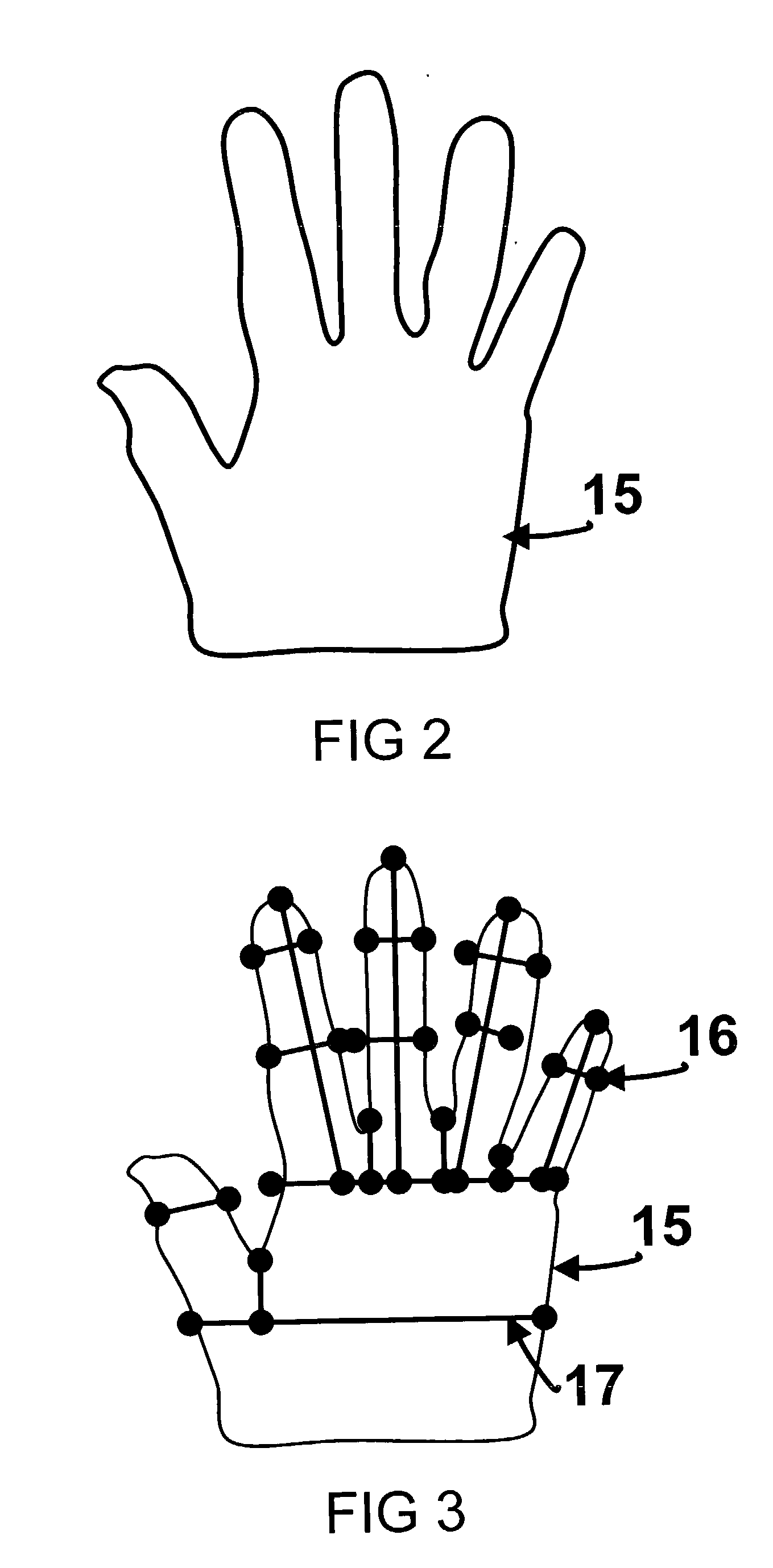

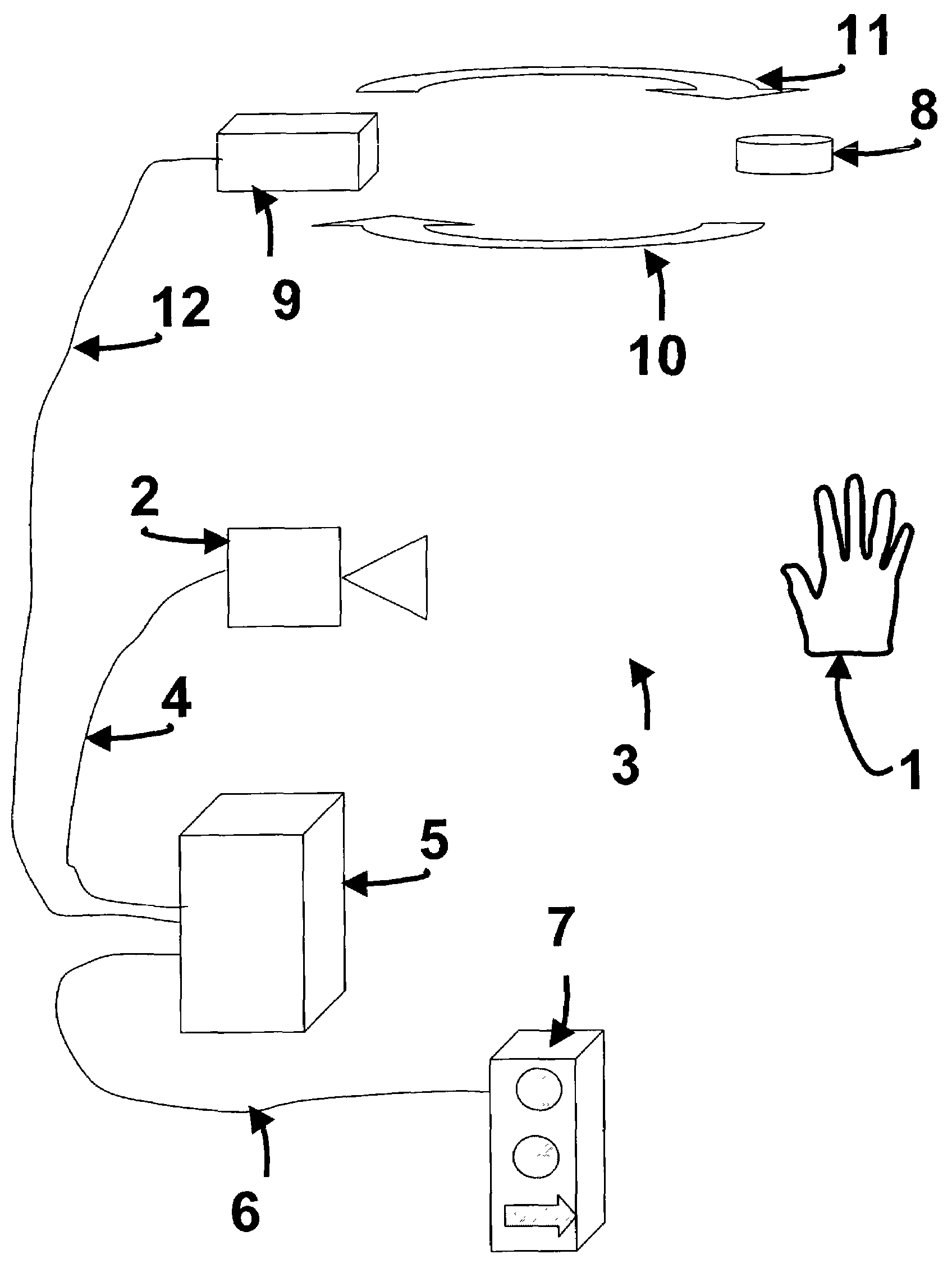

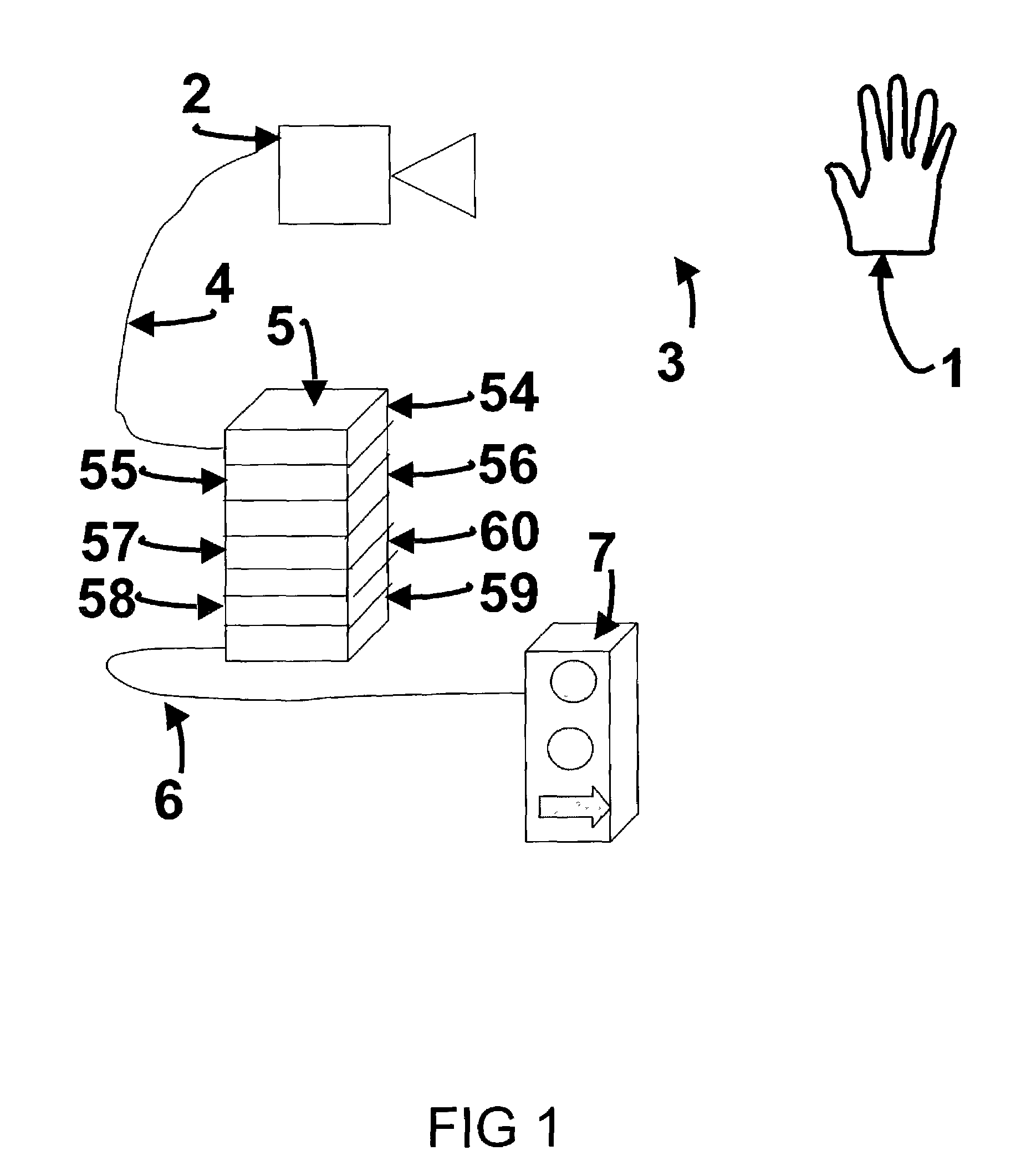

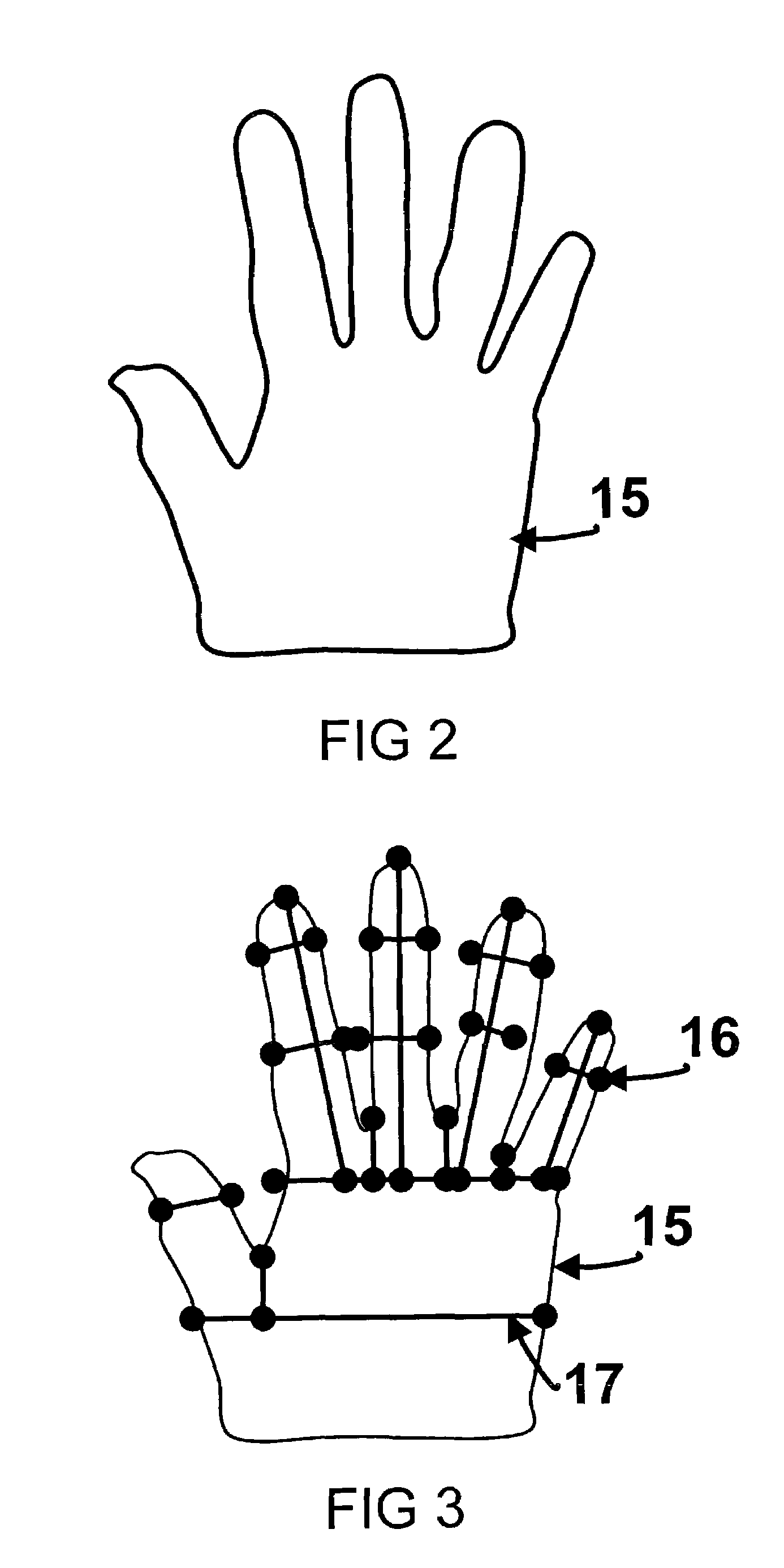

A method and apparatus is provided for Contactless Hand Recognition (CHR) for positive identification of cooperative individuals seeking access to physical, logical, or informational systems. Contactless Hand Recognition (CHR) is based on a novel technique and apparatus that rapidly and contactlessly captures a livescan hand geometry video image with a visible wavelength, infrared, or thermal camera of a person desiring access, then reduces the image to a template, compares the livescan template to a reference template, and determines if there is a match. Contactless Hand Recognition (CHR) is a significant advancement over current state-of-the-art hand recognition systems because authentication is done contactlessly while on the move, and at a distance, while simultaneously verifying liveness. It can also be combined with a personal knowledge process to include the use of a Personnel Identification Number (PIN), a secret contactless sign (SCS), or unique hand / finger position biometrics known only to the user. The CHR invention offers the possibility for users to have a rapid, fully contactless three-factor system of authentication based on contactless tokens, biometrics, and personal knowledge identification signs.

Owner:THE RIGHT PROBLEM

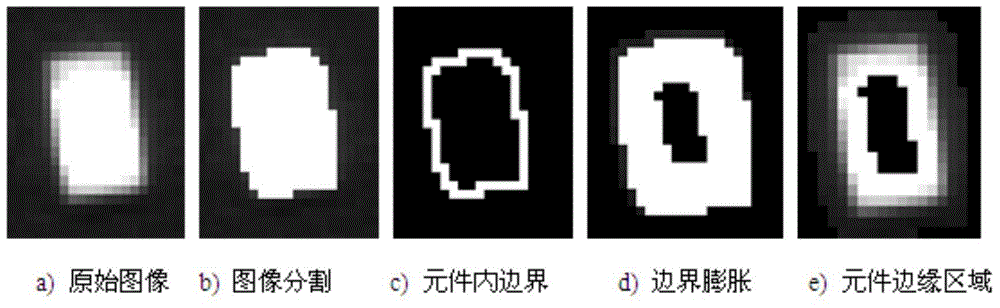

Detecting and error-correcting method capable of rapidly and accurately obtaining element center and deflection angle

ActiveCN104981105AFind out exactlyOvercoming complex shortcomingsPrinted circuit assemblingCircuit board tools positioningCurve fittingEdge extraction

A detecting and error-correcting method capable of rapidly and accurately obtaining an element center and a deflection angle is disclosed. Interested edge area can be rapidly and accurately found out through an automatic edge area extraction method based on combination of binary morphology and image reduction, and subsequent edge extraction image scope is minimized as possible. Pixel level edge is roughly positioned at first, and accordingly a sub-pixel edge is rapidly extracted by one-dimensional curve fitting method. The method overcomes the defect of complex algorithm of a conventional sub-pixel edge extraction algorithm based on two-dimensional images, and the time of extracting accurate sub-pixel edge can be shortened. Weighted least square rectangular edge fitting algorithm based on linear hazen paradigm can detect straight lines on any positions of an image, and effectively minimizes influence of outlier on fitting precision due to uneven edges. The central positions of a plurality of elements and deflect angles can be rapidly and accurately detected at once, and the efficiency of visual detection is improved.

Owner:GUANGDONG UNIV OF TECH

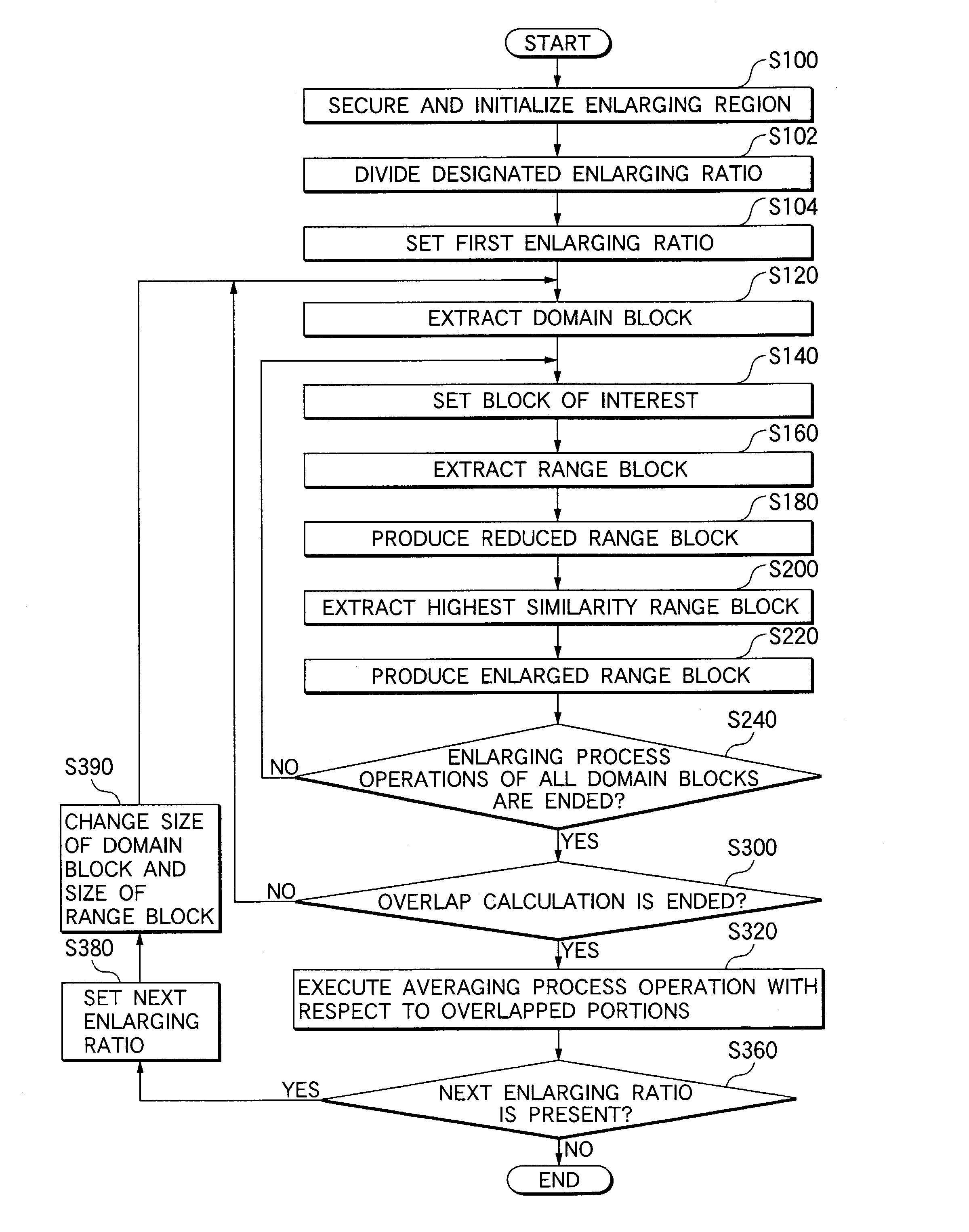

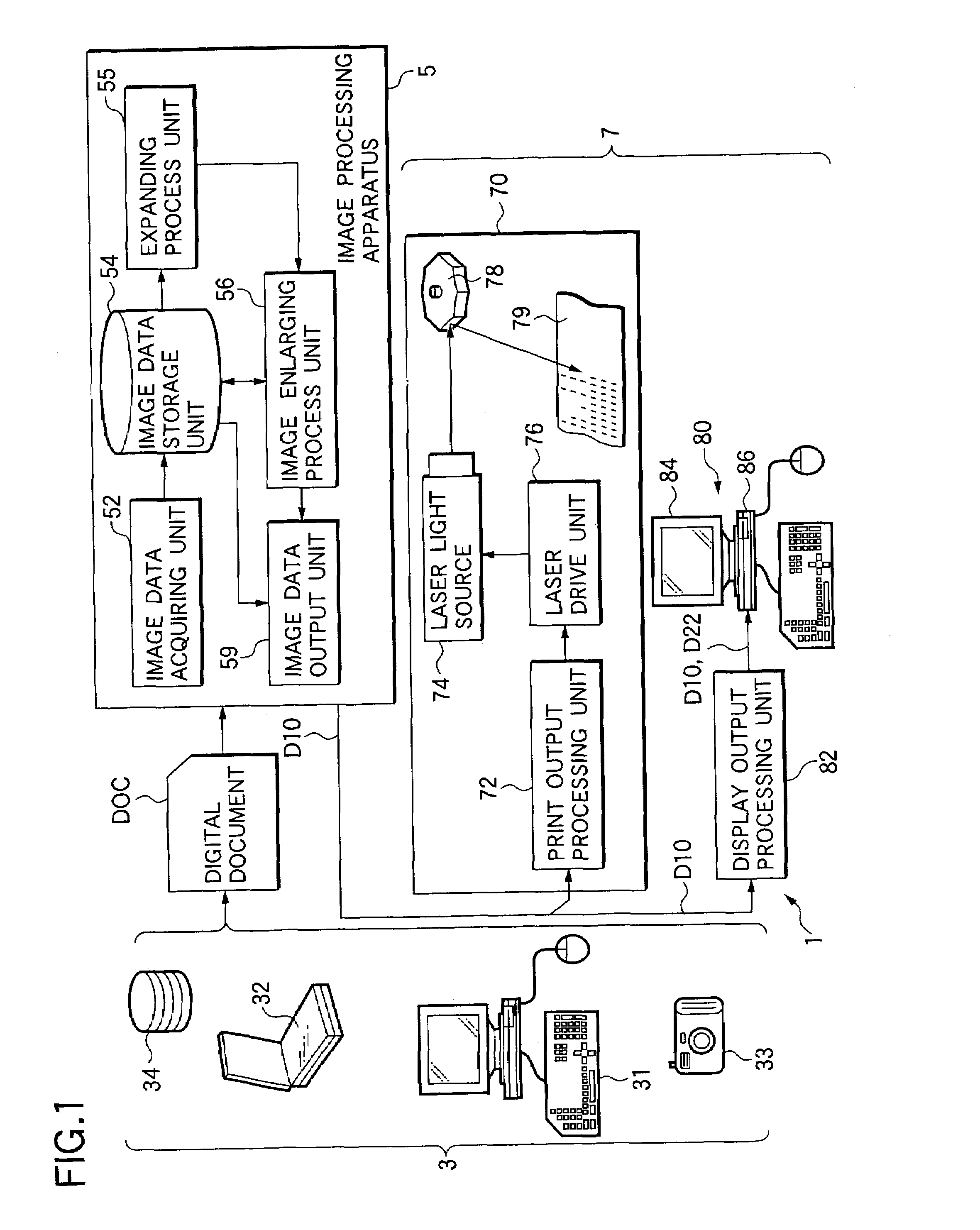

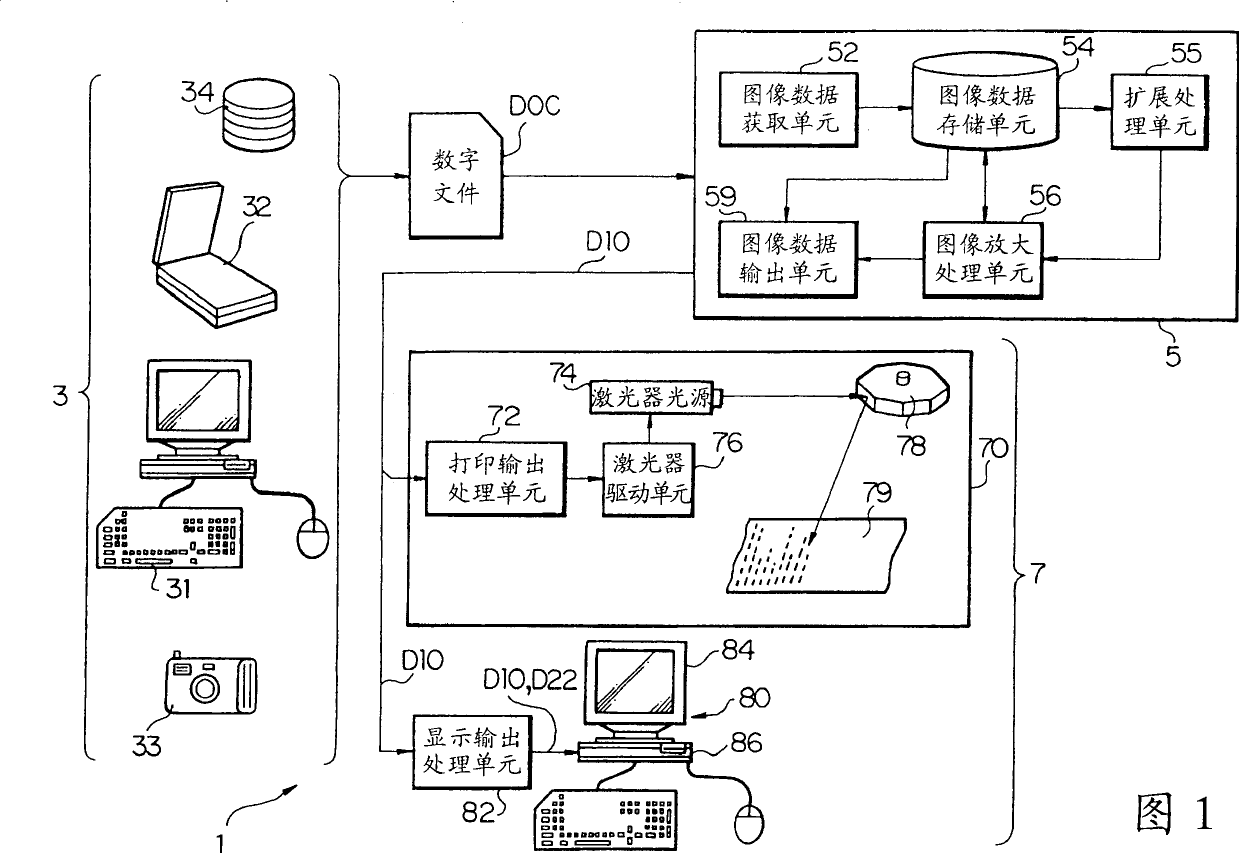

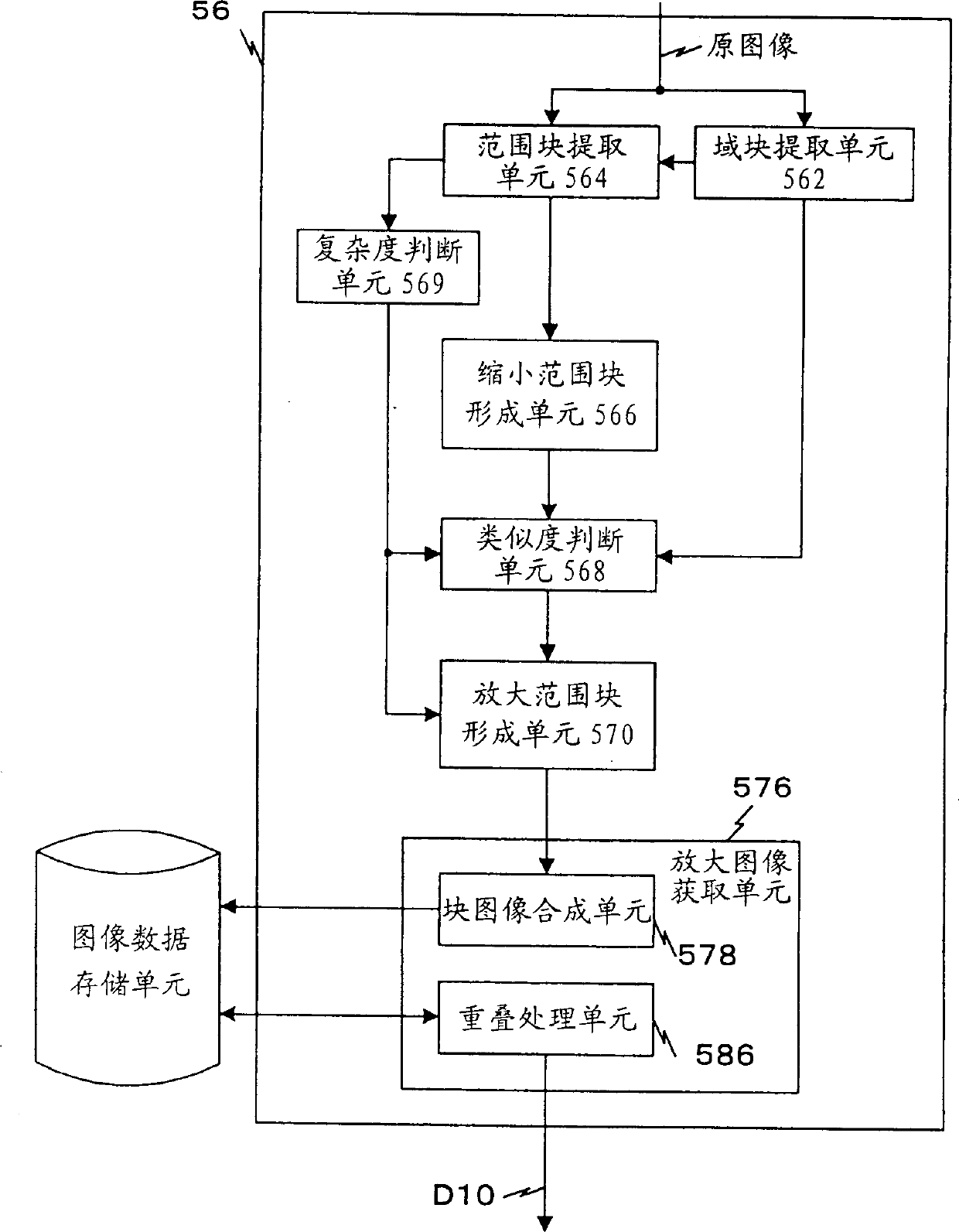

Image processing apparatus and program

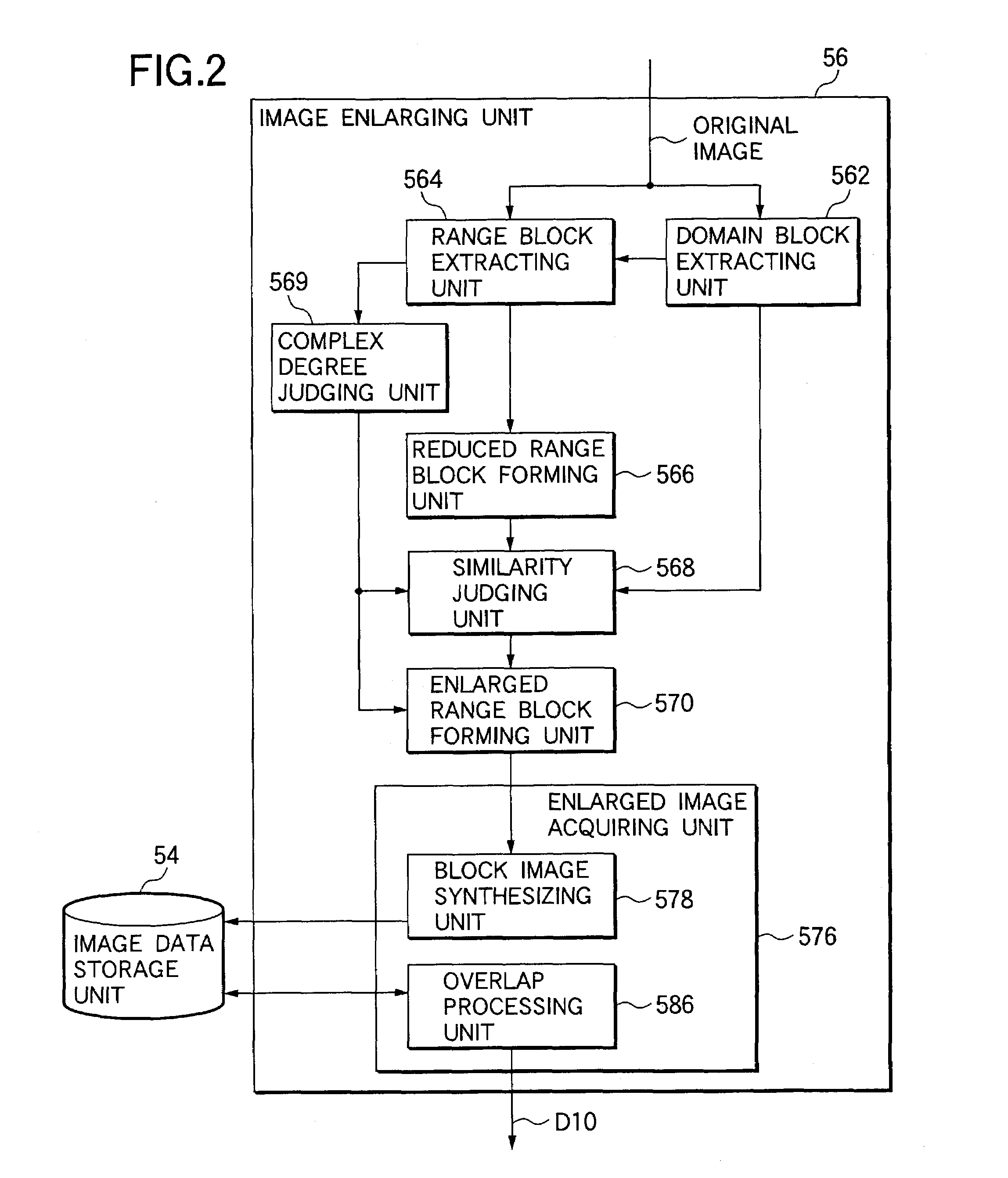

ActiveUS7046862B2Enhance the imageEffectively using featureTelevision system detailsGeometric image transformationPattern recognitionImaging processing

A domain block extracting unit extracts a domain block image from an original image. A range block extracting unit extracts a range block image from an area in the vicinity of the domain block image. The range block image has size being larger than a domain size and being smaller than an enlarged size. A reduced range block forming unit reduces the range block image to the domain size to produce a reduced range block image. A similarity judging unit compares each of the reduced range block images with the domain block image to select the highest similarity range block image. An enlarged range block forming unit forms an enlarged range block image by enlarging the size of the highest similarity range block image to an enlarged size thereof. An enlarged image acquiring unit produces an enlarged image of an original image by employing the respective enlarged range block images.

Owner:FUJIFILM BUSINESS INNOVATION CORP

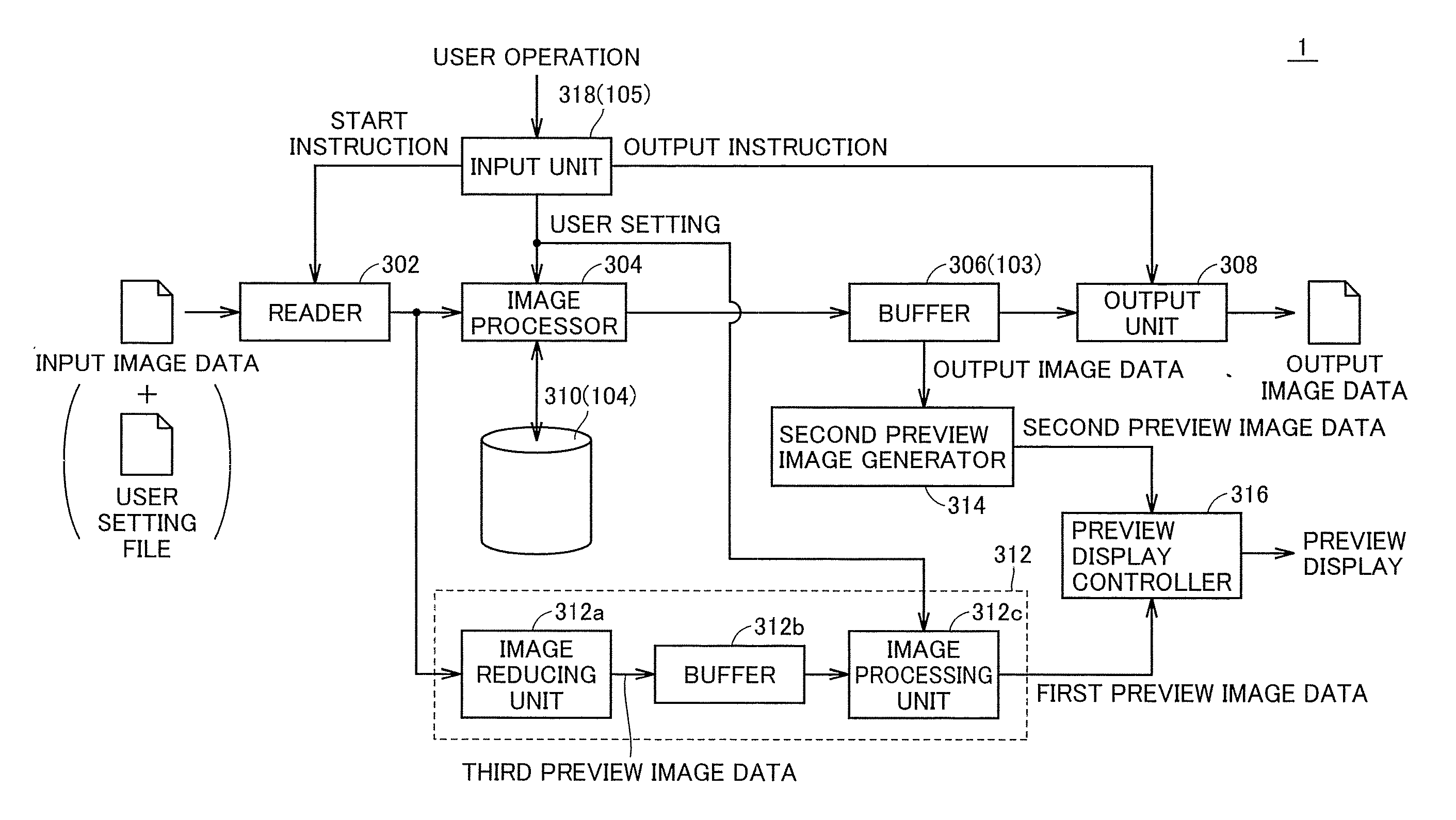

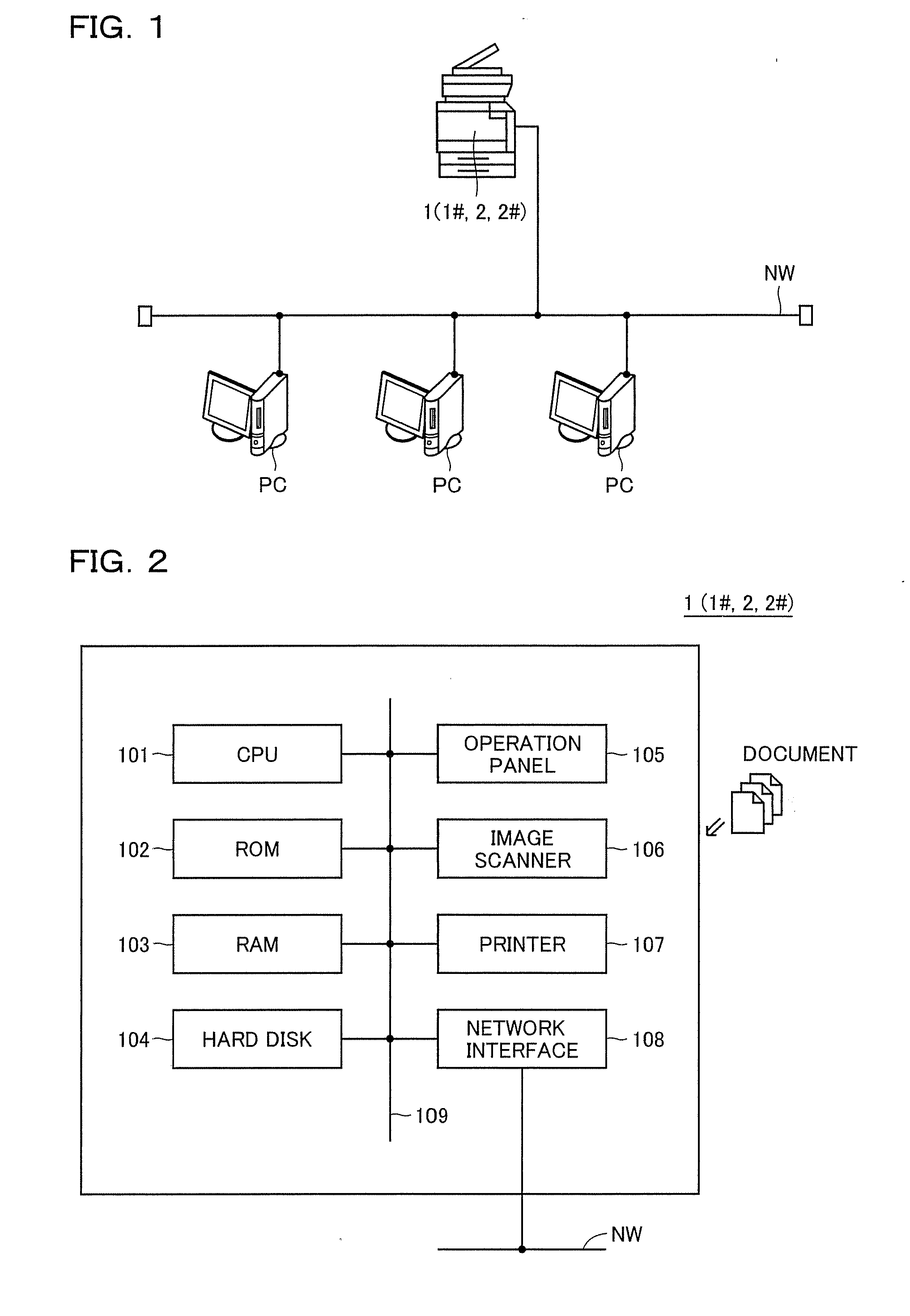

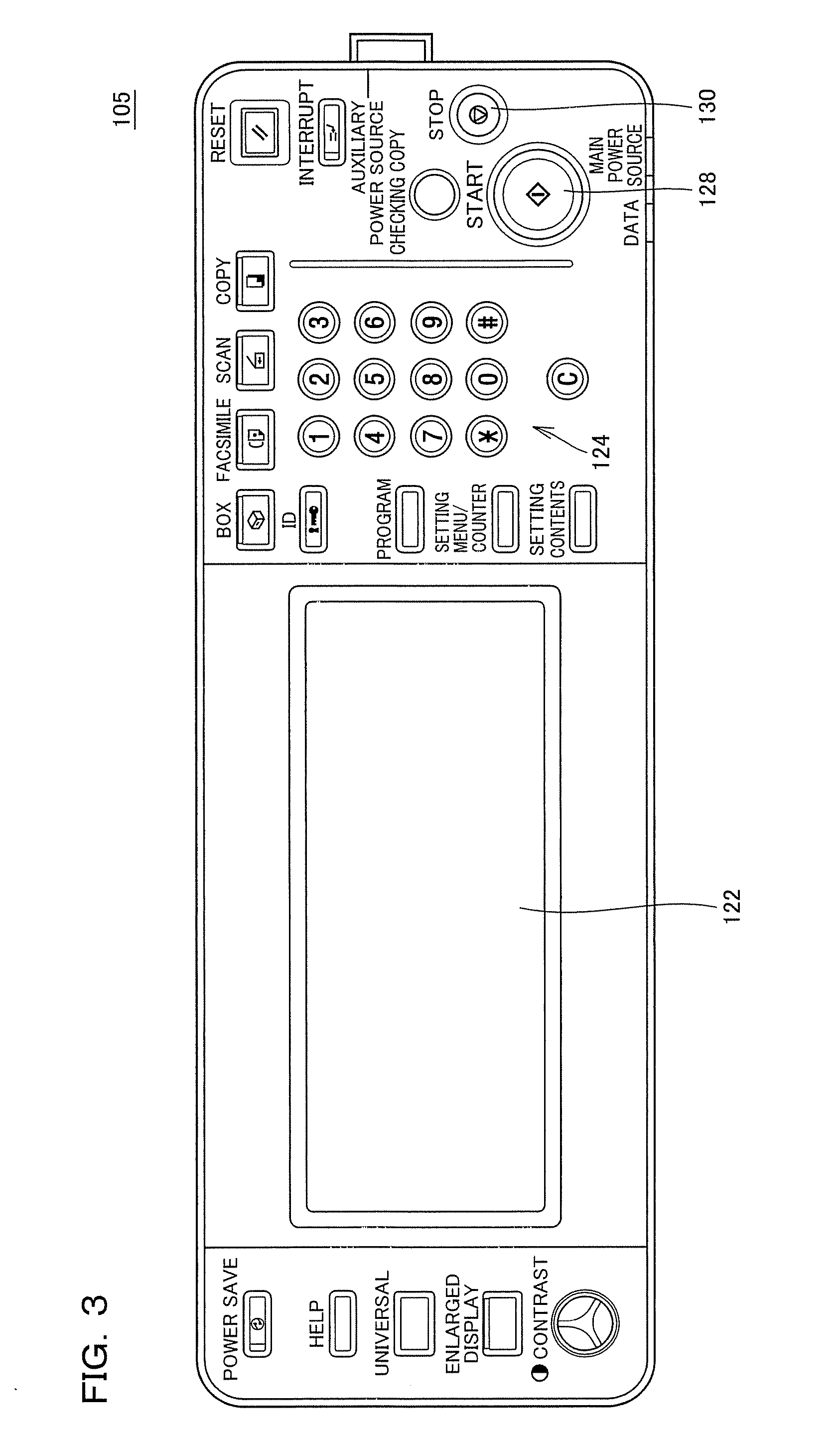

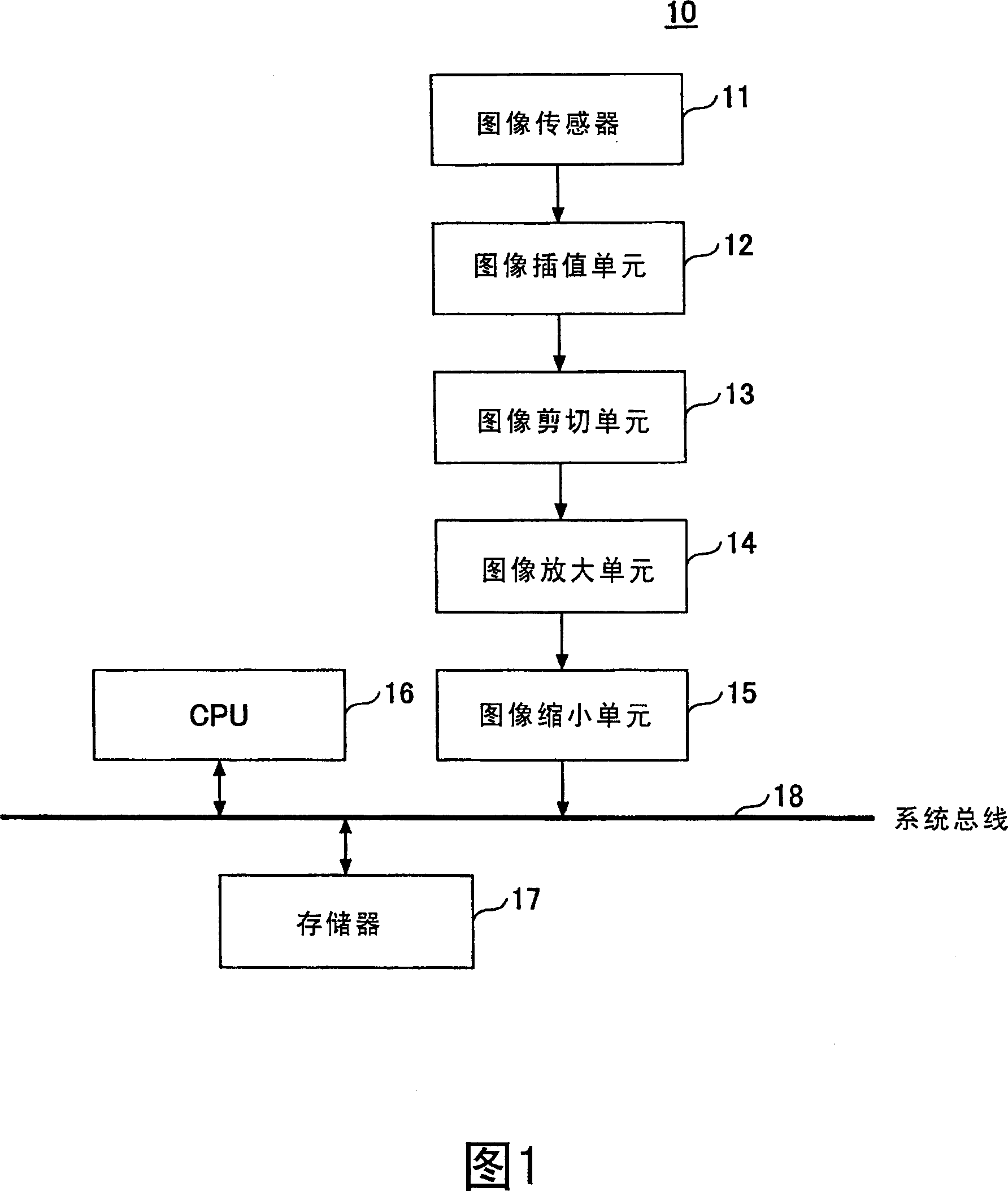

Image processing apparatus with preview display function, image processing method, and image processing program

ActiveUS20090290182A1Quick previewQuick displayDigitally marking record carriersDigital computer detailsImaging processingComputer graphics (images)

On an operation panel, a preview image based on first preview image data generated by a first preview image generator is displayed (first stage), and then, a preview image based on second preview image data generated by a second preview image generator is displayed (second stage). An image reducing unit reduces input image data into an image size appropriate for the preview image to generate third preview image data. When image synthesis processing is set as user setting, an image processing unit changes, in accordance with the user setting, a display aspect of at least a portion of an area on the third preview image data corresponding to an area on the input image data in which another image data (a fixed pattern or the like) is to be synthesized.

Owner:KONICA MINOLTA BUSINESS TECH INC

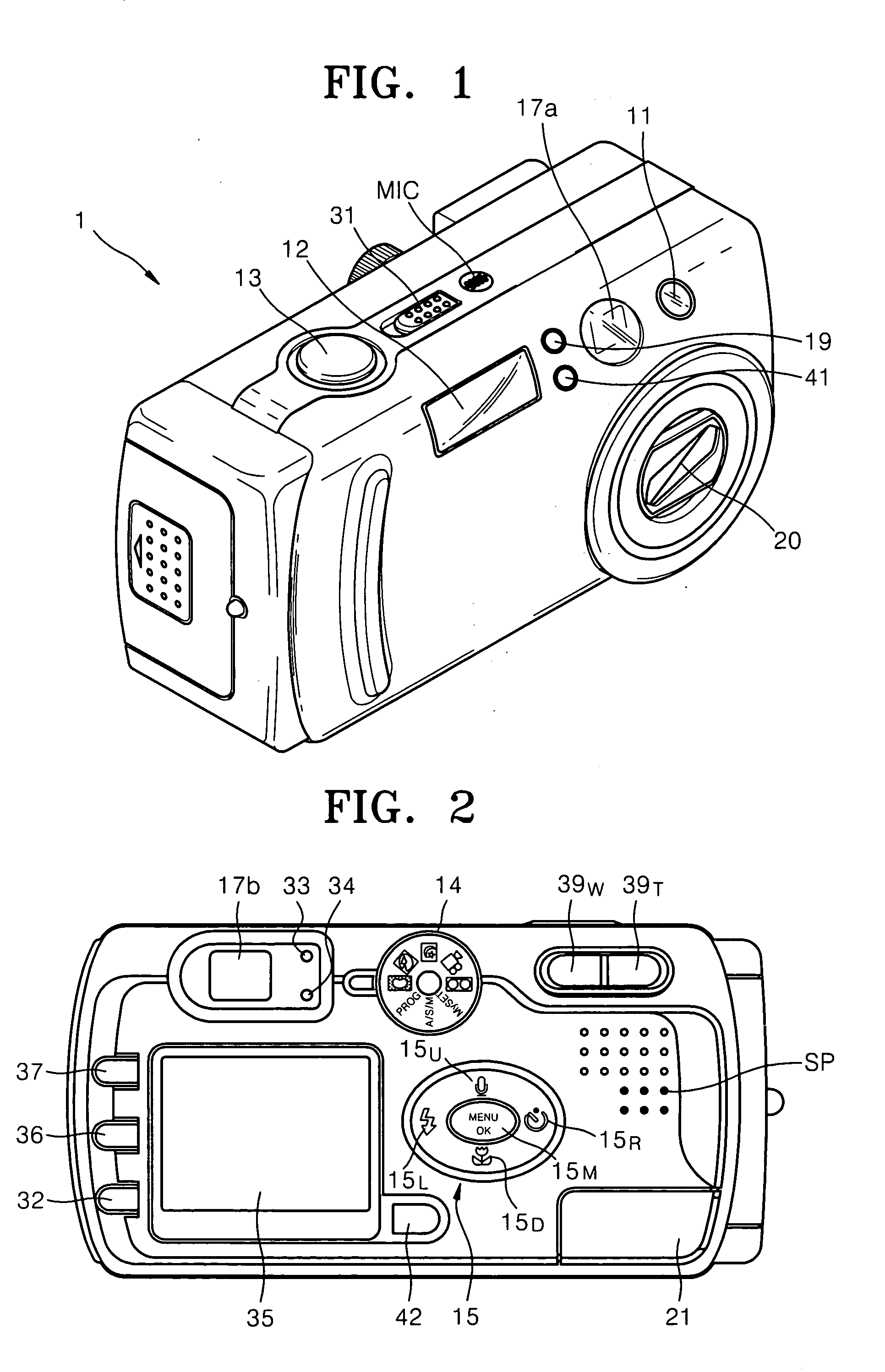

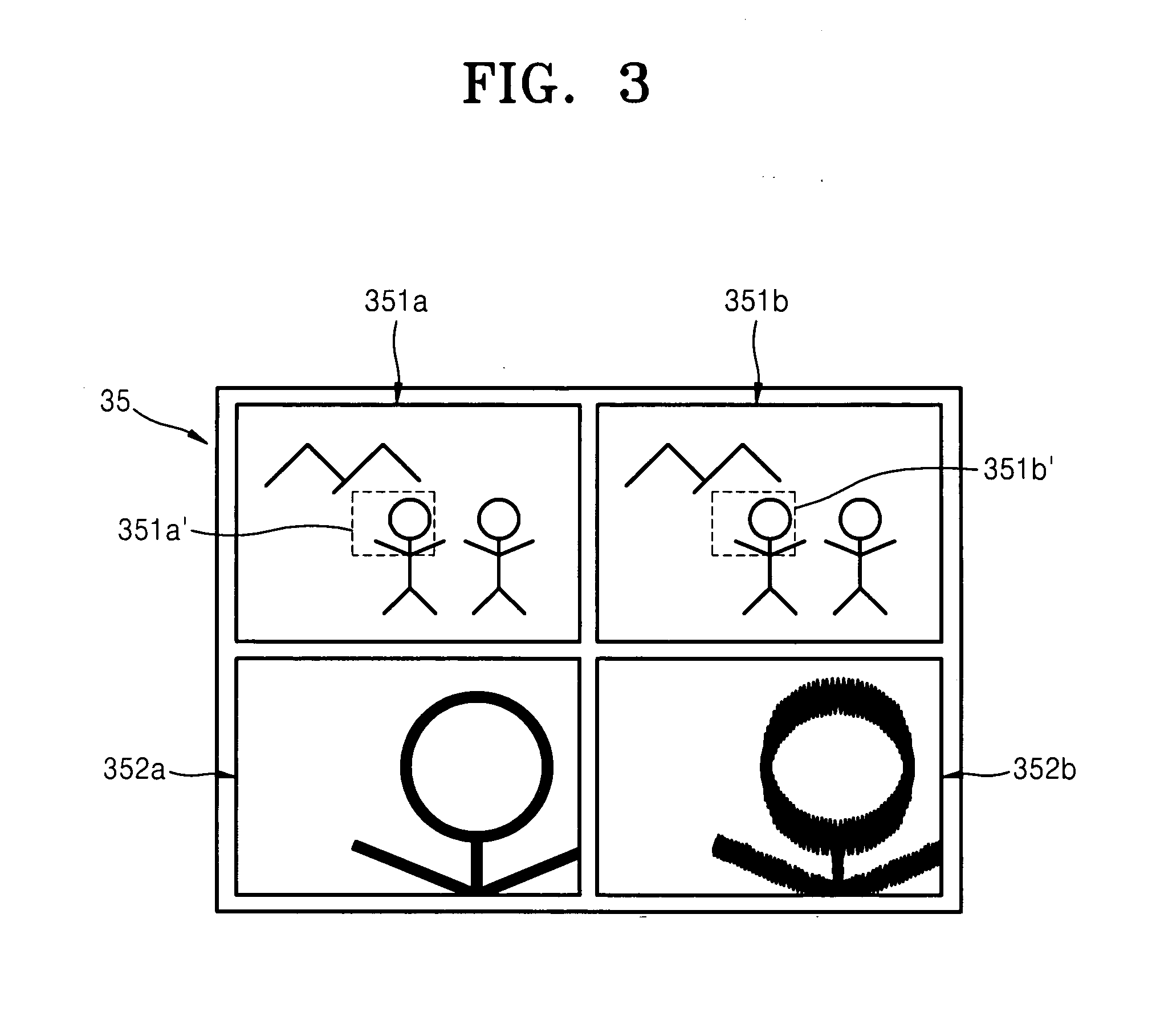

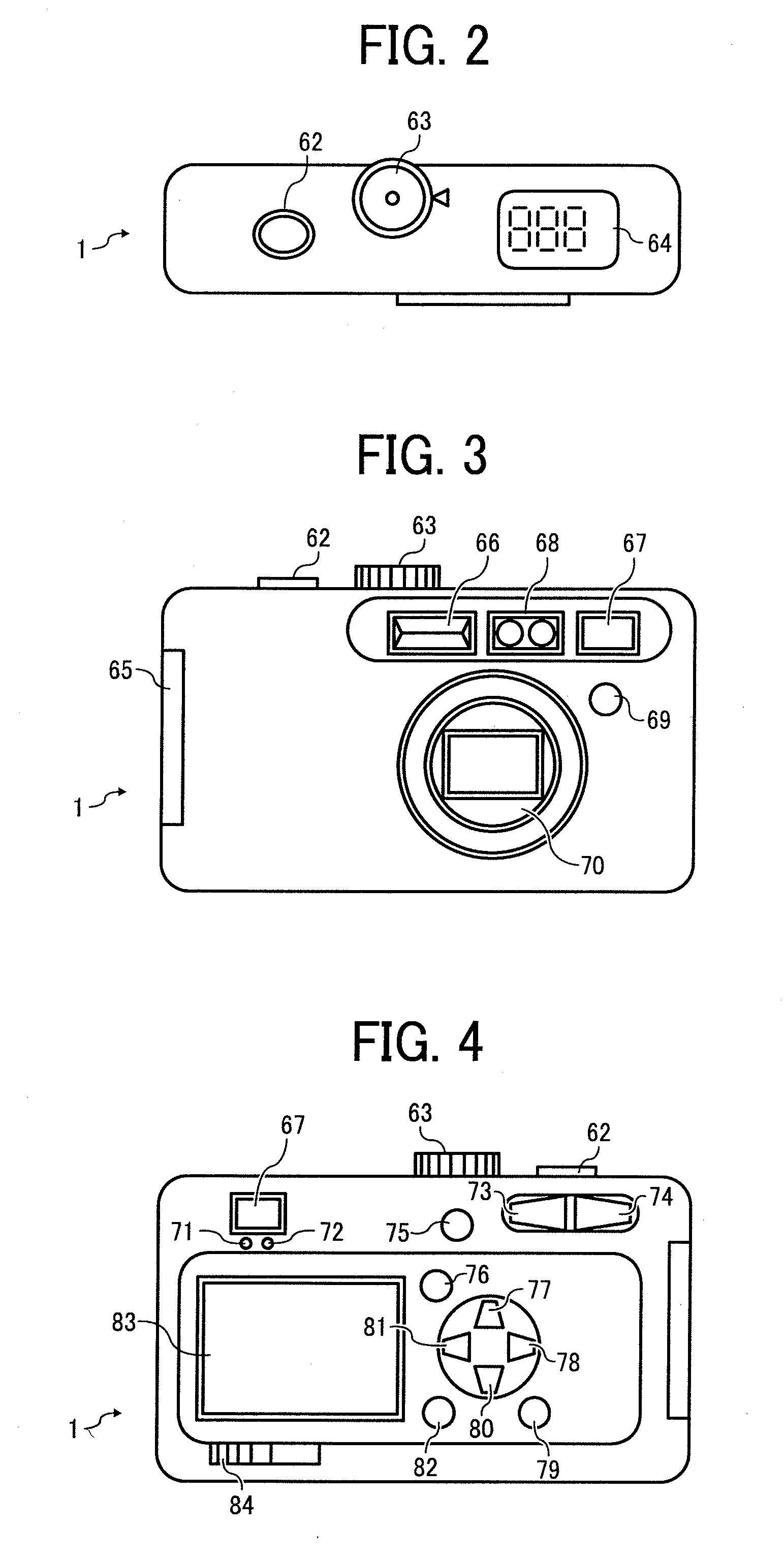

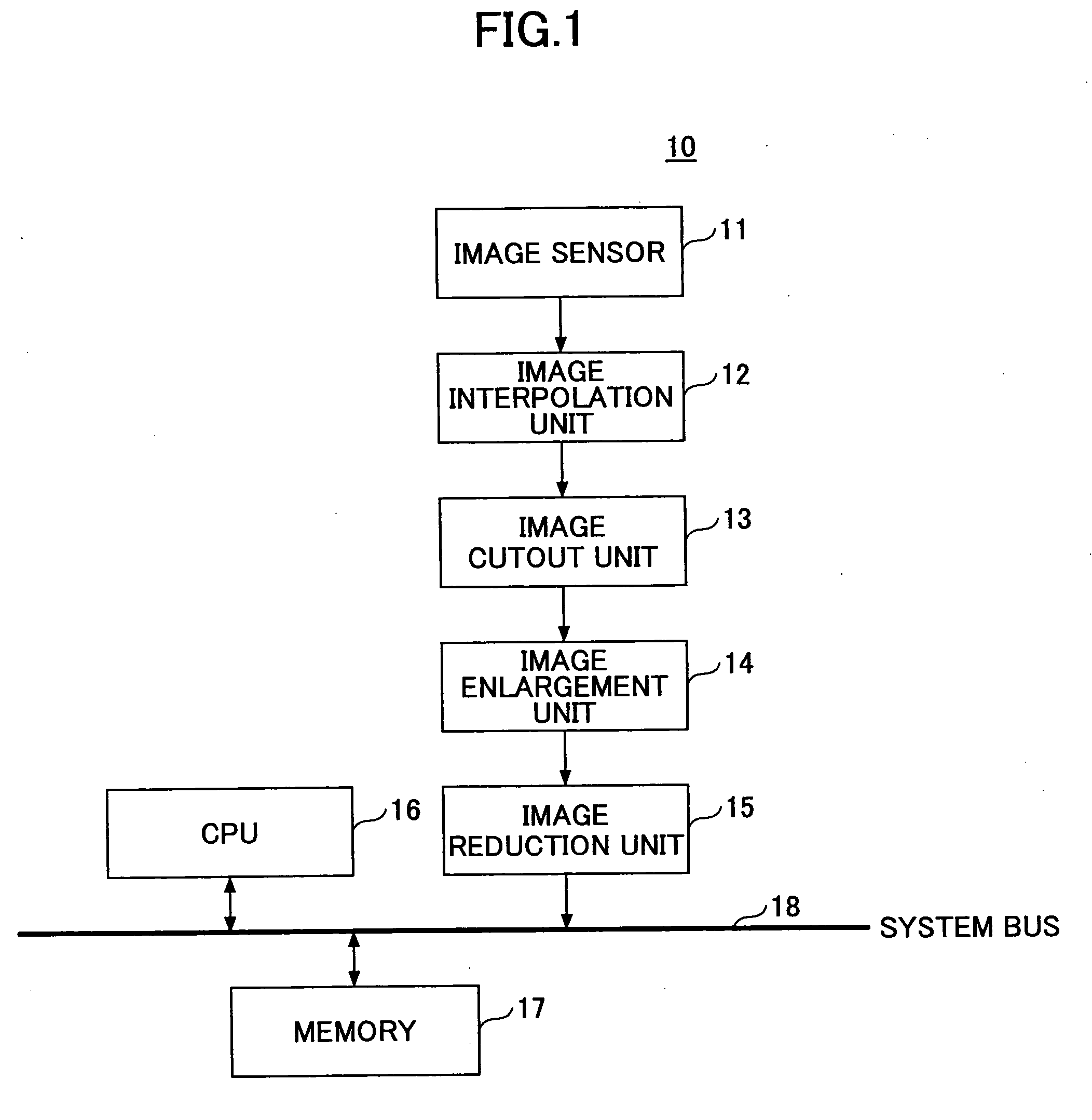

Method of controlling digital photographing apparatus, and digital photographing apparatus using the method

ActiveUS20070291154A1Sure easyImage degradationTelevision system detailsColor television detailsComputer graphics (images)Biological activation

A method of controlling a digital photographing apparatus that can easily determine a quality of a photographed image from an image displayed on a display panel included in the digital photographing apparatus, and the digital photographing apparatus using the method. The method includes: performing photographing operation in two or more photographing modes to obtain photographed images in response to a single activation of a shutter button; and displaying simultaneously: (1) a plurality of first images obtained by reducing the photographed images or by reducing the photographed images that are corrected, and (2) a plurality of second images that correspond to parts of the first images.

Owner:SAMSUNG ELECTRONICS CO LTD

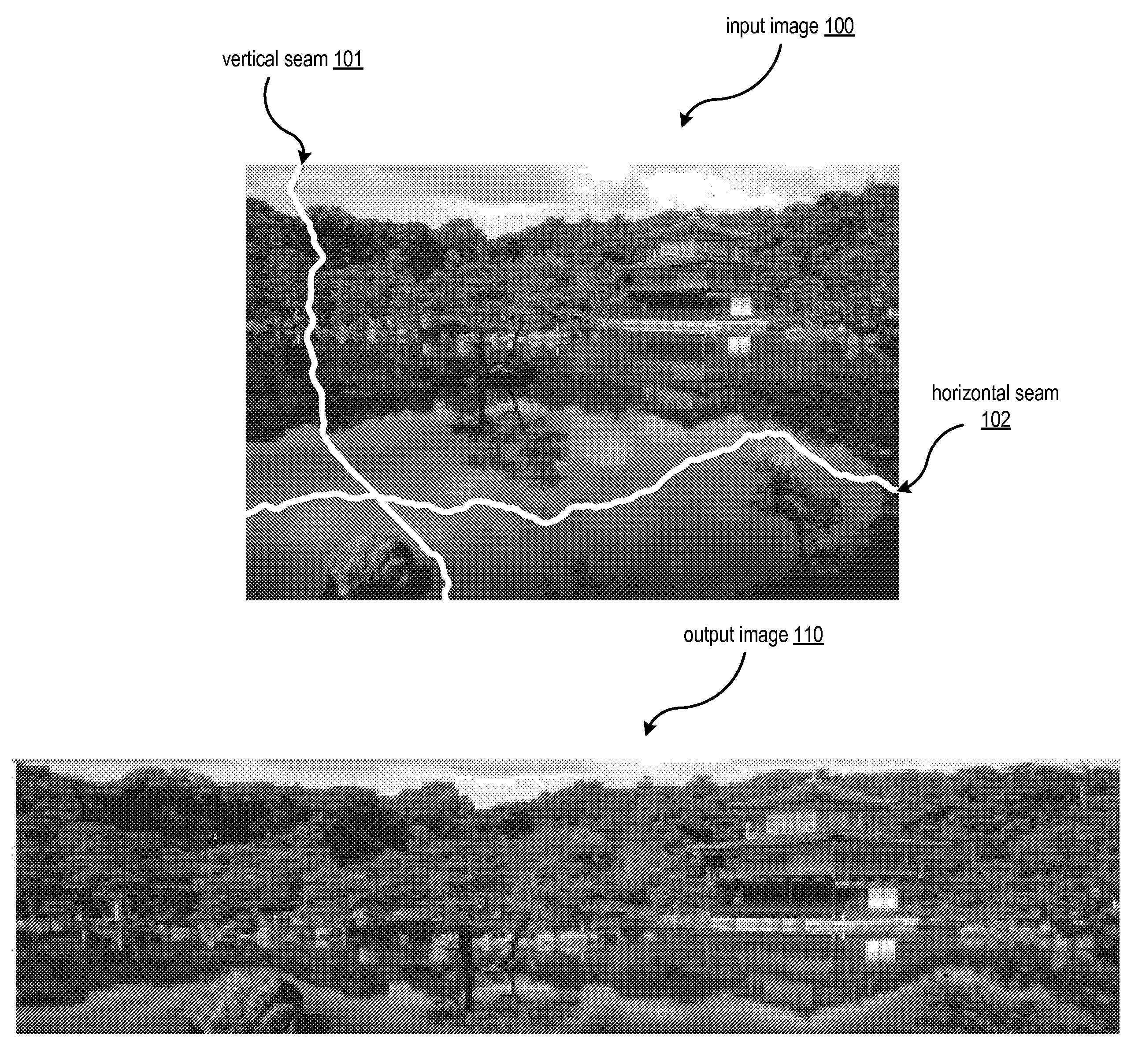

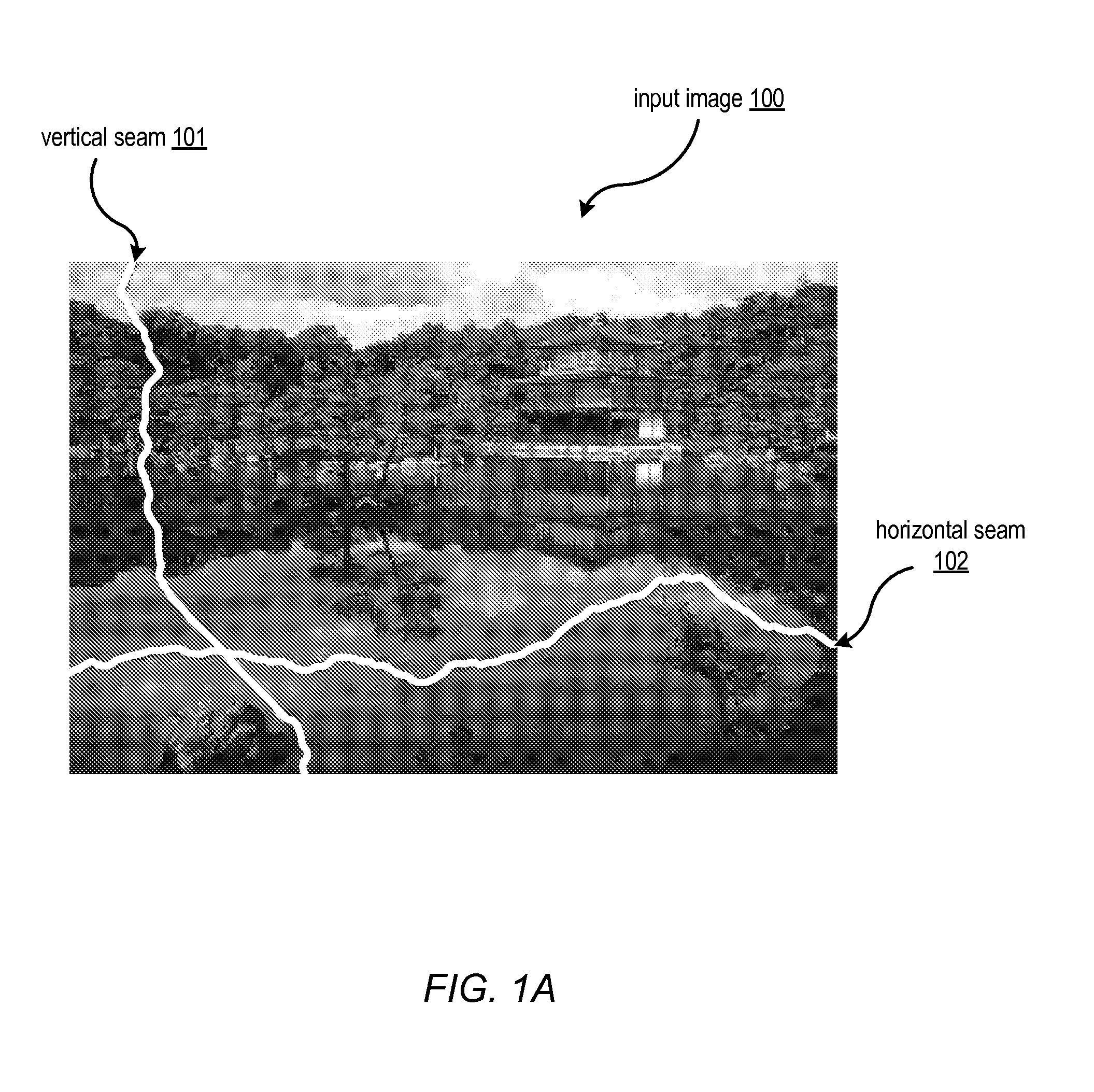

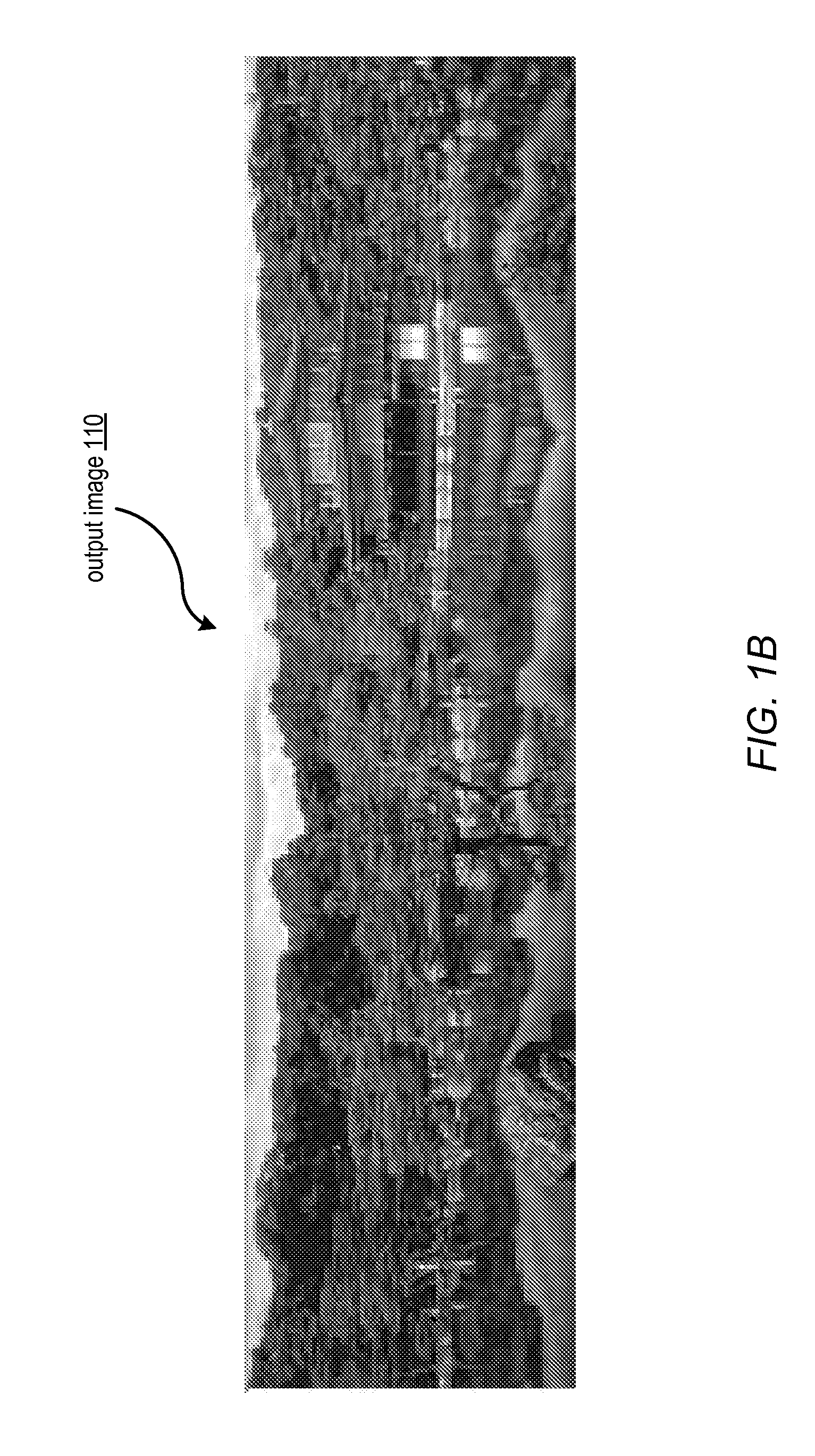

Seam-Based Reduction and Expansion of Images With Color-Weighted Priority

ActiveUS20100027876A1High energy valueLow costGeometric image transformationCharacter and pattern recognitionHigh energyComputer vision

A system and method for expansion and reduction of images uses an absolute value associated with each pixel of an input image (e.g., a color and / or intensity value) to determine a respective energy value for each pixel. For example, a given color or range of colors (e.g., skin tones, or other high-priority colors) may be assigned higher energy values than other colors and / or color ranges, and may be protected during image reduction and / or expansion. These energy values may be used to determine a cost associated with various seams of the image, which may represent the priority of the seams in the image. One or more low-cost seams may be identified for removal or replication to produce a resized image. The methods may be used in conjunction with an automated skin tone detector or a user interface that allows selection of one or more high priority colors or color ranges.

Owner:ADOBE INC

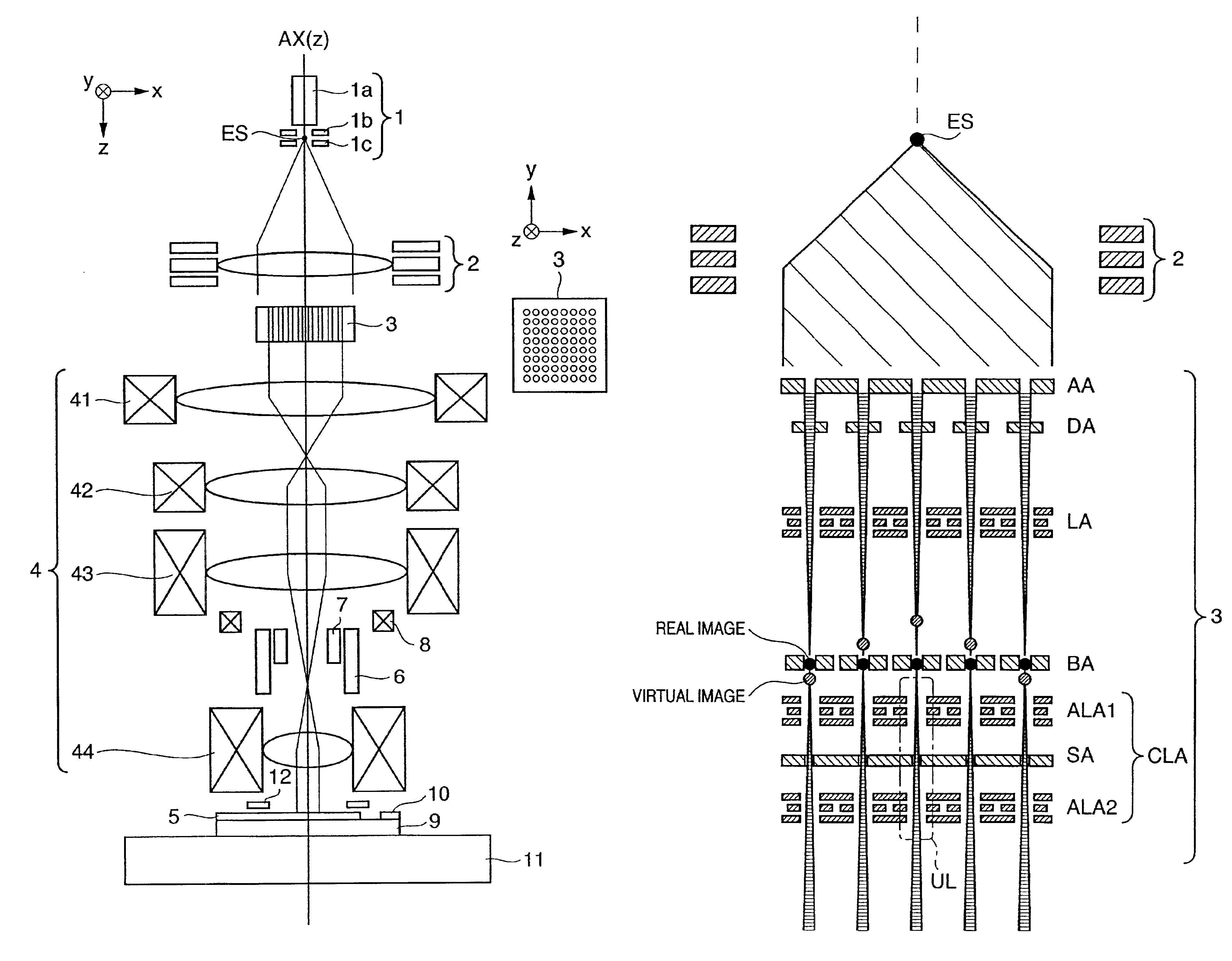

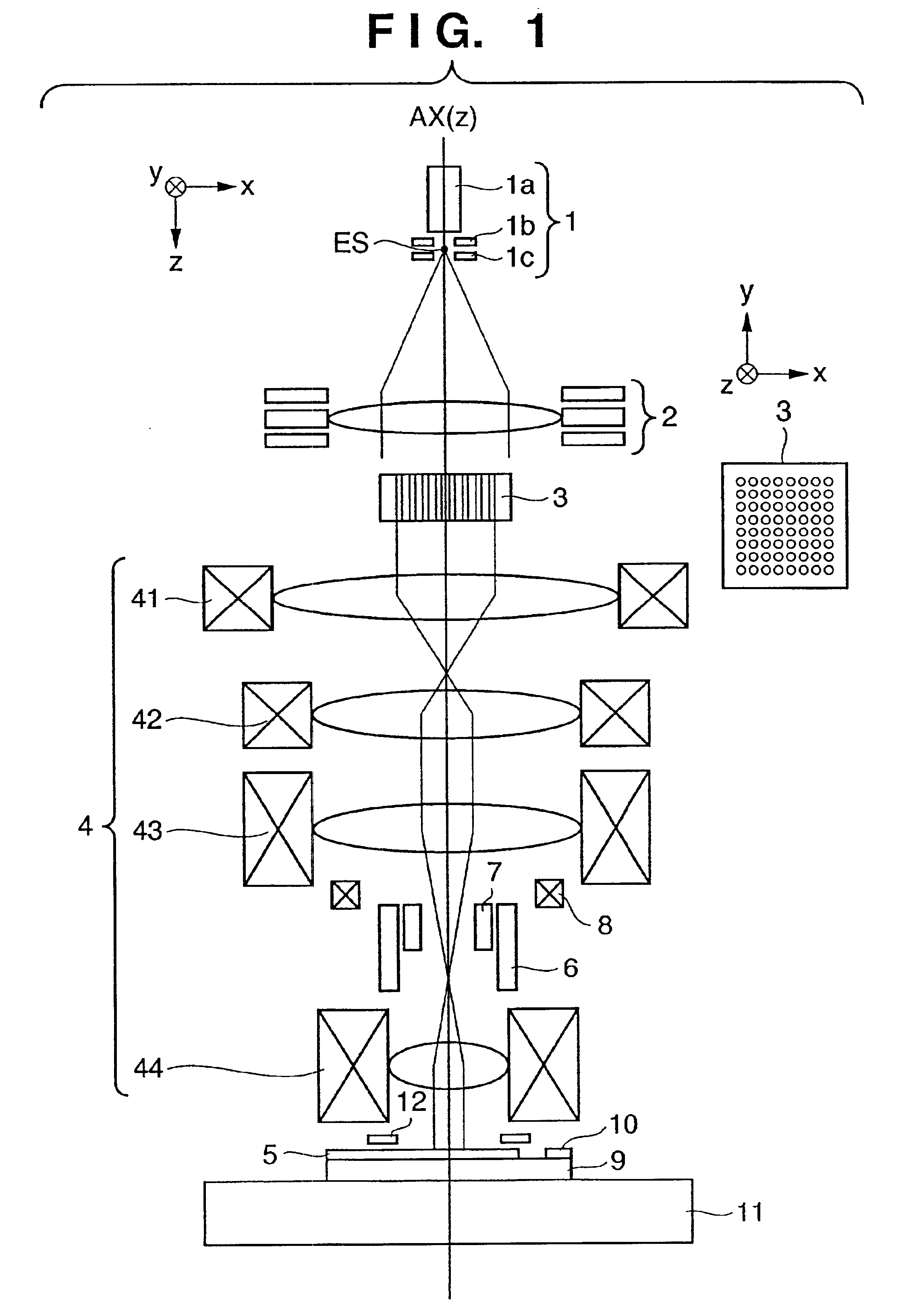

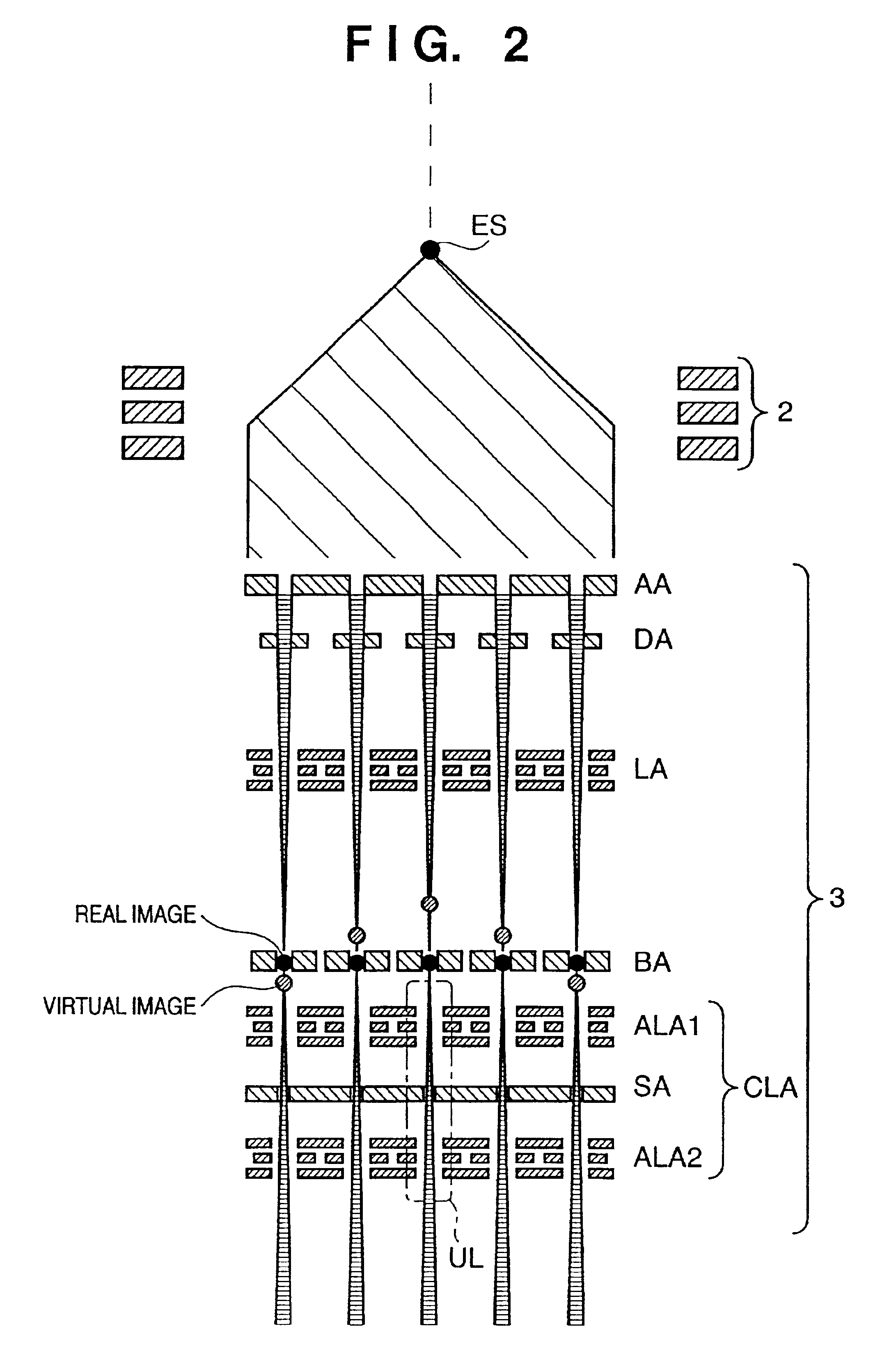

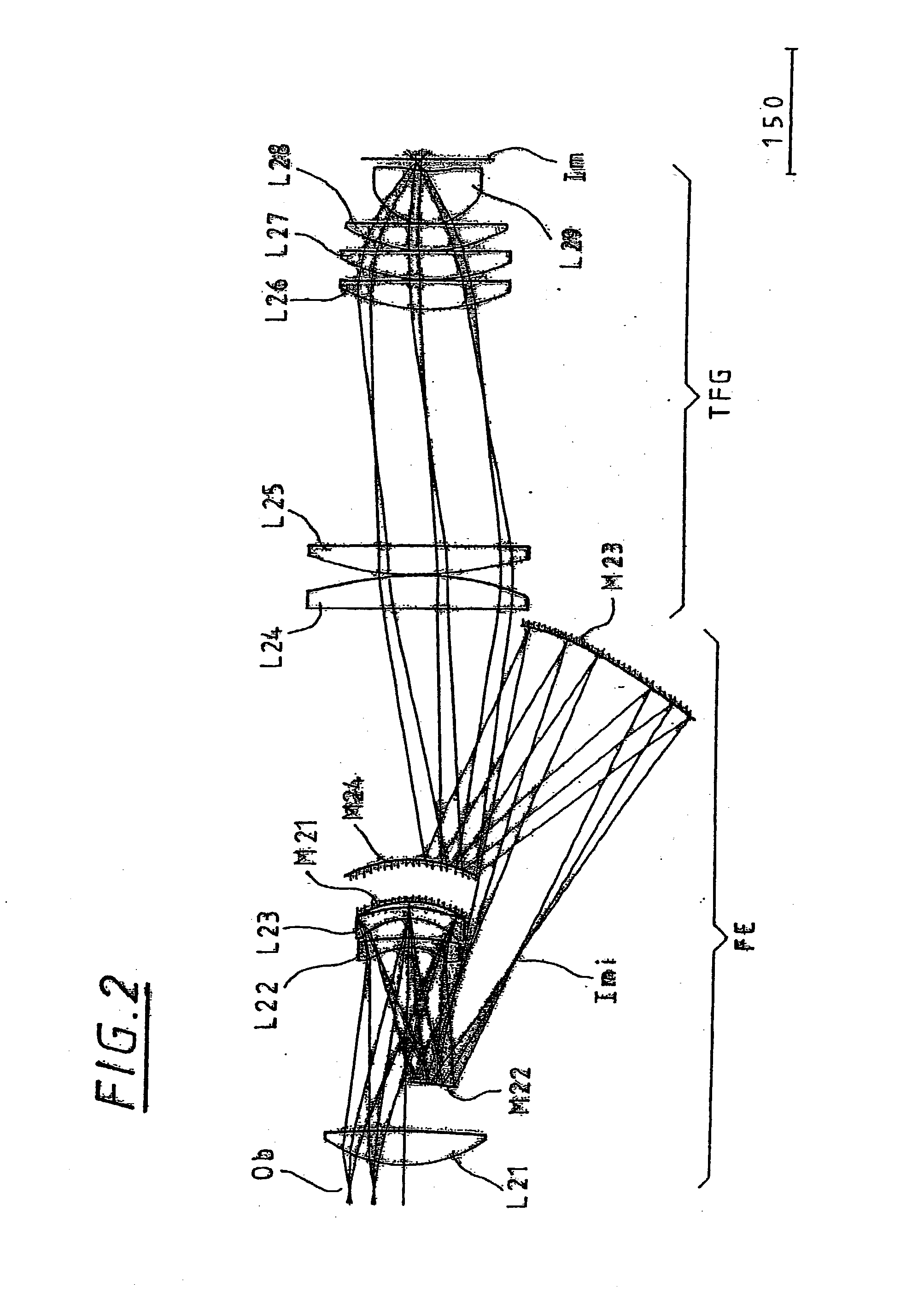

Charged particle beam exposure apparatus, device manufacturing method, and charged particle beam applied apparatus

InactiveUS6903353B2Without increasing performanceImprove performanceStability-of-path spectrometersNanoinformaticsIntermediate imageMolecular physics

A high-precision multi-charged-particle-beam exposure apparatus has a charged particle source (ES) that emits a charged particle beam. An aperture array (AA) having plural apertures divides the charged particle beam from the charged particle source (ES) into plural charged particle beams and a lens array (LA) having plural electron lens forms plural intermediate images of the charged particle source (ES) on substantially one plane with the plural charged particle beams from the aperture array (AA). A blanker array (BA) located on the plane where the plurality of intermediate images are to be formed has plural blankers, and a reduction electron optical system that reduces and projects the images of the charged particle source (ES) onto a substrate.

Owner:ADVANTEST CORP +1

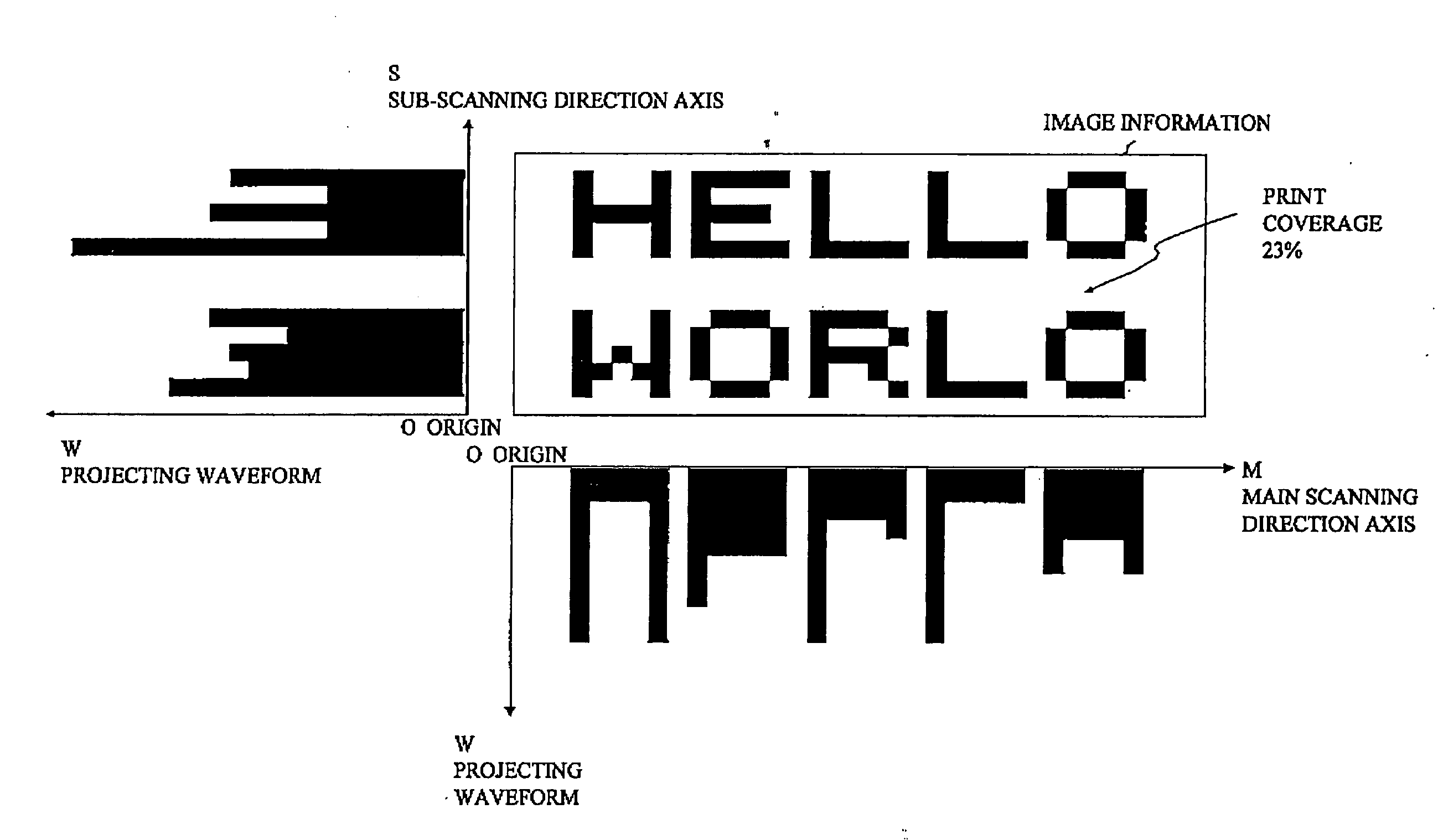

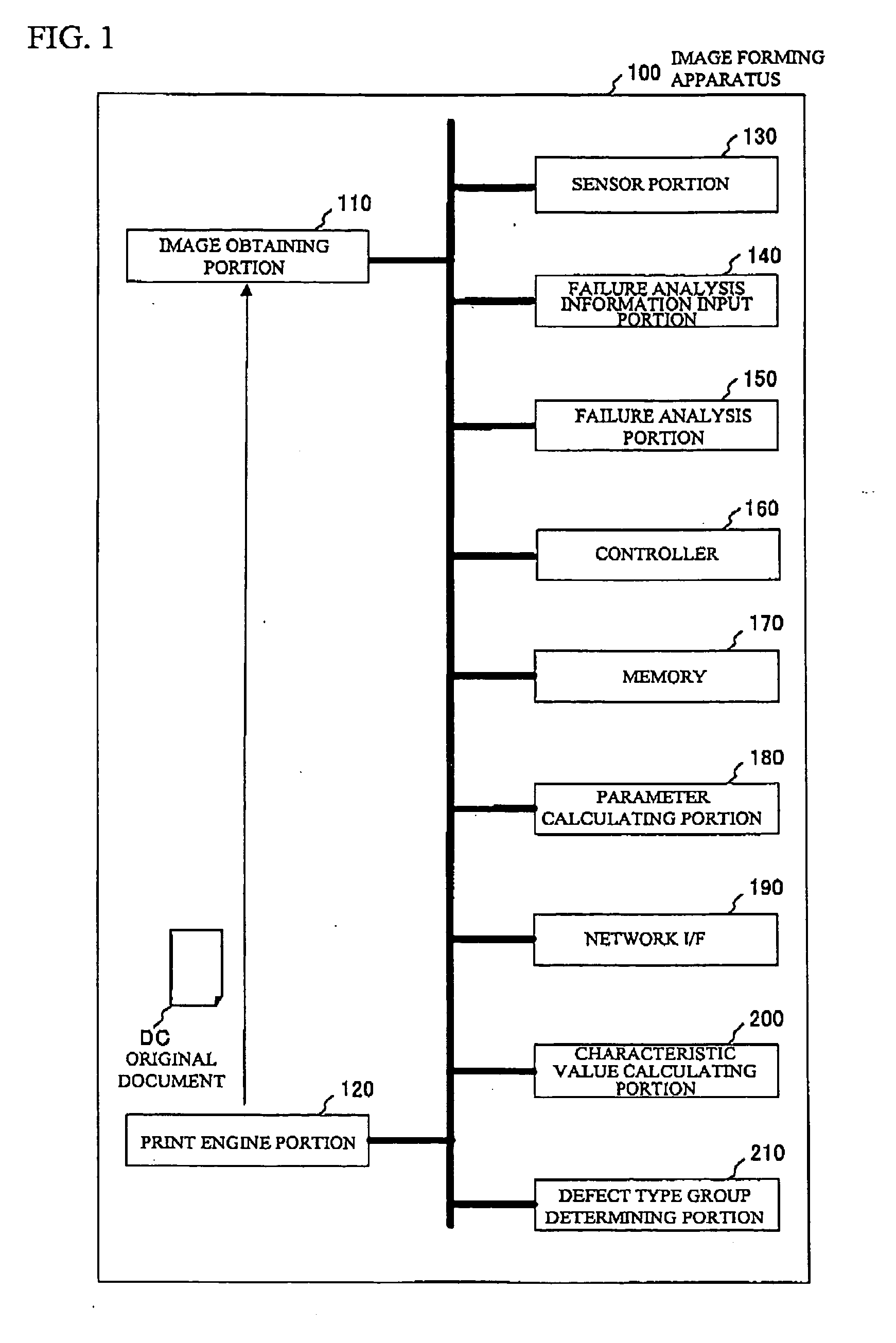

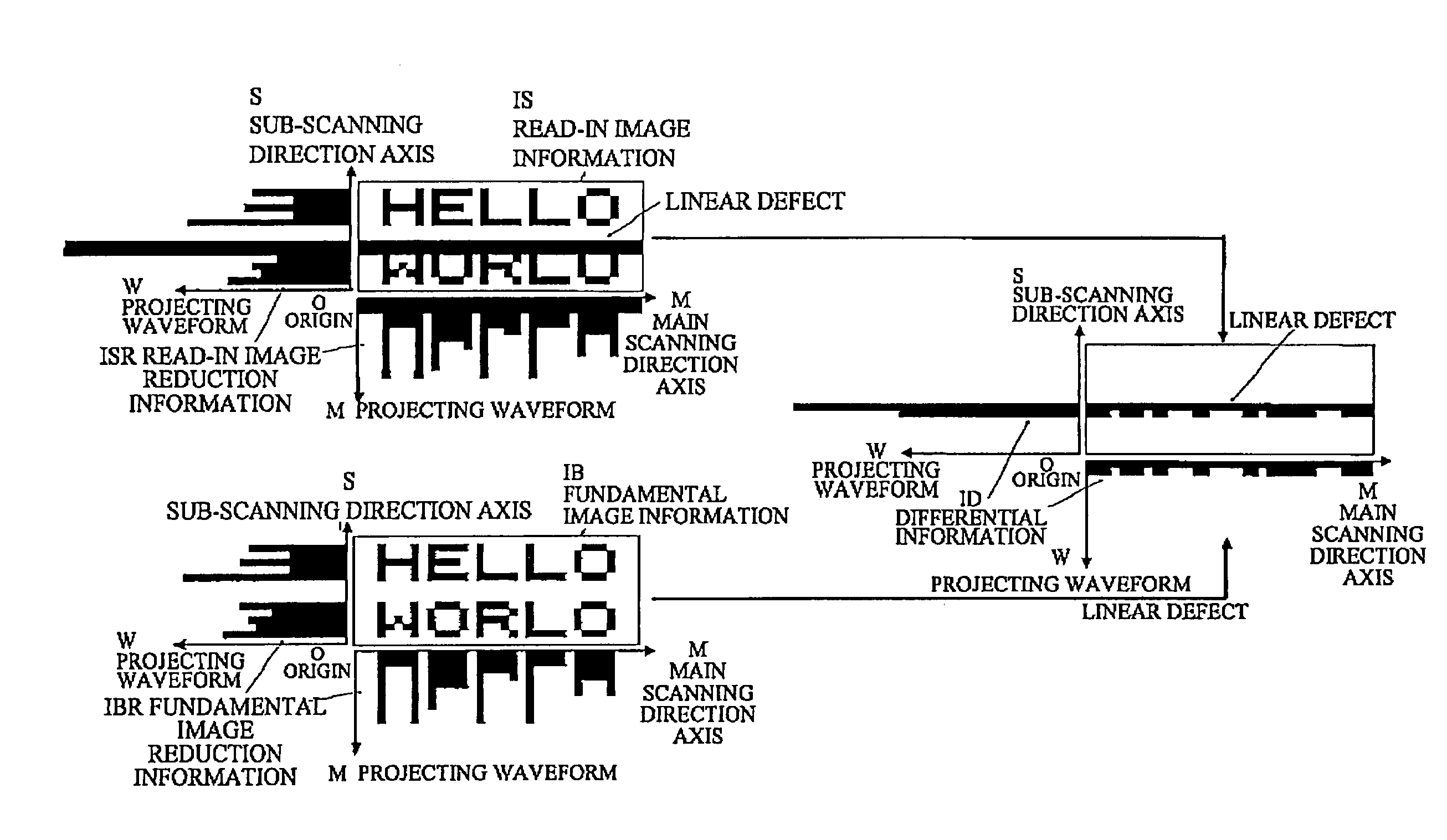

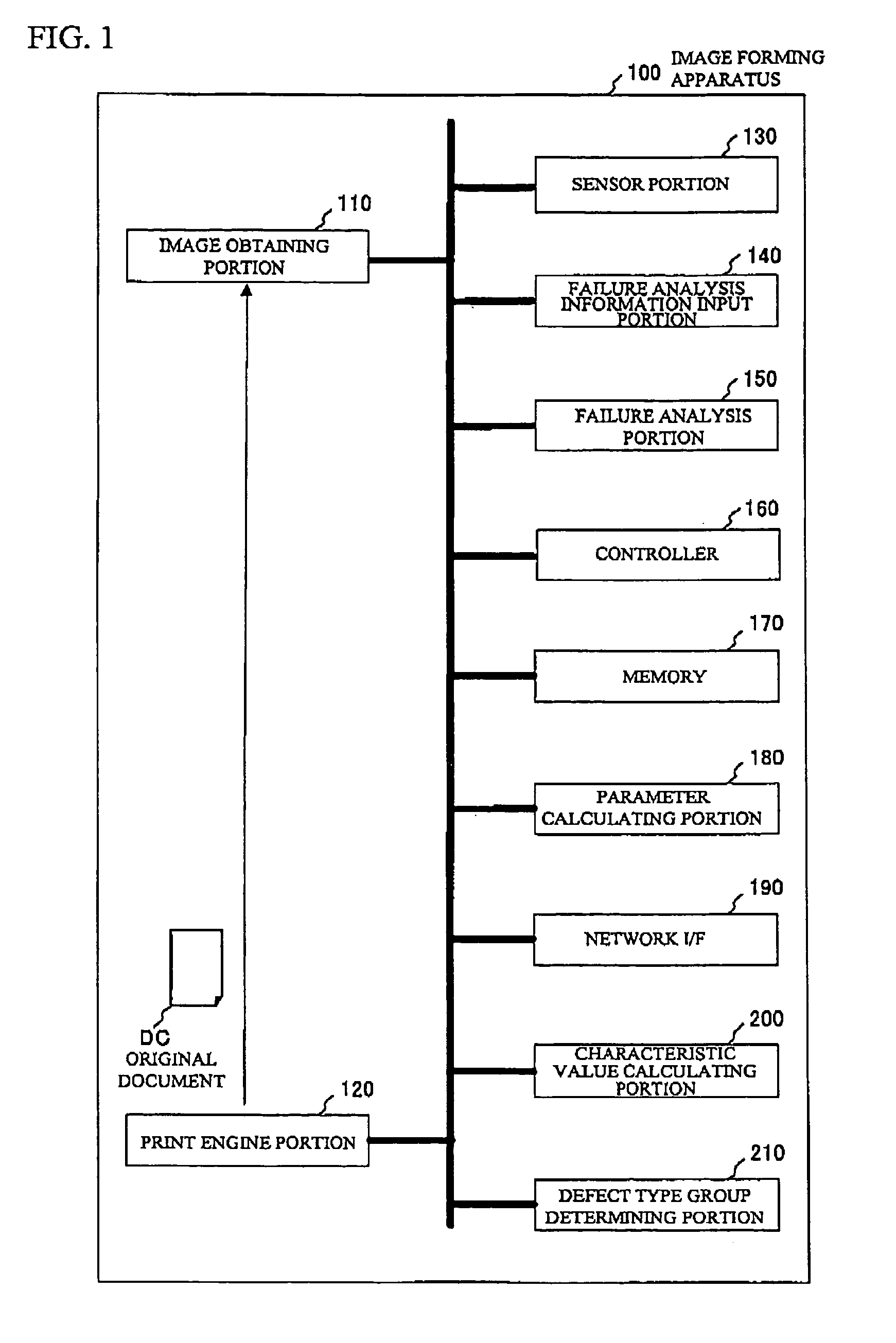

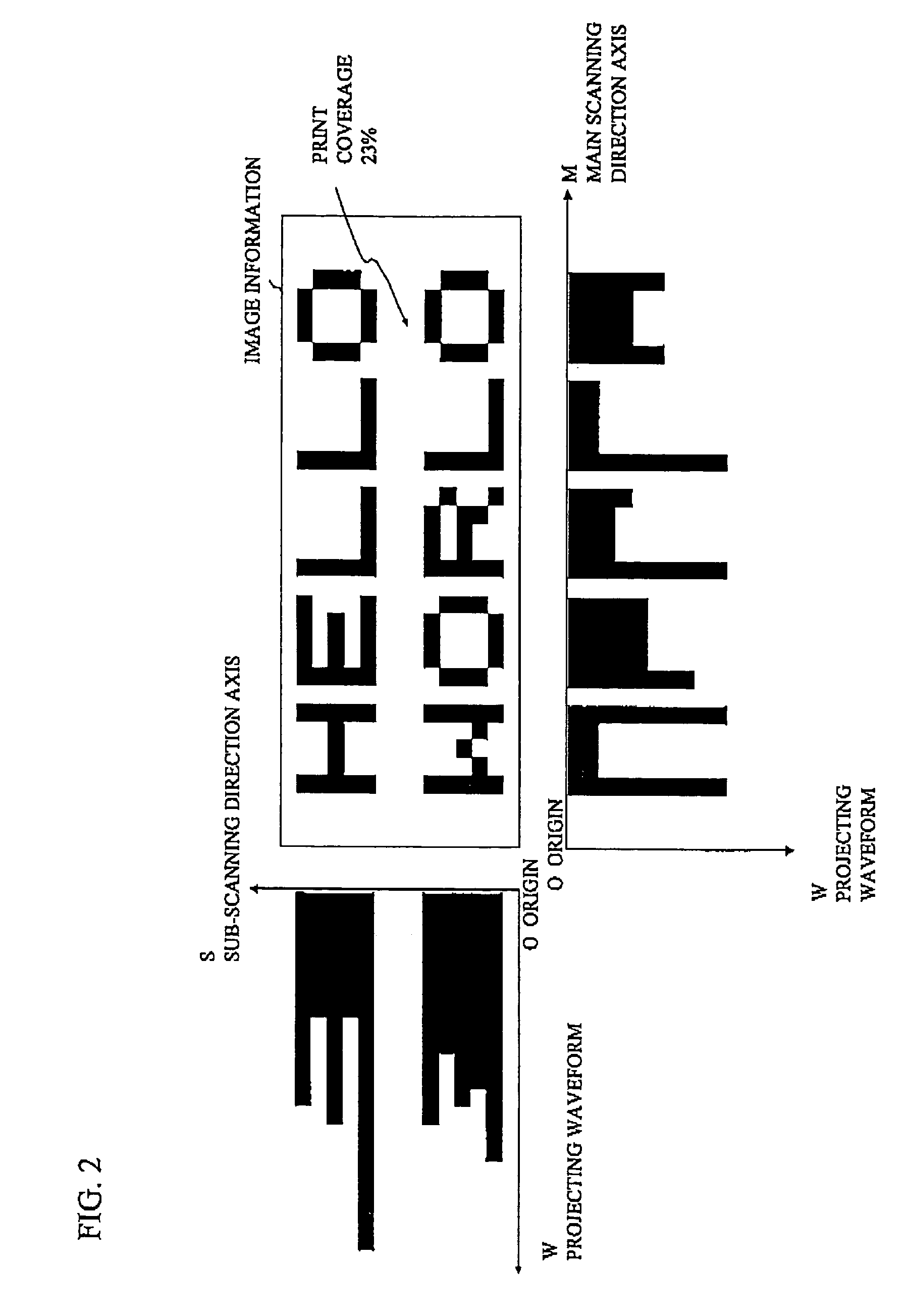

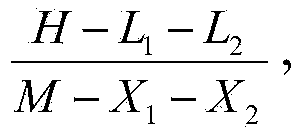

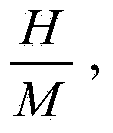

Failure analysis system, failure analysis method, and program product for failure analysis

InactiveUS20070237399A1Reduce the amount of informationImage enhancementImage analysisAlgorithmFailure analysis

A failure analysis system includes an obtaining portion that obtains read-in image information that is image information obtained by reading an output image, a memory that stores fundamental image reduction information that is information in which an information amount of fundamental image information is reduced, the fundamental image information serving as a fundamental of the output image, a calculating portion that calculates a characteristic value of a projecting waveform by use of differential information between read-in image reduction information and the fundamental image reduction information, the read-in image reduction information being information in which the information amount of the read-in image information obtained by the obtaining portion is reduced, the fundamental image reduction information being stored in the memory; and a determining portion that determines a defect type group that is a group of defect types of elements included in the output image by use of a clustering process.

Owner:FUJIFILM BUSINESS INNOVATION CORP

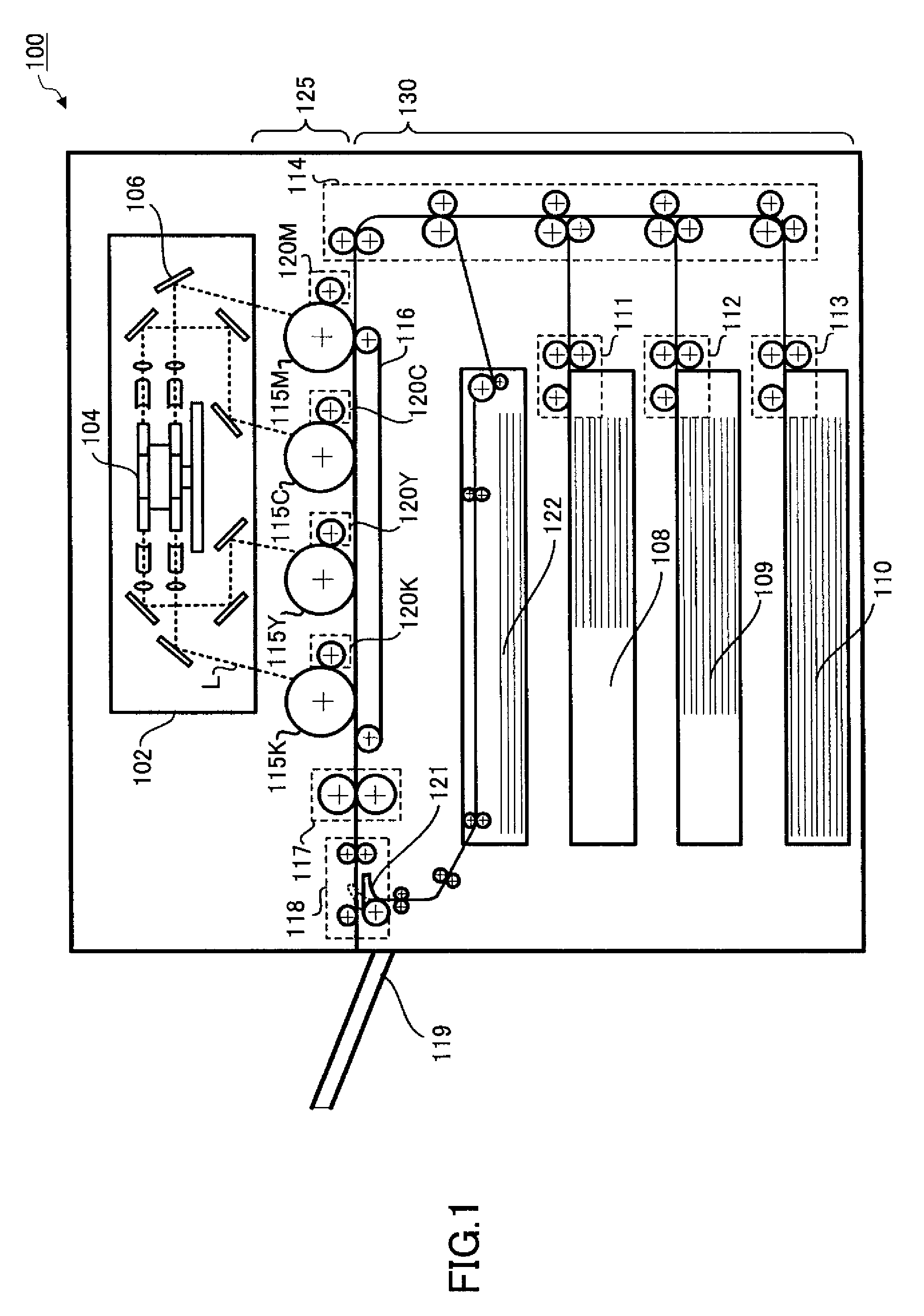

Failure analysis system, failure analysis method, and program product for failure analysis

A failure analysis system includes an obtaining portion that obtains read-in image information that is image information obtained by reading an output image, a memory that stores fundamental image reduction information that is information in which an information amount of fundamental image information is reduced, the fundamental image information serving as a fundamental of the output image, a calculating portion that calculates a characteristic value of a projecting waveform by use of differential information between read-in image reduction information and the fundamental image reduction information, the read-in image reduction information being information in which the information amount of the read-in image information obtained by the obtaining portion is reduced, the fundamental image reduction information being stored in the memory; and a determining portion that determines a defect type group that is a group of defect types of elements included in the output image by use of a clustering process.

Owner:FUJIFILM BUSINESS INNOVATION CORP

Image processing method and device

The invention discloses an image processing method and device. The image processing method is applied to a display unit comprising an optical amplification part. The method includes the steps that a marginal area in an image area is determined, and the image area except the marginal area serves as a middle area; image reduction processing is conducted on images in the marginal area in the image boundary direction; image magnification processing is conducted on images in the middle area in the image boundary direction; the images which are reduced and magnified are displayed through the display unit, and therefore the display unit can present images in the same proportion. According to the image processing method and device, under the effect of the optical amplification part, the images with the marginal areas reduced are magnified in vision, the magnification proportion of the images is equal to that of the images in the middle area, so that the display unit presents the images which are consistent in proportion, and therefore the images are displayed in a non-deformation mode in overall vision.

Owner:HISENSE VISUAL TECH CO LTD

Video signal processing circuit inhibiting display of distorted images

InactiveUS6160590ATelevision system detailsTelevision system scanning detailsComputer hardwareSignal processing circuits

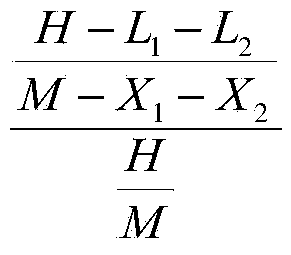

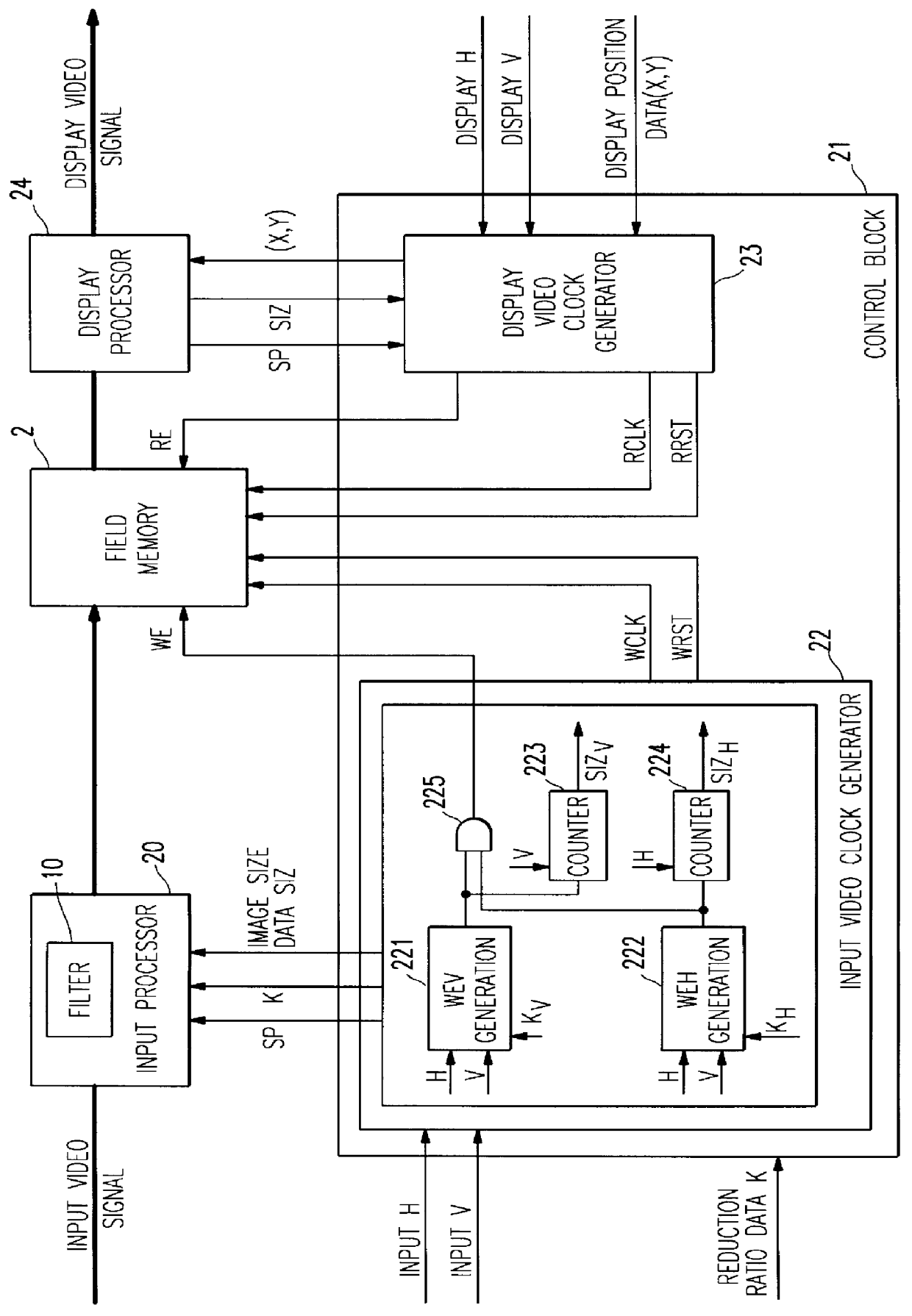

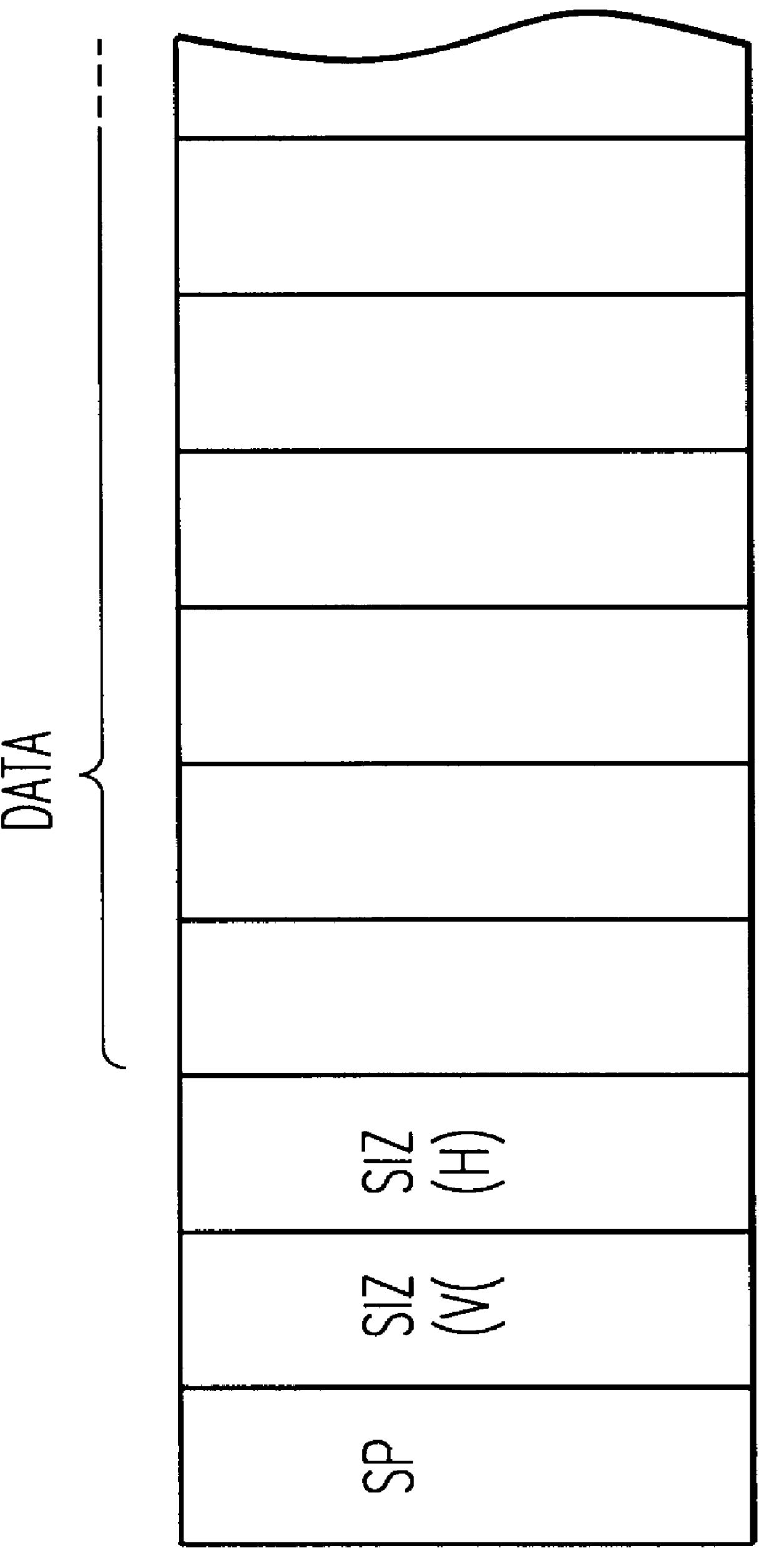

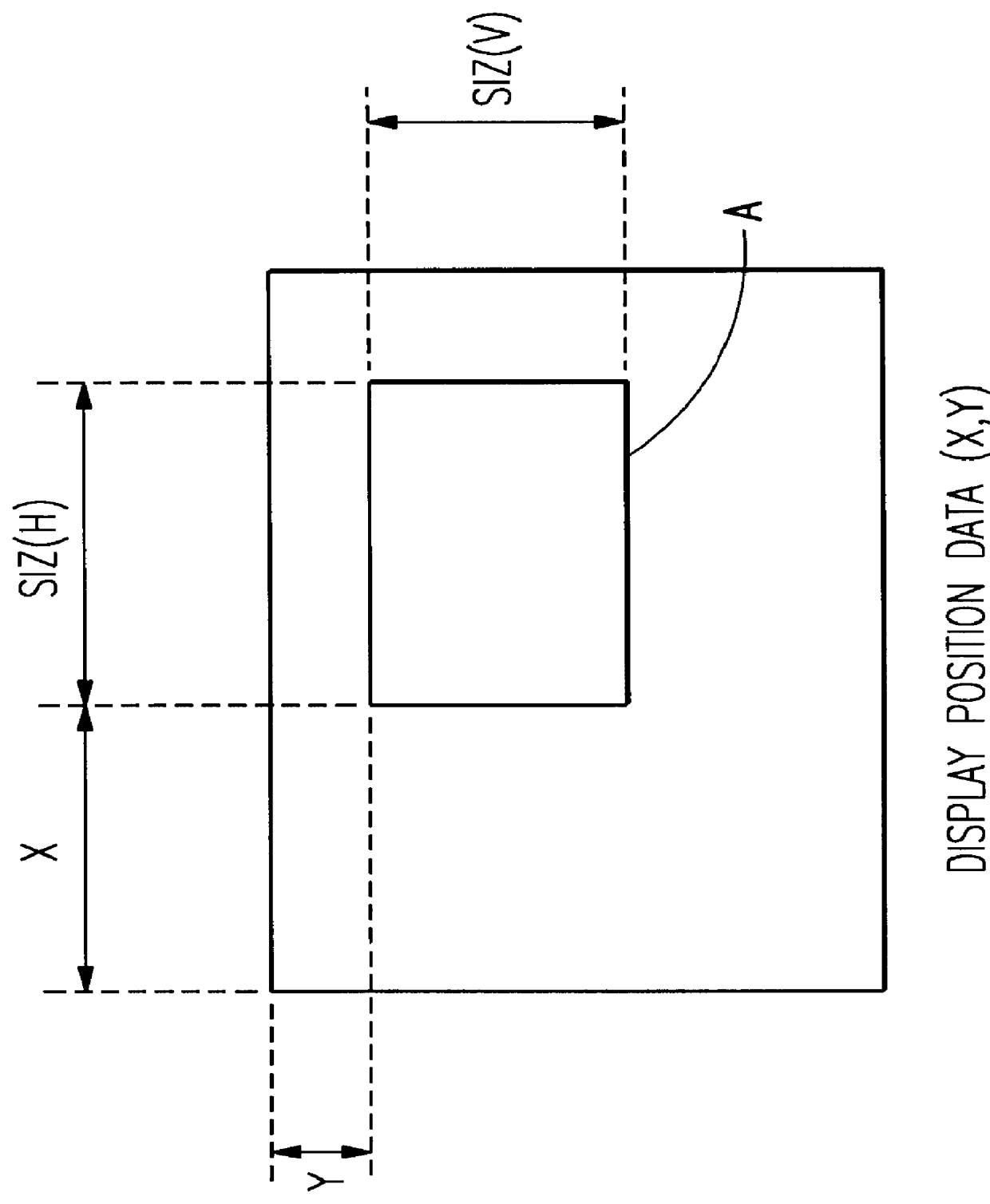

A video signal processing circuit uses a buffer memory for reducing or expanding video signals in the generation of child images to be displayed within a display window. Image size data, stored in a header within the buffer memory, and a reduced video signal are prevented from representing different image reduction ratios which might otherwise occur when the reduction ratio is changed. At the time of changing the reduction ratio, image size data SIZ are calculated from a write enable signal based on reduction ratio data K, for a one-field period just after the change by an input video clock generator 22. The calculated image size data are written to a header together with a reduced video signal in a field memory 2, and a flag bit SP indicating the change in the reduction ratio is also written to the header for the one-field period just after the change. When data are read from the buffer memory, the flag bit SP is detected by a display video clock generator 23 to mute a video signal output when there is a likelihood of displaying distorted data. On the other hand, writing to the field memory 2 is inhibited for the one-field period just after the change in the image magnification data so that the muting period of the video signal output can be shortened.

Owner:SEMICON COMPONENTS IND LLC

Method and apparatus for contactless hand recognition

A method and apparatus is provided for Contactless Hand Recognition (CHR) for positive identification of cooperative individuals seeking access to physical, logical, or informational systems. Contactless Hand Recognition (CHR) is based on a novel technique and apparatus that rapidly and contactlessly captures a livescan hand geometry video image with a visible wavelength, infrared, or thermal camera of a person desiring access, then reduces the image to a template, compares the livescan template to a reference template, and determines if there is a match. Contactless Hand Recognition (CHR) is a significant advancement over current state-of-the-art hand recognition systems because authentication is done contactlessly while on the move, and at a distance, while simultaneously verifying liveness. It can also be combined with a personal knowledge process to include the use of a Personnel Identification Number (PIN), a secret contactless sign (SCS), or unique hand / finger position biometrics known only to the user. The CHR invention offers the possibility for users to have a rapid, fully contactless three-factor system of authentication based on contactless tokens, biometrics, and personal knowledge identification signs.

Owner:THE RIGHT PROBLEM

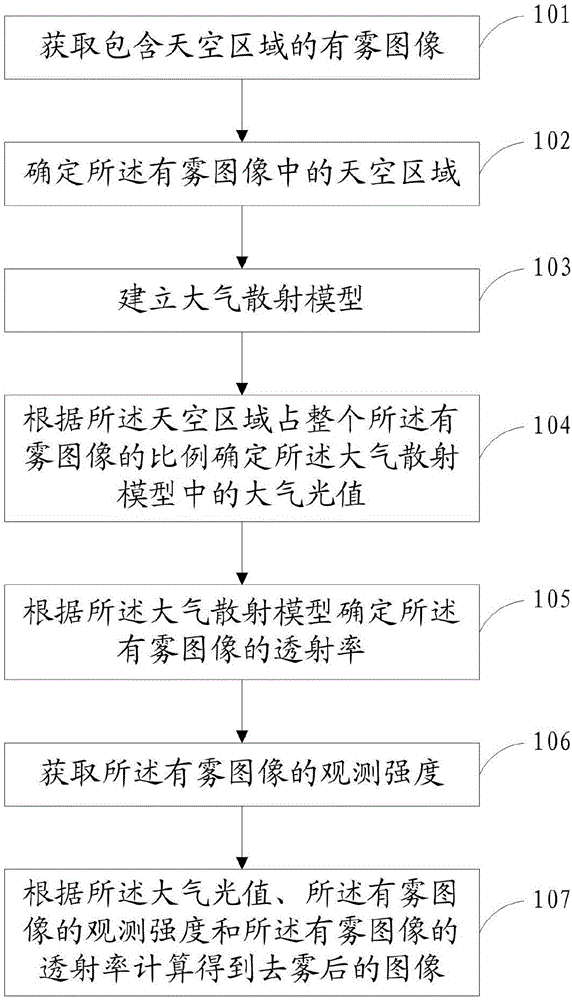

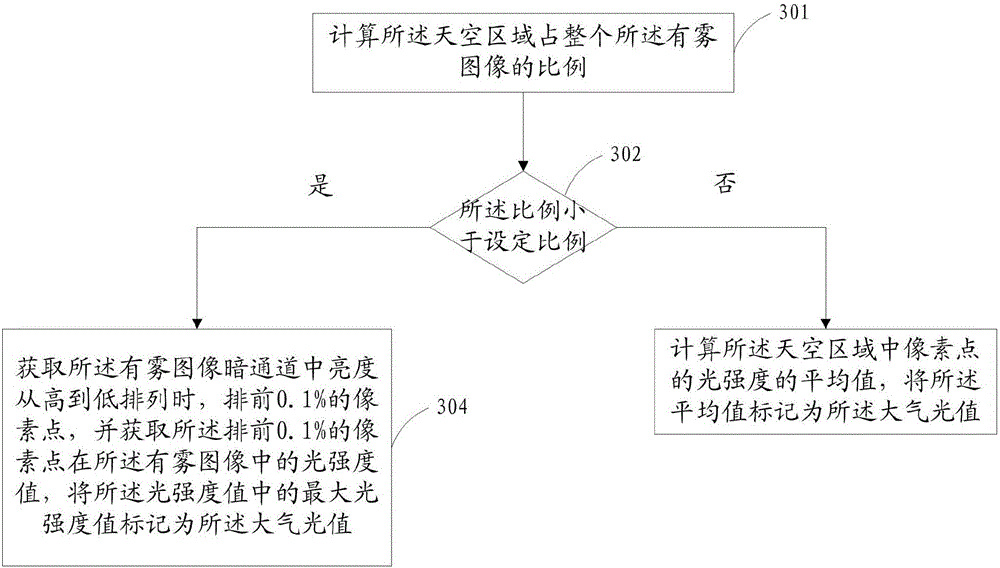

Image defogging method and system

The invention discloses an image defogging method and system. The method comprises the steps: obtaining a fog image comprising a sky area; determining the sky area in the fog image; building an atmospheric scattering model; determining an atmospheric light value in the atmospheric scattering model according to the proportion of the sky area to the whole fog image, wherein the atmospheric light value is the atmospheric light intensity at an infinity place; determining the transmissivity of the fog image according to the atmospheric scattering model; and obtaining the observation intensity of the fog image. The method and system can carry out good defogging of the sky area in the fog image, are high in image reduction precision, are low in defogging complexity, and is high in processing speed.

Owner:程建 +1

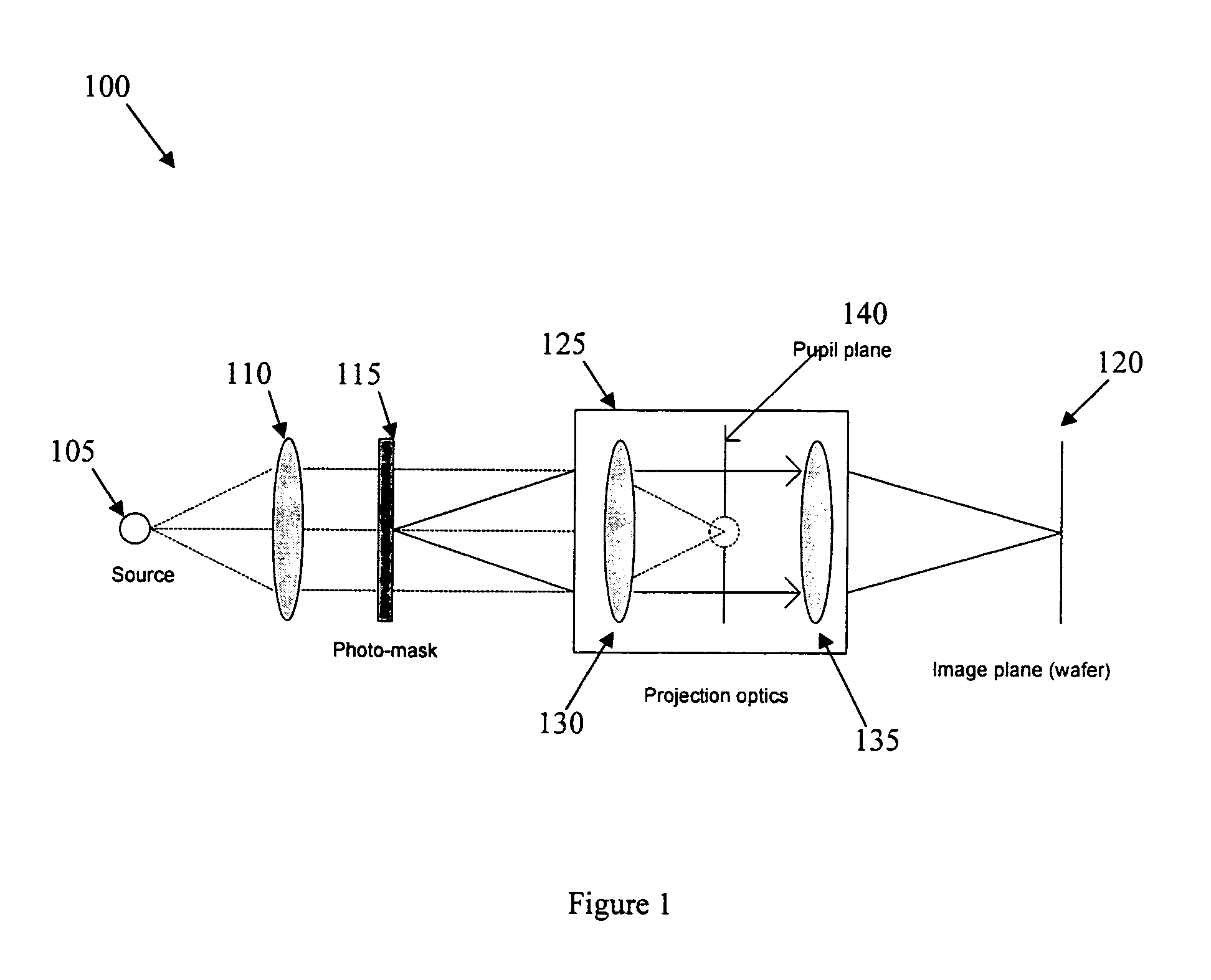

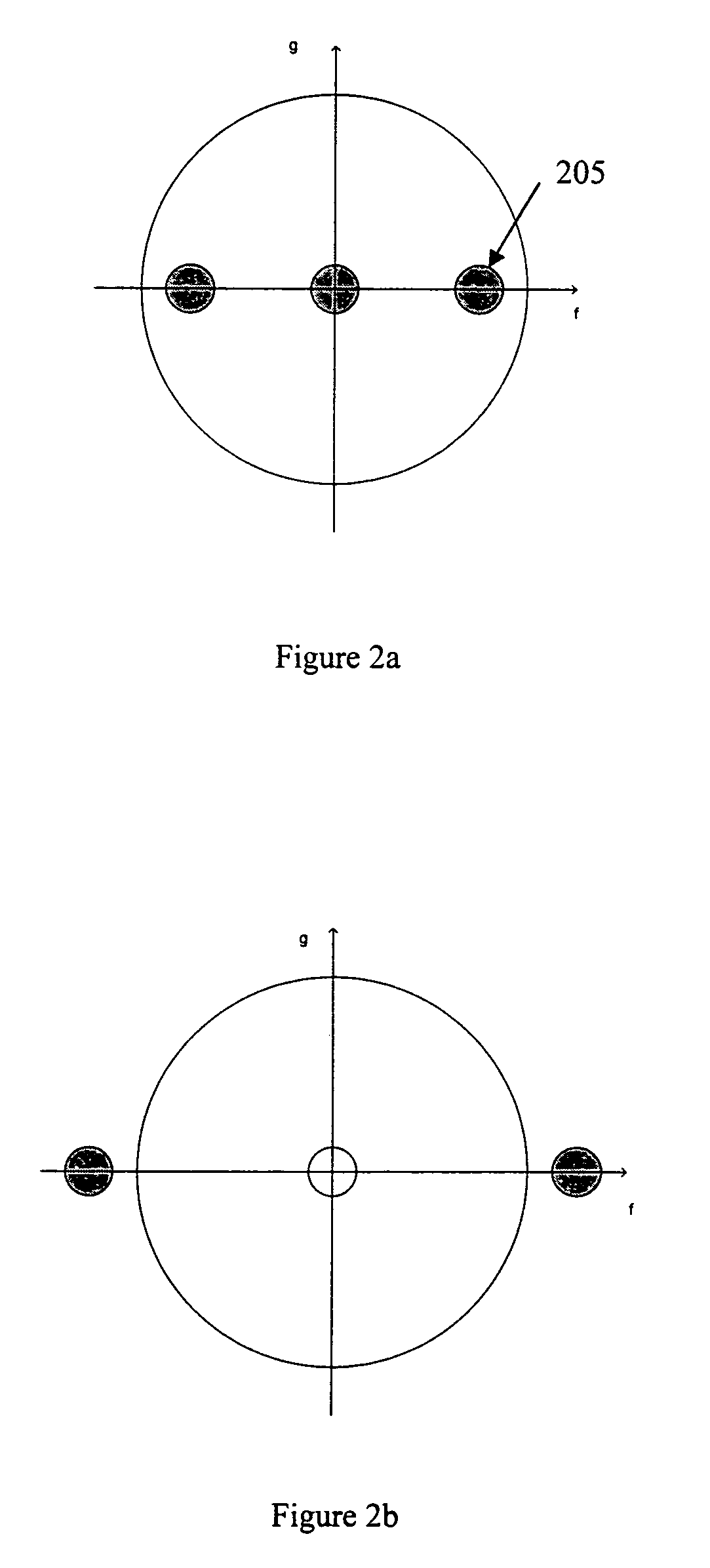

Micro-sculpting using phase masks for projection lithography

InactiveUS7585596B1Increase depth of focusPhotomechanical apparatusSemiconductor/solid-state device manufacturingMicro structurePrism

Owner:JOHNSON ERIC G

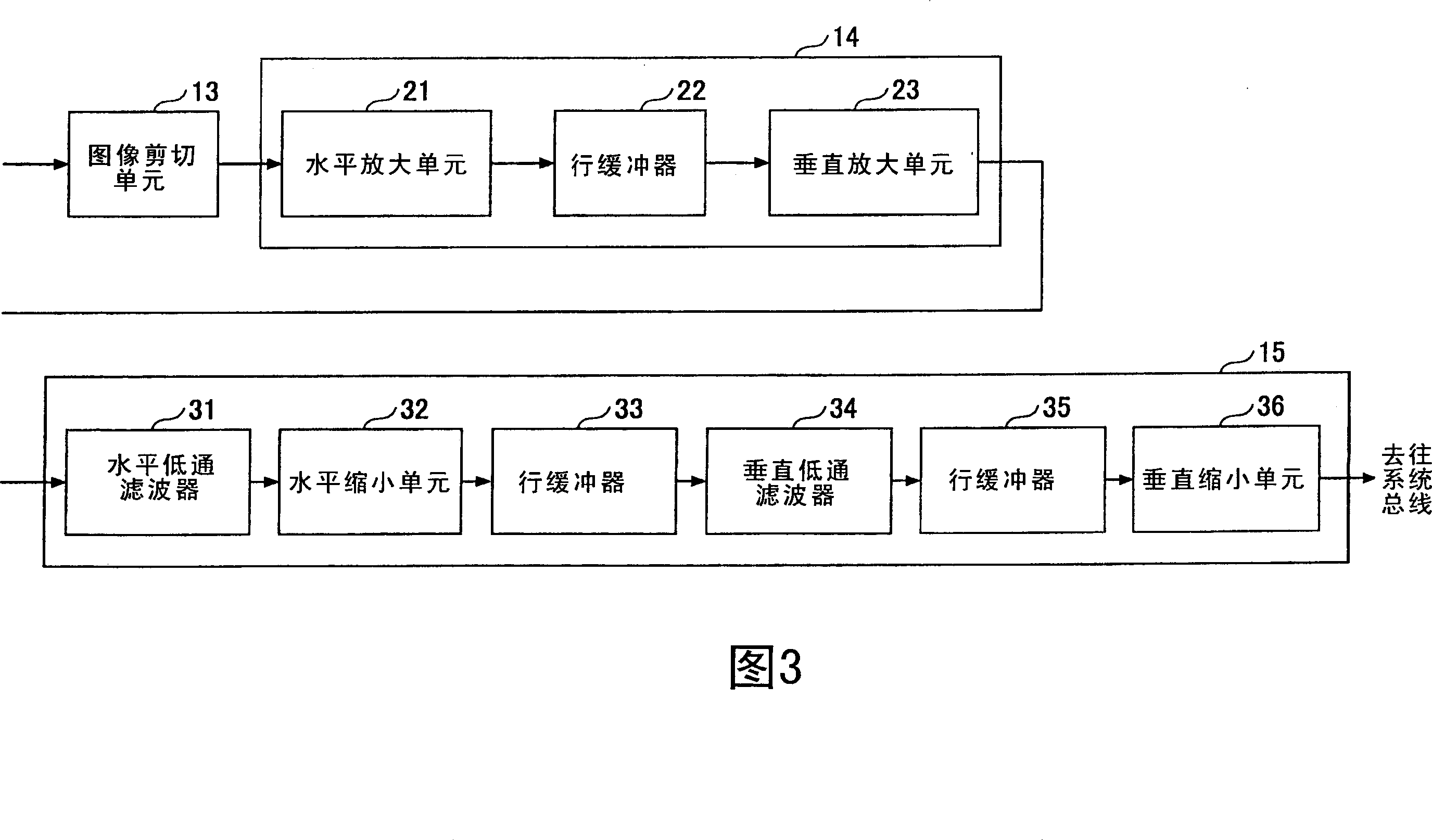

Image processing apparatus and method for image resizing matching data supply speed

InactiveCN1933540AEasy to handleTelevision system detailsGeometric image transformationImaging processingReduction factor

The invention discloses an image processing device, which comprises: a data providing node, used for receiving line data scanned in the main scanning direction of an image; an image amplifying unit coupled to the data providing node, used for applying an upscaling process to produce amplified data at an output node, the upscaling process for enlarging the image with an upscaling factor equal to an integer; and an image downscaling unit coupled to the output node of the image upscaling unit for applying A downscaling process is used to downscale the upscaled image by a desired downscaling factor to produce downscaled data at the output node.

Owner:CYPRESS SEMICON CORP

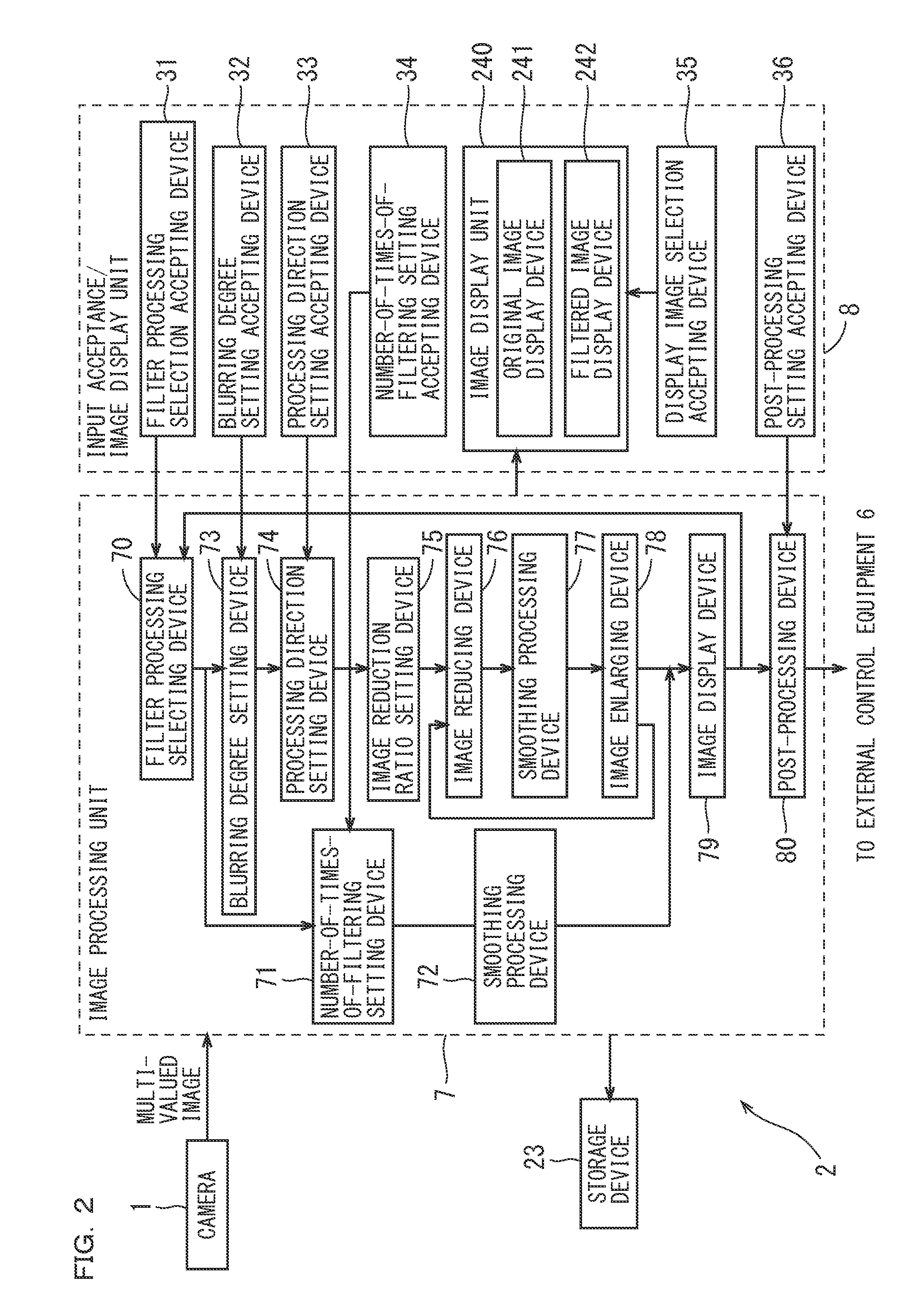

Image Processing Apparatus, Image Processing Method, and Computer Program

ActiveUS20100080484A1Improve blurShorter arrival timeImage enhancementDigitally marking record carriersImaging processingComputer graphics (images)

An image processing apparatus capable of executing filter processing with a desired blurring degree selected in accordance with an application from a multi-valued image captured an object surface, the image processing apparatus comprises: a first filter processing device for executing smoothing processing on the multi-valued image, a second filter processing device for creating a reduced image reduced from the multi-valued image with an image reduction ratio, executing smoothing processing on the reduced image, and creating an enlarged image of the smoothed image enlarged with an image enlargement ratio corresponding to the image reduction ratio, and an image display device for displaying a processed image by the first filter processing device or the second filter processing device.

Owner:KEYENCE

Image processing equipment and program

InactiveCN1417745ALarge blur componentSuppression of distortionTelevision system detailsGeometric image transformationPattern recognitionImaging processing

A domain block extracting unit extracts a domain block image from an original image. A range block extracting unit extracts a range block image from an area in the vicinity of the domain block image. The range block image has size being larger than a domain size and being smaller than an enlarged size. A reduced range block forming unit reduces the range block image to the domain size to produce a reduced range block image. A similarity judging unit compares each of the reduced range block images with the domain block image to select the highest similarity range block image. An enlarged range block forming unit forms an enlarged range block image by enlarging the size of the highest similarity range block image to an enlarged size thereof. An enlarged image acquiring unit produces an enlarged image of an original image by employing the respective enlarged range block images.

Owner:FUJIFILM BUSINESS INNOVATION CORP

Image processing apparatus, image forming apparatus, and recording medium

InactiveUS20090168109A1Degradation of image qualityReduce degradationImage enhancementDigitally marking record carriersImaging processingImage formation

An image processing apparatus for performing image reduction correction on target image data corresponding to pixels, includes a deletion position specifying unit configured to specify, as deletion positions of deletion pixels in the target image data, predetermined positions in image regions including the pixels having gradation values that are more than or equal to a predetermined density; and a pixel deleting unit configured to delete the deletion pixels at the deletion positions specified by the deletion position specifying unit, and to shift the pixels subsequent to the deletion pixels in a reduction direction as the deletion pixels are deleted.

Owner:RICOH KK

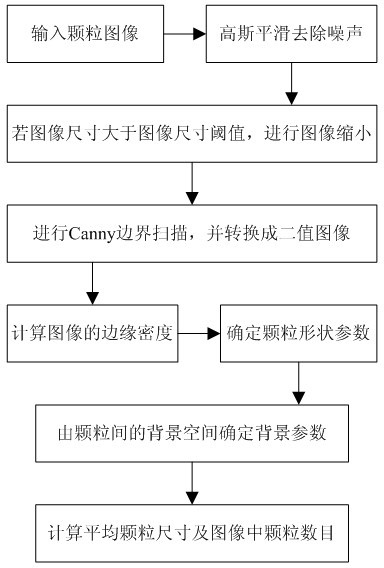

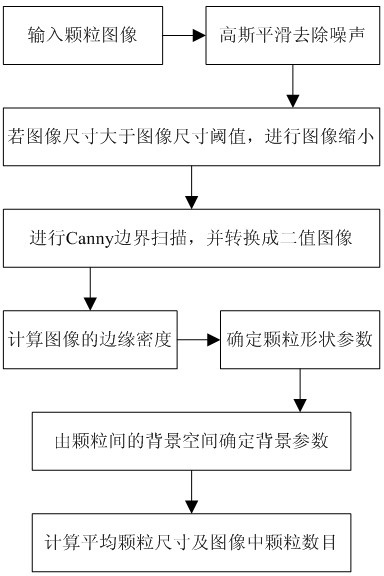

Method for measuring average size of complicated particles based on Canny boundary detection

InactiveCN102608016AAccurate detectionApplicable Statistical MeasuresImage enhancementIndividual particle analysisImaging processingNoise removal

The invention relates to the technical field of image processing, in particular to a method for measuring an average size of complicated particles based on Canny boundary detection. The method comprises the following steps of 1, inputting an image of moving particles; 2, performing Gaussian smoothing noise removal; 3, when the image size is greater than an image size threshold value, shrinking the image; 4, performing Canny boundary scanning, and converting the image into a binary image; 5, calculating the particle edge density of the image, and determining an average shape parameter of the particles and a background space parameter of the image; and 6, calculating the average size of the detected particles and the number of detected particles. through adoption of the method, the average size and the number of the particles in the image can be detected quickly and accurately; and the method is very suitable to statistics and measurement of a plurality of complicated particles at real time on line and can be used for pre-partitioning acomplicated particle image.

Owner:FUZHOU UNIV

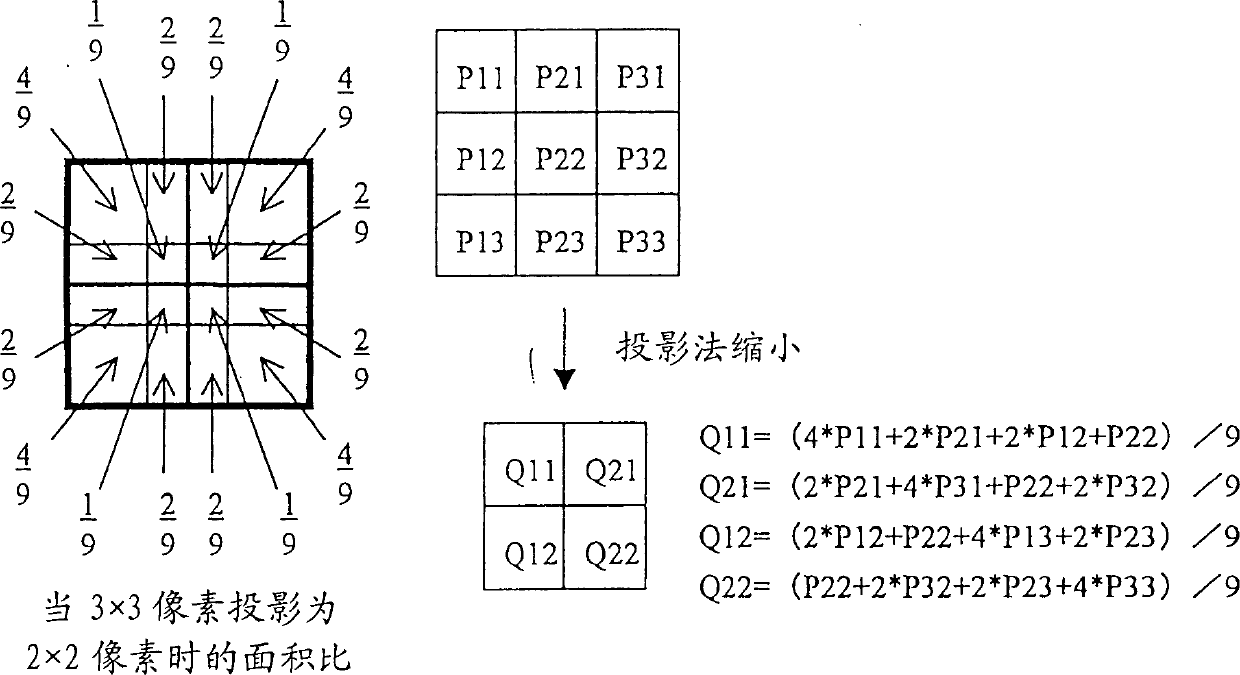

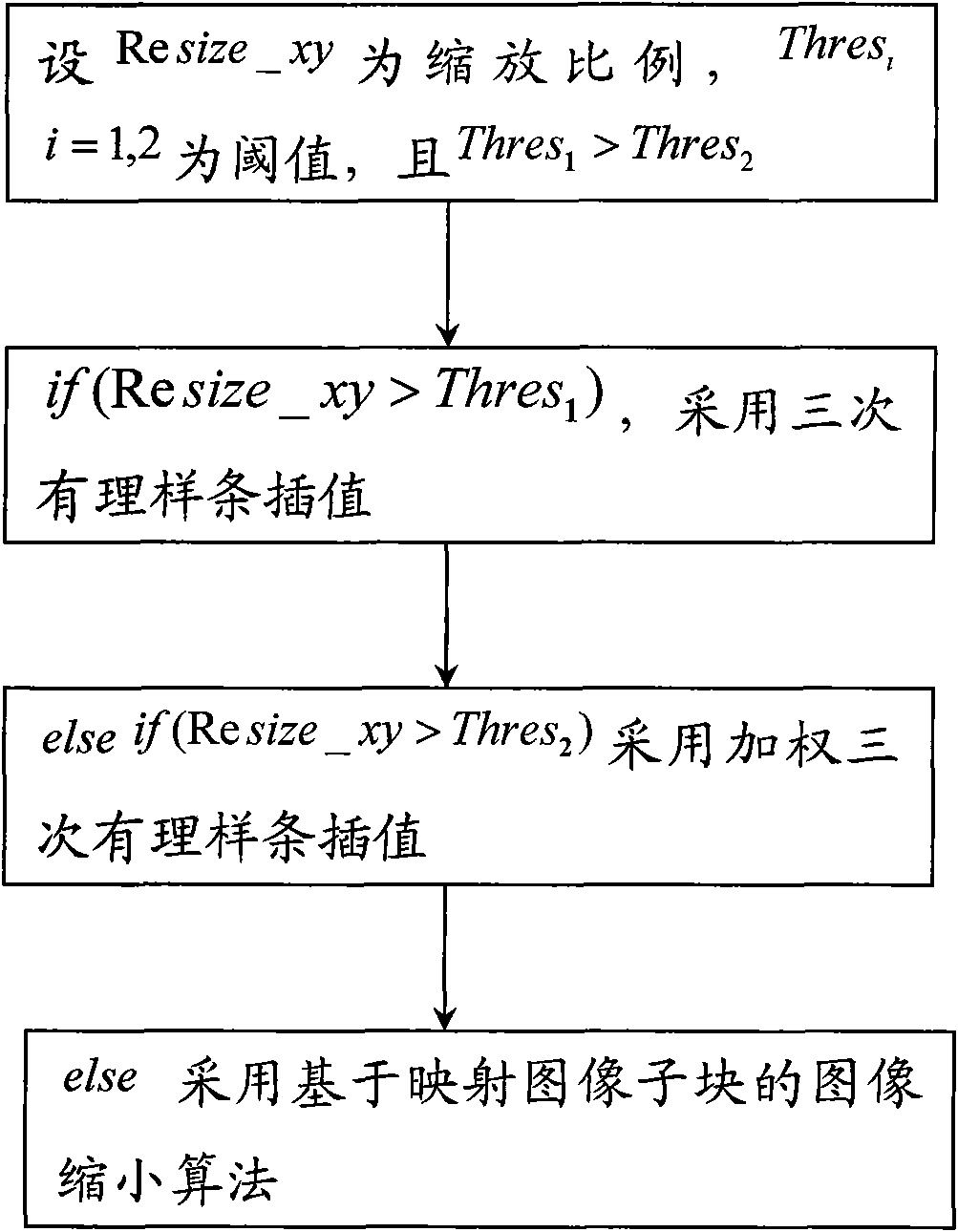

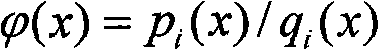

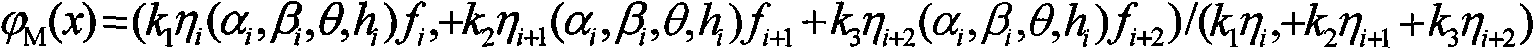

Adaptive image scaling method

InactiveCN101923704AImprove visual effectsImprove clarityGeometric image transformationImage scaleVisual perception

The invention relates to a adaptive image scaling method which comprises the following steps: Re size_xy is set as the scaling ratio, Thresi i=1, 2 is set as the threshold values, wherein Thres1 is more than Thres2; if Re size_xy is more than thres1, triple rational spline interpolation is adopted; if Re size_xy is more than Thres2, then weight triple rational spline interpolation is adopted; and as for other conditions, the image reduction algorithm based on a mapping image sub-block is adopted. On one hand, the new algorithm of multi-mode image scaling can self-adaptively choose a scaling algorithm according to the scaling ratio and enable the image scaling effect to achieve fine visual effect. On the other hand, the weight triple rational spline interpolation can improve the situations in which edge sawtooth emerges and part of information is lost after an image is reduced and maintain fine definition of other regions.

Owner:融创天下(上海)科技发展有限公司

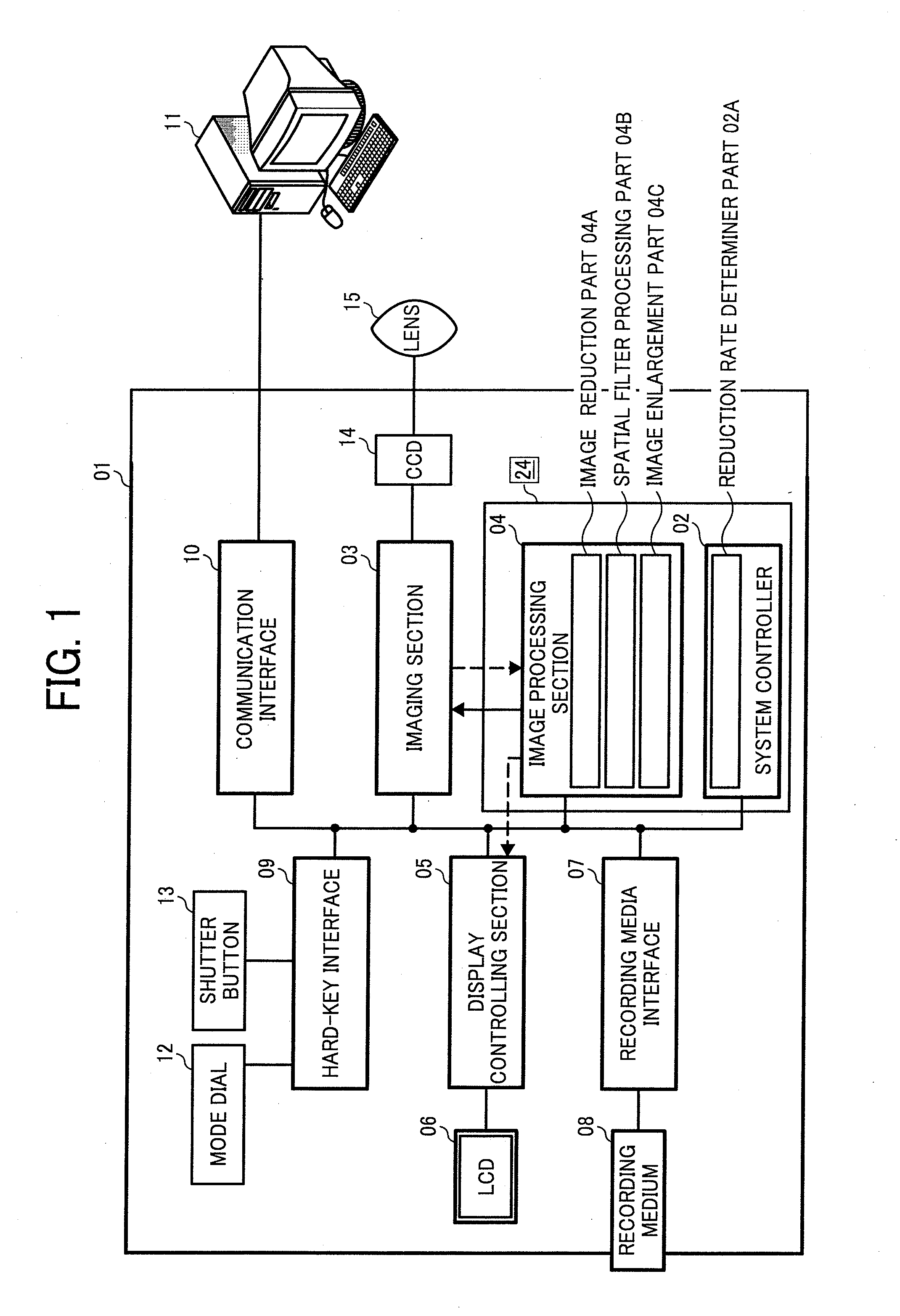

Image processor, imaging apparatus including the same, and image processing method

InactiveUS20100007759A1Good effectSimplify image processingTelevision system detailsImage enhancementReduction rateImaging processing

An image processor performs blurring processing on an image acquired via a lens system and including a main subject image and a background image, and includes an image processing section having a reduction rate determiner part which determines a reduction rate of the background image based on at least one of a focal length of the lens system, a distance between the main subject image and the background image, level of the blurring processing, and an image size of the background image; an image reduction part which reduces the background image at the reduction rate determined by the reduction rate determiner part; a spatial filter processing part which performs spatial filter processing on the background image reduced by the image reduction part; and an image enlargement part which enlarges the background image processed by the spatial filter processing part at an enlargement rate as an inverse of the reduction rate.

Owner:RICOH KK

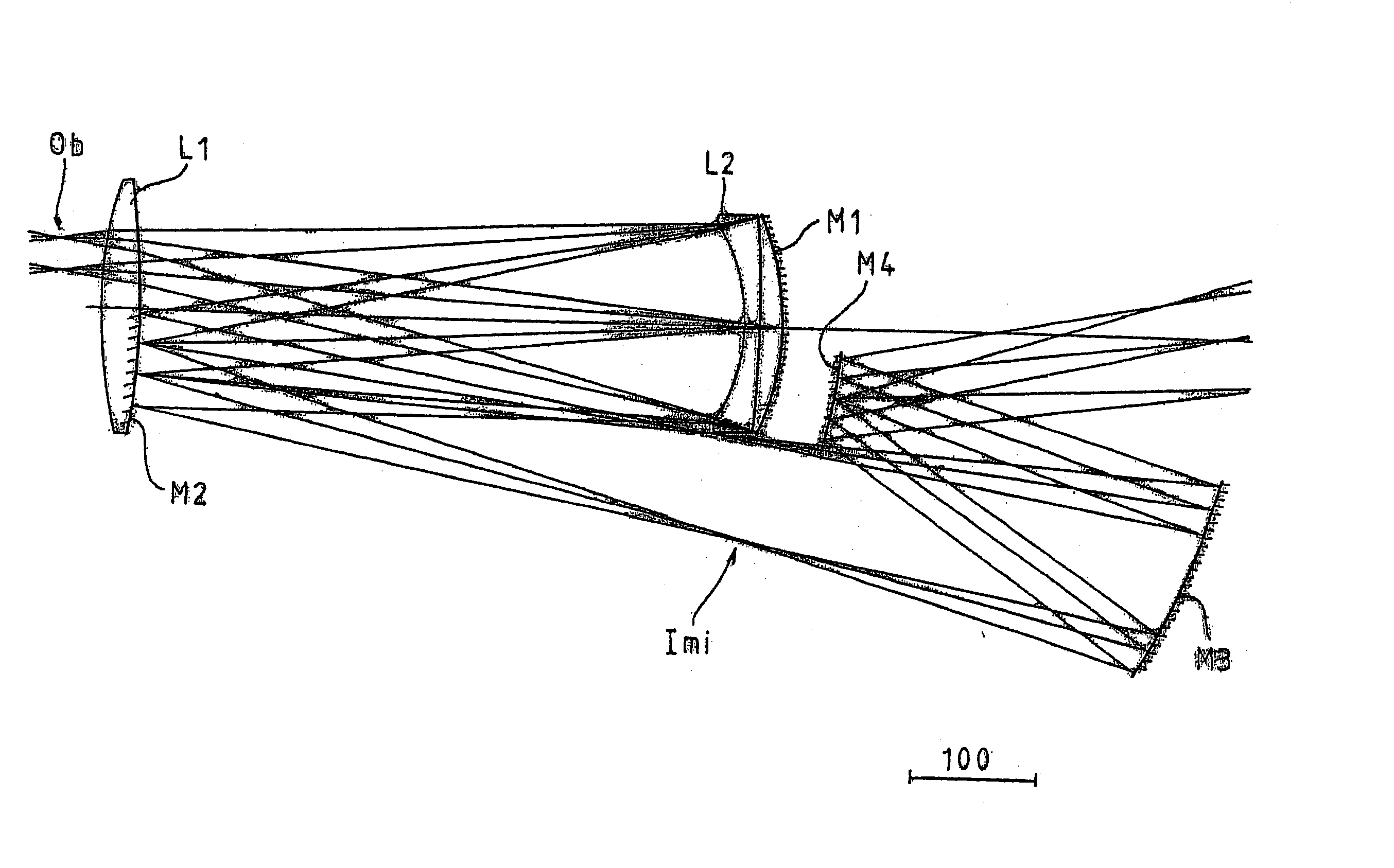

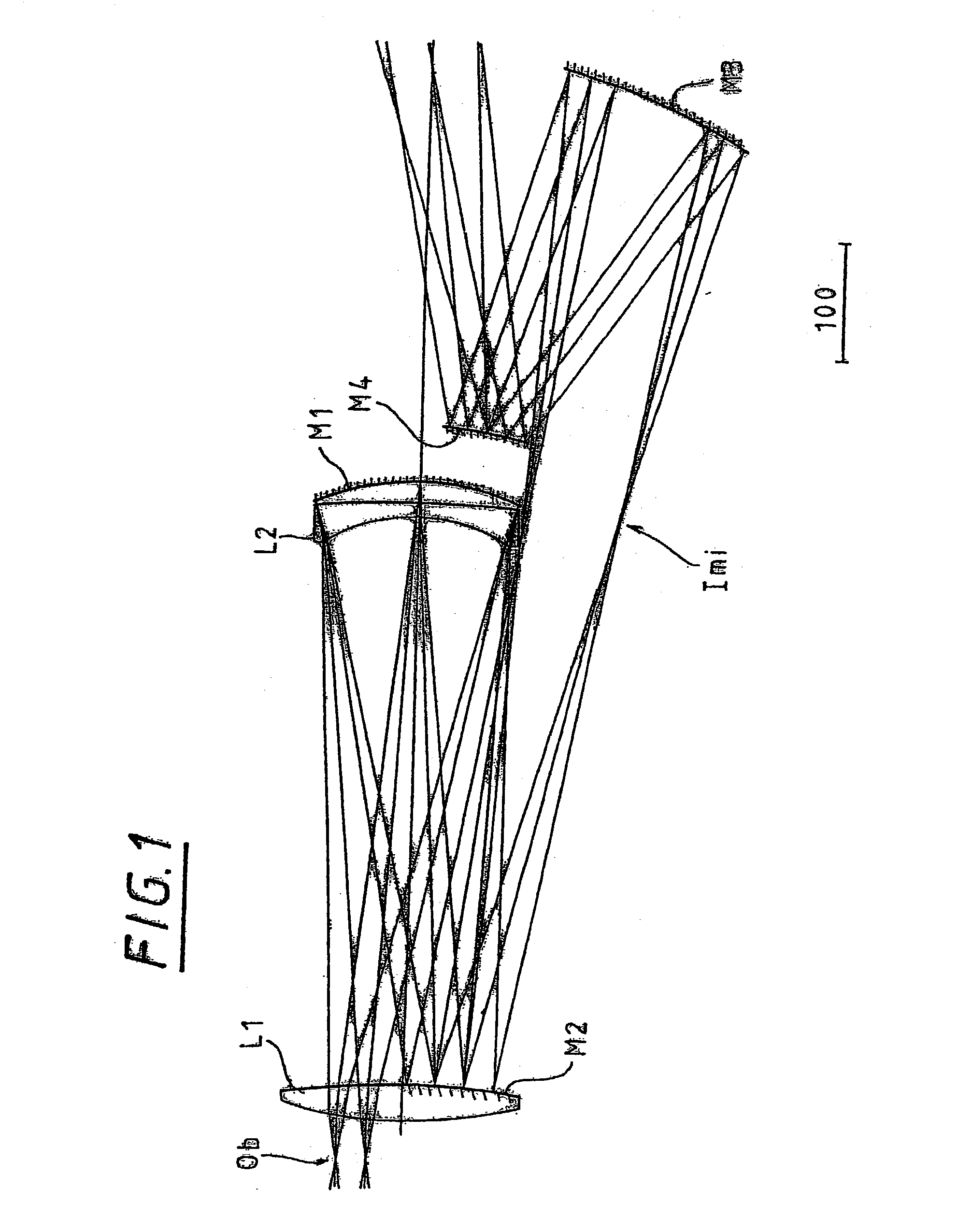

Microlithographic reduction projection catadioptric objective

InactiveUS20040027653A1Easy to controlImprove performanceSemiconductor/solid-state device manufacturingMicroscopesNumerical aperturePhysics

A photolithographic reduction projection catadioptric objective includes a first optical group having an even number of at least four mirrors and having a positive overall magnifying power, and a second substantially refractive optical group more image forward than the first optical group having a number of lenses. The second optical group has a negative overall magnifying power for providing image reduction. The first optical group provides compensative aberrative correction for the second optical group. The objective forms an image with a numerical aperture of at least substantially 0.65, and preferably greater than 0.70 or still more preferably greater than 0.75.

Owner:MASCHFAB KEMPER

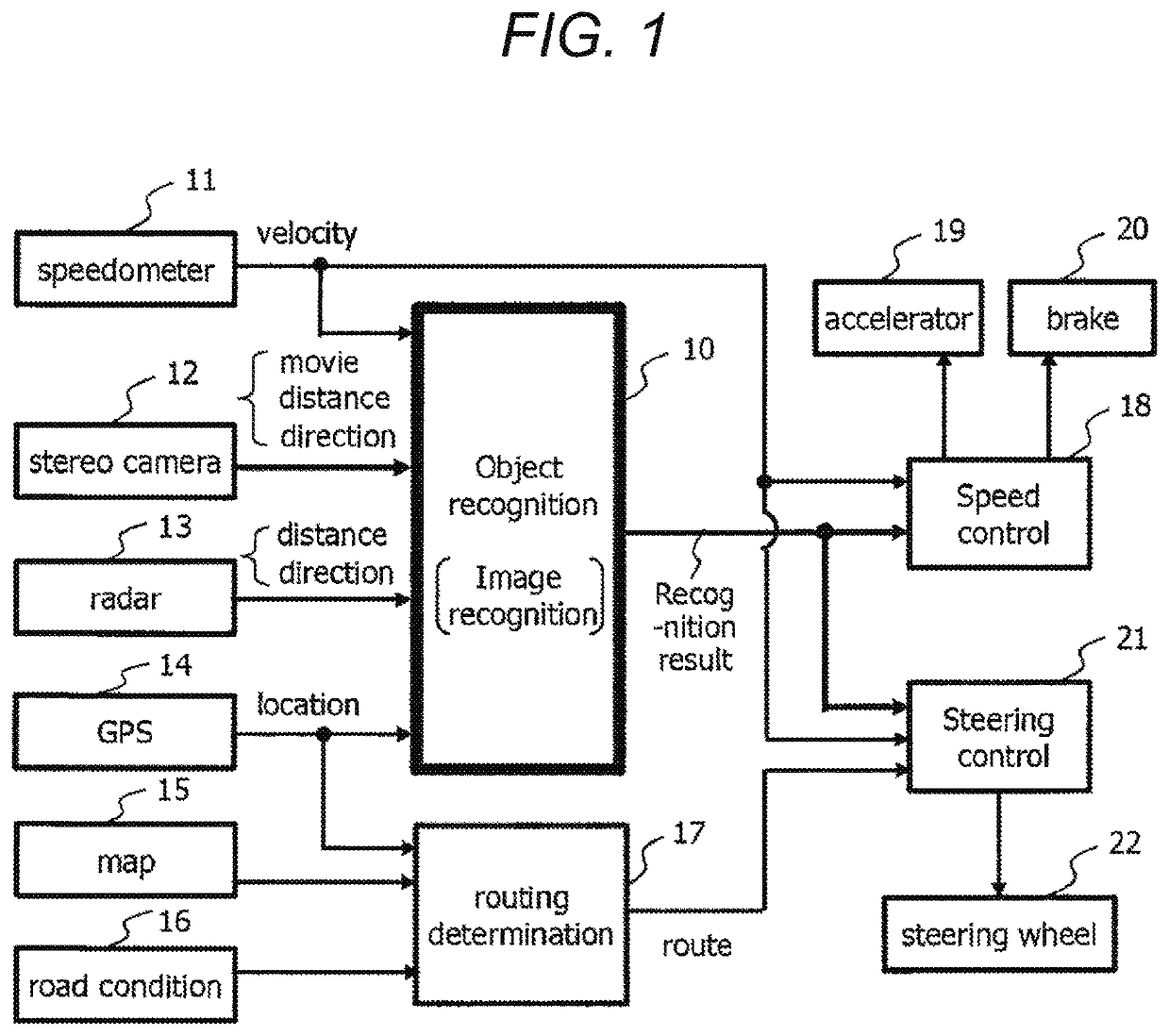

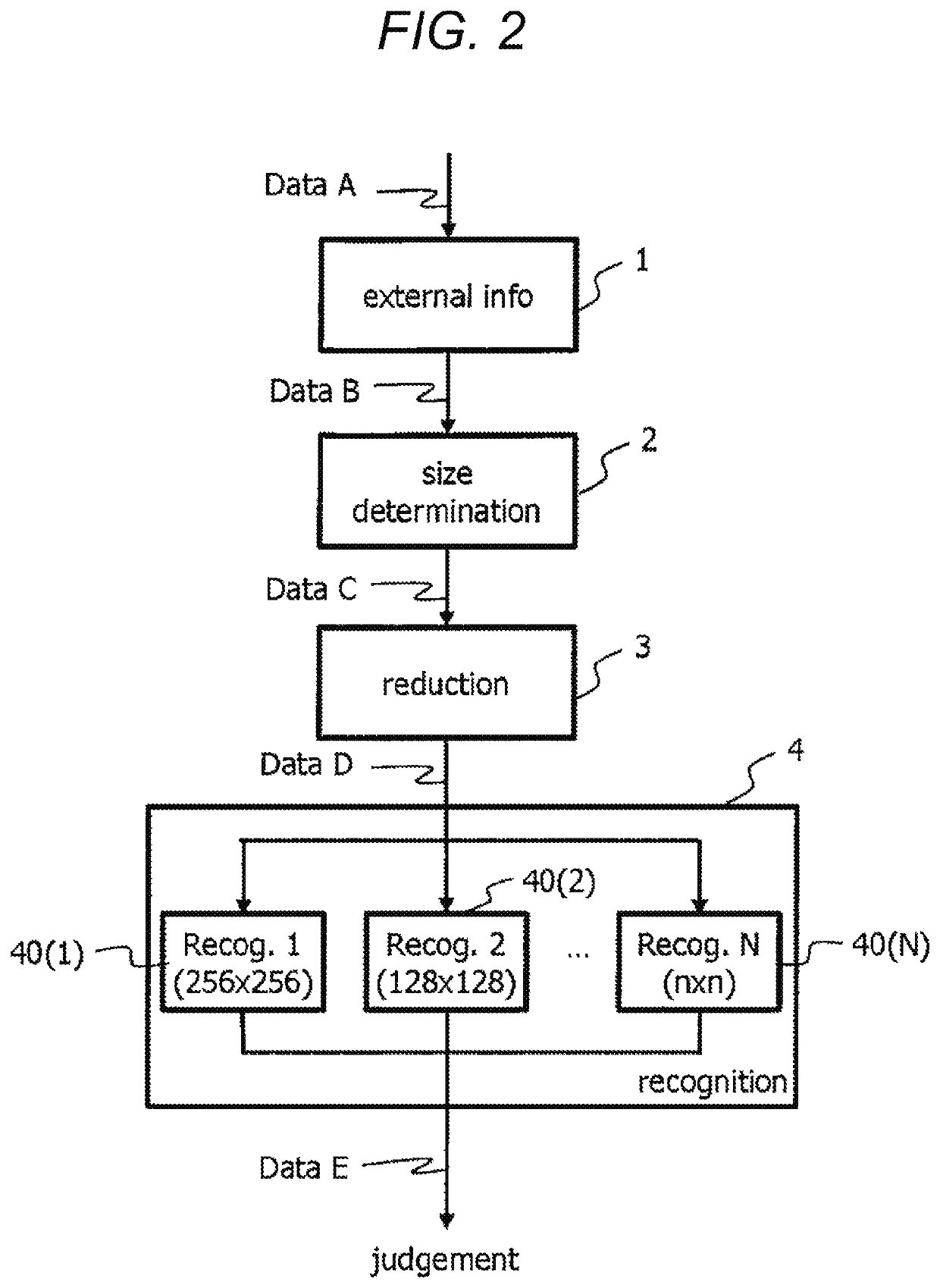

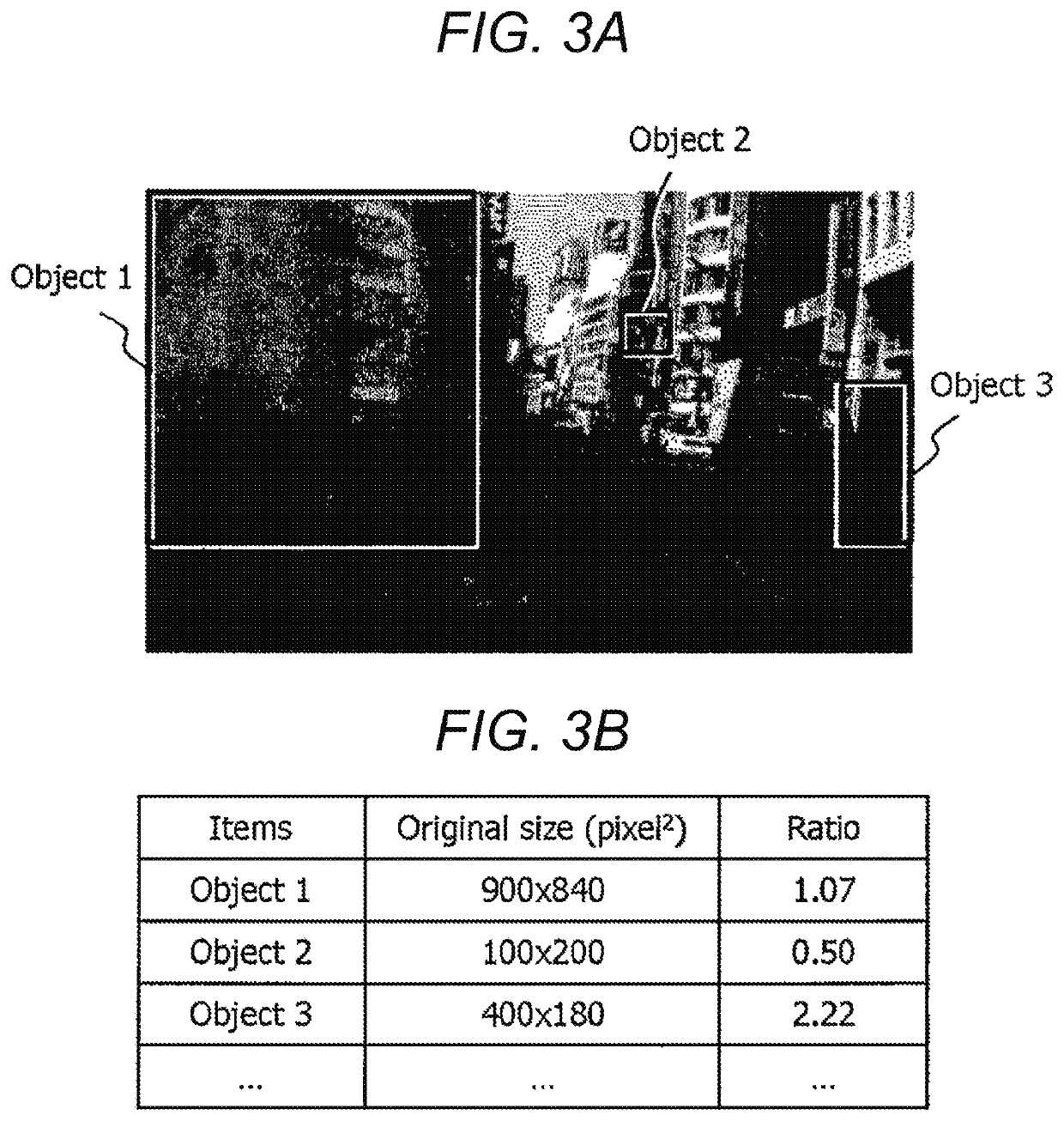

Image recognition system

ActiveUS10636161B2Reduce memory capacityImprove accuracyTelevision system detailsImage enhancementRadiologyNuclear medicine

An image recognition system includes an external information detection unit detecting a distance to a target to be recognized included in an image, a reduced image size determination unit deriving a reduced size of the image based on the distance to the target to be recognized, an image reduction unit reducing the image based on the reduced size of the image, and an image recognition unit including a plurality of recognition process units corresponding to sizes of the images to be recognized and executing the recognition process of the target to be recognized included in the reduced image by means of the recognition process unit corresponding to a size of the image. Instead of the distance to the target to be recognized, a size and a shape of the image, or a clip position of the image from an entire image, may be used.

Owner:HITACHI LTD

Seam-based reduction and expansion of images with table-based priority

ActiveUS8280186B1Geometric image transformationCharacter and pattern recognitionComputer visionComputer science

A system and method for expansion and reduction of images uses a look-up table to define an arbitrary mapping of data (e.g., pixel values) representing an image to respective energy values. Each pixel value may represent an absolute color or intensity value, a difference in color or intensity values, or an average, derivative, minimum, or maximum of two or more pixel values. The energy values may then be used to determine one or more low-cost seams of the image to be removed for an image reduction operation or replicated for an image expansion operation, where the cost of each seam is dependent on the energy values of the pixels of the seam. The look-up table may be used to apply a threshold and / or cap on the energy values mapped to pixel values. The look-up table may also provide a mechanism for reconfiguring mappings, thresholds, and / or caps.

Owner:ADOBE INC

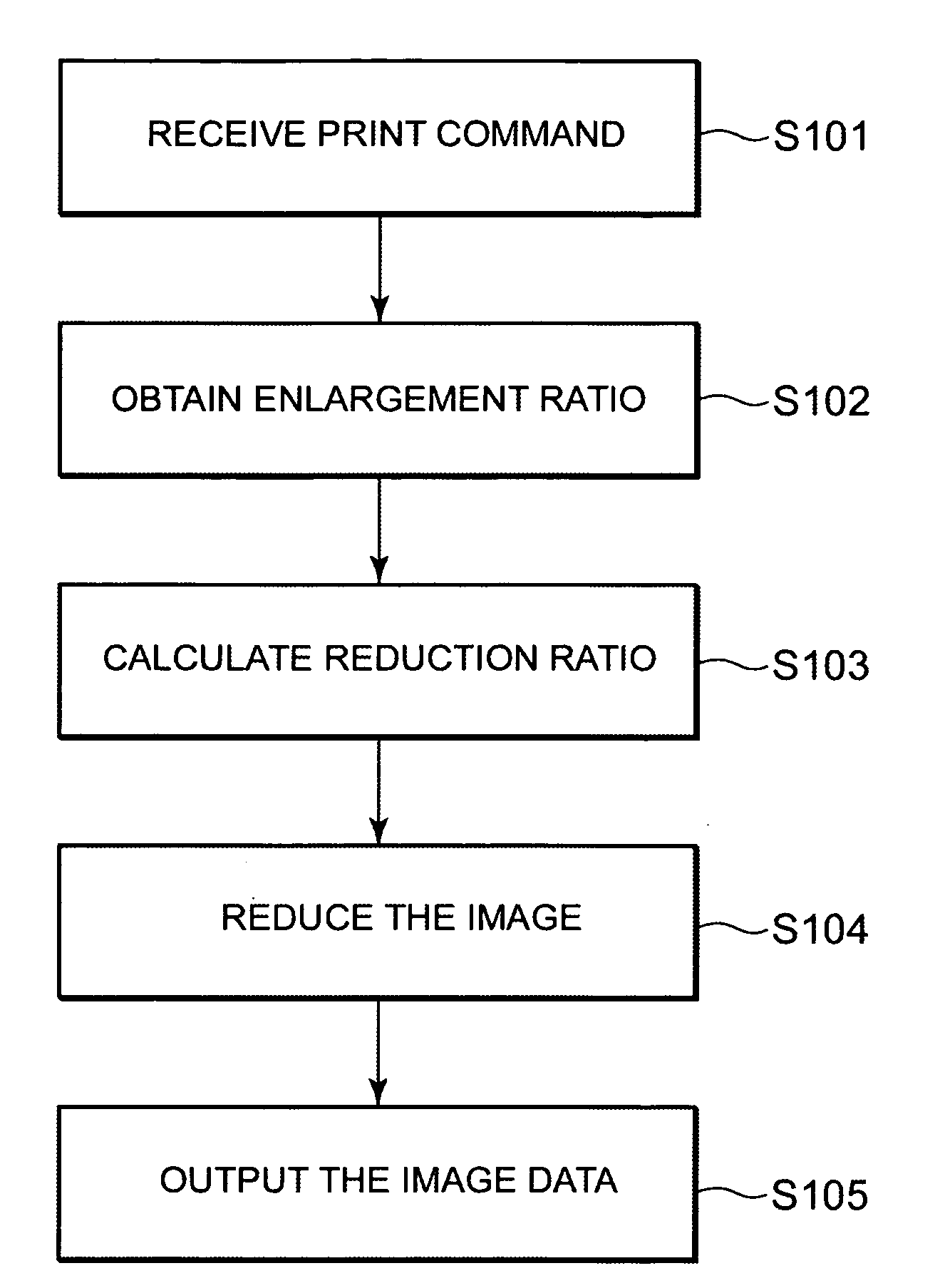

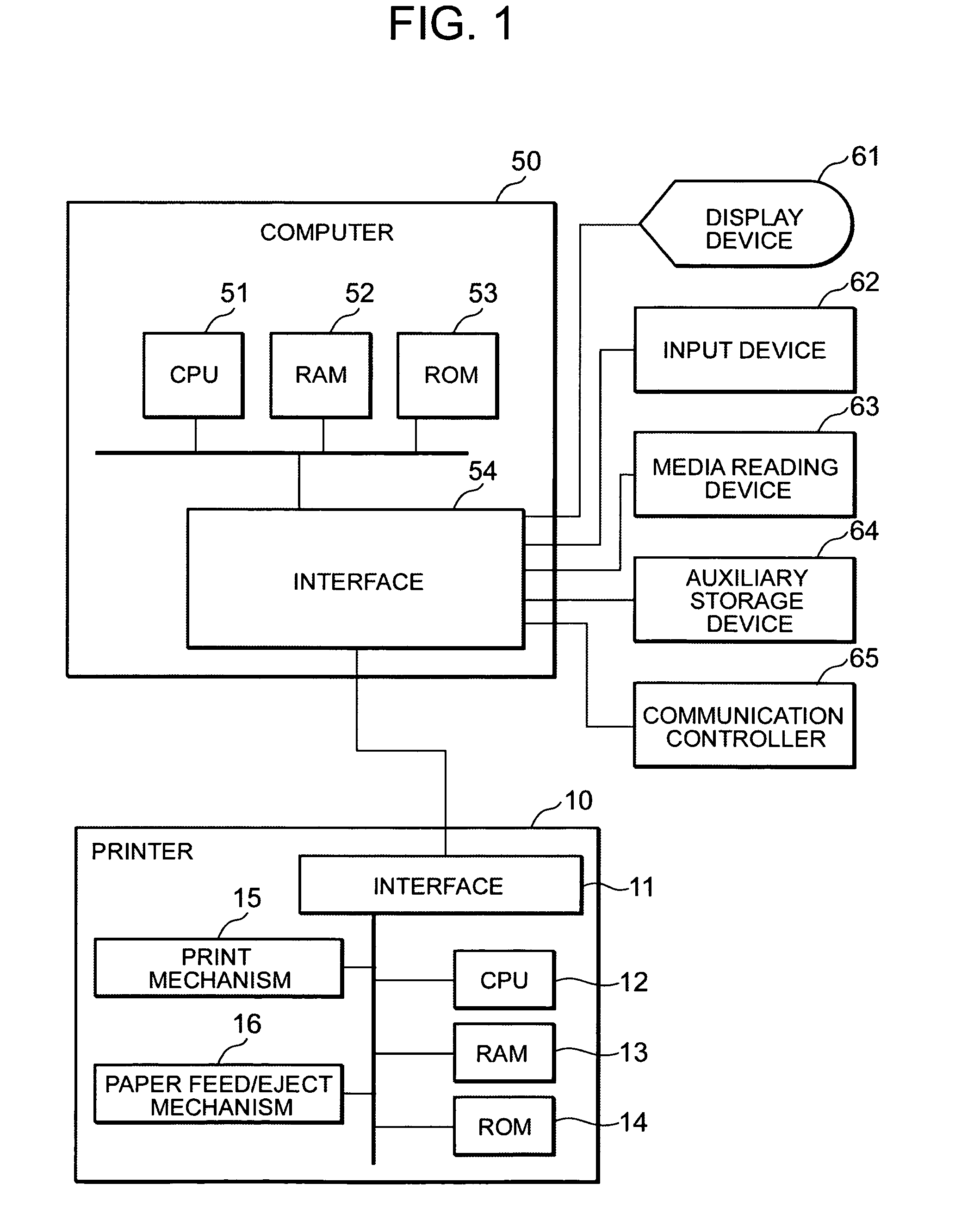

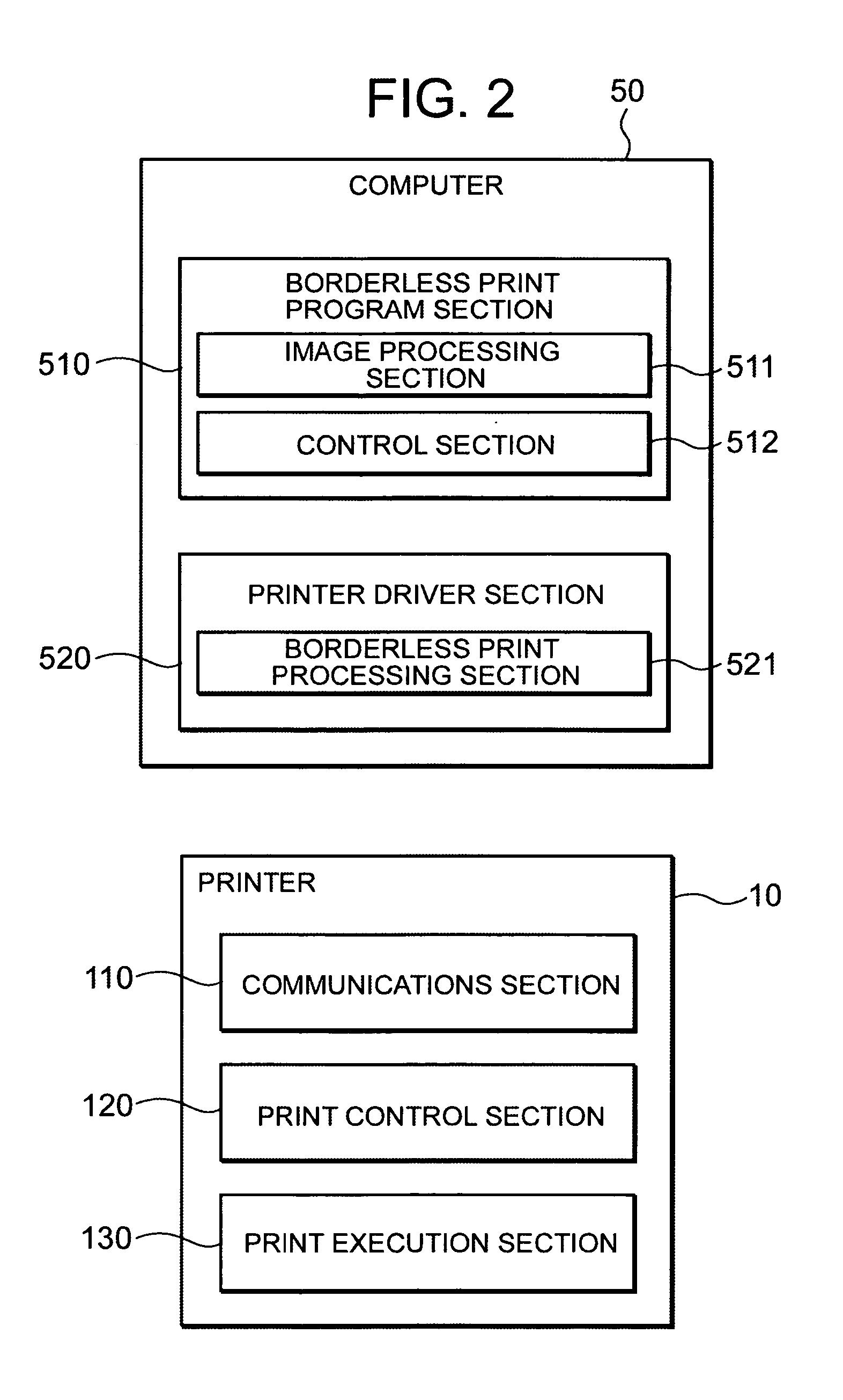

Print system, printer host and print support program product

InactiveUS20050225779A1Reduce processAvoid missingDigitally marking record carriersDigital computer detailsComputer printingComputer science

When a four-sided borderless printing is carried out, in order to print a region as it looks on the screen without generating any margins, the print system according to the present invention is directed to a system to carry out the four-sided borderless printing by enlarging the image larger than a print sheet, and the system is provided with an image display means which displays a print target image in a region narrower than an actual region, an image reduction means which reduces the print target image, a print data generation means which generates print data on the basis of the image which is obtained by enlarging the already reduced print target image, and a print execution means which executes printing on the basis of the print data.

Owner:SEIKO EPSON CORP

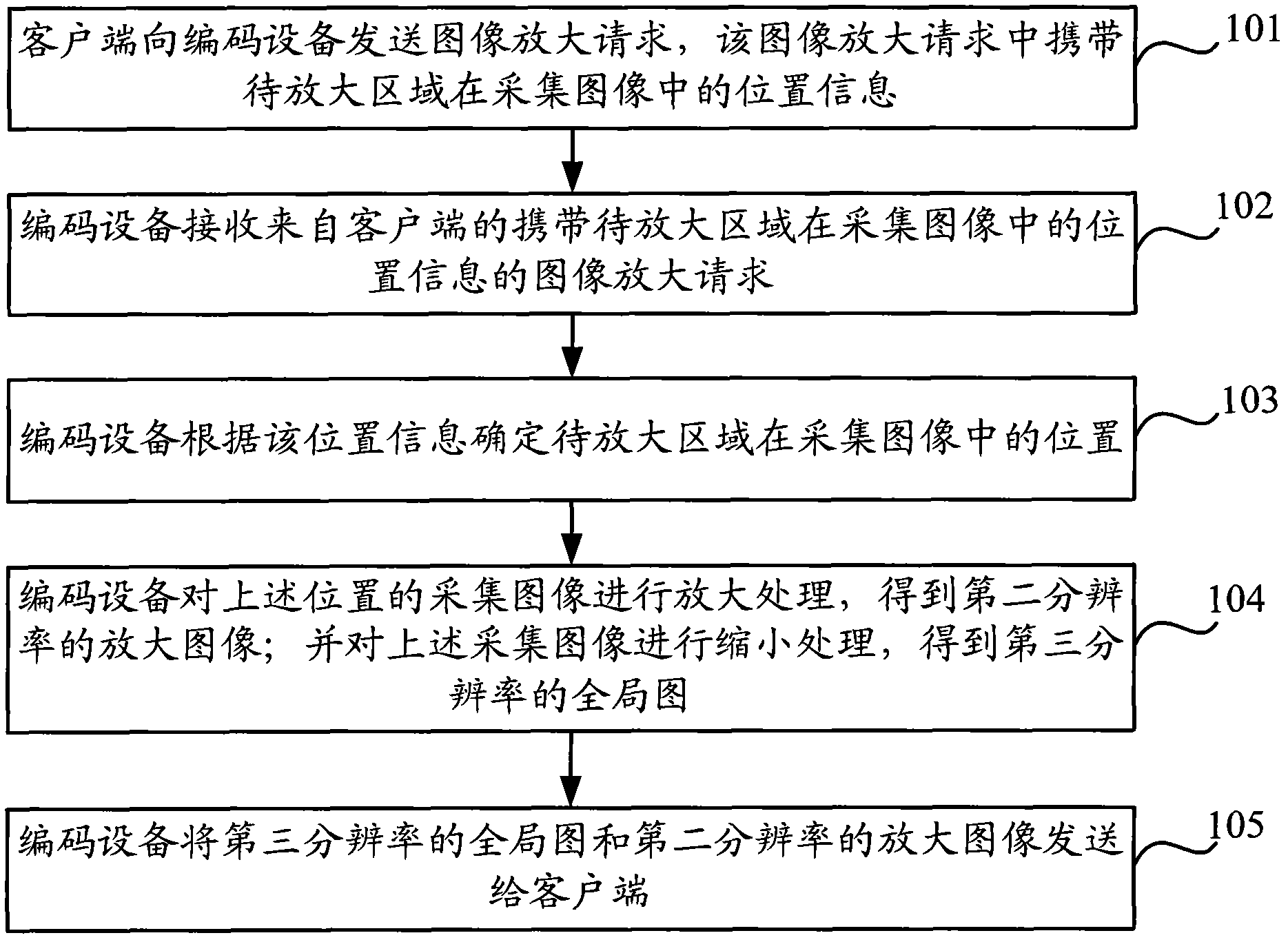

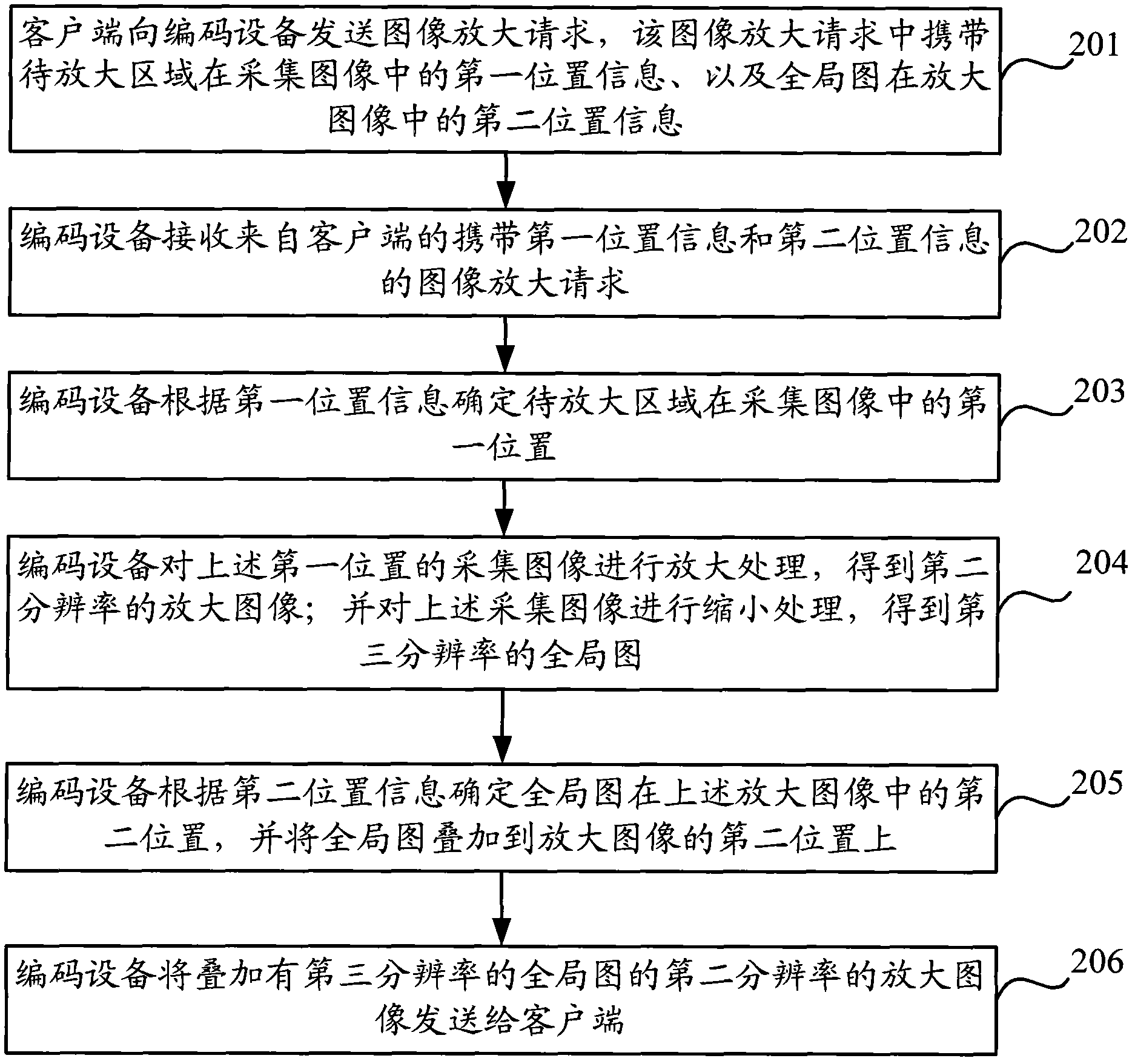

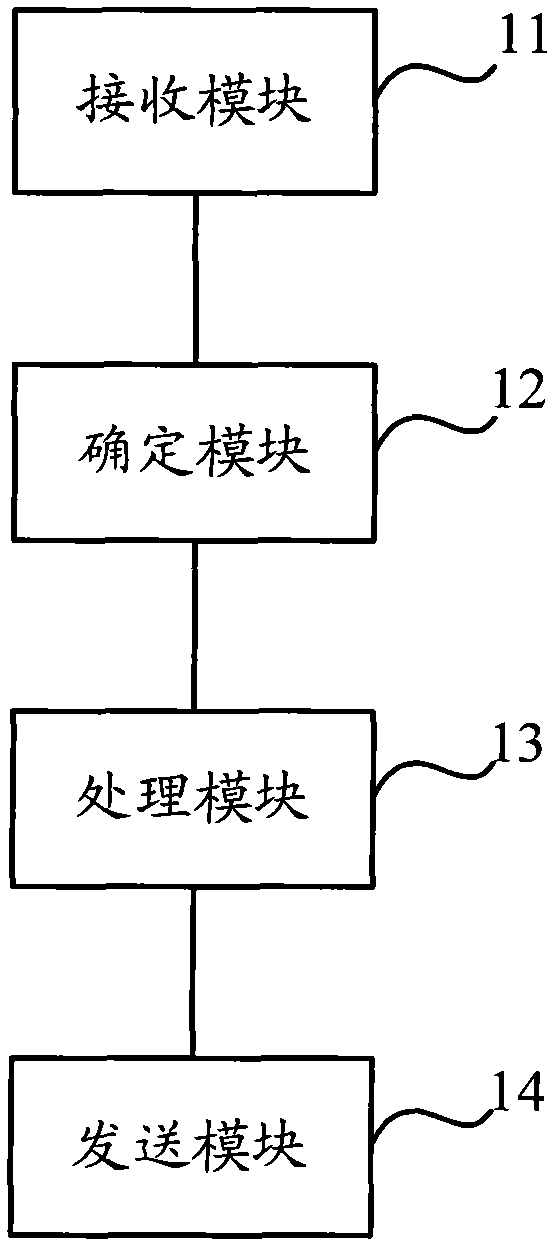

A method and device for enlarging local area images

InactiveCN102300083AReduce lossGeometric image transformationClosed circuit television systemsComputer visionImage reduction

The invention discloses a method and device for enlarging a partial area image, the method comprising: an encoding device receives an image enlarging request from a client, the image enlarging request carries position information of the area to be enlarging in the collected image; the encoding The device determines the position of the region to be enlarged in the captured image according to the position information; the encoding device performs zoom processing on the captured image at the position to obtain an enlarged image; and performs shrink processing on the collected image to obtain a global Figure; the coding device sends the global picture and the enlarged image to the client. In the present invention, the loss of image information can be reduced, so that the enlarged image displayed by the client terminal is clearer.

Owner:NEW H3C TECH CO LTD

A batch repair method aiming at damaged plant leaves

ActiveCN109242791AImprove repair accuracyAvoid the impact of subsequent experimentsImage enhancementImage analysisBatch processingComputer science

The invention discloses a batch repair method aiming at damaged plant leaves. Firstly, image data is pretreated. The pretreatment comprises the following steps: image reduction -grayscale transformation - Gaussian filter - binarization; Contour trimming: canny edge detection -finding edge contour- circumscribing minimum quadrilateral - ROI region trimming; Watershed segmentation: foreground marking-background marking- unknown region marking- watershed segmentation; Then, the image to be repaired is replaced by the same color, and the mask of the region to be repaired is made. Finally, the repaired part is repaired by FMM algorithm. Compared with the prior art, the invention can complete the incomplete part of the leaf, has high repair accuracy, and avoids the influence of the leaf incomplete caused by the force majeure on the subsequent experiment. The invention solves the problem of batch production of a mask through a series of image preprocessing operations, and realizes batch processing operation of damaged plant leaves.

Owner:NORTHEAST AGRICULTURAL UNIVERSITY

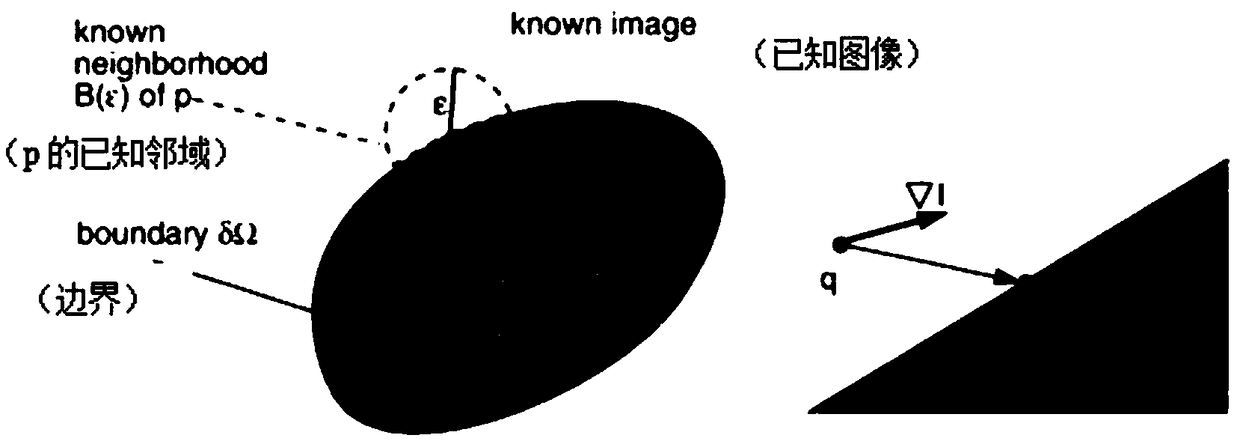

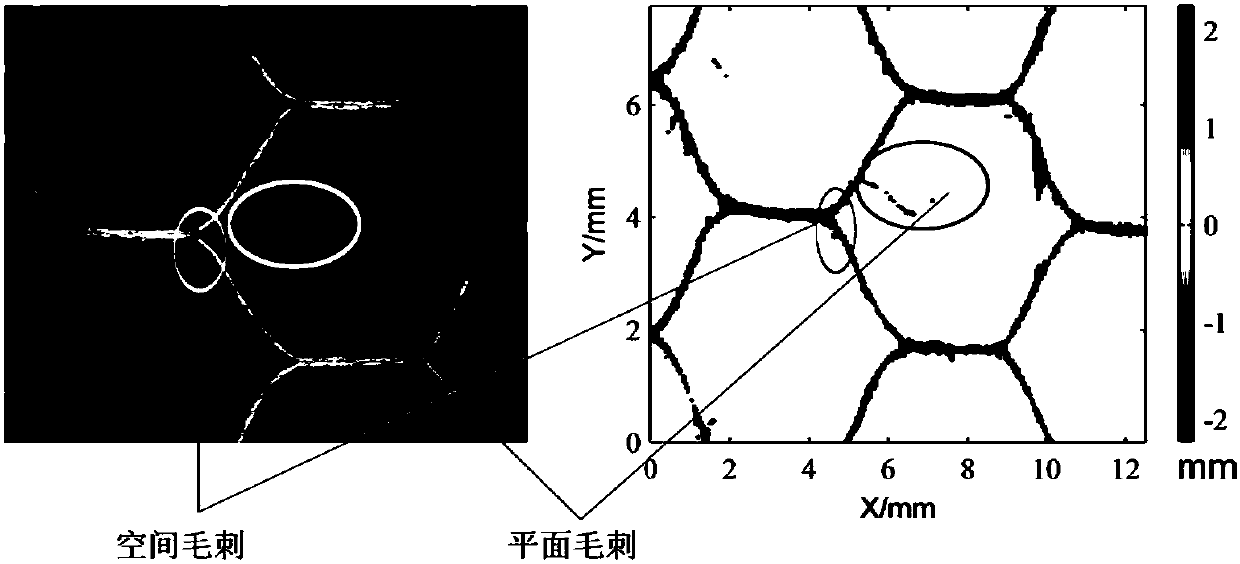

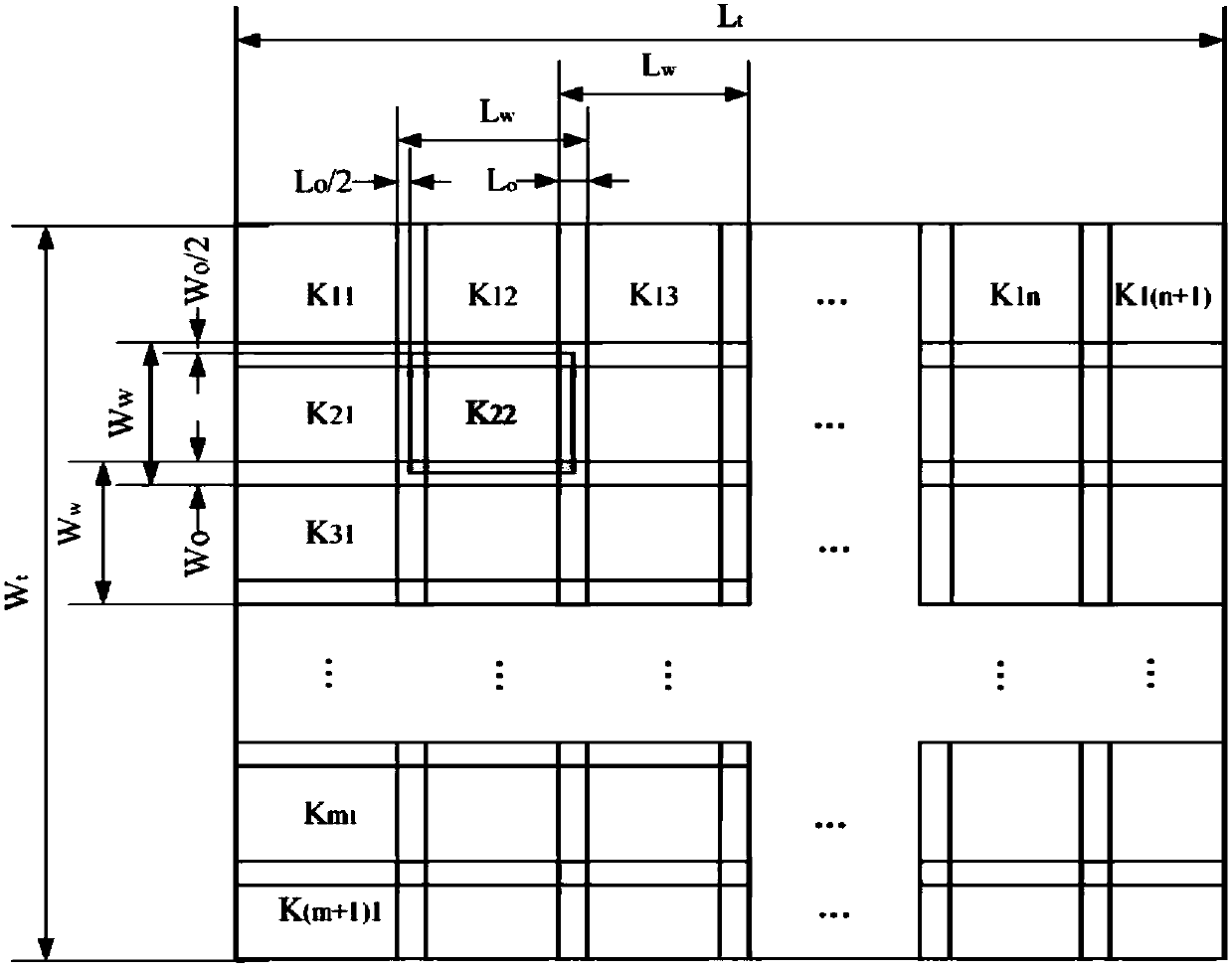

Honeycomb core surface shape measurement data burr removal method

The present invention discloses a honeycomb core surface shape measurement data burr removal method. The method comprises the following steps of: obtaining three-dimensional surface shape data of a honeycomb core surface; arranging mobile windows in an integrated honeycomb measurement data xOy plane, only processing data covered by the mobile windows each time; establishing a plane image of the honeycomb core, and performing identification of apexes of the honeycomb core; performing image reduction for a certain proportion to identify the apexes; determining a threshold of a corner detection algorithm according to the measurement data; performing analysis of the identified apexes one by one, and determining honeycomb edges taking the apexes as end points; establishing search windows for analysis corner points; determining types of the analysis corner points; determining target corner points of the analysis corner points; establishing rectangular regions for the honeycomb edges; performing plane burr removal in each honeycomb edge measurement data; and performing space burr removal in each honeycomb edge measurement data.

Owner:DALIAN UNIV OF TECH

Image processing apparatus and method for image resizing matching data supply speed

ActiveUS20070071360A1Easy to processSimple circuit configurationGeometric image transformationCharacter and pattern recognitionImaging processingReduction factor

An image processing apparatus includes a data supply node to receive line data scanned in a main scan direction of an image, an image enlargement unit coupled to the data supply node to apply to the line data an enlargement process for enlarging the image by an enlargement factor equal to an integer so as to produce enlarged data at an output node, and an image reduction unit coupled to the output node of the image enlargement unit to apply to the enlarged data a reduction process for reducing the enlarged image by a desired reduction factor so as to produce reduced data at an output node.

Owner:CYPRESS SEMICON CORP

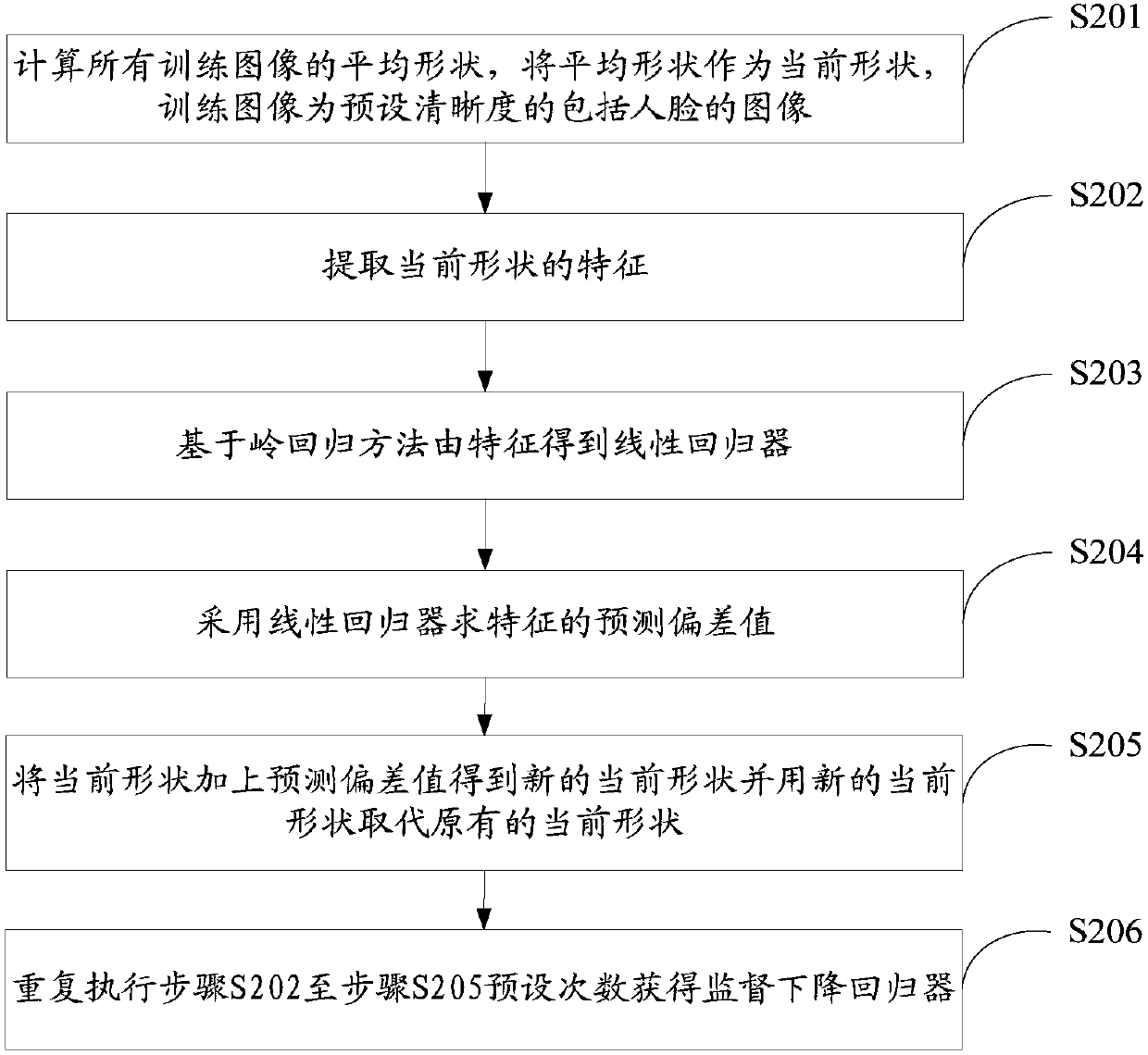

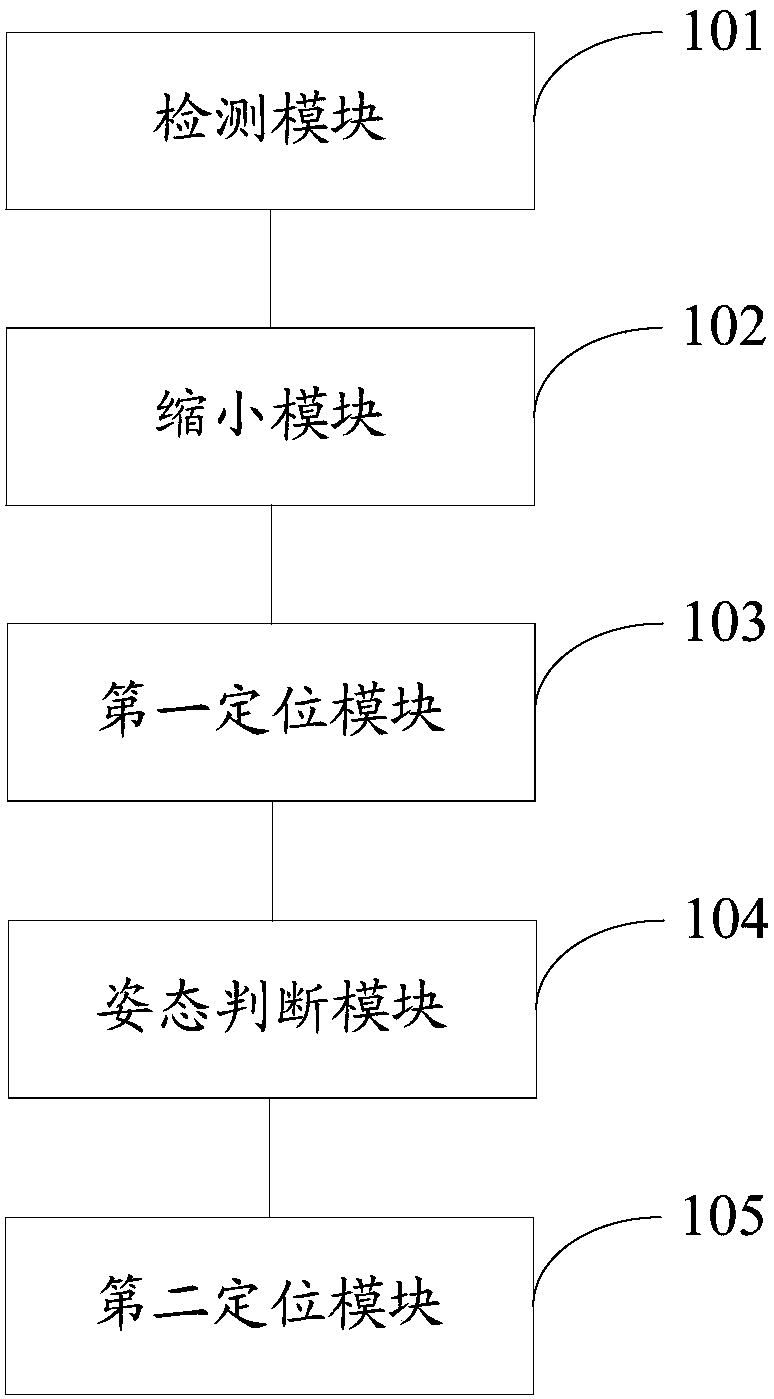

Human face key point positioning method and device

InactiveCN107766851AHigh precisionHigh speedCharacter and pattern recognitionPattern recognitionFace detection

The invention discloses a human face key point positioning method. The human face key point positioning method comprises the following steps: carrying out human face detection on an objective image toobtain a human face image; shrinking the human face image into a shrunk image with preset definition; extracting a first-stage key point from the shrunk image by a supervision descending regressor; mapping the first-stage key point to the human face image so as to judge a three-dimensional posture of the human face image; and selecting the corresponding combined random tree regressor to extract asecond-stage key point from the human face image on the basis of the three-dimensional posture. By a mode of combination of a supervision descending method and a combined random tree algorithm, the human face key points in the image are positioned, and meanwhile, high precision and high speed are ensured.

Owner:BEIJING SOHU NEW MEDIA INFORMATION TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com