Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

49results about How to "Facilitate resource sharing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

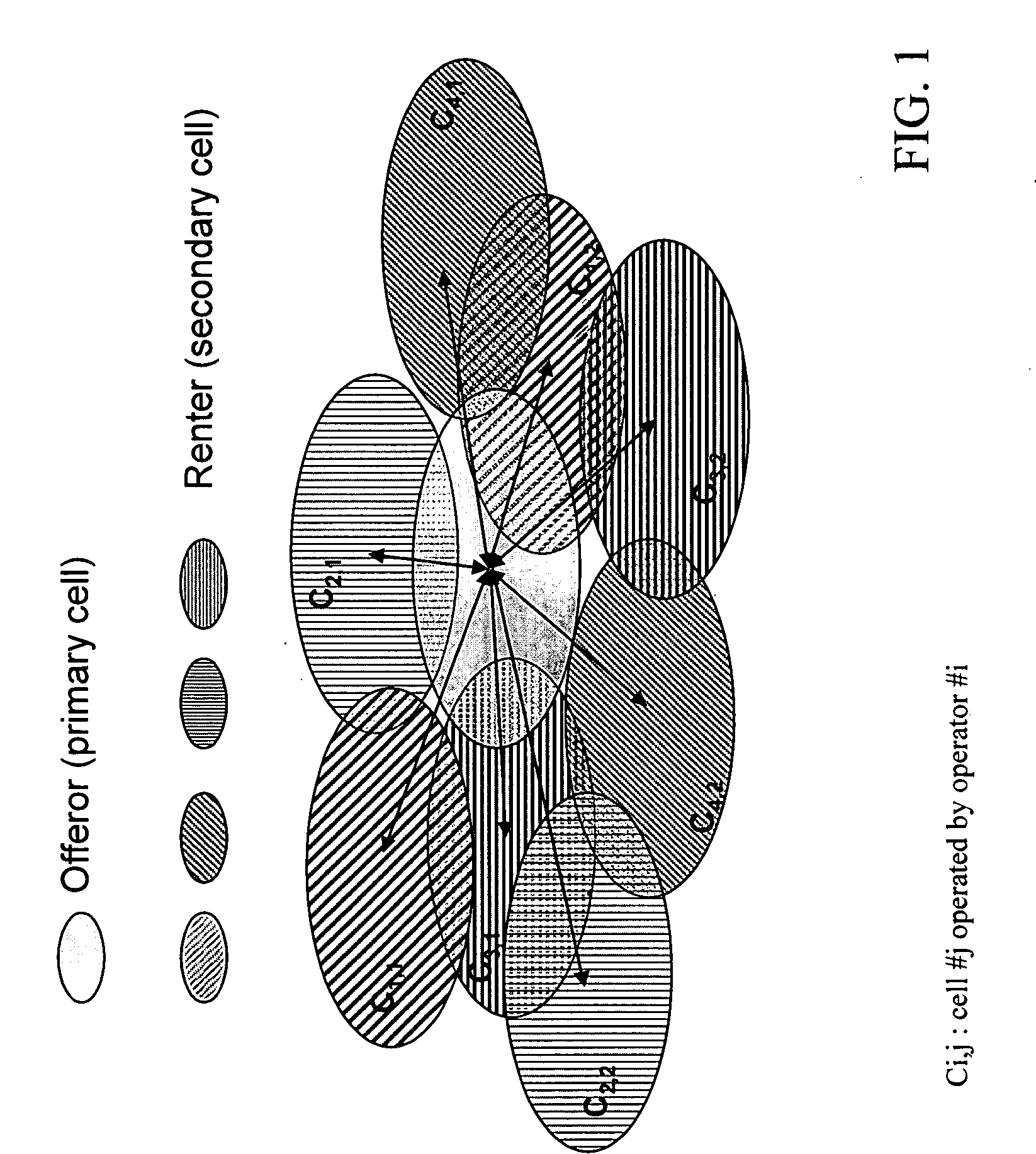

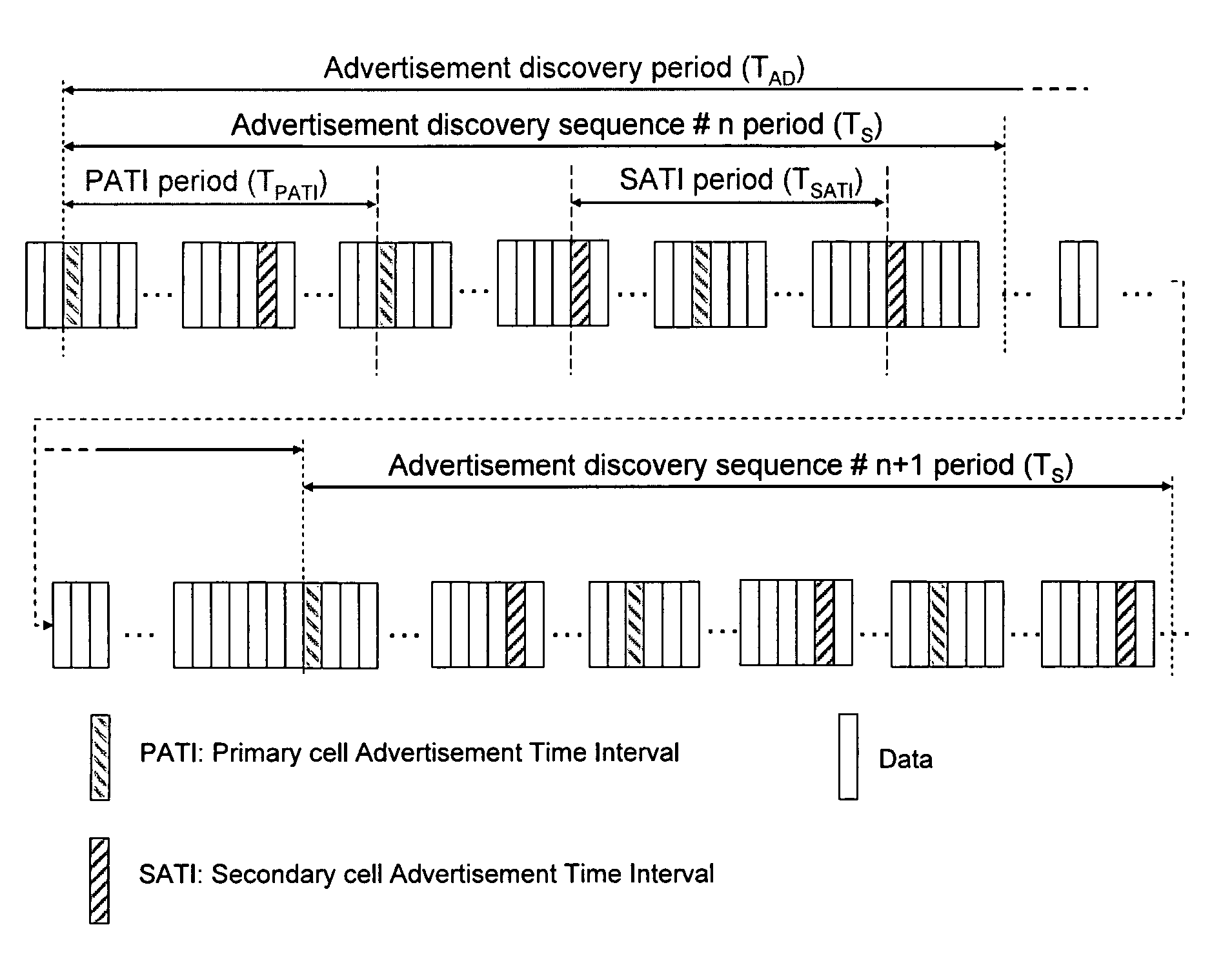

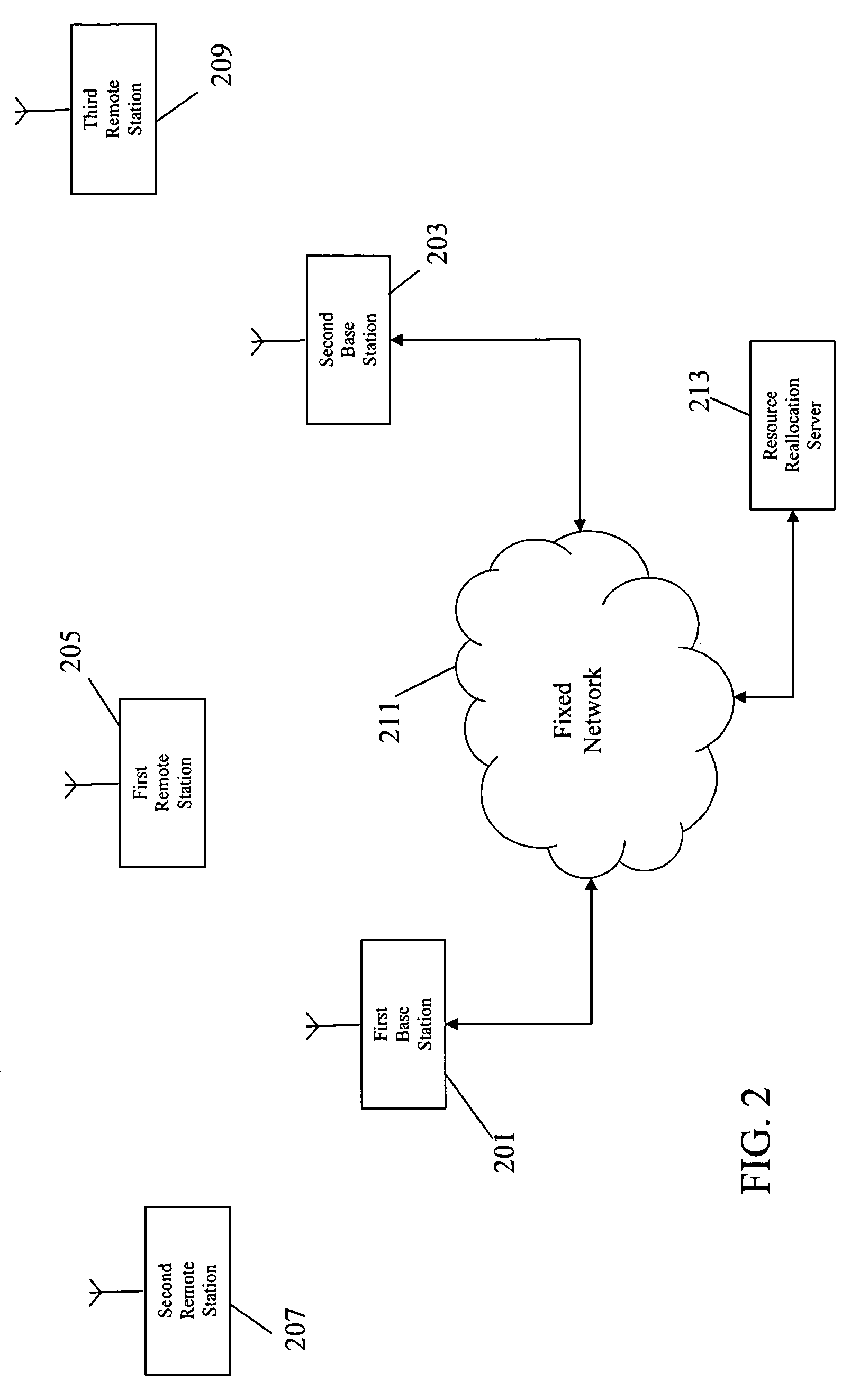

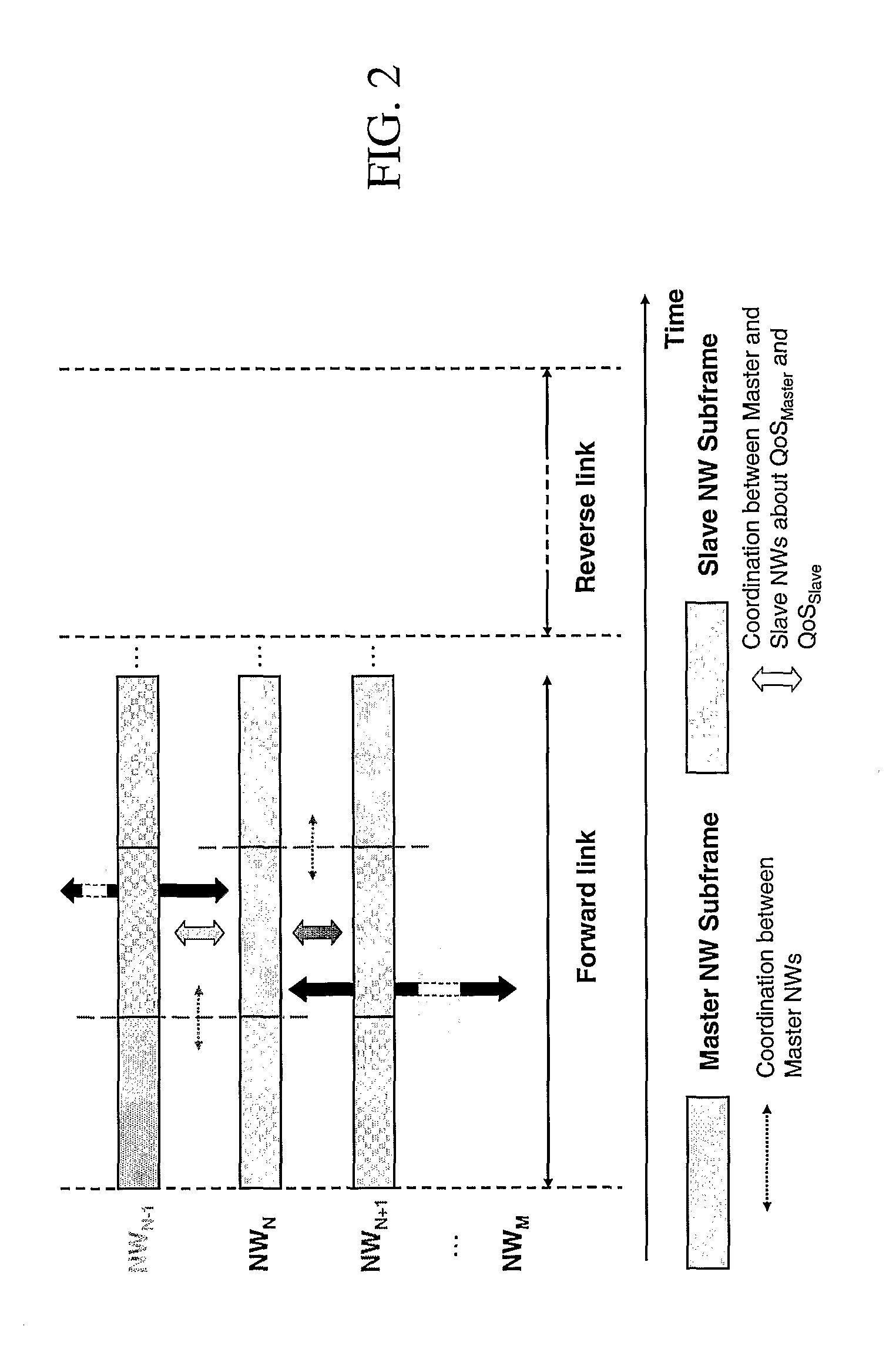

Resource exchange discovery in a cellular communication system

ActiveUS20090161614A1Efficient disseminationEasy to useConnection managementWireless commuication servicesAir interfaceStructure of Management Information

A cellular communication system comprises a set of base stations (201,203) which transmit downlink resource exchange discovery messages to remote terminals in resource allocations of a Media Access Control, MAC, frame structure. The discovery messages may indicate that a base station has resource available for reallocation to another base station or that a base station is seeking resource to be allocated from another base station. A remote terminal (205) comprises a receiver (401, 403) which receives a first message of the downlink resource exchange discovery messages from at least a first base station (201). A discovery message transmit processor (407) generates a second message, which is an uplink resource exchange message comprising resource exchange data determined from the first message, and transmits this to a second base station (203). The second base station (203) then initiates a temporary air interface resource reallocation with the first base station in response to receiving the second message.

Owner:MOTOROLA SOLUTIONS INC

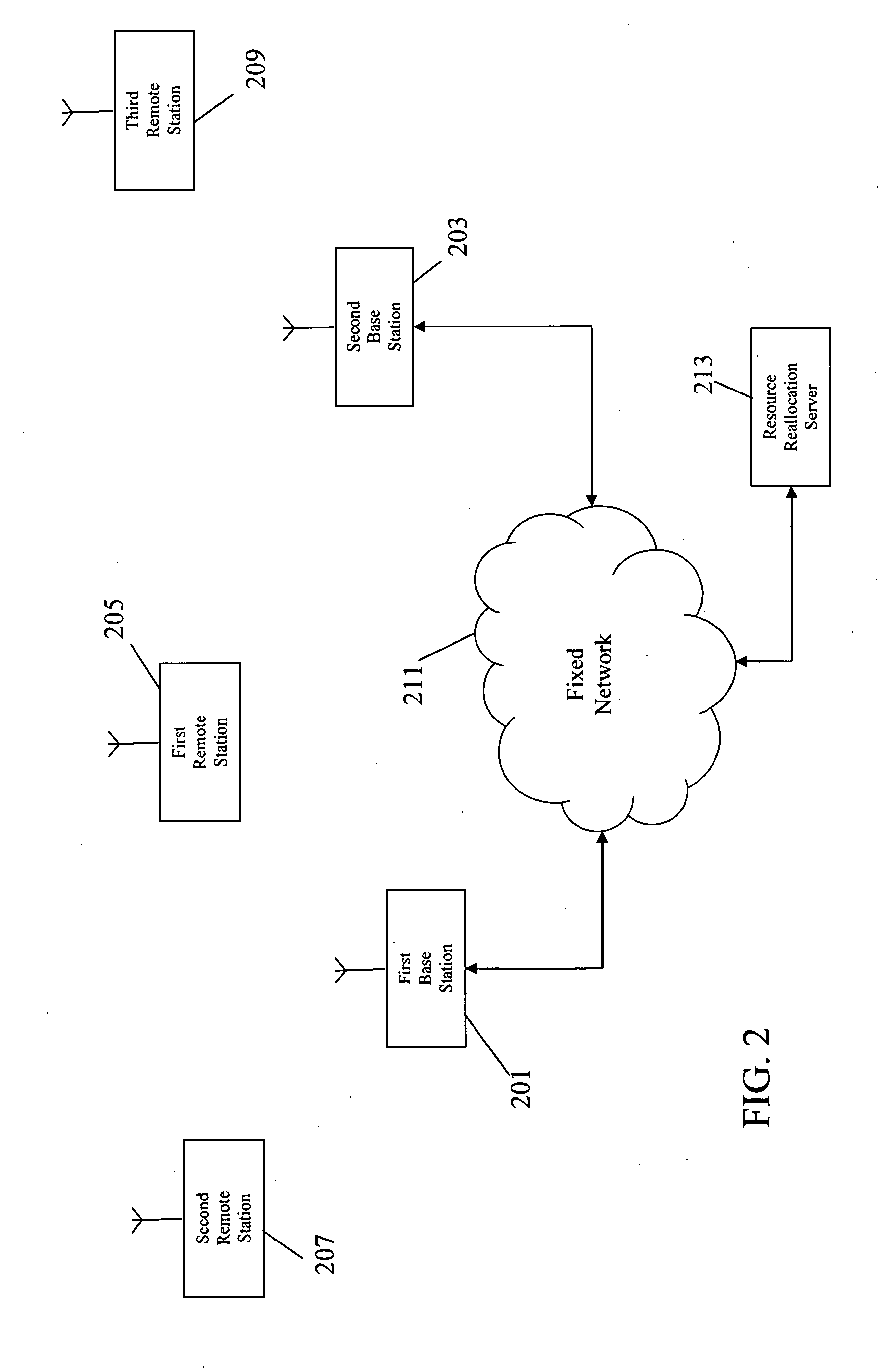

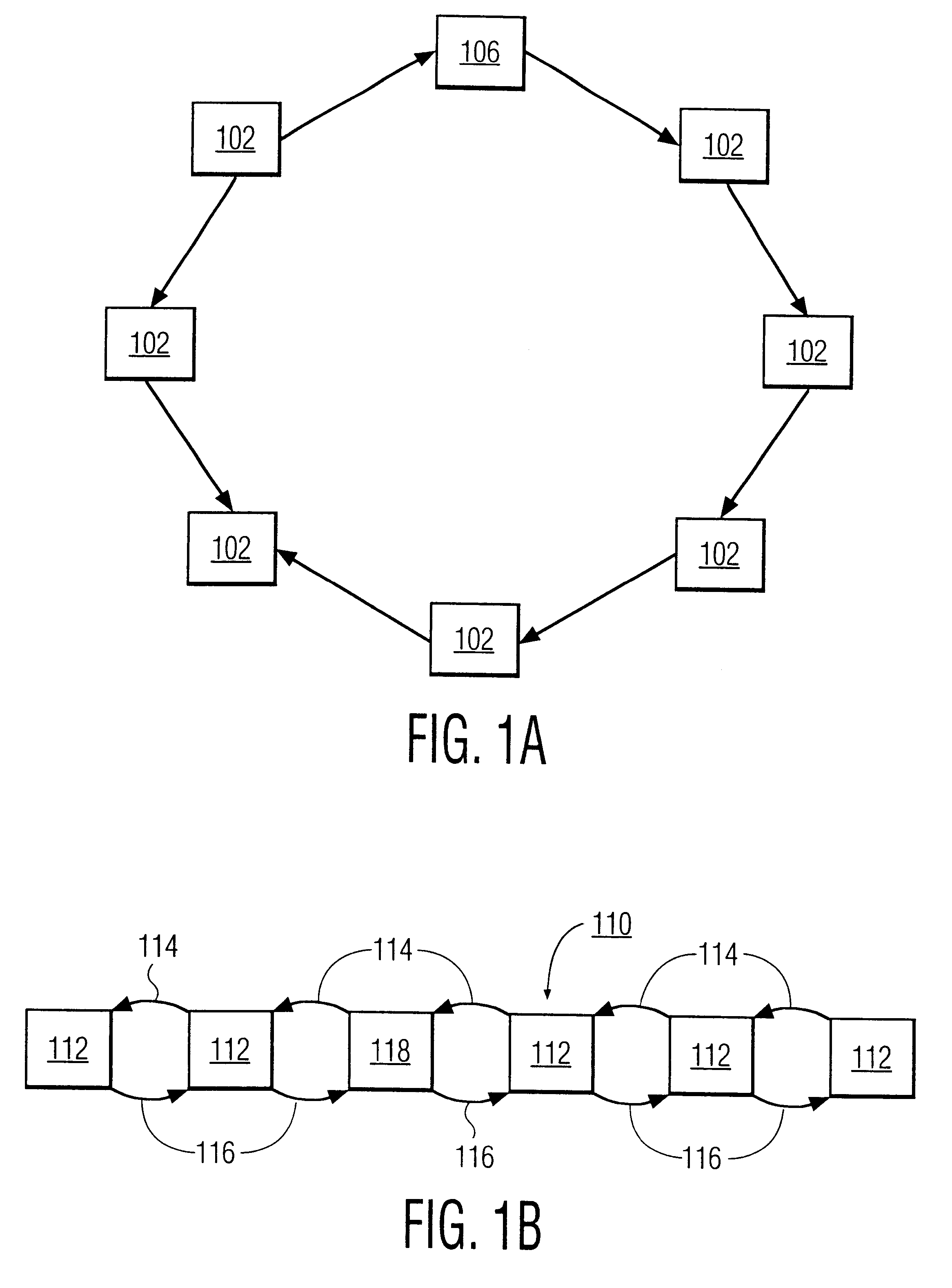

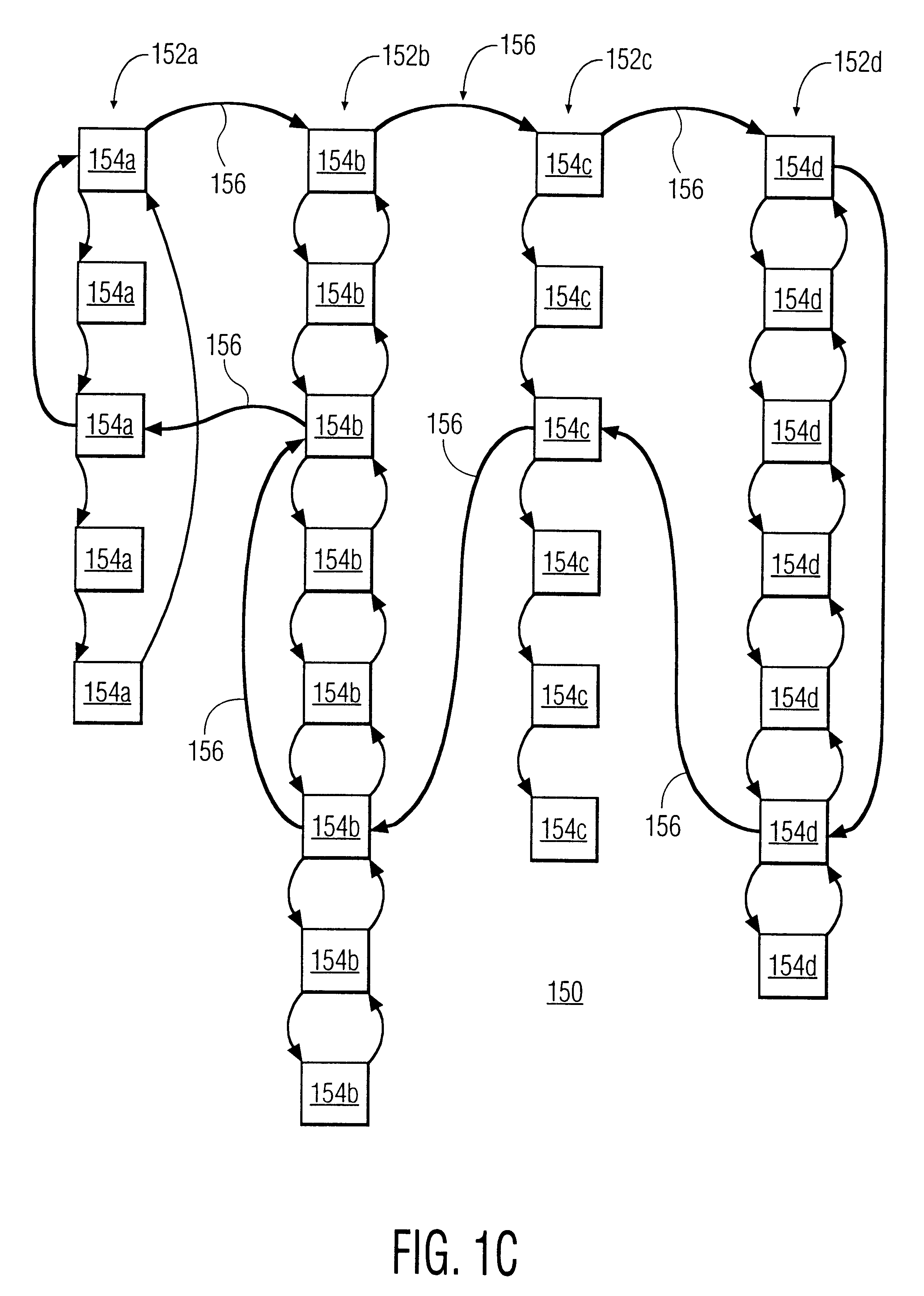

Verification of active nodes in an open network

InactiveUS6480473B1Facilitate resource sharingLong rangeError preventionFrequency-division multiplex detailsComputer networkLinear sequence

The present invention involves a network polling protocol which treats the network as a logical ring or linear sequence of nodes linked together so that a polling request is simply propagated down or around the network one node at a time until a complete inventory of active nodes is achieved. The protocols also includes procedures for curing or repairing breaks in the linking protocol and for adding new nodes to the linking protocol. The linking protocol can also be used to establish hierarchal linked networks where top level hierarchies includes addresses to a permanent member of a linked network and bottom level hierarchies are a given linked network.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

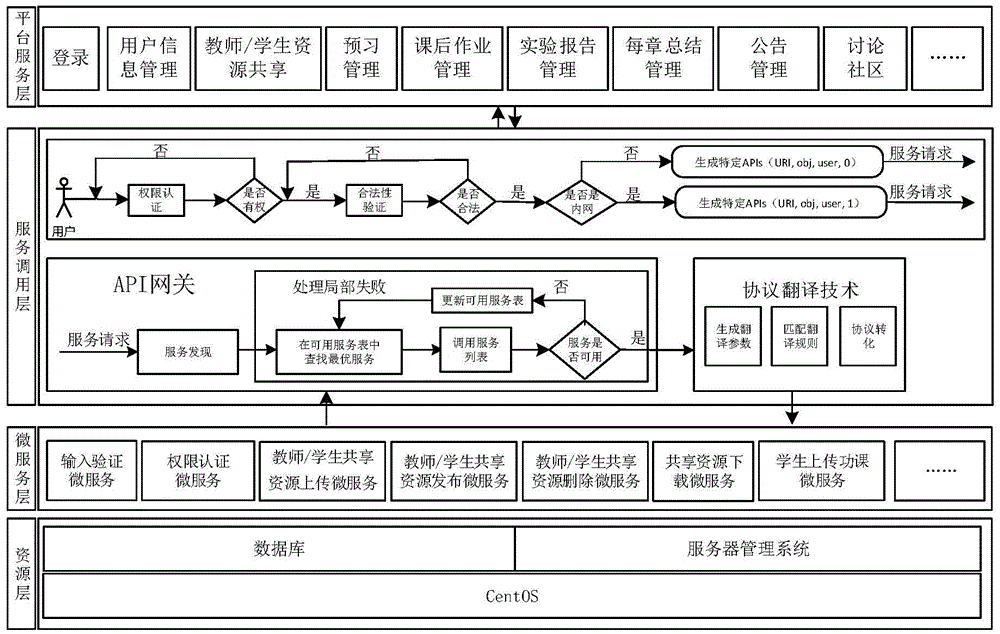

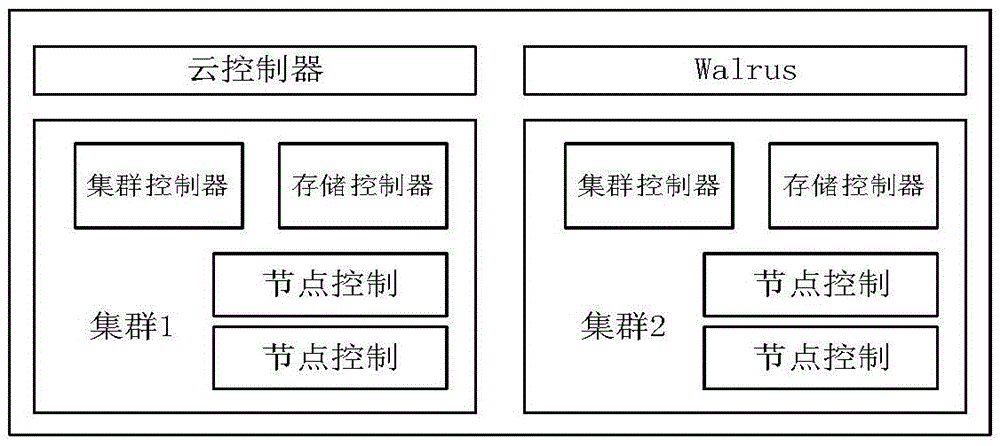

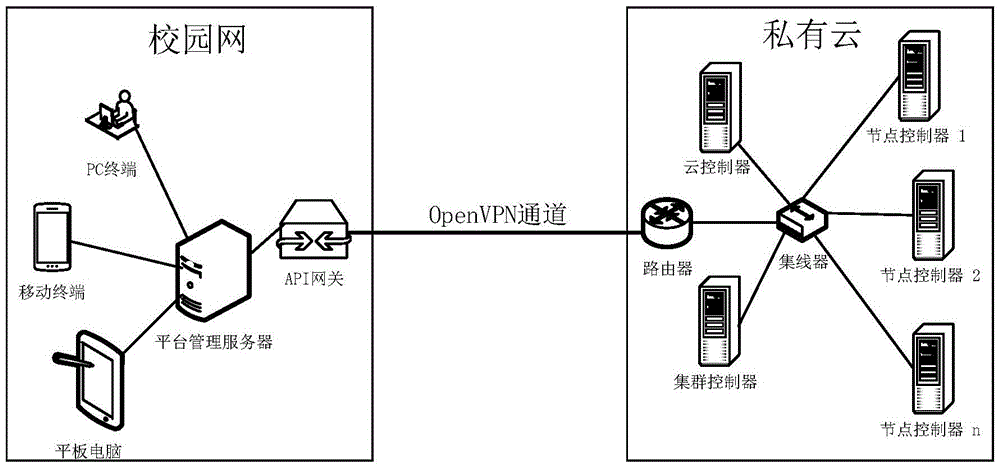

College teaching cloud platform based on micro services

InactiveCN105577780AFast and efficient deliveryImprove efficiencyTransmissionPrivate networkOpen source

The invention discloses a college teaching cloud platform based on micro services. A campus network and private cloud are combined through a virtual private network to build a cloud platform, and a micro service architecture is utilized to build services of the cloud platform; using an open source project Eucalyptus developed by the Department of Computer Science of the University of California to set up private cloud; and all requests of a client first pass through an API gateway, then the API gateway routes the requests to appropriate micro services, and generally the APT gateway calls a plurality of micro services and merges a result to process a request. According to the invention, the micro service architecture is used for the college teaching cloud platform, application of the teaching cloud platform is decoupled into micro services of different functions, thereby enabling each link of teaching to be called in a micro service mode, the response is quick, and the efficiency is high; and the private cloud and the campus network are connected through the virtual private network to form the college teaching cloud platform, thereby providing better resource sharing for teachers and students, and the college teaching cloud platform has good elasticity and expansibility.

Owner:WUHAN UNIV OF TECH

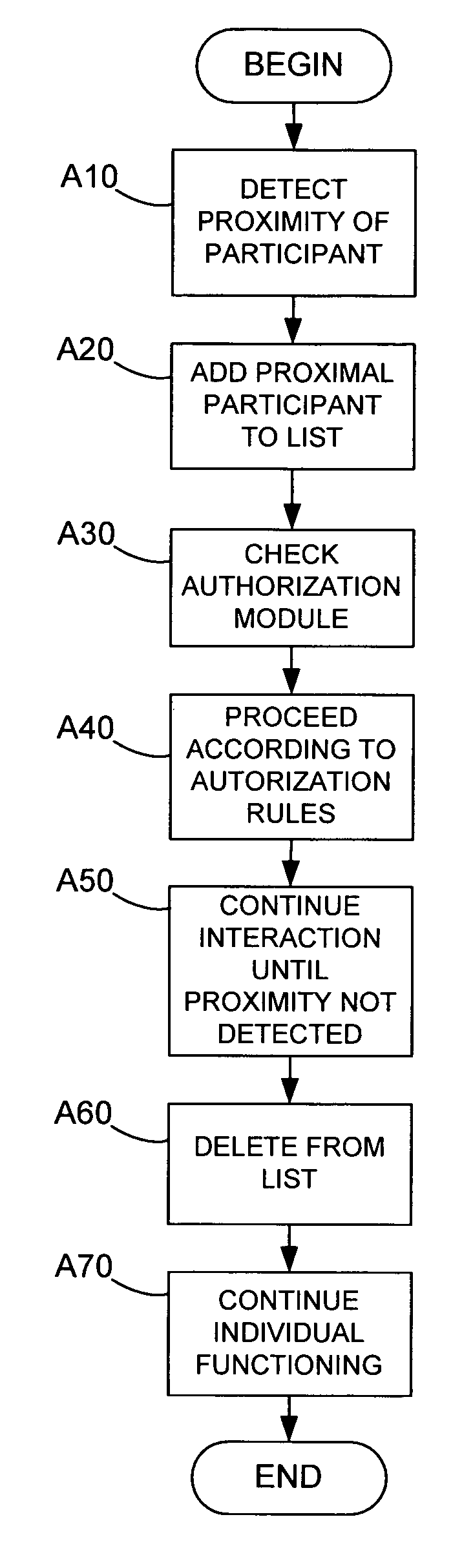

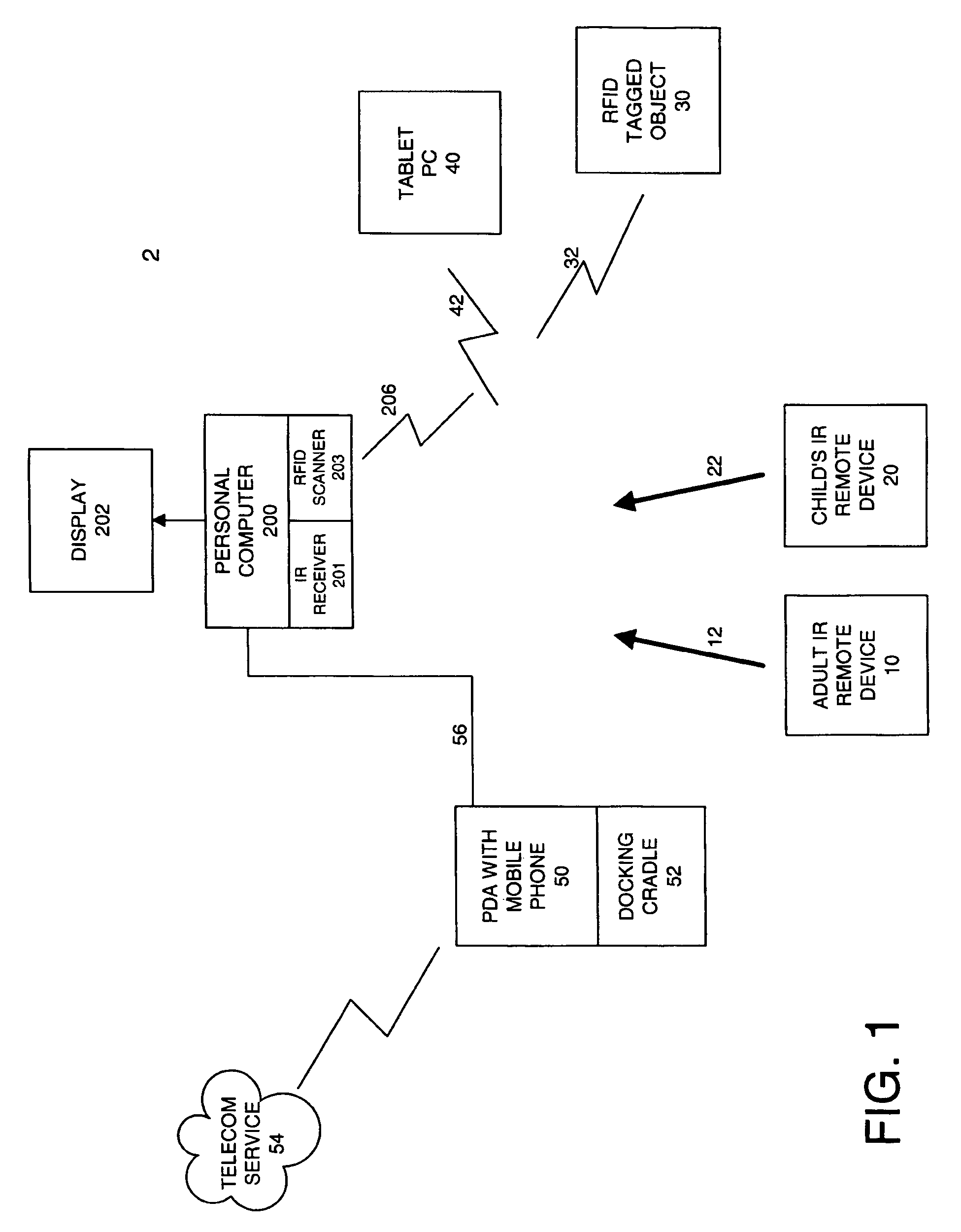

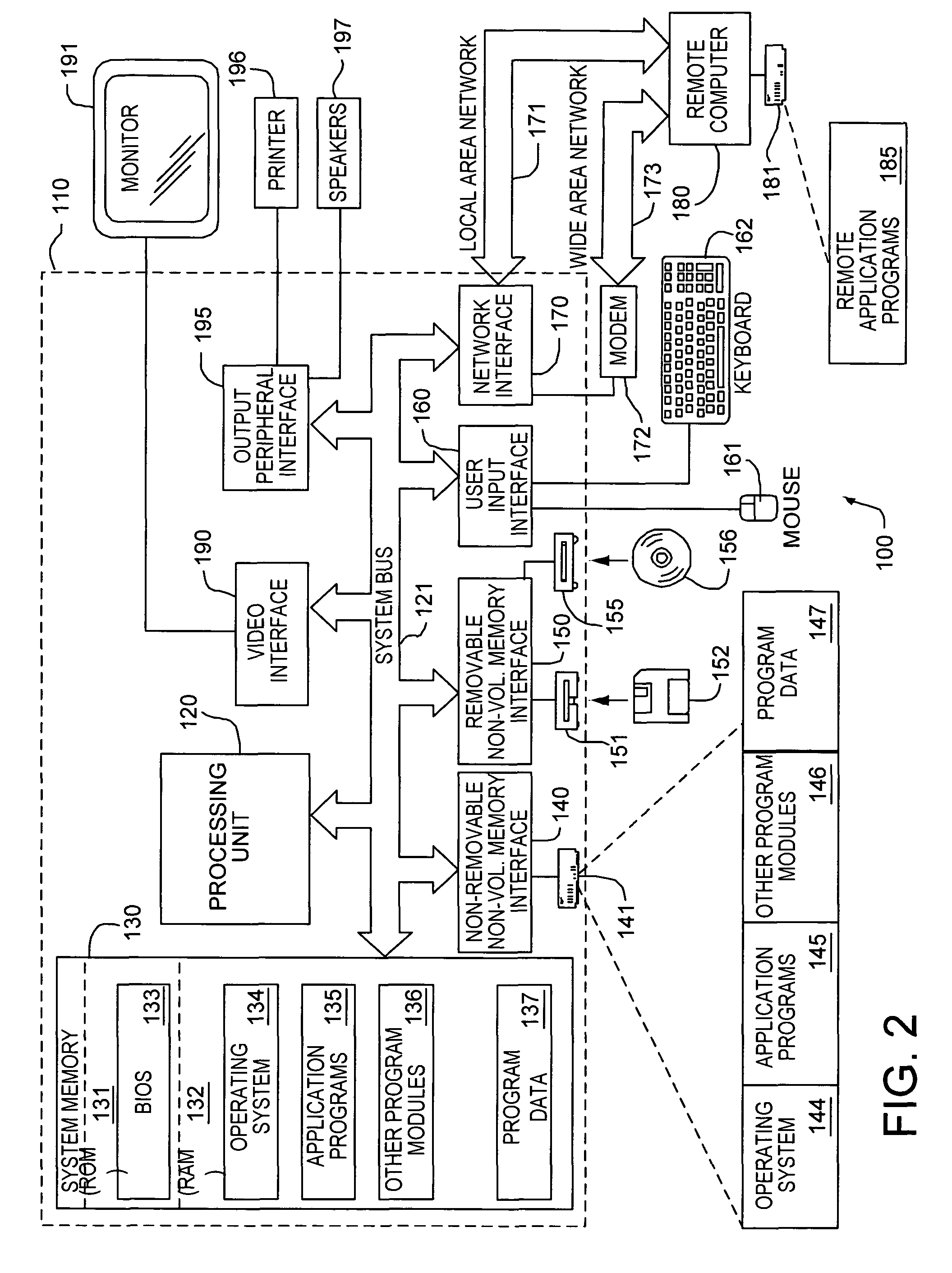

System and method for sharing information based on proximity

ActiveUS7996514B2Enhanced interactionFacilitate resource sharingDigital data processing detailsMultiple digital computer combinationsShared resourceAuthorization

A method and system are provided for facilitating interaction between a device and a device environment. The system may include a detection module for automatically detecting proximity of a participant within the device environment. The system may additionally include a user-configurable authorization module for authorizing the device to adjust a device user interface in a pre-determined manner in response to the detection of the participant. The system may also provide for sharing resources among multiple participating devices, wherein each of the multiple participating devices has a device specific set of application resources. The system may additionally include a configurable resource regulation mechanism for making the device specific application resources from the second participating device available to the first participating device.

Owner:MICROSOFT TECH LICENSING LLC

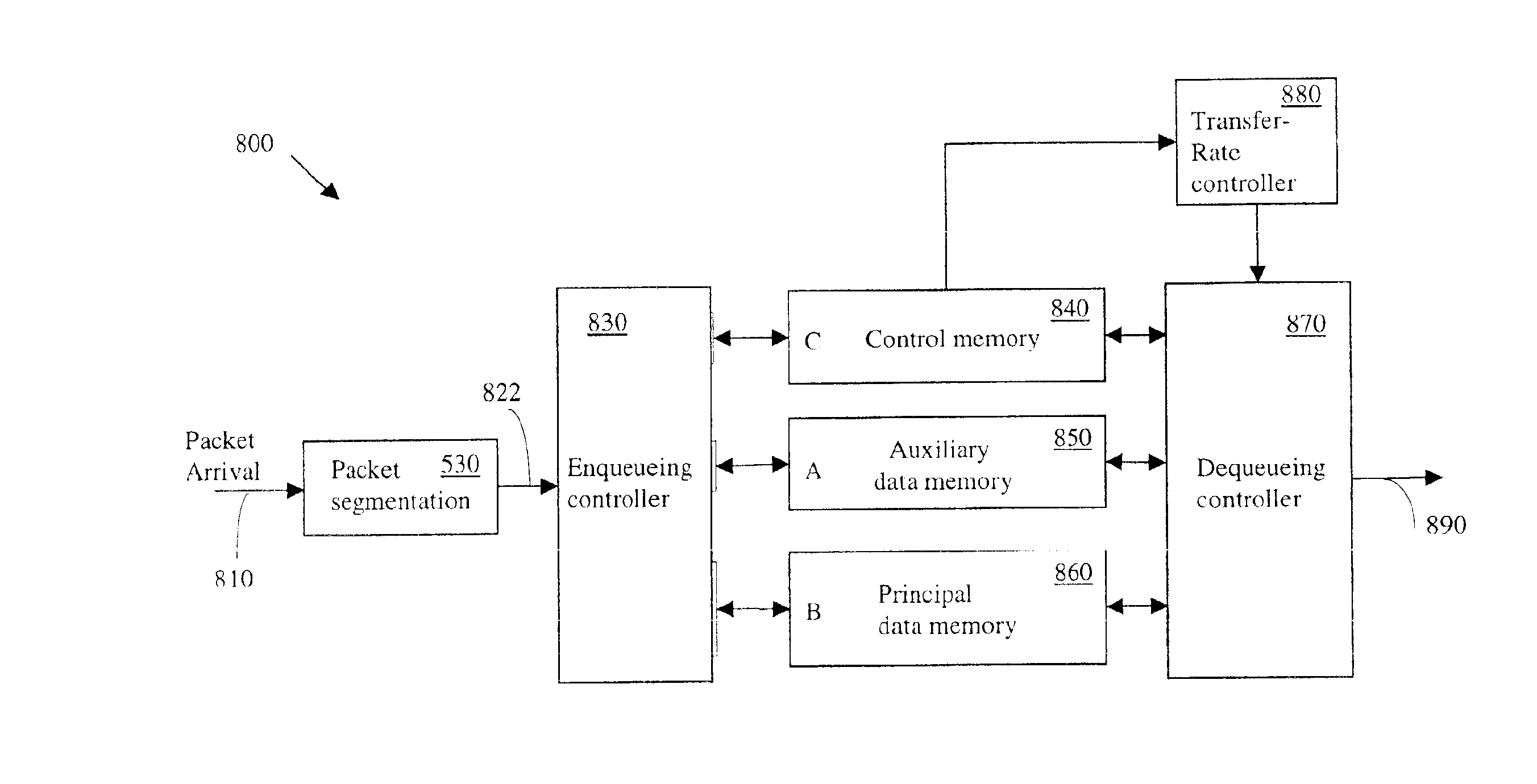

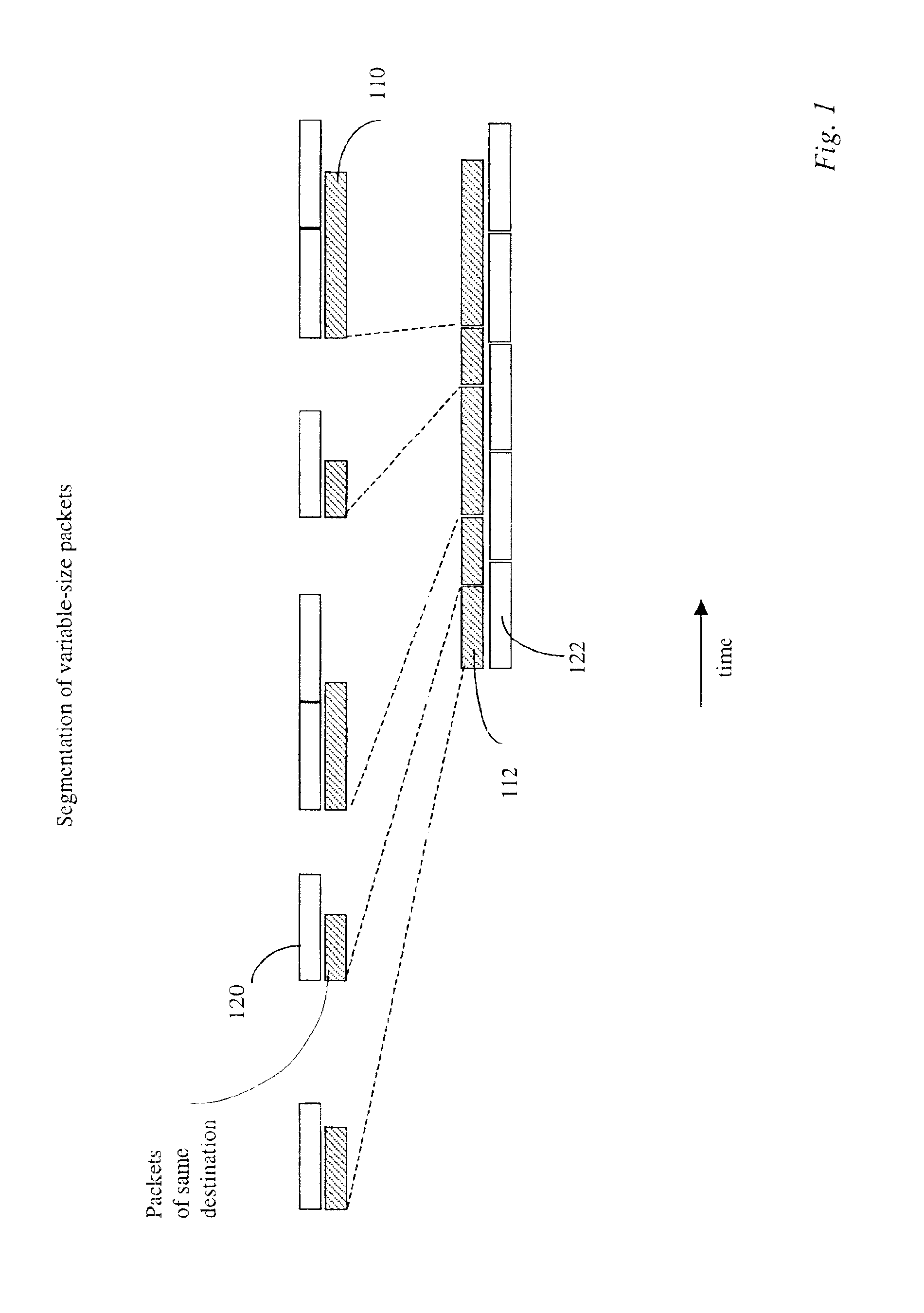

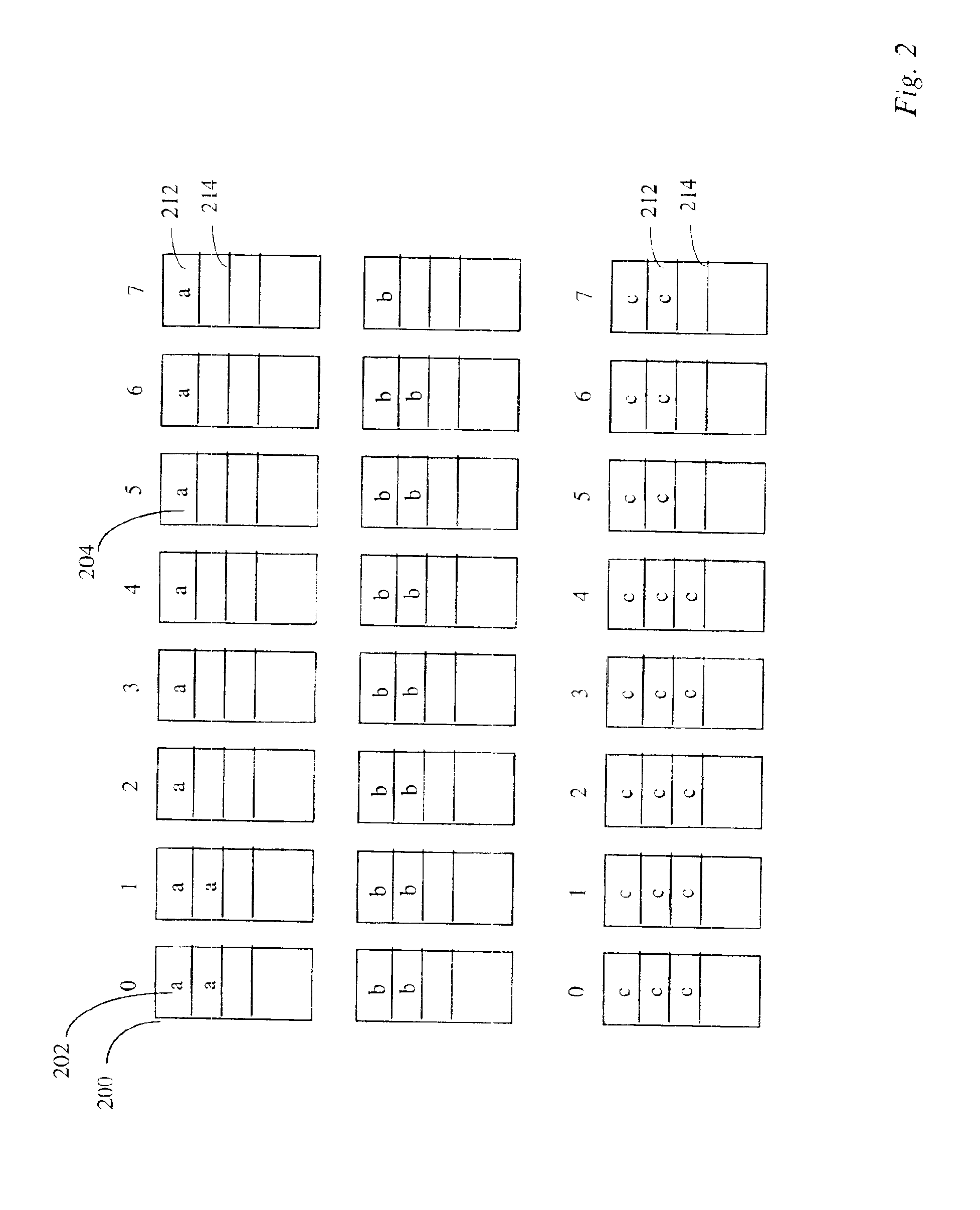

Compact segmentation of variable-size packet streams

InactiveUS6888848B2Unacceptable delayFacilitate resource sharingMultiplex system selection arrangementsError preventionQuality of serviceData stream

A method is described for segmenting a data stream comprising variable-size packets, a data stream being defined by its source node, sink node, assigned network route, and other attributes. The segments are of equal size and the method concatenates the packets in successive segments in a manner that attempts to minimize segmentation waste without undue delay. The method facilitates the construction of efficient networks that scale to very high capacities while respecting service-quality specifications. Apparatus for implementing the method are also described.

Owner:RPX CLEARINGHOUSE

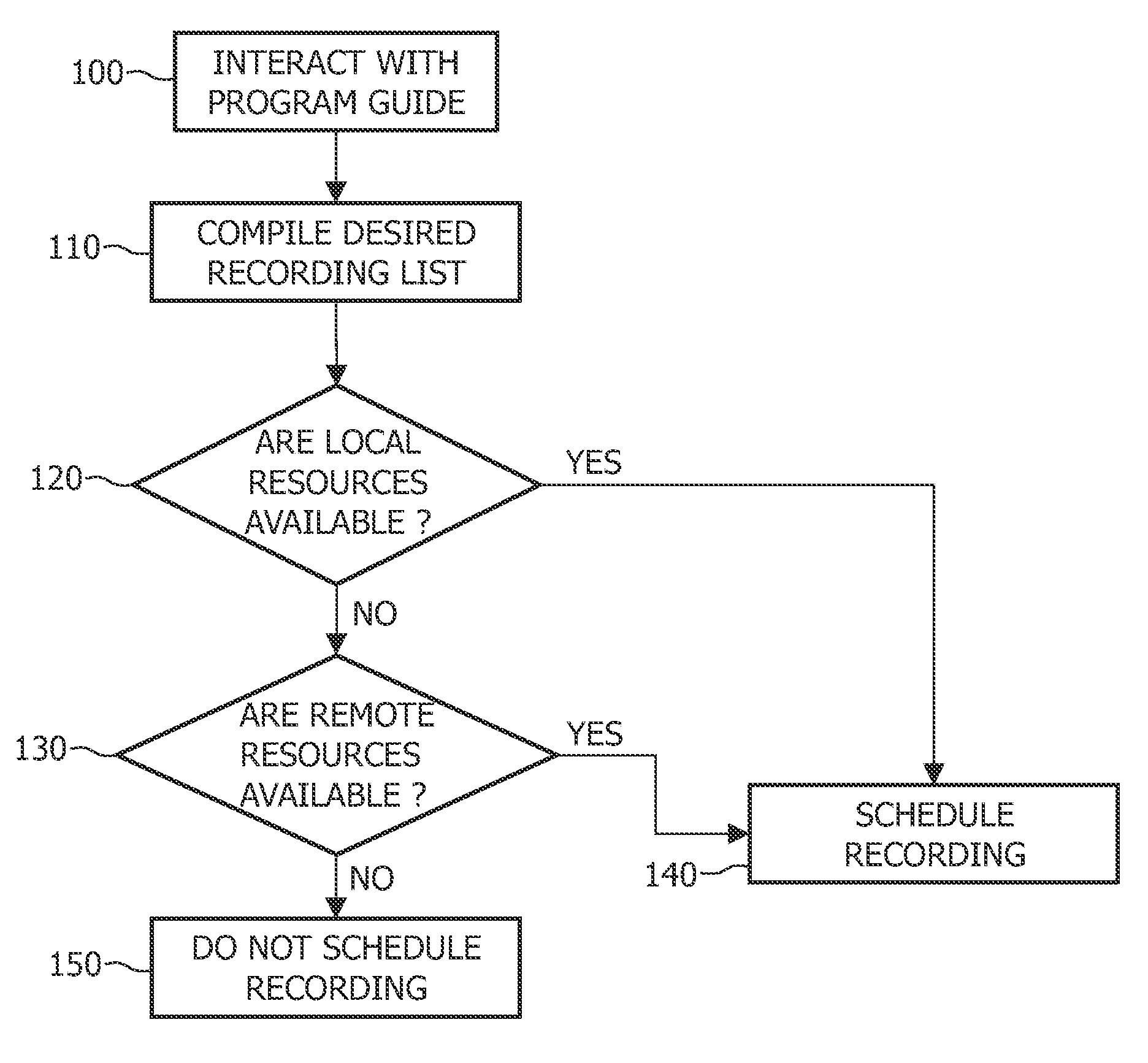

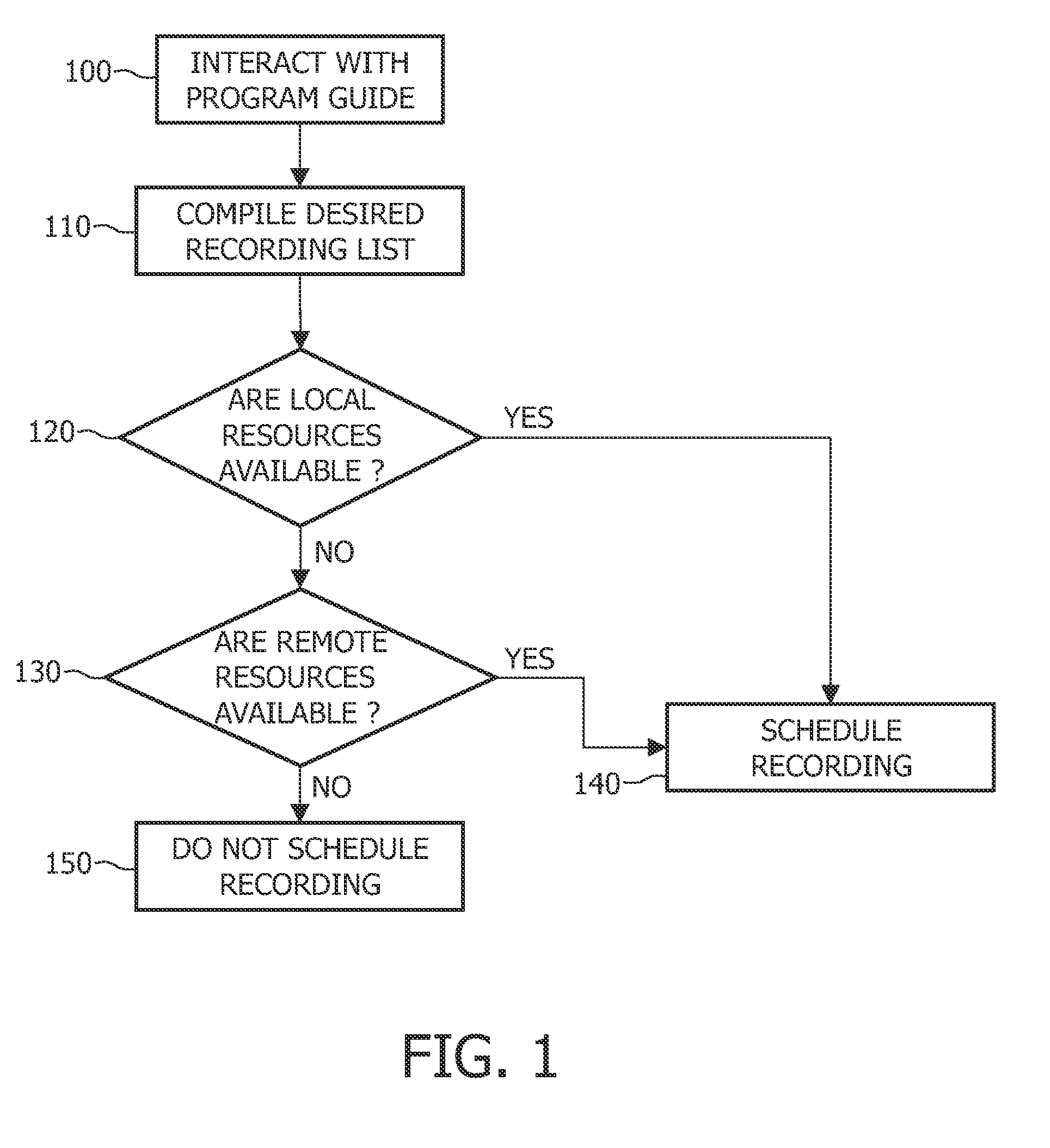

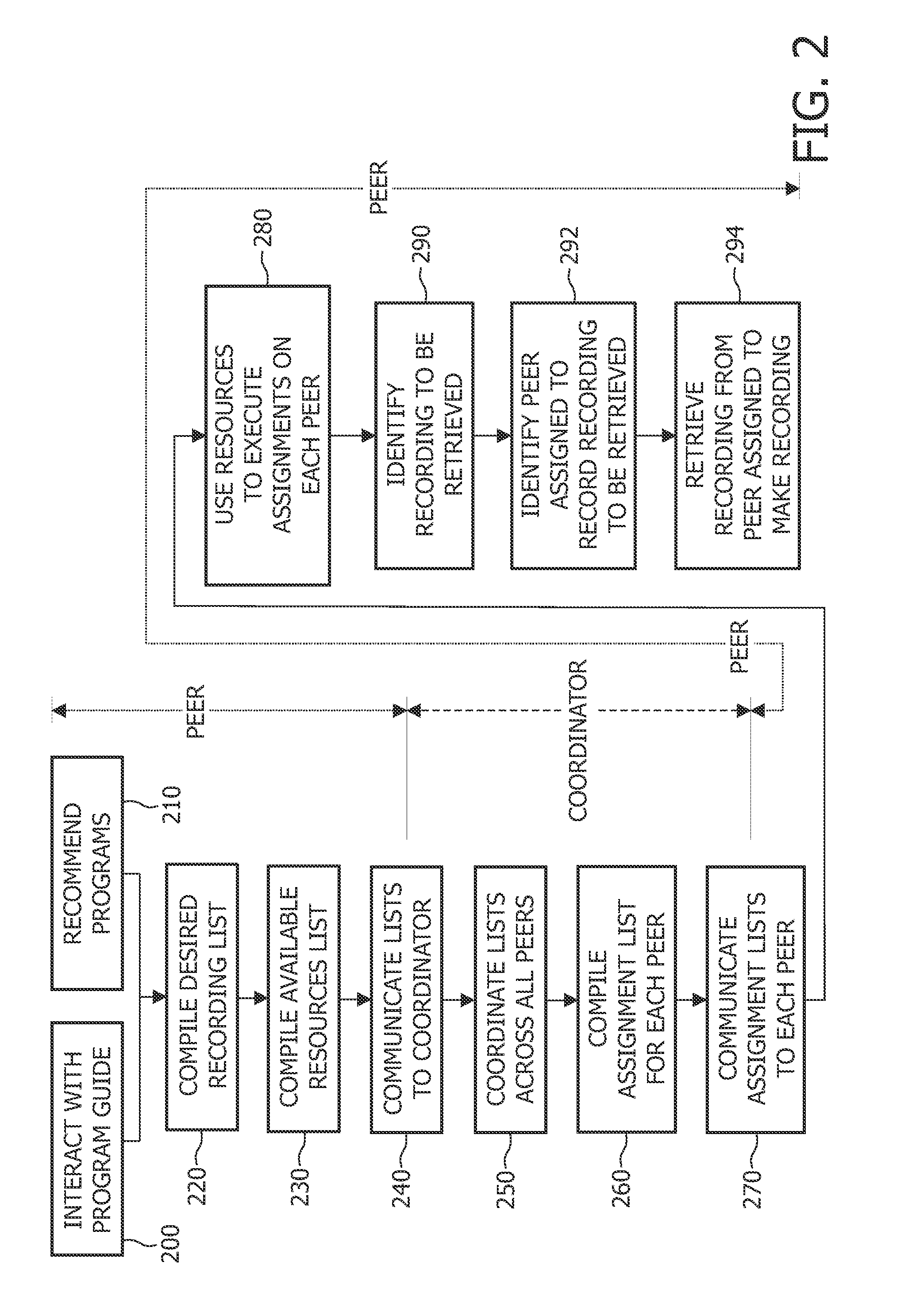

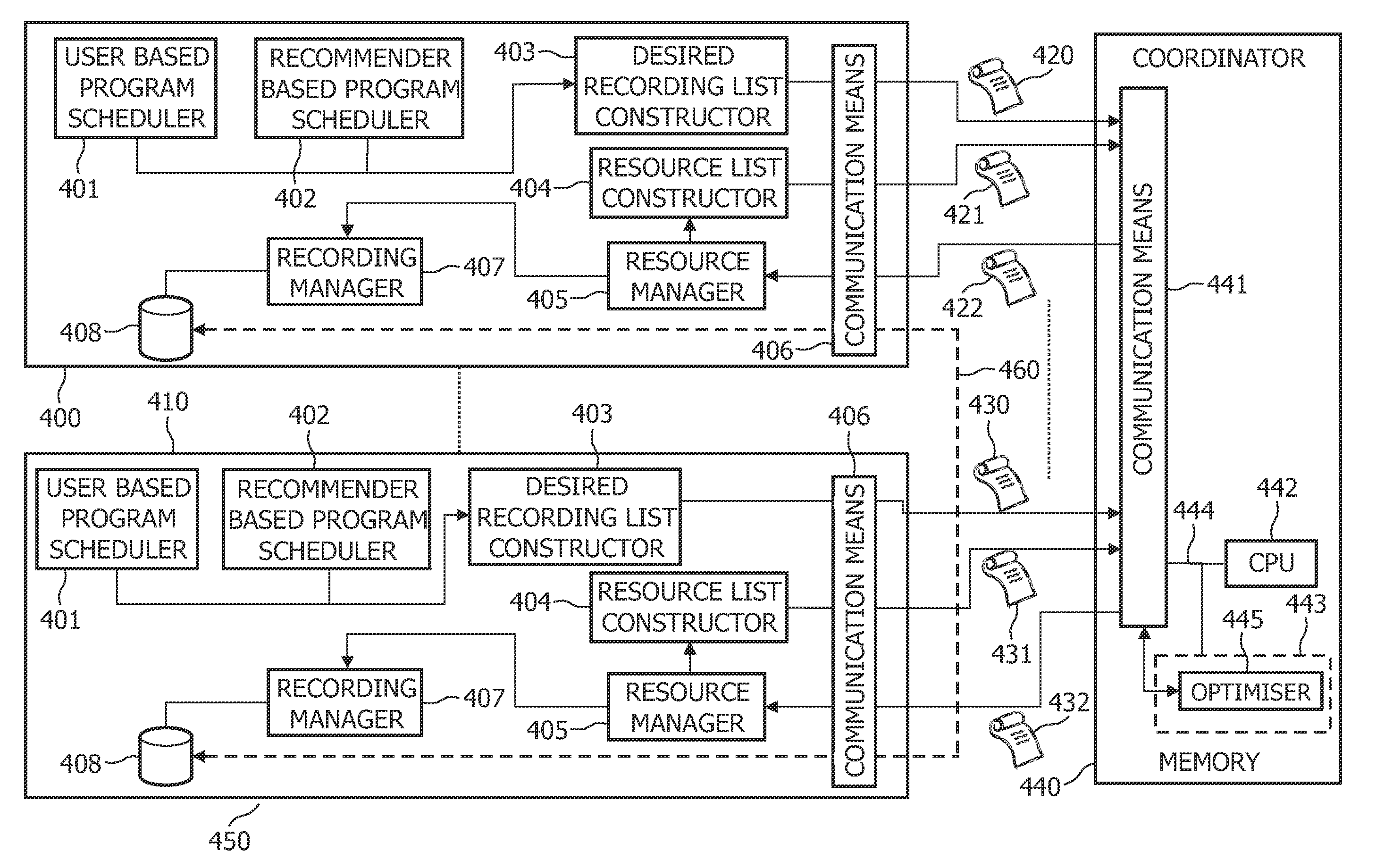

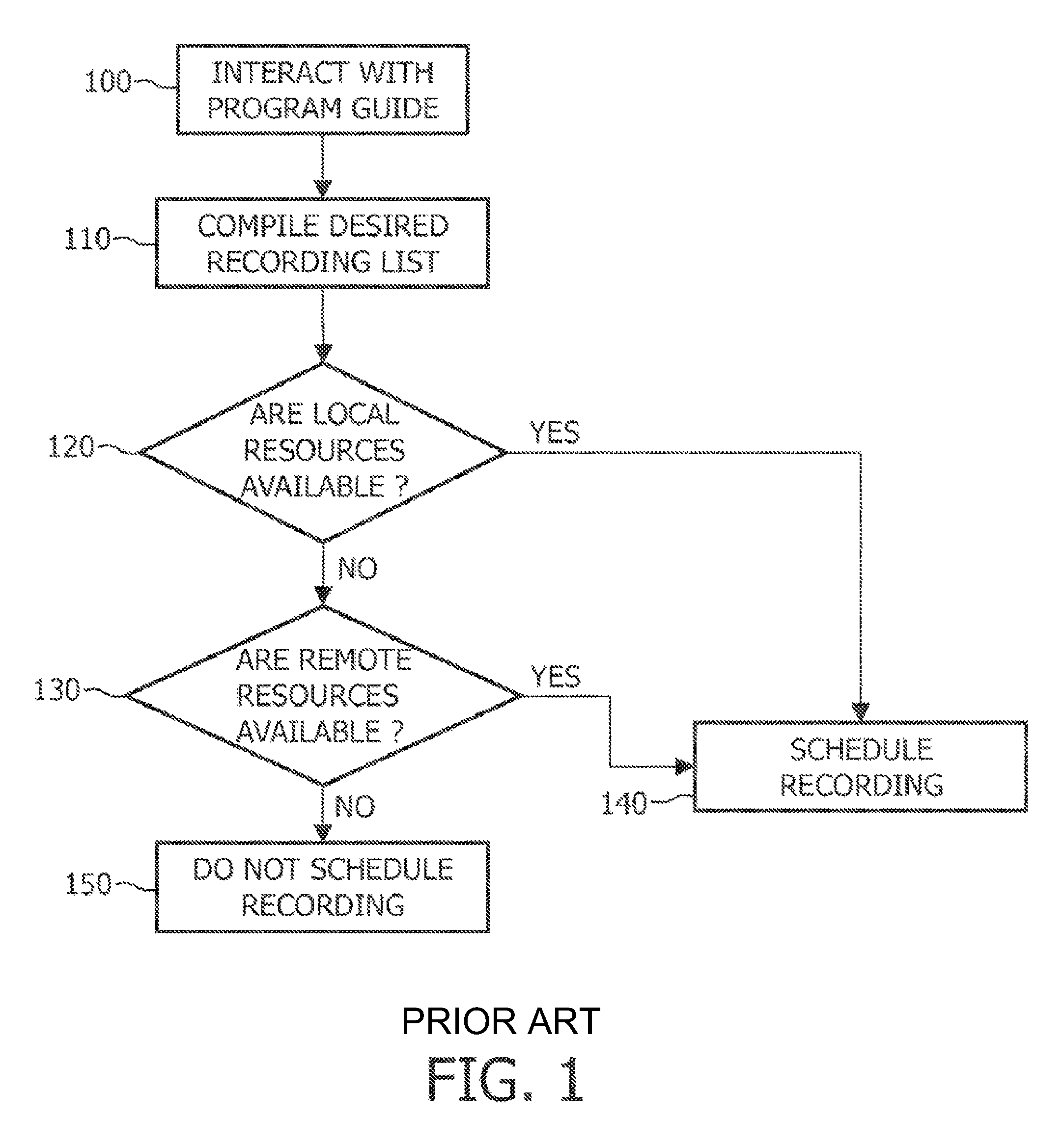

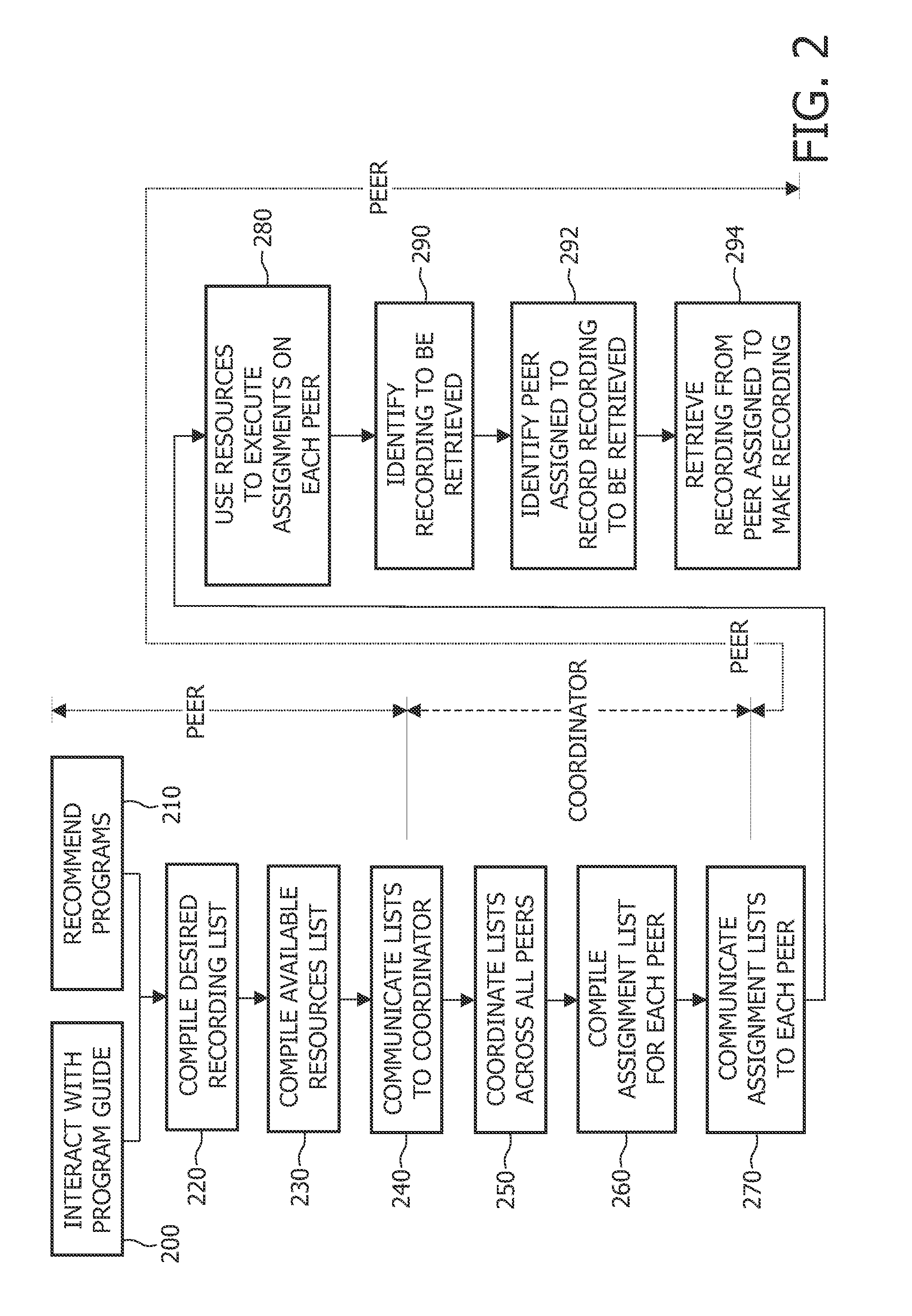

Device and a method for sharing resources in a network of peers

InactiveUS20090210533A1Facilitate resource sharingDigital data information retrievalDigital computer detailsUser deviceProgram planning

A device and a method for sharing resources in a network of peers are disclosed. A user may compile a wish list (420) of programs to be recorded on a recording device (400) that is a peer in the network. A resource list (421) is compiled of resources that the device shares within the network. The wish list and resource list are communicated to a coordinator (440) comprised within the network. The coordinator makes assignments of who records what and communicates an assignment list (422) to each peer. Each peer plans (405) and executes (407) the assigned recordings, which can be retrieved from a peer (410), or sent to the user device. Deletion control is applied to prevent the loss of recordings by deletion on a local peer. The coordinator may be comprised within a peer, as a standalone service within the network or implemented as a distributed algorithm between the peers.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

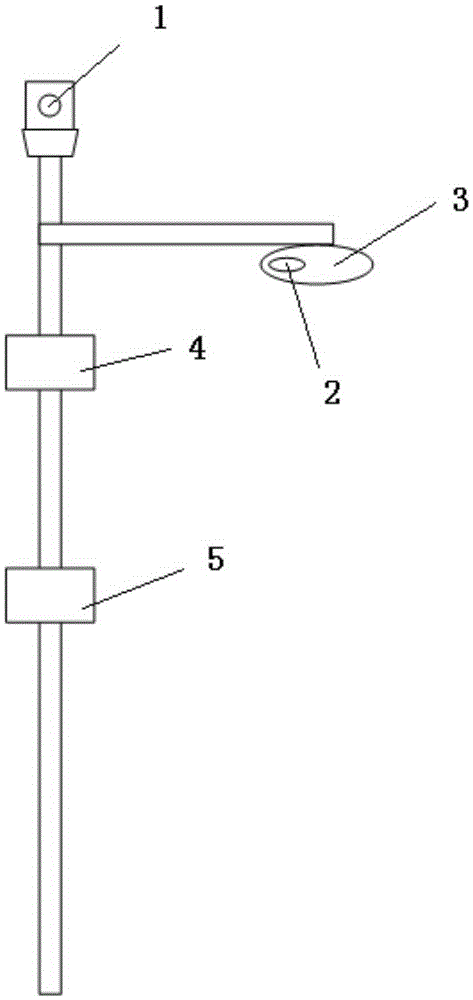

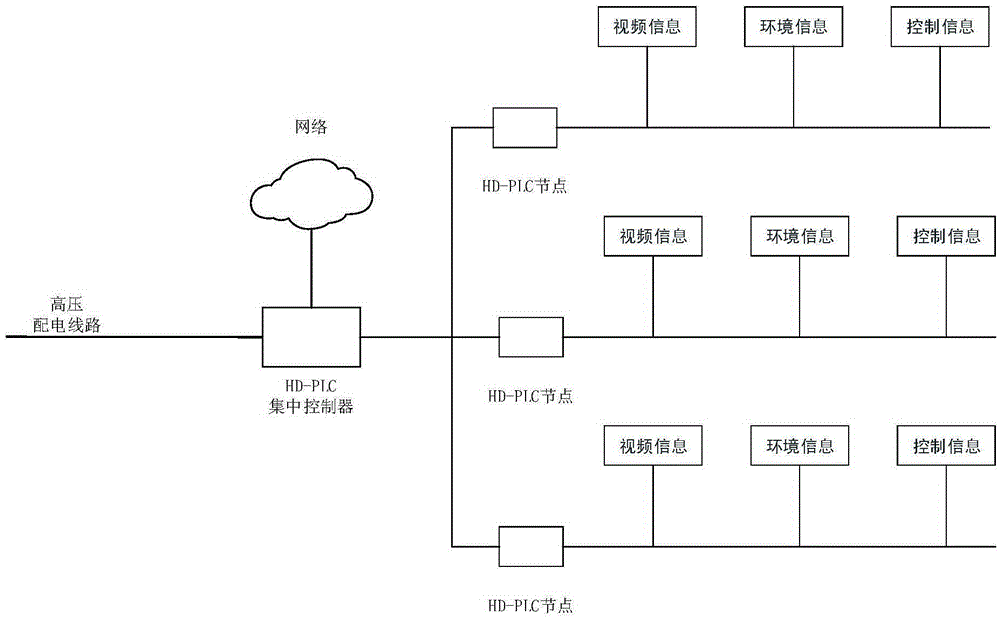

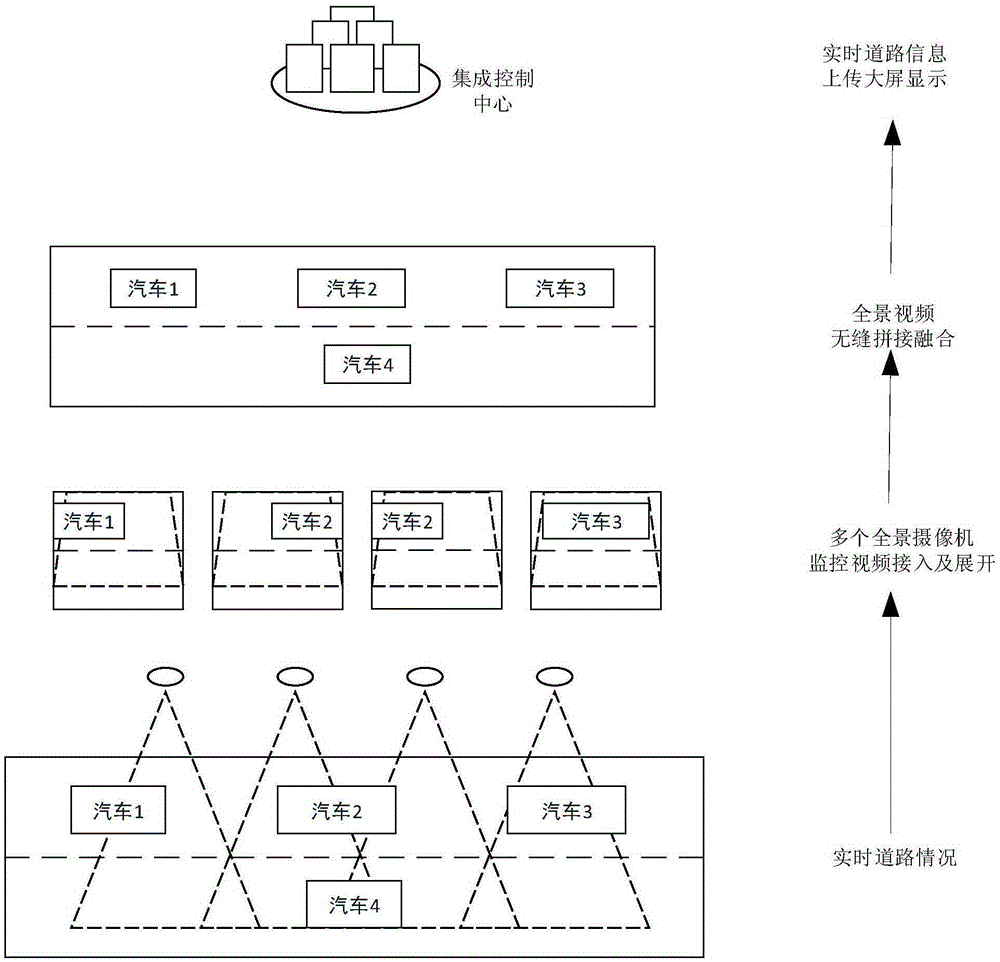

Road full-covering panoramic intelligent video monitoring system and method based on Internet of Things

InactiveCN105262987AAchieve integrationFacilitate big data analysisTelevision system detailsColor television detailsIntelligent lightingVideo monitoring

The invention provides a road full-covering panoramic intelligent video monitoring system based on Internet of Things. The system comprises an acquisition unit, a panoramic video monitoring camera, a holder monitoring camera, a transmission unit, and an integrated control center, the integrated control center processes information obtained by the acquisition unit, the panoramic video monitoring camera, and the holder monitoring camera unit, and manages street lamps and controls the holder monitoring camera via the transmission unit, and required positions or targets on road sections can be monitored. According to the scheme, the street lamps are regarded as the infrastructure, the panoramic video monitoring equipment and the holder monitoring camera are combined, the Internet of Things is regarded as a carrier, technologies of road full-covering panoramic intelligent video monitoring, intelligent illumination, intelligent sensing detection, and novel data transmission, etc. are integrated, and the combination of urban road full-covering intelligent video monitoring based on street lamp facilities and urban smart illumination, comprehensive prevention and control, and network communication coverage is realized.

Owner:北京尚易德科技有限公司

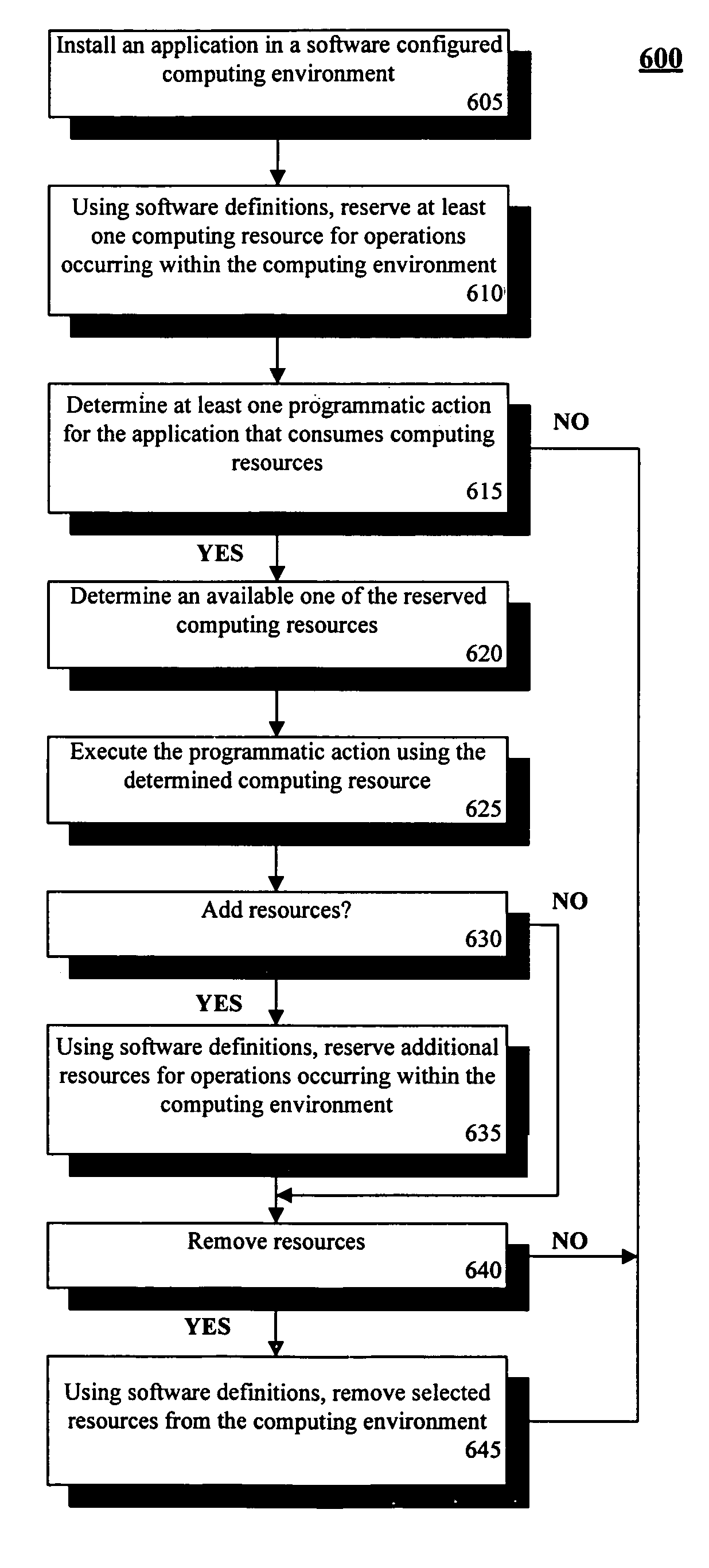

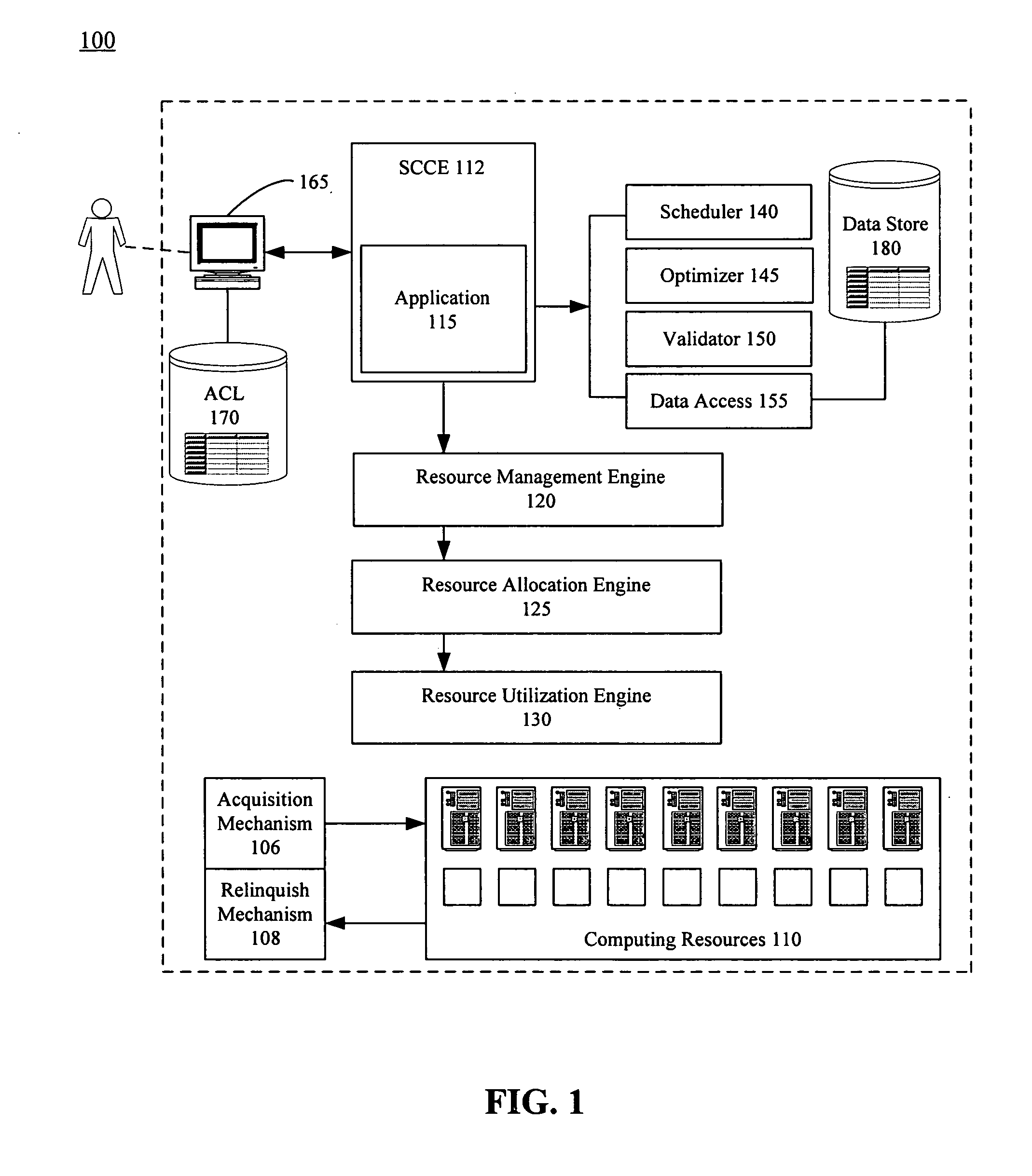

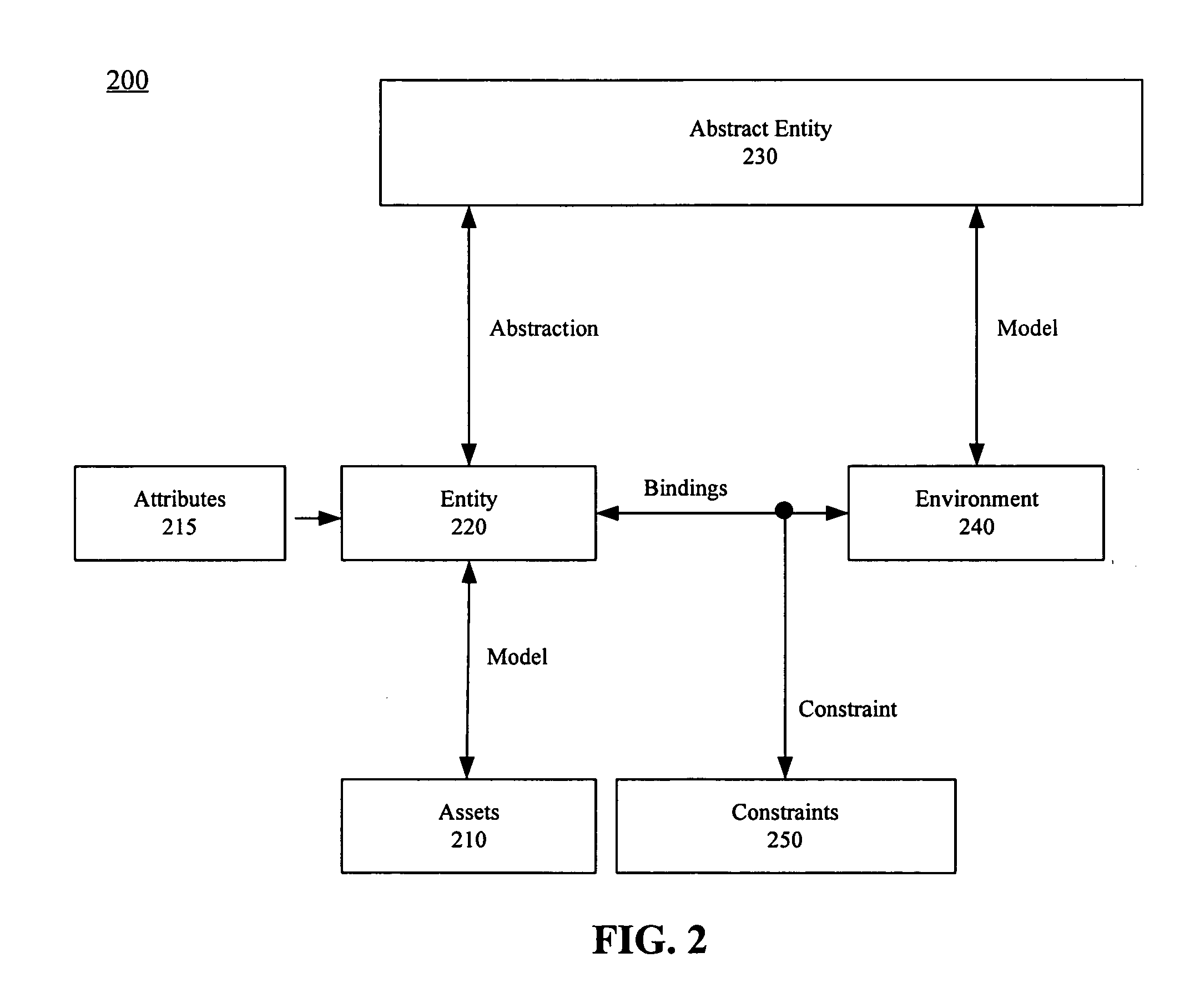

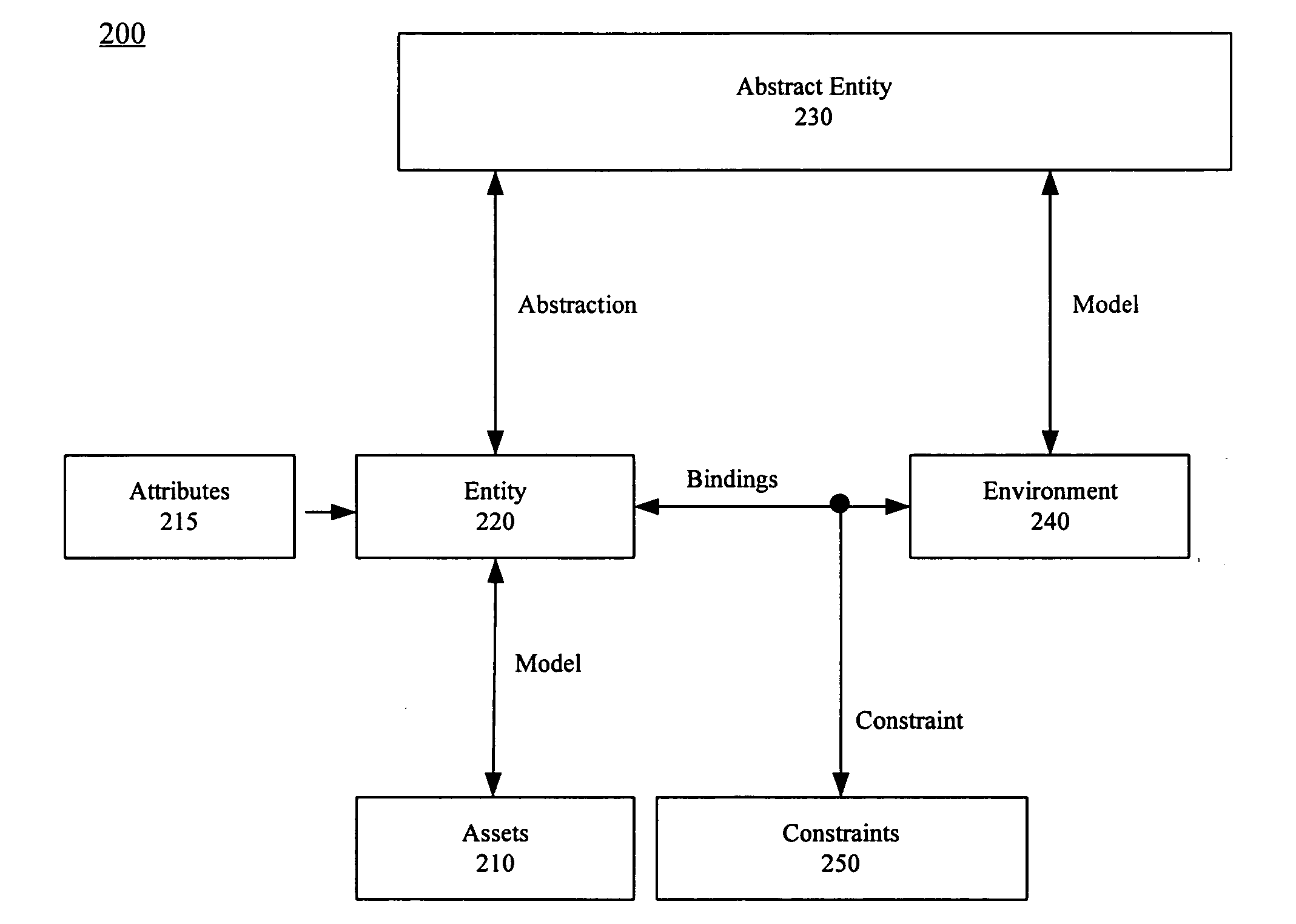

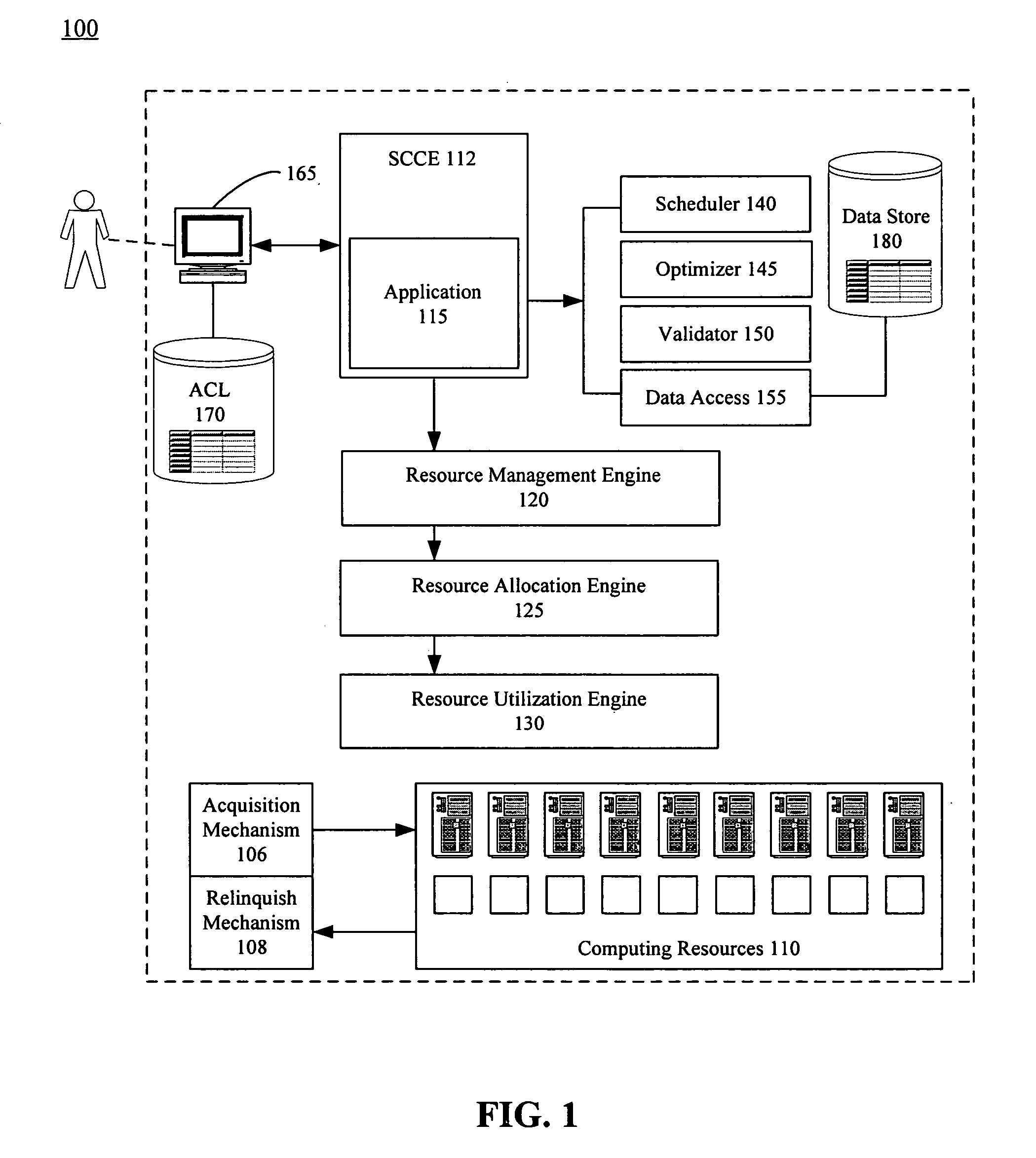

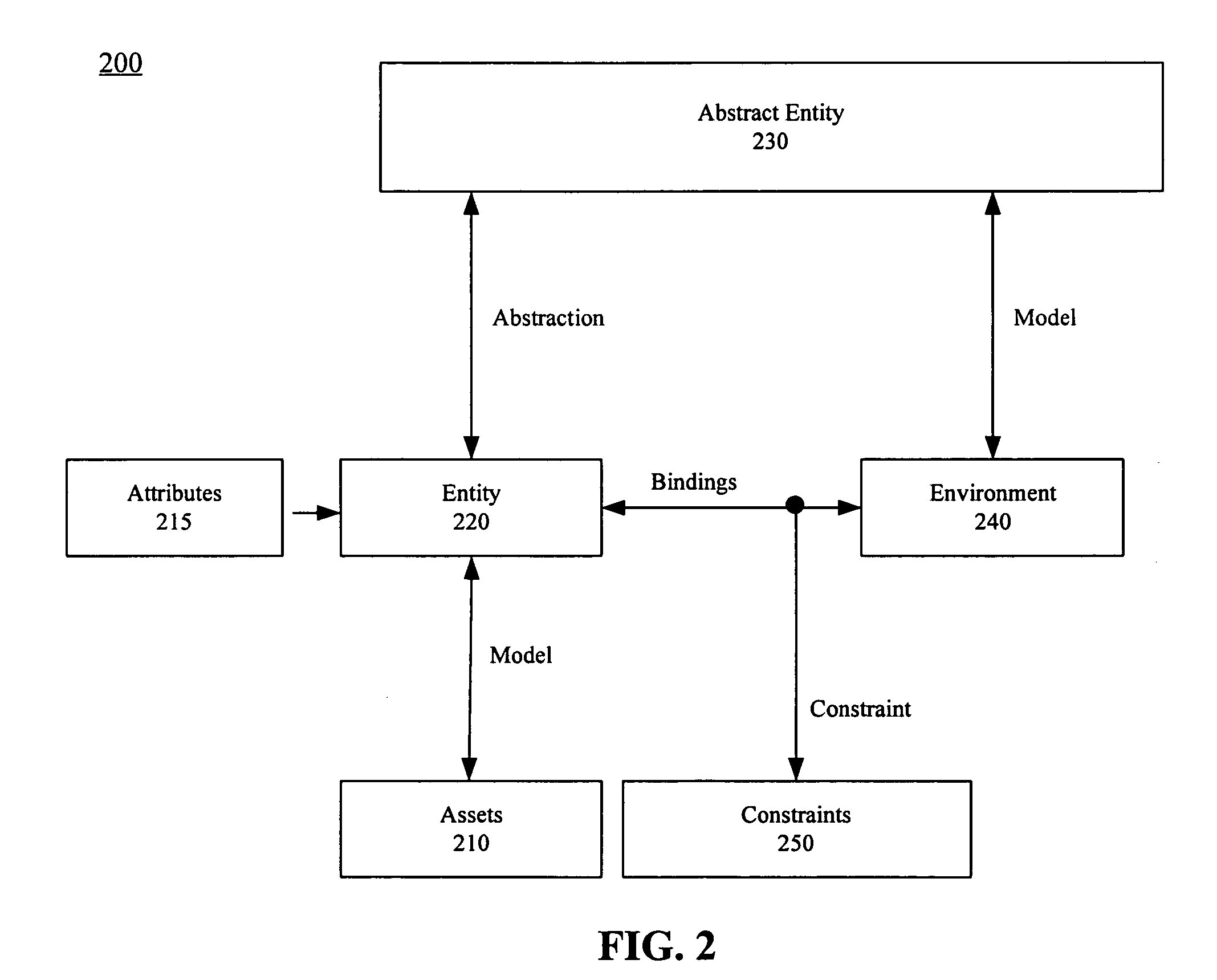

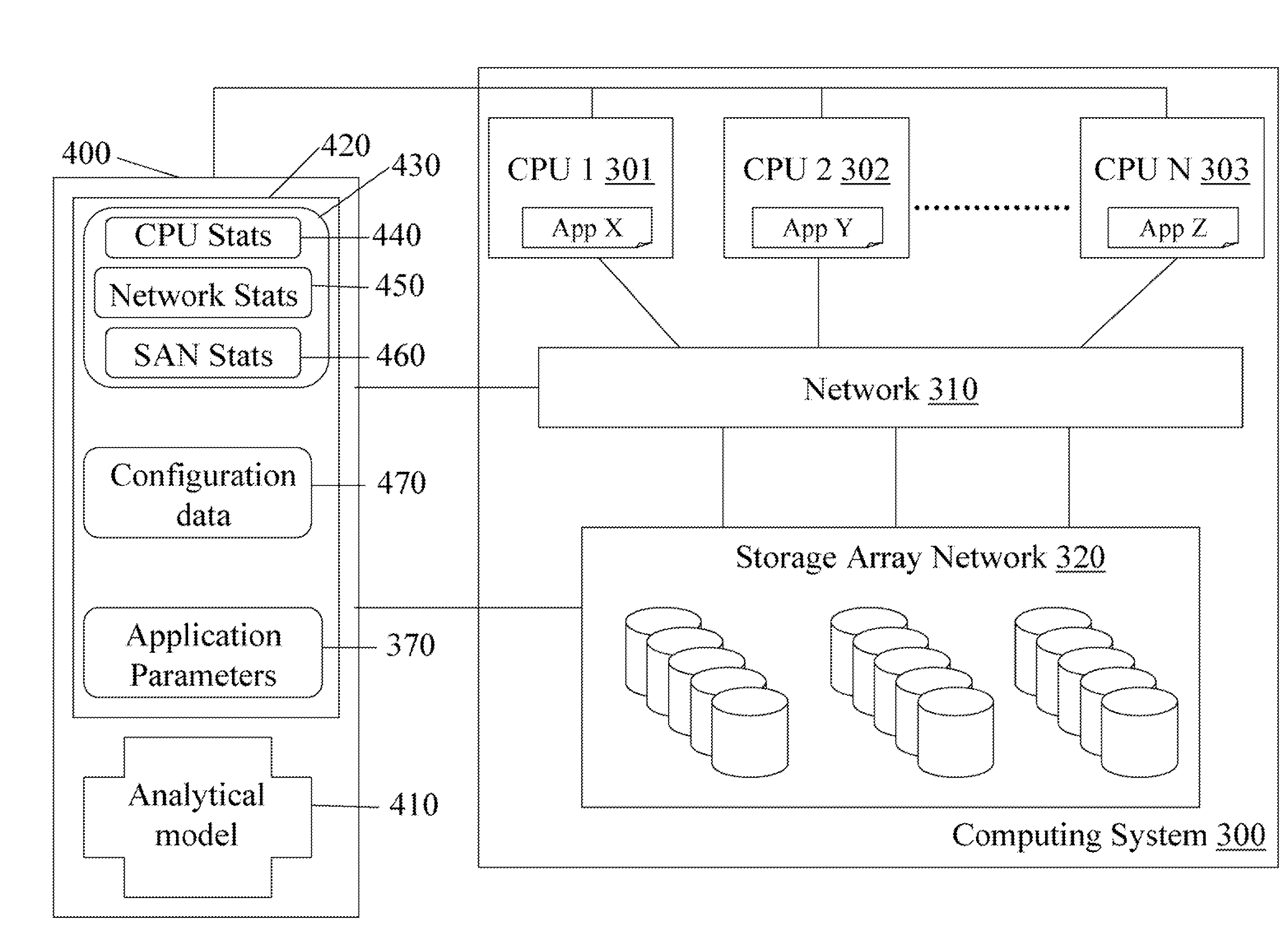

Method, system, and apparatus for establishing a software configurable computing environment

ActiveUS20060090162A1Facilitate resource sharingResource allocationSoftware engineeringResource utilizationResource management

A software configurable computing environment can include at least one application disposed within the software configurable computing environment. The environment can also include a resource management engine configured to define at least one computing resource for the software configurable computing environment. A resource allocation engine can allocate the computing resources defined by the resource management engine for use in the software configurable computing environment. A resource utilization engine can perform at least one programmatic action for the application using available ones of the resources allocated by the resource allocation engine.

Owner:IBM CORP +1

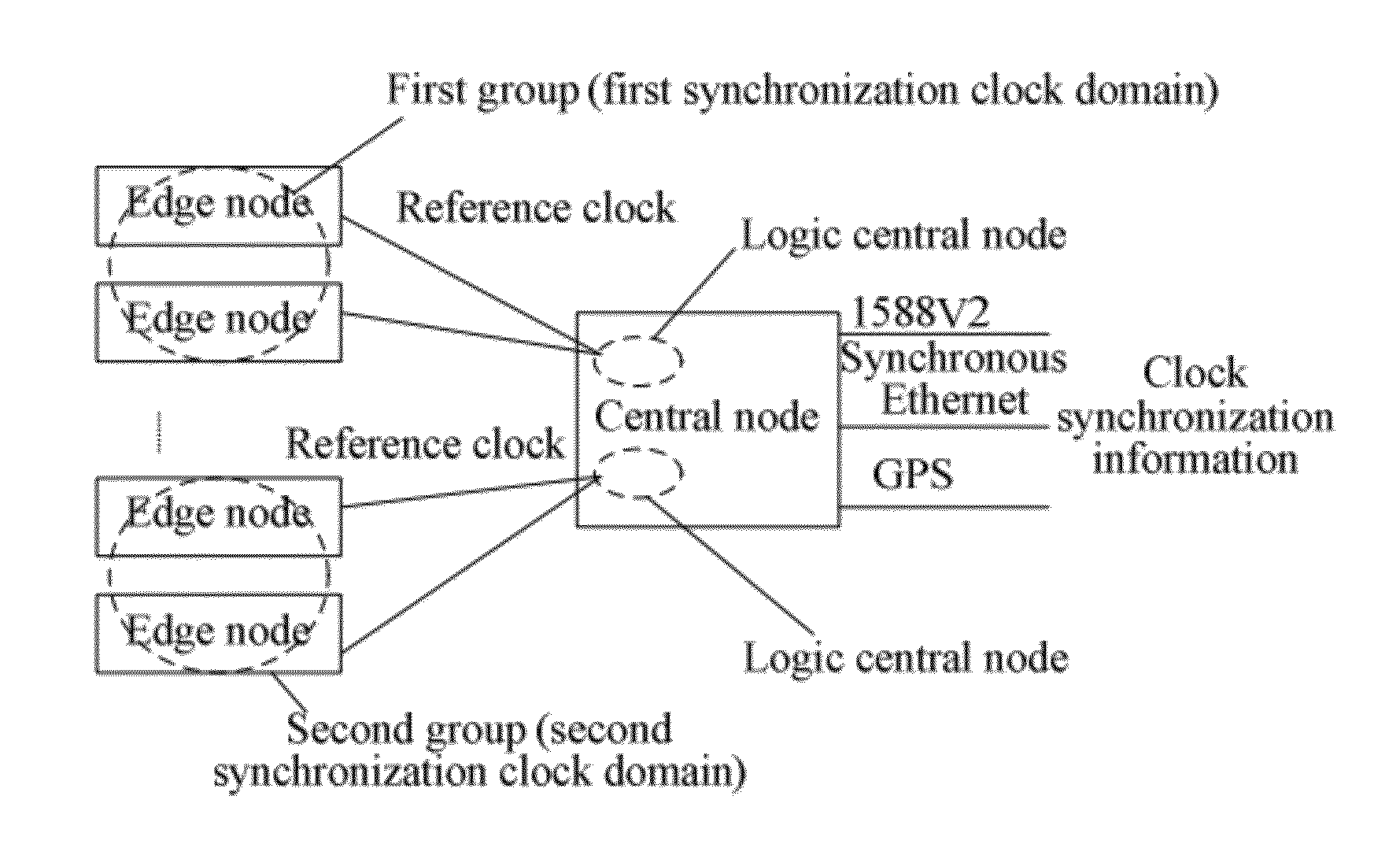

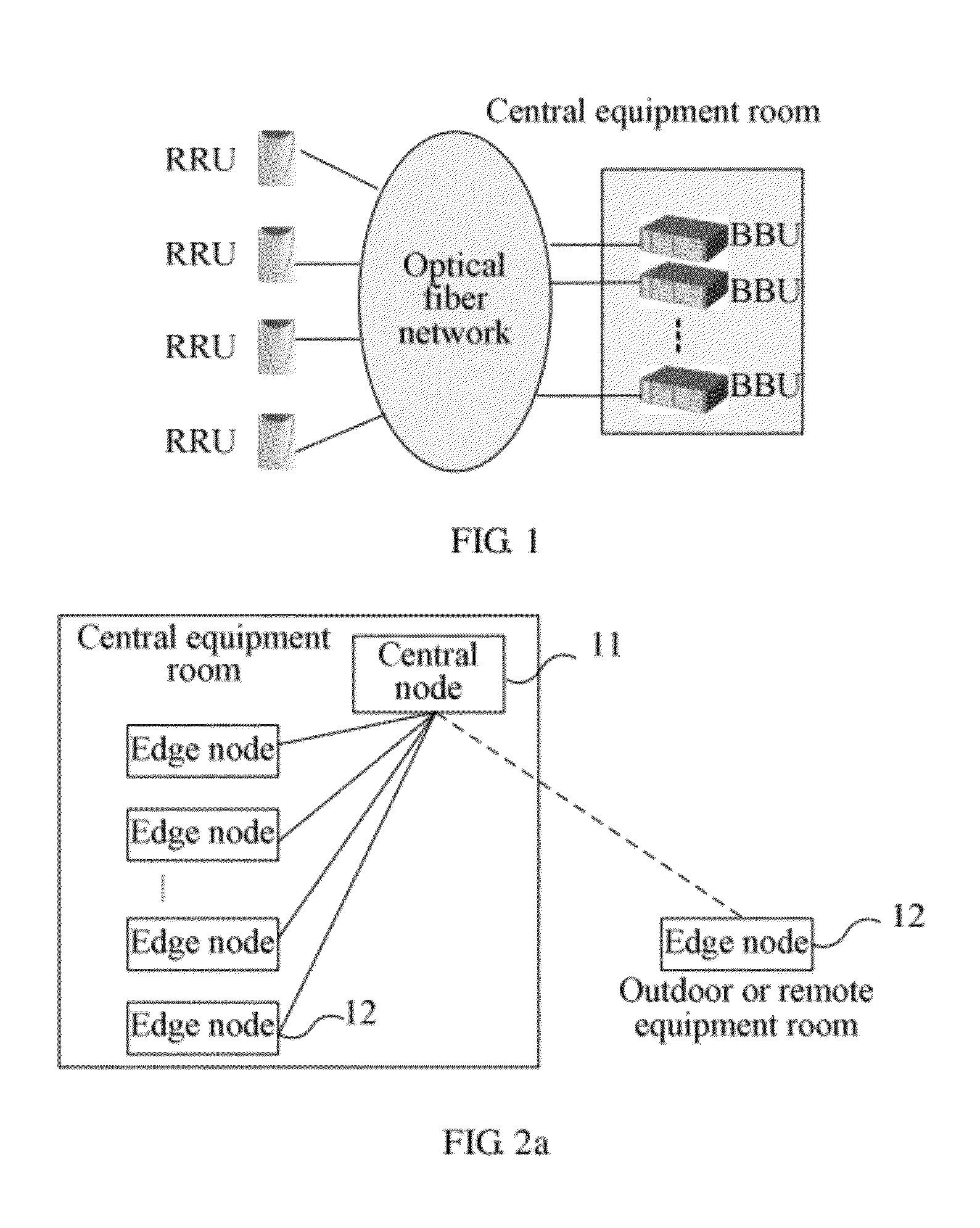

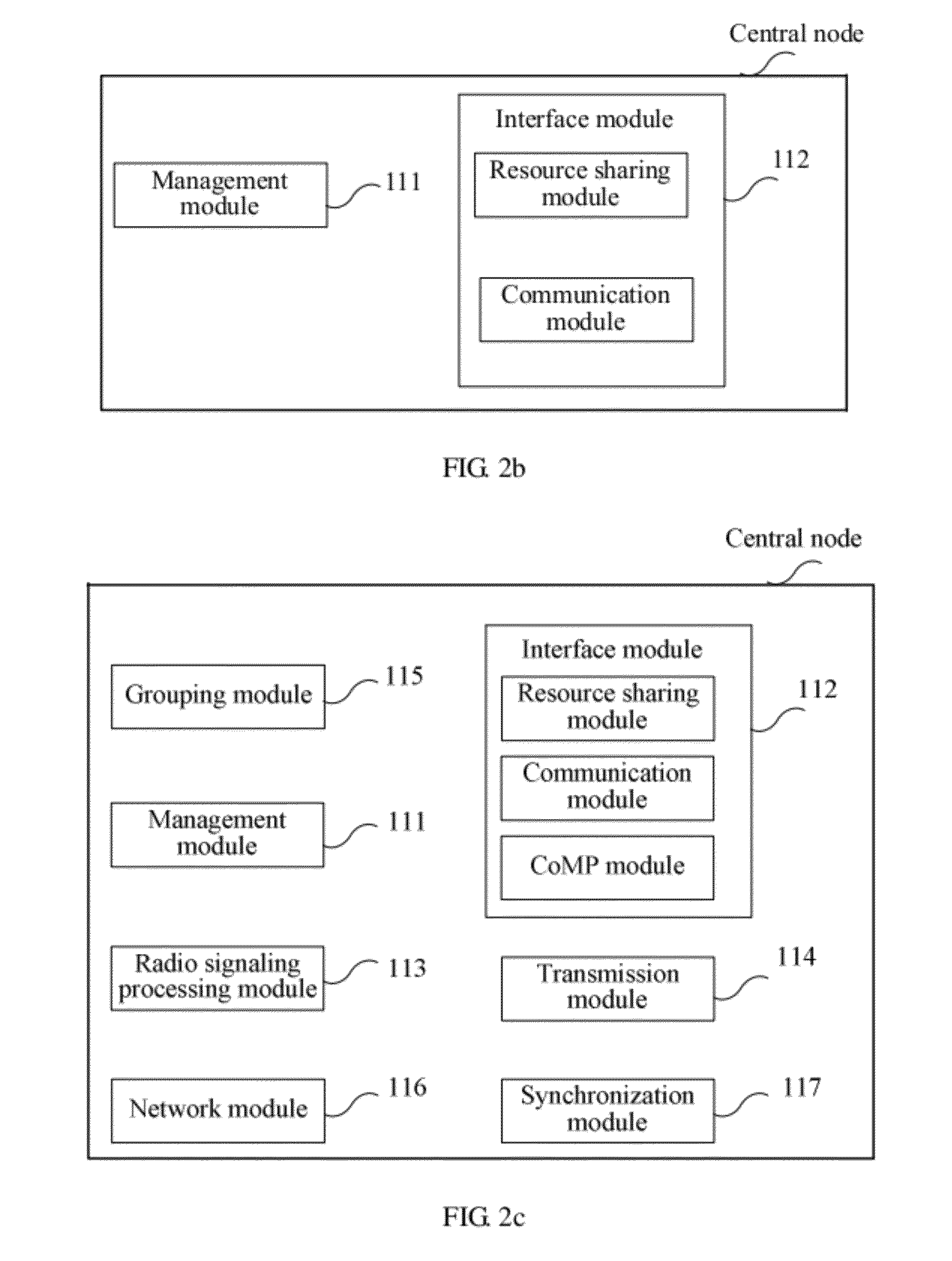

Base station, network system, and implementation method

ActiveUS20120230282A1Facilitate resource sharingHigh degreeSite diversityNetwork traffic/resource managementMultiple edgesNetworked system

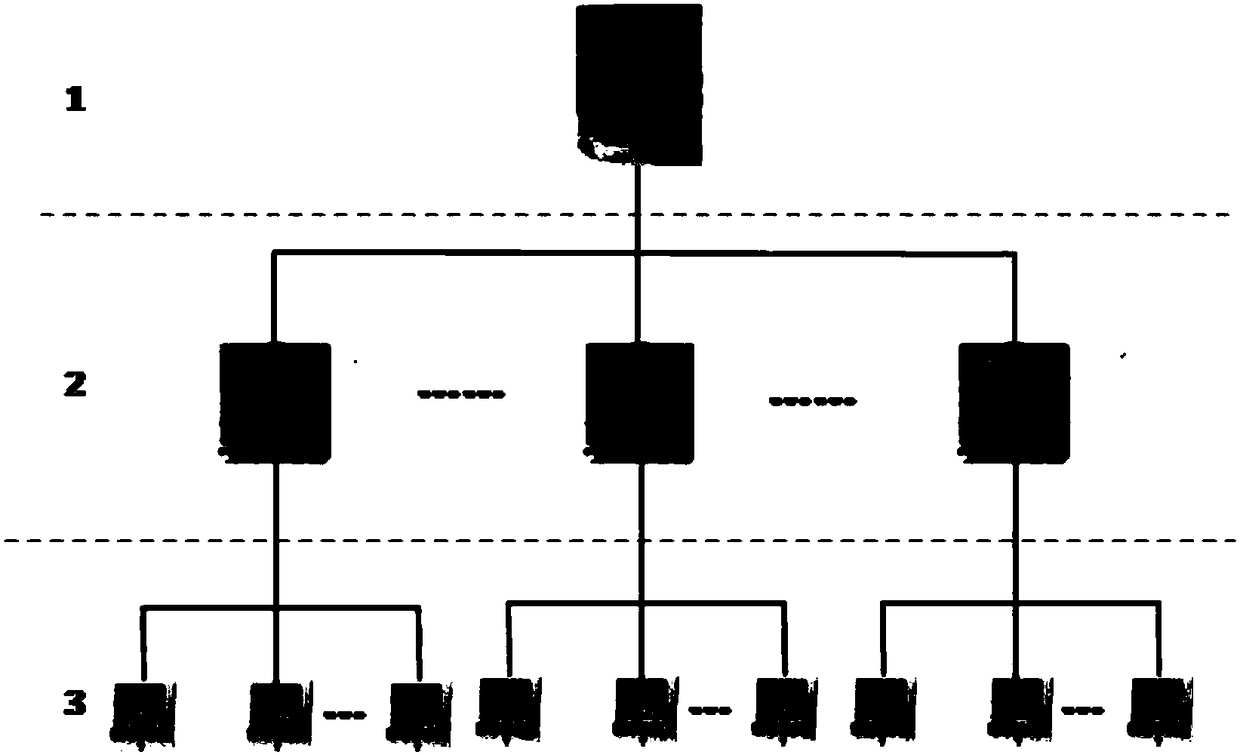

A base station includes multiple edge nodes and a central node. The edge nodes are configured to perform communication with a user equipment, and execute baseband processing and mutual conversion between baseband data and radio data, in which the multiple edge nodes belong to one or more edge node groups, and each edge node group includes at least one edge node. The central node is configured to perform communication with the multiple edge nodes, manage the multiple edge nodes, and perform resource sharing so that resources are shared by the multiple edge nodes. The base station is divided into two levels of architecture, namely, a central node and an edge node, and the central node implements resource sharing so that resources are shared by the edge nodes, so that a resource sharing degree in the base station is enhanced.

Owner:HUAWEI TECH CO LTD

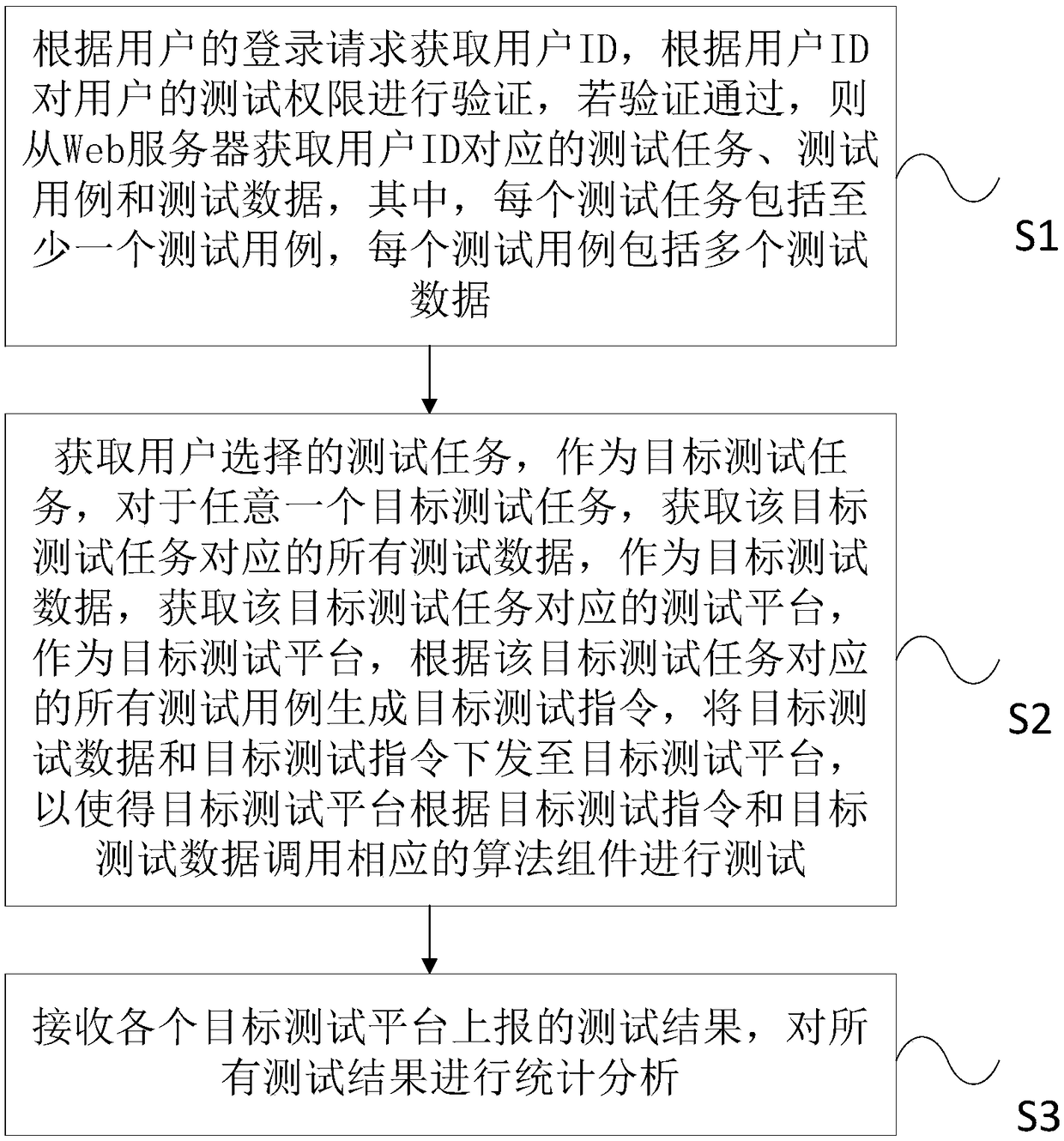

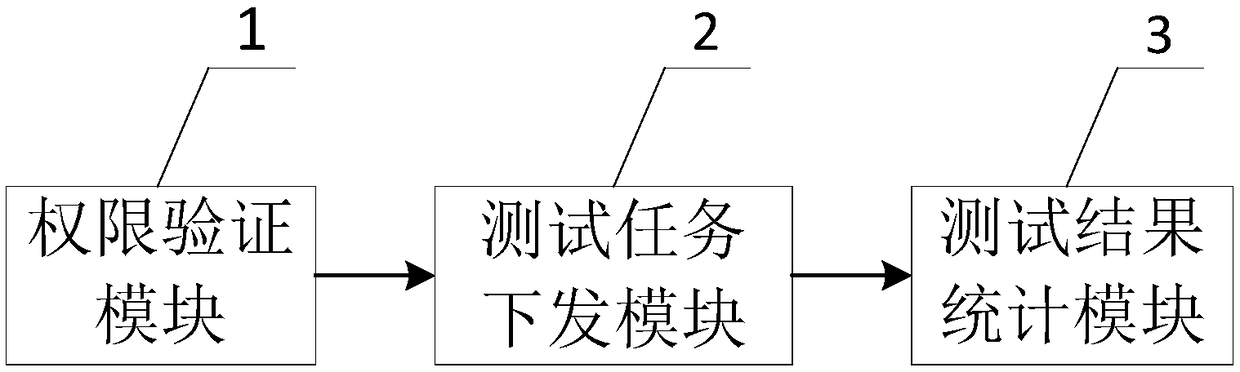

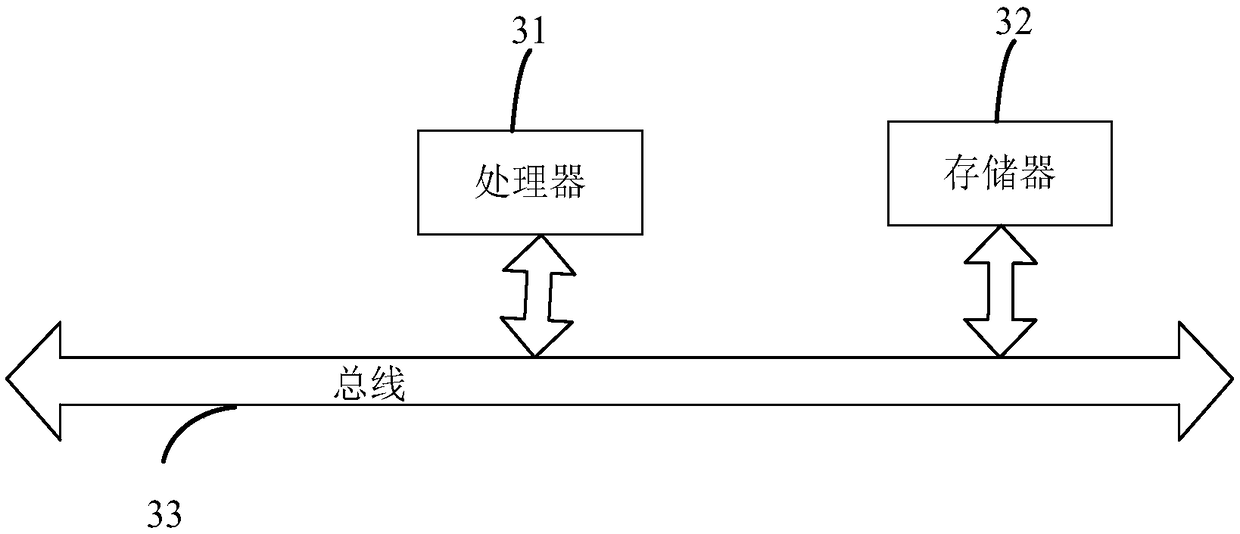

Cross-platform algorithm testing method and system

InactiveCN109144857AReduce computing burdenReduce storage burdenSoftware testing/debuggingWeb serviceStatistical analysis

The invention provides a cross-platform algorithm testing method and a system thereof. The method comprises steps: after a user logs on a testing client, if the testing authority is verified to be passed, the testing client obtaining a testing task corresponding to the user ID from a Web server, a test case and test data for the user to select; obtaining the test task selected by the user, as a target test task, the target test data and the target test platform corresponding to the target test task being obtained for any target test task, the target test instructions corresponding to the target test task being generated, and the target test data and the target test instructions being sent to the target test platform for testing; receiving the test results reported by each target test platform, and making statistical analysis on all the test results. The method and the system can support a plurality of platforms and a plurality of algorithms, and can dynamically expand and adapt to newrequirements. To a certain extent, it reduces the burden of operation and storage of the test platform, and is conducive to the sharing of resources among the test platforms.

Owner:武汉普利商用机器有限公司 +1

Method, system, and apparatus for establishing a software configurable computing environment

ActiveUS8555286B2Facilitate resource sharingResource allocationSoftware engineeringResource utilizationResource management

A software configurable computing environment can include at least one application disposed within the software configurable computing environment. The environment can also include a resource management engine configured to define at least one computing resource for the software configurable computing environment. A resource allocation engine can allocate the computing resources defined by the resource management engine for use in the software configurable computing environment. A resource utilization engine can perform at least one programmatic action for the application using available ones of the resources allocated by the resource allocation engine.

Owner:INT BUSINESS MASCH CORP +1

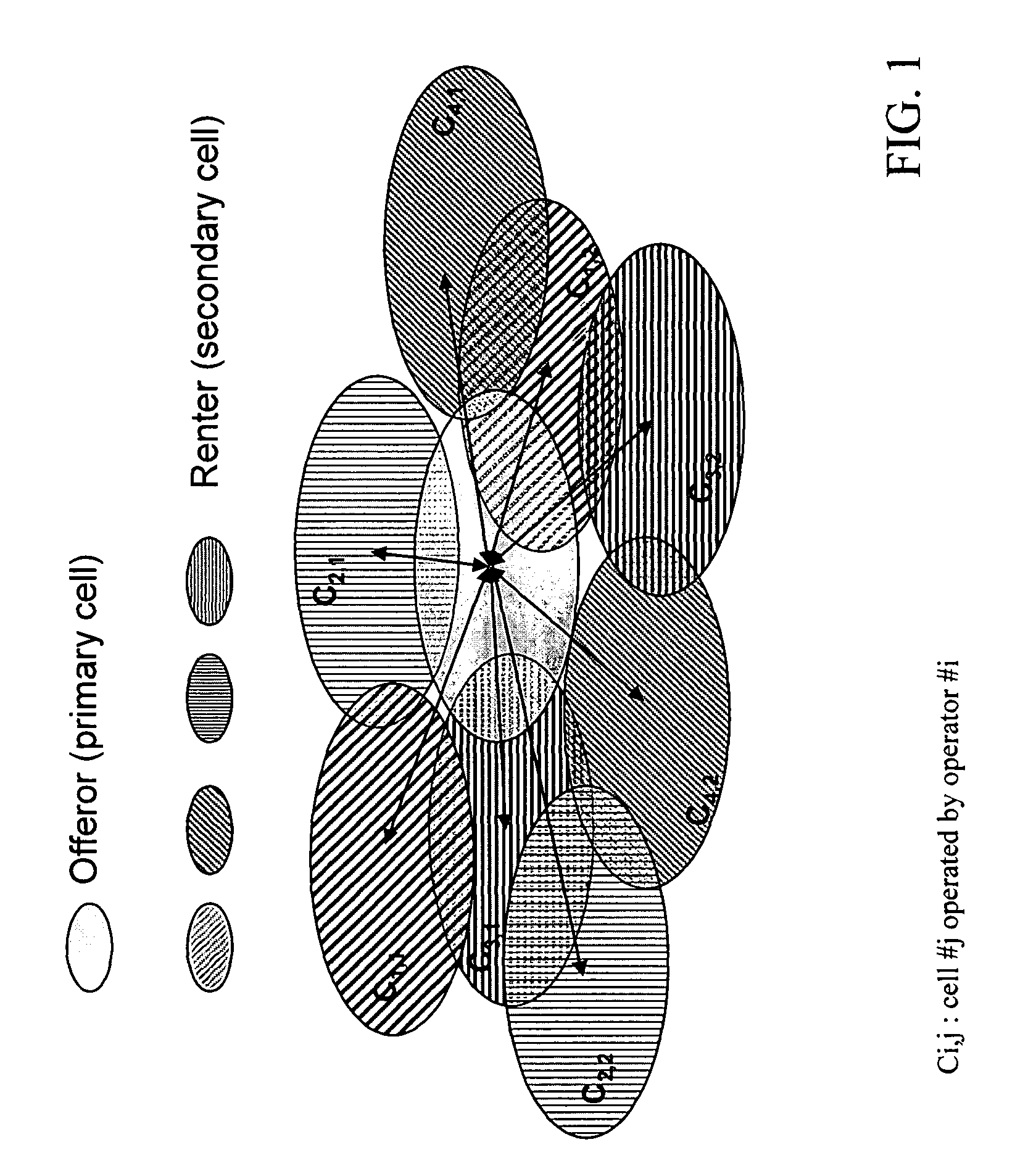

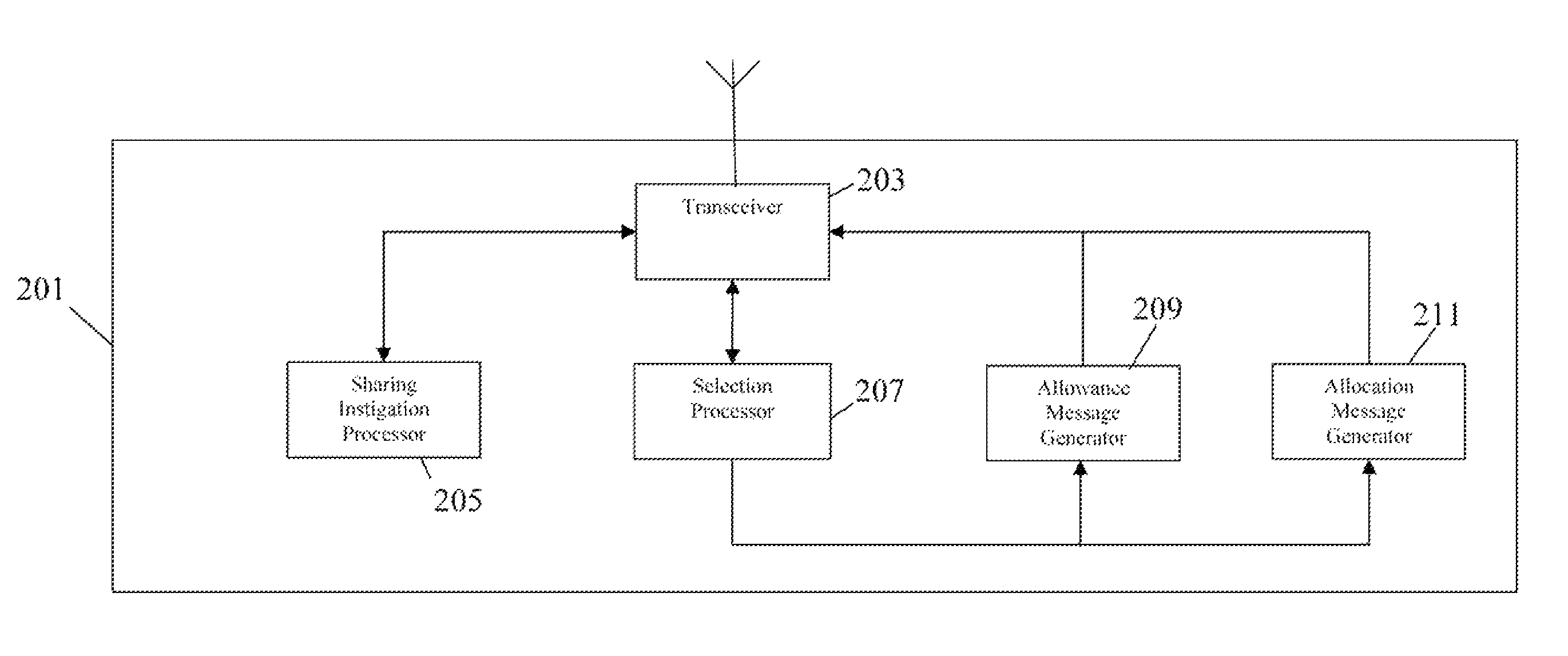

Resource exchange discovery in a cellular communication system

ActiveUS7792533B2Efficient managementEfficient disseminationConnection managementNetwork planningAir interfaceStructure of Management Information

A cellular communication system comprises a set of base stations (201,203) which transmit downlink resource exchange discovery messages to remote terminals in resource allocations of a Media Access Control, MAC, frame structure. The discovery messages may indicate that a base station has resource available for reallocation to another base station or that a base station is seeking resource to be allocated from another base station. A remote terminal (205) comprises a receiver (401, 403) which receives a first message of the downlink resource exchange discovery messages from at least a first base station (201). A discovery message transmit processor (407) generates a second message, which is an uplink resource exchange message comprising resource exchange data determined from the first message, and transmits this to a second base station (203). The second base station (203) then initiates a temporary air interface resource reallocation with the first base station in response to receiving the second message.

Owner:MOTOROLA SOLUTIONS INC

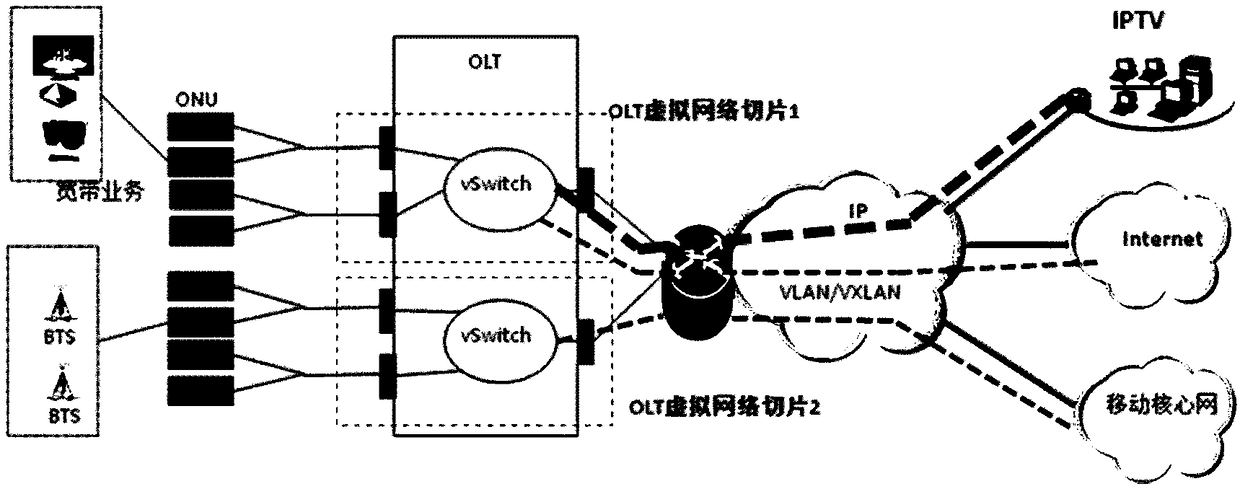

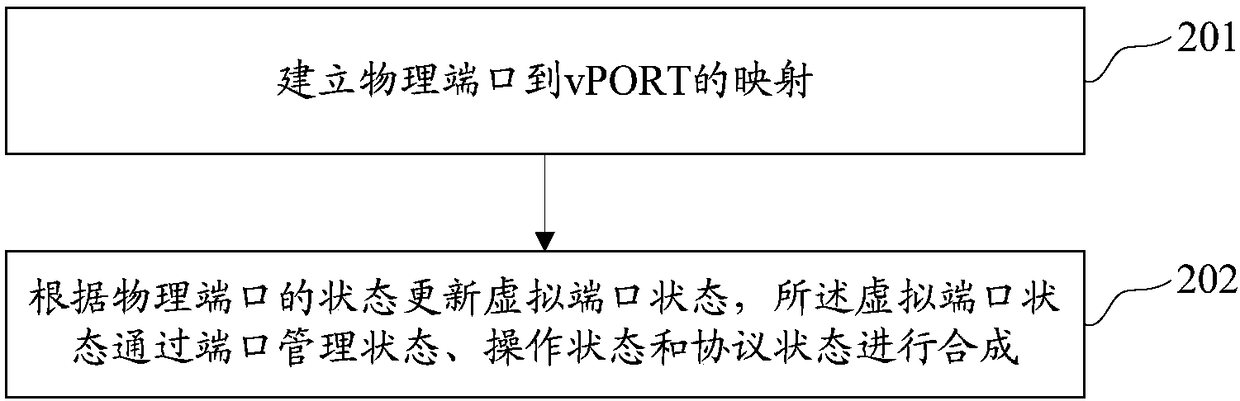

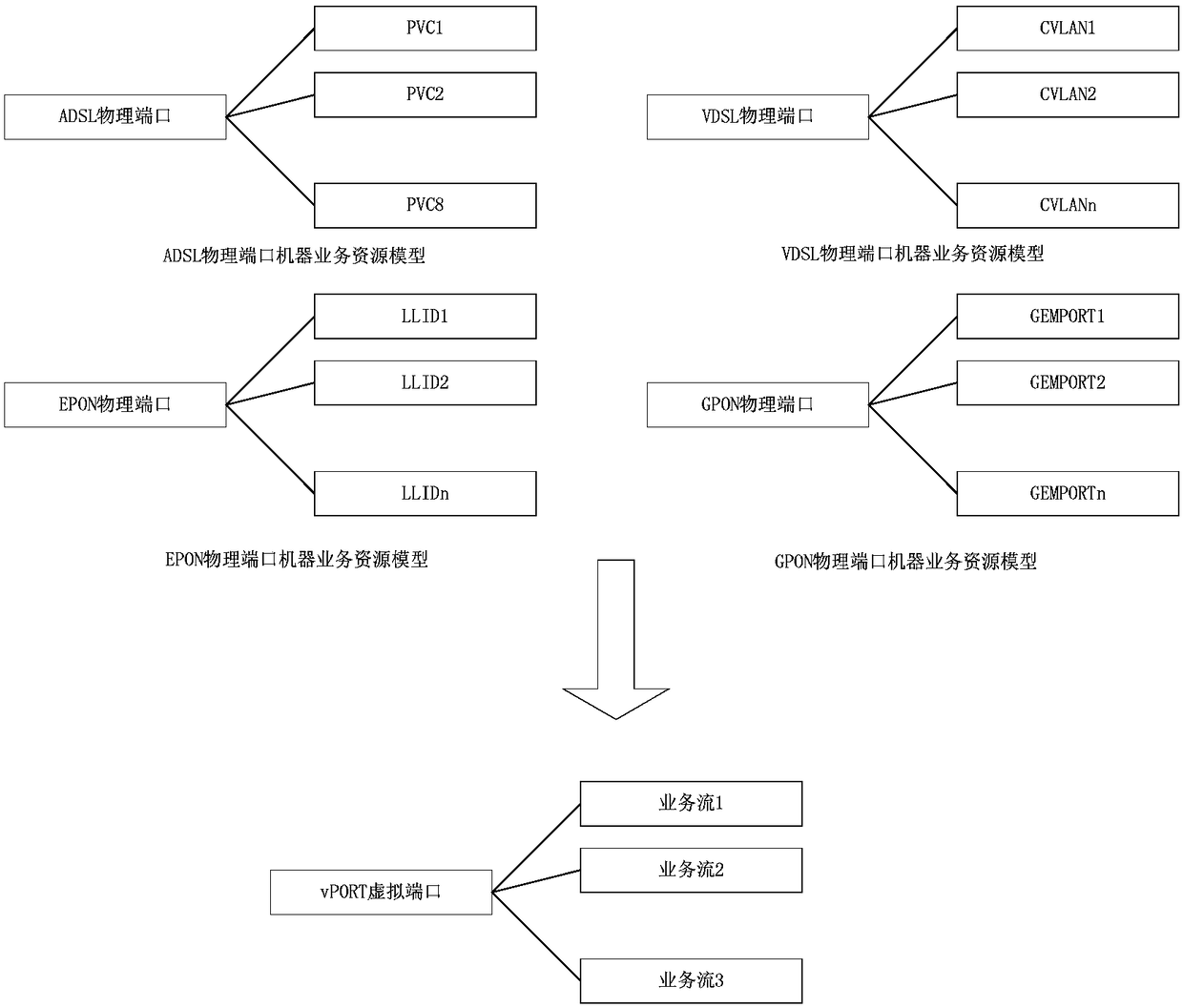

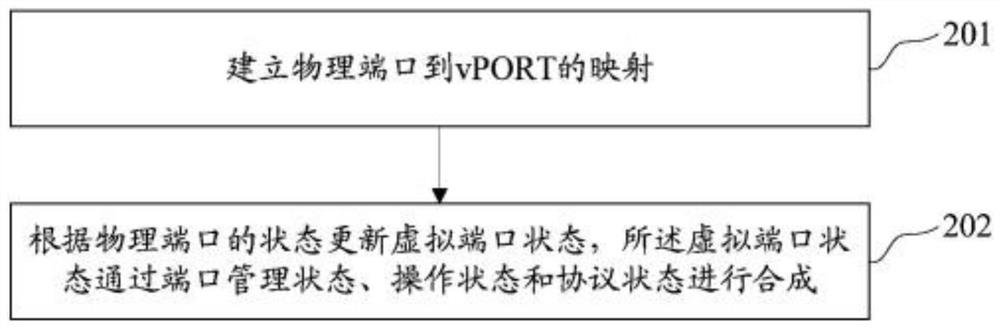

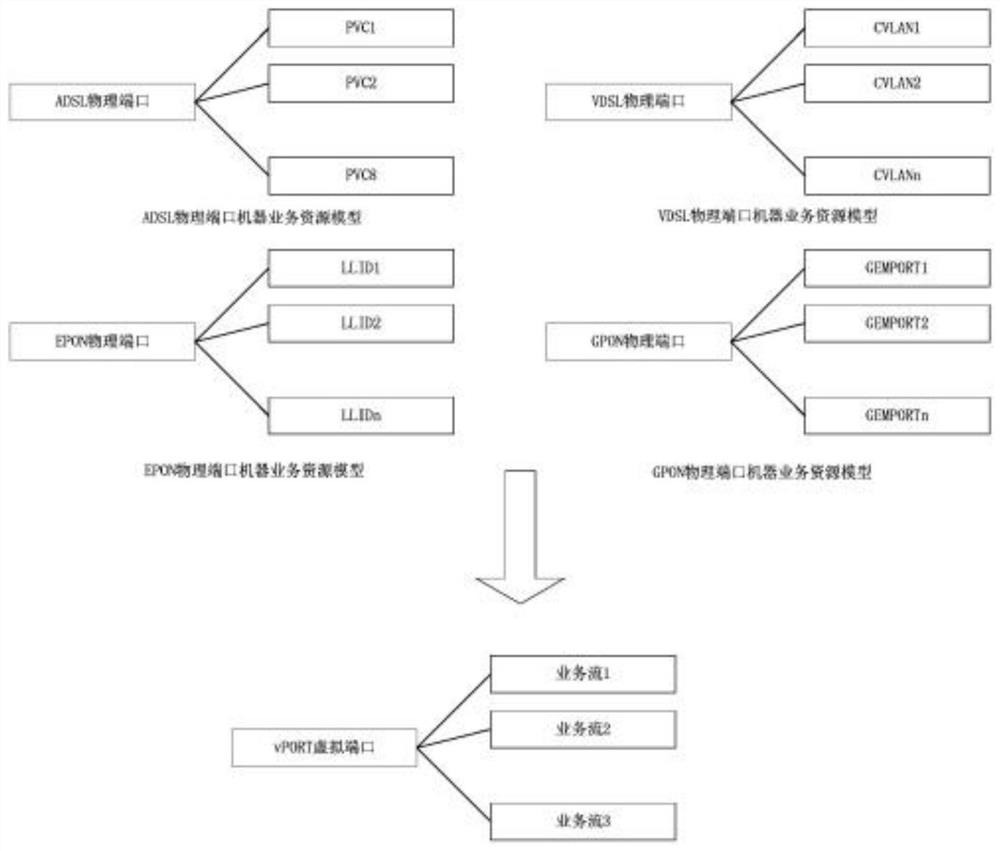

Virtual port management method and device

ActiveCN108809672AEasy to achieve unified managementFacilitate resource sharingElectromagnetic transmissionData switching networksComputer hardwareSoftware define network

The invention discloses a virtual port management method and device. The method comprises the following steps: establishing a mapping between a physical port and a virtual port vPORT; and updating thestate of the virtual port according to the state of the physical port, and synthesizing the state of the virtual port through a port management state, an operation state and a protocol state. The virtual port management method provided by the invention facilitates network resource sharing and unified management of interfaces of an SDN (Software Defined Network) OLT (optical line terminal).

Owner:ZTE CORP

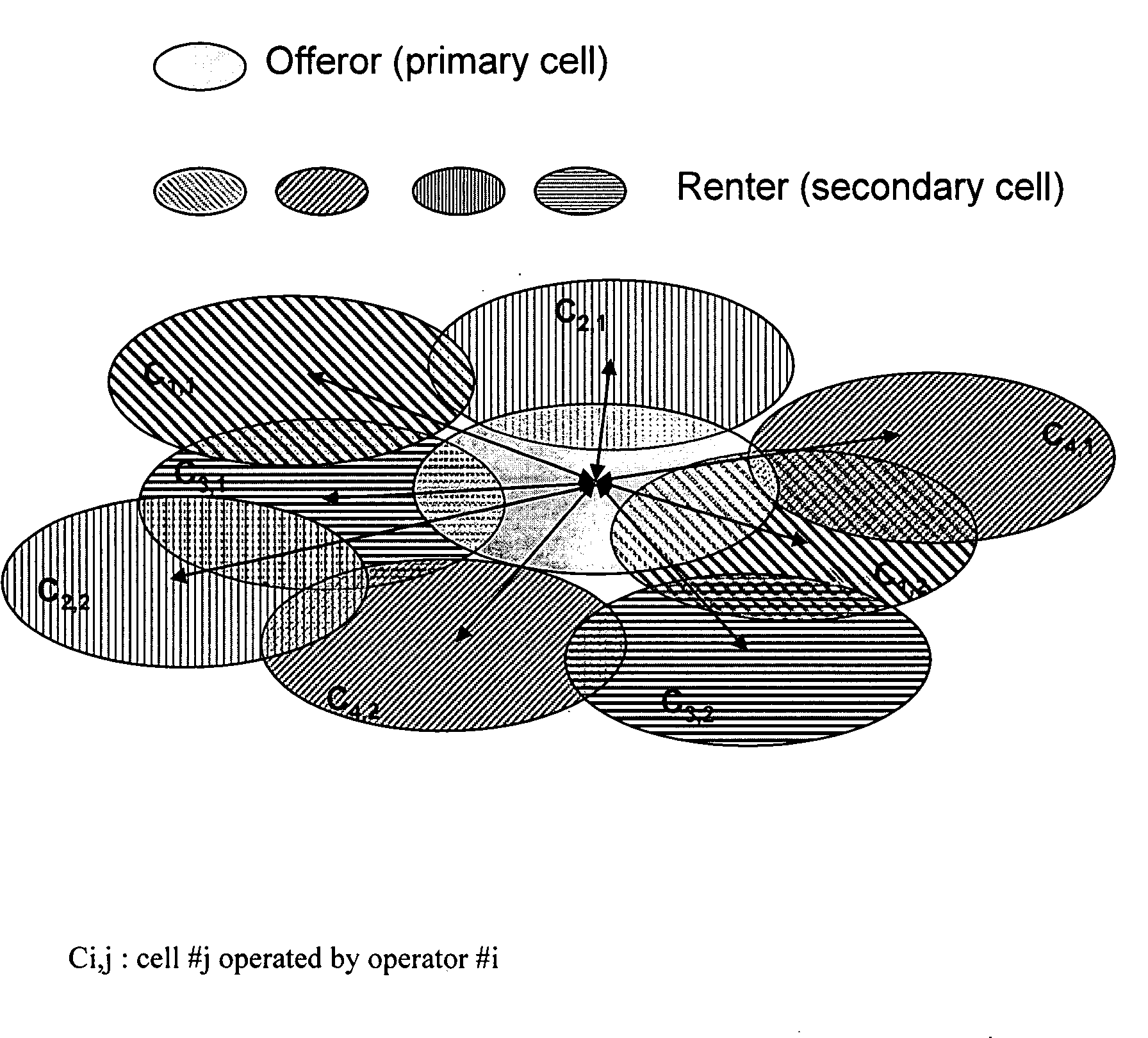

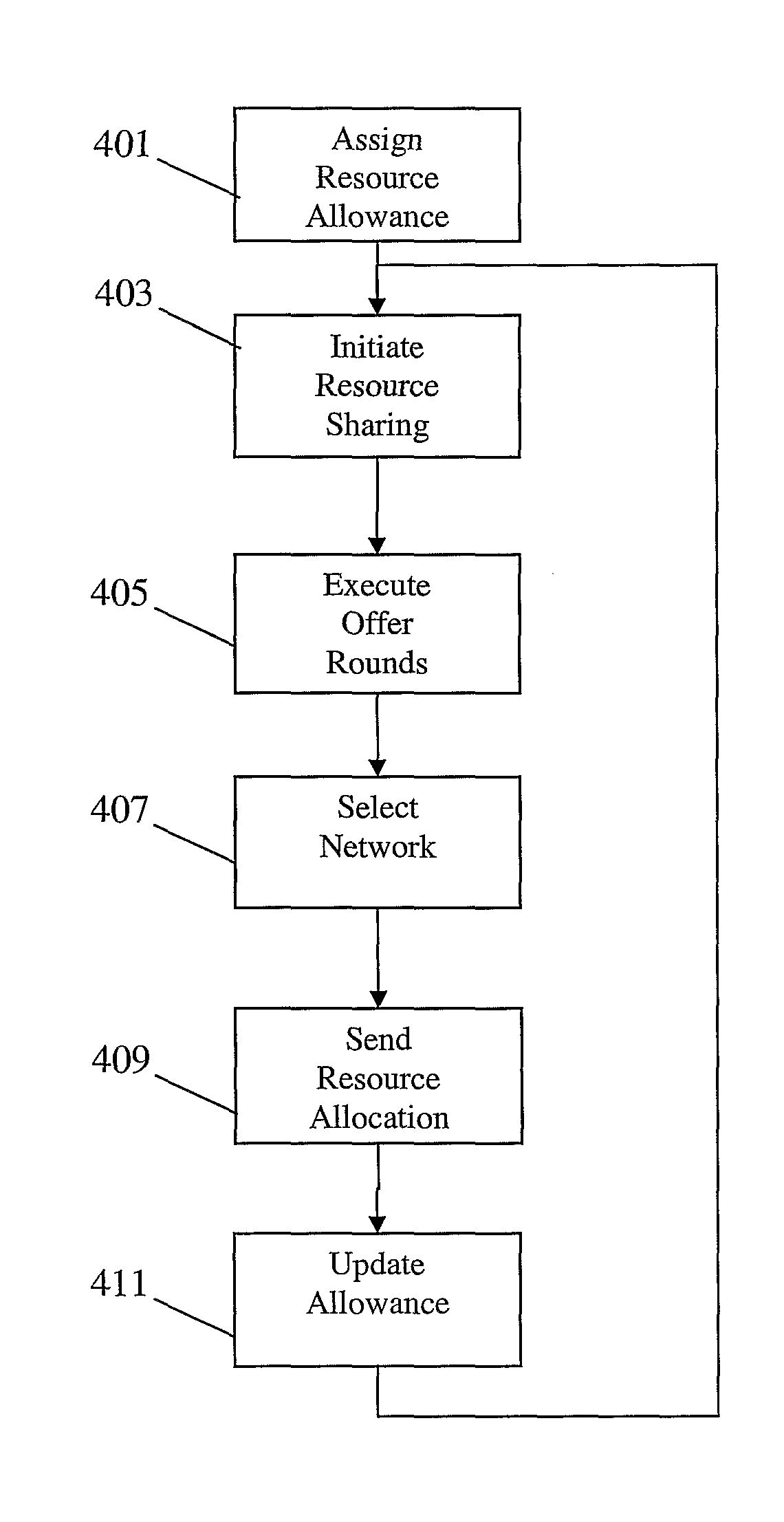

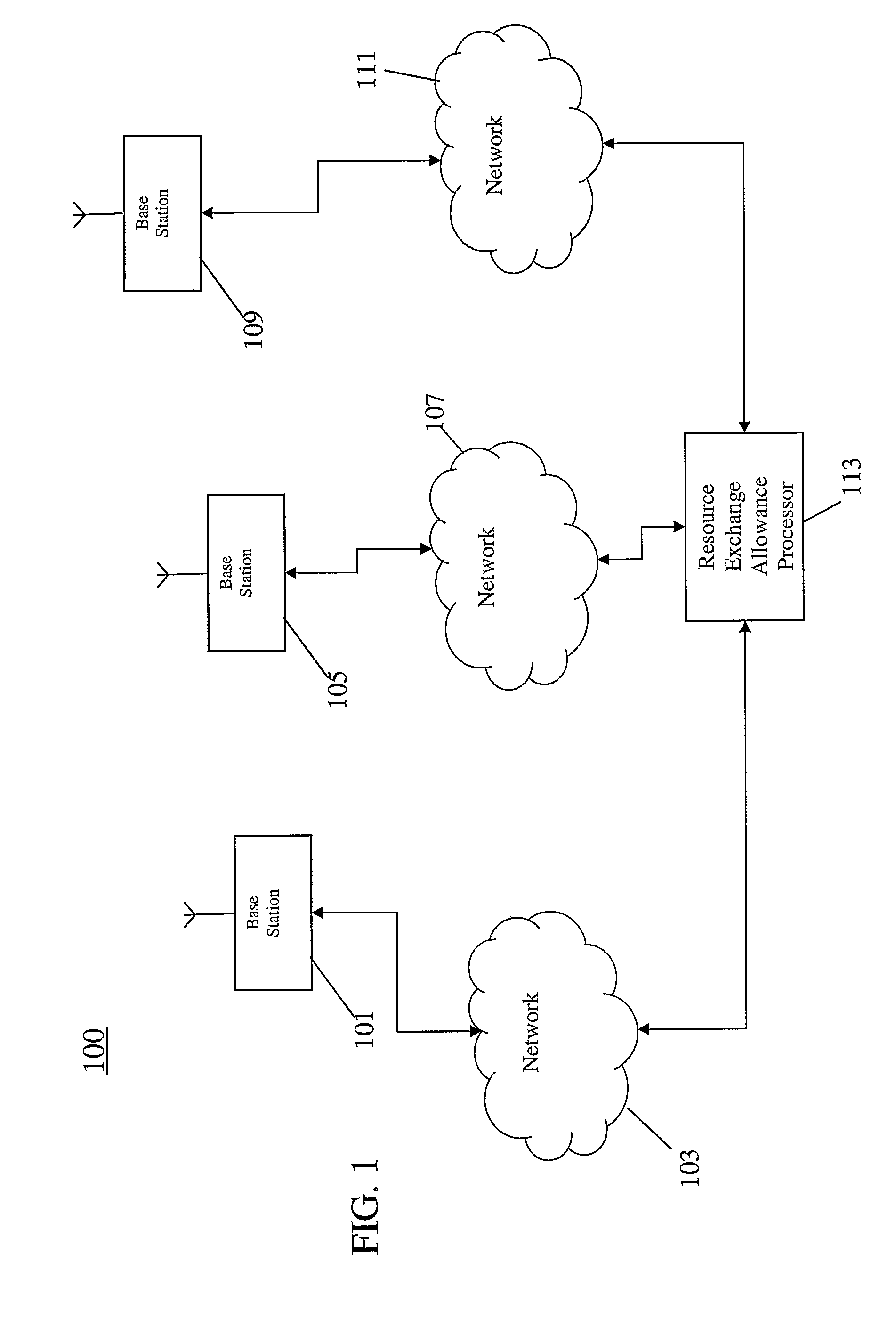

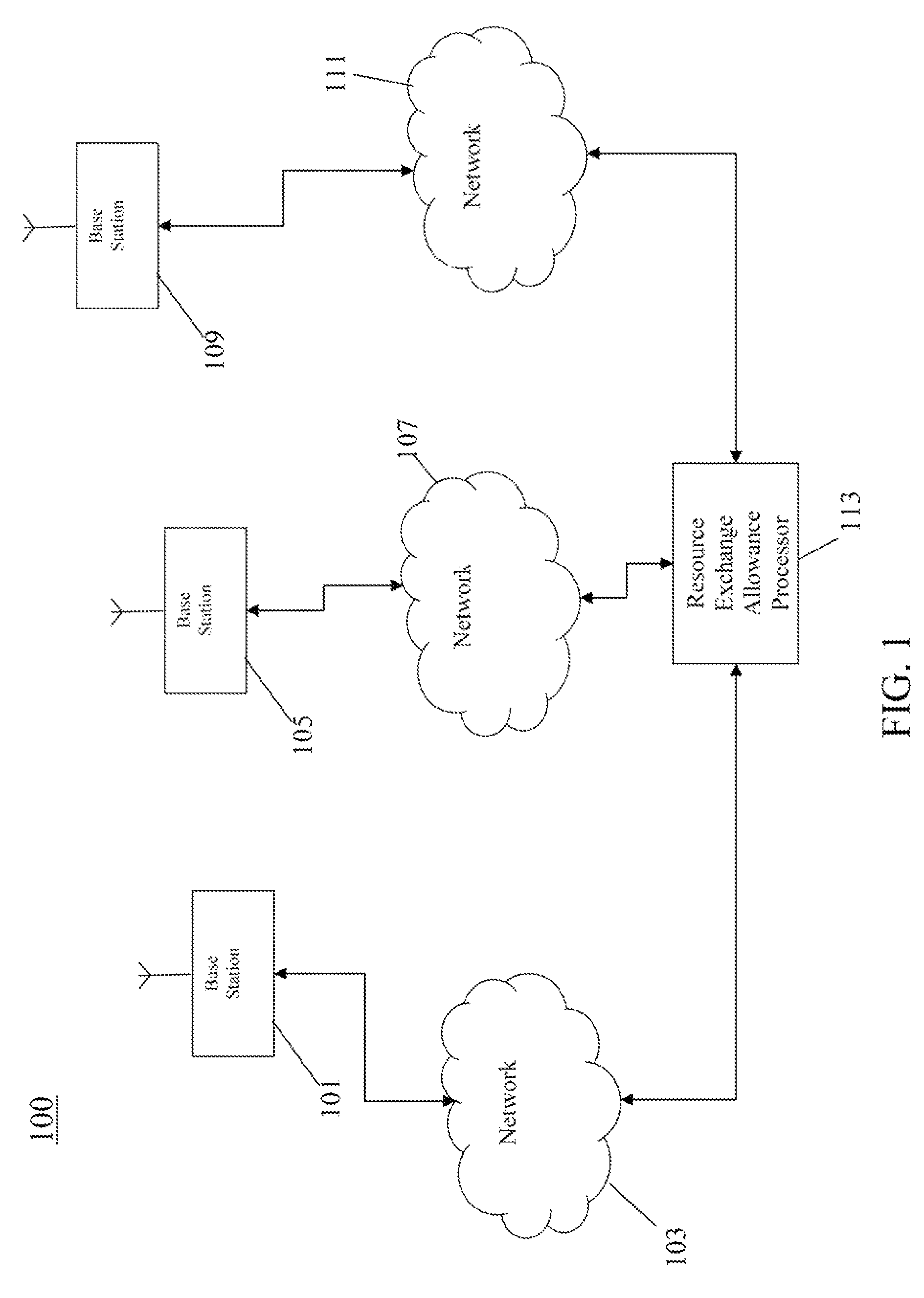

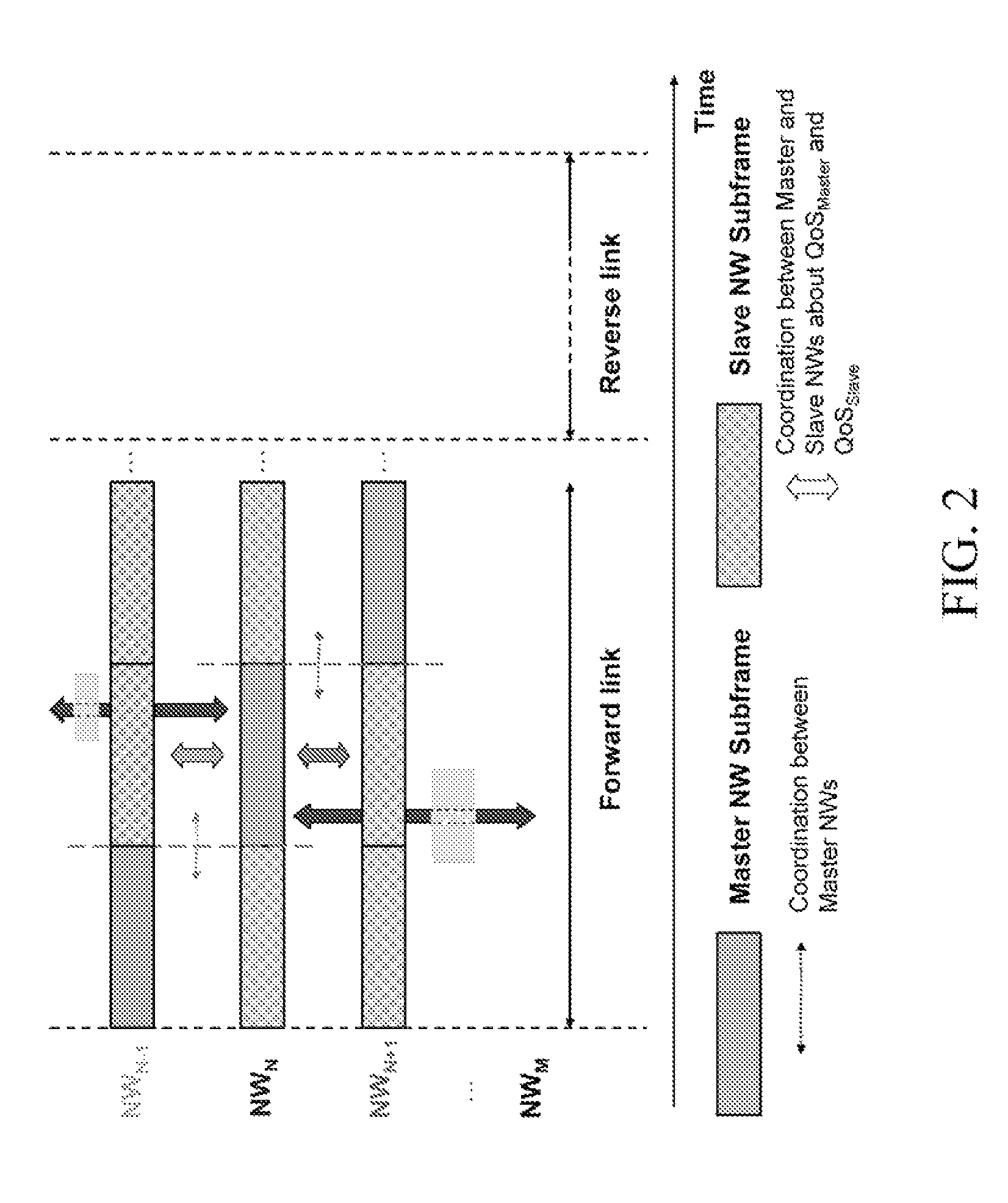

Resource sharing between a plurality of communication networks

ActiveUS20110002274A1Simple and efficientMaximise offer valueError preventionTransmission systemsAir interfaceResource exchange

A method of resource sharing between a plurality of communication networks each having a nominal resource allocation of a shared air interface resource and a resource exchange allowance is provided. A temporary resource allocation of a first air interface resource from a nominal resource allocation of a first network is initiated (403). Subsequently, a plurality of offer rounds are executed (405) with each offer round comprising determining offer values for the first air interface resource. A second network is then selected (407) in response to the determined offer values and subsequently a resource allocation message is transmitted (409) to the second network. The resource allocation message indicates a temporary allocation of at least part of the first air interface resource from the first network to the second network. Consequently, the resource exchange allowance of the second network is reduced (411) accordingly. Each offer round comprises receiving new offer values from the first plurality of networks.

Owner:MOTOROLA SOLUTIONS INC

Managing application system load

InactiveUS20110060827A1Facilitate resource sharingError detection/correctionDigital computer detailsInformation resourceApplication procedure

An improvement in a networked digital computing system comprises an Information Resource Manager (IRM) operable to communicate with elements of the digital computing system to obtain performance information regarding operation of and resources available in the computing system, and to utilize this information to enable the IRM to adjust the application parameters relating to application execution, thereby to optimize execution of the at least one application program.

Owner:AKORRI NETWORKS

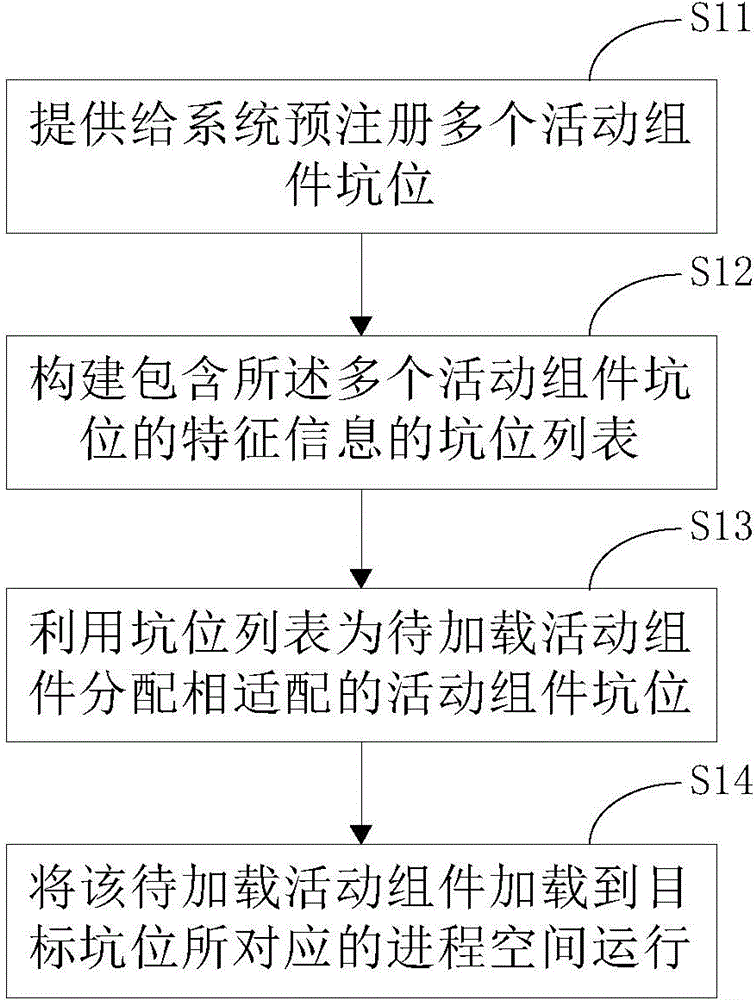

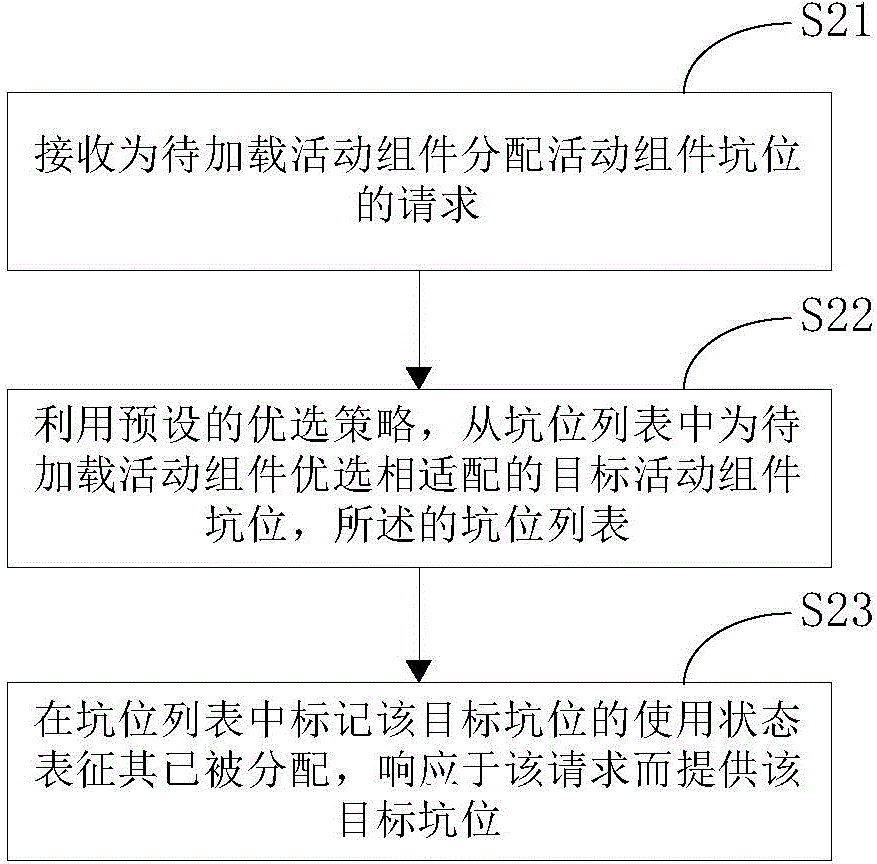

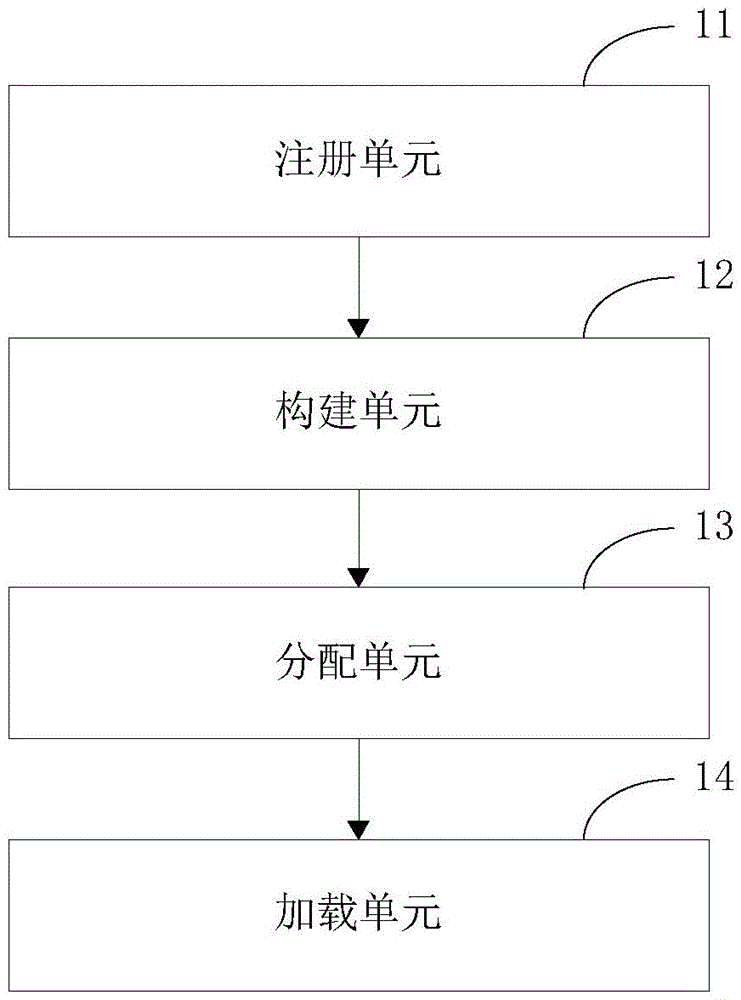

Active assembly progress space distributing method and corresponding device thereof

ActiveCN104699536AImplement customizationUnlimited function expansionProgram initiation/switchingDistribution methodActive component

The invention provides an active assembly progress space distributing method which includes the following steps: receiving a request for distributing active assembly pits for active components to be loaded; utilizing a preset preferable strategy to preferably select matched target active assembly pits for the active assemblies to be loaded from a pit list, wherein the pit list is used for storing characteristic information of the pre-registered active assembly pits; marking the use state of the target pit in the pit list to show that target pit is distributed and providing the target pit in response to the request. In addition, the device matched with the method is provided based on modularization programming thought. Reserved pits matched with the active assemblies to be loaded can be distributed efficiently, flexible expanding and loading of the active assemblies of the application program is facilitated, upgrading of the application program can be simplified, and resource load of the cloud service system is simplified.

Owner:BEIJING QIHOO TECH CO LTD

Device and a method for sharing resources in a network of peers

InactiveUS8103777B2Facilitate resource sharingDigital data information retrievalDigital computer detailsDistributed algorithmShared resource

A device and a method for sharing resources in a network of peers are disclosed. A user may compile a wish list (420) of programs to be recorded on a recording device (400) that is a peer in the network. A resource list (421) is compiled of resources that the device shares within the network. The wish list and resource list are communicated to a coordinator (440) comprised within the network. The coordinator makes assignments of who records what and communicates an assignment list (422) to each peer. Each peer plans (405) and executes (407) the assigned recordings, which can be retrieved from a peer (410), or sent to the user device. Deletion control is applied to prevent the loss of recordings by deletion on a local peer. The coordinator may be comprised within a peer, as a standalone service within the network or implemented as a distributed algorithm between the peers.

Owner:KONINK PHILIPS ELECTRONICS NV

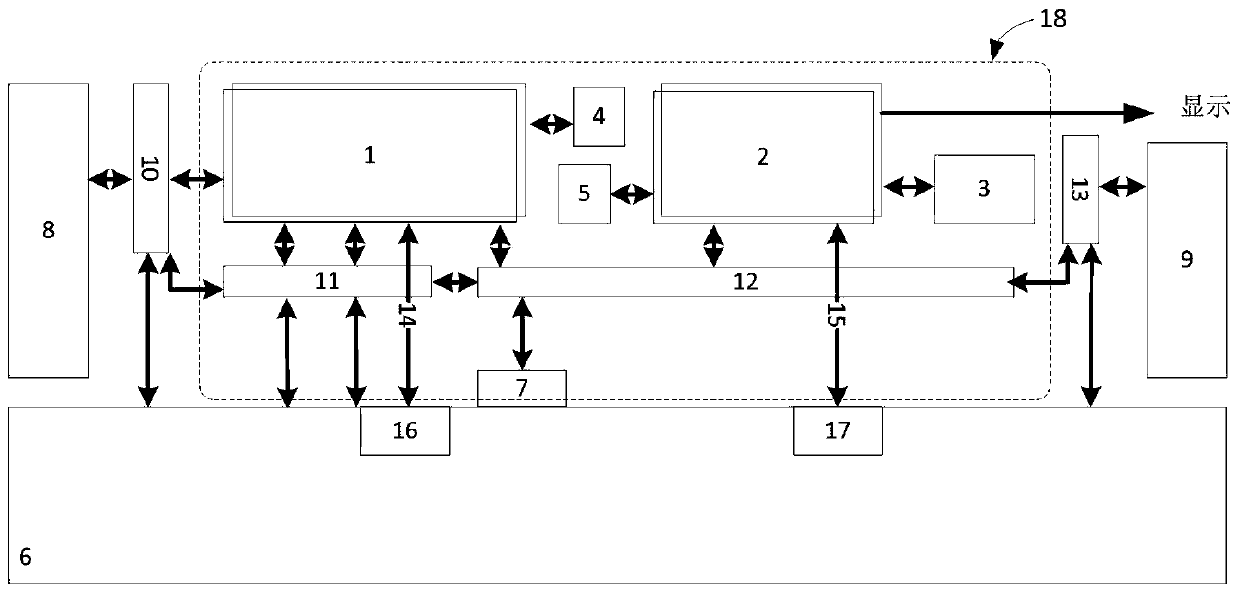

Hardware programmable heterogeneous multi-core system-on-chip

ActiveCN111506540AUniform structureSimple structureArchitecture with single central processing unitElectric digital data processingComputer hardwareComputer architecture

The invention discloses a hardware programmable heterogeneous multi-core system-on-chip, and belongs to the technical field of integrated circuits. According to the system-on-chip, a multi-core DSP, amulti-core MPU, a GPU, an FPGA and a plurality of IP components are organically combined together through an on-chip high-speed bus interconnection network to form a hardware-programmable and processor-multi-core heterogeneous system-on-chip chip, and the specialty of each heterogeneous core is brought into full play. Through an area formed by the multi-core DSP and the FPGA, services such as high-throughput-rate data preprocessing, dense data operation and a bottom-layer algorithm are realized; and an area formed by the multi-core MPU, the GPU and the FPGA accelerator is used for achieving services such as a user interface, a high-level algorithm, application program running and network transmission. The FPGA can also realize a hardware acceleration function required in a multi-core DSPand a multi-core MPU. Based on hardware reconfiguration, the chip architecture improves the flexibility of system-on-chip integration and the expandability and upgradability of later products.

Owner:58TH RES INST OF CETC

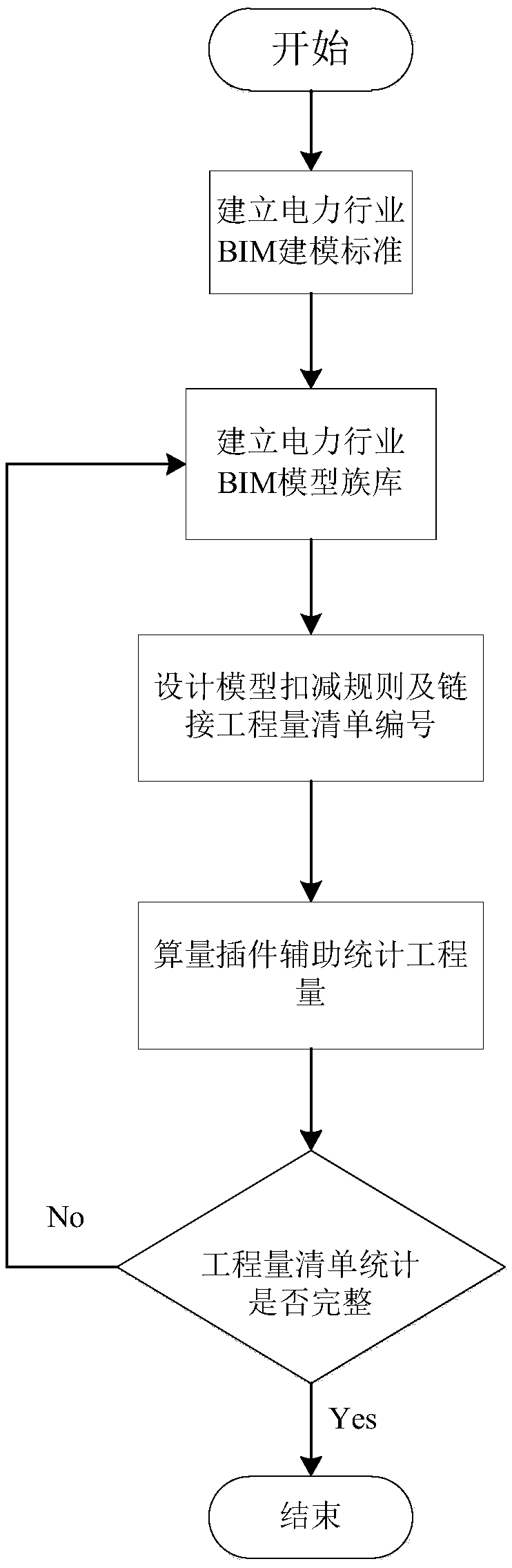

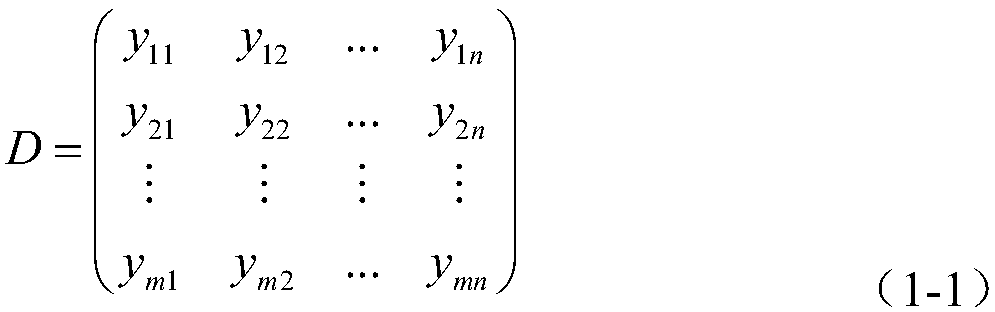

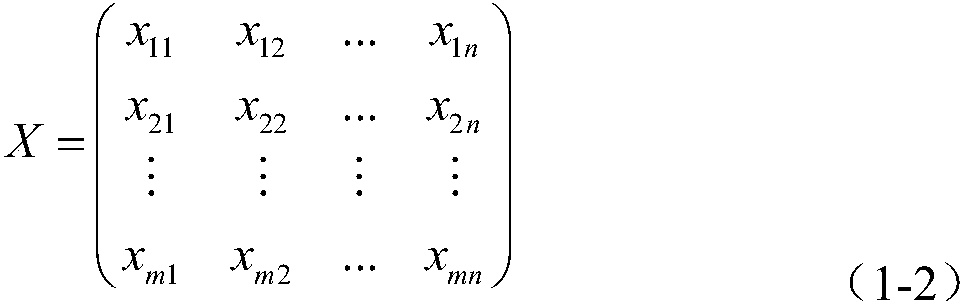

The method of exporting standard bill of quantities of electric power engineering based on BIM technology

The invention discloses a method for exporting standard bill of quantities of electric power engineering based on BIM technology, based on the attribute information of the components in the BIM model,the model is automatically associated with the standard bill of quantities for the electric power industry, by establishing the BIM modeling standard of electric power industry-establishing the BIM model family library of electric power industry-designing the deduction rules of the model and linking the bill of quantities number-calculating the plug-in auxiliary statistics of the quantity of thestandard bill of quantities, exporting of standard bill of quantities is realized. There is no need for manual calculation and secondary refining operations, which greatly improves the work efficiencyon the basis of guaranteeing the quality of the extracted quantities.

Owner:STATE GRID TIANJIN ELECTRIC POWER +1

APP based financial reimbursement method

InactiveCN107368953ASimplify the reimbursement processEasy to standardizeOffice automationResourcesStatistical processingComputer science

The invention belongs to the technical field of financial reimbursement and especially relates to an APP based financial reimbursement method. According to the invention, networking of a reimbursement process is achieved by adopting an APP reimbursement method, so that the reimbursement process is simplified substantially; real time and on site financial reimbursement operation is facilitated; normalization of financial reimbursement management is facilitated; reimbursement data check by the finance department and department year-end statistical processing are facilitated; reimbursement accuracy is improved; resource share among an enterprise and employees is realized. At the same time, convenience is made for department leaders to know financial reimbursement condition of the department.

Owner:苏州吉耐特信息科技有限公司

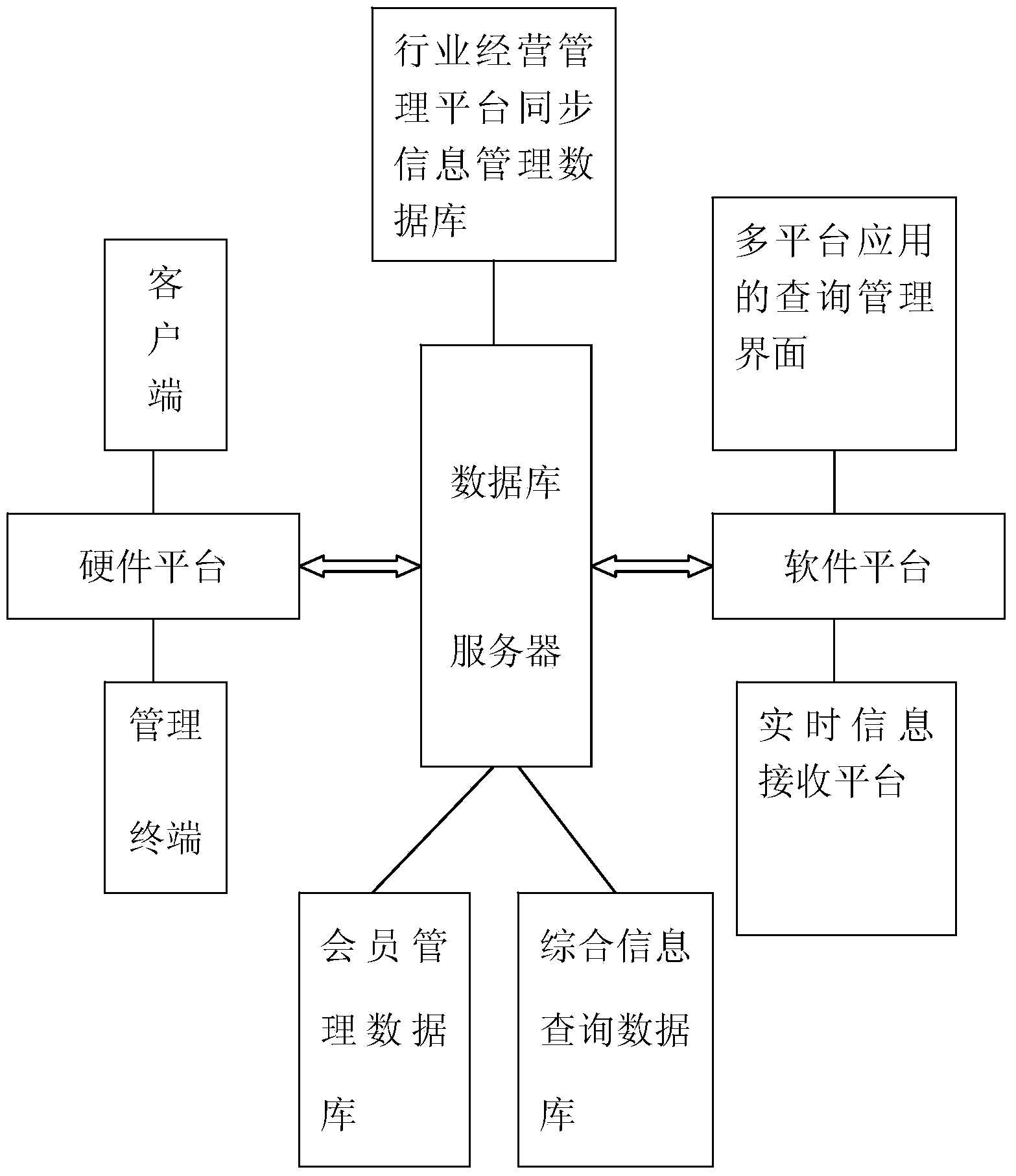

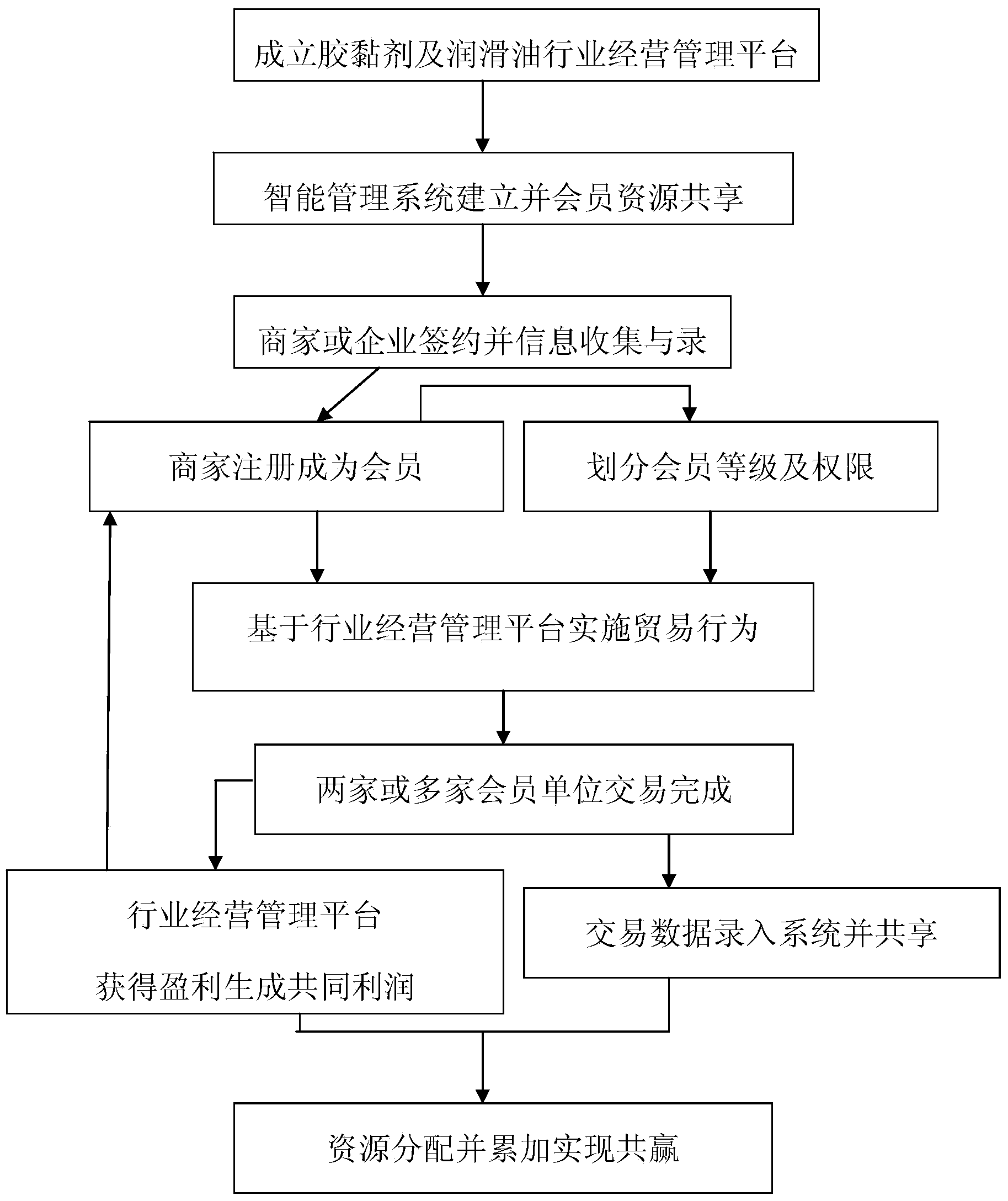

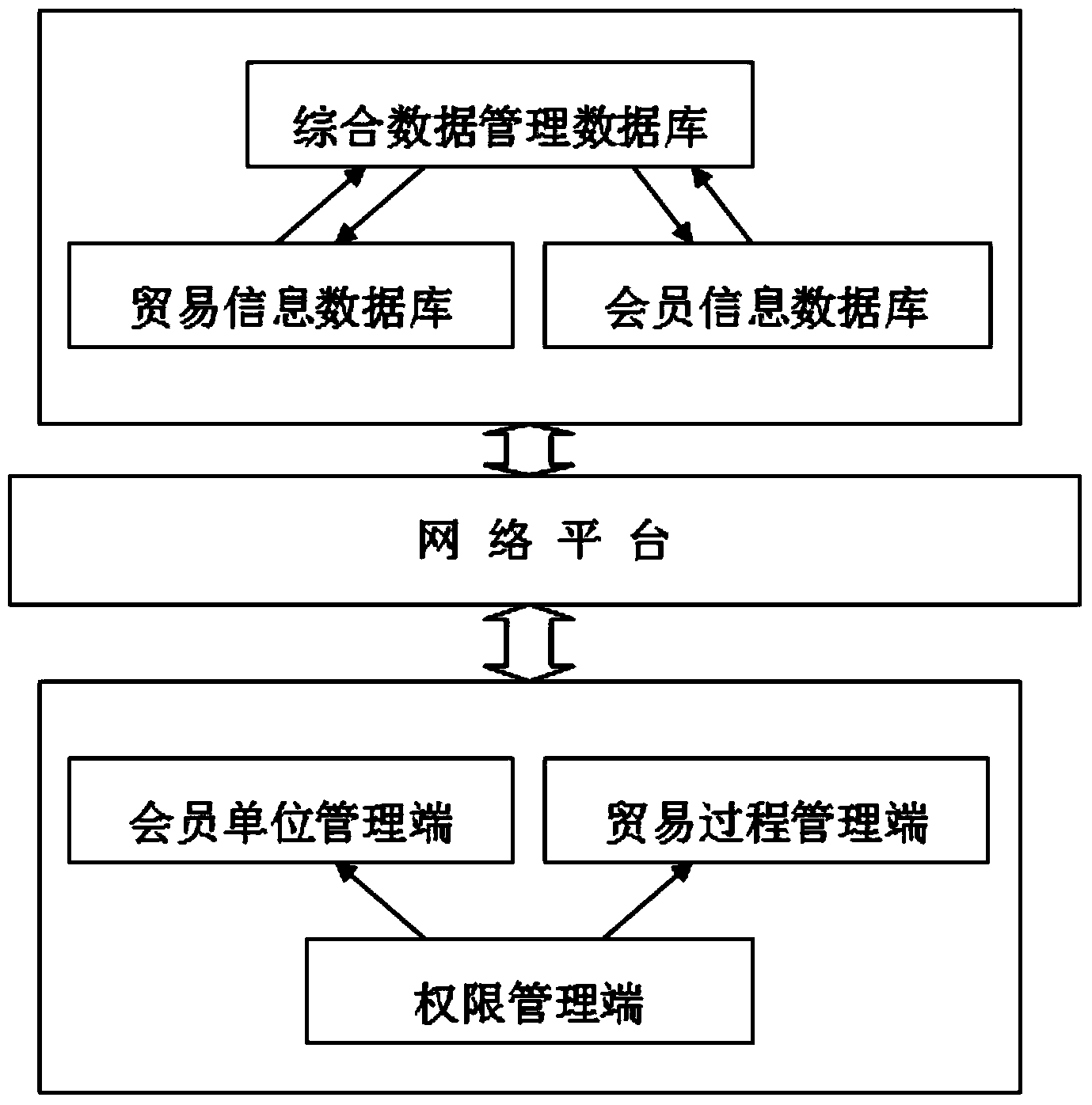

Trade management method based on industry operation management platform and intelligent management system

InactiveCN103810569ARealize the whole process controlPromote high-quality developmentResourcesCommerceTransaction dataIntelligent management

The invention discloses a trade management method based on an industry operation management platform and an intelligent management system. The method comprises the following steps: setting the intelligent management system, wherein the system comprises a server and a client, and the server consists of one or more groups of classification management databases; setting the industry operation management platform, wherein the platform comprises member units which consist of a plurality of merchants and are managed in a hierarchical and right-based way; inputting merchant information into the intelligent management system in an industry classifying way, and effectively saving in a classification management database; recording and timely updating or sorting the trade details of the member units in the industry operation management platform by using the intelligent management system, converting all trade data values and saving; carrying out product trade behaviors under the restriction of the industry operation management platform according to different trade requirements by taking the industry operation management platform as a platform through the member units, and generating a price difference value in a step-by-step way, wherein the price difference value belongs to the industry operation management platform; checking the price difference value of the industry operation management platform periodically by using the intelligent management system, checking the common profit of the member units and allocating.

Owner:曾祥辉

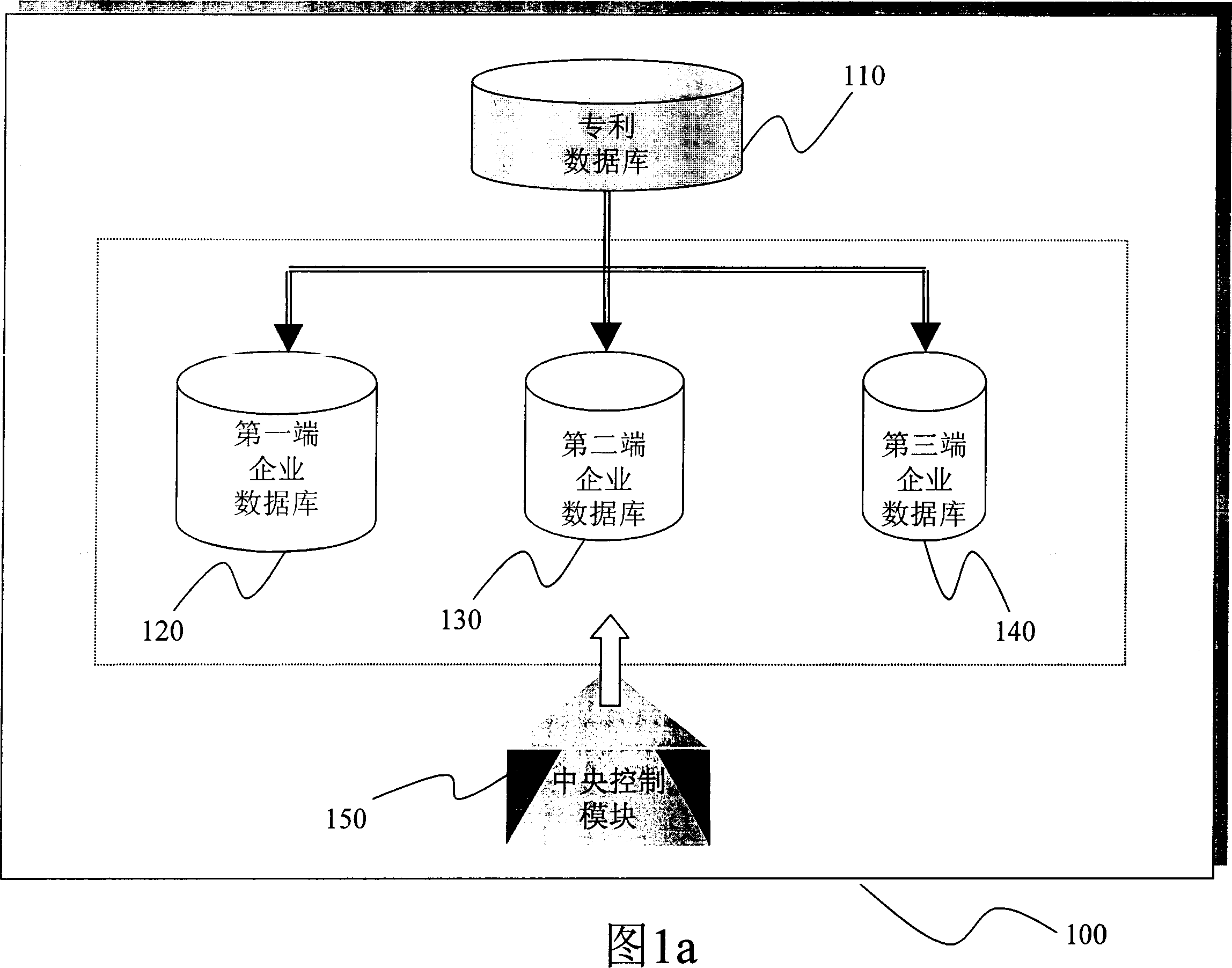

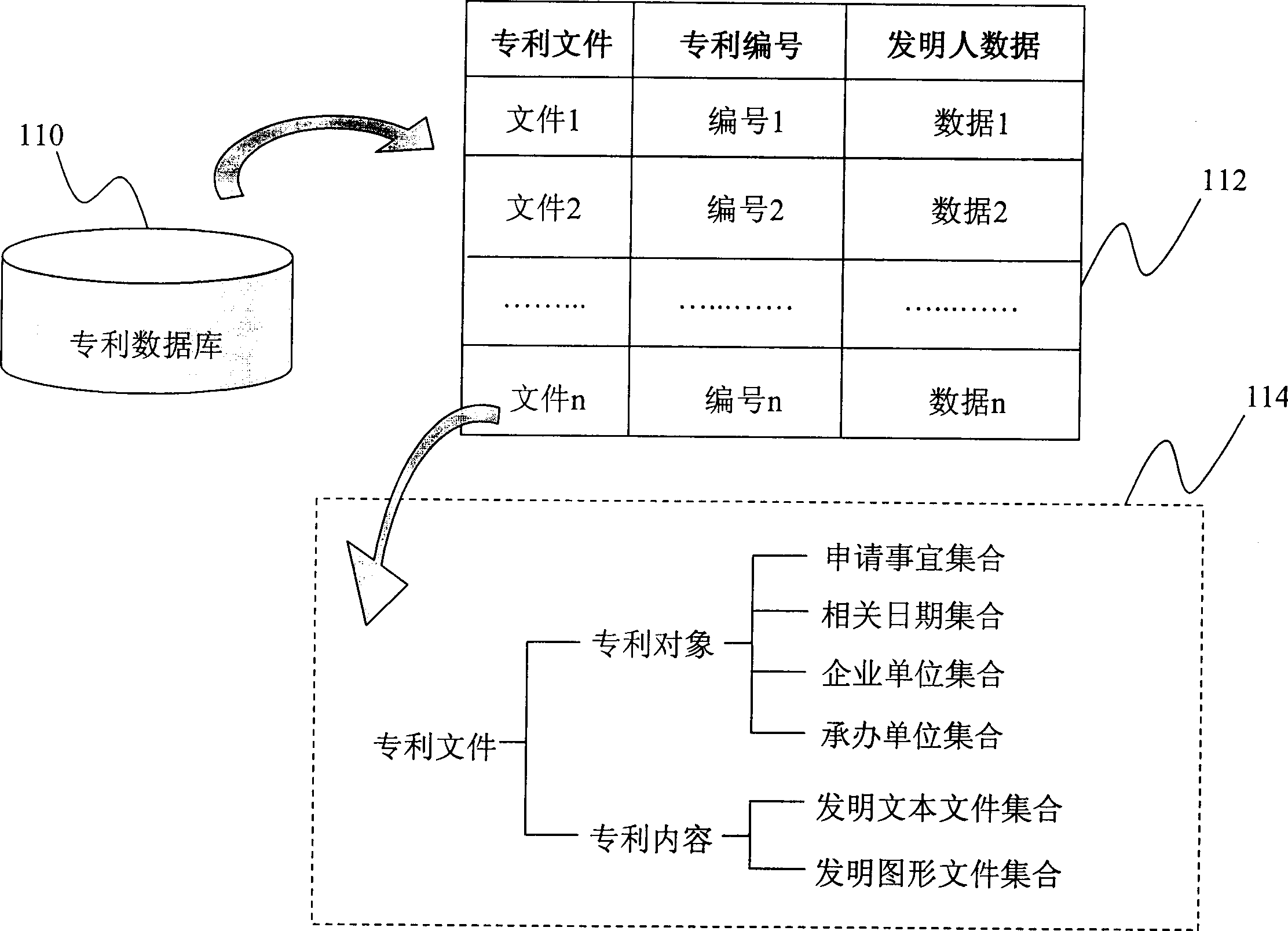

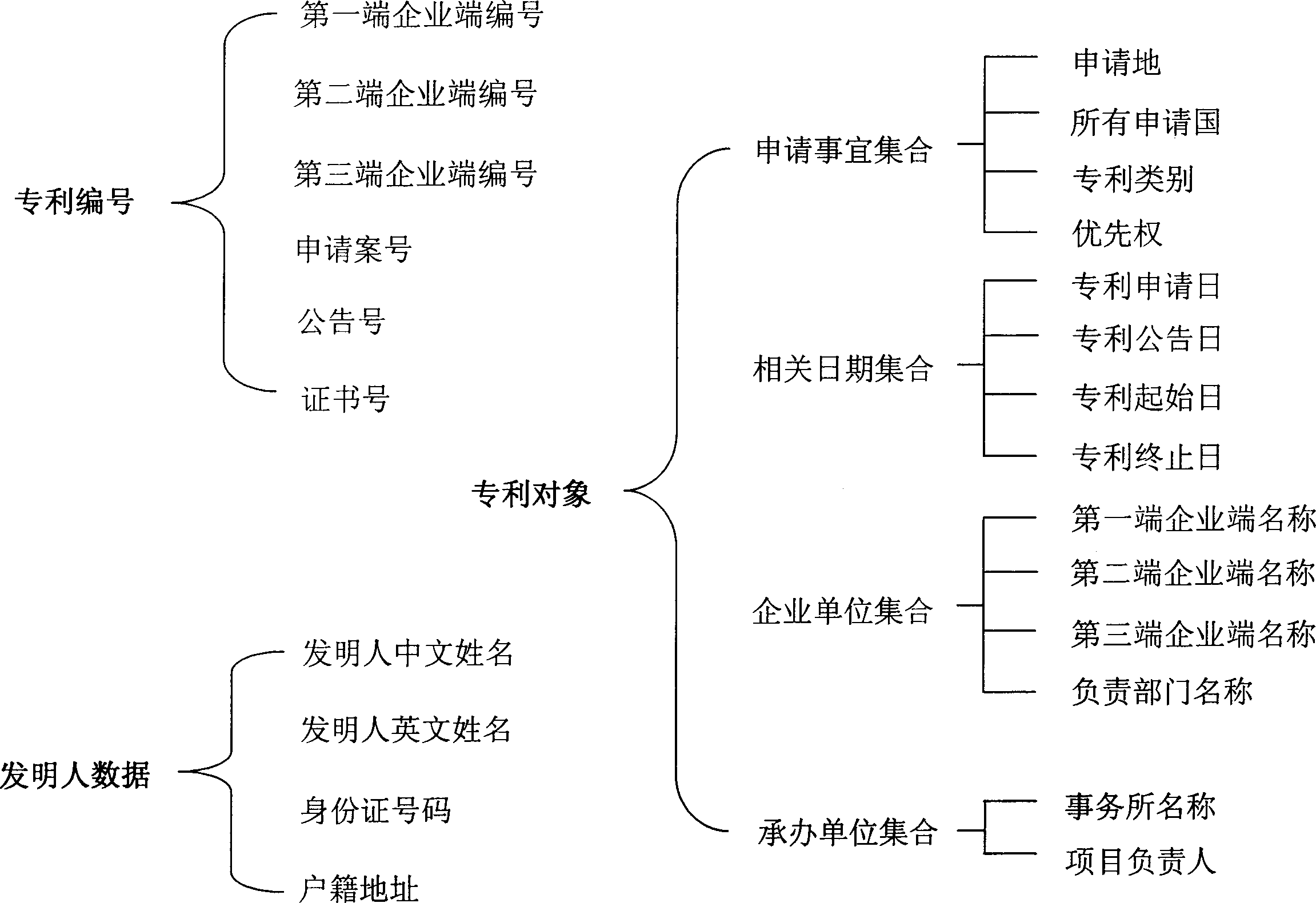

Data-coding control management system and its method

InactiveCN1428722AEasy to manageFacilitate resource sharingSpecial data processing applicationsData encodingData system

The present invention relates to a data encoding control management system and its method. It is a patent data system used in the interior of enterprise. The user terminal can utilize the patent data base provided by said invention to implement various instructions of newly addition, modification and enquiry, and can utilize said system to automatically number the patent file, and can prevent the number of the patent from jumping over, and can utilize said invention to store the patent file. Said invention at least includes the following steps: firstly, creating patent data system and at least one patient file, receiving instruction inputted by user terminal and finally implementing said instruction by said patent data system.

Owner:INVENTEC CORP

Resource sharing between a plurality of communication networks

ActiveUS8194700B2Facilitate resource sharingEfficient managementError preventionNetwork traffic/resource managementAir interfaceResource allocation systems

A method of resource sharing between a plurality of communication networks each having a nominal resource allocation of a shared air interface resource and a resource exchange allowance is provided. A temporary resource allocation of a first air interface resource from a nominal resource allocation of a first network is initiated. Subsequently, a plurality of offer rounds are executed with each offer round comprising determining offer values for the first air interface resource. A second network is then selected in response to the determined offer values and subsequently a resource allocation message is transmitted to the second network. The resource allocation message indicates a temporary allocation of at least part of the first air interface resource from the first network to the second network. Consequently, the resource exchange allowance of the second network is reduced accordingly. Each offer round comprises receiving new offer values from the first plurality of networks.

Owner:MOTOROLA SOLUTIONS INC

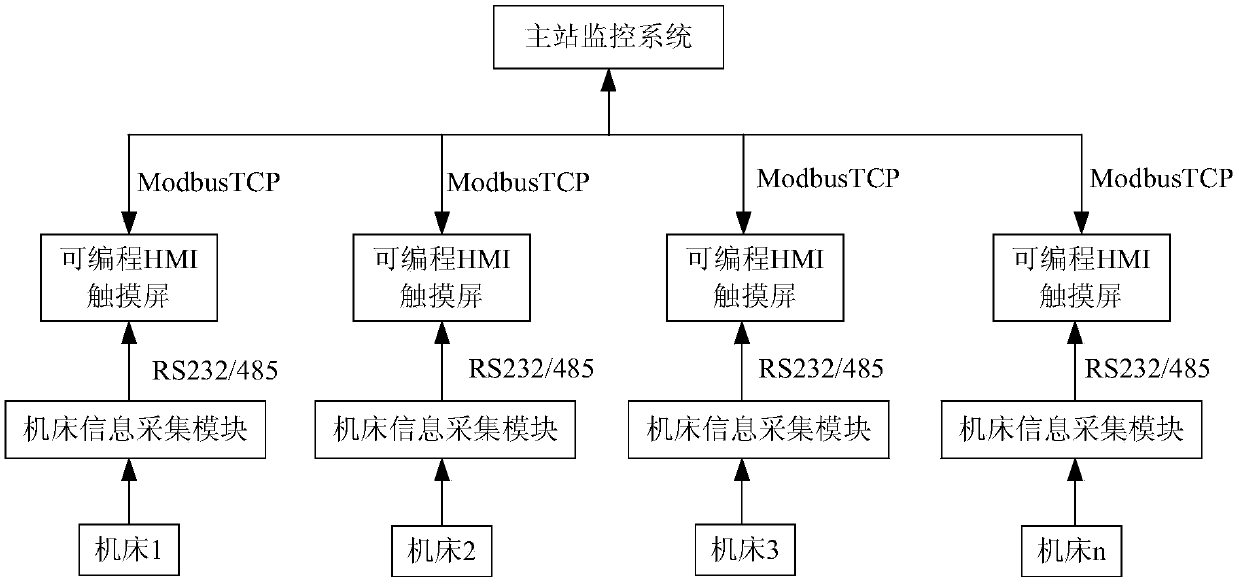

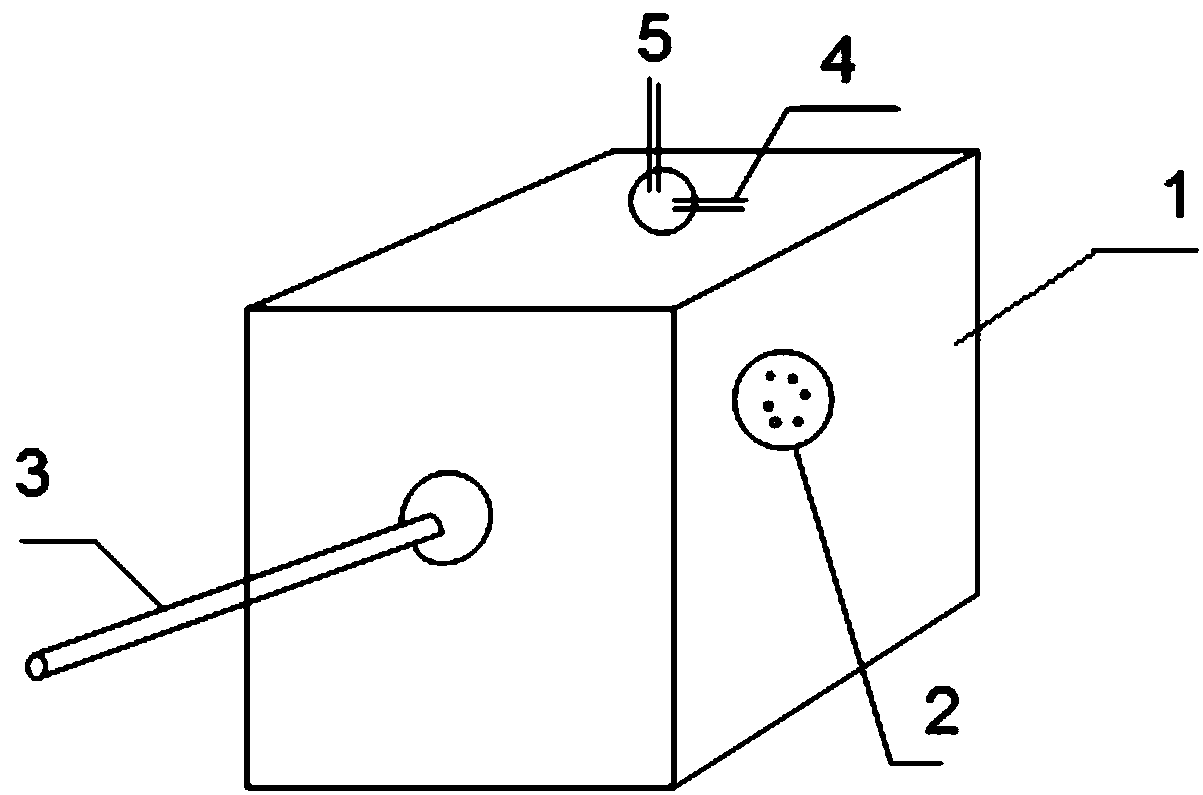

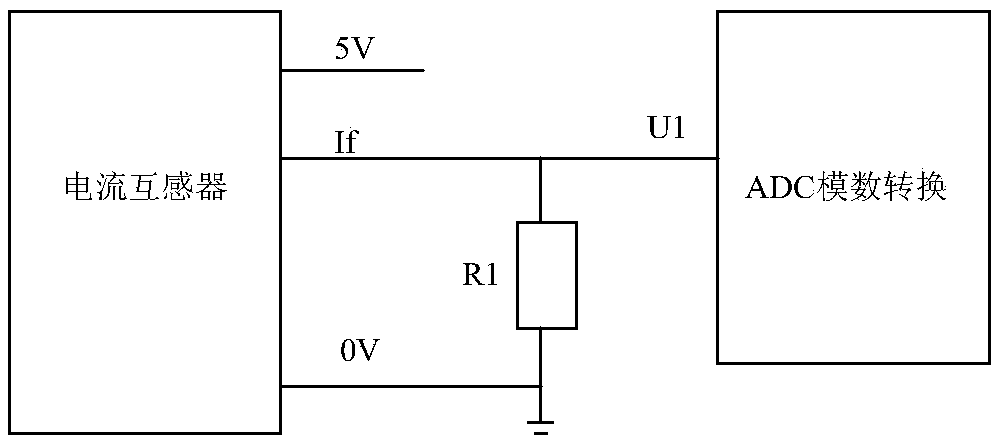

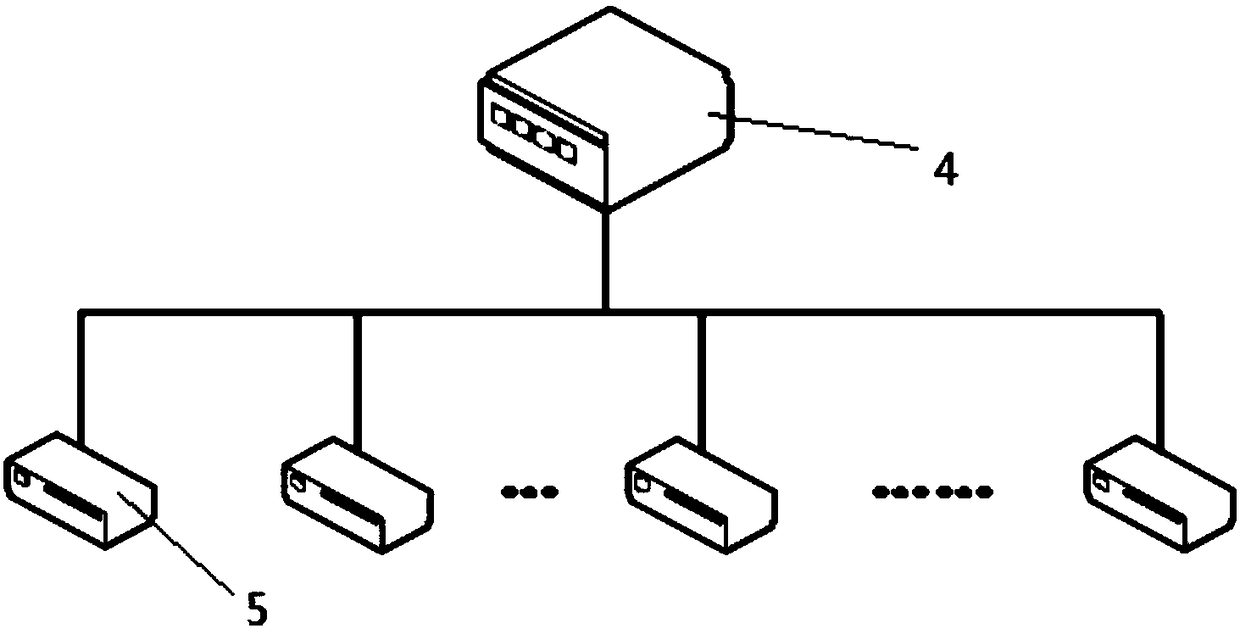

Machine tool networking information acquisition system and method based on touch screen

InactiveCN109637108AFull and comprehensive understanding of operationsFacilitate resource sharingElectric signal transmission systemsData switching networksNumerical controlManagement process

The invention provides a machine tool networking information acquisition system and method based on a touch screen, and relates to the technical field of equipment monitoring and management. Accordingto the method, on-line interconnection of non-numerical control machine tool equipment can be realized, the state of a non-numerical control machine tool is monitored and managed, and the situation that the production conditions of each part of an enterprise is poor in synchronism is improved, and the production efficiency of the enterprise is improved. The system comprises a main server, a programmable touch screen and a signal collector, wherein the collecting end of the signal collector is connected with a machine tool and is used for collecting machine tool information, the output end isconnected with the programmable touch screen to transmit the machine tool information to the touch screen, the programmable touch screen is connected with the main server so as to send the machine tool information to the main server for being processed in a response command mode. According to the technical scheme, the system is suitable for the on-line interconnection management process of the non-numerical control machine tool equipment.

Owner:BEIJING XINGHANG MECHANICAL ELECTRICAL EQUIP

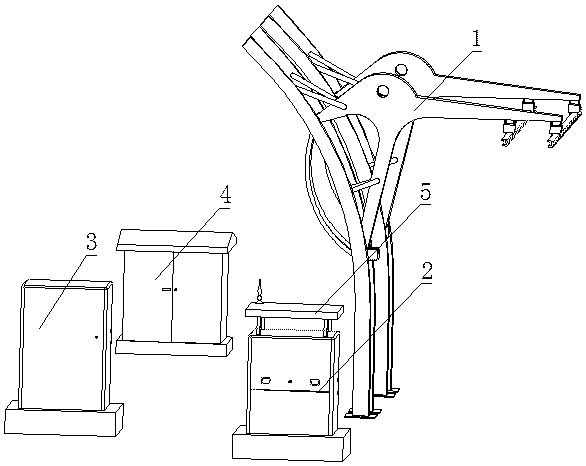

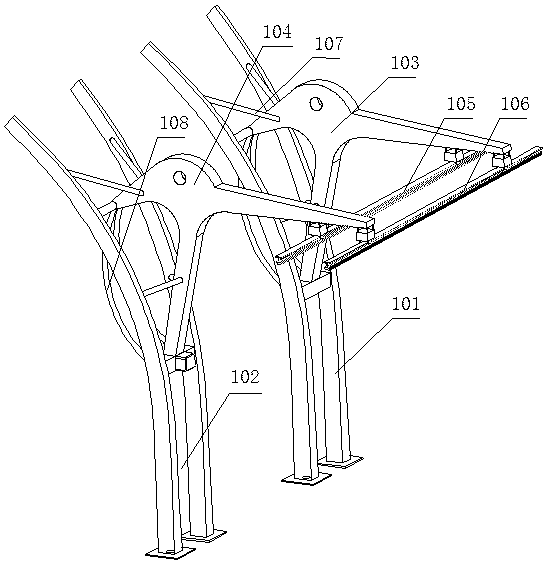

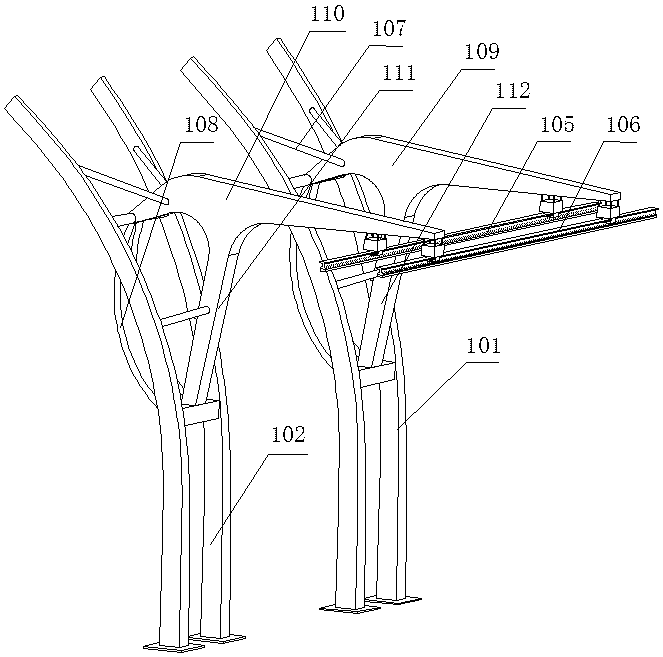

Platform type charging system

ActiveCN106160088AFacilitate resource sharingImprove charging efficiencyCharging stationsMobile unit charging stationsElectricityDistribution system

A platform type charging system includes a charging system for providing electricity for a power receiving system; a power transformation system for providing electricity for the charging system; a power distribution system for providing electricity for the power transformation system; and an operation control system for controlling the charging system to work. The power receiving system includes a support connected to a ground foundation; and a power receiving row connected to the support through an insulating plate. The power receiving row includes a first power receiving rail and a second power receiving rail. The first power receiving rail is connected to a positive output electrode of the charging system through a cable, and the second power receiving rail is connected to a negative output electrode of the charging system through a cable. The technical scheme provided by the invention employs a high power intelligent direct current fast charging principle, charges pure power-driven urban automobiles, and has the characteristics of high charging efficiency, simple operation, and short charging time. A charging station can be constructed in combination with reconstruction of a present bus station without requisition of land, and the construction cost is low. The platform type charging system is provided with the operation control system, and it is in favor of charging station resource sharing.

Owner:谢镕安

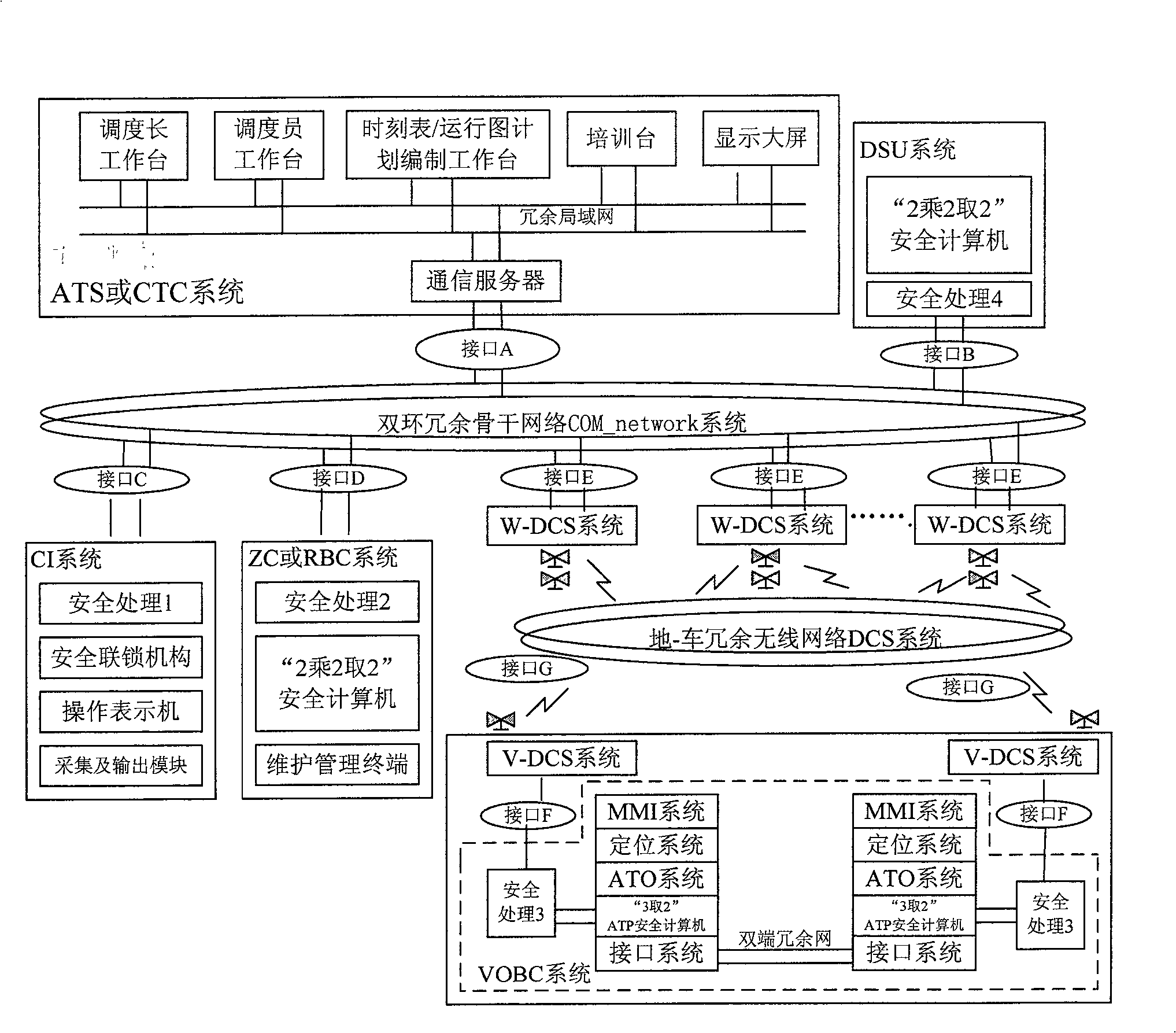

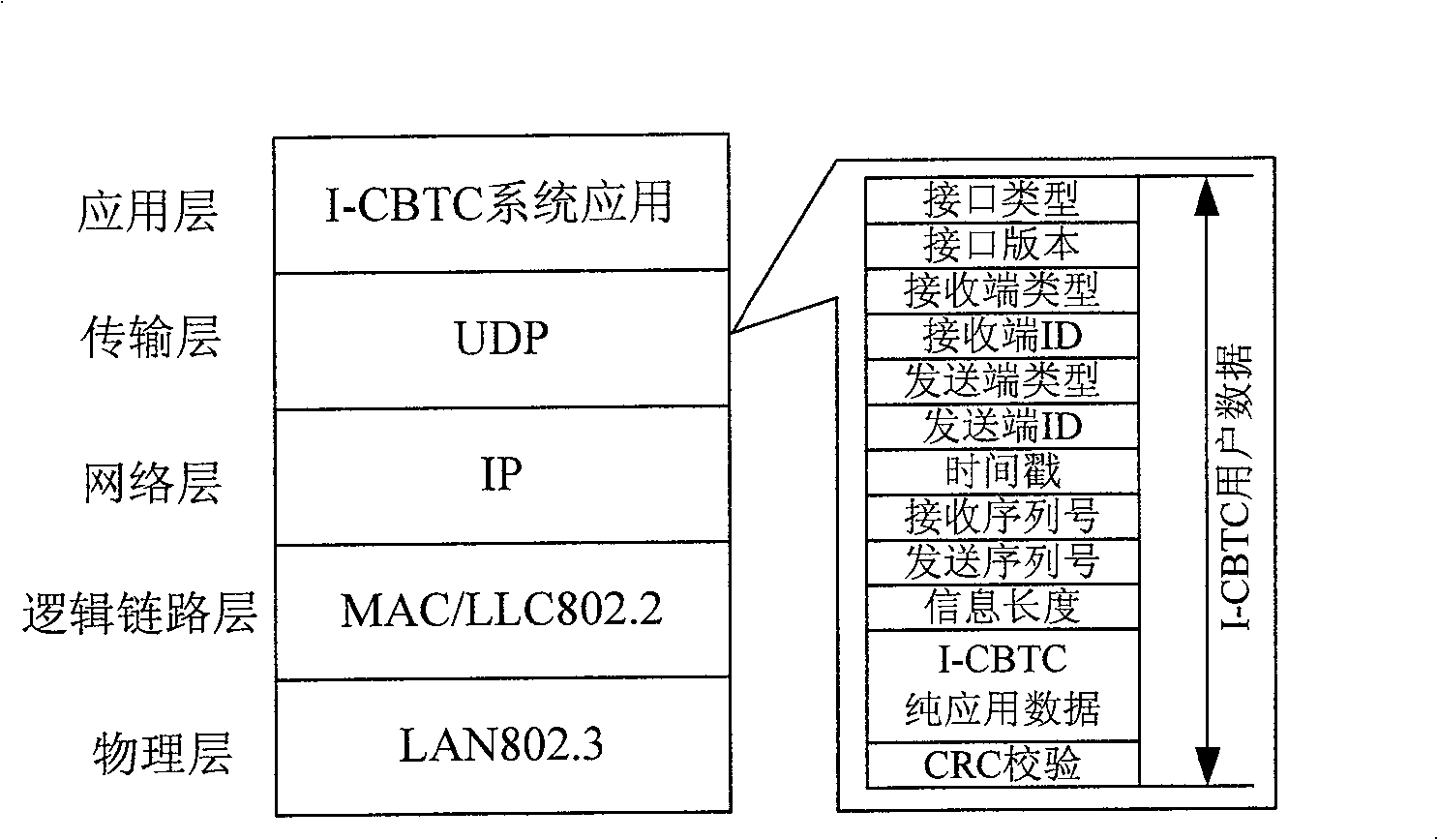

Communication-based interconnected and intercommunicated I-CBIT train operation control system

ActiveCN100536456CFacilitate resource sharingMaintain "transparencyVehicle route interaction devicesTransmissionOperational costsSafety control

The invention discloses a communication-based interconnected I-CBTC train operation control system, which is a mobile block safety control system that uses wireless communication to realize information transmission between the ground control center and the train, and the ATS or CTC is automatically supervised by the ground train System, database storage unit DSU system, computer interlocking CI system, ground area controller ZC or RBC system, vehicle controller VOBC system, double-ring redundant backbone network COM_network system, ground-vehicle redundant wireless network DCS system and network nodes The present invention standardizes and standardizes the functions, performance indicators and interfaces of the above systems. The beneficial effect of the invention is that users can purchase standard modular equipment from different suppliers, thereby providing a basis for interconnection and intercommunication for the construction and operation of the entire road network, and greatly reducing construction and operation costs.

Owner:TRAFFIC CONTROL TECH CO LTD

Carrier resource distribution method and device based on broadband OFDM power line communication

ActiveCN108092756AFacilitate resource sharingIncrease profitTransmission path divisionPower distribution line transmissionResource utilizationDistribution method

The invention discloses a carrier resource distribution method and device based on broadband OFDM power line communication. At least one cluster node CL is included, and each cluster node is connectedwith M leaf nodes LFm; the method comprises the following steps: firstly, the carrier resource is sold to M leaf nodes by taking the cluster node as an auctioneer of the carrier resource, and the bandwidth distributed for the cluster node is Btot; secondly, the M leaf nodes are used as bidders to acquire a channel for transmitting data by mutually competing the carrier resource of the cluster node, and the bandwidth bidding price submitted by the leaf node LFm is bm; and then, the cluster node distributes the bandwidth bm for the leaf node LFm according to the bandwidth bidding price submitted by the leaf node LFm. Through the distribution method and device disclosed by the invention, the carrier distribution fairness and the resource utilization maximation in the broadband OFDM power line communication are solved, the good resource sharing between the cluster node and the leaf nodes is realized, and the utilization factor of the carrier reaches the maximum.

Owner:北京中宸微电子有限公司

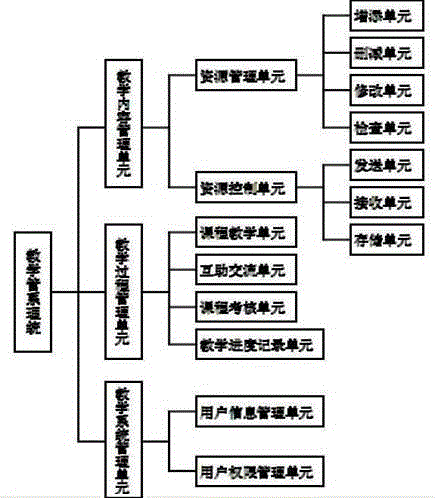

Mathematics learning management system

InactiveCN105844560AConducive to resource sharingReal-time grasp of learning situationData processing applicationsTransmissionContent managementLearning Management

The invention discloses a mathematics learning management system, comprising: a teaching content management unit, a teaching process management unit and a teaching system management unit connected through a network, the teaching content management unit includes a resource management unit and a resource control unit, the teaching The process management unit includes a course teaching unit, an interactive communication unit and a course assessment unit, and the teaching system management unit includes a user information management unit and a user authority management unit. The present invention connects cumbersome teaching management to the Internet, builds a management platform, and implements humanized management. On the premise of ensuring the teaching quality, it saves a lot of resources for teaching management, which not only ensures the novelty and originality of teaching content, but also improves It improves students' learning enthusiasm, teachers' teaching efficiency and teaching quality, and the operating system is safe and practical.

Owner:传学信息技术(苏州)有限公司

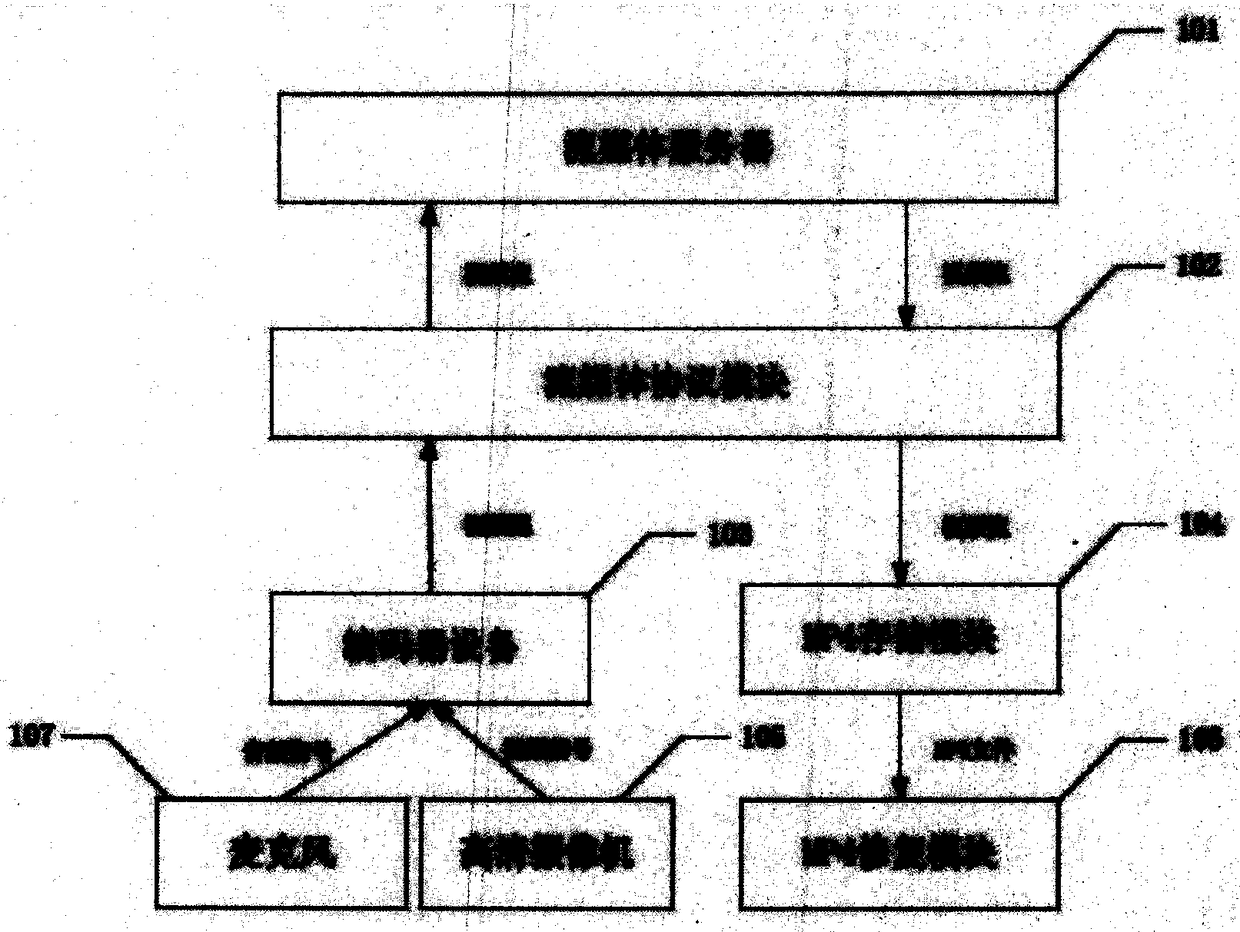

High-reliability streaming media storage system and method thereof

InactiveCN108111512AImprove stability and robustnessIntegrity guaranteedTransmissionInformation technologyPaper document

The invention discloses a high-reliability streaming media storage system and a method thereof, and relates to the information technology. The system is as follows: a high-definition camera (105) is connected with encoder equipment (103); a microphone (107) is connected with the encoder equipment (103); the encoder equipment (103), a streaming media protocol module (102) and a streaming media server (101) are connected in order; the streaming media server (101), a streaming media protocol module (102), a MP4 storage module (104) and a MP4 repairing module (106) are connected in order. The storage format is a standard MP4 format, thereby facilitating the resource sharing among various different system platforms; the system can reliably repair the MP4 files damaged under the outage and abnormal and like situations in the system operation period, the stability and the robustness of the system are improved, and the document integrity is guaranteed; the system is suitable for various application scenes needing to store audio-video data as the MP4 format.

Owner:NINGBO SHENGWEI INFORMATION TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com