Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

114results about How to "Eliminate the effect of error" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

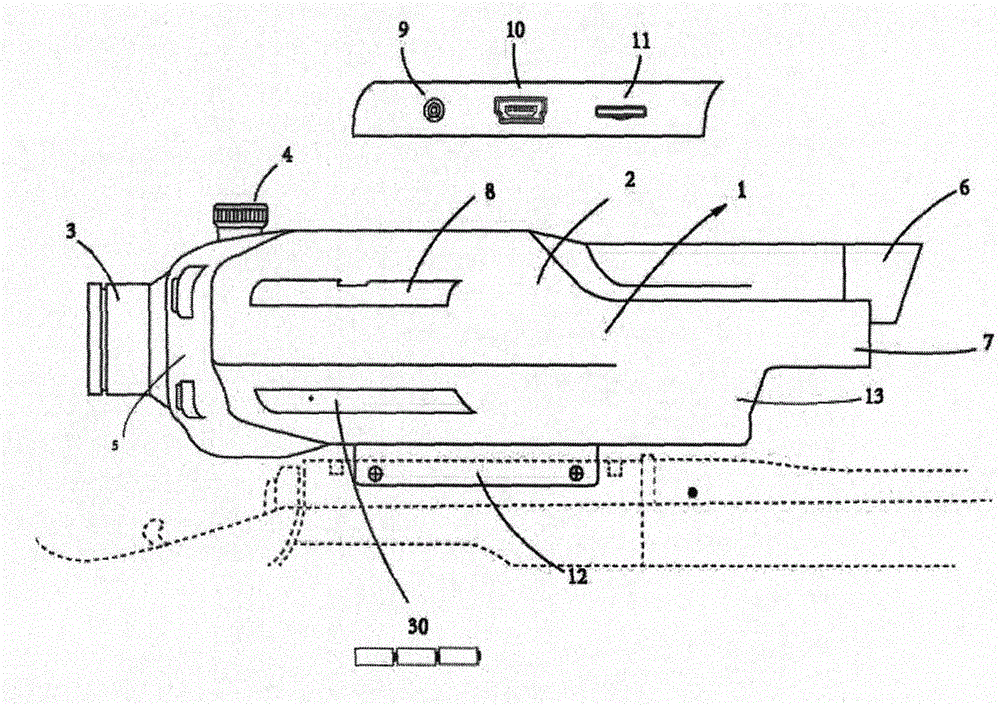

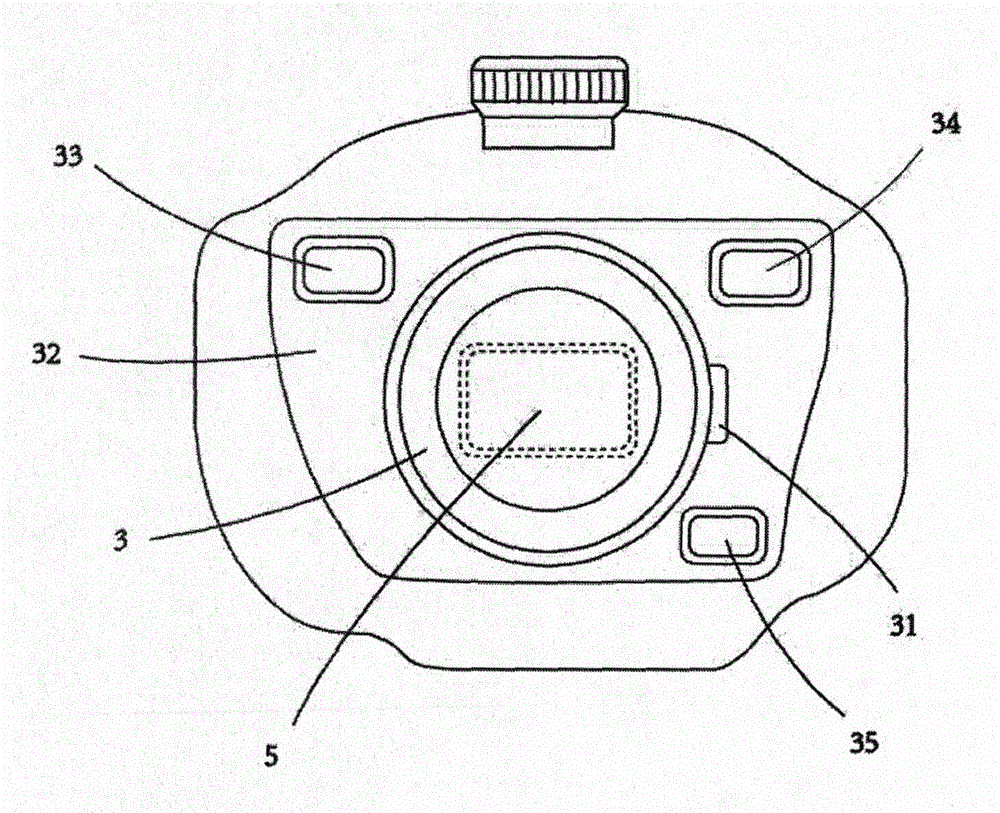

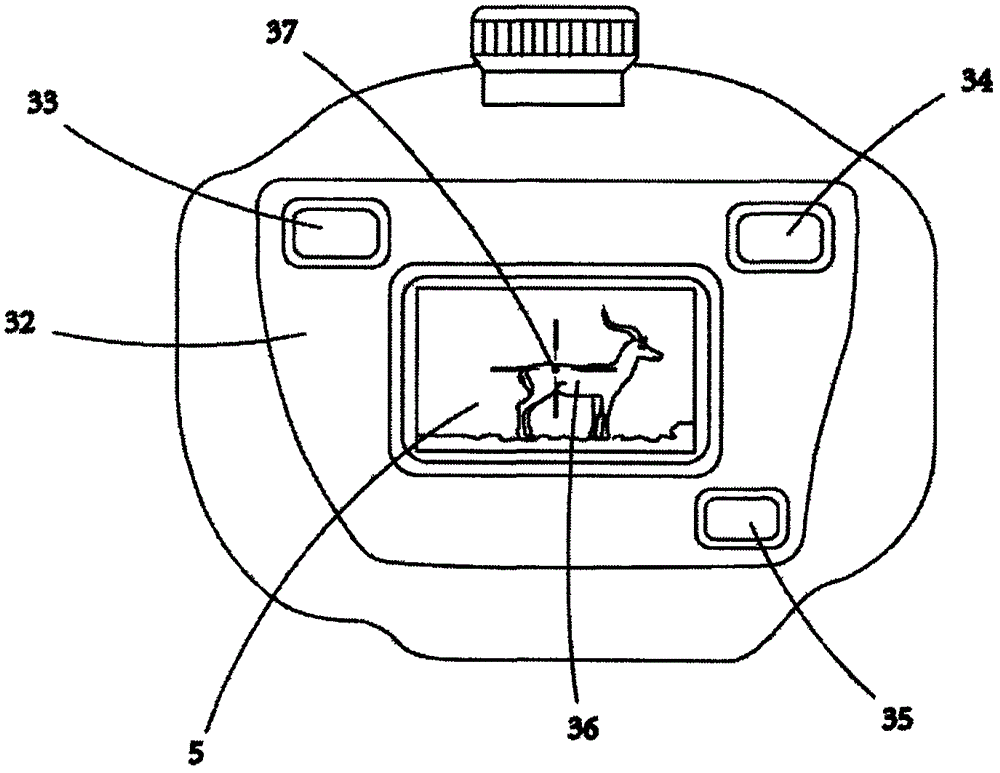

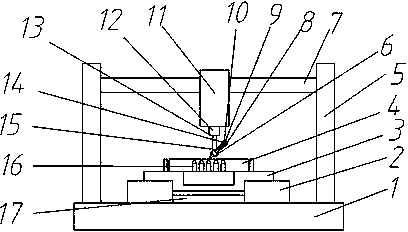

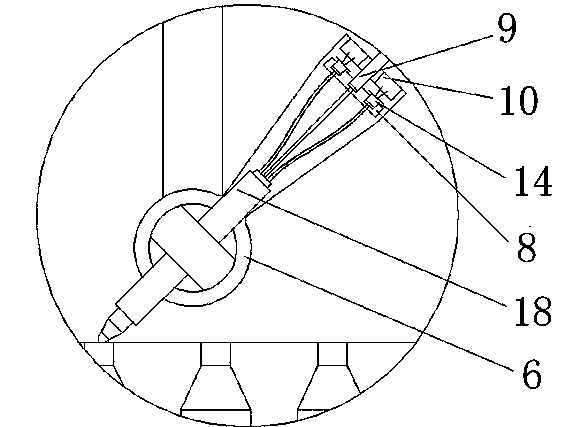

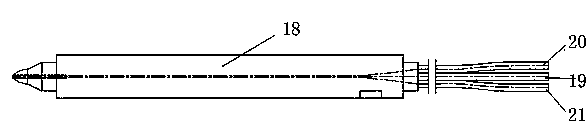

Digital optical sight and method for achieving target tracking, locking and precise shooting through same

The invention discloses a novel digital optical sight. A network topology core structure of the optical sight is mainly composed of a digital optical sight body, a mobile terminal application program (APP), a cloud server and a social network, and an outdoor shooting and hanging internet of things (OSHN) is established based on an intelligent mobile interconnection technology. When a user shoots a target, a bullet hits the target region displayed in a partition mode undoubtedly and precisely due to the fact that partition is displayed with the impact point of the corrected actual bullet as the center point. Due to the fact that in the process, basically no manual participation is needed, a camera of the digital optical sight is aligned with a target to be shot, the follow-up processes are conducted through a digital sighting telescope, the digital optical sight aims at the target, computes the target distance, focuses automatically and locks the target automatically, the hit point is very precise as well, and the purposes of quickly tracking, automatically locking and precisely shooting the target are truly achieved.

Owner:ZHEJIANG GONGSHANG UNIVERSITY

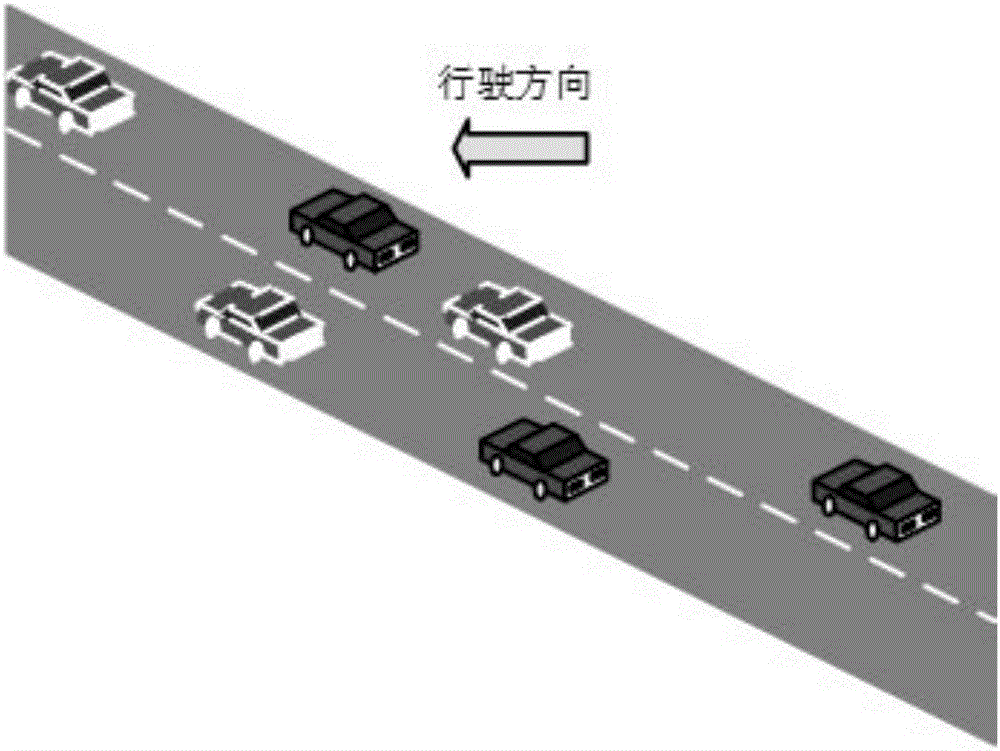

Vehicle location positioning information fusion method based on vehicular ad hoc network

ActiveCN105682222AEliminate the effect of errorImprove target positioning accuracyNetwork topologiesWireless commuication servicesSelf-organizing networkSingle vehicle

The invention discloses a vehicle location positioning information fusion method based on a vehicular ad hoc network. The method comprises the following steps of S1, determining the number of vehicles around a target vehicle in the ad hoc network, if the number of the vehicles is n, running a single vehicle data fusion method for n times, and if four vehicles are located around the target vehicle, running the single vehicle data fusion method for four times; and S2, using a fuzzy nearness fusion method to remove negligent data therein, and working out a weight according to a close degree to obtain the vehicle location positioning information. According to the method, the error influence on ranging caused by network delay is reduced and eliminated through the difference between relative driving distances within the delay, and it assumes that the own vehicle image ranging and radar ranging are real-time. When the data such as distance and the like is used for fusing, the received positioning information of the other vehicles in the system is pre-corrected, the data fusion is performed, and at last fusion is performed again aiming at each auxiliary vehicle fusion result, thus the target positioning accuracy is improved.

Owner:XIDIAN UNIV

Overlapped domain dual-camera target tracking system and method

InactiveCN103997624ASolve the problem of easy to loseImprove anti-interference abilityImage analysisCharacter and pattern recognitionAlgorithmObject tracking algorithm

The invention discloses an overlapped domain dual-camera target tracking system and method. According to the system, an HSV-based space background weighted Meanshift algorithm is connected with an improved visual field boundary target. According to the target tracking algorithm, a relatively-independent tracking task is executed on a video sequence collected by each camera within the visual field range of the camera through a front-end single-camera tracking subsystem, relevant information of the tacked target is obtained, data communication between the cameras is achieved by utilizing a target connection algorithm, and then high-class video processing processes like behavior judgment are carried out.

Owner:JIANGSU UNIV

Long-distance distributed optical fiber positioning interference structure based on wavelength division multiplexing (WDM)

ActiveCN102064884AEliminate positioning effectsEliminate the effect of errorTransmission monitoring/testing/fault-measurement systemsFrequency spectrumLength wave

The invention provides a distributed optical fiber positioning structure and method used for long-distance monitoring and in particular relates to a distributed optical fiber positioning interference technology based on wavelength division multiplexing (WDM). The interference technology is characterized in that two rays with different wavelengths are injected into the same sensing optical fiber, are transmitted to the port of the optical fiber, are separated by a WDM device and respectively reach own reflecting terminals along own independent optical fiber paths; and two optical waves respectively form different interferences. The disturbance position information is obtained by comparing the spectrum characteristics obtained by the two interferences, of phase signals. The structure and the method have the following advantages: the structure is simple; the rear end does not have special requirements for signal processing; and by comparing the spectrum characteristics to obtain the position information, the impact of disturbing signal amplitude variation on detection is eliminated, the average position value can be obtained by utilizing a plurality of frequency points, thus obtaining high positioning precision.

Owner:FUDAN UNIV

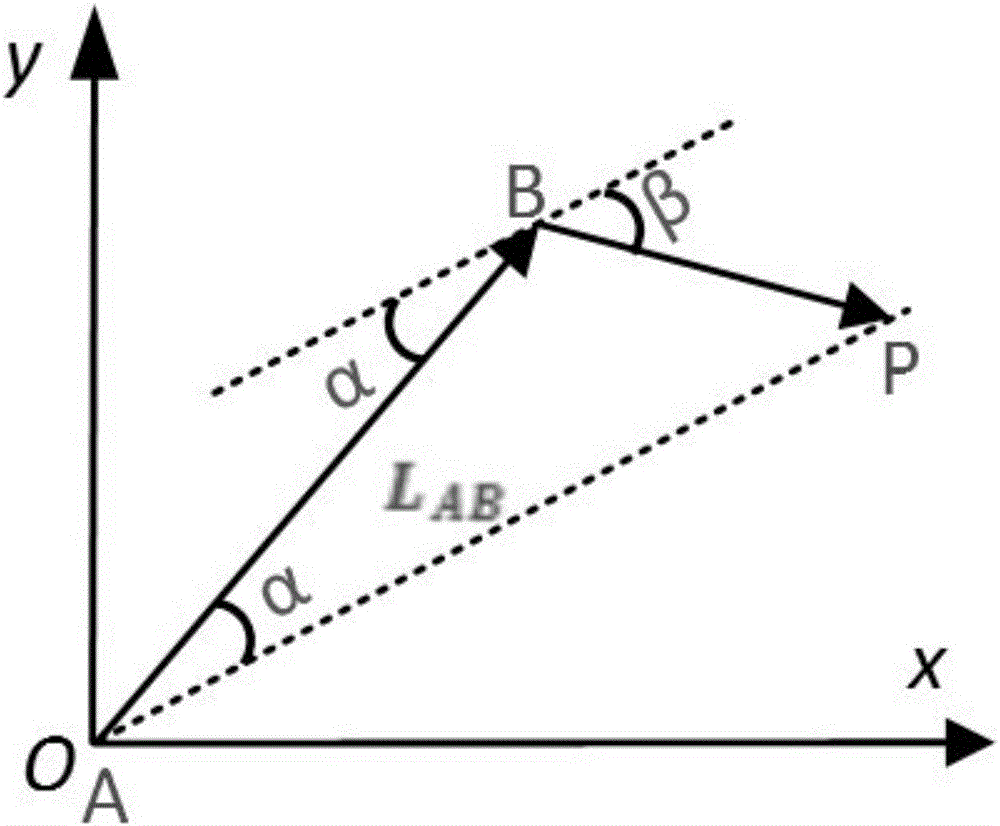

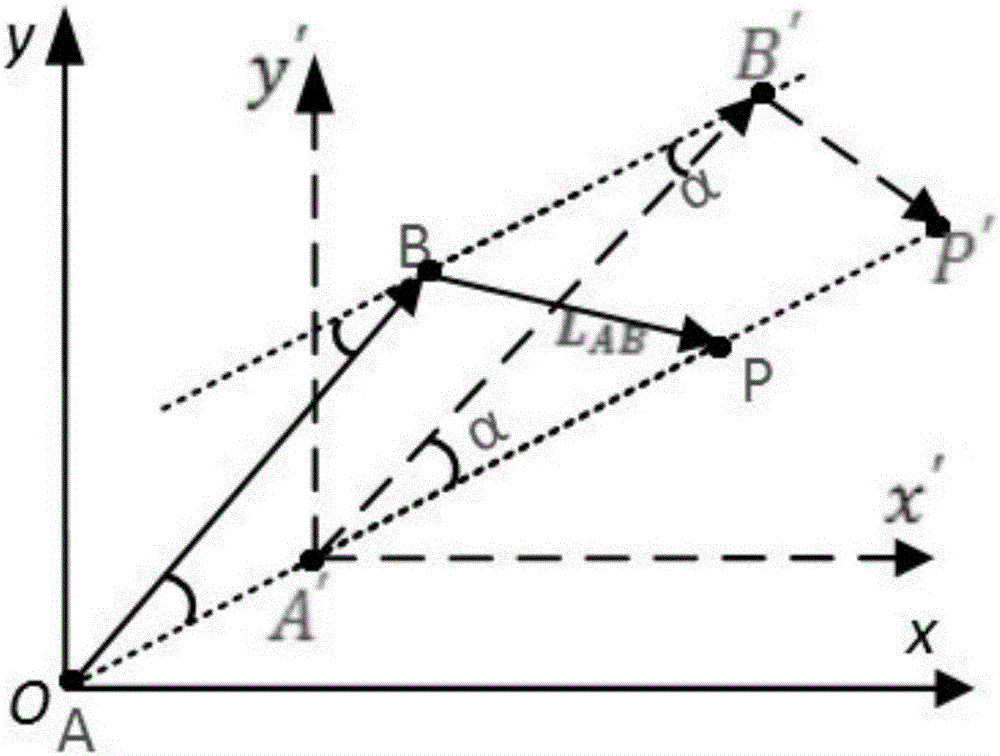

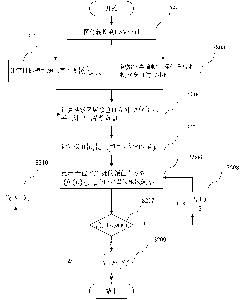

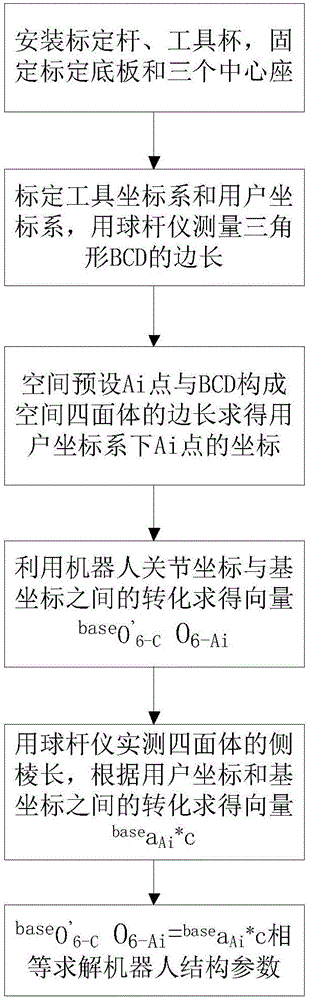

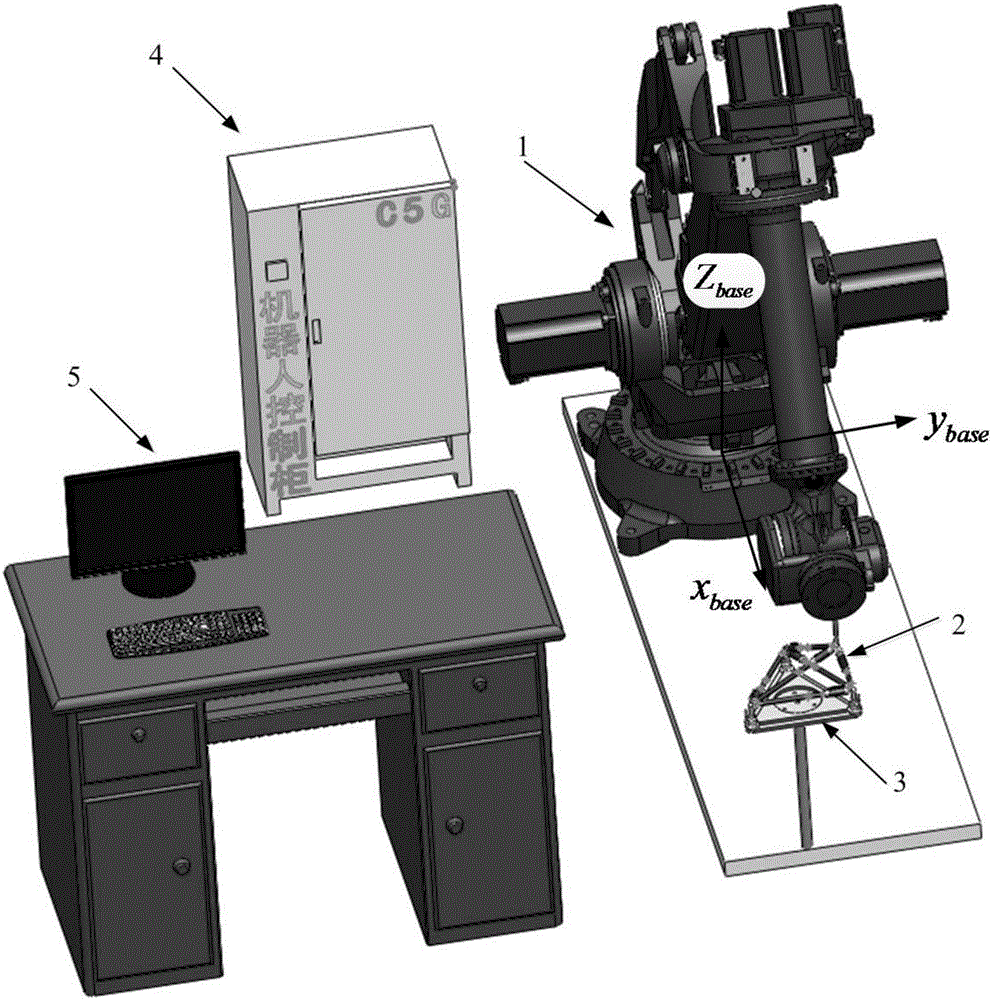

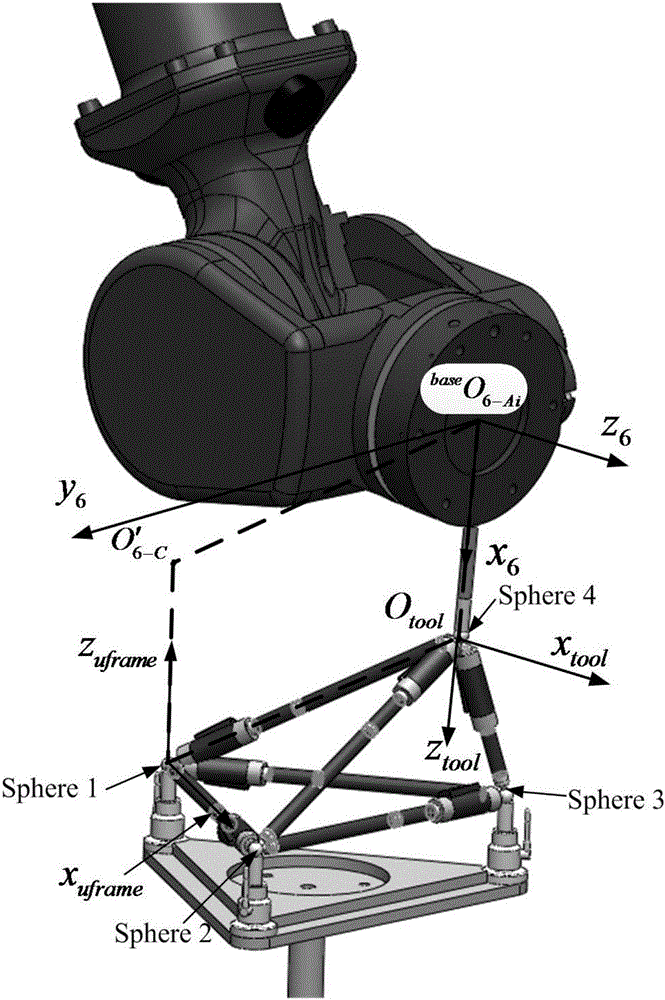

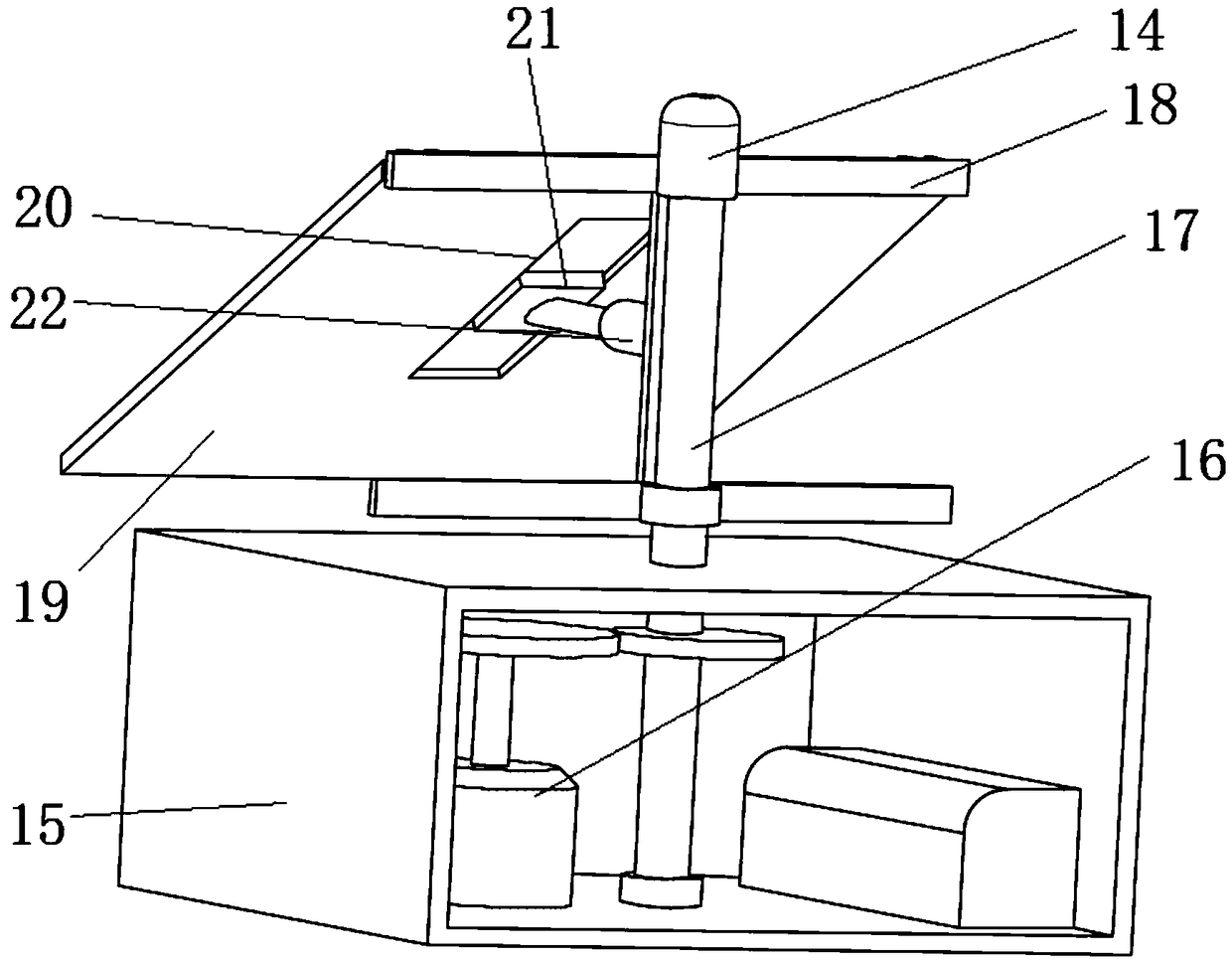

Method for calibrating structural parameters of robot using double-ball-bar

ActiveCN106393174ARealize CalibrationEliminate the effect of errorManipulatorEngineeringCalibration result

The present invention belongs to the field of robot structural parameter calibration, and discloses a method for calibrating structural parameters of a robot using a double-ball-bar. The method comprises the following steps: (a) mounting a calibration rod and a tool cup, and fixing a calibration baseplate and three central seats; (b) calibrating a tool coordinate system and a user coordinate system, and measuring the lengths of the sides of a triangle BCD using the double-ball-bar; (c) presetting a point A in space to form a spatial tetrahedron with the BCD, and obtaining the coordinates of point A under the user coordinate system according to the lengths of the sides of the tetrahedron; (d) obtaining vector <base>O'6-CO6-Ai through conversion of coordinates of robot joints to base coordinates; (e) measuring the lengths of the lateral sides of the tetrahedron using the double-ball-bar, and obtaining vector <base>aAi*c according to conversion of user coordinates to base coordinates; and (f) obtaining the structural parameters of the robot according to the parallelogram principle. According to the present invention, the calibration of the structural parameters of a six-degree-of-freedom articulated robot using the double-ball-bar is achieved simply and quickly, and the calibration result has high accuracy.

Owner:HUAZHONG UNIV OF SCI & TECH

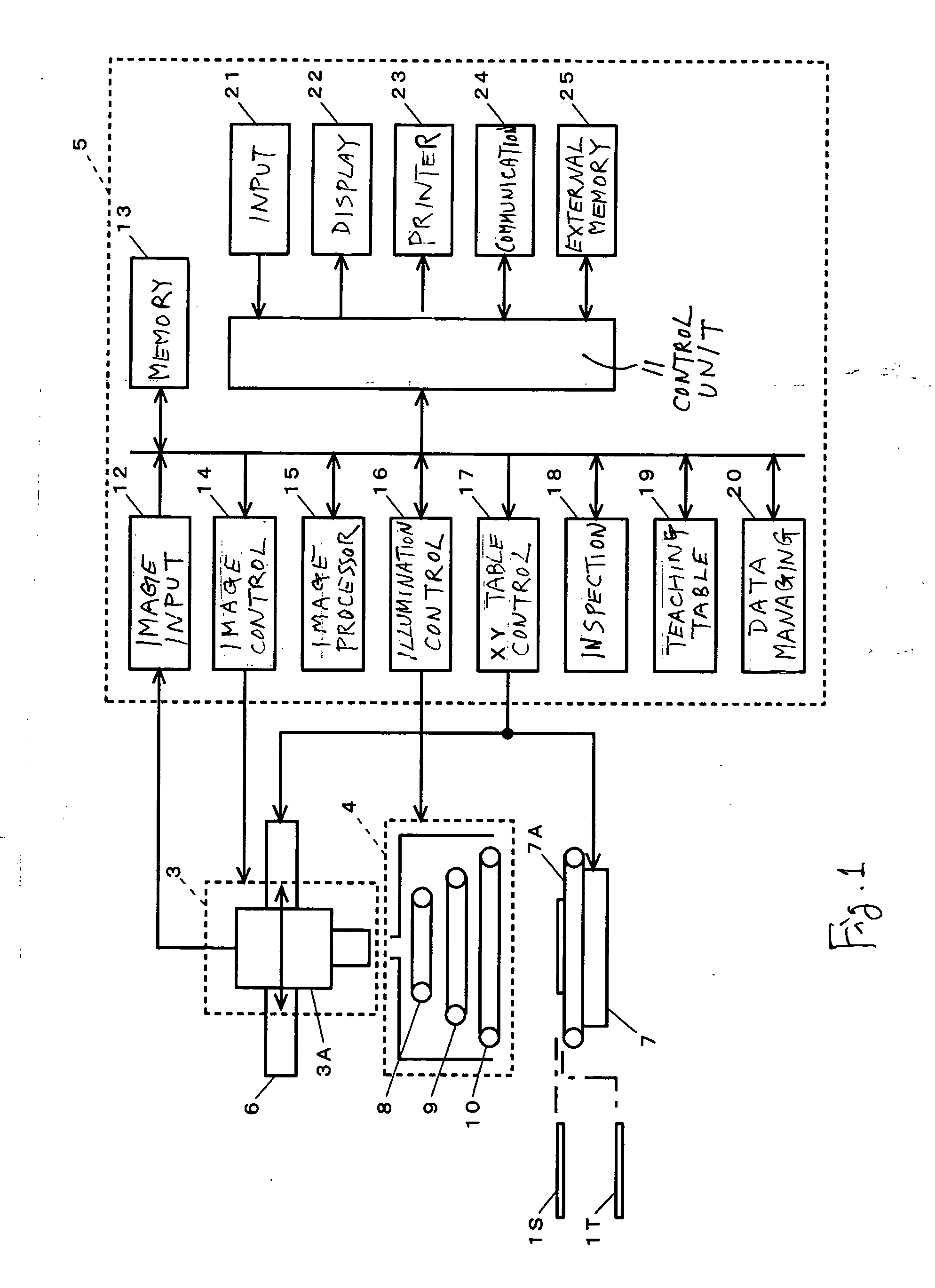

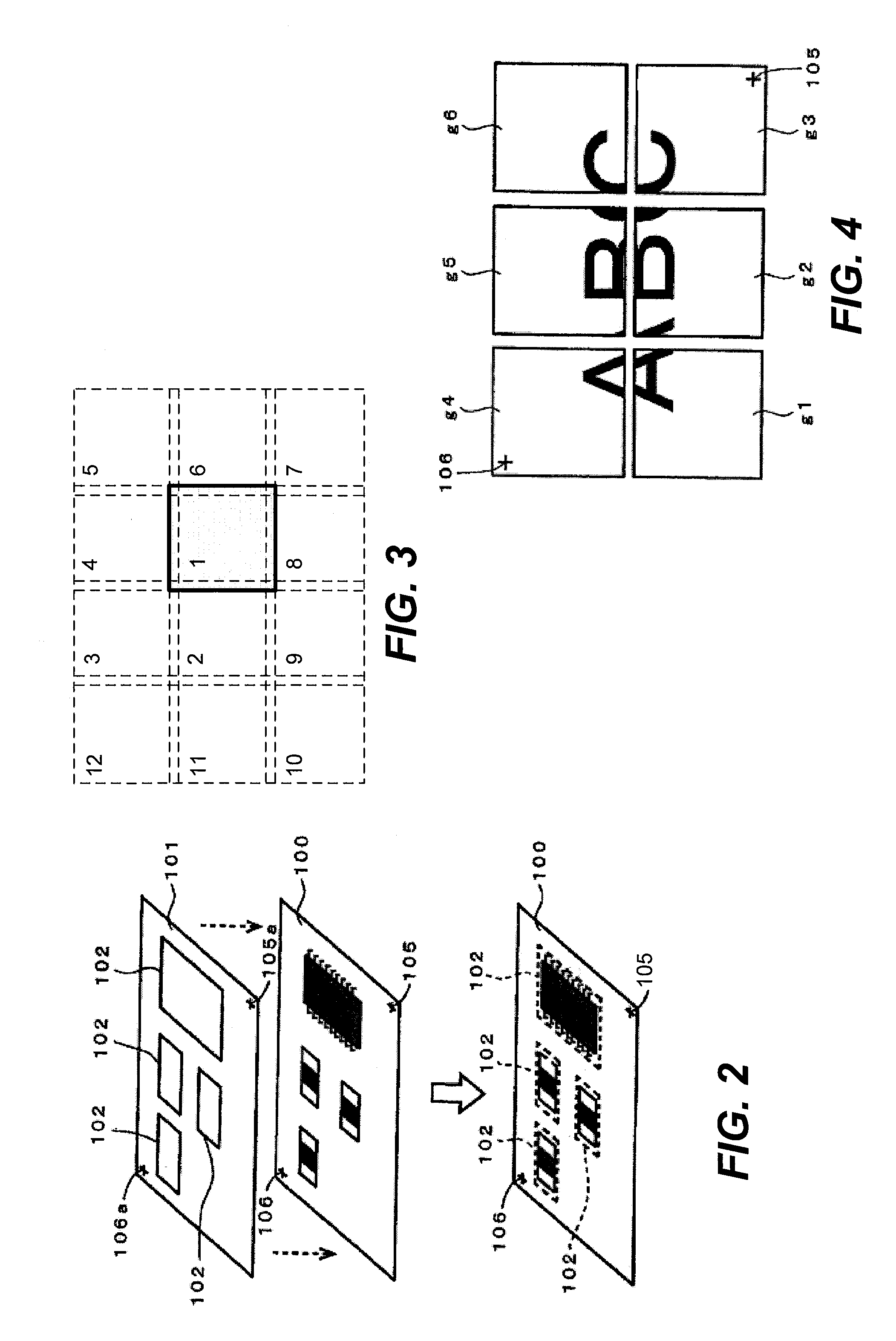

Substrate inspection method and apparatus

InactiveUS20060050267A1Improve detection accuracyEliminate displacementImage enhancementImage analysisComputer graphics (images)Image based

Preparation steps are taken before a substrate with components is inspected and a whole image of a standard substrate is prepared preliminarily and inspection areas are determined for target portions to be inspected on this whole image. At the time of the inspection, a camera is positioned corresponding to a target portion to obtain a target image and an area corresponding to the target image is extracted from the whole image and displacement values of this area are calculated relative to the target image. The setting position of the inspection area is corrected by the calculated displacement values and an inspection area is set on the target image based on the corrected coordinates.

Owner:ORMON CORP

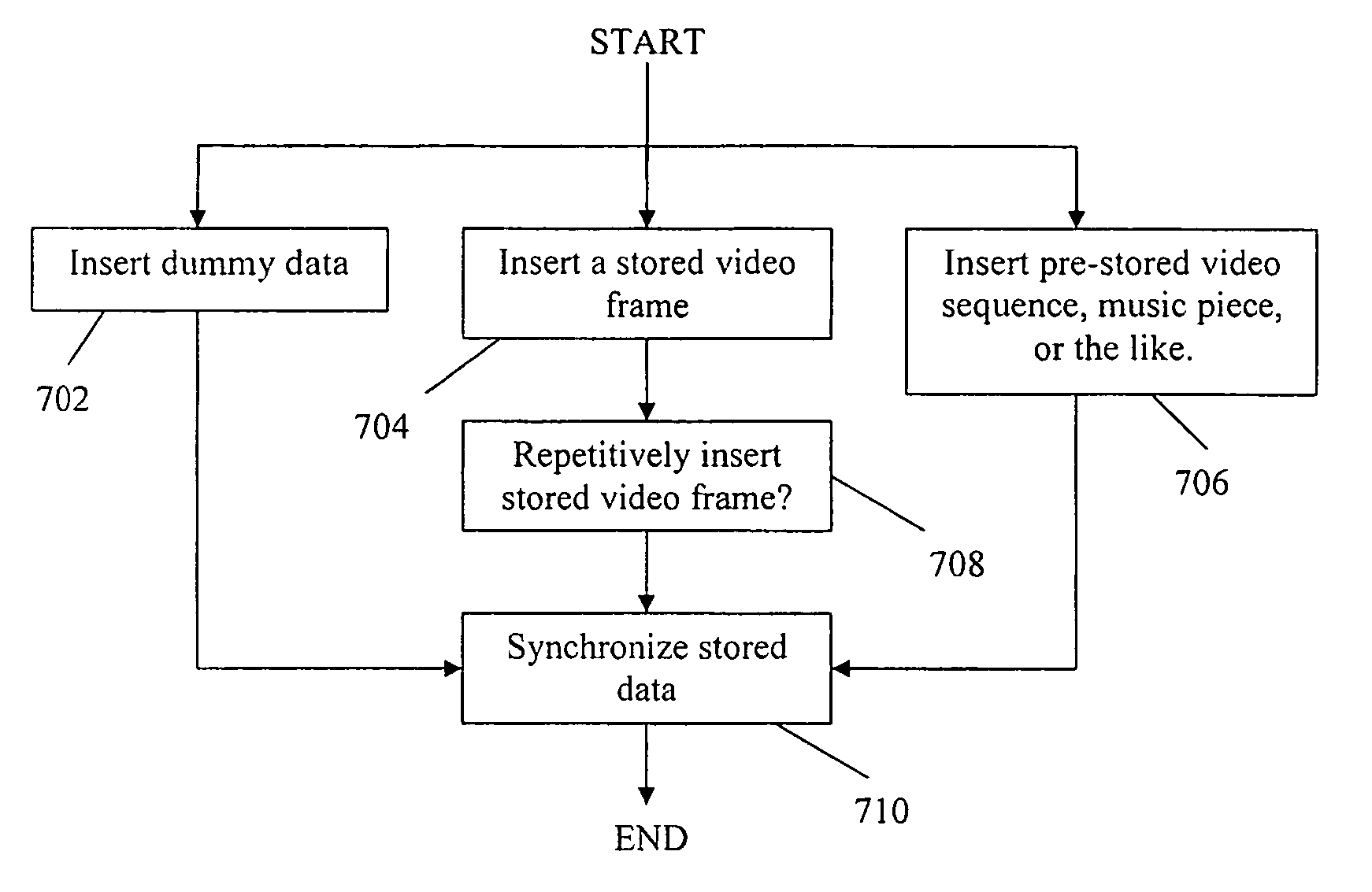

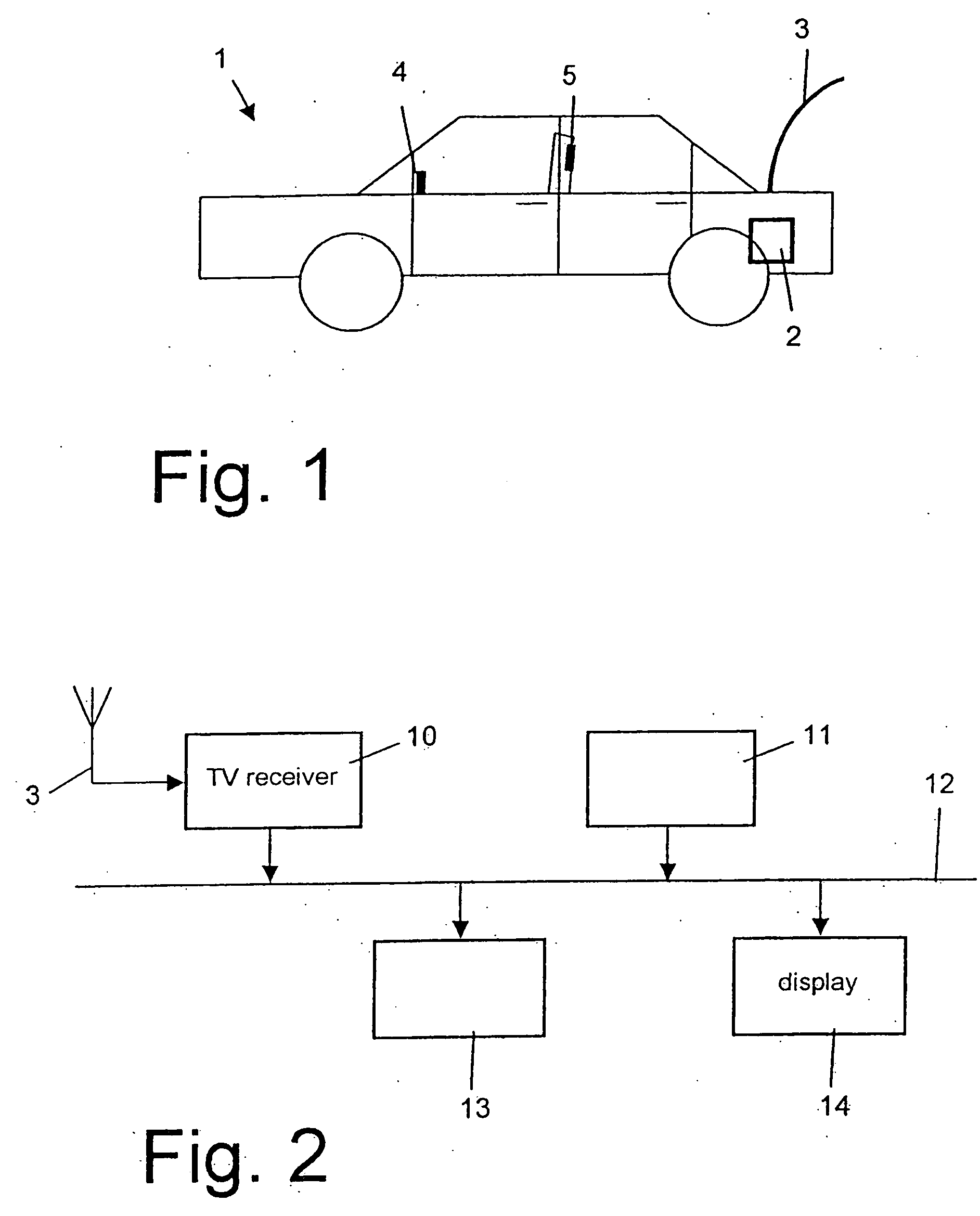

Mobile television receiver

InactiveUS20060195870A1Audio quality be reducedEliminate the effect of errorTelevision system detailsPulse modulation television signal transmissionDigital dataTelecommunications link

The invention relates to the reproduction of a television signal on a distant reproduction device. The received television signal is encoded and transmitted in a digital data format over a communication link to the reproduction device. The reproduction device decodes the received video information for display on a display screen. The invention is particularly intended for use in mobile vehicles, coaches and trains, where the signal strength of a received television signal during travel is continuously varying and signal distortions occur frequently. In order to reduce the effect of signal distortions on the perceived image and audio quality, the invention inserts a compressed pre-stored video or audio data into the data stream transmitted from the television receiver to the reproduction device upon detection of a television signal distortion. Thus, the decoding procedure at the display device can be maintained in spite of a received television signal of insufficient signal strength.

Owner:HARMAN BECKER AUTOMOTIVE SYST

Method for deciding urban rail transit kilometer posts

ActiveCN105882684AEliminate the effect of errorImprove calibration accuracyRailway auxillary equipmentRailway profile gaugesData fileTrackway

The invention discloses a method for deciding urban rail transit kilometer posts. The method includes creating basic data files with the route station kilometer posts and station-to-station distances; measuring the running distances of a train away from previous stops in real time; calculating the difference between k running distances, between two adjacent stops, of the train and the continuous k station-to-station distances in the basic data files by the aid of an annular sliding search matching method so as to determine whether the difference satisfies a specified error range or not, and determining k matched continuous stations; acquiring the sum of the current running distance of the train away from the previous stop and the identified station kilometer posts of the previous stops to decide the kilometer posts of the real-time running of the train. The method has the advantages that the location kilometer posts where the urban rail transit train run can be quickly, accurately and automatically decided by the aid of the method without depending on any external conditions such as a train signal system and sensing devices on a route, and accordingly the fault location kilometer posts necessary for online monitoring steel rail faults from the operating train can be decided.

Owner:TANGZHI SCI & TECH HUNAN DEV CO LTD

Method for measuring particle grain diameter

InactiveCN101295024ALaser Intensity Stability LimitationsImprove accuracyPhotogrammetry/videogrammetryRadiation particle trackingOptical measurementsForward angle

The invention relates to a method for measuring grain diameter by utilizing binocular vision matching and particle picture gray scale difference, pertaining to the technical field of optical grain diameter measurement. According to the characteristic that different forward angle scattered lights have light intensity differences and by utilizing a digital particle image velocimetry (DPIV) imaging system provided with dual-cameras, the method obtains two particle pictures with gray scale difference, the flow fields of which are formed by single exposure; after the particle pictures are pre-treated by an image processing technique, the mating of a same particle corresponding to two particle image points on the two particle pictures is realized according to a binocular vision matching principle; the grain diameter of the particle is obtained by substituting the gray scale value summation of the two particle image points into a grain diameter solving formula, thus obtaining the particle size information of the whole flow field; the method has the reduced requirement to the light intensity and the stability of laser and the particle mating method is simple and convenient, thus reducing the influence of system errors, the digital graphic processing technique and laser diffraction on the measurement result of the particle size, overcoming the deficiencies and defects in the prior art and having substantial characteristics and prominent advancement.

Owner:TONGJI UNIV

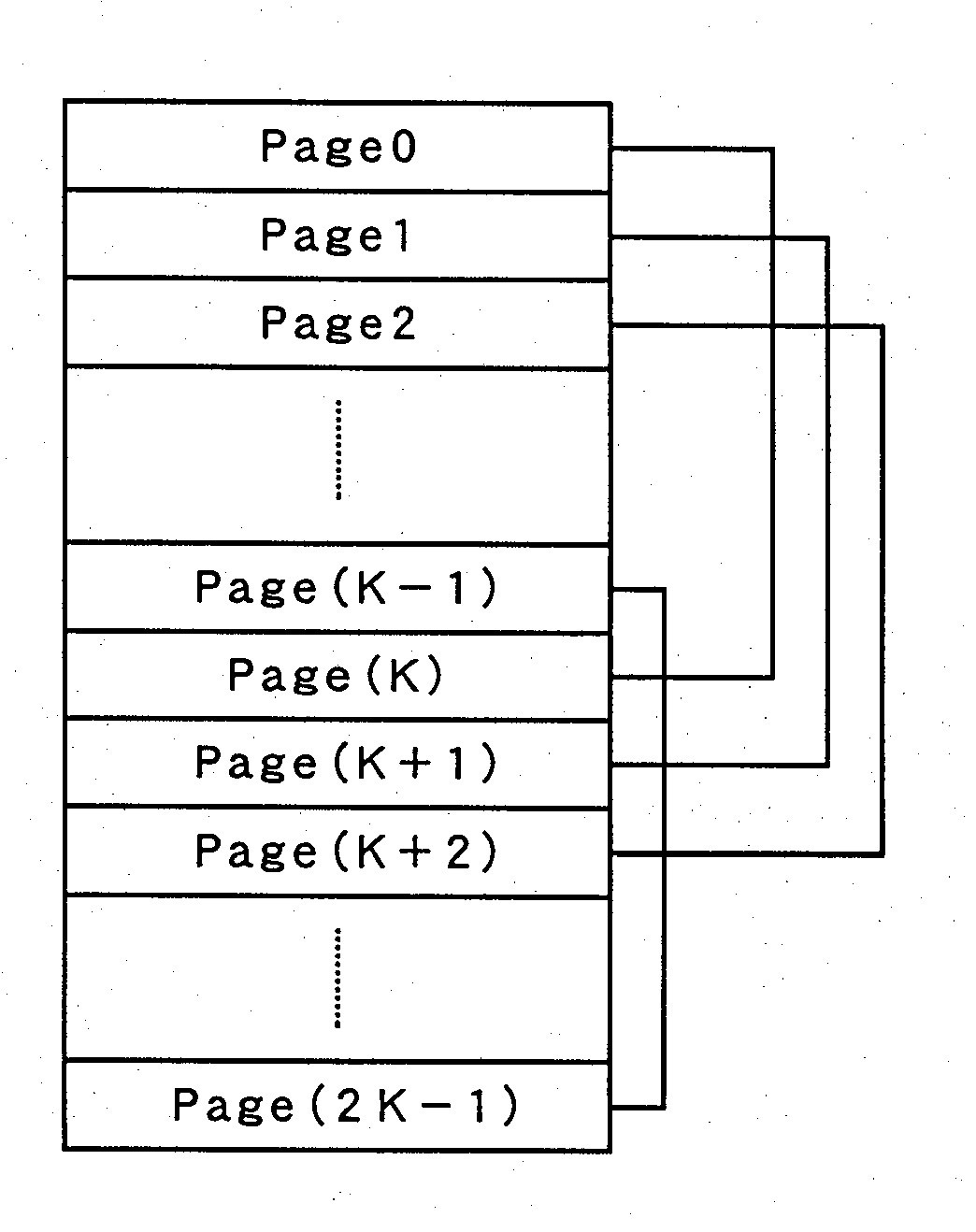

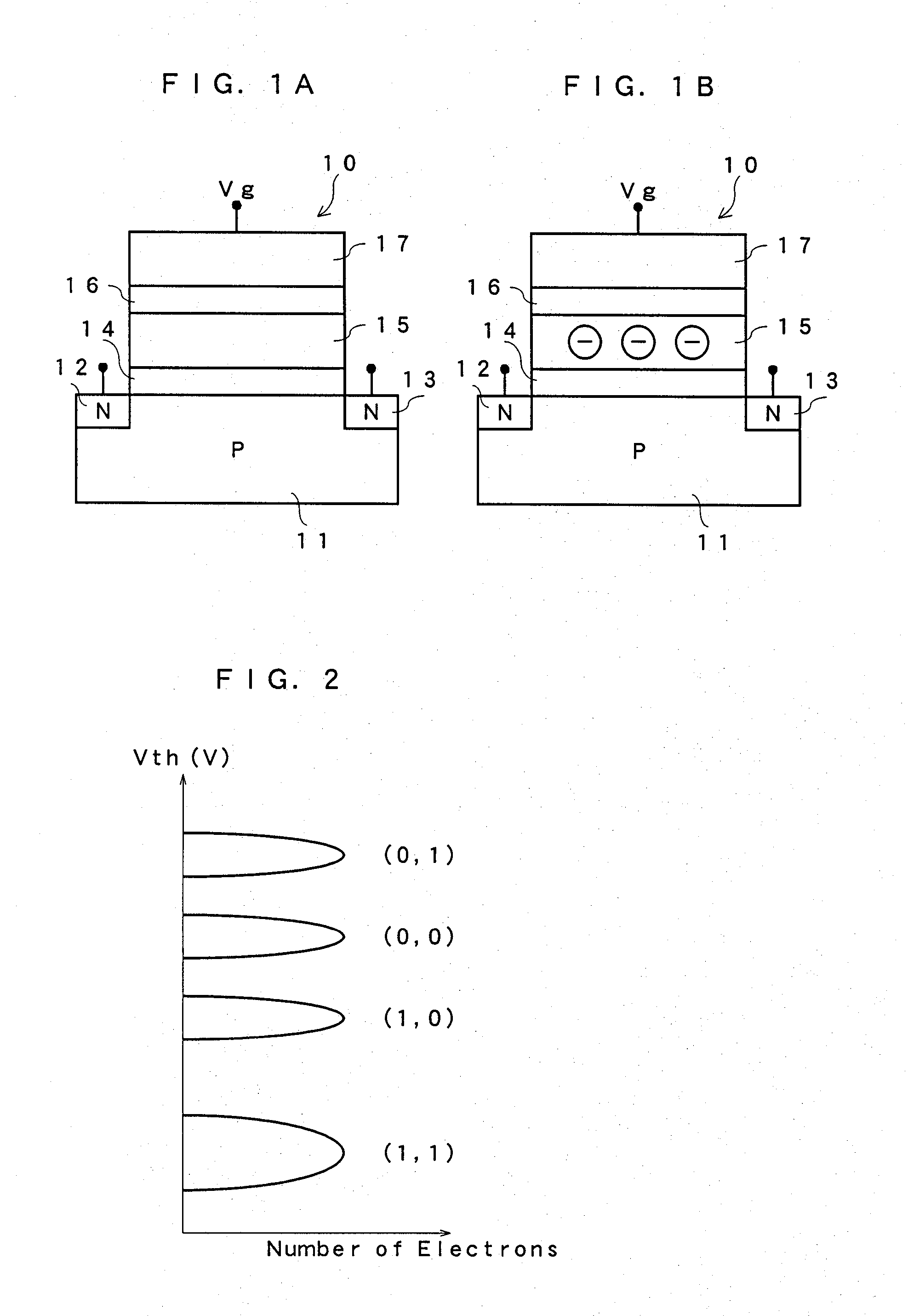

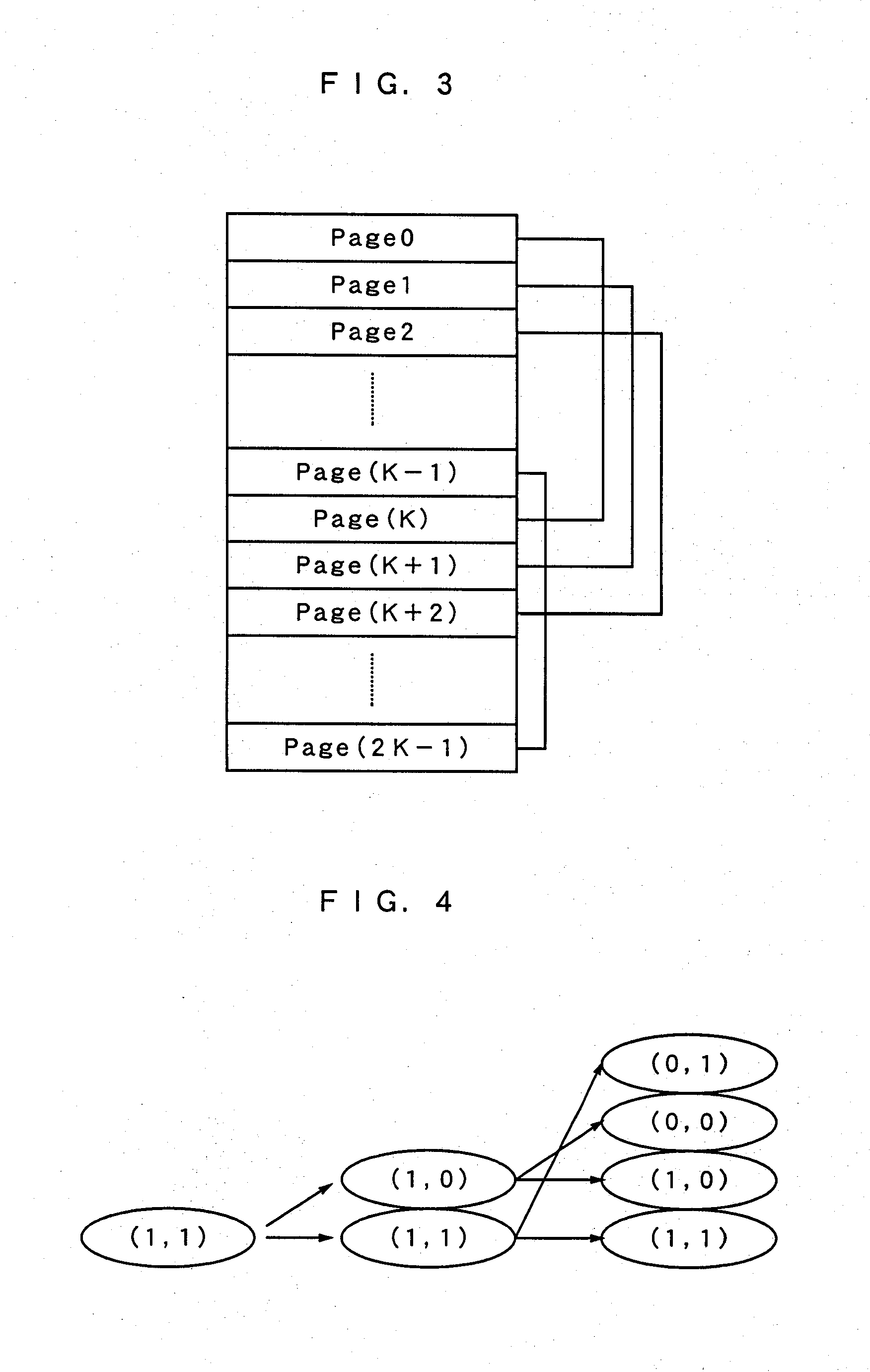

Semiconductor memory device, host device and semiconductor memory system

ActiveUS20100174951A1Avoid data corruptionEliminate the effect of errorMemory architecture accessing/allocationMemory adressing/allocation/relocationSemiconductorSemiconductor device

A host device 200A includes a data buffer 250. When data has been already written to a part of a physical block and data is additionally written to the physical block, it is determined whether or not the data written to the physical block is held in the data buffer. When the data is held, data is written to the block, and when an error exists, data in unit of physical blocks is rewritten. When the data is not held in the data buffer, a new physical block is required to be secured and then, data is written to the new block. Thereby, even when power is shut off or an error occurs during writing in the semiconductor memory device, destruction of data already written is prevented.

Owner:PANASONIC CORP

Textile machine

With a textile machine including a large number of yarn processing units that produce packages, in spite of an attempt to make the yarn lengths of packages uniform on the basis of a yarn speed detected for each unit by a yarn speed sensor, the yarn length of an actually produced package varies among the units as a result of an inherent error in the yarn speed sensor. The present invention includes a setting member 41 that transmits correction information for each of the yarn speed sensors 7 to the corresponding sequencer 12. Each of the sequencers 12 corrects the detected value from a corresponding one of the yarn speed sensors 7 on the basis of the correction information to calculate a correction value for a corresponding yarn speed to calculate the yarn length of the corresponding winding package 4 on the basis of the correction value for the corresponding yarn speed. The winding units 1 each have a yarn speed sensor 7 that detects a yarn speed, a sequencer 12 that calculates the yarn length of a winding package 4 on the basis of the detected value from the yarn speed sensor 7, and a winding device 20 that forms a winding package 4.

Owner:MURATA MASCH LTD

High-voltage static voltage measurement device

ActiveCN104237605ASimple structureImprove performanceCurrent/voltage measurementVoltage dividersCapacitanceMeasurement device

The invention provides a high-voltage static voltage measurement device which comprises an induction pole plate, a partial voltage capacitor and a measuring circuit. The output of the induction pole plate is divided into two branch circuits, one branch circuit is grounded through the partial voltage capacitor, and the other branch circuit is connected with the measuring circuit; the measuring circuit comprises a low-bias input amplifier, an in-phase proportional amplifier, a low-pass filter, a measurement display module, an equipotential shielding ring, a follower amplifier and a switch; an input pin on the low-bias input amplifier is surrounded by the equipotential shielding ring; each output branch circuit of the induction pole plate is connected with the low-bias input amplifier, the in-phase proportional amplifier, the low-pass filter and the measurement display module in sequence through the switch; the reverse input end of the low-bias input amplifier is connected with the input end of the follower amplifier, and the output end of the follower amplifier is connected with the equipotential shielding ring. The high-voltage static voltage measurement device can well solve the electric leakage problem of electric charges in the high-voltage static voltage measurement process.

Owner:LANZHOU INST OF PHYSICS CHINESE ACADEMY OF SPACE TECH

Method and device for detecting roughness of inner surface of micro-pore

InactiveCN103615992AImprove detection efficiencyEnables parallel measurementsUsing optical meansRough surfaceLinear relationship

The invention provides a method and device for detecting the roughness of the inner surface of a micro-pore. The method comprises the steps that diffuse scattering luminous fluxes of different positions modulated through the rough surface intensity are collected so that the roughness can be evaluated; a non-linear relationship exists between the ratio of voltages generated by two sets of luminous fluxes and the roughness, a micro-pore with the known roughness is calibrated, the micro-pore to be detected is compared with a calibration value, and then the roughness of the micro-pore to be detected is detected. By the adoption of the method and device for detecting the roughness of the inner surface of the micro-pore, the problem that a sensor cannot extend into the micro-pore in the prior art is solved, the angle of the sensor can be changed flexibly and conveniently, the measurement accuracy is high, and efficiency is high.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

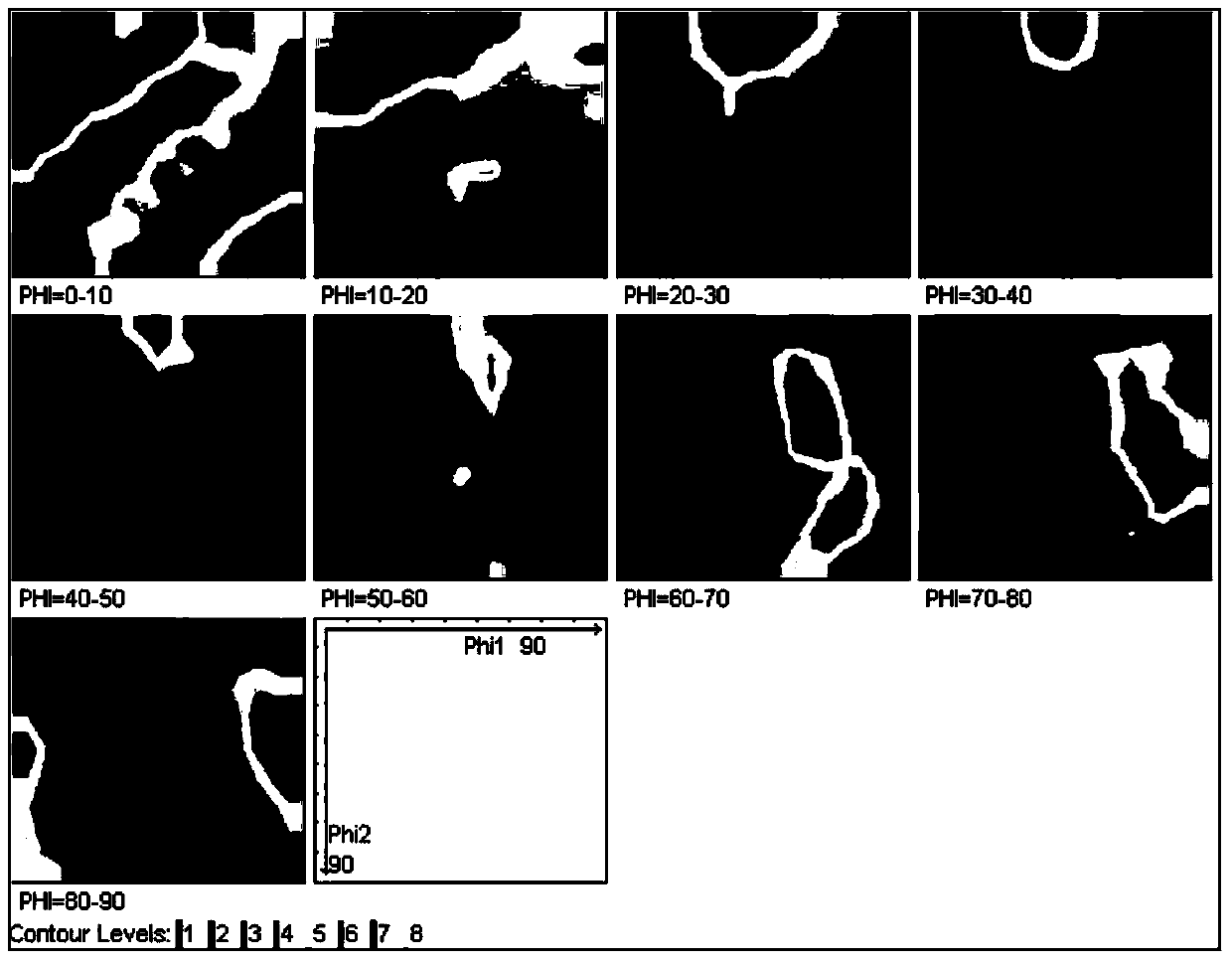

Silicon steel texture measuring method

InactiveCN103389316AThe sample preparation process is simpleEasy to measureMaterial analysis using wave/particle radiationSheet steelAnalysis sample

The invention discloses a silicon steel texture measuring method. The silicon steel texture measuring method comprises the following steps of preparing an EBSD analysis sample, measuring orientation distribution diagrams of half-thickness areas at three or more different positions of a longitudinal section of the sample by EBSD equipment, dividing a measured area into at least 10 equal-area zones from the steel plate surface to the plate thickness center, carrying out analysis to obtain ODF diagrams of the different positions, calculating density fractions f (hkl) of all crystal faces {hkl}, calculating an average value of the density fractions f (hkl) of the crystal faces {hkl} which are in different positions and have the same thickness, and drawing a data diagram of the silicon steel texture along a plate thickness direction. Through measurement of the ODF diagrams and quantitative calculation of the density fractions f (hkl) of the crystal faces {hkl}, the problem of high difficulty of XRD quantitative analysis is solved. Through measurement of data of multiple zones, the error caused by a too small EBSD measuring zone is eliminated and data is more accurate.

Owner:武汉钢铁有限公司

Frequency characteristic detecting system of electronic type voltage transformer

ActiveCN103499800AFrequency characteristic detectionImprove frequency transfer performanceElectrical measurementsVoltage amplitudeTransformer

The invention discloses a frequency characteristic detecting system of an electronic type voltage transformer. The frequency characteristic detecting system comprises a frequency conversion power supply, a boosting unit, a high frequency voltage divider, a merging unit and a frequency characteristic detecting unit. The nominal voltage of the output end of the frequency conversion power supply adjusts the voltage amplitude of a power supply through the boosting unit to supply the primary side high voltage U1 used in an experiment to the electronic type voltage transformer to be detected; the primary side high voltage U1 is converted into the low voltage U2 through the high frequency voltage divider, and the low voltage U2 is used as standard source signals of the frequency characteristic detecting unit; the sampling value of the electronic type voltage transformer to be detected is sent to the frequency characteristic detecting unit through the merging unit, and the sampling value is used as detected signals of the frequency characteristic detecting unit. The frequency characteristic detecting system of the electronic type voltage transformer can reliably and perfectly detect the frequency characteristics of the electronic type voltage transformer, and aims to improve the frequency transmission performance of the electronic type voltage transformer and provide the technical guarantee for safe and stable operation of the electronic type voltage transformer.

Owner:STATE GRID CORP OF CHINA +2

Path delay on-line measurement circuit

ActiveCN102495349AEliminate distractionsRealize high-precision measurementElectronic circuit testingTotal delayComputer module

A path delay on-line measurement circuit comprises a measurement trigger module connected with a to-be-detected circuit, a to-be-detected source selection module connected with the measurement trigger module and controlling signals sent by the measurement trigger module to selectively pass, a delay measurement module connected with the to-be-detected source selection module and carrying out delay measurement to signals sent by the to-be-detected source selection module, a storage module connected with the delay measurement module and storing delay measurement information of the delay measurement module, and a control module for controlling operation of the measurement trigger module, the to-be-detected source selection module and the storage module. The path delay on-line measurement circuit is connected to the to-be-detected circuit, the control module controls the path delay on-line measurement circuit to work in a probe path delay measurement mode so as to measure and obtain delay of each probe path and controls the path delay on-line measurement circuit to work in an on-line delay measurement mode so as to measure and obtain total delay. Finally, the measured probe path delay is subtracted from the total delay, and the delay of the to-be-detected path is obtained.

Owner:SHENZHEN INST OF ADVANCED TECH CHINESE ACAD OF SCI

Underground engineering disturbance similarity model test bench and test method

The invention discloses an underground engineering disturbance similarity model test bench and a test method. The underground engineering disturbance similarity model test bench comprises a model box.The model box comprises an inner frame, a middle frame and an outer frame, the inner frame is sleeved in the middle frame, and the middle frame is sleeved in the outer frame. Multiple hydraulic loading devices are arranged at the inner top of the inner frame. Multiple horizontal first linear sliding rails are arranged at the inner bottom of the inner frame, and the tops of the first linear sliding rails are connected in a sliding manner with first sliding blocks. A sample box is arranged at the tops of the first sliding blocks. Protection springs are fixedly arranged between the first slidingblocks and the sample box. A buffer protection layer is further arranged between the inner bottom of the inner frame and the sample box. Wave absorbing layers are arranged on the side and at the bottom of the sample box. Multiple vertical second linear sliding rails are arranged on the inner side of the middle frame. Second sliding blocks are arranged on the outer side of the inner frame and connected with the second linear sliding rails in a sliding mode. A first actuator and a plurality of supporting springs are arranged at the inner bottom of the middle frame, and the top of the first actuator and the tops of the supporting springs are connected with the outer bottom of the inner frame.

Owner:SHANDONG JIANZHU UNIV

High-speed parallel D/A clock synchronization apparatus

ActiveCN105094014AStable and synchronous workGood stability and reliabilityProgramme controlComputer controlRadio frequency circuitsSignal production

The invention discloses a high-speed parallel D / A clock synchronization apparatus. The high-speed parallel D / A clock synchronization apparatus comprises a signal conditioning unit for adjusting the amplitude size of clock signals, increasing the amplitude of the clock signals to a saturation degree of an amplification unit before a switch unit is energized and then reducing the amplitude after a state is stable so as to enable the amplification unit to work at a linear interval, and the switch unit and the amplification unit. The invention further discloses a high-speed parallel D / A clock synchronization method. According to the apparatus and method provided by the invention, synchronization of a multichannel signal generation system can only be concentrated on on-off of a radio frequency switch, the transition time at the moment when the switch is turned on and turned off is substantially compressed, the influences of errors caused by clock jittering at D / A conversion initial time, and the stability and the reliability are good. On the other hand, by use of the feature of small noise of a radio frequency circuit, low-noise conversion of high-speed clock signals from a single end to a differential is finished, and the application requirement of circuit difference signals can be met.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

Base line-based subway tunnel horizontal displacement deformation monitoring method

ActiveCN106643673AEliminate the effect of errorSimple and flexible testing processSurveying instrumentsTotal stationEngineering

The invention discloses a base line-based subway tunnel horizontal displacement deformation monitoring method. The base line-based subway tunnel horizontal displacement deformation monitoring method comprises following steps: 1, erection of a total station is carried out, and the total station is used for acquiring two stage controlling point coordinate data; 2, two stage control base line vectors are calculated based on the two stage controlling point coordinates respectively; 3, a base line coordinate system is established based on the two stage control base line vectors; 4, the total station is used for acquiring two stage monitoring point plane coordinate data; 5, monitoring base line vectors are calculated based on controlling point coordinates and monitoring point coordinates; 6, projection of the monitoring base line vectors onto the base line coordinate system is carried out so as to obtain the components of the monitoring base line vectors in the X coordinate axis direction and the Y coordinate axis direction; and 7, the components of a same monitoring base line vector in two stages in the base line coordinate system are compared so as to obtain the deformation of the monitoring point in directions parallel to track and vertical to track in adjacent two stages. The base line-based subway tunnel horizontal displacement deformation monitoring method is capable of eliminating influences of errors caused by rendezvous and directional introduction, test process is simple and flexible, operation time is shortened greatly, and working efficiency is increased.

Owner:HOHAI UNIV

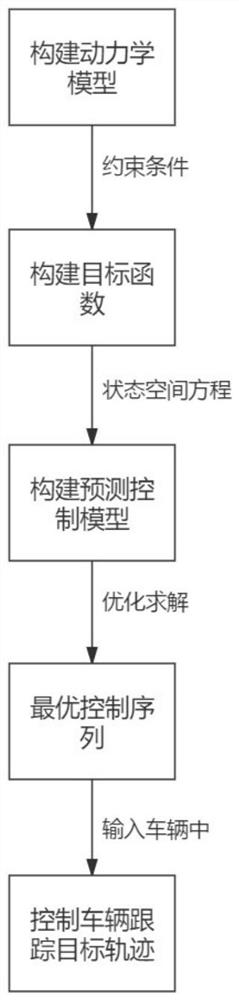

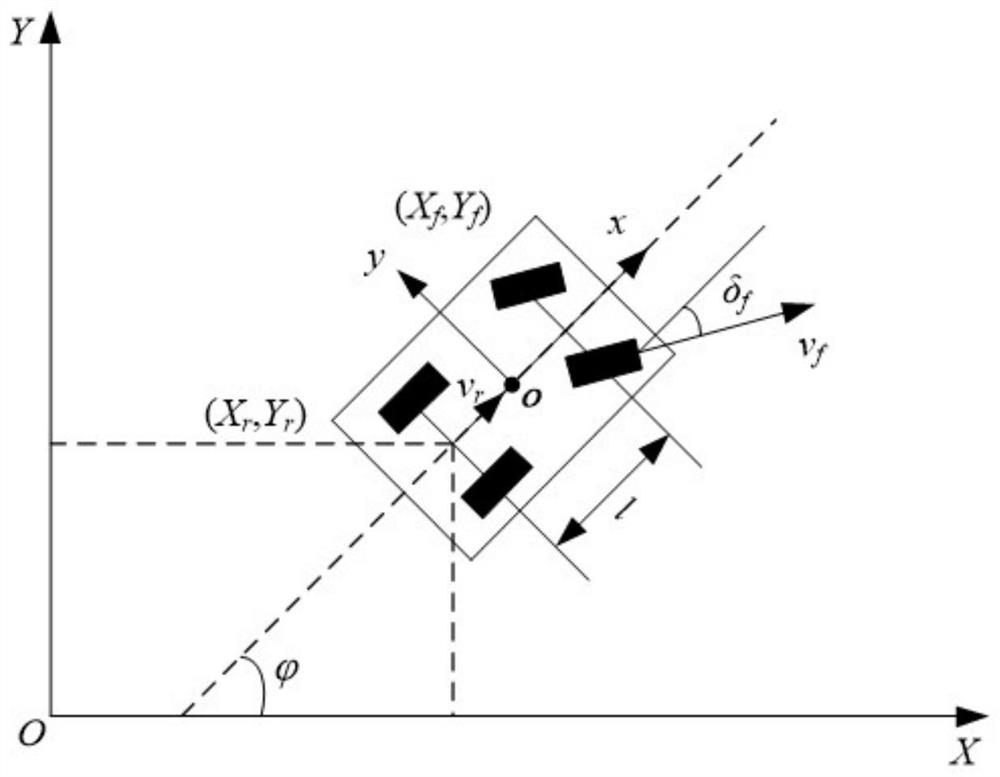

MPC-based intelligent vehicle path tracking control method and system

InactiveCN111930112AImprove stabilityEliminate the effect of errorPosition/course control in two dimensionsVehiclesOptimal controlControl engineering

The invention discloses an MPC-based intelligent vehicle path tracking control method and system. The method comprises the steps of: building a three-degree-of-freedom kinetic model according to an entity intelligent vehicle structure, and analyzing the three-degree-of-freedom kinetic model to obtain a geometric constraint condition meeting the movement and driving of a vehicle; constructing an objective function by using a multi-objective optimization strategy, and converting the nonlinear kinetic model into a linear model to obtain a state-space equation; constructing a predictive control model based on the state-space equation, and performing optimal solution according to the objective function and the constraint condition to generate an optimal control sequence; and inputting the optimal control sequence into the intelligent vehicle to control the vehicle to track a target trajectory. The vehicle driving stability is improved, the control requirement and stability of an existing intelligent vehicle are met, high constraint processing capacity is achieved, and high feasibility and stability are achieved.

Owner:GUANGXI UNIVERSITY OF TECHNOLOGY

Ambiguity calculating method used under medium-long baseline of Beidou system

ActiveCN104749597AEliminate the effect of errorExtension of timeSatellite radio beaconingAmbiguityIonosphere

Owner:ACAD OF OPTO ELECTRONICS CHINESE ACAD OF SCI

A range finding method and system for a direct current rail transit power supply line short circuit fault

ActiveCN107015102AAvoid the disadvantages of short-circuit faultsThe ranging result is accurateElectrical testingMaterial resourcesEngineering

The invention relates to a range finding method and system for a direct current rail transit power supply line short circuit fault. The method comprises the following steps: S1, whether a permanent short-circuit fault occurs on a DC rail transit power supply line is detected; S2, when the permanent short-circuit fault occurs on the DC rail transit power supply line and the pantograph falling of a vehicle does not does not occur, the distance between a sampling point and a short-circuit fault point is obtained through short circuit fault range finding carried out on the sampling point on the direct current rail transit power supply line. The method of the invention can avoid the shortcomings in the prior art which require the vehicle to stop to find the short circuit fault with a lot of manpower and material resources. The method of the invention can quickly find out the short circuit fault point, which is important for the safety of rail transportation and economic operation.

Owner:WUHAN ZHONGZHI ELECTRIC

Medium-long baseline single-epoch ambiguity resolution method, system and device and storage medium

InactiveCN108508468AAvoid features with less precisionSolve the rank deficit problemSatellite radio beaconingDouble differenceNatural satellite

The invention discloses a medium-long baseline single-epoch ambiguity resolution method, system and device and a storage medium and belongs to the technical field of global navigational satellite positioning. The method comprises the steps that a single-epoch double-difference wide-lane combined observation equation is established according to observation data of global navigational satellites; coordinate correction parameters are constrained through a regularization method, the morbidity of matrixes is improved; by combining with a lambda algorithm, single-epoch wide-lane ambiguity fixation is achieved; a double-difference ionized-layer-free combined observation equation is represented by using wide-lane ambiguity and original carrier ambiguity and is substituted based on fixed wide-laneambiguity; original carrier ambiguity fixation is achieved by using the lambda algorithm. According to the technical scheme of the embodiment, only carrier observation values are adopted, the characteristic is avoided that the precision of pseudo-range observation values is poorer, and meanwhile the rank defect problem of a normal equation in single-epoch ambiguity resolution is solved by adoptingthe regularization method. In addition, by combining with ionized-layer-free combination, the influence of ionization layer errors is better eliminated, and the success rate of ambiguity fixation isimproved.

Owner:ANHUI UNIV OF SCI & TECH

Substrate inspection method and apparatus

InactiveUS7512260B2Eliminate the effect of errorAccurate settingImage enhancementImage analysisComputer graphics (images)Image based

Preparation steps are taken before a substrate with components is inspected and a whole image of a standard substrate is prepared preliminarily and inspection areas are determined for target portions to be inspected on this whole image. At the time of the inspection, a camera is positioned corresponding to a target portion to obtain a target image and an area corresponding to the target image is extracted from the whole image and displacement values of this area are calculated relative to the target image. The setting position of the inspection area is corrected by the calculated displacement values and an inspection area is set on the target image based on the corrected coordinates.

Owner:ORMON CORP

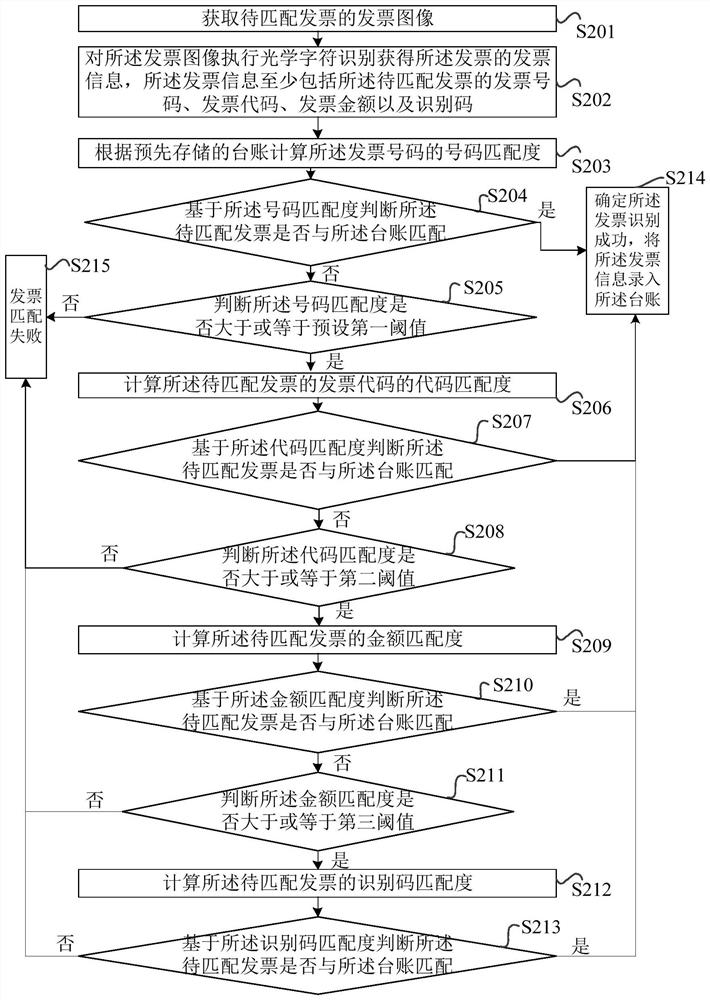

Invoice matching method and device, electronic equipment and storage medium

PendingCN111784423AEliminate the effect of errorImprove exact matchBilling/invoicingCharacter recognitionCharacter recognitionOptical character recognition

The embodiment of the invention discloses an invoice matching method and device, electronic equipment and a storage medium. The method comprises the steps: performing optical character recognition onan invoice image to obtain invoice information of an invoice, the invoice information comprising an invoice number, an invoice code, an invoice amount and an identification code, and calculating the number matching degree of the invoice number according to a pre-stored standing book; judging whether the to-be-matched invoice matches the standing book or not based on the number matching degree; ifso, determining that invoice matching succeeds, and inputting the invoice information into the standing book; and if not, when the number matching degree is greater than or equal to a first threshold,matching the to-be-matched invoice according to the invoice code, the invoice amount and the identification code in sequence to identify the to-be-matched invoice. Due to the fact that when invoice number matching fails, the invoice code, the invoice amount and the identification code are sequentially adopted for matching, the problem that invoice matching is skipped due to matching failure is solved, accurate invoice matching can be achieved through multiple matching invoices, and manual sufficient insertion processing is not needed.

Owner:MEIZHOU POWER SUPPLY BUREAU OF GUANGDONG POWER GRID CORP

Soil moisture monitoring device and method

InactiveCN109490506AEffective against rain and moistureEliminate the effect of errorEarth material testingUsing optical meansMultiple pointEngineering

The invention discloses a soil moisture monitoring device and method and relates to the technical field of monitoring devices. The soil moisture monitoring device comprises a fixing pole; a master control box is fixedly connected to the circumference of the fixing pole; a rainproof cover is fixedly connected to one surface of the master control box; a heating plate is fixedly connected to one surface of the rainproof cover; a temperature and humidity sensor, an information acquisition unit and a wireless transmitter are fixedly connected to the inner surface of the master control box respectively; an input end of the information acquisition unit is connected with a plurality of junction boxes fixedly through conductor wires; input ends of the junction boxes are fixedly connected with a plurality of tubular moisture detectors through conductor wires respectively. With the arrangement design of the junction boxes and the tubular moisture detectors, and designs of the the wireless transmitter and moisture monitoring probes, the device can realize multiple-point sampling, error influence caused by single-point sampling can be eliminated, monitoring results can be more representative and accurate; with designs of the rainproof cover, water guide slots and the electric heating plate, the electric appliance box of the device can be protected against rain and damp effectively.

Owner:NORTH CHINA UNIV OF WATER RESOURCES & ELECTRIC POWER

High-speed parallel acquisition system clock synchronization device

InactiveCN105116413AMiniaturizationImprove utilization efficiencyRadio wave reradiation/reflectionLow noisePhase noise

The invention relates to a high-speed parallel acquisition system clock synchronization device. According to the synchronization device, a signal conditioning unit is configured; a clock input amplitude range is set; before a switch unit is switched on, signal amplitude is increased to be sufficient to make a post-amplifier saturate; and therefore, clock signals at a triggering initial time point can be consistently identified at each channel, and the synchronization of a multi-channel data acquisition system can be realized. With the synchronization device adopted, the synchronism of the data acquisition system is concentrated on the switching on and switching off of a radio frequency switch, and the transient time of the switching on and switching off of the switch can be substantially compressed, and error influences caused by clock jitter at an A / D sampling starting position can be eliminated, and therefore, clock signal amplitude can be consistently identified at each channel, and excellent stability and reliability can be realized; and the extremely-low phase noise characteristic of a radio frequency circuit is utilized, so that single ended-to-differential low noise conversion of high-speed clock signals can be completed, and the utilization efficiency of the device can be improved, and the size of the device can be effectively reduced, and the realization of the miniaturization of circuits can be benefitted.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

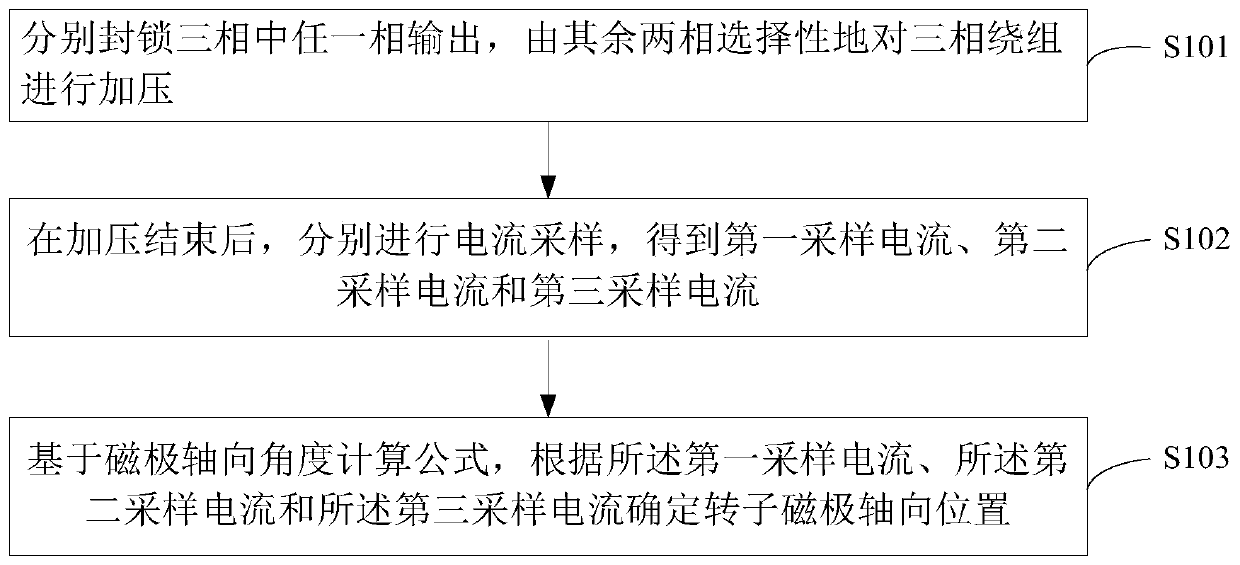

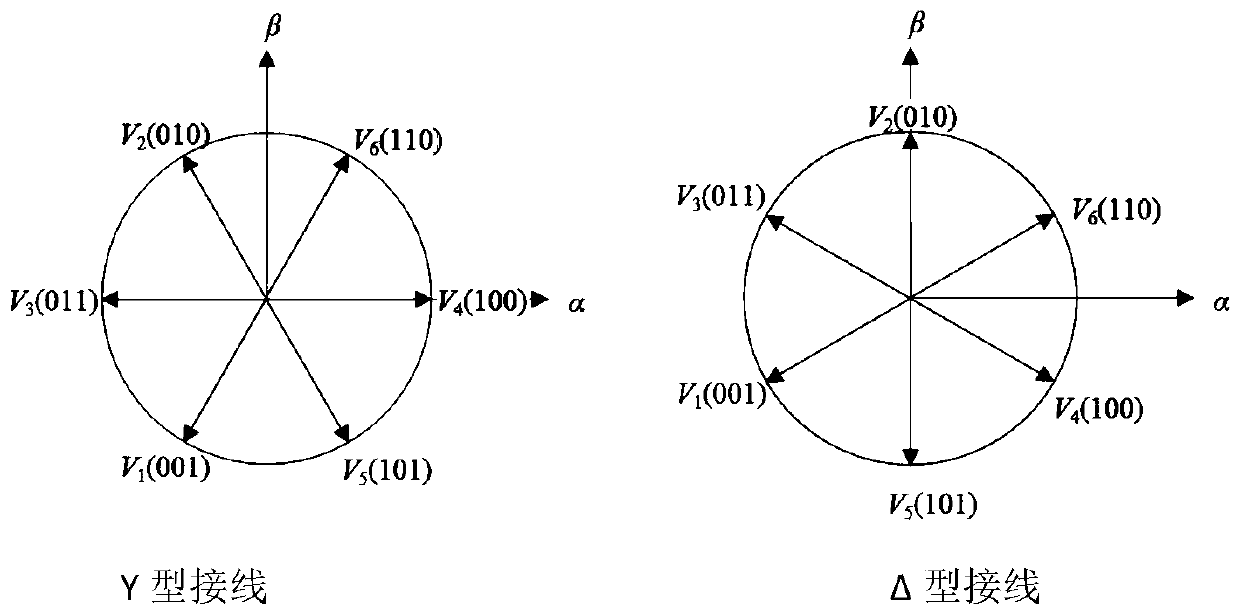

Method and device for detecting initial position of rotor of permanent magnet synchronous motor and frequency converter

InactiveCN110855192AEasy to detectEliminate the effect of errorElectric motor controlElectronic commutatorsFrequency changerPermanent magnet synchronous motor

The invention discloses a permanent magnet synchronous motor rotor initial position detection method and device, a frequency converter and a storage medium, and relates to the technical field of rotorinitial position detection. The method comprises the steps: respectively blocking the output of any one phase in three phases, and enabling the other two phases to selectively pressurize three-phasewindings; after the pressurization is finished, respectively carrying out current sampling to obtain a first sampling current, a second sampling current and a third sampling current; and determining the axial position of the rotor magnetic pole according to the first sampling current, the second sampling current and the third sampling current based on a magnetic pole axial angle calculation formula. According to the permanent magnet synchronous motor rotor initial position detection method, the permanent magnet synchronous motor rotor initial position detection device and the frequency converter, modulation of a plurality of voltage vectors is not needed, so that the detection process is greatly simplified, and the influence of control errors is thoroughly eliminated.

Owner:青岛斑科变频技术有限公司

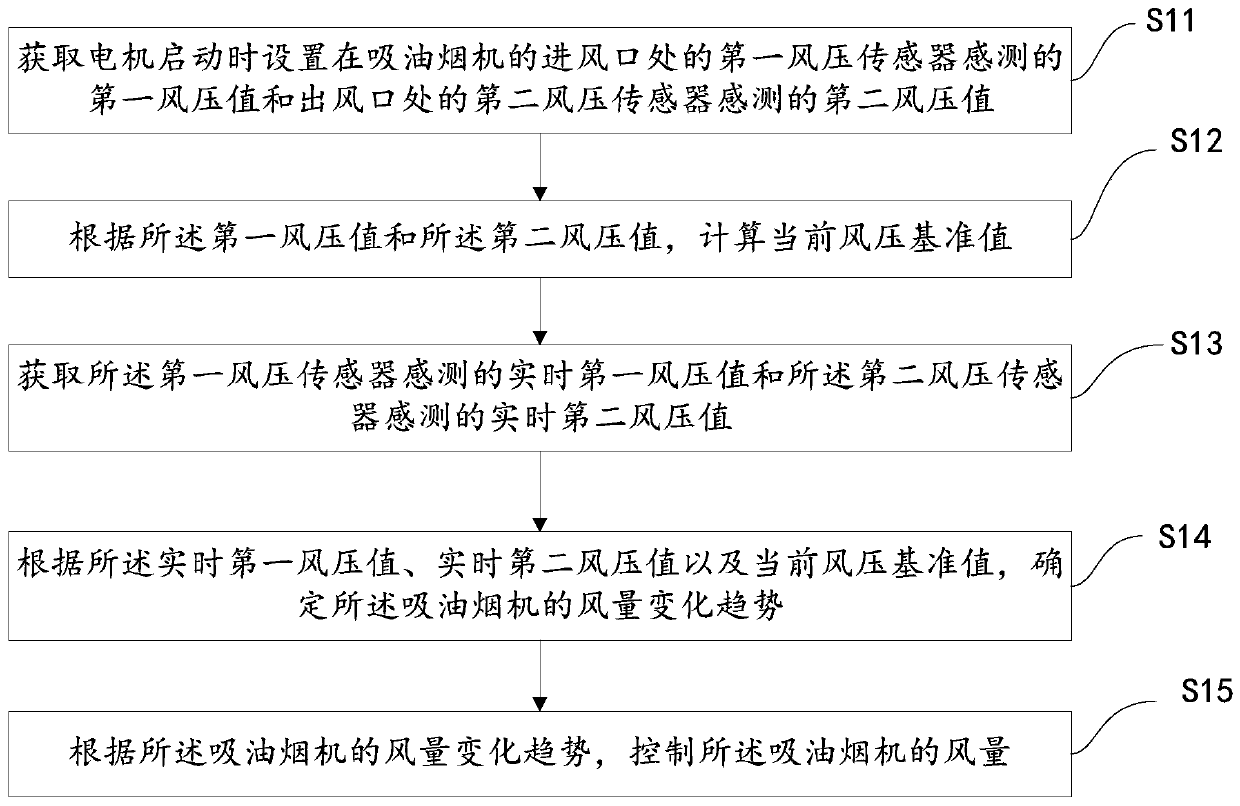

Method, device and equipment for detecting and controlling wind pressure of range hood and storage medium

ActiveCN109974059AGuaranteed accuracyEliminate the effects of systematic errorsDomestic stoves or rangesLighting and heating apparatusAir volumeCurrent range

The invention discloses a method, device and equipment for detecting and controlling wind pressure of a range hood and a storage medium. The method for detecting and controlling the wind pressure of the range hood comprises the following steps that a first wind pressure value sensed by a first wind pressure detection module arranged at an air inlet of the range hood and a second wind pressure value sensed by a second wind pressure detection module arranged at an air outlet of the range hood are acquired when a motor is started; a current wind pressure reference value is calculated according tothe first wind pressure value and the second wind pressure value; a real-time first wind pressure value sensed by the first wind pressure detection module and a real-time second wind pressure value sensed by the second wind pressure detection module are acquired; according to the real-time first air pressure value, the real-time second air pressure value and the current air pressure reference value, the air volume change trend of the range hood is determined; according to the air volume change trend of the range hood, the air volume of the range hood is controlled; by updating the wind pressure reference value at each motor startup, the running status of a whole flue system and a wind cabinet system of the current range hood is reflected, the influence of system errors is eliminated, misjudgment is avoided, and the accuracy of wind pressure detection is improved.

Owner:GUANGDONG WANHE THERMAL ENERGY TECH CO LTD

Roadside equipment clock accuracy test method and system based on floating vehicle

ActiveCN112153574AImprove accuracyImprove stabilitySynchronisation arrangementParticular environment based servicesTime informationSimulation

The invention relates to a roadside equipment clock accuracy test method and system based on a floating vehicle, and the method comprises the steps: retrieving and recording GPS records nearby roadside equipment, including vehicle GPS positioning information and time information; forming a passing track record of the vehicle passing by the roadside equipment based on the obtained GPS record; basedon the GPS positioning information of the vehicle passing through the roadside equipment each time, establishing a fitting model to predict the real GPS time of the vehicle passing through the roadside equipment; and matching data records of the same vehicle passing through the same road side equipment, and checking whether the observation time of the road side equipment is consistent or not by utilizing the real GPS time when an event occurs. The method and the system are low in cost and easy to implement, and have good accuracy and stability.

Owner:NANJING MICROVIDEO TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com