Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

365results about "Protection and storage accessories" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

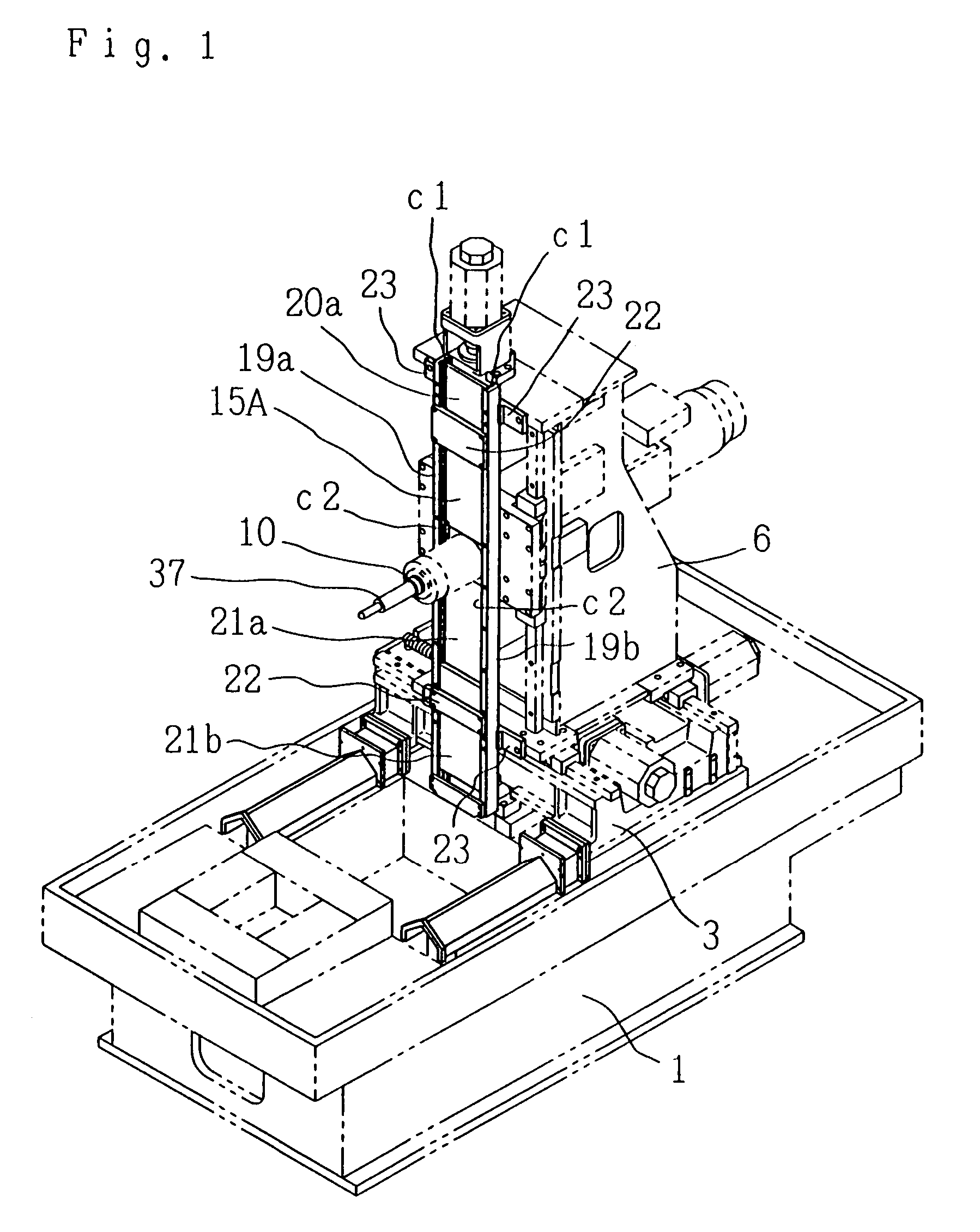

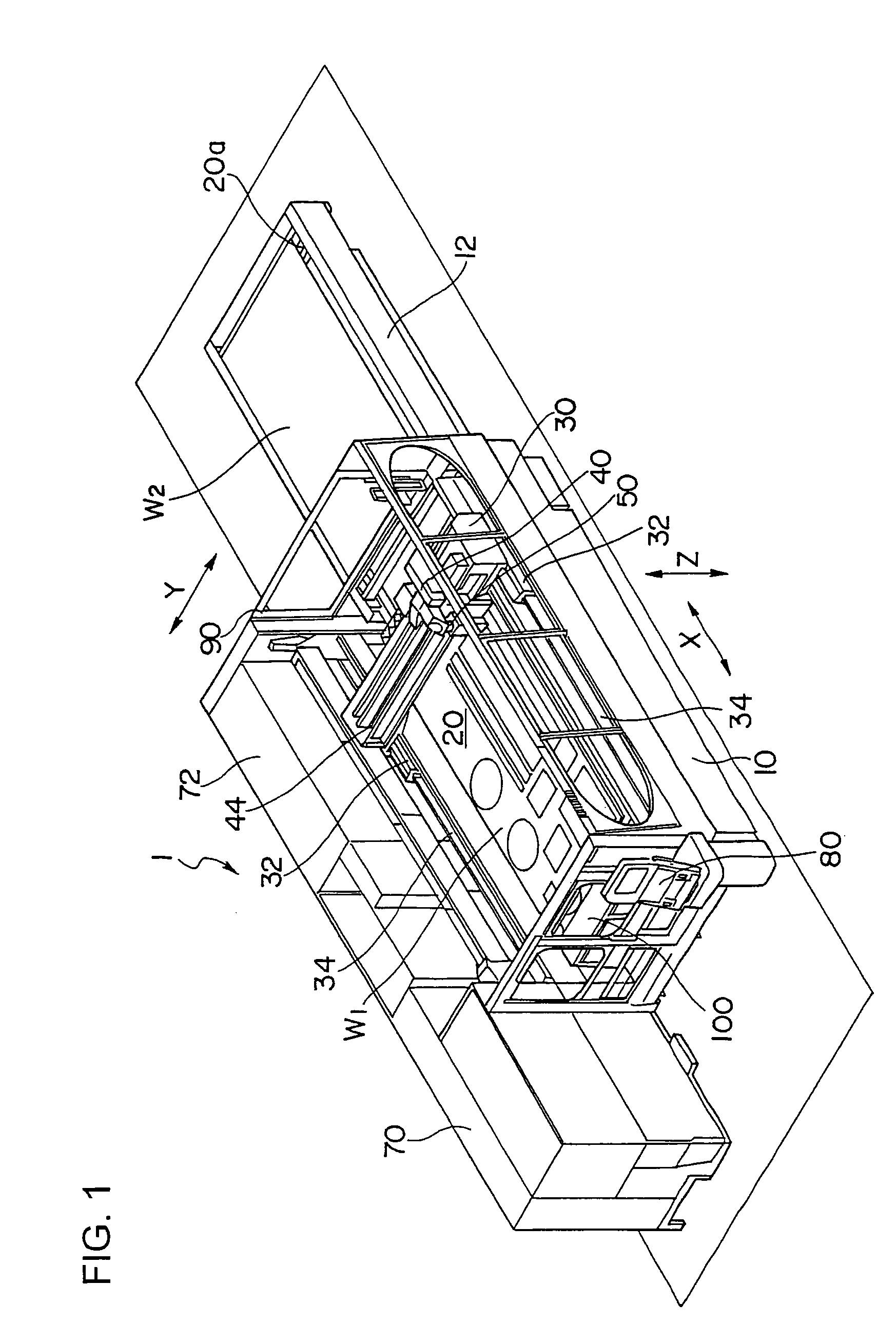

Machine Tool

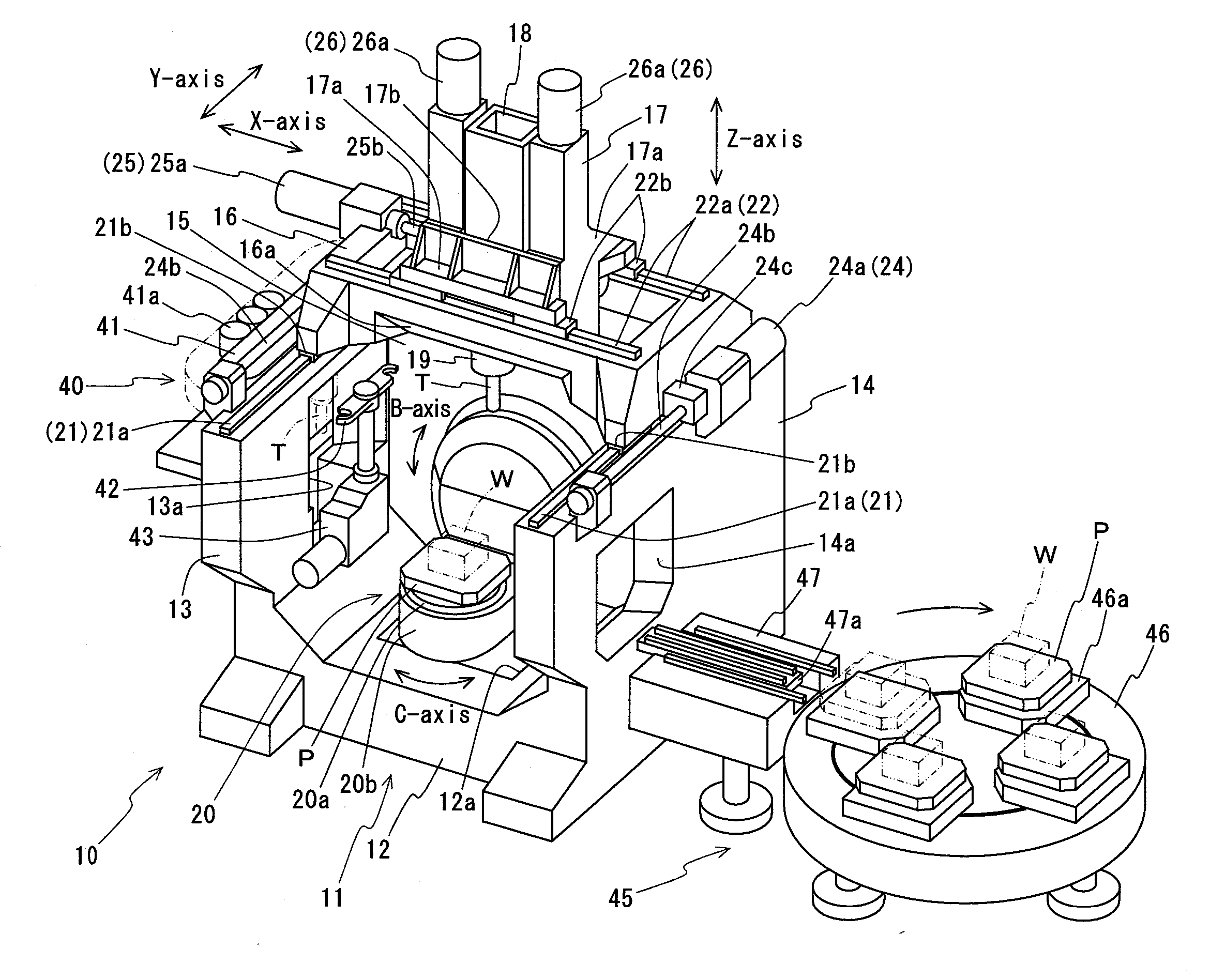

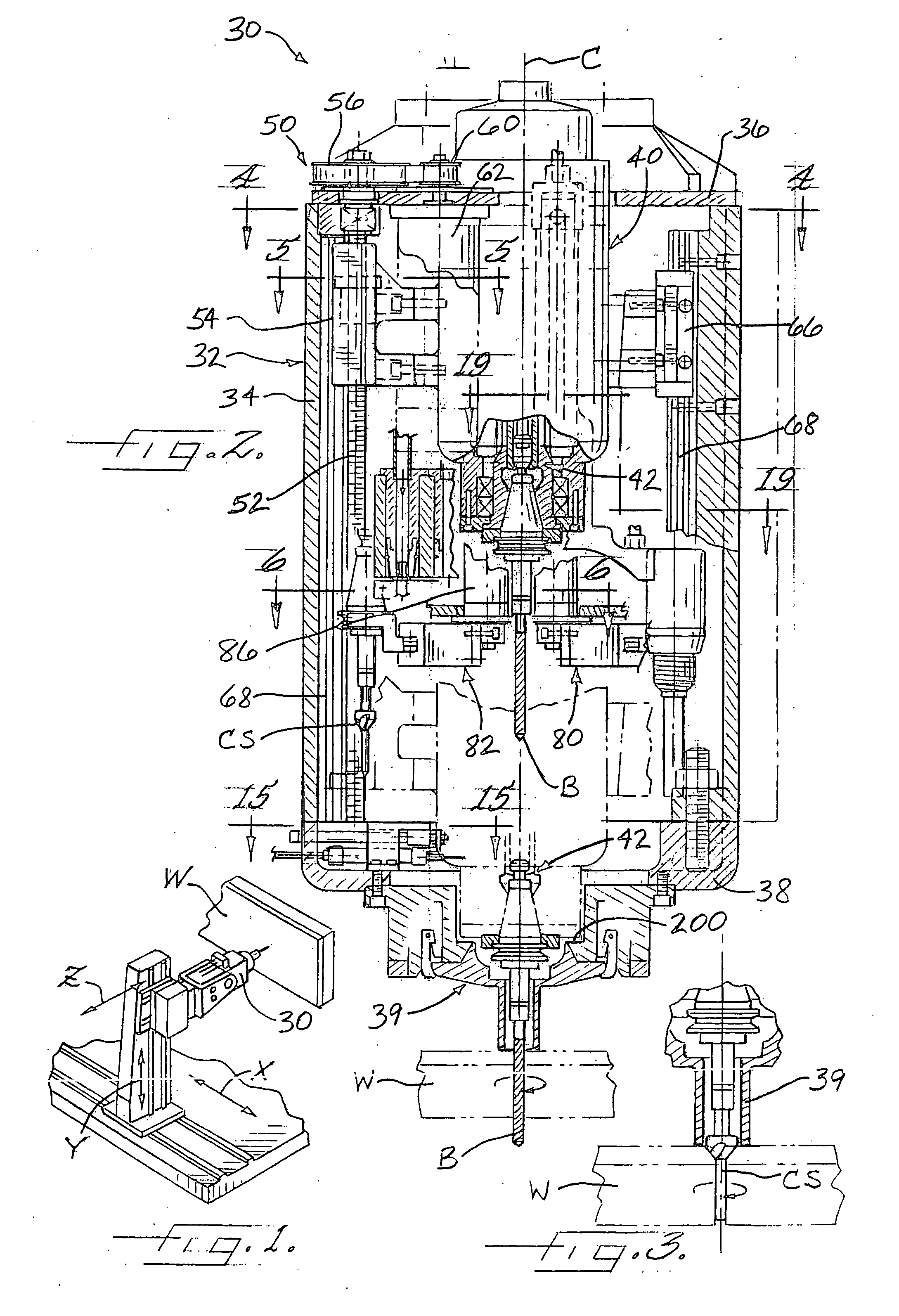

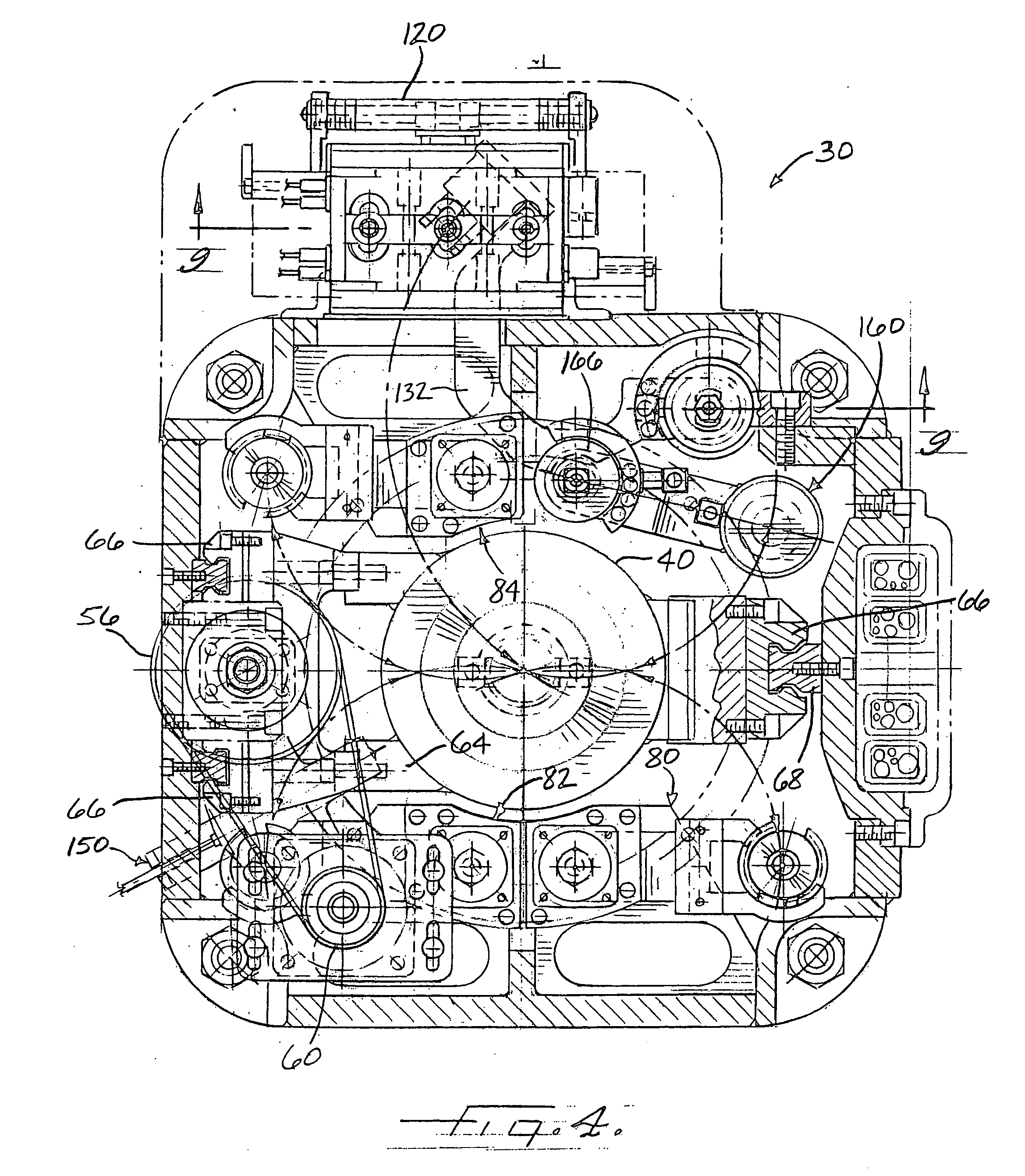

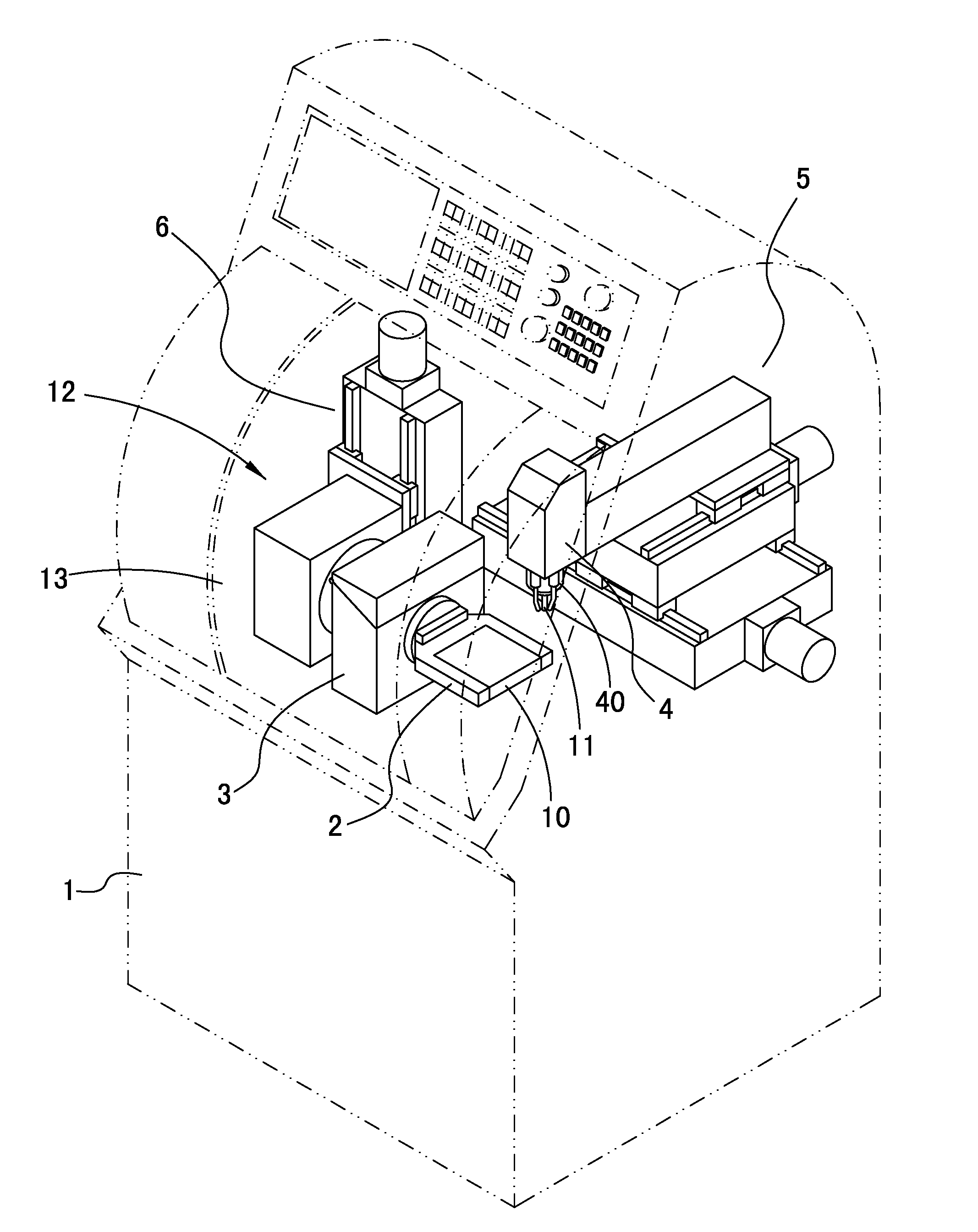

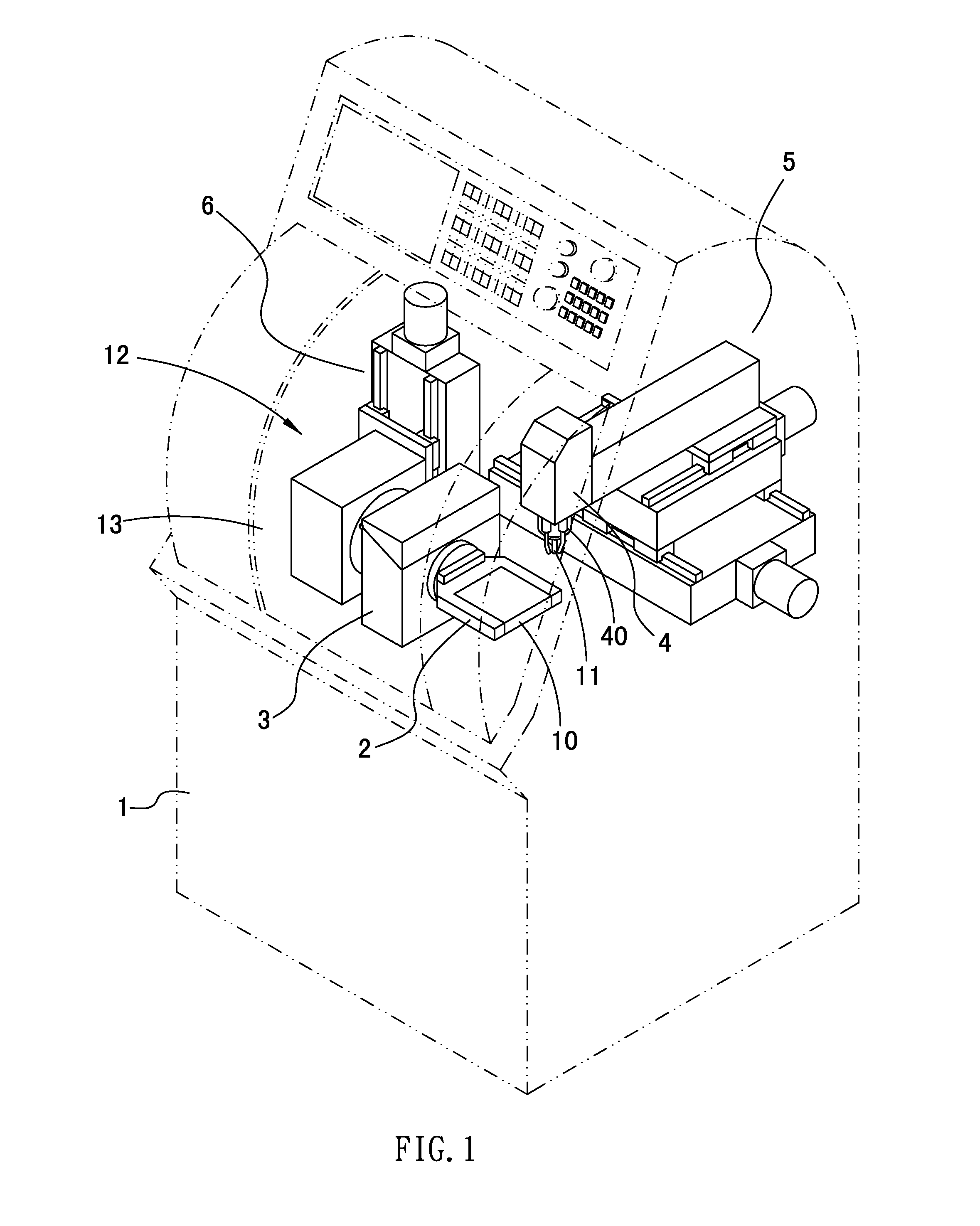

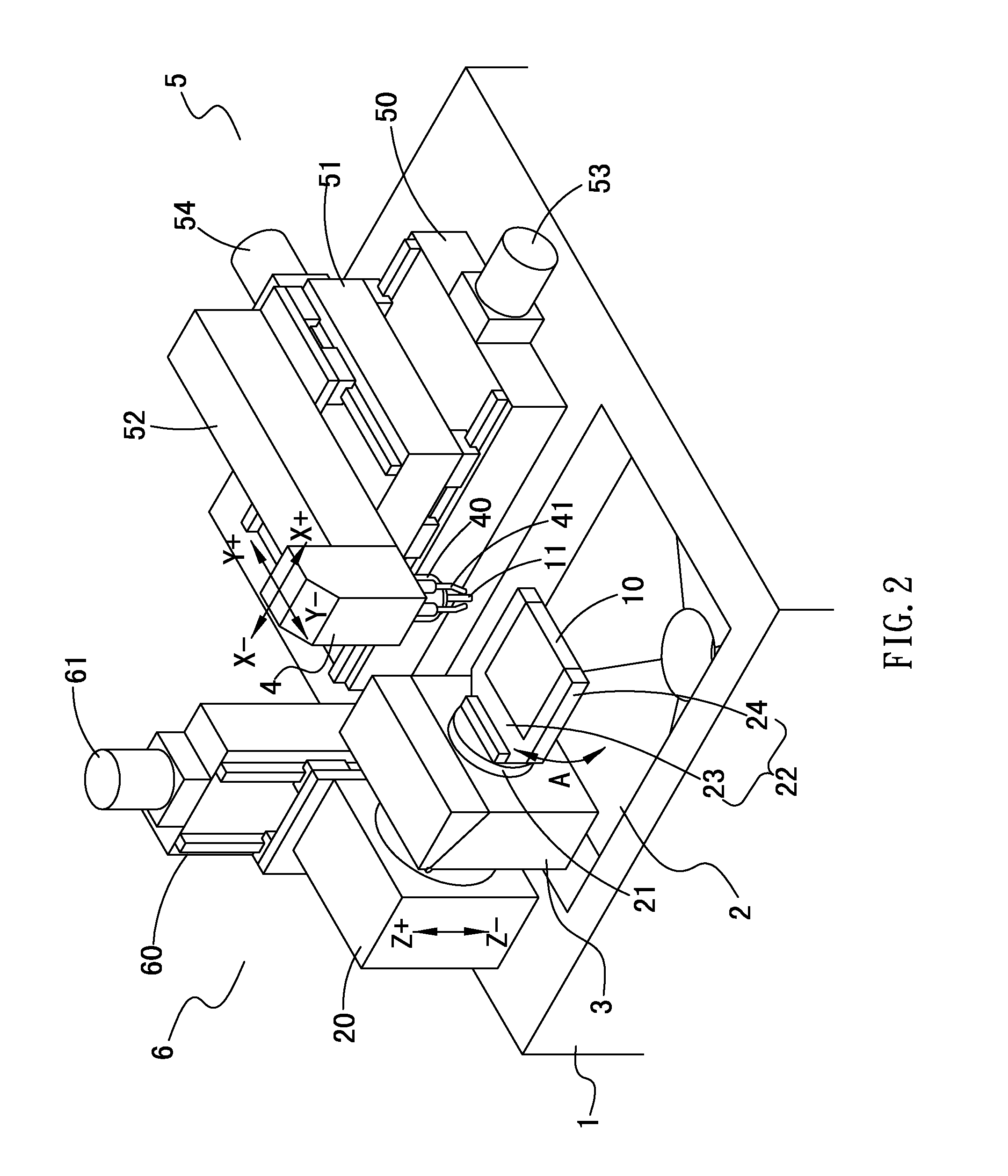

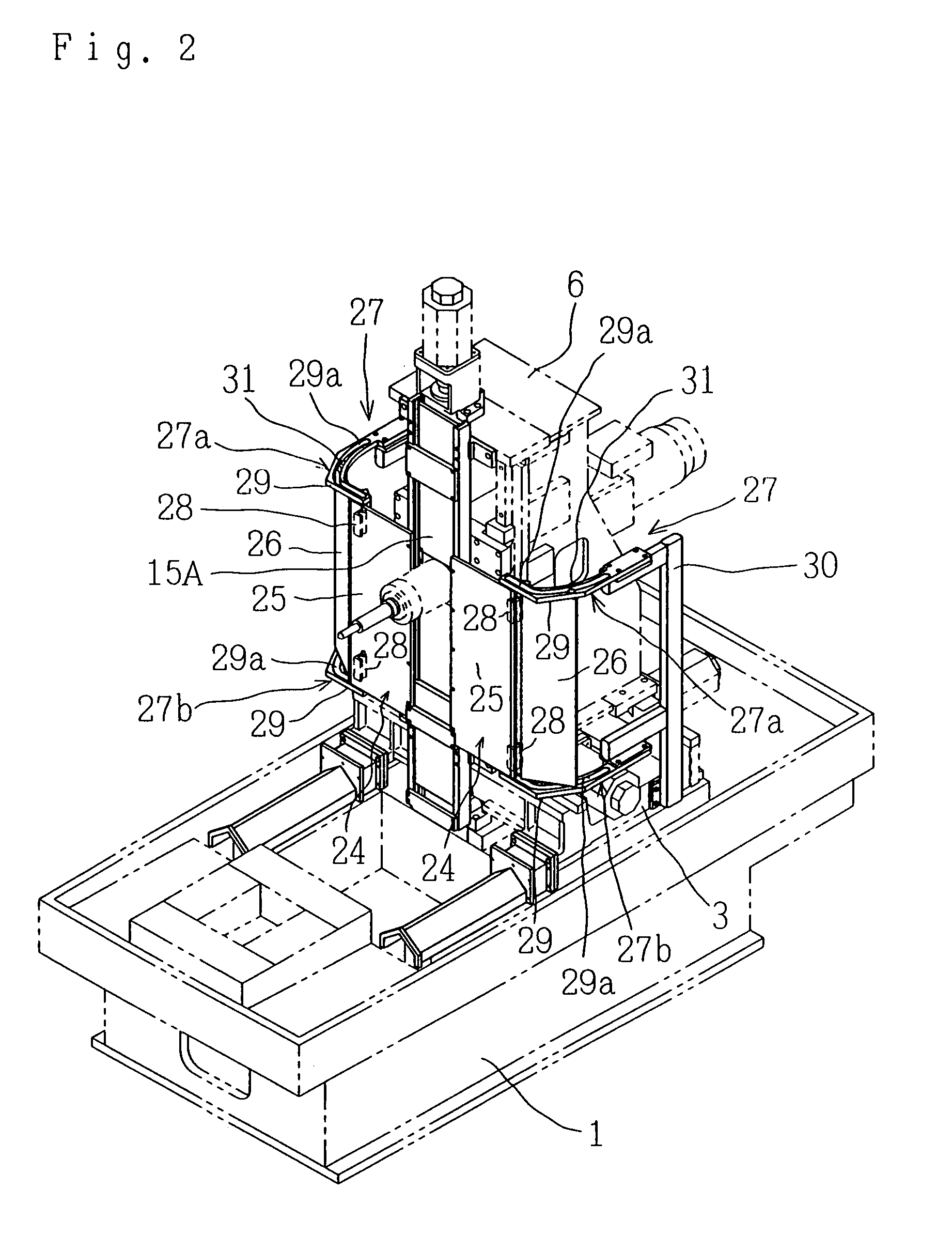

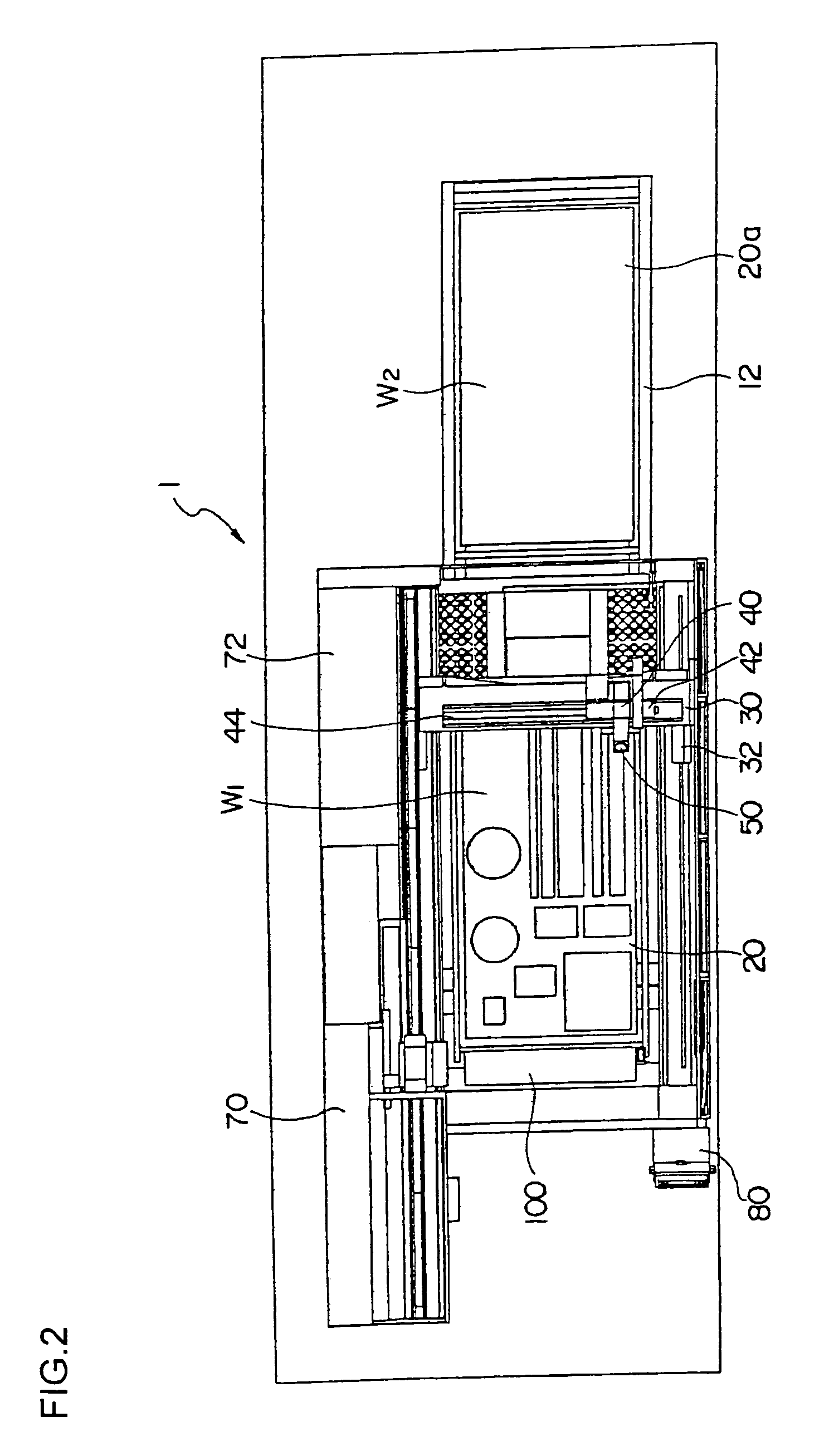

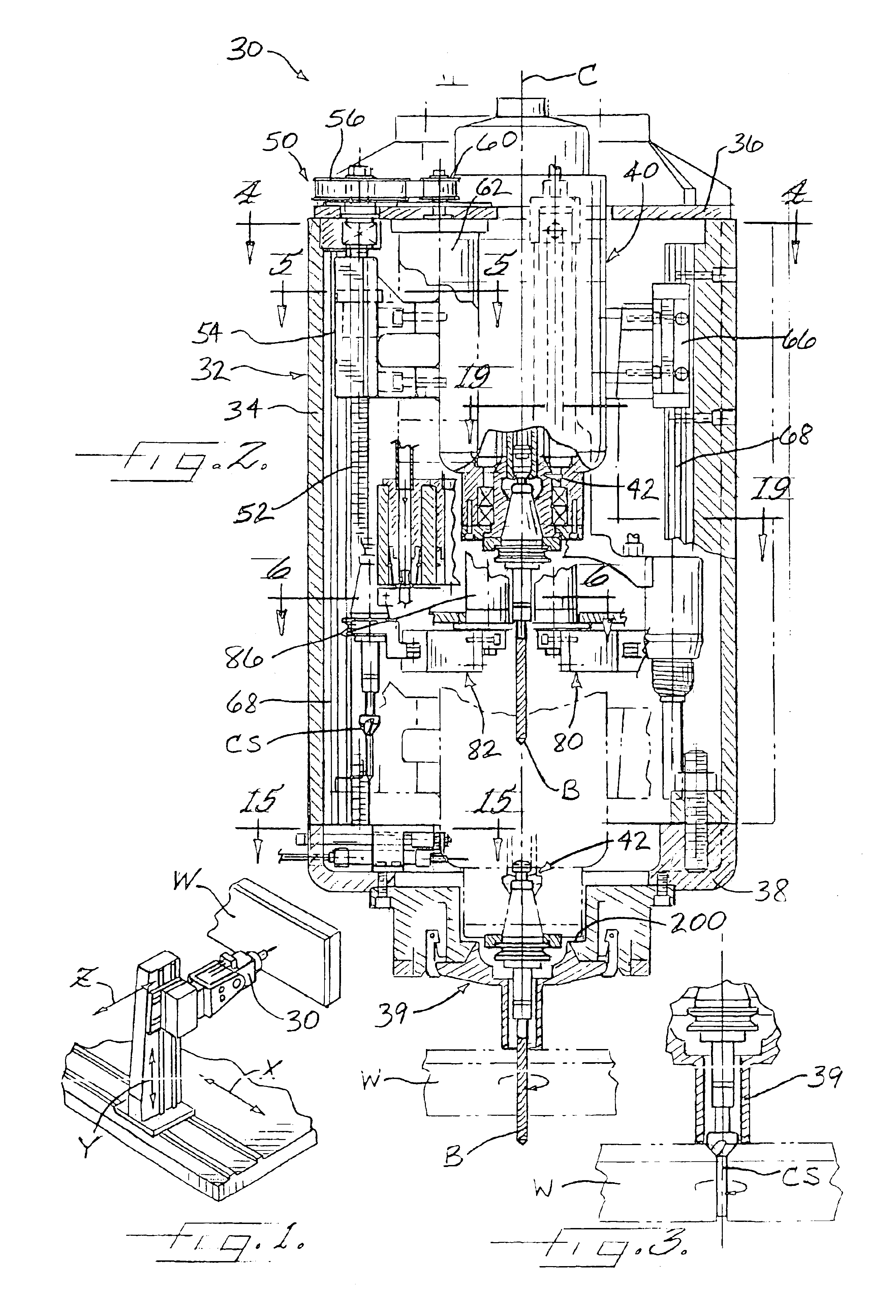

ActiveUS20060270540A1Easy maintenanceReduce manufacturing costPlaning/slotting machinesMilling machinesFree rotationSaddle shape

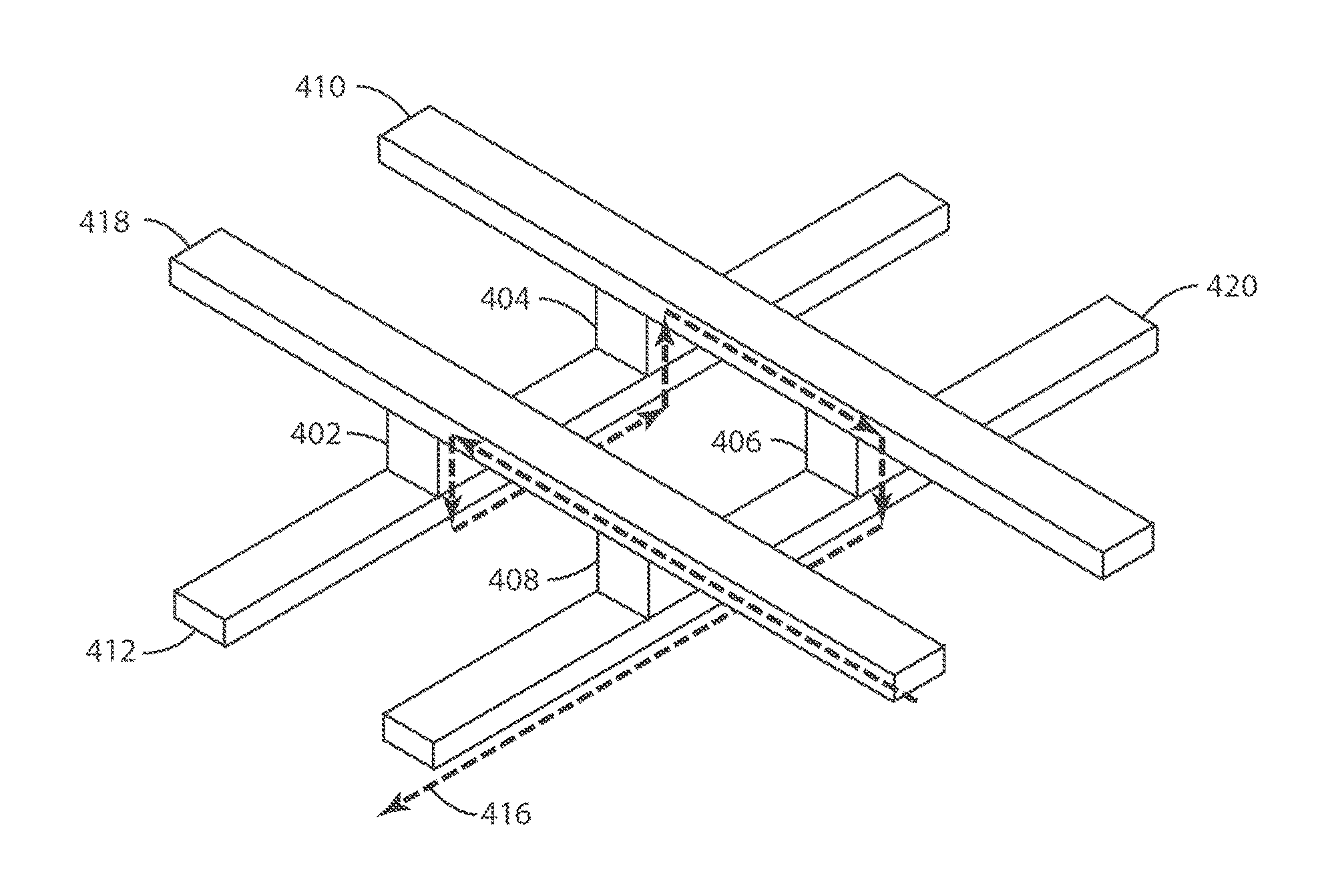

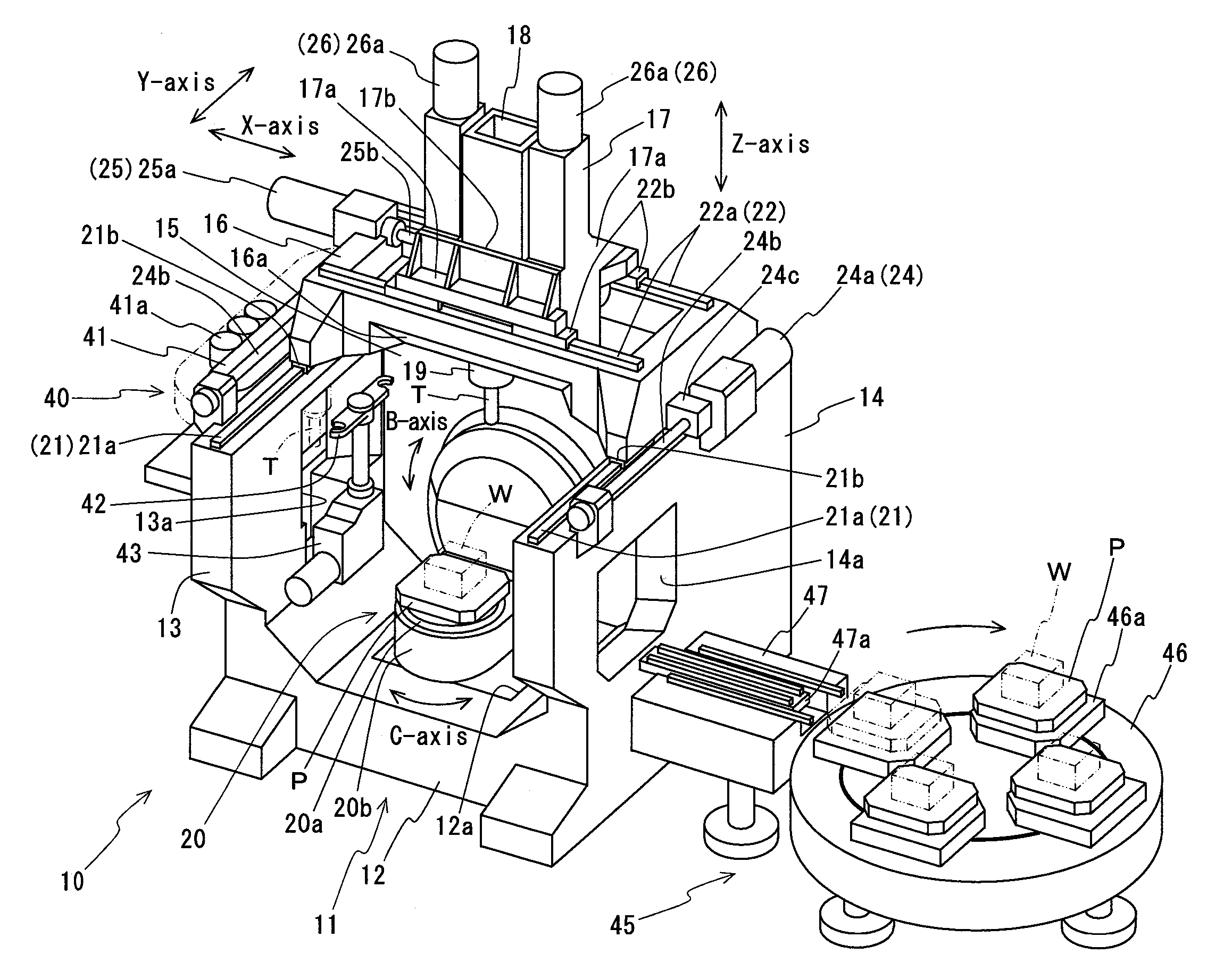

Machine tool simplifying maintenance, reducing manufacturing costs, and enabling high precision machining. The machine tool is equipped with: a bed furnished with a rectangular base, right and left sidewalls provided standing either side of the base, and a rear sidewall provided standing along the back of the base; a table disposed in the space surrounded by the three sidewalls; a first saddle shaped in the form of a rectangular frame shape, provided free to shift back and forth supported on the tops of the left and right sidewalls; a second saddle penetrated by a perpendicular through-hole and arranged free to shift sideways inside the first saddle frame; and a spindle head arranged free to shift perpendicularly inside the through-hole in the second saddle; and a main spindle arranged over the table and supported by the spindle head free to rotate centered on its axis.

Owner:DMG MORI SEIKI CO LTD

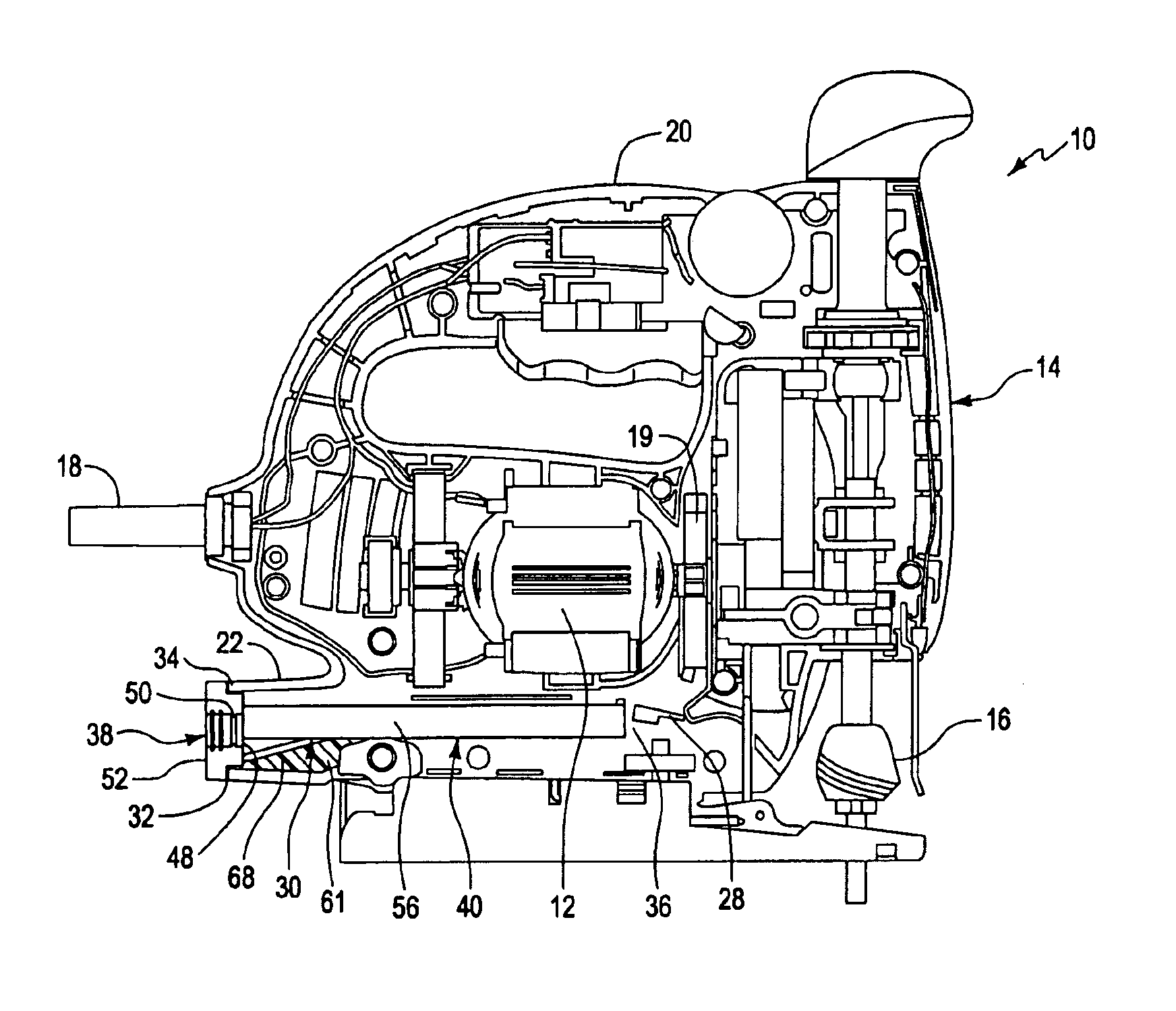

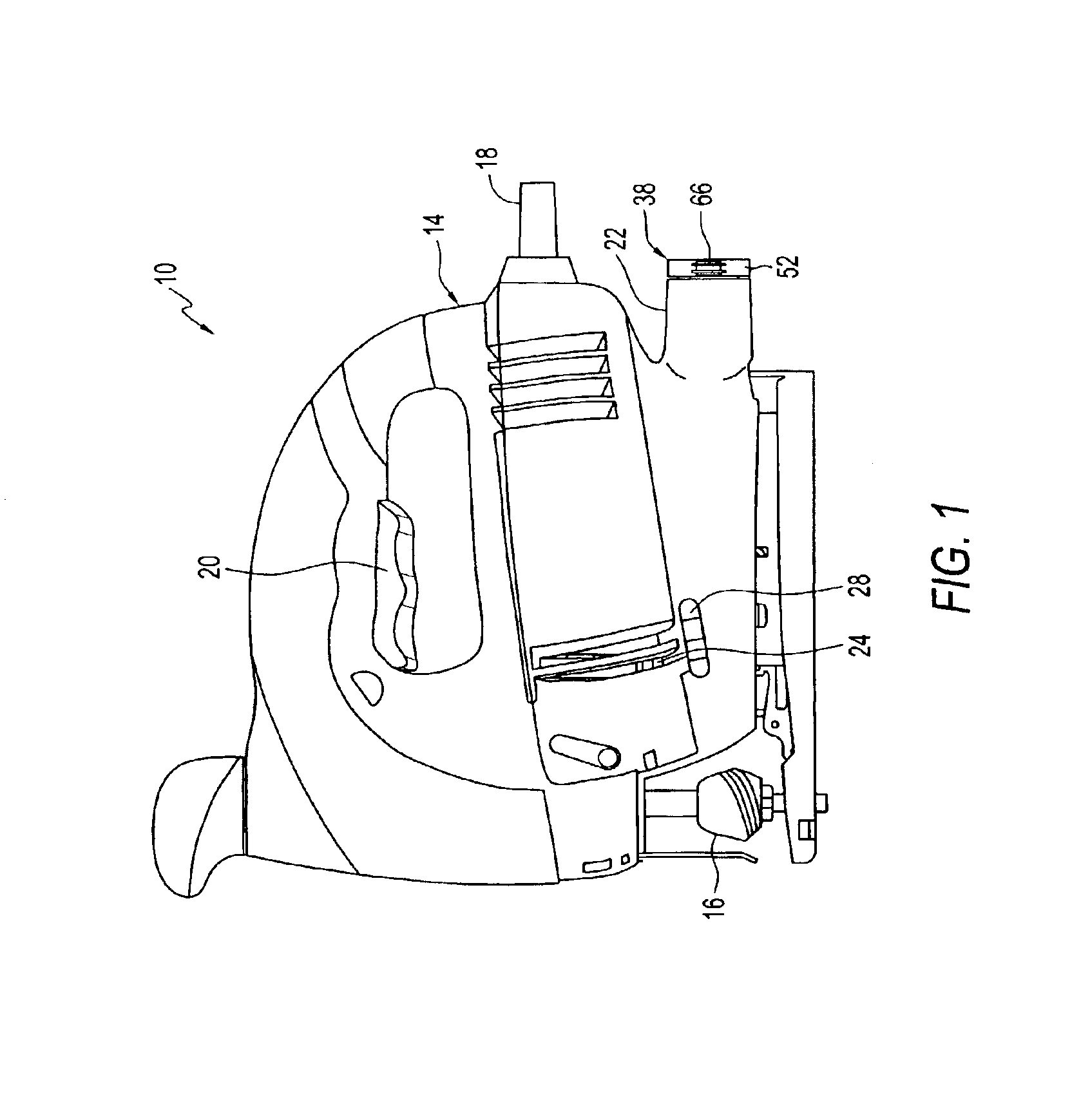

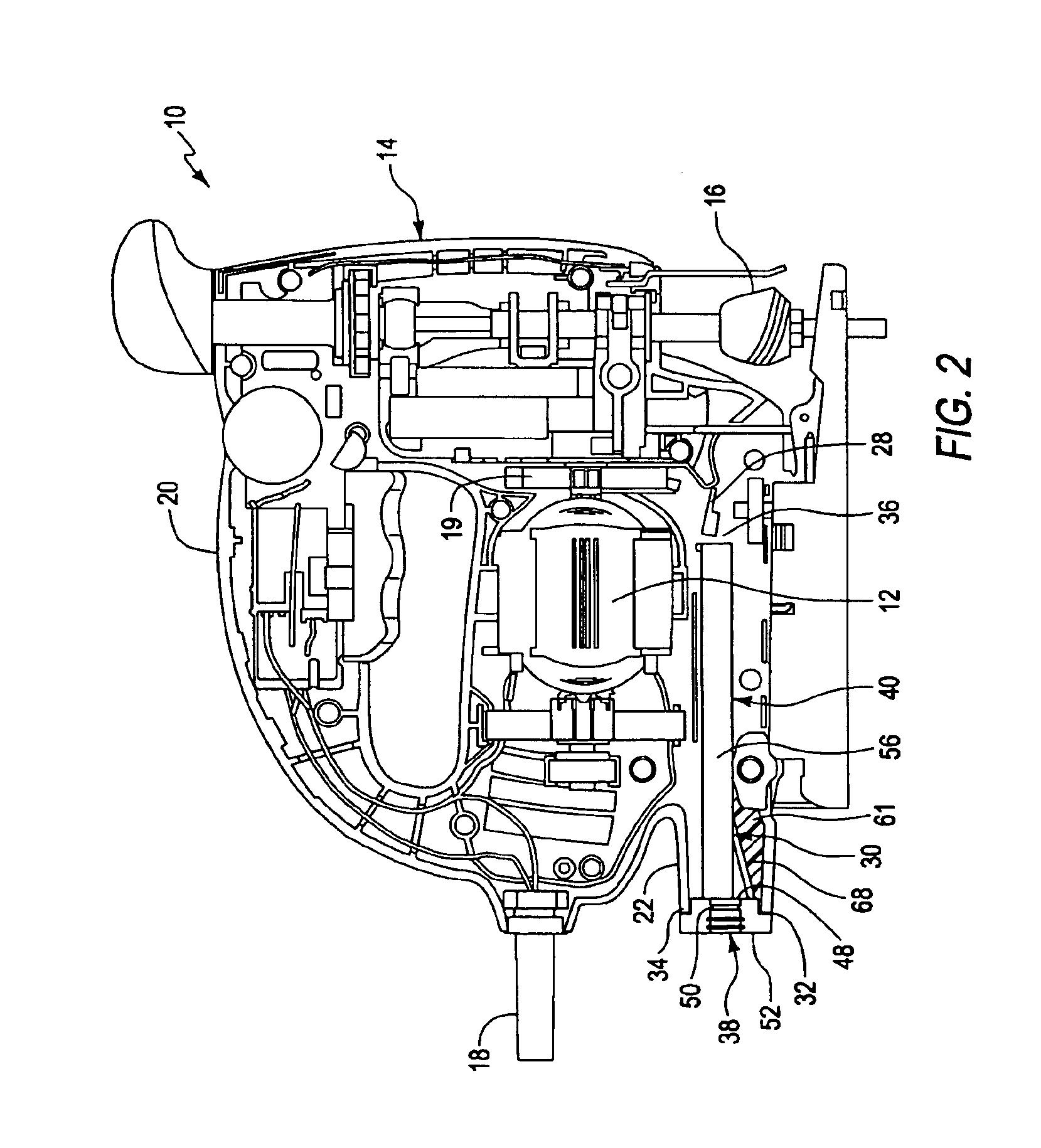

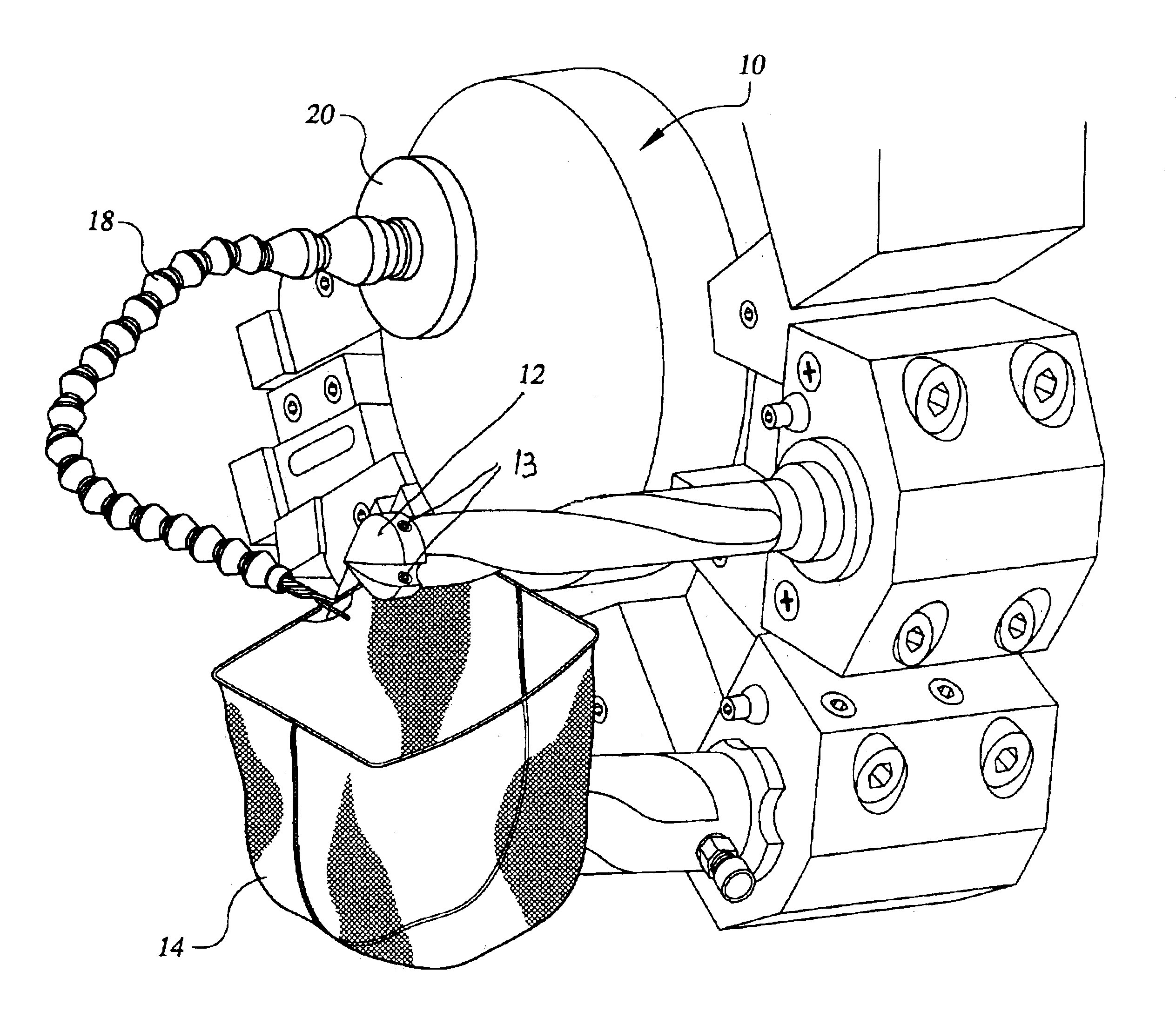

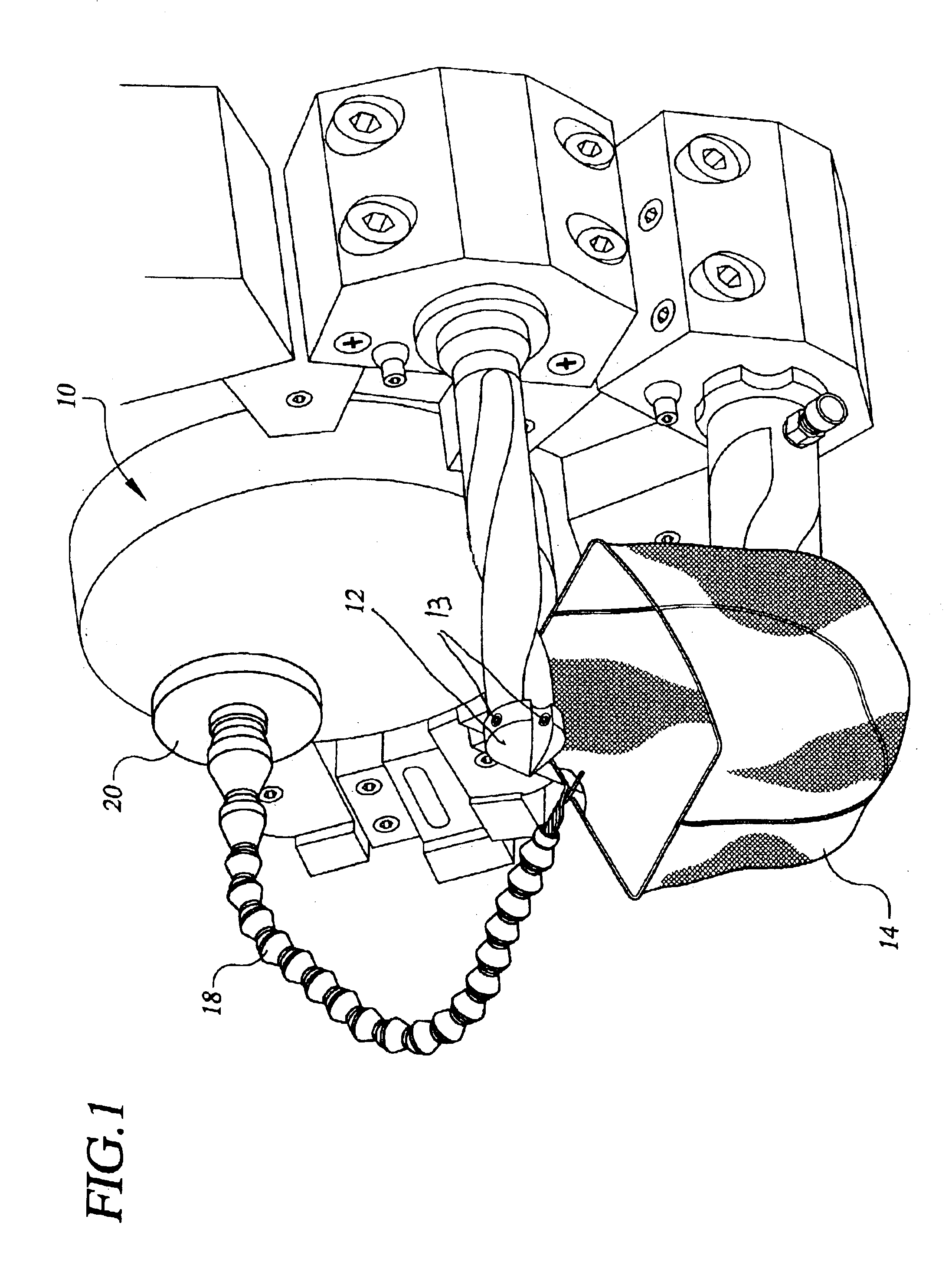

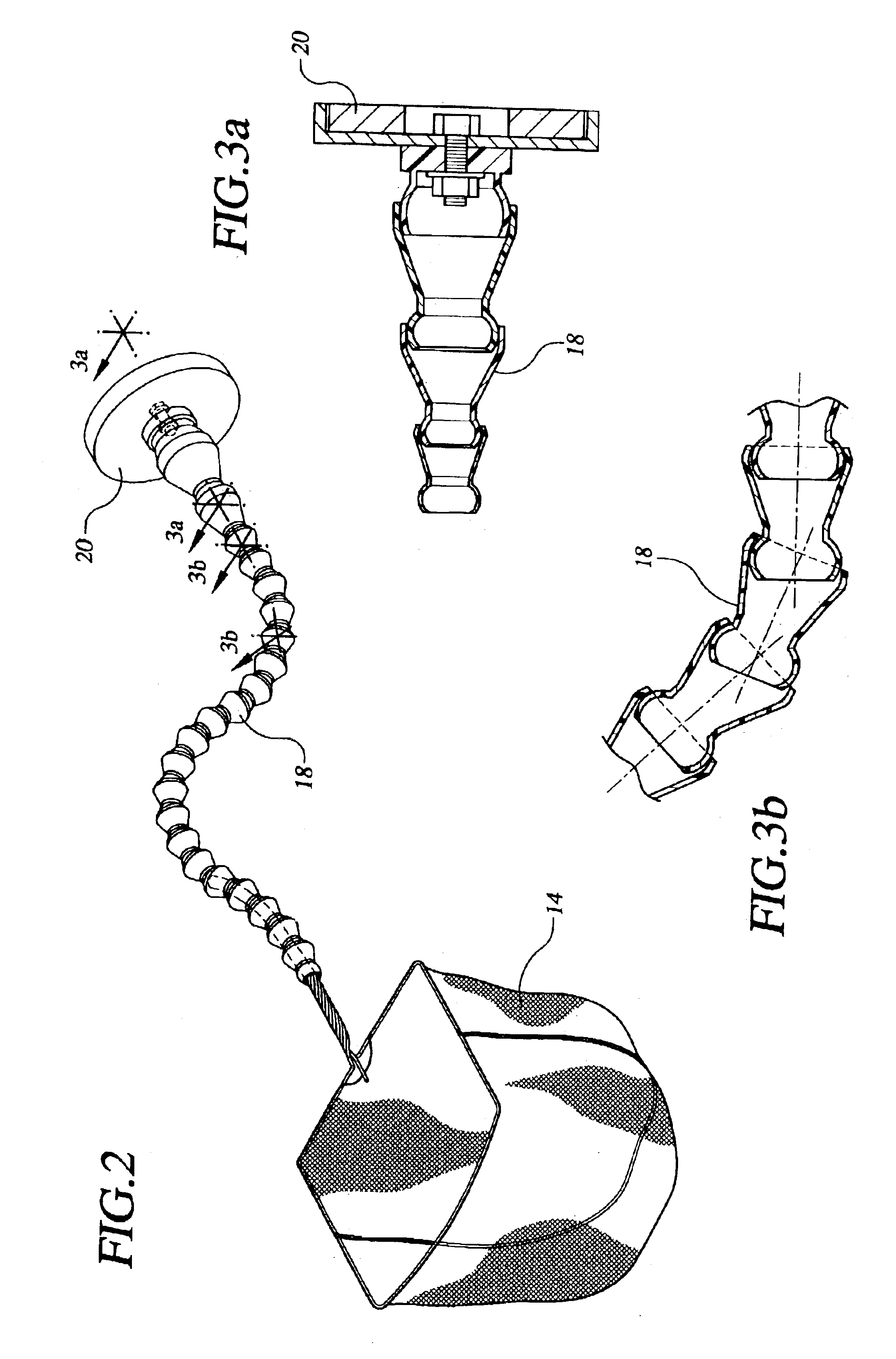

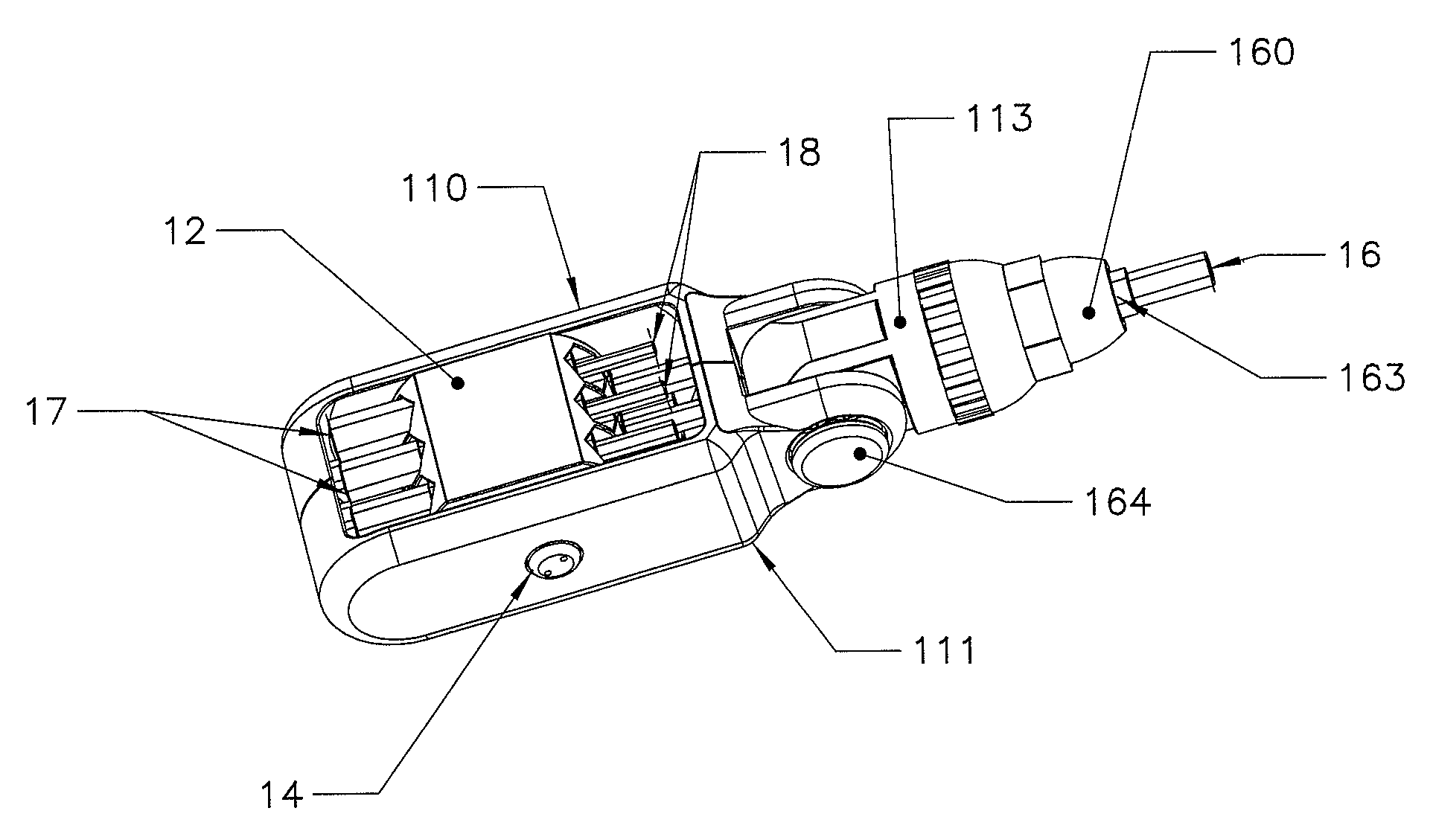

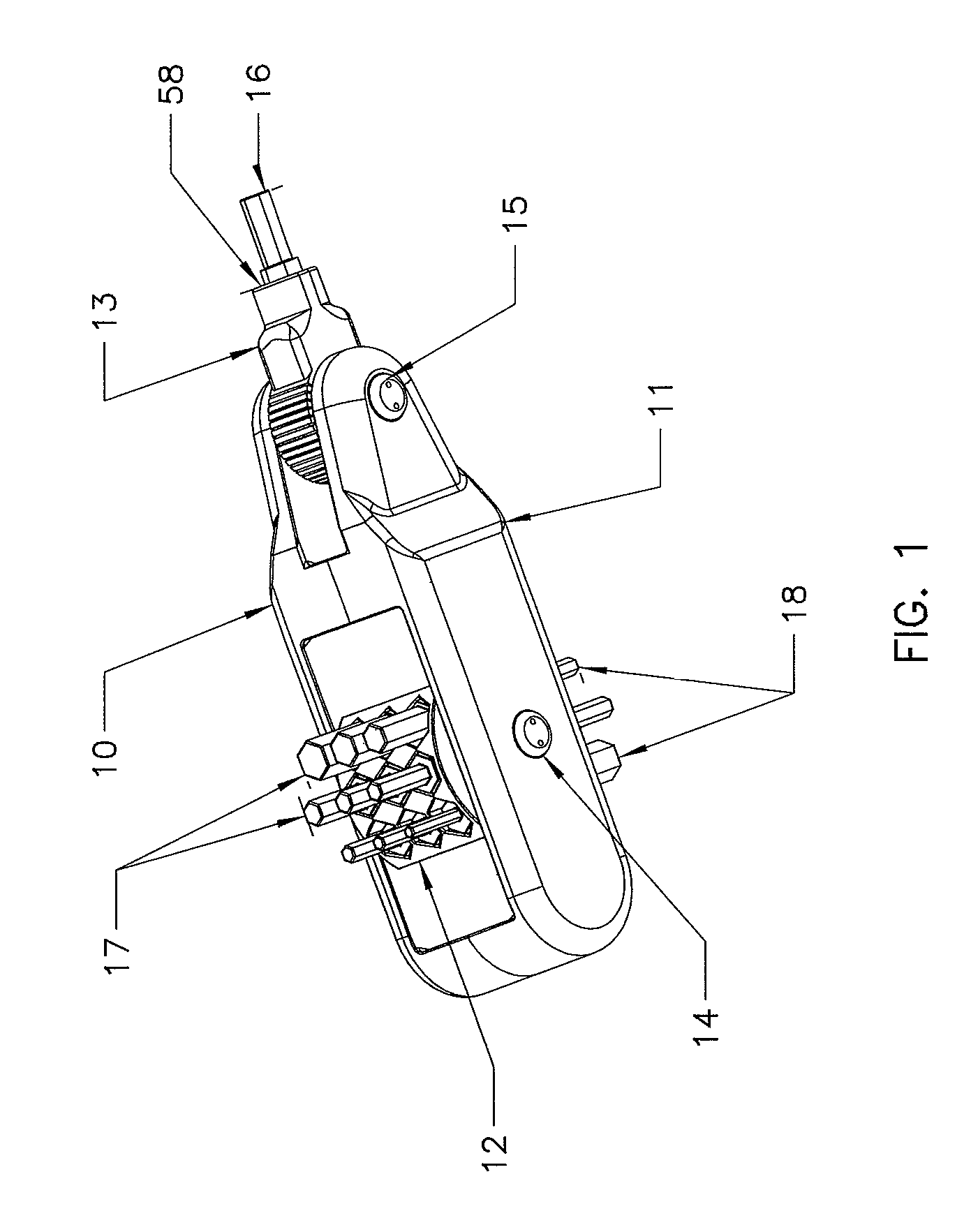

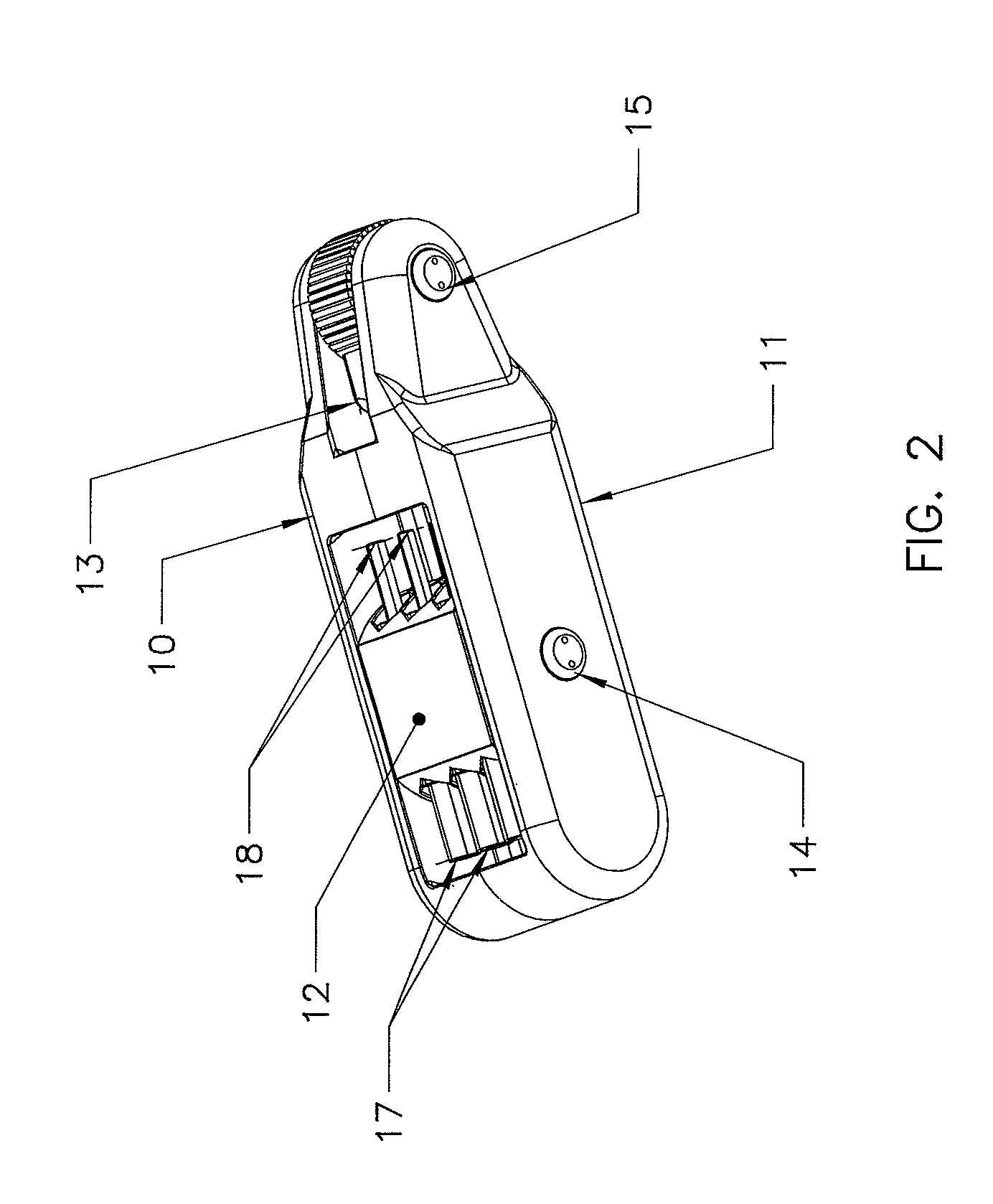

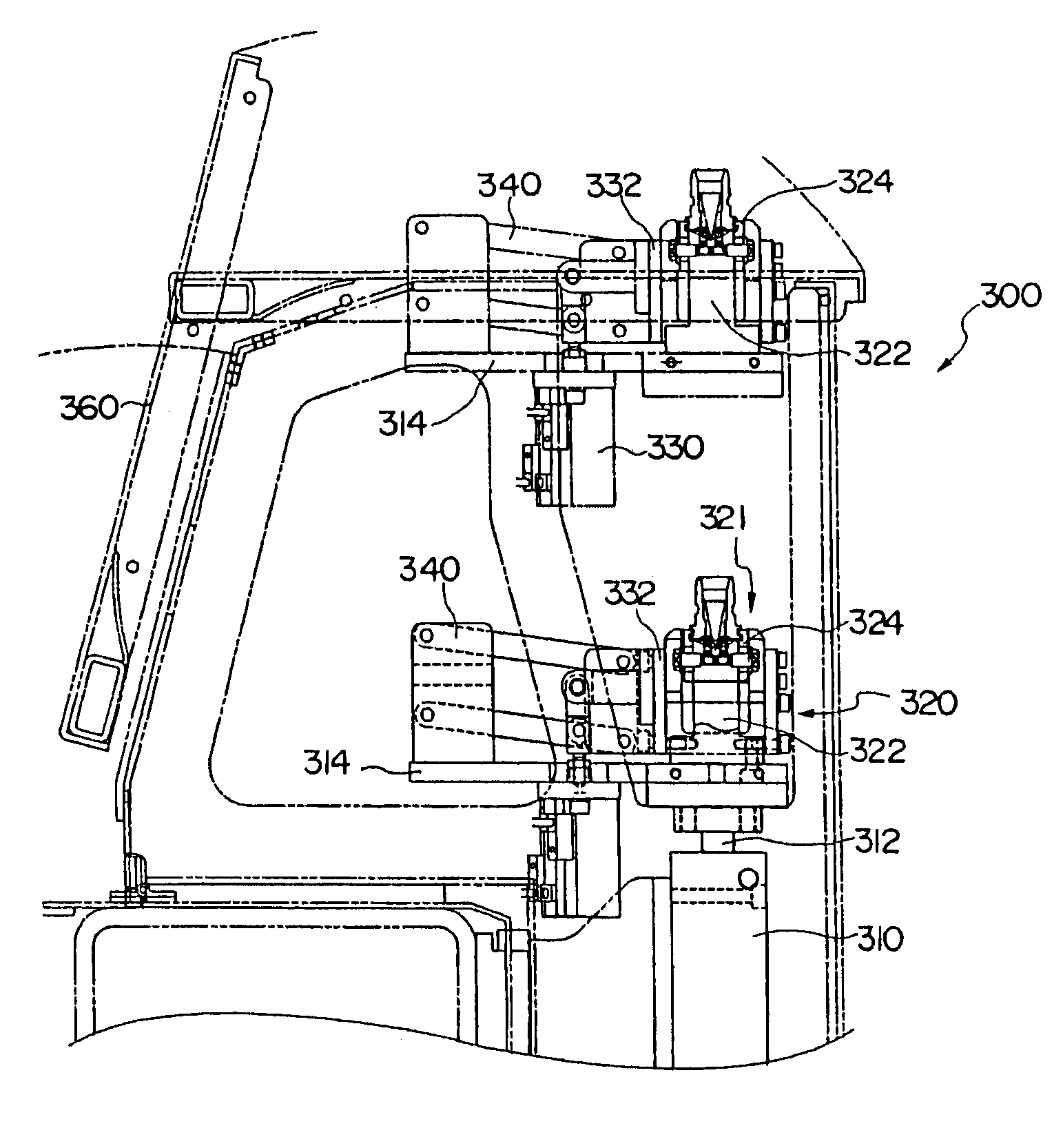

Multi-function end effector

A multi-function end effector includes a plurality of tool change mechanisms in a housing in which a spindle is also mounted for translation along an axis of the spindle. Each tool change mechanism has a gripper that releasably grips a tool holder in which a tool is mounted. The gripper of each tool change mechanism is movable between a stowed position to a tool-change position in which the gripper is coaxially aligned with the axis of the spindle for placing a tool holder held in the gripper in a position to be received by the spindle and for positioning the gripper to receive a tool holder from the spindle. The tools mounted in the tool holders include a drill bit, a countersink tool, and a fastener insertion tool. The end effector also includes a fastener feed system, a hammer device, and a sealant applicator.

Owner:THE BOEING CO

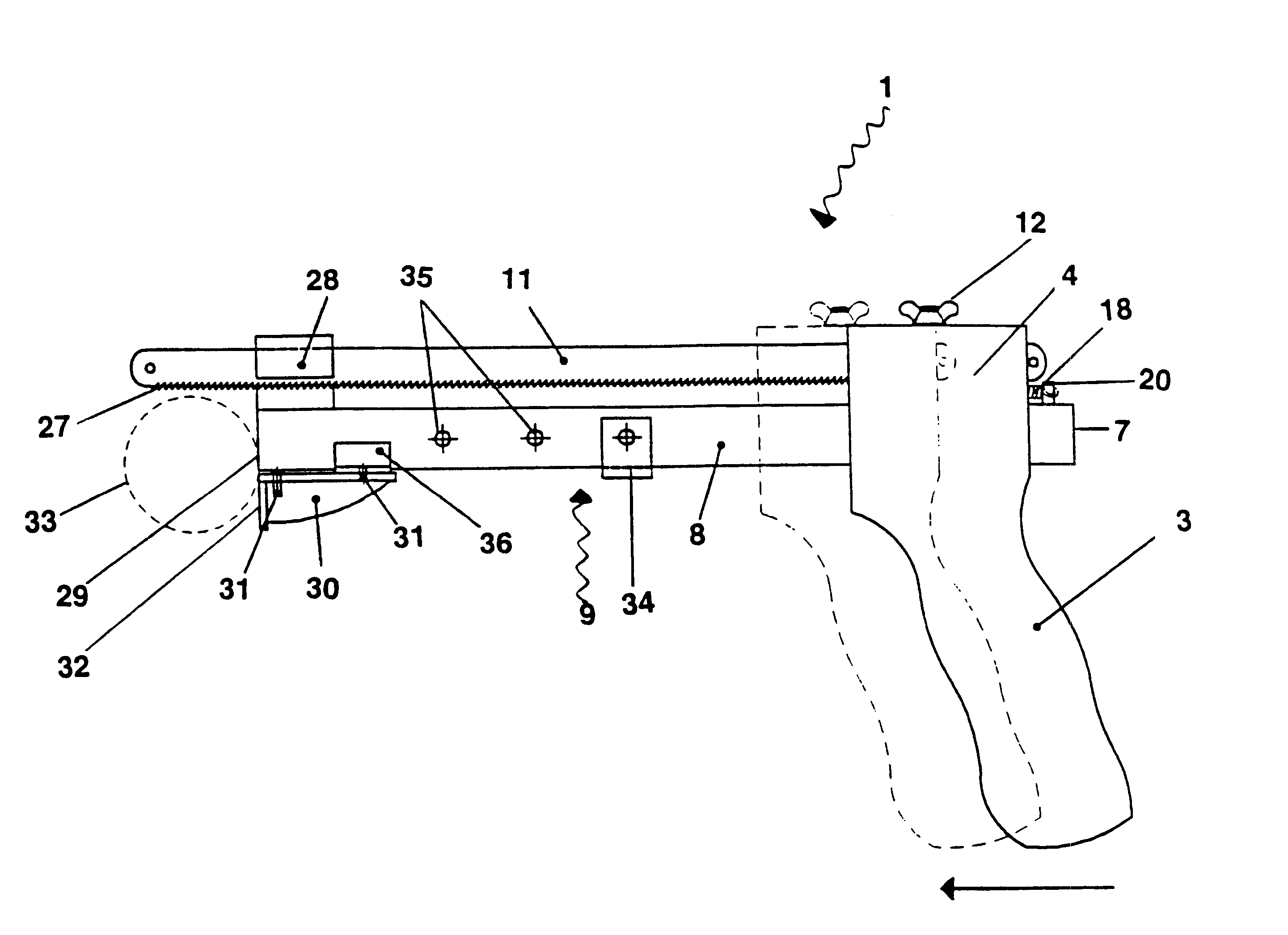

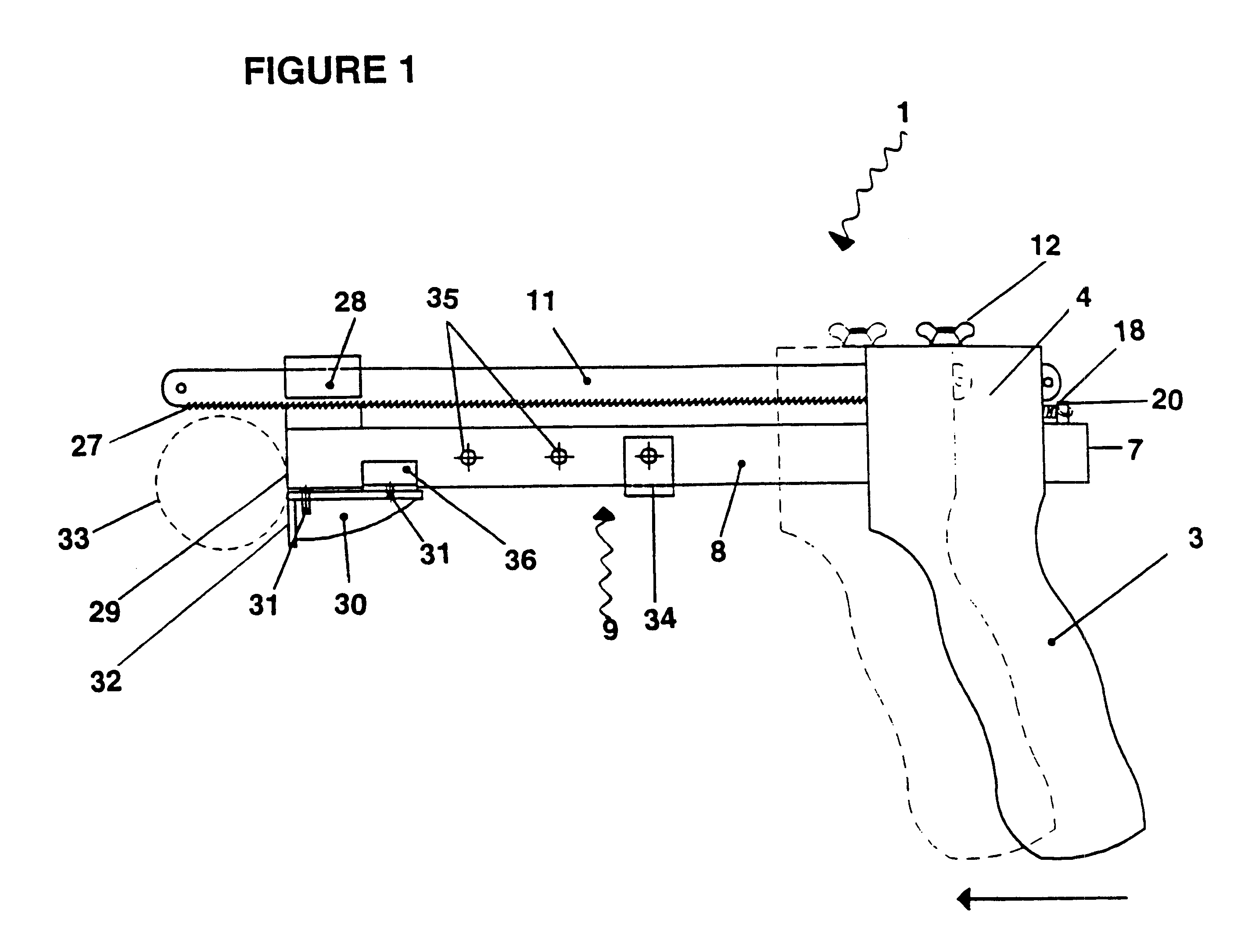

Tool

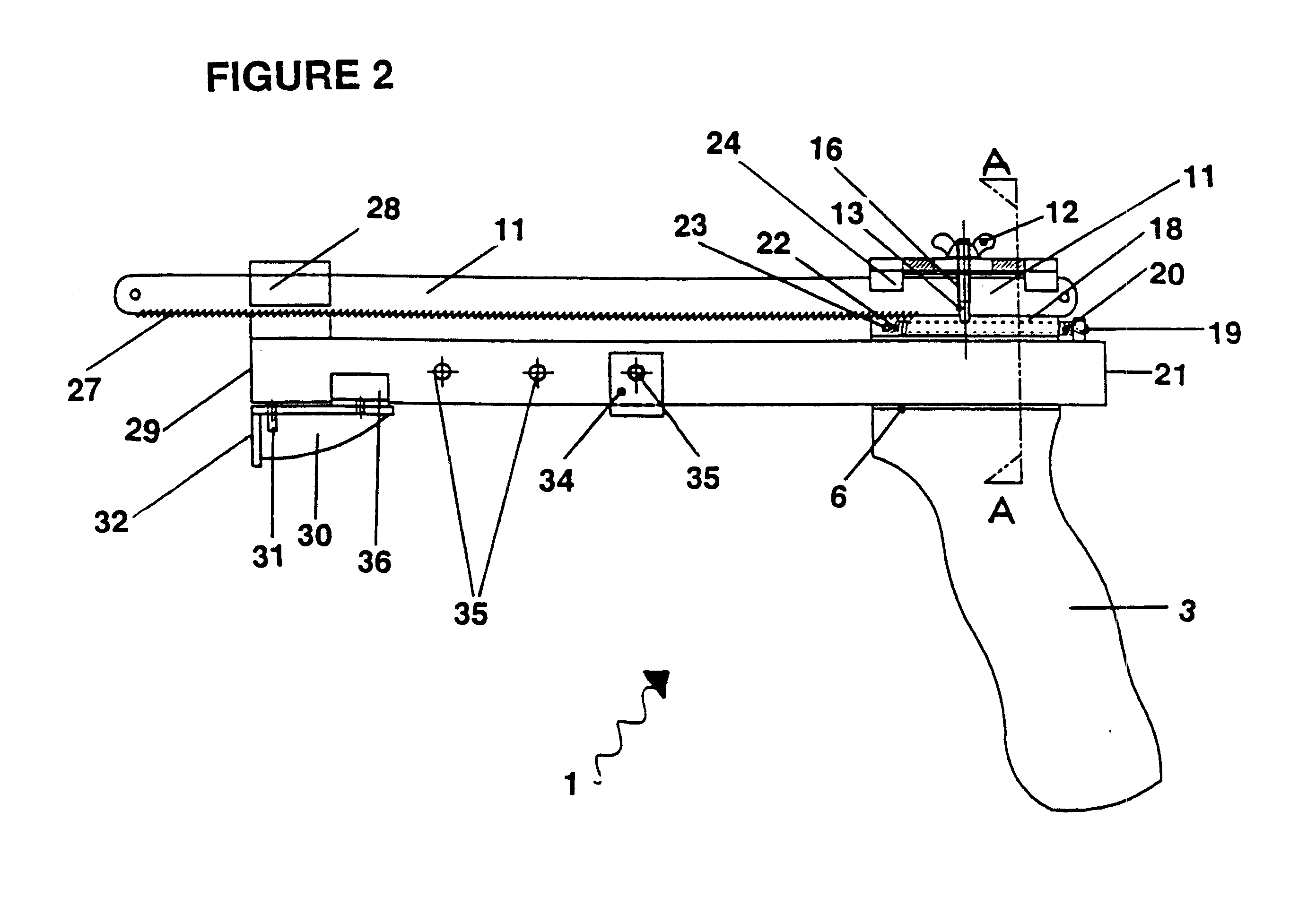

InactiveUS6578268B2Easy to disassembleEasy to slideTurning machine accessoriesPad sawsEngineeringHand tool

A hand tool includes a replaceable cutting portion having an elongate cutting surface, a body and a handle. The body receives displaceable protecting apparatus for shielding the cutting surface of the cutting portion when not in use. A forward distal end of the protecting apparatus contacts a portion of the surface of the object to be cut such that when pressure is applied against the object surface displacement of the protecting apparatus relative to the replaceable cutting portion is effected to expose only as much of the cutting surface as needed to effect the required cut. Alignment means maintain alignment of the replaceable cutting portion relative to the protecting apparatus throughout the cutting. When the cutting action is completed resilience means facilitates return of the protecting apparatus so the cutting surface is no longer exposed.

Owner:HAWKETTS GEOFFREY

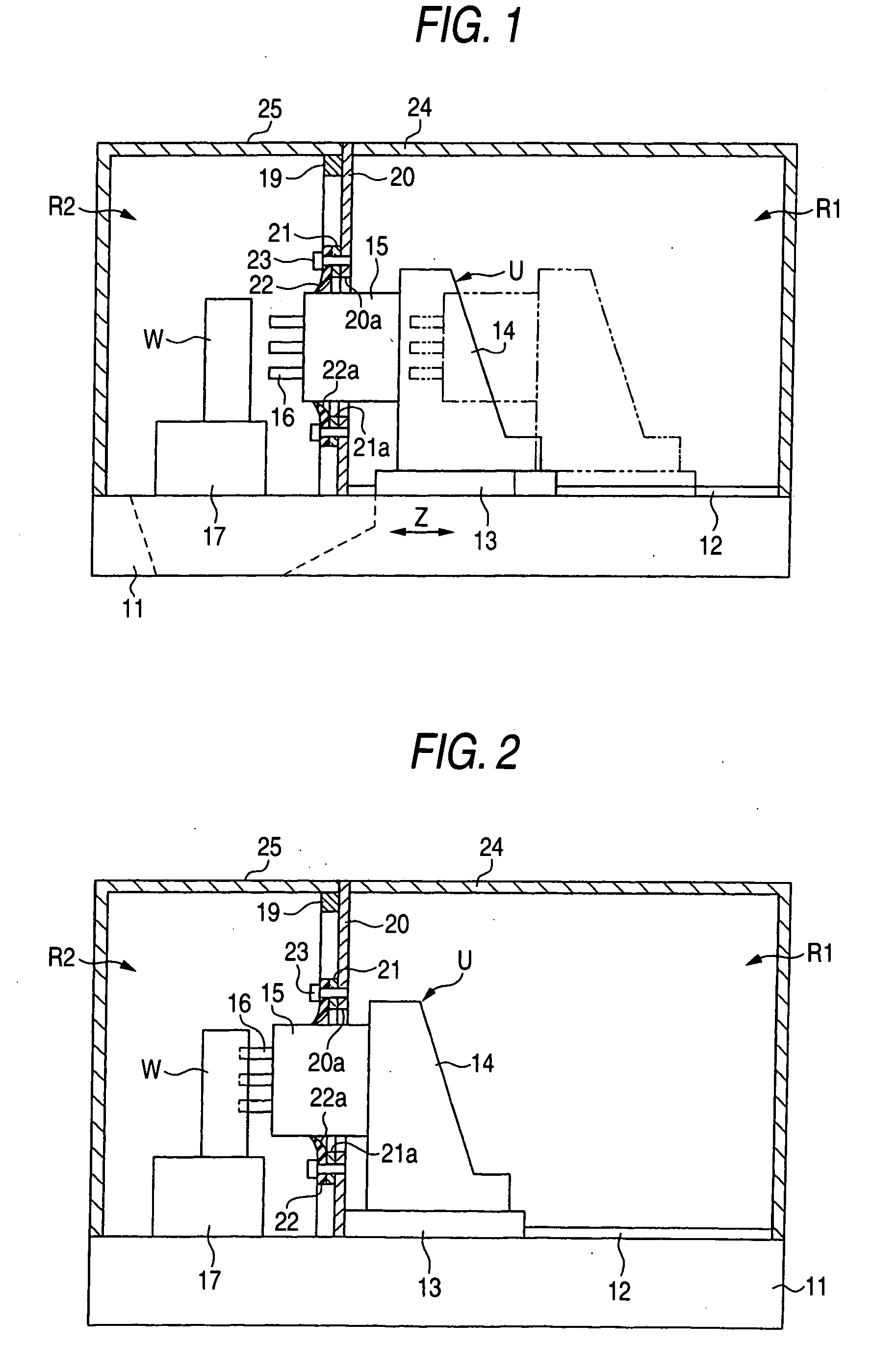

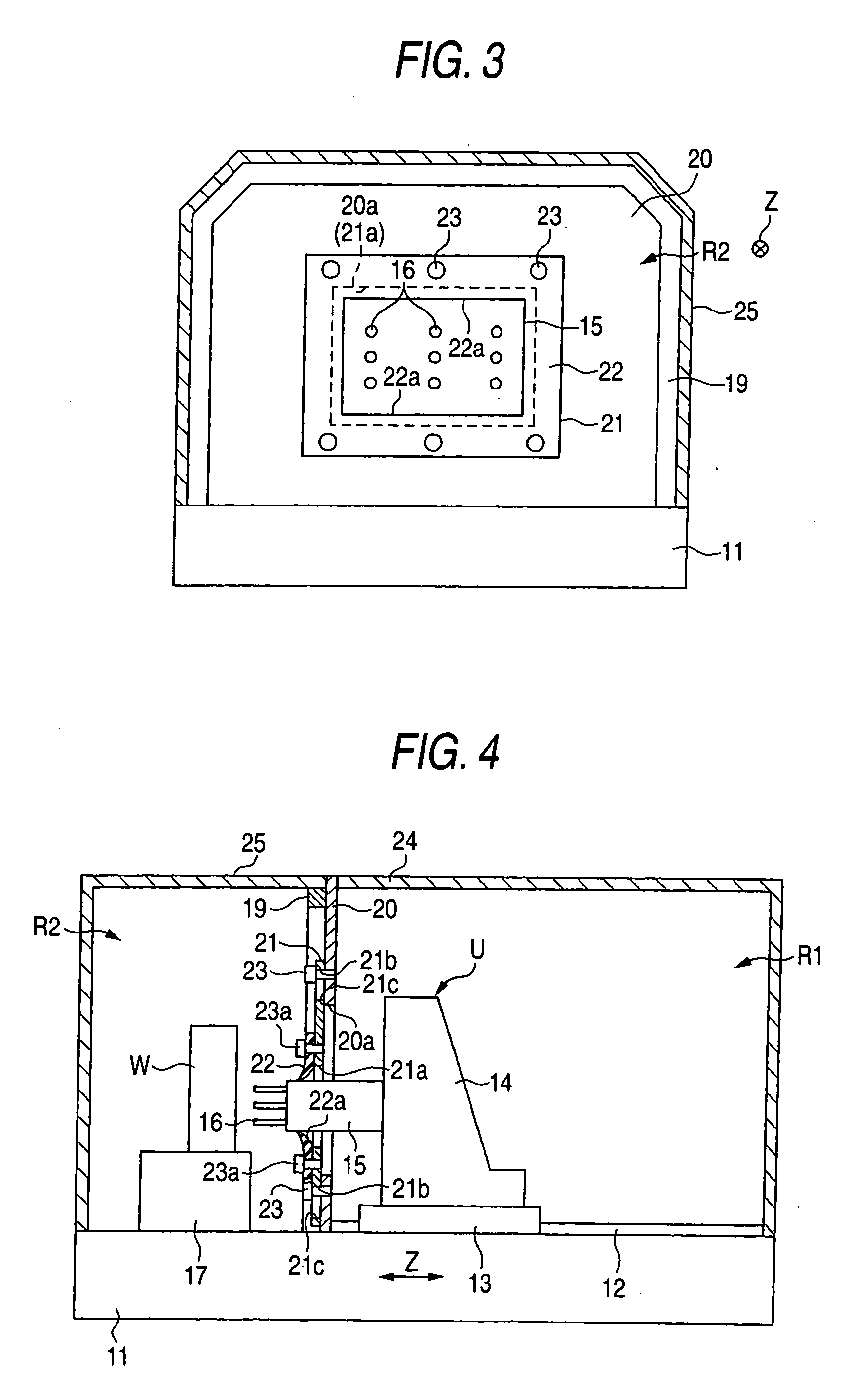

Machine Tool

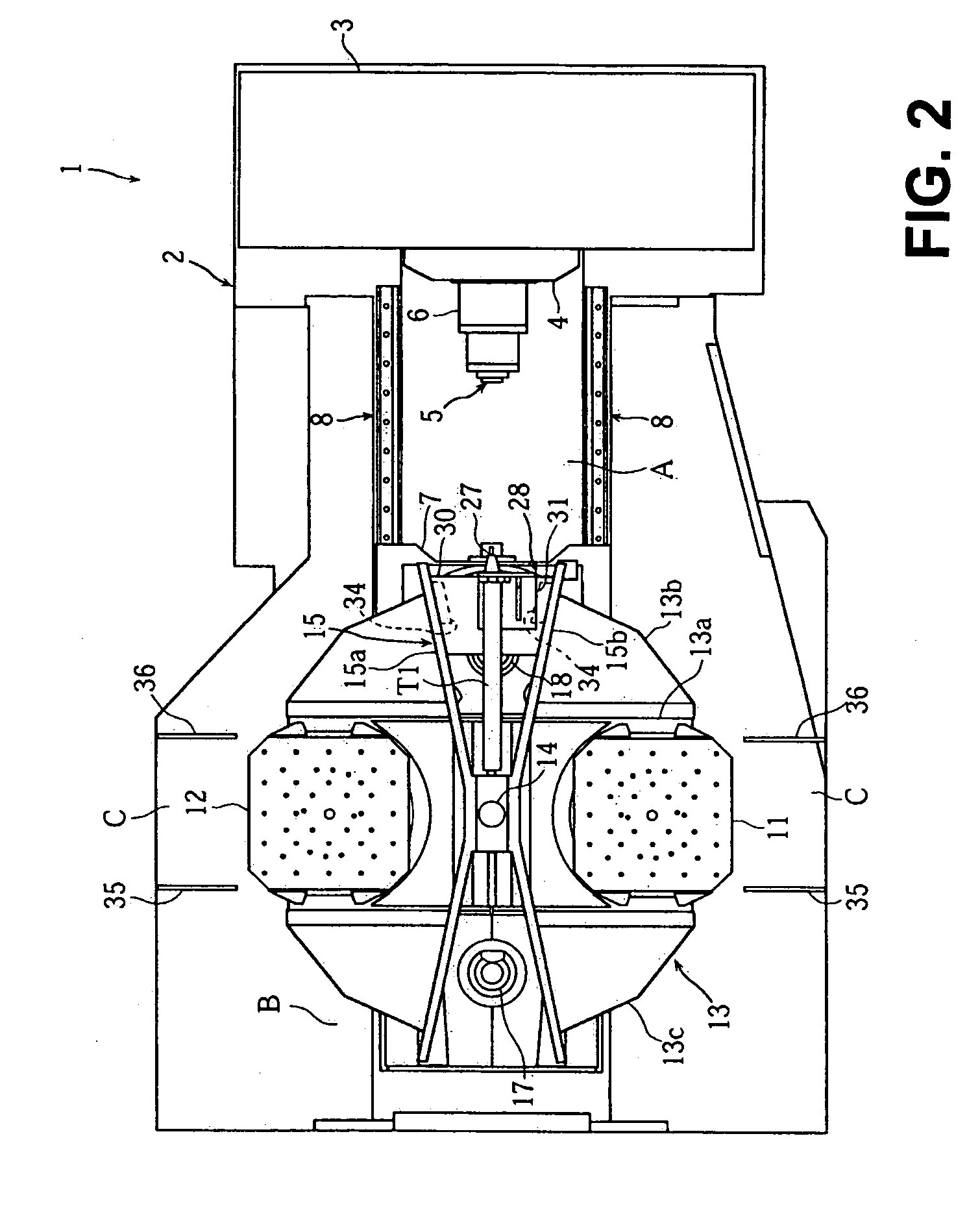

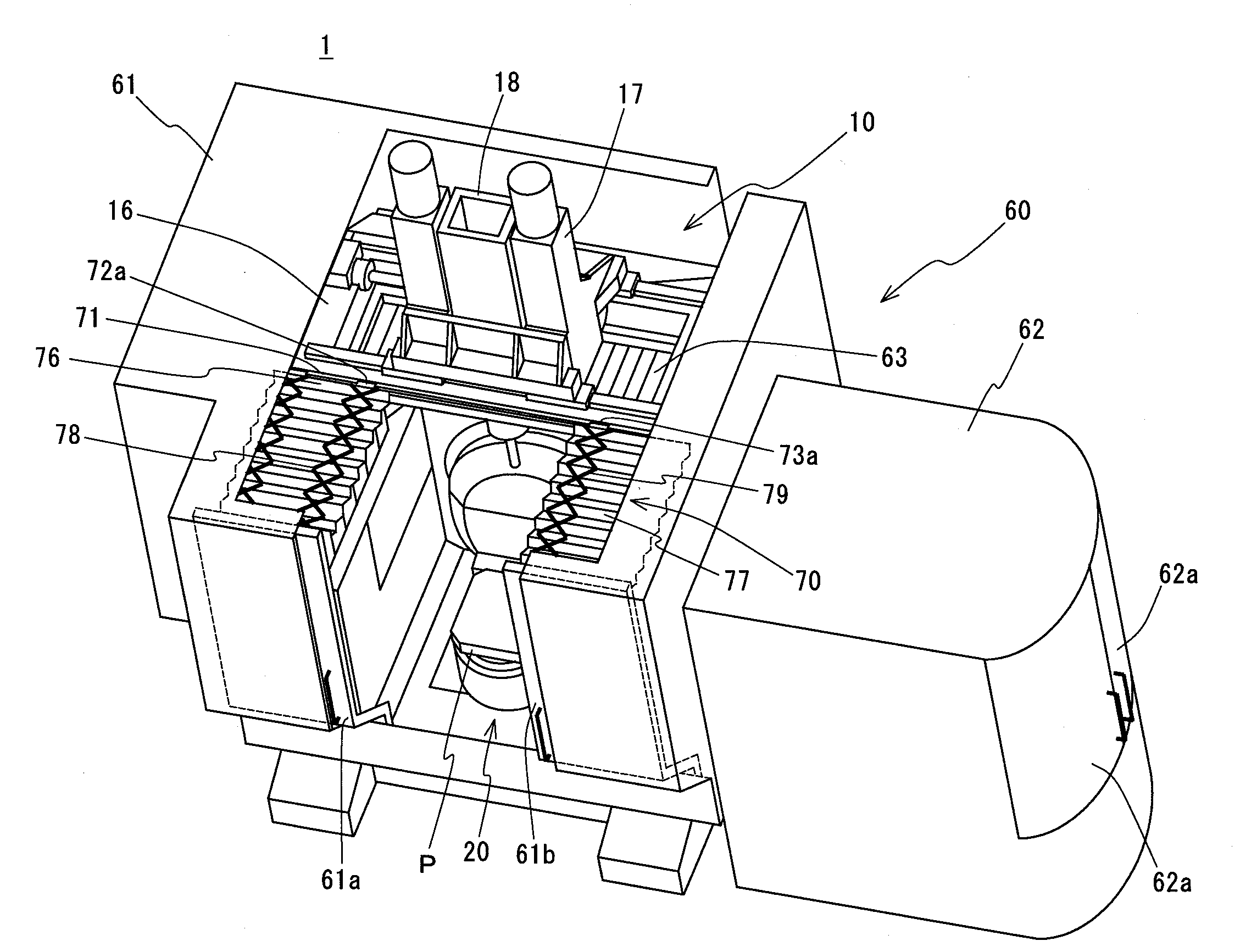

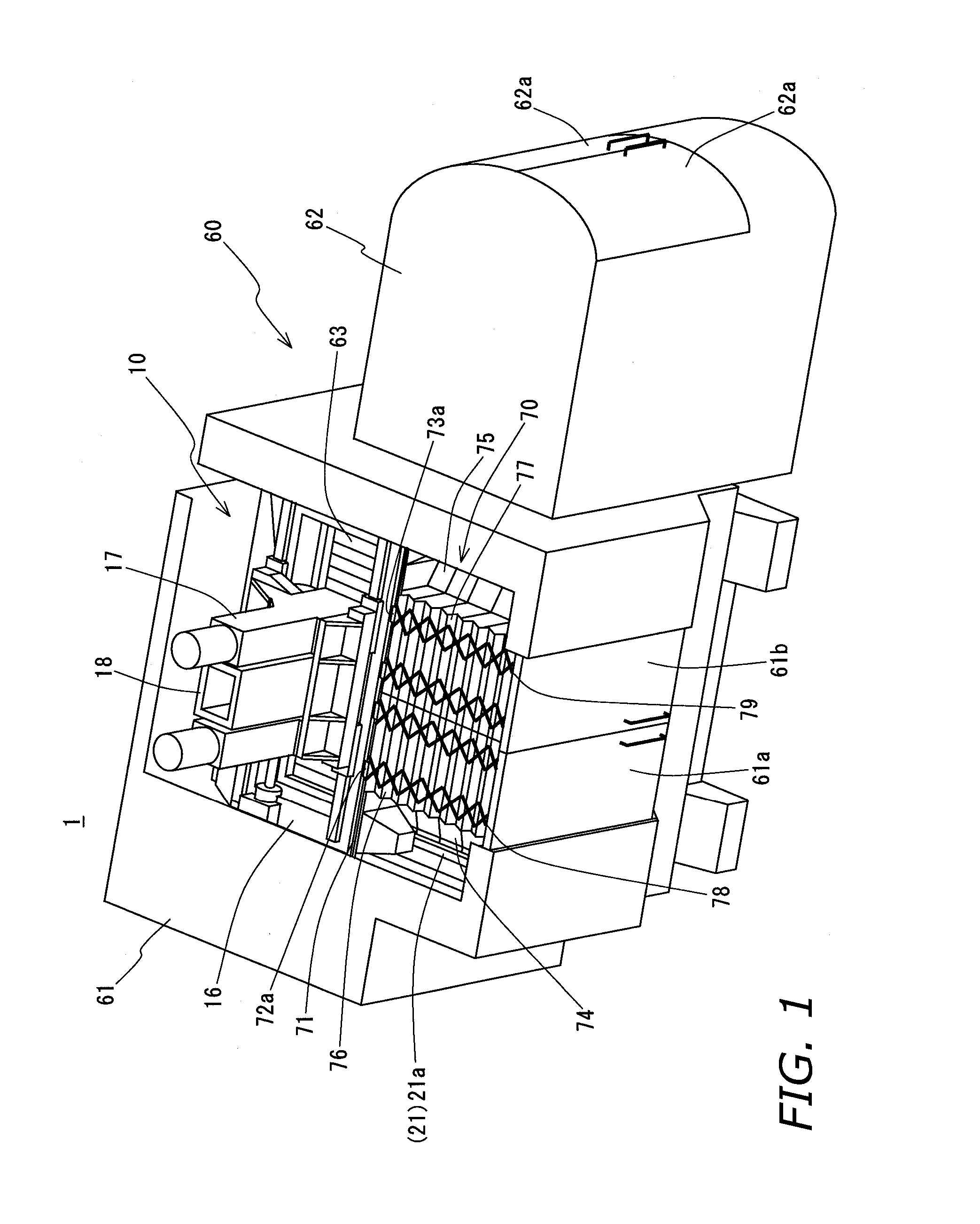

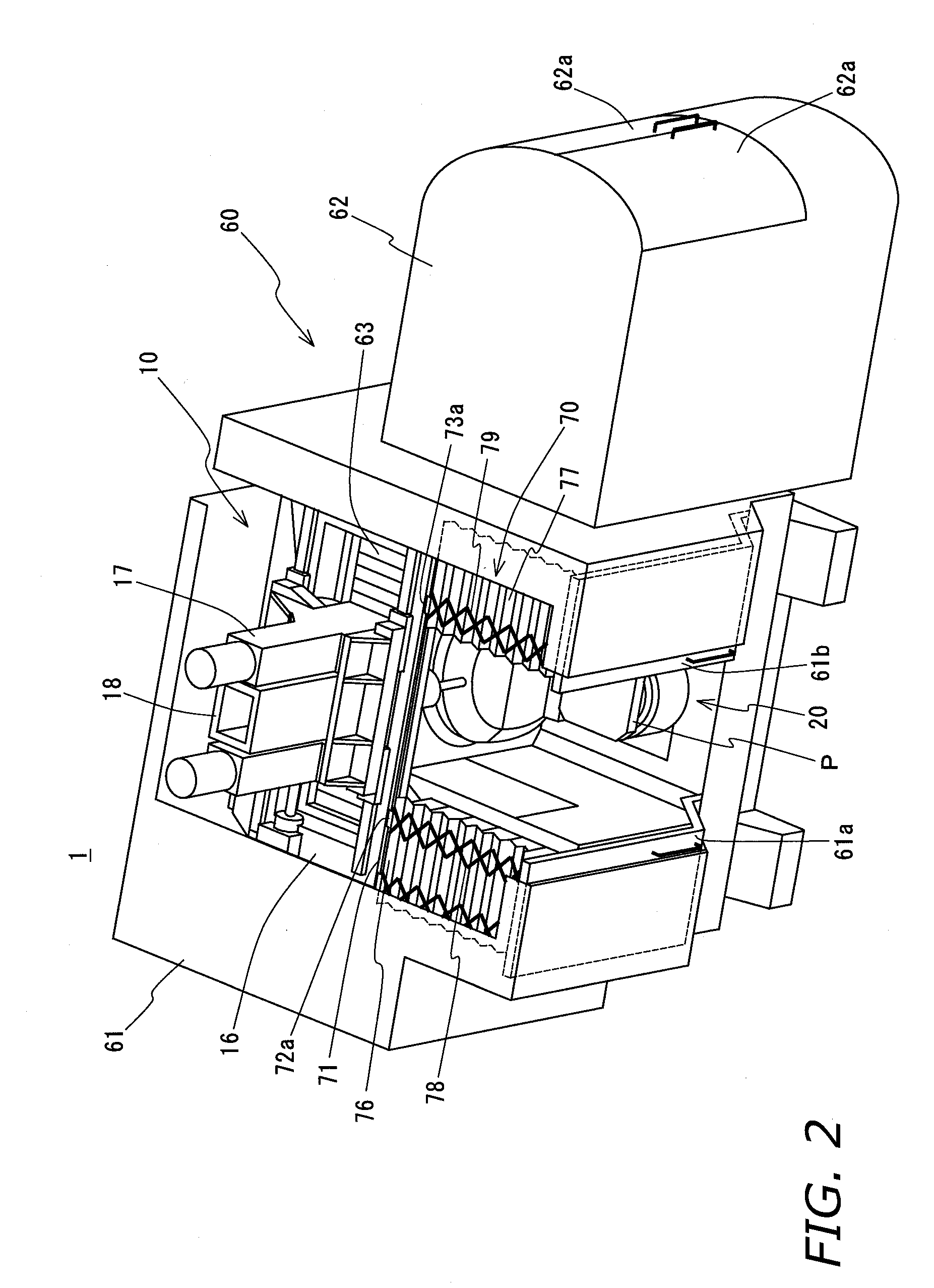

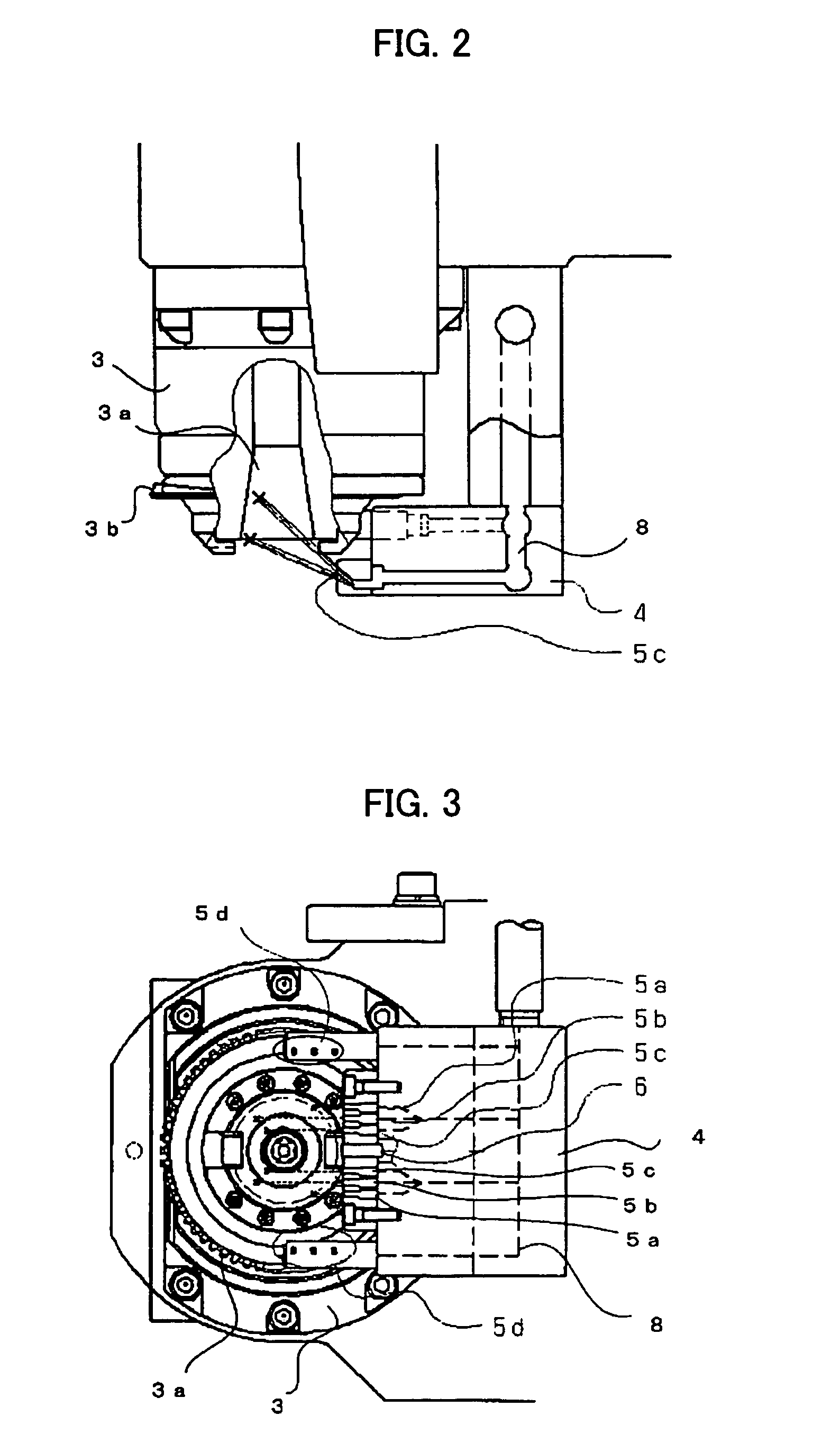

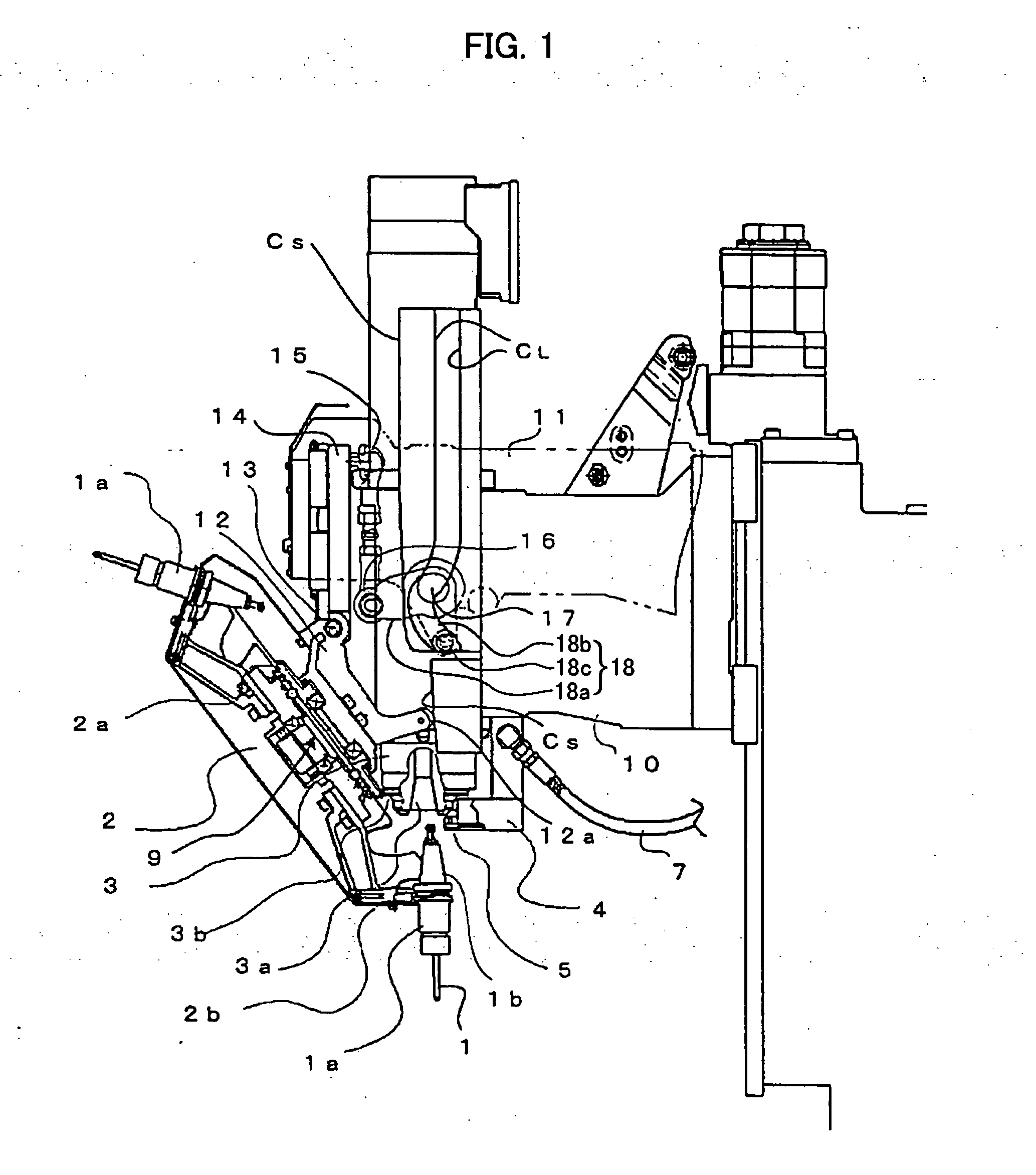

InactiveUS20060269375A1Easy to openEasy to closeControl mechanismProtection and storage accessoriesFree rotationEngineering

Machine tool having a bed, a table arranged on the bed, a first saddle provided free to travel back and forth, a second saddle supported on the first saddle and provided free to travel side to side, a spindle head provided free to travel perpendicularly on the second saddle, a main spindle situated above the table and by the spindle head supported free to rotate on its center axis, a front cover provided on the front side of the bed and furnished with doors that open and close sideways, and top covers configured with one end sideways shiftably connected to the front side of the first saddle, and with another end connected extensibly / retractably to the top of the front-cover doors, therein being configured for permitting back-and-forth-directed movement of the first saddle.

Owner:DMG MORI SEIKI CO LTD

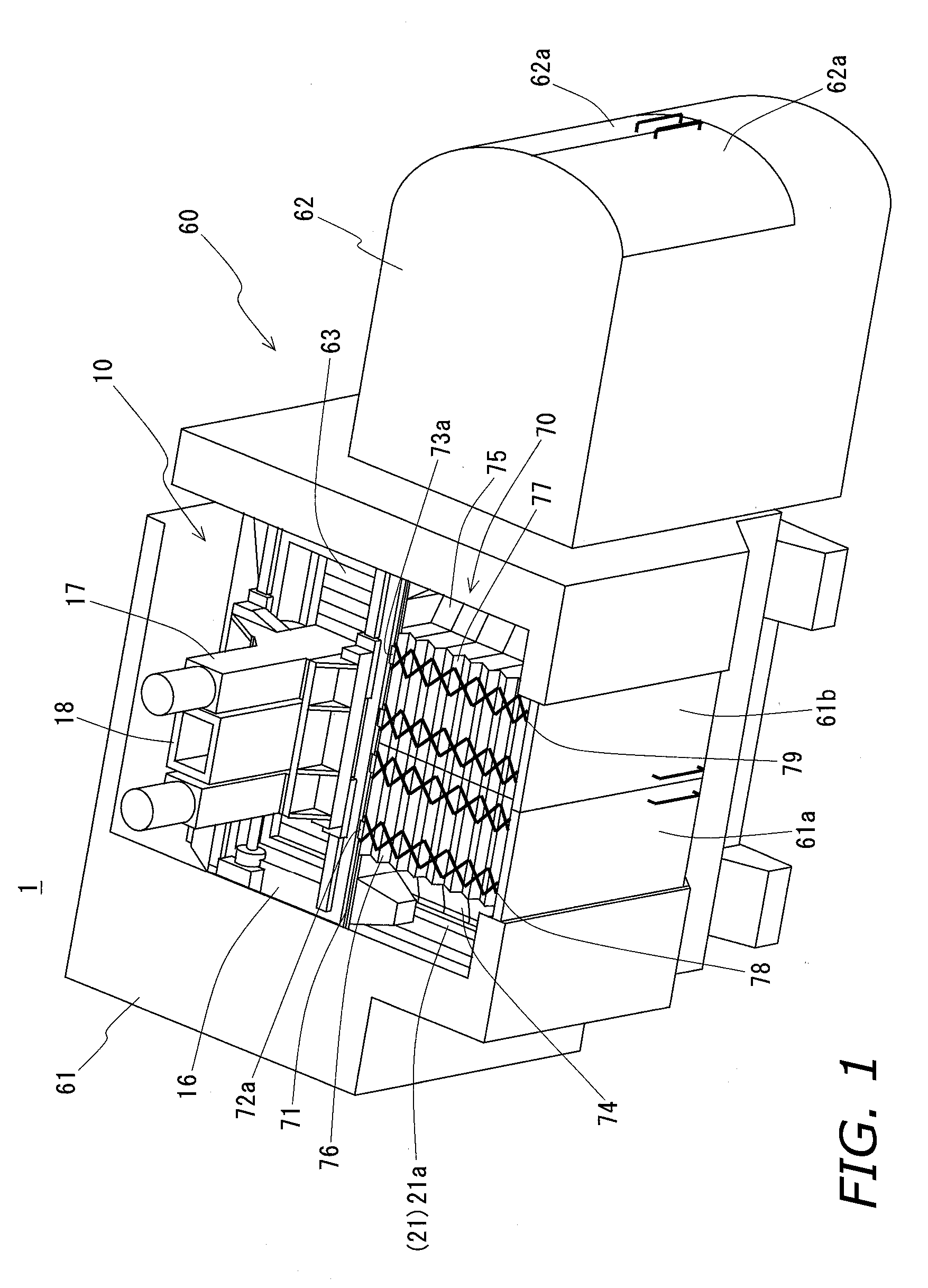

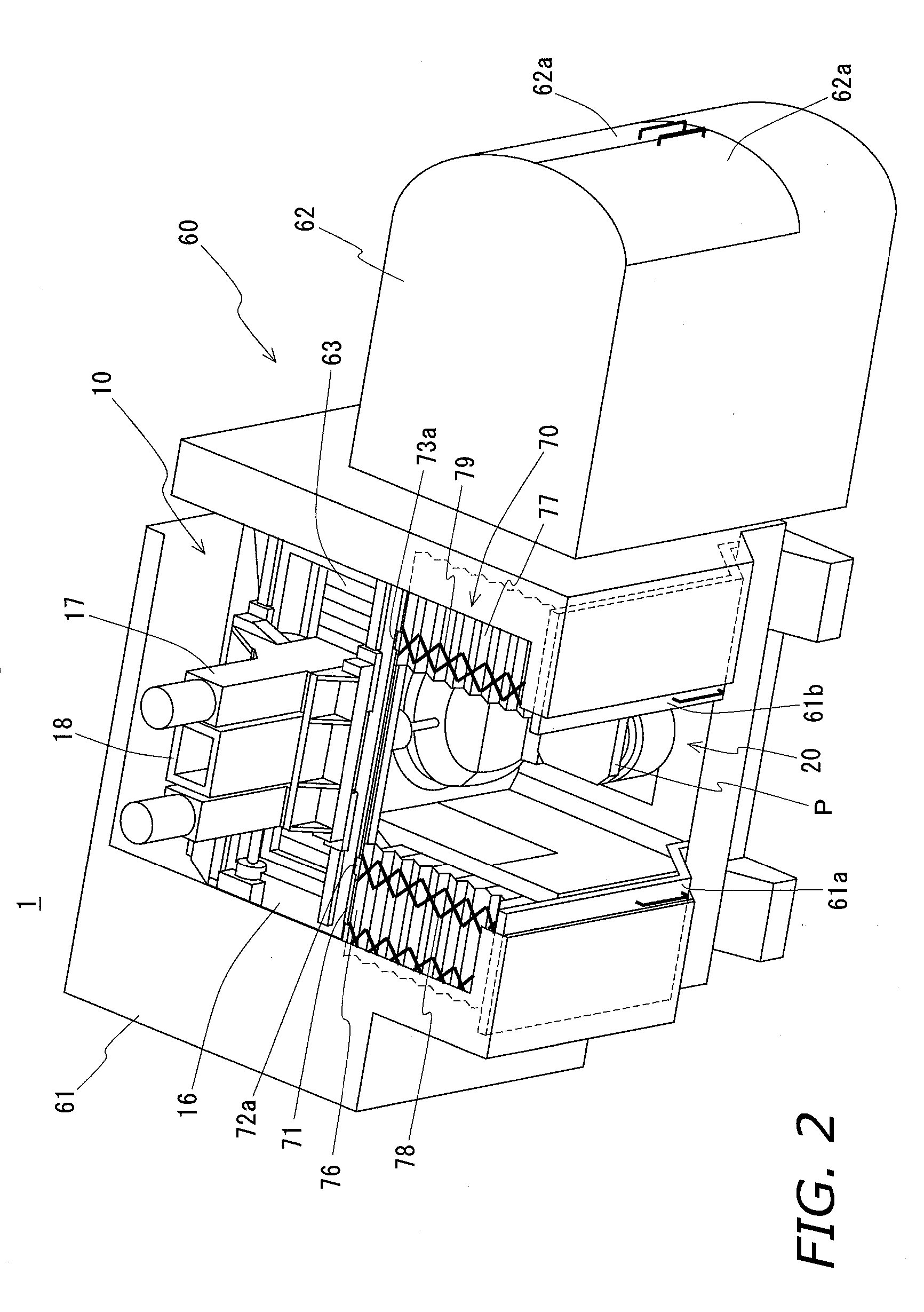

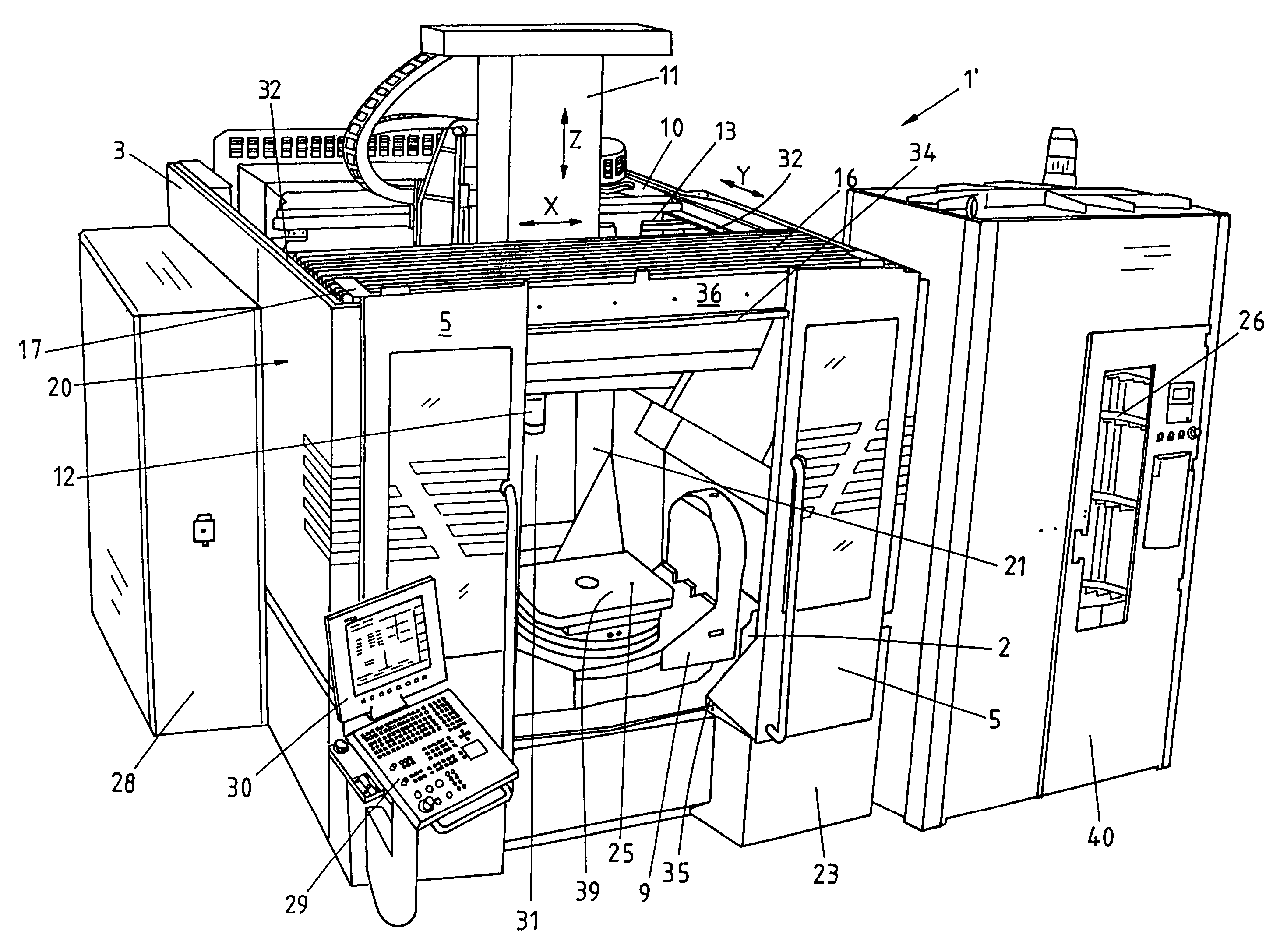

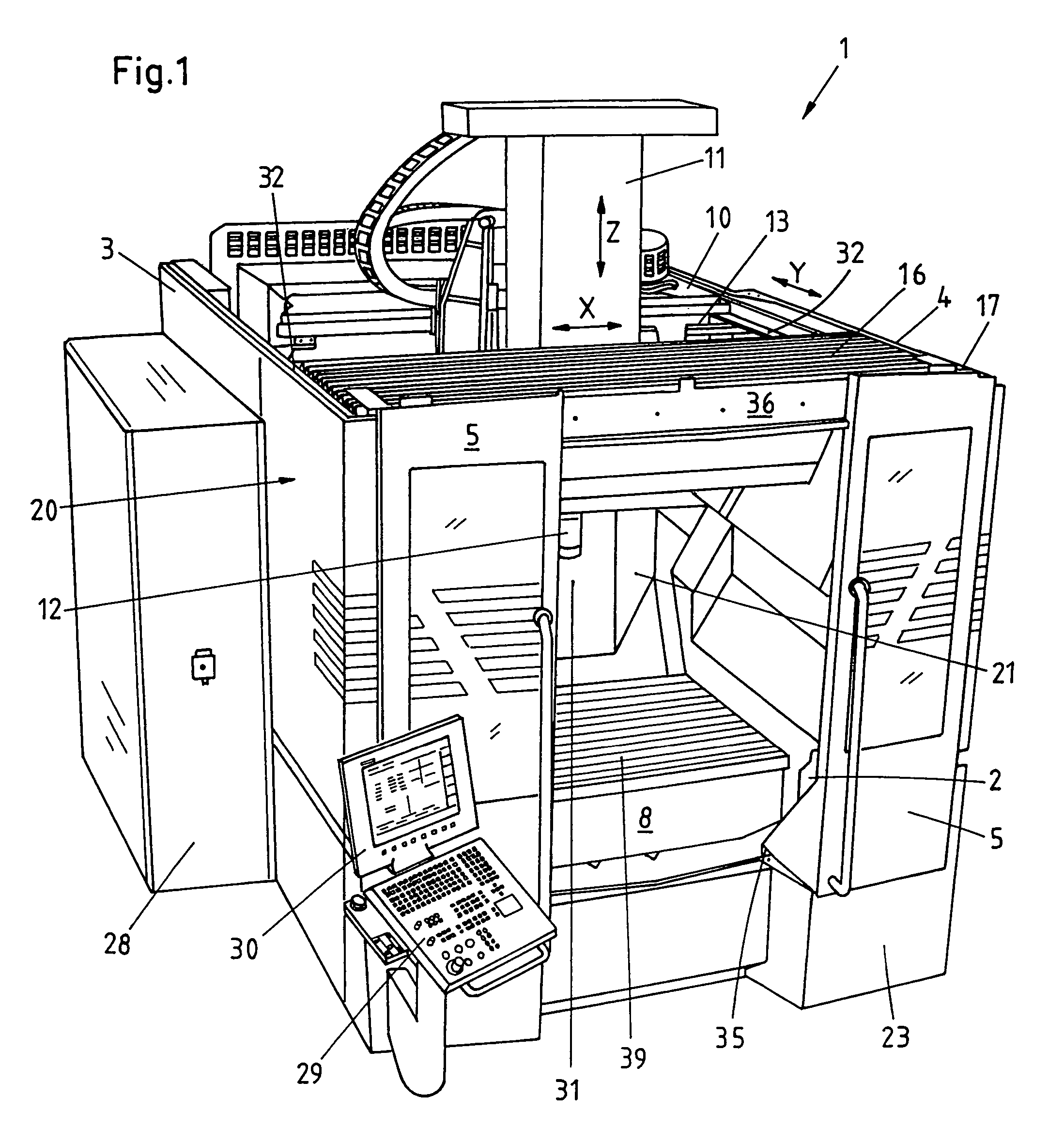

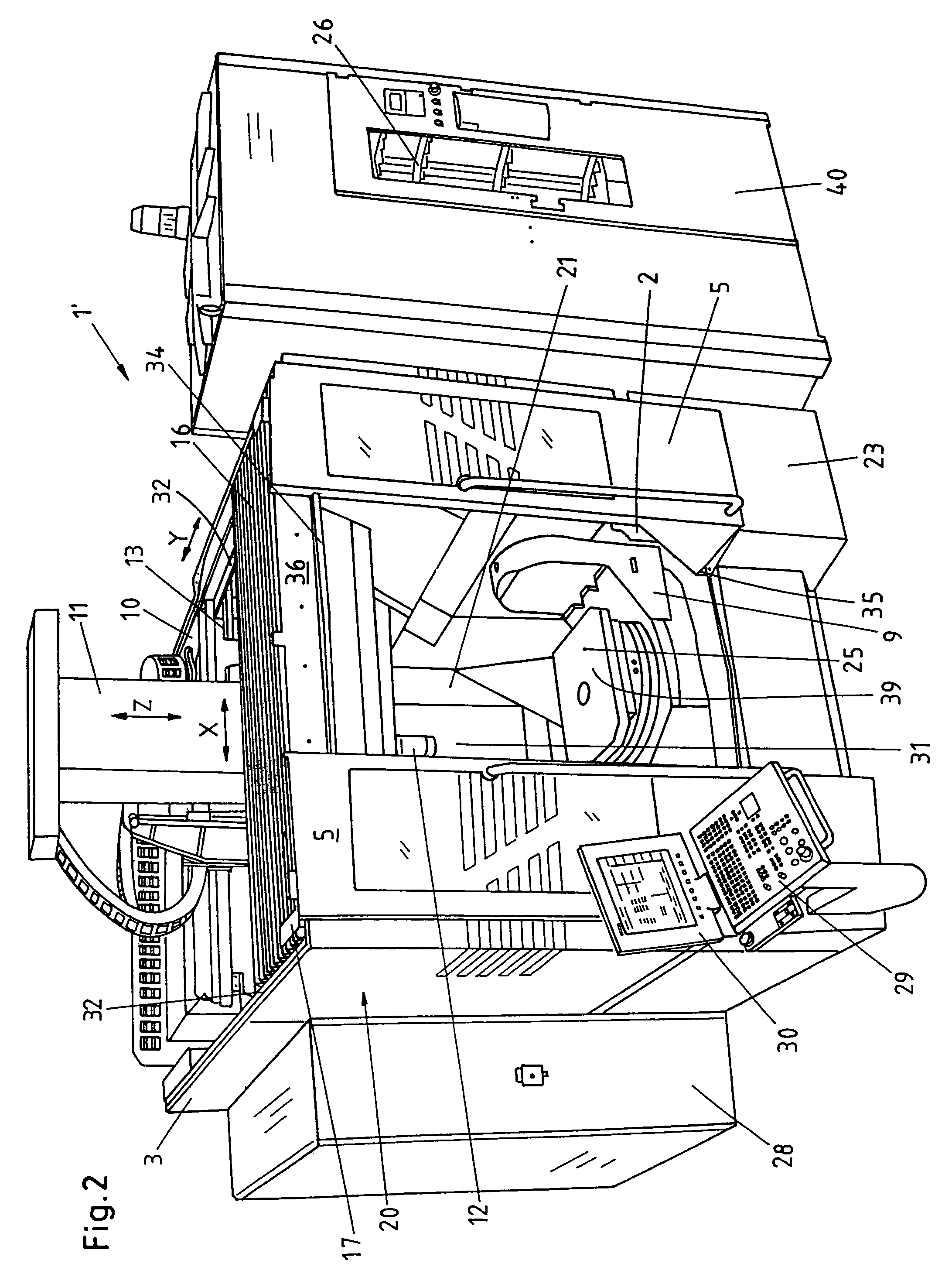

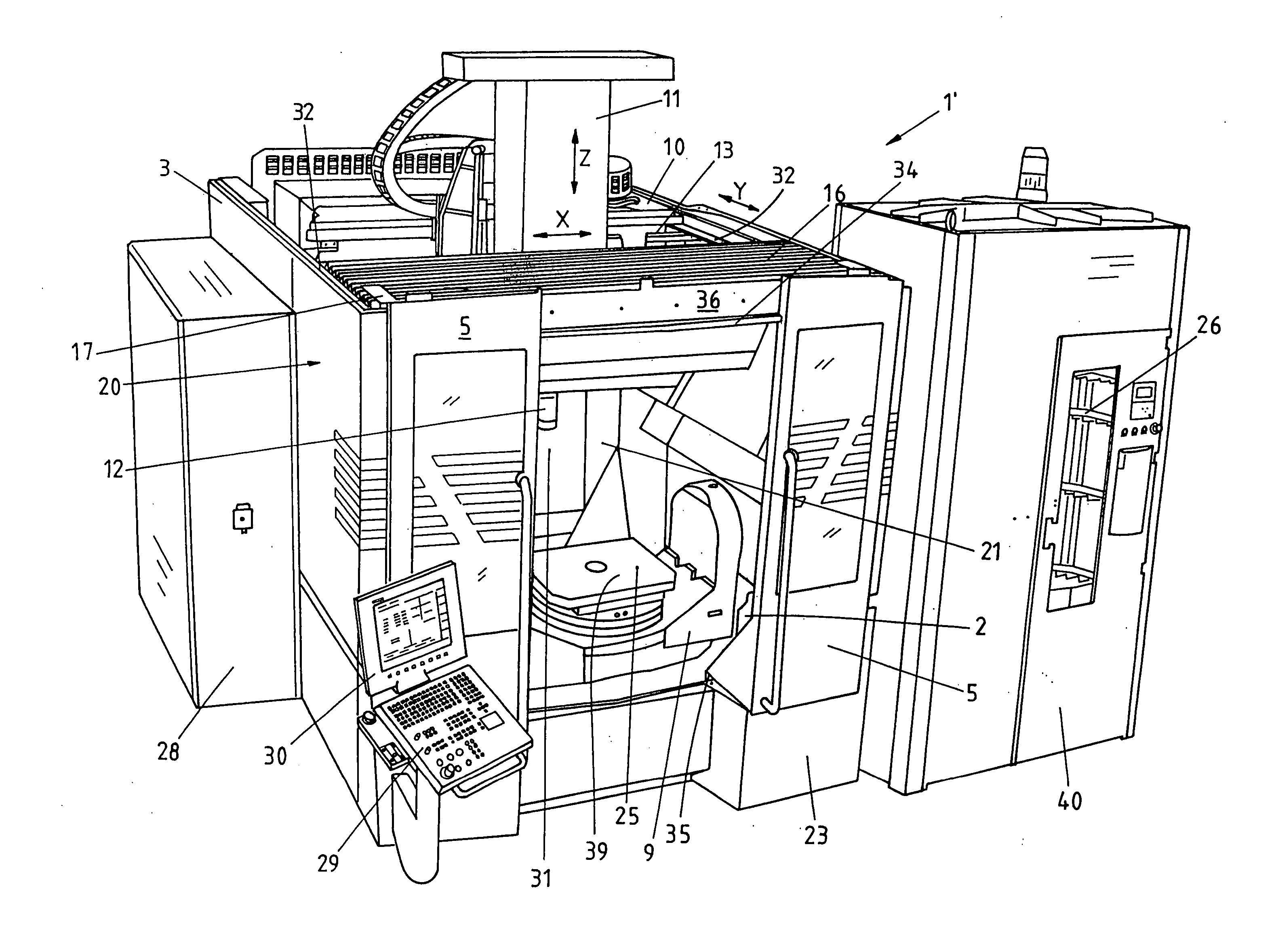

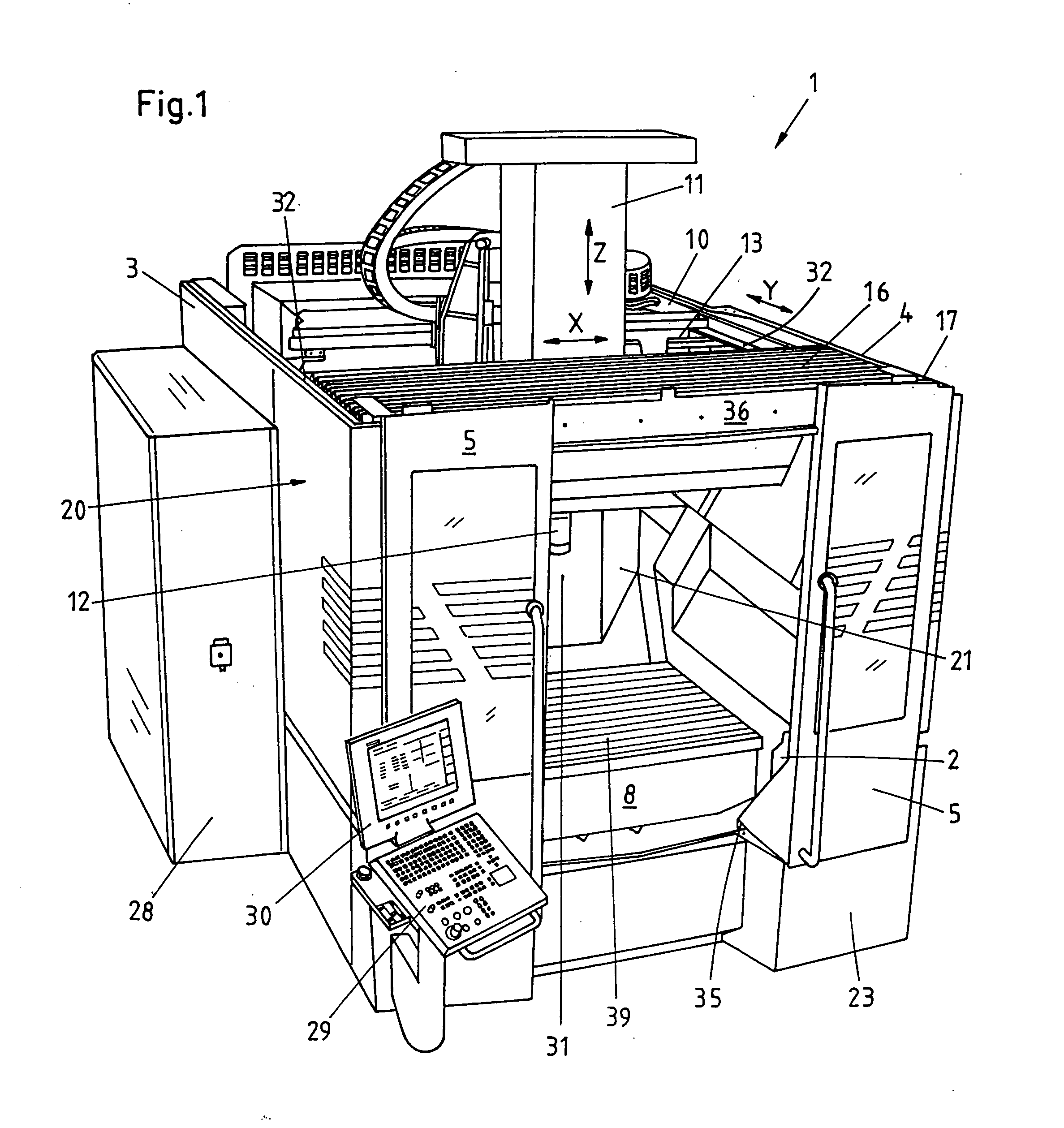

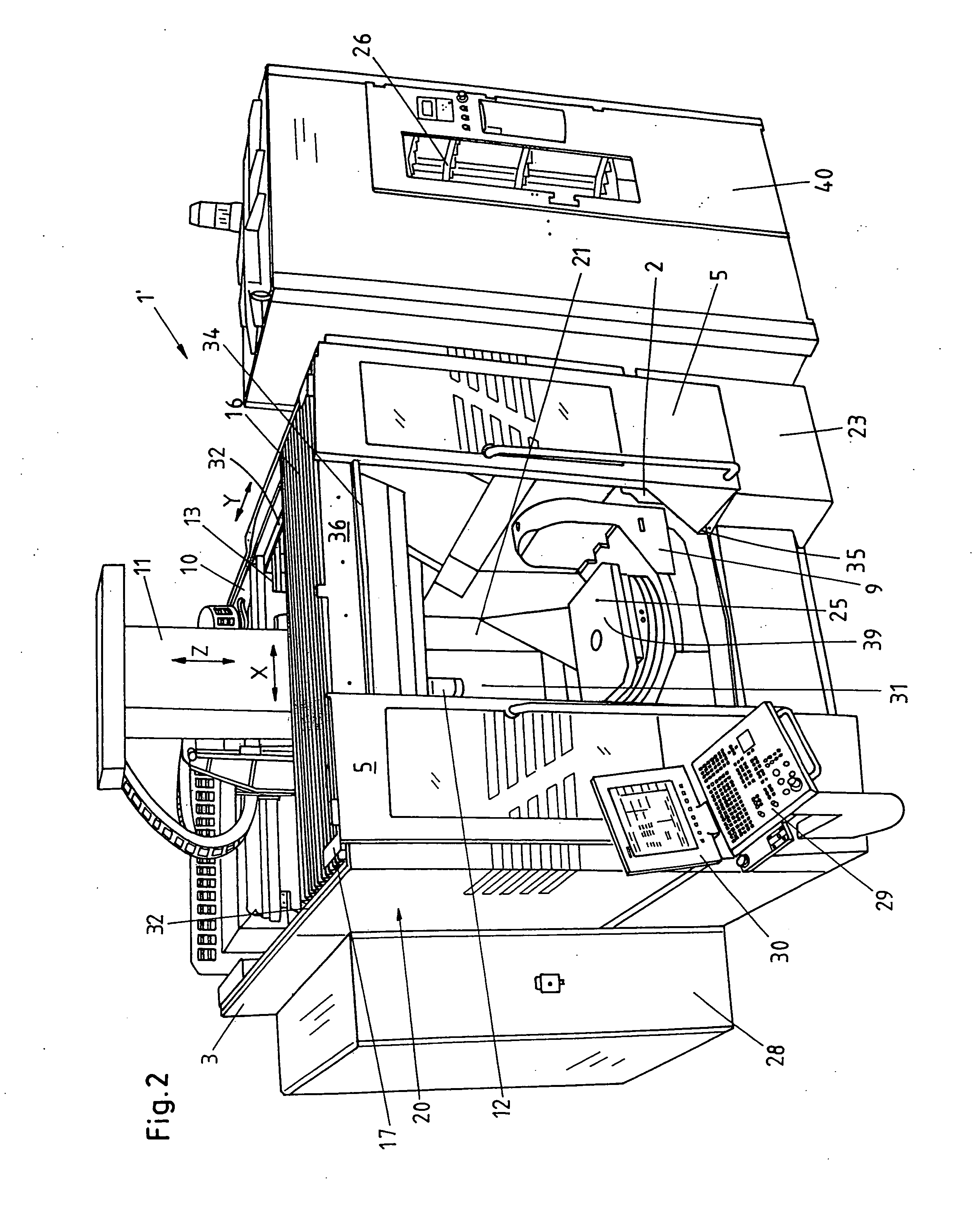

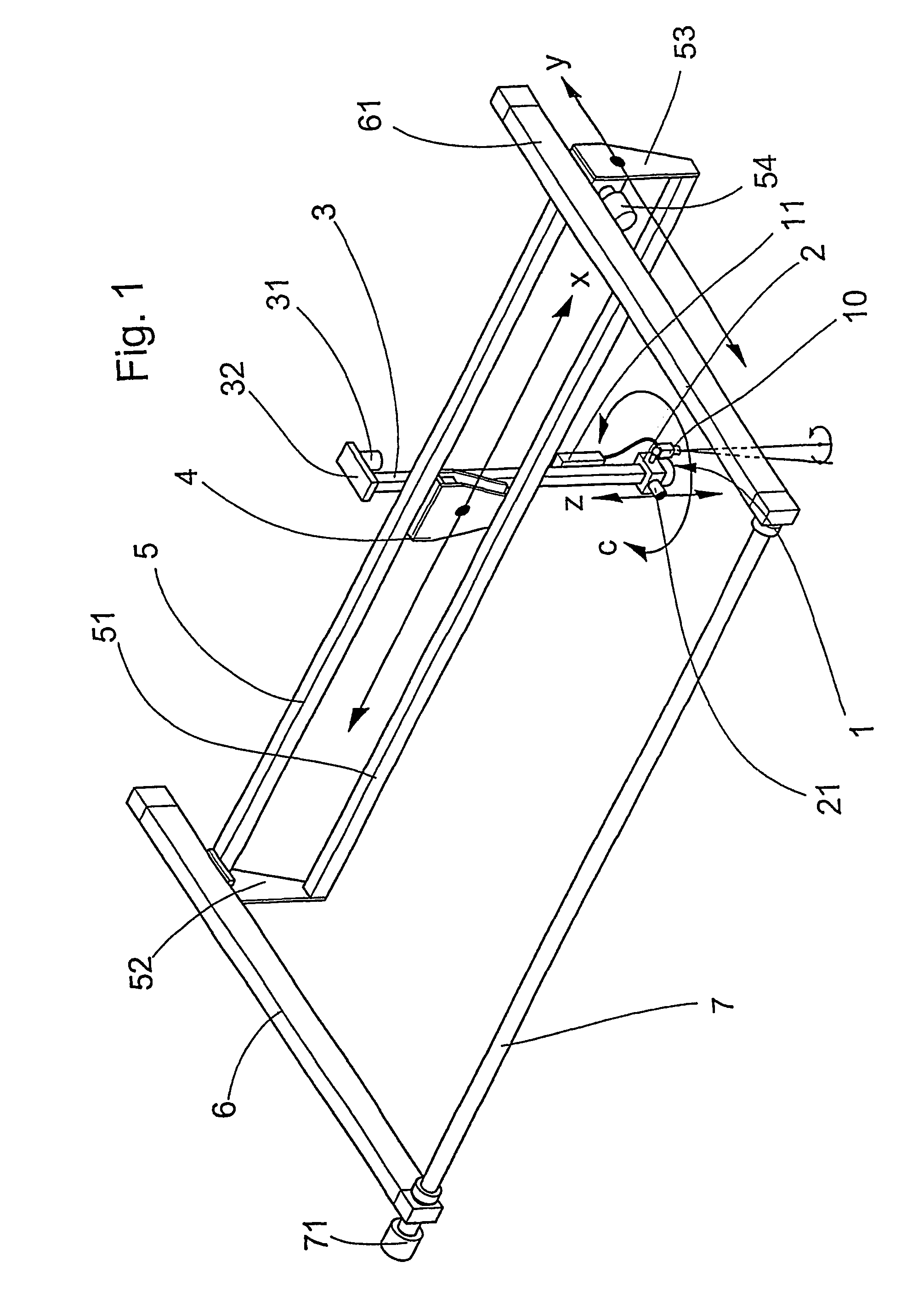

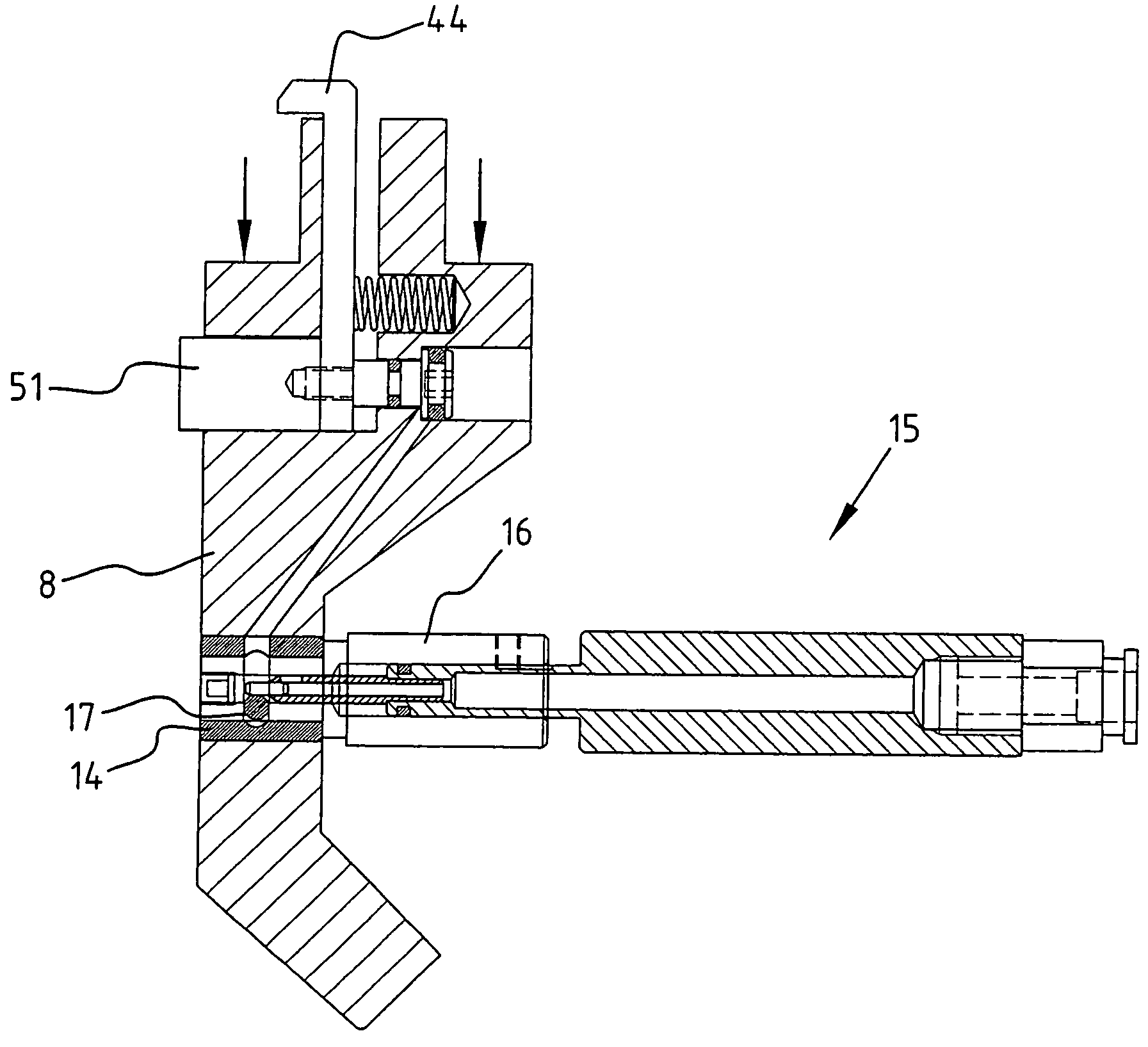

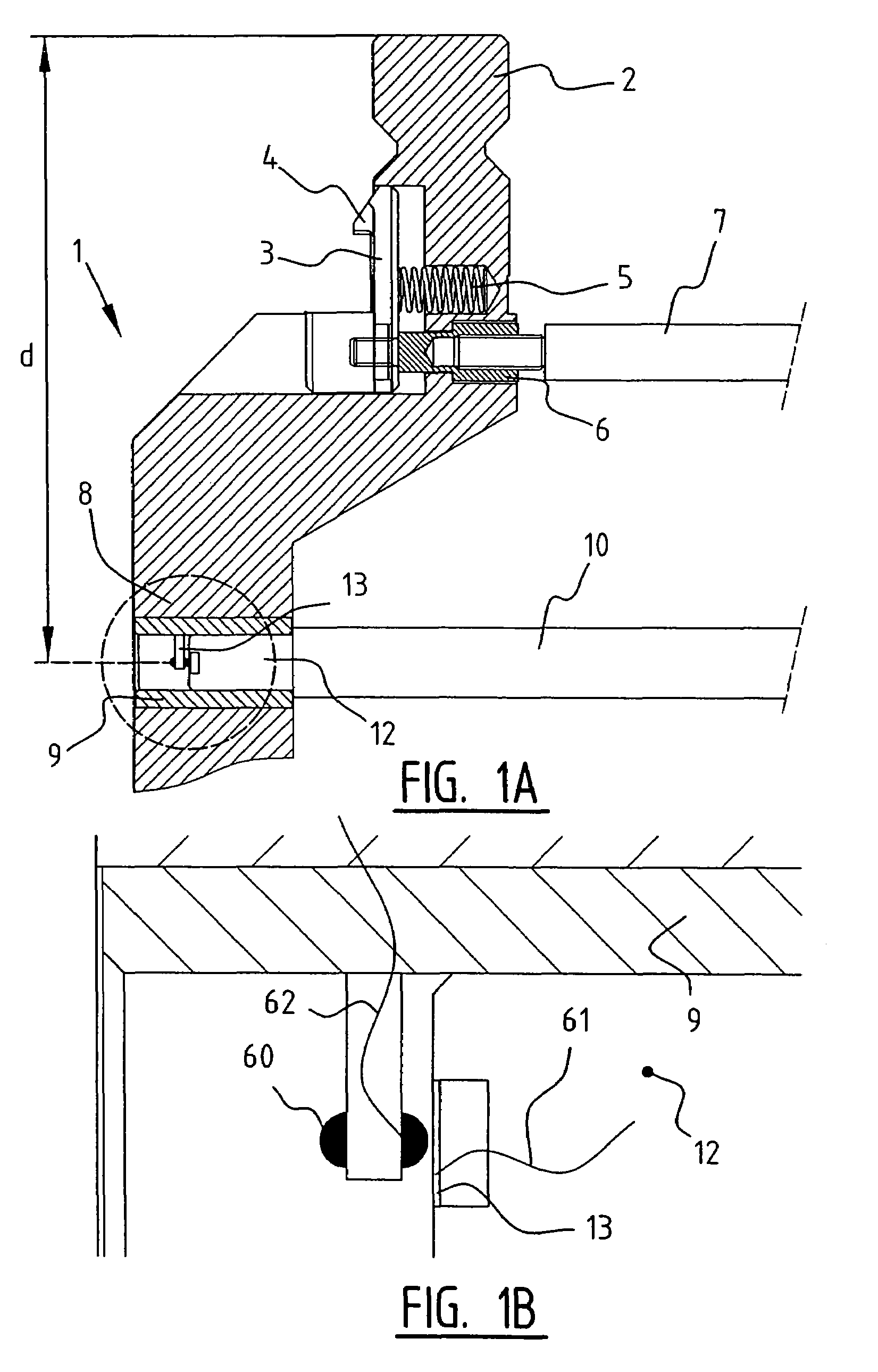

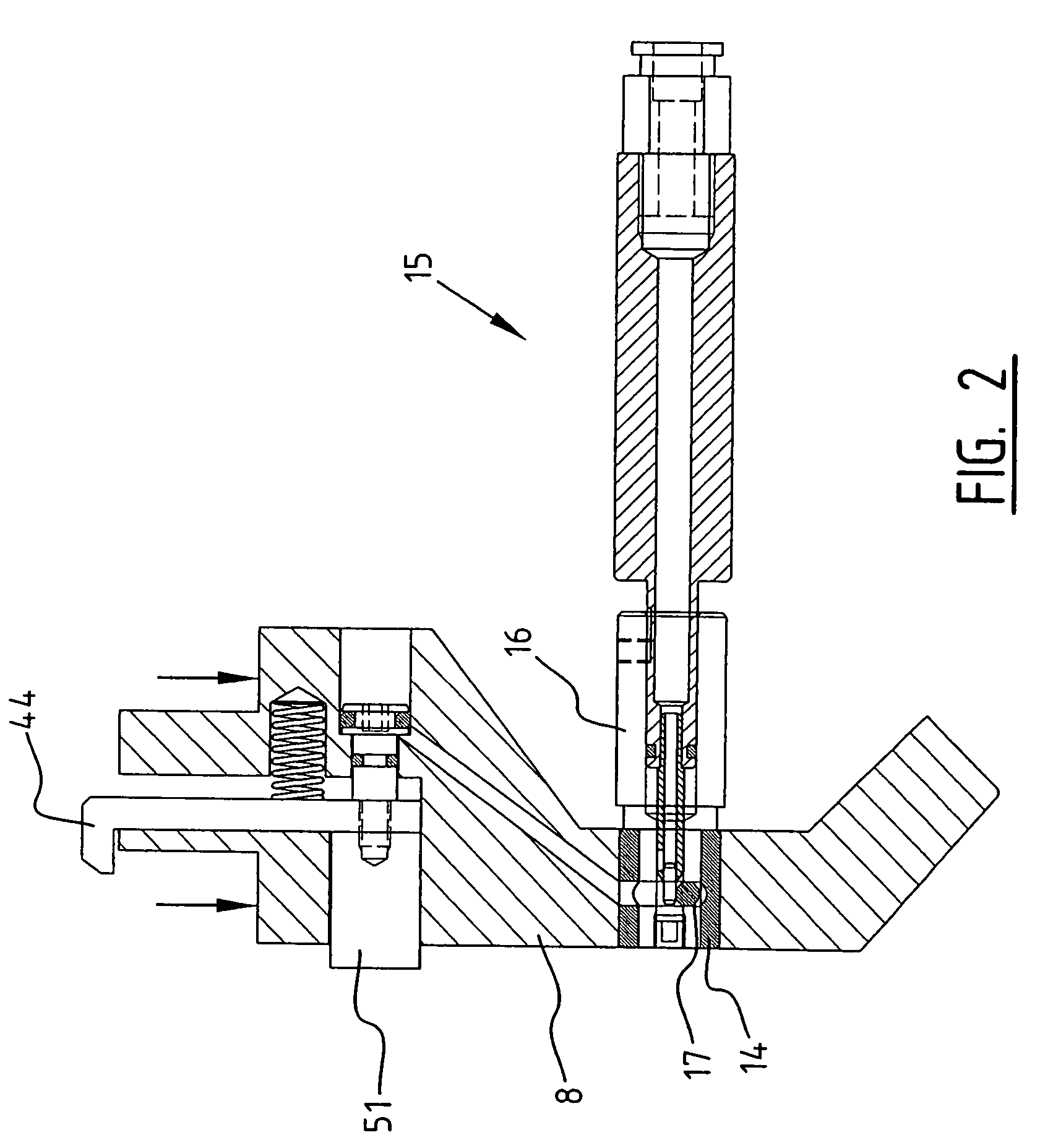

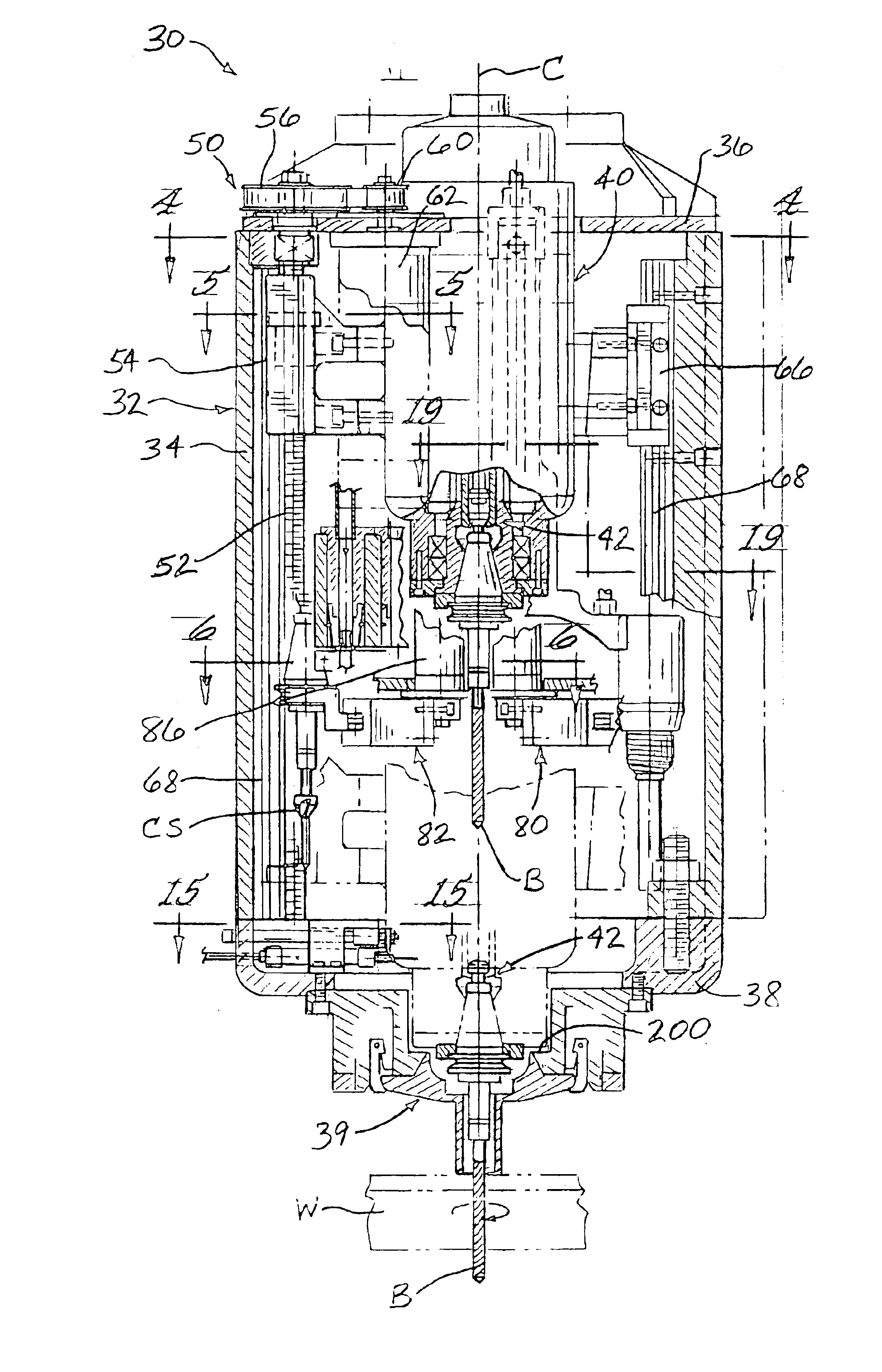

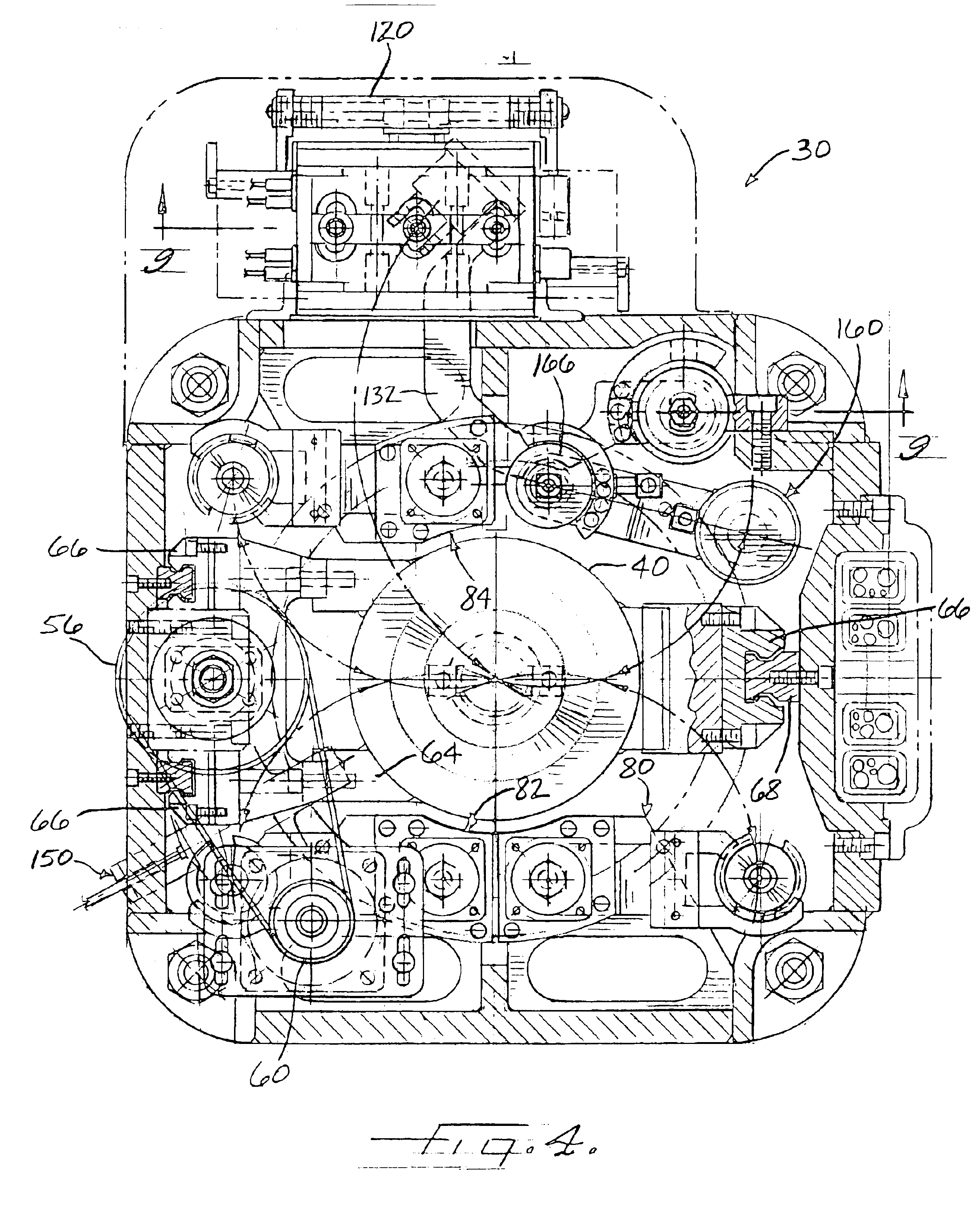

Machine tool, in particular a drilling and milling machine

ActiveUS7226403B2Simple processing technologyCharge manipulationMilling machinesEngineeringMachine tool

A machine tool (1, 1′), in particular a drilling and milling machine, comprising a housing (20) having a machine bed (2), together with side walls (3, 4) and doors (5, 6, 7), comprising a fixed, pivotable or rotatable work table (8, 9), and comprising a slide (10), transportable in the y direction, for the reception of a spindle head (11), transportable in the x-z direction, for the reception of tools (12), wherein the front door (5), for the enlargement of the working and loading area (21) in the upward direction, is of transomless configuration, the roof region (13) of the machine (1, 1′) has an automatically operable cover (16), the rear region (22) of the machine (1, 1′) has an integrable automatic pallet changer (14), and the machine (1, 1′) is assigned an automatic tool changer (15).

Owner:MIKRON AGIE CHARMILLES

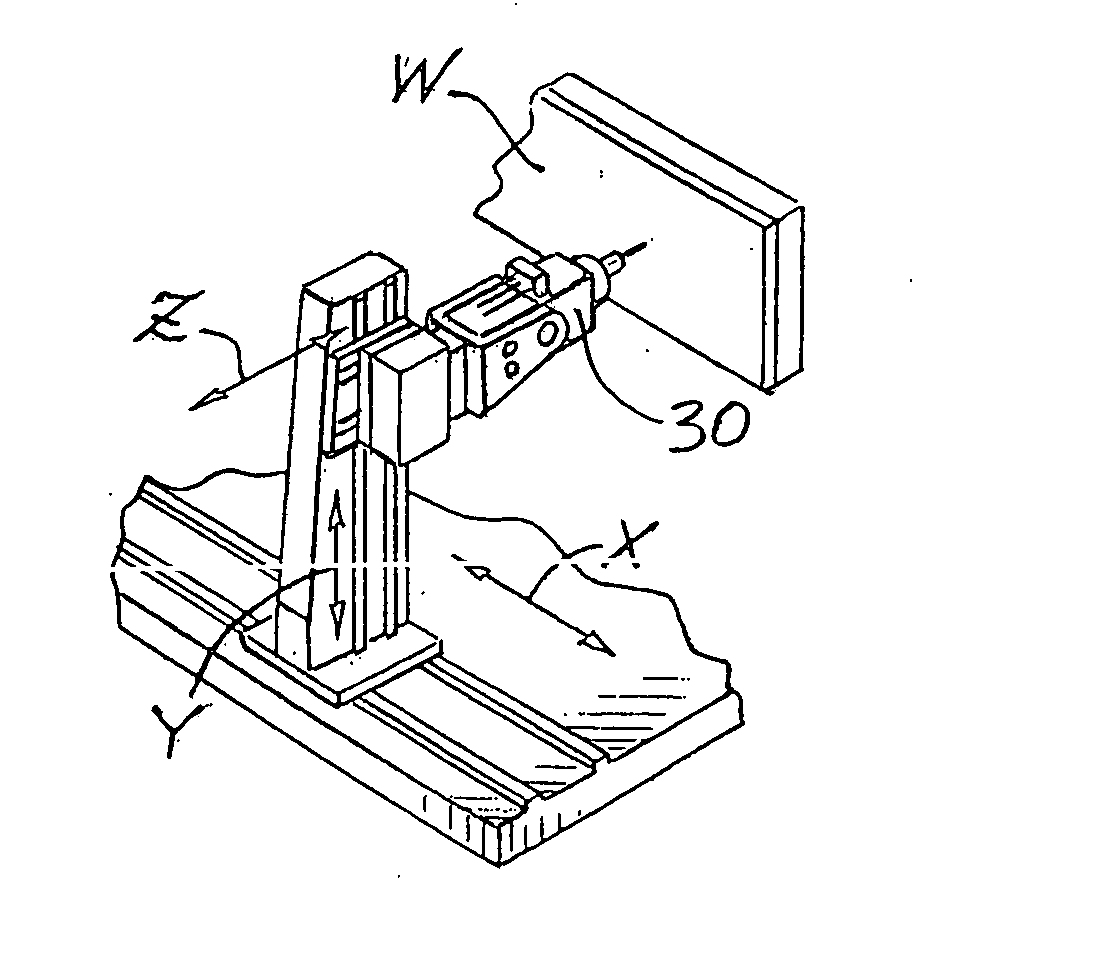

Machine tool

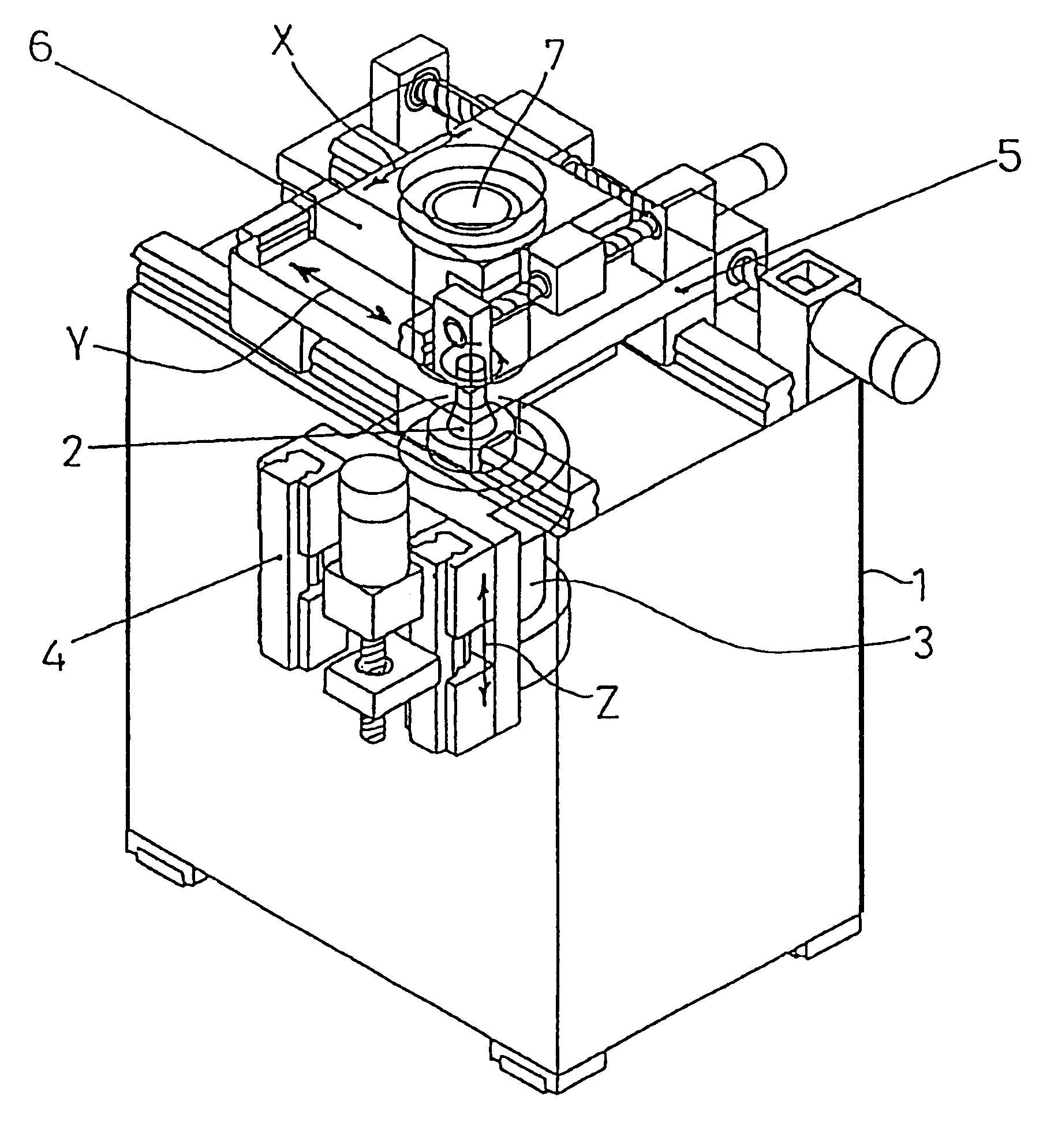

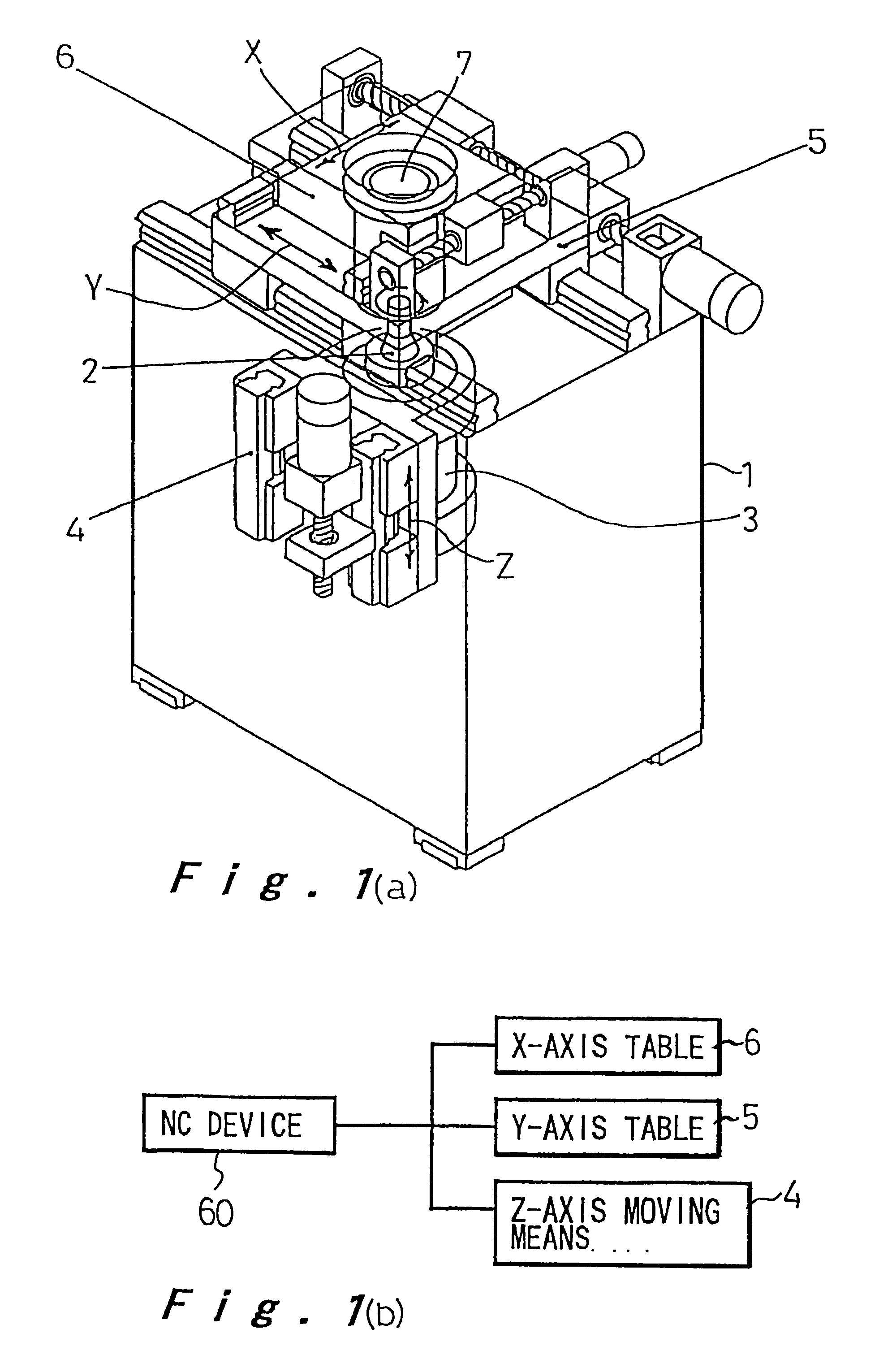

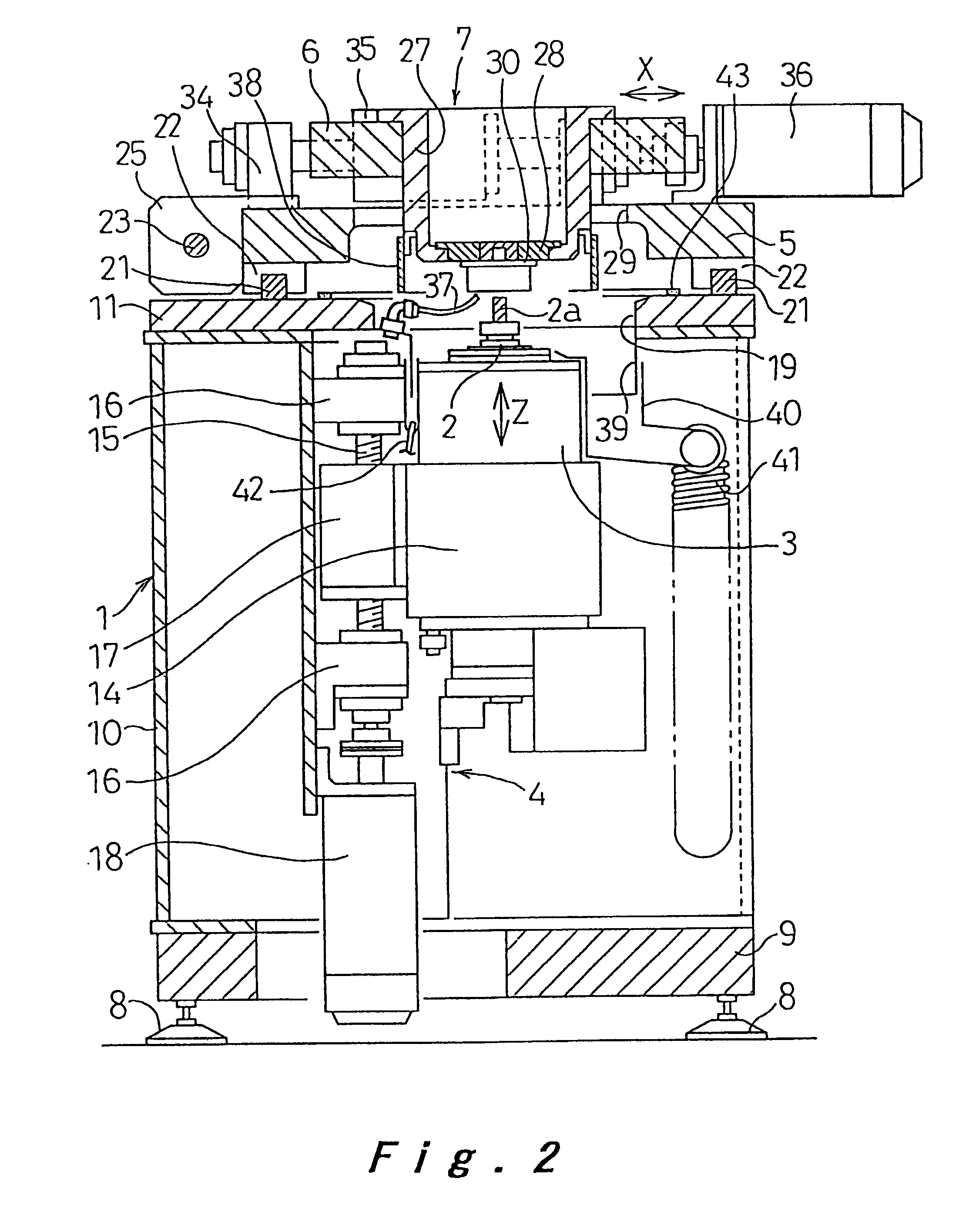

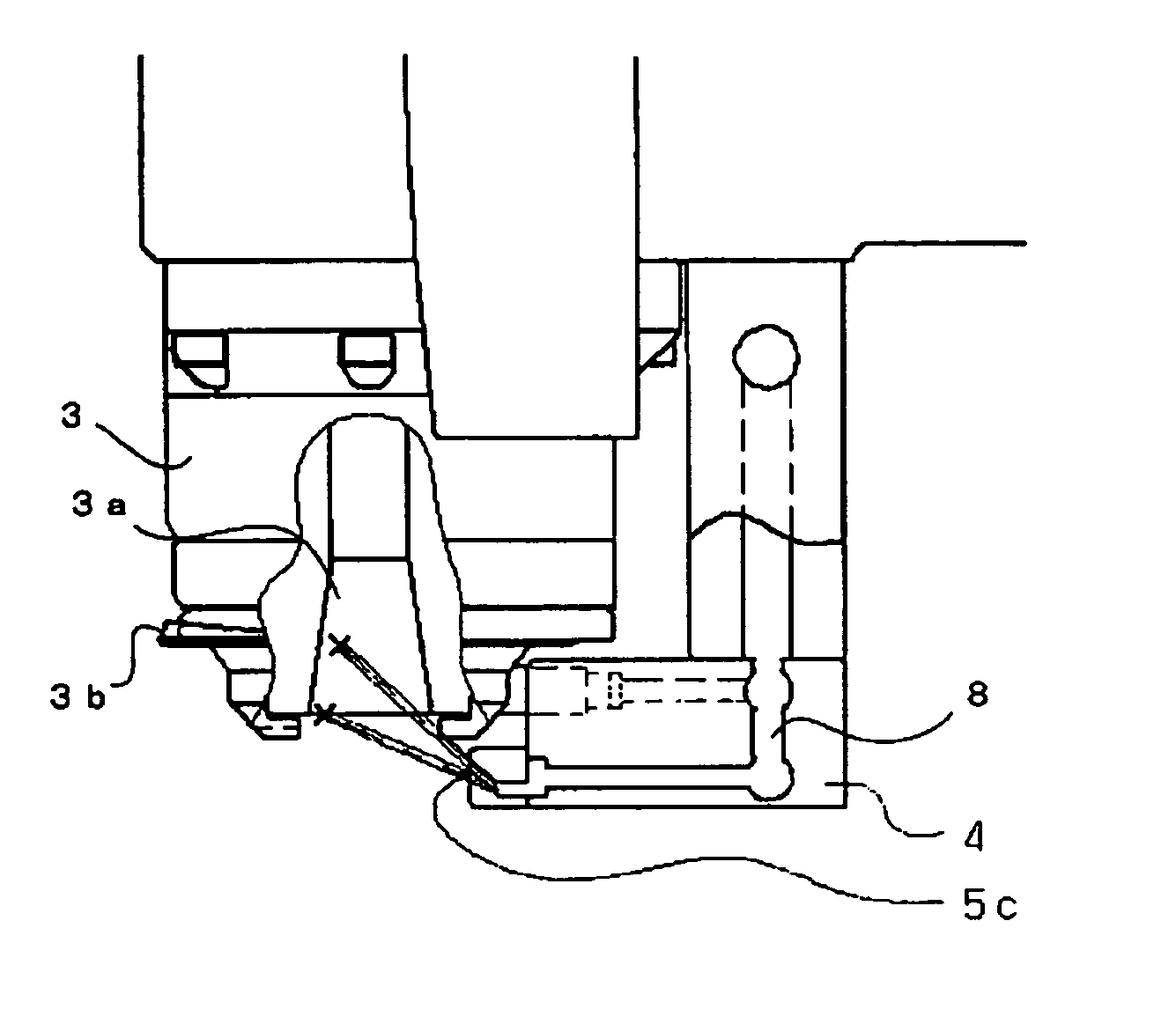

InactiveUS6220799B1Compact structureInhibit bad effectsPlaning/slotting machinesMilling machinesEngineeringMachine tool

A machine tool of small scale, light weight, and low cost, yet accomplishing a high degree of precision in machining. A spindle (2) is encased in a body frame (1) and disposed preferably in such a manner that the spindle (2) is movable along an axial center thereof or Z-axis direction by means of a Z-axis moving means (4). Either Y-axis table (5) or an X-axis table (6), at least being capable of moving along X-axis or Y-axis direction, or both is provided at one end of the spindle (2) on one side of the body frame (1) and arranged to be vertical with respect to the axial center of the spindle (2).

Owner:PANASONIC CORP

Machine tool, in particular a drilling and milling machine

ActiveUS20070042882A1Simple processing technologyCharge manipulationMilling machinesMachine toolDrilling machines

A machine tool (1, 1′), in particular a drilling and milling machine, comprising a housing (20) having a machine bed (2), together with side walls (3, 4) and doors (5, 6, 7), comprising a fixed, pivotable or rotatable work table (8, 9), and comprising a slide (10), transportable in the y direction, for the reception of a spindle head (11), transportable in the x-z direction, for the reception of tools (12), wherein the front door (5), for the enlargement of the working and loading area (21) in the upward direction, is of transomless configuration, the roof region (13) of the machine (1, 1′) has an automatically operable cover (16), the rear region (22) of the machine (1, 1′) has an integrable automatic pallet changer (14), and the machine (1, 1′) is assigned an automatic tool changer (15).

Owner:MIKRON AGIE CHARMILLES

Quick change tool holder

Owner:AMERICAN FLASHLIGHT TIP

Multi-spindle machining machine with tool changing mechanism

InactiveUS20110083307A1Low production costReduce sizing costsDrilling machinesTransportation and packagingRotational axisEngineering

A multi-spindle machining machine with a tool changing mechanism comprising a base; a carrier including a seat to move in Z axis, a rotary shaft fixed on the seat laterally to drive the seat to rotate in A axis, and a fixing holder coupled to an end portion of the rotary shaft to fix a workpiece; a tool changing mechanism including a mount mounted to the rotary shaft to rotate with the rotary shaft and a monitor fixed on the seat to measure a length of the tool clamped on the driving spindle, and including a plurality of slots to receive the tools respectively; a working head moving above the carrier and the tool changing mechanism in X and Y axes and including a driving spindle mounted on a lower end thereof to rotate axially, and the lower end of the driving spindle allowing to engage and disengage the tool.

Owner:SHENQ FANG YUAN TECH

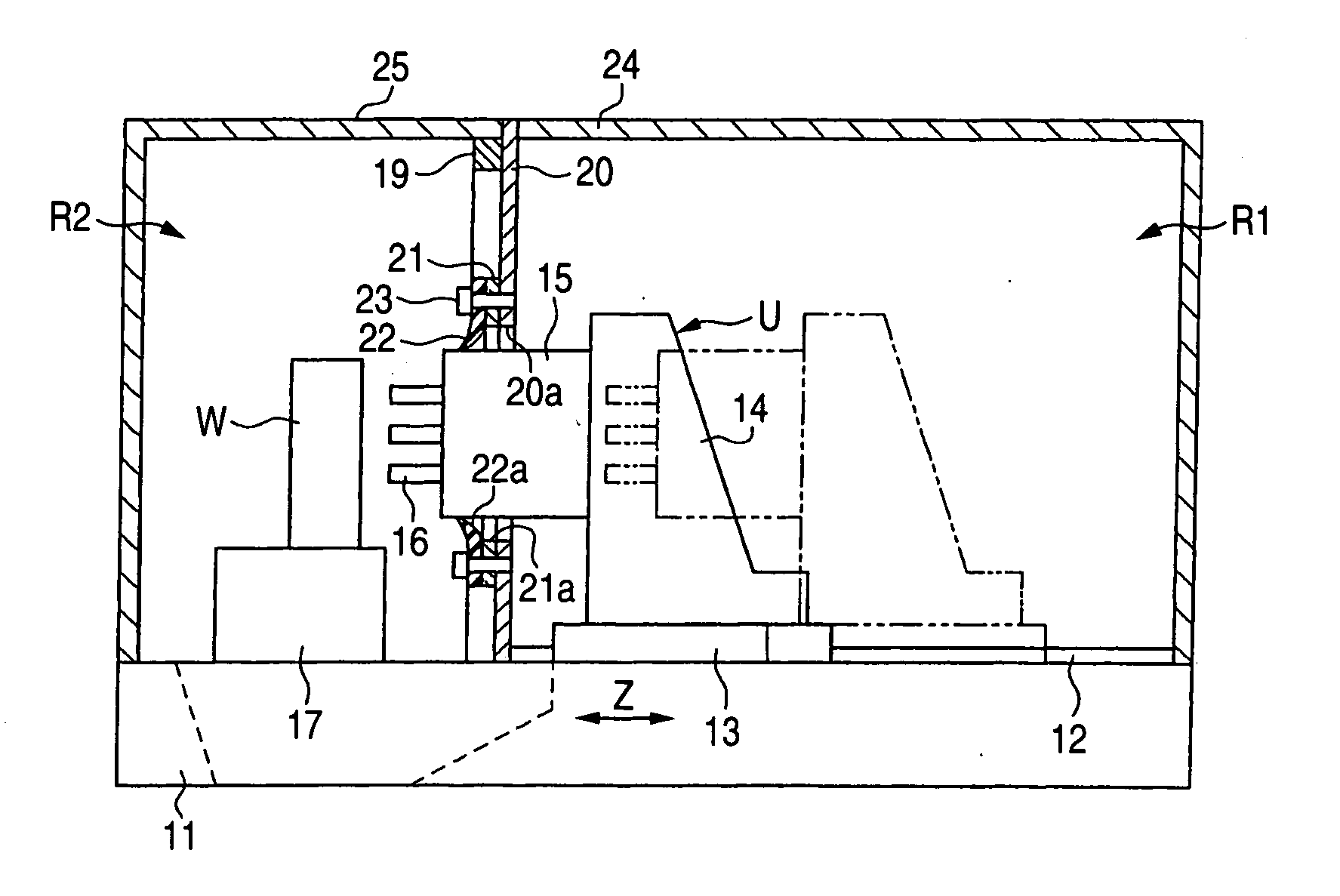

Machine tool

InactiveUS20060133903A1Surely preventAvoid enteringThread cutting toolsTransportation and packagingEngineeringMachine tool

A machine tool has a support table provided on an upper surface of a bed to support a work, a Z-axis saddle, a machining unit mounted on the Z-axis saddle and provided with a machining head, a compartment cover arranged on the bed to compartment a region and a machine region, an opening window provided on the compartment cover to permit the machining head to go in and out therethrough, and a seal member in the form of a closed ring to be mounted on an inner peripheral edge of the opening window of the compartment cover, wherein an entire periphery of an outer peripheral surface of the machining head is brought into sliding contact with an inner peripheral edge of the seal member in a state, in which the machining head is moved into the machining region from a tool exchange position within the machine region.

Owner:KOMATSU NTC LTD

Blade storage compartment for power tool vacuum port

A power hand tool of the type adapted to operate with one of a variety of elongated blades and being configured for vacuuming debris from an area near the blade during operation of the tool, wherein the tool includes a housing, a motor located within the housing, a port within said housing configured to receive a vacuum attachment, and a storage receptacle configured to carry at least one elongated blade and to matingly engage the port.

Owner:NANJING CHERVON IND

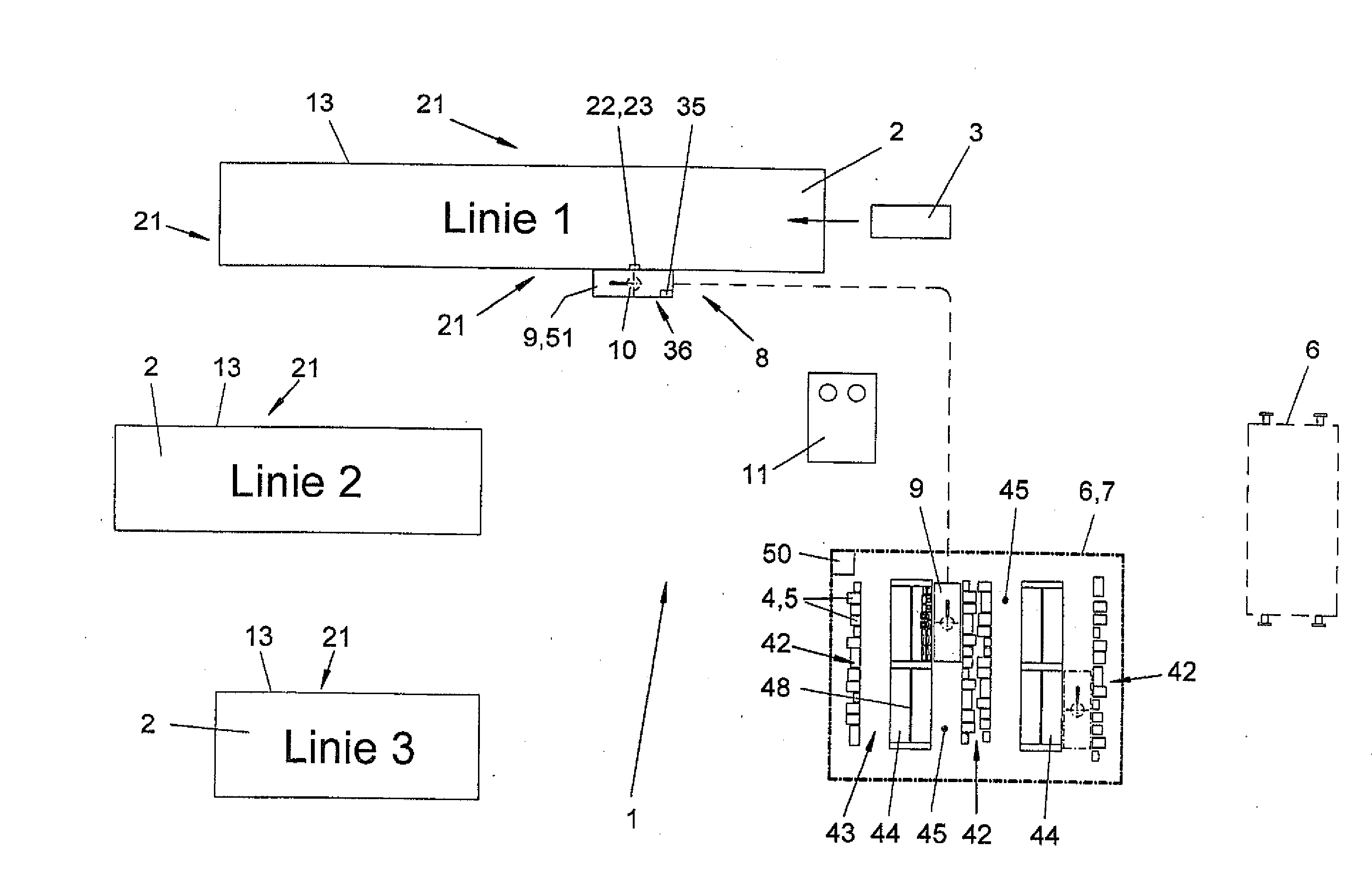

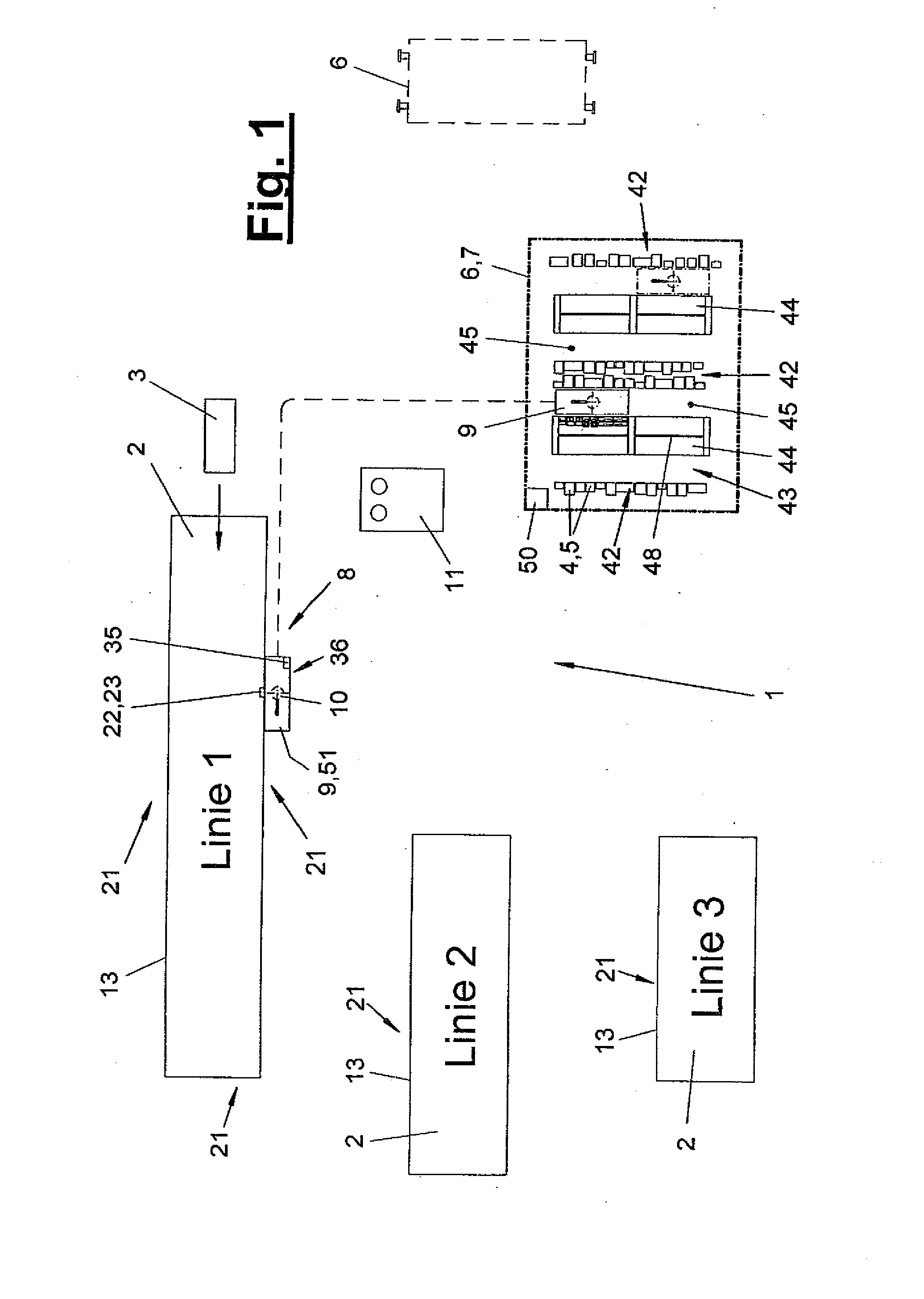

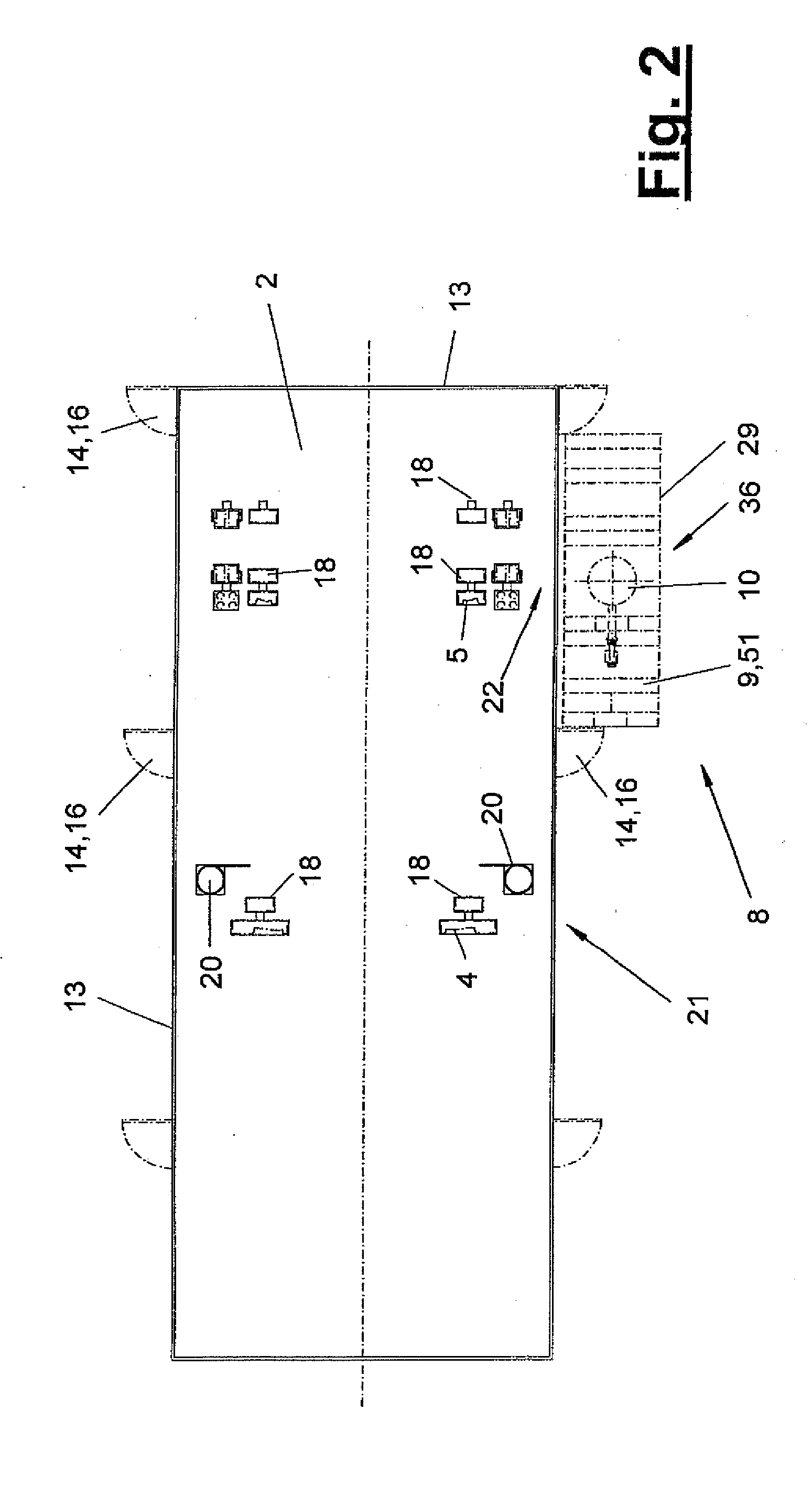

Processing Plant

InactiveUS20080274865A1Improve component logisticsAdditional componentProtection and storage accessoriesAssembly machinesProcessing plantsMachining

A machining or processing plant (1) is provided including one or several machining stations (2) that are surrounded by a protective partition (13) and are supplied with components (4, 5) from at least one external supply (6) by a feeding mechanism (8). The feeding mechanism (8) is provided with one or several distribution vehicles (9) which can be moved between the supply (6) and the processing stations (2). The distribution vehicles (9) are equipped with a multi-shaft manipulator (10) and a device (36) for surmounting the protective partitions (13). The distribution vehicles (9) are also equipped with one or several receptacles (30) for component supports (24, 25).

Owner:KUKA SYSTEMS

Switching device having a non-linear element

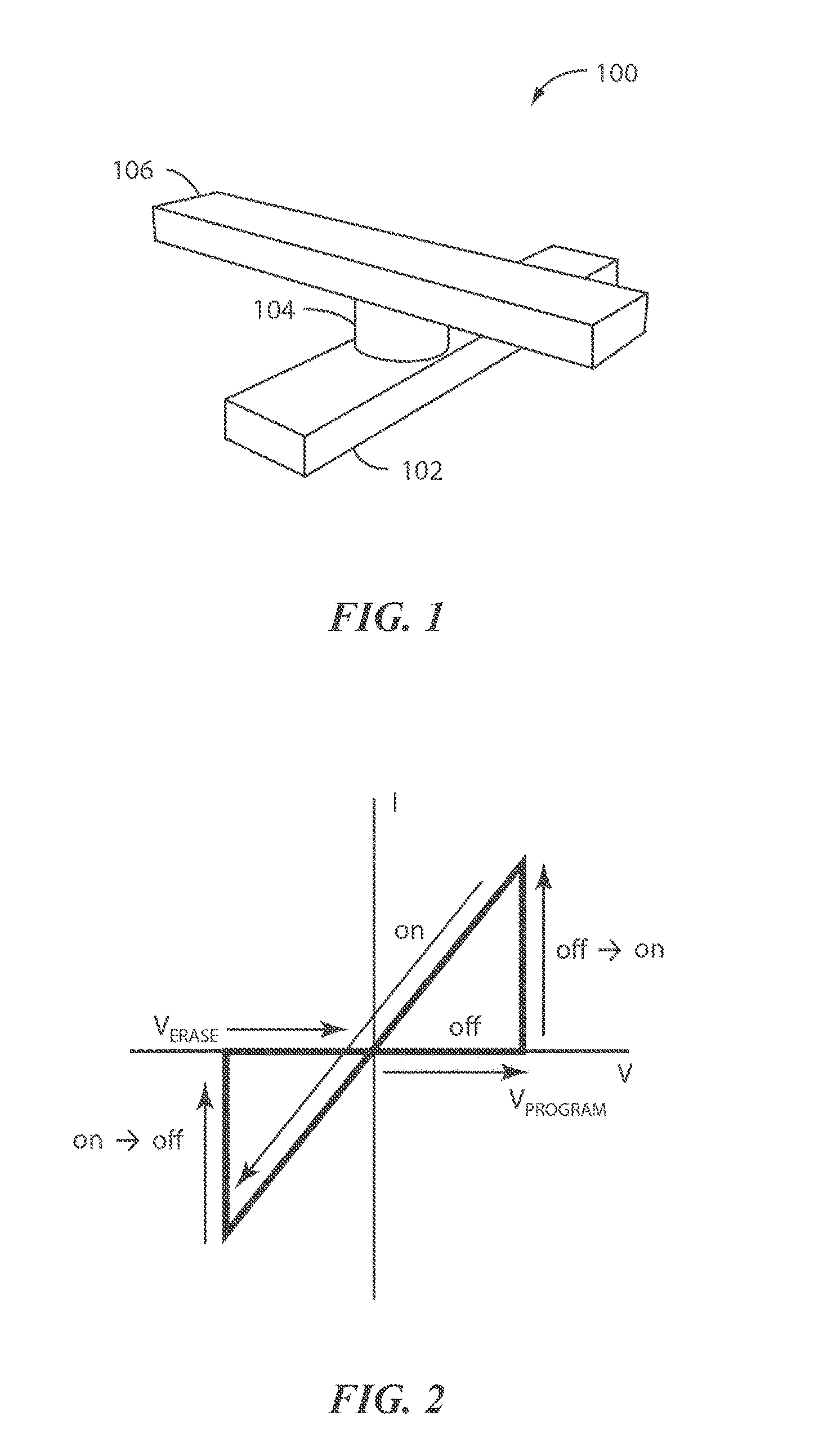

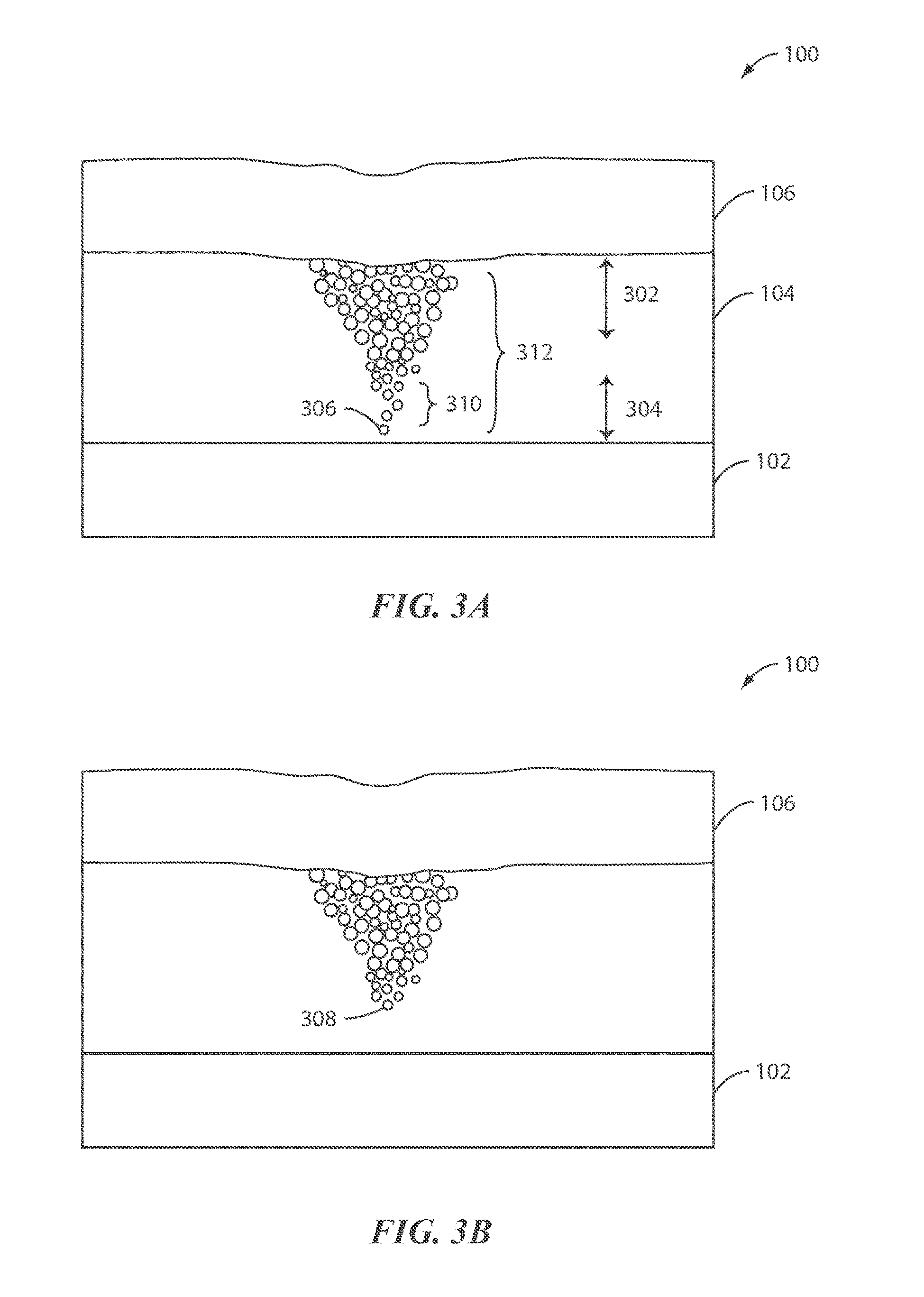

ActiveUS8767441B2High densityFast switching speedSolid-state devicesDigital storageLinear elementResistive switching

Method for a memory including a first, second, third and fourth cells include applying a read, program, or erase voltage, the first and second cells coupled to a first top interconnect, the third and fourth cells coupled to a second top interconnect, the first and third cells coupled to a first bottom interconnect, the second and fourth cells are to a second bottom interconnect, each cell includes a switching material overlying a non-linear element (NLE), the resistive switching material is associated with a first conductive threshold voltage, the NLE is associated with a lower, second conductive threshold voltage, comprising applying the read voltage between the first top and the first bottom electrode to switch the NLE of the first cell to conductive, while the NLEs of the second, third, and the fourth cells remain non-conductive, and detecting a read current across the first cell in response to the read voltage.

Owner:CROSSBAR INC

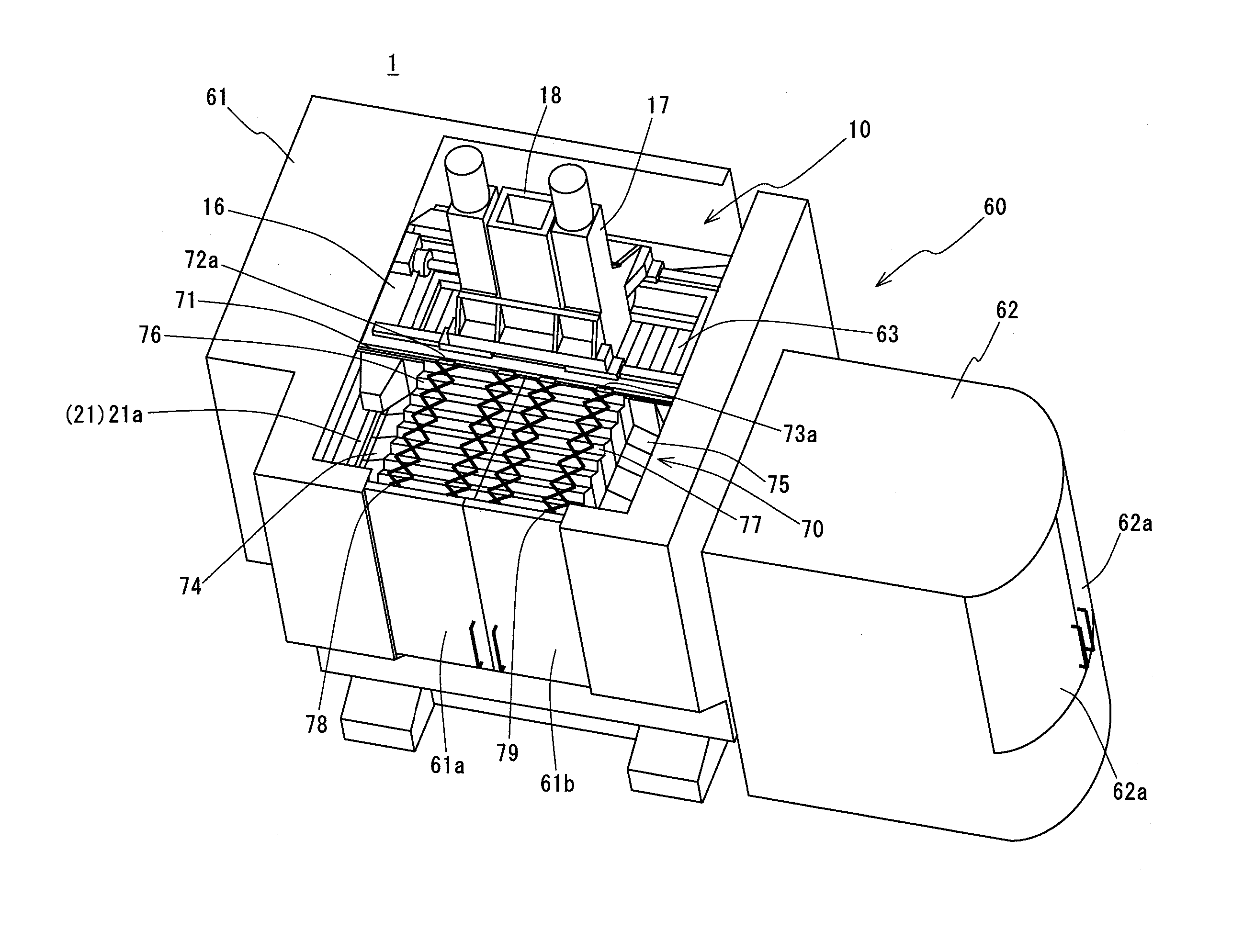

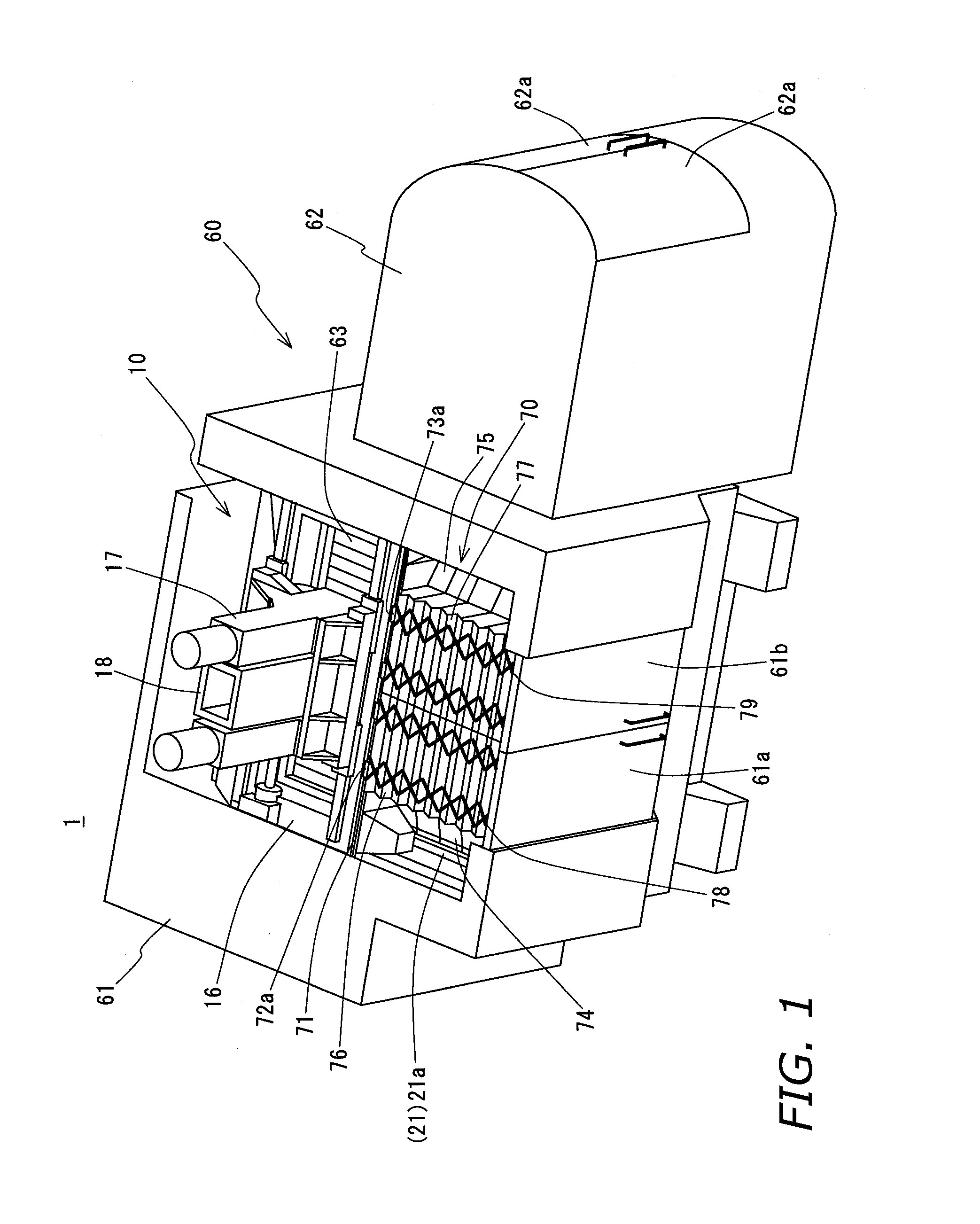

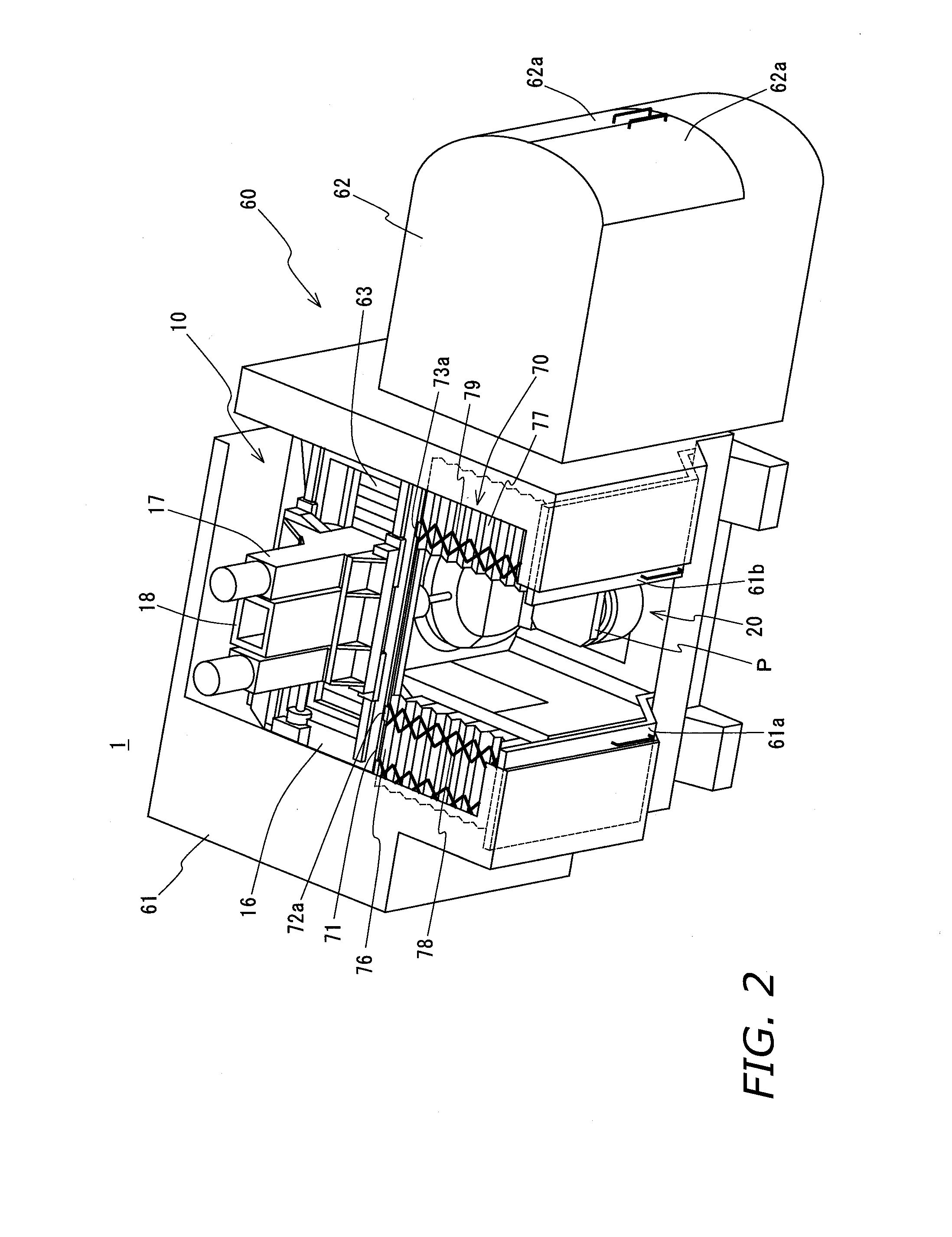

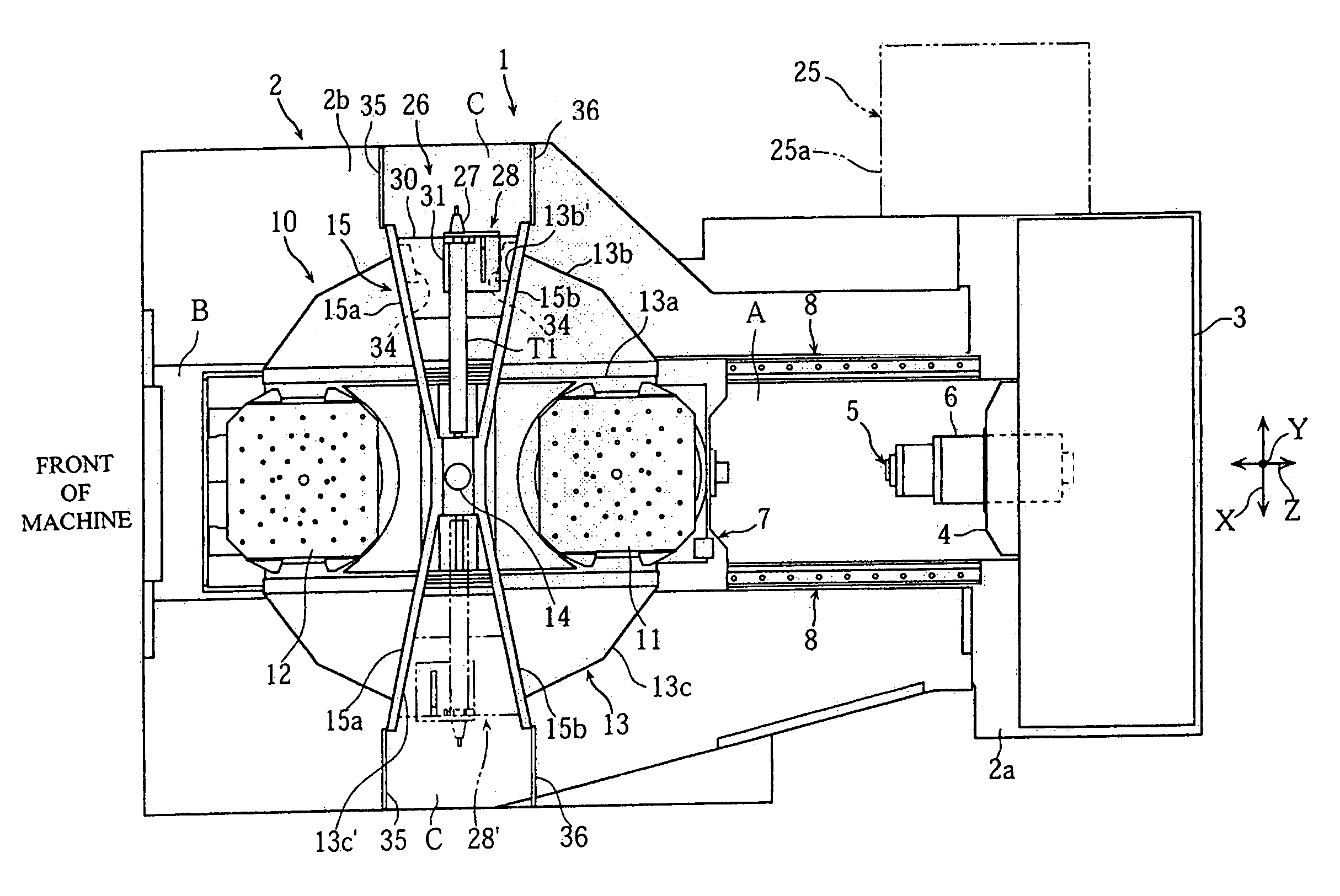

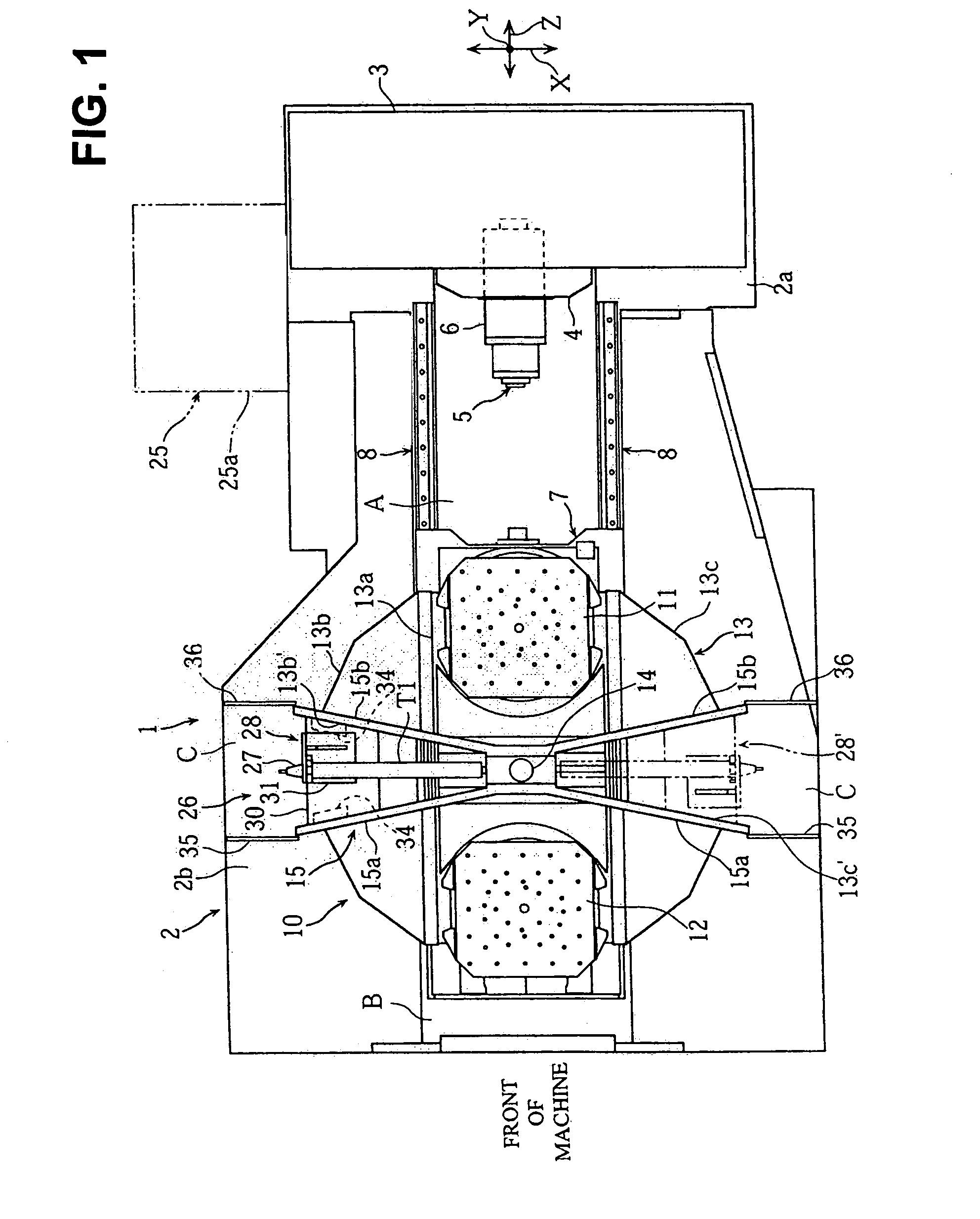

Machine tool

ActiveUS7357769B2Easy maintenanceReduce manufacturing costPlaning/slotting machinesMilling machinesEngineeringSaddle shape

Machine tool simplifying maintenance, reducing manufacturing costs, and enabling high precision machining. The machine tool is equipped with: a bed furnished with a rectangular base, right and left sidewalls provided standing either side of the base, and a rear sidewall provided standing along the back of the base; a table disposed in the space surrounded by the three sidewalls; a first saddle shaped in the form of a rectangular frame shape, provided free to shift back and forth supported on the tops of the left and right sidewalls; a second saddle penetrated by a perpendicular through-hole and arranged free to shift sideways inside the first saddle frame; and a spindle head arranged free to shift perpendicularly inside the through-hole in the second saddle; and a main spindle arranged over the table and supported by the spindle head free to rotate centered on its axis.

Owner:DMG MORI CO LTD

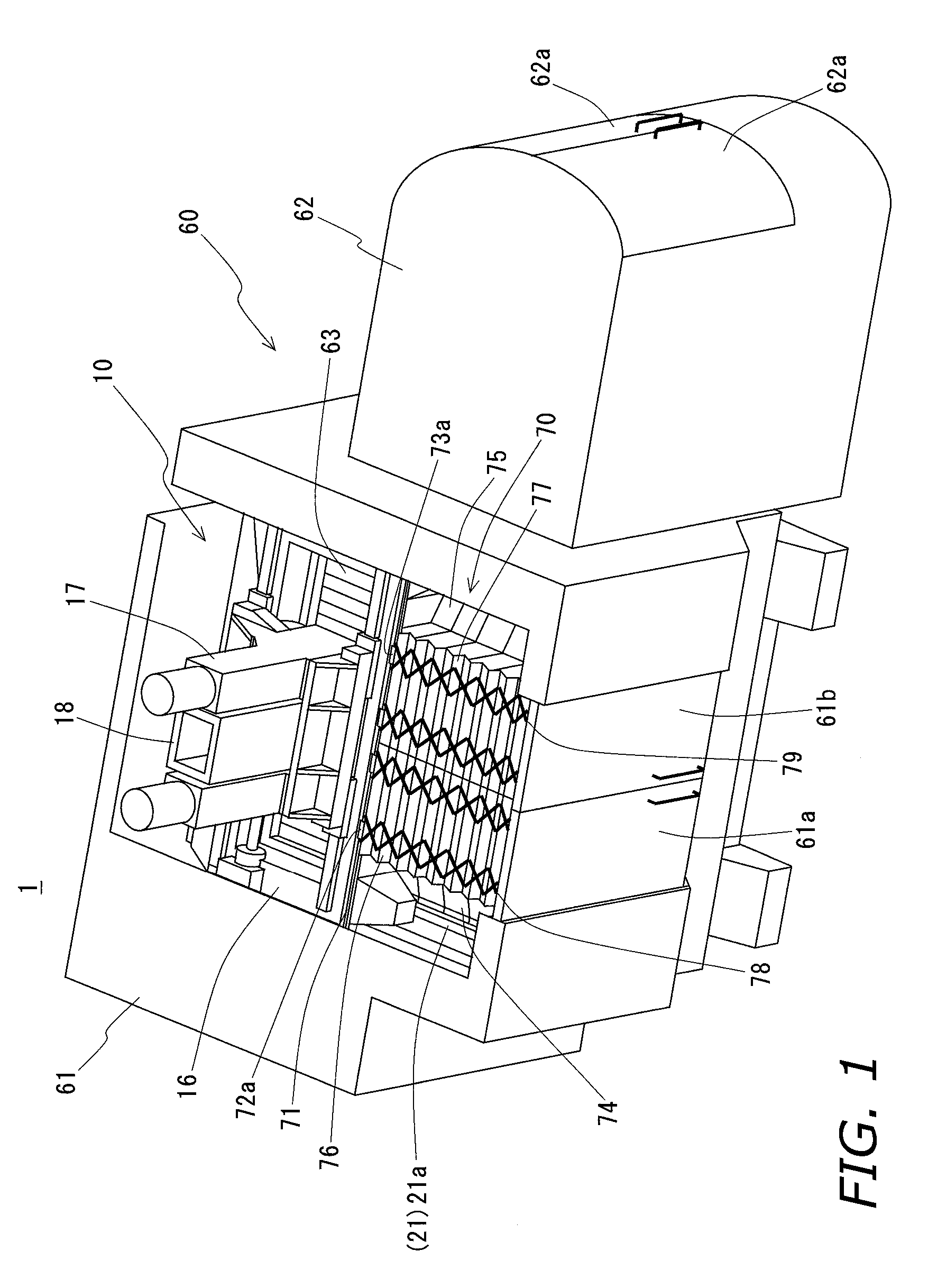

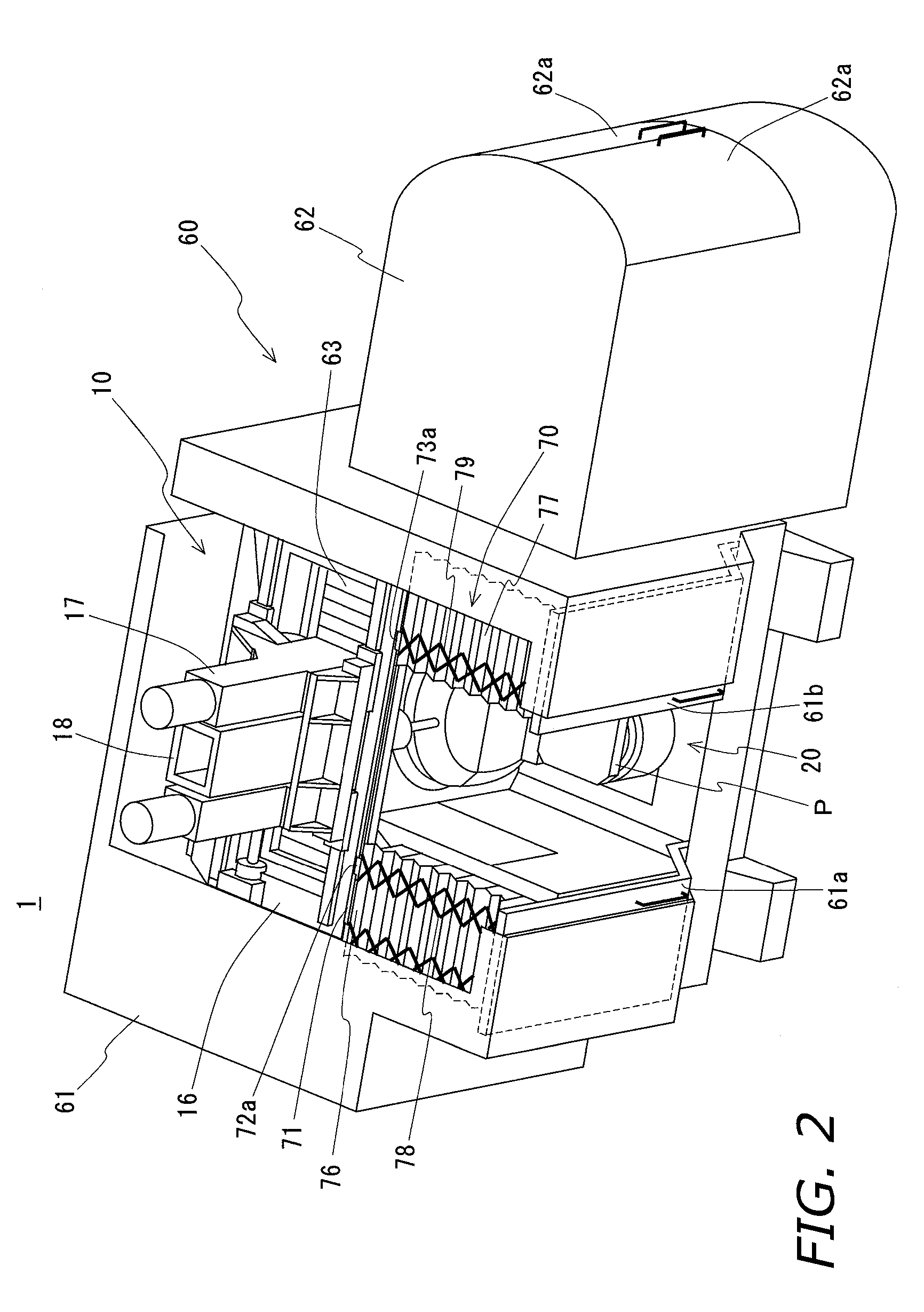

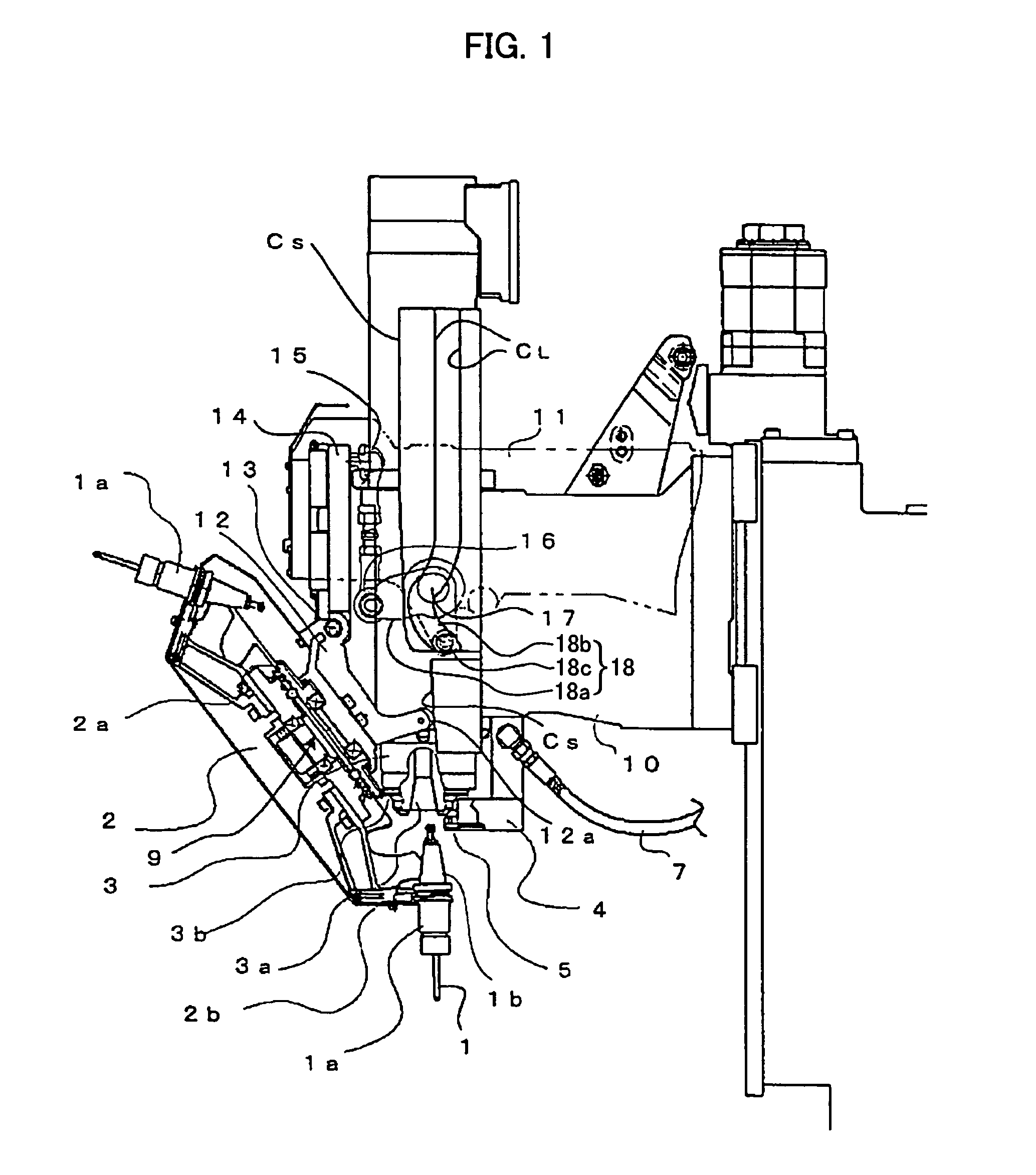

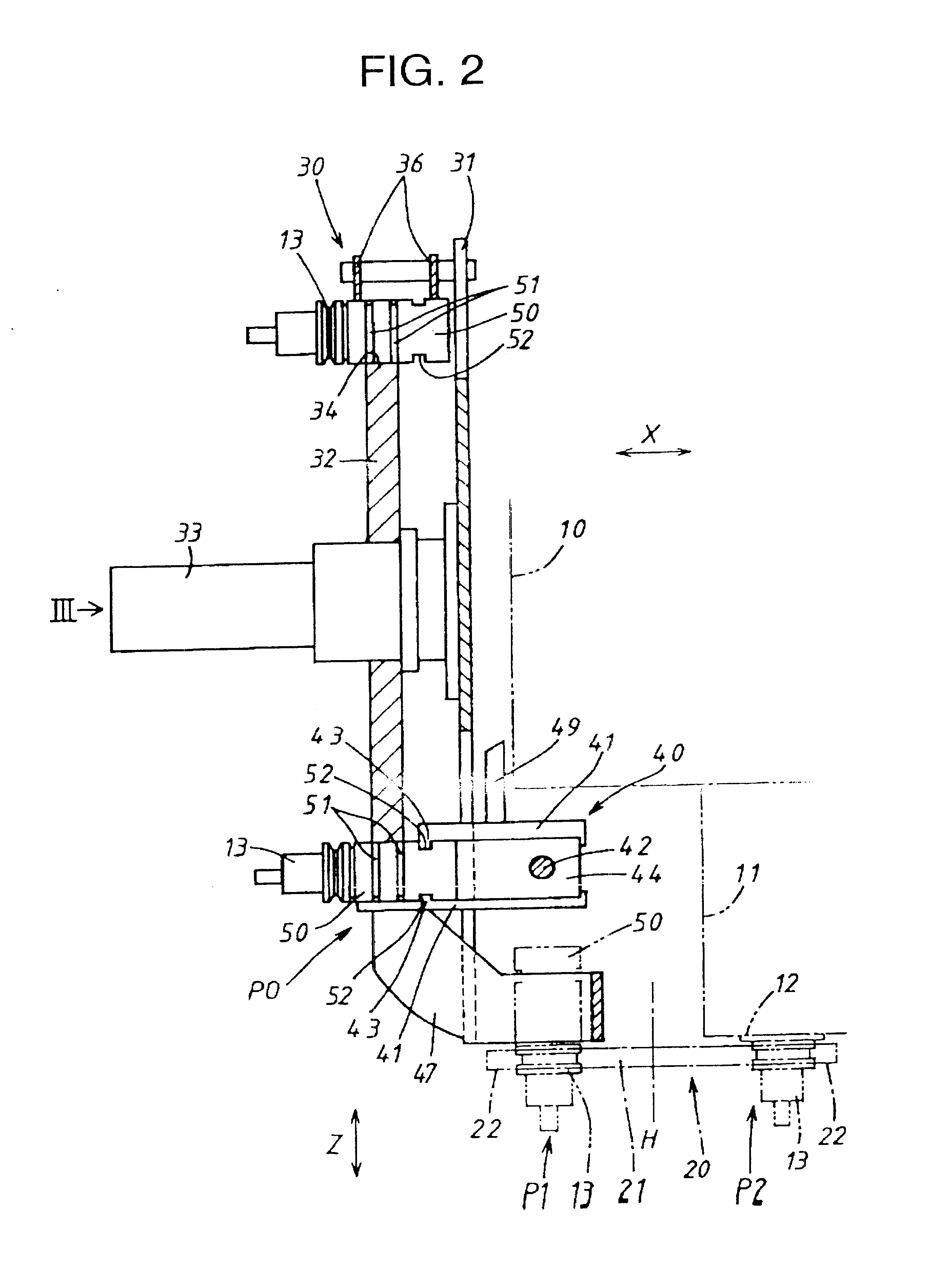

Tool changer of machine tool

InactiveUS7108647B2Small sizeCost containmentAutomatic control devicesProtection and storage accessoriesSize increaseEngineering

The present invention provides a tool changer of a machine tool capable of suppressing cost increase and preventing size increase of the machine when a tool magazine is mounted. In a tool changer of a machine tool provided with a pallet change mechanism 10 in which a machining-side pallet 11 disposed on a machining area A side and a standby-side pallet 12 disposed on a standby area B side are turned around a turn shaft 14 by a turning member 13 to be automatically changed, a tool magazine 28 holding a plurality of tools T1 to T4 is disposed between the machining-side pallet 11 and the standby-side pallet 12 in the turning member 13 and the tool magazine 28 is turned by the turning member 13 so that the tools T1 to T4 face a spindle 5 disposed on the machining area A side.

Owner:DMG MORI CO LTD

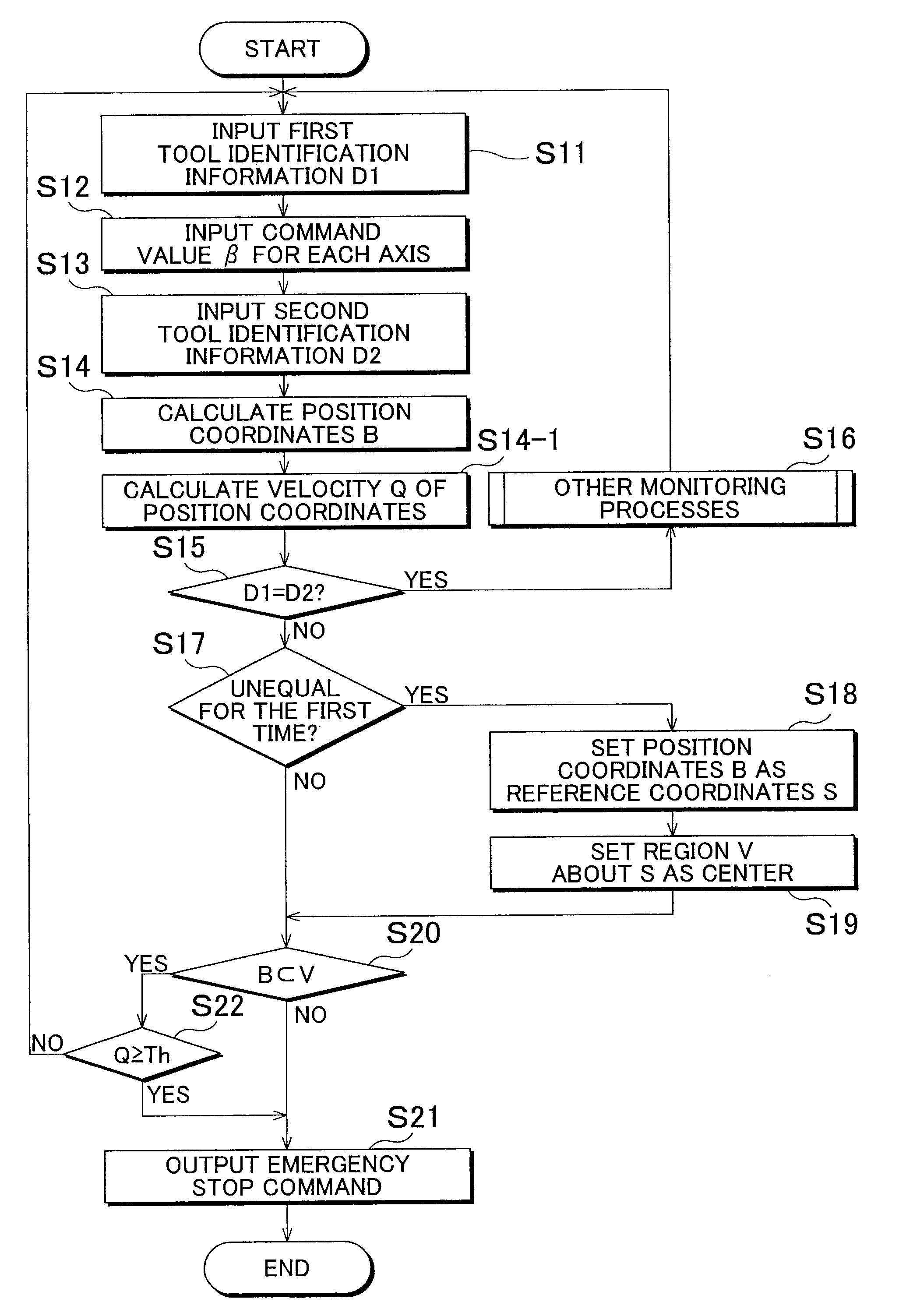

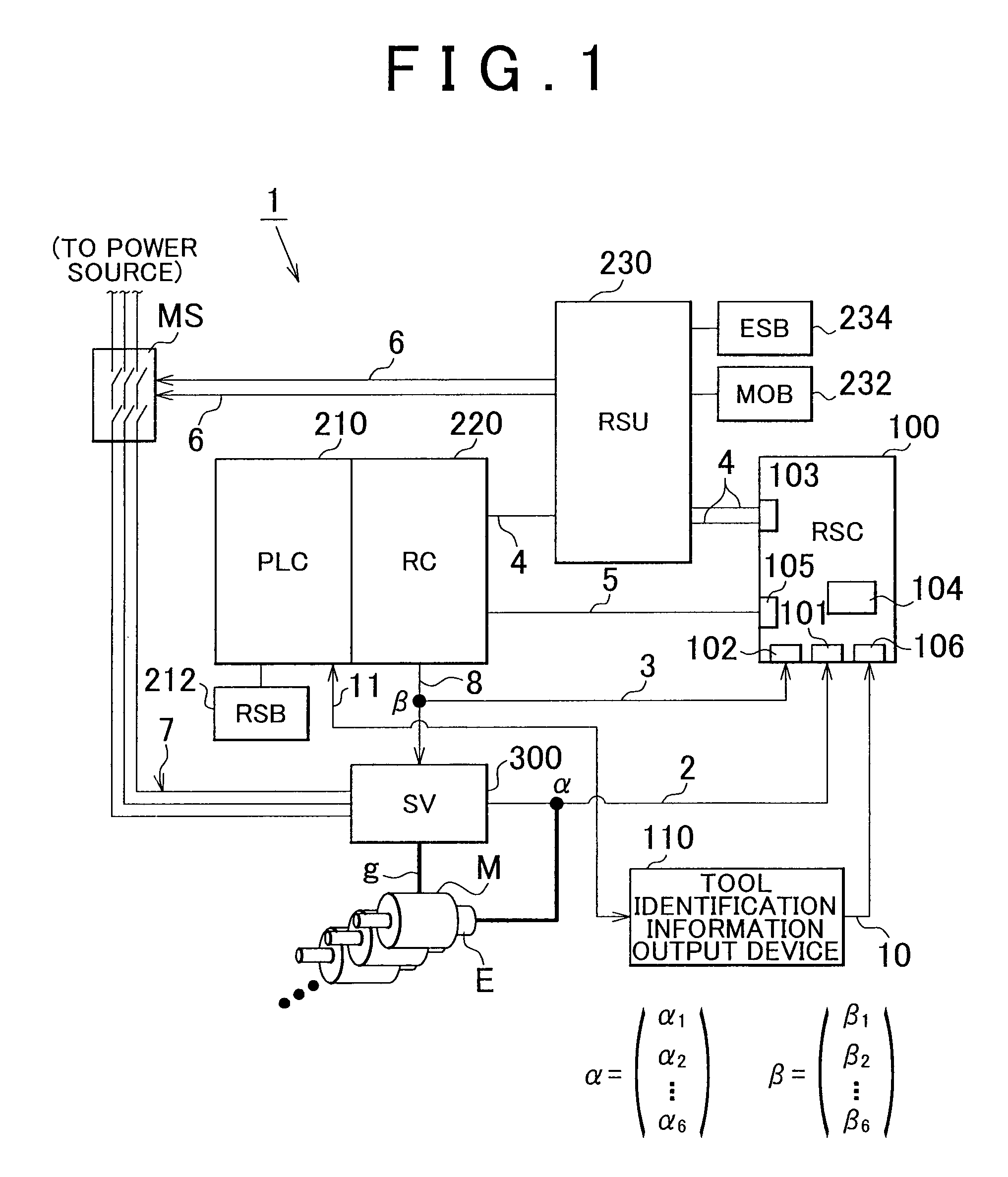

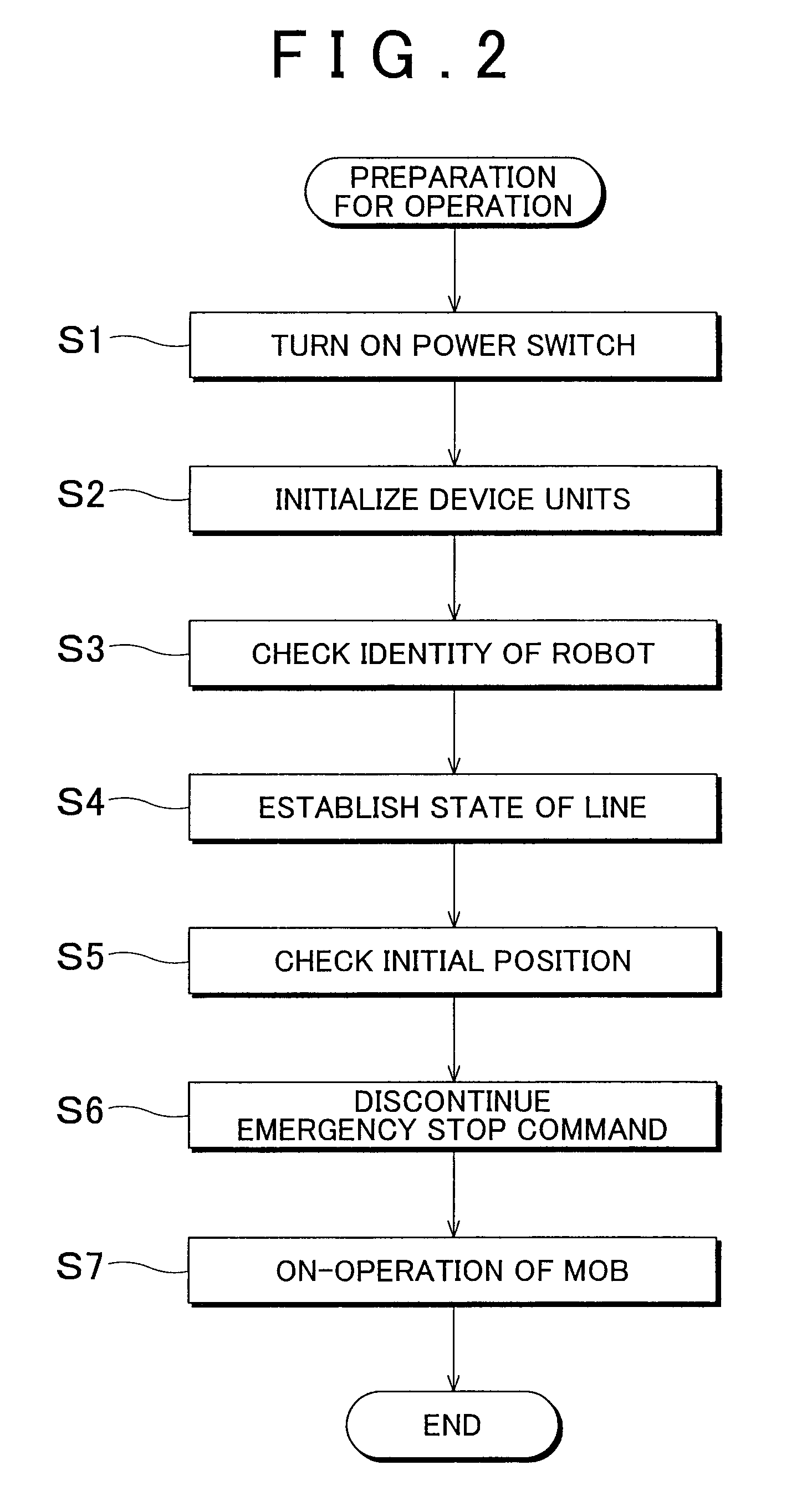

Robot safety monitor device, and robot safety monitor method

InactiveUS20090198379A1Improve securityImprovement of the safety regarding tool changeProgramme-controlled manipulatorElectric testing/monitoringEngineeringRobot control

It is determined whether the first tool identification information that is output from a robot control device, and that indicates a present tool and the second tool identification information for detecting and identifying a tool attached to the robot are unequal to each other. The position coordinates of the taught reference point in an actual space of the robot occurring at the time when the unequalness therebetween is first detected are set as reference coordinates, and a region that contains the reference coordinates is set as a predetermined region. If the position coordinates of the taught reference point have come to exist outside the predetermined region during a period during which it is determined that the foregoing two pieces of information are unequal, an emergency stop signal for causing the robot to be in a safe state is output.

Owner:JTEKT CORP

Screw/insert saver

Owner:SANCHEZ JAVIER

High density tool and locking system

InactiveUS8430003B1Good flexibilityMinimization requirementsSleeve/socket jointsProtection and storage accessoriesHigh densityEngineering

A compact folding hand tool system wherein the storage of replaceable tool driver bits in a multi-chambered tool bit cartridge and / or extended tools are contained within the confines of the tool handle in high density organized multiple rows along stepped planes defined by an X, Y and Z axis. The storage of driver bits and / or extended tools does not exceed beyond the physical width, height and length or contour design of the tool handle and can be accessed from one or two sides of the tool handle. The use of compact multi-chambered tool bit fixed or pivoting cartridge and / or pivoting extended tools equipped with multiple locations including a home position with semi secure positioning features or positive locking position features. Folding hand tool driver(s) either equipped with a singular or multiple locations including a home position with semi secure positioning features or positive locking position features. This system allows for a greater number of tools to be grouped together within the tool handle and minimize the need for additional tool containers such as tool boxes or pouches.

Owner:BASELINE REDEFINED

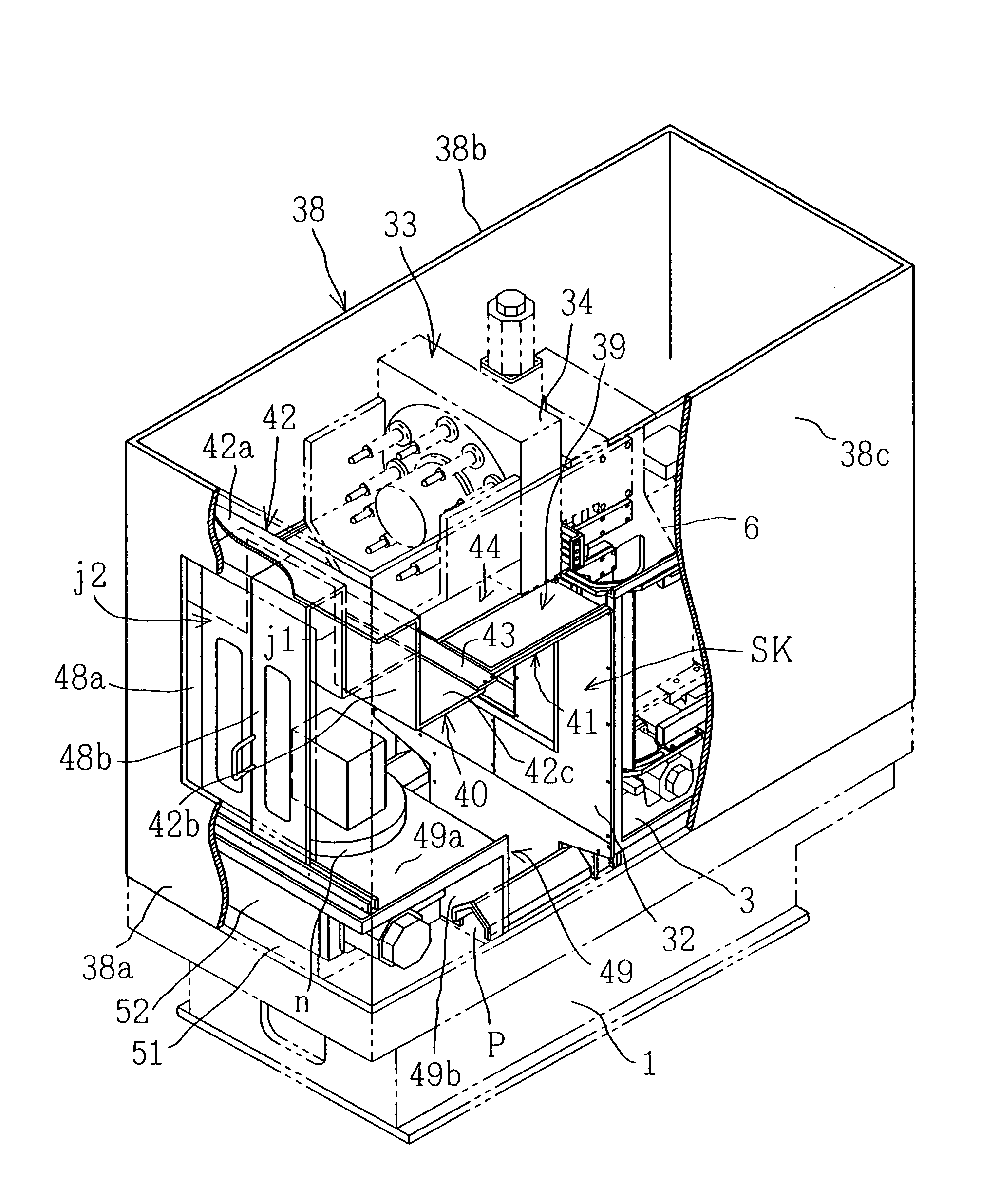

Column moving type machine tool with shield machining space

InactiveUS7223221B2Effective interceptionPrevent splashProtection and storage accessoriesGuardEngineeringMachine tool

A machine tool capable of reducing the lateral width of the upper part thereof by reducing the lateral width of a bed (1) while machining through the same lateral moving distance of a spindle (10) as before, comprising longitudinal guide rails (2) installed on the bed (1), a slide (3) installed through the guide rails (2) movably in a longitudinal direction, a column (6) movable in vertical direction, wherein first cover plates (25) are fixed at the right and left sides of a vertical moving route for the spindle (10), side cover plates (26) are installed continuously with the outer end edges of the first cover plates (25) so as to be turnable rearward, a second cover plate (32) is installed at the front sides of the first cover plates (25) and the side cover plates (26) integrally with the slide (3) so as to cover the front side of the moving range of the column (6), and a shielded machining space (SK) is formed at the front of the second cover plate (32).

Owner:HORKOS

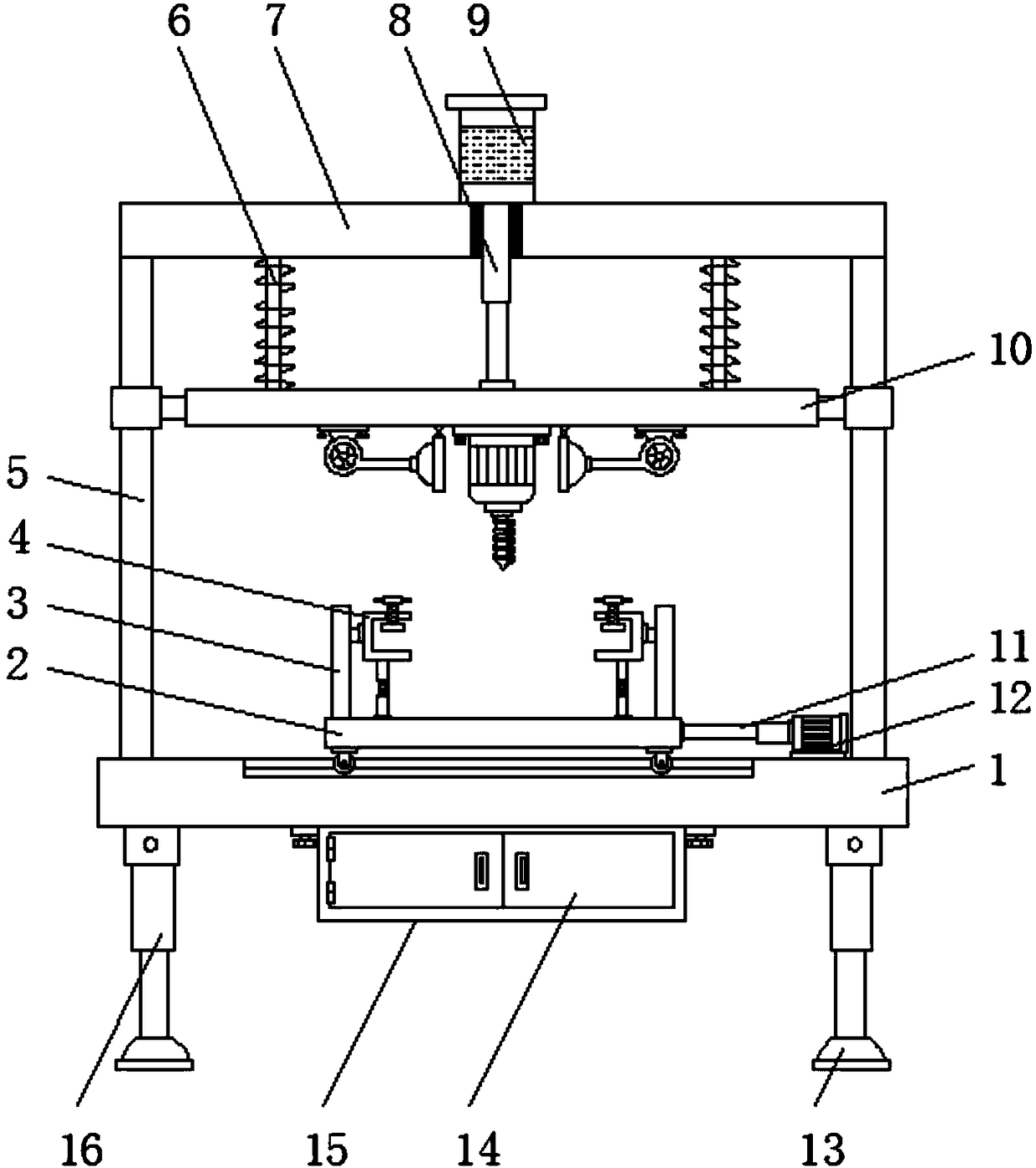

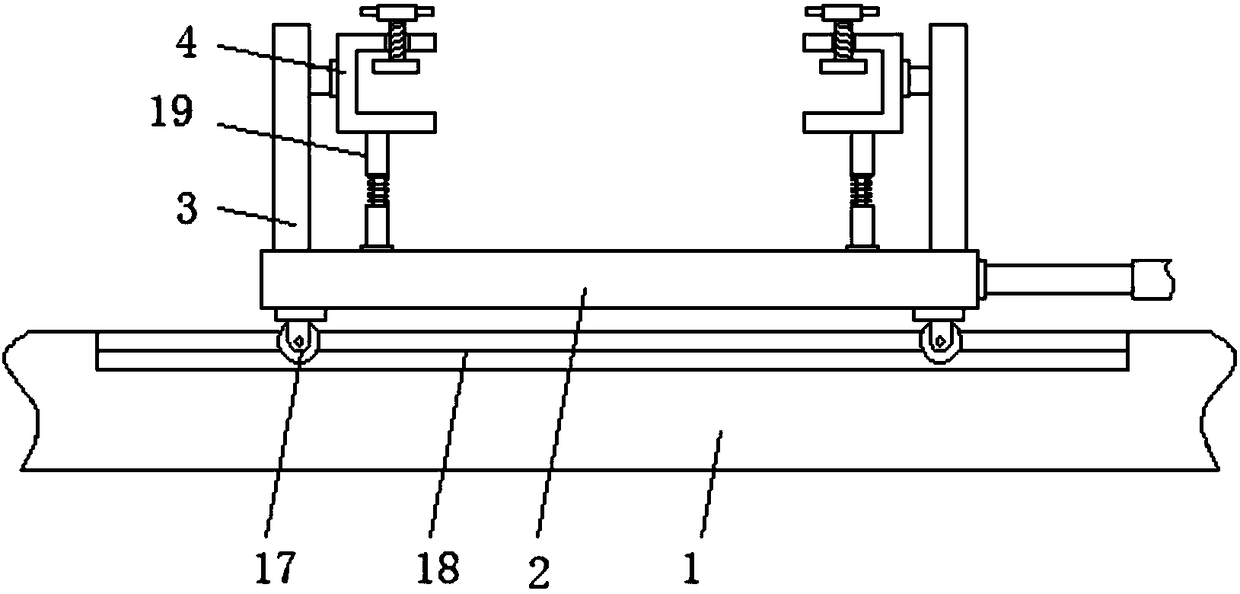

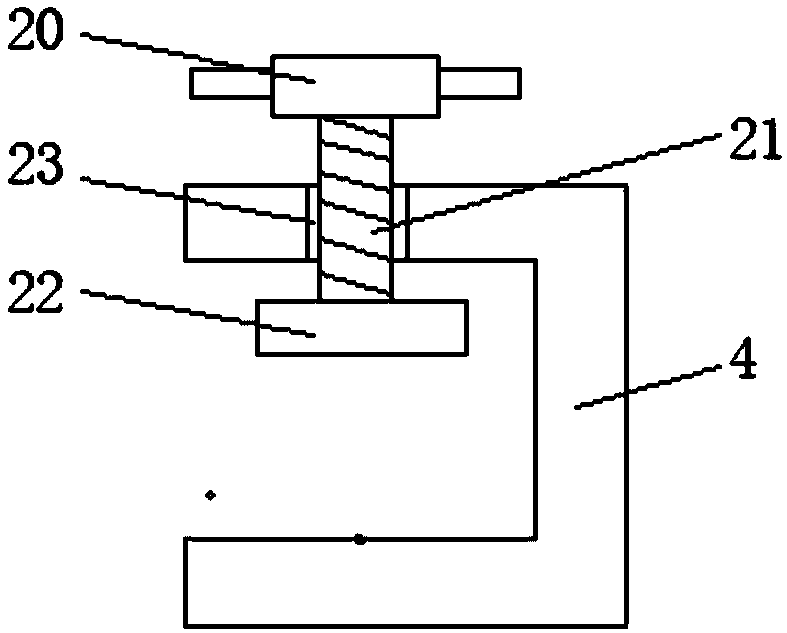

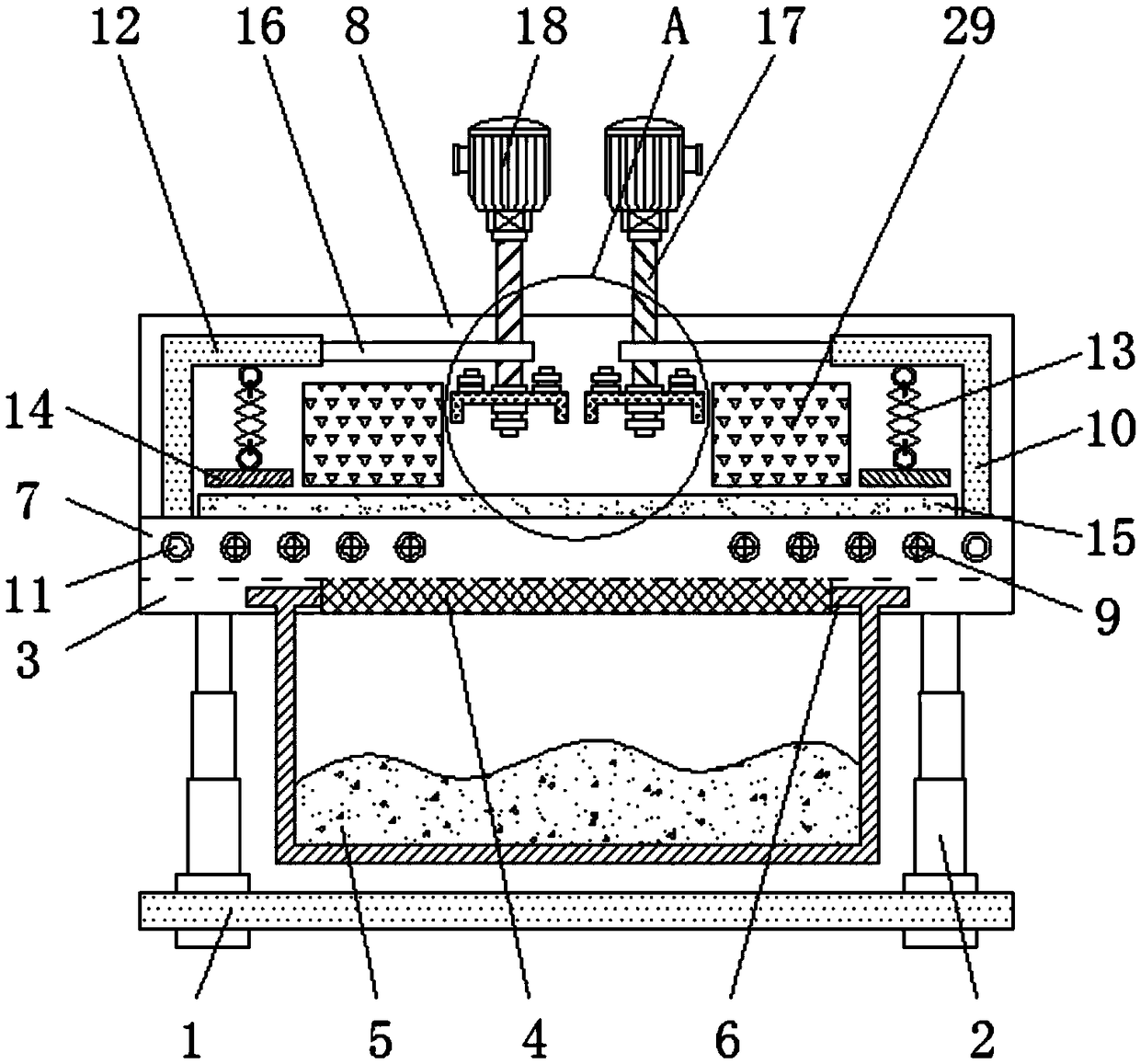

Drilling device for board machining

PendingCN108608032ARealize multi-point drillingReduce labor intensityProtection and storage accessoriesPositioning apparatusDrive motorScrew thread

The invention discloses a drilling device for board machining. The device comprises a base and a supporting top plate, a movable plate is arranged below the supporting top plate, a drilling motor is arranged on the bottom of the movable plate, a machining table is arranged on the upper surface of the base in a sliding manner, a drive motor is arranged on one side of the machining table, the drivemotor is connected with the machining table through an electric push rod, baffles are arranged on the two sides of the top of the machining table, concave opening clamping plates are arranged on the upper end of the inner wall of the baffles, thread holes are formed in the top sides of the concave opening clamping plates in a penetrating manner, thread rods are in threaded connection into the thread holes, and pressing blocks are arranged on the bottom ends of the thread holes. Under cooperation use of the concave opening clamping plates, the thread rods and the pressing blocks, the board canbe firmly fixed to the machining table, the phenomenon that in the drilling process, the board slides, and moves, and the drilling precision is affected is avoided, drilling effect is improved, the structure is simple, use is convenient, multi-point drilling of the board is achieved, and the drilling efficiency is high.

Owner:ZHEJIANG JUFENG WOOD IND

Machine tool

InactiveUS7192225B2Opens and closes easilyControl mechanismProtection and storage accessoriesFree rotationEngineering

Machine tool having a bed, a table arranged on the bed, a first saddle provided free to travel back and forth, a second saddle supported on the first saddle and provided free to travel side to side, a spindle head provided free to travel perpendicularly on the second saddle, a main spindle situated above the table and by the spindle head supported free to rotate on its center axis, a front cover provided on the front side of the bed and furnished with doors that open and close sideways, and top covers configured with one end sideways shiftably connected to the front side of the first saddle, and with another end connected extensibly / retractably to the top of the front-cover doors, therein being configured for permitting back-and-forth-directed movement of the first saddle.

Owner:DMG MORI CO LTD

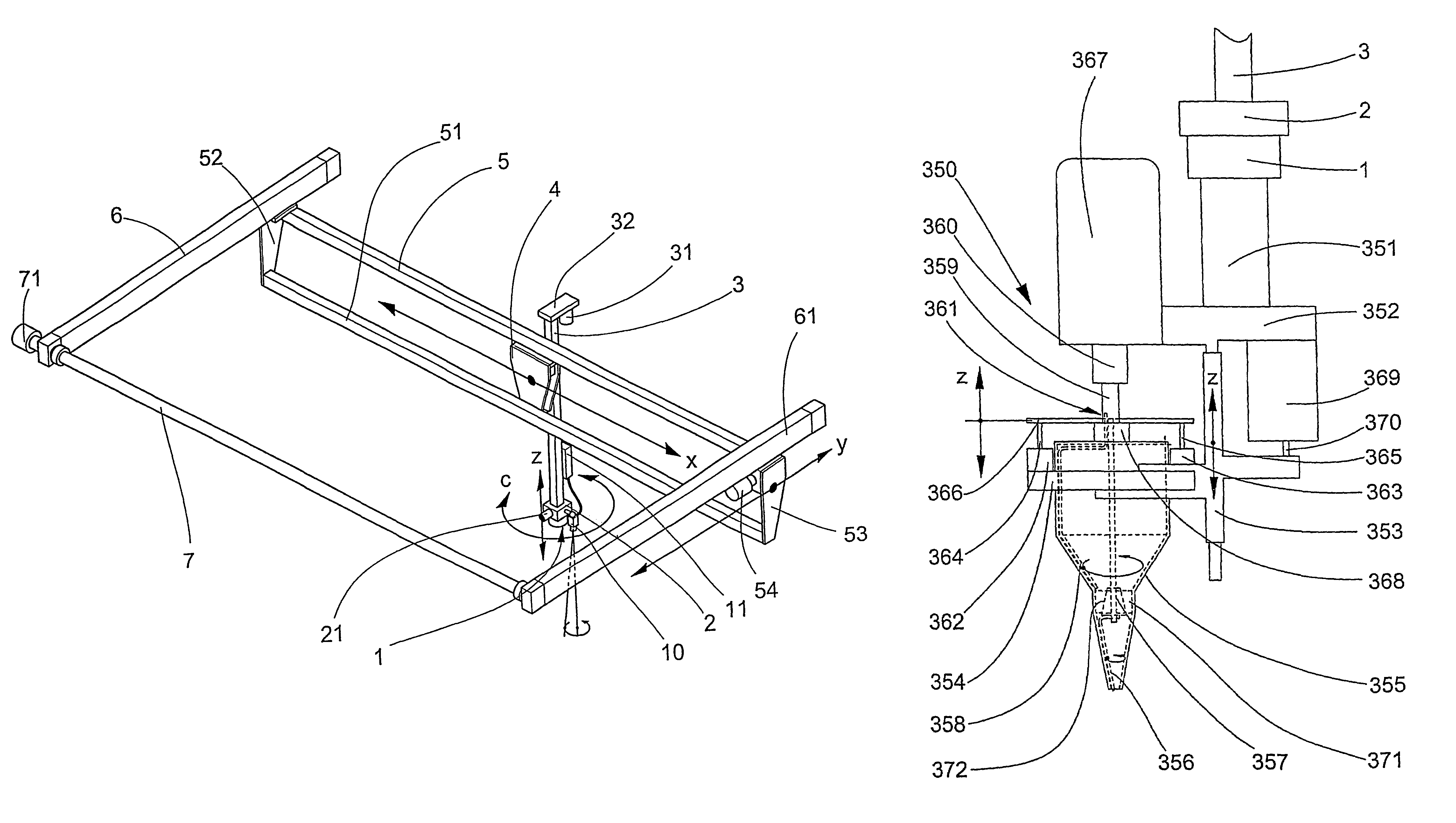

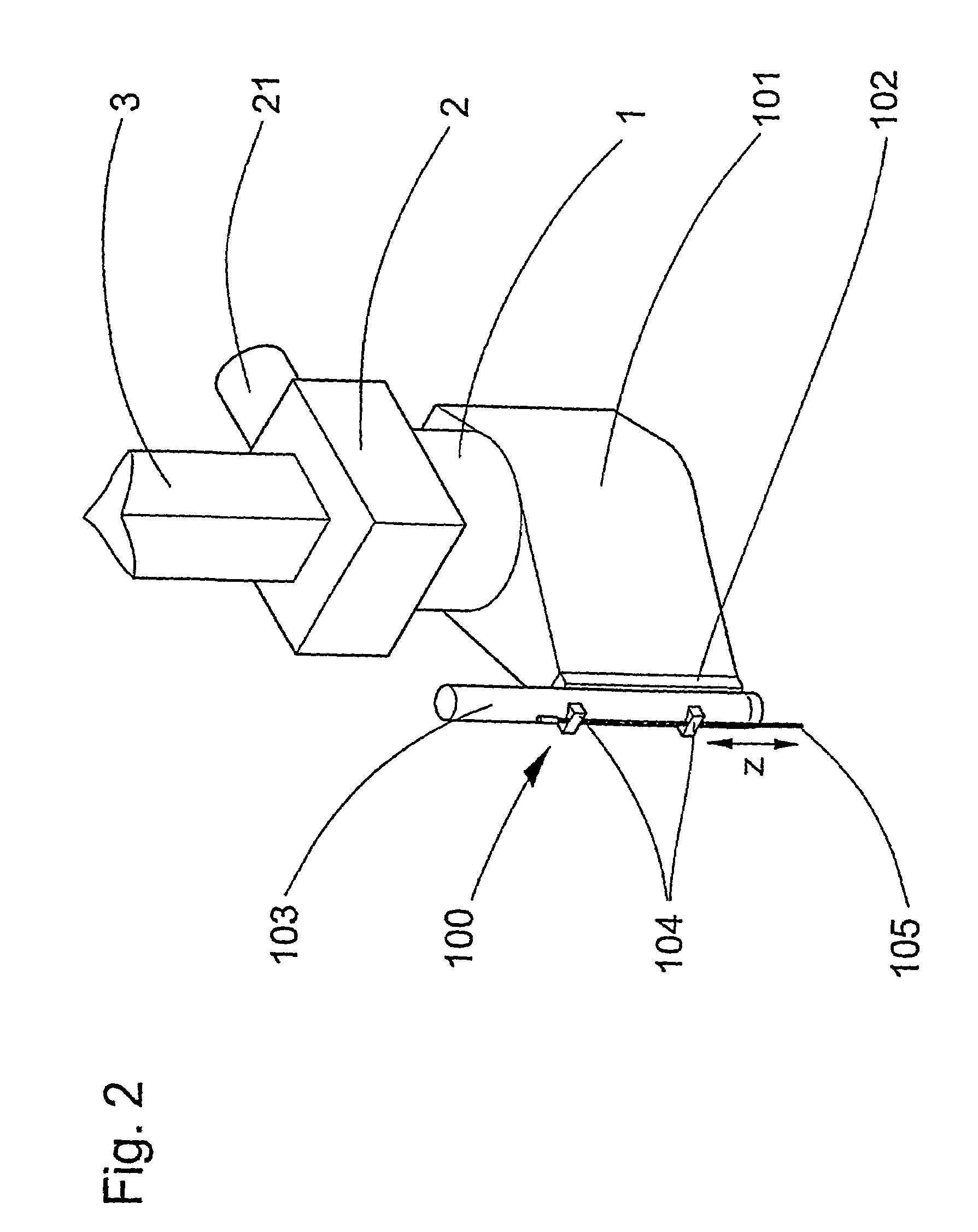

Device having a tool holder and a tool which can be secured removeably

InactiveUS7513857B2RiskMultiply speedTurning machine accessoriesWeighing apparatus for materials with special property/formEngineeringSolid matter

The inventive device comprises a tool holder, which can be displaced in an x-direction, in a y-direction that is perpendicular thereto, and in a z-direction that is perpendicular to both the x-direction and the y-direction, and which can rotate about the z-direction A solid matter dosing head, provided as a tool, is automatically attached in a removable manner to the tool holder by means of a permanent magnet. The tool can be easily exchanged for another tool due to this automatic removable attachment of said tool to the tool holder involving the use of a permanent magnet.

Owner:CHEMSPEED TECH

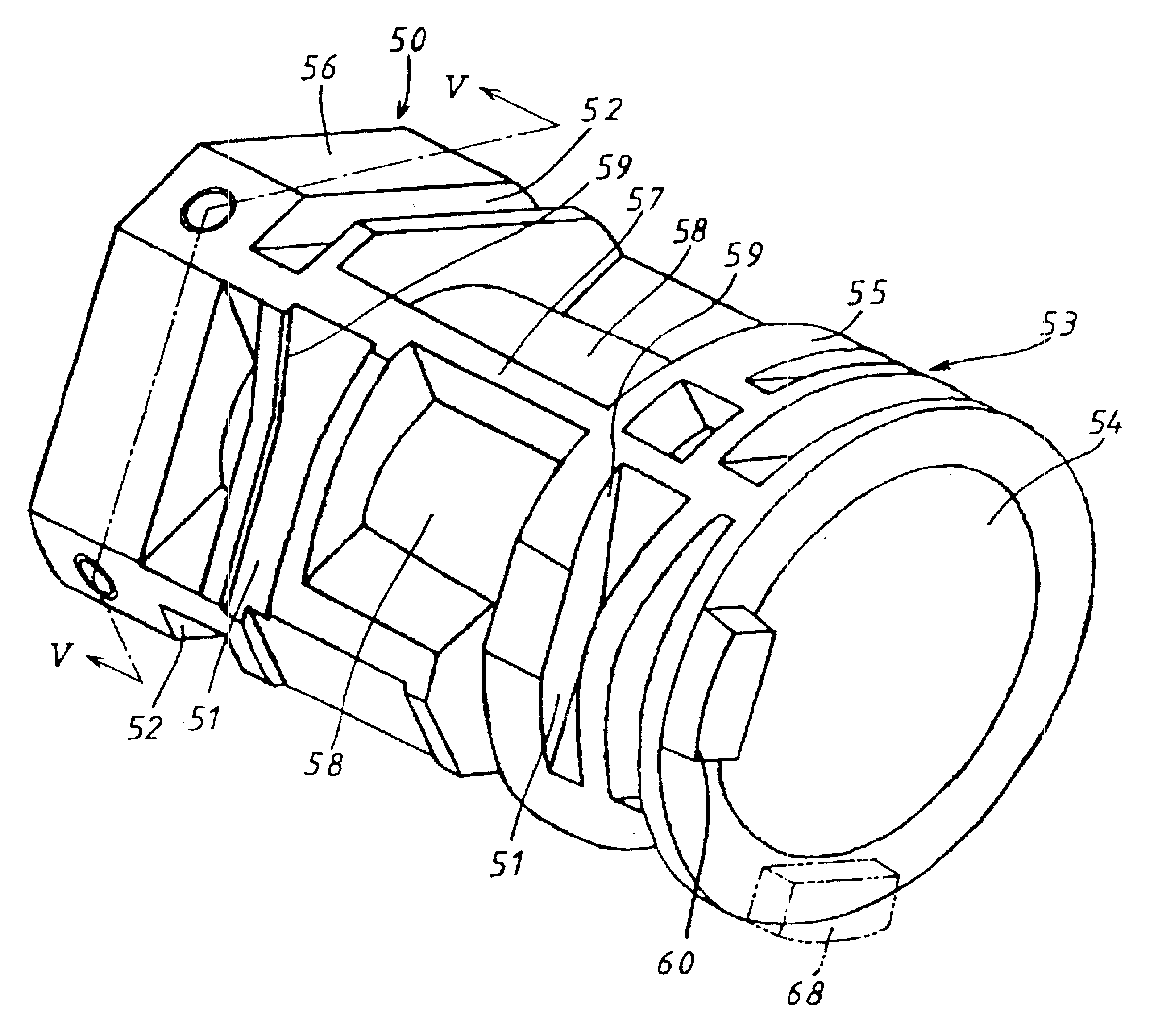

Nozzle change magazine for laser beam machine

A nozzle change magazine for laser beam machine which improves machining efficiency of a laser beam machine by installing a nozzle change magazine for laser machining tools equipped with a torch and a nozzle replaceably attached to the tip of the torch. A setup station for laser machining tools is installed outside a machining area of a laser beam machine. It includes a nozzle station which replaces a nozzle at the tip of the torch. The nozzle change station has a large number of magazines and changes the nozzle at the tip of the laser machining tool.

Owner:YAMAZAKI MAZAK KK

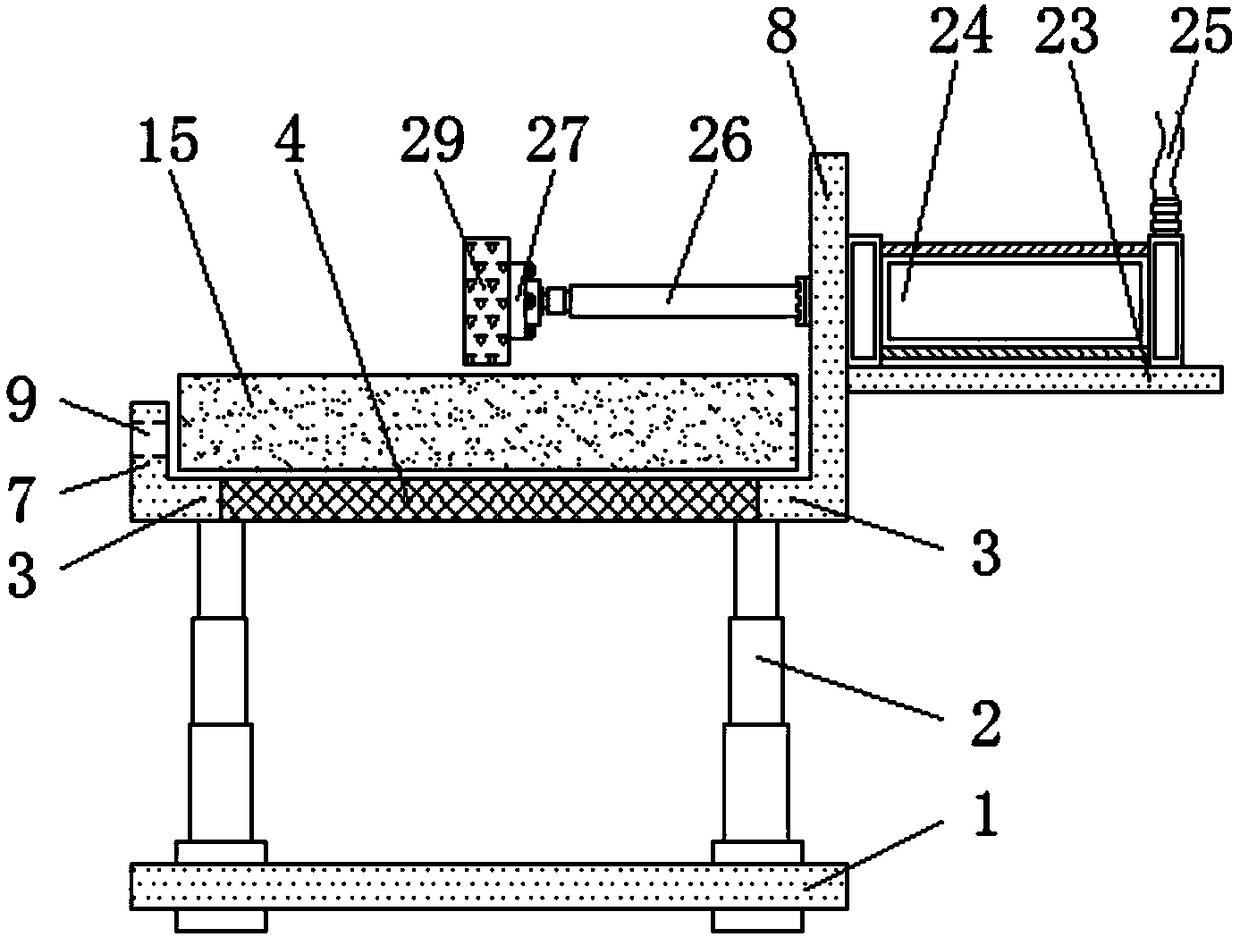

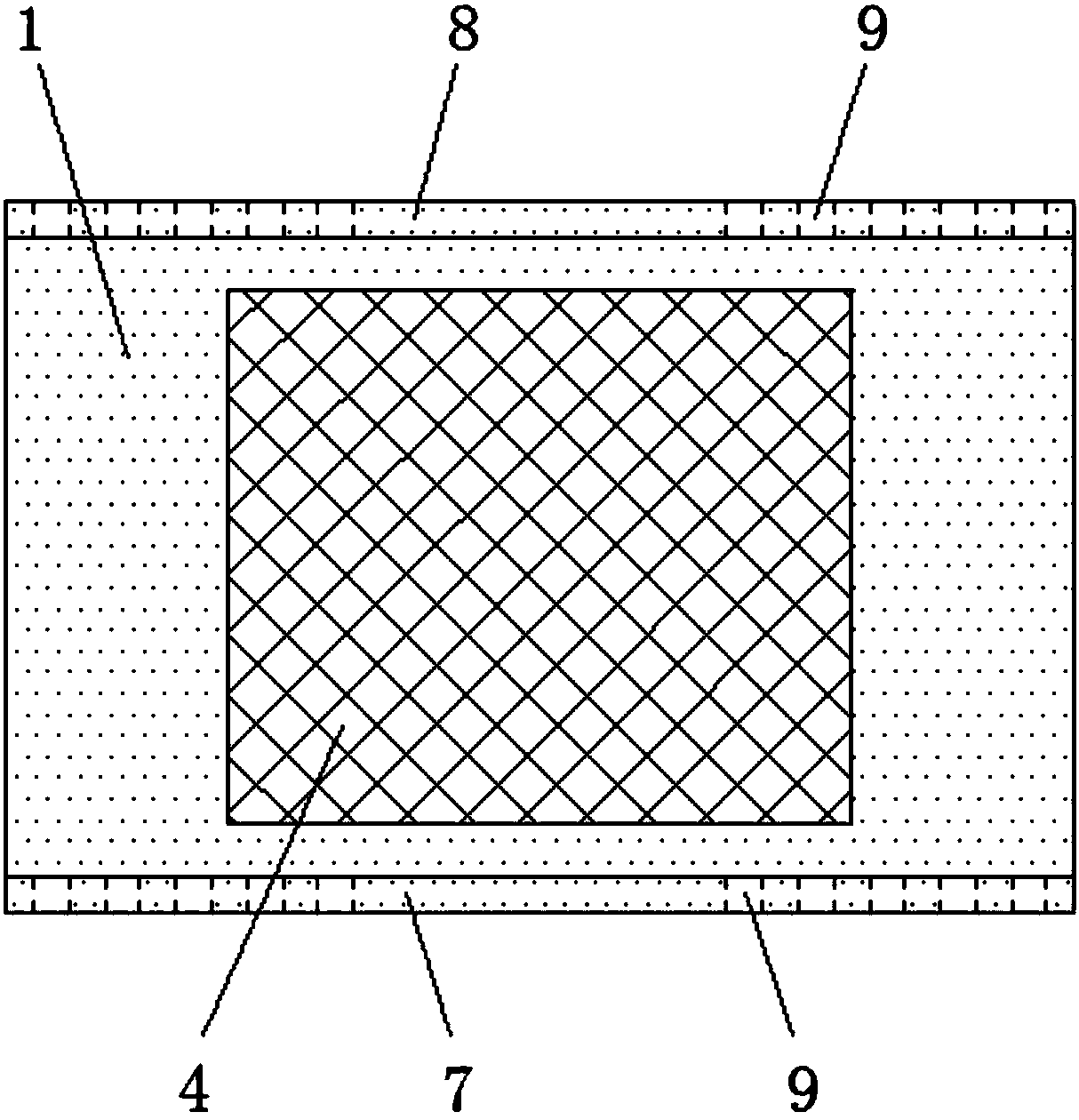

Drilling and polishing-integrated machine for aluminum sheet production and processing

InactiveCN108161471APrevent splashEasy to clean upProtection and storage accessoriesOther manufacturing equipments/toolsHydraulic cylinderPiston rod

The invention discloses a drilling and polishing-integrated machine for aluminum sheet production and processing. The machine includes a bottom plate, a chipping collecting tank, side plates, movableplates, a supporting plate, a piston rod and a polishing plate; the corner of the top of the bottom plate is connected with a working table through an electric telescopic rod, the chipping collectingtank is installed below a filter screen, the front and back sides of the bottom end of each side plate are both provided with elastic lugs, the inner side of the top end of each side plate is welded with a top plate, the movable plates are installed inside the top plates, the upper and lower ends of each screw rod are connected with a motor and a drill placement disk respectively, the supporting plate is welded at the back end of a rear-positioned baffle, the piston rod and a hydraulic cylinder are installed on the inner side and outer side of the rear-positioned baffle respectively, and the back end of the polishing plate is connected with a slide block through a slide groove. According to the drilling and polishing-integrated machine for aluminum sheet production and processing, drillingand polishing are integrated, an aluminum sheet can be firstly drilled and then polished, and therefore the surface of the aluminum sheet is shinier.

Owner:钱富良

Exchangeable tool

ActiveUS7632224B2Prevents possible rotationPrevent rotationShaping toolsGripping headsManipulatorEngineering

The invention relates to an exchangeable tool having a tool body with a receiving end for holding the tool in a receiving structure, wherein a connector is arranged in the tool body for providing a substantially non-rotatable connection with a manipulator for manipulating the tool into and out from the receiving structure,to a combination of such tool with a manipulator for manipulating the tool into and out from a receiving structure,and to a method for manipulating such tool into and out from a receiving structure.

Owner:WILA

Multi-function end effector

A multi-function end effector includes a plurality of tool change mechanisms in a housing in which a spindle is also mounted for translation along an axis of the spindle. Each tool change mechanism has a gripper that releasably grips a tool holder in which a tool is mounted. The gripper of each tool change mechanism is movable between a stowed position to a tool-change position in which the gripper is coaxially aligned with the axis of the spindle for placing a tool holder held in the gripper in a position to be received by the spindle and for positioning the gripper to receive a tool holder from the spindle. The tools mounted in the tool holders include a drill bit, a countersink tool, and a fastener insertion tool. The end effector also includes a fastener feed system, a hammer device, and a sealant applicator.

Owner:THE BOEING CO

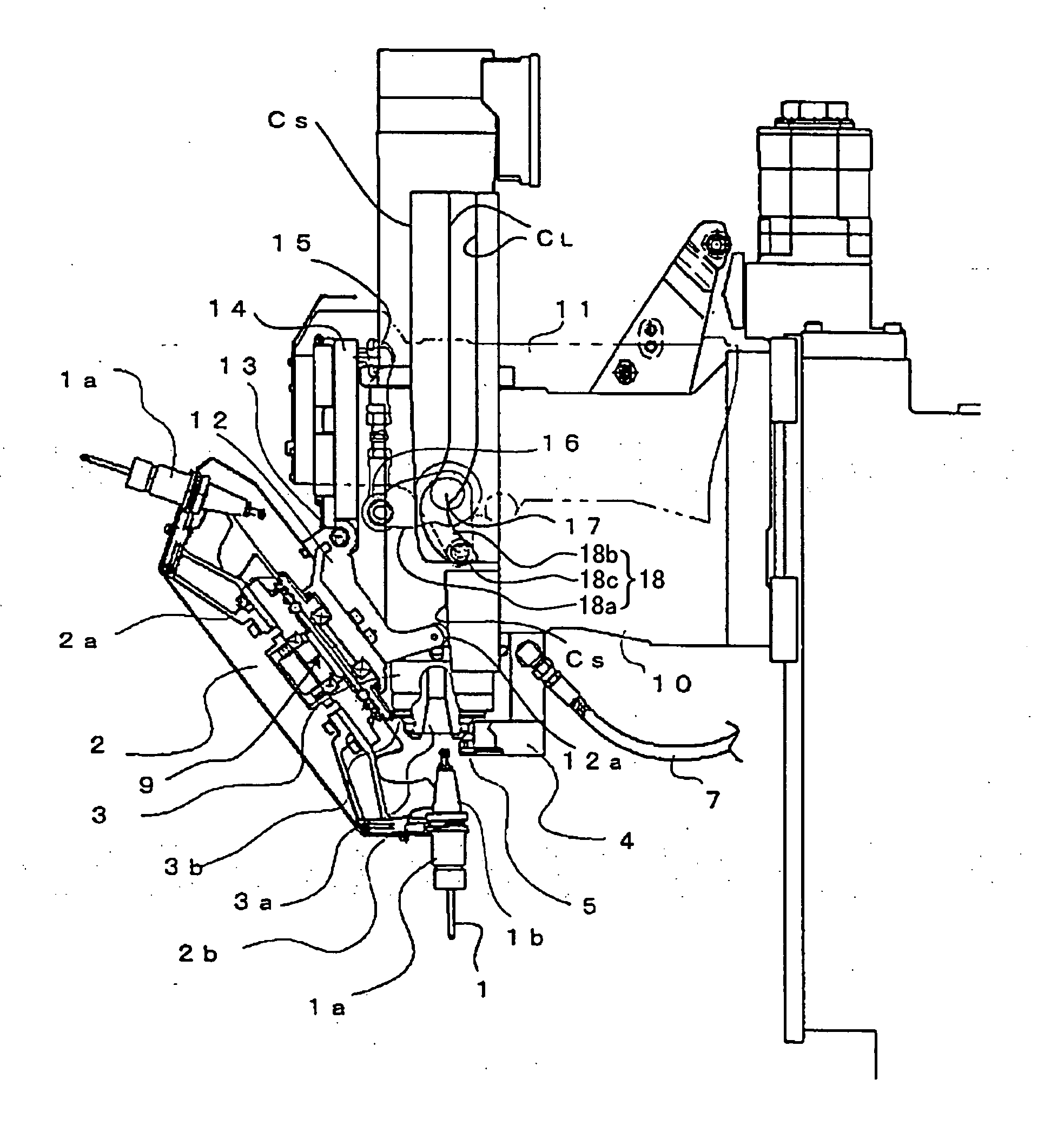

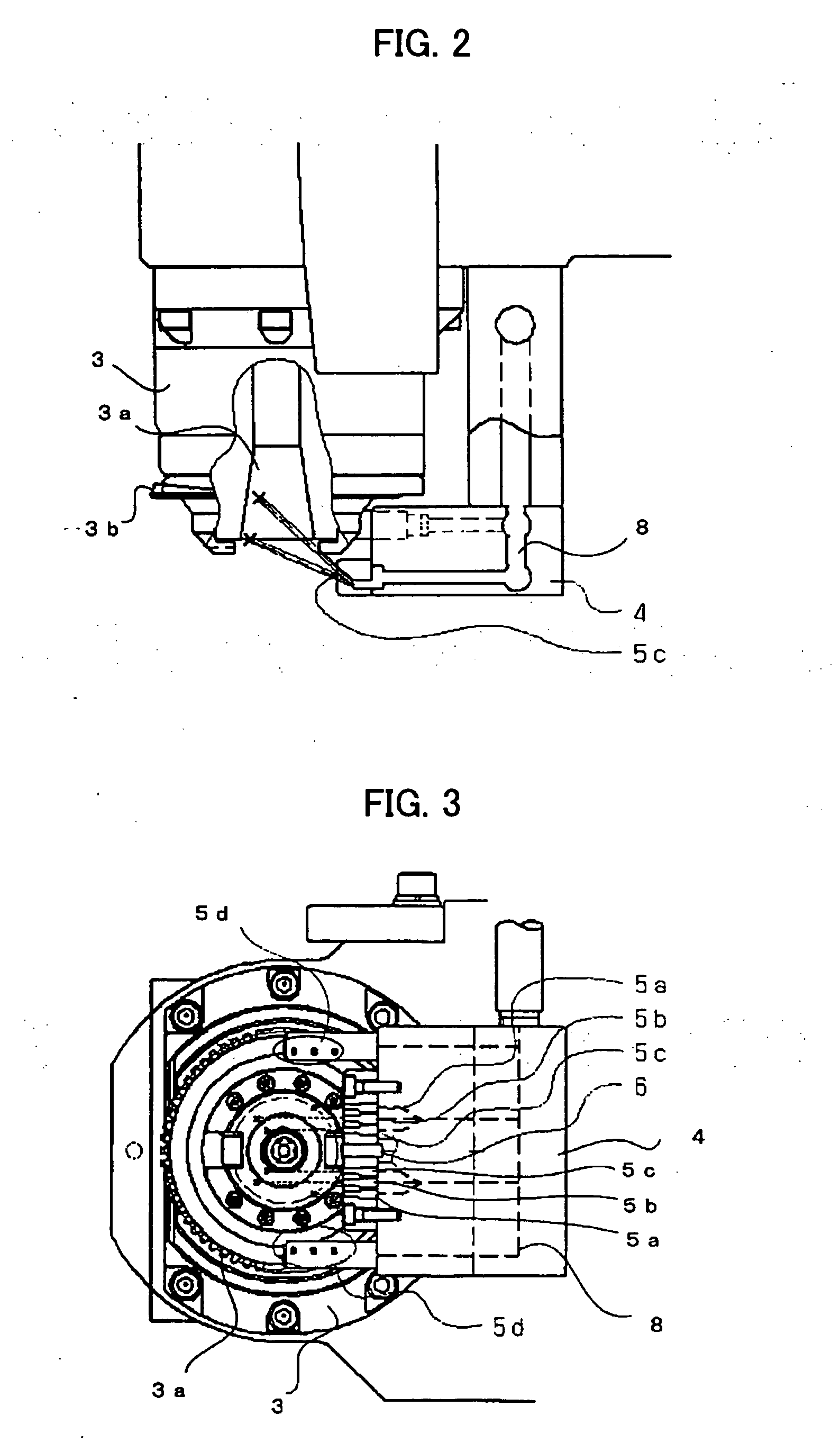

Automatic tool changing device for machine tool

ActiveUS7033308B2Accurate measurementAccurate detectionPrecision positioning equipmentProtection and storage accessoriesEngineeringMachine tool

An automatic tool changing device capable of cleaning a contact surface of a spindle, which is to be in contact with a tool holder, with a simple structure. The device includes a turret having a plurality of grippers on its outer circumference and holding the tool holder by means of the grippers. At the time of tool change, the grippers grip and pull out the tool holder fixed to the spindle. Rotation of the spindle causes the turret to rotate through a spindle gear, a turret gear, and a decelerating device, to thereby select a tool. At this moment, a coolant is spouted from a nozzle portion of a manifold toward a spindle taper hole in which the tool holder is interfitted and washes the taper hole. Due to the rotation of the spindle, the coolant is spouted onto the whole circumference of the taper hole, and the surface to be in contact with the tool holder is surely washed. Therefore, it is possible to perform the cleaning with a simple structure in which the nozzle portion is arranged near the spindle without machining the spindle and the tool holder.

Owner:FANUC LTD

Automatic tool changing device for machine tool

ActiveUS20050009679A1Accurate measurementAccurate detectionPrecision positioning equipmentProtection and storage accessoriesGear wheelEngineering

An automatic tool changing device capable of cleaning a contact surface of a spindle, which is to be in contact with a tool holder, with a simple structure. The device includes a turret having a plurality of grippers on its outer circumference and holding the tool holder by means of the grippers. At the time of tool change, the grippers grip and pull out the tool holder fixed to the spindle. Rotation of the spindle causes the turret to rotate through a spindle gear, a turret gear, and a decelerating device, to thereby select a tool. At this moment, a coolant is spouted from a nozzle portion of a manifold toward a spindle taper hole in which the tool holder is interfitted and washes the taper hole. Due to the rotation of the spindle, the coolant is spouted onto the whole circumference of the taper hole, and the surface to be in contact with the tool holder is surely washed. Therefore, it is possible to perform the cleaning with a simple structure in which the nozzle portion is arranged near the spindle without machining the spindle and the tool holder.

Owner:FANUC LTD

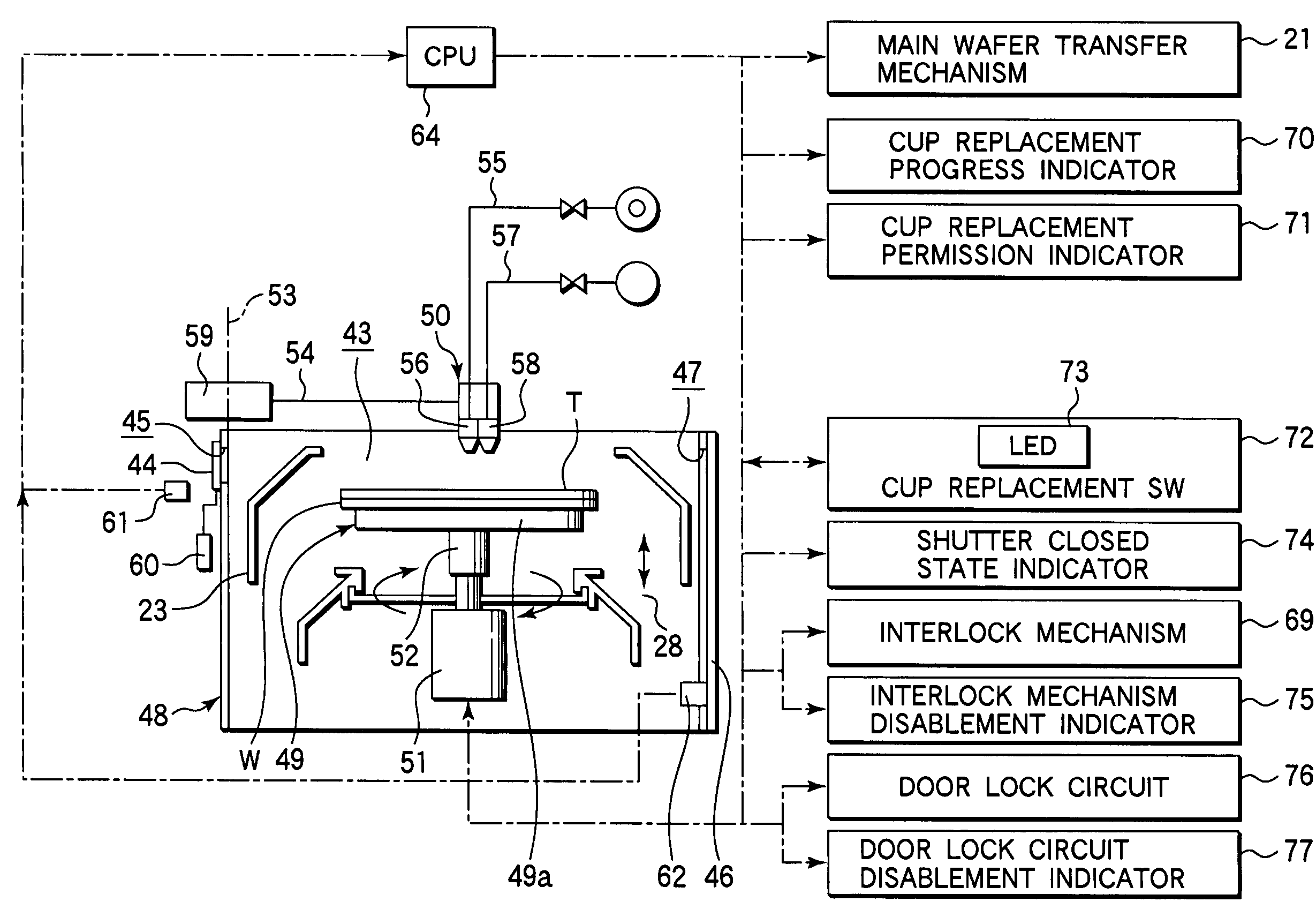

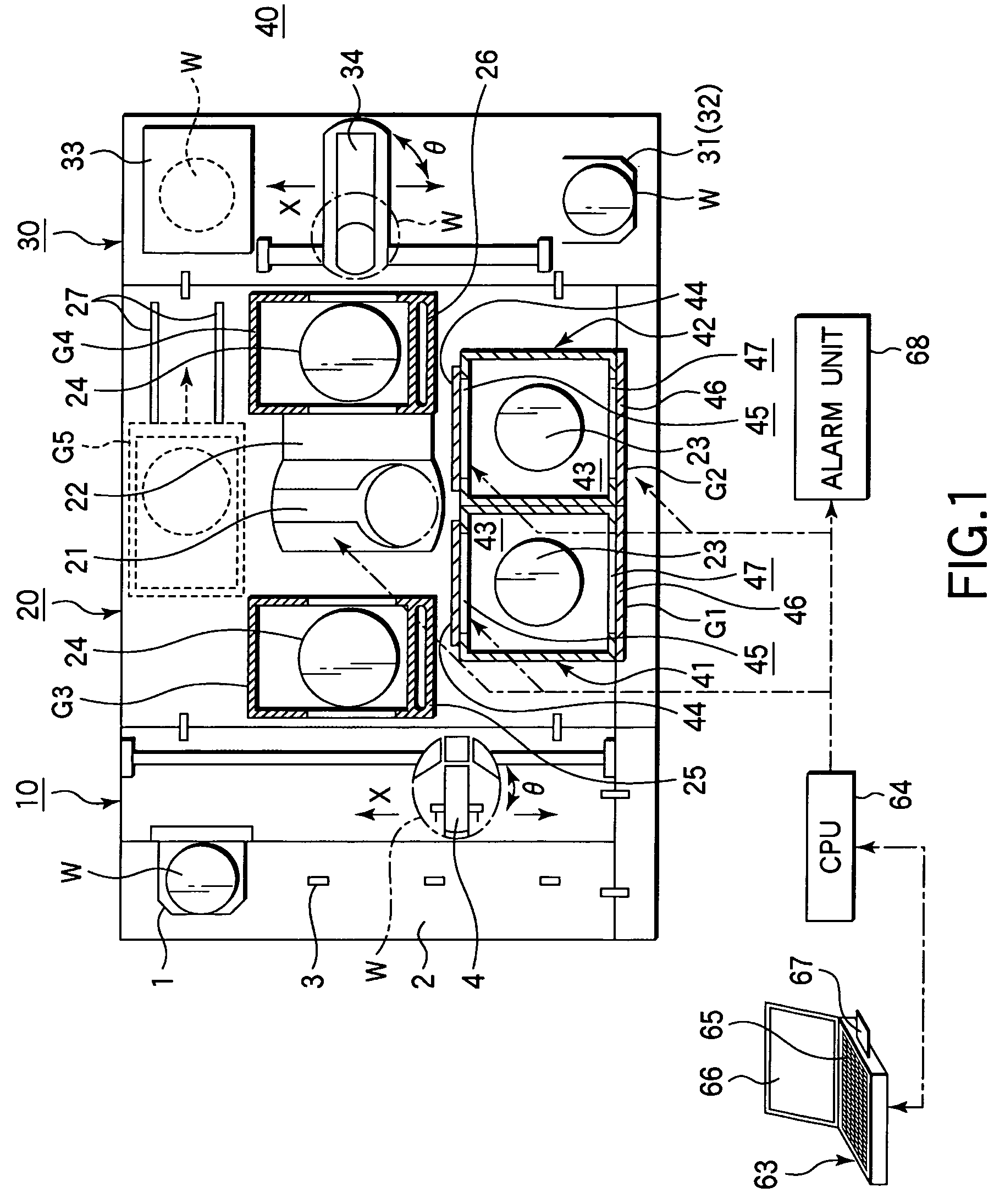

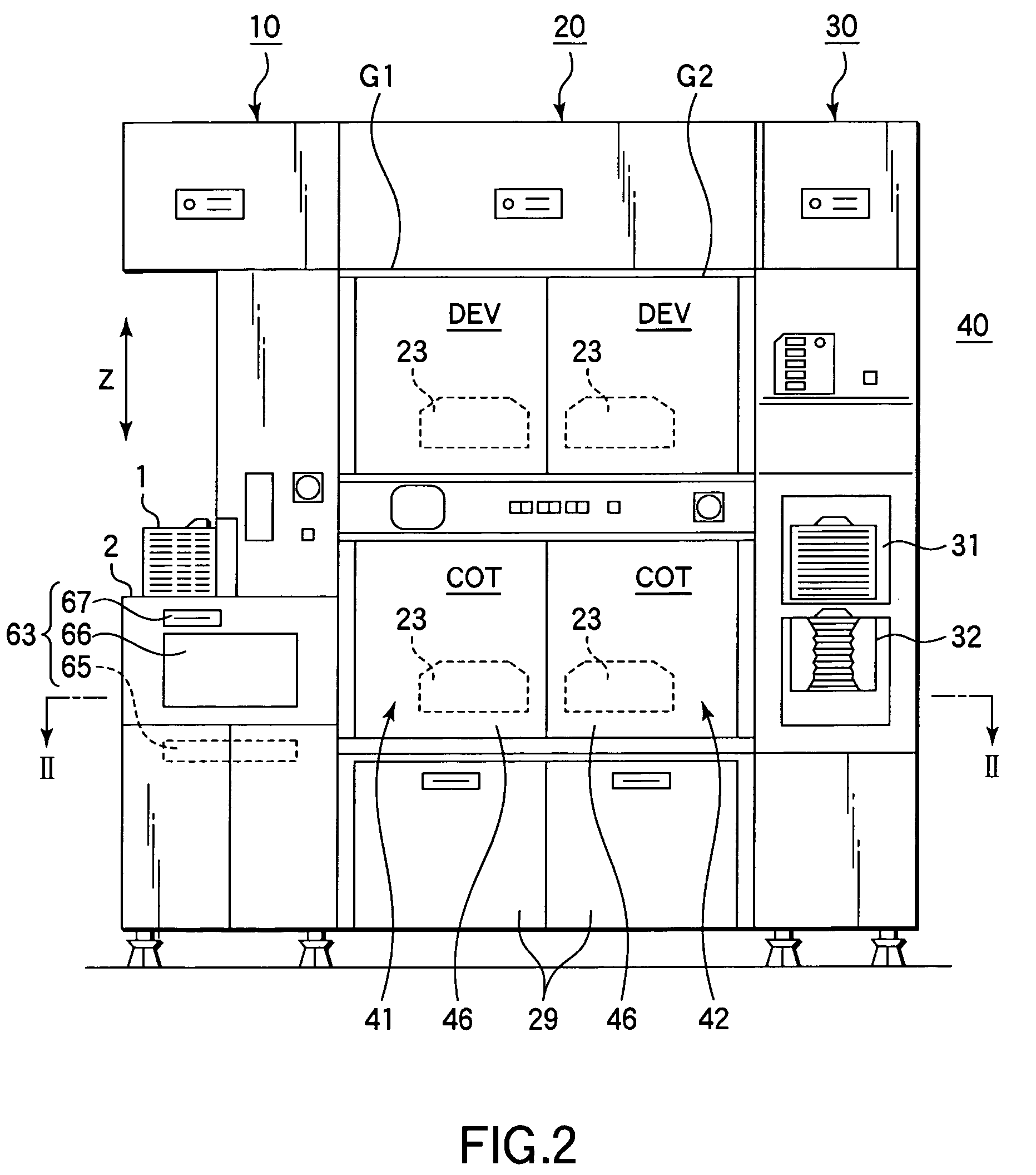

Method and storage medium for replacing process instrument in processing apparatus

ActiveUS7815558B2More processedLiquid surface applicatorsLiquid processingTransfer mechanismComputer science

Disclosed is a method for replacing a process instrument in a processing apparatus, in which a target object is loaded by a transfer mechanism into a processing unit and is subjected to a process by use of the process instrument. The method includes confirming that a process on the target object is finished in a processing unit designated as a process instrument replacement target, and providing information that a process instrument replacing operation is permitted to start. The method further includes, when a shutter of the processing unit designated as the process instrument replacement target is closed to perform a process instrument replacing operation and an operation prohibition state is thereby applied to the transfer mechanism, canceling the operation prohibition state to allow the transfer mechanism to perform a load / unload operation relative to a processing unit not designated as a process instrument replacement target.

Owner:TOKYO ELECTRON LTD

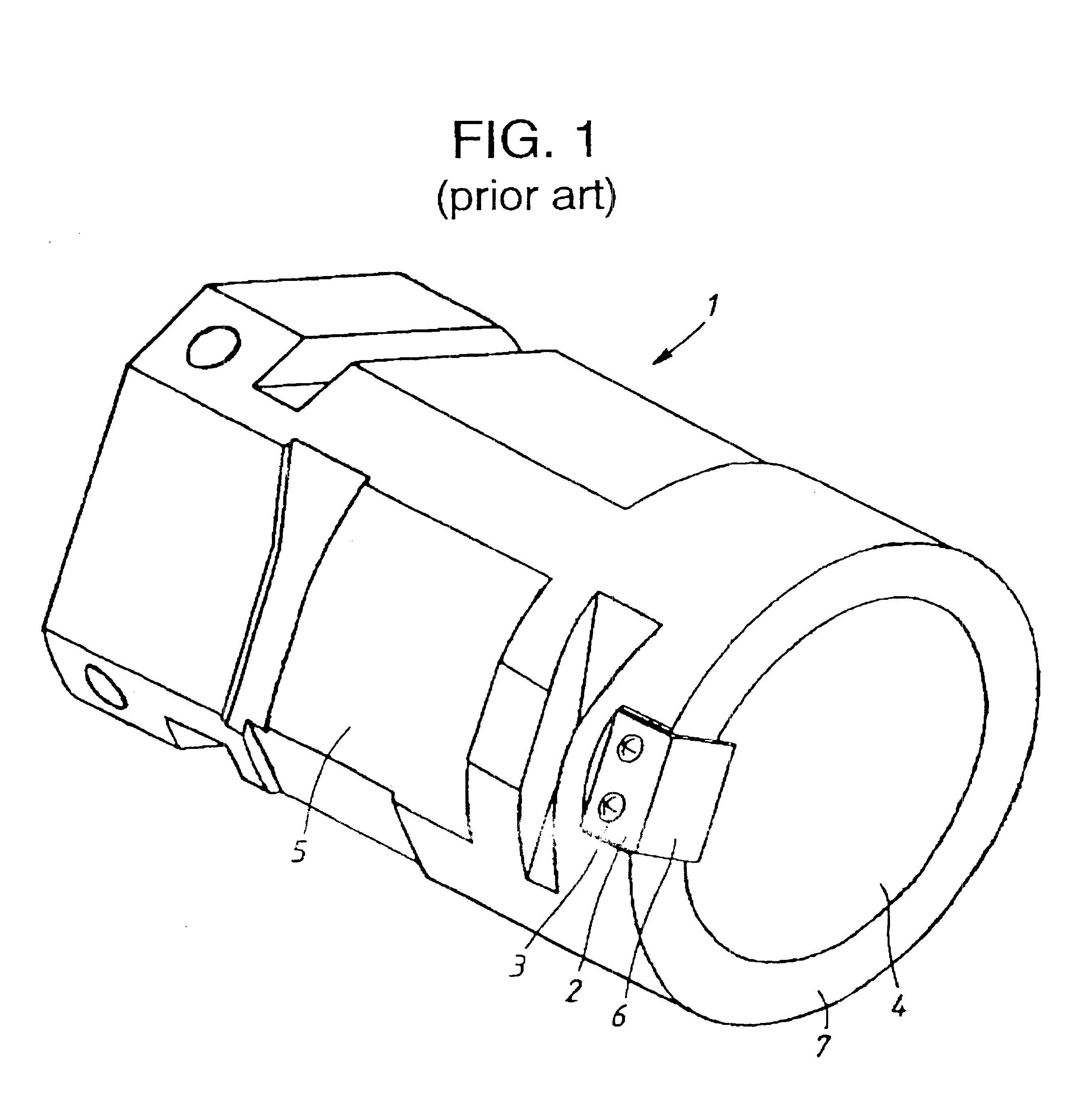

Tool pot for tool magazine

InactiveUS6620083B2Sleeve/socket jointsProtection and storage accessoriesGlass fiberHigh wear resistance

A tool pot used for a tool magazine of a machine tool to removably hold a tool is disclosed. A main body of the tool pot is constructed a cylindrical wall defining a holing aperture for holding the tool, end ribs formed at opposed ends of the cylindrical wall and a plurality of longitudinal ribs formed between the end ribs on the outer periphery of the cylindrical wall. And the main body is integrally molded from a glass-fiber reinforced thermoplastic resin material such as crystalline nylon-type resin. Therefore, the tool pot has high wear resistance and light weight, and it can be recycled.

Owner:TOYODA MASCH WORKS LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com