Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

296 results about "Receiver front end" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

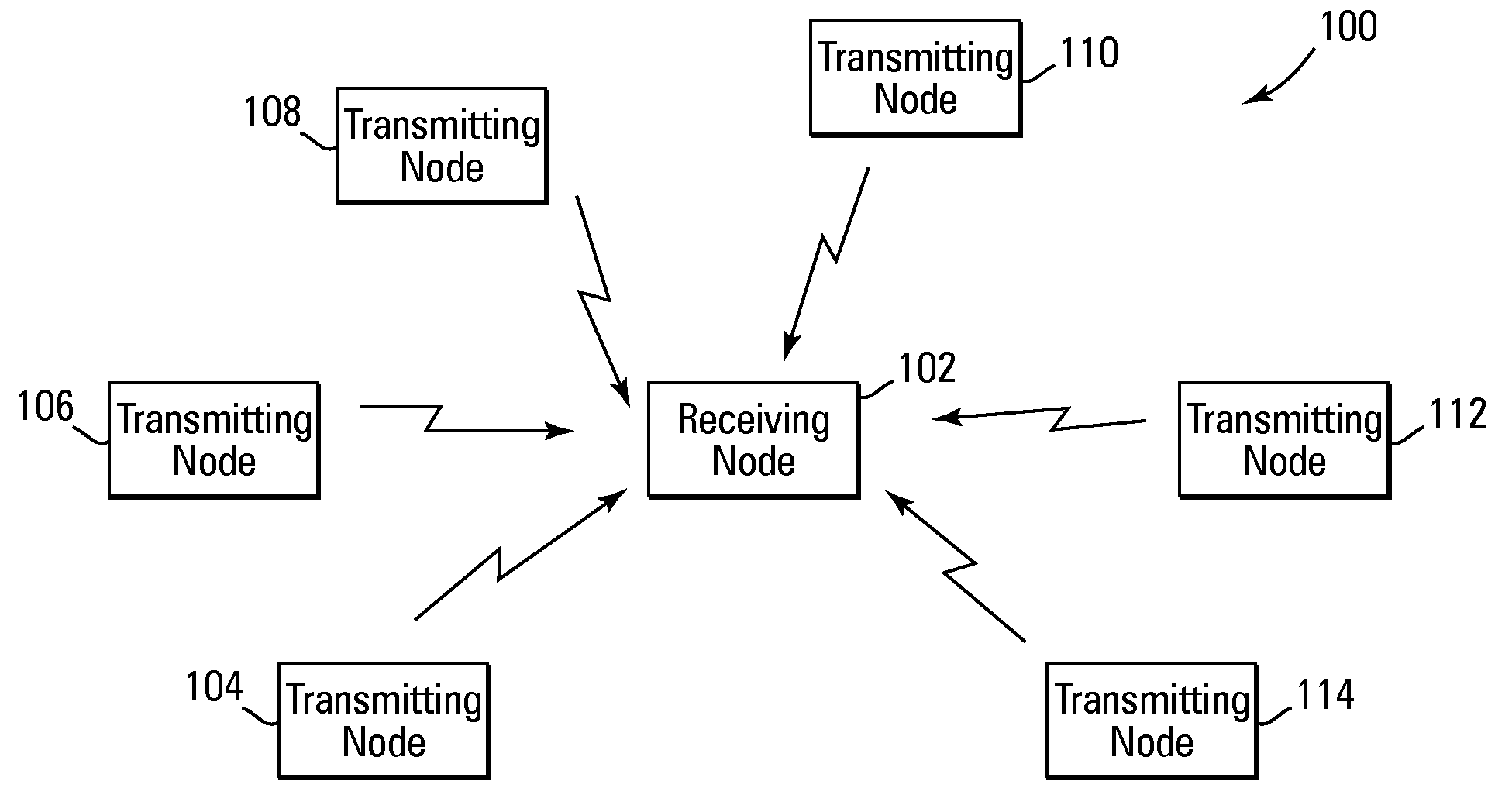

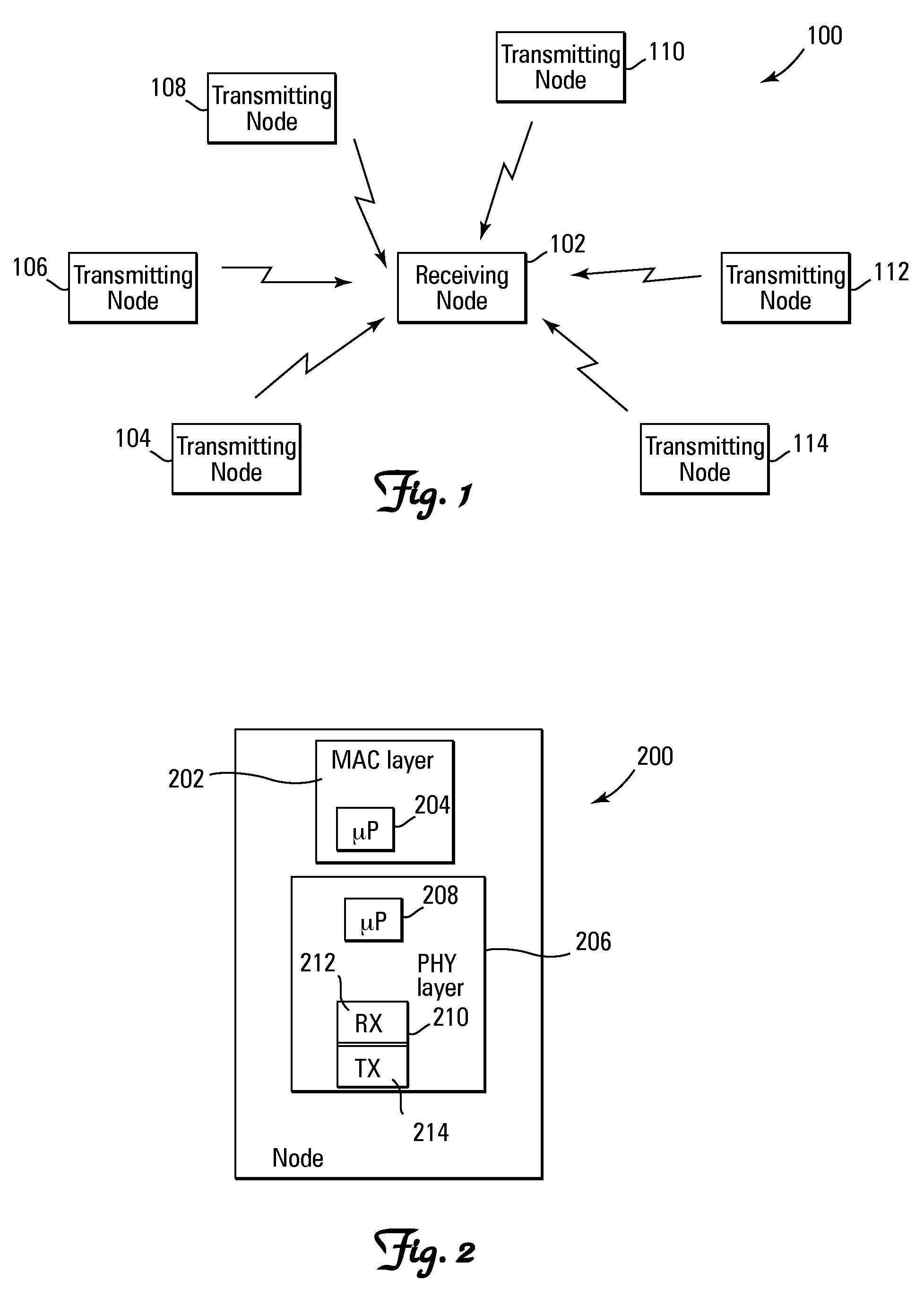

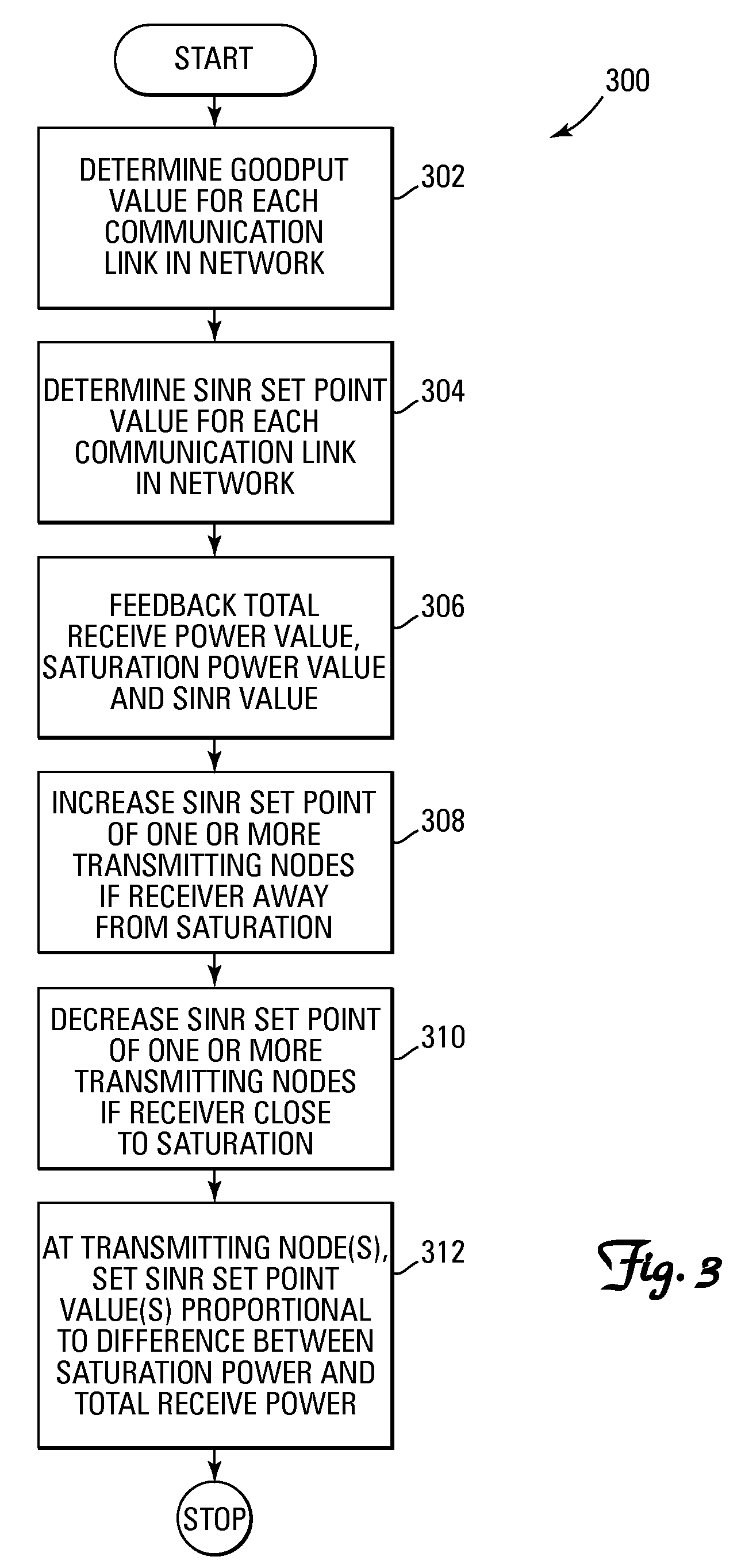

Method and system for performing distributed outer loop power control in wireless communication networks

InactiveUS20090093267A1Improve signal-to-noise ratioReduce signal to noise ratioPower managementRadio/inductive link selection arrangementsSignal-to-interference-plus-noise ratioReceiver front end

A method and system for performing distributed outer loop power control in a wireless communication network are disclosed. The method includes the steps of determining a transmit power for a plurality of transmitting nodes such that signals sent from each of the transmitting nodes are received at a receiver associated with a receiving node at a predetermined signal-to-interference plus noise ratio (SINR) set point, increasing the SINR at the receiving node of one or more transmitting nodes of the plurality of transmitting nodes if a saturation value for a front end of the receiver associated with the receiving node is not near a predetermined saturation value, and decreasing the SINR at the receiving node of the one or more transmitting nodes of the plurality of transmitting nodes if the saturation value for the front end of the receiver associated with the receiving node is near the predetermined saturation value.

Owner:HONEYWELL INT INC

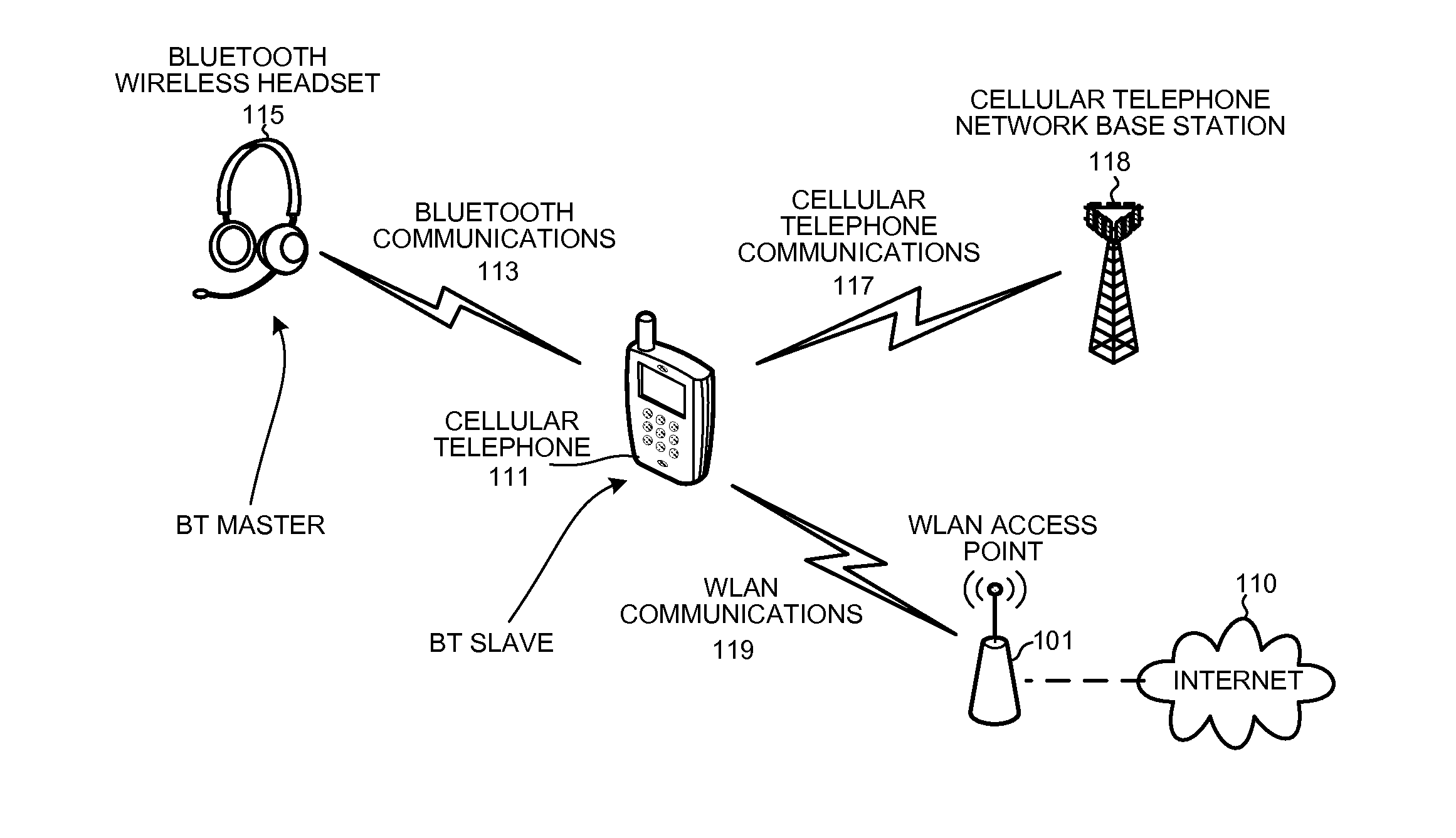

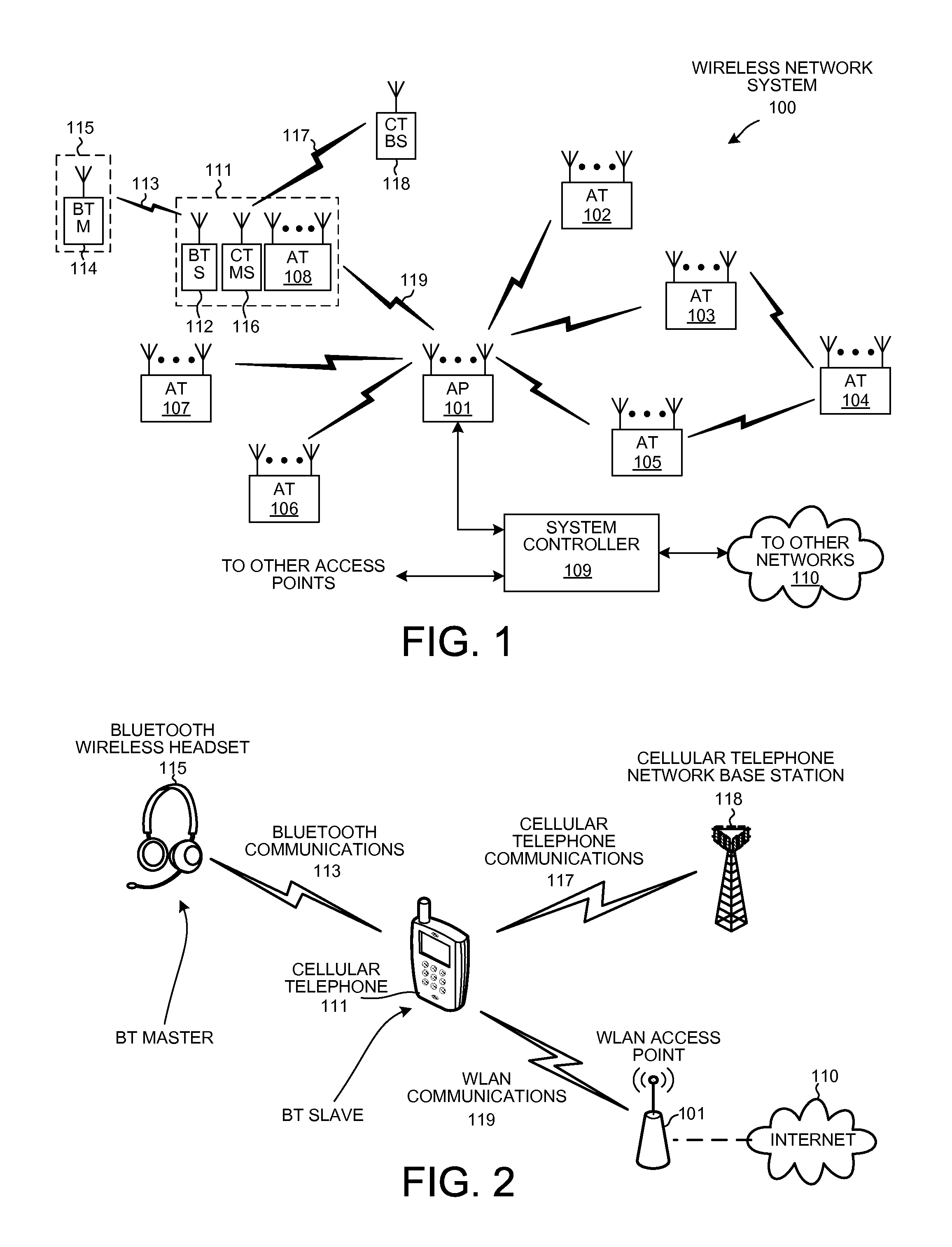

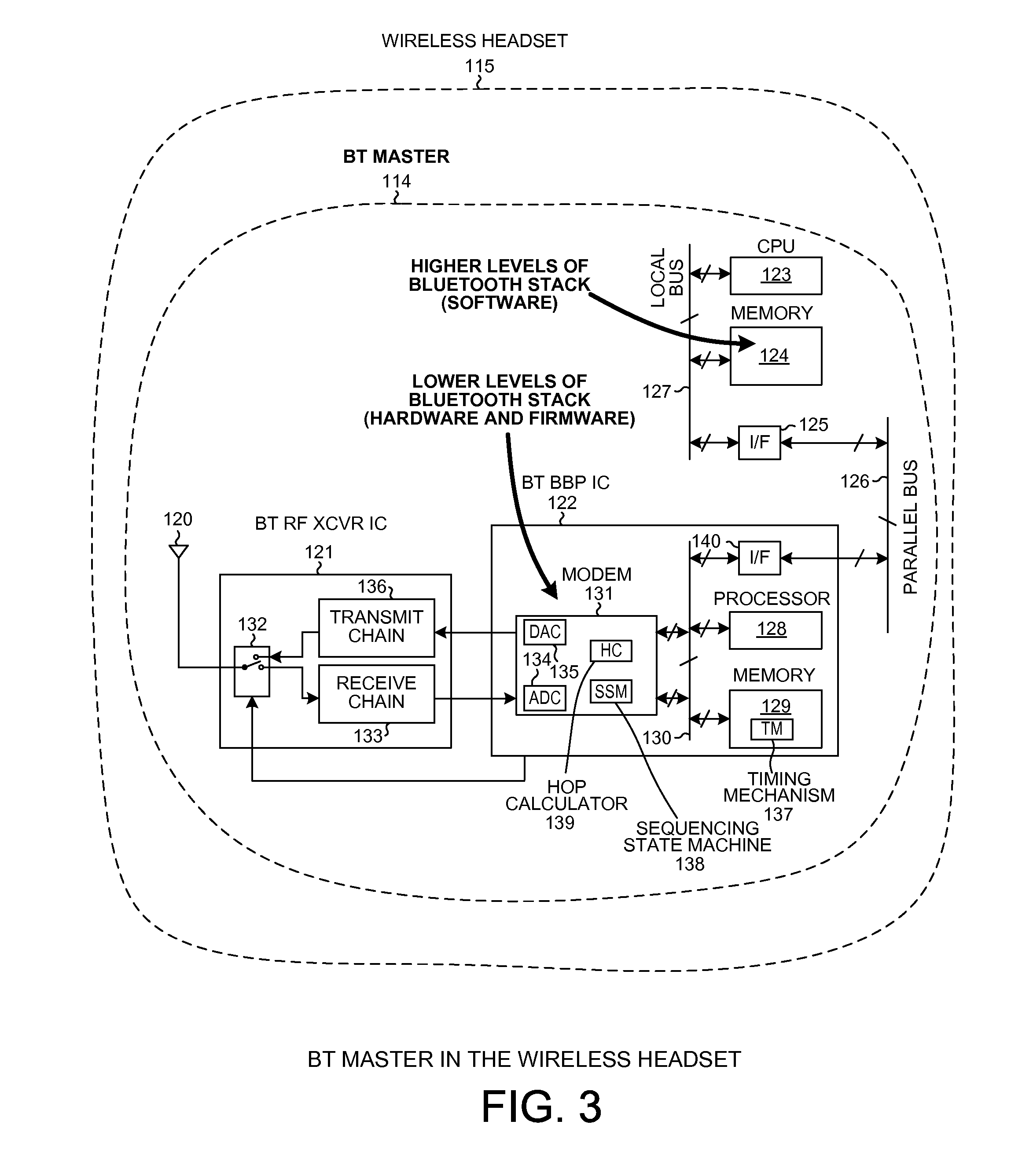

Detecting a WLAN signal using a bluetooth receiver during bluetooth scan activity

InactiveUS20110274021A1Reduce resolutionSignal bandwidthPower managementEnergy efficient ICTTransceiverRF front end

A BT receiver RF front end receives RF energy in a sequence of BT scan windows. Throughout a scan window, the front end is tuned to one hop frequency. Before and after the window the front end is in a disabled state. A WLAN energy detector processes an output of the front end during the window and determines whether more than a predetermined amount of RF energy was received onto the front end during the window. A BT baseband processor attempts to demodulate the output of the front end. If the WLAN energy detector determines that the predetermined amount of RF energy was received and if a BT signal could not be demodulated, then a WLAN wake-up signal is asserted, thereby causing a WLAN transceiver to be powered up to receive WLAN signals. BT scan intervals are varied in duration to facilitate a BT scan window overlapping a WLAN beacon.

Owner:QUALCOMM INC

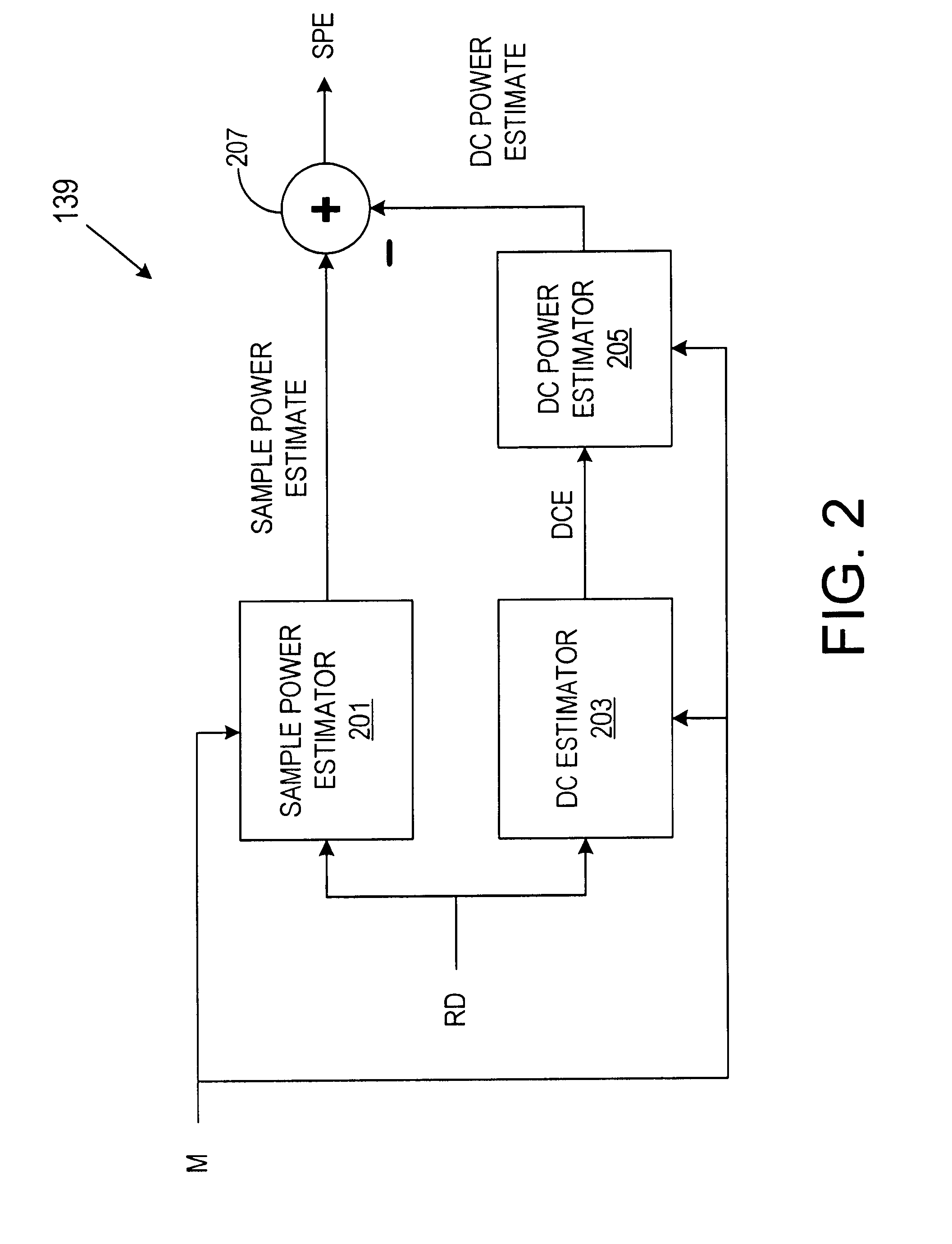

Automatic gain control system and method for a ZIF architecture

A system and method for controlling amplification of a signal received by a ZIF radio having a power level within a full power range relative to a minimum noise floor. The ZIF radio includes a ZIF receiver front end, an overload detector, an ADC, a saturation detector, a DC and power estimator, and control logic. The control logic utilized full visibility of the ADC to limit gain of the baseband amplifier to a maximum gain setting sufficient to view the minimum noise floor and to view a received signal having a power level within any of several segments of the power spectrum. The segmentation of the power spectrum is based on an overload condition of the ZIF receiver front end and a saturation condition of the ADC. The control logic further employs limited gain stepping of the baseband amplifier to avoid exceeding a DC budget of the ADC.

Owner:M RED INC

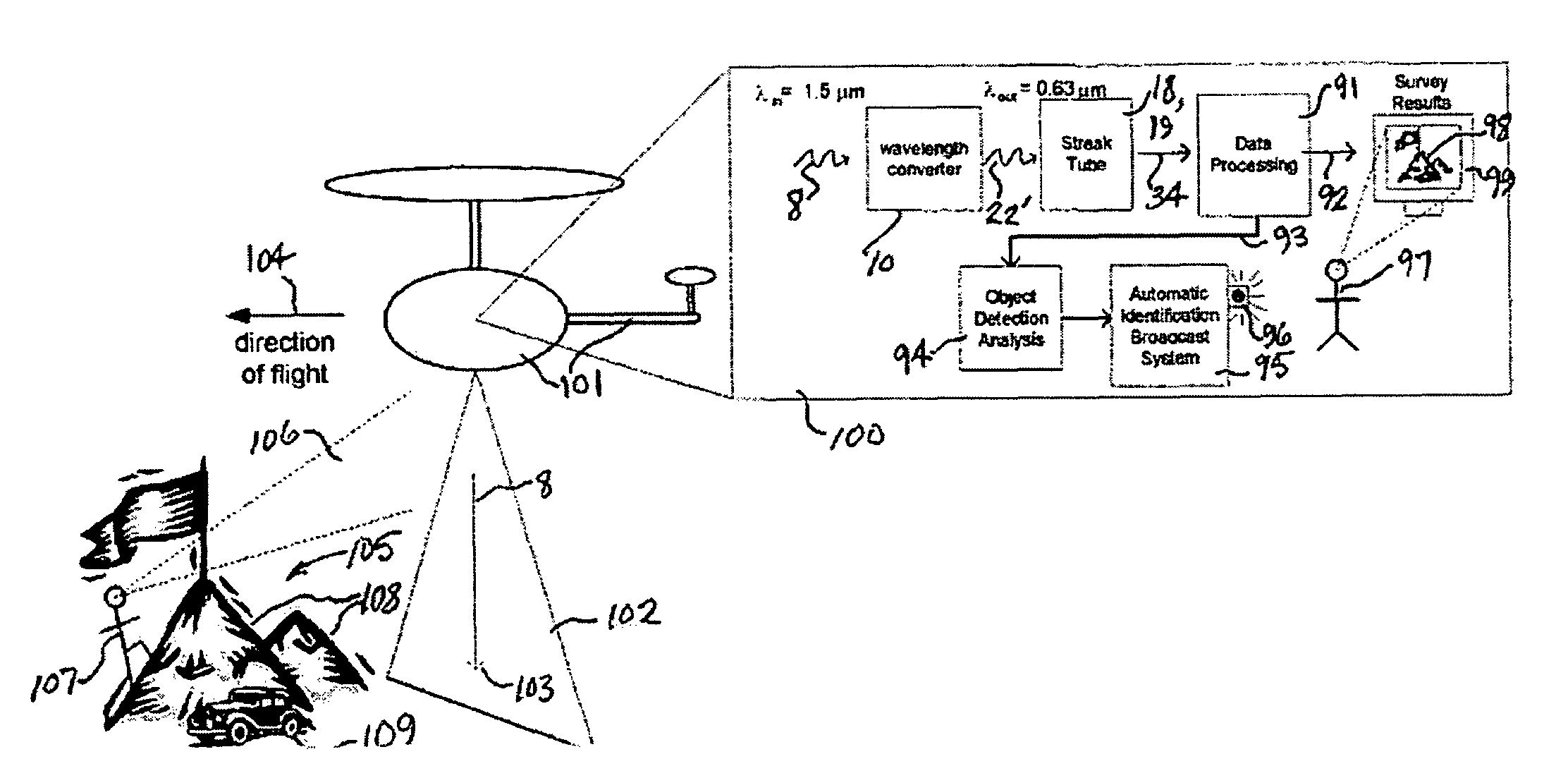

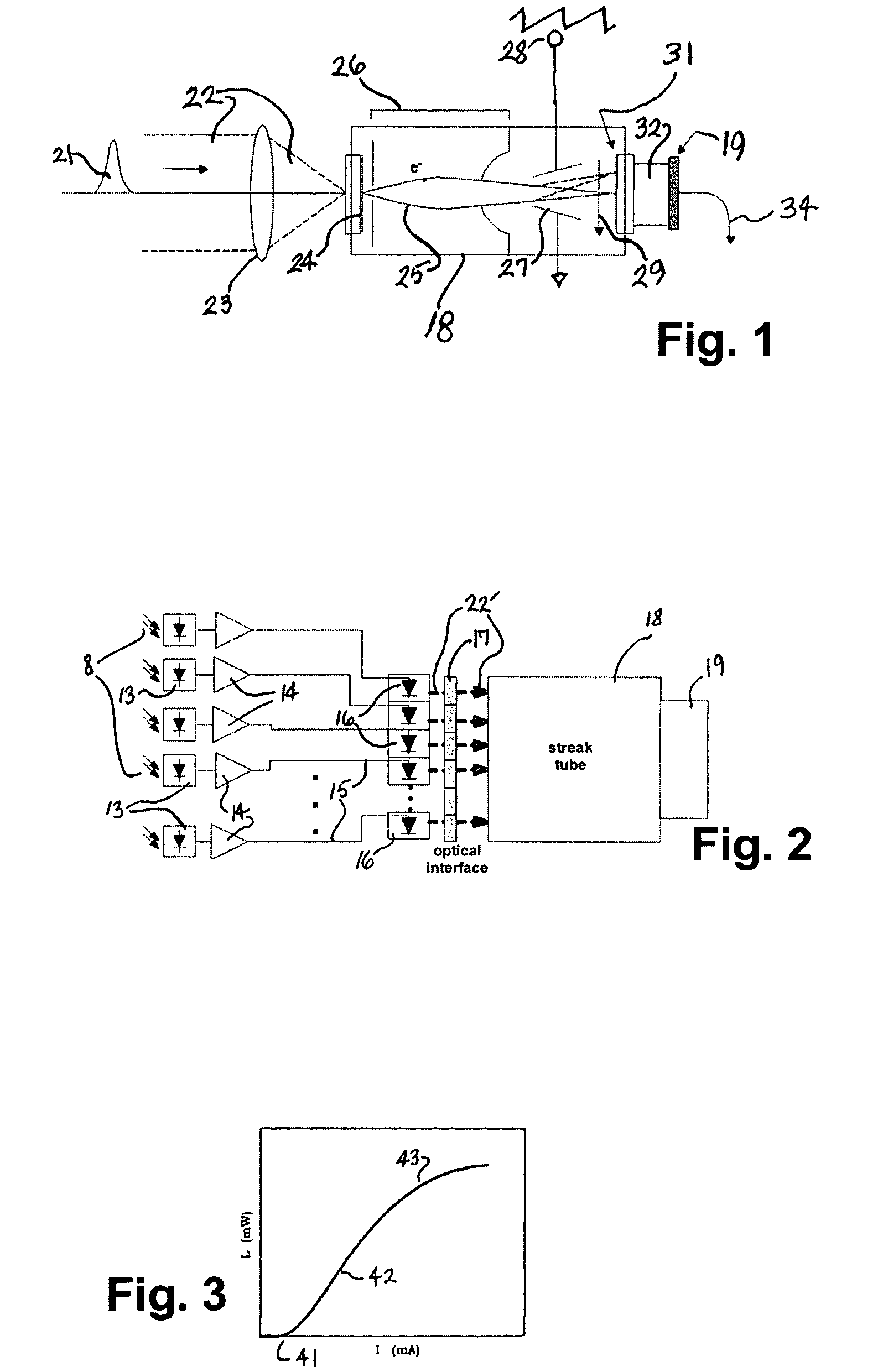

Ultraviolet, infrared, and near-infrared lidar system and method

Pushbroom and flash lidar operations outside the visible spectrum, most preferably in near-IR but also in IR and UV, are enabled by inserting—ahead of a generally conventional lidar receiver front end—a device that receives light scattered from objects and in response forms corresponding light of a different wavelength from the scattered light. Detailed implementations using arrays of discrete COTS components—most preferably PIN diodes and VCSELs, with intervening semicustom amplifiers—are discussed, as is use of a known monolithic converter. Differential and ratioing multispectral measurements, particularly including UV data, are enabled through either spatial-sharing (e. g. plural-slit) or time-sharing.

Owner:ARETE ASSOCIATES INC

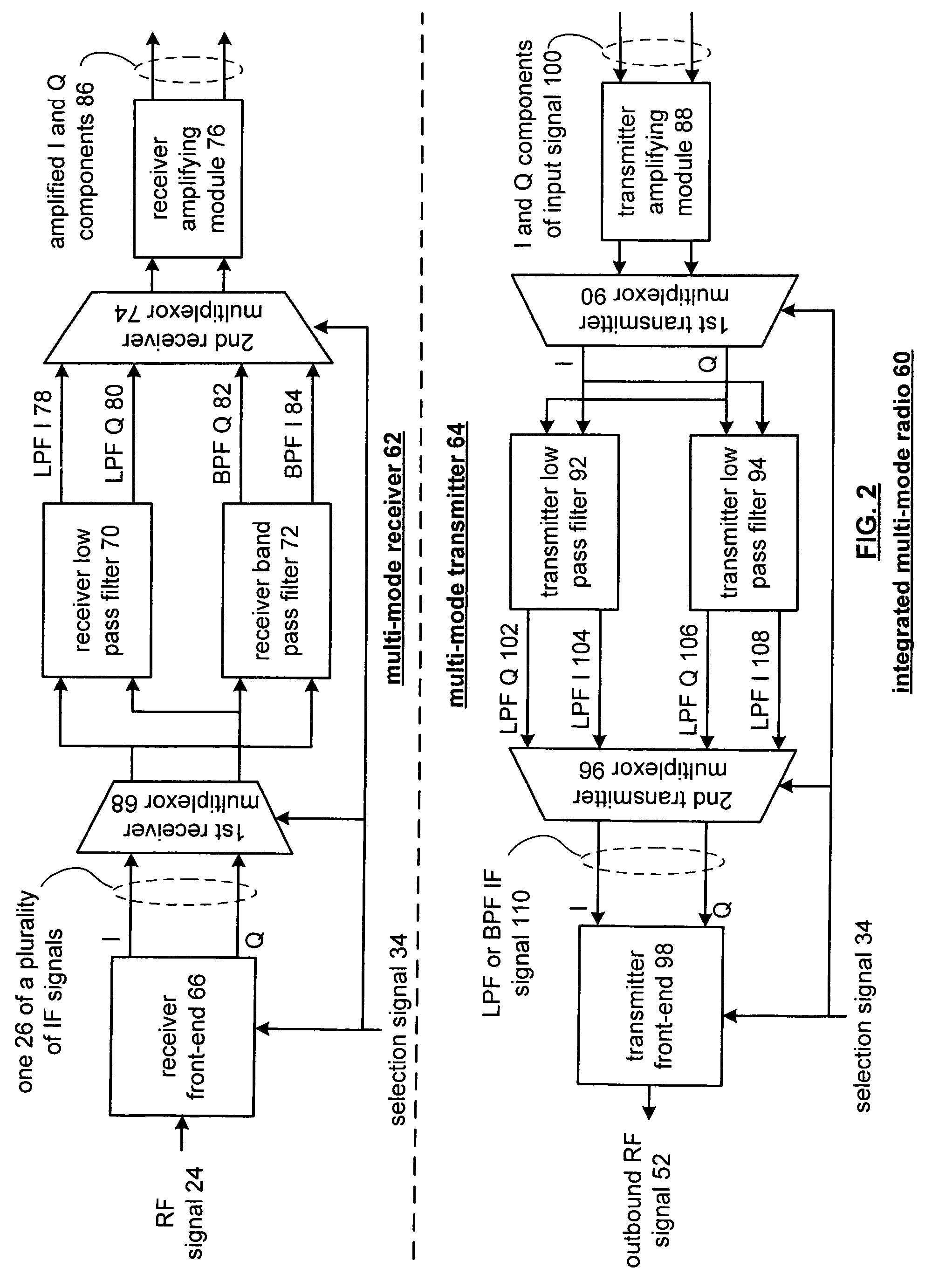

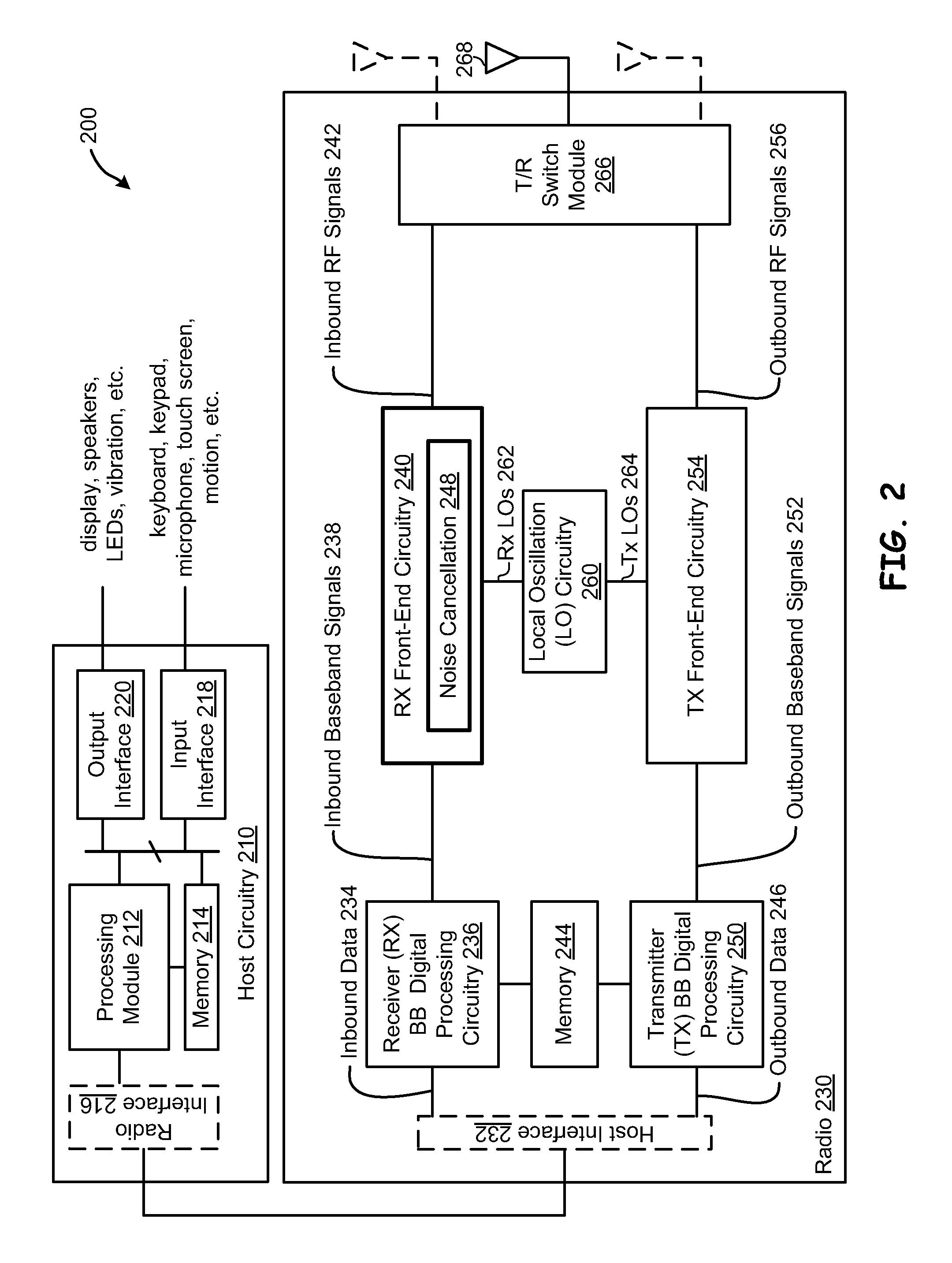

Integrated multimode radio and components thereof

InactiveUS6970681B2Amplitude demodulation by homodyne/synchrodyne circuitsModulated-carrier systemsReceiver front endTransmitter

An integrated multimode radio includes a multimode receiver and a multimode transmitter. The multimode receiver includes a shared receiver front-end, a receiver multiplexor, and a plurality of receiver IF stages. The multimode transmitter includes a shared transmitter front-end, a transmitter multiplexor, and a plurality of transmitter IF stages.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

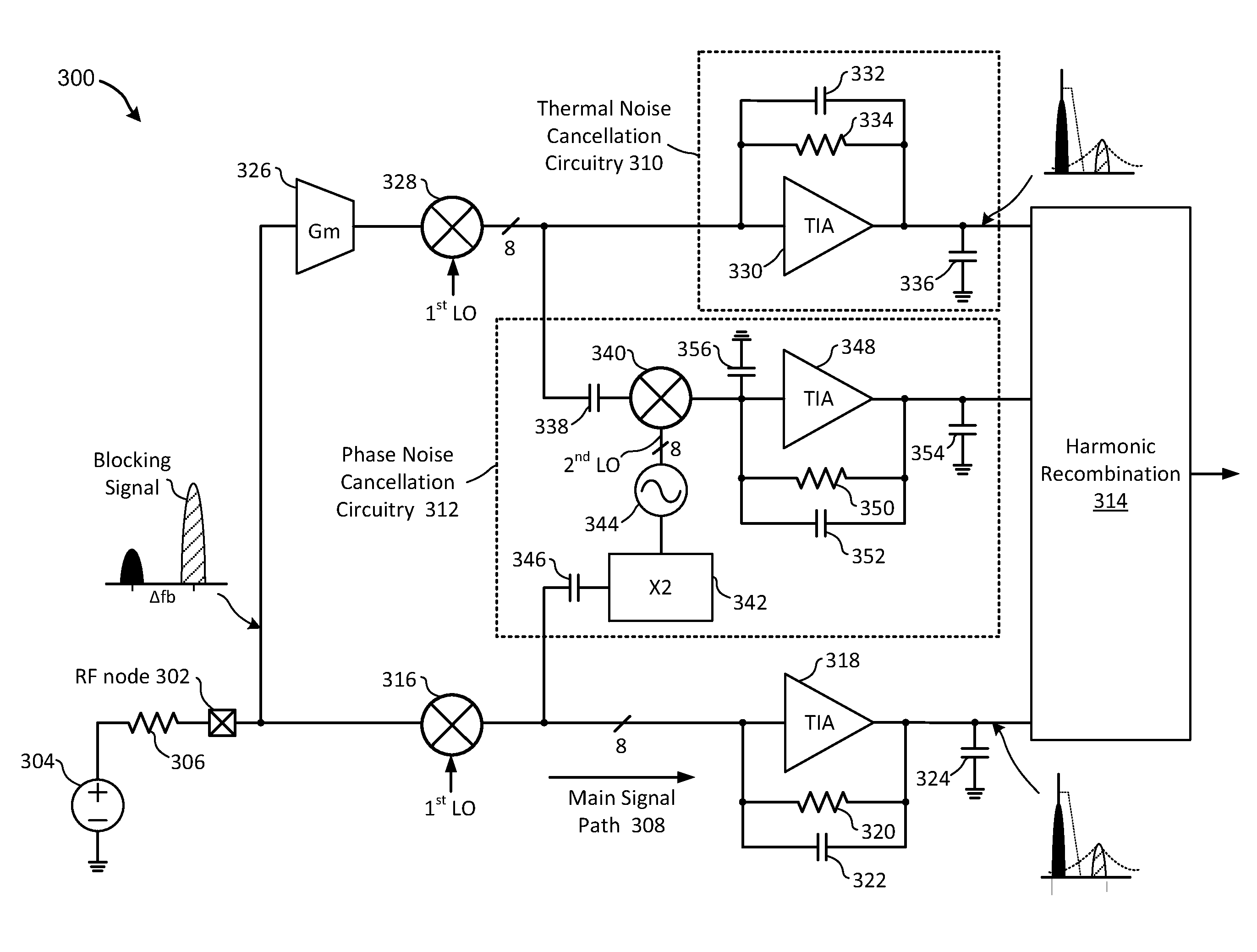

Highly linear receiver front-end with thermal and phase noise cancellation

InactiveUS9148186B1Error preventionDc level restoring means or bias distort correctionPhase noiseRadio reception

A radio receiver supporting cancellation of thermal and phase noise in a down-converted RF signal. An inbound RF signal and blocking signal are provided directly to a passive mixer for down-conversion into a first baseband signal having data, thermal noise, and reciprocal mixing (RM) noise components. The inbound signals are also provided to a transconductance circuit, the output of which is provided to a second passive mixer for conversion into a current signal having data and blocking signal components, and a RM image. The blocking signal component and the RM image are mixed with a second LO signal, derived from the blocking signal, to produce a RM noise cancellation signal. The data component of the current signal is converted into a second baseband signal having data and thermal noise components. The first baseband signal, second baseband signal and RM noise cancellation signal are then combined through harmonic recombination.

Owner:AVAGO TECH INT SALES PTE LTD

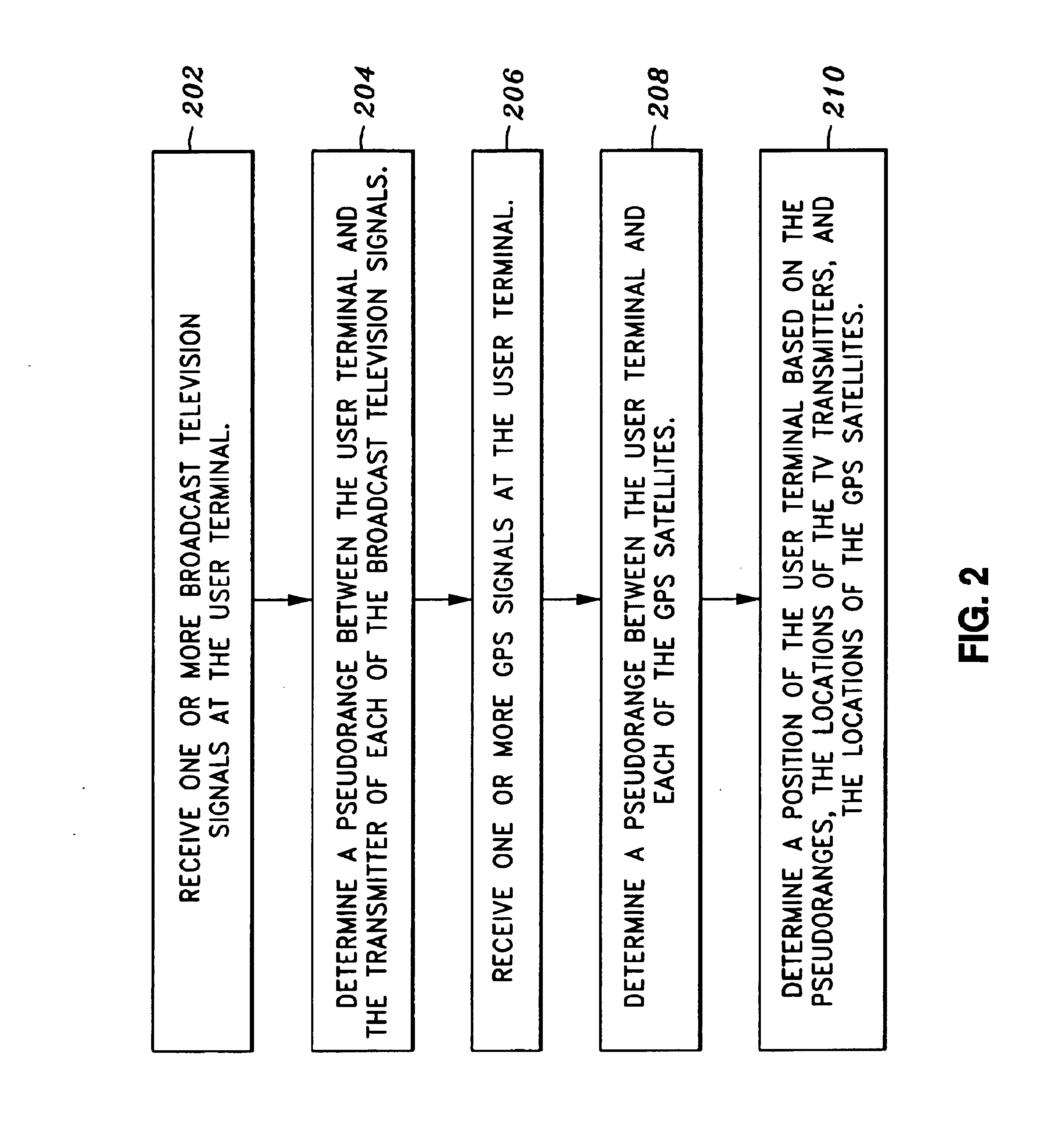

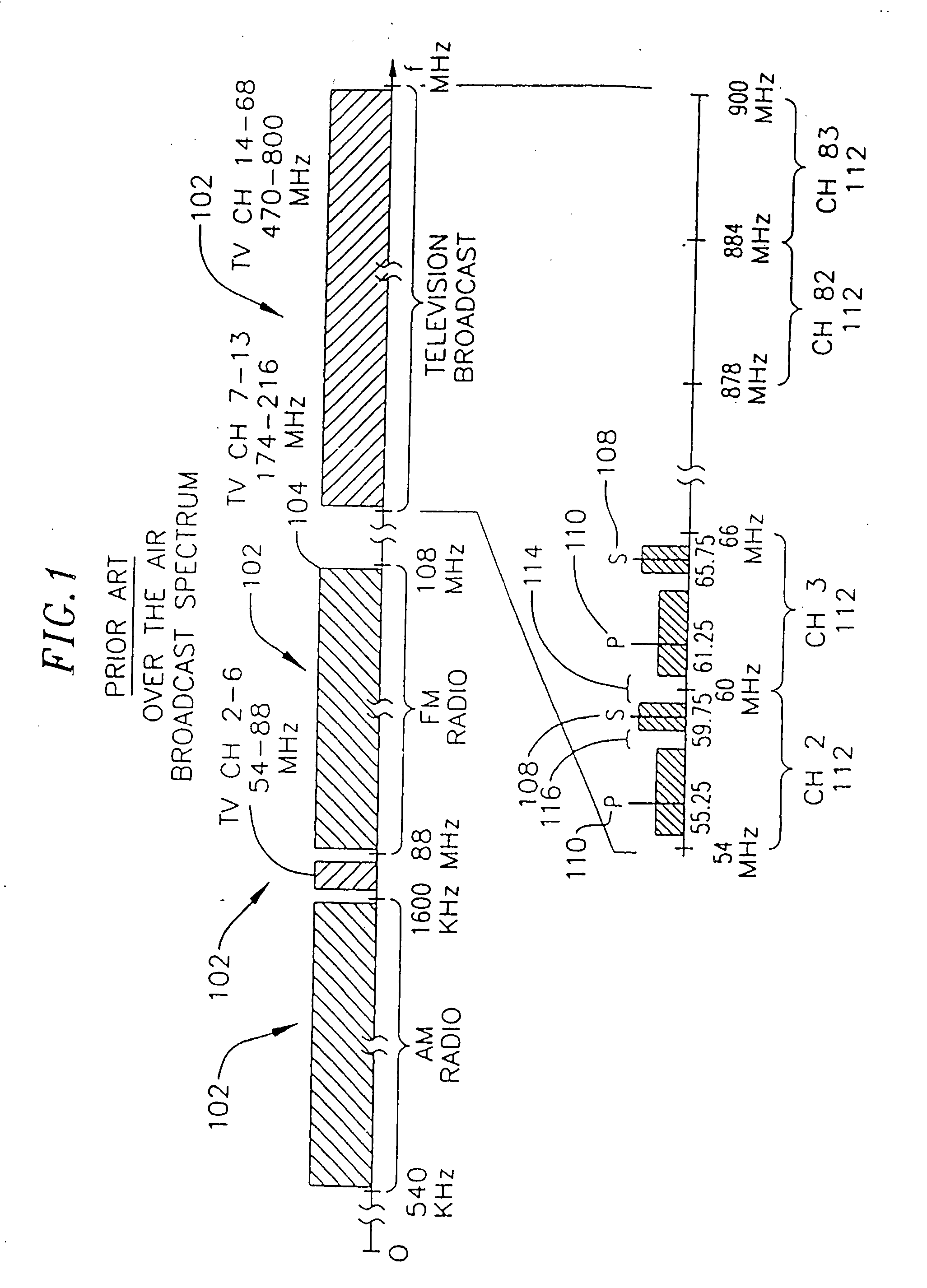

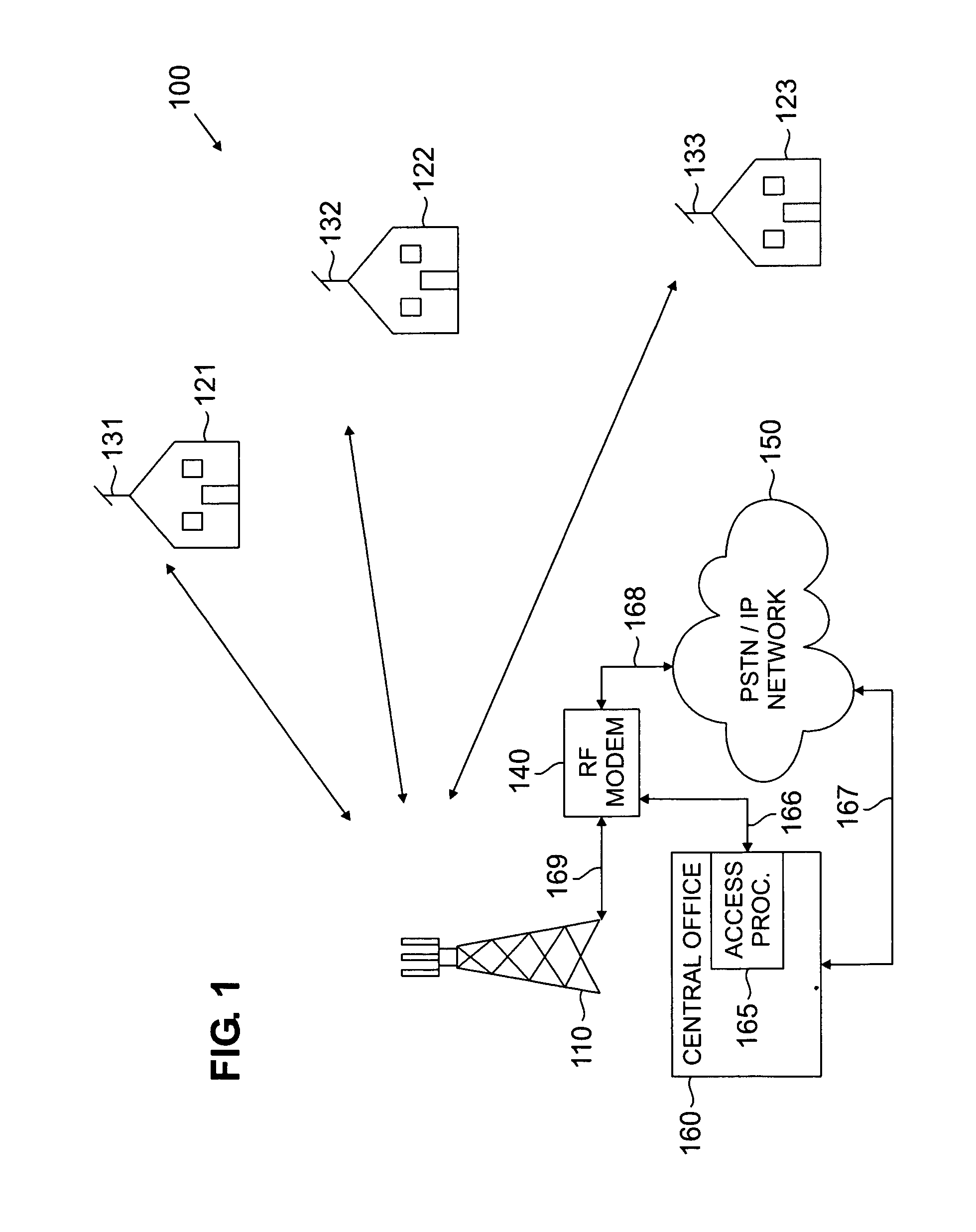

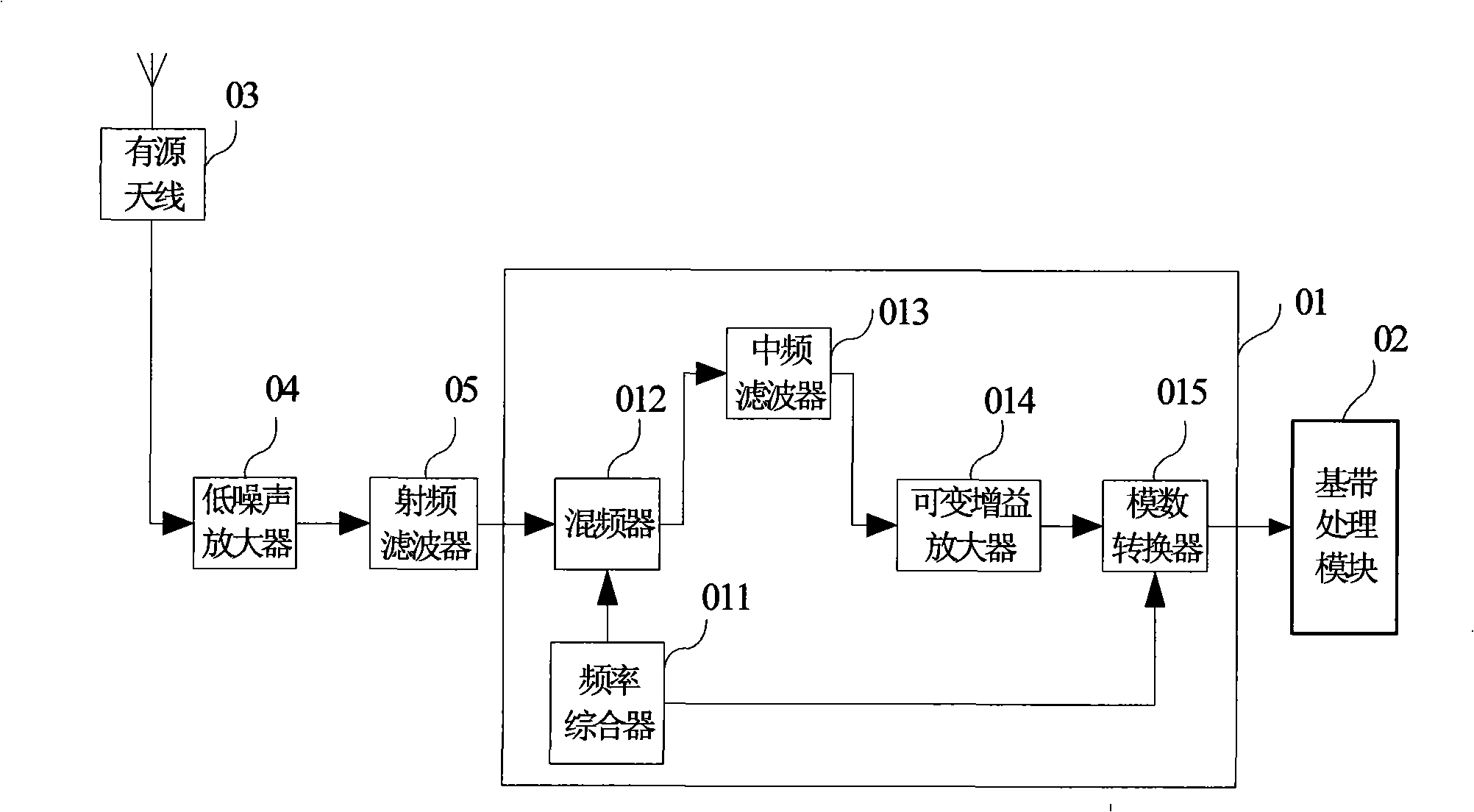

Radio frequency device for receiving TV signals and GPS satellite signals and performing positioning

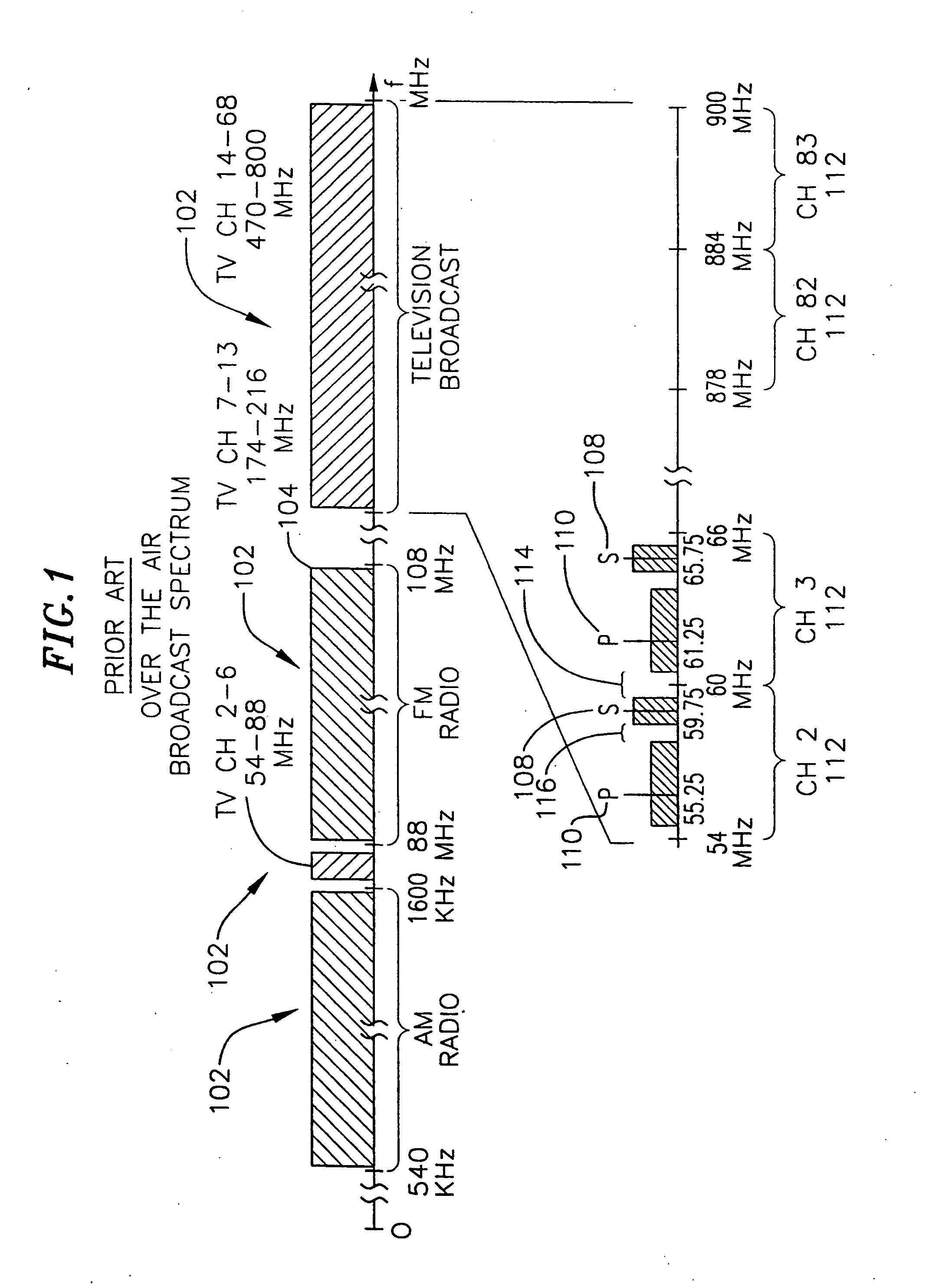

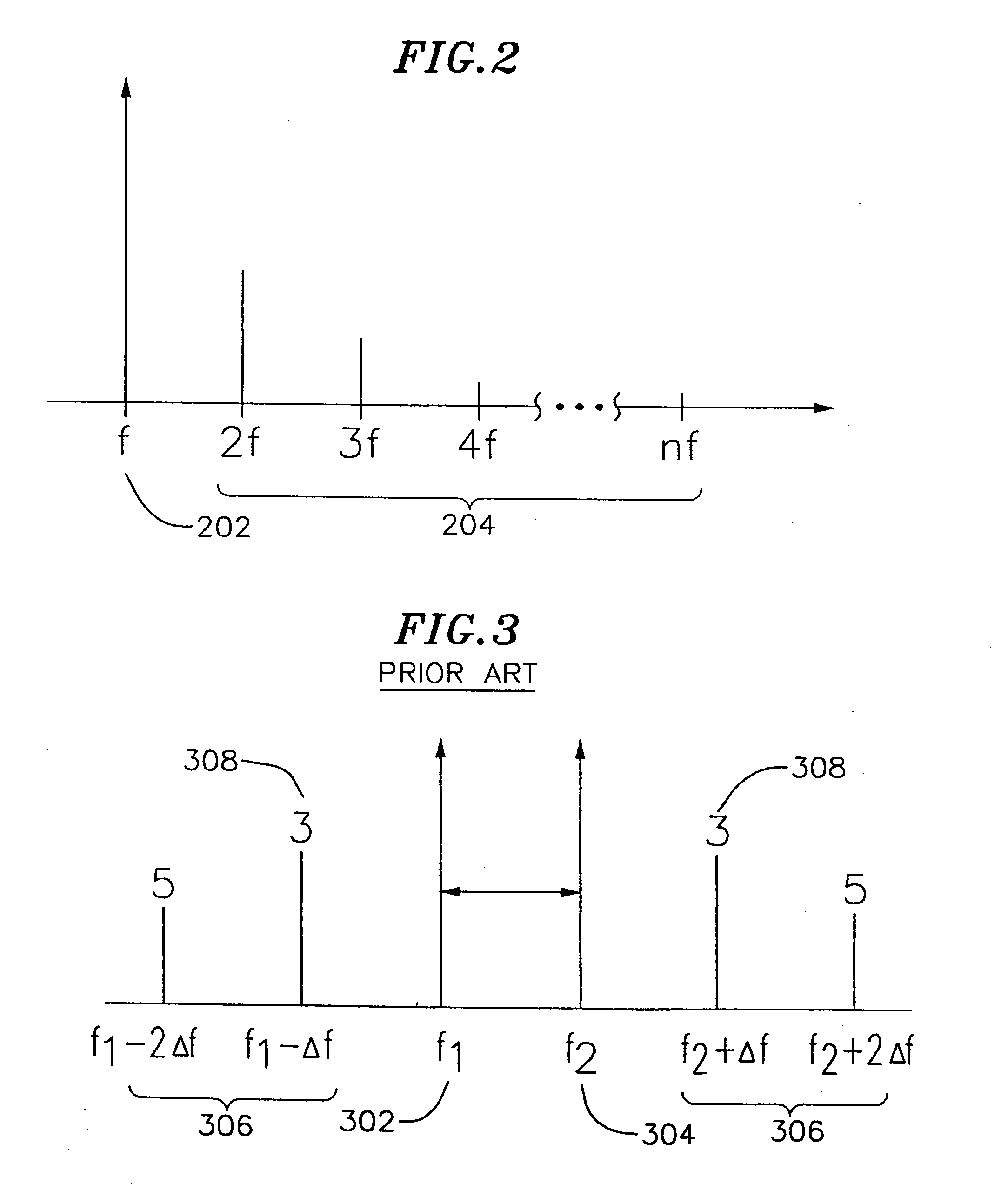

An apparatus and method for determining the position of a user terminal comprise an antenna subsystem which is able to receive signals of GPS and TV, a receiver front end which converts the frequency of the incident signals and filters out unwanted signals so that the desired signals can be sampled, a digital processing component which accommodates the imperfections of the front end and converts the measured signals into a position information. The apparatus is capable of receiving at the user terminal, broadcast television signals from television signal transmitters; determining a first set of pseudo-ranges between the user terminal and the television signal transmitters based on a known component of the broadcast television signals; receiving at the user terminal global positioning signals from a global positioning satellites; determining a second set of pseudo-ranges between the user terminal and the global positioning satellites based on the global positioning signals; and determining a position of the user terminal based on the first and second sets of pseudo-ranges, locations of the television signal transmitters, and locations of the global positioning satellites.

Owner:TRUE POSITION INC

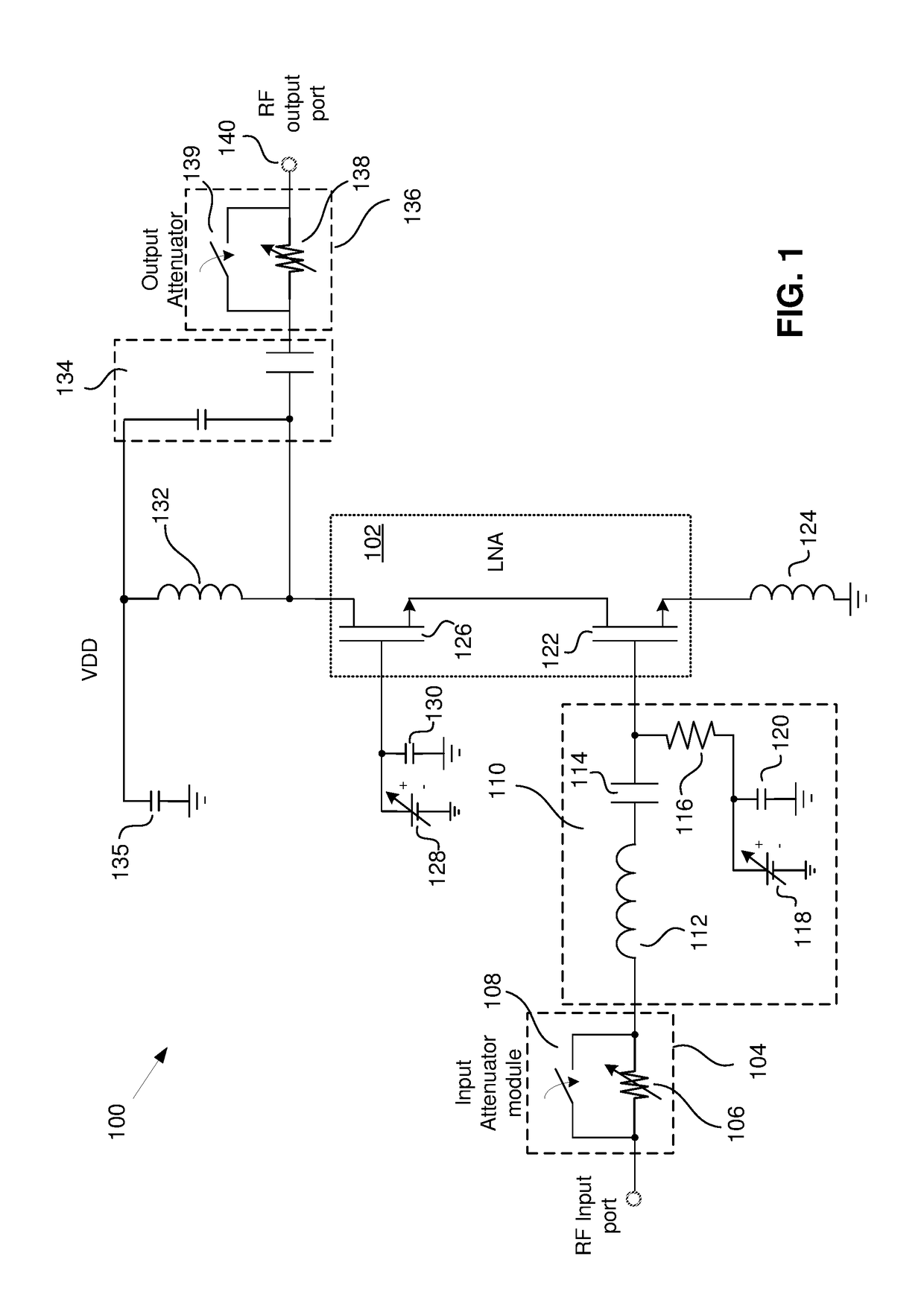

Integrated switchless programmable attenuator and low noise amplifier

InactiveUS6879816B2Multiple-port active networksSwitched capacitor networksCapacitanceLocal oscillator signal

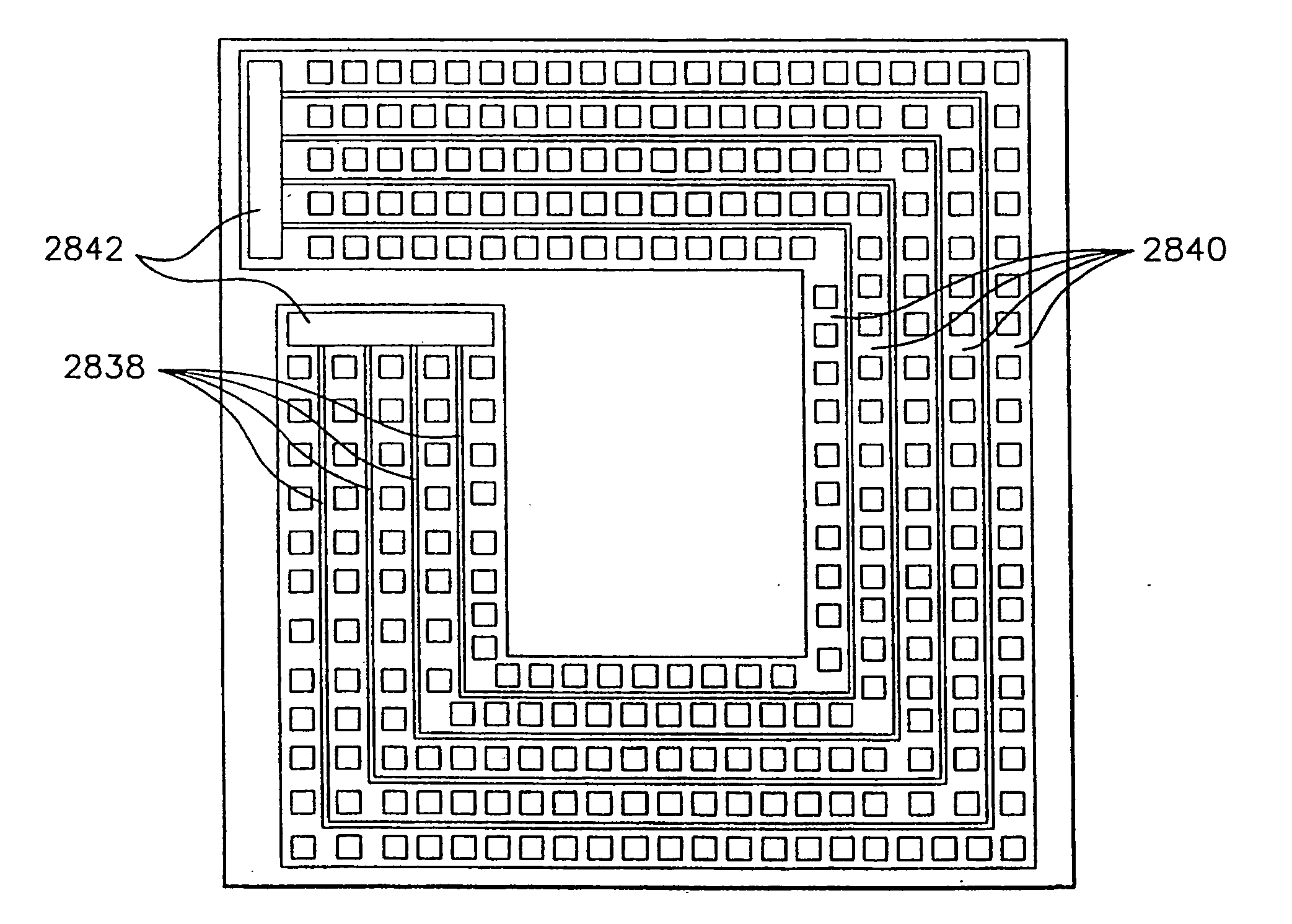

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programmable attenuation and a programmable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

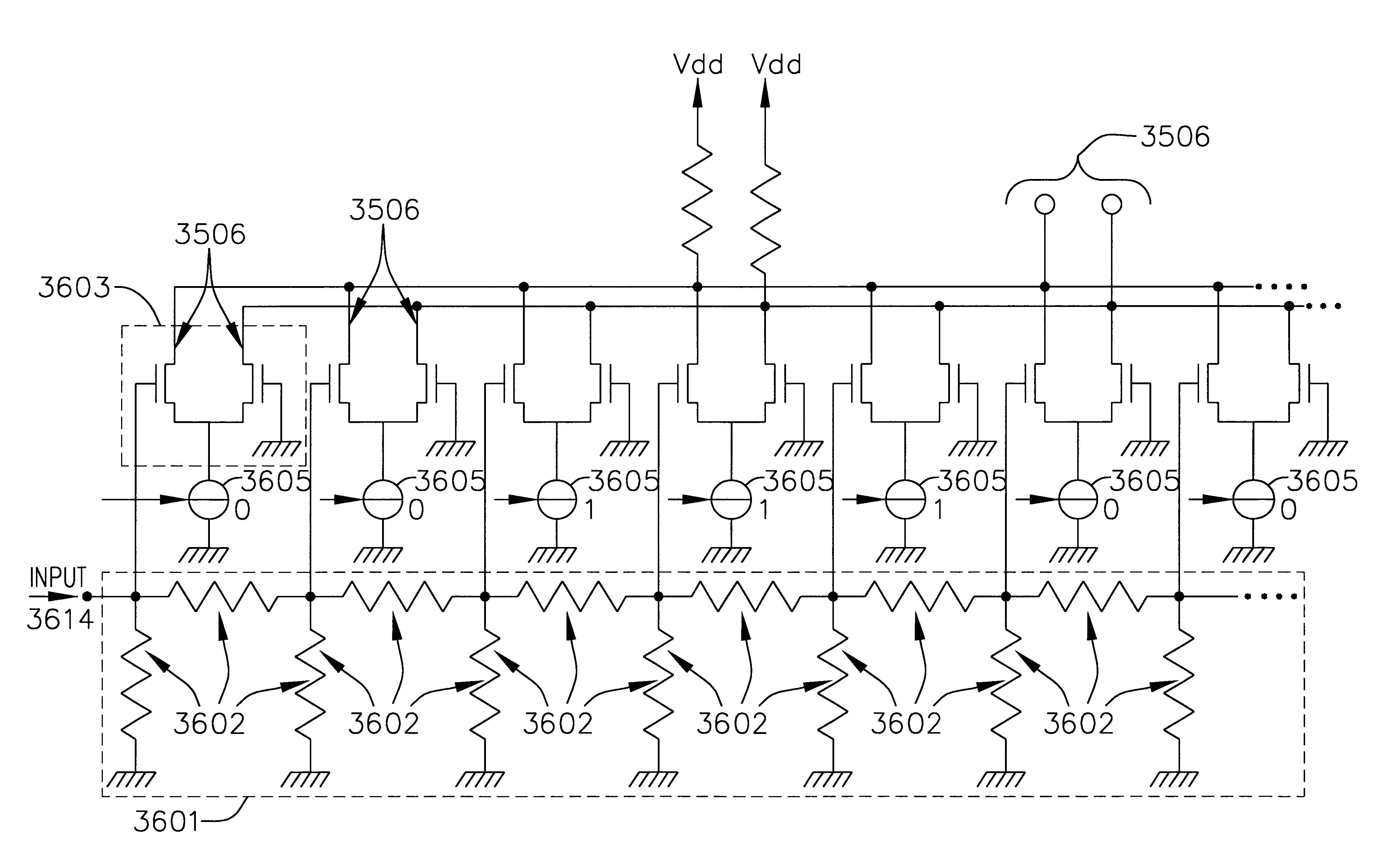

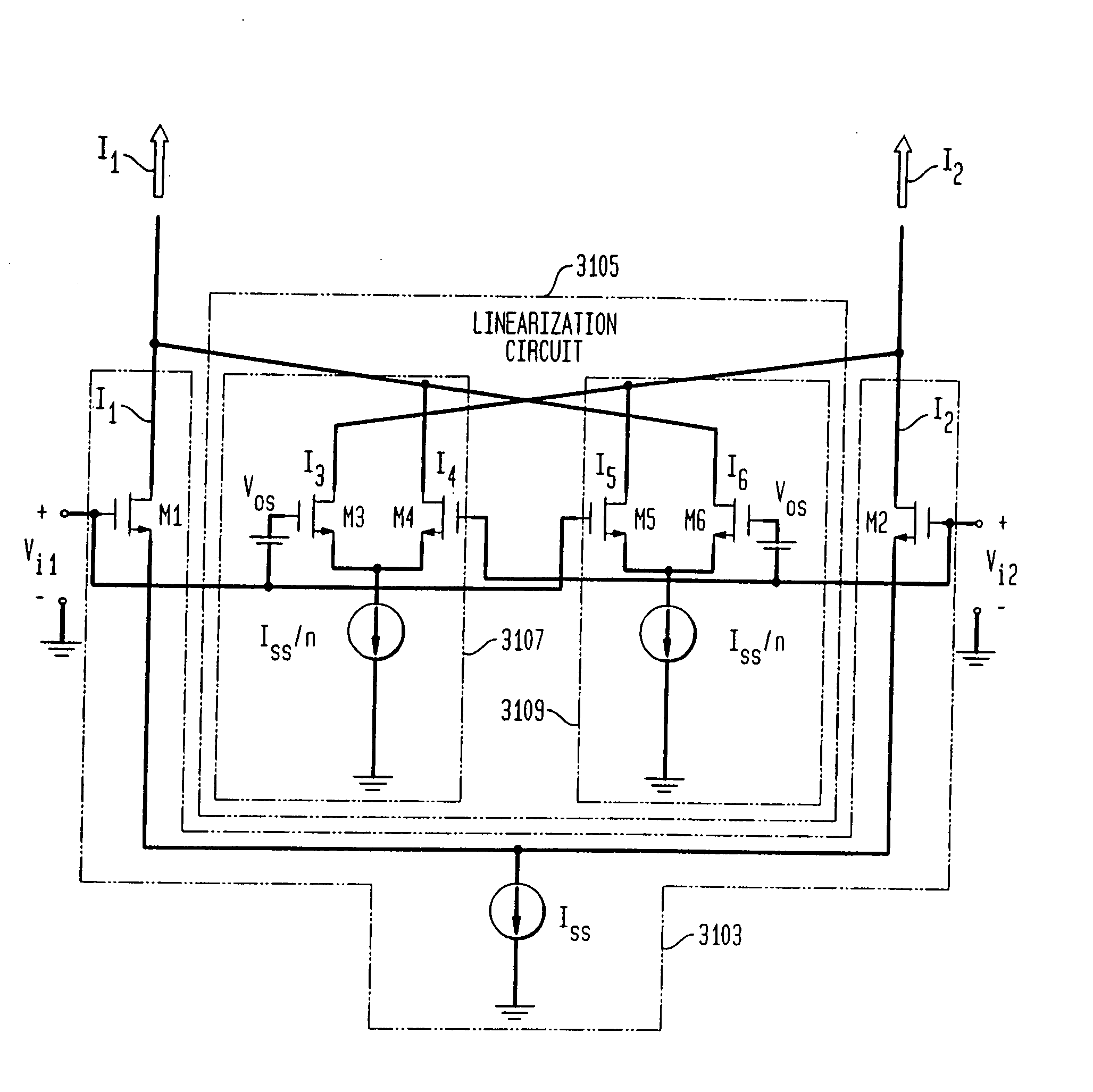

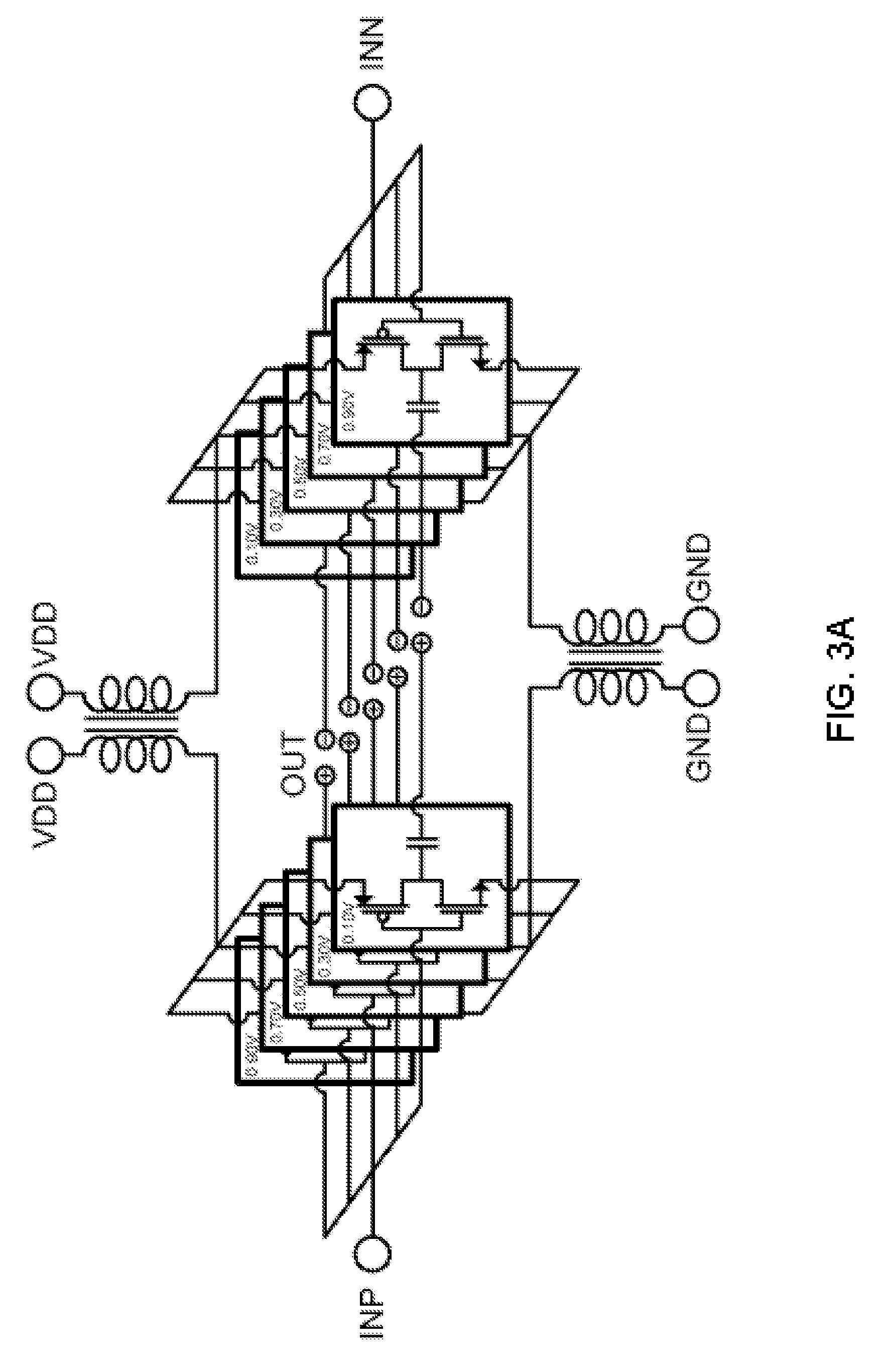

System and method for linearizing a CMOS differential pair

InactiveUS20080036536A1Multiple-port networksSemiconductor/solid-state device detailsShunt DeviceFilter tuning

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit. A receiver front end provides programmable attenuation and a programmable gain low noise amplifier. LC filters integrated onto the substrate in conjunction with image reject mixers provide image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. Active filters utilize multi track spiral inductors with shields to increase circuit Q. The filters incorporate a gain stage that provides improved dynamic range through the use of cross coupled auxiliary differential pair CMOS amplifiers to cancel distortion in a main linearized differential pair amplifier. Frequency planning provides additional image rejection. Local oscillator signal generation methods on chip reduce distortion. A PLL generates needed out of band LO signals. Direct synthesis generates in band LO signals. PLL VCOs are centered automatically. A differential crystal oscillator provides a frequency reference. Differential signal transmission throughout the receiver is used. ESD protection is provided by a pad ring and ESD clamping structure. Shunts utilize a gate boosting at each pin to discharge ESD build up. An IF VGA utilizes distortion cancellation achieved with cross coupled differential pair amplifiers having their Vds dynamically modified in conjunction with current steering of the differential pairs sources.

Owner:AVAGO TECH INT SALES PTE LTD

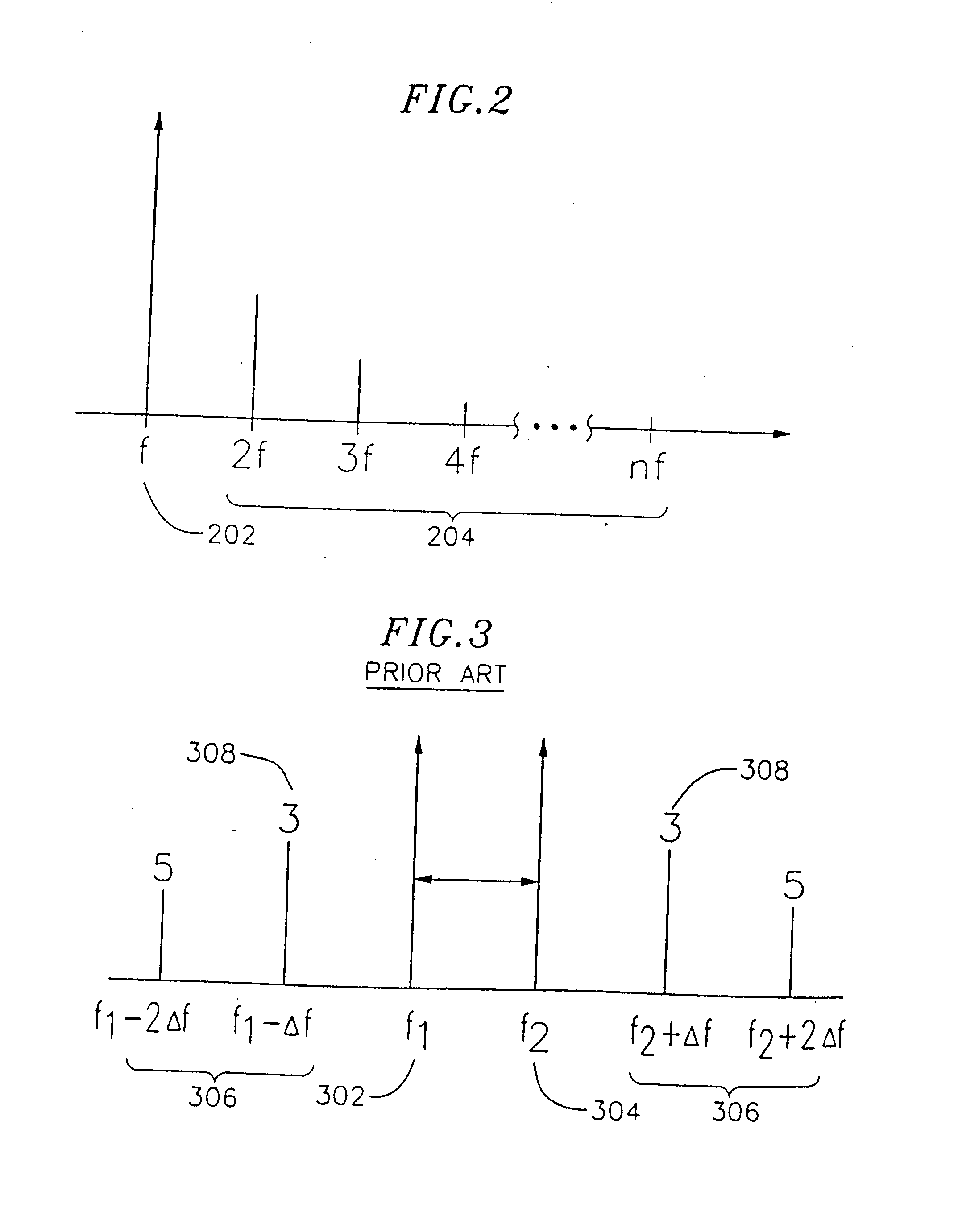

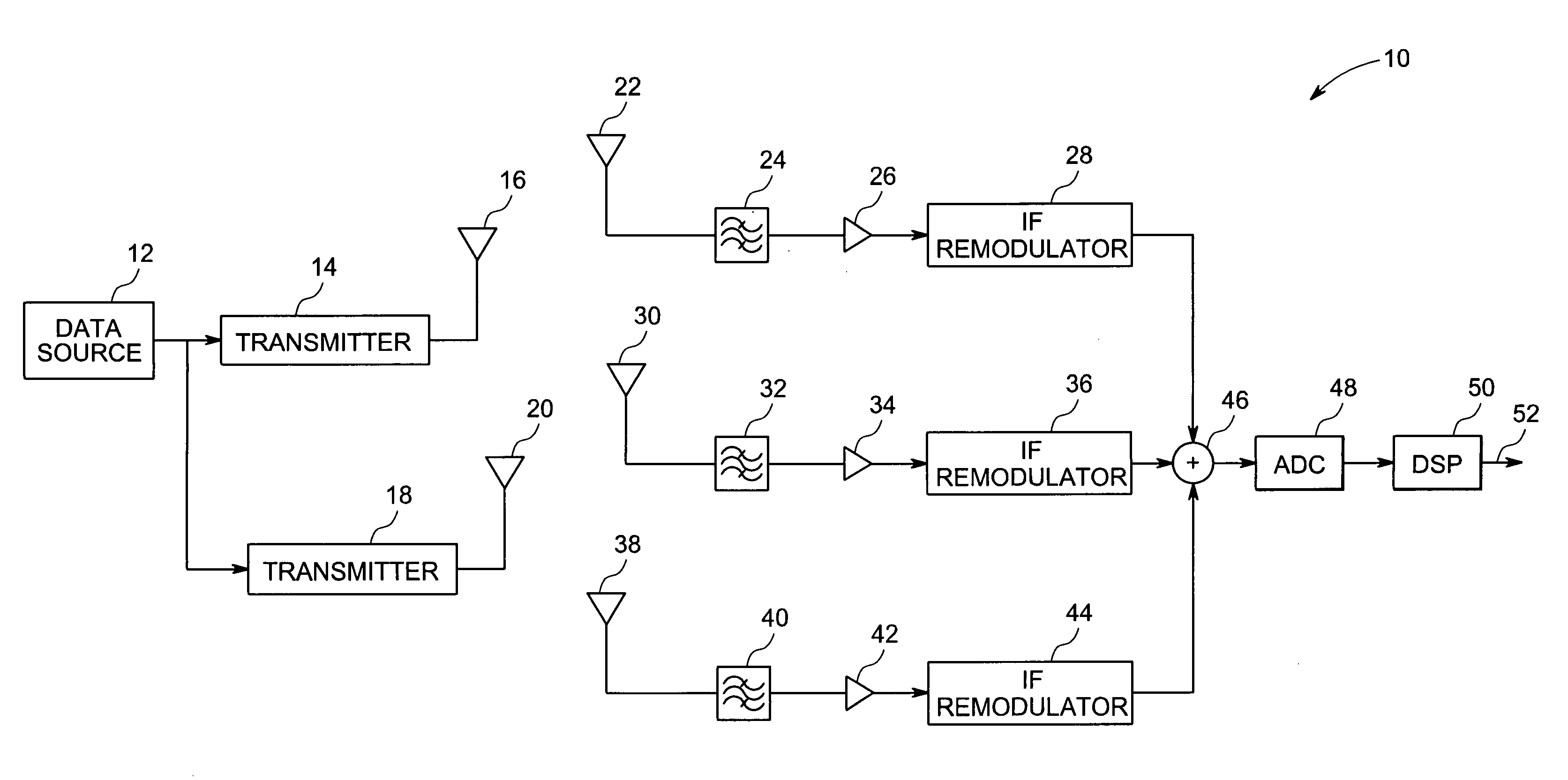

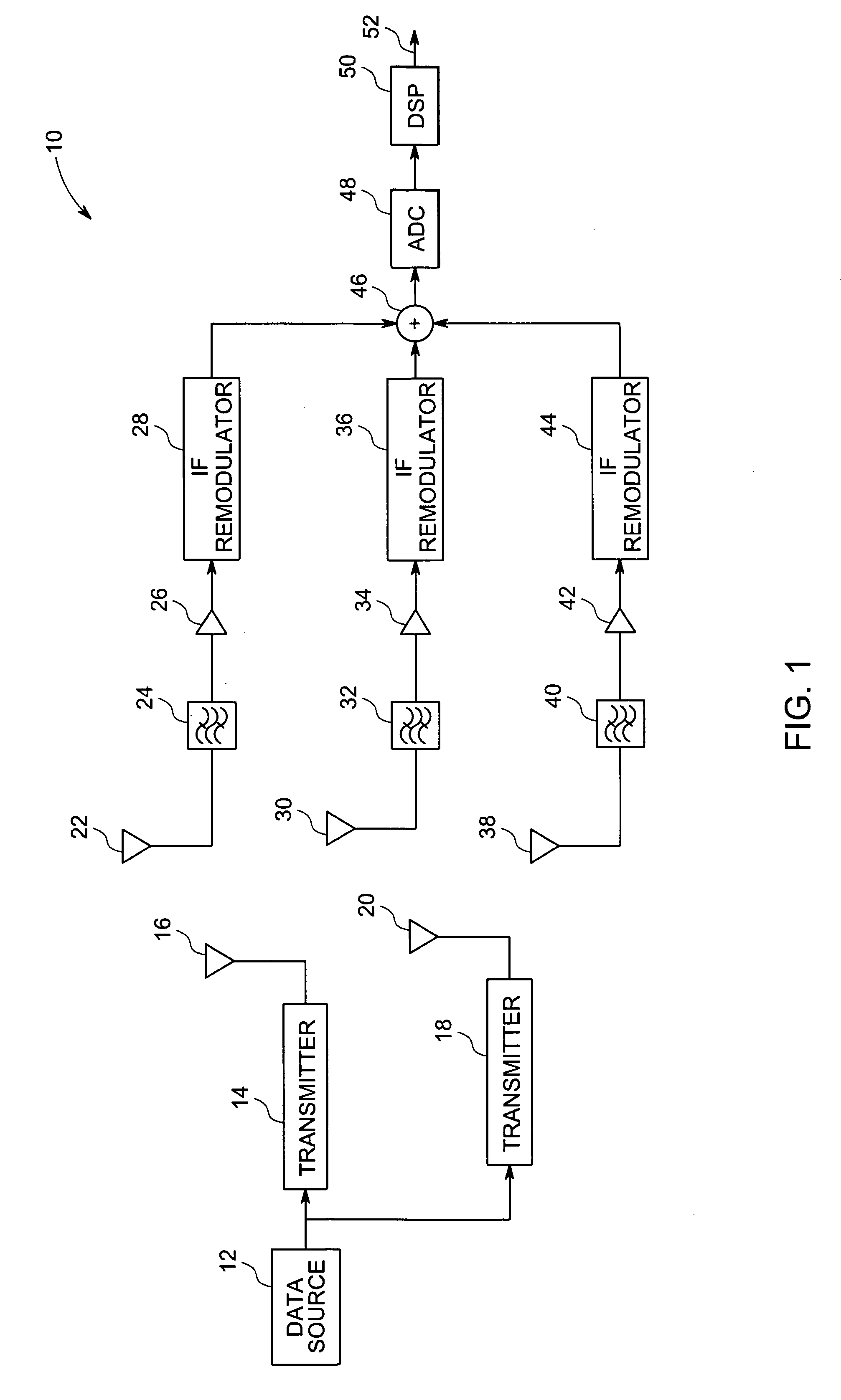

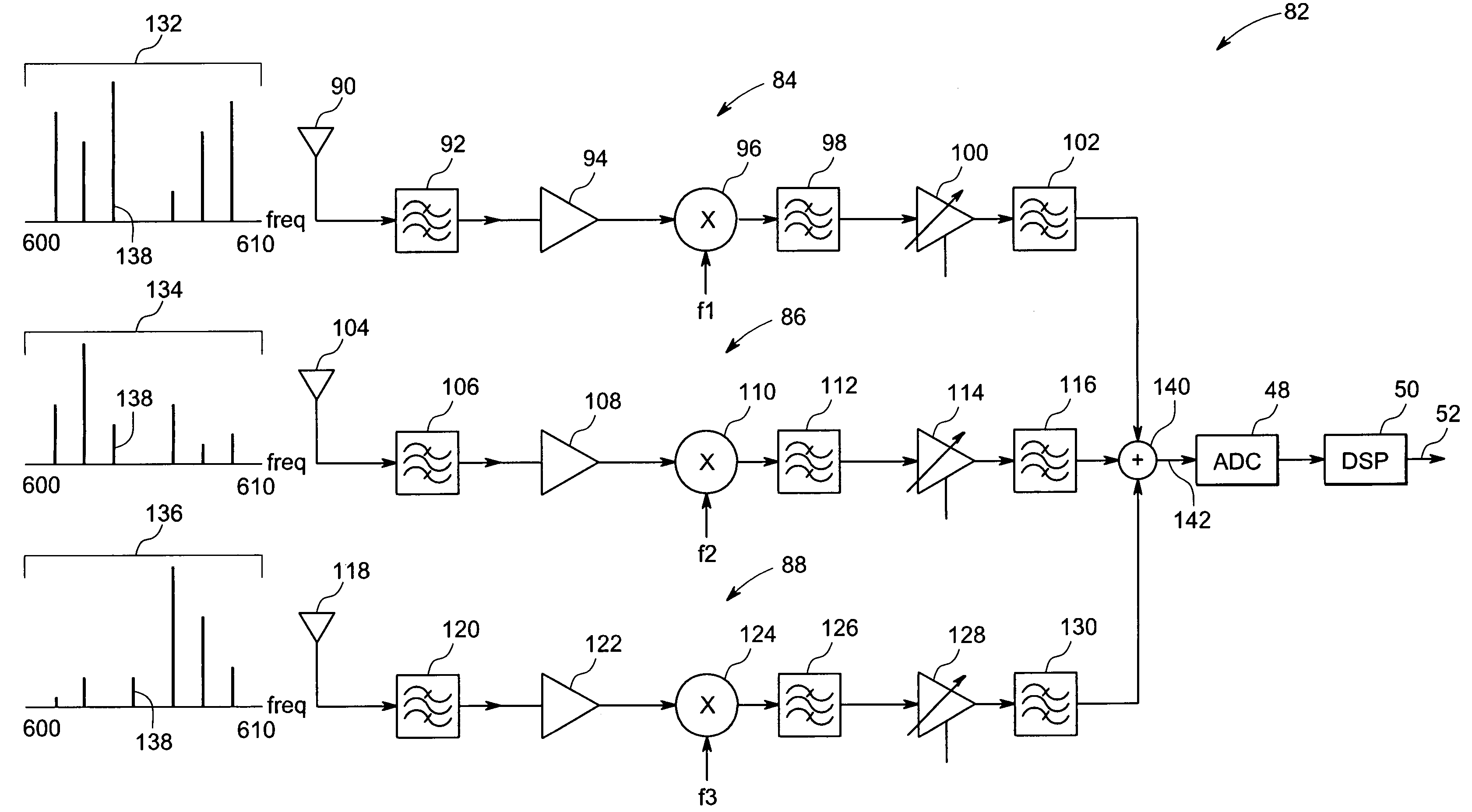

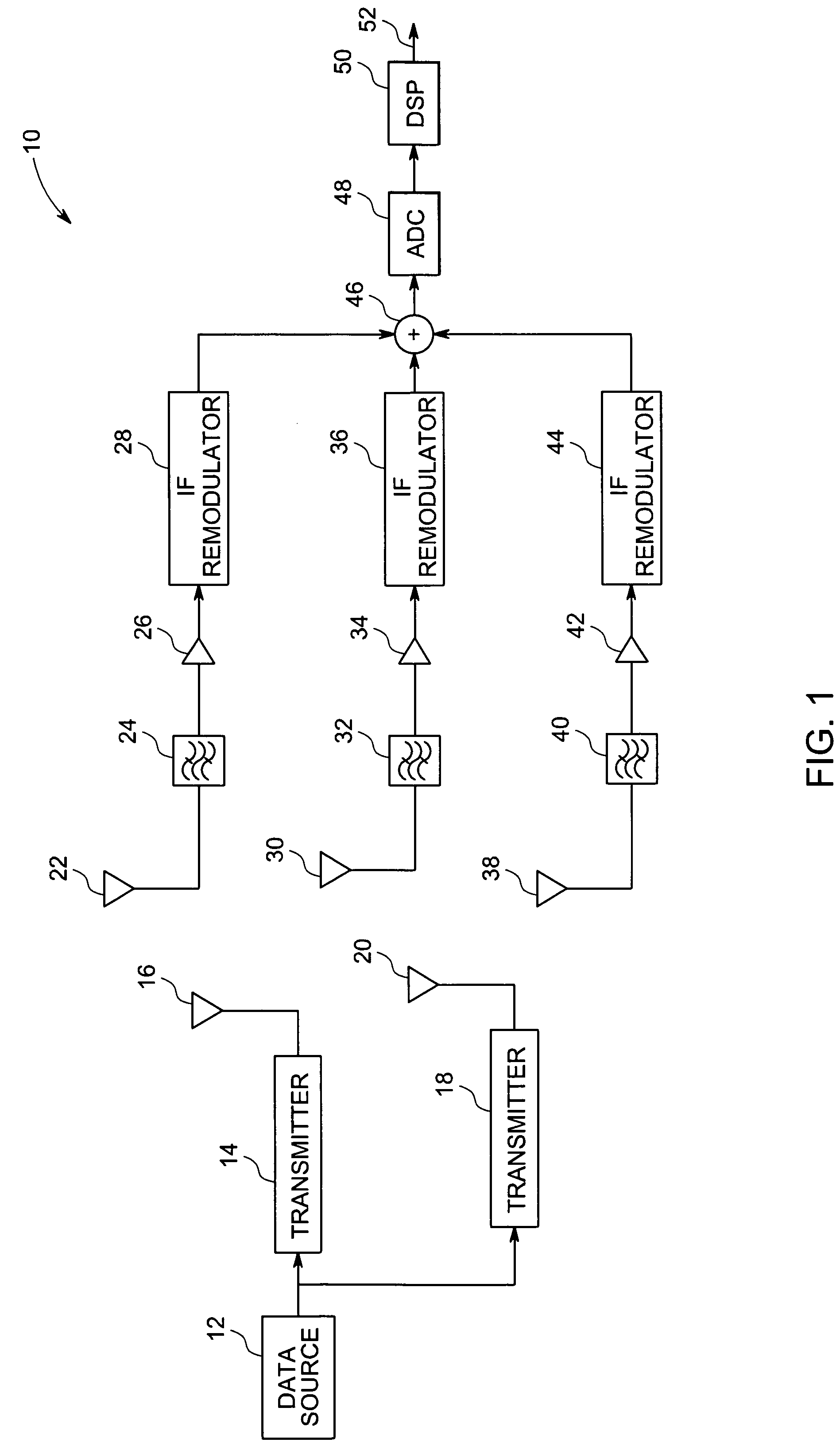

System and method of communicating signals

InactiveUS20070002961A1Reduce the sampling frequencyTransmission systemsPolarisation/directional diversityCommunications systemIntermediate frequency

A communication system is presented. The system includes one or more transmitters configured to transmit a signal, where each of the signals generated by the one or more transmitters corresponds to a respective frequency. Further, the system includes a plurality of receiver front-ends configured to receive the signal transmitted by each of the one or more transmitters. The system also includes a plurality of remodulator modules configured to translate each of the received signals to a signal having a respective intermediate frequency. In addition, the system includes a combining module configured to combine each of the signals having respective intermediate frequencies to generate a single composite signal. Also, the system includes a single analog-to-digital converter configured to process the composite signal and generate a digital output. Additionally, the system includes a digital signal processor module configured to extract the signal transmitted by each of the one or more transmitters.

Owner:GENERAL ELECTRIC CO

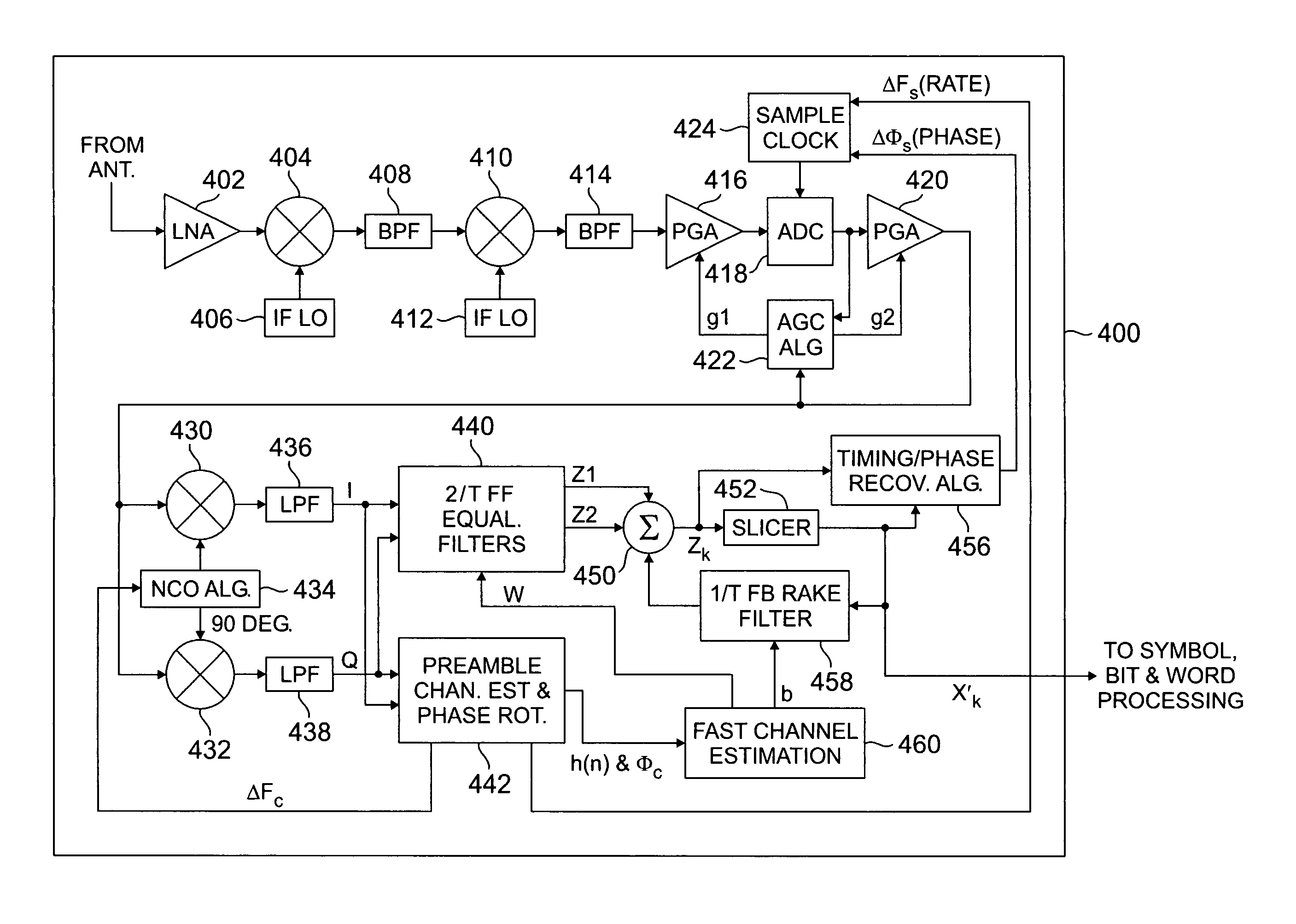

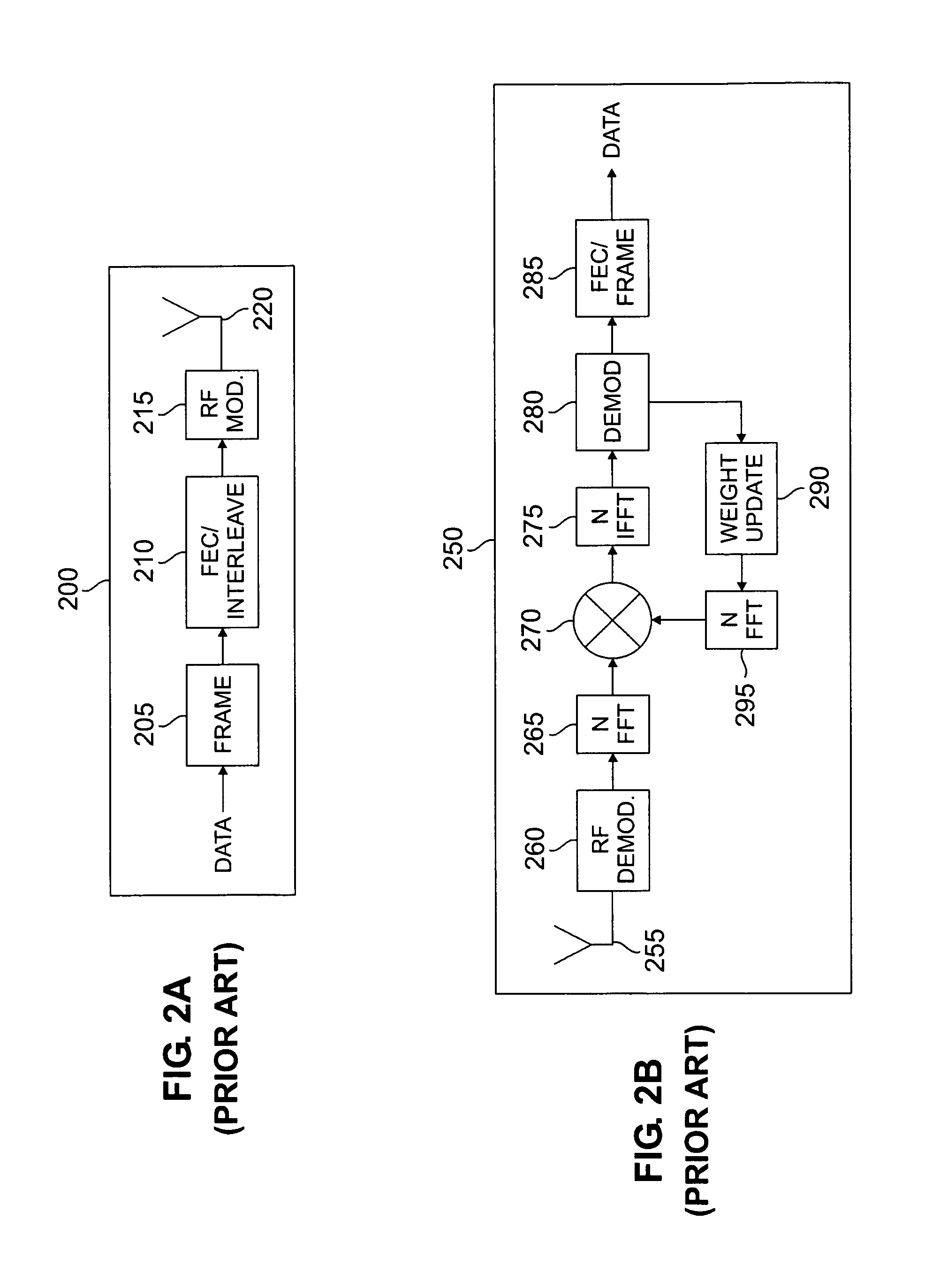

Wireless communication system using block filtering and fast equalization-demodulation and method of operation

InactiveUS7075967B2Minimizing preamble overheadMinimize overheadError prevention/detection by using return channelSite diversityBurst transmissionTransceiver

There is disclosed a transceiver for use in a base station of a fixed wireless network that communicates with a plurality of subscriber transceivers via time division duplex (TDD) channels. The transceiver comprises: 1) a receiver front-end for receiving data burst transmissions from the plurality of subscriber transceivers in an uplink portion of a TDD channel, wherein the receiver front-end demodulates the received data burst transmissions into a digital baseband signal in-phase (I) signal and a digital baseband quadrature (Q) signal; 2) a first frequency domain feedforward equalization filter for receiving the I signal; 3) a second frequency domain feedforward equalization filter for receiving the Q signal; 4) an adder for producing a combined symbol estimate sequence; 5) a slicer for receiving and quantizing the combined symbol estimate sequence; and 6) a time domain feedback filter for generating a symbol correction sequence.

Owner:RAZE TECH

Ultraviolet, infrared, and near-infrared lidar system and method

ActiveUS20070024840A1Eliminate the problemOptical rangefindersCharacter and pattern recognitionInfraredFrequency spectrum

Pushbroom and flash lidar operations outside the visible spectrum, most preferably in near-IR but also in IR and UV, are enabled by inserting—ahead of a generally conventional lidar receiver front end—a device that receives light scattered from objects and in response forms corresponding light of a different wavelength from the scattered light. Detailed implementations using arrays of discrete COTS components—most preferably PIN diodes and VCSELs, with intervening semicustom amplifiers—are discussed, as is use of a known monolithic converter. Differential and ratioing multispectral measurements, particularly including UV data, are enabled through either spatial-sharing (e. g. plural-slit) or time-sharing.

Owner:ARETE ASSOCIATES INC

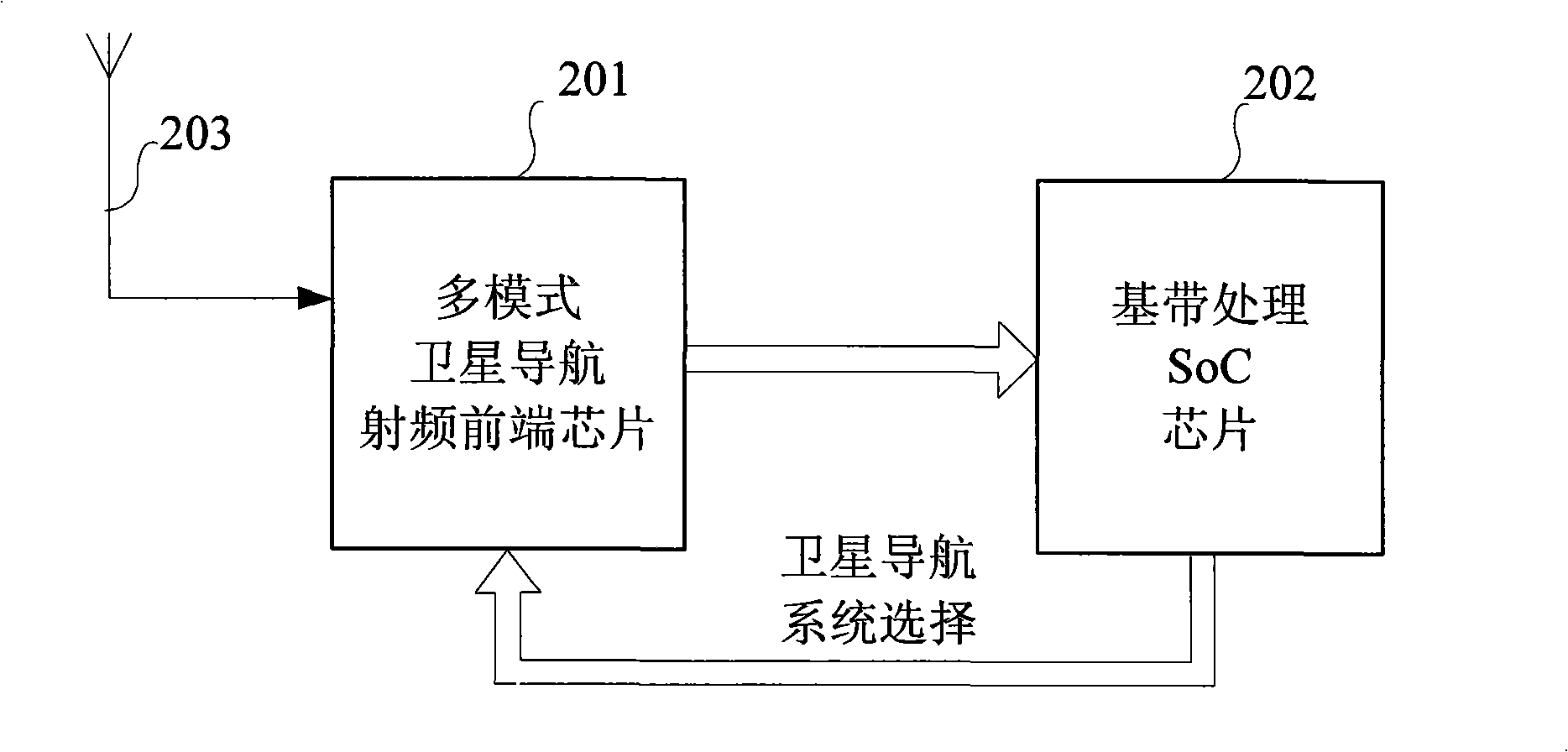

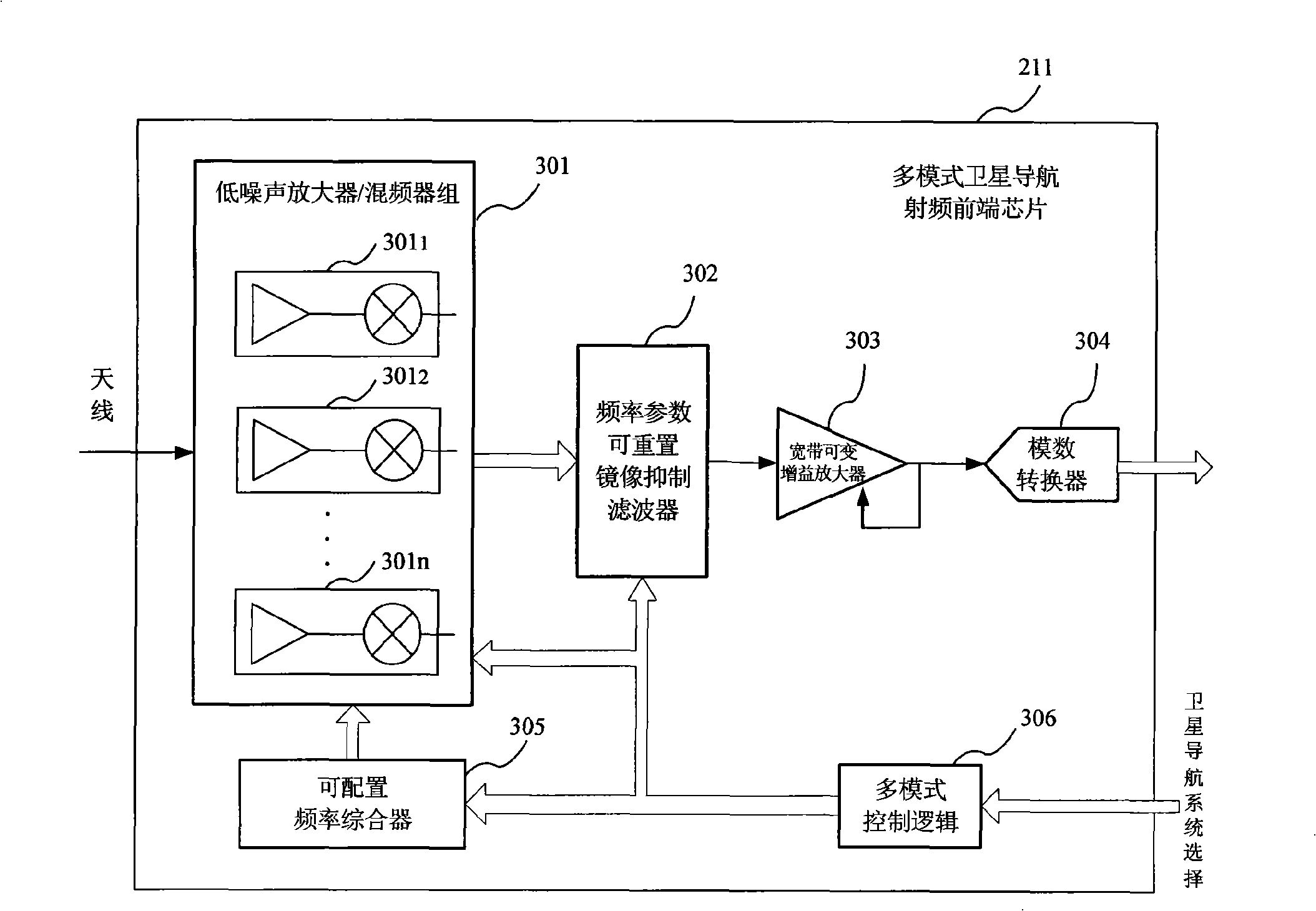

Multi-mode satellite navigation receiving radio frequency front end chip

InactiveCN101303403ASatisfied with bandpass filteringSatisfy InhibitionBeacon systems using radio wavesRF front endNavigation system

The invention provides a framing method of the receiver front-end of multimode satellite navigation, which discloses a frontend chip of the receiving RF of multimode satellite navigation which is applicable to a plurality of satellite navigation systems. The method of the invention comprises six modules which are a multimode PF frontend low-noise amplifier / mixer group of monolithic integrated and completed type, a reconfigurable image rejection filter, a band-variable gain amplifier, an analog-to-digital converser, a configurable frequency synthesizer and a multimode control logic module. The reconfigurable module can realize the distribution of functional parameters according to the requirement through the multimode control logic management, causing the working performance to be optimized and meeting the functional requirement on the RF front end of the receiving platform of multimode satellite navigation. The framing method of the invention requires no external supporting accessories and has the advantages of being easy to carrying out cascade connection with preceding and backward stages, high gain, small noise coefficient and good integration. The invention is applied to the current communication and navigation positioning equipment for receiving multimode satellite navigation signals, has a wide application range and quite remarkable economic benefit, is largely on demand, supports the integration making use of multimode satellite navigation positioning information, improves positioning precision and has large social benefit.

Owner:杭州中科微电子有限公司

Integrated spiral inductor

InactiveUS20050156700A1Resonant circuit detailsSemiconductor/solid-state device detailsCapacitanceShunt Device

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors with shields to increase circuit Q. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH INT SALES PTE LTD

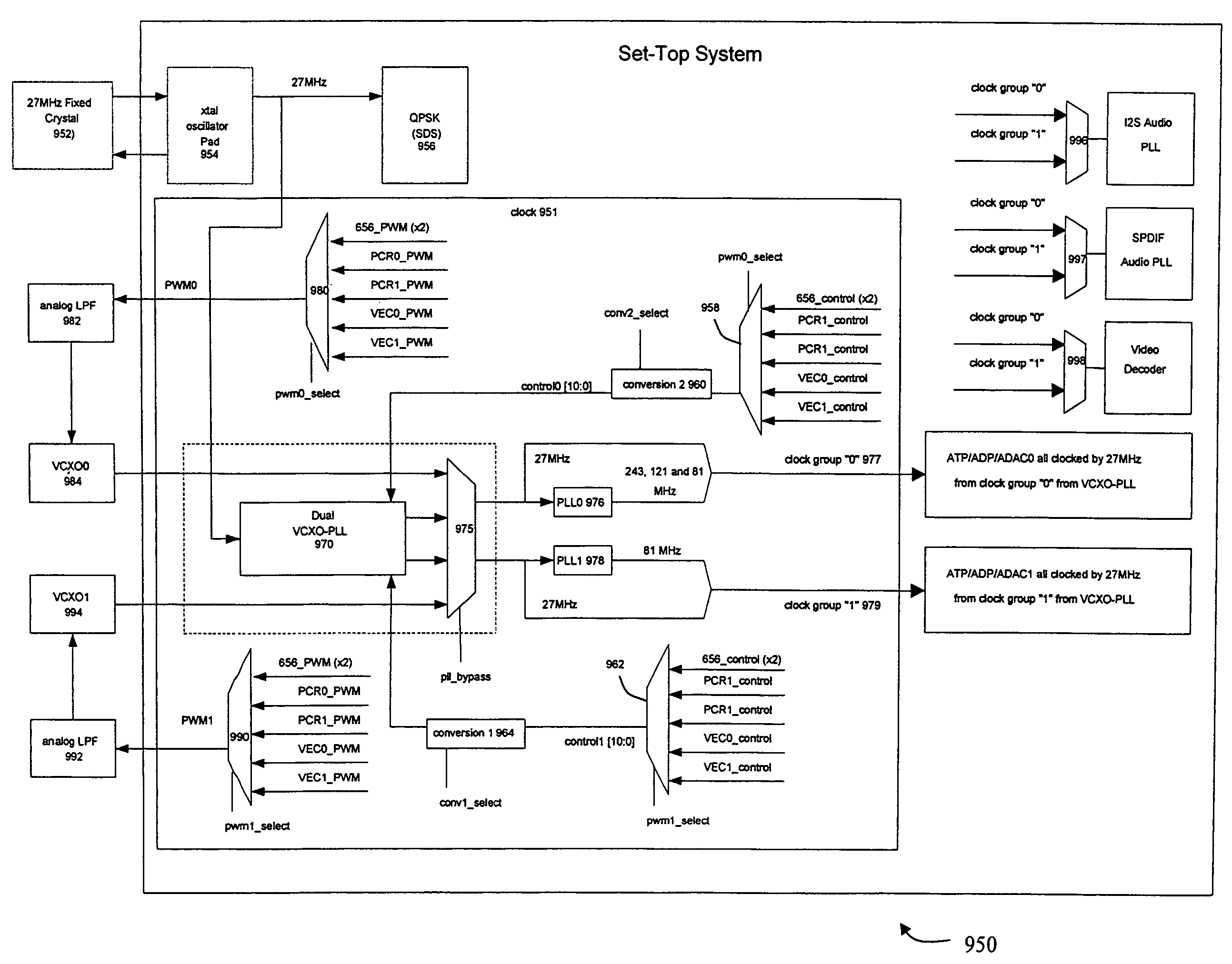

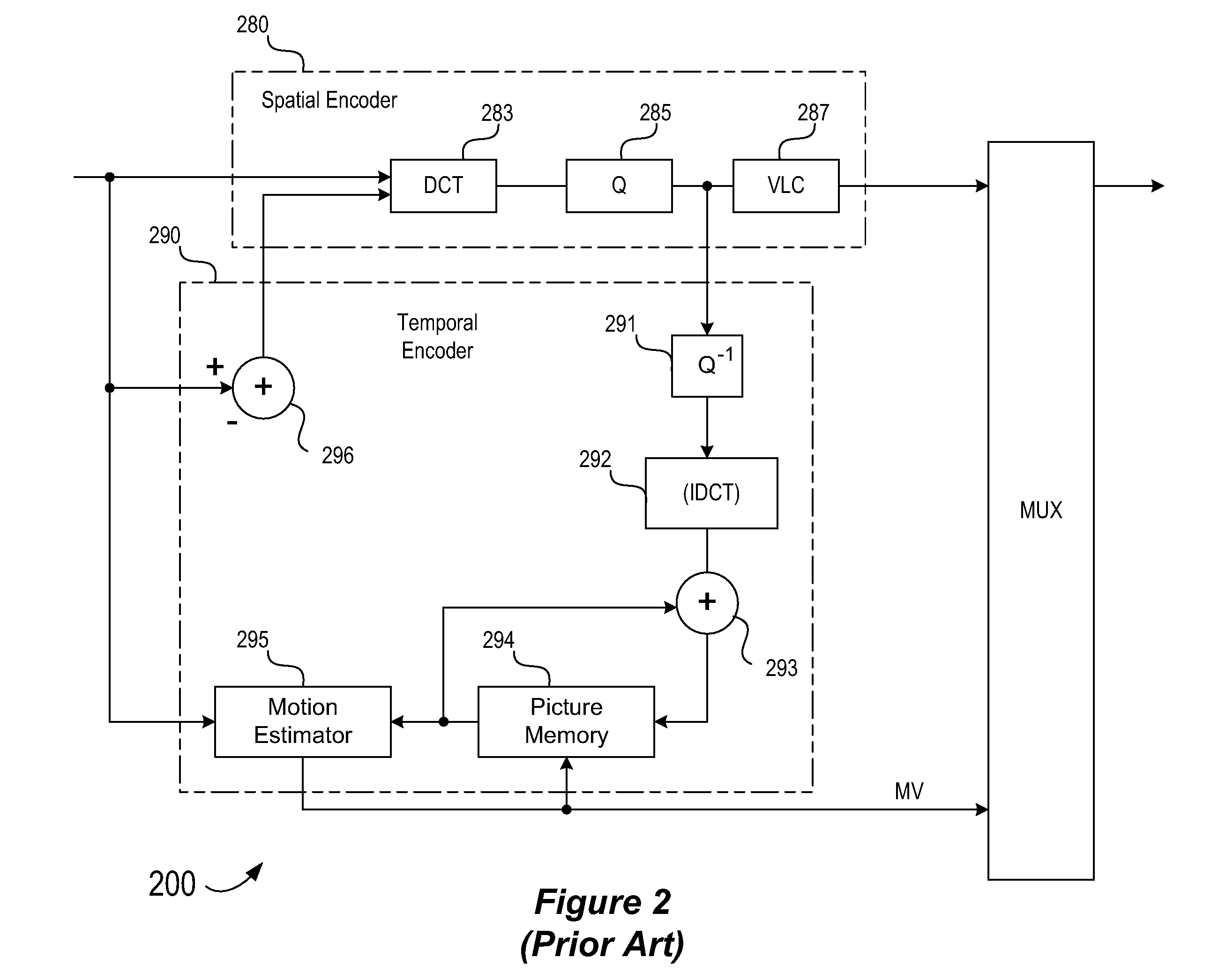

Satellite set-top box decoder for simultaneously servicing multiple independent programs for display on independent display devices

InactiveUS7533402B2Television system detailsColor burst signal generation/insertionSignal onDisplay device

An integrated receiver with dual channel transport stream decoding and delivery substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides multiple time-base clocks for two transport streams. Transport processor circuitry uses multiple PCRs to track transport streams through decoding, storage and or delivery of the decoded signals for display. Provision of a multiple time-base clock for decoding and delivering multiple transport streams allows display of the two decoded audio-video signals on independent monitors.

Owner:AVAGO TECH INT SALES PTE LTD

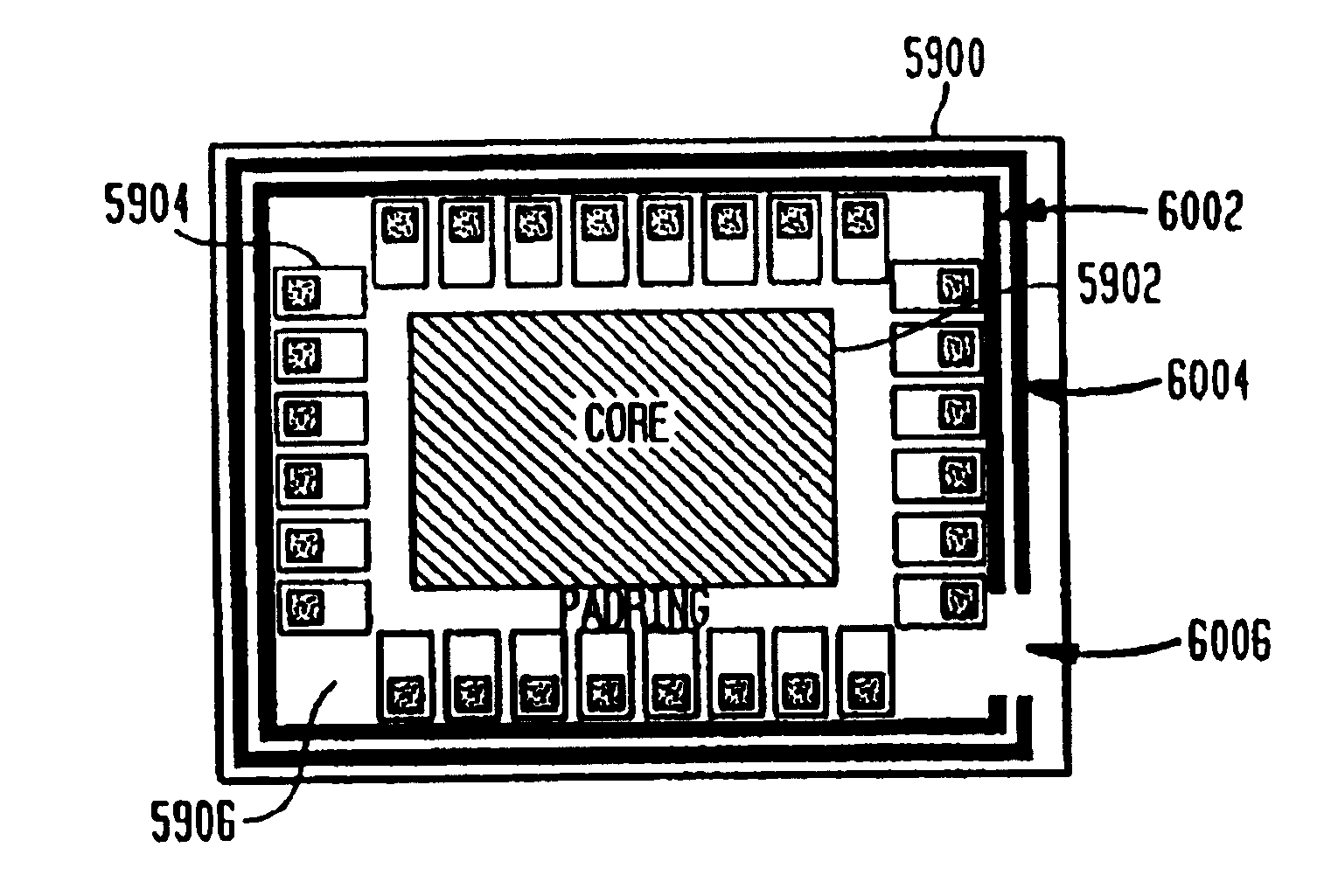

System and method for ESD protection

InactiveUS6963110B2Reduce areaReduce capacitanceResonant circuit detailsSemiconductor/solid-state device detailsShunt DeviceCapacitance

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Incompressible RF receiver

InactiveUS20100316172A1Modulation transferenceError preventionNonlinear distortionAudio power amplifier

An incompressible receiver for minimizing undesired higher-order nonlinear distortion products includes a first receiver path configured to receive an input signal having at least one non-baseband frequency. A second receiver path is also configured to receive the input signal. The second receiver path includes at least one odd-order nonlinear distortion reference component and at least one even-order nonlinear distortion reference component. The distortion reference components are configured to be in an “on” state or in an “off” state. A combining element is configured to combine input signals from the first and second receiver paths such that the higher-order nonlinear distortion signals are substantially attenuated at an output of the combining element. An incompressible receiver that has an odd-order nonlinear distortion reference generator including a cubic term and at least one additional term of order greater than 3 and an incompressible receiver front end amplifier (IRFEA) are also described.

Owner:CALIFORNIA INST OF TECH

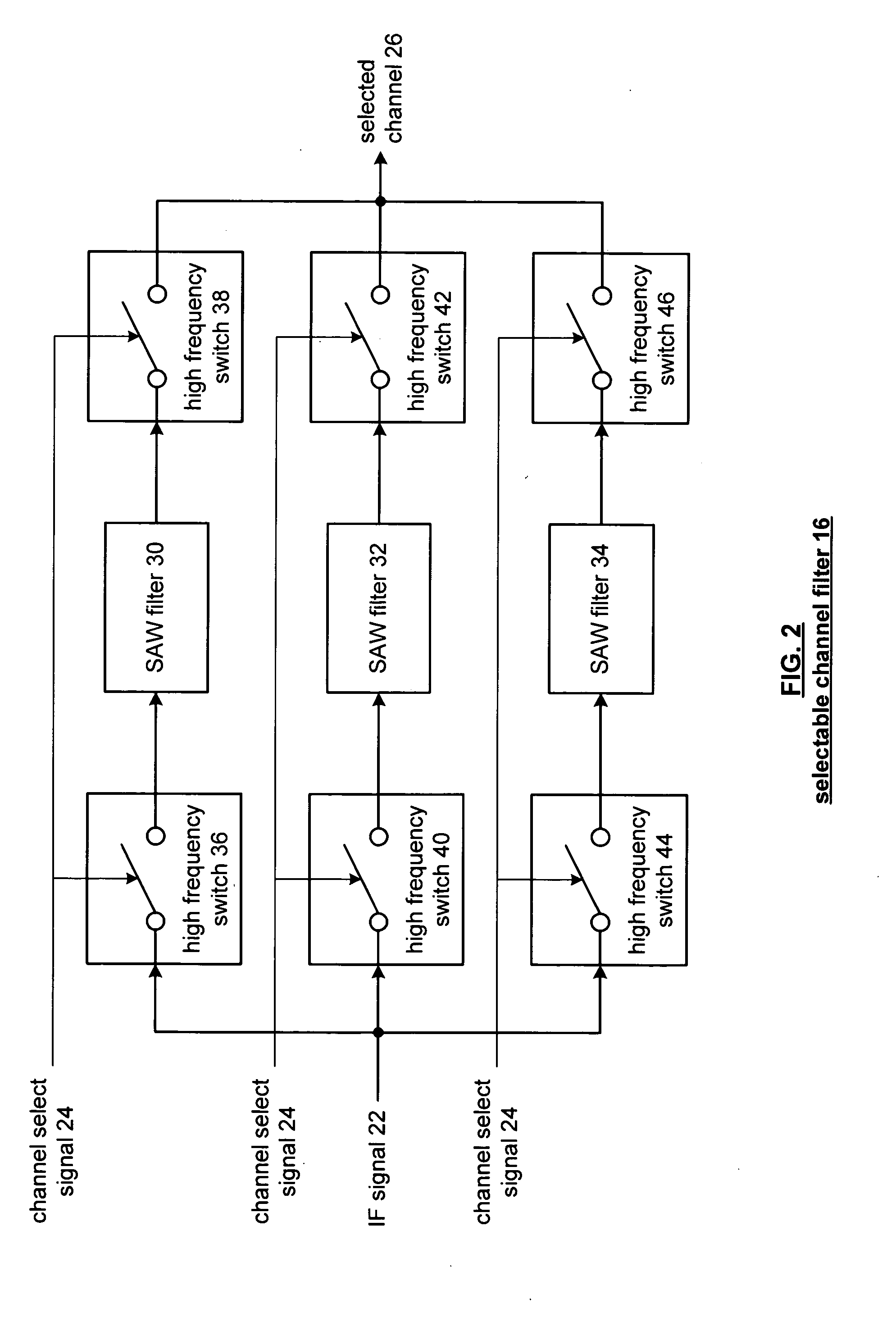

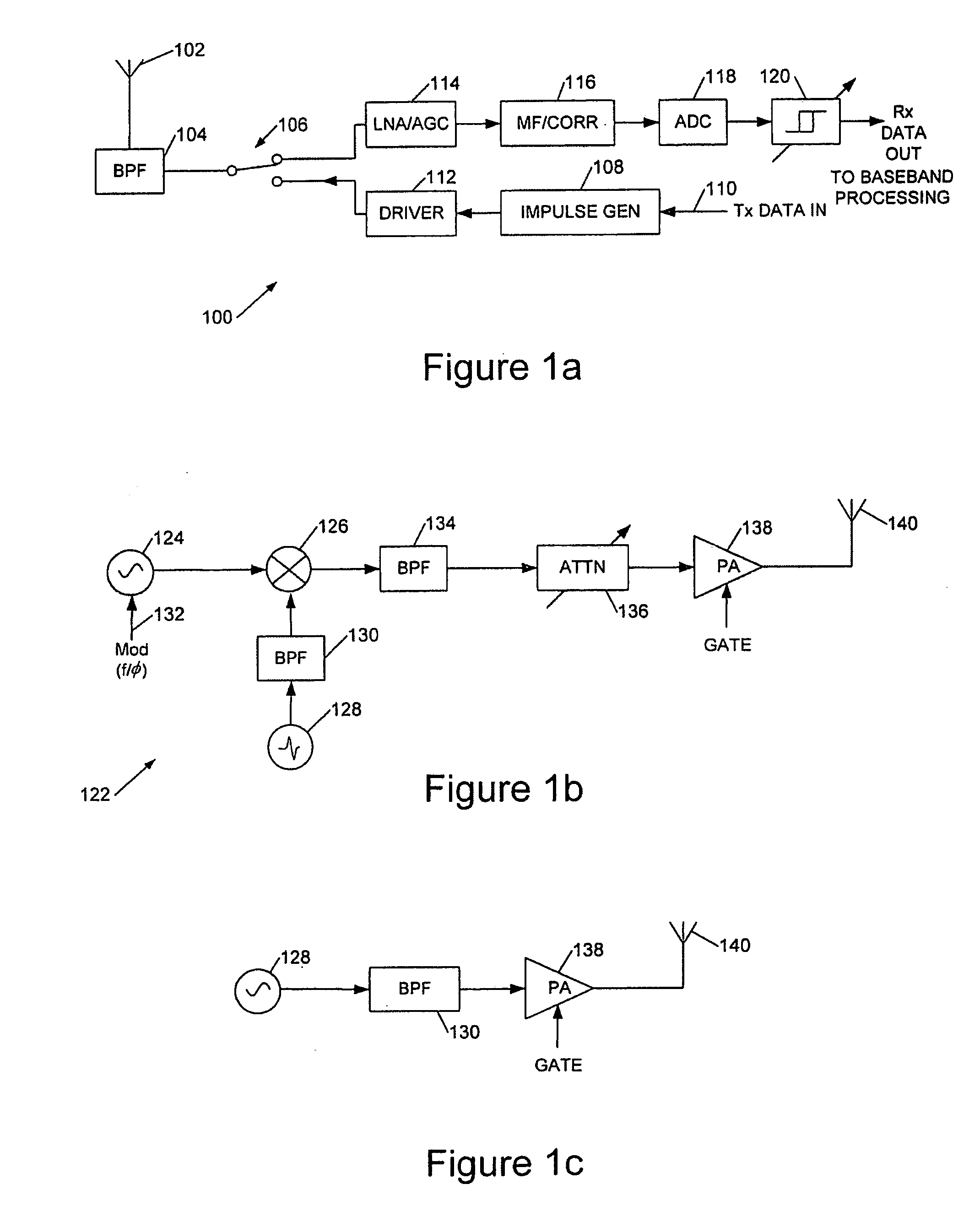

RF transmitter and receiver front-end

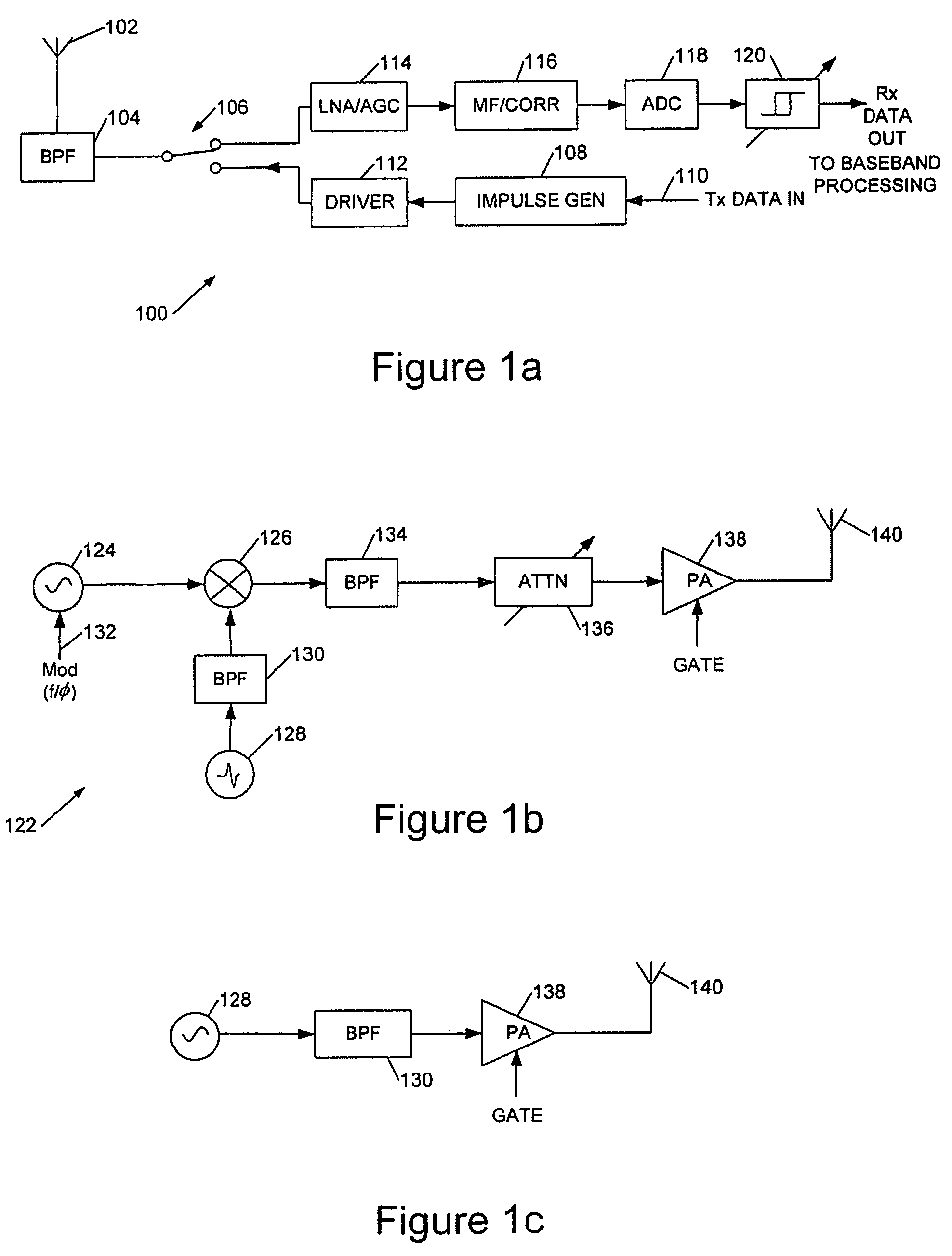

InactiveUS20050136880A1TransmissionInput/output processes for data processingAudio power amplifierIntermediate frequency

A radio frequency receiver front-end includes a low noise amplifier, a mixing stage, and a selectable channel filter. The low noise amplifier is operably coupled to amplify inbound RF signals to produce amplified inbound RF signals. The mixing stage is operably coupled to mix amplified inbound RF signals with a 1st local oscillation to produce a 1st intermediate frequency (IF) signal. The selectable channel filter is operably coupled to pass a 1st channel of the 1st IF signal when a channel select signal is in a 1st state and to pass a 2nd channel of the 1st IF signal when the channel select signal is in a 2nd state to produce a selected channel.

Owner:VIXS SYSTEMS INC

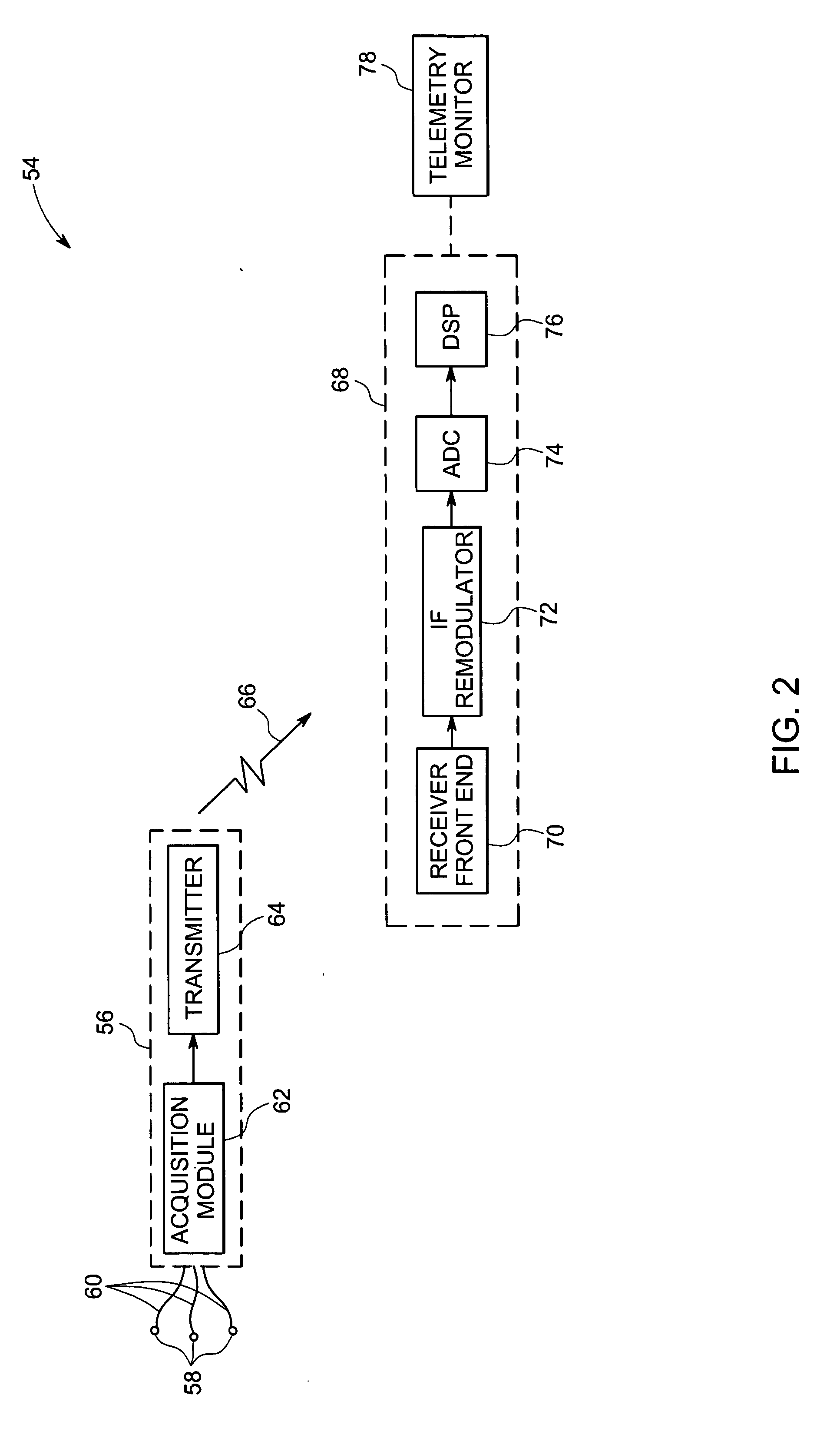

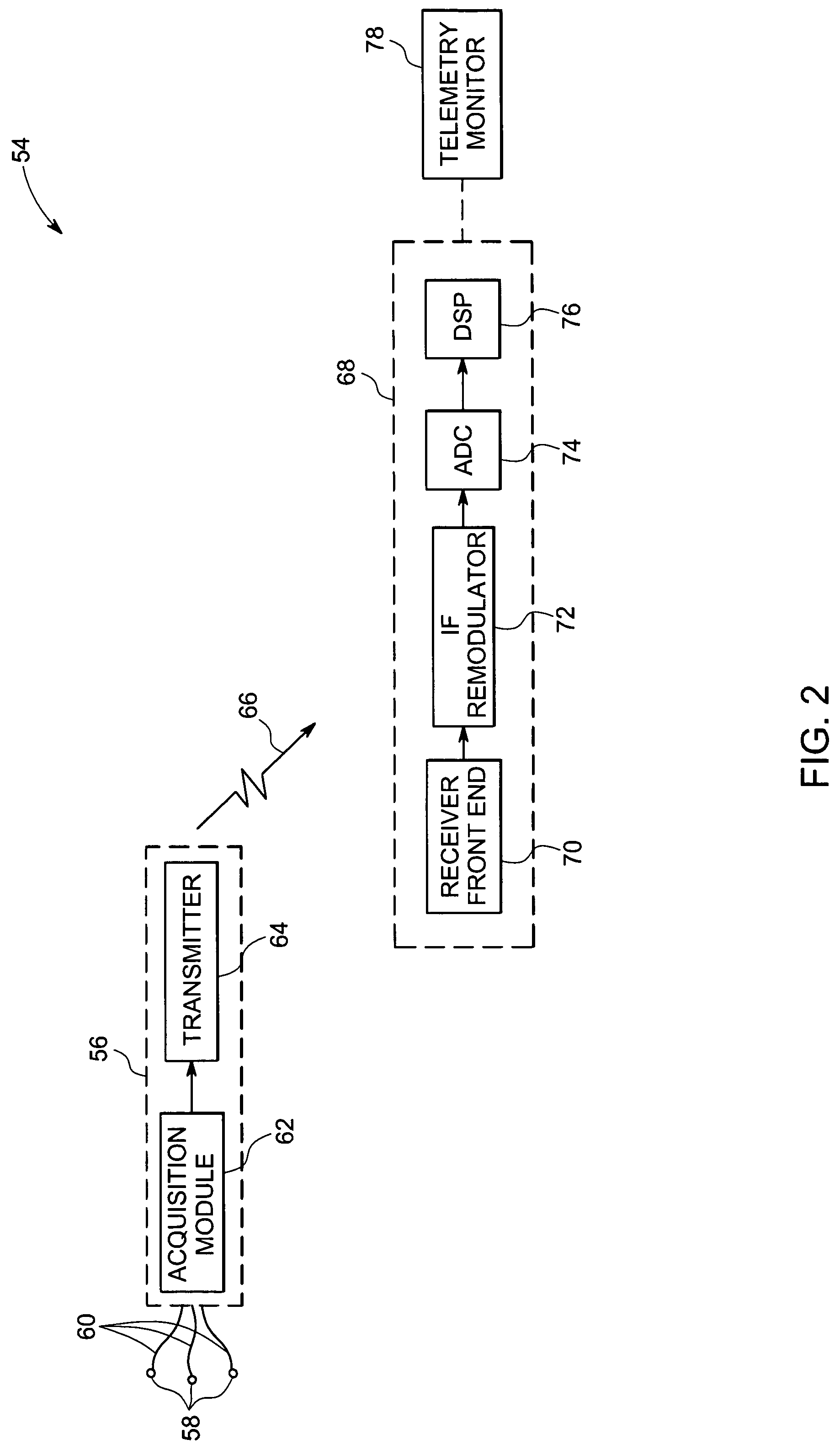

Variable implantable medical device power characteristics based upon implant depth

An implantable medical device (“IMD”) as described herein includes adjustable power characteristics such as variable transmitter output power and variable receiver front end gain. These power characteristics are adjusted based upon the intended or actual implant depth of the IMD. The IMD may process an IMD implant depth value (provided by an external IMD programming device) to generate power scaling instructions or control signals that are interpreted by the IMD transmitter and / or the IMD receiver. Such adjustability enables the IMD to satisfy minimum telemetry requirements in a manner that does not waste power, thus extending the IMD battery life.

Owner:MEDTRONIC INC

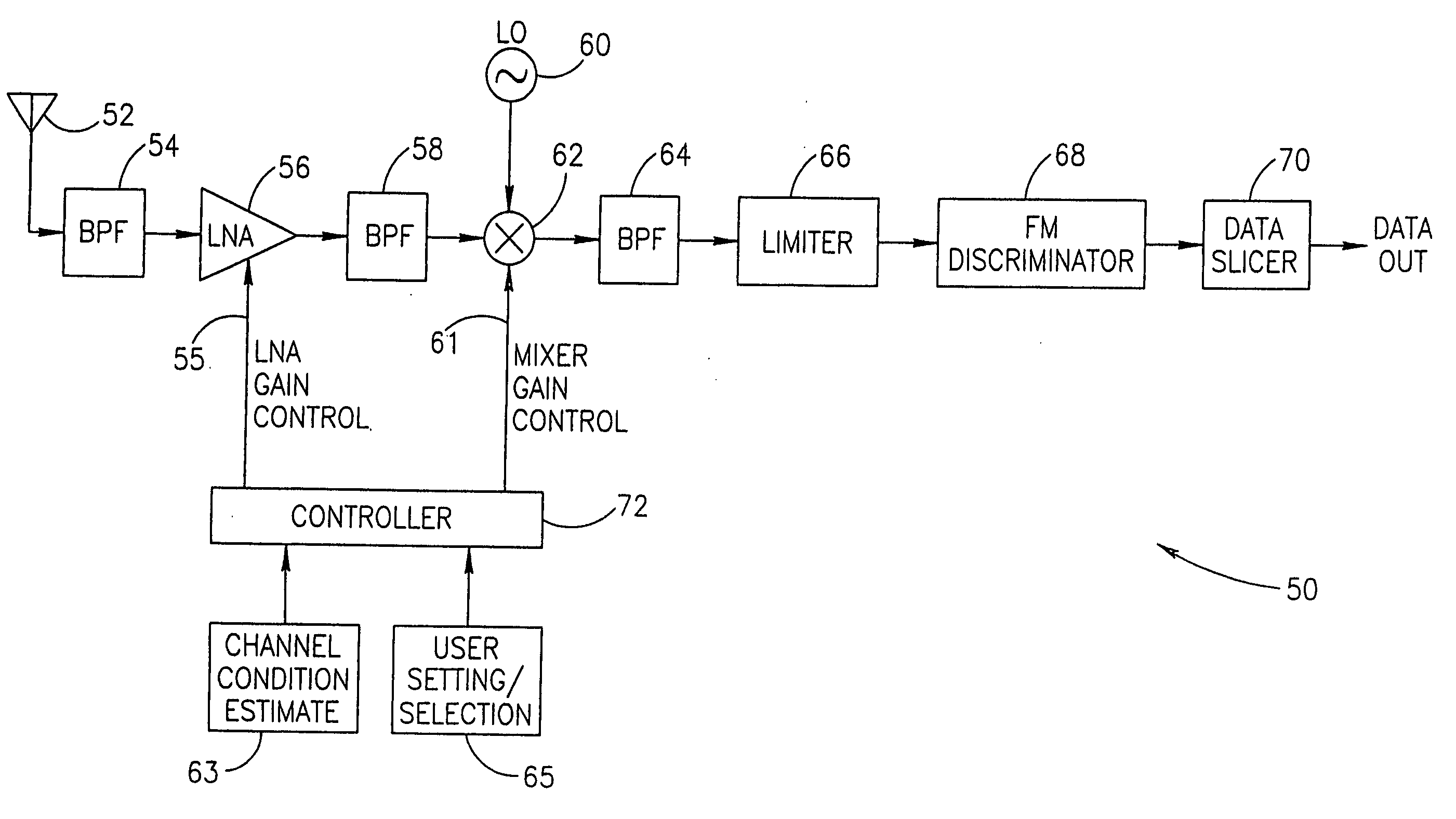

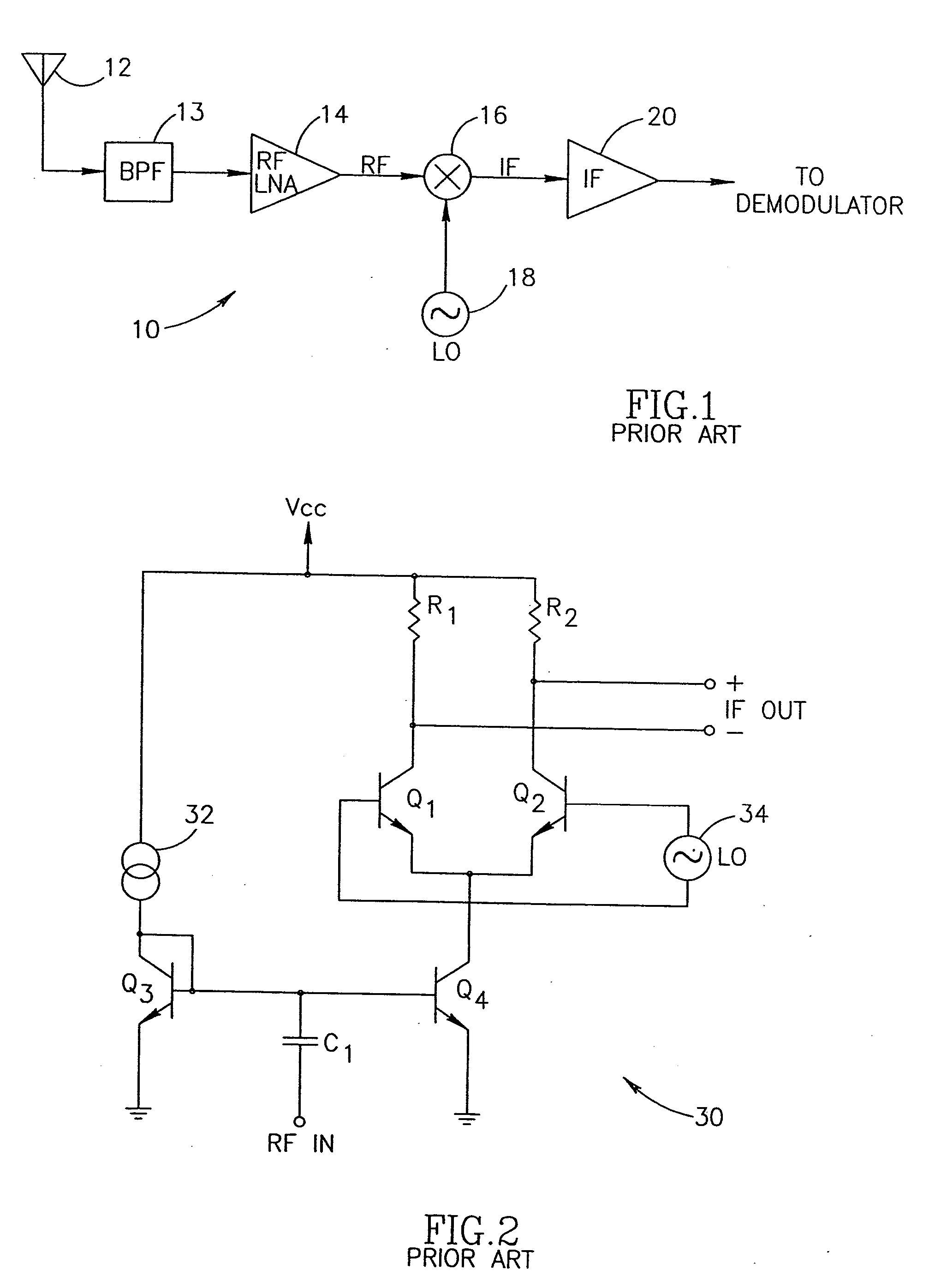

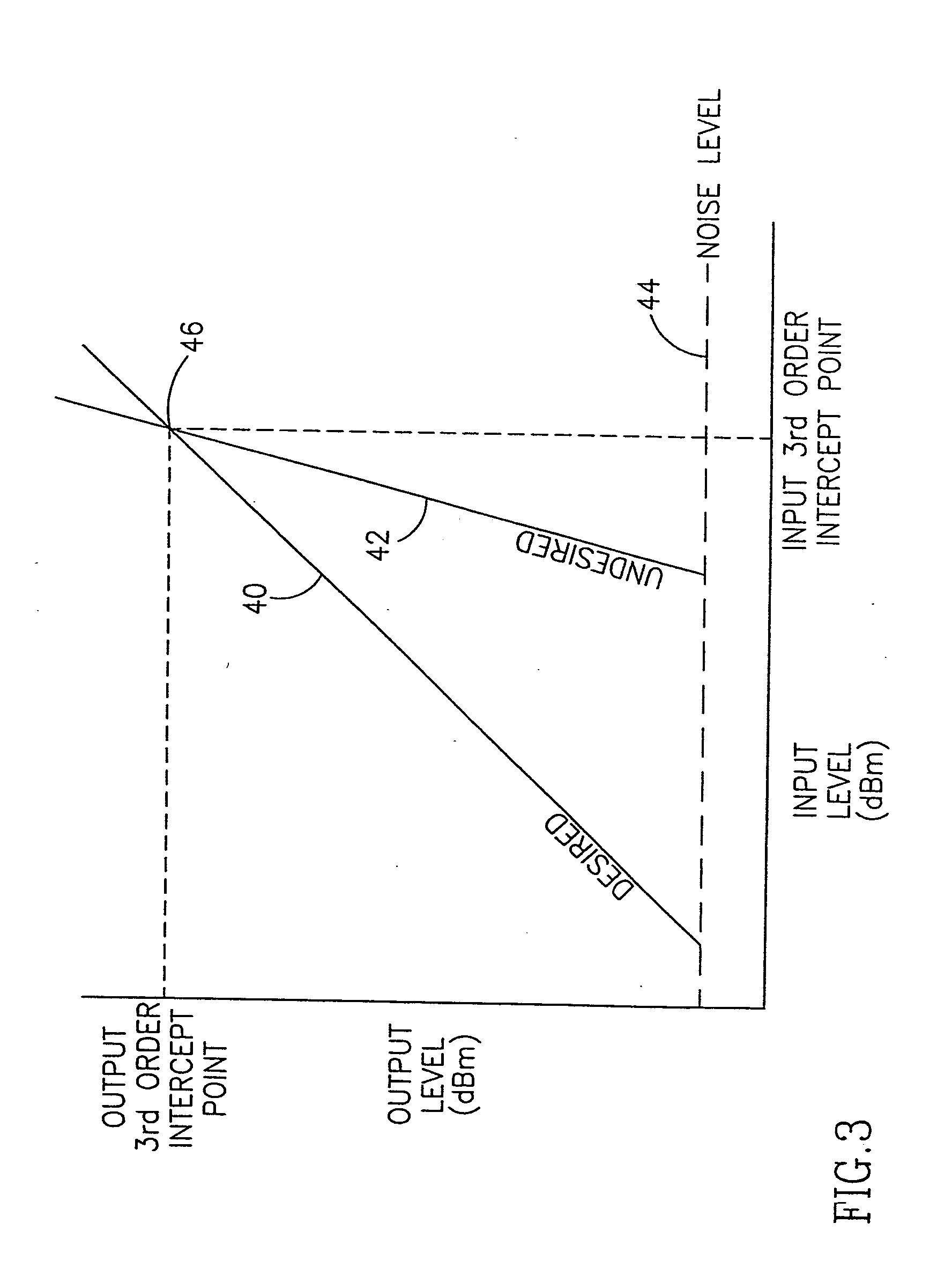

Apparatus for and method of optimizing the performance of a radio frequency receiver in the presence of interference

InactiveUS20060040630A1Improve linearityIncrease flexibilityGain controlAmplifier combinationsFrequency mixerMode control

An apparatus for and method of extending the dynamic range of a RF communications receiver. The invention provides a mechanism for controlling the gain of both the LNA and down conversion mixer in the front end portion of an RF receiver. Both the LNA and the mixer are adapted to have both low and high gain modes of operation. The control mechanism typically comprises a two bit gain control that places both the LNA and mixer in one of four operating gain mode states. The selection of the most appropriate operating gain mode state, is preferably determined in accordance with various metrics such as the received levels of the desired signal, levels of interference signals, bit error rate and receiver RSSI.

Owner:TEXAS INSTR INC

Gfsk receiver architecture and methodology

ActiveUS20120027132A1Simple and cost-effective approachImprove throughputError preventionLine-faulsts/interference reductionDigital filterFrequency modulation

A Gaussian Frequency Shift Key (GFSK) receiver includes a receiver front end to receive a GFSK-modulated signal and convert the received GFSK-modulated signal to a baseband frequency modulated signal, a channel filter to reduce channel interference which is adjacent to a desired channel of the baseband frequency modulated signal, a demodulator to demodulate the channel filtered baseband modulated signal and to recover a sequence of symbols, a digital filter to reduce inter-symbol interference (ISI) from the sequence of symbols, a slicer to produce symbol decisions based on the filtered sequence of symbols, and a symbol-to-bit mapper to map the symbol decisions to data bits.

Owner:SENSUS USA

Integrated load impedance sensing for tunable matching networks

ActiveUS7586384B2Limitations and drawbacks associated with prior art are eliminated or reducedReduce complexityMultiple-port networksTransmissionImpedance matchingCommunication device

Owner:NOKIA TECH OY

Integrated multimode radio and components thereof

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

System and method of communicating signals

InactiveUS7573398B2Reduce the sampling frequencyElectric signal transmission systemsPolarisation/directional diversityCommunications systemIntermediate frequency

A communication system is presented. The system includes one or more transmitters configured to transmit a signal, where each of the signals generated by the one or more transmitters corresponds to a respective frequency. Further, the system includes a plurality of receiver front-ends configured to receive the signal transmitted by each of the one or more transmitters. The system also includes a plurality of remodulator modules configured to translate each of the received signals to a signal having a respective intermediate frequency. In addition, the system includes a combining module configured to combine each of the signals having respective intermediate frequencies to generate a single composite signal. Also, the system includes a single analog-to-digital converter configured to process the composite signal and generate a digital output. Additionally, the system includes a digital signal processor module configured to extract the signal transmitted by each of the one or more transmitters.

Owner:GENERAL ELECTRIC CO

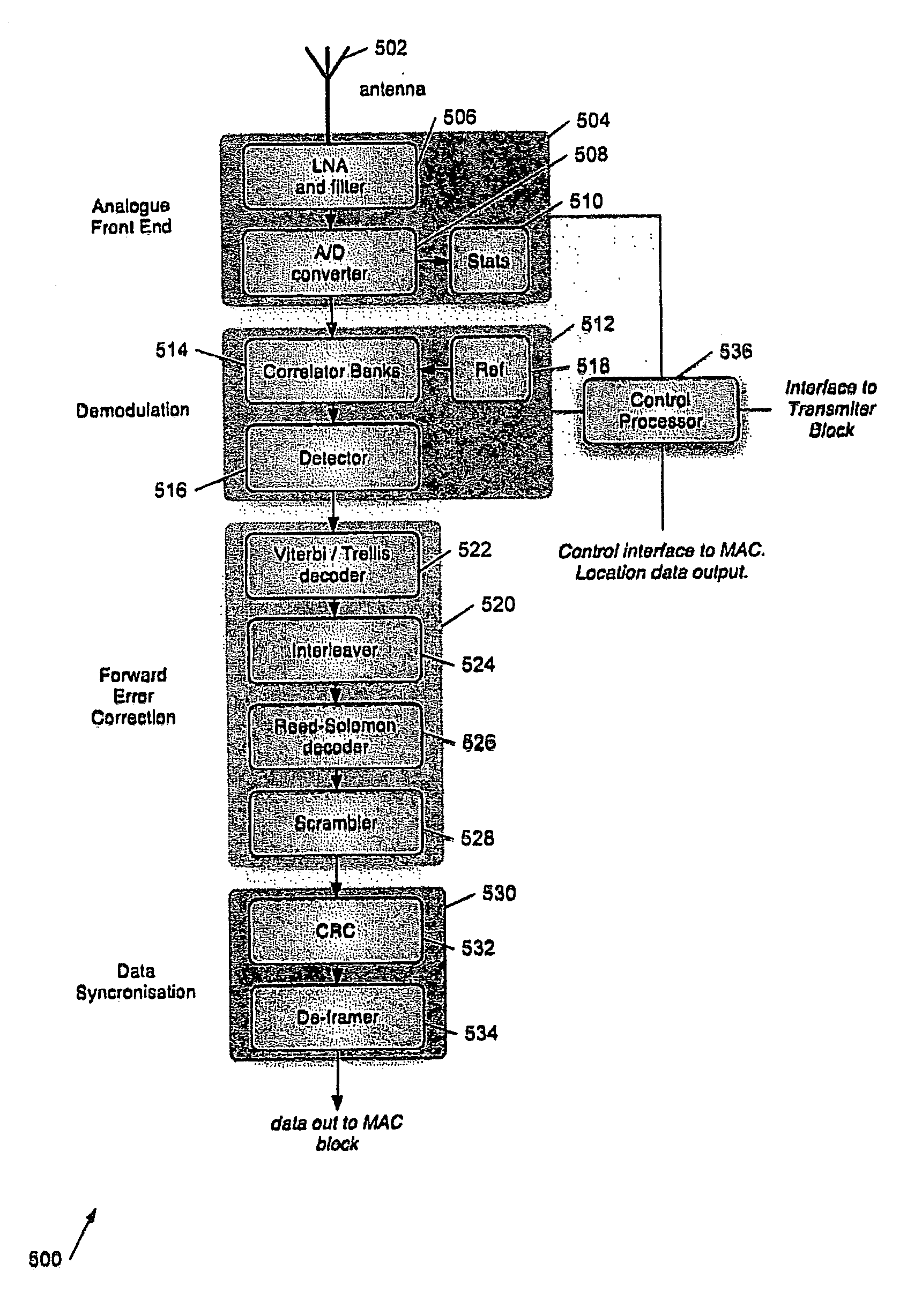

Communications systems and methods

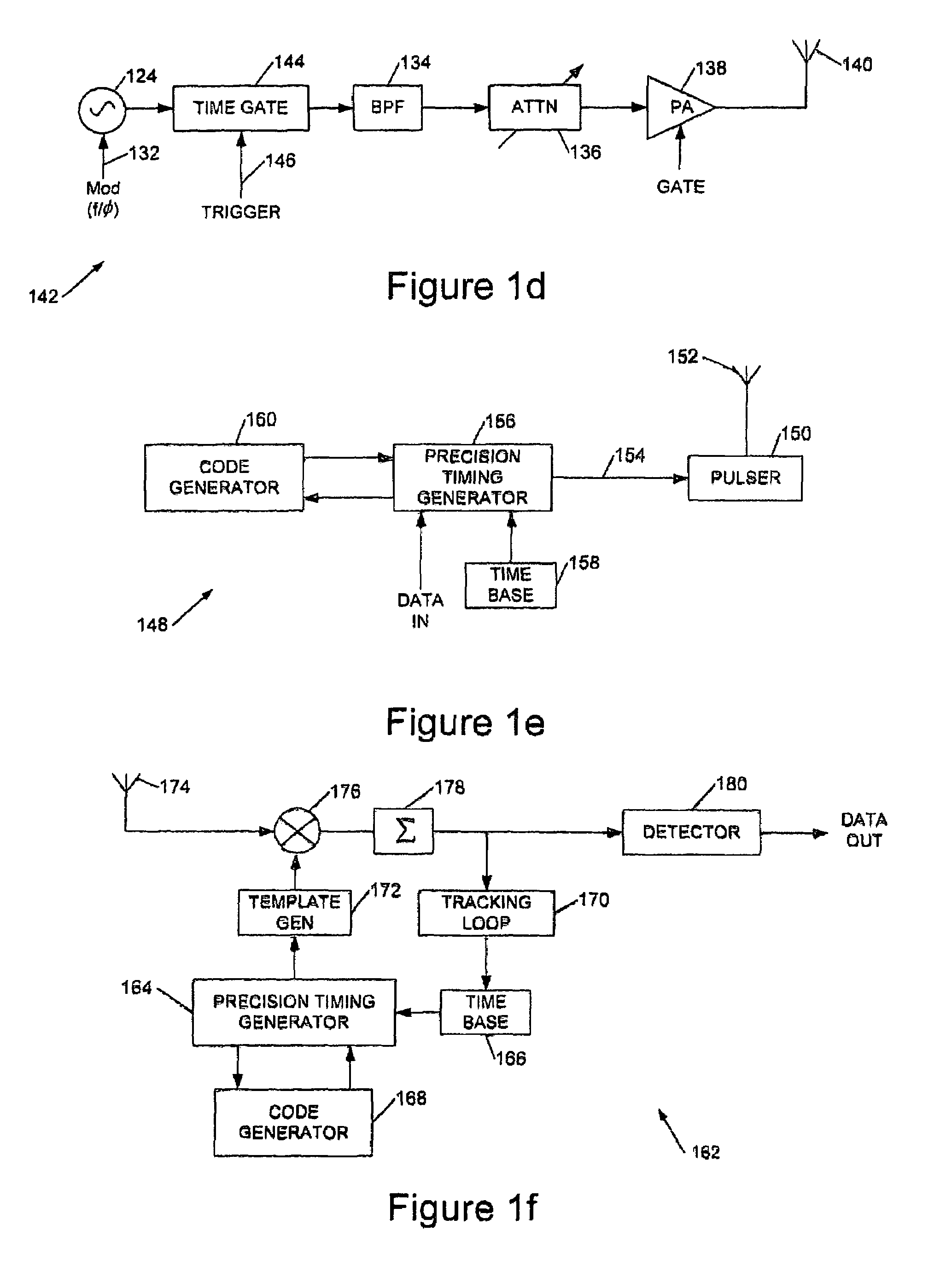

ActiveUS20050111524A1Simple demodulationCorrelated delayFrequency/rate-modulated pulse demodulationAmplitude-modulated carrier systemsUltra-widebandCommunications system

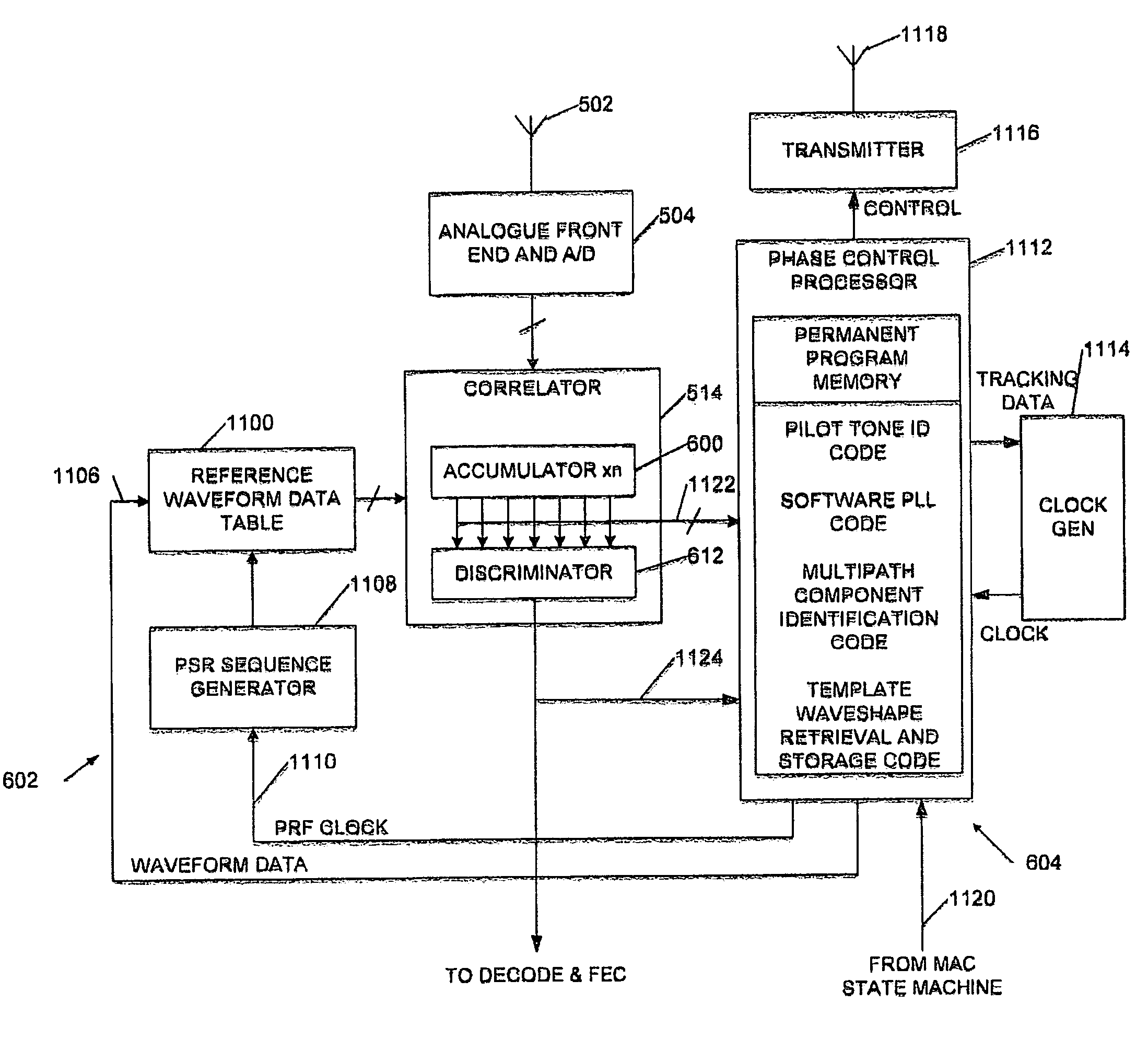

This invention generally relates to wired and wireless ultra wideband (UWB) data communications apparatus and methods, and in particular to UWB receiver systems and architectures, and to correlators therefore. An ultra wideband (UWB) receiver system comprising: a receiver front end to receive a UWB signal having a plurality of multipath components; and a correlator coupled to said receiver front end to correlate said UWB signal with a reference signal; and wherein said UWB signal comprises a plurality of pulses; wherein each said pulse has a plurality of multipath components; wherein said reference signal comprises a plurality of multipath components of a said pulse; and wherein said correlator comprises at least one correlator module configured to correlate a plurality of said multipath components of a said pulse with said reference signal.

Owner:TAHOE RES LTD +1

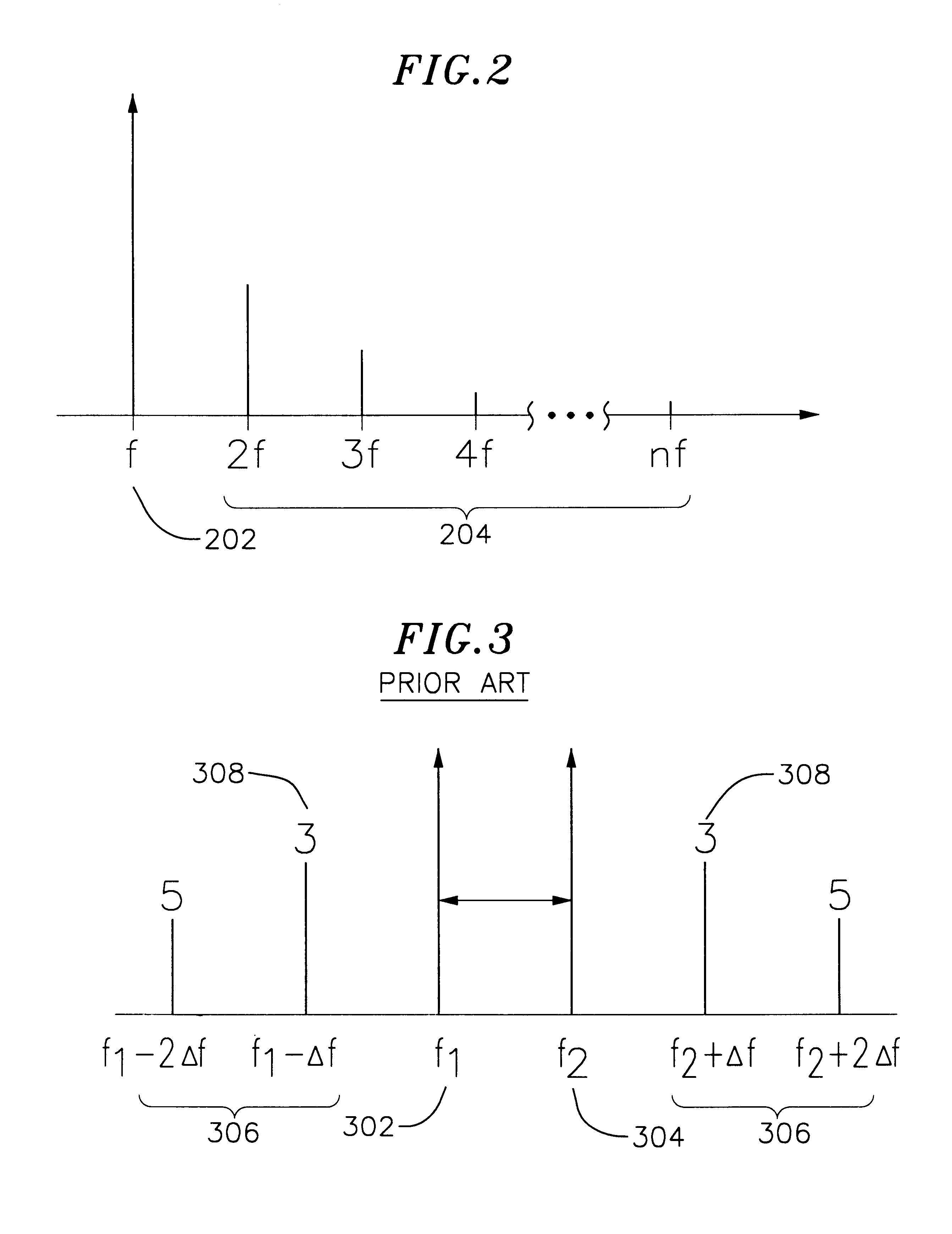

System and method for radar calibration using antenna leakage

InactiveUS20060227040A1Simple meansRadio wave reradiation/reflectionFrequency spectrumAlternative methods

The system and method for radar calibration using antenna leakage is a simplified means of calibrating the channels in amplitude and phase using natural signal leakage between antennas. It utilizes as calibration signal a wideband sinusoidal Frequency Modulated Continuous Wave (FMCW) waveform with a modulation index and modulation frequency chosen to generate spectral components (or discrete signal frequencies) that fall within the receiver Doppler passband of the radar. The calibration signal is radiated out of the transmitting antenna and enters the radar receiver front-end through the transmit-to-receive antenna leakage which occurs naturally. This technique provides a low-complexity (simpler hardware realization) means for achieving a wideband calibration rapidly and is a practical alternative to the conventional calibration approach that relies on generating offset Doppler signals that are coupled into the radar receiver front-end through the use of couplers and cabling within the radar.

Owner:UNITED STATES OF AMERICA THE AS REPRESENTED BY THE SEC OF THE ARMY

Communications systems and methods

InactiveUS20050031021A1Increase the number ofReduce spectral spikeFrequency/rate-modulated pulse demodulationAmplitude-modulated carrier systemsUltra-widebandCommunications system

This invention generally relates to wired and wireless ultra wideband (UWB) data communications apparatus and methods, and in particular to UWB receiver systems and architectures, and to UWB transmission systems and signals. A UWB receiver system for receiving a UWB signal comprising a plurality of pulses, the system comprising: a receiver front end to receive a UWB signal; a reference UWB signal store for storing a reference UWB signal; and a correlator configured to correlate said received UWB signal with a plurality of differently delayed versions of said stored reference signal to co-determine a timing and a phase of a received UWB signal pulse; whereby a UWB signal carrying data encoded by both pulse position and pulse phase is decodeable.

Owner:ARTIMI

Communications systems and methods

ActiveUS7457350B2Simple demodulationFrequency/rate-modulated pulse demodulationAmplitude-modulated carrier systemsUltra-widebandCommunications system

Described herein are ultra wideband (UWB) receiver systems, and applications thereof. Such a UWB receiver includes a receiver front end and a correlator coupled to the receiver front end. The receiver front end is configured to receive a UWB signal having a plurality of multipath components. The correlator is configured to correlate the UWB signal with a reference signal. The UWB signal includes a plurality of pulses, wherein each pulse has a plurality of multipath components. The reference signal also includes a plurality of multipath components of the pulse. The correlator includes at least one correlator module configured to correlate a plurality of the multipath components of the pulse with the reference signal.

Owner:TAHOE RES LTD +1

System and method for linearizing a CMOS differential pair

InactiveUS20050258901A1Resonant circuit detailsSemiconductor/solid-state device detailsShunt DeviceFilter tuning

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit. A receiver front end provides programable attenuation and a programable gain low noise amplifier. LC filters integrated onto the substrate in conjunction with image reject mixers provide image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. Active filters utilize multi track spiral inductors with shields to increase circuit Q. The filters incorporate a gain stage that provides improved dynamic range through the use of cross coupled auxiliary differential pair CMOS amplifiers to cancel distortion in a main linearized differential pair amplifier. Frequency planning provides additional image rejection. Local oscillator signal generation methods on chip reduce distortion. A PLL generates needed out of band LO signals. Direct synthesis generates in band LO signals. PLL VCOs are centered automatically. A differential crystal oscillator provides a frequency reference. Differential signal transmission throughout the receiver is used. ESD protection is provided by a pad ring and ESD clamping structure. Shunts utilize a gate boosting at each pin to discharge ESD build up. An IF VGA utilizes distortion cancellation achieved with cross coupled differential pair amplifiers having their Vds dynamically modified in conjunction with current steering of the differential pairs sources.

Owner:AVAGO TECH INT SALES PTE LTD

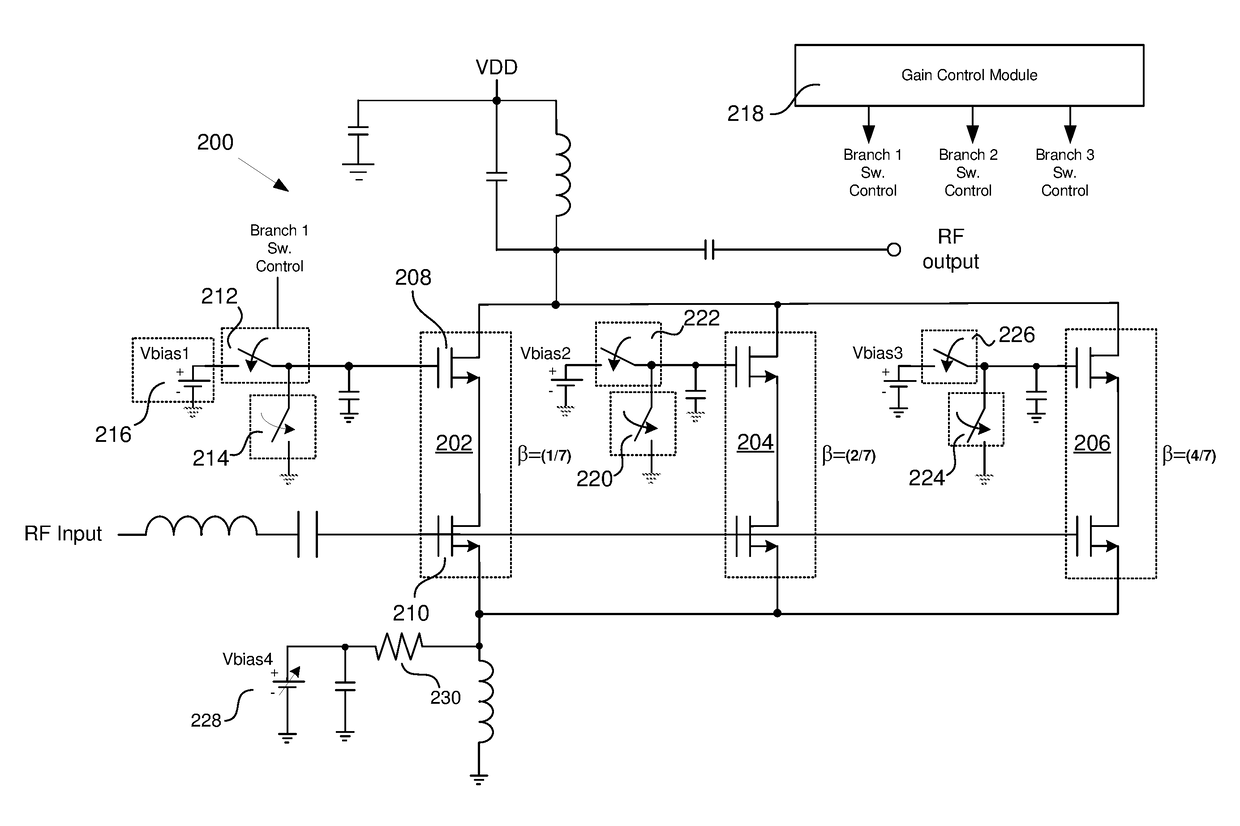

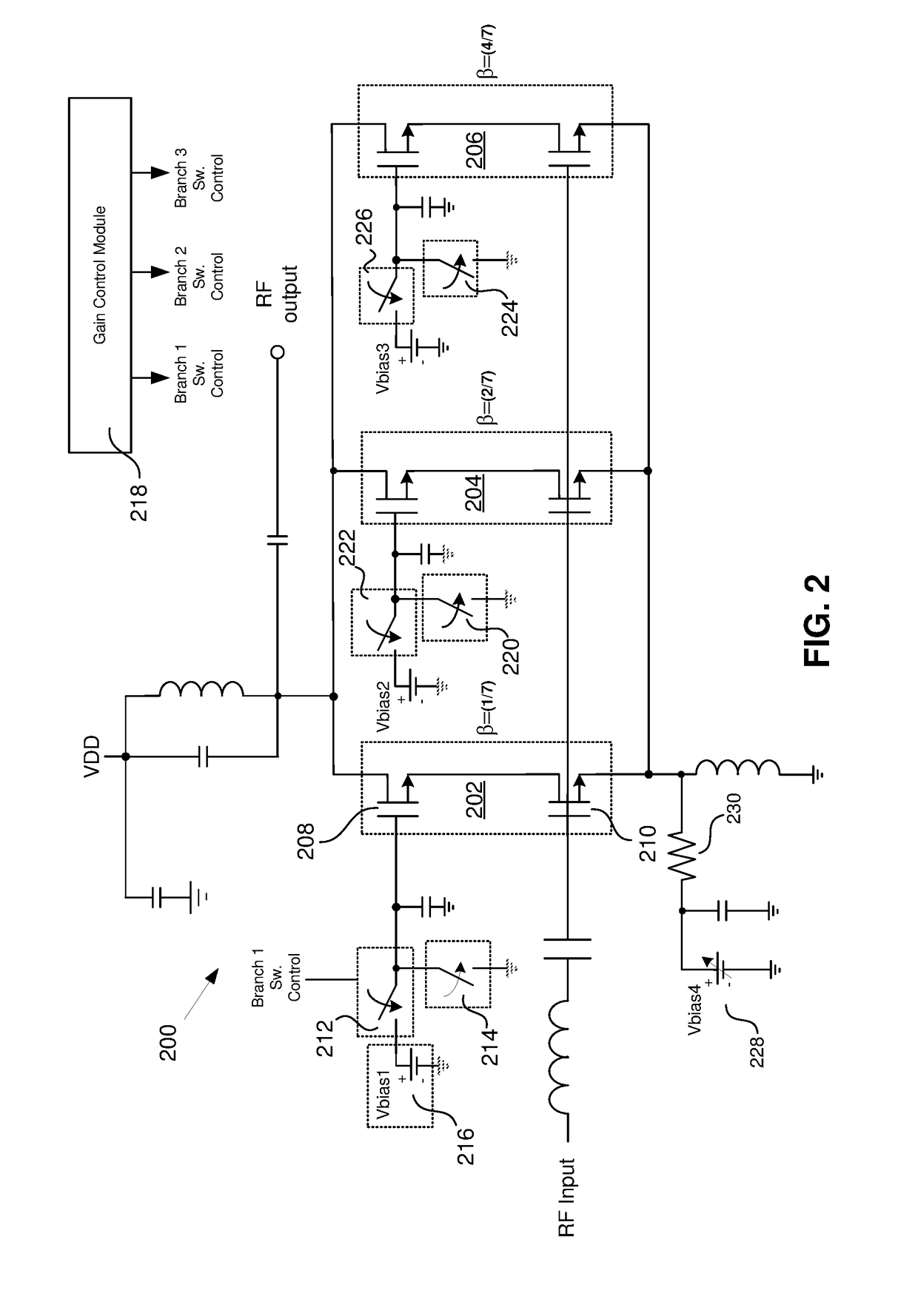

LNA with Programmable Linearity

A receiver front end capable of receiving and processing intraband non-contiguous carrier aggregate (CA) signals using multiple low noise amplifiers (LNAs) is disclosed herein. A cascode having a “common source” input stage and a “common gate” output stage can be turned on or off using the gate of the output stage. A first switch is provided that allows a connection to be either established or broken between the source terminal of the input stage of each cascode. Further switches used for switching degeneration inductors, gate / sources caps and gate to ground caps for each legs can be used to further improve the matching performance of the invention.

Owner:PSEMI CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com