Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

162 results about "Physics processing unit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

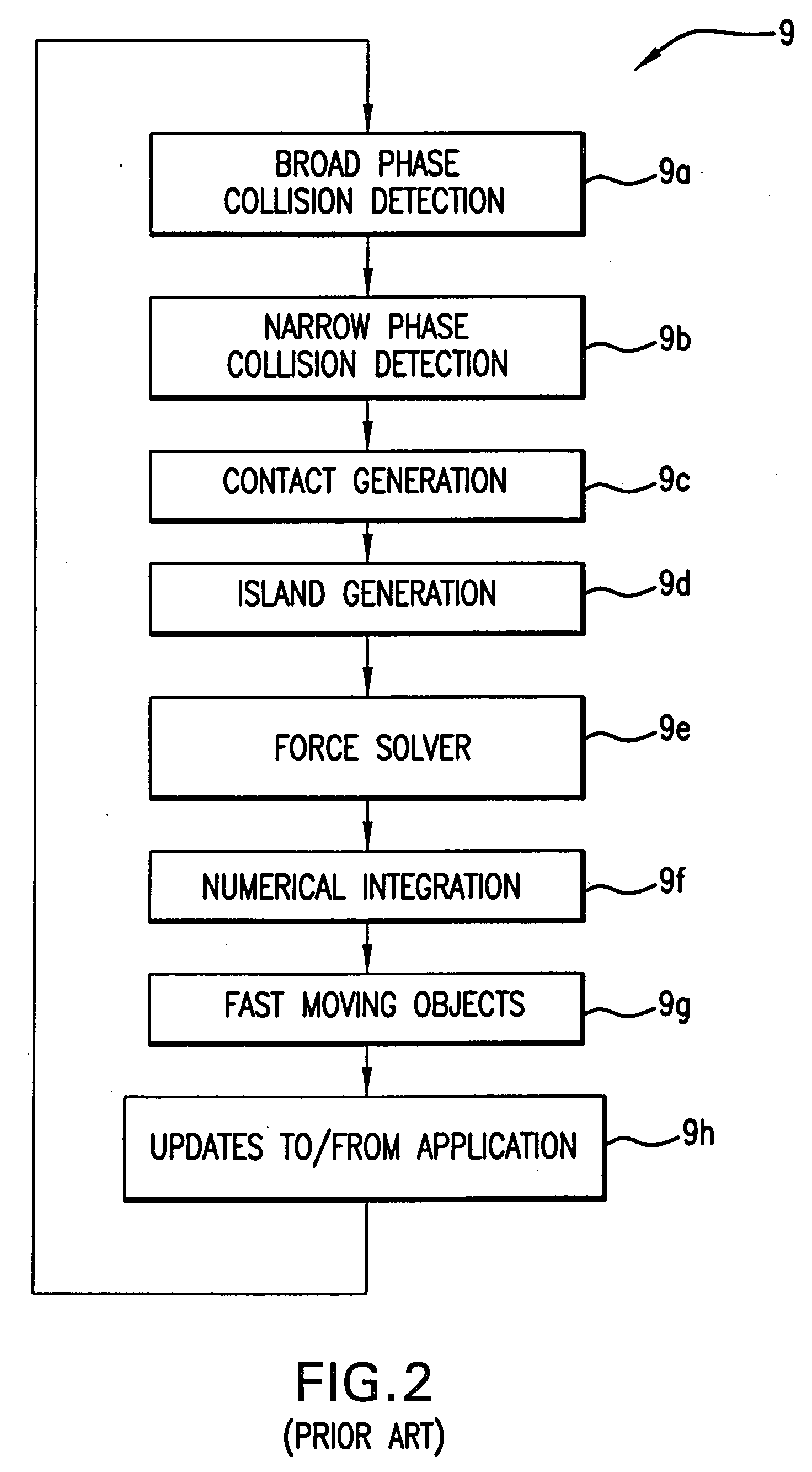

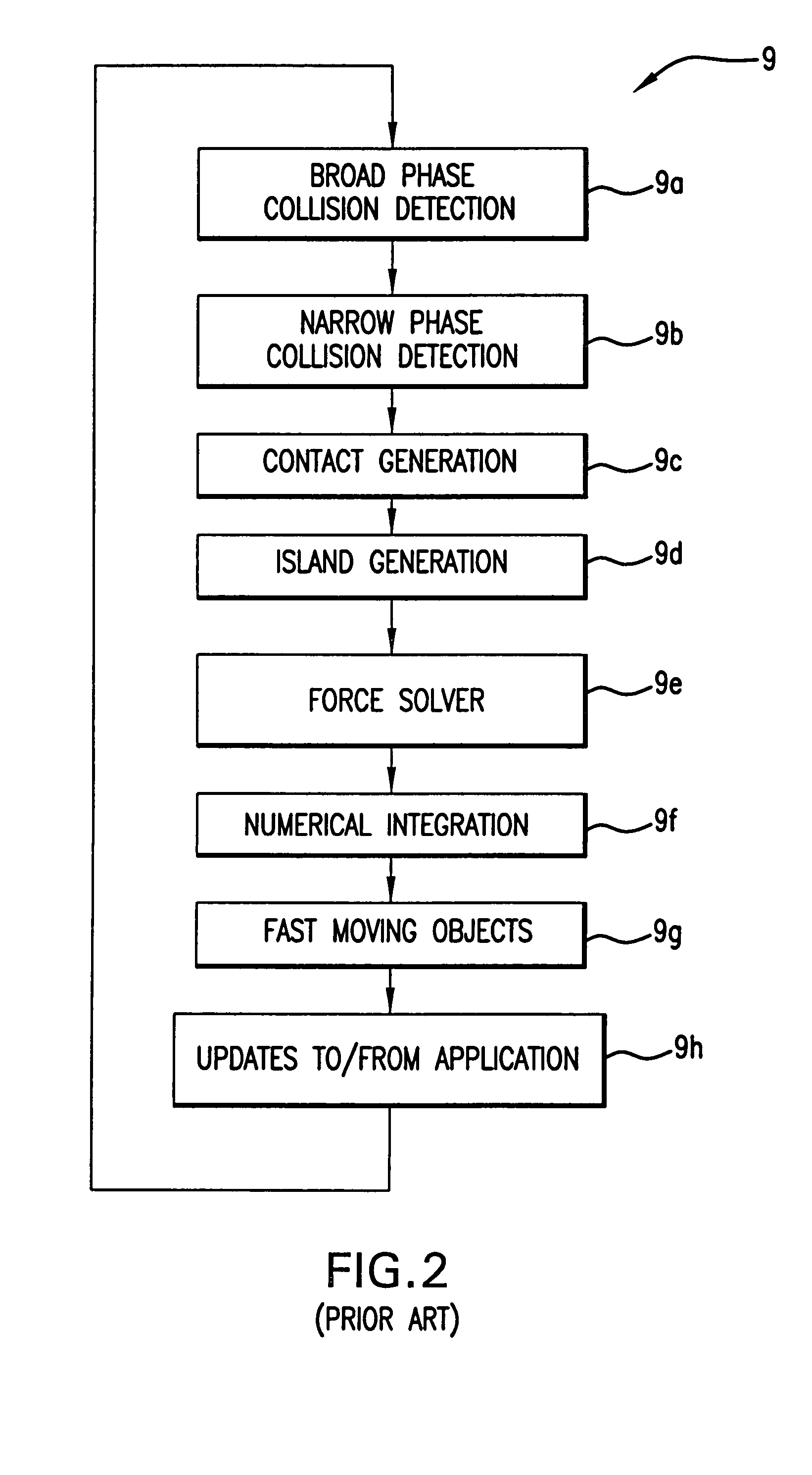

A physics processing unit (PPU) is a dedicated microprocessor designed to handle the calculations of physics, especially in the physics engine of video games. It is an example of hardware acceleration.

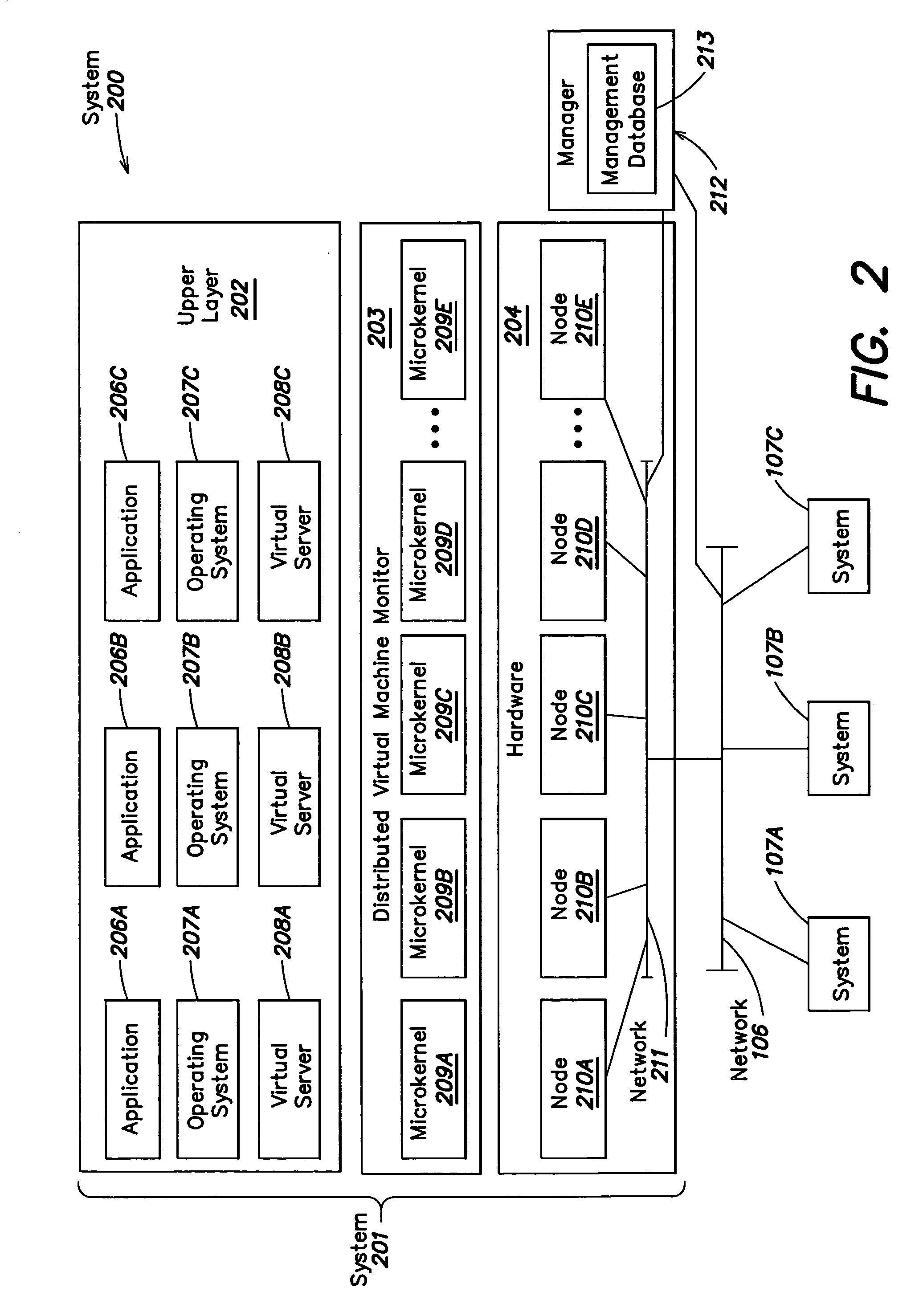

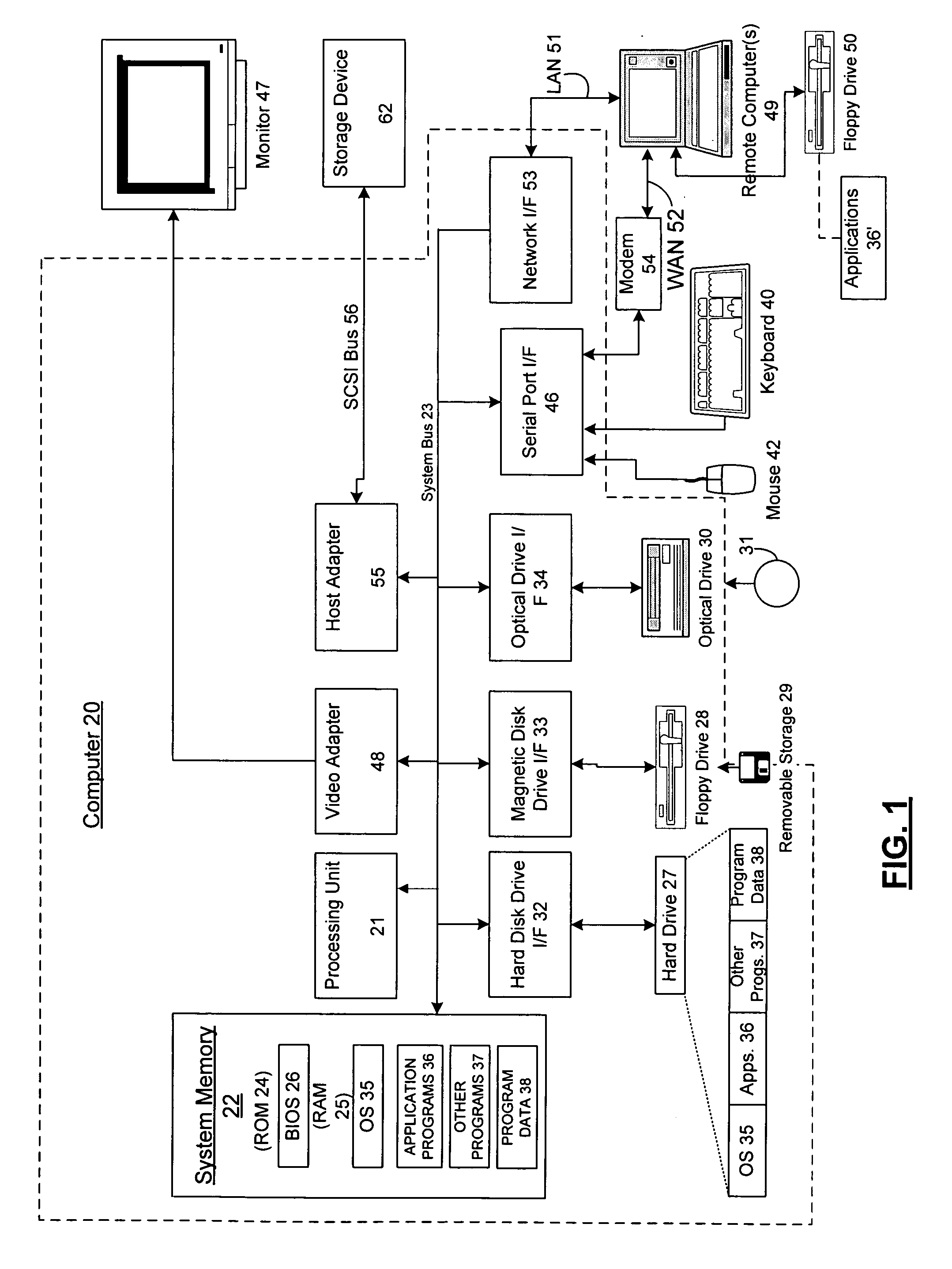

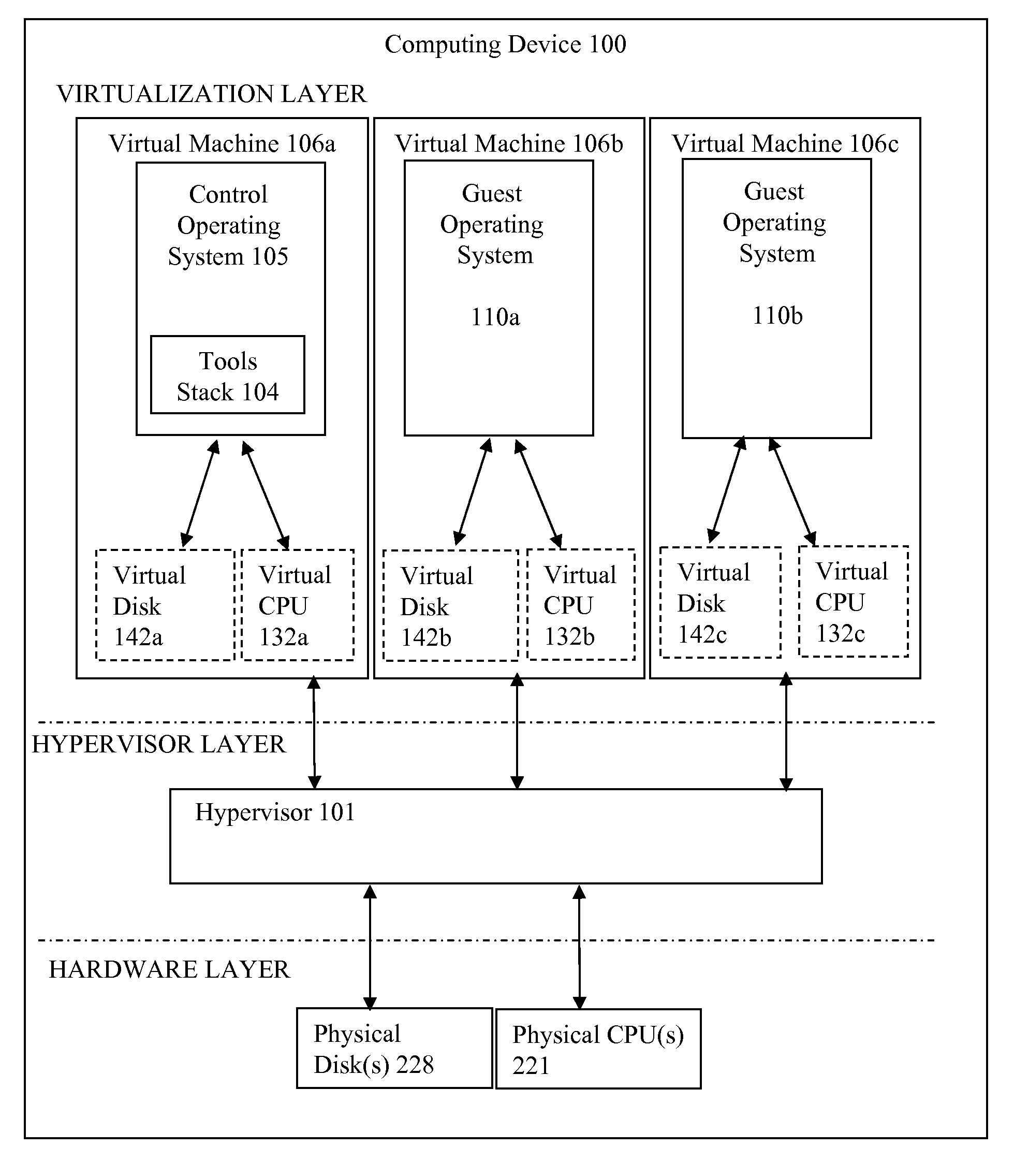

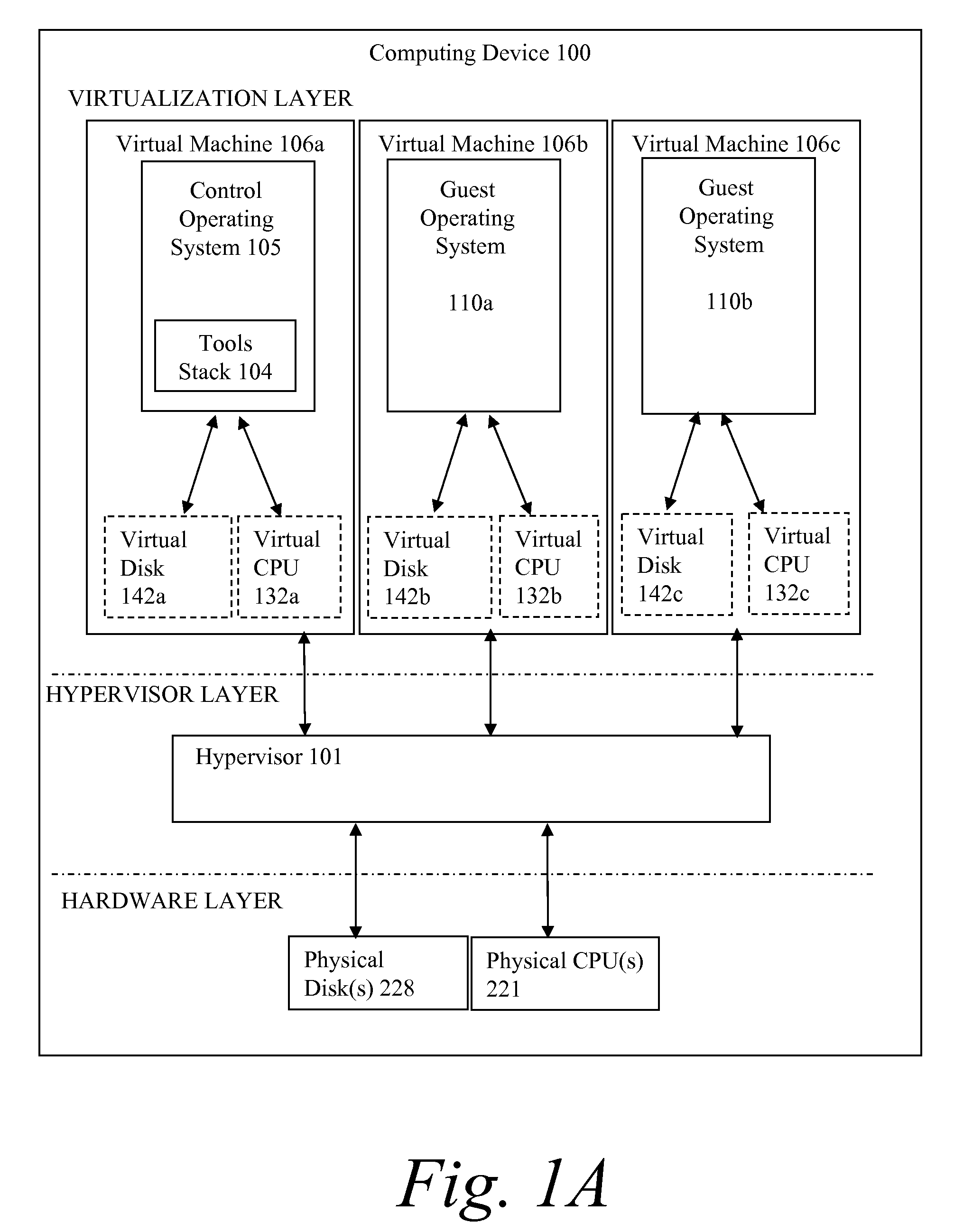

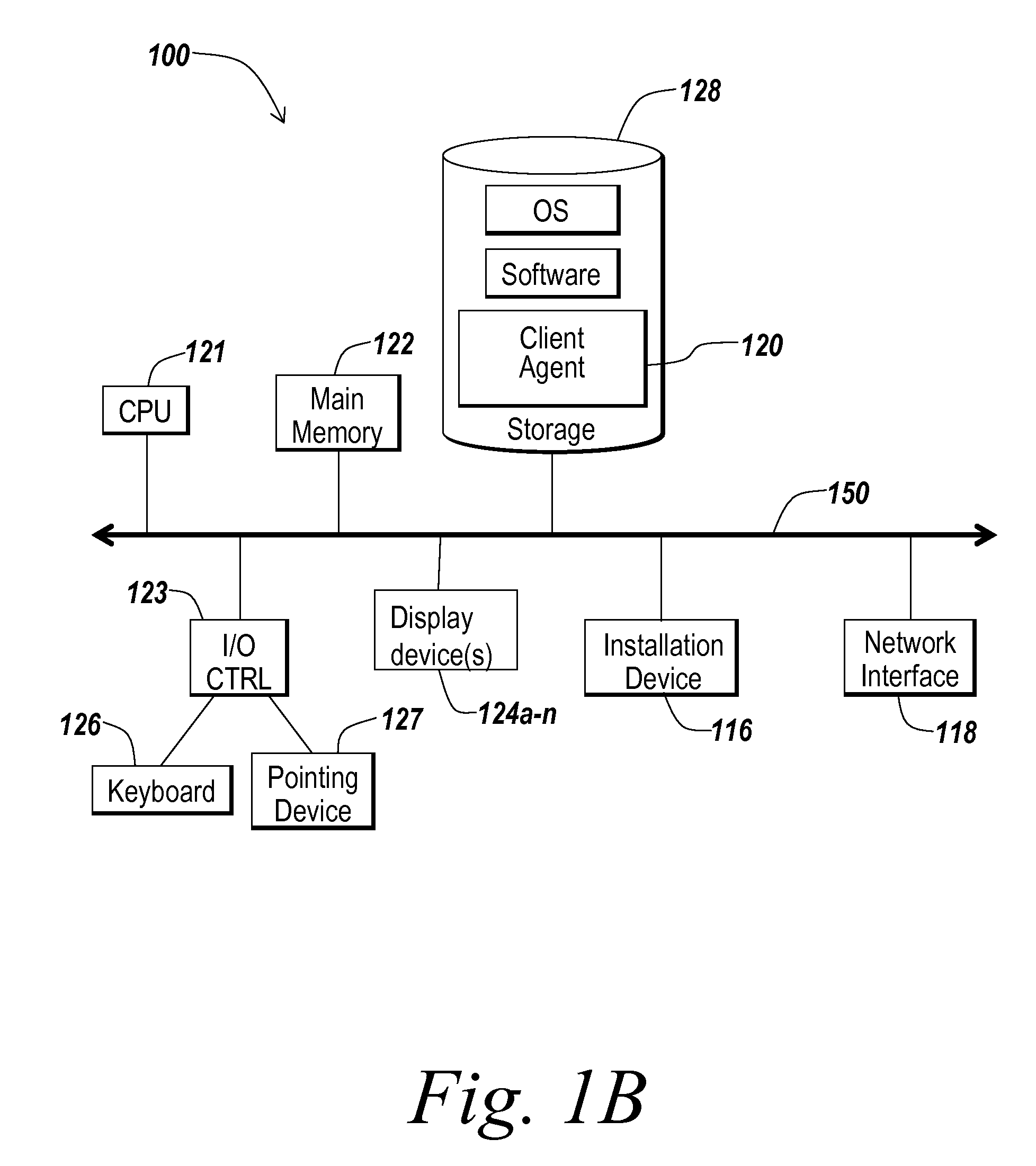

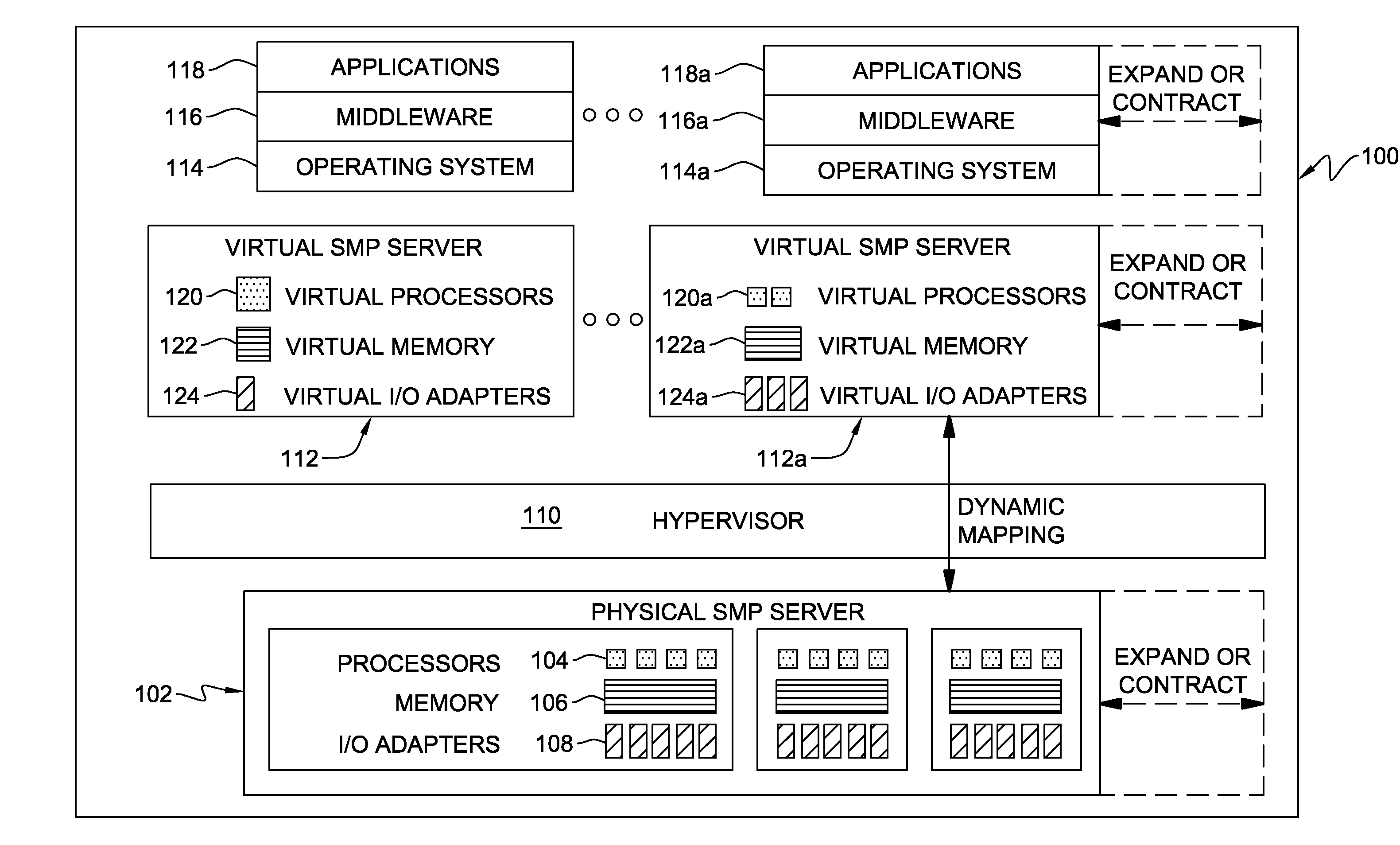

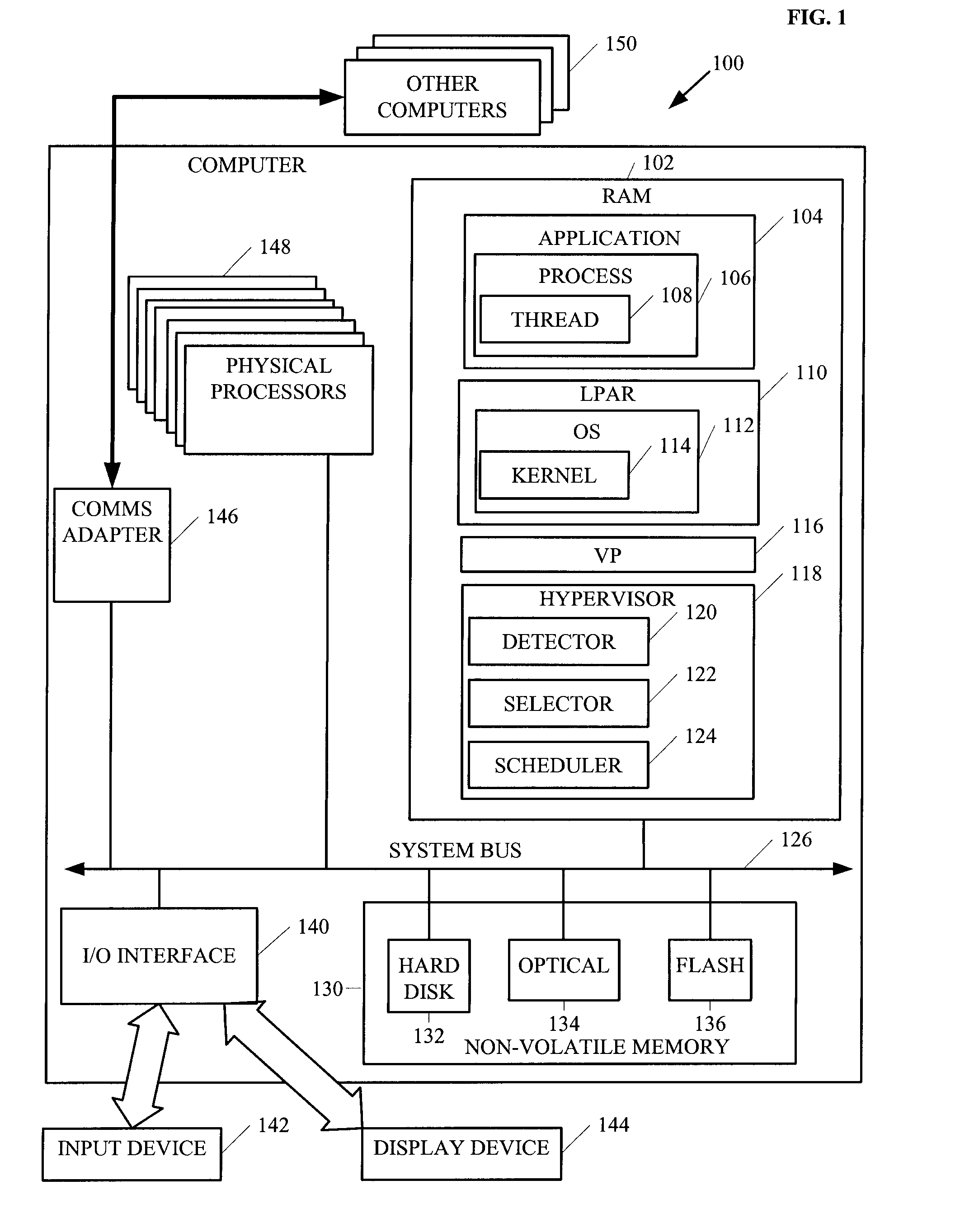

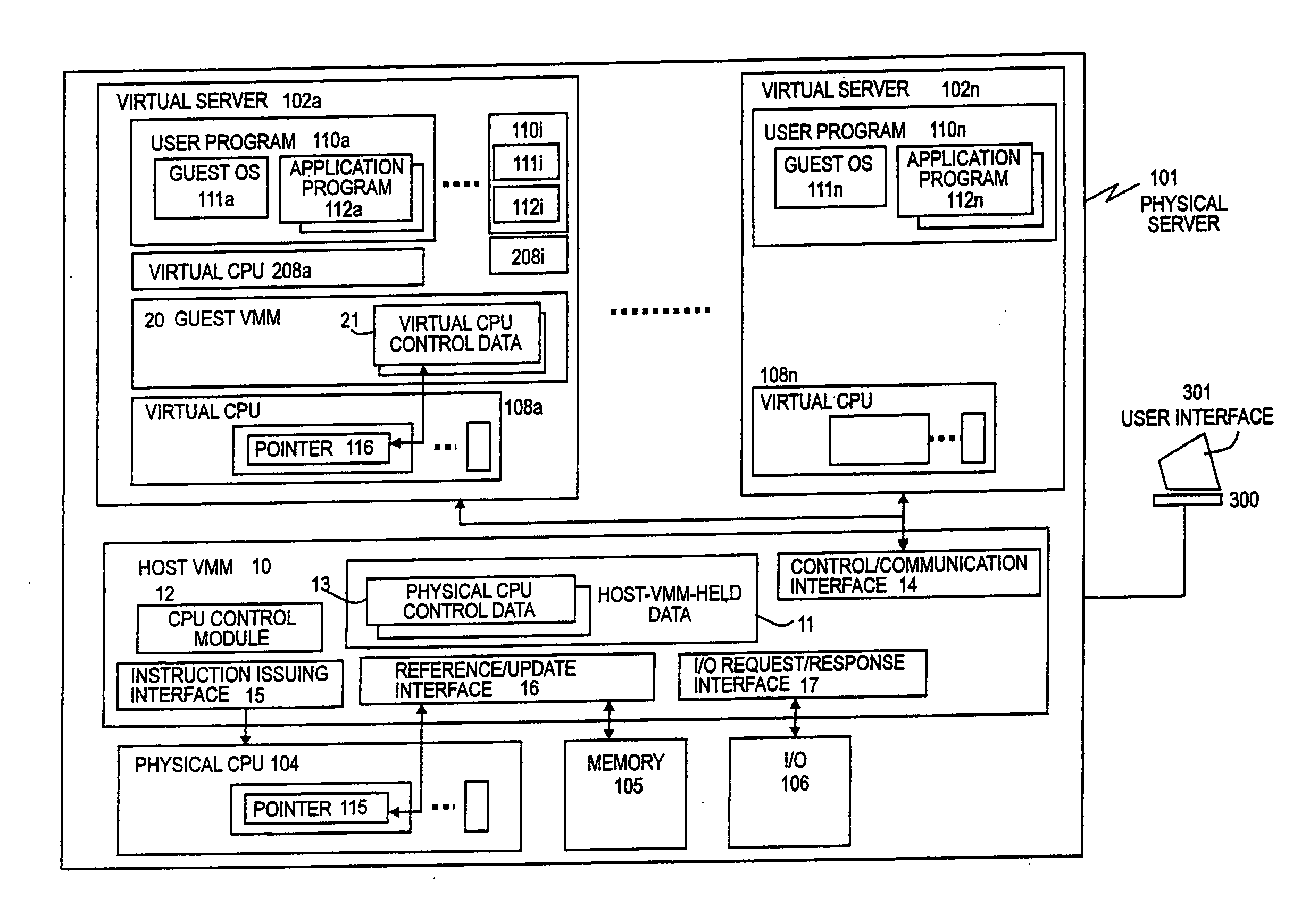

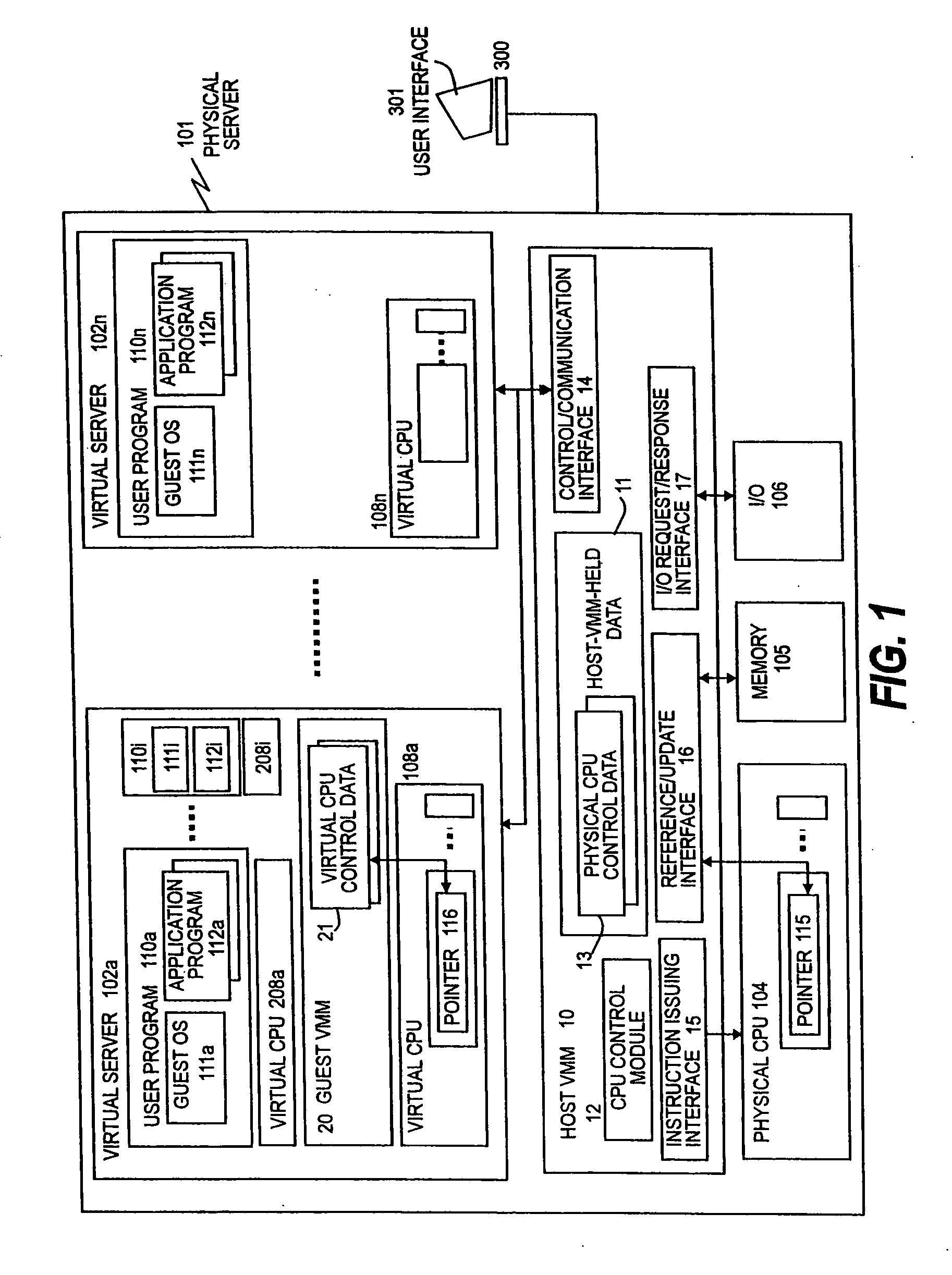

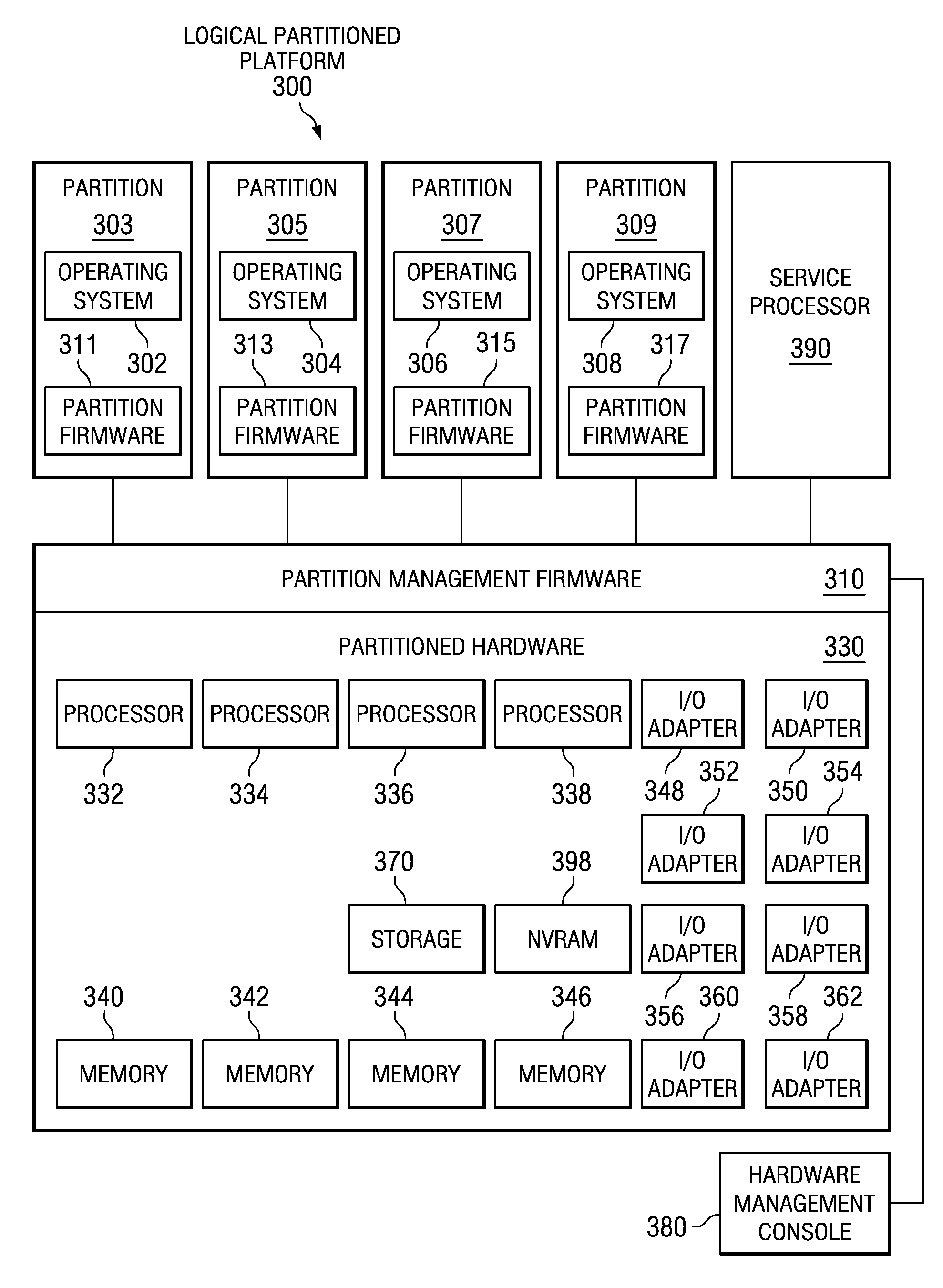

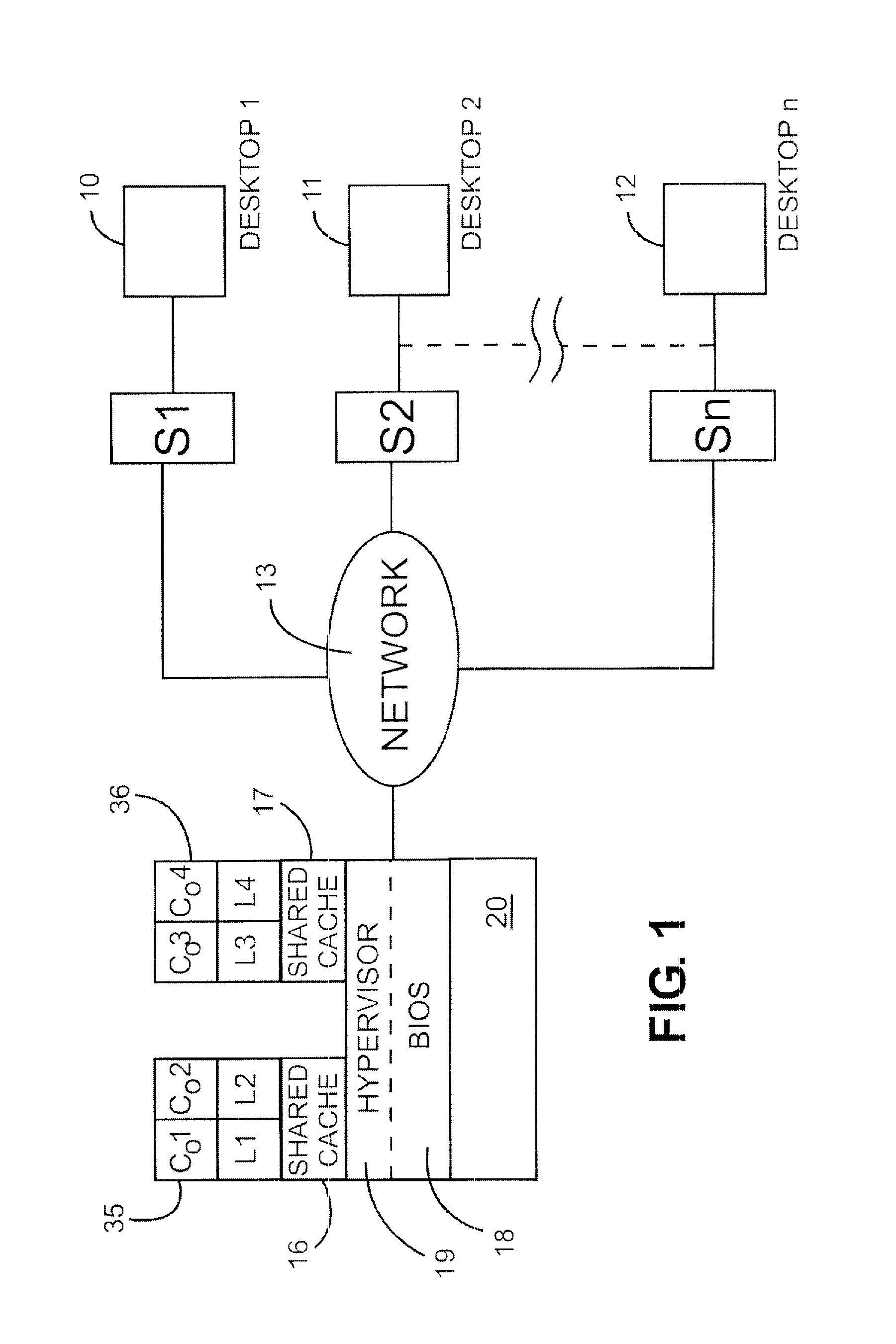

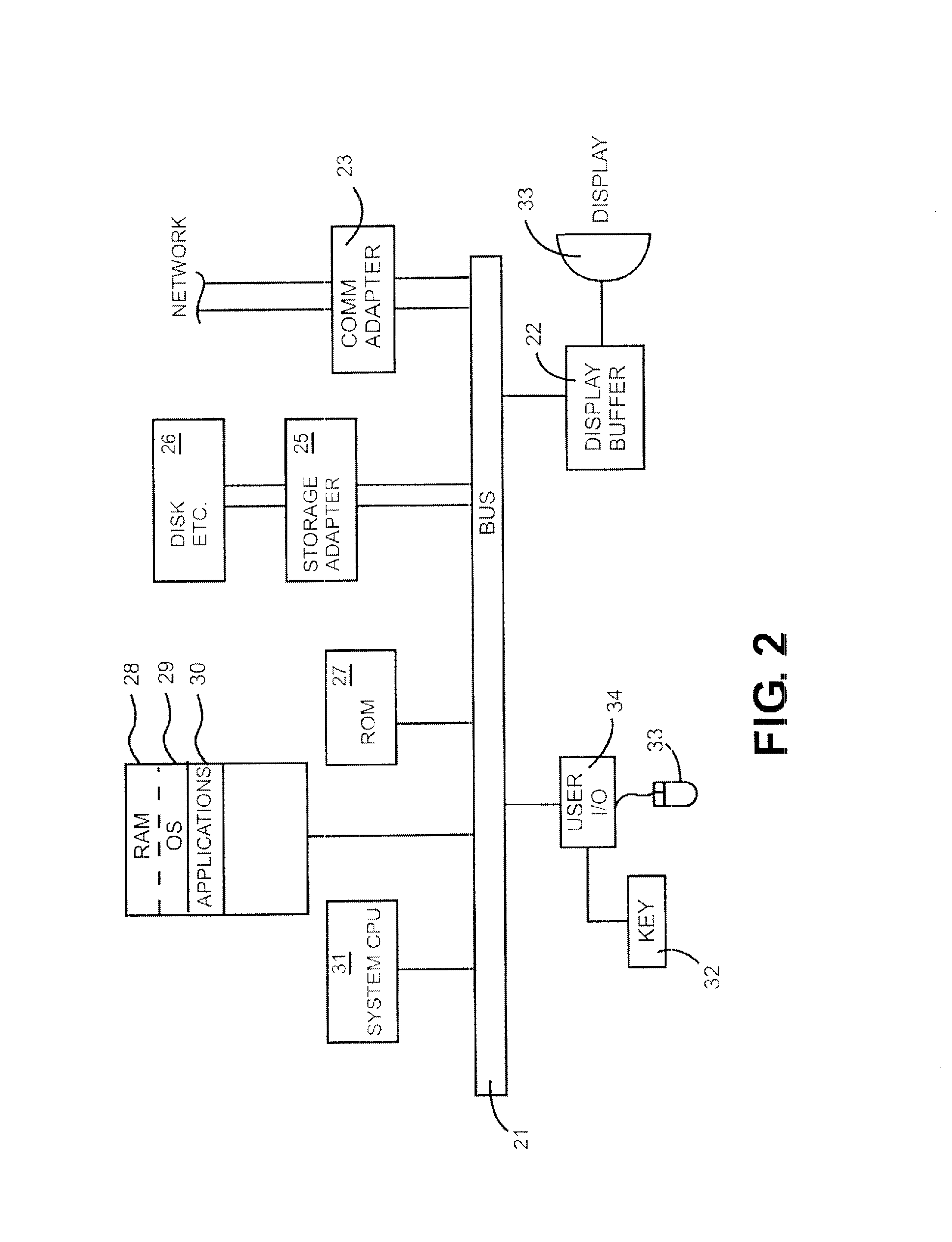

System and method for managing virtual servers

ActiveUS20050120160A1Grow and shrink capabilityMaximize useResource allocationMemory adressing/allocation/relocationOperational systemPrimitive state

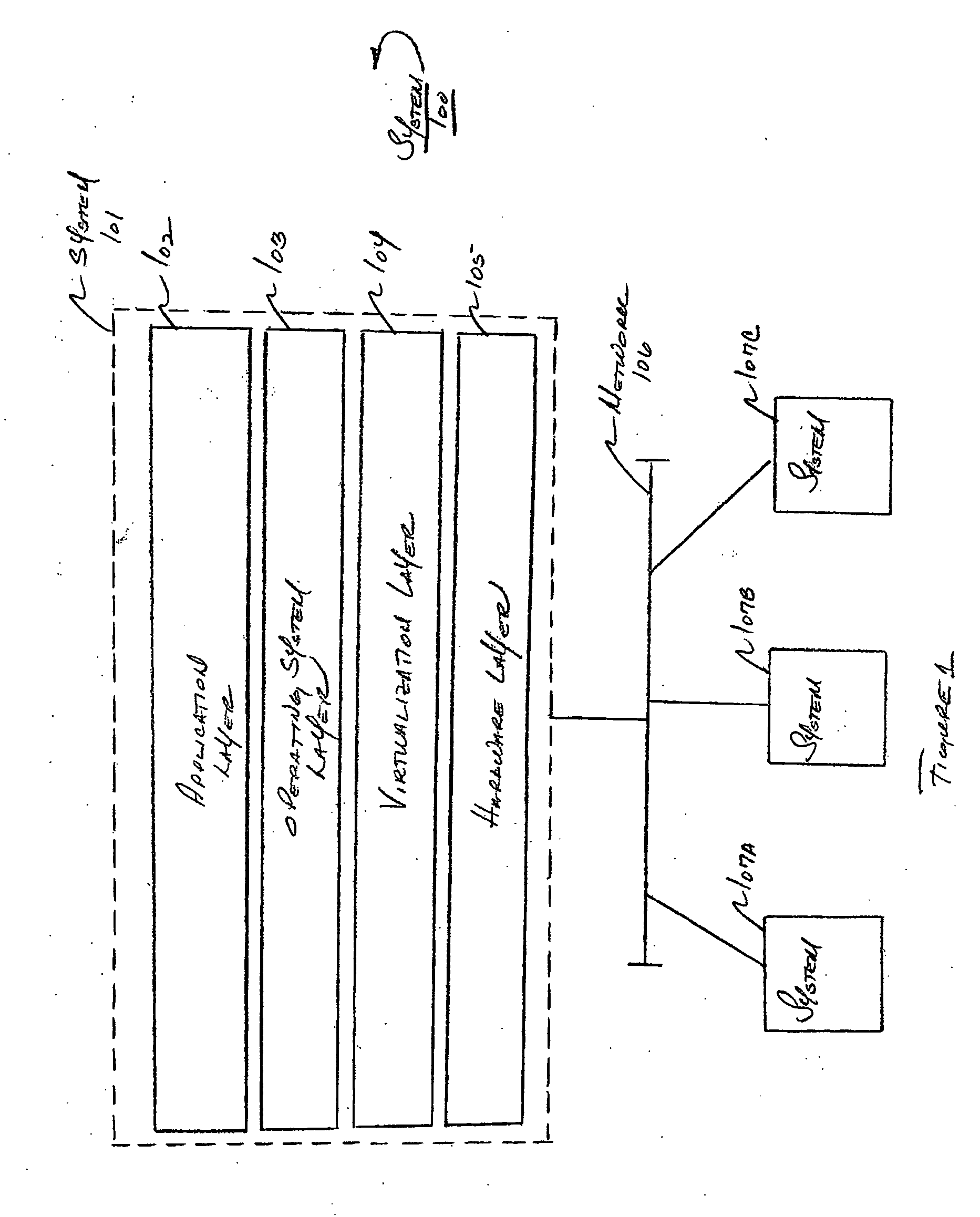

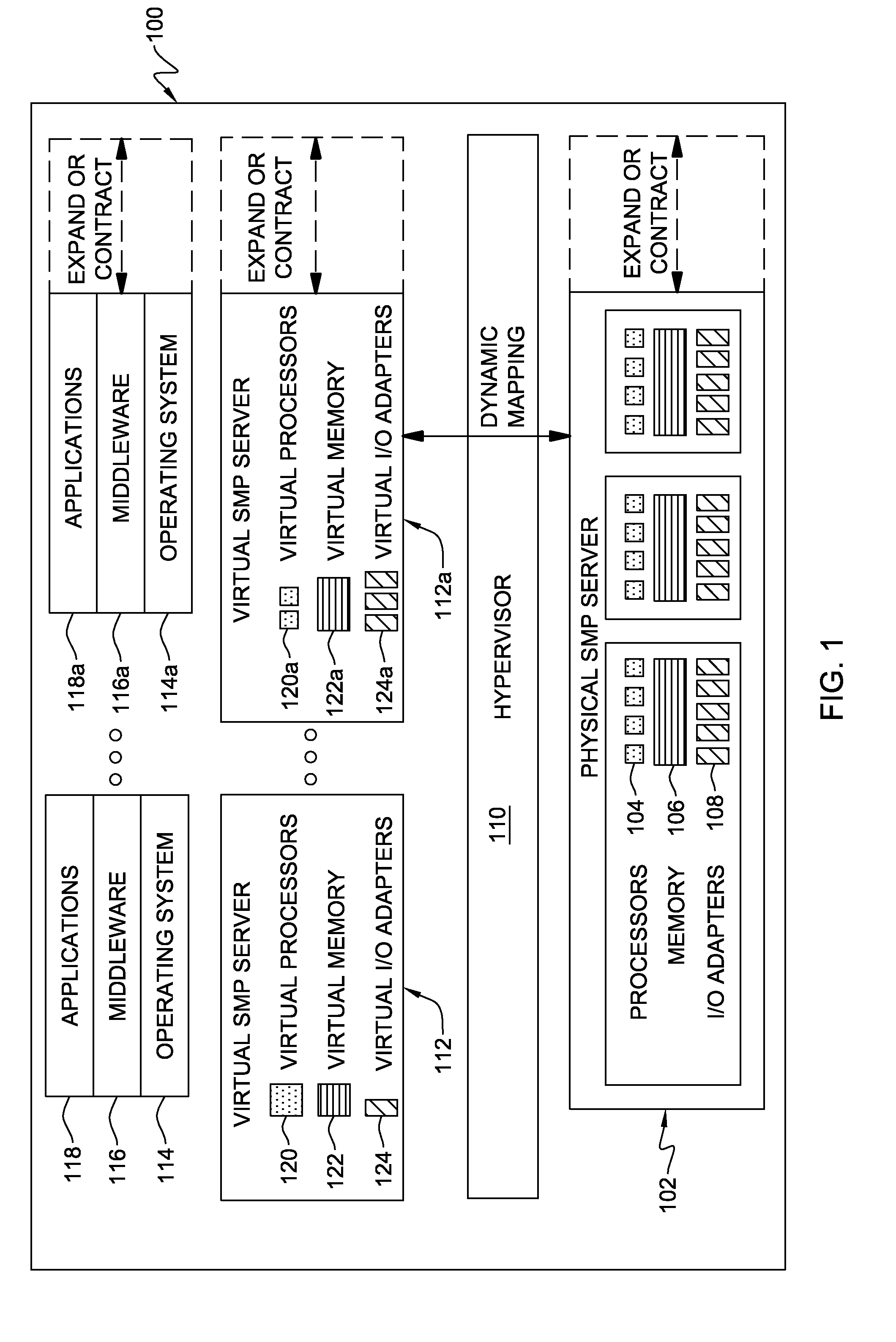

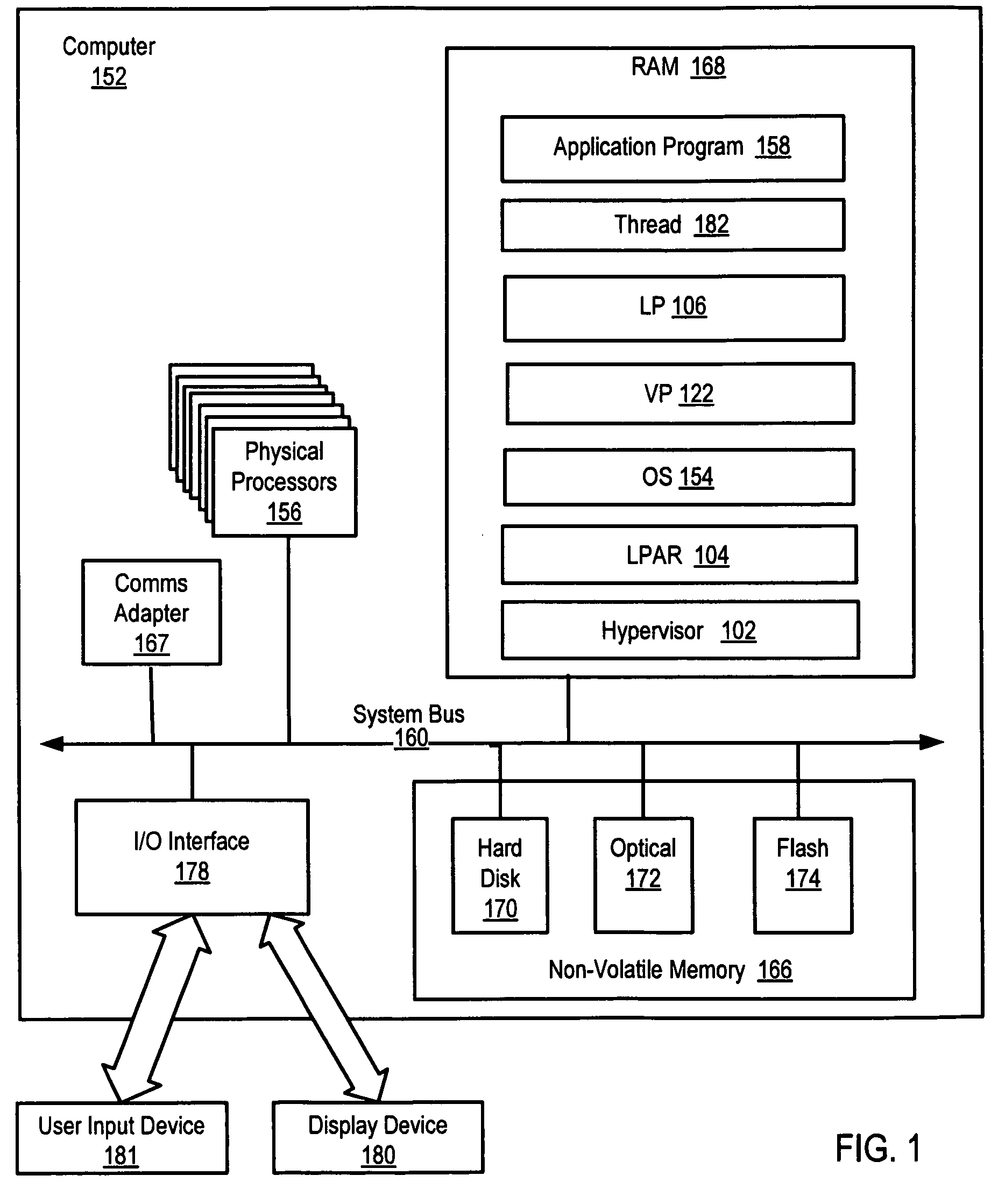

A management capability is provided for a virtual computing platform. In one example, this platform allows interconnected physical resources such as processors, memory, network interfaces and storage interfaces to be abstracted and mapped to virtual resources (e.g., virtual mainframes, virtual partitions). Virtual resources contained in a virtual partition can be assembled into virtual servers that execute a guest operating system (e.g., Linux). In one example, the abstraction is unique in that any resource is available to any virtual server regardless of the physical boundaries that separate the resources. For example, any number of physical processors or any amount of physical memory can be used by a virtual server even if these resources span different nodes. A virtual computing platform is provided that allows for the creation, deletion, modification, control (e.g., start, stop, suspend, resume) and status (i.e., events) of the virtual servers which execute on the virtual computing platform and the management capability provides controls for these functions. In a particular example, such a platform allows the number and type of virtual resources consumed by a virtual server to be scaled up or down when the virtual server is running. For instance, an administrator may scale a virtual server manually or may define one or more policies that automatically scale a virtual server. Further, using the management API, a virtual server can monitor itself and can scale itself up or down depending on its need for processing, memory and I / O resources. For example, a virtual server may monitor its CPU utilization and invoke controls through the management API to allocate a new processor for itself when its utilization exceeds a specific threshold. Conversely, a virtual server may scale down its processor count when its utilization falls. Policies can be used to execute one or more management controls. More specifically, a management capability is provided that allows policies to be defined using management object's properties, events and / or method results. A management policy may also incorporate external data (e.g., an external event) in its definition. A policy may be triggered, causing the management server or other computing entity to execute an action. An action may utilize one or more management controls. In addition, an action may access external capabilities such as sending notification e-mail or sending a text message to a telephone paging system. Further, management capability controls may be executed using a discrete transaction referred to as a “job.” A series of management controls may be assembled into a job using one or management interfaces. Errors that occur when a job is executed may cause the job to be rolled back, allowing affected virtual servers to return to their original state.

Owner:ORACLE INT CORP

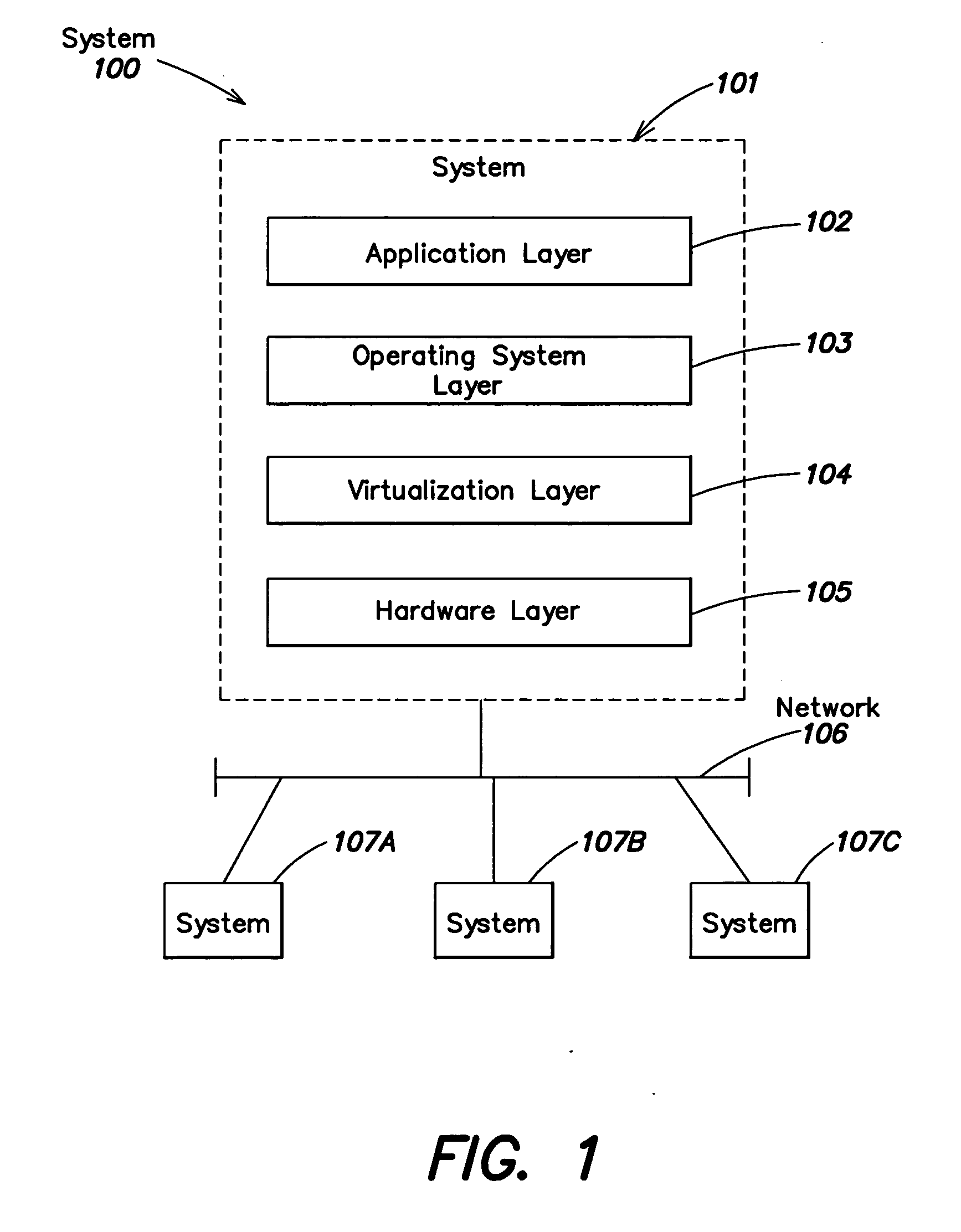

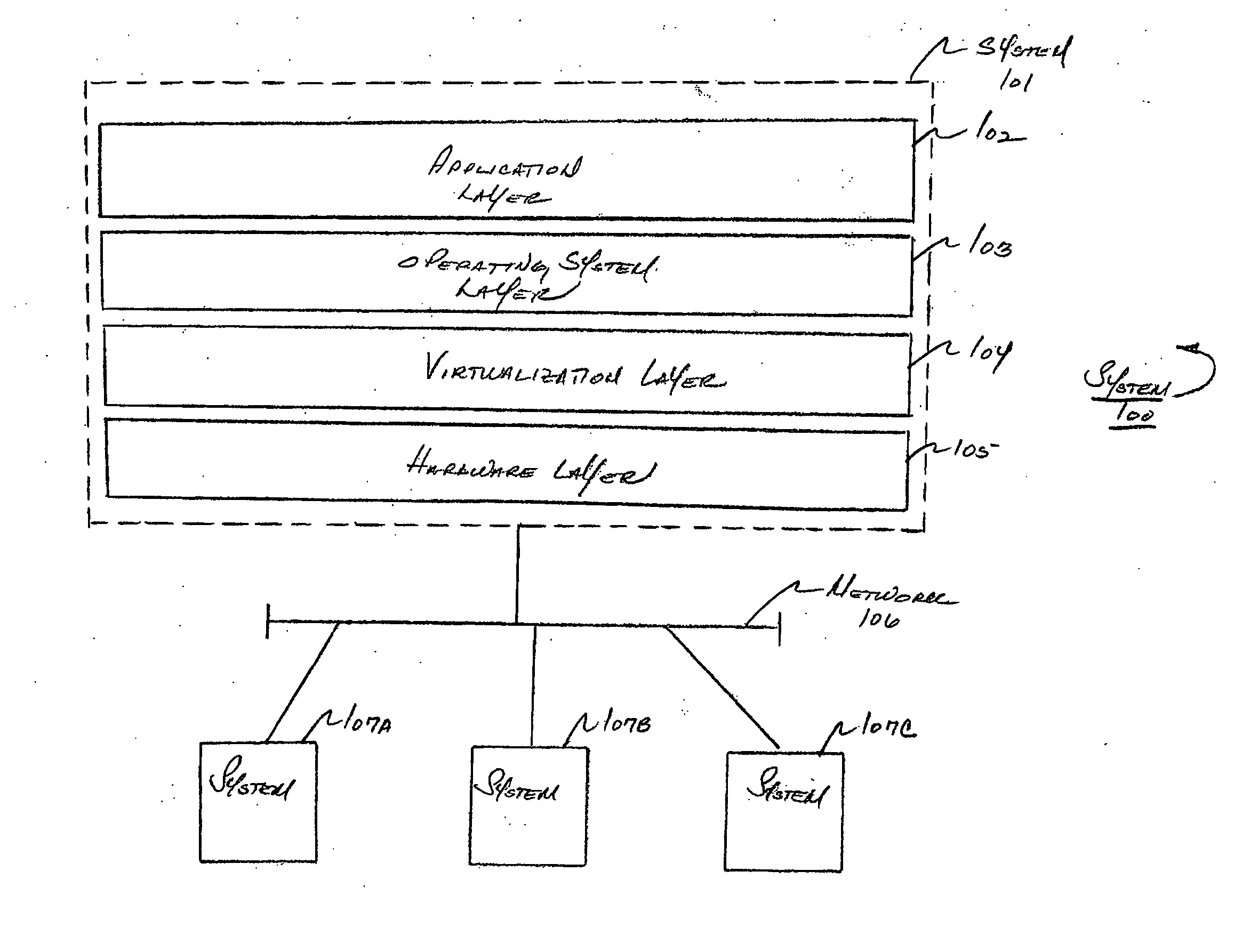

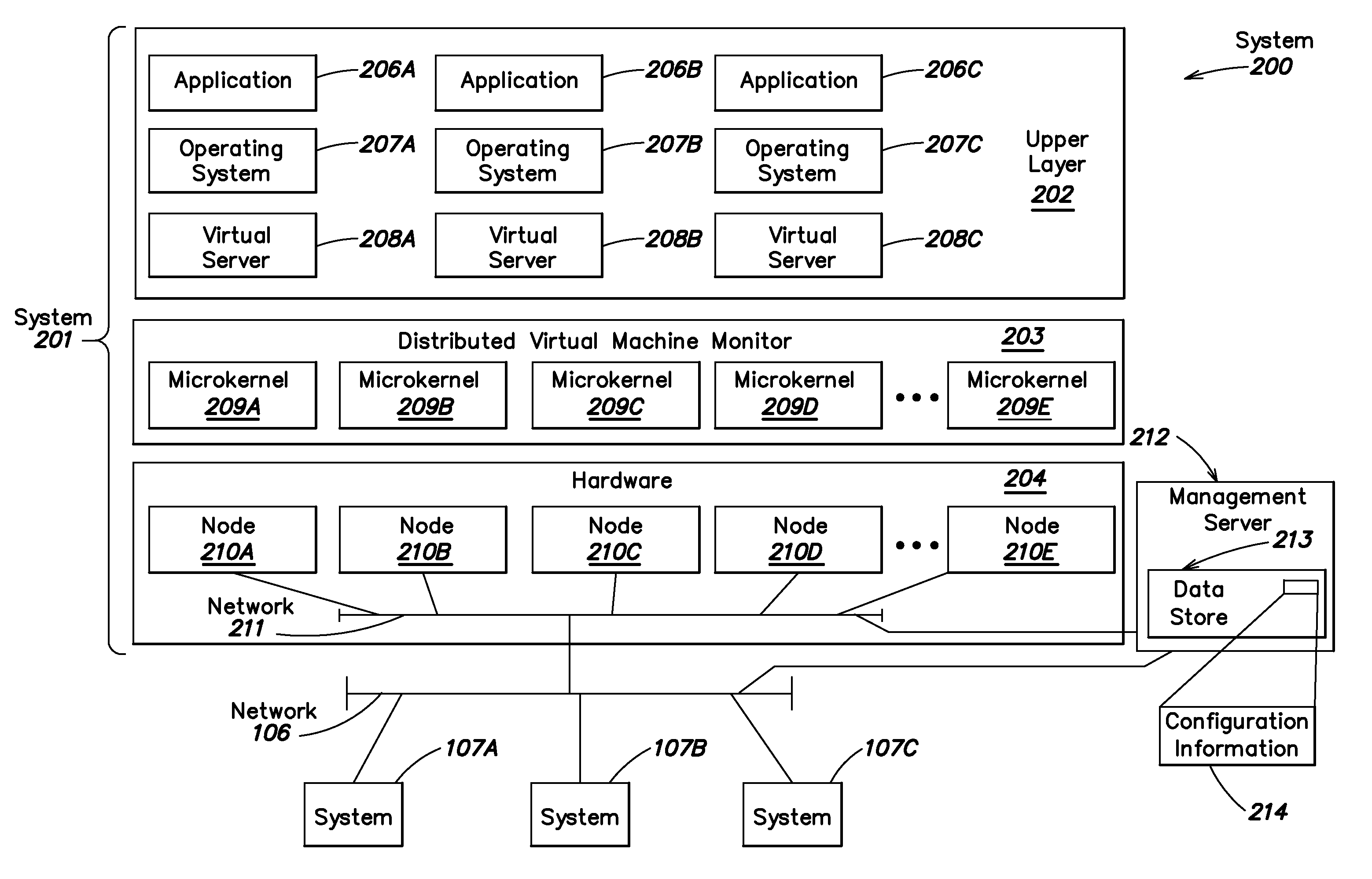

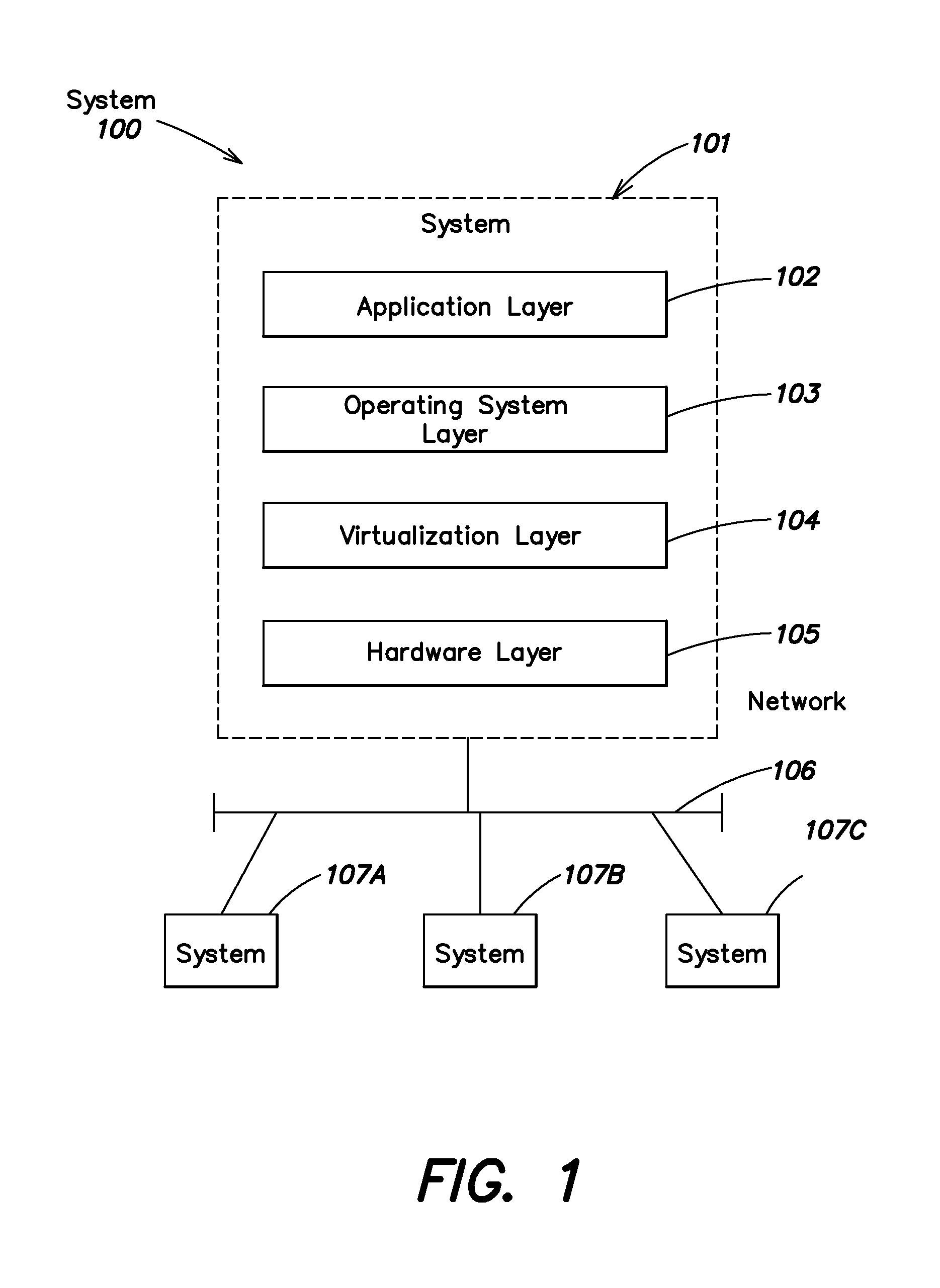

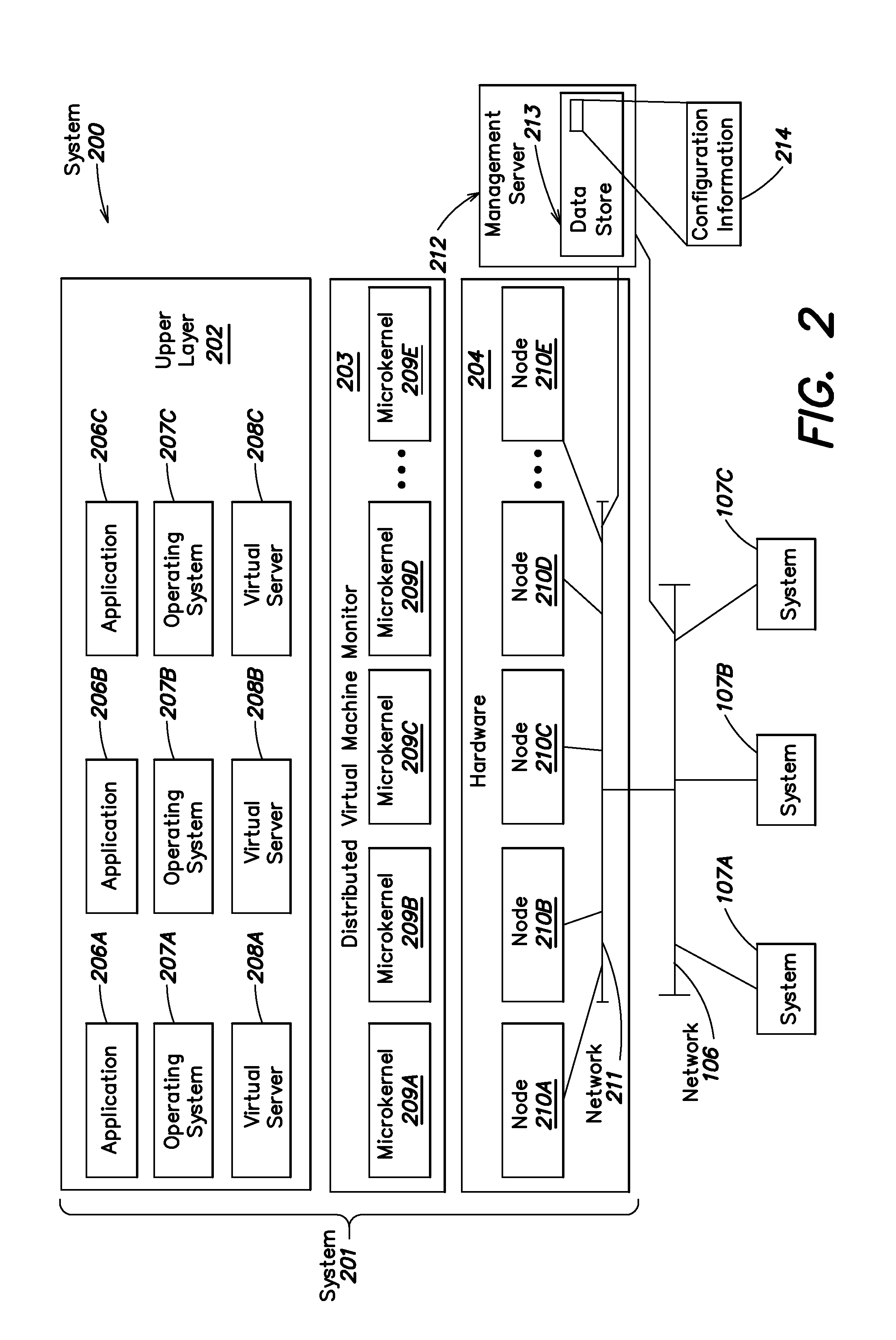

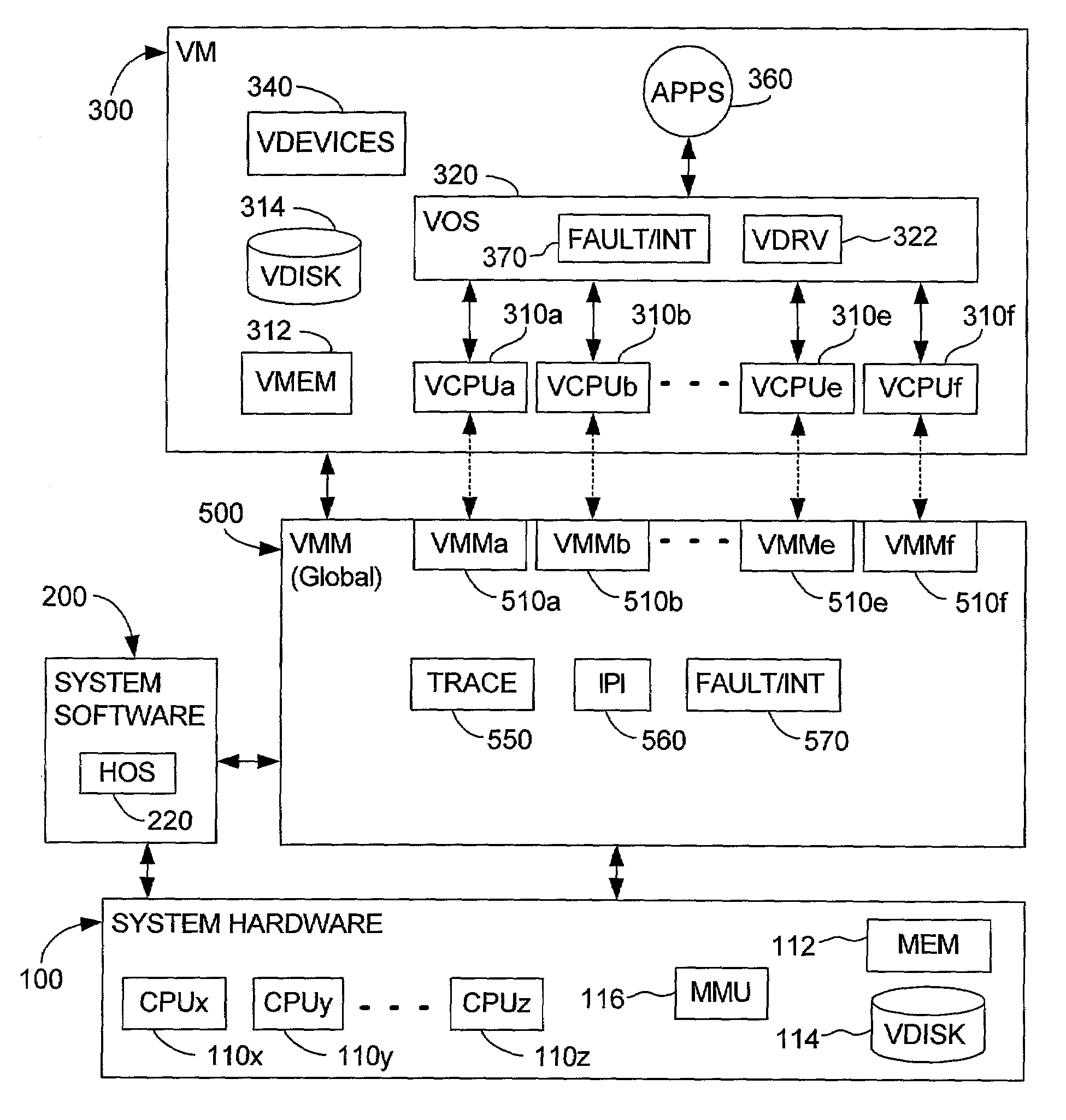

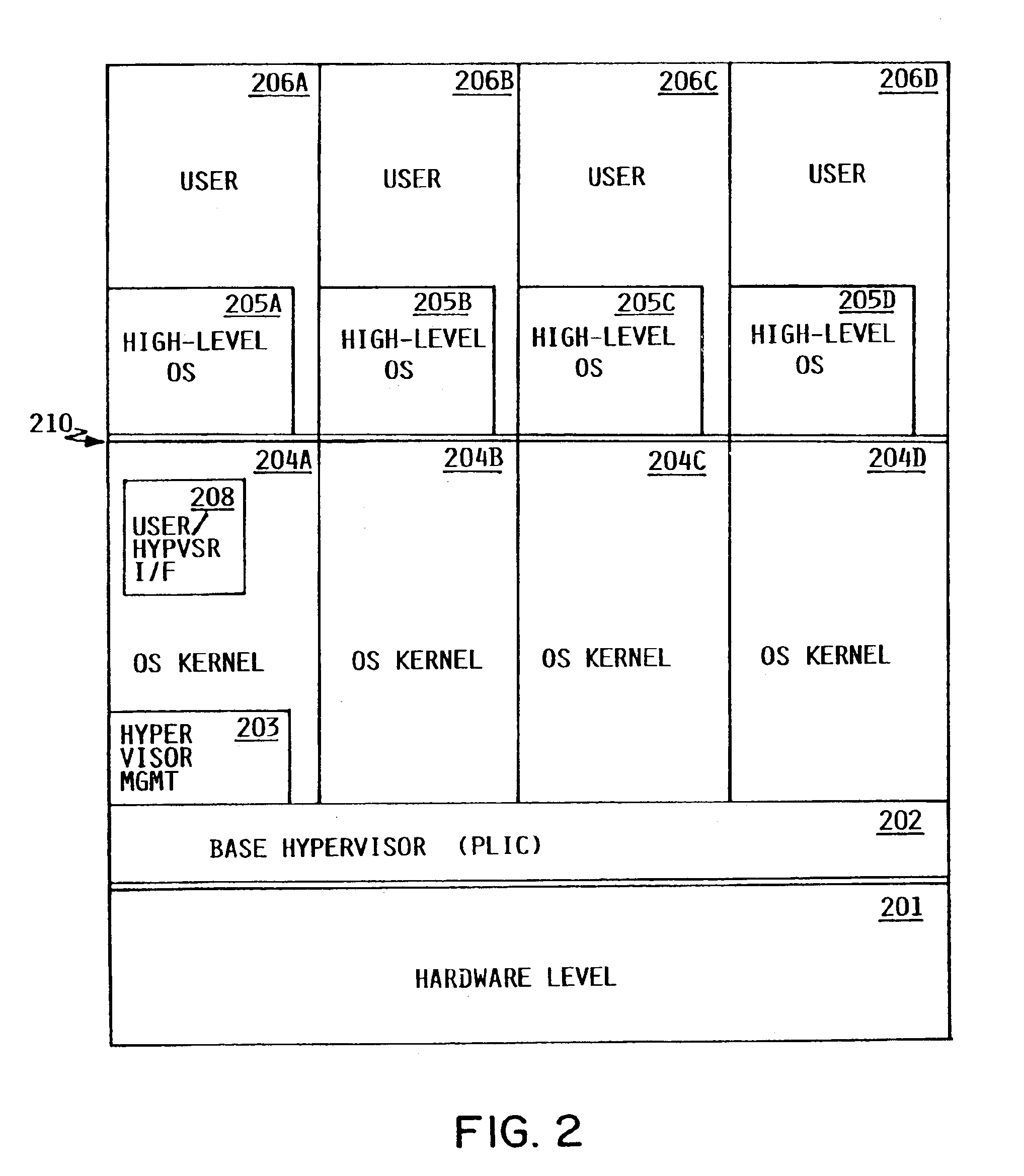

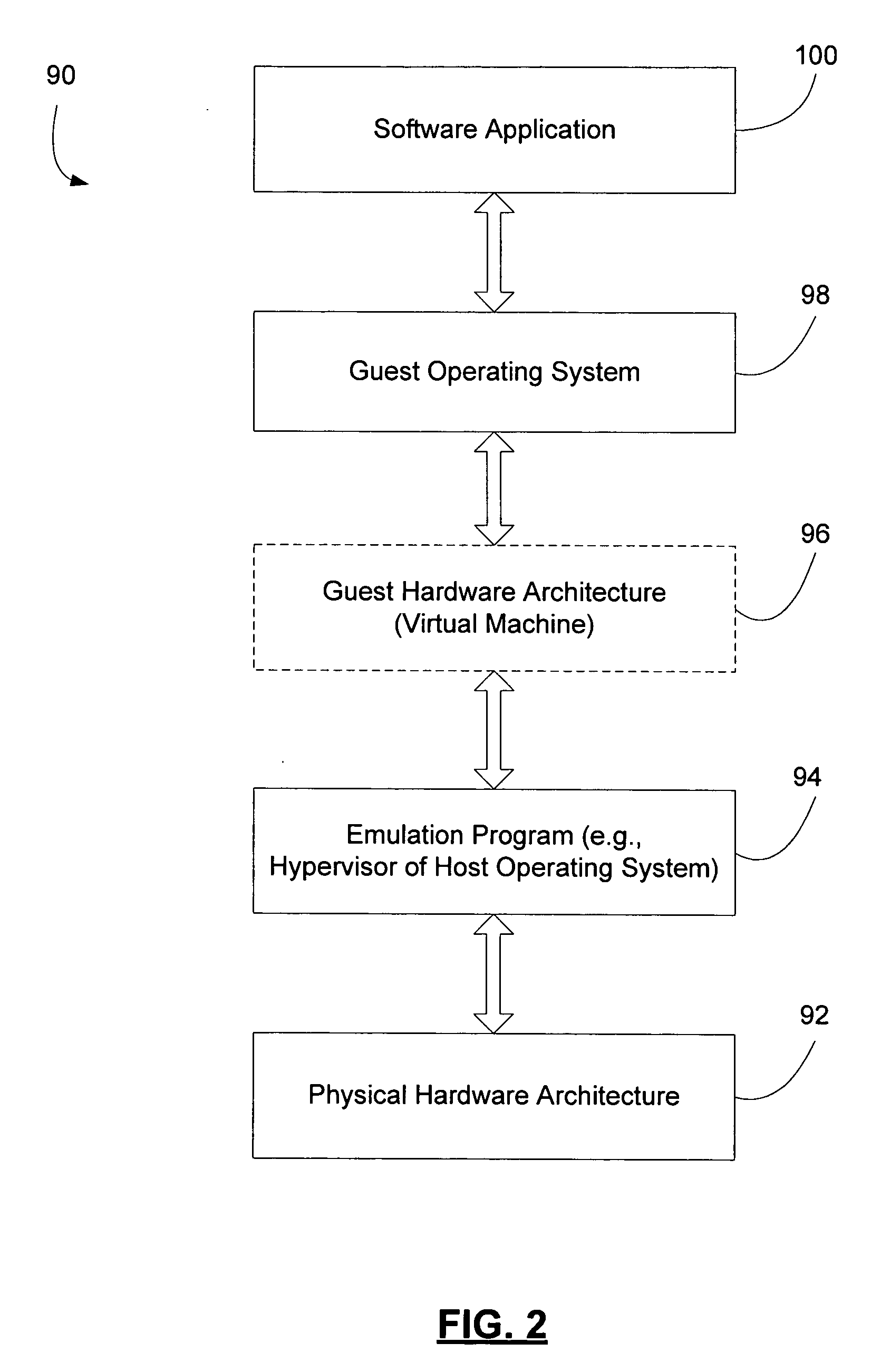

Method and apparatus for providing virtual computing services

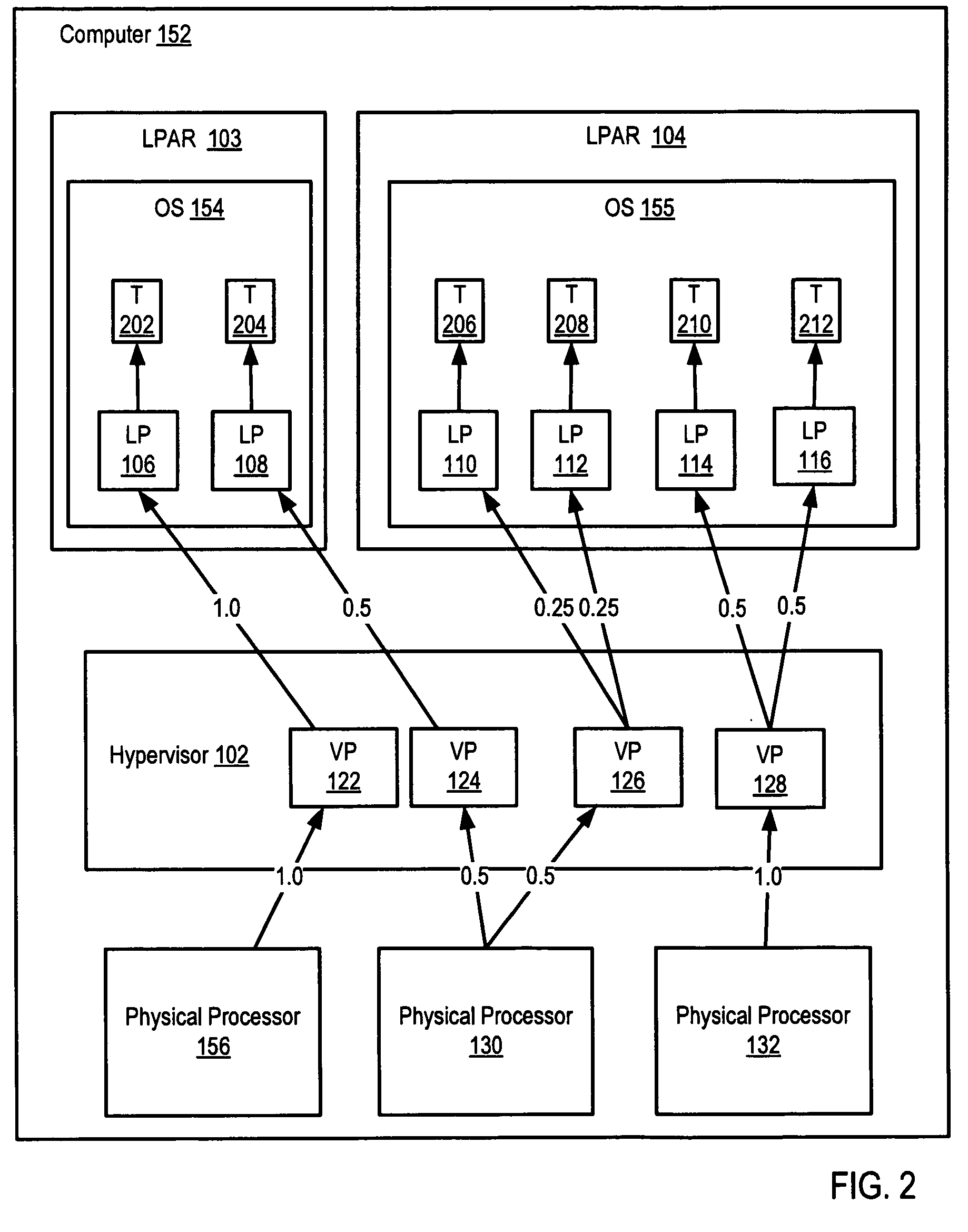

InactiveUS20050044301A1Easy to manageLow costResource allocationMemory adressing/allocation/relocationVirtualizationOperational system

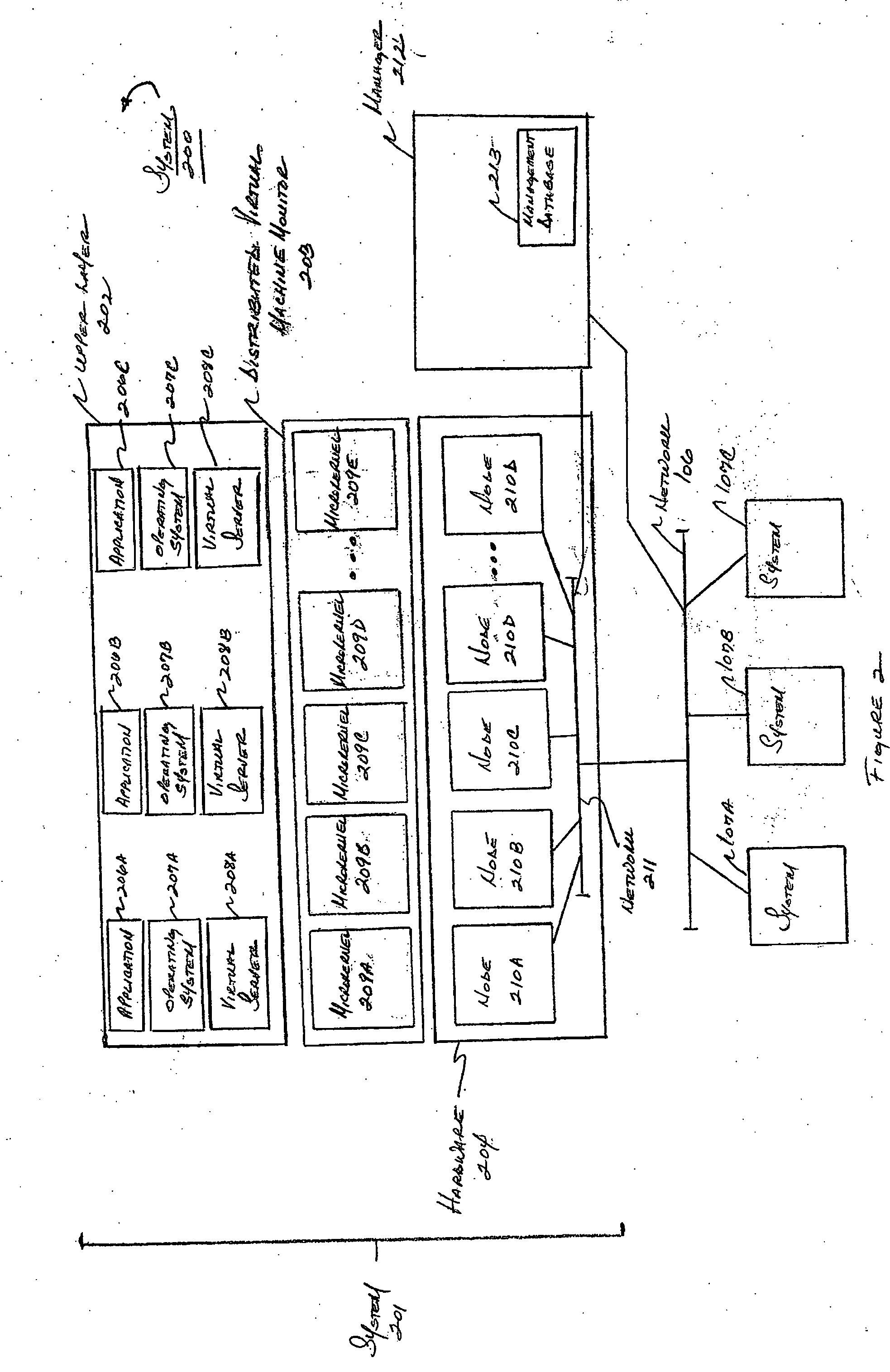

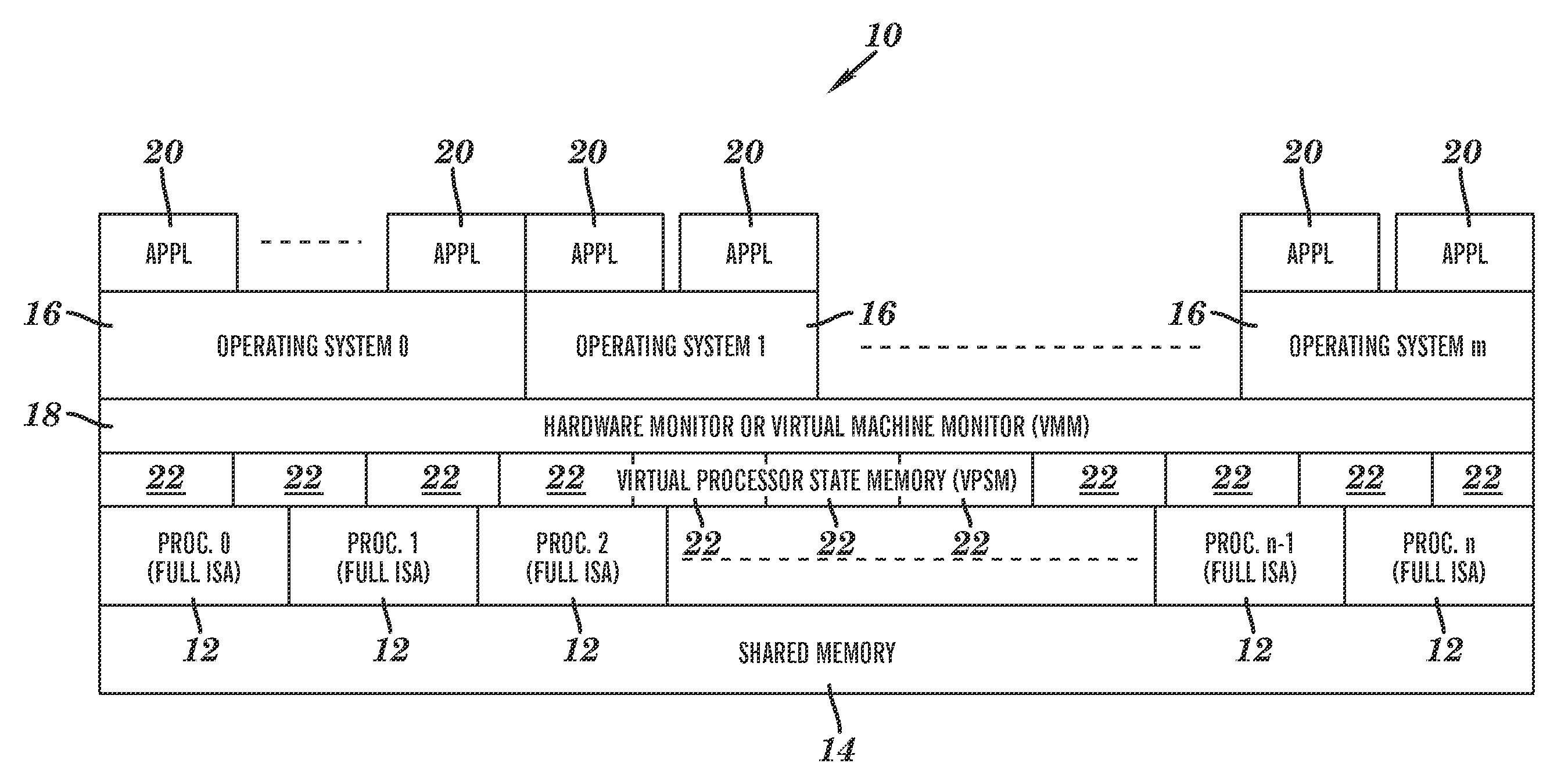

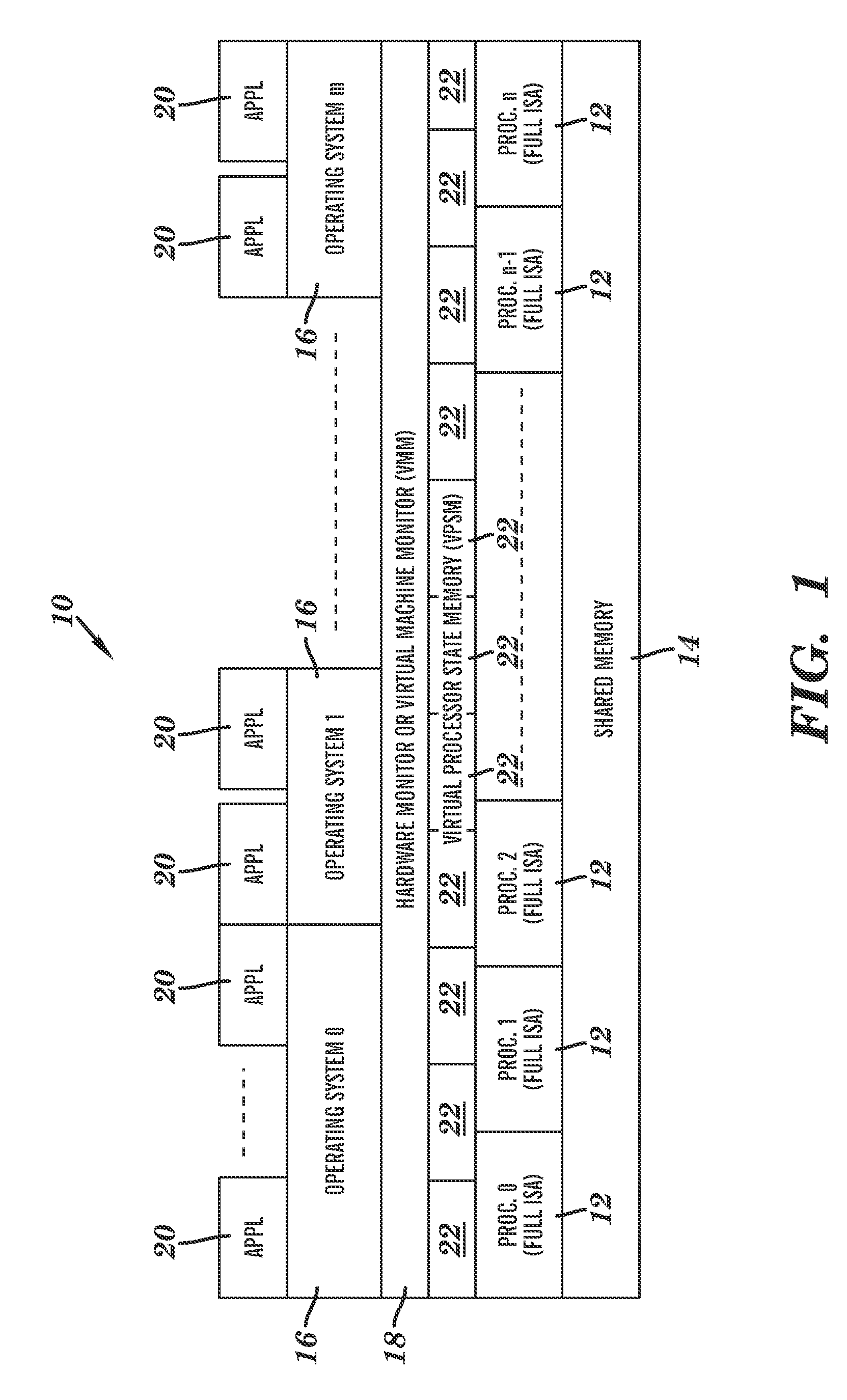

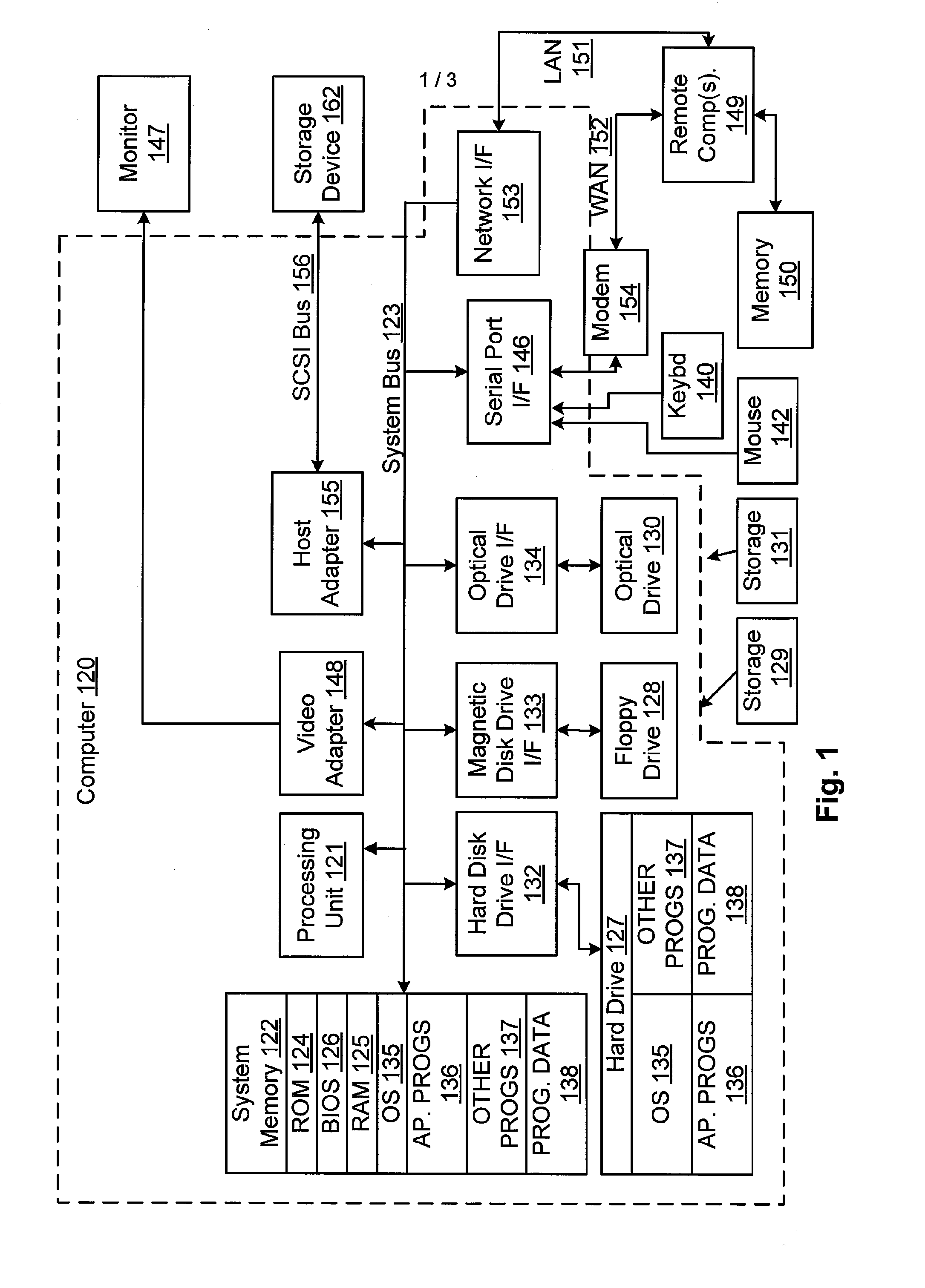

A level of abstraction is created between a set of physical processors and a set of virtual multiprocessors to form a virtualized data center. This virtualized data center comprises a set of virtual, isolated systems separated by a boundary referred as a partition. Each of these systems appears as a unique, independent virtual multiprocessor computer capable of running a traditional operating system and its applications. In one embodiment, the system implements this multi-layered abstraction via a group of microkernels, each of which communicates with one or more peer microkernel over a high-speed, low-latency interconnect and forms a distributed virtual machine monitor. Functionally, a virtual data center is provided, including the ability to take a collection of servers and execute a collection of business applications over a compute fabric comprising commodity processors coupled by an interconnect. Processor, memory and I / O are virtualized across this fabric, providing a single system, scalability and manageability. According to one embodiment, this virtualization is transparent to the application, and therefore, applications may be scaled to increasing resource demands without modifying the application.

Owner:ORACLE INT CORP

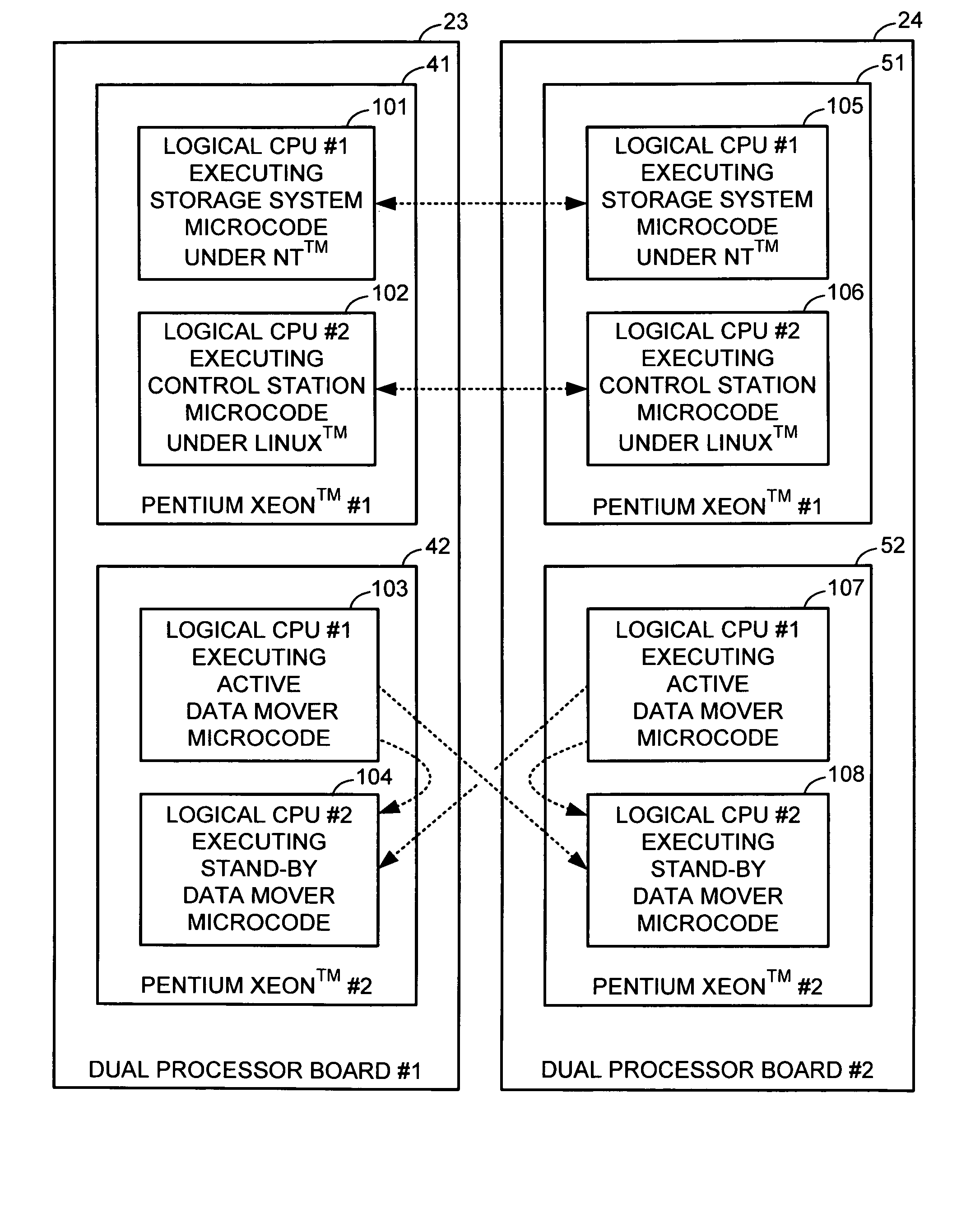

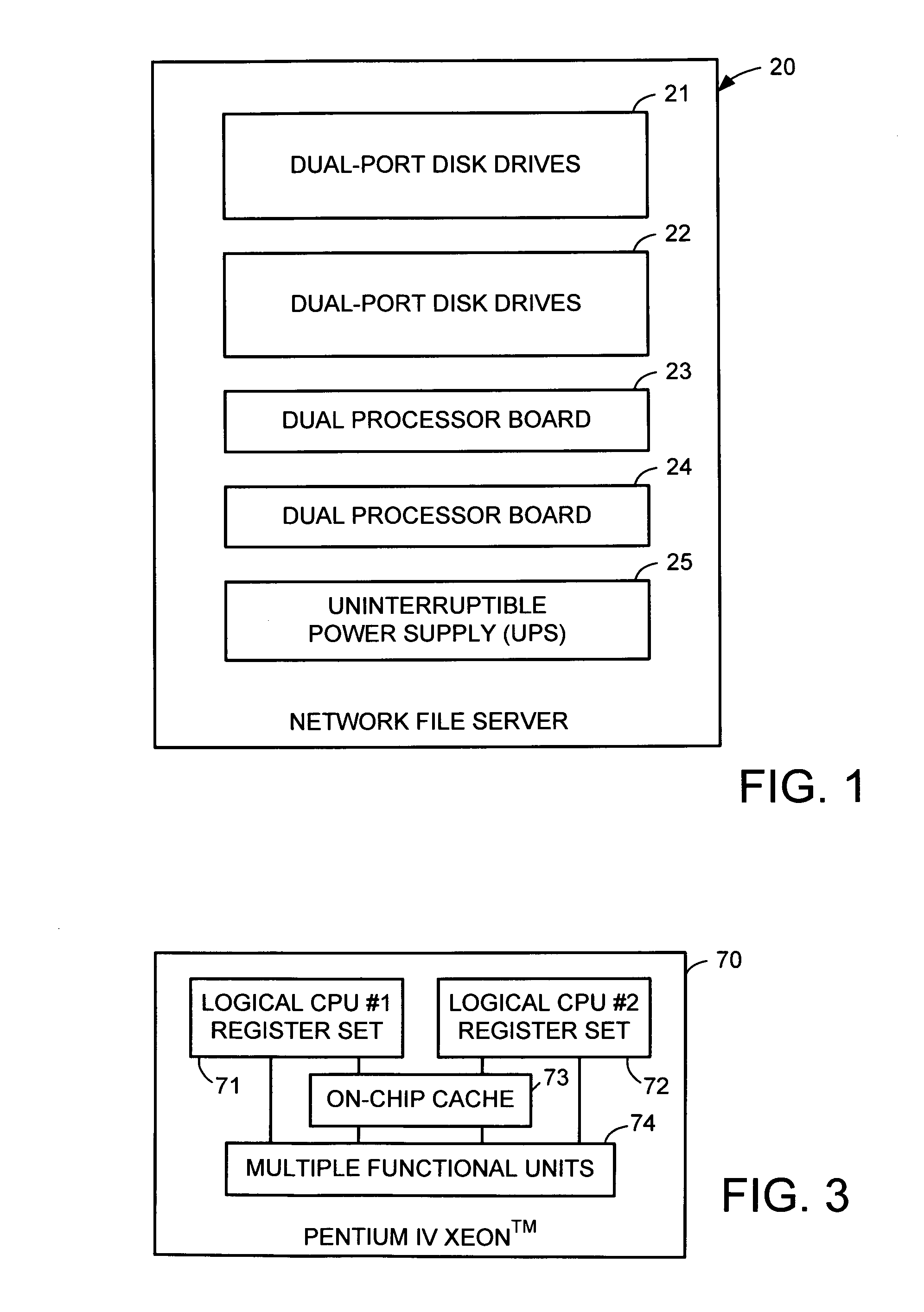

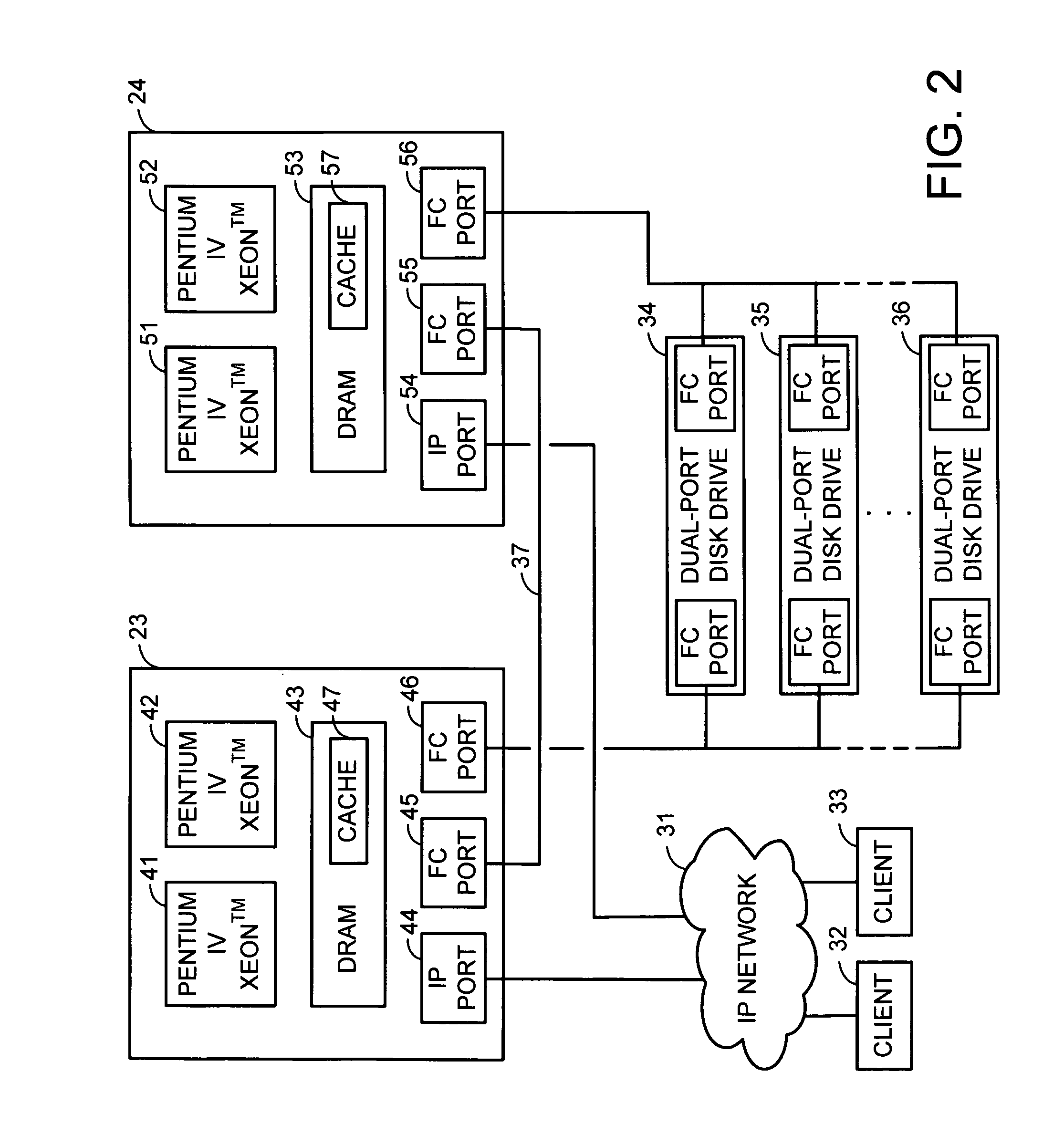

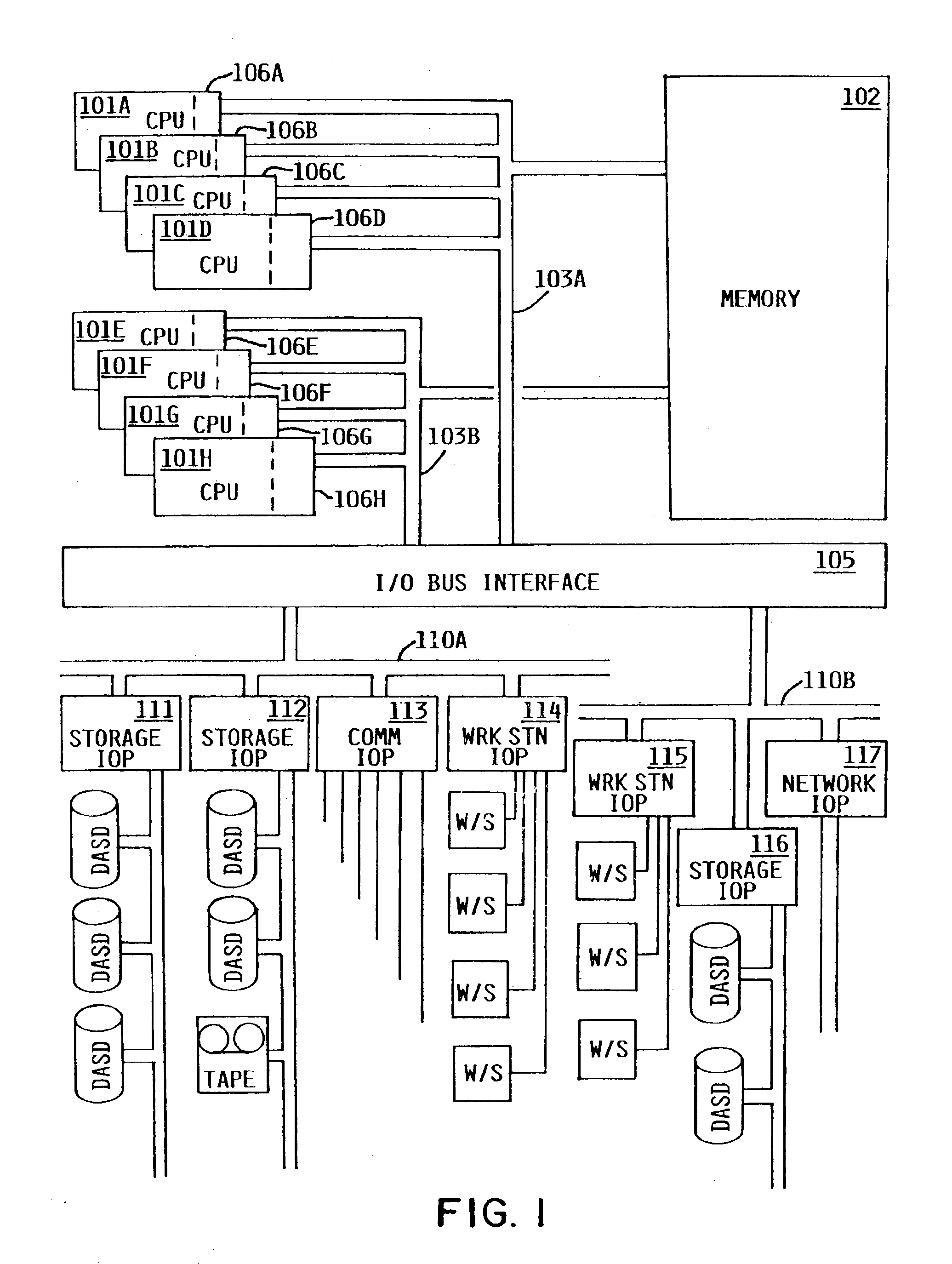

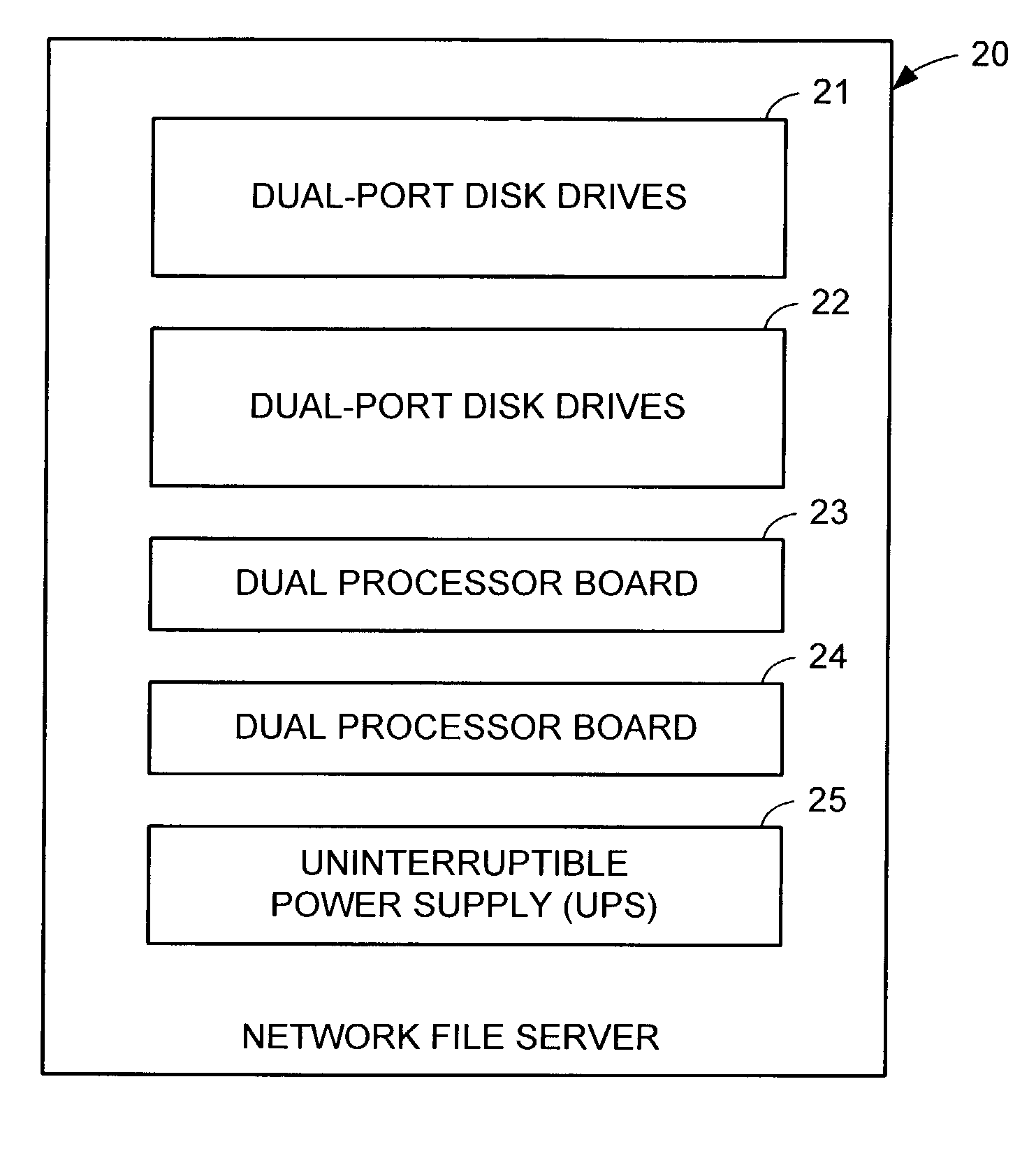

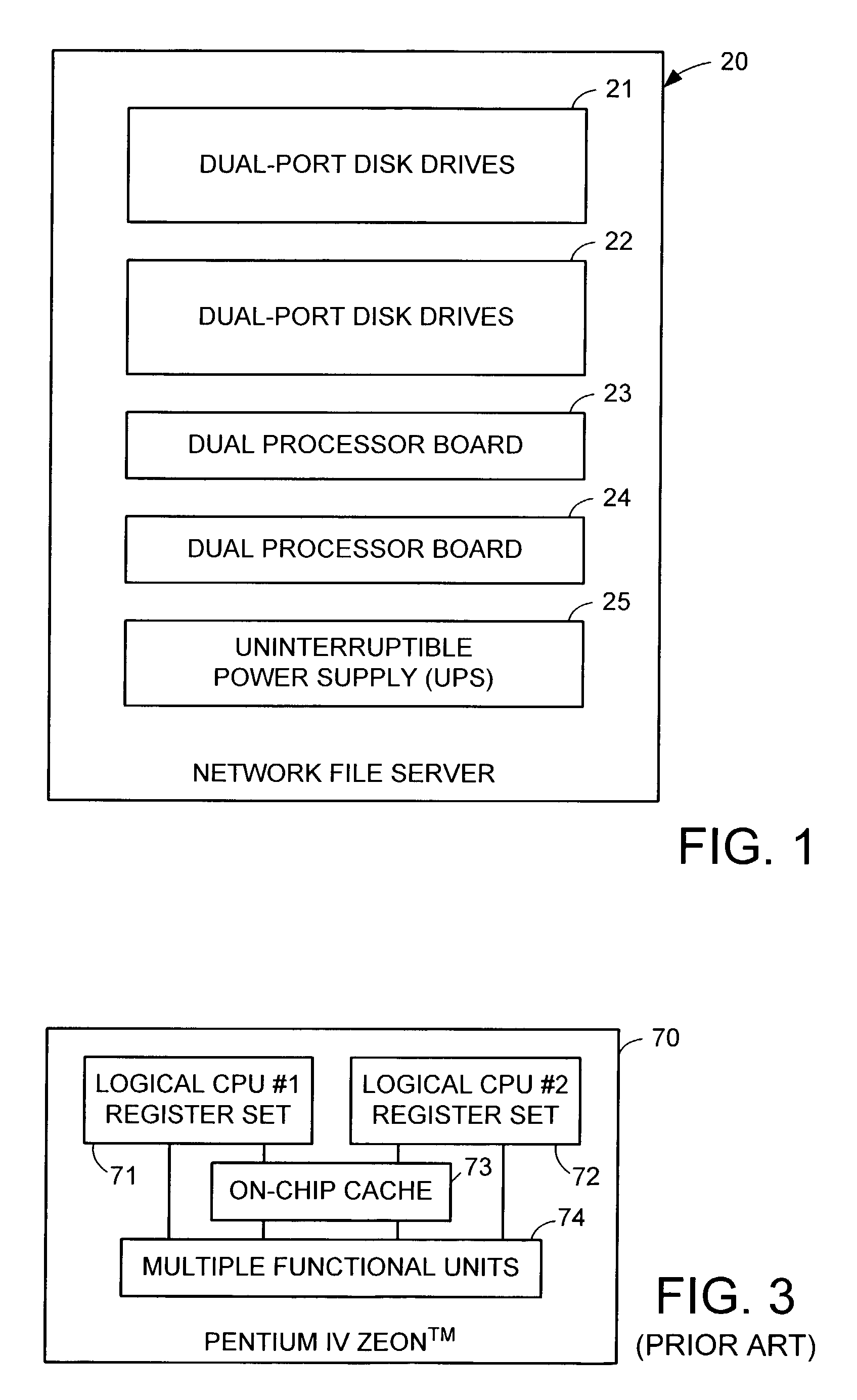

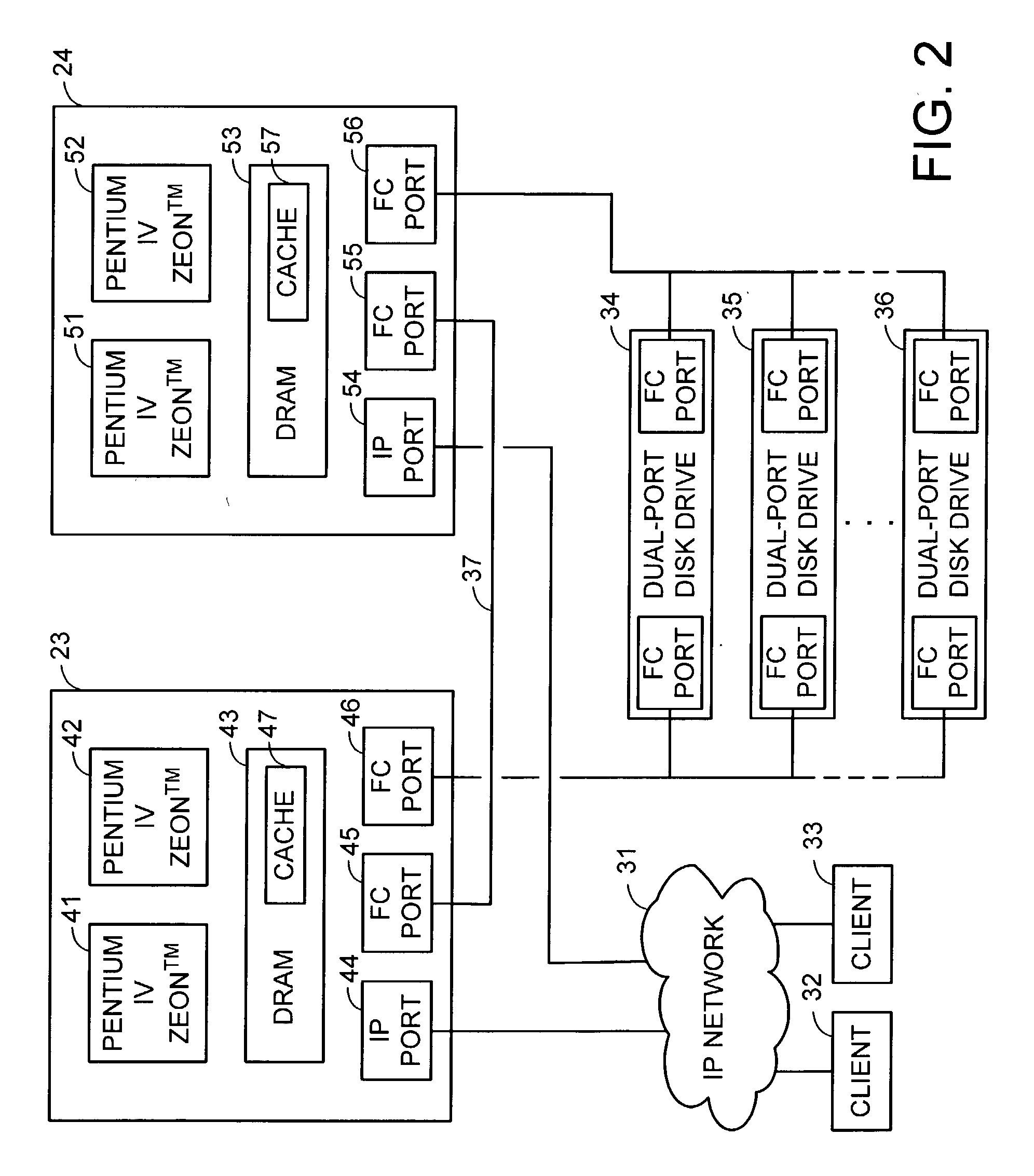

Redundant multi-processor and logical processor configuration for a file server

A redundant file server includes at least two dual processor boards. Each physical processor has two logical processors. The first logical processor of the first physical processor of each board executes storage system code under the Microsoft NT™ operating system. The second logical processor of the first physical processor of each board executes control station code under the Linux operating system. The first logical processor of the second physical processor of each board executes data mover code. The second logical processor of the second physical processor of each board is kept in a stand-by mode for assuming data mover functions upon failure of the first logical processor of the second physical processor on the first or second board.

Owner:EMC IP HLDG CO LLC

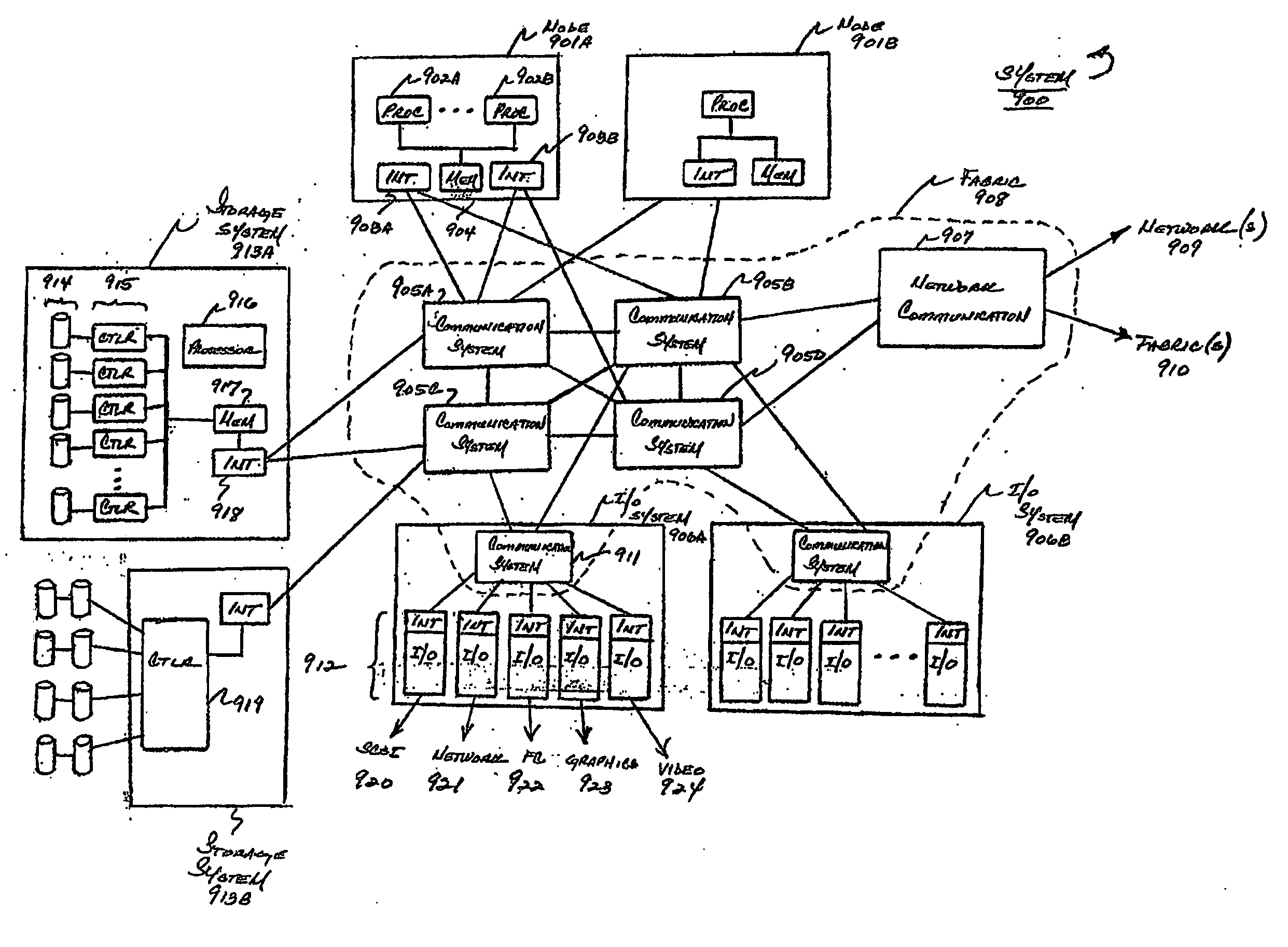

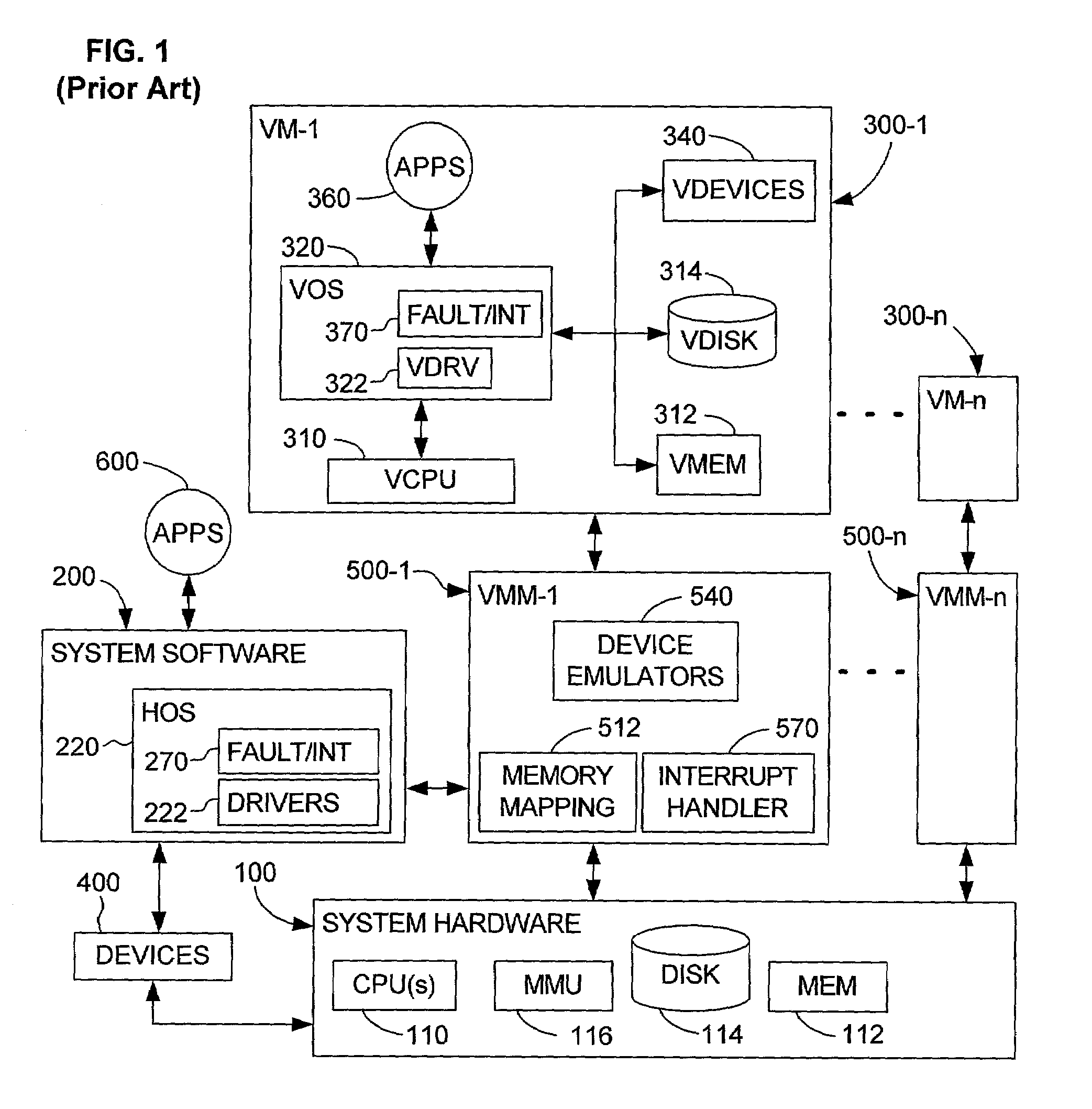

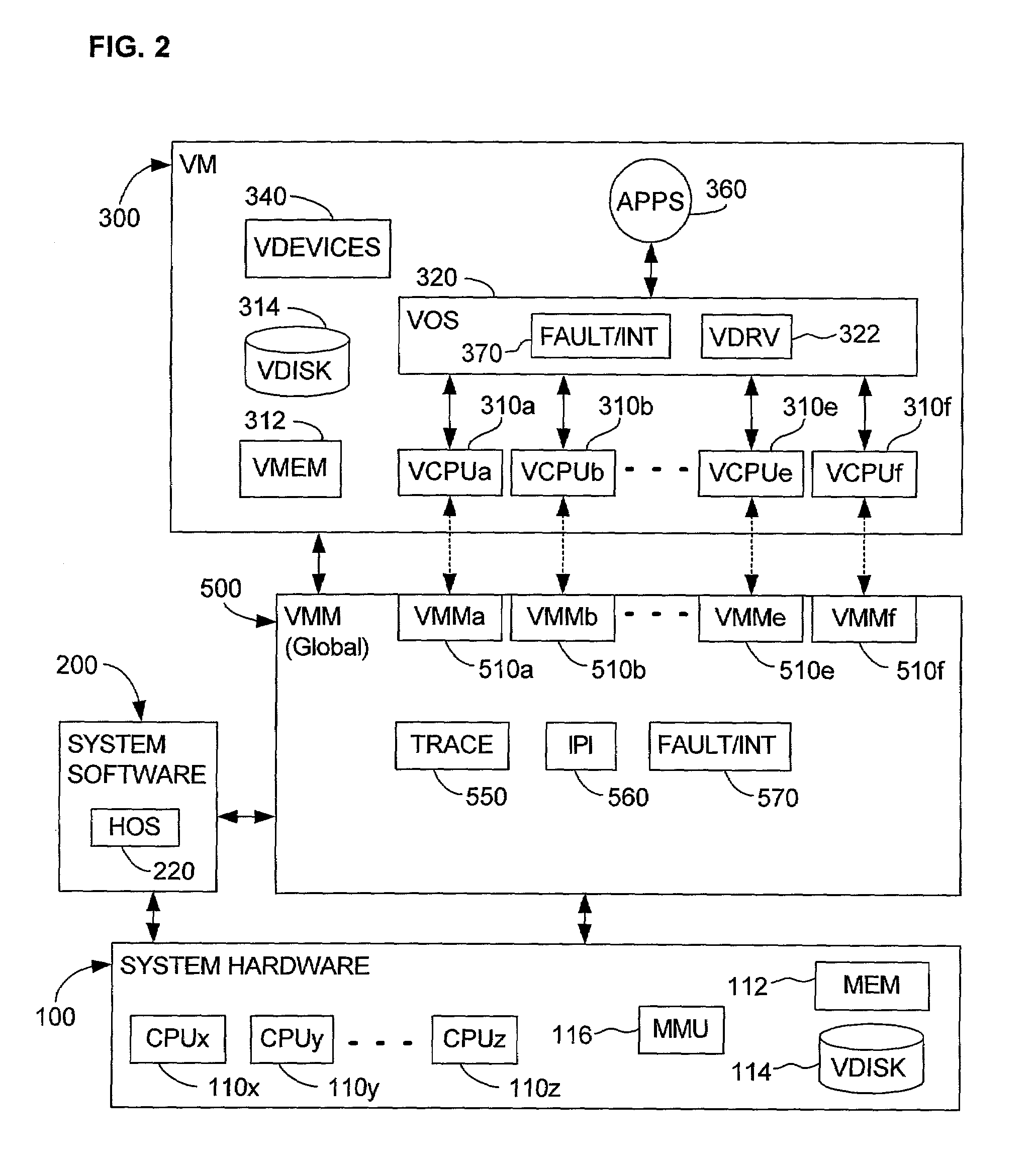

Distributed virtual machine monitor for managing multiple virtual resources across multiple physical nodes

ActiveUS8776050B2Grow and shrink capabilityMaximize useResource allocationMemory adressing/allocation/relocationOperational systemGNU/Linux

A management capability is provided for a virtual computing platform. In one example, this platform allows interconnected physical resources such as processors, memory, network interfaces and storage interfaces to be abstracted and mapped to virtual resources (e.g., virtual mainframes, virtual partitions). Virtual resources contained in a virtual partition can be assembled into virtual servers that execute a guest operating system (e.g., Linux). In one example, the abstraction is unique in that any resource is available to any virtual server regardless of the physical boundaries that separate the resources. For example, any number of physical processors or any amount of physical memory can be used by a virtual server even if these resources span different nodes.

Owner:ORACLE INT CORP

System and method for detecting access to shared structures and for maintaining coherence of derived structures in virtualized multiprocessor systems

A computer system includes at least one virtual machine that has a plurality of virtual processors all running on an underlying hardware platform. A software interface layer such as a virtual machine monitor establishes traces on primary structures located in a common memory space as needed for the different virtual processors. Whenever any one of the virtual processors generates a trace event, such as accessing a traced structure, then a notification is sent to at least the other virtual processors that have a trace on the accessed primary structure. In some applications, the VMM derives and maintains secondary structures corresponding to the primary structures, such as where the VMM converts, through binary translation, original code intended to run on a virtual processor into code that can be run on an underlying physical processor of the hardware platform. In these applications, the VMM may rederive or invalidate the secondary structures as needed upon receipt of the notification of the trace event. Different semantics are provided for the notification, providing different choices of performance versus guaranteed consistency between primary and secondary structures. In the preferred embodiment of the invention, a dedicated sub-system is included within the VMM for each virtual processor; each sub-system establishes traces, senses trace events, issues the notification, and performs other operations relating specifically to its respective virtual processor.

Owner:VMWARE INC

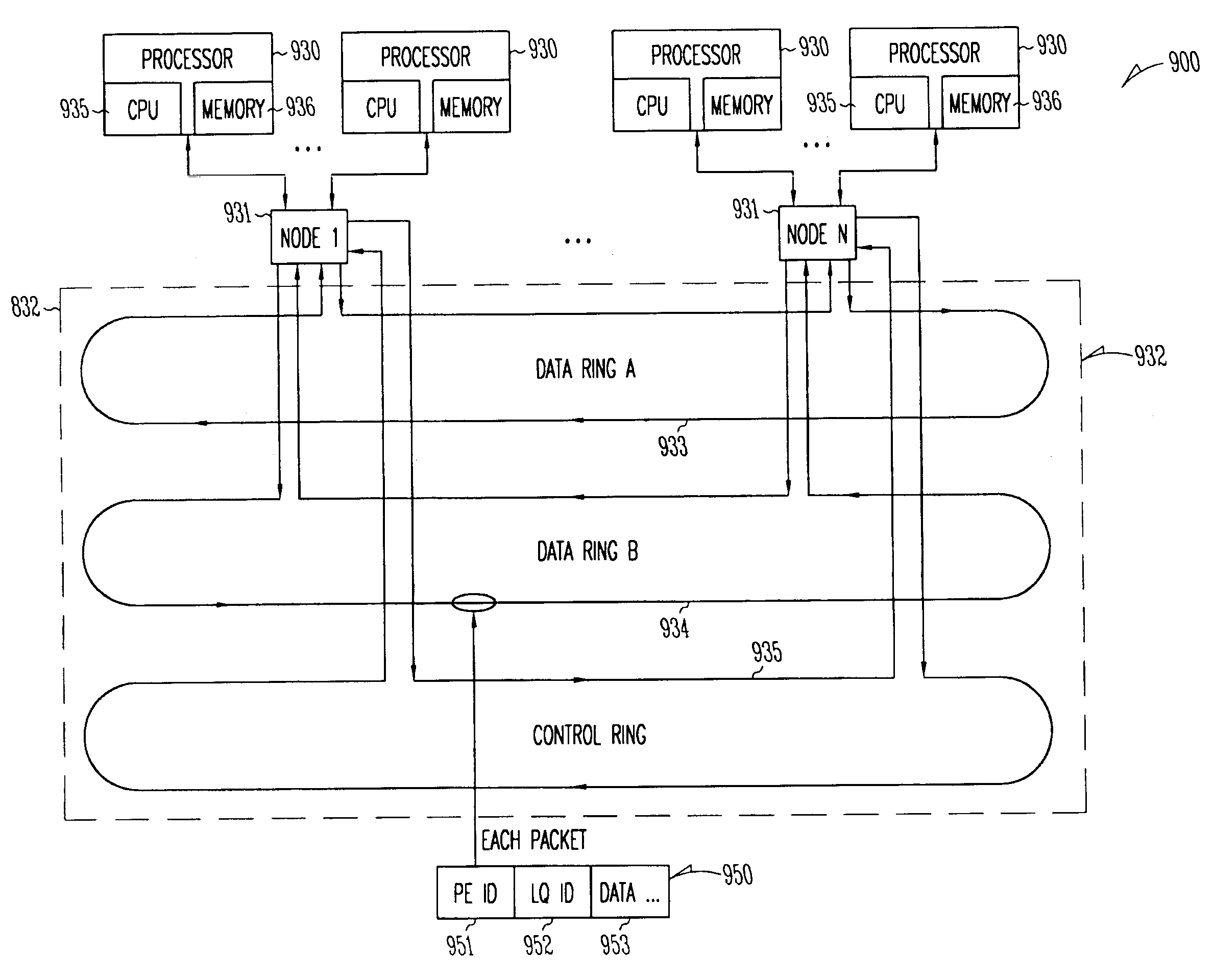

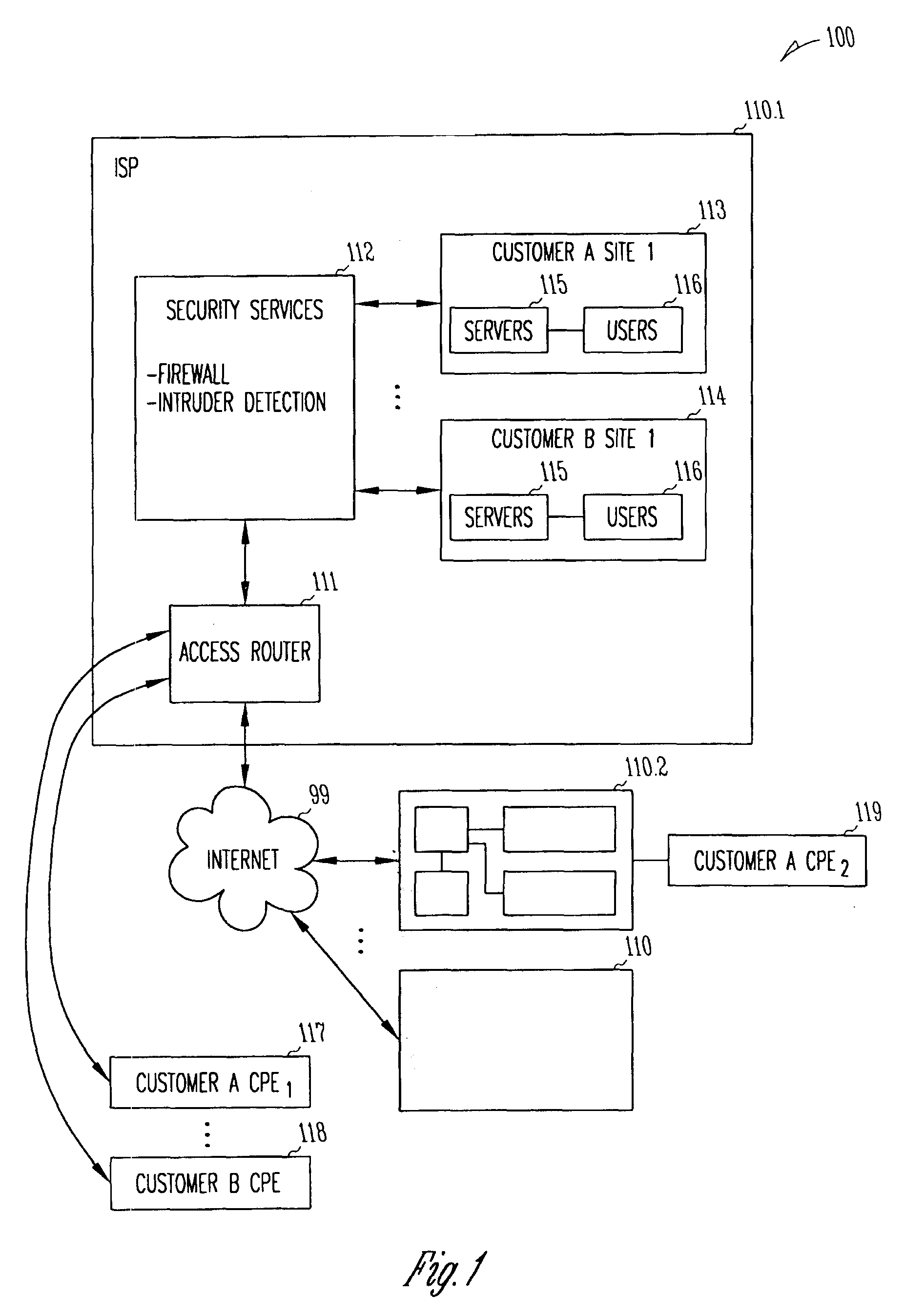

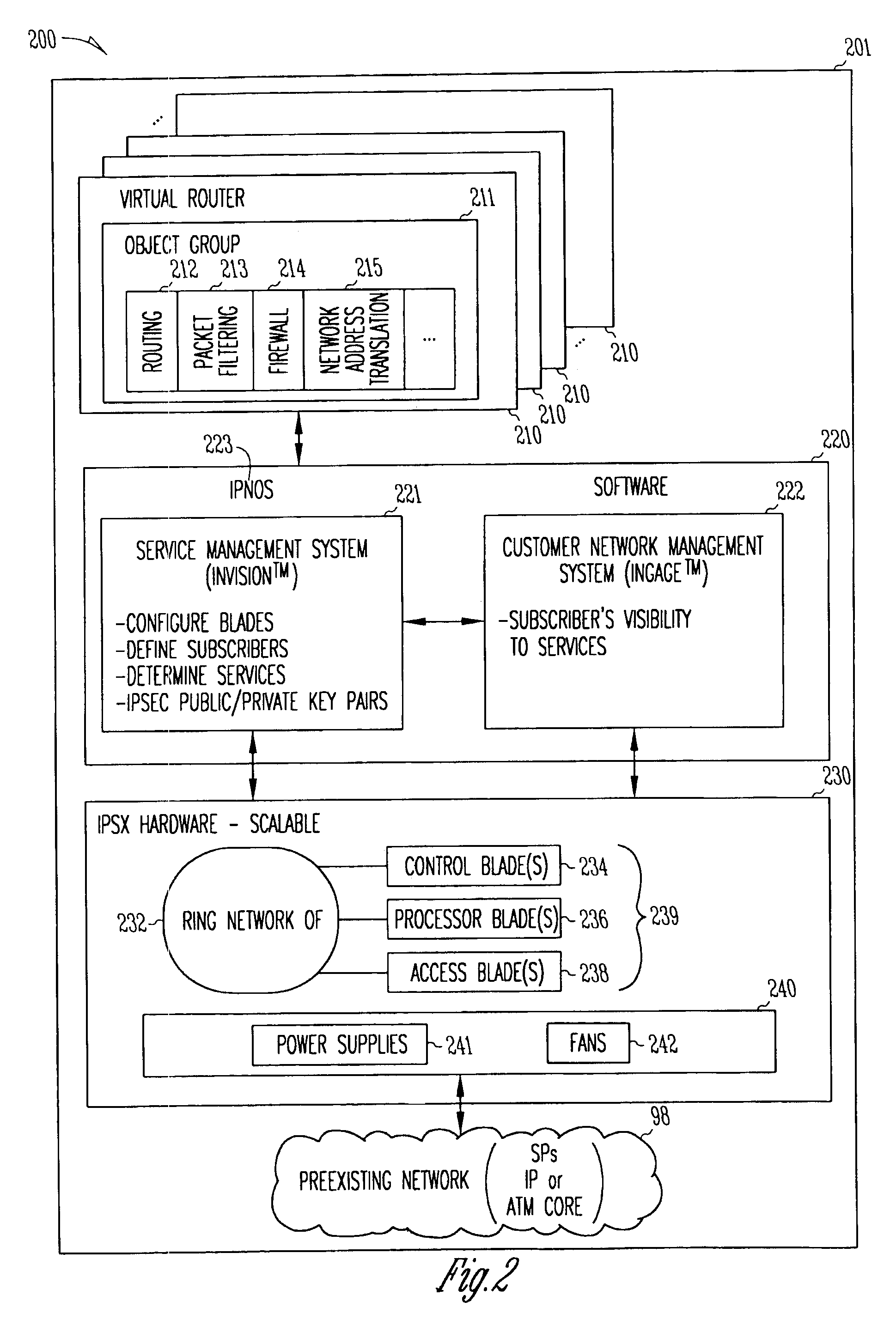

Packet routing system and method

InactiveUS7111072B1Multiple digital computer combinationsLoop networksComputer hardwarePrivate network

A flexible, scalable hardware and software platform that allows a service provider to easily provide internet services, virtual private network services, firewall services, etc., to a plurality of customers. One aspect provides a method and system for delivering security services. This includes connecting a plurality of processors in a ring configuration within a first processing system, establishing a secure connection between the processors in the ring configuration across an internet protocol (IP) connection to a second processing system to form a tunnel, and providing both router services and host services for a customer using the plurality of processors in the ring configuration and using the second processing system. a packet routing system and method is described that includes a processor identifier in each packet to route the packets to a physical processor, and a logical queue identifier to route the packets to the destination object within that processor.

Owner:FORTINET

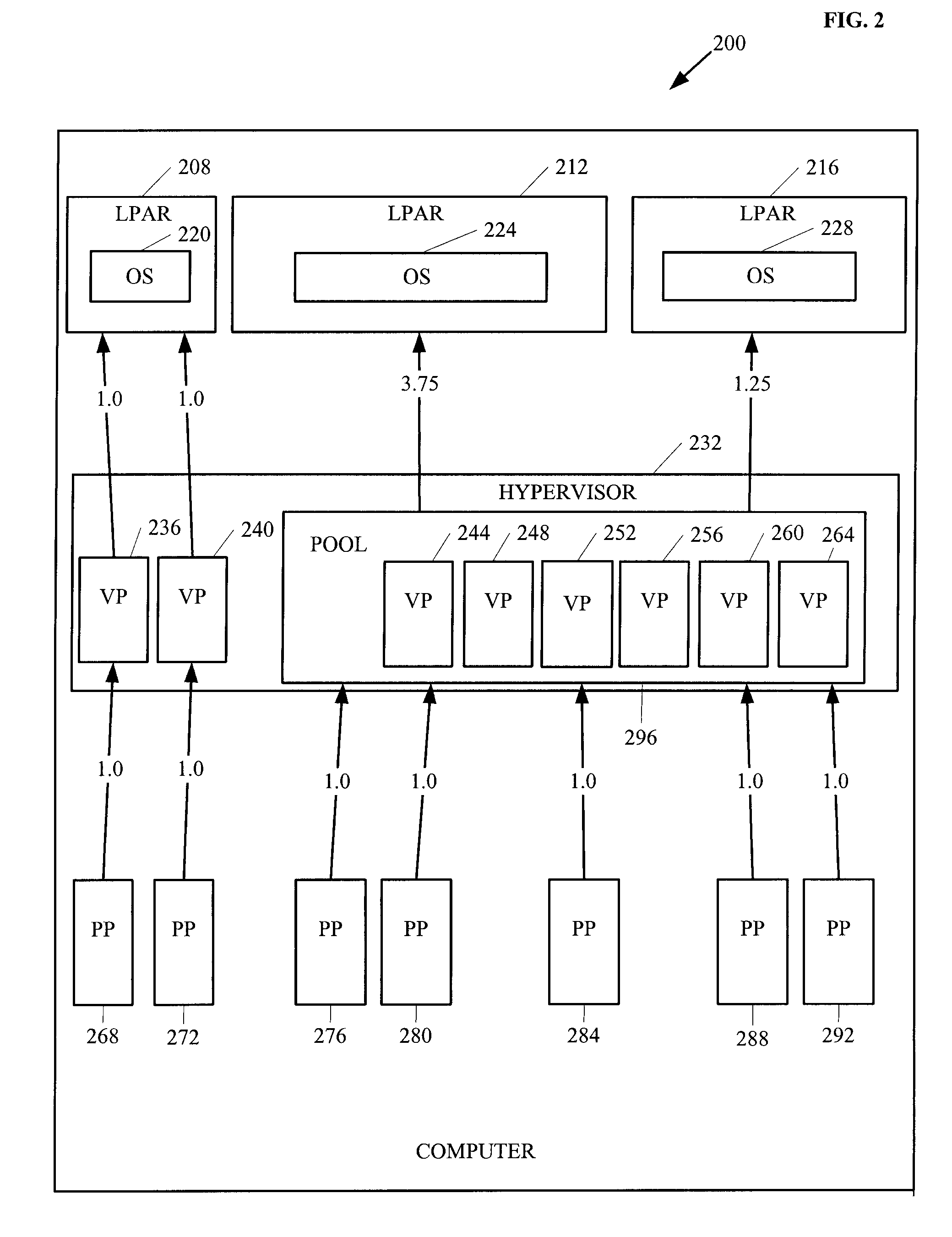

Method and apparatus for allocating processor resources in a logically partitioned computer system

InactiveUS6957435B2Efficient interfaceResource allocationGeneral purpose stored program computerComputer architectureComputerized system

A processor allocation mechanism for a logically partitionable computer system allows an administrator to specify processing capability allocable to each partition as an equivalent number of processors, where the processing capability may be specified as a non-integer value. This processing capability value is unaffected by changes to the processing capability values of other partitions. The administrator may designate multiple sets of processors, assigning each physical processor of the system to a respective processor set. Each logical partition is constrained to execute in an assigned processor set, which may be shared by more than one partition. Preferably, the administrator may designate a logical partition as either capped, meaning that a partition can not use excess idle capacity of the processors, or uncapped, meaning that it can.

Owner:IBM CORP

Systems and methods for exposing processor topology for virtual machines

ActiveUS20060136653A1Multiprogramming arrangementsComputer security arrangementsOperational systemPhysics processing unit

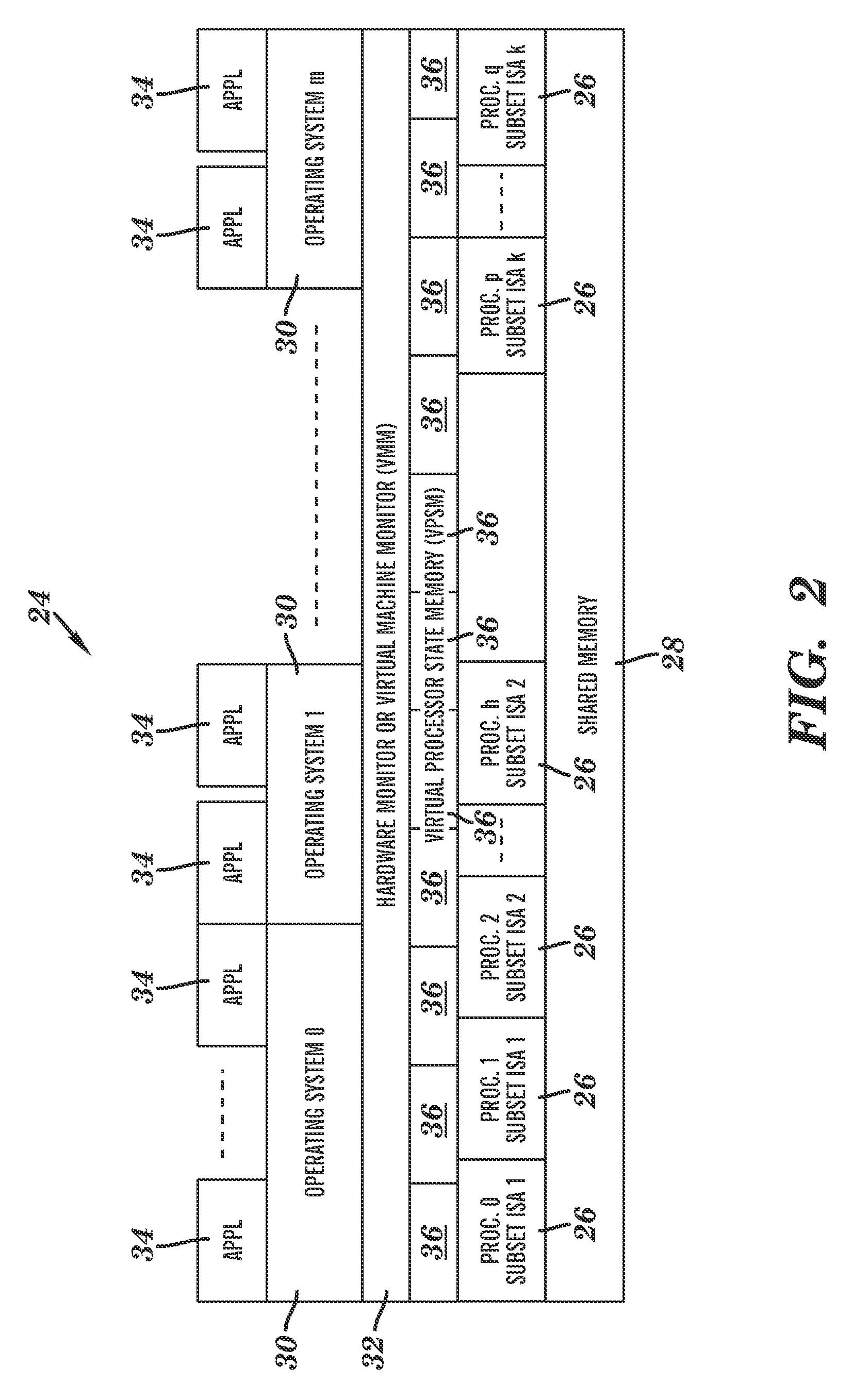

The present invention is directed to making a guest operating system aware of the topology of the subset of host resources currently assigned to it. At virtual machine boot time a Static Resource Affinity Table (SRAT) will be used by the virtualizer to group guest physical memory and guest virtual processors into virtual nodes. Thereafter, in one embodiment, the host physical memory behind a virtual node can be changed by the virtualizer as necessary, and the virtualizer will provide physical processors appropriate for the virtual processors in that node.

Owner:MICROSOFT TECH LICENSING LLC

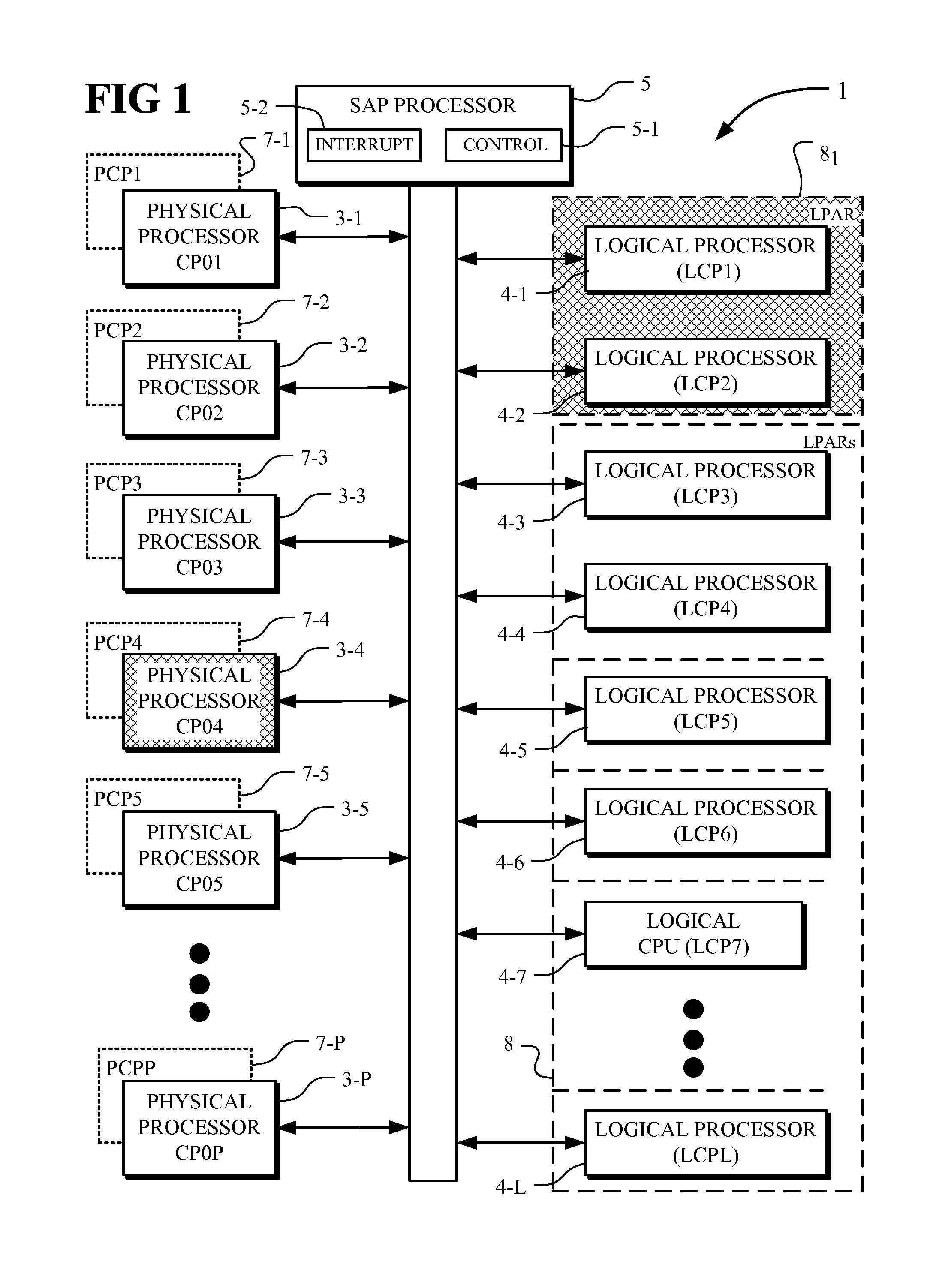

Processor exclusivity in a partitioned system

ActiveUS20090013153A1Eliminating all formMeet changing requirementsSoftware simulation/interpretation/emulationMemory systemsVirtualizationComputerized system

A computer system including a plurality of physical processors (CPs) having physical processor performances (PCPs), a plurality of logical processors (LCPs), a plurality of logical partitions (LPARs) where each partition includes one or more of the logical processors (LCPs), and a system assist processor having a control element. The control element controls the virtualization of the physical processors (CPs), the logical partitions (LPARs) and the logical processors (LCPs) and allocates the physical processor performances (PCPs) to the logical partitions (LPARs). The control element operates to exclusively bind logical processors (LCPs) to the physical processors (CPs). For a logical processor (LCP) exclusively bound to a physical processor (CP), the logical processor (LCP) has exclusive use of the underlying physical processor (CP) and no other logical processor (LCP) can be dispatched on the underlying physical processor (CP) even if the underlying physical processor (CP) is otherwise available.

Owner:IBM CORP

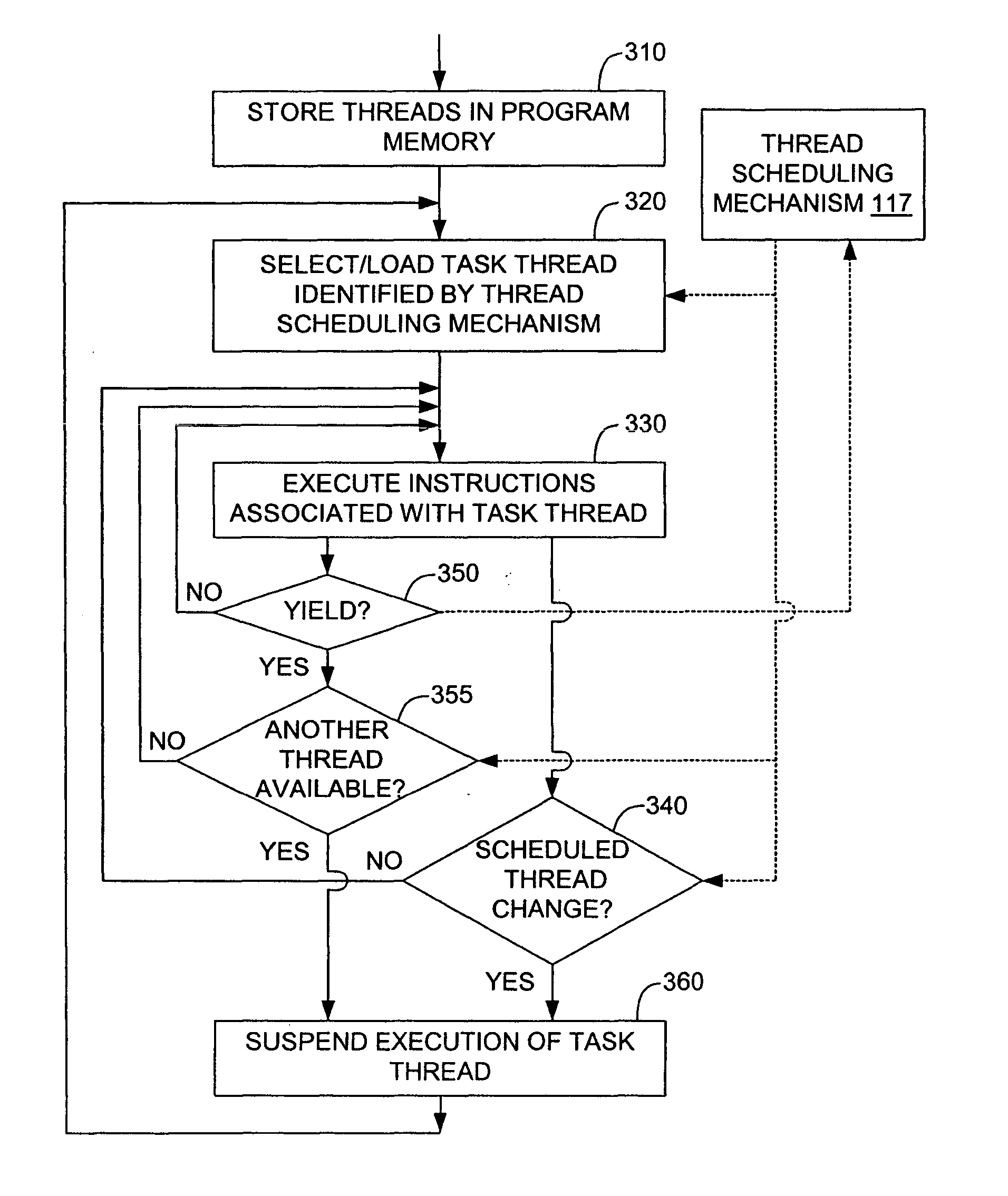

Machine instruction for enhanced control of multiple virtual processor systems

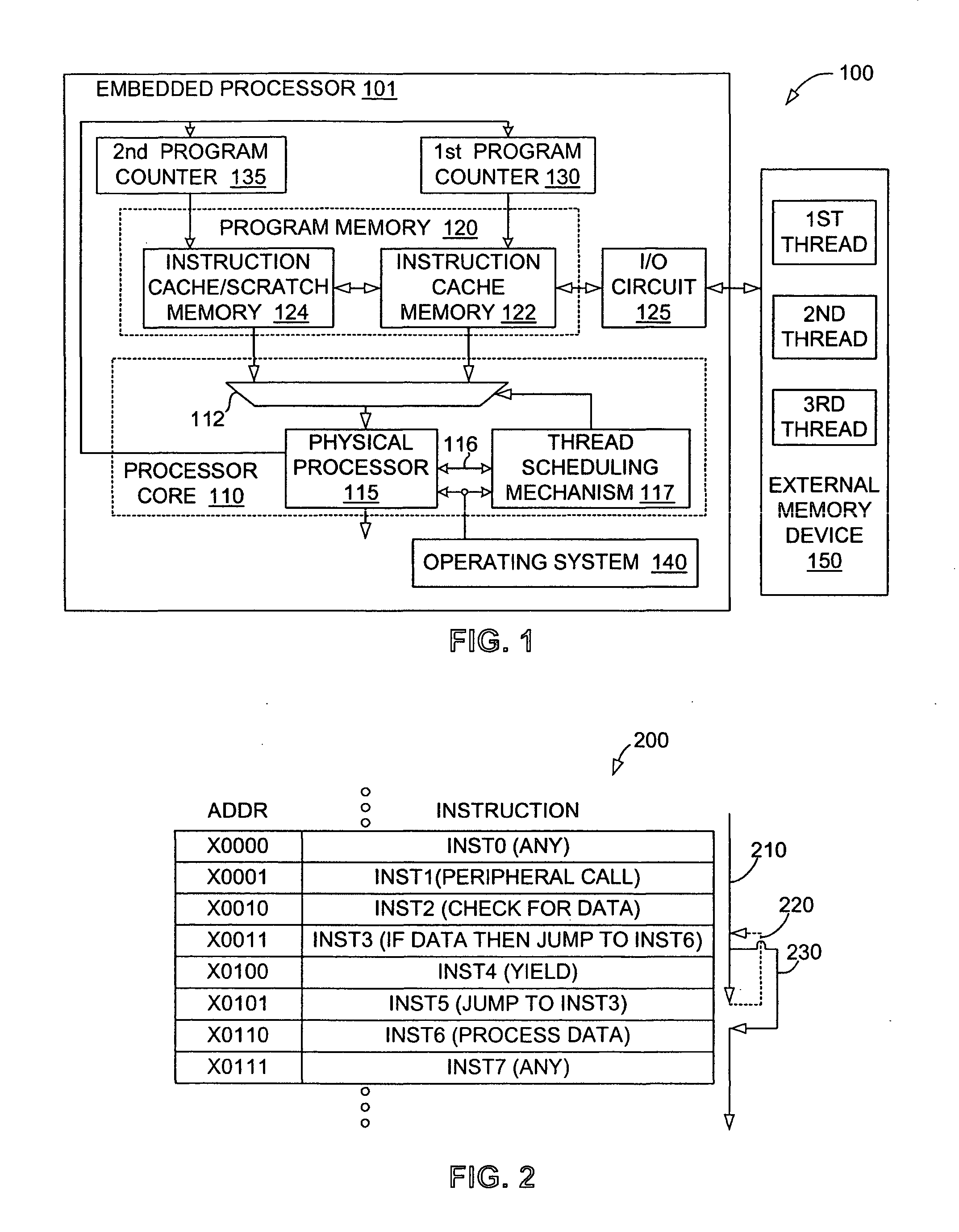

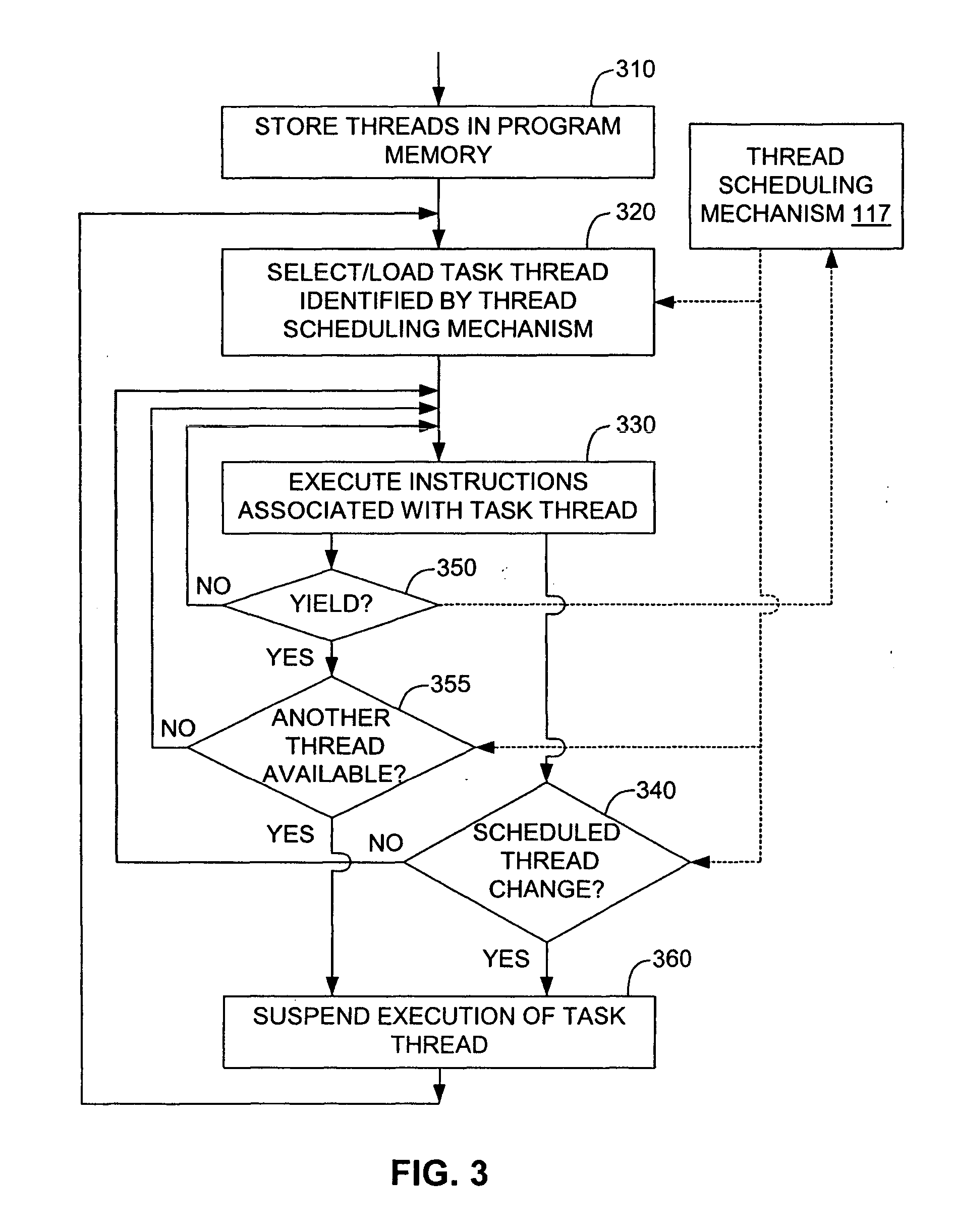

InactiveUS20050108711A1Facilitates increased processor efficiencyEasy to cleanMultiprogramming arrangementsConcurrent instruction executionControl systemThread scheduling

Owner:INFINEON TECH AG

Redundant multi-processor and logical processor configuration for a file server

A redundant file server includes at least two dual processor boards. Each physical processor has two logical processors. The first logical processor of the first physical processor of each board executes storage system code under the Microsoft NT(TM) operating system. The second logical processor of the first physical processor of each board executes control station code under the Linux operating system. The first logical processor of the second physical processor of each board executes data mover code. The second logical processor of the second physical processor of each board is kept in a stand-by mode for assuming data mover functions upon failure of the first logical processor of the second physical processor on the first or second board.

Owner:EMC IP HLDG CO LLC

Systems and Methods for Facilitating Virtualization of a Heterogeneous Processor Pool

ActiveUS20100138828A1Multiprogramming arrangementsSoftware simulation/interpretation/emulationPhysics processing unitFunctional type

A system for facilitating virtualization of a heterogeneous processor pool includes a processor allocation component and a hypervisor, each executing on a host computer. The processor allocation component identifies a plurality of physical processors available for computing and determines a set of flags, each of the set of flags identifying a type of functionality provided by each of a subset of the plurality of physical processors. The hypervisor, in communication with the processor allocation component, allocates, to at least one virtual machine, access to one of the subset of the plurality of physical processors.

Owner:CITRIX SYST INC

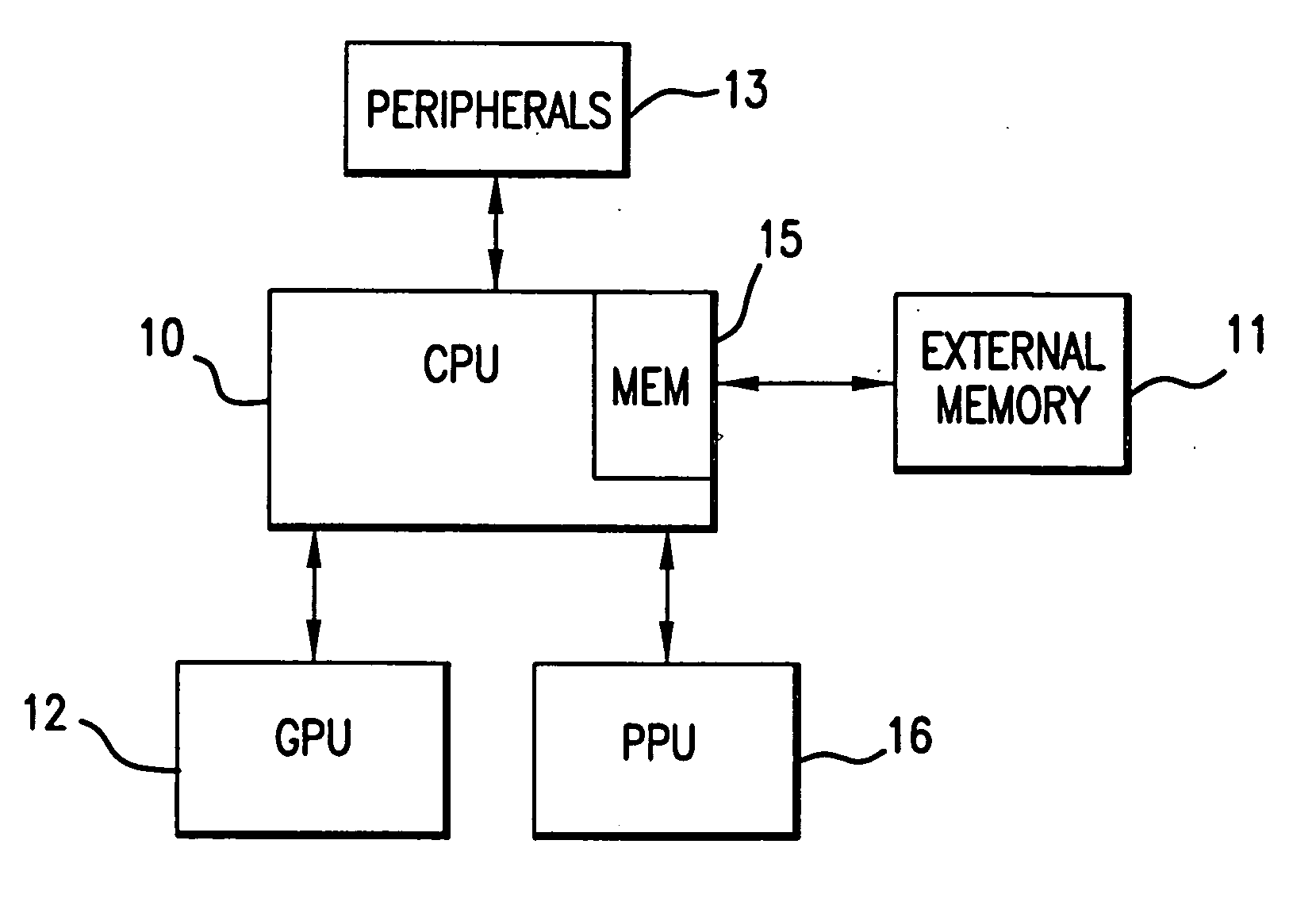

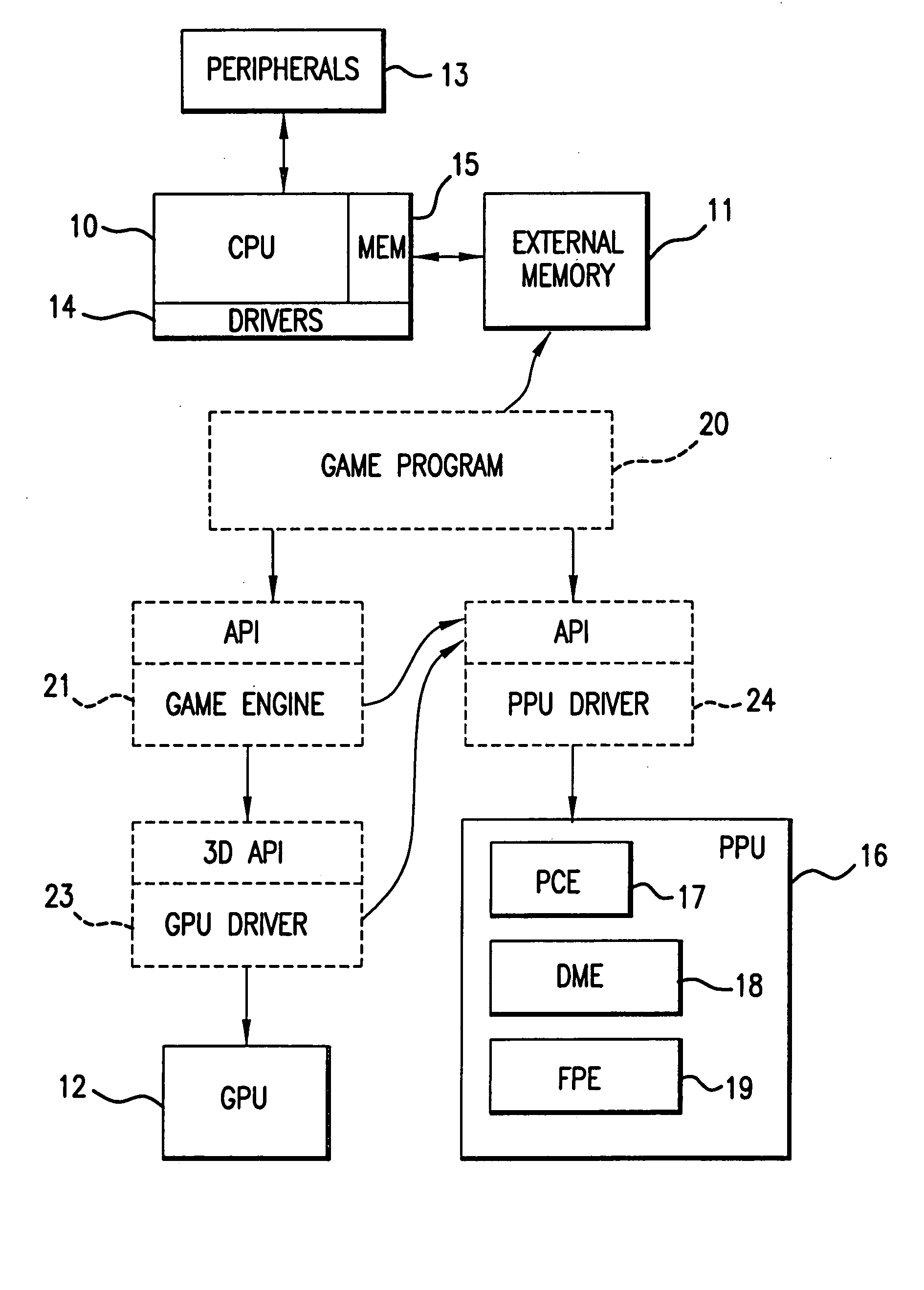

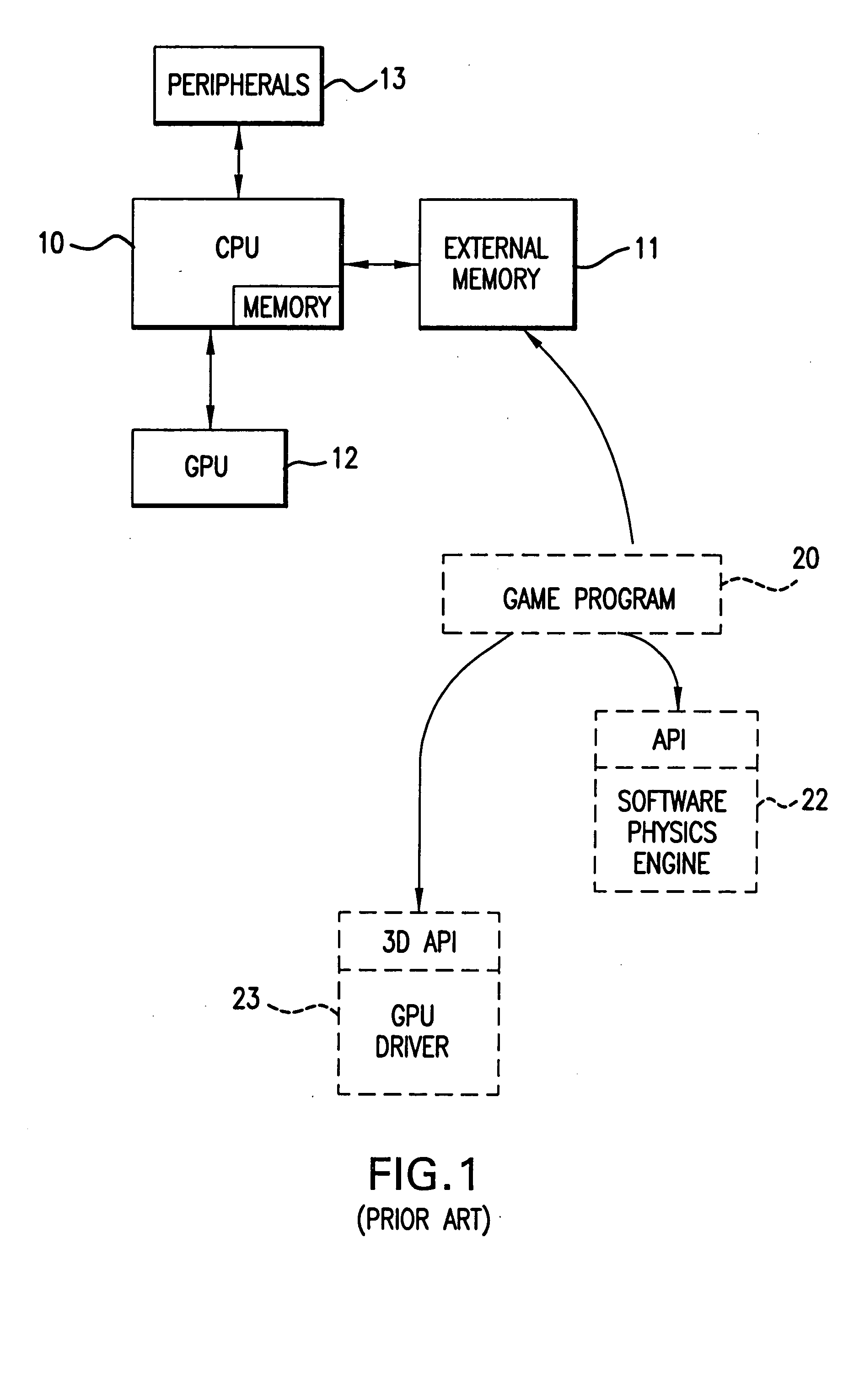

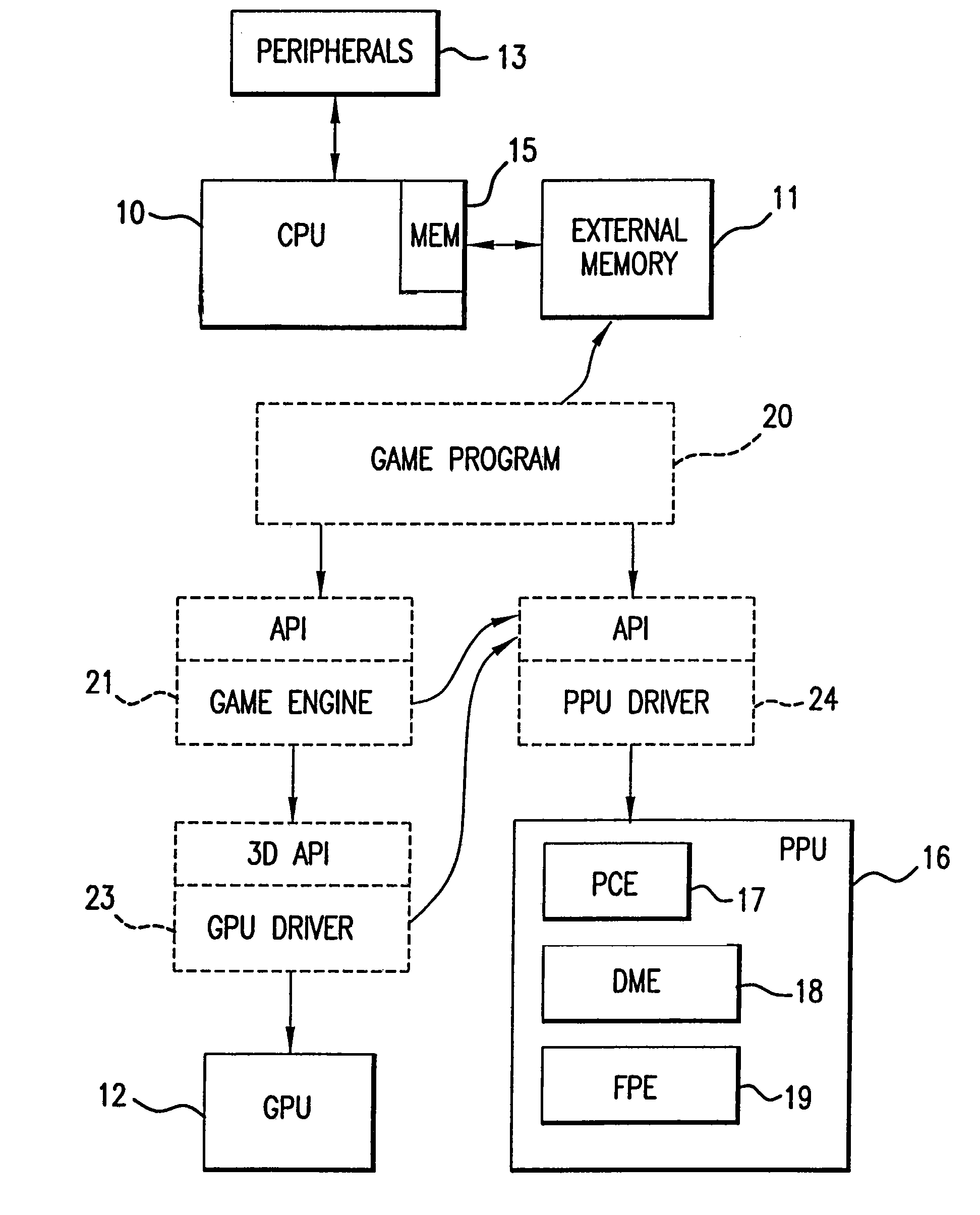

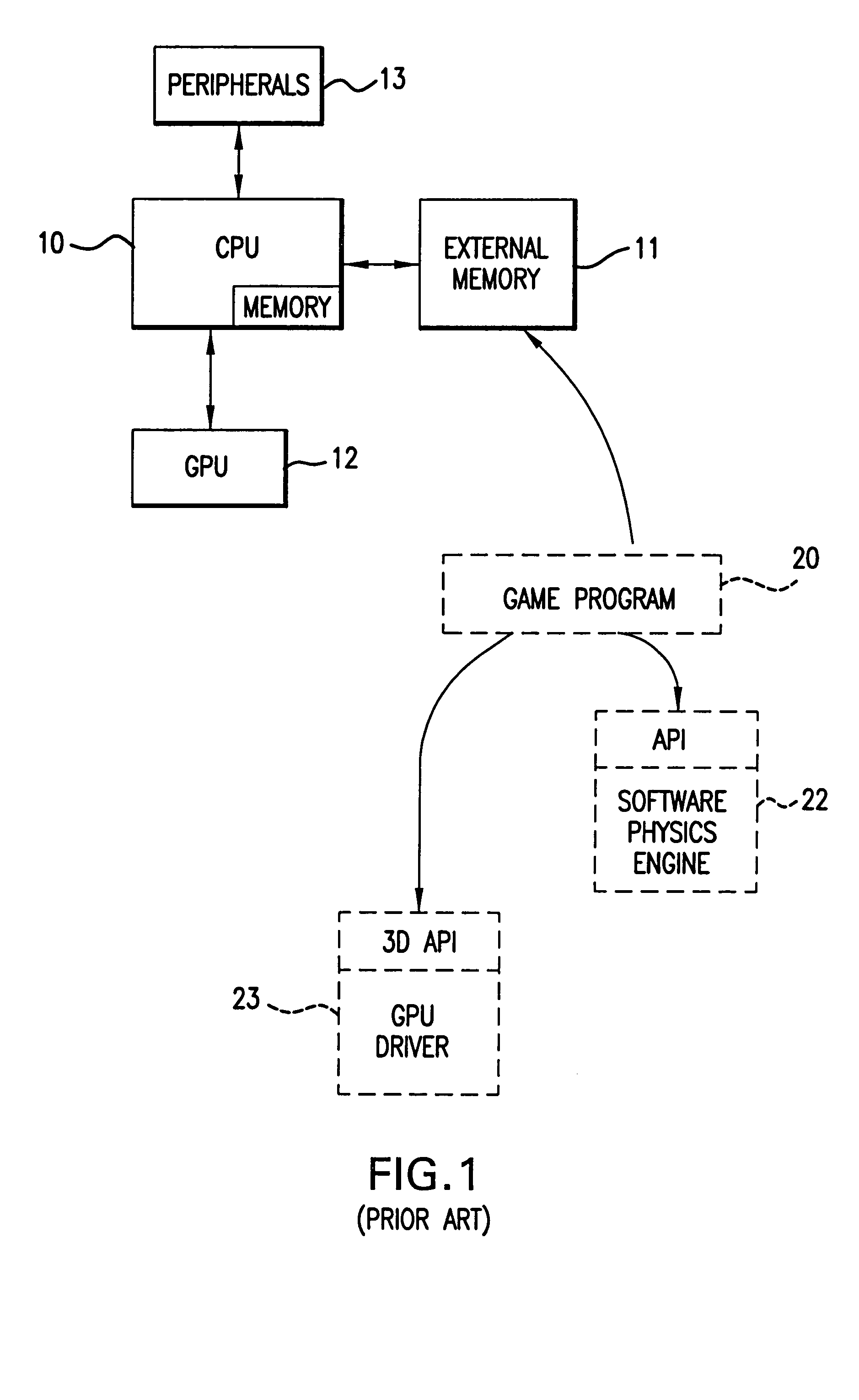

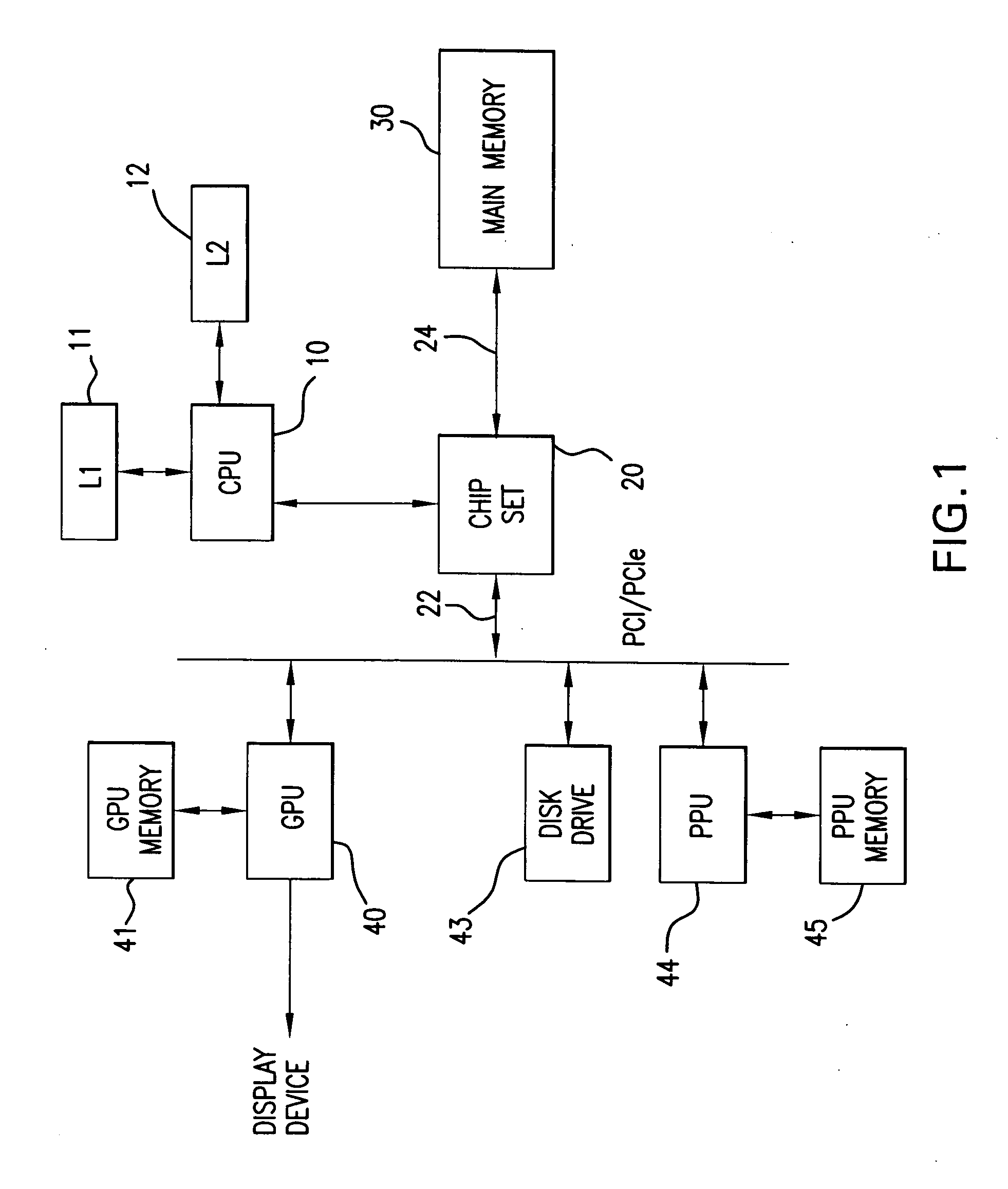

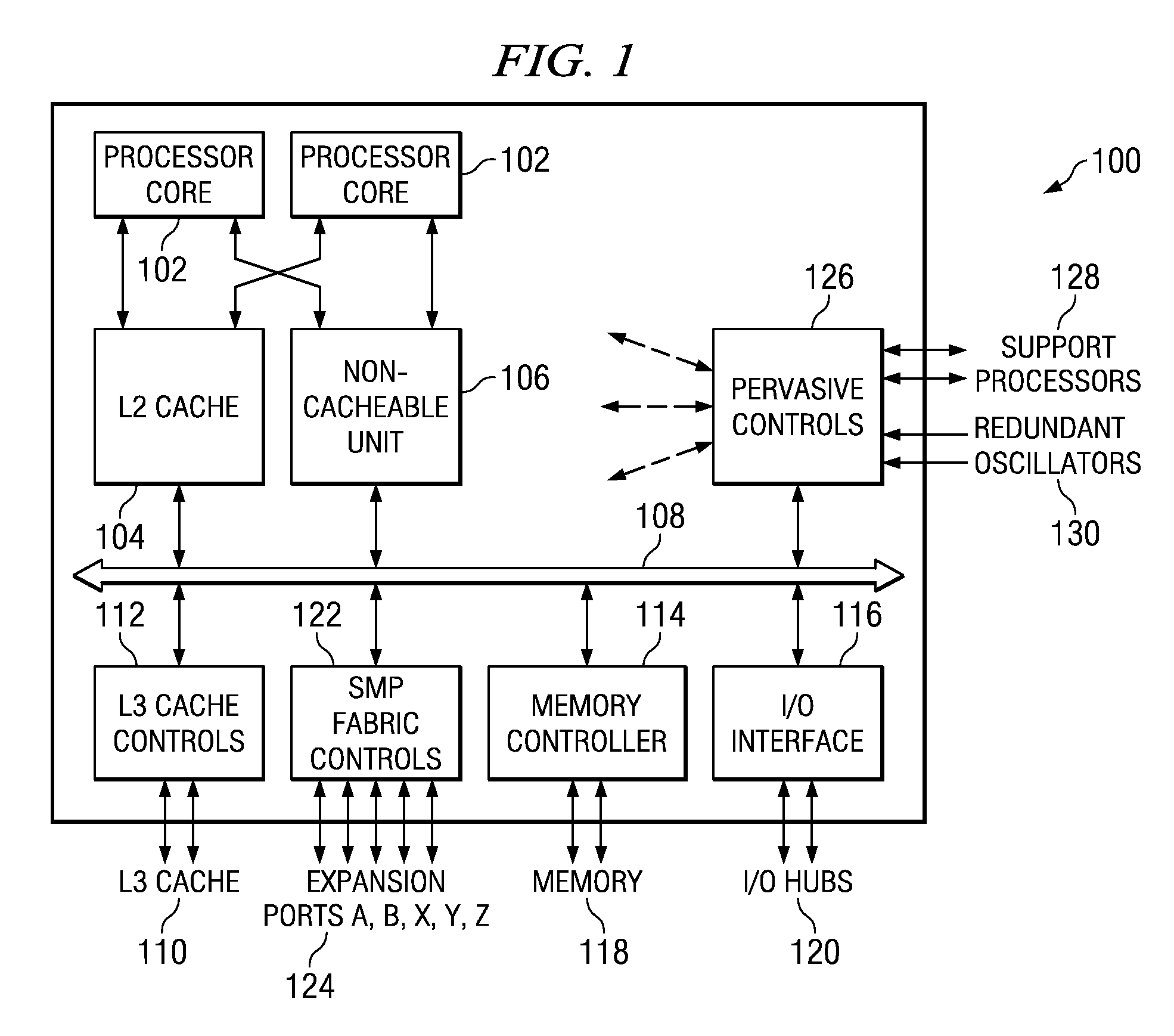

System incorporating physics processing unit

InactiveUS20050086040A1Efficient communicationEffective calculationProcessor architectures/configurationProgram controlAnimationPhysics processing unit

A system, such as a PC, incorporating a dedicated physics processing unit adapted to generate physics data for use within a physics simulation or game animation. The hardware-based physics processing unit is characterized by a unique architecture designed to efficiently calculate physics data, including multiple, parallel floating point operations.

Owner:NVIDIA CORP

Dynamic Control of Partition Memory Affinity in a Shared Memory Partition Data Processing System

InactiveUS20090307439A1Multiprogramming arrangementsNon-redundant fault processingData processing systemPhysics processing unit

Dynamic control of memory affinity is provided for a shared memory logical partition within a shared memory partition data processing system having a plurality of nodes. The memory affinity control approach includes: determining one or more home node assignments for the shared memory logical partition, with each assigned home node being one node of the plurality of nodes of the system; determining a desired physical page level per node for the shared memory logical partition; and allowing the shared memory partition to run and using the home node assignment(s) and its desired physical page level(s) in the dispatching of tasks to physical processors in the nodes and in hypervisor page memory management to dynamically control memory affinity of the shared memory logical partition in the data processing system.

Owner:IBM CORP

Hetergeneous processor apparatus and method

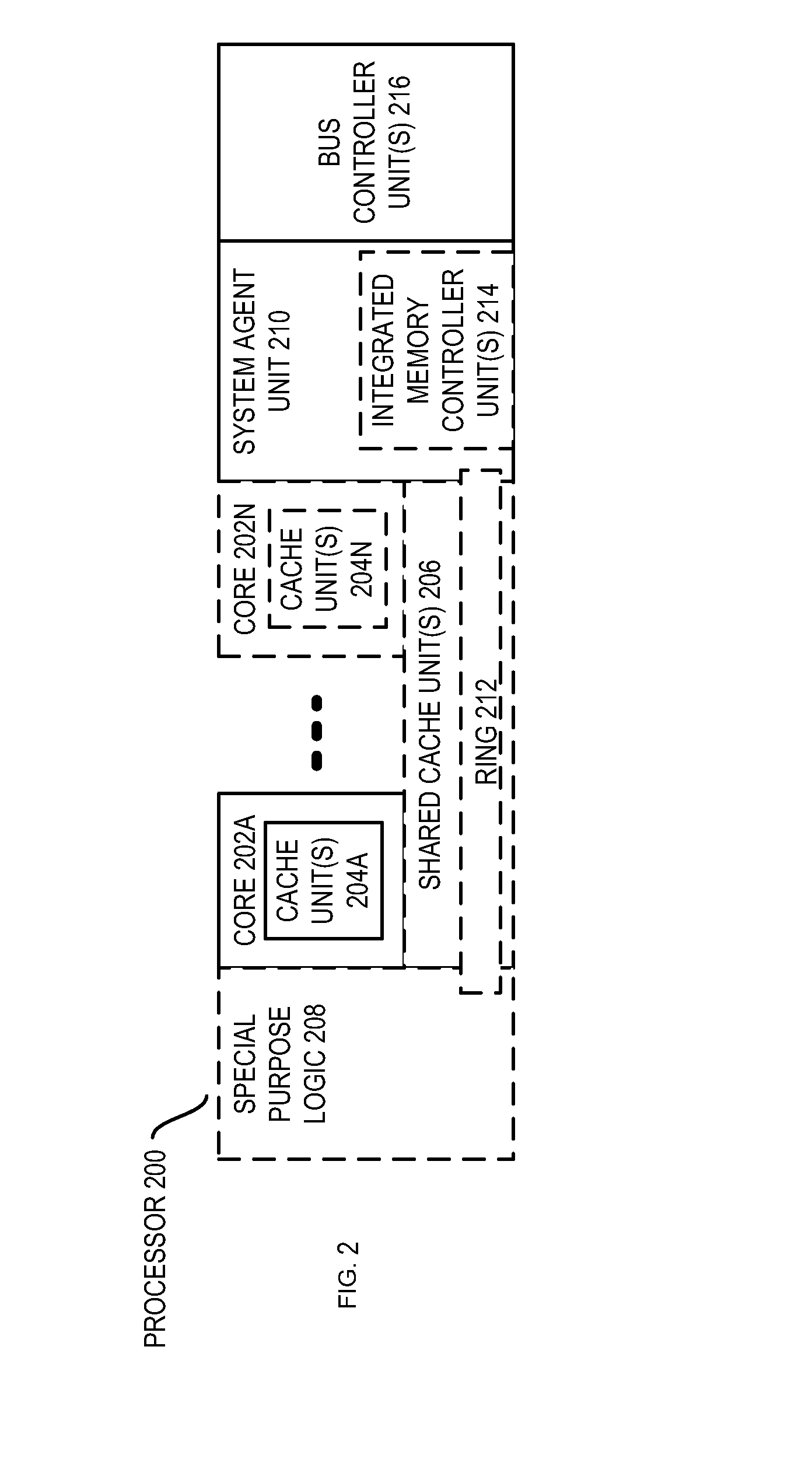

A heterogeneous processor architecture is described. For example, a processor according to one embodiment of the invention comprises: a first set of one or more physical processor cores having first processing characteristics; a second set of one or more physical processor cores having second processing characteristics different from the first processing characteristics; virtual-to-physical (V-P) mapping logic to expose a plurality of virtual processors to software, the plurality of virtual processors to appear to the software as a plurality of homogeneous processor cores, the software to allocate threads to the virtual processors as if the virtual processors were homogeneous processor cores; wherein the V-P mapping logic is to map each virtual processor to a physical processor within the first set of physical processor cores or the second set of physical processor cores such that a thread allocated to a first virtual processor by software is executed by a physical processor mapped to the first virtual processor from the first set or the second set of physical processors.

Owner:INTEL CORP

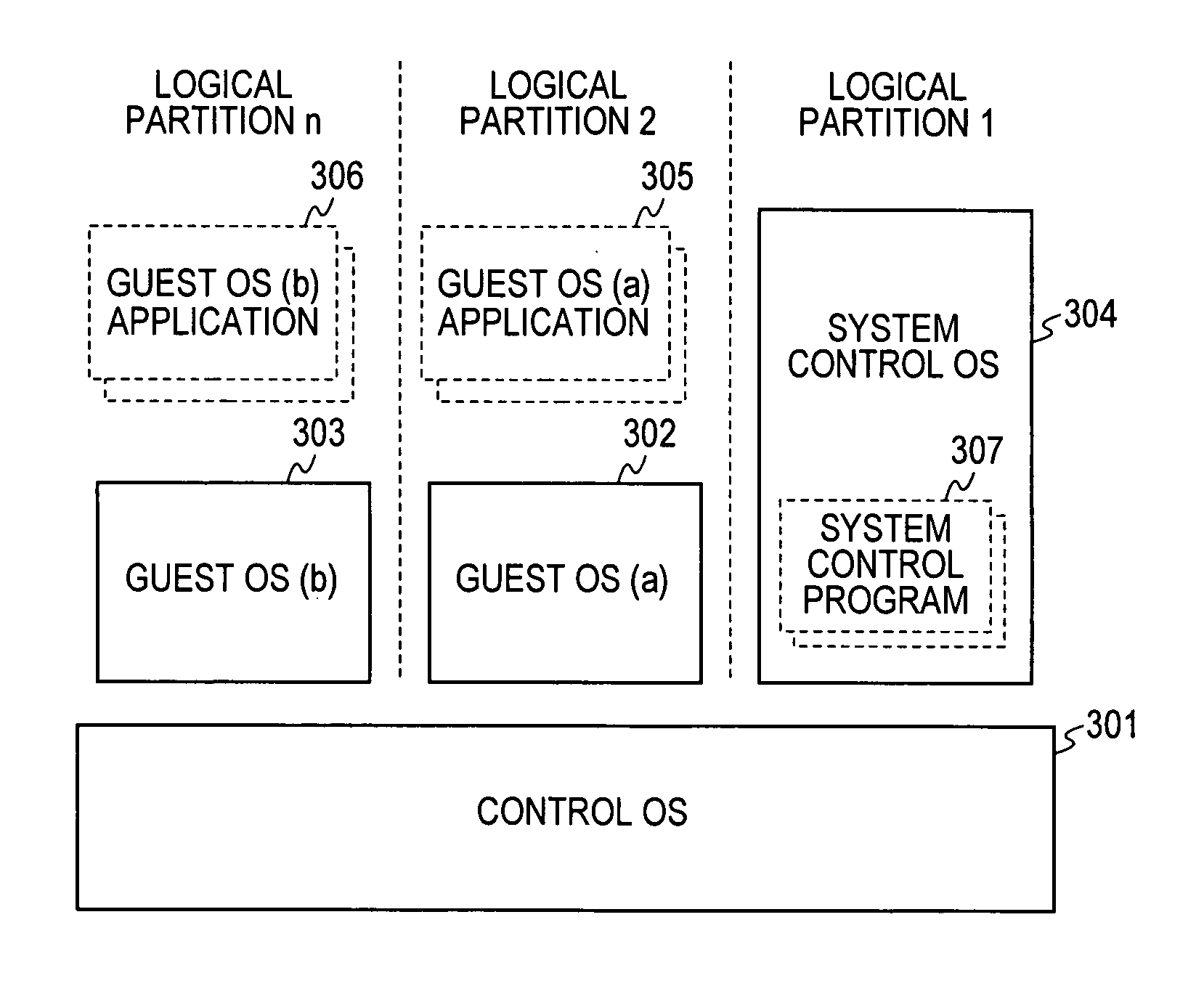

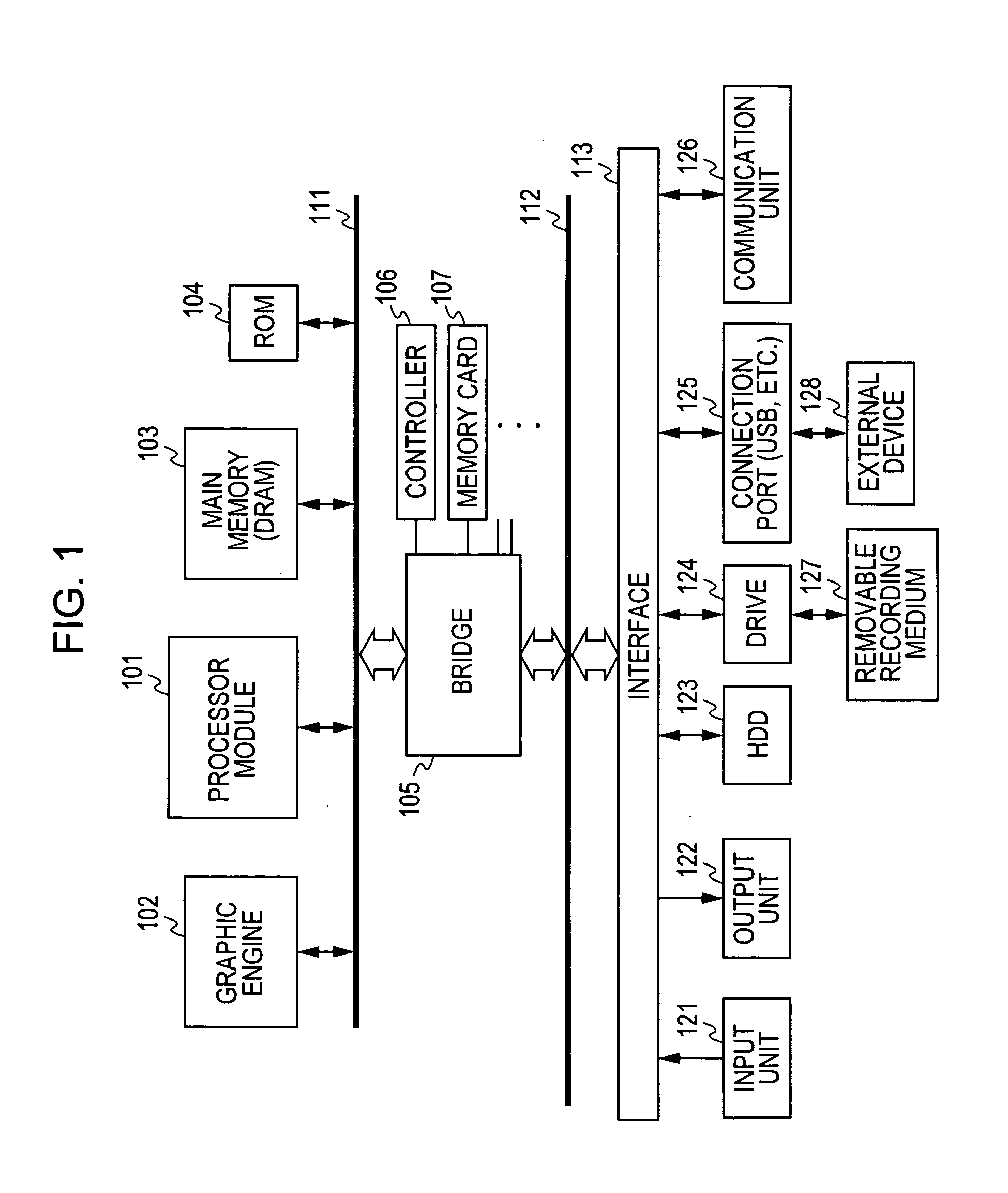

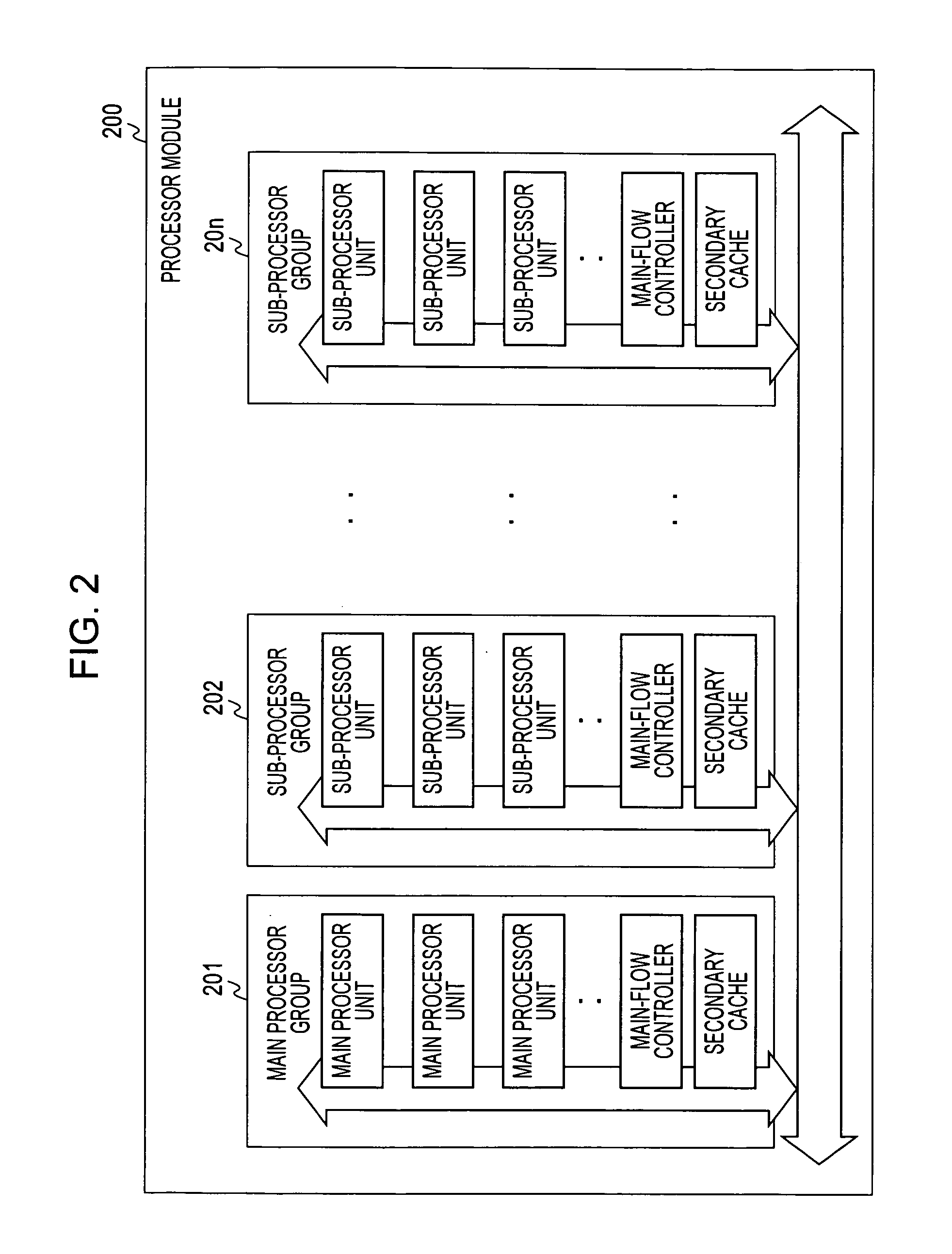

Information processing apparatus, process control method, and computer program

InactiveUS20060075207A1Efficient data processingHigh access frequencyMemory adressing/allocation/relocationMultiprogramming arrangementsInformation processingOperational system

An information processing apparatus includes a control operating system executing a process for allocating a plurality of logical processors to a physical processor in a time division manner, and a guest operating system for which a logical partition as an application entity of the logical processor is set. The control operating system sets and updates, as address conversion tables for determining an allocation relationship between the logical processor and the physical processor, two address conversion tables of a first conversion table that sets an allocation relationship between a logical partition address space and a physical address space and a second conversion table that sets an allocation relationship between a virtual address space in the guest operating system and the physical address space.

Owner:SONY CORP

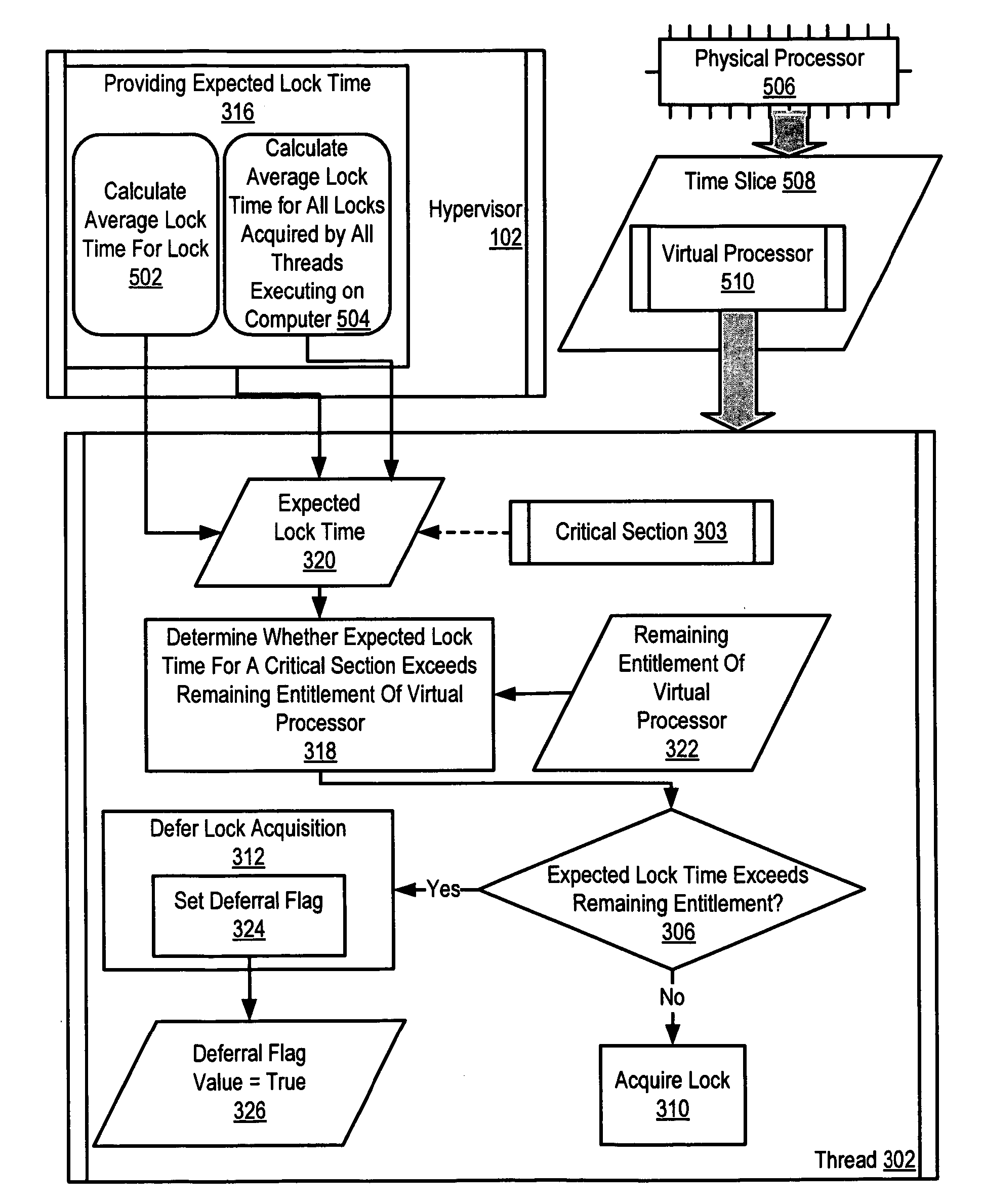

Administration of locks for critical sections of computer programs in a computer that supports a multiplicity of logical partitions

InactiveUS20060277551A1Multiprogramming arrangementsSoftware simulation/interpretation/emulationCritical sectionPhysics processing unit

Administration of locks for critical sections of computer programs in a computer that supports a multiplicity of logical partitions that include determining by a thread executing on a virtual processor executing in a time slice on a physical processor whether an expected lock time for a critical section of the thread exceeds a remaining entitlement of the virtual processor in the time slice and deferring acquisition of a lock if the expected lock time exceeds the remaining entitlement.

Owner:IBM CORP

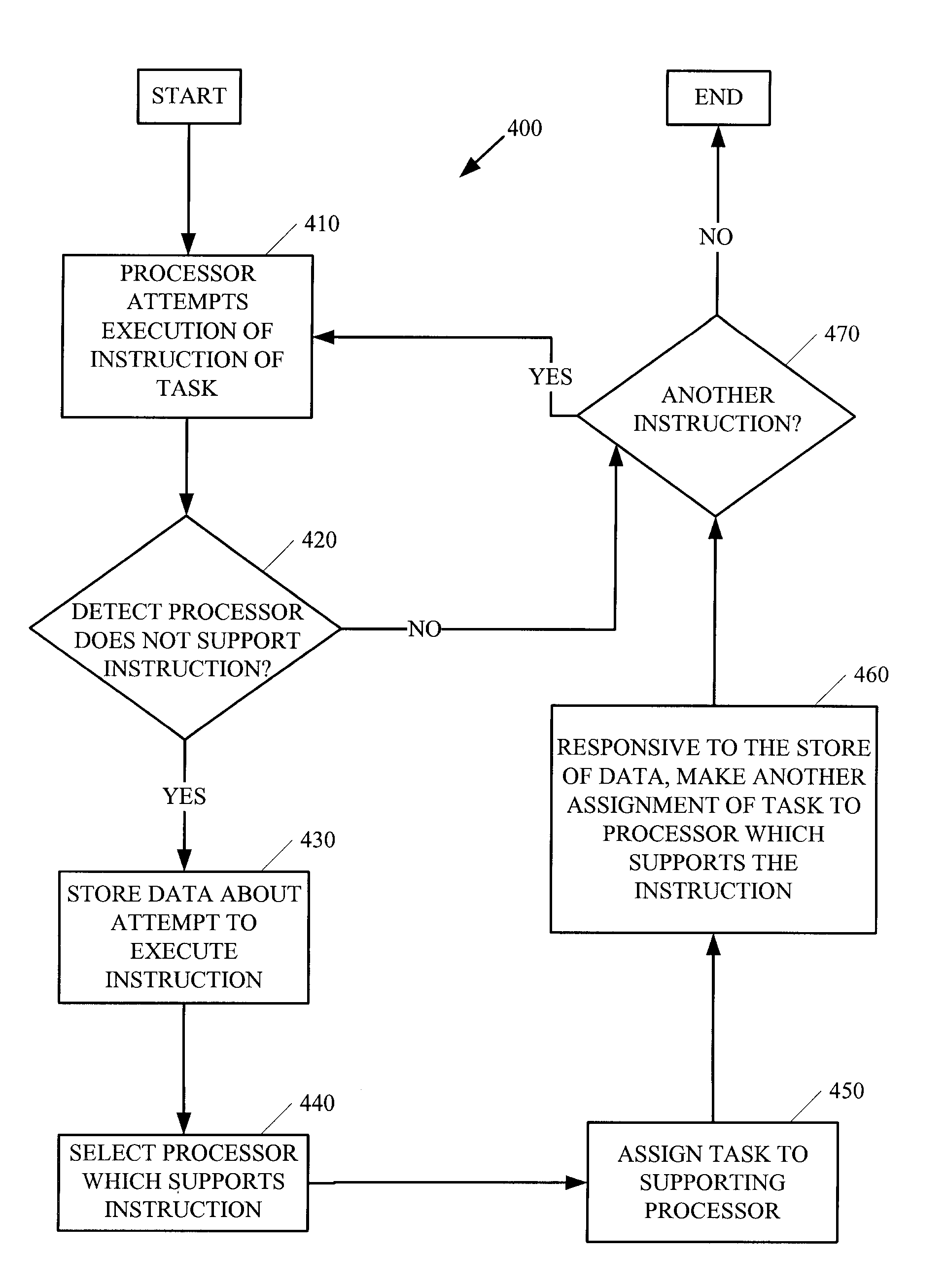

Assigning tasks to processors in heterogeneous multiprocessors

ActiveUS20090037911A1General purpose stored program computerMultiprogramming arrangementsPhysics processing unitInstruction set

Methods and arrangements of assigning tasks to processors are discussed. Embodiments include transformations, code, state machines or other logic to detect an attempt to execute an instruction of a task on a processor not supporting the instruction (non-supporting processor). The method may involve selecting a processor supporting the instruction (supporting physical processor). In many embodiments, the method may include storing data about the attempt to execute the instruction and, based upon the data, making another assignment of the task to a physical processor supporting the instruction. In some embodiments, the method may include representing the instruction set of a virtual processor as the union of the instruction sets of the physical processors comprising the virtual processor and assigning a task to the virtual processor based upon the representing.

Owner:IBM CORP

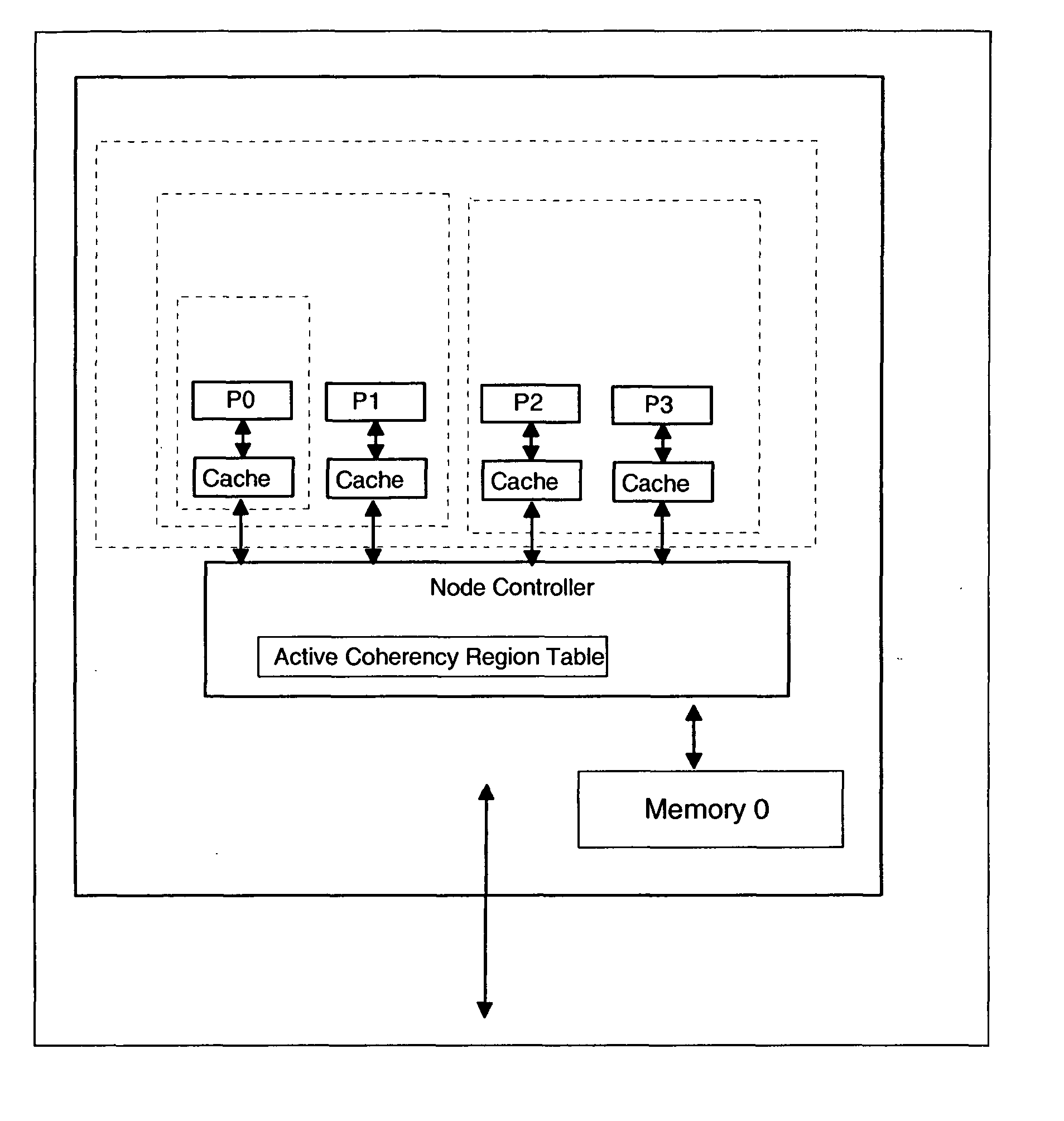

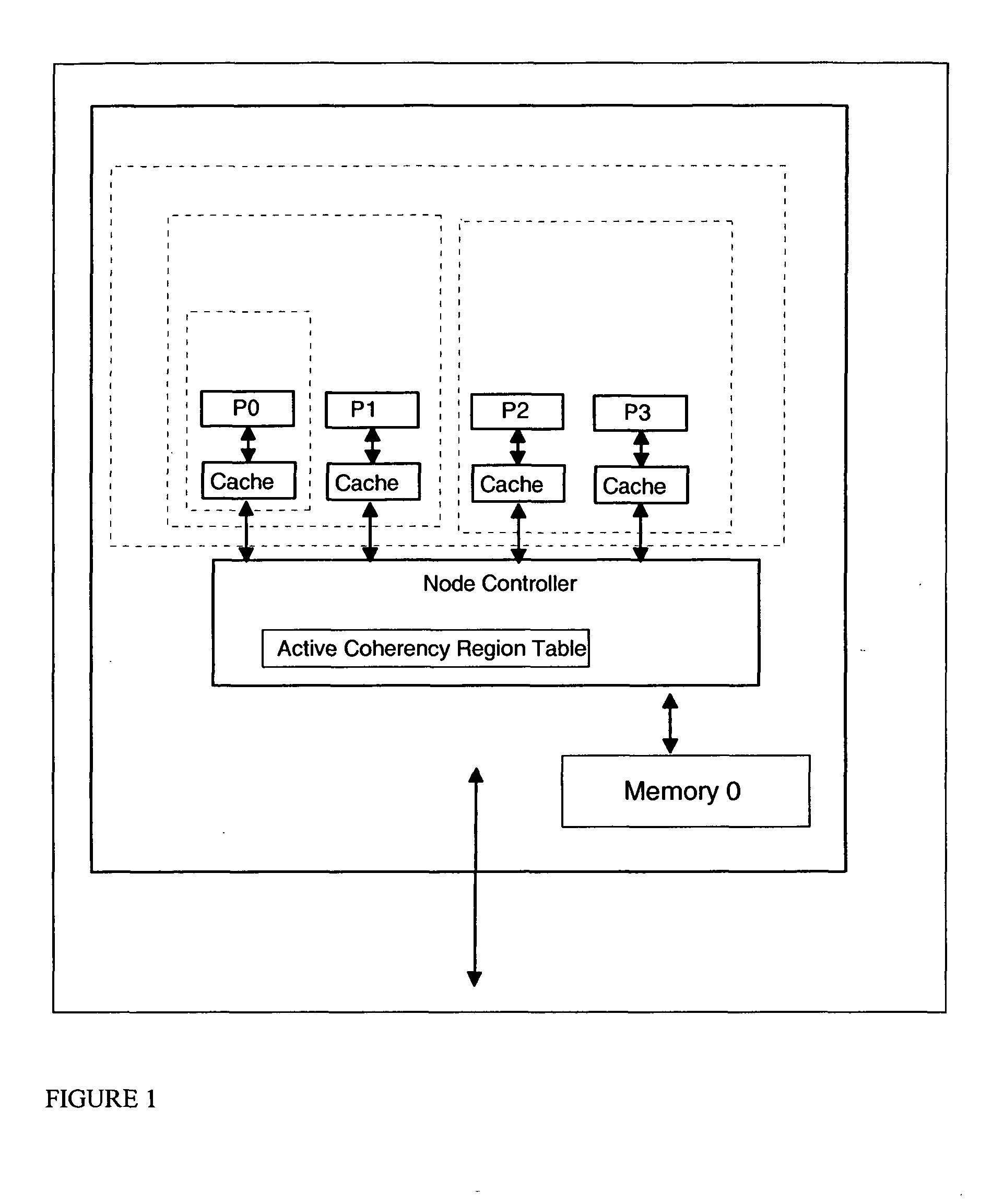

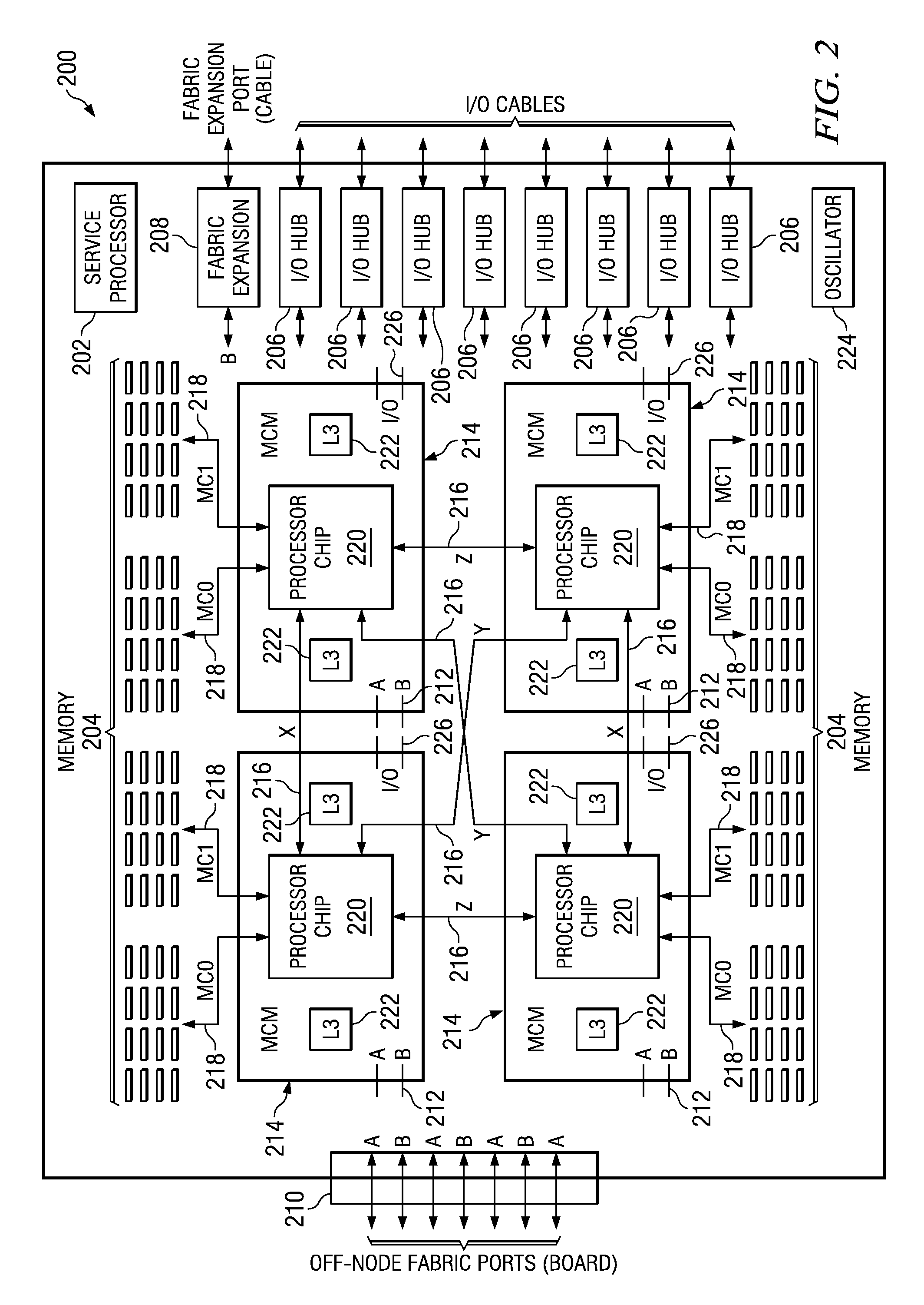

Multiprocessor computer system having multiple coherency regions and software process migration between coherency regions without cache purges

InactiveUS20050021913A1Eliminate needMemory architecture accessing/allocationMemory adressing/allocation/relocationMulti processorPhysics processing unit

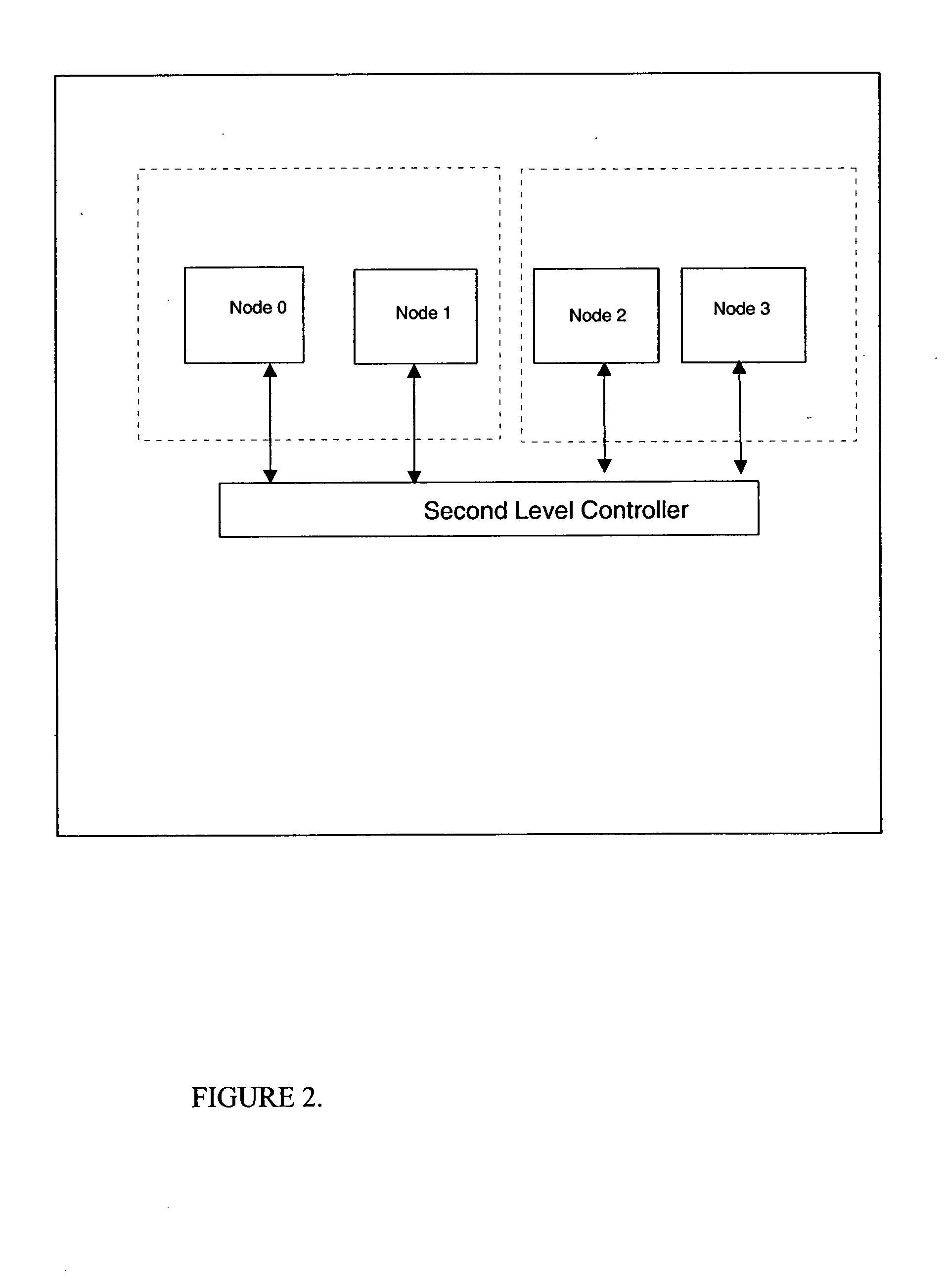

A multiprocessor computer system has a plurality of processing nodes which use processor state information to determine which coherent caches in the system are required to examine a coherency transaction produced by a single originating processor's storage request. A node of the computer has dynamic coherency boundaries such that the hardware uses only a subset of the total processors in a large system for a single workload at any specific point in time and can optimize the cache coherency as the supervisor software or firmware expands and contracts the number of processors which are being used to run any single workload. Multiple instances of a node can be connected with a second level controller to create a large multiprocessor system. The node controller uses the mode bits to determine which processors must receive any given transaction that is received by the node controller. The second level controller uses the mode bits to determine which nodes must receive any given transaction that is received by the second level controller. Logical partitions are mapped to allowable physical processors. Cache coherence regions which encompass subsets of the total number of processors and caches in the system are chosen for their physical proximity. A distinct cache coherency region can be defined for each partition using a hypervisor.

Owner:IBM CORP

Virtualizing the execution of homogeneous parallel systems on heterogeneous multiprocessor platforms

InactiveUS20080163206A1SavingClosely matchedEnergy efficient ICTError detection/correctionVirtualizationPhysics processing unit

A method of virtual processing includes running a virtual processor (1), which when the virtual processor (1) encounters a faulting instruction unmaps the virtual processor (1) from the physical processor (A), and generates a list of other of the physical processors that could execute the instruction. Then determines if one of the other of the physical processors in the list is currently idle, and when one of the other of the physical processors in the list is determined to be currently idle, maps the virtual processor (1) to a physical processor (B) which is the one of the other of the physical processors in the list that was determined to be currently idle.

Owner:IBM CORP

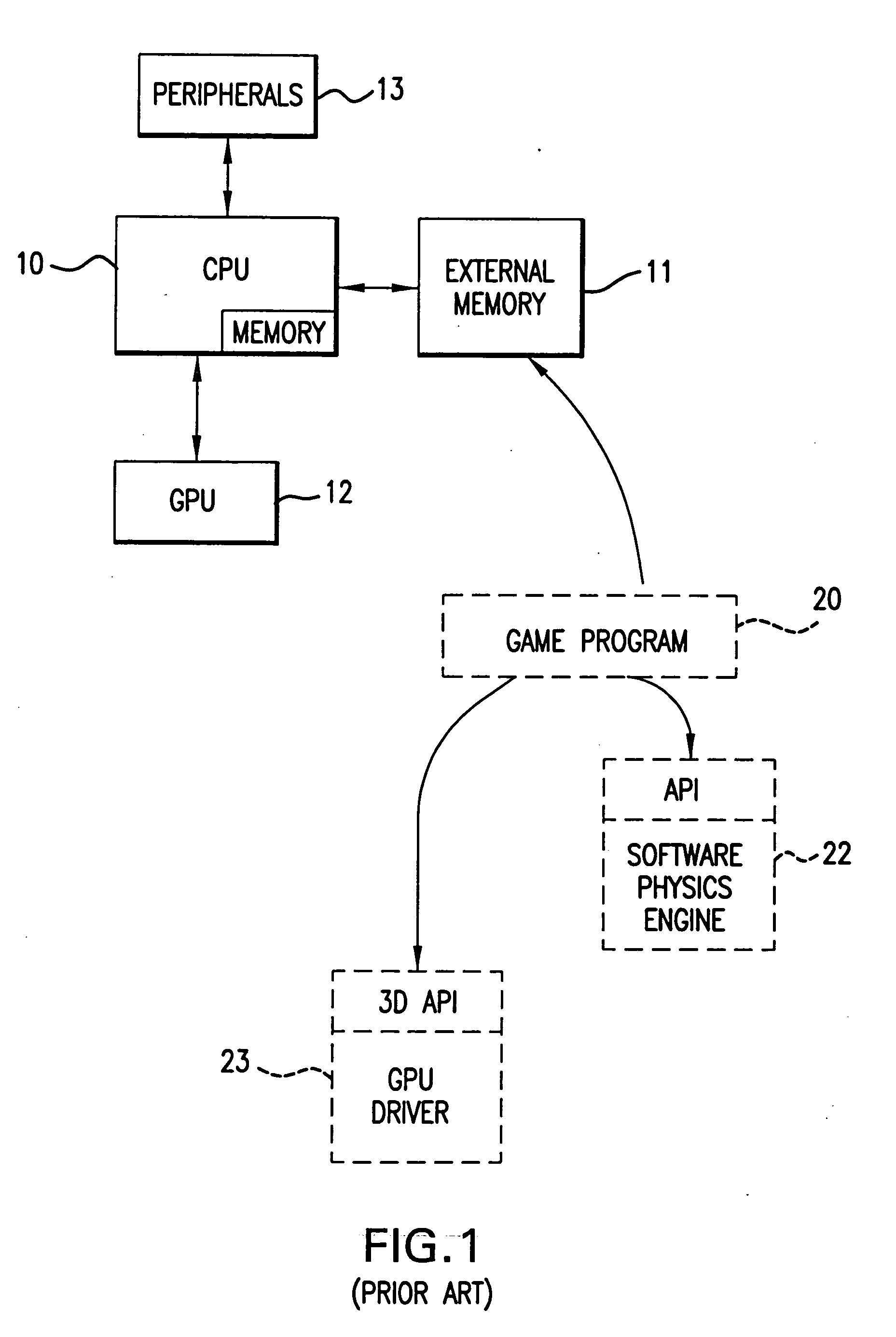

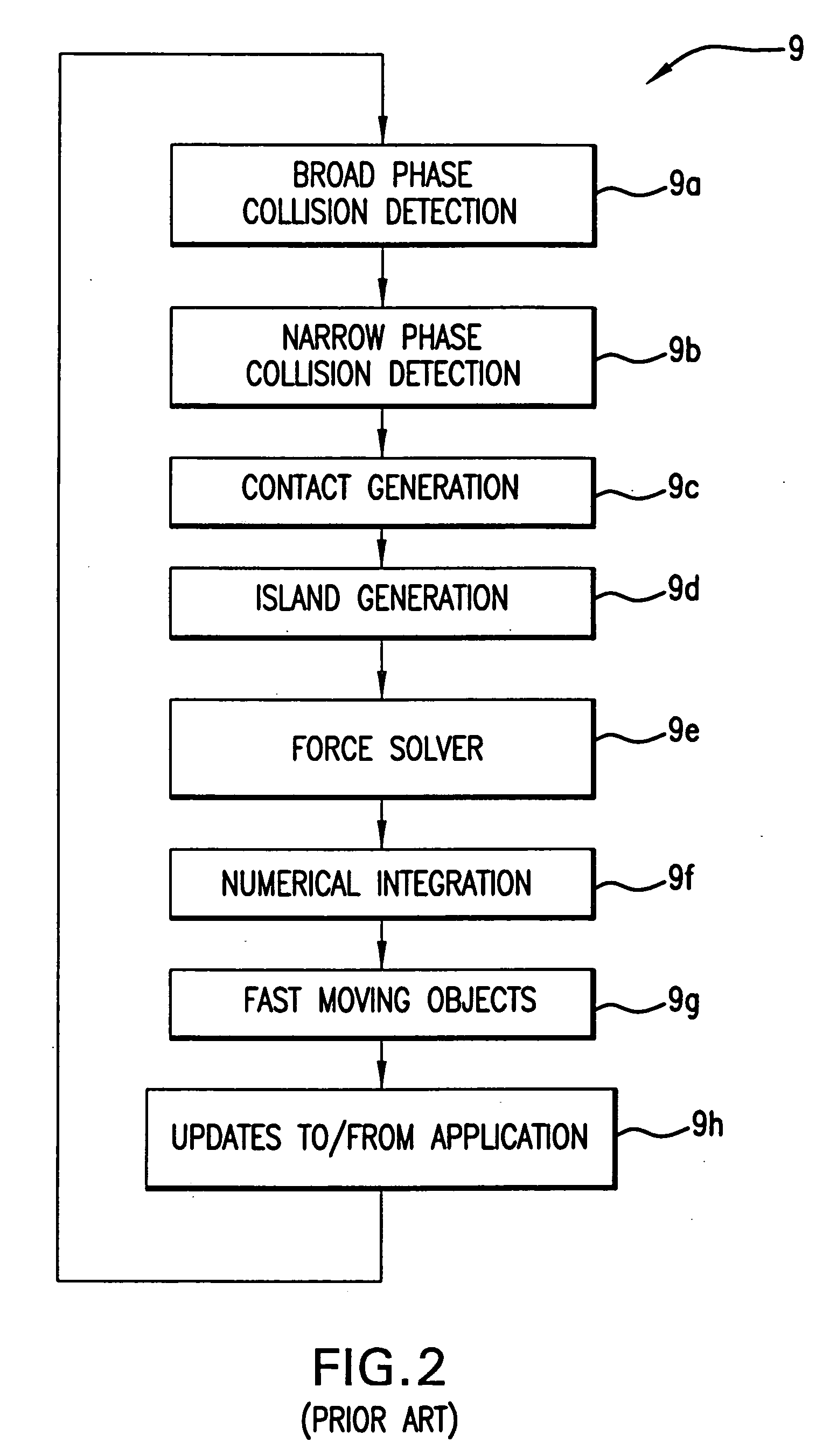

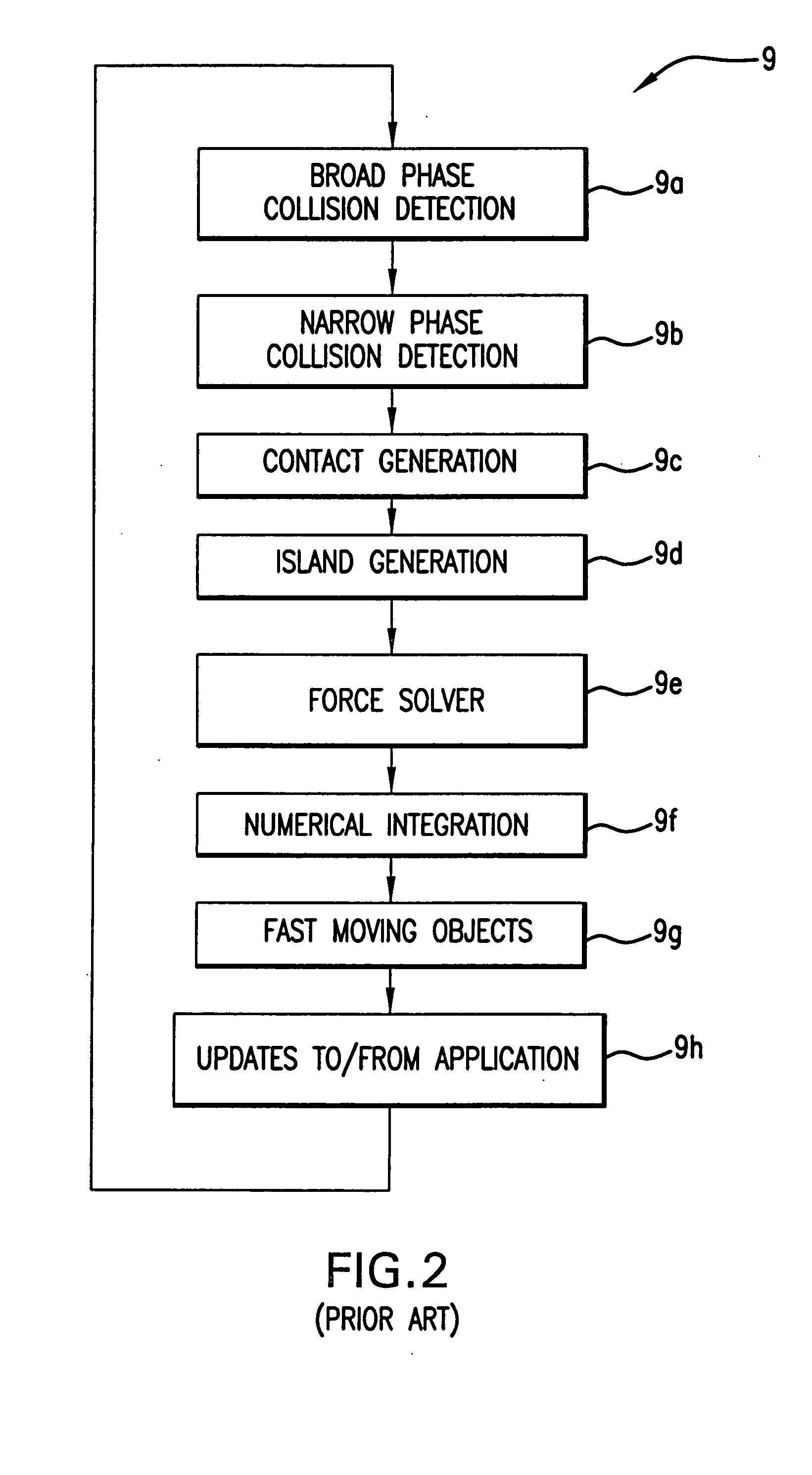

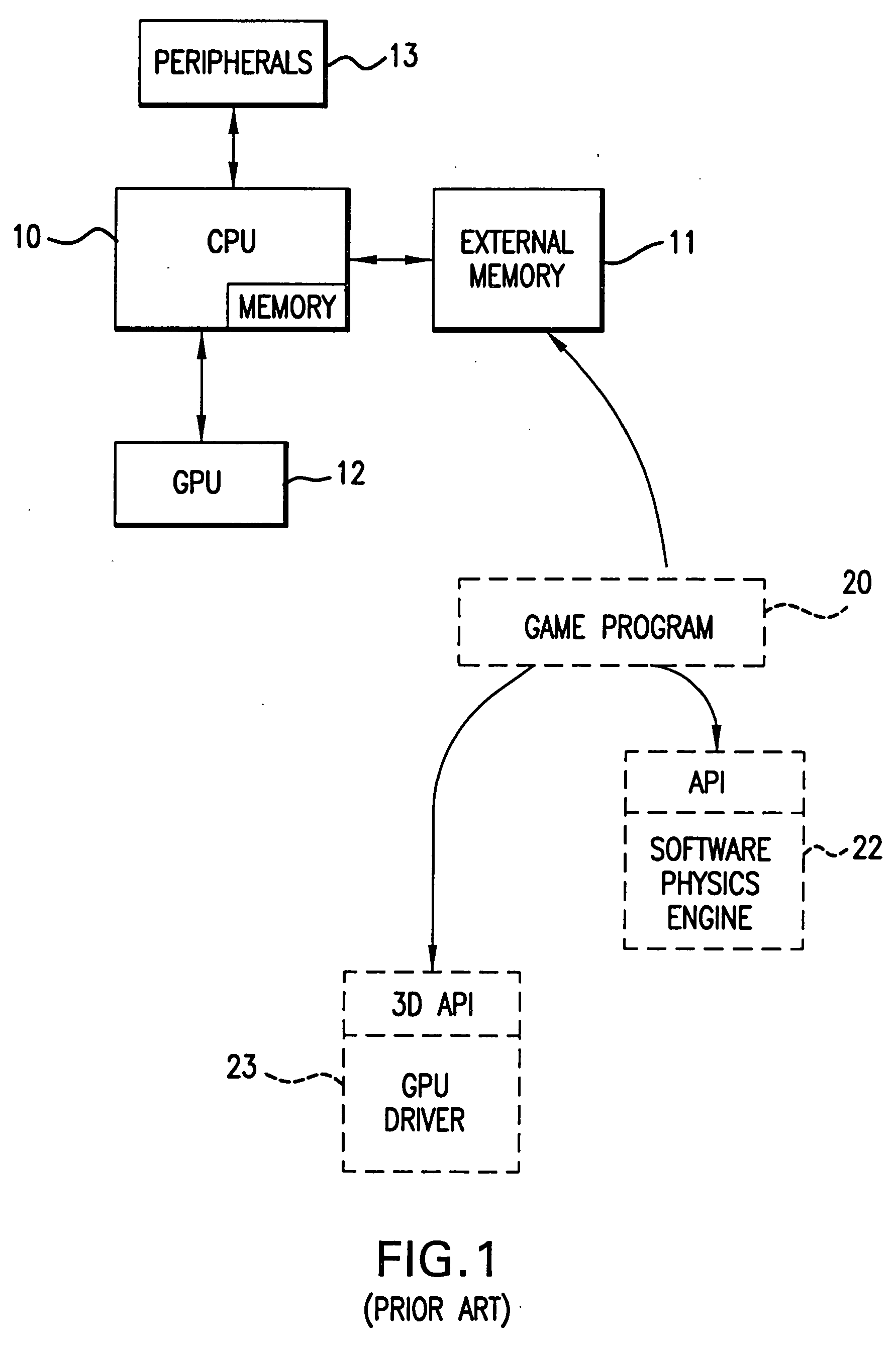

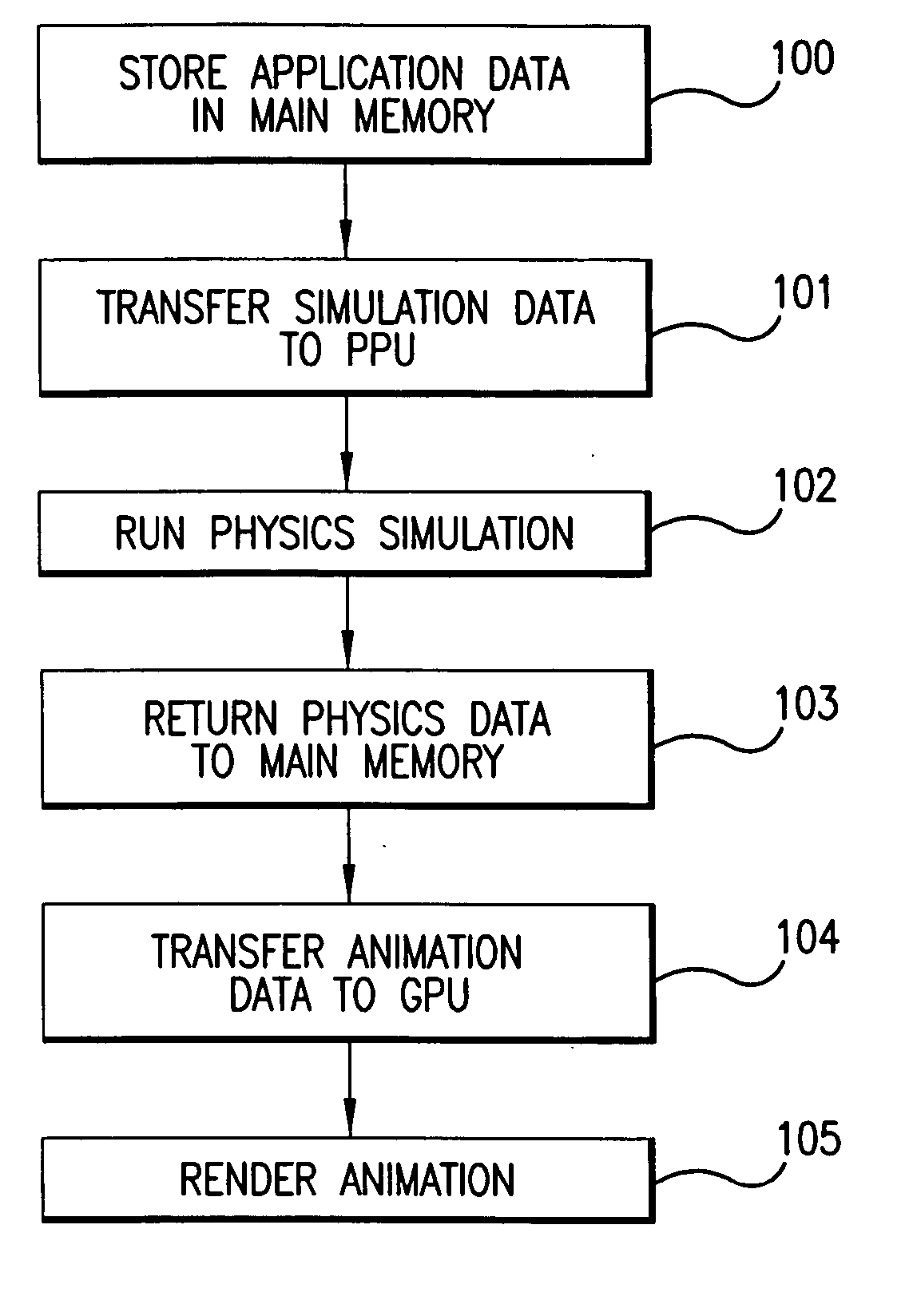

Method for providing physics simulation data

ActiveUS20050075154A1Maximize efficiencyEfficient communicationVideo gamesSpecial data processing applicationsProcessing elementPhysics processing unit

A method of providing physics data within a game program or simulation using a hardware-based physics processing unit having unique architecture designed to efficiently calculate physics related data.

Owner:NVIDIA CORP

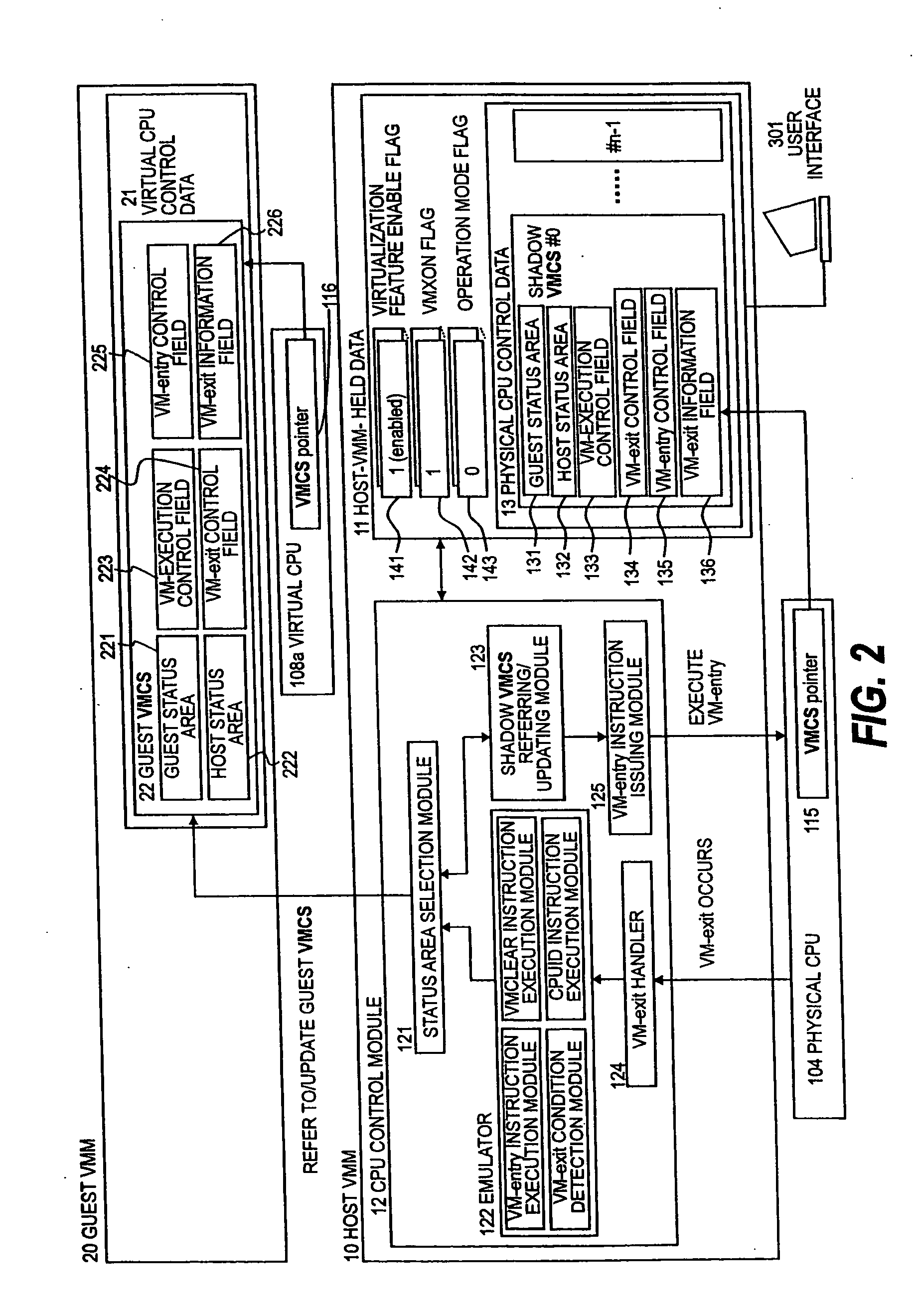

Method for controlling a virtual machine and a virtual machine system

InactiveUS20090007112A1Improve performanceSoftware simulation/interpretation/emulationMemory systemsVirtualizationPhysics processing unit

A next-generation OS with a virtualization feature is executed as a user program on a first virtual processor by selecting, in response to a cause of a call for a host VMM, one of a guest status area (221) for executing a user program on a second virtual processor and a host status area (222) for executing the guest VMM, and by updating a guest status area (131) of a shadow VMCS for controlling a physical processor. Accordingly, without a decrease in performance of a virtual computer, the next-generation OS incorporating the virtualization feature is executed on a virtual server, and the next-generation OS and an existing OS are integrated on a single physical computer.

Owner:HITACHI LTD

Physics processing unit

ActiveUS20050075849A1Reduce pointsEfficient communicationGeneral purpose stored program computerComputation using non-denominational number representationPhysics processing unit

A hardware-based physics processing unit having unique architecture designed to efficiently calculate physics data.

Owner:NVIDIA CORP

Method for providing physics simulation data

ActiveUS7739479B2Efficient communicationEffective calculationMultiple digital computer combinationsProgram controlPhysics processing unit

A method of providing physics data within a game program or simulation using a hardware-based physics processing unit having unique architecture designed to efficiently calculate physics related data.

Owner:NVIDIA CORP

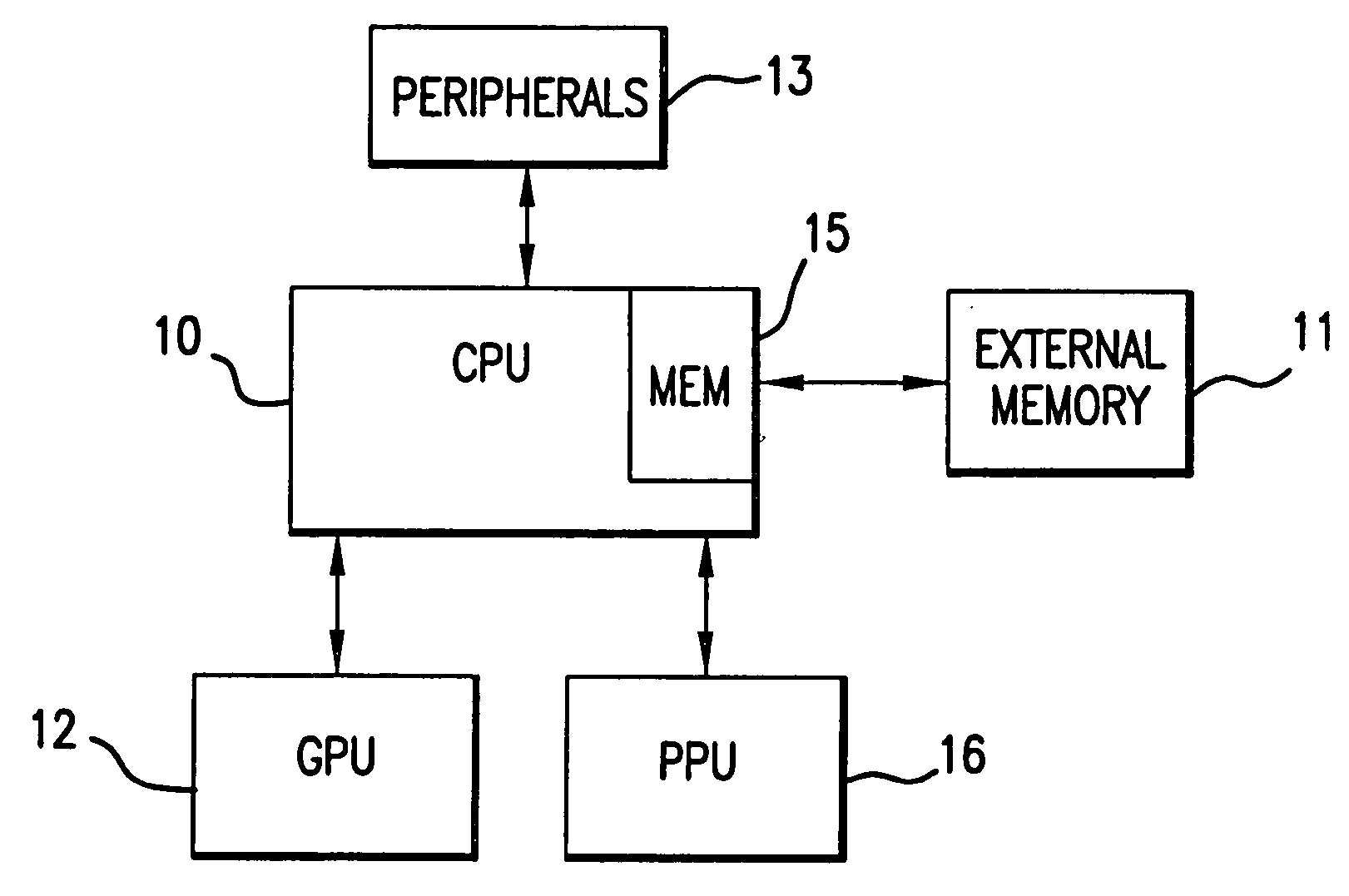

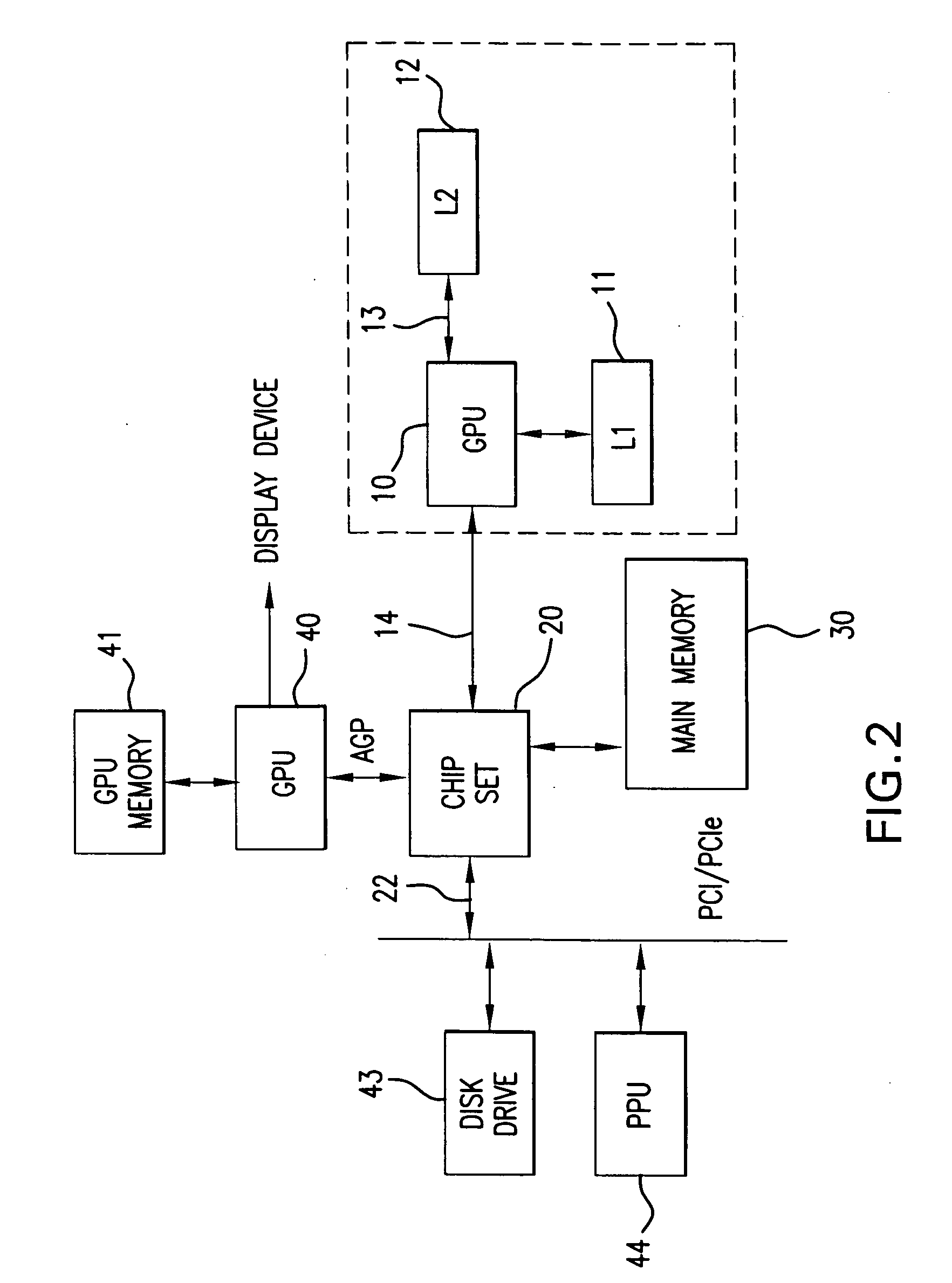

System with PPU/GPU architecture

ActiveUS20060106591A1Generate efficientlyComputing modelsMultiple digital computer combinationsComputational scienceGraphics

A PPU-enhanced system is described in which a Physics Processing Unit (PPU) and a Graphics Processing Unit (GPU) are connected with the system.

Owner:NVIDIA CORP

Virtual machine dispatching to maintain memory affinity

InactiveUS20080163203A1Software simulation/interpretation/emulationMemory systemsData processing systemPhysics processing unit

A computer implemented method, data processing system, and computer usable program code are provided for dispatching virtual processors. A determination is made as to whether a physical processor in a set of physical processors is idle, and, if so, a determination is made as to whether an affinity map for the idle physical processor exists. Responsive to an existence of the affinity map, a determination is made as to whether a virtual processor last mapped to the idle physical processor is ready to run using the affinity map and a dispatch algorithm. Responsive to identifying a ready-to-run virtual processor whose affinity map indicates that the idle physical processor is mapped to this virtual processor in its preceding dispatch, the ready-to-run virtual processor is dispatched to the idle physical processor. Thus, memory affinity is maintained between physical and virtual processors when the memory affinity is not expired.

Owner:IBM CORP

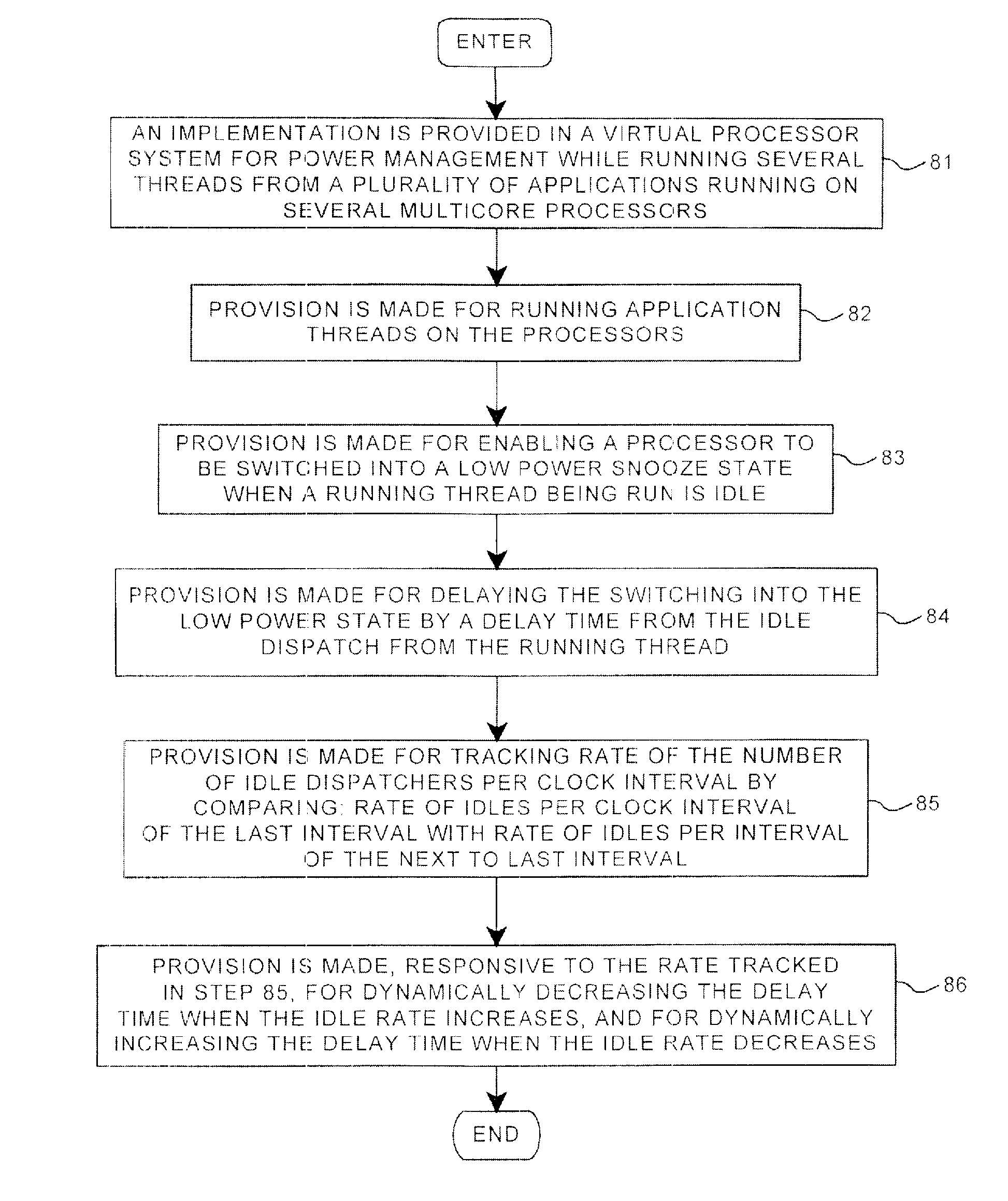

Optimizing power management in multicore virtual machine platforms by dynamically variable delay before switching processor cores into a low power state

InactiveUS20110246800A1Easy to useImprove effectivenessEnergy efficient ICTVolume/mass flow measurementDelayed timePhysics processing unit

Distributing a thread for running on a physical processor and enabling the physical processor to be switched into a low power snooze state when said running thread is IDLE. However, this switching into said low power state is enabled to be delayed by a delay time from an IDLE dispatch from said running thread; such delay is determined by tracking the rate of the number of said IDLE dispatches per processor clock interval and dynamically varying said delay time wherein the delay time is decreased when said rate of IDLE dispatches increases and the delay time is increased when said rate of IDLE dispatches decreases.

Owner:IBM CORP

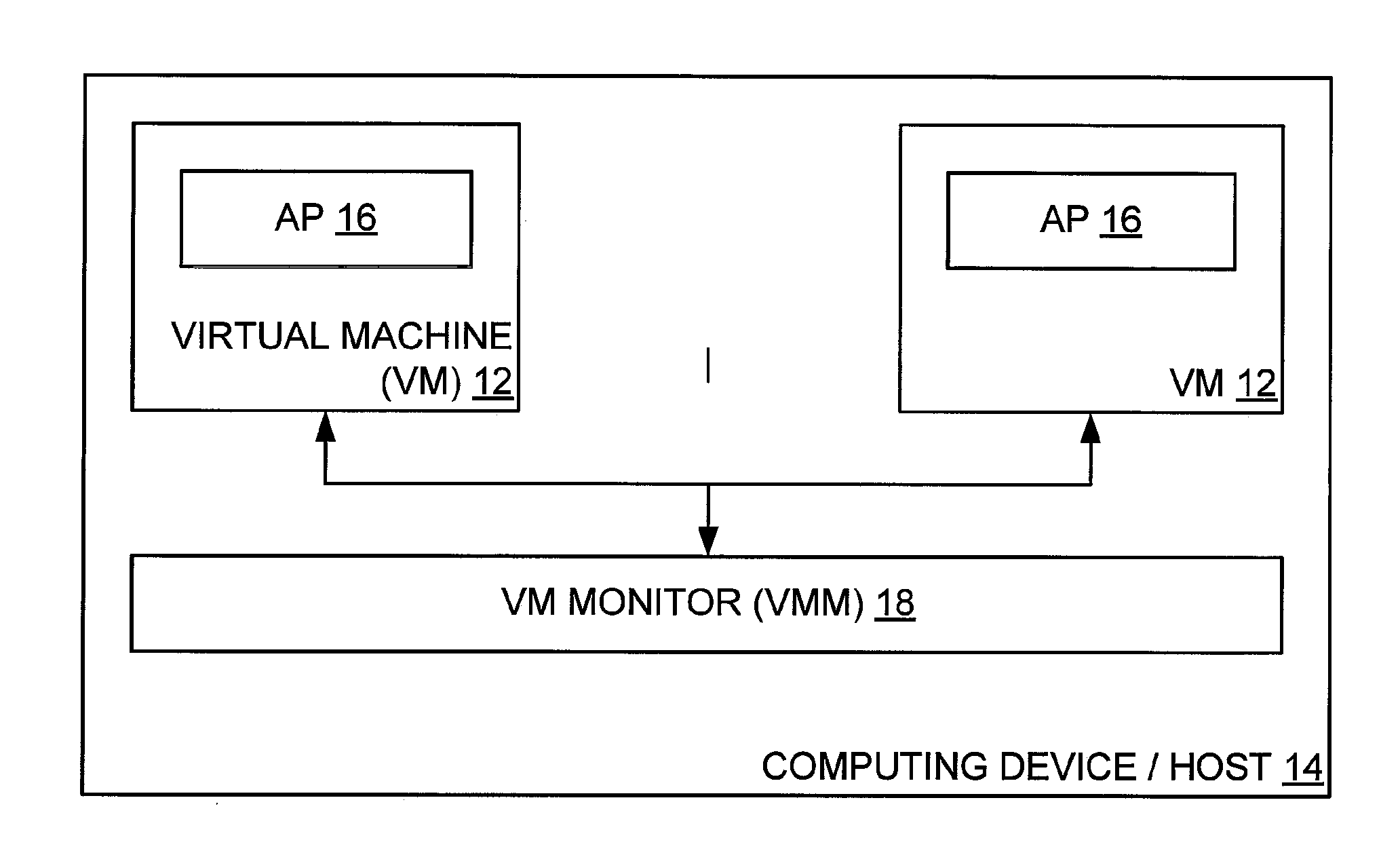

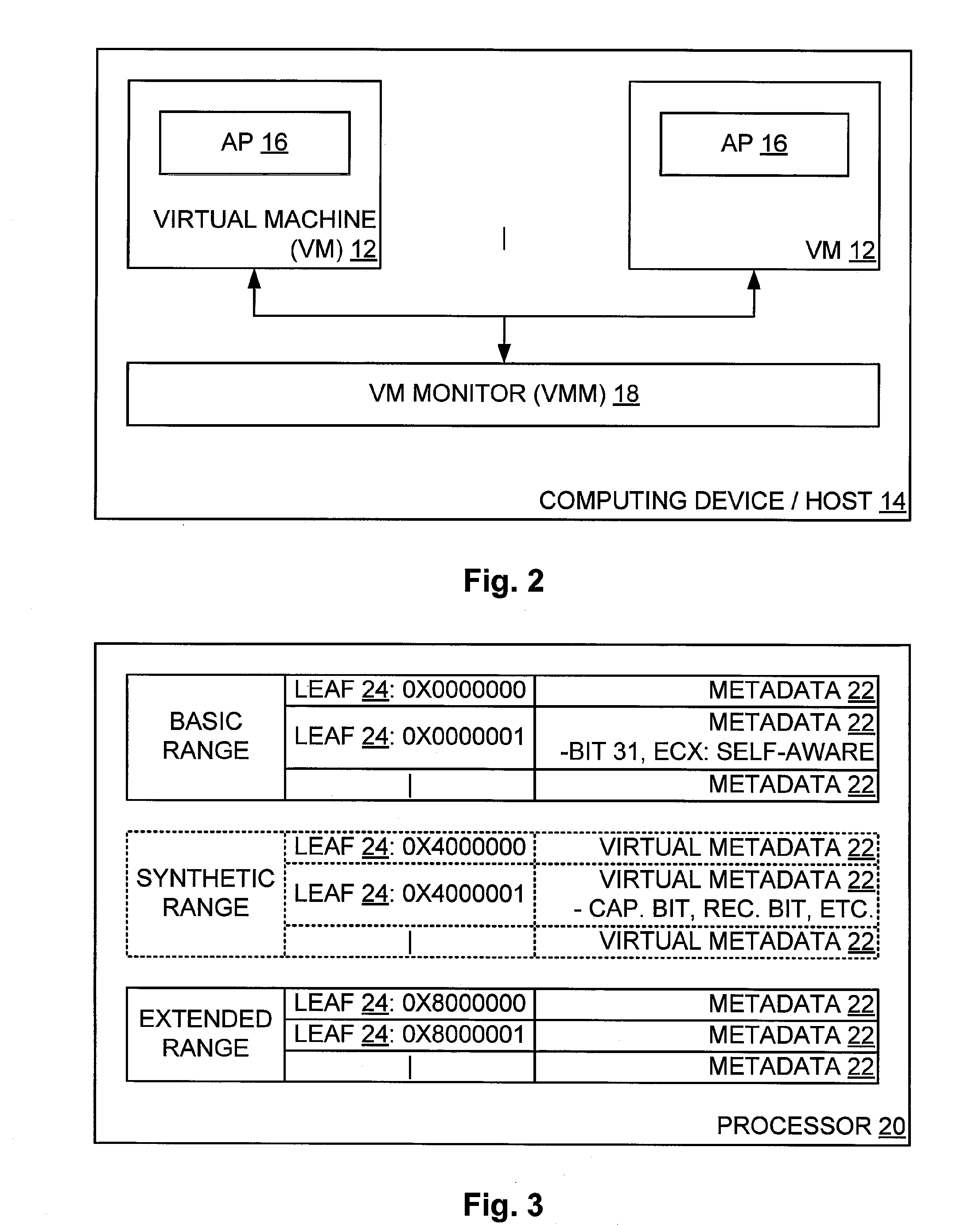

Allowing Virtual Machine to Discover Virtual Status Thereof

InactiveUS20080104586A1Easy to operateSoftware simulation/interpretation/emulationMemory systemsPhysics processing unitApplication software

A host computing device has a virtual machine (VM) instantiated thereon. The VM has a virtual application instantiated thereon and a virtual processor. The host also has a virtual machine monitor (VMM) instantiated thereon to oversee the VM and to intercept instructions from a virtual entity comprising one of the virtual application and the VM to the virtual processor of such VM. The virtual entity becomes self-aware of the virtual status thereof based on a self-aware flag as obtained from the VMM, and based thereon obtains particular virtual metadata from a Synthetic range of the virtual processor by way of the VMM to operate efficiently. The Synthetic range of the virtual processor is implemented by the VMM and does not correspond to any defined range of the physical processor corresponding to the virtual processor.

Owner:MICROSOFT TECH LICENSING LLC

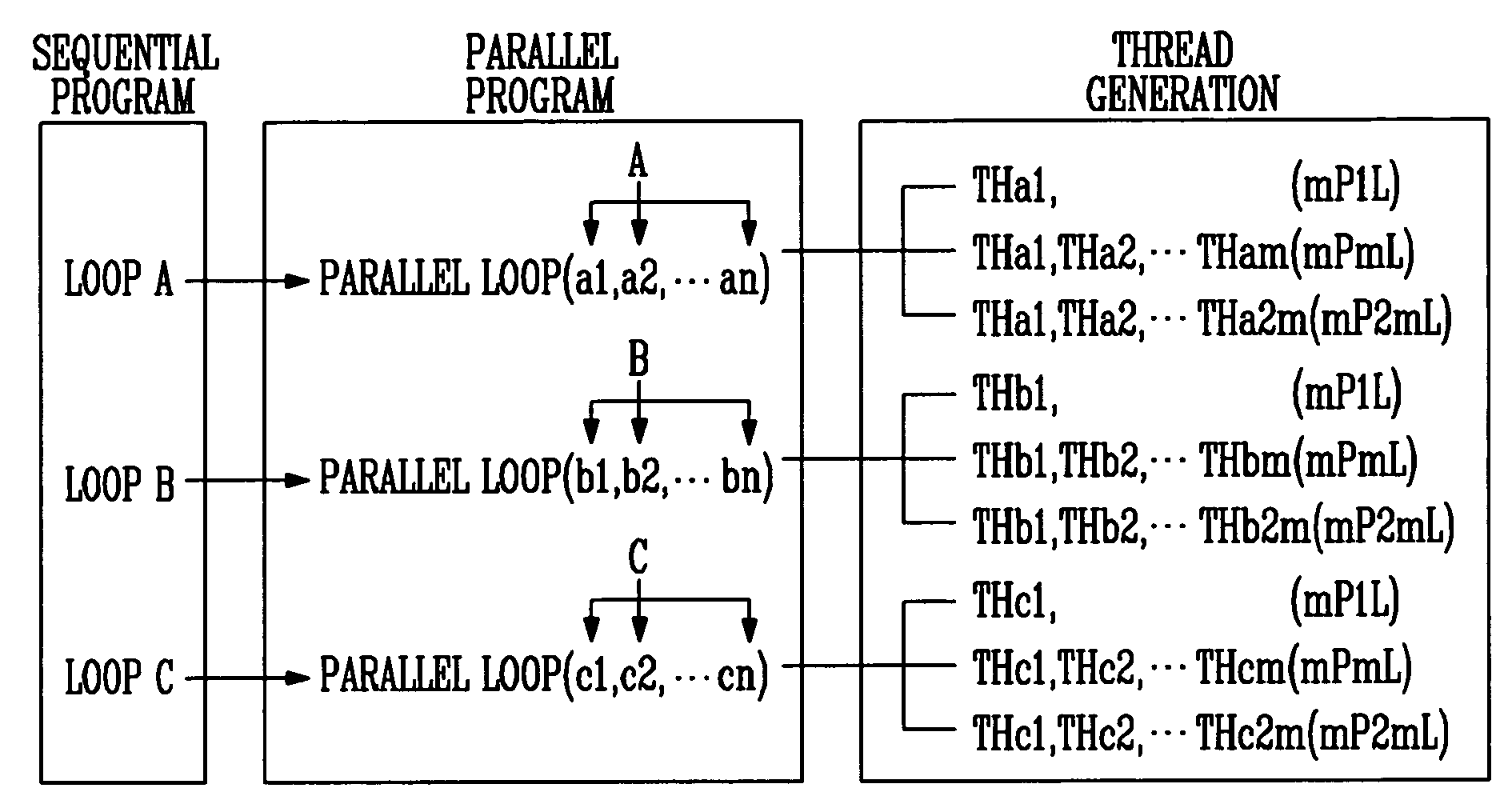

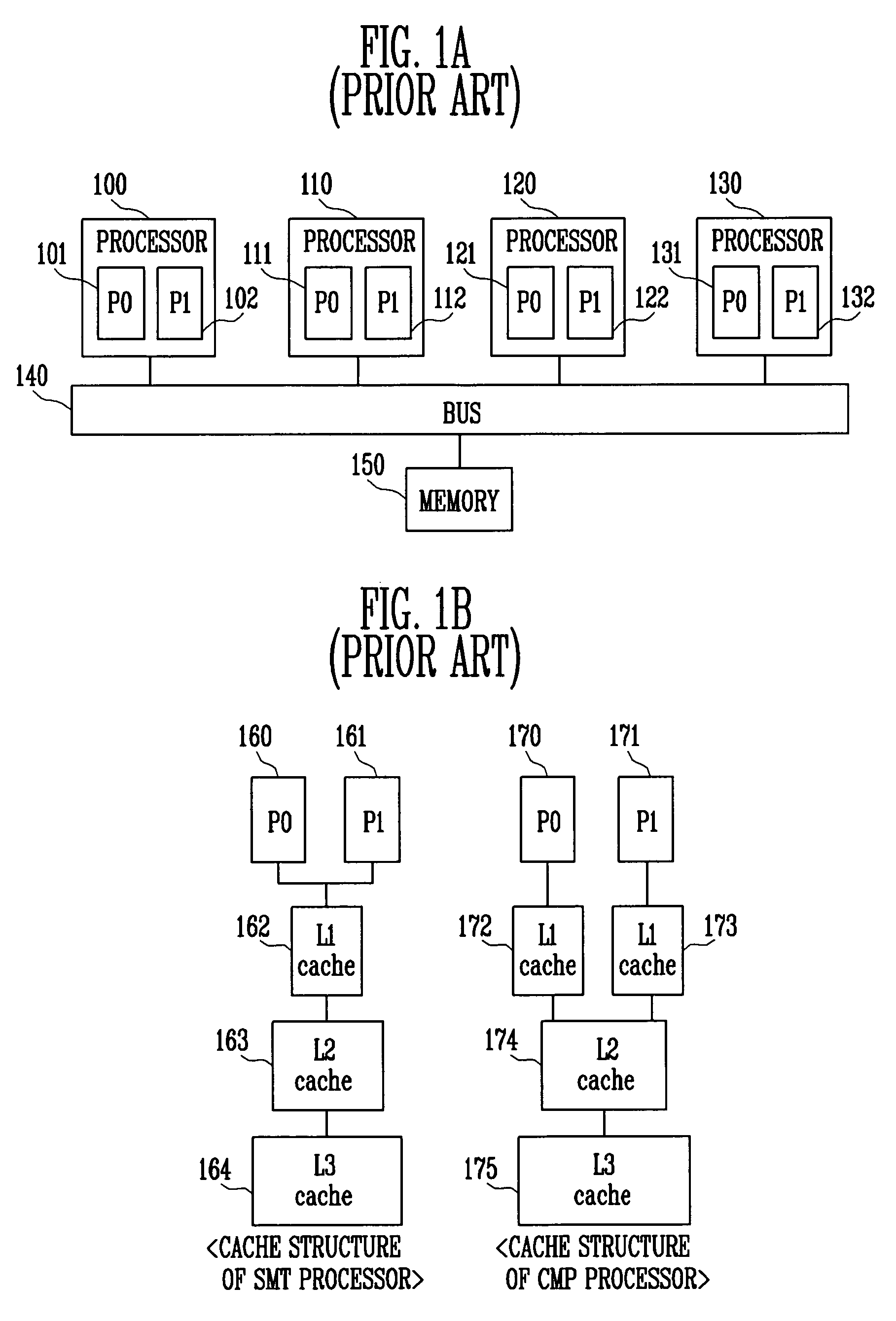

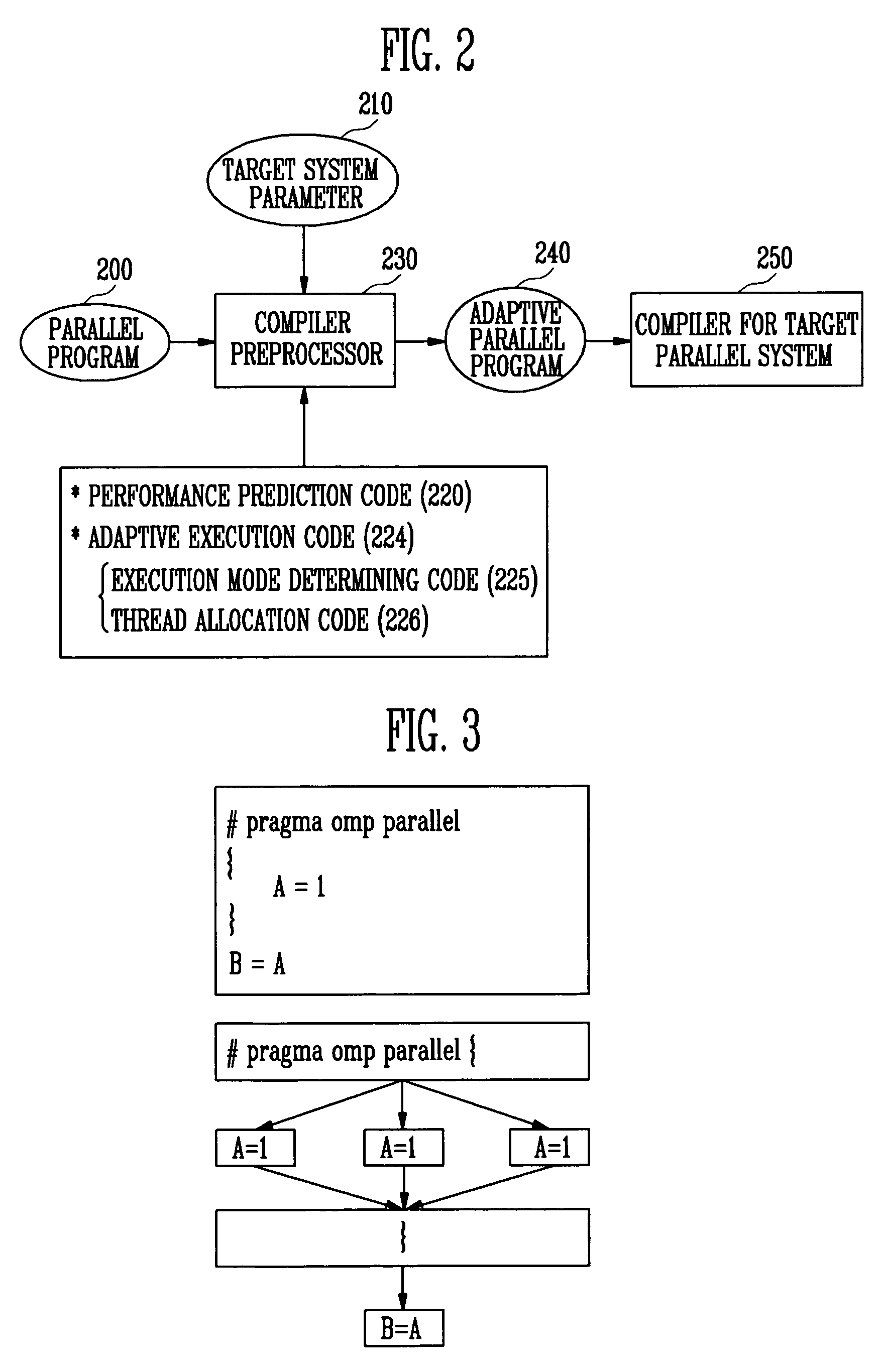

Adaptive execution method for multithreaded processor-based parallel system

InactiveUS7526637B2Error detection/correctionSoftware engineeringPhysics processing unitSelf adaptive

Owner:ELECTRONICS & TELECOMM RES INST

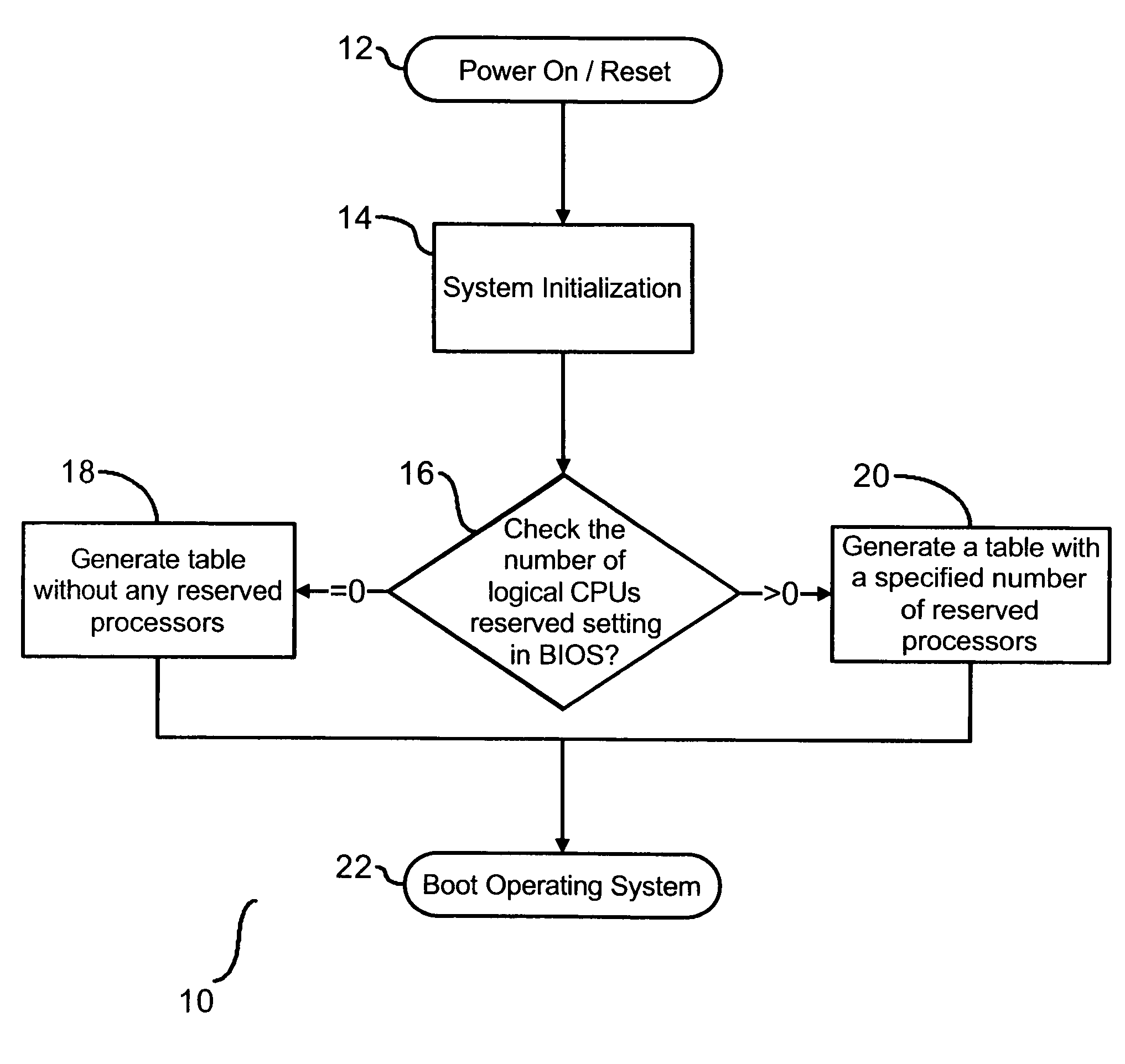

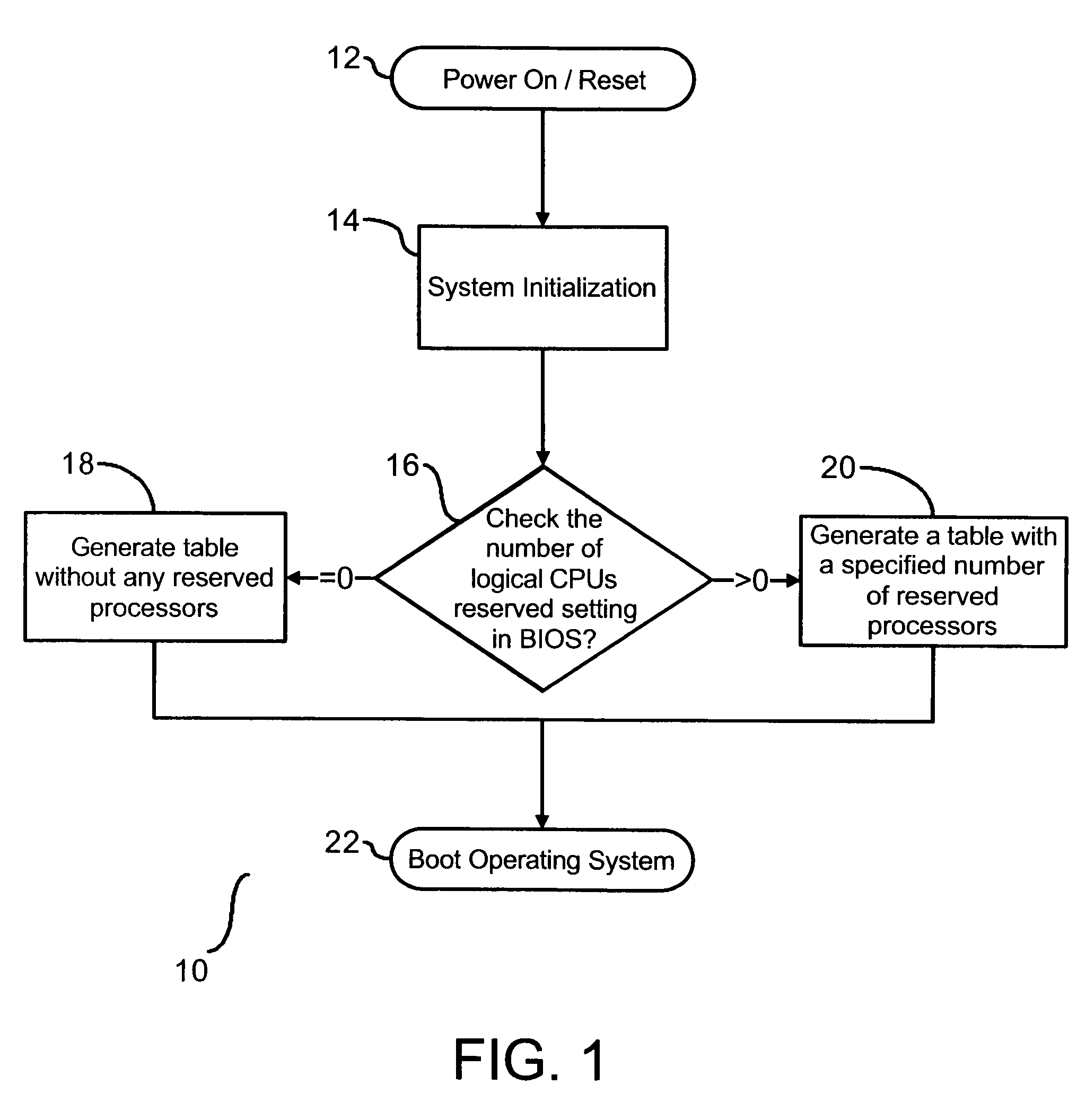

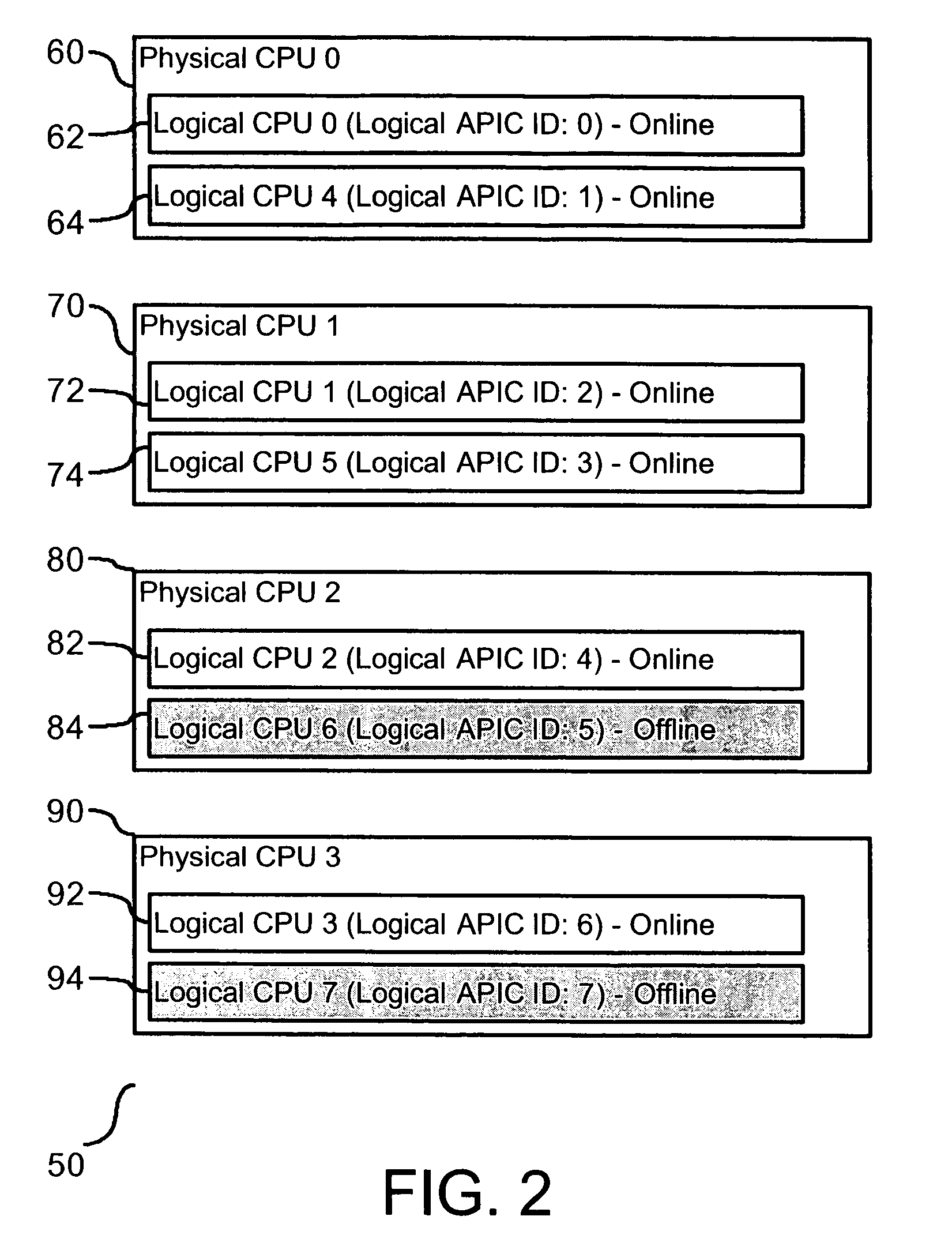

High availability multi-processor system

A method and system are provided for enabling replacement of a failed processor without requiring redundancy of hardware. The system is a multiprocessing computer system that includes one or more processor chips. Each processor chip may include one or more logical processors. During system initialization, one or more logical processors may be reserved in an inactive state. In the event an error is detected on a logical or physical processor, one or more reserved logical processors may have execution context transferred from the processor experiencing the error. Thereafter, the active processor is designated as inactive and replaced by the inactive processor to which the execution context has been transferred.

Owner:IBM CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com