Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

33 results about "Delay encoding" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In telecommunications, delay encoding is the encoding of binary data to form a two-level signal where a "0" causes no change of signal level unless it is followed by another "0" in which case a transition to the other level takes place at the end of the first bit period; and a "1" causes a transition from one level to the other in the middle of the bit period. Delay encoding is used primarily for encoding radio signals because the frequency spectrum of the encoded signal contains less low-frequency energy than a conventional non-return-to-zero signal and less high-frequency energy than a biphase signal. Delay encoding is an encoding using only half the bandwidth for biphase encoding but features all the advantages of biphase encoding: To be rewritten: It is guaranteed to have transitions every other bit, meaning that decoding systems can adjust their clock/DC threshold continuously. One drawback is human readability. Delay encoding is also known as Miller encoding. <US Pat. # 3,108,261> Some RFID cards, in particular EPC UHF Gen 2 RF cards, use a variant called "Miller sub-carrier coding".

Robust mode staggercasting

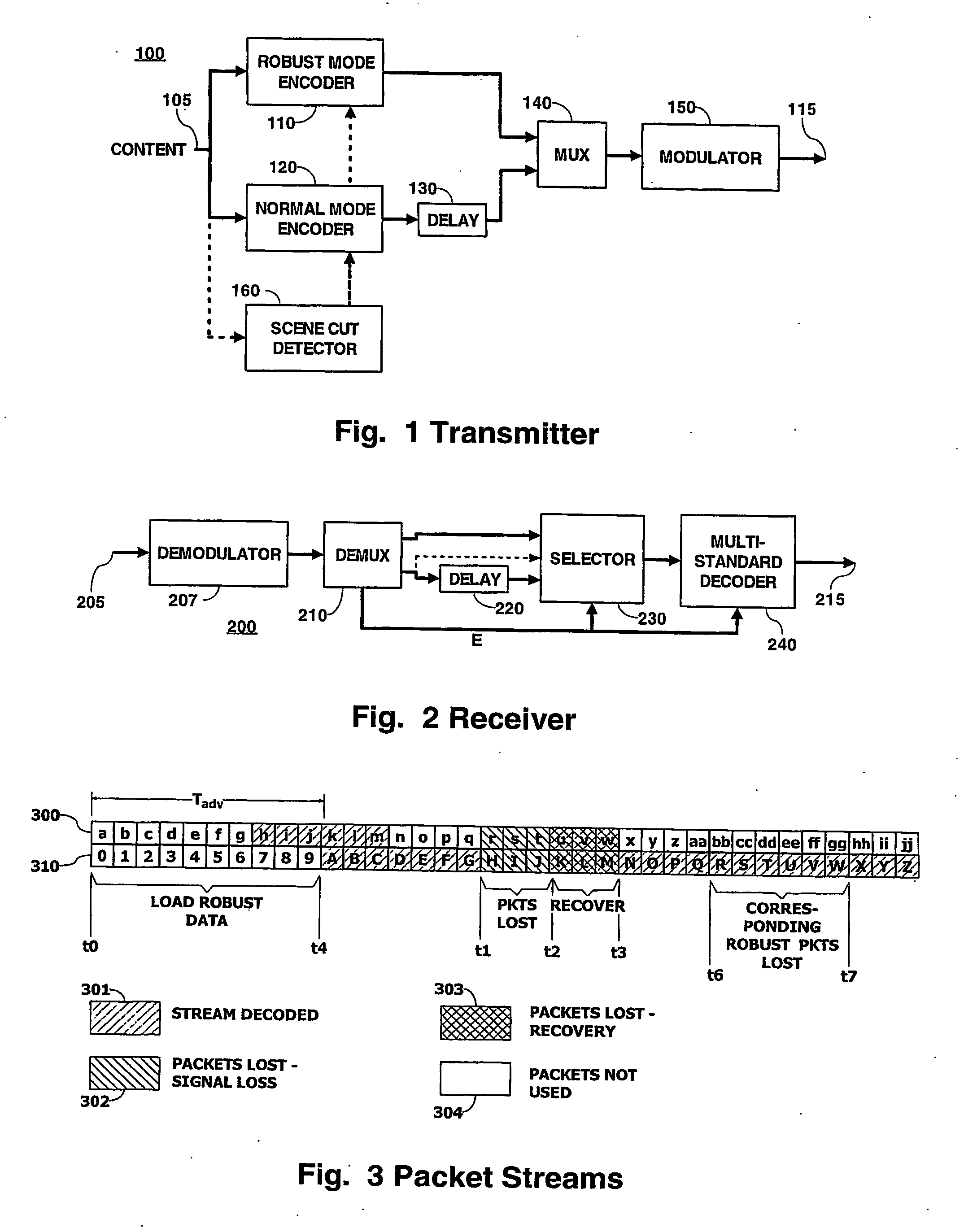

ActiveUS20060056505A1Improve performanceAnalogue/digital conversionTelevision system detailsBroadcastingComputer science

Owner:INTERDIGITAL CE PATENT HLDG

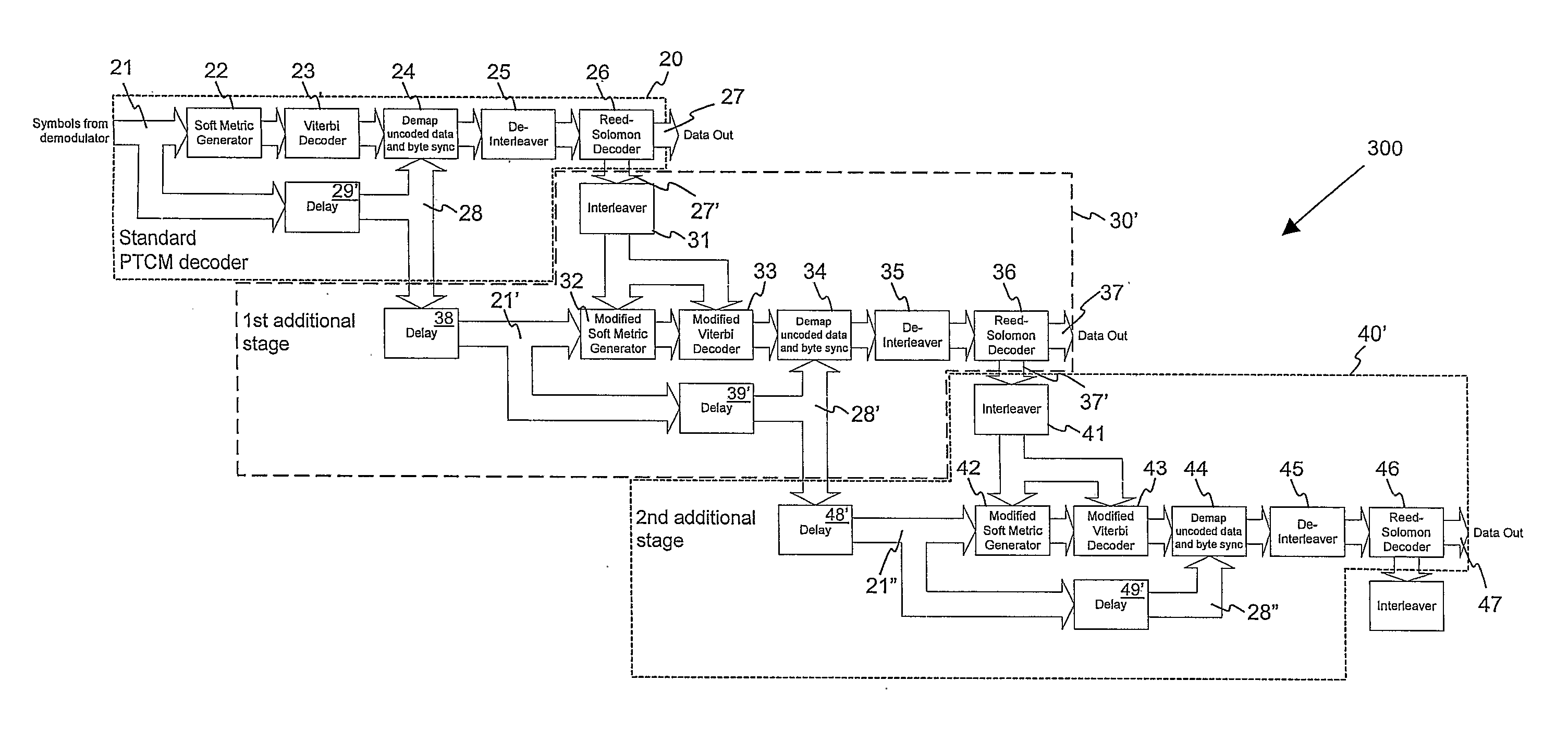

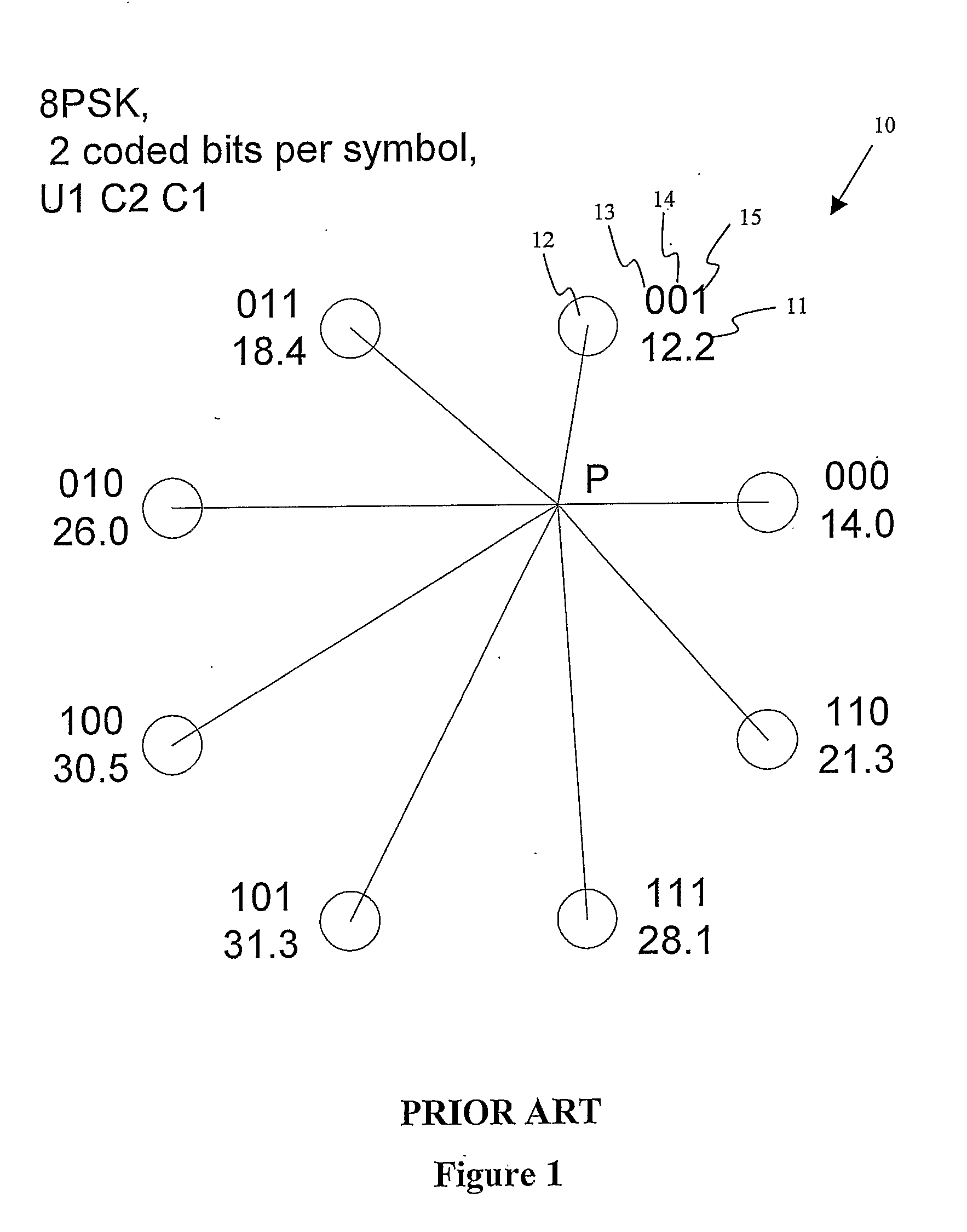

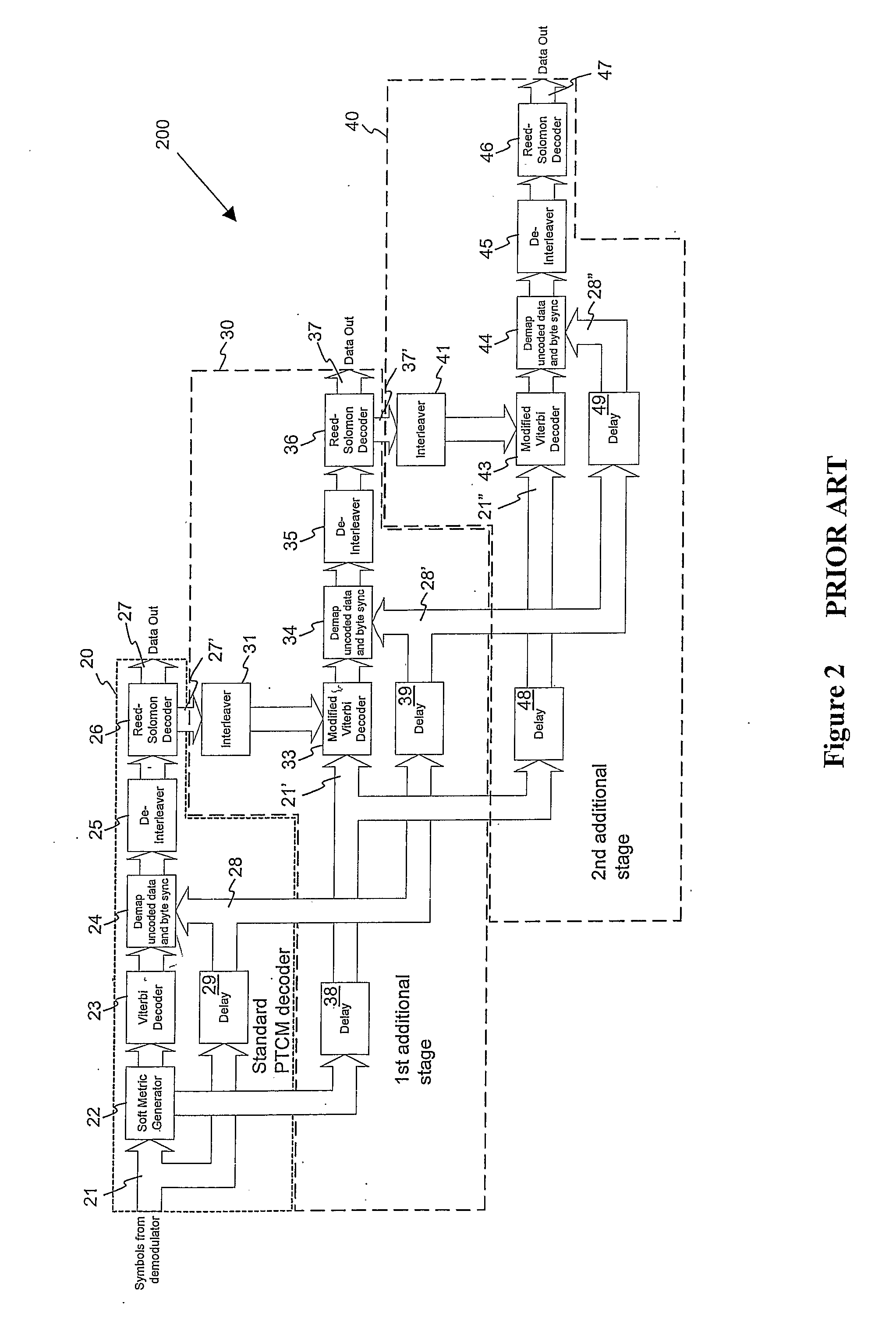

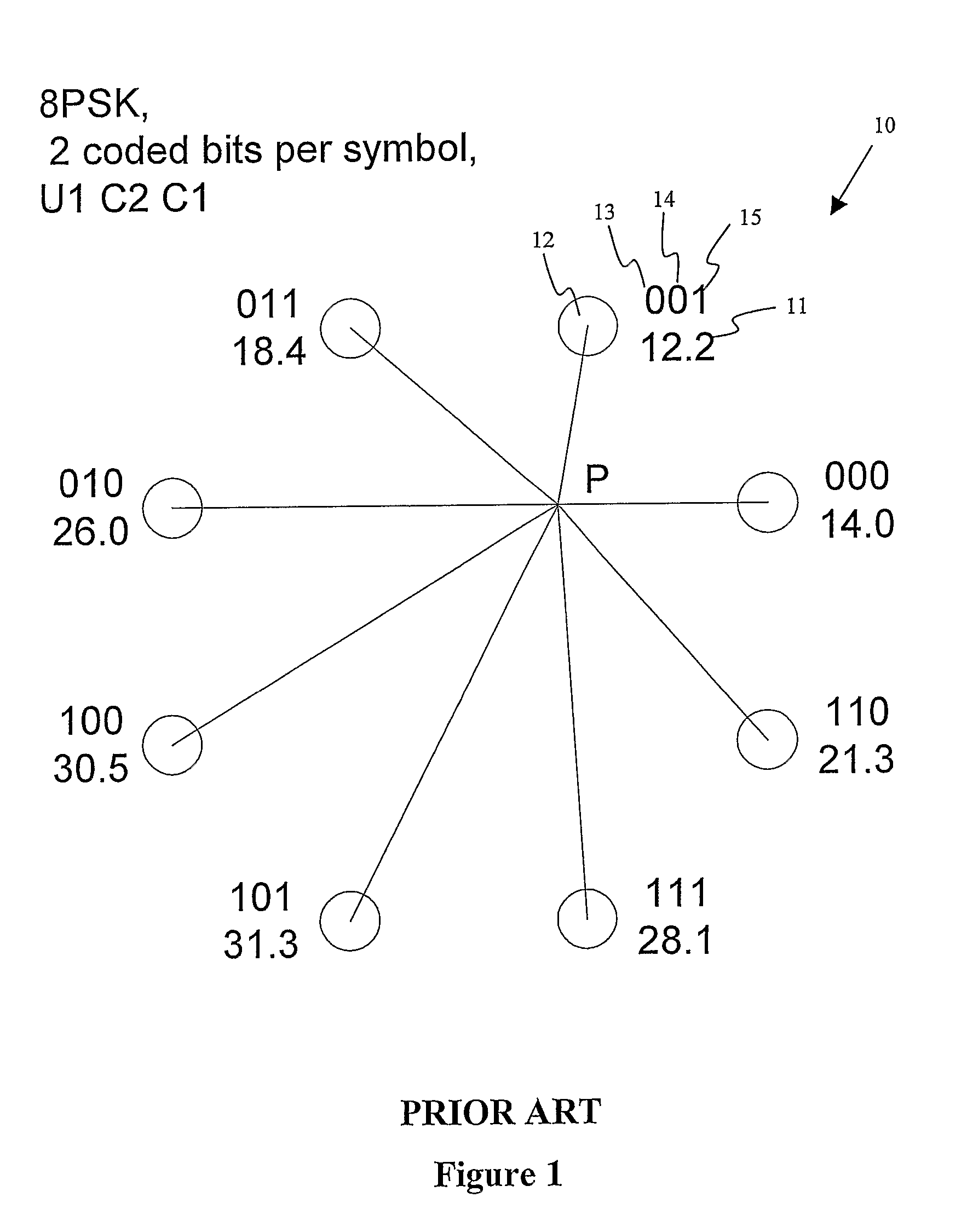

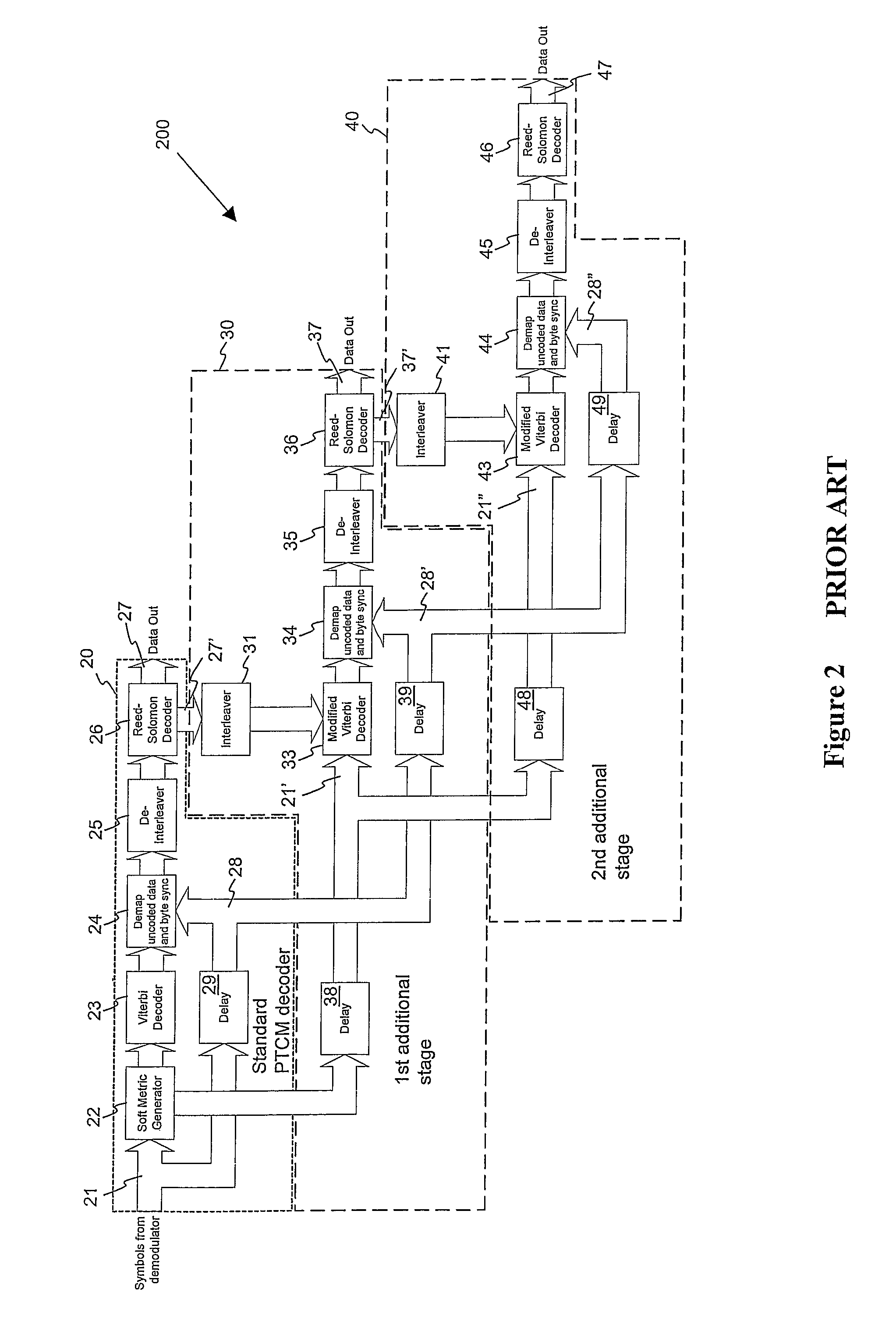

Decoding a Concatenated Convolutional-Encoded and Block Encoded Signal

ActiveUS20070220408A1Improve efficiencySpeed up the decoding processData representation error detection/correctionOther decoding techniquesViterbi decoderReed solomon decoder

Encoded symbols of a concatenated convolutional-encoded and block encoded signal are presented to a conventional first stage of a concatenated decoder, comprising in sequence a soft metric generator, a Viterbi decoder, a first de-interleaver and a first block decoder such as a Reed-Solomon decoder. The encoded symbols are also presented to a delay chain to produce progressively delayed encoded symbols. Where an output block of the conventional decoder is indicated as being a valid codeword by the first block decoder, the bytes in this block are marked as being correct. These bytes that are known to be correct are then used after interleaving and serialisation as known bits input to a second stage of the decoder process operating on the delayed encoded symbols and incorporating a modified soft metric generator constrained by the known bits. This process can be extended to further iterations as required. A modified Viterbi decoder, which is also constrained by the known bits, may also be used in the second and subsequent iterative stages.

Owner:MK SYST USA INC

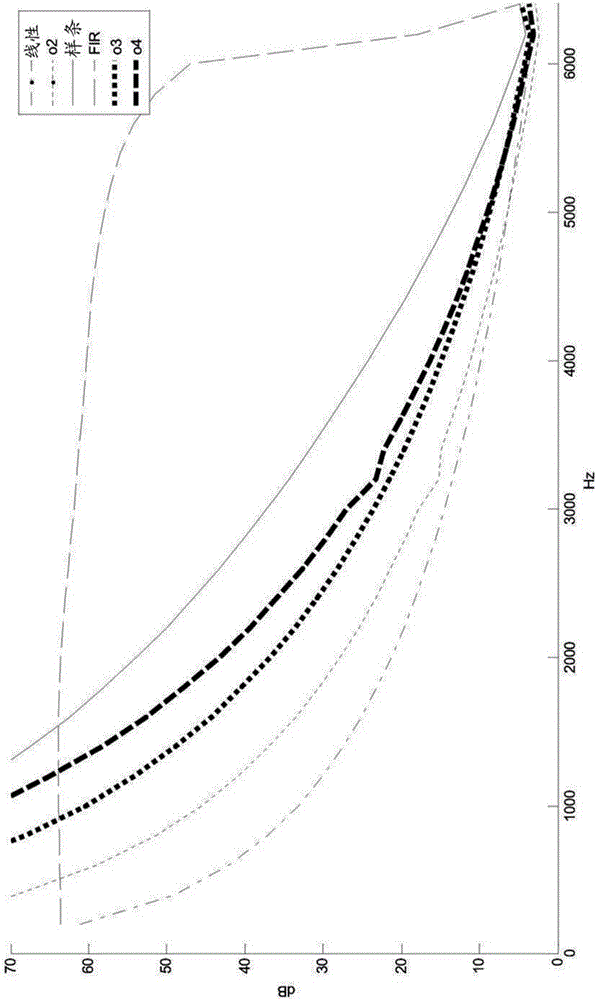

Resampling of an audio signal by interpolation for low-delay encoding/decoding

A method is provided for resampling an audio-frequency signal in an audio-frequency signal encoding or decoding operation. The resampling is carried out by a method of interpolation of an order greater than one. The method is such that the interpolated samples are obtained by calculating a weighted average of possible interpolation values calculated over a plurality of intervals covering the time location of the sample to be interpolated. A resampling device is provided, which implements the method, and also an encoder and decoder including at least one resampling device.

Owner:ORANGE SA (FR)

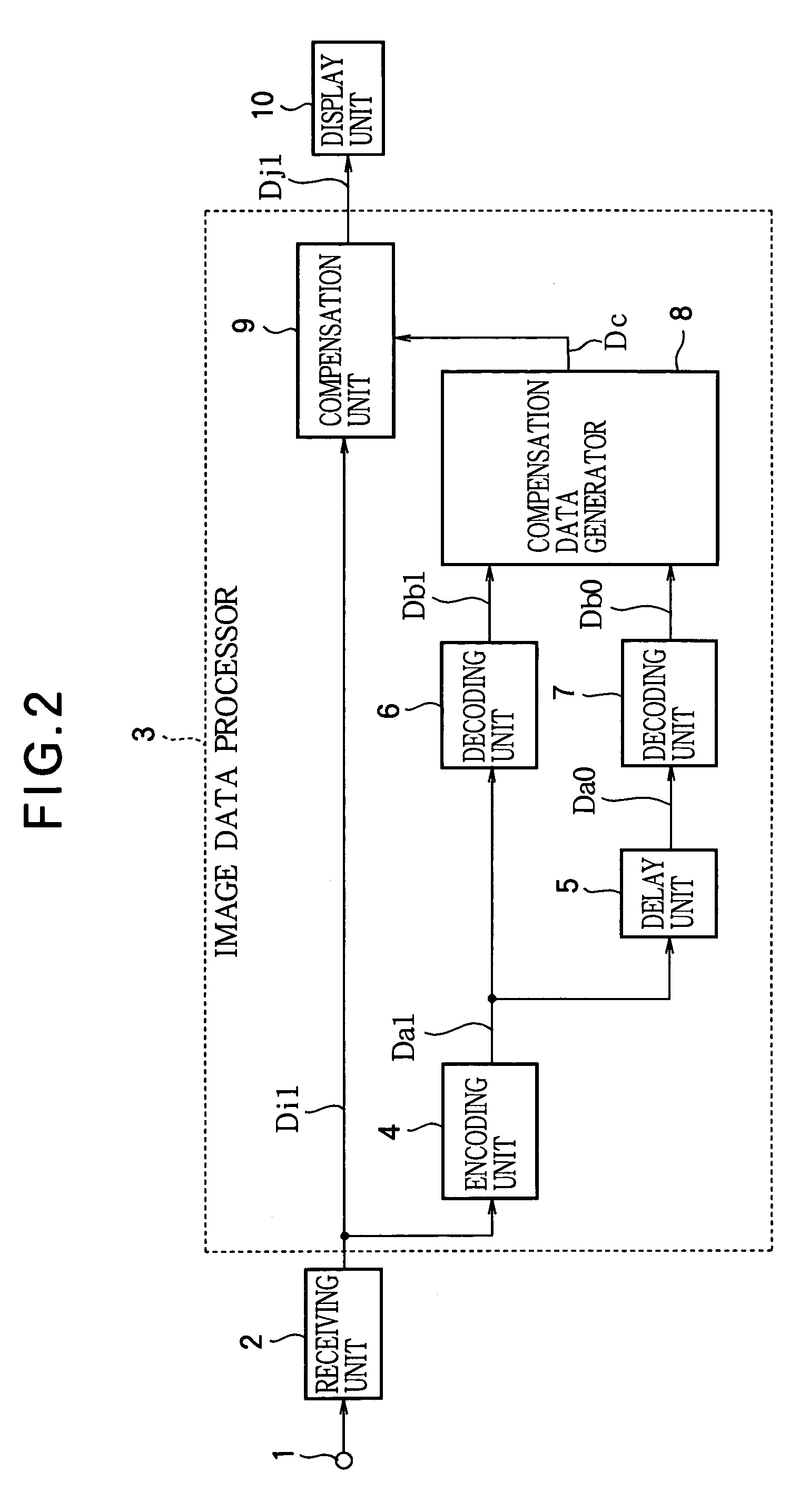

Liquid-crystal driving circuit and method

InactiveUS7327340B2Controls are responsiveEasy to controlTelevision system detailsCathode-ray tube indicatorsTransmittanceData treatment

A liquid-crystal driving circuit has an image data processor that, for example, encodes the present image, decodes the encoded image, delays the encoded image by one frame interval, decodes the delayed encoded image, and uses the two decoded images to generate compensation data for adjusting the gray-scale values in the present image. The encoding process reduces the amount of image data, thereby reducing the size of the frame memory needed to delay the image. The compensation data preferably cause the liquid crystal to reach transmissivity values corresponding to the gray-scale values of the present image within substantially one frame interval. This enables the response speed of the liquid crystal to be controlled accurately.

Owner:TRIVALE TECH

Resampling of an Audio Signal by Interpolation for Low-Delay Encoding/Decoding

ActiveUS20170133027A1Not costlyIncreased complexityDigital technique networkSpeech analysisLow delayAudio frequency

A method is provided for resampling an audio-frequency signal in an audio-frequency signal encoding or decoding operation. The resampling is carried out by a method of interpolation of an order greater than one. The method is such that the interpolated samples are obtained by calculating a weighted average of possible interpolation values calculated over a plurality of intervals covering the time location of the sample to be interpolated. A resampling device is provided, which implements the method, and also an encoder and decoder including at least one resampling device.

Owner:ORANGE SA (FR)

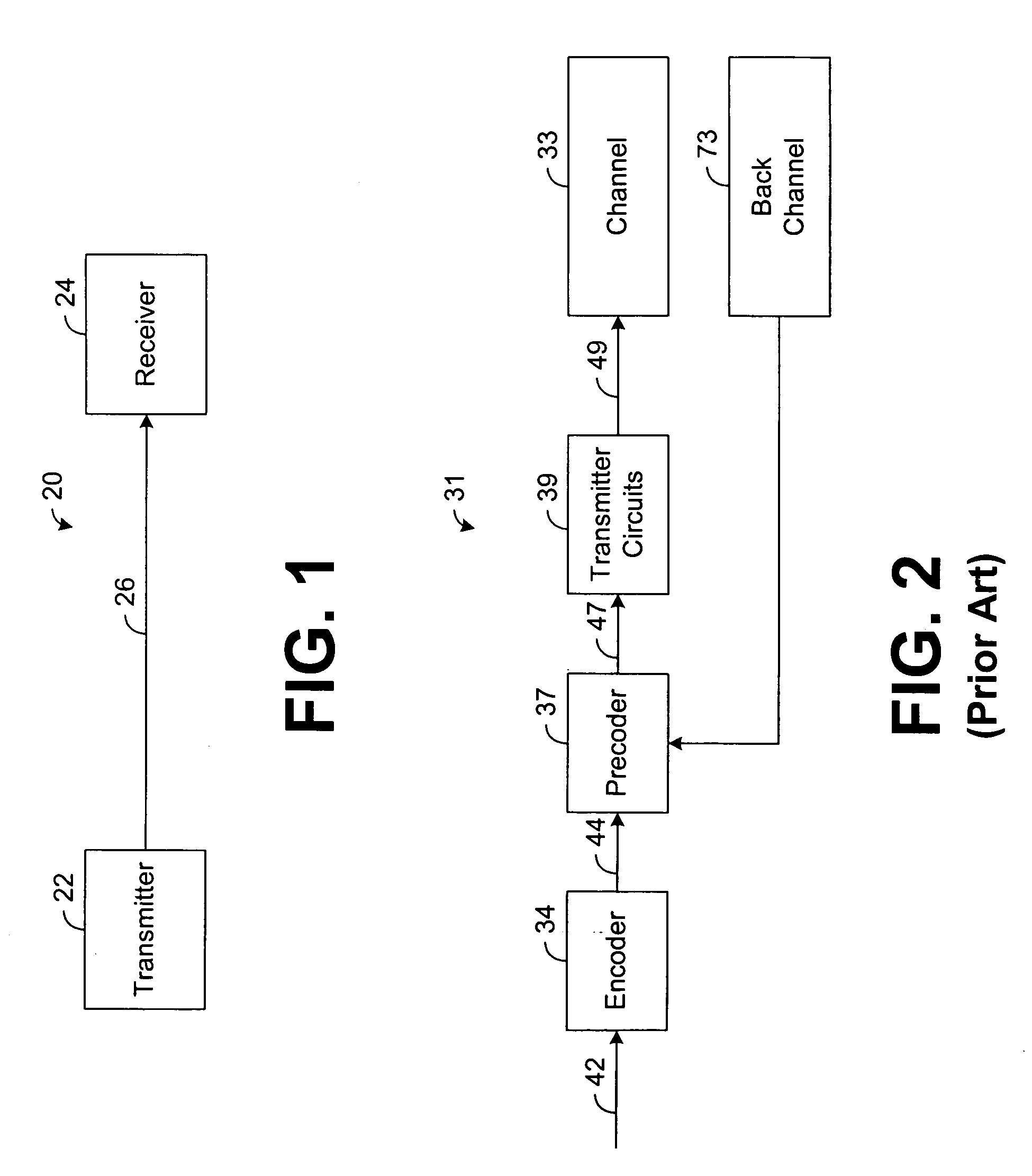

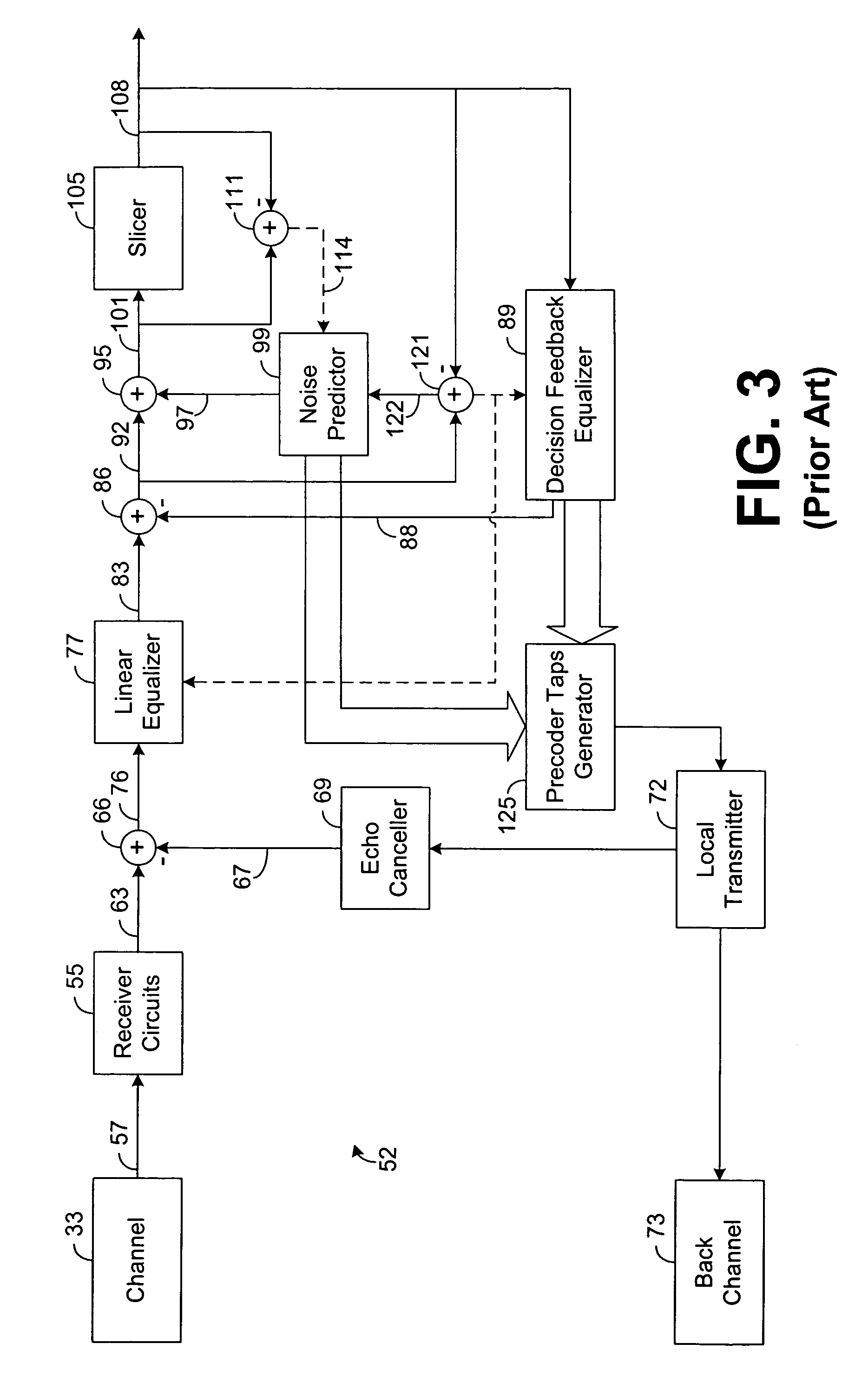

System and method for adaptively updating precoder taps

A system for adaptively updating precoder taps comprises a first signal path, a second signal path, a delay mechanism, and logic. The first signal path is configured to receive encoded signals. The first signal path has a decoder that is configured to decode the encoded signals thereby recovering data originally transmitted from a remote transmitter. The delay mechanism is configured to receive and delay the encoded signals. The second signal path is connected in parallel with the first signal path and is configured to receive the encoded signals delayed by the delay mechanism. The second signal path has an adaptive filter configured to filter the encoded signals received by the second signal path based on a set of coefficients of the adaptive filter. The adaptive filter is configured to adaptively update the coefficients based on the data recovered by the first signal path. The logic is configured to adaptively generate new precoder taps based on the coefficients and to transmit the new precoder taps to a precoder.

Owner:ADTRAN

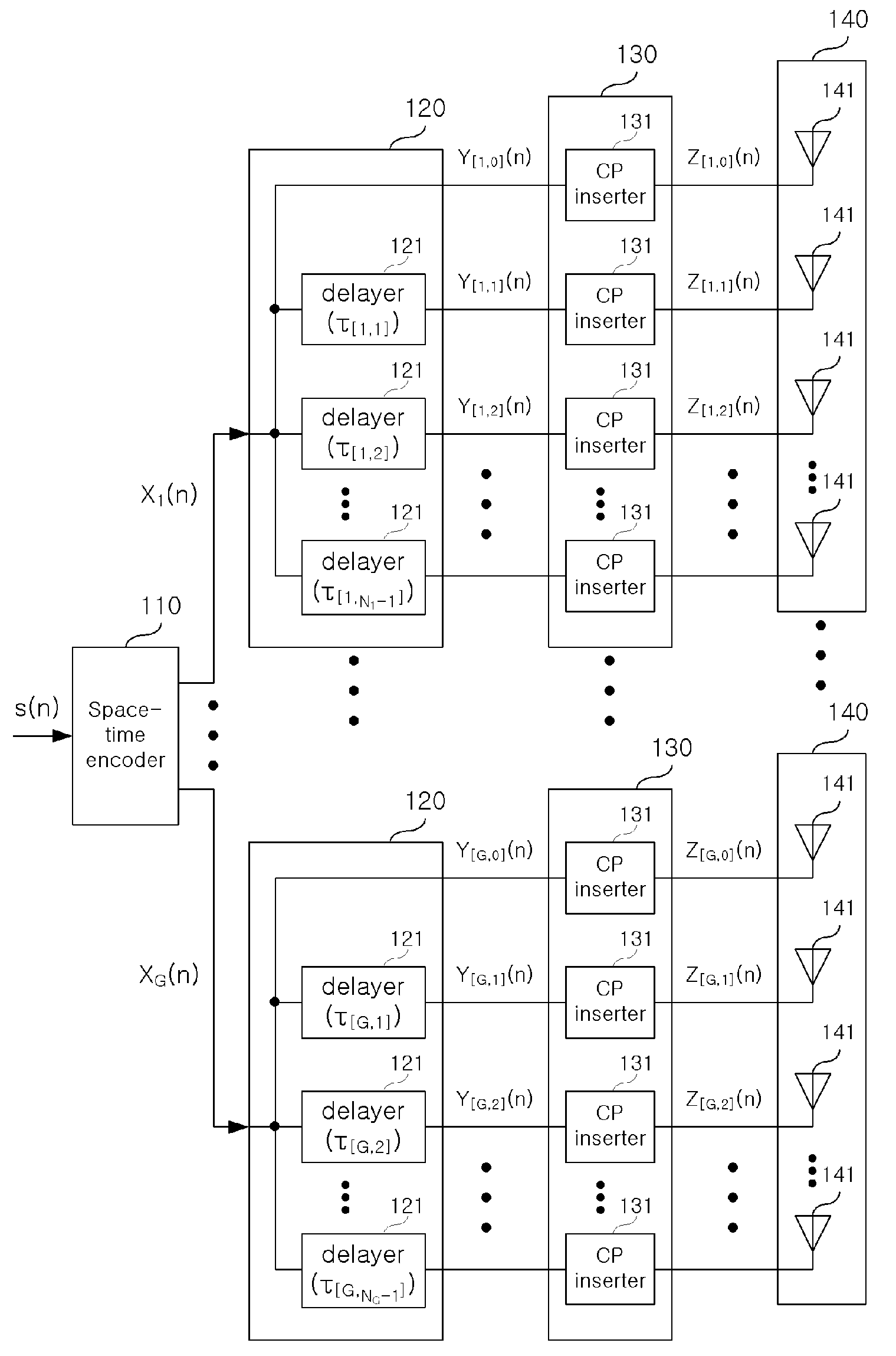

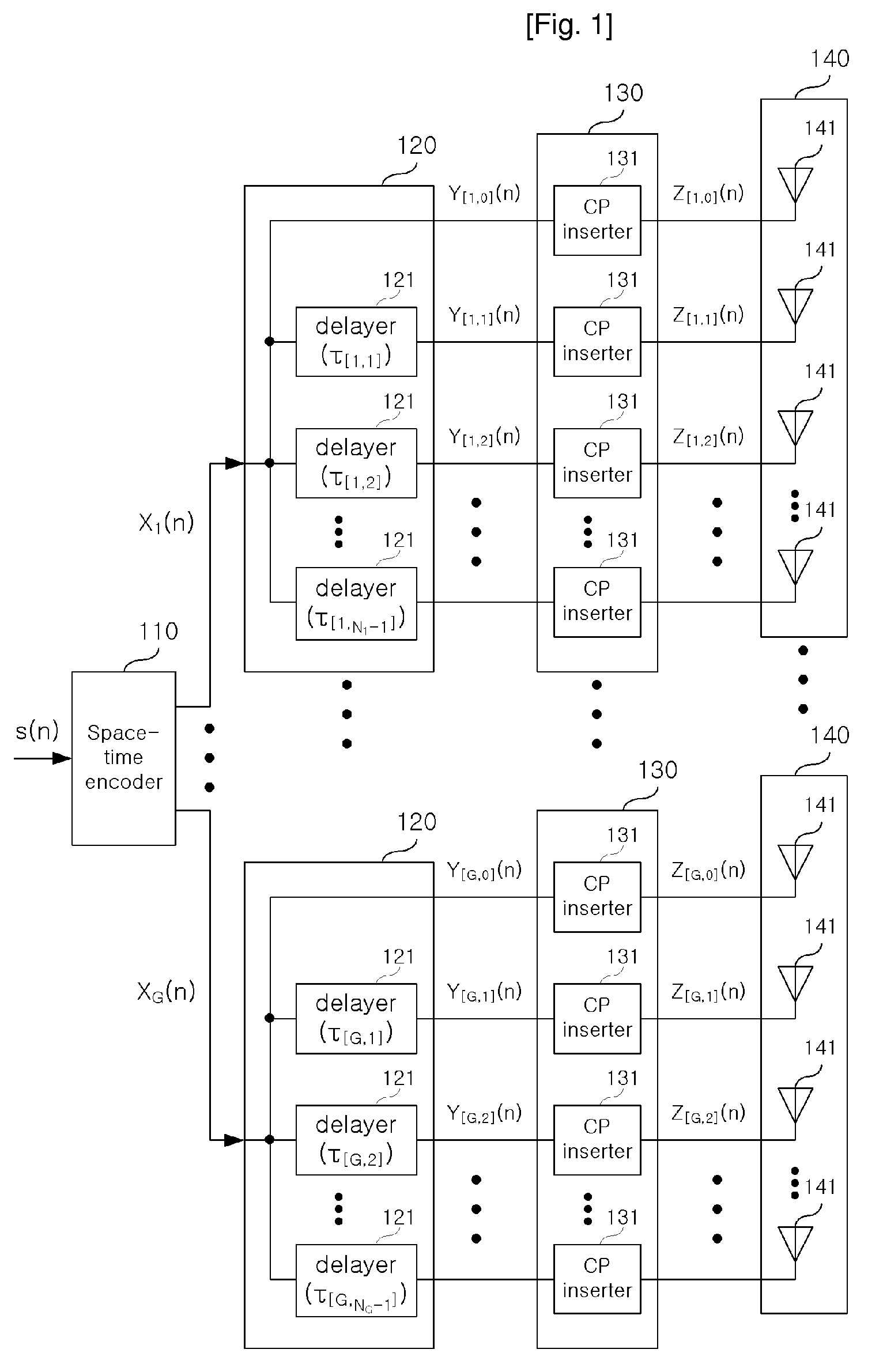

Apparatus and Method For Transmitting Signals With Multiple Antennas

ActiveUS20080285677A1Low reception complexityEasy to numberSemiconductor/solid-state device detailsSolid-state devicesDelay encodingElectrical and Electronics engineering

An apparatus for transmitting signals with multiple antennas is disclosed. The multiple antenna transmission apparatus performs space-time encoding or space-frequency encoding, and cyclically delays the encoded symbol with a plurality of delay-values to generate a plurality of delayed symbols. The multiple antenna transmission apparatus transmits the plurality of delayed symbols to the channel through a plurality of antennas. By changing the number of space areas for encoding and the number of delay-values for delaying, the number of antennas for the multiple antenna transmission apparatus is easily expanded.

Owner:ELECTRONICS & TELECOMM RES INST

Method for optimizing time domain rate-distortion in low-delay video coding

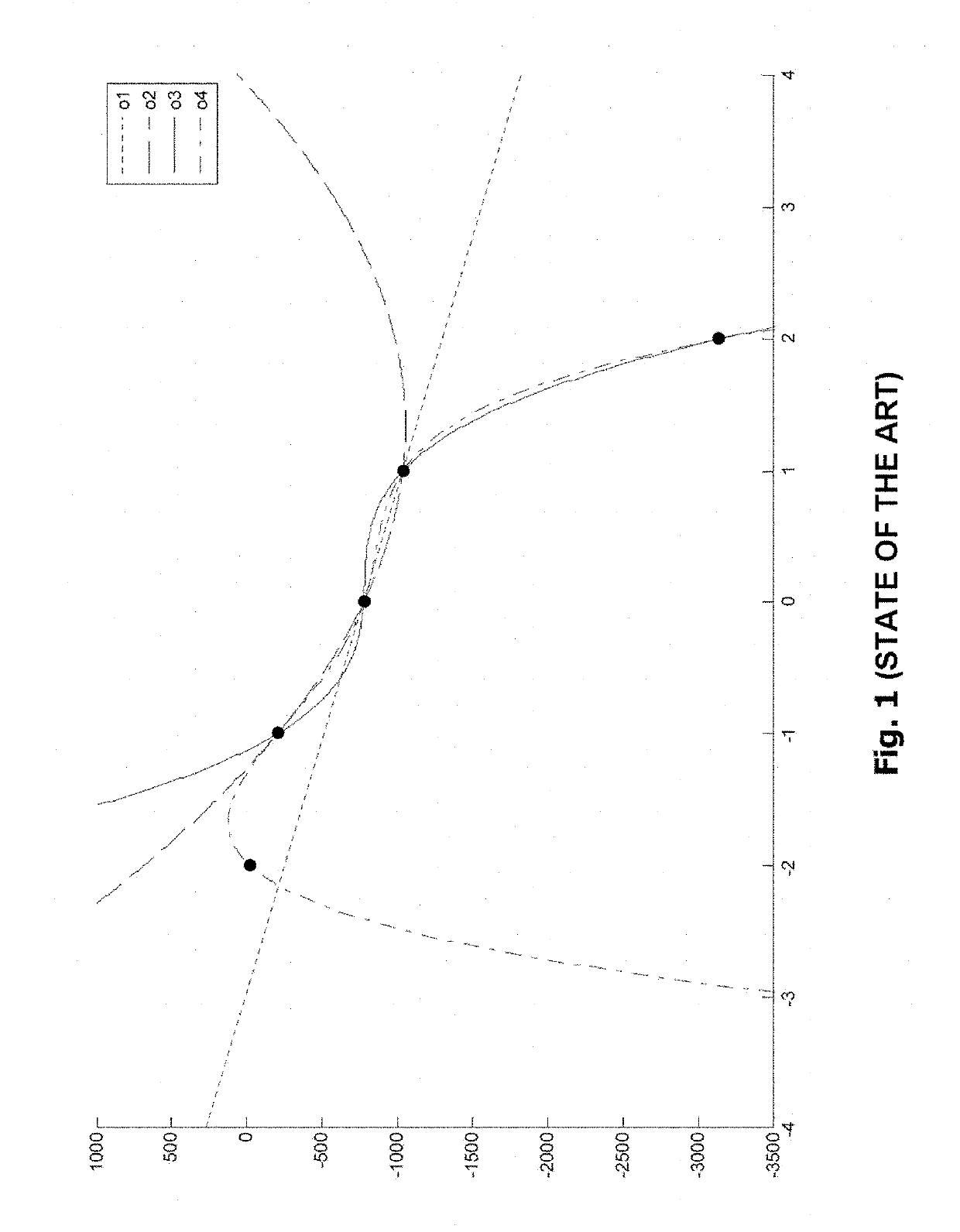

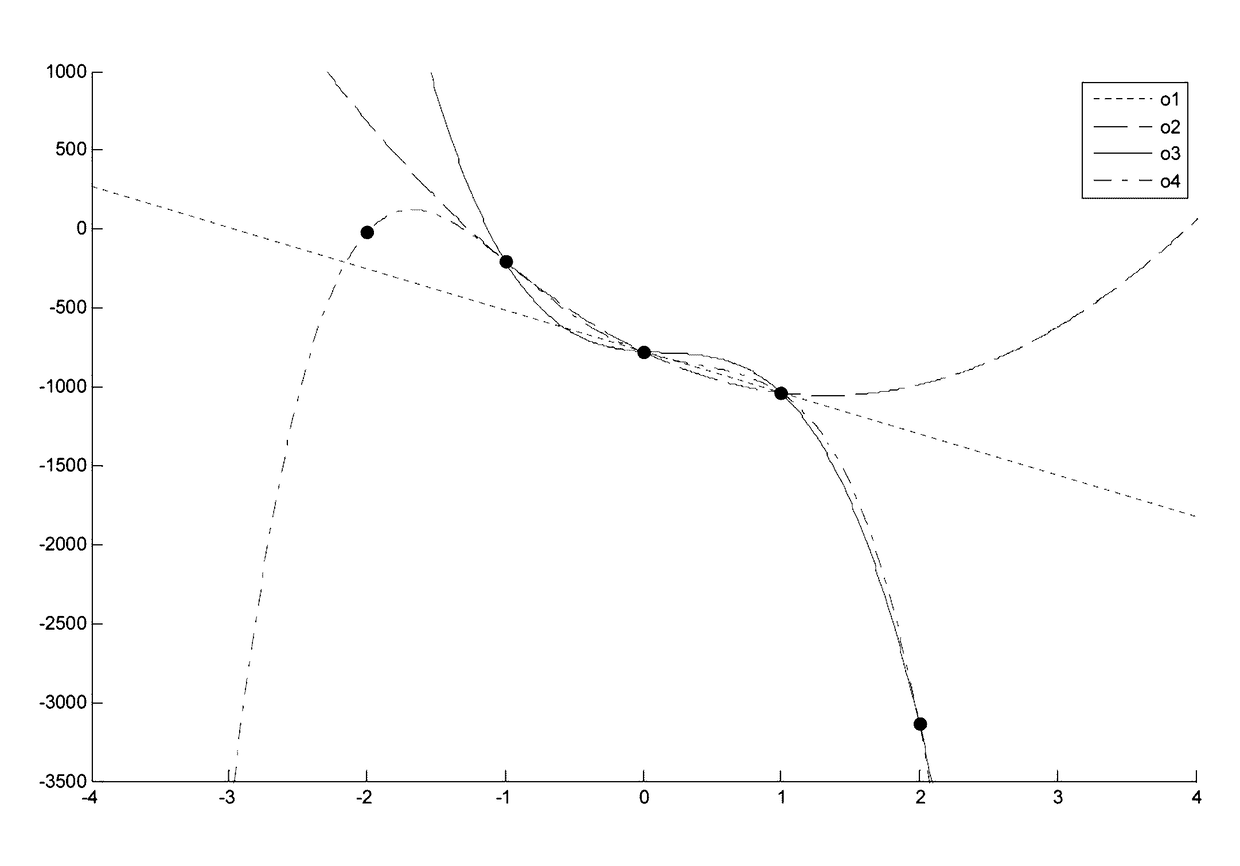

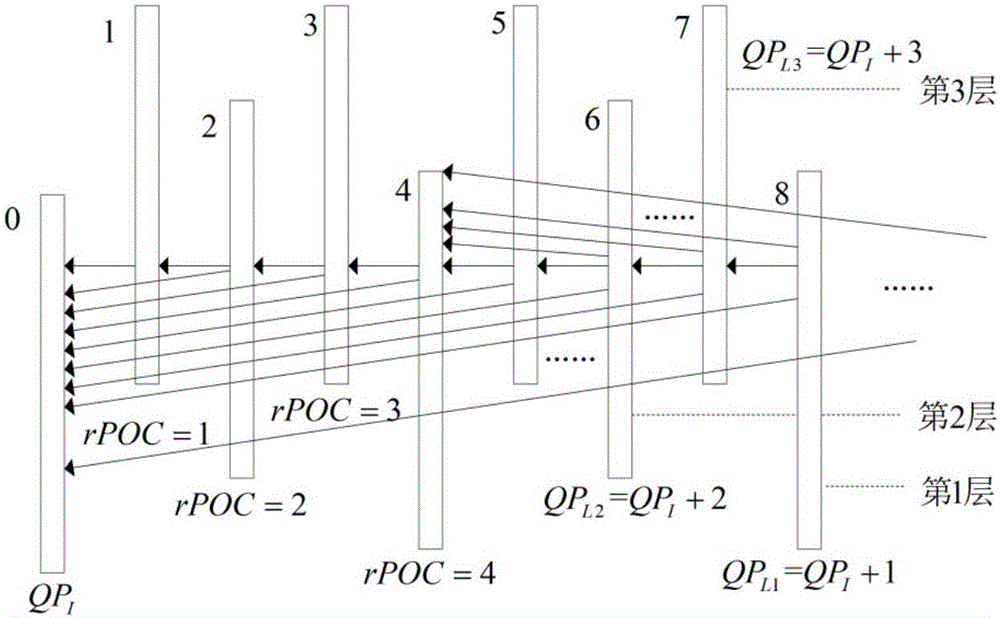

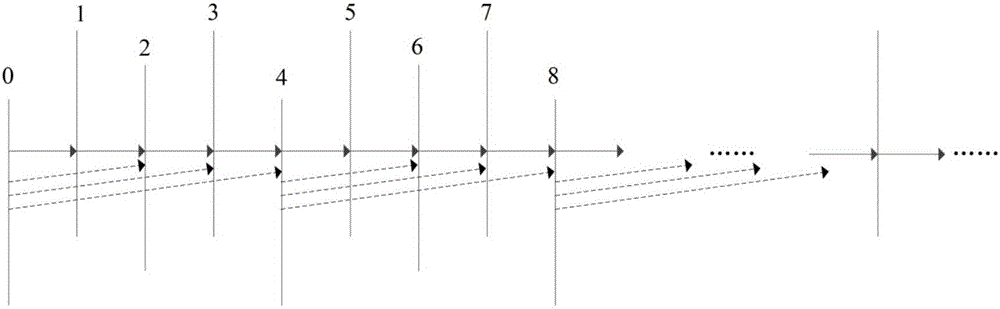

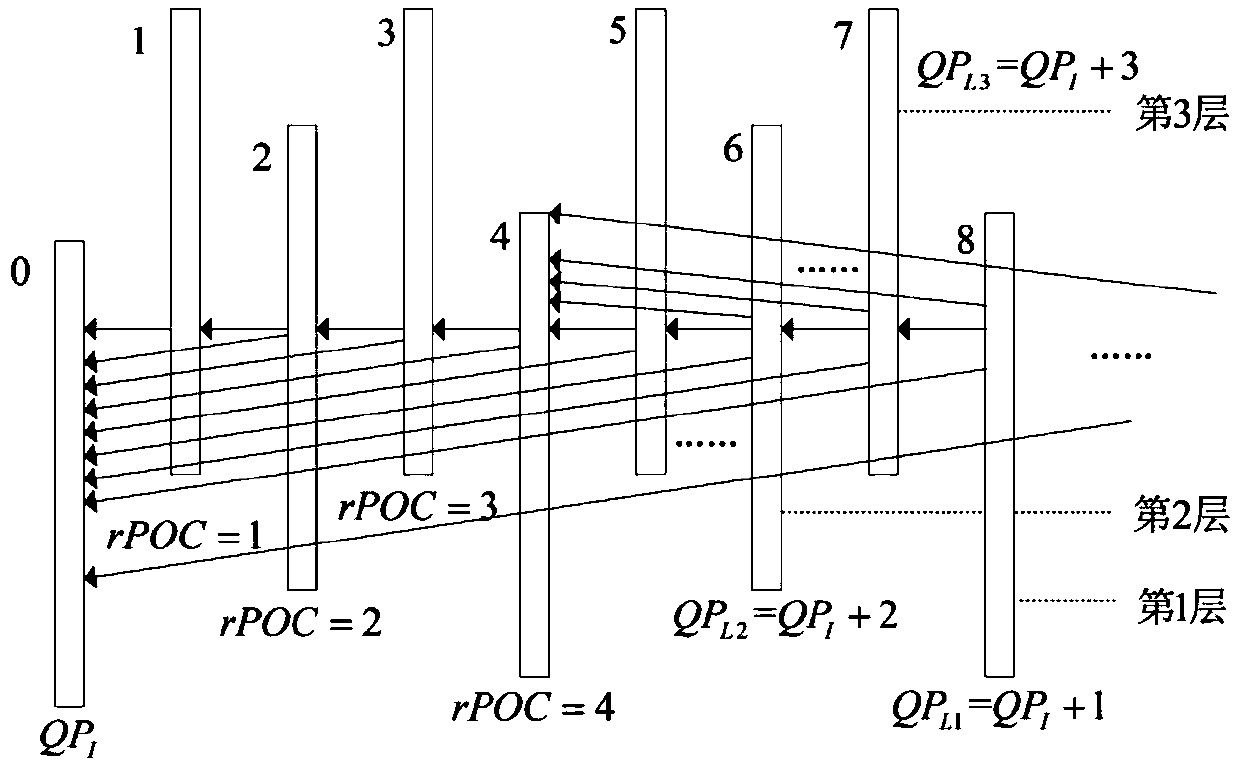

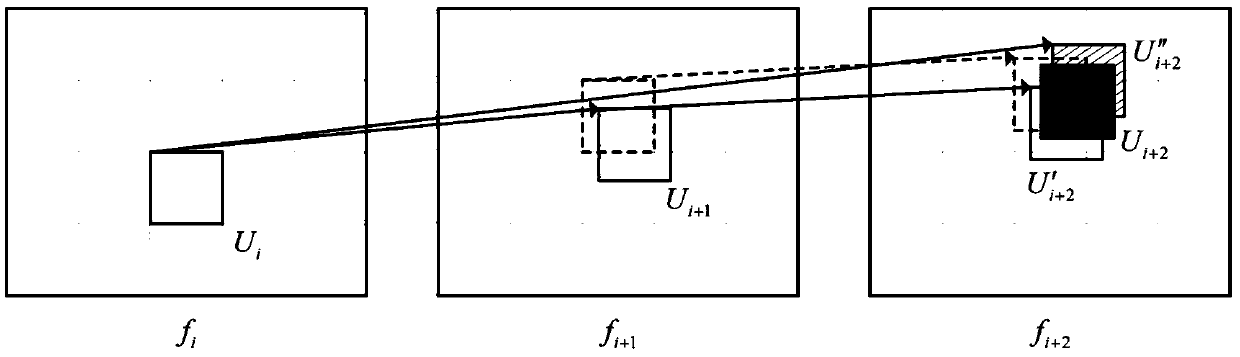

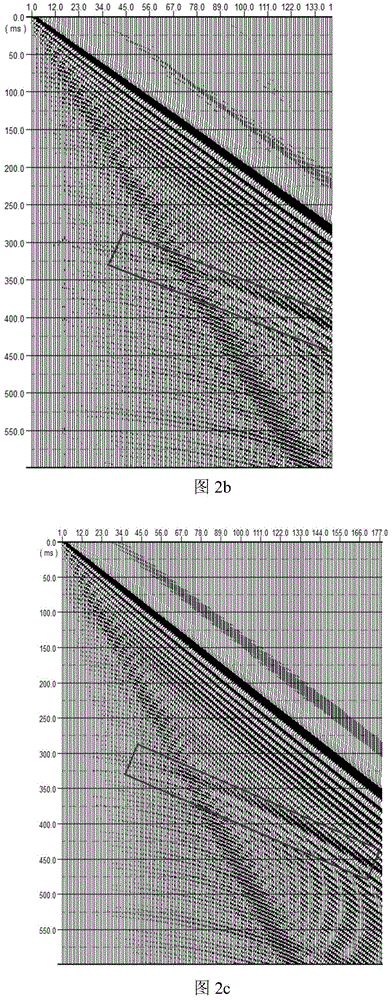

The invention belongs to the technical field of video coding, and particularly relates to a rate-distortion optimizing method based on time domain dependence in low-delay video coding. A circulating group of picture (GOP) structure is adopted, a GOP is formed by every four frames, the frames in the GOPs are allocated to different layers, and the frames in the same layer follow the similar reference frame and QP allocation rule. The time domain dependence of a hierarchical structure in the low-delay video coding is analyzed, a time domain propagation chain shown in picture 2 is established according to the time domain dependence in the low-delay coding, and then rate-distortion optimal modeling of time domain dependence is carried out. A propagation factor omega a and global lagrangian multiplier lambda g are got. Finally, according to the propagation factor omega a, time domain rate-distortion optimizing is achieved only by adjusting the global lagrangian multiplier lambda g.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

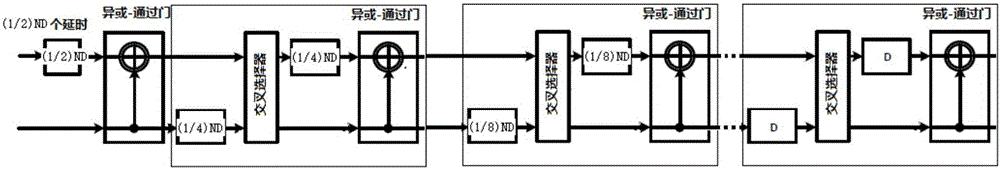

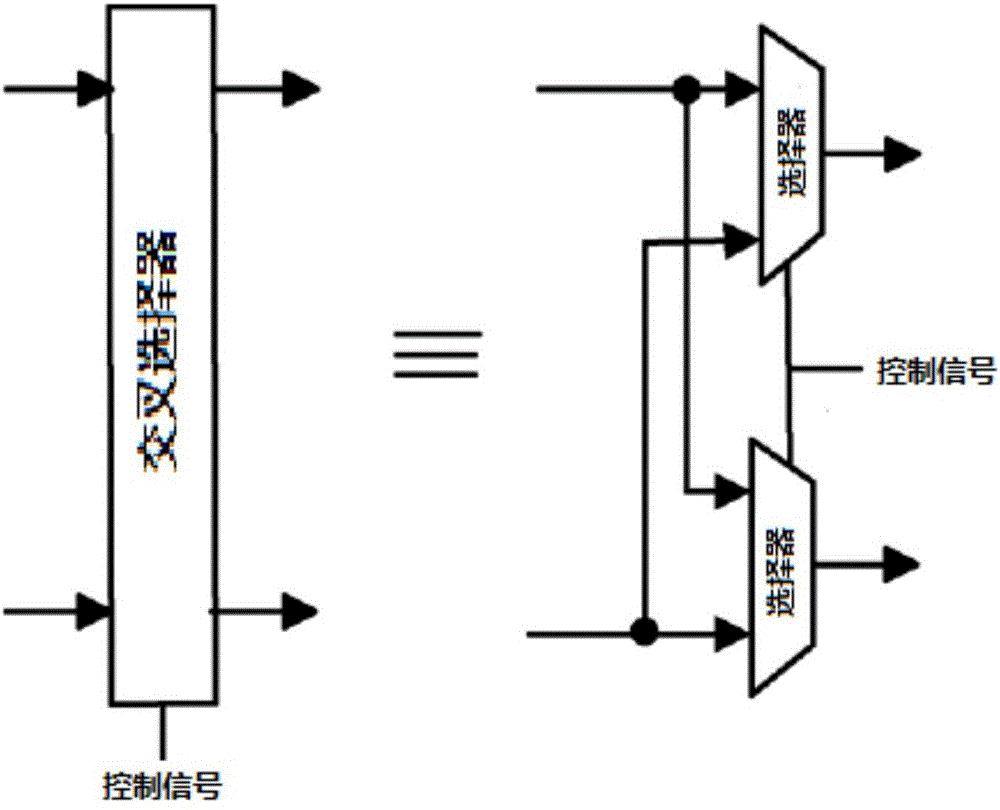

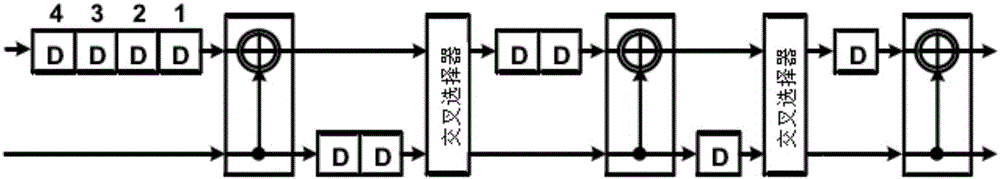

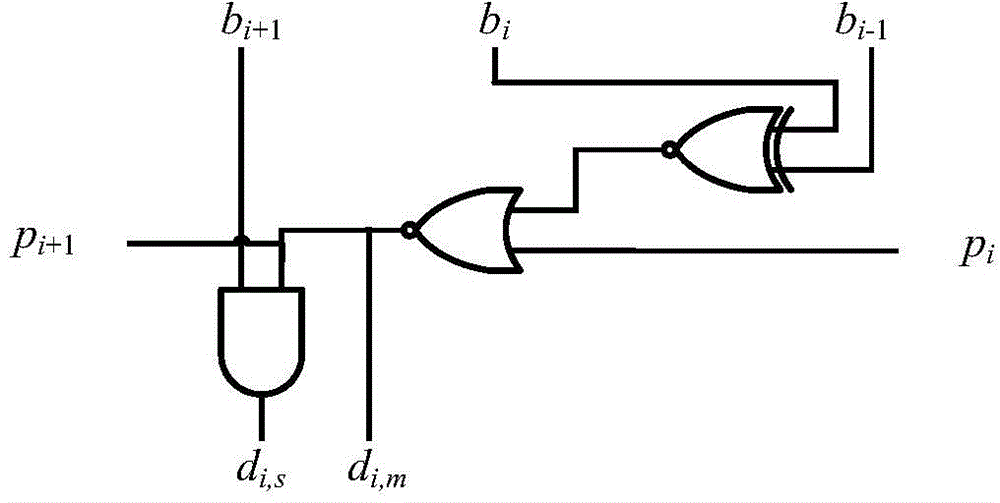

Pipeline polar code encoder

ActiveCN105049064AReduce complexityHigh speedError preventionOther decoding techniquesRound complexityComputer architecture

The present invention puts forward a pipeline polar code encoder, comprising log<2>N groups of delay encoding modules which are connected successively, wherein each delay encoding module comprises one XOR-passing gate and a plurality of delay units which are connected with each other, wherein the N is the number of digits of the polar code encoder. The pipeline polar code encoder of the present invention, according to the principle of a folding technology, achieves encoding of polar codes through adoption of successive connection of the delay encoding modules consisting of the delay units, the XOR-passing gates and so on. The pipeline polar code encoder effectively reduces complexity of hardware, improves encoding speed and processing frequency, and has huge potential in actual application.

Owner:SOUTHEAST UNIV

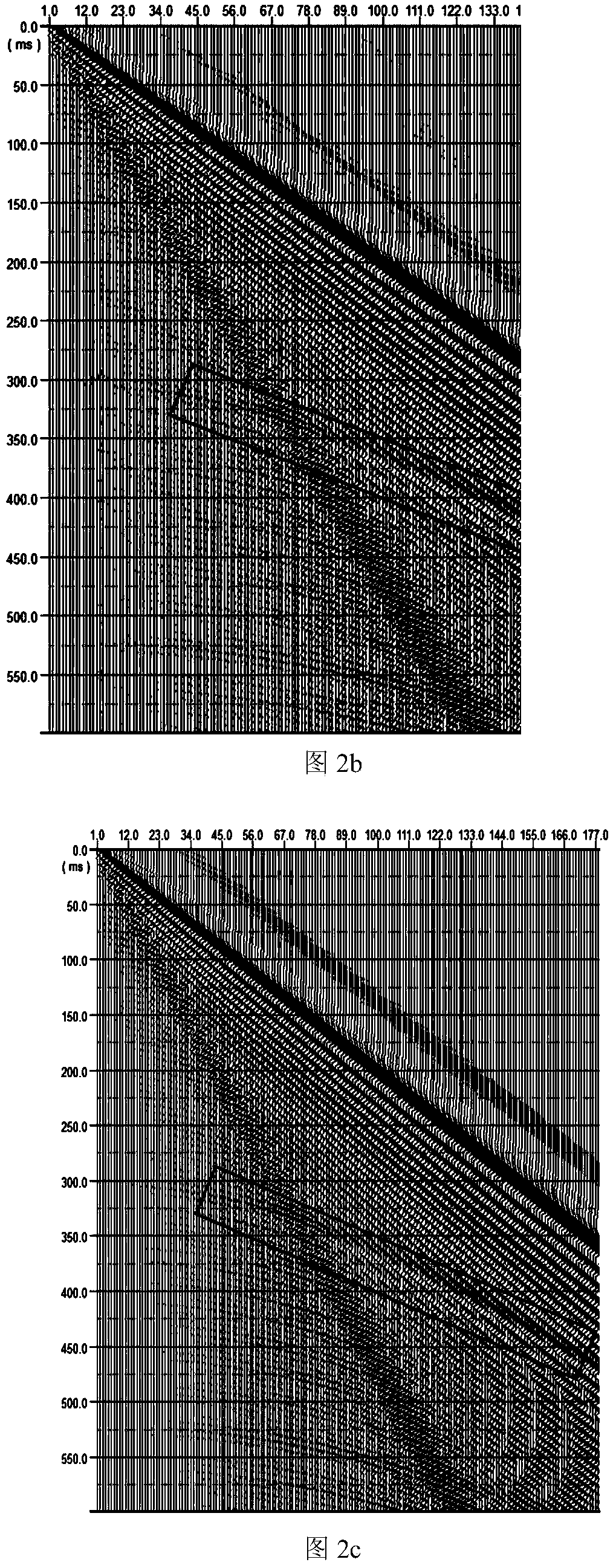

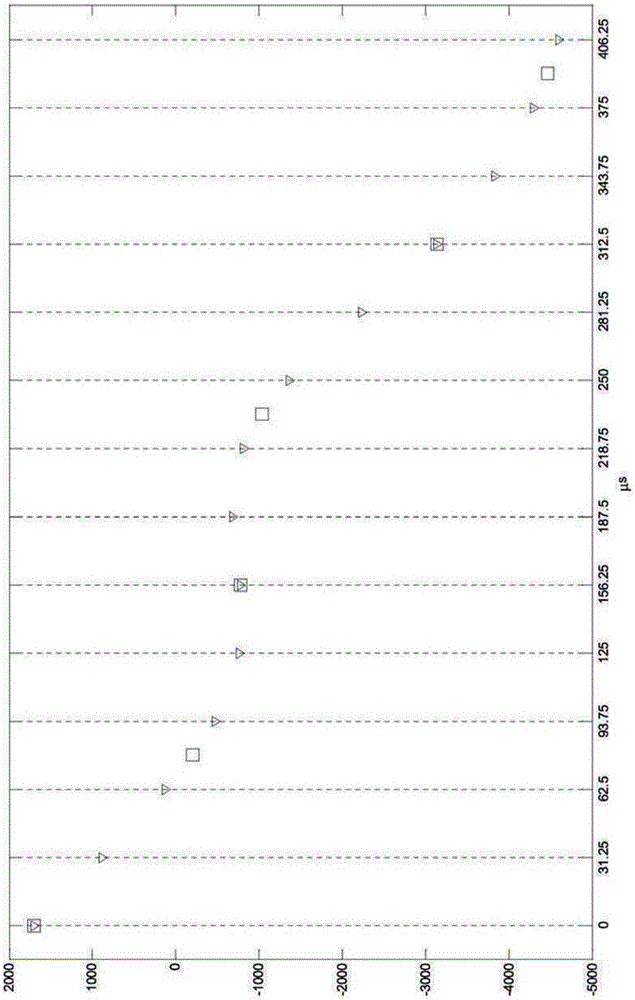

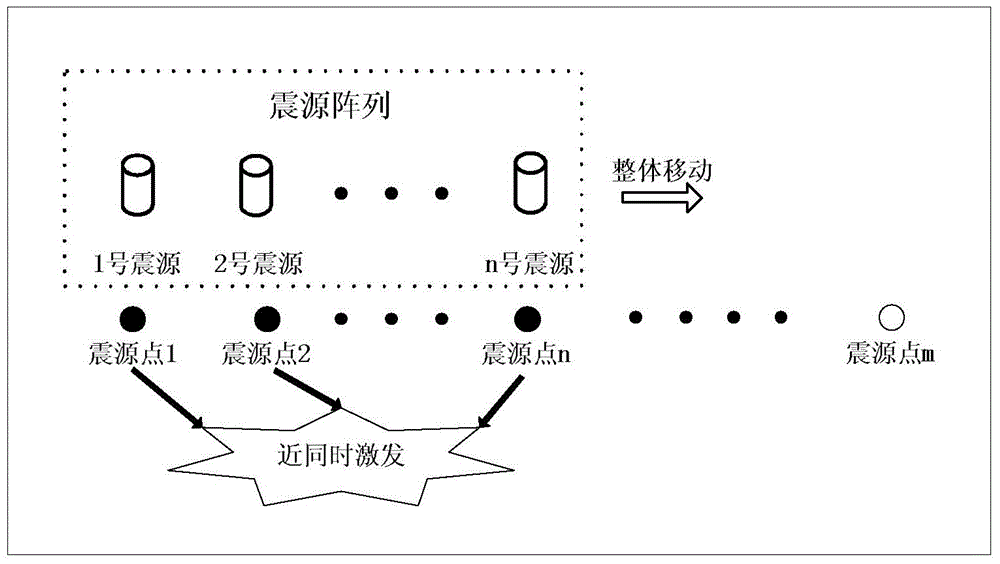

Electromagnetic type vibroseis parallel stimulation collecting and mixing record separating method

InactiveCN103984025AAchieve separationIntegrity guaranteedSeismic signal processingVIT signalsInitial phase

The invention relates to an electromagnetic type vibroseis parallel stimulation collecting and mixing record separating method. The method comprises the steps that focus points and an observing system are designed according to a common single focus collecting method, and the number n of vertical stacking times is determined through the experiment to serve as the number of focuses of parallel stimulation; n electromagnetic type vibroseises are arranged on the n focus points along a measuring line, the initial phase and stimulation delay encoding is carried out on scanning signals, the n focuses can be stimulated n times nearly at the same time, and n mixing records are obtained; the n focuses are integrally moved to the subsequent n focus points along the measuring line, and parallel stimulation continues to be carried out. Compared with an existing common single focus collecting method, if n focus parallel stimulation is utilized, a same number of focus points are collected, the work finishing time is 1 / n of the working finishing time of the common single focus collecting method, and in other words, the production efficiency is improved by n times. Production efficiency is greatly improved, effective signals in the obtained single focus records are clear, and waveforms are consistent. The vibroseis earthquake exploring working efficiency can be improved, and the construction cost of the field earthquake exploring is greatly reduced.

Owner:JILIN UNIV

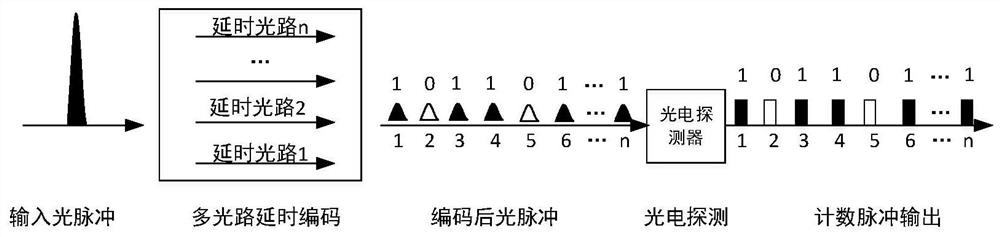

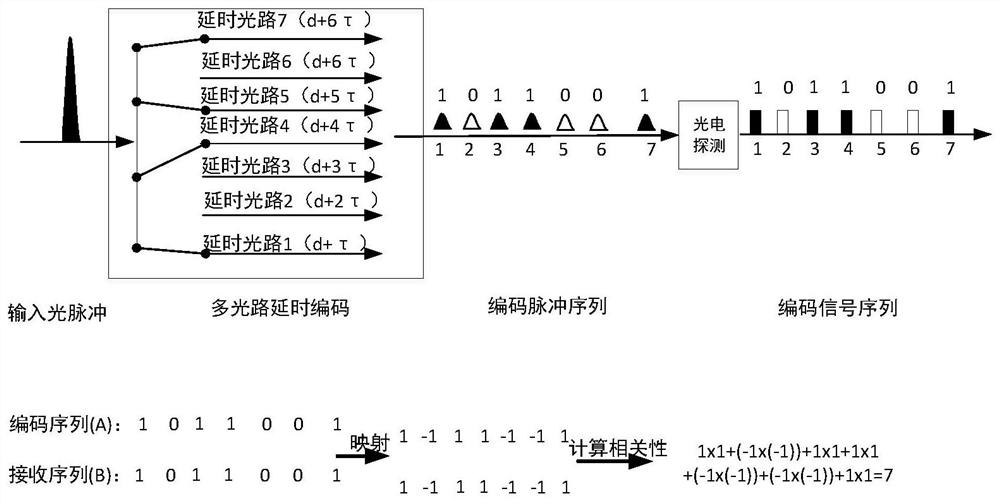

Optical fiber array neutron position sensitiveness detection system and method based on delay encoding

ActiveCN104090293ACost controlDark emission suppressionMeasurement with scintillation detectorsConverting sensor output opticallyTime informationFluorescence

The invention relates to an optical fiber array neutron position sensitiveness detection system and method based on delay encoding. The delay encoding is performed through pulse fluorescence signals sent by different lengths of optical fibers and having the effect on a neutron and a scintillator, so that the arrival times of pulse fluorescence signals transmitted by different lengths of optical fibers arriving at a rear-end photoelectric detector can be different. Therefore, the pulse fluorescence signals transmitted by the optical fibers can be confirmed by measuring the time differences of multiple pulse current signals output by the photoelectric detector and combining an encoding technology, finally the neutron acting position is determined according to the signals transmitted by the optical fibers, and time information can be determined according to the arrival time of the first pulse current signal and through back-stepping of the obtained neutron acting position. By adopting the method, an original multi-path paralleling signal reading mode can be changed into a single-channel serial signal reading mode, and accordingly a neutron acting position and time united measurement system is remarkably simplified.

Owner:NORTHWEST INST OF NUCLEAR TECH

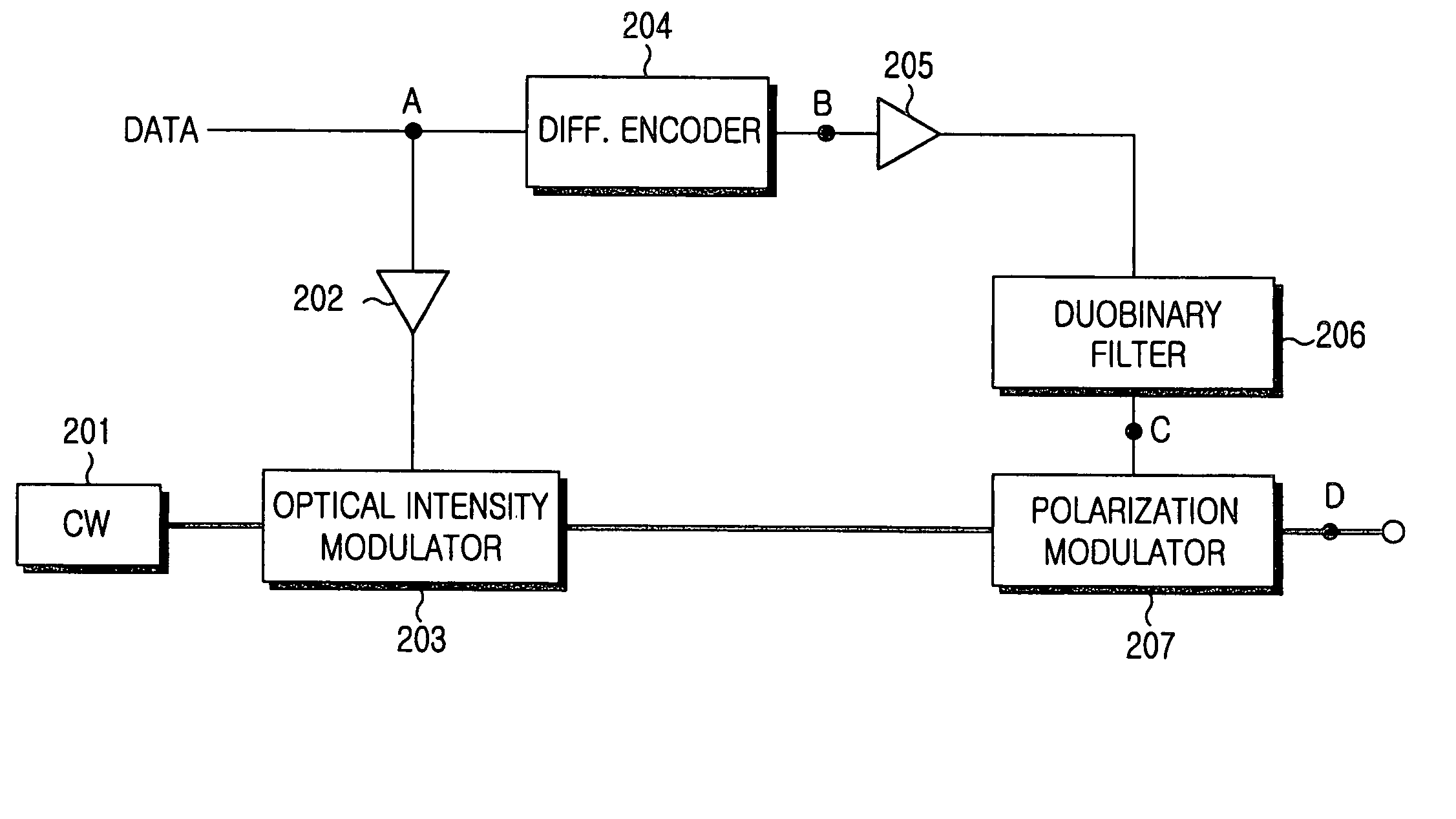

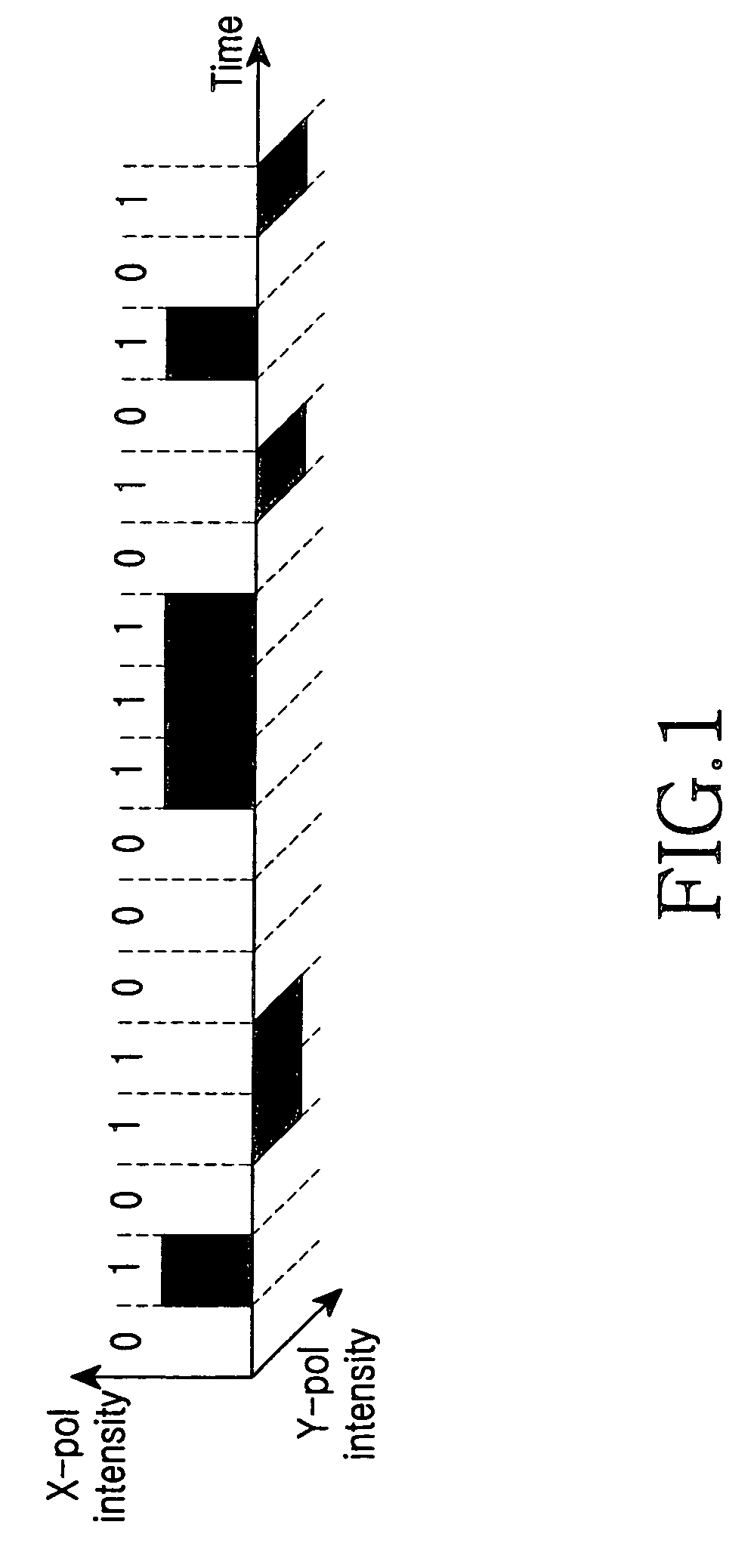

Polarization-shaped duobinary optical transmission apparatus

InactiveUS7212691B2Low implementation costReduce complexityCoupling light guidesElectromagnetic transmittersContinuous waveDifferential coding

A polarization-shaped duobinary optical transmission apparatus is disclosed. The apparatus includes a light source that generates light having a continuous wave, an optical intensity modulator that converts the light into an optical intensity signal based upon an input electric signal and a differential encoder that encodes the input electric signal. The apparatus also includes a delay element that delays the encoded electric signal and a polarization-shaped modulator that polarization-modulates the signal modulated optical intensity by using the delayed signal.

Owner:SAMSUNG ELECTRONICS CO LTD

Decoding a concatenated convolutional-encoded and block encoded signal

ActiveUS7783963B2Speed up the decoding processReduce rateData representation error detection/correctionOther decoding techniquesViterbi decoderReed solomon decoder

Encoded symbols of a concatenated convolutional-encoded and block encoded signal are presented to a conventional first stage of a concatenated decoder, comprising in sequence a soft metric generator, a Viterbi decoder, a first de-interleaver and a first block decoder such as a Reed-Solomon decoder. The encoded symbols are also presented to a delay chain to produce progressively delayed encoded symbols. Where an output block of the conventional decoder is indicated as being a valid codeword by the first block decoder, the bytes in this block are marked as being correct. These bytes that are known to be correct are then used after interleaving and serialization as known bits input to a second stage of the decoder process operating on the delayed encoded symbols and incorporating a modified soft metric generator constrained by the known bits. This process can be extended to further iterations as required. A modified Viterbi decoder, which is also constrained by the known bits, may also be used in the second and subsequent iterative stages.

Owner:MK SYST USA INC

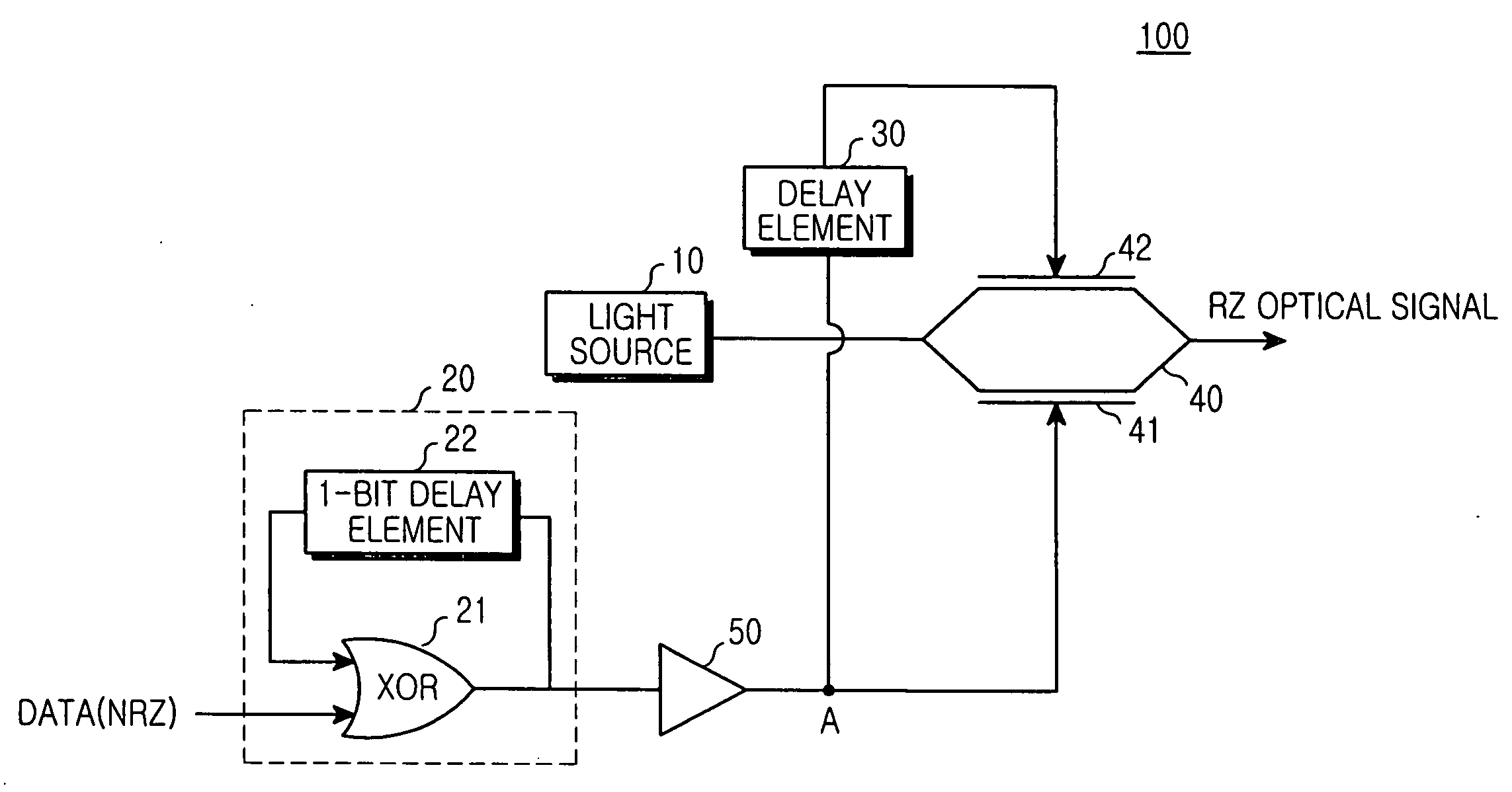

Return-to-zero optical transmission device

InactiveUS20050069331A1Improve receiver sensitivityReduce signal distortionElectromagnetic transmittersNon-linear opticsReturn-to-zeroCarrier signal

Disclosed is a return-to-zero (RZ) optical transmission device. A light source outputs a carrier wave. A precoder encodes an inputted non-return-to-zero (NRZ) electrical signal. A delay element delays the encoded signal. A Mach-Zehnder interferometer modulator has two electrodes. The Mach-Zehnder interferometer modulator configured to modulate phase and intensity of the carrier wave using respective output signals of the precoder the delay element applied, and output an RZ optical signal.

Owner:SAMSUNG ELECTRONICS CO LTD

Resampling of an audio signal by interpolation for low-delay encoding/decoding

The invention relates to a method for resampling an audio-frequency signal in an audio-frequency signal encoding or decoding operation, the resampling being carried out by a method of interpolation of an order greater than one. The method is such that the interpolated samples are obtained (E702) by calculating a weighted average of possible interpolation values (E701) calculated over a plurality of intervals covering the time location of the sample to be interpolated. The invention also relates to a resampling device implementing the described method, and an encoder and decoder comprising at least one device.

Owner:ORANGE SA

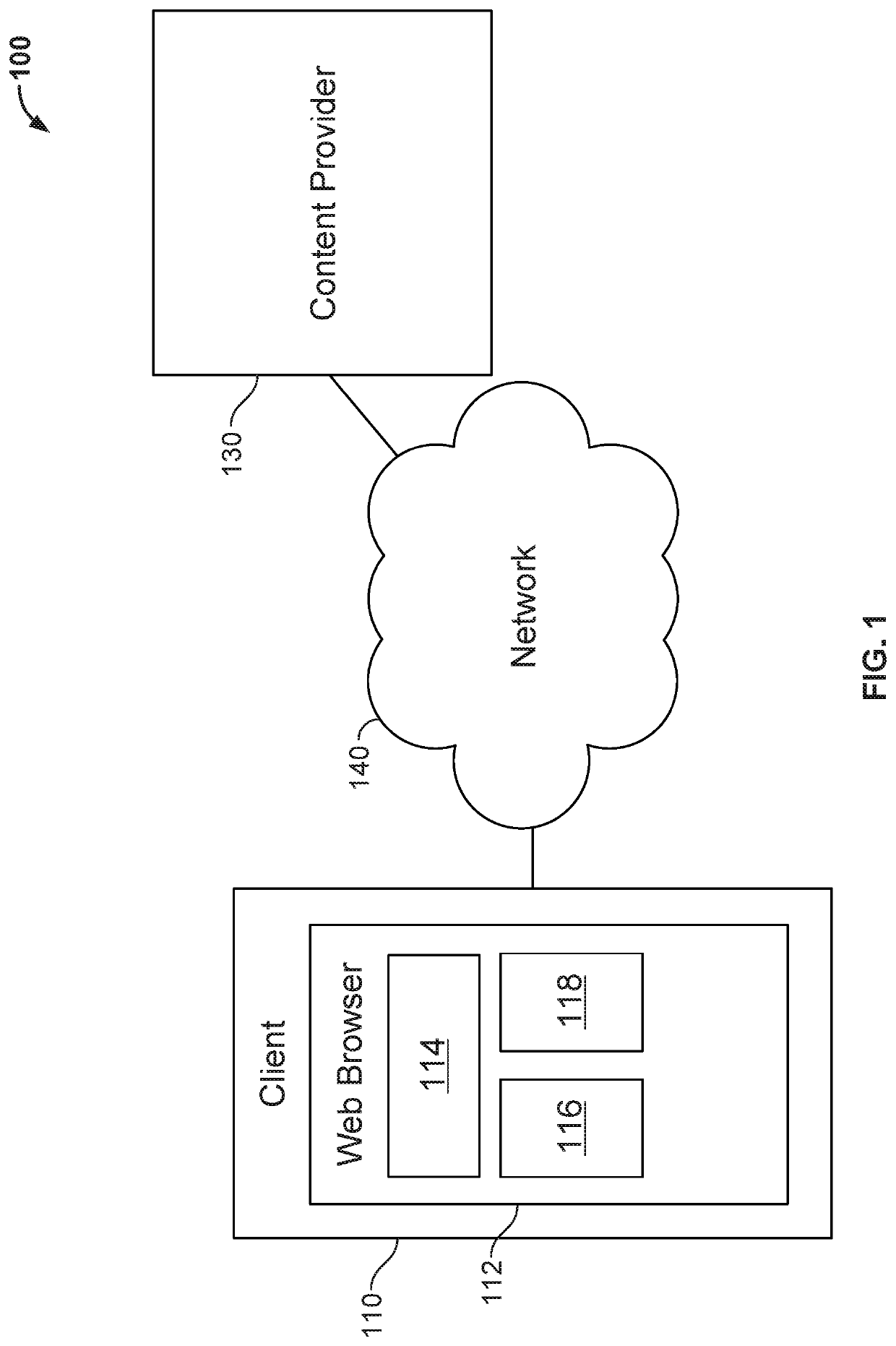

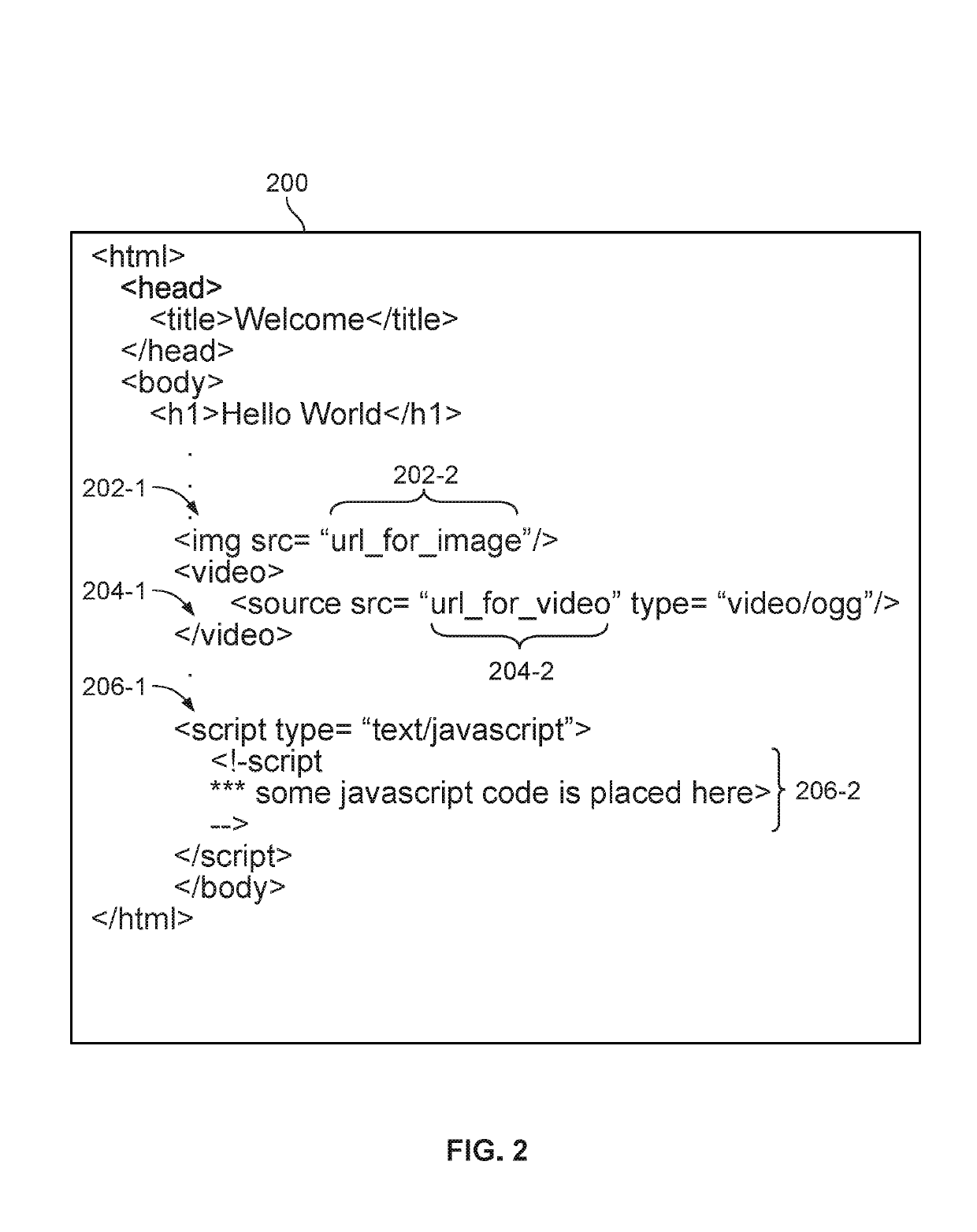

Delayed encoding of resource identifiers

ActiveUS20200065341A1User identity/authority verificationDigital data protectionWeb browserEngineering

A resource identifier to be encoded dynamically upon detection of a triggering event is identified. The resource identifier is allowed to remain not encoded prior to detection of the triggering event. The triggering event that will cause the resource identifier to be consumed by a web browser is detected. In response to detecting the triggering event, the resource identifier is encoded, and an encoded version of the resource identifier is provided for consumption by the web browser.

Owner:AKAMAI TECH INC

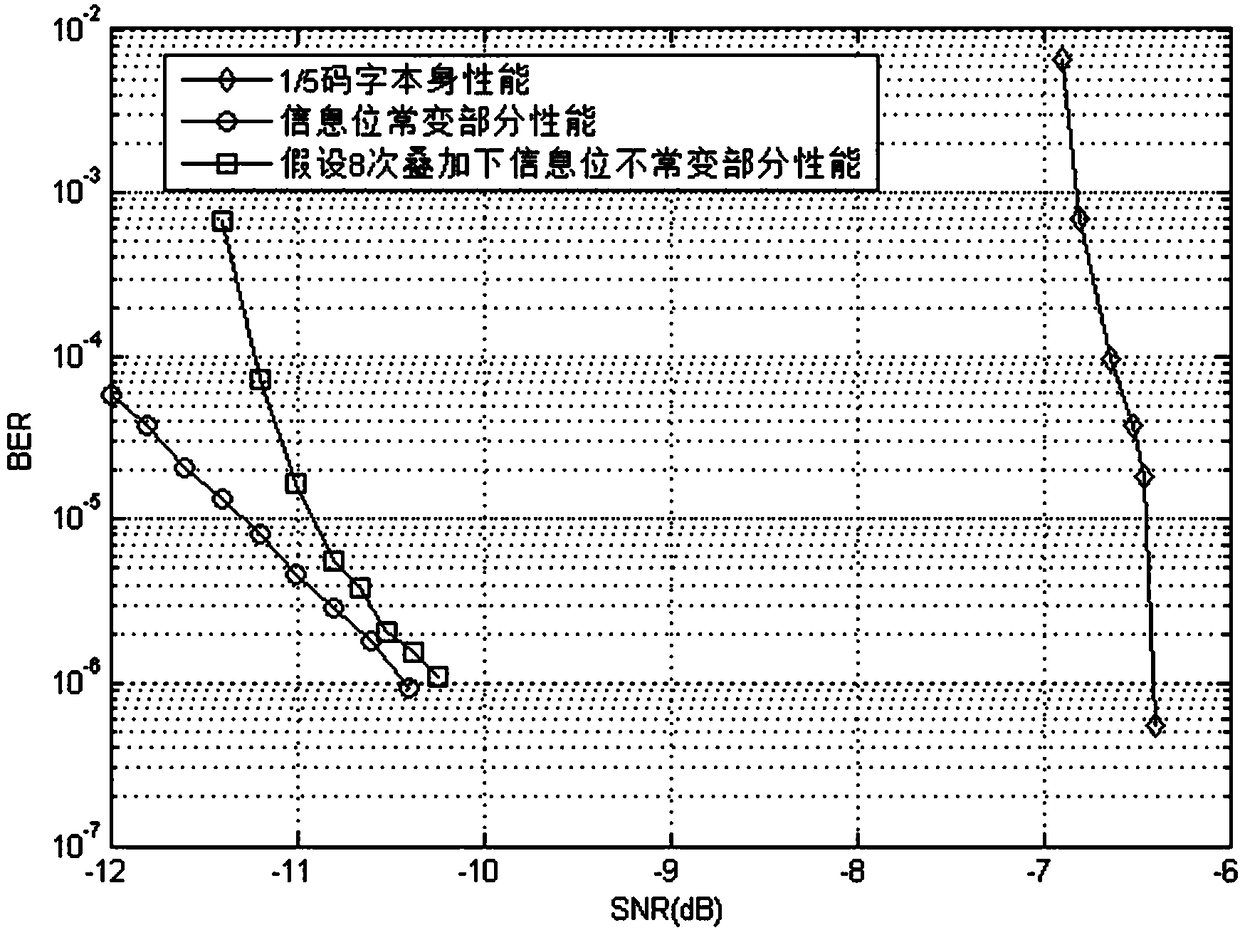

Signaling code encoding method applied to broadcast communication system and corresponding decoding method

ActiveCN108111251AImprove noise immunityForward error control useCommunications systemComputer science

The invention provides a signaling code encoding method applied to a broadcast communication system and a corresponding decoding method. Used code words for signaling code encoding are LDPC code wordswhich have a code length of N and an information bit length of K and are of a raptor-like structure. Generally, when noise exceeds a threshold that the code words can be decoded, a signaling code ina system completely cannot normally work and the system can be in a non-working state, but according to the signaling code encoding method applied to the broadcast communication system and the corresponding decoding method which are provided by the invention, when the noise exceeds the threshold that the code words can be decoded, superposition decoding is started up, after superposition encodingis successful in decoding, constantly changeable bits are decoded according to inconstantly changeable bits, and finally, all the word codes can be successfully decoded. A case that the system cannotnormally work when receiving the first several frames of data can be caused, but after sufficient frames, the system can normally work, so that noise resistance performance of the system is greatly improved.

Owner:SHANGHAI JIAO TONG UNIV

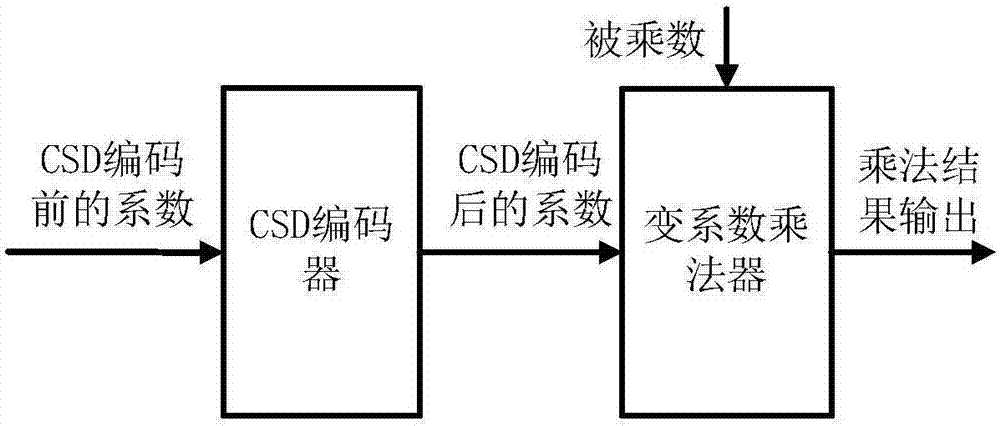

Parallel pseudo CSD encoder for variable coefficient multiplier

InactiveCN104536719AFast operationImprove data throughputComputation using non-contact making devicesBinary multiplierComputer science

The invention relates to the technical field of integrated circuits, in particular to a parallel pseudo CSD encoder for a variable coefficient multiplier. The parallel pseudo CSD encoder comprises an arithmetic logic circuit and an output logic circuit. The input end of the arithmetic logic circuit is connected with external input data, and the output end of the arithmetic logic circuit is connected with the first input end of the output logic circuit. The second input end of the output logic circuit is connected with external input data, and the output end of the output logic circuit is connected with the coefficient input end of a backward-stage multiplier. The parallel pseudo CSD encoder has the advantages that it is ensured that a code system formed after pseudo CSD encoding has the same nonzero digit number as a traditional CSD encoding, and meanwhile the parallel arithmetic logic is adopted to eliminate carry transmission logic produced in the traditional CSD encoding process, so that the pseudo CSD encoder arithmetic speed is increased, the parallel pseudo CSD encoder is unrelated with the binary digit bit length needing to be encoded, the fixed-delay encoding circuit is formed, and the data throughput of the pseudo CSD encoder is greatly improved. The parallel pseudo CSD encoder is especially applicable to variable coefficient multipliers.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

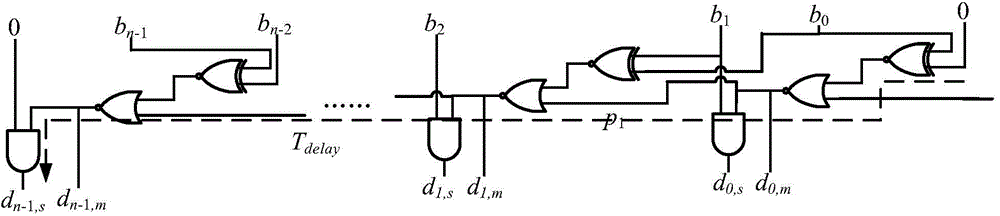

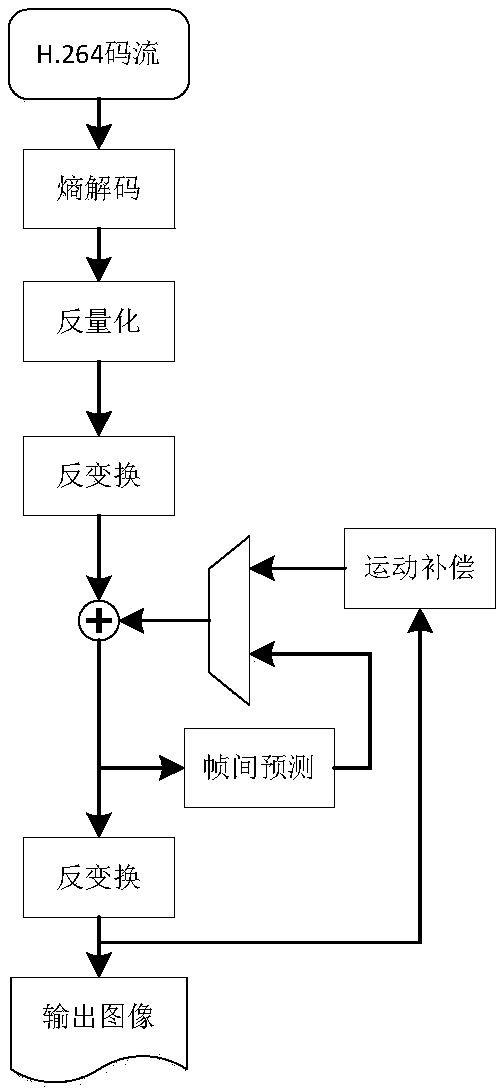

Low-delay encoding/decoding method based on H264 standard and image data transmission method

The invention discloses a low-delay encoding / decoding method based on H264 standard and an image data transmission method. The low-delay encoding / decoding method comprises the following steps: performing conversion and quantization processing on an image domain of an input image to obtain a first image; performing prediction encoding on space domain and time domain of the first image so as to obtain the second image, wherein the prediction coding specifically comprises intra-frame prediction and inter-frame prediction; performing optimization memory mapping on the second image to obtain imagedata, wherein the optimization memory mapping specifically comprises the steps of distributing memory space at first, and then cyclically reading the second image and performing data processing on thesecond image; breaking the circulation and releasing the memory; performing entropy encoding on the image data, and outputting H264 encoded stream. After the memory optimization, the execution efficiency is improved, the image encoding / decoding delay is reduced, the encoding / decoding can be performed under low frequency, and the system power consumption and radiated heat can be reduced

Owner:西安思丹德信息技术有限公司

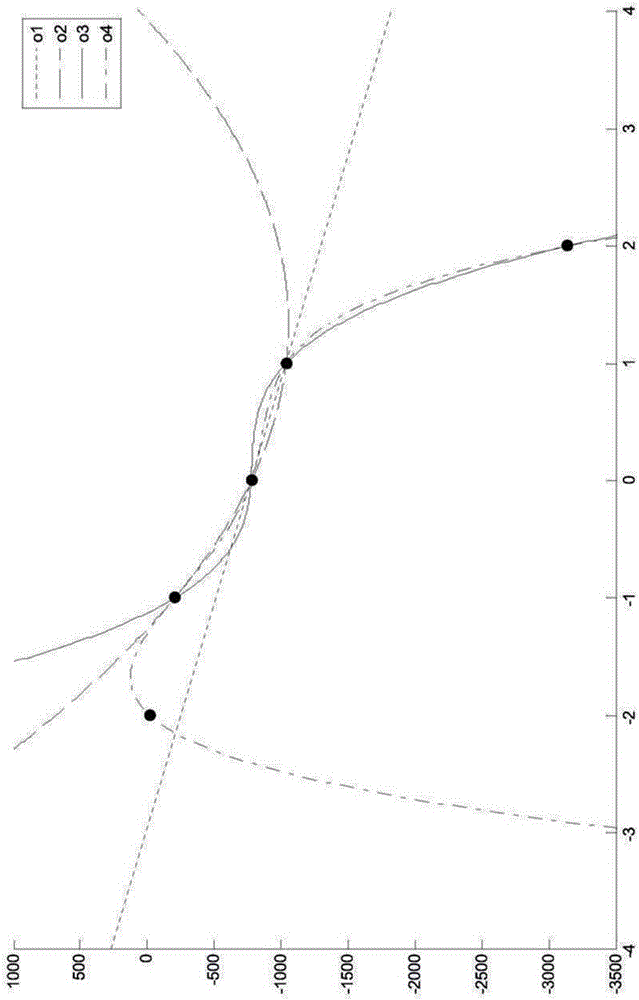

Time Domain Rate-Distortion Optimization Method in Low-Latency Video Coding

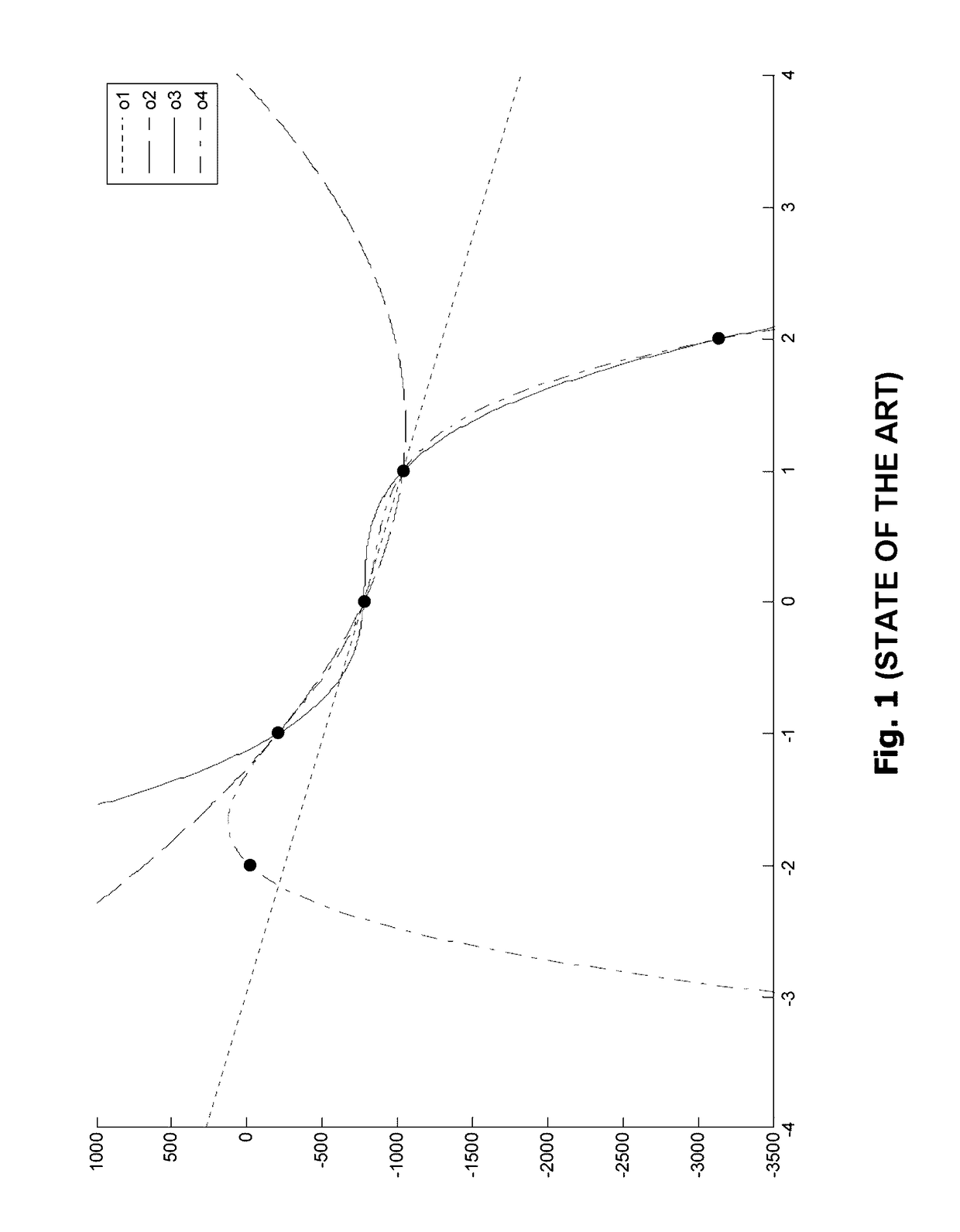

The invention belongs to the technical field of video coding, in particular to a rate-distortion optimization method based on time-domain dependence in low-delay video coding. The present invention adopts a cyclic group of picture (GOP) structure, and every 4 frames is a GOP, and the frames in the GOP are allocated to different layers, and the frames of the same layer follow similar reference frames and QP allocation rules . Analyze the time-domain dependence of the hierarchical structure in low-delay coding, and establish a time-domain propagation chain according to the time-domain dependence in low-delay coding, as shown in Figure 2, and then perform time-domain dependent rate-distortion optimization modeling. Calculate the propagation factor ωa and the global Lagrangian multiplier λg. Finally, according to the propagation factor ωa, the present invention realizes time-domain rate-distortion optimization only by adjusting the global Lagrangian multiplier λg.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

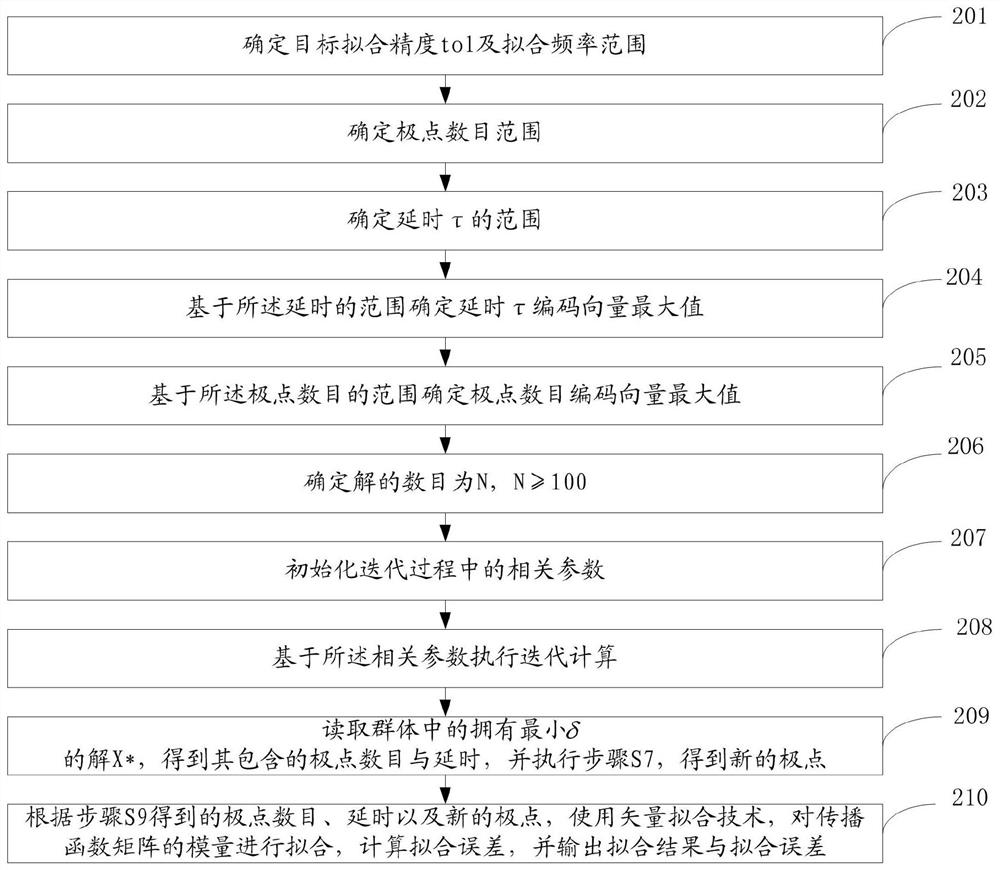

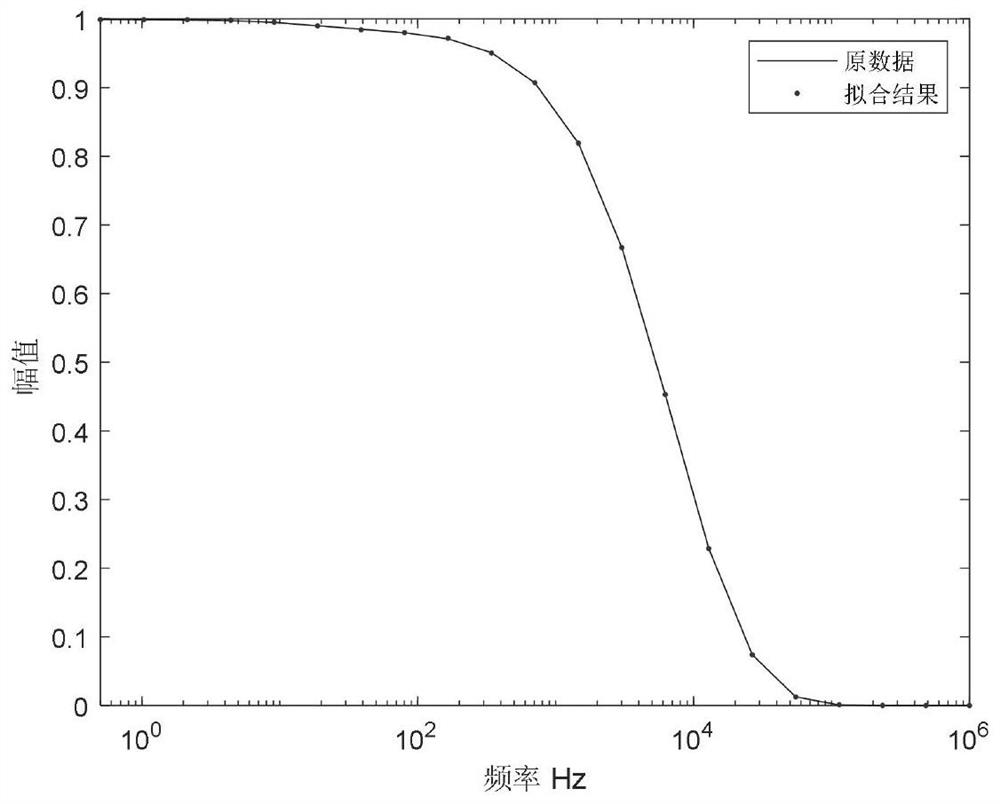

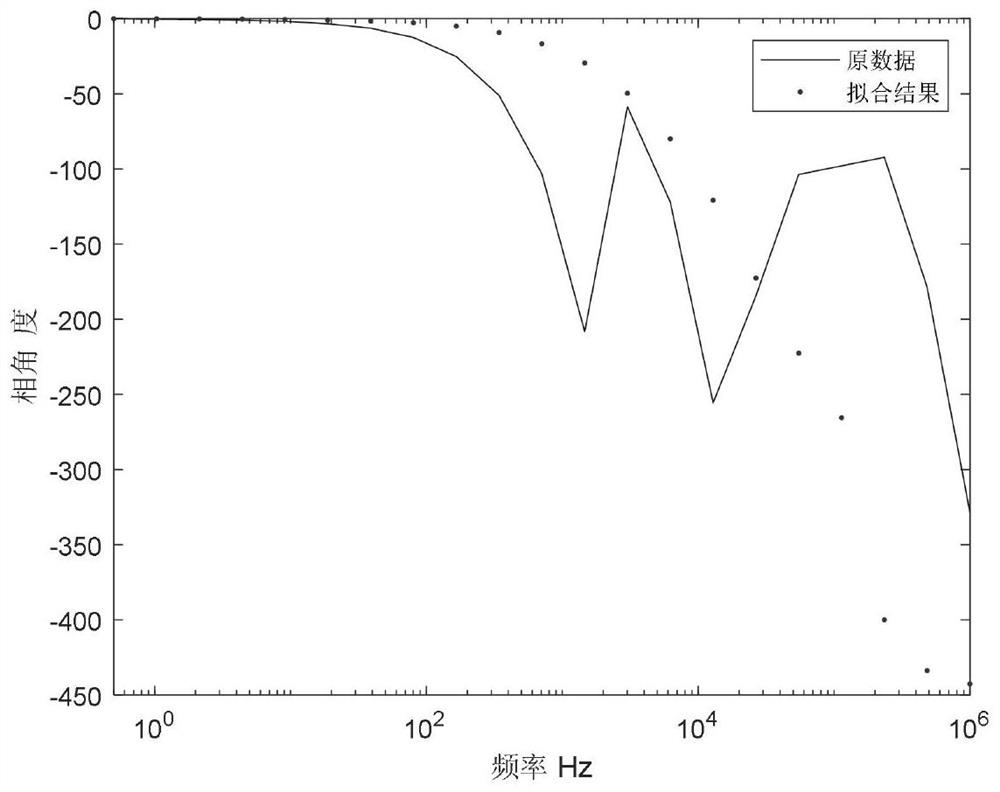

Optimal Fitting Method and System of Propagation Matrix Modulus Based on Differential Evolution Algorithm

ActiveCN111259329BEasy to solveSatisfied with the combinationComplex mathematical operationsGenetic algorithmsPropagation matrixAlgorithm

The present invention relates to a propagation matrix modulus optimization fitting method and system based on differential evolution algorithm, comprising: determining target fitting accuracy tol and fitting frequency range; determining the range of pole numbers; determining the range of delay τ; The range of τ determines the maximum value of the delay encoding vector; the maximum value of the pole number encoding vector is determined based on the range of the number of poles; the number of solutions is determined to be N; the relevant parameters in the initial iteration process are initialized; the iterative calculation is performed based on the relevant parameters; The solution x in the population with the smallest δ * , get the number of poles and delays it contains, and perform the above steps to get new poles; according to the number of poles, delays and new poles obtained by the above steps, use vector fitting technology to calculate the modulus of the propagation function matrix Fitting, calculate the fitting error, and output the fitting result and fitting error. The above-mentioned method in the present invention introduces a differential evolution algorithm, which can solve this nonlinear optimization problem well, and improves efficiency.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

A Parallel Pseudo-CSD Encoder for Variable Coefficient Multipliers

InactiveCN104536719BFast operationImprove data throughputComputation using non-contact making devicesBinary multiplierCarry propagation

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

An optical path delay encoding method and encoding system

Owner:SICHUAN JIUZHOU ELECTRIC GROUP

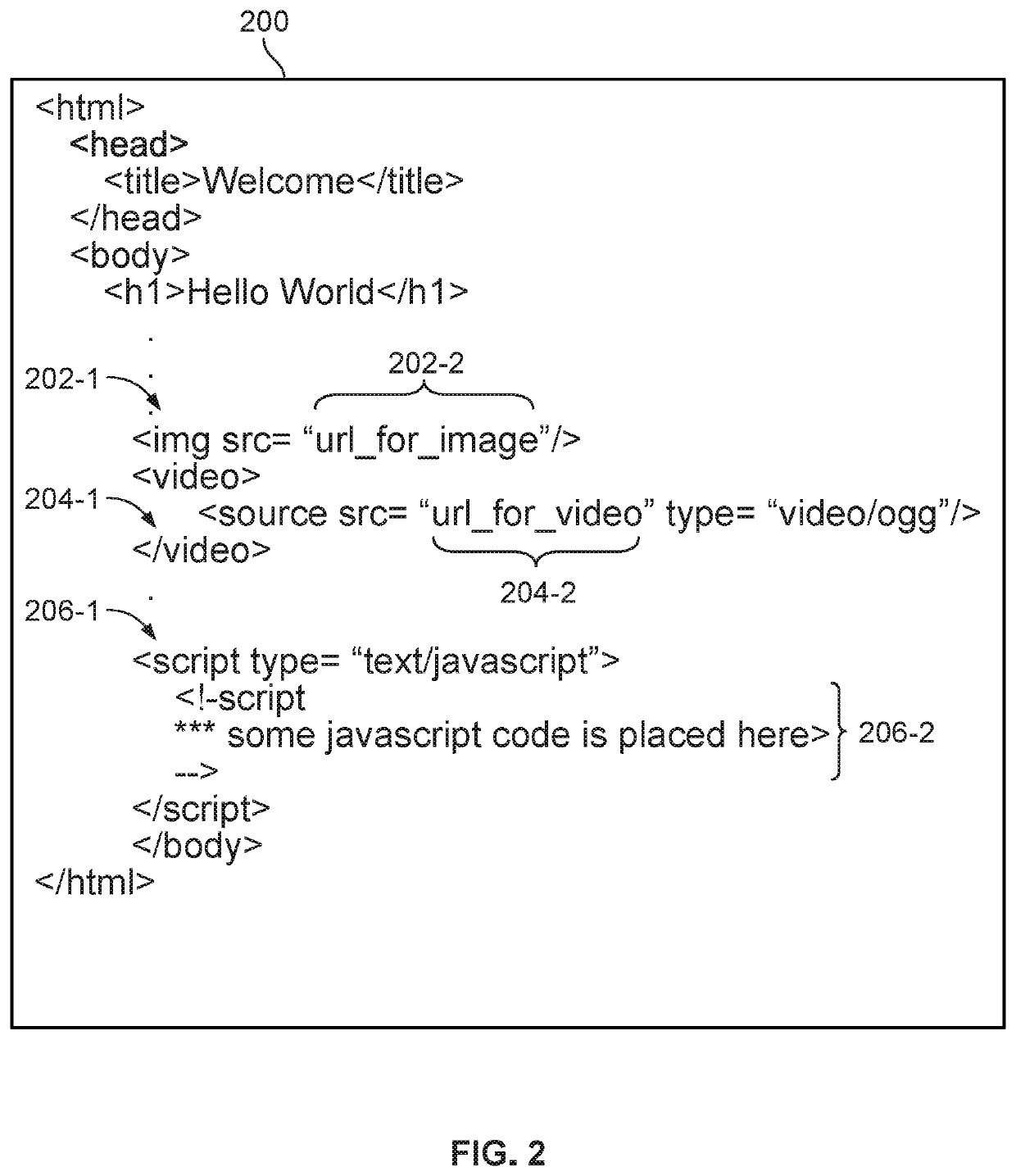

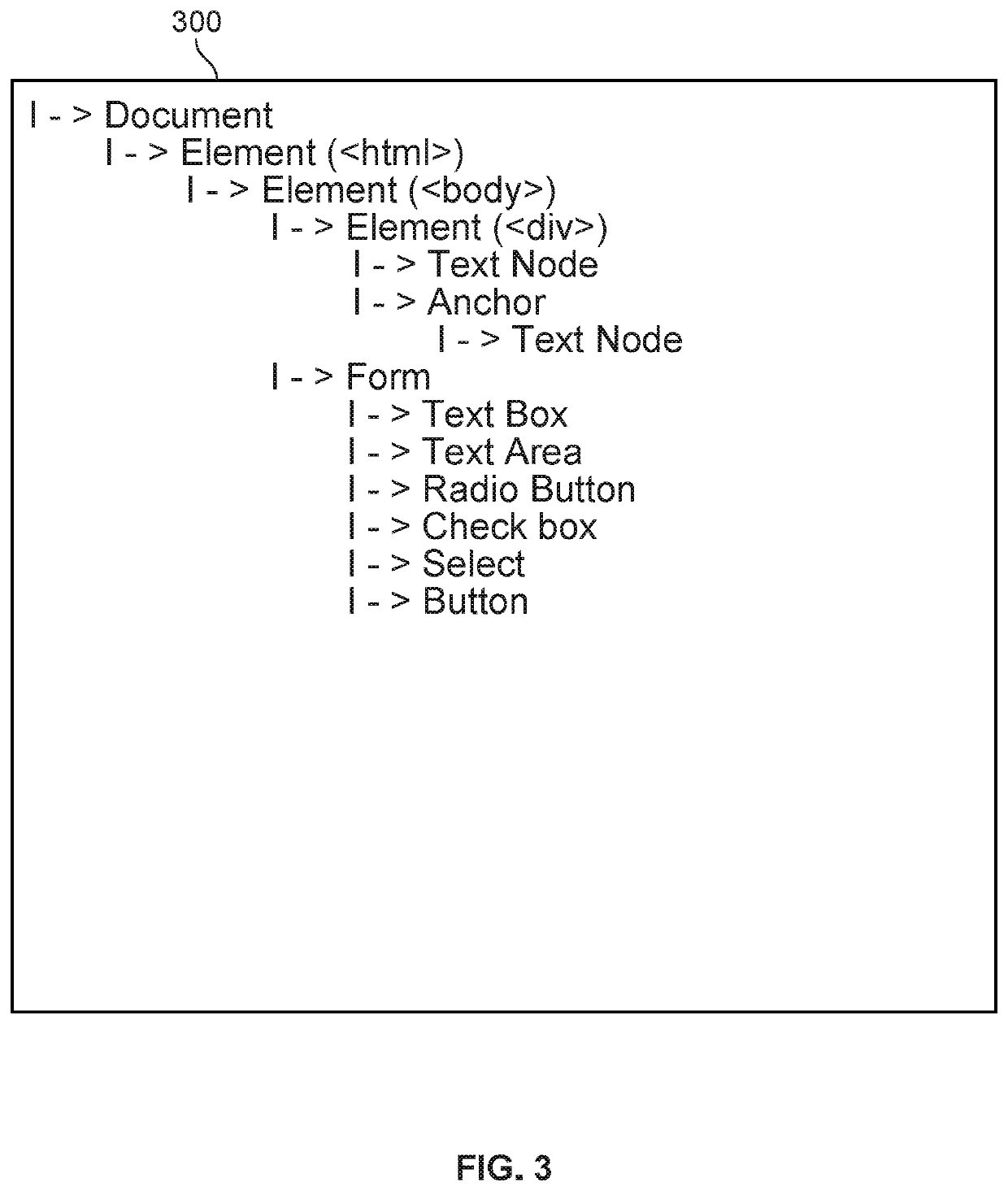

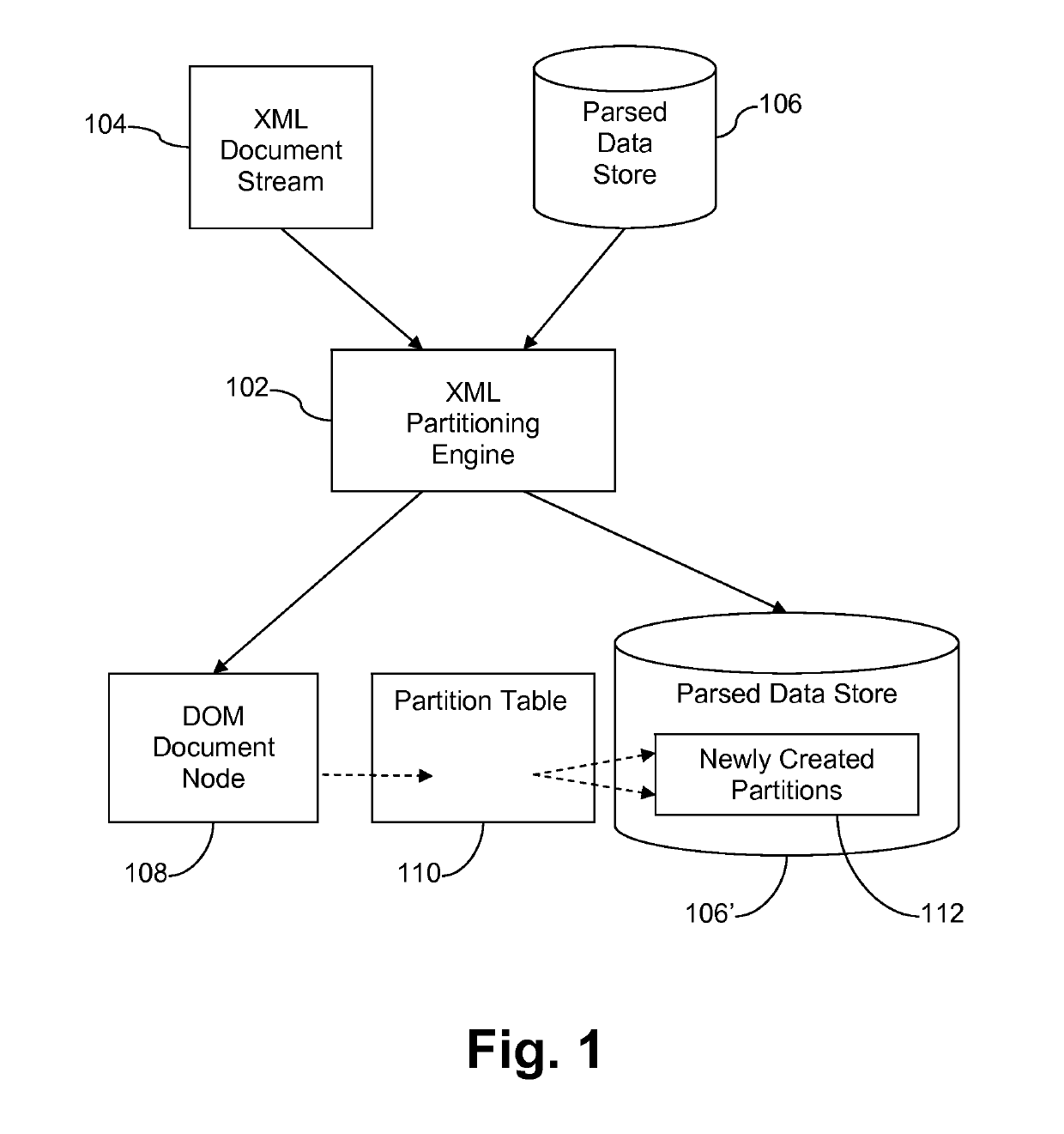

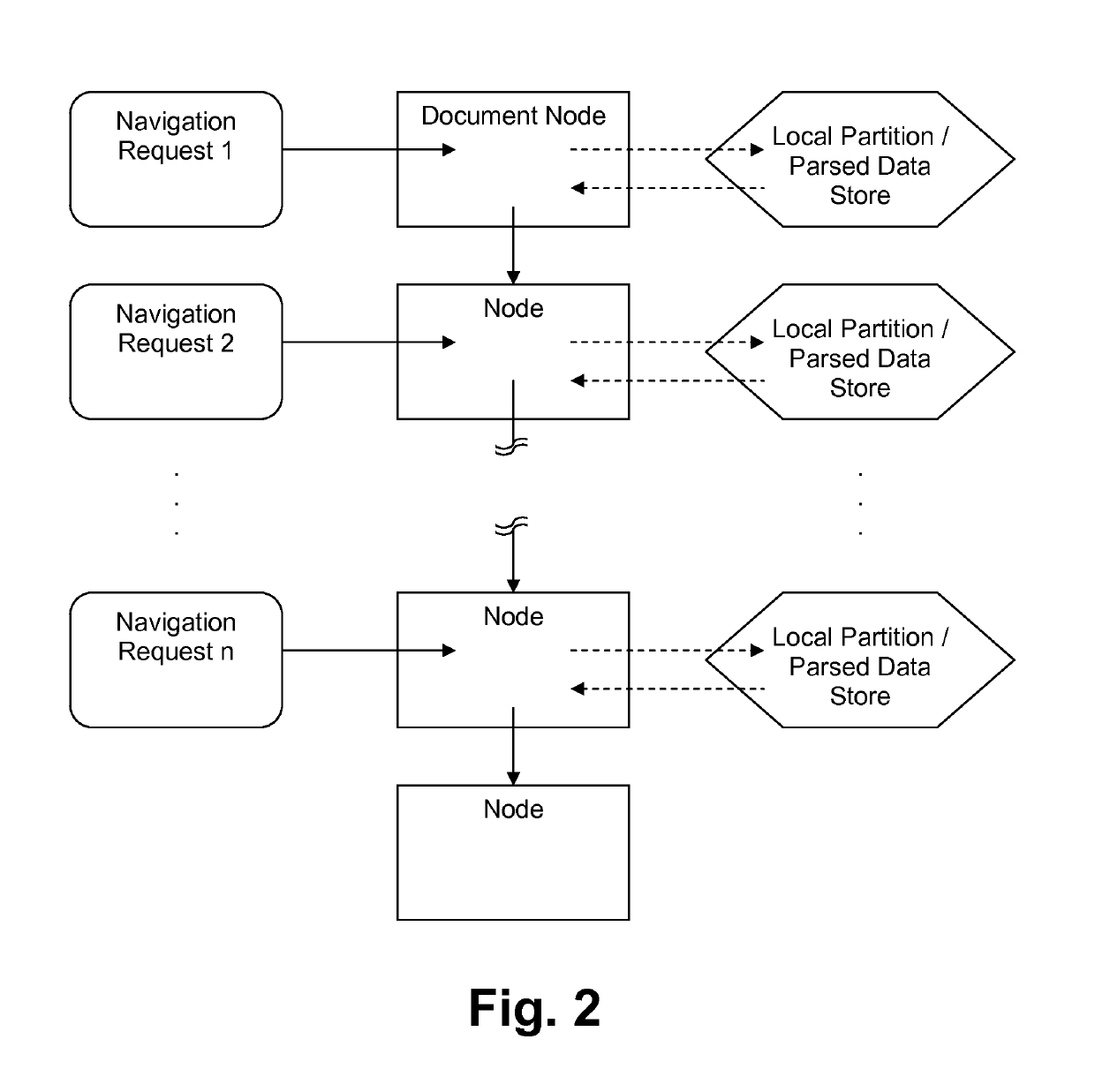

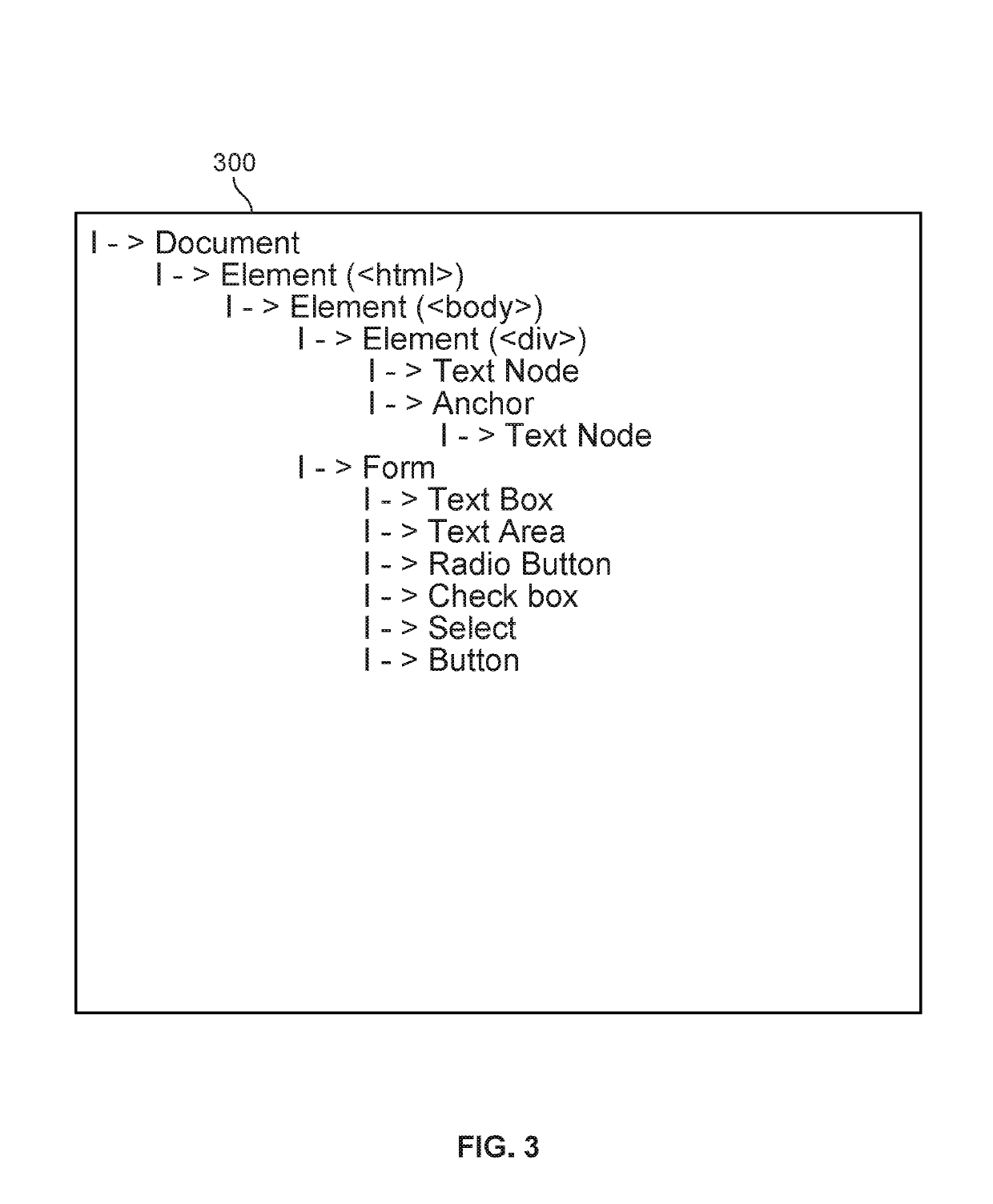

Systems and/or methods for delayed encoding of XML information sets

ActiveUS10515141B2Improve performanceAvoid creatingText processingSpecial data processing applicationsMemory addressMemory hierarchy

Certain example embodiments described herein relate to techniques for processing XML documents of potentially very large sizes. For instance, certain example embodiments parse a potentially large XML document, store the parsed data and some associated metadata in multiple independent blocks or partitions, and instantiate only the particular object model object requested by a program. By including logical references rather than physical memory addresses in such pre-parsed partitions, certain example embodiments make it possible to move the partitions through a caching storage hierarchy without necessarily having to adjust or encode memory references, thereby advantageously enabling dynamic usage of the created partitions and making it possible to cache an arbitrarily large document while consuming a limited amount of program memory. Additionally, certain example embodiments relate to, in addition to delaying the instantiation of nodes, delaying the encoding of respective segments of the XML document until associated nodes are referenced.

Owner:SOFTWARE AG USA

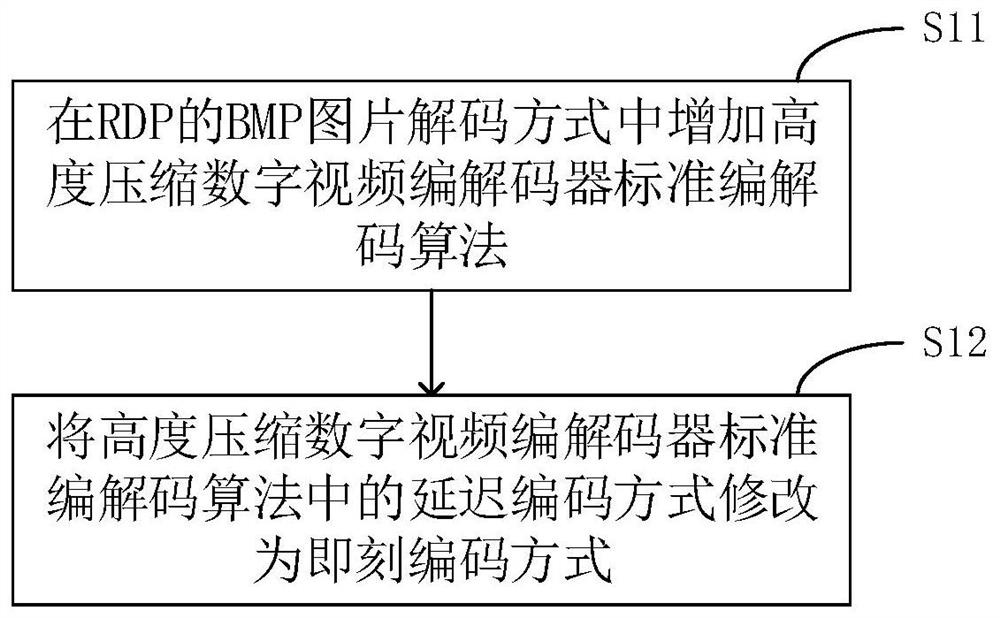

Cloud application opening optimization method and equipment based on RDP

ActiveCN113873253ASolve the problem of decoding failureSolve the problem of blurred screenDigital video signal modificationEnergy efficient computingDigital videoAlgorithm

The invention relates to a cloud application opening optimization method and equipment based on an RDP, and the method comprises the steps: adding a highly compressed digital video codec standard coding and decoding algorithm in a BMP picture decoding mode of the RDP, and modifying a delay coding mode in the highly compressed digital video codec standard coding and decoding algorithm into an immediate coding mode. The problem of decoding failure caused by frame missing is solved through an immediate coding mode, and the problem of blurred screen caused by frame missing due to various factors such as network instability is solved.

Owner:龙思云(北京)科技有限公司

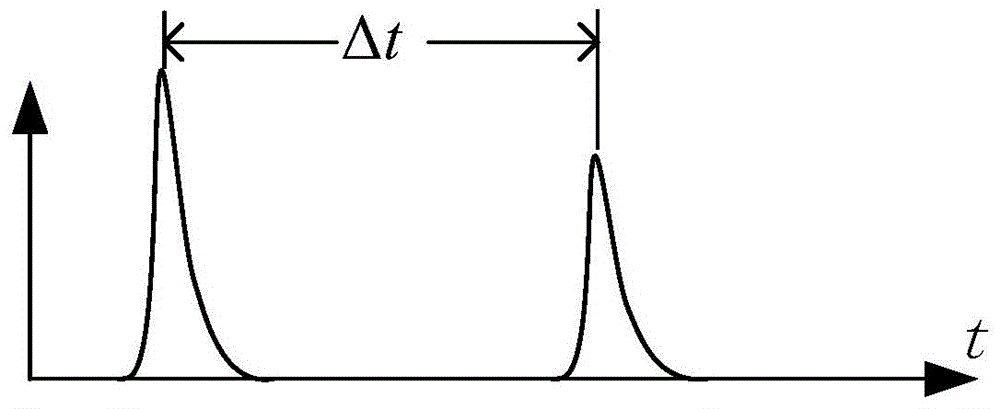

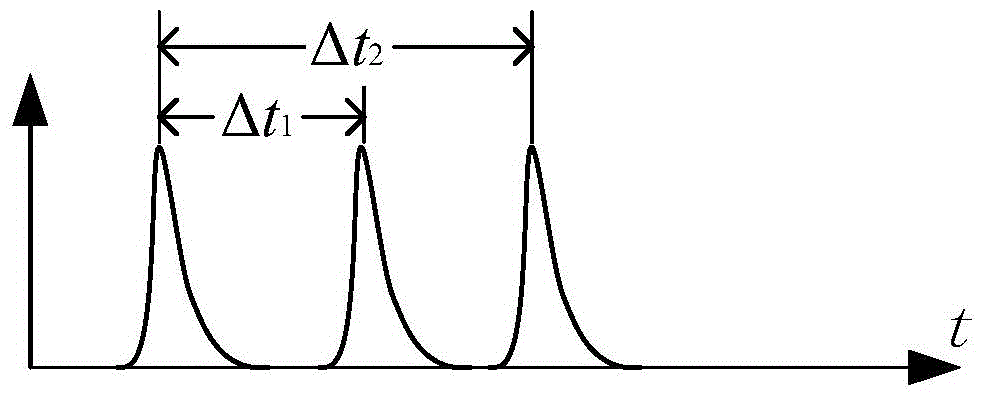

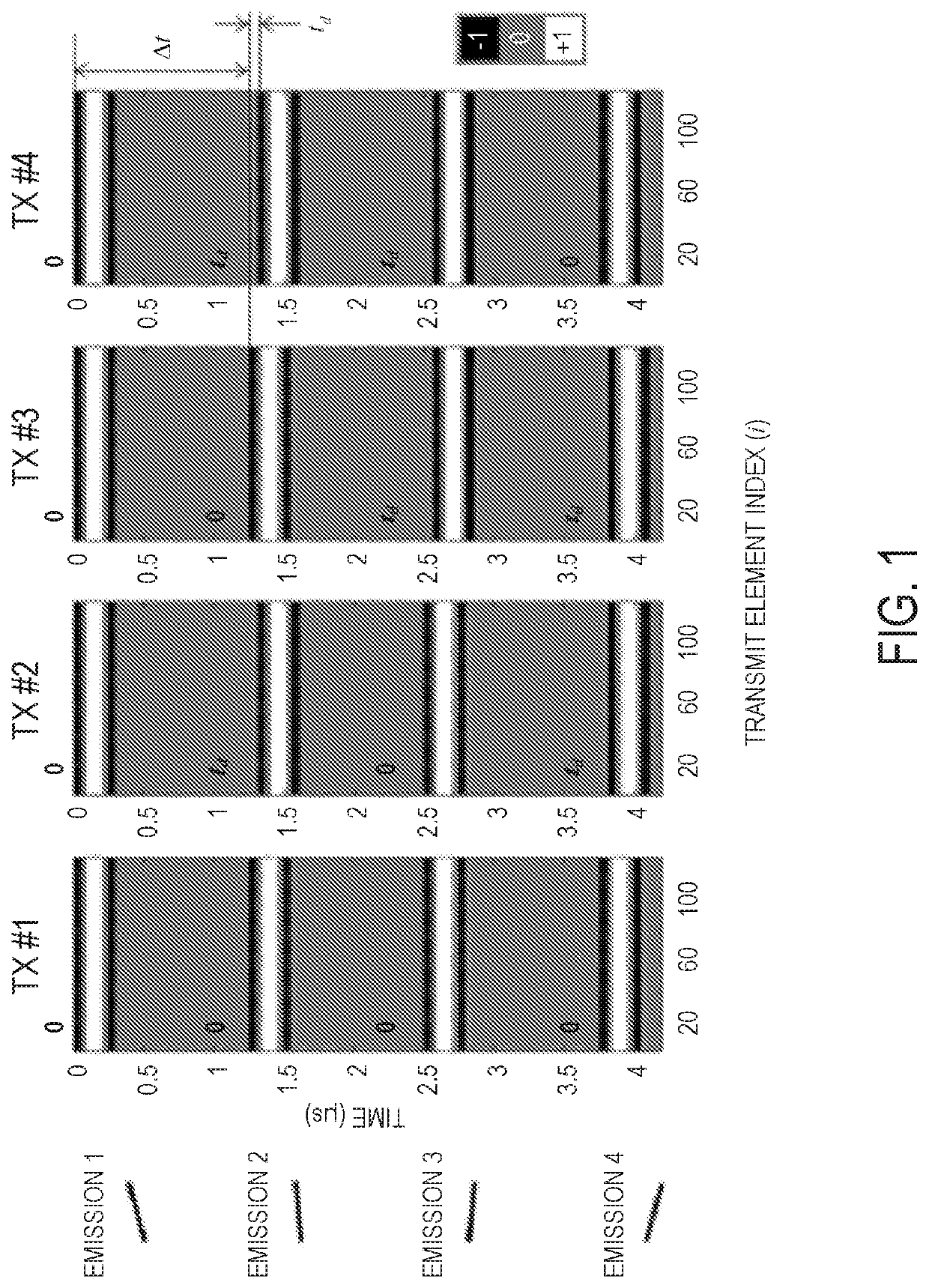

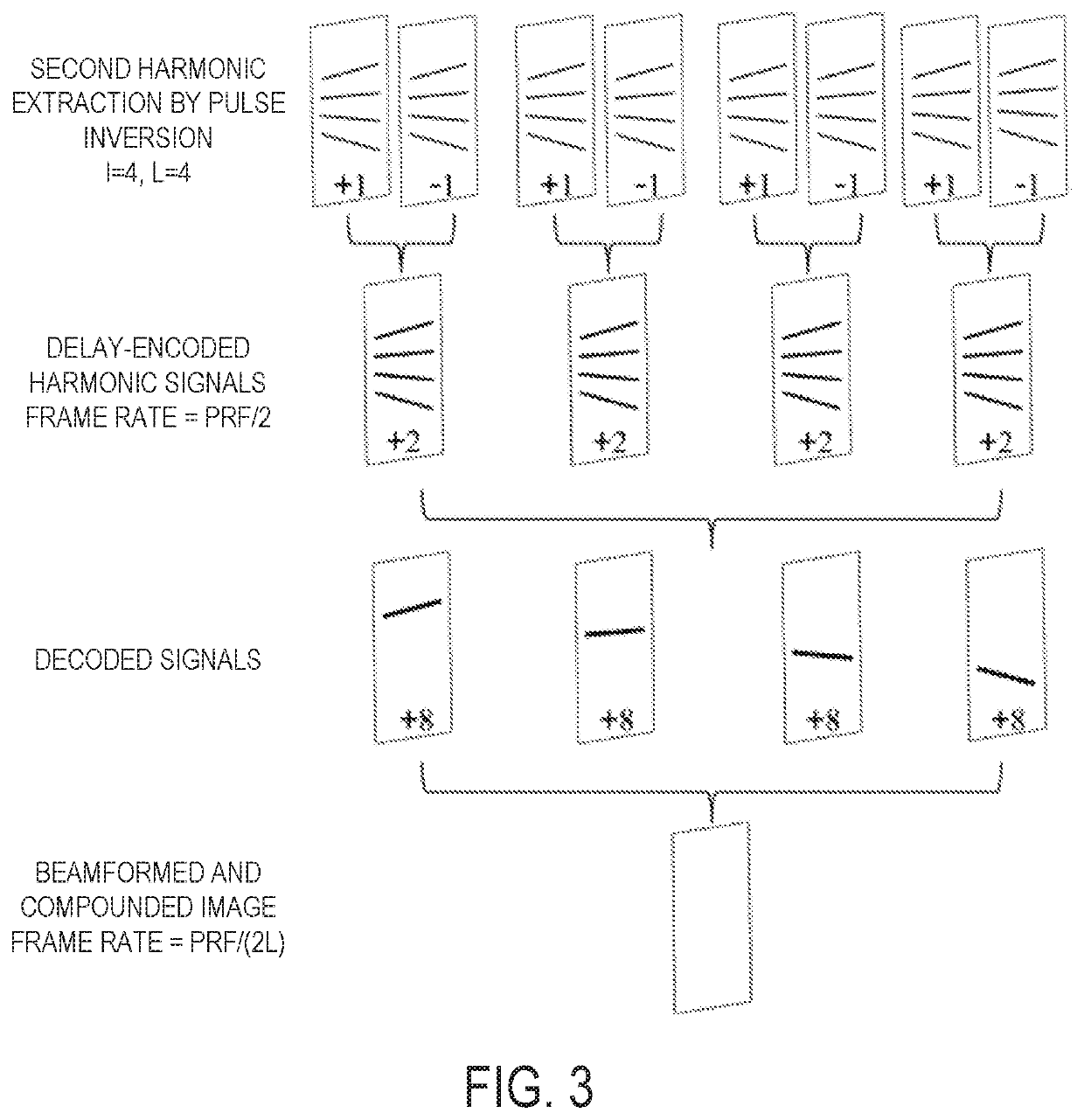

Delay-encoded harmonic imaging with an ultrasound system

ActiveUS11385349B2Complex mathematical operationsAcoustic wave reradiationUltrasound imagingRadio frequency signal

Systems and methods for ultrasound imaging using a delay-encoded harmonic imaging (“DE-HI”) technique is provided. An ultrasound pulse sequence is coded using temporal delays between ultrasound emissions within a single transmission event. This coded scheme allows for harmonic imaging to be implemented. The temporal time delay-codes are applied temporally to multiple different ultrasound emissions within a single transmission event, rather than spatially across different transmitting elements. The received radio frequency (“RF”) signals undergo a decoding process in the frequency domain to recover the signals, as they would be obtained from standard single emissions, for subsequent compounding. As one specific example, a one-quarter period time delay can be used to encode second harmonic signals from each angle emission during a single multiplane wave (“MW”) transmission event, rather than inverting the polarity of the pulses as in conventional MW imaging.

Owner:MAYO FOUND FOR MEDICAL EDUCATION & RES

Delayed encoding of resource identifiers

ActiveUS10474729B2User identity/authority verificationDigital data protectionWeb browserWorld Wide Web

A resource identifier to be encoded dynamically upon detection of a triggering event is identified. The resource identifier is allowed to remain not encoded prior to detection of the triggering event. The triggering event that will cause the resource identifier to be consumed by a web browser is detected. In response to detecting the triggering event, the resource identifier is encoded, and an encoded version of the resource identifier is provided for consumption by the web browser.

Owner:AKAMAI TECH INC

Separation Method of Electromagnetic Vibroseis Parallel Excitation Acquisition and Hybrid Recording

InactiveCN103984025BImproving the efficiency of seismic exploration workReduce construction costsSeismic signal processingWork timeDelay encoding

The invention relates to an electromagnetic type vibroseis parallel stimulation collecting and mixing record separating method. The method comprises the steps that focus points and an observing system are designed according to a common single focus collecting method, and the number n of vertical stacking times is determined through the experiment to serve as the number of focuses of parallel stimulation; n electromagnetic type vibroseises are arranged on the n focus points along a measuring line, the initial phase and stimulation delay encoding is carried out on scanning signals, the n focuses can be stimulated n times nearly at the same time, and n mixing records are obtained; the n focuses are integrally moved to the subsequent n focus points along the measuring line, and parallel stimulation continues to be carried out. Compared with an existing common single focus collecting method, if n focus parallel stimulation is utilized, a same number of focus points are collected, the work finishing time is 1 / n of the working finishing time of the common single focus collecting method, and in other words, the production efficiency is improved by n times. Production efficiency is greatly improved, effective signals in the obtained single focus records are clear, and waveforms are consistent. The vibroseis earthquake exploring working efficiency can be improved, and the construction cost of the field earthquake exploring is greatly reduced.

Owner:JILIN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com