Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

99results about How to "Not set it low" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

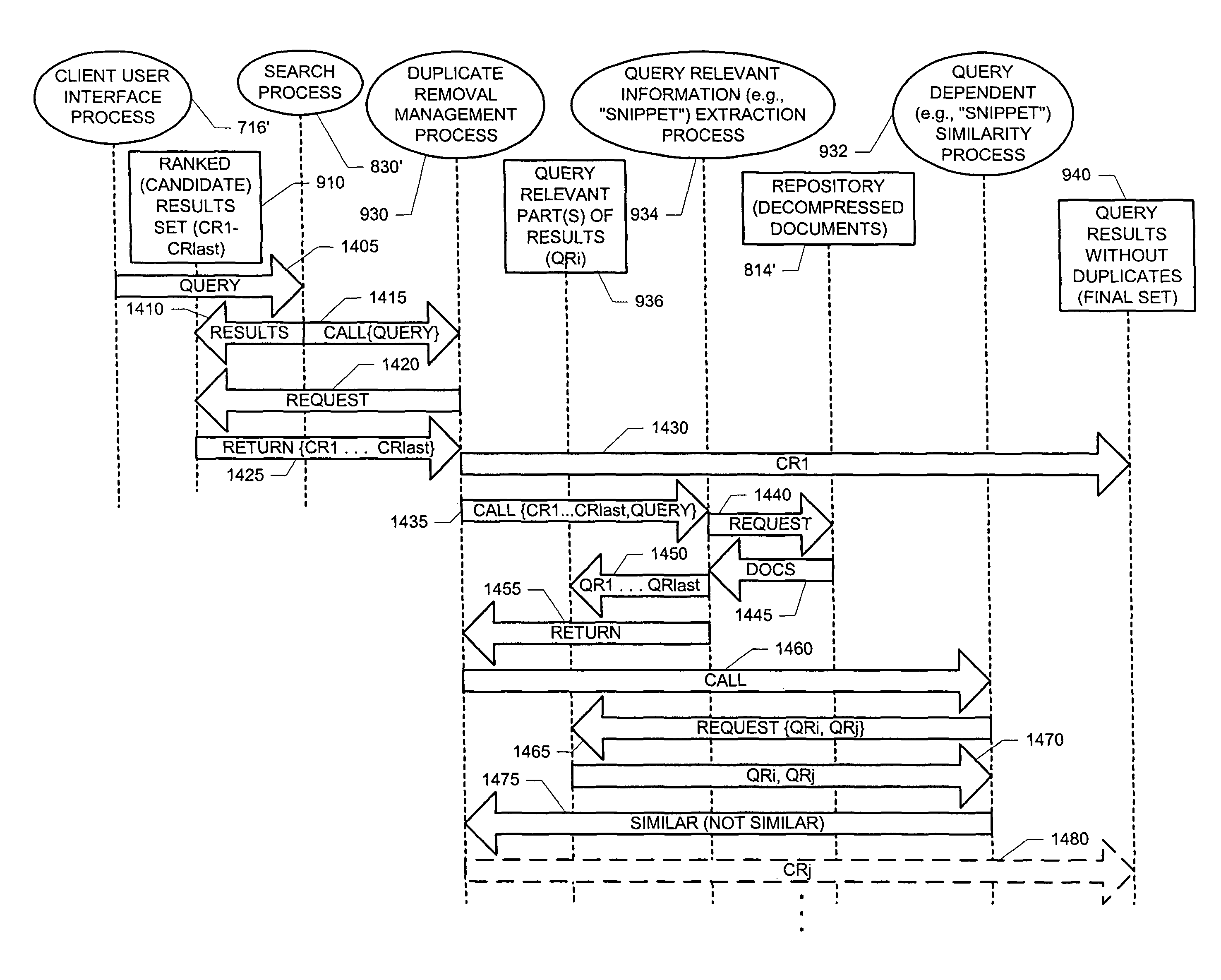

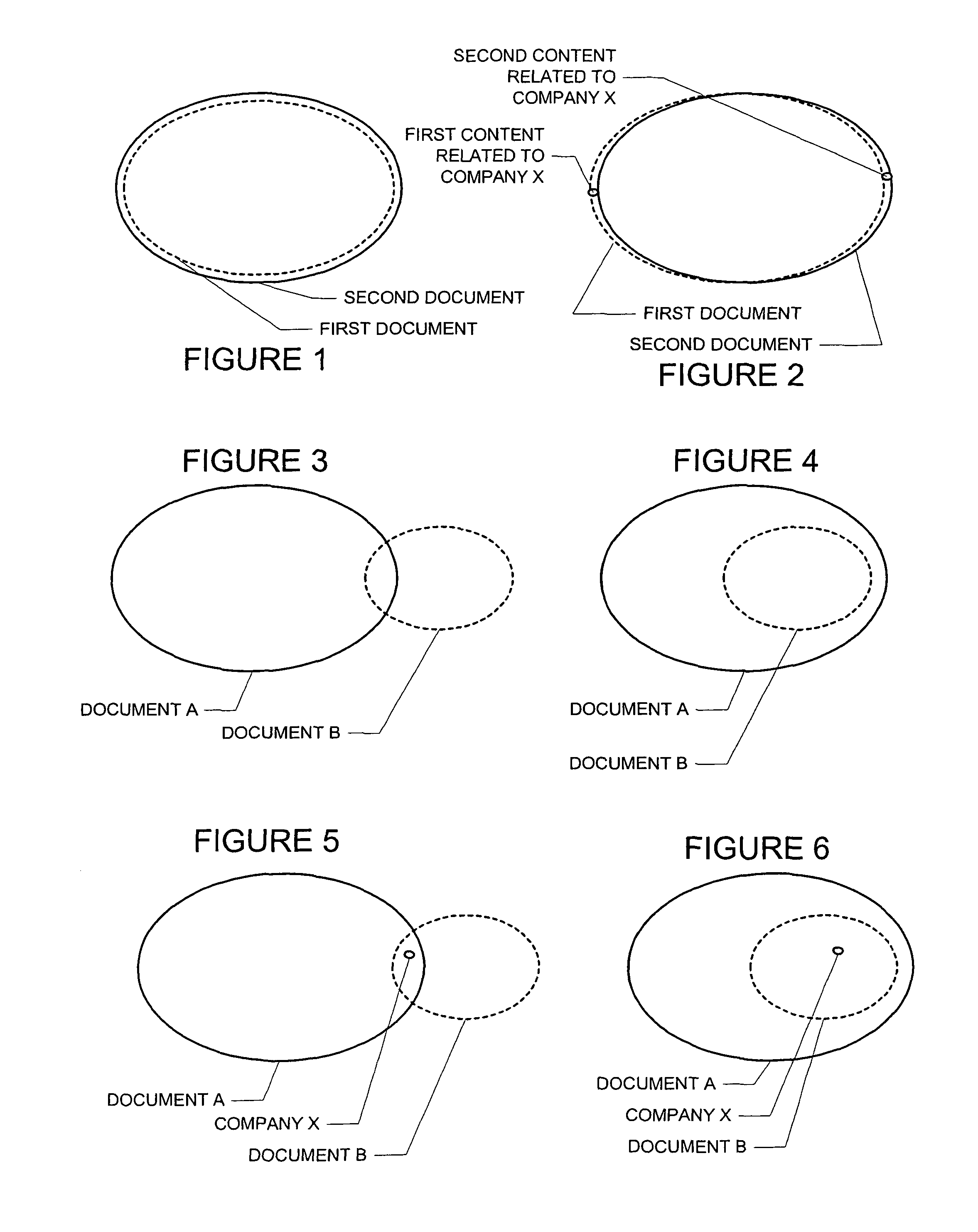

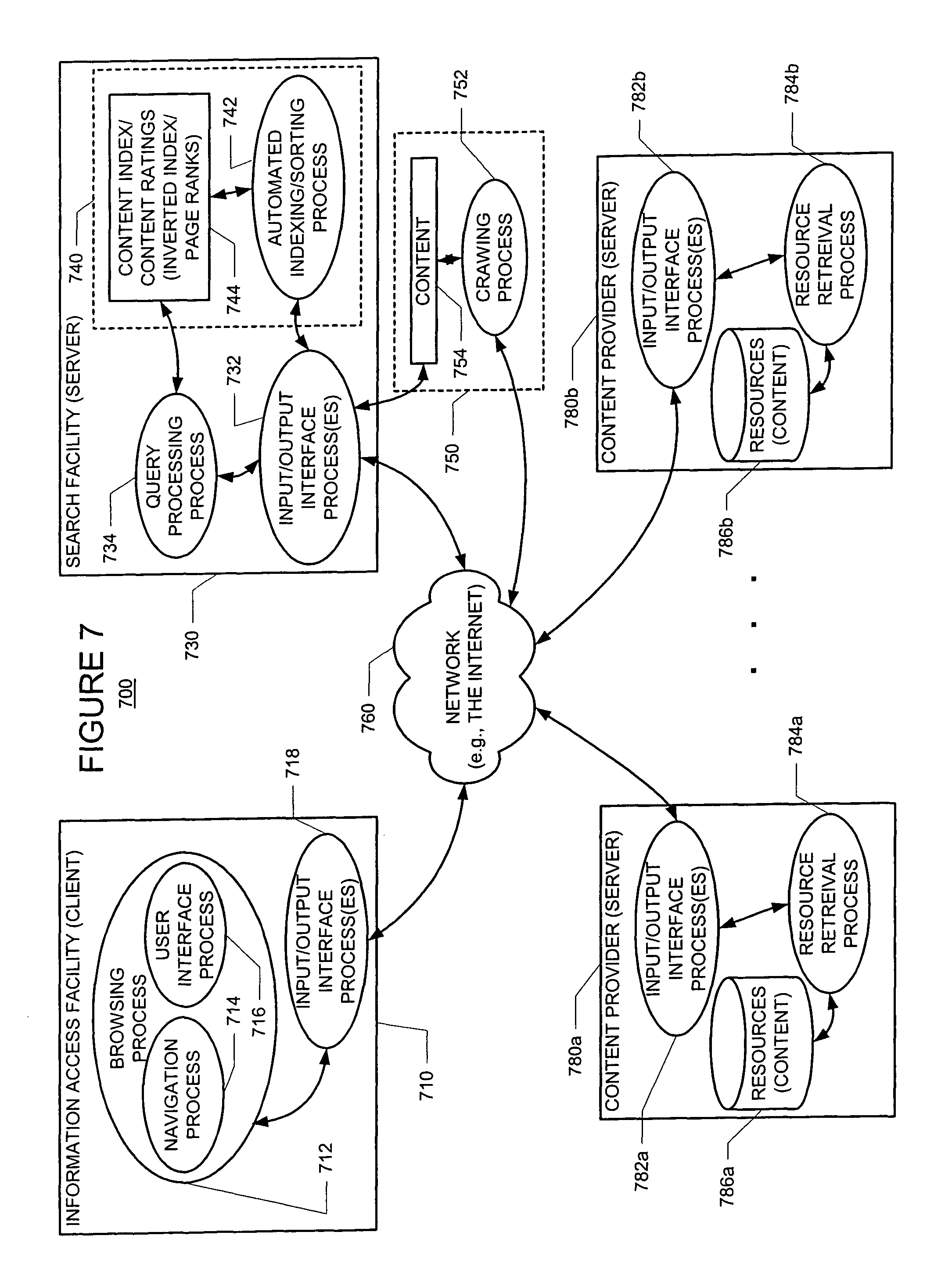

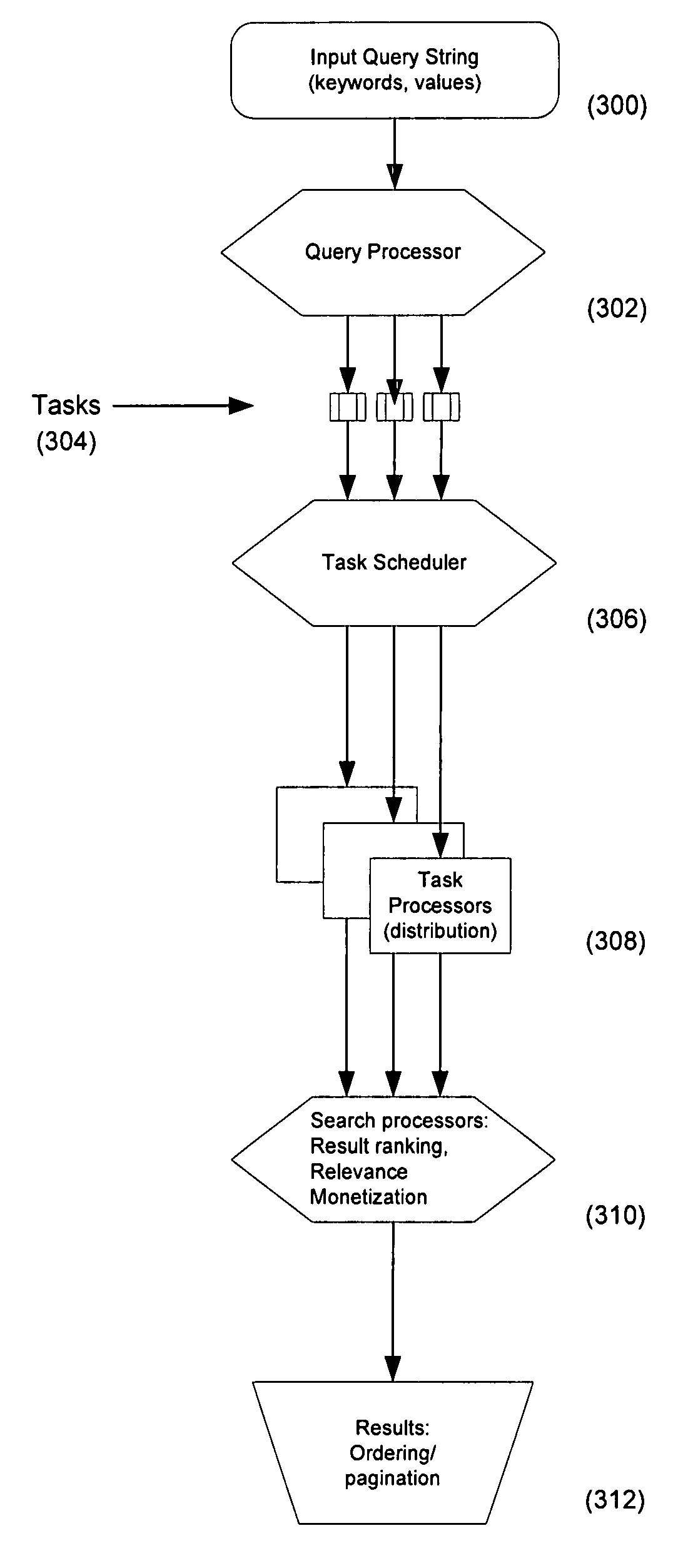

Detecting query-specific duplicate documents

InactiveUS6615209B1Decrease in numberLow thresholdMetadata text retrievalData processing applicationsDocument preparationDuplicate detection

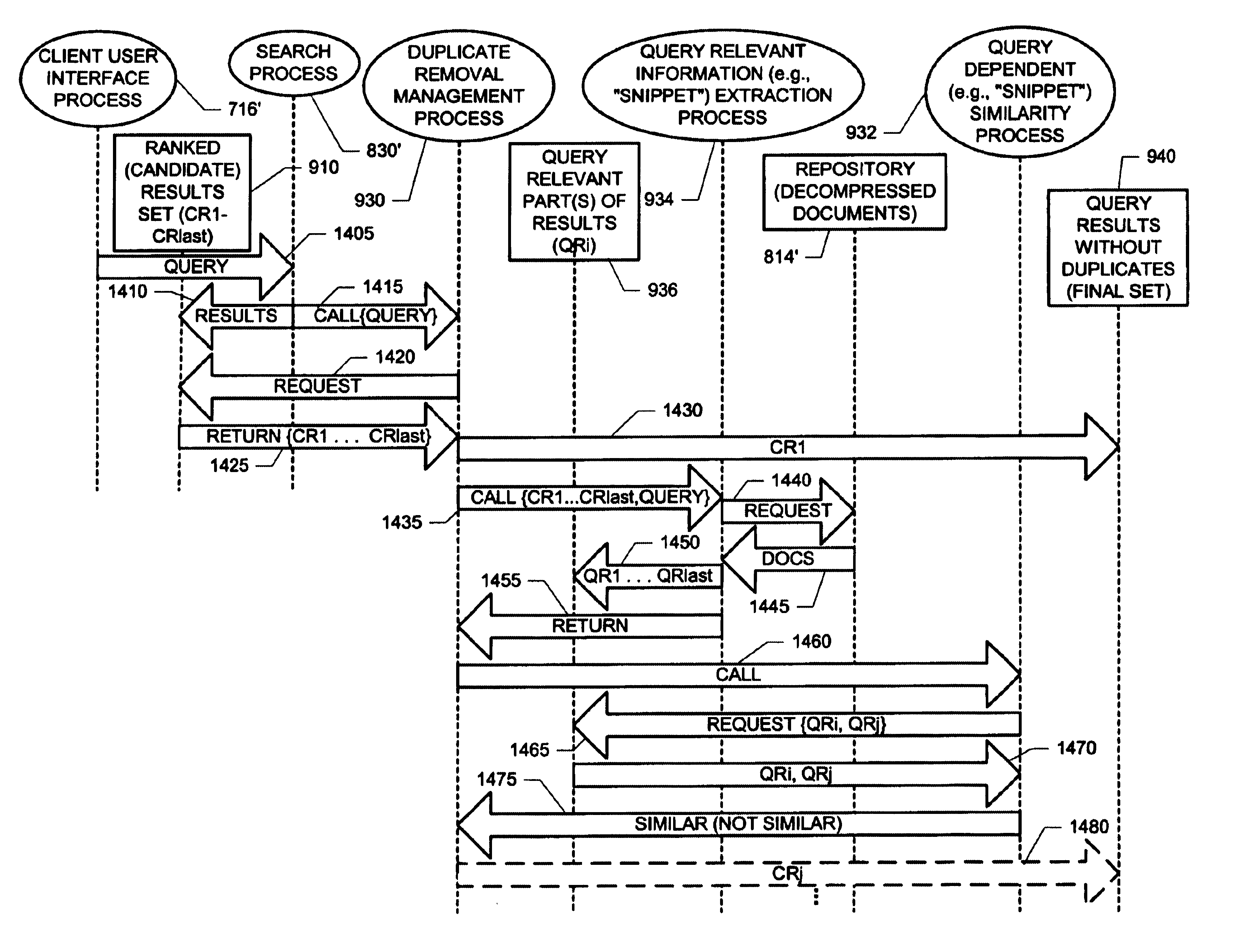

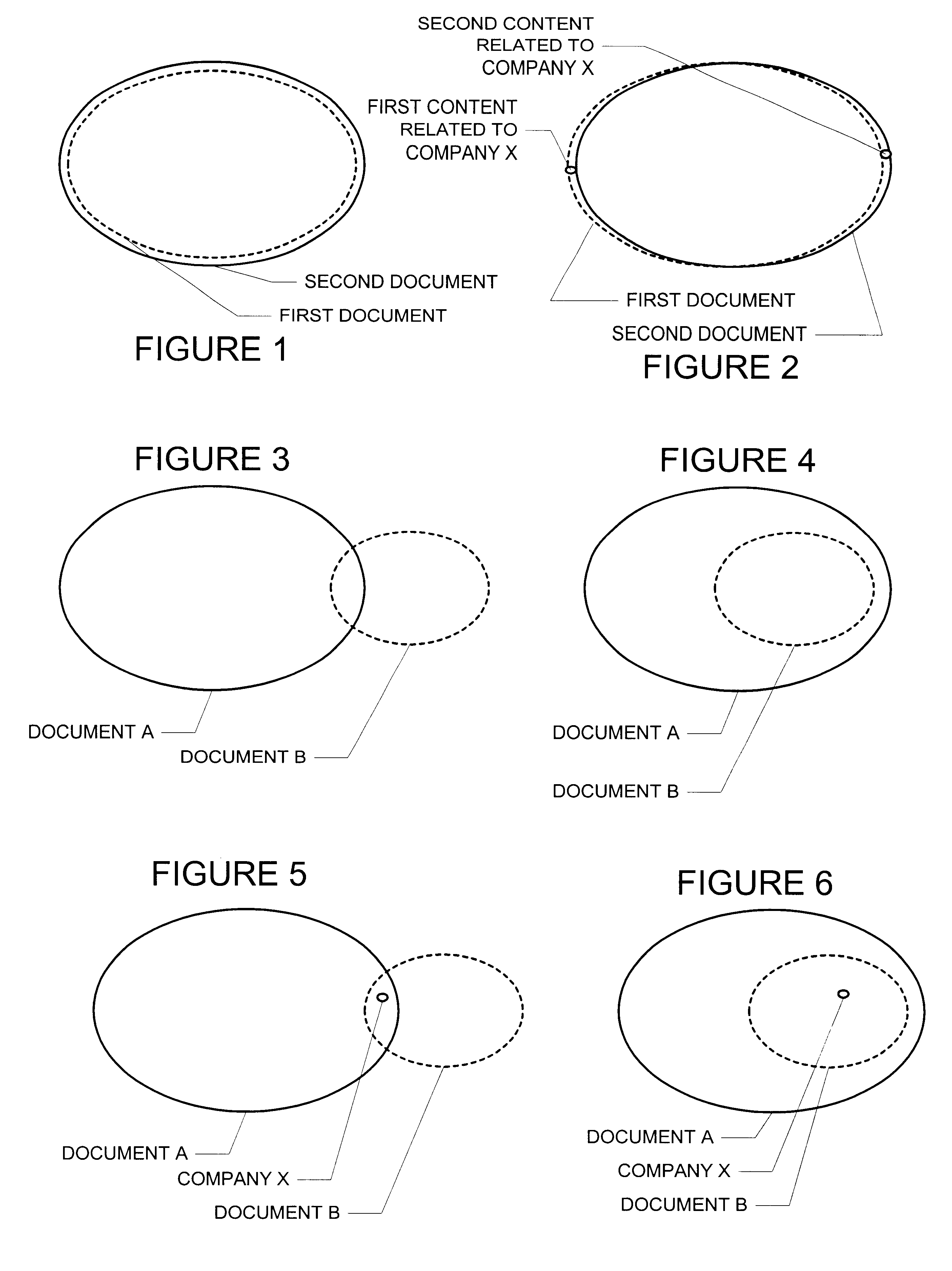

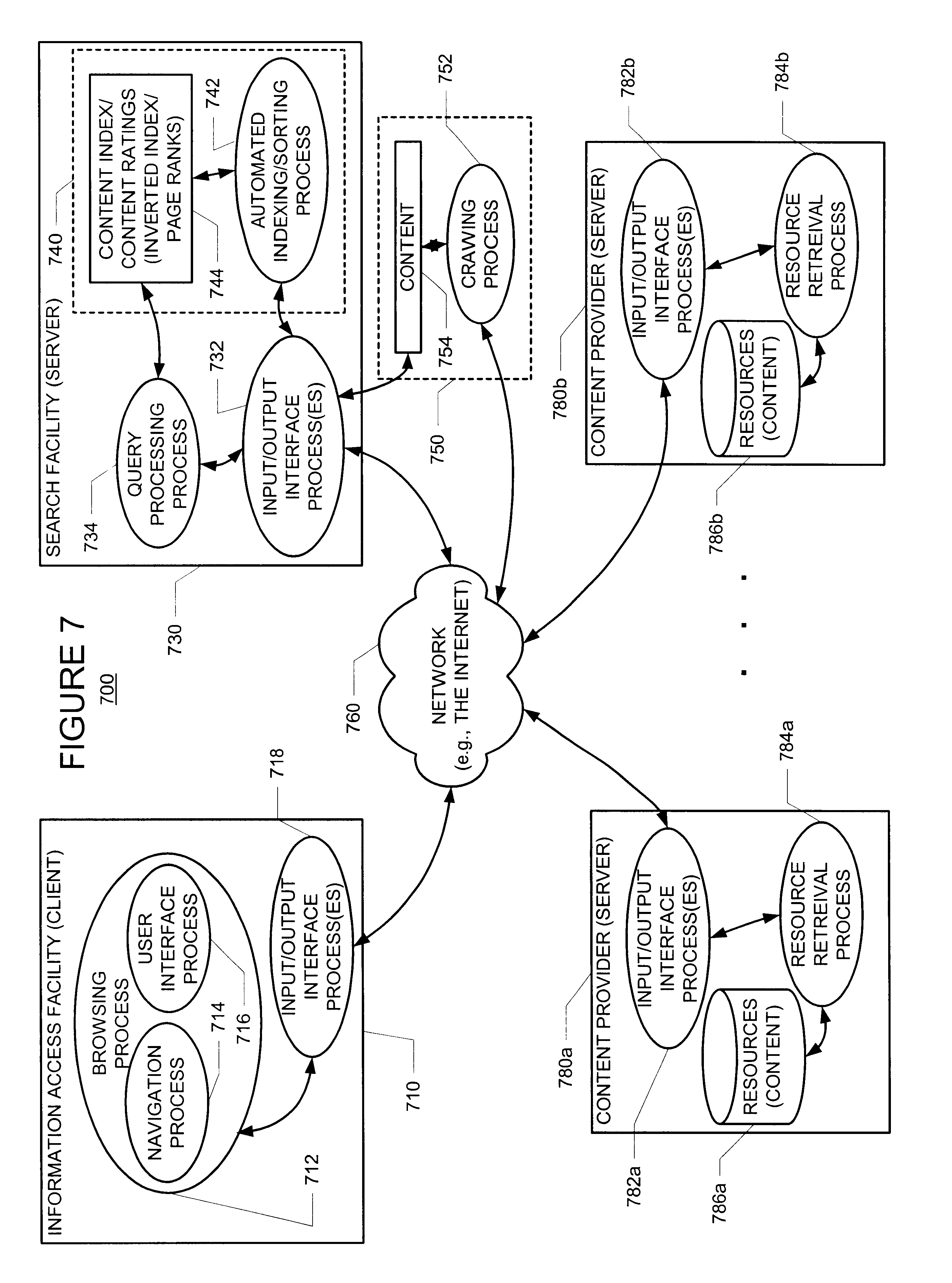

An improved duplicate detection technique that uses query-relevant information to limit the portion(s) of documents to be compared for similarity is described. Before comparing two documents for similarity, the content of these documents may be condensed based on the query. In one embodiment, query-relevant information or text (also referred to as "snippets") is extracted from the documents and only the extracted snippets, rather than the entire documents, are compared for purposes of determining similarity.

Owner:GOOGLE LLC

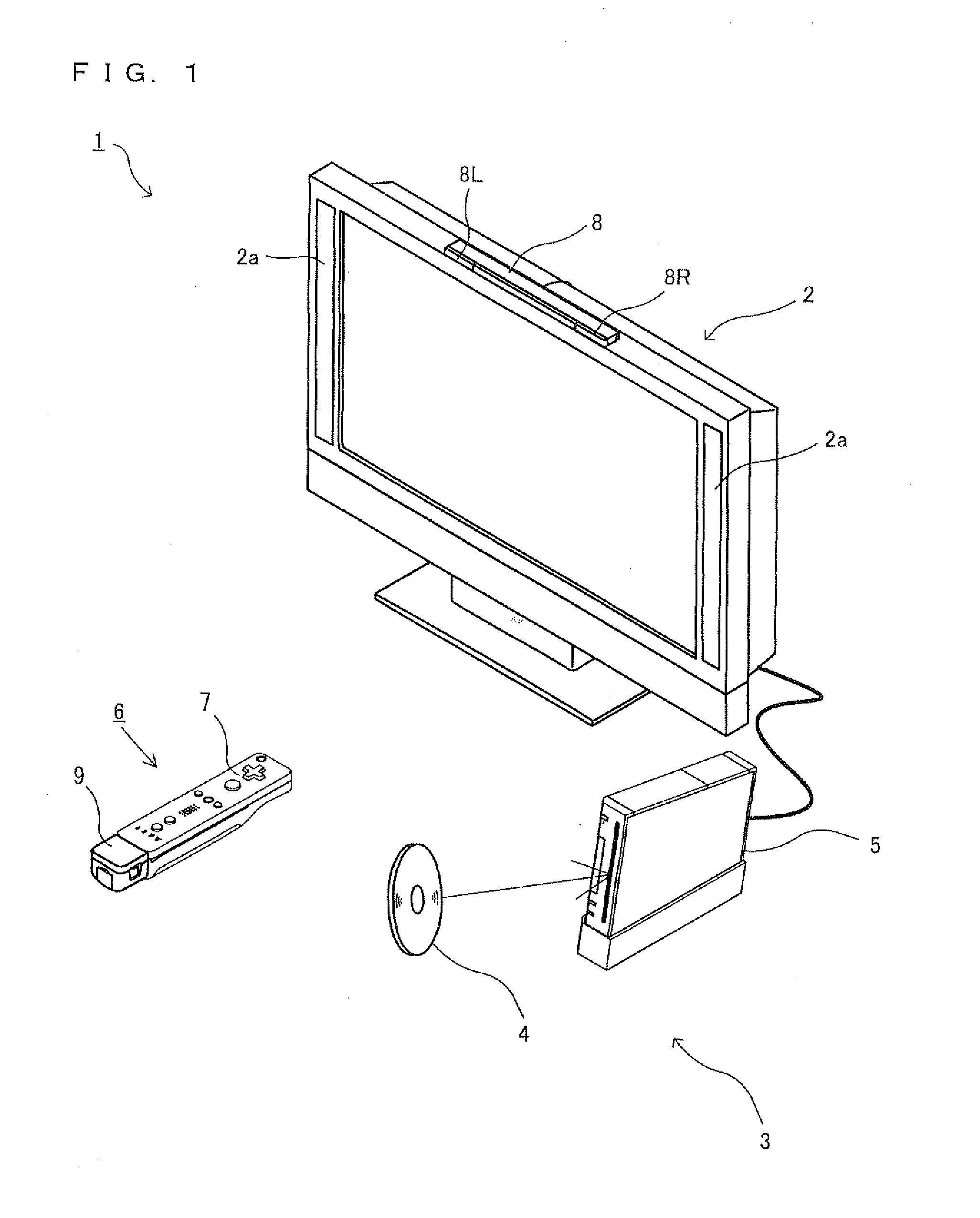

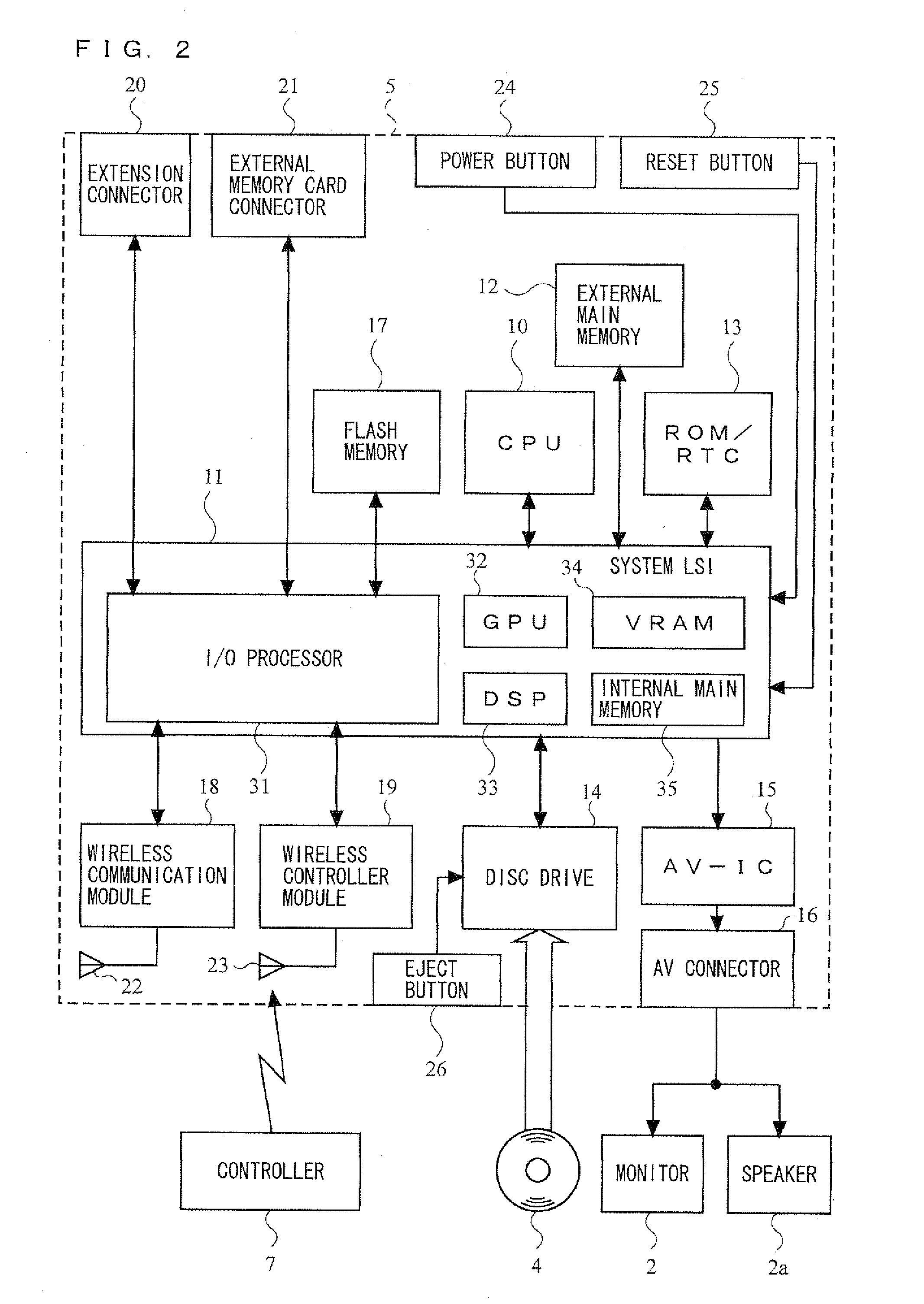

Game apparatus and storage medium having stored thereon game program

ActiveUS20100323783A1Appropriate settingNot set it lowVideo gamesSpecial data processing applicationsAngular velocityAcceleration Unit

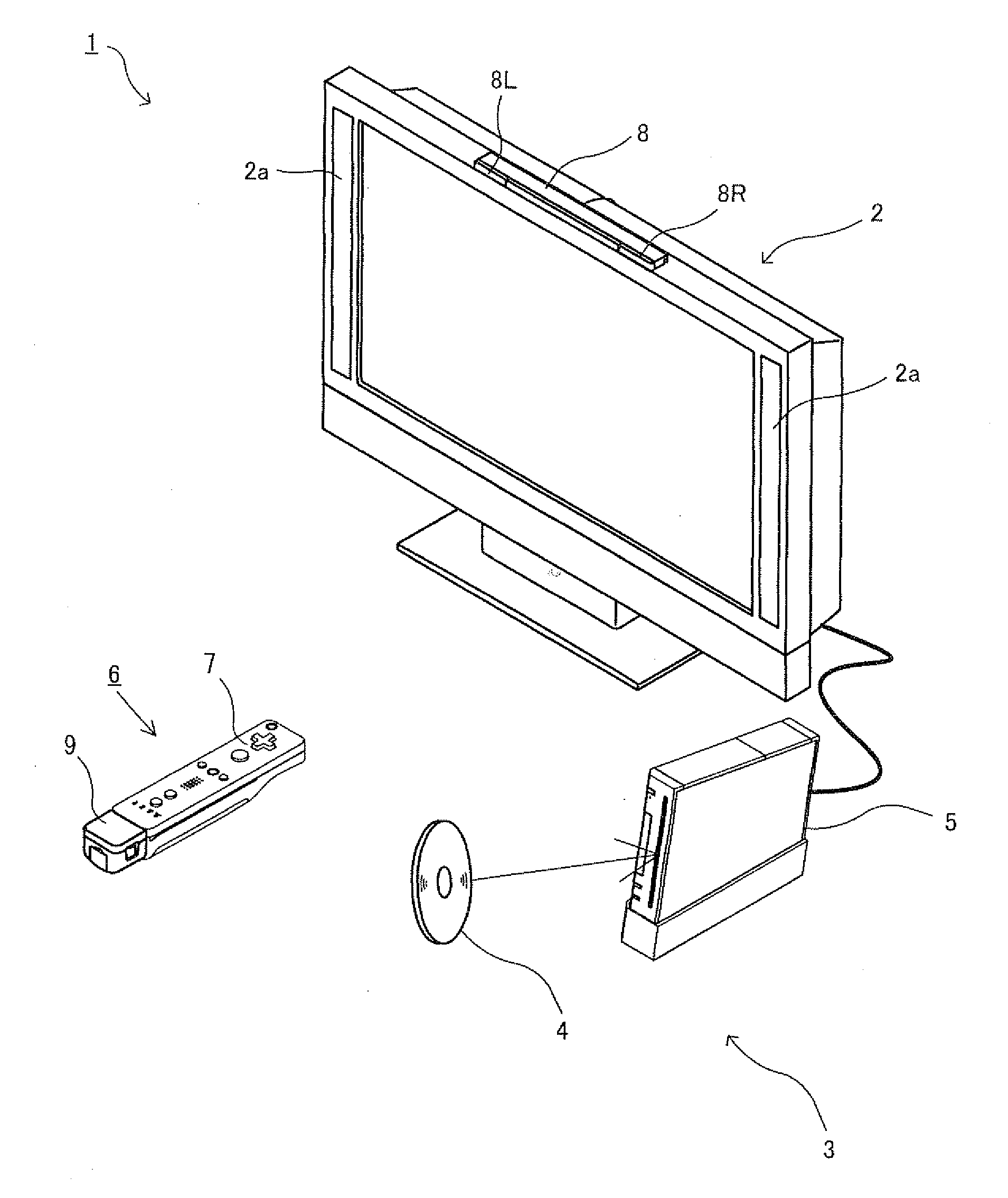

Whether or not an angular velocity detected by an angular velocity sensor is used for a game process is determined, and a difficulty level of a game to be subjected to a game process is set so as to vary depending on whether the angular velocity is determined to be used or the angular velocity is determined not to be used. When the angular velocity is determined not to be used, a process of specifying a motion direction of an input device is performed by using acceleration detected by an acceleration sensor, whereas when the angular velocity is determined to be used, at least a part of the process of specifying the motion of the input device is performed by using the angular velocity detected by the angular velocity sensor. Accordingly, based on the specified motion direction, the game process is performed while the set difficulty level is applied.

Owner:NINTENDO CO LTD

Detecting query-specific duplicate documents

InactiveUS7779002B1Reduce in quantityNot set it lowMetadata text retrievalData processing applicationsRelevant informationDocument preparation

An improved duplicate detection technique that uses query-relevant information to limit the portion(s) of documents to be compared for similarity is described. Before comparing two documents for similarity, the content of these documents may be condensed based on the query. In one embodiment, query-relevant information or text (also referred to as “snippets”) is extracted from the documents and only the extracted snippets, rather than the entire documents, are compared for purposes of determining similarity.

Owner:GOOGLE LLC

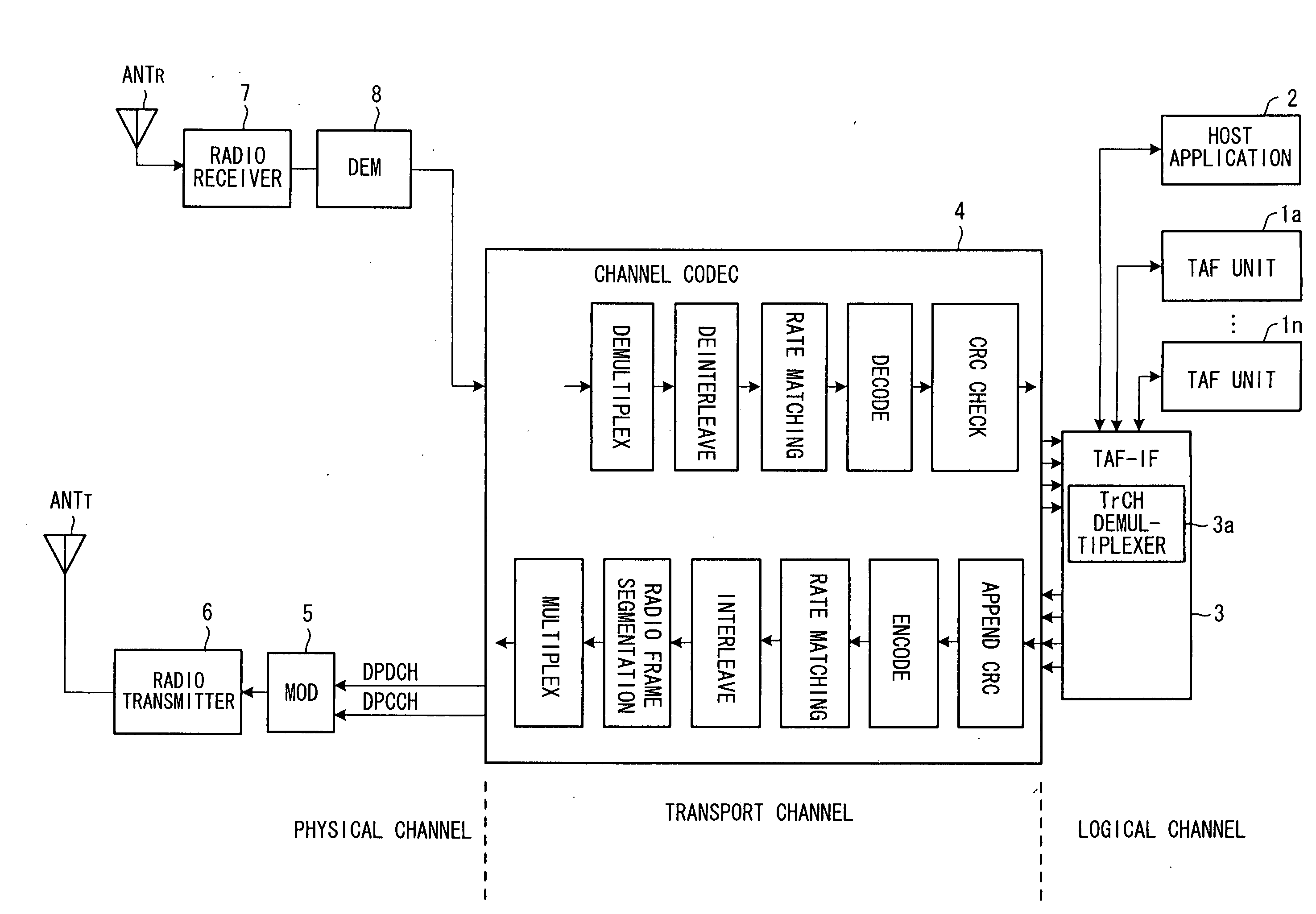

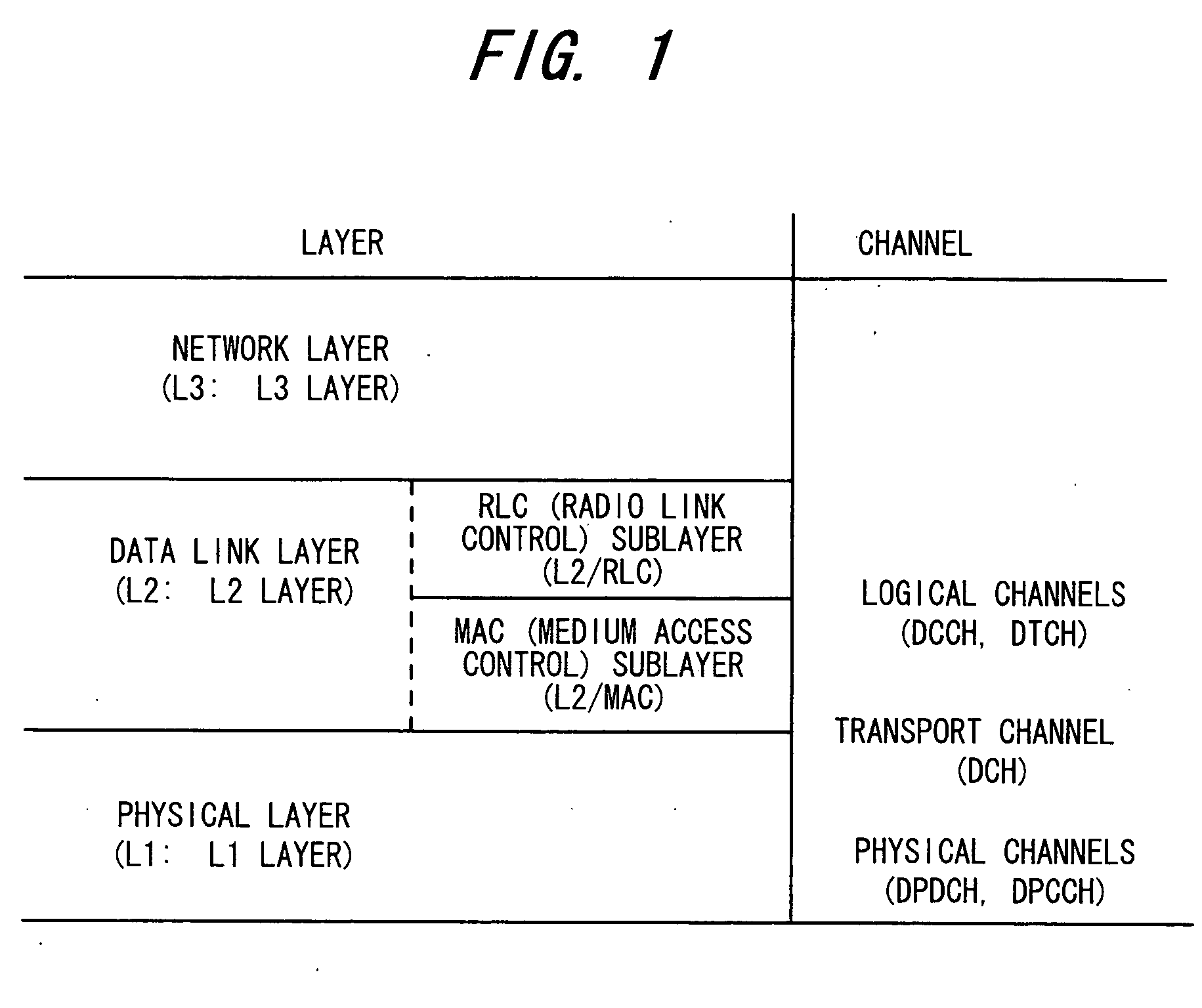

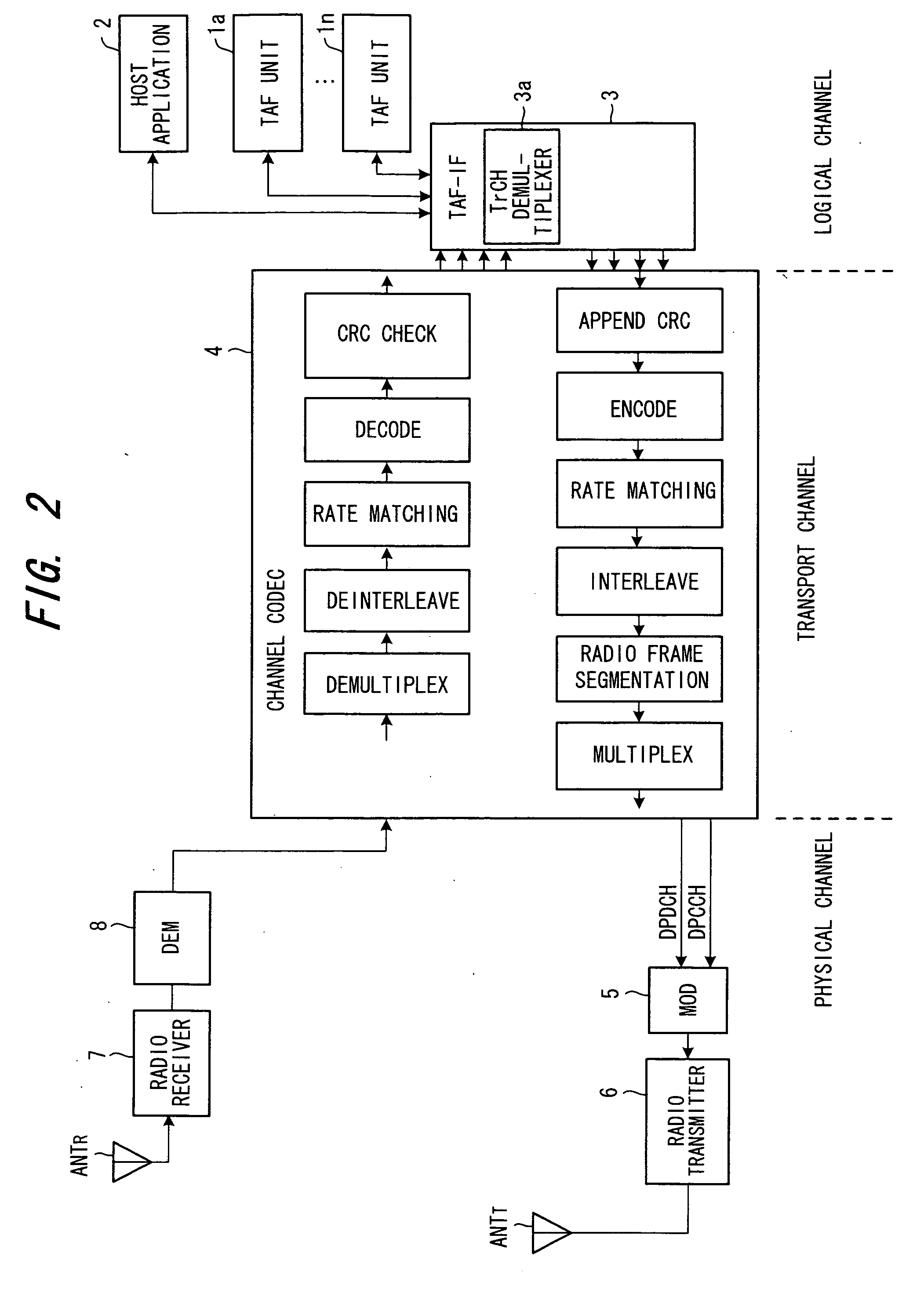

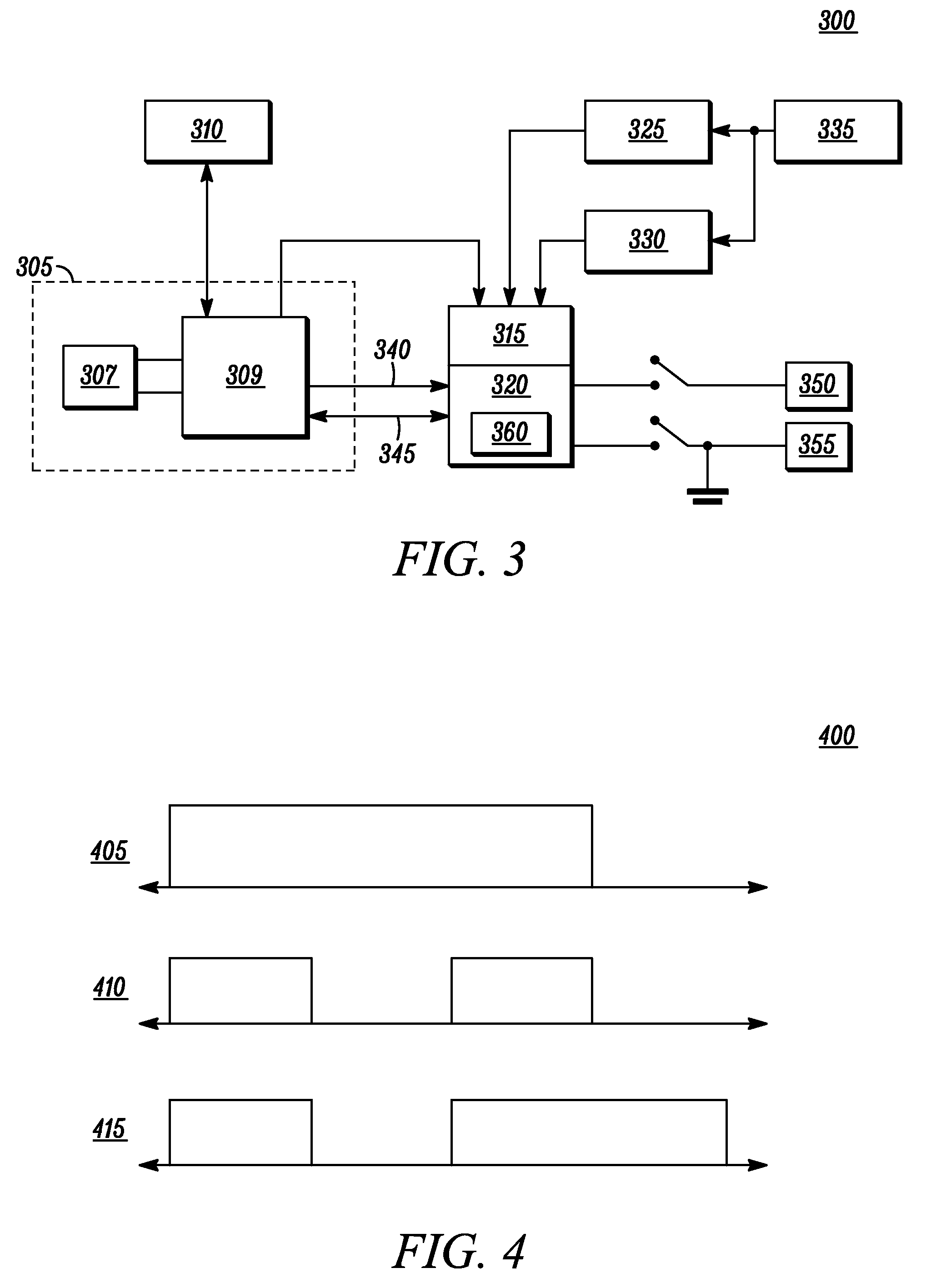

Power control method and apparatus

InactiveUS20050099968A1Quality improvementImprove reception qualityPower managementTransmission systemsPower controllerClosed loop

An open-loop power controller of a transmission power control apparatus investigates whether a dedicated control channel DCCH and a synchronization channel SCH overlap. If the channels overlap, the open-loop power controller suspends ordinary open-loop power control processing, increases a target SIR by a satisfactory level and indicates this to a closed-loop power controller. The closed-loop power controller maintains the indicated target SIR and executes closed-loop transmission power control processing based upon the target SIR. The open-loop power controller resumes ordinary open-loop transmission power control processing after DCCH reception ends.

Owner:FUJITSU LTD

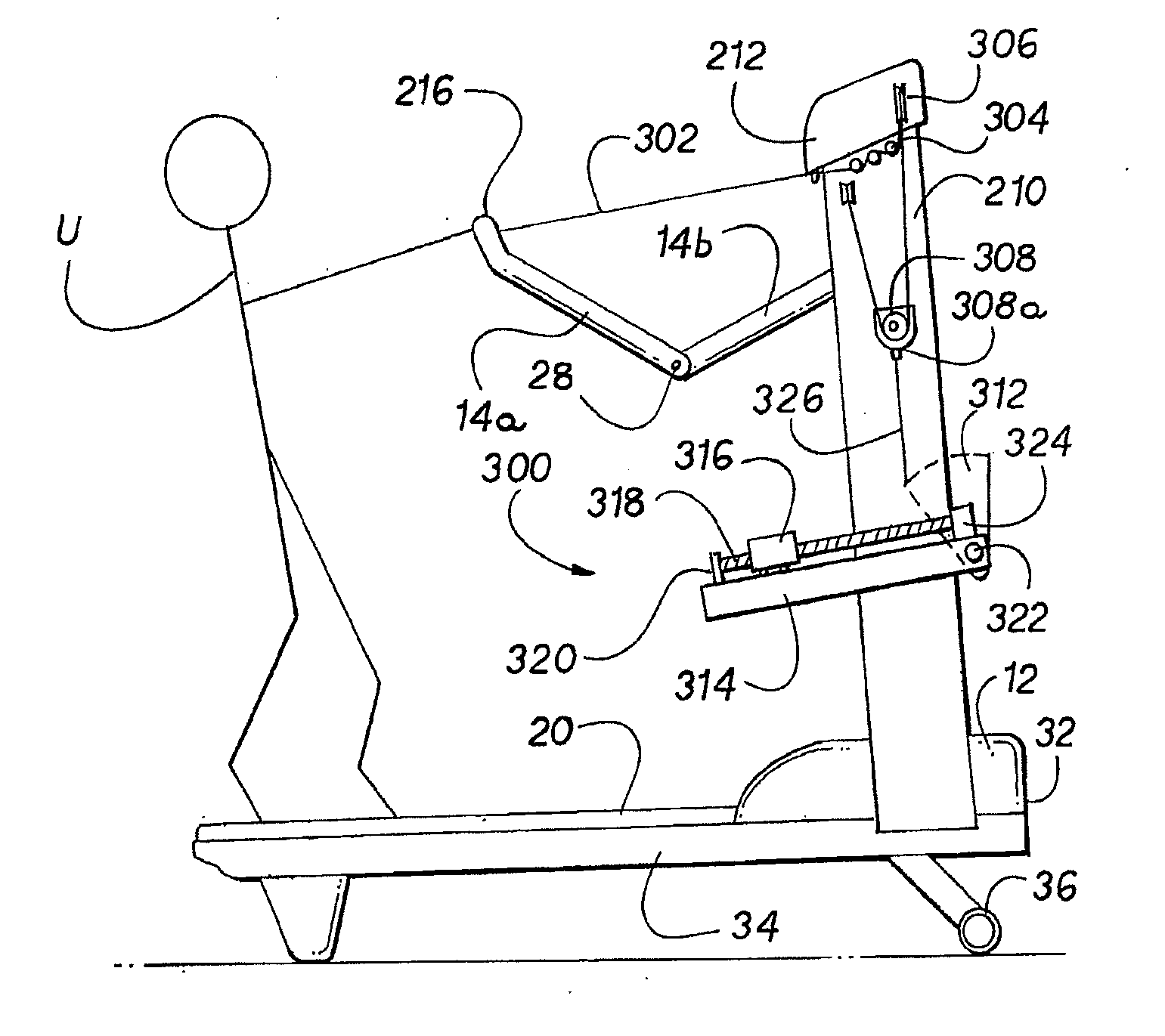

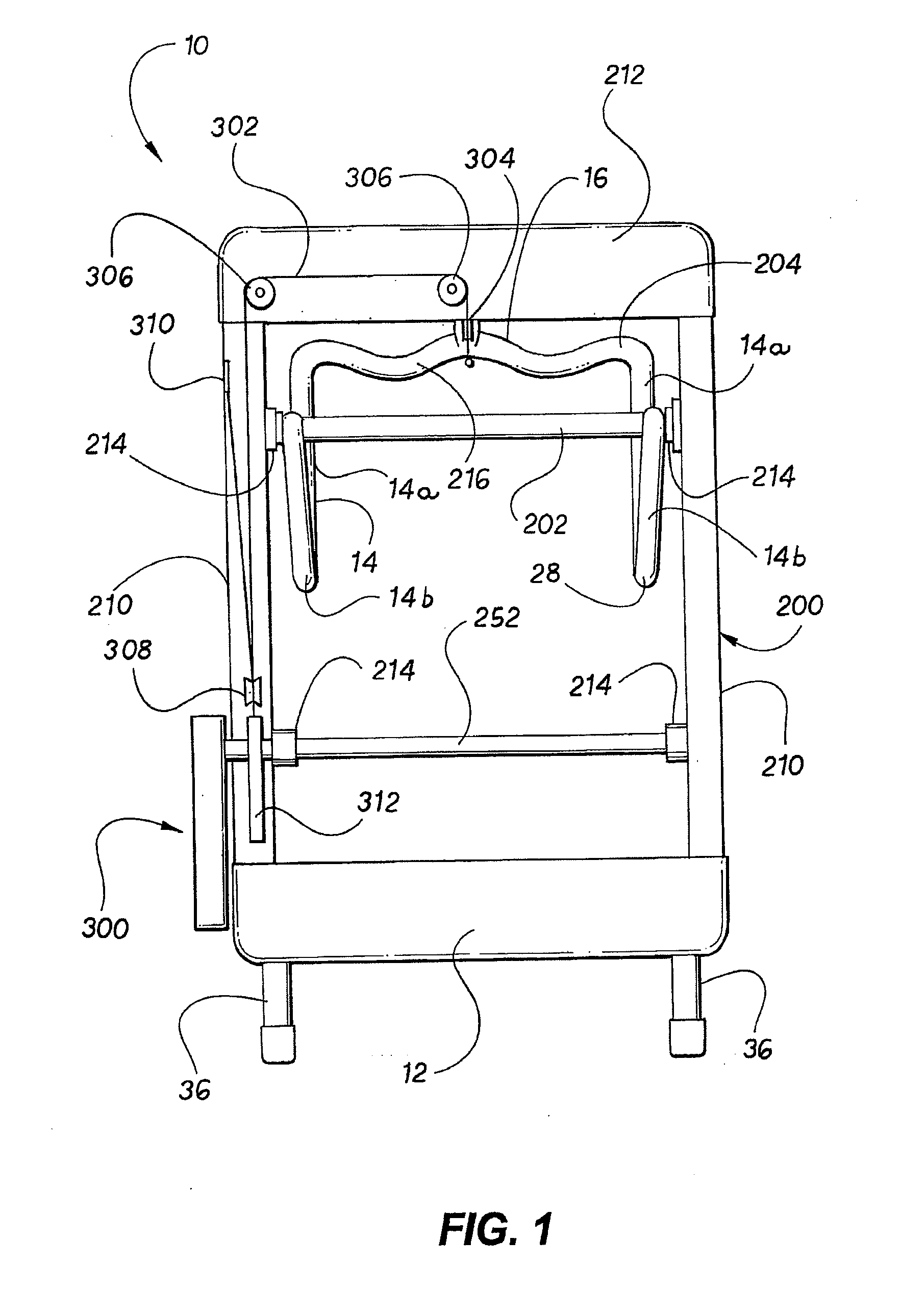

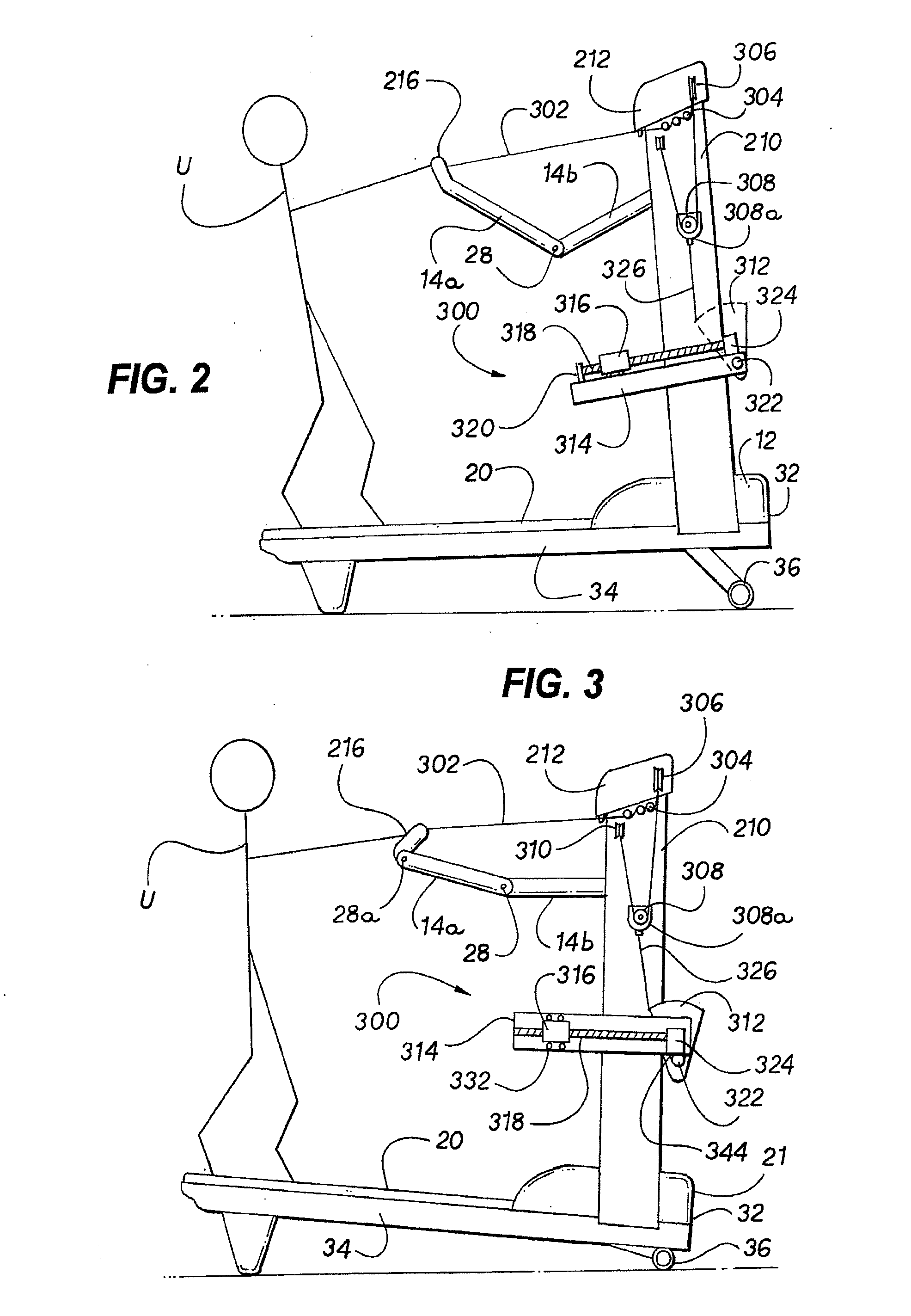

Dual direction exercise treadmill with moment arm resistance

InactiveUS20110118089A1High activityIncrease ratingsResilient force resistorsMovement coordination devicesEngineeringPulley

An exercise treadmill for simulating a dragging or pulling action, having an endless moveable surface looped around rollers or pulleys to form an upper run and a lower run, with an exercise surface for walking or running on while operating the treadmill; and a moment arm weight resistance means for simulating the dragging or pulling of a load.

Owner:ELLIS JOSEPH K

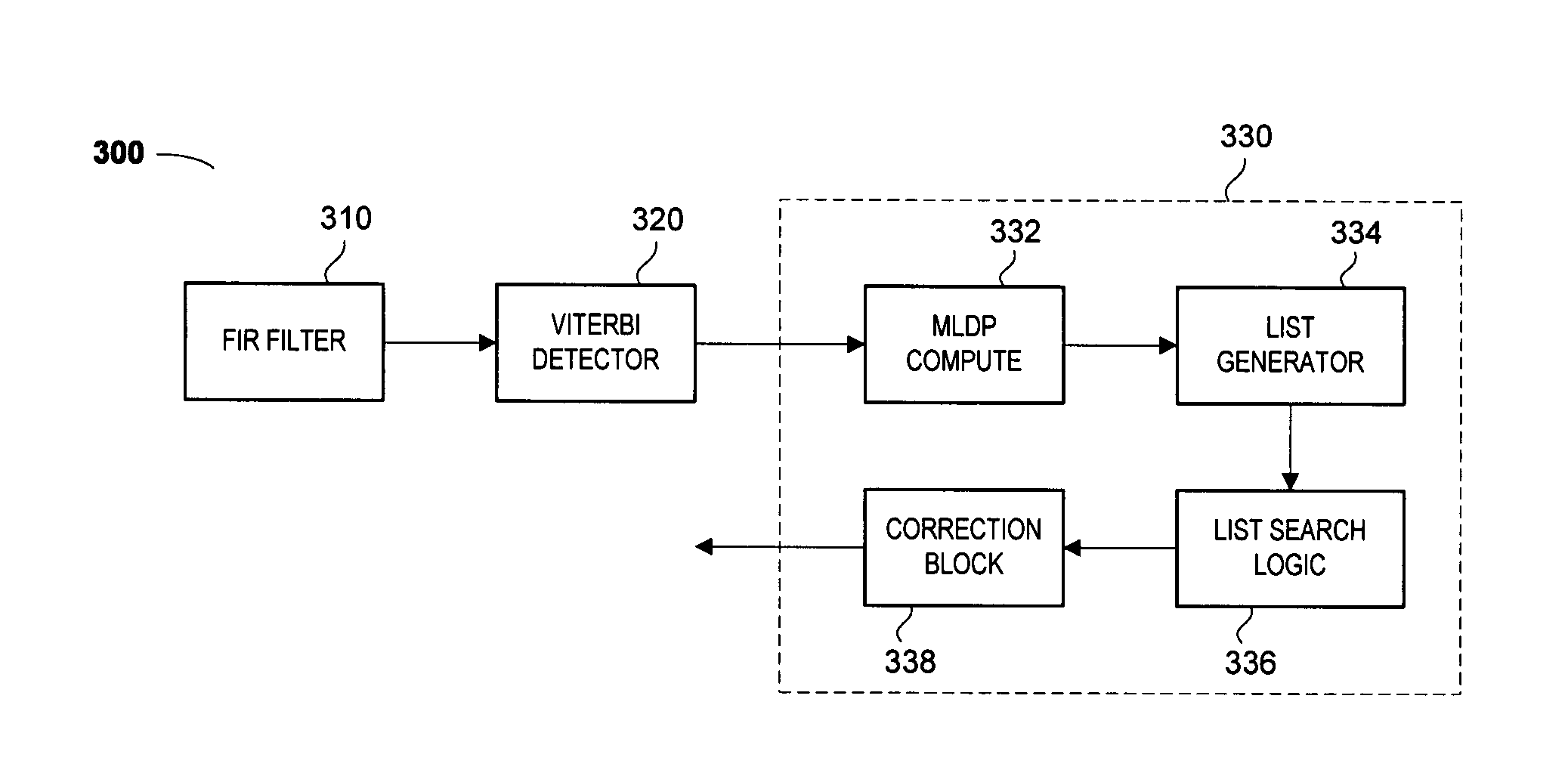

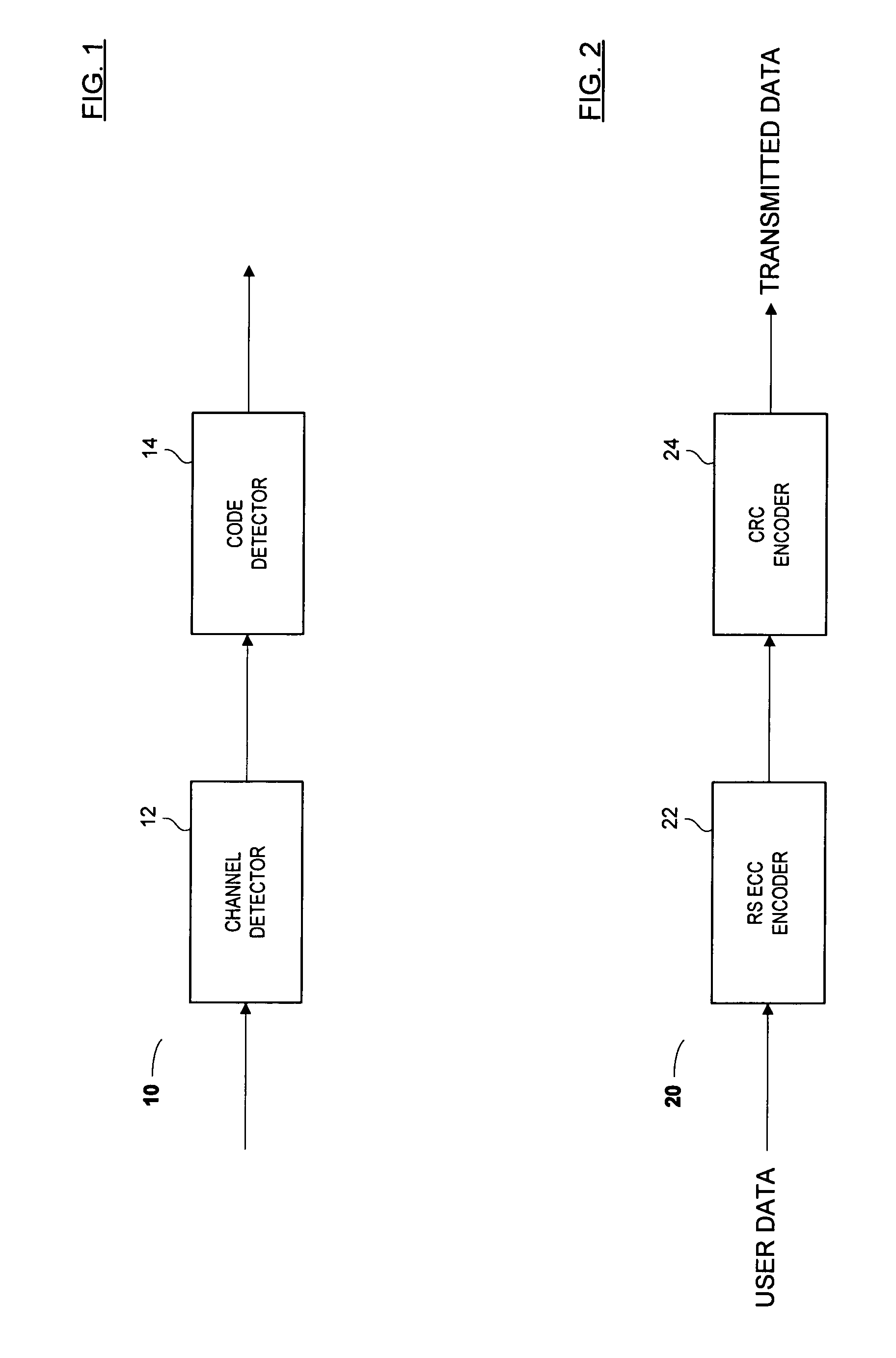

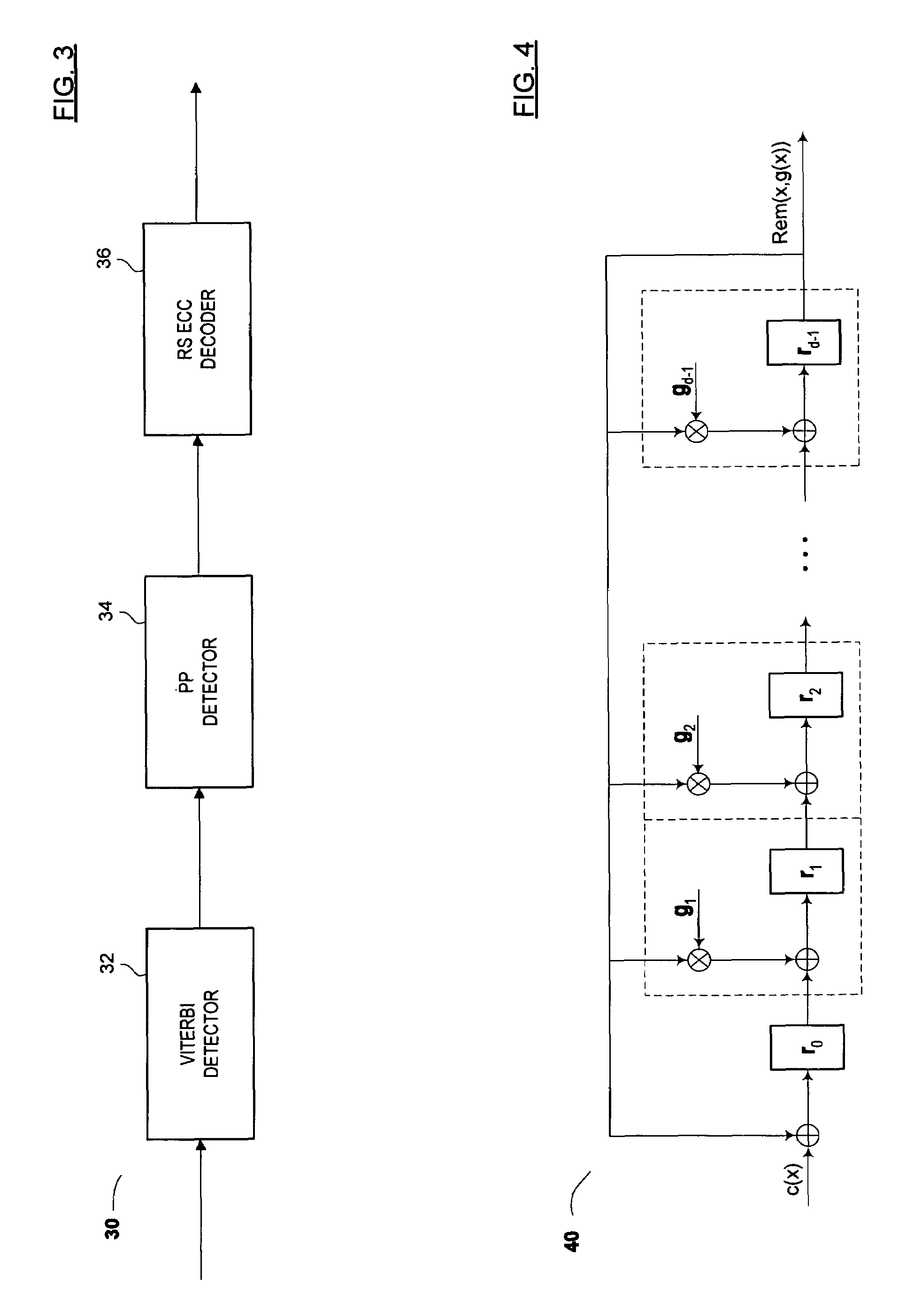

Methods and algorithms for joint channel-code decoding of linear block codes

ActiveUS7571372B1Facilitates PP implementationNot set it lowCode conversionRecord information storageError checkAlgorithm

Circuits, architectures, methods and algorithms for joint channel-code decoding of linear block codes, and more particularly, for identifying and correcting one or more errors in a code word and / or for encoding CRC (or parity) information. In one aspect, the invention focuses on use of (i) remainders, syndromes or other polynomials and (ii) Gaussian elimination to determine and correct errors. Although this approach may be suboptimal, the present error checking and / or detection scheme involves simpler computations and / or manipulations than conventional schemes, and is generally easier to implement logically. Since the complexity of parity-based error correction schemes increases disproportionately to the number of potential error events, the present invention meets a long-felt need for a scheme to manage error detection and / or correction in systems (such as magnetic recording applications) where there may be a relatively large number of likely error events, thereby advantageously improving reliability and / or performance in channel communications.

Owner:MARVELL ASIA PTE LTD

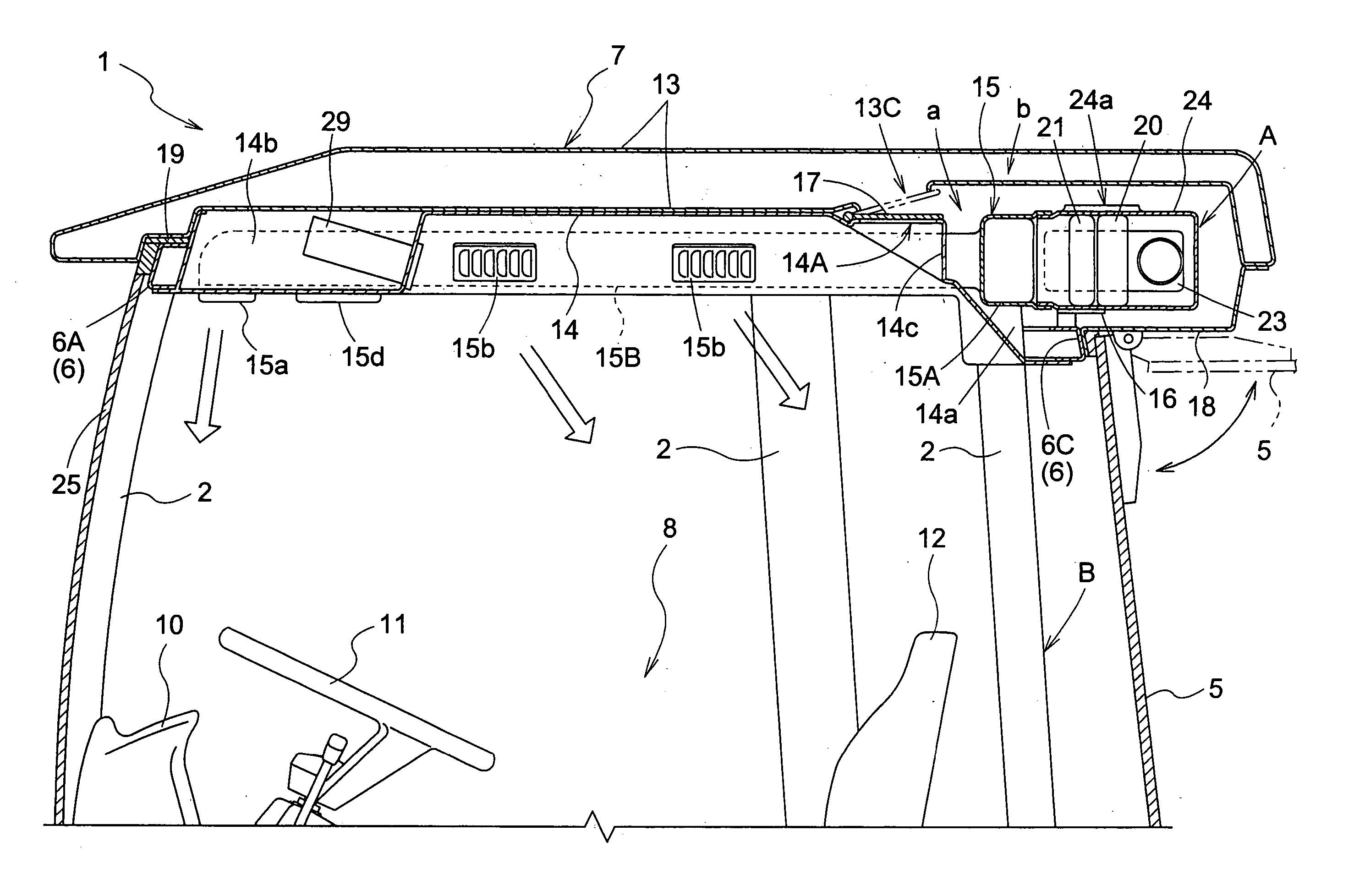

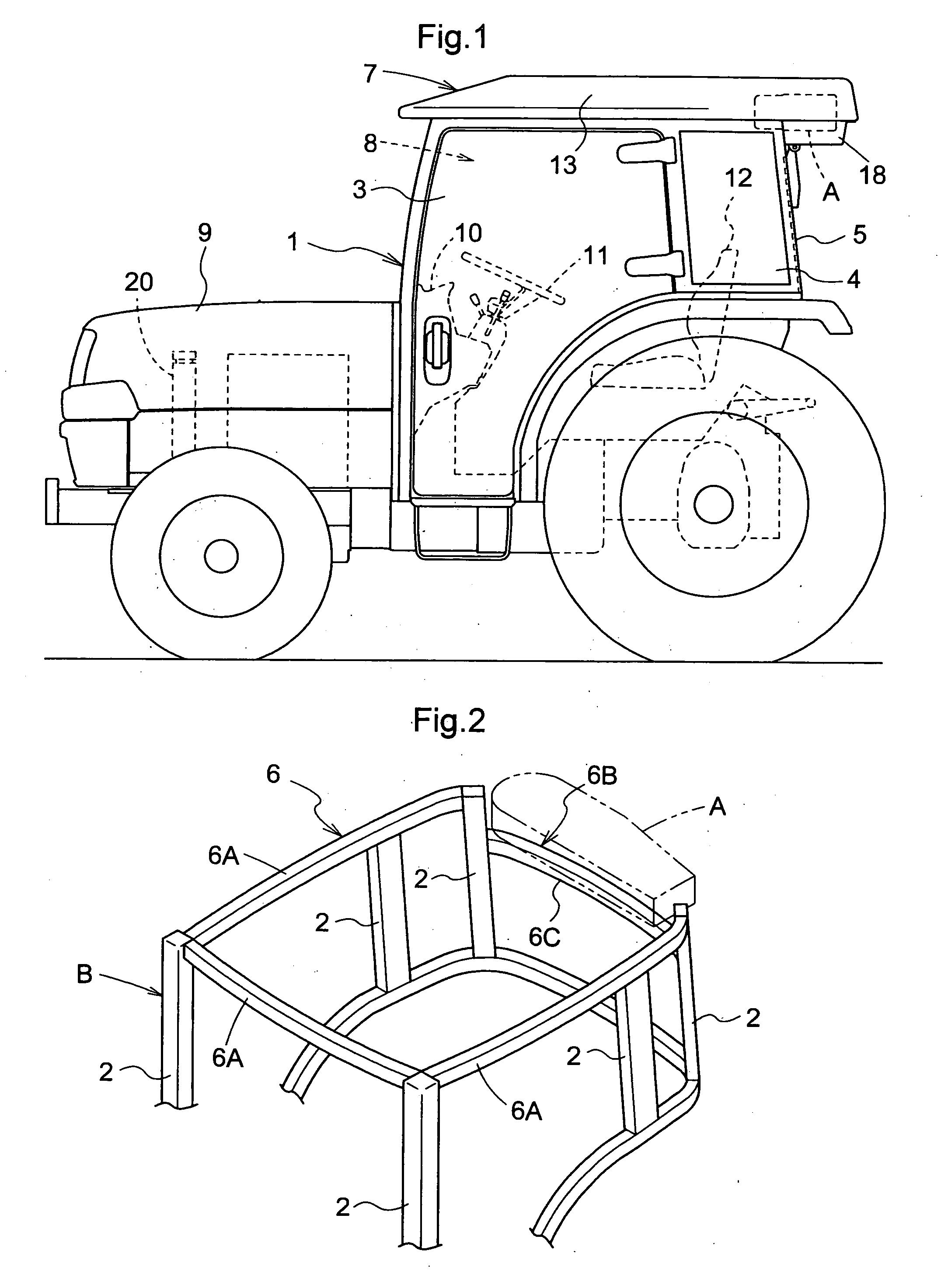

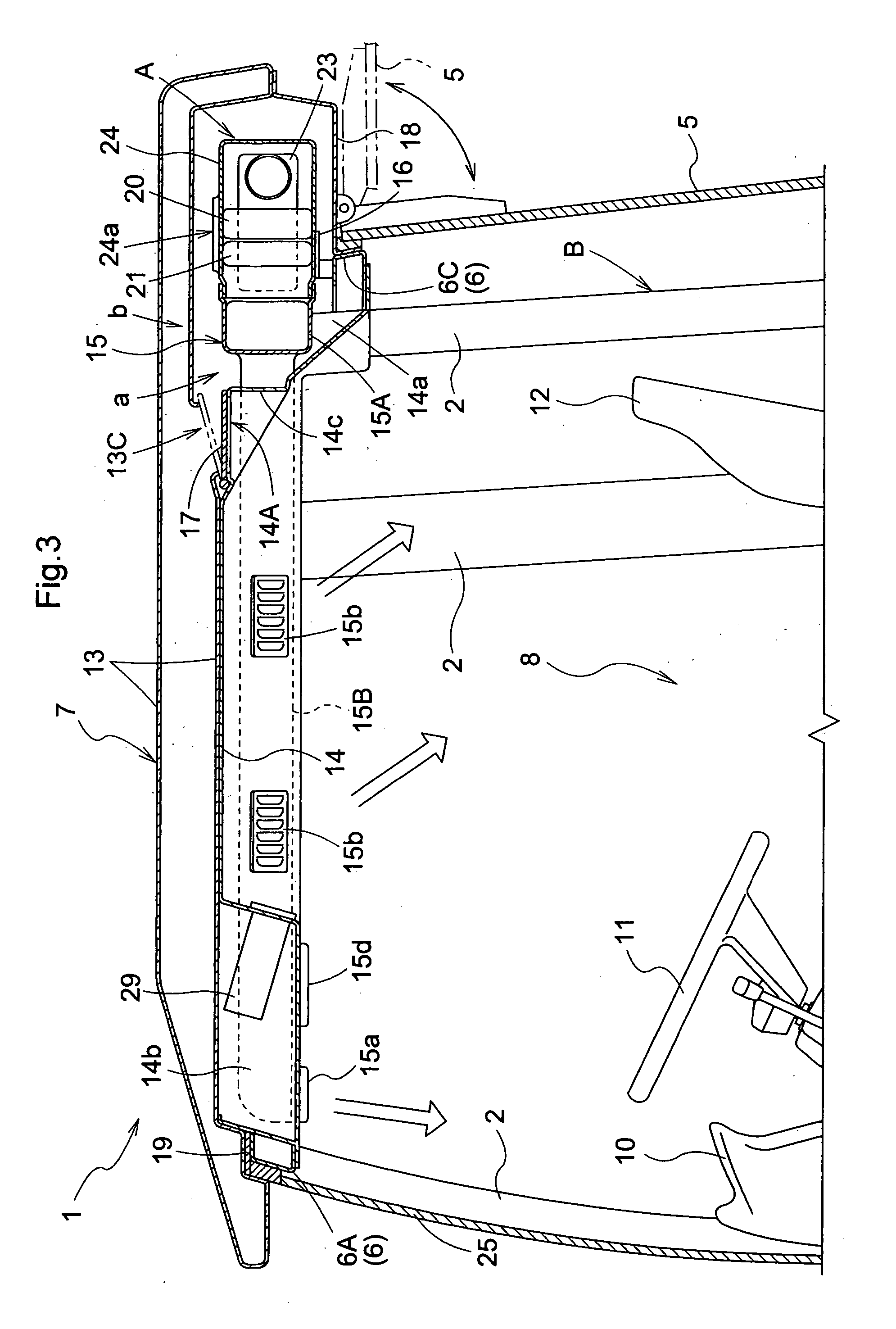

Cabin for a work vehicle

ActiveUS20070044492A1Improved upper forward field of viewNot set it lowAuxillariesFlexible-parts wheelsAir conditioningEngineering

A cabin for a work vehicle comprises: a driver's seat positioned within the cabin; cabin frames including at least a transverse frame located in a rear region of the cabin; a roof supported by at least some of the cabin frames; at least one air-conditioning duct located within the roof; an air conditioning unit located rearwardly with respect to a rearward end of a seat portion of the driver's seat and adjacent the transverse frame for conditioning air and for feeding air-conditioned air into the at least one air-conditioning duct.

Owner:KUBOTA LTD

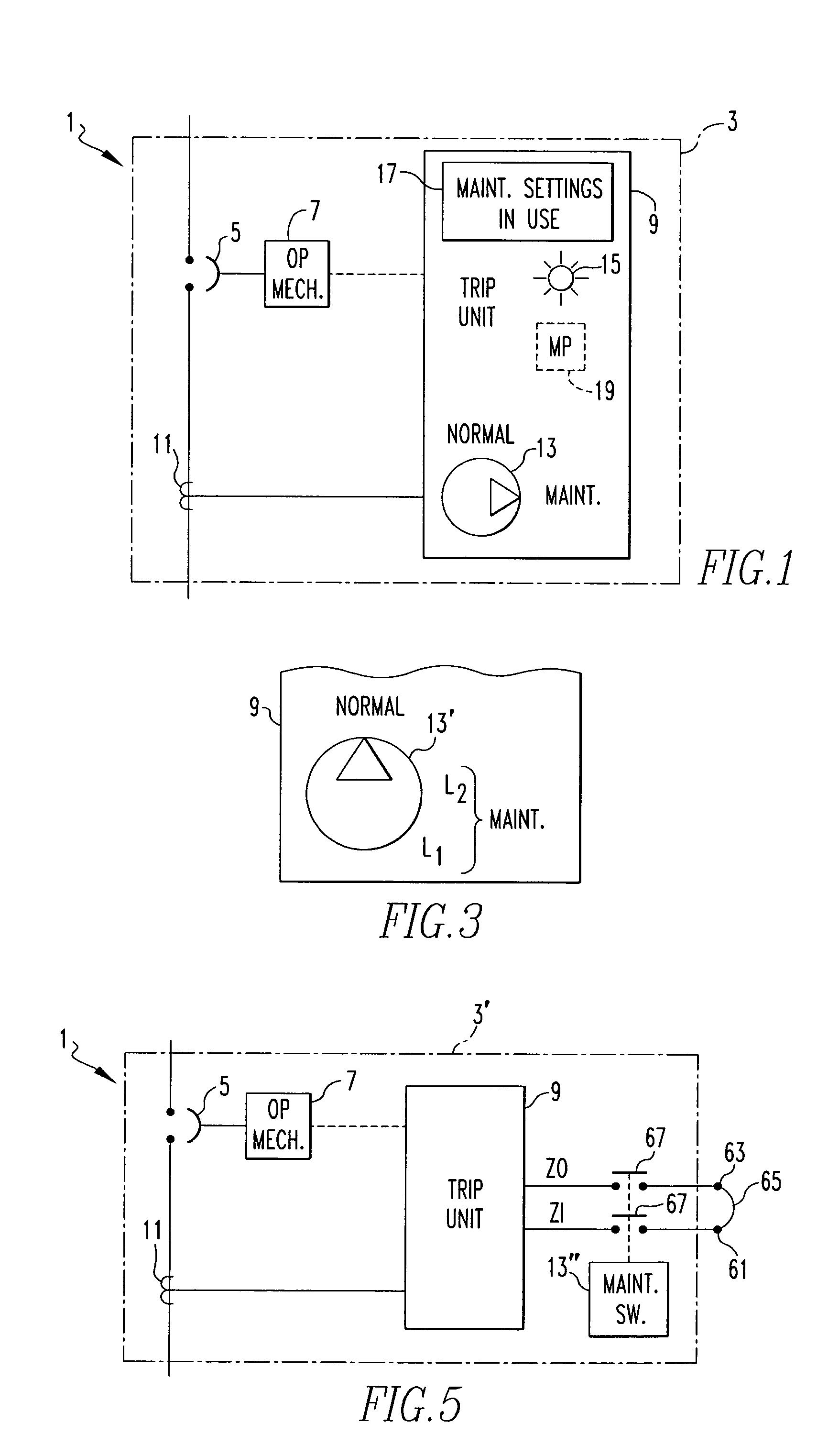

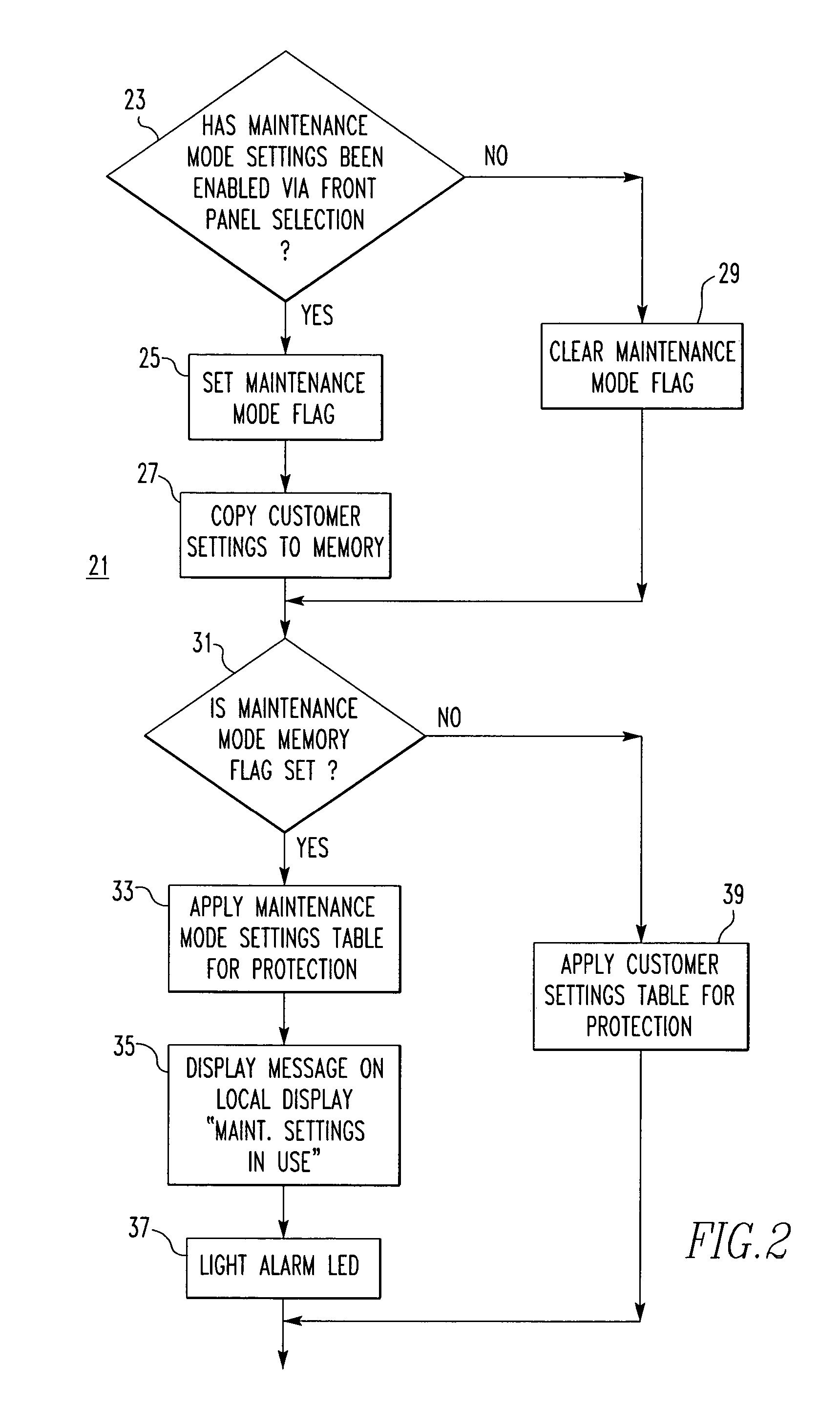

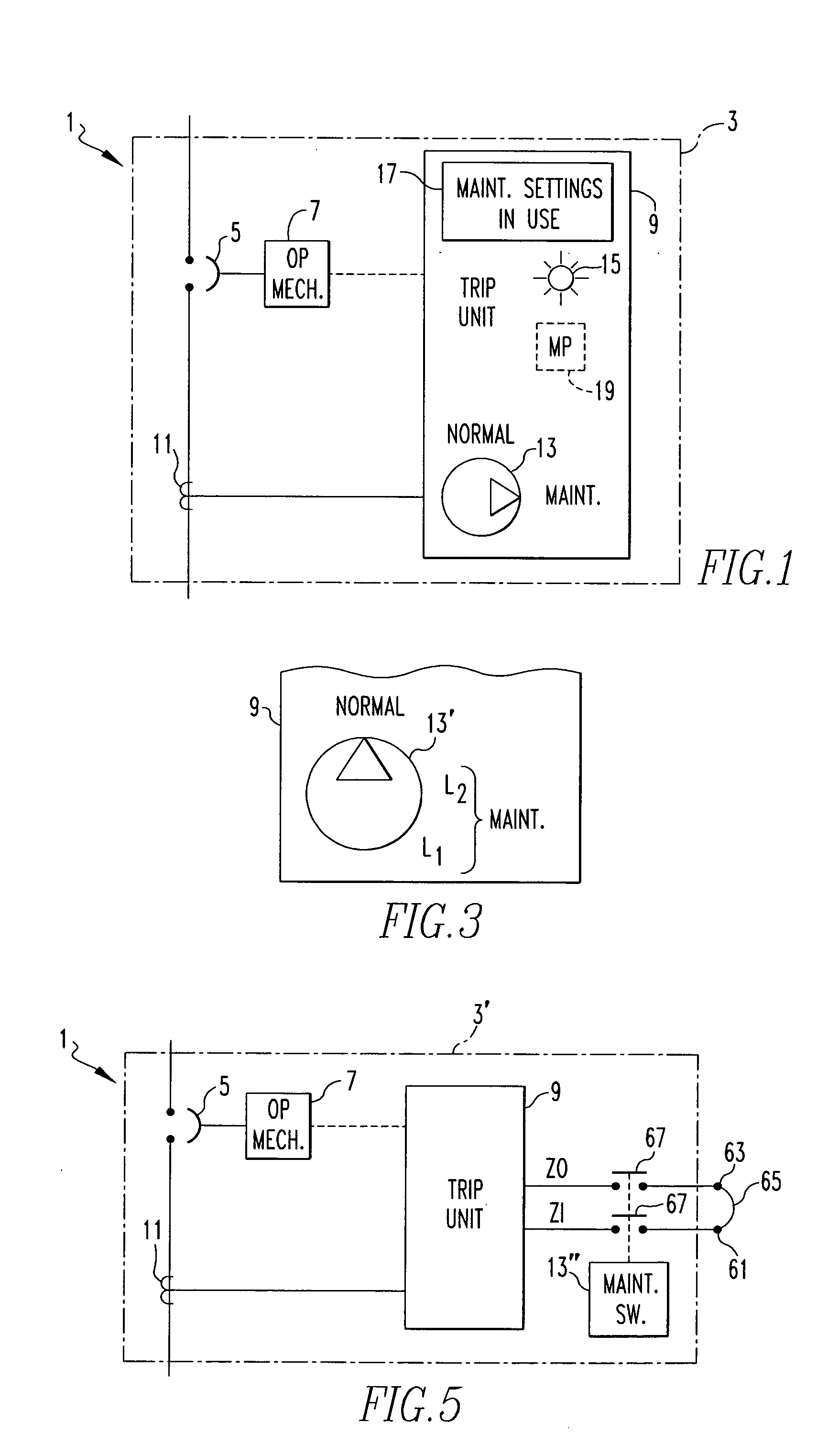

Method and circuit breaker for reducing arc flash during maintenance in a low voltage power circuit

ActiveUS7203040B2Low levelReduce arc energyParameter calibration/settingProvisions for user interfaceLow voltage circuitsArc flash

Owner:EATON INTELLIGENT POWER LTD

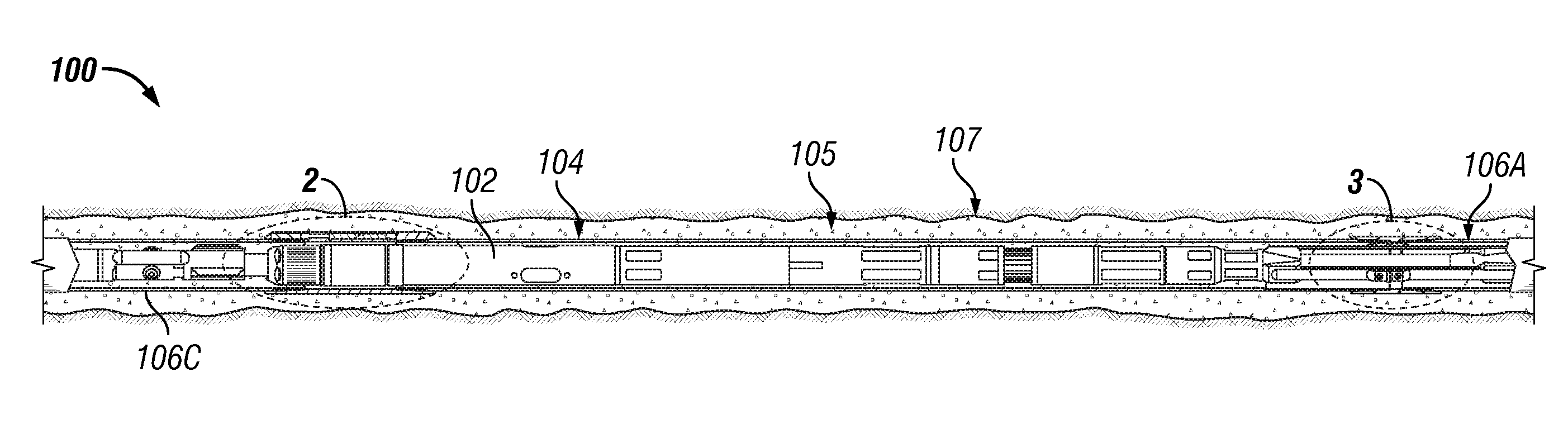

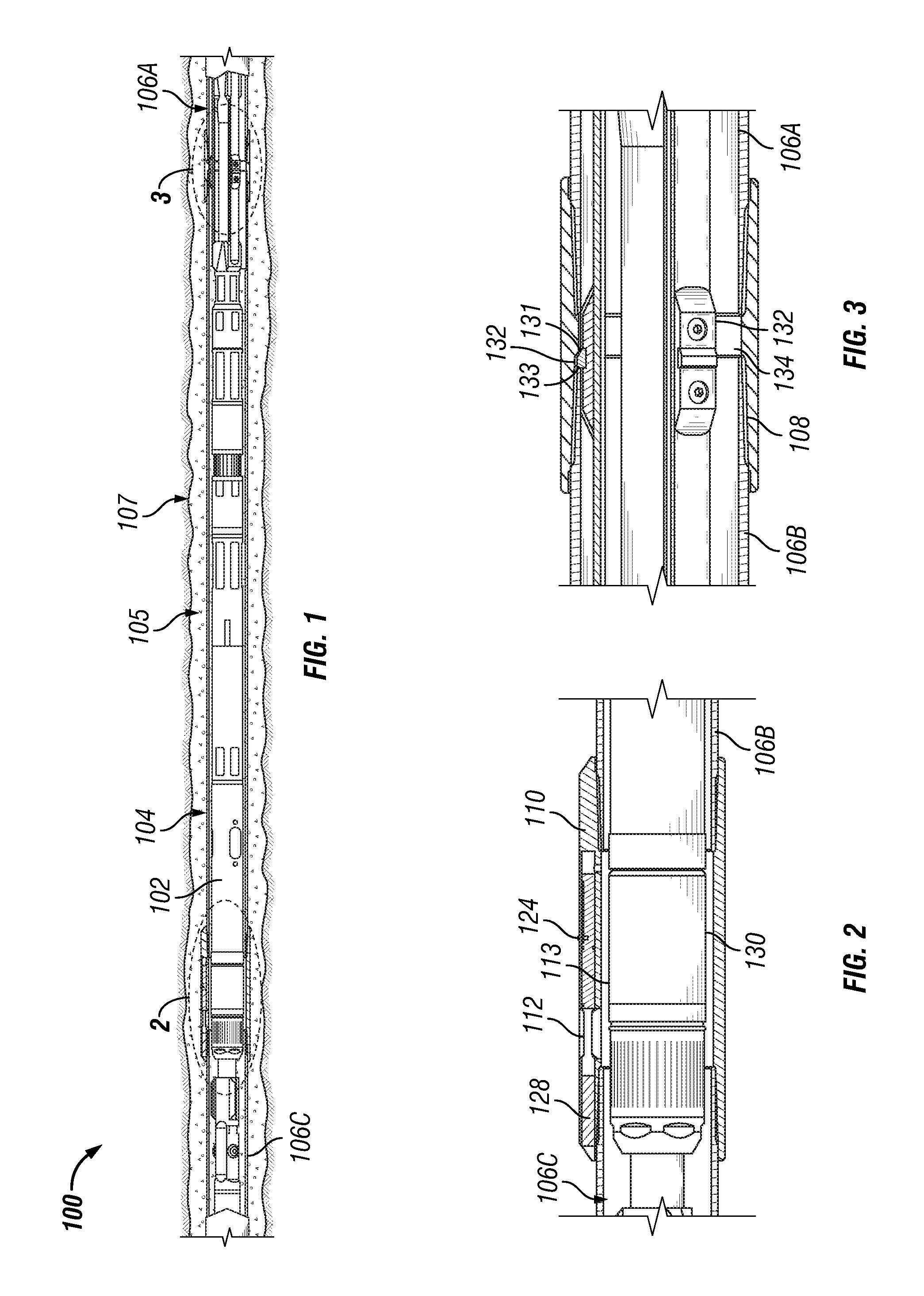

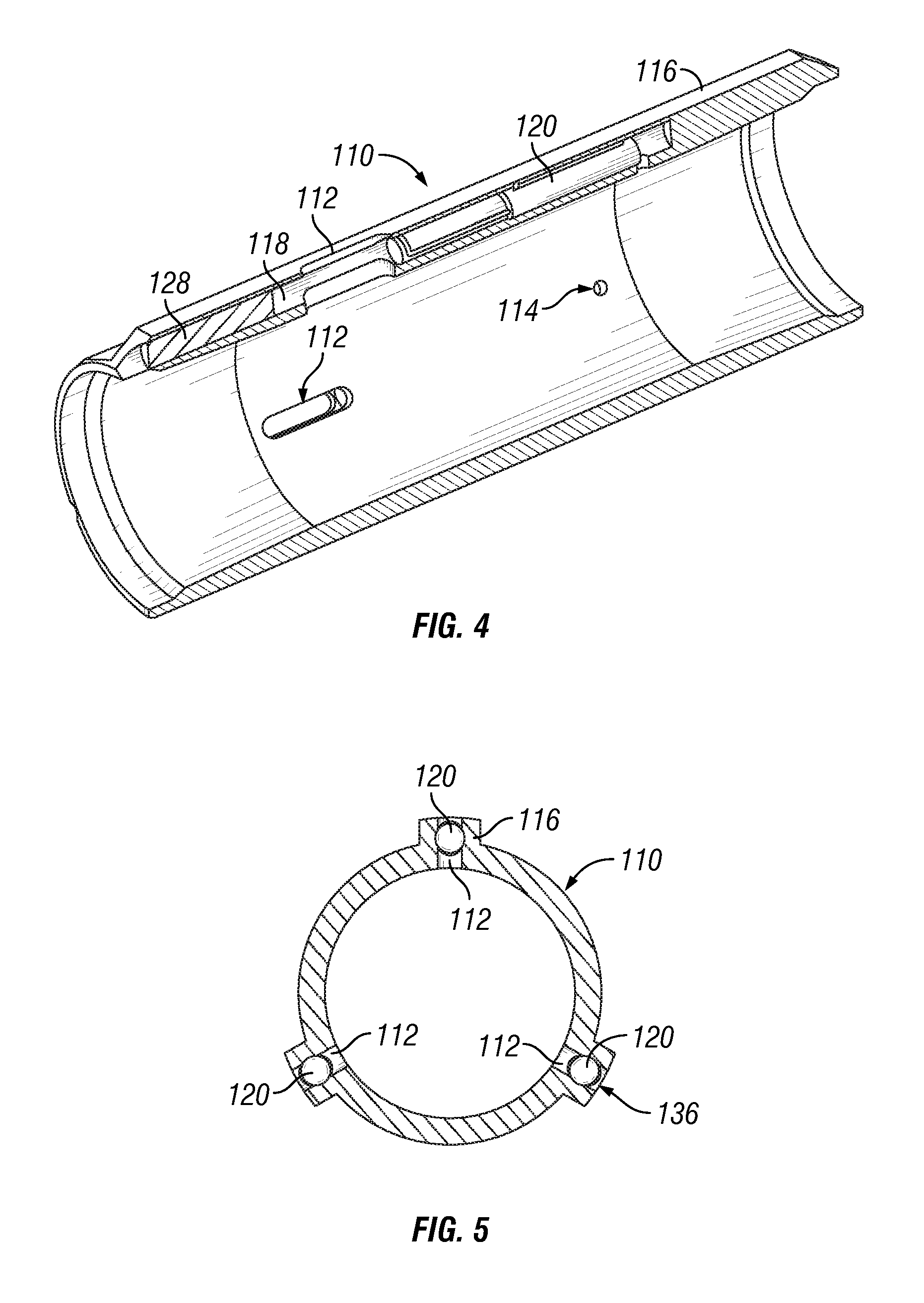

Bottom hole assembly with ported completion and methods of fracturing therewith

ActiveUS20110174491A1Improve fracture treatmentIncrease the differential pressureConstructionsGenetic material ingredientsEngineeringPressure difference

A ported completion and method for use in fracturing multi-zone wells. A casing assembly having a plurality of casing lengths and one or more collars positioned so as to couple together the casing lengths. The collars may be a tubular body having an inner flow path, one or more fracture ports configured to provide fluid communication between an outer surface of the collar and the inner flow path, one or more valve holes intersecting the fracture ports, one or more valve vent holes positioned to provide fluid communication between the valve holes and the inner flow path, and one or more valves positioned in the valve holes for opening and closing the fracture ports. The valves are configured to open when a pressure differential is created between the fracture ports and the valve vent holes. The valve vent hole may be an annulus around the perimeter of the tubular body.

Owner:BAKER HUGHES INC

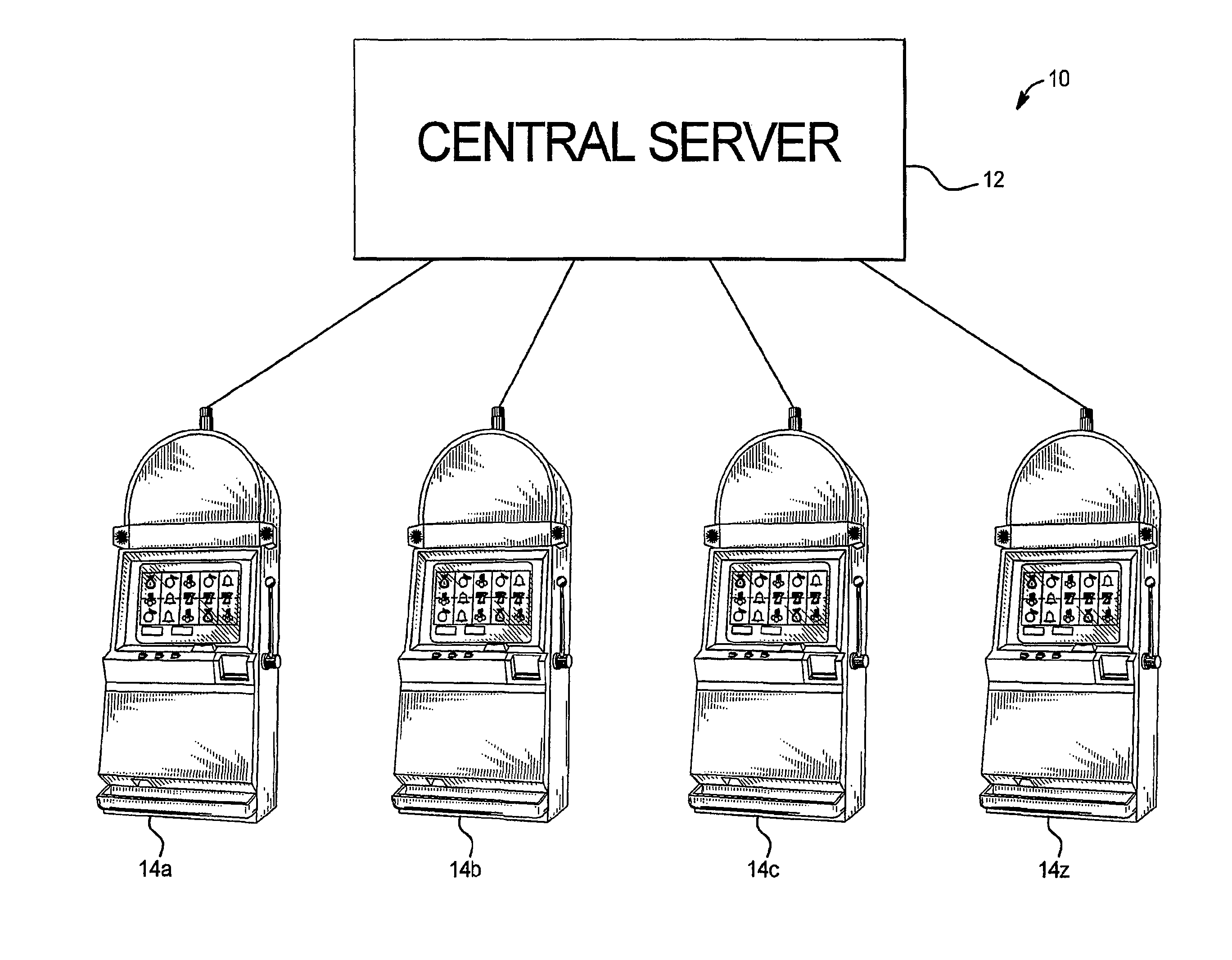

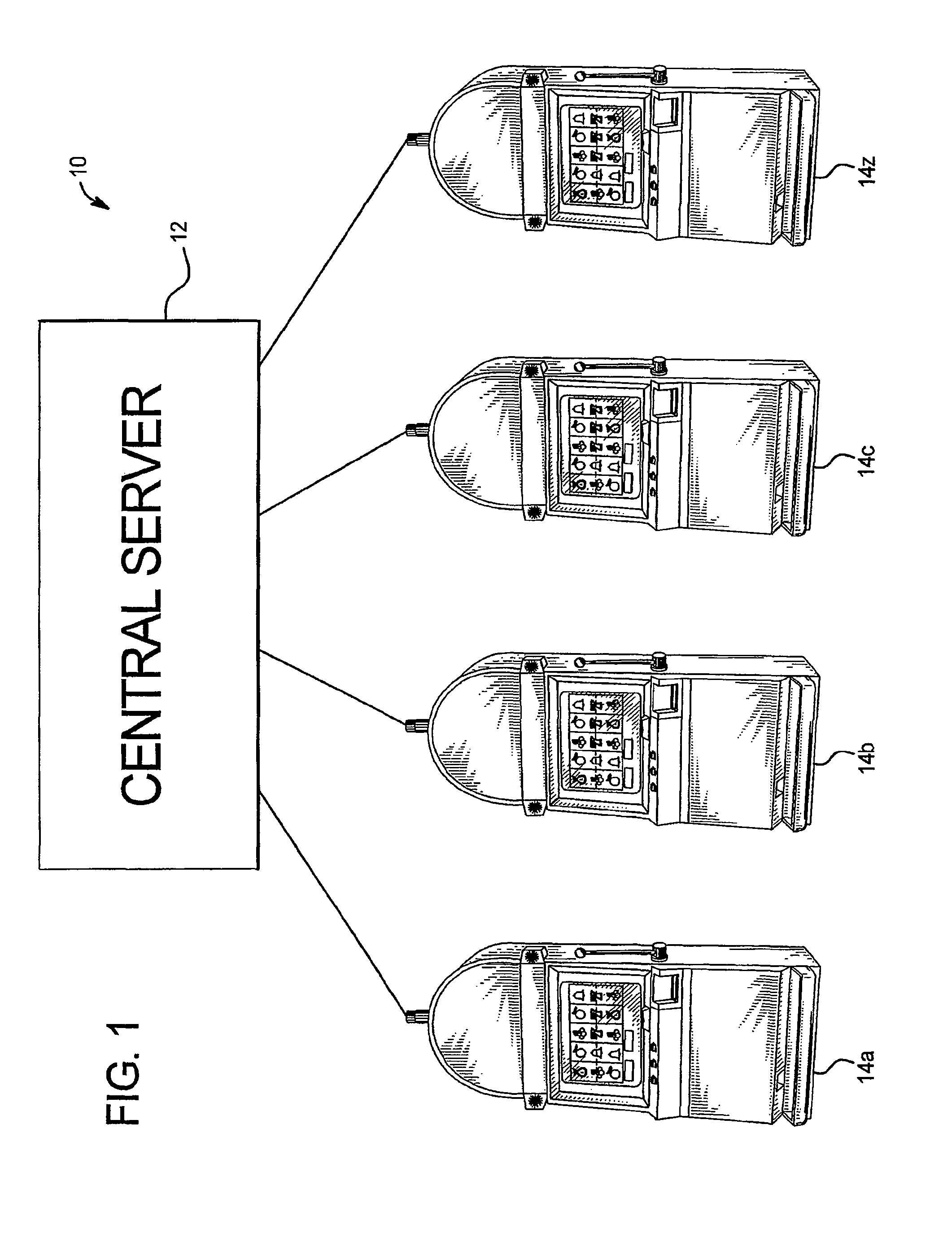

Server based gaming system having system triggered loyalty award sequences

ActiveUS8012009B2Enhances one or more gaming parametersIncrease the player's excitement at the win potentialApparatus for meter-controlled dispensingVideo gamesHuman–computer interactionOperations research

A gaming system including a central server linked to a plurality of gaming tables. In one embodiment, the gaming system provides players with one or more loyalty incentives, such as one or more loyalty awards, utilizing one or more loyalty incentive award sequences. In one embodiment, the gaming system determines a loyalty award to provide to a player and then determines an appropriate loyalty award sequence to utilize to provide the player the determined loyalty award, wherein the loyalty award sequence is determined based on the individual gaming table at which that the player is currently playing.

Owner:IGT

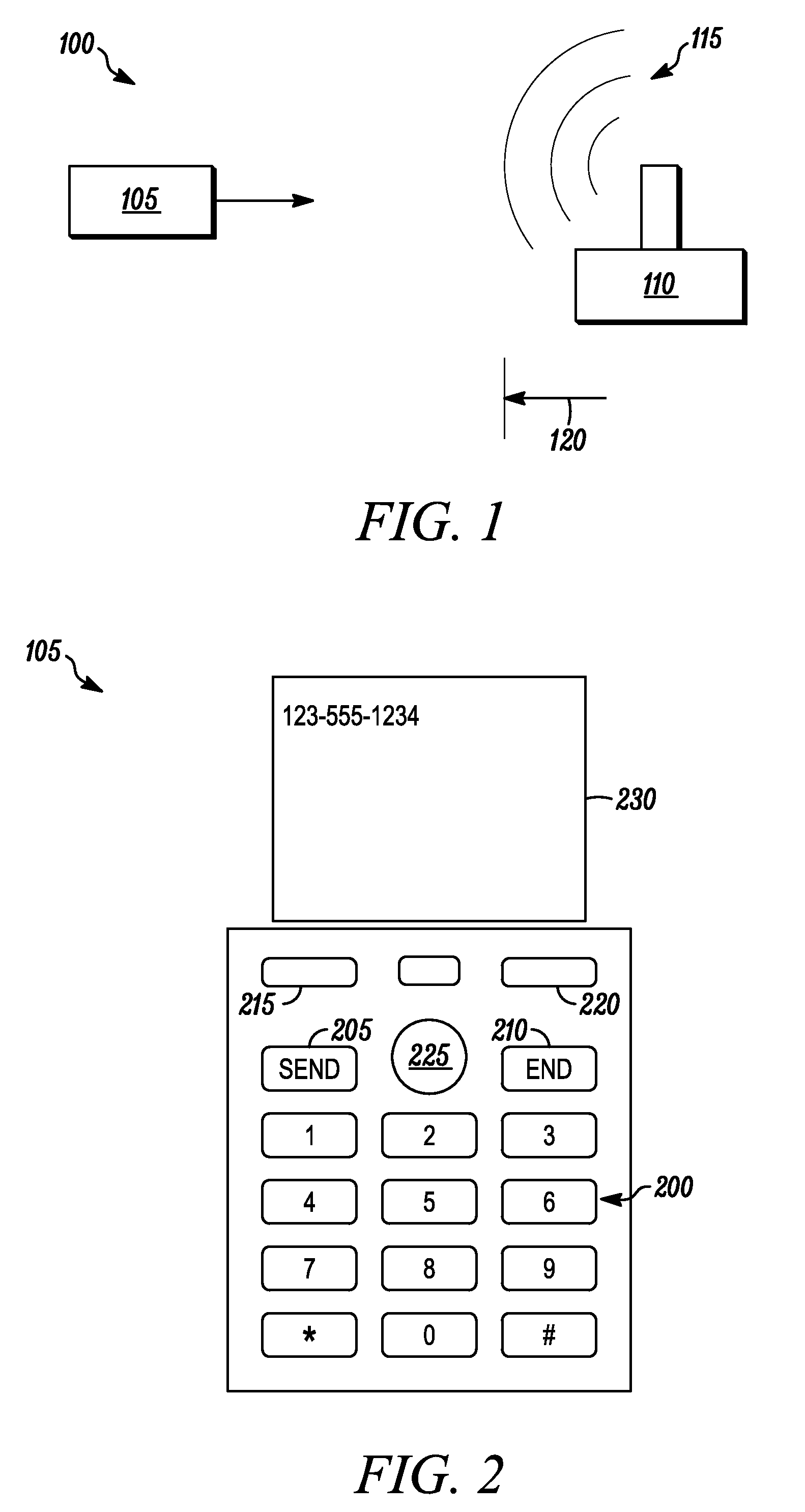

Methods, Systems and Apparatus for Selecting an Application in Power-Off Mode

ActiveUS20100248710A1Not set it lowPower managementNear-field transmissionMobile deviceEmbedded system

An embodiment relates generally to a method of selecting applications. The method includes positioning a powered-down mobile device into a close proximity of a near field communication device and selecting an application from a plurality of applications stored on the powered-down mobile device. The method also includes executing the application in the powered-down mobile device to interact with the near field communication device.

Owner:GOOGLE TECH HLDG LLC

Method and circuit breaker for reducing arc flash during maintenance in a low voltage power circuit

ActiveUS20050219775A1Eliminate delaysLow levelParameter calibration/settingProvisions for user interfaceArc flashLow voltage circuits

Maintenance trip functions override the normal or specified trip functions of a low voltage circuit breaker to reduce pickup currents and / or time delays to effect faster trips, which reduces arc energy produced by faults during maintenance or testing on a live circuit breaker.

Owner:EATON INTELLIGENT POWER LIMITED

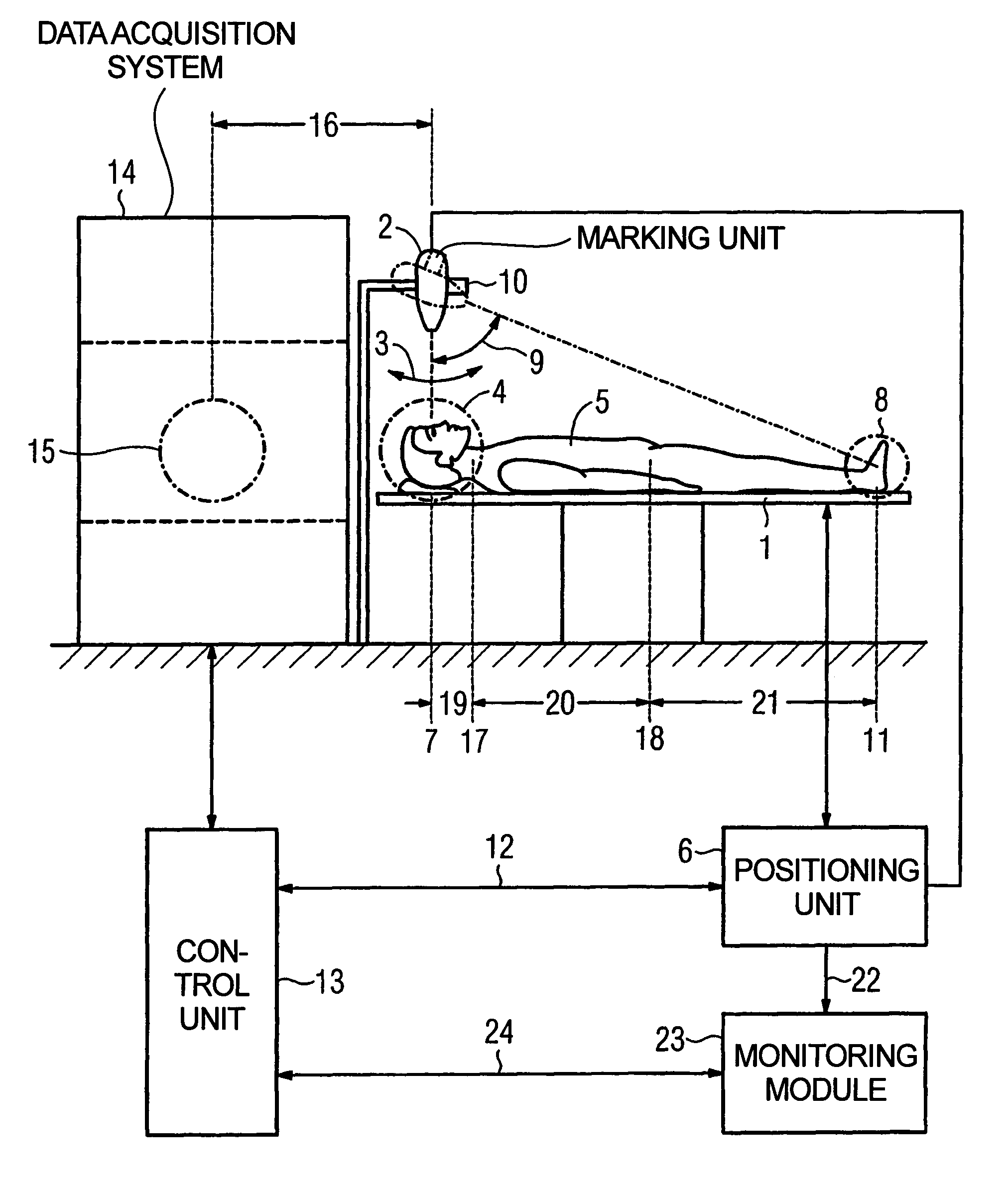

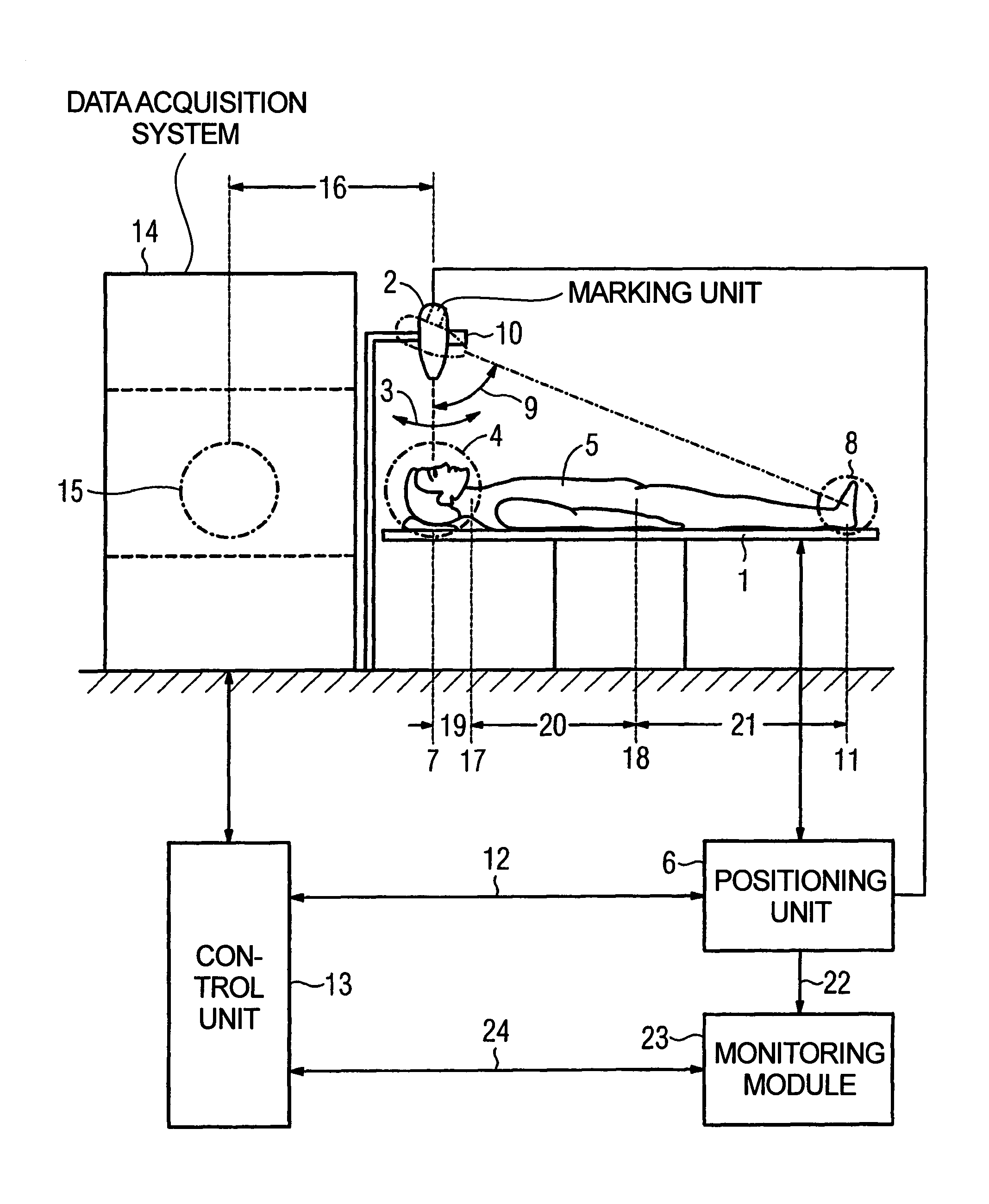

Magnetic resonance apparatus with a positioning unit

InactiveUS20050218896A1Simple procedureImprove securityMagnetic property measurementsDiagnostic recording/measuringDiagnostic dataResonance

A magnetic resonance apparatus has a positioning unit and a patient bed. The positioning unit can store a number of positions of the patient bed and can automatically position in an imaging volume the associated examination regions established by a marking unit in a diagnostic data acquisition procedure predetermined by a measurement control unit. The positioning unit can detect dimensions of a patient by evaluation of the number of positions of the patient bed and transfer these dimensions to a monitoring module. The monitoring module adapts the RF transmitting power to the patient according to the dimensions.

Owner:SIEMENS AG

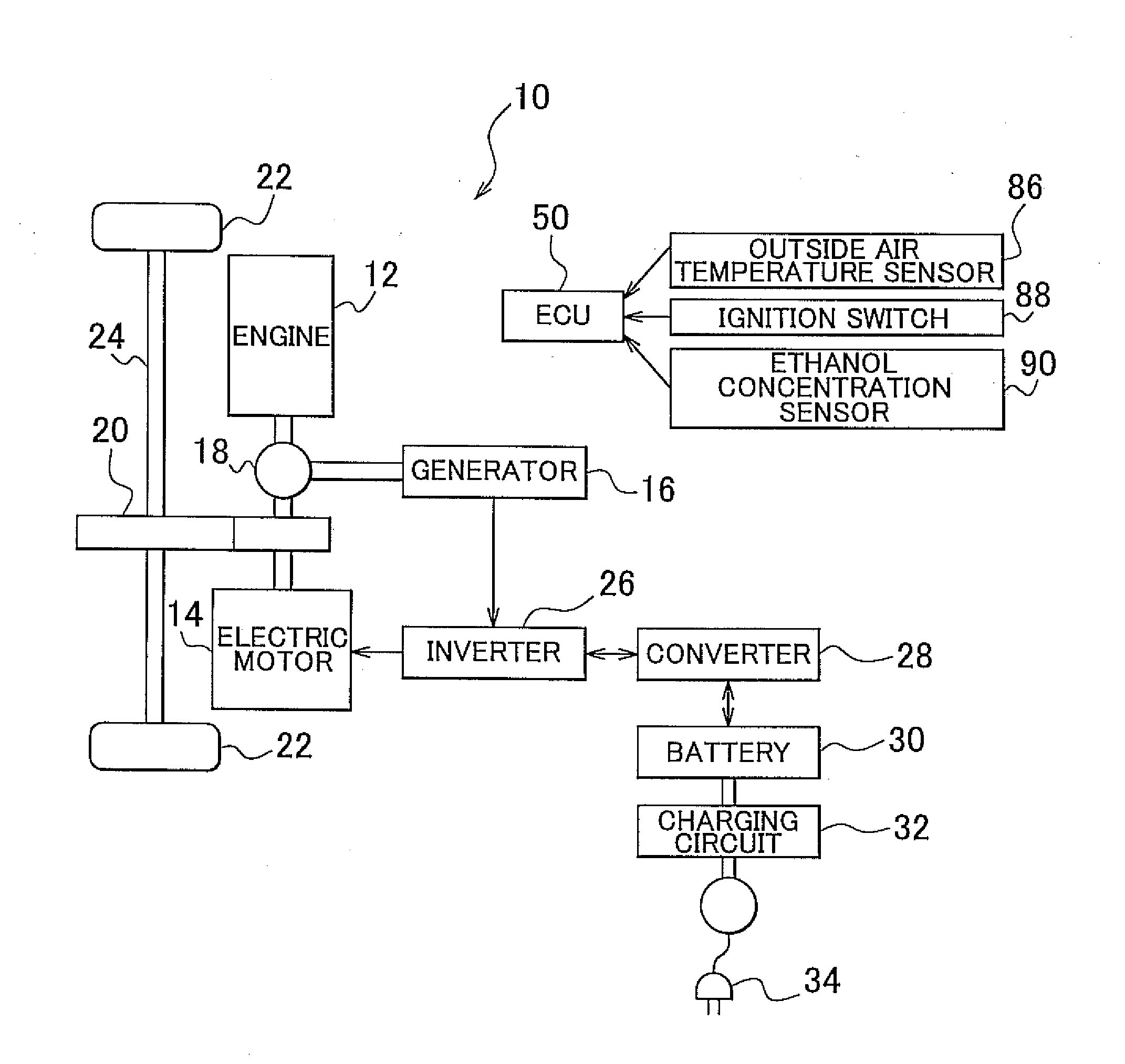

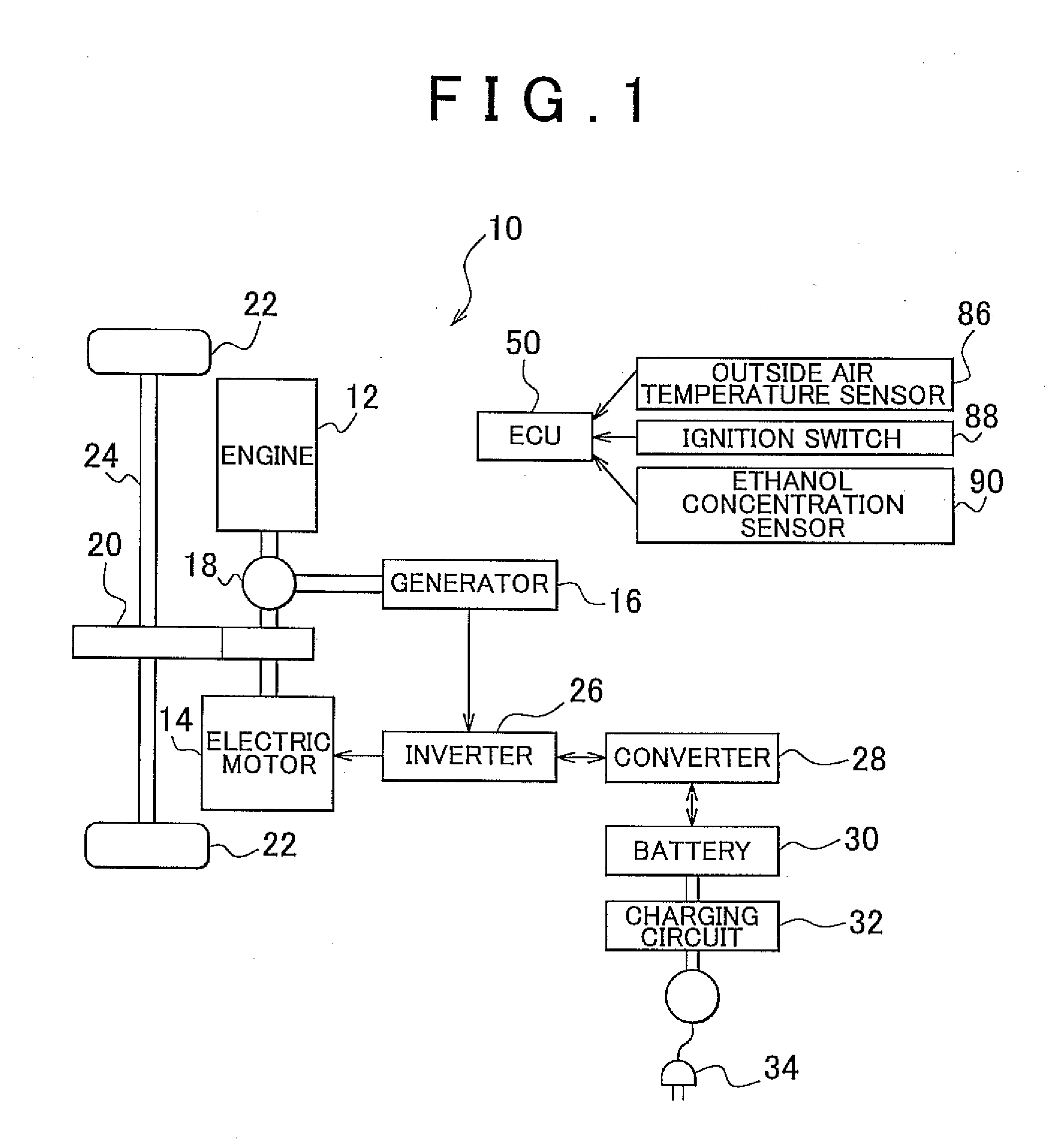

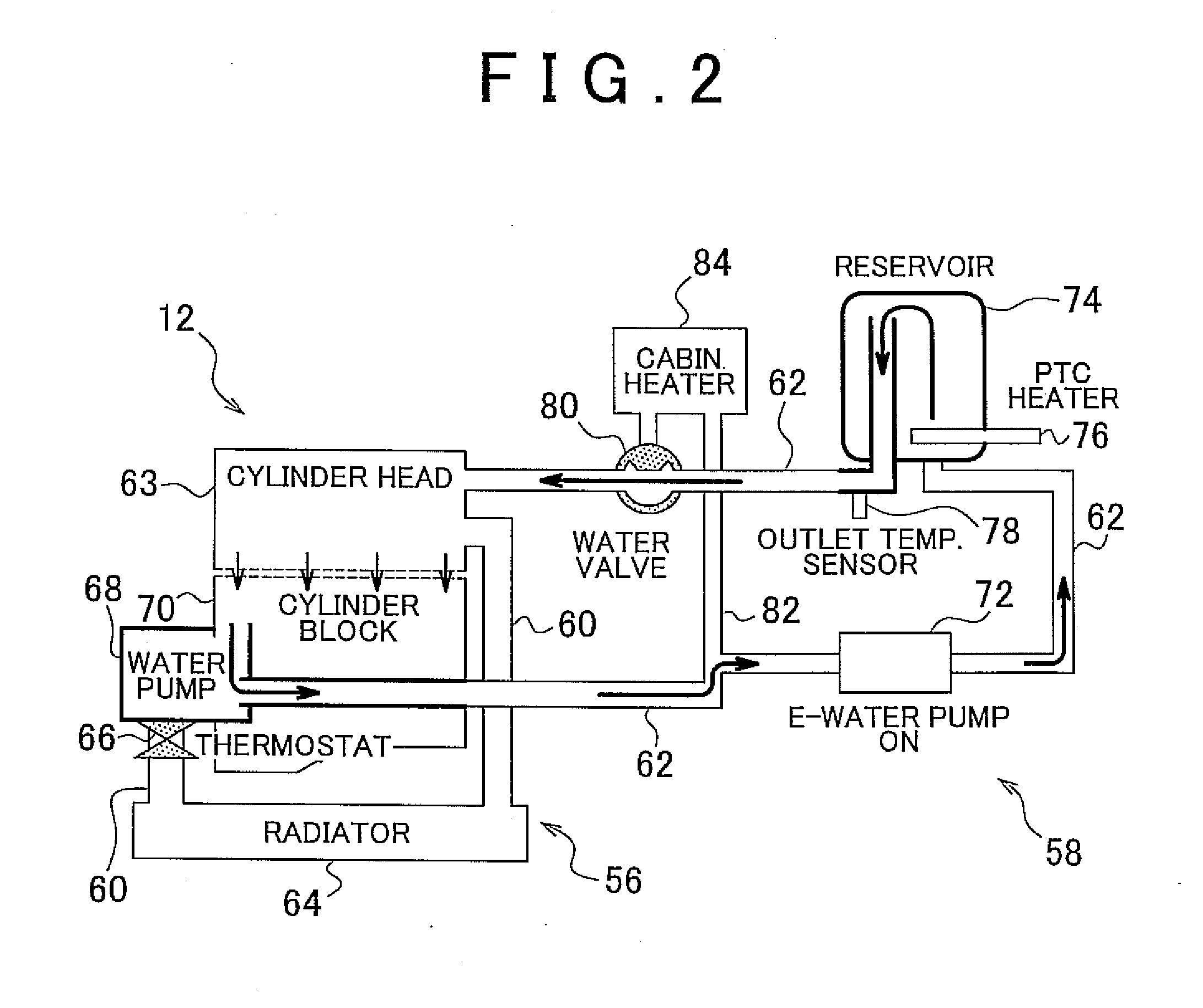

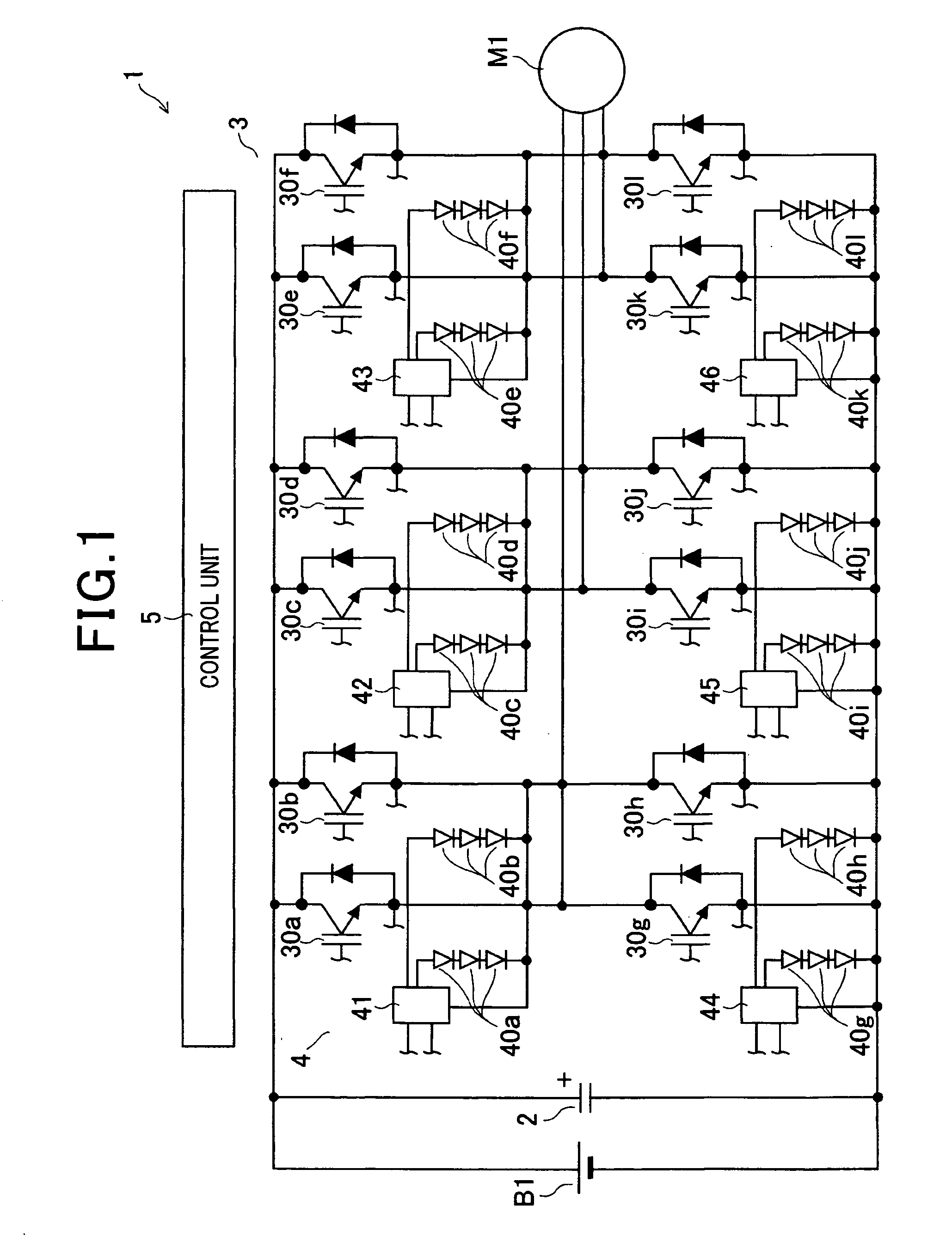

Controller for hybrid system

InactiveUS20110178665A1Startability is improvedHigh concentrationHybrid vehiclesDigital data processing detailsHybrid systemAlcohol

A controller for the hybrid system includes: an alcohol concentration detector that detects alcohol concentration of fuel; a demanded coolant temperature setting device that sets a demanded coolant temperature higher as the alcohol concentration increases; an internal combustion engine stopped state determination device that determines whether an internal combustion engine is stopped; an external electric power source connection determination device that determines whether a storage battery is connected to an external electric power source; and a coolant pre-heating device that supplies electric power to a coolant heater until coolant temperature of the coolant reaches the demanded coolant temperature if the internal combustion engine is in the stopped state and the storage battery is connected to the external electric power source.

Owner:TOYOTA JIDOSHA KK

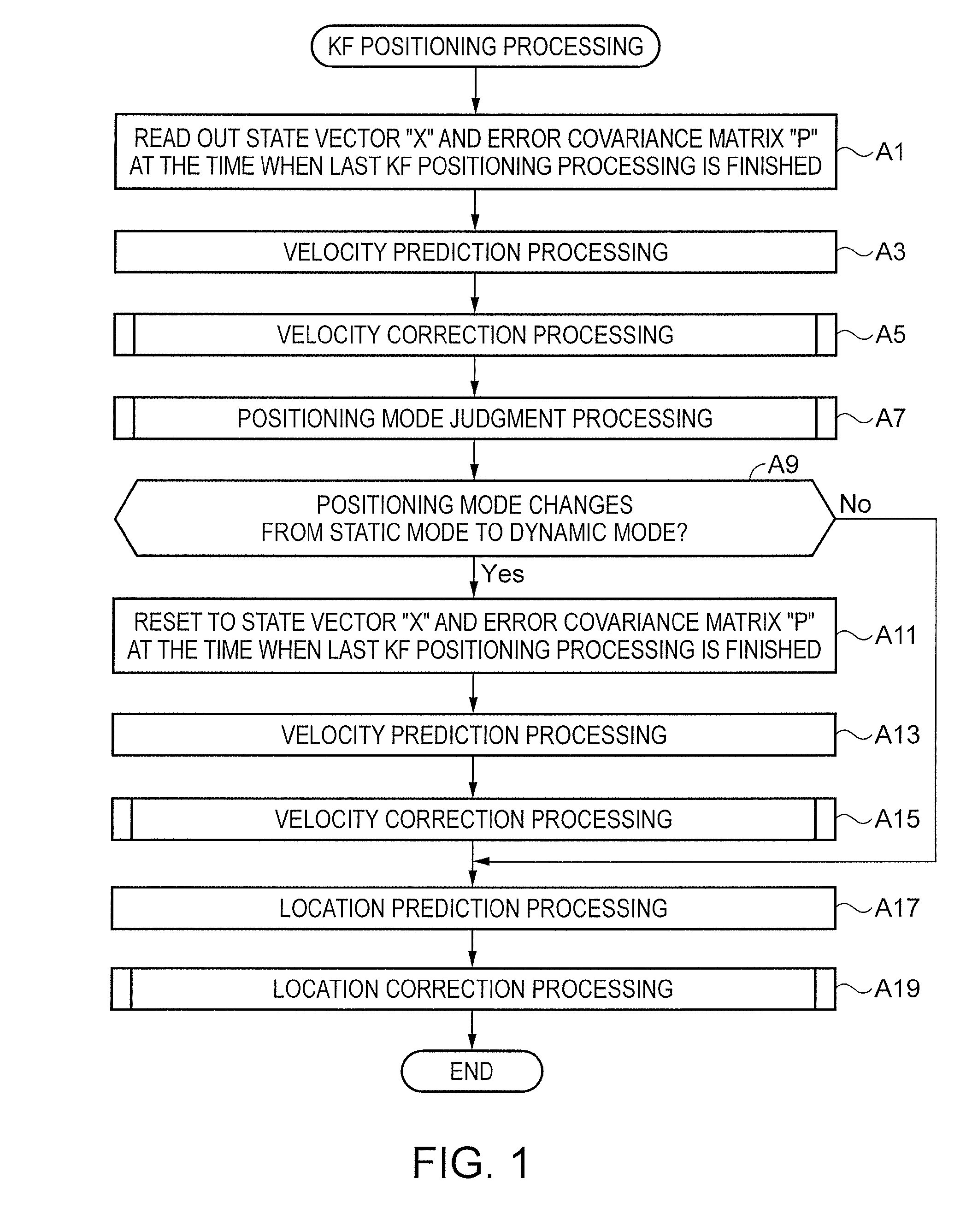

Positioning method, computer program, positioning device, and electronic apparatus

InactiveUS20090167603A1Solve the real problemLow accuracyBeacon systemsSatellite radio beaconingCovarianceComputer program

A positioning method in a positioning device that calculates a location of the positioning device by executing Kalman filtering includes, acquiring a satellite signal from a positioning satellite; predicting a state vector including a velocity component of the positioning device, and error covariance of the state vector; correcting the velocity component using a difference between a measured value and a predicted value of the reception signal frequency from the positioning satellite; determining accuracy of the corrected velocity component based on the error covariance; setting a velocity condition based on the determined accuracy; judging a moving state of the positioning device by comparing the corrected velocity component and the velocity condition; and calculating the location by executing the Kalman filtering with a filter characteristic changed according to the judged moving state.

Owner:SEIKO EPSON CORP

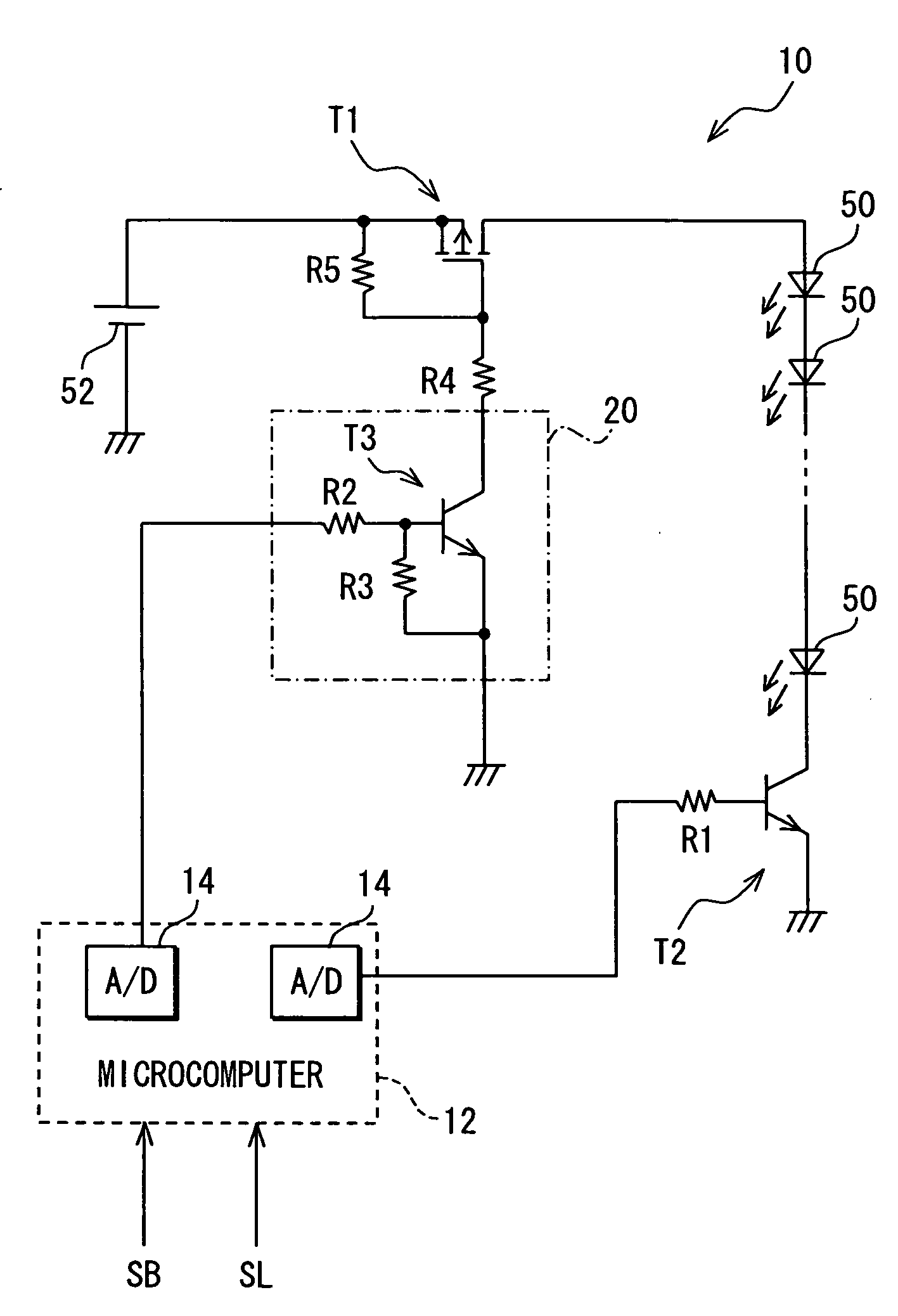

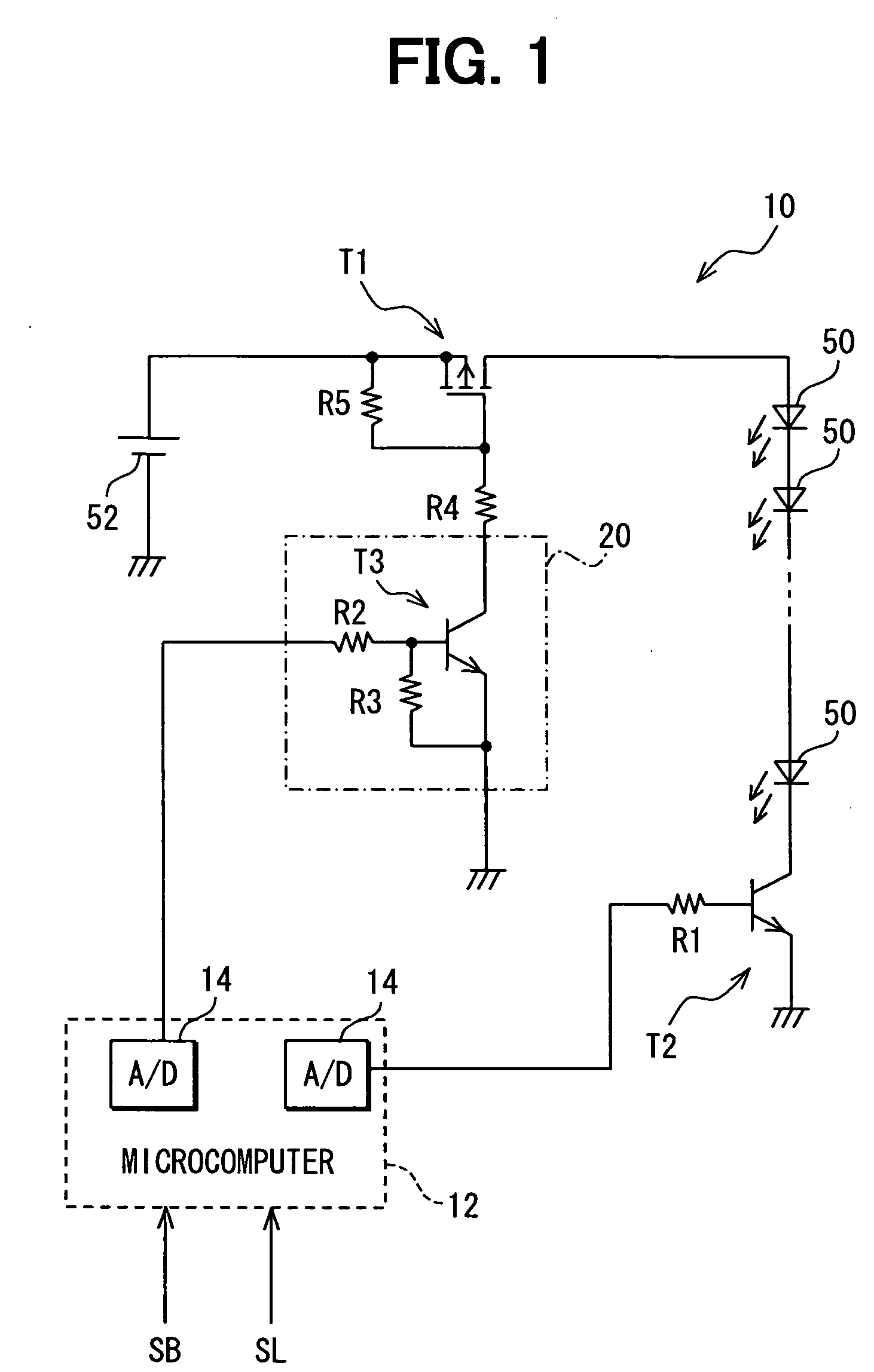

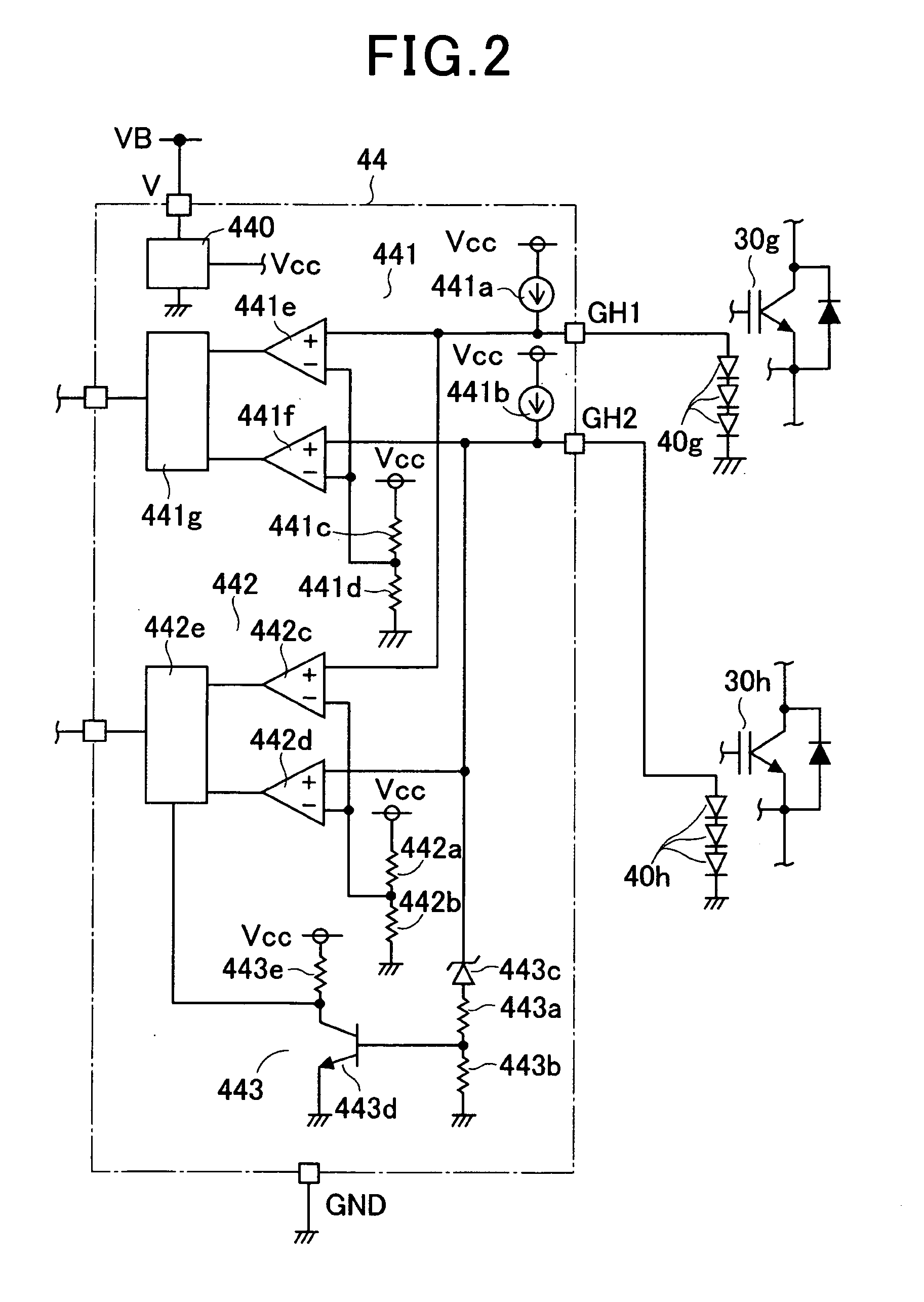

Luminance control apparatus for light emitting device

InactiveUS20070115209A1Not set it lowLow luminance rangeStatic indicating devicesElectroluminescent light sourcesEngineeringPulse width modulated

A luminance control apparatus for a backlight of a display device in a vehicle has a first transistor and a second transistor connected to the backlight. The first transistor is controlled by pulse-width modulation control, and the second transistor is controlled to supply a low level current at nighttime and a high level current at daytime under a condition that the first transistor is ON. The duty ratio of the first transistor is varied over a full range from 0% to 100% at the nighttime, while the duty ratio of the same is varied only in a partial range at the daytime.

Owner:DENSO CORP

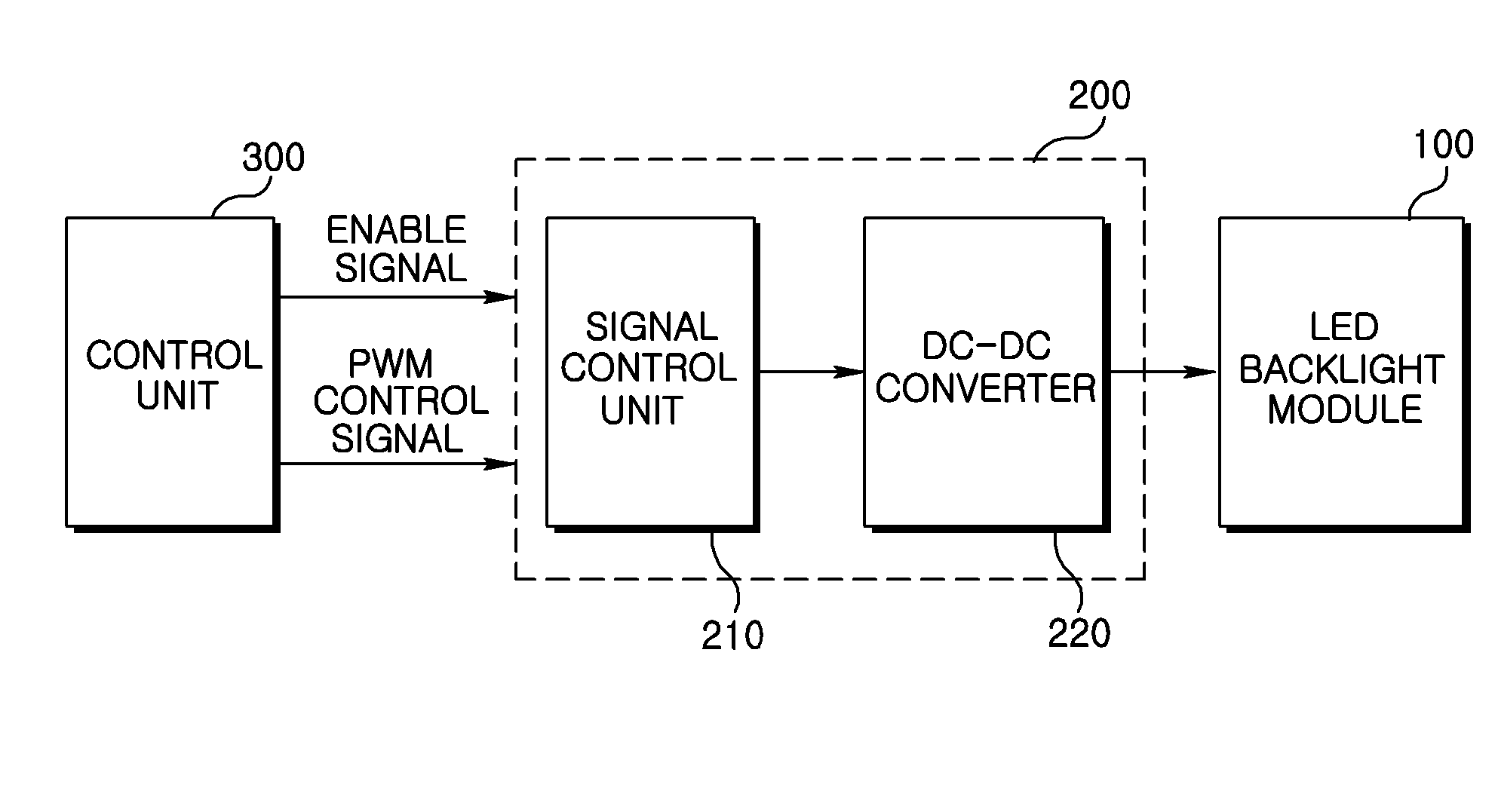

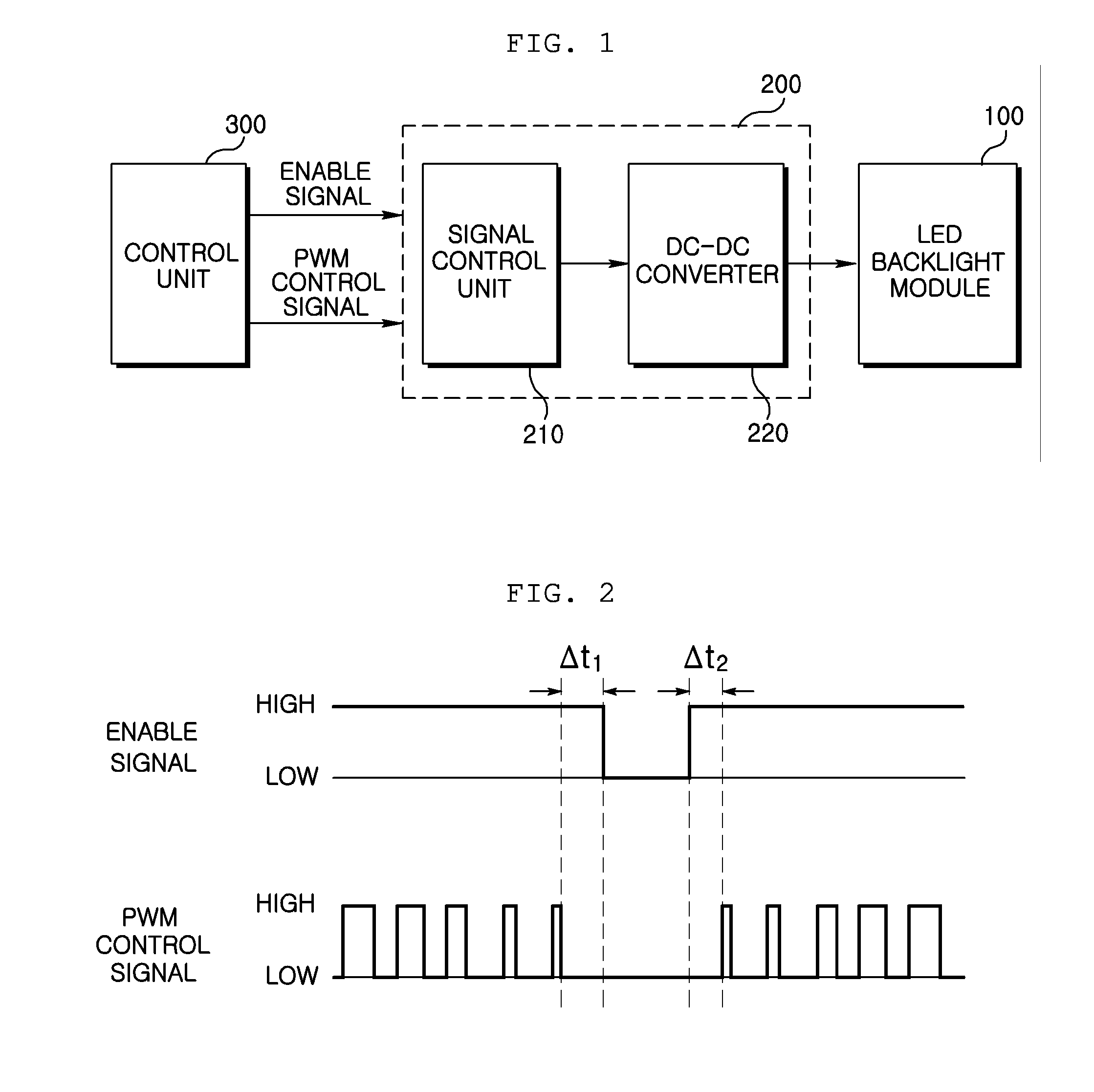

Apparatus and method for controlling back light

InactiveUS20110298834A1Reducing duty ratioLow setCathode-ray tube indicatorsInput/output processes for data processingControl signalEngineering

Disclosed herein is a backlight control apparatus, including an LED backlight drive unit driving an LED backlight module and a control unit outputting an enable signal deterministic of whether to drive the LED backlight drive unit or not to the LED backlight drive unit, and stepwisely decreasing or increasing the duty ratio of a PWM control signal to control the brightness of the LED backlight module and outputting it to the LED backlight drive unit.

Owner:LG ELECTRONICS INC

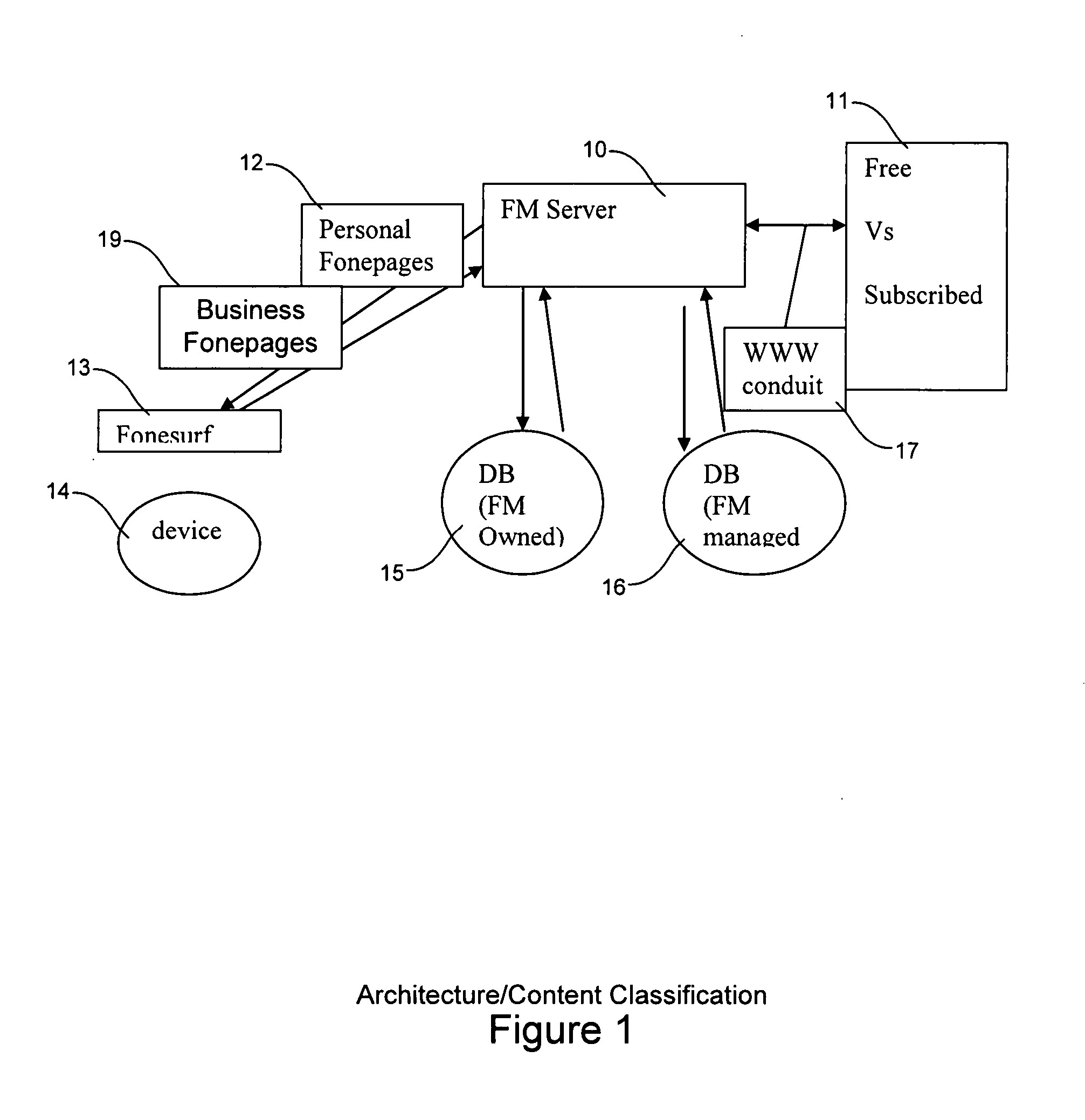

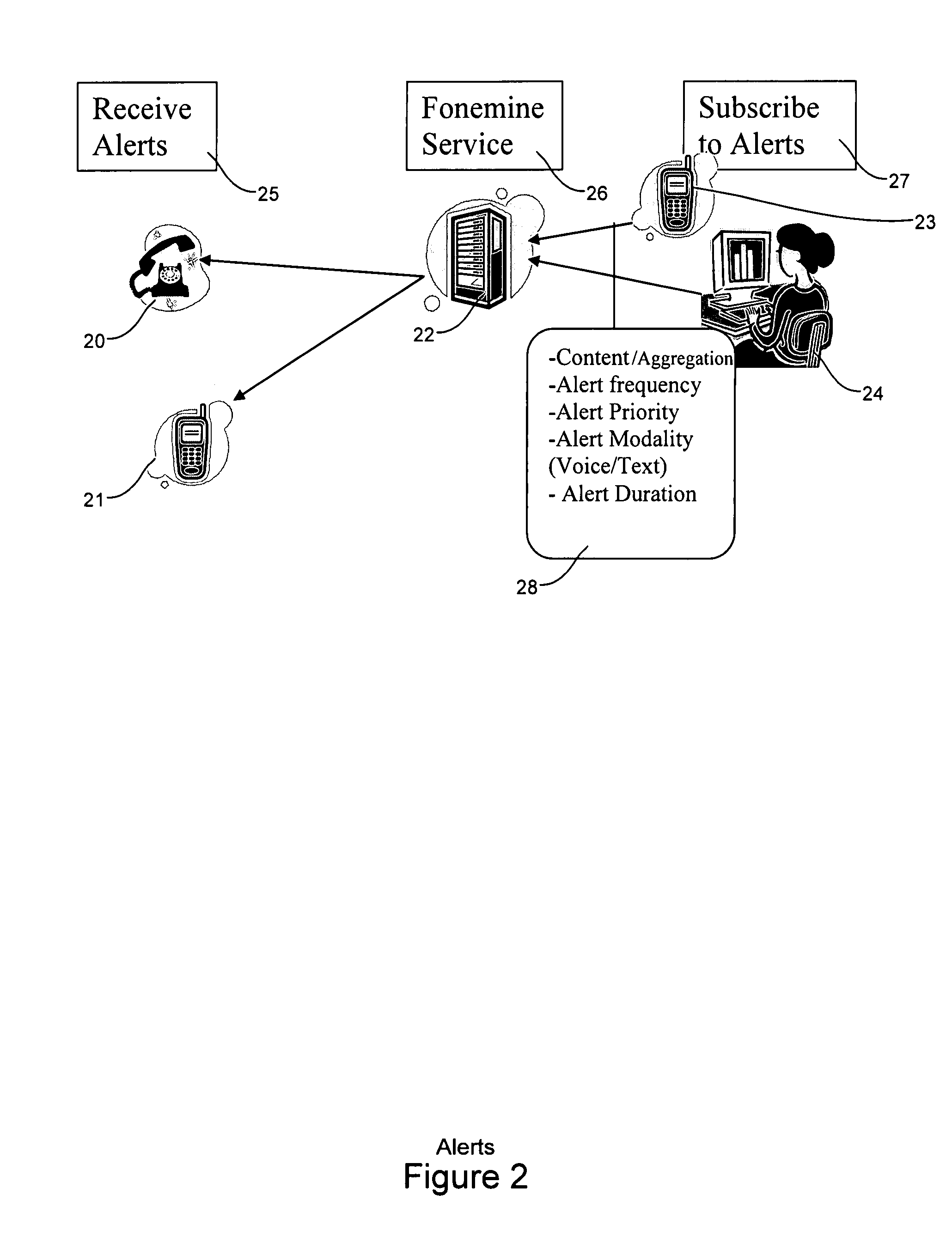

Telephony based publishing, search, alerts & notifications, collaboration, and commerce methods

InactiveUS20070208688A1Easily viewed/heardNot set it lowDigital data processing detailsMarketingService protocolTelephone network

Systems, apparatus and methods are described that provide data services including publication and viewing of personal and business content on phone devices via phone networks. The invention provides systems, methods, tools and delivery systems useful in the publication, sharing, viewing, searching, communication, transmission, alerting, notification & feedback, collaboration and commerce on telephone networks.—Subscribers may publish content specifically targeted for phones and view such content on existing phone devices, on phone networks. Subscribers may search for relevant content on phone devices and may send / receive alerts that can be tied to their search operations. Subscribers may also create, join, participate in communities via their phone devices as well as, view, and update content designed specifically for such phone communities. Commerce can also be initiated and automated end-to-end via Fonemine services, protocols, and abstractions that are described in this invention. The systems, methods and apparatus for such data services can be optimized for use in mobile devices and may be accessed using existing telephones and telephone networks.

Owner:FONEMINE

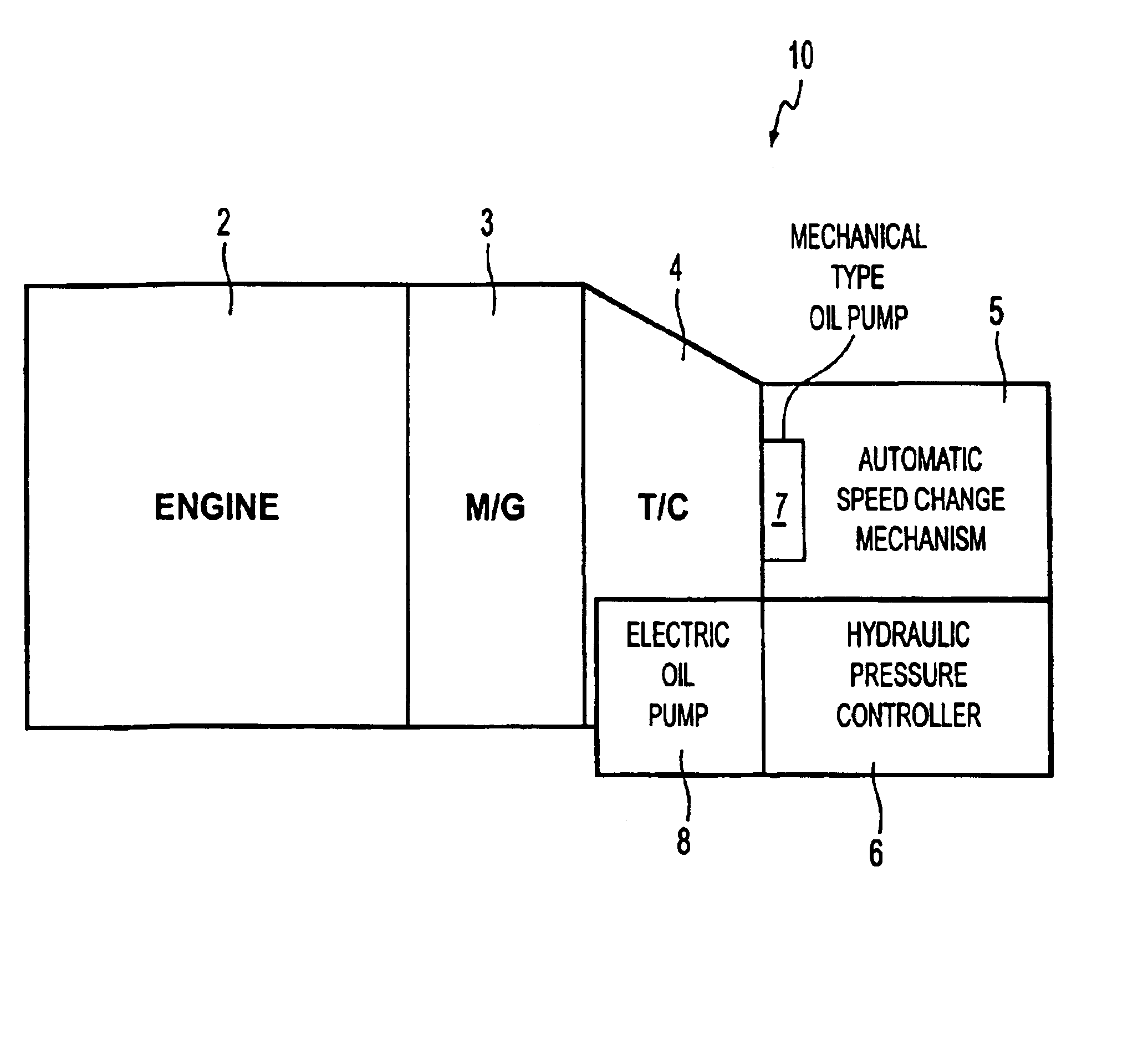

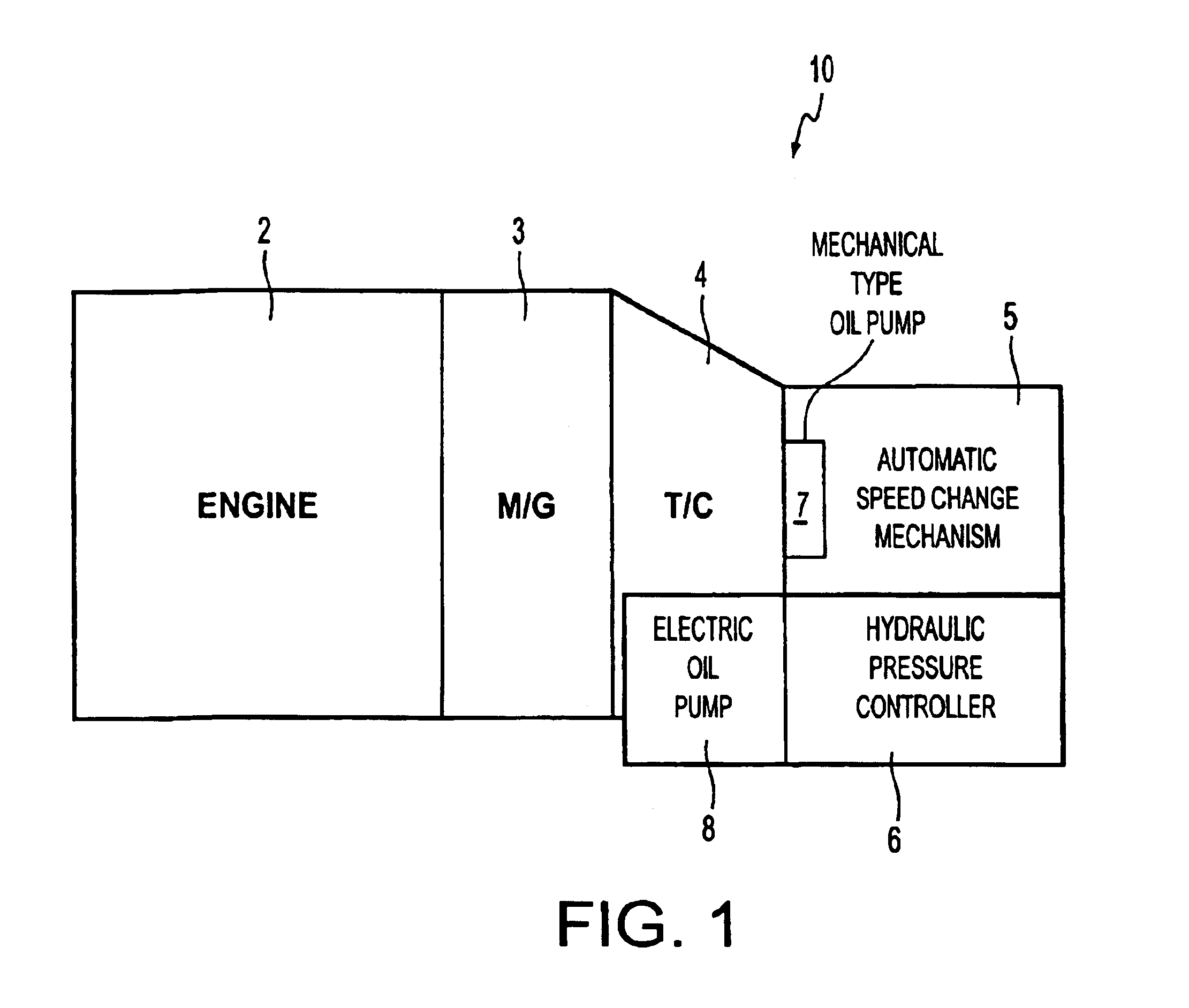

Controller of vehicle

InactiveUS6952057B2Reduce power consumptionElectric power consumptionPower operated startersDC motor speed/torque controlLow speedLoad torque

A controller of a vehicle for igniting, i.e., starting-up an engine on the basis of a load condition. When a starting condition judging device judges that the vehicle is advanced, i.e., starts moving, during an idle stop, an engine water temperature detector and a lubricating oil temperature detector of a load condition detector detect, e.g., the water temperature of the engine and the temperature of lubricating oil of an automatic speed change gear as a load condition having an influence on the magnitude of the load torque given to a motor. When an ignition condition setting device sets an ignition condition for starting the engine on the basis of the load condition and an ignition condition judging device judges that the ignition condition occurs, an engine ignition device ignites the engine. Thus, when the load with respect to the motor is large, the engine is ignited from low speed rotation and electric power consumption is reduced. In contrast to this, when the load is small, the engine is ignited by high speed rotation and the consumption of fuel is reduced. Thus, fuel cost of the vehicle is improved.

Owner:AISIN AW CO LTD

Magnetic resonance apparatus with a positioning unit

InactiveUS7030615B2Simple procedureImprove securityMagnetic property measurementsDiagnostic recording/measuringDiagnostic dataResonance

A magnetic resonance apparatus has a positioning unit and a patient bed. The positioning unit can store a number of positions of the patient bed and can automatically position in an imaging volume the associated examination regions established by a marking unit in a diagnostic data acquisition procedure predetermined by a measurement control unit. The positioning unit can detect dimensions of a patient by evaluation of the number of positions of the patient bed and transfer these dimensions to a monitoring module. The monitoring module adapts the RF transmitting power to the patient according to the dimensions.

Owner:SIEMENS AG

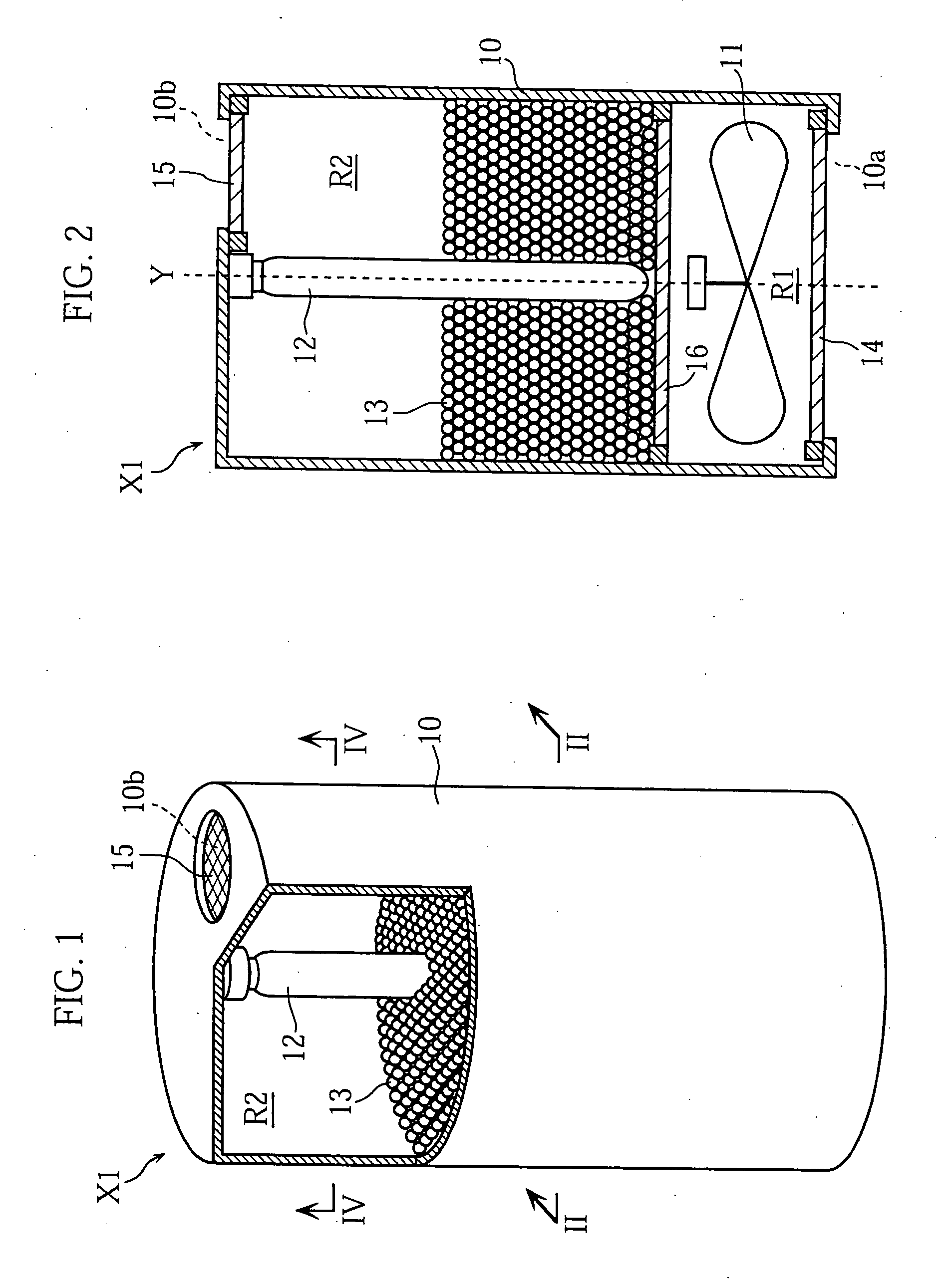

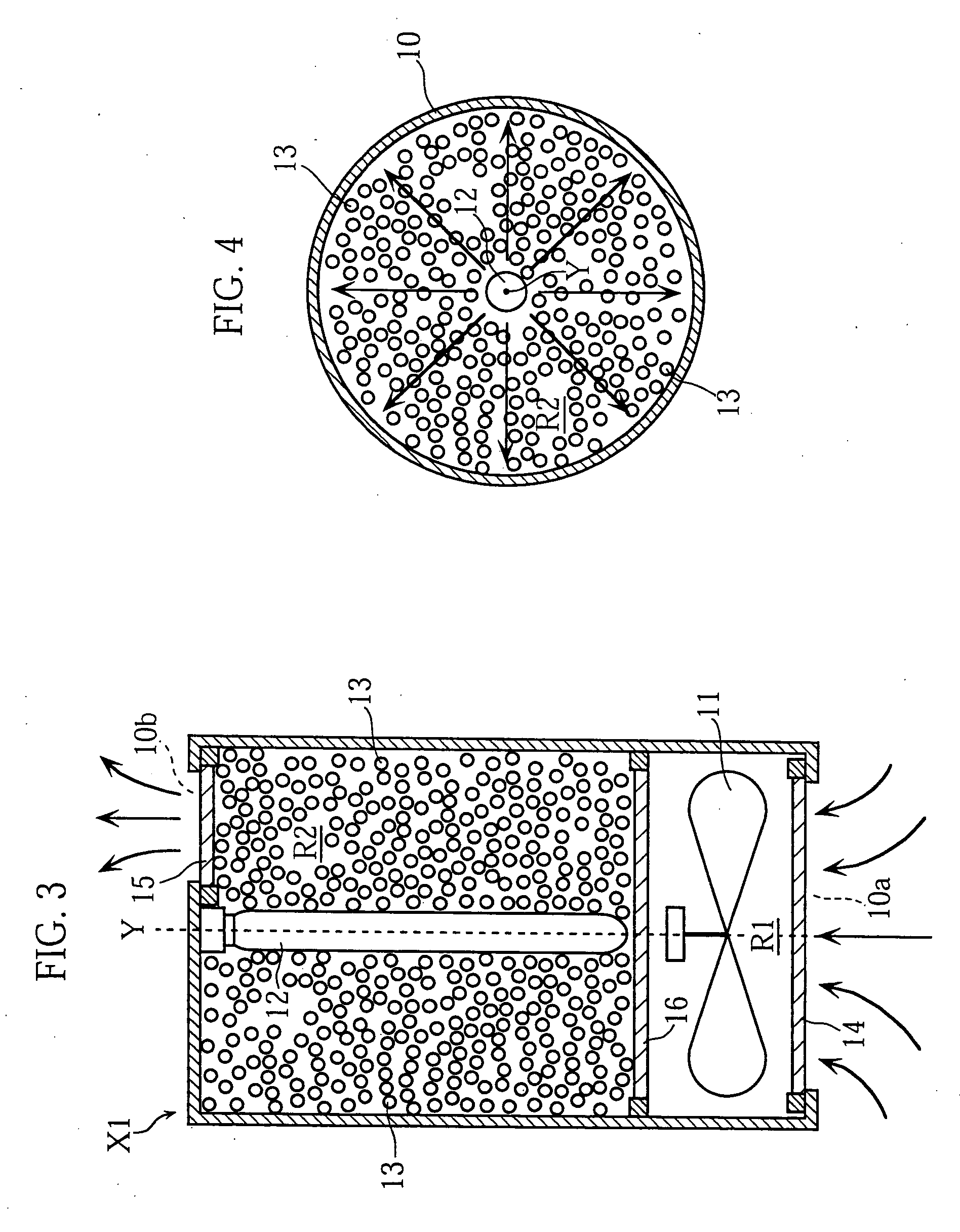

Air cleaner

ActiveUS20050201907A1High contact efficiencyClean efficiency be highMechanical apparatusLighting and heating apparatusAir cleanersAirflow

An air cleaner X1 includes a cleaning chamber (R2) through which air can pass, an ultraviolet light source (12) provided in the cleaning chamber (R2), a flow generator (11) for generating an air flow in the cleaning chamber (R2) by passing air through the cleaning chamber (R2), and photocatalyst granules (13) having a photocatalytic function, held in the cleaning chamber (R2), and displaceable by the air flow.

Owner:FUJITSU LTD

Apparatus for detecting temperature of switching elements

ActiveUS20120219033A1Detection be disabledDetection is disabledThermometers using electric/magnetic elementsUsing electrical meansEngineeringDetection threshold

A temperature detecting apparatus includes an integrated circuit that integrates an overheating detecting circuit, a breakage detecting circuit and a disabling circuit, and an element connection terminal connecting a temperature sensing element. The disabling circuit disables the breakage detecting circuit from detecting a breakage of wire when a voltage at the element connection exceeds a disabling threshold which is set higher than an overheating detection threshold and a breakage detection threshold. A predetermined voltage higher than the disabling threshold is applied to the element connection terminal when the temperature sensing element is not connected to the element connection terminal.

Owner:DENSO CORP

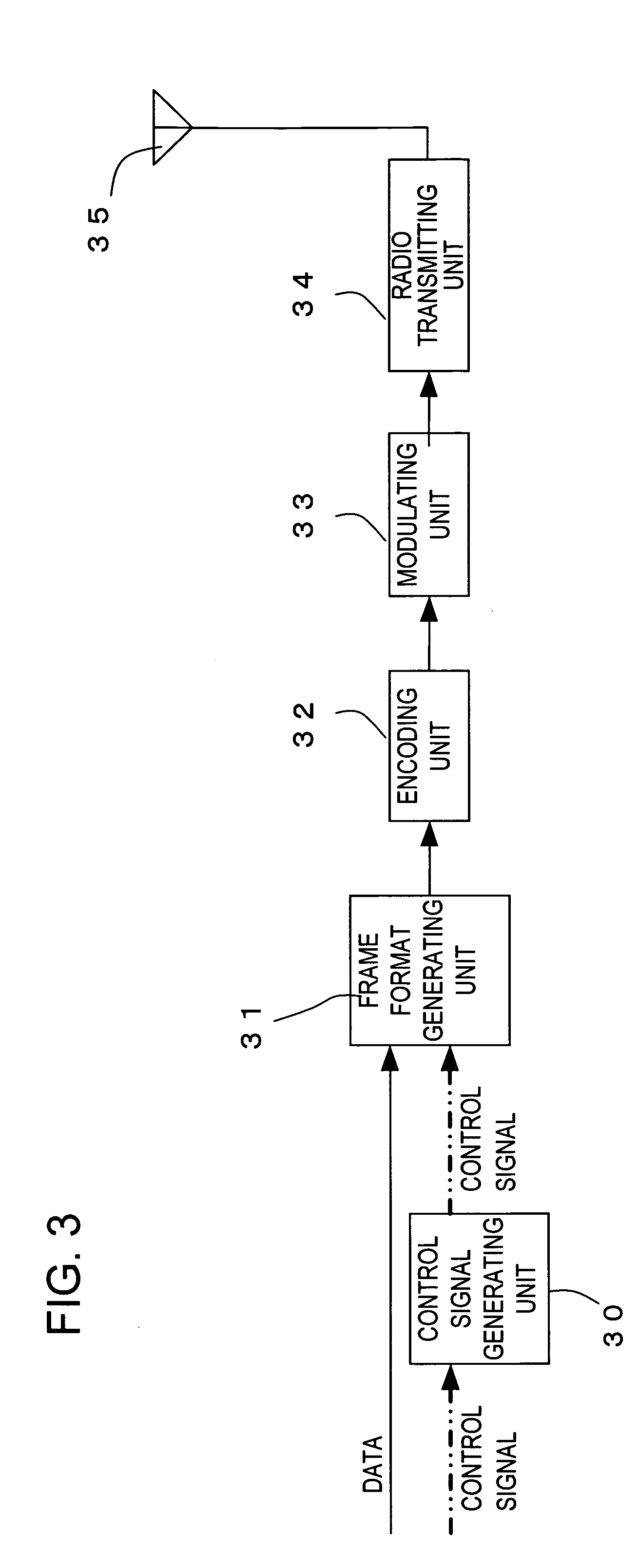

Radio communication system

ActiveUS20070178928A1Reduce transmit powerPAPR can also be reducedPower managementEnergy efficient ICTCommunications systemControl signal

A frame format is generated which can constrain the PAPR at a lower level without limitation in code selections in a radio communication system. The radio communication system with each radio channel constituted by a control channel and a data channel divides a plurality of the radio channels in a frequency direction for mapping to a radio frame format. A control signal position on the control channel is controlled in the radio frame format for each user or service to reduce peak transmission power or a peak-to-average power ratio of a radio communication apparatus.

Owner:FUJITSU LTD

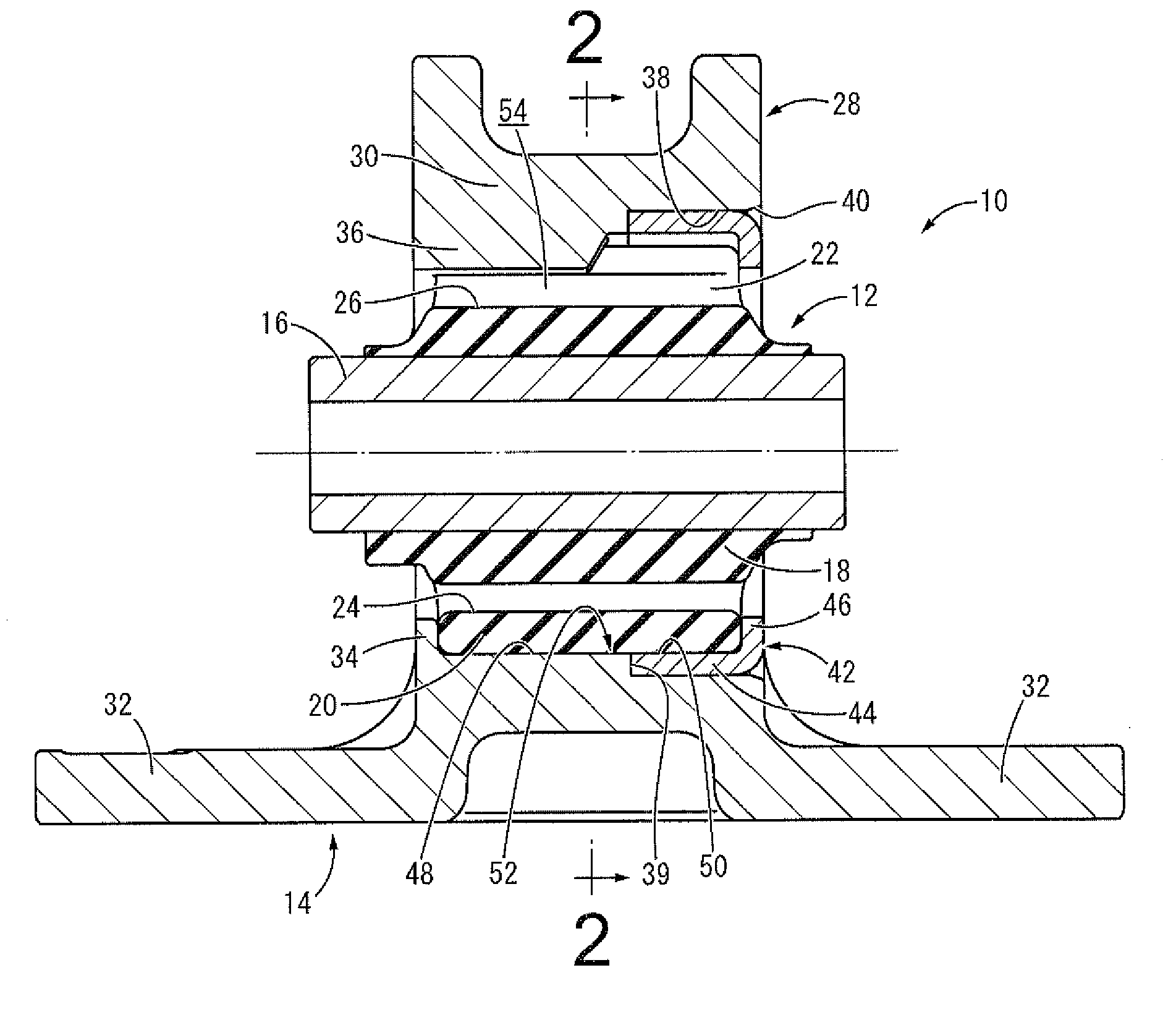

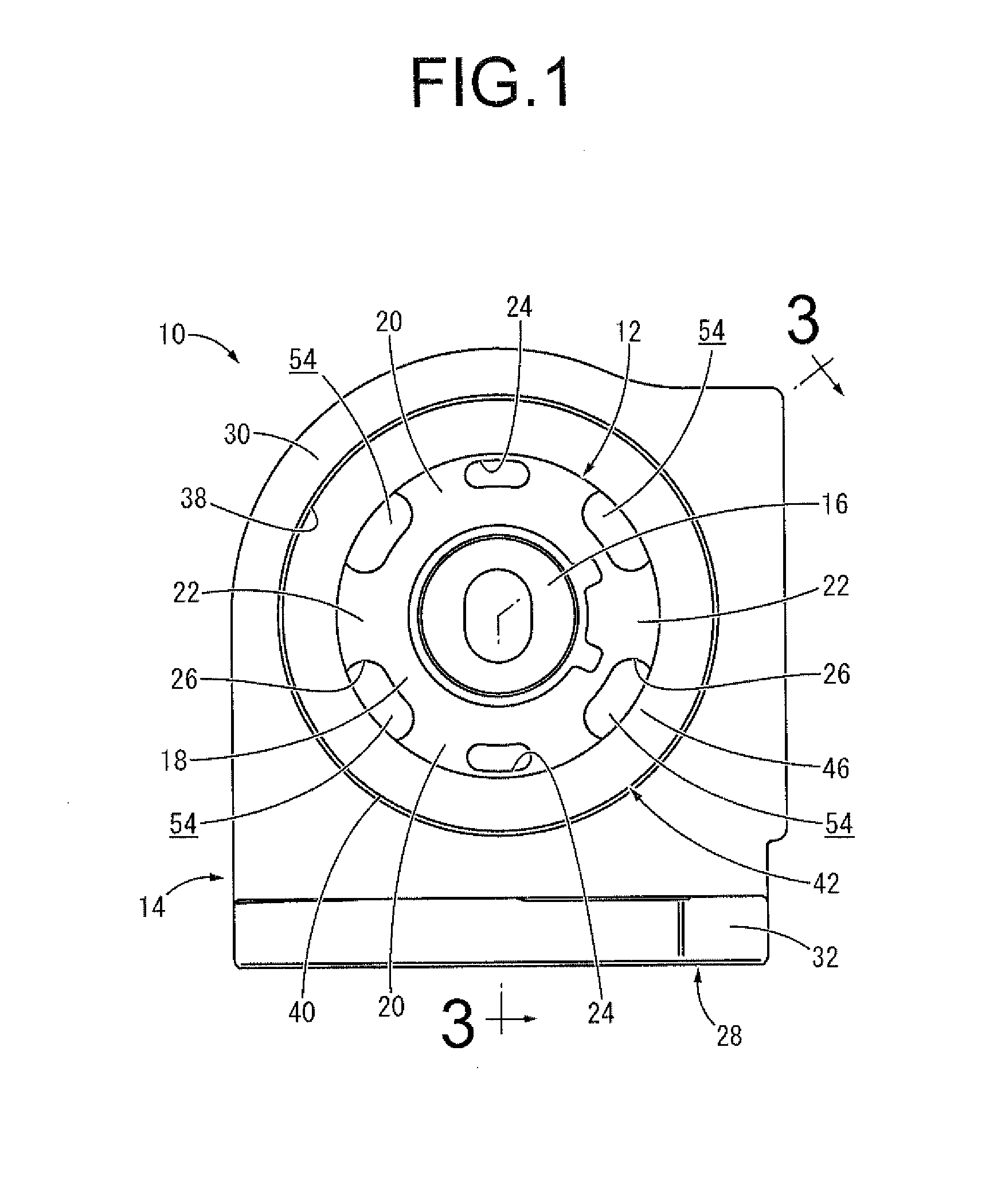

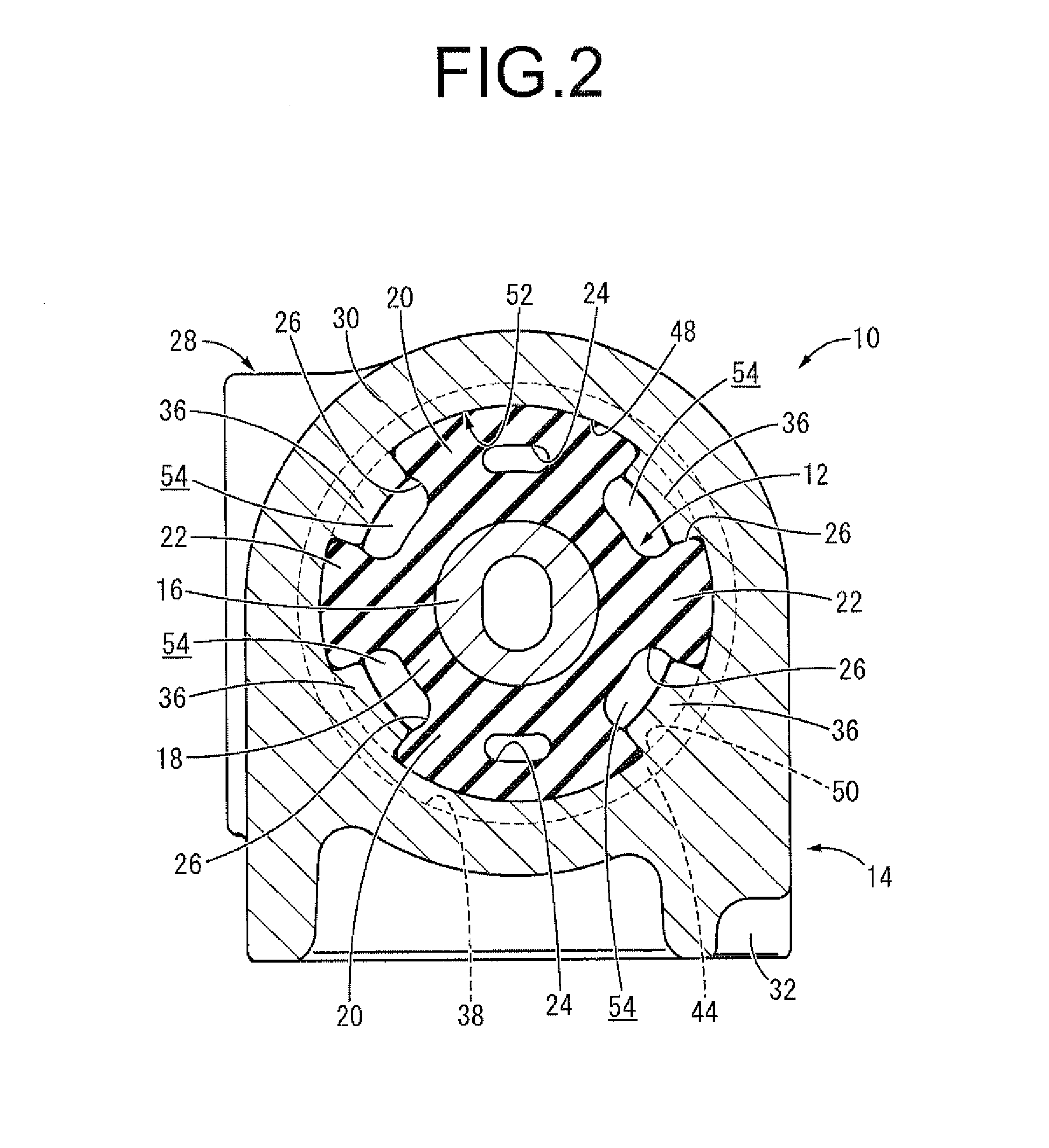

Vibration damping device

ActiveUS20140367546A1Good dispersionIncreased durabilitySpringsNon-rotating vibration suppressionElastomerEngineering

A vibration damping device including: an inner shaft member; a main rubber elastic body fixed to an outer circumference surface of the inner shaft member; and an outer bracket attached to an outer circumference surface of the main rubber elastic body. At least one locking projection formed to an inner circumference surface on a bracket main unit provided to the outer bracket is inserted and locked in a circumference direction in at least one locking groove formed on the outer circumference surface of the main rubber elastic body. The main rubber elastic body is held between axially opposed surfaces of an abutting protruding part formed on one axial end of the bracket main unit and a retaining protruding part formed on a press fit metal fitting press fit and fixed to another axial end of the bracket main unit.

Owner:TOYOTA JIDOSHA KK +1

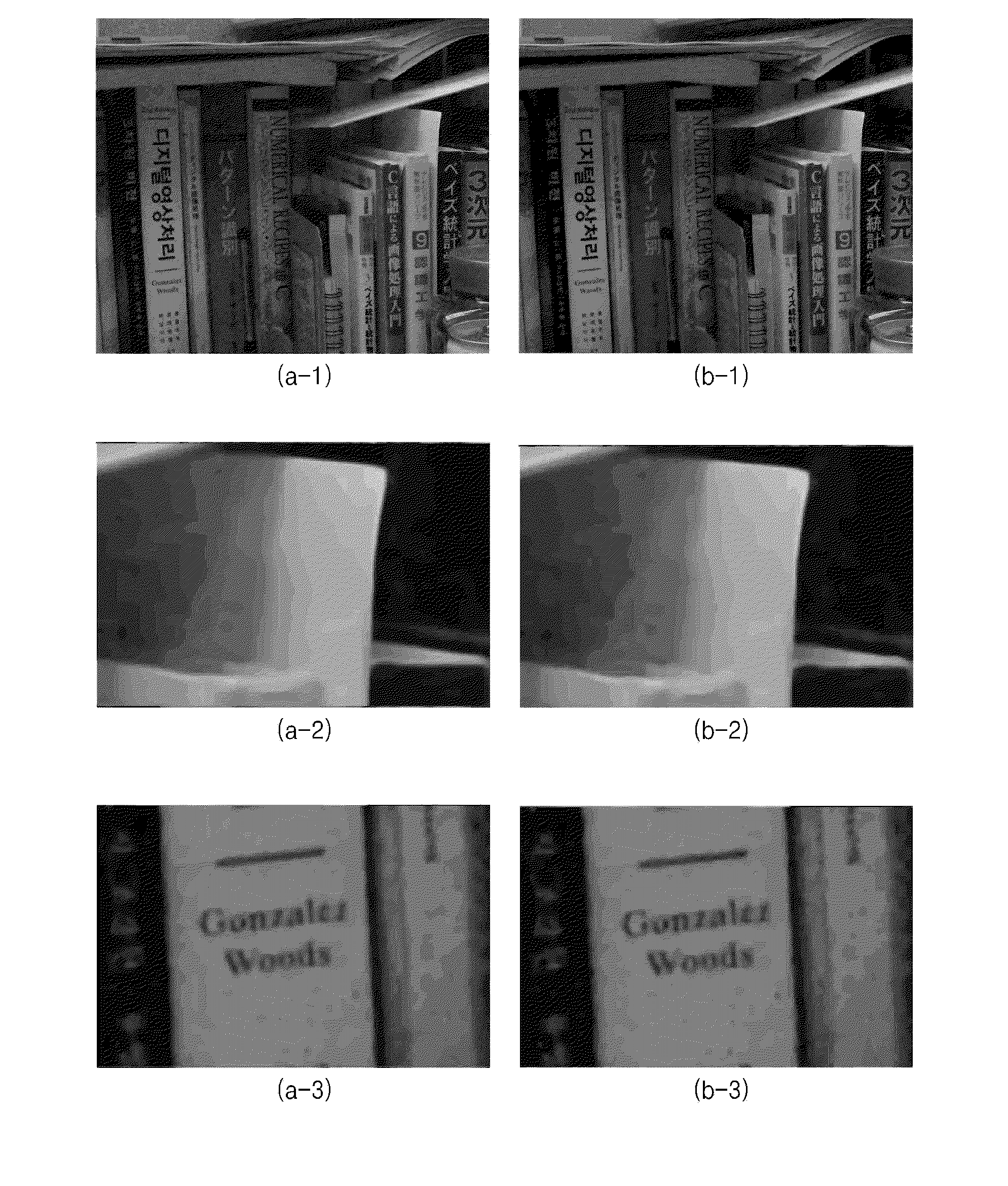

Image processing method and image processing apparatus

InactiveUS20130071025A1Reduce brightnessHigh sensitivityTelevision system detailsImage enhancementImaging processingLightness

An image processing method and an image processing apparatus for removing noise from an image are disclosed. A provided image processing method includes: dividing an input image into a luminance signal and a chrominance signal; removing noise from the luminance signal; restoring luminance signal present in the noise removed from the luminance signal; removing noise from the chrominance signal; and combining the luminance signal and the chrominance signal from which the noises are removed. Accordingly, an image of which an edge component is well preserved and a degree of color noise is low is generated not only in a general environment but also in a low light level and high sensitivity environment having a large amount of noise.

Owner:SAMSUNG ELECTRONICS CO LTD +1

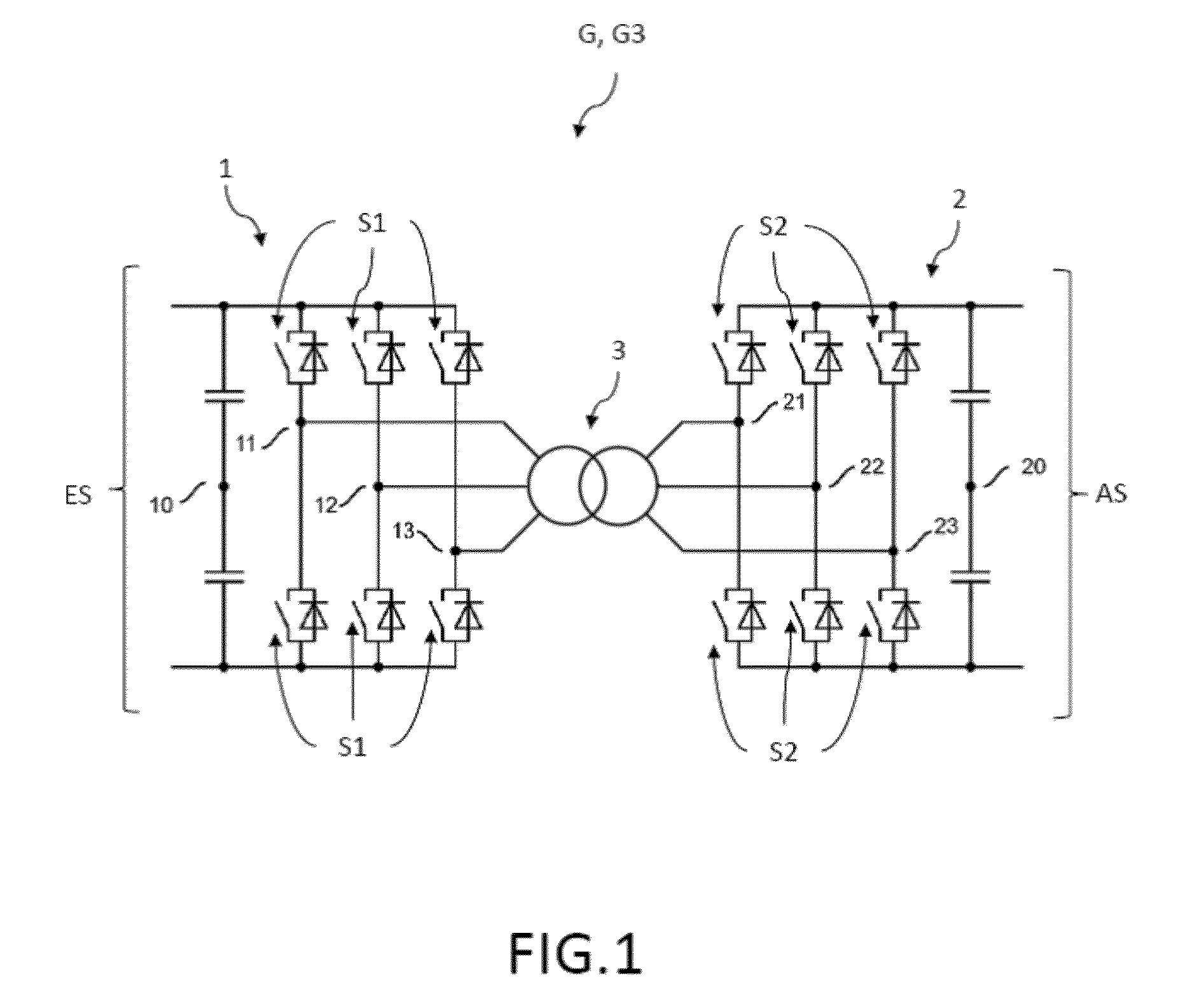

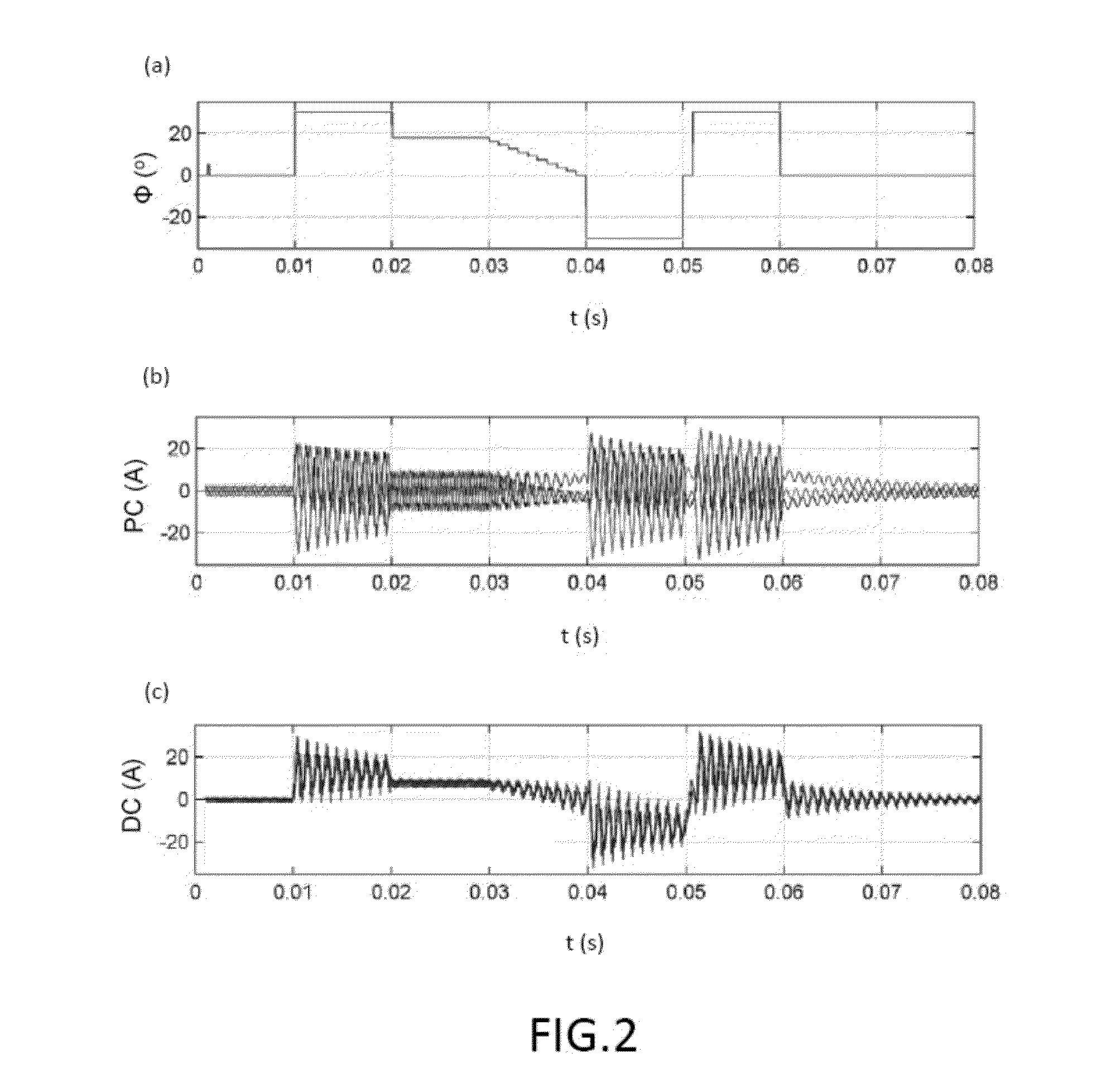

Current control for dc-dc converters

InactiveUS20150146455A1Easy to adjustMinimize oscillationDc-dc conversionElectric variable regulationPower flowDc dc converter

A DC-DC converter having a primary side comprising at least three actively switched primary voltage bridges with several active switches for converting a DC input voltage into primary alternating voltages for each of the primary voltage bridges, and having a secondary side comprising at least three actively switched secondary voltage bridges with several active switches for converting the secondary alternating voltages into a shared DC output voltage for each of the secondary voltage bridges. The primary and secondary alternating voltages are each shifted by a phase angle φ with the periods T, and each of the primary and secondary voltage bridges is coupled to an appertaining phase via one or more transformers.

Owner:FLEXIBLE ELEKTRISCHE NETZE FEN GMBH

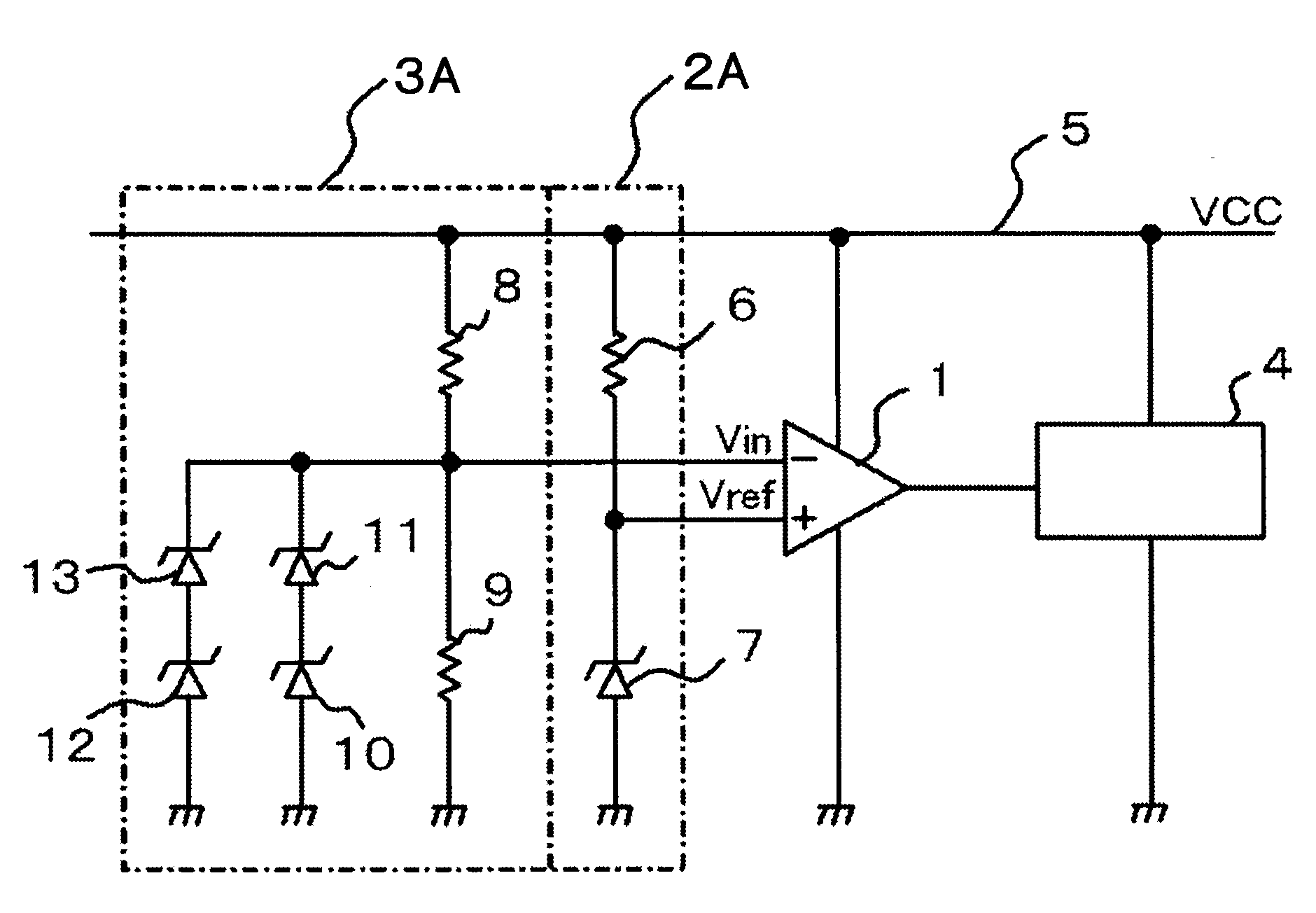

Undervoltage lockout circuit

InactiveUS20080247110A1Highly-reliable undervoltage lockout circuitNot set it lowArrangements responsive to undervoltageGate driverVoltage reference

An objective is to provide a highly-reliable undervoltage lockout circuit which can block and permit normal gate-driver output even when a supply voltage steeply increases. The undervoltage lockout circuit includes a reference-voltage circuit for outputting a reference voltage, a monitor-voltage circuit for outputting a monitor voltage, and a comparator for outputting, the reference voltage and the monitor voltage being inputted thereinto, a high / low signal, according to a comparison result of the reference voltage and the monitor voltage, in which the time constant of the monitor-voltage circuit for determining an increasing rate of the monitor voltage is set higher than that of the reference-voltage circuit for determining that of the reference voltage.

Owner:MITSUBISHI ELECTRIC CORP

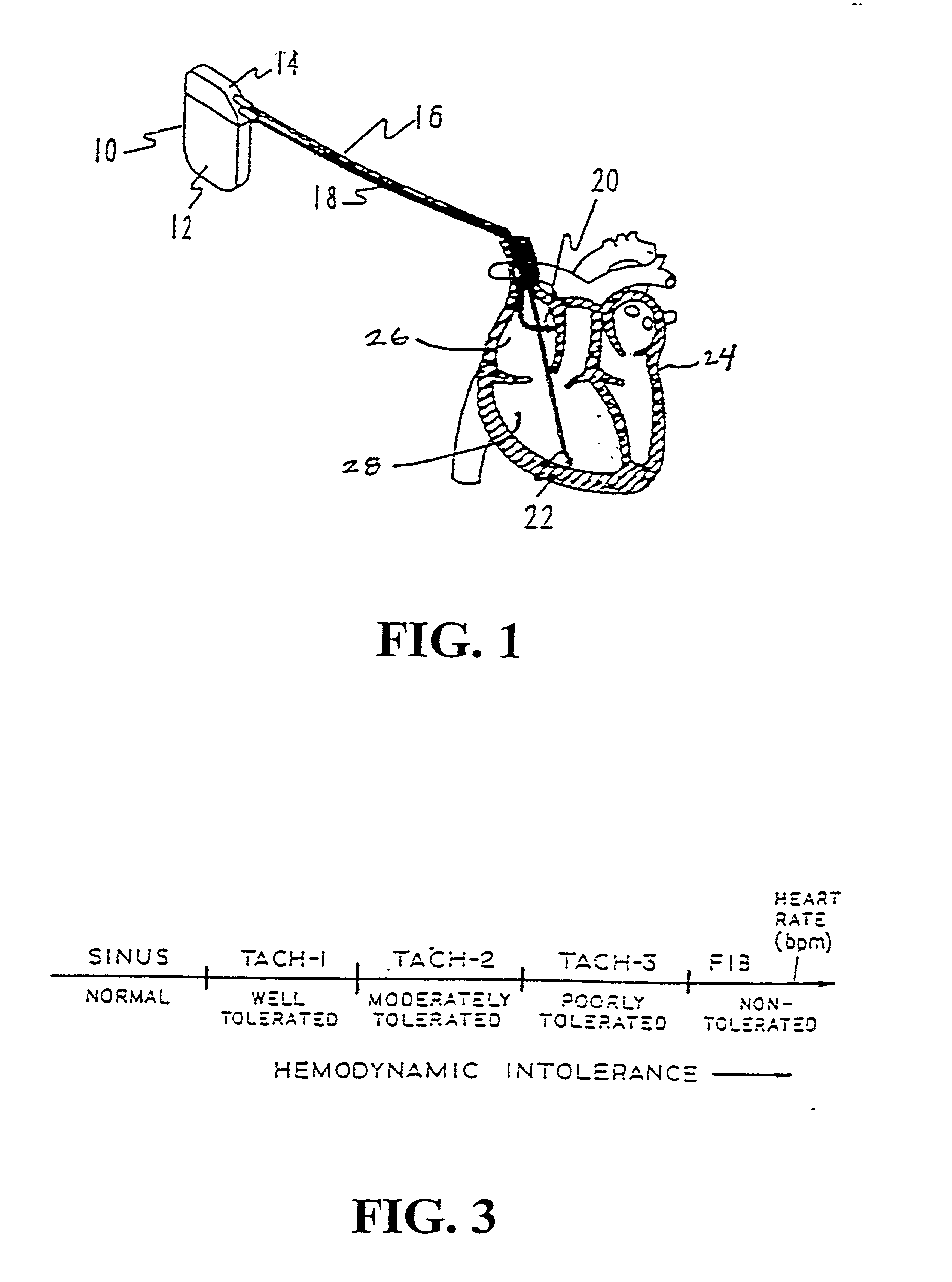

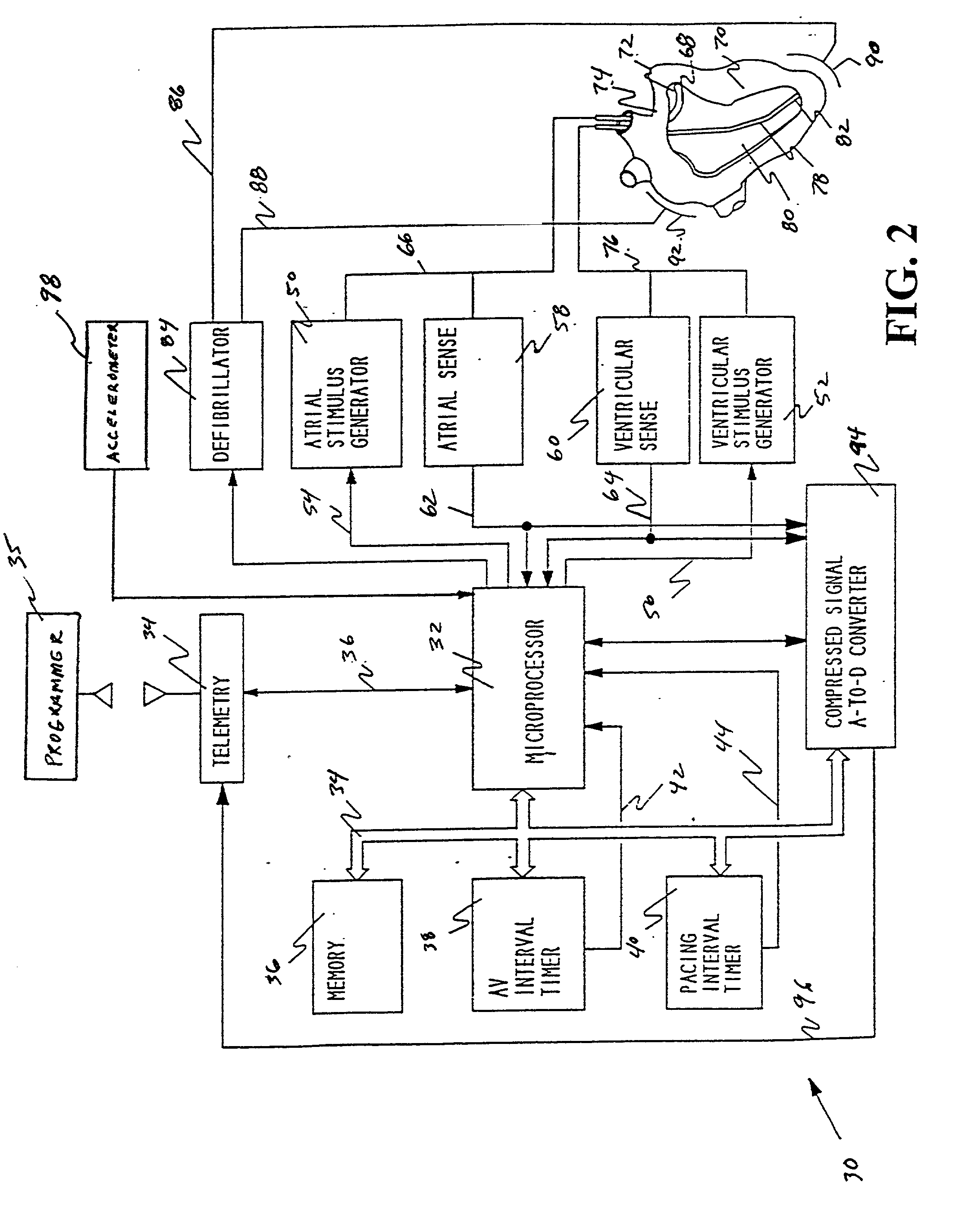

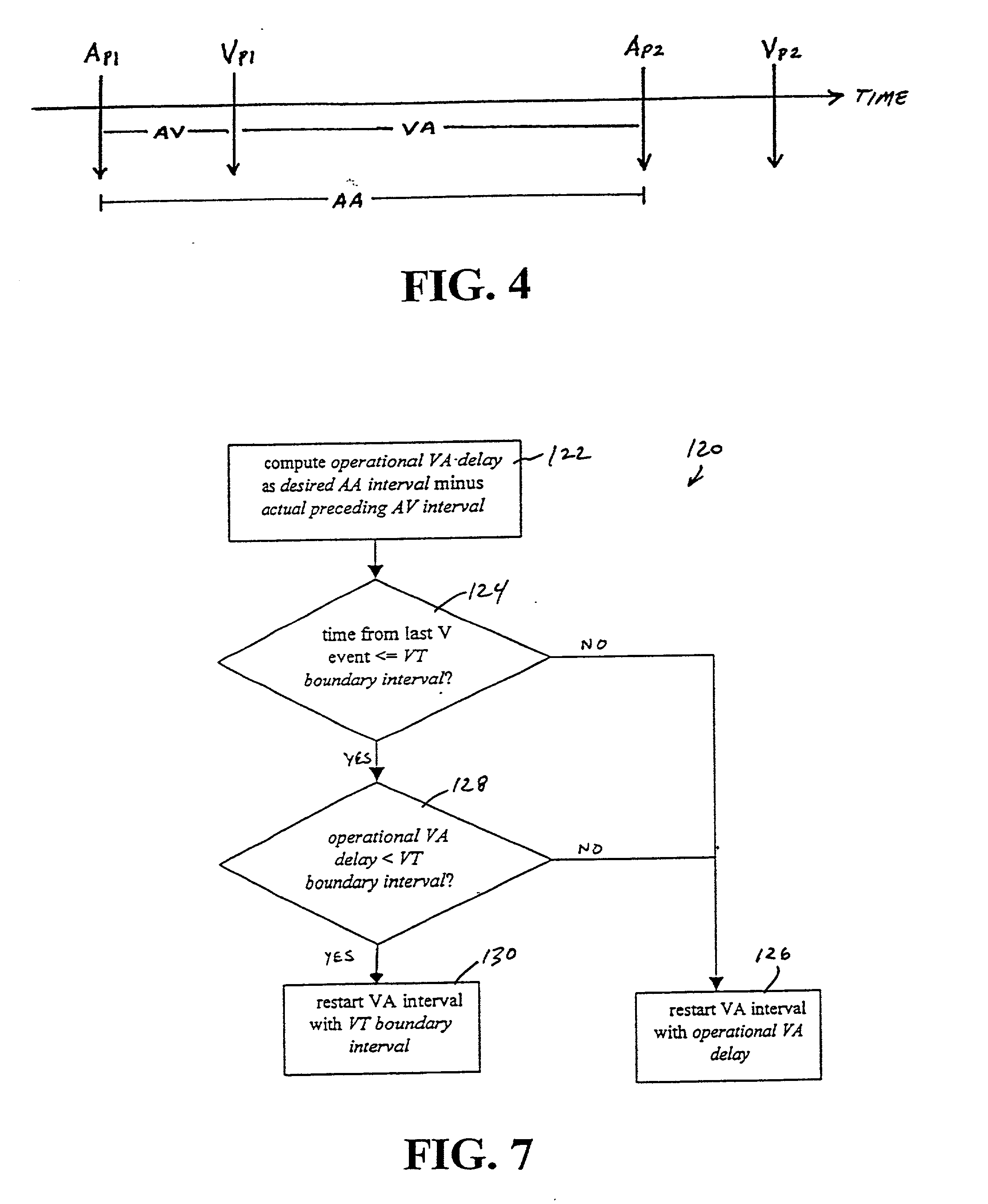

Methods and apparatus for tachycardia rate hysteresis for dual-chamber cardiac stimulators

InactiveUS20010014817A1Delay detectionNot set it lowHeart stimulatorsHysteresisVentricular Tachyarrhythmias

It has been determined that certain dual-chambered cardiac stimulators may operate in a region in which an atrial pacing event may obscure the detection of a ventricular tachyarrhythmia. Various exemplary techniques may be used to improve the ability of dual-chamber cardiac stimulators to detect such ventricular events. In accordance with one technique, it is determined whether a ventricular event should be classified as a ventricular tachyarrhythmia. If not, the VA interval is restarted as usual. However, if the ventricular event may be classified as a ventricular tachyarrhythmia, it is determined whether the ventricular event falls within the region in which an atrial pacing event may obscure its detection. If not, then the VA interval is restarted as usual. However, if the ventricular event falls within this region, the VA interval is restarted with the VT rate detection boundary. This has the effect of lengthening the VA interval and the AA interval in this region so that atrial pacing events will not obscure the sensing and treatment of ventricular tachyarrhythmias in the region.

Owner:INTERMEDICS

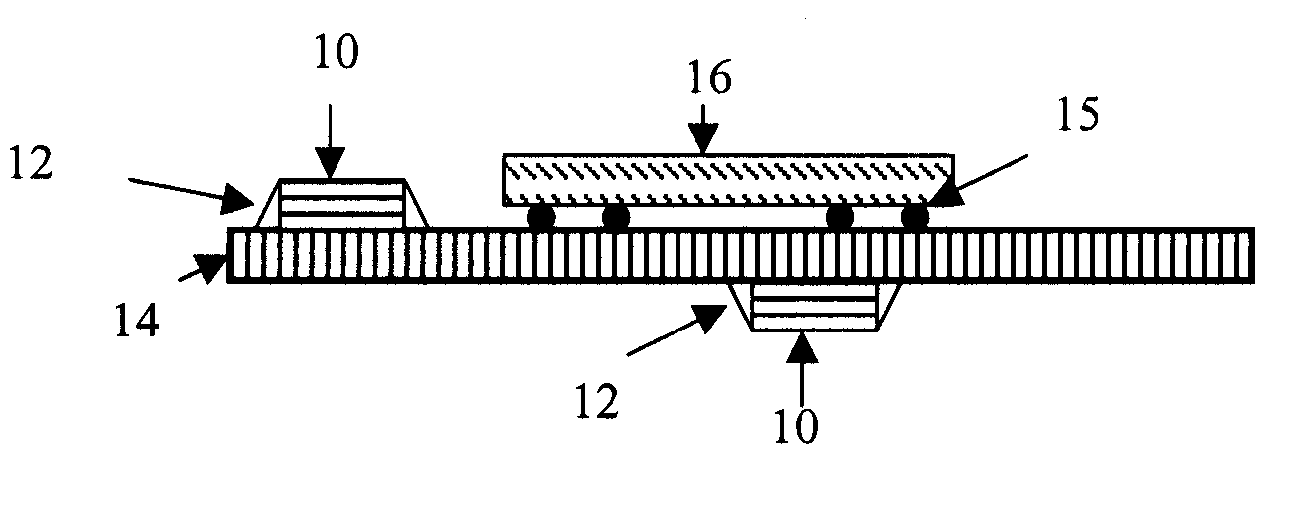

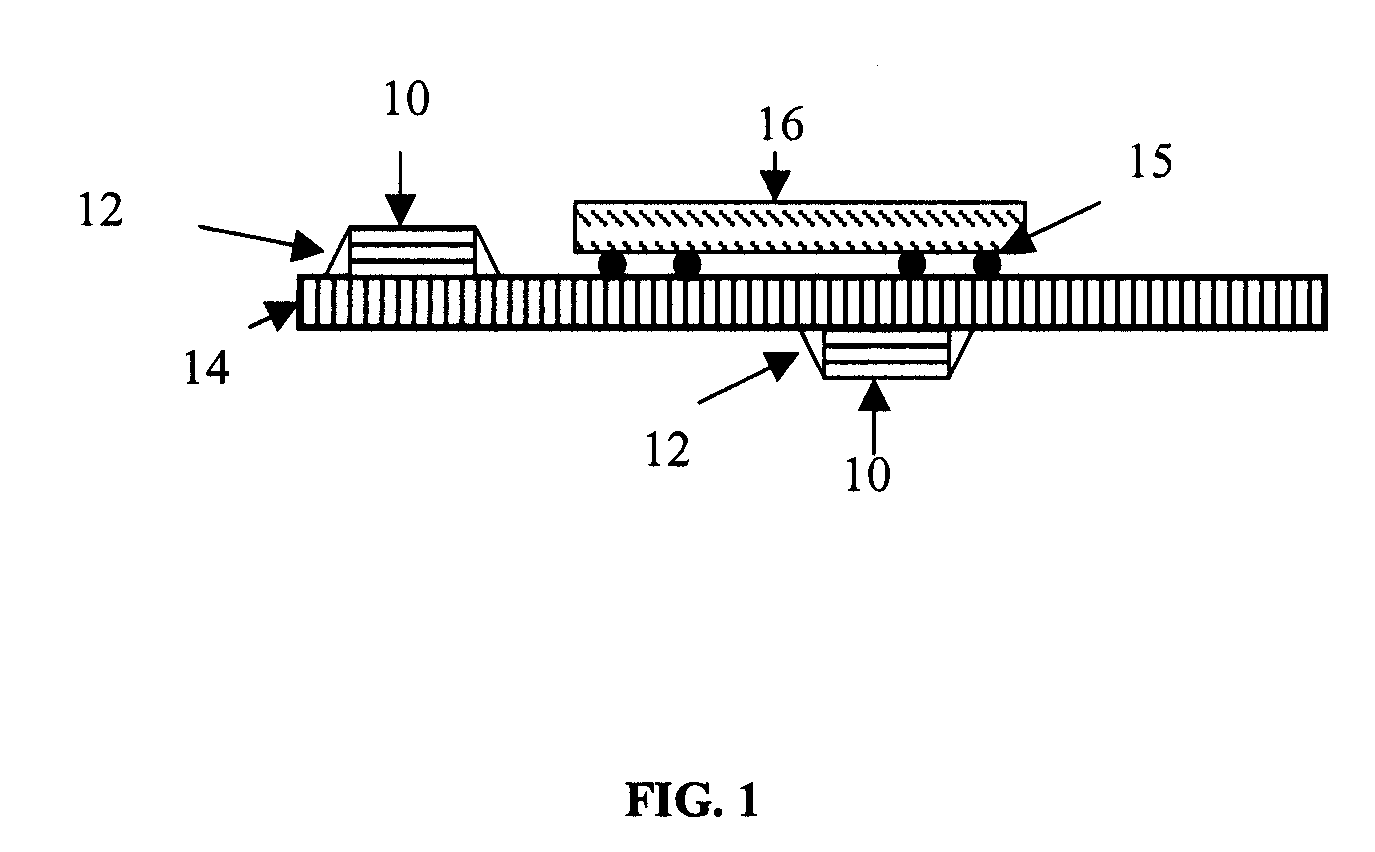

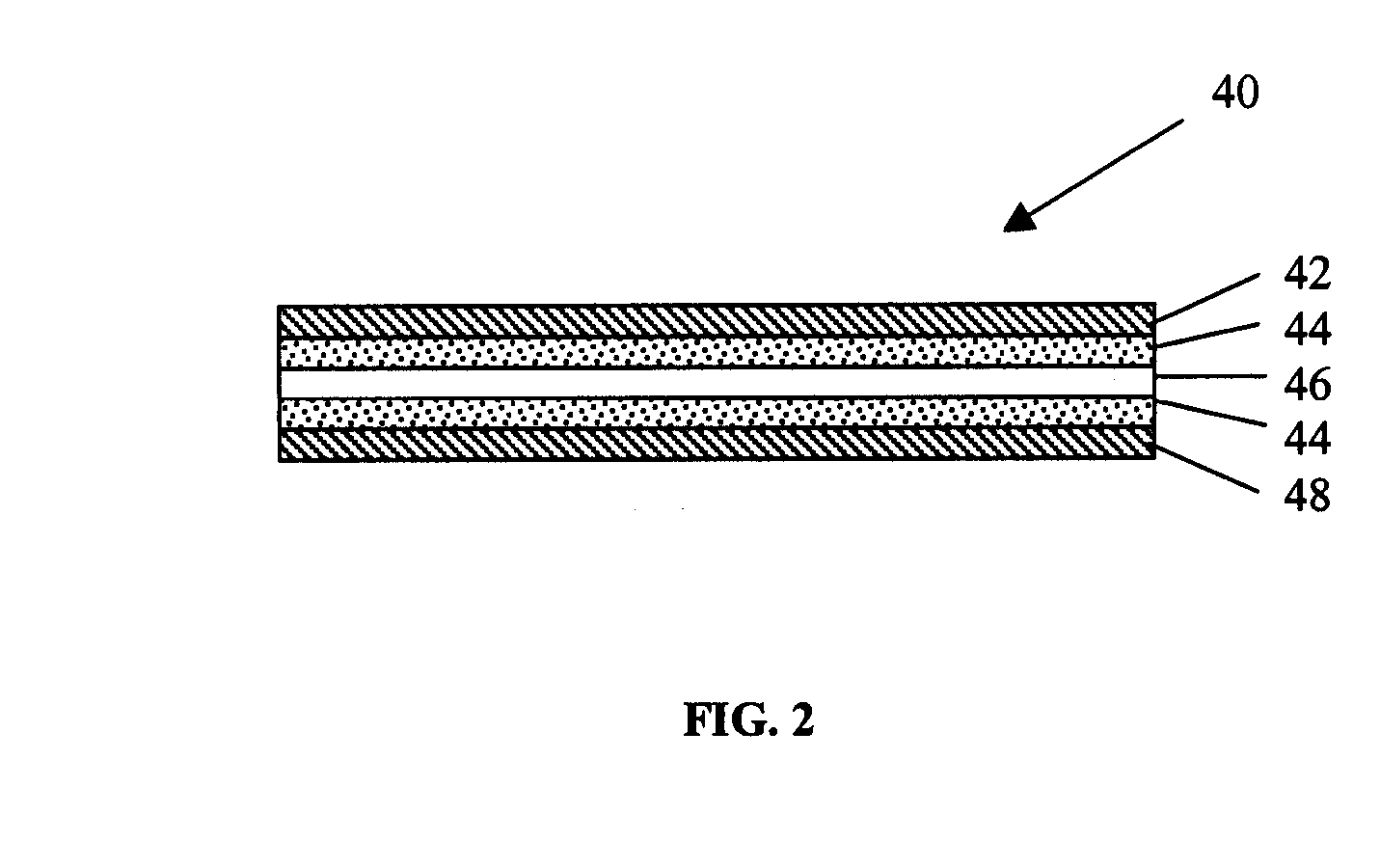

Integrated capacitor for wafer level packaging applications

InactiveUS20060258048A1Minimize the numberReduce device form factorSemiconductor/solid-state device detailsSolid-state devicesCapacitanceEngineering

A capacitor design, which incorporates a material set that is adaptable to standard substrate or electronic packaging fabrication methods, uses copper as a base and electrode, mesoporous nanocomposite materials or other adhesion promoting materials combined with a high dielectric material specific to the application's capacitance requirements. This capacitor is then used as a basis for forming a capacitor in substrate or package or wafer level package or die or wafer.

Owner:EKUBIK CONSULTING

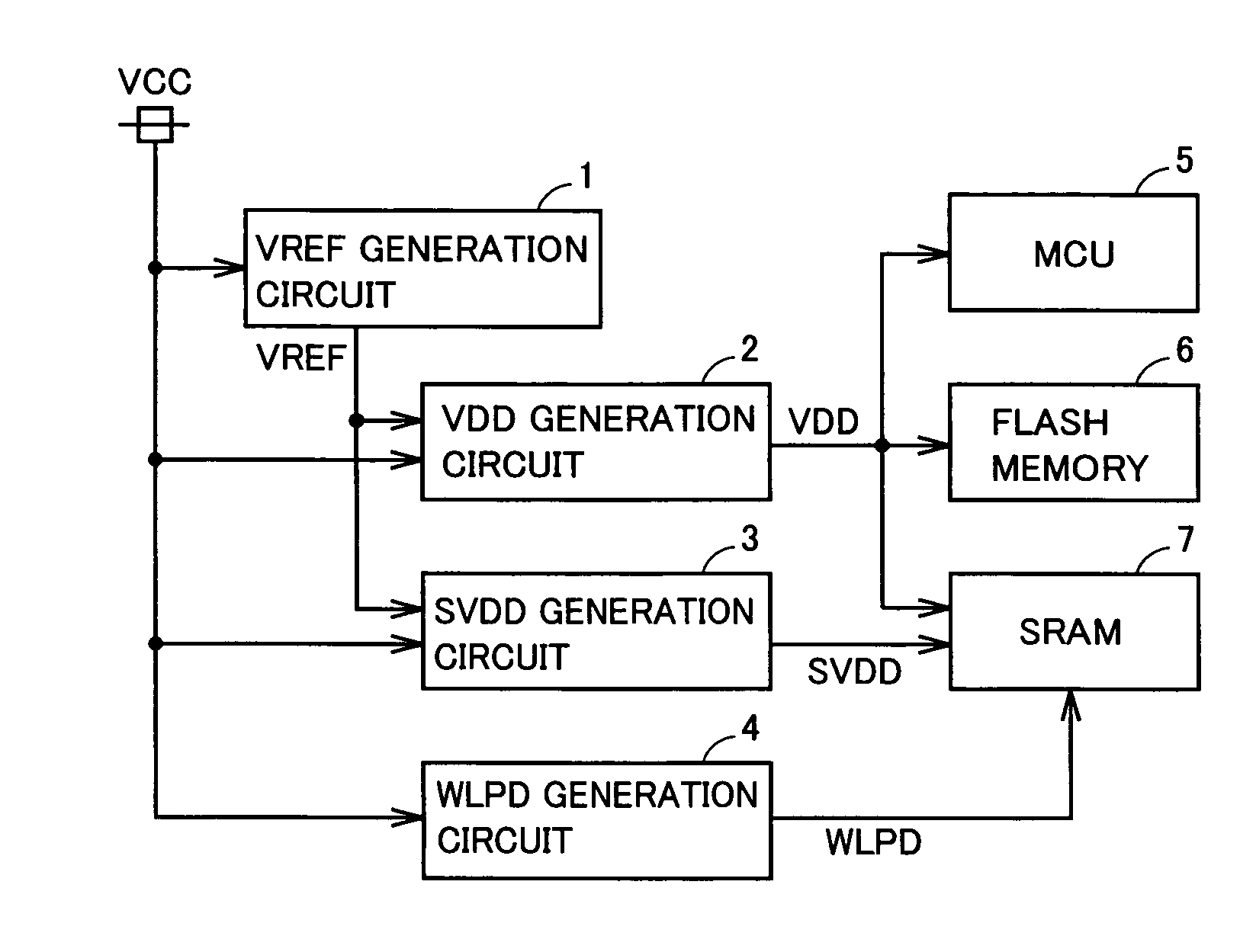

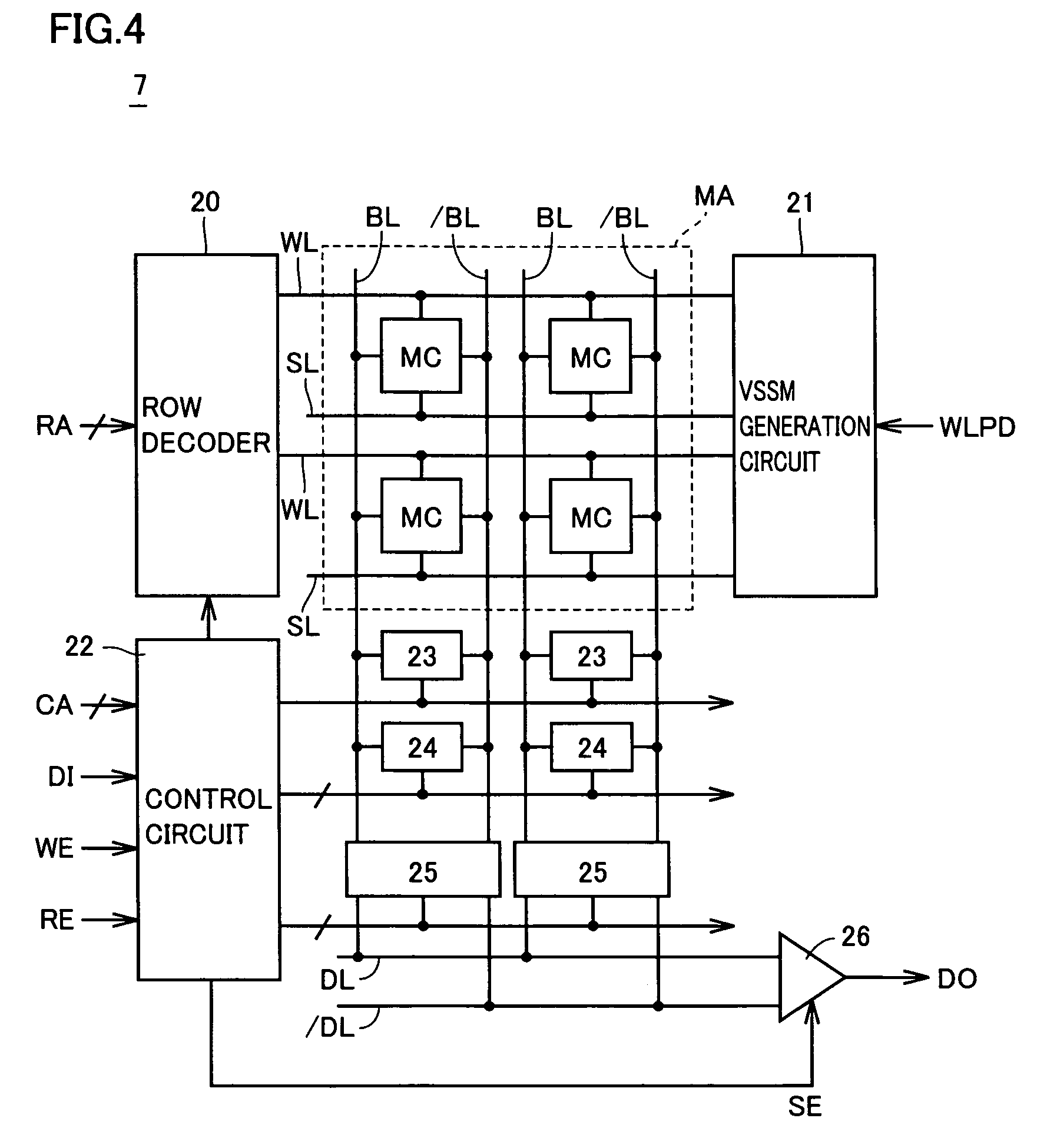

Semiconductor memory device with low standby current

ActiveUS7826298B2Not set it lowSmall amount requiredRead-only memoriesDigital storageCurrent consumptionDrain current

In an SRAM according to the present invention, an internal power supply voltage for a memory cell is applied to a back gate of each of P-channel MOS transistors included in an equalizer, a write driver, and a column select gate. Therefore, even if an internal power supply voltage for a peripheral circuit is shut off to reduce current consumption during standby, a threshold voltage of each of the P-channel MOS transistors is maintained at a high level, and hence a leakage current is small.

Owner:RENESAS ELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com