Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

38results about How to "Minimize latency" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

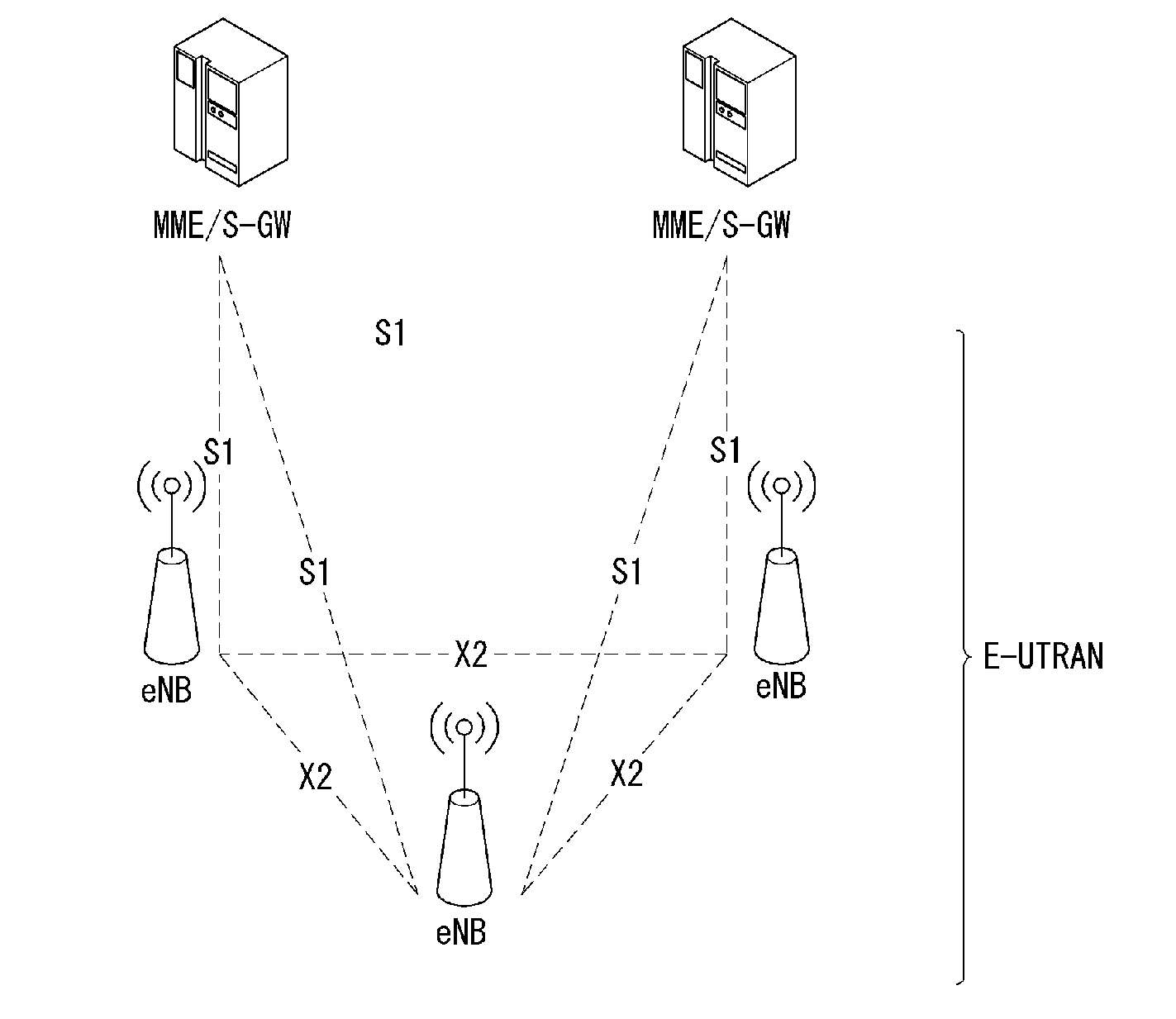

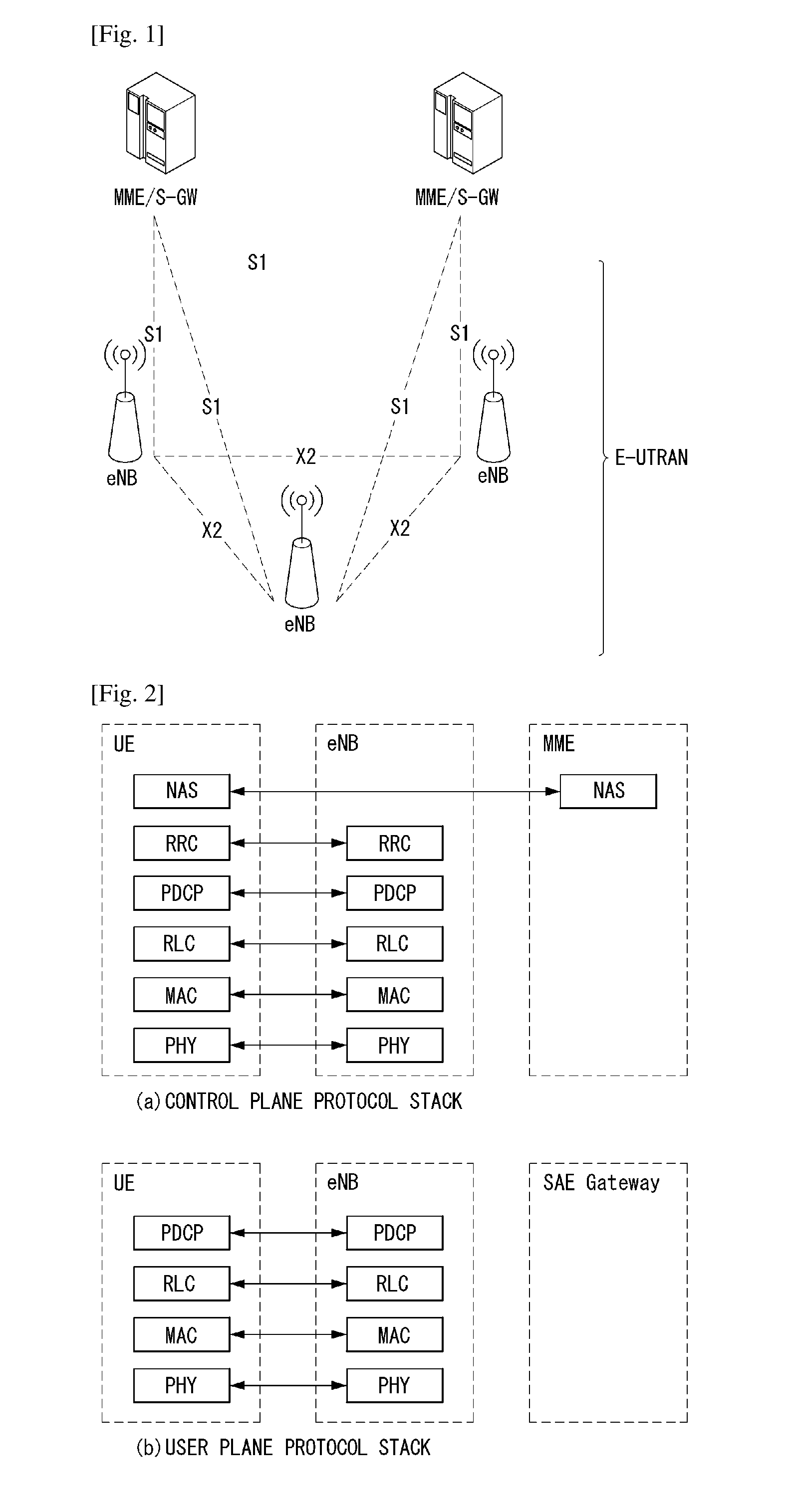

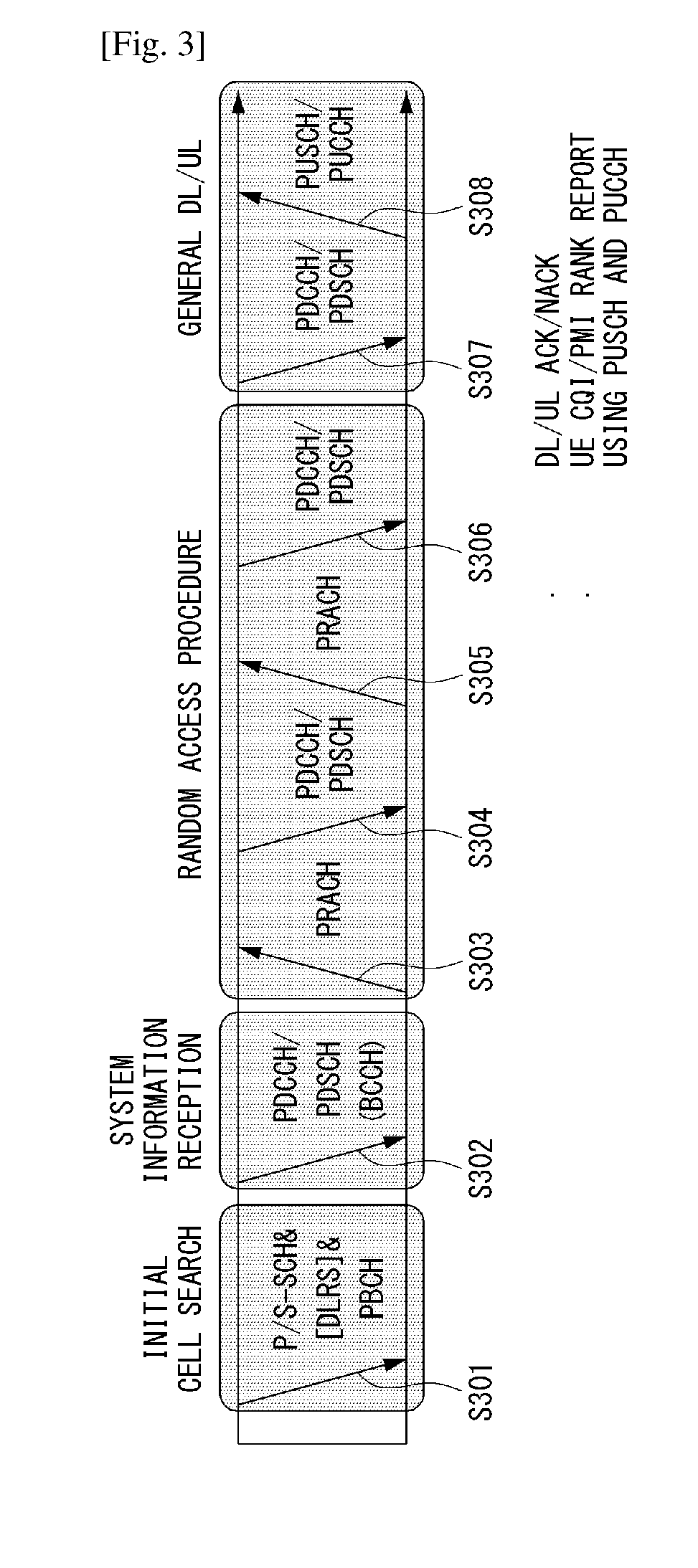

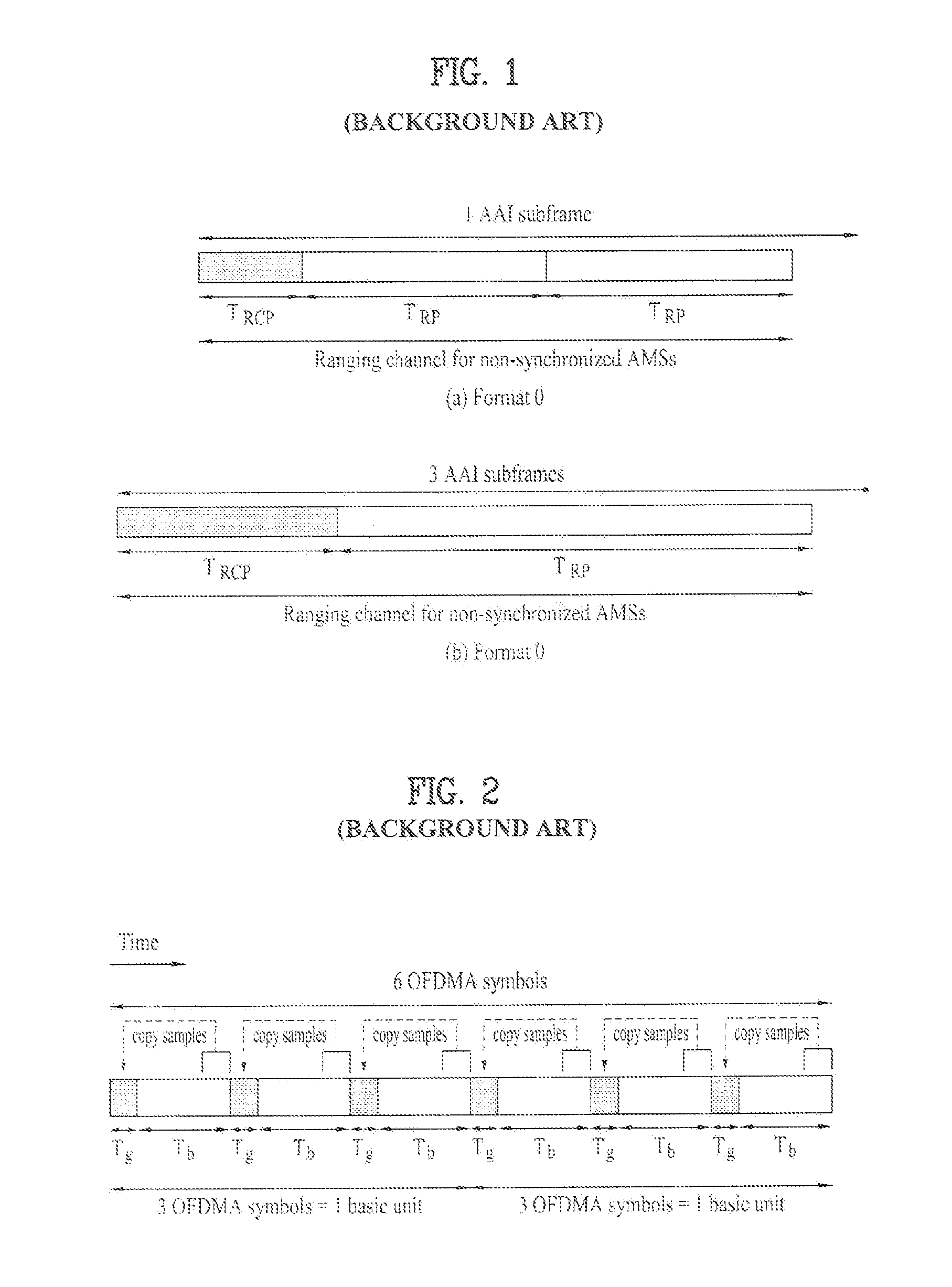

Method for allocating temporary identifier to terminal in random access procedure in wireless communication system and apparatus tehrefor

ActiveUS20170019930A1Minimize latencyOverall latency of an initial access procedure can be minimizedConnection managementNetwork data managementPreambleRadio Resource Control

Provided are a method for allocating a temporary radio network temporary identifier to a terminal within a random access procedure in a wireless communication system, and an apparatus supporting the same. The method for allocating a temporary radio network temporary identifier (T-RNTI) to a user equipment (UE) within a random access procedure in a wireless communication system, includes transmitting, by the UE, a random access preamble to a base station (BS), transmitting, by the UE, a radio resource control (RRC) request message to the BS through a contention-based physical uplink shared channel (PUSCH) resource block in which uplink data can be transmitted without uplink resource allocation scheduling, and receiving, by the UE, an RRC connection setup message identified by a T-RNTI allocated to the UE in response to the RRC request message, wherein the T-RNTI is allocated on the basis of the contention-based PUSCH resource block in which the RRC request message has been transmitted.

Owner:LG ELECTRONICS INC

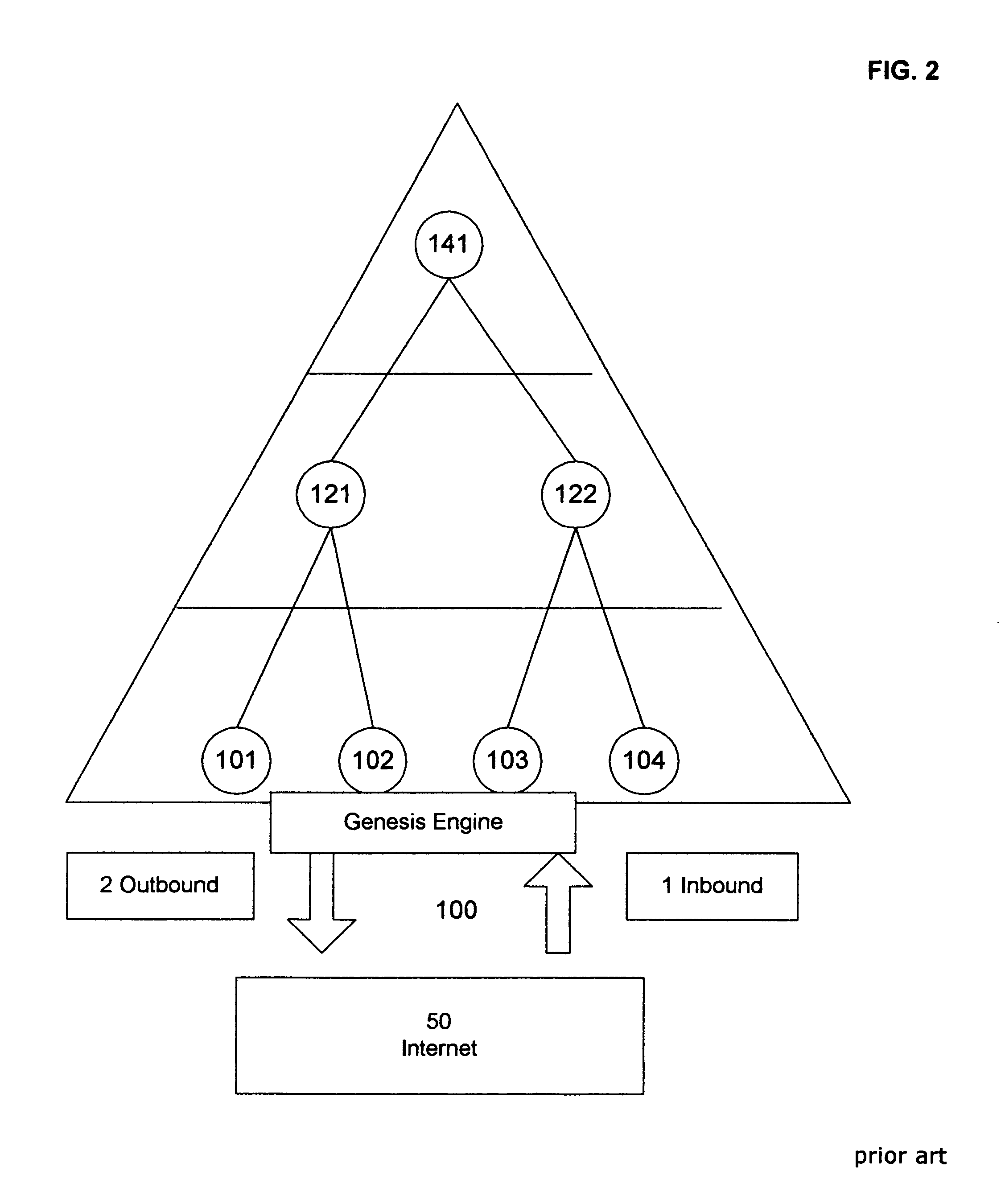

Method for presenting optimal internet keyword based search result sets using an environmental bitmap and environmental bitmap pyramid structure

InactiveUS7809659B1Minimize latencyLower informational entropyDigital computer detailsDigital dataClustering searchResult set

A method for simulating the entire superset of potential valid keyword regular expression requests constructed during an Internet browser search and converting the result sets into Environmental Bitmap data to enable efficient and accurate searching without requiring Browser Engine supercomputer cluster searching capabilities.

Owner:PAIZ RICHARD S

Data partitioning for multi-link transmission

ActiveUS7203206B2Enhanced interleavingMinimize latencyMultiplex system selection arrangementsChannel dividing arrangementsData partitioningMulti link

A method for transmitting a stream of data over a channel made up of a plurality of subchannels having respective subchannel rates. The method includes partitioning the data among the subchannels, such that successive words of the data are mapped to the subchannels in alternation responsive to the respective subchannel rates. The words of the data are transmitted over the subchannels to which they are mapped, and are then received and processed to recover the stream of data.

Owner:STMICROELECTRONICS INT NV

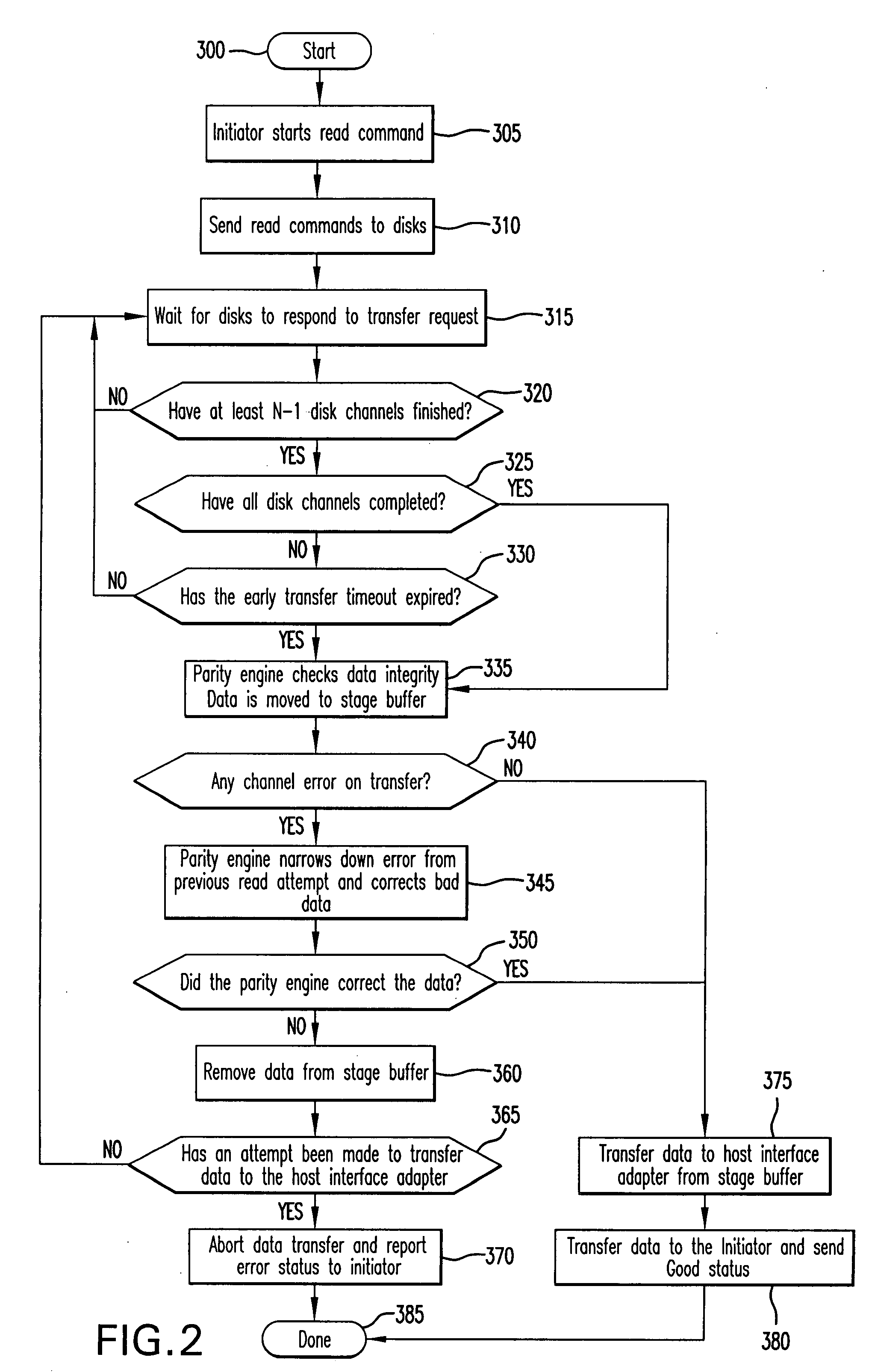

Method for reducing latency in a raid memory system while maintaining data integrity

ActiveUS20090106491A1Reduce latencyMinimize latencyError prevention/detection by using return channelTransmission systemsReduction methodsDisk storage

A latency reduction method for read operations of an array of N disk storage devices (210) having n disk storage devices (210A-210H) for data storage and p of disk storage devices (210I, 210J) for storing parity data is provided. Utilizing the parity generation engine's (230) fault tolerance of for a loss of valid data from at least two of the N disk storage devices (210A-210J), the integrity of the data is determined when N−1 of the disk storage devices (210A-210J) have completed executing a read command. If the data is determined to be valid, the missing data of the Nth disk storage device is reconstructed and the data transmitted to the requesting processor (10). By that arrangement the time necessary for the Nth disk storage device to complete execution of the read command is saved, thereby improving the performance of memory system (200).

Owner:DATADIRECT NETWORKS

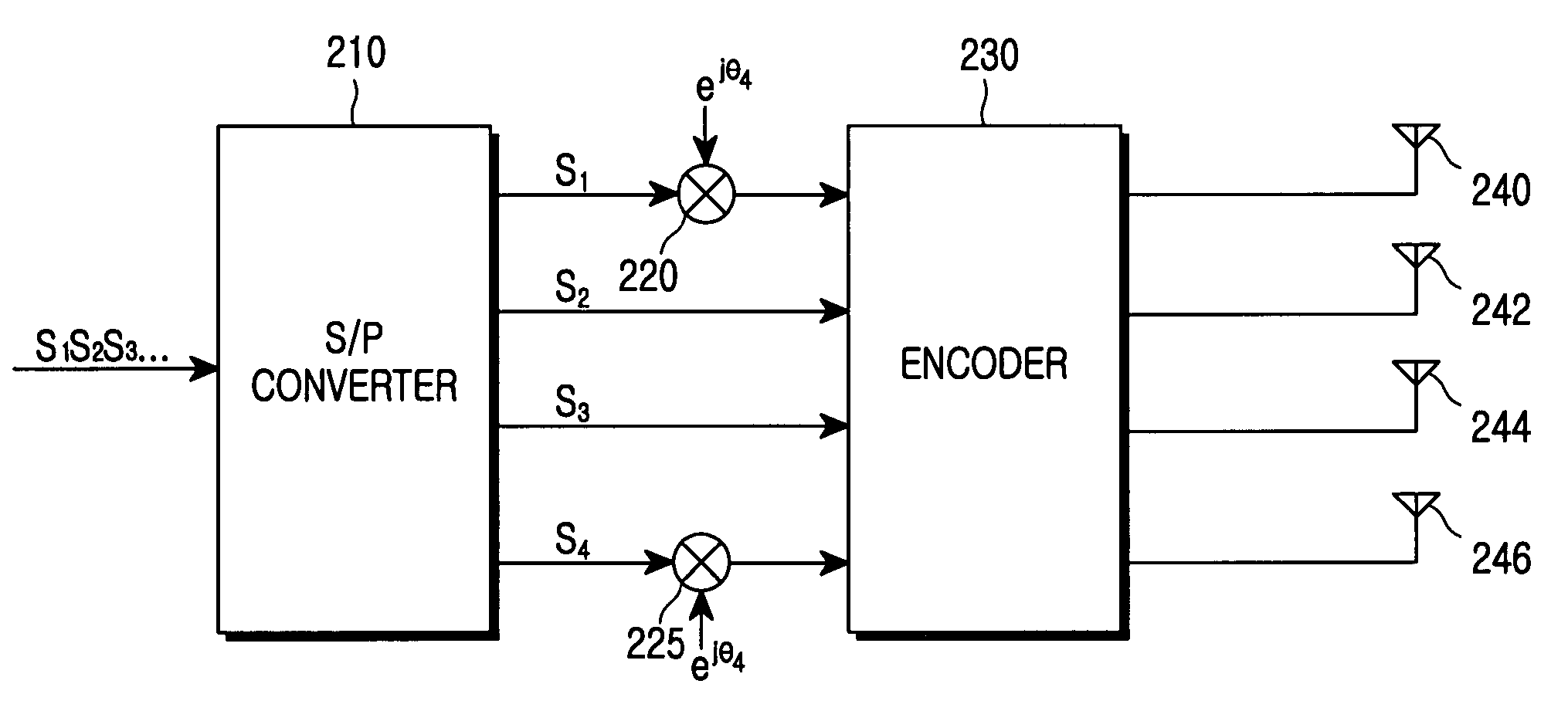

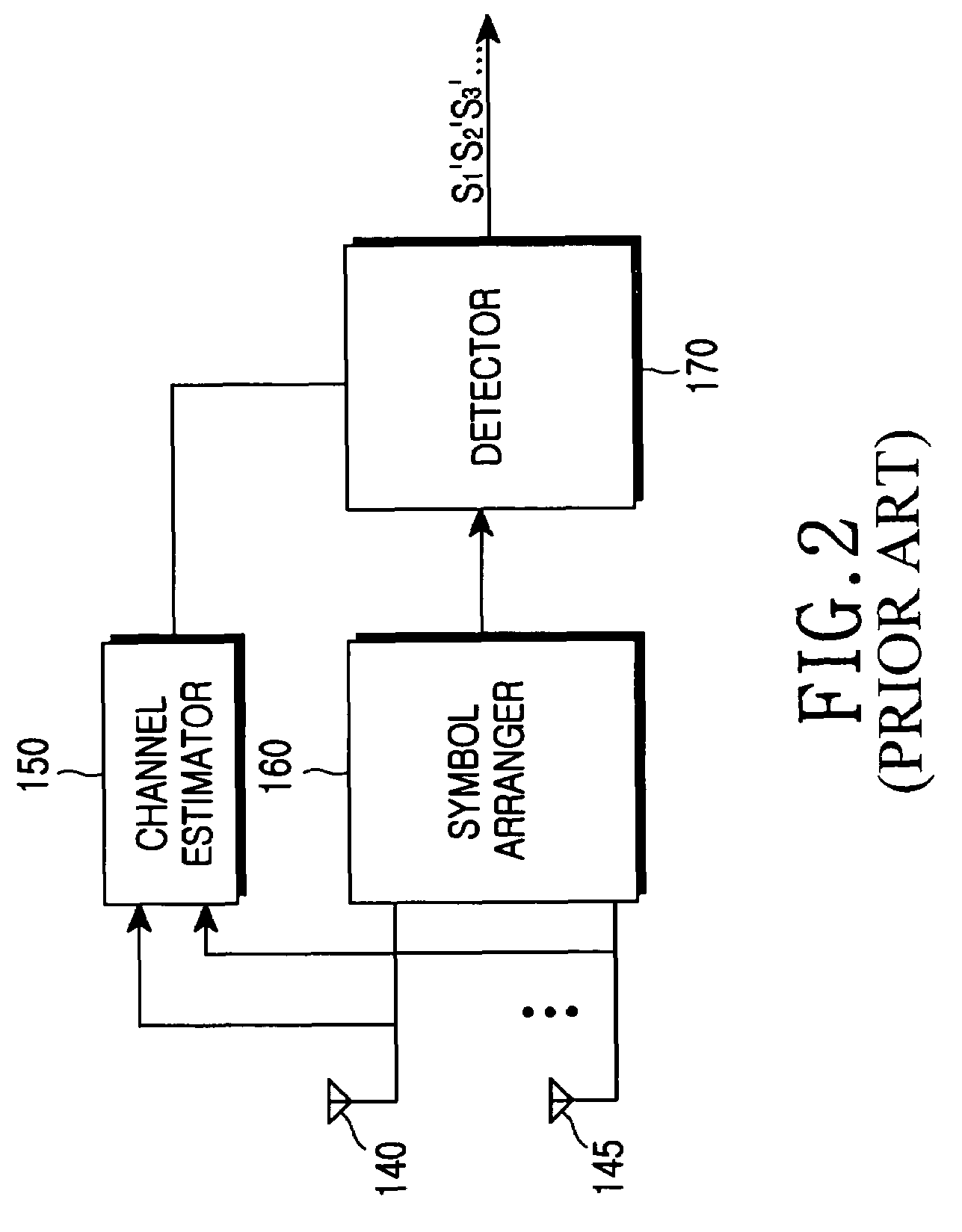

Transmitter and receiver provided in wireless communication system using four transmitting antennas

ActiveUS7298797B2Low transfer rateLarge transmission rateSpatial transmit diversityOther decoding techniquesTransmission delayDiversity scheme

An apparatus using transmitting antenna diversity to combat degradation due to fading in a wireless communication system. At least two symbols of four symbols to be transmitted through four transmitting antennas are rotated by predetermined phase values. An encoder configures four combinations for four input symbols so that a sequence of four symbols can be transmitted once by each transmitting antenna during each time interval. The combinations are transferred to the four transmitting antennas during four time intervals. Before the four input symbols are transmitted to the transmitting antennas, at least two symbols selected from the four input symbols are rotated by predetermined phase values. Therefore, the maximum diversity order can be obtained, a transmission delay time can be reduced, and the effect of fast fading can be reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

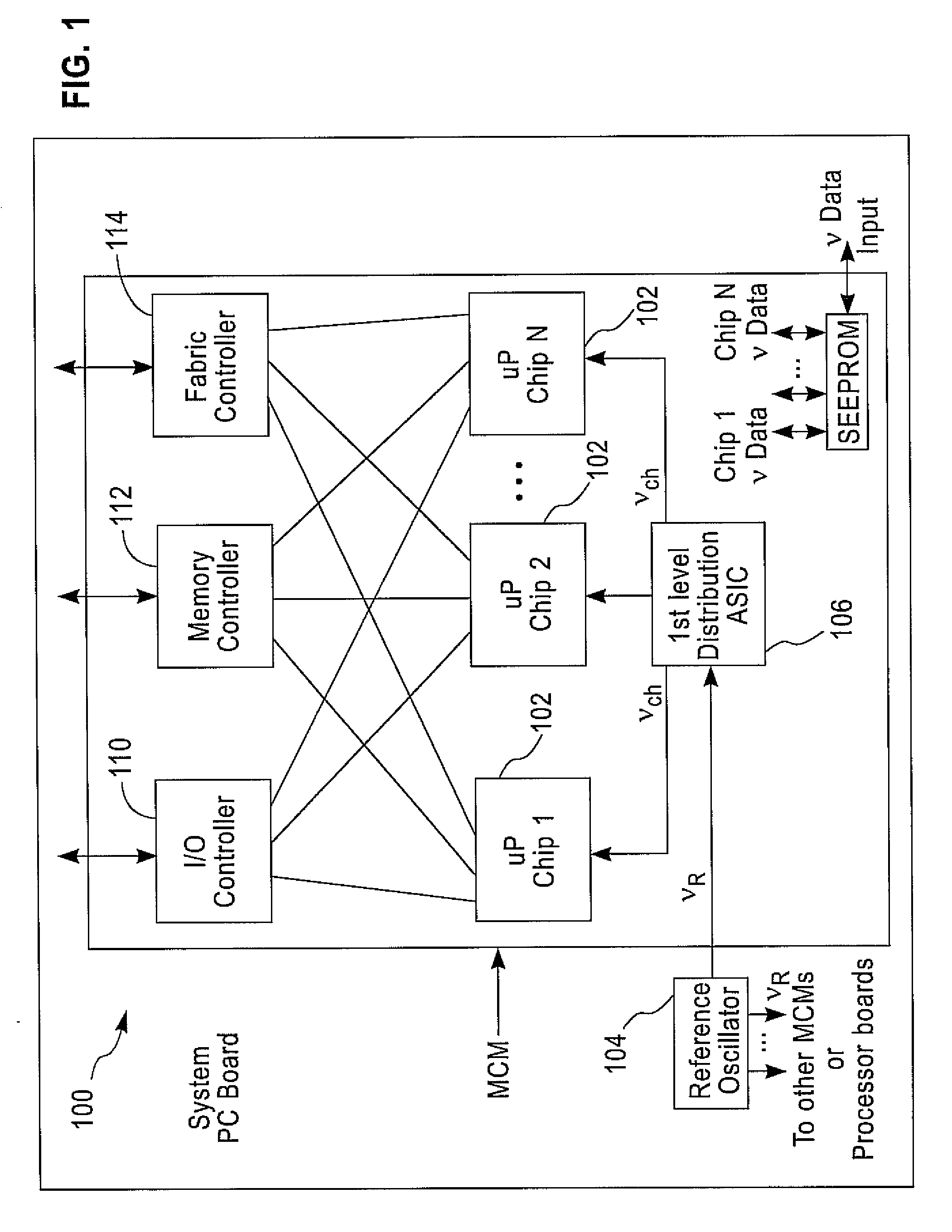

Method and system for analog frequency clocking in processor cores

ActiveUS20080256381A1Minimize latencyIncreased latencyPulse automatic controlGenerating/distributing signalsClock signalControl data

A method of and system for frequency clocking in a processor core are disclosed. In this system, at least one processor core is provided, and that at least one processor core has a clocking subsystem for generating an analog output clock signal at a variable frequency. Digital frequency control data and an analog signal are both transmitted to that at least one processor core; and that processor core uses the received analog signal and digital frequency control data to set the frequency of the output clock signal of the clocking subsystem. In a preferred implementation, multiple cores are asynchronously clocked and the core frequencies are independently set.

Owner:IBM CORP

Maintaining portlet data currency while minimizing latency

ActiveUS20080040450A1Minimize latencyMinimize unnecessary trafficDigital data processing detailsMultiple digital computer combinationsInformation typeTransient storage

Providing data to portlets can include a step of registering a plurality of portlets to determine a type of data required by the portlets. The registering can establish a portlet context for handling future data requests for the portlets. A type of information associated with one of the portlets can be determined. A data acquisition process can be initialized to obtain the determined type of information from a data source. A data request can be received for data of the determined type from the associated portlet. Data can be acquired from the data source using the initialized process. The data request can be responded to using the acquired data. In one embodiment, the acquisition of data from the source and the updating of the portlets can occur asynchronously, where a cache is used to temporarily store data acquired from the data source that is used to update the portlets.

Owner:MAPLEBEAR INC

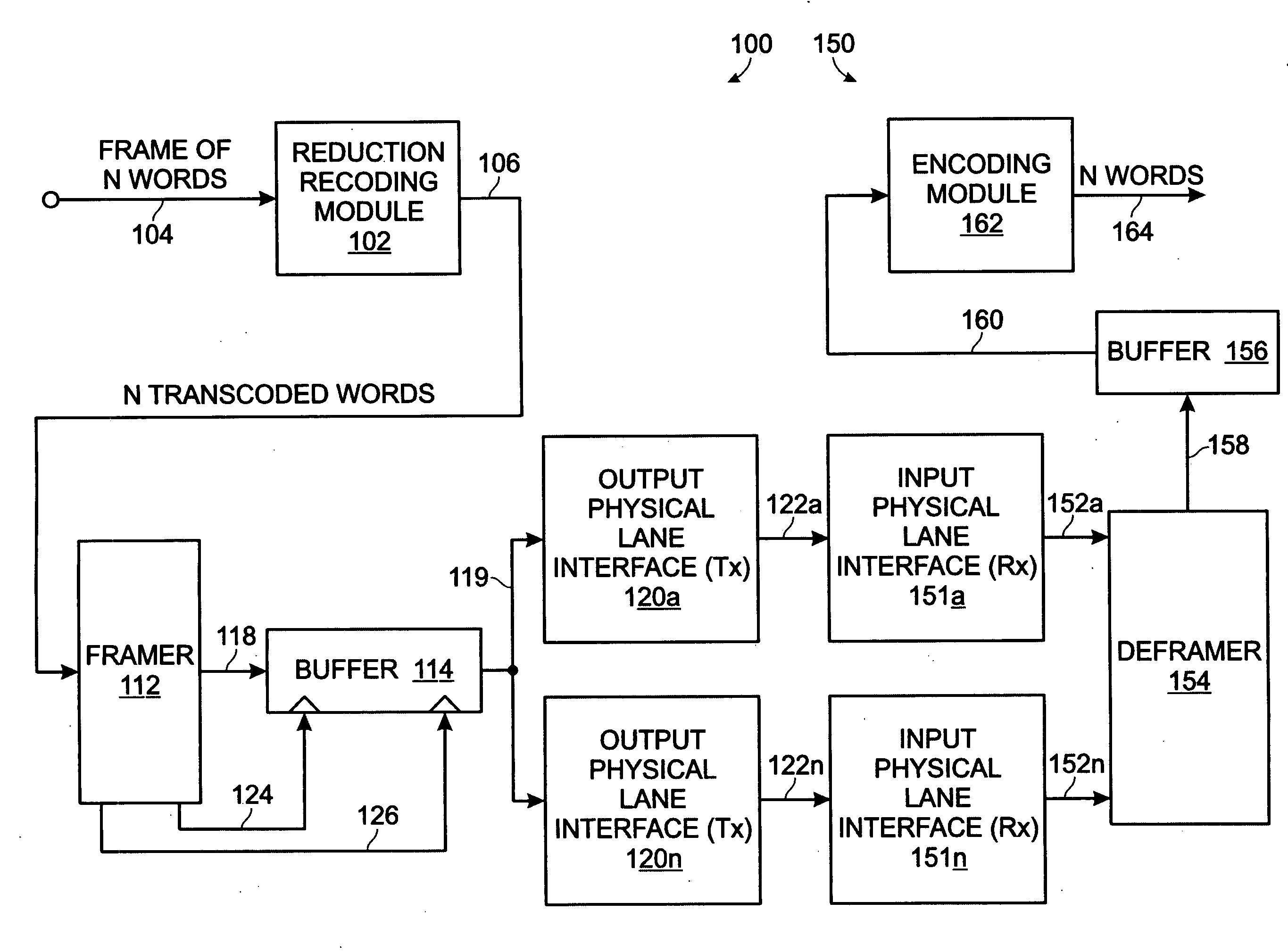

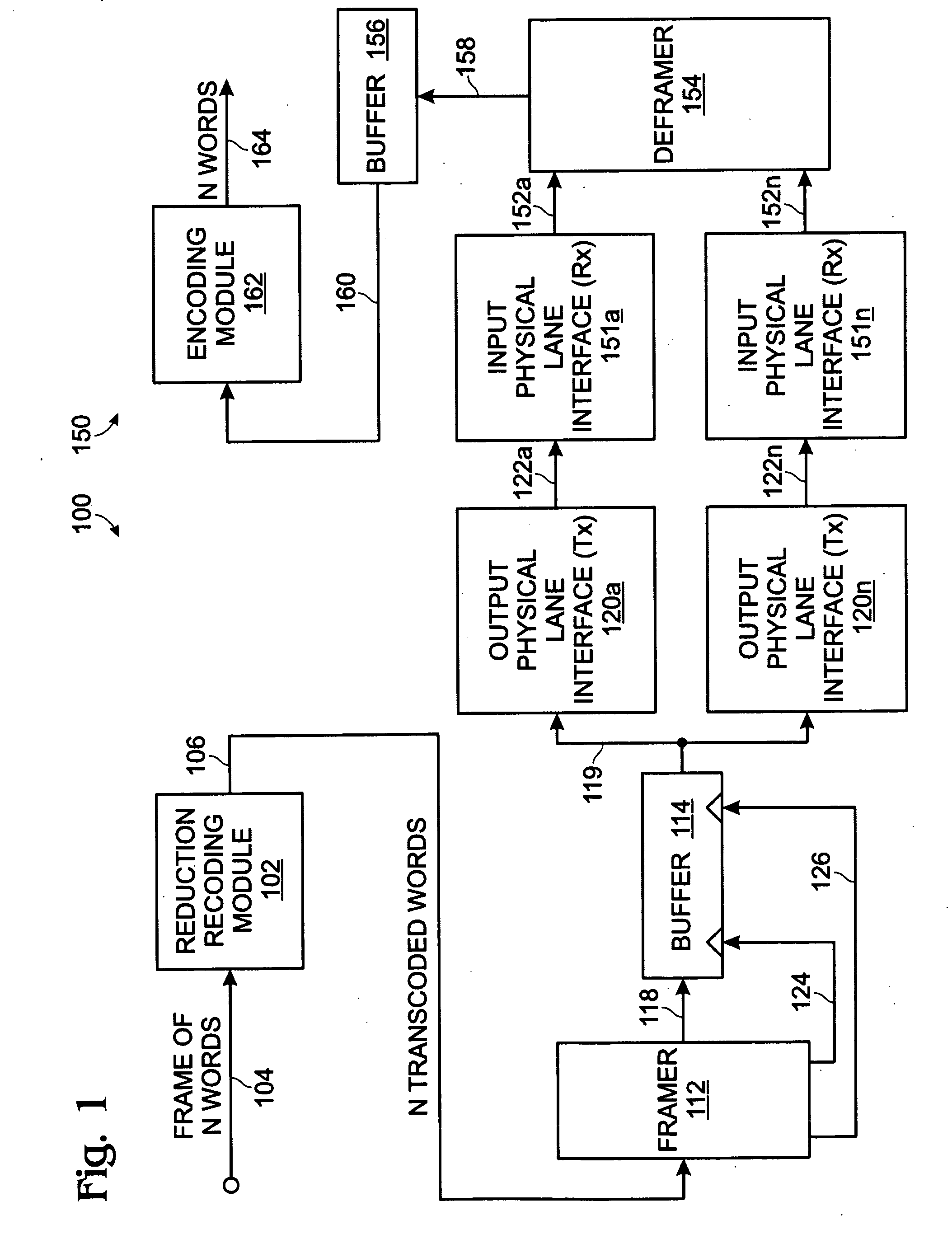

System and Method for Inverse Multiplexing Using Transcoding and Frame Alignment Markers

ActiveUS20100208753A1Minimize latencyFrequency-division multiplex detailsTime-division multiplexReal-time computingTranscoding

A system and method are provided for framing messages in a data streams encoded with redundant information for transmission and recovering the messages at a receiver. The transmission method accepts an energy waveform representing N words at a first bit rate, encoded with redundant information, where each word includes P number of bits. The N words are transformed, creating N transcoded words, where each transcoded word includes Q number of bits, and where Q<P. The N transcoded words are mapped into M lanes in a buffer memory, where M>1 and each lane receives a frame of N / M transcoded words. A frame alignment marker is generated and mapped into each frame. Each frame is represented as an energy waveform that is transmitted on a corresponding physical lane at the first bit rate divided by M.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

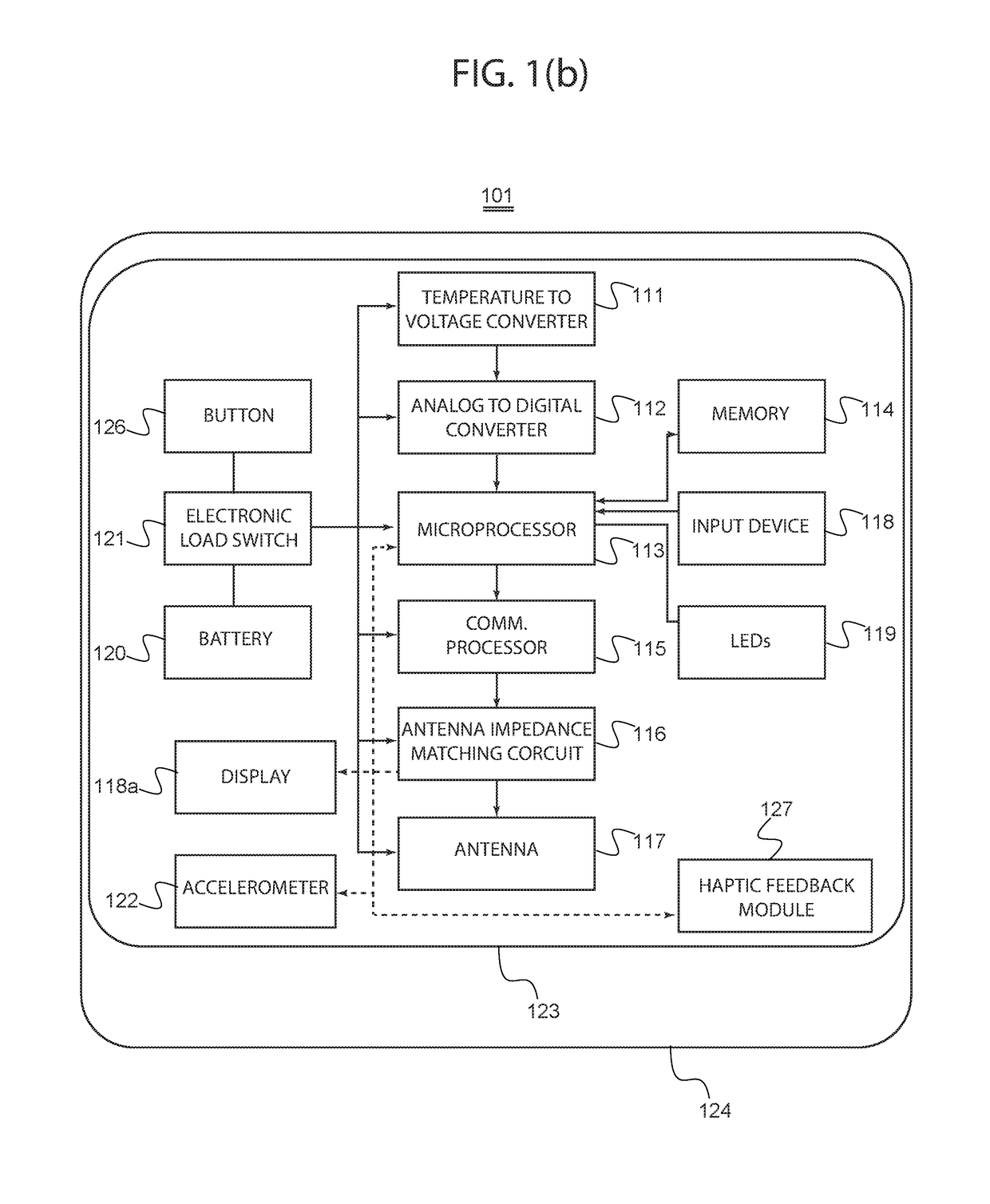

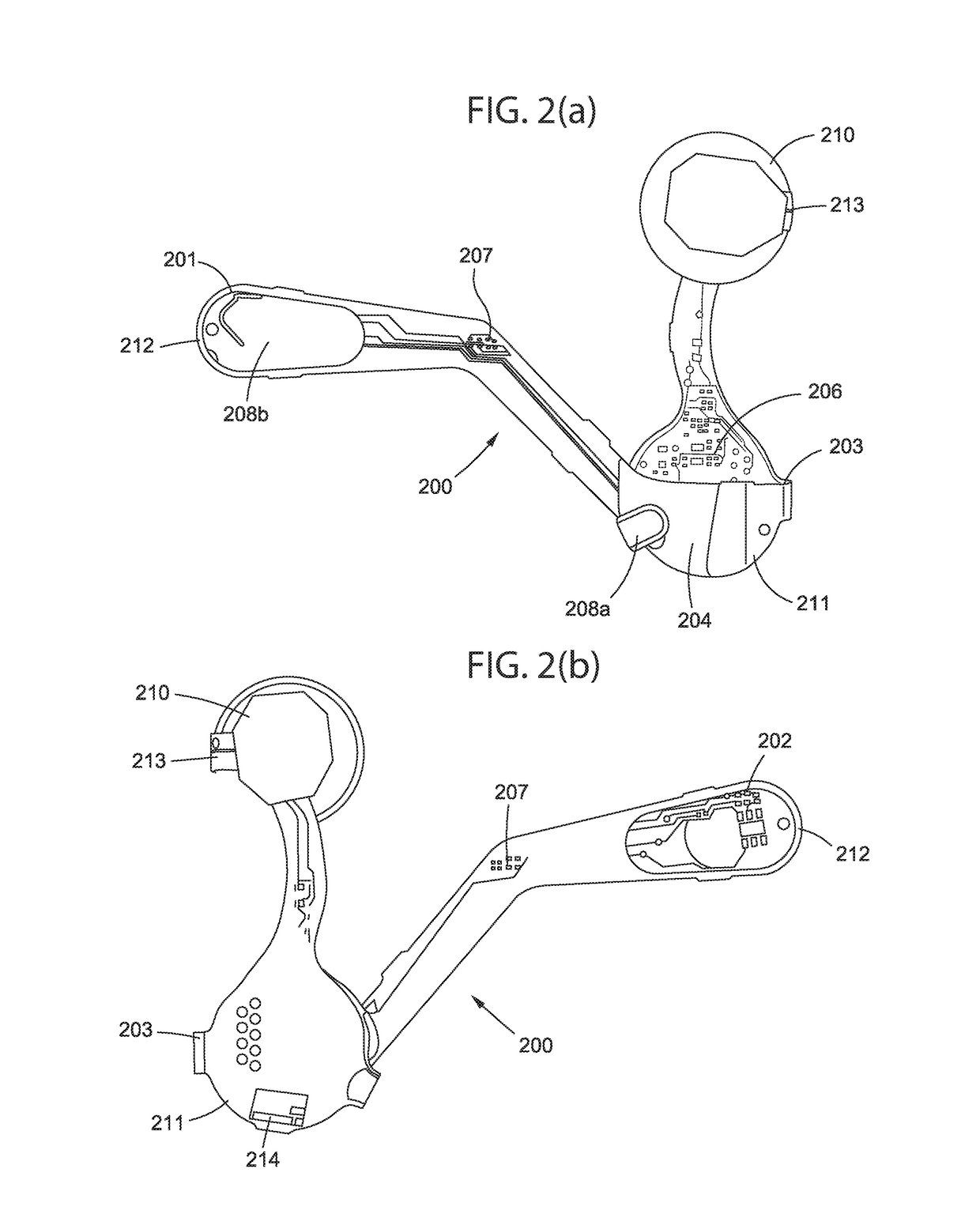

System and method of continuous health monitoring

InactiveUS20190082968A1Minimize latencyProlong battery lifePhysical therapies and activitiesMedical communicationFlexible electronicsPrinted circuit board

The invention involves a system and method implementing a wearable device that employs a flexible printed circuit board (PCB), which includes a temperature sensor. The PCB may be printed on a flexible substrate that may be folded to form multiple layers configured to house the sensor and an antenna. The sensor may be housed within said layers and situated at a terminal end of a pathway that may be printed on the PCB, wherein the pathway acts as a contact as well as a conduit of heat from the body of the user to the sensor. The antenna may be housed within the layers of the flexible PCB in a manner such that proper signal transmission is preserved and latency is minimized. Temperature readings may be wirelessly communicated to one or more client devices, which implement one or more algorithms suitable for generating insights regarding health aspects of the user.

Owner:KARNIK PRASAD +1

Autonomic SMT System tuning

ActiveUS20060085368A1Increase throughputMinimize latencyGeneral purpose stored program computerMultiprogramming arrangementsGenetic libraryWorkload

Methods, systems, and media are disclosed for autonomic system tuning of simultaneous multithreading (“SMT”). In one embodiment, the method for autonomic tuning of at least one SMT setting for an optimized processing, such as via throughput, latency, and power consumption, of a workload on a computer system includes calling, by a kernel, an SMT scheduler having at least one hook into a genetic library. Further, the method includes obtaining, by the SMT scheduler through the at least one hook, genetic data from the genetic library for the optimized processing of the workload. Further still, the method includes tuning, by the SMT scheduler and based on the obtaining, the at least one SMT setting for at least one cpu of the computer system.

Owner:TWITTER INC

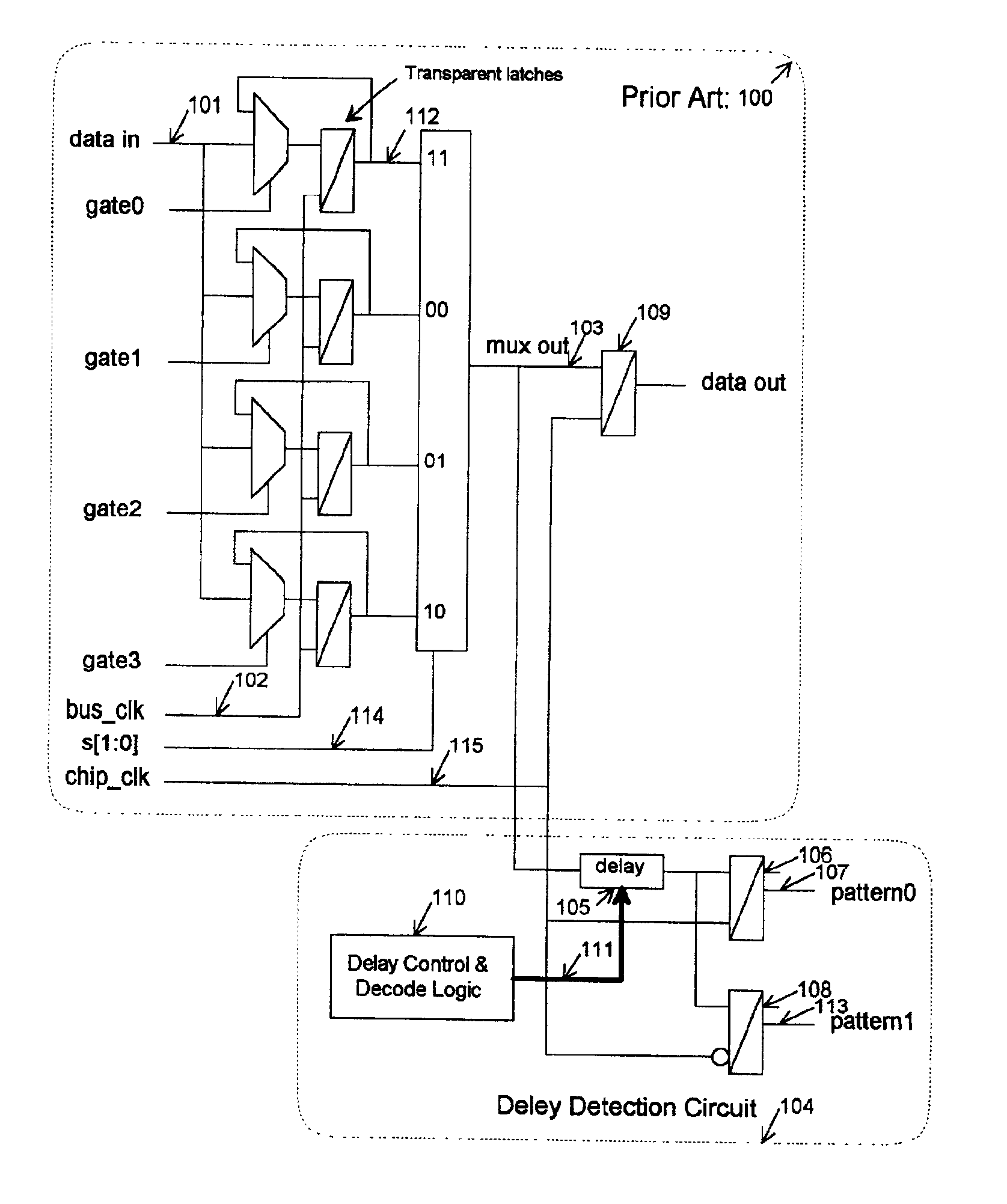

Method for receiver delay detection and latency minimization for a source synchronous wave pipelined interface

InactiveUS6954870B2Minimize latencyDelay minimizationSynchronisation information channelsSynchronisation signal speed/phase controlPhase shiftedEmbedded system

A method of calibrating an elastic interface is provided to automatically achieve a minimal cycle delay through the interface. An existing self-alignment interface (i.e. elastic interface) is used to de-skew within a cycle and stage the data to have it arrive on a given, programmed target cycle. However, this target cycle must be calculated in advance and may be larger than it needs to be, causing more latency on the interface. This method is used to determine the earliest target cycle (with or without additional guard-band). This target cycle is used to adjust the interface automatically to achieve this earliest target cycle. The determination of earliest target cycle can be done once, continuously, or using a sample window. The method also can be used for interfaces that have frequency multipliers or phase shifts at its boundaries.

Owner:IBM CORP

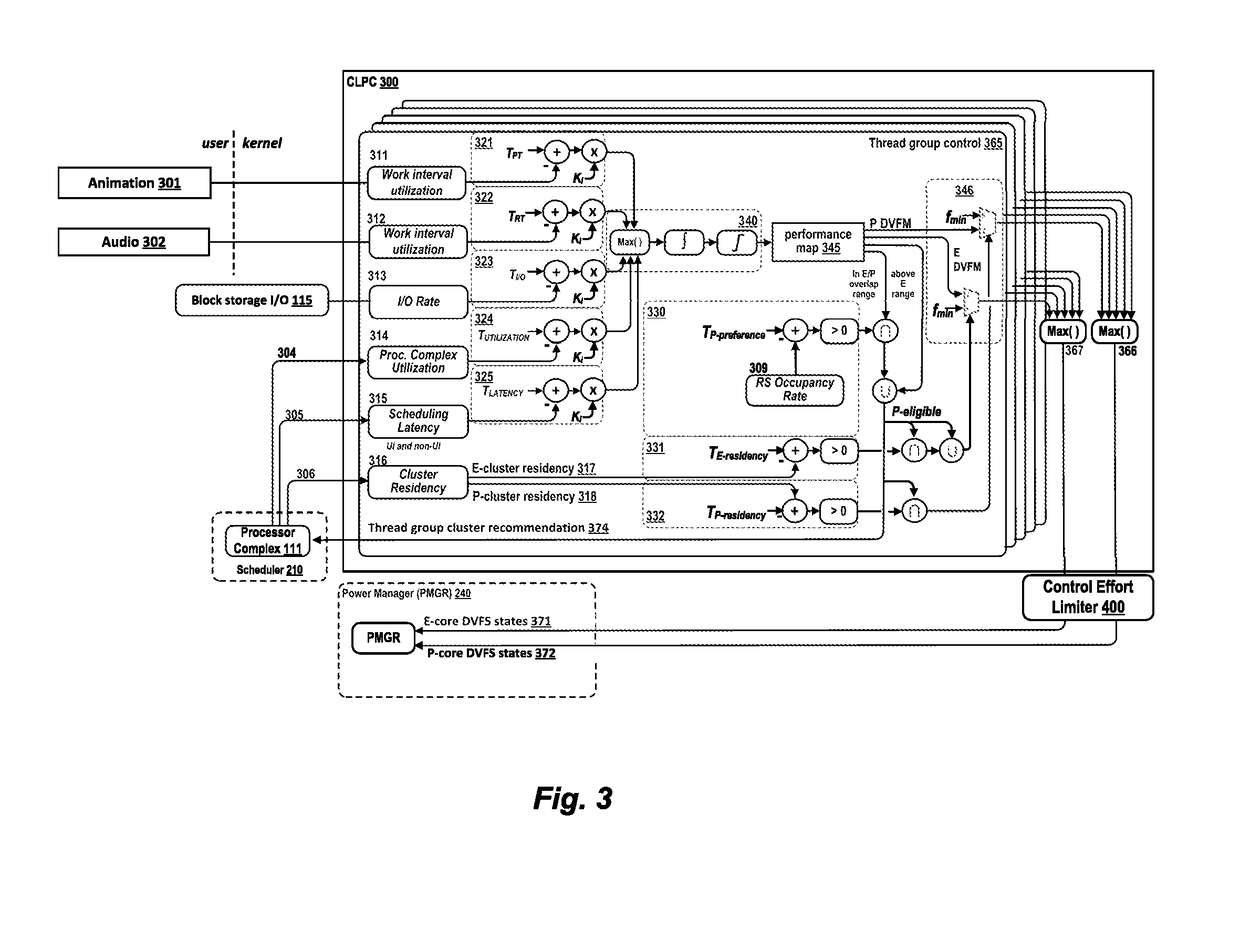

Scheduler for amp architecture using a closed loop performance controller and deferred inter-processor interrupts

ActiveUS20180349177A1Minimize latencyMaximize throughputProgram initiation/switchingResource allocationPower management systemClosed loop

Systems and methods are disclosed for scheduling threads on a processor that has at least two different core types, such as an asymmetric multiprocessing system. Each core type can run at a plurality of selectable voltage and frequency scaling (DVFS) states. Threads from a plurality of processes can be grouped into thread groups. Execution metrics are accumulated for threads of a thread group and fed into a plurality of tunable controllers for the thread group. A closed loop performance control (CLPC) system determines a control effort for the thread group and maps the control effort to a recommended core type and DVFS state. A closed loop thermal and power management system can limit the control effort determined by the CLPC for a thread group, and limit the power, core type, and DVFS states for the system. Deferred interrupts can be used to increase performance.

Owner:APPLE INC

Systems and methods for managing tape drive operation

InactiveUS20090077300A1Balance loadMinimize latencyInput/output to record carriersMemory systemsTape driveData source

Owner:L 3 COMM INTEGRATED SYST

Scheduler for amp architecture using a closed loop performance and thermal controller

ActiveUS20180349191A1Minimize latencyMaximize throughputResource allocationInstruction analysisPower management systemEngineering

Systems and methods are disclosed for scheduling threads on an asymmetric multiprocessing system having multiple core types. Each core type can run at a plurality of selectable voltage and frequency scaling (DVFS) states. Threads from a plurality of processes can be grouped into thread groups. Execution metrics are accumulated for threads of a thread group and fed into a plurality of tunable controllers. A closed loop performance control (CLPC) system determines a control effort for the thread group and maps the control effort to a recommended core type and DVFS state. A closed loop thermal and power management system can limit the control effort determined by the CLPC for a thread group, and limit the power, core type, and DVFS states for the system. Metrics for workloads offloaded to co-processors can be tracked and integrated into metrics for the offloading thread group.

Owner:APPLE INC

LED driver circuit and method, and system and method for estimating junction temperature of light emitting diode

ActiveCN101926224AMinimize latencyHigh precisionElectrical apparatusThermometers using electric/magnetic elementsDriver circuitJunction temperature

A driver circuit (10) for a light emitting diode comprises a first driver circuit (32, 32', 32') for generating a first current output for driving the light emitting diode, wherein the first driver circuit has a control switch for interrupting the supply of the first current output. A second driver circuit (50) is for generating a second current output for driving the light emitting diode, and the second driver circuit also has a control switch for interrupting the supply of the second current output. The overall output of the driver circuit comprises a pulse width modulated output current which alternates between a high current (Ihigh) generated by the first driver circuit and a low current (I|OW) generated by the second driver circuit. By providing separate driver circuits for two different current requirements, the circuits can be optimised for each function. For example the high current value can comprise an LED operation current, and the low current value can comprise a non-zero measurement current.

Owner:NXP BV

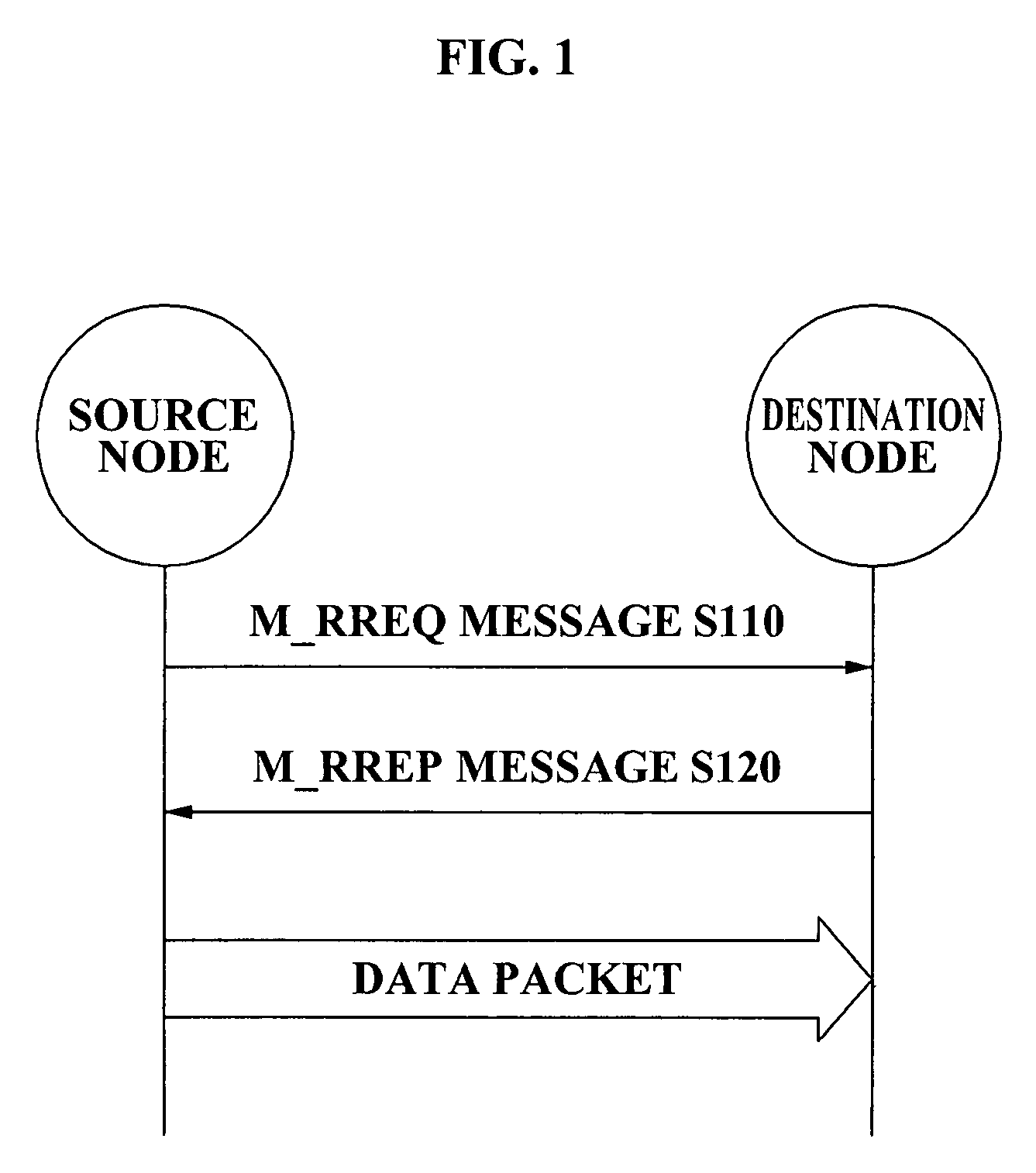

Control message processing method in wireless mesh network and control message processing apparatus using the method

ActiveUS20080117885A1Minimize overheadMinimize unnecessary latencyConnection managementData switching by path configurationWireless mesh networkMessage processing

A control message processing method and a control message processing apparatus using the method on a wireless mesh network are provided where a neighbor solicitation (NS) information is generated by extracting a part or an entire NS message, the NS message having been generated to request a medium access control (MAC) address of a destination node. A modified route request (RREQ) message, including the NS information, is generated to request the MAC address of the destination node and a routing path to the destination node, and is broadcasted.

Owner:SAMSUNG ELECTRONICS CO LTD

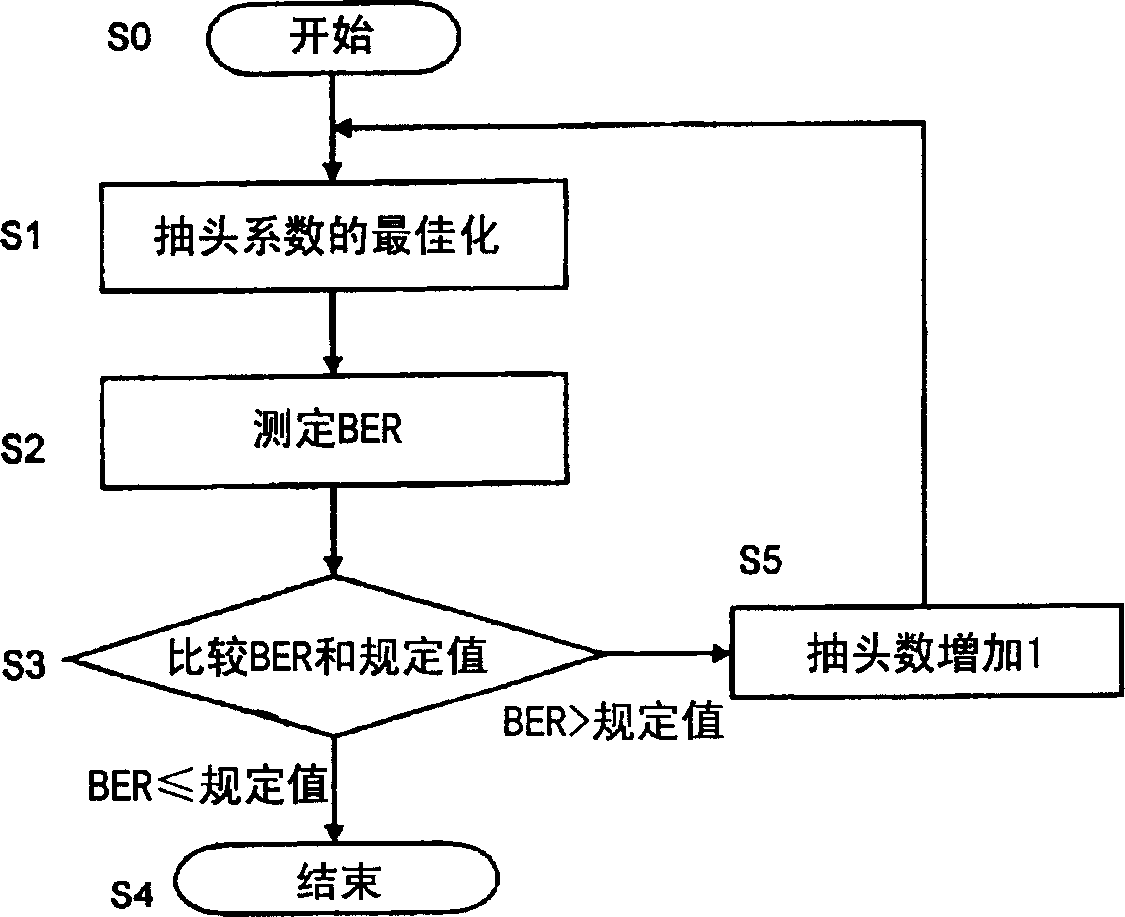

Transversal filter, transmitter and receiver with transversal filter

InactiveCN1870427AMinimize LatencyTransmission control/equlisationTransversal filtersComputer scienceTransmitter

Provided is a transversal filter, in which delayers and multipliers are connected in series, includes: a first multiplier for multiplying a first tap coefficient set by a tap coefficient register module and an input signal to output a result of multiplication; a first delayer for delaying the value output from the first multiplier by a predetermined time to output the delayed value; a second multiplier for multiplying a second tap coefficient set by the tap coefficient register module and an input signal to output a result of multiplication; a first adder for adding the value output from the delayer situated upstream to the value output from the second multiplier to output a result of addition; a second delayer for delaying the value output from the first adder by a predetermined time to output the delayed value; and a selector for selecting one of the input signal, the value output from the first delayer, and the value output from the second delayer to output the selected one.

Owner:HITACHI LTD

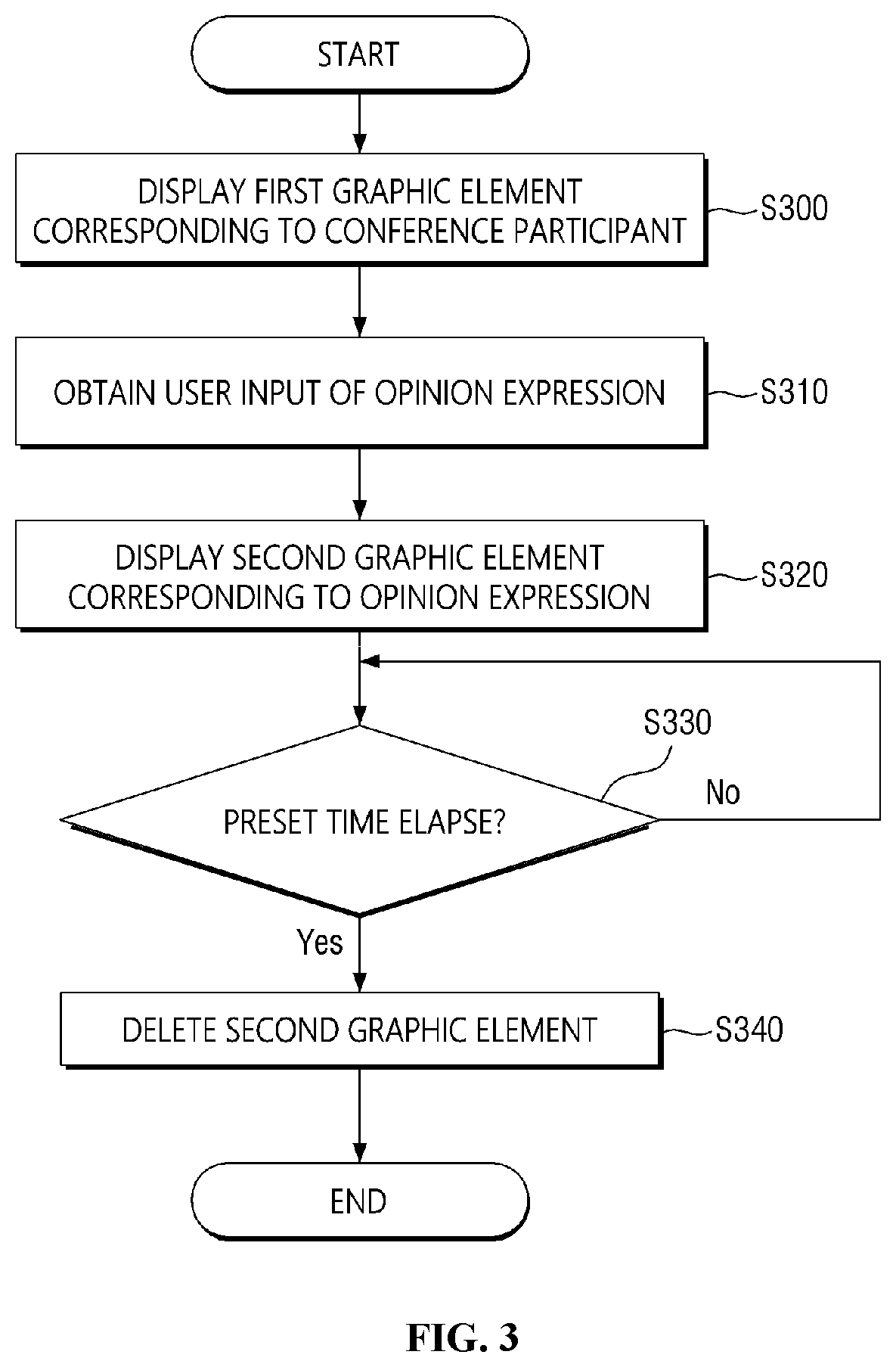

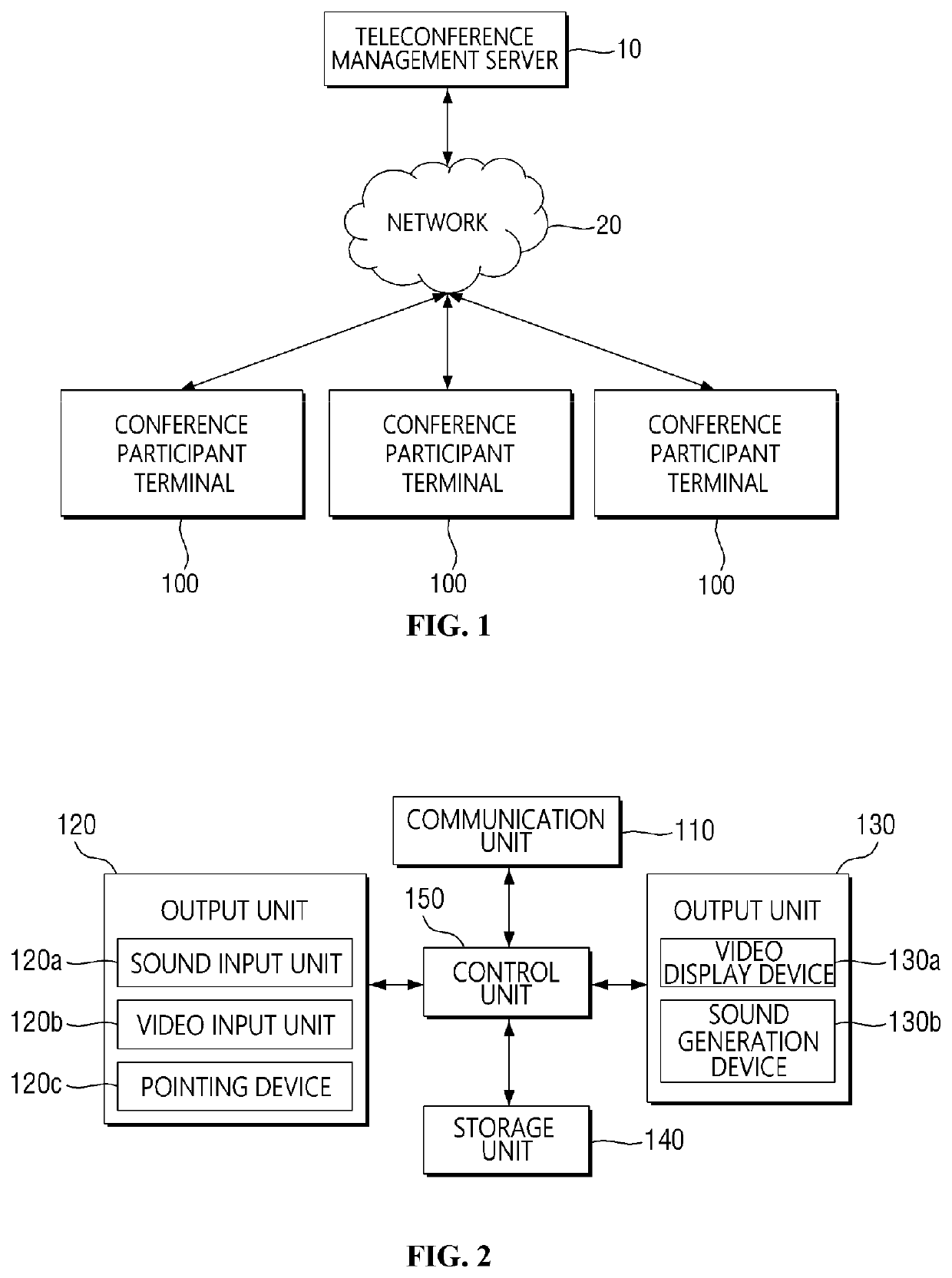

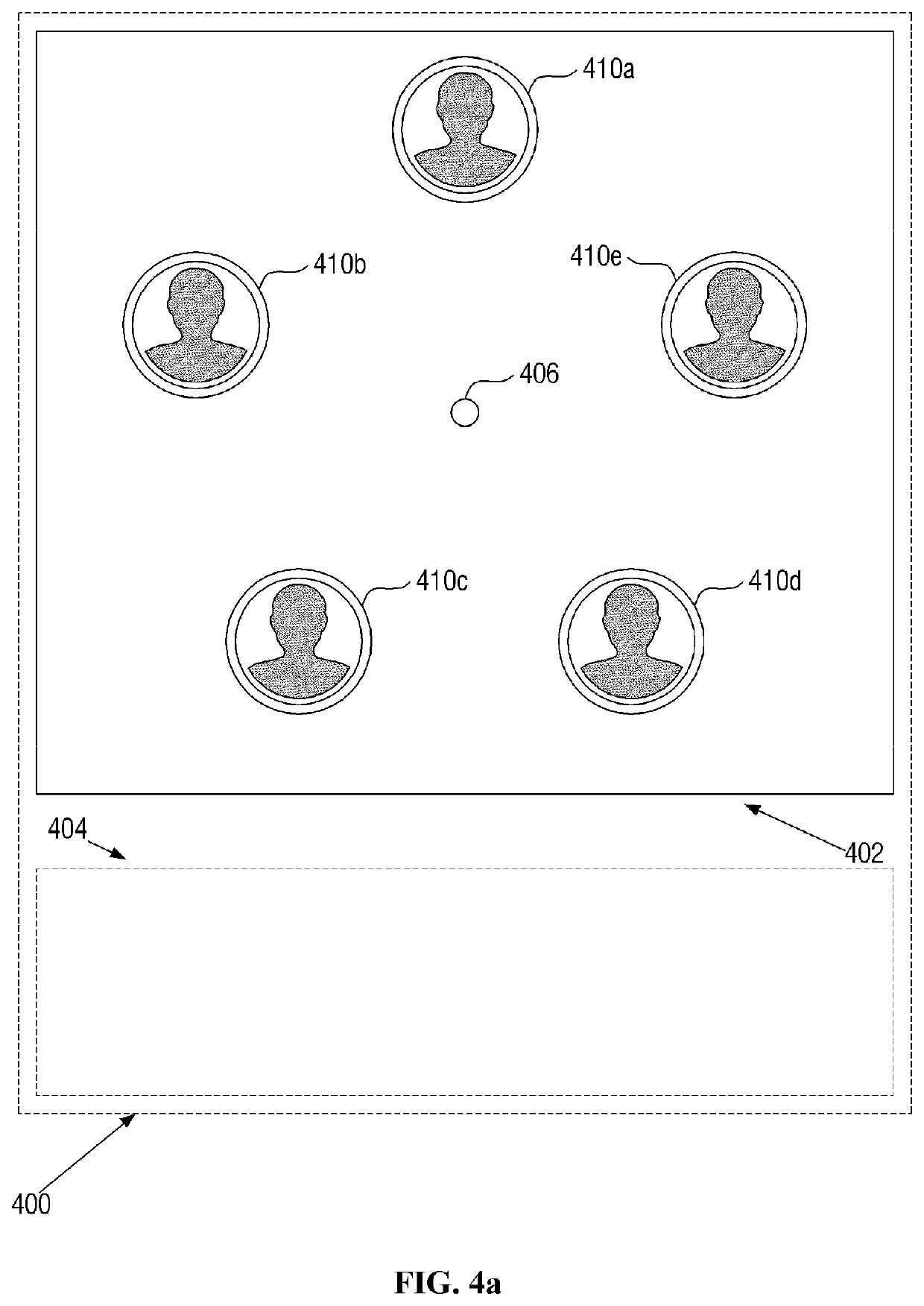

Method and system for providing virtual whiteboard based collaboration service

ActiveUS20210120053A1Prevent loss of editing contentMinimize latencyTransmissionExternal applicationEngineering

A content joint editing method according to an embodiment of the inventive concept may preserve the real-time property of update of edits as much as possible even if the number of editors increases when multiple editors simultaneously edit content. A content editing method can share and edit various contents without calling a separate external application in an online collaboration service. A content sharing method can manage each user's access rights to a content in individual content units in collaboration service that displays a plurality of contents at the same time in the collaboration space for sharing contents among multiple users.

Owner:SAMSUNG SDS CO LTD

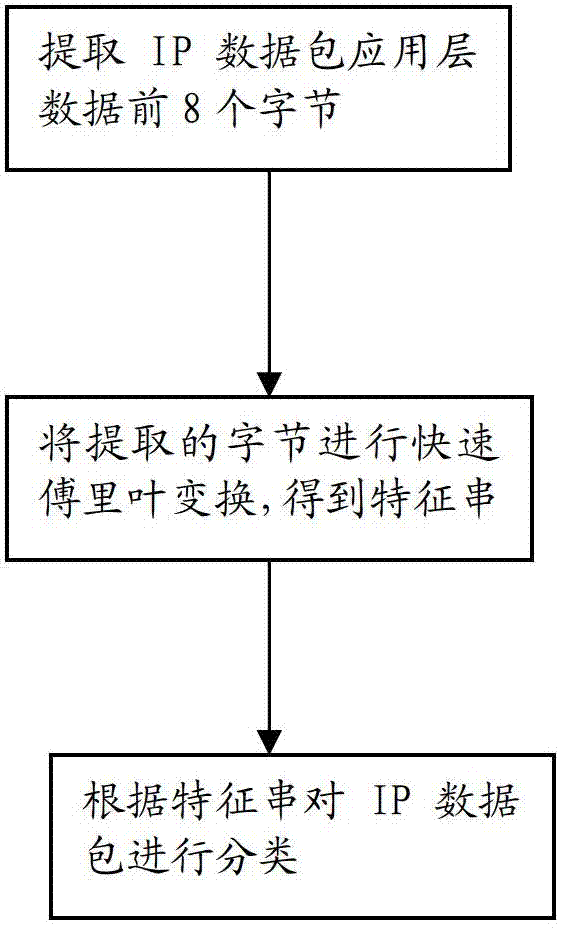

IP data packet identification method and gateway

The invention discloses an IP data packet identification method and a gateway, which are designed to solve the problems that the existing IP data packet identification method and the gateway are low in accuracy rate, low in efficiency and large in time delay. The IP data packet identification method comprises the following steps: extracting the front N bytes of data of an IP data packet application layer, and converting the extracted bytes into a frequency domain signal through Fourier transformation to obtain a characteristic string of the frequency domain, and sorting the IP data packets according to the characteristic string by a machine learning algorithm. The gateway in the invention at least comprises an identifying unit which comprises an extracting module, a Fourier transforming module and a sorting module which are connected orderly. The IP data packet identification method and the gateway have the advantages of high accuracy rate, high efficiency and easy implementation.

Owner:北京中科晶上科技股份有限公司

Scheduler for amp architecture with closed loop performance controller

ActiveUS20180349176A1Minimize latencyMaximize throughputProgram initiation/switchingResource allocationPower management systemClosed loop

Systems and methods are disclosed for scheduling threads on a processor that has at least two different core types, such as an asymmetric multiprocessing system. Each core type can run at a plurality of selectable voltage and frequency scaling (DVFS) states. Threads from a plurality of processes can be grouped into thread groups. Execution metrics are accumulated for threads of a thread group and fed into a plurality of tunable controllers for the thread group. A closed loop performance control (CLPC) system determines a control effort for the thread group and maps the control effort to a recommended core type and DVFS state. A closed loop thermal and power management system can limit the control effort determined by the CLPC for a thread group, and limit the power, core type, and DVFS states for the system. Deferred interrupts can be used to increase performance.

Owner:APPLE INC

Systems and methods for managing tape drive operation

InactiveUS7809880B2Minimize latencyManage minimizeInput/output to record carriersMemory systemsMagnetic tapeData source

Owner:L 3 COMM INTEGRATED SYST

Linear electric motor controller and system for providing linear control

InactiveUS7265516B2Increase fuel economyReduce weight and sizeAC motor controlDC motor speed/torque controlDigital-to-analog converterLinear control

The invention relates to a method of, and system for, linear speed control for an electric motor, in which a digital to analog converter means is used for converting an 8-bit digital signal to an analog voltage for setting voltage across a motor, a digital state machine means is used for converting the duty cycle of an input signal for output to the digital to analog converter means, and a closed loop feedback loop means is used for monitoring and setting the voltage across the motor. An over-current sense circuit can be used for monitoring the current across the electric motor. An over / under voltage sense circuit can be used for monitoring voltage of the electric motor. The resulting 8-bit digital control signal is converted to an analog voltage for the electric motor. Such methods and systems find particular use in automotive applications.

Owner:2112376 ONTARIO

Linear electric motor controller and system for providing linear control

InactiveUS20080024084A1Small and lighter in weightReduce weight and sizeAC motor controlVector control systemsLinear controlControl signal

The invention relates to a method of, and system for, linear speed control for an electric motor, in which a digital to analog converter means is used for converting an 8-bit digital signal to an analog voltage for setting voltage across a motor, a digital state machine means is used for converting the duty cycle of an input signal for output to the digital to analog converter means, and a closed loop feedback loop means is used for monitoring and setting the voltage across the motor. An over-current sense circuit can be used for monitoring the current across the electric motor. An over / under voltage sense circuit can be used for monitoring voltage of the electric motor. The resulting 8-bit digital control signal is converted to an analog voltage for the electric motor. Such methods and systems find particular use in automotive applications.

Owner:2112376 ONTARIO

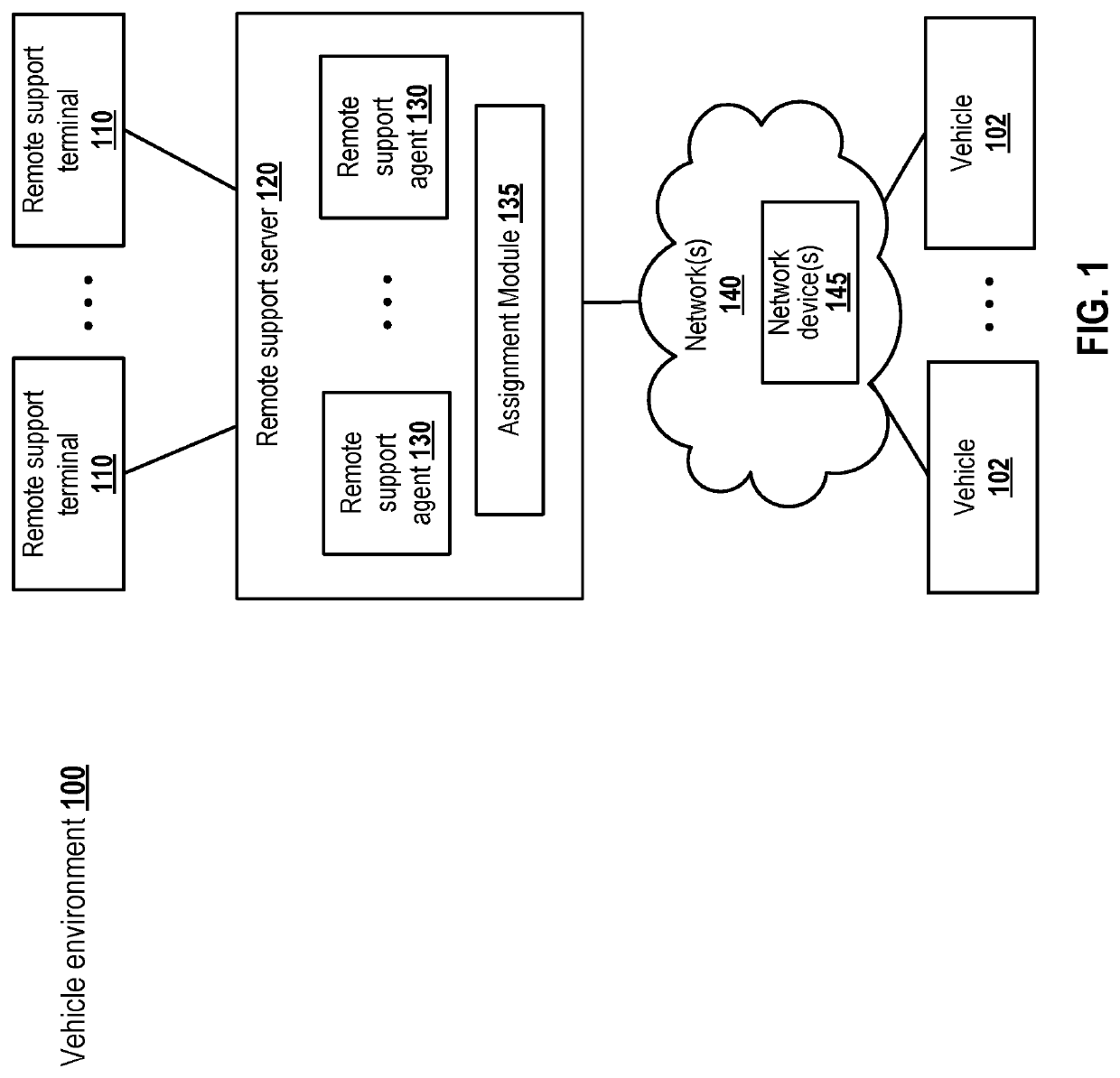

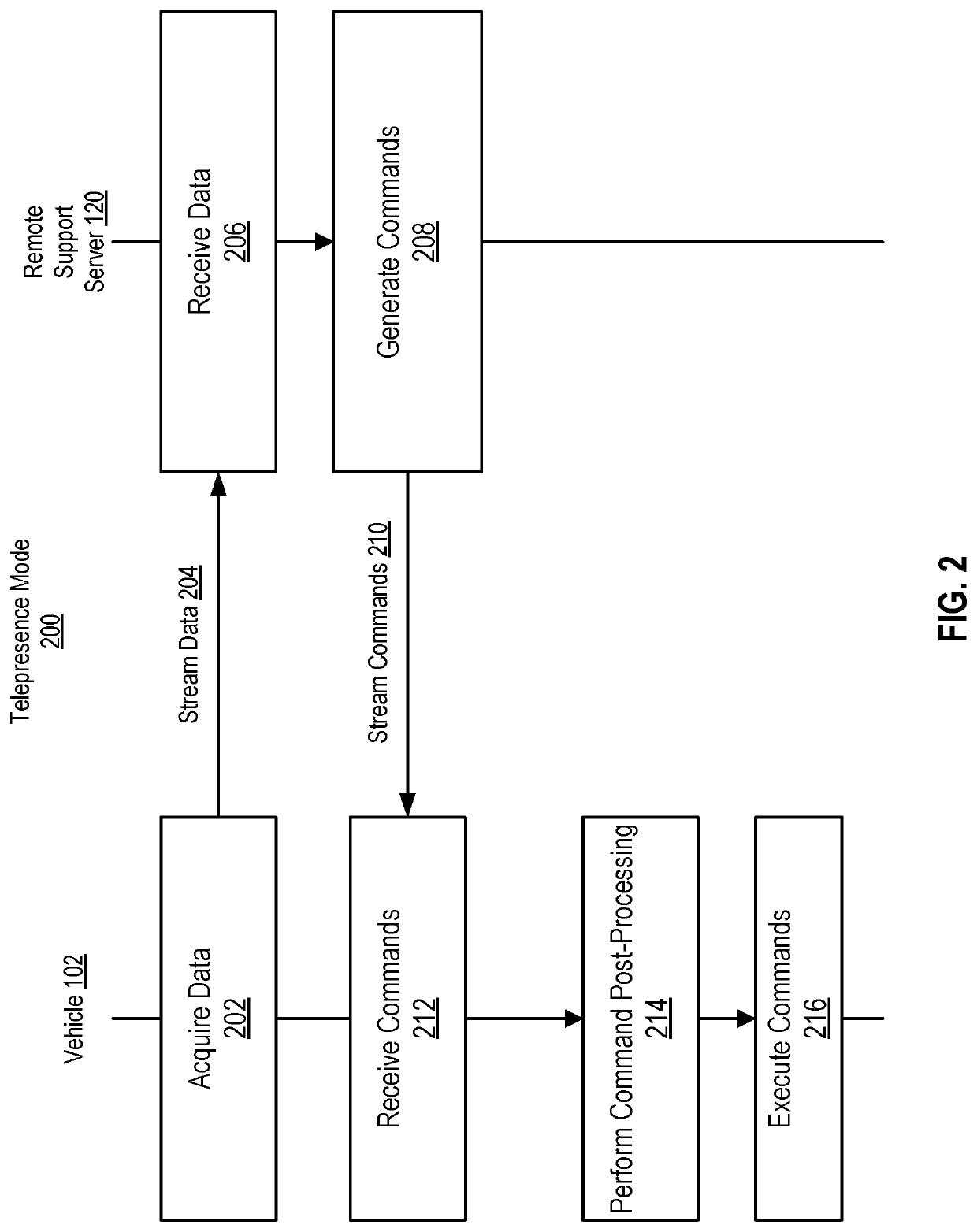

Mapping of intelligent transport systems to remote support agents

PendingUS20210078595A1Minimize latency and another performance parameterMinimize latencyRegistering/indicating working of vehiclesRoad vehicles traffic controlIntelligent transportIntelligent transportation system its

A remote support system facilitates assignment of vehicles to remote support agents for providing teleoperation or other remote support services. The remote support system may generate assignments based on a mapping function that optimizes various parameters based on sensed data associated with the vehicle, a requested service mode of the vehicle, or other factors. In some situations, the remote support server assigns a redundant set of remote support agents to a vehicle that provide similar command streams. The vehicle selects between the command streams to minimize latency or another performance parameter. Alternatively, the remote support server assigns multiple diverse remote support agents to a vehicle that generate diverse command streams. A proxy agent then generates a consensus command stream for providing to the vehicle.

Owner:PHANTOM AUTO INC

Control message processing method in wireless mesh network and control message processing apparatus using the method

ActiveUS8706072B2Minimize latencyMinimize overheadError preventionFrequency-division multiplex detailsWireless mesh networkMessage processing

A control message processing method and a control message processing apparatus using the method on a wireless mesh network are provided where a neighbor solicitation (NS) information is generated by extracting a part or an entire NS message, the NS message having been generated to request a medium access control (MAC) address of a destination node. A modified route request (RREQ) message, including the NS information, is generated to request the MAC address of the destination node and a routing path to the destination node, and is broadcasted.

Owner:SAMSUNG ELECTRONICS CO LTD

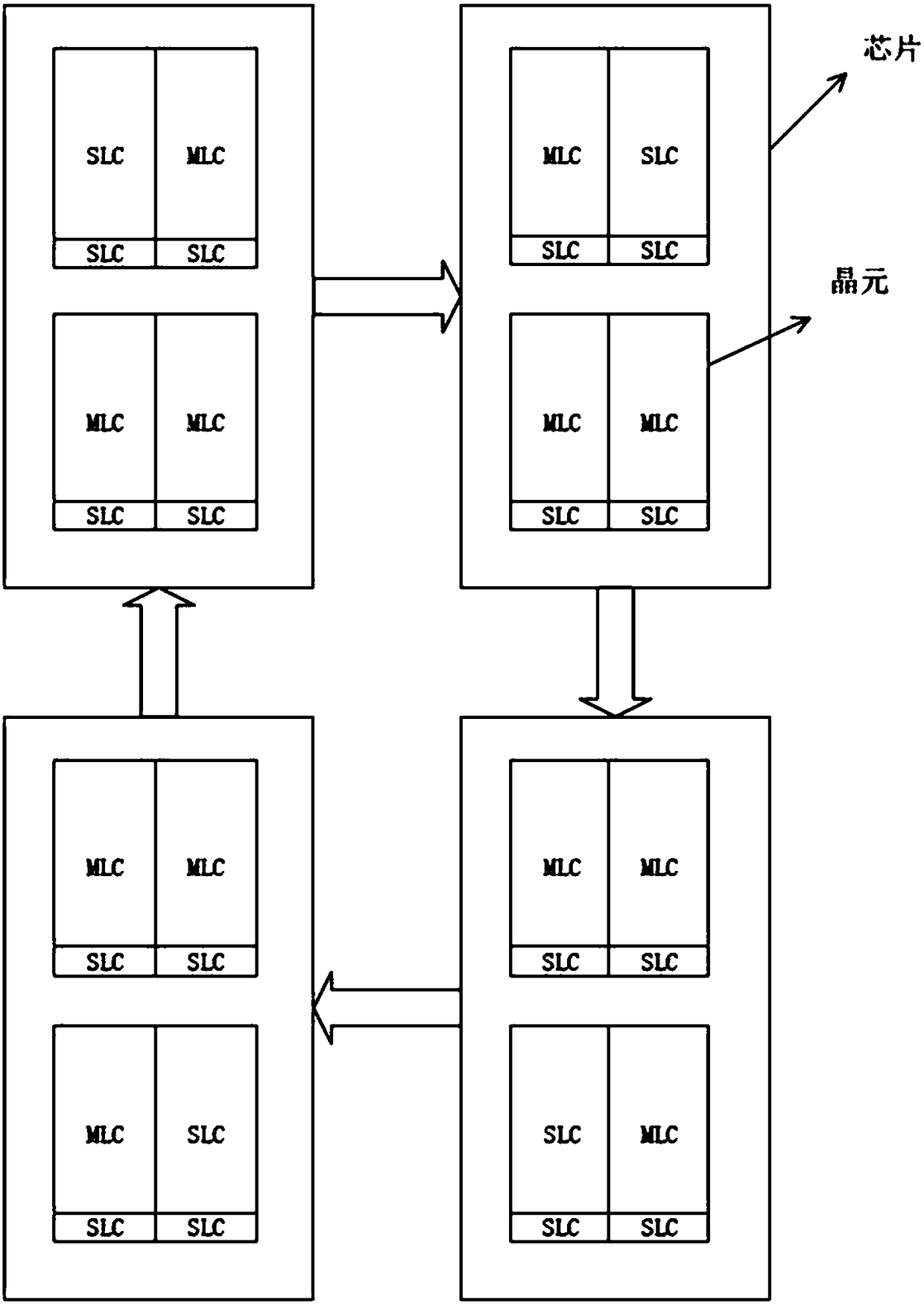

Request handling method of 3D MLC flash device

ActiveCN108572924AExtended service lifeGood write performanceMemory adressing/allocation/relocationRead-only memoriesDelay timeFlash memory

The invention discloses a request handling method of a 3D MLC flash device. The method comprises the following steps: performing a read request by a read request fir mode; performing a write request while a wafer is idle; ensuring that the working mode of the related wafer is consistent with the working mode of the related block during performing the read / write request; performing trash recoveryrequest while the wafer is idle; selecting the block with the least active pages in the block under an SLC mode as the block to be recovered in case of insufficient current capacity of the device; selecting an idle block of the SLC mode as a target block in case of jam in current array of the device; setting the wiped working mode of the block to be recovered as the MLC mode in case of insufficient current capacity of the device; and circularly setting the working mode of the next wafer as the SLC mode in case that the total wiping quantity of all wafers is certainly increased. According to the method, the new properties of a 3D MLC flash chip can be fully utilized, so that the delay time in trash recovery can be decreased, and the service life of the flash device is prolonged.

Owner:HUAZHONG UNIV OF SCI & TECH

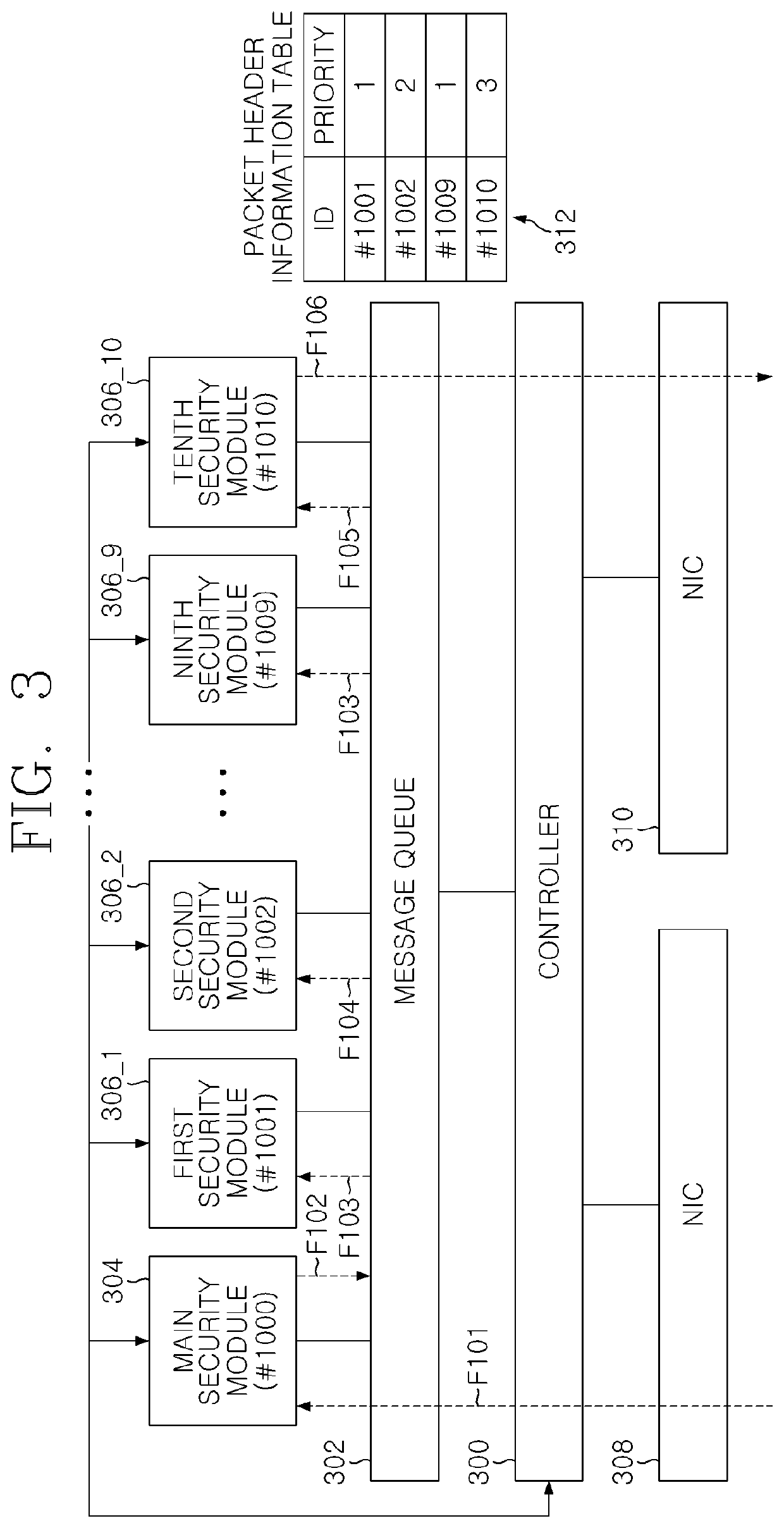

Apparatus and method for traffic security processing in 5g mobile edge computing slicing service

PendingUS20220295283A1Improve processing speedMinimize latencyNetwork traffic/resource managementTransmissionData packMobile edge computing

An apparatus for traffic security processing in a slicing service of mobile edge computing according to an embodiment of the present invention includes: a plurality of security modules for analyzing a received packet to respectively execute security functions suitable for slicing security of mobile edge computing; a controller for managing a slicing security module list in the mobile edge computing; and a main security module for analyzing a received packet on the basis of the slicing security module list to determine a security function to be executed and priority of the security function to be executed, wherein the controller transmits the received packet to at least one corresponding security module among the plurality of security modules according to the priority of the security function to be executed, which is determined by the main security module.

Owner:WINS CO LTD

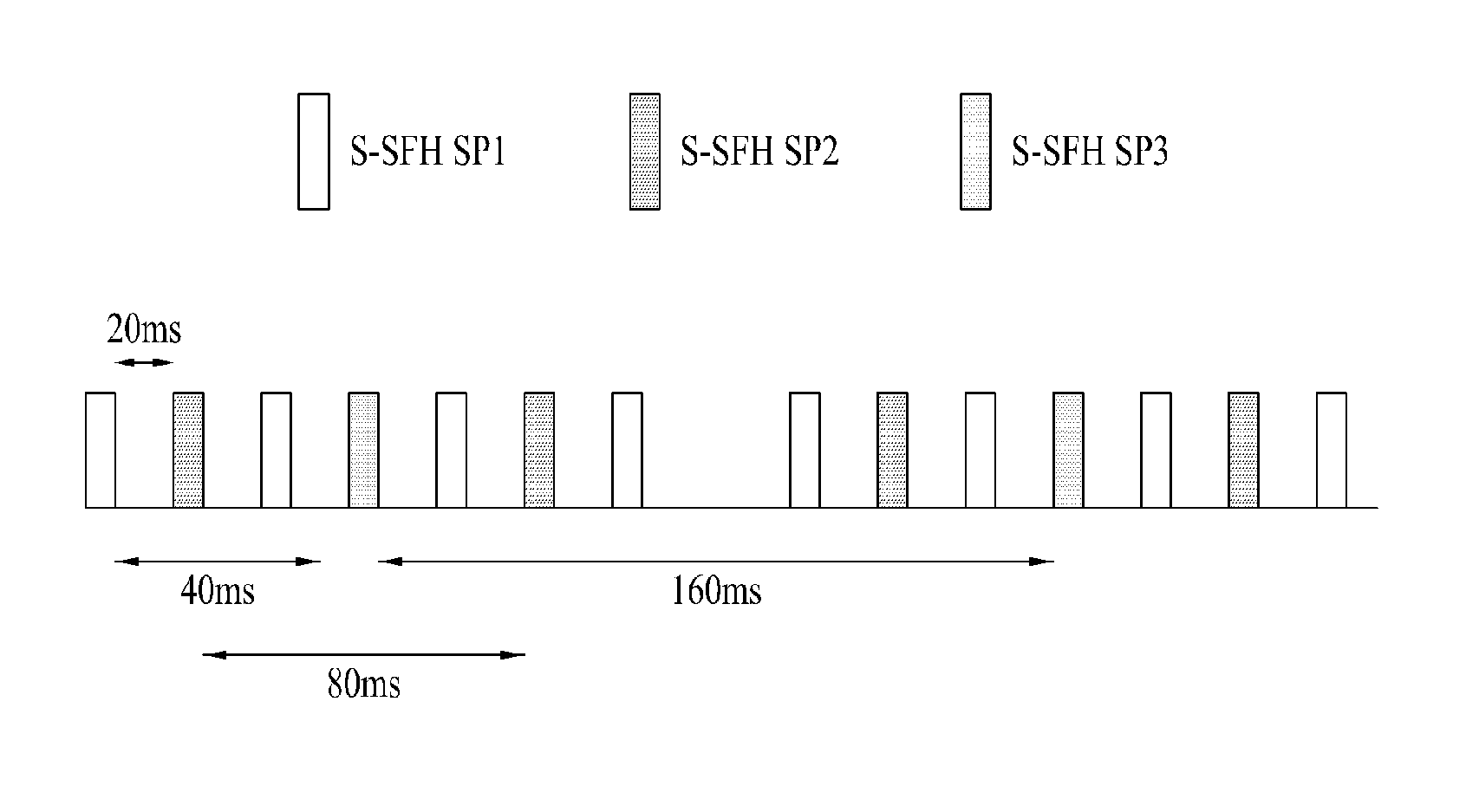

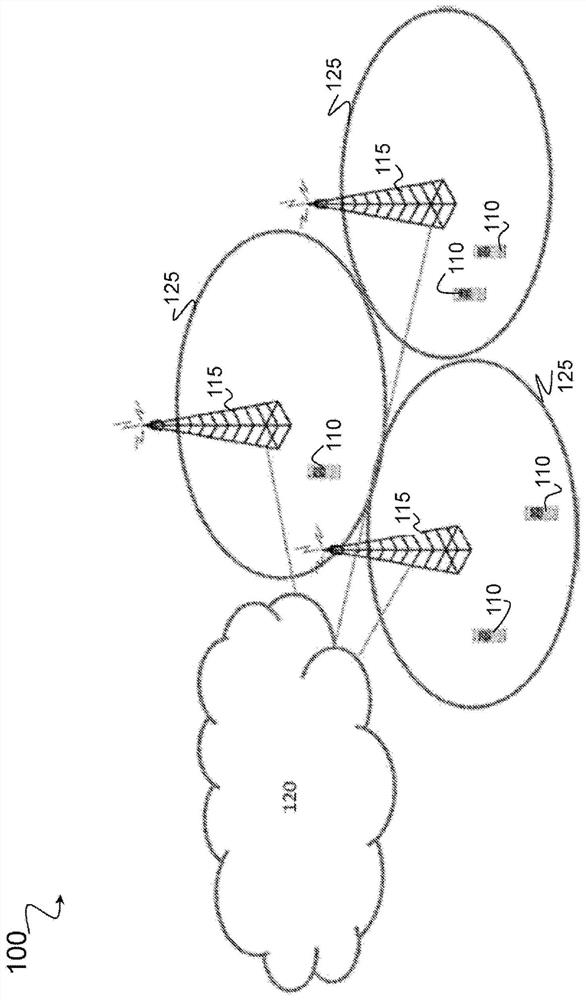

Ranging by mobile station in femto system

InactiveUS8369282B2Minimize delayMinimize latencyTransmission path divisionCriteria allocationMobile stationFemto-

A ranging method in a mobile station of a femto system is disclosed. According to the present invention, a femto base station enables non-synchronized ranging channel (NS-RCH) information to be carried on S-SFH SP1. A mobile station receives S-SFH and then determines whether a base station is a femto base station. If the base station is the femto base station, the mobile station is able to perform a periodic ranging using the NS-RCH information within the S-SFH as well as an initial / handover ranging.

Owner:LG ELECTRONICS INC

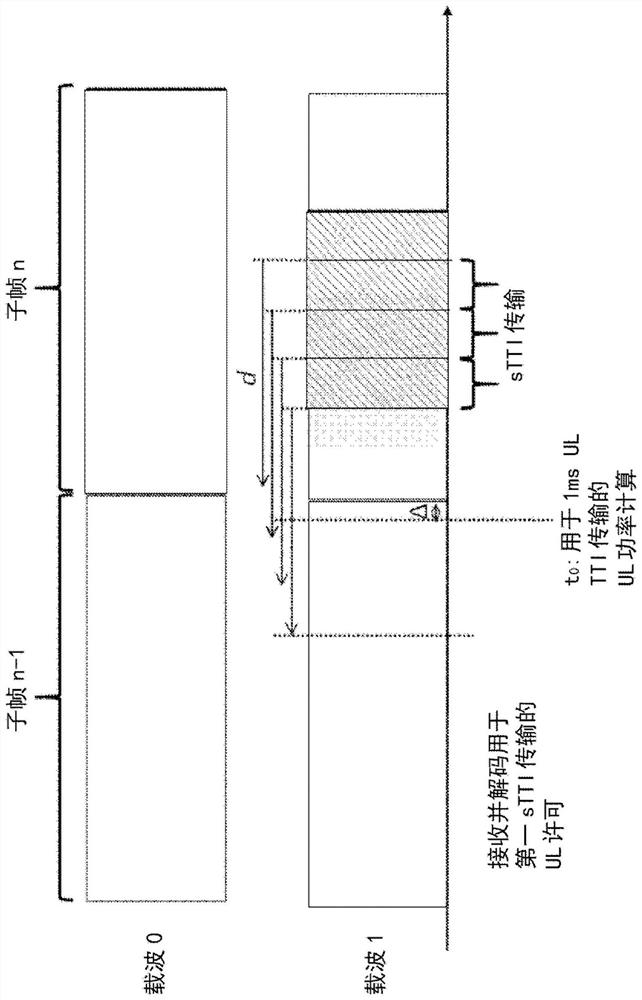

Uplink power prioritization for short tti

Certain embodiments relate to a method for use in a wireless device. The method includes allocating uplink power between parallel transmissions during subframes that the wireless device has scheduled on two or more uplink physical channels. The parallel transmissions include one or more short transmission time interval sTTI transmissions, and the UL power is allocated according to at least one prioritization rule. According to one of said prioritization rules, sTTI transmissions comprising control information are prioritized over sTTI transmissions comprising data but without any control information. According to another of the prioritization rules, transmissions with shorter transmission time intervals are prioritized over transmissions with longer transmission time intervals.

Owner:TELEFON AB LM ERICSSON (PUBL)

Method and system for providing virtual whiteboard based collaboration service

ActiveUS11418551B2Minimize latencyLoad minimizationData switching networksExternal applicationEngineering

A content joint editing method according to an embodiment of the inventive concept may preserve the real-time property of update of edits as much as possible even if the number of editors increases when multiple editors simultaneously edit content. A content editing method can share and edit various contents without calling a separate external application in an online collaboration service. A content sharing method can manage each user's access rights to a content in individual content units in collaboration service that displays a plurality of contents at the same time in the collaboration space for sharing contents among multiple users.

Owner:SAMSUNG SDS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com