Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

42results about How to "Improve package integration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

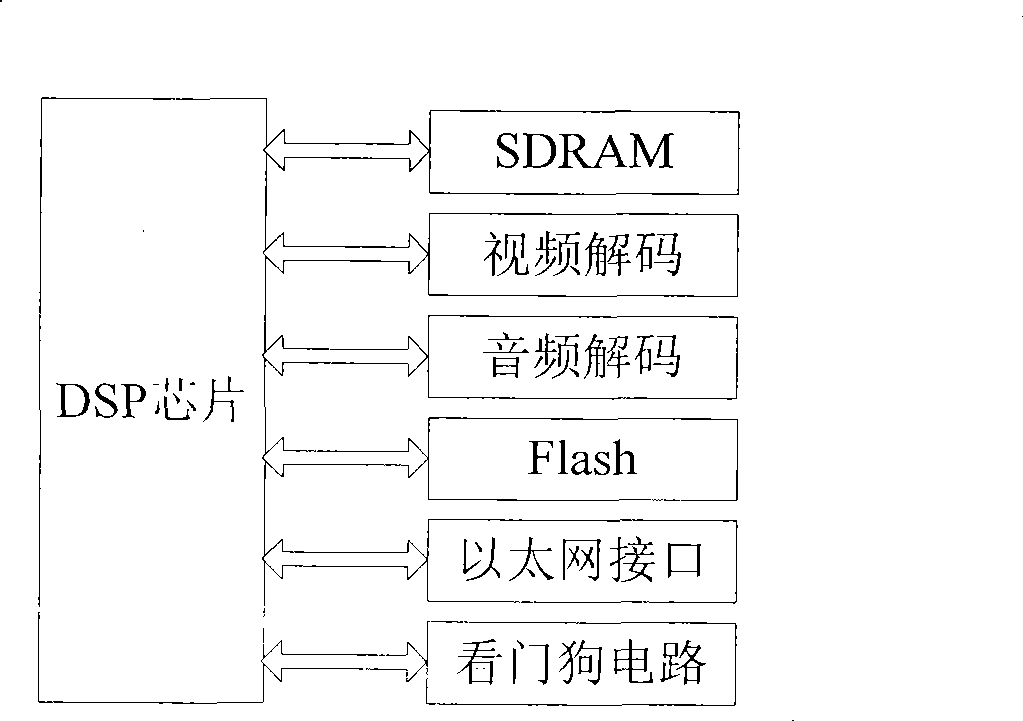

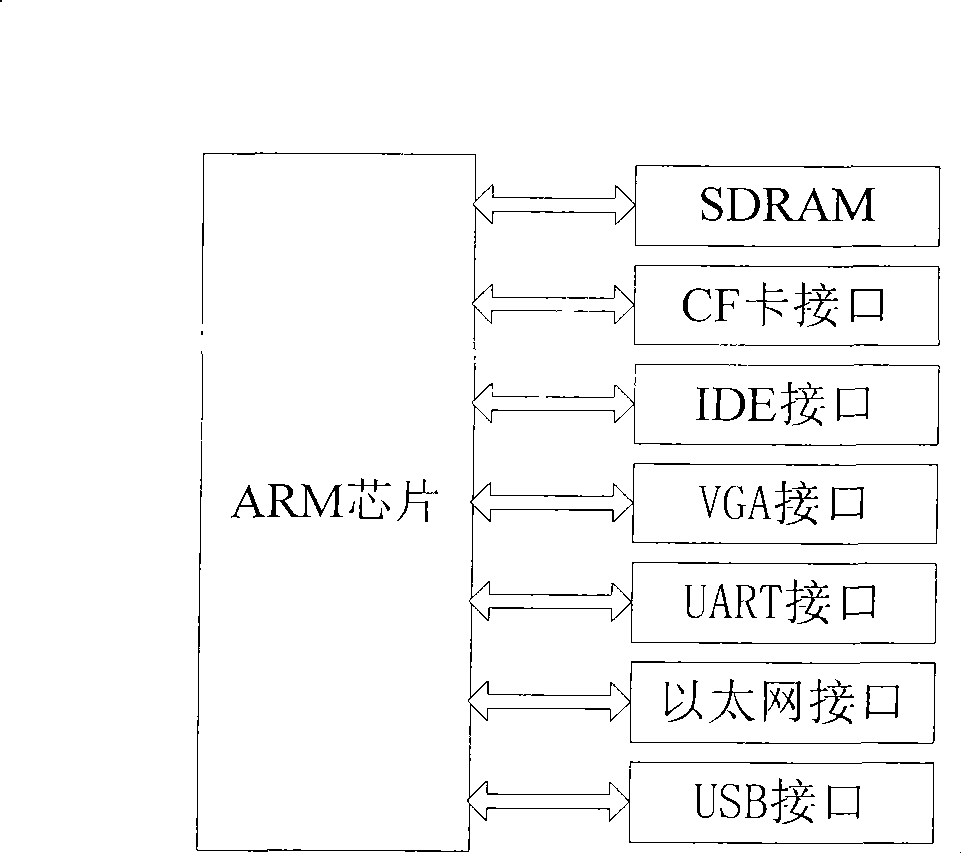

Embedded real-time intelligent traffic monitoring system based on video stream

InactiveCN101364346AHigh speed processingVarious communication methodsDetection of traffic movementImaging processingMonitoring system

The invention provides an embedded-type real-time intelligent traffic monitoring system based on video streaming technique, which mainly comprises two DSP modules, an ARM module and an FPGA logic control module. The two DSP modules perform the high-speed real-time processing of video images. The ARM module controls the operating mode of the two DSP modules and transmits an image processing result to the peripheral equipment via a peripheral interface. The FPGA logic control module supports the coordination control of the system and the cache storage of the images. The embedded-type real-time intelligent traffic monitoring system integrates the functions of the DSP, the ARM and the FPGA, has the advantages of high computing capacity, various interfaces and flexible communication mode, is applicable to various complex traffic conditions, and has wide application range.

Owner:HUAZHONG UNIV OF SCI & TECH

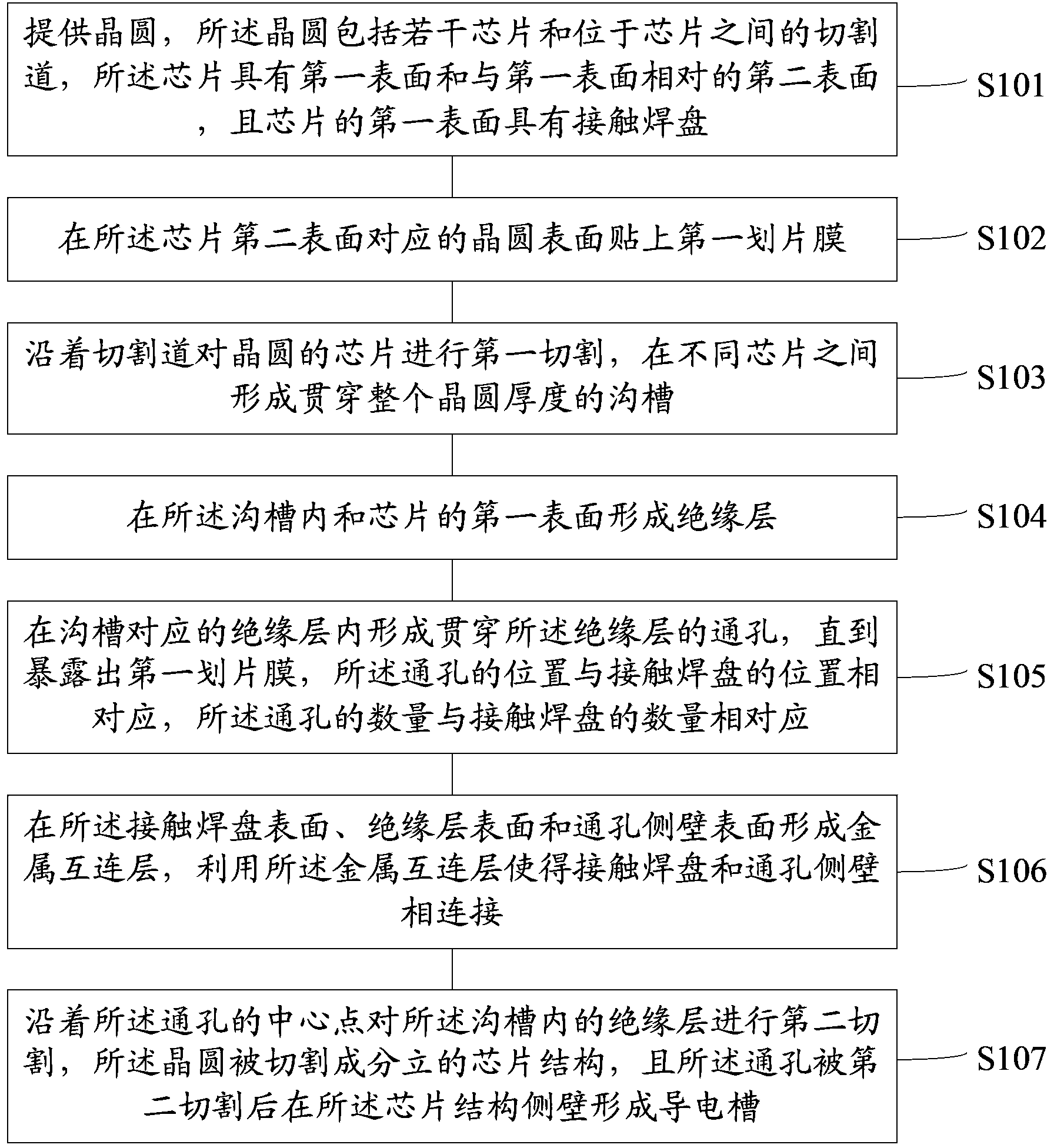

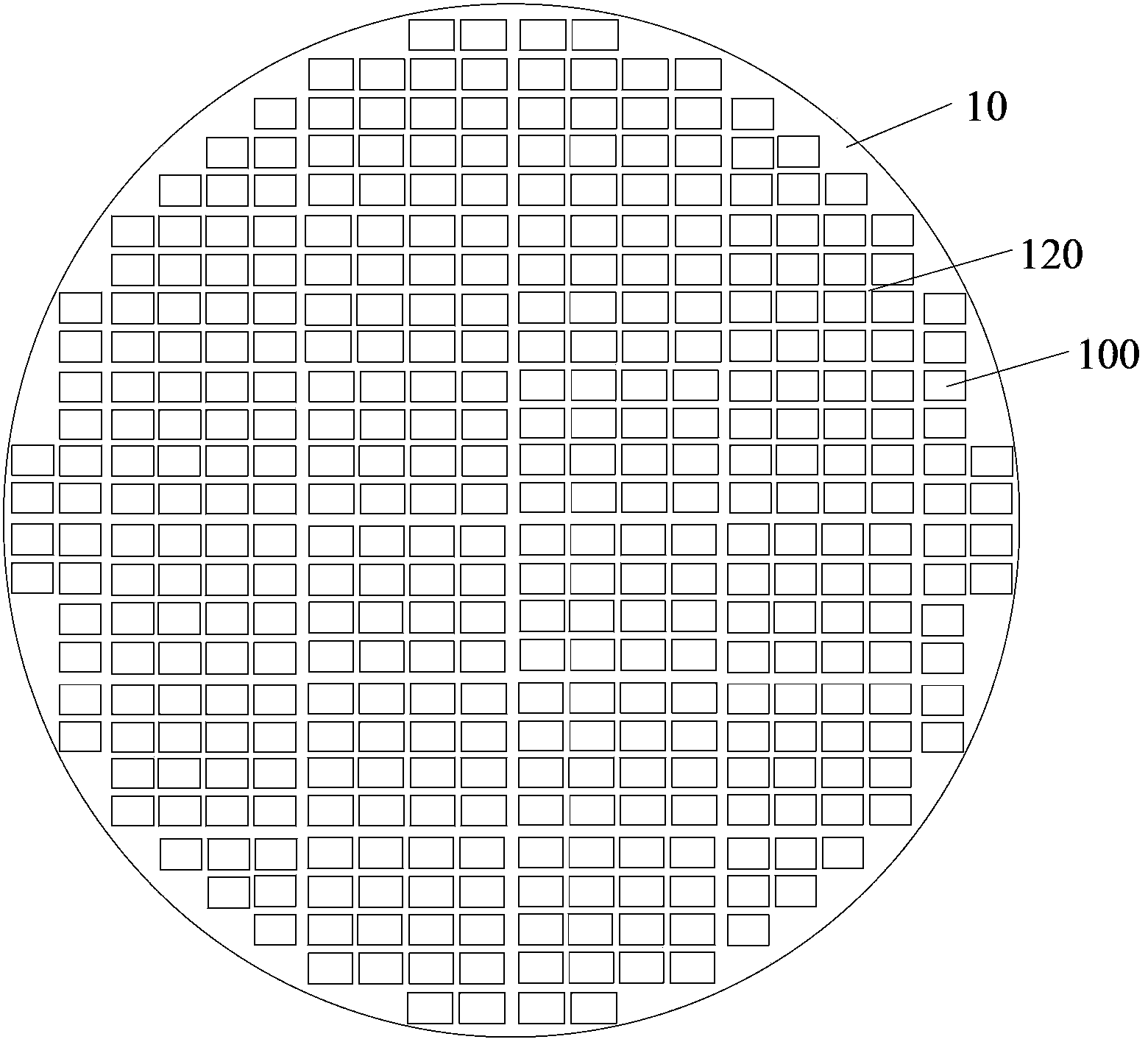

Chip cutting method and chip packaging method

ActiveCN103413785AReduce areaNo short circuitSolid-state devicesSemiconductor/solid-state device manufacturingAdhesiveInterconnection

Provided are a chip cutting method and a chip packaging method. The chip packaging method includes the steps that at least two chip structures are provided, wherein each chip structure comprises a chip and an insulating layer at least located on the side wall of the chip, the side wall of the insulating layer of each chip structure is provided with a conductive groove, the chip structures are stacked, and the conductive grooves of the different chip structures correspond to each other in position; the insides of the conductive grooves are filled with conductive adhesives, wherein circuits in the different chip structures are electrically connected through the conductive adhesives. Due to the fact that the conductive grooves are formed in the side walls of the insulating layers, the conductive adhesives formed in the conductive grooves cannot be in direct contact with the chips, and short-circuit phenomena cannot occur; due to the fact that the conductive grooves and contact welding plates are connected through metal interconnection layers on the surfaces of the insulating layers, the insulating layers cannot influence layout design of other metal interconnection structures in the chips, the chip area occupied by the metal interconnection structures can be saved, and the component integration degree of the chips can be beneficially improved.

Owner:NANTONG FUJITSU MICROELECTRONICS

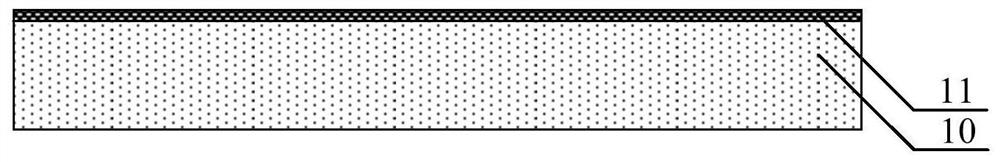

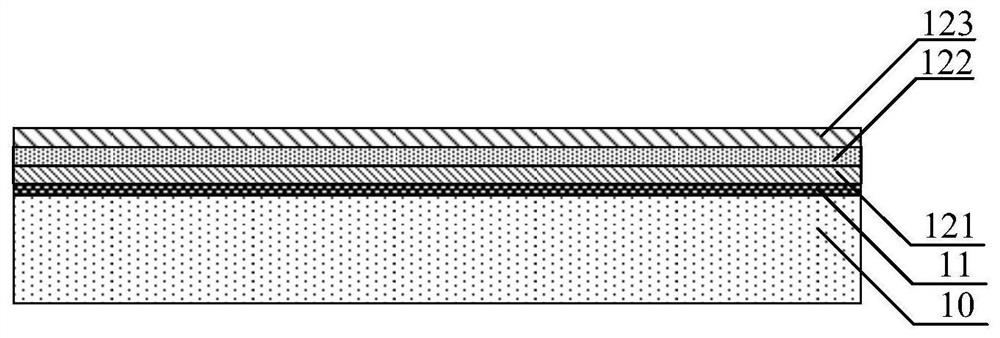

MEMS gas sensor and manufacturing method thereof

ActiveCN105987935AImprove package integrationHigh precisionDecorative surface effectsMaterial resistanceHigh volume manufacturingOptoelectronics

The invention relates to the technical field of gas detection, and provides an MEMS gas sensor and a manufacturing method thereof. The MEMS gas sensor comprises: a monocrystalline silicon substrate; an upper silicon nitride layer and an upper silicon oxide layer which are superposed on the upper surface of the monocrystalline silicon substrate from bottom to top; a lower silicon nitride layer placed on the lower surface of the monocrystalline silicon substrate; a heating electrode placed on the silicon oxide layer; an insulating layer placed on the heating electrode; a measurement electrode placed on the insulating layer; a gas-sensitive layer placed on the measurement electrode and electrically connected with the measurement electrode; and a heat insulation chamber positioned under the upper silicon nitride layer and formed by etching the lower silicon nitride layer and the monocrystalline silicon substrate. The gas sensor has the advantages of high precision, light weight, small dimension, low power dissipation, high usefulness, low cost, and realization of large-batch production.

Owner:郑州炜盛电子科技有限公司

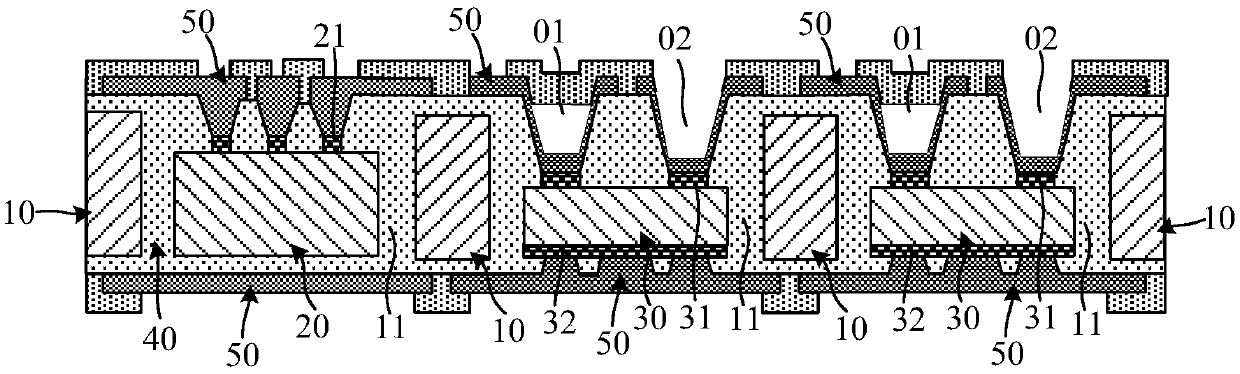

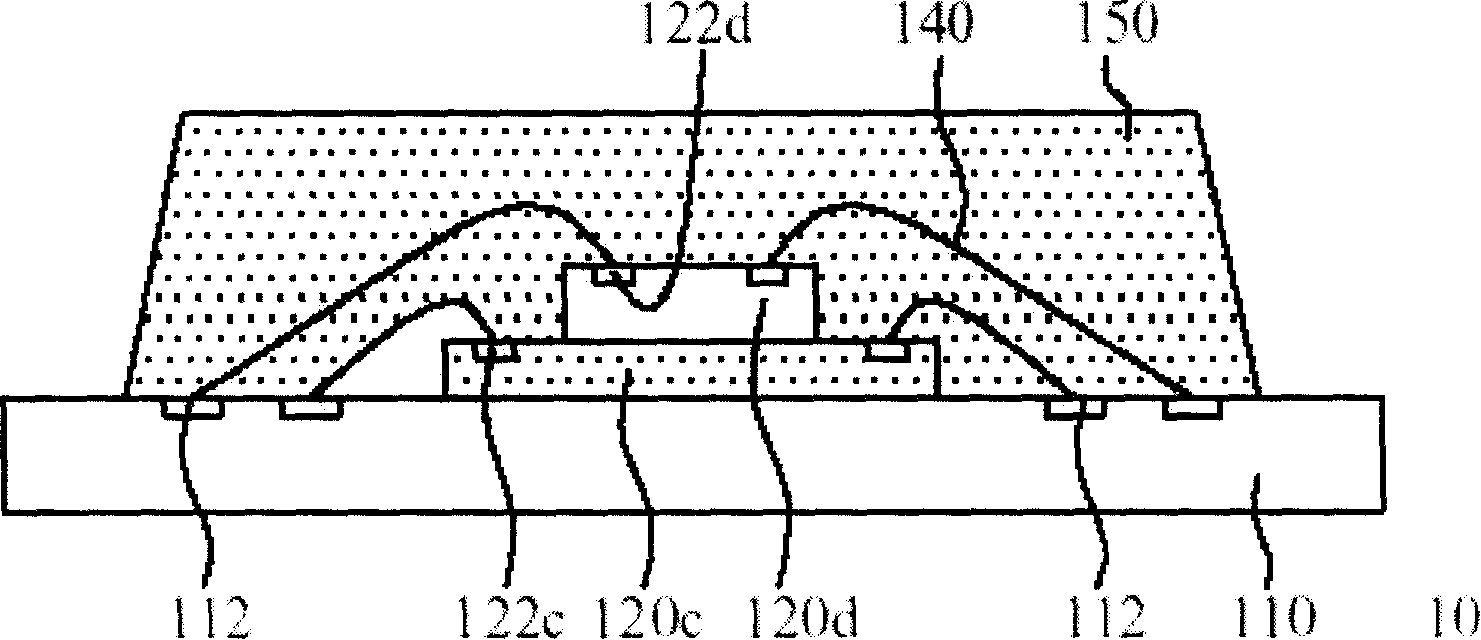

Chip structure and chip packaging structure

ActiveCN103413798AReduce areaNo short circuitSemiconductor/solid-state device detailsSolid-state devicesAdhesiveInterconnection

Provided are a chip structure and a chip packaging structure. The chip packaging structure comprises at least two chip structures and conductive adhesives located in conductive grooves, wherein the side walls of the chip structures are provided with the conductive grooves, the chip structures are stacked, the conductive grooves of the stacked chip structures correspond in position, and circuits in the stacked chip structures are electrically connected through the conductive adhesives. Due to the fact that the conductive grooves are formed in the side walls of insulating layers, the conductive adhesives formed in the conductive grooves later cannot be in direct contact with chips, and short-circuit phenomena cannot occur; due to the fact that the conductive grooves and contact welding plates are connected through metal interconnection layers on the surfaces of the insulating layers, the insulating layers cannot influence layout design of other metal interconnection structures in the chips, the practice that extra metal interconnection structures are designed due to positions of the contact welding plates is needless, the chip area occupied by the metal interconnection structures can be saved, and the component integration degree of the chips can be beneficially improved.

Owner:NANTONG FUJITSU MICROELECTRONICS

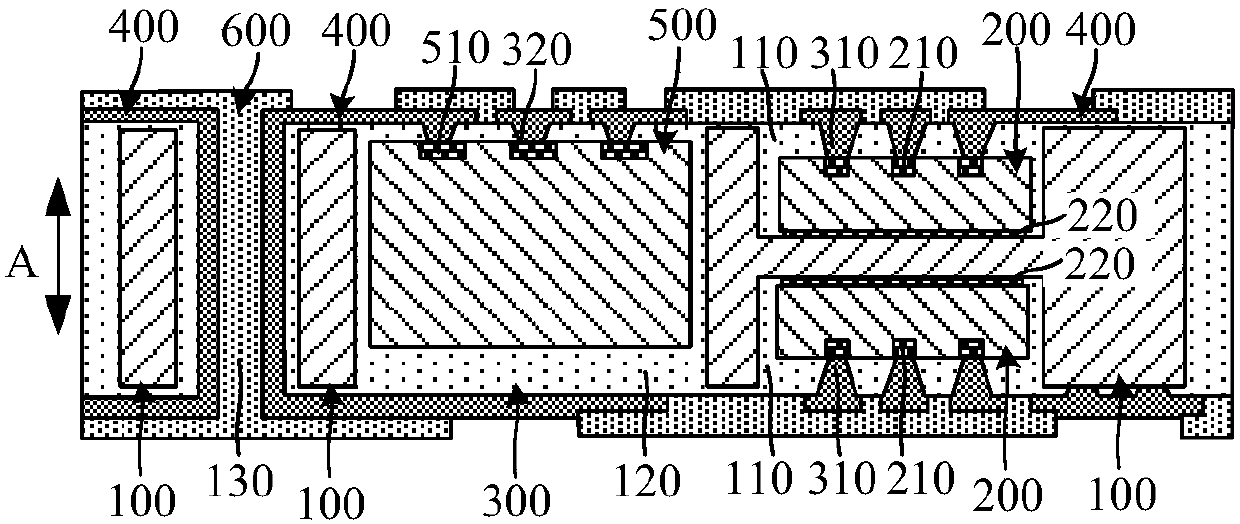

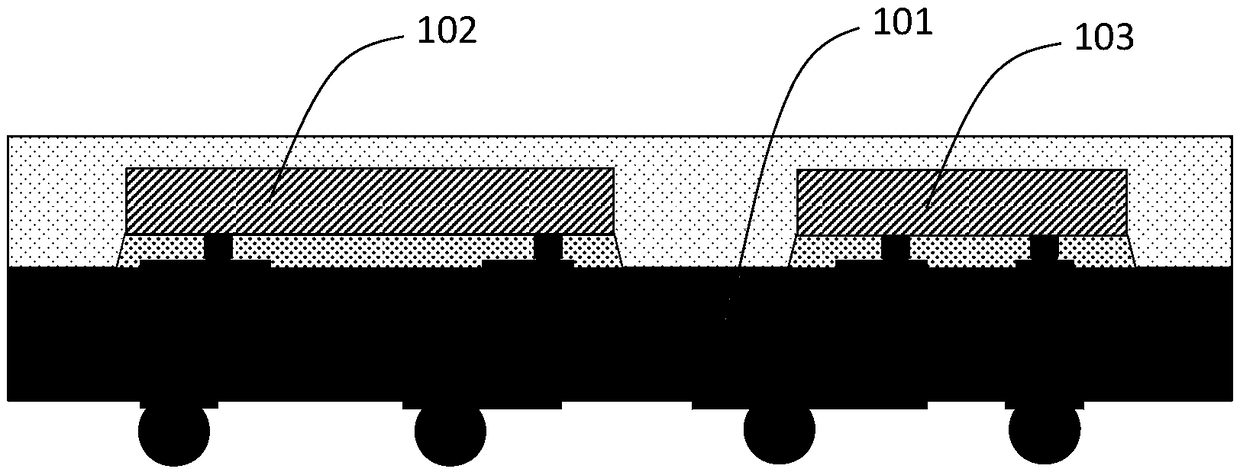

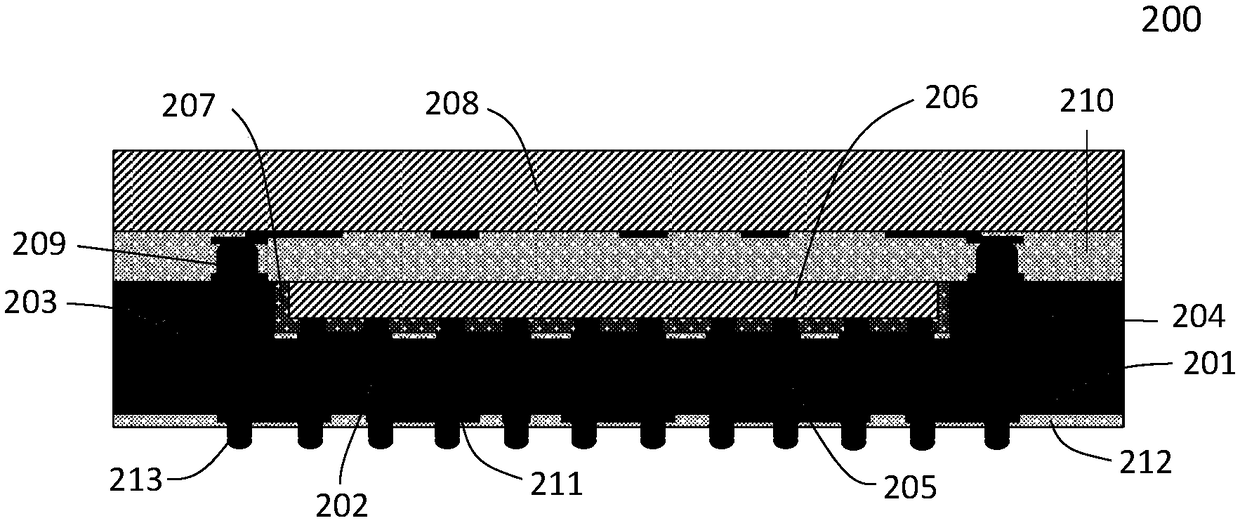

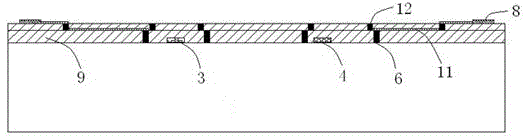

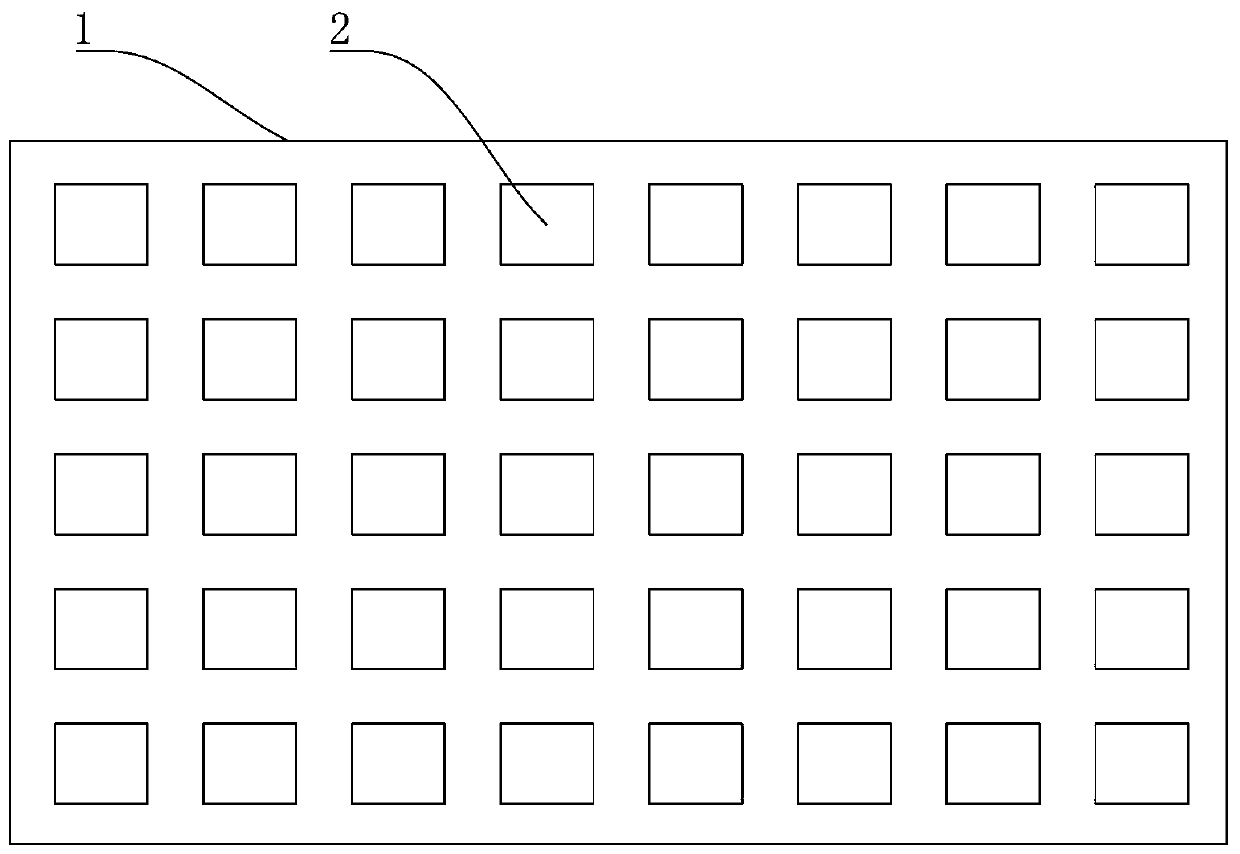

Embedded substrate

ActiveCN107611114AHighly integratedImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesState of artComputer science

The invention relates to the technical field of integrated circuits, and discloses an embedded substrate. The embedded substrate is used for solving a problem that an embedded substrate limits the further improvement of the packaging integration degree in the prior art because all chips of the embedded substrate occupies a bigger space and the reliability of products is lower. The embedded substrate comprises a substrate, wherein two sides of the substrate in the thickness direction are respectively provided with at least one first cavity and at least two first electronic devices, and each first electronic device is corresponding to one first cavity; packaging layers which are respectively disposed in each first cavity and respectively wrap the first electronic devices in the first cavities, and is provided with a plurality of first connection holes, wherein each first connection hole is corresponding to one pin of one first electronic device, and is connected with a corresponding pin;and a conductive circuit layer, wherein a part of the conductive circuit layer is disposed in the first connection holes to be connected with the pins corresponding to the first connection holes.

Owner:HUAWEI DIGITAL POWER TECH CO LTD

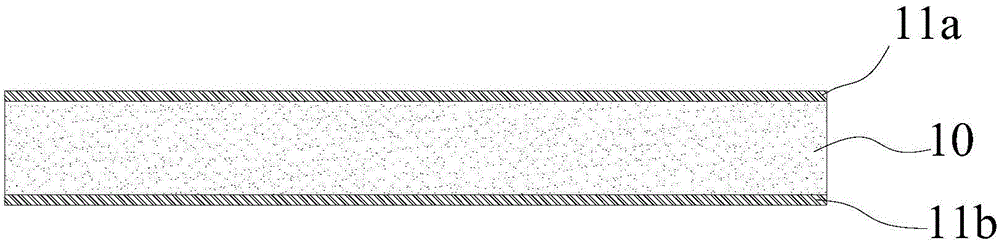

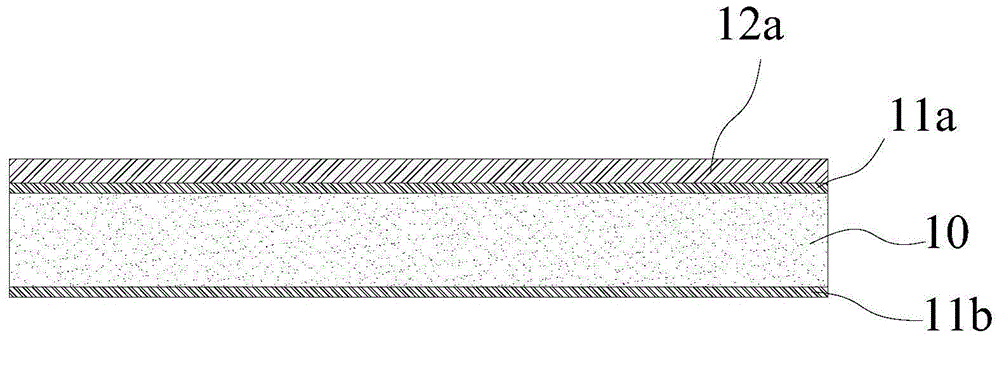

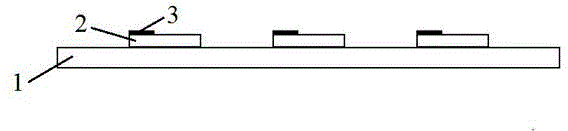

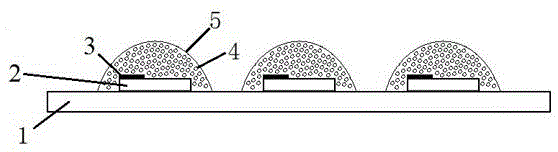

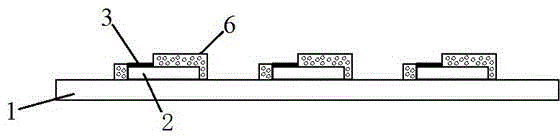

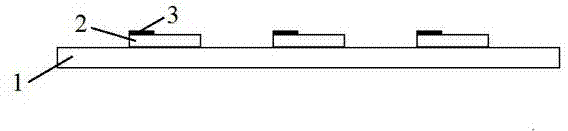

Integrated preparation method for LED fluorescent powder coating

The invention discloses an integrated preparation method for an LED fluorescent powder coating, which belongs to the photoelectric technical field. The method comprises the following steps: (1), preparing fluorescent powder and sensitive colloid dispersion; (2), spinning the fluorescent powder to form a fluorescent powder-sensitive colloid dispersion coating; (3), obtaining fluorescent powder-sensitive colloid dispersion coating patterns in required shapes and thickness through exposure and development; (4), displacing a fluorescent powder dispersion medium; and (5), removing a coating residue on the surface of an electrode, and showing a chip pattern. The invention provides a wafer level packaging fluorescent powder coating slurry method and a realization method (cleaning and exposing) of the chip electrode pattern, and the problem of applying the fluorescent powder coating technology into LED chip integrated package to realize the separation of the electrode pattern and the fluorescent powder coating in the prior art is solved.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

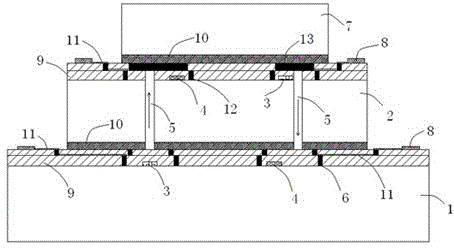

A 3D system integrate structure and a manufacturing method thereof

ActiveCN109003961AReduce depthImprove package integrationSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical and Electronics engineering

The invention discloses a 3D system integration structure, comprising: an adapter board; A first silicon through hole arranged on the front face of the adapter board; A second silicon through hole arranged on the front face of the adapter board; A cavity arranged on the back surface of the adapter plate; A first relayout wiring layer and a pad arranged on a bottom surface of the cavity, the firstrelayout wiring layer and the pad being electrically connected with the first silicon via; A first chip disposed within the cavity, the first chip electrically connected to the first relayout wiring layer and the pad; A plastic filling layer arranged around the first chip and having a gap between the bottom and the adapter board; A second chip arranged on the back surface of the adapter board, thesecond chip being electrically connected to the second silicon through hole; A second relayout wiring layer disposed on a front face of the adapter board; And a welding structure provided on the front face of the adapter plate, the welding structure being electrically connected to the second relayout wiring layer.

Owner:NAT CENT FOR ADVANCED PACKAGING

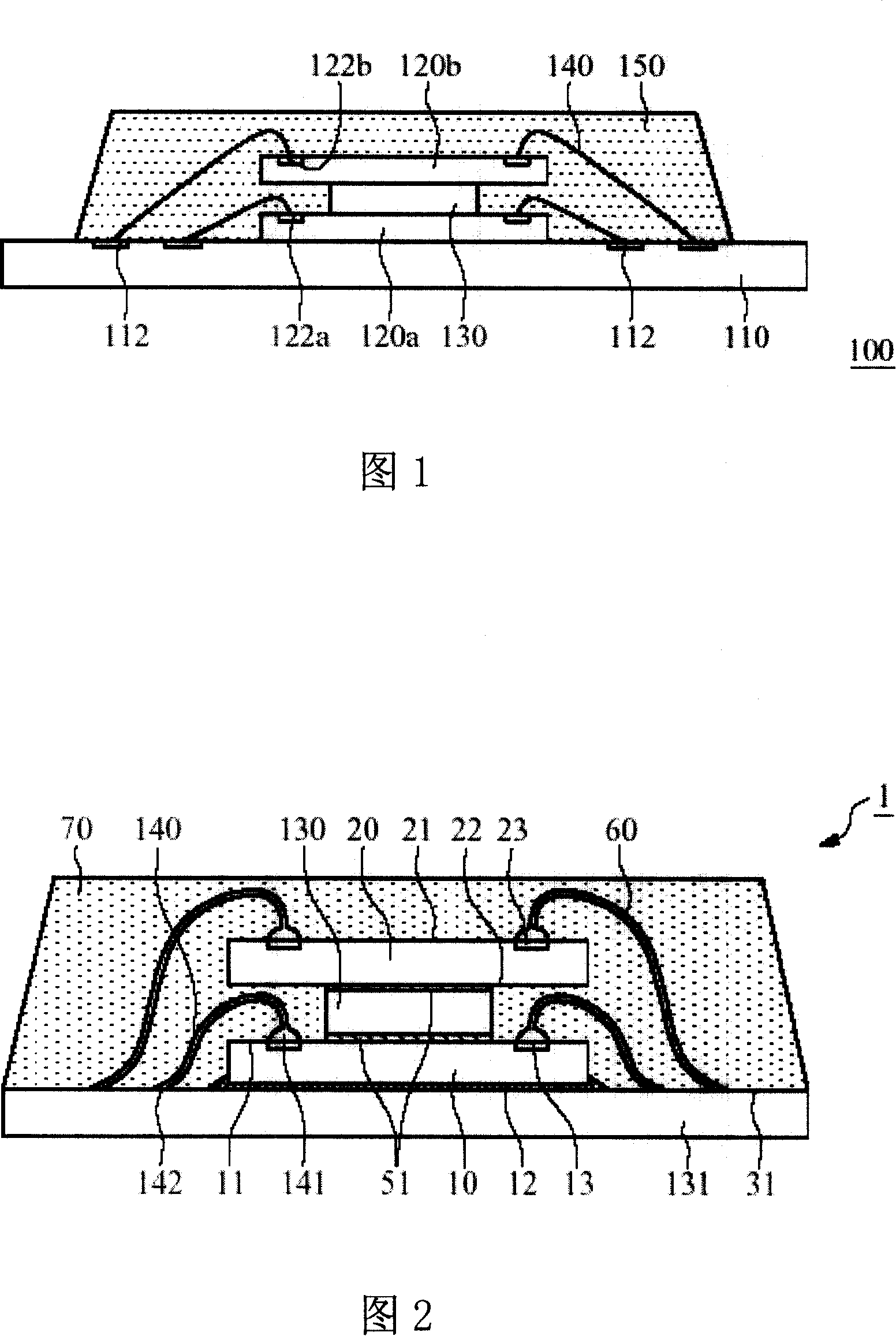

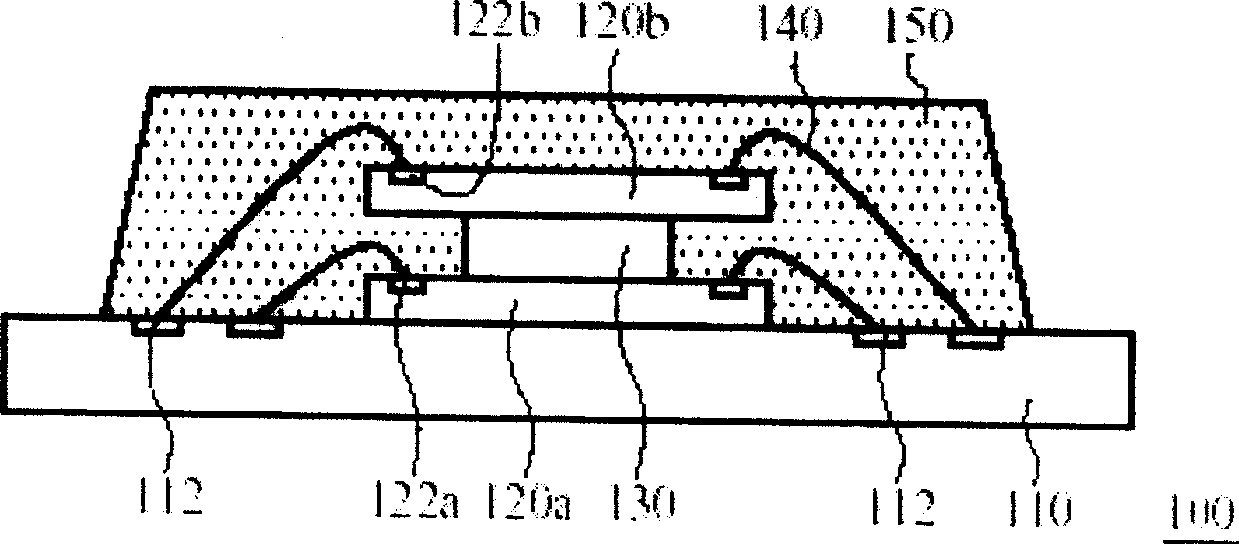

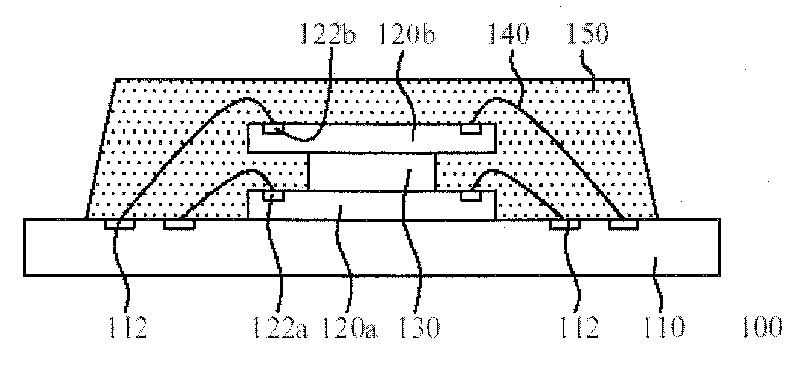

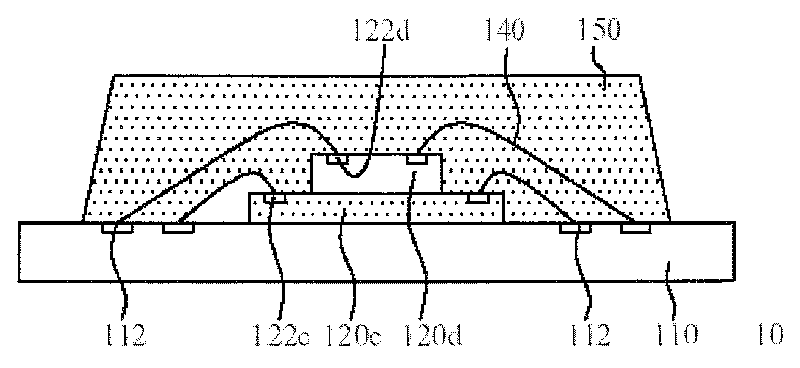

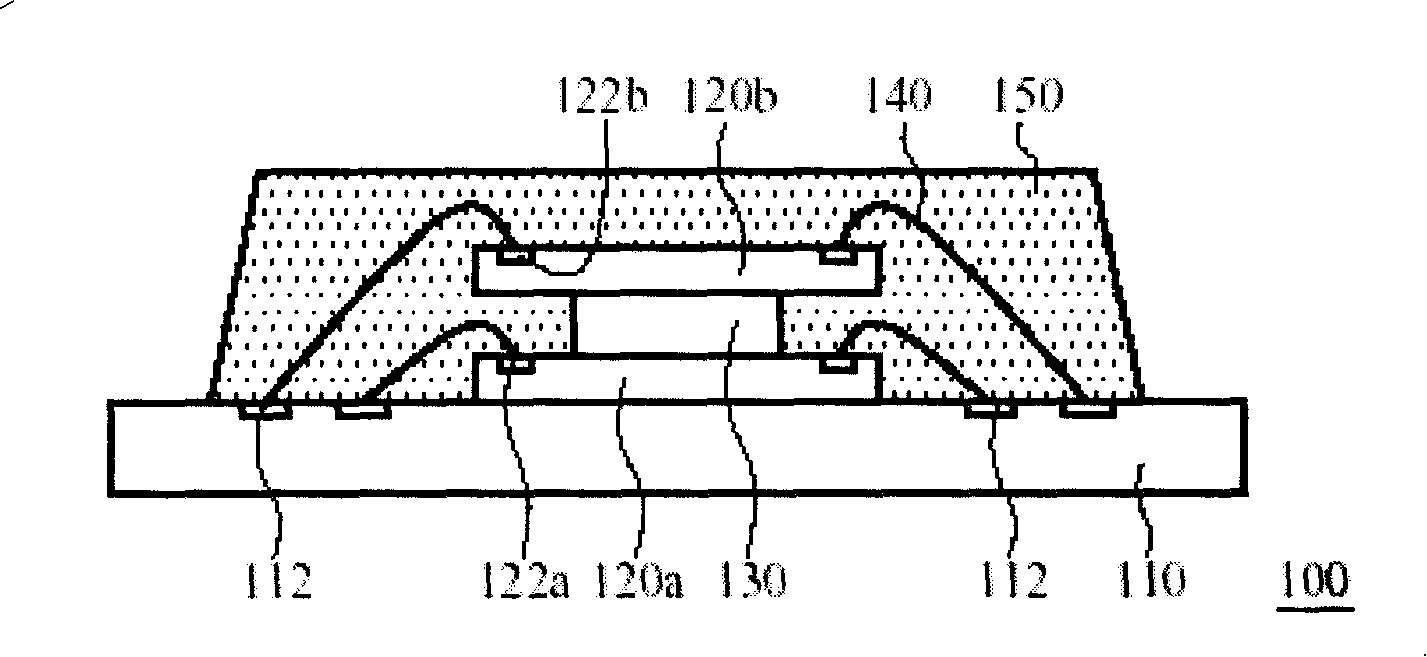

Multi-chip stacking type packaging structure

InactiveCN101131992AImprove package integrationThe overall thickness is thinSemiconductor/solid-state device detailsSolid-state devicesChip stackingMetal

The present invention provides a multi-chip-stacked package, and includes: a substrate set with several metal terminals and a multi-chip-stacked package are provided; the multi-chip-stacked package is fixed on substrate, of which active surface of each chip is set with several welding pads, and each chip is set with insulating layer on its back; a clinging layer combines the active surface of each chip and the insulating layer set on the back of the other chip to form stack structure; several metal wires joins the several welding pads on the several chips and the several metal terminals on the substrate.

Owner:CHIPMOS TECH INC

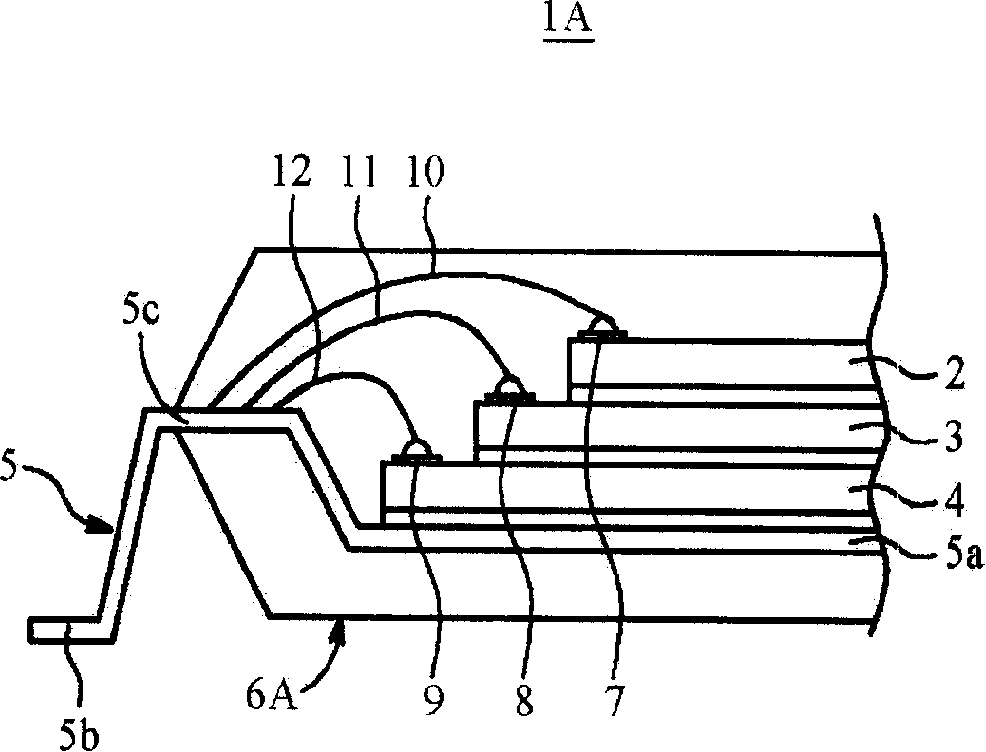

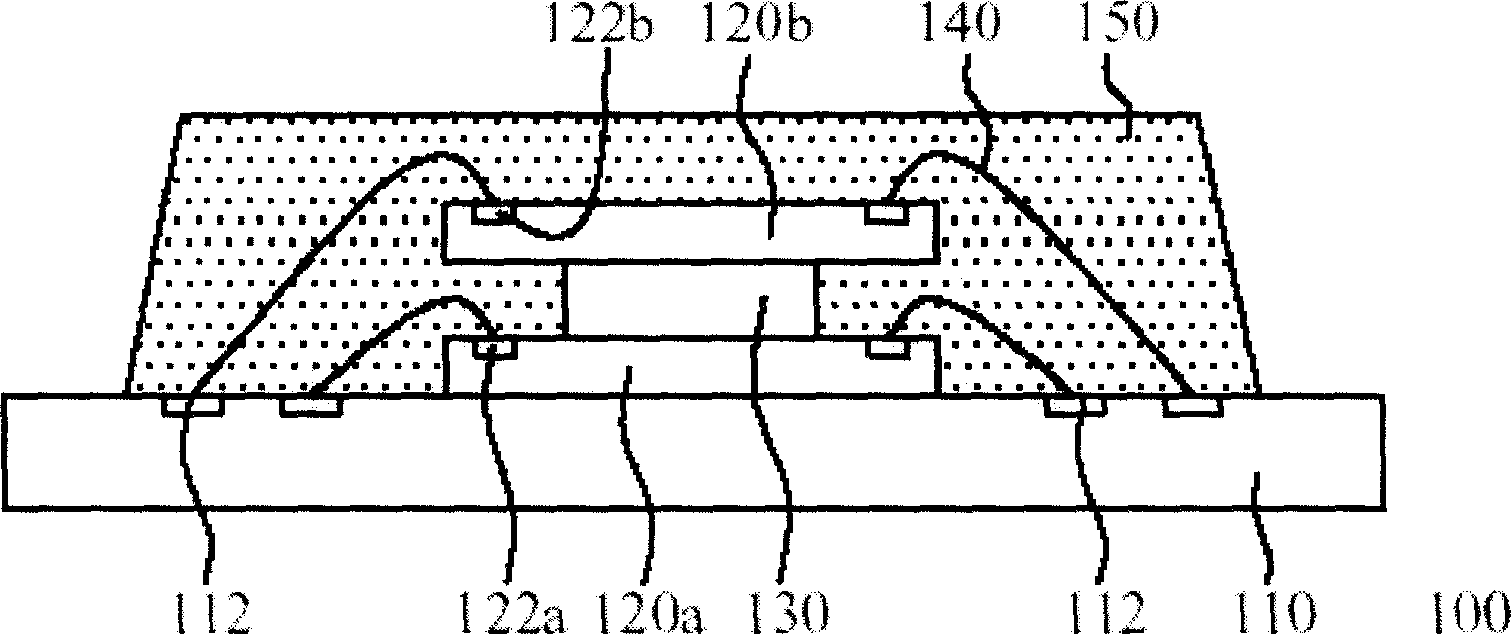

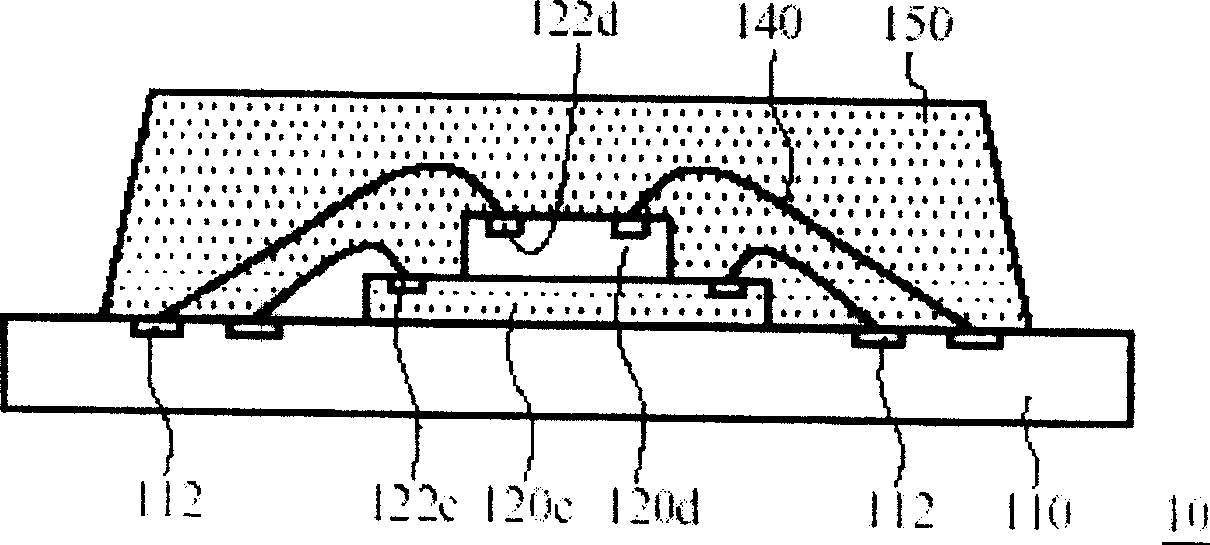

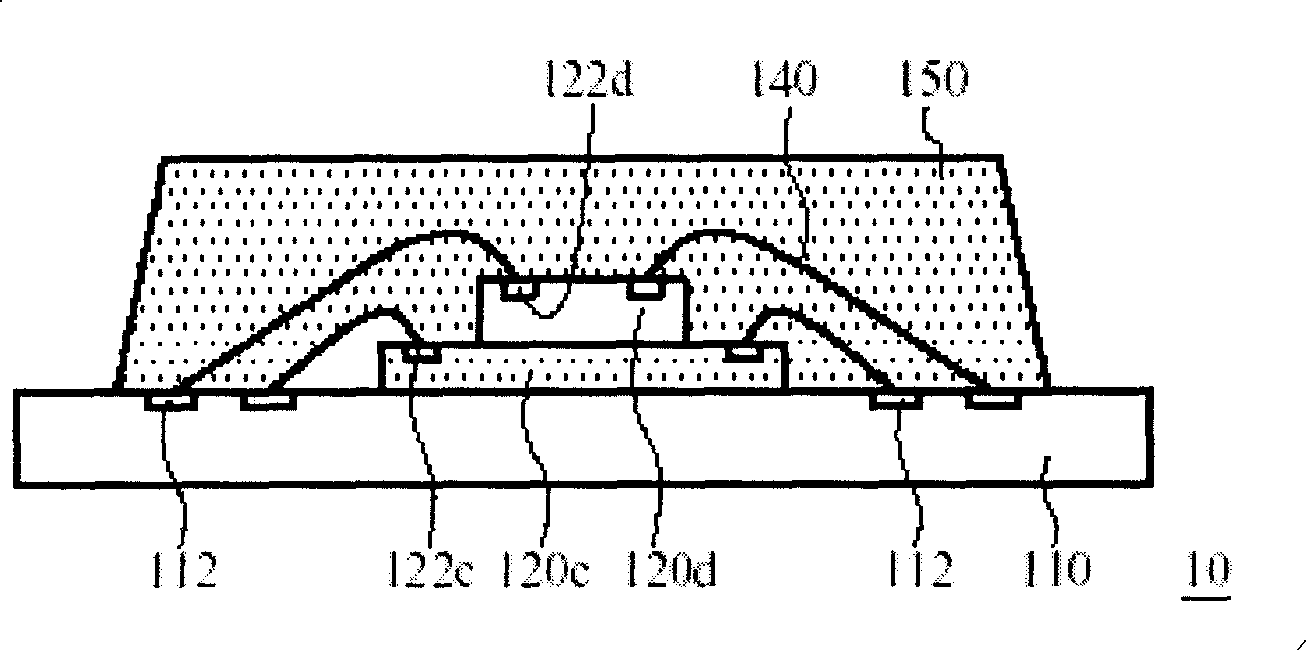

Multi-chip stack packaging structure with asymmetric conductive wire rack

ActiveCN101174614AImprove package integrationThe overall thickness is thinSemiconductor/solid-state device detailsSolid-state devicesSealantChip stacking

The invention relates to a stacked chip packaging structure, comprising a wire rack, wherein, the wire rack comprises a plurality of internal pins and a plurality of external pins; the internal pins comprise a plurality of first parallel internal pin clusters and second parallel internal pin clusters, the tail ends of the first internal pin clusters and the second internal pin clusters are arranged oppositely with an interval; the tail ends of the first internal pin clusters and the tail ends of the second internal pin clusters have different vertical height due to the sink-arranged structure of the first internal pin clusters; the multi-chip stacked structure is connected fixedly with the first internal pin clusters; the metal welding points on the edge of the same side of the multi-chip stacking structure are connected electrically with the first internal pin clusters and the second internal pin clusters via a plurality of metal wires; the multi-chip stacked structure and the internal pins are packaged with sealant; and the packaging structure is provided with a top surface and a bottom surface.

Owner:CHIPMOS TECH INC

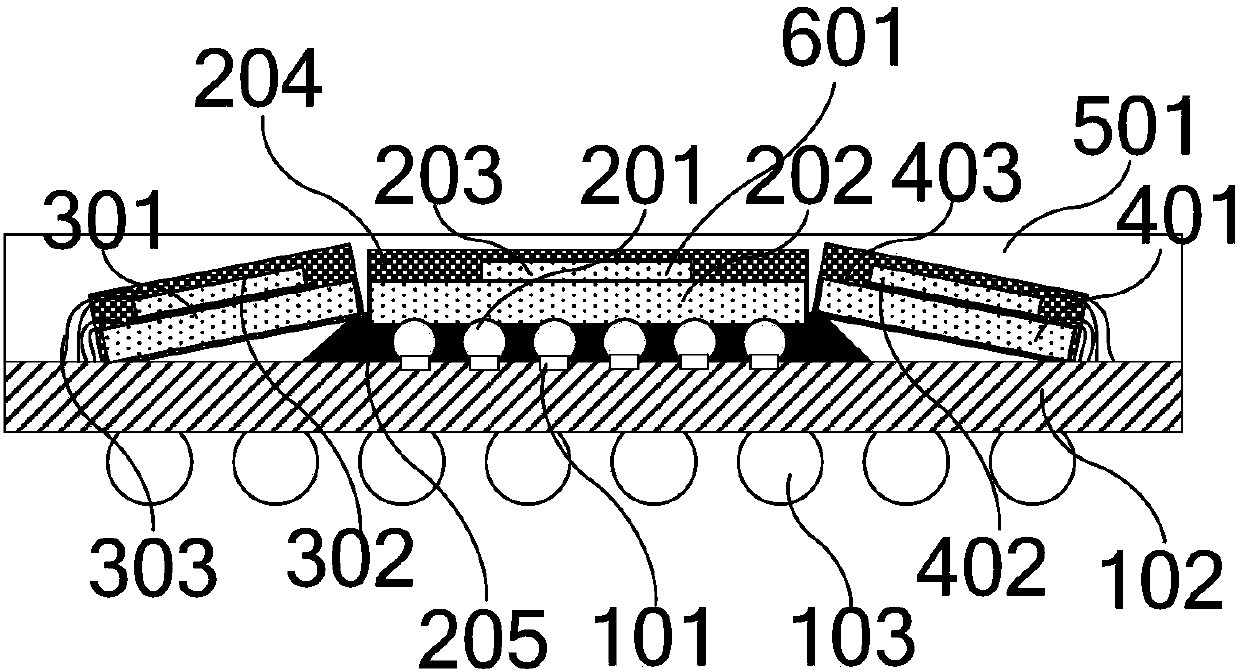

Flexible packaging structure and preparation method thereof, and wearable equipment

ActiveCN108022887AImprove package integrationGuaranteed Signal Integrity RequirementsSemiconductor/solid-state device detailsSolid-state devicesBiomedical engineering

The invention discloses a flexible packaging structure which comprises a flexible packaging substrate, a first hard packaging body and at least one second hard packaging body; the first hard packagingbody comprises at least one first chip and a hard packaging material for wrapping the at least one first chip; the second hard packaging body comprises at least one third chip and a hard packaging material for wrapping the at least one third chip; and the first hard packaging body and the at least one second hard packaging body are arranged in the upper surface of the flexible packaging substrate. A flexible packaging material is further included, and packages the first and second hard packaging bodies at least. The invention also discloses a preparation method of the flexible packaging structure and wearable equipment.

Owner:SANECHIPS TECH CO LTD

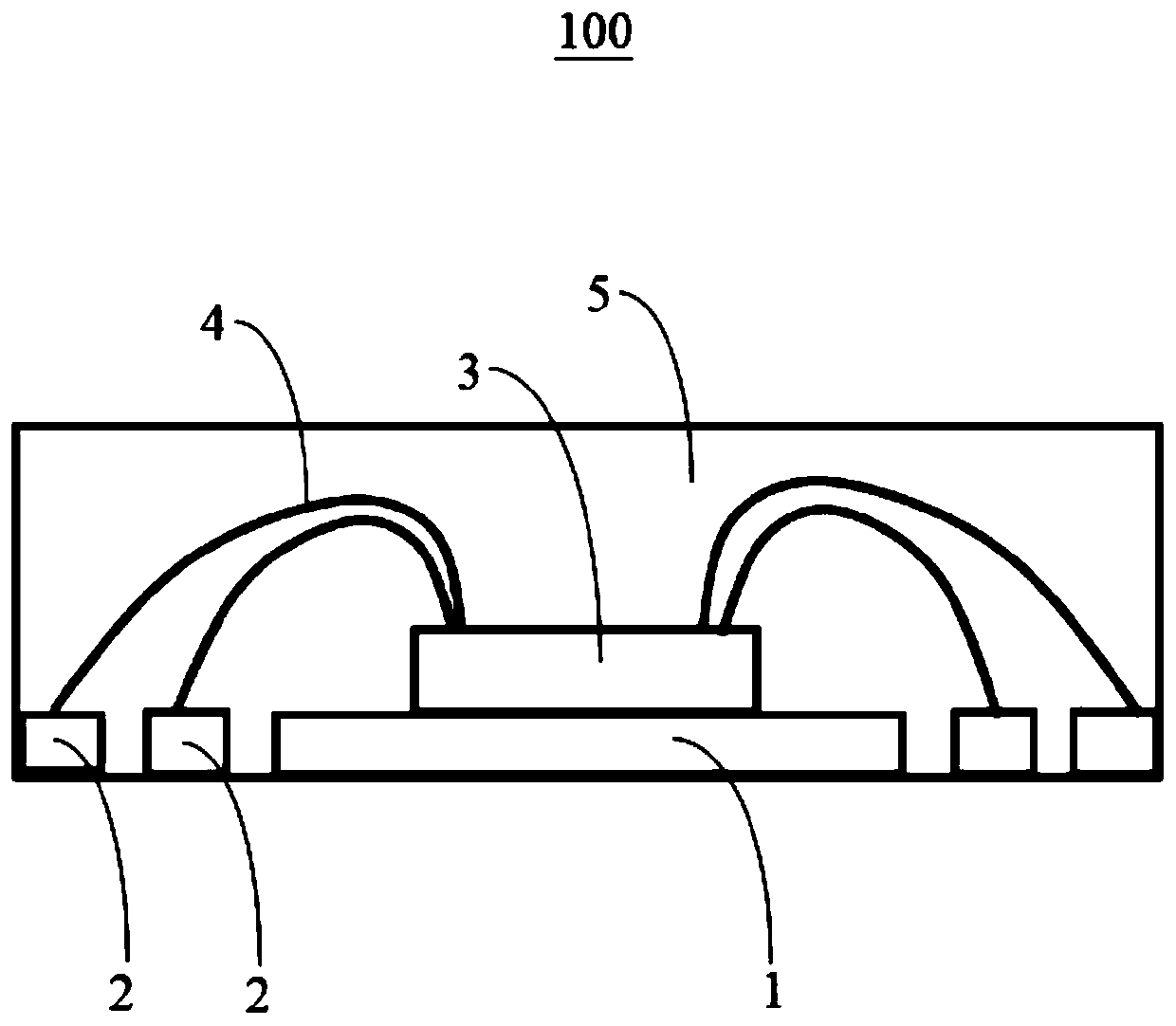

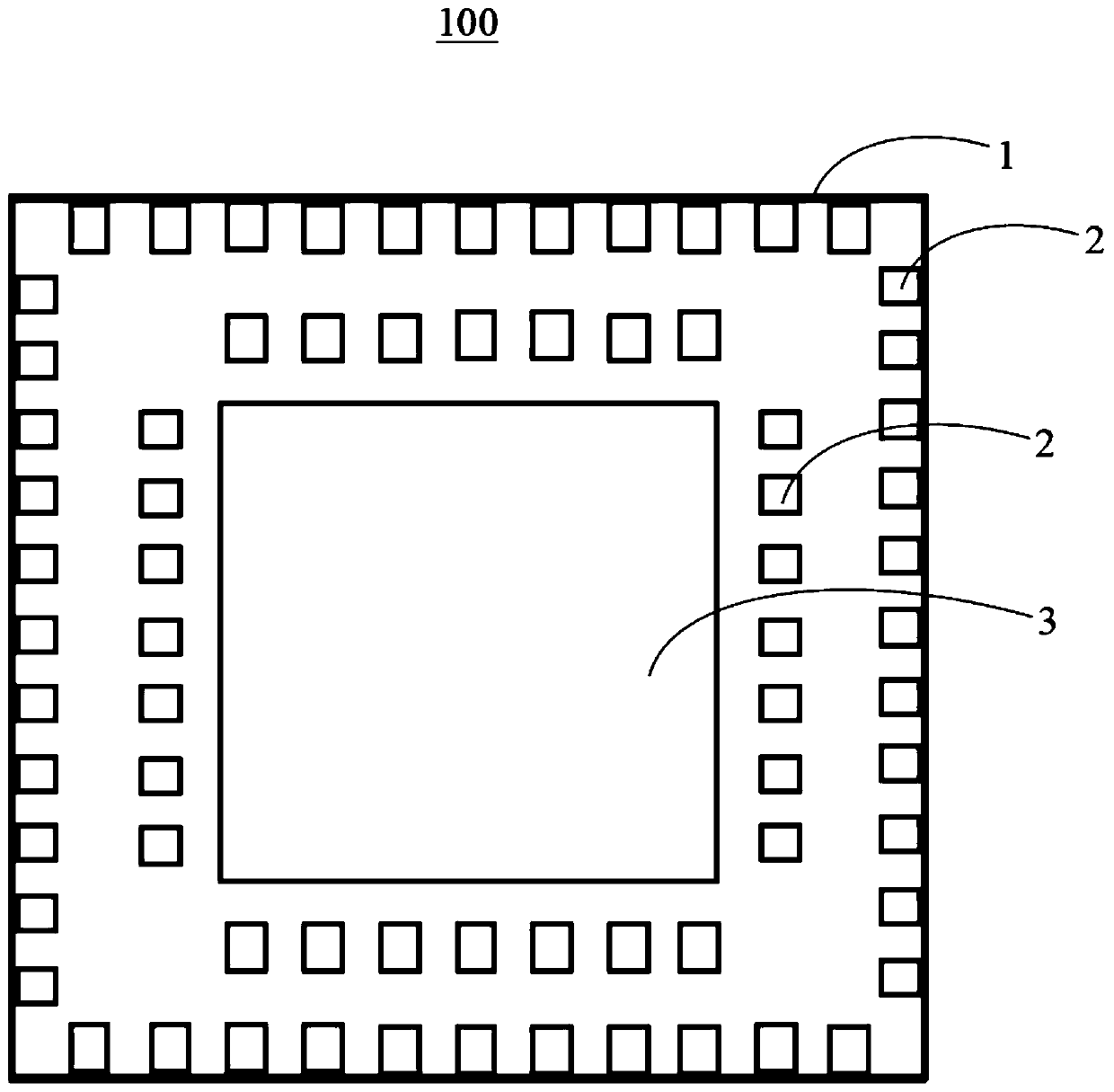

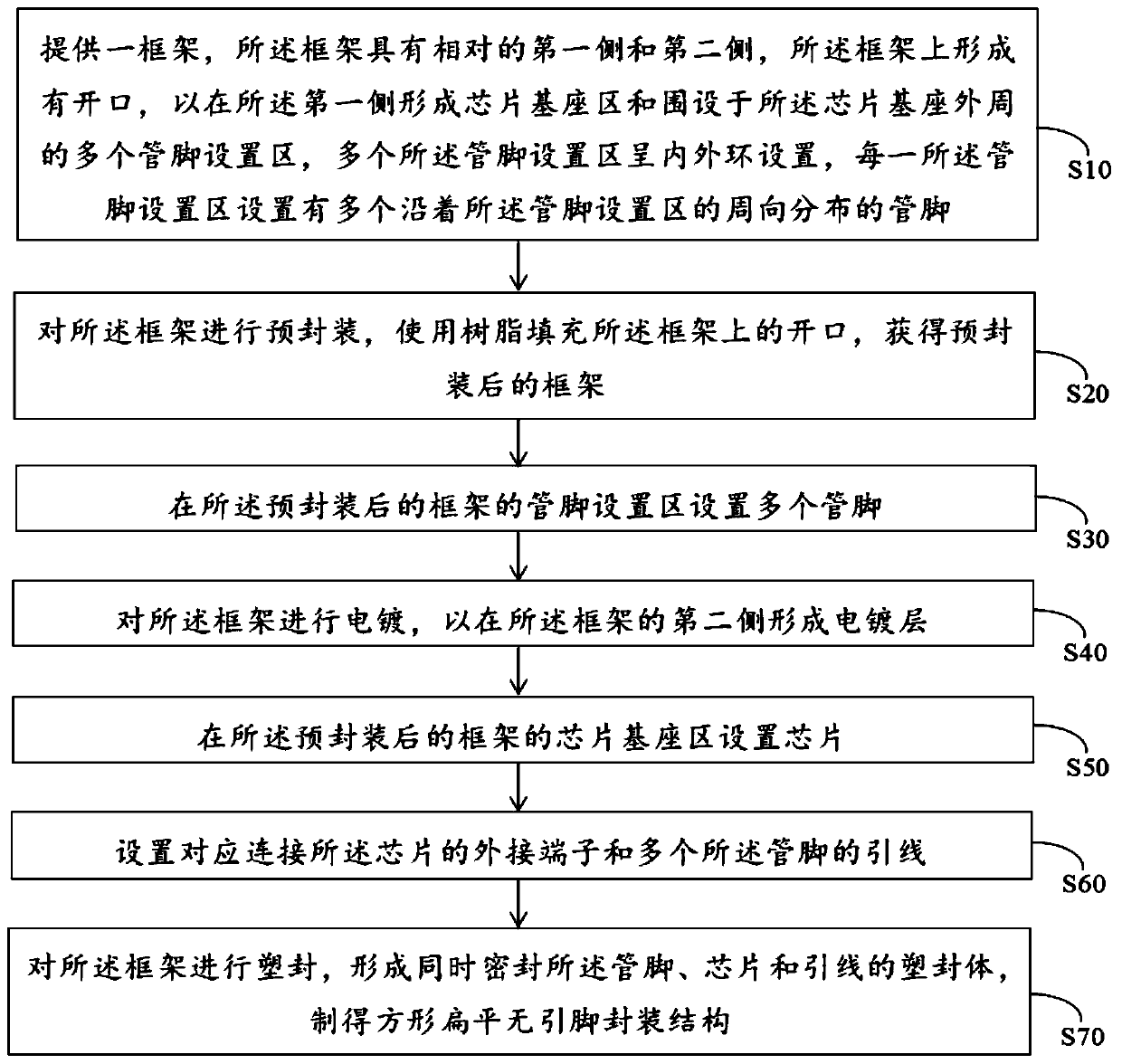

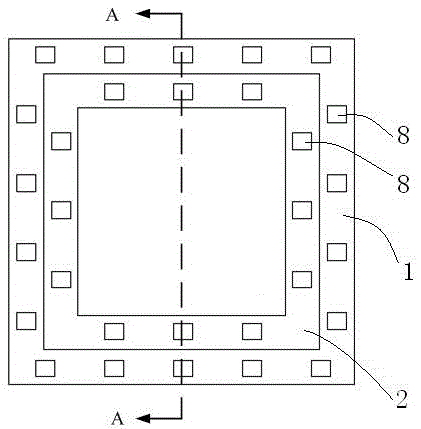

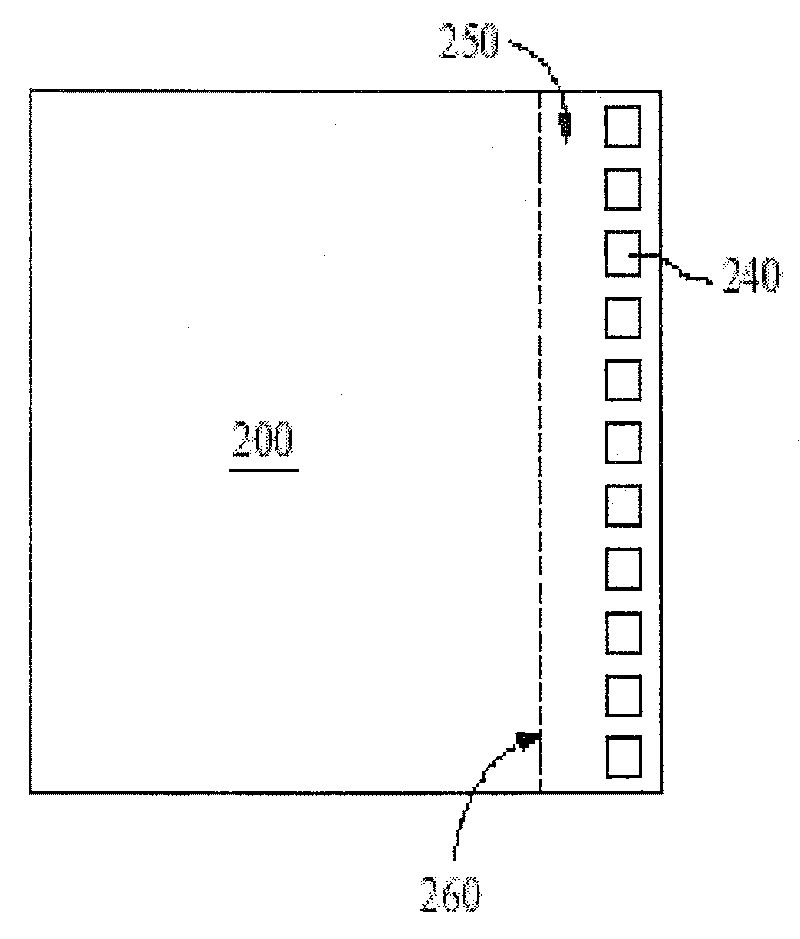

Square flat pin-free packaging structure, preparation method thereof and electronic device

InactiveCN111276461AHigh densityImprove package integrationSemiconductor/solid-state device detailsSolid-state devicesPlastic packagingStructural engineering

The invention discloses a square flat pin-free packaging structure, a preparation method thereof and an electronic device. The square flat pin-free packaging structure comprises a frame, a chip, leadsand a plastic packaging body, wherein the frame is provided with a first side and a second side which are opposite to each other, the first side is provided with a chip base and a plurality of pin setting areas arranged at the periphery of the chip base in a surrounding manner, the plurality of pin setting areas are arranged in an inner and outer ring manner, and each pin setting area is providedwith a plurality of pins distributed along the circumferential direction of the pin setting area; wherein the chip is arranged on the chip base; the pin is correspondingly connected with an externalterminal of the chip and the plurality of pins; the plastic package body is arranged on the frame and seals the pins, the chip and the pins at the same time. According to the invention, the pluralityof pin groups arranged in the inner and outer rings are arranged around the chip, so that the pin density of the square flat pin-free packaging structure is improved, and the improvement of the packaging integration level is facilitated.

Owner:QINGDAO GOERTEK MICROELECTRONICS RES INST CO LTD

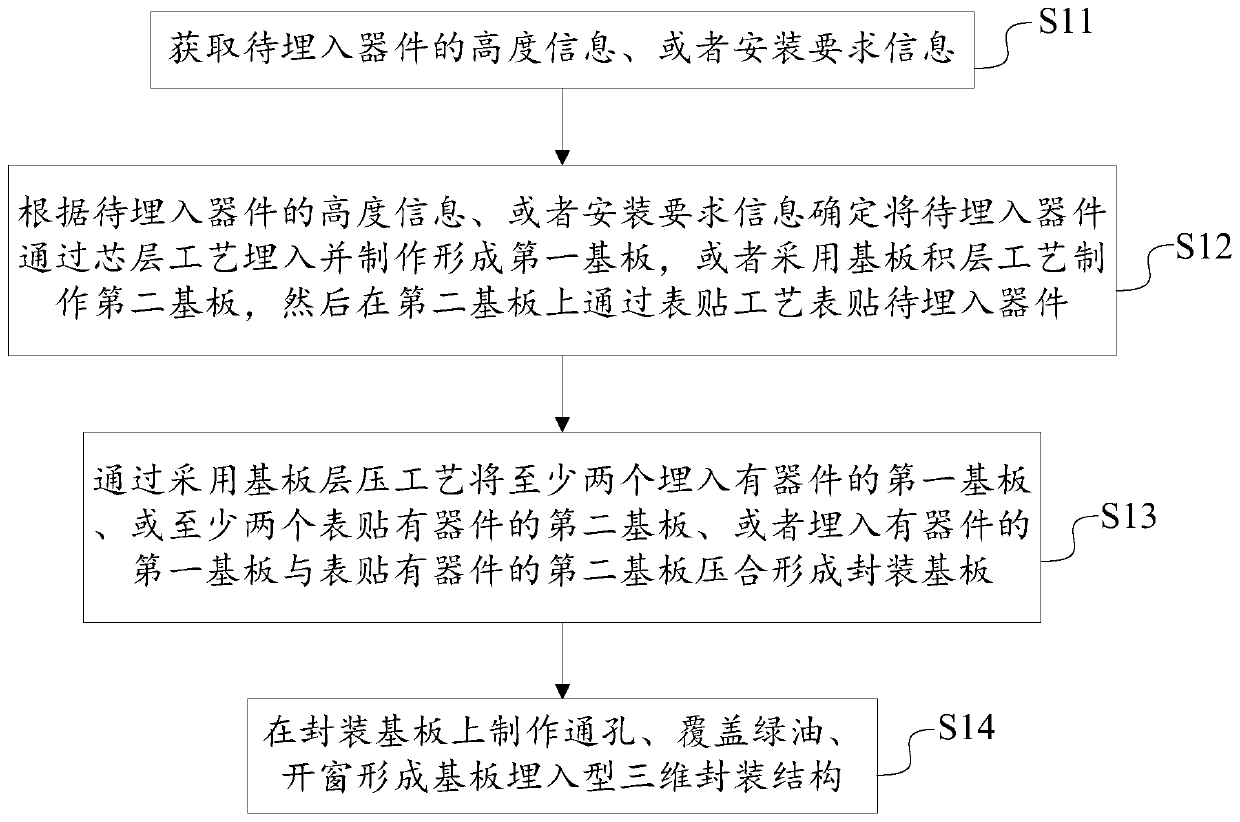

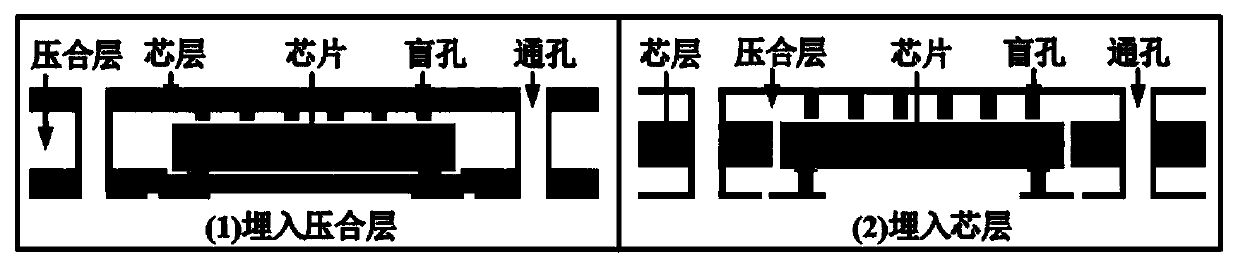

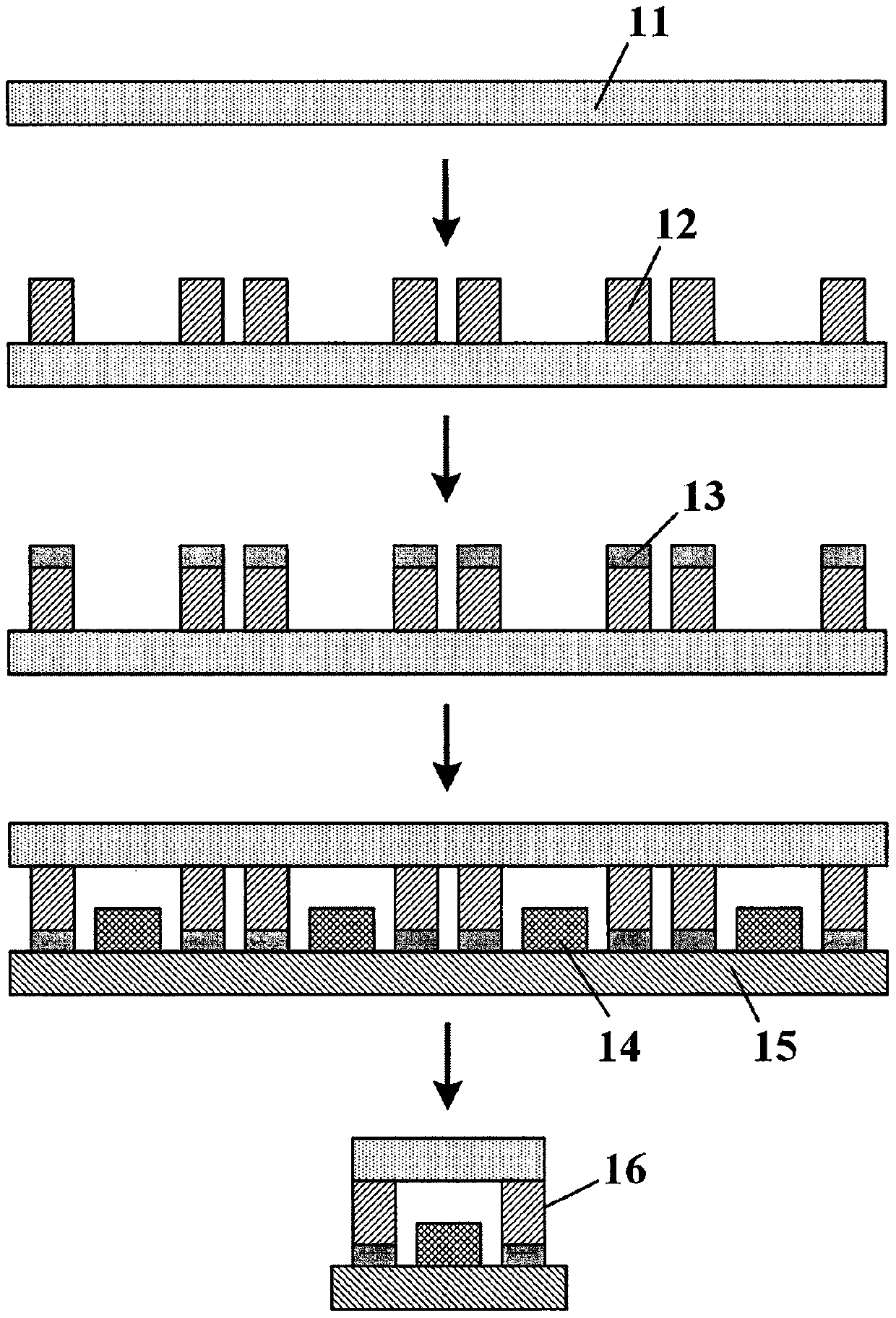

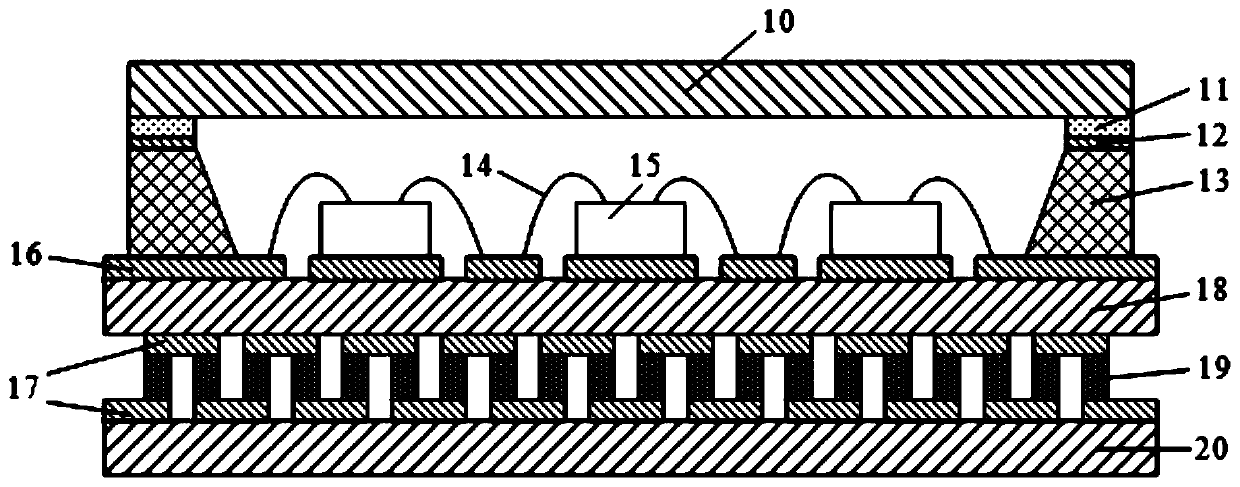

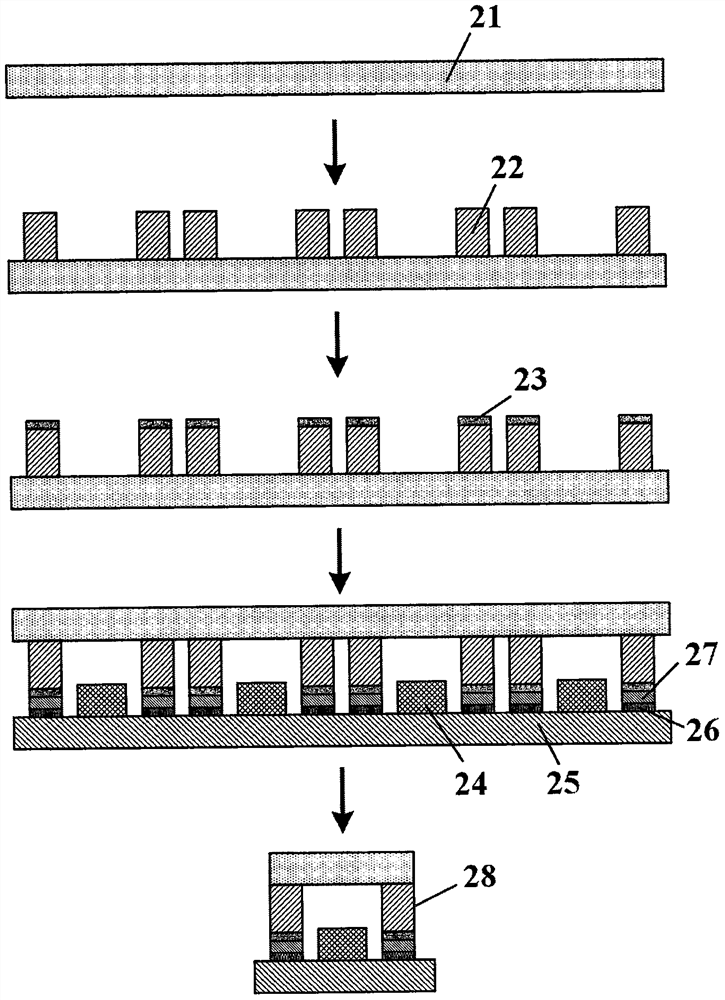

Substrate embedding type three-dimensional system-level packaging method and structure

ActiveCN109904082ASave spaceImprove package integrationSemiconductor/solid-state device detailsSolid-state devicesElectromagnetic interferenceMiniaturization

The invention provides a substrate embedding type three-dimensional system-level packaging method and structure; the method comprises the following steps that height information or installation requirement information of a to-be-embedded device is acquired; according to the height information or the installation requirement information, it is determined that the to-be-embedded device is embedded through a core layer process and is made to form a first substrate, or a second substrate is manufactured by adopting a substrate lamination process, and then the to-be-embedded device is attached to and mounted on the second substrate through a surface attaching process; at least two first substrates, or at least two second substrates or the first substrate and the second substrate are laminated to form a packaging substrate by adopting a substrate lamination process; a through hole is manufactured in the packaging substrate, and then green oil covering, and window opening are carried out to form the substrate embedding type three-dimensional packaging structure. According to the method, most of the space can be effectively saved on the surface, the packaging integration level is improved,and miniaturization is realized; and a natural electromagnetic shielding and isolation structure can be formed in the packaging structure, so that the electromagnetic interference performance of thesystem is effectively improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

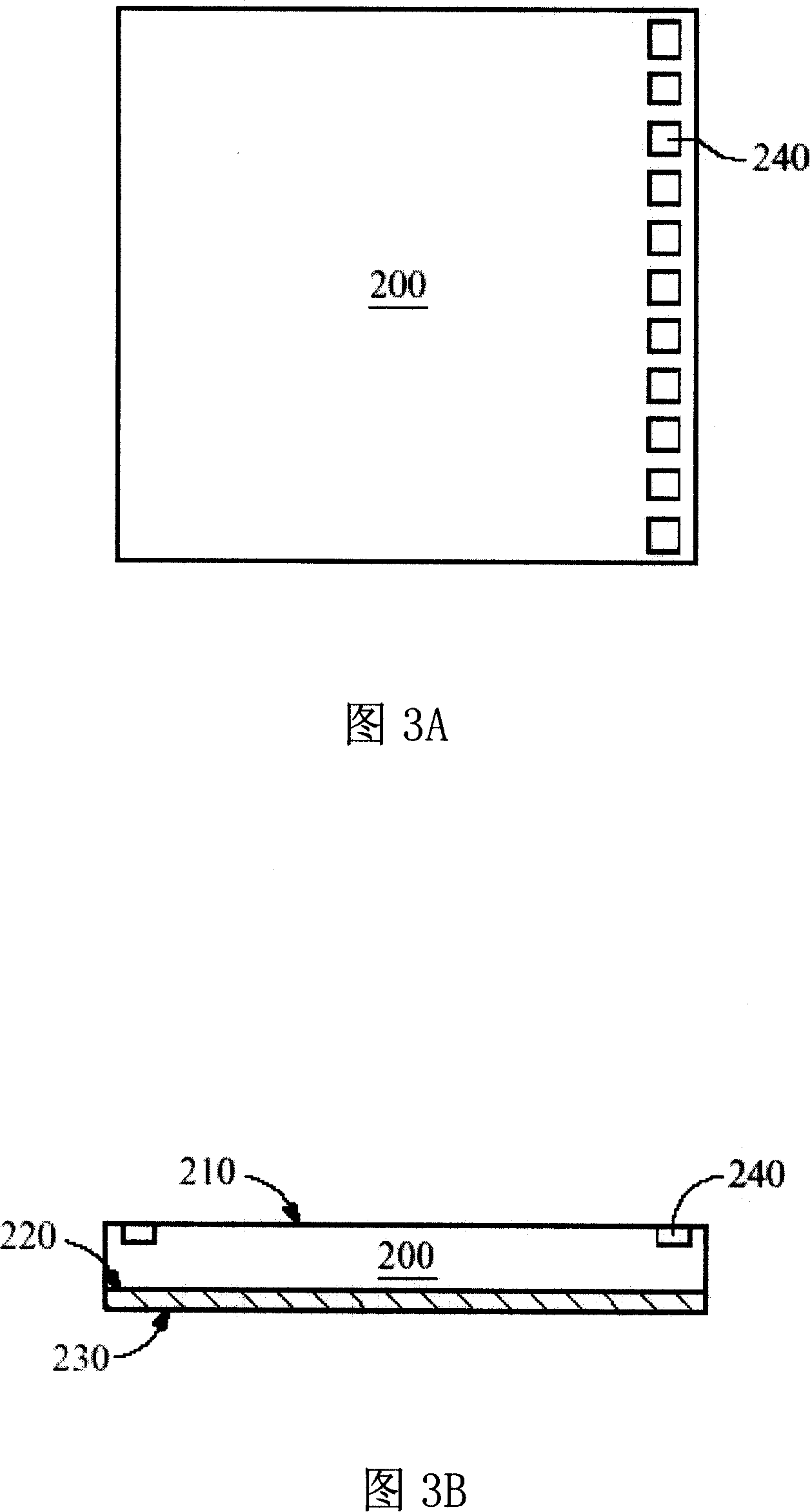

Full-inorganic ultraviolet LED wafer-level package method

ActiveCN109888081AMeet long-term reliability requirementsImprove package integrationSemiconductor devicesGlass coverSurface mounting

The invention belongs to the technical field of semiconductor manufacturing, and discloses a full-inorganic ultraviolet LED wafer-level package method. The full-inorganic ultraviolet LED wafer-level package method comprises the steps of firstly, forming a plurality of glass paste rings on a glass cover plate by a printing or 3D printing technology, and obtaining a plurality of glass cavity structures by low-temperature sintering; secondly, surface-mounting a plurality of ultraviolet LED chips onto a cooling substrate; thirdly, achieving reliable bonding of the glass cavities in the glass coverplate and the cooling substrate by inorganic paste or a metal welding material; and finally, cutting to obtain a full-inorganic ultraviolet LED package product. The invention also discloses a corresponding ultraviolet LED package structure. By the full-inorganic ultraviolet LED wafer-level package method, the problems of ultraviolet aging and failure of an organic package material are effectivelyprevented, the long-term reliability of an ultraviolet LED device is improved, the ultraviolet LED package integration is improved, and the package cost is reduced.

Owner:武汉高星紫外光电科技有限公司

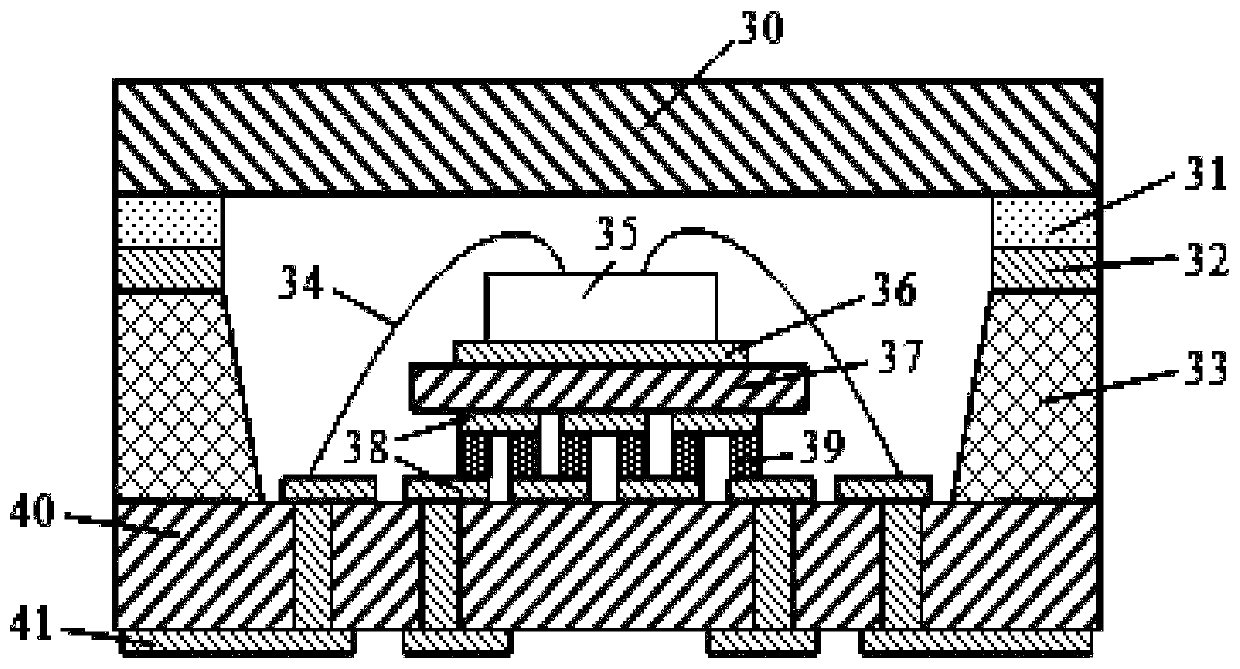

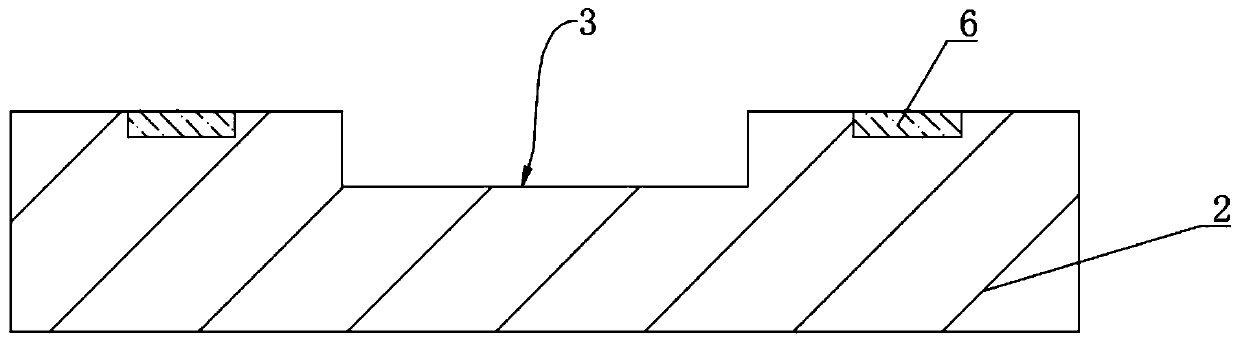

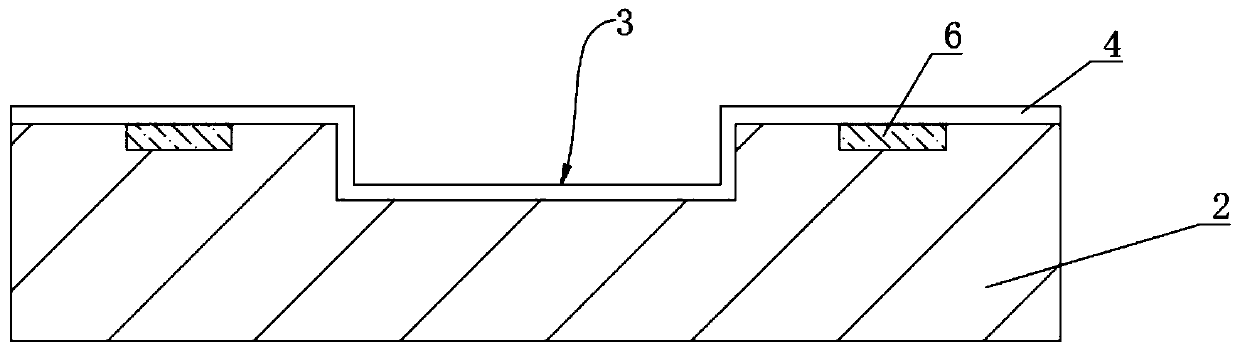

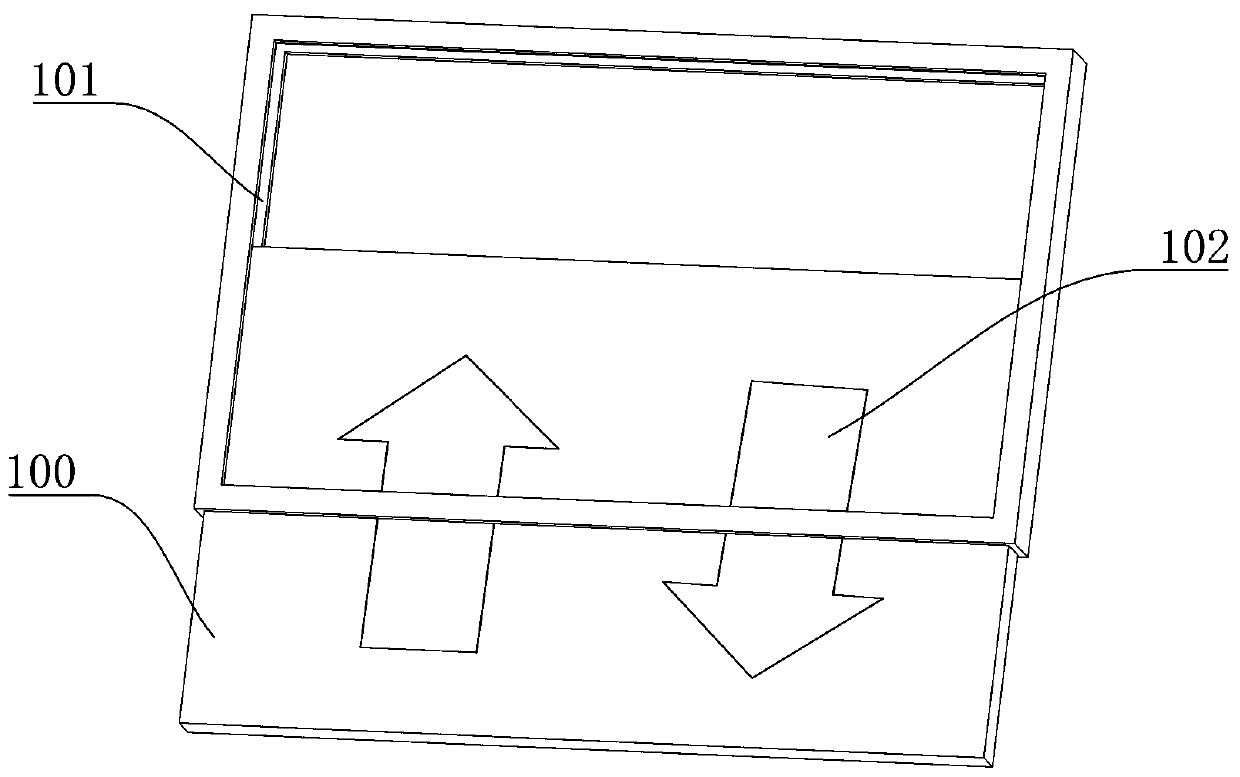

Airtight packaging structure of integrated thermoelectric refrigerator and preparation method thereof

ActiveCN111403376AImprove cooling effectReduce soldering interfaceSemiconductor/solid-state device detailsSolid-state devicesCeramic substrateComposite material

The invention belongs to the related technical field of microelectronic packaging, and discloses an airtight packaging structure of an integrated thermoelectric refrigerator and a preparation method thereof. The airtight packaging structure of the integrated thermoelectric refrigerator comprises a packaging cover plate, a chip, the thermoelectric refrigerator and a three-dimensional ceramic substrate, a cavity is formed in the three-dimensional ceramic substrate, the chip is arranged in the cavity, and the packaging cover plate is in airtight connection with the three-dimensional ceramic substrate so as to package the chip in the cavity; the three-dimensional ceramic substrate is connected with the thermoelectric refrigerator, and the three-dimensional ceramic substrate and the thermoelectric refrigerator share one ceramic substrate, so that the heat dissipation refrigerator and the three-dimensional ceramic substrate are combined to form an airtight packaging structure. According to the airtight packaging structure, the three-dimensional DPC ceramic substrate is used, and interconnection between the inside and the outside of the cavity is realized by utilizing the cavity structureand the vertical interconnection characteristic of the three-dimensional DPC ceramic substrate; the three-dimensional DPC ceramic substrate is used as a ceramic substrate of the TEC, that is, the thermoelectric refrigerator and the three-dimensional ceramic substrate share the ceramic substrate, so that one layer of ceramic substrate and one layer of welding interface are reduced, the heat dissipation capability of the device is improved, the thermal resistance can be reduced, and the packaging integration degree is improved.

Owner:HUAZHONG UNIV OF SCI & TECH

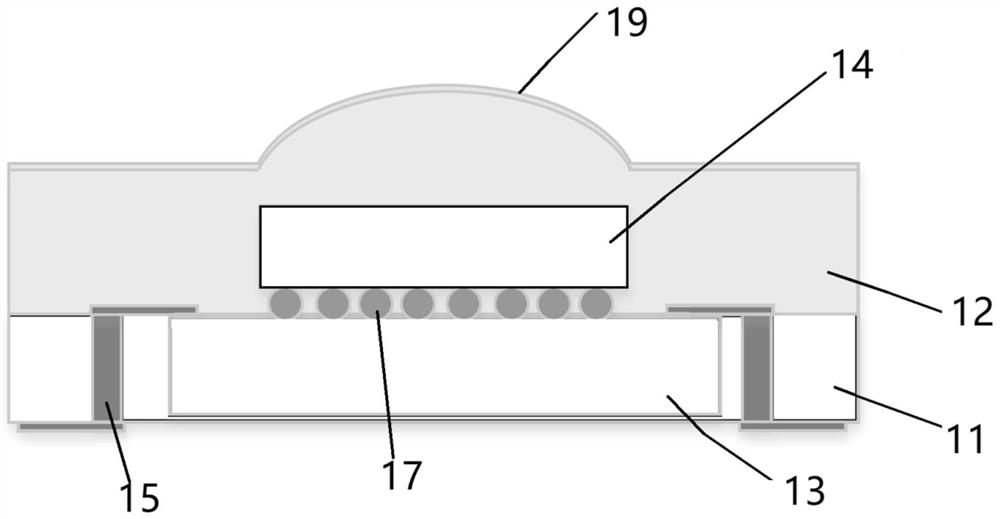

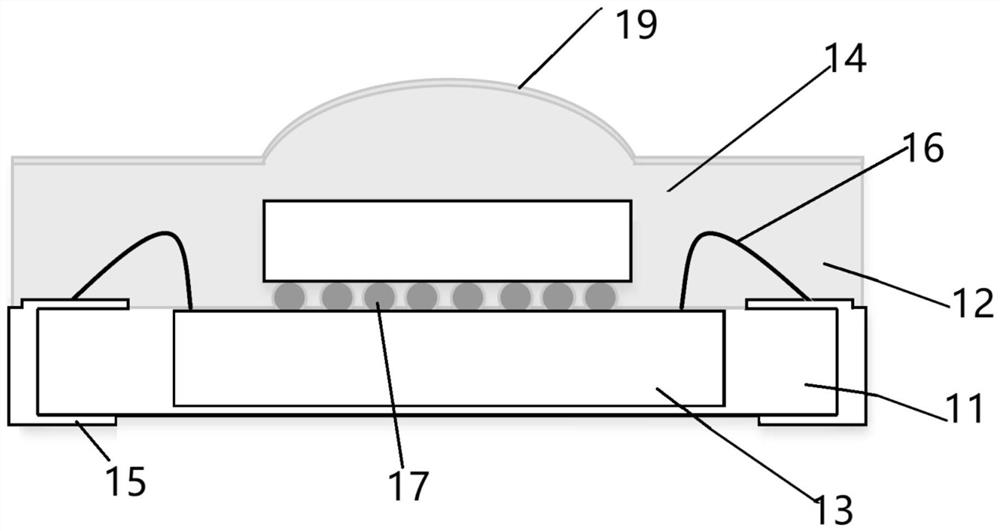

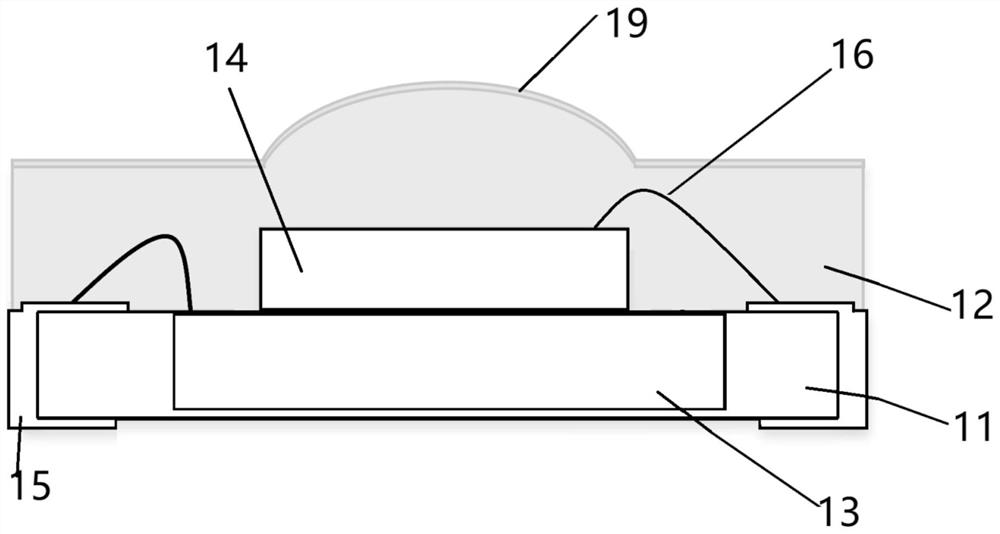

Laser radar chip packaging structure and packaging method

ActiveCN112820725AHighly integratedSmall sizeWave based measurement systemsSemiconductor/solid-state device detailsElectric propertiesEmbedded system

The invention provides a laser radar chip packaging structure and method, and the structure comprises an optical chip which is disposed in a first packaging body, wherein the first packaging body is provided with a lens shape; and an electric chip which is arranged in a second packaging body, wherein the second packaging body is internally provided with a first electric interconnection structure, the first electric interconnection structure leads out the electric property of the electric chip, and the first packaging body and the second packaging body are arranged through a lamination layer.

Owner:NAT CENT FOR ADVANCED PACKAGING

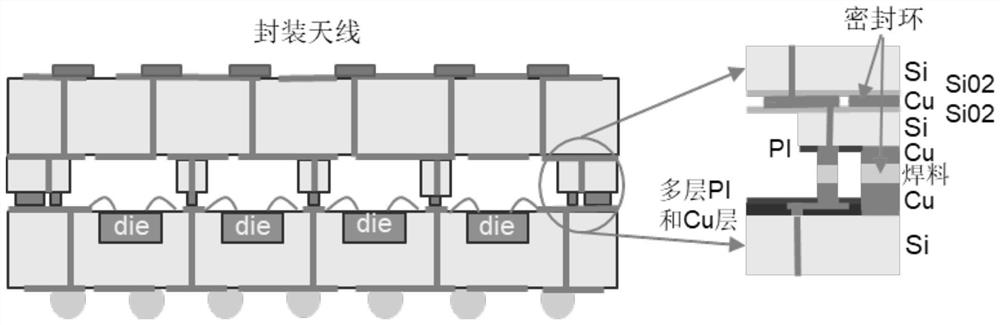

Optical communication interconnection txv 3D integrated packaging and packaging method

InactiveCN103745969BSimplify the integrated packaging processRealize interconnectionSemiconductor/solid-state device detailsSolid-state devicesCapacitanceElectronic systems

Owner:INST OF ELECTRONICS ENG CHINA ACAD OF ENG PHYSICS

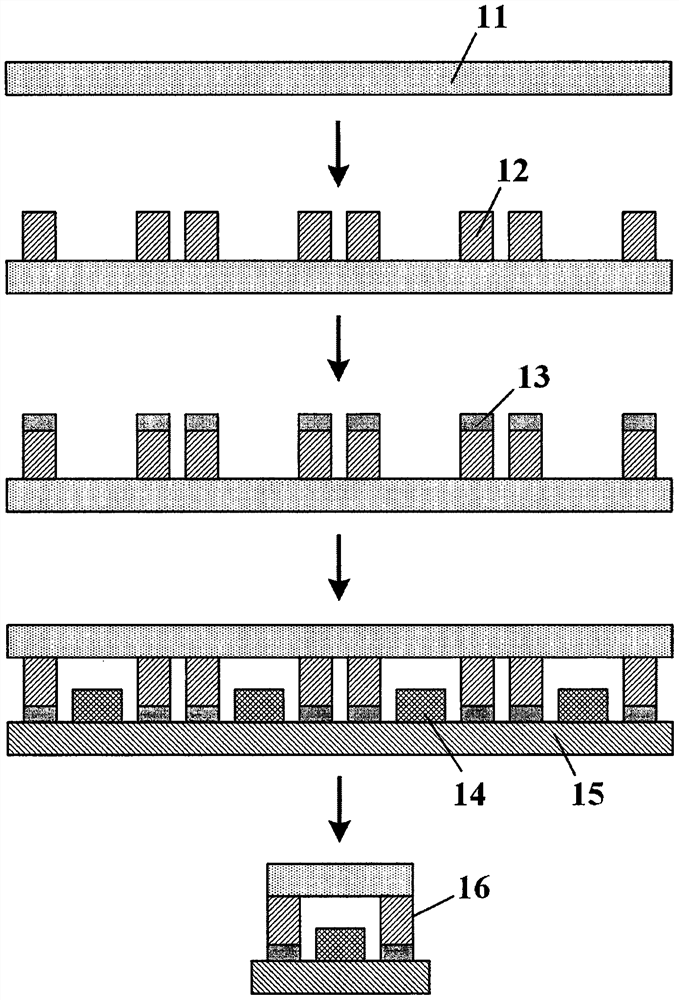

Fan-out type packaging method and fan-out type packaging structure of embedded chip

InactiveCN111048503AReduce power consumptionHigh speedSemiconductor/solid-state device detailsSolid-state devicesMechanical engineeringEmbedded system

The invention provides a fan-out packaging method of an embedded chip. The method can remarkably improve element density, has fewer process steps, can be realized by utilizing a fan-out packaging process, and can reduce production cost. The method comprises the following steps that: 1, a first chip and a second chip are provided, the second chip is slotted, and a functional region on the second chip is avoided during the slotting; 2, a layer of adhesive covers the slotted surface of the second chip and a formed slot; 3, the first chip is embedded into the slot of the second chip; 4, the firstchip and the second chip are covered with a layer of insulating resin, and the I / O ports of the first chip and the second chip are exposed; and 5, a rewiring layer is manufactured, the rewiring layeris connected to the I / O ports of the first chip and the second chip. In addition, the invention also provides a fan-out packaging structure of the embedded chip.

Owner:HUATIAN TECH KUNSHAN ELECTRONICS

Stacking chip encapsulation structure with multi-section bus bar in lead rack

ActiveCN101170104AImprove package integrationThe overall thickness is thinSemiconductor/solid-state device detailsSolid-state devicesHeight differenceLead frame

The invention provides a stacked chip encapsulation structure with a multi-stage collecting bar in a lead frame, which includes a lead frame consisting of a plurality of inner pin groups arranged relatively, a plurality of outer pin groups and a chip bearing seat, wherein, the chip bearing seat is arranged among a plurality of inner pin groups arranged relatively and forms height difference with the inner pin groups; the stacked chip device is formed by a plurality of chip stacks and arranged on the chip bearing seat and is electrically connected with the inner pin groups; and an encapsulationbody, used to wrap the stacked chip device and the lead frame, wherein, the lead frame includes at least one collecting bar in multi-stage type and is arranged among the inner pin groups and the chipbearing seat.

Owner:CHIPMOS TECH INC

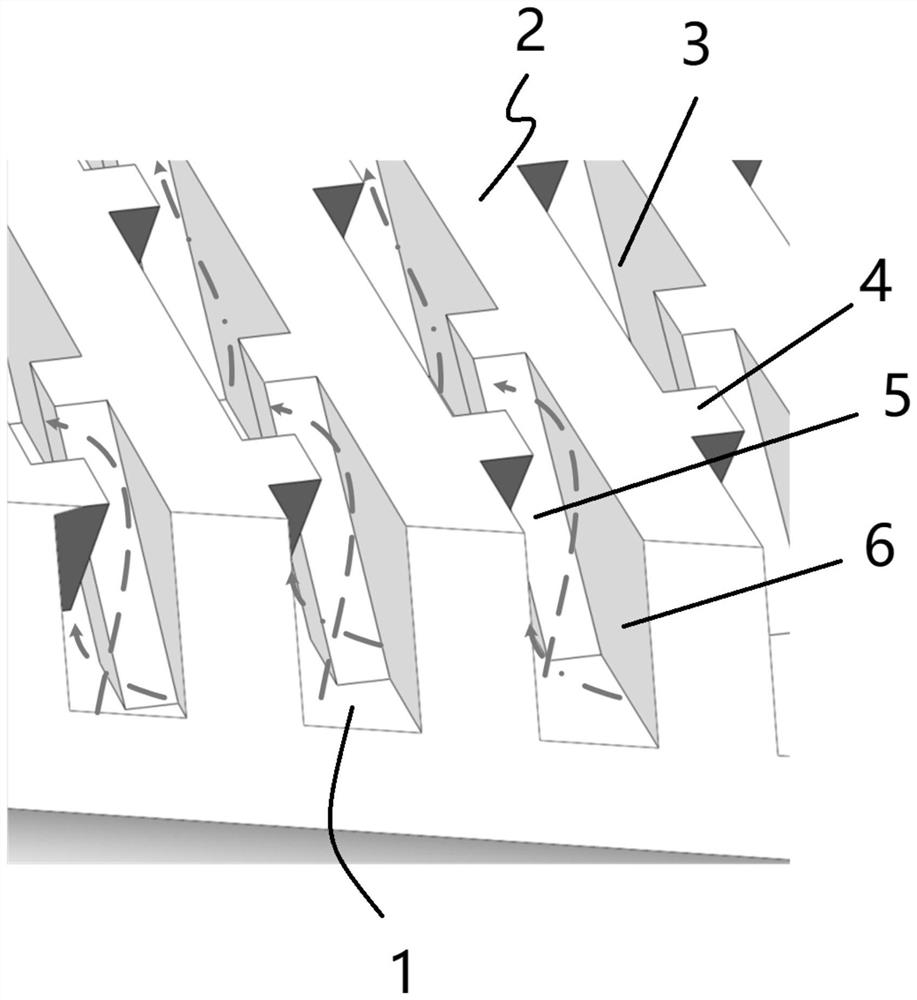

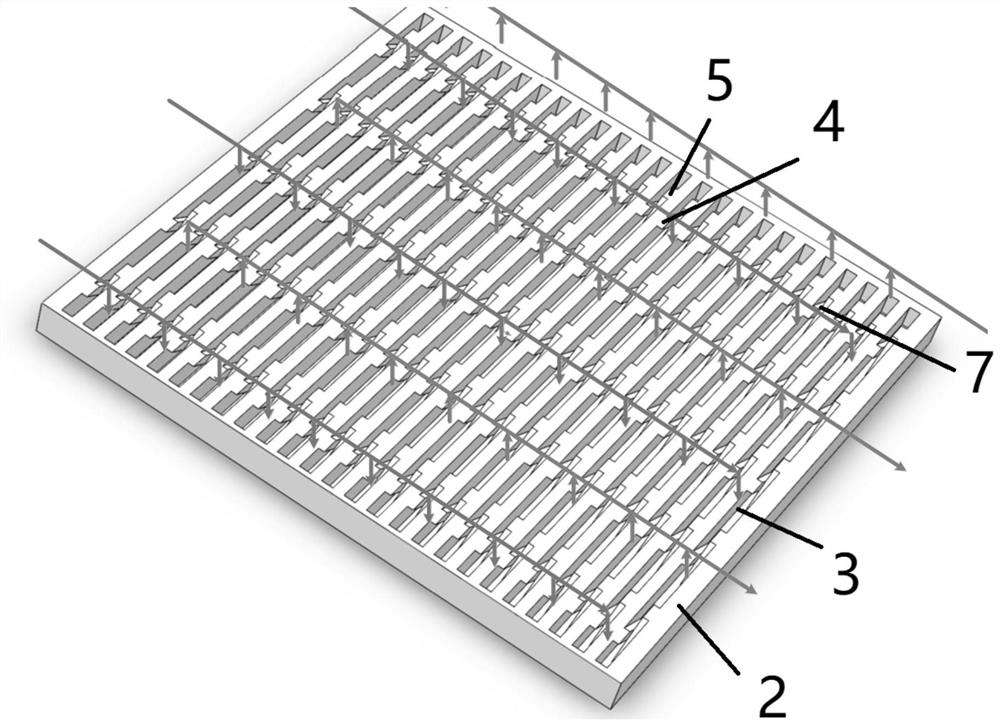

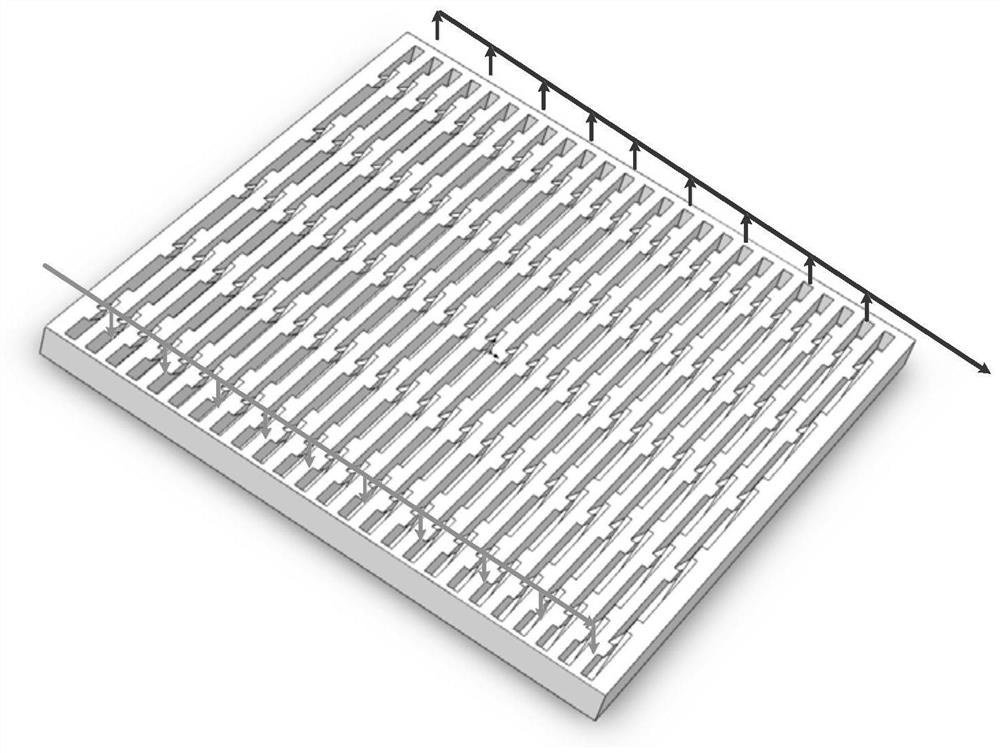

Runner structure for chip cooling and manufacturing method thereof

ActiveCN114245583AThermal Capacity LimitationImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesEngineeringCooling fluid

The invention provides a flow channel structure for chip cooling and a manufacturing method thereof, and the structure comprises at least one first fin which is disposed on a first side wall surface of a flow channel and extends along a first direction so as to guide a cooling liquid in the flow channel along the first direction; the first fins are arranged on the first side wall face of the flow channel, the second fins are arranged on the second side wall face of the flow channel, the second fins extend in the second direction so as to be used for guiding cooling liquid in the flow channel in the second direction, and the first fins and the second fins intersect with each other and communicate with each other at the intersection.

Owner:NAT CENT FOR ADVANCED PACKAGING +1

Active light-emitting film, active light-emitting signboard and preparation method thereof

PendingCN111128984AConvenience for immediate upgradeReduce volumeSolid-state devicesIlluminated signsLed arrayEngineering

The invention discloses an active light-emitting film, an active light-emitting signboard and a preparation method thereof, and aims to solve the technical problems that an existing active light-emitting signboard is complex in structure and difficult to manufacture, and resources cannot be reasonably utilized. The active light-emitting film comprises a substrate, an LED array, a scattering layer,fluorescent powder glue and a retro-reflection layer, the LED array is arranged on the substrate, the scattering layer is fixed above the LED array, the space between the substrate and the scatteringlayer is filled with the fluorescent powder glue, and the retro-reflection layer is arranged on the side face, back on to the LED array, of the scattering layer; and the active light-emitting sign comprises a support, a signboard panel, a bottom film and an active light-emitting film, the signboard panel is fixedly connected with the support, the bottom film is adhered to the front surface of thesignboard panel, and the active light-emitting film is adhered to the bottom film. The active light-emitting film is directly pasted on an existing signboard, the size is reduced, manufacturing is convenient, and brightness is uniform.

Owner:河南车路智通信息技术有限公司

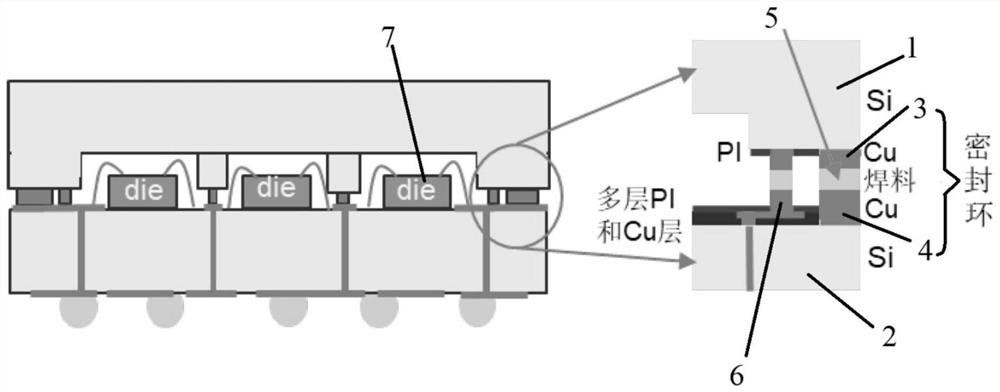

Three-dimensional integrated airtight packaging interconnection structure and manufacturing method thereof

PendingCN114156237AHermetic packaging achievedImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesStructural engineeringMechanical engineering

The invention provides a three-dimensional integrated airtight packaging interconnection structure and a manufacturing method thereof, and the structure comprises an airtight silicon cavity upper cover which is configured to be capable of being connected with a first part of a sealing bonding ring; the airtight bottom silicon substrate is configured to be connected with the second part of the sealing bonding ring; and the sealing bonding ring is provided with an annular first part and an annular second part, and the first part and the second part are configured to be capable of forming an airtight silicon-based cavity between the airtight silicon cavity upper cover and the airtight bottom silicon substrate under the condition that the first part and the second part are jointed with each other.

Owner:NAT CENT FOR ADVANCED PACKAGING +1

Stack type chip package with radiation structure

ActiveCN100505248CImprove package integrationThe overall thickness is thinSemiconductor/solid-state device detailsSolid-state devicesHeight differenceLead frame

The invention discloses a stack package structure with a confluence frame on a lead frame, which includes: a lead frame, a plurality of inner pin groups and outer pin groups arranged face to face and a chip holder, wherein, the chip holder is arranged among the inner pin groups and a height difference is formed between the chip holder and the inner pin groups; at least a confluence frame with an upper surface and a lower surface is positioned between the inner draw feet groups and the chip holder; a multi-chip offset stack structure is formed by the stack of a plurality of chips. The multi-chip offset stack structure is fixedly connected with the a first surface of the chip holder and is electrically connected with the plurality of inner pin groups; and an package body coats the multi-chip offset stack structure, the inner pin groups, the first surface of the chip holder and the upper surface of the confluence frame, and exposes a second surface of the chip holder and the lower surface of the confluence frame and juts the plurality of outer pin groups out of the package body.

Owner:CHIPMOS TECH INC

Lidar chip packaging structure and packaging method

ActiveCN112820725BHighly integratedSmall sizeWave based measurement systemsSemiconductor/solid-state device detailsFisheryMechanical engineering

The present invention provides a lidar chip packaging structure and packaging method, including: an optical chip, which is arranged in a first package, and the first package has a lens shape; an electrical chip, which is arranged in the second package, The second package body has a first electrical interconnection structure, and the first electrical interconnection structure leads out the electrical properties of the electrical chip; the first package body and the second package body are arranged by stacking.

Owner:NAT CENT FOR ADVANCED PACKAGING CO LTD

Stacking chip encapsulation structure with multi-section bus bar in lead rack

ActiveCN101170104BImprove package integrationThe overall thickness is thinSemiconductor/solid-state device detailsSolid-state devicesHeight differenceLead frame

The invention provides a stacked chip encapsulation structure with a multi-stage collecting bar in a lead frame, which includes a lead frame consisting of a plurality of inner pin groups arranged relatively, a plurality of outer pin groups and a chip bearing seat, wherein, the chip bearing seat is arranged among a plurality of inner pin groups arranged relatively and forms height difference with the inner pin groups; the stacked chip device is formed by a plurality of chip stacks and arranged on the chip bearing seat and is electrically connected with the inner pin groups; and an encapsulationbody, used to wrap the stacked chip device and the lead frame, wherein, the lead frame includes at least one collecting bar in multi-stage type and is arranged among the inner pin groups and the chipbearing seat.

Owner:CHIPMOS TECH INC

Low-stress bottom filling method of laminating device

ActiveCN101814444BGuaranteed performanceImproved thermodynamic reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesInterconnectionMaterials science

The invention discloses a low-stress bottom filling method of a laminating device, which comprises the following steps of: selecting epoxy glue; (2) removing air bubbles generated when the epoxy glue is mixed; (3) applying the glue on the laminating device; (4) curing the epoxy glue in two stages: (a) hardening and molding the epoxy glue; (b) strengthening and curing the epoxy glue; and (5) detecting whether the epoxy glue is completely cured. The method enables the layers of the laminating device to have higher bonding force and mechanical strength; and the glue layer can not generate process residual stress. The method is widely applied to packaging multichips in a laminating way, inverse welding interconnection devices, a micro-electro-mechanical system (MEMS) device, a liquid crystal box, and the like, reduces the curing residual stress for filling the epoxy glue of the laminating device, ensures the mechanical strength and reduces the damage probably caused by stress to the minimum, thereby improving the thermodynamic reliability of the laminating device.

Owner:中航凯迈上海红外科技有限公司

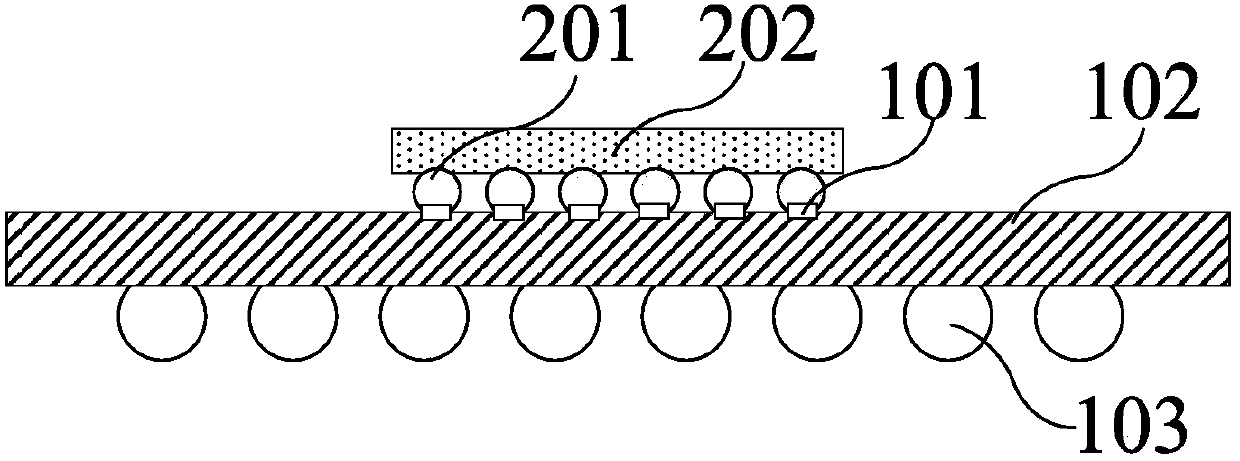

3D chip packaging structure and preparation method thereof

PendingCN112053964ALow costImprove package integrationSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerSolder ball

The invention provides a 3D chip packaging structure and a preparation method thereof. The 3D chip packaging structure comprises: a rewiring layer; a chip which is bonded on the upper surface of the rewiring layer in a flip-chip manner; a first electric connection structure which is located on the upper surface of the rewiring layer; a first plastic package layer which is positioned on the upper surface of the rewiring layer and is used for carrying out plastic package on the chip and the first electric connection structure; a second electric connection structure which is located on the uppersurface of the first plastic package layer; a second plastic package layer which is located on the upper surface of the first plastic package layer; a third electric connection structure which is located on the upper surface of the second plastic package layer; a third plastic package layer which is positioned on the upper surface of the second plastic package layer and is used for carrying out plastic package on the third electric connection structure; a top metal wire layer which is positioned on the upper surface of the third plastic package layer; and a solder ball bump located on the lower surface of the redistribution layer. According to the 3D chip packaging structure, 3D packaging of the chip is achieved, the cost is low, the packaging integration degree is high, and the requirement for the miniaturization development trend can be met.

Owner:SJ SEMICON JIANGYIN CORP

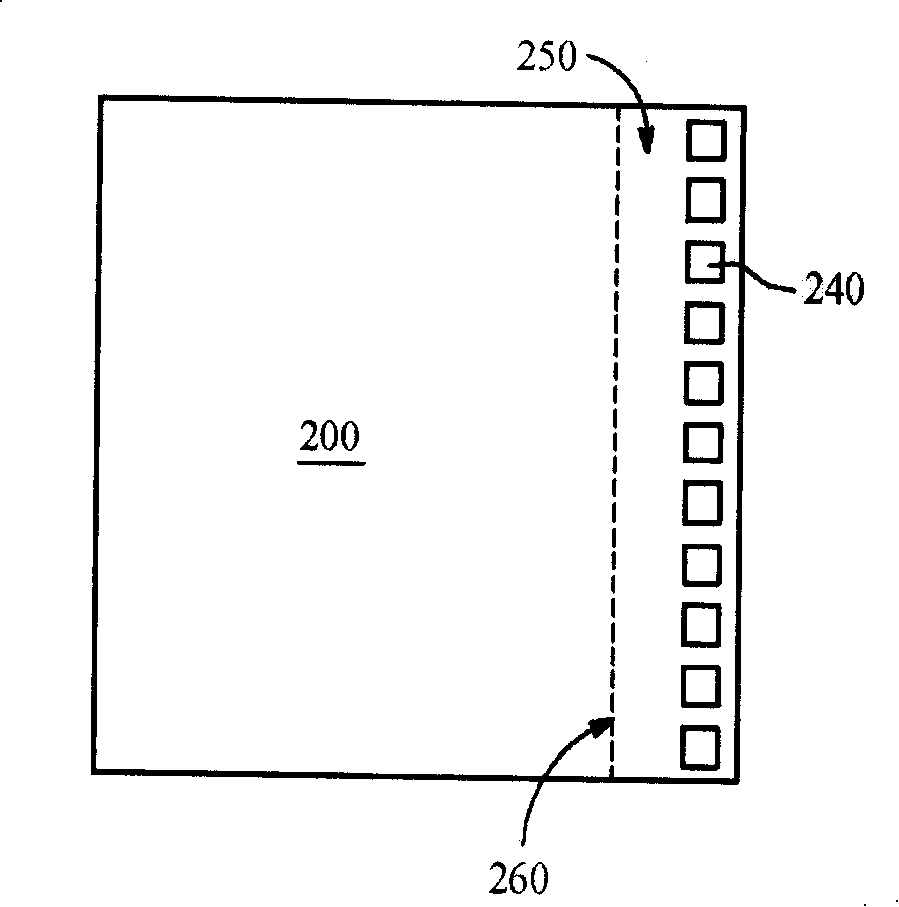

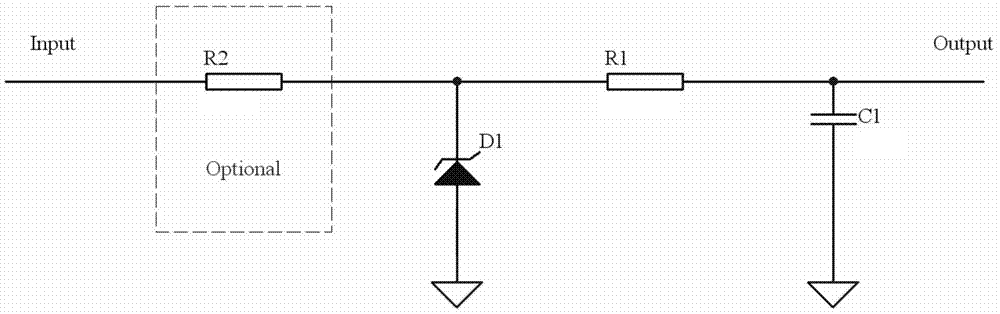

Resistive touch screen protecting circuit

InactiveCN106992507AImprove package integrationSimple structureEmergency protective arrangements for limiting excess voltage/currentInput/output processes for data processingOvervoltageCapacitance

The invention relates to a resistive touch screen protecting circuit which is arranged on a driving line between a resistive touch screen control board and a resistive touch screen and is used for preventing instantaneous high voltage on a resistive screen driving line. The protecting circuit comprises a transient voltage inhibition diode, a first resistor and a capacitor. The signal output end of the resistive touch screen control board, the first resistor and the resistive touch screen signal input end are successively connected. The anode of the transient voltage inhibition diode is grounded, and the cathode is connected between the first resistor and the signal output end of the resistive touch screen control board. One end of the capacitor is grounded, and the other end is connected between the first resistor and the signal input end of the resistive touch screen. Compared with prior art, the resistive touch screen protecting circuit has advantages of high integration degree, small size, high convenience and high flexibility in use, effective ESD overvoltage protection, etc.

Owner:PIXY SHANGHAI CO LTD

Integrated preparation method for LED fluorescent powder coating

The invention discloses an integrated preparation method for an LED fluorescent powder coating, which belongs to the photoelectric technical field. The method comprises the following steps: (1), preparing fluorescent powder and sensitive colloid dispersion; (2), spinning the fluorescent powder to form a fluorescent powder-sensitive colloid dispersion coating; (3), obtaining fluorescent powder-sensitive colloid dispersion coating patterns in required shapes and thickness through exposure and development; (4), displacing a fluorescent powder dispersion medium; and (5), removing a coating residue on the surface of an electrode, and showing a chip pattern. The invention provides a wafer level packaging fluorescent powder coating slurry method and a realization method (cleaning and exposing) of the chip electrode pattern, and the problem of applying the fluorescent powder coating technology into LED chip integrated package to realize the separation of the electrode pattern and the fluorescent powder coating in the prior art is solved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

An all-inorganic UV LED wafer-level packaging method

ActiveCN109888081BMeet long-term reliability requirementsImprove package integrationSemiconductor devicesGlass coverUltraviolet

The invention belongs to the technical field of semiconductor manufacturing, and discloses a full-inorganic ultraviolet LED wafer-level package method. The full-inorganic ultraviolet LED wafer-level package method comprises the steps of firstly, forming a plurality of glass paste rings on a glass cover plate by a printing or 3D printing technology, and obtaining a plurality of glass cavity structures by low-temperature sintering; secondly, surface-mounting a plurality of ultraviolet LED chips onto a cooling substrate; thirdly, achieving reliable bonding of the glass cavities in the glass coverplate and the cooling substrate by inorganic paste or a metal welding material; and finally, cutting to obtain a full-inorganic ultraviolet LED package product. The invention also discloses a corresponding ultraviolet LED package structure. By the full-inorganic ultraviolet LED wafer-level package method, the problems of ultraviolet aging and failure of an organic package material are effectivelyprevented, the long-term reliability of an ultraviolet LED device is improved, the ultraviolet LED package integration is improved, and the package cost is reduced.

Owner:武汉高星紫外光电科技有限公司

Stack type chip package with radiation structure

ActiveCN101192600AImprove package integrationThe overall thickness is thinSemiconductor/solid-state device detailsSolid-state devicesHeight differenceEngineering

The invention discloses a stack package structure with a confluence frame on a lead frame, which includes: a lead frame, a plurality of inner pin groups and outer pin groups arranged face to face and a chip holder, wherein, the chip holder is arranged among the inner pin groups and a height difference is formed between the chip holder and the inner pin groups; at least a confluence frame with an upper surface and a lower surface is positioned between the inner draw feet groups and the chip holder; a multi-chip offset stack structure is formed by the stack of a plurality of chips. The multi-chip offset stack structure is fixedly connected with the a first surface of the chip holder and is electrically connected with the plurality of inner pin groups; and an package body coats the multi-chip offset stack structure, the inner pin groups, the first surface of the chip holder and the upper surface of the confluence frame, and exposes a second surface of the chip holder and the lower surface of the confluence frame and juts the plurality of outer pin groups out of the package body.

Owner:CHIPMOS TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com