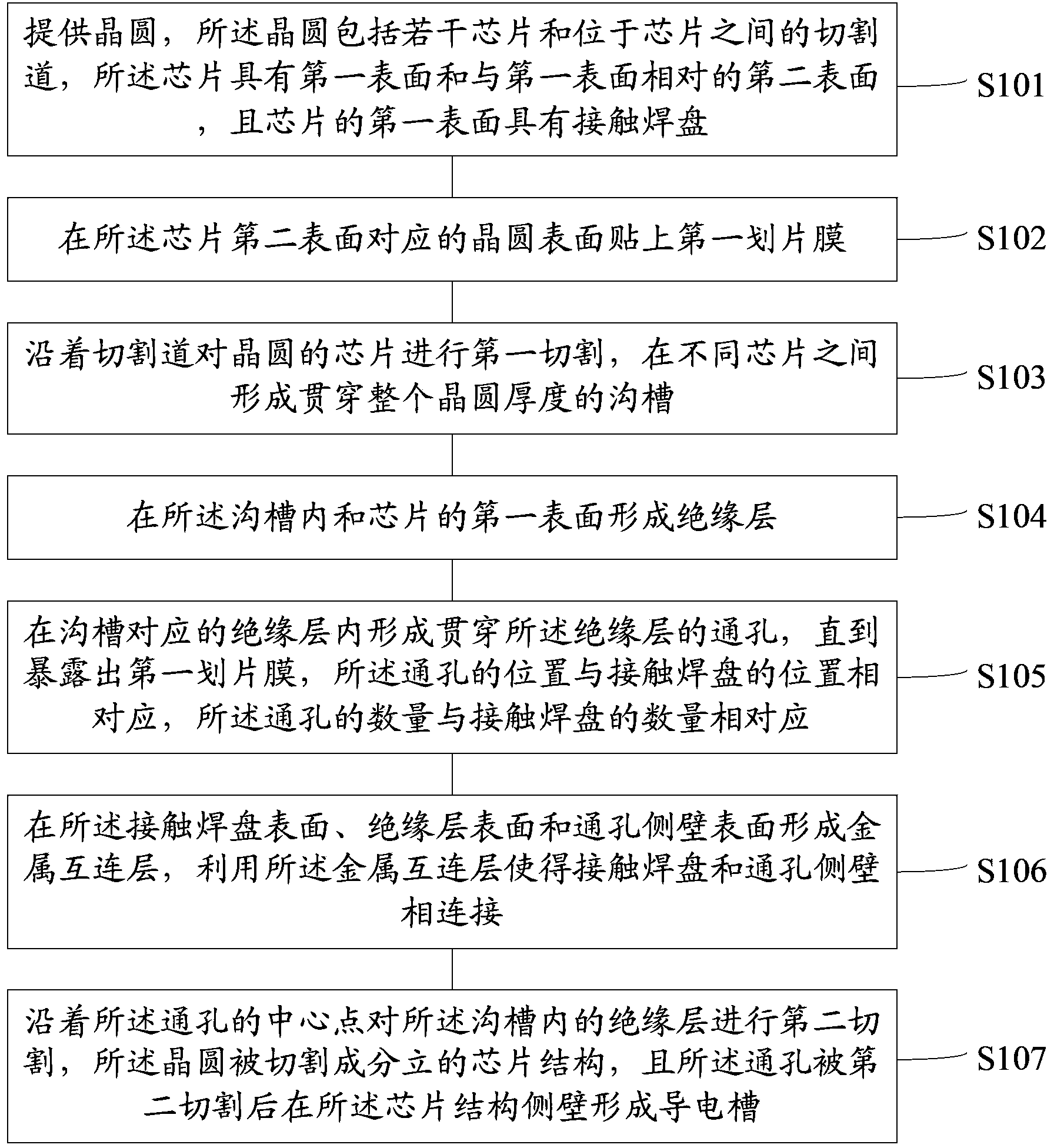

Chip cutting method and chip packaging method

A cutting method and chip technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of waste of chip area, poor mechanical strength of chips, and large differences in thermal expansion coefficients, etc., to improve the integration of devices , The effect of saving chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

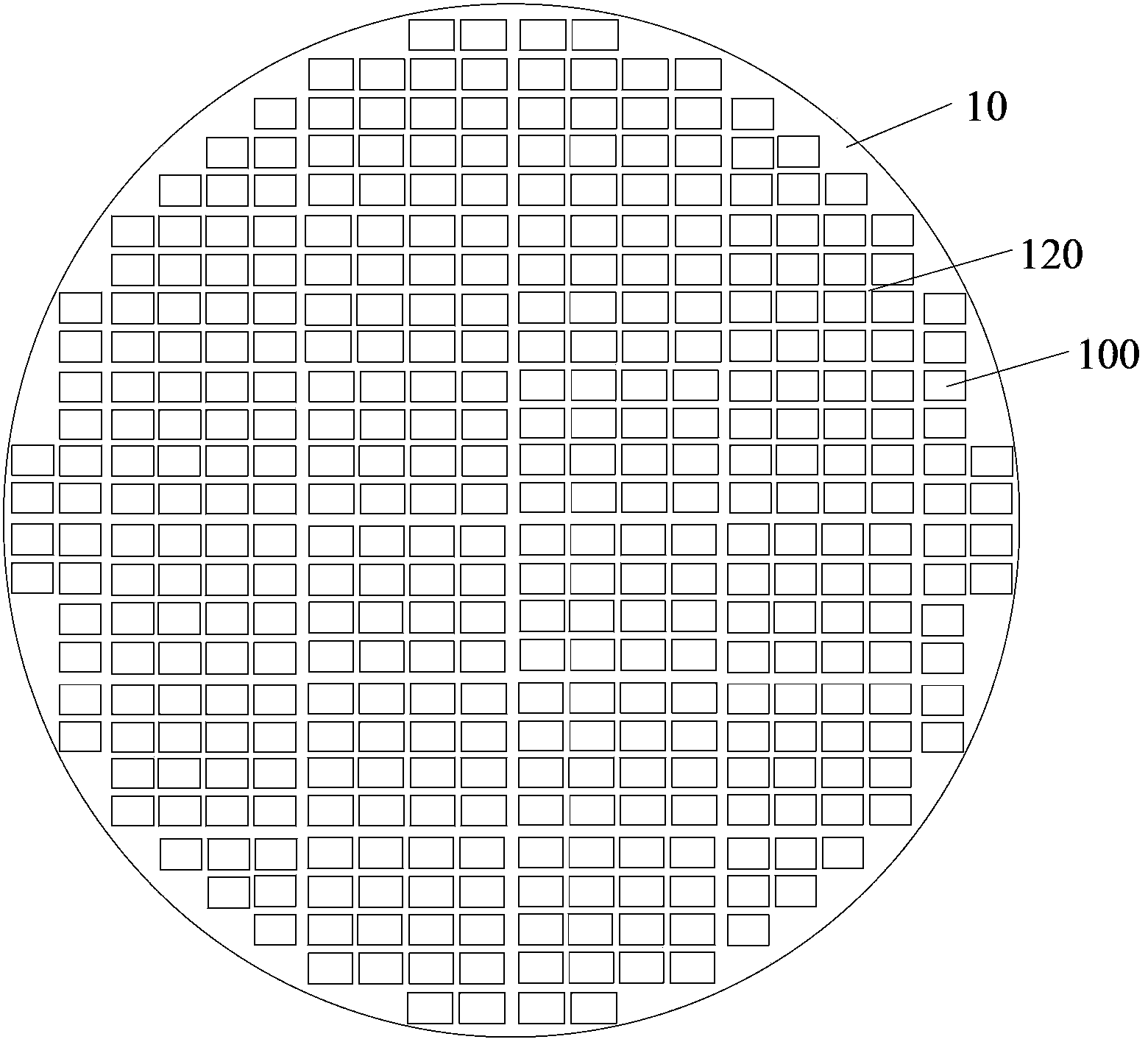

[0023] Since the process cost of the three-dimensional stacking technology based on through-silicon vias is large, it will cause waste of chip area, and the chip needs to be thinned, so that the mechanical strength of the chip will deteriorate. Therefore, the present invention provides a chip cutting method and a chip packaging method. The sidewall of the chip structure formed by the cutting method has a conductive groove. When a plurality of chip structures are stacked, the conductive groove is filled with conductive glue, and the conductive glue is used to make different chip structures The circuits are electrically connected to form a chip package structure. Since the present invention does not need to form through-silicon holes in the chip, the process of forming through-silicon holes can be saved, and the cost can be reduced; at the same time, since the conductive groove is formed on the side wall of the chip structure, only the conductive groove needs to be formed in the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com