Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1740results about "Signal processing using self-clocking codes" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

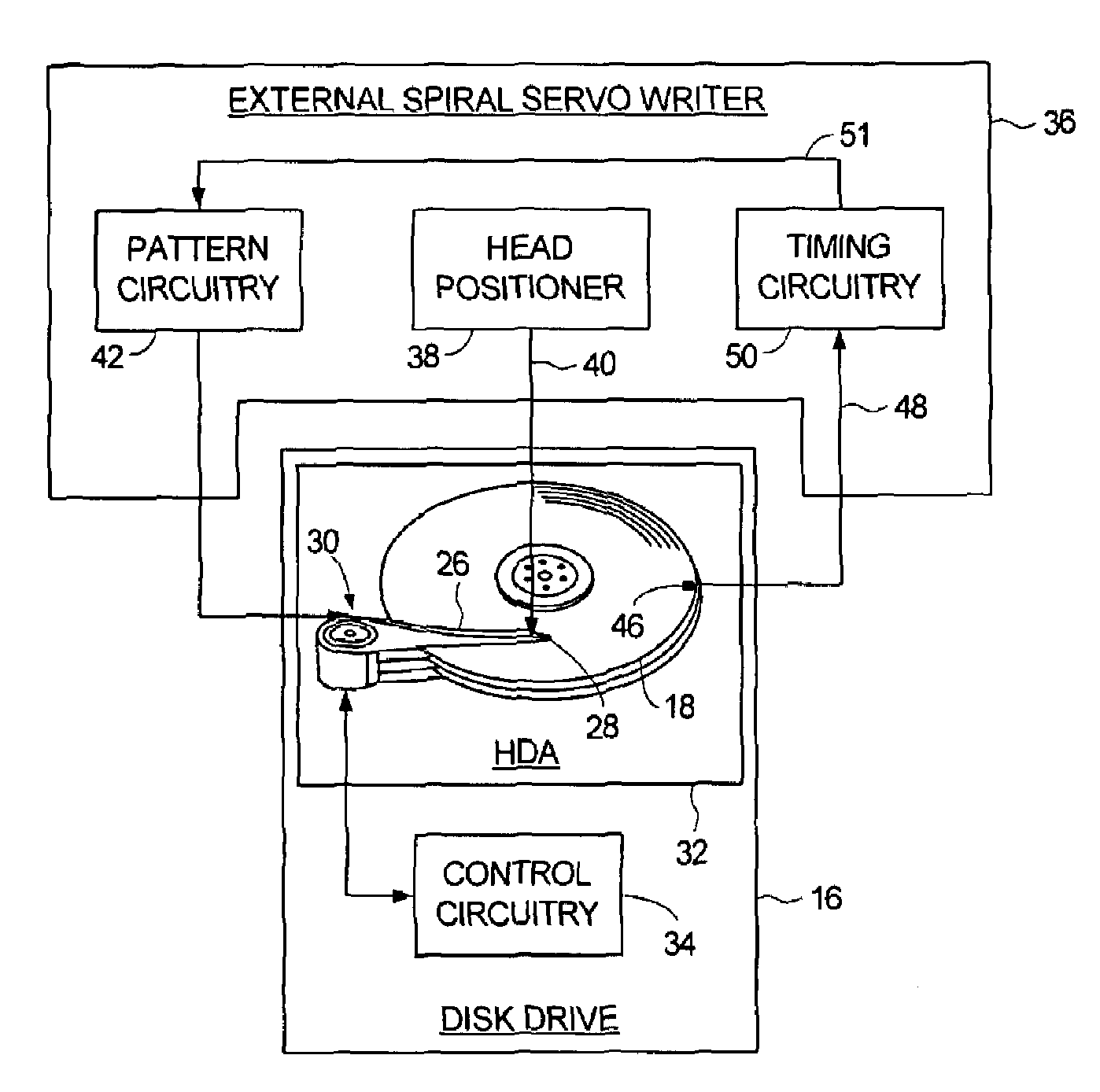

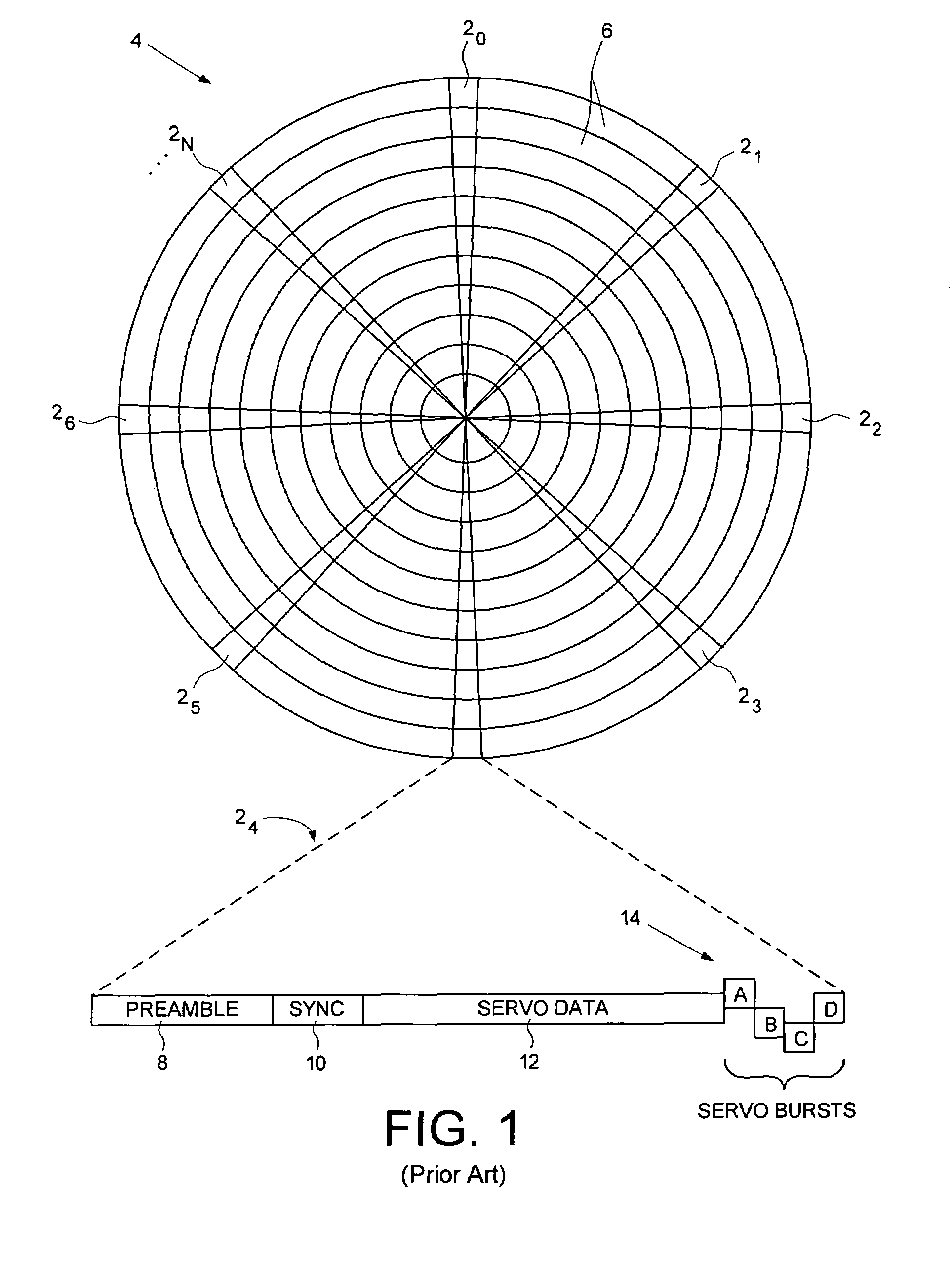

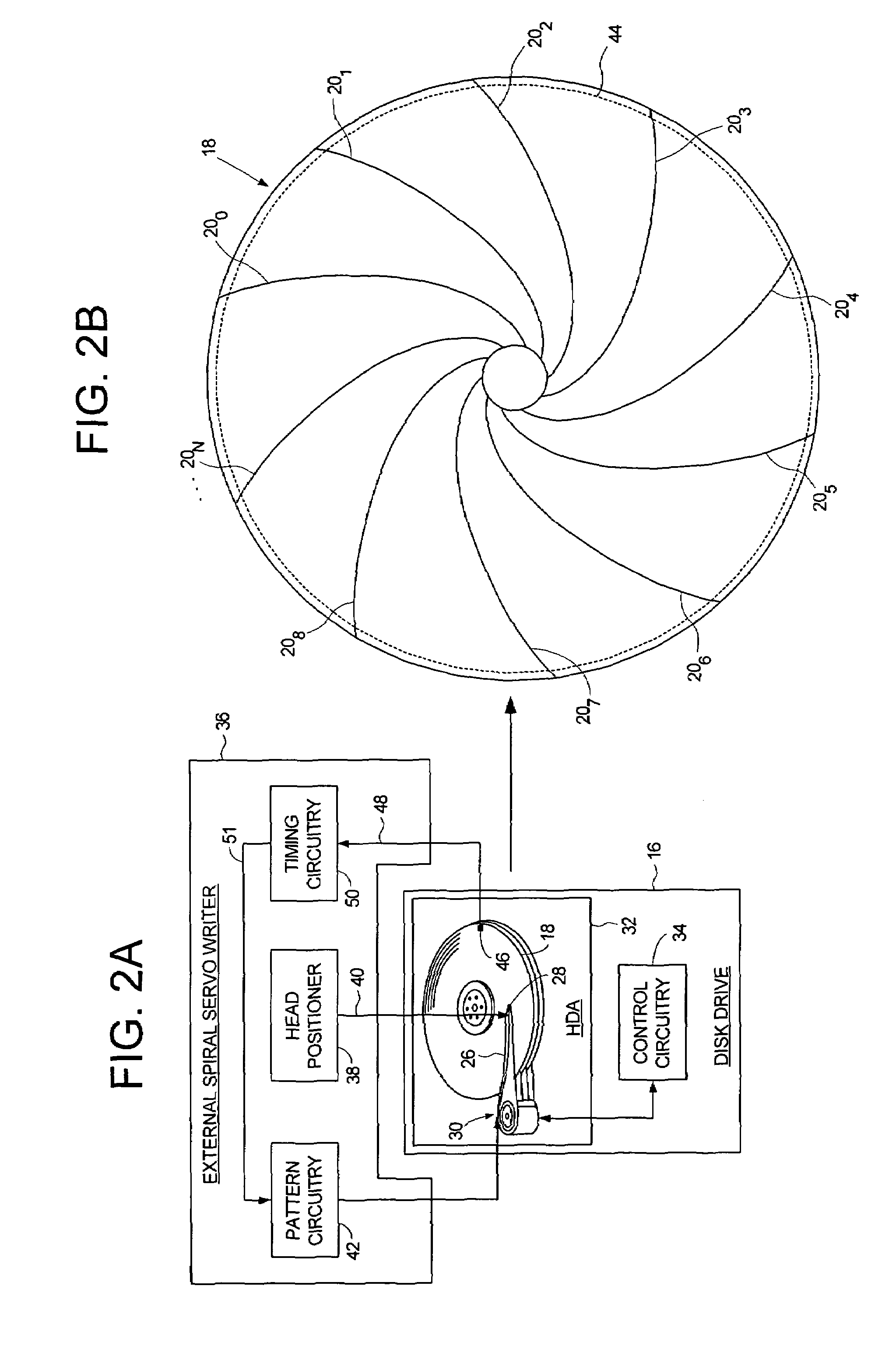

Servo writing a disk drive by integrating a spiral track read signal

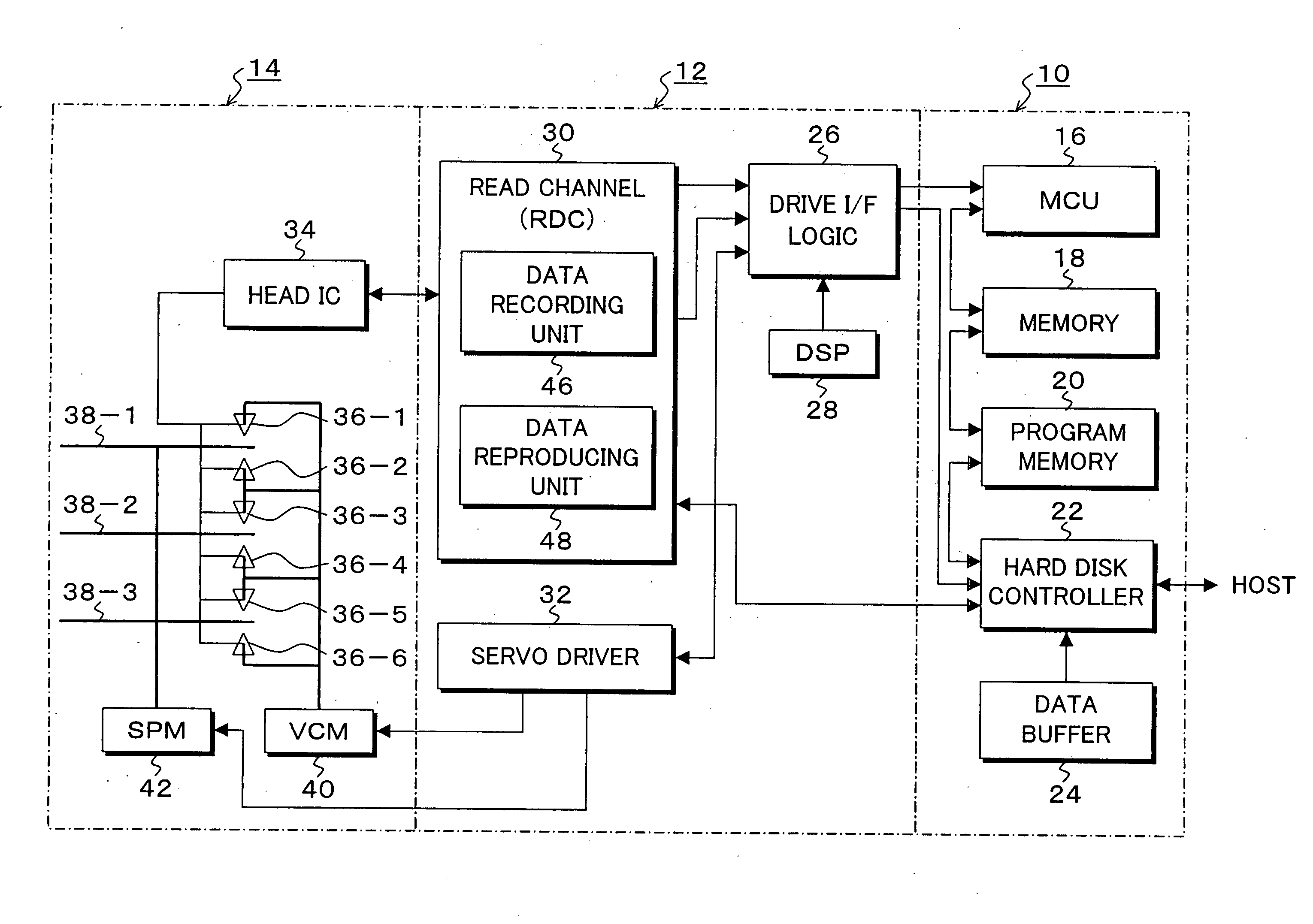

InactiveUS7301717B1Driving/moving recording headsRecord information storageControl theoryPosition error signal

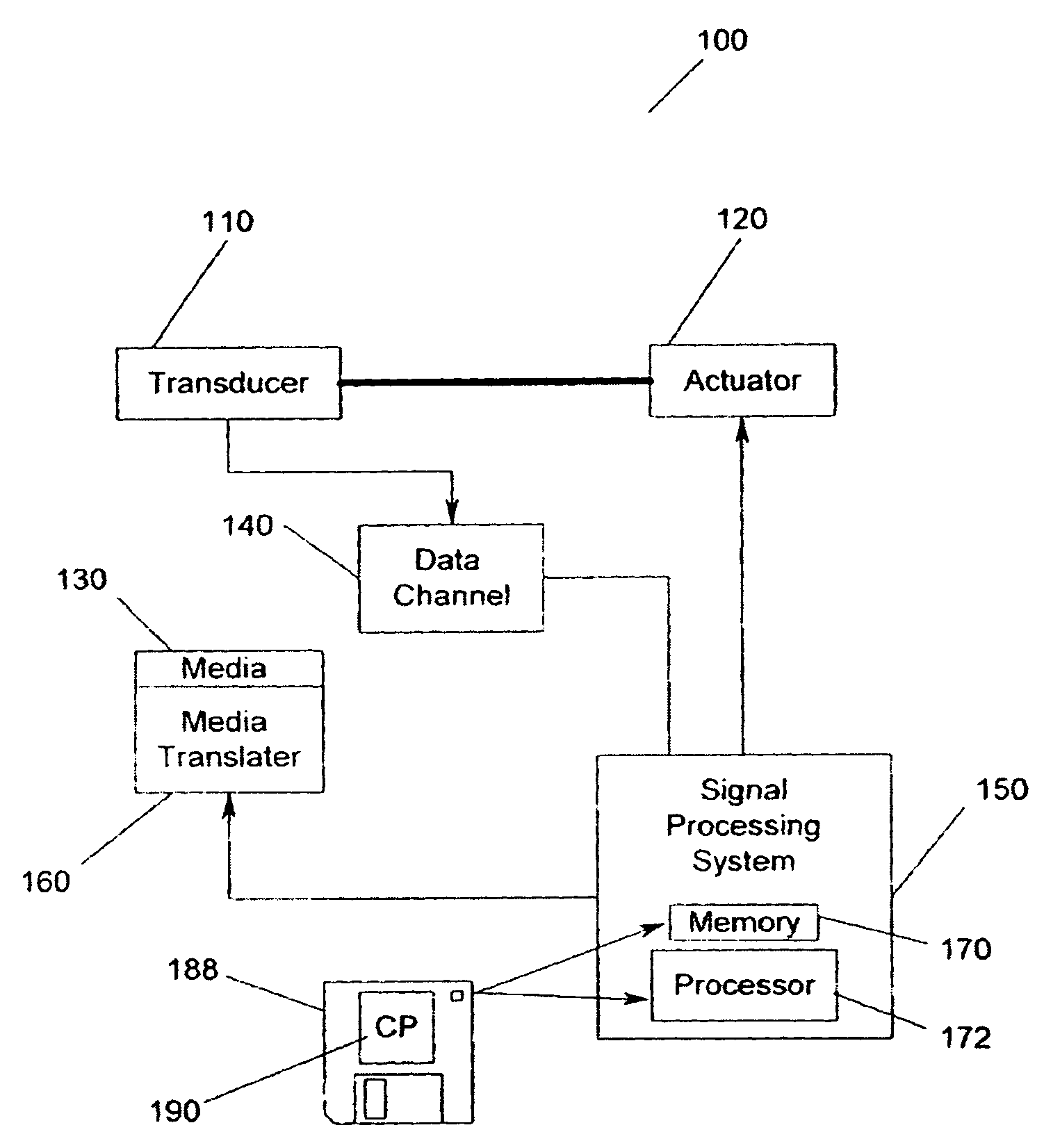

A method of writing product servo sectors to a disk of a disk drive is disclosed. The disk comprises a plurality of spiral tracks, wherein each spiral track comprises a high frequency signal interrupted by a sync mark at a sync mark interval. The head internal to the disk drive is used to read the spiral tracks to generate a read signal. The read signal is integrated to generate a ramp signal, wherein a position error signal is generated from the ramp signal. The position error signal is used to maintain the head internal to the disk drive along a servo track while writing product servo sectors along the servo track.

Owner:WESTERN DIGITAL TECH INC

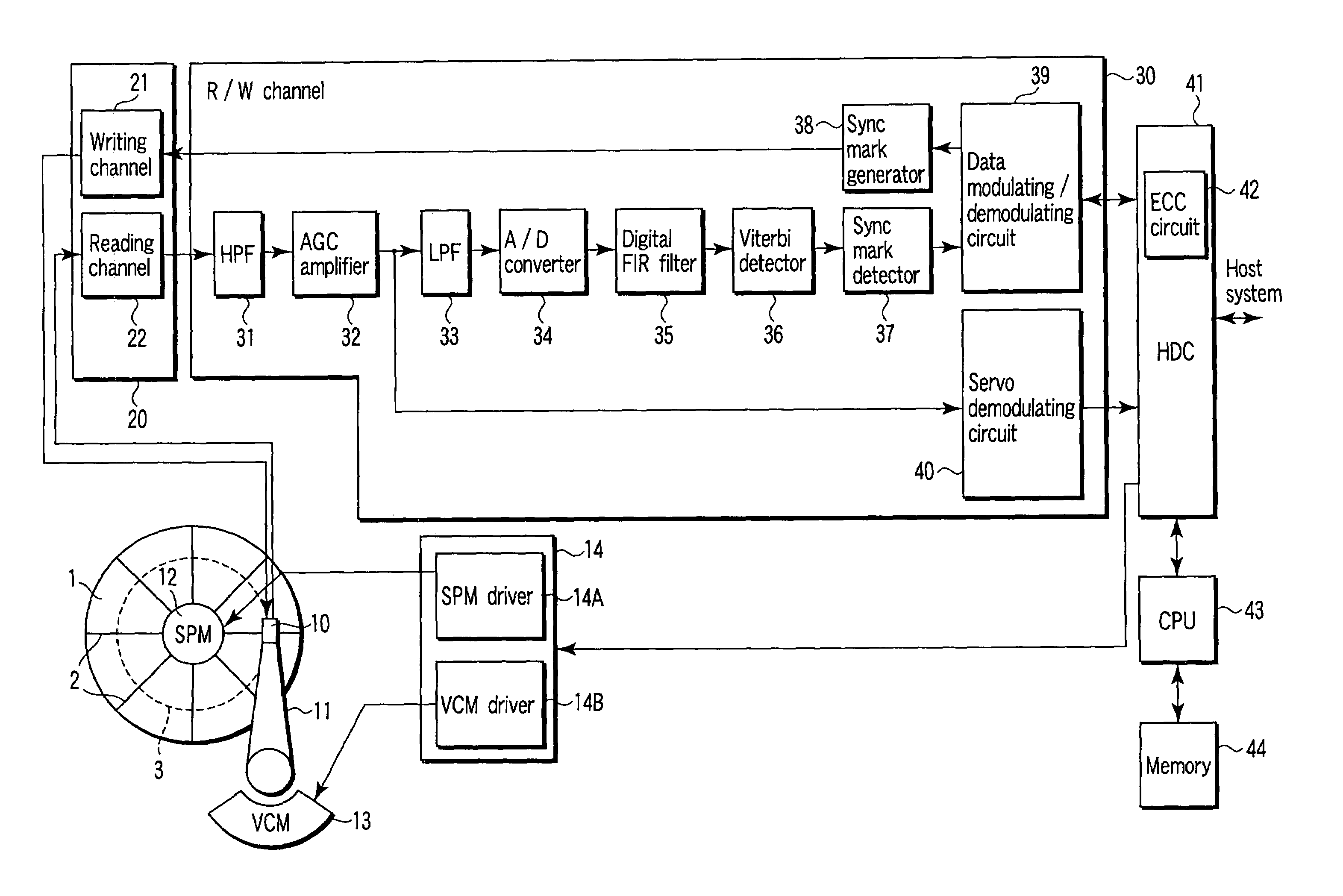

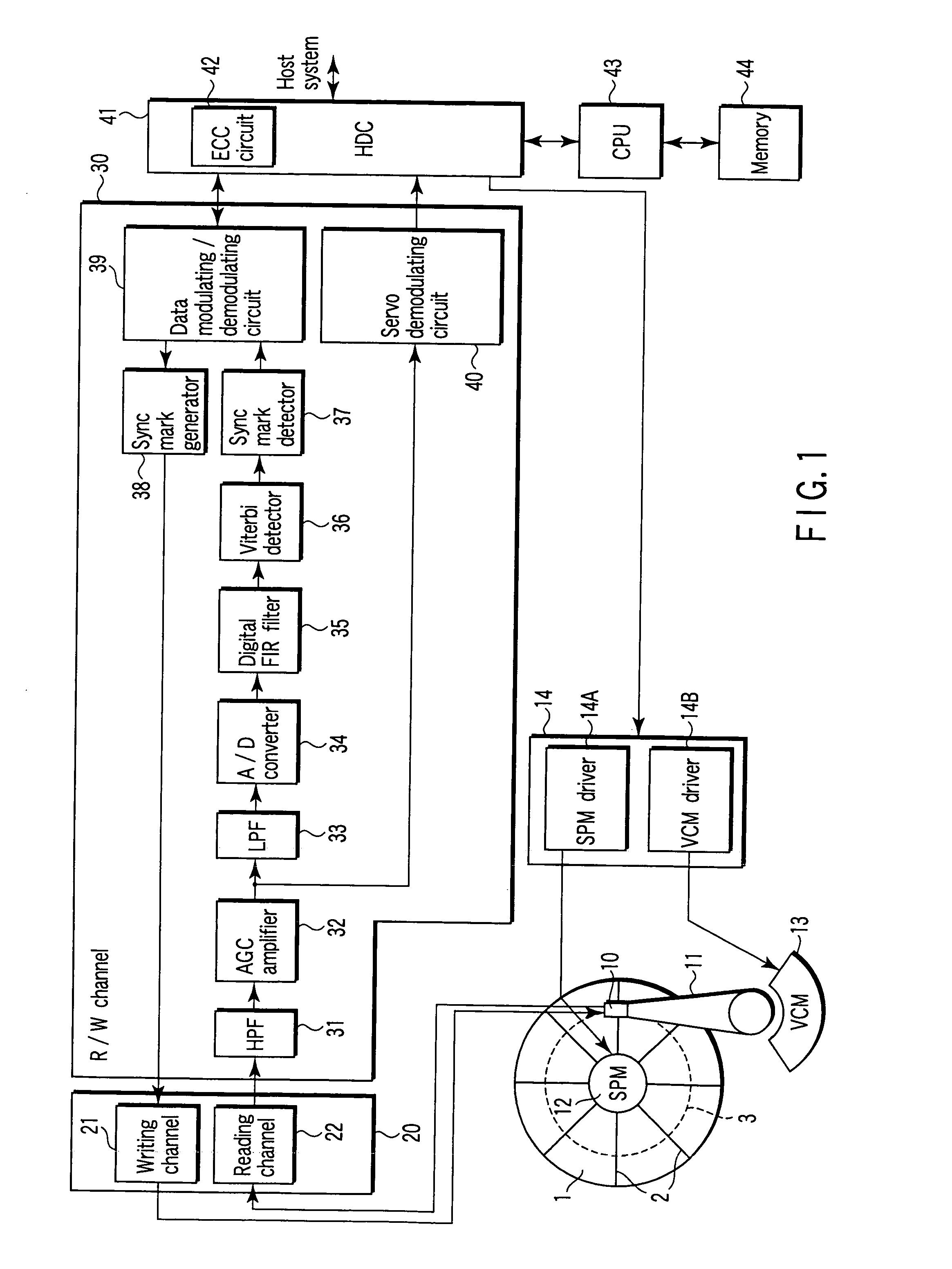

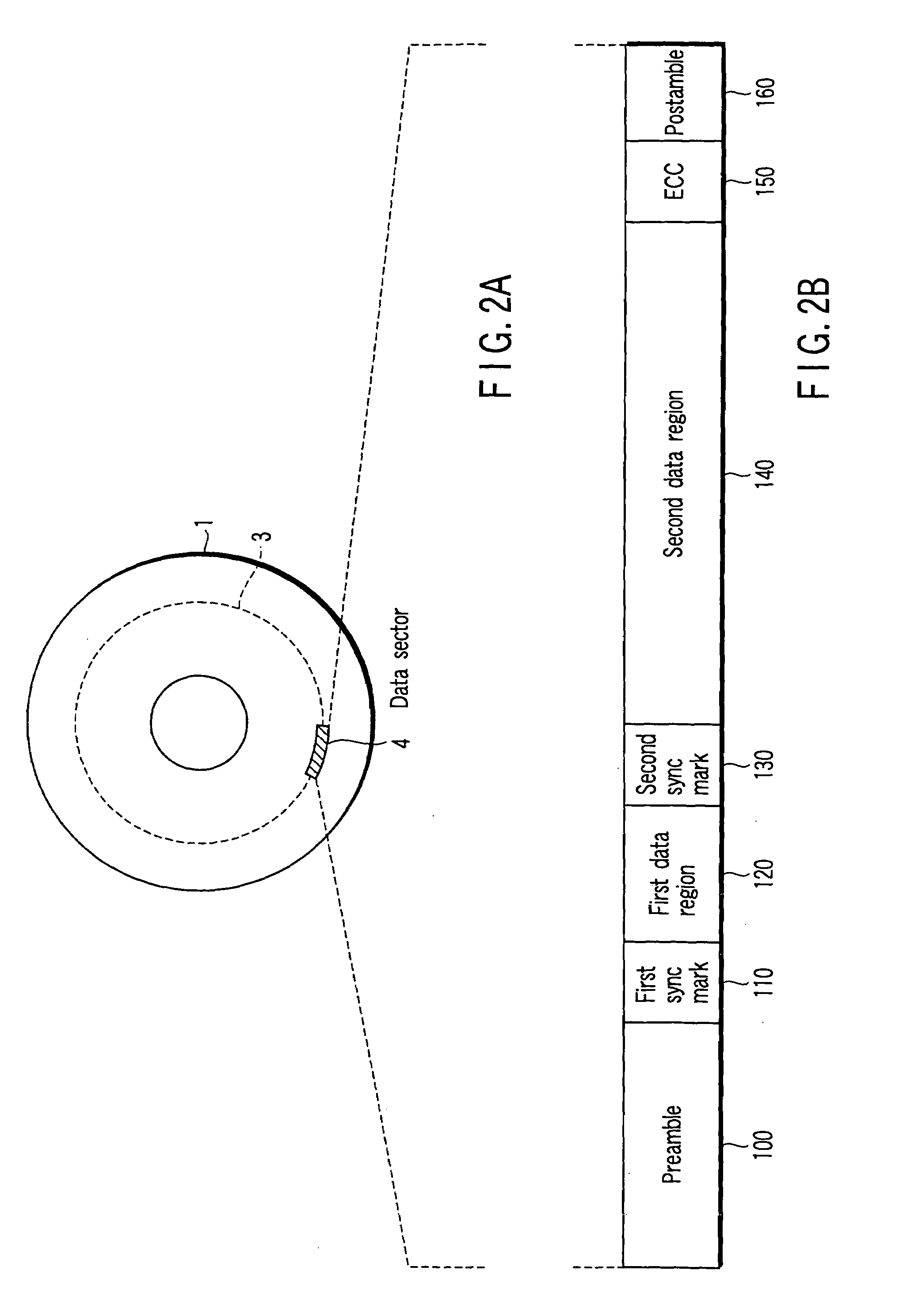

Method and apparatus for decoding sync marks in a disk

InactiveUS7203015B2High error rateIncrease probabilityModification of read/write signalsDisc-shaped record carriersComputer scienceBit-length

In a disk drive that performs perpendicular magnetic recording, the read / write channel has a sync mark generator. The sync mark generator generates a second sync mark before the read / write channel operates to write data on a disk. The second sync mark has a bit pattern including a series of bits representing positive polarity and a series of bits representing negative polarity. The series of bits, which is longer than the other, has a bit length that is at least 50% but less than 85% of the total bit length of the second sync mark.

Owner:KK TOSHIBA

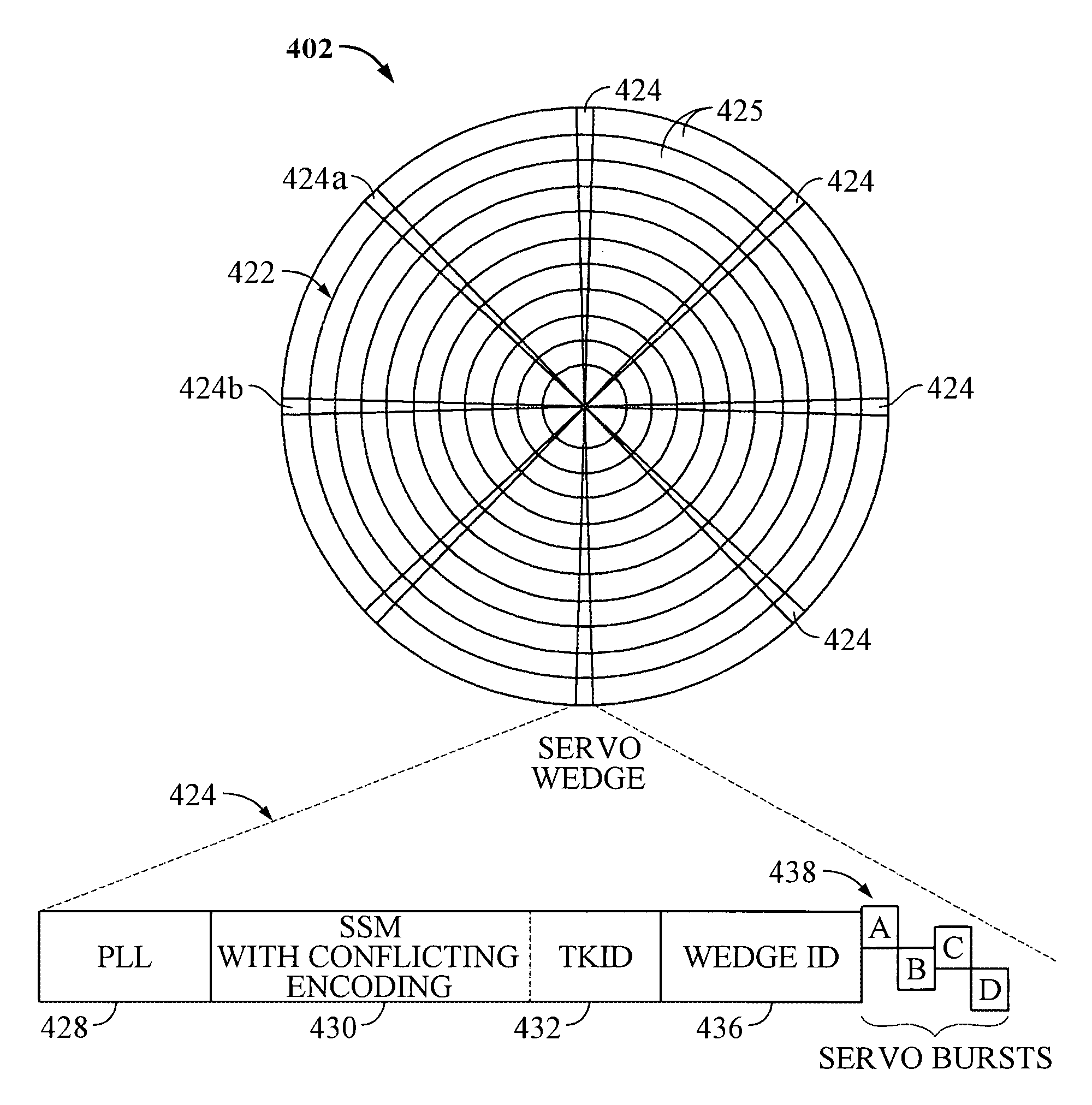

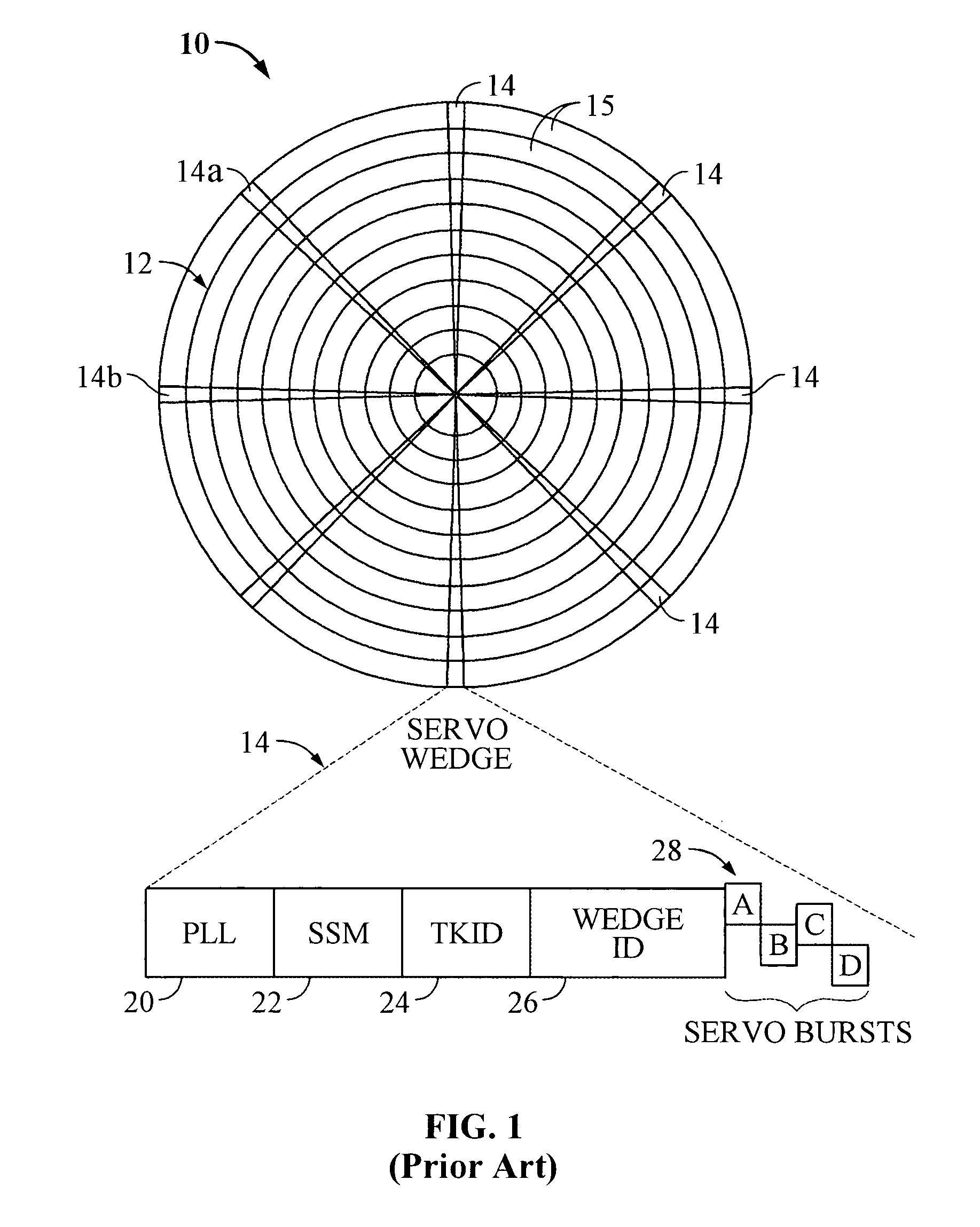

Servo synchronization based on a servo synch mark that conflicts with self-clocking encoding algorithms

InactiveUS6934104B1Disc-shaped record carriersRecord information storageEncoding algorithmComputer science

Disclosed is a rotatable media storage device (RMSD) that performs servo synchronization based on a servo synch mark (SSM) that conflicts with self-clocking encoding algorithms. The RMSD includes a disk having a plurality of tracks wherein each track comprises a plurality of data regions interspersed between servo wedges. The servo wedges comprise a servo synch mark field including a servo synch mark (SSM) and a track identification field including a track identifier (TKID). The TKID is encoded in accordance with a self-clocking encoding algorithm whereas the SSM is encoded in accordance with a second algorithm that conflicts with the self-clocking encoding algorithm of the TKID. Thus, the SSM is prevented from being decoded as a portion of the TKID.

Owner:WESTERN DIGITAL TECH INC

Methods and Apparatus for Map Detection with Reduced Complexity

ActiveUS20090185643A1Reduce complexityDependence moreDriving/moving recording headsError preventionLog likelihoodComputer science

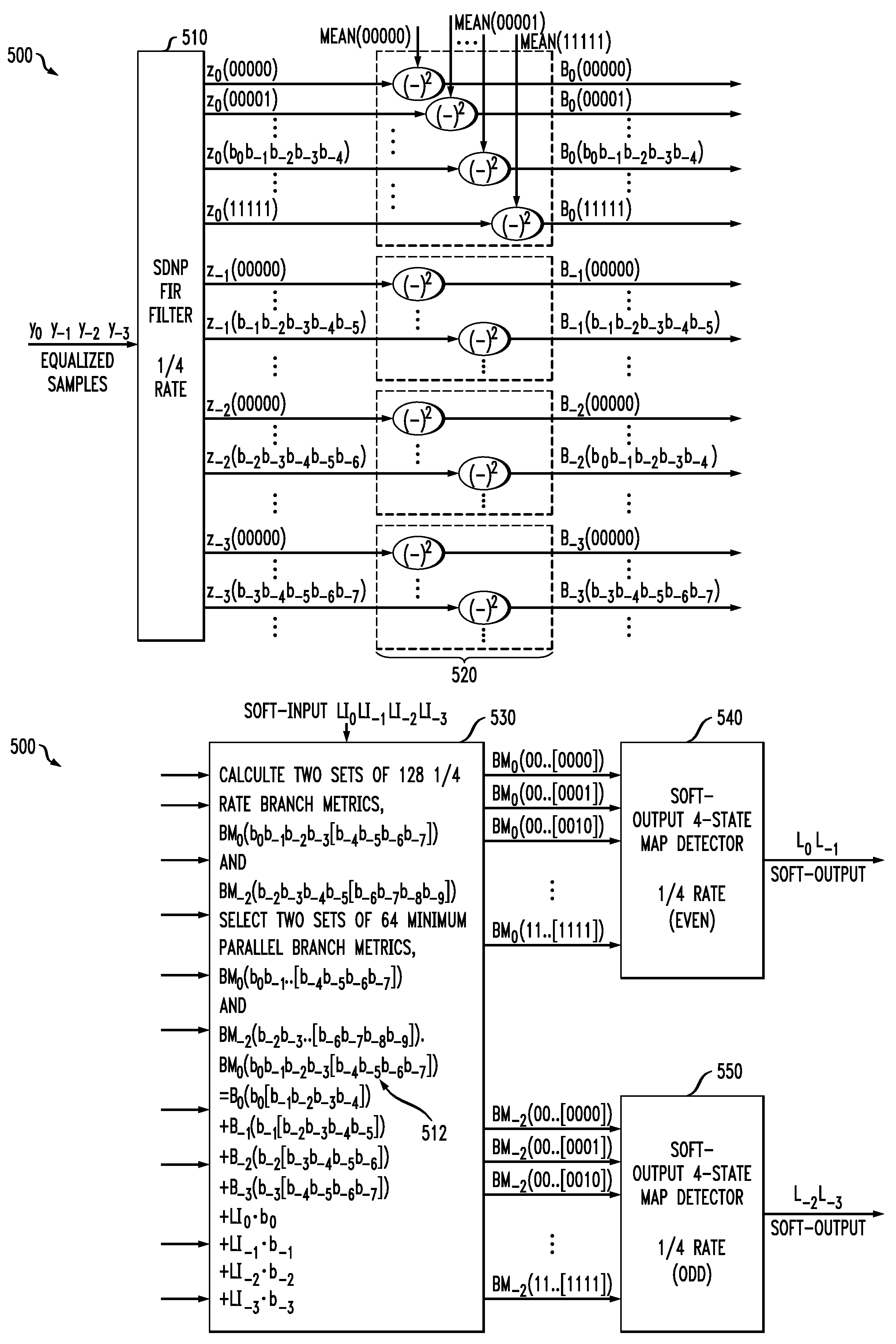

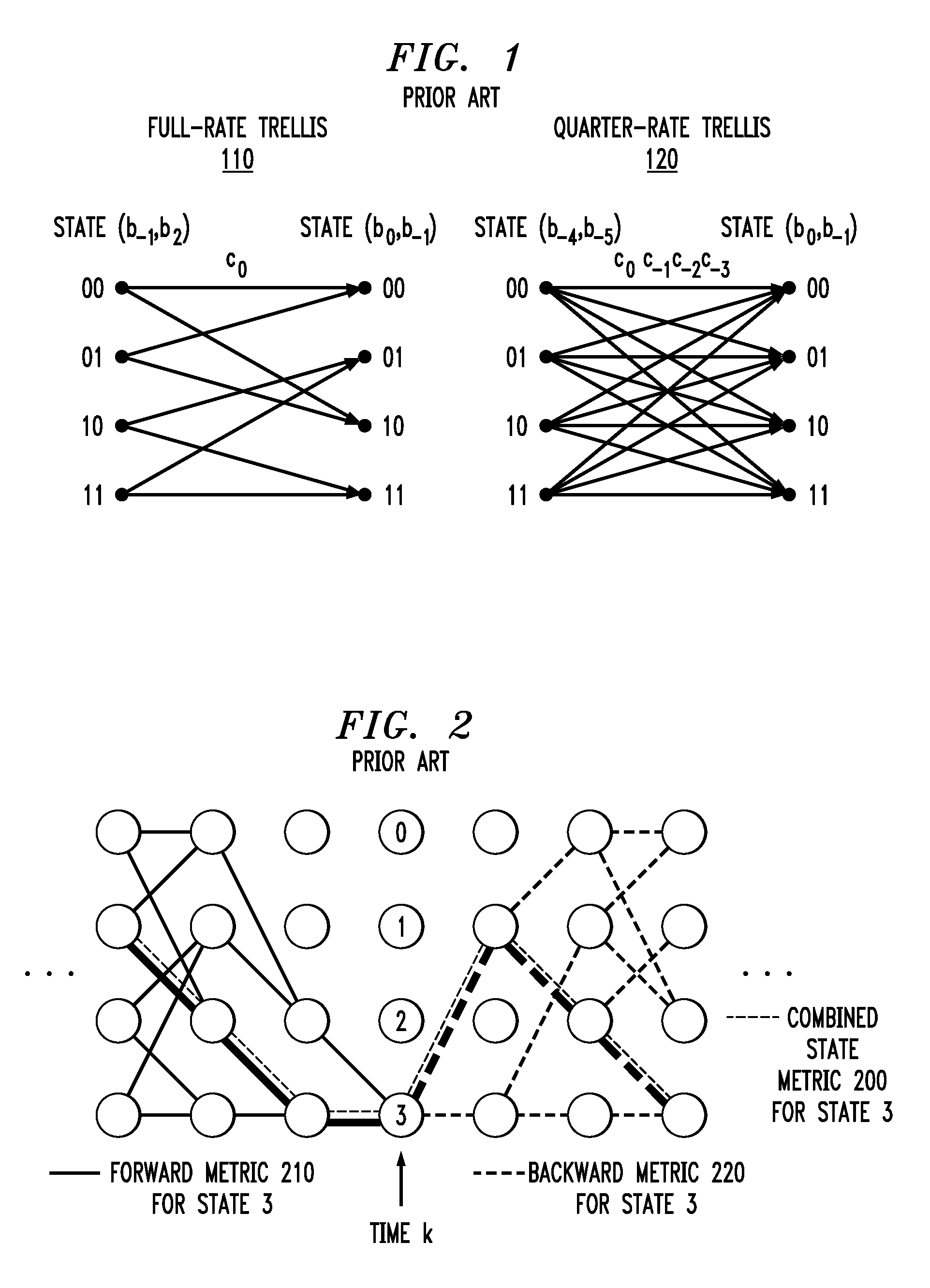

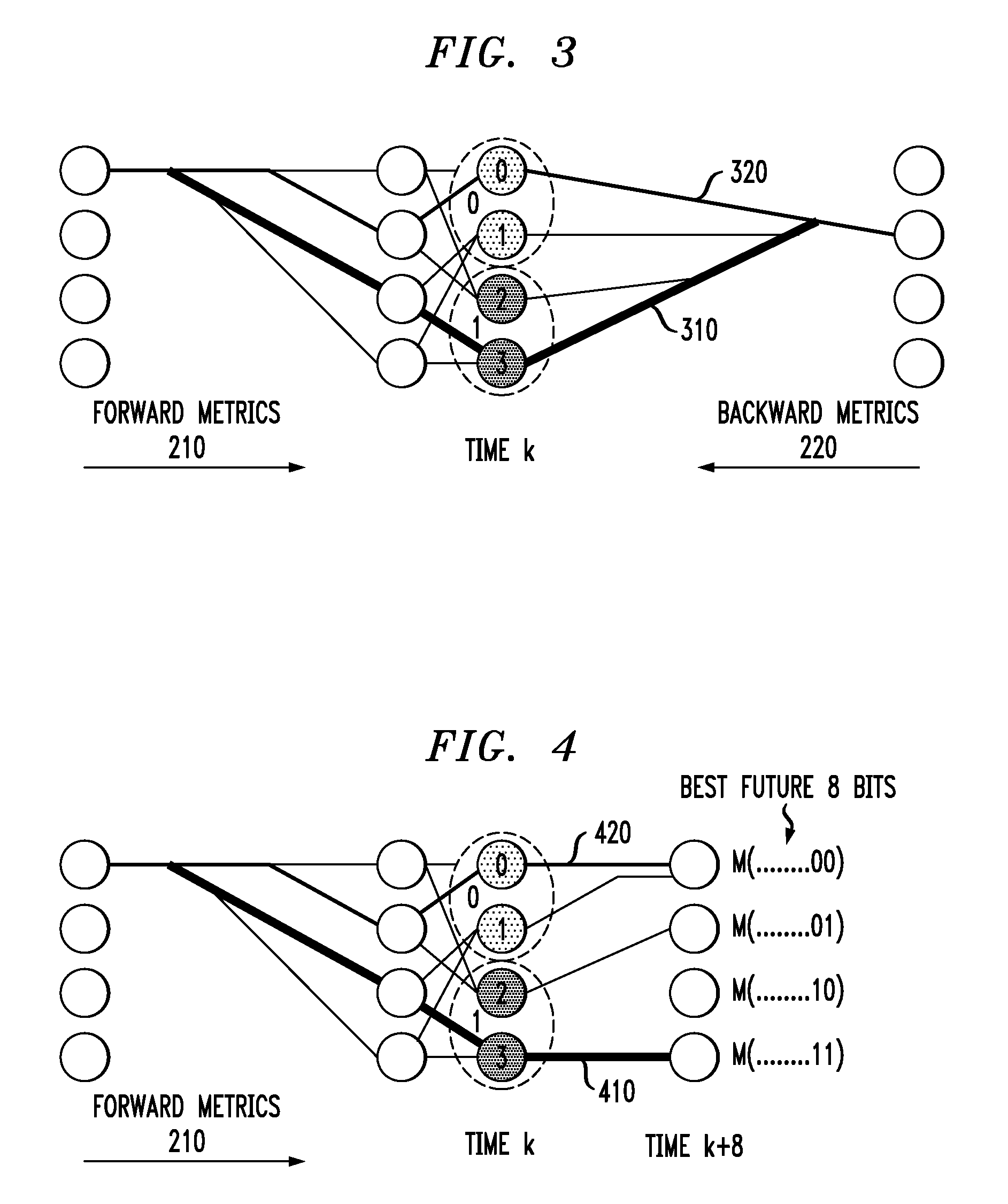

Methods and apparatus are provided for high-speed, low-power, high-performance channel detection. A soft output channel detector is provided that operates at a rate of 1 / N and detects N bits per 1 / N-rate clock cycle. The channel detector comprises a plurality, D, of MAP detectors operating in parallel, wherein each of the MAP detectors generates N / D log-likelihood ratio values per 1 / N-rate clock cycle and wherein at least one of the plurality of MAP detectors constrains each of the bits. The log-likelihood ratio values can be merged to form an output sequence. A single MAP detector is also provided that comprises a forward detector for calculating forward state metrics; a backward detector for calculating backward state metrics; and a current branch detector for calculating a current branch metric, wherein at least two of the forward detector, the backward detector and the current branch detector employ different trellis structures.

Owner:AVAGO TECH INT SALES PTE LTD

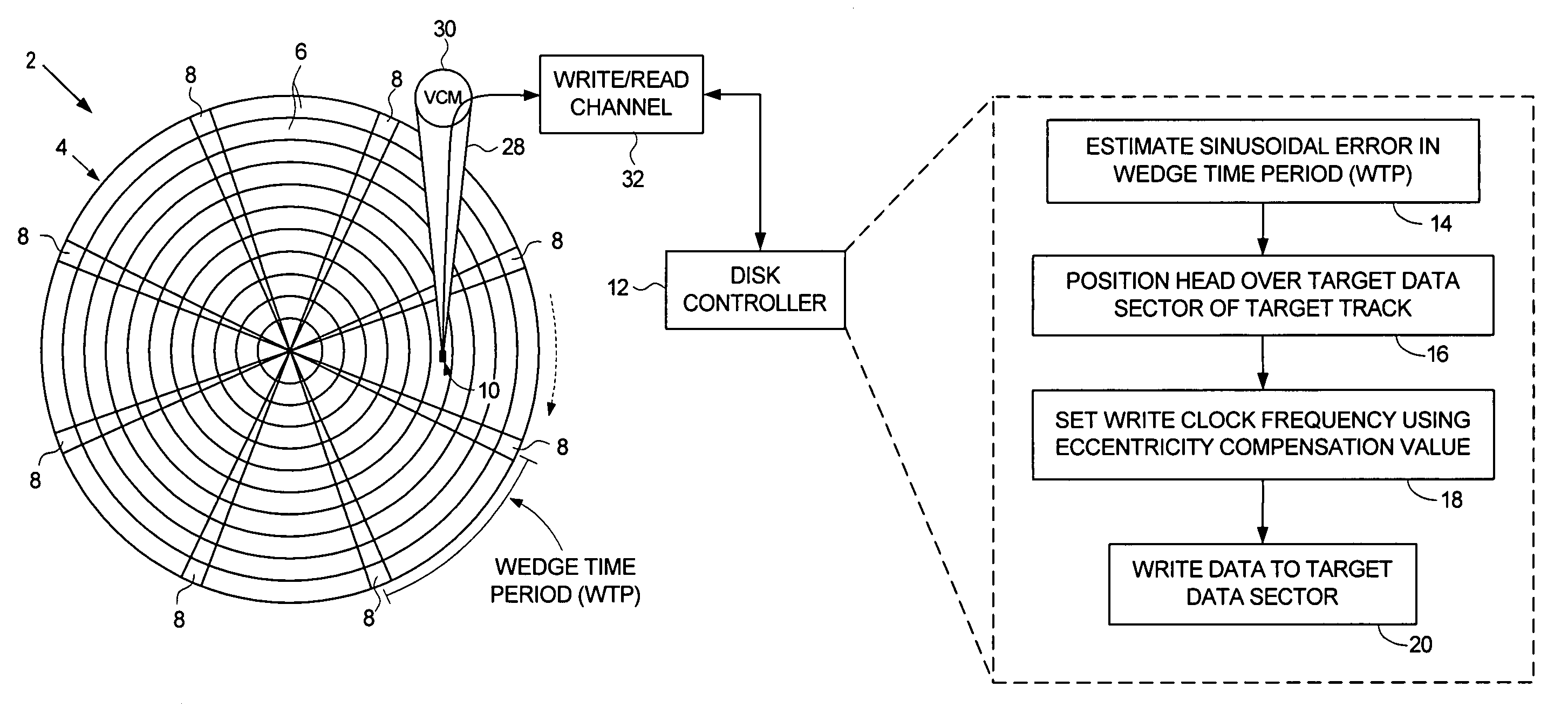

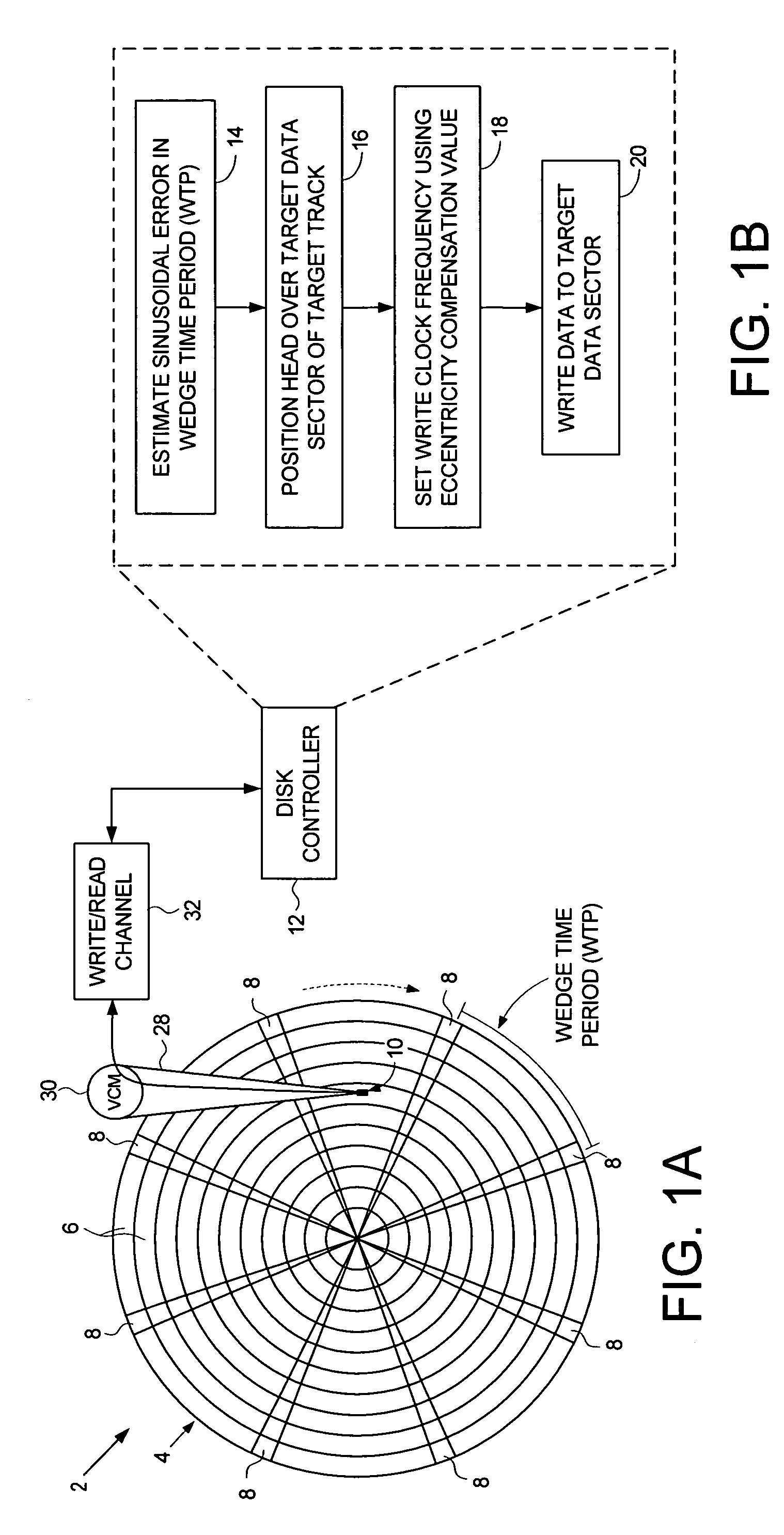

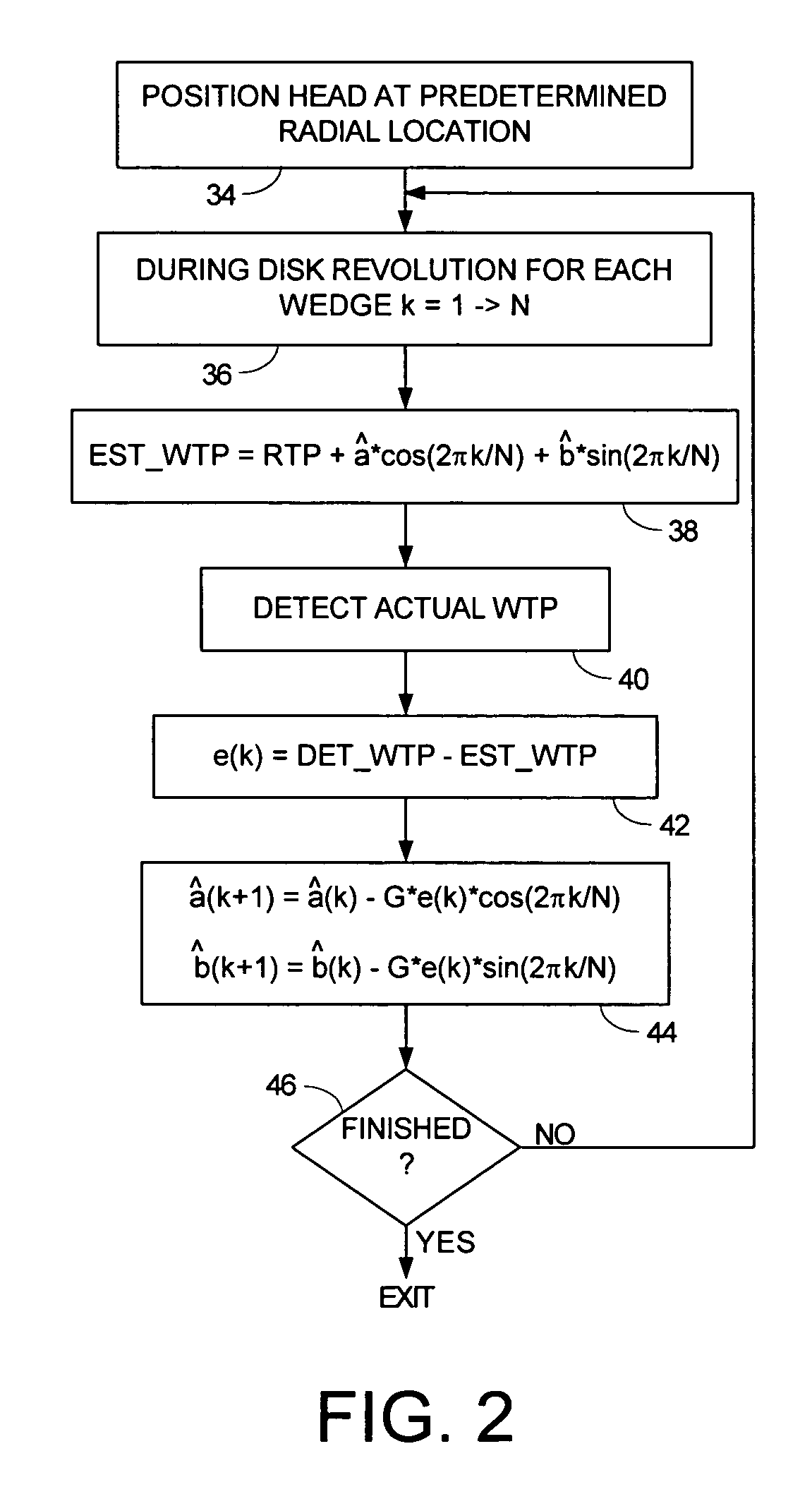

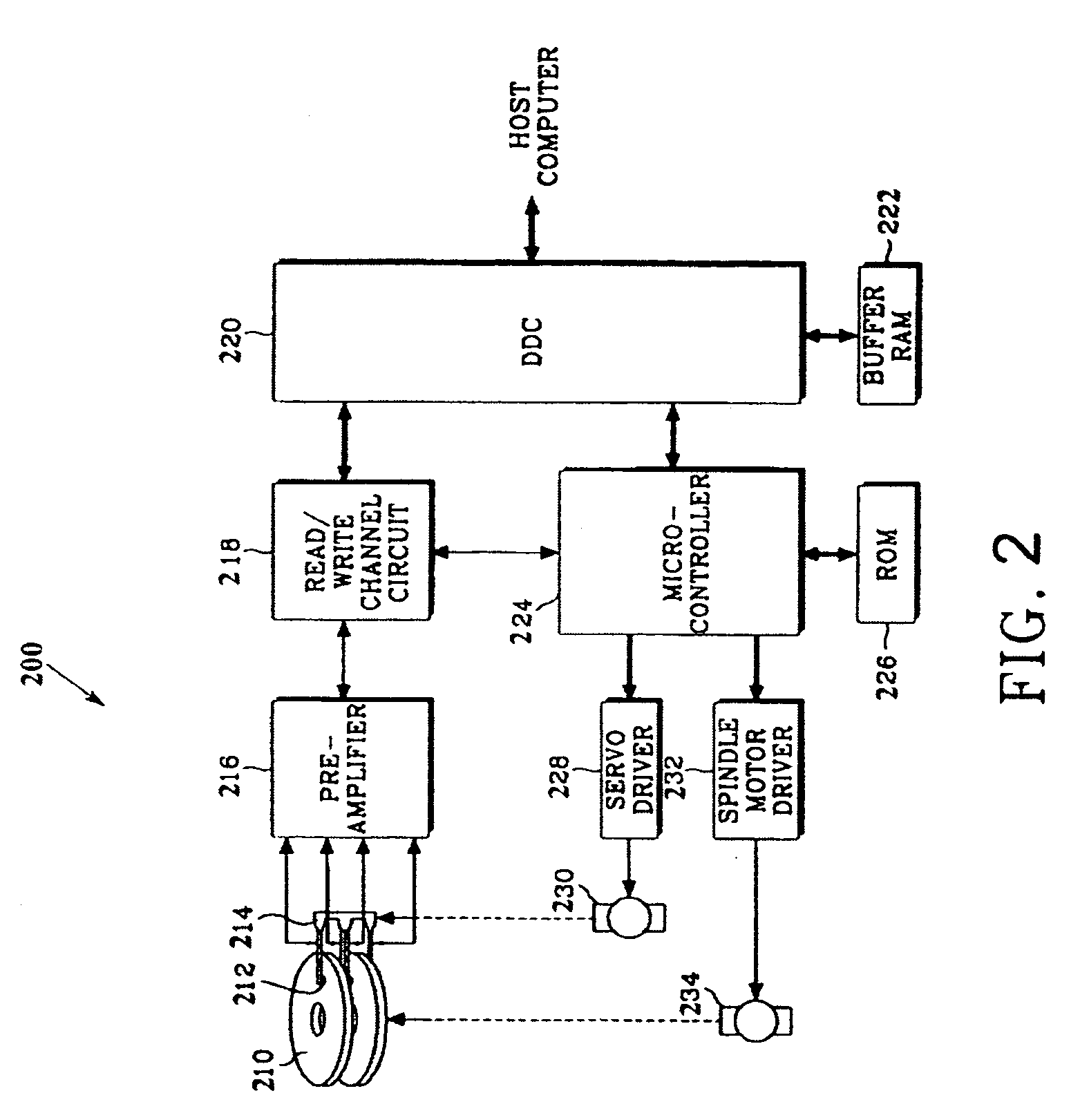

Disk drive adjusting write clock frequency to compensate for eccentricity in disk rotation

InactiveUS7251098B1Record information storageAlignment for track following on disksClock rateTime segment

A disk drive is disclosed that estimates a sinusoidal error in a wedge time period due to eccentricity in the disk rotating to generate eccentricity compensation values. During a write operation a head is positioned over a target data sector within a target track, a write clock frequency is set using an eccentricity compensation value corresponding to the target data sector, and data is written to the target data sector using the write clock frequency. In this manner, the eccentricity compensation value adjusts the write clock frequency to better optimize the linear bit density from the inner to outer diameter tracks.

Owner:WESTERN DIGITAL TECH INC

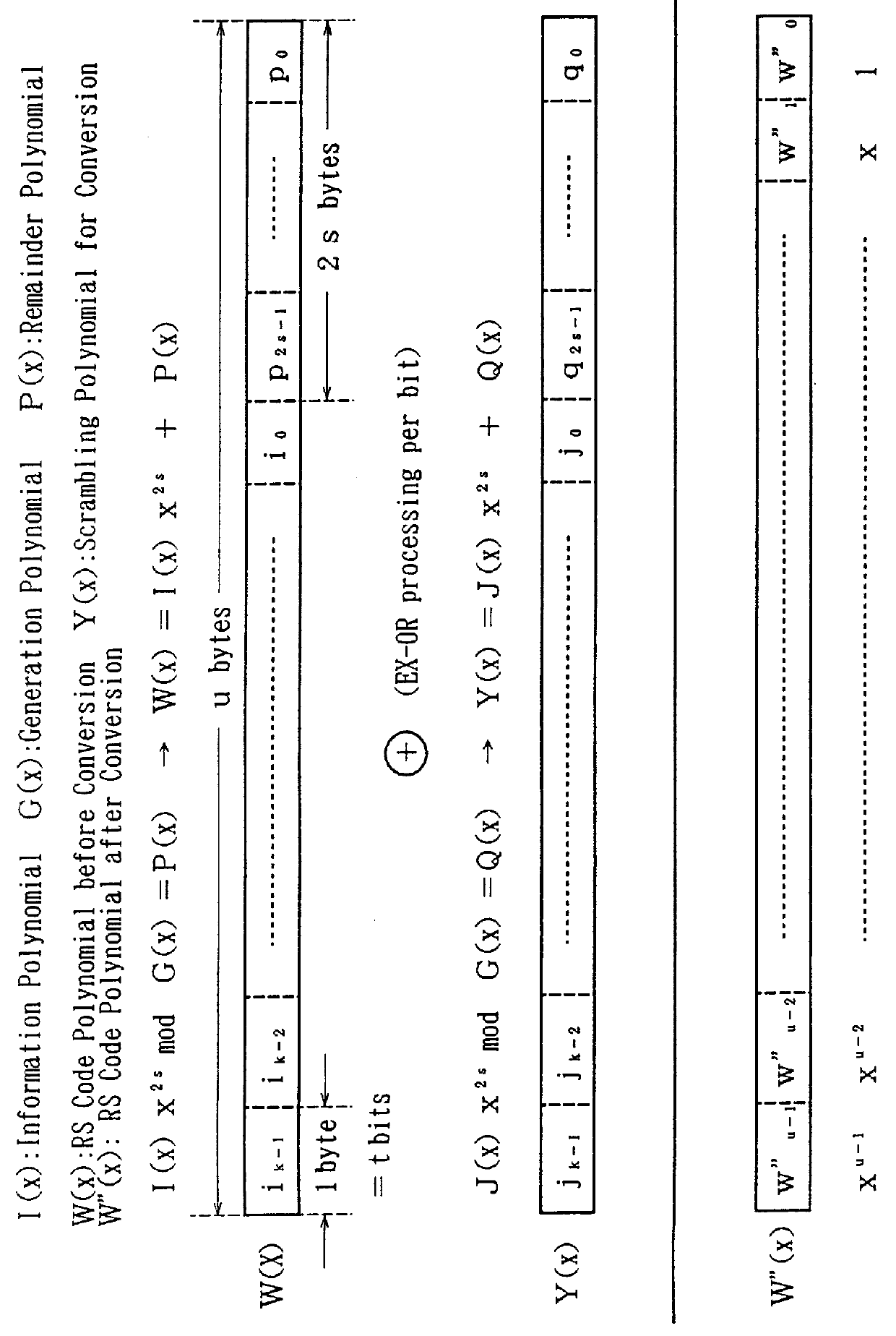

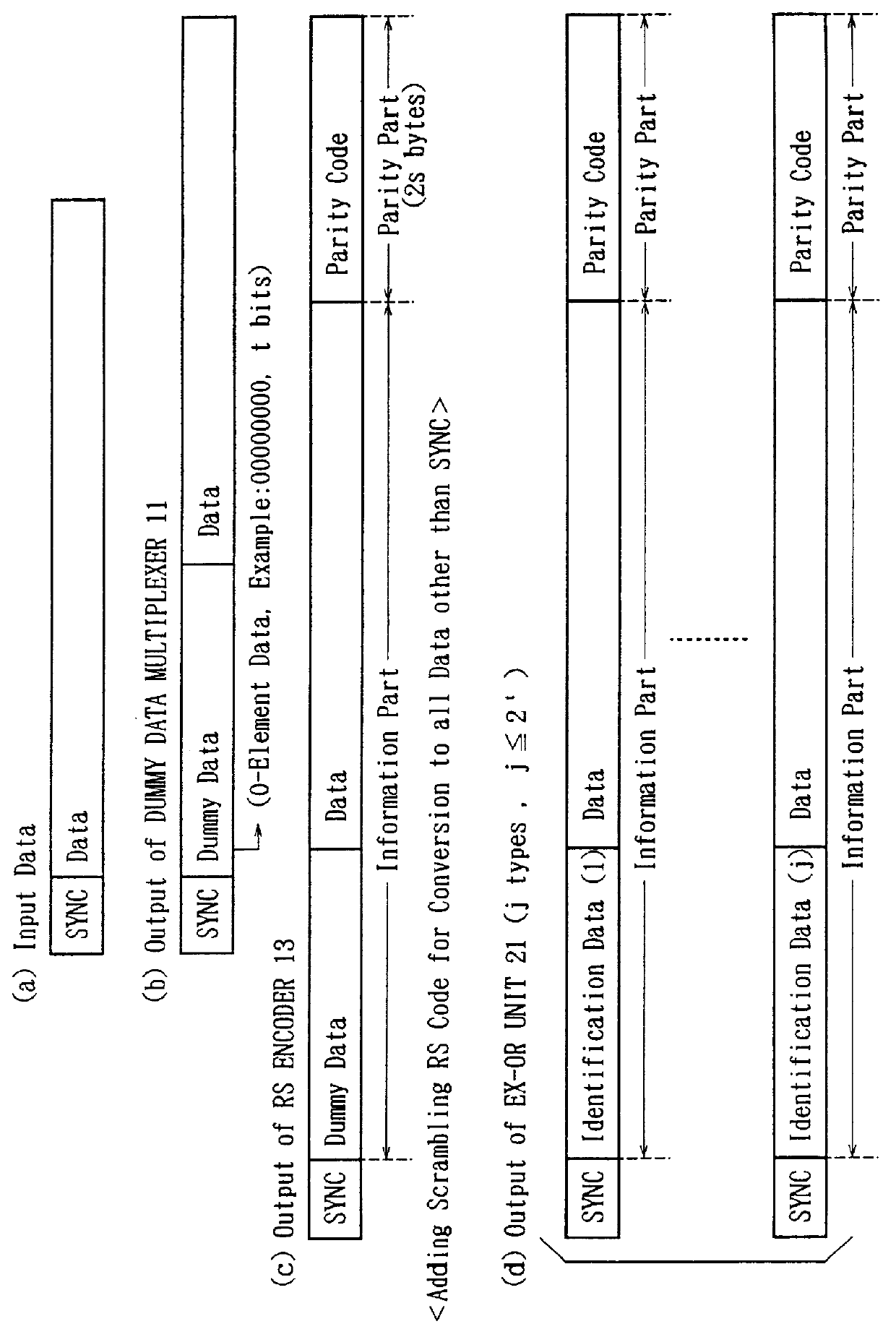

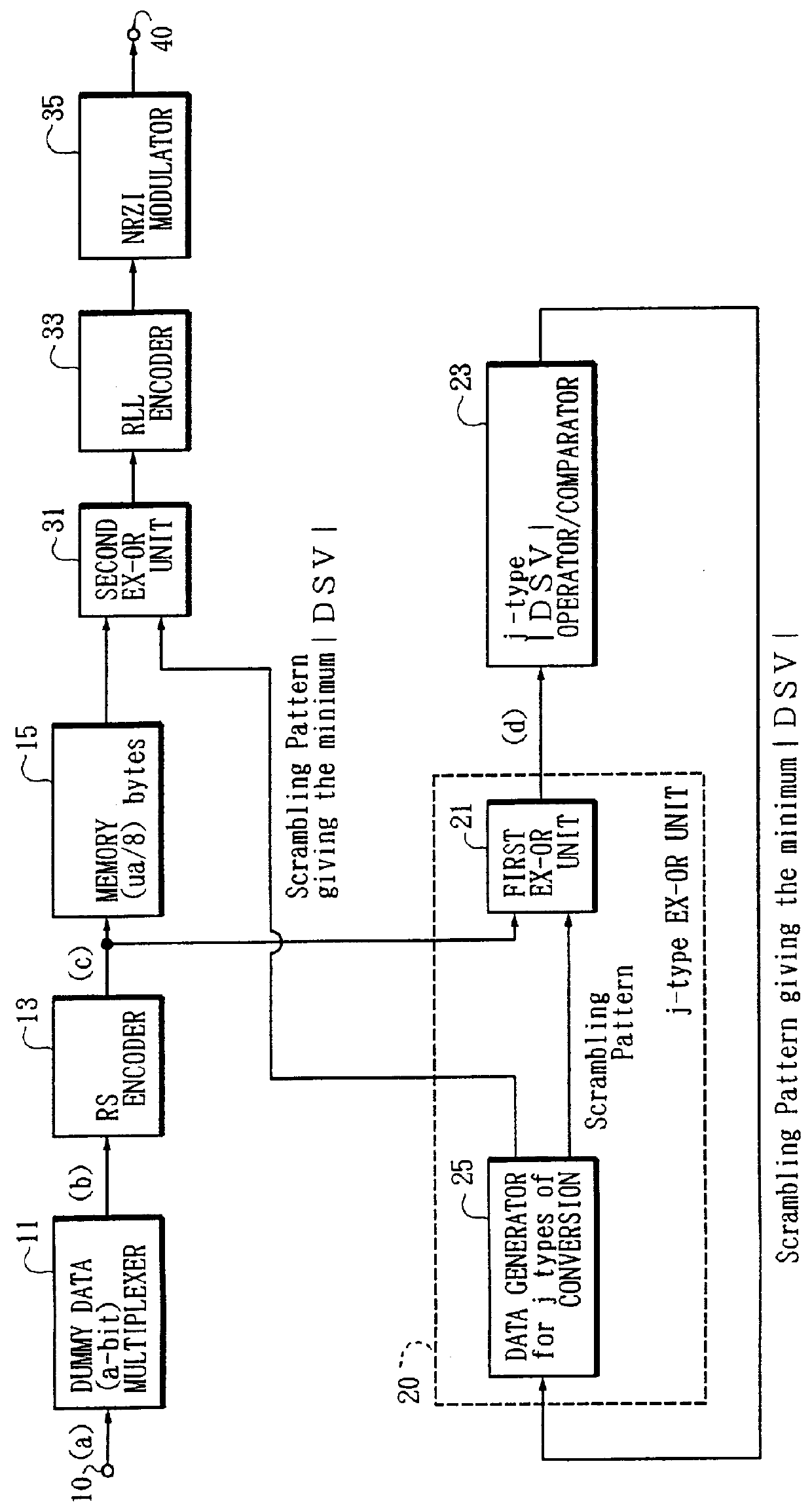

Digital modulation and demodulation

A digital modulator which inputs a data stream to convert to a channel bit stream. The multiplexed data block is generated by multiplexing dummy data to any position within each data block cut out of the data stream one by one. The first Reed-Solomon code is generated by Reed-Solomon-encoding the multiplexed data block as an information part. A plurality of second Reed-Solomon codes are generated by adding a plurality of Reed-Solomon codes for scrambling each of which has identification data showing its scrambling pattern in the same position as that of the dummy data, and the code length of information part and parity part is the same as the first Reed-Solomon code. The second Reed-Solomon code in which the characteristics becomes desirable after modulation among the plurality of the second Reed-Solomon codes is set for output.

Owner:SANYO ELCETRIC CO LTD +1

Detection of synchronization mark from output of matched filter upstream of viterbi detector

InactiveUS20090274247A1Avoid delayAccurate startModification of read/write signalsOther decoding techniquesViterbi detectorMatched filter

Embodiments of the present invention relate to the detection of synchronization marks in data storage and retrieval. According to one embodiment, synchronization marks are detected from the output of a matched filter, upstream of the Viterbi detector. This approach avoids the delay associated with the latency of the Viterbi output, thereby allowing time to align parity framing and to properly start the time-varying trellis. Certain embodiments disclose 34- and 20-bit primary synchronization marks located at the beginning of a data region. Other embodiments disclose 16-, 20-, and 24-bit embedded synchronization marks located within a data region.

Owner:WESTERN DIGITAL TECH INC

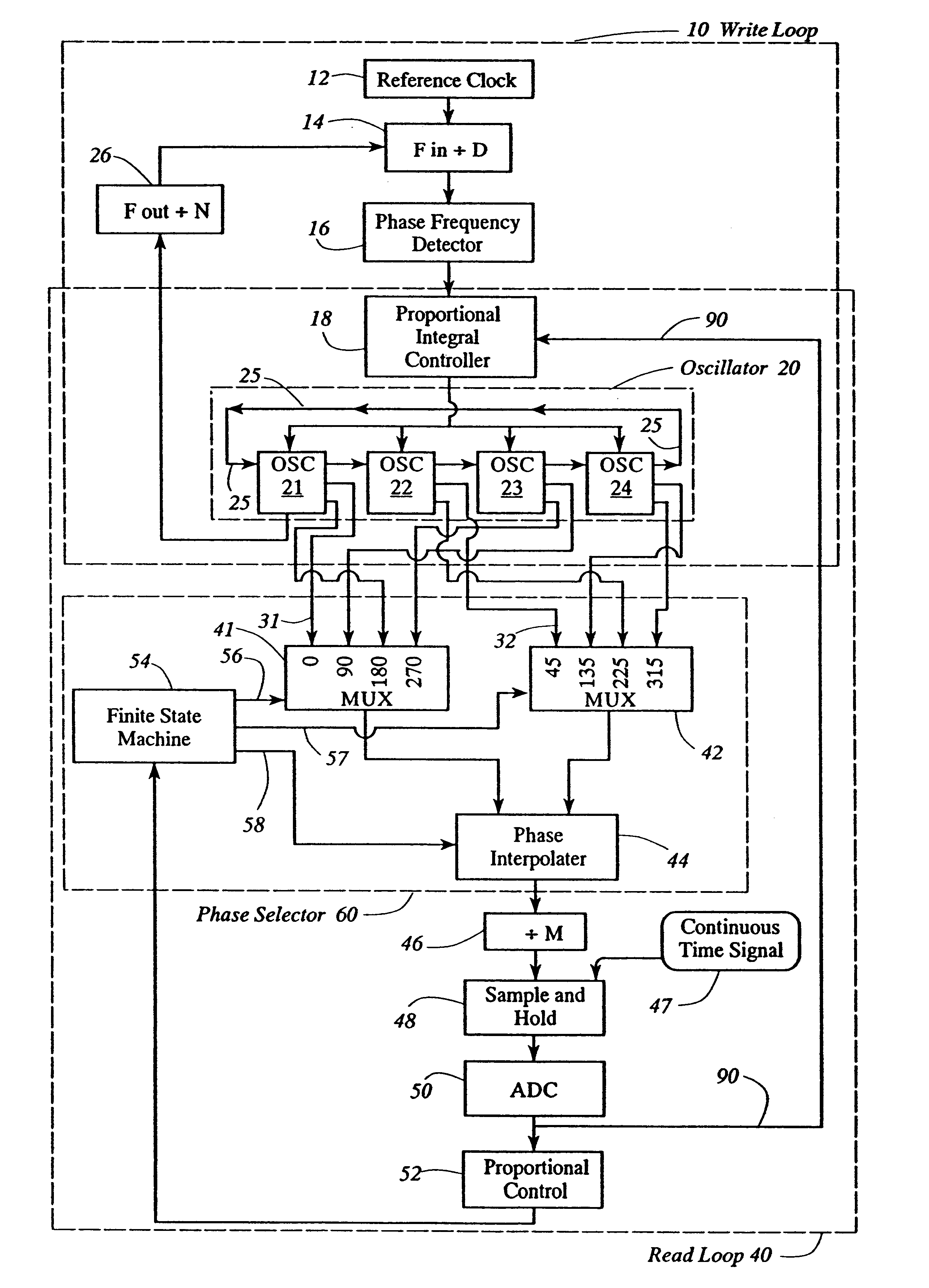

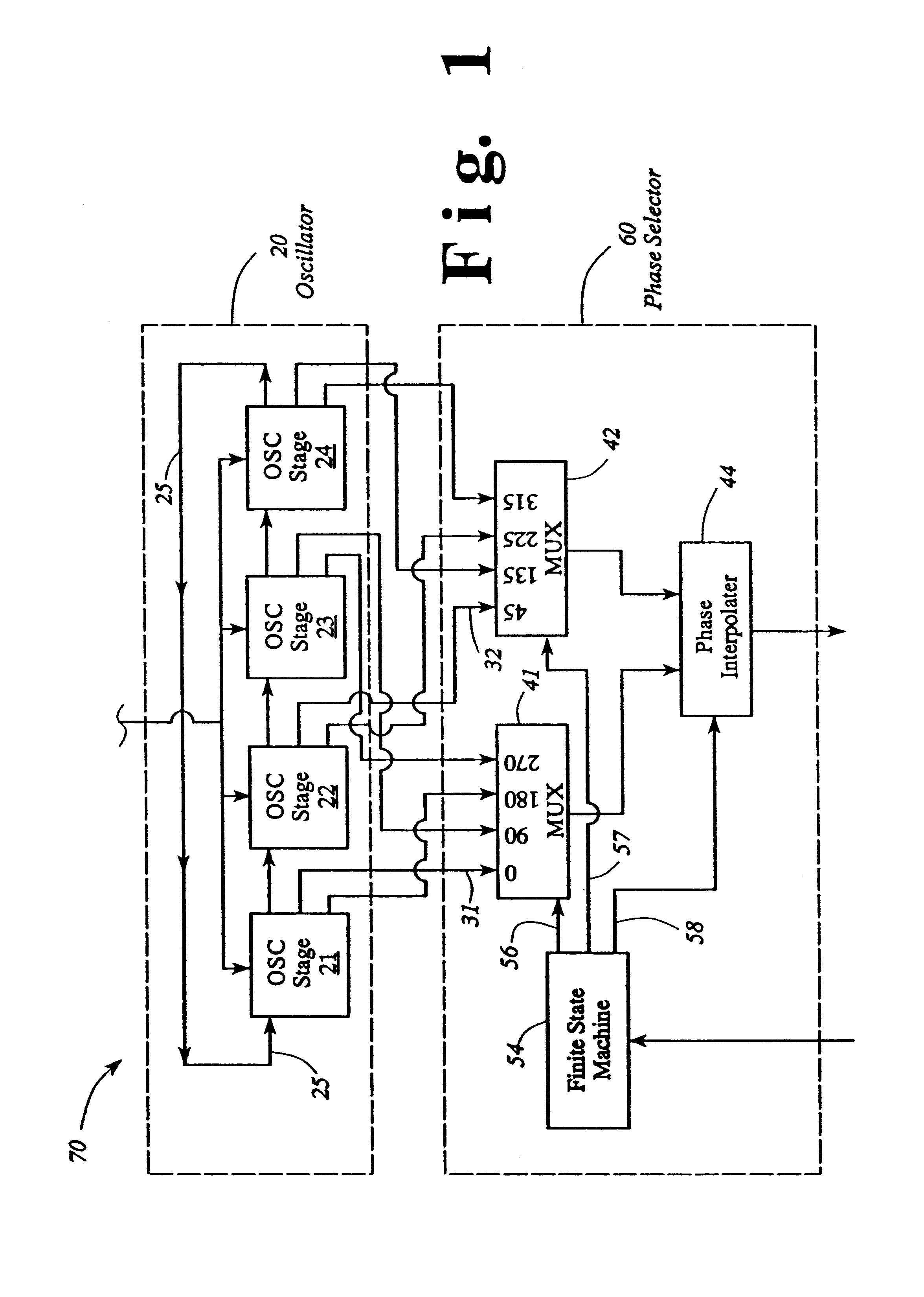

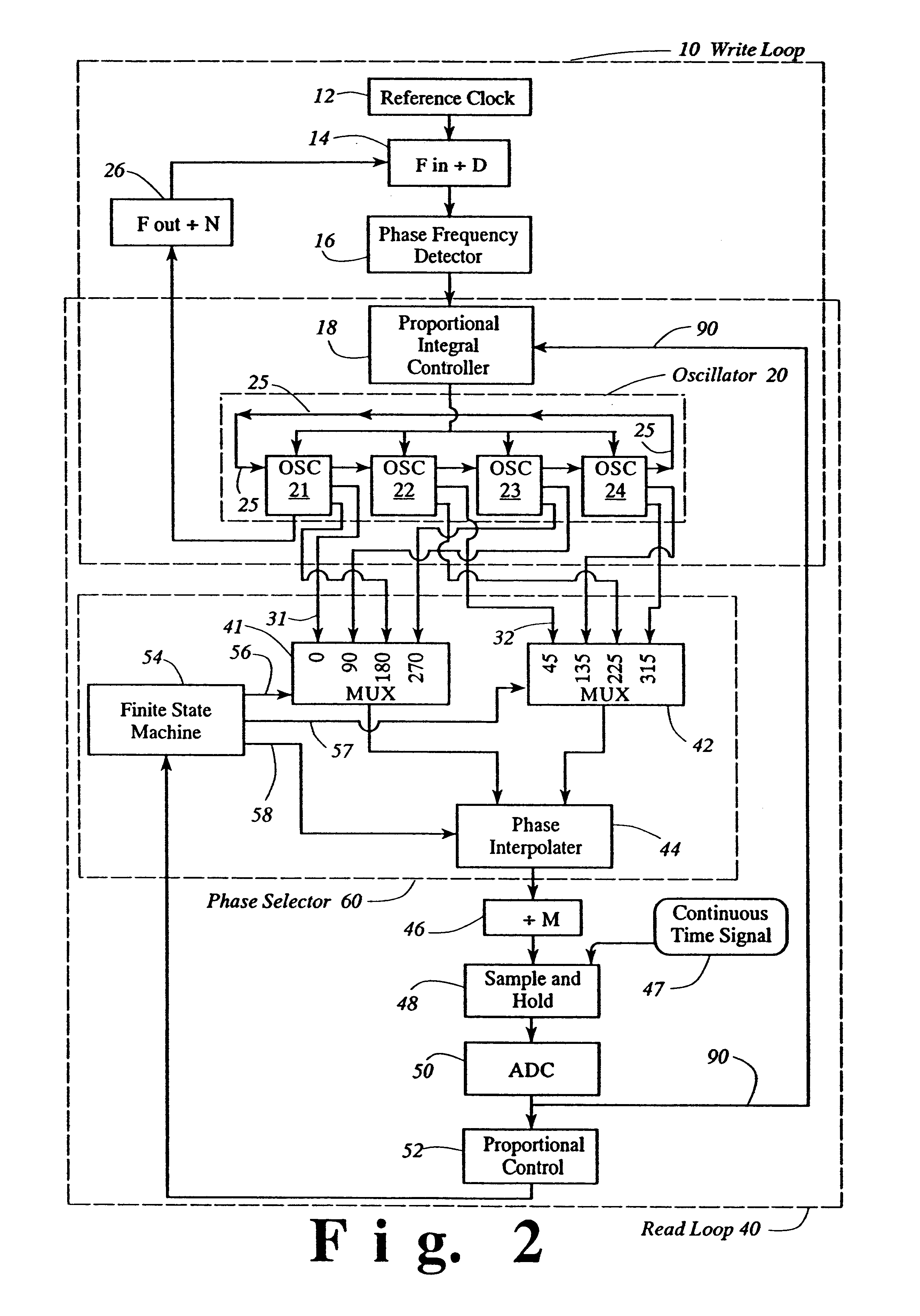

Oscillator with digitally variable phase for a phase-locked loop

InactiveUS6525615B1Disposition/mounting of recording headsPulse automatic controlMultiplexerImproved method

The present invention provides an improved method and apparatus for independently controlling phase and frequency using an oscillator having a plurality of stages in combination with a phase selector within a digitally controlled phase-locked loop, preferably, a read phase locked loop. The present invention provides a digitally controlled variable phase of the read timing loop in read channel integrated circuits associated with data storage devices. The phase selector has a digitally controlled fine interpolator with 12 states for further fine interpolation between at least two multiplexer phase outputs to provide a single phase output selected from a range comprising at least 2pi in selectable variable phase increments of 2pi / 96 radian. The combined oscillator with the phase selector within a phase locked loop controls phase by exact fractional increments of equally space phases of the operating frequency within the phase locked loop, therein controlling phase at all operating frequencies.

Owner:GLOBALFOUNDRIES INC

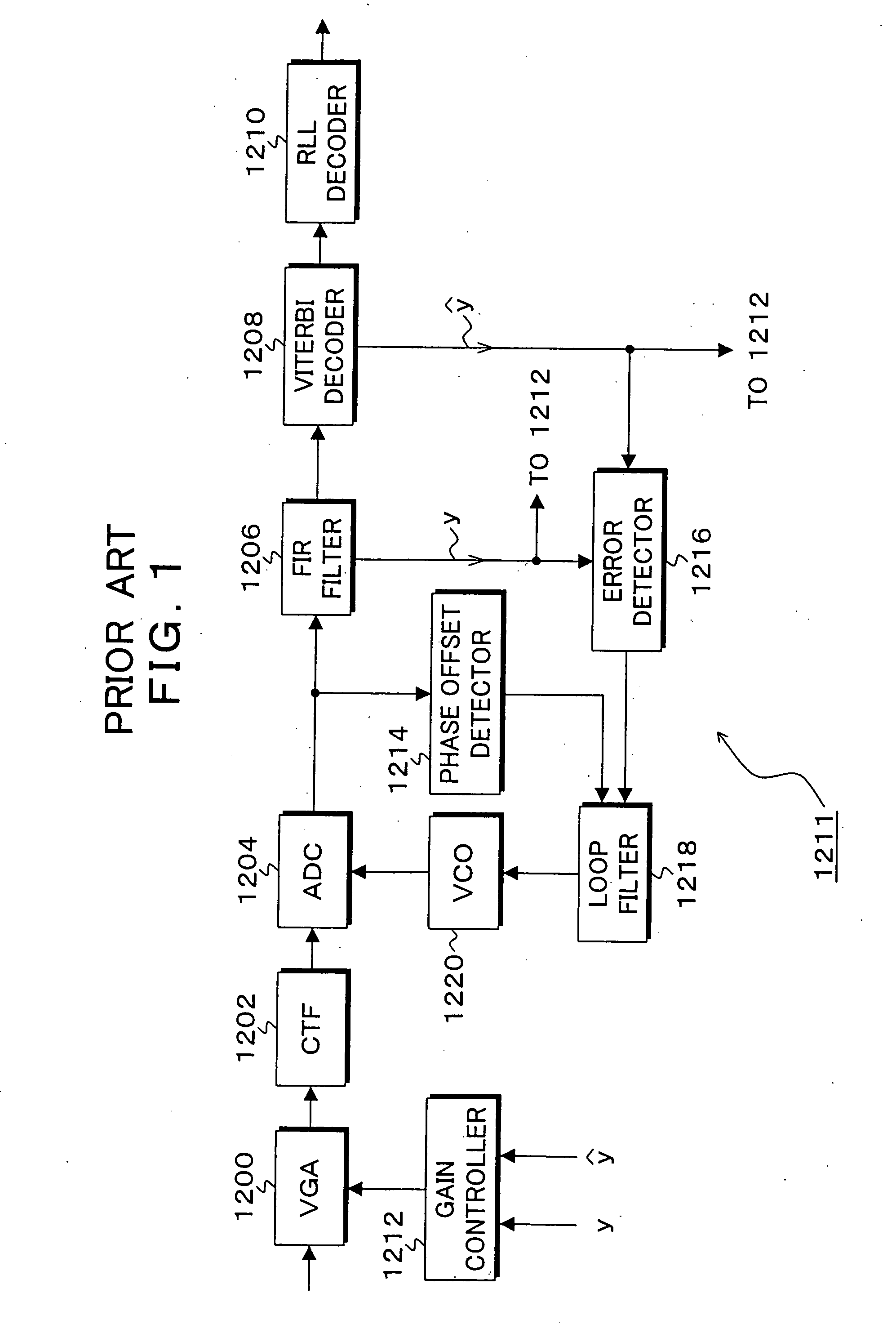

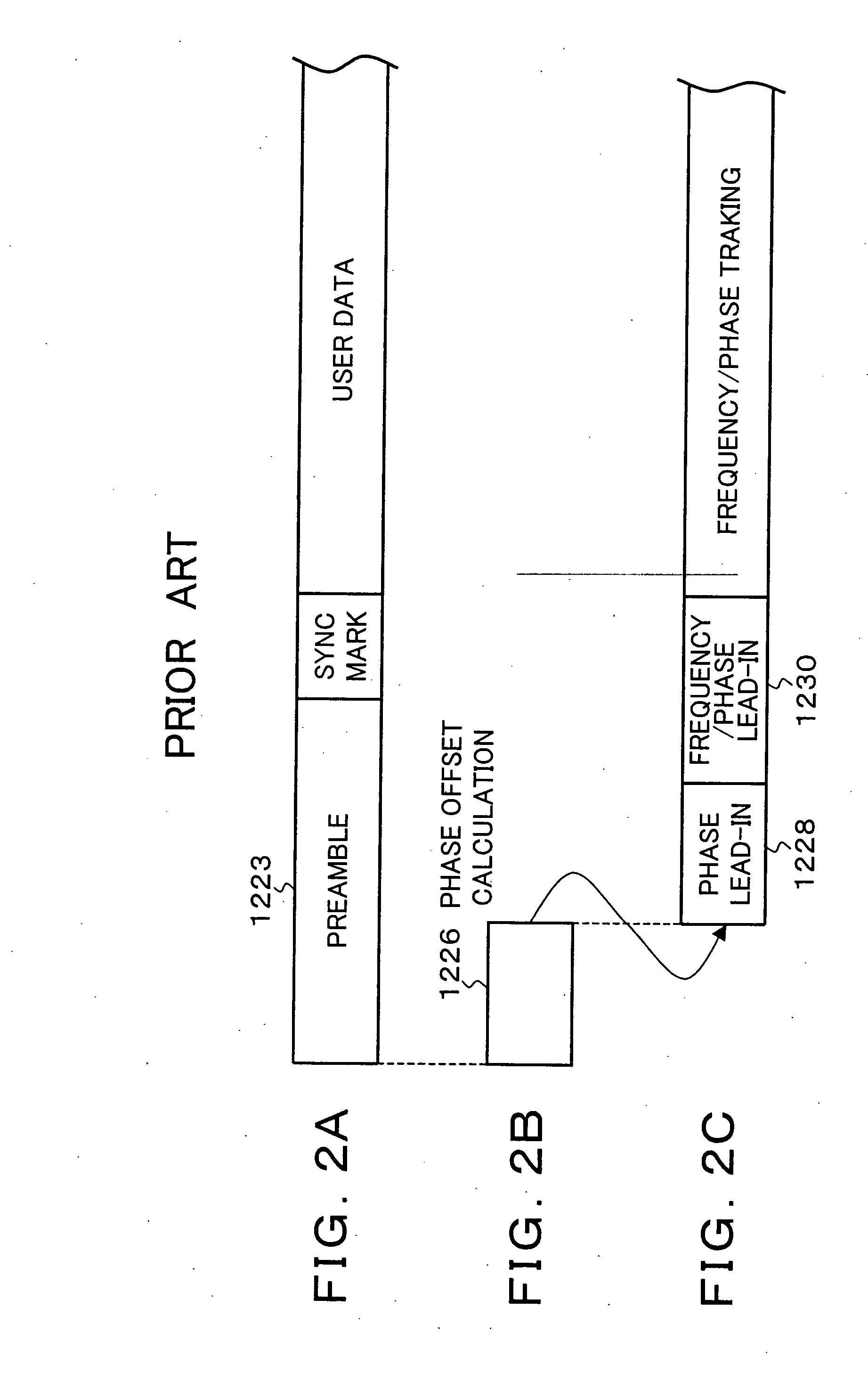

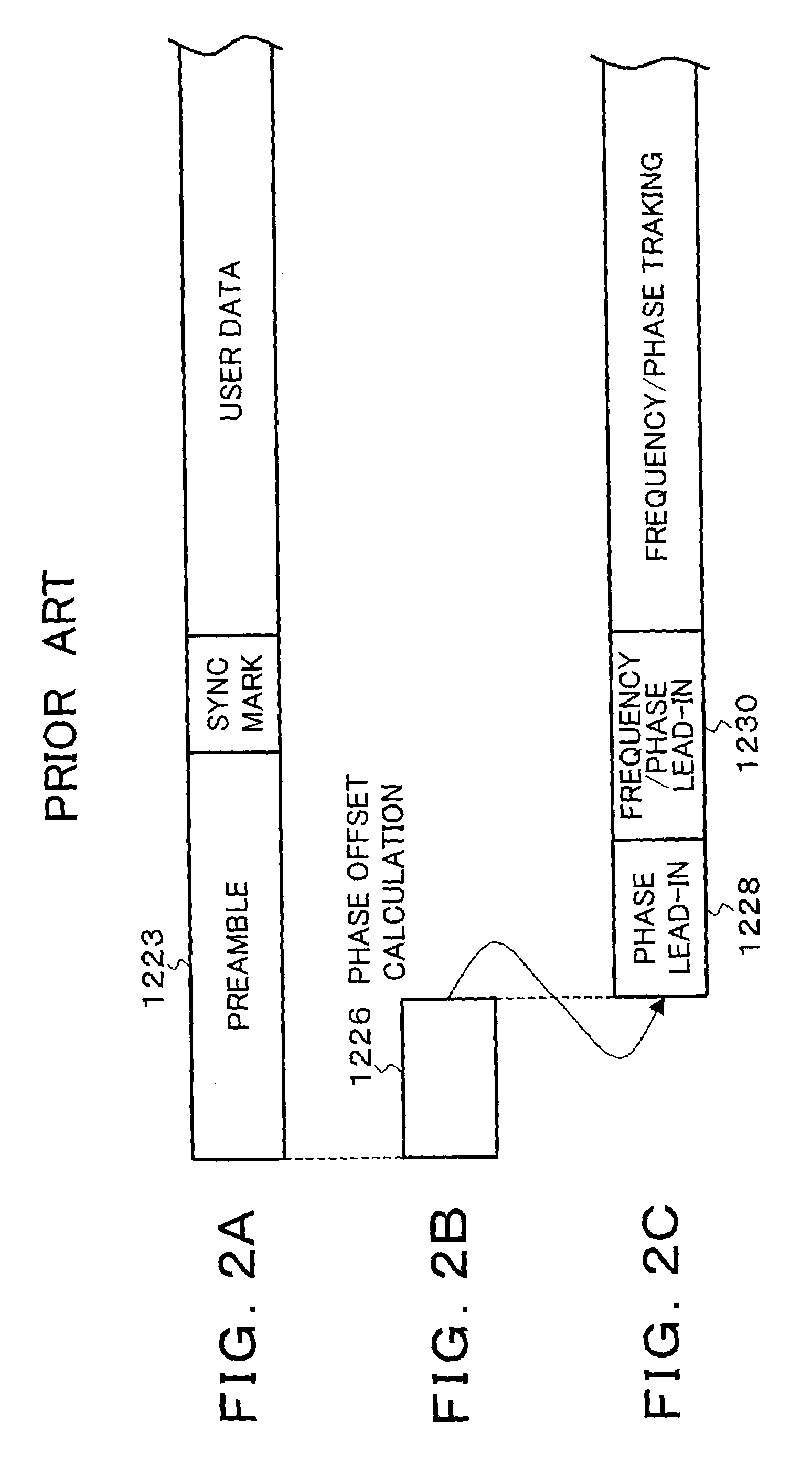

Information recording and reproducing apparatus and method, and signal decoding circuit for performing timing recovery

InactiveUS20060181797A1Shorten the lengthIncrease rangeModification of read/write signalsTransmission control/equlisationPhase leadComputer science

A timing recovery unit detects a phase offset and a frequency offset from a head area of reproduction data and initially corrects them. The timing recovery unit stores data in which a head reproduction signal has been made to be discrete by a fixed clock into a buffer. A phase offset detector detects the phase offset from the data head area in parallel with the operation for writing the data into the buffer. At the same time, a frequency offset detector detects the frequency offset from the data head area in parallel with the operation for writing the data into the buffer. A correction value of the detected phase offset and a correction value of the detected frequency offset are initially set into a digital PLL. While the data is read out from the buffer, a frequency lead-in and a phase lead-in are executed in the head area.

Owner:TOSHIBA STORAGE DEVICE CORP

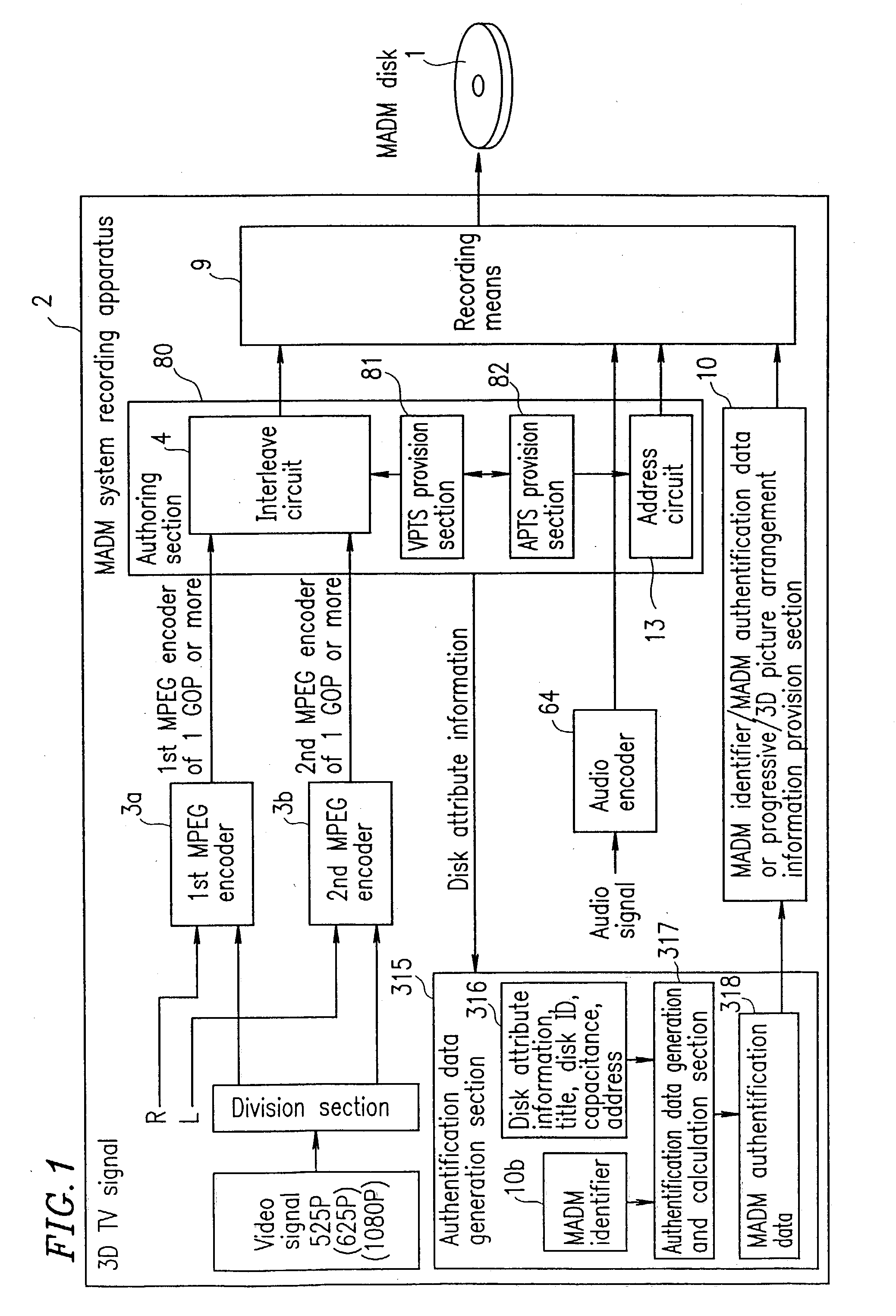

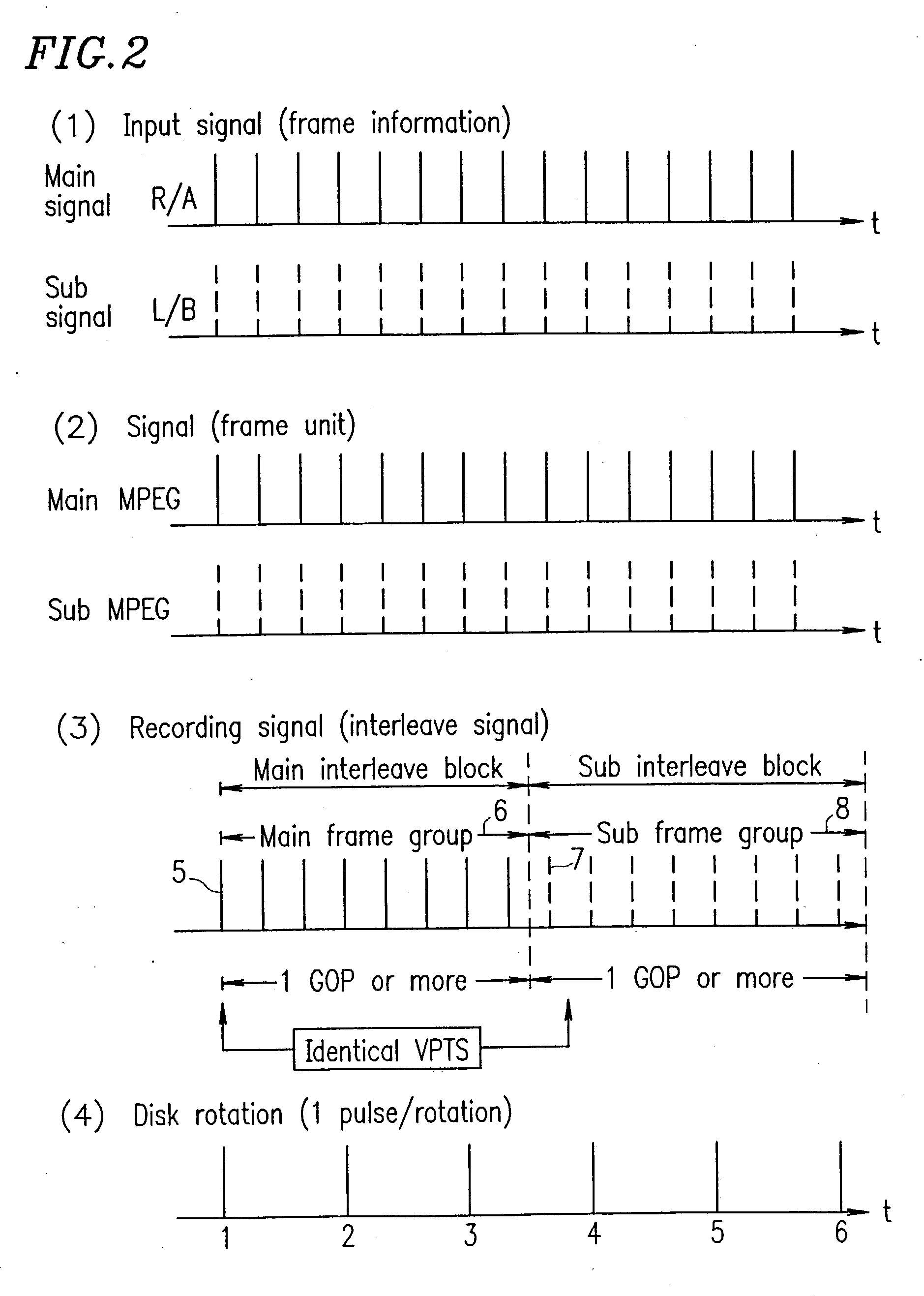

Optical disk for high resolution and three-dimensional video recording, optical disk reproduction apparatus, and optical disk recording apparatus

InactiveUS20030108341A1Precise positioningWithout any changeTelevision system detailsTelevision system scanning detailsImage resolutionImage segmentation

The present invention has an objective of providing an optical disk having a high resolution picture and a system for reproducing data on the optical disk, which are compatible with a conventional system for reproducing an ordinary resolution picture. A high resolution signal is divided into a main signal and a sub signal by picture division means and MPEG-encoded. The main signal and the sub signal are divided into frames each having 1 GOP or more. The resultant first interleave block 54 and second interleave block 55 are recorded alternately on an optical disk. A high resolution reproduction apparatus reproduced both the first and second interleave blocks, so that a high resolution picture is obtained. A non-high resolution reproduction apparatus reproduces only the first or second interleave block, so that an ordinary resolution picture.

Owner:PANASONIC CORP

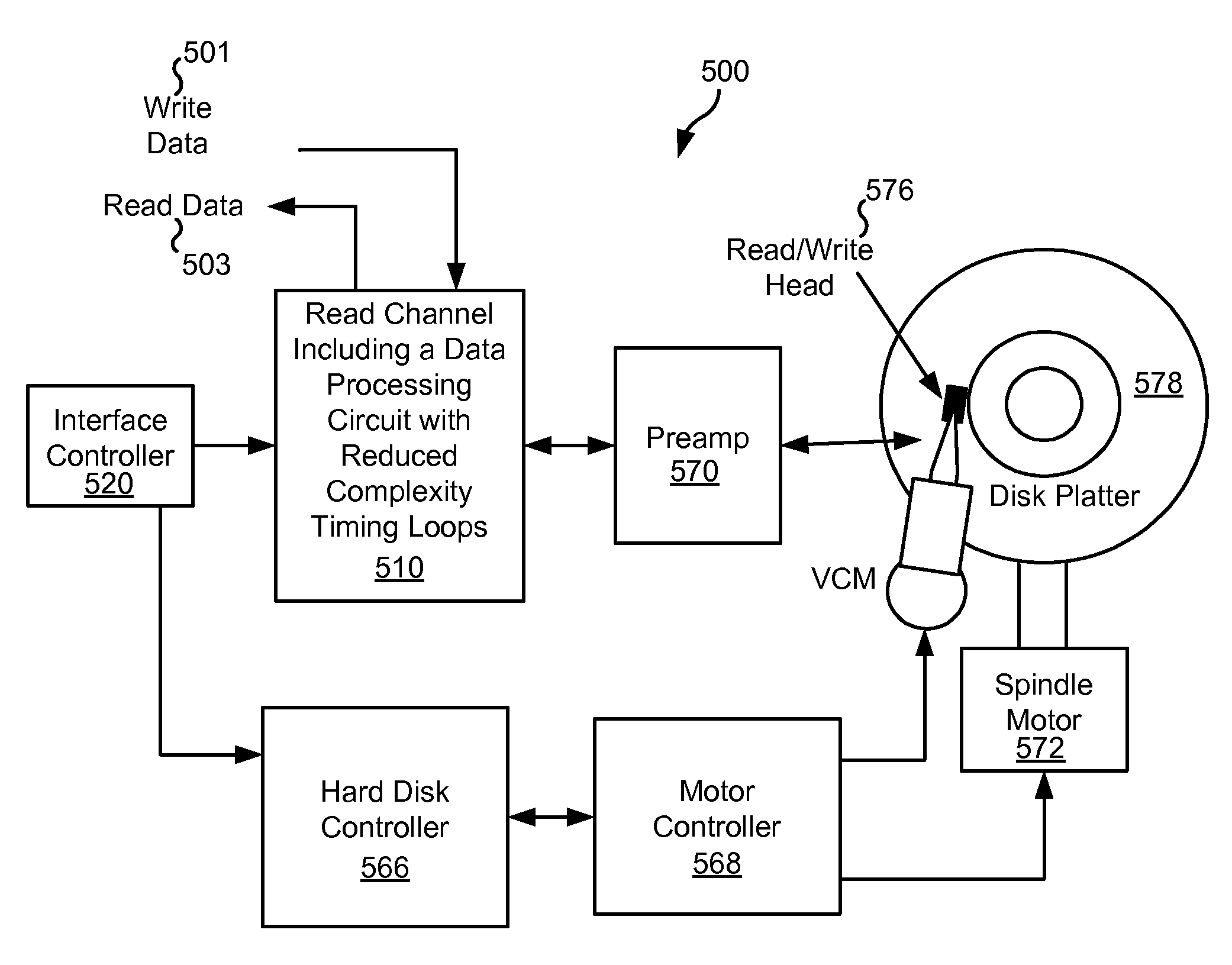

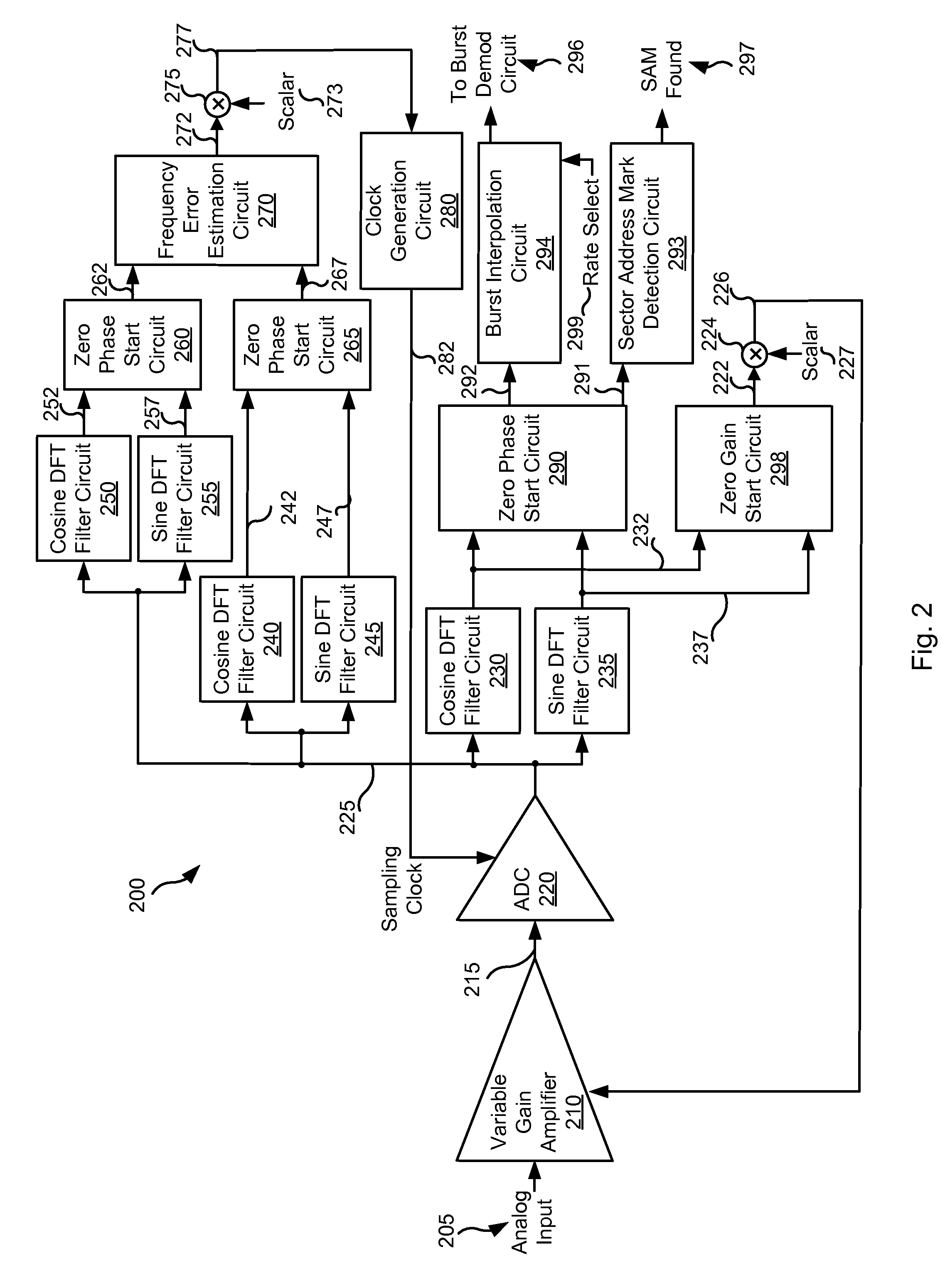

Systems and Methods for Reduced Format Data Processing

InactiveUS20120182643A1Record information storageAlignment for track following on disksAudio power amplifierVariable-gain amplifier

Various embodiments of the present invention provide systems and methods for data processing. For example, some embodiments of the present invention provide data processing circuits that include a variable gain amplifier circuit, an analog to digital conversion circuit, a cosine component calculation circuit, a sine calculation circuit, and a zero gain start calculation circuit. The variable gain amplifier circuit is operable to apply a gain to a data input corresponding to a gain feedback value and providing an amplified output. The analog to digital conversion circuit is operable to convert the amplified output to a corresponding series of digital samples. The cosine component calculation circuit is operable to calculate a cosine component from the series of digital samples, and the sine component calculation circuit operable to calculate a sine component from the series of digital samples. The zero gain start calculation circuit is operable to calculate a raw gain error value based on the cosine component and the sine component, where the gain feedback value is derived from the raw gain error value.

Owner:BROADCOM INT PTE LTD

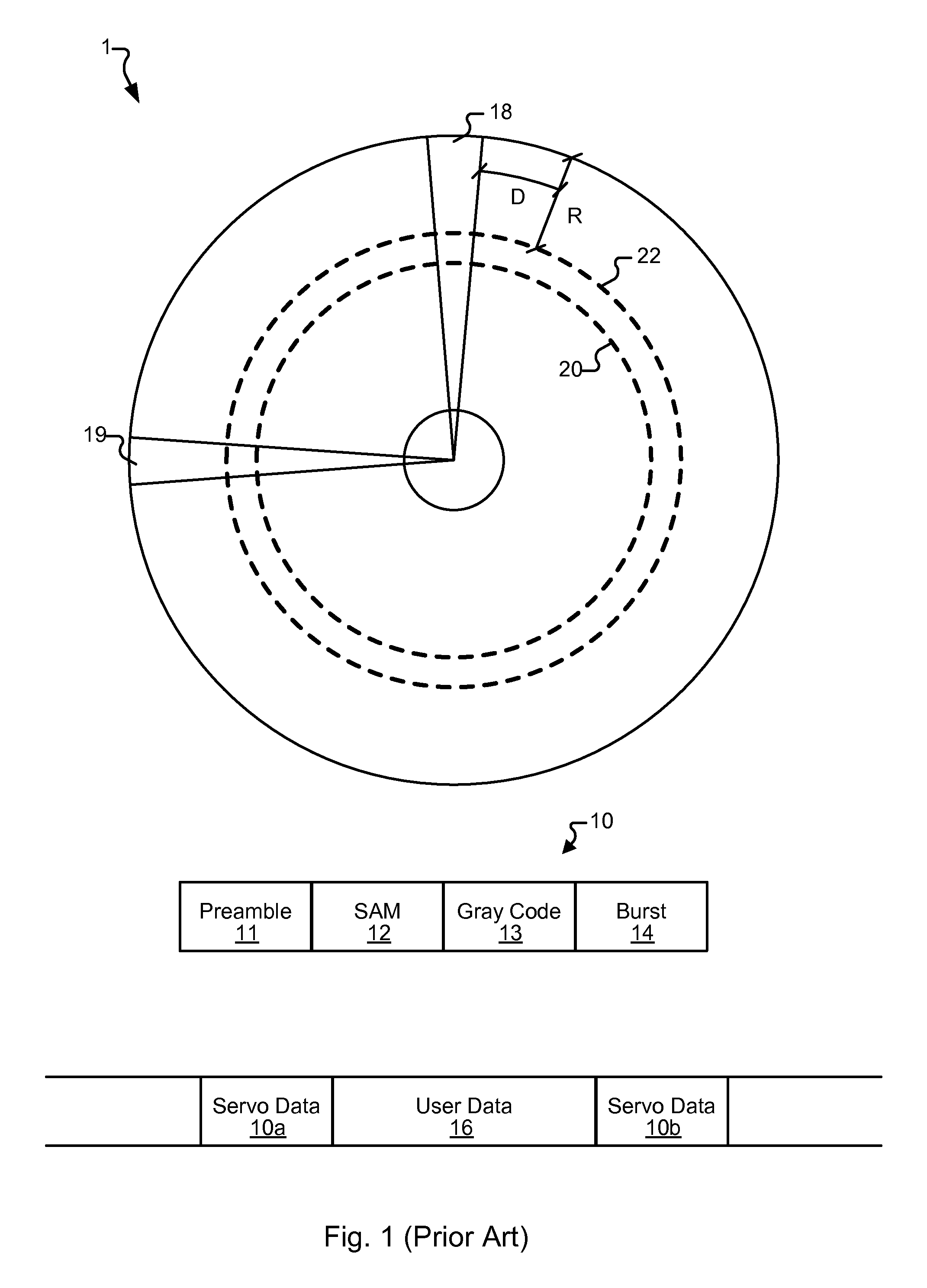

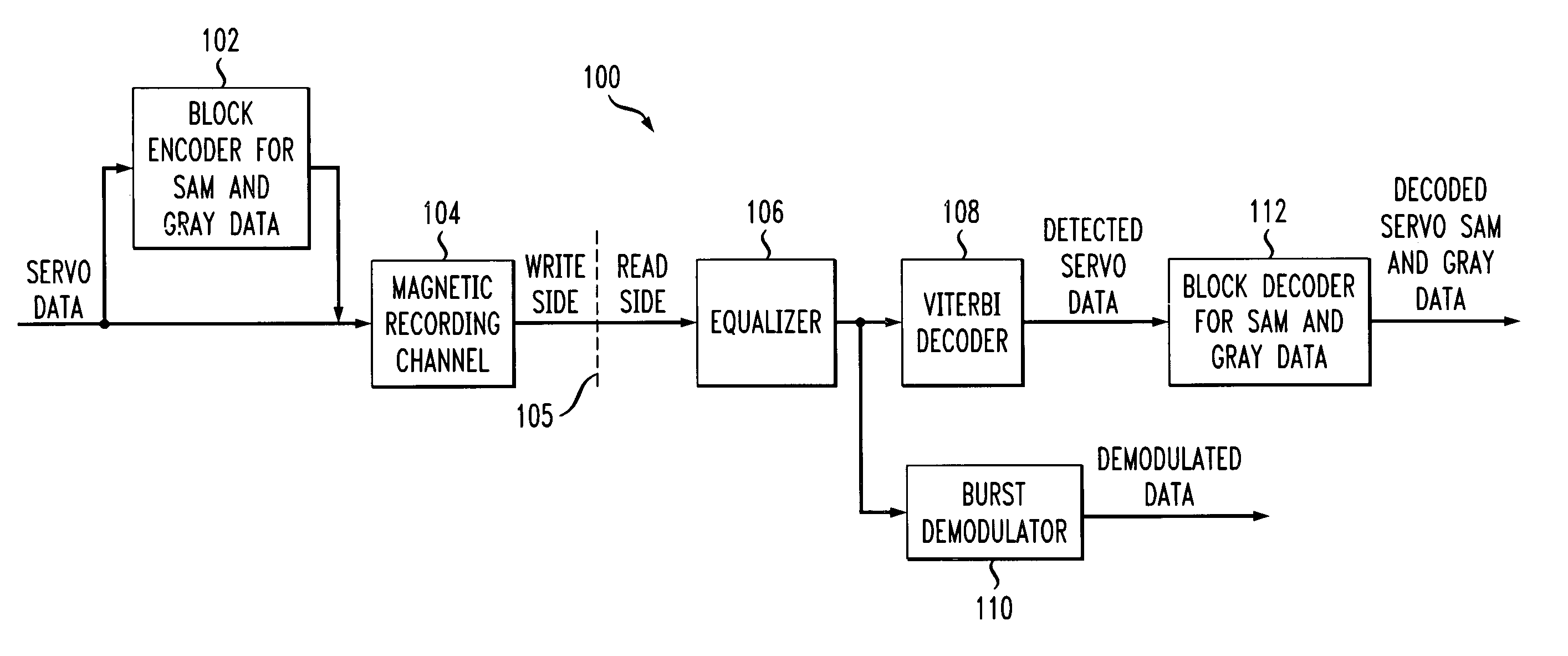

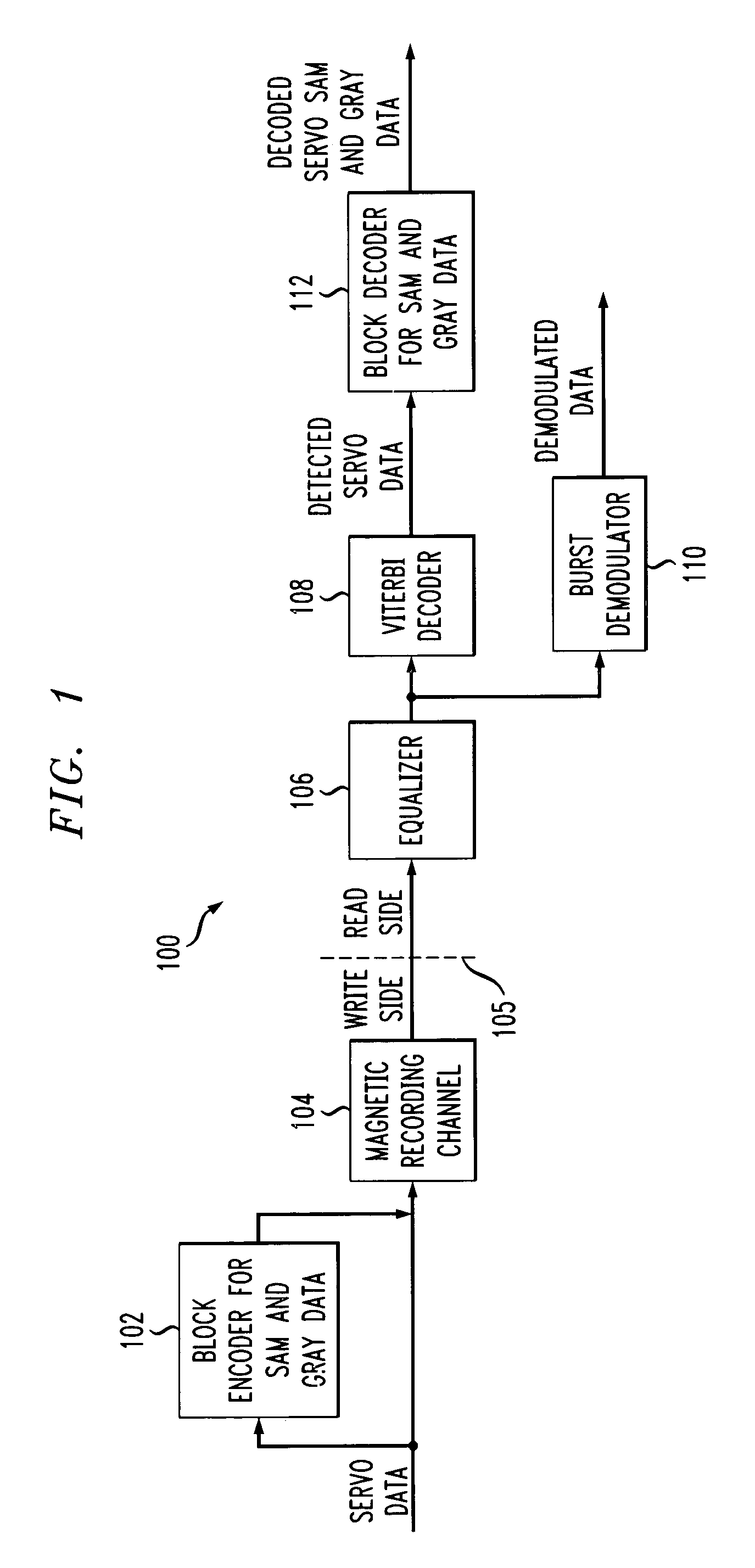

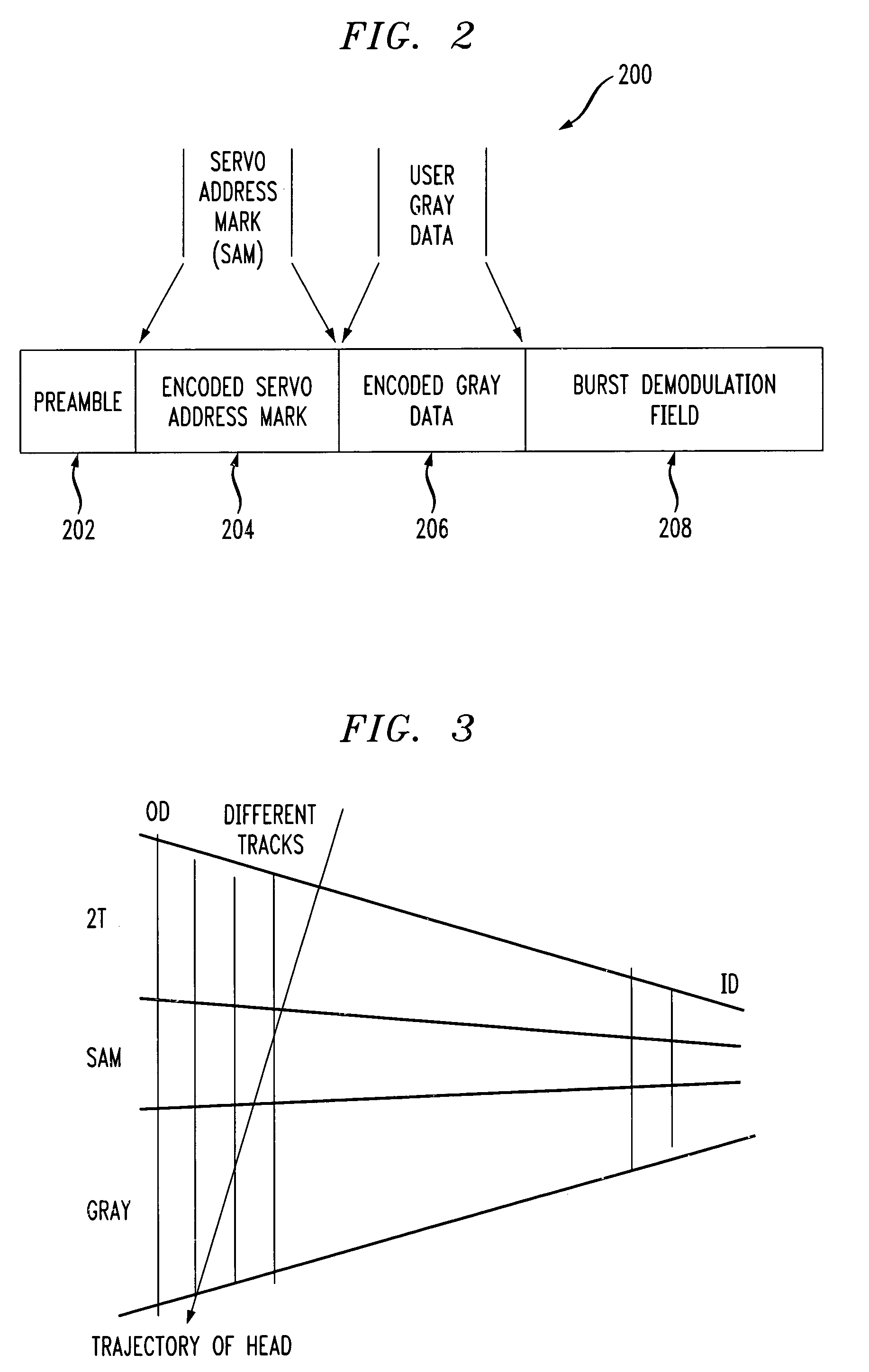

Servo data detection in the presence or absence of radial incoherence using digital interpolators

ActiveUS7082005B2Improve performanceSeek time increaseModification of read/write signalsRecord information storagePhase correlationData storing

Techniques for detecting data, such as servo data, from input or incoming data read from a transmission medium, such as magnetic recording medium, in the presence or absence of radial incoherence. In one illustrative recording medium-based aspect of the invention, such a technique for detecting data from input data stored on a recording medium comprises the following steps. First, one or more samples are interpolated from one or more samples which have been generated from the input data at a given symbol rate. The one or more interpolated samples have one or more phases associated therewith which differ from a phase associated with the one or more samples generated at the given symbol rate. Then, an optimum or best phase is selected from the symbol rate phase and the one or more interpolated phases such that at least a portion of the one or more samples associated with the optimum phase are identified as representative of detected data.

Owner:AVAGO TECH INT SALES PTE LTD

Record carrier and apparatus for scanning the record carrier

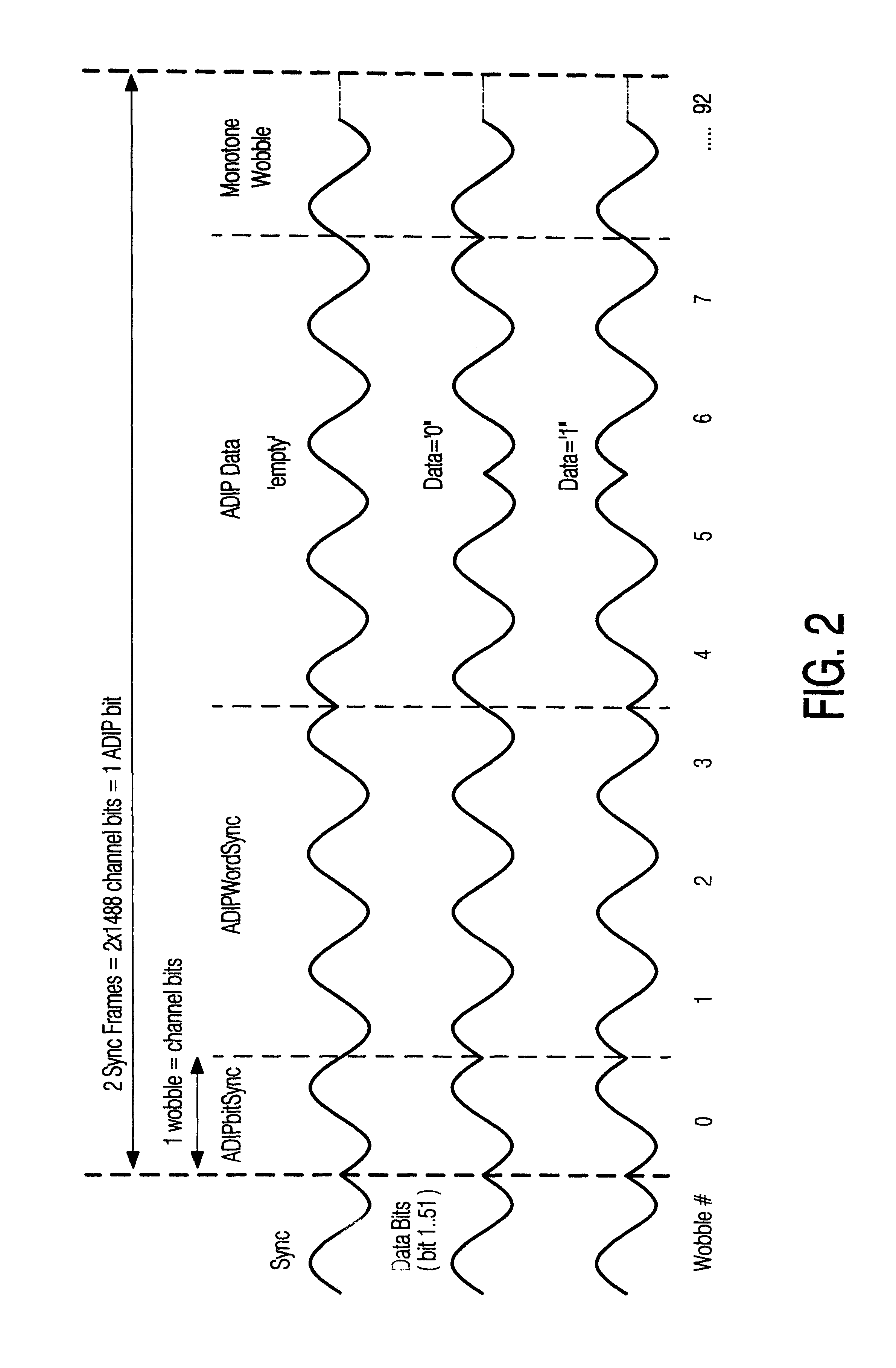

InactiveUS6538982B1Reliable and rapid and accurate mannerHigh positioning accuracyTelevision system detailsFilamentary/web record carriersCarrier signalEngineering

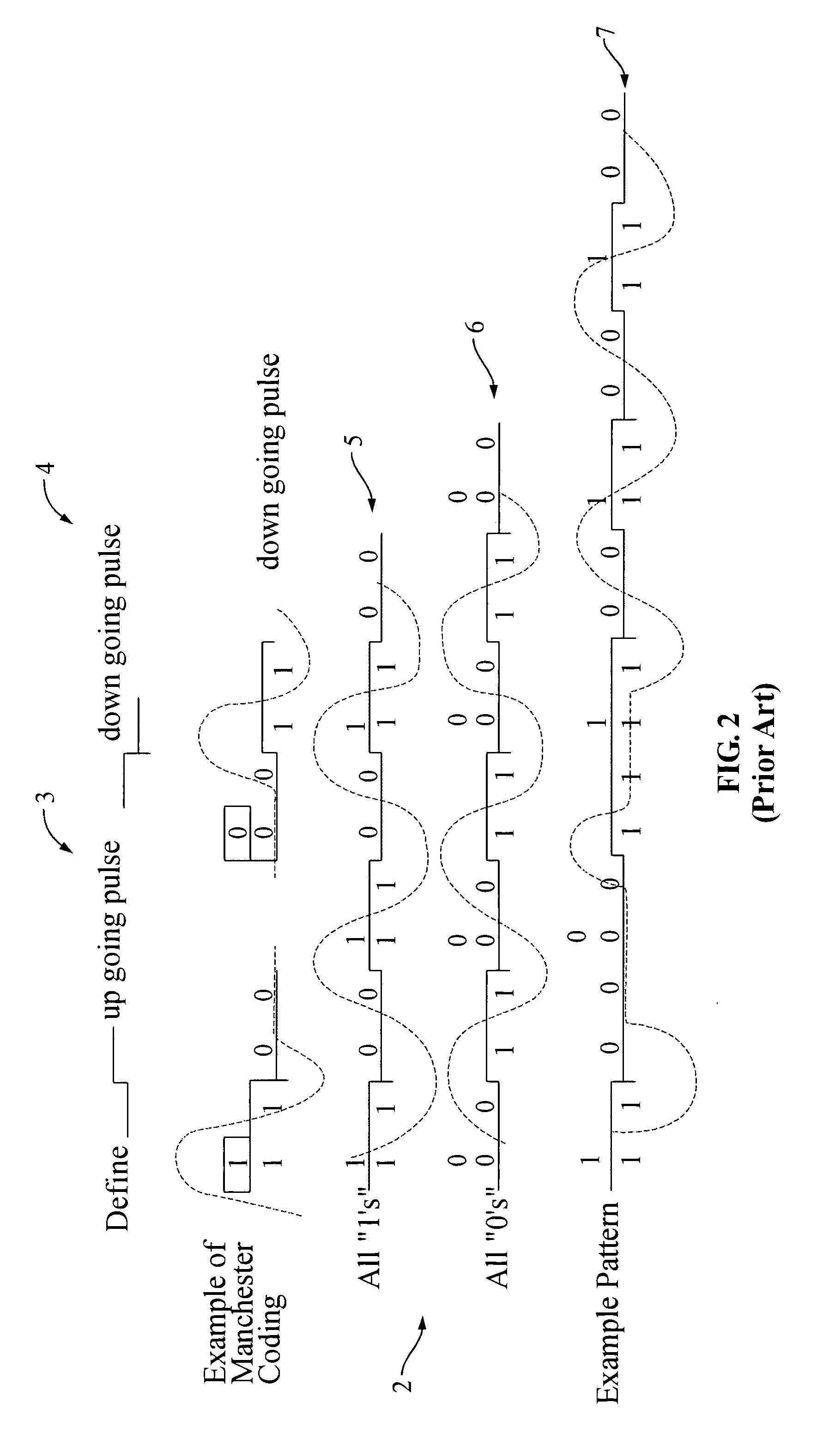

A record carrier is described comprising a servo track indicating an information track intended for recording information blocks represented by marks having lengths expressed in channel bits, which servo track has a periodic variation of a physical parameter. The periodic variation is modulated for encoding record carrier information, such as addresses. The modulation is a bi-phase modulation in which a data bit of the record carrier information is encoded by a first predetermined number of variations of a first phase followed by the same number of variations of a second phase inverse to the first phase. A recording and / or playback device has a demodulator for retrieving data bits of the record carrier information from a first predetermined number of variations of a first phase followed by the same number of variations of a second phase inverse to the first phase.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

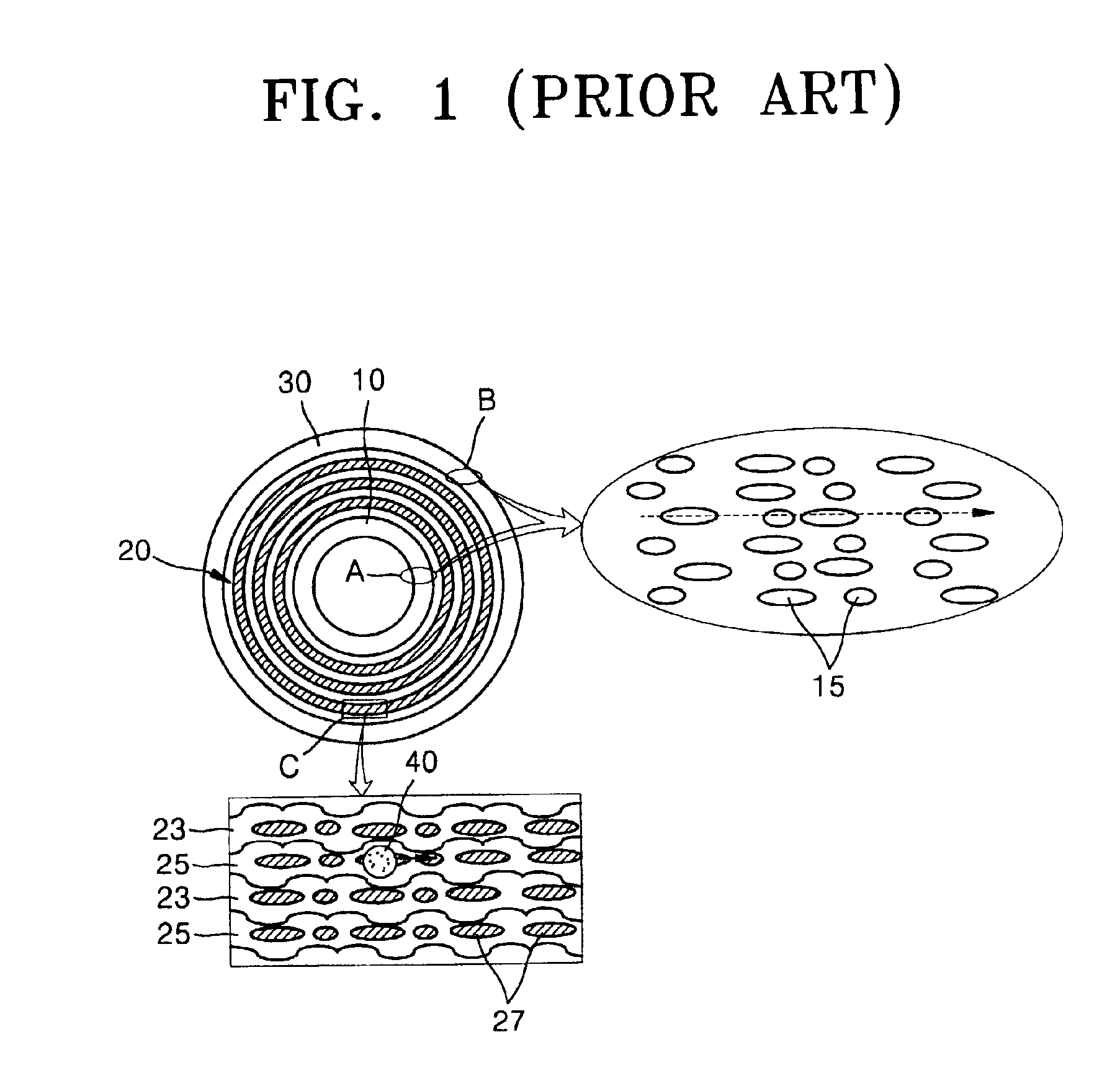

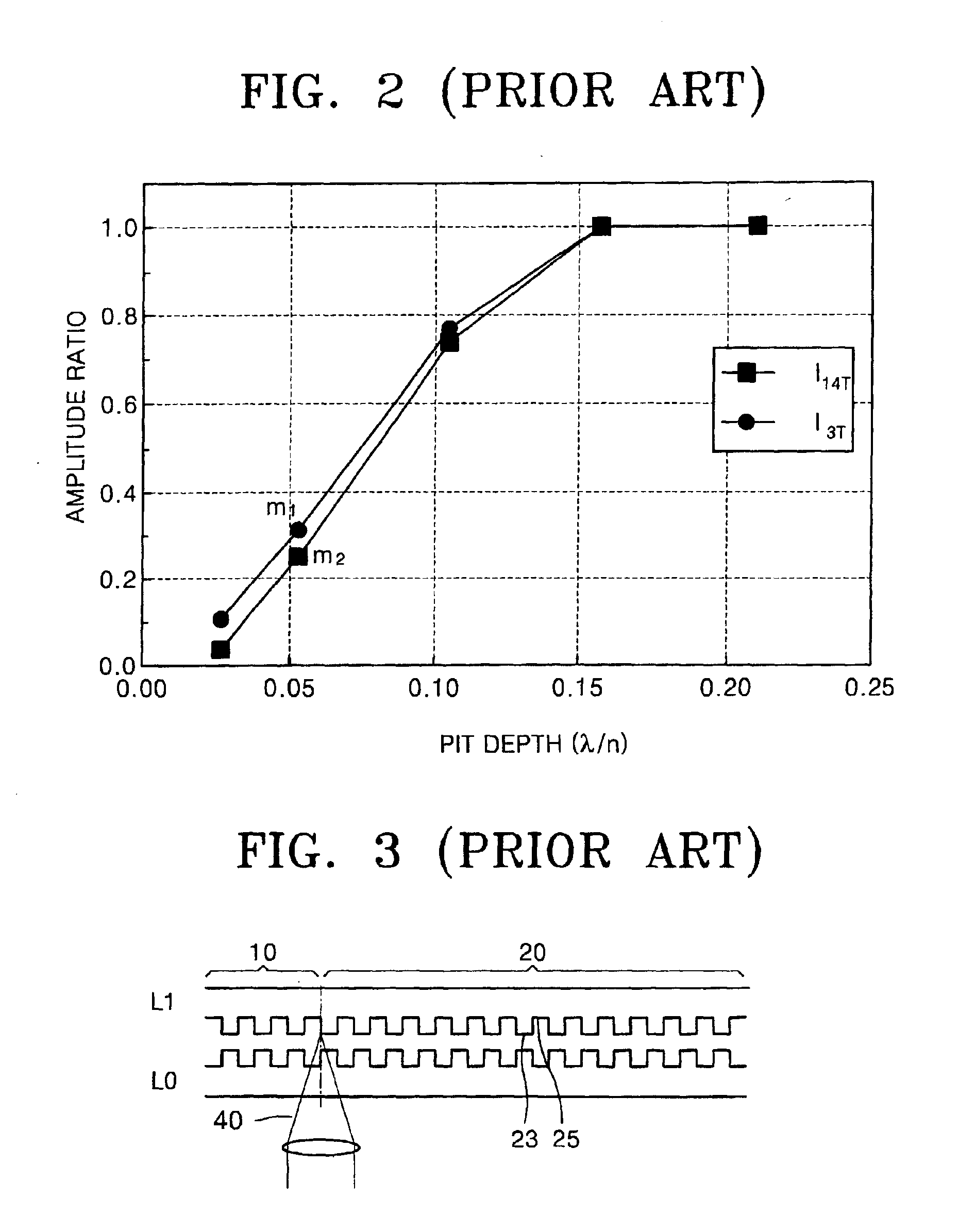

Optical disc having uniform structure

InactiveUS7065015B2Increase productionReduce manufacturing costFilamentary/web record carriersRecord information storageManufacturing cost reductionEngineering

An optical disc is manufactured under a uniform condition by forming grooves and lands on the entire surface of the disc. The optical disc is configured to obtain a reliable reproduction signal, and the grooves and lands are formed on a lead-in area, a user data area and a lead-out area of the optical disc. Since the same manufacturing condition can be adopted in mastering discs, the yield can be enhanced and the manufacturing cost can be reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

Information recording and reproducing apparatus and method, and signal decoding circuit for performing timing recovery

InactiveUS7054088B2High density recordingShorten the lengthModification of read/write signalsTransmission control/equlisationPhase leadComputer science

A timing recovery unit detects a phase offset and a frequency offset from a head area of reproduction data and initially corrects them. The timing recovery unit stores data in which a head reproduction signal has been made to be discrete by a fixed clock into a buffer. A phase offset detector detects the phase offset from the data head area in parallel with the operation for writing the data into the buffer. At the same time, a frequency offset detector detects the frequency offset from the data head area in parallel with the operation for writing the data into the buffer. A correction value of the detected phase offset and a correction value of the detected frequency offset are initially set into a digital PLL. While the data is read out from the buffer, a frequency lead-in and a phase lead-in are executed in the head area.

Owner:TOSHIBA STORAGE DEVICE CORP

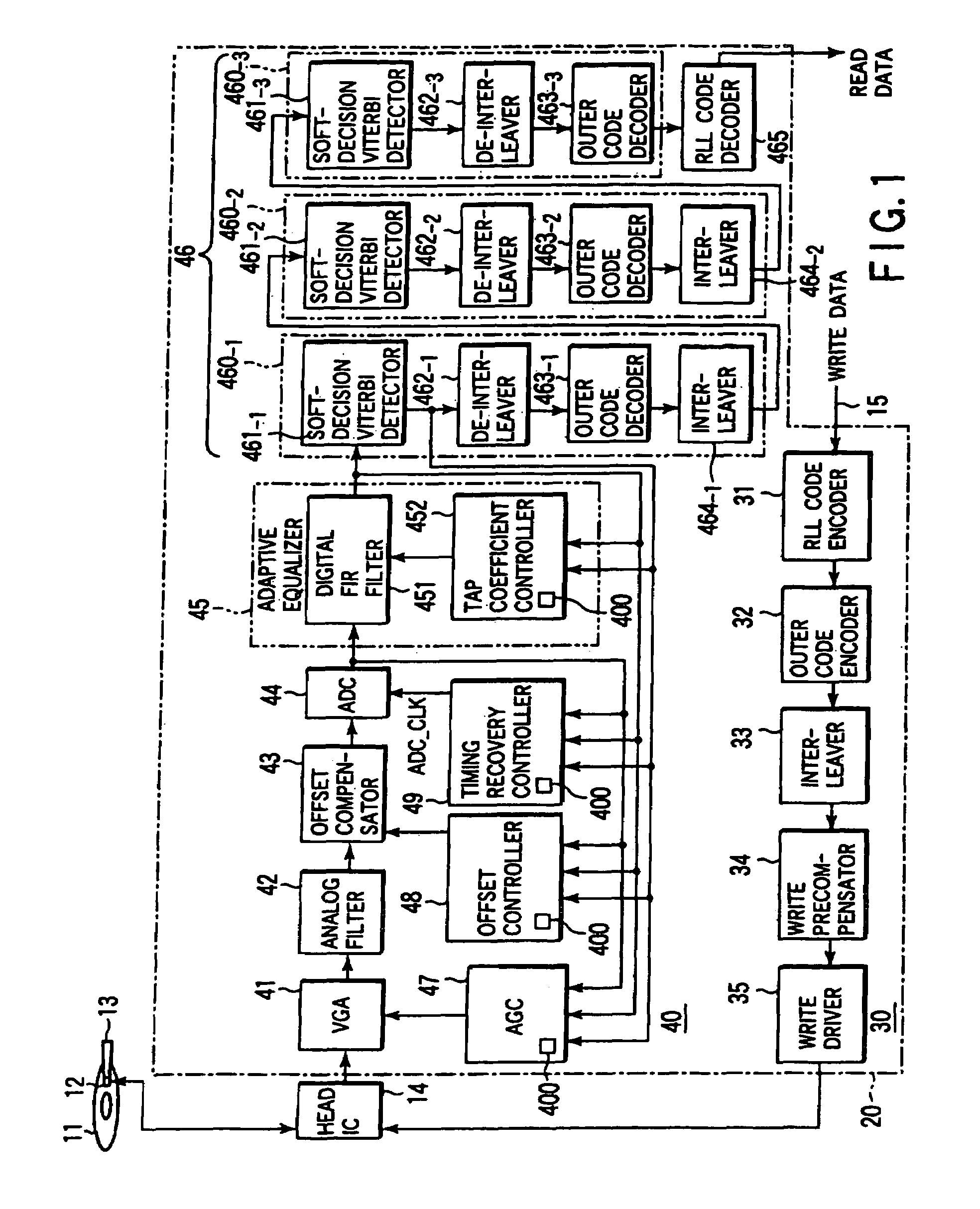

Signal processing device utilizing partial response maximum likelihood detection

InactiveUS7257172B2Other decoding techniquesRecord information storageControl objectiveViterbi detector

A partial response (PR) waveform generator generates a digital value sequence of an expected PR waveform based on the output of a soft-decision Viterbi detector included in, for example, a first-stage decoder unit incorporated in an iterative decoder. The generator also generates flag information indicative of whether reliability of the digital value sequence is low or high, in parallel with the generation of the digital value sequence. An error detector detects error values in a PR equalized sample value sequence, needed for feedback control of a control target, using the digital value sequence of the expected PR waveform as a digital value sequence of a reference waveform. An error output controller controls the output of the error values detected by the error detector in accordance with the state of the flag information generated by the generator.

Owner:KK TOSHIBA

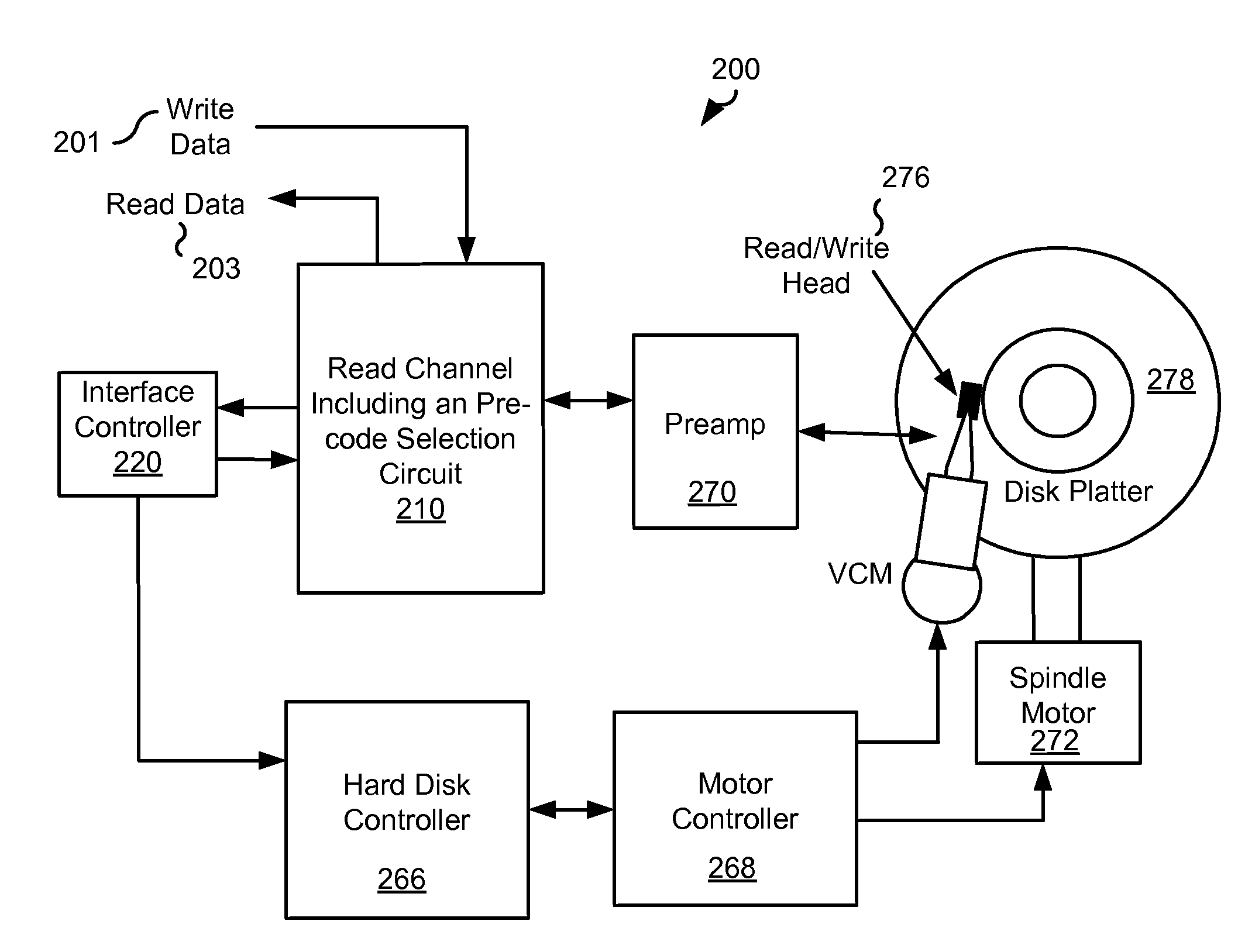

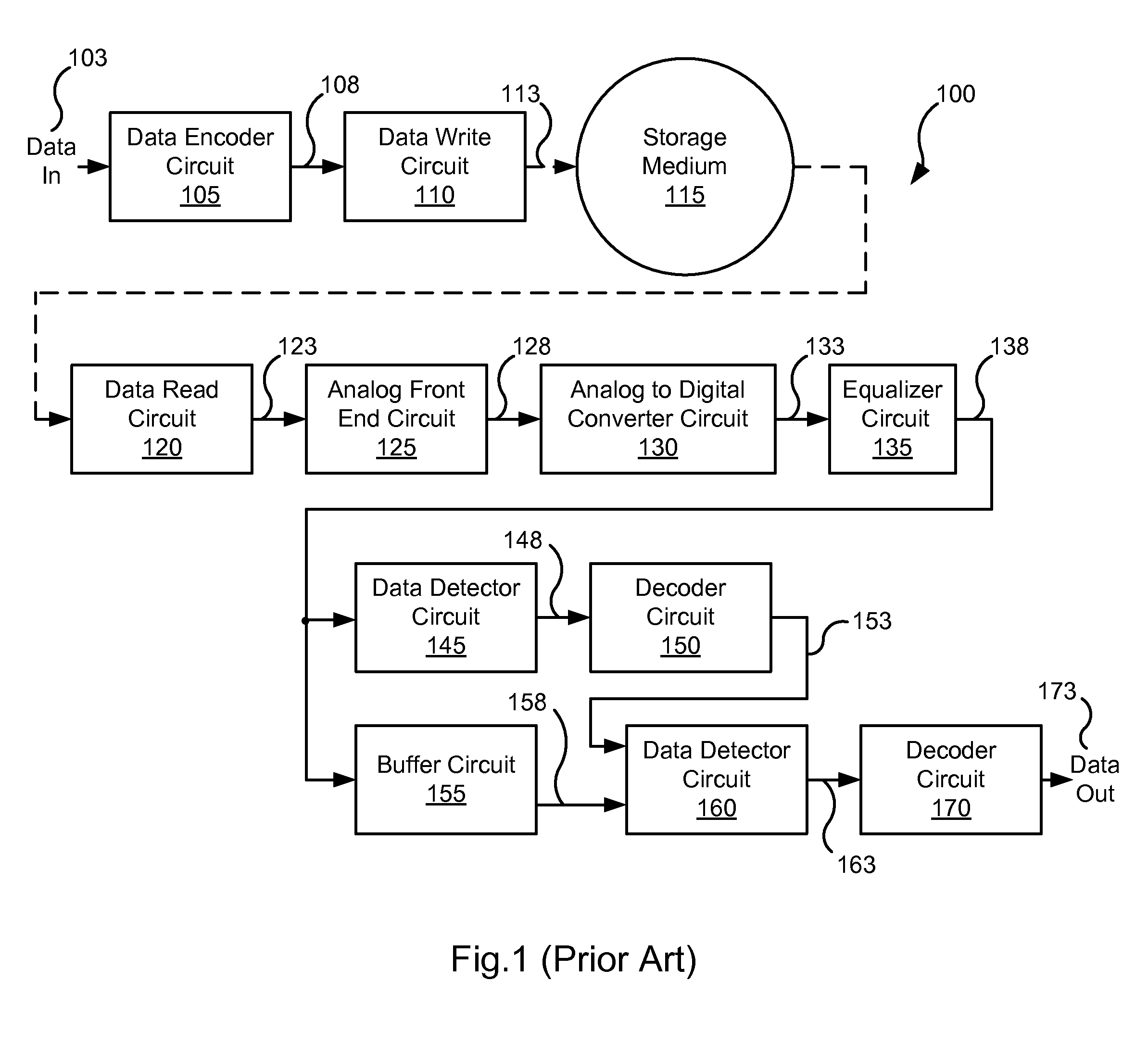

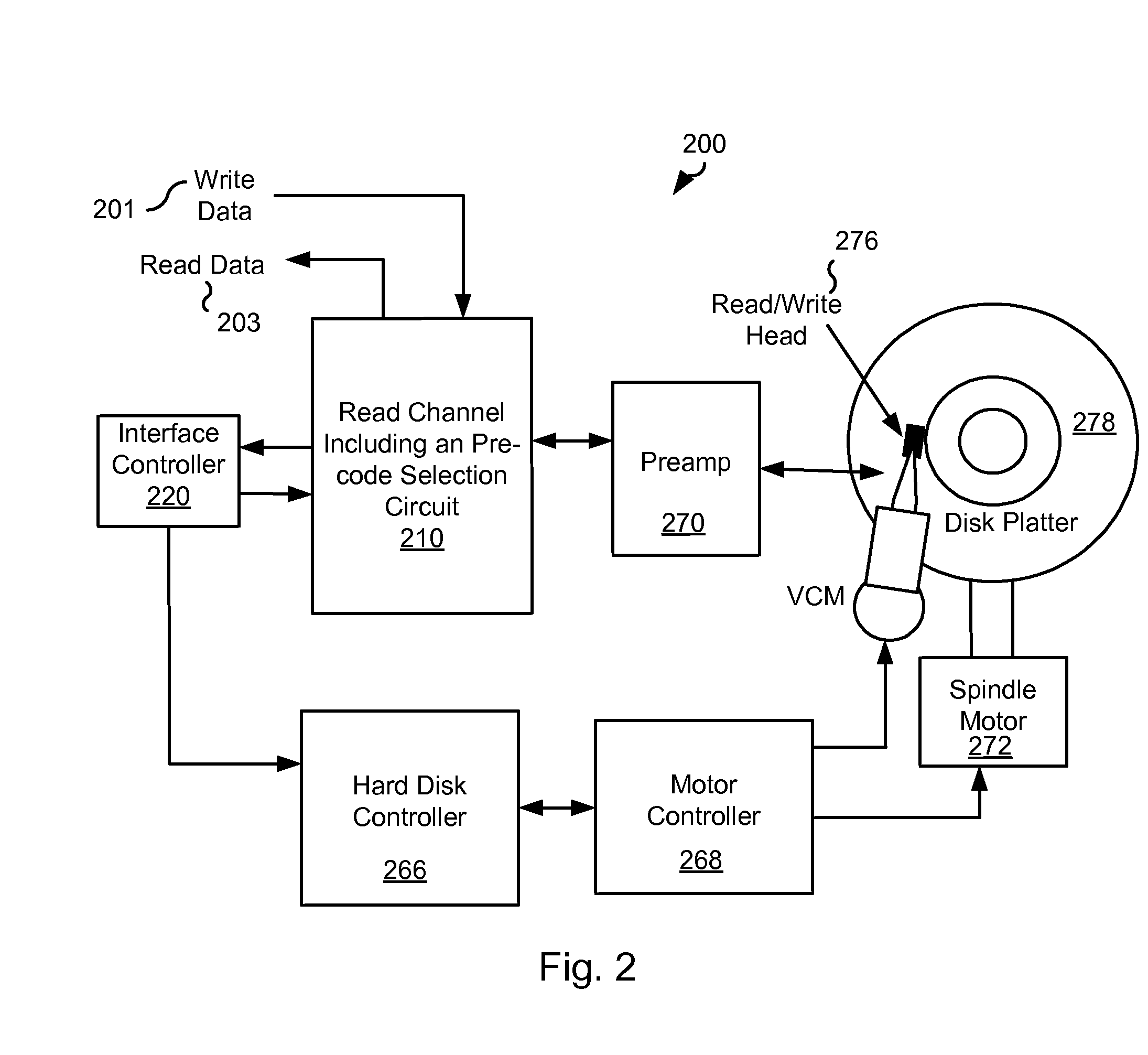

Systems and Methods for Data Pre-Coding Calibration

ActiveUS20120212849A1Multiple-port networksData representation error detection/correctionPrecodingDetector circuits

Various embodiments of the present invention provide systems and methods for selecting between pre-coding and non-pre-coding. As an example, a data processing circuit is disclosed that includes: a first data detector circuit, a second data detector circuit, a first comparator circuit, a second comparator circuit, and a pre-code selection circuit. The first data detector circuit is selectably configurable to operate in a pre-coded state, and operable to apply a data detection algorithm on a data input to yield a first detected output. The second data detector circuit operable to apply the data detection algorithm to the data input to yield a second detected output without compensating for pre-coding. The first comparator circuit operable to compare the first detected output against a known input to yield a first comparison value, and the second comparator circuit operable to compare the second detected output against the known input to yield a second comparison value. The pre-code selection circuit is operable to determine a selectable configuration of the first data detector circuit based at least in part on the first comparison value and the second comparison value.

Owner:AVAGO TECH INT SALES PTE LTD

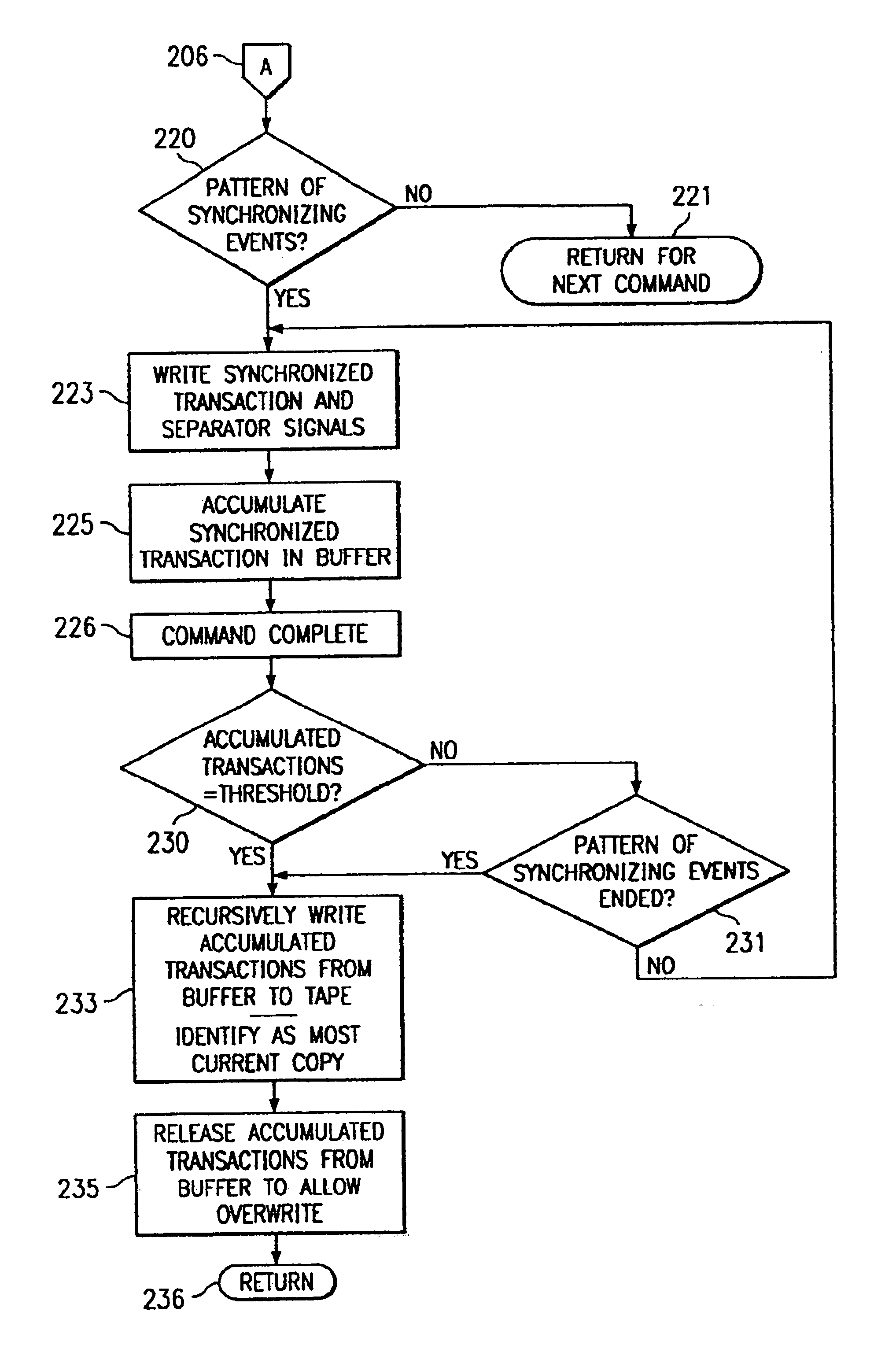

Writing synchronized data to magnetic tape

InactiveUS6856479B2Reduce in quantityInput/output to record carriersData buffering arrangementsMagnetic tapeDatabase

Synchronized data is written to magnetic tape while reducing the number of backhitches. A controller detects a pattern of synchronizing events for received data records to be written to tape; writes each transaction of data records to the magnetic tape; accumulates the synchronized transactions in a buffer; and subsequently recursively writes the accumulated transactions of data records from the buffer to the magnetic tape in a sequence. A single backhitch may be employed to place the recursively written accumulated data records following the preceding data, maximizing performance and capacity.

Owner:IBM CORP

Read channel apparatus for asynchronous sampling and synchronous equalization

ActiveUS20070047121A1Television system detailsModification of read/write signalsA d converterAnalog signal

A read channel and method using that read channel are disclosed. The read channel comprises an analog to digital converter which asynchronously samples at a fixed rate an analog signal formed by reading a data track, where that data track was written to a data storage medium at a symbol rate and an interpolator interconnected with the analog to digital converter. The read channel further comprises a fractionally-spaced equalizer, where the interpolator provides an interpolated signal to the fractionally-spaced equalizer at an interpolation rate, where that interpolation rate is greater than the symbol rate. The fractionally-spaced equalizer forms a synchronous equalized signal. The read channel further comprises a gain control module interconnected with the fractionally-spaced equalizer, and a sequence detector interconnected with the gain control module.

Owner:META PLATFORMS INC

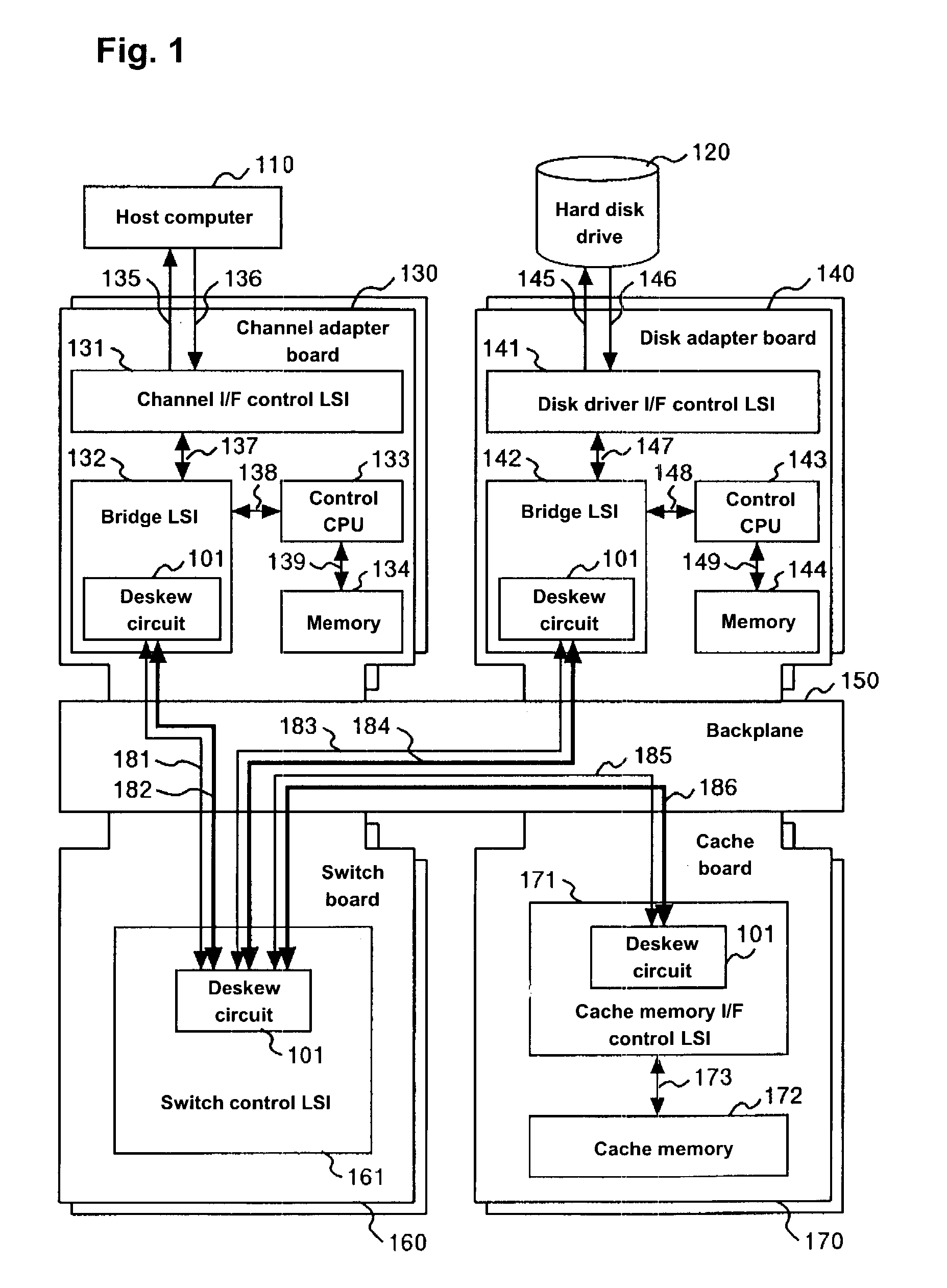

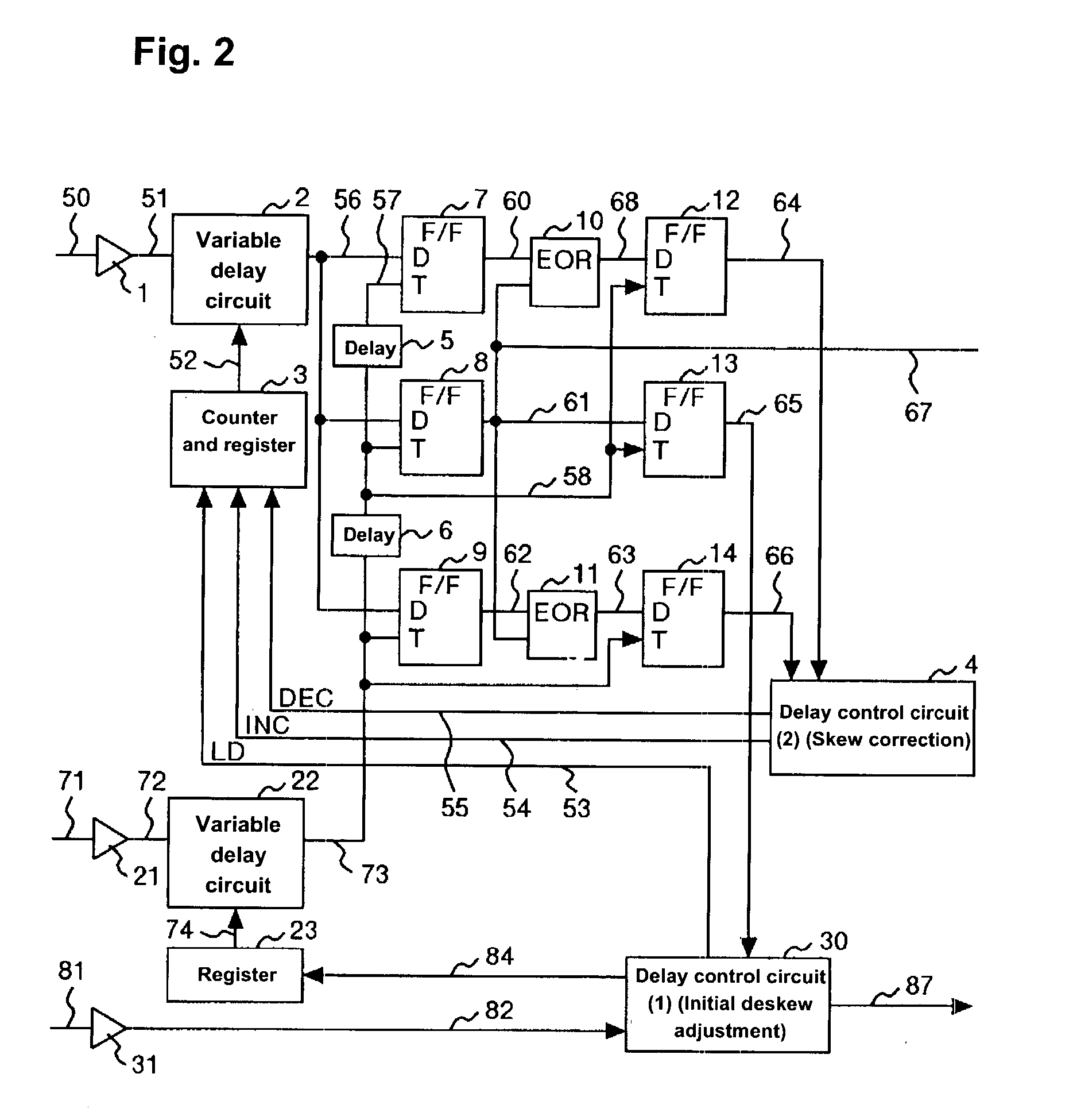

Deskew circuit and disk array control device using the deskew circuit, and deskew method

InactiveUS20040068682A1Input/output to record carriersElectronic circuit testingDisk arrayData transmission

A deskew circuit includes, for clock and every bit of data, a variable delay circuit between a receiver that receives data and a flip-flop that first latches the data, in which a detecting pattern to detect a stable region for receiving data is repeatedly sent before implementing a data transfer, a delay value with which the starting edge and ending edge of the data match the rising edge of the clock is found for the variable delay circuit, and a delay value with which the transfer data can be received in a stable manner is set based on the delay value of the variable delay circuit.

Owner:HITACHI LTD

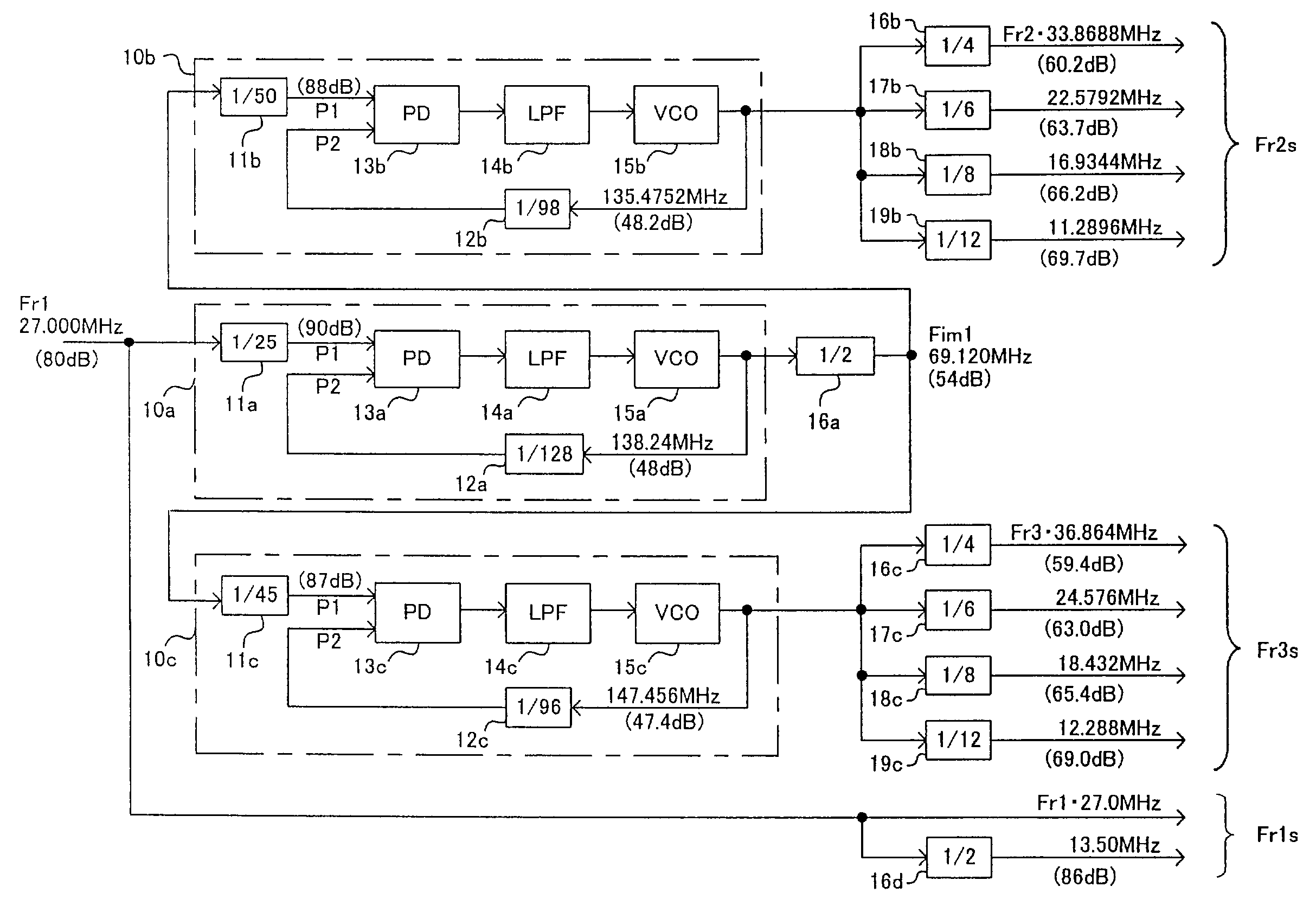

Clock generation system

ActiveUS7216249B2Elimination of the limitation,Weaken influencePulse automatic controlError detection/correctionIntermediate frequencyNoise floor

A clock generation system for generating a first-, a second-, and a third-reference frequency clocks having respective frequencies having predetermined ratios to the reference frequency of a reference clock, using PL circuits in such a way that the clocks have sufficient S / N ratios in spite of the S / N ratio limitation by the noise floor. A first reference frequency clock is supplied to a first PLL circuit to generate an intermediate-frequency clock having an intermediate frequency having a predetermined ratio to the reference clock. The intermediate-frequency clock is supplied to a second and a third PLL circuits to generate a second and a third reference frequency clocks having frequencies respectively having a second and a third ratios to the intermediate frequency, respectively.

Owner:ROHM CO LTD

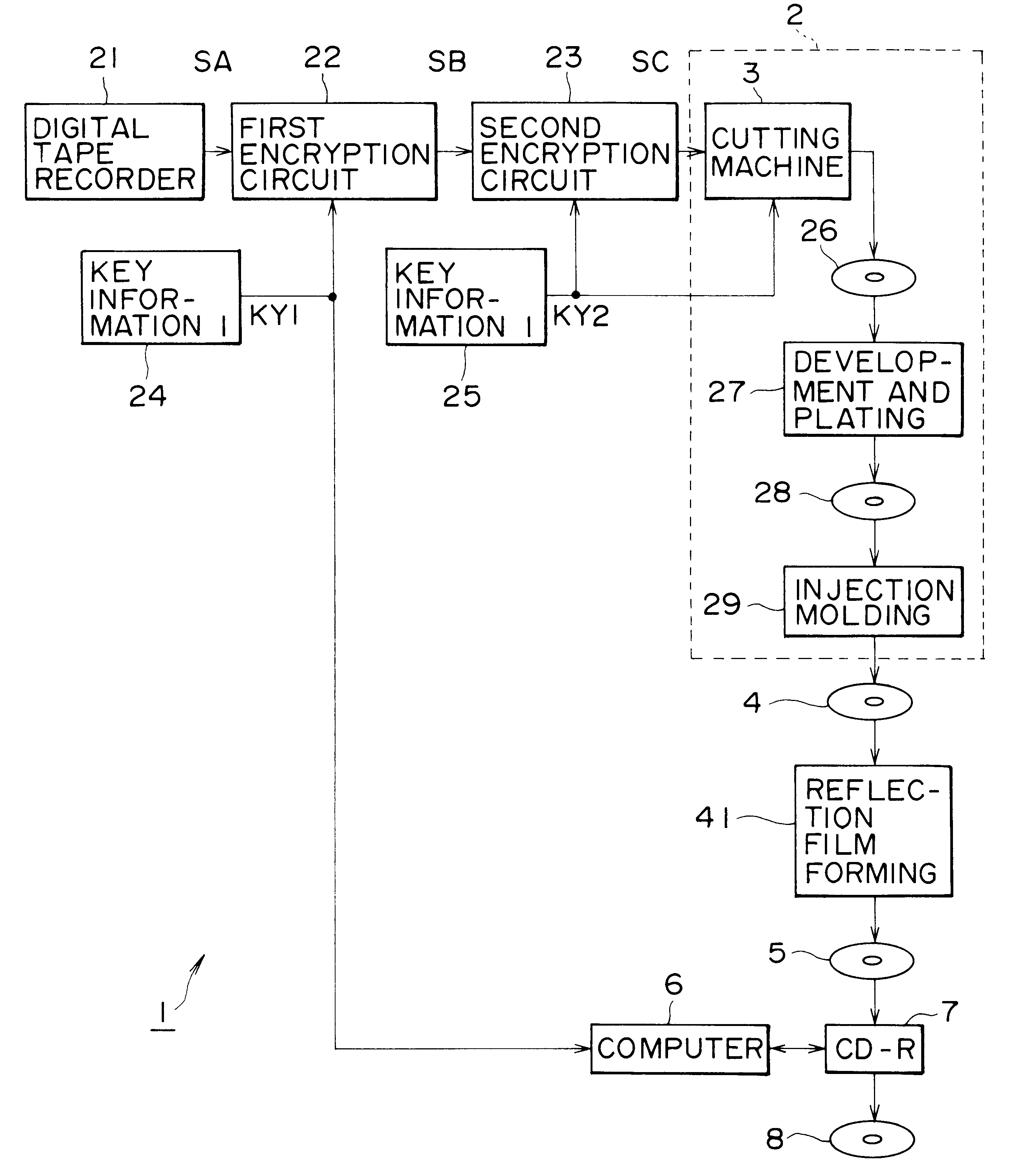

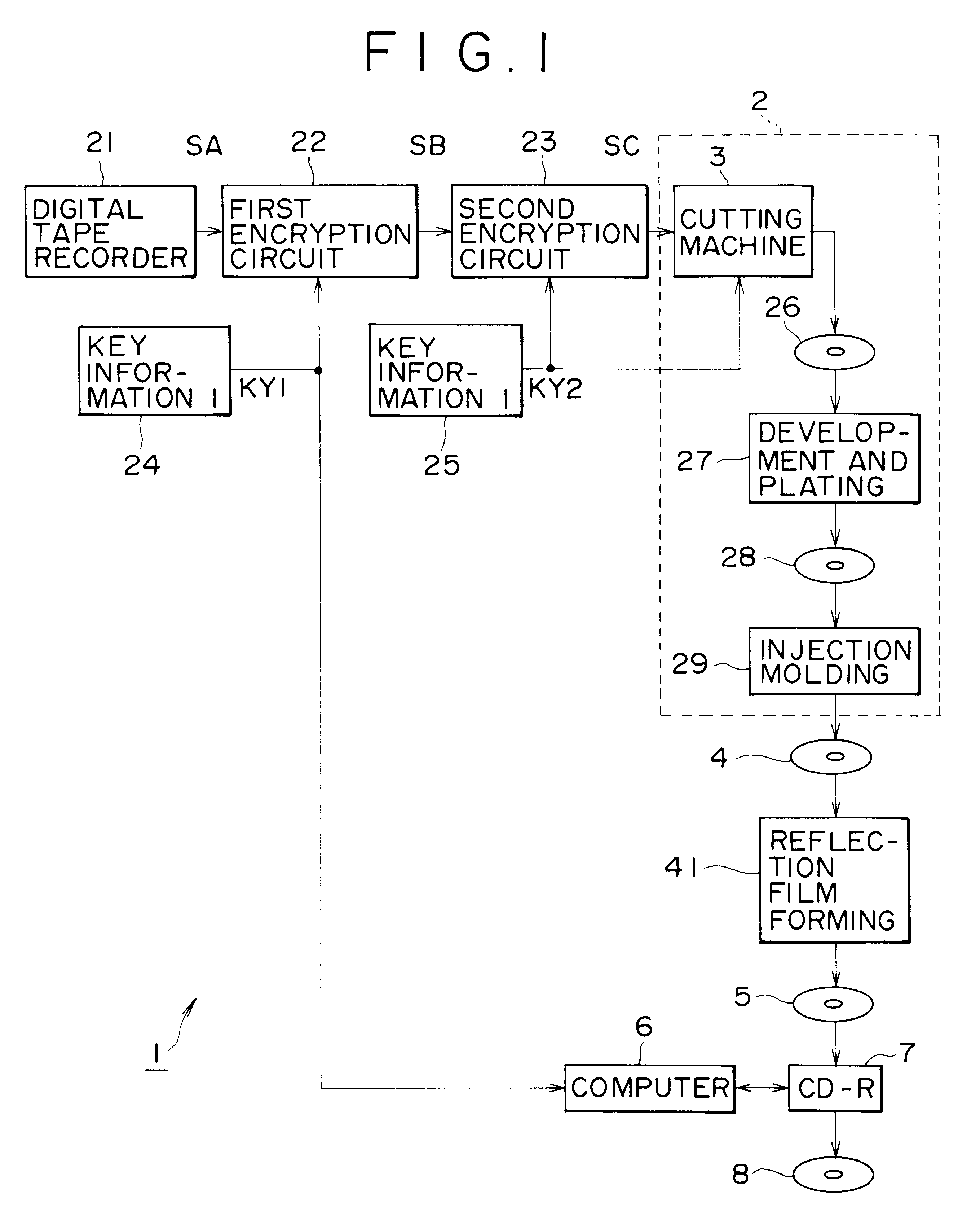

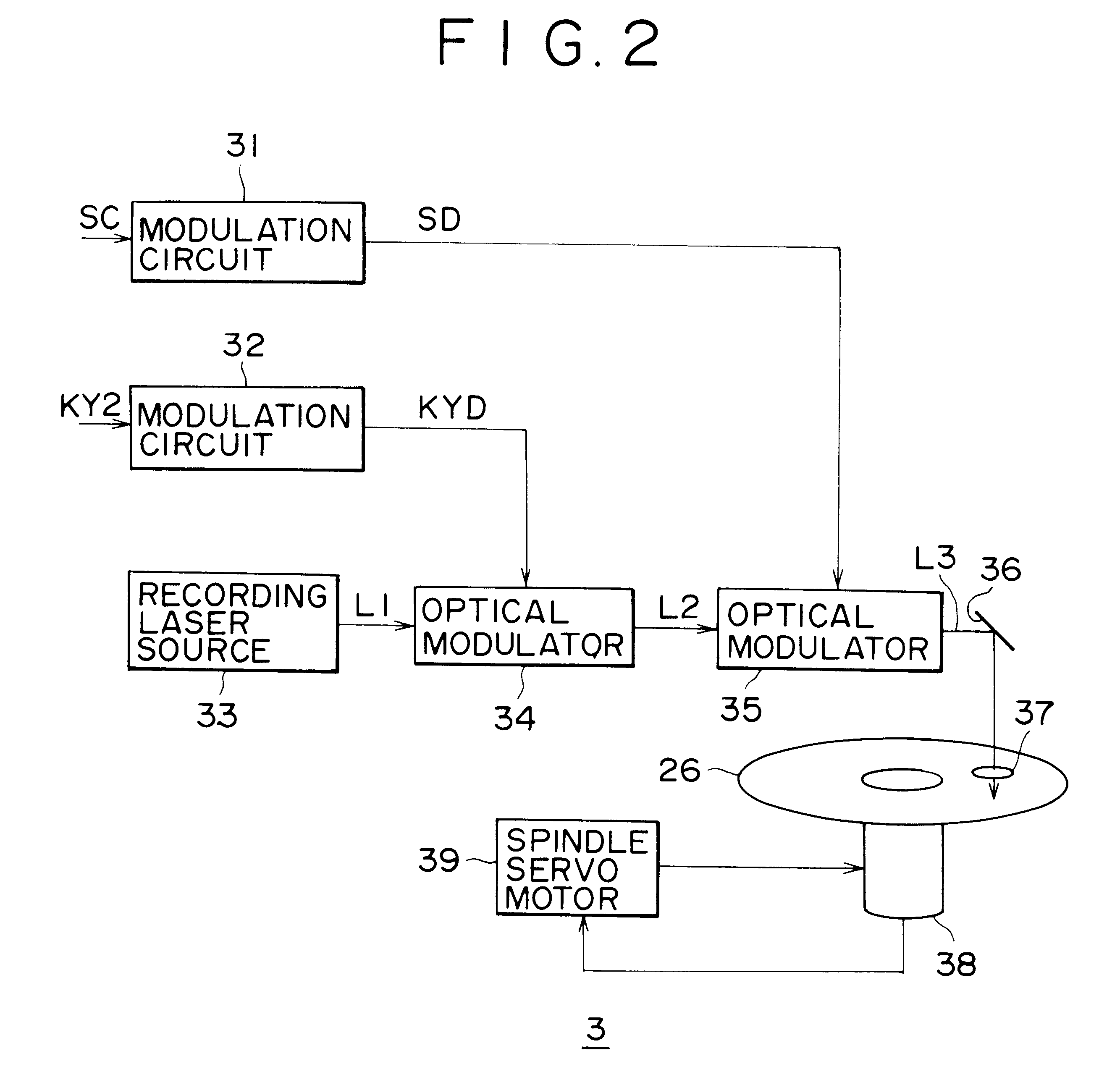

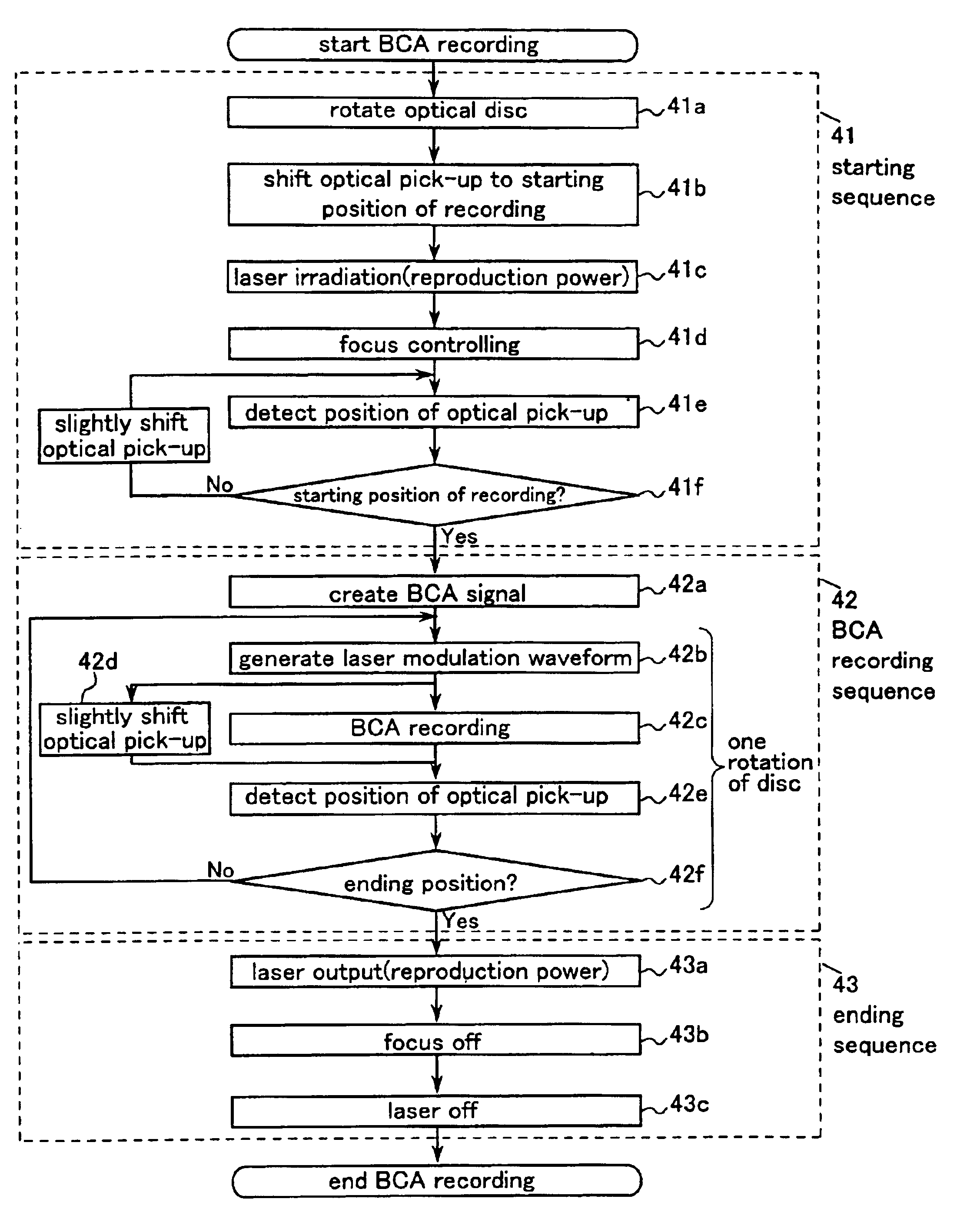

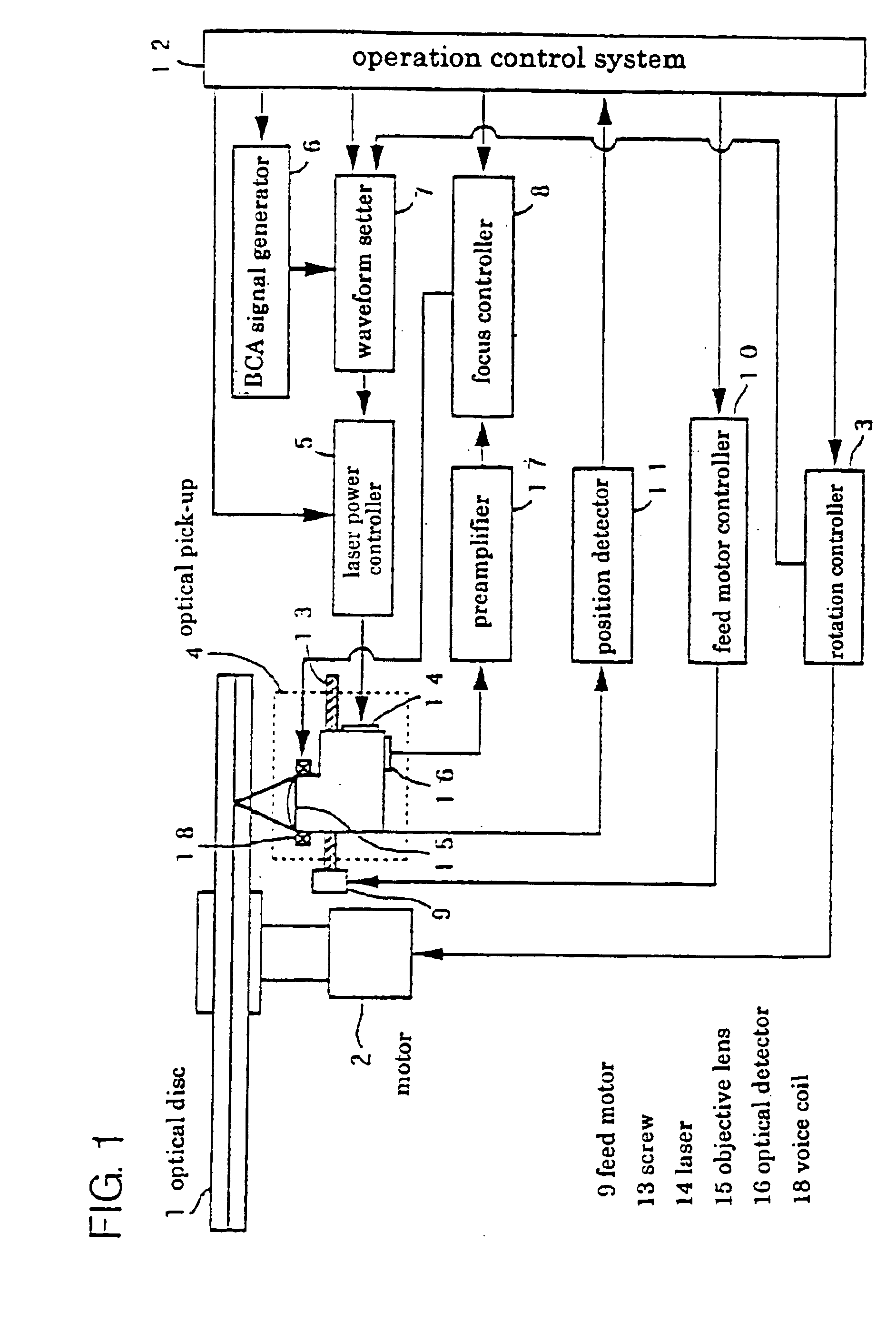

Apparatus and method for manufacturing optical disks, apparatus and method for recording data on optical disks, apparatus and method for reproducing data from optical disks, and optical disk

InactiveUS6665240B1Television system detailsAccessories for auxillary signalsDigital dataCompact Disc manufacturing

Described herewith is an optical disk manufacturing apparatus for reading recorded digital data from an optical disk, comprising an encryption unit (22, 23) for encrypting entered digital data according to a plurality of key information; an optical disk substrate manufacturing unit 2 for manufacturing an optical disk substrate 4 on which the encrypted digital data and key information are recorded in the form of physical form changes; a reflection film forming unit 41 for forming a reflection film on the optical disk substrate 4; and a key information recording unit 7 for recording key information on the optical disk substrate on which the reflection film is formed. The reflection factor of the optical disk is changed locally, thereby giving a jitter to the position information of each pit edge, and desired data is recorded additionally according to this jitter. Pits, etc. are disposed so as to be deviated from the track center towards the inner / outer region of the optical disk 2, thereby recording such subdata as key information KY, etc.

Owner:SONY CORP

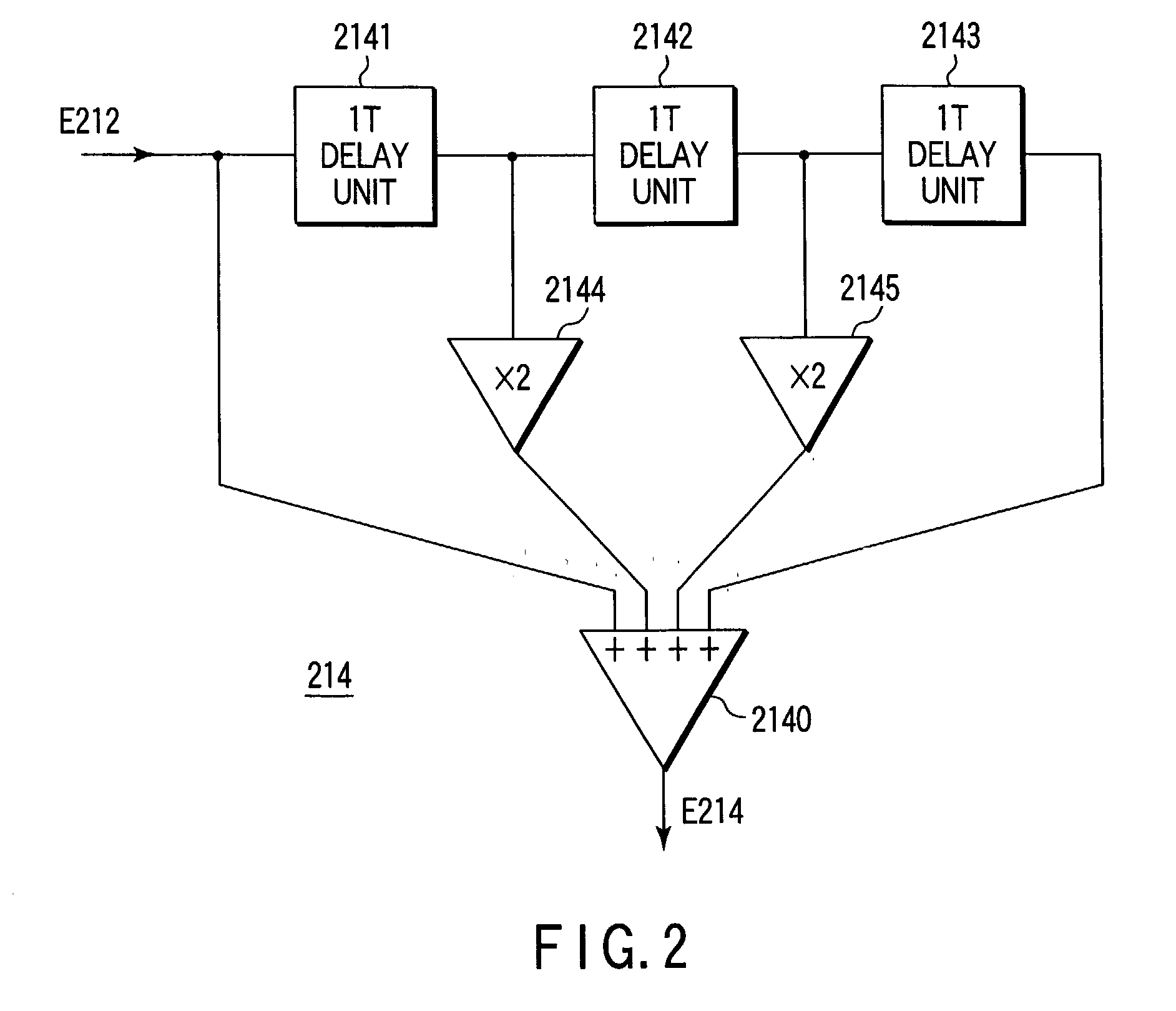

Information read device and read signal processing circuit

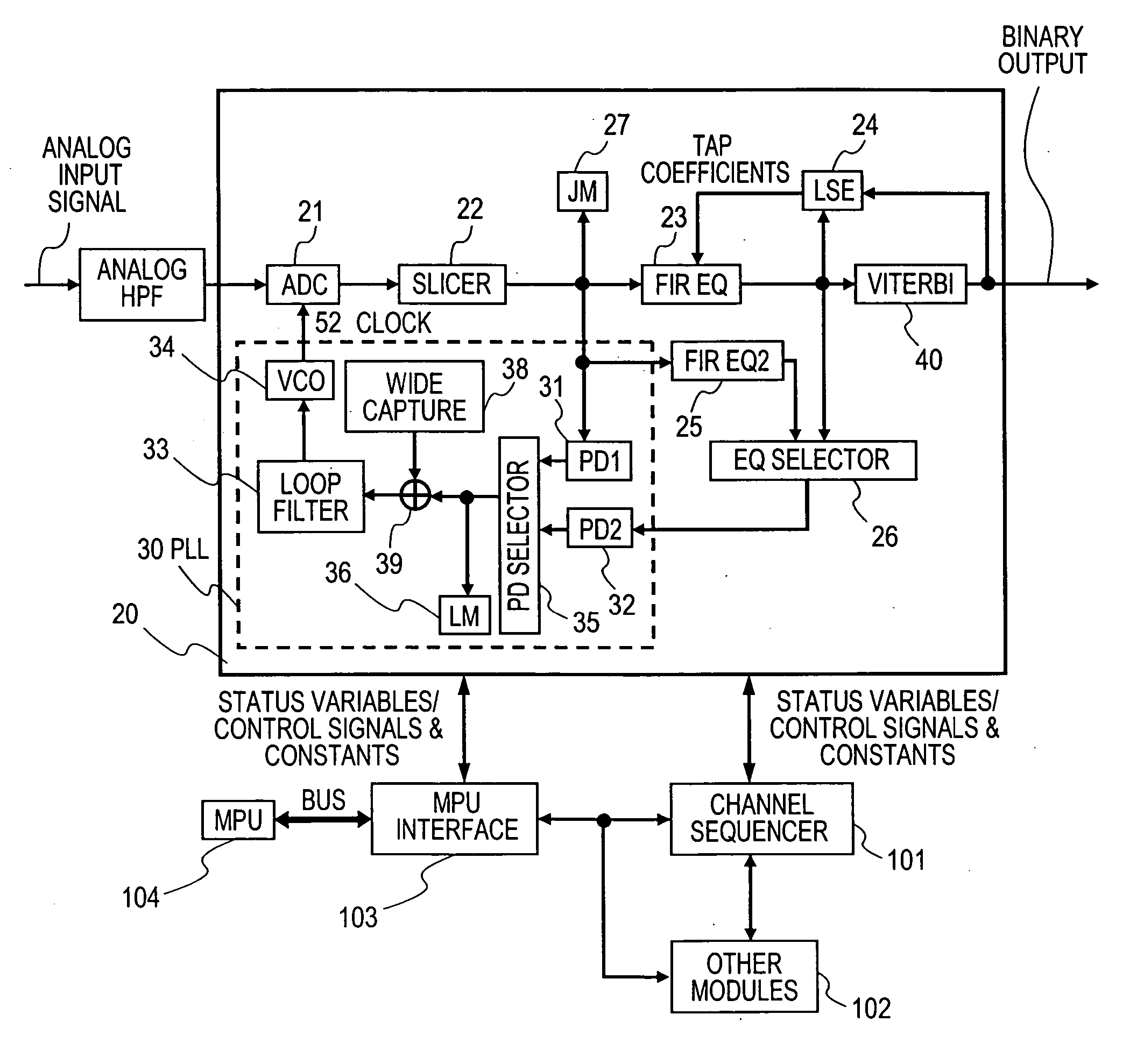

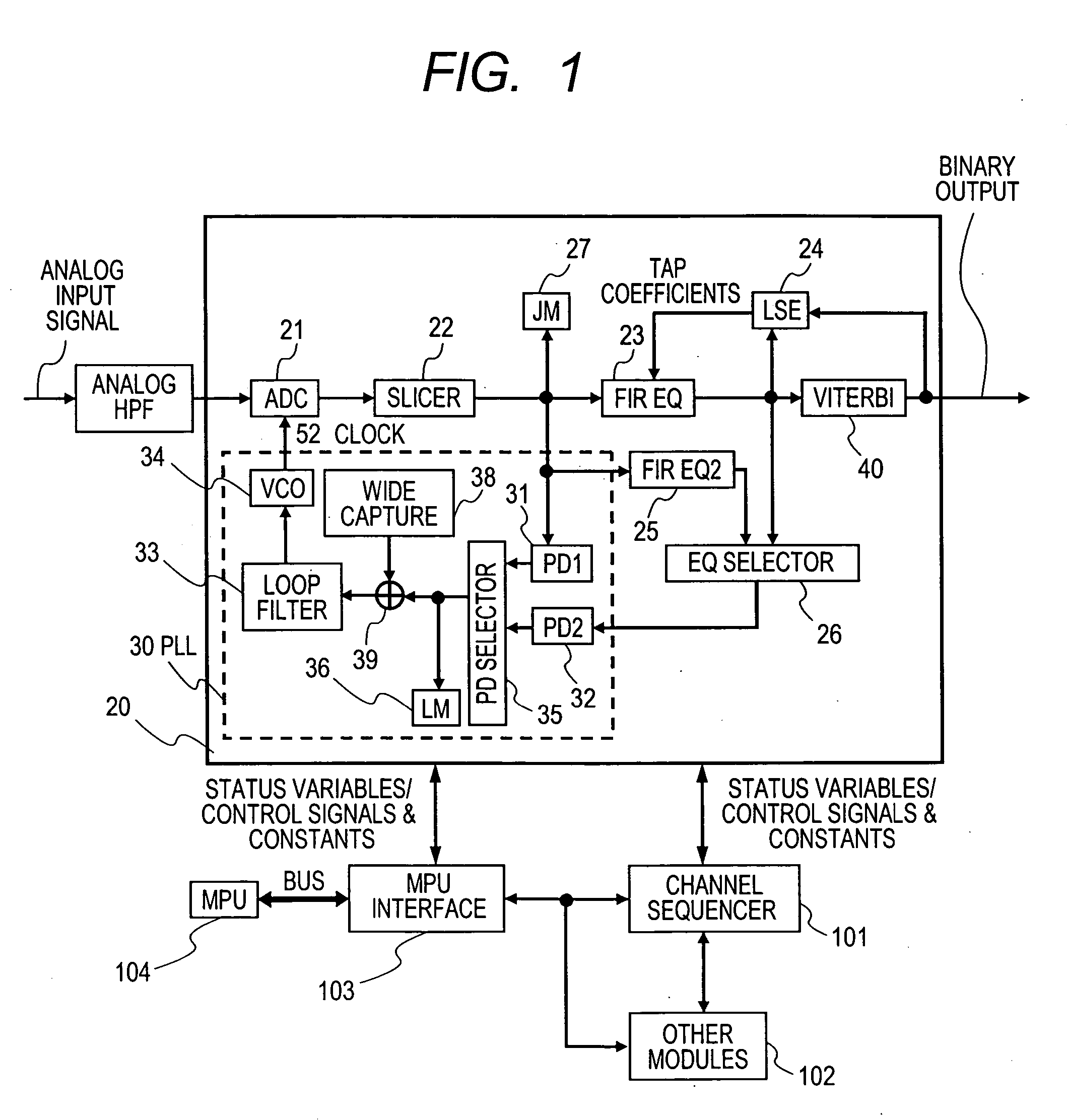

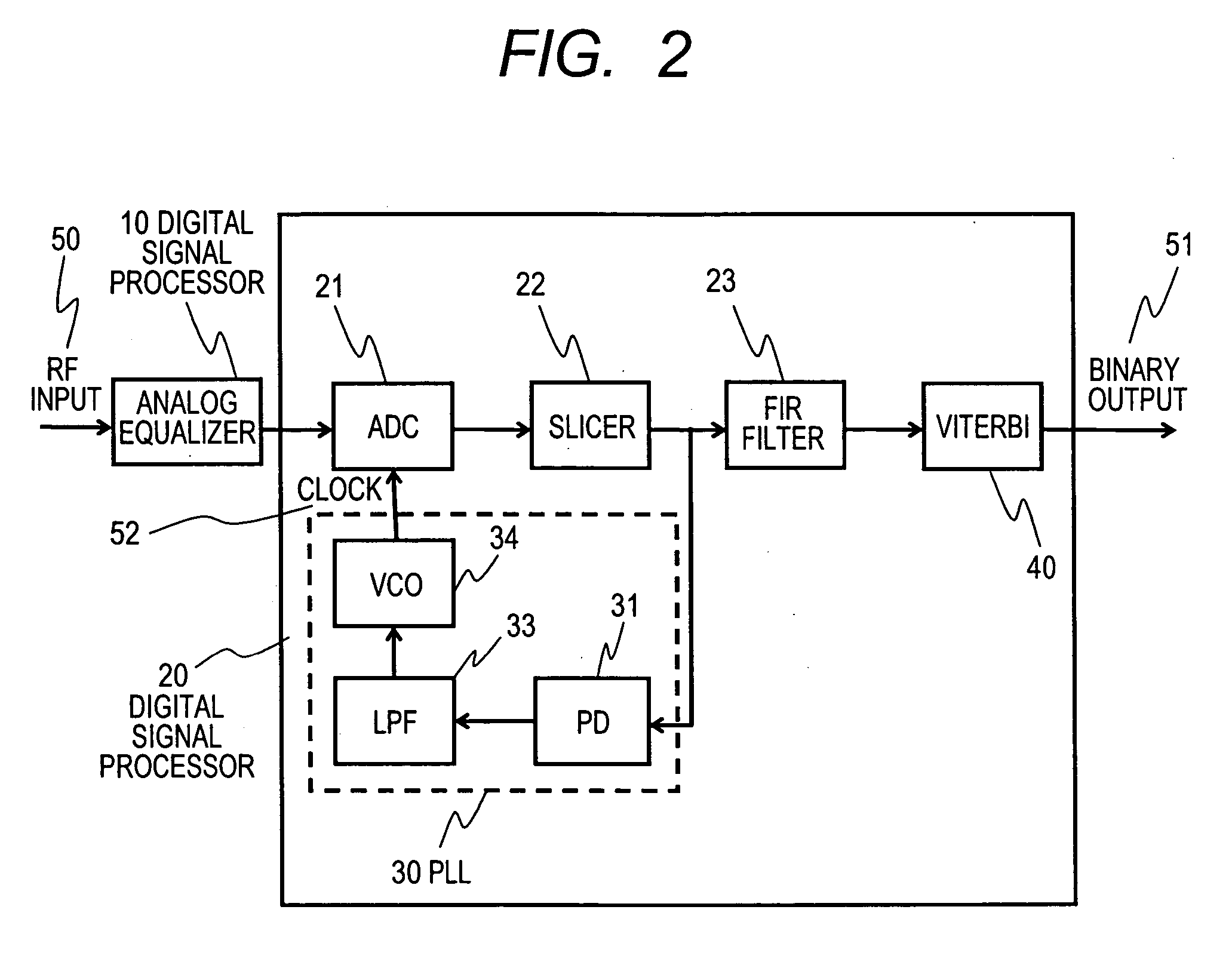

ActiveUS20060280240A1High error rateSatisfied with the effectMultiple-port networksFilamentary/web record carriersSignal processing circuitsSignal-to-noise ratio (imaging)

An optical disk read signal processing system for Blu-ray disc systems to ensure stable phase-locked locked operation even with a low signal-to-noise ratio. This system changes a loop configuration of a phase lock loop circuit according to the operating state, and utilizes a FIR equalizer for phase detection. This system attains a low error rate even when the signal-to-noise ratio of an input signal is low, and avoids pulse edges with low phase detection accuracy or signal pulse streams with a high possibility of being mistakenly detected as an edge in conventional methods, and also supports diverse types of input signals.

Owner:HITACHI CONSUMER ELECTRONICS CORP

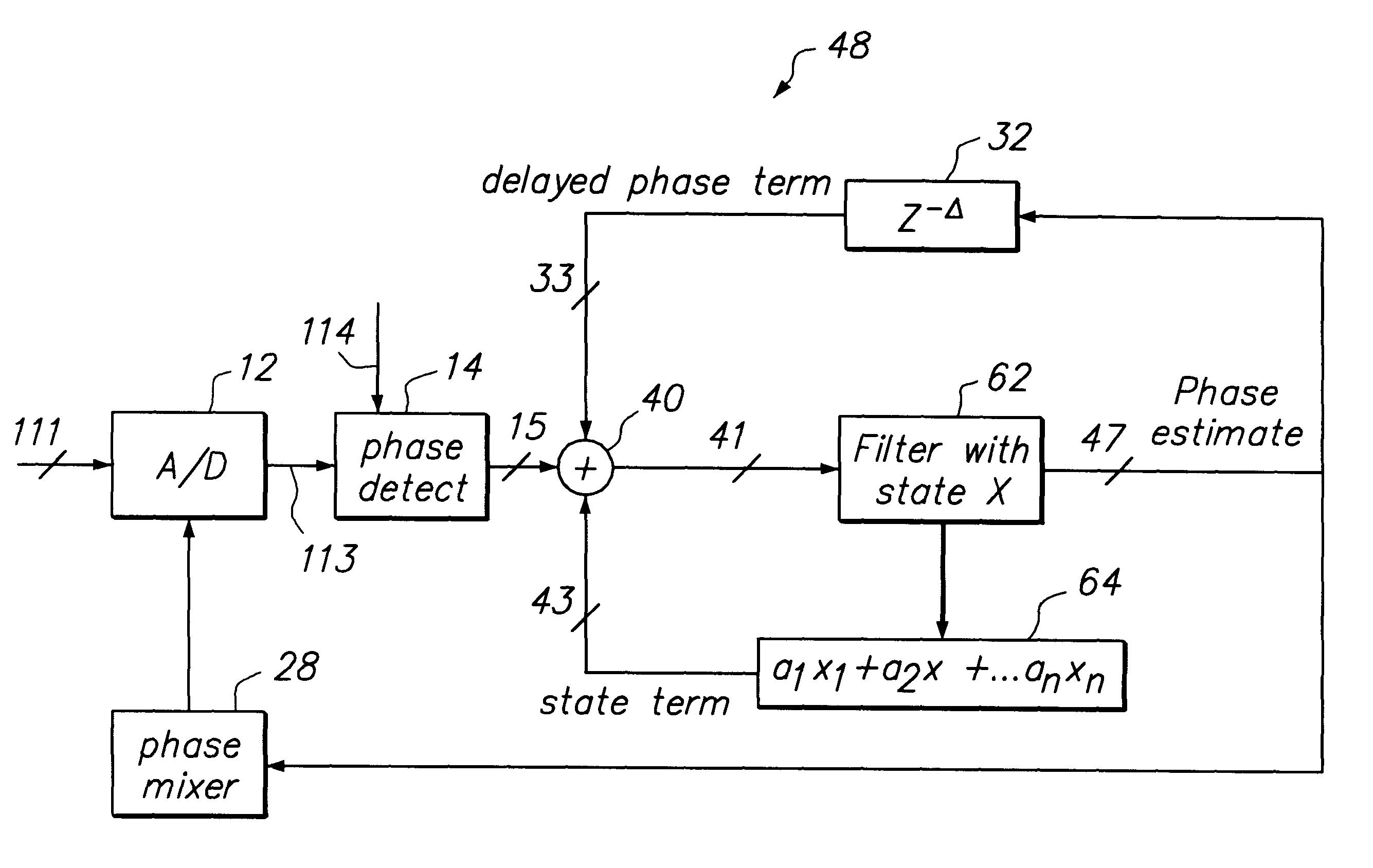

Loop latency compensated PLL filter

InactiveUS6236343B1Minimize jitterReduce sensitivityAnalogue/digital conversionElectric signal transmission systemsPhase detectorSquare waveform

The loop latency compensated PLL filter comprising two additional feedback terms, a delayed phase compensation signal and a state compensation signal, that are provided as input of a PLL filter. Accordingly, the PLL filter input comprises two additional compensation input signals: the delayed phase compensation signal and the state compensation signal in addition to a phase estimated error output from a phase detector that is also coupled to the input of the PLL filter. Consequently, PLL filter thus is able to provide a latency compensated phase error control output that is fedback to control a phase mixer to generate a square waveform used to drive an A / D of the PLL in accordance with the principles of this invention. The loop latency compensated PLL of this invention thus minimizes the jitter of the PLL circuit, provides higher format efficiency, and also has reduced sensitivity to large bursty noises.

Owner:MAXTOR

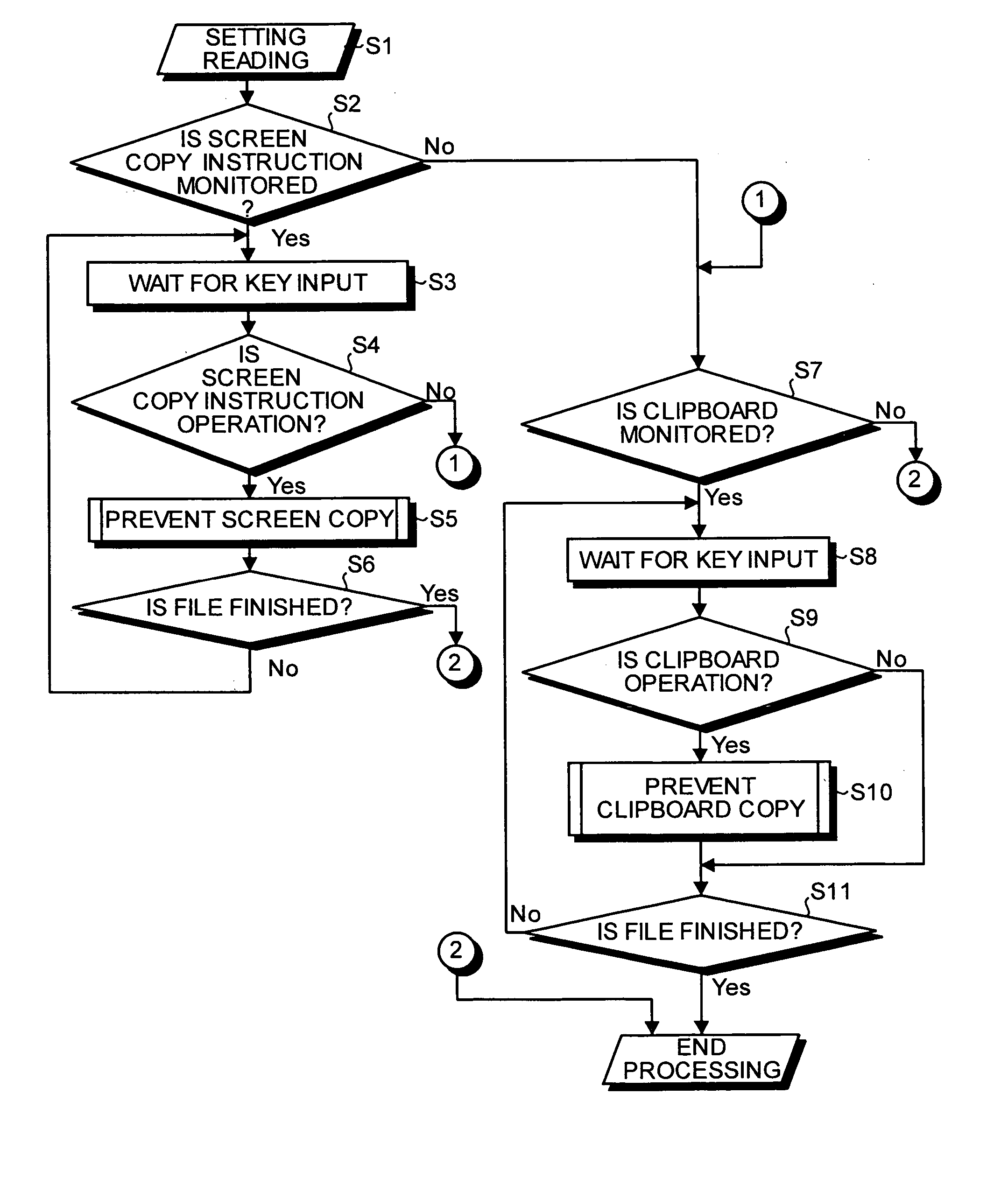

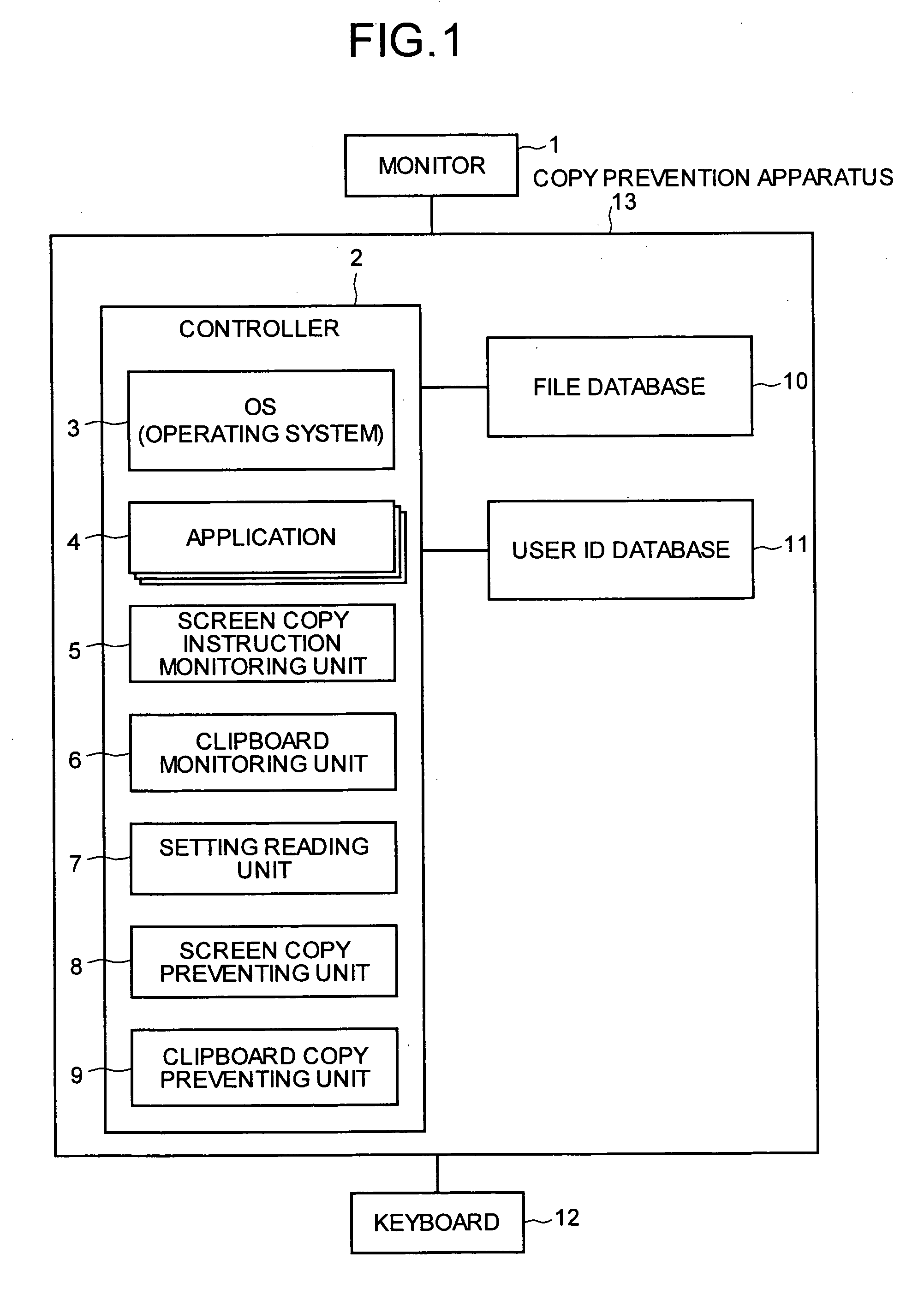

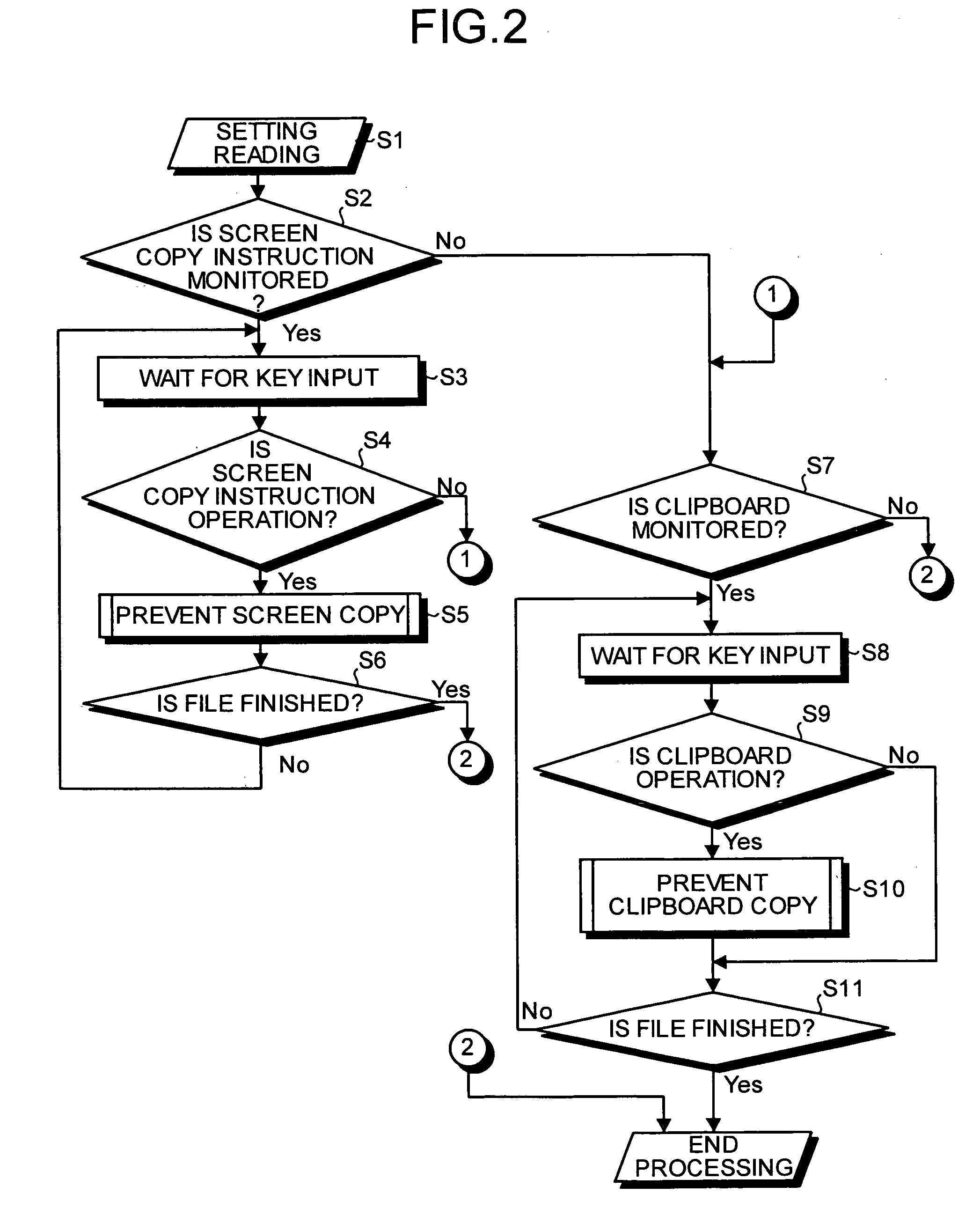

Apparatus, method and computer product for preventing copy of data

InactiveUS20050265548A1Avoid data duplicationOptical beam sourcesUnauthorized memory use protectionComputer hardwareOperational system

A copy prevention apparatus is provided by an operating system. A data area is shared by a plurality of applications that operate on the operating system. A data area monitoring unit monitors storing of copy prevention data into the data area and a data area copy preventing unit prevents copying of the copy prevention data from the data area based on a result of the monitoring by the data area monitoring unit.

Owner:FUJITSU LTD

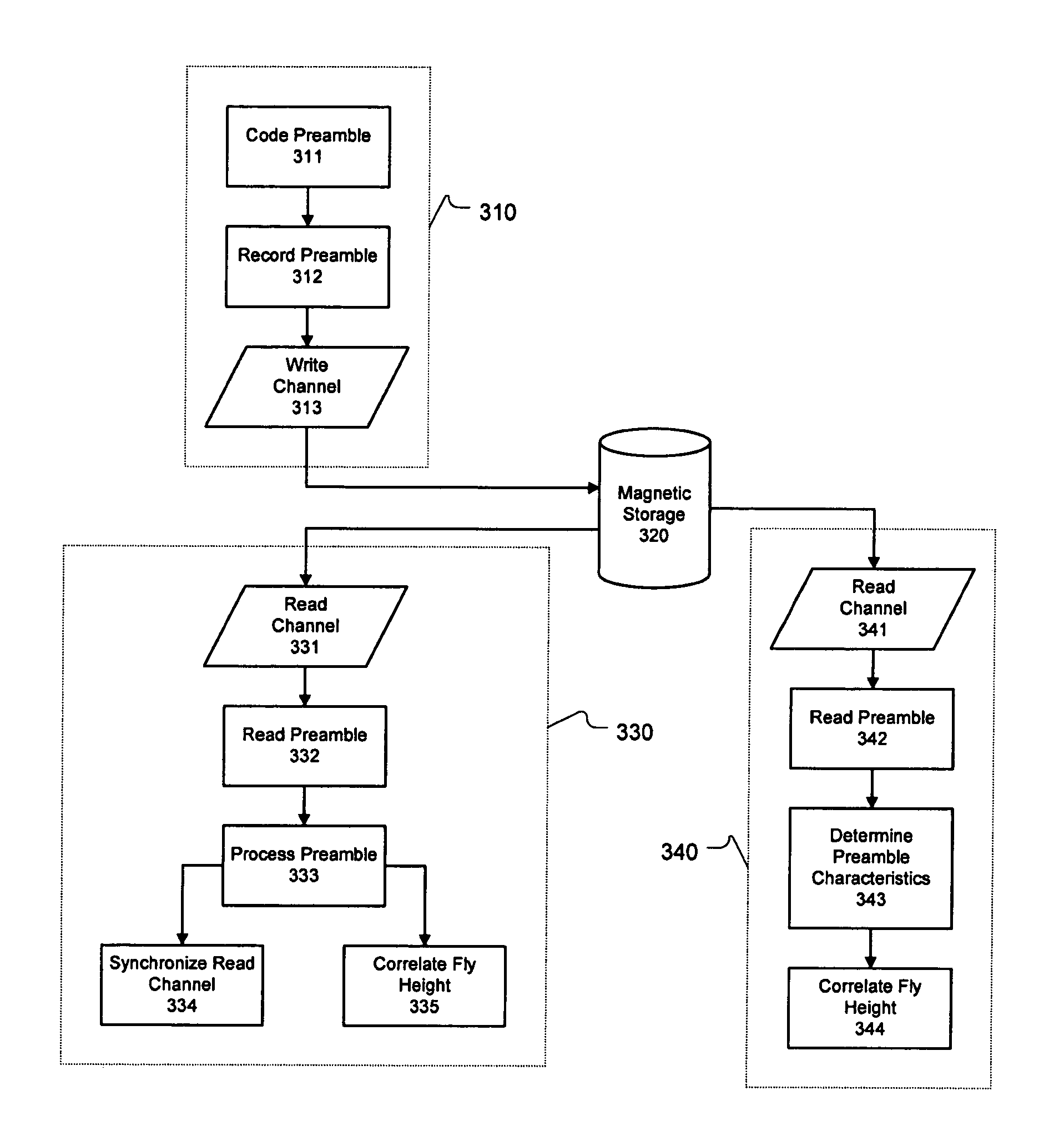

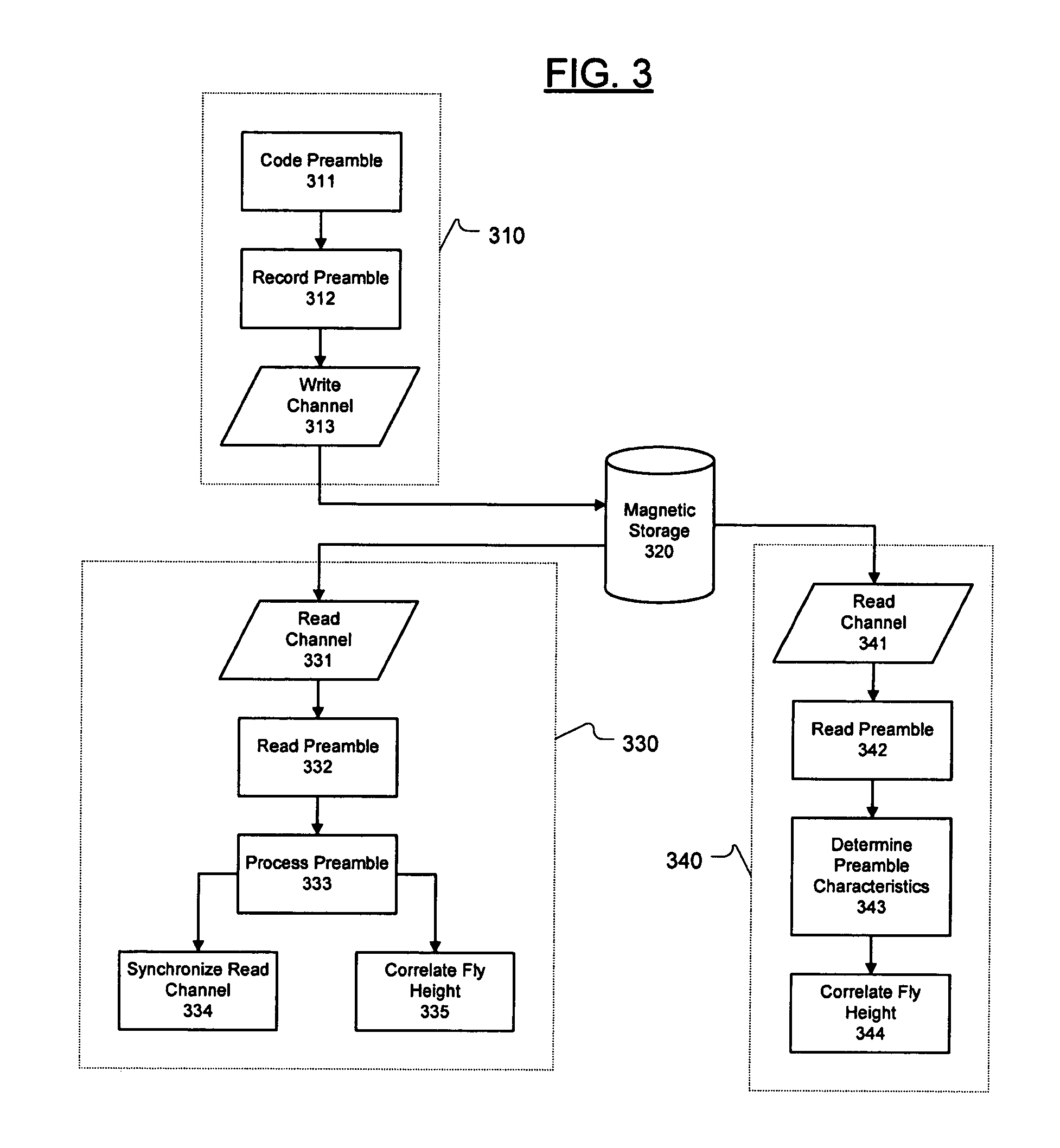

Methods, circuits, apparatus, and systems for read channel synchronization and/or fly height measurement

ActiveUS7715135B1High signal resolutionGood synchronizationDriving/moving recording headsRecord information storageHard disc driveHarmonic

Methods, circuits, and systems for processing a preamble field in a read channel (e.g., in a magnetic storage device such as a hard disk drive). The methods generally include the steps of (a) reading the preamble field, wherein the preamble field comprises a repetitive bit pattern having a logical transition every x bit periods, where x is an integer of at least 3 when d is 0 or 1, or where x is an integer of at least d+2 when d is greater than 1, and (b) processing the repetitive bit pattern. The methods may further relate to processing the preamble for synchronization with the read channel and / or for measuring the fly height of a read / write head. The invention also relates to methods of enabling read channel synchronization and / or fly height measurement. The circuitry for fly height measurement generally includes (a) reading logic configured to read a preamble field from a read channel, wherein the preamble field comprises a repetitive bit pattern, (b) determination logic configured to determine a characteristic of the repetitive bit pattern, and (c) correlation logic configured to correlate the characteristic to the fly height. The systems generally comprise those that include a circuit embodying one or more of the inventive concepts disclosed herein. The present invention advantageously provides improved resolution of signals resulting from the preamble fields and of harmonics of said signals, and enables fly height measurement and improved channel synchronization without consuming dedicated tracks, platters, etc. on a magnetic recording medium.

Owner:MARVELL ASIA PTE LTD

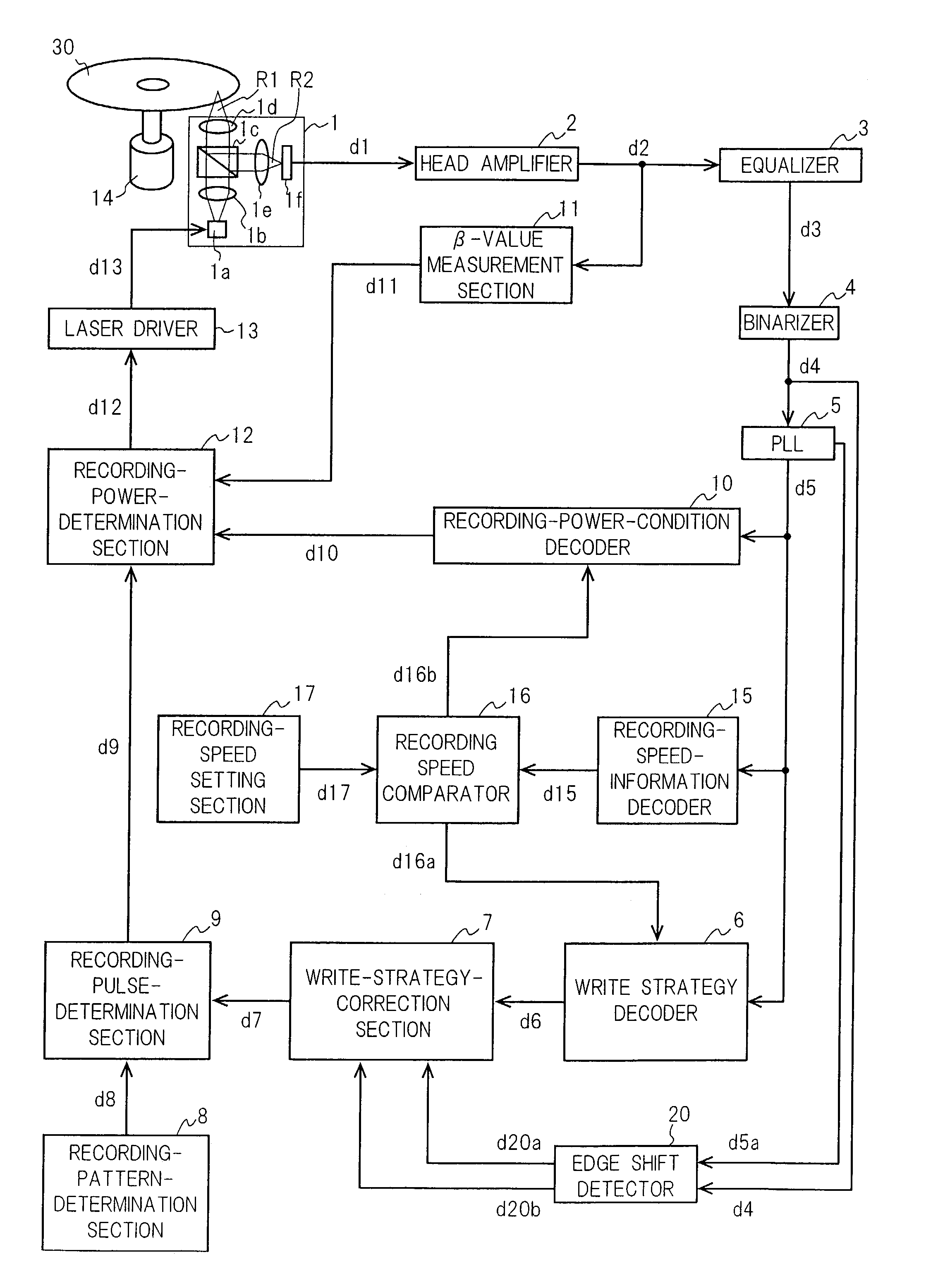

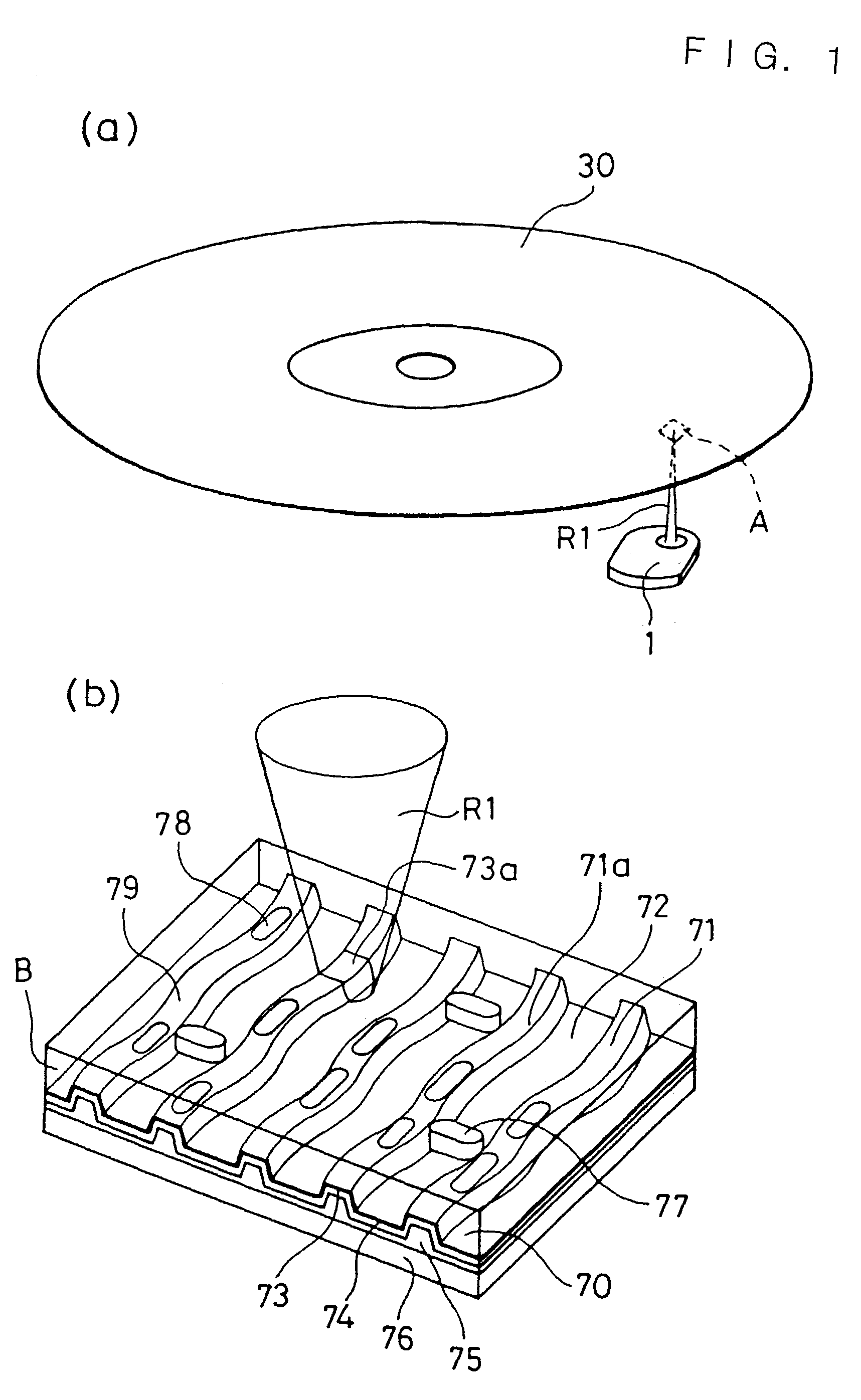

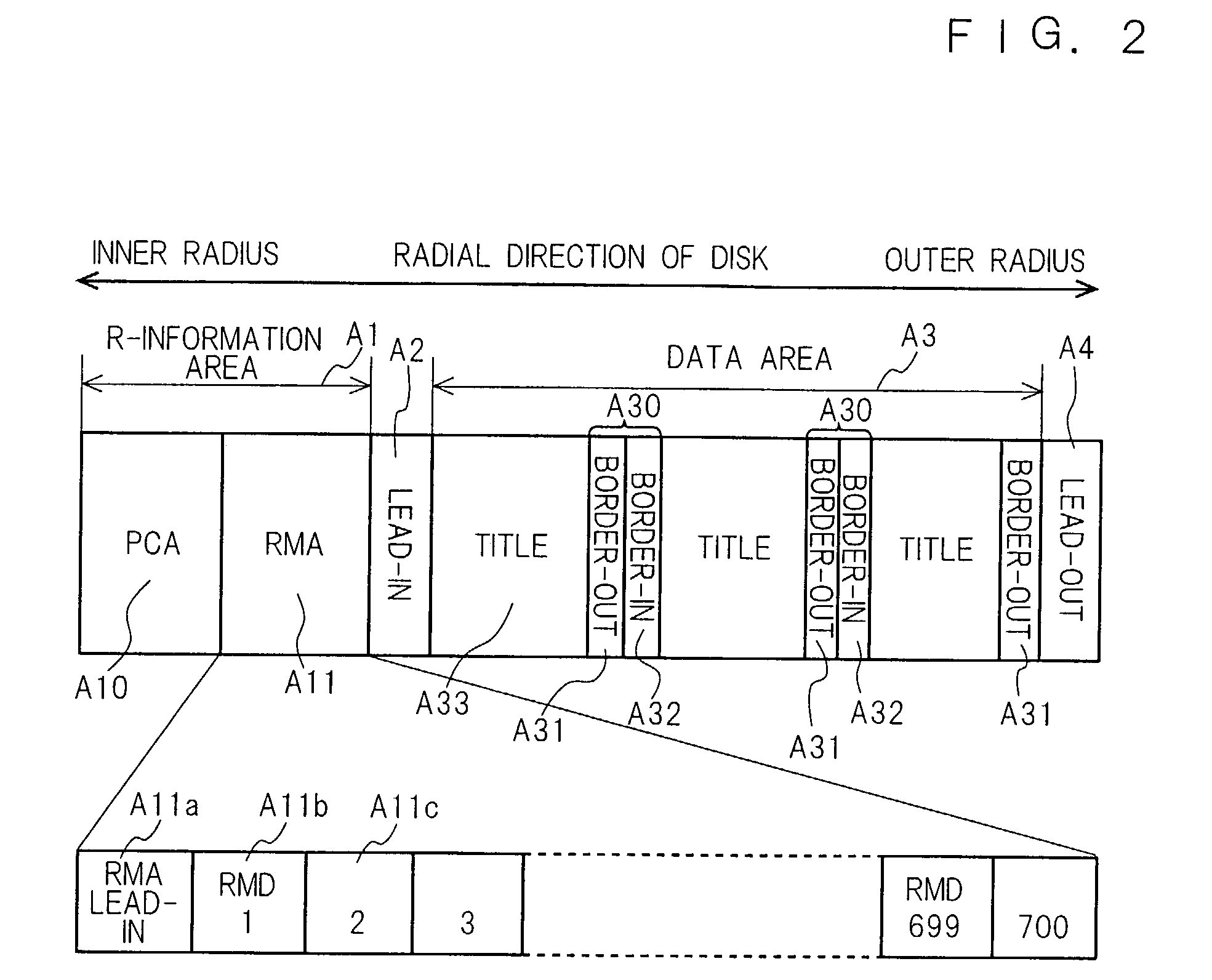

Recordable optical disc, optical disc recording apparatus, optical disc reproduction apparatus, and method for recording data onto recordable optical disc

InactiveUS7068579B2DataRecording strategiesTelevision system detailsRecordable compact discData recording

A DVD-R recorder according to the invention detects an item of recording speed information (d15) from a DVD-R (30) on which histories of recording speed information, write strategy, and recording power condition are stored. When the decoded item of recording speed information (d15) agrees with a set item of recording speed information (d17), the recorder detects the write strategy (d6) and the recording power condition (d10) corresponding to the decoded item of recording speed information (d15). A recording-pulse-determination section (9) converts a recording pattern (d8) into a recording pulse (d9) according to the write strategy (d6). A recording-power-determination section (12) performs an OPC based on the recording power condition (d10). The recording power condition (d10) may include information specifying that a recording pulse corresponding to the front edge of a recorded mark has a larger recording power than other recording pulses.

Owner:PANASONIC CORP

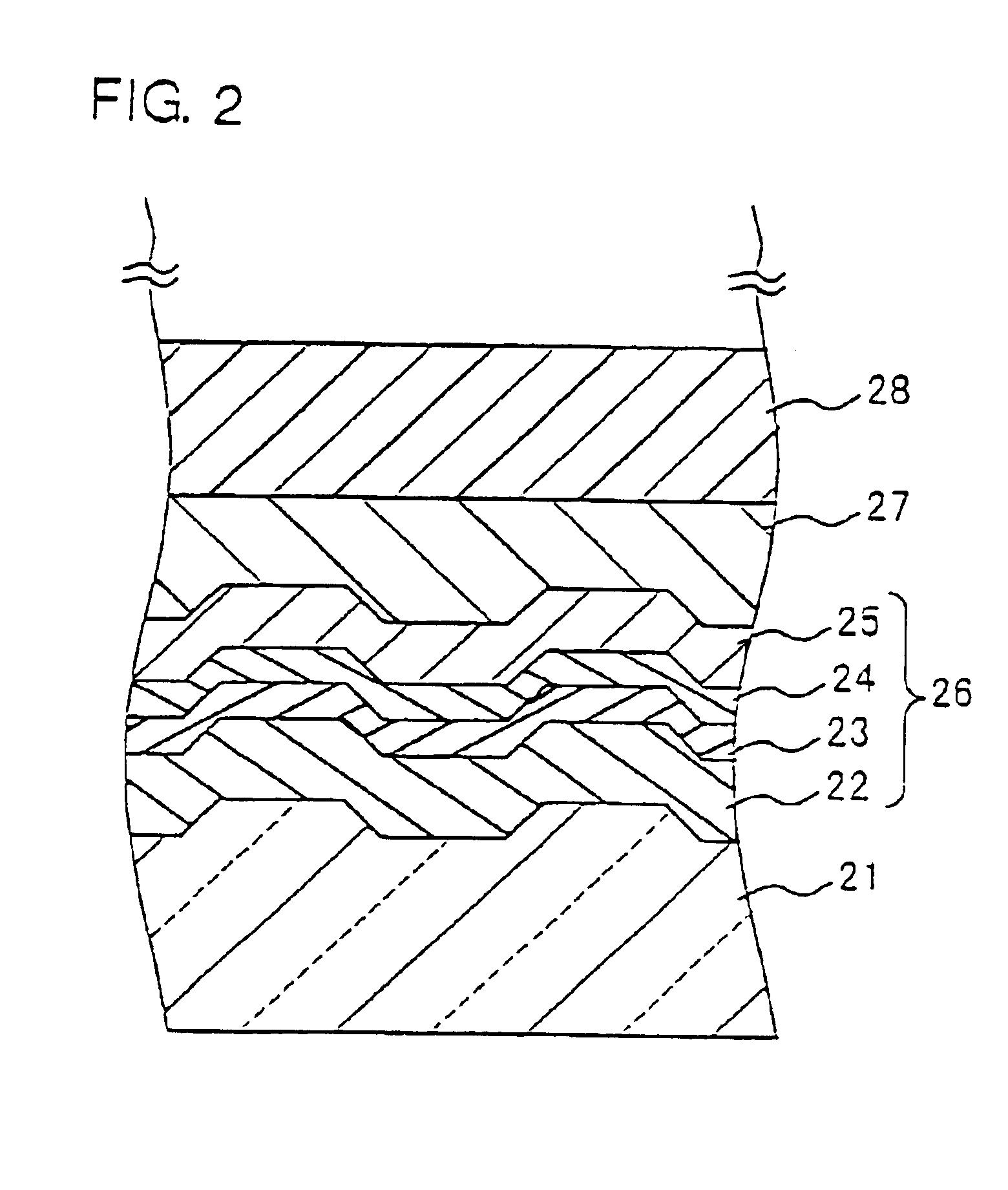

Optical recording medium and recording method for the same

InactiveUS7061850B1Television system detailsDisc-shaped record carriersInformation layerComputer hardware

A main information area 31 capable of recording an information signal and a subsidiary information area 32 for recording subsidiary information that is different from the information signal are divided in one principal plane direction of a substrate, and an information layer for recording the information signal in the main information area 31 is provided also in the subsidiary information area 32, and medium identification information for distinguishing the medium optically is recorded in the information layer of the subsidiary information area 32 without changing the shape of the information layer. As a result, the medium identification information can be recorded in an optical recording medium 1 stably. In particular, the initialization of a phase change type optical recording medium and the recording of the medium identification information can be performed at the same time, so that the production process can be simplified, and the production costs can be reduced.

Owner:PANASONIC CORP

Signal quality evaluation method, information recording/reproducing system, and recording compensation method

InactiveUS20030090980A1Television system detailsData representation error detection/correctionSignal qualityComputer science

Signal quality evaluation is performed using a predetermined reproduction signal, a first pattern corresponding to a signal waveform pattern of the reproduction signal, and a given pattern corresponding to the signal waveform pattern of the reproduction signal and being different from the first pattern.

Owner:KK TOSHIBA

Information recording carrier and method of reproducing the same

ActiveUS7088670B2Effectively buryingMultilayered discsInformation arrangementDigital recordingEngineering

Plural grooves or lands formed in an information recording carrier include at least a wobbling region and data is recorded wobblingly in this wobbling region by frequency shift modulation while recorded digitally with a single or multiple waves as a channel bit.

Owner:JVC KENWOOD CORP A CORP OF JAPAN

Popular searches

Digital signal formatting Digital recording Signal processing using self-clocking codes Record carrier types Using detectable carrier information Recording on magnetic disks Special recording techniques Code conversion Error correction/detection by combining multiple code structures Amplitude-modulated carrier systems

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com