Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

32 results about "Word clock" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A word clock or wordclock (sometimes sample clock, which can have a broader meaning) is a clock signal used to synchronise other devices, such as digital audio tape machines and compact disc players, which interconnect via digital audio signals. Word clock is so named because it clocks each audio sample. Samples are represented in data words.

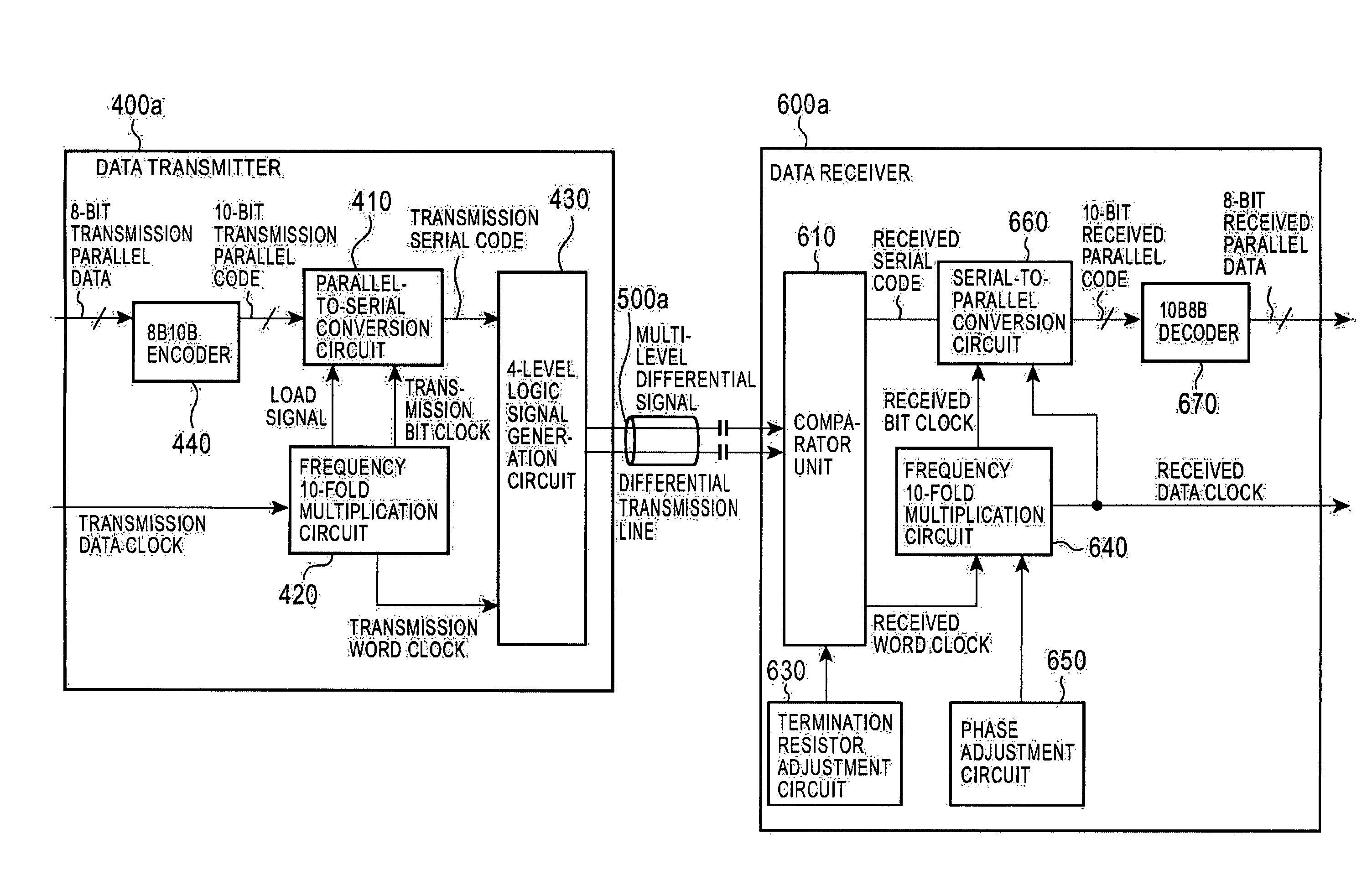

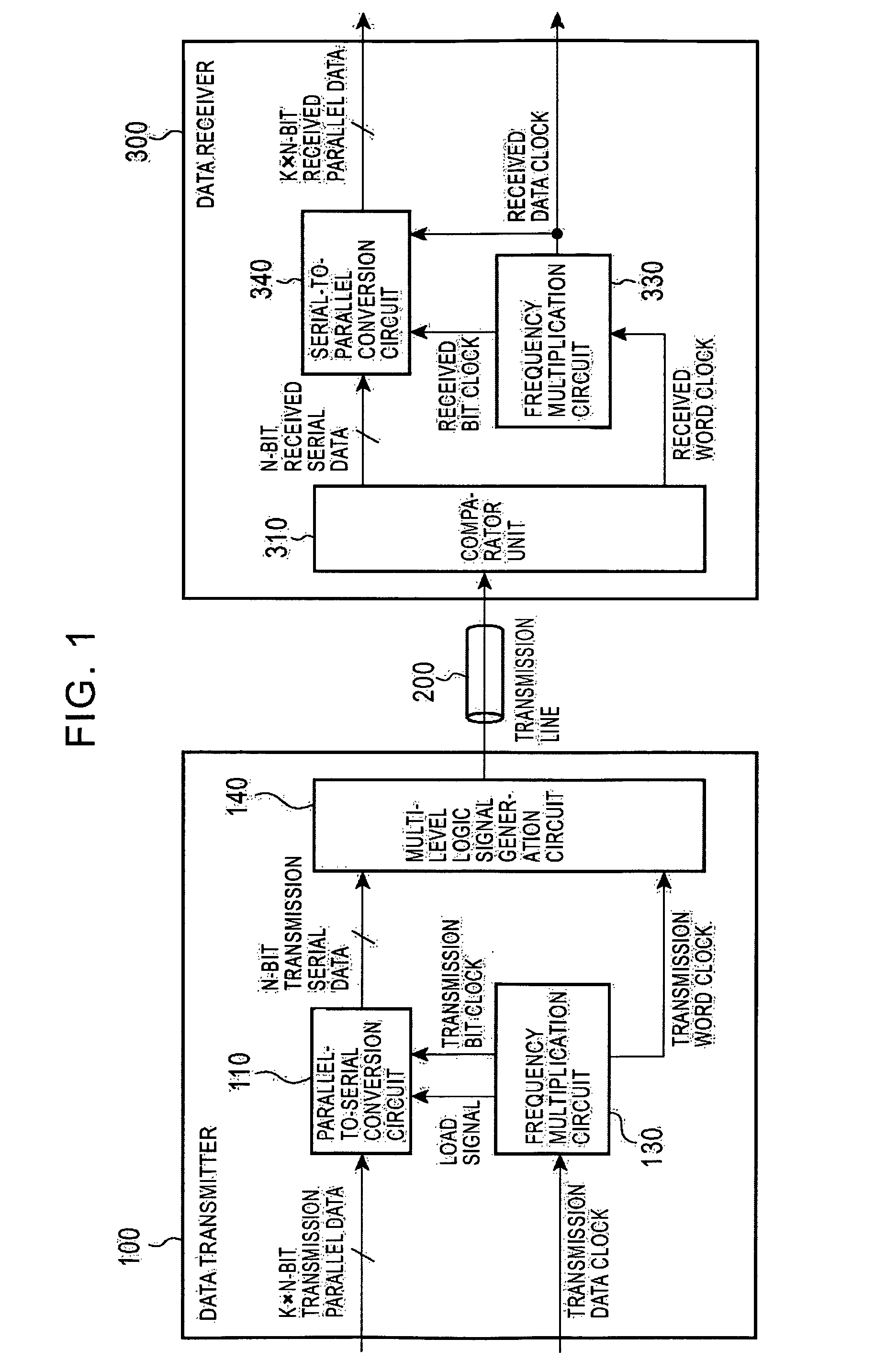

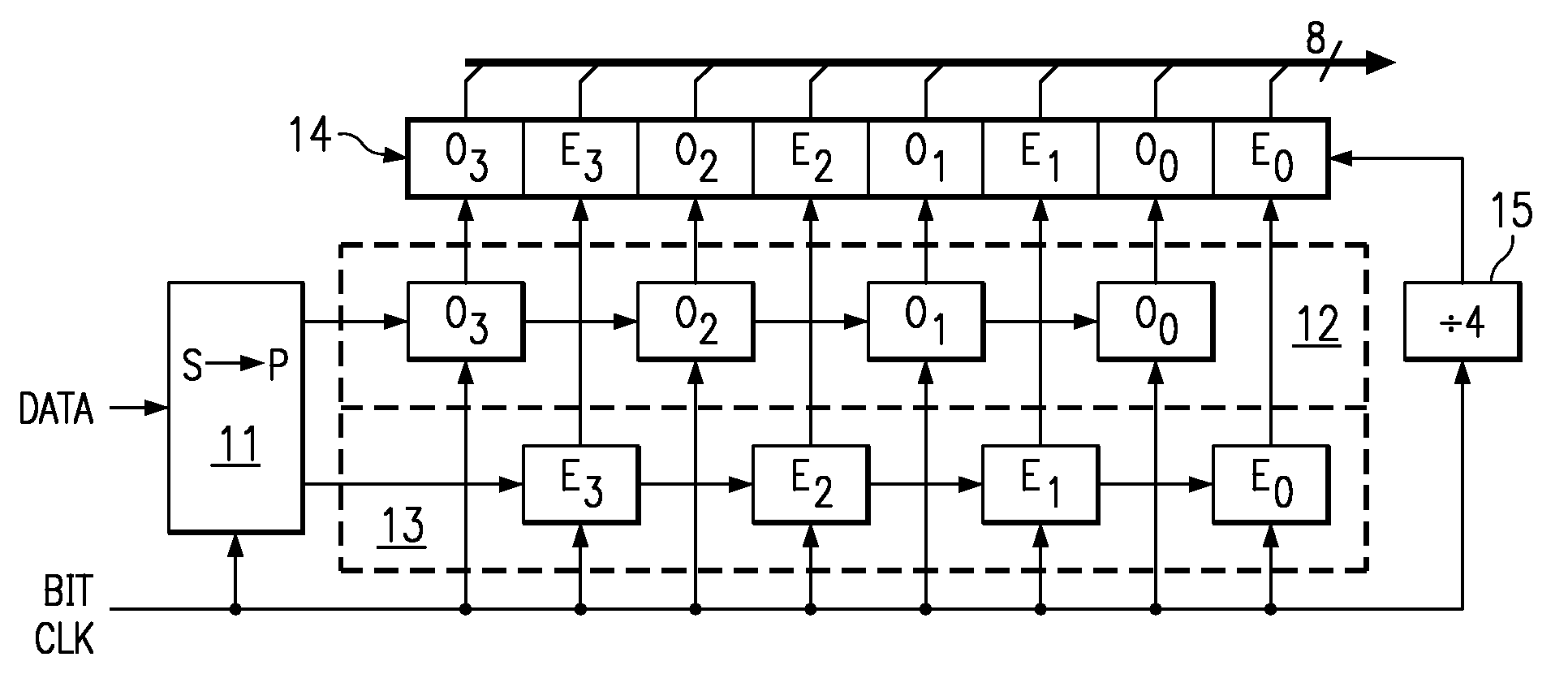

Data transfer system and method, data transmitter, data receiver, data transmission method, and data reception method

ActiveUS20050147178A1Simple structureReduce componentsParallel/series conversionLogic circuits characterised by logic functionTransfer systemWord clock

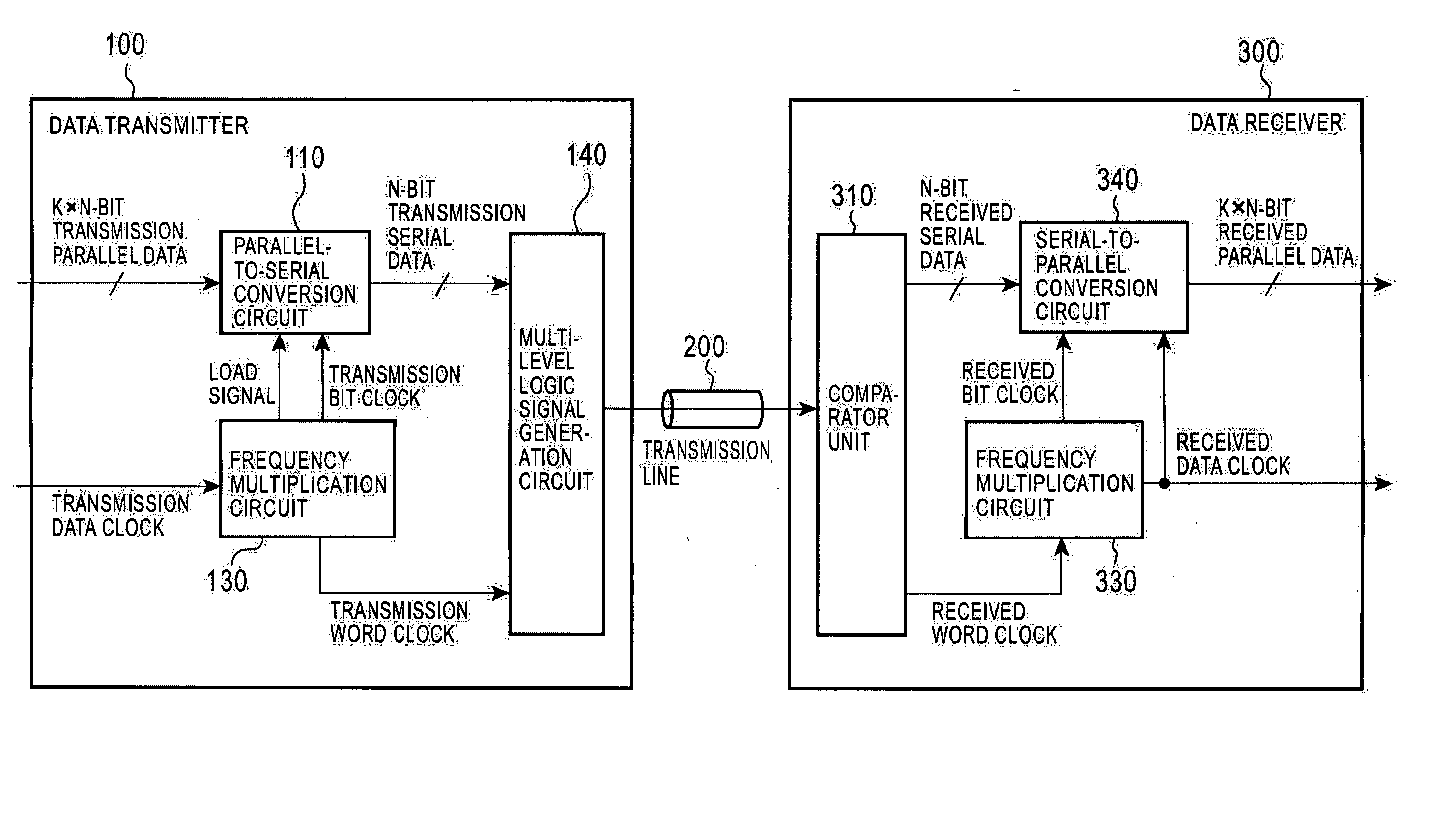

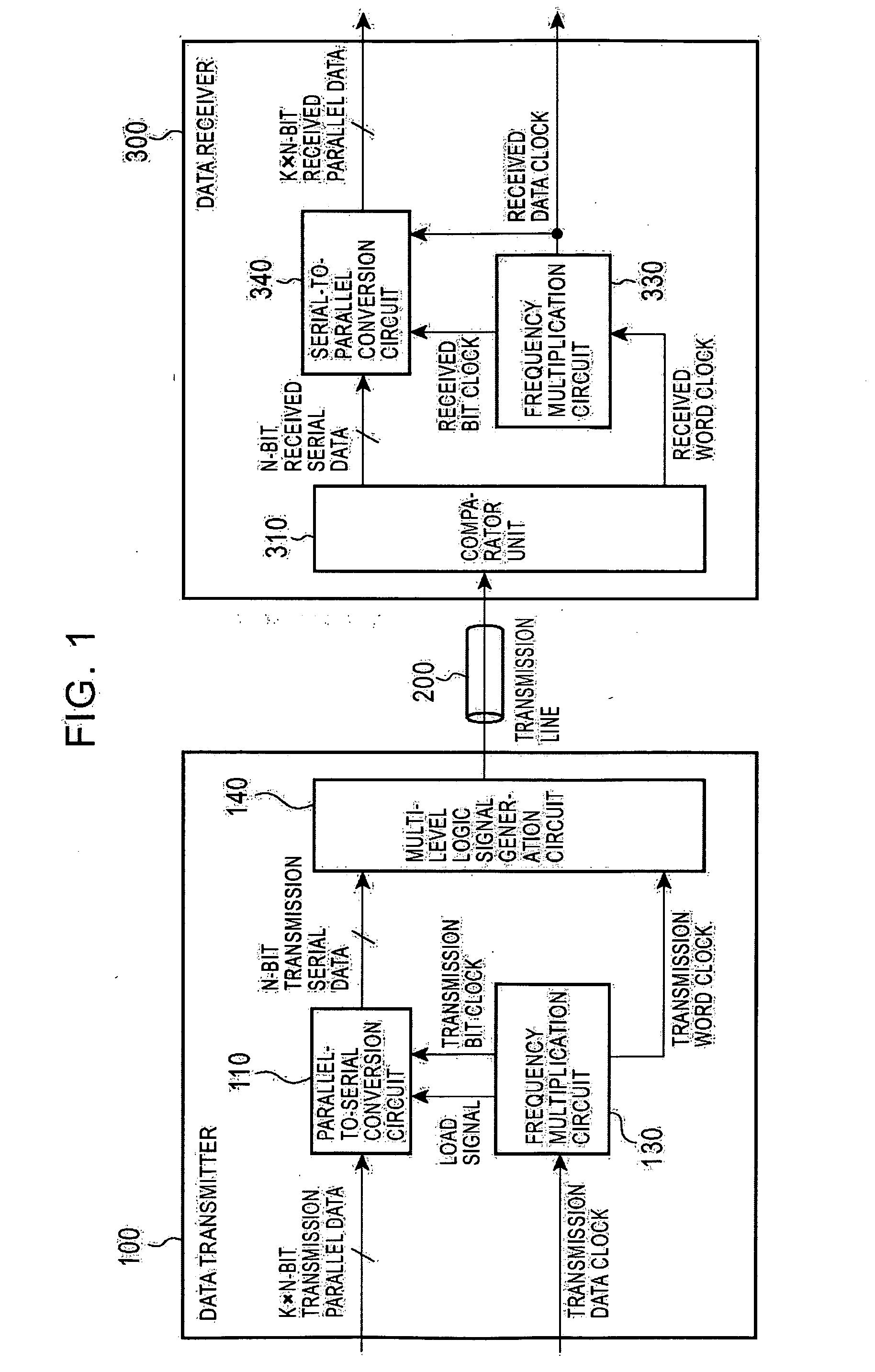

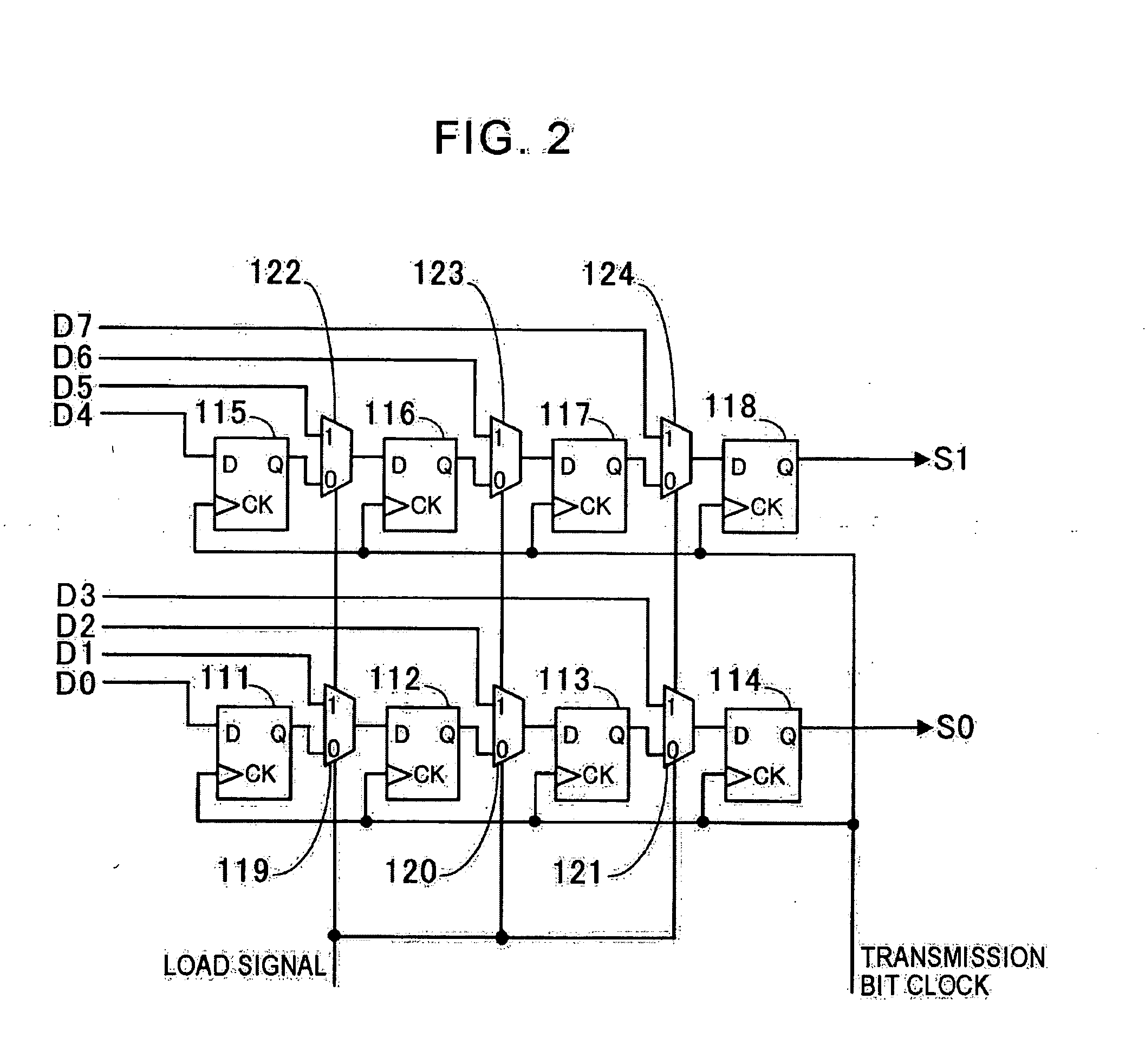

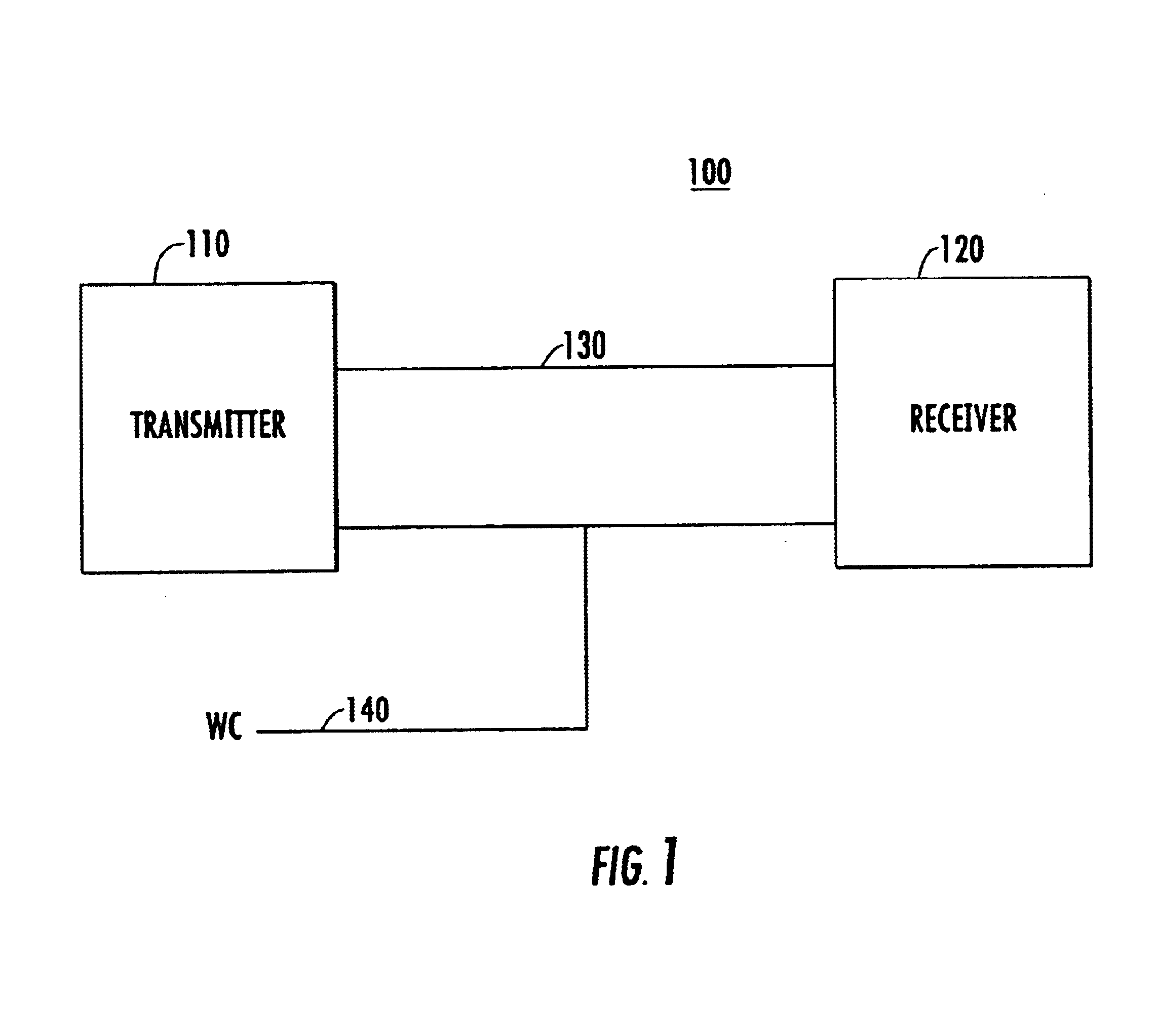

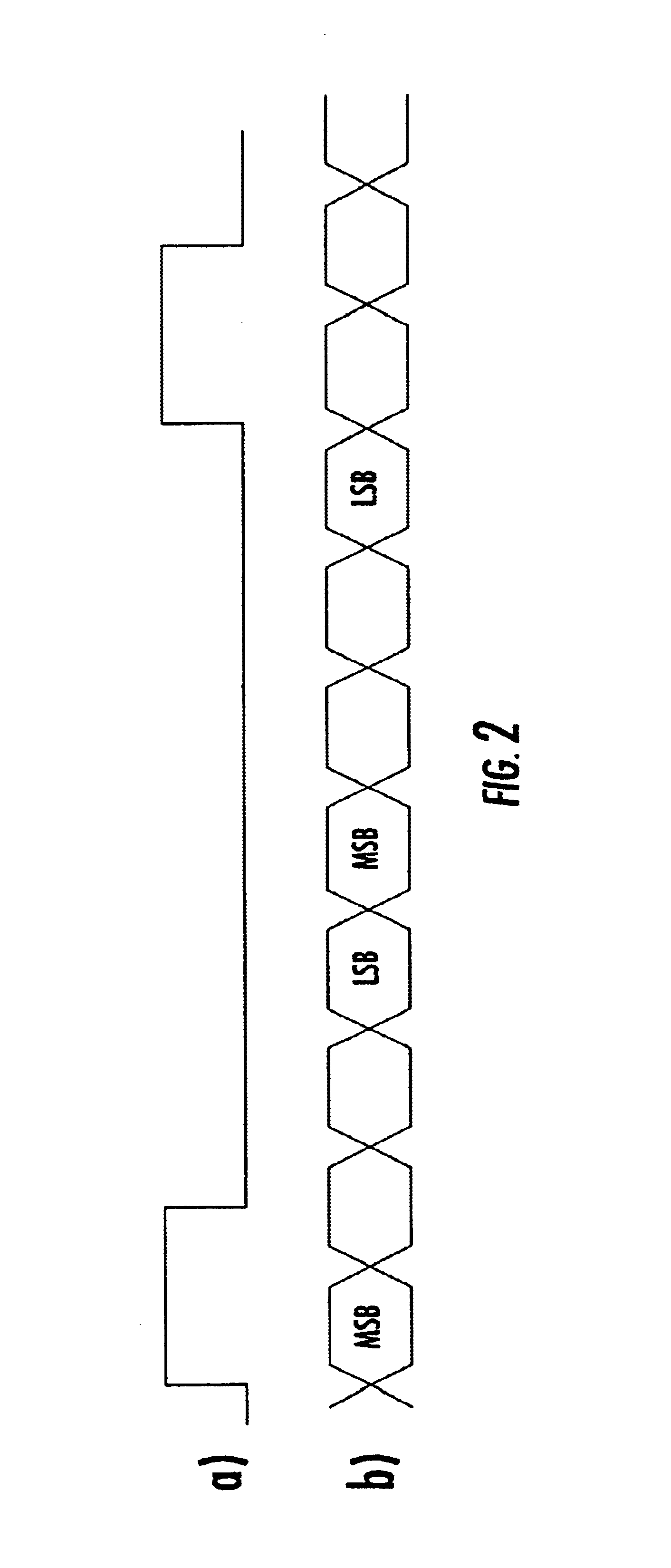

The present invention provides a data transfer system including a data transmitter and a data receiver. The data transmitter converts a plurality of bits of transmission parallel data into serial data and generates a multi-level logic signal representing a plurality of bits of information in one symbol, the information being obtained by combining the serial data with a word clock as one-bit information. The word clock indicates a word delimiter in the serial data. The data receiver receives the transmitted multi-level logic signal, extracts the serial data and the word clock from the signal, and reproduces the parallel data based on the extracted word clock. In the data transfer system, a multi-bit digital signal can be transmitted as one signal including a word clock. Thus, components and mounting space to be allocated to transfer can be reduced.

Owner:SONY CORP

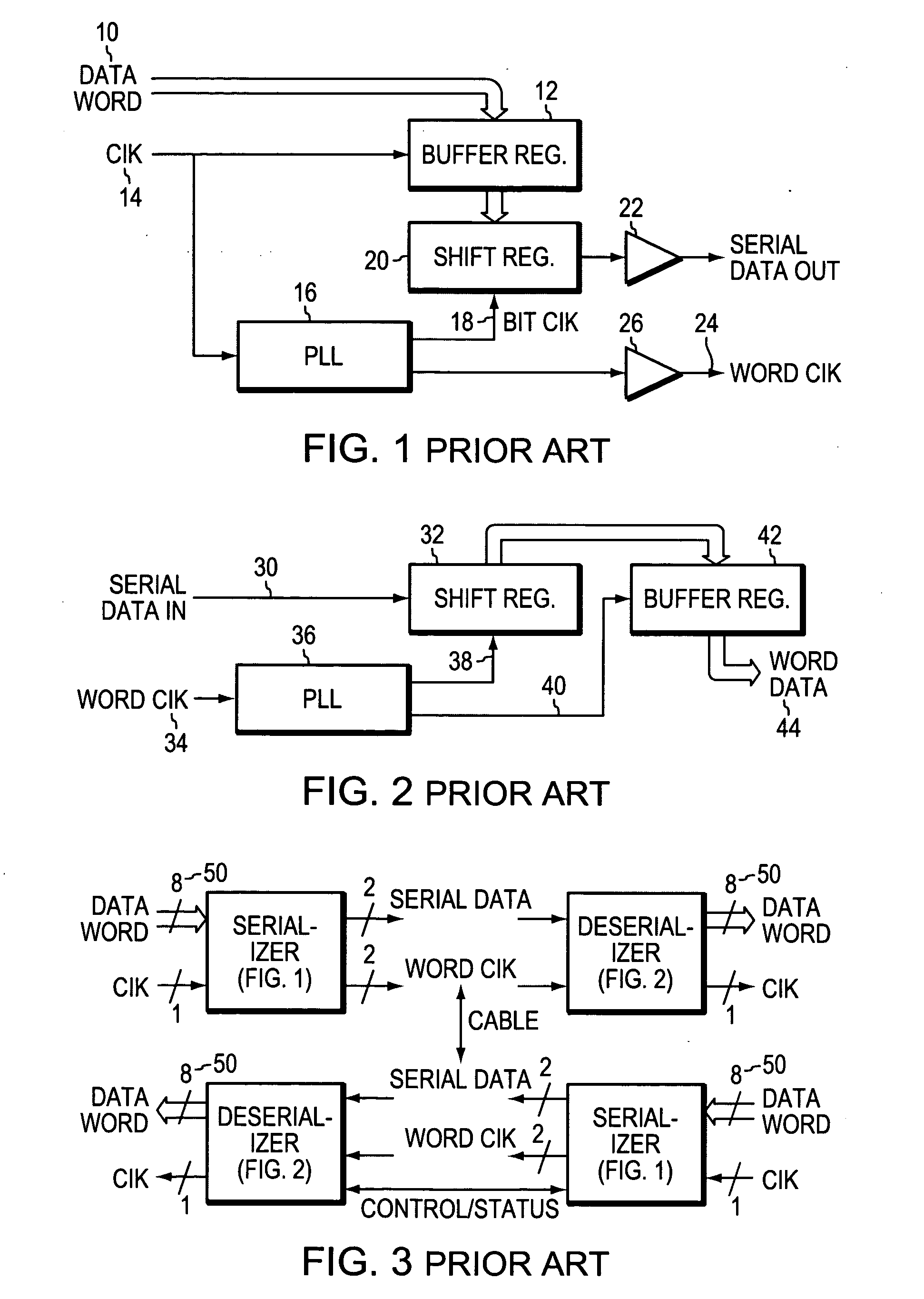

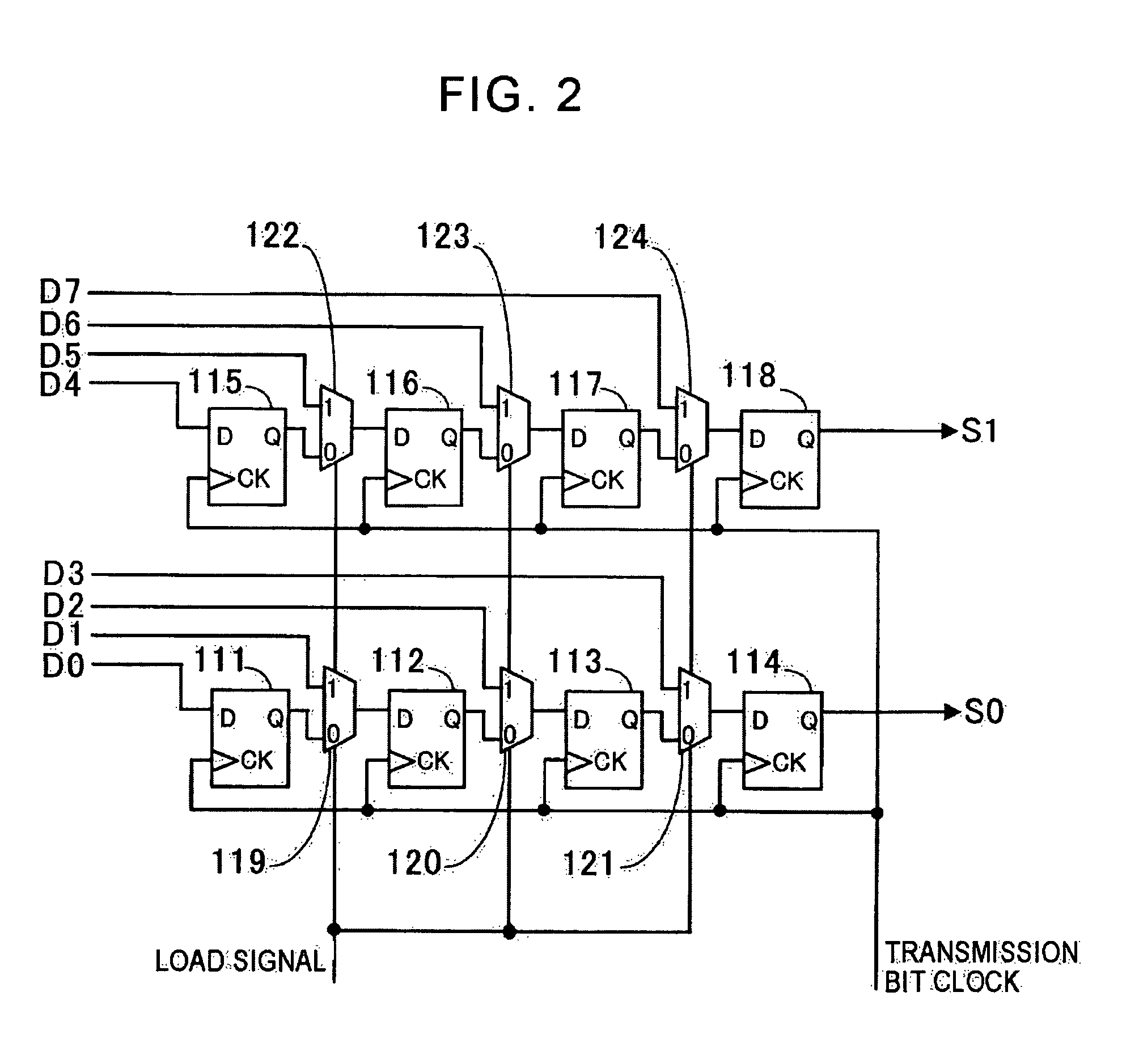

Bit clock with embedded word clock boundary

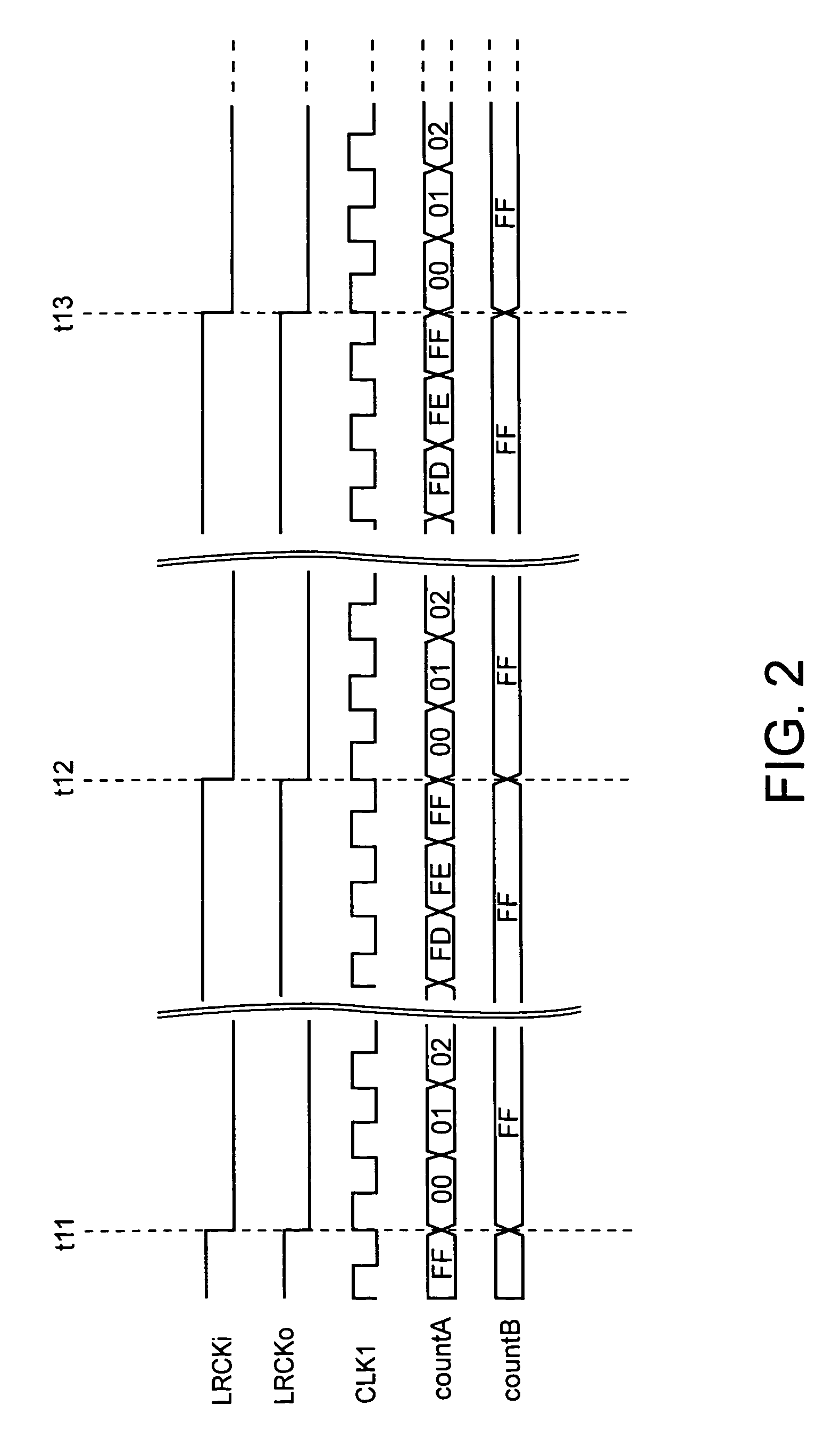

InactiveUS20050207280A1Easy to controlParallel/series conversionSynchronisation information channelsShift registerSensing data

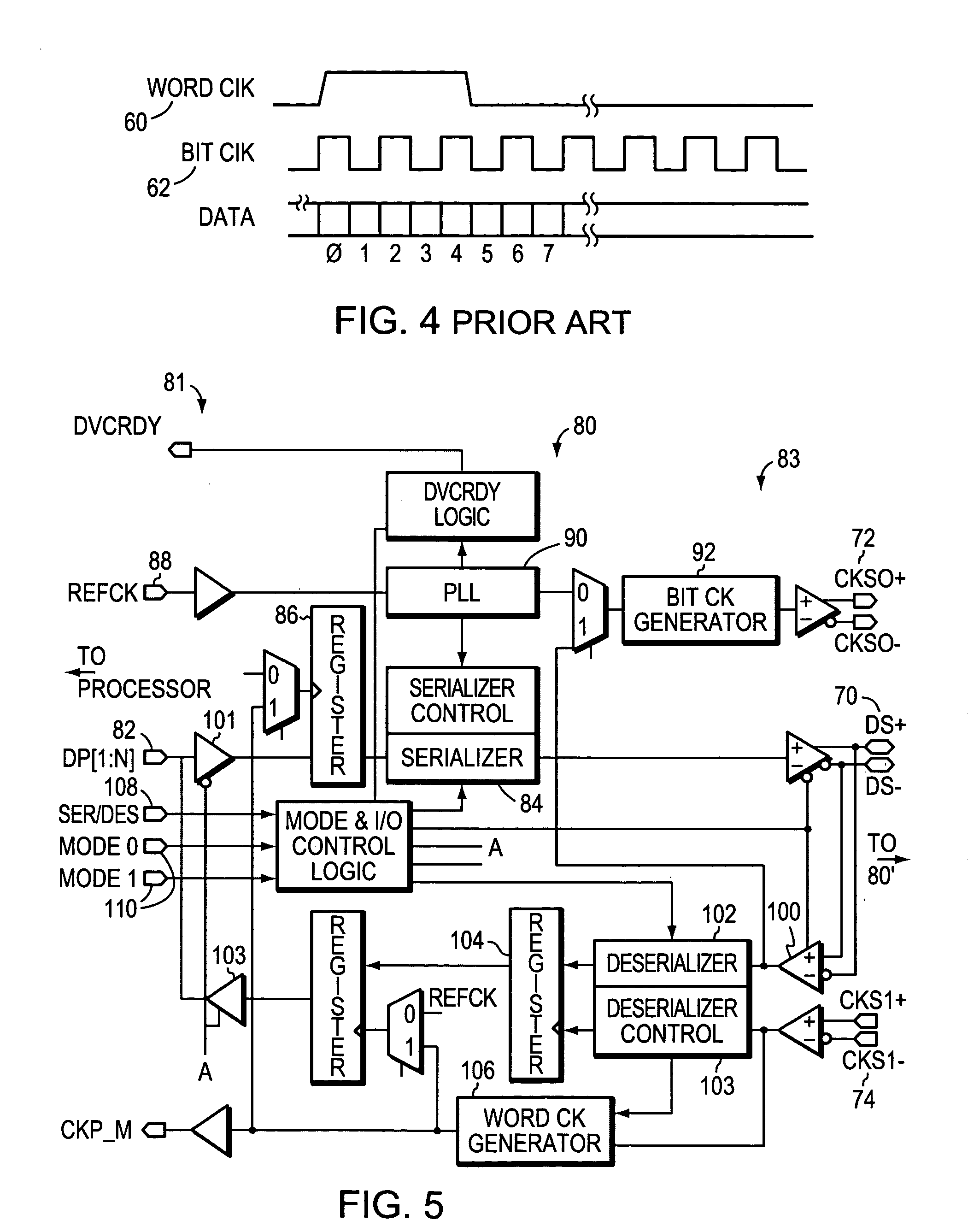

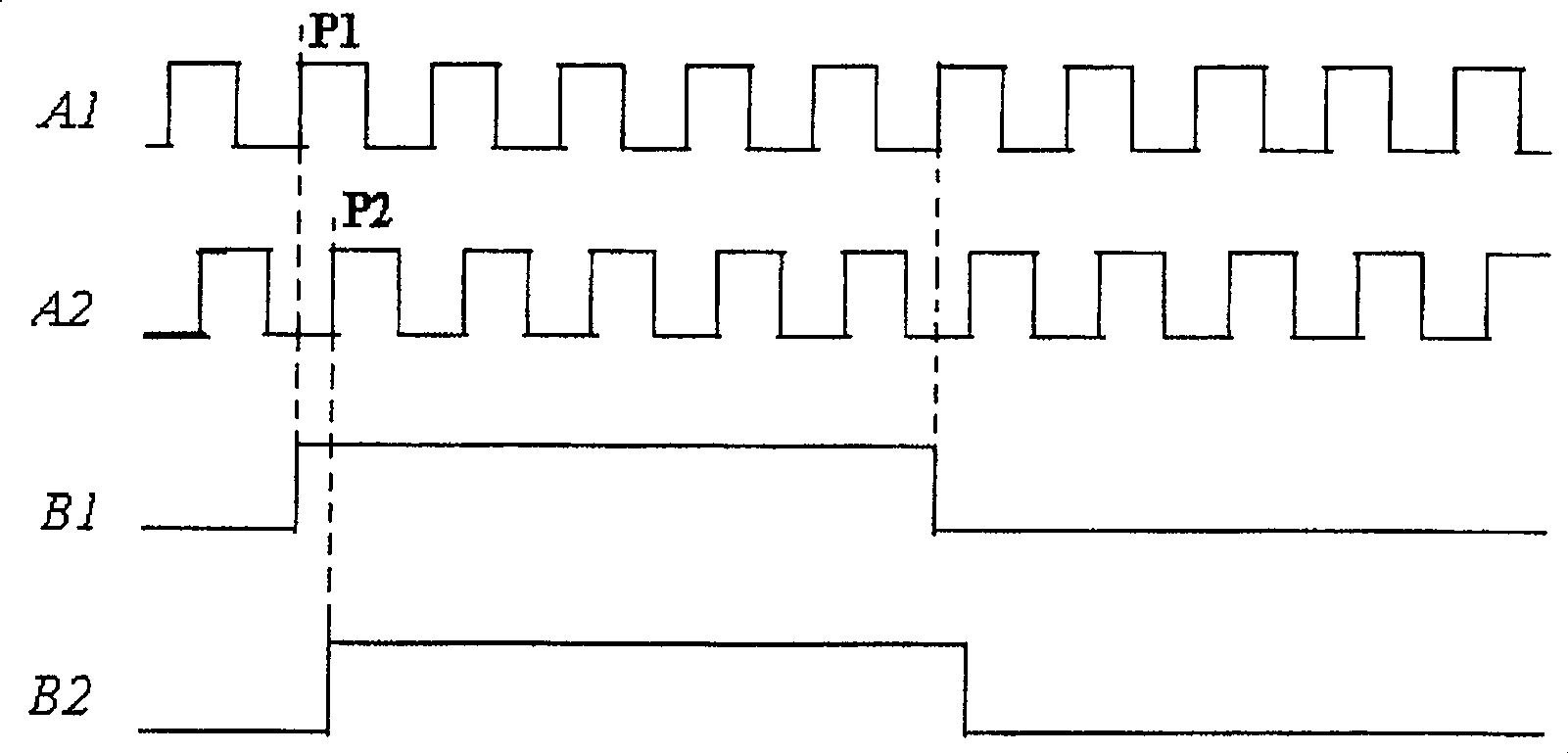

A bi-directional serializer / deserializer is disclosed using a single bi-directional data line and a single bi-directional clock line. Gated buffers are controlled to operate either sending or receiving data, and a phase locked loop provides a clock to shift data out from a shift register. A reference clock is supplied to the PLL and the PLL generates a synchronous bit clock. The bit clock is sent over the clock line in parallel with the serial data bits, and the PLL bit clock is synchronized to the data bits. Two data boundary bits are inserted between the word data bits, the boundary data bits are arranged with a logic level transition between the two data boundary bits. Also, at the boundary of the words during the sending of the two boundary data bits, the synchronous bit clock is arranged to have no logic level transition. The receiving system will use the bit clock to serial load the received word and boundary data bits into a shift register. A word boundary is detected by sensing a data bit transition while there is no bit clock.

Owner:SEMICON COMPONENTS IND LLC

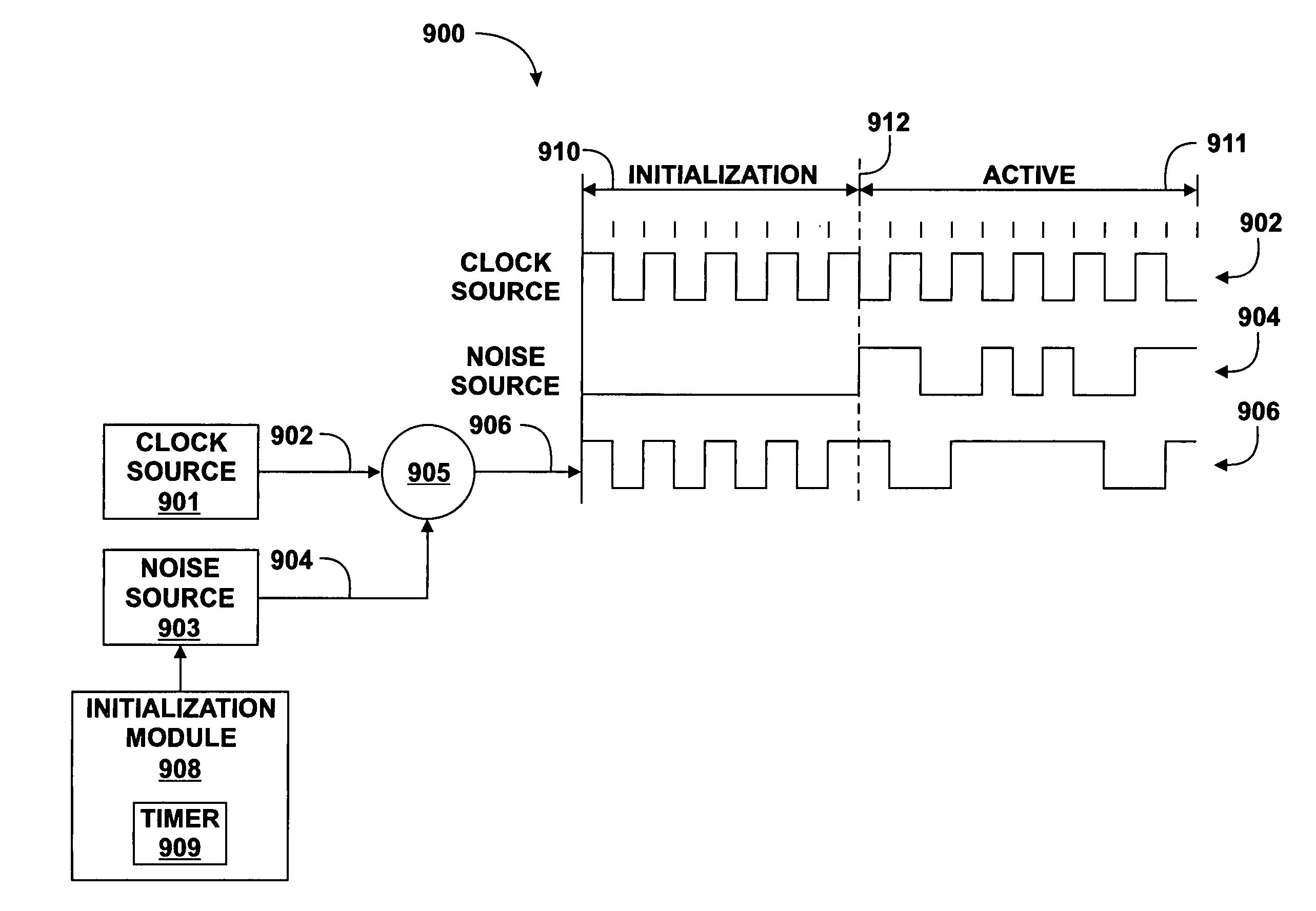

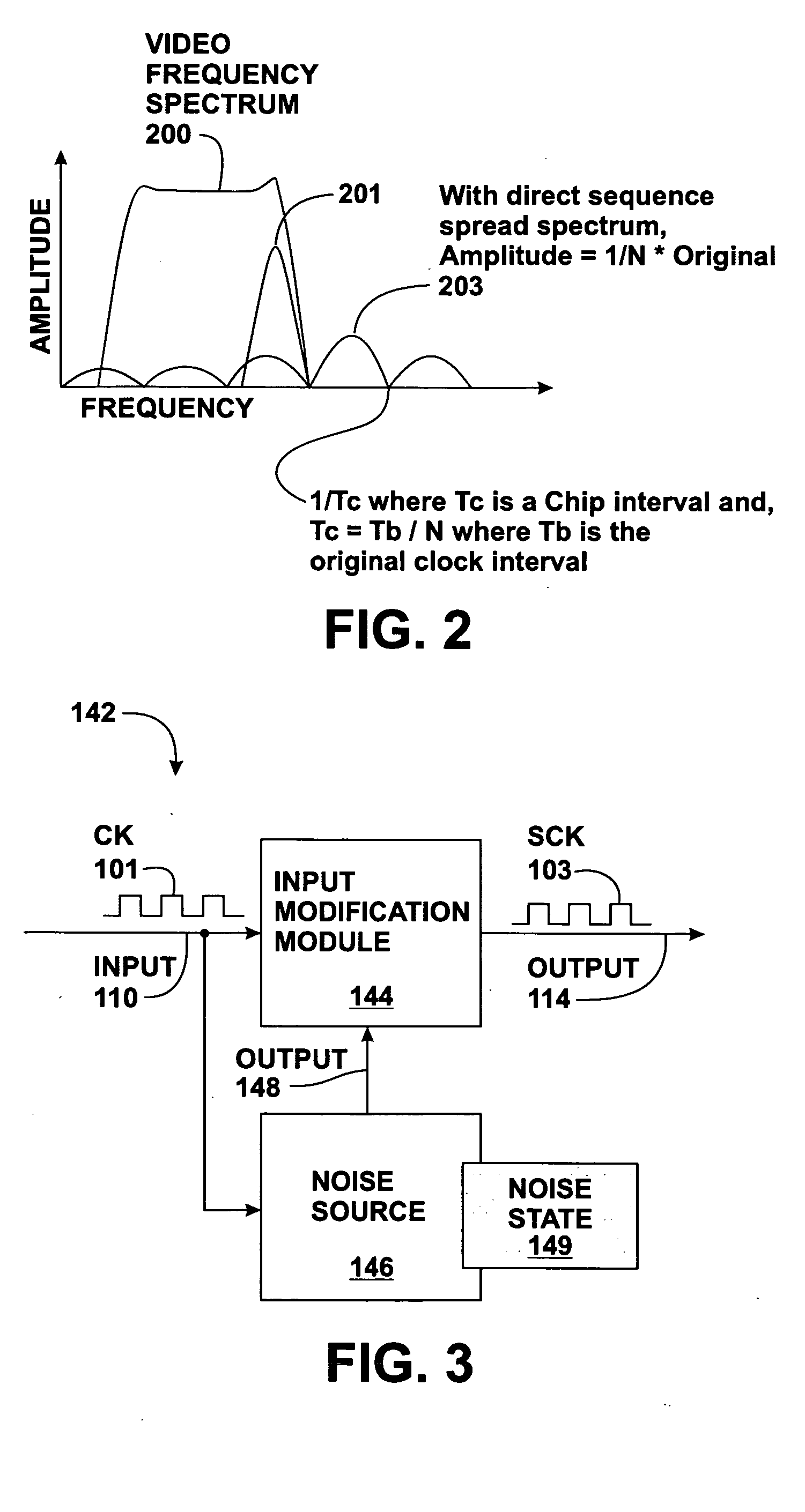

Noise source synchronization for power spread signals

A method and system is disclosed for spreading the power associated with digital signals being transmitted to reduce electromagnetic interference (EMI) by operating a digital noise generator in an initialization state between a first time and a second time, operating the digital noise generator in an active state between the second time and a third time, modifying a digital clock signal based on an output of the digital noise generator, and providing the modified digital clock signal between the first time and the third time.

Owner:VIZIONWARE

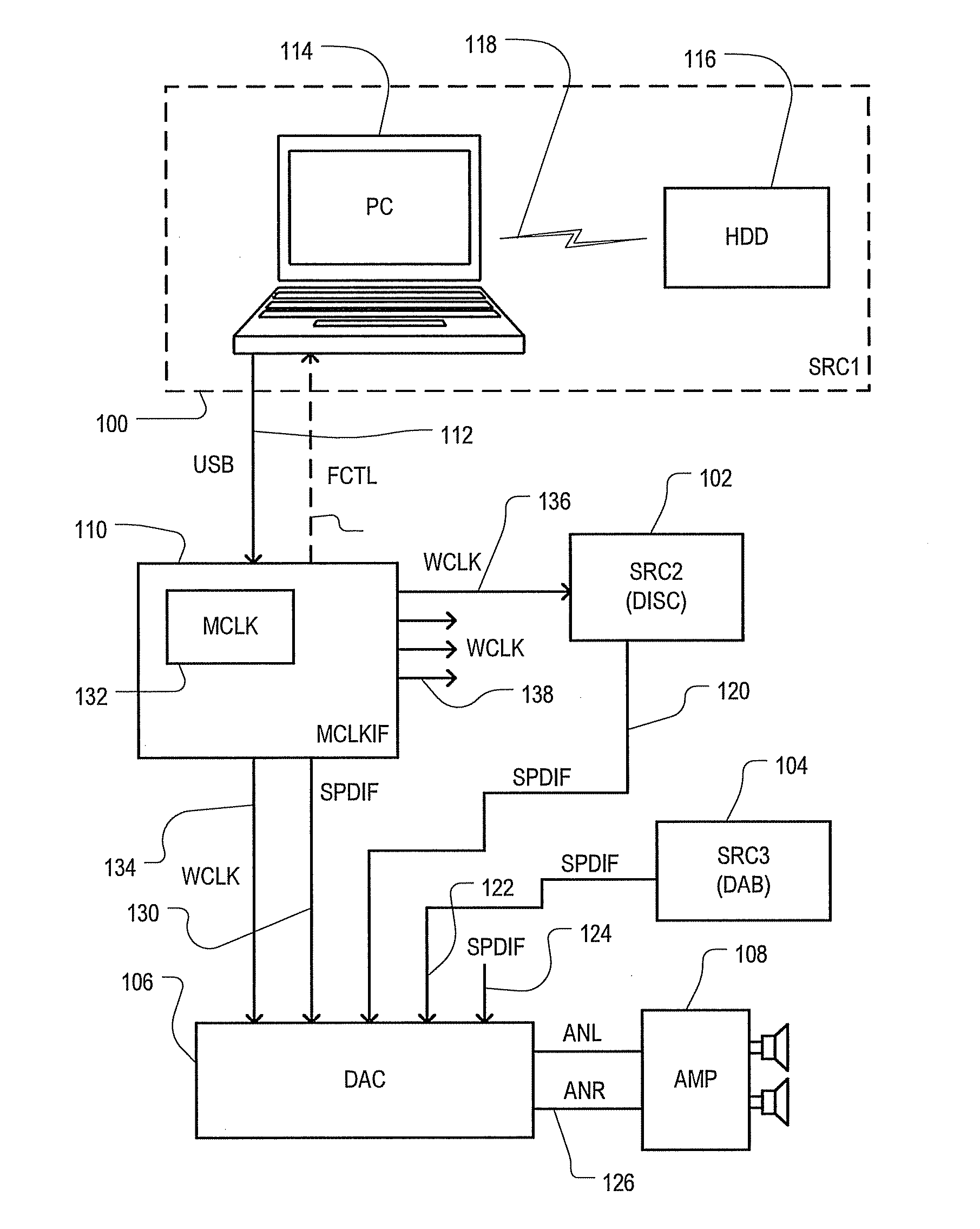

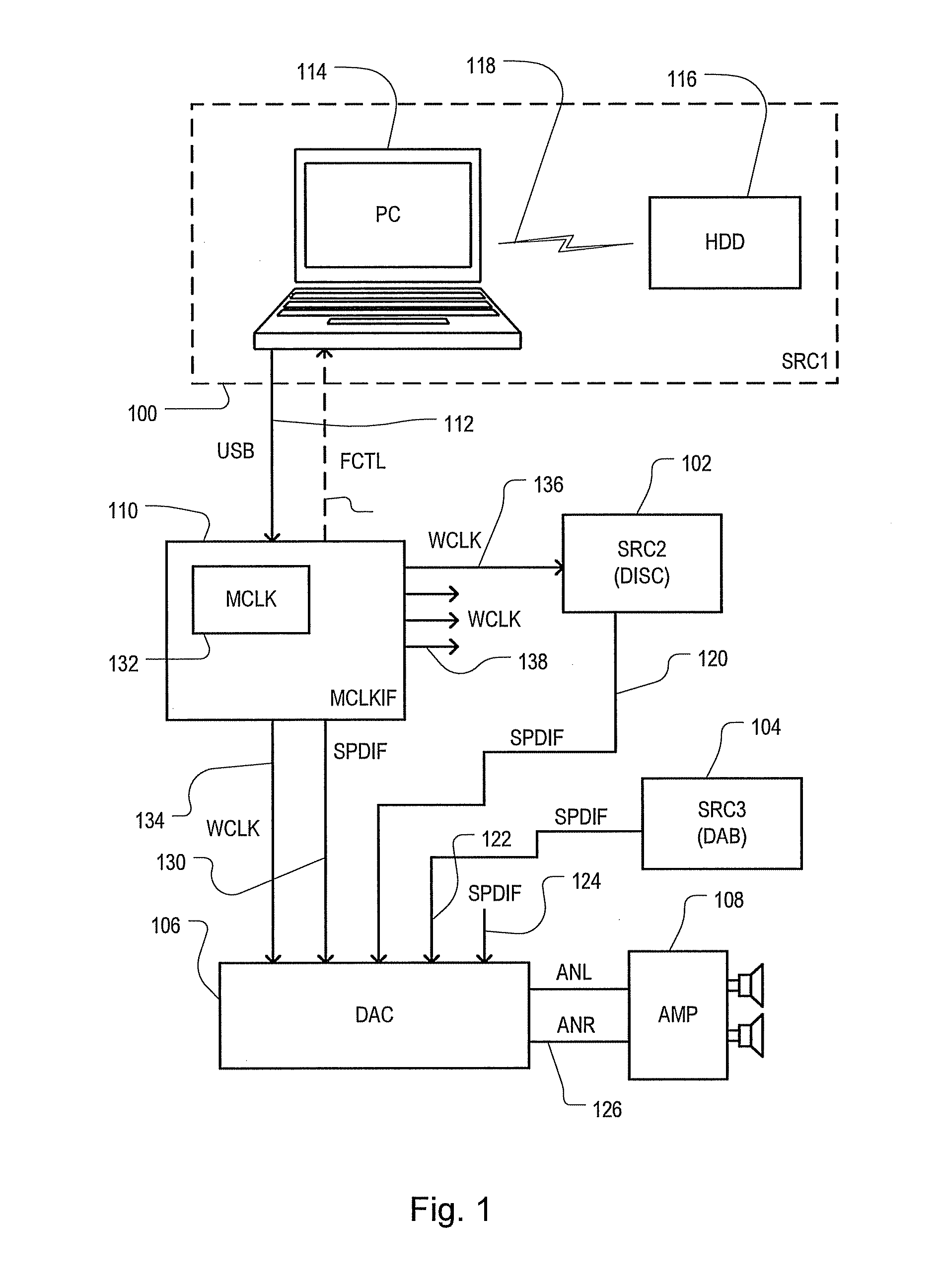

Computer audio interface units and systems

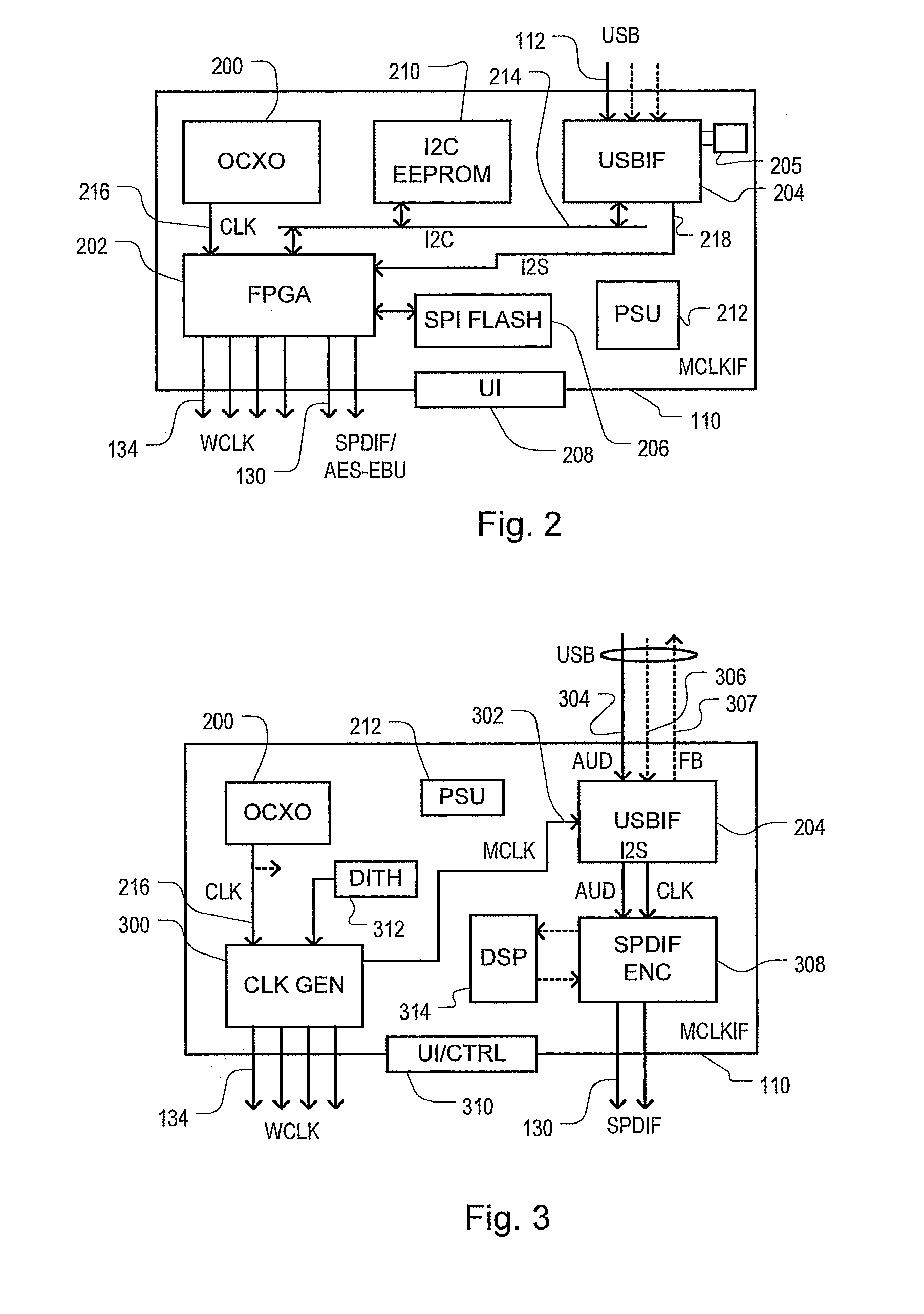

InactiveUS20100077247A1Without qualityCost-effective and flexibleGenerating/distributing signalsTransmission path multiple useSerial computerWord clock

A computer audio interface unit (110) comprises a serial computer interface (e.g. USB) (204) providing a connector (112) for connection to an external, computer-based source (100) of digital audio data samples. A digital audio output connector (130) provides a digital audio output signal to external audio reproduction apparatus (106, 108). A word clock output connector (134) provides a word clock signal to external audio reproduction apparatus, in parallel with said digital audio output signal. An encoder (202 / 308) receives digital audio data via said USB interface and outputs said digital audio output signal. Clocking circuitry (202 / 300, 312) is responsive to a timing reference signal (200) independent of said external source (100), and generates said word clock signal for output to the external reproduction apparatus. Said clocking circuitry further generates a clock signal (302) for the USB interface (204) so as to synchronise the drawing of said audio data samples via said USB interface with the generated external word clock signal and the digital audio output signal. Interface and encoder functions may be housed separately from a master clock function.

Owner:DATA CONVERSION SYST

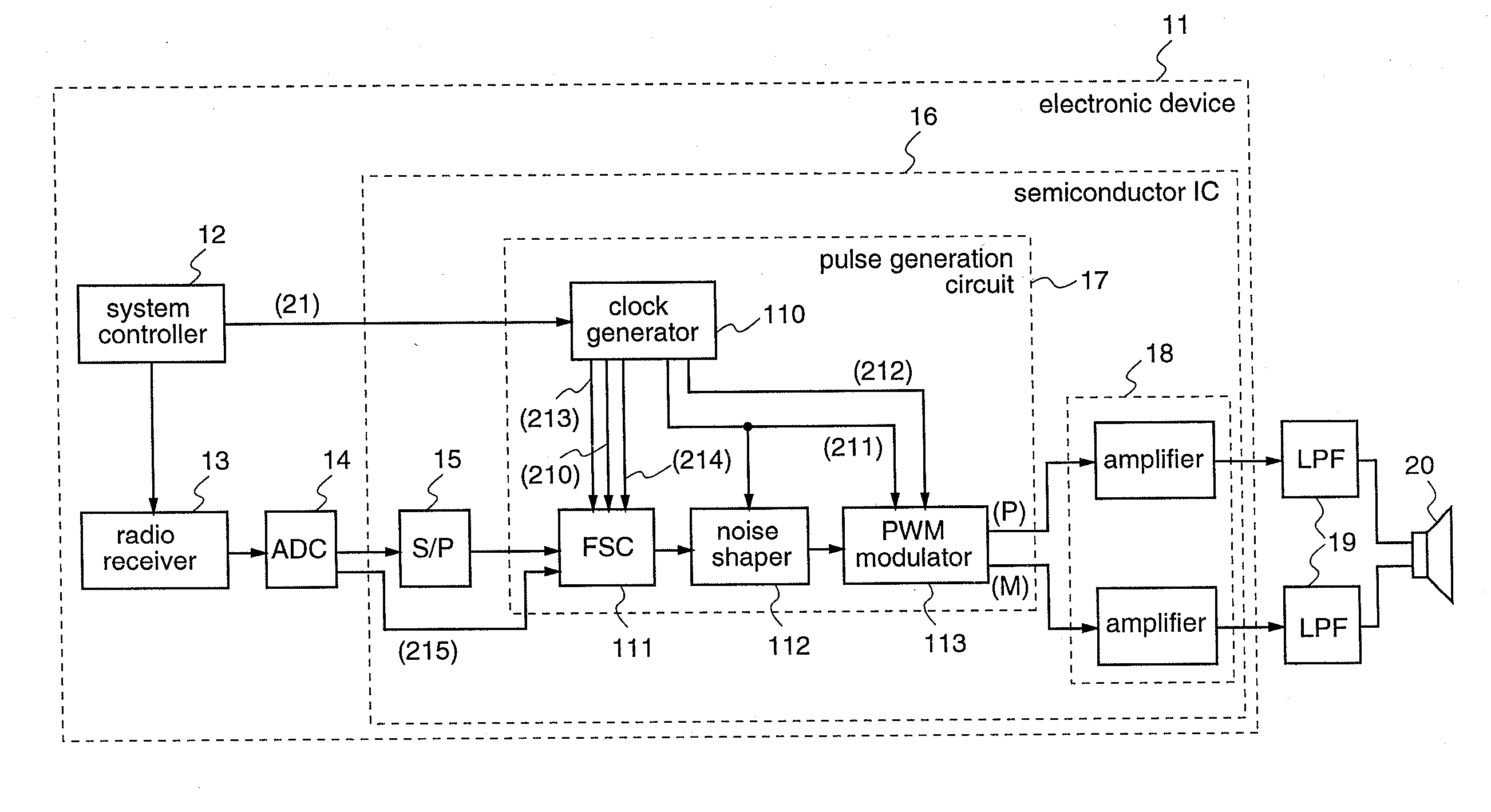

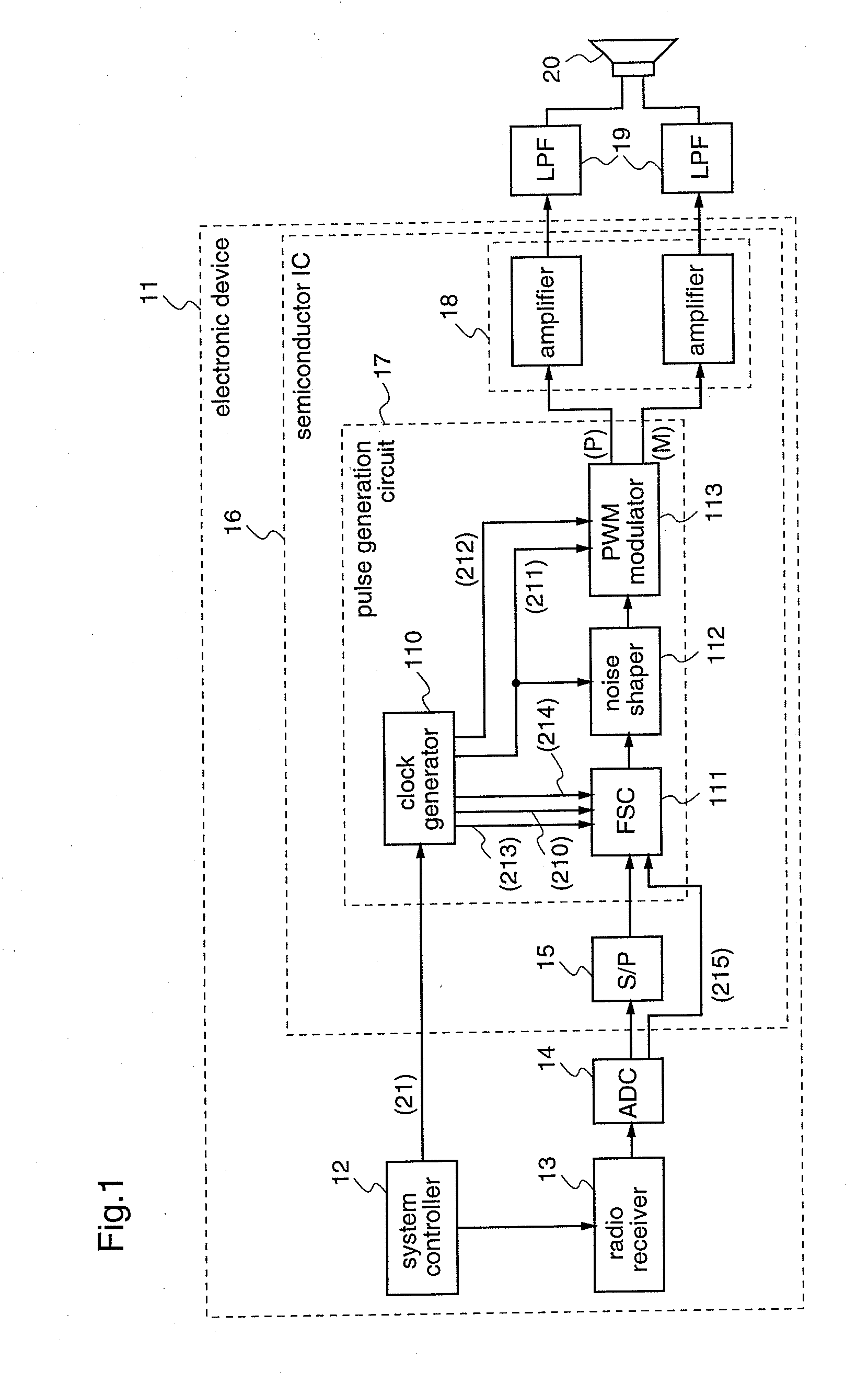

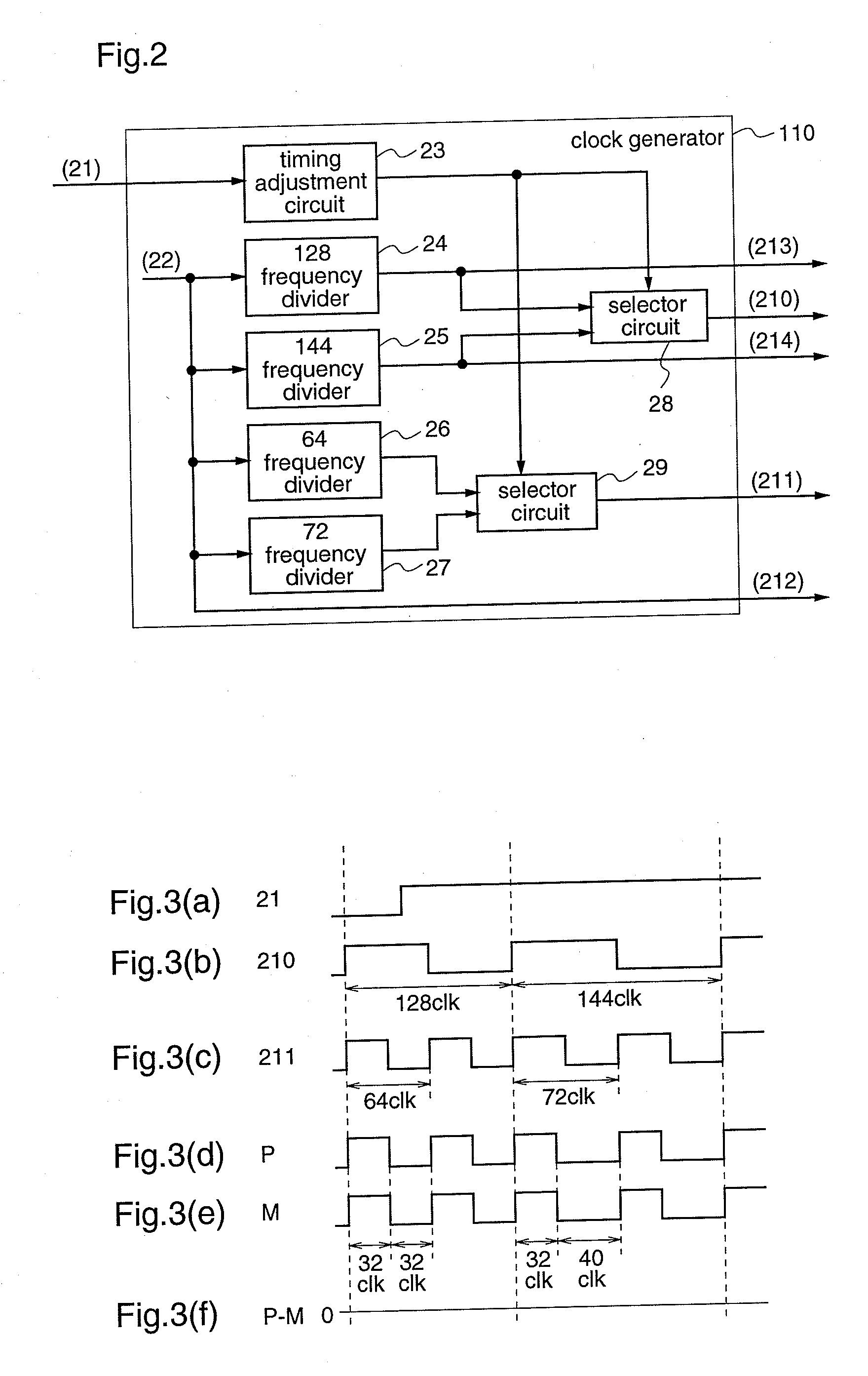

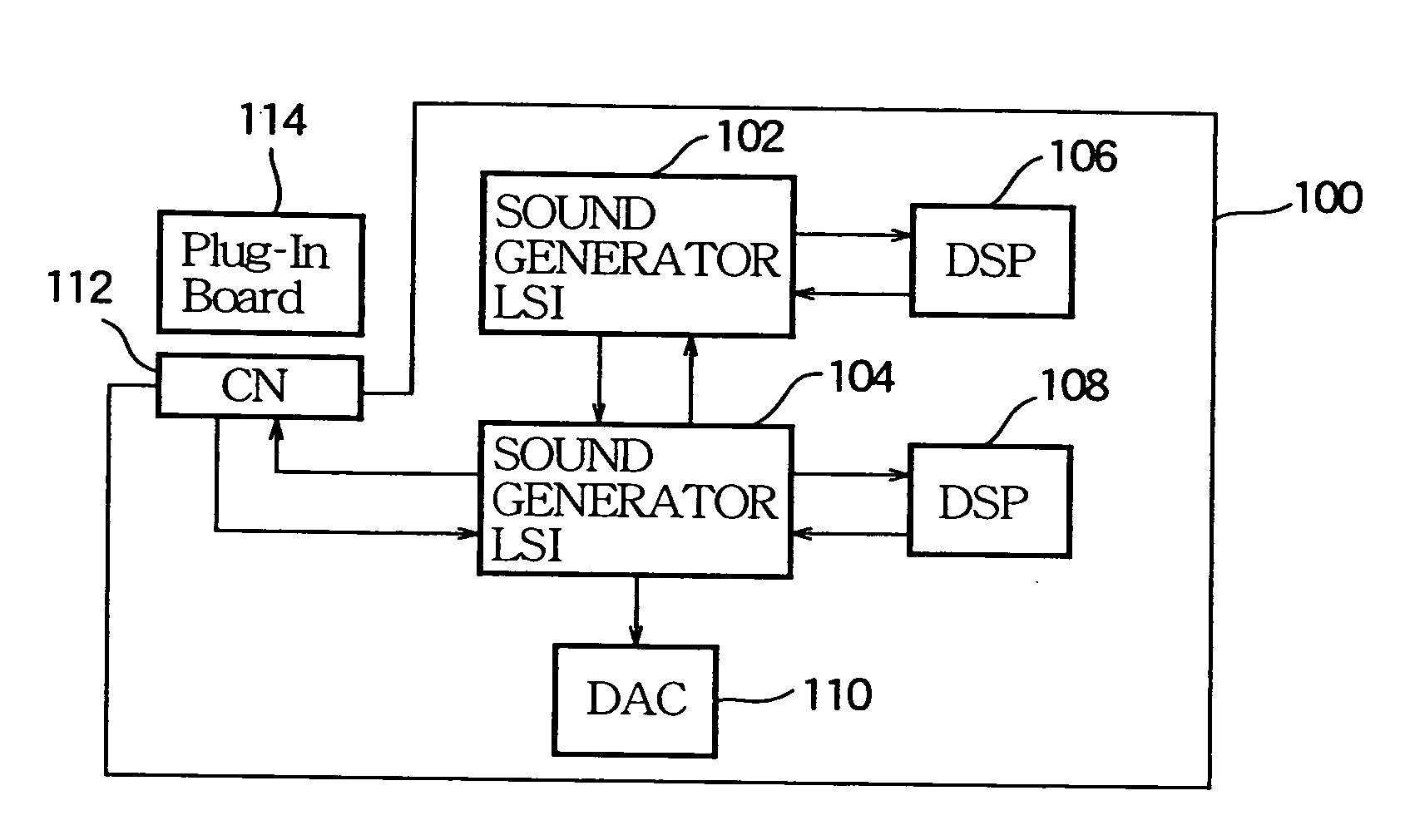

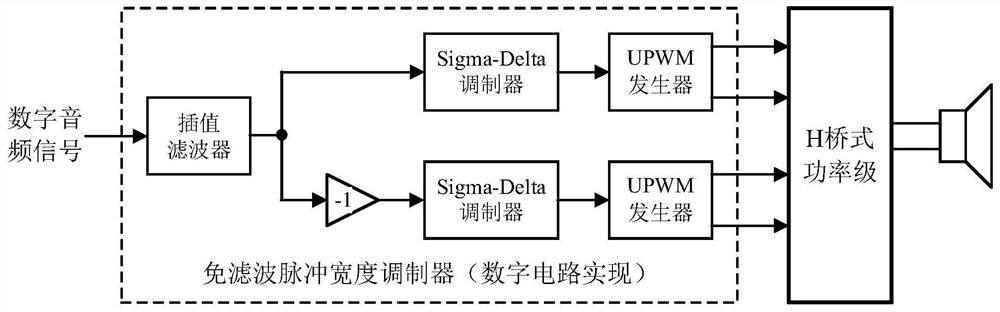

Semiconductor integrated circuit and electronic device

InactiveUS20090135897A1Avoid interferenceSuppress mutationAmplifier with semiconductor-devices/discharge-tubesDuration/width modulated pulse demodulationRadio receptionRadio receiver

An electronic device (11) according to the present invention includes a semiconductor integrated circuit (16) on which a pulse conversion circuit (17) for converting an acoustic signal received by a radio receiver (13) into a pulse signal is integrated. The pulse conversion circuit (17) includes a clock generator (110) which generates plural clocks and selects word clocks (210,211) according to the reception frequency of the radio receiver (13), an FSC (111) which performs sampling frequency conversion so as to make a sample sequence of an A / D converted acoustic signal have the same frequency as that of the word clock (210), a noise shaper (112) for performing noise shaping to the sample sequence outputted from the FSC (111) using the word clock (211), and a PWM modulator (113) for generating a pulse signal from the output of the noise shaper (112) using the word clock (211). Therefore, it is possible to avoid radio reception interference which may caused by the pulse signal when driving a speaker with the pulse signal.

Owner:PANASONIC CORP

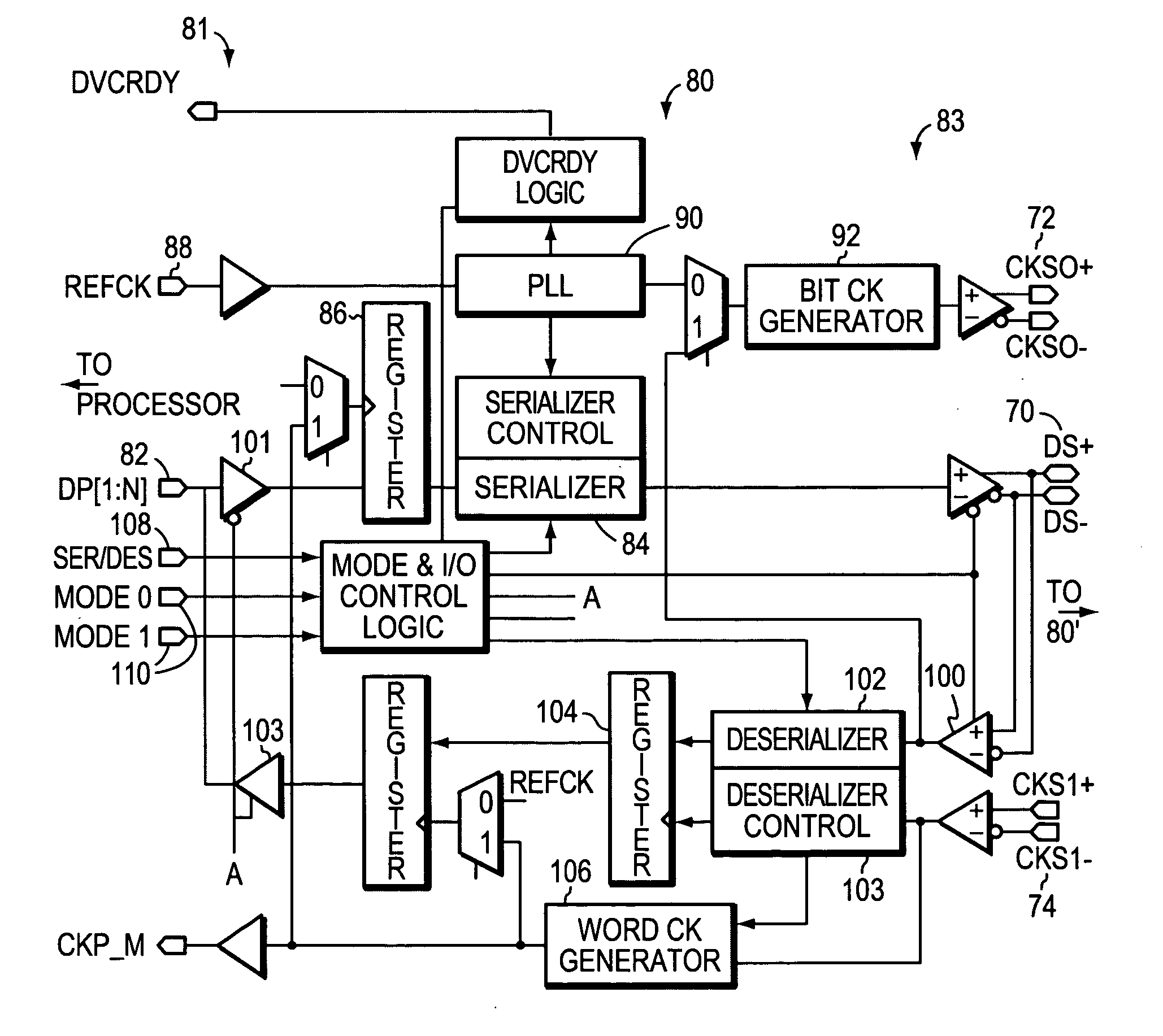

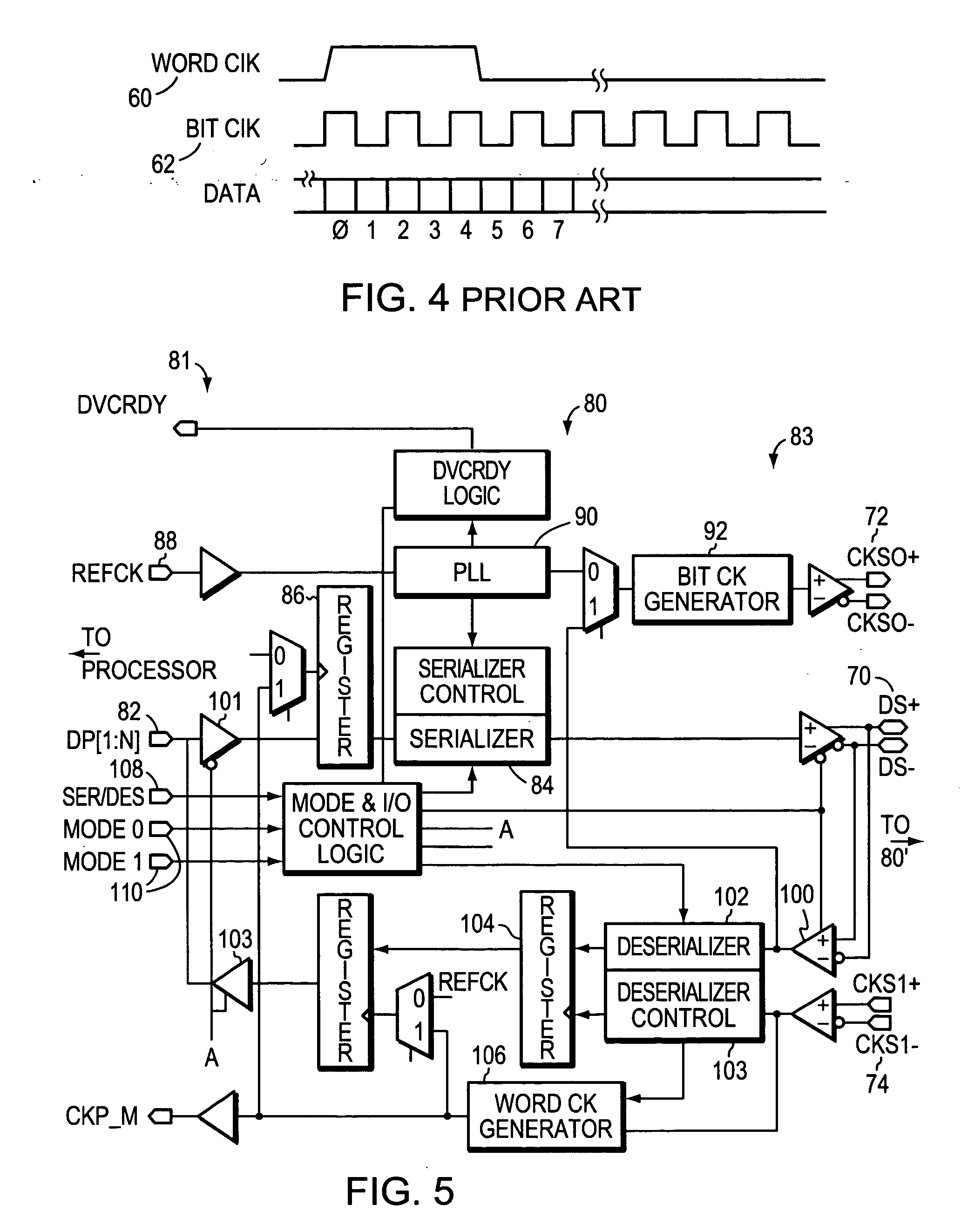

Architecture for bidirectional serializers and deserializer

InactiveUS20050219083A1Easy to controlParallel/series conversionSynchronisation information channelsShift registerWord clock

A bi-directional serializer / deserializer is disclosed using a single bi-directional data line and a single bi-directional clock line. Gated buffers are controlled to operate either sending or receiving data, and a phase locked loop provides a clock to shift data out from a shift register. A reference clock is supplied to the PLL and the PLL generates a synchronous bit clock. The bit clock is sent over the clock line in parallel with the serial data bits, and the PLL bit clock is synchronized to the data bits. The receiving system will use the bit clock to serial load a receiving shift register. When a word is received a word clock is available to inform the receiving system. An embodiment of the system sends data to a receiving system using a clock generated at the sending system. Another embodiment receives data but uses a clock that is sent from the receiving system to the sending system, wherein the sending system uses the received clock to generate a clock to send the data and a synchronous clock that is sent back to the receiving system to load the data from the data line.

Owner:SEMICON COMPONENTS IND LLC

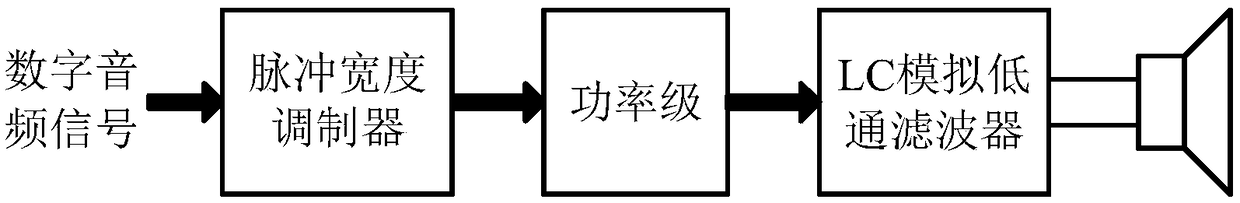

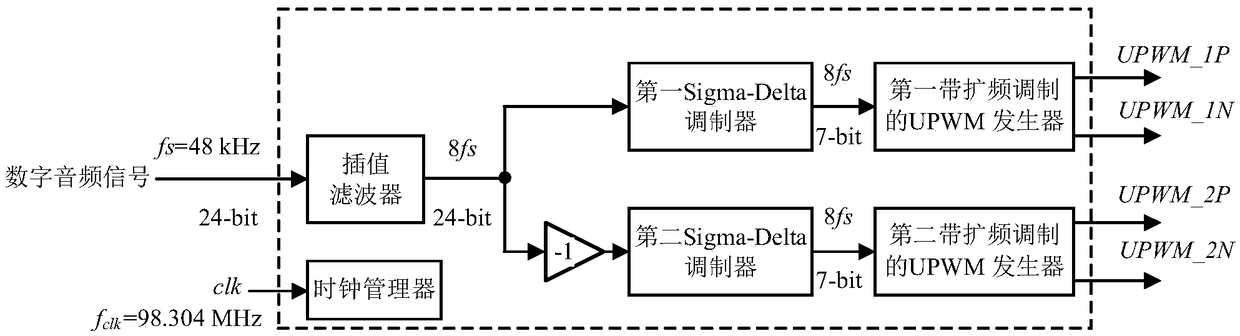

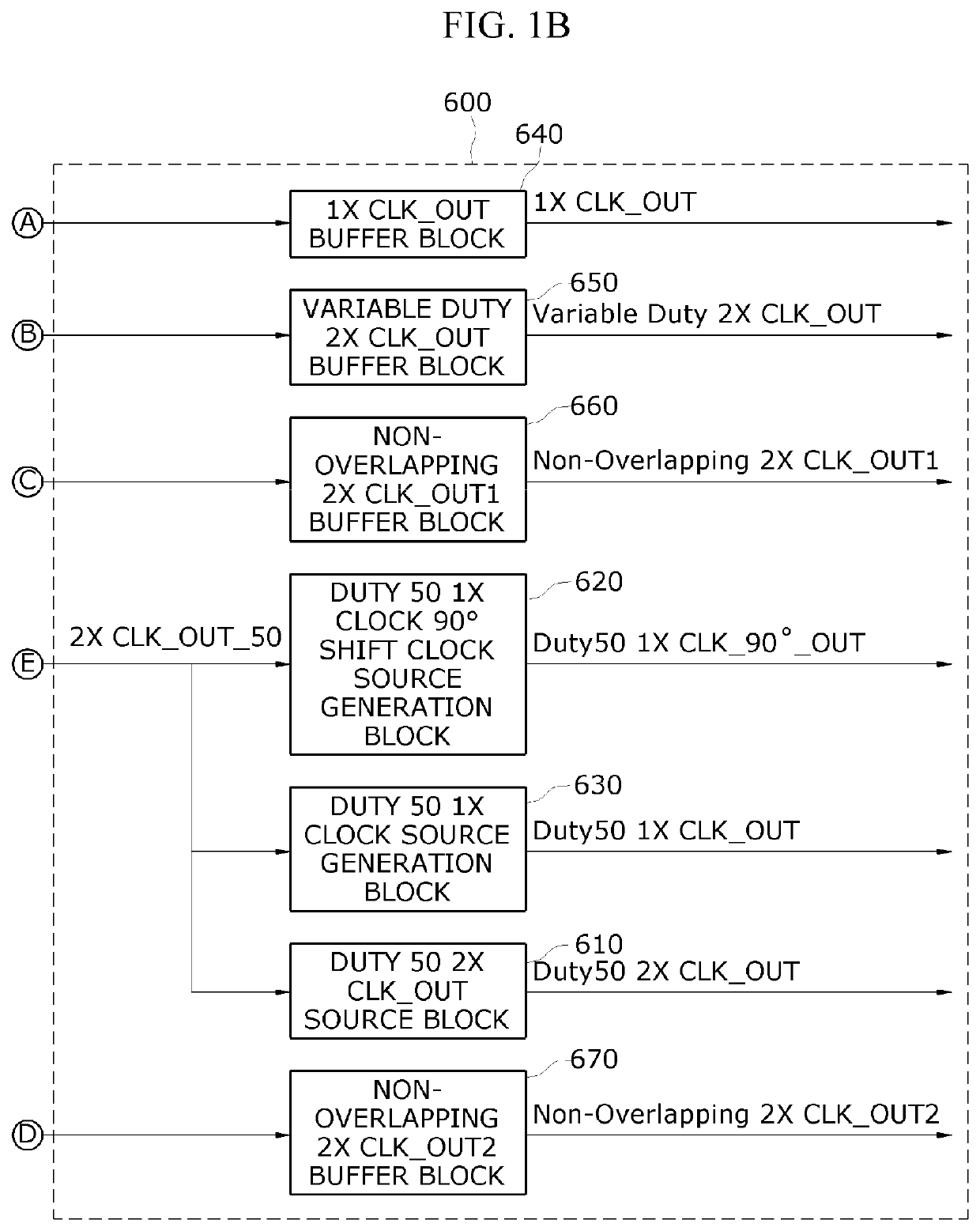

Spread spectrum modulation method for filterless digital D class audio power amplifier

ActiveCN108832917AImprove power efficiencyReduce high frequency peak amplitudeAmplifier modifications to reduce non-linear distortionLow frequency amplifiersNumber generatorSpread spectrum modulation

The invention provides a spread spectrum modulation method for a filterless digital D class audio power amplifier. A power amplifier main clock signal clk and an UPWM generator are used input a synchronous word clock signal clk_s1, another clock signal clk_s2 is synthesized according to a certain rule, and then a pseudo random number generator is constructed to generate a series of pseudo random number sequences. By judging the parities of the pseudo random number sequences, the clock signal clk_s1 and the clock signal clk_s2 are used to form a frequency variable clock signal clk_c through synthesis, and finally a PRF variable left-growth double-edge UPWM signal is processed and outputted through a threshold calculator, a counter and a comparator by using the amplitudes of the main clock signal clk, the clock signal clk_c and the UPWM generator input signal. At the same time, a corresponding filter-free pulse width modulator is designed based on the above spread spectrum modulation method. According to the method, the amplitude of a high-frequency component of a power amplifier output UPWM signal can be obviously reduced, thereby an EMI is reduced, the implementation is easy, and few hardware resources are needed.

Owner:ZHENGZHOU UNIVERSITY OF LIGHT INDUSTRY

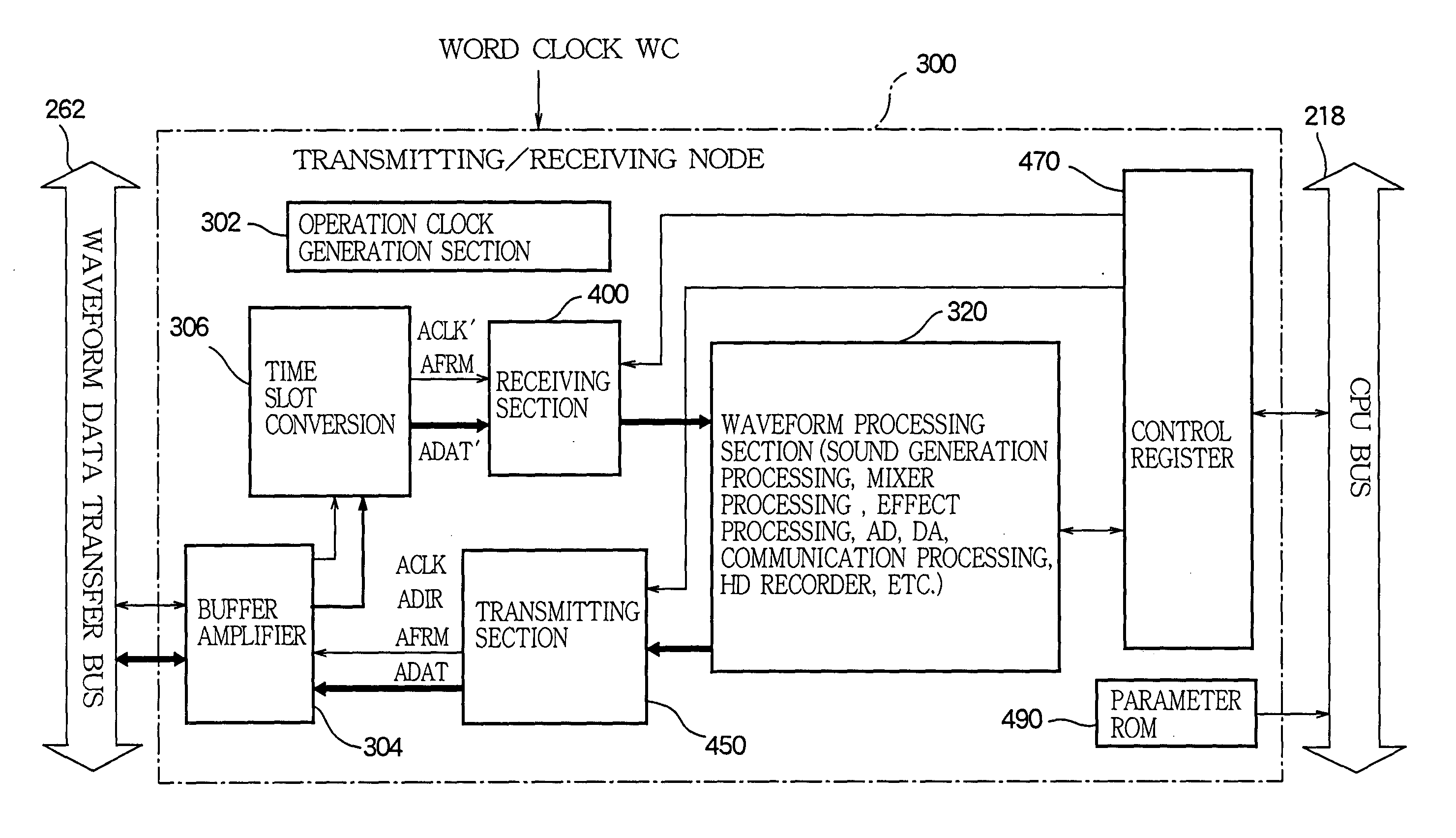

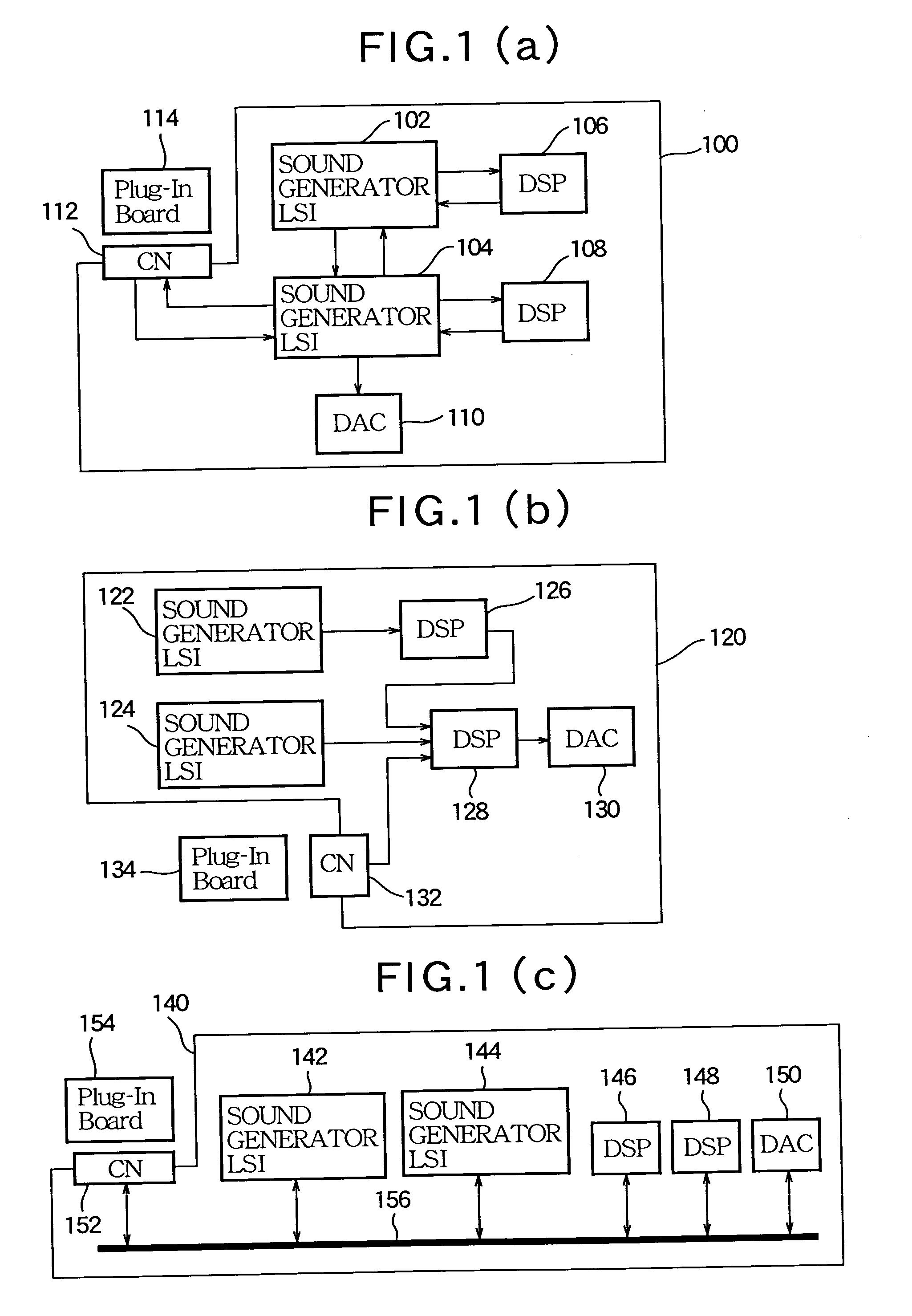

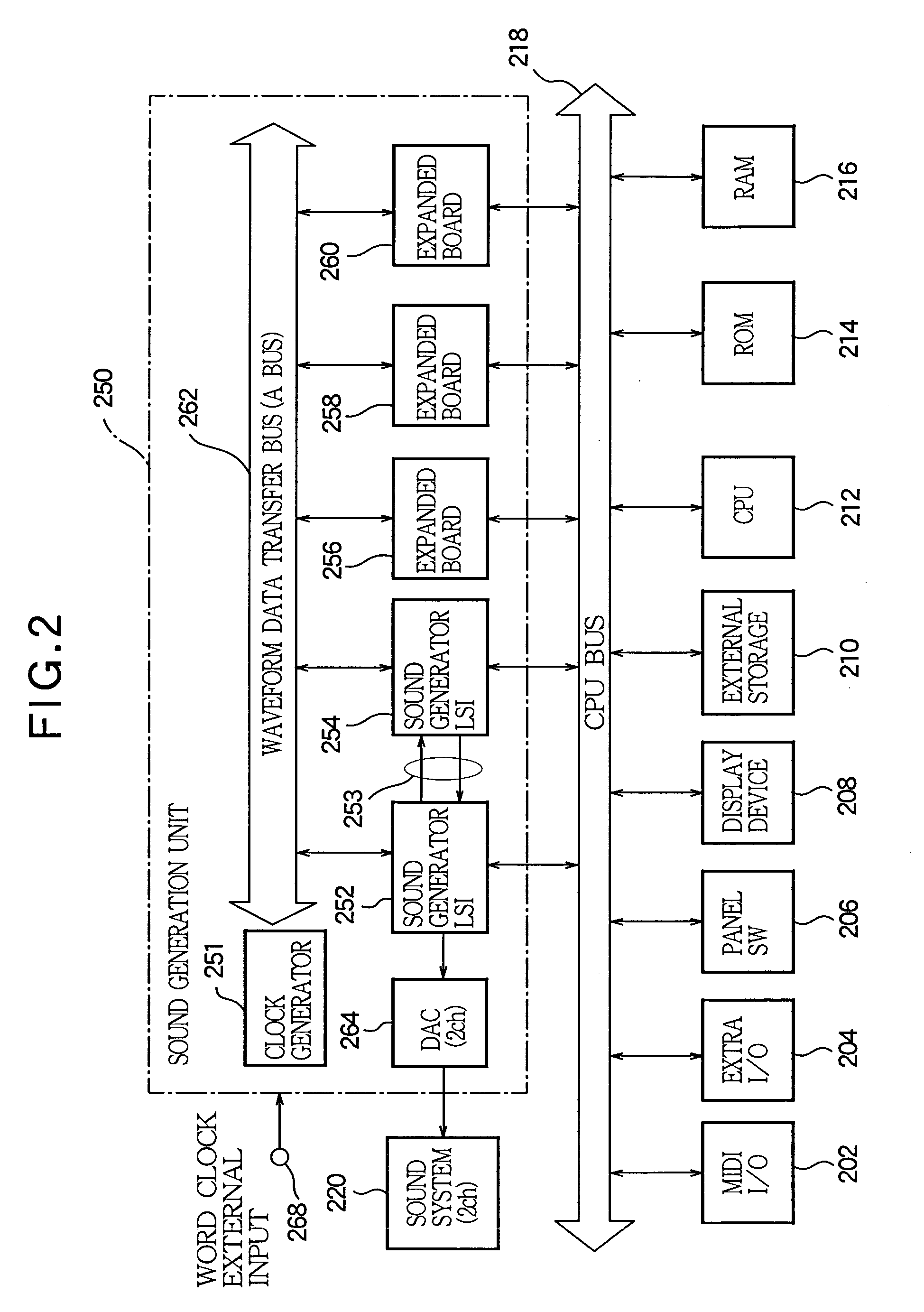

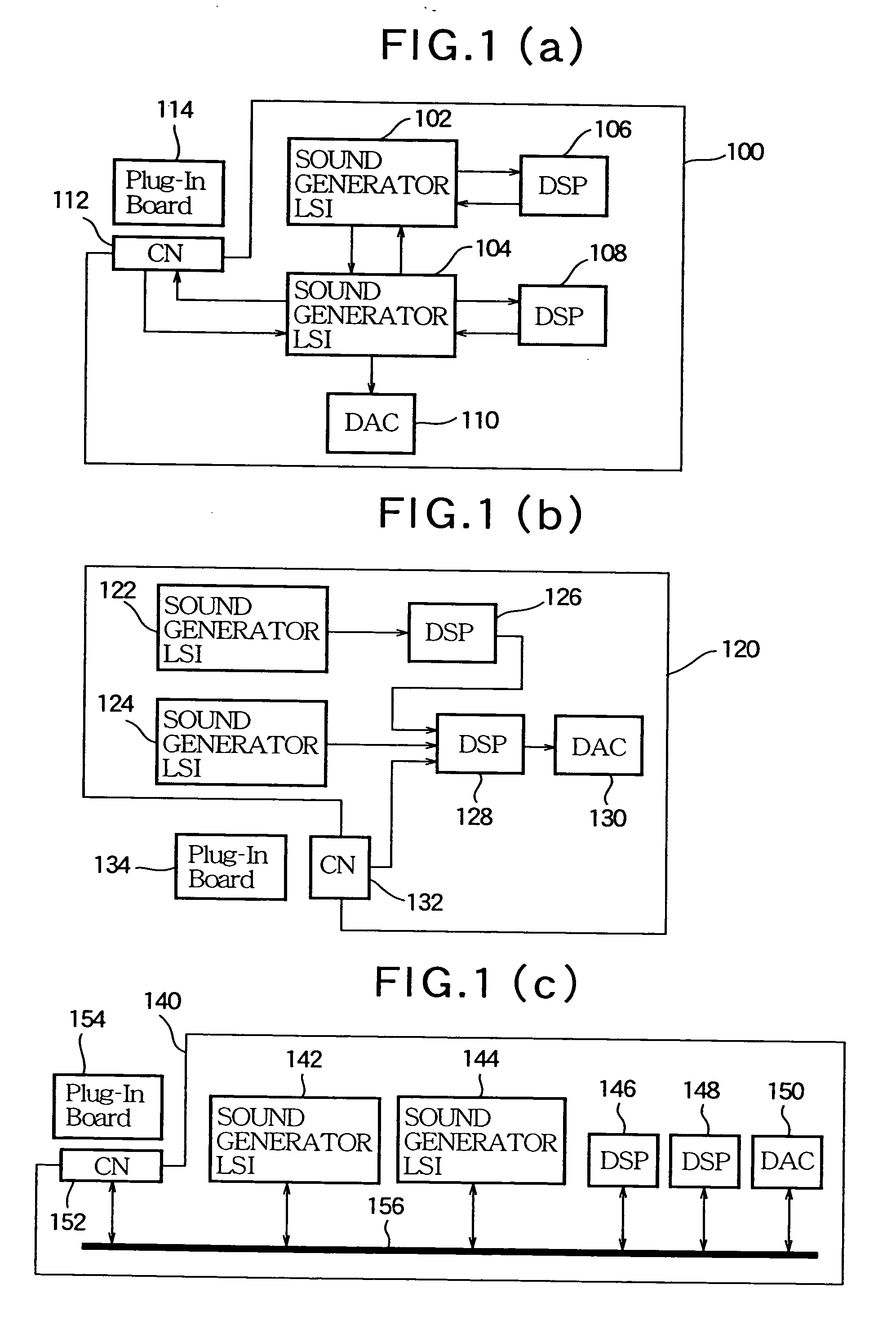

Waveform processing apparatus with versatile data bus

ActiveUS20040050238A1Simple circuit configurationReduce line widthElectrophonic musical instrumentsData signalWord clock

A waveform data processing apparatus has a bus that transfers data signals representative of waveform data. A plurality of transmitting nodes transmit the data signals to the bus. A plurality of receiving nodes receive the data signals from the bus. A clock generator generates a word clock signal at each sampling period. A controller is responsive to the word clock signal for conducting a session of transferring the data signals within a sampling period, such that the transmitting nodes sequentially transmit the data signals in an order predetermined by the controller so as to avoid collision of the data signals within the sampling period, and each of the receiving nodes selectively admits a necessary one of the data signals outputted from the transmitting nodes and processes the admitted data signal within the sampling period.

Owner:YAMAHA CORP

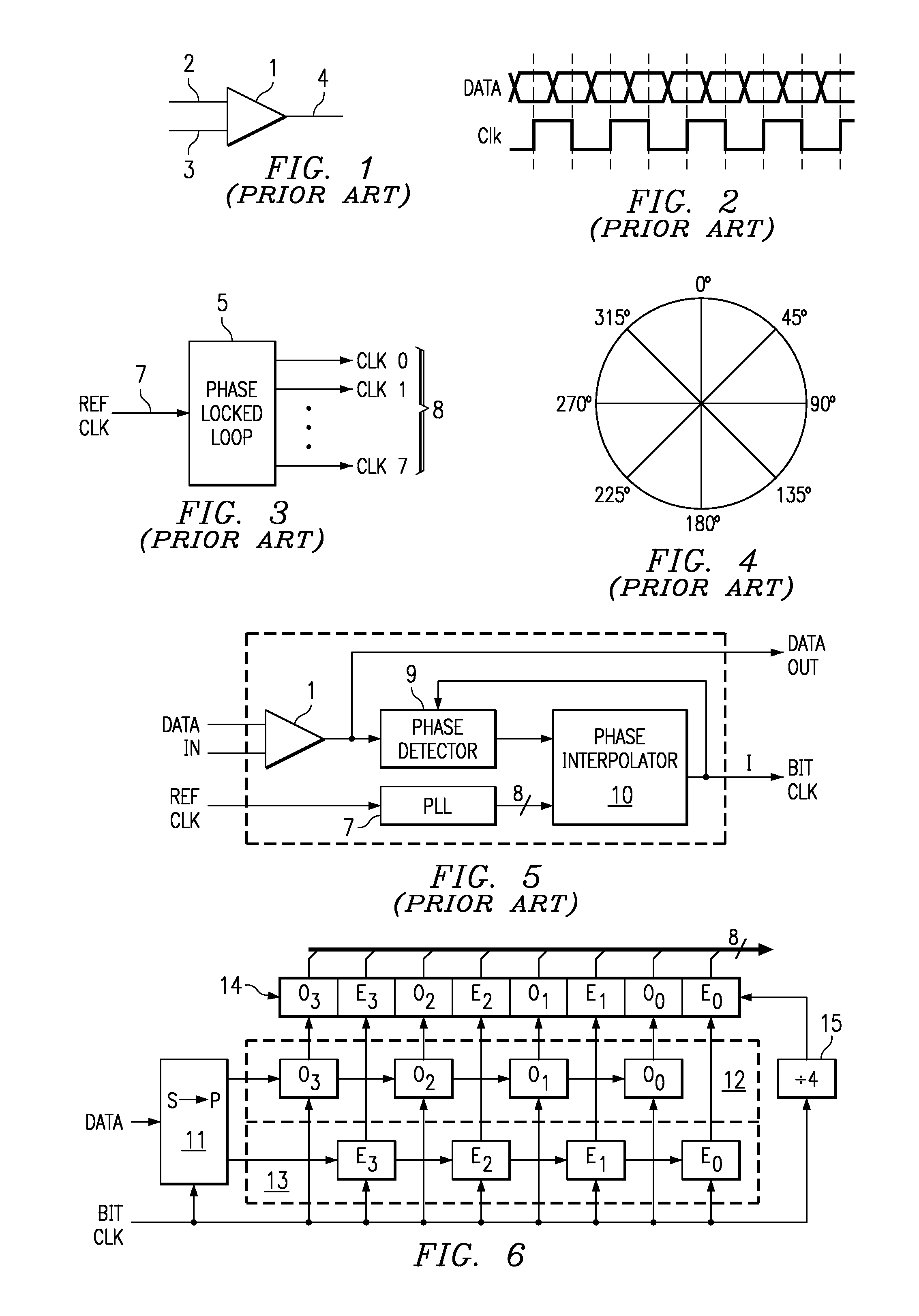

Data transmission

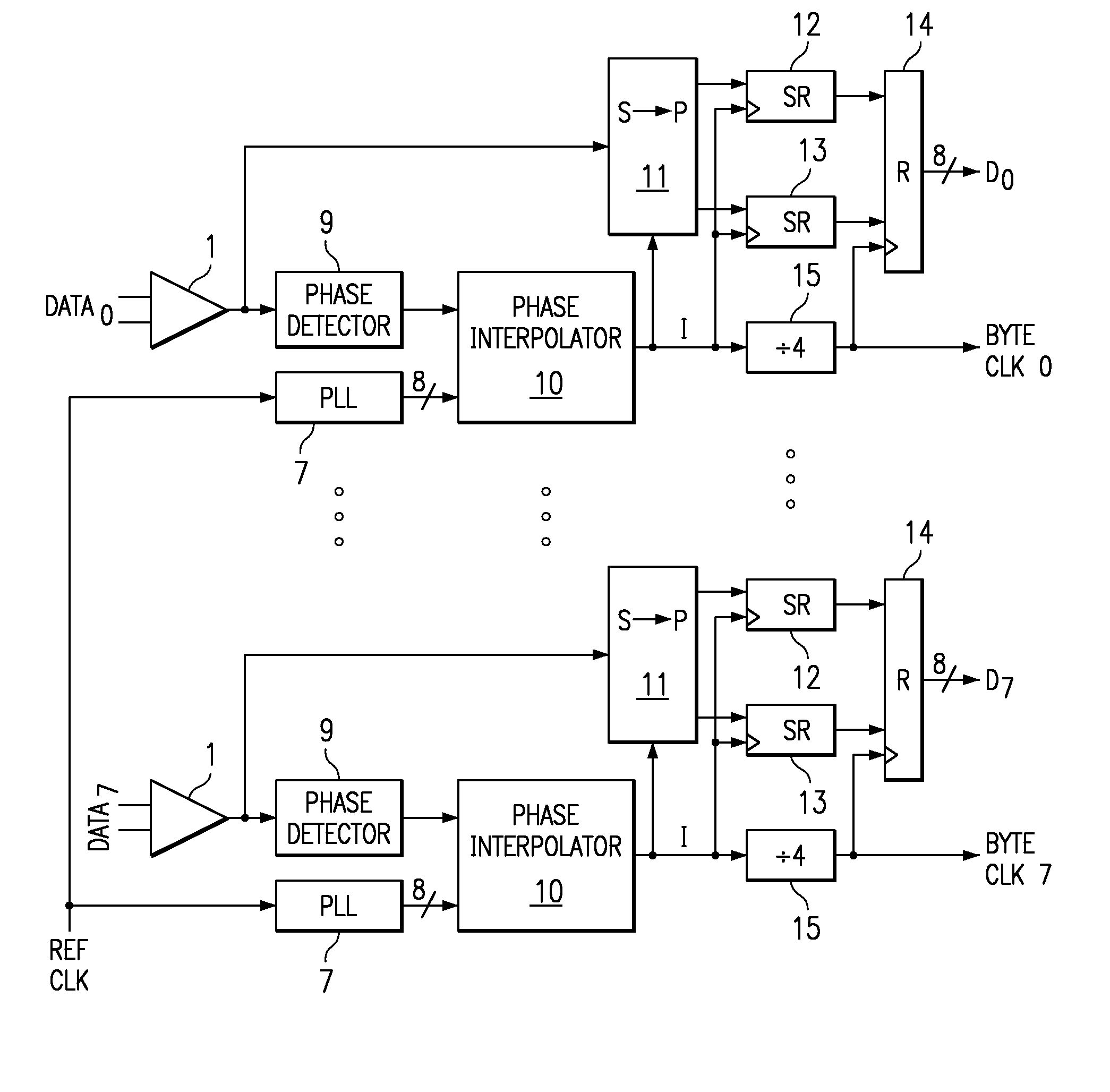

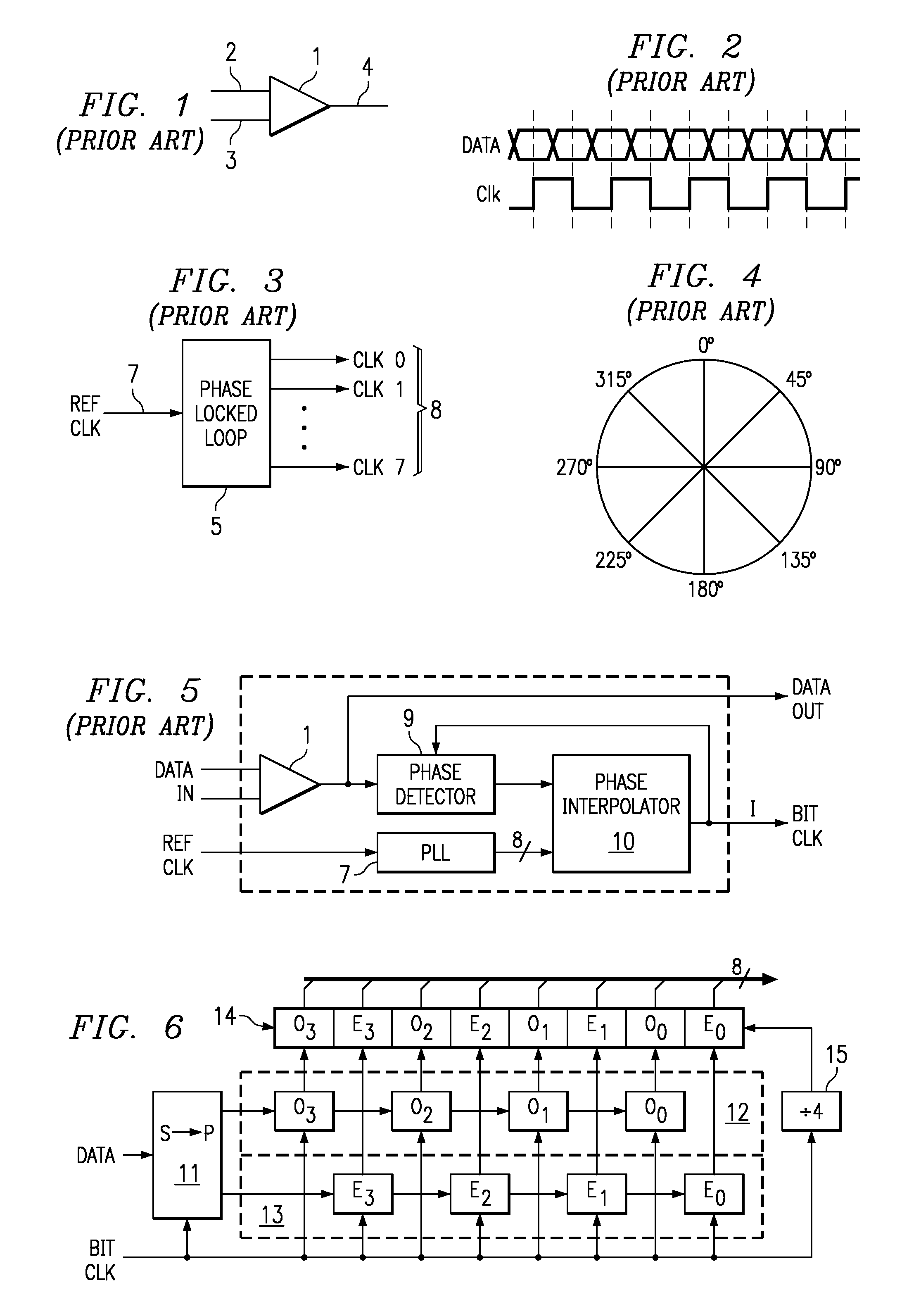

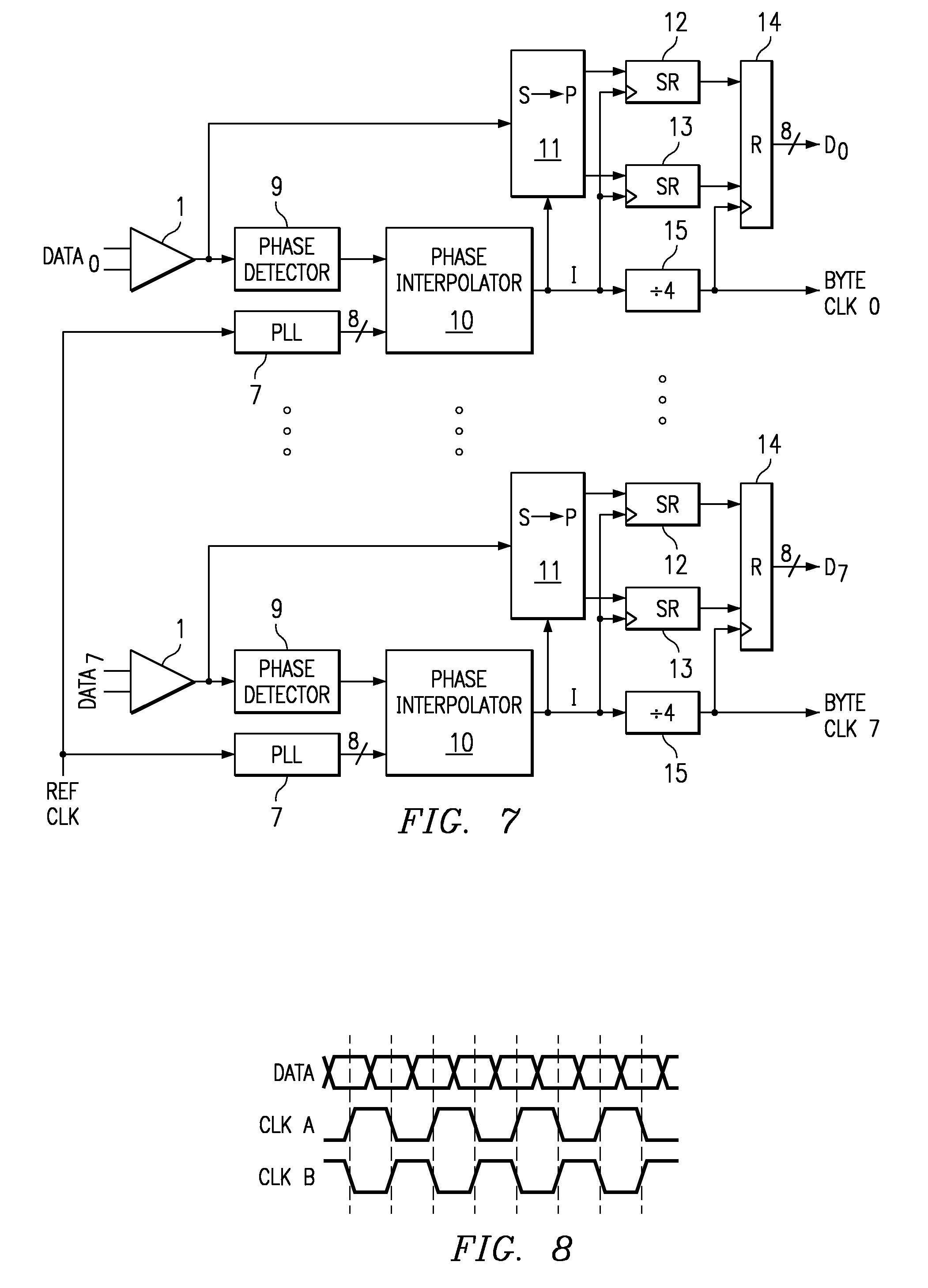

A circuit for receiving multiple serial datastreams in parallel is disclosed. A bit clock is recovered from each data stream, there being one data bit for ach transition of the clock signal both positive and negative going. The phases of the bit clocks are compared and are adjusted by 180 degrees so that the positive going edges of all occur close to each other. The bits of each stream are assembled into words under the control of a word clock. In one embodiment a common word clock is derived form the set of bit clocks as a whole. In another embodiment each stream is provided with its own word clock which is aligned to positive edges of the respective bit clocks that are close to each other.

Owner:TEXAS INSTR INC

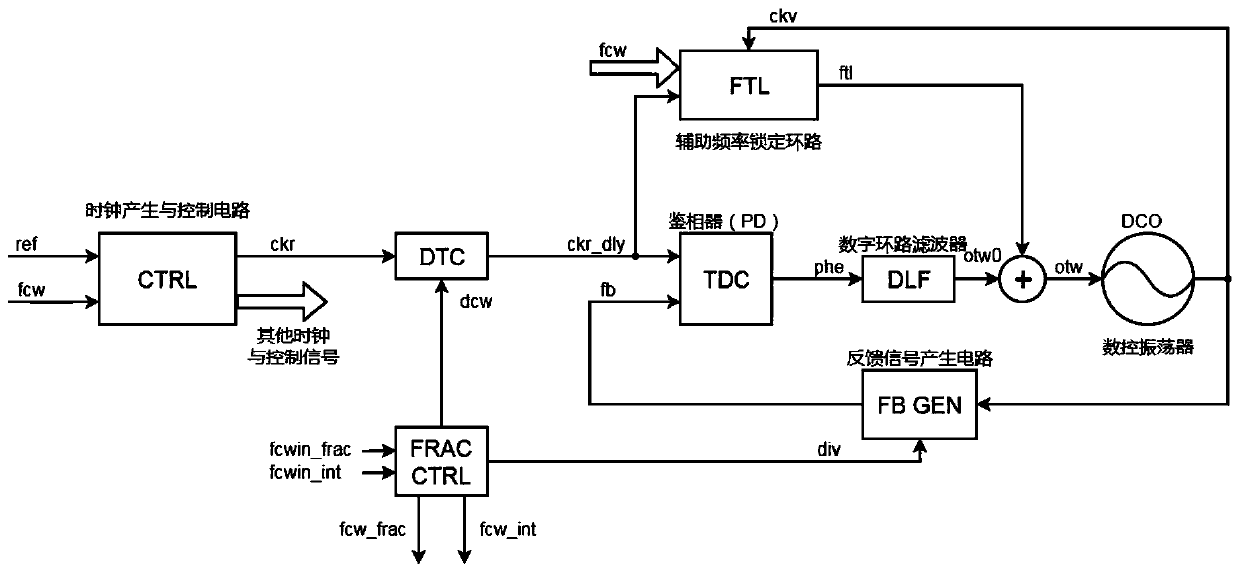

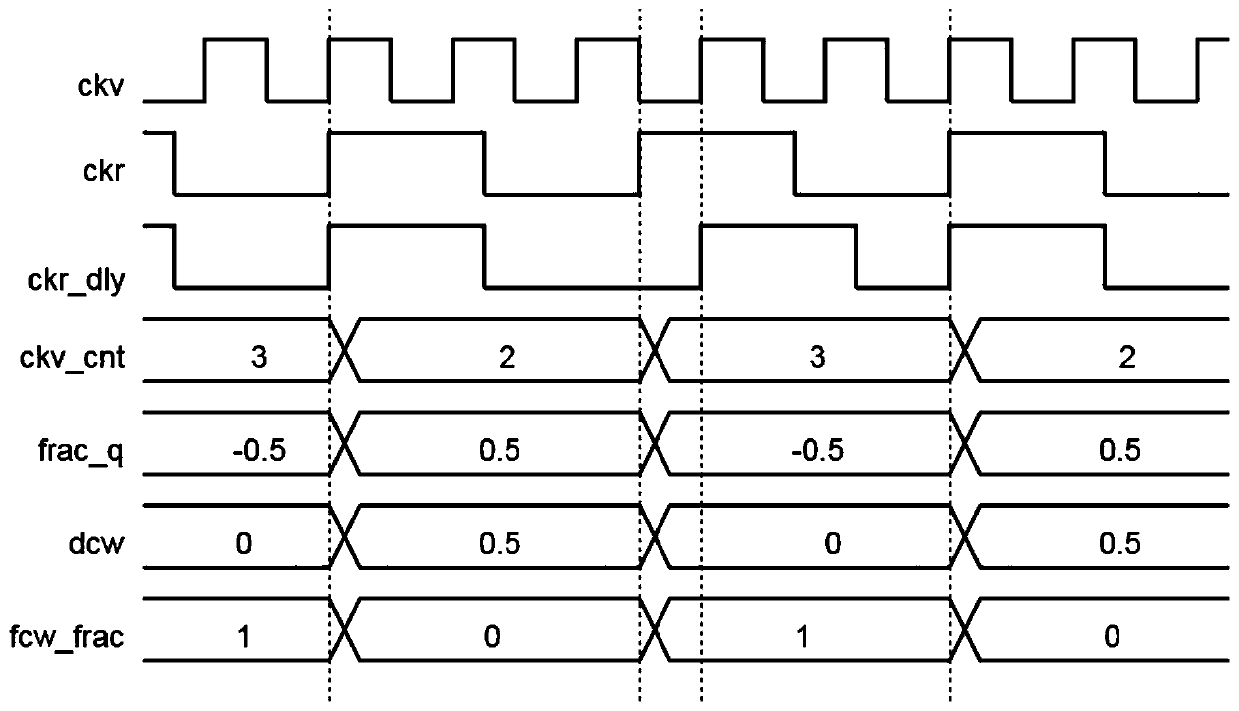

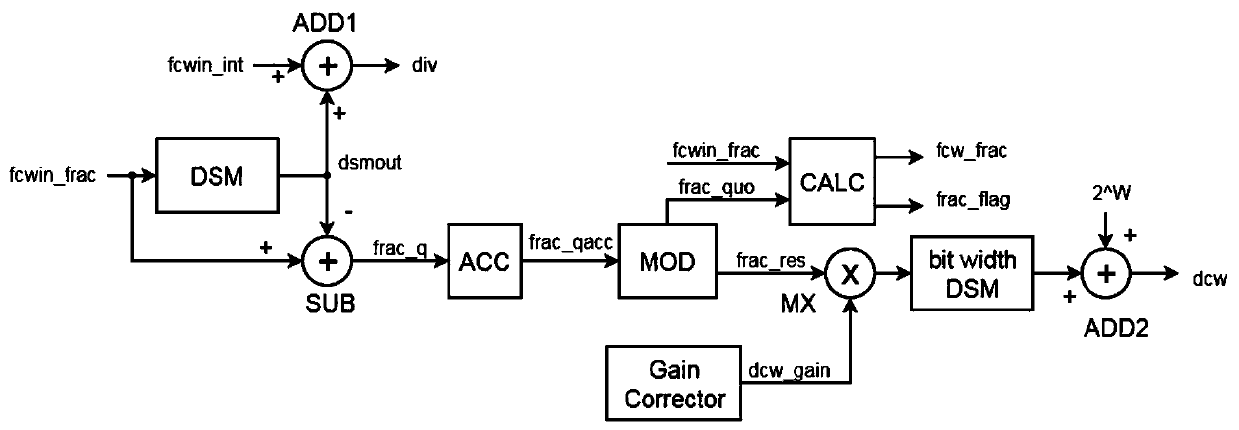

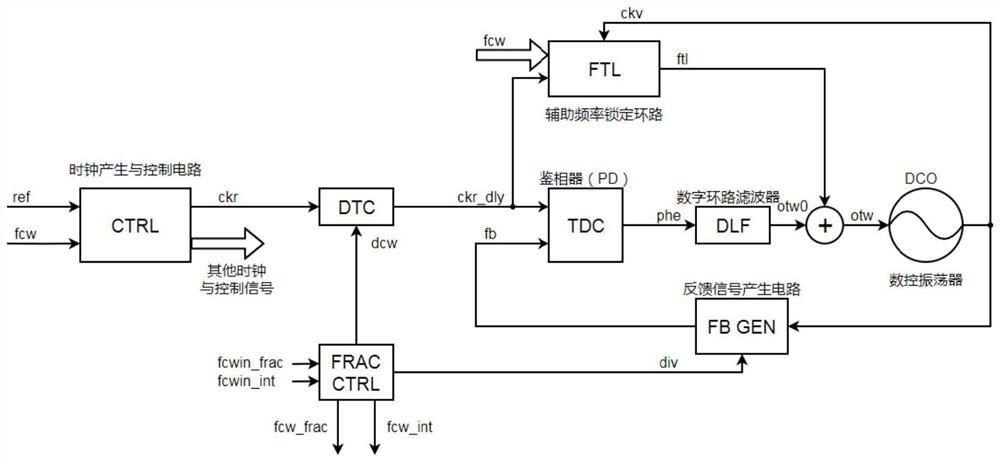

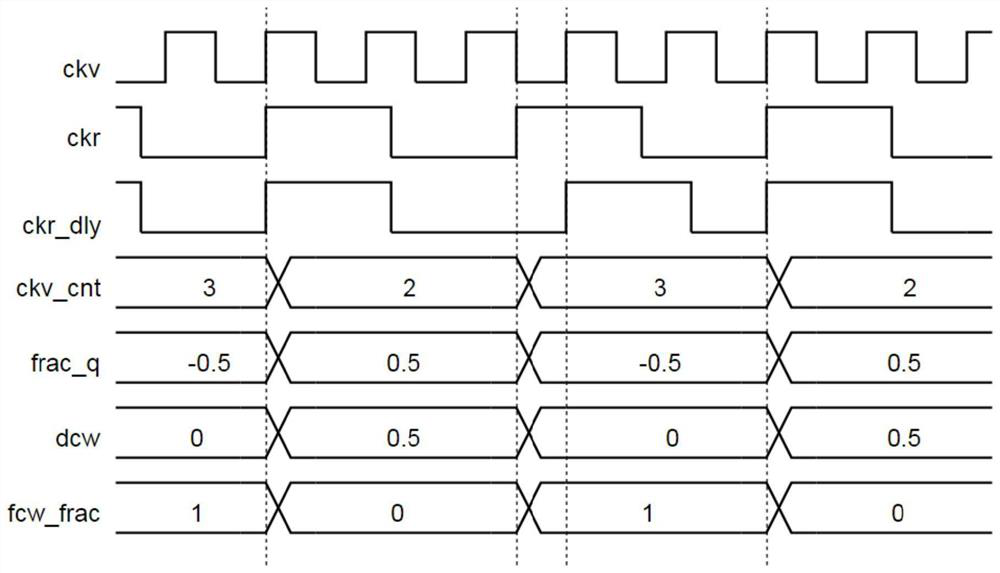

Fractional frequency all-digital phase-locked loop and control method thereof

ActiveCN110719100ARequirements for reducing output delay time rangeReduce design difficultyPulse automatic controlConvertersNumerical control

The invention provides a fractional frequency all-digital phase-locked loop and a control method thereof. The method comprises the following steps: S1, a fractional frequency controller generates a delay control word, a frequency division ratio control word, an integer frequency control word and a fractional frequency control word according to an external fractional frequency control word; s2, theclock generation and control circuit generates a clock signal ckr according to the reference clock and the frequency control word; s3, the digital time converter generates a low-frequency clock signal according to the ckr and the delay control word; s4, the feedback signal generation circuit outputs a feedback signal fb according to the frequency division ratio control word and a high-frequency clock signal ckv generated by the numerical control oscillator; s5, the phase discriminator generates phase error digital signals phe of ckr and fb; s6, the auxiliary frequency locking loop outputs a control signal ft1 according to the integer frequency control word, the fractional frequency control word and the low-frequency clock signal, and the numerical control oscillator updates ckv accordingto the sum of ft1 and phe.

Owner:FUDAN UNIV

Systems and method for transfering digital data and transfering parallel digital data in a serial data stream including clock information

ActiveUS7822143B2Reduce componentsReduce transferParallel/series conversionLogic circuits characterised by logic functionDigital dataData stream

The present invention provides a data transfer system including a data transmitter and a data receiver. The data transmitter converts a plurality of bits of transmission parallel data into serial data and generates a multi-level logic signal representing a plurality of bits of information in one symbol, the information being obtained by combining the serial data with a word clock as one-bit information. The word clock indicates a word delimiter in the serial data. The data receiver receives the transmitted multi-level logic signal, extracts the serial data and the word clock from the signal, and reproduces the parallel data based on the extracted word clock. In the data transfer system, a multi-bit digital signal can be transmitted as one signal including a word clock. Thus, components and mounting space to be allocated to transfer can be reduced.

Owner:SONY CORP

Data transmission

ActiveUS7170962B2Channel dividing arrangementsSynchronisation signal speed/phase controlData streamWord clock

A circuit for receiving multiple serial datastreams in parallel is disclosed. A bit clock is recovered from each data stream, there being one data bit for each transition of the clock signal both positive and negative going. The phases of the bit clocks are compared and are adjusted by 180 degrees so that the positive going edges of all occur close to each other. The bits of each stream are assembled into words under the control of a word clock. In one embodiment a common word clock is derived form the set of bit clocks as a whole. In another embodiment each stream is provided with its own word clock which is aligned to positive edges of the respective bit clocks that are close to each other.

Owner:TEXAS INSTR INC

Waveform processing apparatus with versatile data bus

InactiveUS20060219088A1Improve versatilitySimple circuitElectrophonic musical instrumentsData signalWord clock

A waveform data processing apparatus has a bus that transfers data signals representative of waveform data. A plurality of transmitting nodes transmit the data signals to the bus. A plurality of receiving nodes receive the data signals from the bus. A clock generator generates a word clock signal at each sampling period. A controller is responsive to the word clock signal for conducting a session of transferring the data signals within a sampling period, such that the transmitting nodes sequentially transmit the data signals in an order predetermined by the controller so as to avoid collision of the data signals within the sampling period, and each of the receiving nodes selectively admits a necessary one of the data signals outputted from the transmitting nodes and processes the admitted data signal within the sampling period.

Owner:YAMAHA CORP

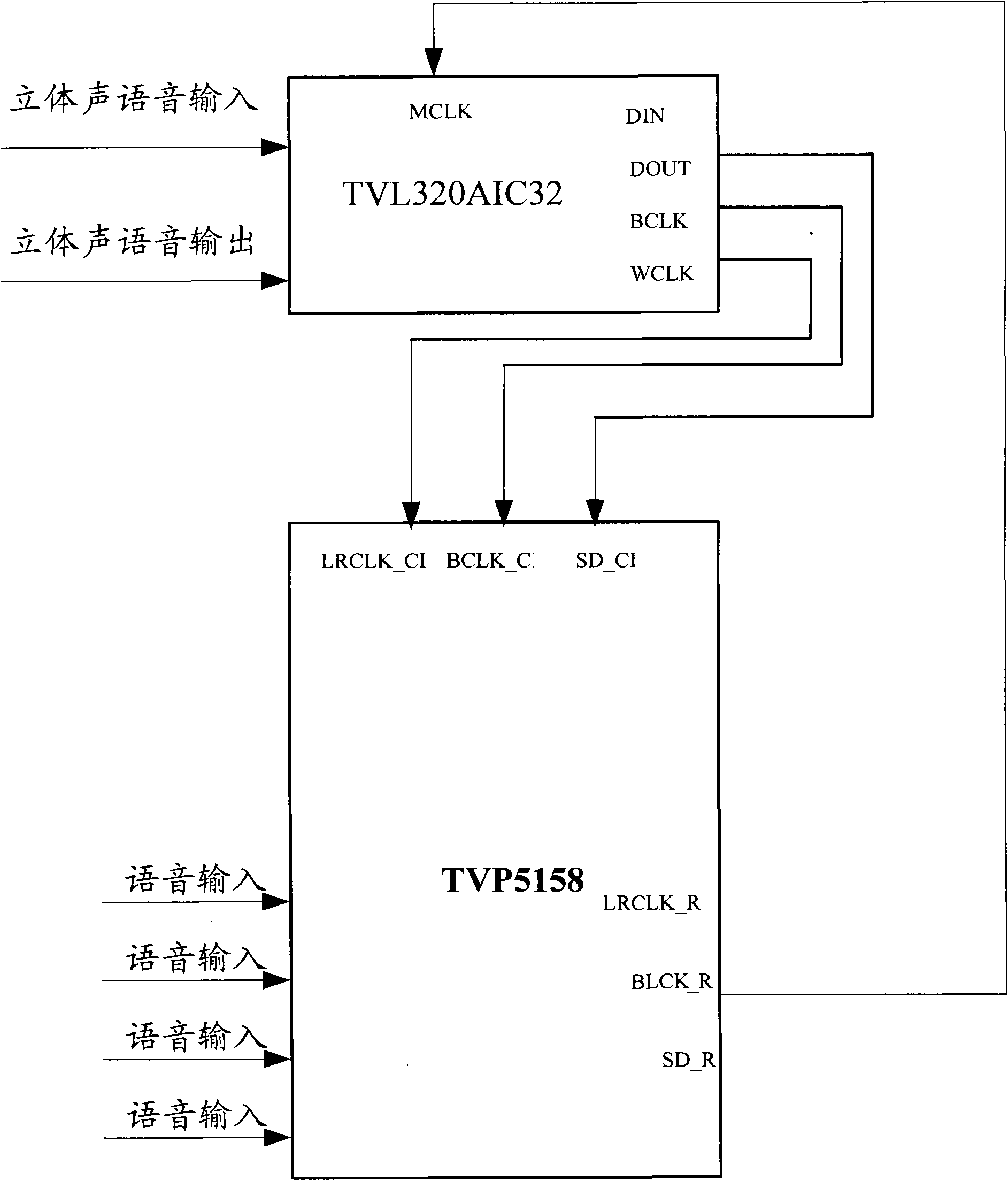

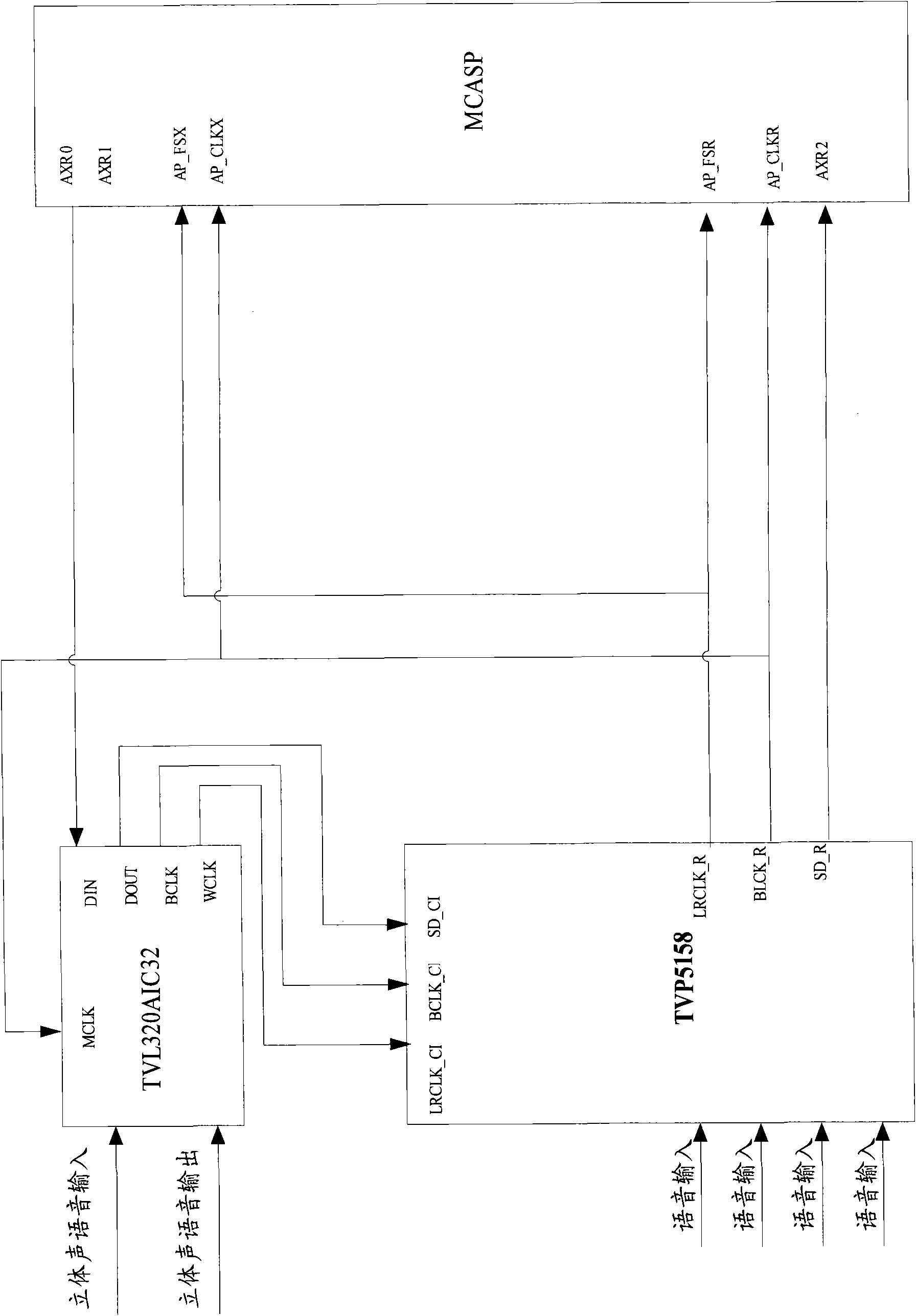

Multi-path audio collecting system

InactiveCN101635857ALow costTake advantage ofPulse modulation television signal transmissionWord clockSpeech sound

The invention provides a multi-path audio collecting system comprising a TVL320AIC32 chip and a TVP5158 chip which are arranged in a cascade connection way, wherein a bit clock record pin of the TVP5158 is connected with a master clock pin of the TVl320AIC32; and a serial data output pin, a bit clock input pin in a cascade connection mode and a word clock pin of the TVl320AIC32 are respectively connected with a serial data input pin, a bit clock input pin in a cascade connection mode and a word clock input pin in a cascade connection mode of the TVP5158. The TVP5158 can process four-path video signals and four-path audio signals, therefore, one-path stereophony (two-path single-channel voice) signals, four-path voice signals and four-path video signals can be processed after the TVL320AIC32 and the TVP5158 are connected in a cascade connection way. The function of the TVP5158 is fully utilized, thereby not only saving the cost of hardware, but also reducing the size of products and enabling the products to develop in a smaller way.

Owner:NETPOSA TECH

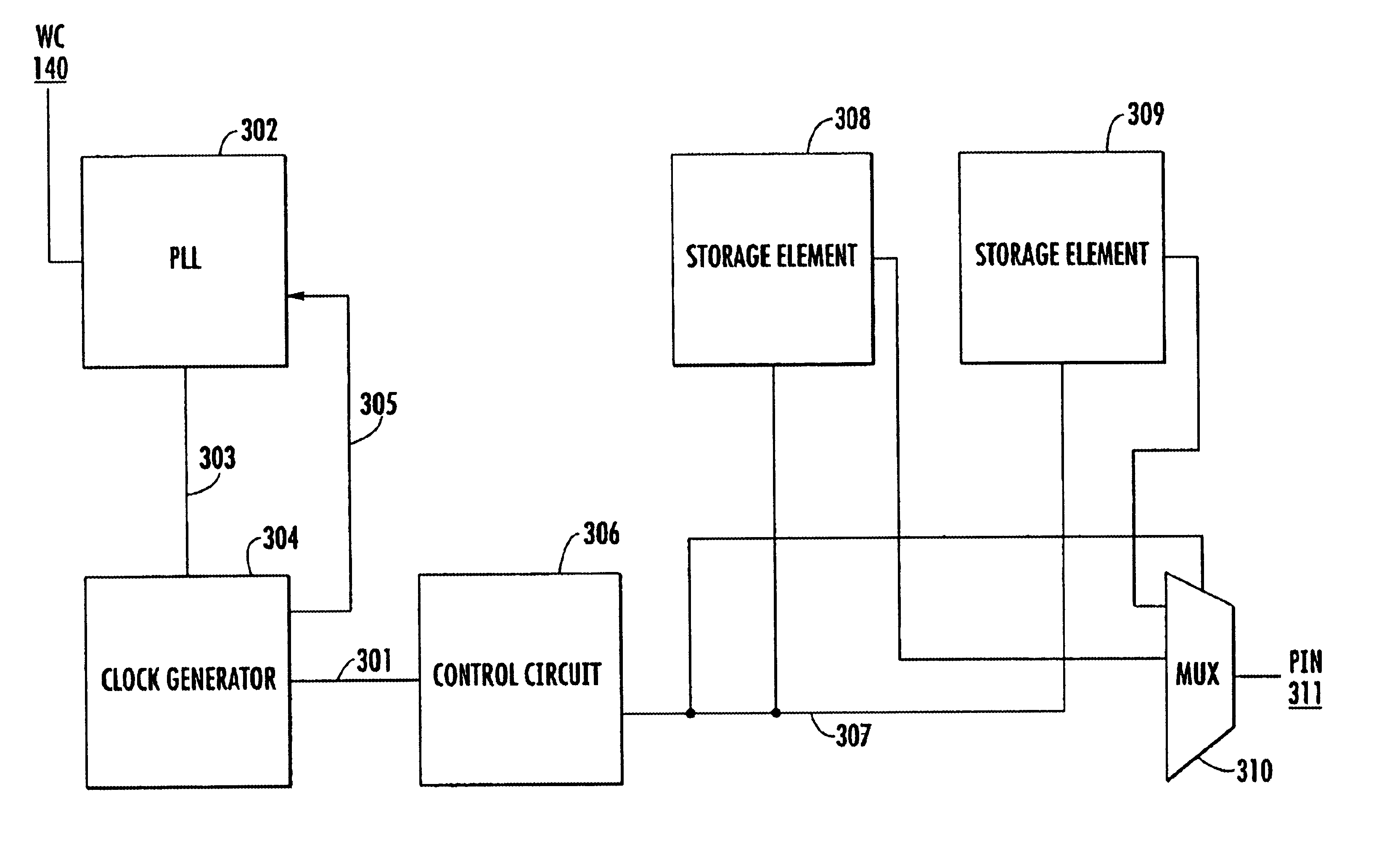

Serial data transmission system using minimal interface

InactiveUS6871051B1Simple interfacePulse automatic controlSynchronisation signal speed/phase controlWord clockSingle chip

A data transmission system comprising a transmitter and a receiver that use a single external word clock to generate all needed clocks locally using a clock generator and a phase locked loop. Data words are transmitted on a transmission line based on a single transition of the word clock. The transmitter and receiver may each be incorporated on a single chip.

Owner:INMUSIC BRANDS +2

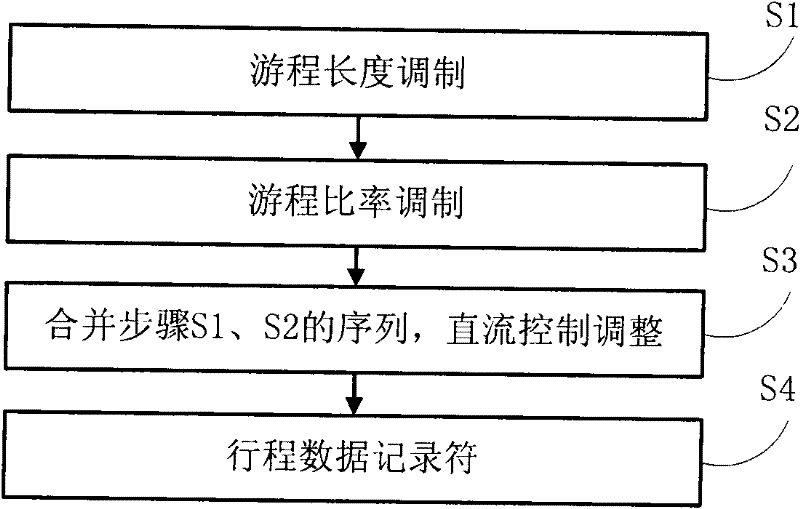

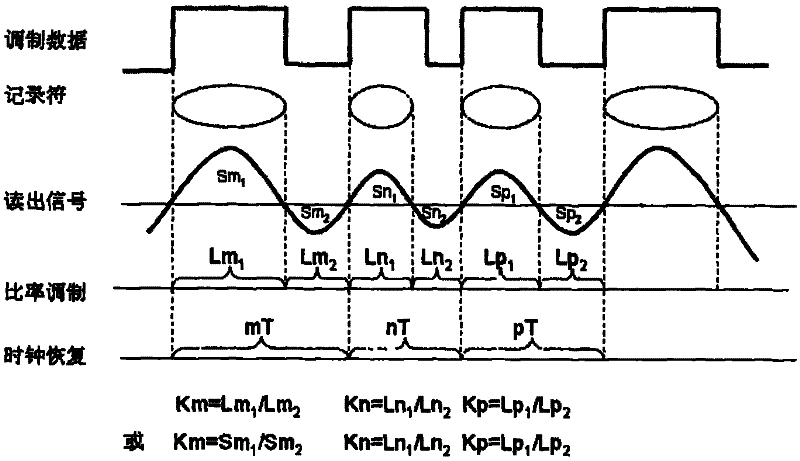

Run length rate (RLR) modulation data recording method

The invention relates to a method for realizing modulation coding of a digital storage product. In the digital storage product, modulation coding is required to be performed on user information to meet channel transmission limit and digital clock restoring performance, and a digital clock can be well restored by generally adopting a run length limit coding form. The method designs a method for realizing modulation coding on the basis of meeting a clock restoring requirement, i.e., a run length rate (RLR) modulation coding method. The method comprises the following steps of: (1) performing RLR modulating coding on binary information which is subjected to error correction coding; and (2) controlling the recording mark length of a physical recording medium and the formation of a microstructure by using data information which is subjected to RLR rate modulation coding.

Owner:北京同方光盘股份有限公司

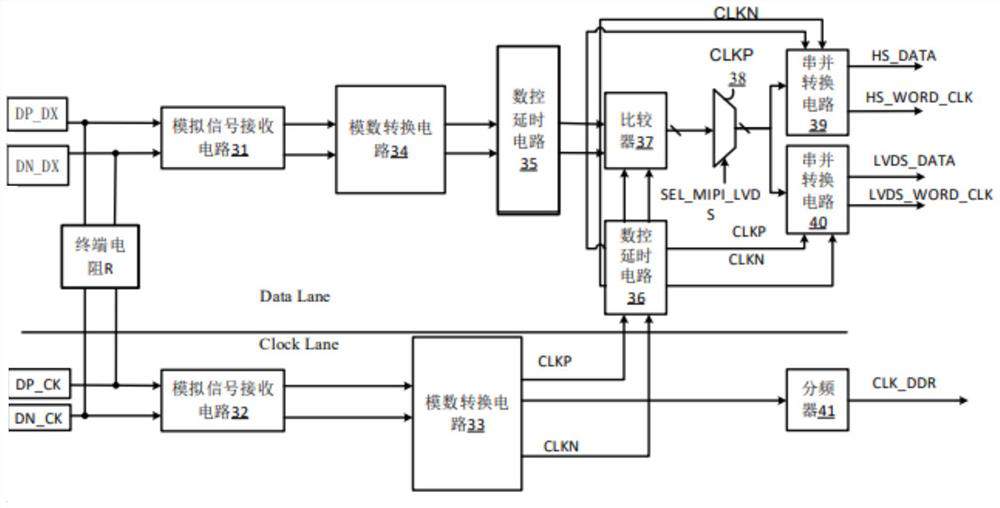

Serial communication device and method for removing data clock skew therein

A serial communication device and a method of removing data clock skew therein are provided. The device comprises an MIPI D-PHY physical layer, and the physical layer comprises a clock receiving device which is used for receiving an analog clock signal from a first channel of a serial link of the MIPI D-PHY physical layer and processing the analog clock signal to obtain a digital initial clock signal; each data receiving device receives an analog data signal from a second channel of the serial link of the MIPI D-PHY physical layer, obtains an initial clock signal from the clock receiving device, and outputs a digital data signal and a corresponding word clock signal after processing; and the synchronous processing device is used for respectively determining starting points of respective effective data from the plurality of received data signals and correcting phase deviation between each effective data and a first word clock signal according to the starting points, and the first word clock signal is selected from a plurality of word clock signals output by the plurality of data receiving devices. The device aligns data signals in all data channels to a specific clock signal.

Owner:MAXIO TECH HANGZHOU LTD

Sampling frequency conversion device and sampling frequency conversion method

A sampling frequency conversion device comprises an internal circuit for executing in synchronization with an internal clock a signal processing of input data fetched in accordance with an input word clock, and for outputting the input data having undergone the signal processing as output data, a clock generation circuit for generating from the internal clock an output word clock and a counter clock having a frequency which is equal to that of the output word clock multiplied by n (n: integer equal to two or more), a counter for counting the counter clock, and a register for holding a counter value of the counter in synchronization with the input word clock, and for outputting the held counter value to the internal circuit

Owner:KK TOSHIBA

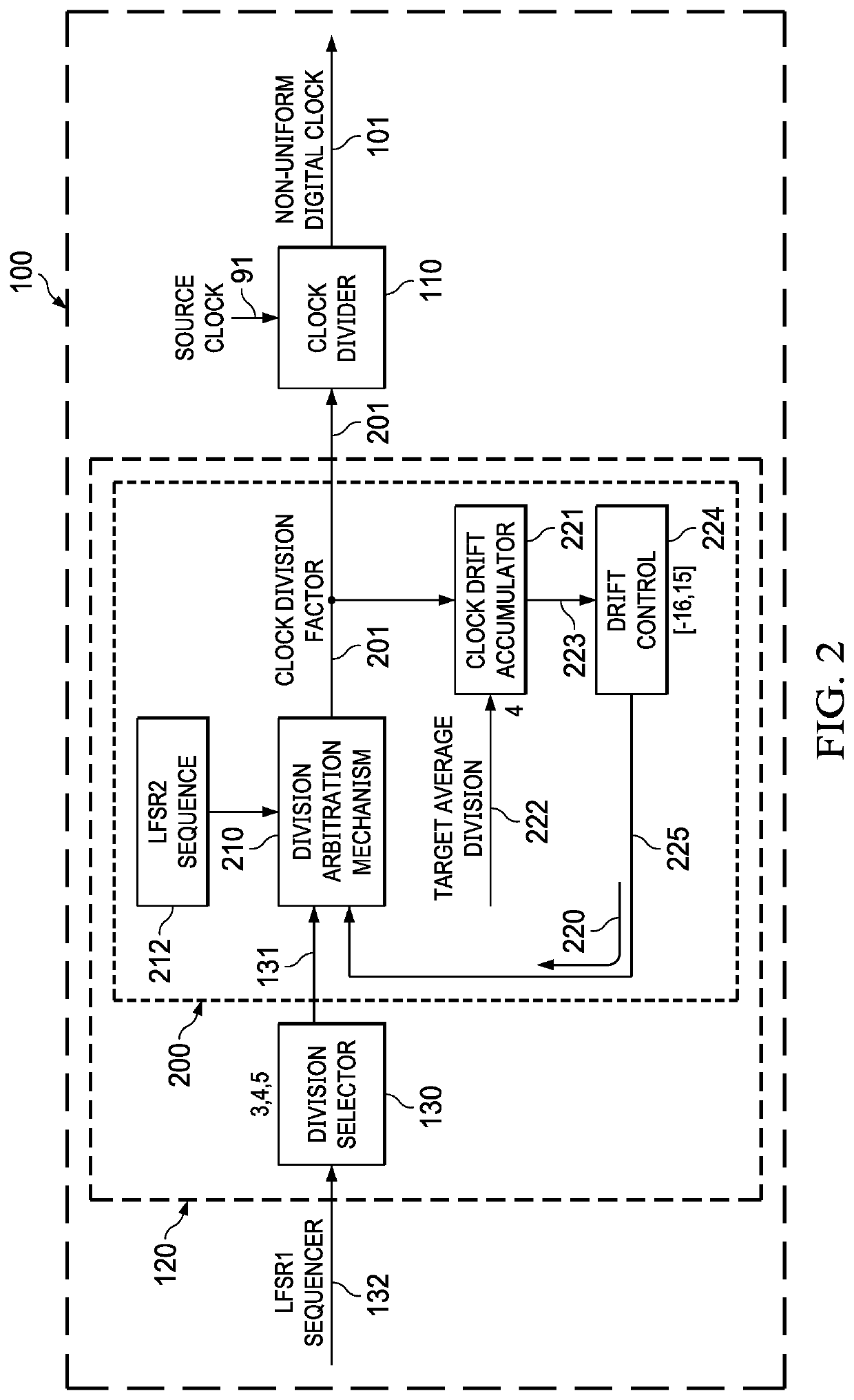

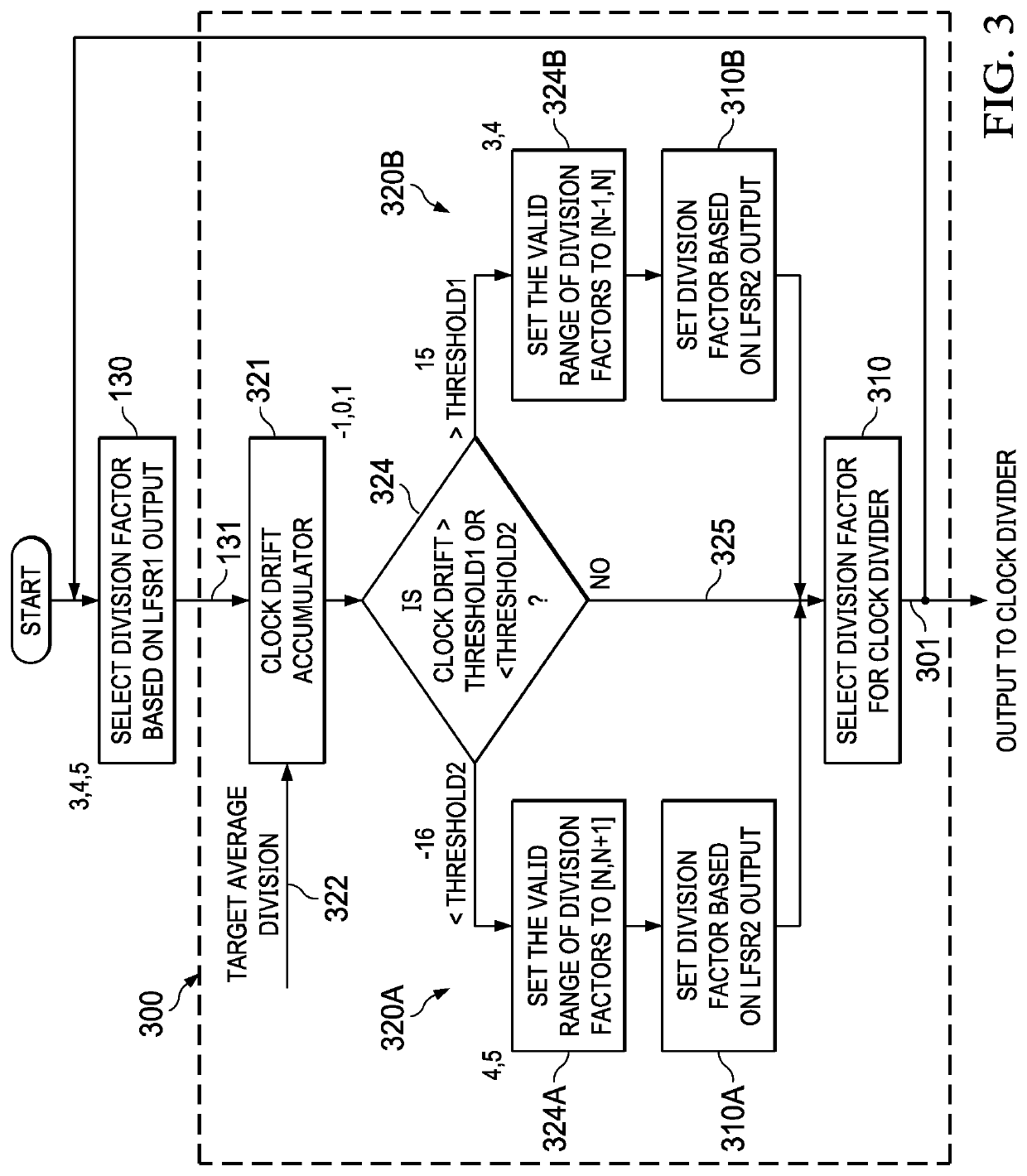

Digital clock generation with randomized division of a source clock

A digital clock generator for a digital clock domain interfaced to another clock domain through a FIFO, includes division selector circuitry to provide an input randomizing sequence of clock division factors, selected from a defined set of clock division factors corresponding to a target average clock division, and division arbitration circuitry to generate a drift-corrected randomizing sequence of clock division factors, based at least in part on the input randomizing sequence of clock division factors, and an accumulated drift correction signal. A clock drift control loop generates the accumulated drift correction signal, based at least in part on an accumulated clock drift relative to the target average clock division. Clock generation can be based on randomized division with the drift-corrected randomizing sequence of clock division factors. The drift-corrected randomizing sequence of clock division factors can be generated so that clock drift is bounded based on a FIFO depth.

Owner:TEXAS INSTR INC

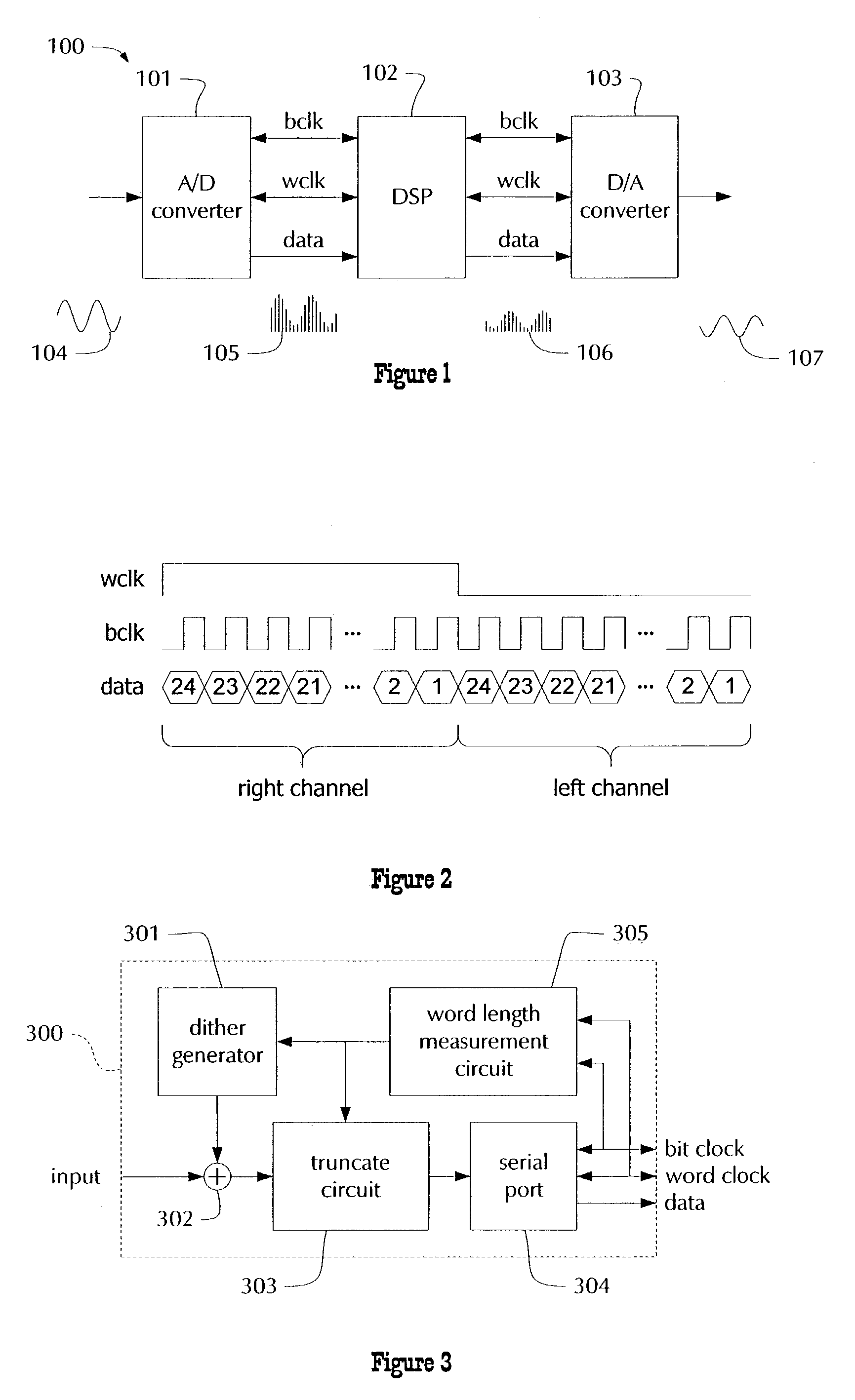

Method and apparatus for automatic word length conversion

ActiveUS7350001B1Reduce distortionReduce quantization artifactCode conversionGenerating/distributing signalsWord clockComputer science

Methods and Apparatuses are provided for automatically converting a word length of sample data being transmitted over a serial link. A serial interface transmits and / or receives one or more data words comprising digital signals, a bit clock synchronizes transmission of individual bits, and a word clock is used to group the bits into sample words. A desired word length is determined based on the relationship between the bit clock and the word clock during the transmission or reception of a data word. Based on the desired word length, the sample data is either truncated or padded, and an appropriate amount of dither is added to the sample words to reduce the distortion and quantization artifacts introduced by the word length conversion.

Owner:CIRRUS LOGIC INC

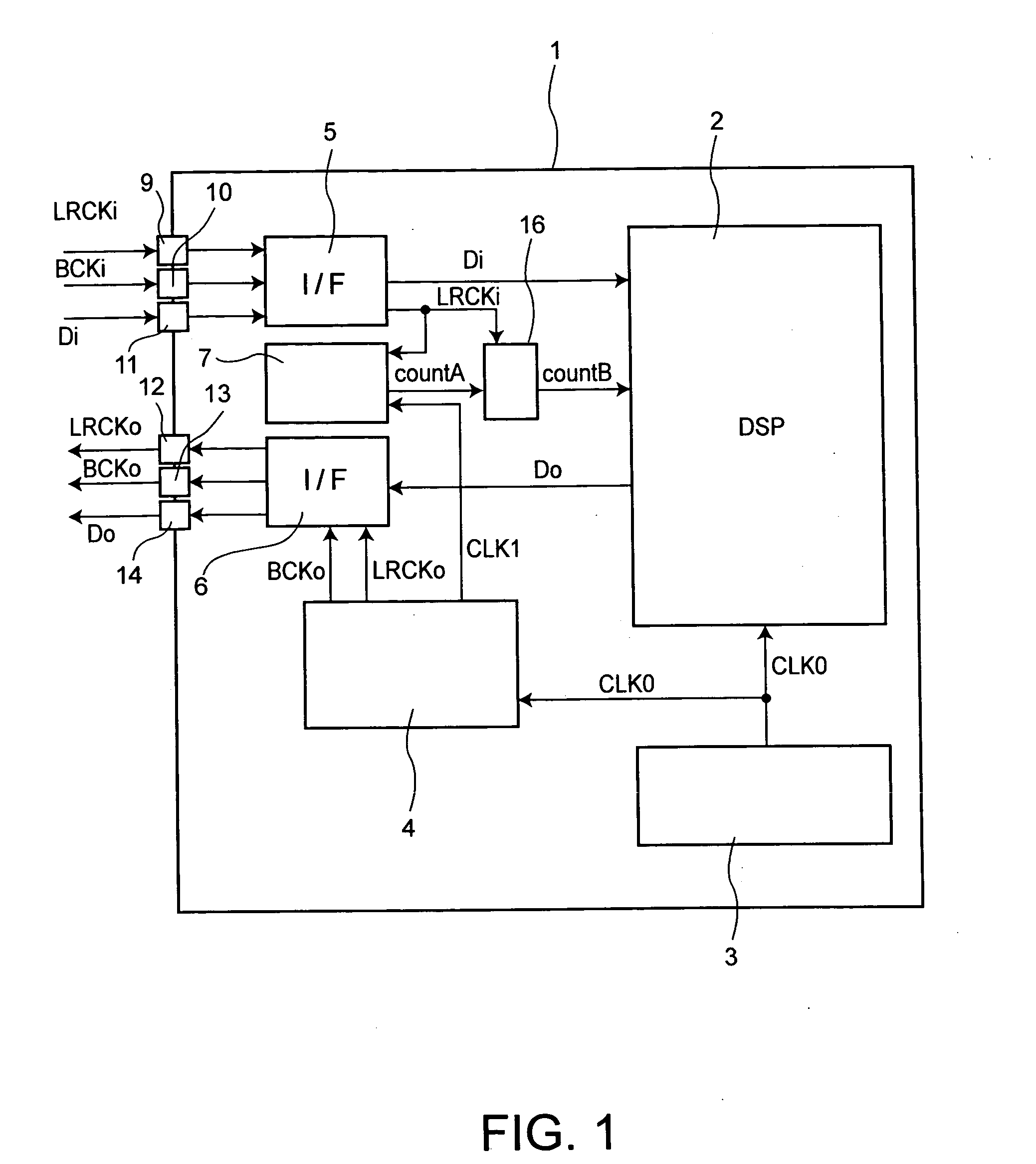

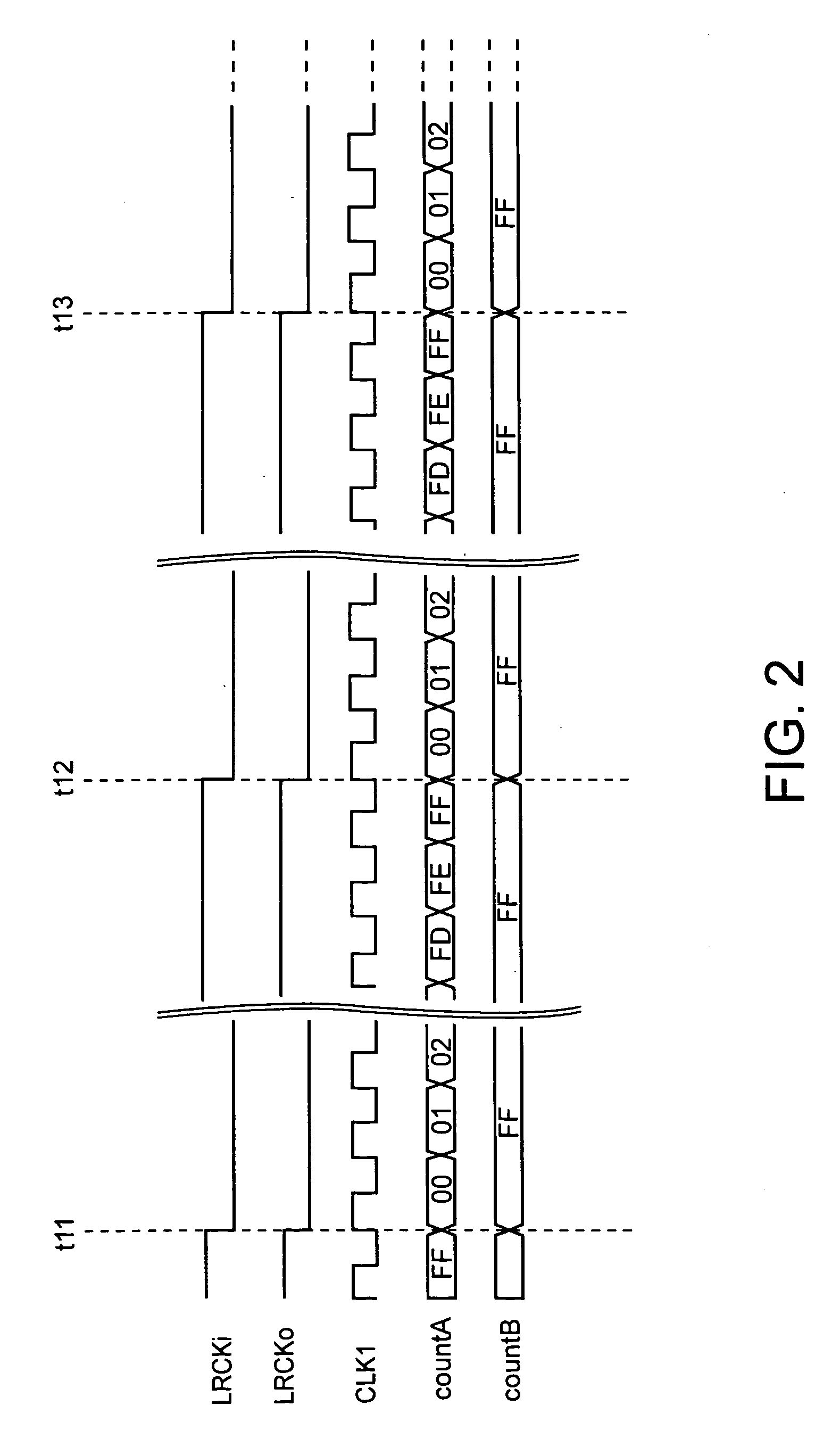

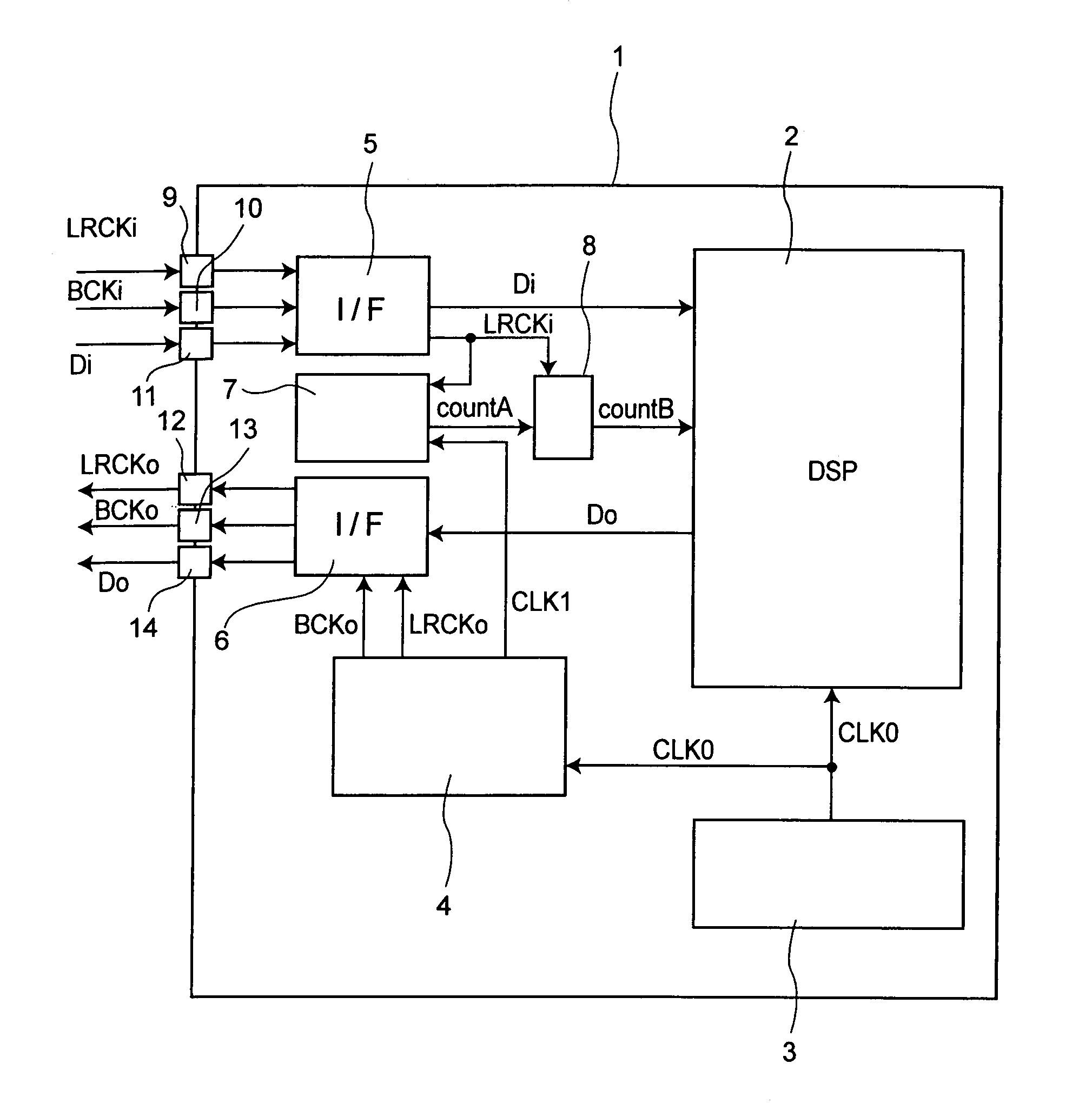

Audio processing apparatus

InactiveUS9753689B2Improve featuresTime-division multiplexSound input/outputWord clockAudio frequency

In an audio processing apparatus configured to supply audio data to a processor configured to process audio data, a plurality of receivers, each configured to receive audio data and a work clock carried with the audio data and to supply the audio data to the processor; a plurality of PLL circuits corresponding to the plurality of receivers, each PLL circuit being configured to generate a clock signal based on a word clock received by the corresponding receiver; and a selector configured to select a clock signal from among a plurality of clock signals generated by the plurality of PLL circuits, and to supply the selected clock signal to the processor, the processor outputting the processed audio data at timing synchronized with the selected clock signal are provided.

Owner:YAMAHA CORP

Sampling frequency conversion device and sampling frequency conversion method

A sampling frequency conversion device comprises an internal circuit for executing in synchronization with an internal clock a signal processing of input data fetched in accordance with an input word clock, and for outputting the input data having undergone the signal processing as output data, a clock generation circuit for generating from the internal clock an output word clock and a counter clock having a frequency which is equal to that of the output word clock multiplied by n (n: integer equal to two or more), a counter for counting the counter clock, and a register for holding a counter value of the counter in synchronization with the input word clock, and for outputting the held counter value to the internal circuit.

Owner:KK TOSHIBA

A fractional frequency all-digital phase-locked loop and its control method

ActiveCN110719100BRequirements for reducing output delay time rangeReduce design difficultyPulse automatic controlNumerical controlConverters

The invention provides a fractional frequency all-digital phase-locked loop and a control method of the fractional frequency all-digital phase-locked loop. The method includes: S1, the fractional frequency controller generates a delay control word, a frequency division ratio control word, an integer frequency control word and a fractional frequency control word according to an external fractional frequency control word; S2, the clock generation and control circuit is based on the reference clock, The frequency control word generates the clock signal ckr; S3, the digital time converter generates the low frequency clock signal according to the ckr and the delay control word; S4, the feedback signal generating circuit outputs the high frequency clock signal ckv generated according to the frequency division ratio control word and the numerical control oscillator The feedback signal fb; S5, the phase detector generates the phase error digital signal phe of ckr and fb; S6, the auxiliary frequency locked loop outputs the control signal ftl according to the integer frequency control word, the fractional frequency control word and the low frequency clock signal, and the numerical control oscillator according to The addition of ftl and phe and the update of ckv.

Owner:FUDAN UNIV

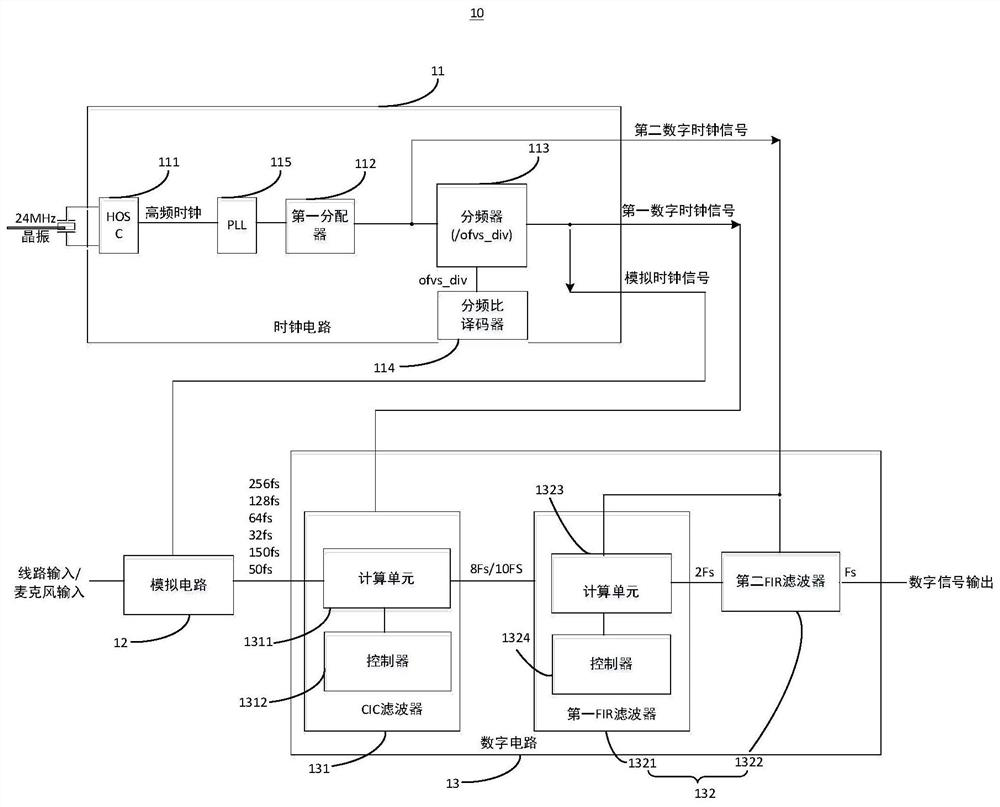

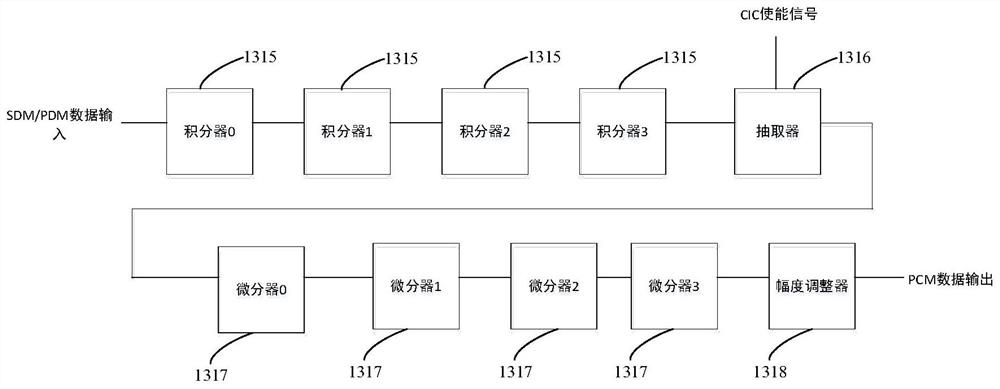

Analog-to-digital conversion system and audio equipment

PendingCN113078902AImprove performanceIncrease the oversampling rateSpeech analysisAnalogue-digital convertersSoftware engineeringOversampling

The invention discloses an analog-to-digital conversion system and audio equipment. The analog-to-digital conversion system comprises a clock control circuit which is used for providing clock signals according with each design ratio according to different preset oversampling rates, wherein the clock signal comprises a first digital clock signal, a second digital clock signal and an analog clock signal; an analog circuit which is used for outputting corresponding oversampling signals according to different analog clock signals; and a digital circuit which is used for performing first extraction on the oversampling signal according to the first digital clock signal to obtain a first extraction signal, and further performing second extraction on the first extraction signal according to the second digital clock signal to output a second extraction signal meeting the sampling rate requirement. Therefore, the oversampling rate of the system can be improved and higher performance can be obtained in an application requiring high performance, and the working frequency of the system can be reduced and power consumption can be saved by using a low oversampling rate in a low-power-consumption application.

Owner:ACTIONS ZHUHAI TECH CO

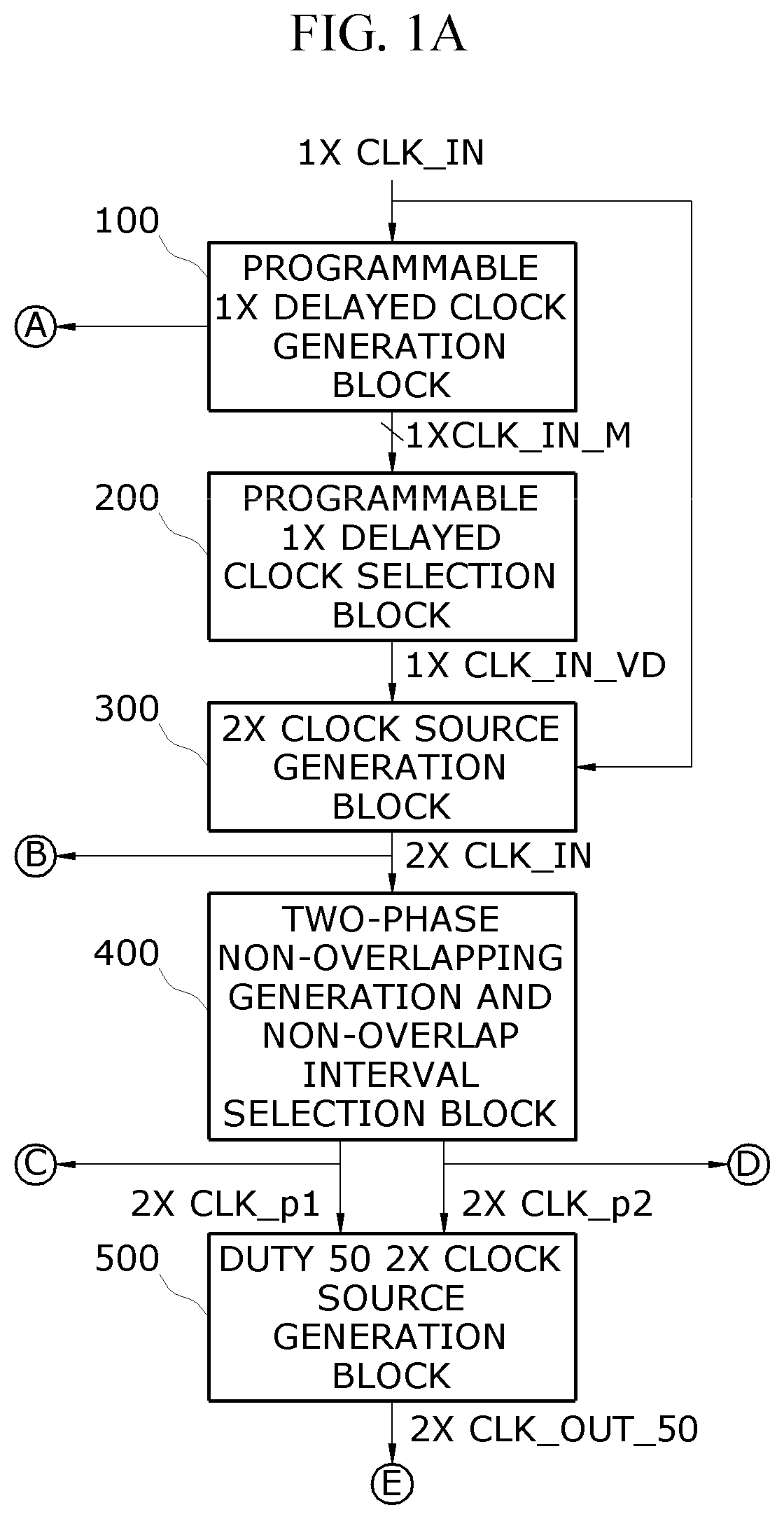

Digital clock generation apparatus and method

ActiveUS10819326B1Easy to controlHardware is simpleElectric pulse generatorManipulation for frequency changeDigital clockWord clock

The present invention relates to a digital clock generation apparatus. The digital clock generation apparatus is directed to providing a digital clock generation apparatus in which hardware is simple, duty cycles are easily controlled, and various duty cycles and various frequency clocks (n× clocks) are provided as compared to a 1× single-phase clock generation apparatus or a 1× multi-phase clock generation apparatus based on the conventional programmable delay element chain.

Owner:ELECTRONICS & TELECOMM RES INST

A Spread Spectrum Modulation Method for Filter-free Digital Class-D Audio Power Amplifier

ActiveCN108832917BImprove power efficiencyReduce high frequency peak amplitudeAmplifier modifications to reduce non-linear distortionLow frequency amplifiersSoftware engineeringNumber generator

The present invention proposes a spread-spectrum modulation method for a filter-free digital class D audio power amplifier, which utilizes the main clock signal of the power amplifier clk and UPWM generator input synchronous word clock signal clk_s 1 Synthesize another clock signal according to certain rules clk_s 2. Then build a pseudo-random number generator to generate a series of pseudo-random numbers, by judging the parity of the pseudo-random numbers, using the clock signal clk_s 1 and the clock signal clk_s 2 Synthesize a clock signal with variable frequency clk_c , and finally using the master clock signal clk , clock signal clk_c And the amplitude of the input signal of the UPWM generator is processed by the threshold calculator, counter and comparator to output the PRF variable left-increasing double-edge UPWM signal; at the same time, the corresponding filter-free pulse width modulator is designed based on the above-mentioned spread spectrum modulation method. The invention can obviously reduce the amplitude of the high-frequency component of the UPWM signal output by the power amplifier, thereby reducing EMI, and is simple to implement and requires less hardware resources.

Owner:ZHENGZHOU UNIVERSITY OF LIGHT INDUSTRY

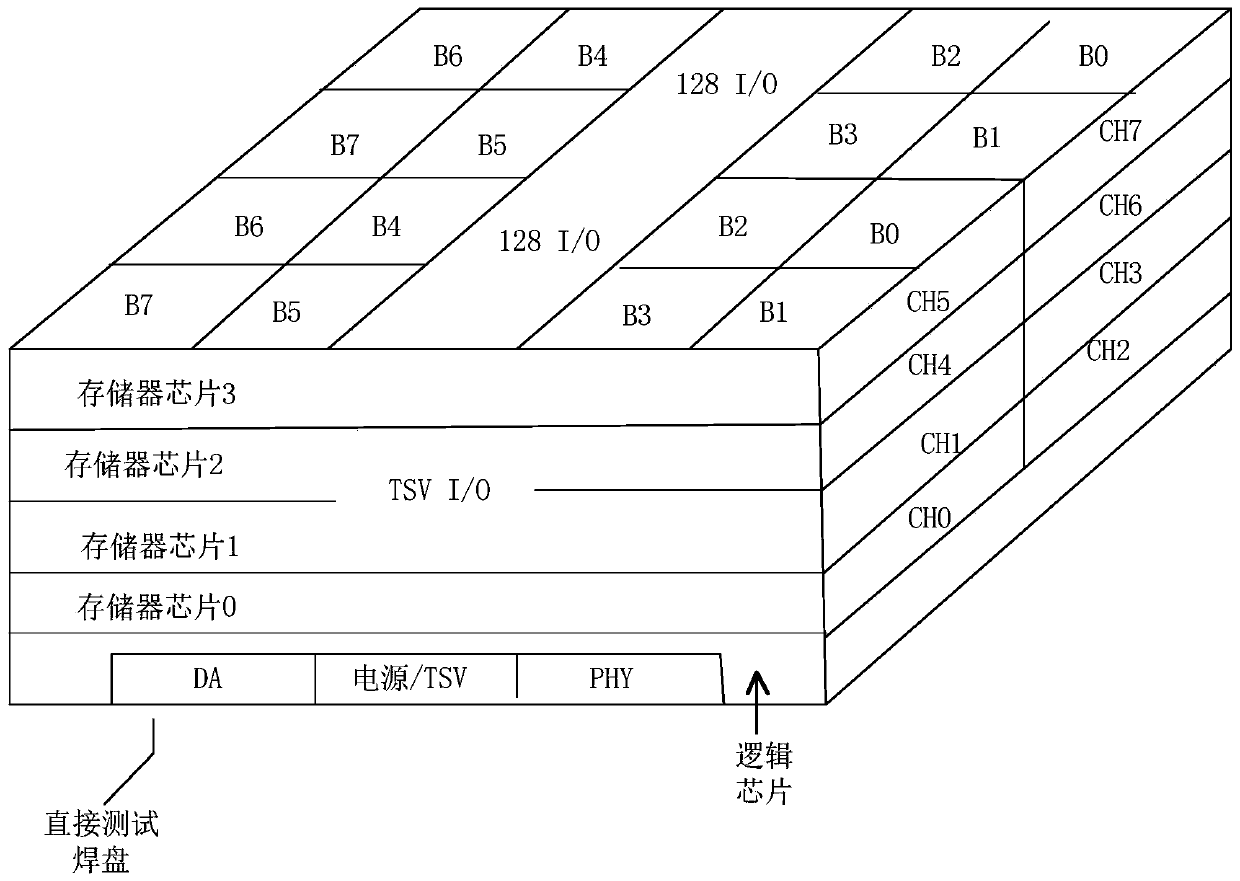

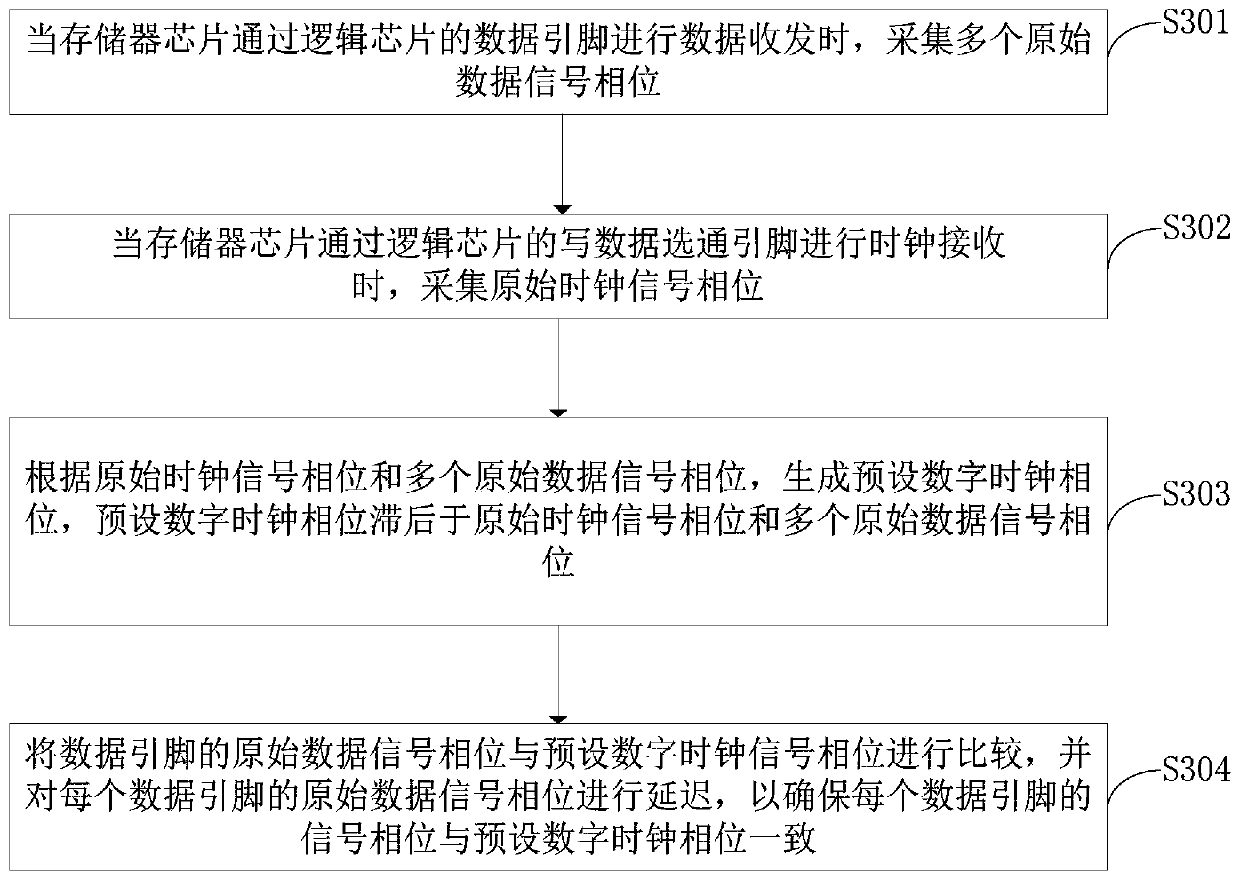

3D stacked memory, clock skew elimination method and clock skew elimination circuit

ActiveCN111179987AReduce standby lossEliminate skew errorsDigital storageComputer architectureDigital clock

The invention discloses a clock skew elimination method of a 3D stacked memory, a clock skew elimination circuit of the 3D stacked memory and the 3D stacked memory. The clock skew elimination method comprises the following steps: generating a preset digital clock phase according to an original signal phase of a write data gating pin and original signal phases of all data pins, so as to enable thepreset digital clock phase to lag behind the original signal phase of the data gating pin and the original signal phase of each data pin; comparing the original signal phase of each data pin with a preset digital clock phase, and delaying the original signal phase of each data pin to ensure that the signal phase of each data pin is consistent with the preset digital clock phase. According to the embodiment, delay control is carried out on each data pin according to the preset digital clock phase, so that pin deflection is eliminated, and the data transmission reliability of the 3D stacked memory is improved.

Owner:SHENZHEN STATE MICROELECTRONICS CO LTD

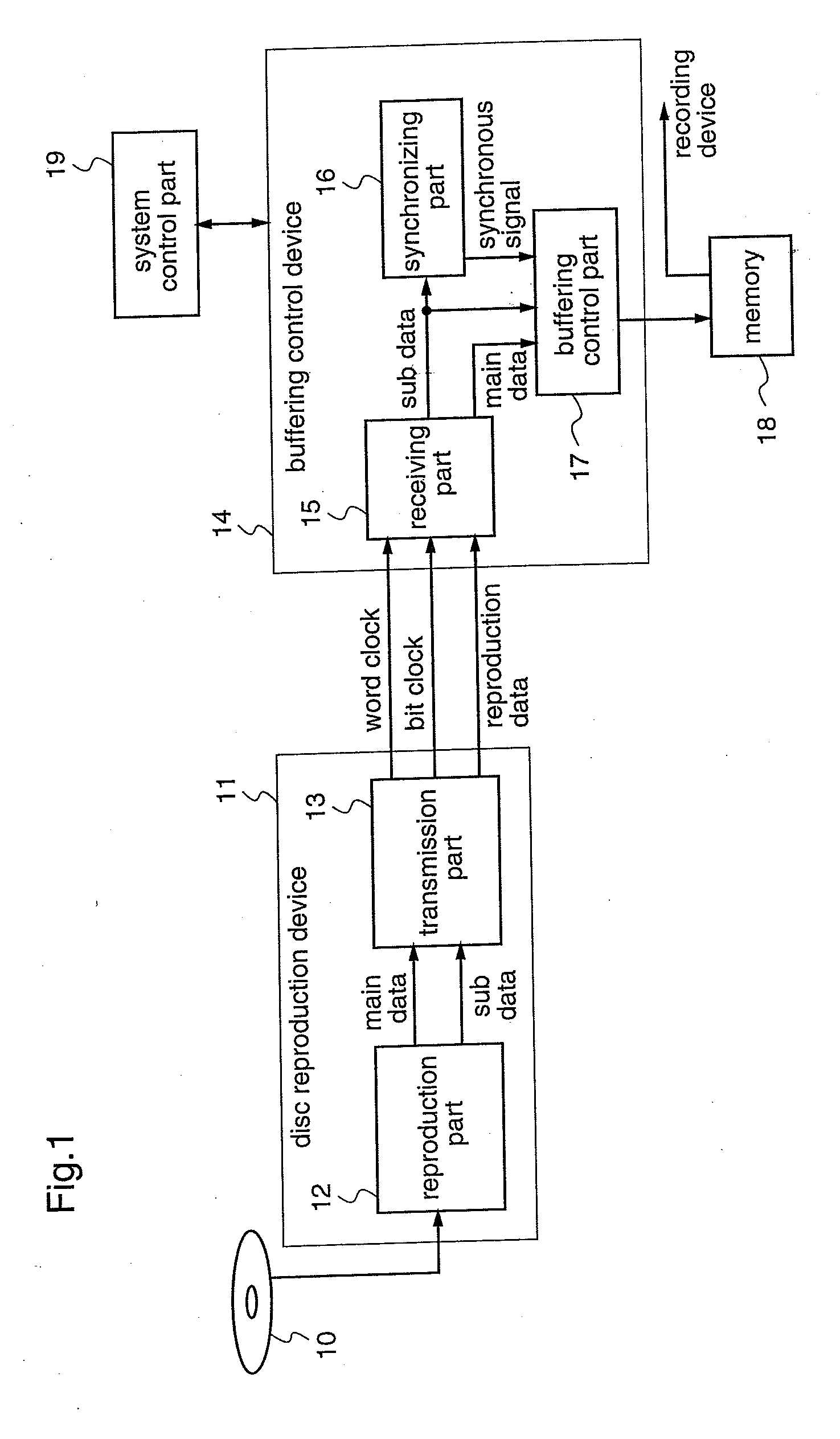

Buffering control method, and buffering control device

ActiveUS20100027389A1Reduce memoryOptical re-recordingFilamentary/web record carriersWord clockComputer science

When receiving the reproduced data from the optical disc and buffering same, the buffering from the correct position can be started on the basis of the synchronous signal and the address information included in the sub data which was received simultaneously.There is provided a method for controlling the buffering of the main data which is reproduced from the optical disc, in which the main data and the sub data are received with taking word clocks which are partitioning timings having plural bits of the main data as a unit as references, a synchronous signal which is in synchronization with the main data is generated, and the buffering of the main data is started on the basis of the synchronous signal.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

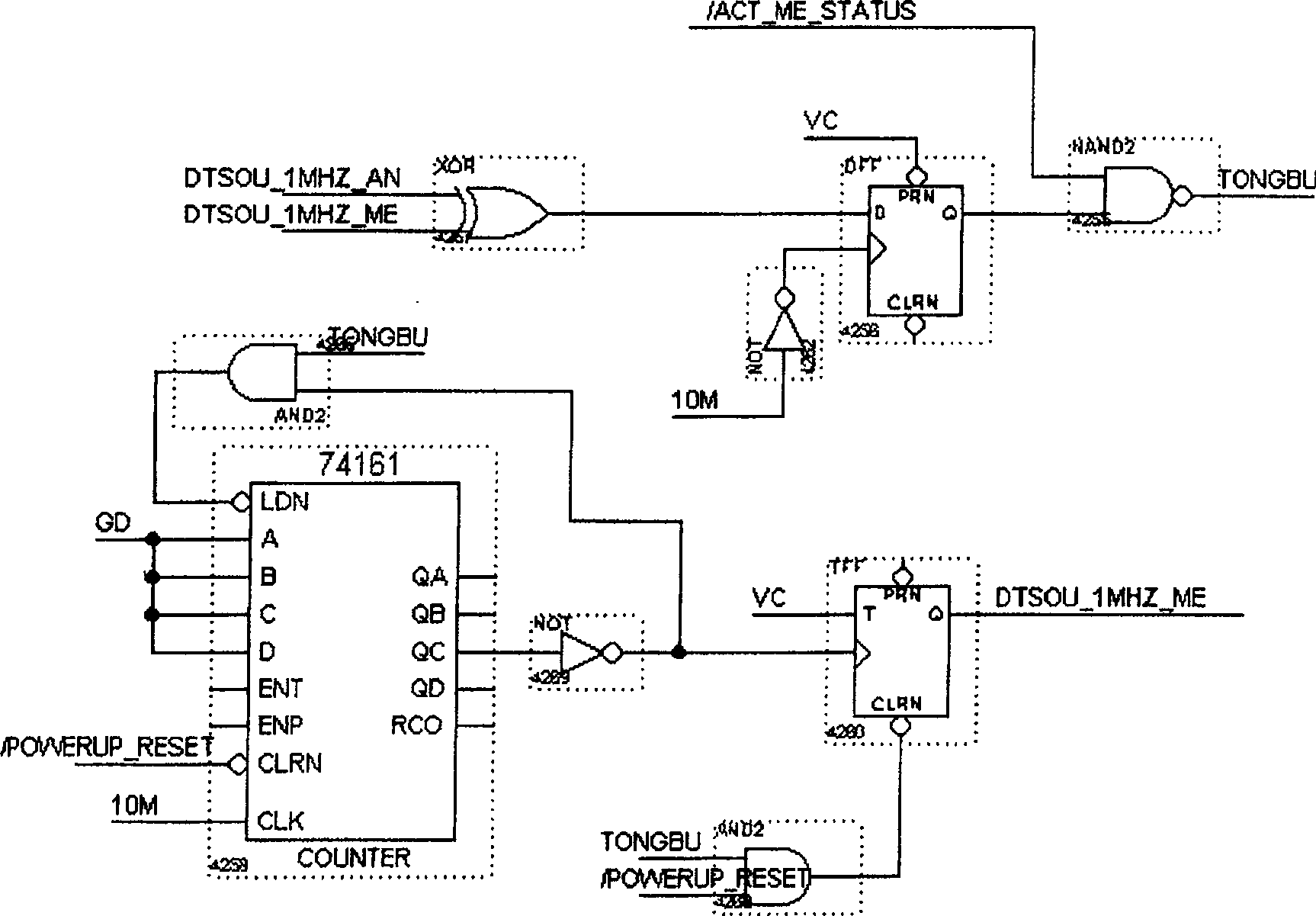

Method for implemention of master-spare clock phase alignment in communication equipment

ActiveCN100525173CImproved phase discontinuity performanceLow synchronization requirementSynchronising arrangementSlave clockFrequency synthesizer

A method for phase alignment of active and standby clocks in a communication device, wherein at least one frequency-modulated direct digital frequency synthesizer (DDS) and at least one phase-modulated DDS are respectively arranged on the main clock board and the standby clock board, wherein the frequency-modulated DDS tracks an external clock The reference source synthesizes the frequency required by the output clock, and writes the frequency adjustment word that is the same as the frequency adjustment word of the frequency modulation DDS or has a fixed proportional relationship on the phase modulation DDS, and outputs the clock of the corresponding frequency; The relationship is detected, and the value of the phase register of the phase modulation DDS on the standby clock board is adjusted according to the detection result, and the output phase of the standby clock board is adjusted to align the phases of the main and standby output clocks. The invention improves the precision of the phase alignment, reduces the frequency synchronization requirements of the main and standby clock phase alignment, and improves the reliability of the clock system.

Owner:HUAWEI TECH CO LTD

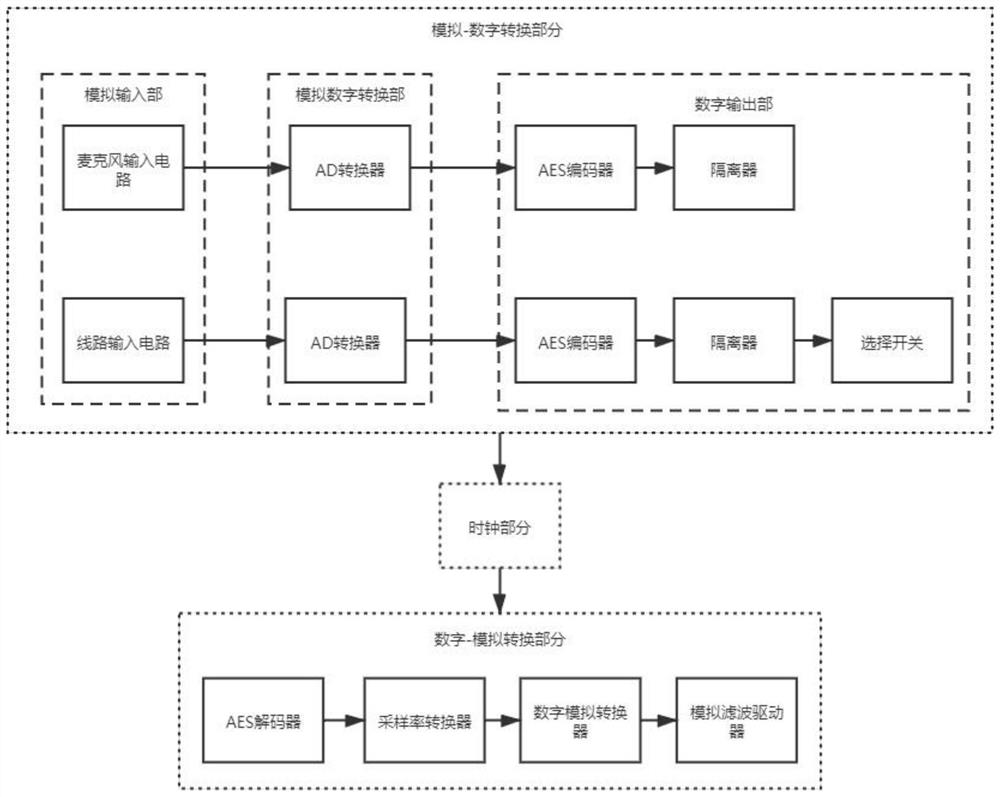

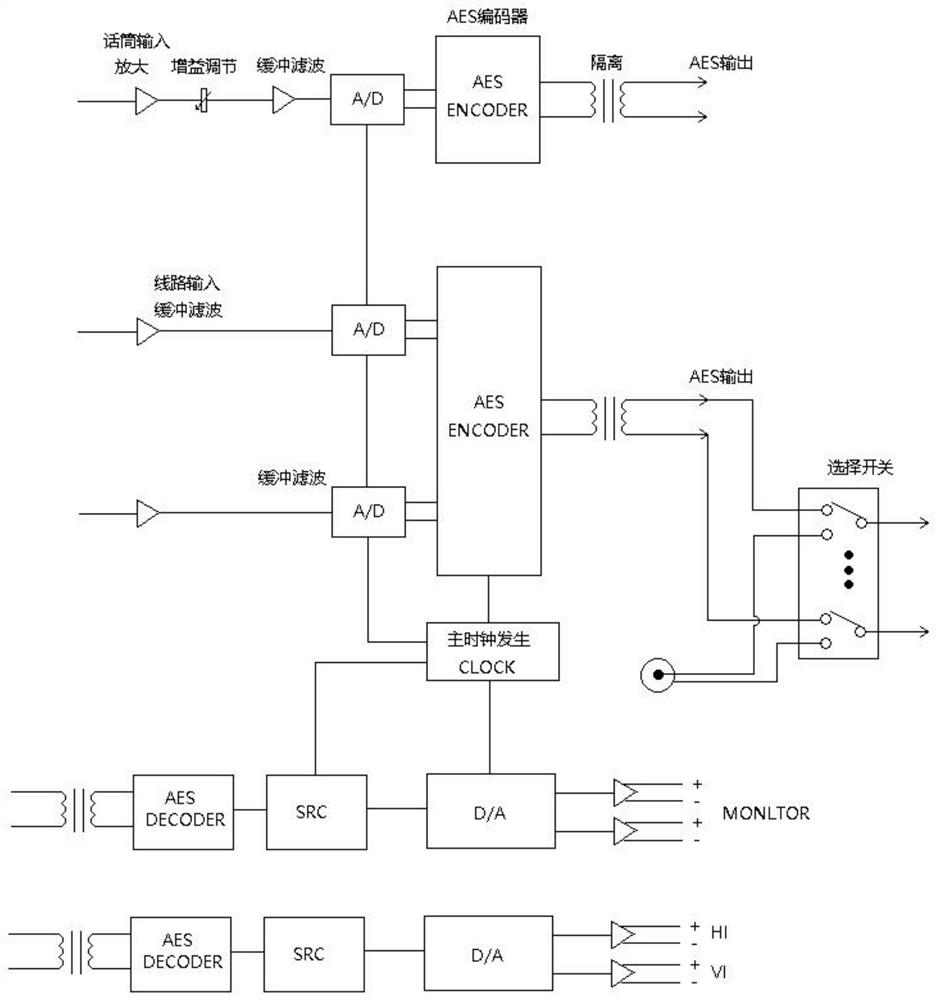

Bidirectional audio signal converter

PendingCN113207057ARealize functions such as monitoringEasy implementation of auxiliary audio functionsTransducer circuitsConvertersWord clock

The invention discloses a bidirectional audio signal converter, and the converter comprises a shell, an analog-digital conversion part, a digital-analog conversion part and a clock part; the analog-digital conversion part, the digital-analog conversion part and the clock part are arranged in the shell, and the analog-digital conversion part comprises an analog input part, an analog-digital conversion part and a digital output part which are connected in sequence; the analog input part is used for inputting a level signal, the analog-to-digital conversion part is electrically connected with the analog input part and is used for converting an analog signal into a digital signal with independent word clock, bit clock and data, and the digital output part is electrically connected with the analog-to-digital conversion part and is used for synthesizing the digital signal into a digital audio signal meeting the AES-3 standard. The converter can be used as an A / D converter for converting a received audio analog signal into a digital signal, and can also be used as a D / A converter for converting a digital audio signal into an analog signal for connecting a monitoring loudspeaker and a cinema audio-visual disability system.

Owner:上海森仝贸易有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com