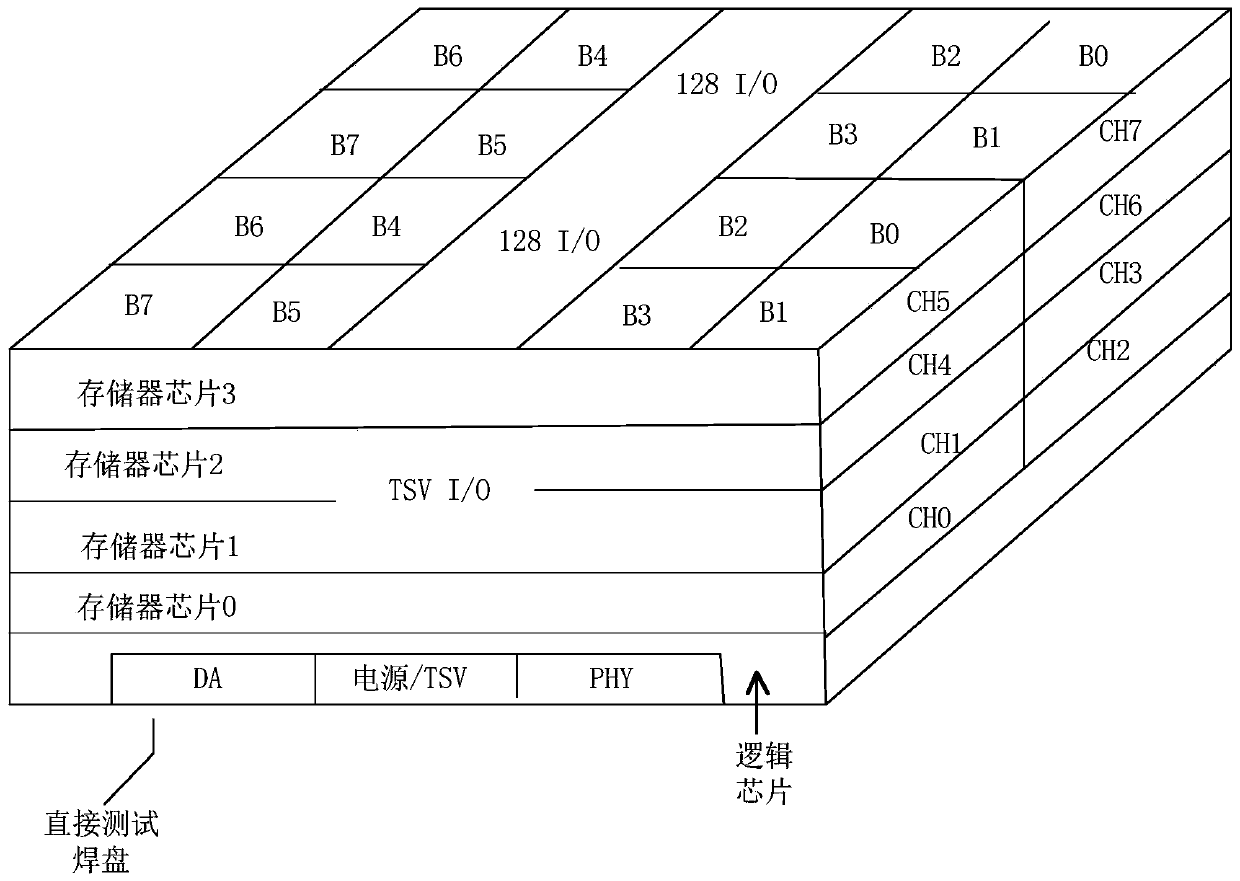

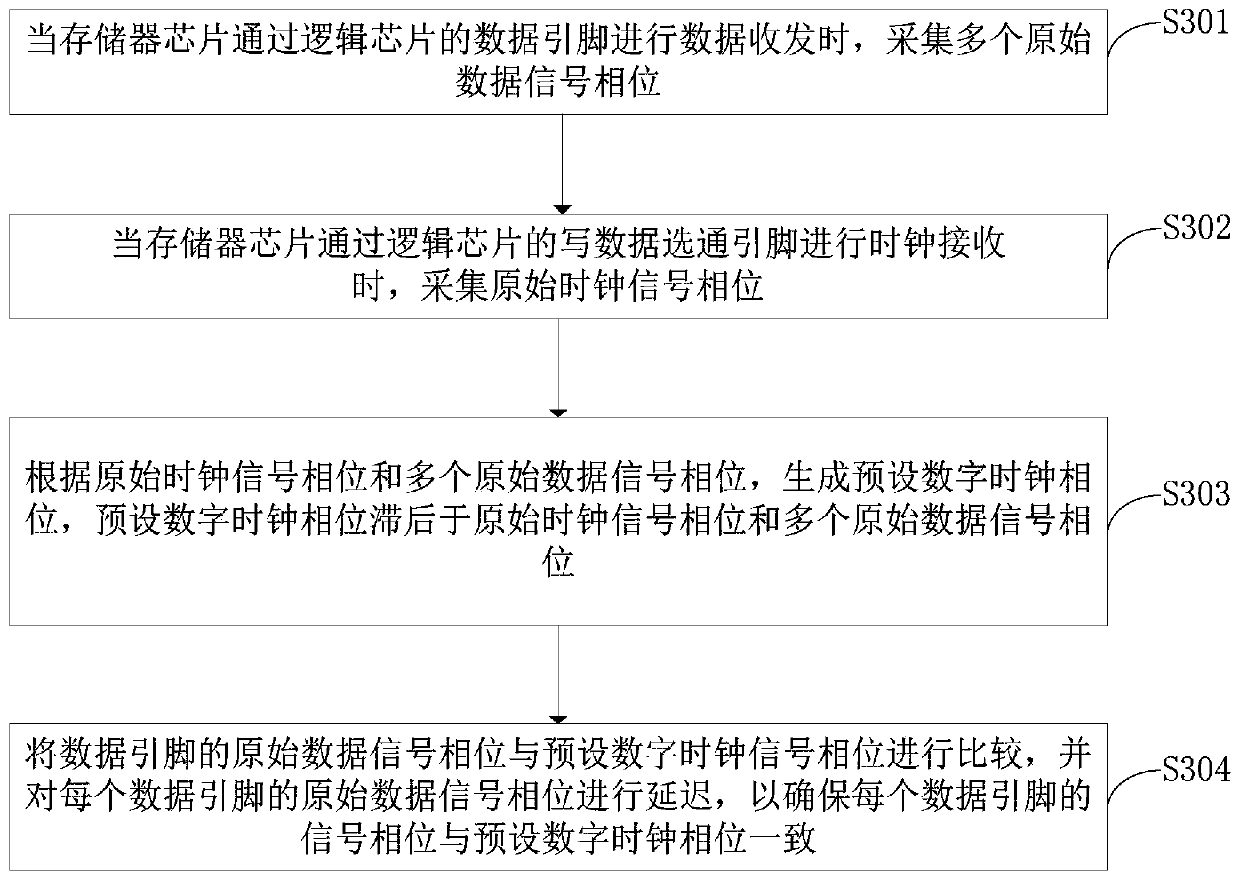

3D stacked memory, clock skew elimination method and clock skew elimination circuit

A clock skew and circuit elimination technology, applied in static memory, digital memory information, information storage, etc., can solve the problem of large storage standby power consumption, reduce standby loss, eliminate pin skew error, accuracy and reliability. Reliable effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In order to make the purpose, technical solution and advantages of the present application clearer, the present application will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present application, and are not intended to limit the present application.

[0033] In recent years, the accumulation of big data, the innovation of theoretical algorithms, the improvement of computing power and the evolution of network facilities have made the artificial intelligence industry, which has been accumulated for more than half a century, usher in revolutionary progress again, and the research and application of artificial intelligence have entered the A new stage of development; with the active promotion of the government and the industry, artificial intelligence technology has advanced by leaps and bounds in large-scale industrial appl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com