Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

44 results about "Serial computer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A serial computer is a computer typified by bit-serial architecture – i.e., internally operating on one bit or digit for each clock cycle. Machines with serial main storage devices such as acoustic or magnetostrictive delay lines and rotating magnetic devices were usually serial computers.

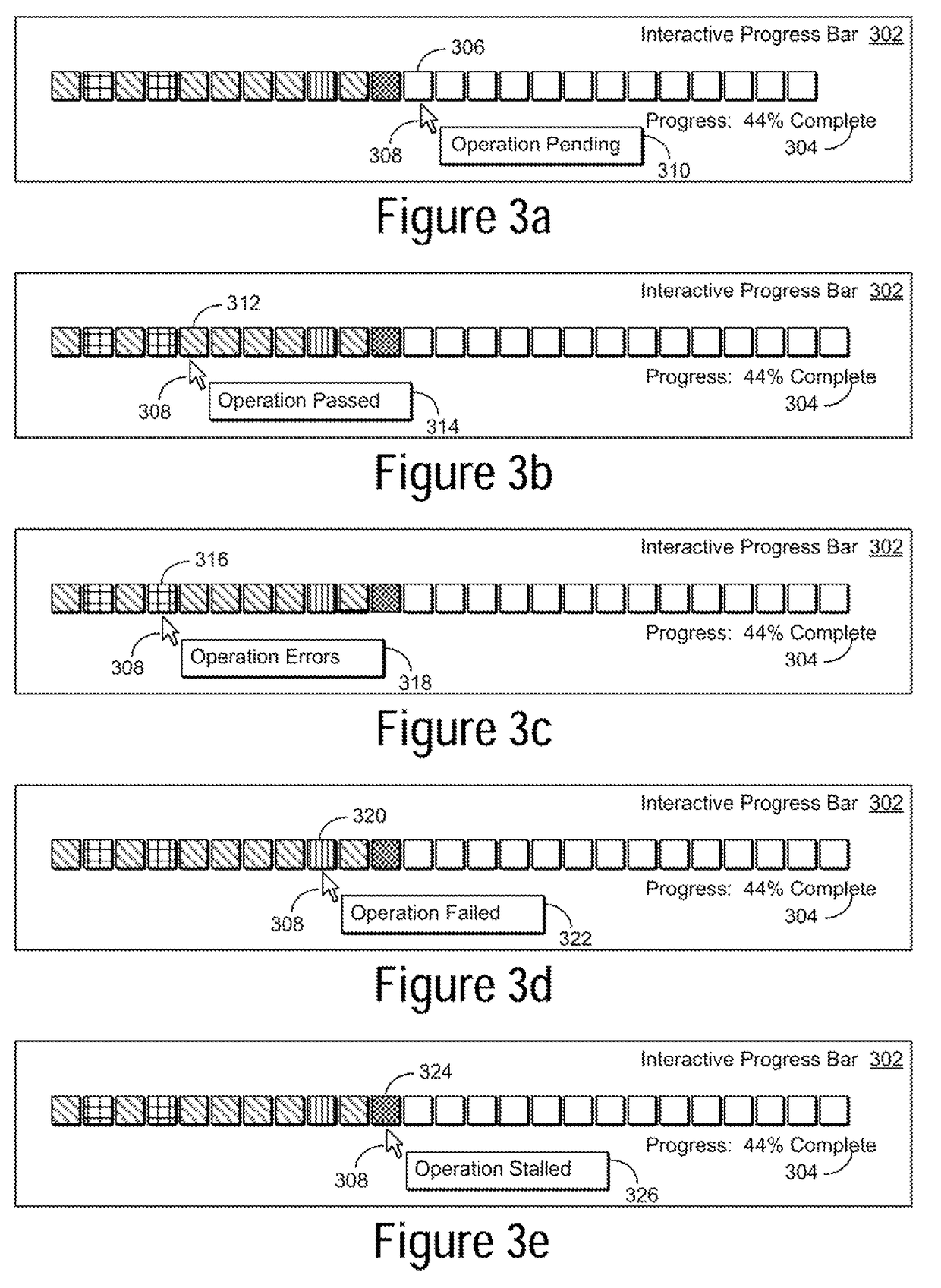

System and Method to Facilitate Progress Forking

InactiveUS20090113334A1Insufficient resourceProgram loading/initiatingExecution for user interfacesCompletion StatusGraphics

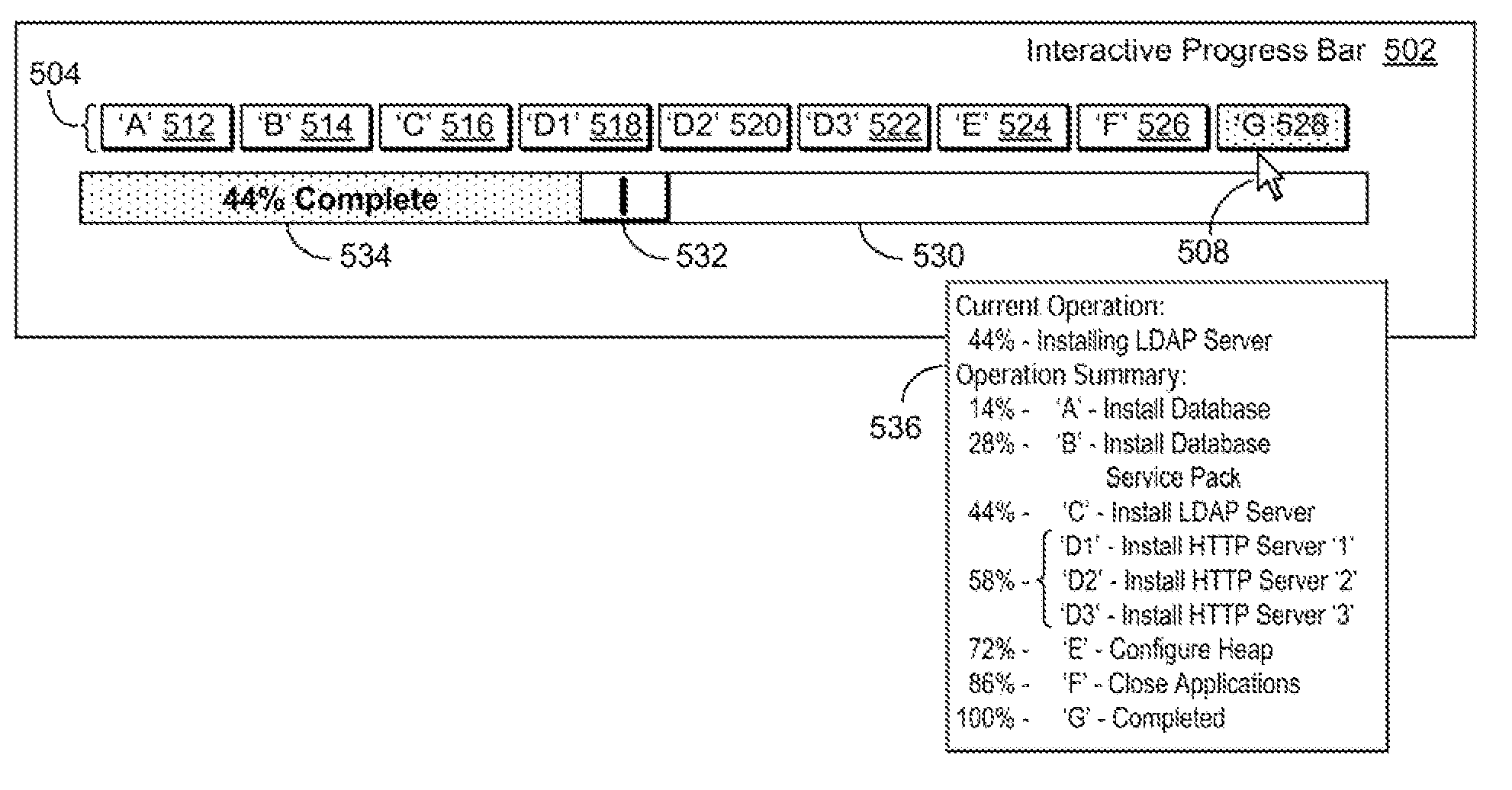

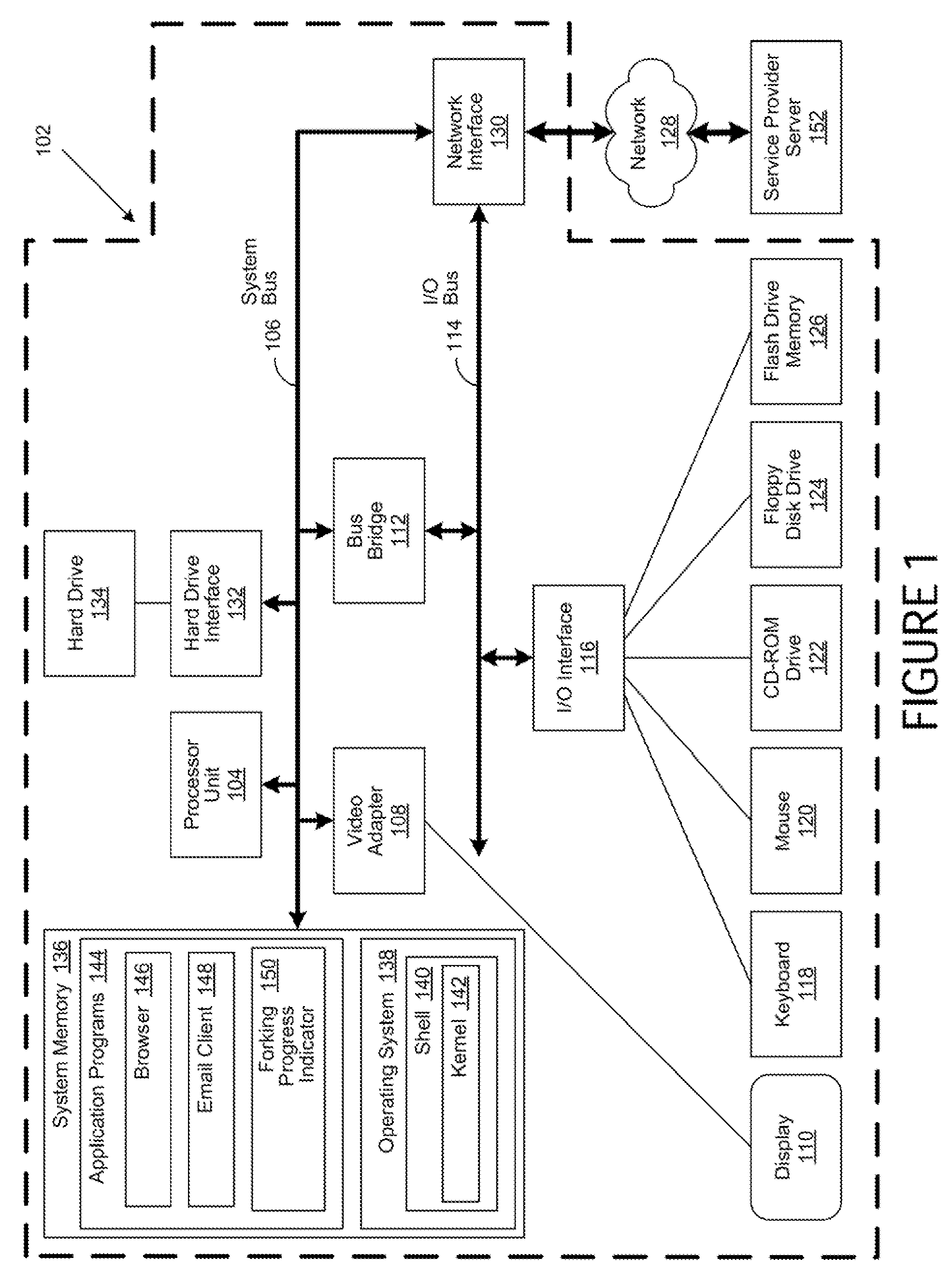

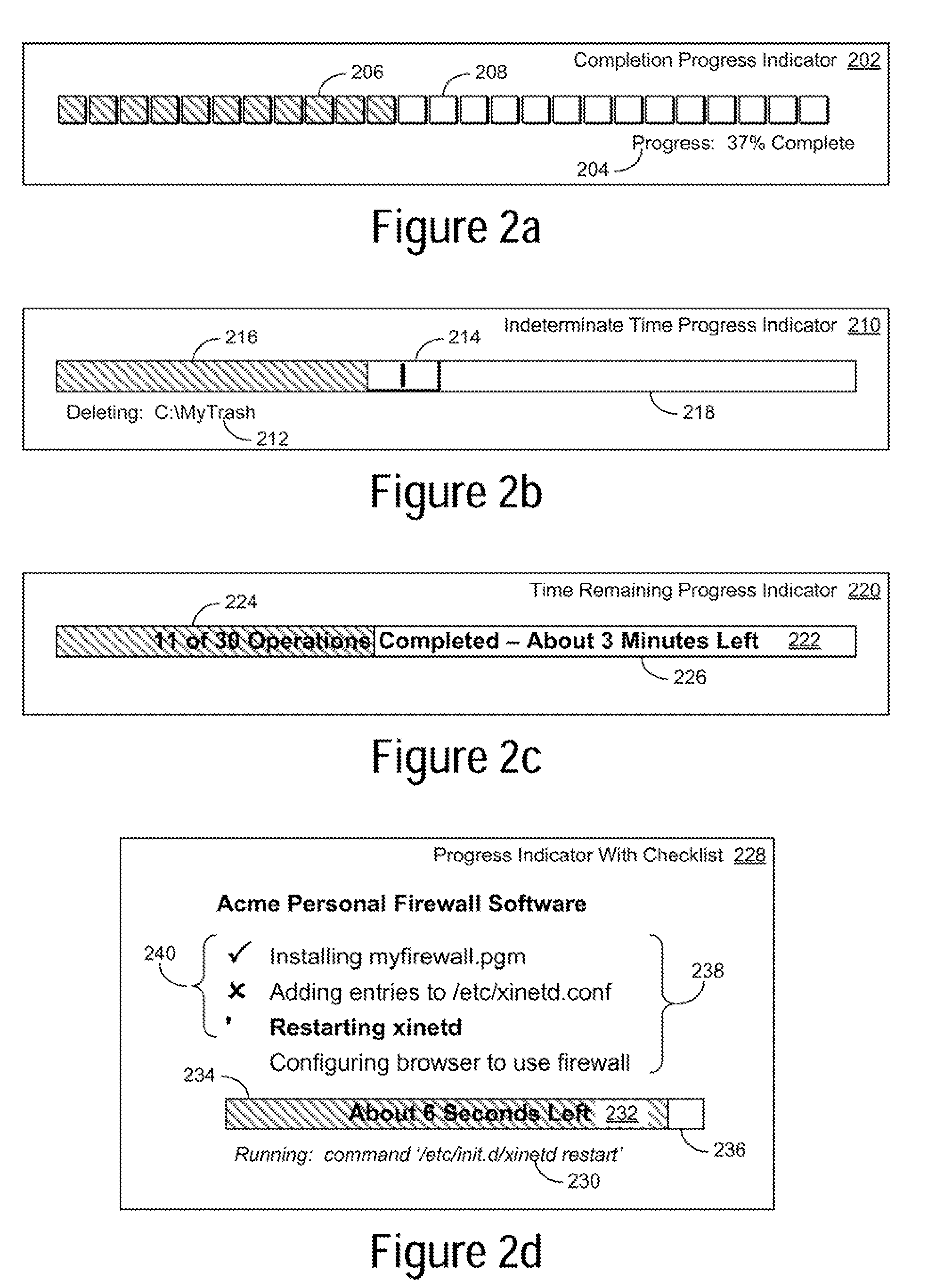

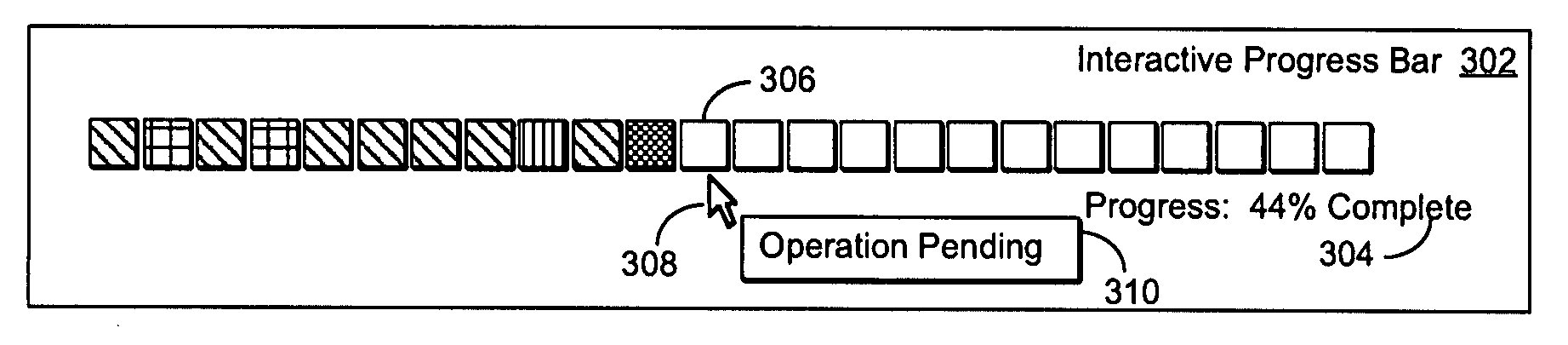

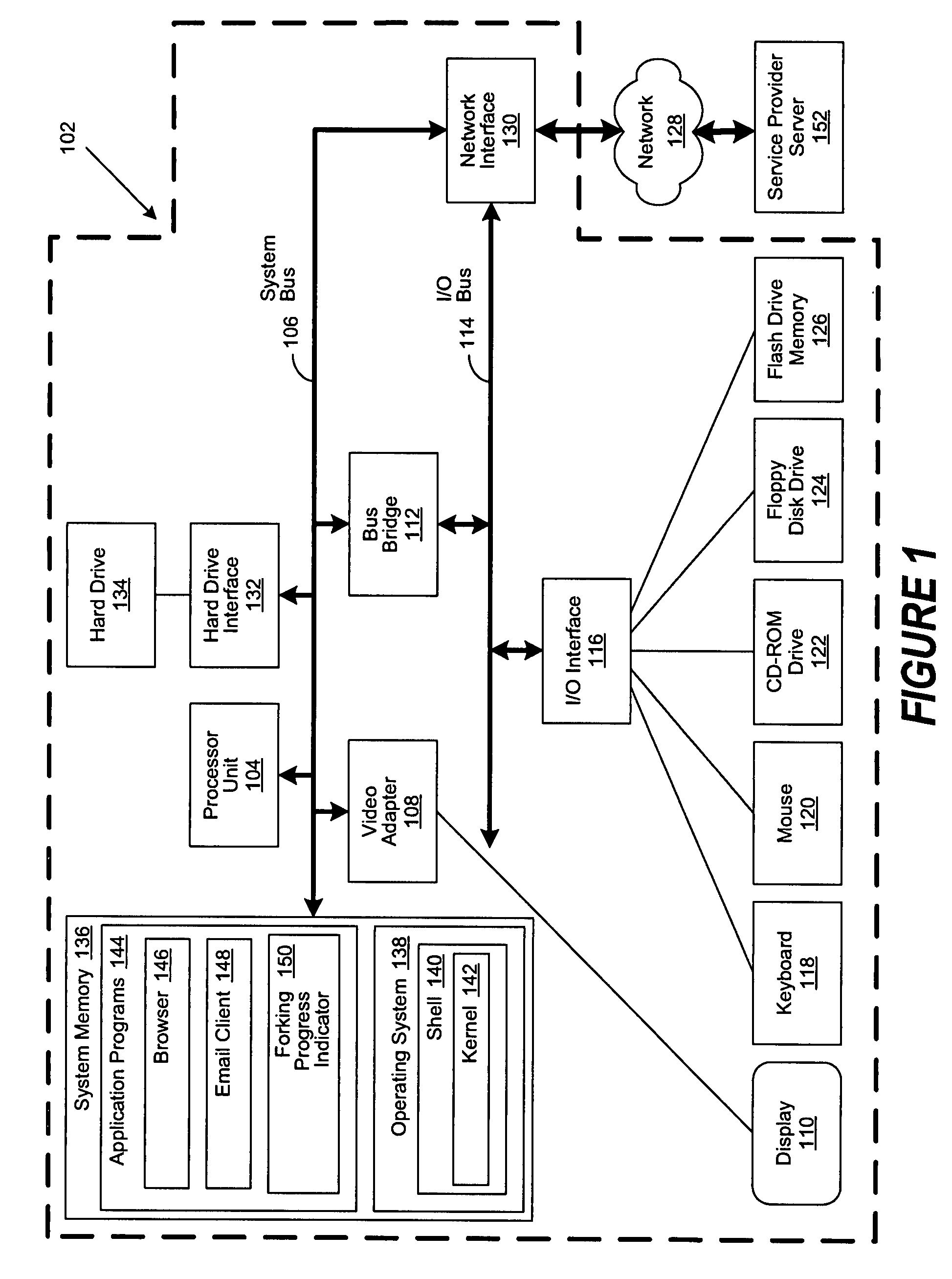

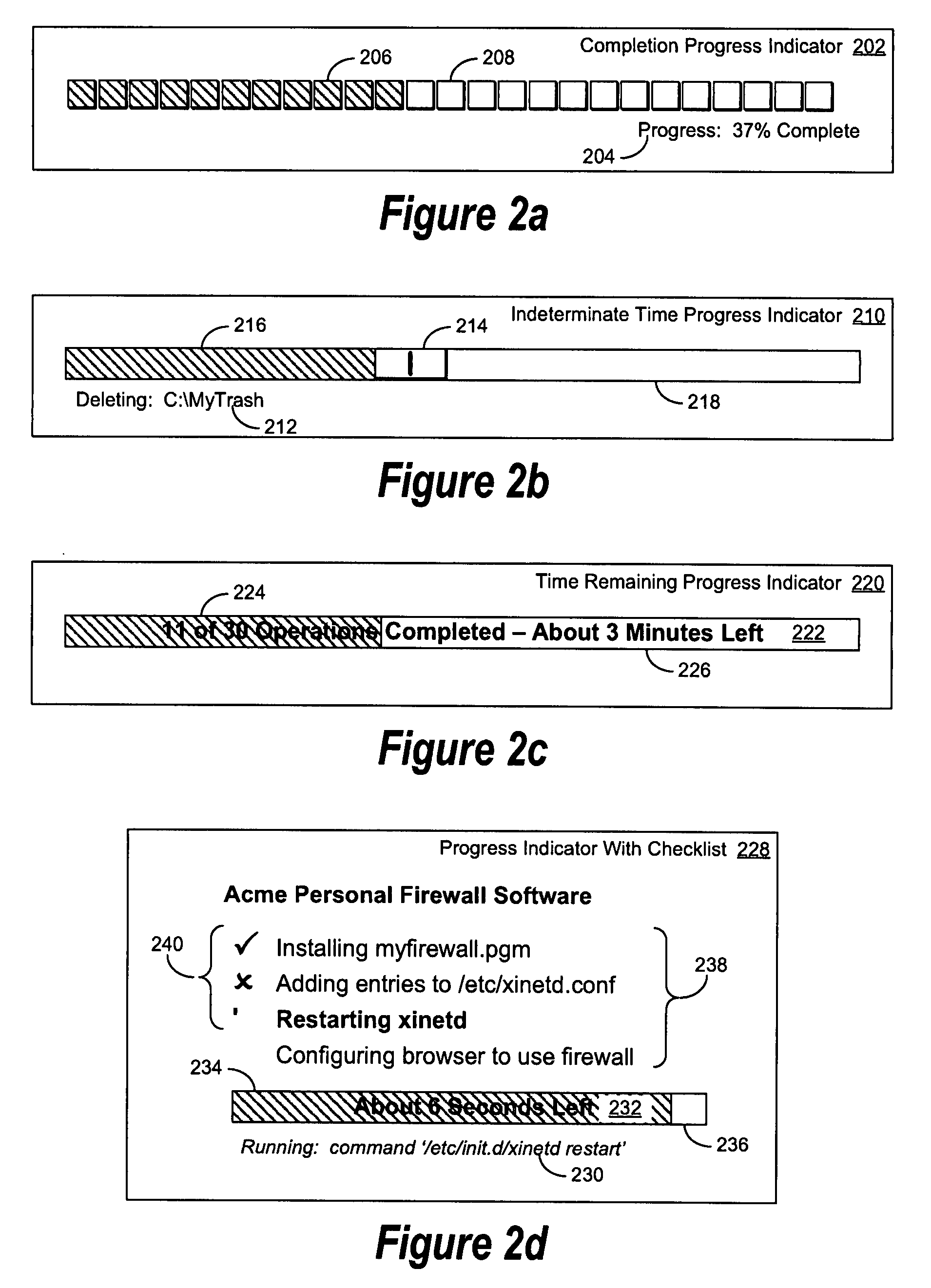

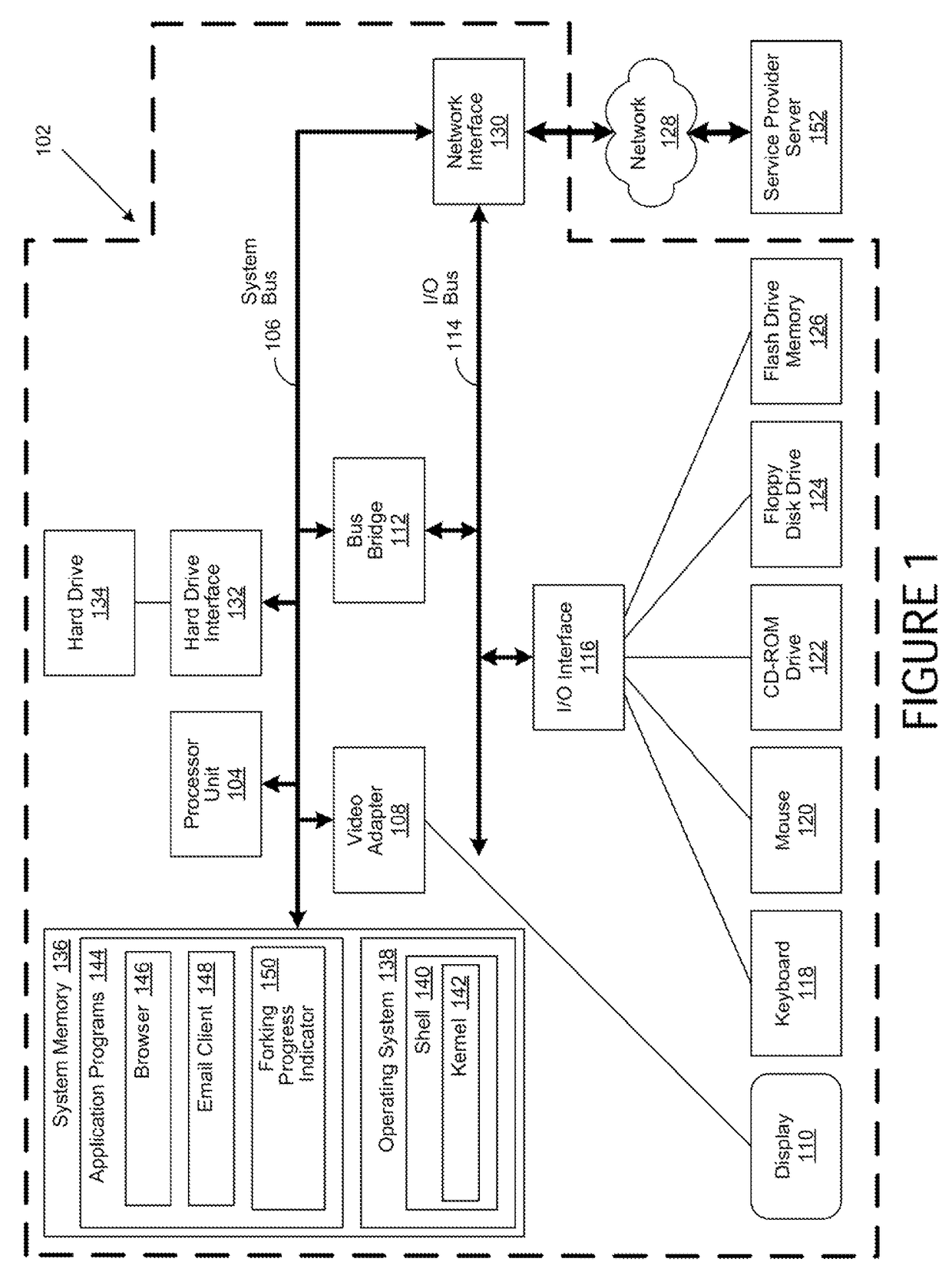

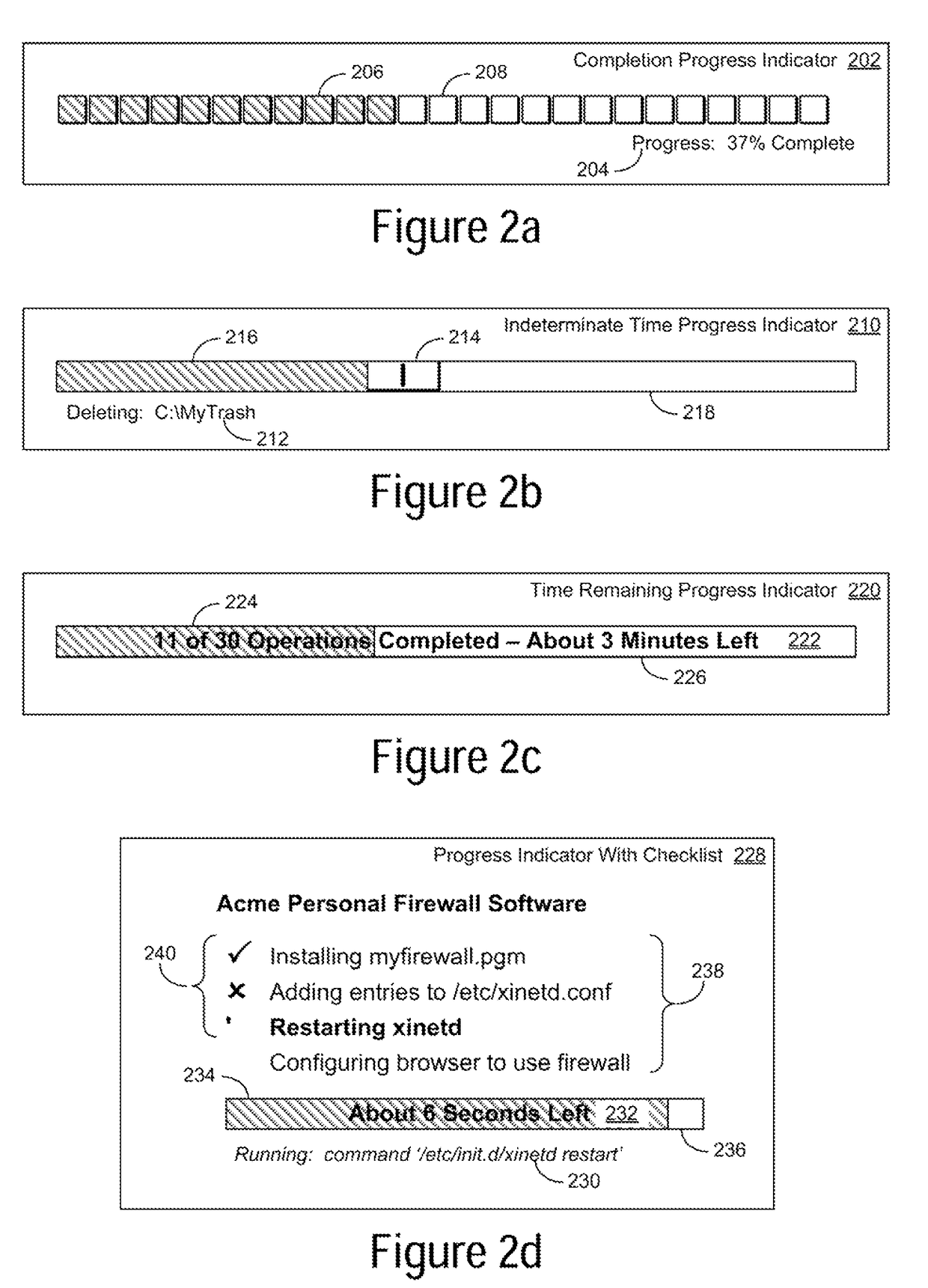

A method, system and computer-usable medium are disclosed for providing graphical completion status information for the management of serial computer operations that are forked into parallel operations. A first interactive progress bar, comprising a plurality of progress indicator segments, is implemented to show the completion status of a composite application. A second progress bar is implemented for each element of the composite application as it is executed. Elements that are serially executed may require prerequisite or dependent operations. Forking operations are performed to execute elements in parallel. One or more progress indicator segments are selected to display information about their related computer operations. The user interacts with the information to pause, modify, reorder, reverse, retarget, or reverse the selected computer operations.

Owner:IBM CORP

System and Method to Facilitate Progress Forking

A method, system and computer-usable medium are disclosed for providing graphical completion status information for the management of serial computer operations that are forked into parallel operations. A first interactive progress bar, comprising a plurality of progress indicator segments, is implemented to show the completion status of a composite application. A second progress bar is implemented for each element of the composite application as it is executed. Elements that are serially executed may require prerequisite or dependent operations. Forking operations are performed to execute elements in parallel. One or more progress indicator segments are selected to display information about their related computer operations. The user interacts with the information to pause, modify, reorder, reverse, retarget, or reverse the selected computer operations.

Owner:IBM CORP

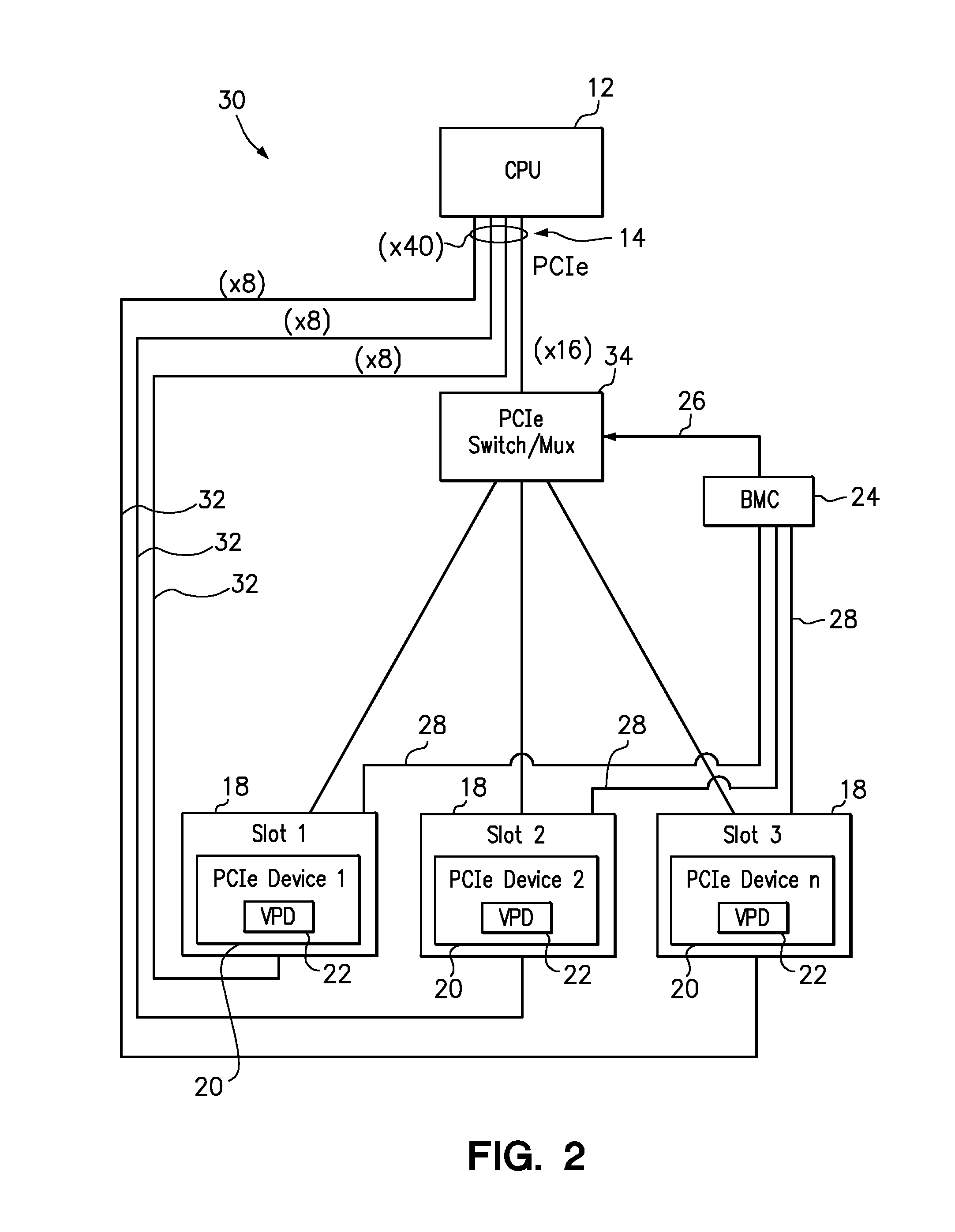

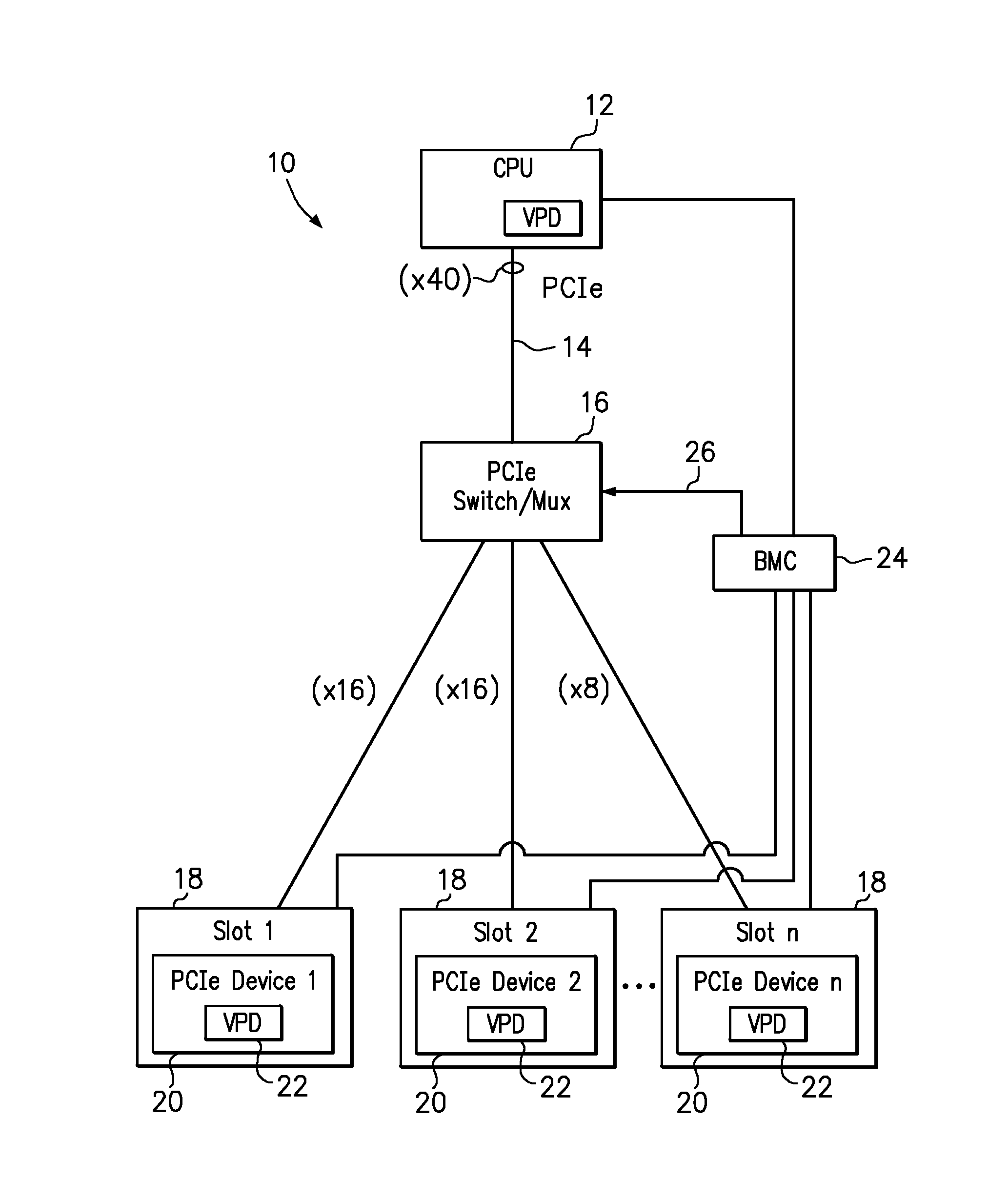

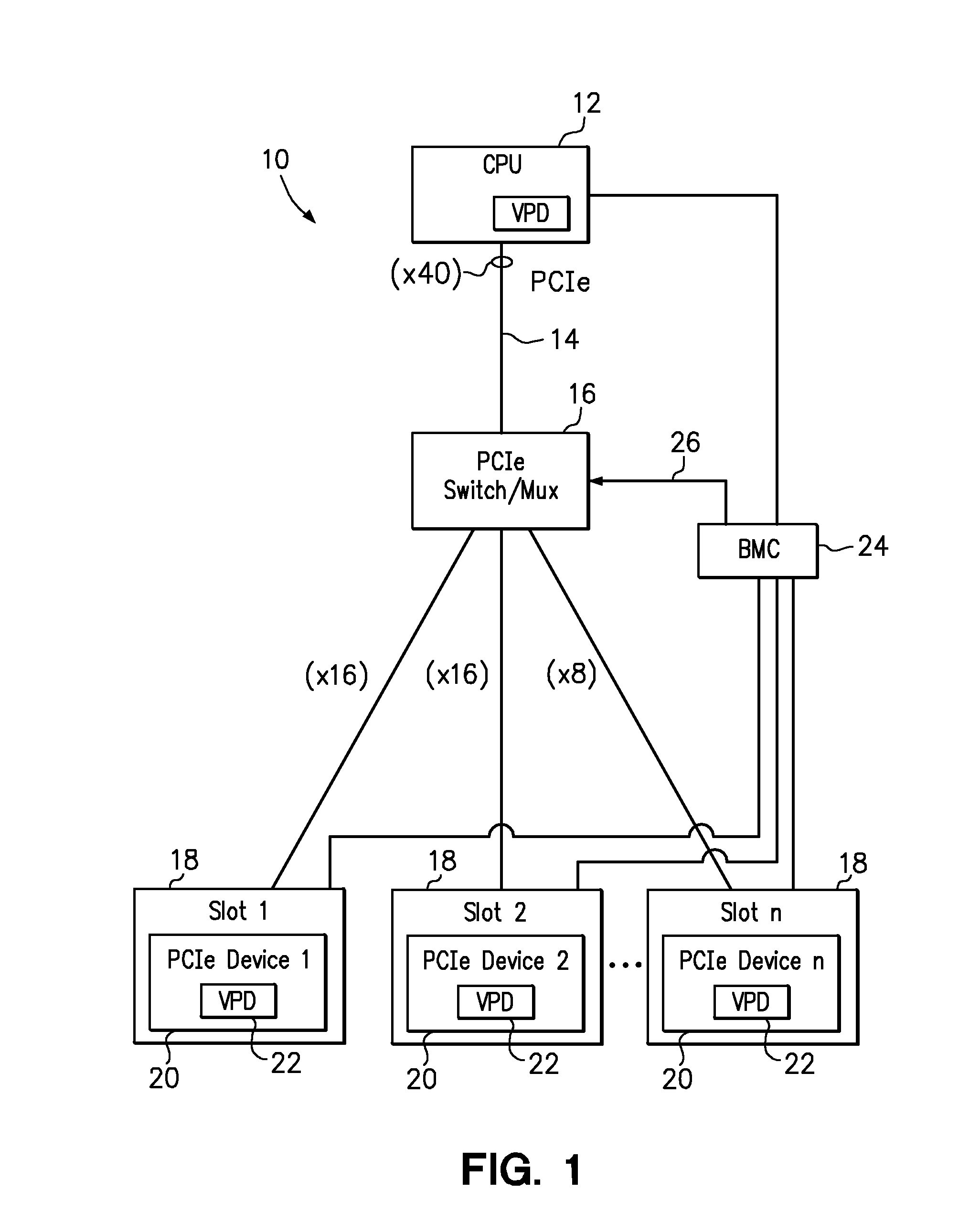

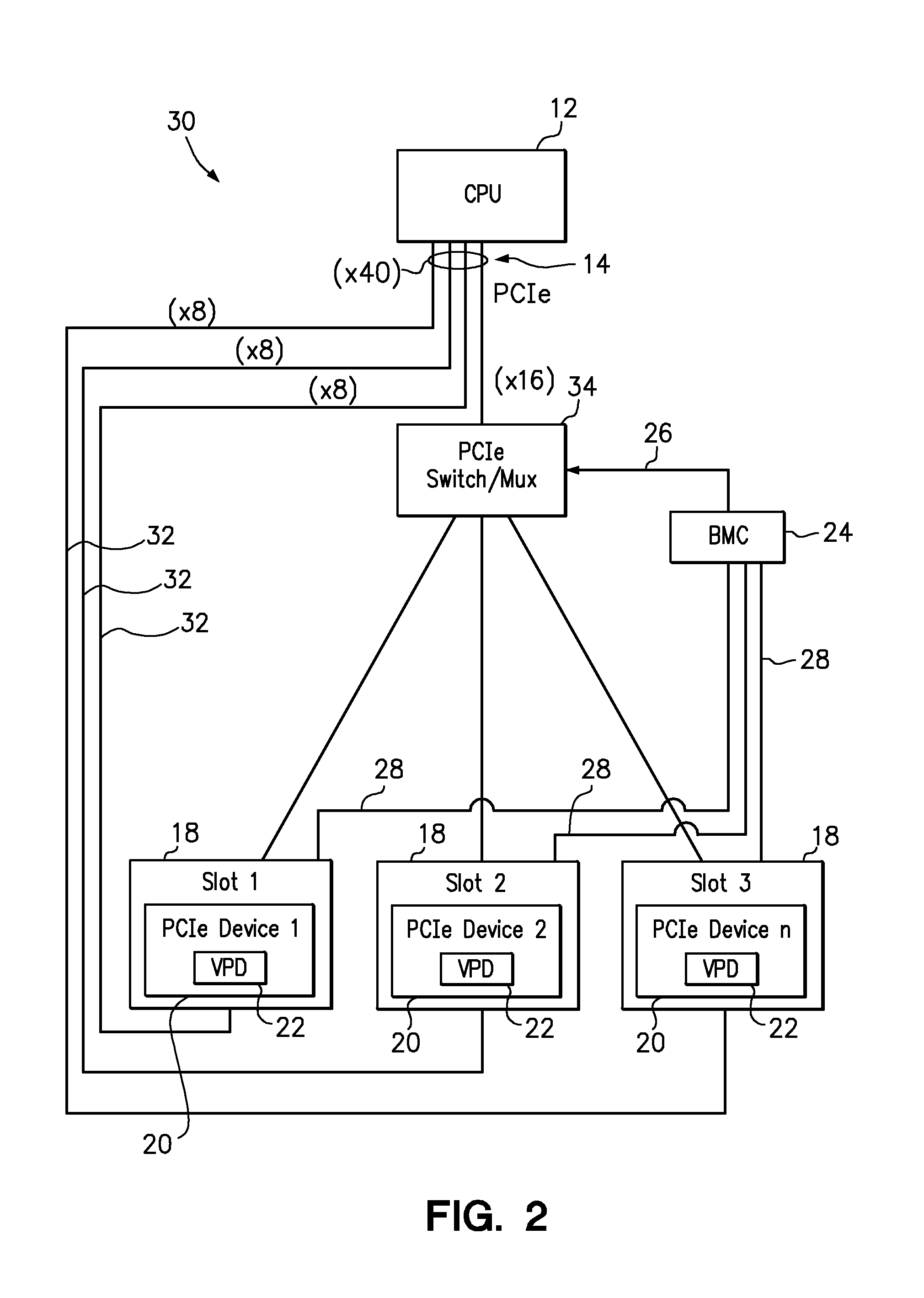

Allocating lanes of a serial computer expansion bus among installed devices

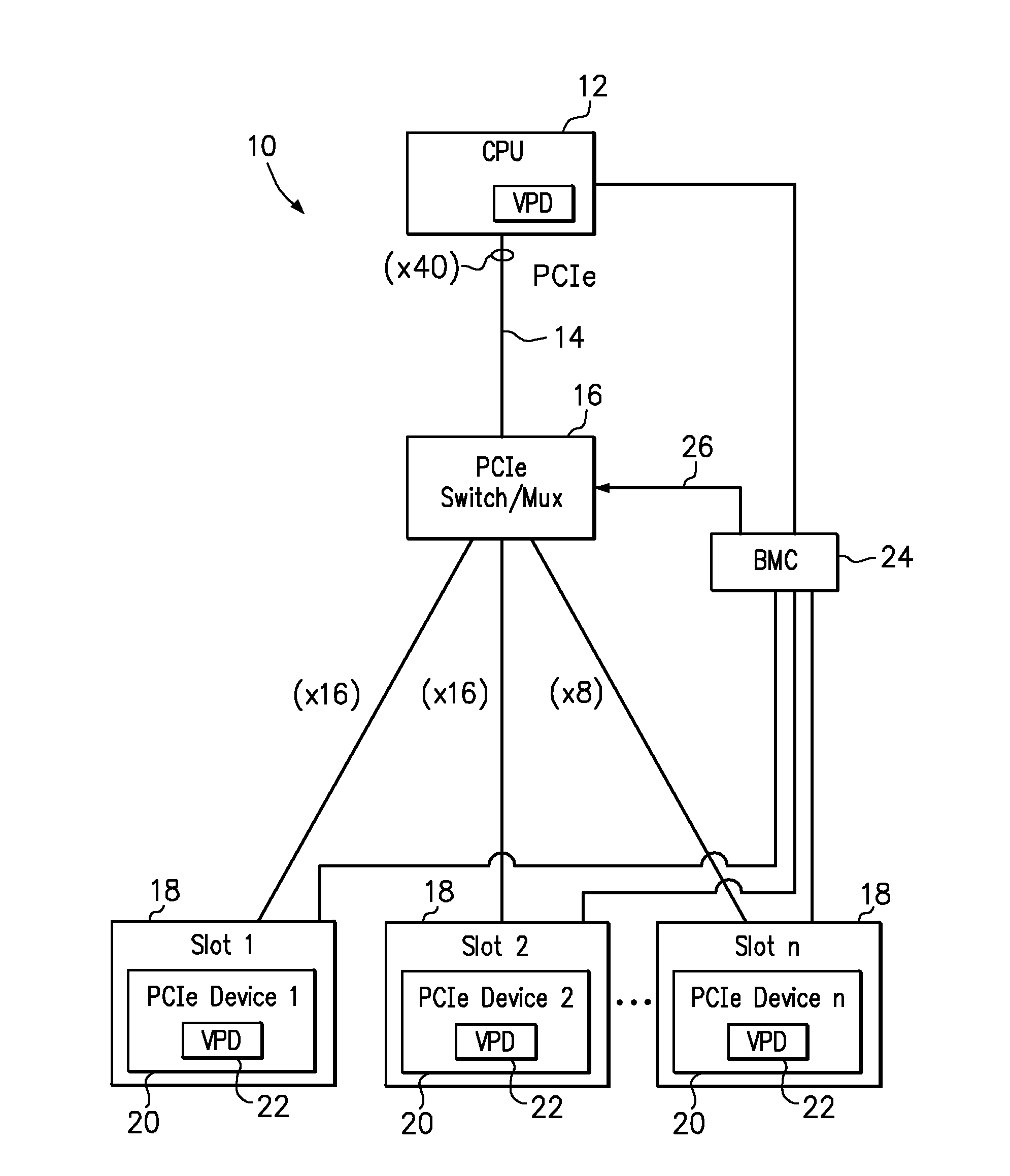

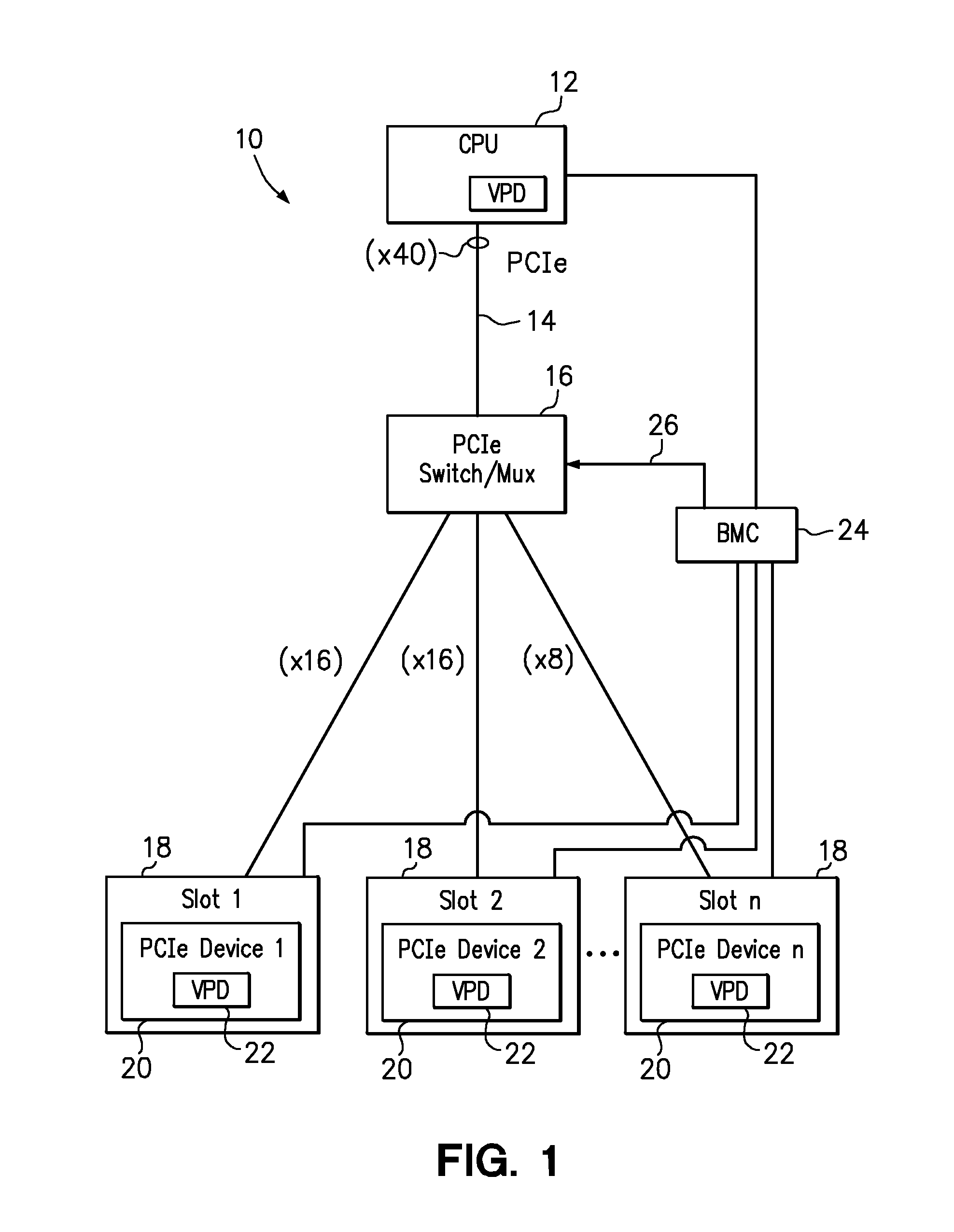

A method includes a supervisory controller within a computer identifying a plurality of PCIe devices installed within the computer and identifying one or more configurable link width for each of the identified PCIe devices, wherein each of the identified PCIe devices is determined to be installed in a particular PCIe slot. The method further includes the supervisory controller granting a higher priority to a first one of the PCIe devices than to a second one of the PCIe devices, and the supervisory controller controlling the allocation of a fixed number of serial communication lanes from a processor to the plurality of PCIe devices, wherein the first PCIe device is allocated the maximum configurable link width identified for the first PCIe device and the second PCIe device is allocated a link width less than the maximum configurable link width identified for the second PCIe device.

Owner:LENOVO ENTERPRISE SOLUTIONS SINGAPORE

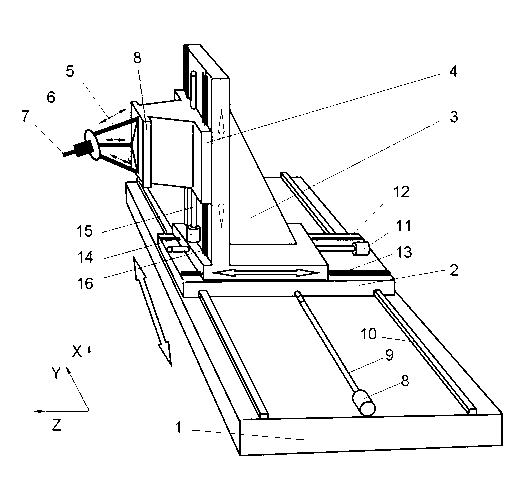

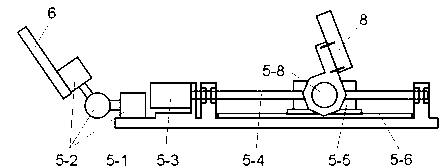

Horizontal type six-shaft parallel-serial computer numerical control milling machine

InactiveCN103252673AEasy to placeIncrease the Z-direction processing rangeFeeding apparatusNumerical controlThree degrees of freedom

The invention discloses a horizontal type six-shaft parallel-serial computer numerical control milling machine, and relates to machining tools for large workpieces with complex curved surfaces. The horizontal type six-shaft parallel-serial computer numerical control milling machine is provided with a base, and a Y-direction slide platform, a Z-direction slide platform and an X-direction slide platform are mounted on the base through rails in sequence. A Y-direction drive motor is arranged on the base, and the Y-direction drive motor is connected with a Y-direction drive screw rod and drives the Y-direction slide platform to move in the Y direction. A Z-direction drive motor is arranged on the Y-direction slide platform, and the Z-direction drive motor is connected with a Z-direction drive screw rod and drives the Z-direction slide platform to move in the Z direction. An X-direction drive motor is arranged on the Z-direction slide platform, and the X-direction drive motor is connected with an X-direction drive screw rod and drives the X-direction slide platform to move in the X direction. An RPS parallel mechanism with three degrees of freedom is arranged on the X-direction slide platform, and a machining tool is mounted at the executing end of the parallel mechanism. The horizontal type six-shaft parallel-serial computer numerical control milling machine has the advantages of being large in working space, good in stiffness property, low in cost and high in machining accuracy. Further, the horizontal type six-shaft parallel-serial computer numerical control milling machine can be used for large stroke machining in the Y direction.

Owner:HARBIN INST OF TECH AT WEIHAI

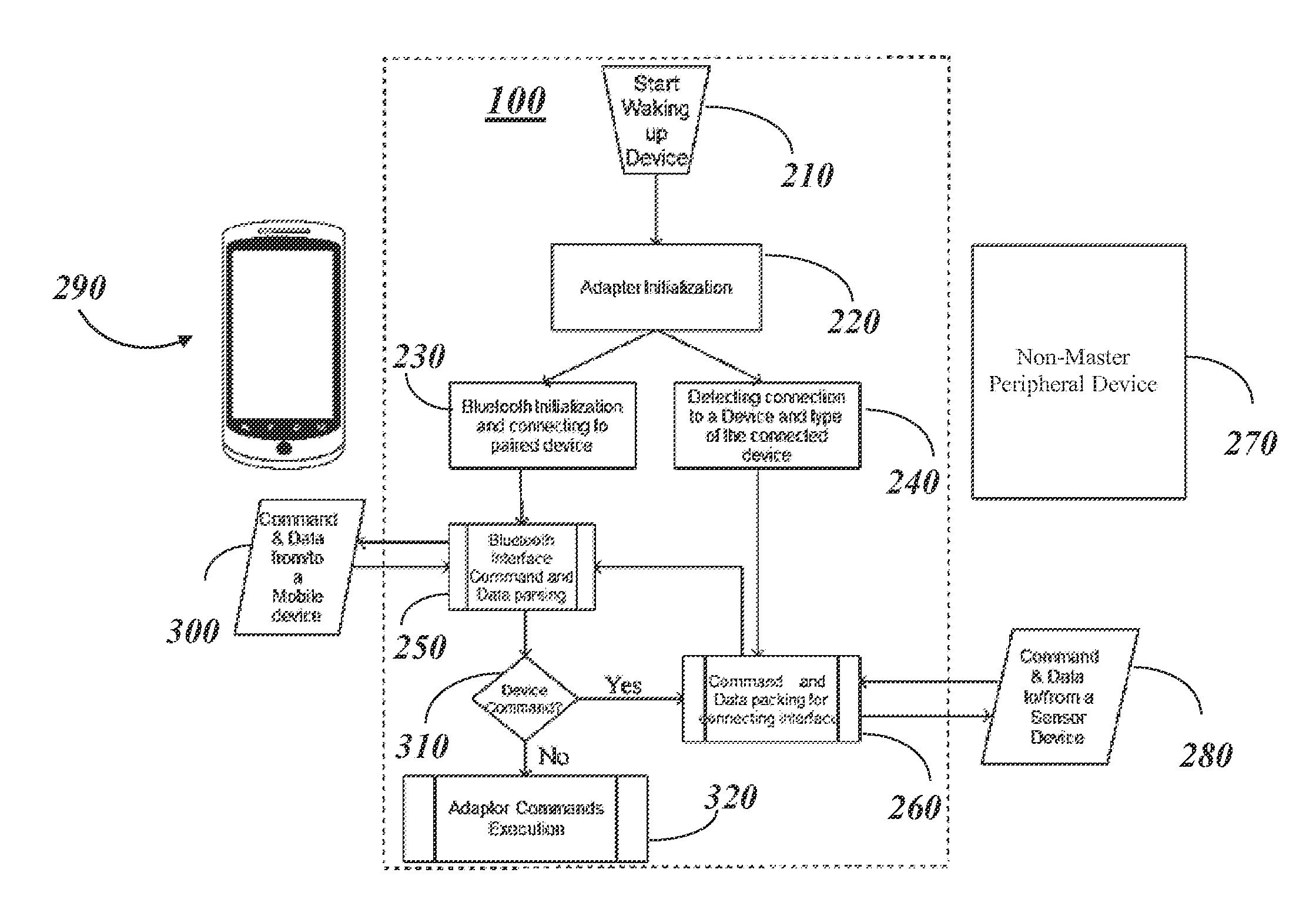

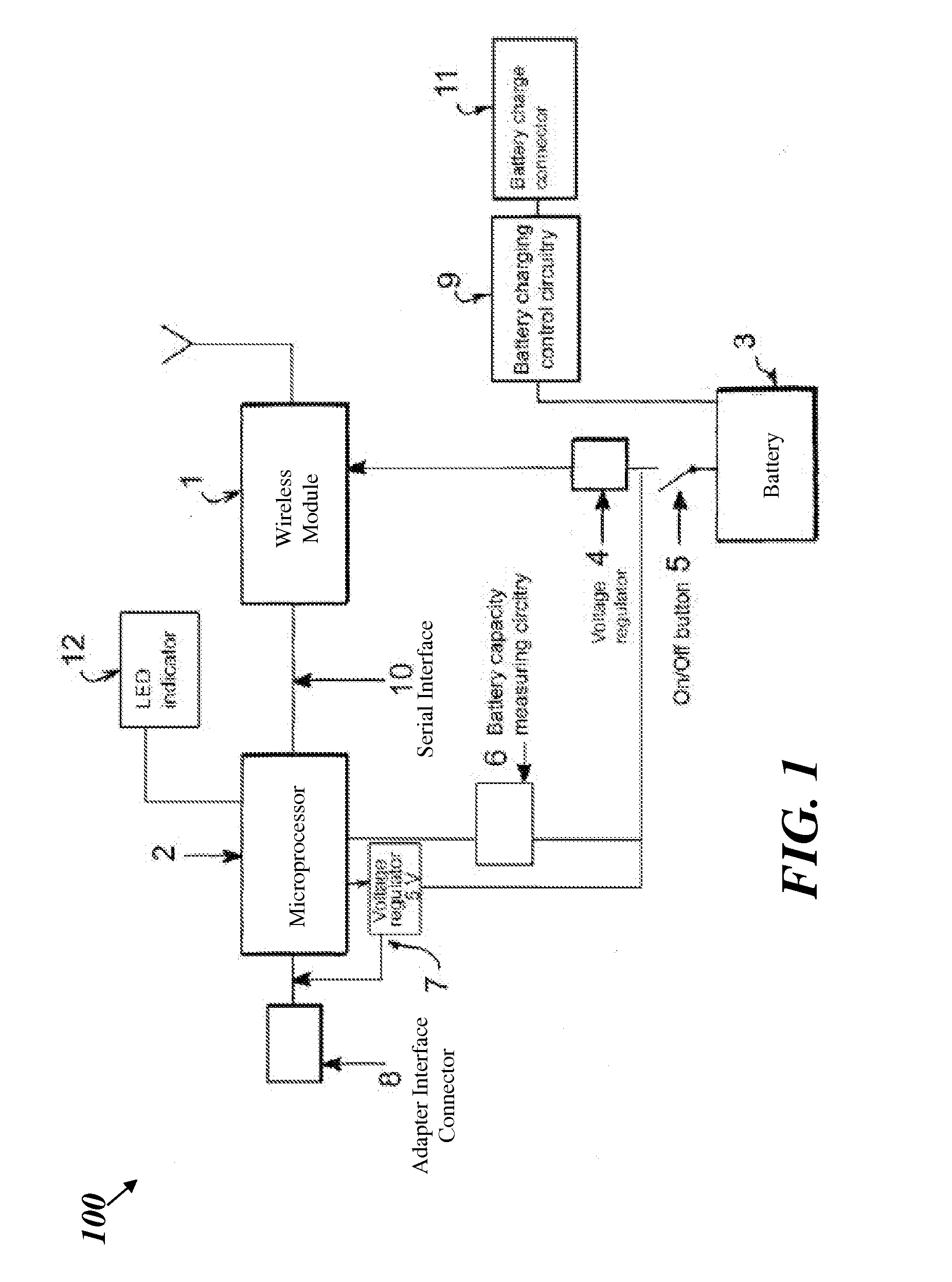

Wireless adapter for connecting a computing device directly to a non-master peripheral device with legacy interface and method of use

InactiveUS20130282928A1Reduce power consumptionImprove mobilityInput/output to record carriersSerial computerComputer module

A wireless adapter and method of using the adapter for wireless connection via communication protocols, communication and data exchange between non-master peripheral devices that have legacy interface such as legacy wired serial computer interfaces and computing devices. The wireless adapter includes a wireless module such as a radio transmission / reception module that supports one or more wireless interfaces and has embedded software stack with at least one or several communication protocols. The wireless module is connected to a microprocessor emulating role of a master device. The adapter interface connector plugs into the legacy interface connector of the non-master peripheral device. The microprocessor emulates a master device in legacy interface in combination with a voltage regulator / converter so the wireless adapter plays a role of a master device in legacy interface with the non-master peripheral device acting as a non-master device in interface. This establishes a wireless connection between the computing device and the non-master peripheral device across the wireless adapter.

Owner:HEALTHMOB

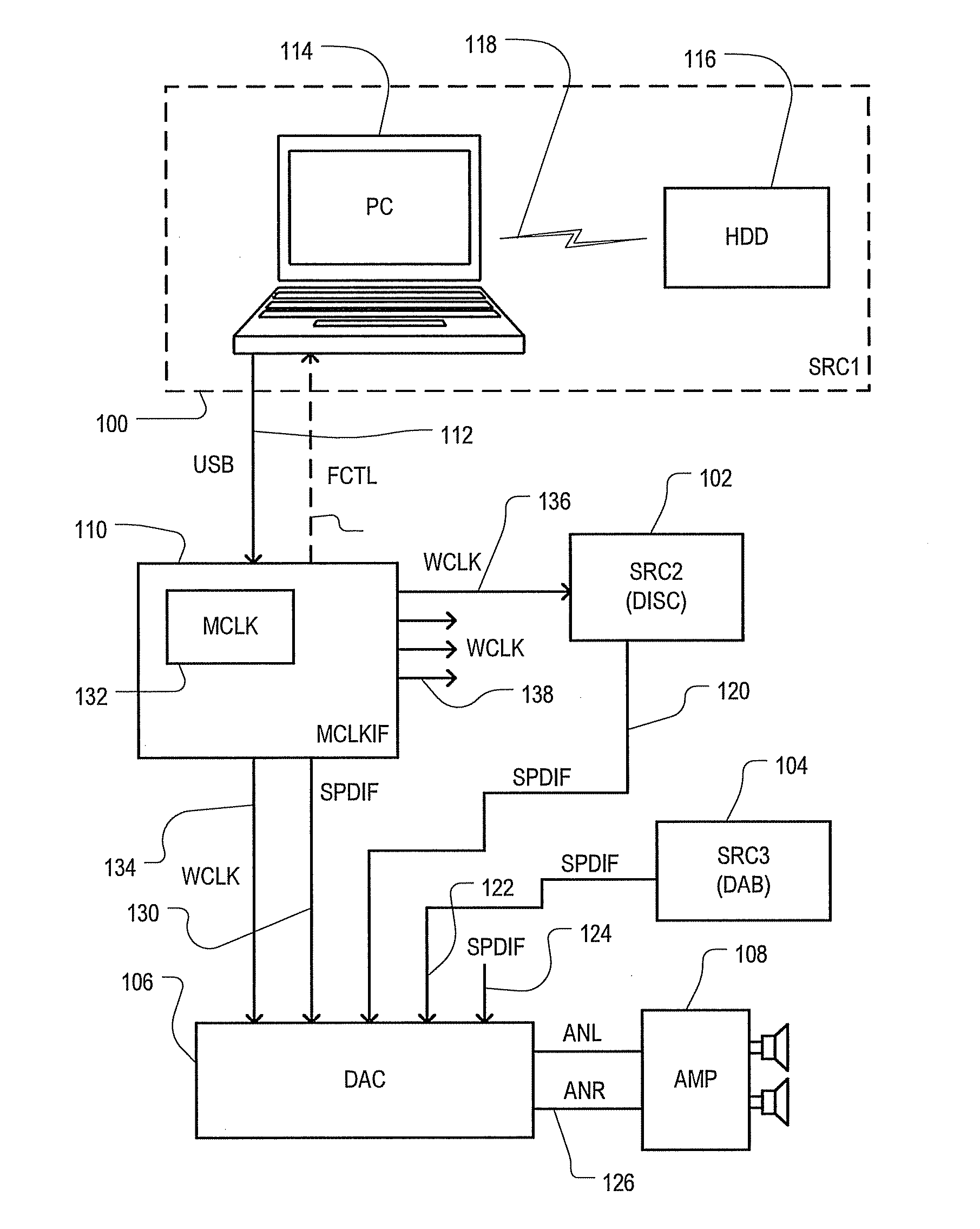

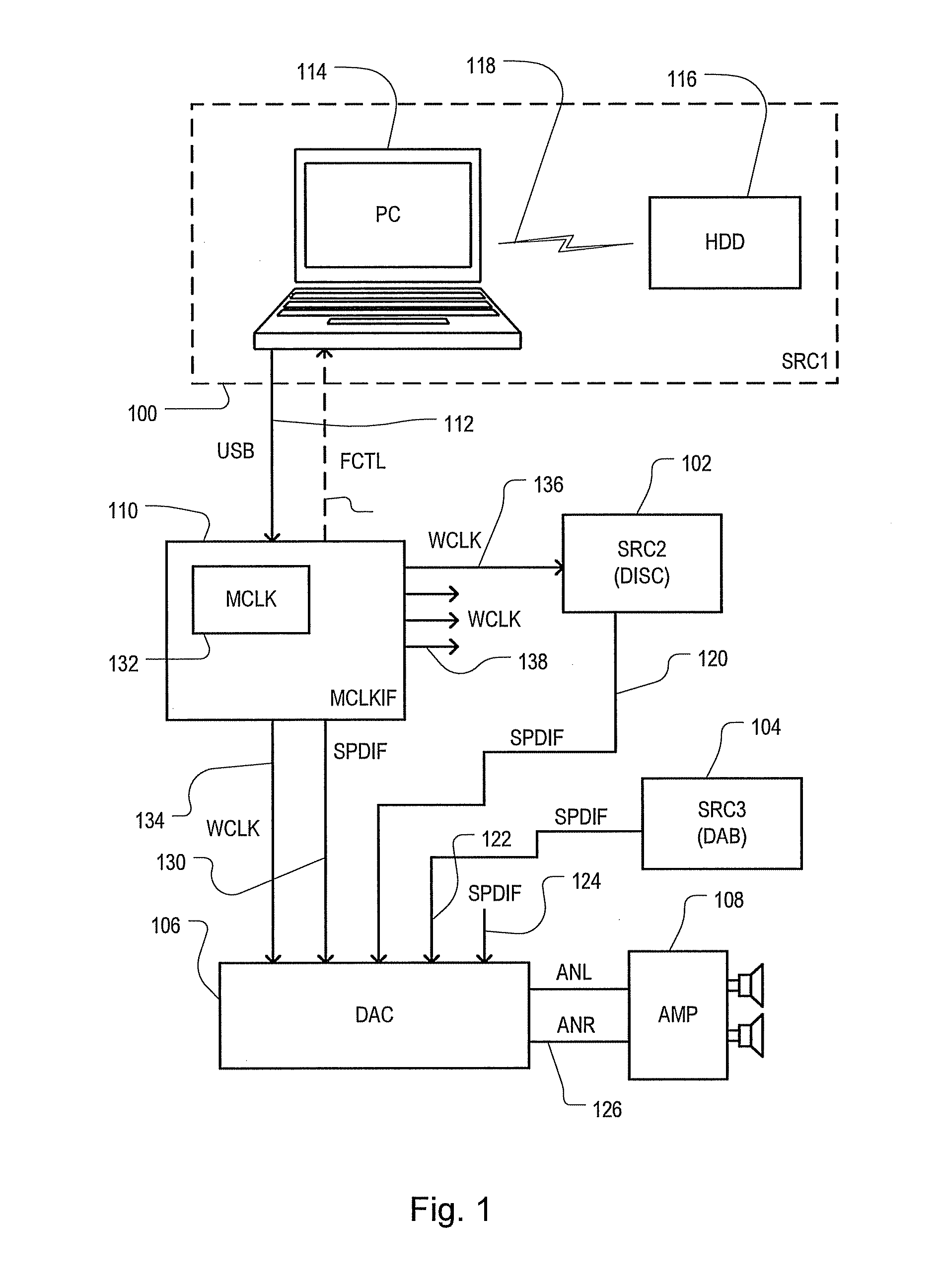

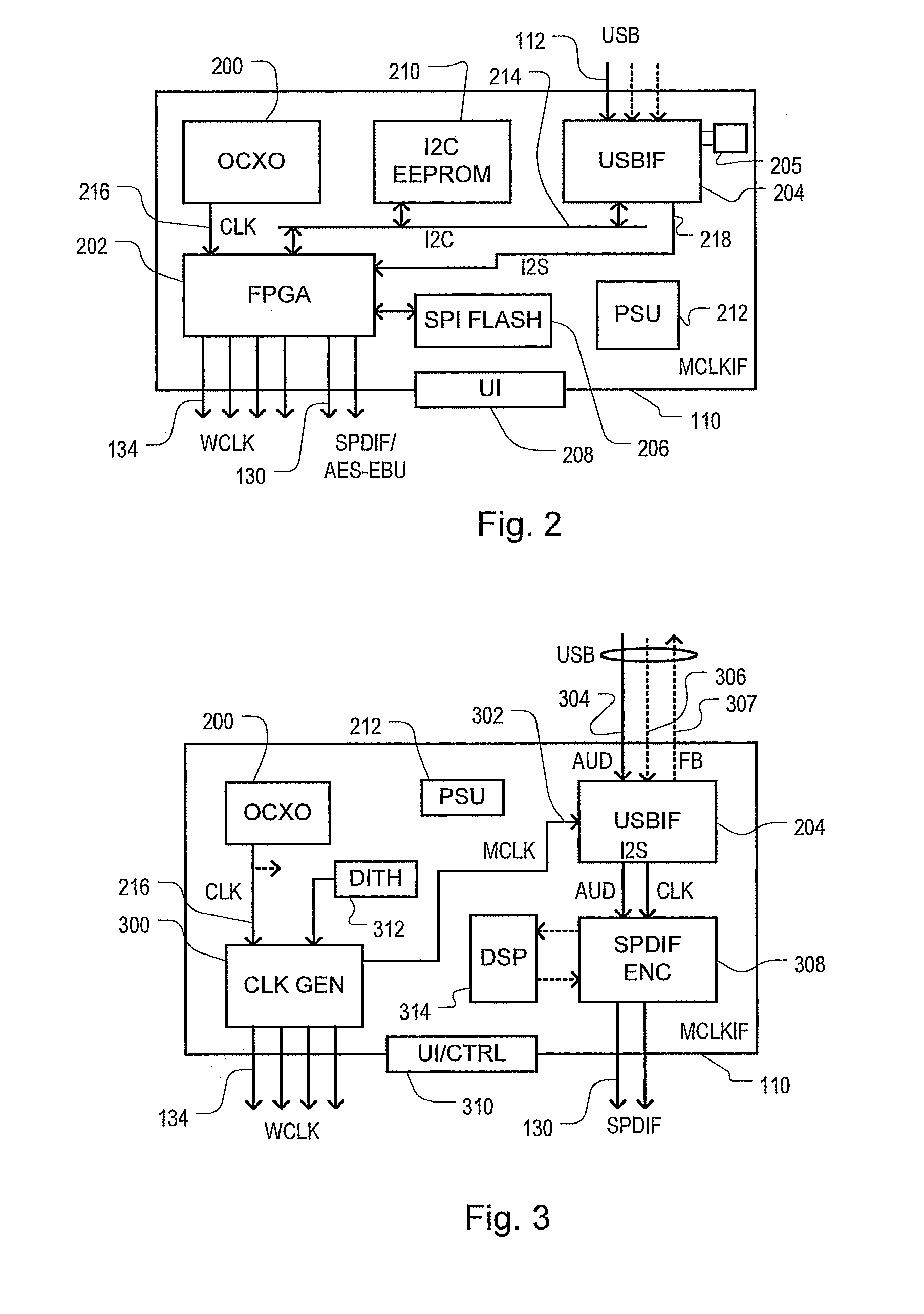

Computer audio interface units and systems

InactiveUS20100077247A1Without qualityCost-effective and flexibleGenerating/distributing signalsTransmission path multiple useSerial computerWord clock

A computer audio interface unit (110) comprises a serial computer interface (e.g. USB) (204) providing a connector (112) for connection to an external, computer-based source (100) of digital audio data samples. A digital audio output connector (130) provides a digital audio output signal to external audio reproduction apparatus (106, 108). A word clock output connector (134) provides a word clock signal to external audio reproduction apparatus, in parallel with said digital audio output signal. An encoder (202 / 308) receives digital audio data via said USB interface and outputs said digital audio output signal. Clocking circuitry (202 / 300, 312) is responsive to a timing reference signal (200) independent of said external source (100), and generates said word clock signal for output to the external reproduction apparatus. Said clocking circuitry further generates a clock signal (302) for the USB interface (204) so as to synchronise the drawing of said audio data samples via said USB interface with the generated external word clock signal and the digital audio output signal. Interface and encoder functions may be housed separately from a master clock function.

Owner:DATA CONVERSION SYST

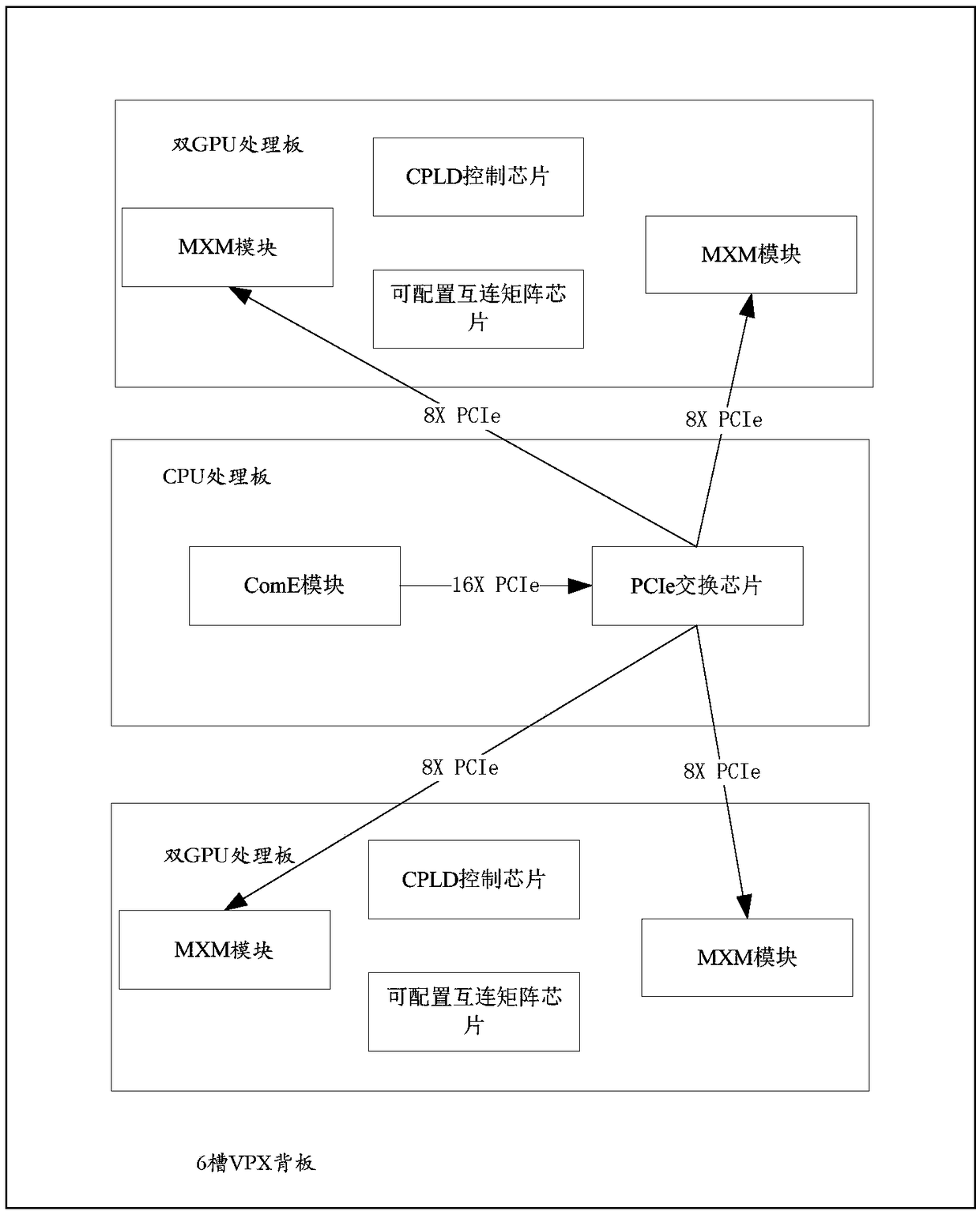

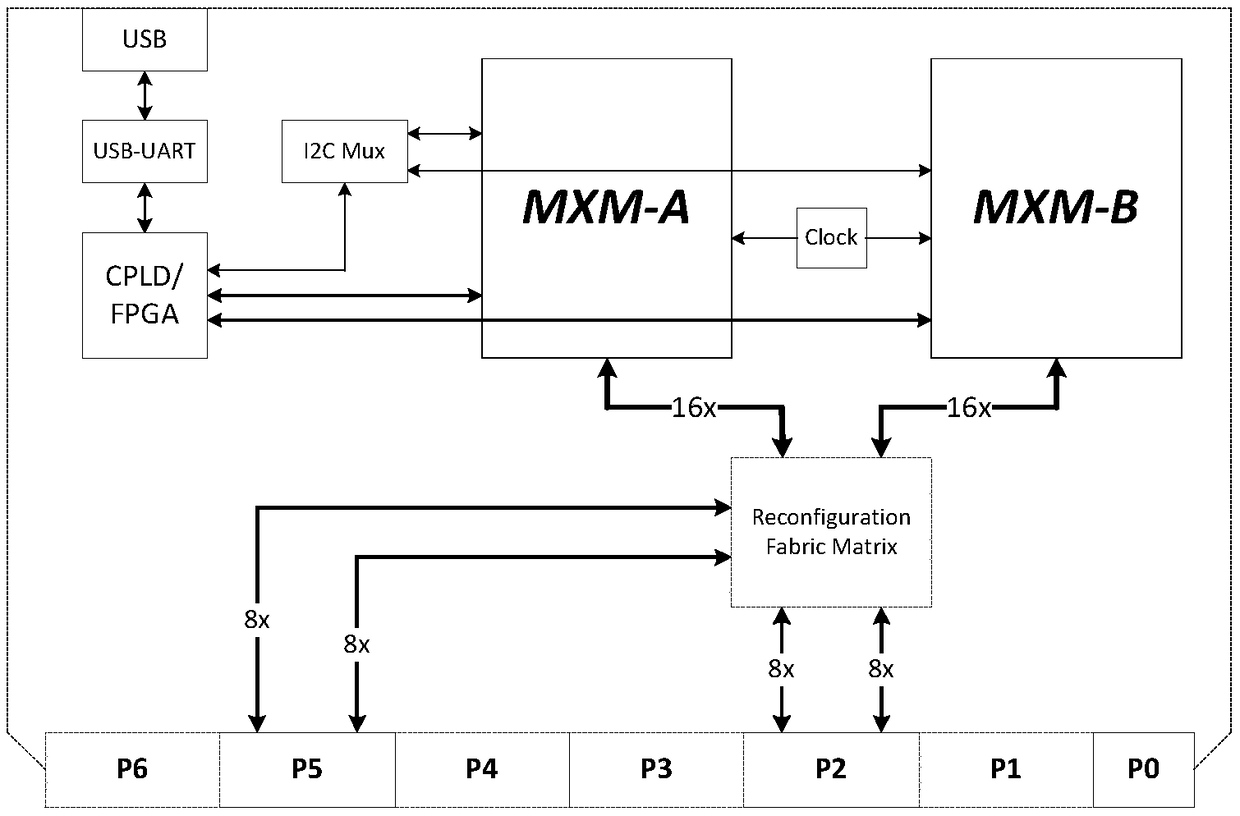

A multi-GPU high performance processing system based on OpenVPX platform

ActiveCN109242754AGood internet communicationMeet different needsProcessor architectures/configurationElectric digital data processingGraphicsSerial computer

The invention discloses a multi-GPU high-performance processing system based on an OpenVPX platform. The system comprises two dual-graphics processor GPU processing boards, a central processing unit CPU processing board and a 6-slot VPX backboard. The dual GPU processing board has two MXM modules equipped with GPU and a CPLD control chip. The 6-slot VPX backplane includes seven VPX connectors fromP0 to P6, of which P2 and P5 are configured as VPX connectors supporting the high-speed serial computer expansion bus standard PCIe communication standard, and P2 and P5 each have two 8x PCIe interfaces. CPU CPU processing board with a CPU mounted on the ComE module and a 64-channel PCIe switch chip; the ComE module is connected to the PCIe switch chip via 16x PCIE. A total of four MXM modules onthe two GPU processing boards are respectively connected to a total of four 8x PCIe interfaces on P2 and P5 on the VPX backplane through 8x PCIe; a total of four 8x PCIe interfaces for P2 and P5 on the 6-slot VPX backplane are connected to the PCIe switch chip.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

System and method to facilitate progress forking

A method, system and computer-usable medium are disclosed for providing graphical completion status information for the management of serial computer operations that are forked into parallel operations. A first interactive progress bar, comprising a plurality of progress indicator segments, is implemented to show the completion status of a composite application. A second progress bar is implemented for each element of the composite application as it is executed. Elements that are serially executed may require prerequisite or dependent operations. Forking operations are performed to execute elements in parallel. One or more progress indicator segments are selected to display information about their related computer operations. The user interacts with the information to pause, modify, reorder, reverse, retarget, or reverse the selected computer operations.

Owner:IBM CORP

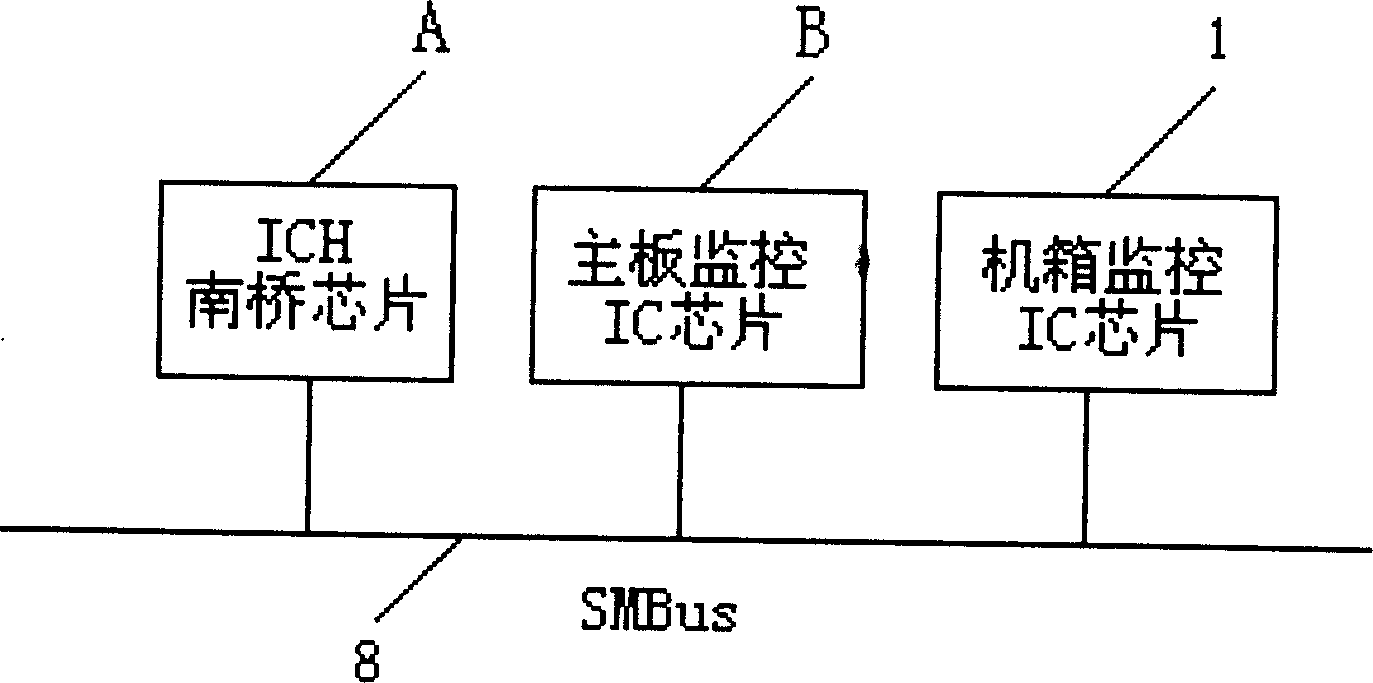

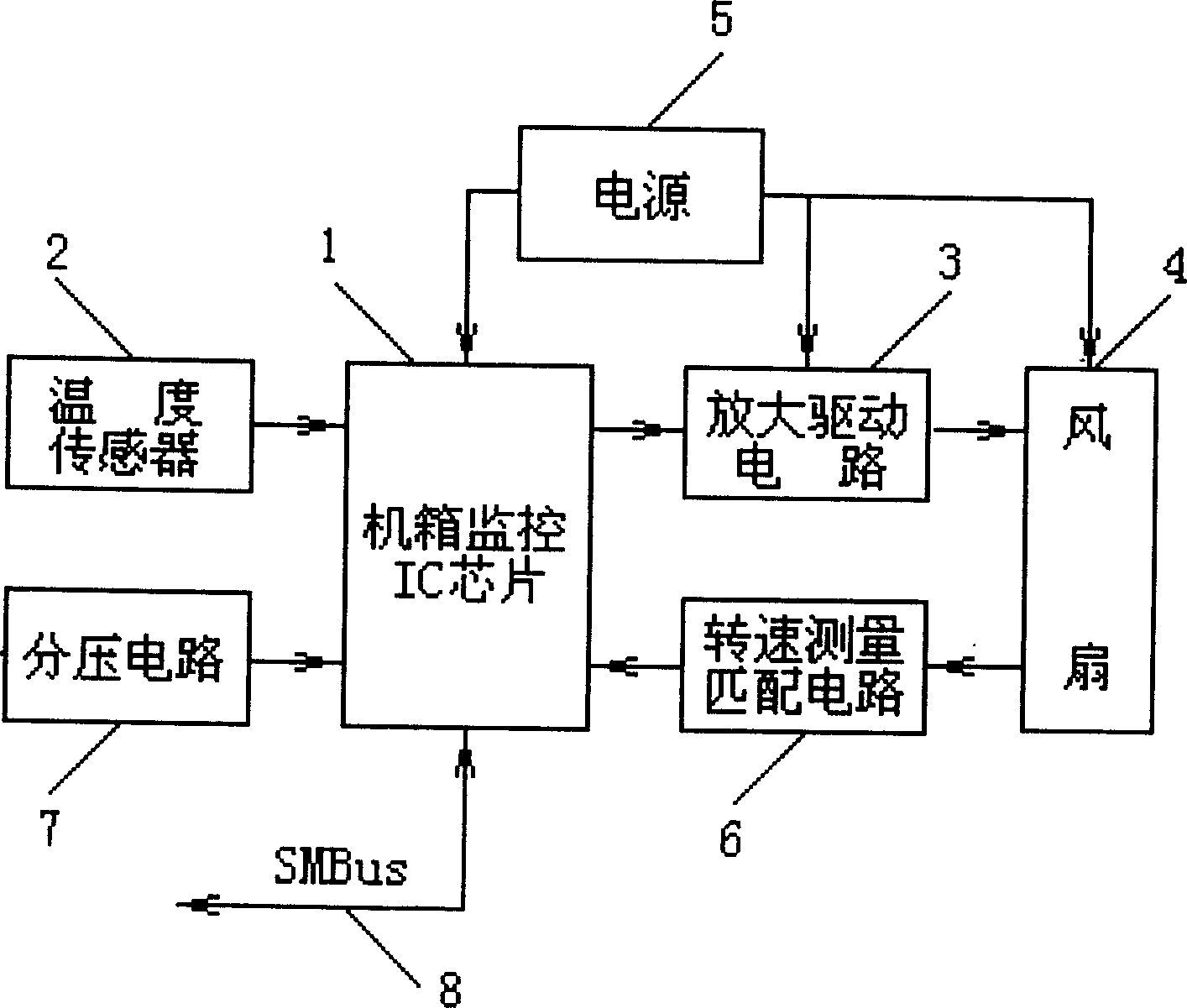

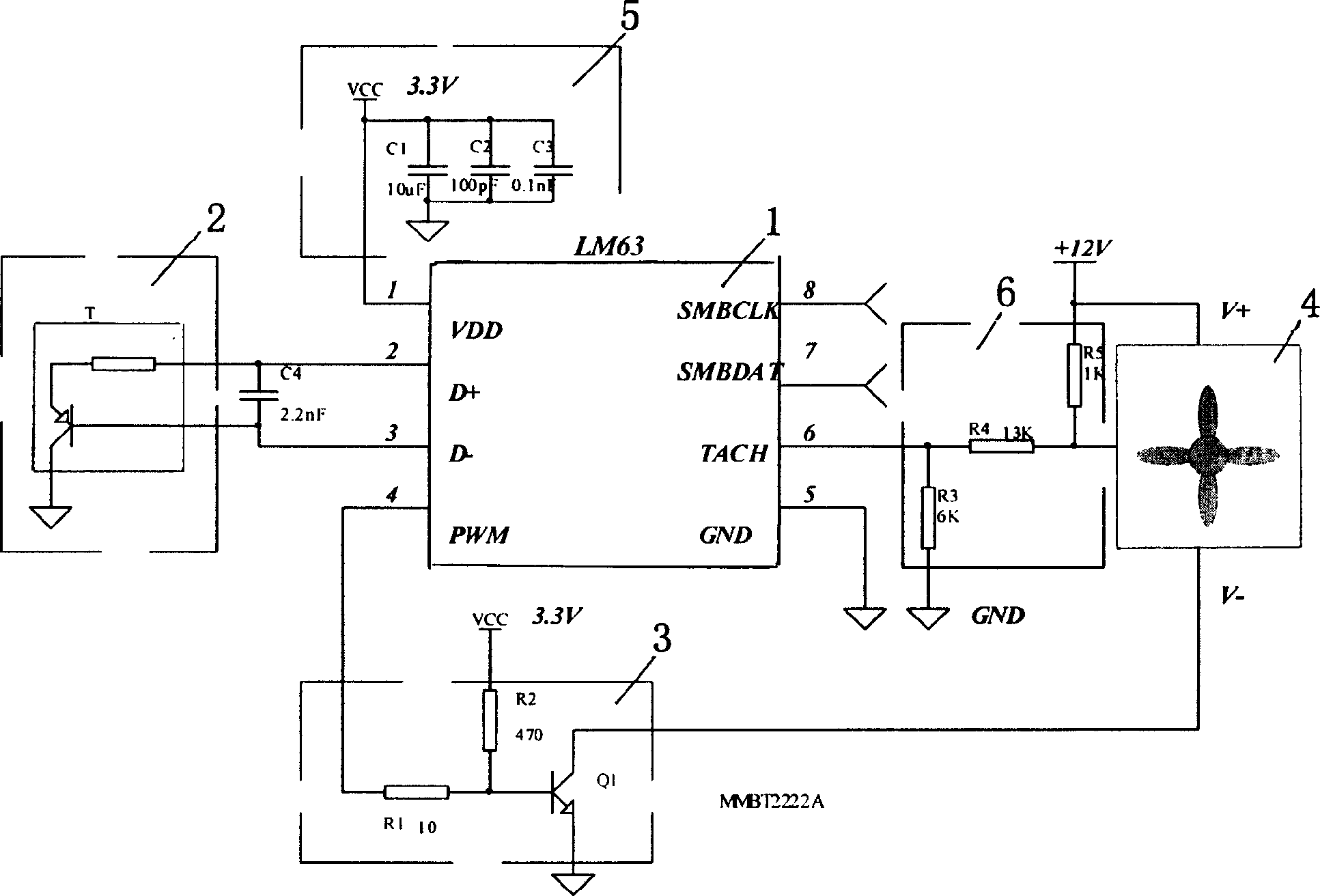

Method and its device for monitoring and controlling computer casing using system managing bus chip

InactiveCN1617105ASimple methodSimple and easy deviceDigital data processing detailsHardware monitoringControl systemSerial computer

The present invention relates to serial computer bus, its device and expanding application. The present invention adopts the built-in control function of SMBus IC chip, and has temperature sensors to measure the temperature of devices inside casing, temperature feedback signal to the IC chip for calculation and amplifier circuit to amplify the outer of the IC chip for controlling the fan to constitute one closed-loop control system. The device consists of casing monitoring IC chip, temperature sensors, amplifying and driving circuit, fan, power source, rotation speed measuring and matching circuit, voltage dividing circuit and SMBus. The present invention has the beneficial effects of constitution of intelligent casing system, measurement and control of fan rotation speed, lowering noise, environment protection, saving in energy, and management of devices inside the casing via communication between SMBus and system unit.

Owner:李谦

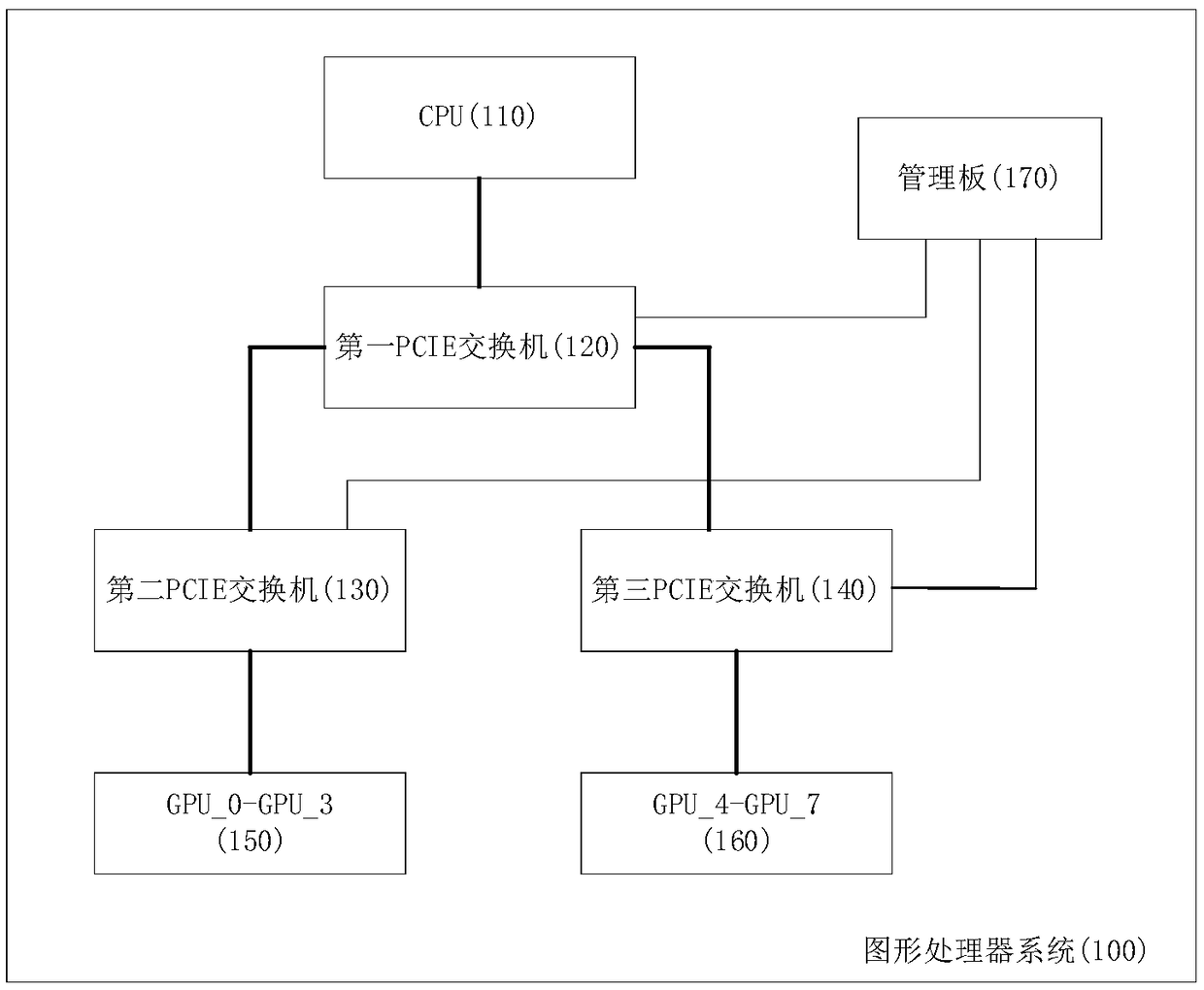

Graphics processor system

ActiveCN109410117ASolve the problem of low P2P communication bandwidthHigh bandwidthProcessor architectures/configurationElectric digital data processingGraphicsSerial computer

The invention provides a graphic processor system. The graphic processor system comprises a central processing unit; A first high-speed serial computer expansion bus standard switch is connected withthe central processing unit; A second high-speed serial computer expansion bus standard switch is connected with the first high-speed serial computer expansion bus standard switch and is in downlink connection with a plurality of graphic processors; A third high-speed serial computer expansion bus standard switch is connected with the first high-speed serial computer expansion bus standard switchand is in downlink connection with a plurality of graphic processors; and a management board is respectively connected with the first high-speed serial computer expansion bus standard switch, the second high-speed serial computer expansion bus standard switch and the third high-speed serial computer expansion bus standard switch for management setting. According to the invention, flexible communication between multiple hosts and multiple terminals is realized, and the problem of low P2P communication bandwidth between GPUs is solved.

Owner:INVENTEC PUDONG TECH CORPOARTION +1

Onboard graphics processor control method and device

ActiveCN110399328AEasy to handleMultiple digital computer combinationsProcessor architectures/configurationGraphics processing unitEmbedded system

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

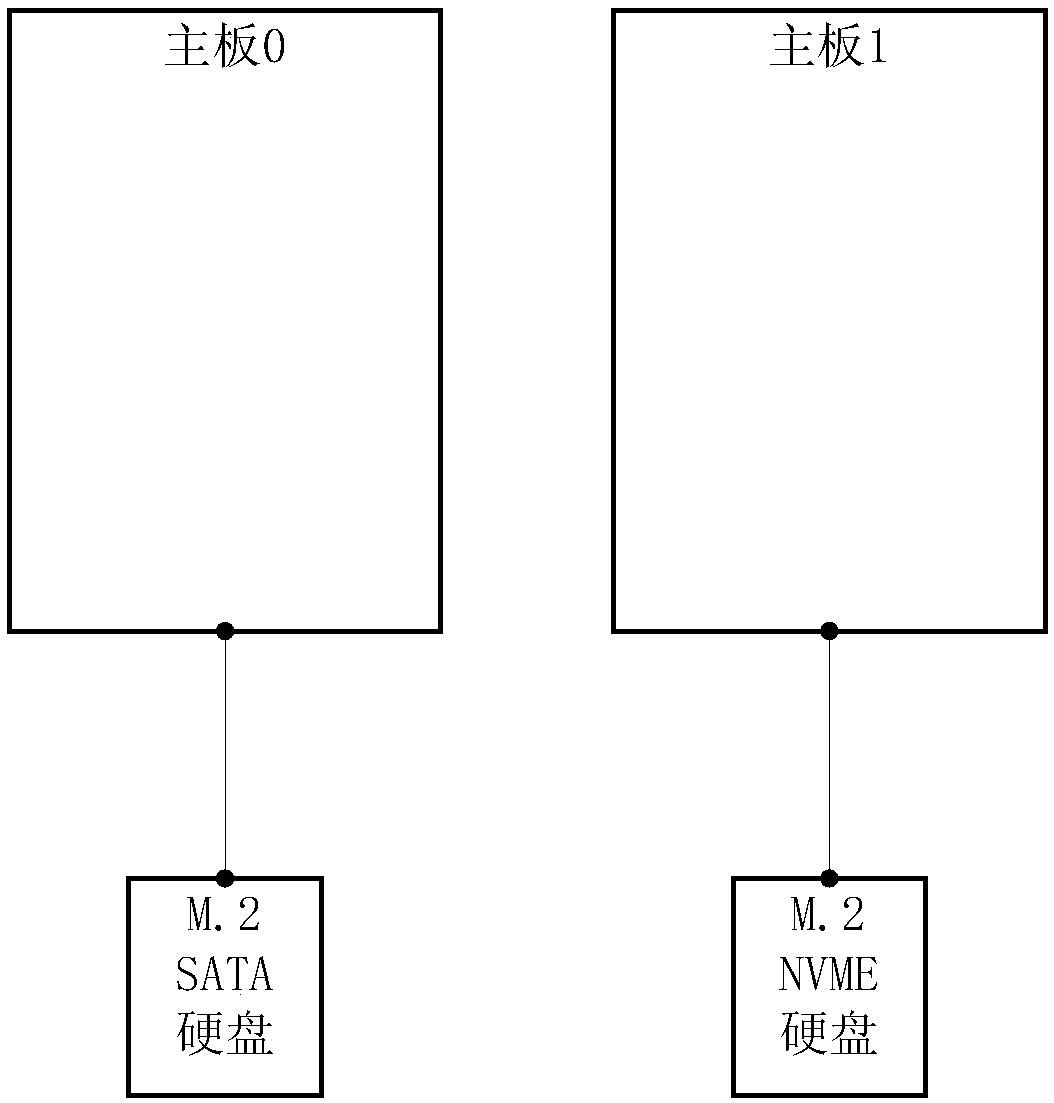

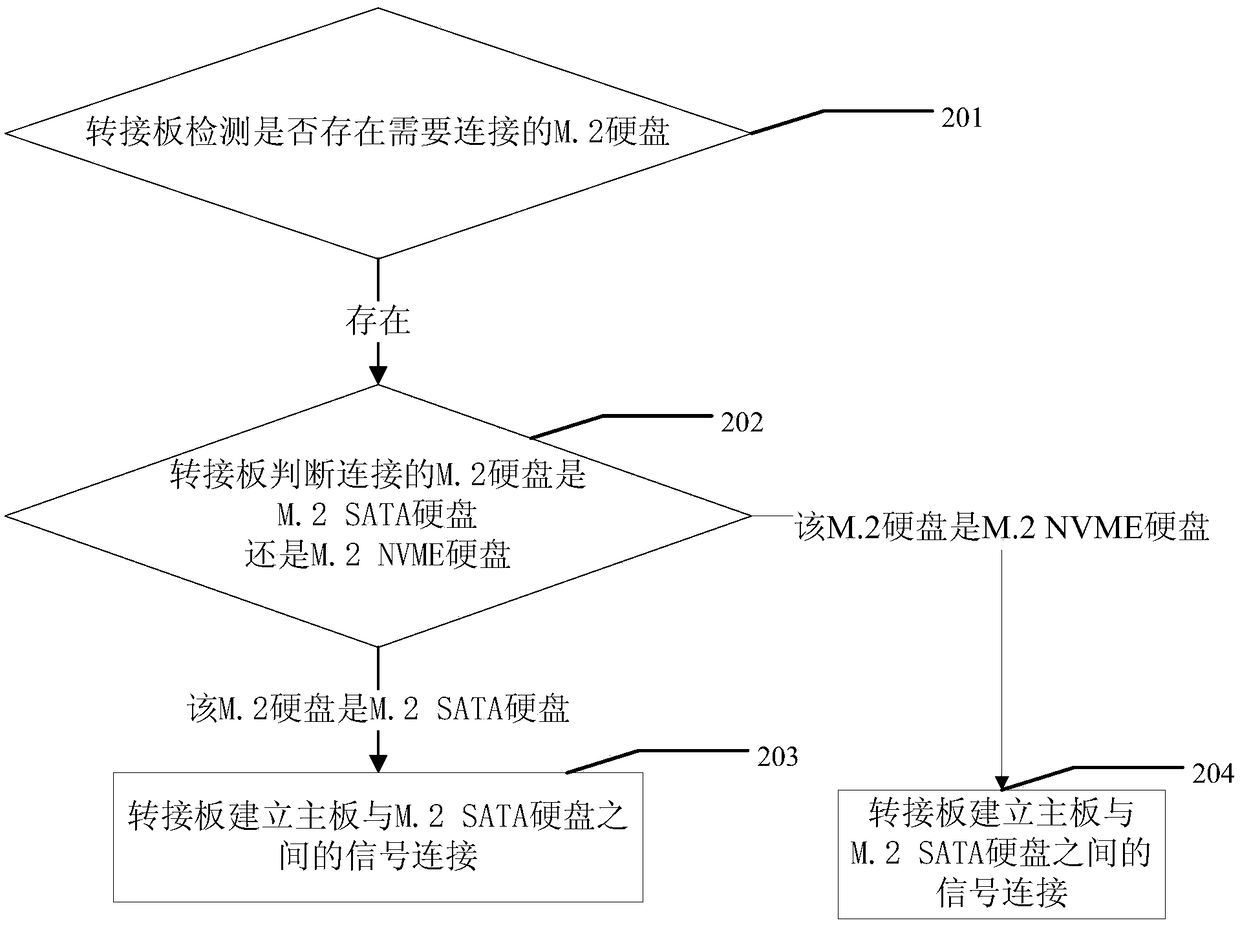

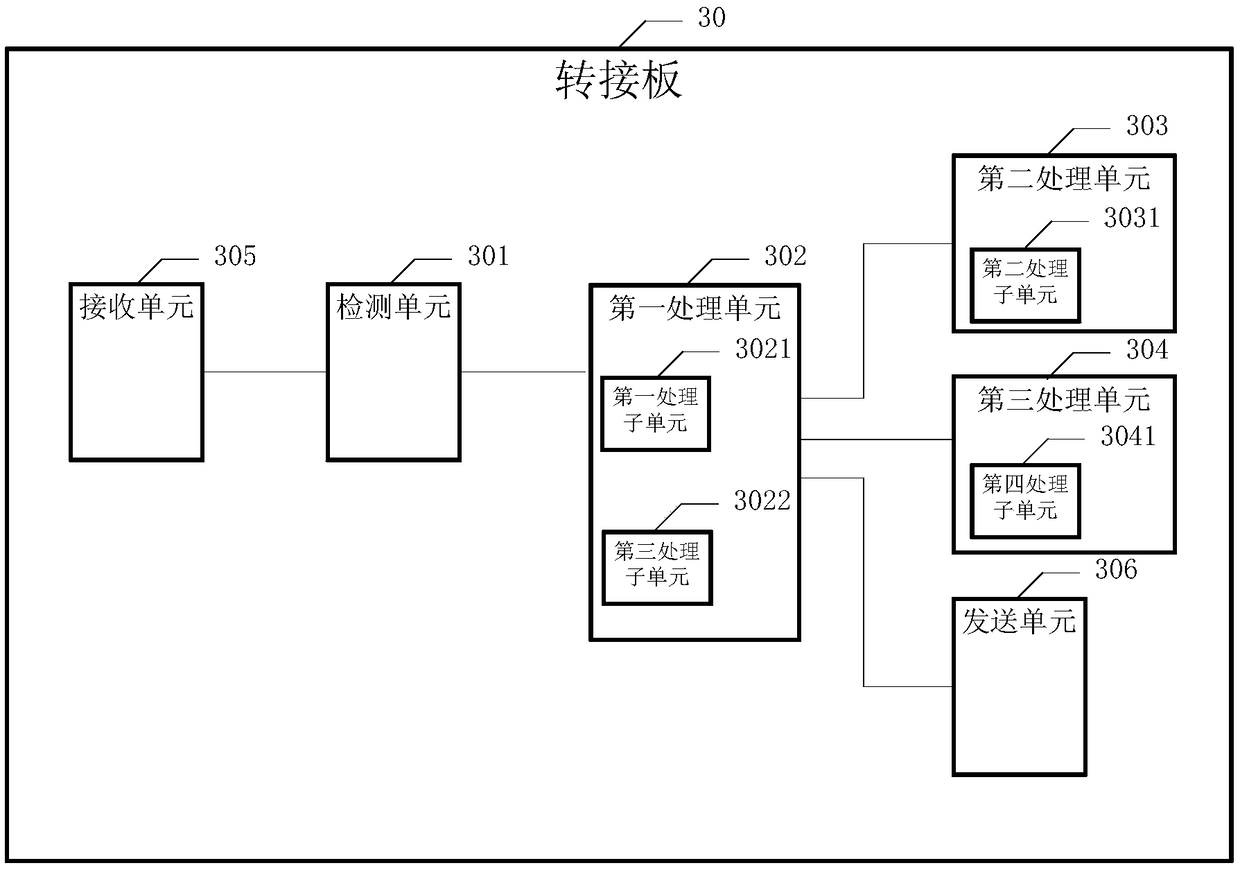

Method, adapter board and system for adaptively switching hard disk

InactiveCN109240953AImprove connection efficiencyElectric digital data processingSerial computerHost controller interface

The embodiment of the present application discloses a method for adaptively switching a hard disk, which comprises the following steps: an adapter board detects whether there is a new generation interface standard M.2 hard disk which needs to be connected; If yes, the adapter board judges whether the connected M.2 hard disk is an M.2 serial advanced technology accessory SATA hard disk or an M.2 non-volatile memory host controller interface specification NVME hard disk; If the M.2 hard disk is an M.2 SATA hard disk, the adapter board establishes a SATA signal connection between the main board and the M.2 SATA hard disk; If the M.2 hard disk is an M.2 NVME hard disk, the adapter board establishes a high-speed serial computer expansion bus standard PCIE signal connection between the main board and the M.2 NVME hard disk. The embodiment of that present application also provides a corresponding adapter board and system. The adapter board in the embodiment of the present application can adaptively connect the M.2 hard disk with the motherboard, thereby improving the connection efficiency.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

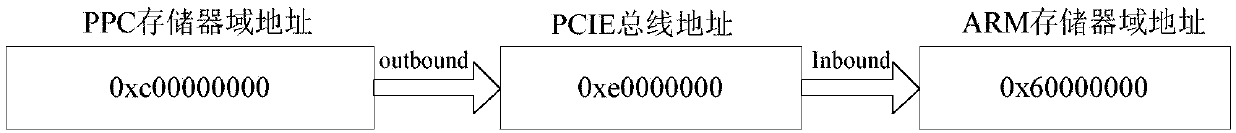

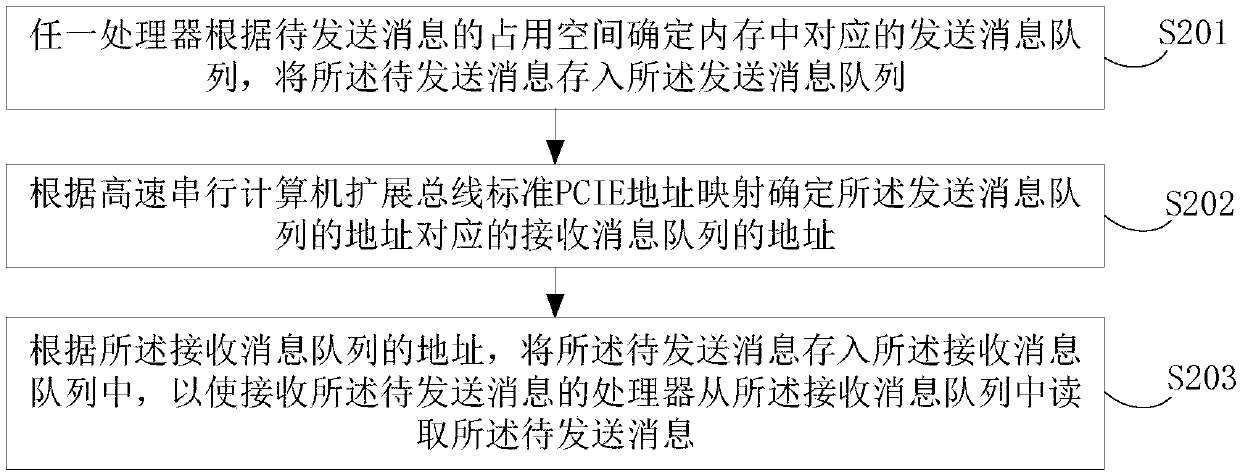

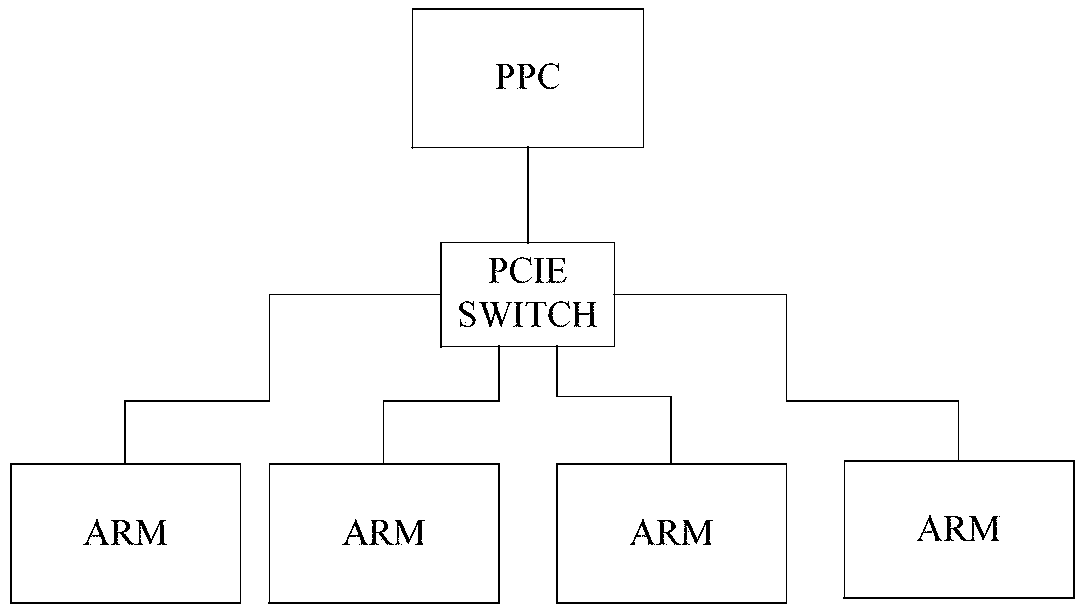

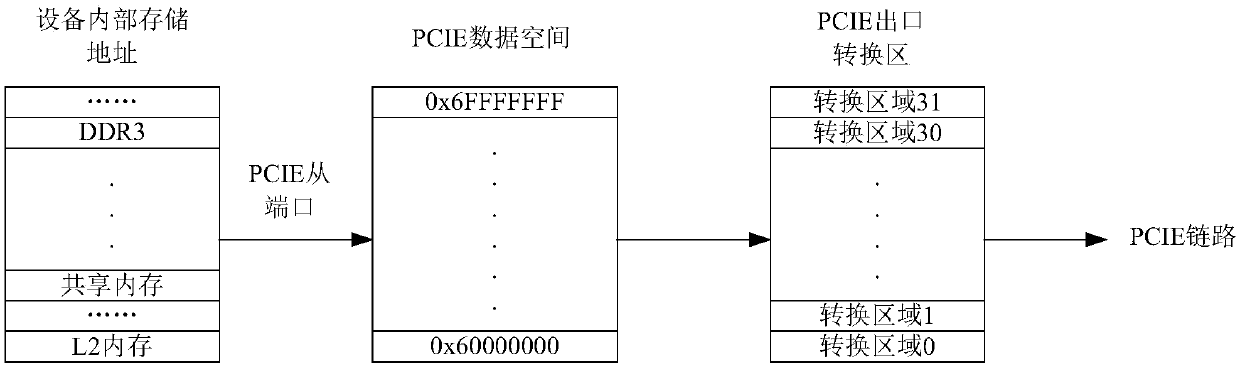

Method and device for data communication among multiple processors

ActiveCN110457251AEasy to operateEasy maintenanceElectric digital data processingMessage queueSerial computer

The embodiment of the invention discloses a method and device for data communication among multiple processors, and the method comprises: enabling any processor to determine a corresponding message sending queue in a memory according to the occupied space of a to-be-sent message, and storing the to-be-sent message into the message sending queue; determining an address of a received message queue corresponding to the address of the sent message queue according to high-speed serial computer extension bus standard PCIE address mapping; and storing the to-be-sent message into the received messagequeue according to the address of the received message queue, so as to enable a processor receiving the to-be-sent message to read the to-be-sent message from the received message queue. According tothe embodiment of the invention, the message sending queues and the message receiving queues are arranged in the memories of the processors, message-based data communication between the two processorsis completed through PCIE address mapping, data receiving and sending interfaces of the processors are unified, data reading and writing are convenient to operate and maintain, and the communicationefficiency between the processors is greatly improved.

Owner:DATANG MOBILE COMM EQUIP CO LTD

Allocating lanes of a serial computer expansion bus among installed devices

Owner:LENOVO ENTERPRISE SOLUTIONS SINGAPORE

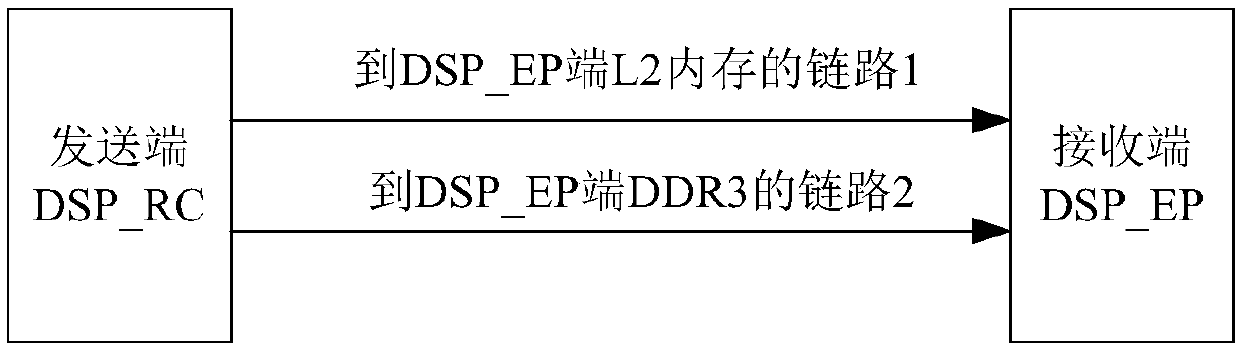

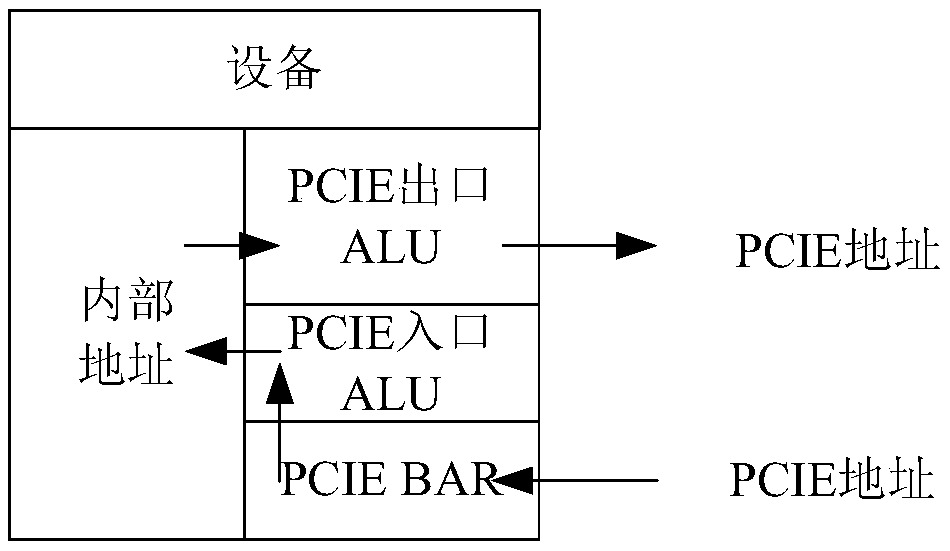

A method for standard interface transmission of high-speed serial compute expansion bus

The invention discloses a method for standard interface transmission of a high-speed serial compute expansion bus, which is used between two digital signal processing chips (DSP). The method including: step 1, establishing a transmission system;2, starting that power / clock of the high-speed serial compute bus standard (PCIE); 3, setting that root complex mode or the endpoint mode as the operationmode of the high-speed serial computer bus standard (PCIE) and configuring a serial / deserialization register (SERDE); Step 4, configuring the size of the base address memory (Base Address Register); 5, setting an exit or entry register; 6, establishing a transmission link connection. The invention overcomes the problem that the communication between two pieces of digital signal processing is transmitted to a field programmable gate array (FPGA) through one piece of digital signal processing, and the field programmable gate array (FPGA) transmits another piece of digital signal processing circuitous communication.

Owner:BEIJING INST OF REMOTE SENSING EQUIP

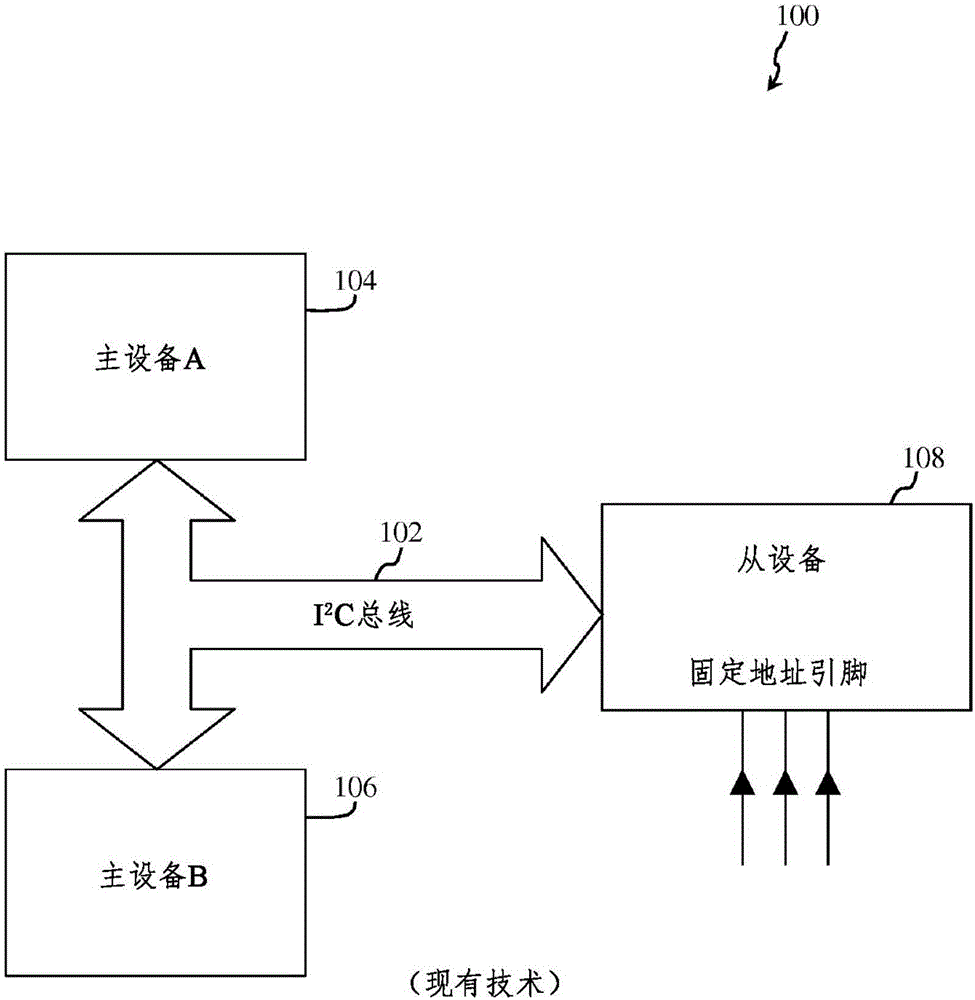

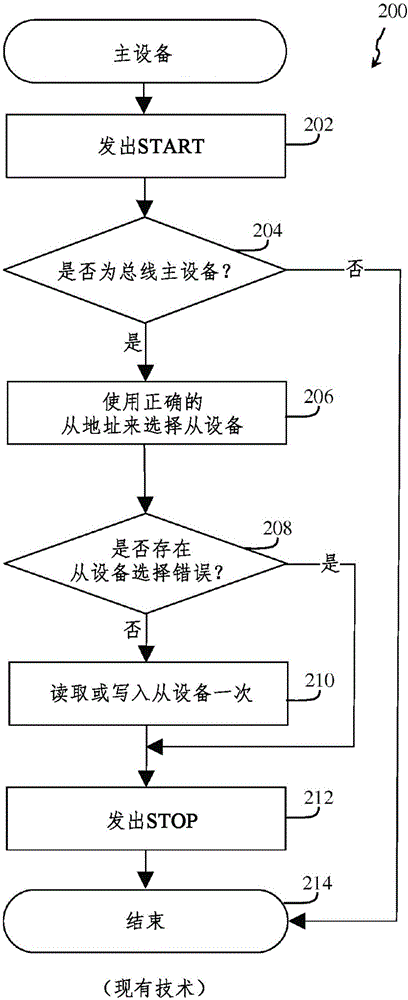

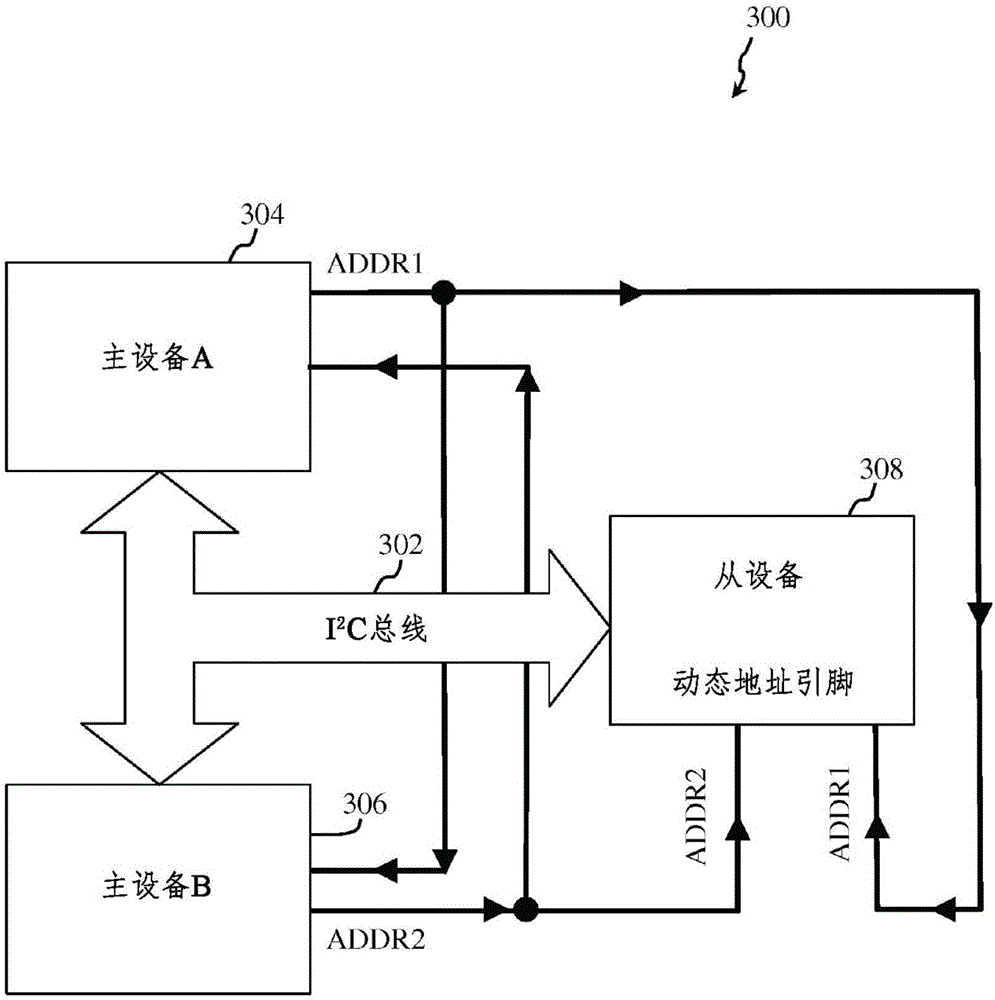

Methods and apparatus for a multiple master bus protocol

ActiveCN106462526AFully understandElectric digital data processingSerial computerProtocol for Carrying Authentication for Network Access

Embodiments of the invention provide systems, methods, and apparatus for arbitrating a multi-master computer bus. The embodiments include a multi-master serial computer bus; a first master coupled to the bus; a second master coupled to the bus; a slave device coupled to the bus; a first I / O line from the first master going to the second master and the slave device; and a second I / O line from the second master going to the first master and the slave device. A bus arbitration protocol for arbitrating use of the bus restricts the masters to a single transaction each time either master becomes a bus master, and the masters are each adapted to use the I / O lines to signal to each other not to become a bus master. Numerous other aspects are disclosed.

Owner:ASCENSIA DIABETES CARE HLDG AG

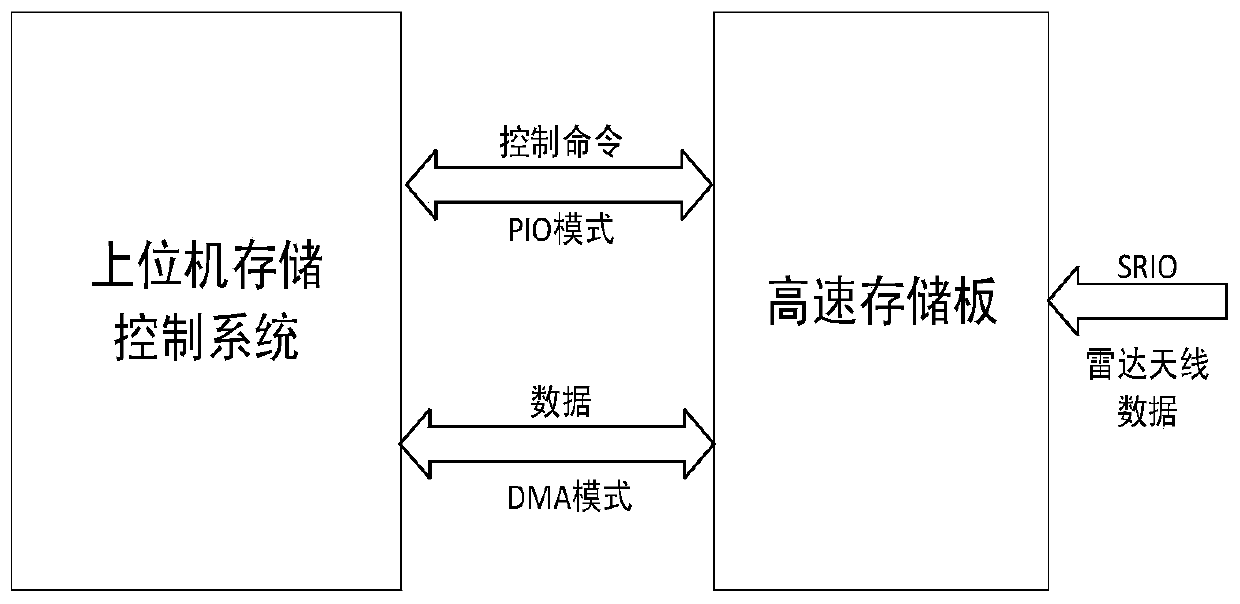

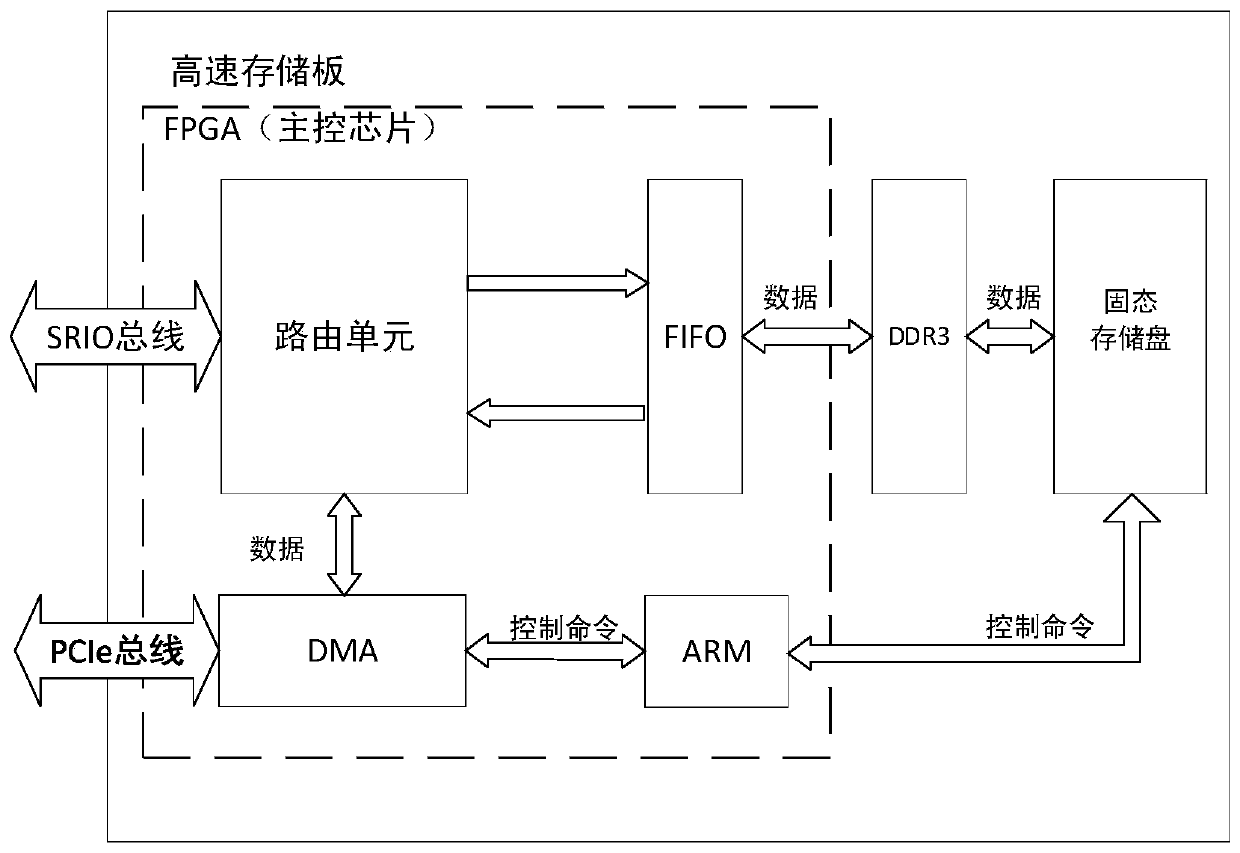

Storage control system based on SATA interface solid state disk

ActiveCN111258504AConvenient real-time storageSolve the loss of collected dataInput/output to record carriersEnergy efficient computingData controlRadar antennas

The invention belongs to the field of radar storage systems, and particularly relates to a storage control system based on an SATA interface solid state disk, which comprises an upper computer storagecontrol system; a high-speed storage board which is used for receiving external radar antenna data and carrying out signal transmission with the upper computer storage control system through a high-speed serial computer expansion bus standard interface, and the upper computer storage control system and the high-speed storage board carry out interaction of user layer data and control commands; anda high-speed storage board which comprises a main control chip and a storage medium, the main control chip is connected with the upper computer storage control system, and the main control chip sendsa control signal to the storage medium to receive a feedback signal of the storage medium. Through data storage and data control of the high-speed storage system, the problems of acquired data loss in radar work and correctness verification in the research and development process are solved, the front-end acquired data can be conveniently stored in real time in the airborne radar work, and testing in the early-stage radar research and development process and later-stage data analysis are facilitated.

Owner:XIDIAN UNIV

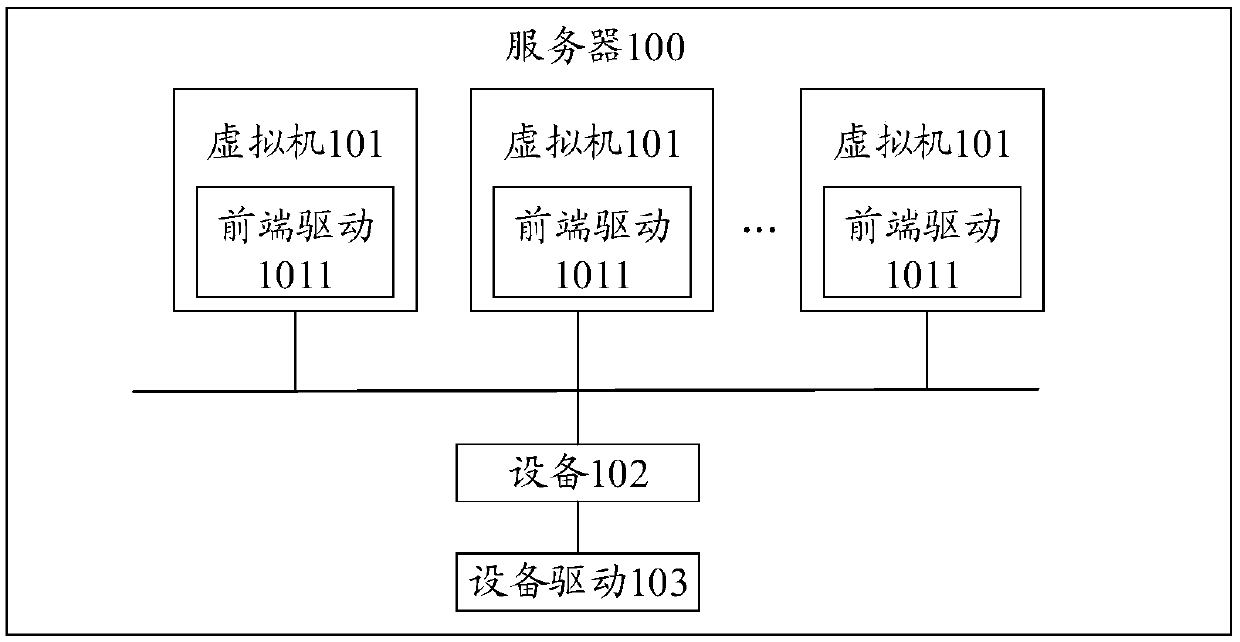

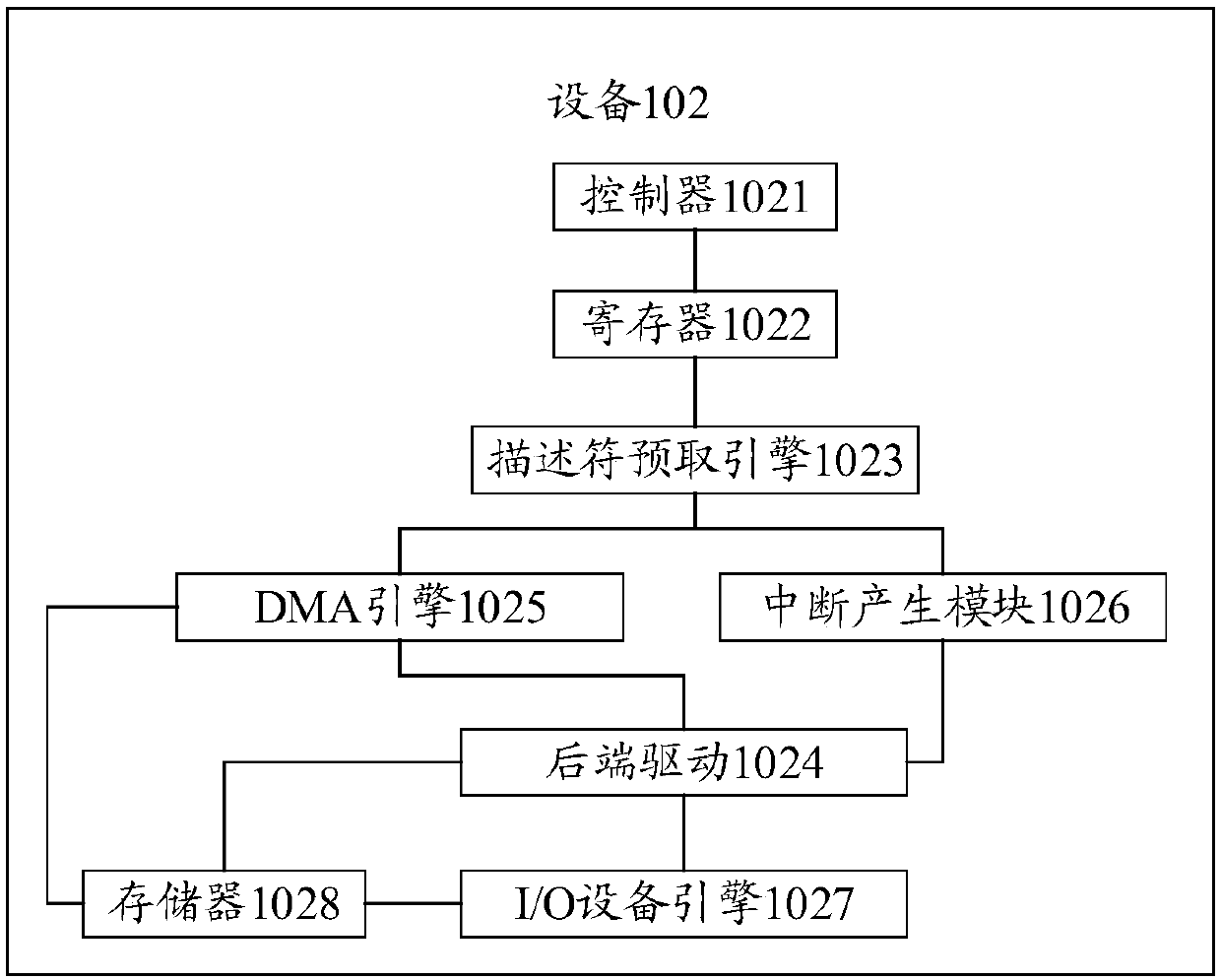

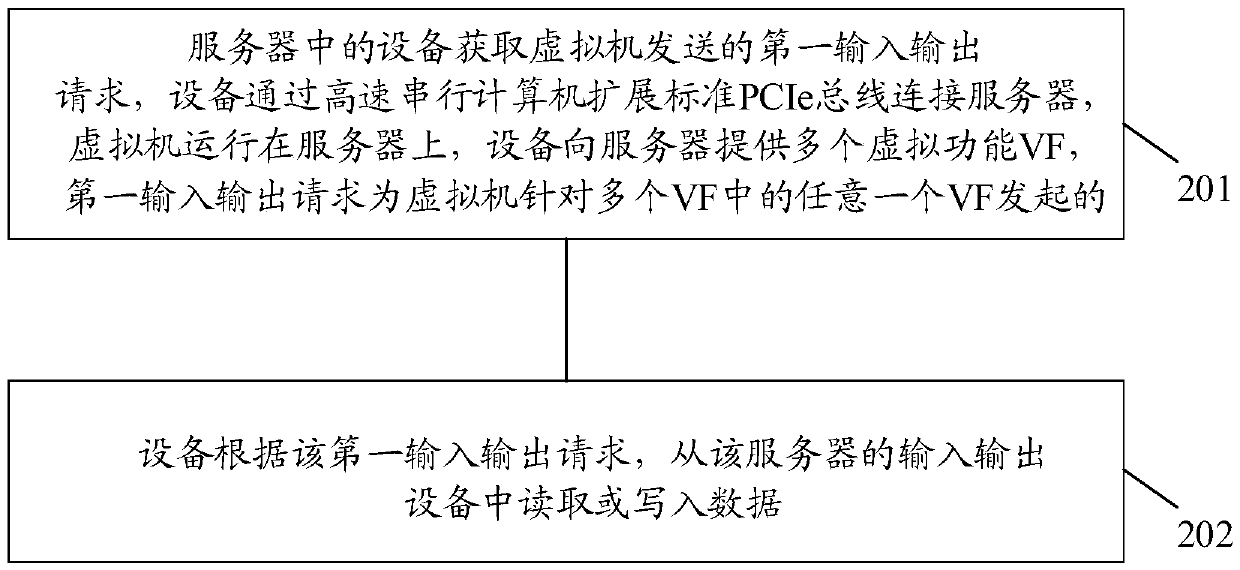

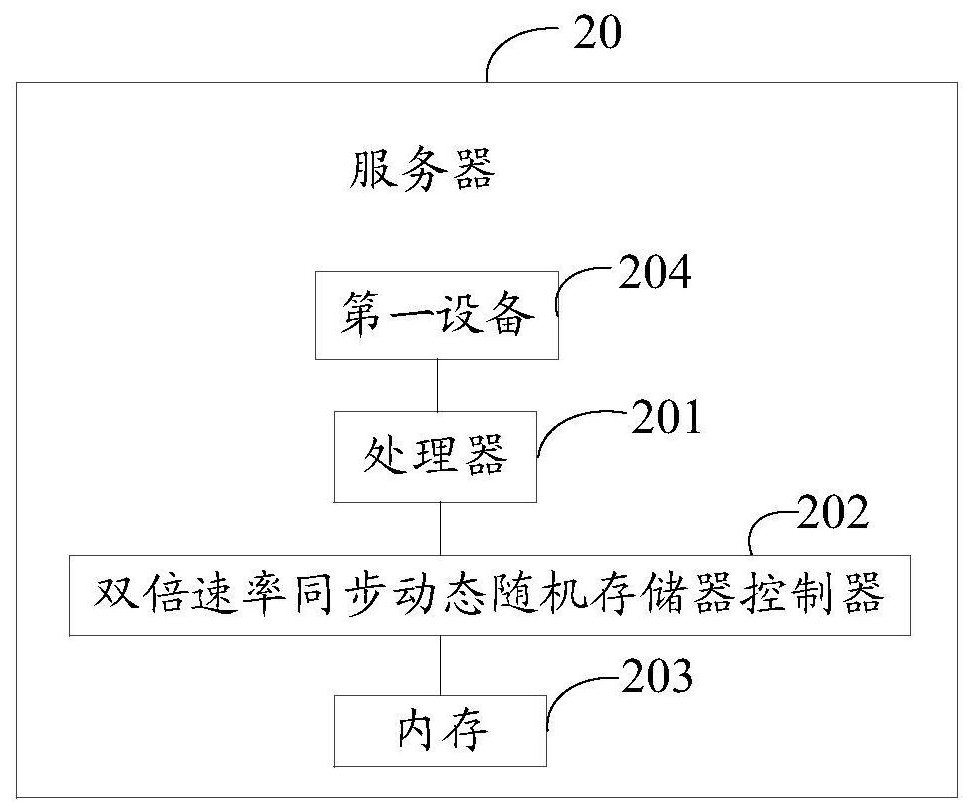

Data processing method, equipment and server

InactiveCN110825485AReduce loadEasy to handleSoftware simulation/interpretation/emulationVirtualizationSerial computer

The invention provides a data processing method. The method comprises: equipment in a server obtaining a first I / O request sent by a virtual machine, the device being connected with a server through ahigh-speed serial computer extension standard PCIe bus; the virtual machine running on a server, a device providing a plurality of virtual functions (VFs) to a server, wherein the first I / O request is initiated by the virtual machine for any one VF in the plurality of VFs, the first I / O request comprises a read operation or a write operation, the read operation is used for executing a data read operation on an I / O device of the server, and the write operation is used for executing a data write operation on the I / O device of the server; and the device reading or writing data from the I / O device of the server according to the first I / O request. According to the method, the I / O processing process can be optimized, the load of the processor of the server is reduced, and the I / O request of thevirtual machine is directly processed by the equipment, so that the virtualization I / O performance is further improved.

Owner:HUAWEI TECH CO LTD

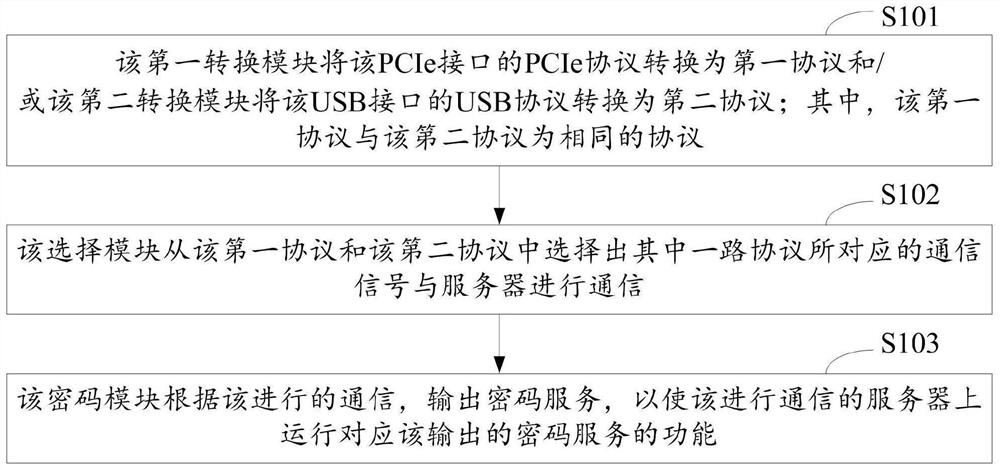

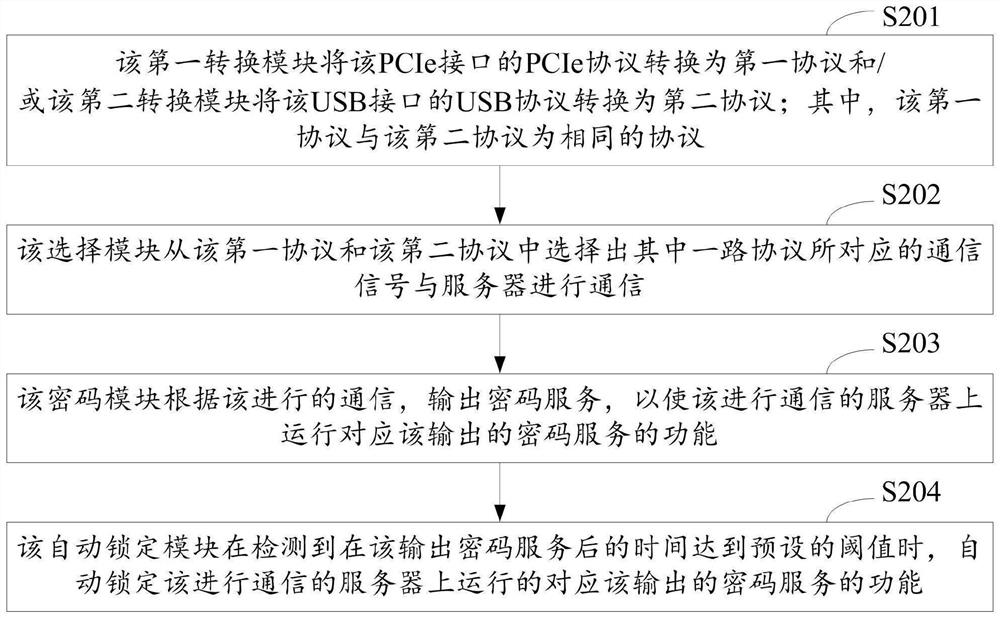

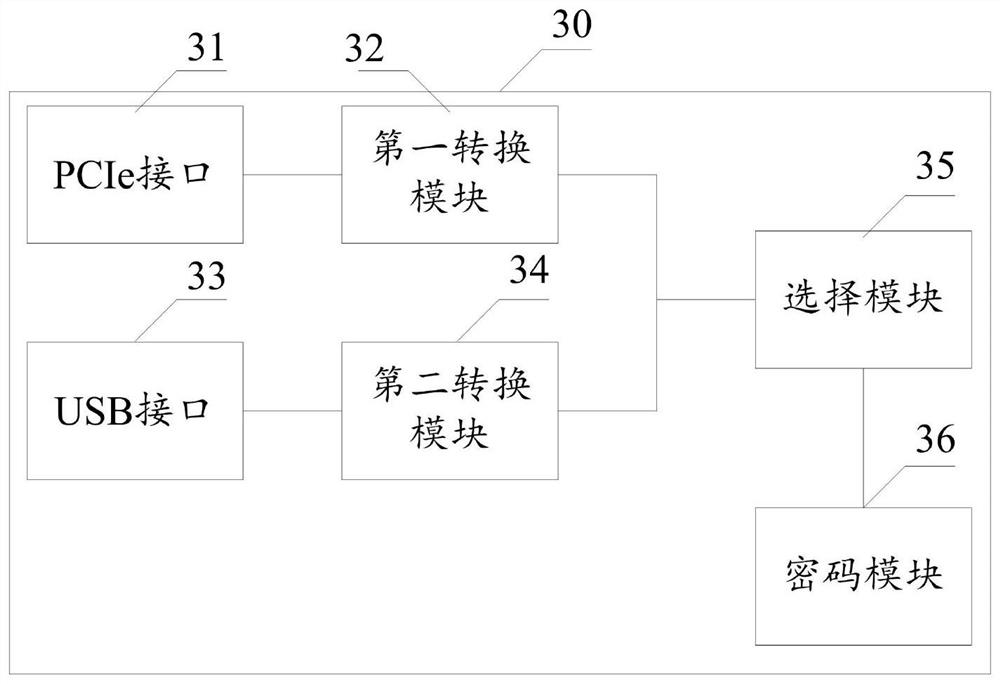

Password card communication method, password card and computer equipment

PendingCN111934859AImprove securityKey distribution for secure communicationElectric digital data processingSerial computerPassword

The invention discloses a password card communication method, a password card and computer equipment. The method comprises the following steps that: the password card comprises a PCIe interface, a first conversion module, a USB interface, a second conversion module, a selection module and a password module; the first conversion module converts a PCIe protocol of the PCIe interface into a first protocol and / or the second conversion module converts a USB protocol of the USB interface into a second protocol, wherein the first protocol and the second protocol are the same protocol; the selection module selects a communication signal corresponding to one protocol from the first protocol and the second protocol to communicate with a server, and the password module outputs a password service according to the performed communication, and therefore a function corresponding to the output password service is operated on the server performing the communication. In this way, dual-protocol communication based on a high-speed serial computer expansion bus standard and a universal serial bus can be achieved.

Owner:BEIJING SANSEC TECH DEV

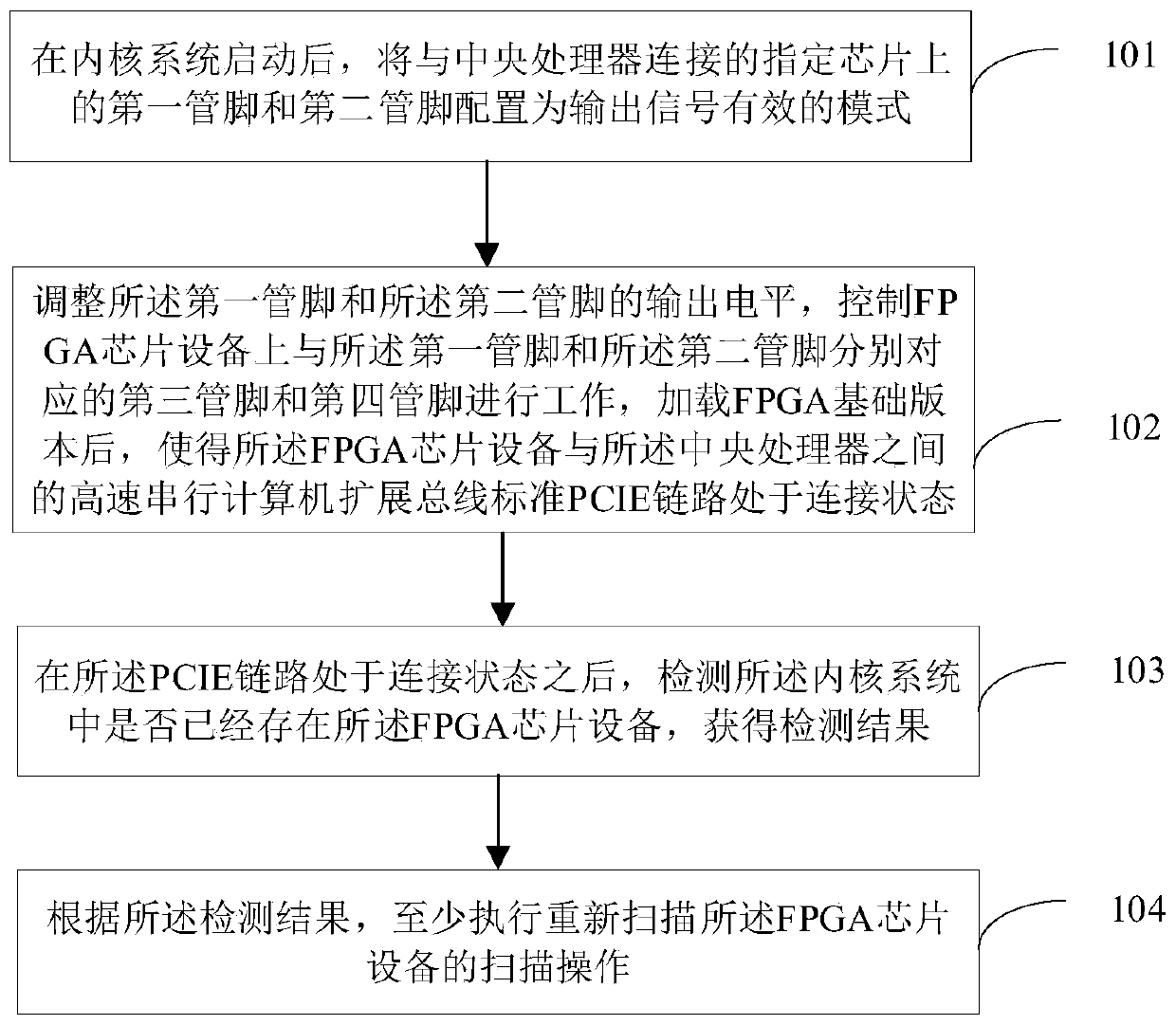

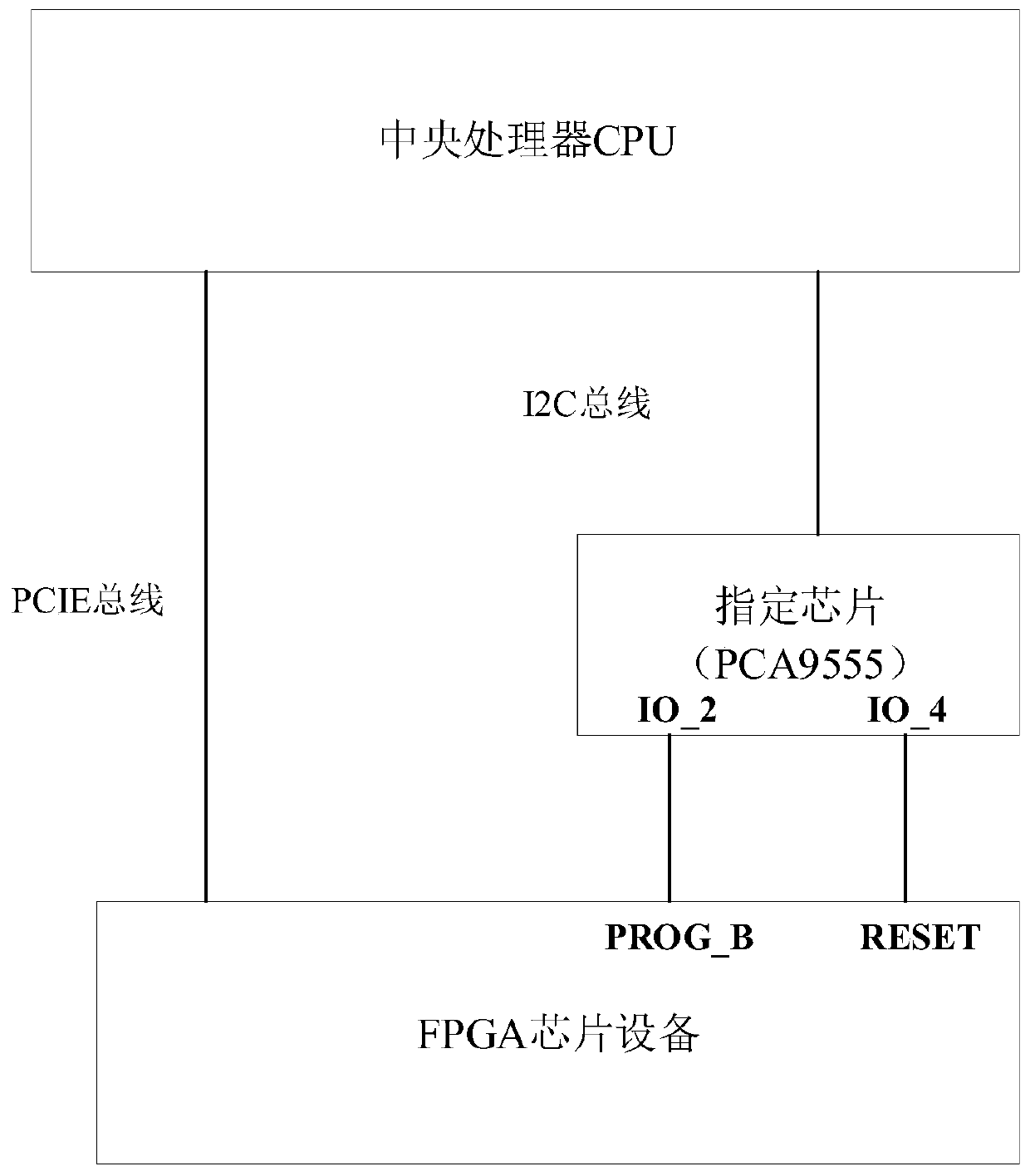

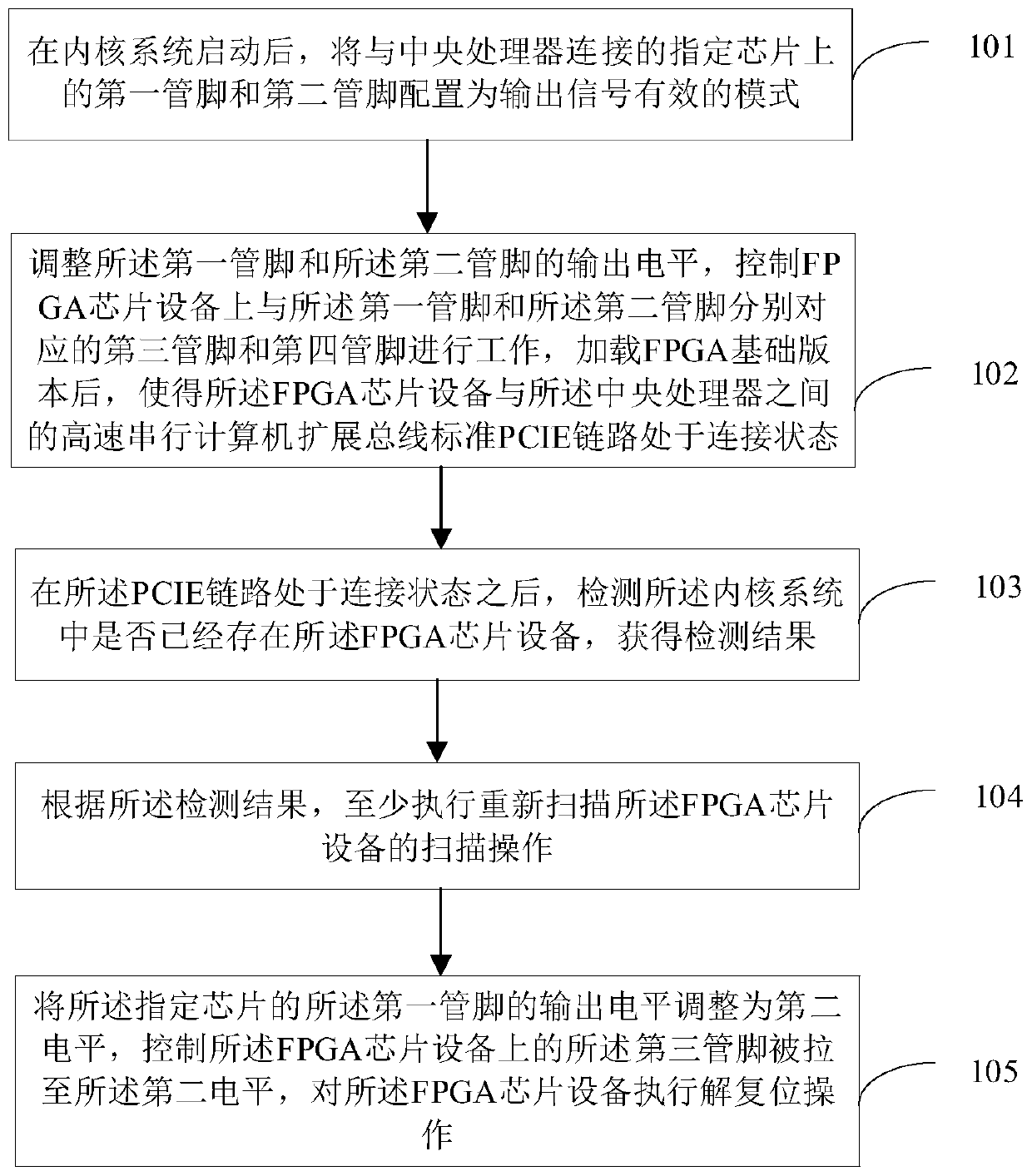

FPGA version loading method and device and storage medium

The invention provides an FPGA version loading method and device and a storage medium. The method comprises the steps: configuring a first pin and a second pin on a specified chip connected with a central processing unit into a mode that an output signal is valid after a kernel system is started; adjusting the output levels of the first pin and the second pin; and controlling a third pin and a fourth pin respectively corresponding to the first pin and the second pin on the FPGA chip equipment to work, after the FPGA basic version is loaded, enabling a high-speed serial computer extension bus standard PCIE link between the FPGA chip device and the central processing unit to be in a connected state; after the PCIE link is in a connected state, detecting whether the FPGA chip equipment existsin the kernel system or not, and obtaining a detection result; and at least executing a scanning operation of re-scanning the FPGA chip device according to the detection result. According to the method and the device, the stability of loading the FPGA version through the PCIE bus is improved.

Owner:HANGZHOU DPTECH TECH

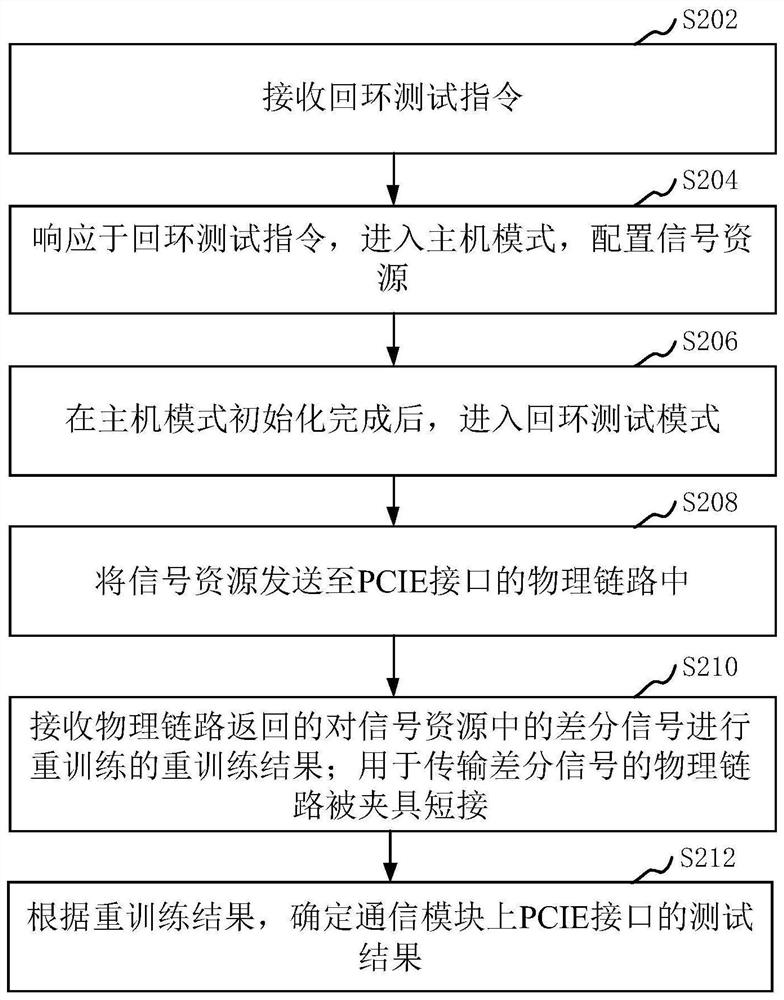

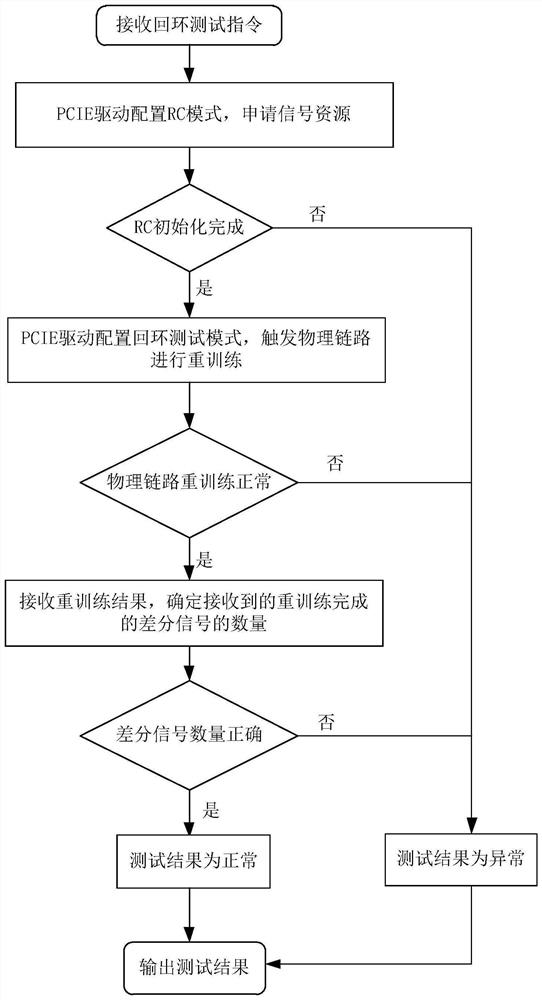

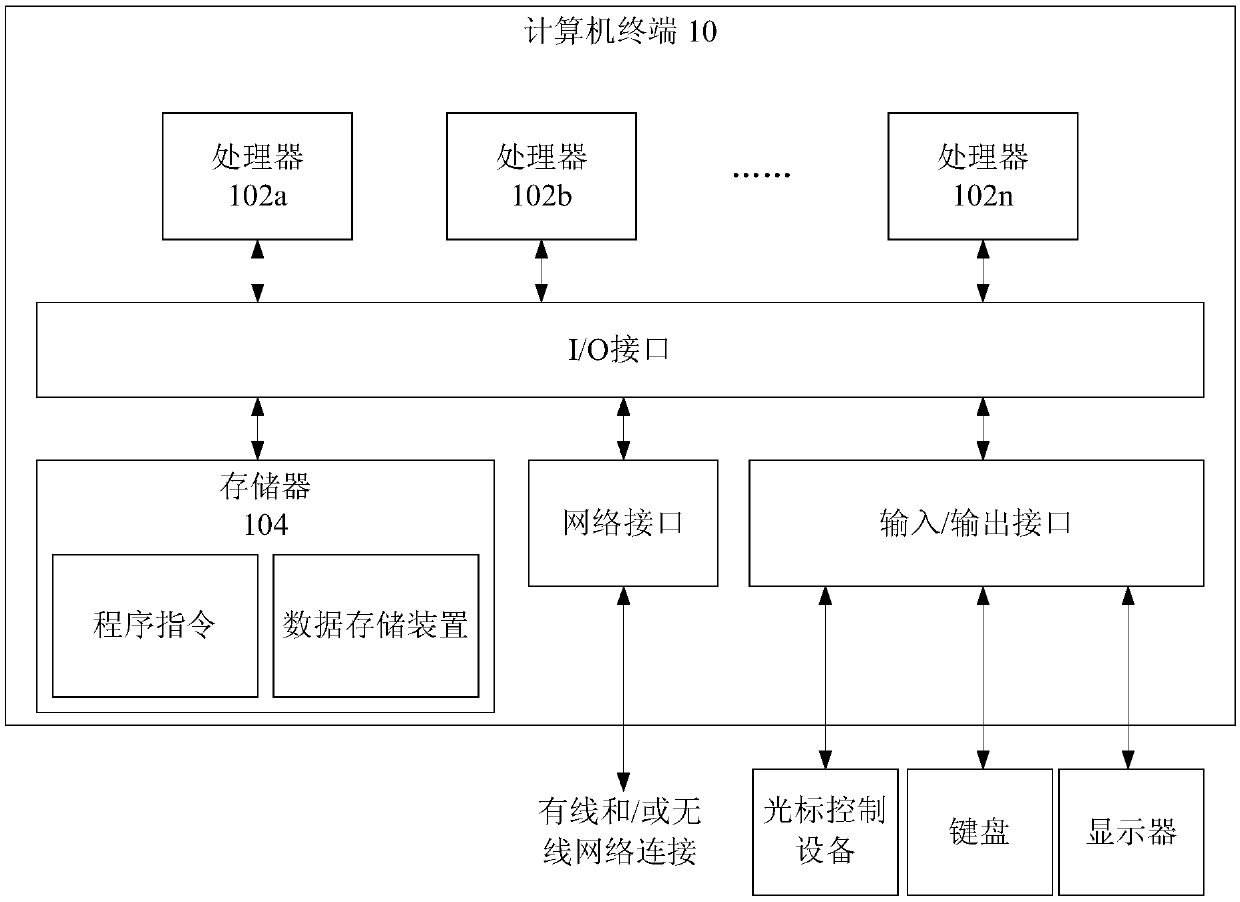

Communication module interface test method and device, computer equipment and storage medium

PendingCN112231155AImprove test efficiencyAvoid enum matchingDetecting faulty computer hardwareTest efficiencyComputer architecture

The invention relates to a communication module interface test method and device, computer equipment and a storage medium. The method is applied to a communication module with an expansion bus standard PCIE interface of a high-speed serial computer. The method comprises the following steps: receiving a loopback test instruction; entering a host mode in response to the loopback test instruction, and configuring signal resources; entering a loop-back test mode after the host mode is initialized; sending the signal resources to a physical link of a PCIE interface; receiving a retraining result which is returned by the physical link and is used for retraining the differential signal in the signal resources; wherein the physical link used for transmitting the differential signal is short-circuited by a clamp; and determining a test result of the PCIE interface on the communication module according to the retraining result. By adopting the method, the test efficiency can be improved.

Owner:FIBOCOM WIRELESS

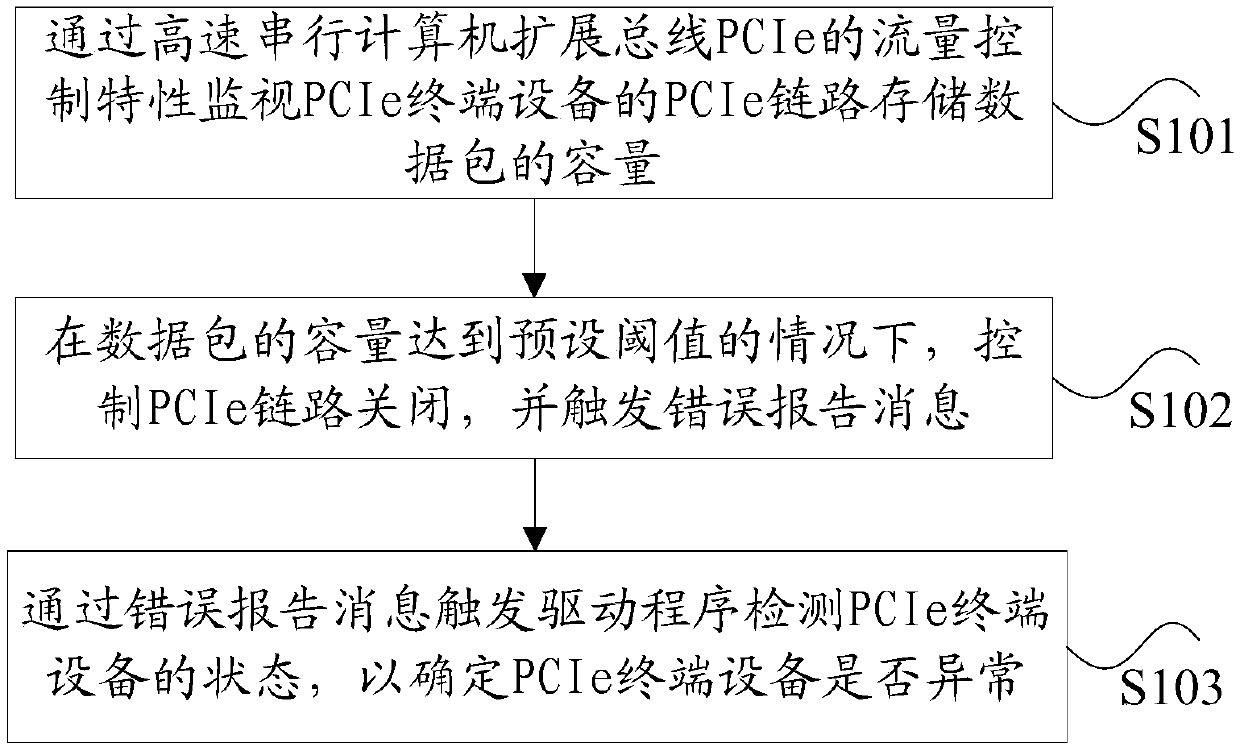

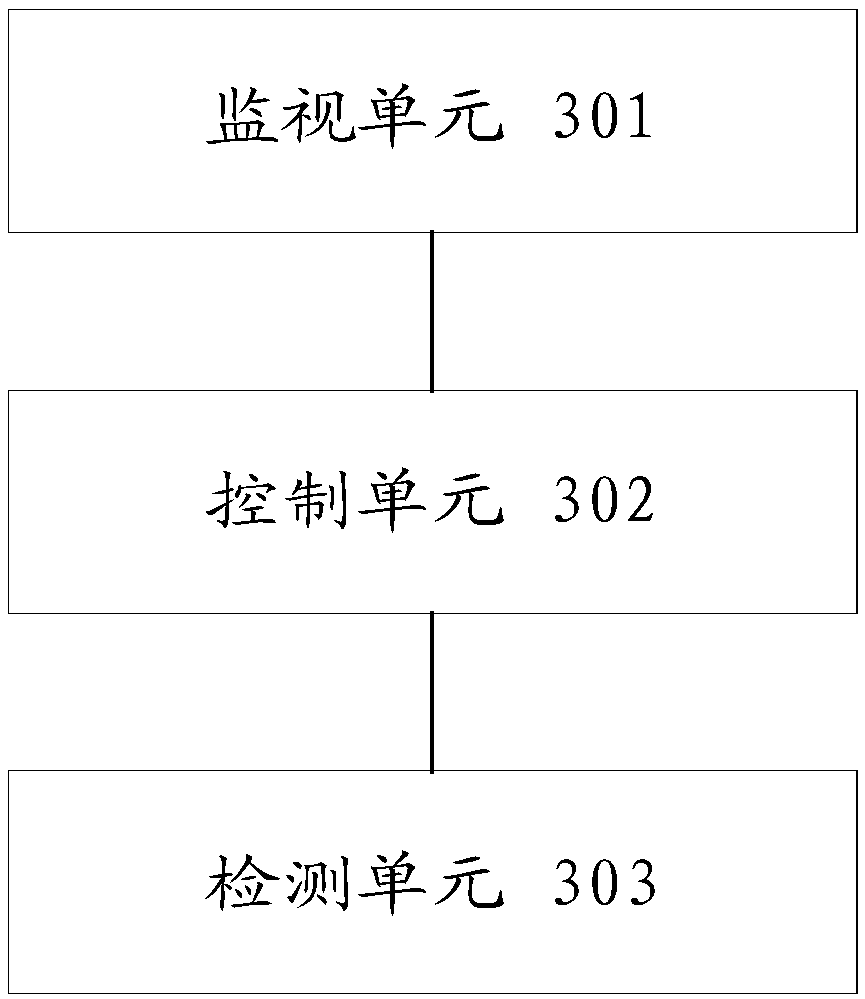

Equipment exception detection method and device

ActiveCN110968443AAvoid the risk of downtimeDowntime risk resolutionFault responseData packSerial computer

The invention discloses an equipment exception detection method and device. The method comprises the following steps: monitoring the capacity of a PCIe link storage data packet of PCIe terminal equipment through the flow control characteristic of a high-speed serial computer extension bus PCIe; under the condition that the capacity of the data packet reaches a preset threshold value, controlling the PCIe link to be closed, and triggering an error report message, the error report message being an error report message triggered by an error report mechanism of PCIe; and triggering the driver to detect the state of the PCIe terminal device through the error report message so as to determine whether the PCIe terminal device is abnormal or not. According to the method and the device, the technical problem that the downtime risk of the host machine caused by hardware cannot be processed and repaired in time due to slow response of the AER drive program in related technologies is solved.

Owner:ALIBABA GRP HLDG LTD

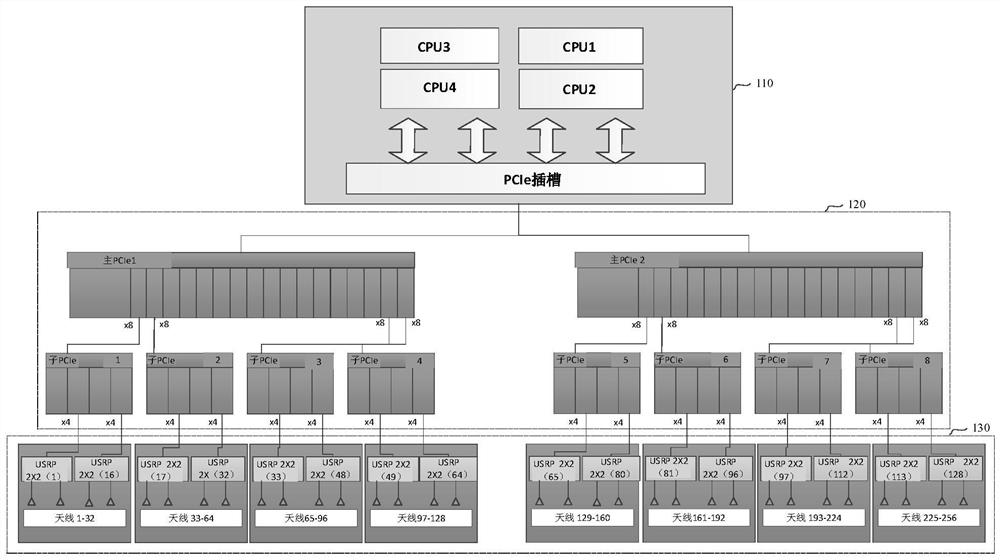

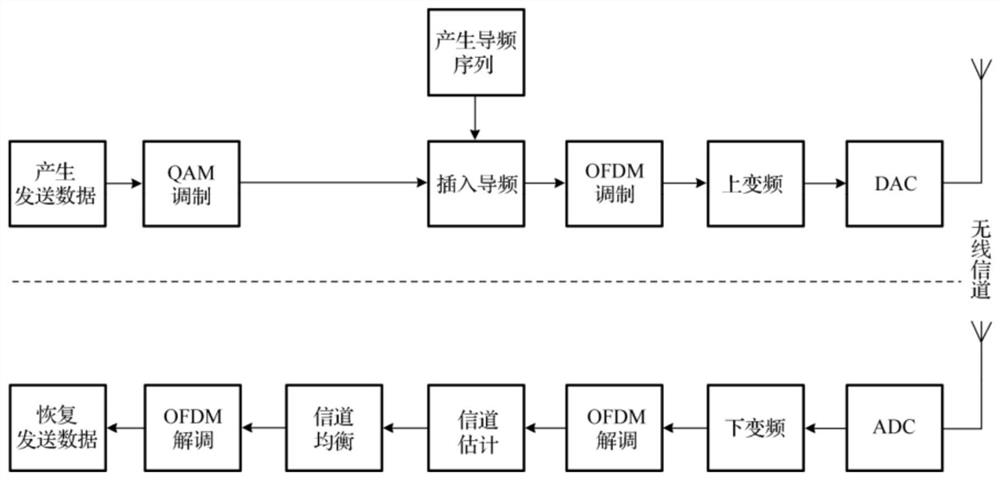

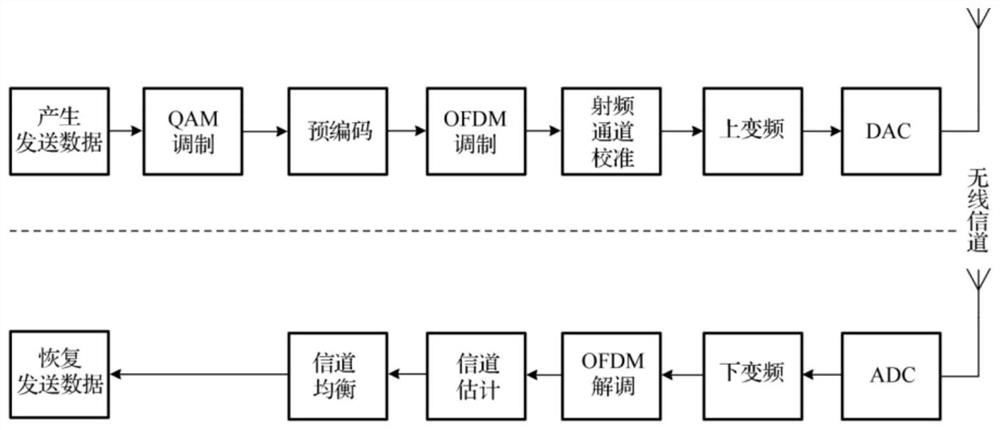

Simulation test system of large-scale MIMO system

InactiveCN113132038AFirmly connectedResolve connectionTransmission monitoringRadio transmissionComputer hardwareSerial computer

The invention discloses a simulation test system of a large-scale MIMO system. The simulation test system comprises universal software radio peripherals (USRP), a high-speed serial computer expansion bus standard PCIe case and a high-performance universal processor, wherein the PCIe case comprises a plurality of main PCIe cases and a plurality of sub PCIe cases; one main PCIe case is connected with a plurality of sub PCIe cases; one sub PCIe case is connected with a plurality of USRPs; each USRP is used for collecting antenna data and sending the collected antenna data to the sub PCIe case connected with the USRP; each sub PCIe case is used for collecting the received antenna data and sending the collected antenna data to the main PCIe case connected with the sub PCIe case; and each main PCIe case is used for collecting the received antenna data and sending the collected antenna data to the high-performance universal processor connected with the main PCIe case, so that the high-performance universal processor processes the received antenna data to obtain a processed baseband signal.

Owner:TSINGHUA UNIV

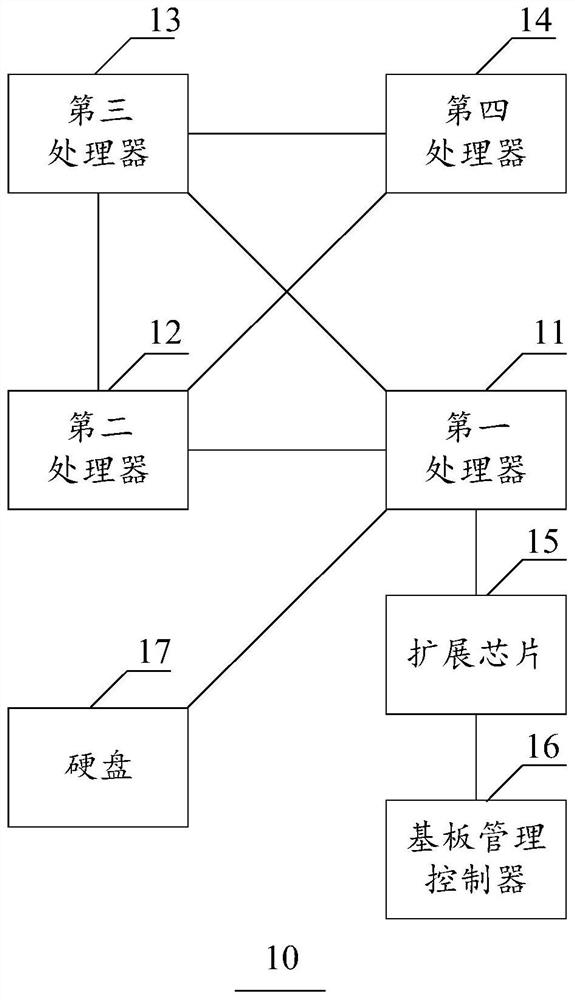

Four-way server and four-way service equipment

PendingCN113553284AVolume/mass flow measurementDigital computer detailsSerial computerMemory interface

The invention discloses a four-way server and four-way service equipment. The four-way server comprises a first processor, a second processor, a third processor, a fourth processor, an expansion chip, a substrate management controller and a hard disk, the first processor, the second processor, the third processor and the fourth processor respectively support at most eight memory channels, and each memory supports at most two memory interfaces. The expansion chip is configured with a high-speed serial computer expansion bus standard mode to expand nine groups of high-speed serial computer expansion bus standard buses, the substrate management controller is connected with the expansion chip through one group of high-speed serial computer expansion bus standard buses to execute a server far-end management controller, and the hard disk is connected with the first processor, so that the high-speed serial computer expansion bus standard function is converted into a serial port hard disk function. By means of the mode, the four-way server with the independent technology can be achieved.

Owner:SHENZHEN TONGTAIYI INFORMATION TECH CO LTD

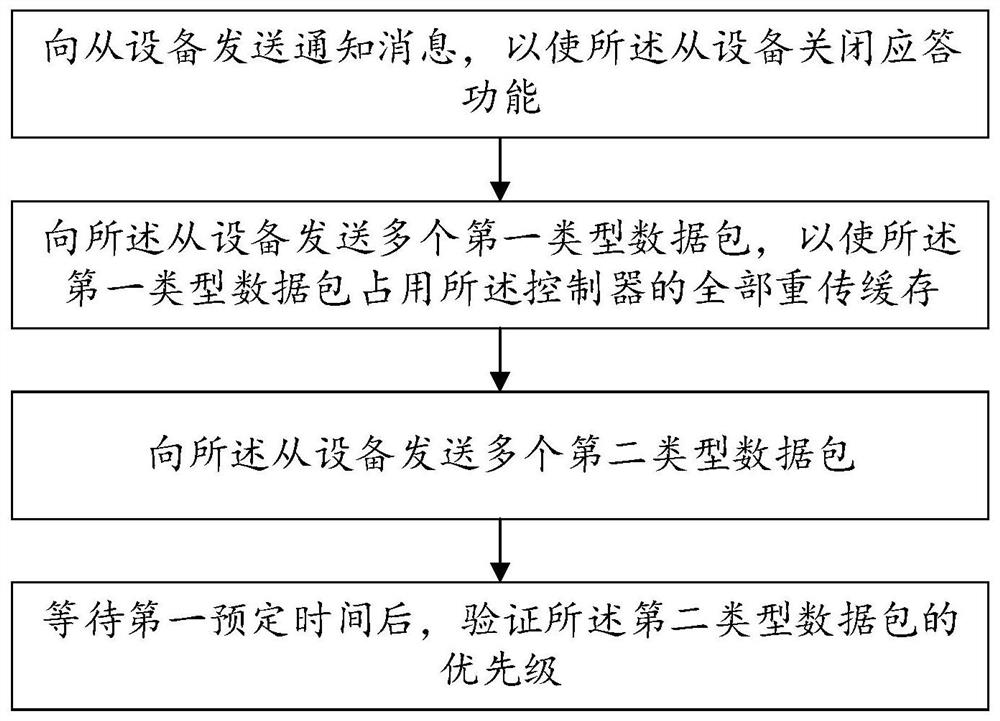

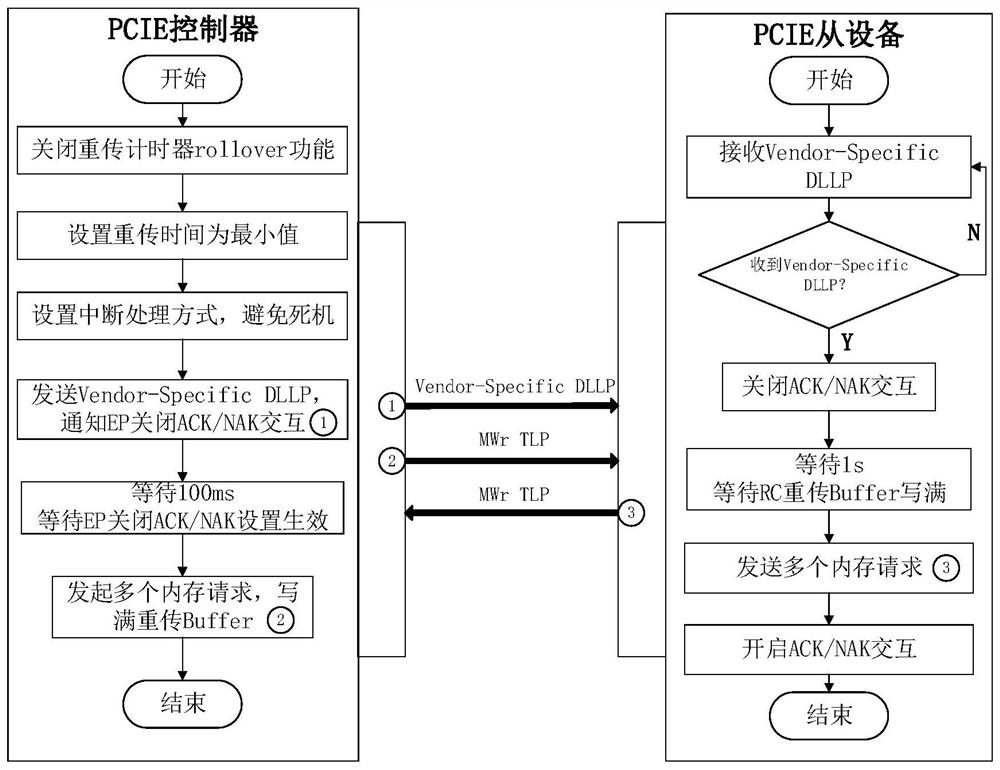

Method and device for testing expansion bus of high-speed serial computer

ActiveCN113297022ARaise priorityCorrectly enforce priority change rulesDetecting faulty computer hardwareEnergy efficient computingData packSerial computer

The invention provides a method for testing an expansion bus of a high-speed serial computer, which is applied to a controller of a high-speed serial computer expansion bus PCIE (Peripheral Component Interface Express) bus, and comprises the following steps: sending a notification message to slave equipment, so that the slave equipment closes a response function aiming at a first type of data packet; sending a plurality of first type data packets to the slave device, so that the first type data packets occupy all retransmission caches of the controller; sending a plurality of second type data packets to the slave device; and after waiting for a first preset time, verifying the priority of the second type of data packets. According to the invention, the occupation state of the link can be accurately created, and the change rule of the priority of the data packet is verified.

Owner:HYGON INFORMATION TECH CO LTD

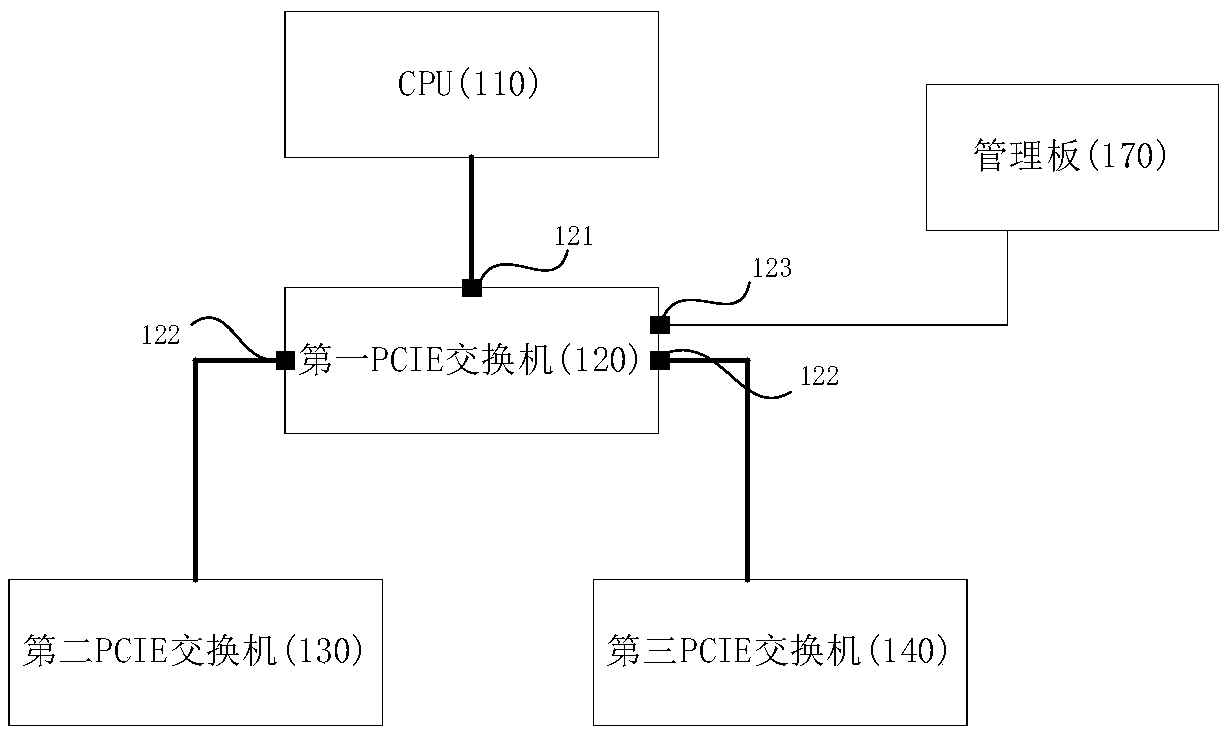

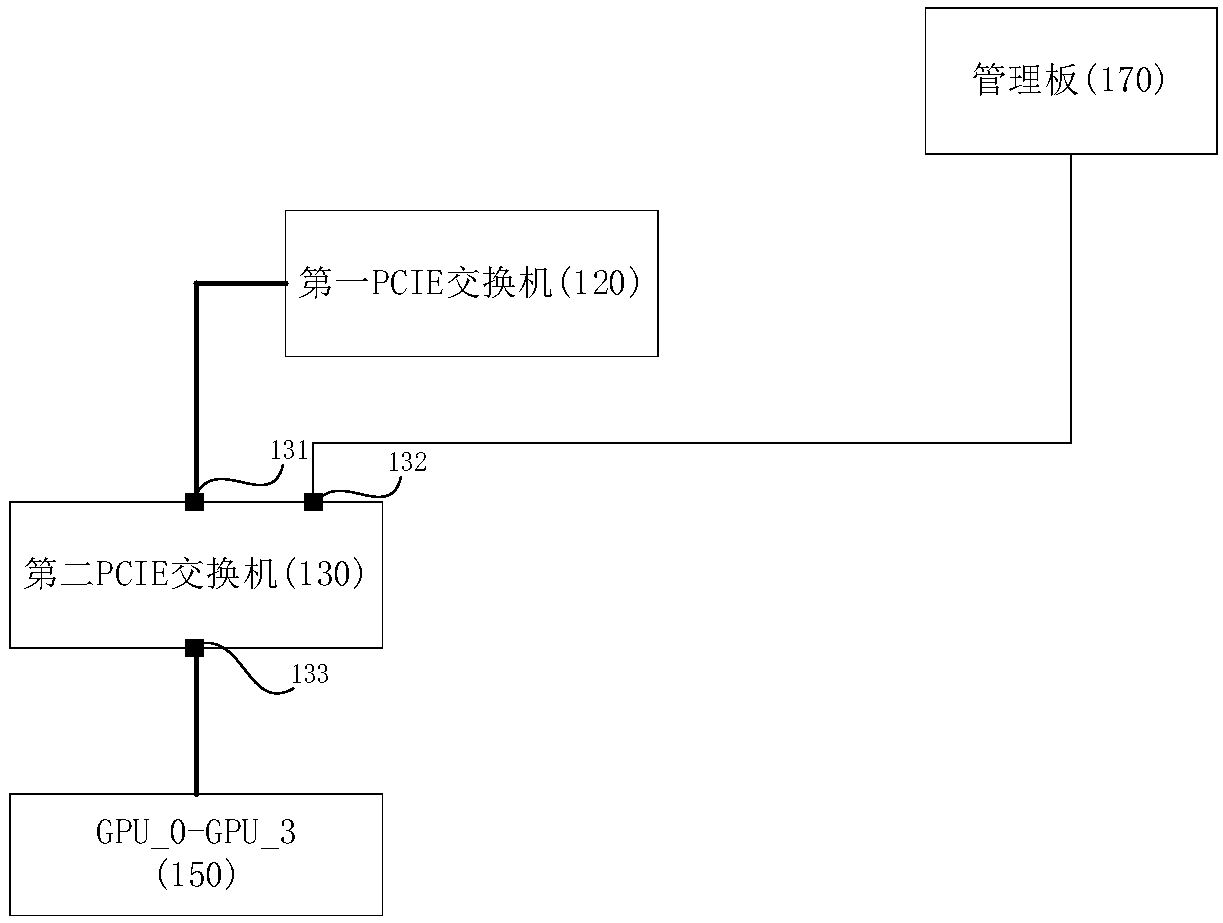

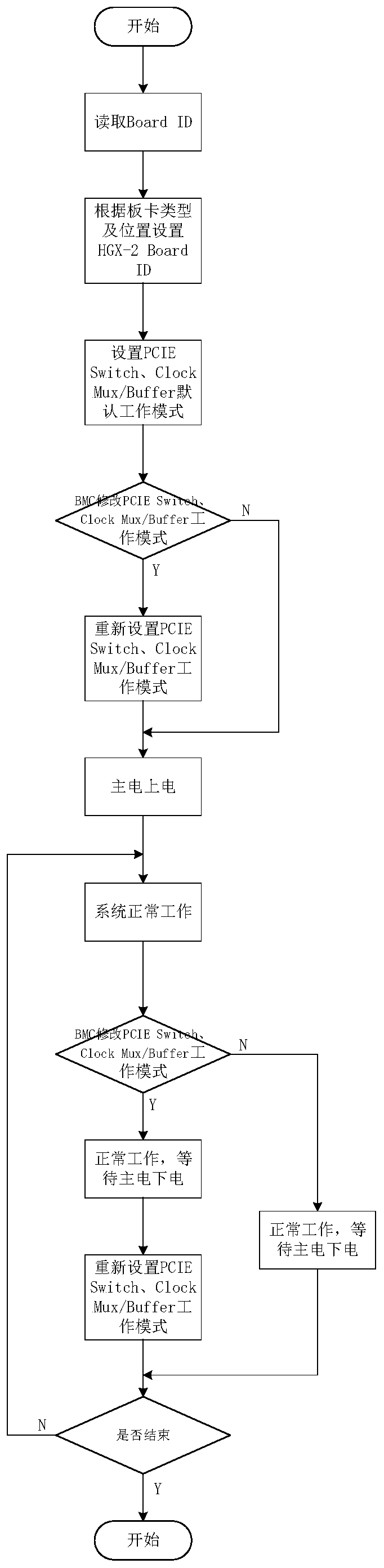

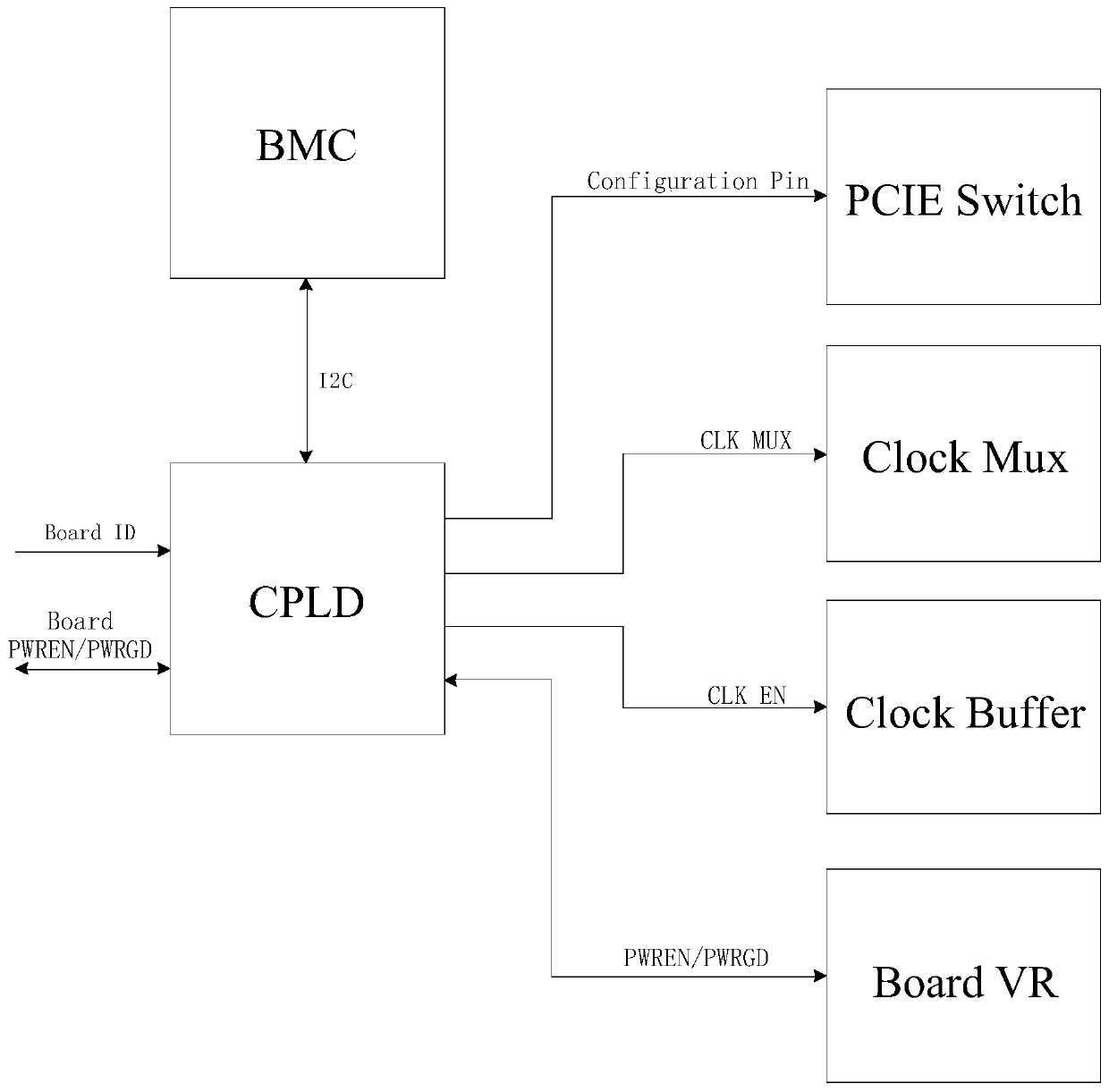

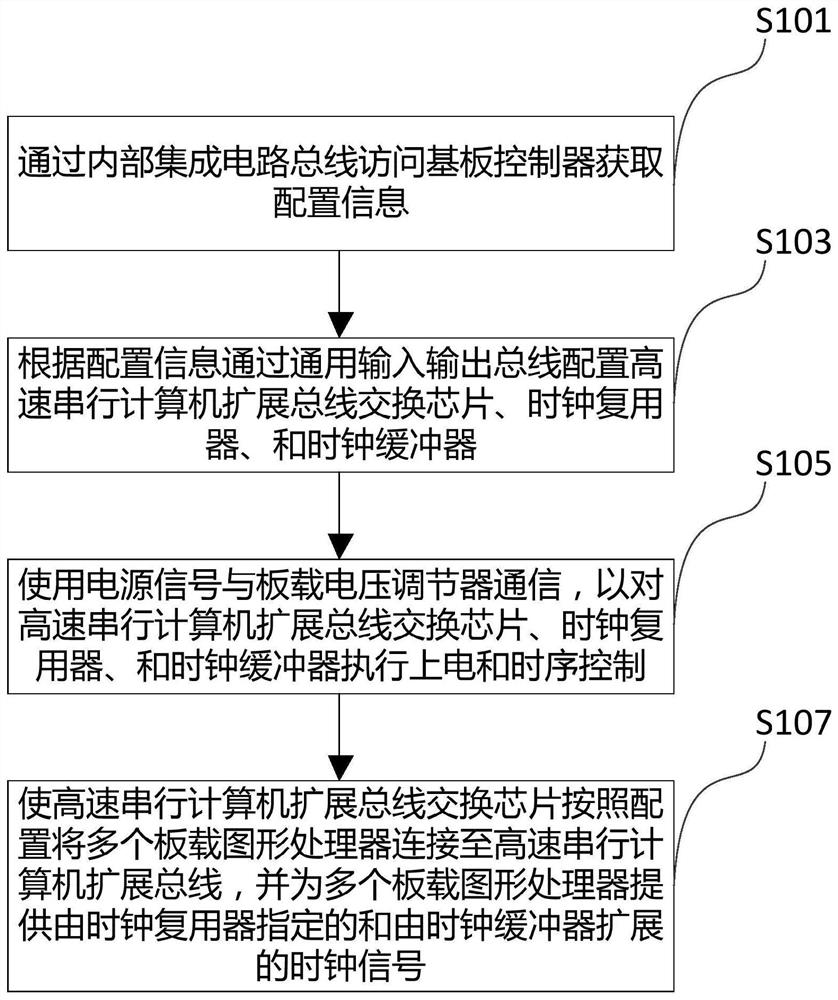

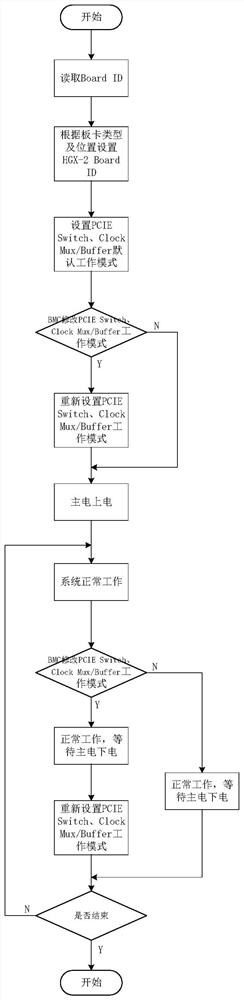

A kind of onboard graphics processor control method and device

ActiveCN110399328BEasy to handleMultiple digital computer combinationsProcessor architectures/configurationGraphicsMultiplexer

The invention discloses a method and device for controlling an onboard graphics processor, comprising: accessing a substrate controller to obtain configuration information, configuring a high-speed serial computer expansion bus switching chip, a clock multiplexer, and a clock buffer, using a power supply signal to communicate with the board The on-board voltage regulator communicates to perform power-on and timing control, so that the high-speed serial computer expansion bus switch chip connects a plurality of onboard graphics processors to the high-speed serial computer expansion bus and provides clock signals according to the configuration information. The invention can provide PCIE interface and clock signal according to multiple different GPUs or different working states of GPU, control the onboard graphics processor to work normally according to its performance requirements, and improve the processing capability of the onboard graphics processor.

Owner:INSPUR SUZHOU INTELLIGENT TECH CO LTD

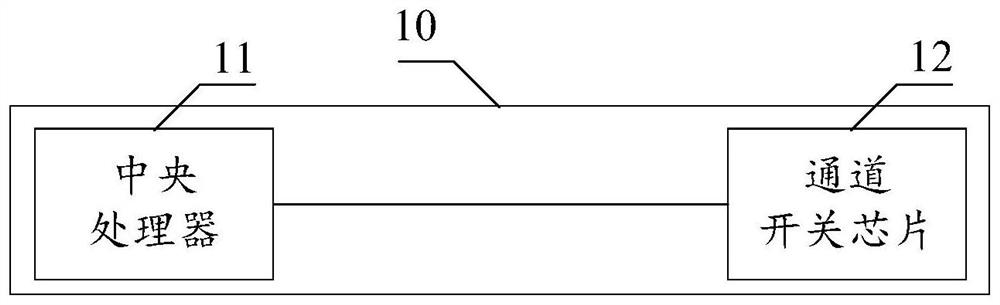

Two-way server and connection method thereof

PendingCN113553283ACompatibilityDigital computer detailsElectric digital data processingSerial computerEmbedded system

The invention discloses a two-way server and a communication method thereof. The two-way server comprises a central processing unit and a channel switch chip, a high-speed serial computer expansion bus standard channel of the central processing unit is connected with the channel switch chip, and the central processing unit provides a high-speed serial computer expansion bus standard channel function. And the channel switch chip provides a high-speed serial computer expansion bus standard channel function which is the same as that of the central processing unit. By means of the mode, the two-way server can have the same high-speed serial computer expansion bus standard channel function of two ways of central processing units when being matched with one way of central processing unit.

Owner:SHENZHEN TONGTAIYI INFORMATION TECH CO LTD

Method, device and server for processing identity secret key

ActiveCN109525396BKey distribution for secure communicationUser identity/authority verificationSerial computerSoftware engineering

A method, device, and server for processing an identity key, comprising: a processing device for an identity key obtains a first identity key of a virtual machine, the first identity key is used for identity authentication of the virtual machine, and the processing device passes The high-speed serial computer expansion bus standard PCIe is connected to the server, and the virtual machine is deployed in the server; the first identity key is encrypted with the device key to obtain the second identity key, and the device key is generated according to the identification of the processing device The globally unique key, the device key is stored in the storage area of the processing device; the processing device stores the second identity key in the first storage area; the processing device signs the access request of the virtual machine according to the second identity key to This can solve the problem of low security of the identity key.

Owner:HUAWEI TECH CO LTD

Error injection method and device for expansion bus of high-speed serial computer

ActiveCN113032199AFlexible authenticationNote flexibleDetecting faulty computer hardwareData packSerial computer

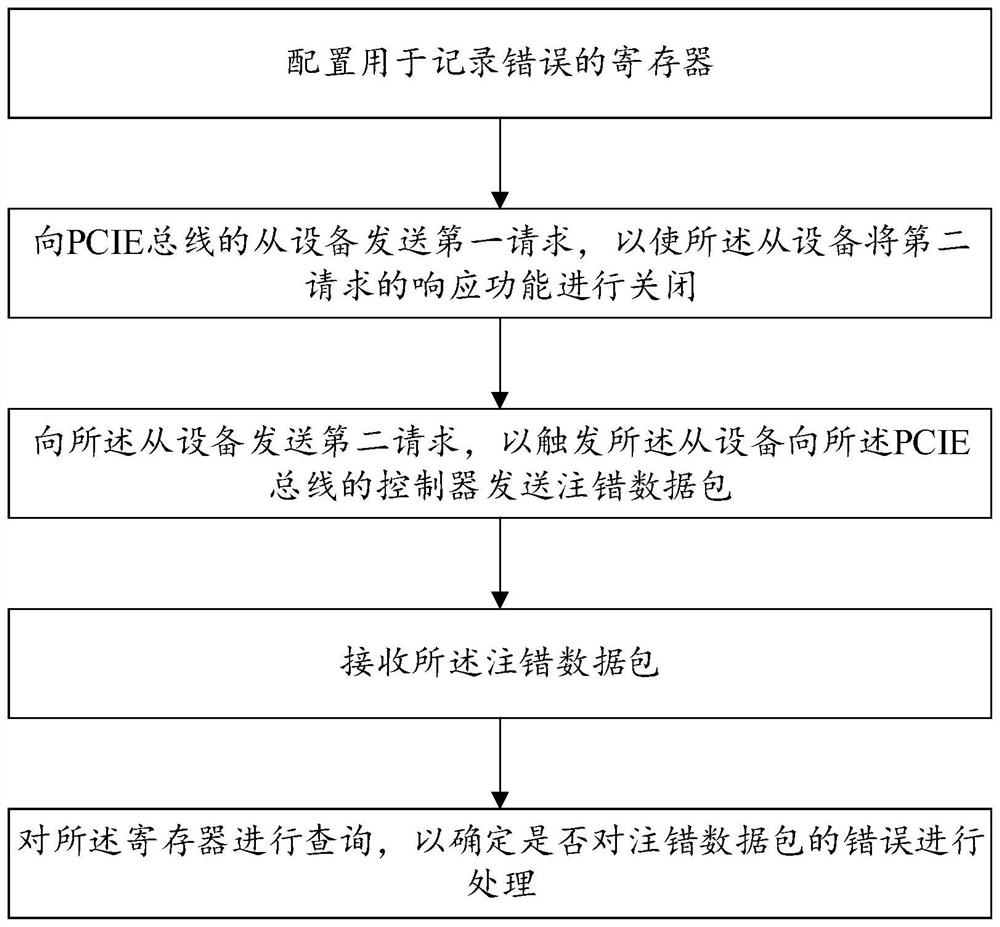

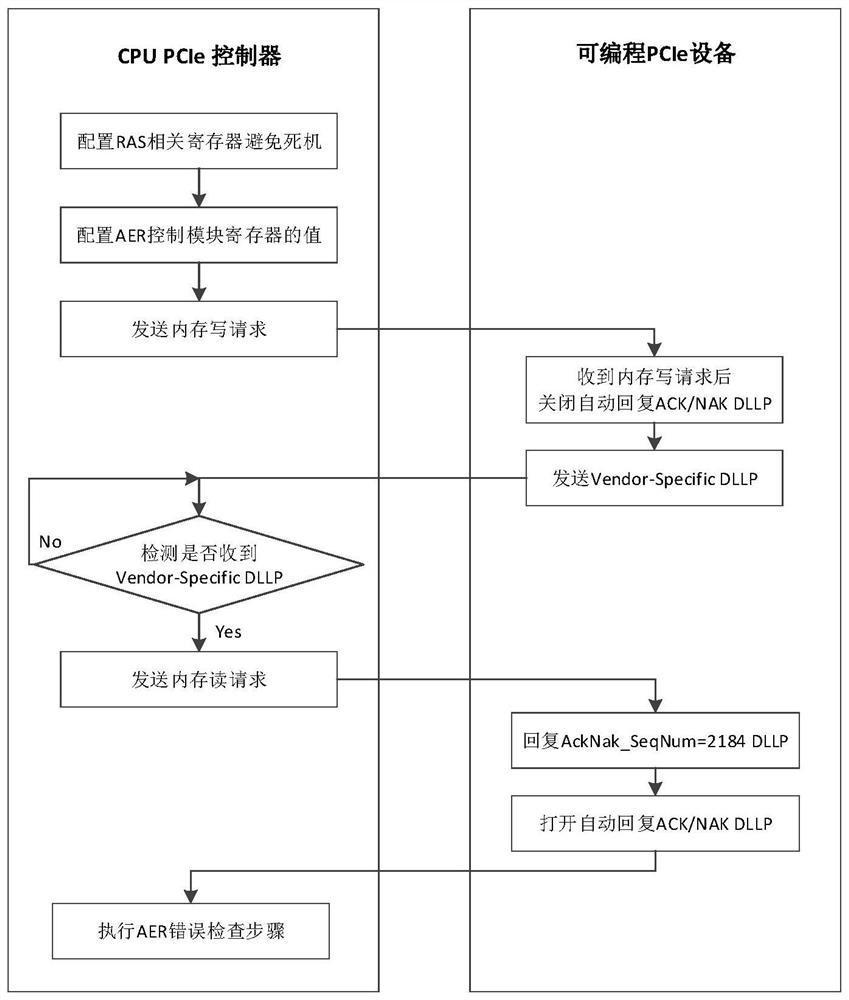

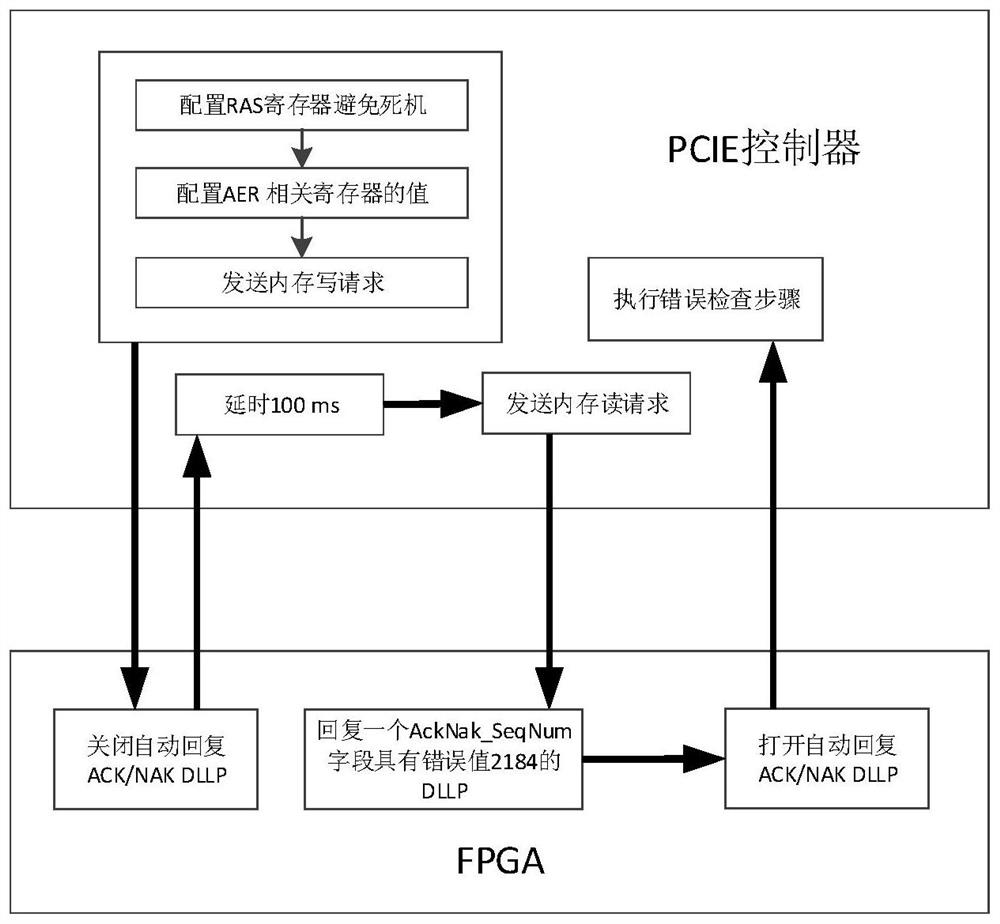

The invention provides an error injection method for an expansion bus of a high-speed serial computer. The method which is applied to a controller of a PCIe bus of the expansion bus of the high-speed serial computer and comprises the following steps: configuring a register for recording errors; sending a first request to slave equipment of the PCIe bus, so that the slave equipment closes the automatic response function of a second request; sending the second request to the slave equipment to trigger the slave equipment to send an error injection data packet to a controller of the PCIe bus; receiving the error injection data packet; and querying the register to determine whether the error of the error injection data packet is processed or not. According to the invention, the errors can be flexibly injected into a PCIe controller, so that the processing modes of the PCIe bus on various types of errors are flexibly verified.

Owner:HYGON INFORMATION TECH CO LTD

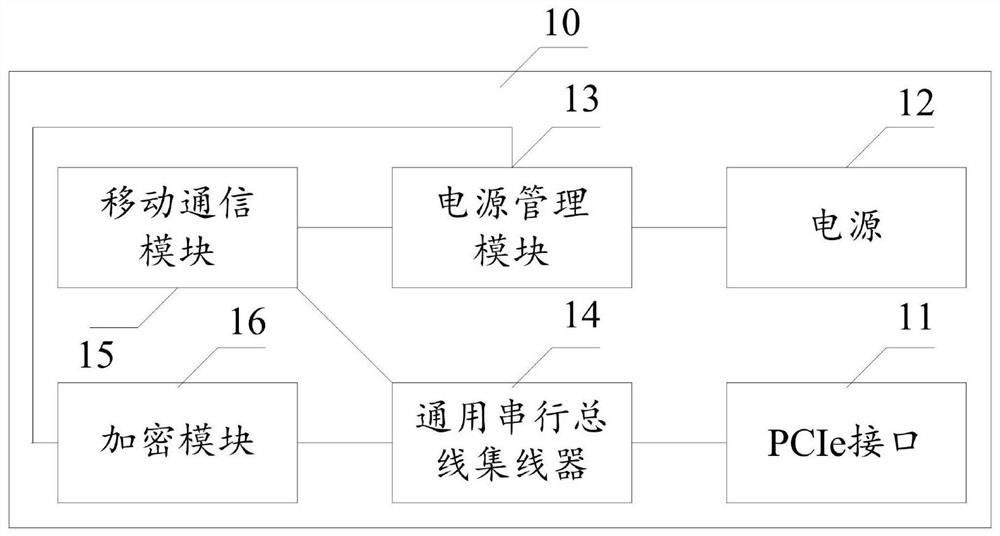

Cryptographic device and cryptographic apparatus

PendingCN111935707AImprove portabilityEasy to carrySecurity arrangementSupply managementSerial computer

The invention discloses a cryptographic device and a cryptographic apparatus. The cryptographic device comprises a PCIe interface, a power supply, a power supply management module, a universal serialbus concentrator, a mobile communication module and an encryption module, wherein the PCIe interface comprises at least one high-speed serial computer expansion bus standard interface and at least oneuniversal serial bus interface. Electric energy is provided by the power supply, and the power supply management module distributes the electric energy to the mobile communication module and the encryption module; the universal serial bus concentrator converts one of the PCIe interfaces into two universal serial bus interfaces, namely a first universal serial bus interface and a second universalserial bus interface; the mobile communication module performs mobile communication based on the first universal serial bus interface, and the encryption module encrypts data of communication betweenthe second universal serial bus interface and a personal computer. In this way, the data encryption function and the mobile communication function can be achieved at the same time.

Owner:BEIJING SANSEC TECH DEV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com