Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

72 results about "Software verification and validation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In software project management, software testing, and software engineering, verification and validation (V&V) is the process of checking that a software system meets specifications and that it fulfills its intended purpose. It may also be referred to as software quality control. It is normally the responsibility of software testers as part of the software development lifecycle. In simple terms, software verification is: "Assuming we should build X, does our software achieve its goals without any bugs or gaps?" On the other hand, software validation is: "Was X what we should have built? Does X meet the high level requirements?"

Pluggable semantic verification and validation of configuration data

ActiveUS20040019670A1Digital computer detailsData switching networksData validationSource Data Verification

A pluggable semantic verification and syntactic validation mechanism for server configuration information. In one embodiment, the data verification and validation mechanism may be implemented as modules that may be plugged into a framework. In one embodiment, the mechanism may include a generic test case framework that may call test cases to verify and validate changes to configuration information. In one embodiment, each test case may implement an interface through which the framework calls a test case. The test case may return results, e.g. whether the test passed or failed, and may return additional information, e.g. why the test failed. If the change is valid, then the change may be made to the configuration information. If the change is not valid, the change is not made or alternatively is made with a warning. If the change is made, one or more other servers may be notified of the change.

Owner:ORACLE INT CORP

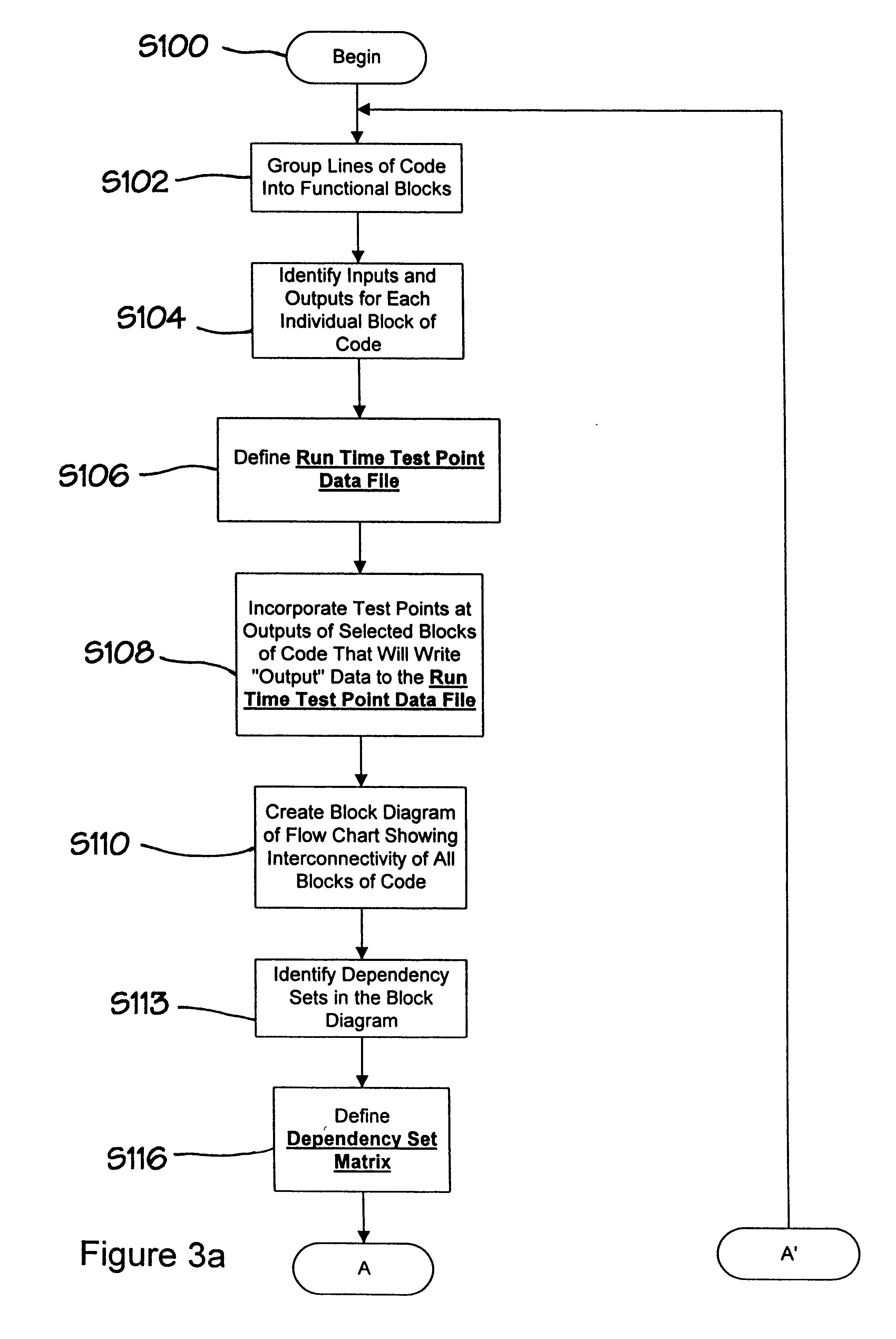

Method and apparatus for debugging, verifying and validating computer software

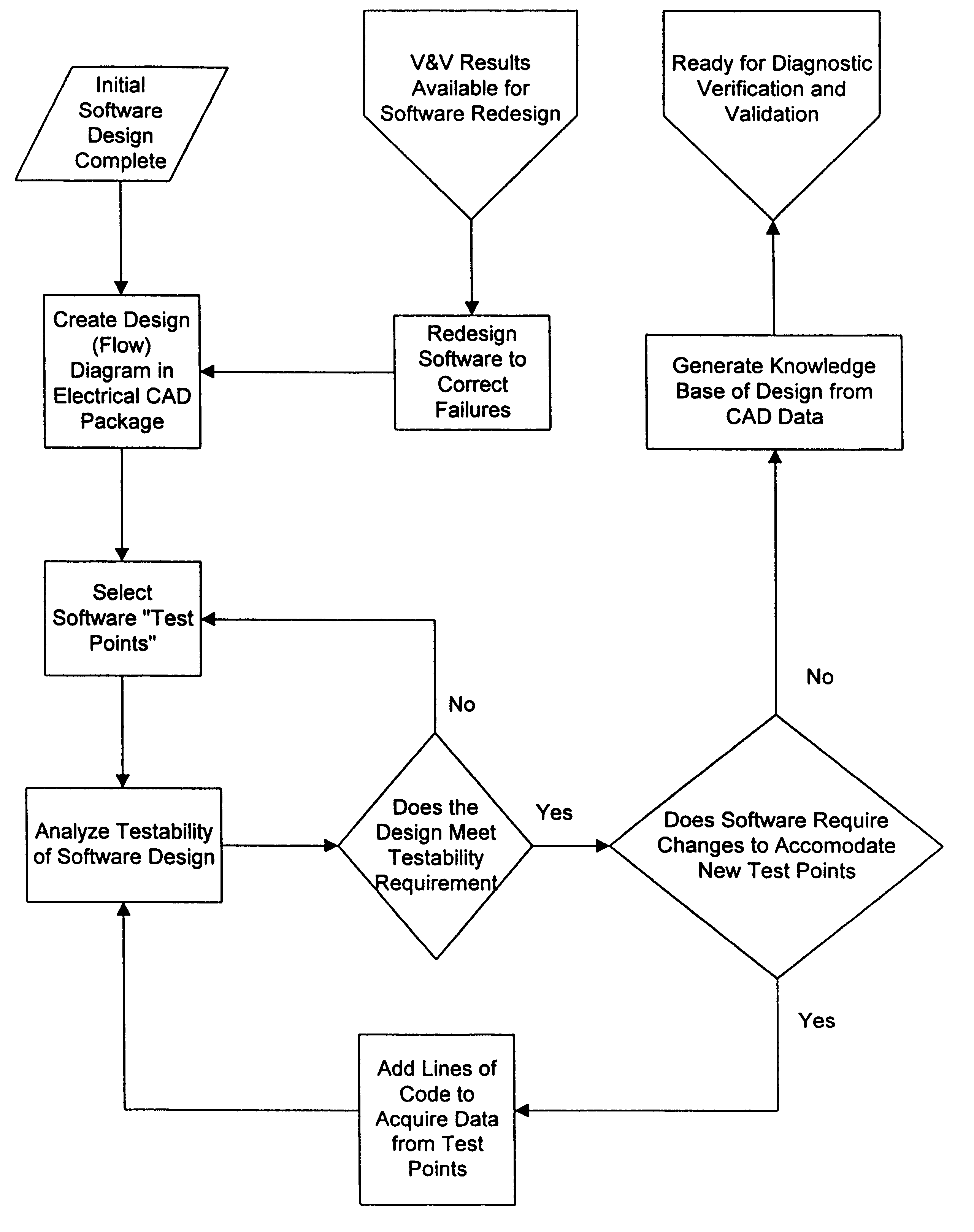

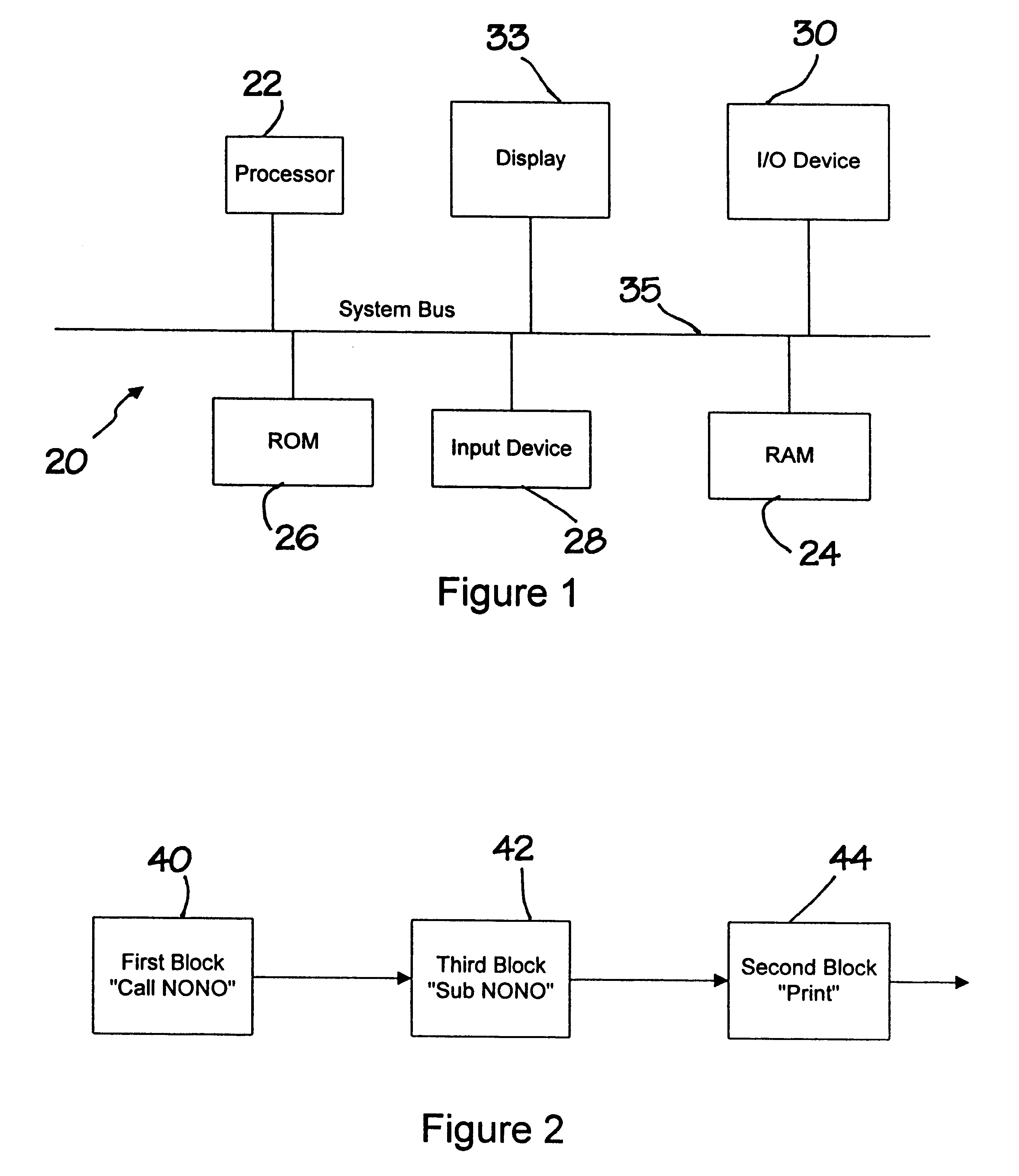

InactiveUS6173440B1Software testing/debuggingProgram loading/initiatingSoftware designVerification procedure

A new approach for software debugging, verification and validation is disclosed. The present invention utilizes a knowledge-based reasoning approach to build a functional model of the software code for identifying and isolating failures in the software code. The knowledge-based reasoning approach of the present invention uses the software design, which is preferably based upon a flow chart or block diagram representation of the software functionality, to build the functional model. The software block diagram contributes to the functional model by defining the inputs and outputs of the various blocks of code, as well as defining data interconnections between the various blocks of code. In accordance with a method of the present invention, test points are strategically inserted throughout the code, and each test point is associated with a corresponding block of code. Expected values of the test points for an expected proper-operation execution of the computer program are generated. The computer program is then executed on a computer, and the actual values of the test points from the program execution are compared with the expected values of the test points. Failed test points which do not agree with corresponding expected values are determined. The functional model, which includes information functionally relating the various test points to one another, is then used to isolate the failed test points to one or more sources of failure in the code.

Owner:MCDONNELL DOUGLAS

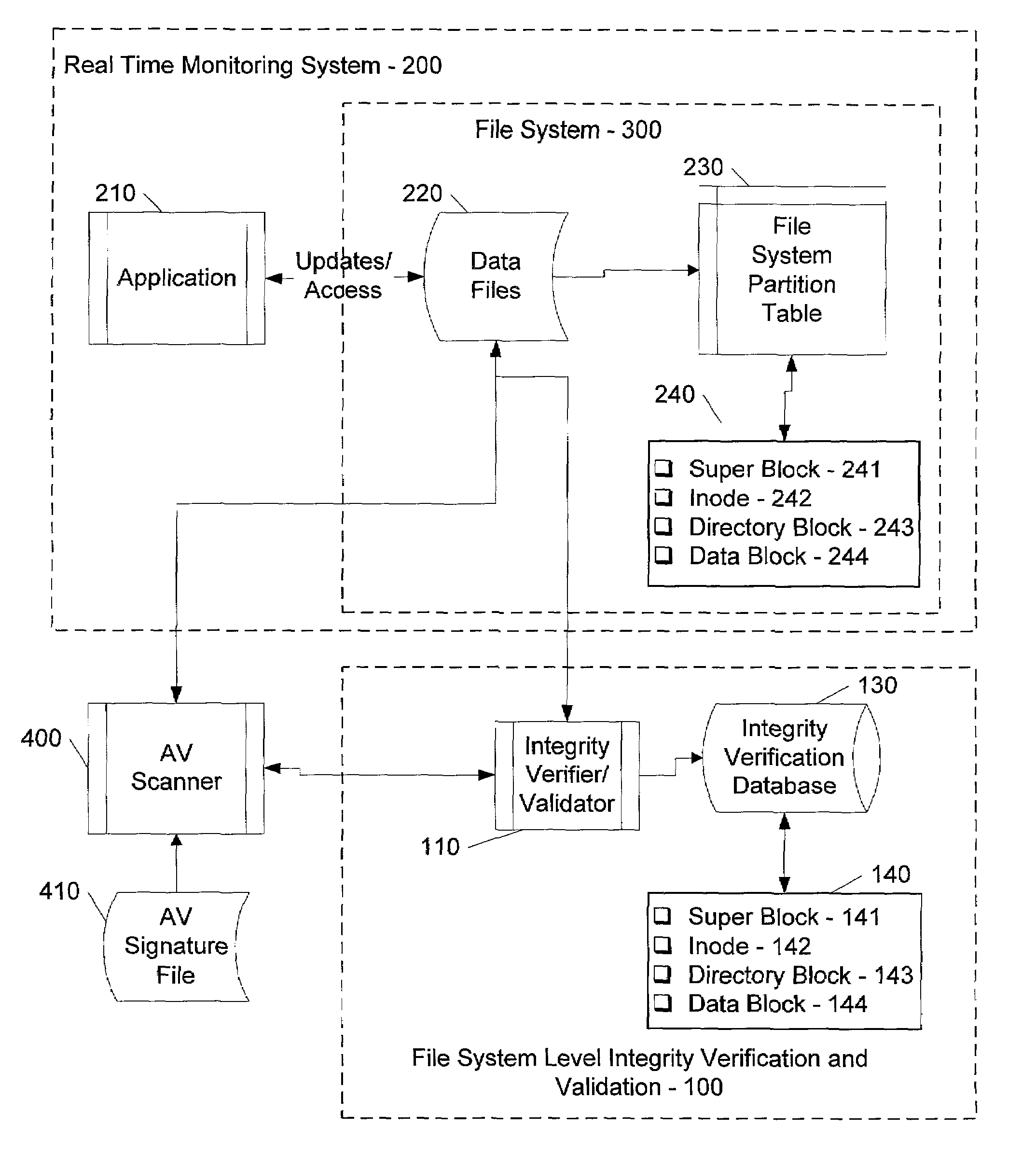

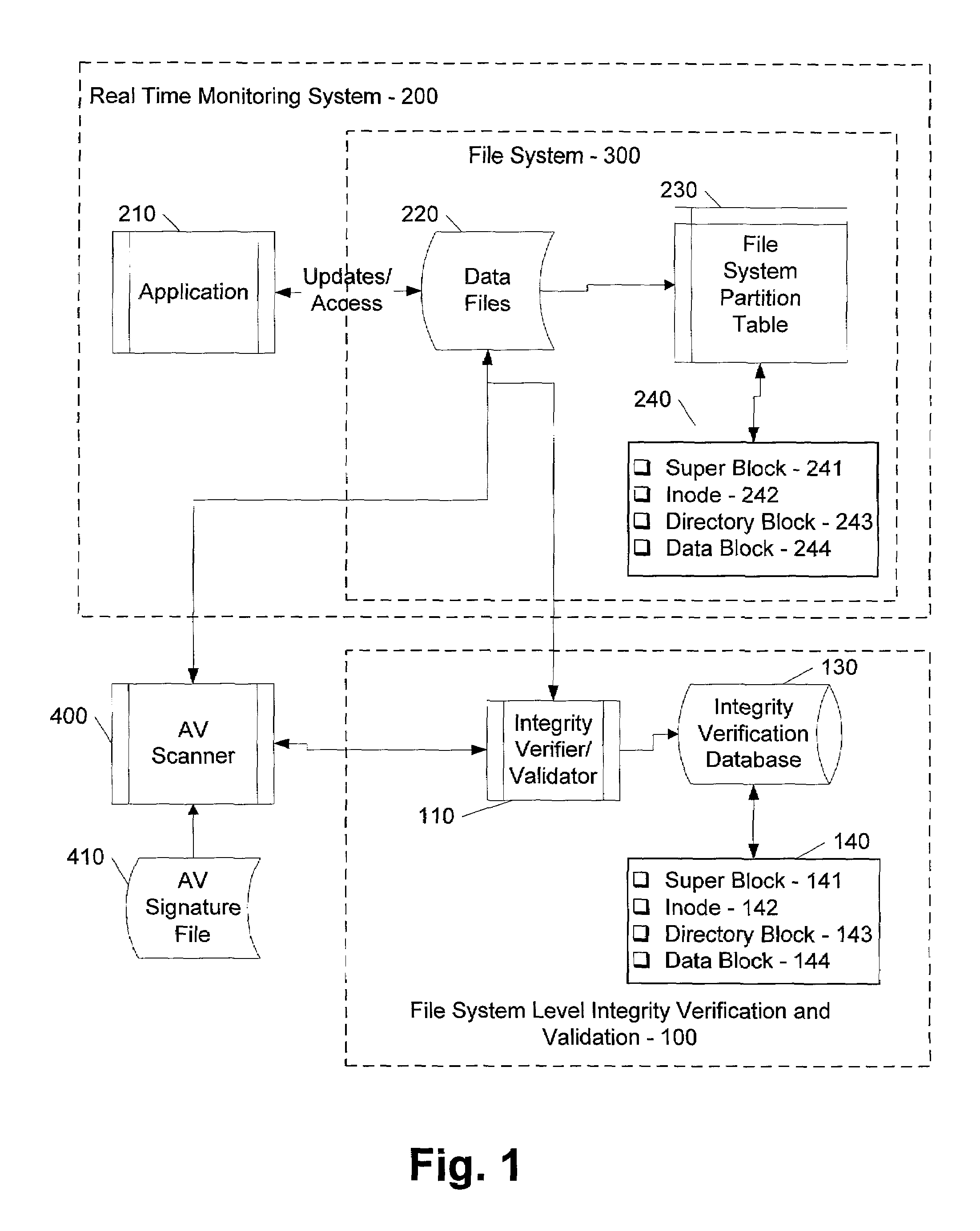

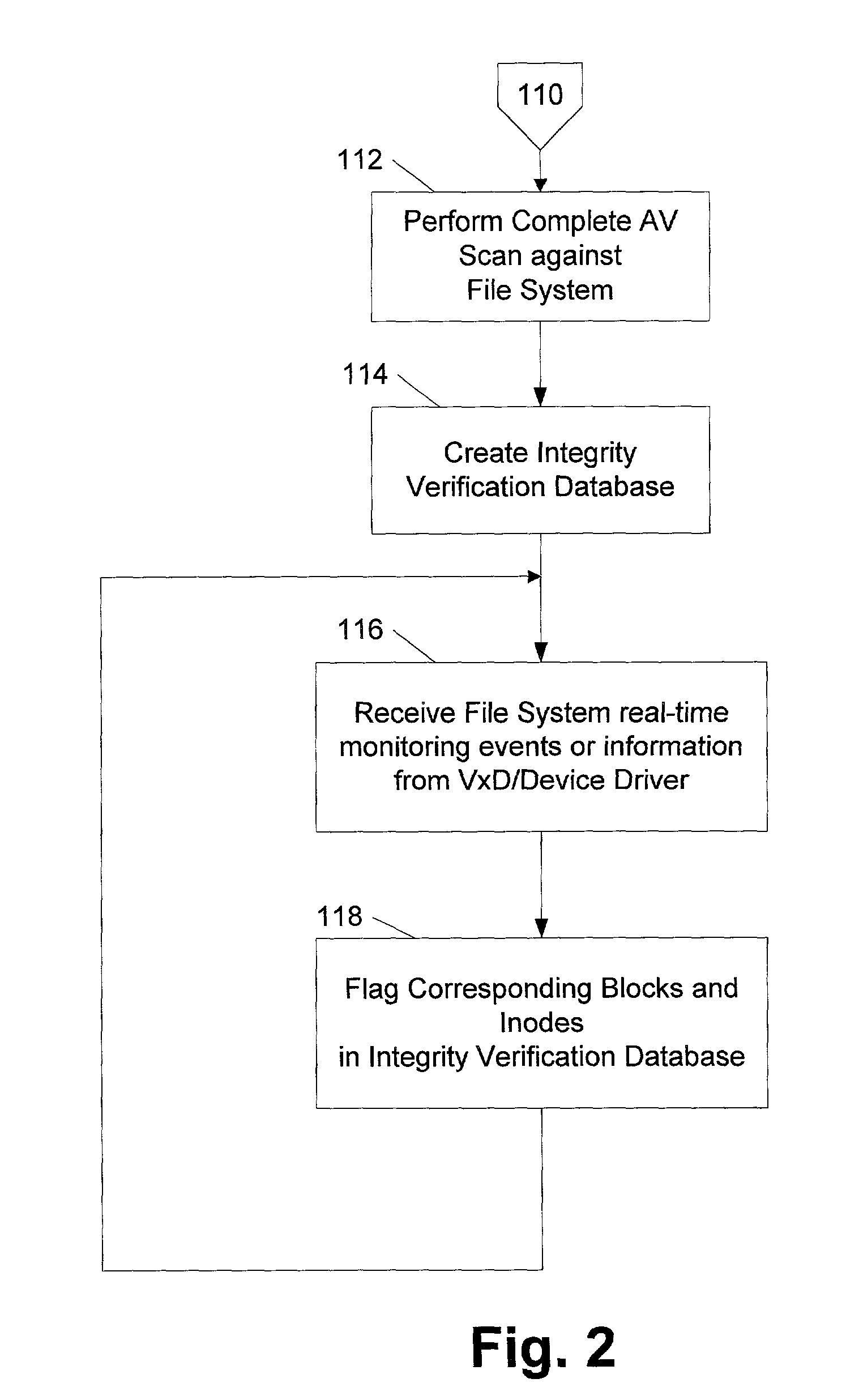

File system level integrity verification and validation

ActiveUS7069594B1Preventing rescanningGood level of efficiencyMemory loss protectionError detection/correctionAnti virusInode

An integrity verifier and validator is provided in which an initial anti-virus scan is performed against an entire file system to verify the integrity of the file system and create a corresponding file system level integrity verification database of known scanned regions of the file system. The database contains a copy of the file system's partition table referencing the range of occupied inodes and directory blocks. When new or updated content is written to the file system the integrity of the corresponding occupied inodes and directory blocks is no longer assured, and the integrity verifier flags them on the database for rescanning. Subsequent attempts to rescan any portion of the file system triggers the integrity validator to scan the database to validate whether that portion of the file system falls within any of the occupied inodes or directory blocks that have been flagged for rescanning. If they are not flagged, then rescanning of that portion of the file system is unnecessary as the integrity of at least that portion is assured. However, if they are flagged, then the anti-virus software rescans that portion of the file system for the presence of viruses.

Owner:MCAFEE LLC

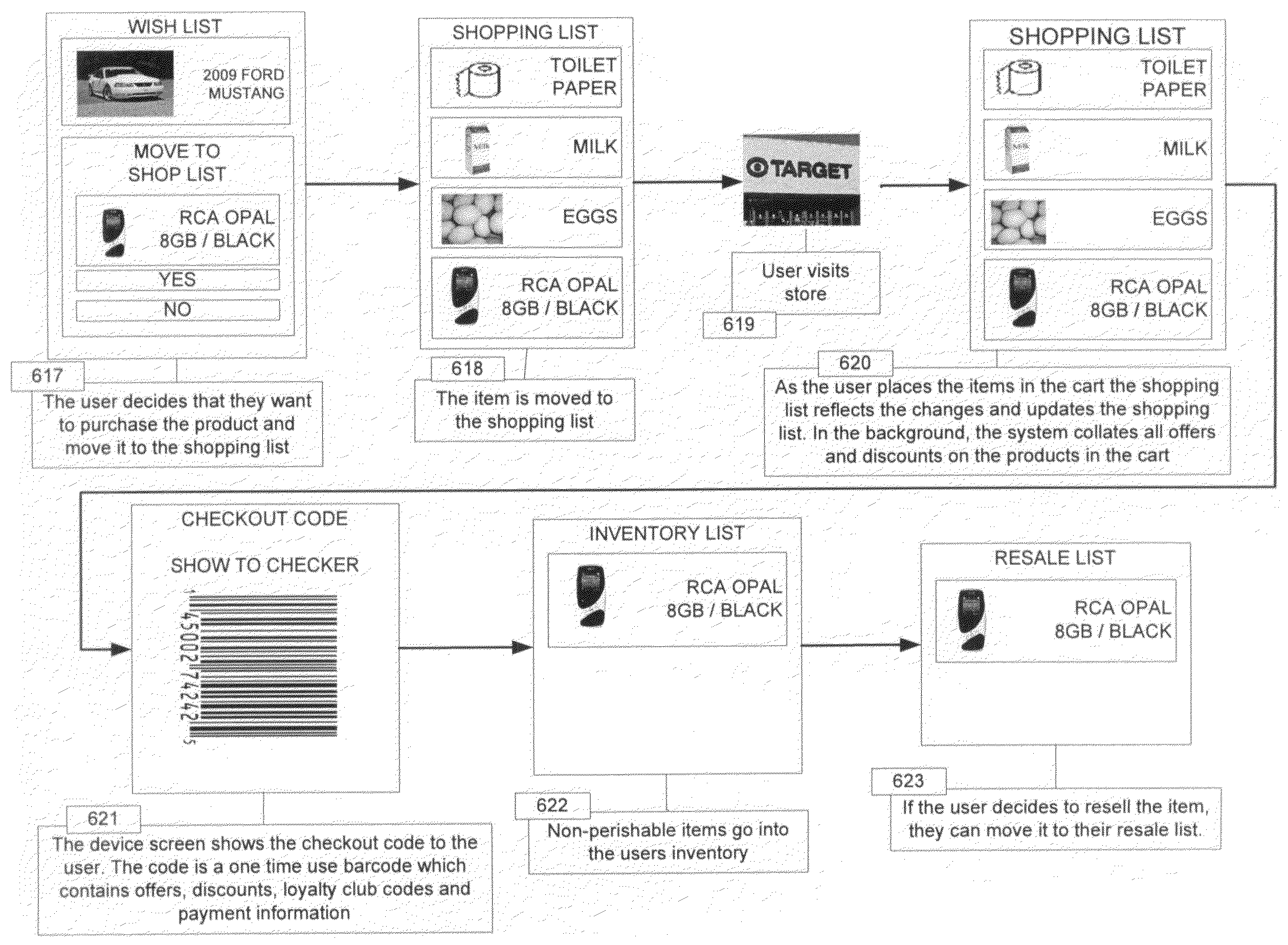

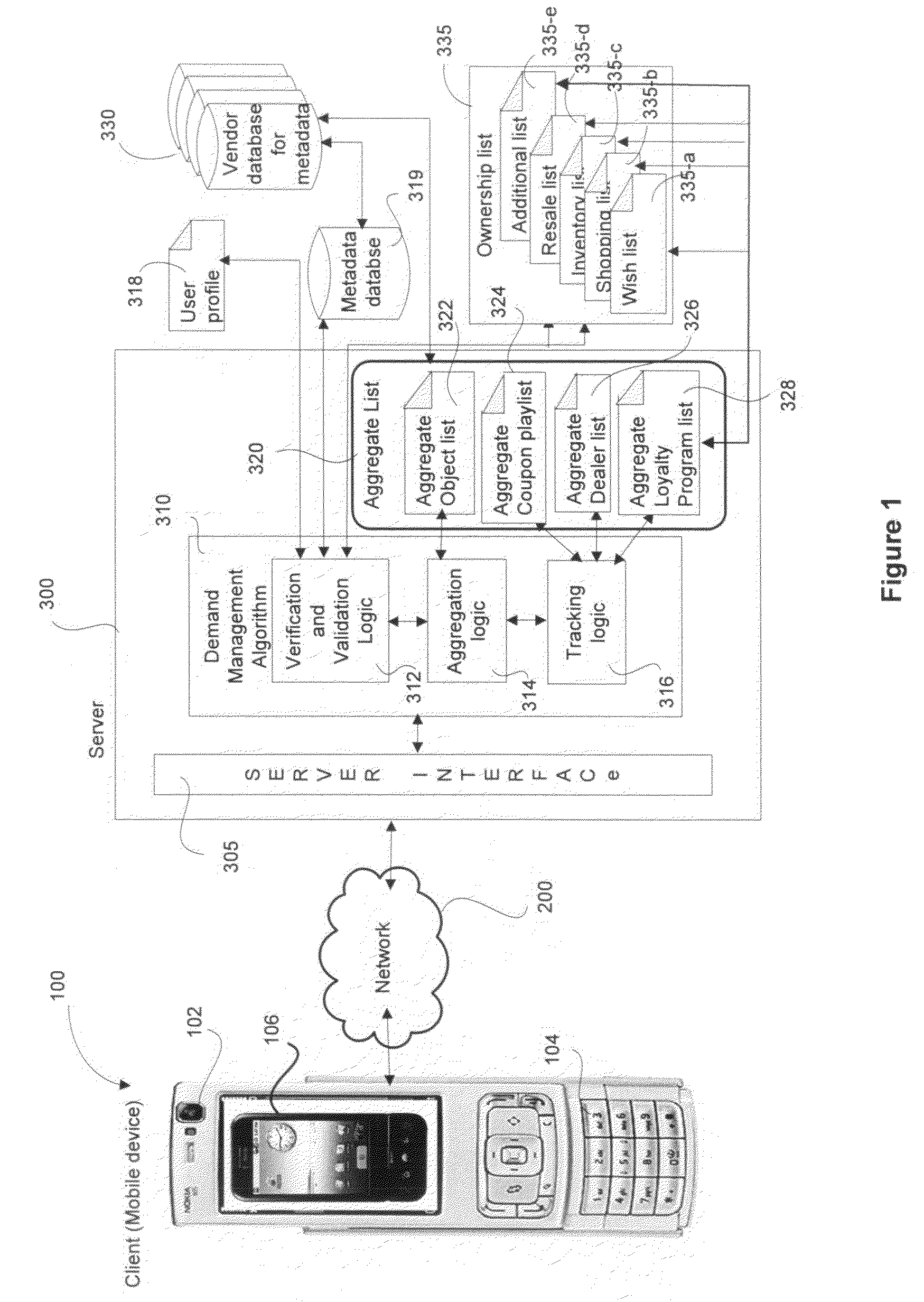

Dynamic Demand Calculation using Captured Data of Real Life Objects

ActiveUS20100179857A1Maximize utilizationAttract more usersHand manipulated computer devicesPayment architectureManagement objectSubject matter

Methods and system for managing demand for an object includes capturing information about the object through a mobile device associated with a user. The mobile device is configured to capture information about the object that include one or more of a spatial, temporal, topical and social attributes of the object. The identity of the object is verified and validated using this metadata captured by the user through the device from the real world object or its proxy. Upon successful verification and validation, the object and its metadata are automatically added to a wish list of the user. An aggregate list is generated using the attributes and metadata of the object from a plurality of users. The aggregate list defines a source of demand for the object. The object is tracked as it progresses through various phases of ownership cycle using dynamic demand calculations based on the information associated with the objects, the users and the aggregate lists.

Owner:R2 SOLUTIONS

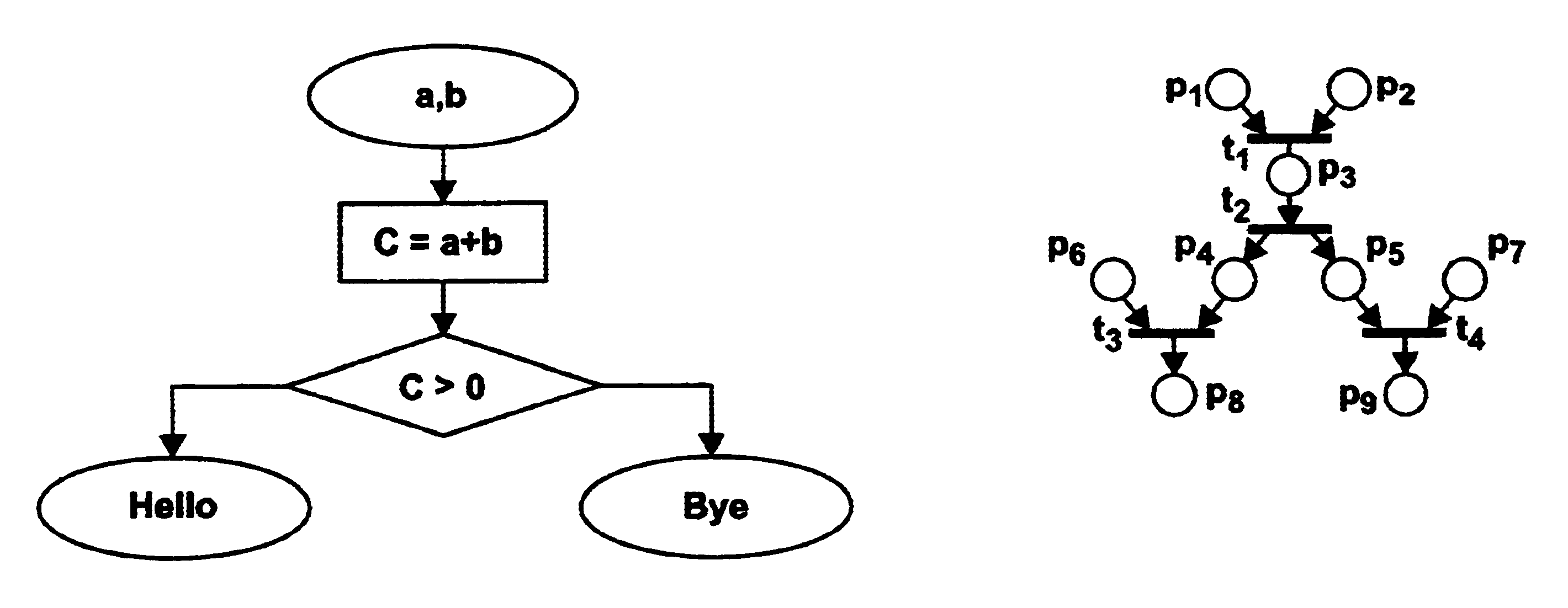

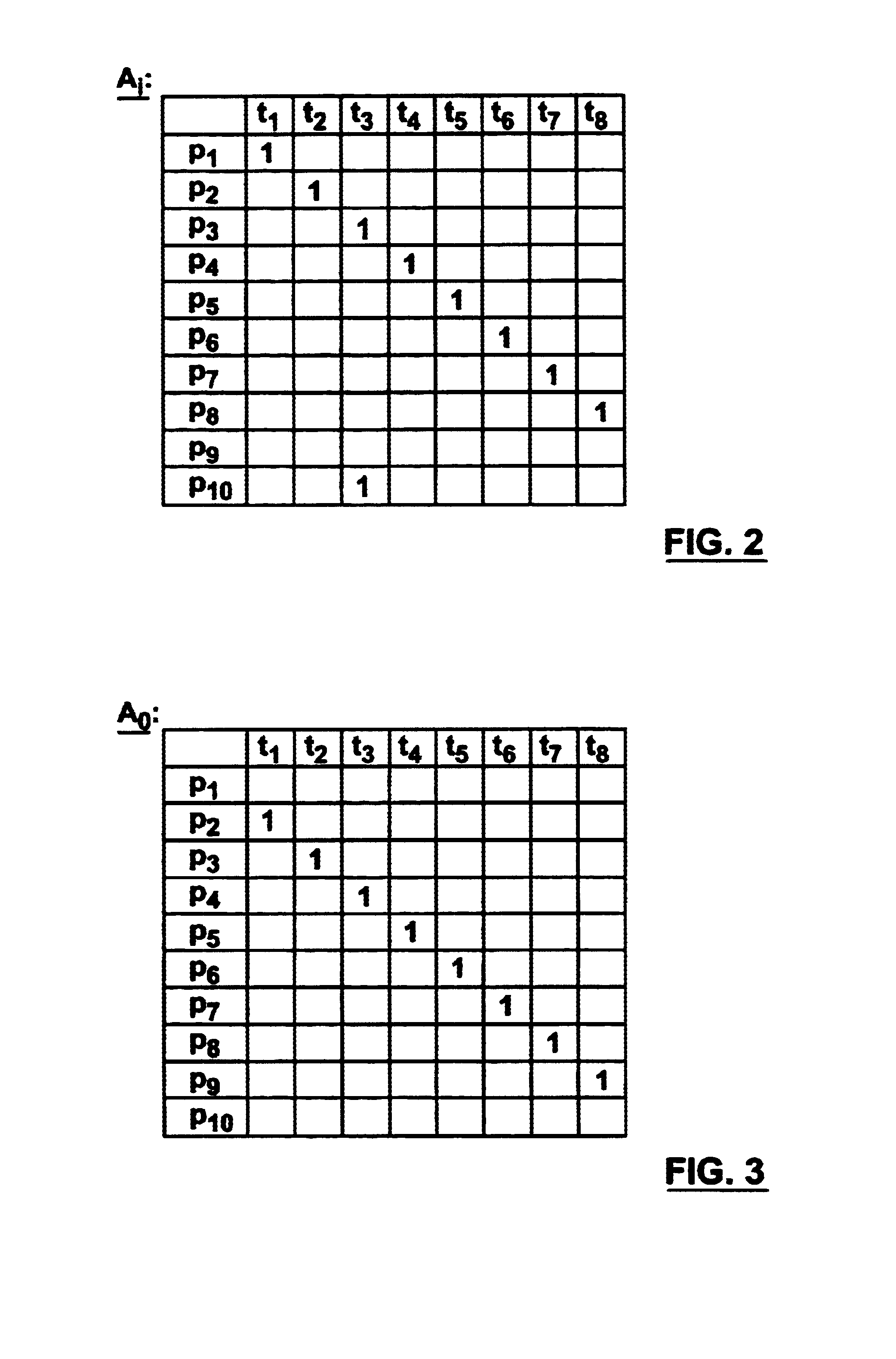

Universal verification and validation system and method of computer-aided software quality assurance and testing

InactiveUS6671874B1Eliminate degradationProgram documentationSoftware testing/debuggingDocumentation procedureSystem requirements

A method of developing a model of a computer program represents the system requirement conditions and events as a set of positions and transitions, maps the system requirements in a table of positions with position and optionally transition designations, tags one or more significant positions in the including any conditional positions, and creates a reference designation associating alternative conditions with their respective conditional positions. A universal software test development method can be applied to the model by mapping the conditions to a set of positions including a starting position which has no input, a terminal position which has no output, and intermediate positions between the starting position and the terminal position, and generating from the set of positions a table of positions, associating each positions with an expression of the position representing the corresponding system requirements. Both the model development method and the test development method can be implemented automatically by computer software, and the test development method allows for automated development of test documentation. These methods can thus be applied for the verification and validation of computer software.

Owner:SOFEA INC

System and method for independent verification and validation

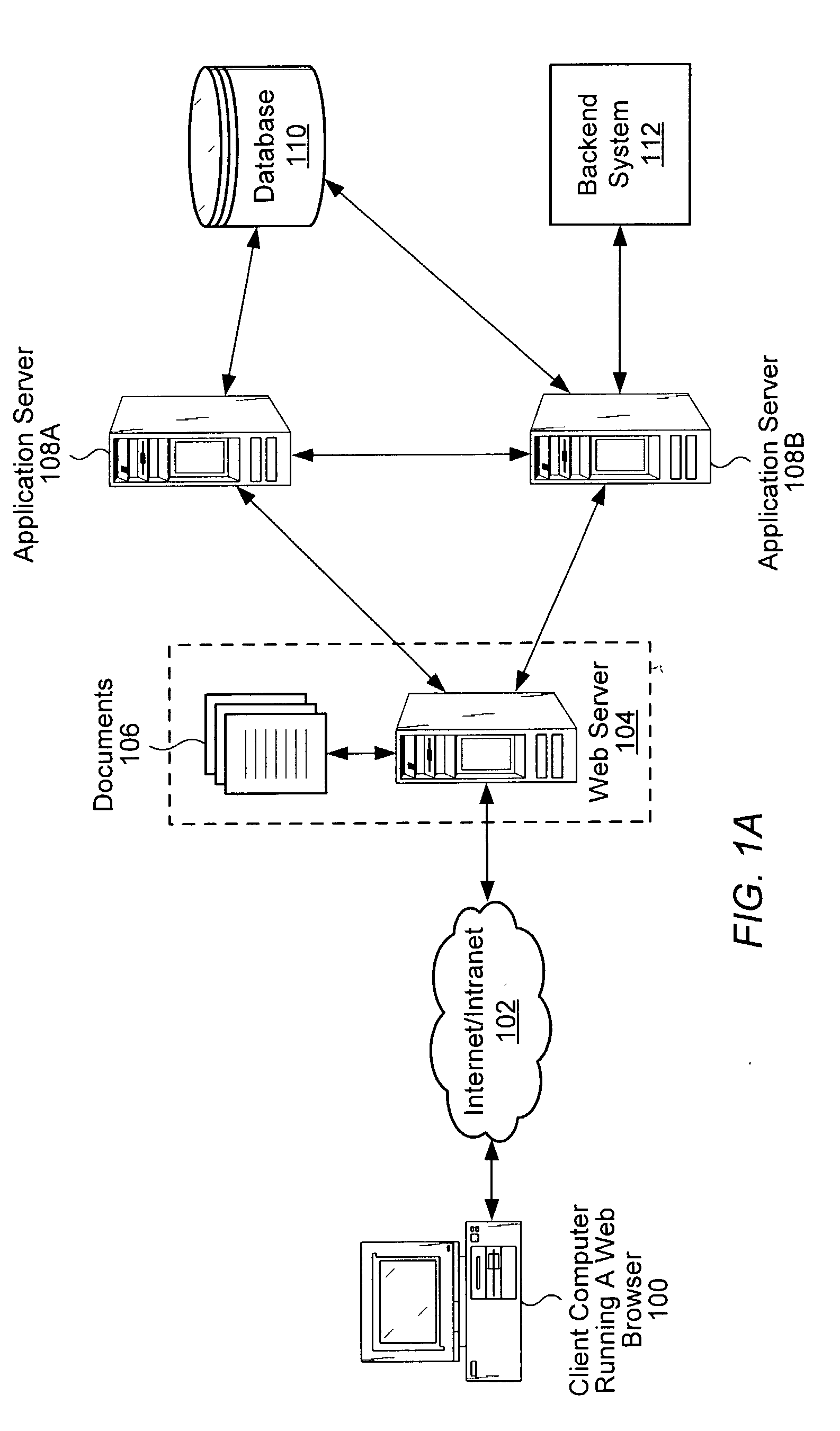

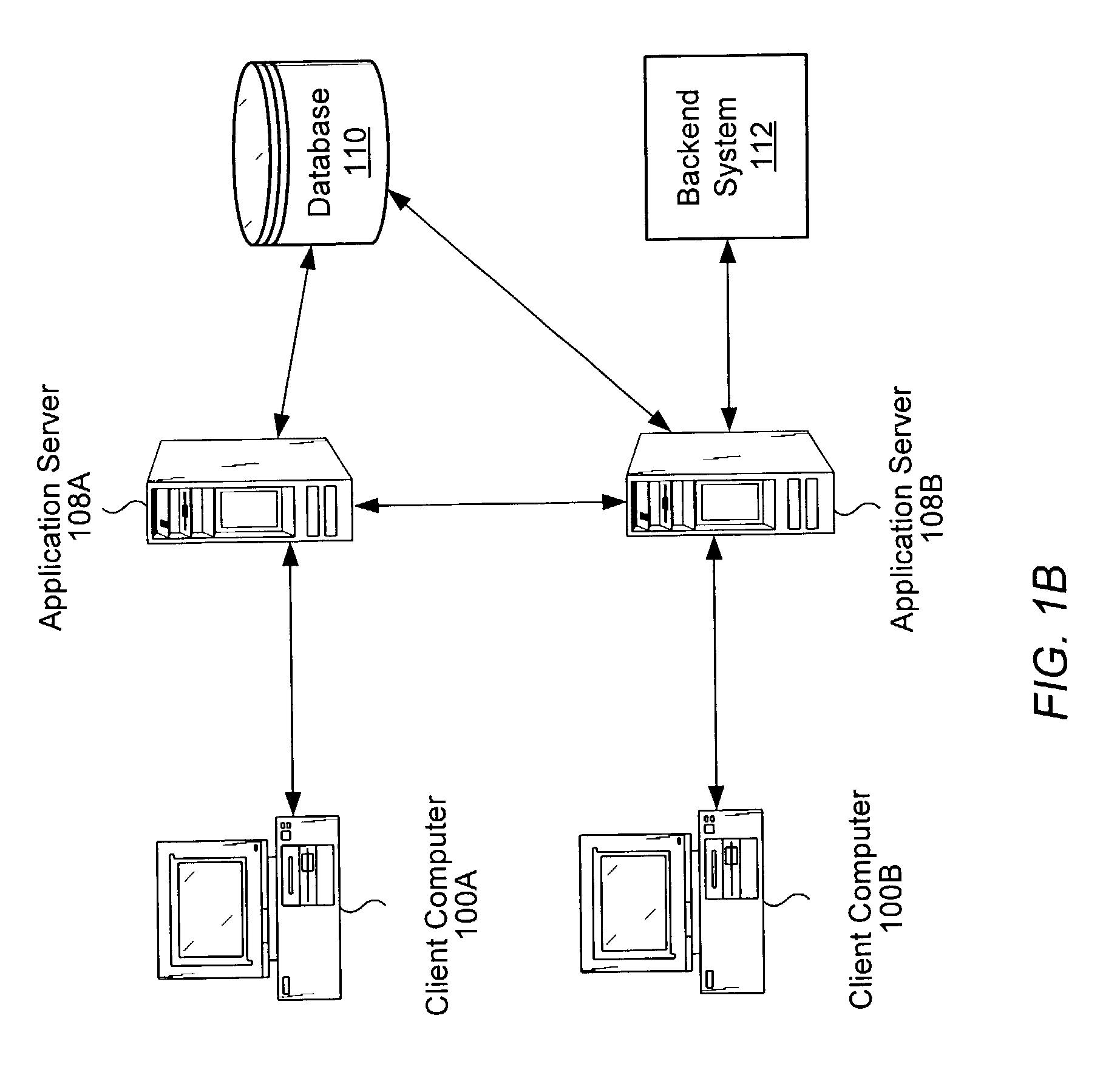

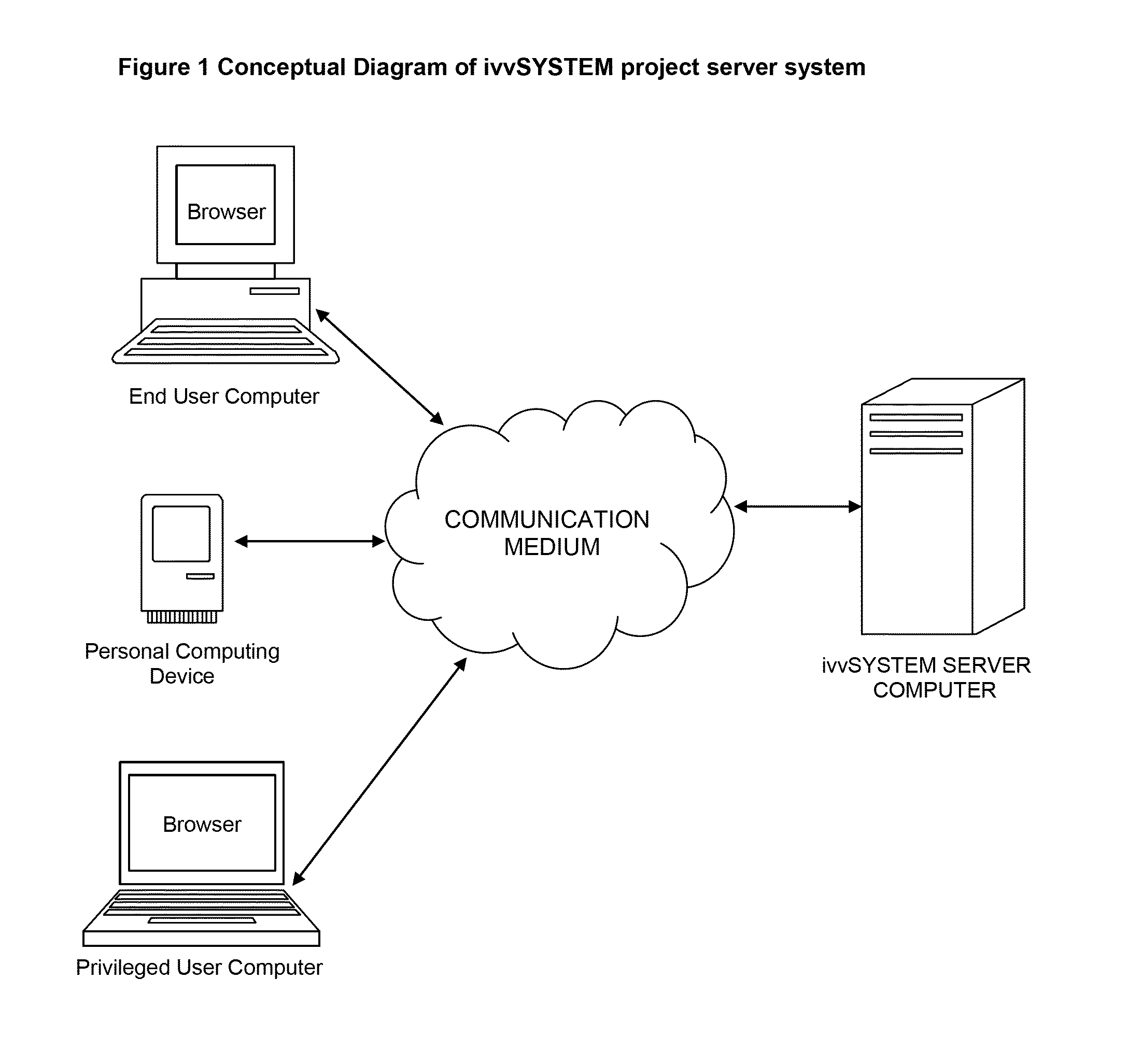

ActiveUS8543620B2Simplifies complex logisticsQuick mapDigital data processing detailsResourcesOperational systemNetwork service

This invention is to solve the high cost of IV&V by simplifying the complex logistics of project management. This is an intelligent project management system comprising a project server computer remotely accessible by a user computing device. The project server computer includes several databases: A database of electronic library which stores documents that are required by the project, a database which stores project data that reflect the state of the project, and a database which stores the user information of privileged users. Several modules are executing in the project server computer to generate the view of the project, to automatically monitor the state of the project, to verify and validate the mapping between multiple documents for requirement traceability, to automatically indicate the state of the project, to automatically provide assistance to the user, to automatically inform the stakeholder on matters related to the project, and to authenticate the privileged user. This intelligent project management system assumes that the server computer contains a standard computer operating system that includes at least a web server, an email server and a search engine facility.

Owner:APLIX RES

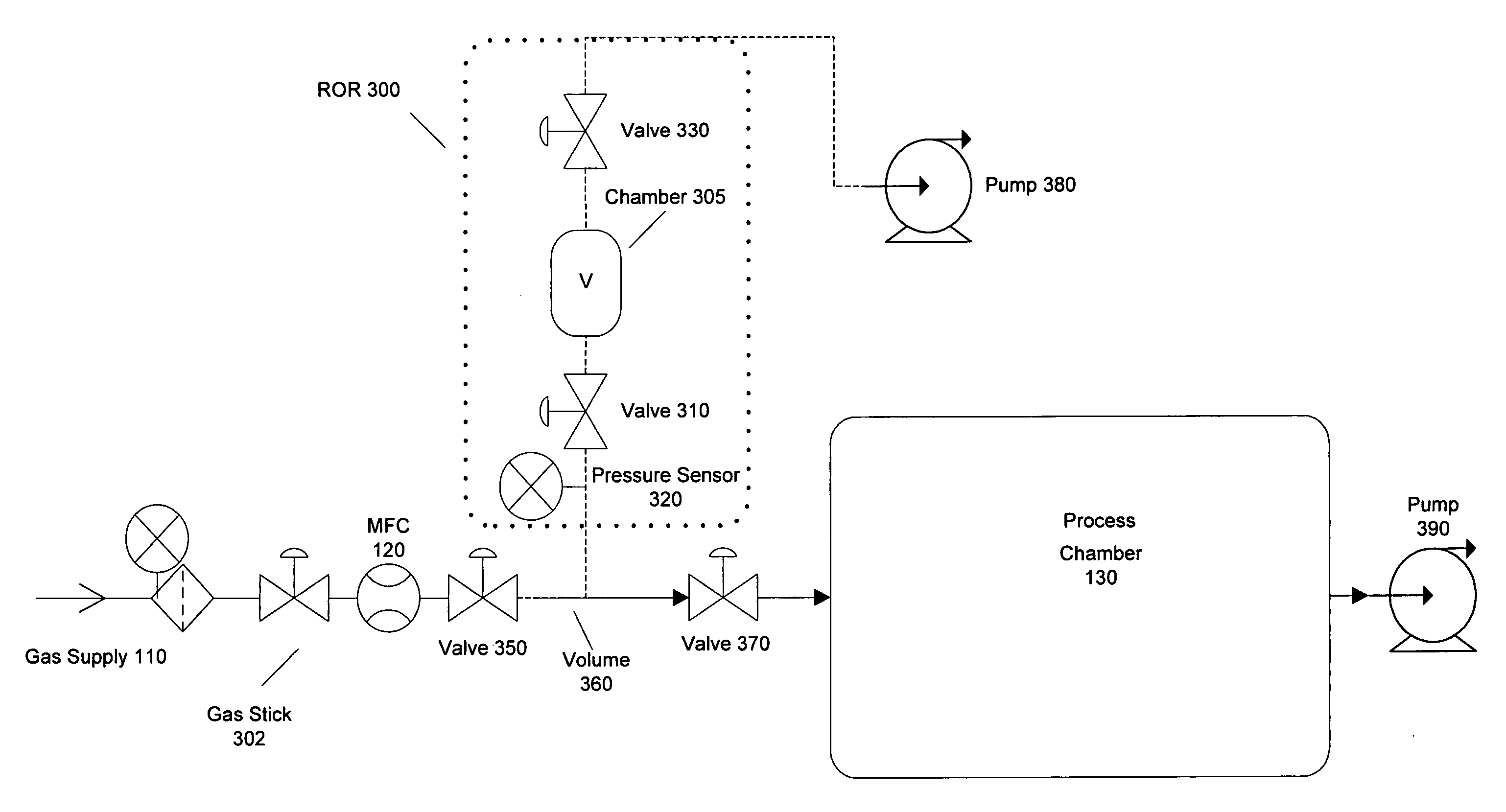

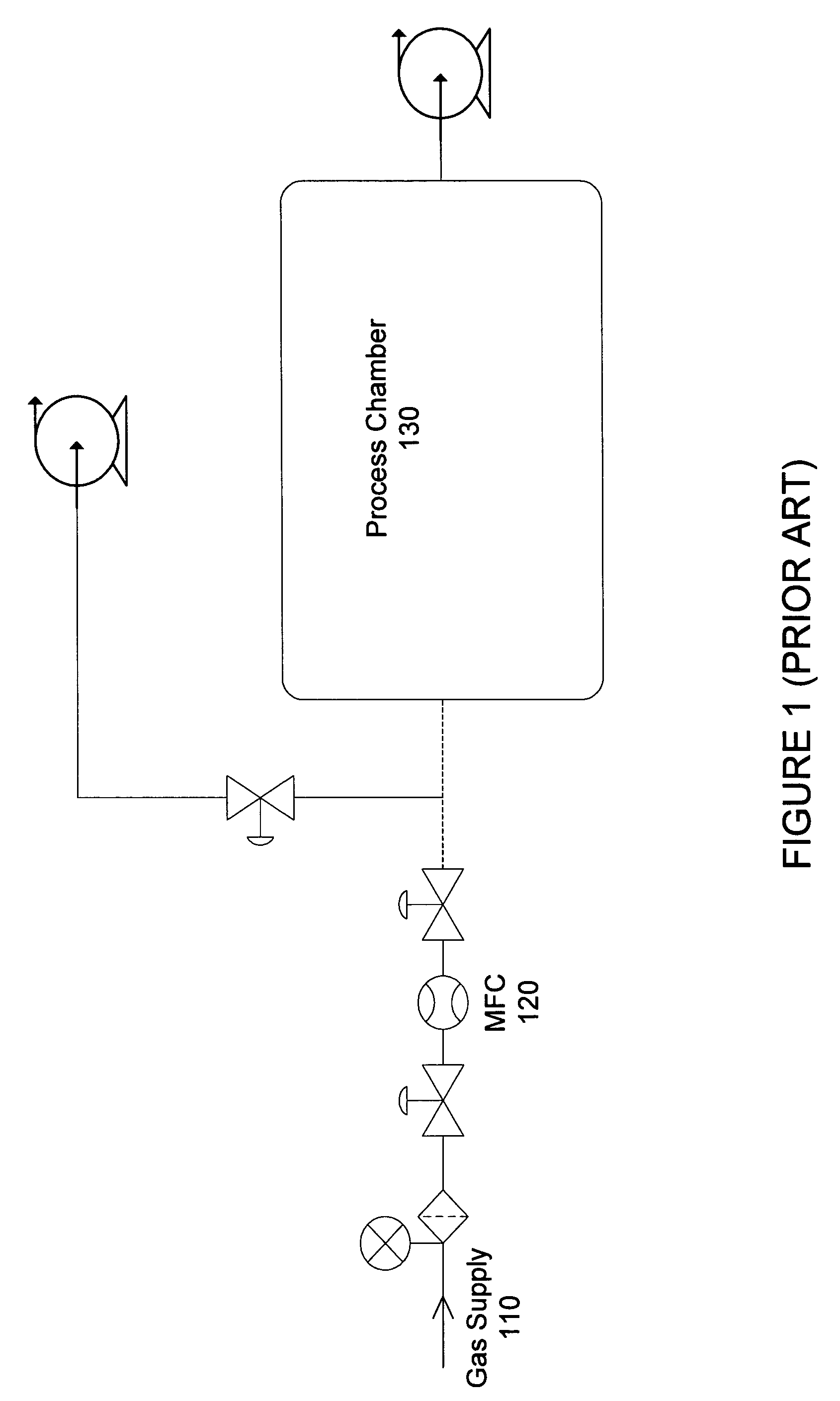

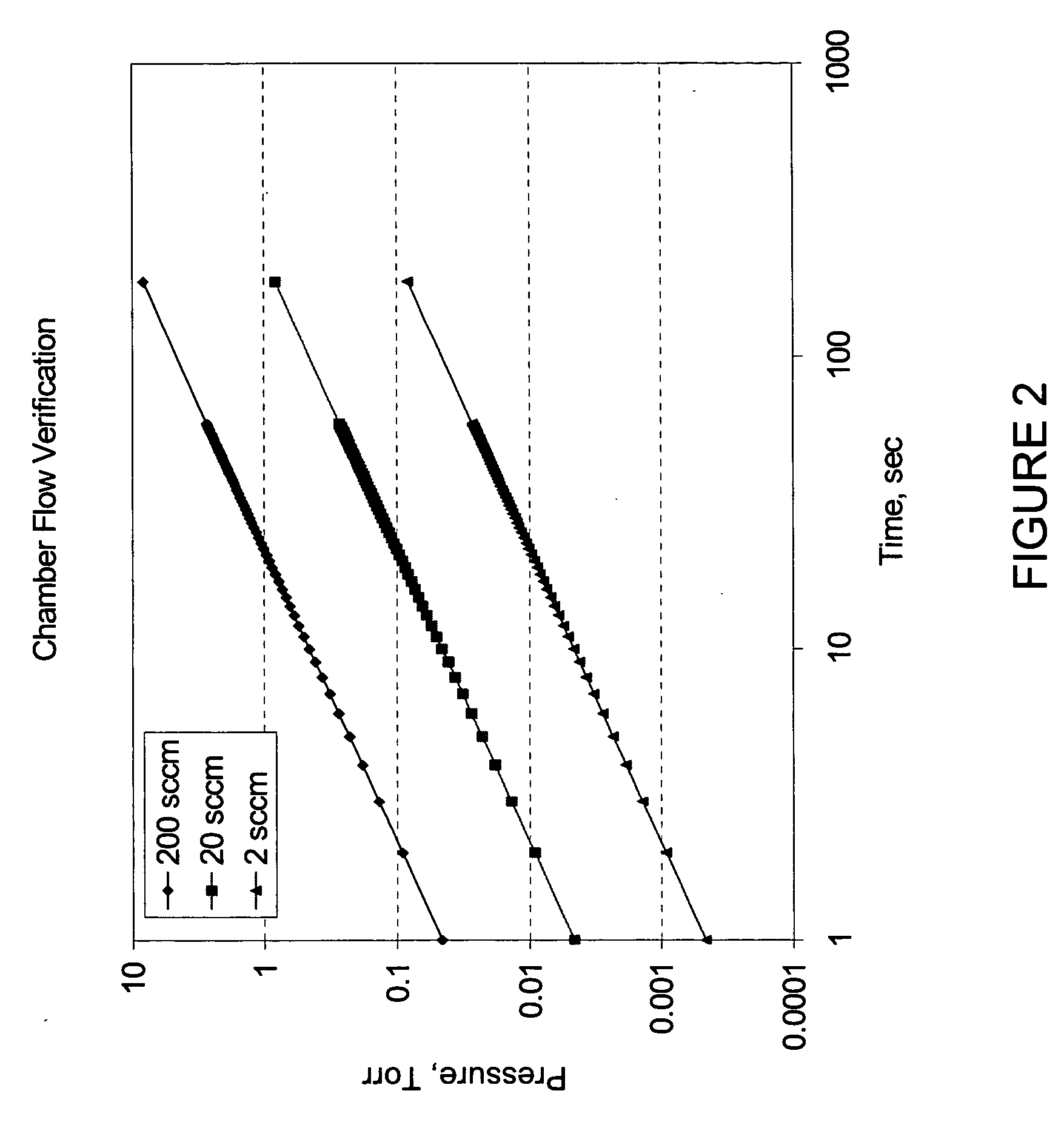

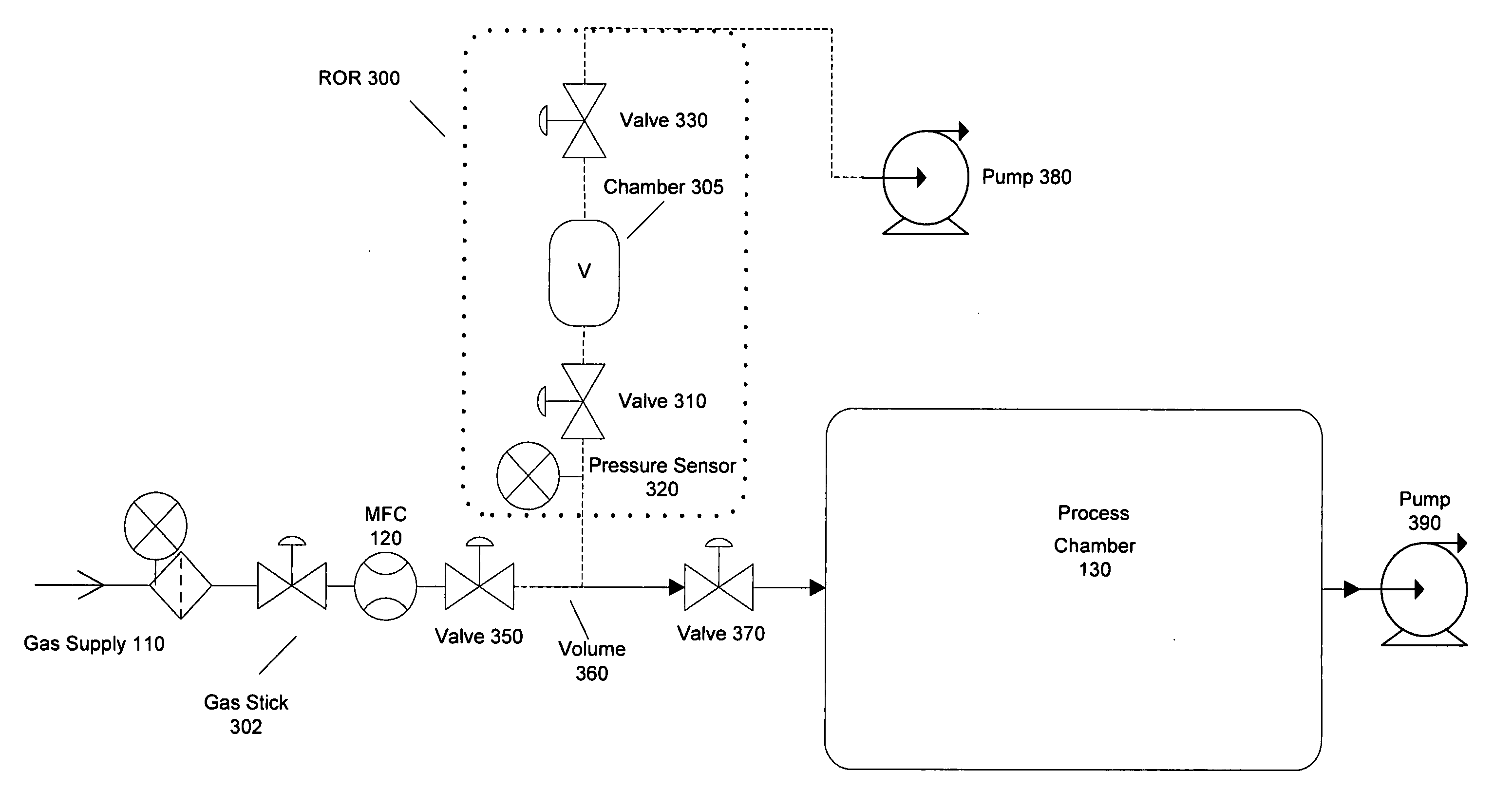

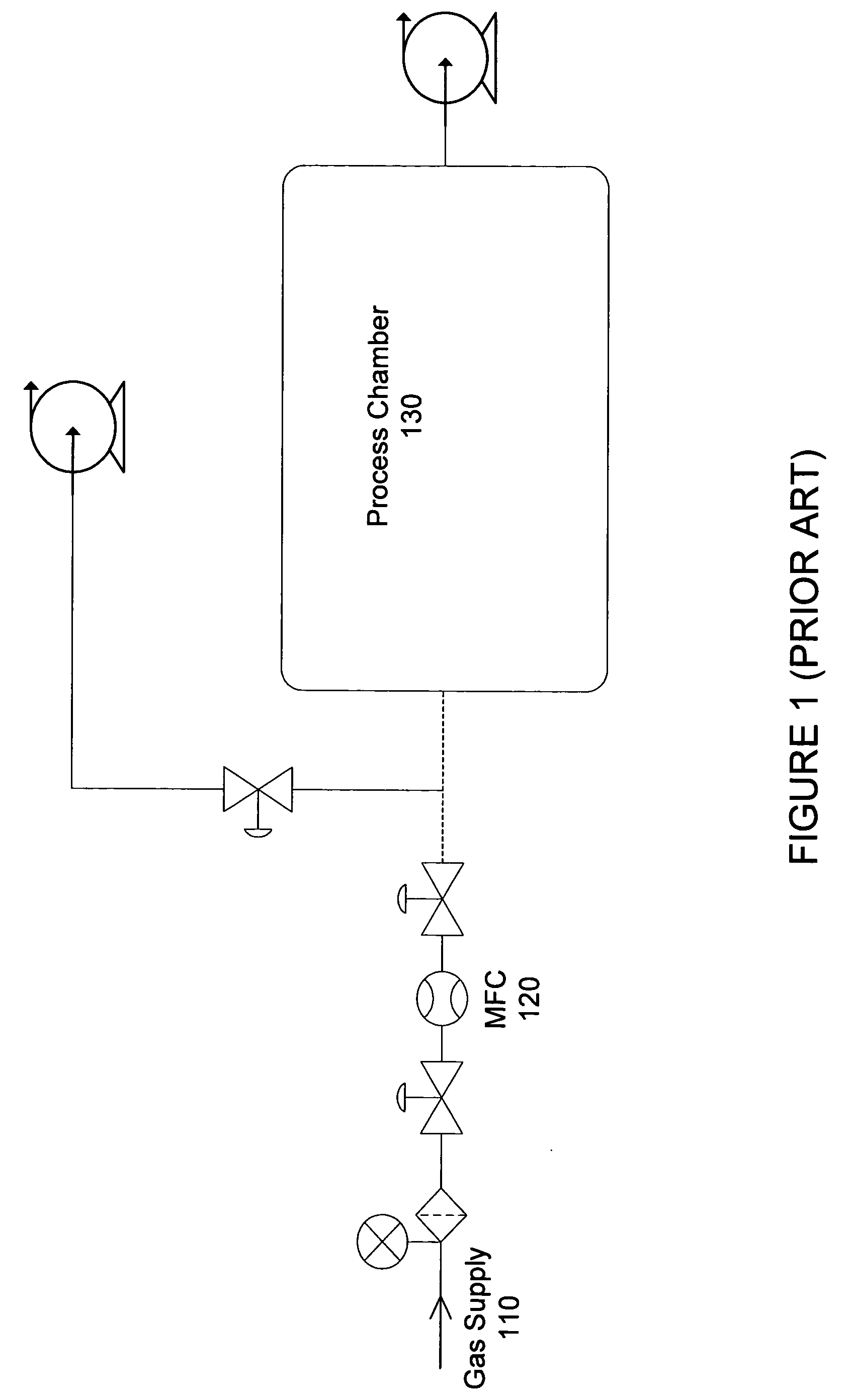

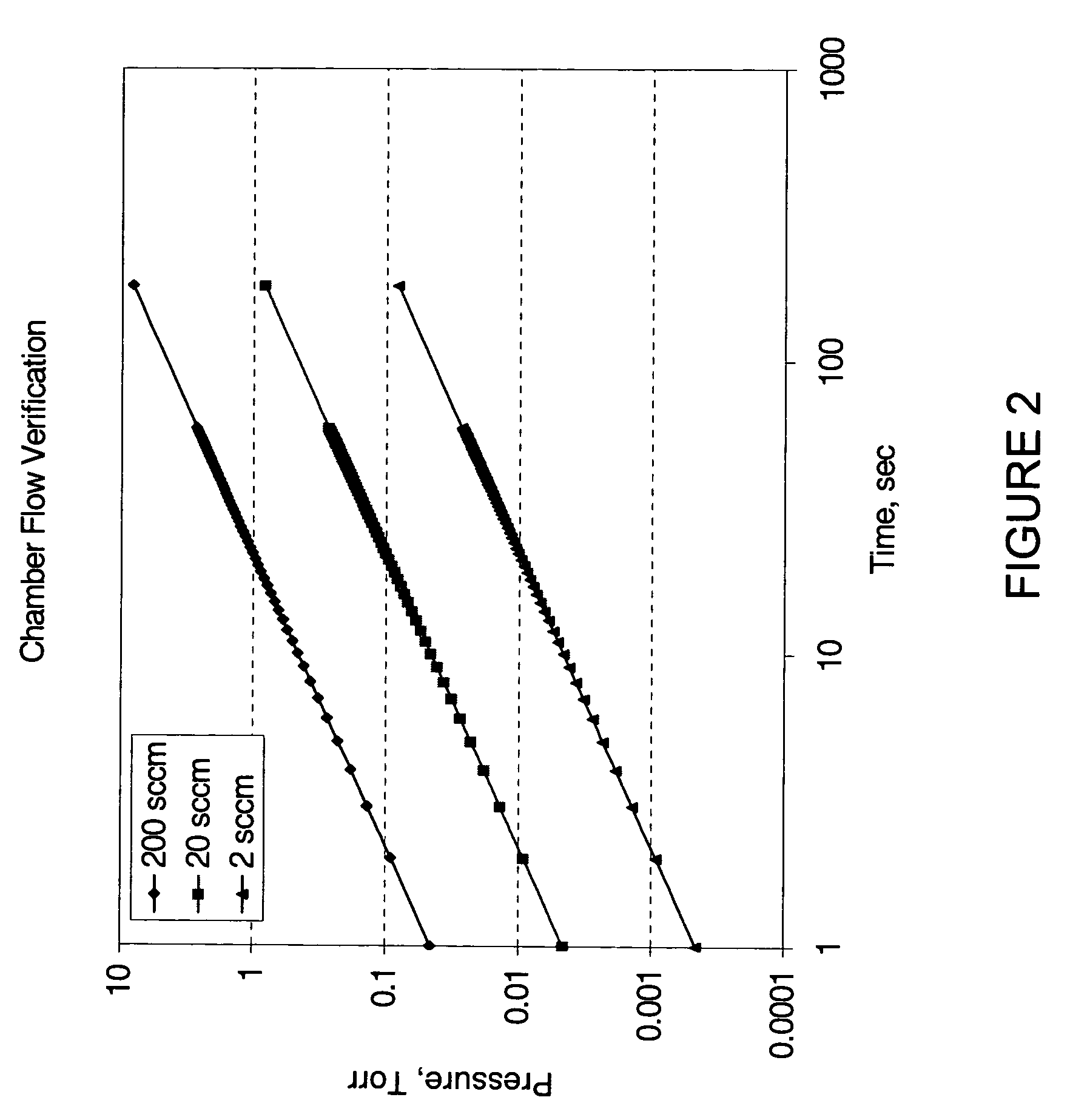

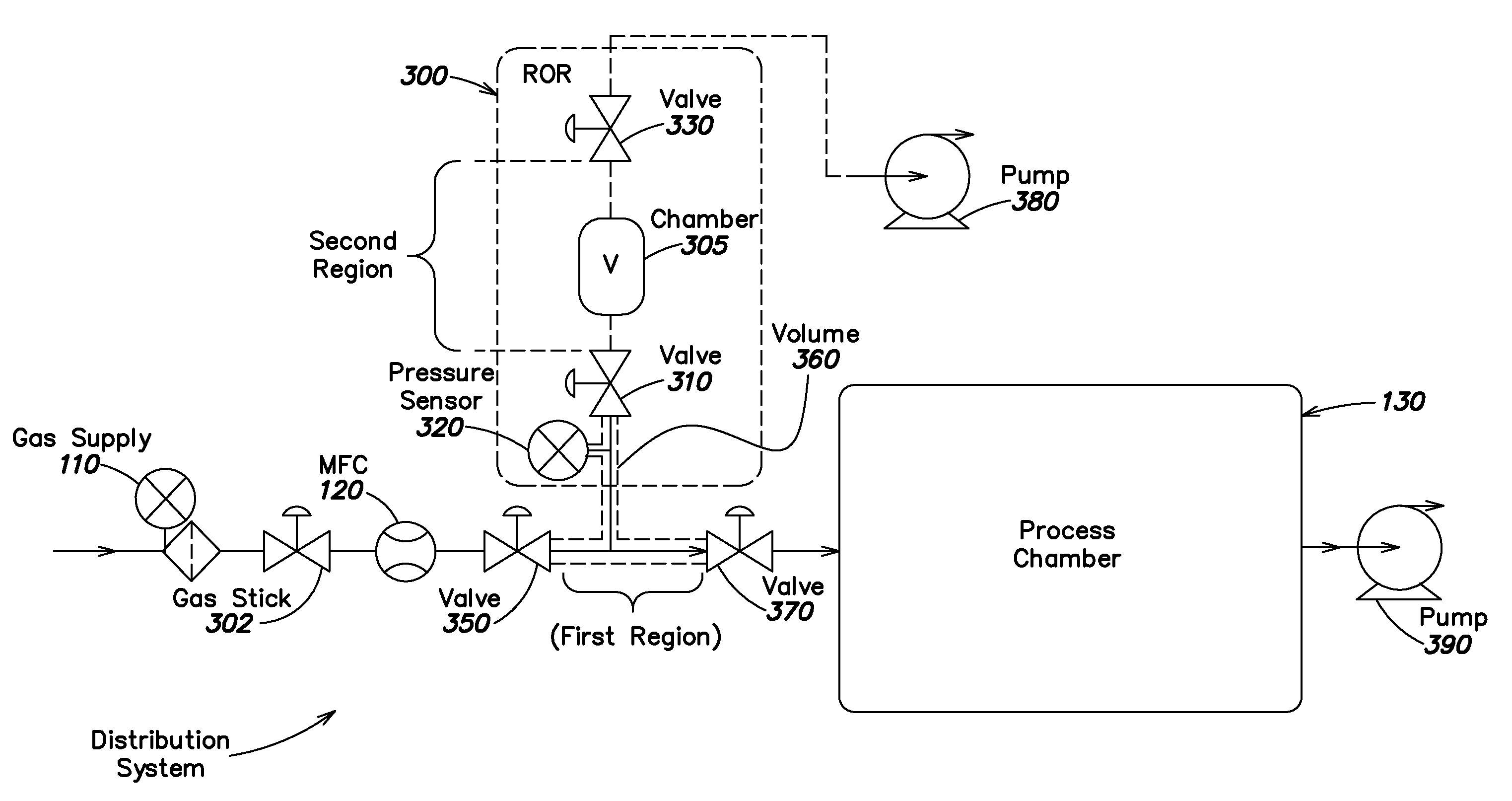

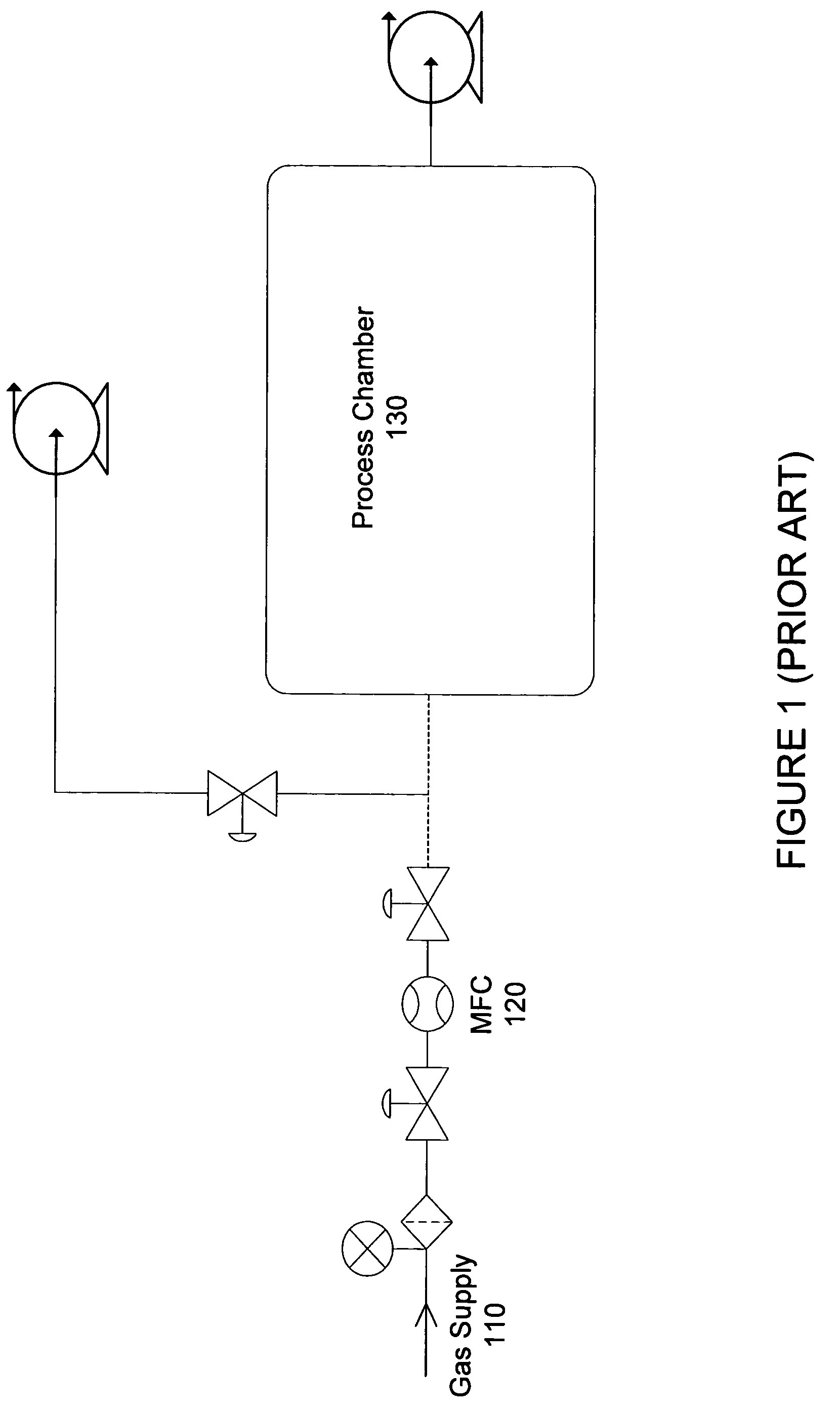

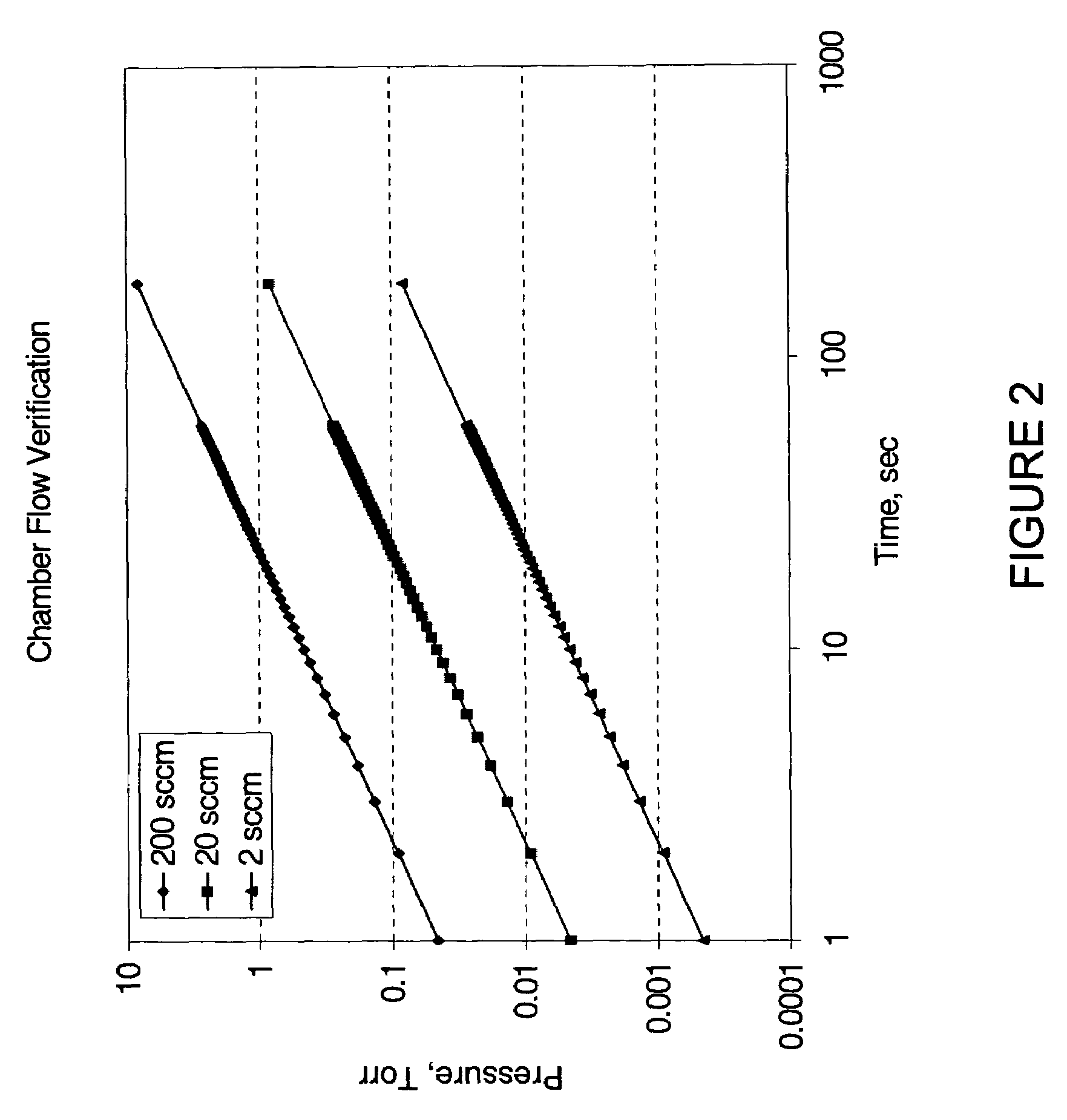

Method and system for flow measurement and validation of a mass flow controller

ActiveUS20060011237A1Operating means/releasing devices for valvesTesting/calibration apparatusEngineeringVerification and validation

Systems and methods for flow verification and validation of mass flow controllers are disclosed. A mass flow controller may be commanded to a specified flow and flow measurement commenced. During an interval, gas is accumulated in a first volume and measurements taken within this volume. The various measurements taken during the interval may then be used to calculate the flow rate. The flow rate, in turn, may be used to determine the accuracy of the mass flow controller relative to a setpoint.

Owner:ENTEGRIS INC +1

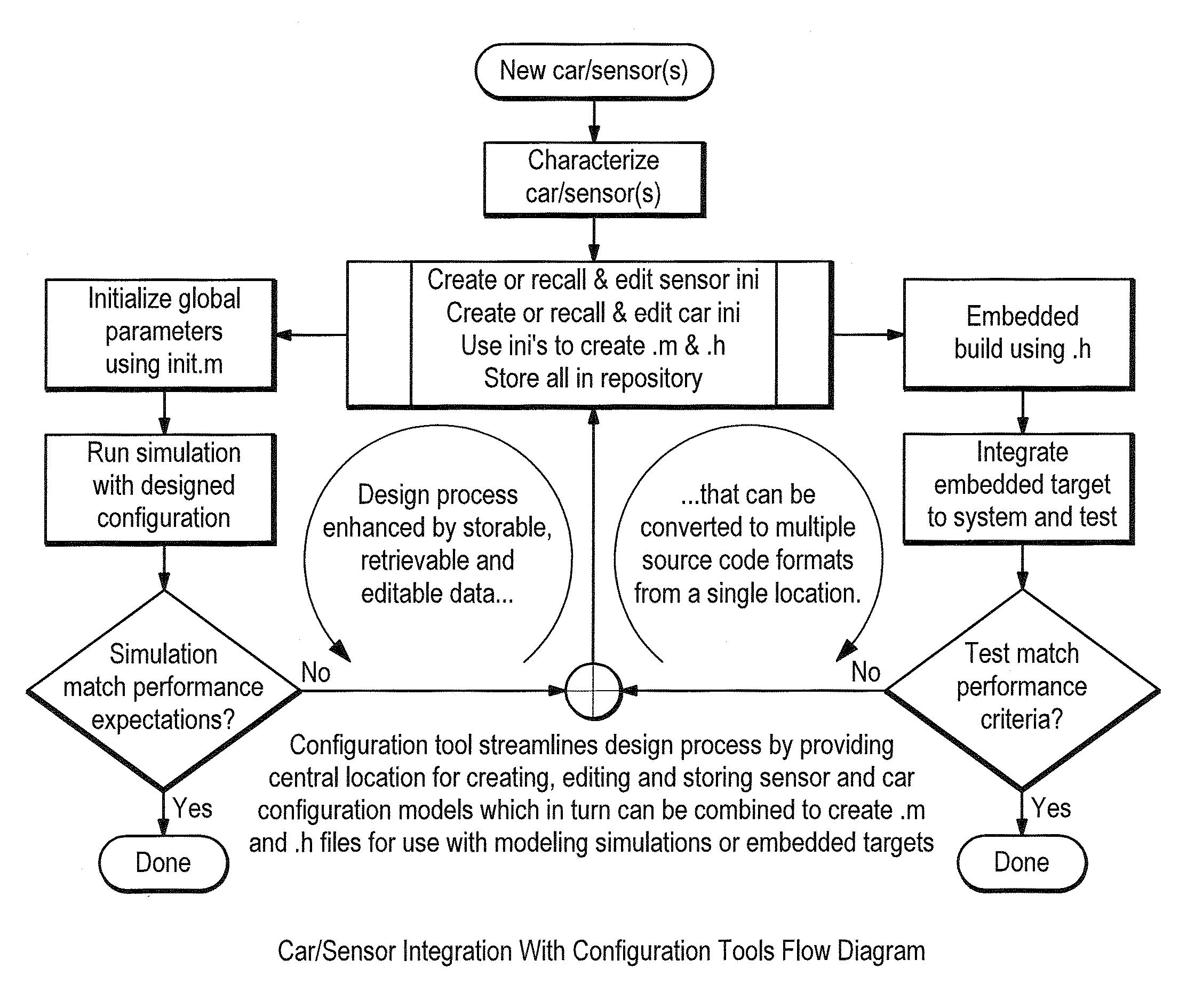

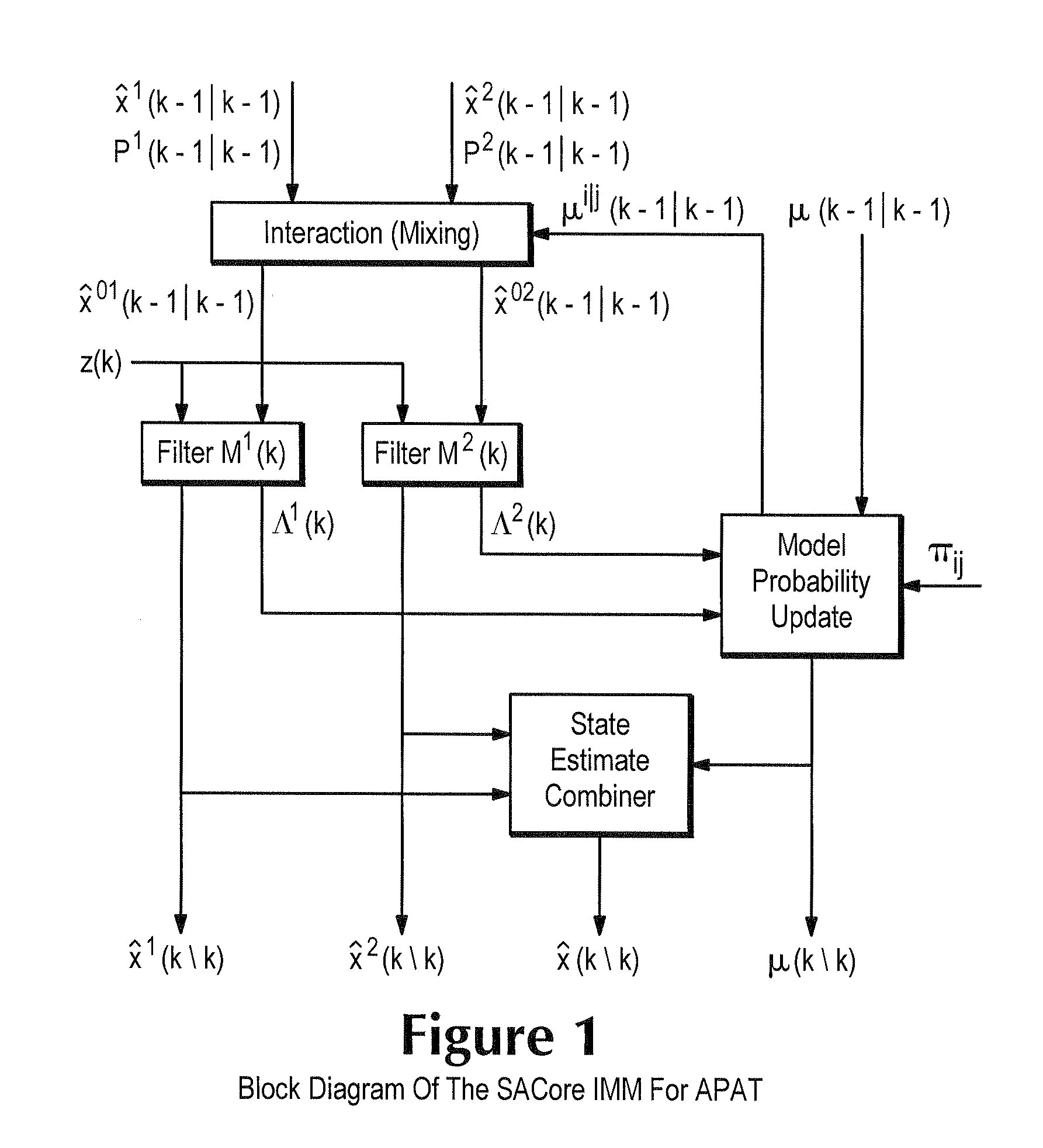

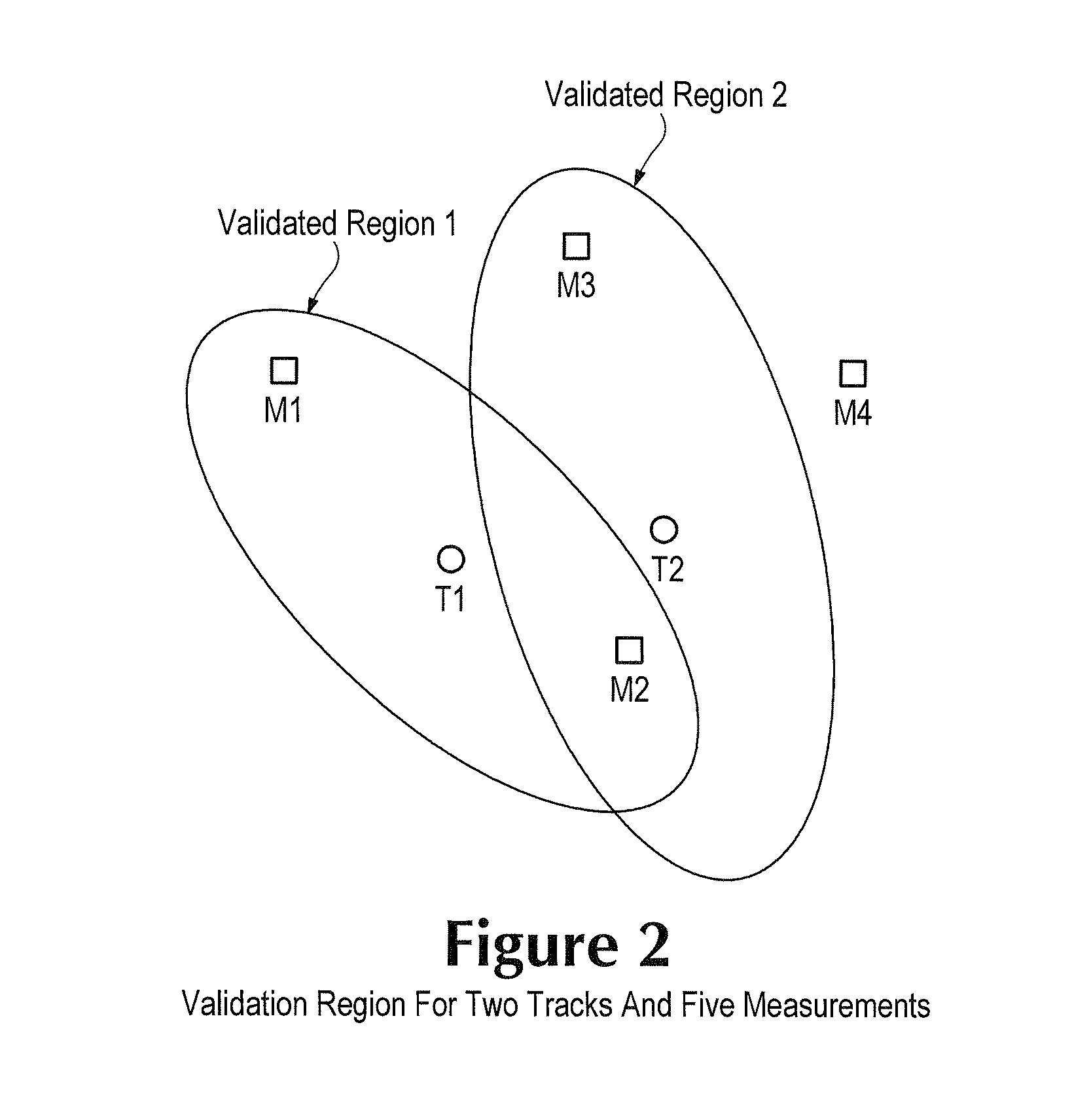

System and method for the configuration of an automotive vehicle with modeled sensors

InactiveUS8417490B1Reduce process complexityProvide functionalityGeometric CADAnalogue computers for vehiclesAutomotive softwareData modeling

A system and methods are disclosed for providing integrated software development environment for the design, verification and validation of advanced automotive safety systems. The system allows automotive software to be developed on a host computer using a collection of computer programs running simultaneously as processes and synchronized by a central process. The software disclosed uses separate synchronized processes, permitting signals from disparate sources to be generated by a simulation running on the host computer or from actual sensors and data bus signals coming from and going to actual vehicle hardware which is connected to their bus counterparts in the host computer on a real-time basis. The methods disclosed are for providing an Algorithm Prototyping, Analysis and Test through an integrated framework for dynamic data modeling and application development.

Owner:AUTOBRILLIANCE LLC +1

Method and system for flow measurement and validation of a mass flow controller

ActiveUS20060005882A1Accurately determineMinimize false flow conditionOperating means/releasing devices for valvesTesting/calibration apparatusStream flowValidation methods

Systems and methods for flow verification and validation of mass flow controllers are disclosed. A mass flow controller may be commanded to a specified flow and flow measurement commenced. Gas is accumulated in a first volume and while measurements are taken within this volume. Gas may then flow into a second volume while measurements are taken. The various measurements taken during the two intervals may then be used to calculate the flow rate. The flow rate, in turn, may be used to determine the accuracy of the mass flow controller relative to a setpoint. Additionally, these systems and methods may utilize only one volume to perform flow verification by flowing gas into this volume, taking measurements, and calculating the flow rate based only upon this set of measurements.

Owner:BROOKS INSTRUMENT +1

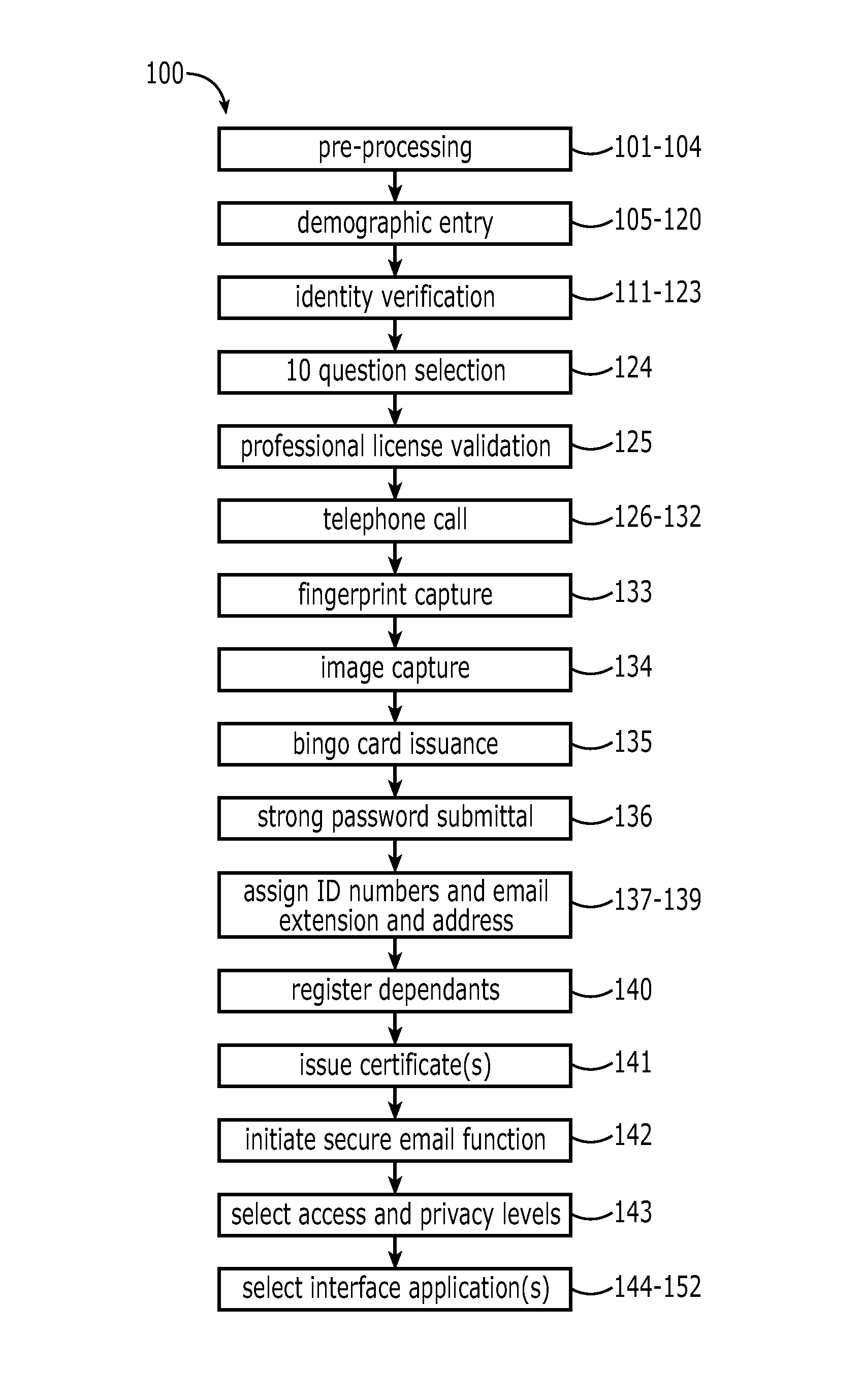

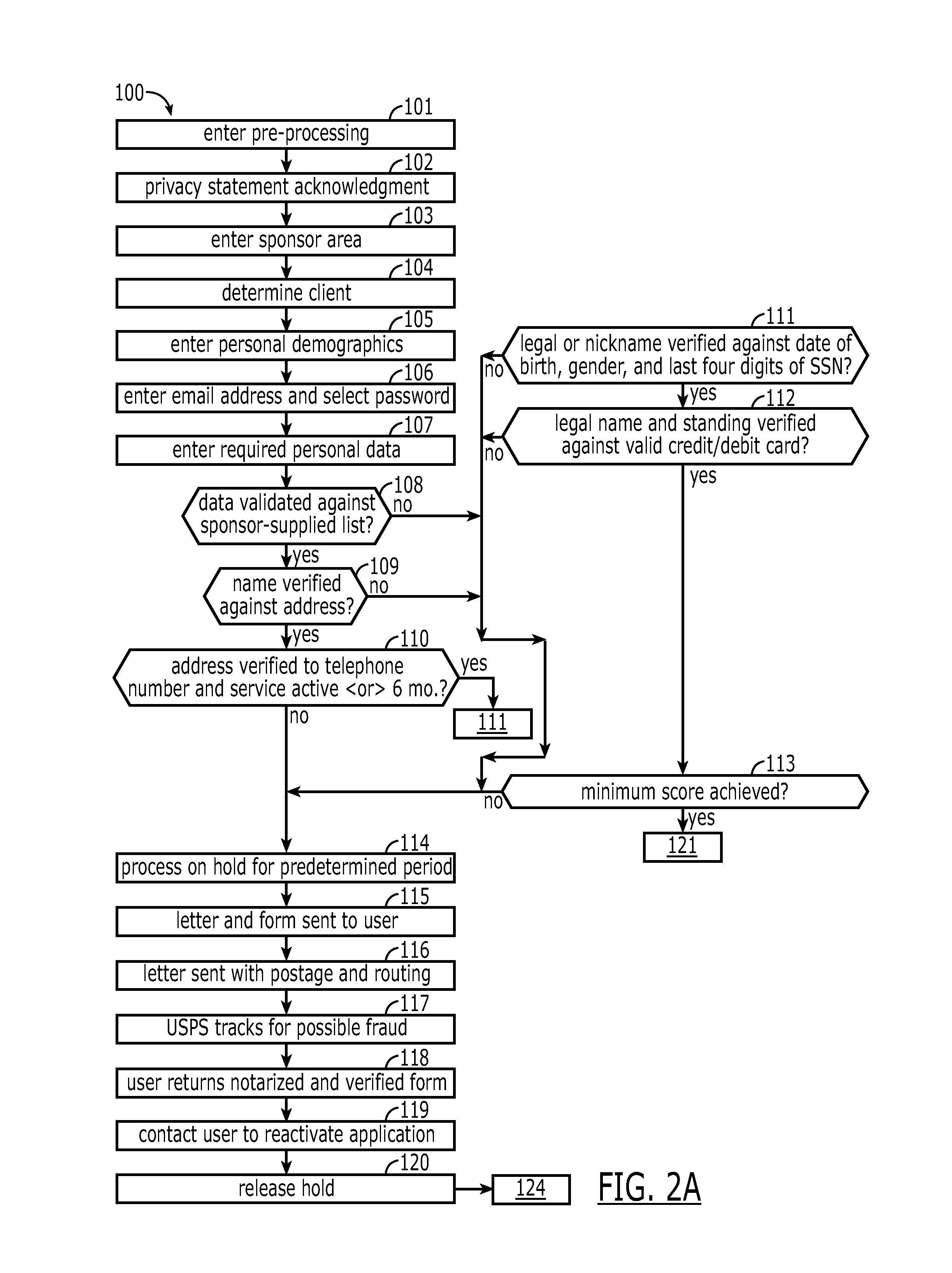

Identity validation and verification system and associated methods

A computer implemented system and method verify and validate a user identity for enrollment in a secure personal dataset accessing system. A personal dataset includes identifiable attributes of the user. Using a computer, authenticity of an asserted user identity includes electronically verified identifiable attributes to form the personal dataset. A biometric identifier of the user is automatically captured for validating the identifiable attributes by confirming that the asserted identity matches the identifiable attributes. A traceable e-audit trail is provided in an enterprise infrastructure and bench mark performance indicator. A digital security element is generated and results in the user electronically receiving a password and a unique electronic address is assigned to the user. The digital security element is then transmitted to the user from the computer and enables electronic access to the personal dataset relating to the user, the personal dataset having been authenticated through the verification and validation.

Owner:KRAGH JAMES F

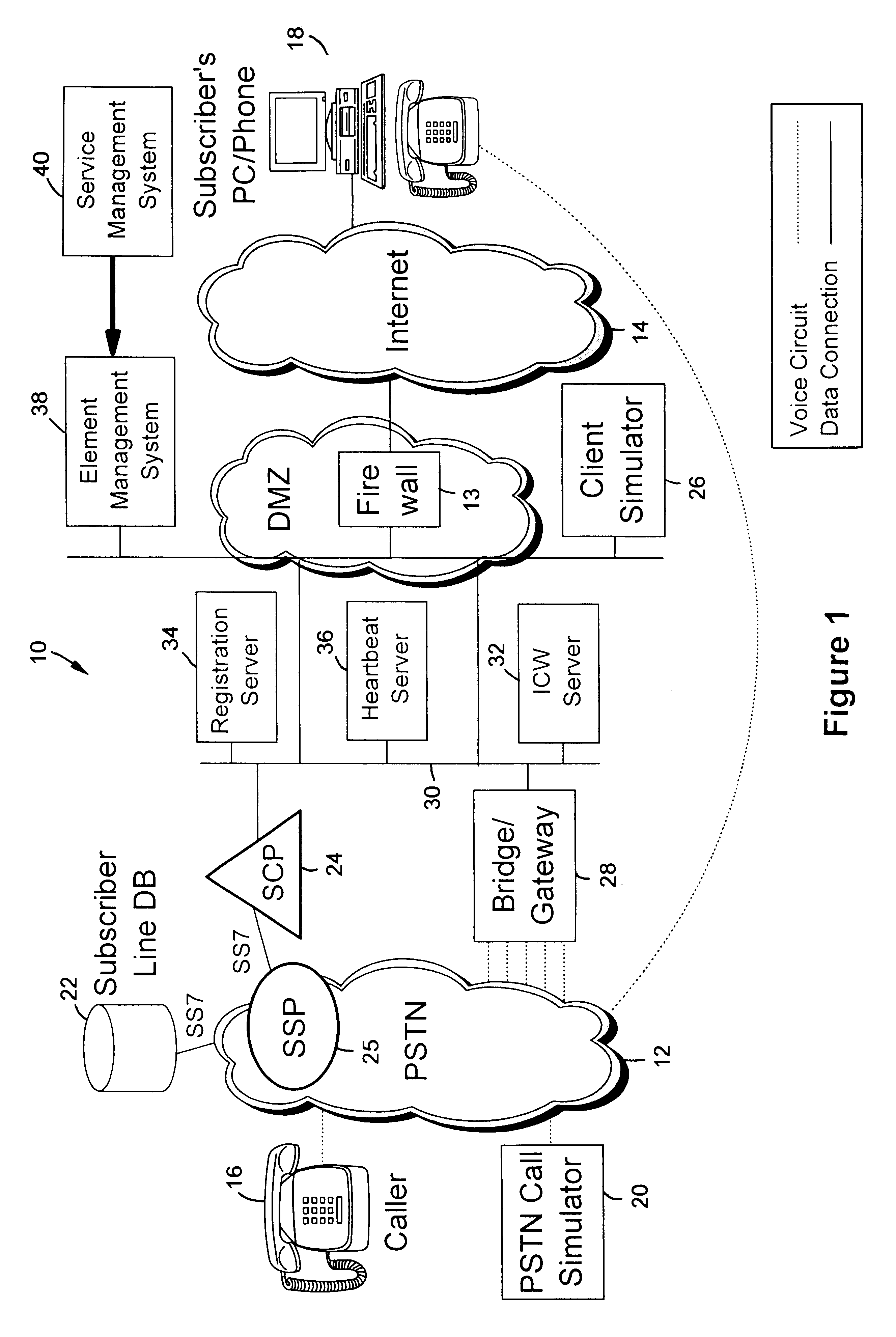

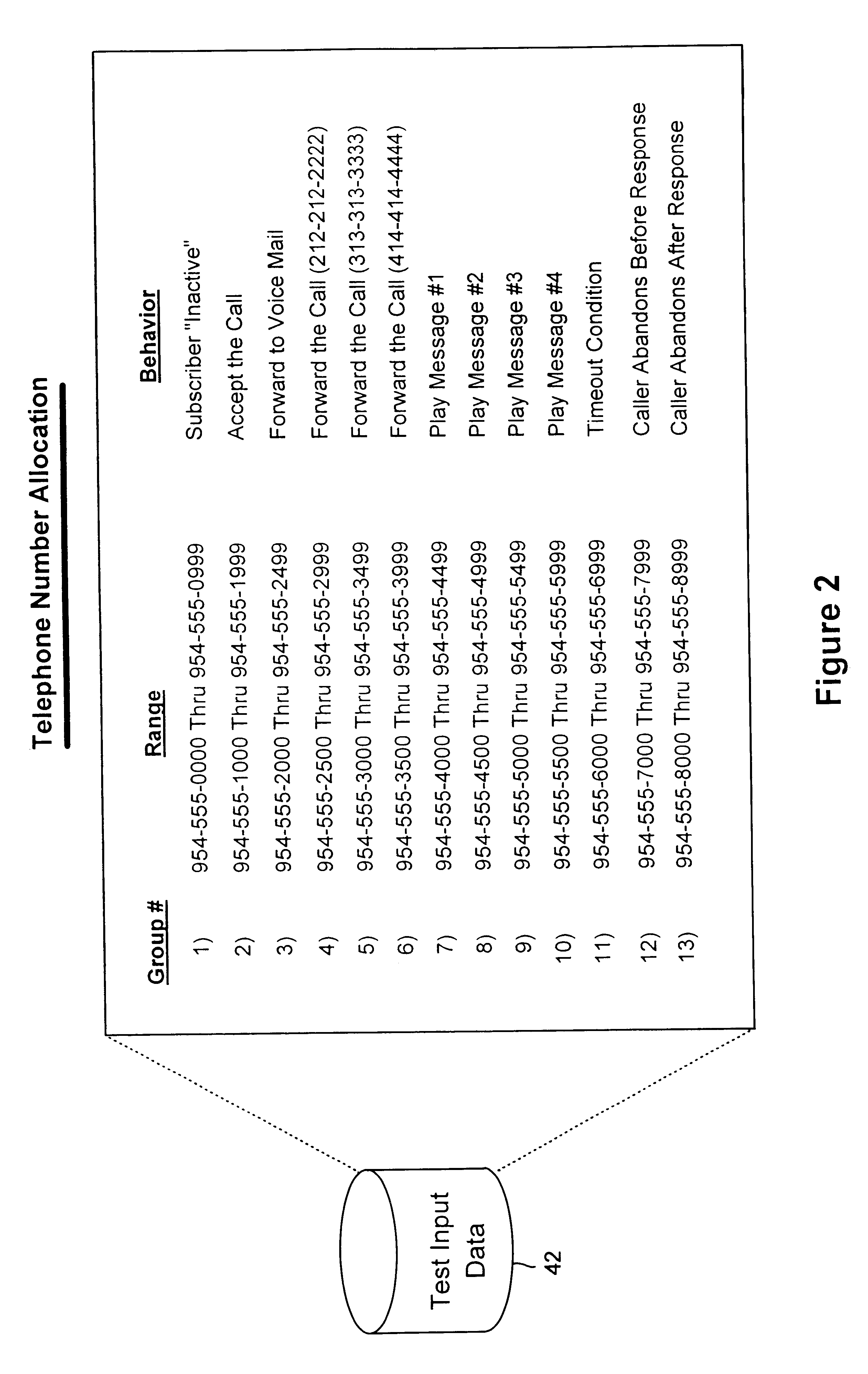

System and method of operation for verifying and validating public switch telephone networks (PSTN) to (IP) network services

A system verifies and validates PSTN to IP Network services prior to the availability of the services to a plurality of subscribers. A PSTN call generator services a plurality of callers coupled to the PSTN and to a test database. An IP client simulator is coupled to the test database and to an IP Network. A data bus couples the PSTN and the IP Network to a registration server for registering the client and a heartbeat server for tracking the system for heartbeat message. An application server processes test service calls from the PSTN call generator whereby PSTN-IP Network services can be executed for all clients or individual clients as represented by the IP Client simulator for verification and validation of PSTN services to IP Network clients prior to the availability of the services to the clients.

Owner:IBM CORP

Method and system for flow measurement and validation of a mass flow controller

ActiveUS7412986B2Operating means/releasing devices for valvesTesting/calibration apparatusDischarge measurementsEngineering

Systems and methods for flow verification and validation of mass flow controllers are disclosed. A mass flow controller may be commanded to a specified flow and flow measurement commenced. Gas is accumulated in a first volume and while measurements are taken within this volume. Gas may then flow into a second volume while measurements are taken. The various measurements taken during the two intervals may then be used to calculate the flow rate. The flow rate, in turn, may be used to determine the accuracy of the mass flow controller relative to a setpoint. Additionally, these systems and methods may utilize only one volume to perform flow verification by flowing gas into this volume, taking measurements, and calculating the flow rate based only upon this set of measurements.

Owner:BROOKS INSTRUMENT +1

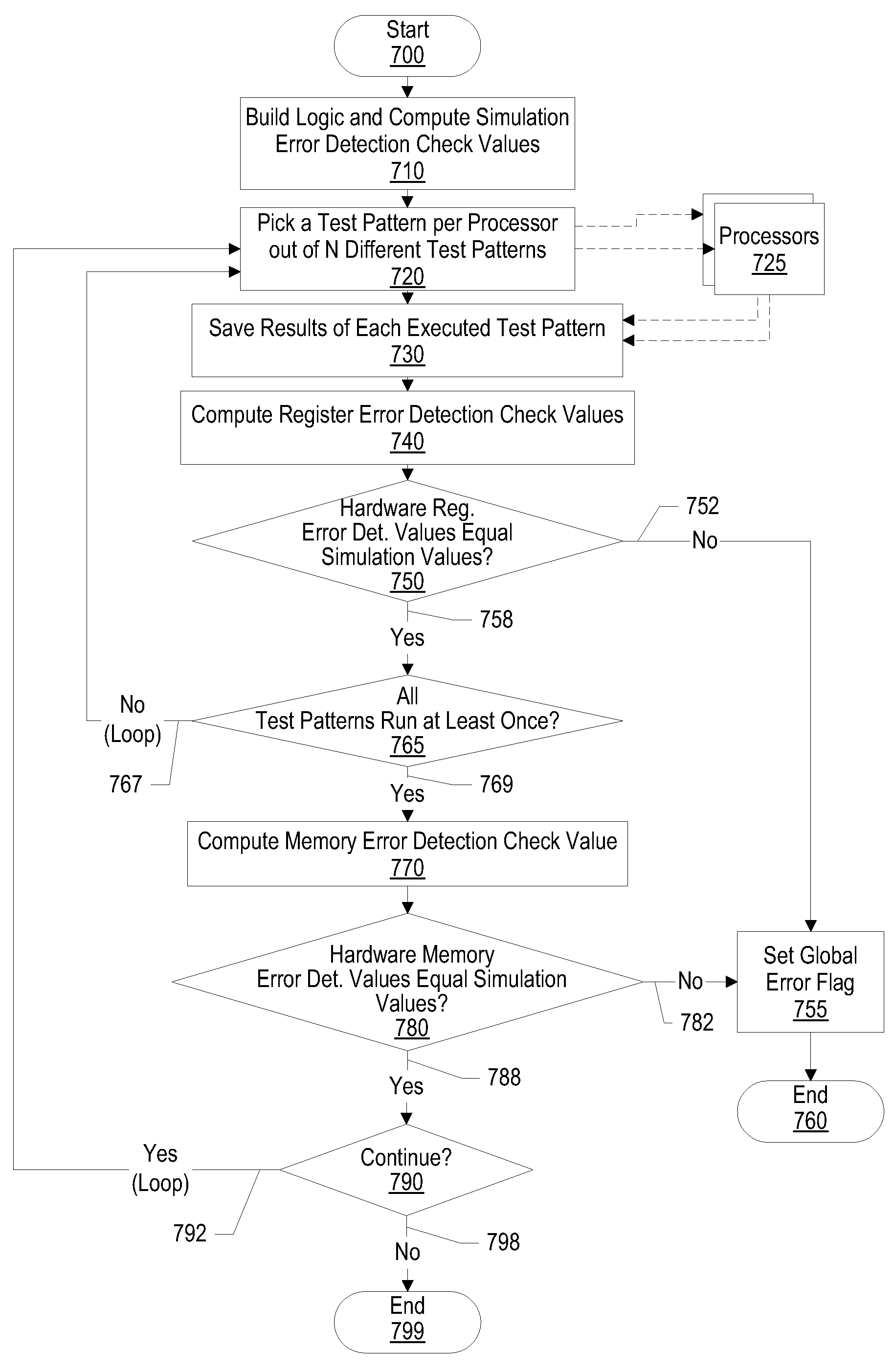

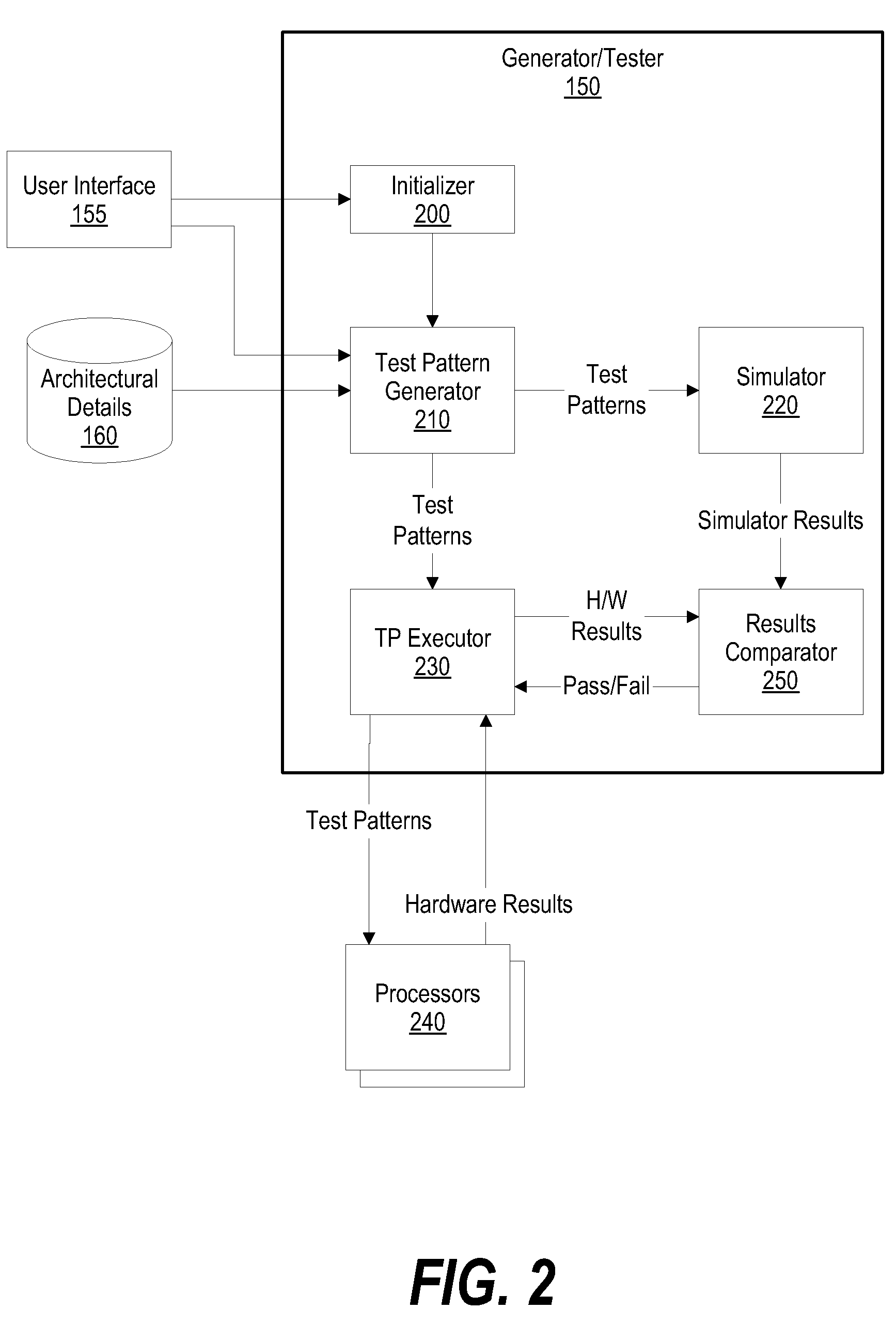

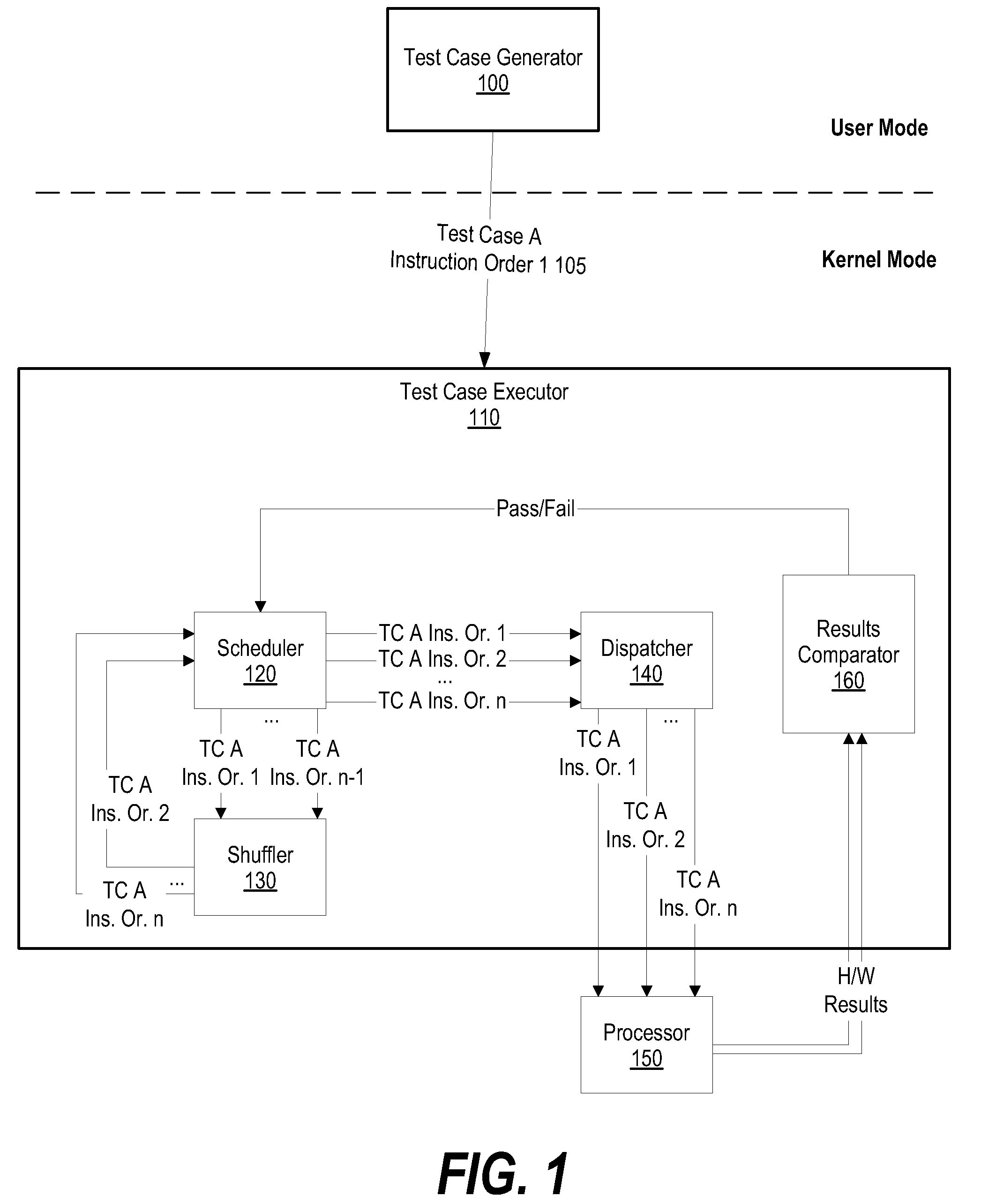

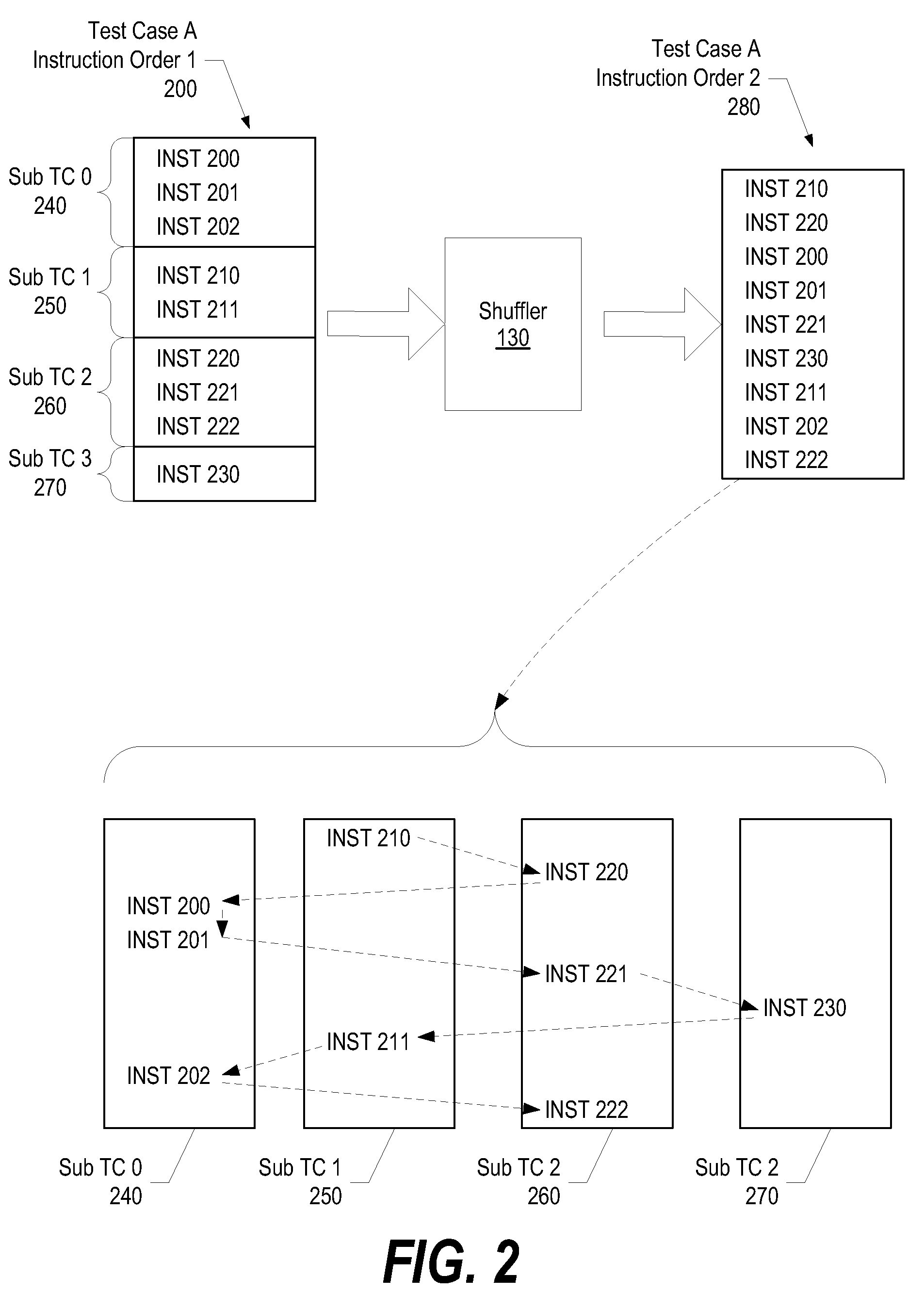

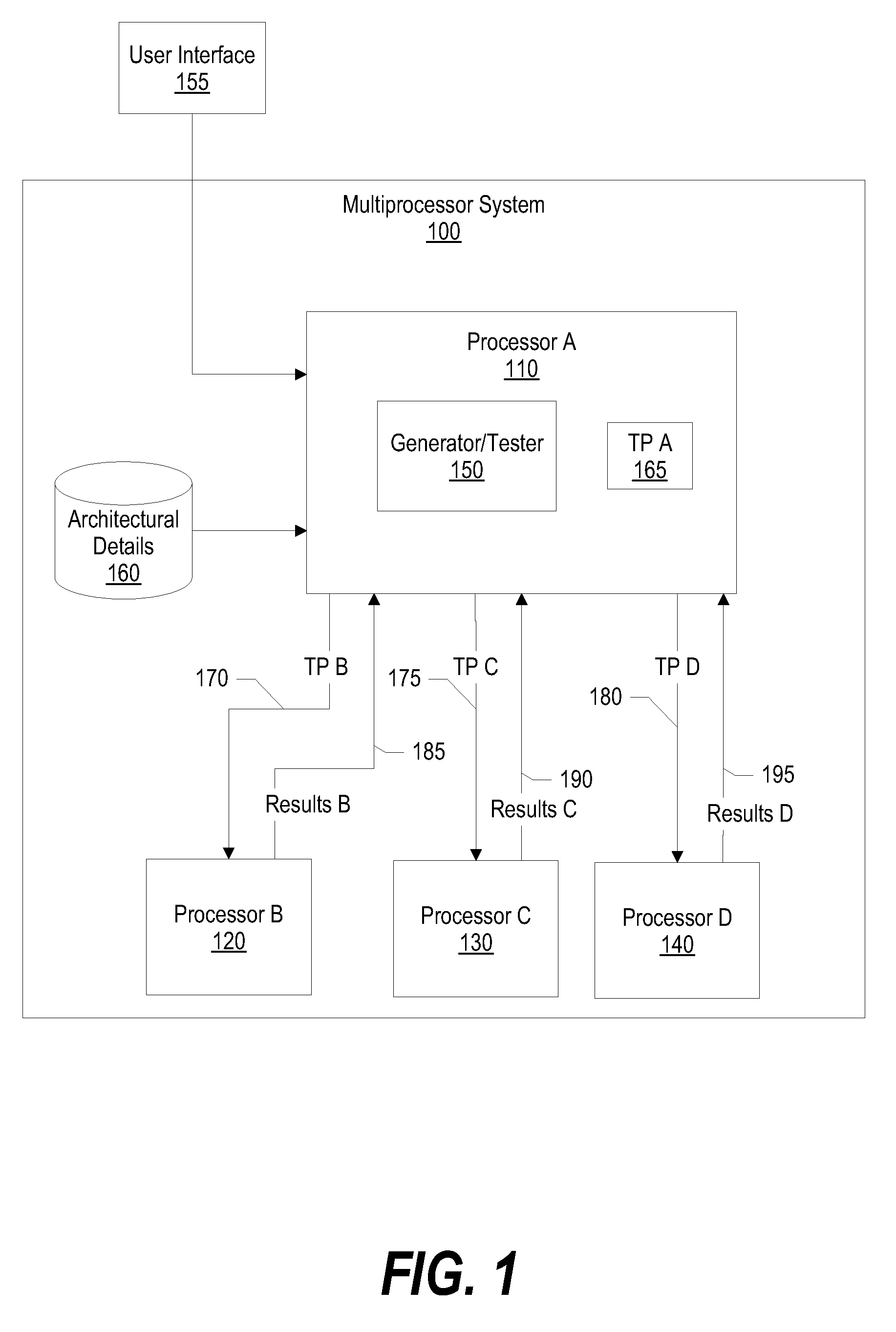

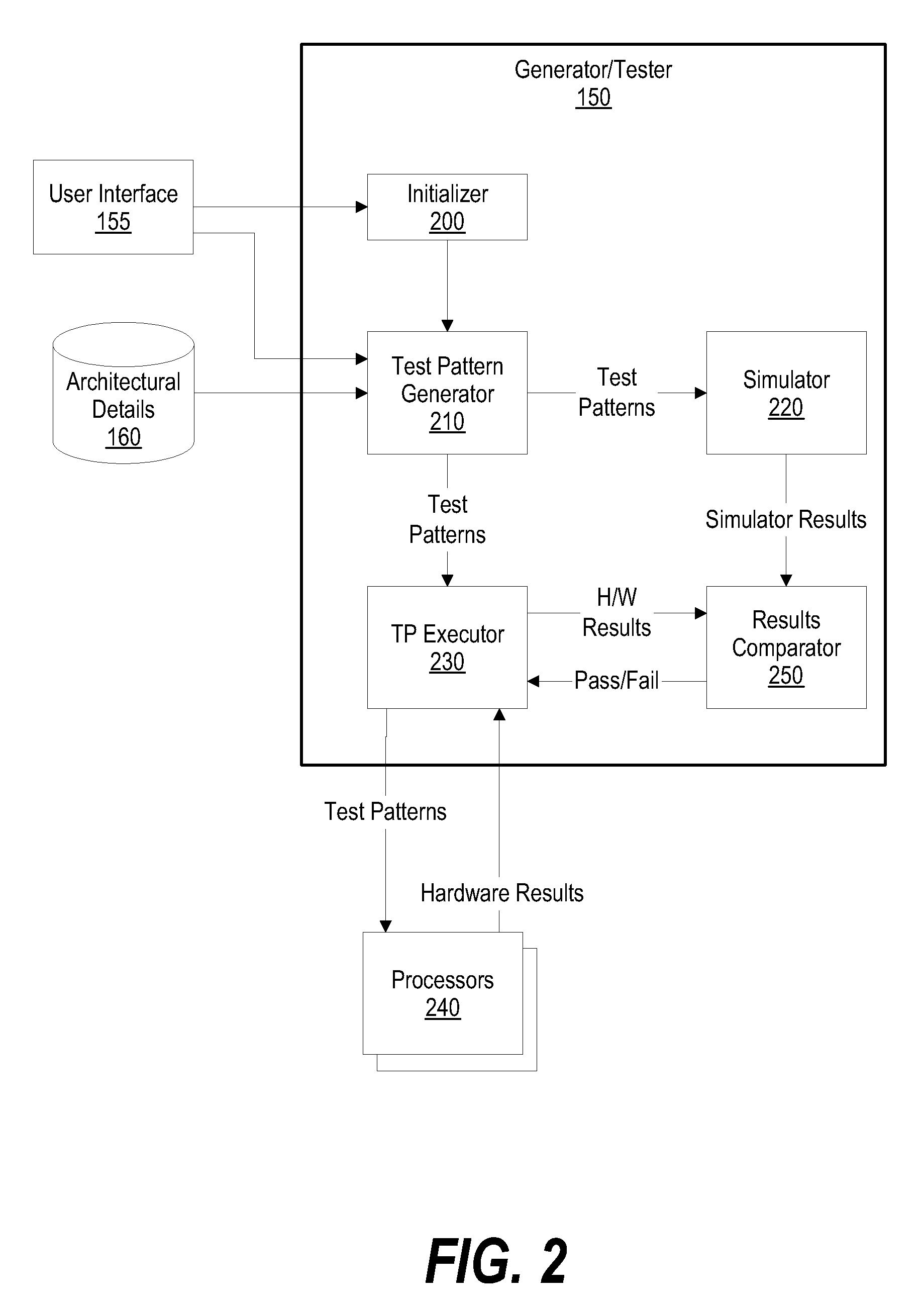

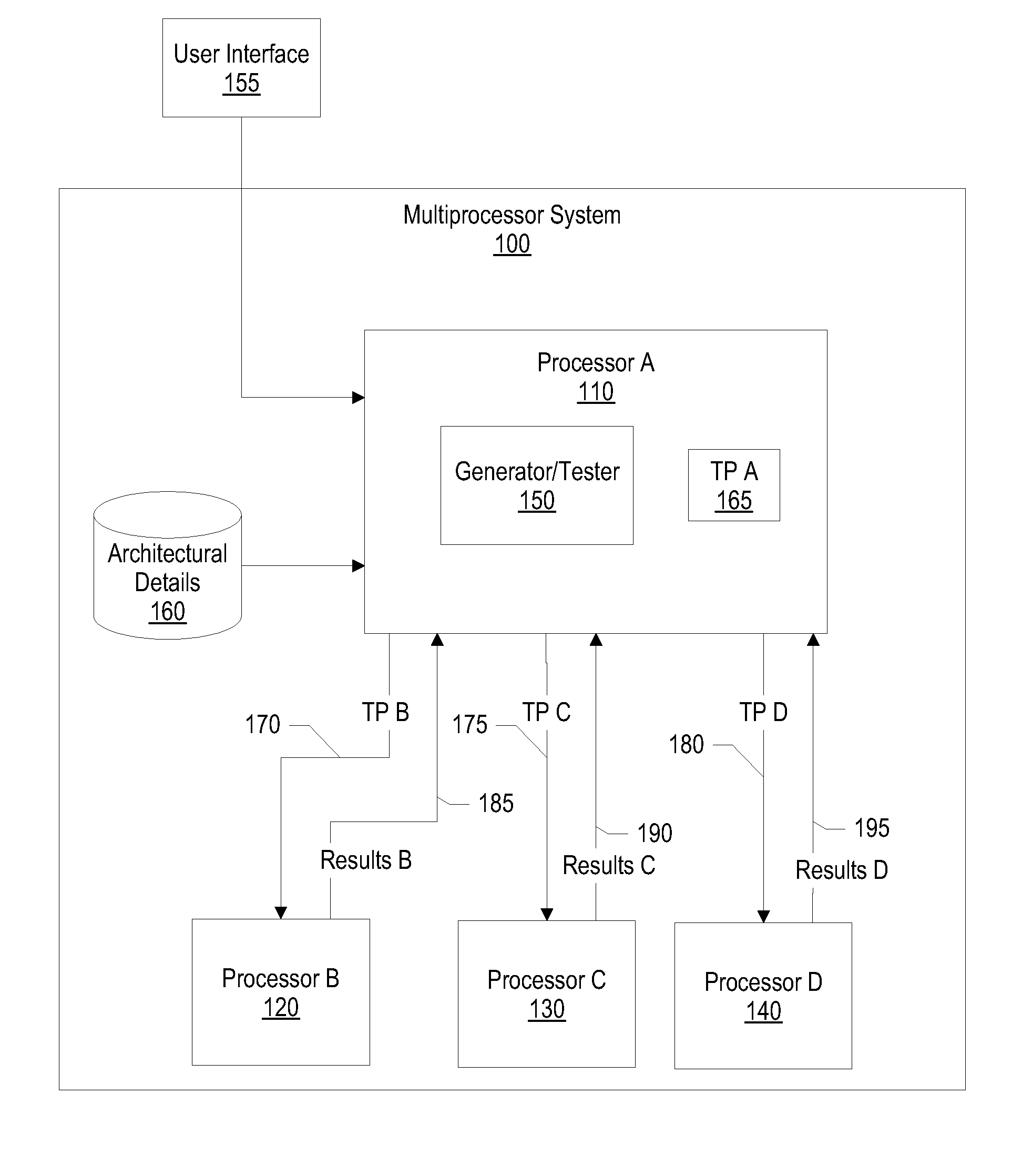

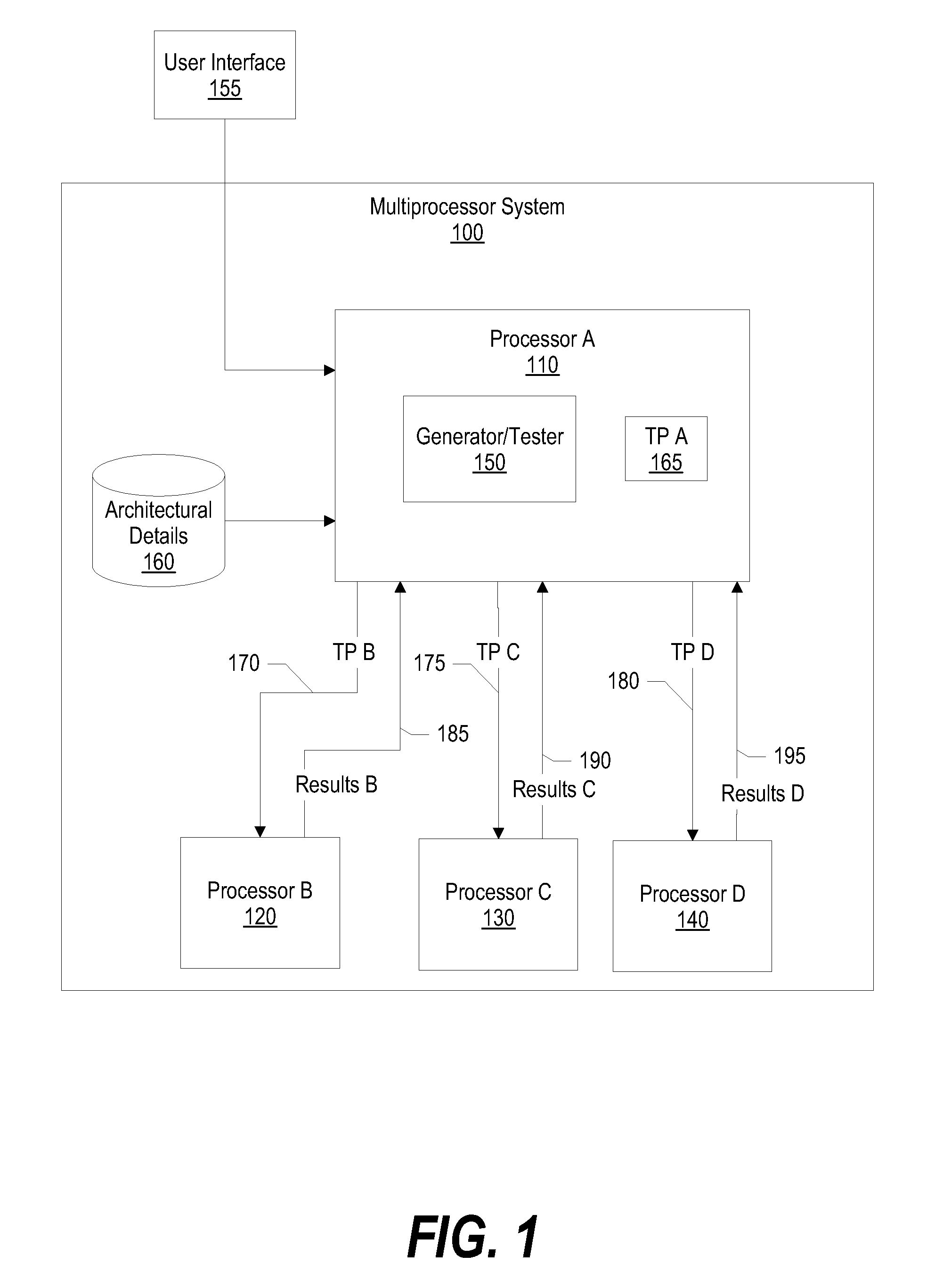

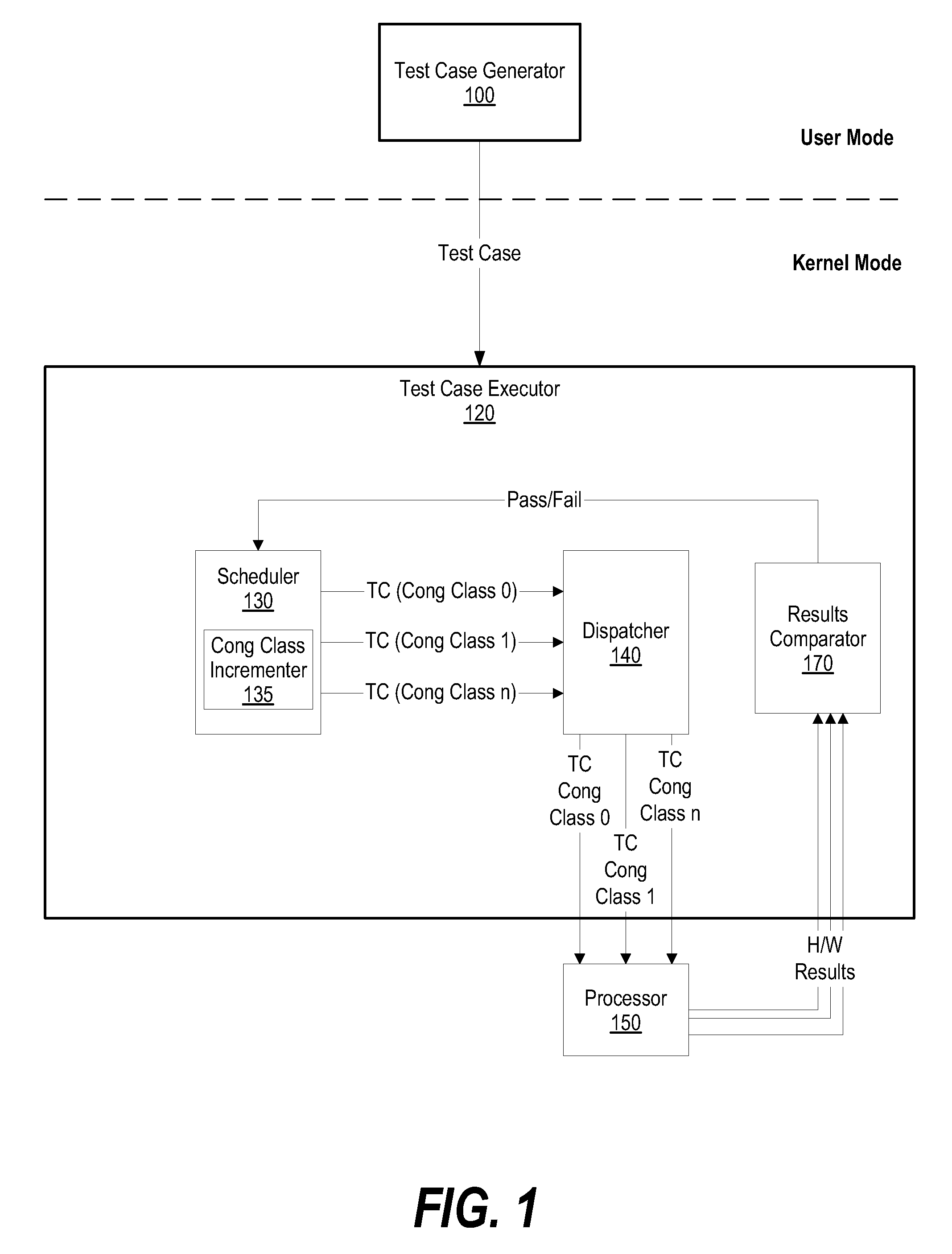

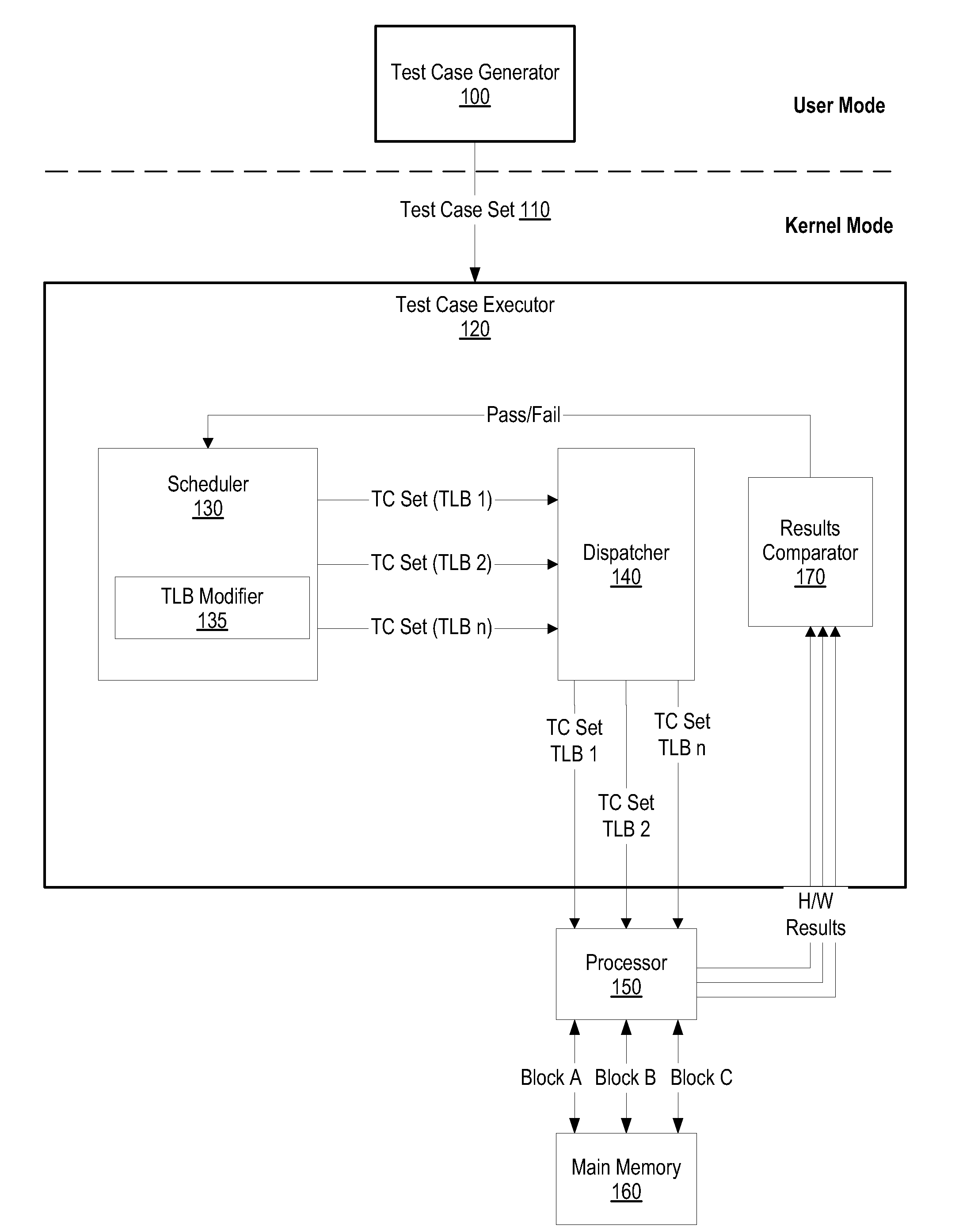

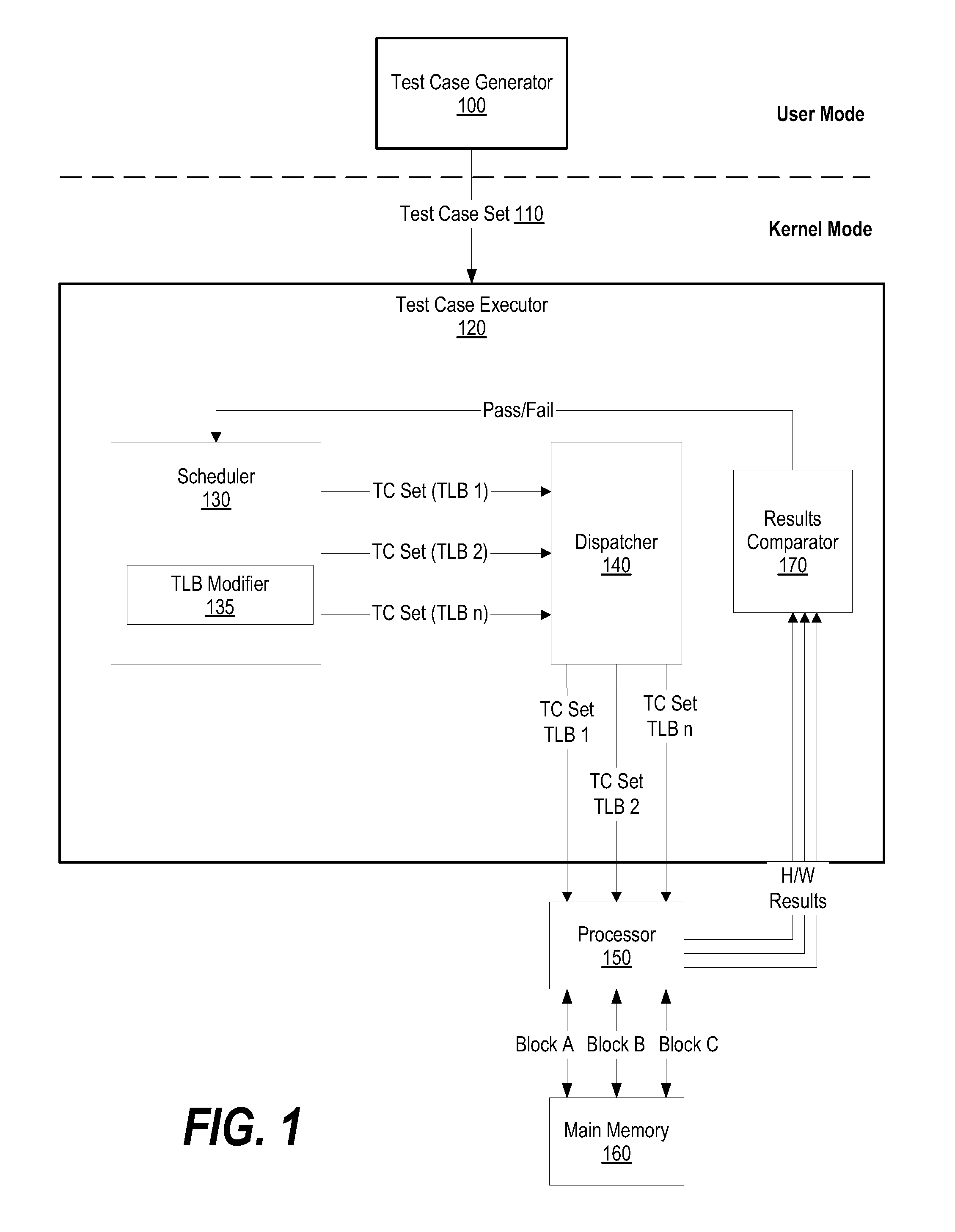

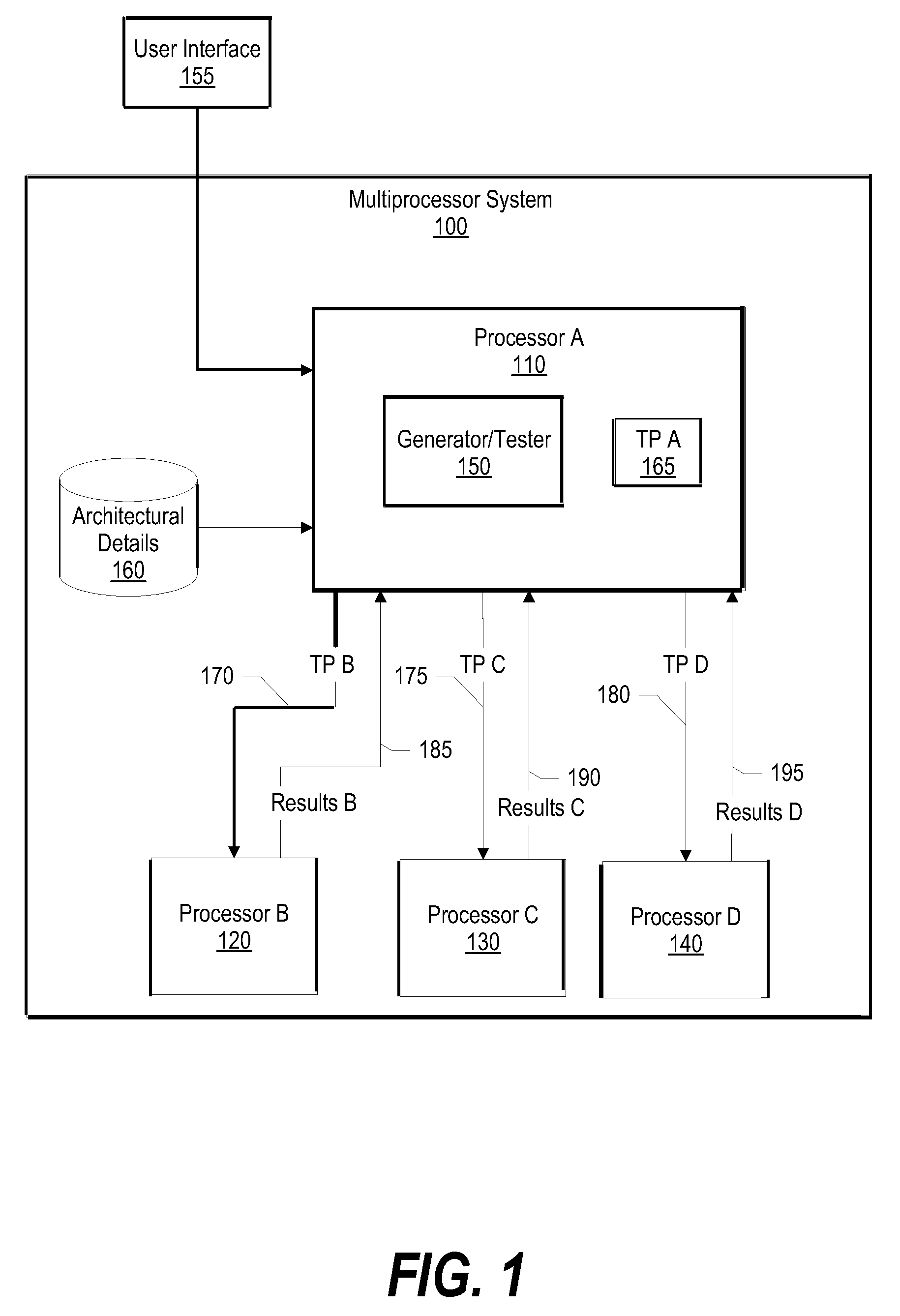

System and method of testing using test pattern re-execution in varying timing scenarios for processor design verification and validation

ActiveUS7647539B2Reduce build timeImprove test coverageElectronic circuit testingError detection/correctionError checkingSystem testing

A system and method processor testing using test pattern re-execution is presented. A processor re-executes test patterns using different timing scenarios in order to reduce test pattern build time and increase system test coverage. The invention described herein varies initial states of a processor's memory (cache, TLB, SLB, etc.) that, in turn, varies the timing scenarios when re-executing test patterns. By re-executing the test patterns instead of rebuilding new test patterns, verification quality is improved since more time is available for execution, verification and validation. In addition, since the test patterns result in the same final state, the invention described herein also simplifies error checking.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

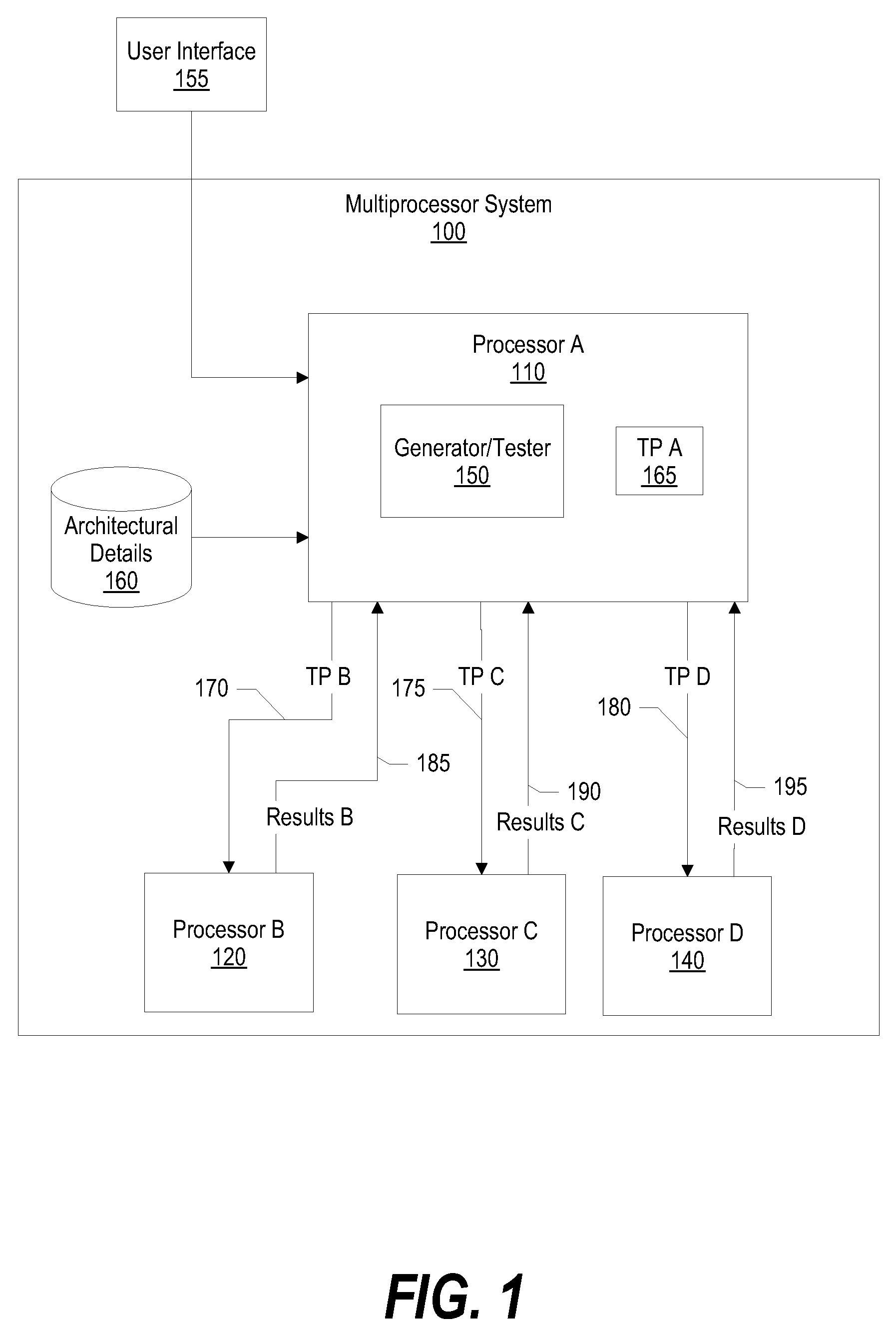

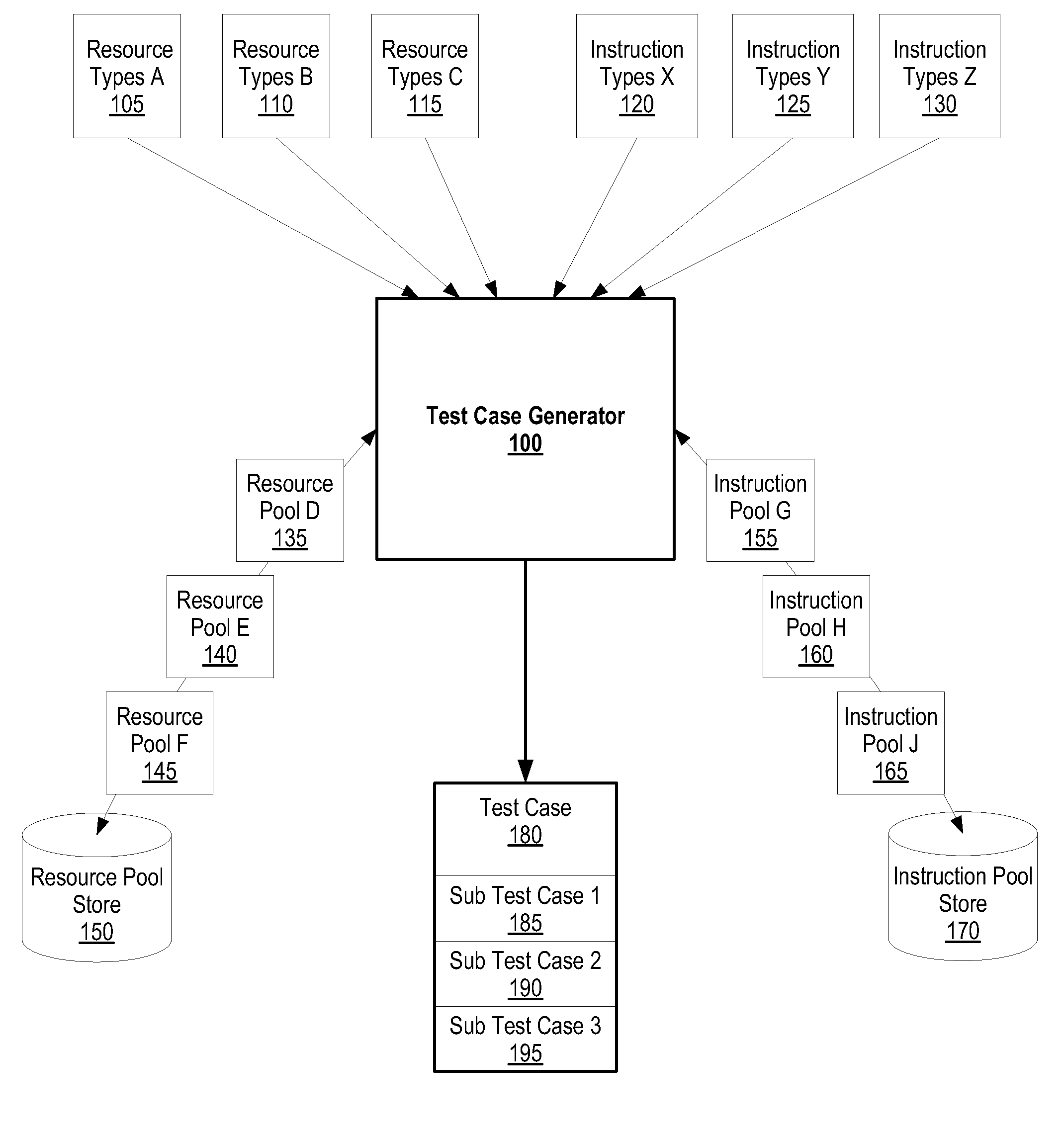

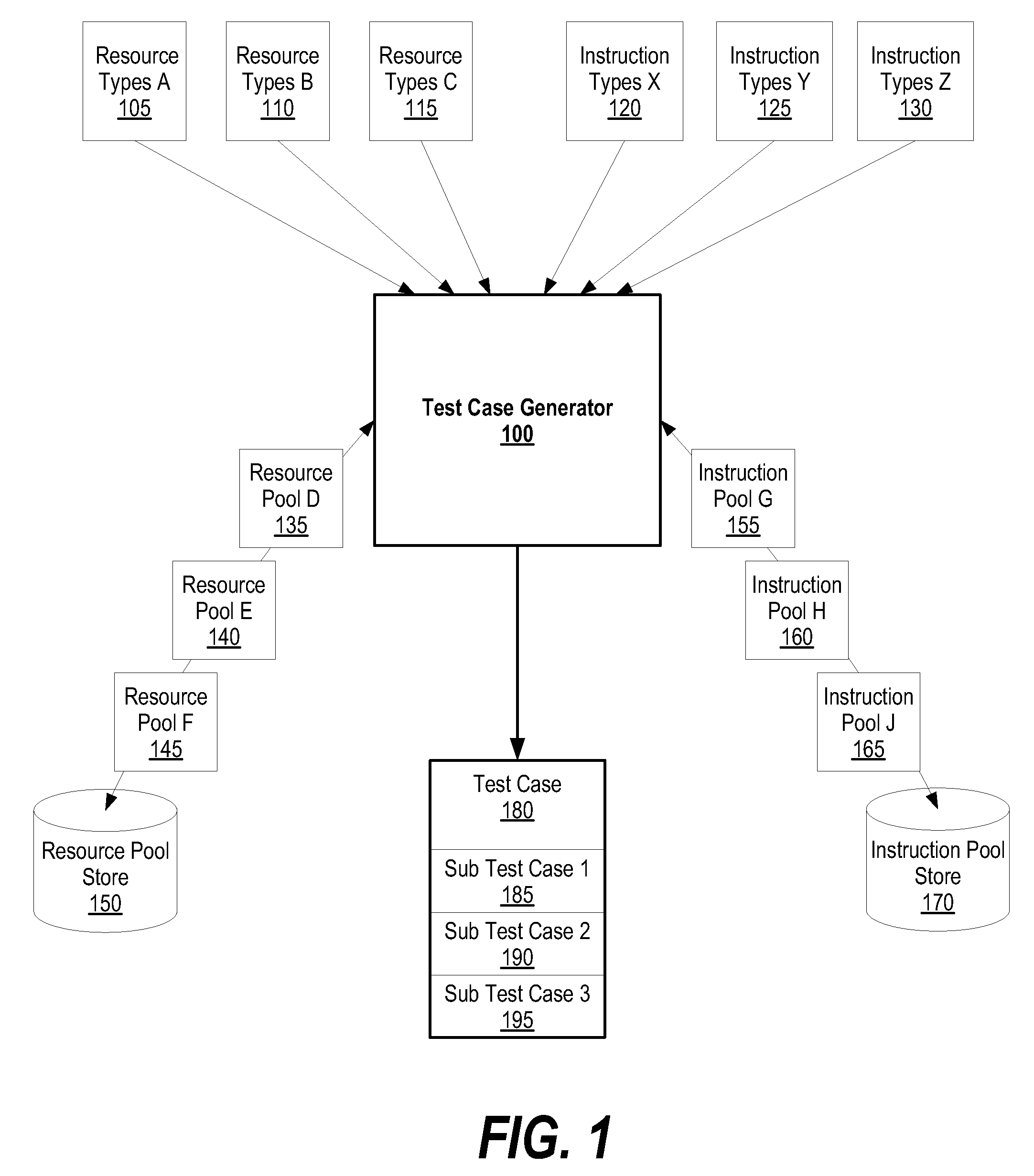

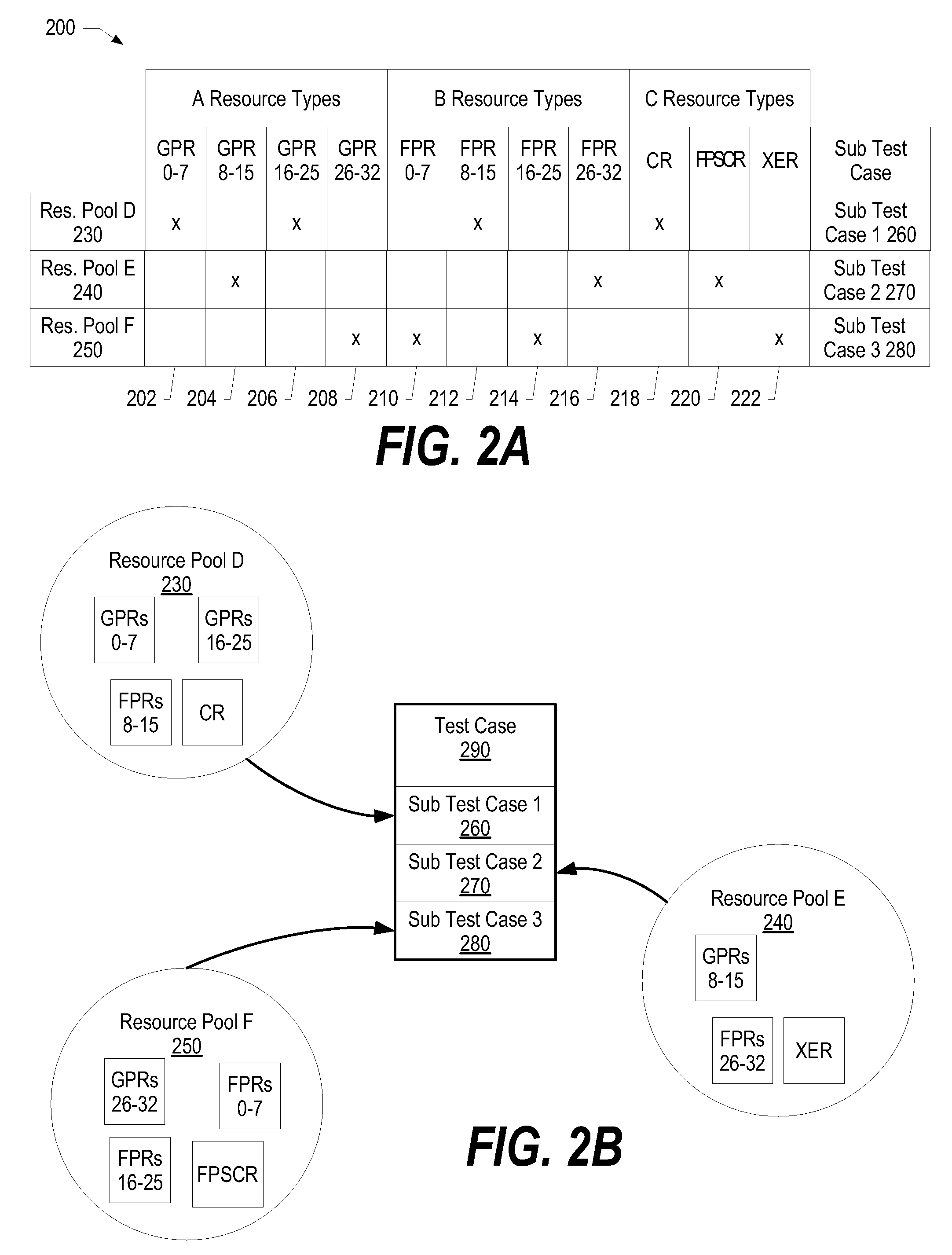

System and method for using resource pools and instruction pools for processor design verification and validation

A system and method for using resource pools and instruction pools for processor design verification and validation is presented. A test case generator organizes processor resources into resource pools using a resource pool mask. Next, the test case generator separates instructions into instruction pools based upon the resources that each instruction requires. The test case generator then creates a test case using one or more sub test cases by assigning a resource pool to each sub test case, identifying instruction pools that correspond the assigned test case, and building each sub test case using instructions included in the identified instruction pools.

Owner:TWITTER INC

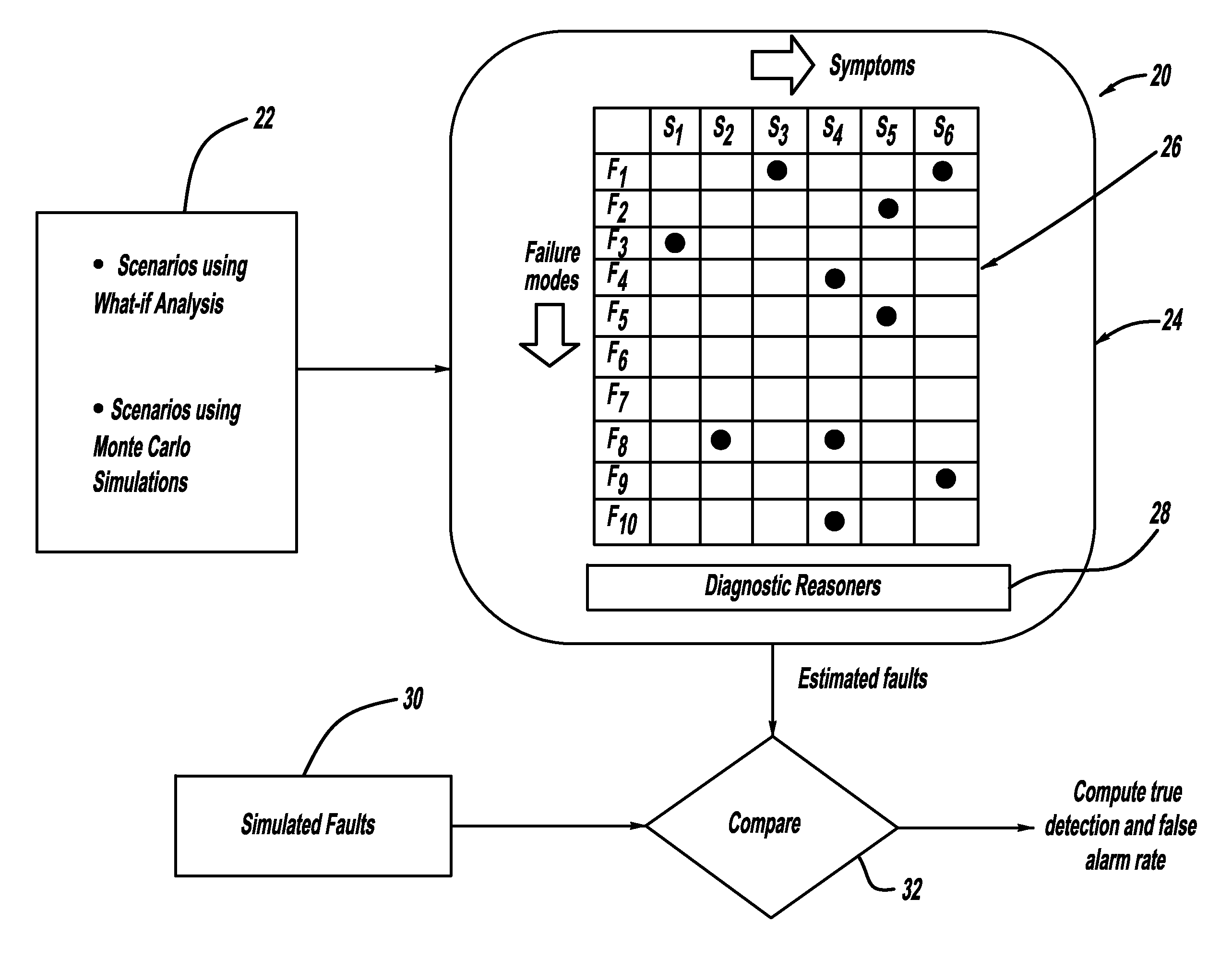

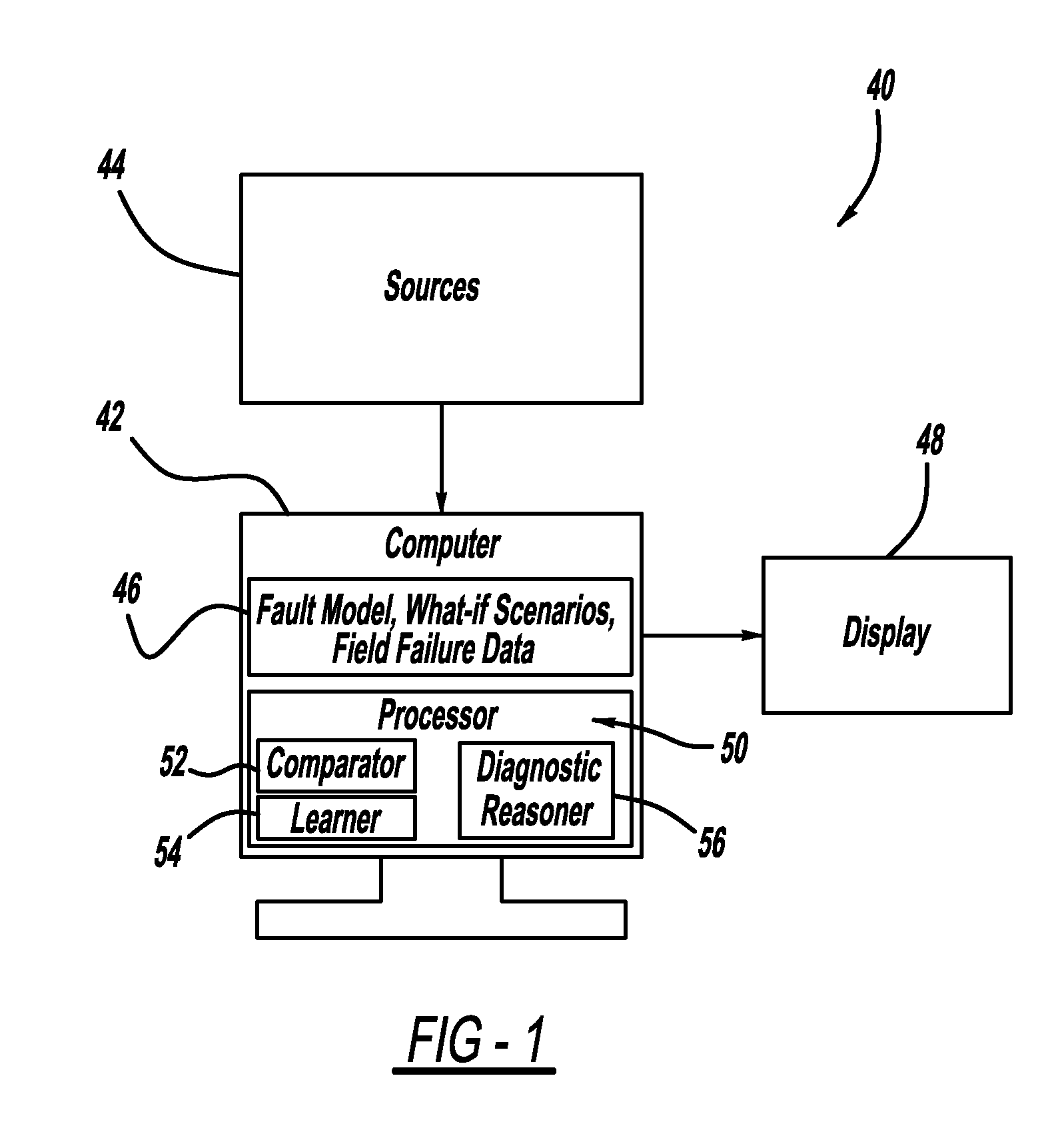

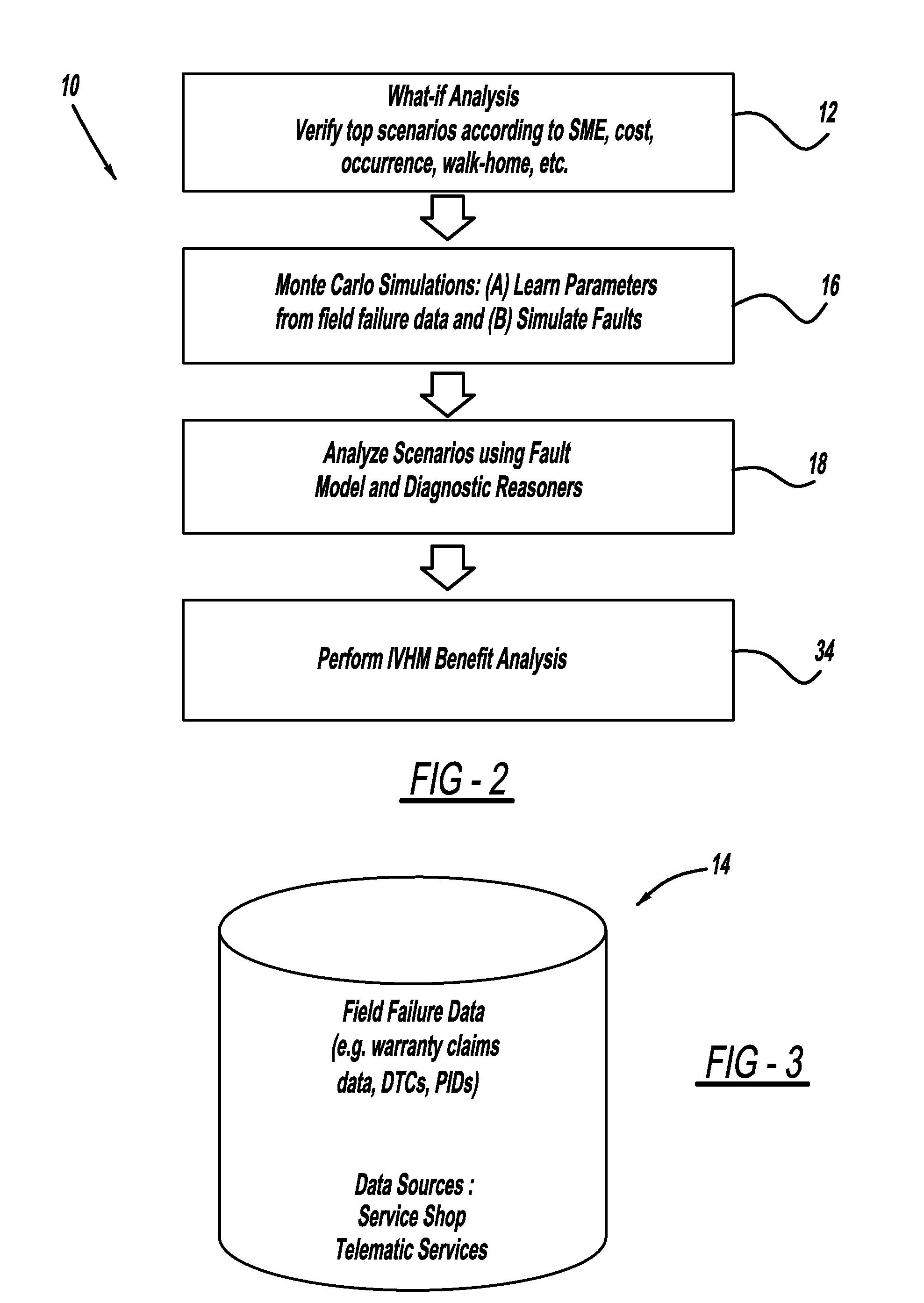

Software-centric methodology for verification and validation of fault models

A method for verifying and improving a vehicle fault model is disclosed. The method includes analyzing the available field failure data that includes vehicle symptoms and failures for many vehicles. The method performs an analysis using the field failure data that includes using subject matter expert knowledge to determine the most significant failure modes and the most significant symptoms. The method also includes learning simulation parameters from the field failure data and simulating faults using the learned simulation parameters. The method further includes verifying and validating the fault model based on the most significant failure modes and the most significant symptoms from the what-if analysis and the faults identifies by the simulation, and using a diagnostic reasoner to analyze the revised fault model to generate estimated faults. The method then compares the estimated faults to the simulated faults to determine true detection and false alarm rates for a benefit analysis.

Owner:GM GLOBAL TECH OPERATIONS LLC

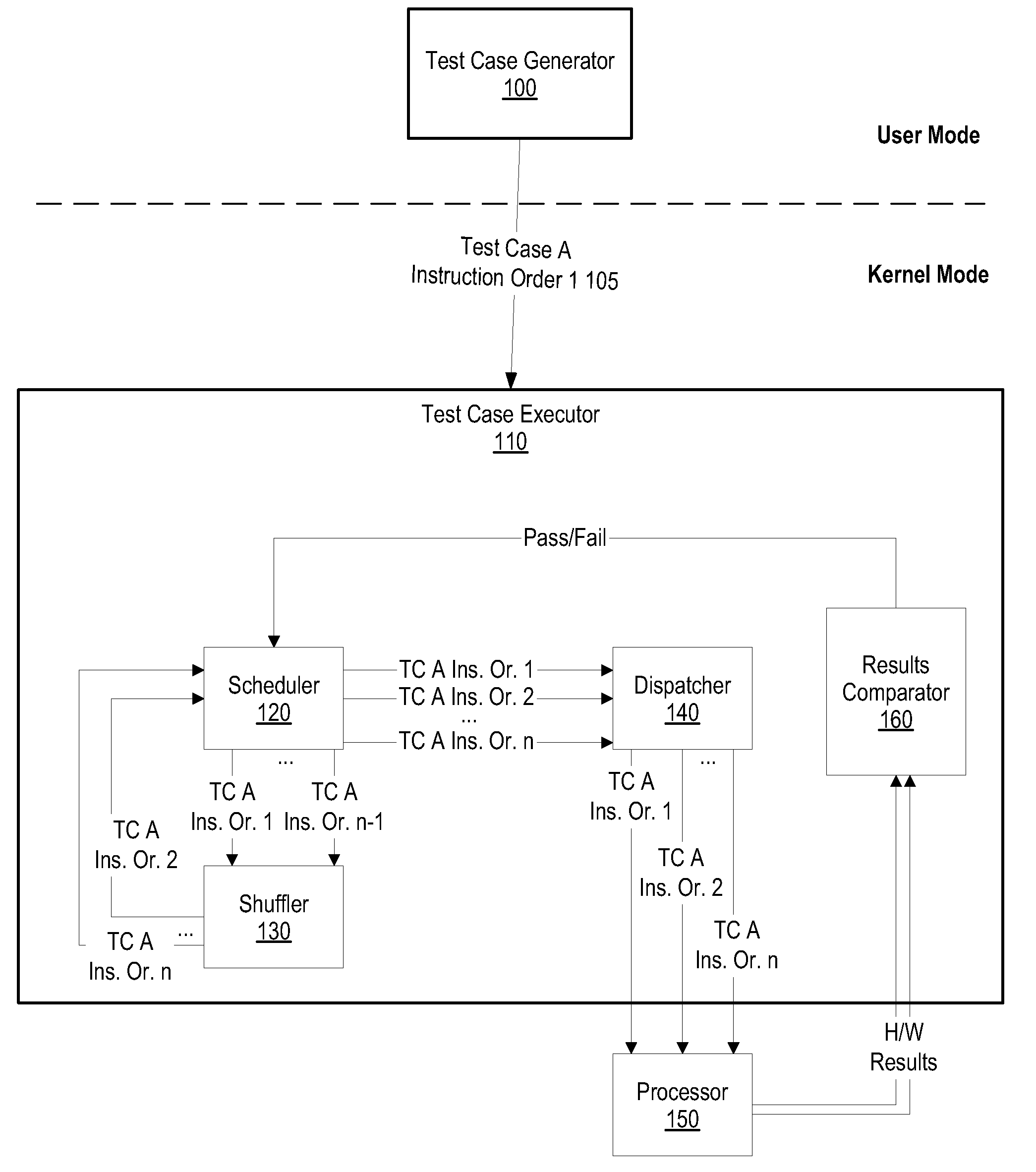

System and method for re-shuffling test case instruction orders for processor design verification and validation

ActiveUS7669083B2Efficient testingMany timesError detection/correctionSpecific program execution arrangementsActuatorTest case generator

A system and method for creating multiple test case scenarios from one test case by shuffling the test case instruction order while maintaining relative sub test case instruction order intact is presented. A test case generator generates and provides a test case that includes multiple sub test cases to a test case executor. In turn, the test case executor recursively schedules and dispatches the test case with different shuffled instruction orders to a processor in order to efficiently test the processor. In one embodiment, the test case generator provides multiple test cases to the test case executor. In another embodiment, the test case generator provides test cases to multiple test case executors that, in turn, shuffle the test cases and provide the shuffled test cases to their respective processor.

Owner:TWITTER INC

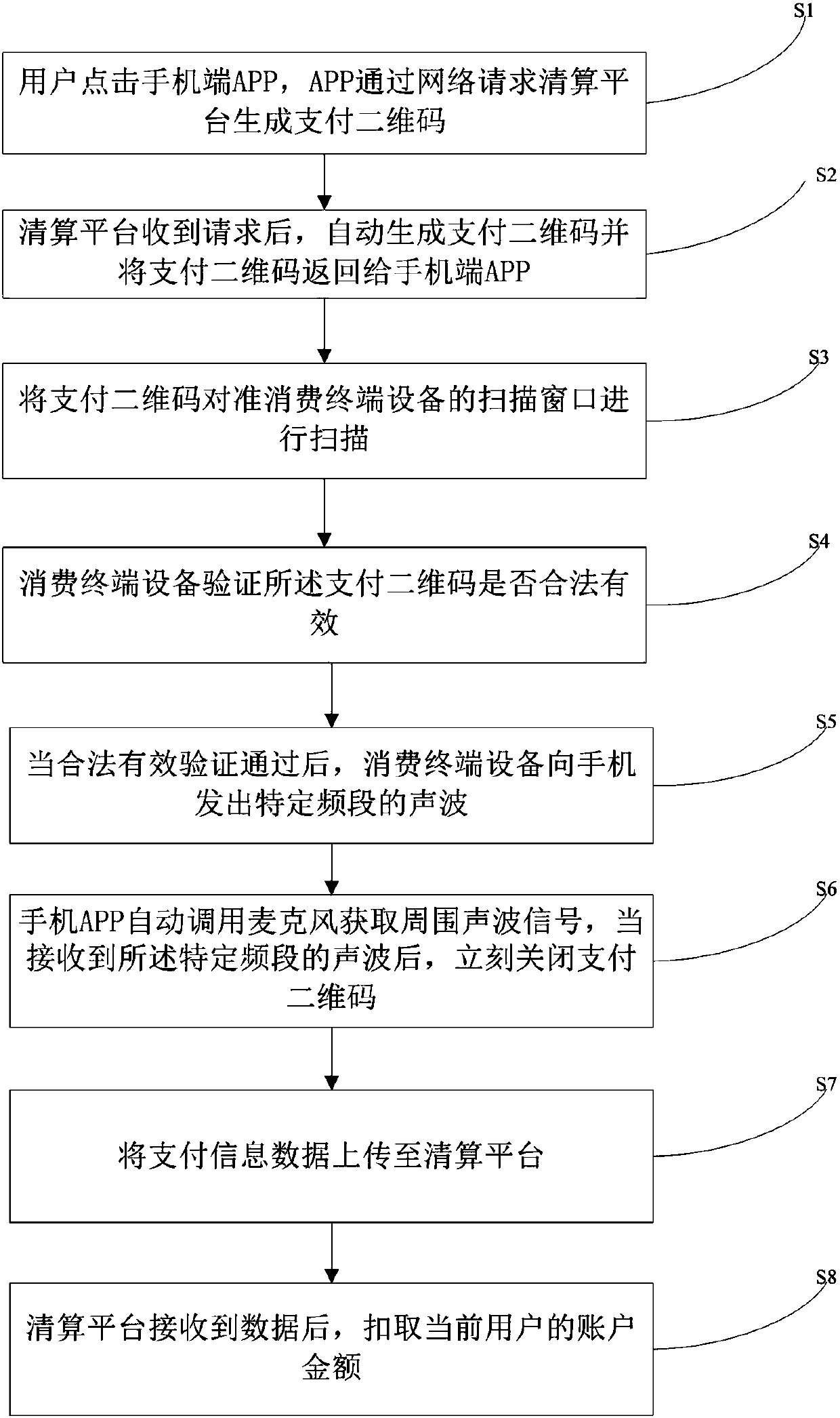

QR code payment system and payment method thereof

ActiveCN107609856AProtection securityTransparent consumer transactionsPayment architectureTerminal equipmentComputer terminal

The invention discloses a QR code payment system and a payment method thereof. The system comprises a clearing platform, a cellphone in communication connection with the clearing platform, and consumption terminal equipment in in communication connection with the clearing platform. The cellphone stores one or more programs, so as to execute the following steps that the cellphone requests the clearing platform for generating a payment QR code through a network when a user clicks a cellphone APP, and the clearing platform automatically generates the payment QR code and returns the payment QR code to the cellphone after the clearing platform receives the request; the consumption terminal equipment scans the payment QR code, and synchronously transmits a sound wave at a specific waveband to the cellphone after verification and validation; the cellphone instantly switches off the QR code after the cellphone receives the sound wave at the specific waveband. According to the invention, afterthe payment is completed, the QR code at the cellphone is instantly switched off, thereby eliminating the potential safety hazards. The system employs the sound wave at the specific waveband for returning the transaction information, is transparent in consumption, is short in payment time, and is especially suitable for the quick payment for public transportation.

Owner:SHENZHEN WONDERFUL STAR TECH LTD

System and Method for Predicting lwarx and stwcx Instructions in Test Pattern Generation and Simulation for Processor Design Verification and Validation

InactiveUS20090024886A1Electronic circuit testingError detection/correctionPredictabilityPattern generation

A system and method for predicting lwarx (Load Word And Reserve Index form) and stwcx (Store Word Conditional) instruction outcome is presented. A lwarx instruction establishes a reservation on an address / granule, and a stwcx instruction targeted to the same address / granule “succeeds” only if the reservation for the granule still exists (conditional store). Since the reservation may be lost due to situations such as, for example, a processor (or another processor) executing a different lwarx or ldarx instruction (or other mechanism), which clears the first reservation and establishes a new reservation, the invention described herein builds test patterns in a manner that ensures, stwcx success and failure predictability. As a result, stwcx instructions are testable during test pattern execution.

Owner:IBM CORP

System and Method for Pseudo-Random Test Pattern Memory Allocation for Processor Design Verification and Validation

InactiveUS20090024891A1Efficient testingElectronic circuit testingHardware monitoringPage tableFalse sharing

A system and method for pseudo-randomly allocating page table memory for test pattern instructions to produce complex test scenarios during processor execution is presented. The invention described herein distributes page table memory across processors and across multiple test patterns, such as when a processor executes “n” test patterns. In addition, the page table memory is allocated using a “true” sharing mode or a “false” sharing mode. The false sharing mode provides flexibility of performing error detection checks on the test pattern results. In addition, since a processor comprises sub units such as a cache, a TLB (translation look aside buffer), an SLB (segment look aside buffer), an MMU (memory management unit), and data / instruction pre-fetch engines, the test patterns effectively use the page table memory to test each of the sub units.

Owner:IBM CORP

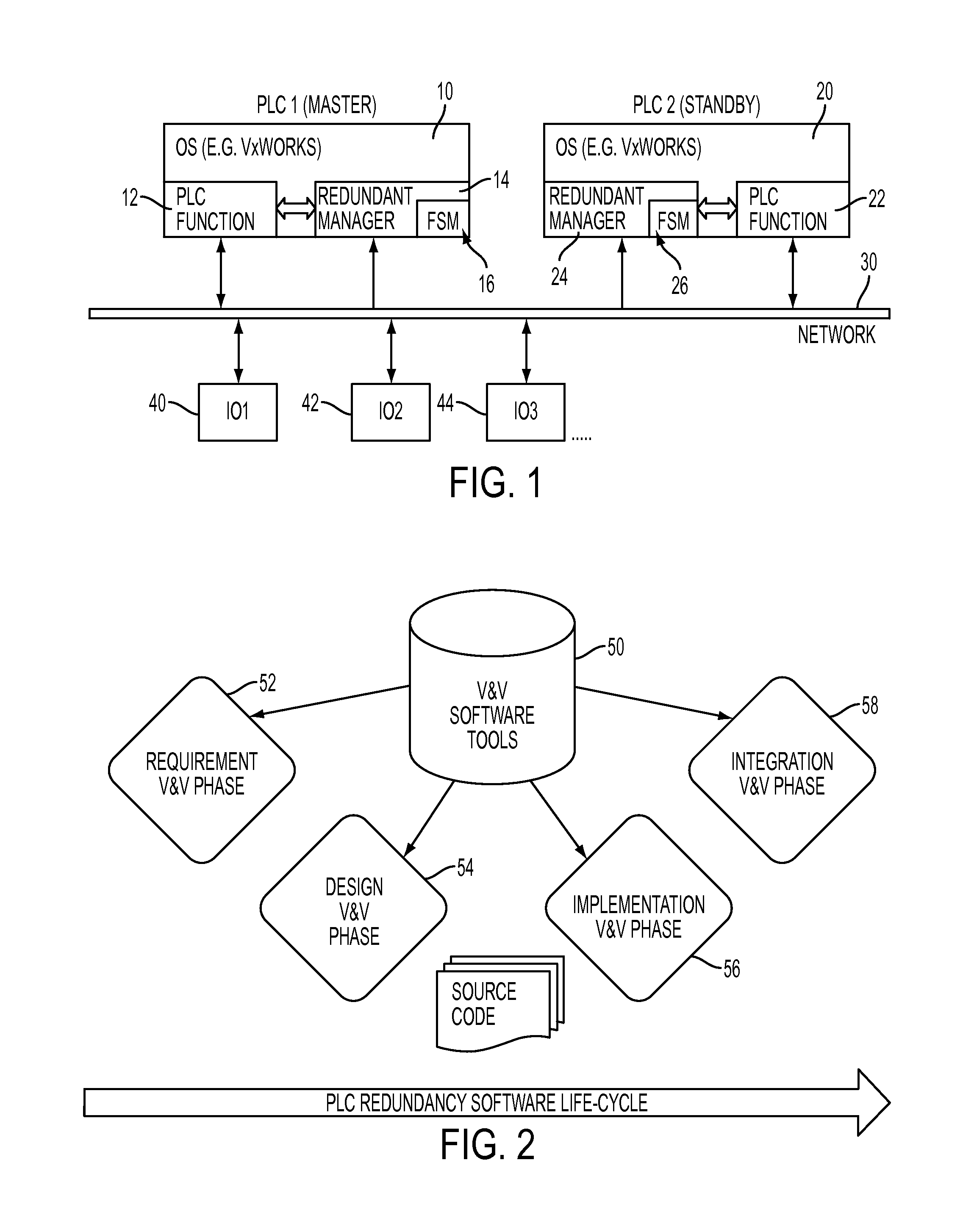

System and method for verification and validation of redundancy software in PLC systems

Formal methods are instituted to verify and validate the finite state machine (FSM) of PLC redundancy software. The method and system is implemented through each phase in the lifecycle of the redundancy software; that is, the requirement phase, design phase, implementation phase and, finally, integration phase (including system integration). At each step along the way, the verification and validation process uses tools such as a checklist-based review and inspection, a requirement traceability analysis, formal verification (model checking) and the like to ensure that the created redundancy software is error-free and will perform as intended when implemented in the redundant PLC system.

Owner:SIEMENS CORP

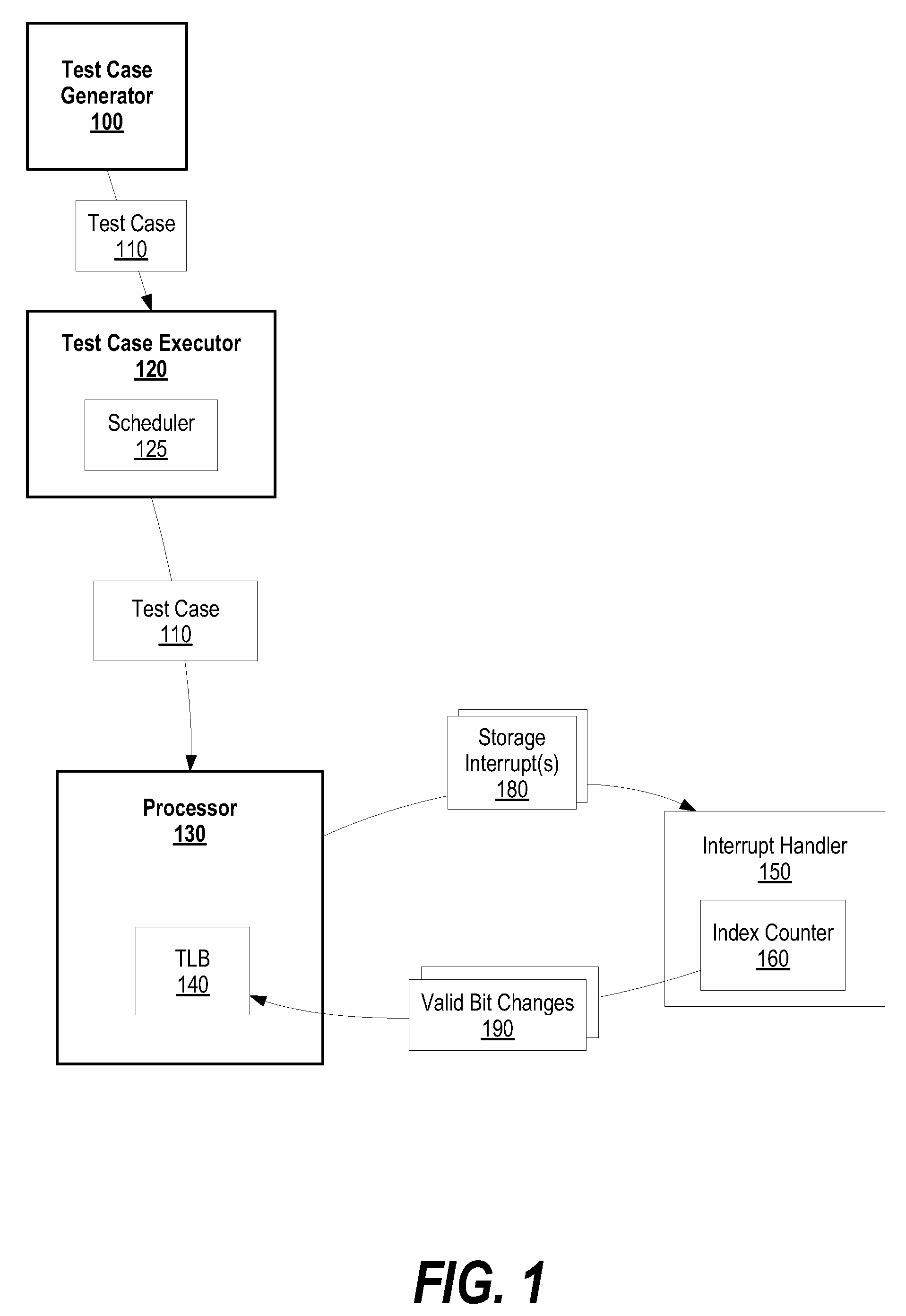

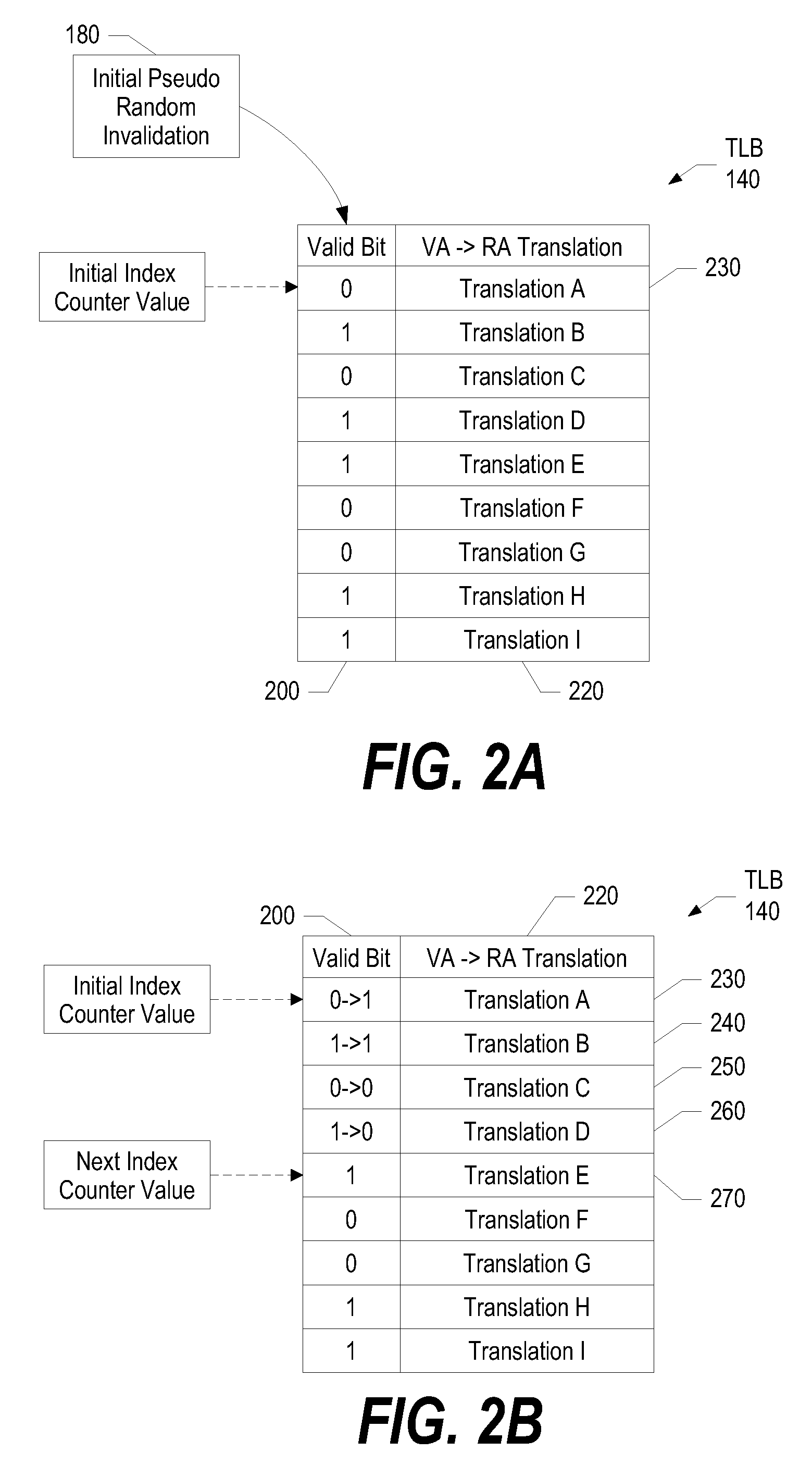

System and Method for Generating Fast Instruction and Data Interrupts for Processor Design Verification and Validation

InactiveUS20090070546A1Memory architecture accessing/allocationError detection/correctionPage tableInterrupt handler

A system and method for intentionally invaliding translation entry valid bits in order to provoke storage interrupts when executing a test case is presented. Prior to executing the test case, an interrupt handler pseudo-randomly invalidates a number of translation entries included in a translation lookaside buffer (TLB) by changing particular valid bits in order to provoke initial storage interrupts, such as an instruction storage interrupt (ISI) or a data storage interrupt (DSI). Once the processor executes the test case that, in turn, triggers a storage interrupt, the interrupt handler uses an index counter to validate particular valid bits and invalidate other valid bits, thus provoking subsequent storage interrupts. In one embodiment, the interrupt handler also changes valid bits in a page table when the processor executes in a mode that accesses the page table in addition to the TLB.

Owner:IBM CORP

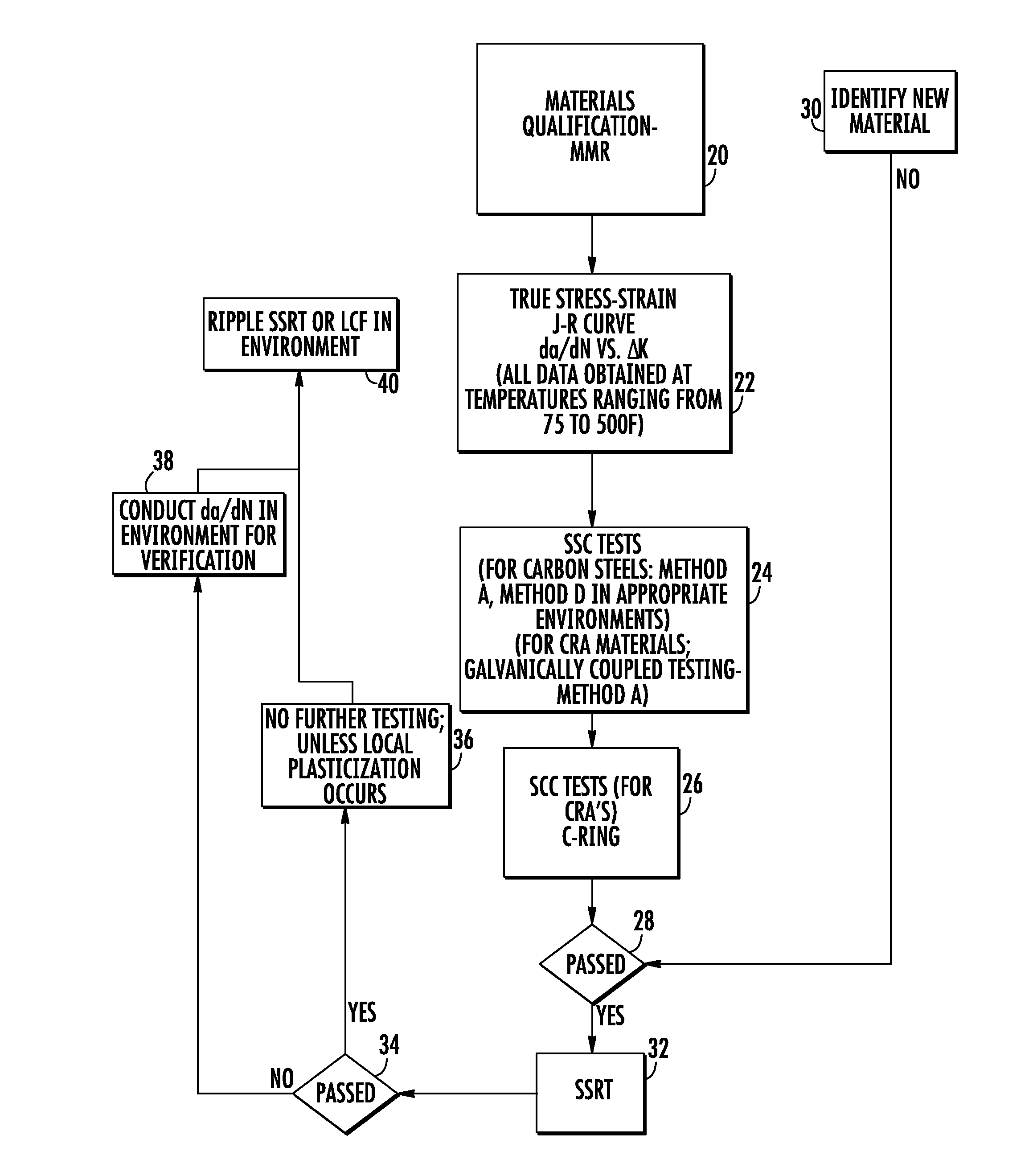

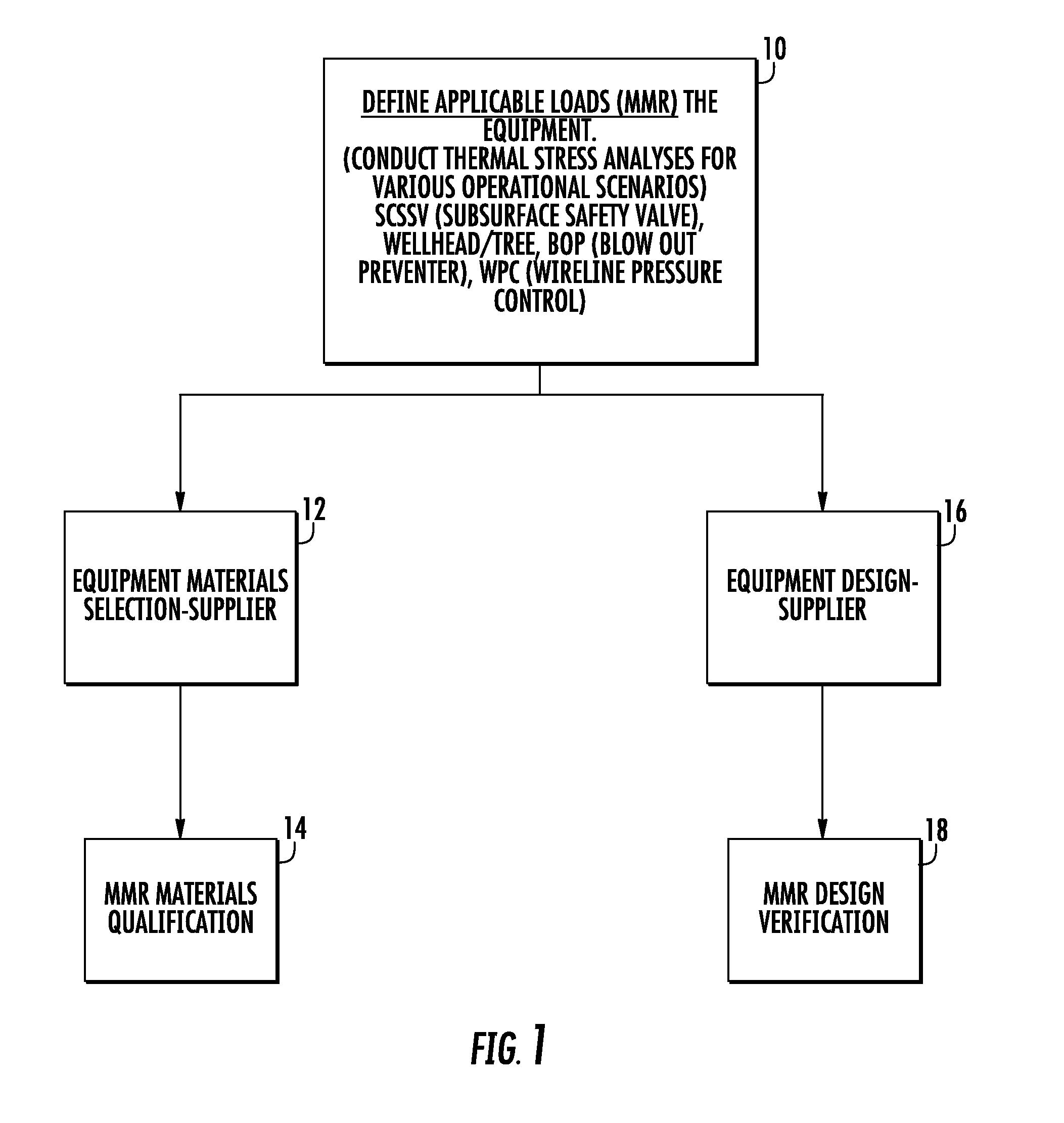

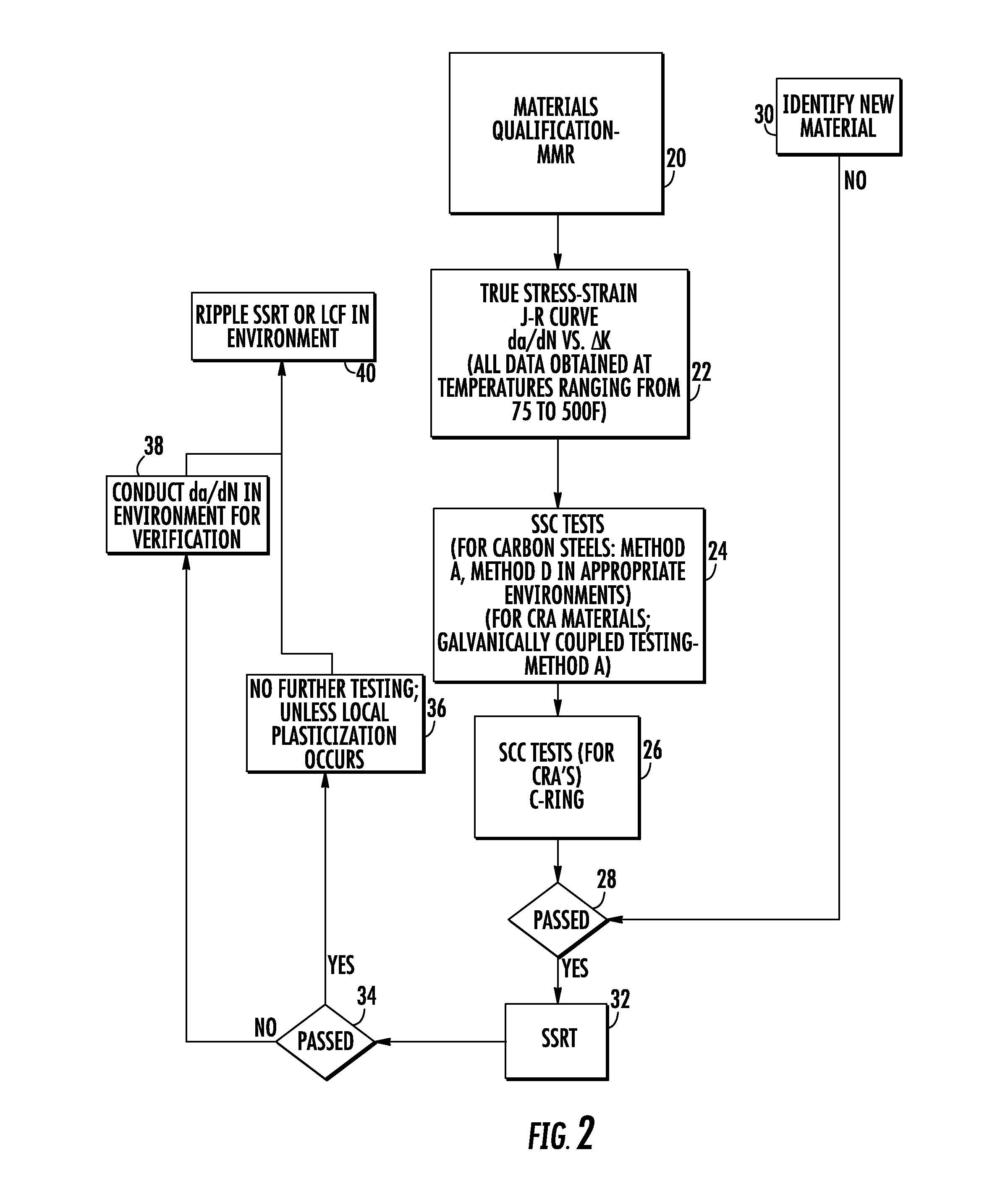

Engineered methodology for design verification and validation of ultra-deep high pressure high temperature oil and gas well control equipment

InactiveUS20130060536A1Geometric CADComputation using non-denominational number representationElement modelElastic plastic

A process for the verification and validation testing of equipment and components for drilling, completion, production and general well construction (typically such as subsurface safety valves, wellhead trees, blowout preventers and wireline pressure control equipment) to determine the suitability of such equipment for use in oil and gas wells in high pressure high temperature environments. In particular, the process of the present invention comprises, among other steps, the steps of analyzing such components using an elastic-plastic finite element model with respect to certain preset load conditions and establishing stable model convergence, conducting a ratcheting assessment by running analysis on such model on all components that exhibit local plasticity, and examining all components to determine fatigue sensitive locations and subjecting such components to a fatigue analysis. The process may further comprise a process for qualifying the materials to be used in the manufacture of the equipment components with respect to their ability to withstand high pressure and high temperature environmental conditions.

Owner:MCMORAN OIL & GAS

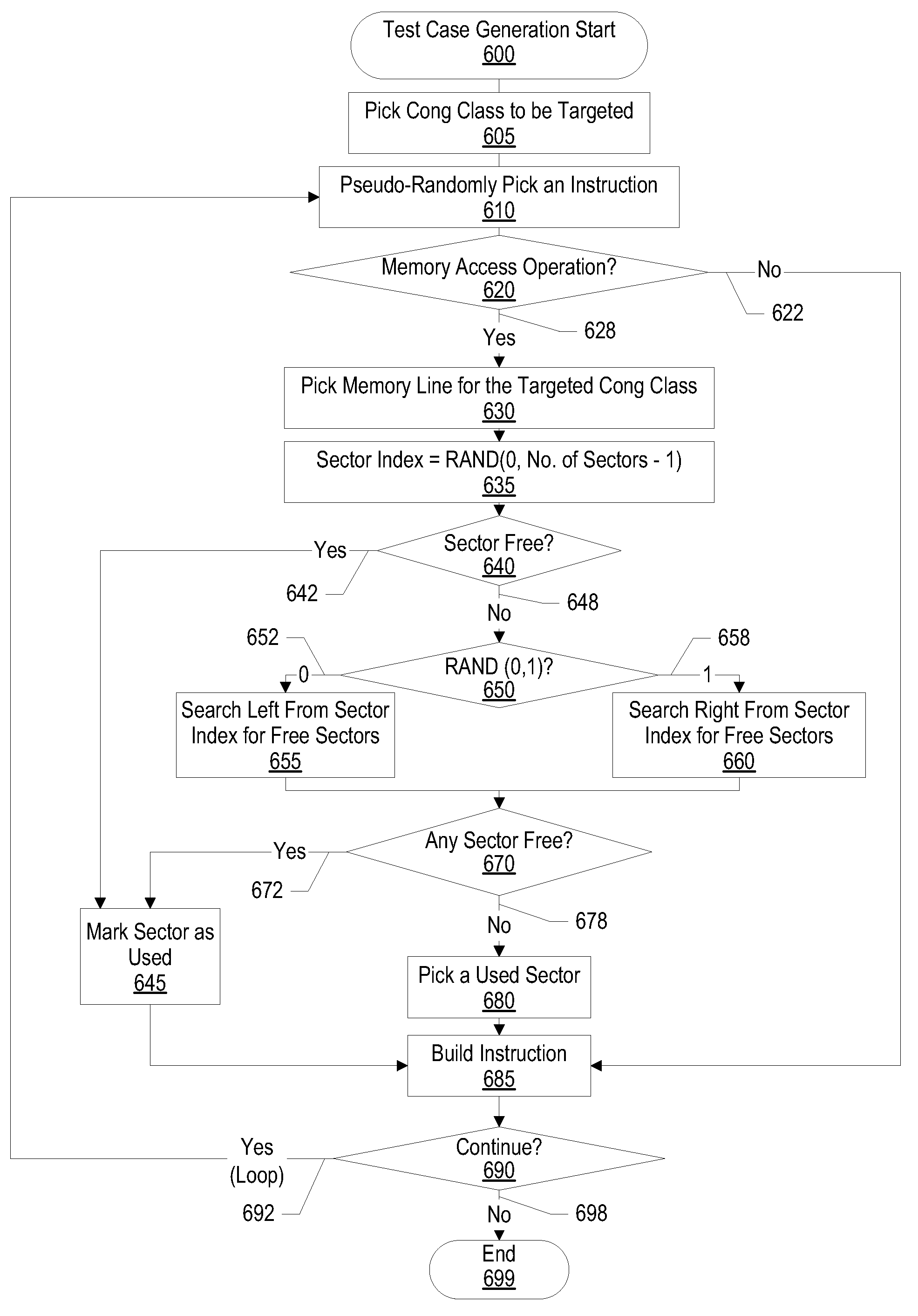

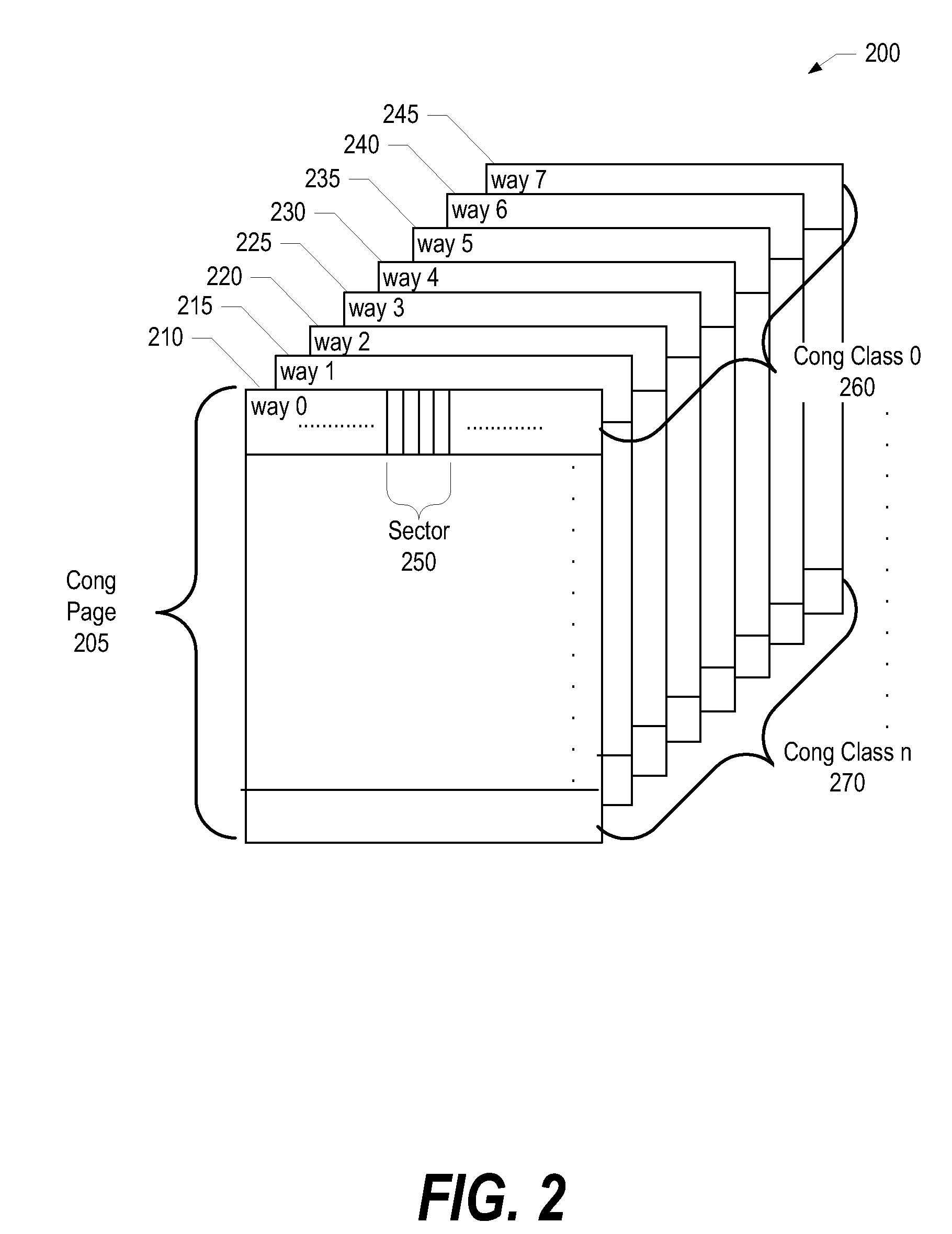

System and Method for Efficiently Testing Cache Congruence Classes During Processor Design Verification and Validation

InactiveUS20090070532A1Resistance/reactance/impedenceMemory adressing/allocation/relocationProgramming languageTest case generator

A system and method for using a single test case to test each sector within multiple congruence classes is presented. A test case generator builds a test case for accessing each sector within a congruence class. Since a congruence class spans multiple congruence pages, the test case generator builds the test case over multiple congruence pages in order for the test case to test the entire congruence class. During design verification and validation, a test case executor modifies a congruence class identifier (e.g., patches a base register), which forces the test case to test a specific congruence class. By incrementing the congruence class identifier after each execution of the test case, the test case executor is able to test each congruence class in the cache using a single test case.

Owner:IBM CORP

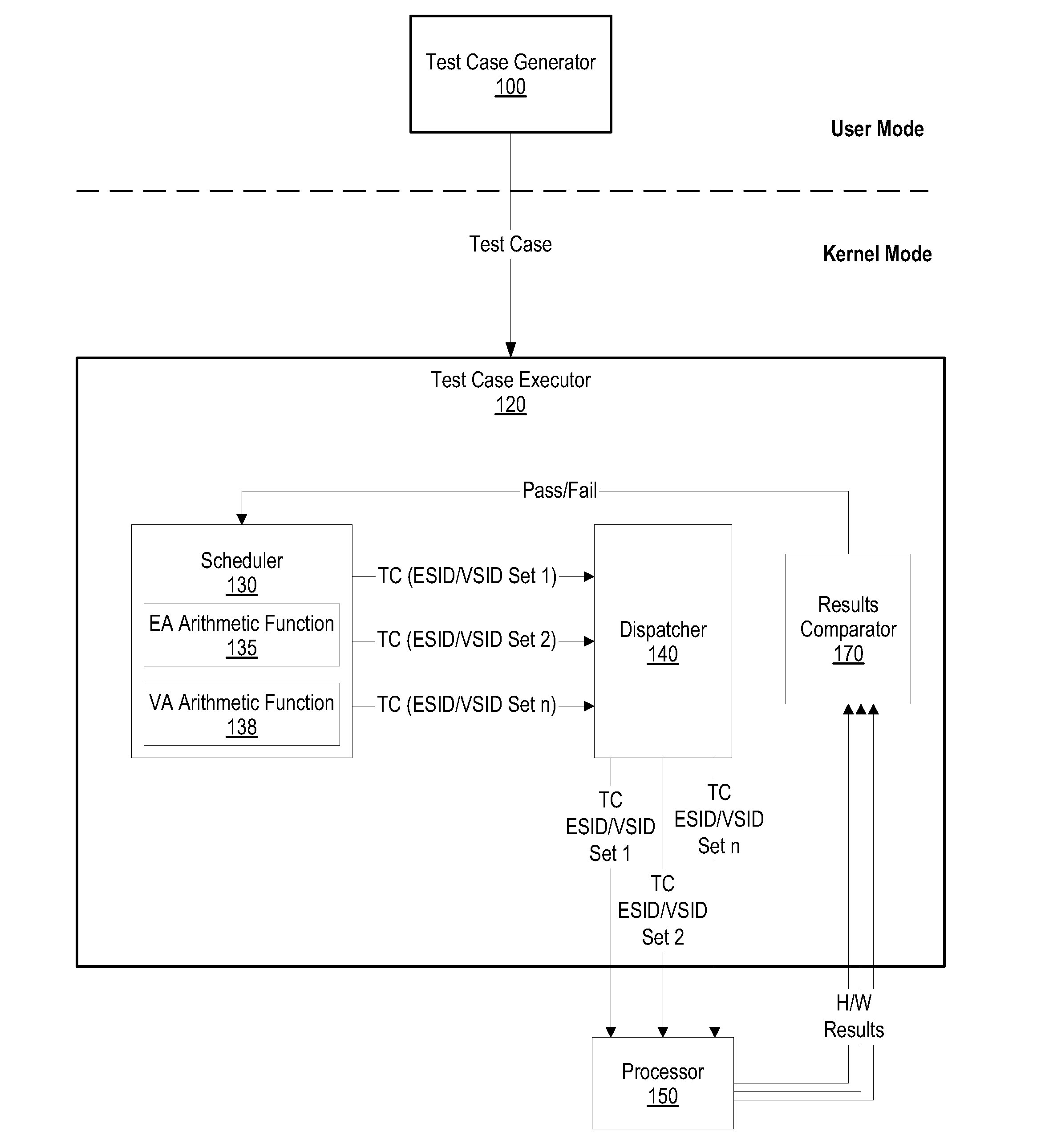

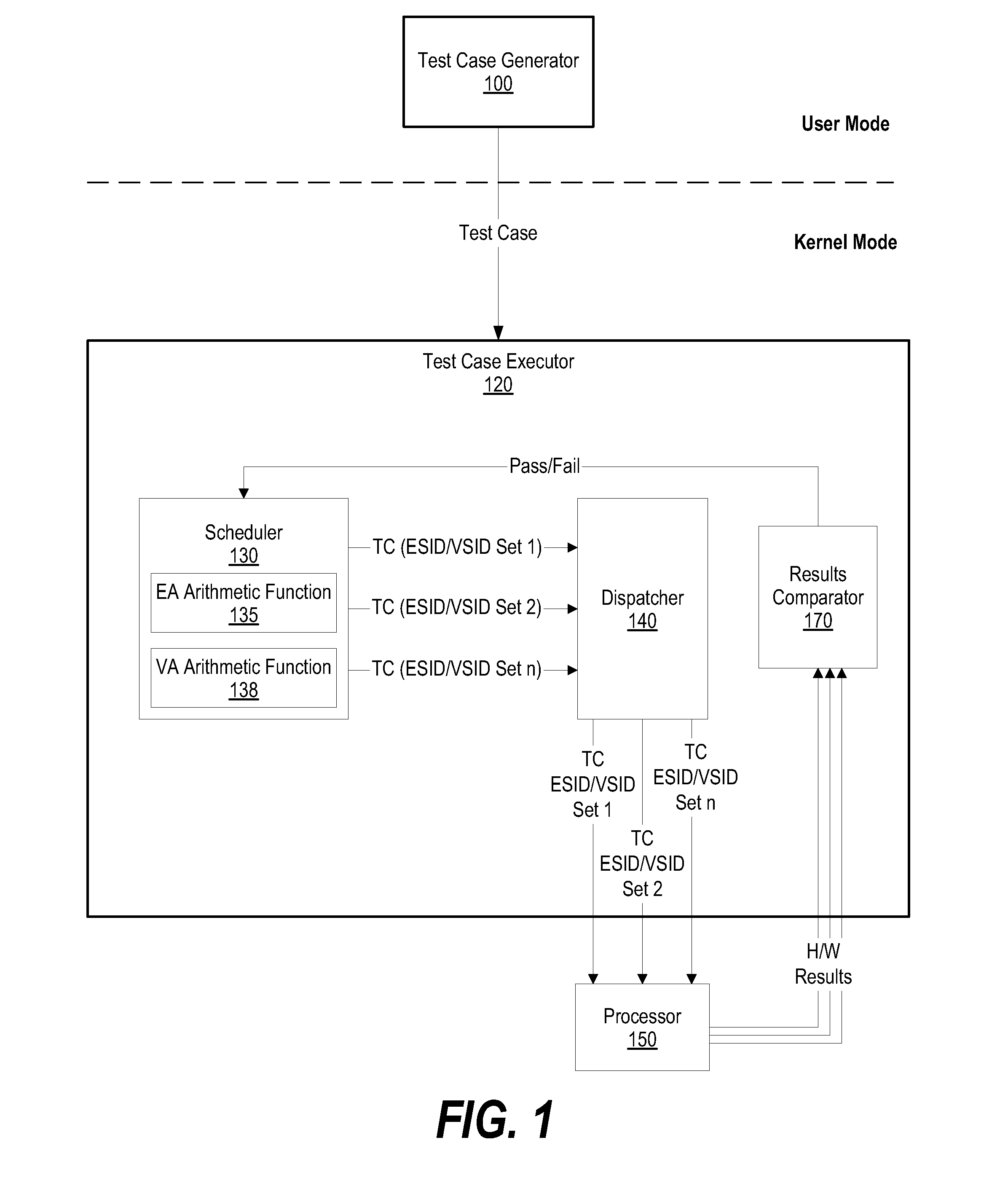

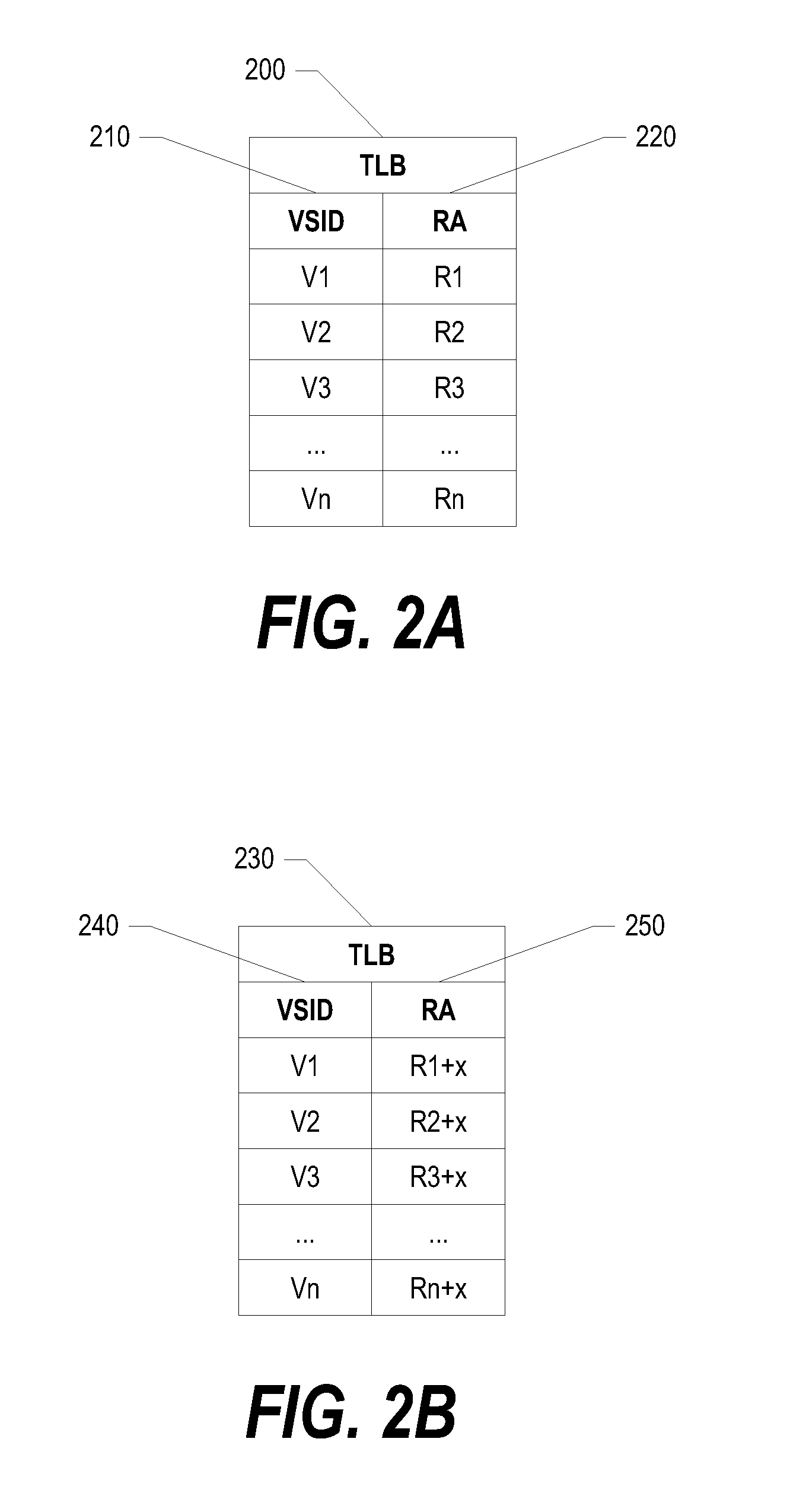

System and Method for Testing SLB and TLB Cells During Processor Design Verification and Validation

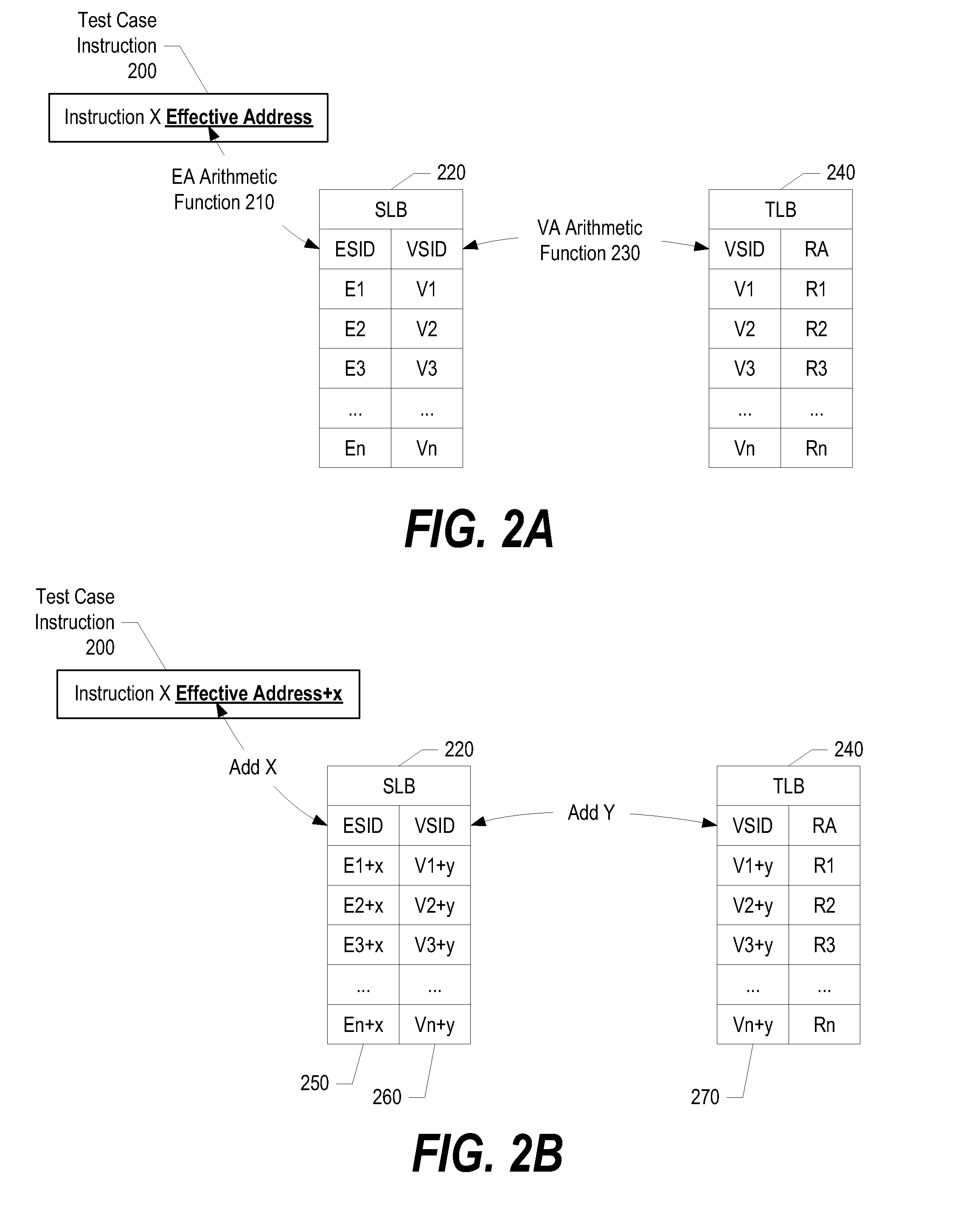

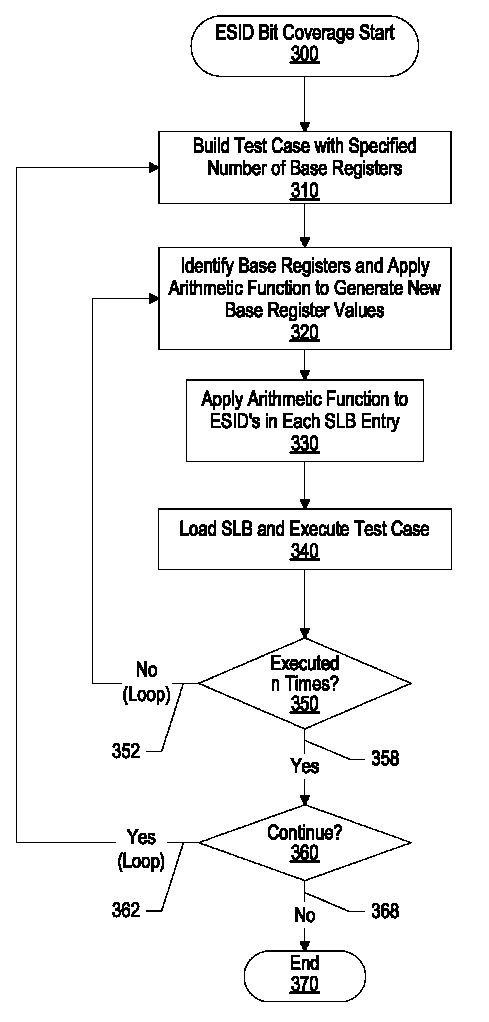

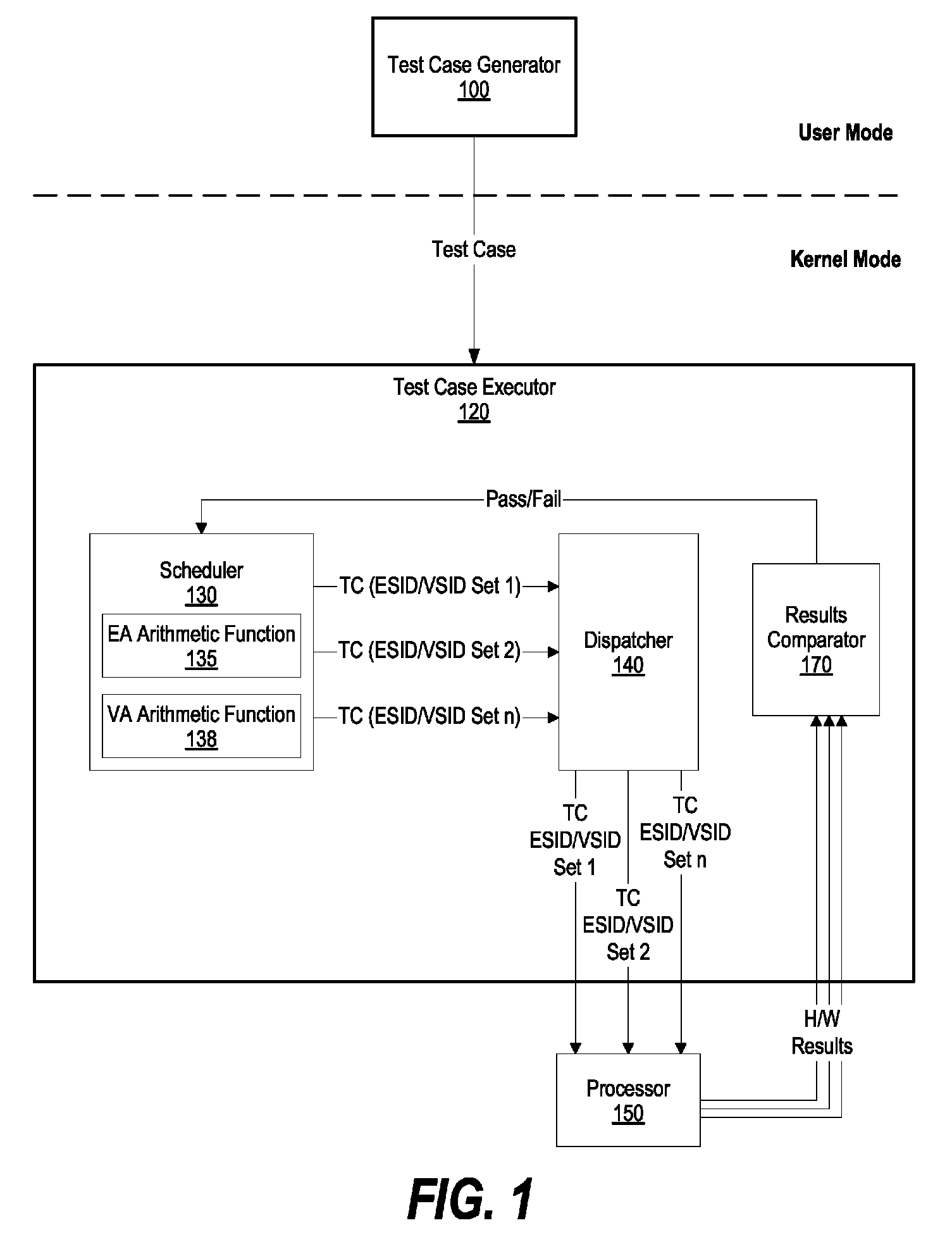

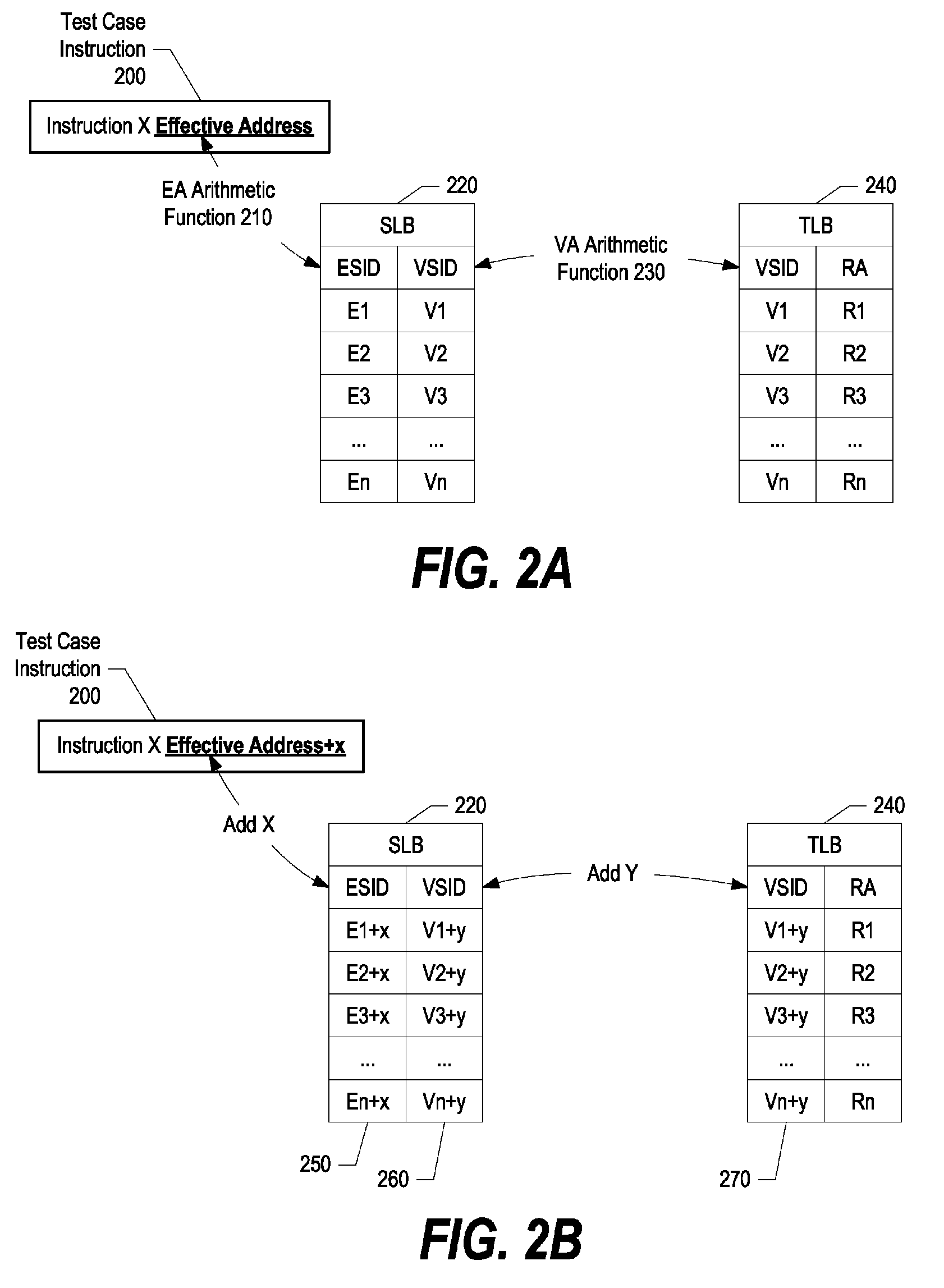

A system and method for re-executing a test case and modifying the test case's effective addresses, effective segment identifiers (ESIDs), and virtual segment identifiers (VSIDs) in order to fully test a processor's SLB and TLB cells is presented. A test case generator generates a test case that includes an initial set of test case effective addresses, an initial set of ESIDs, and an initial set of VSIDs. The test case executor uses an effective address arithmetic function and a virtual address arithmetic function to modify the test case effective addresses, the ESIDs, and the VSIDs on each re-execution that, in turn, sets / unsets each bit within each SLB and TLB entry. In one embodiment, the invention described herein sequentially shifts segment lookaside buffer entries, whose ESIDs are in single bit increments, in order to fully test each ESID bit location within each SLB entry.

Owner:LINKEDIN

Open platform for supporting design, verification and validation of telex flight control system

InactiveCN101750978AShort cycleEliminate design flawsWith power amplificationVehicle position/course/altitude controlControl system designEngineering

The invention relates to an open platform for supporting design, verification and validation of a telex flight control system, which is composed of five function modules, namely 1) a demand analysis, verification and refinement environment module of the telex flight control system; 2) a design, verification and validation environment module of the telex flight control system; 3) a hardware design environment module of the telex flight control system; 4) a project development environment module of flight control software; and 5) a system-level entire digitization, entire duty simulation test and confirmation environment module of the telex flight control system. The open platform can assist flight control system engineers to carry out demand analysis and validation of the telex flight control system, system overall design, verification of a design proposal, system hardware design, system software project development, system-level entire digitization, entire duty simulation test and confirmation to solve the problems of long development cycle, high cost, large risk, and the like brought by development environment. The open platform has wide use value and application prospect in the technical field of system projects.

Owner:BEIHANG UNIV

System and method for testing SLB and TLB cells during processor design verification and validation

Owner:LINKEDIN

System and Method for Testing a Large Memory Area During Processor Design Verification and Validation

InactiveUS20090070643A1Electronic circuit testingError detection/correctionActuatorTest case generator

A system and method for replicating a memory block throughout a main memory and modifying real addresses within an address translation buffer to reference the replicated memory blocks during test case set re-executions in order to fully test the main memory is presented. A test case generator generates a test case set (multiple test cases) along with an initial address translation buffer that includes real addresses that reference an initial memory block. A test case executor modifies the real addresses after each test case set re-execution in order for a processor to test each replicated memory block included in the main memory.

Owner:IBM CORP

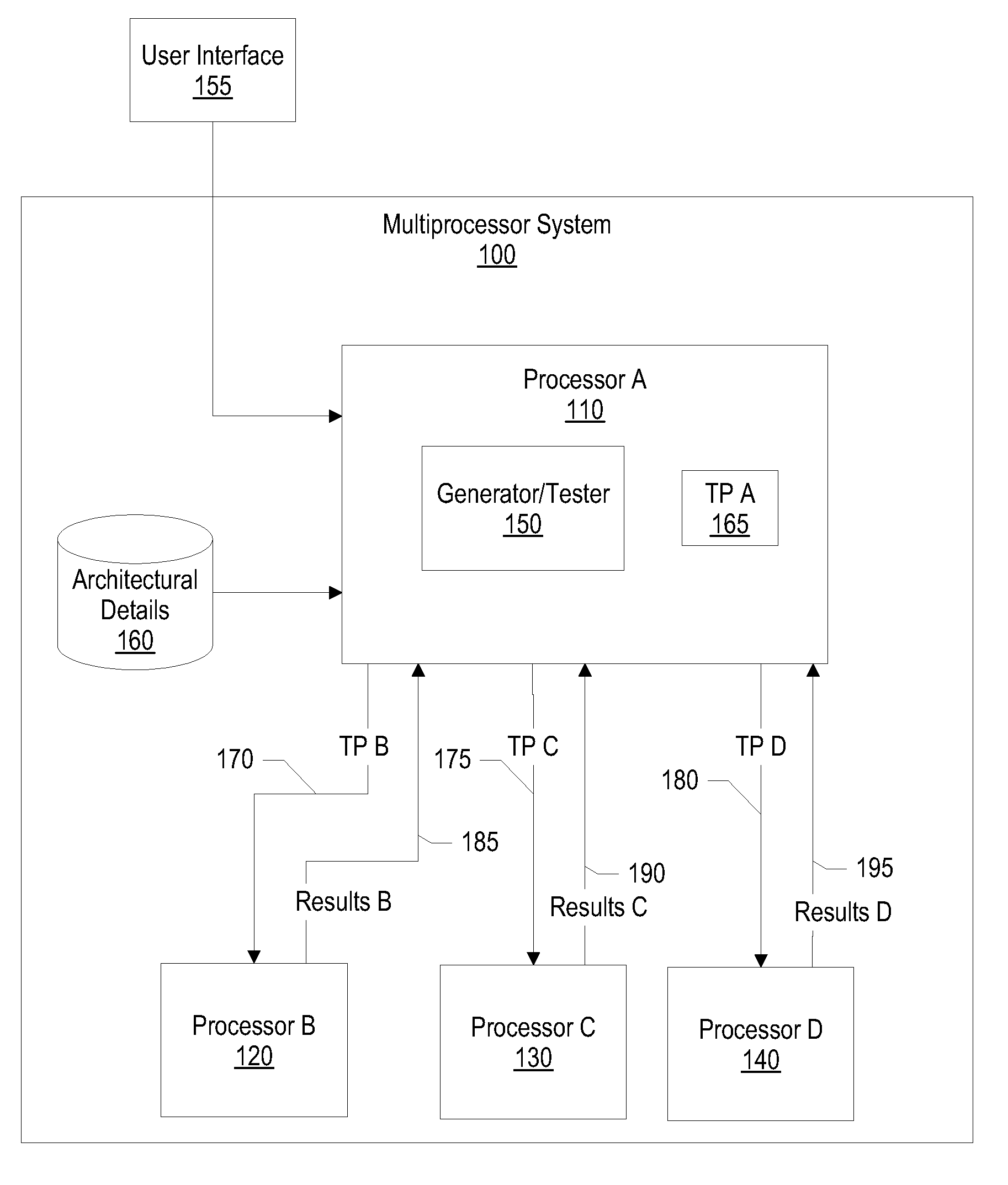

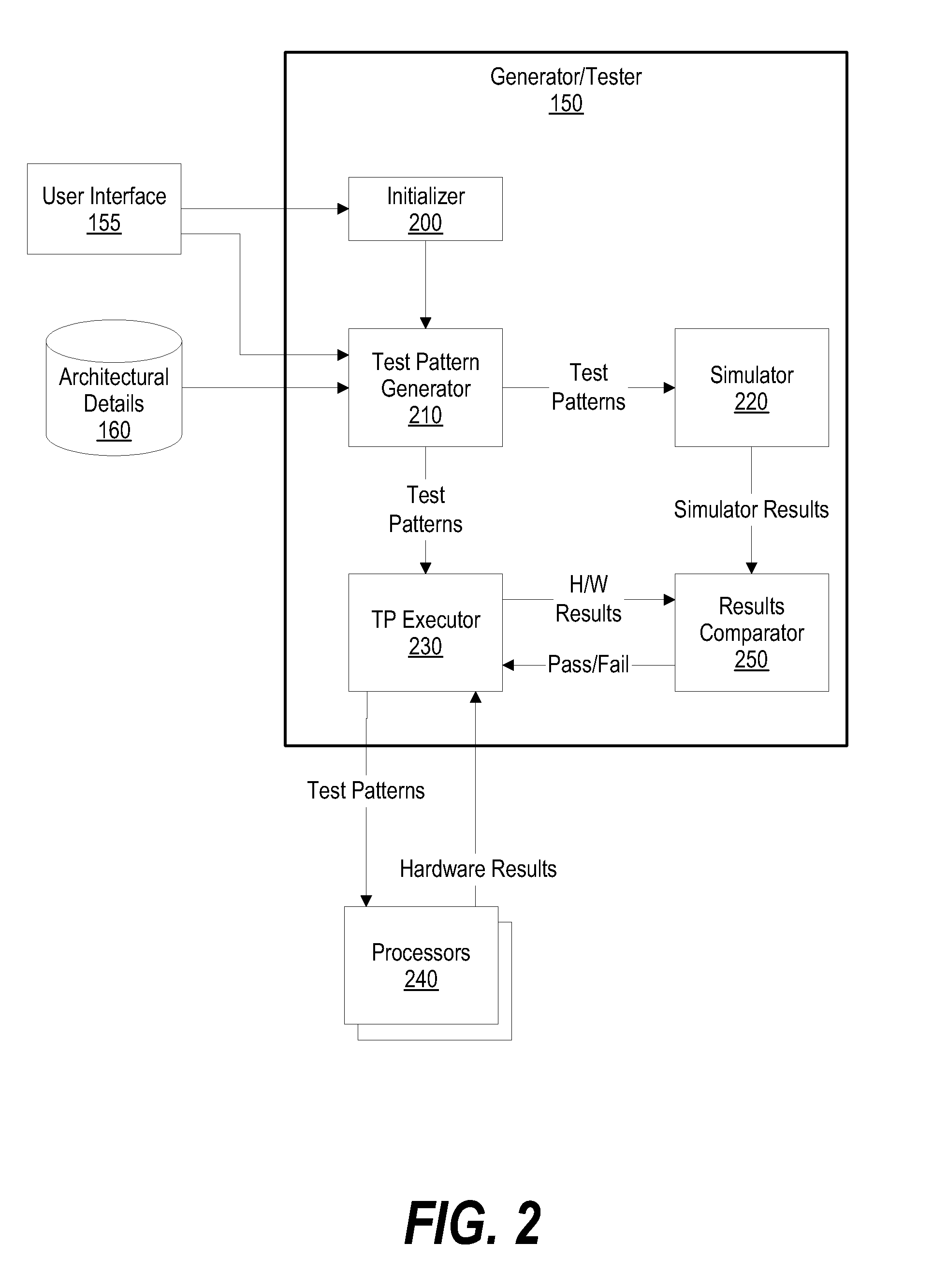

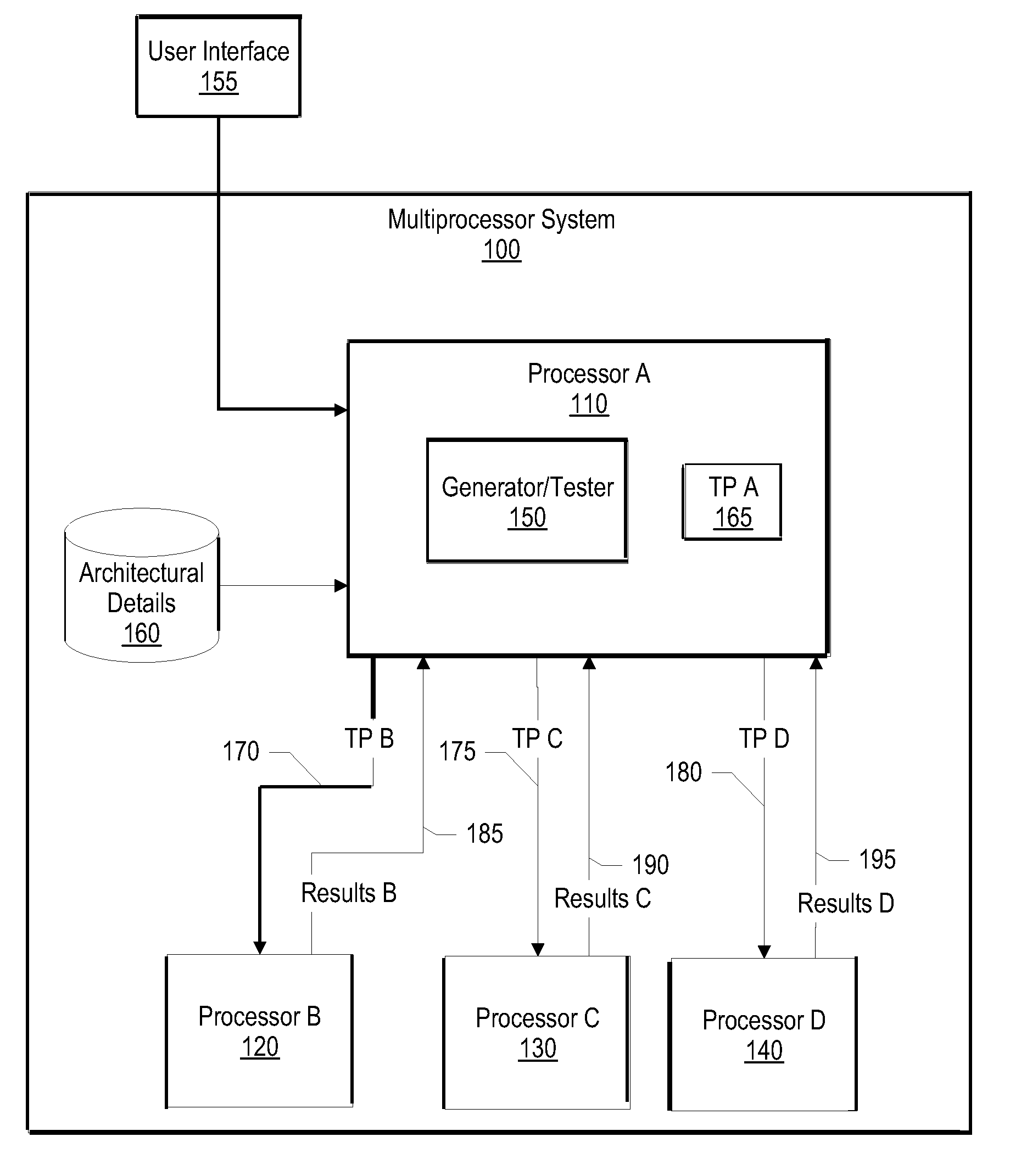

System and method for creating different start cache and bus states using multiple test patterns for processor design verification and validation

ActiveUS7747908B2Increase coverageElectronic circuit testingError detection/correctionMulti processorBroadband

A system and method for creating different start cache and bus states using multiple test patterns for processor design verification and validation is presented. A test pattern generator / tester re-uses test patterns in different configurations that alter cache states and translation lookaside buffer (TLB) states, which produces different timing scenarios on a broadband bus. The test pattern generator / tester creates multiple test patterns for a multi-processor system and executes the test patterns repeatedly in different configurations without rebuilding the test patterns. This enables a system to dedicate more time executing the test patterns instead of building the test patterns. By repeatedly executing the same test patterns in a different configuration, the invention described herein produces different start cache states, different TLB states, along with other processor units, each time the test patterns execute that, in turn, changes the bus timing.

Owner:TWITTER INC

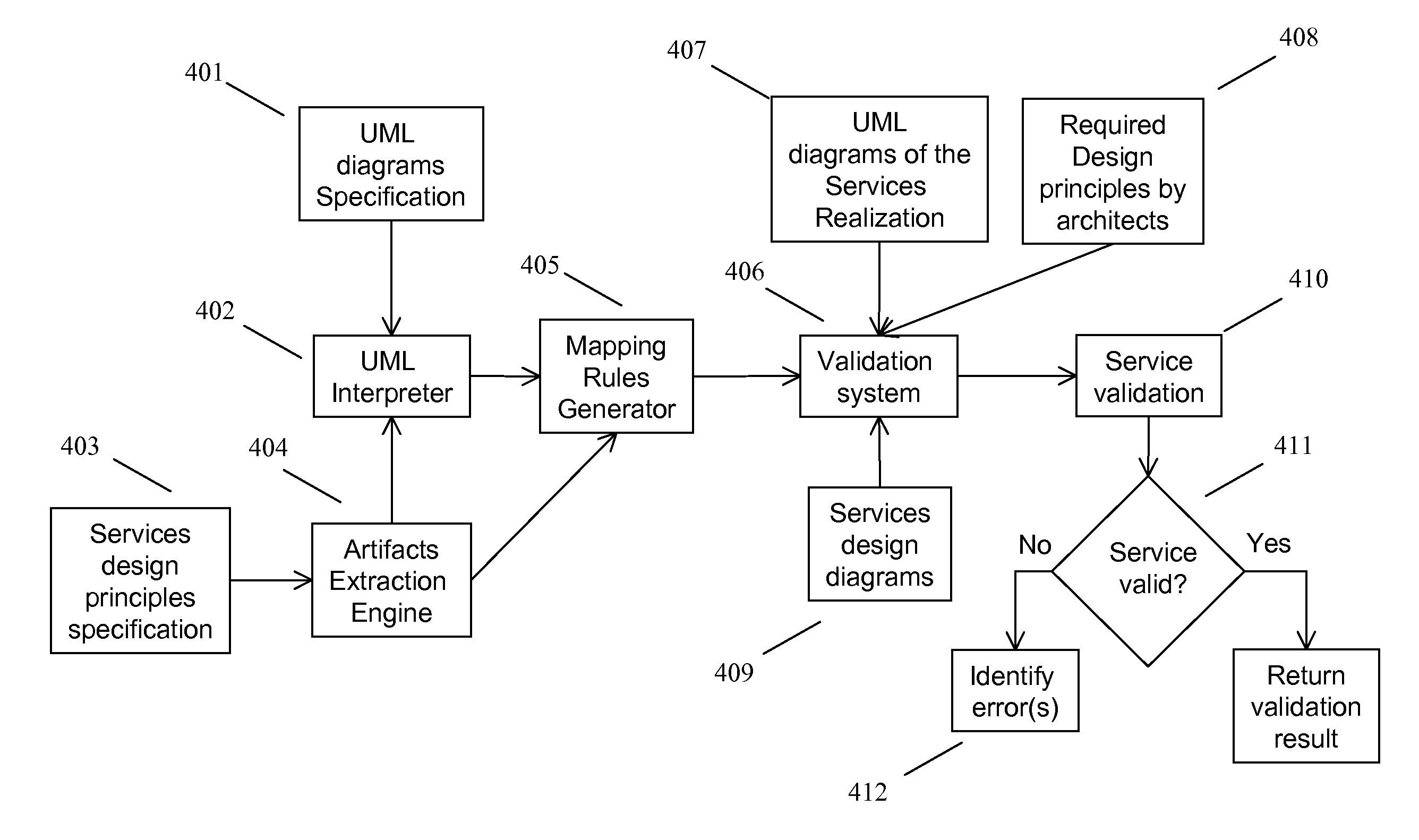

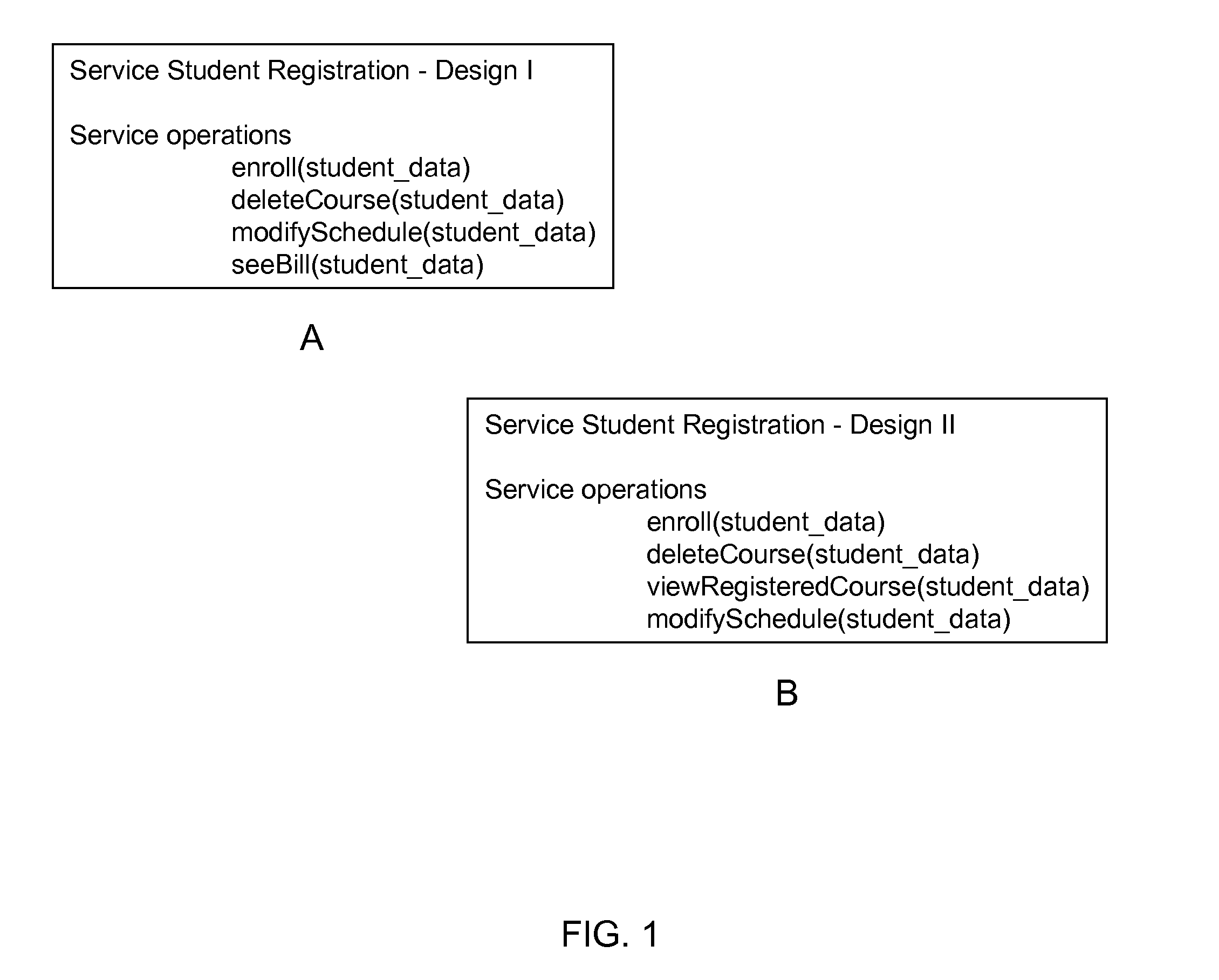

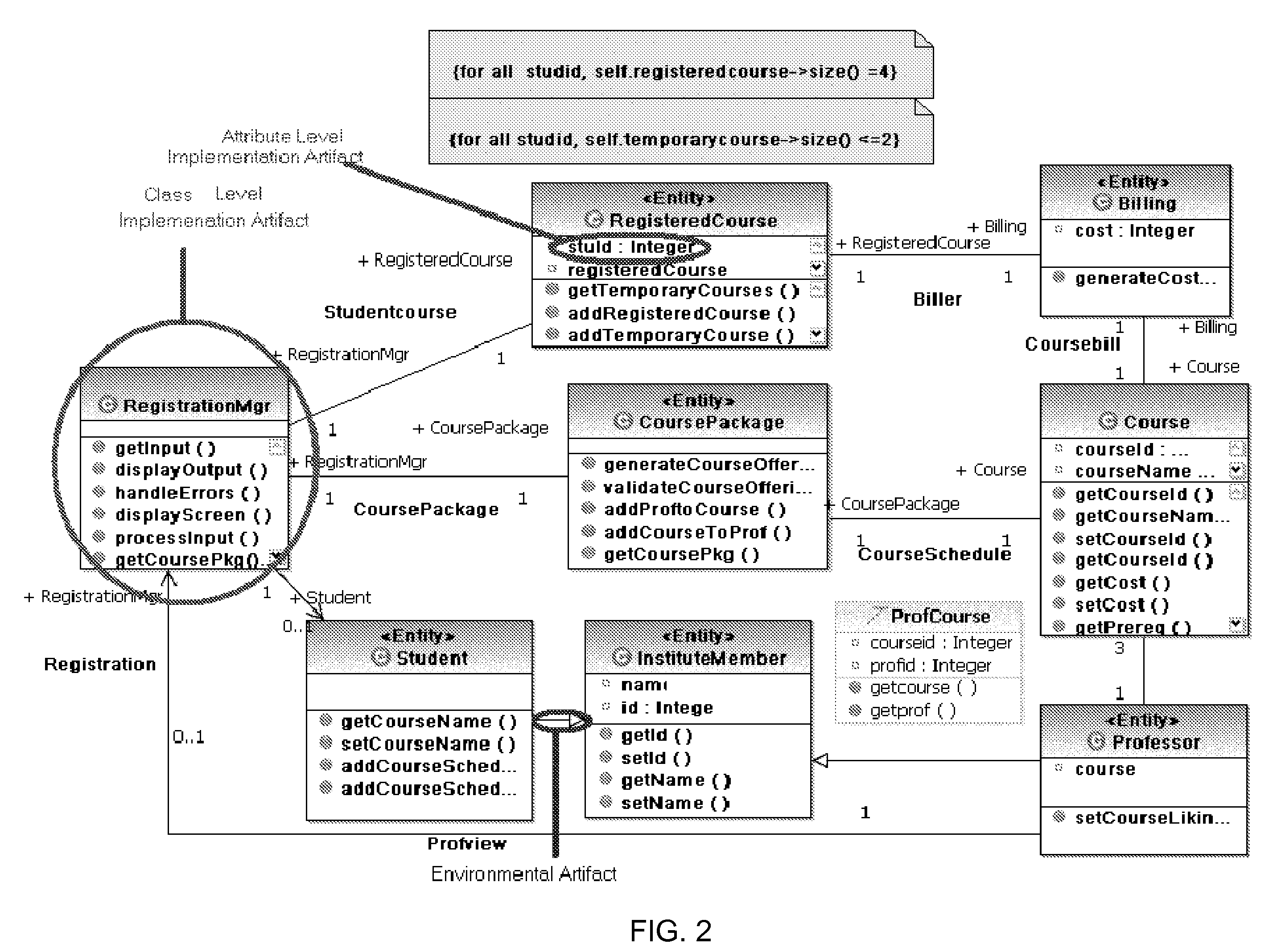

Systems and methods for design time service verification and validation

Design principles of services ensure reliability, scalability and reusability of software components. Services that follow the design principles are robust to changes and are largely reusable in multiple scenarios but in similar domains. To-date there is no systematic approach to apply these design principles to service design that will ensure service quality. Embodiments of the invention provide a formal check for the adherence of the services designed for an enterprise solution to the service orientation principles using design diagrams.

Owner:IBM CORP

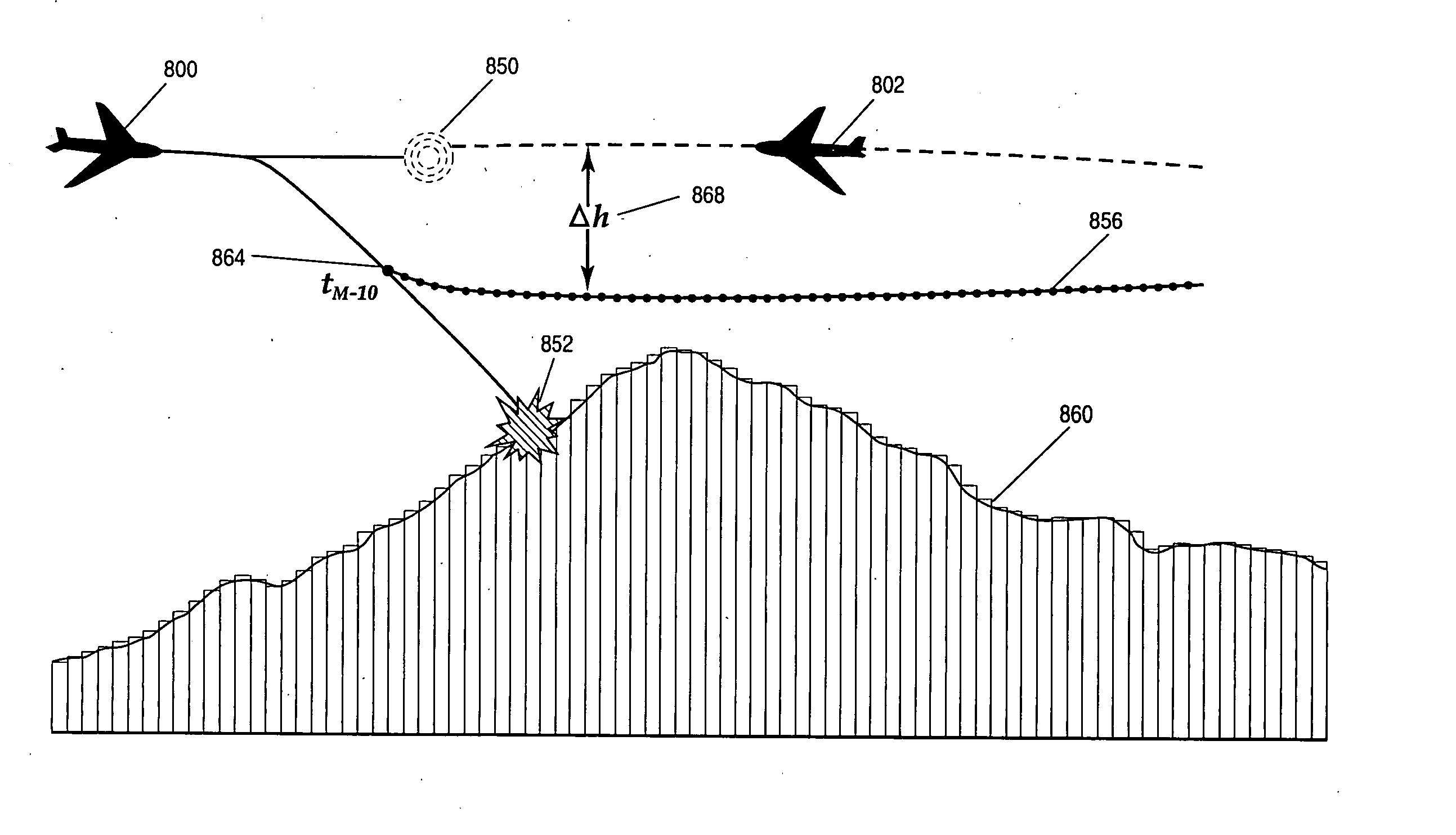

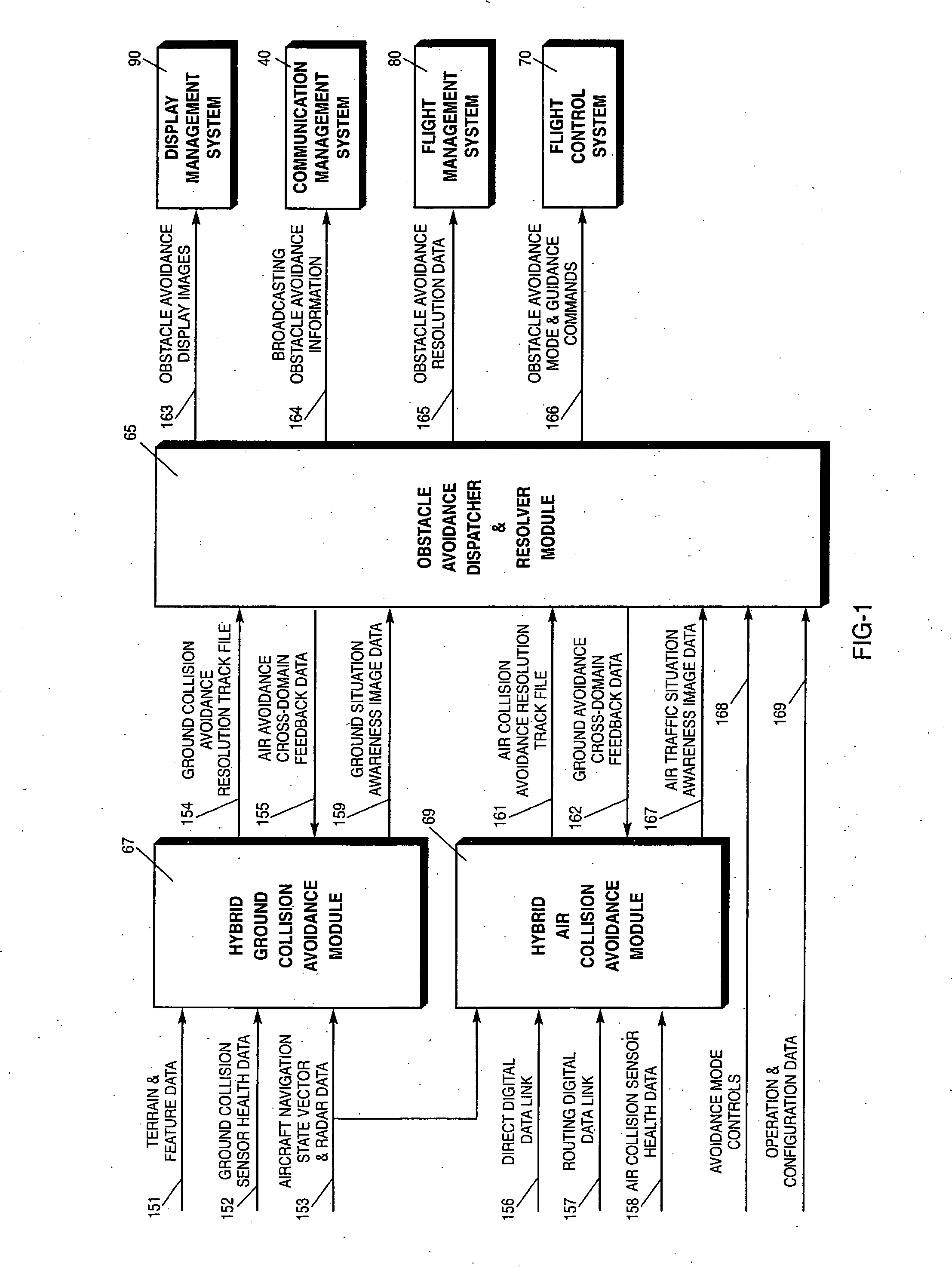

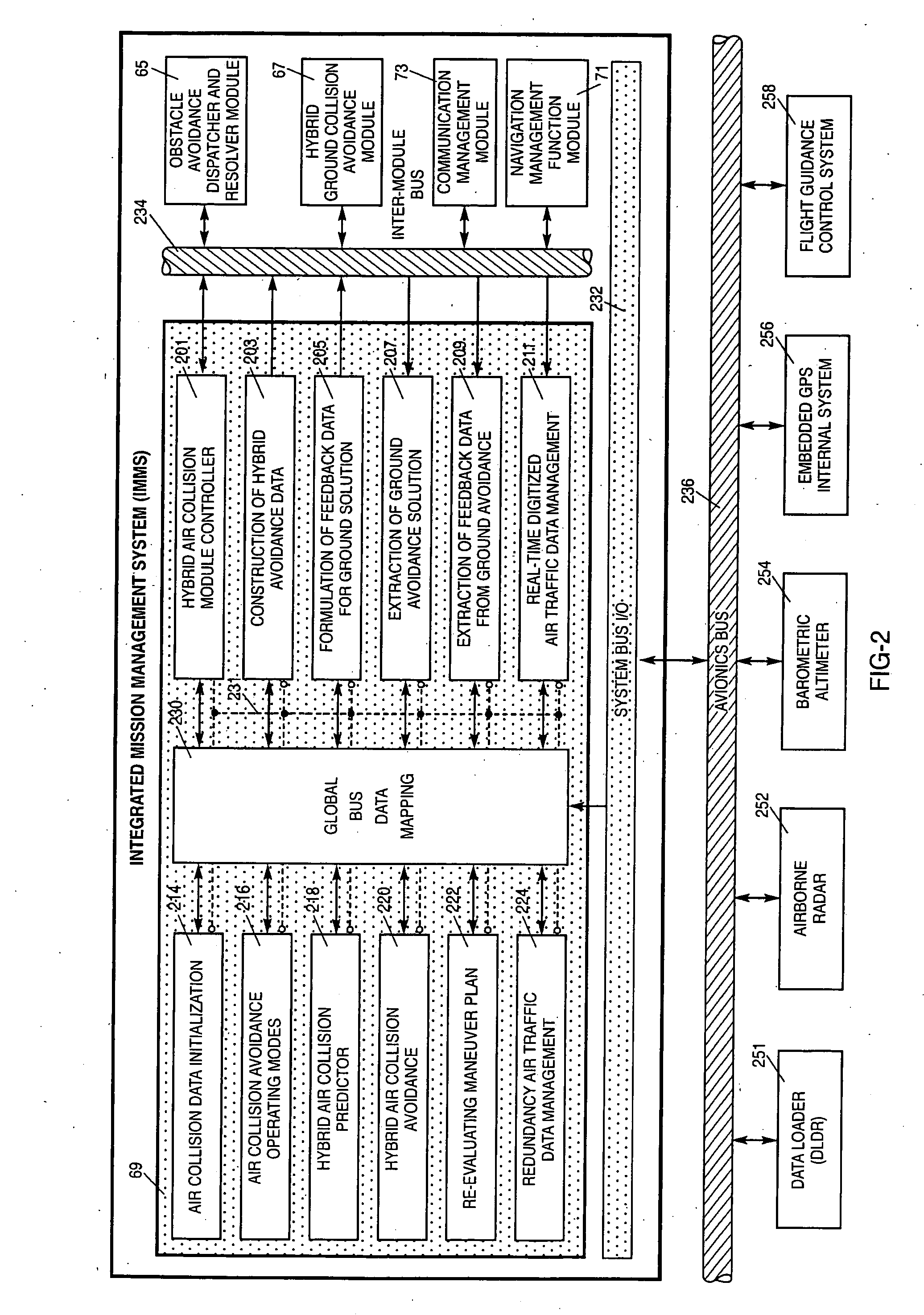

Hybrid air collision avoidance system

InactiveUS20060287827A1Create ambiguityCreate to operationAnalogue computers for vehiclesAnalogue computers for trafficImage resolutionEngineering

A hybrid air collision avoidance system (HACAS) is an air collision avoidance system with extended existing air avoidance capabilities and incorporated with new hybrid capabilities to perform hybrid air collision prediction and hybrid air collision avoidance. This system works in collaboration with two other systems, hybrid ground collision avoidance system, and obstacle avoidance dispatcher and resolver module to form a bi-directional feedback network for processing and exchanging of verification and validation collision avoiding data. With the embedded hybrid prediction and avoidance processing capabilities, the system not only can refine air collision avoidance solution to eliminate any induced ground collision situation, but also provide verification for ground collision avoidance resolution in the air domain; and subsequent validate the final avoidance solution.

Owner:HONEYWELL INT INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com