Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

36 results about "Feed forward equalization" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

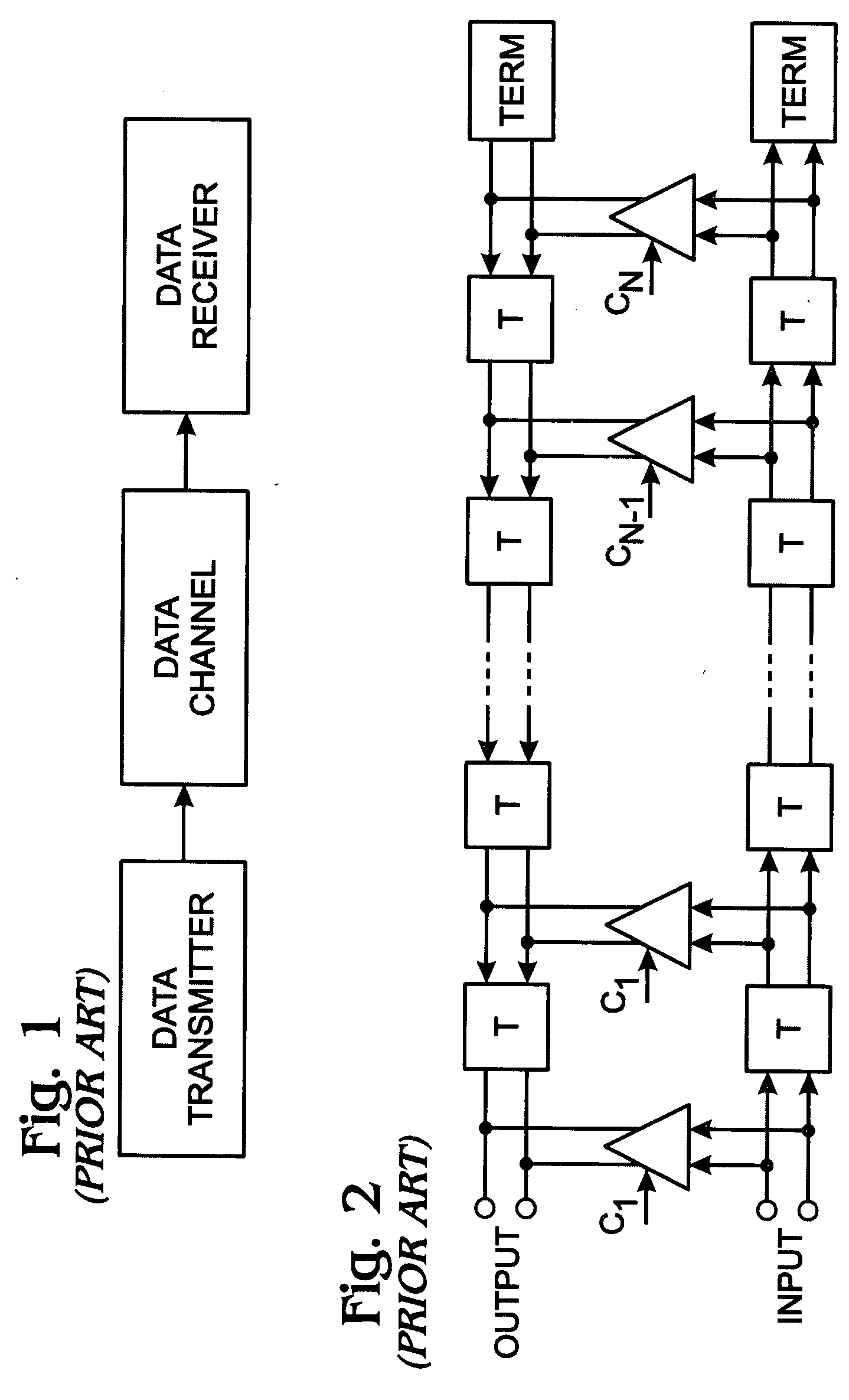

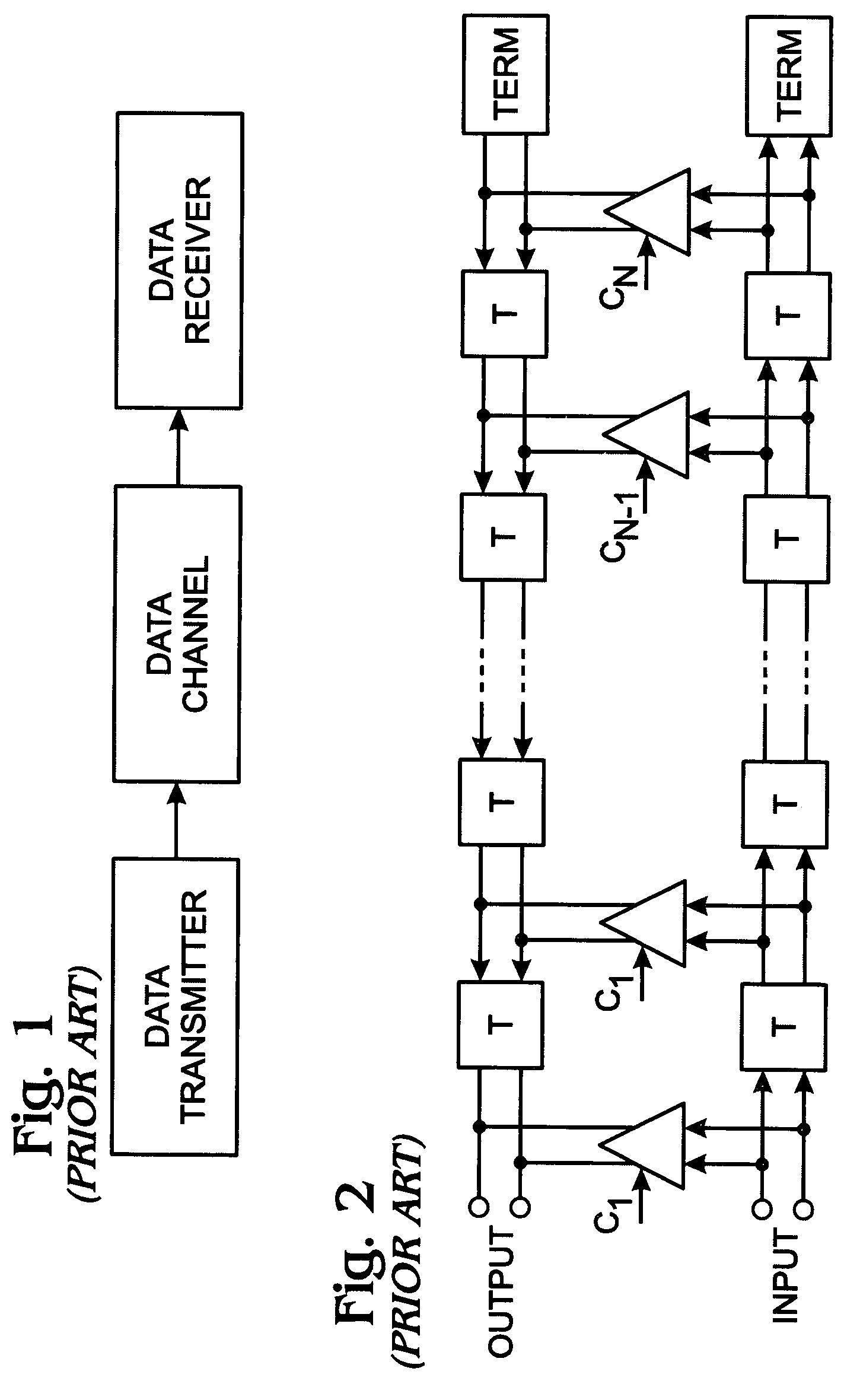

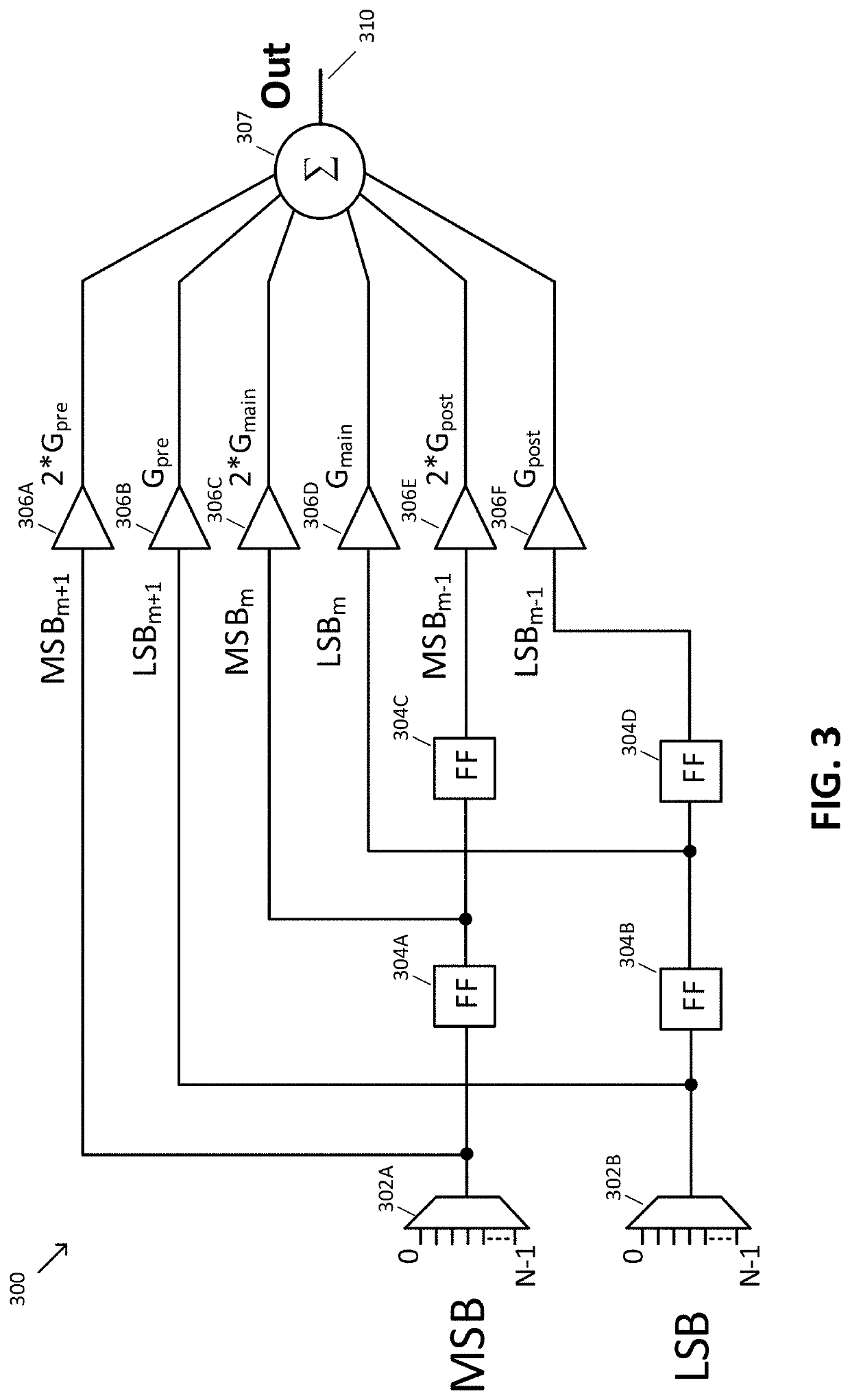

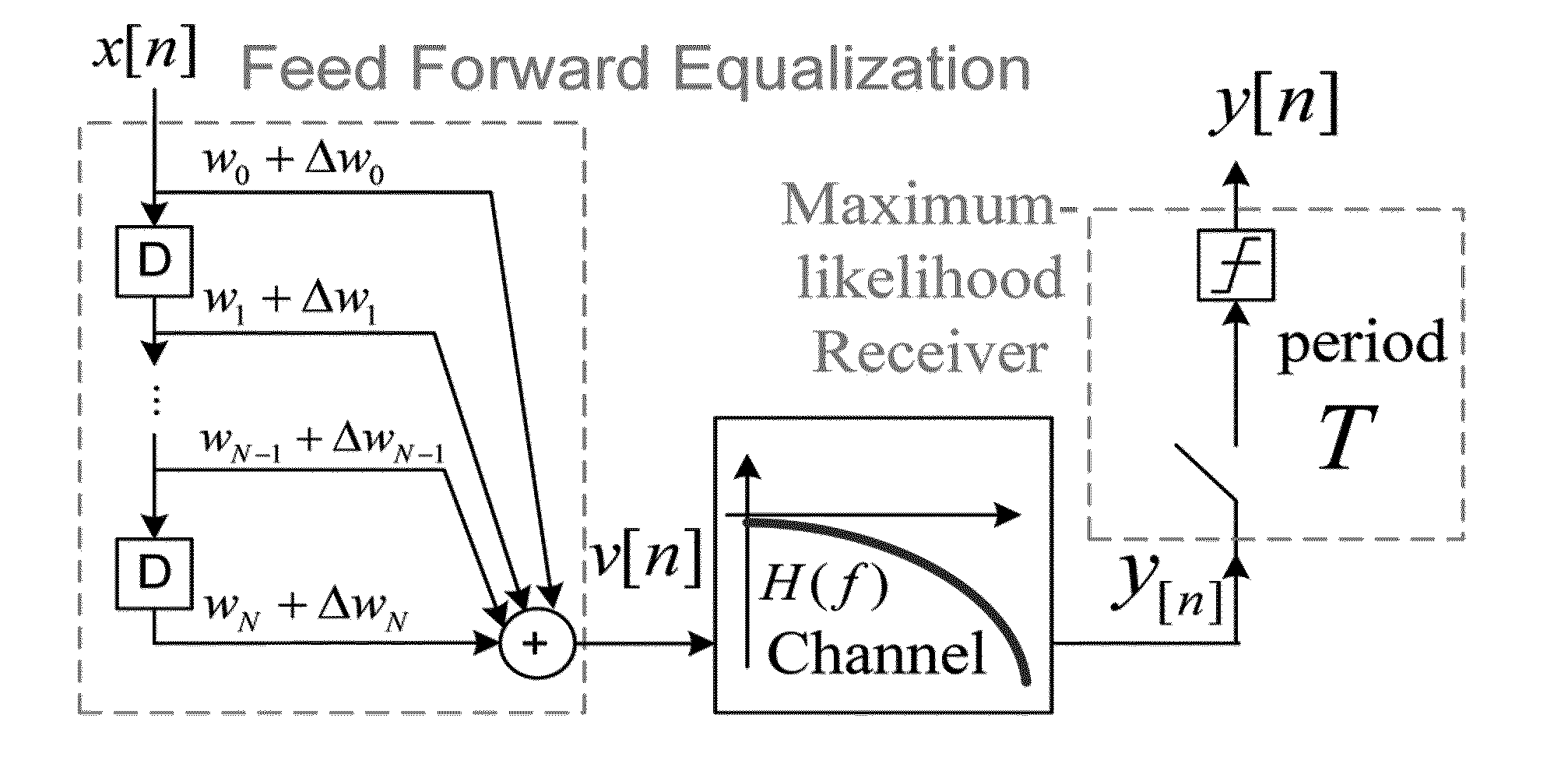

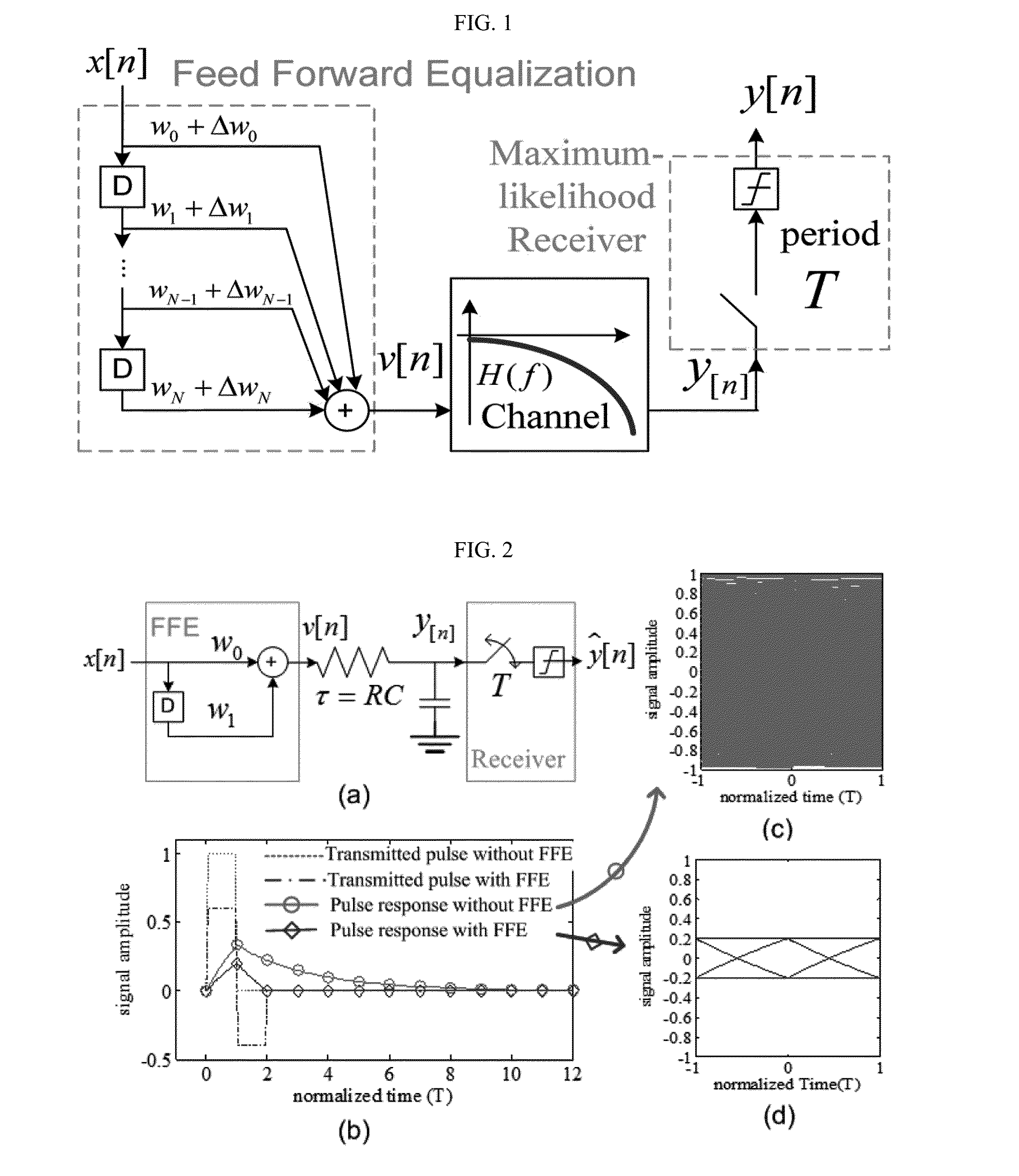

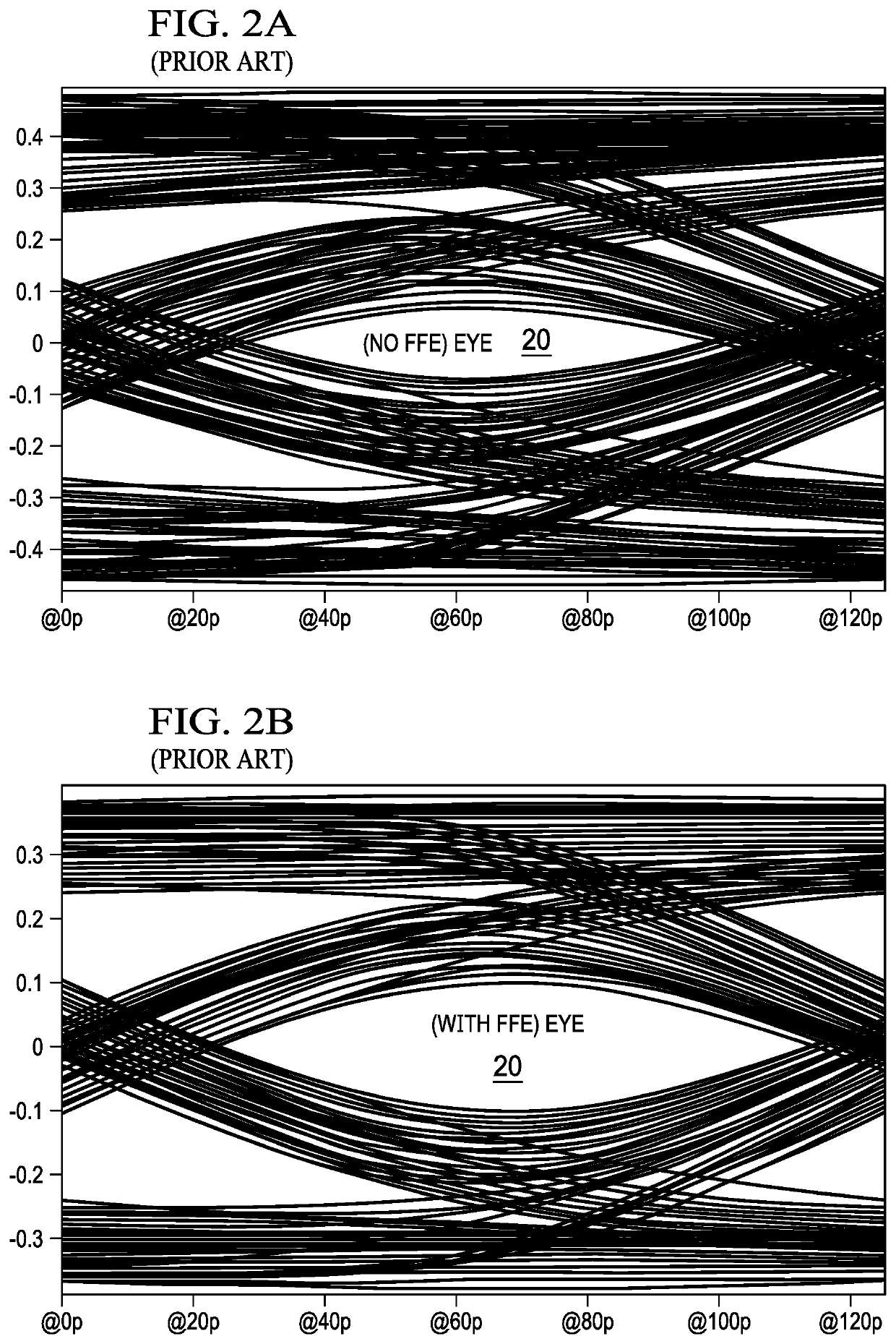

Inventor

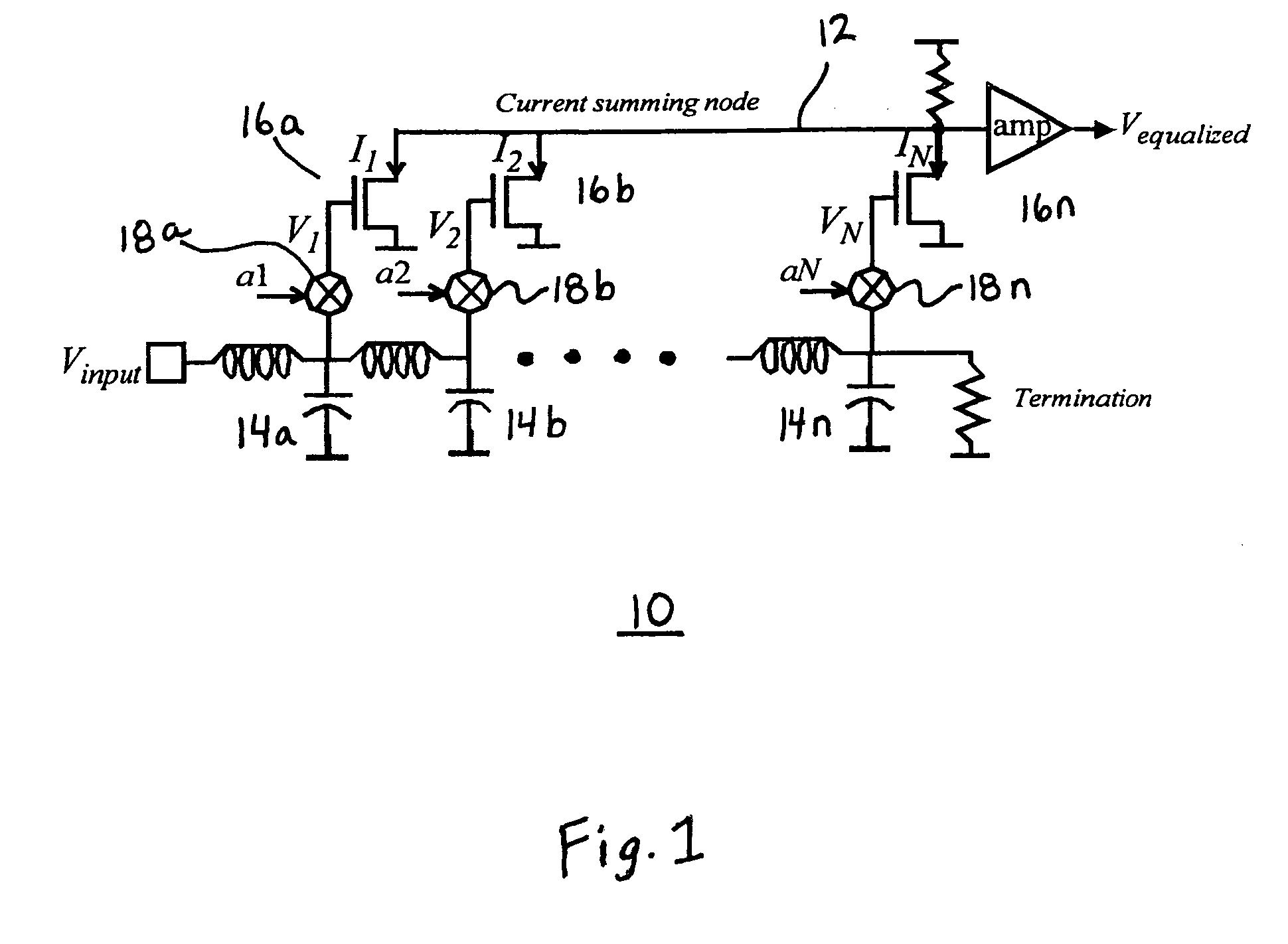

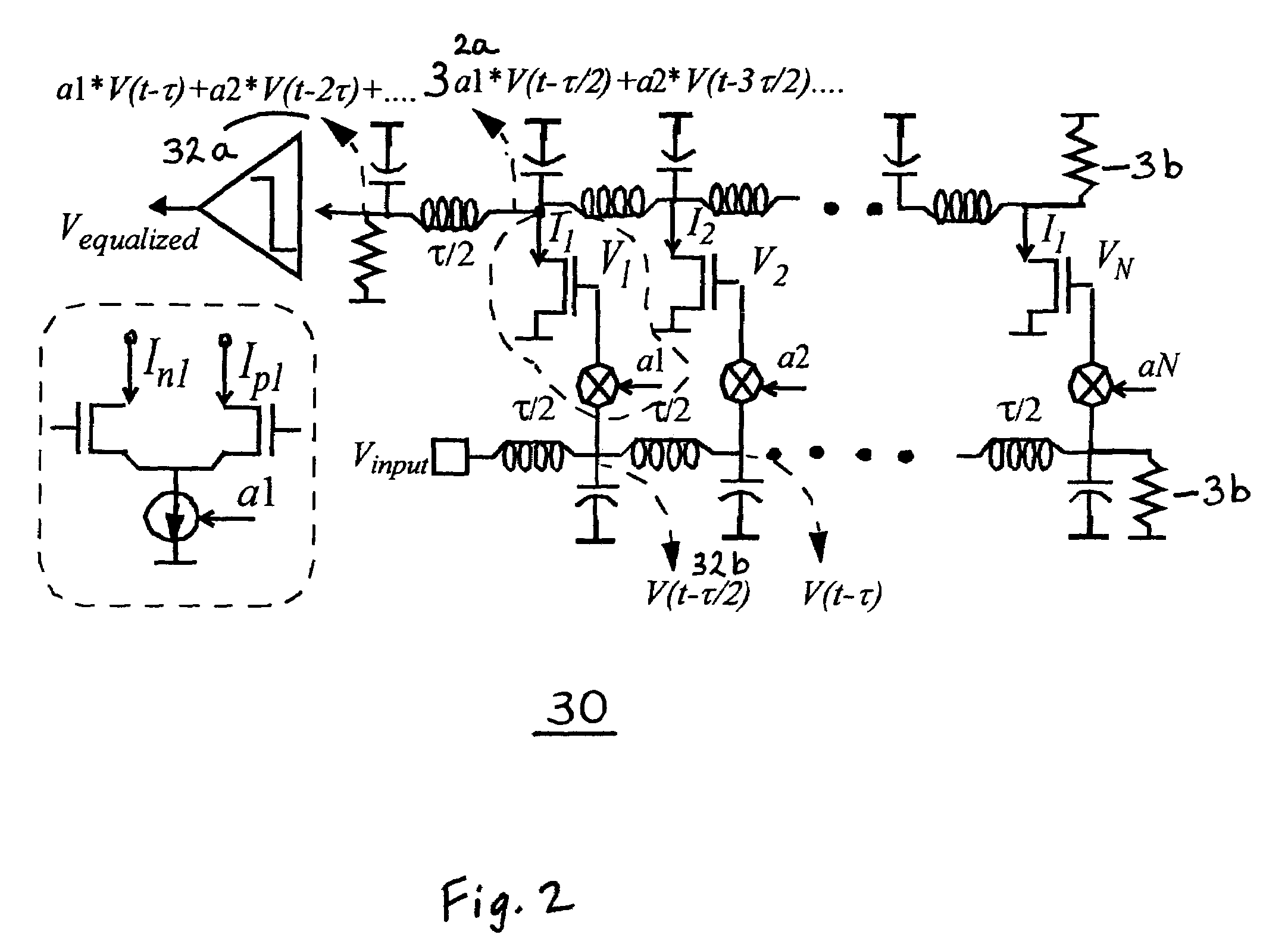

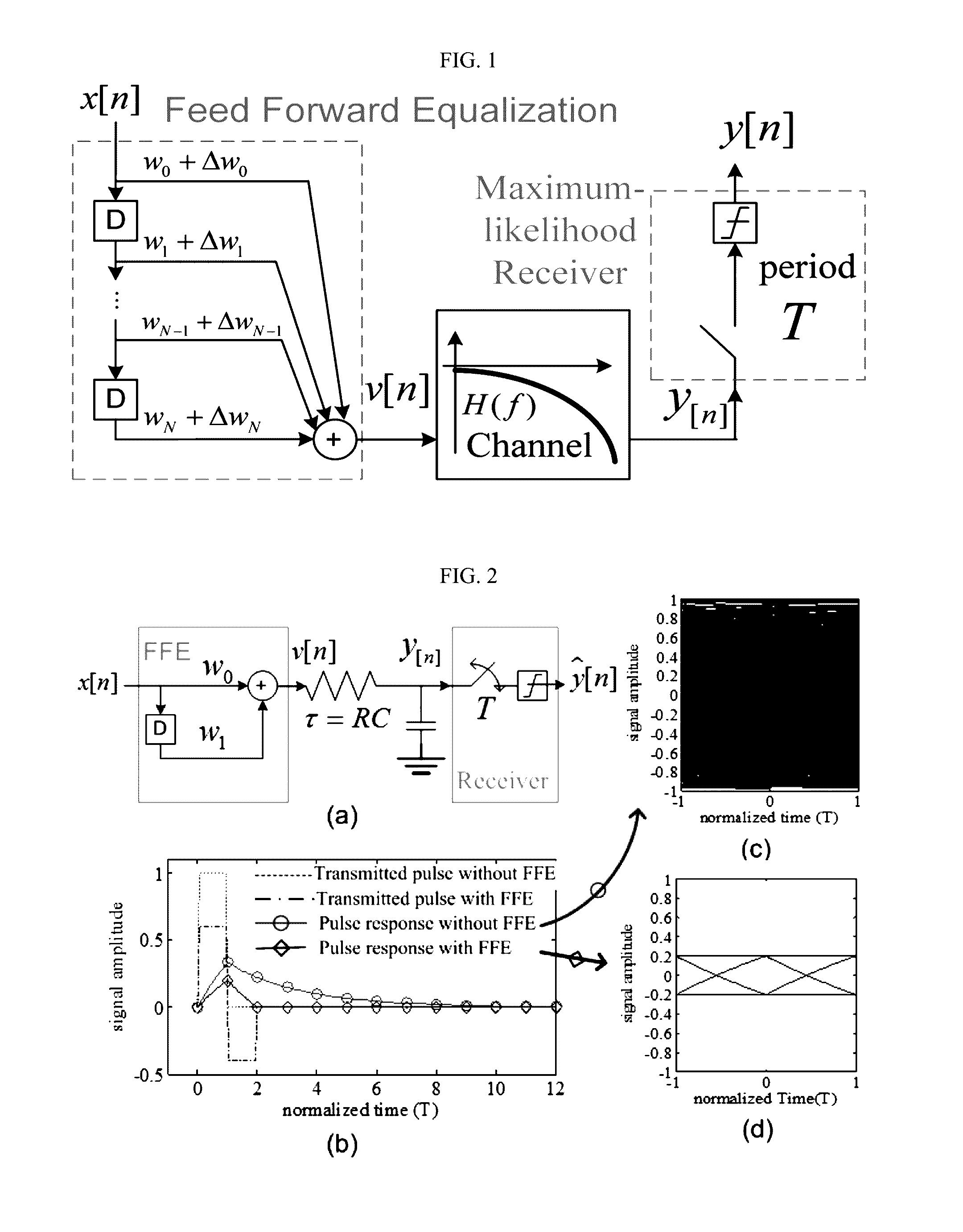

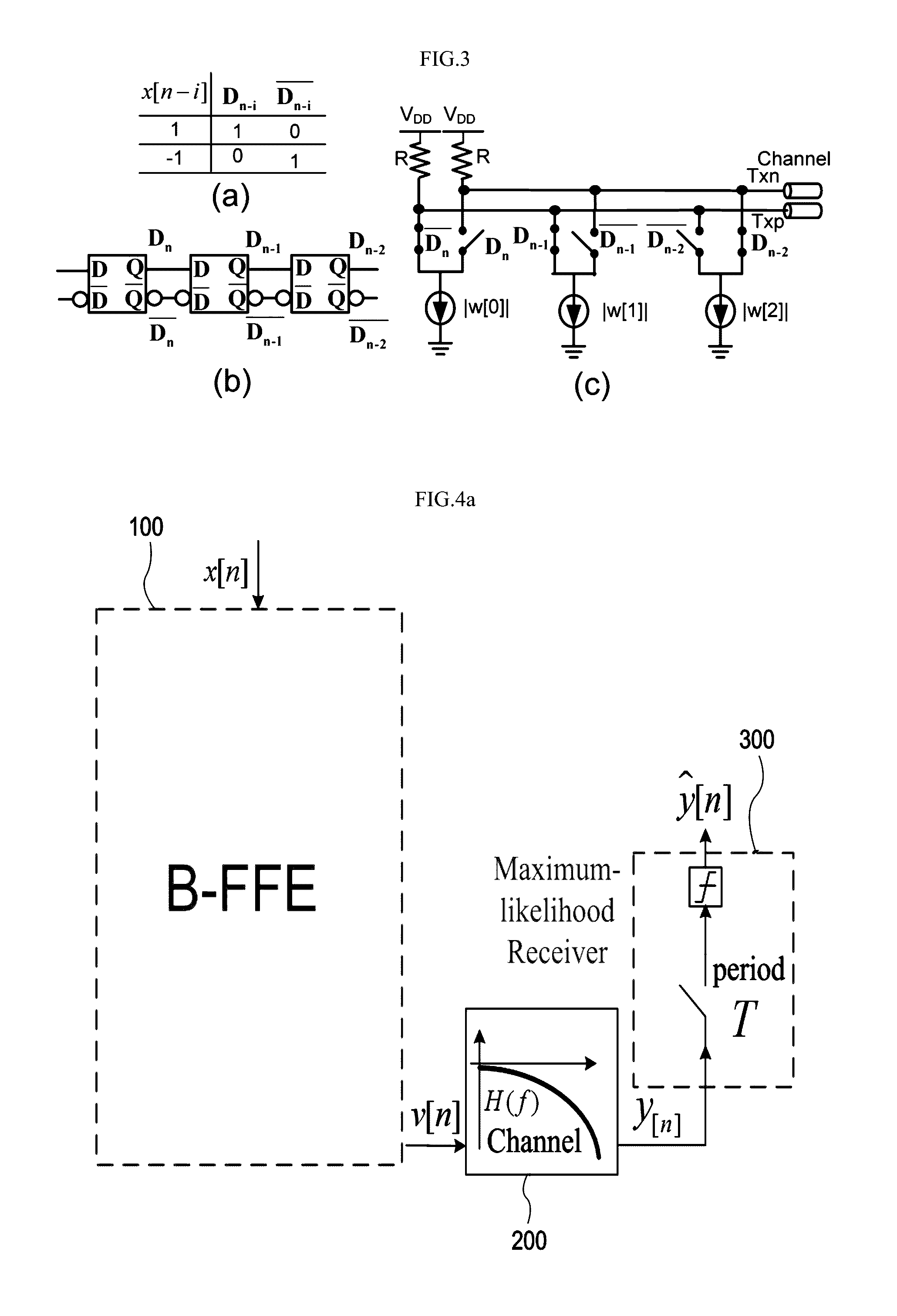

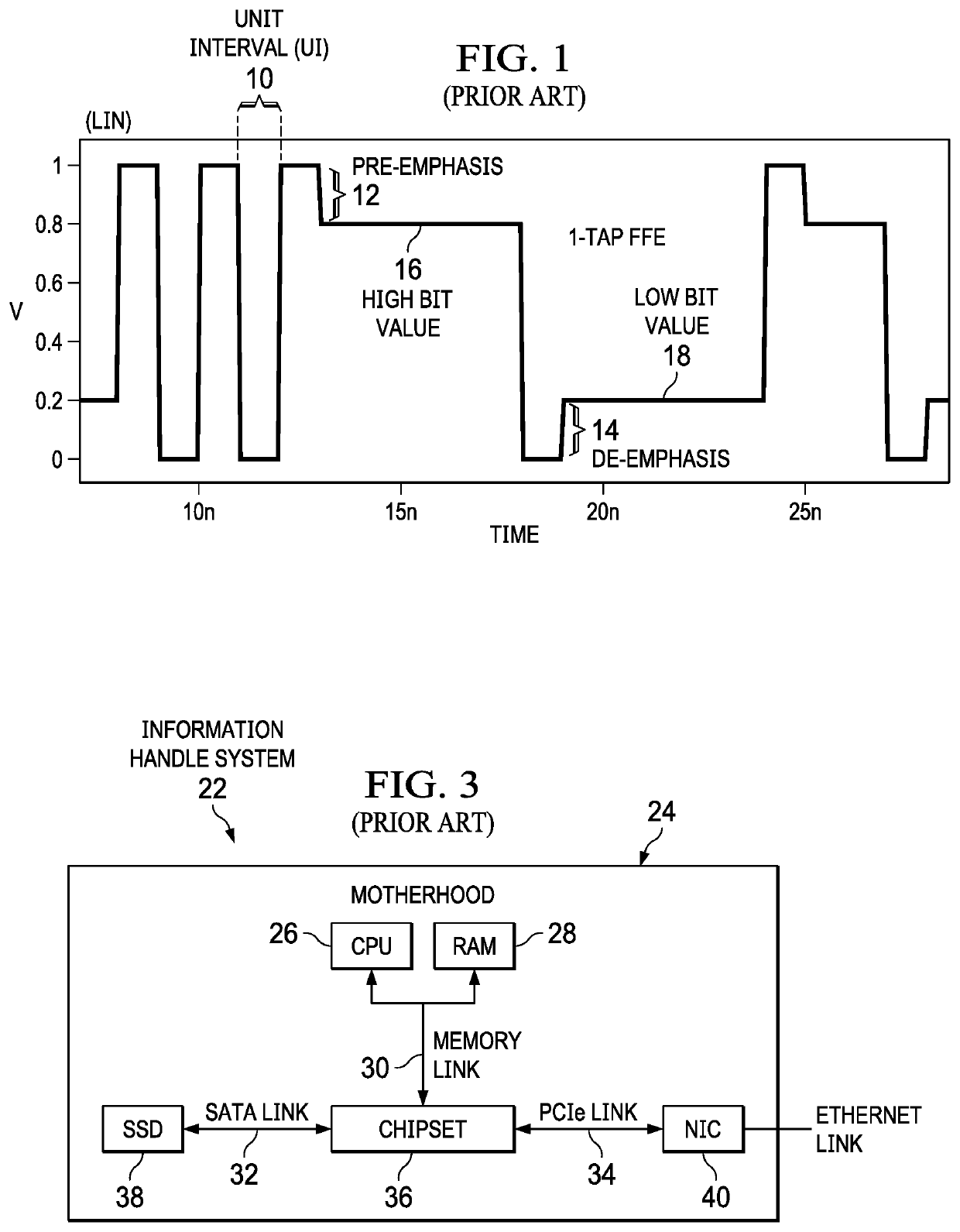

The simplest approach is Feed Forward Equalization (FFE). This employs a finite impulse response filter (FIR) with a series of tap weights programmed to adjust the impulse and, by duality, frequency response (See Figure 3). This is the simplest implementation and can be designed entirely in the analogue domain.

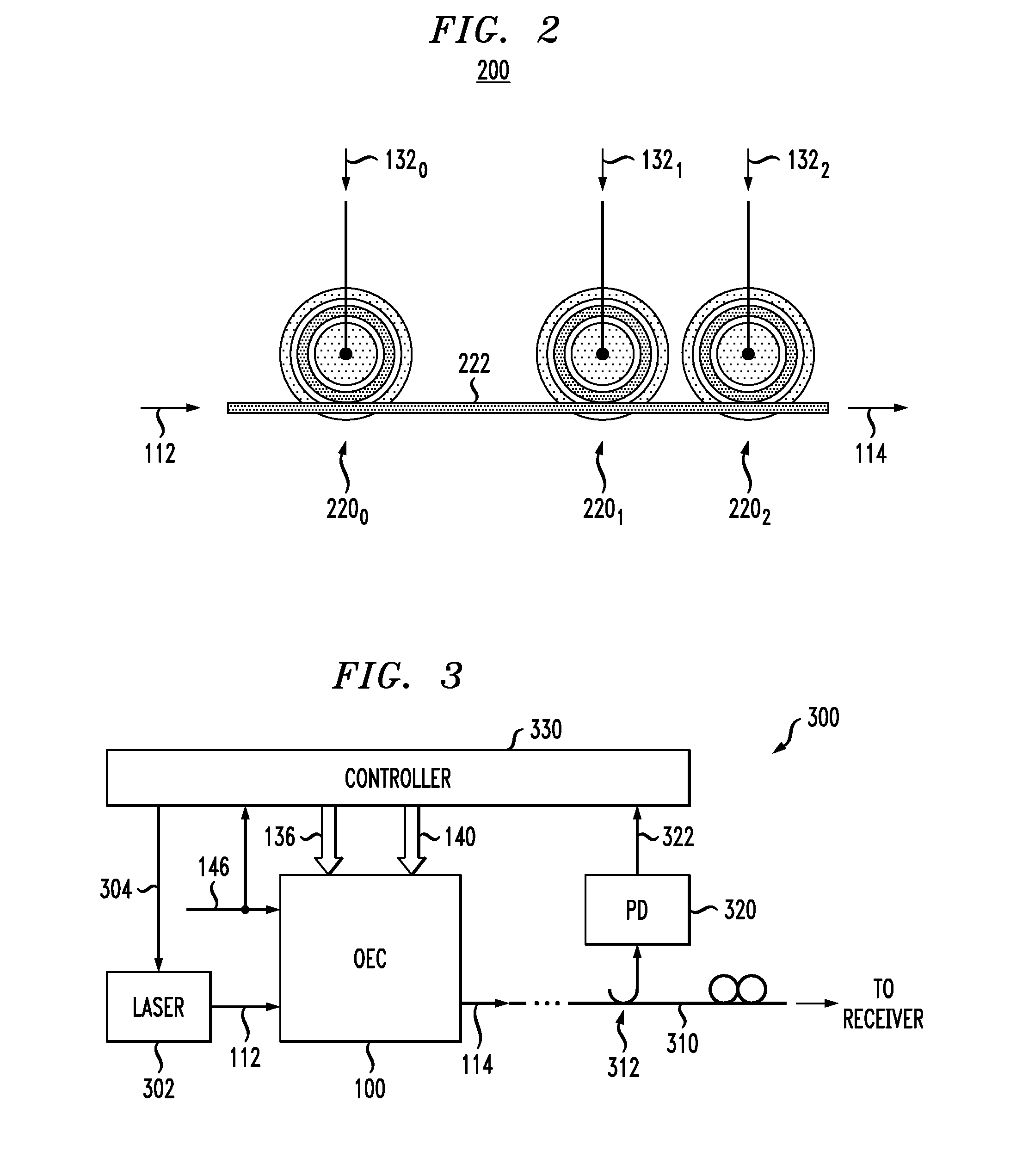

Filter structure for driving an optical modulator

InactiveUS20150295650A1Radio-over-fibreElectromagnetic receiversFinite impulse responseDriver circuit

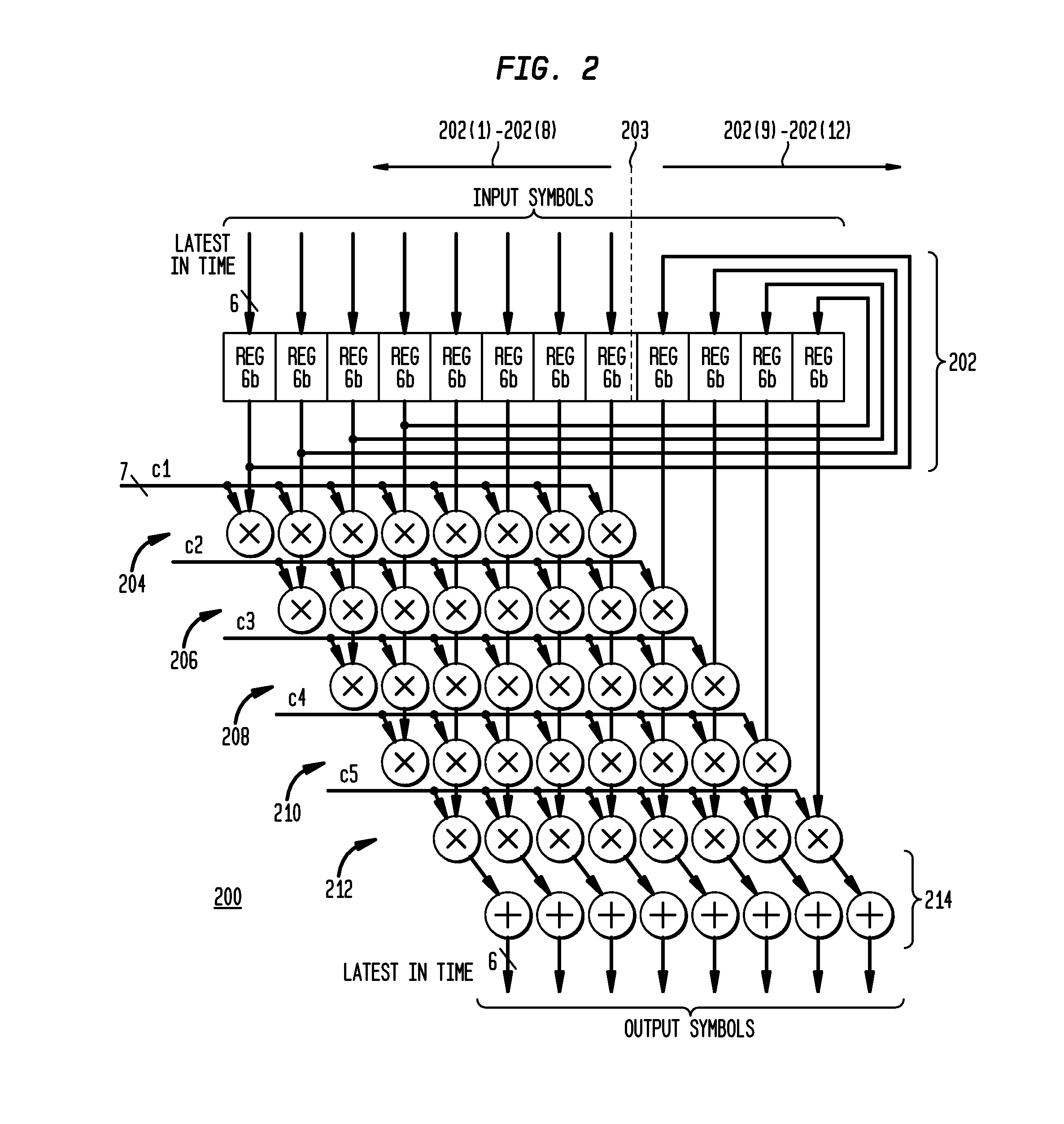

We disclose an opto-electronic circuit having an optical modulator and a driver circuit configured to generate a plurality of electrical drive signals for the optical modulator in a manner that causes the opto-electronic circuit to operate as a finite-impulse-response (FIR) filter. Different electrical drive signals generated by the driver circuit represent different taps of the FIR filter and are individually applied to different respective electrodes in the optical modulator without first being combined with one another prior to said individual application. The optical modulator represents an adder of the FIR filter and is configured to use the applied electrical drive signals to perform signal summation in the optical domain, thereby alleviating some of the limitations associated with the electrical RF circuitry used in the driver circuit. The opto-electronic circuit can be employed in optical transceivers and equalizers and be configured to implement signal pre-emphasis, feed-forward equalization, or decision-feedback equalization.

Owner:ALCATEL LUCENT SAS

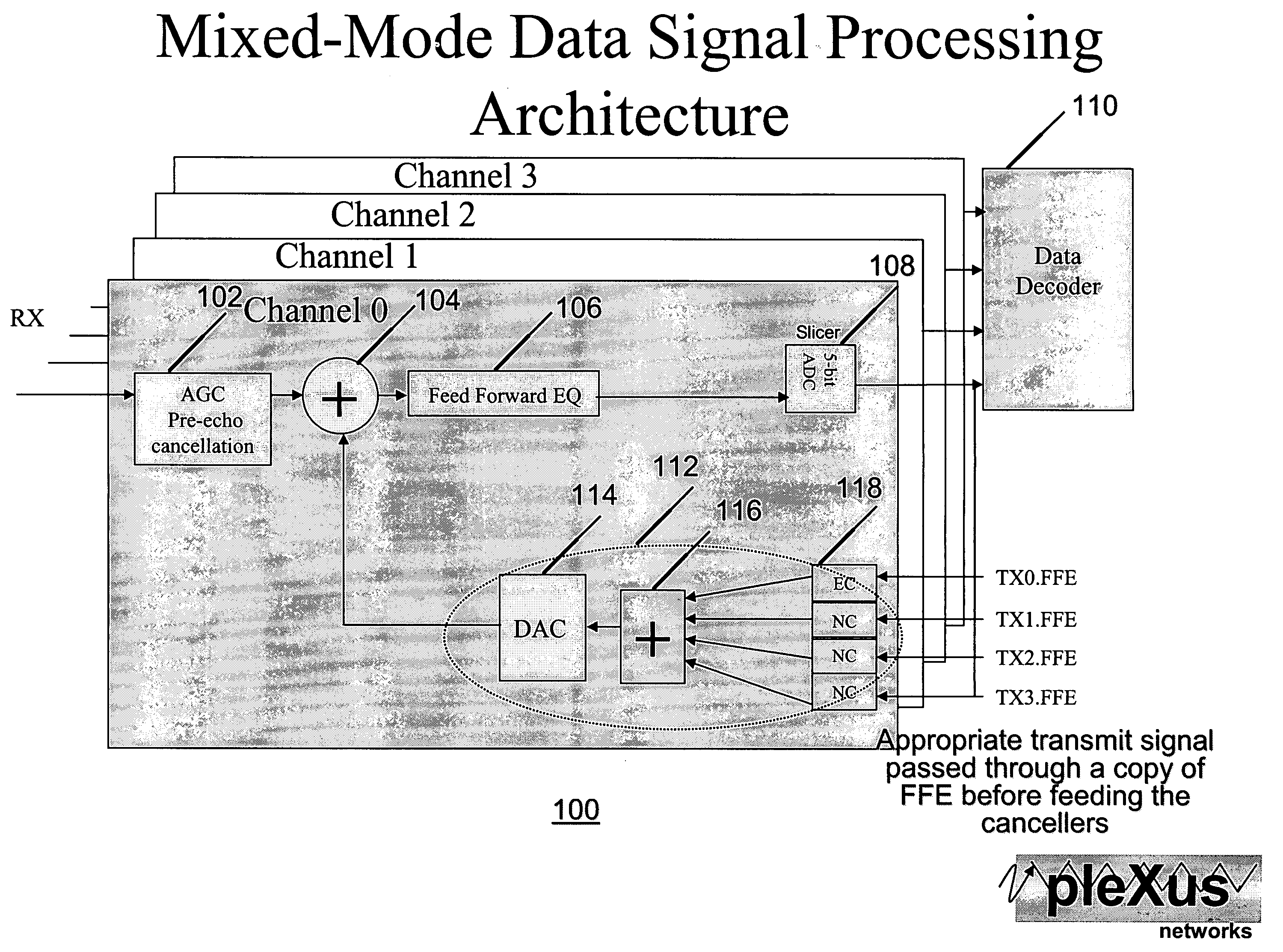

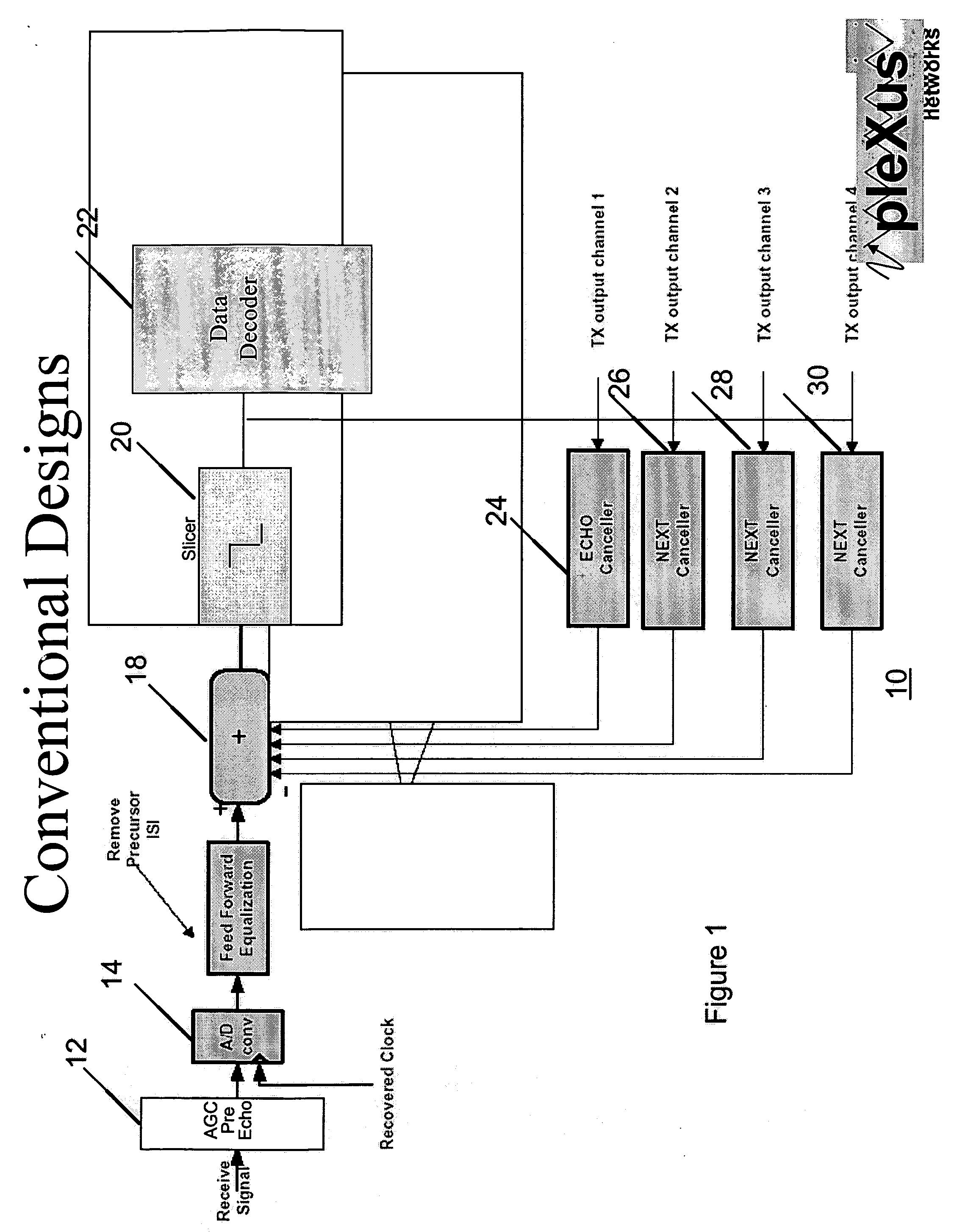

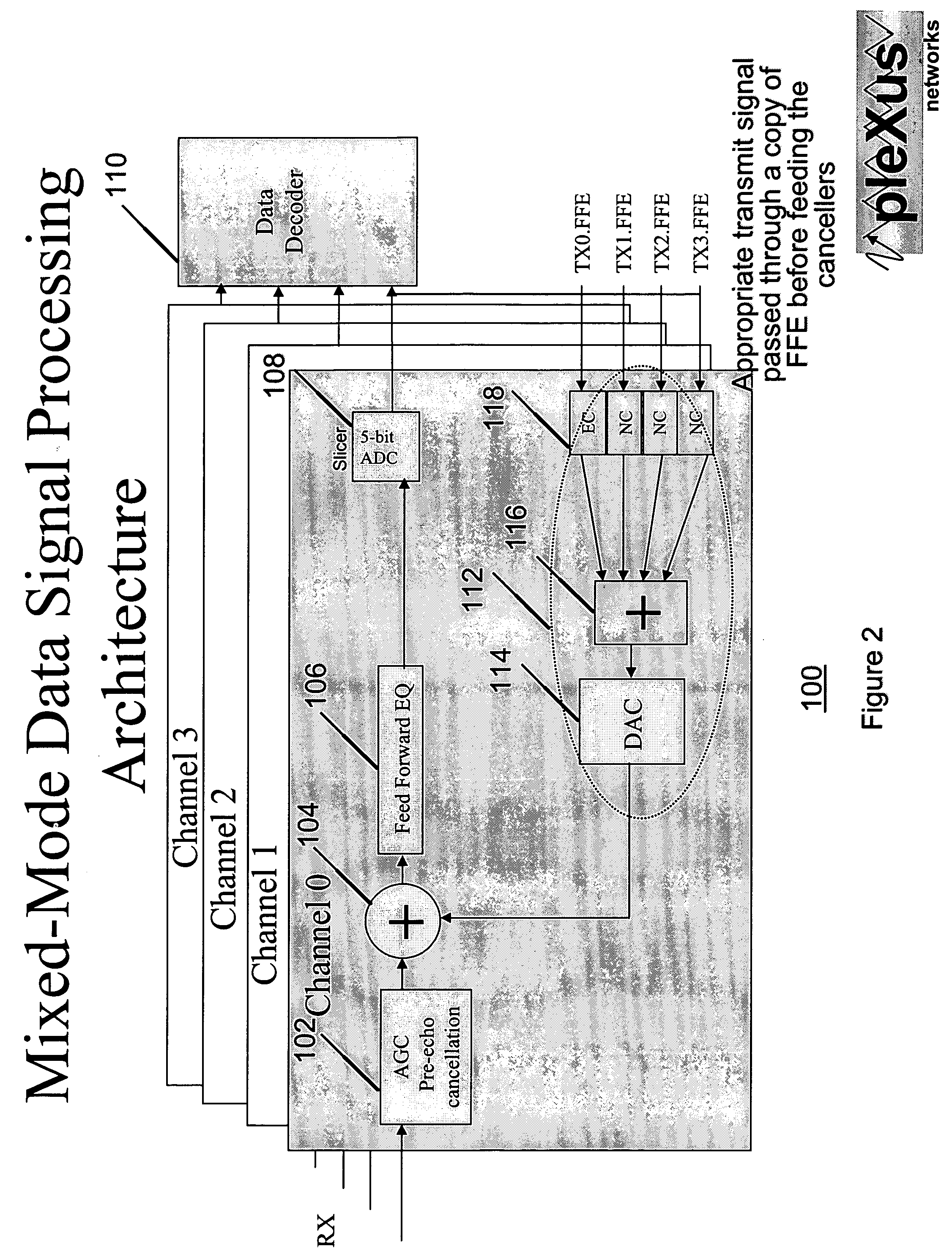

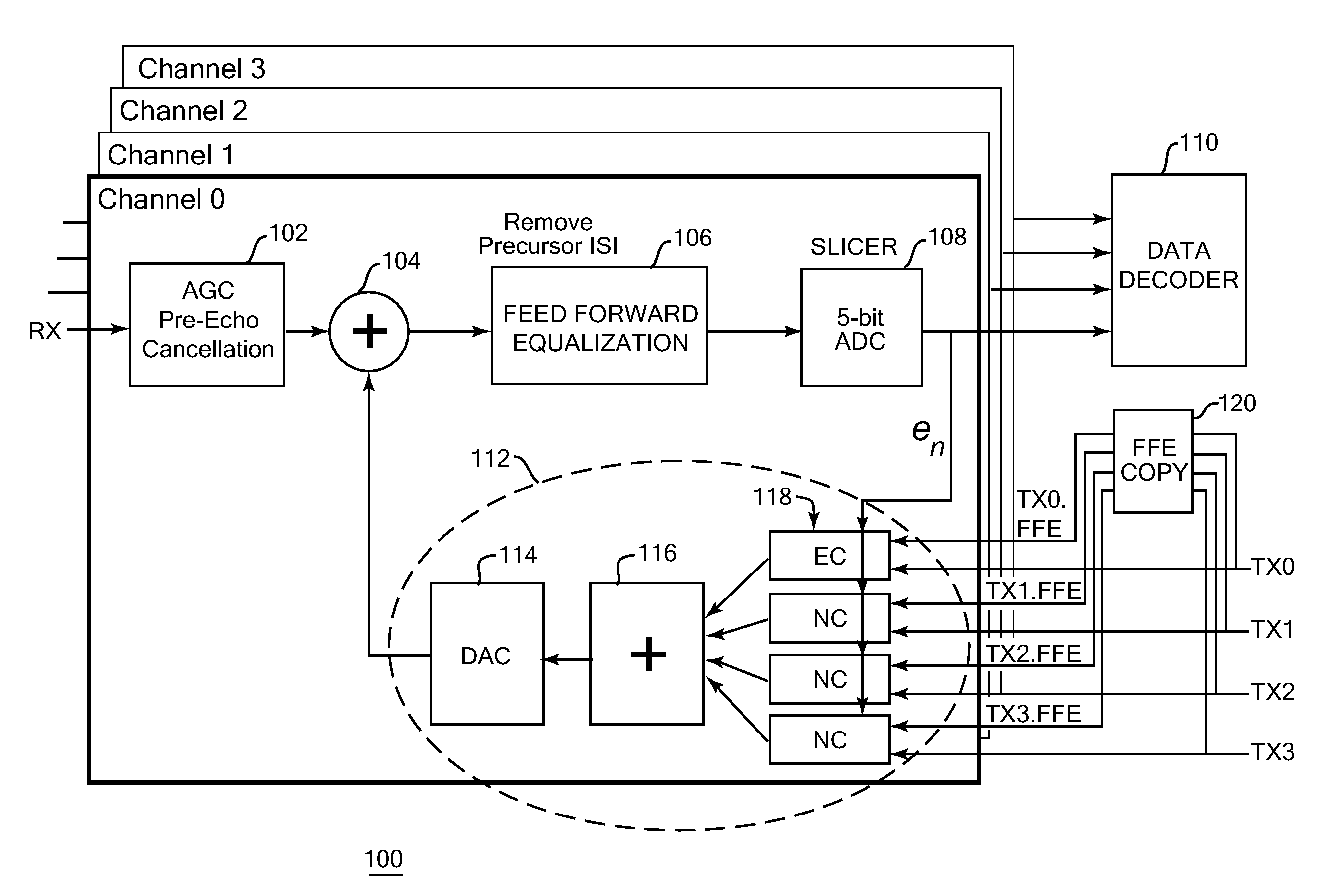

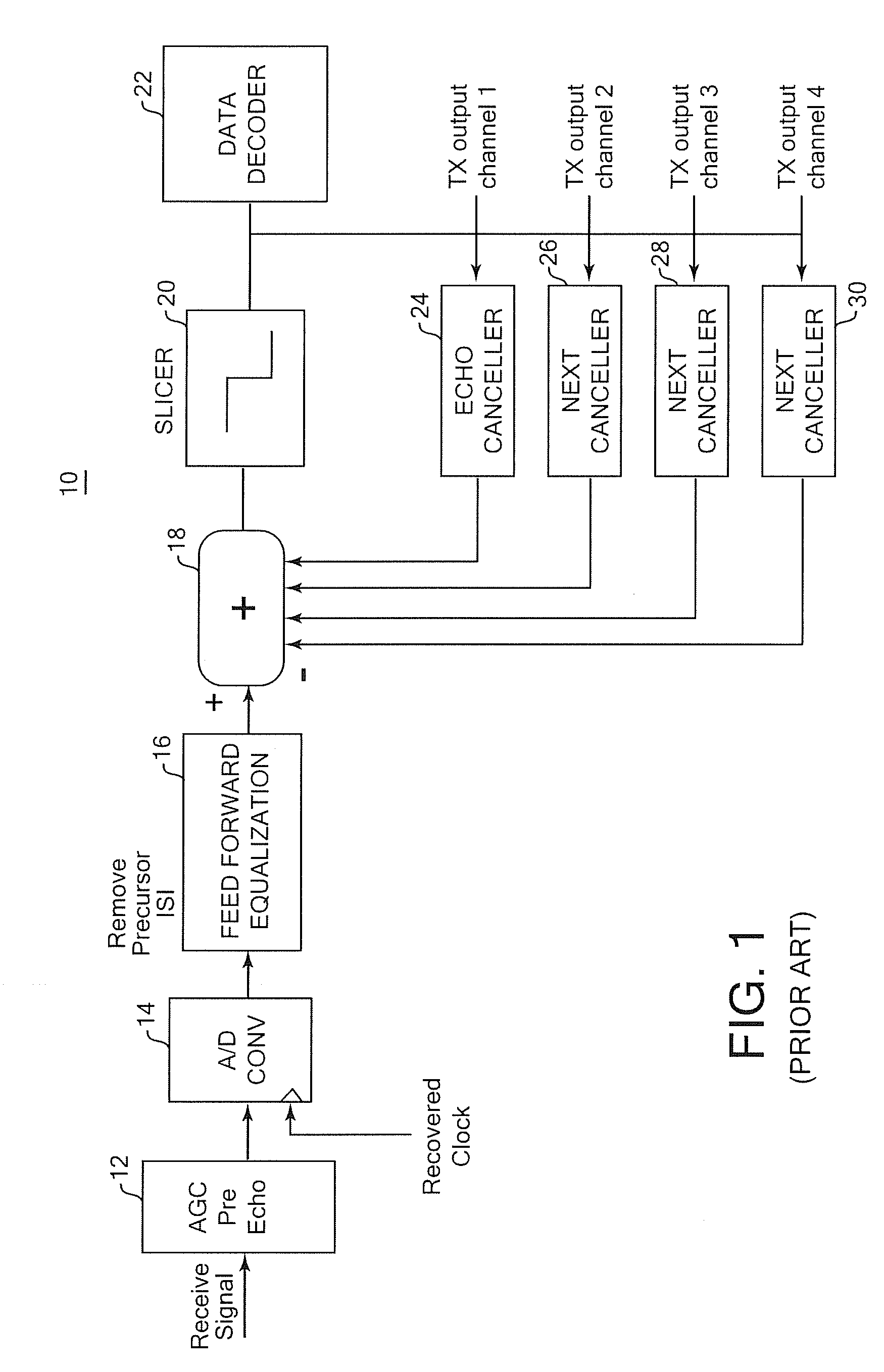

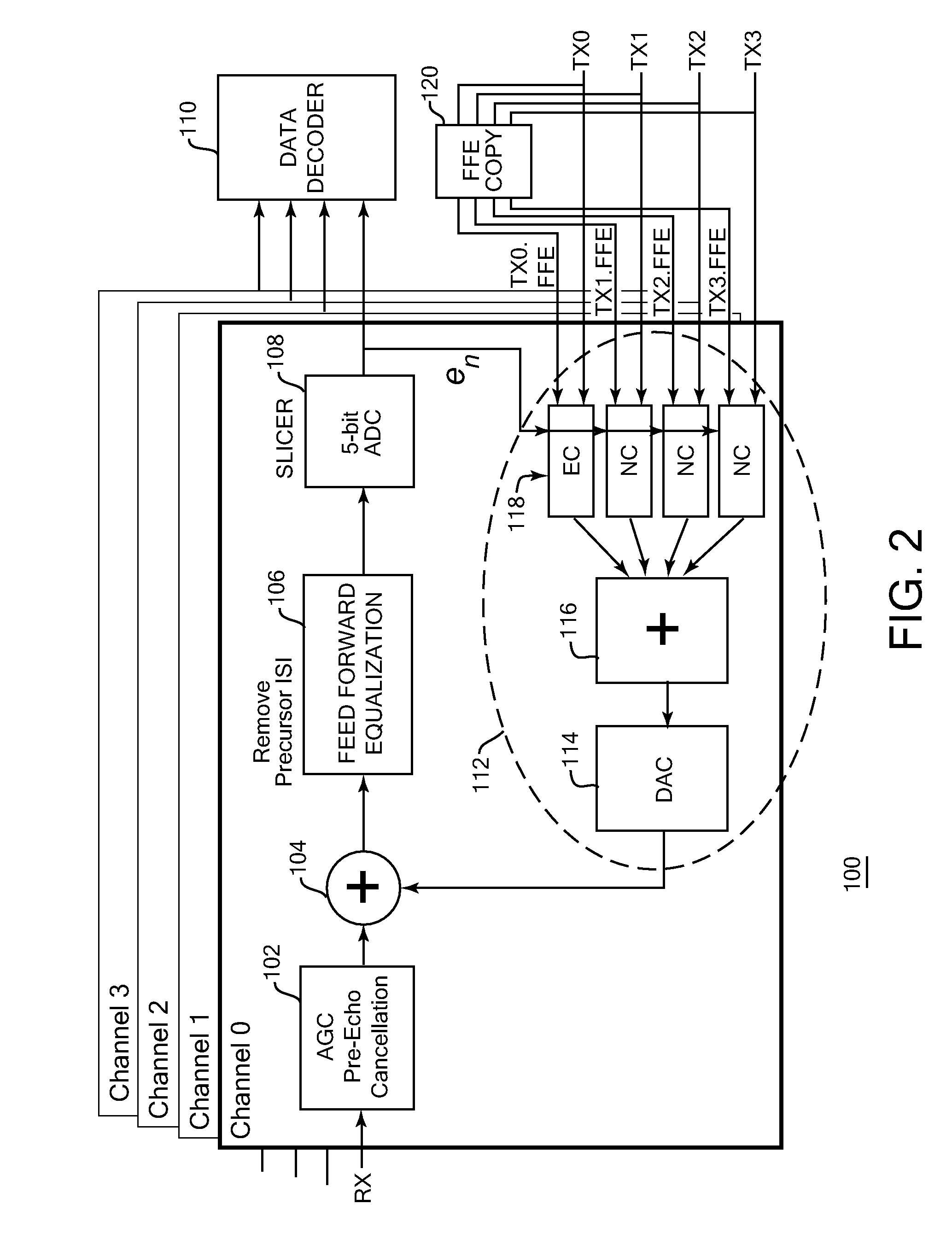

Low-power mixed-mode echo/crosstalk cancellation in wireline communications

ActiveUS20050123081A1Large dynamic rangeMore dynamic rangeMultiple-port networksSubstations coupling interface circuitsCMOSCrosstalk cancellation

A signal processing system is disclosed. The signal processing system comprises an AGC and pre-echo cancellation system for receiving an analog signal, boosting it up (over all frequencies) to a pre-determined range by AGC, and removing the immediate transmit pulse from this received signal by pre-echo canceller to provide a second analog signal. The signal processing system further comprises a summer for receiving the analog signal; a feed forward equalization (FFE) unit for receiving a signal from the summer; and a slicer for receiving a signal from the FFE unit and providing an output signal. The signal processing system also comprises an Echo and NEXT cancellation system for receiving the output signal and for providing a signal to the summer for canceling the echo and crosstalk in the signal processing system. Accordingly, in a system and method in accordance with the present invention the Echo and crosstalk components associated with a signal processing system can be subtracted prior to the FFE. This allows for a practical analog implementation which has a good dynamic range of the signal through the FFE and subsequent analog elements. This system can be utilized to great advantage in low power CMOS designs where supply voltages are limited.

Owner:MARVELL ASIA PTE LTD

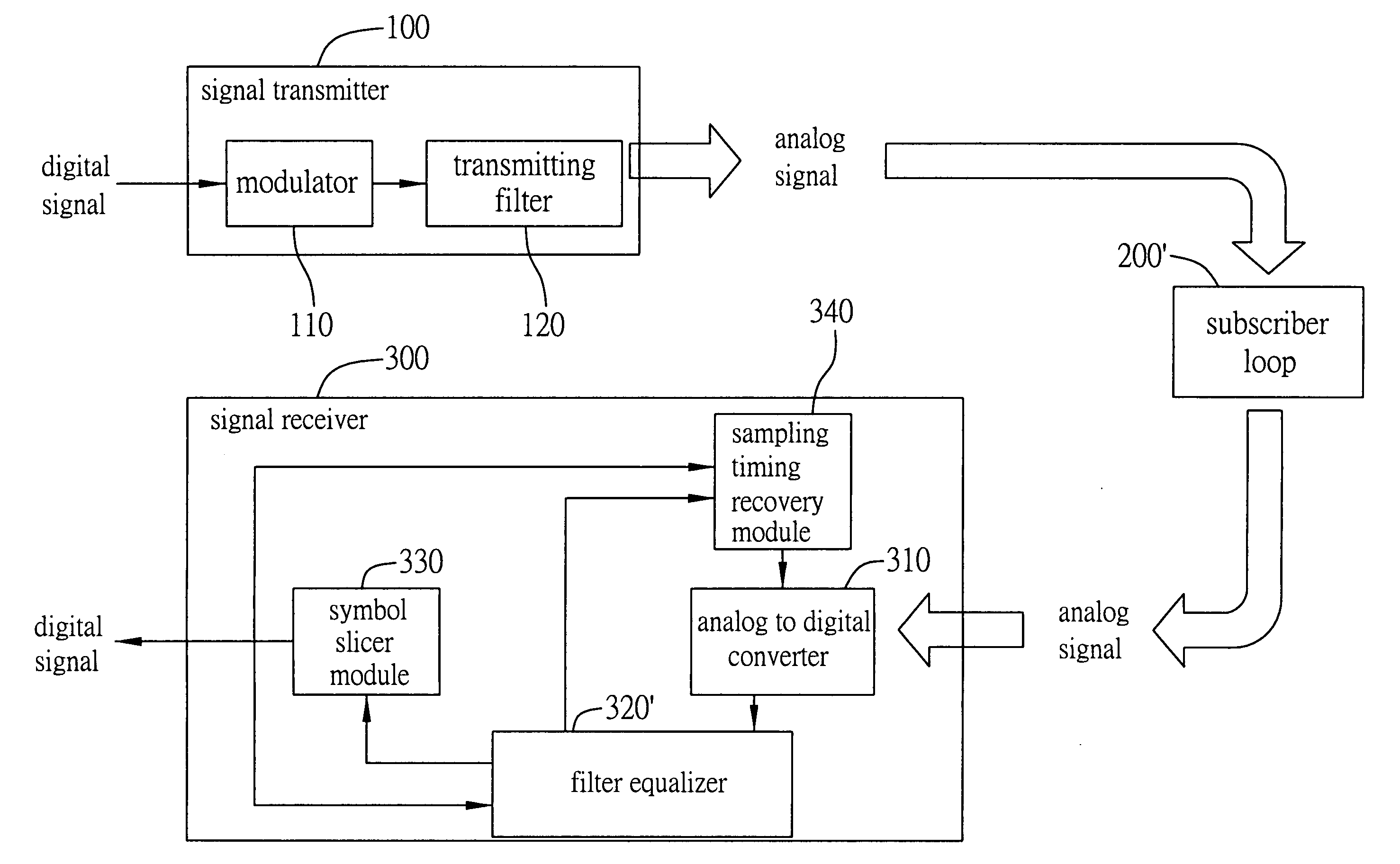

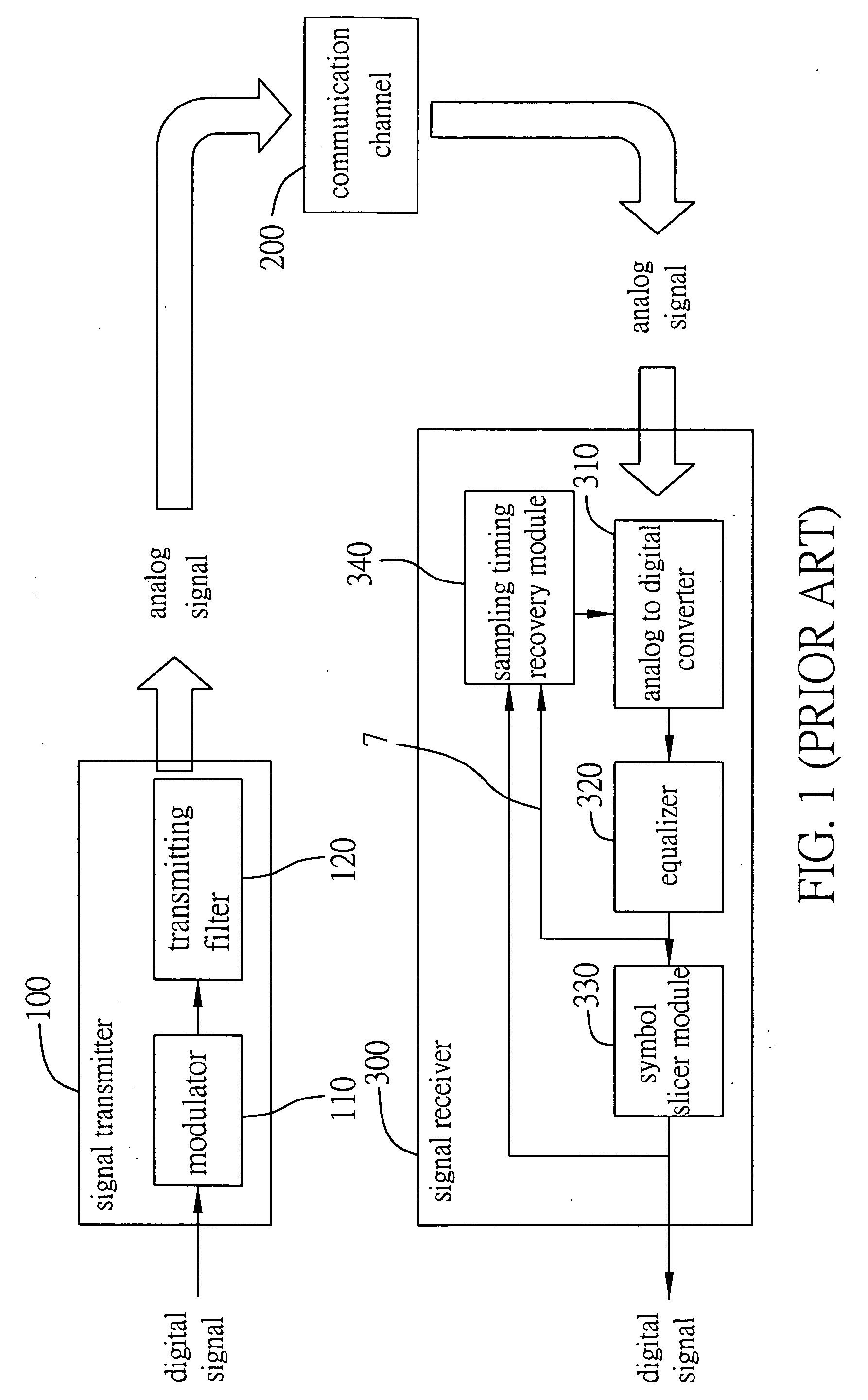

Timing recovery method and device for combining pre-filtering and feed-forward equalizing functions

InactiveUS20050249275A1Multiple-port networksDelay line applicationsRecovery methodCommunications system

Timing recovery method and device for combining pre-filtering and feed-forward equalizer functions are proposed and used in a digital communication system. A signal receiver is provided to receive a signal transmitted from a signal transmitter in the communication system, and recovers a sampling clock phase of the received signal to the phase of the signal transmitted from the signal transmitter. The method is used to control the signal receiver to transform the received signal to a signal similar to a Nyquist pulse after the pre-filtering and feed-forward equalizing operations are performed on the received signal, thereby improving the performance of the following sampling timing recovery process and increasing the signal noise ratio (SNR) of the received signal.

Owner:RDC SEMICON CO LTD

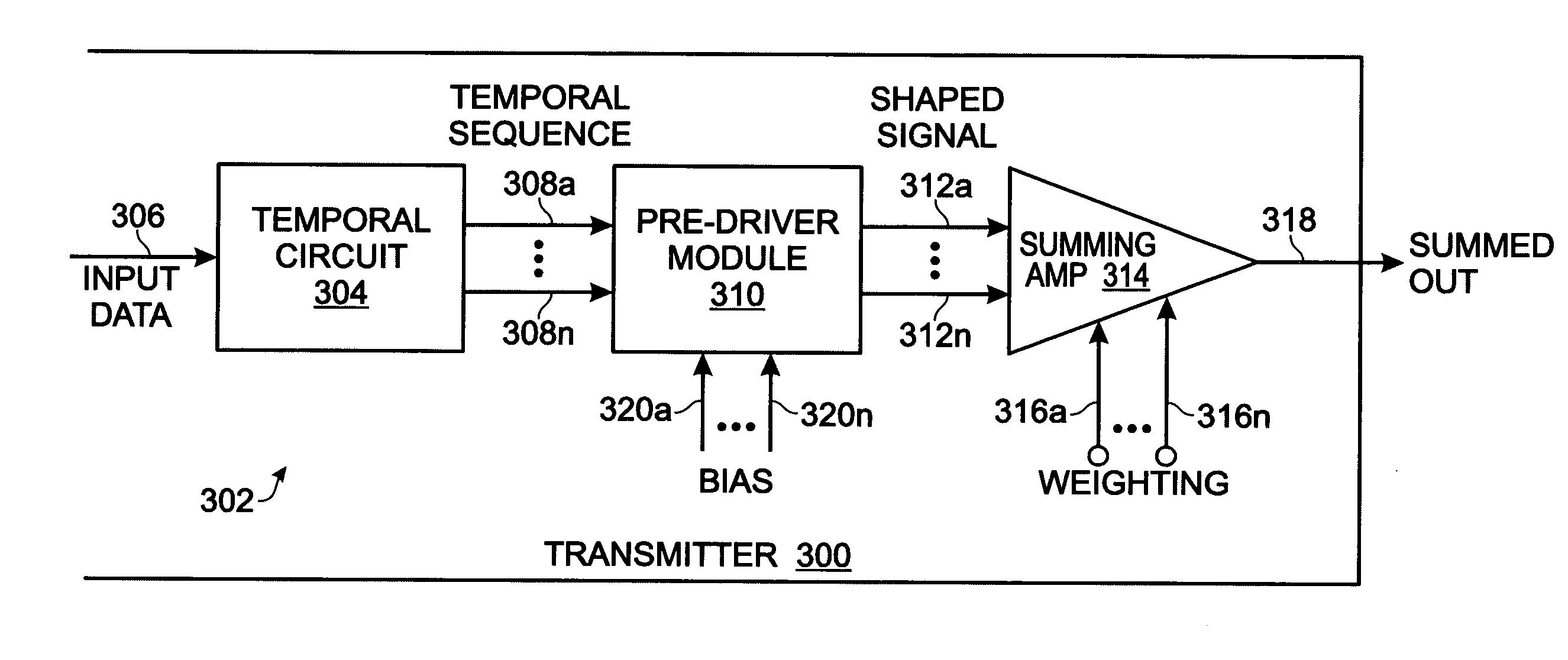

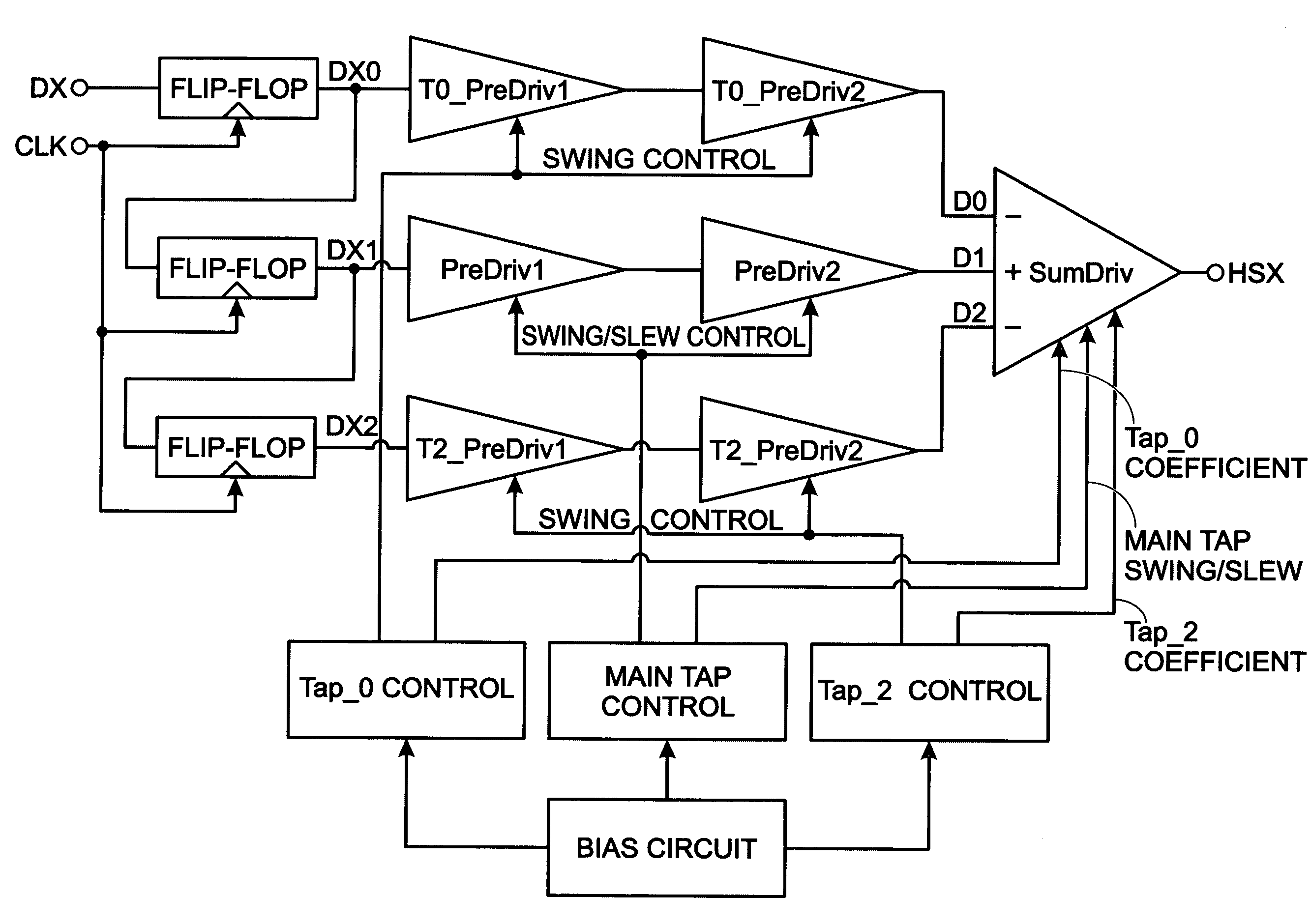

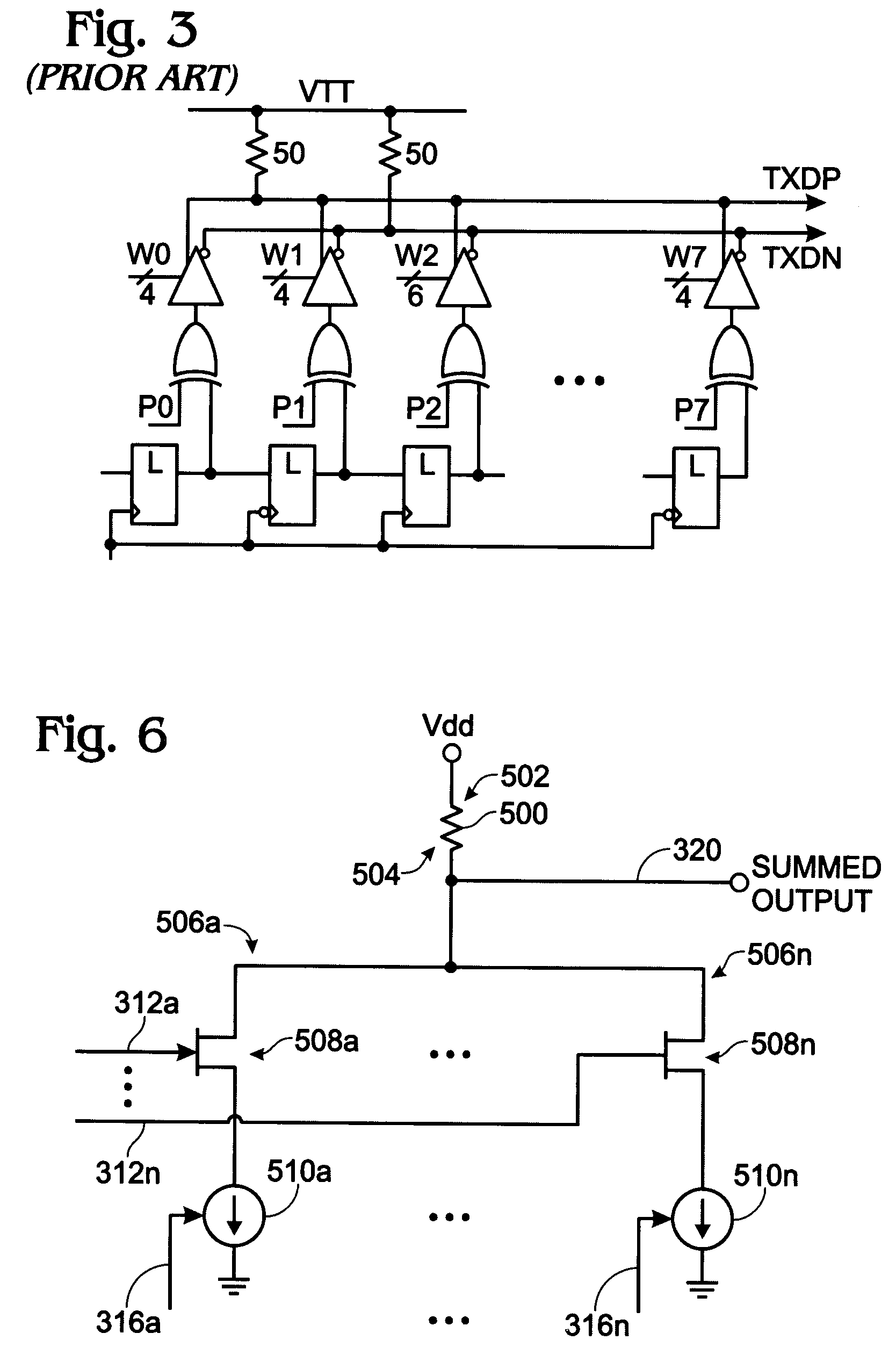

Current mode logic multi-tap feed-forward equalizer

ActiveUS20080247453A1Multiple-port networksModulated-carrier systemsTime delaysFeed forward equalization

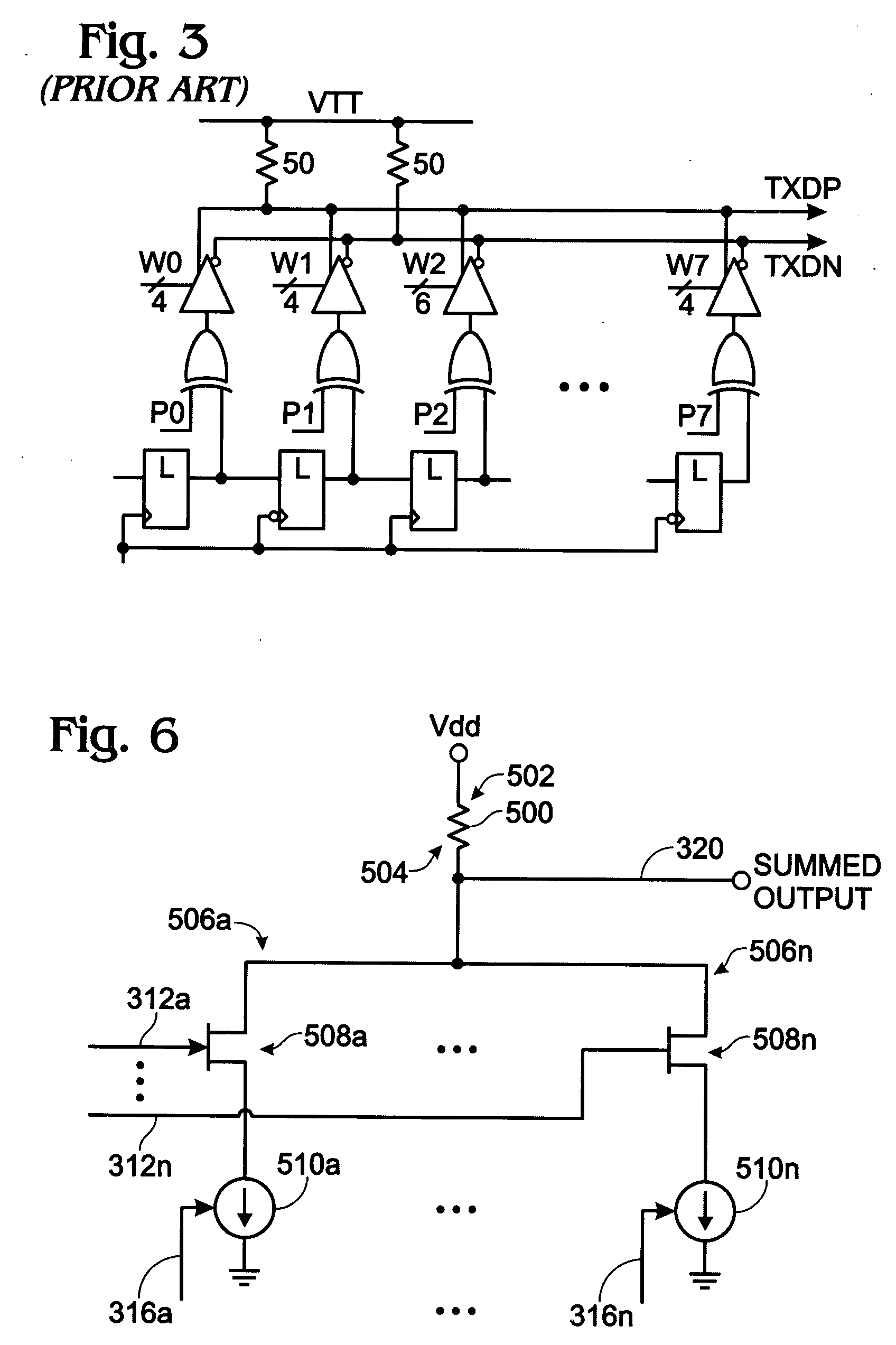

A system and method are provided for feed-forward equalization (FFE) in a transmission system. The method accepts a serial stream of input digital data signals. For each input data signal, a temporal sequence of signals is generated. Each of the signals in the temporal sequence is selectively shaped. Shaping map include varying the degree of amplification, modifying the slew rate, or varying the time delay. The contributions of the selectively shaped signals in the temporal sequence are then selectively weighted, and a summed output signal is transmitted.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

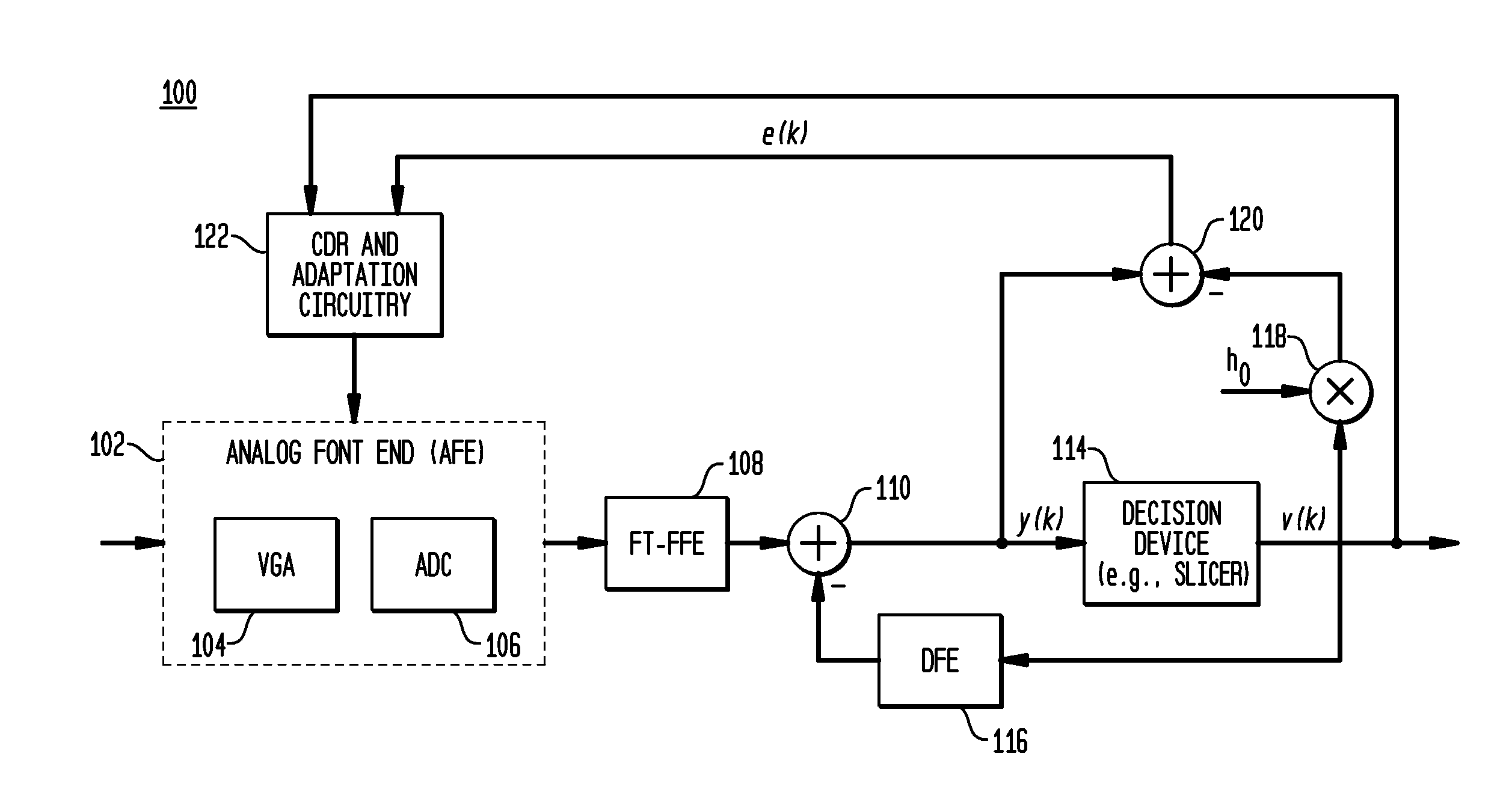

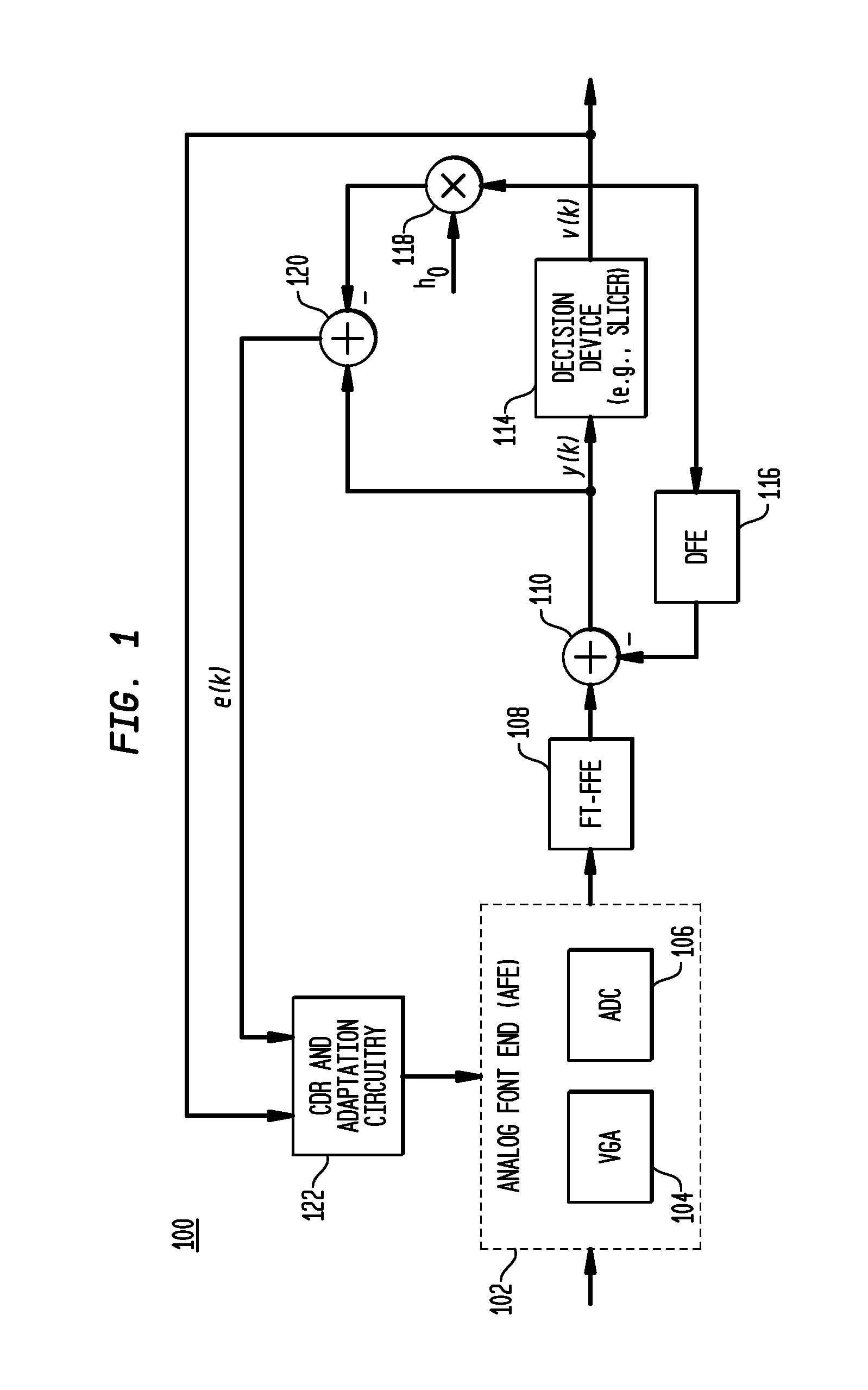

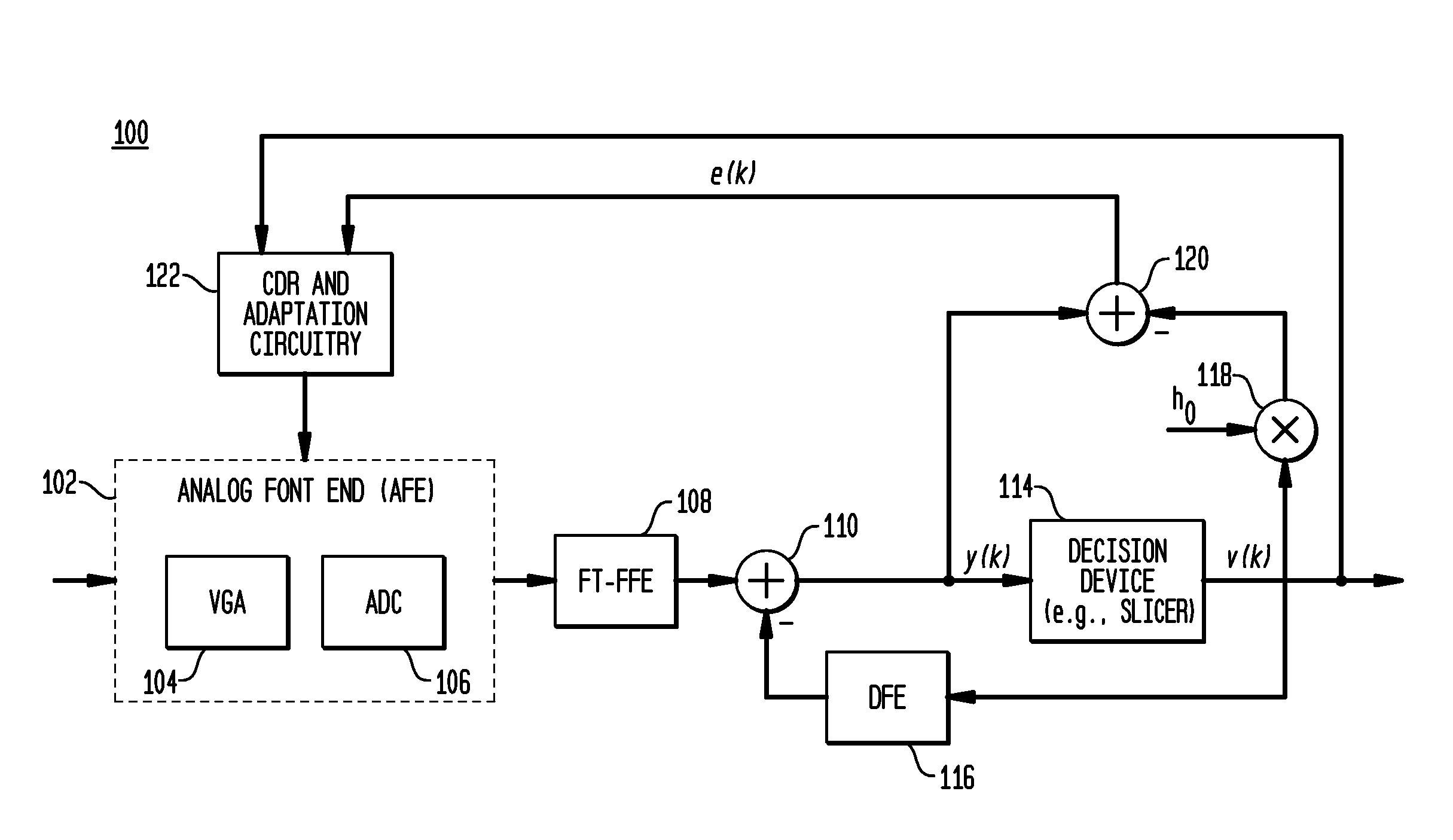

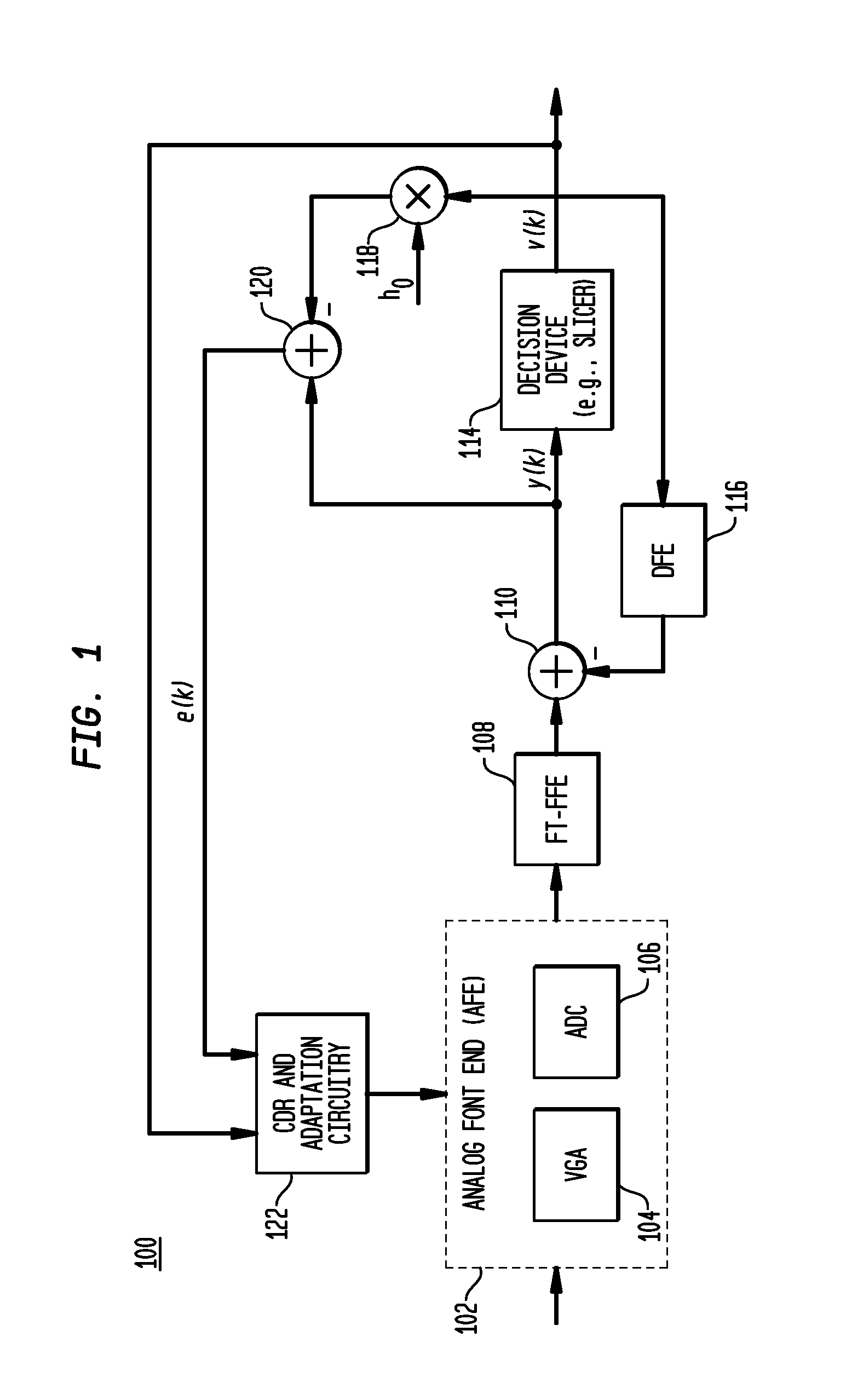

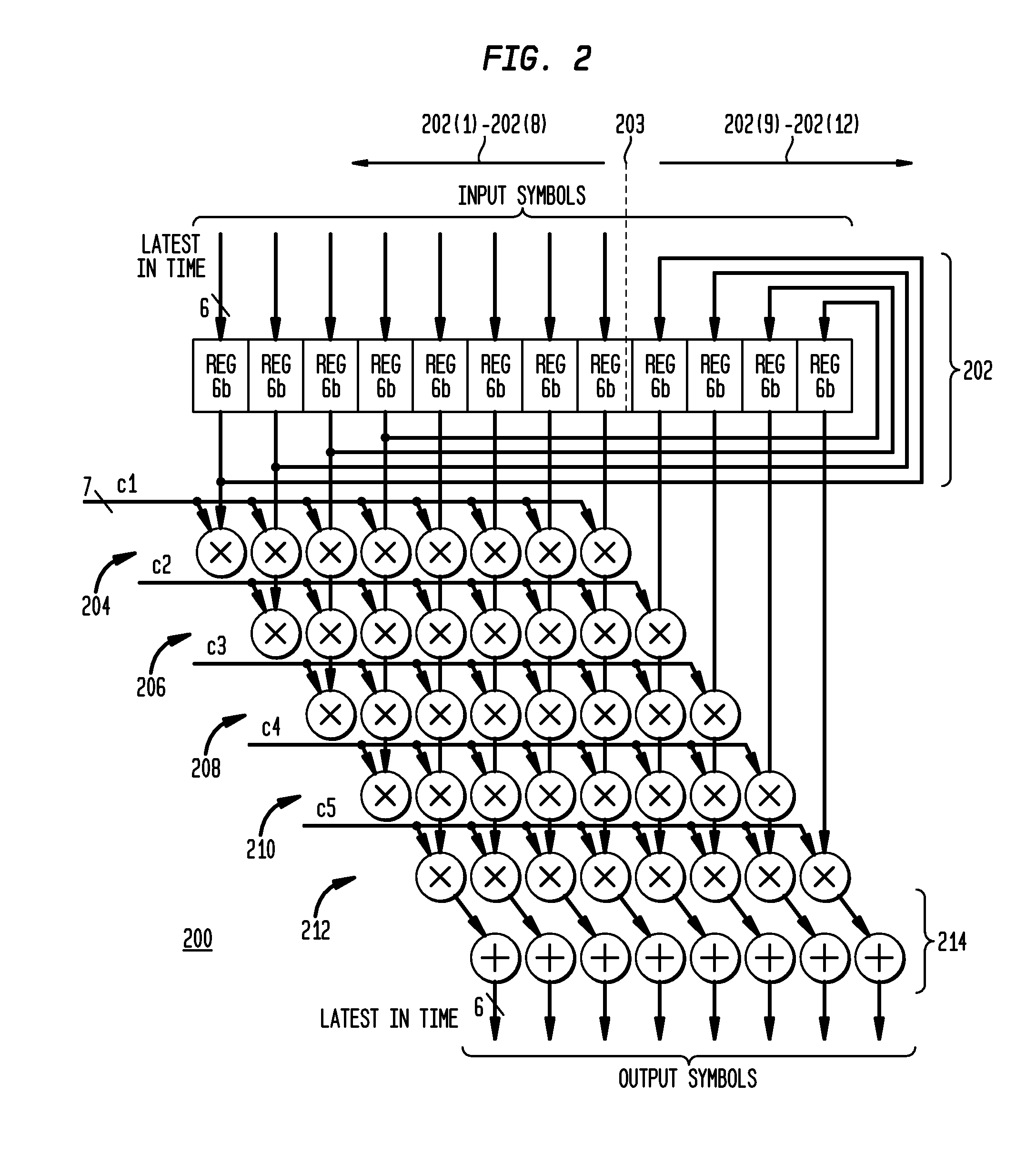

Sparse and reconfigurable floating tap feed forward equalization

In described embodiments, a Floating Tap, Feed Forward Equalizer (FT-FFE) achieves performance comparable to a full size, long FFE when equalizing wire line channels in, for example, SerDes receivers. A FT-FFE might be employed as a standalone datapath equalizer, or might be employed in conjunction with other equalization techniques.

Owner:AVAGO TECH INT SALES PTE LTD

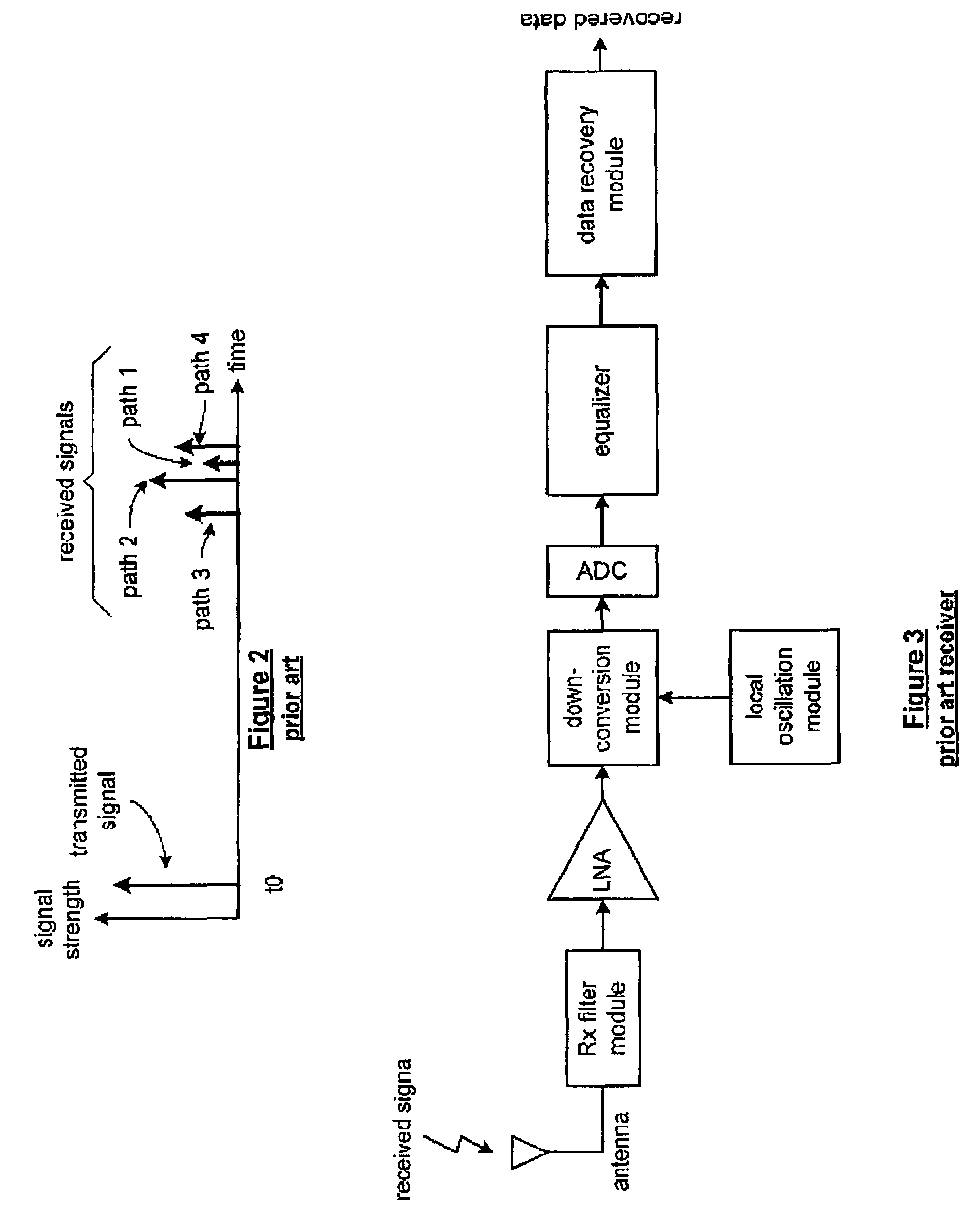

Receiver for high rate digital communication system

InactiveUS7161980B2Without impairing the received signal's energyMultiple-port networksAdaptive networkHigh rateCommunications system

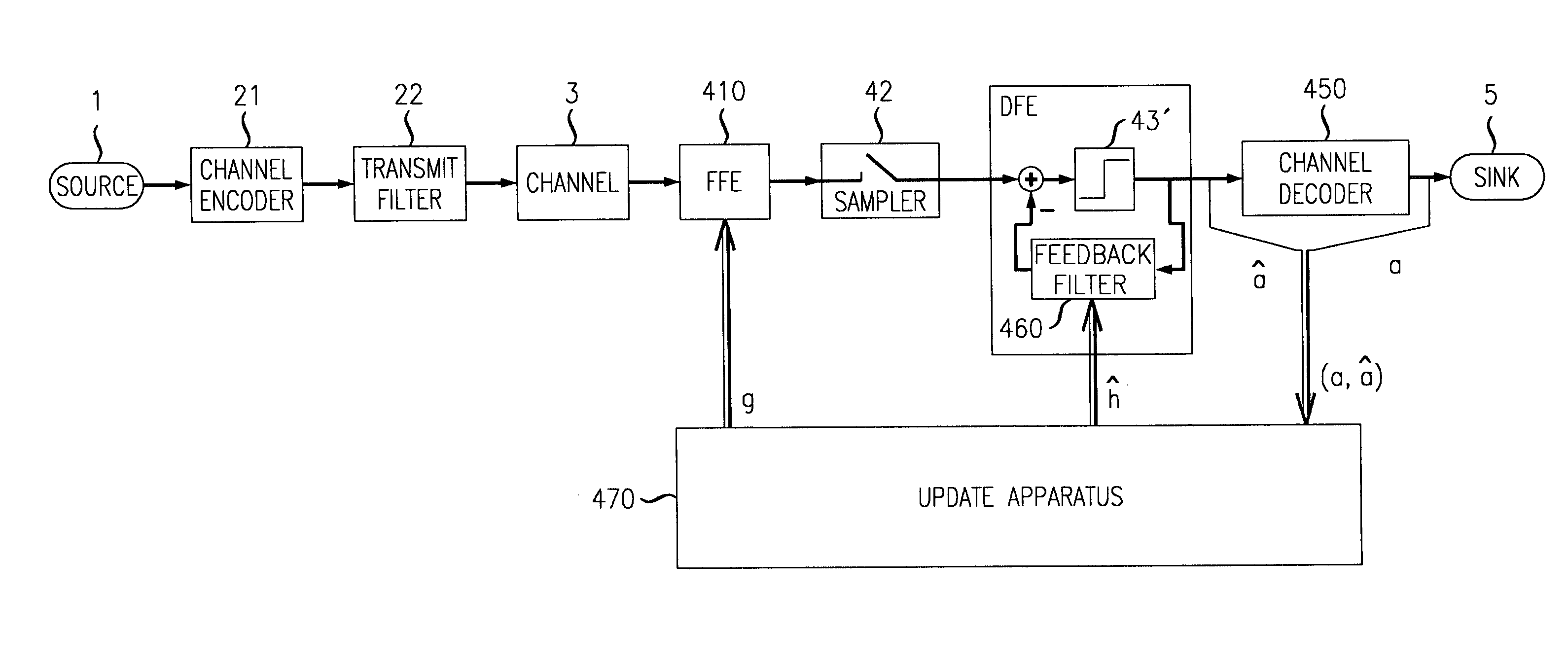

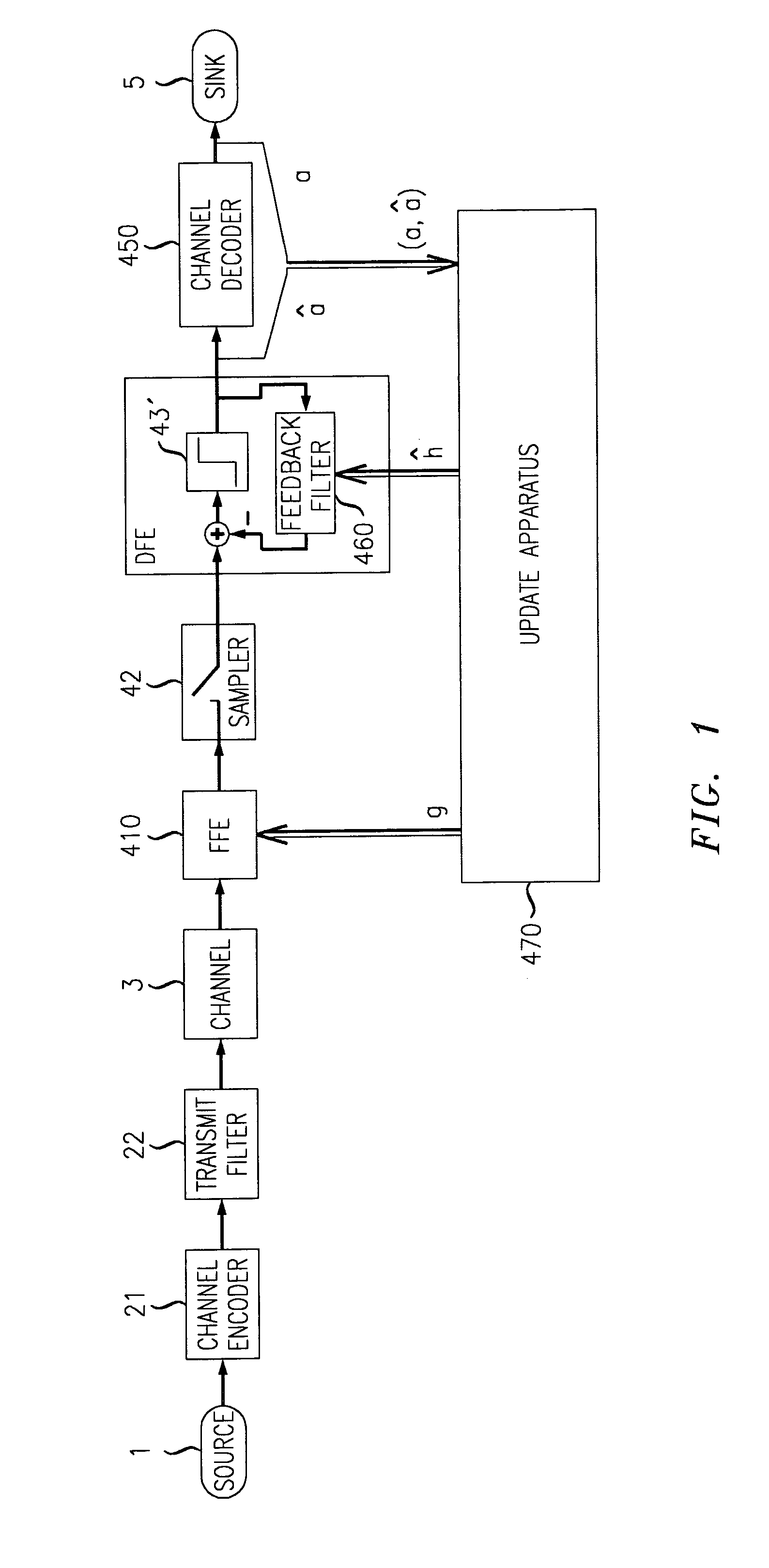

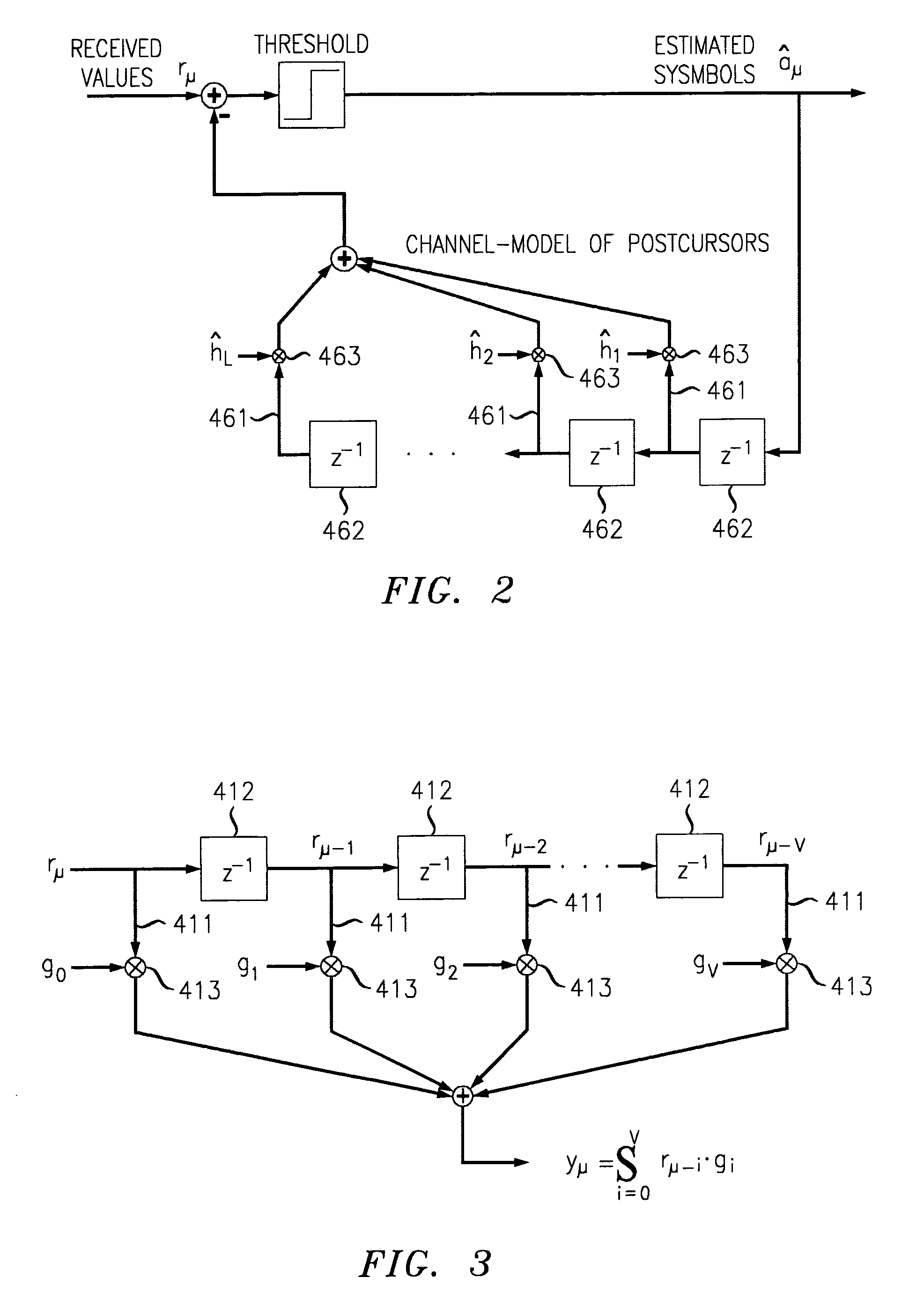

A system and method for processing received transmission signal(s) adapted to be used in high rate communication systems without impairing the received signal energy and without additional expensive components. The system and method are adapted to transmission system(s) having at the receiver-side a compound system of a feed-forward equalizer (FFE) and a subsequent decision feedback equalizer (DFE). A feed forward equalization and / or a decision feedback equalization is performed on the received high rate signal by deriving adaptation information from the equalized signal after a signal decision is performed for adjusting all intended feed forward equalization and / or decision feedback equalization coefficients and / or table entries in dependence on said information.

Owner:LUCENT TECH INC +1

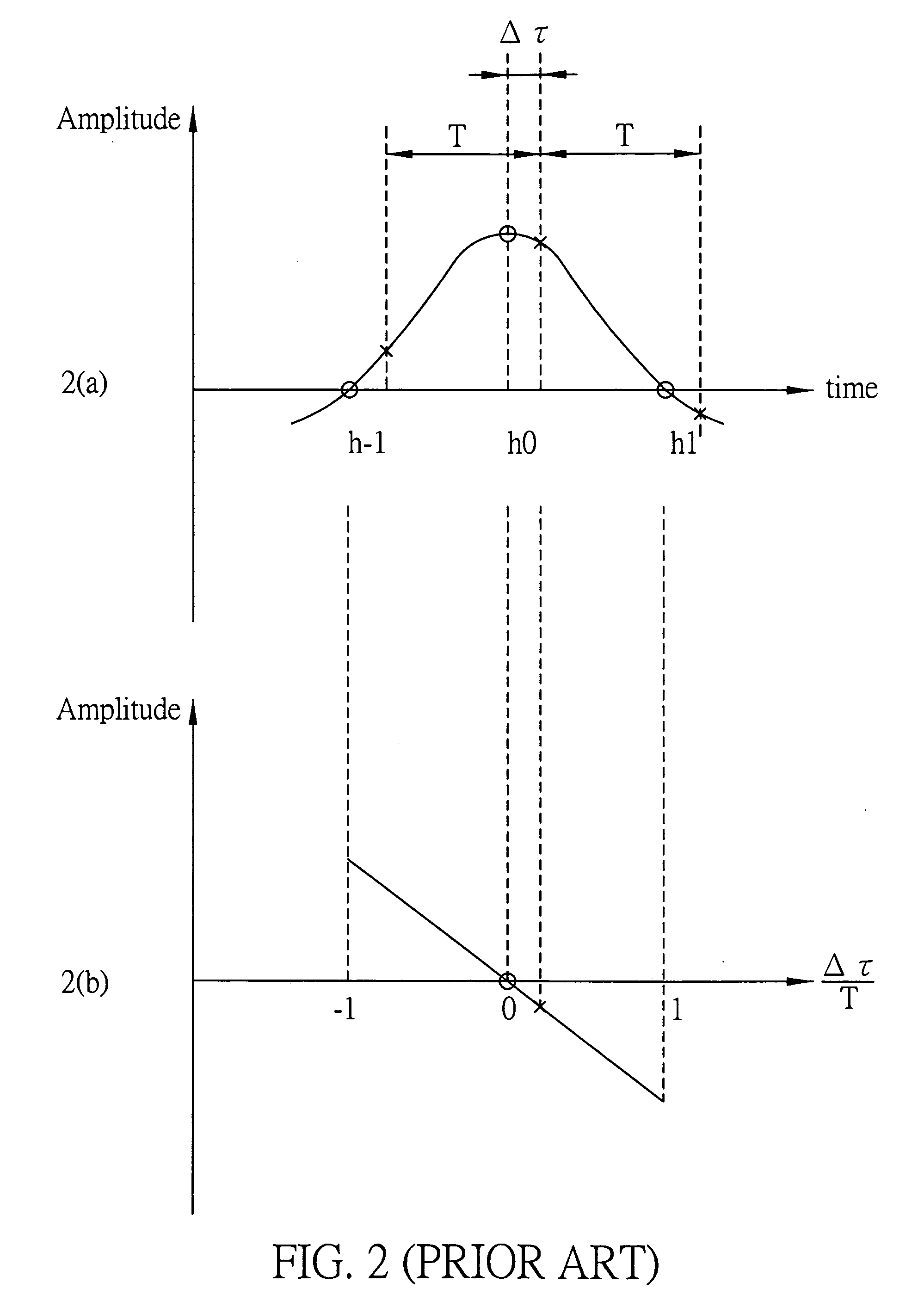

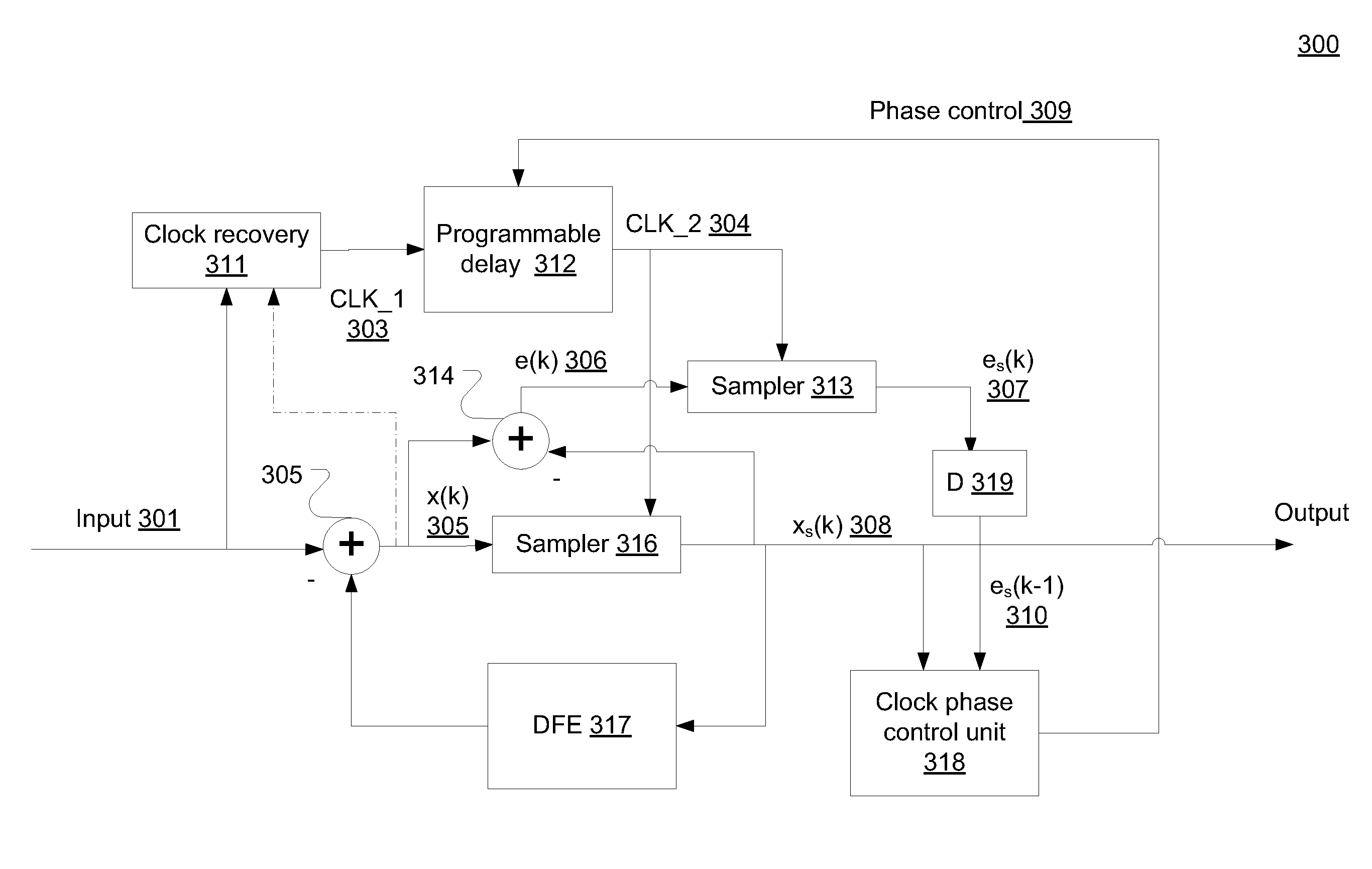

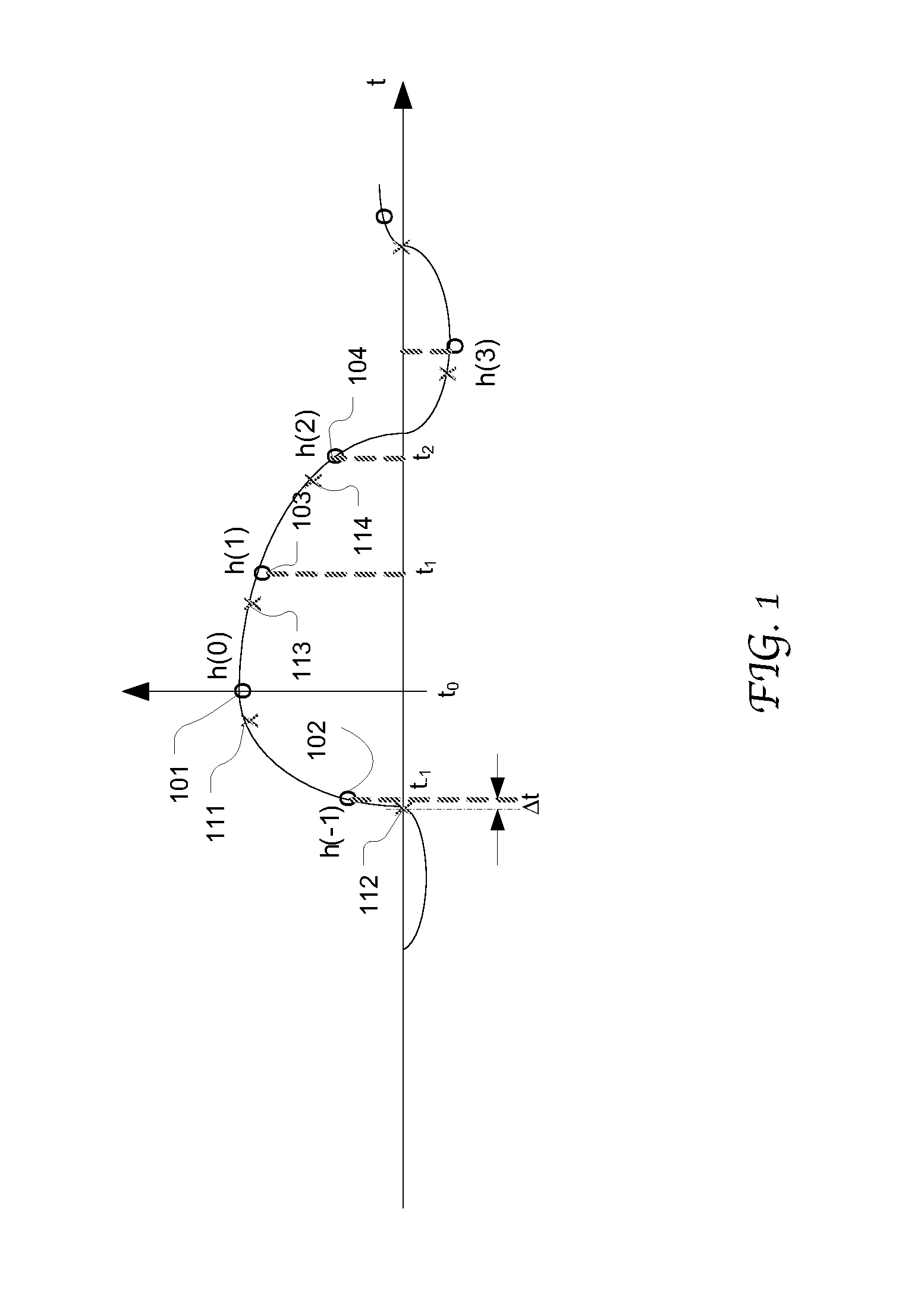

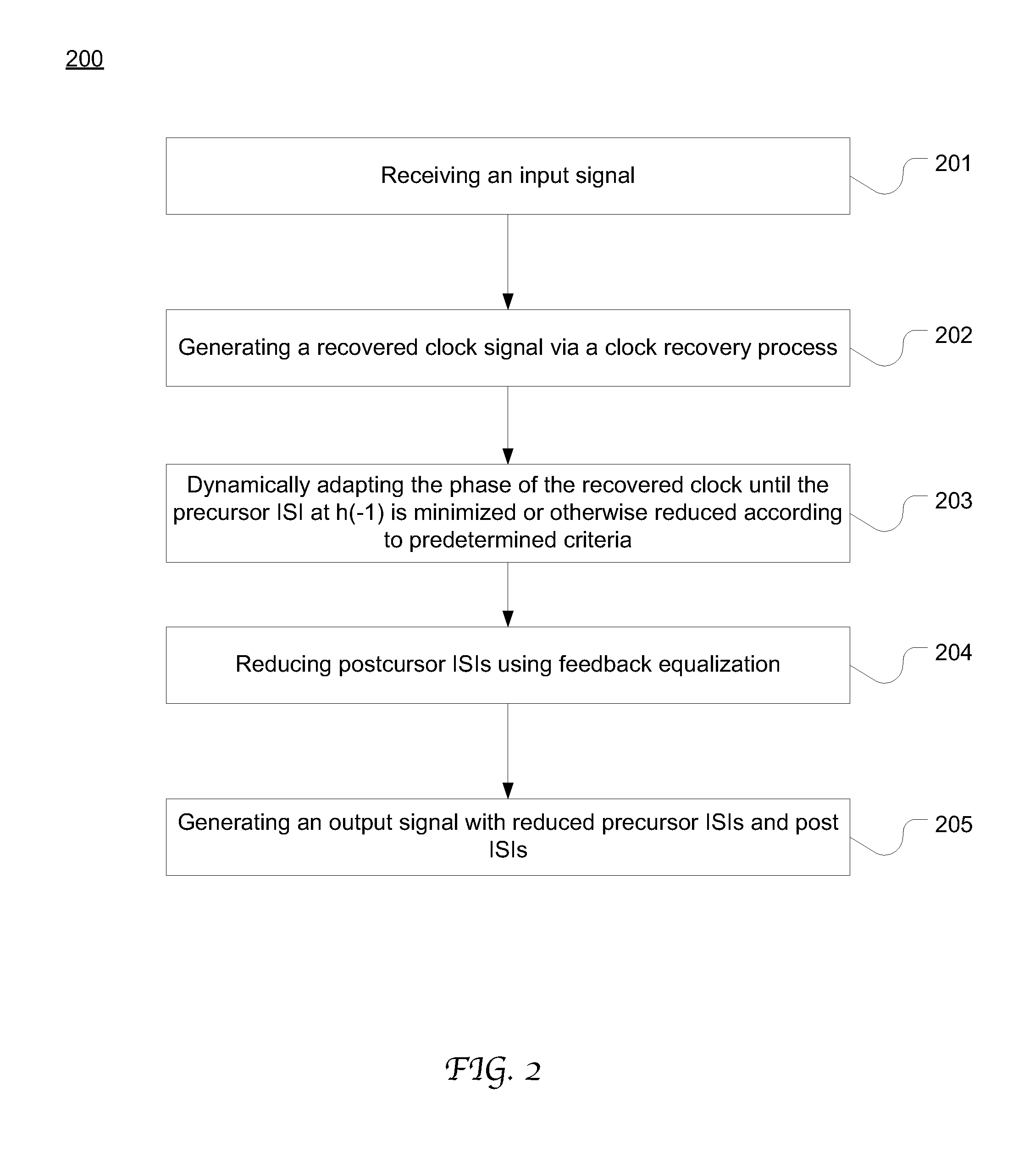

Clock phase adaptation for precursor isi reduction

ActiveUS20160234043A1Advantageous and effectiveSynchronisation receiversTransmitter/receiver shaping networksPhase shiftedMean square

Systems and methods of mitigating precursor ISIs for communication channels having time-variant precursor channel responses using digital circuit designs. A phase adaptation circuit is utilized in a receiver and configured to generate a phase control signal responsive to an input signal and based on the current precursor channel response. The phase control signal controls the phase shift of a recovered clock to a position where the precursor ISI at h(−1) is minimized. The phase control signal corresponds to a “feed-forward equalization (FFE) first tap weight” obtained via a digital least-mean-square (LMS) process.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

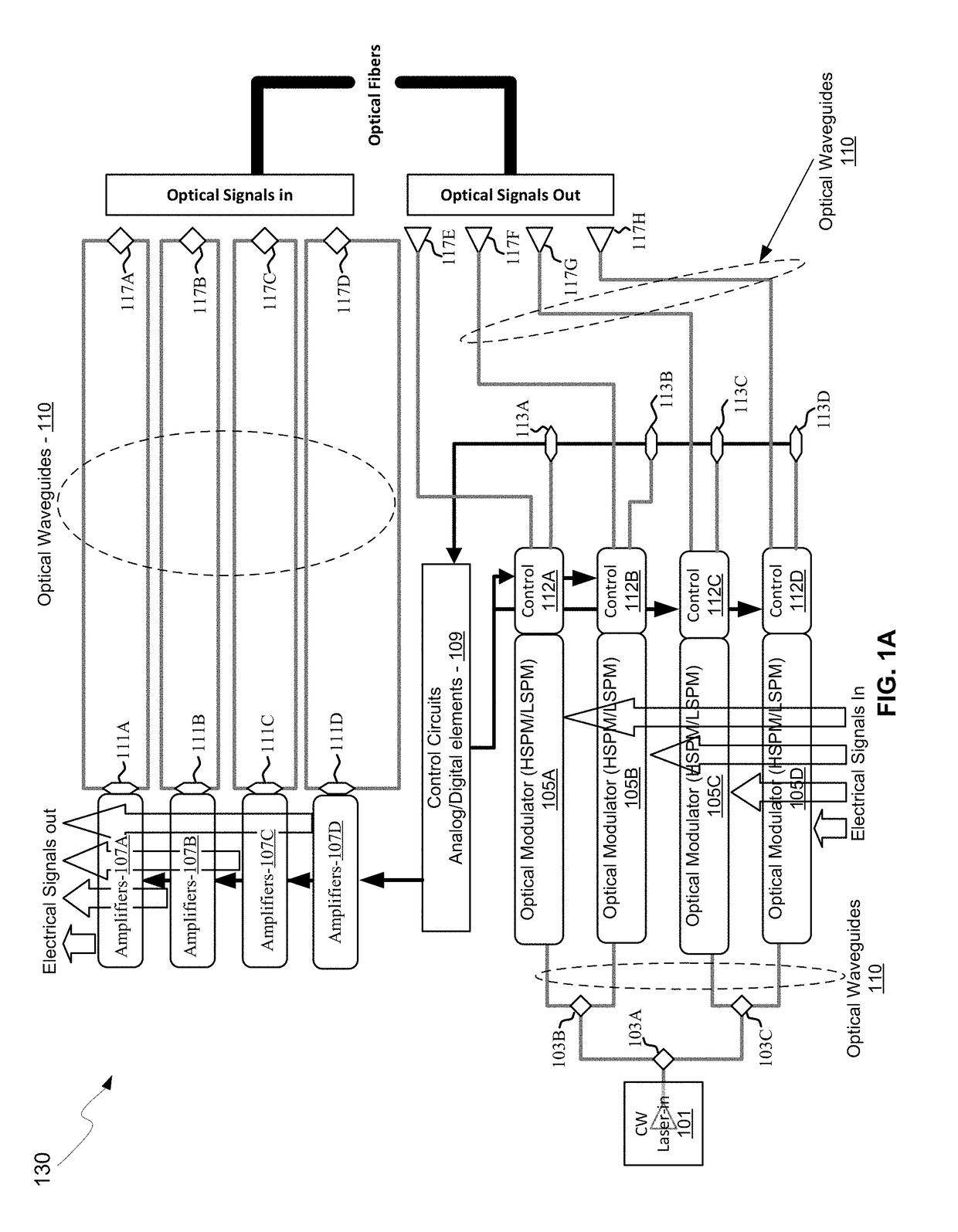

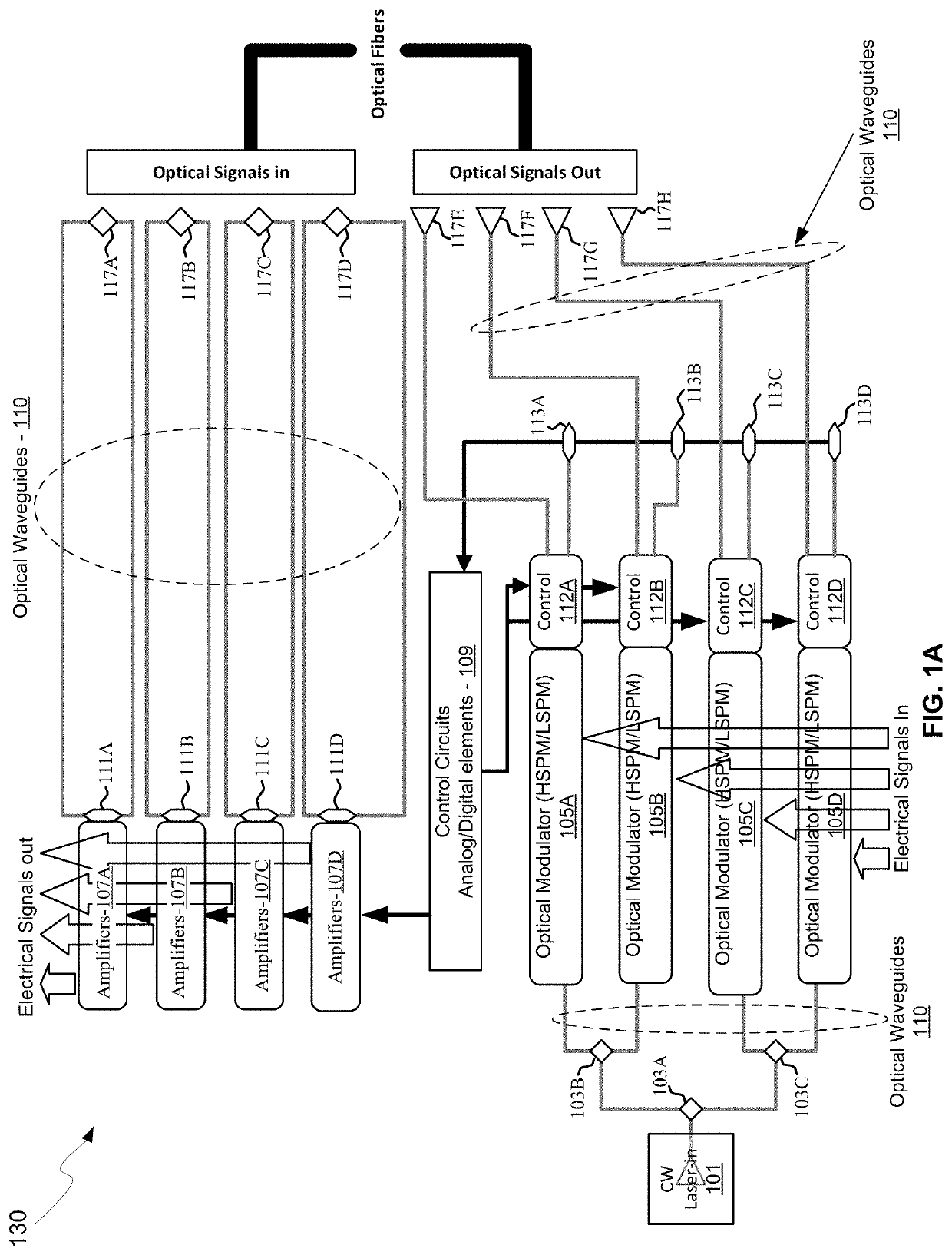

Method And System For A Distributed Mach-Zehnder Interferometer With Integrated Feed Forward Equalizer

Methods and systems for a distributed Mach-Zehnder Interferometer (MZI) with an integrated feed forward equalizer (FFE) may include a photonic chip comprising an optical modulator having diode drivers, local voltage domain splitters, and delay elements, where each is distributed along a length of the optical modulator. Outputs of the delay elements may be coupled to inputs of the local domain splitters, and outputs of the local voltage domain splitters may be coupled to inputs of the diode drivers. A feed forward equalization (FFE) module comprising a configurable delay element with inverted outputs coupled to one of the delay elements along the length of the modulator, may be coupled to a local voltage domain splitter. An input electrical signal may be received and delayed using the delay elements and coupled to the local domain splitters, and input electrical signals for the diode drivers may be generated using the local domain splitters.

Owner:CISCO TECH INC

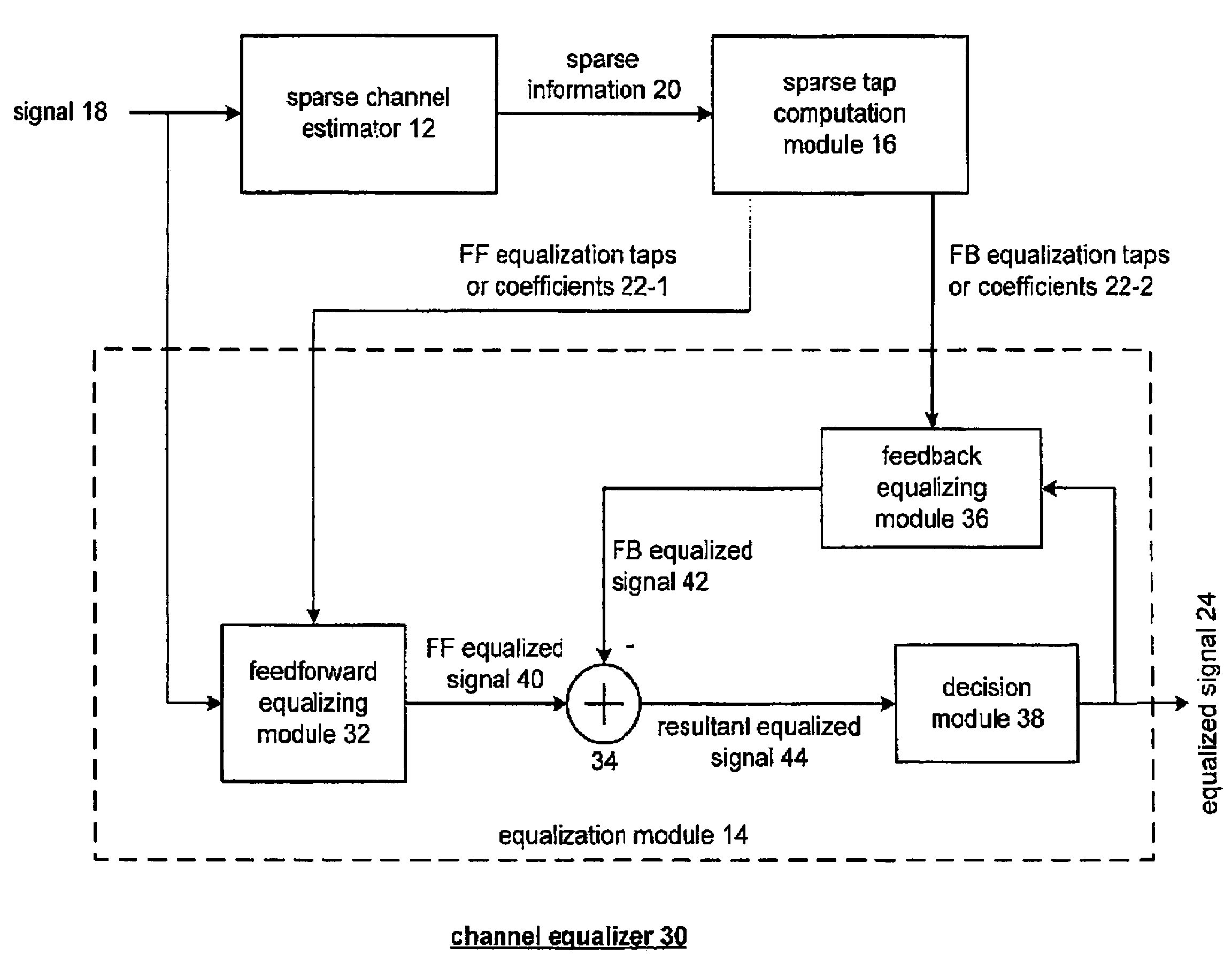

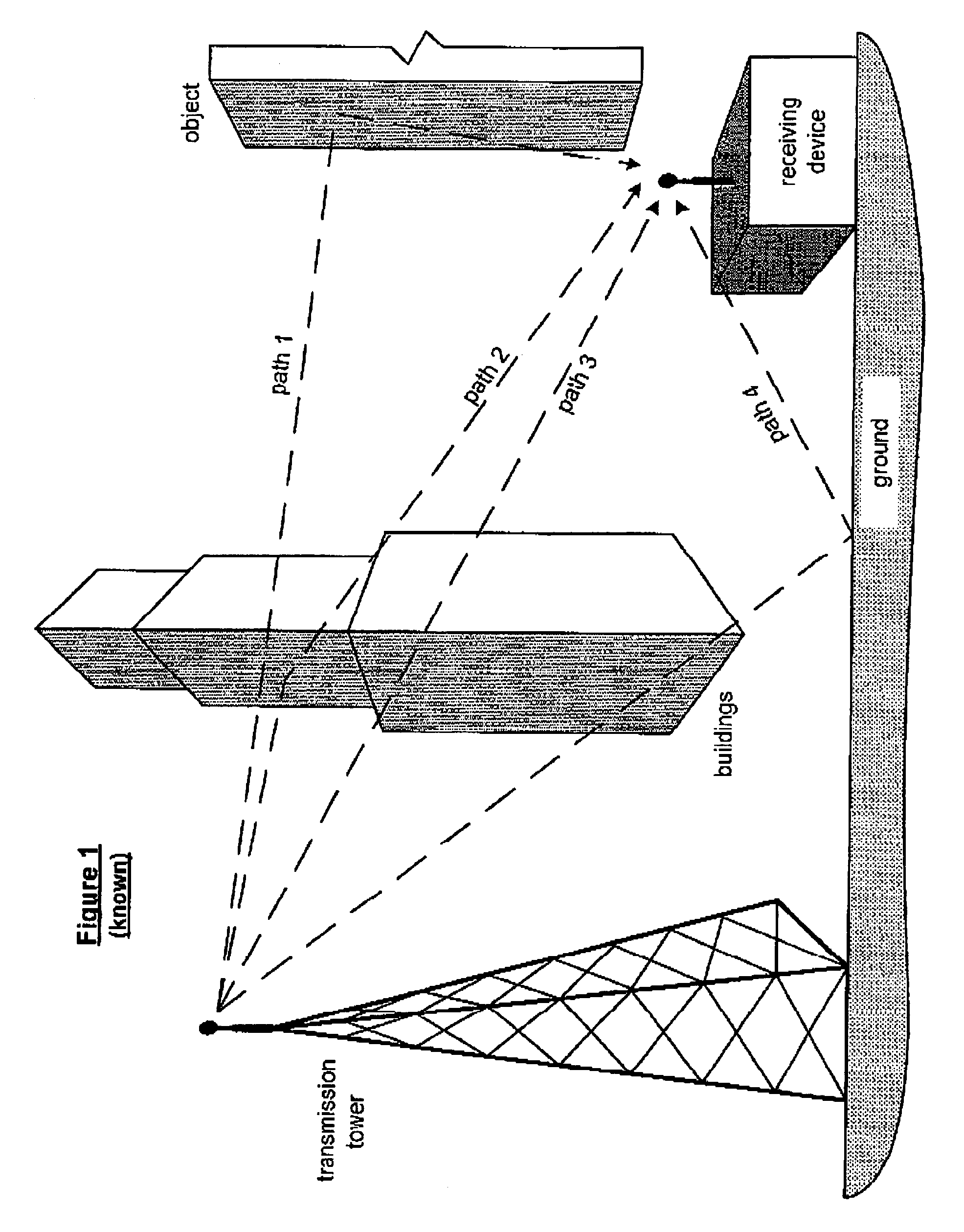

Determine coefficients of a decision feedback equalizer from a sparse channel estimate

InactiveUS7230983B2Reduce in quantityMultiple-port networksDelay line applicationsEqualizationLocation determination

Determination of equalizer coefficients from a sparse channel estimate begins by determining location of significant taps based on the sparse channel estimate of a multiple path communication channel. The sparse channel estimate indicates the positioning of signals received via the various multiple paths of the channel. The method then continues by determining feed-forward equalization coefficients based on the location of the significant taps. The method then continues by determining feedback equalization coefficients based on the feed-forward equalization coefficients and the sparse channel estimate.

Owner:AVAGO TECH INT SALES PTE LTD

Current mode logic multi-tap feed-forward equalizer

A system and method are provided for feed-forward equalization (FFE) in a transmission system. The method accepts a serial stream of input digital data signals. For each input data signal, a temporal sequence of signals is generated. Each of the signals in the temporal sequence is selectively shaped. Shaping map include varying the degree of amplification, modifying the slew rate, or varying the time delay. The contributions of the selectively shaped signals in the temporal sequence are then selectively weighted, and a summed output signal is transmitted.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

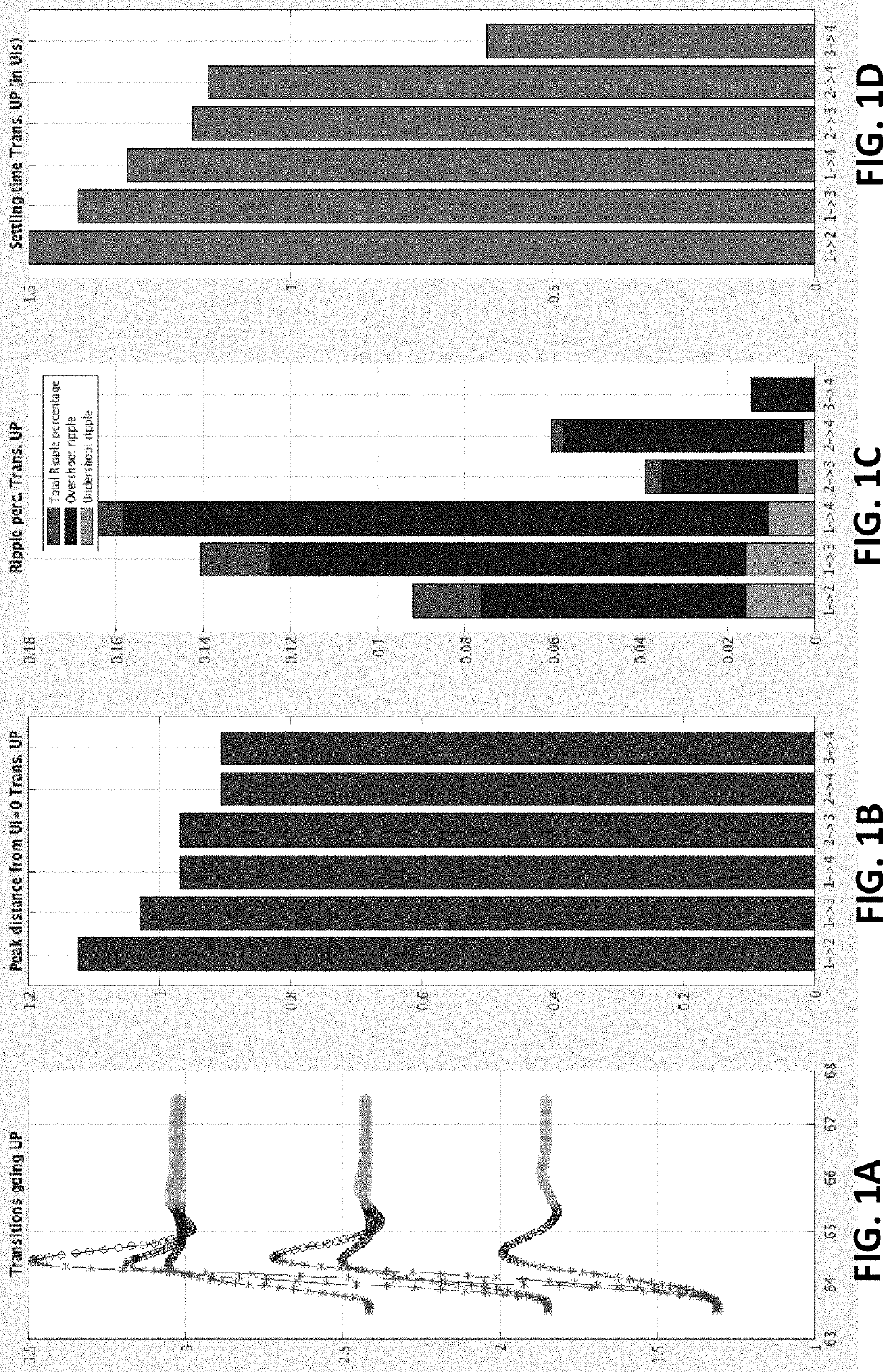

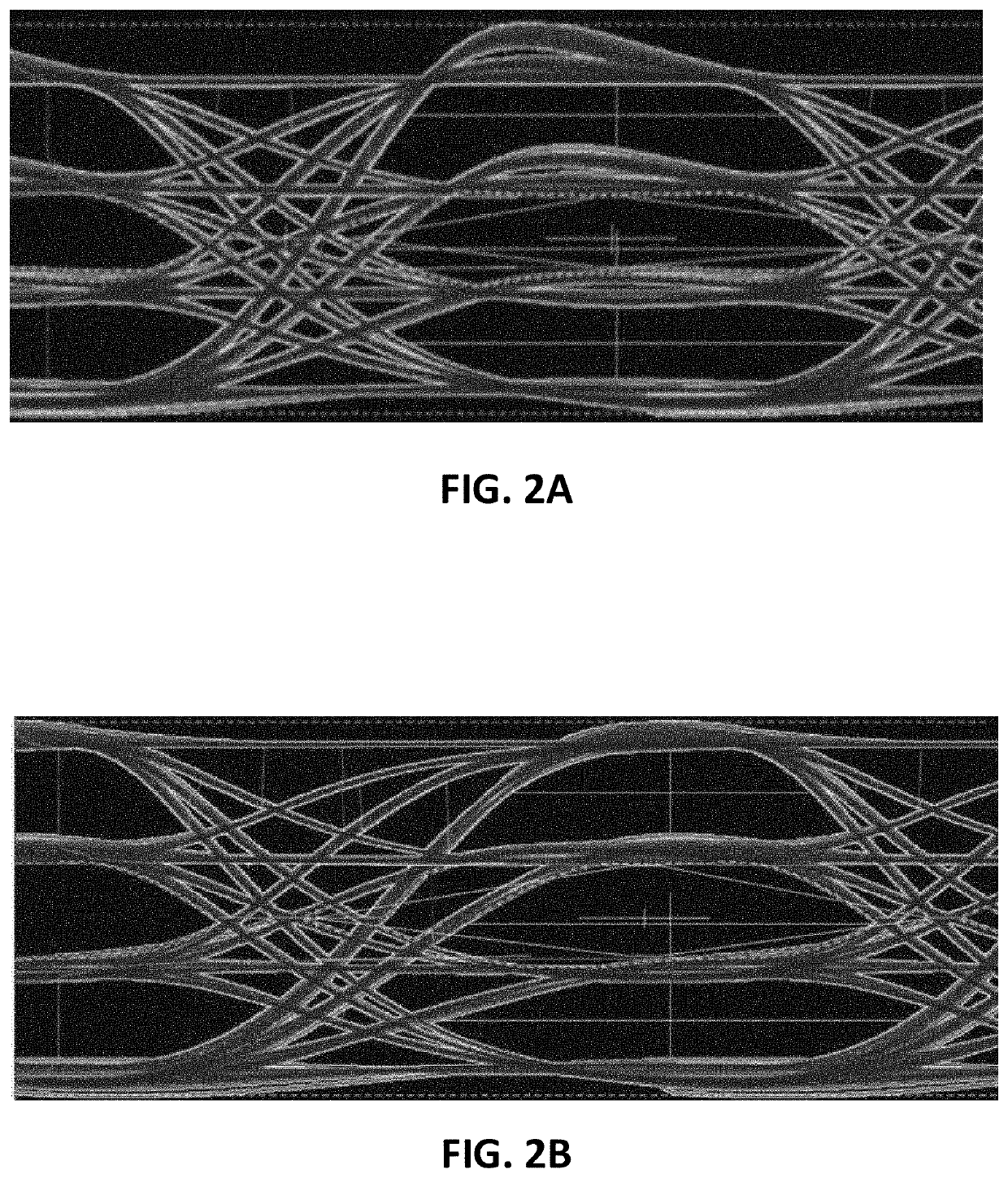

Transition based feedforward equalization method and apparatus implemented with lookup table circuits

Embodiments are disclosed for equalizing input signals for communication systems. An example method includes receiving an input signal. The input signal encodes a plurality of bits in a number of amplitude levels. The example method further includes converting the input signal to an equalized output signal using a plurality of lookup table circuits. The equalized output signal encodes a plurality of symbols in a number of amplitude levels. The example method further includes feeding the equalized output signal to an output driver circuit.

Owner:NVIDIA DENMARK APS

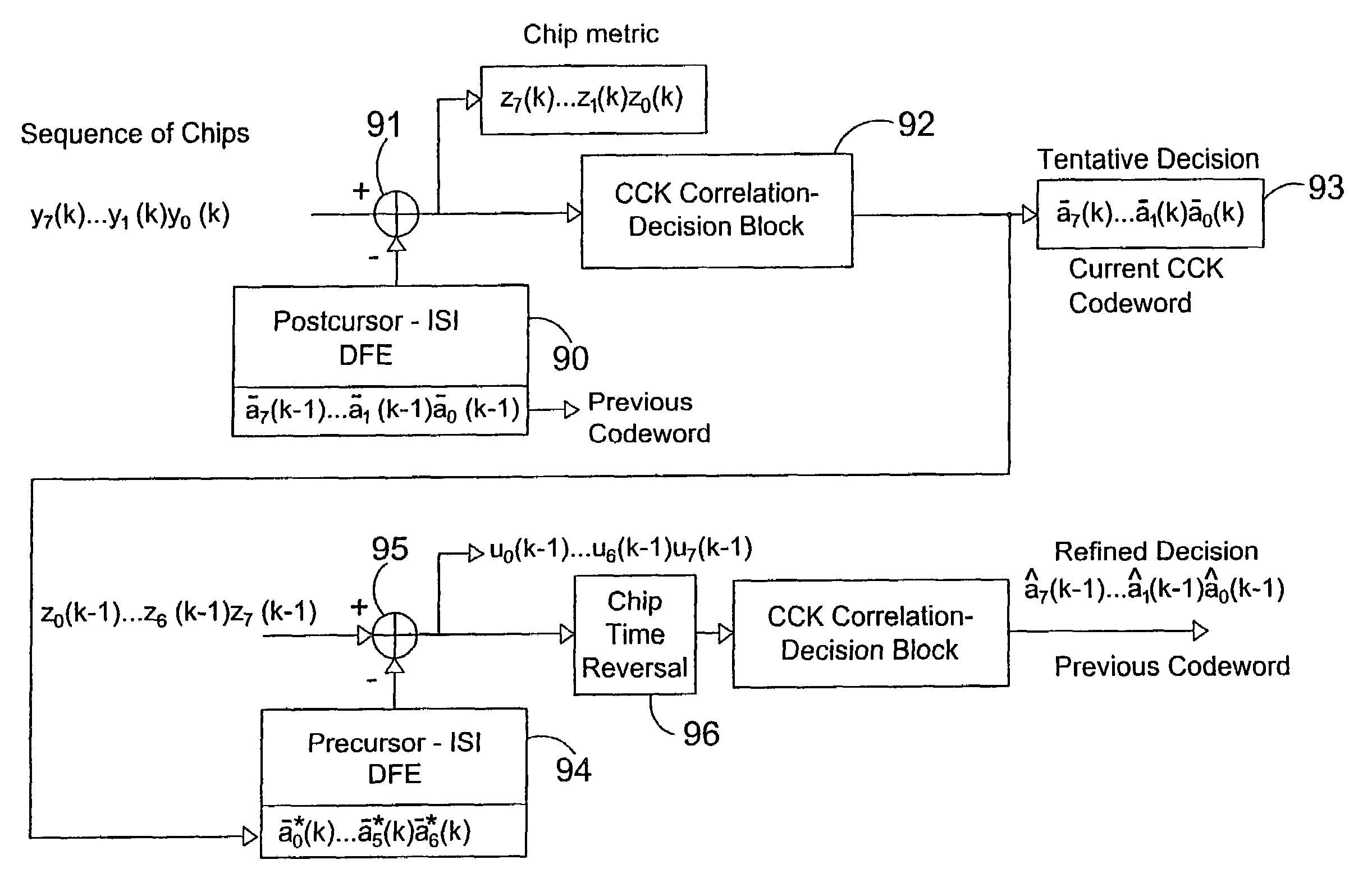

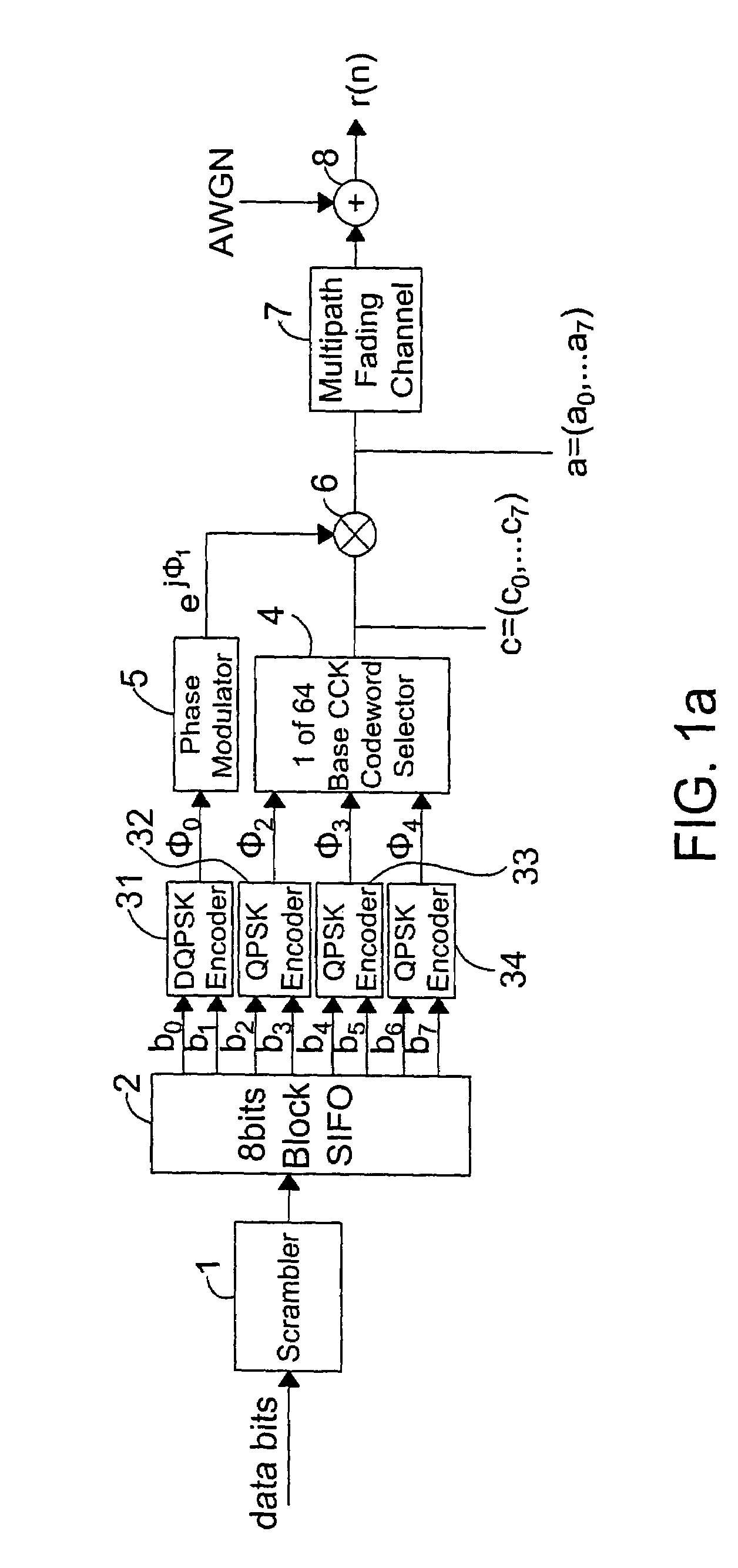

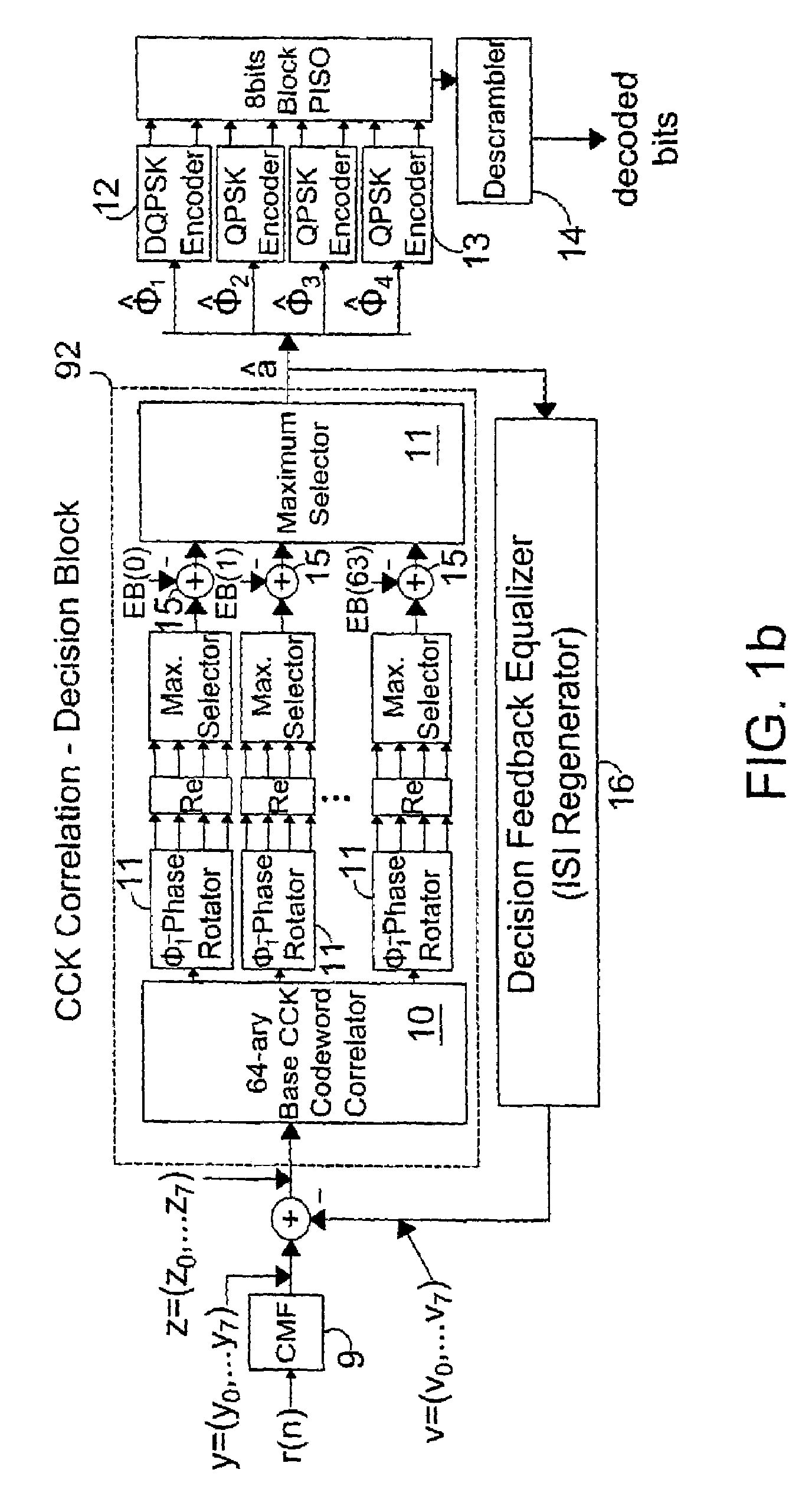

Bidirectional turbo ISI canceller-based DSSS receiver for high-speed wireless LAN

ActiveUS7606293B2Easy to detectSustain performanceMultiple-port networksError correction/detection using convolutional codesWireless lanRake receiver

A bidirectional turbo ISI canceller cancels precursor-ISI as well as postcursor-ISI in a received signal without incorporating a multiplicative feedforward equalization filter. This is accomplished by taking a three-step receiver design approach. In the first step, an optimal single-symbol RAKE receiver is designed to comprise a CMF, a codeword correlator bank, and an energy bias (EB) canceller under the assumption that no ISI is generated by preceding or trailing symbols. In a second step, a DFE is included for suppressing postcursor-ISI caused by a preceding symbol. Finally, a precursor ISI canceler is used to remove the remaining ISI caused by a trailing symbol. All three components may be integrated into a BTIC-based receiver applying turbo-iteration processing.

Owner:GCT SEMICONDUCTOR INC

Low-power mixed-mode echo/crosstalk cancellation in wireline communications

ActiveUS7583724B2More dynamic rangeLimited rangeMultiple-port networksTwo-way loud-speaking telephone systemsCrosstalk cancellationAnalog signal

Owner:MARVELL ASIA PTE LTD

Method and apparatus for cancelling inter-symbol interference (ISI) within a communication channel

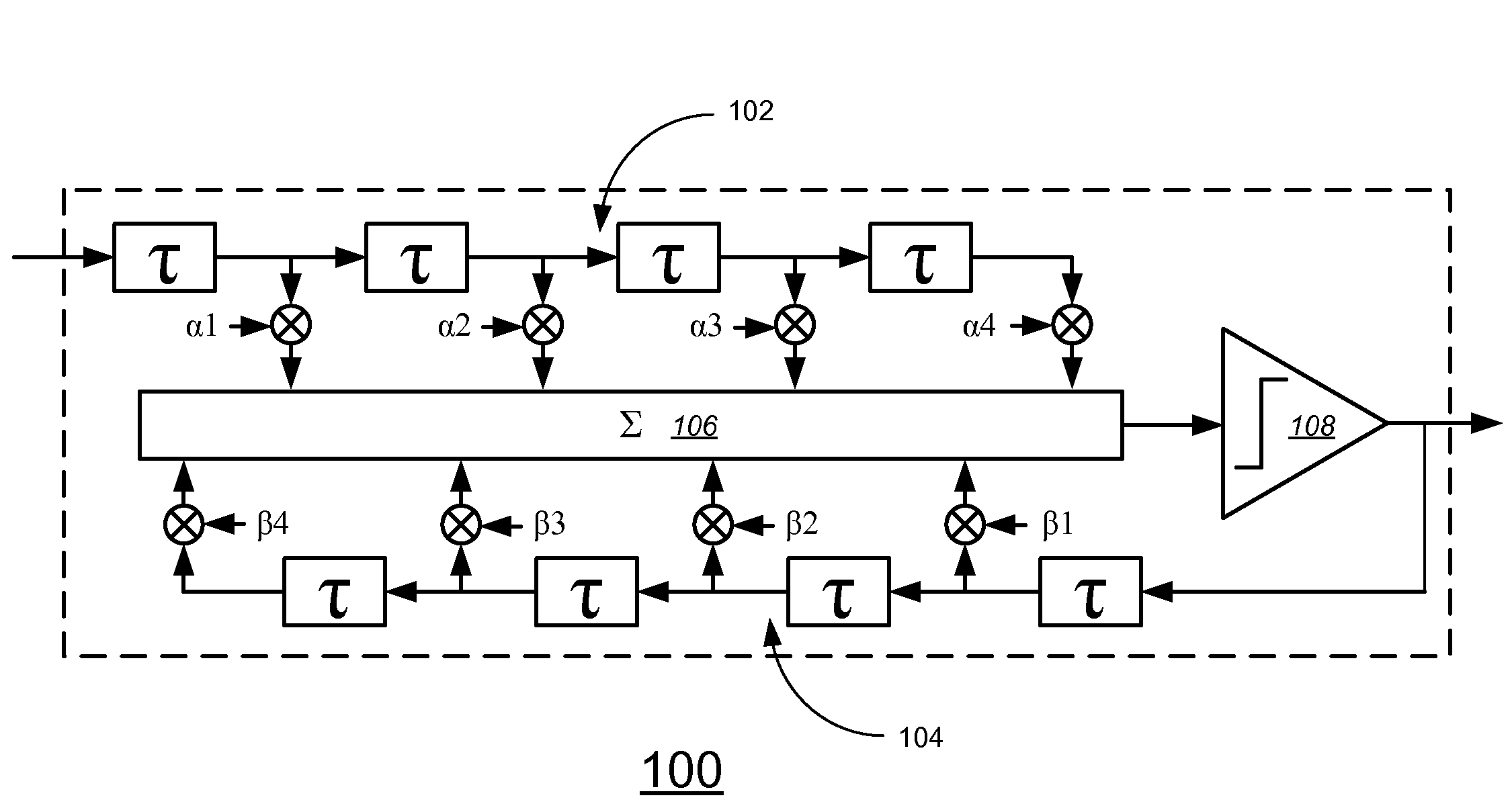

InactiveUS7293057B2Transmission control/equlisationTransmitter/receiver shaping networksFinite impulse responseAudio power amplifier

A decision feedback equalizer finite impulse response (DFE FIR) filter for cancelling inter-symbol interference within a signal transmitted through a communication channel. The DFE FIR filter includes a feed-forward equalization path to receive the signal transmitted through the communication channel and generate a first partially equalized signal from the signal based on a plurality of coefficients associated with the feed-forward equalization path; a feedback equalization path to generate a second partially equalized signal that corrects for the inter-symbol interference within the signal based on an output of the DFE FIR filter; a summer to combine the first partially equalized signal with the second partially equalized signal; and a signal amplifier to receive the combined signal from the summer and generate the output of the DFE FIR filter.

Owner:PLEXUS NETWORKS

Bidirectional turbo ISI canceller-based DSSS receiver for high-speed wireless LAN

A bidirectional turbo ISI canceller removes preceding ISI (94) and following ISI (90) in the received signal without inserting a multiplicative feed-forward equalization filter. This is achieved by employing a three-step receiver design methodology. In the first step, under the assumption that the previous symbol or the tail symbol does not produce ISI, l designs the optimal single-symbol RAKE receiver to include: CMF (9), code word correlator group and energy offset EB, in The second step involves DFE (16) to suppress subsequent ISI (90) produced by previous symbols. Finally, the remaining ISI generated by the tail symbols is removed using a lookahead ISI (94) canceller. All three of these components can be integrated 10 into a BTIC-based receiver employing turbo iterative processing.

Owner:GCT SEMICONDUCTOR INC

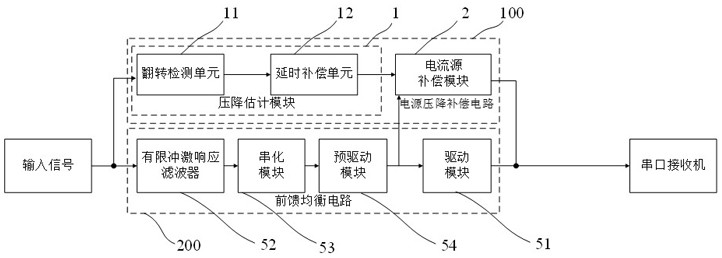

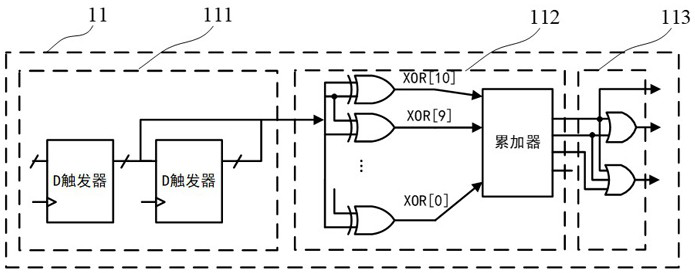

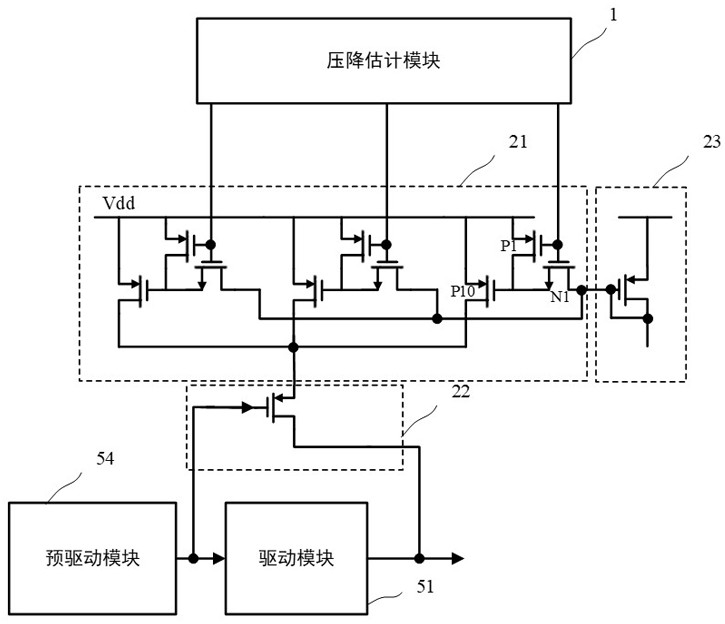

Serial transmitter and voltage drop compensation circuit of feed-forward equalization circuit thereof

ActiveCN114866098AReduce complexityReduce the impactTransmissionEnergy efficient computingControl signalElectrical connection

The invention discloses a serial transmitter and a voltage drop compensation circuit of a feed-forward equalization circuit thereof. The voltage drop compensation circuit comprises a voltage drop estimation module and a current source compensation module. The input end of the voltage drop estimation module is electrically connected with the input end of the feed-forward equalization circuit; the output end of the voltage drop estimation module is electrically connected with the input end of the current source compensation module and the input end of the driving module. The input end of the current source compensation module is also electrically connected with the input end of the driving module; the output end of the current source compensation module is electrically connected with the output end of the driving module; the voltage drop estimation module is used for generating a voltage drop compensation control signal corresponding to a current fluctuation level caused in an input signal transmission process; and the current source compensation module is used for generating compensation current for power supply voltage drop according to the voltage drop compensation control signal and the input signal received by the driving module. The voltage drop compensation circuit is high in compensation accuracy, high in adaptability, low in extra power consumption and low in circuit complexity.

Owner:奉加微电子(昆山)有限公司 +1

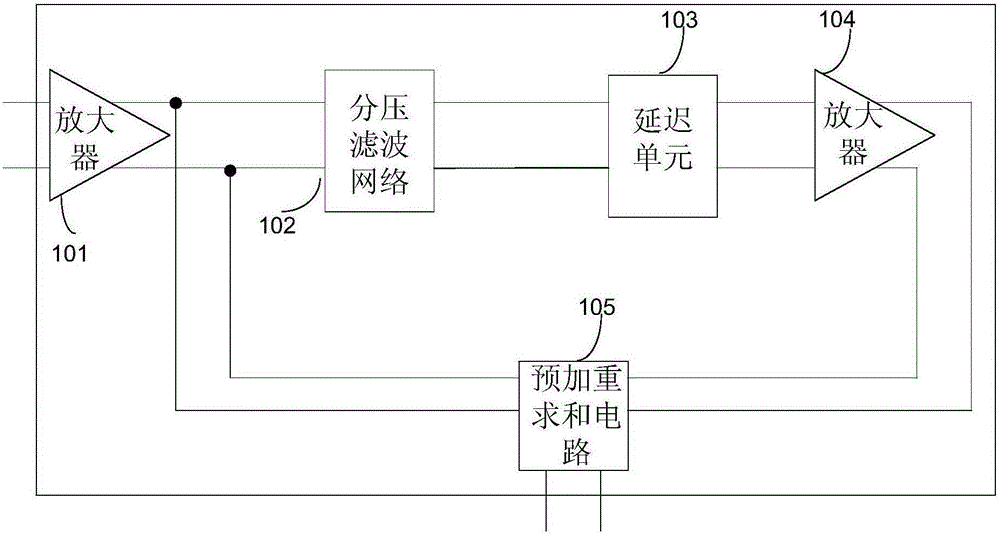

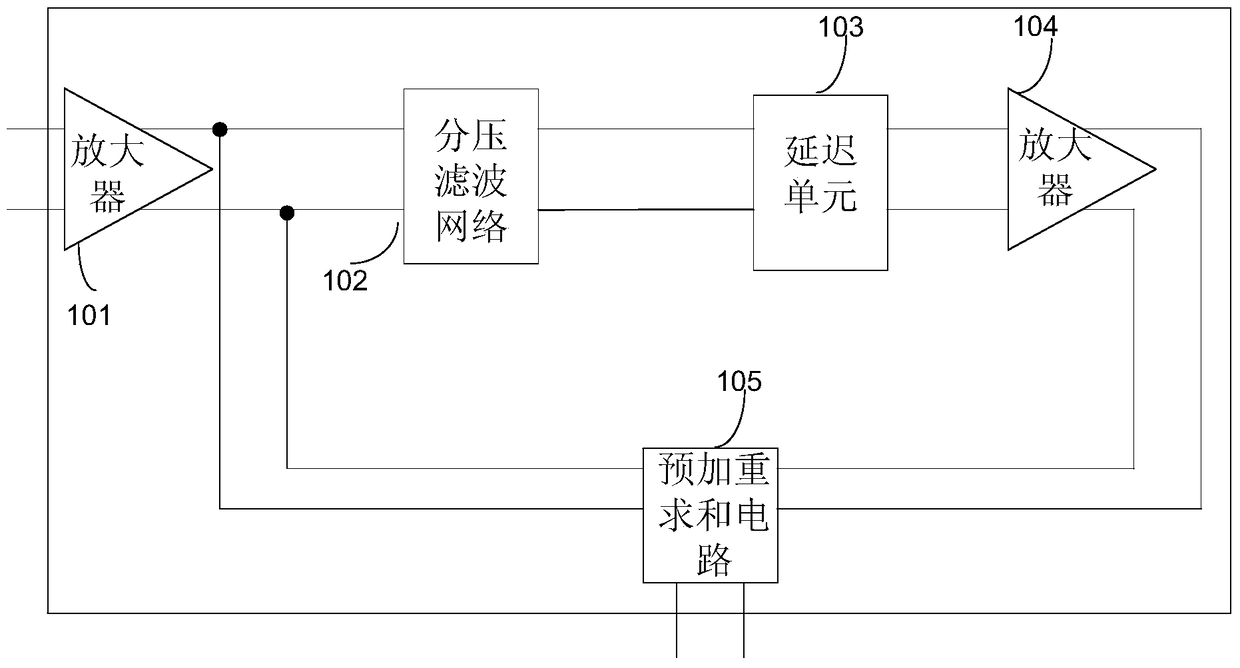

Feedforward equalization pre-emphasis circuit, processing method and USB driver

ActiveCN105243041AAvoid the problem of intersymbol interference and loss of dataGuaranteed communication qualityElectric digital data processingCommunication qualityAudio power amplifier

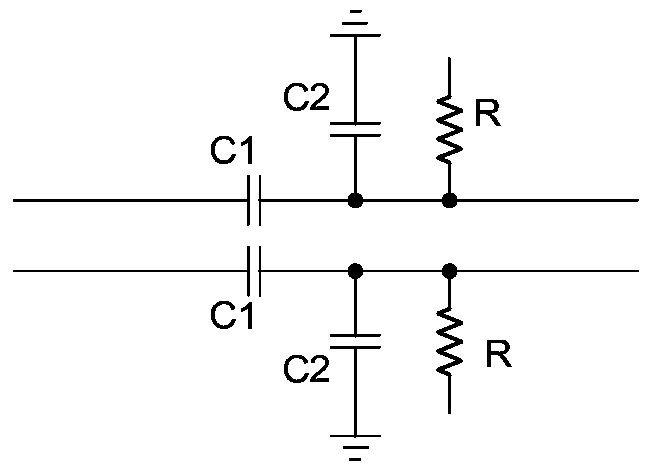

The present invention relates to a feedforward equalization pre-emphasis circuit, a processing method and a USB driver. The circuit comprises: a first-stage amplifier (101), a voltage dividing filter network (102), a delay unit (103), a second-stage amplifier (104), and a pre-emphasis summing circuit (105). The first-stage amplifier (101) is used for amplifying an amplitude of an input signal and outputting a signal; the voltage dividing filter network (102) is used for carrying out filtering, voltage division and outputting on the signal output by the first-stage amplifier (101); the delay unit (103) is used for delaying the signal output by the voltage dividing filter network (102) and outputting the delayed signal; the second-stage amplifier (104) is used for amplifying and recovering the signal output by the delay unit (103); and the pre-emphasis summing circuit (105) is used for receiving the signal output by the first-stage amplifier (101) and the signal output by the second-stage amplifier (104), carrying out the pre-emphasis summation operation and outputting an operation result. The signal is subjected to pre-emphasis processing at an input terminal so as to avoid the problem of data loss caused by intersymbol interference of the signal in the communication channel transmission process, thereby well ensuring communication quality.

Owner:豪威模拟集成电路(北京)有限公司

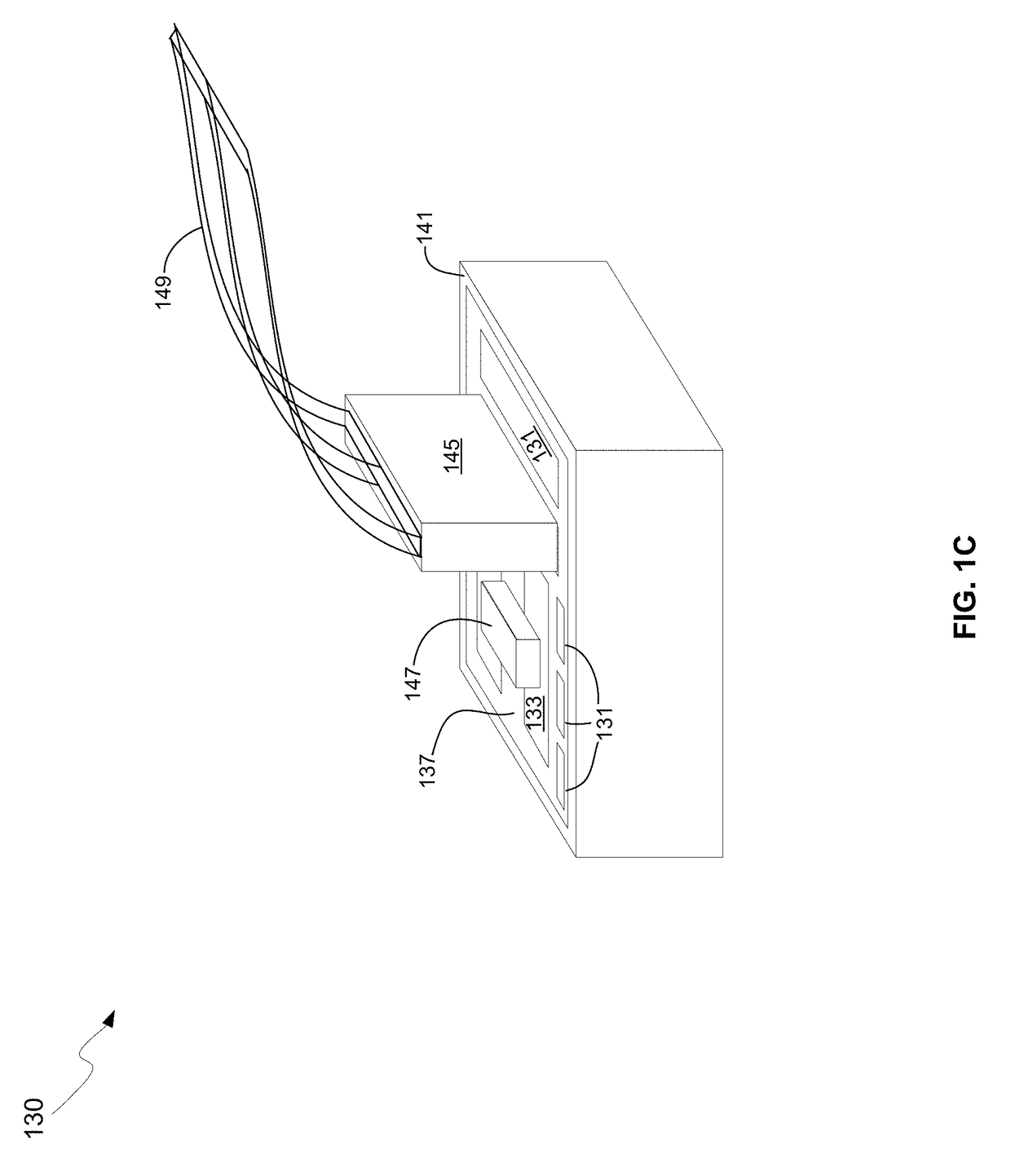

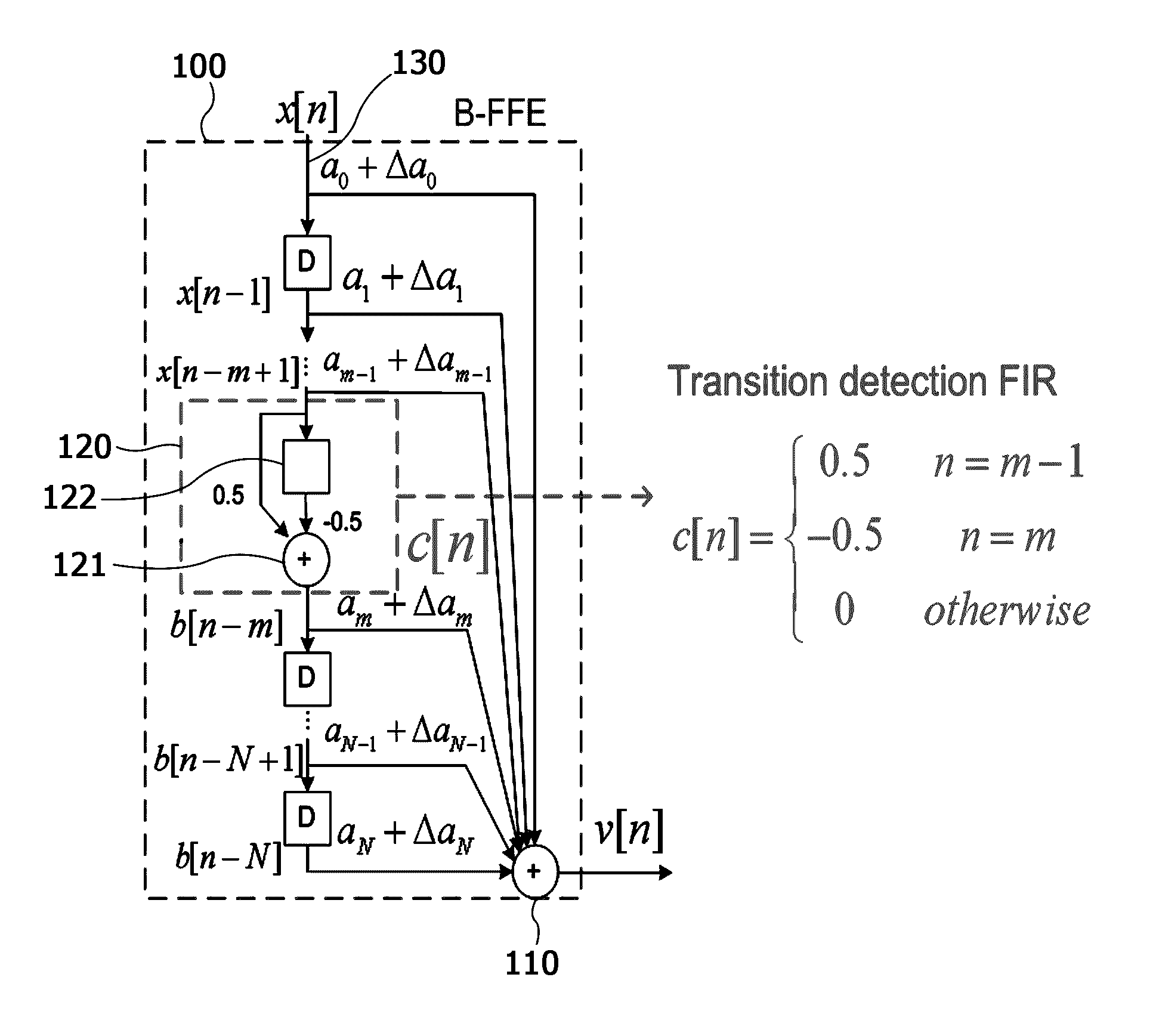

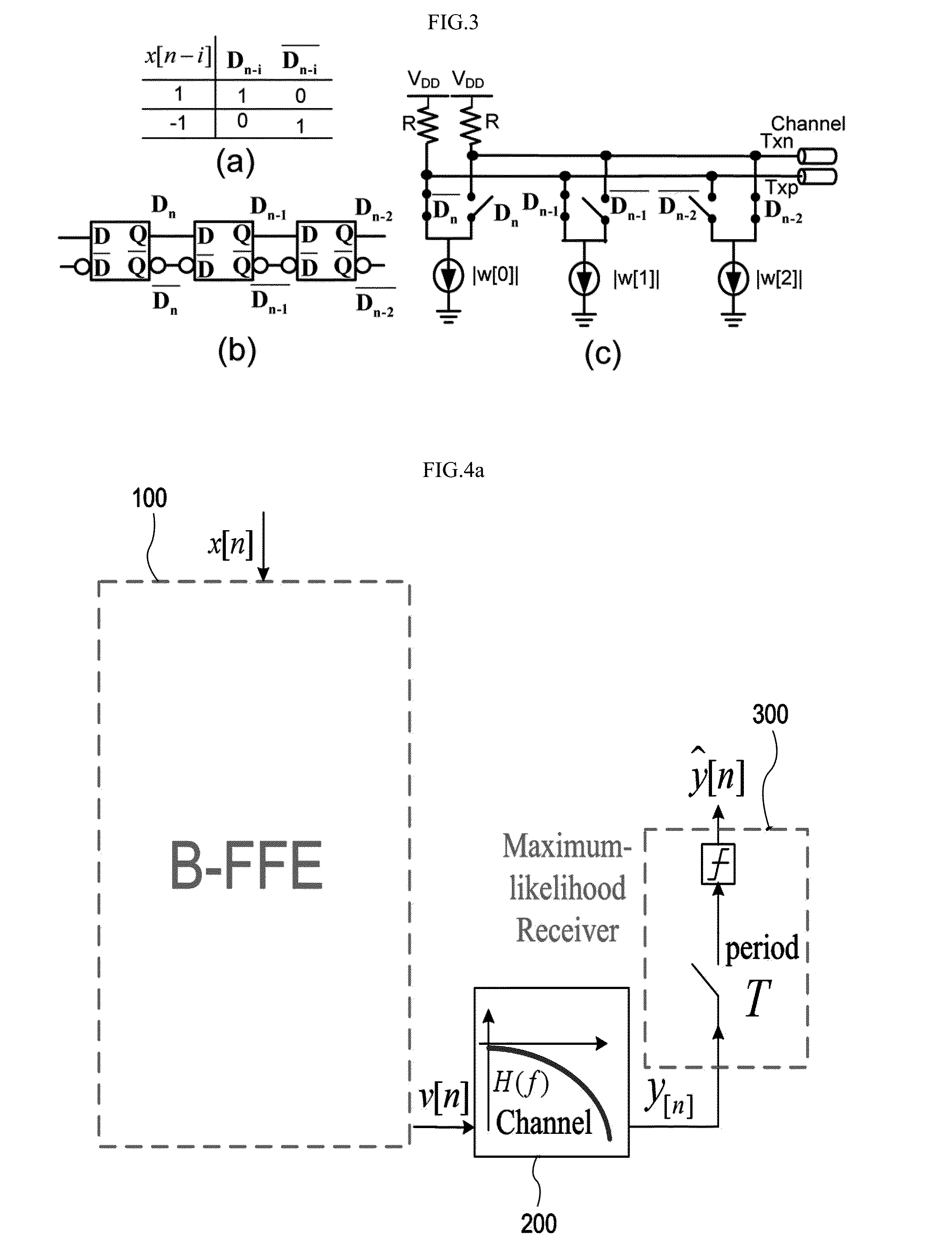

Coefficient error robust feed forward equalizer

ActiveUS9503293B2Improve robustnessLow additional costMultiple-port networksTransmitter/receiver shaping networksWired communicationEngineering

The present invention relates to a coefficient error robust feed forward equalizer and, more specifically, to a feed forward equalizing transmitter for baseband wired communication for preventing the influence of a coefficient error generated by the variation of nano-elements. The coefficient error robust feed forward equalizer according to one embodiment of the present invention comprises: a receiving terminal (130) for receiving input data (x) according to an integer time index (n), N number of delay units (D) connected with the input terminal (130) in series, a first calculator (110) for summing up tap signals outputted respectively from the N number of delay units (D); and a data change detection filter (120) for outputting a data transition value (b) on the basis of the change in the input data (x).

Owner:POSTECH ACAD IND FOUND

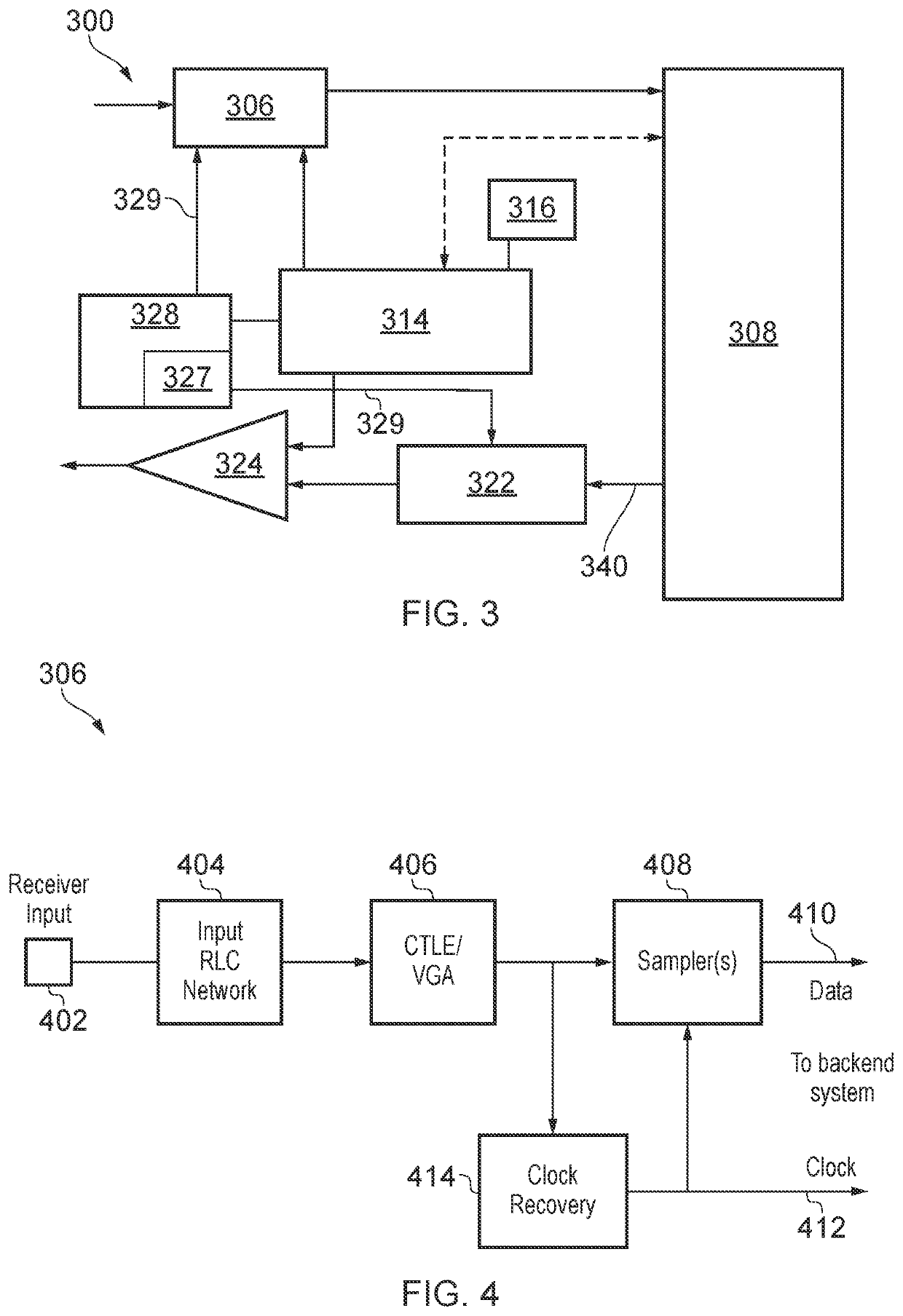

Low power receiver with equalization circuit, communication unit and method therefor

ActiveUS20220103400A1Reduce power consumptionPower overheadDc level restoring means or bias distort correctionTransmitter/receiver shaping networksTelecommunicationsCommunication unit

Owner:MEDIATEK SINGAPORE PTE LTD SINGAPORE

Coefficient error robust feed forward equalizer

ActiveUS20160105298A1Improve robustnessLow additional costMultiple-port networksDelay line applicationsWired communicationFeed forward equalizer

The present invention relates to a coefficient error robust feed forward equalizer and, more specifically, to a feed forward equalizing transmitter for baseband wired communication for preventing the influence of a coefficient error generated by the variation of nano-elements. The coefficient error robust feed forward equalizer according to one embodiment of the present invention comprises: a receiving terminal (130) for receiving input data (x) according to an integer time index (n), N number of delay units (D) connected with the input terminal (130) in series, a first calculator (110) for summing up tap signals outputted respectively from the N number of delay units (D); and a data change detection filter (120) for outputting a data transition value (b) on the basis of the change in the input data (x).

Owner:POSTECH ACAD IND FOUND

Sparse and reconfigurable floating tap feed forward equalization

Owner:AVAGO TECH INT SALES PTE LTD

Method and system for a distributed mach-zehnder interferometer with integrated feed forward equalizer

Owner:CISCO TECH INC

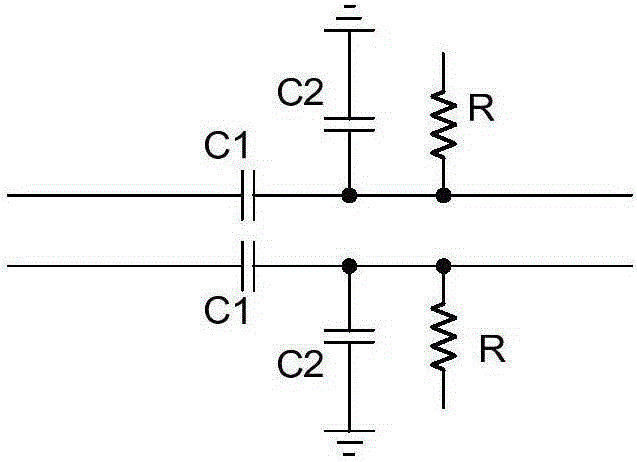

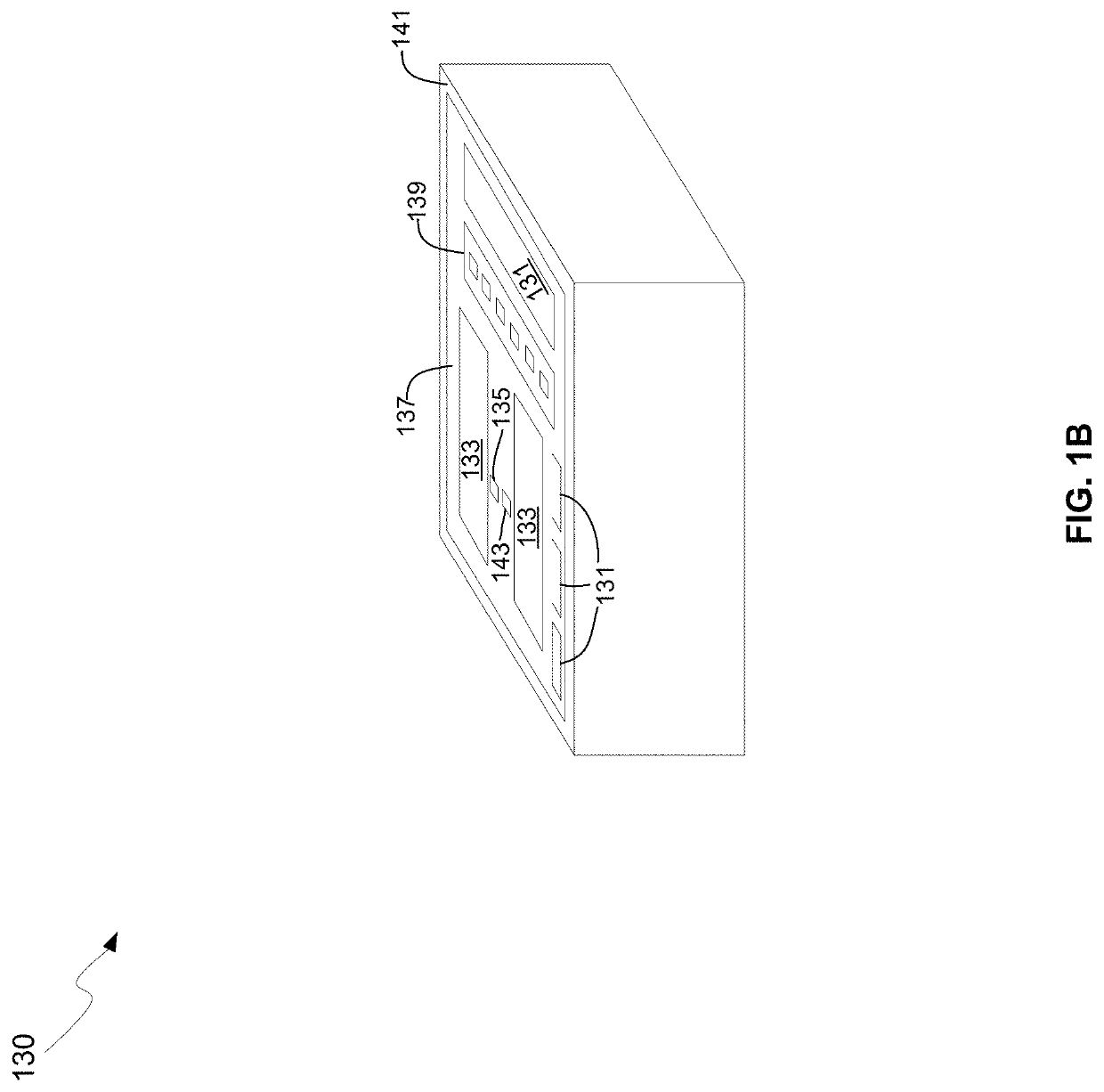

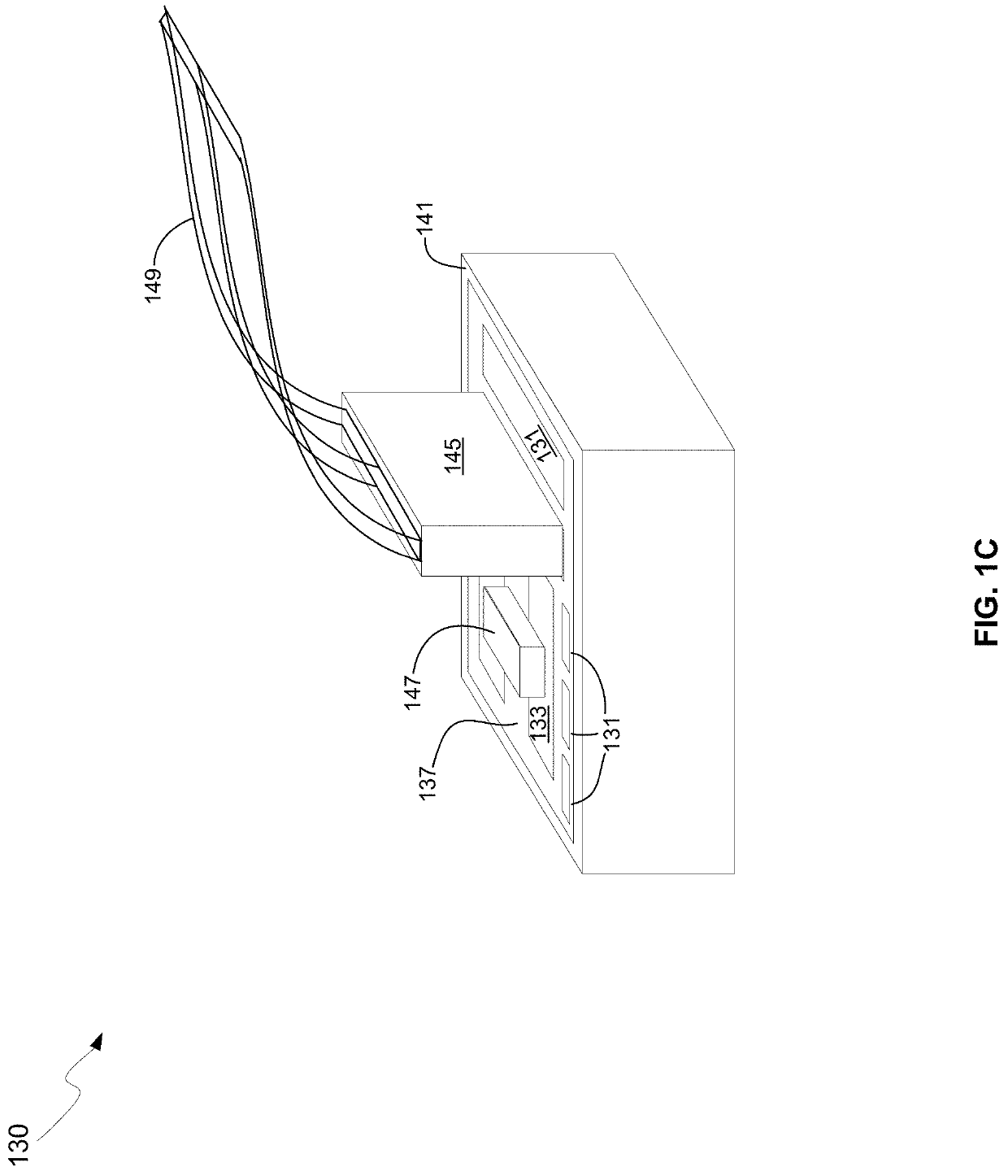

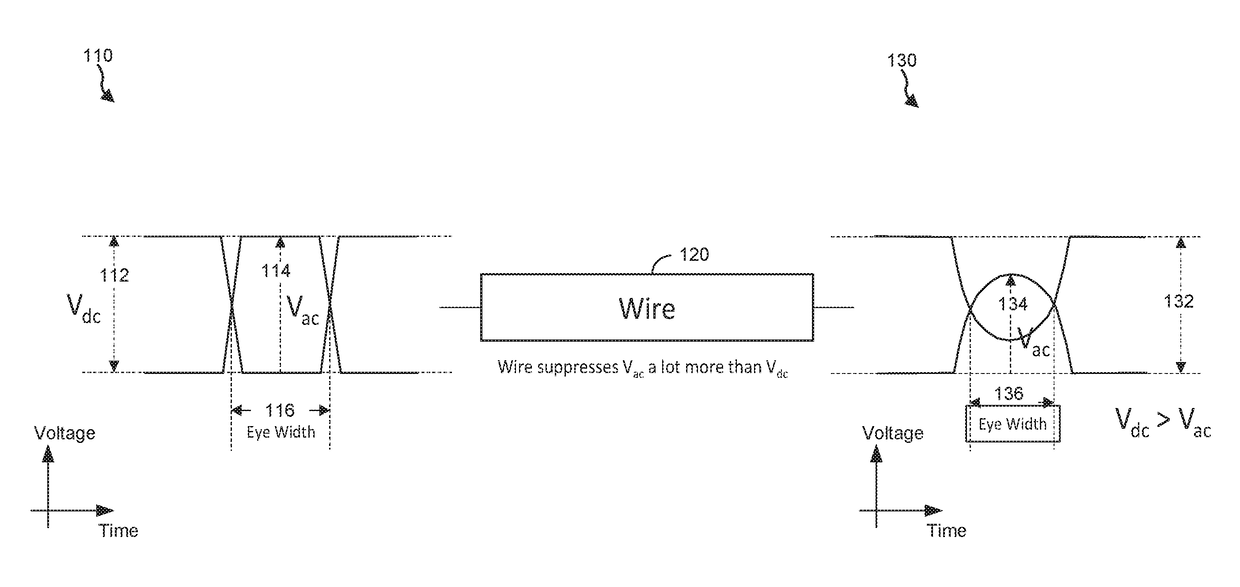

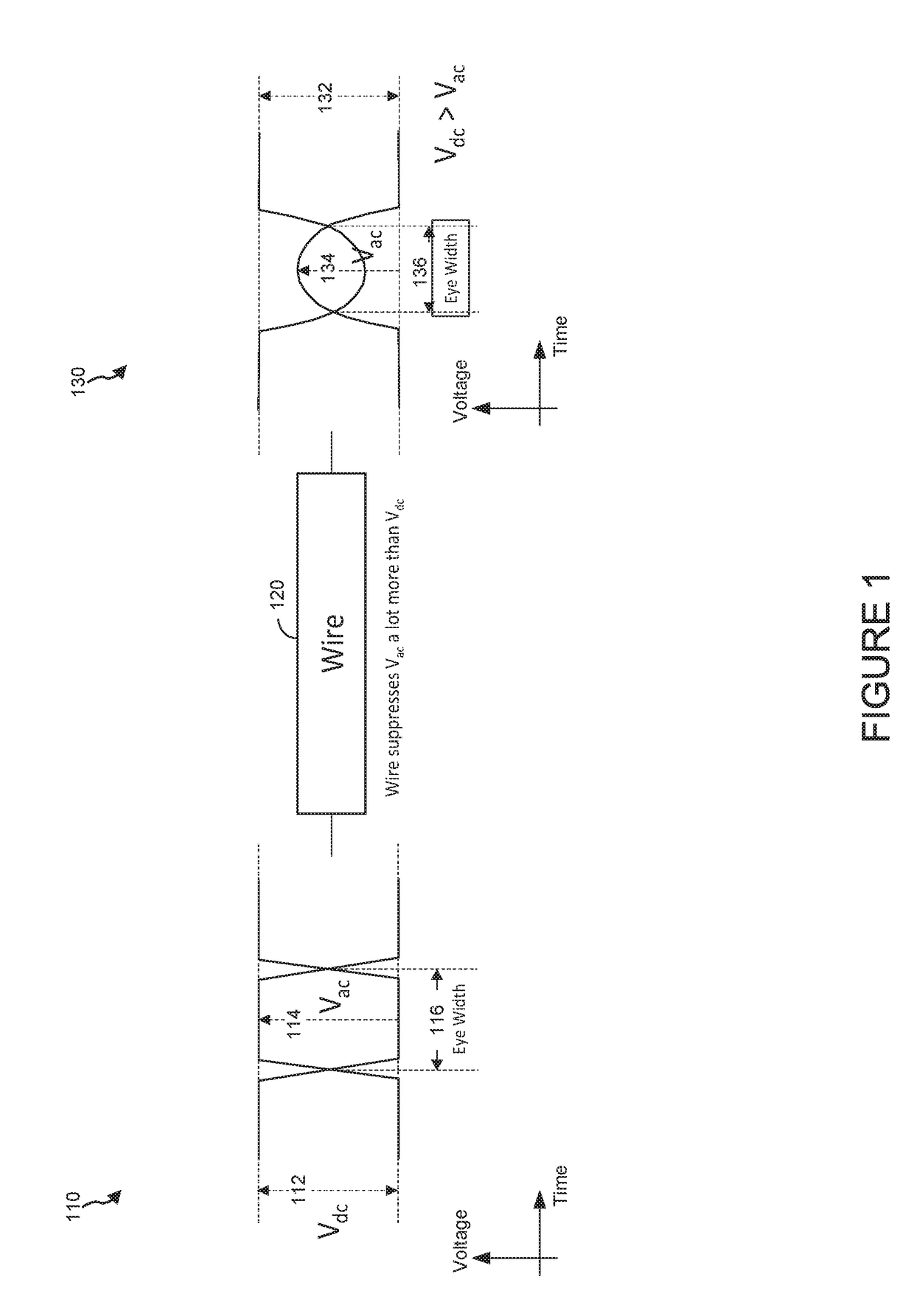

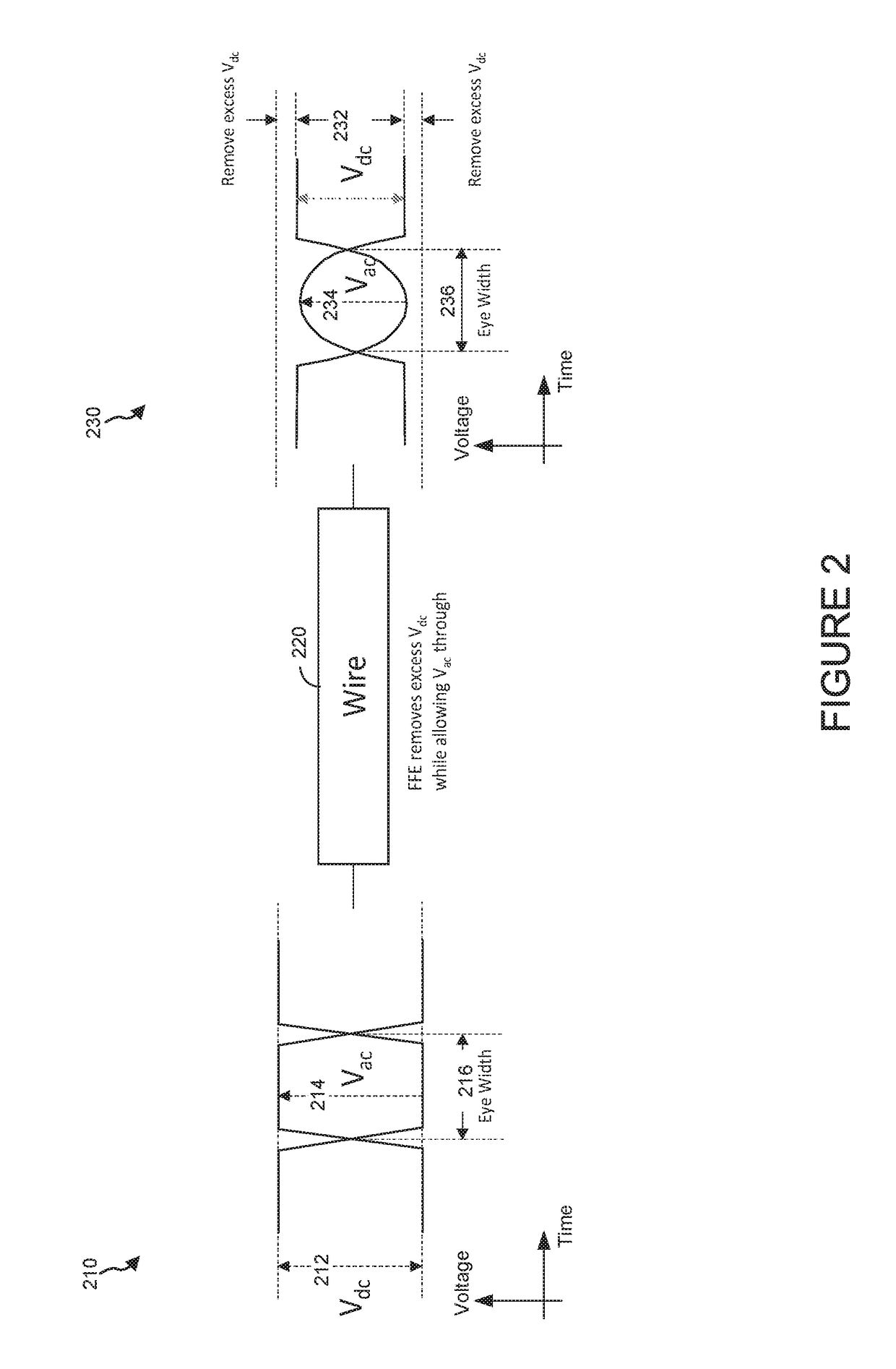

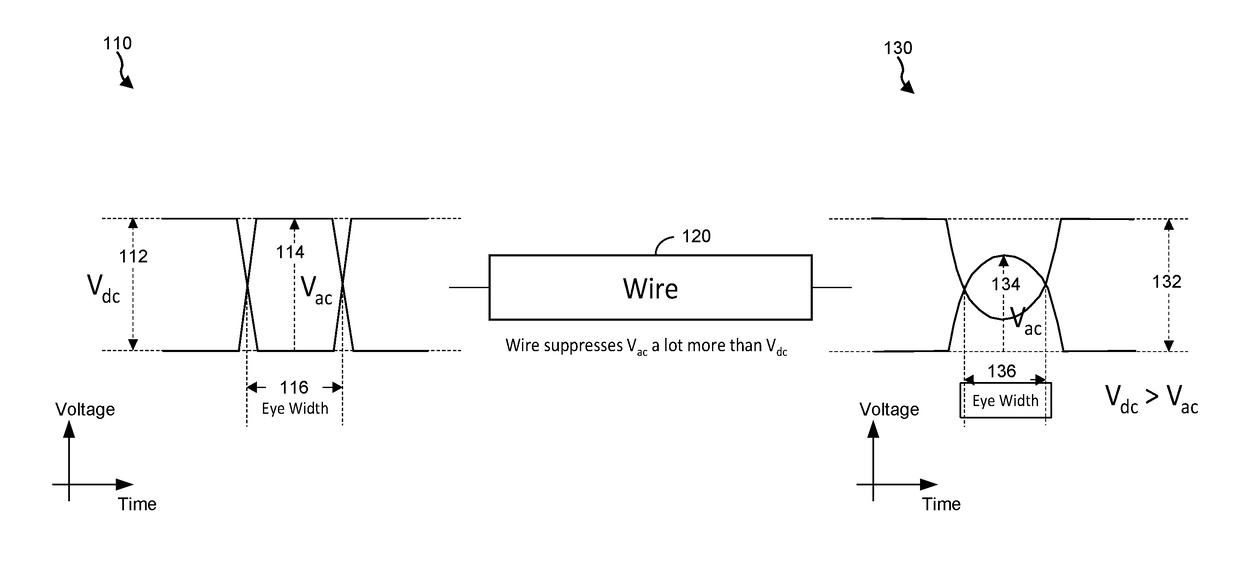

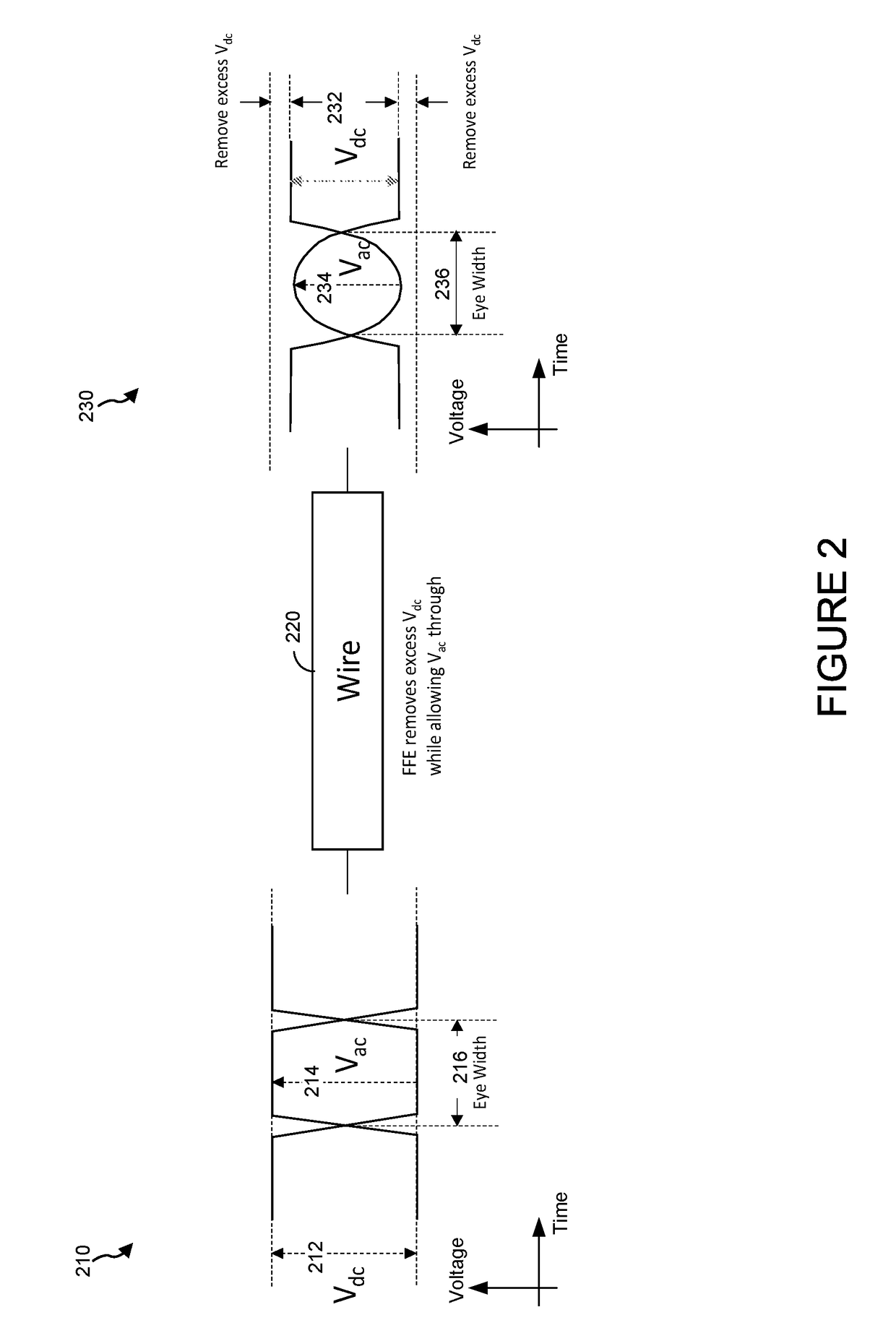

Embedded wire feed forward equalization

ActiveUS20170222837A1Transmission control/equlisationTransmitter/receiver shaping networksElectrical resistance and conductanceCapacitance

Embodiments of the present disclosure provide methods and apparatus for providing feed forward equalization to a communication line by providing a resistance and a capacitance to the communication line. The method includes determining the resistance based on a desired value of feed forward equalization to provide to a communication line, determining the capacitance based on the desired value of feed forward equalization to provide to the communication line, providing a layer of resistive material between a first conductor and a second conductor of the communication line, wherein a dimension of the layer of resistive material is determined based on the determined resistance and providing a layer of dielectric material between the first conductor and the second conductor, wherein a dimension of the layer of dielectric material is determined based on the determined capacitance.

Owner:INT BUSINESS MASCH CORP

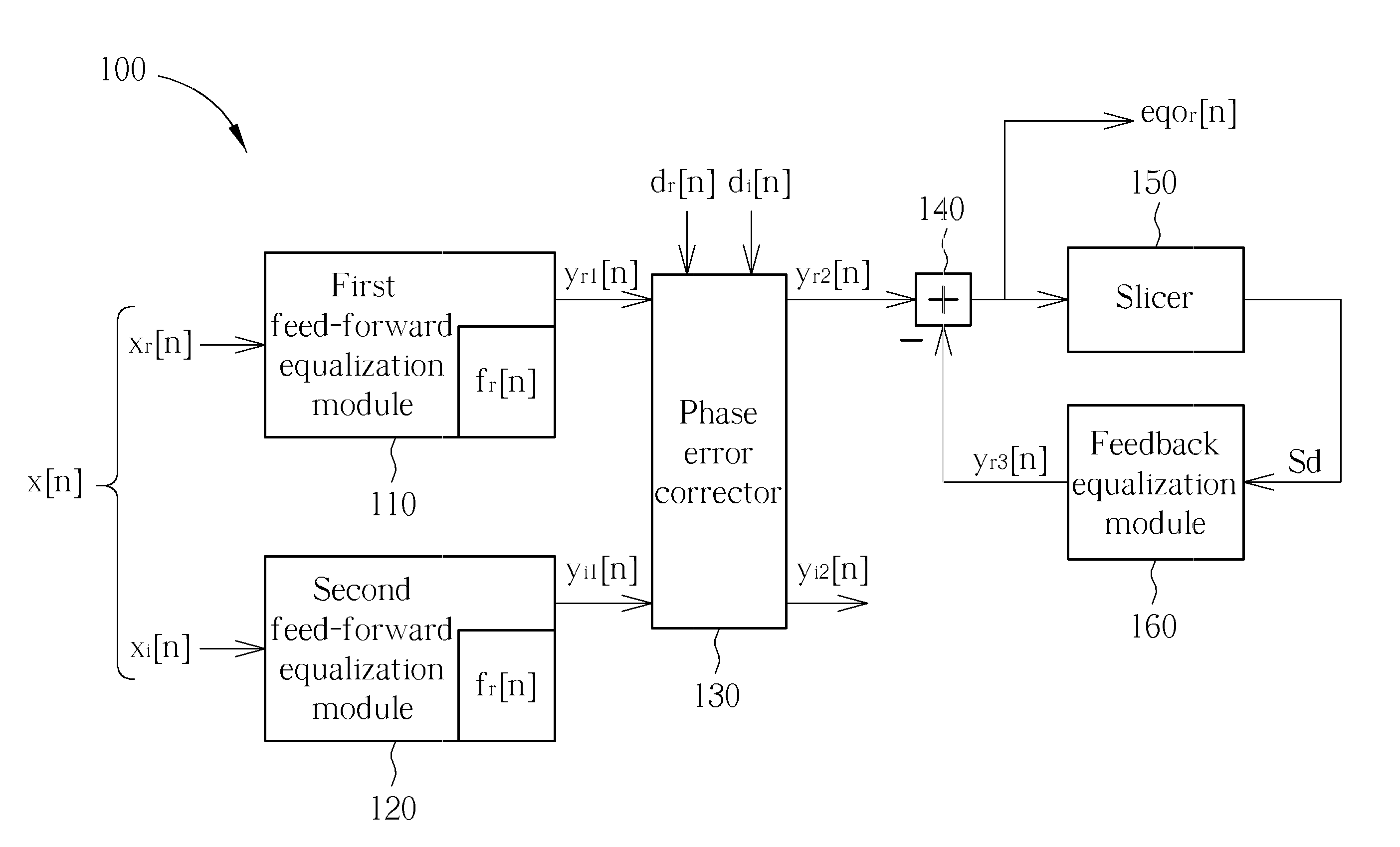

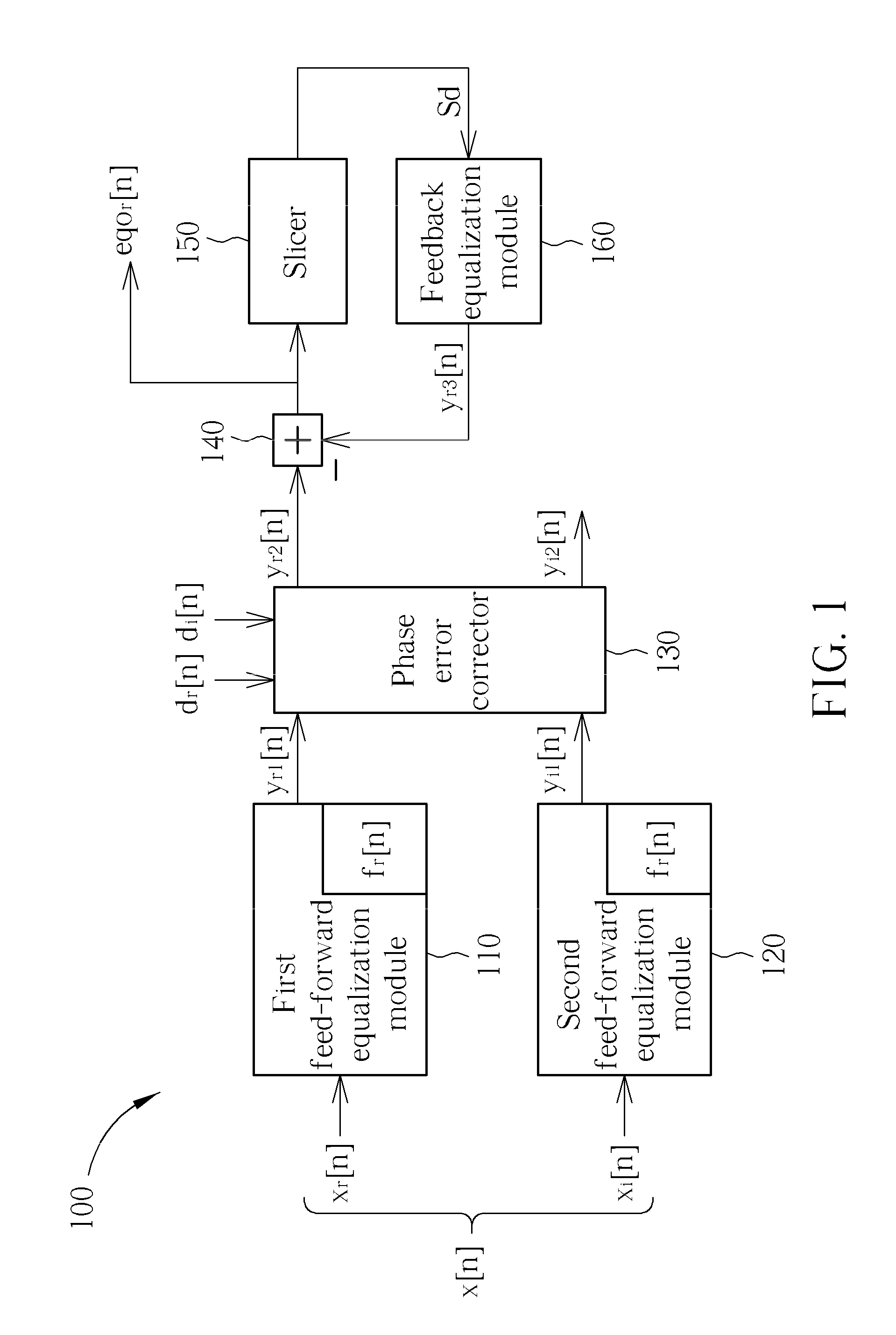

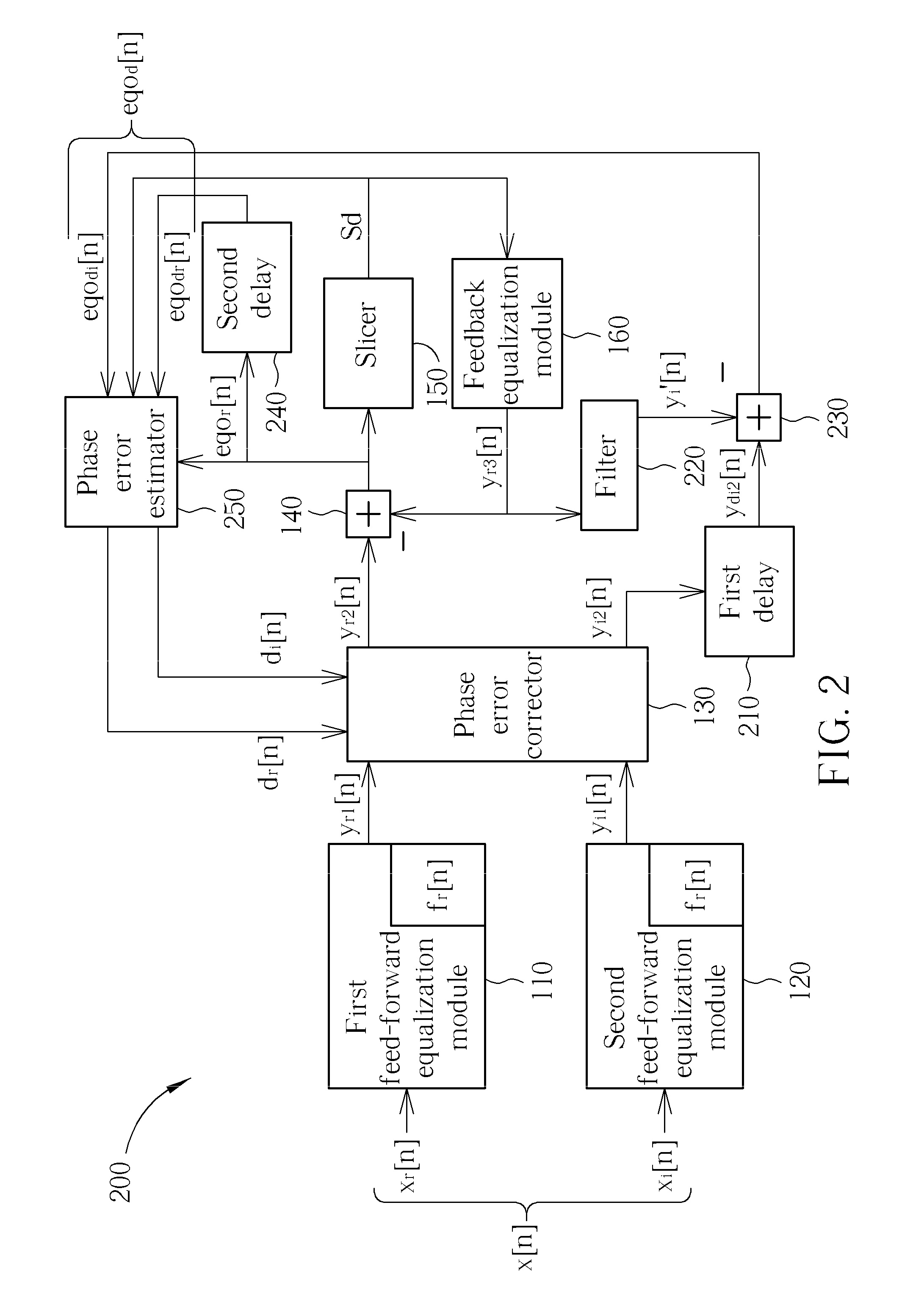

Equalizer and method applied thereto

ActiveUS20100111158A1Multiple-port networksTransmission control/equlisationFeed forward equalizationPhase error

The equalizer presented includes a first feed-forward equalization module, a second feed-forward equalization module, and a phase error corrector. The first and the second feed-forward equalization modules respectively receives an input real-part component signal and an input imaginary-part component signal of a complex input signal and respectively equalizes the input real-part component signal and the input imaginary-part component signal to generate a first real-part component signal and a first imaginary-part component signal. The phase error corrector is coupled to the first and the second feed-forward equalization modules for adjusting a complex phase corresponding to the first real-part component signal and the first imaginary-part component signal to generate a second real-part component signal and a second imaginary-part component signal according to a phase error information.

Owner:REALTEK SEMICON CORP

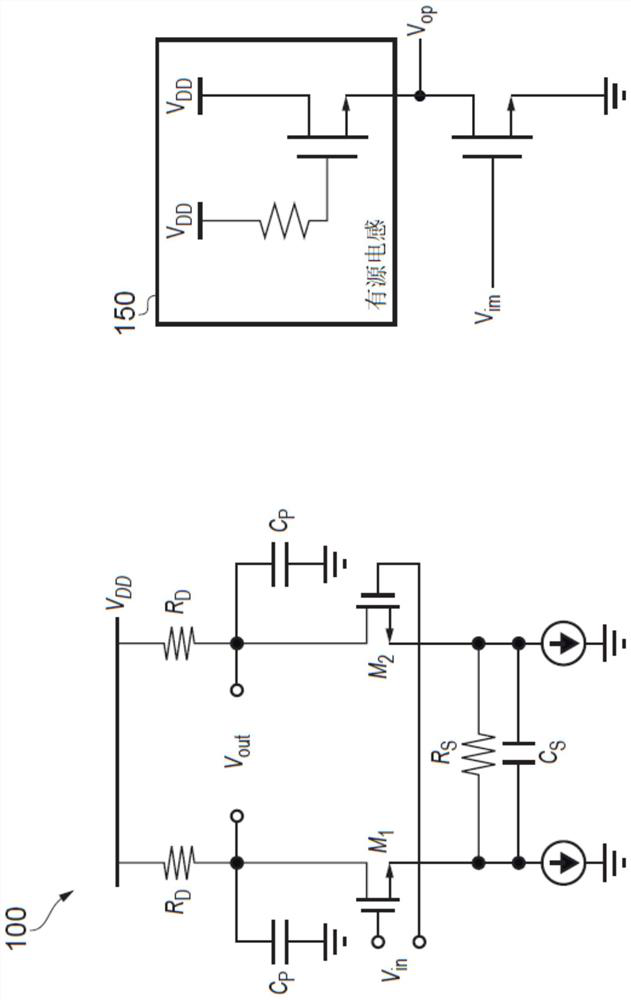

Low power receiver with equalization circuit, communication unit and method thereof

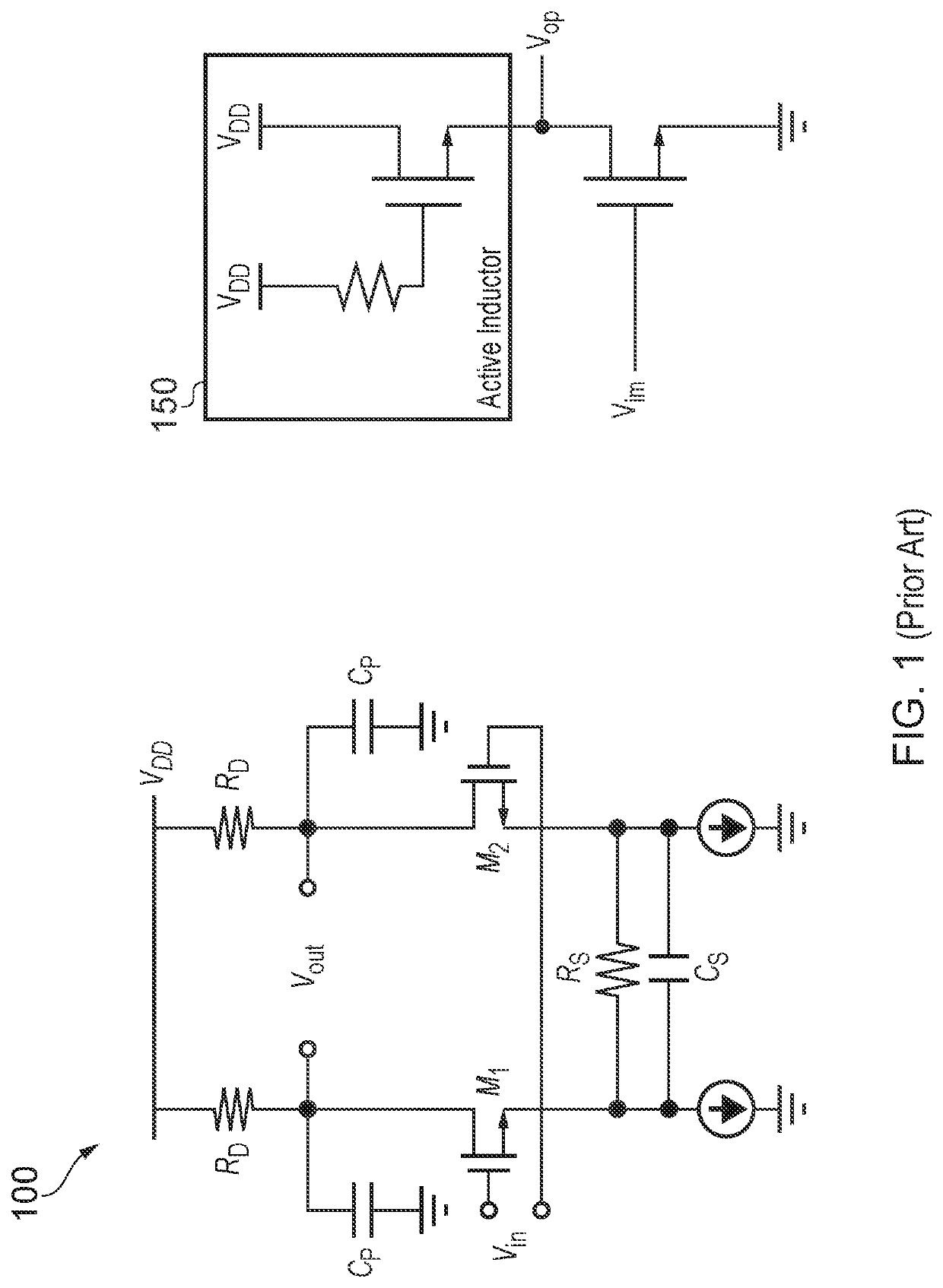

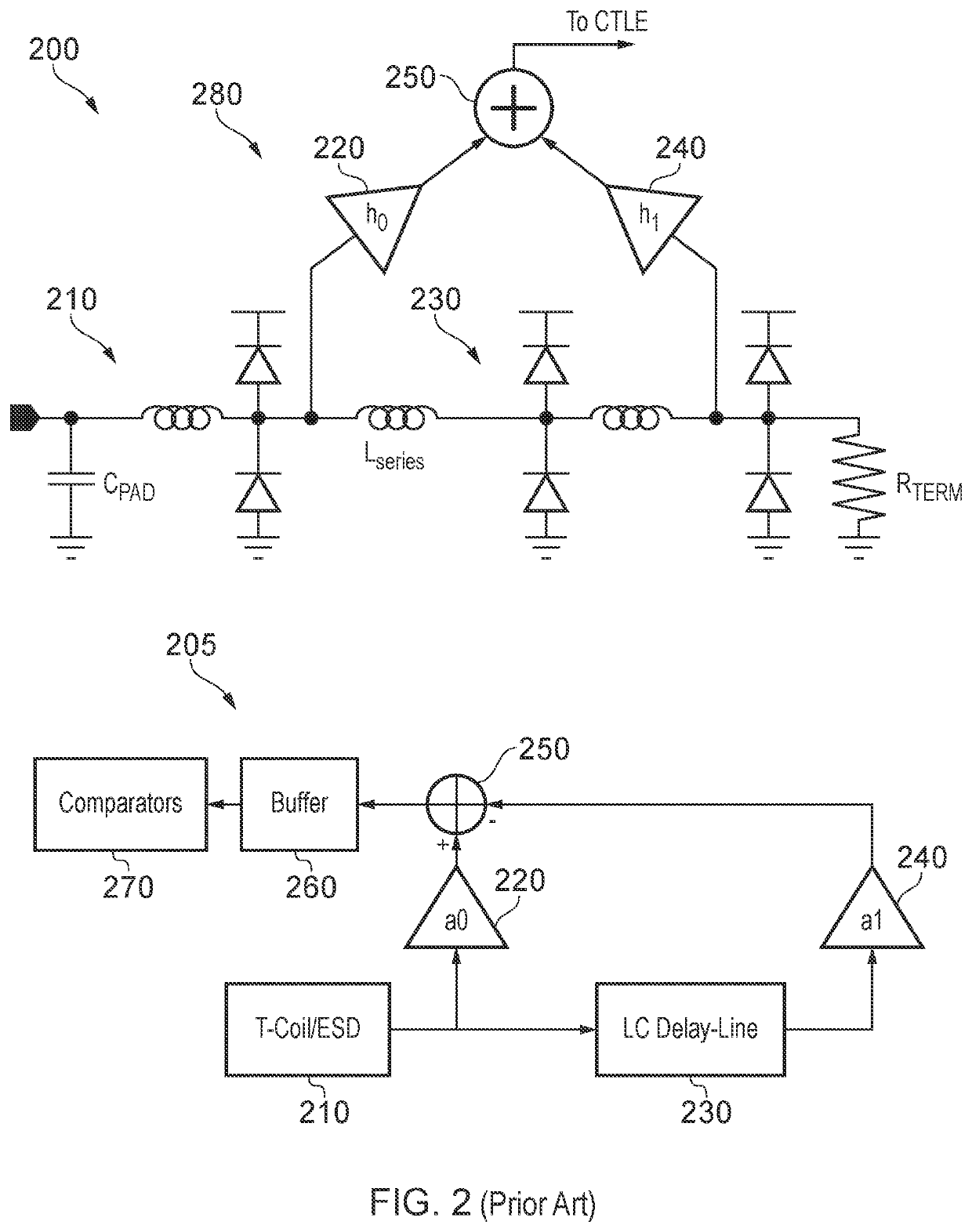

The invention provides a low power receiver with a continuous time linear equalizer (CTLE) based on feed forward equalization (FFE). The FFE CTLE comprises: an input for receiving an input signal; a first main path is operably coupled to the input and includes a source follower transistor arranged to apply a scaling factor to a received input signal; the second path is operably coupled to the input and includes a delayer arranged to delay the received input signal and a common source transistor arranged to apply a scaling factor to the delayed received input signal, where the source follower transistor and the common source transistor are connected as a single SF-CS stage, the output of the common source transistor is arranged to subtract the output of the common source transistor from the output of the source follower transistor.

Owner:MEDIATEK SINGAPORE PTE LTD SINGAPORE

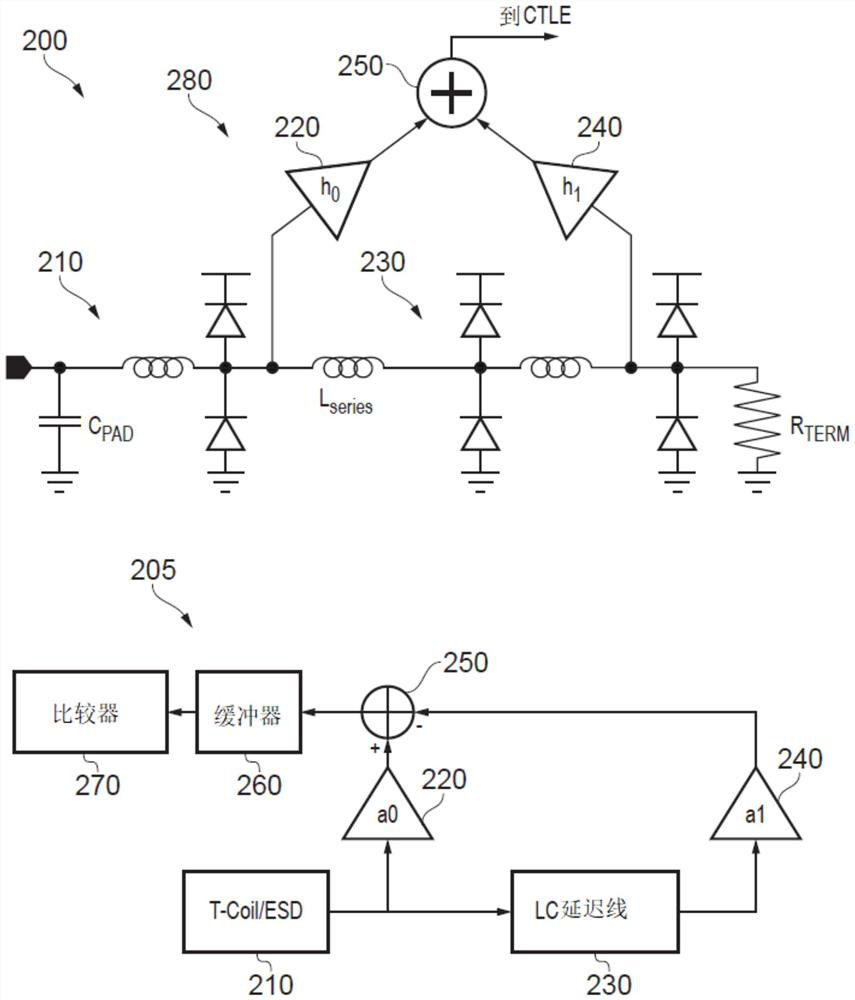

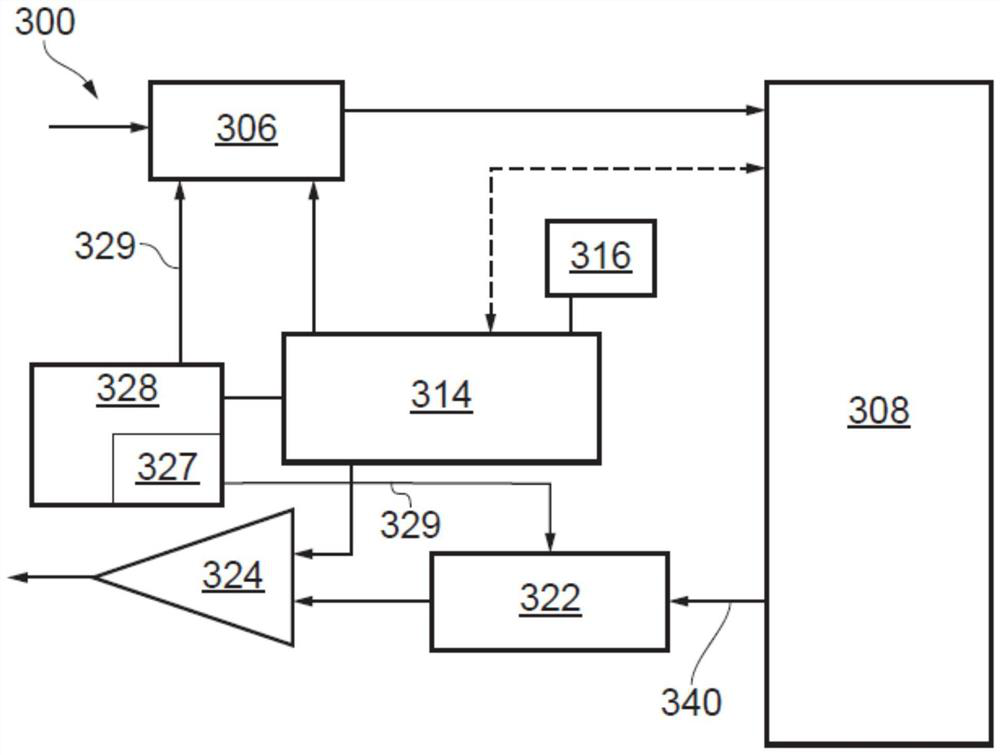

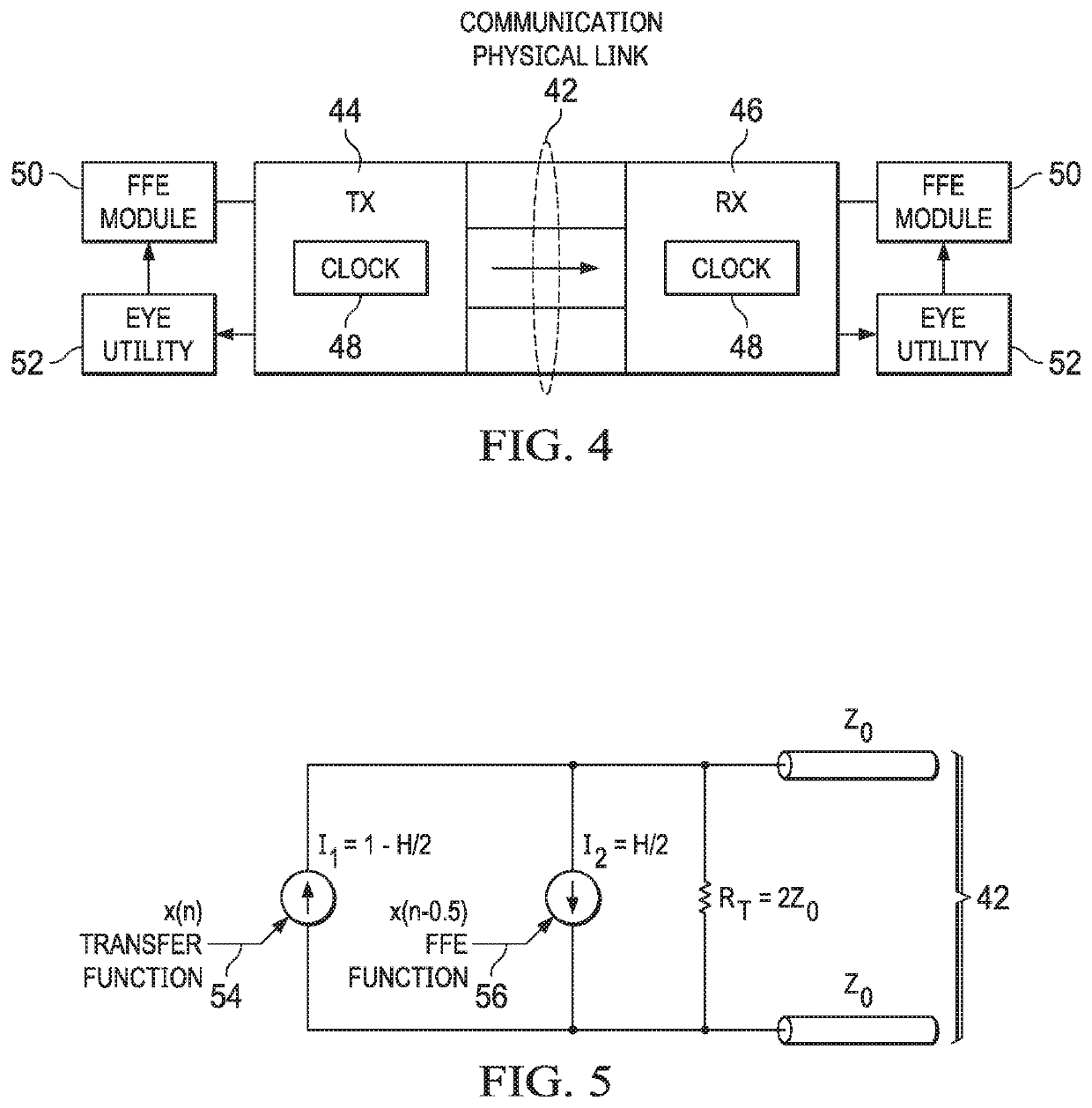

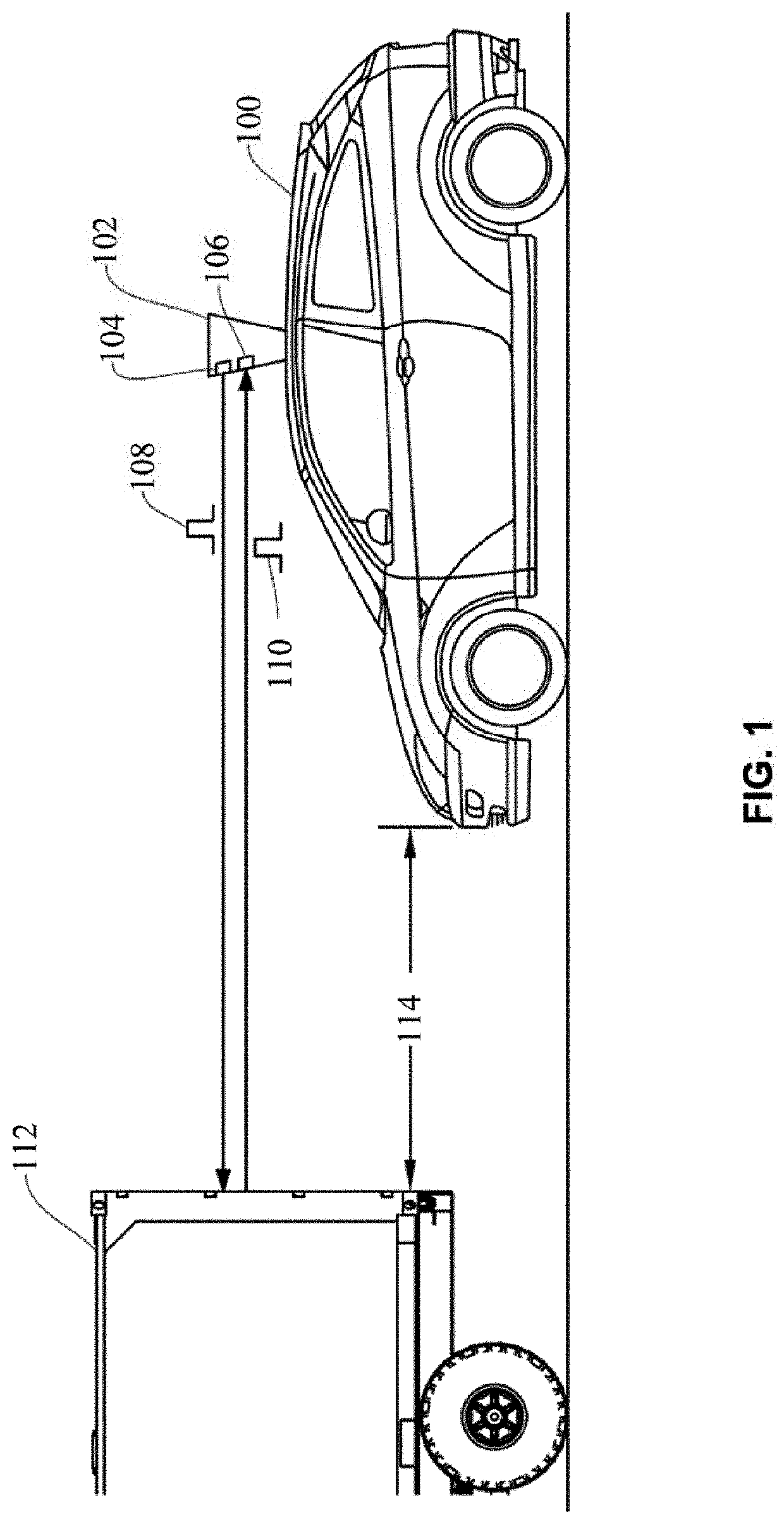

Information handling system half unit interval equalization

ActiveUS10560290B2High strengthReduce disadvantagesTransmitter/receiver shaping networksElectric digital data processingEqualizationInformation handling system

Owner:DELL PROD LP

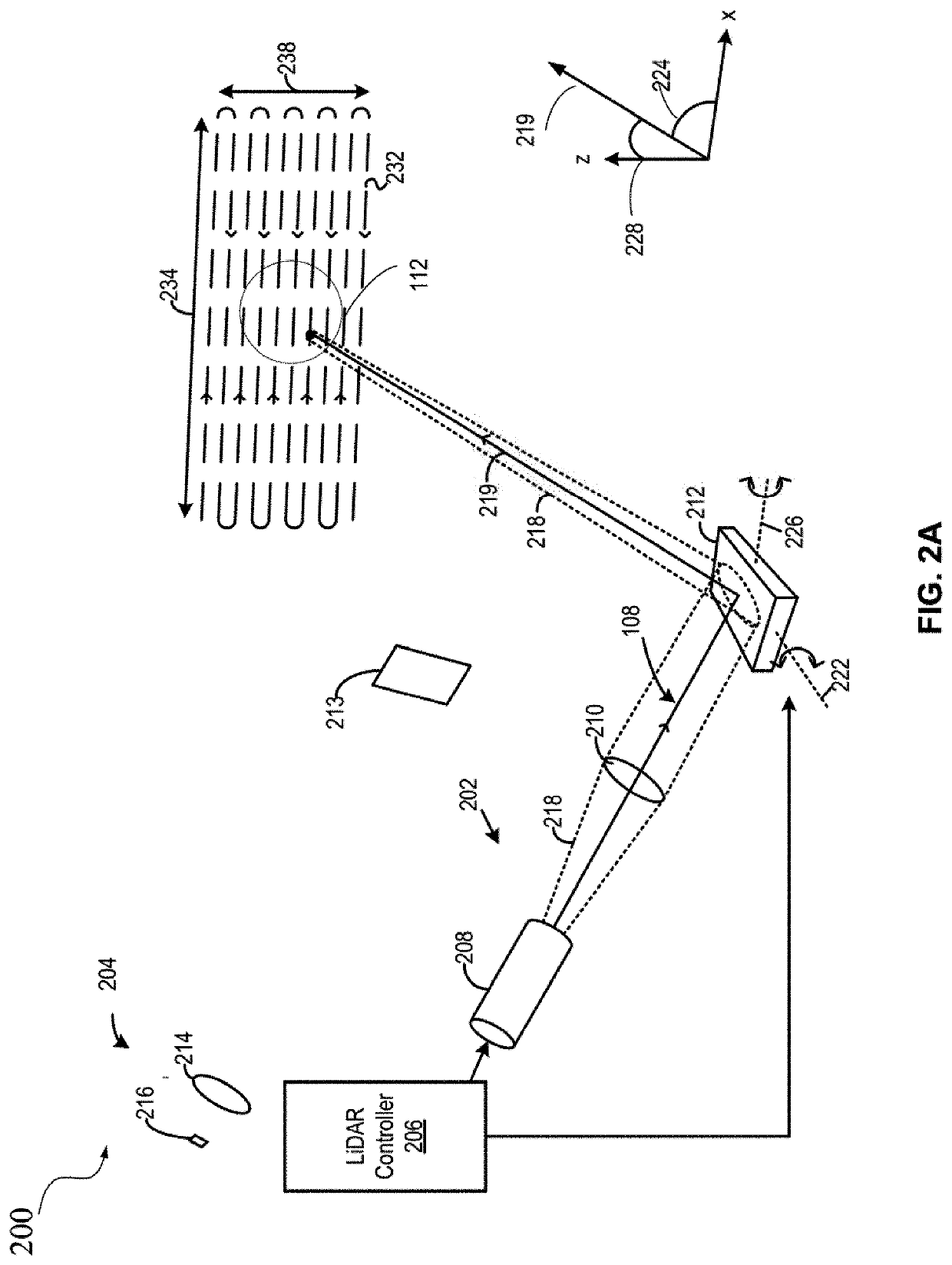

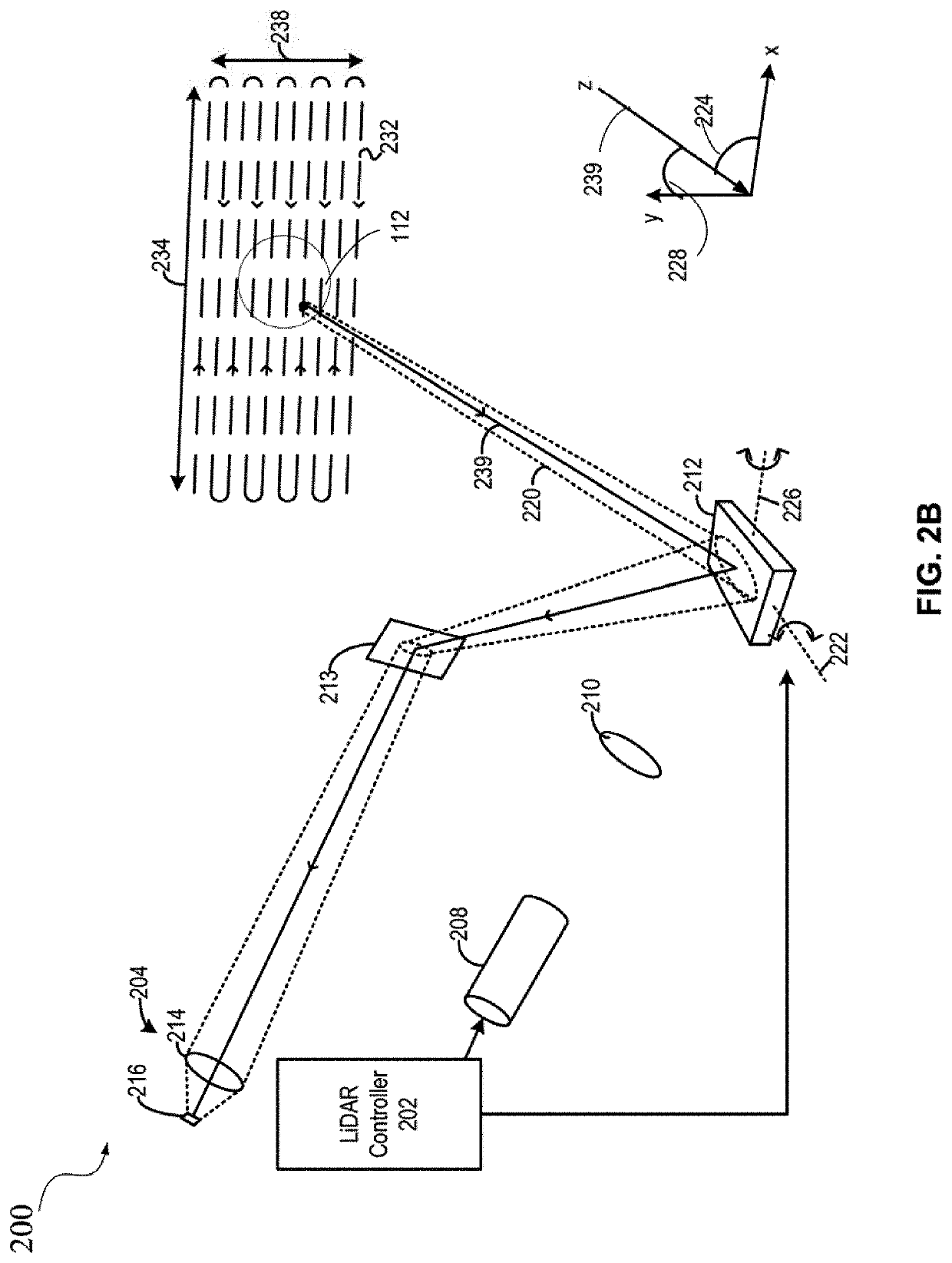

Feed-forward equalization for enhanced distance resolution

PendingUS20220308188A1Reduce Intersymbol InterferenceReduce gainElectromagnetic wave reradiationDetector circuitsPhotodetector

Apparatus and methods for reducing inter symbol interference from reflected laser pulses that are received close in time. A laser is provided to emit a laser beam pulse. A photodetector is mounted to receive a reflected laser beam pulse after reflecting off an object in an external environment, and produce a voltage signal corresponding to the reflected laser beam pulse. The voltage signal is provided to a delay path circuit having a delay line and a gain control circuit to provide a delayed, reduced amplitude voltage signal. The delayed, reduced amplitude voltage signal is subtracted from the voltage signal in a subtraction circuit to produce a truncated pulse. The output of the subtraction circuit is provided to a pulse detector circuit to detect the arrival time of the leading edge of the truncated pulse.

Owner:BEIJING VOYAGER TECH CO LTD

Embedded wire feed forward equalization

ActiveUS20170214556A1Transmitter/receiver shaping networksWaveguidesElectrical resistance and conductanceCapacitance

Embodiments of the present disclosure provide methods and apparatus for providing feed forward equalization to a communication line by providing a resistance and a capacitance to the communication line. The method includes determining the resistance based on a desired value of feed forward equalization to provide to a communication line, determining the capacitance based on the desired value of feed forward equalization to provide to the communication line, providing a layer of resistive material between a first conductor and a second conductor of the communication line, wherein a dimension of the layer of resistive material is determined based on the determined resistance and providing a layer of dielectric material between the first conductor and the second conductor, wherein a dimension of the layer of dielectric material is determined based on the determined capacitance.

Owner:IBM CORP

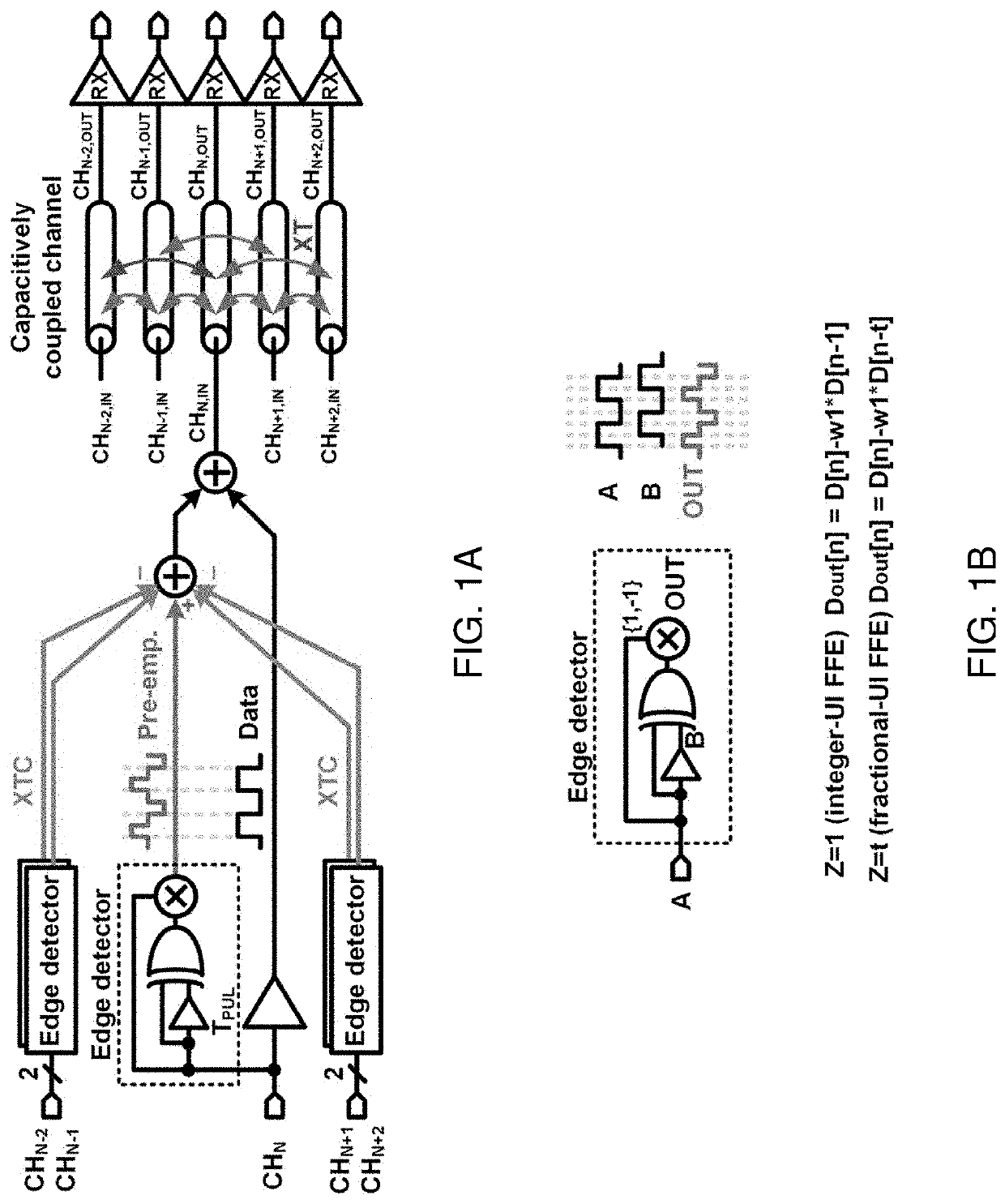

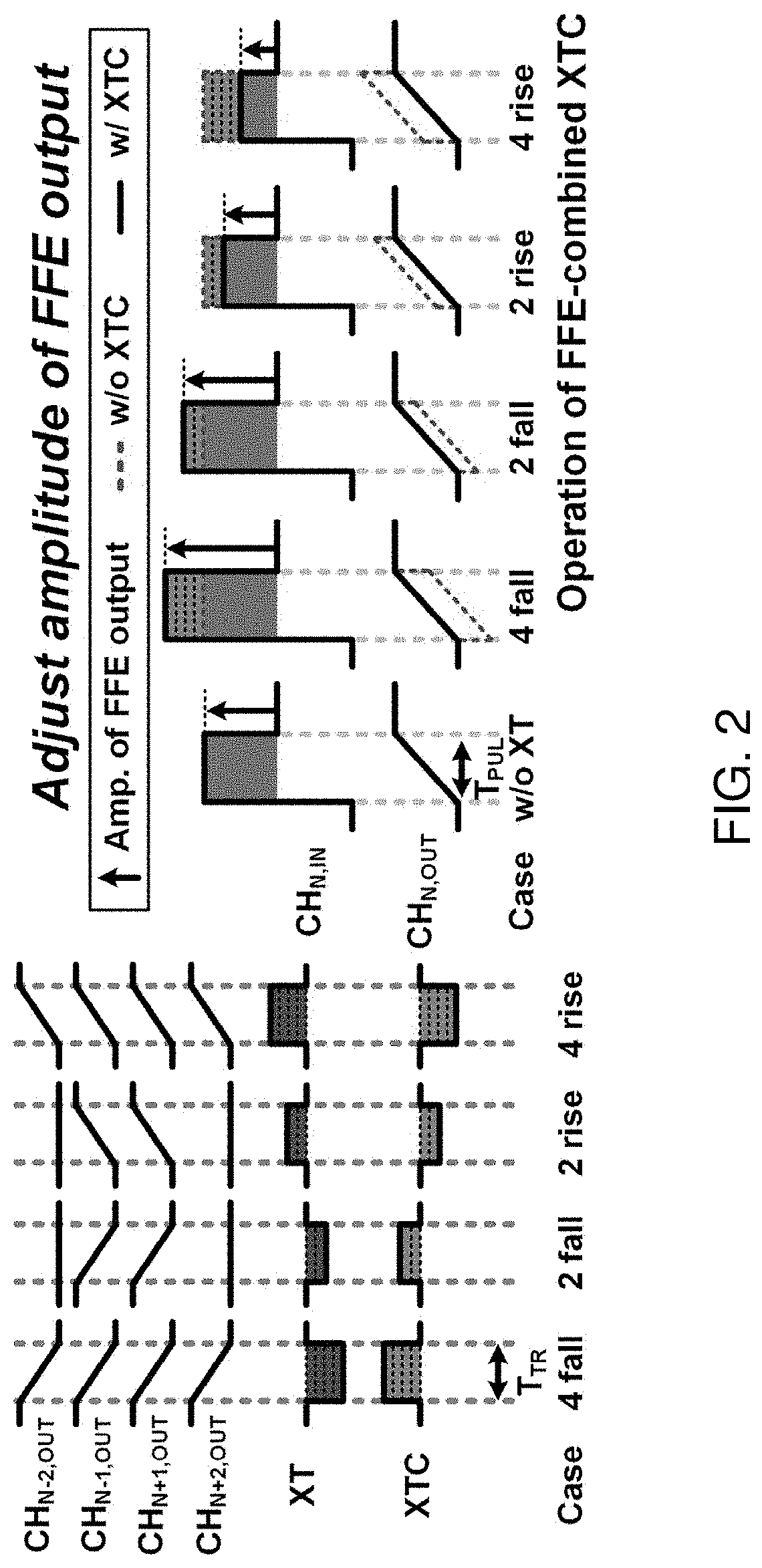

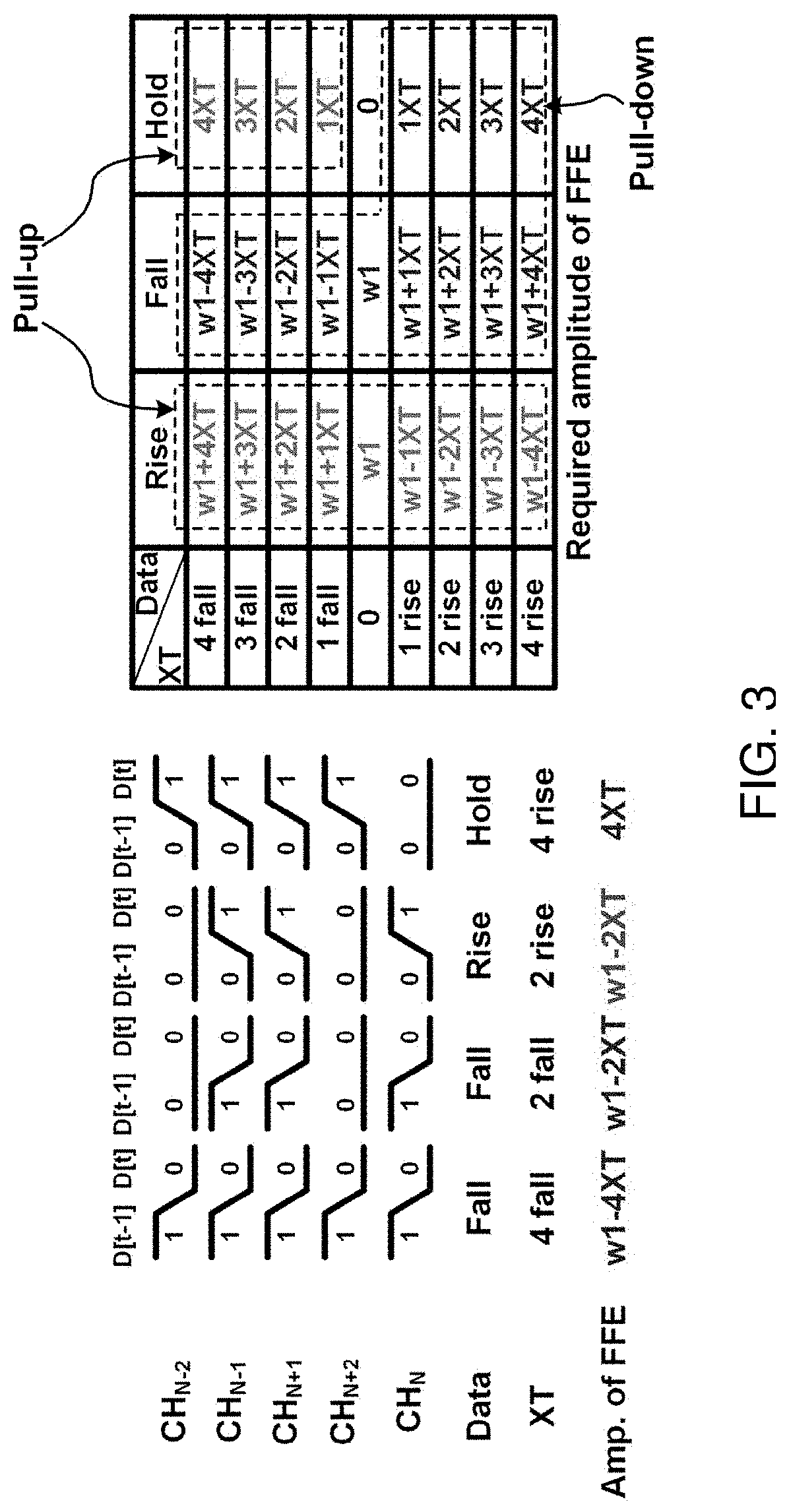

Transmitter having merged FFE and XTC, and transmission method thereof

ActiveUS11283655B2Degree of complexity can be reducedCrosstalk is eliminatedEqualisersLine-faulsts/interference reductionCrosstalk cancellationControl theory

Provided is a transmitter performing at least feed-forward equalizing and crosstalk cancellation, the transmitter including: a main driver (20) generating waveform including data to be transmitted; and an FFE driver block (40) connected to the main driver in parallel, and generating waveform that is acquired by applying a sum of amplitude for feed-forward equalizing and amplitude for crosstalk cancellation, so as to adjust the waveform generated by the main driver.

Owner:SEOUL NAT UNIV R&DB FOUND

A feed-forward equalization pre-emphasis circuit and processing method, usb driver

ActiveCN105243041BAvoid the problem of intersymbol interference and loss of dataGuaranteed communication qualityElectric digital data processingAudio power amplifierCommunication quality

Owner:豪威模拟集成电路(北京)有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com