Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

107 results about "Delay analysis" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Delay Analysis. Forensic delay analysis is the process of carefully sifting through project records in order to measure critical delays and also to identify the causes of, and liability for, those delays.

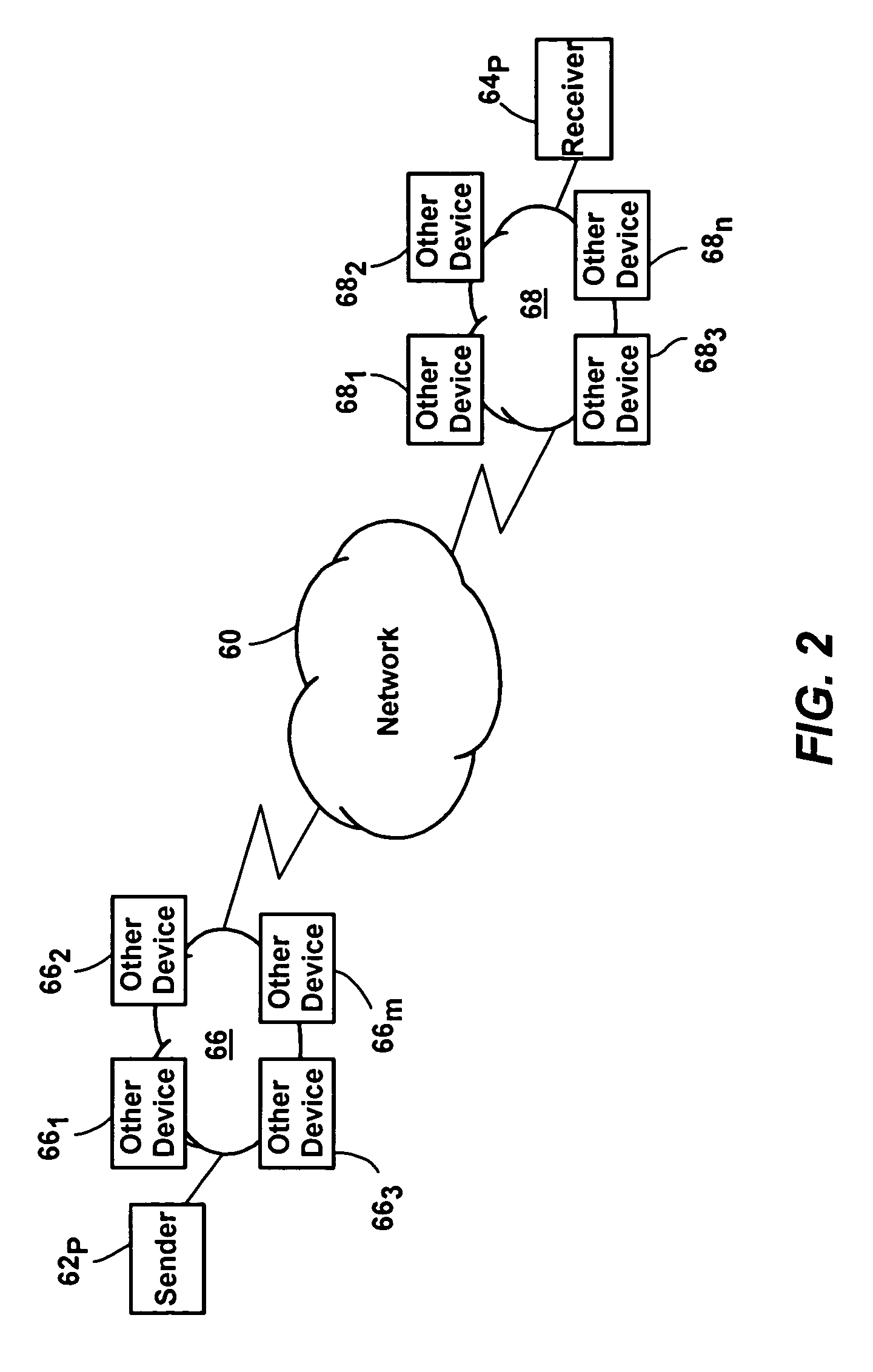

Network latency analysis packet and method

ActiveUS20070274227A1Efficient methodAttenuation bandwidthError preventionTransmission systemsTimestampNetwork packet

A packet and a method for analyzing network latency are disclosed. The disclosed systems and methods measure the latency between nodes in a network and do so while using less bandwidth and processing than traditional methods by using a packet to traverse a network and collect timestamps at various nodes so that the delay in transit time between nodes can be calculated when the packet returns to a server.

Owner:AMERICAN TELEPHONE & TELEGRAPH CO

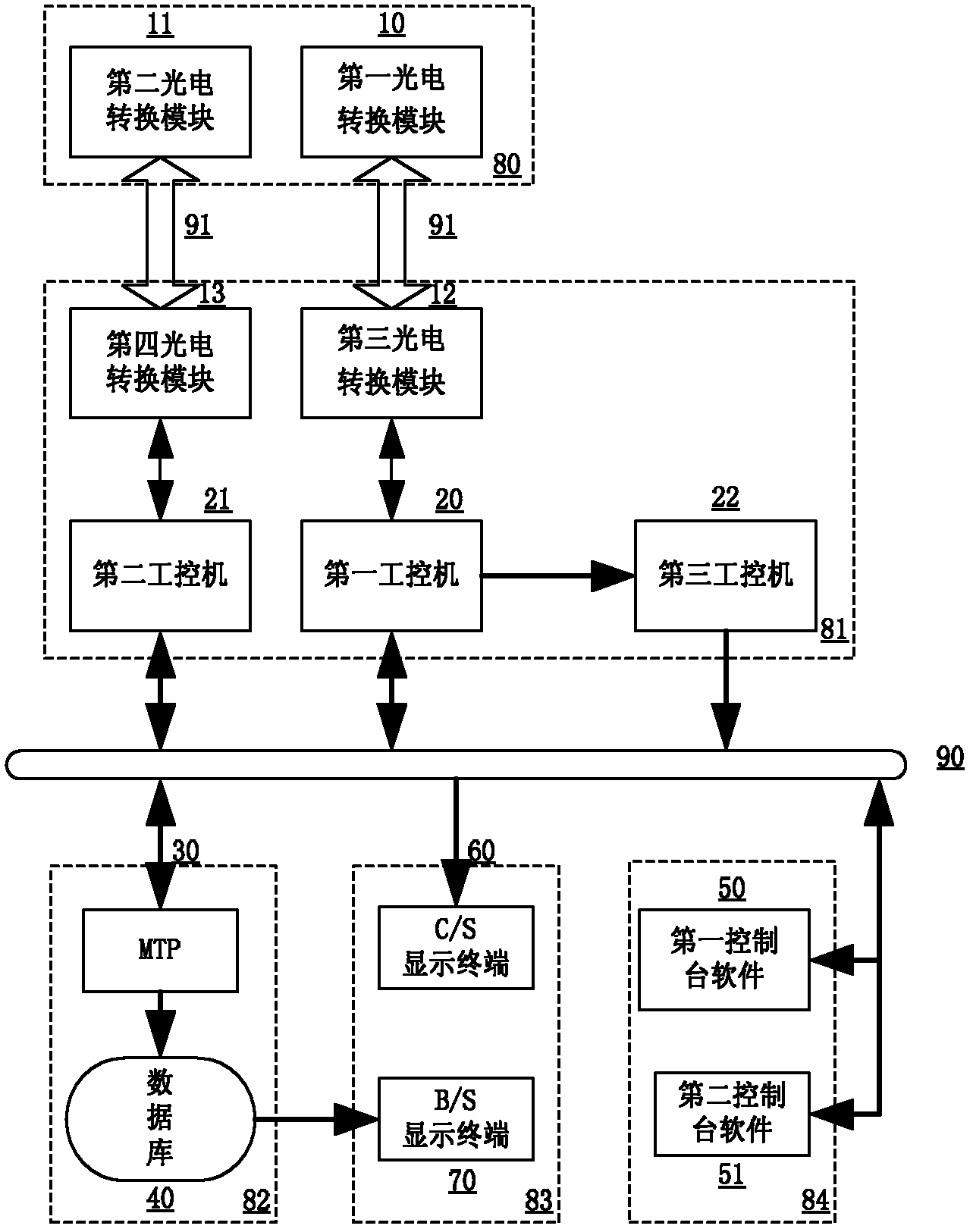

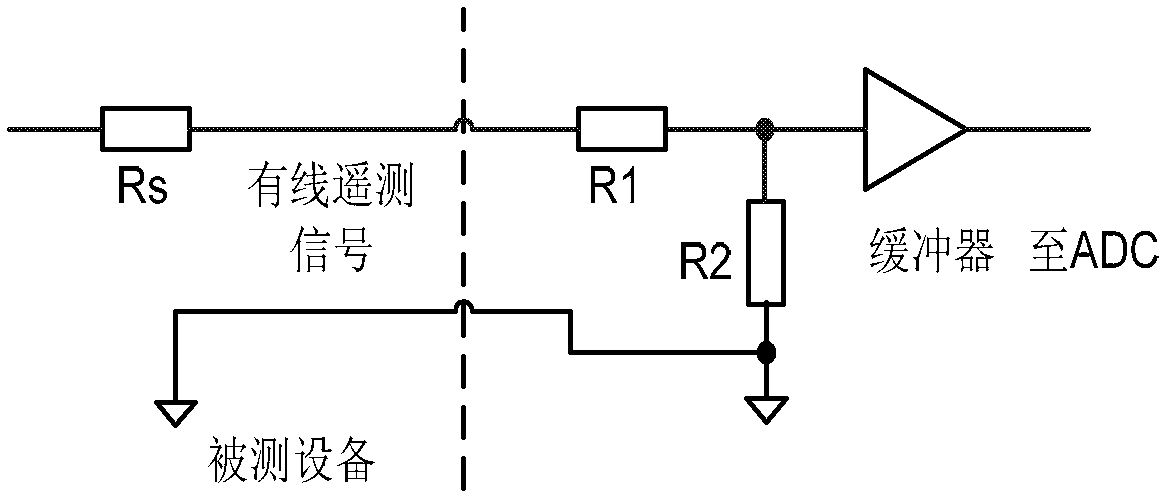

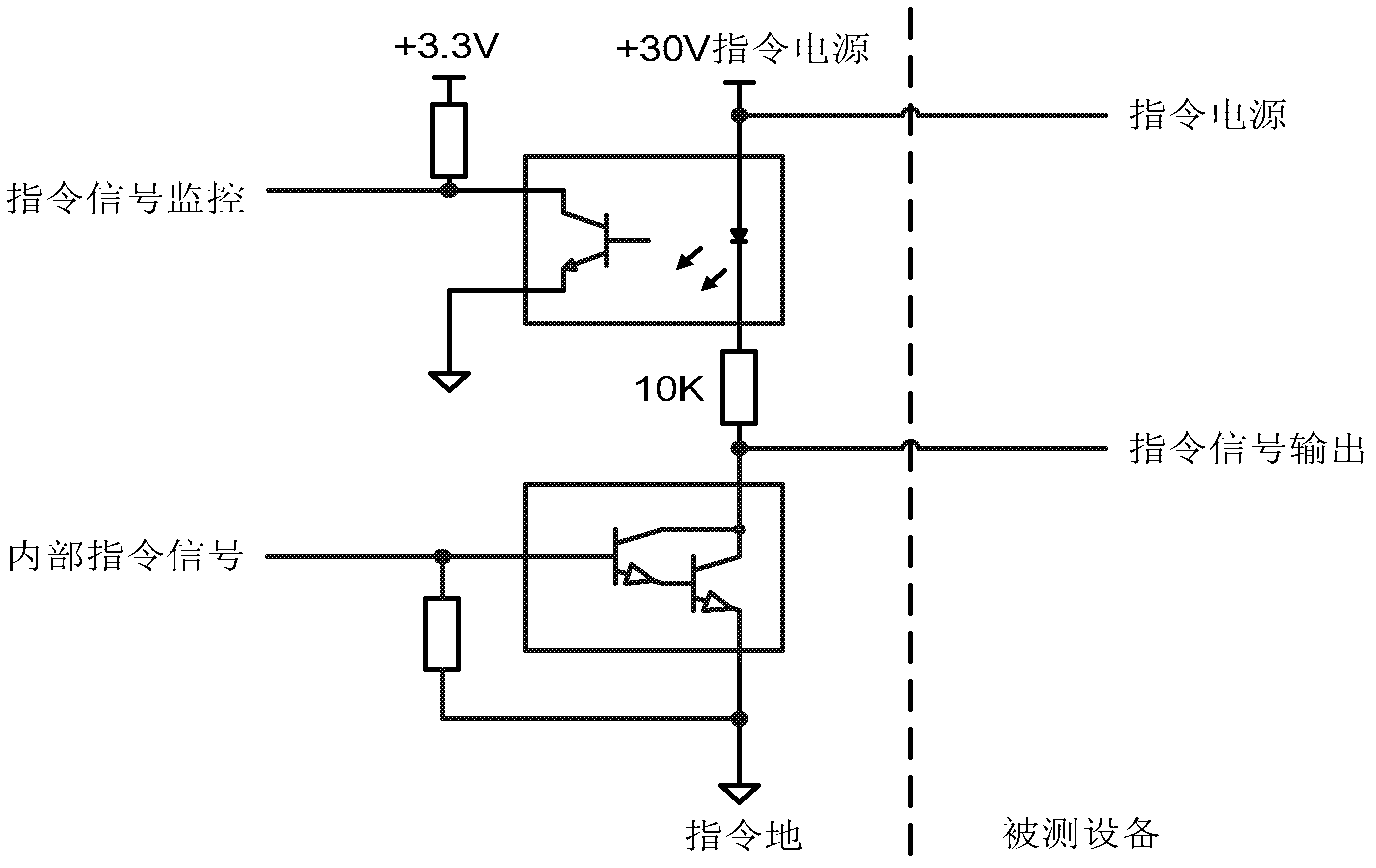

Universal satellite ground overall control test system

ActiveCN102520715AStrong automationStrong generalizationElectric testing/monitoringRemote controlSystem under test

Owner:BEIHANG UNIV

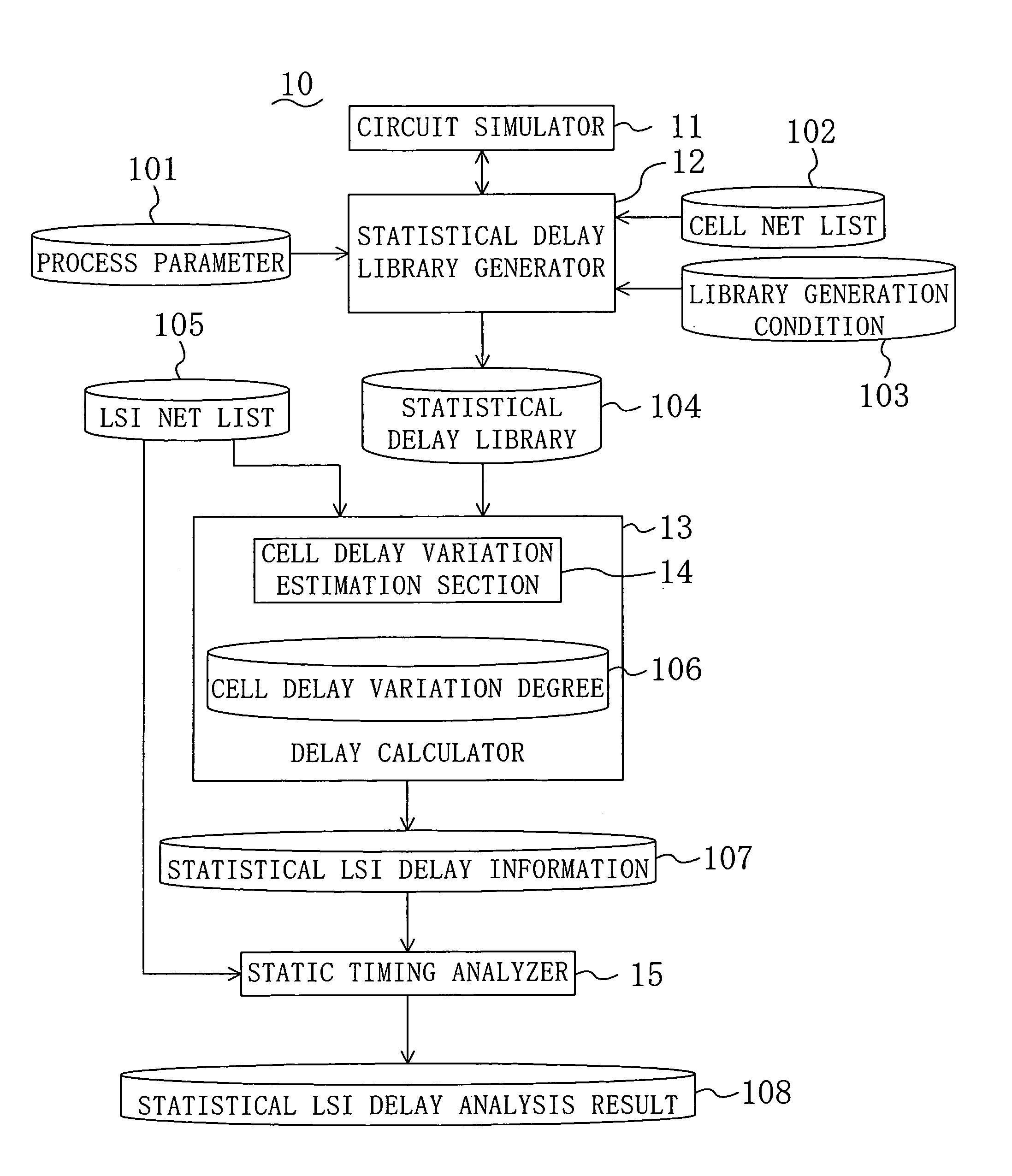

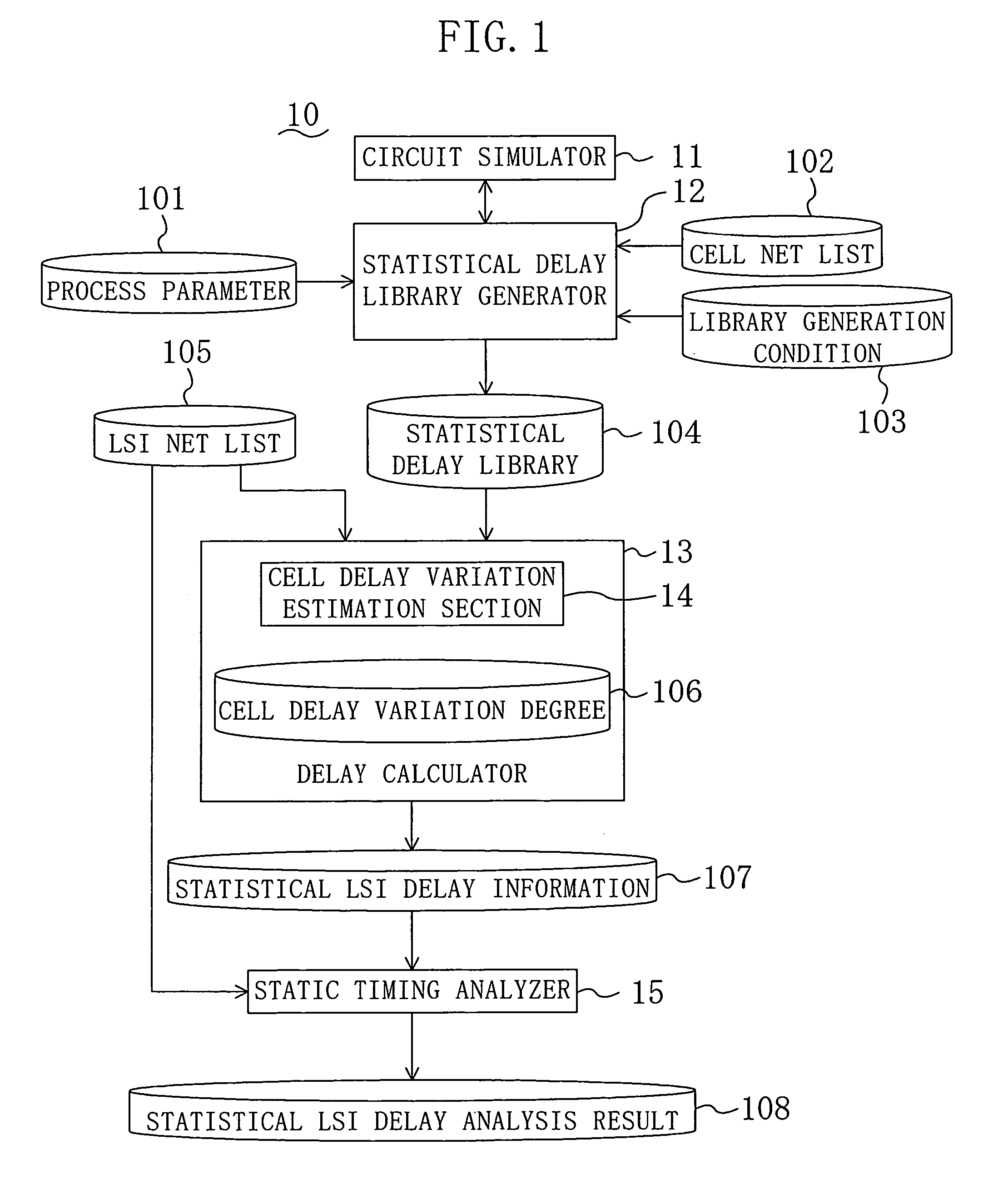

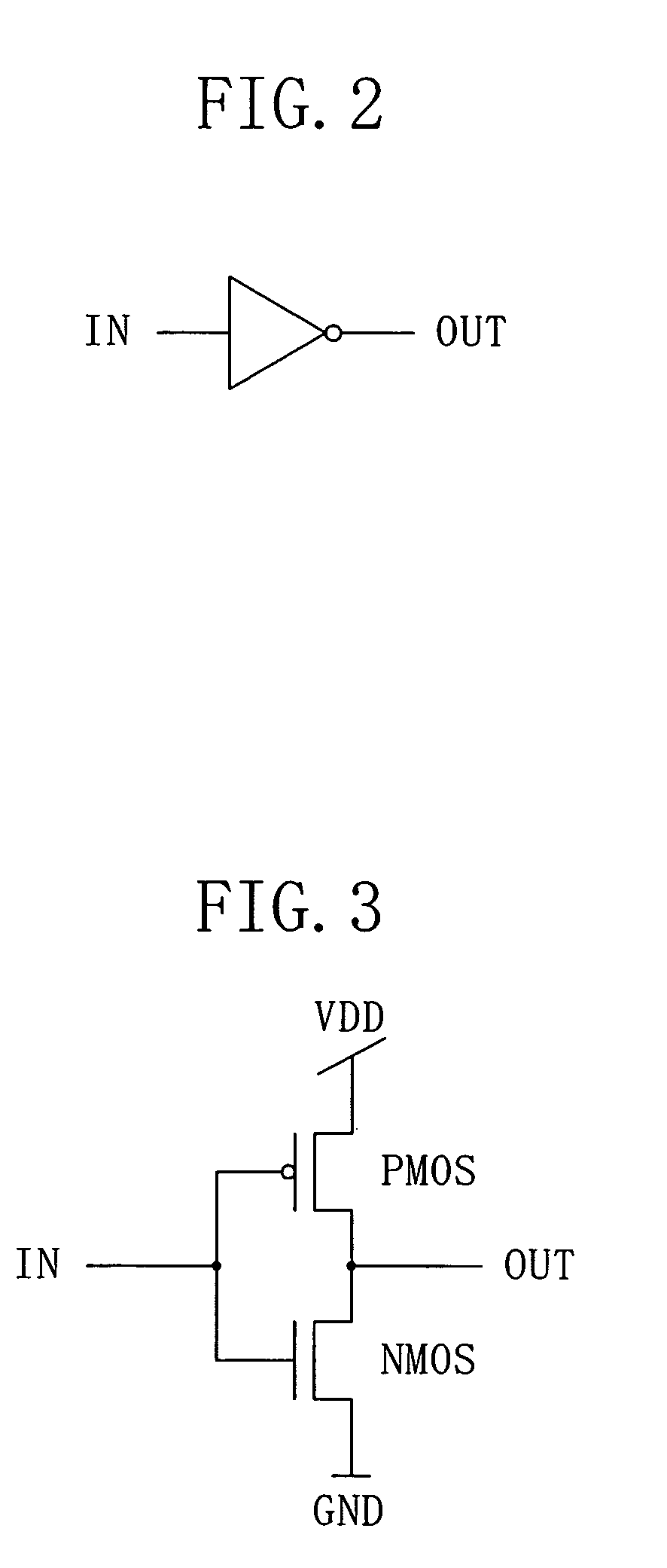

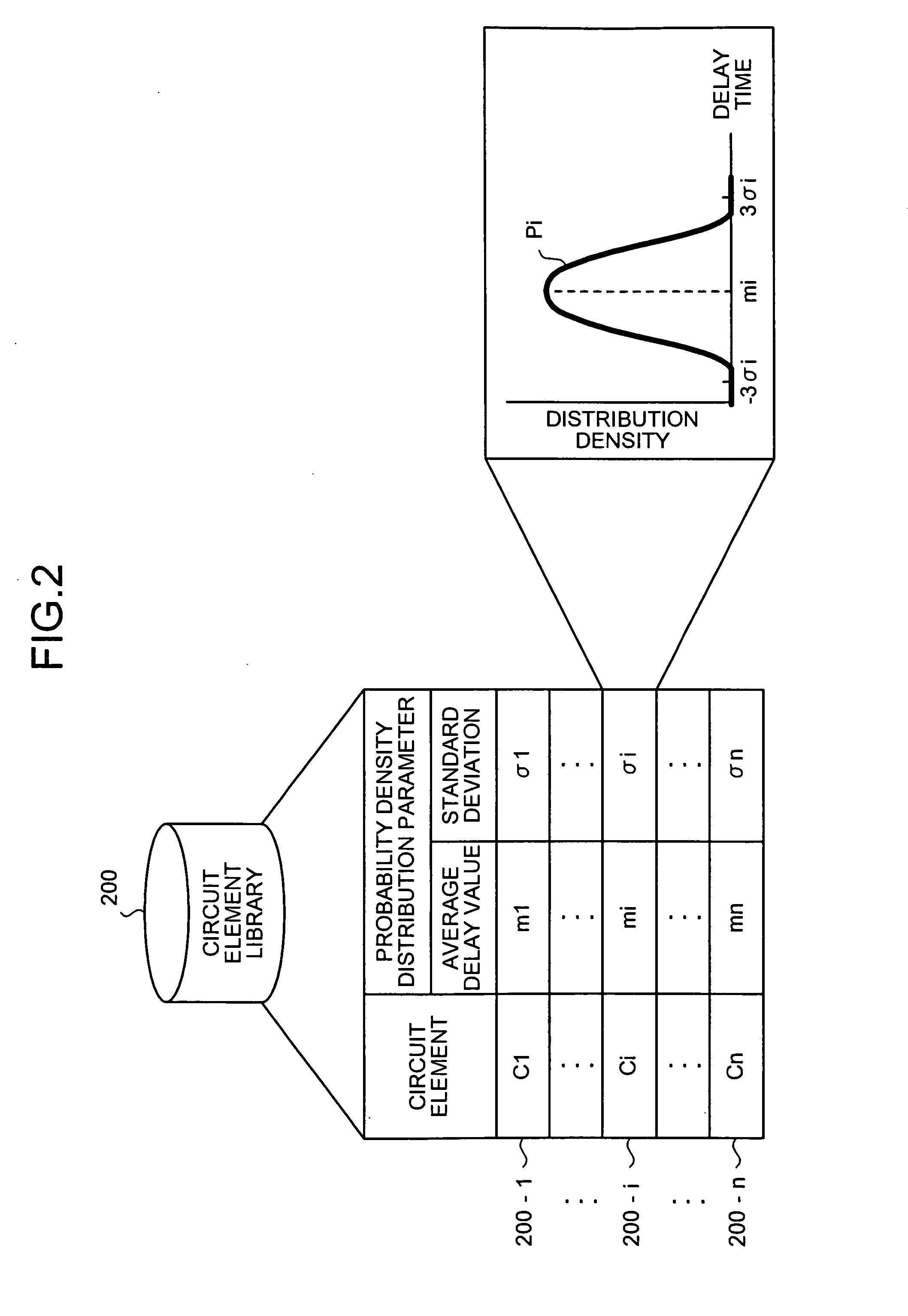

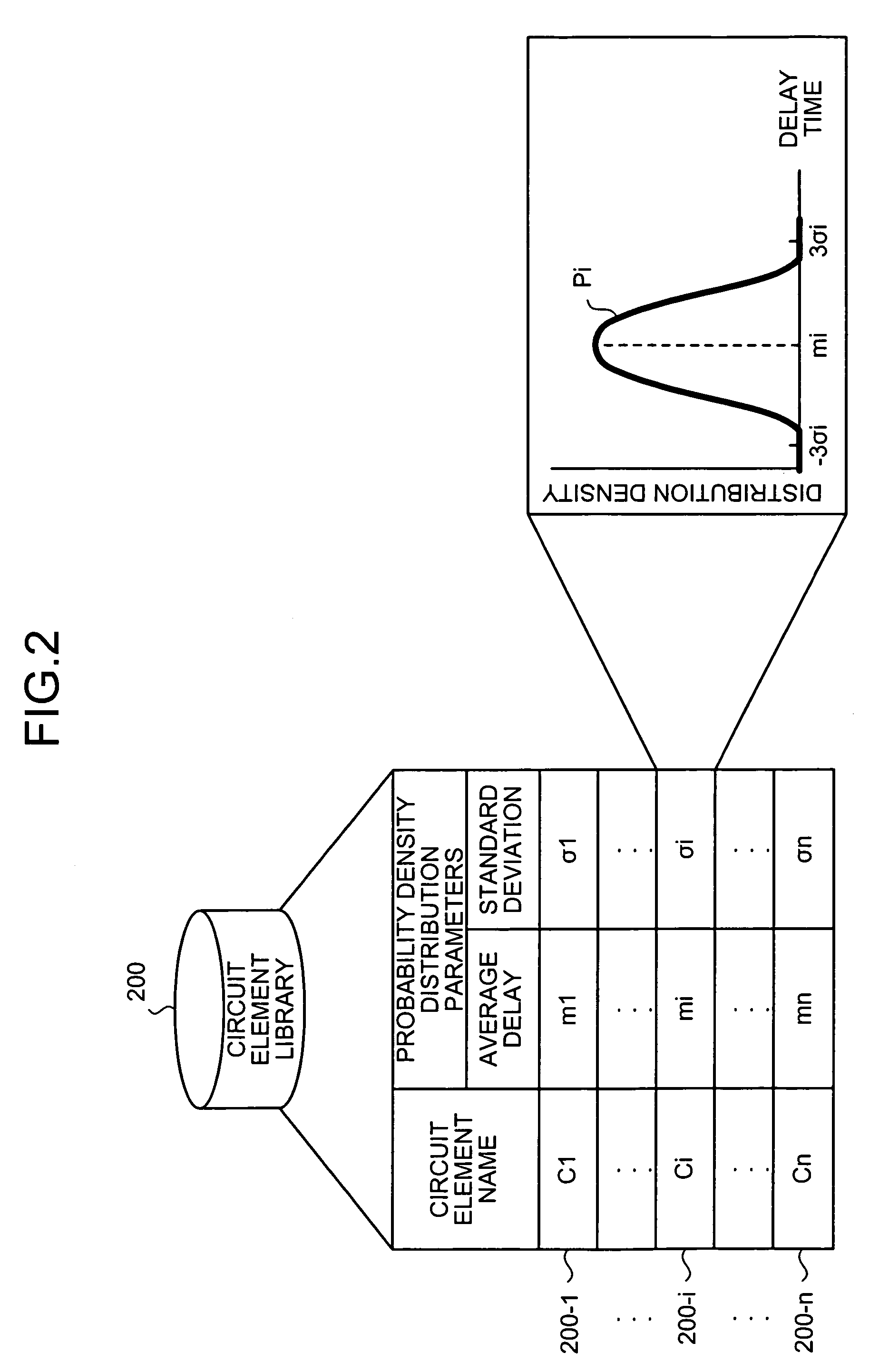

Apparatus for statistical LSI delay simulation

InactiveUS7239997B2Simple wayReliable resultsAnalogue computers for electric apparatusComputation using non-denominational number representationDriver circuitDelay analysis

A statistical delay simulation apparatus includes: a circuit simulator for simulating a circuit operation of a circuit cell constituting an LSI; a statistical delay library generator for driving the circuit simulator and generating, based on a process parameter and the like, a statistical delay library in which the dependency of a delay variation on a predetermined operation condition in each circuit cell is described; a delay calculator for calculating a delay amount of each circuit cell to generate a statistical LSI delay information file containing data on the calculated delay amount; and a static timing analyzer for simulating, based on data of the statistical LSI delay information file, an operation with a delay variation of the LSI to generate a statistical LSI delay analysis result file.

Owner:PANASONIC CORP

Histogram performance counters for use in transaction latency analysis

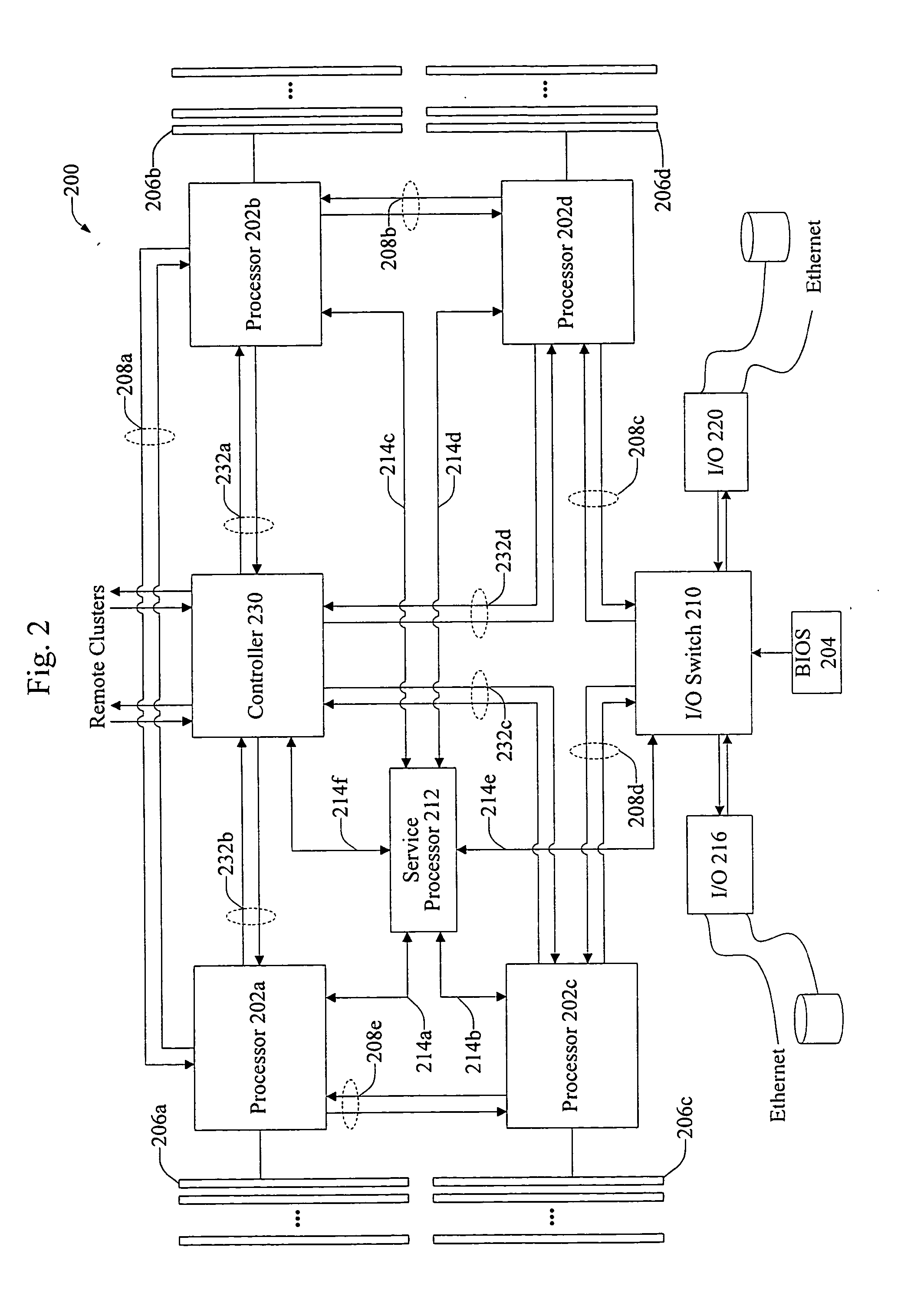

Methods and apparatus are described for measuring latency in computer systems. A computer system includes a processor, memory, and I / O. The processor is operable to initiate transactions involving the memory and the I / O. The computer system further includes a latency counter operable to measure a latency for each of selected ones of the transactions. The system also includes a plurality of histogram counters. Each histogram counter is operable to count the latencies corresponding to an associated latency range.

Owner:SANMINA-SCI CORPORATION

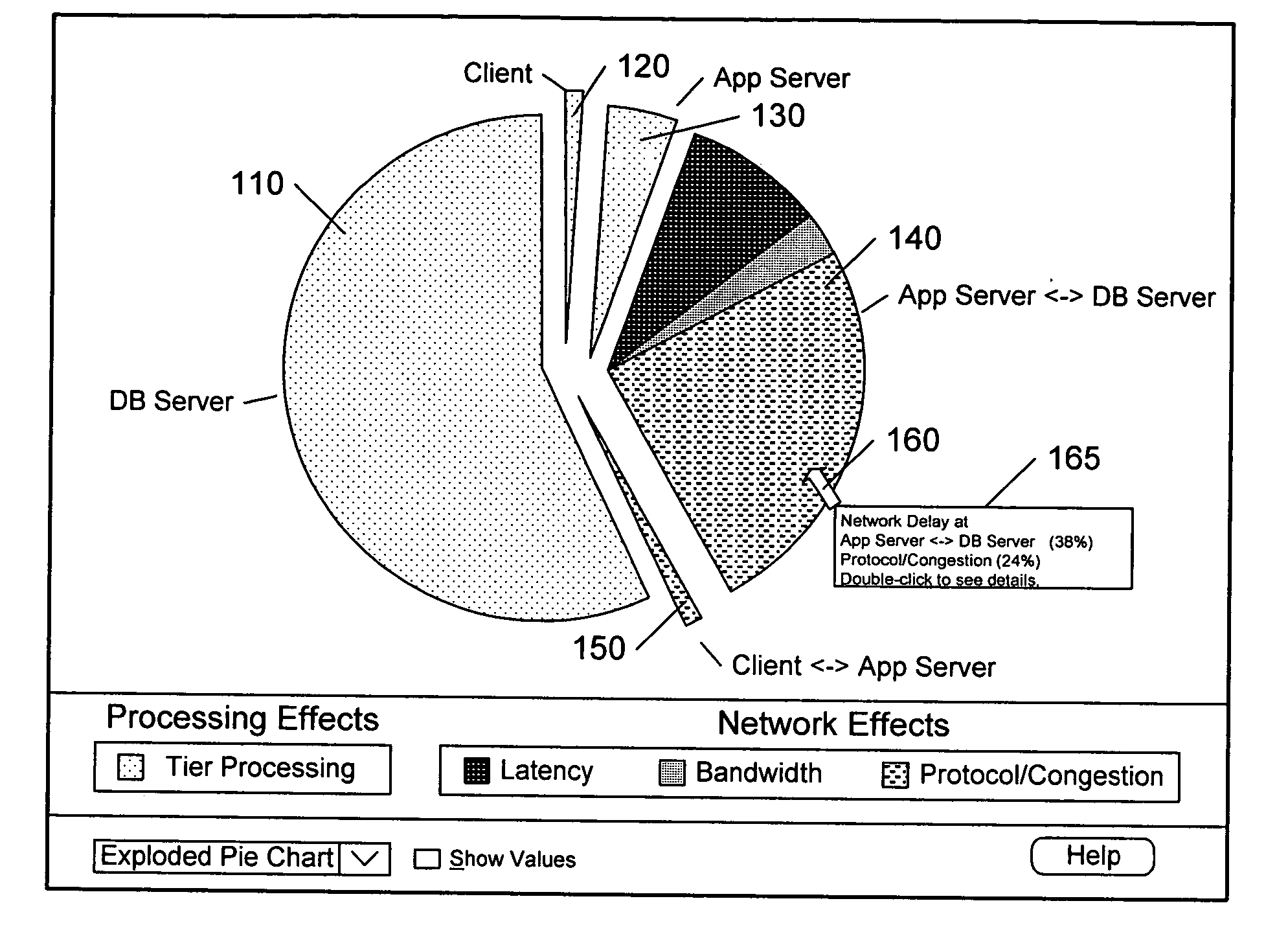

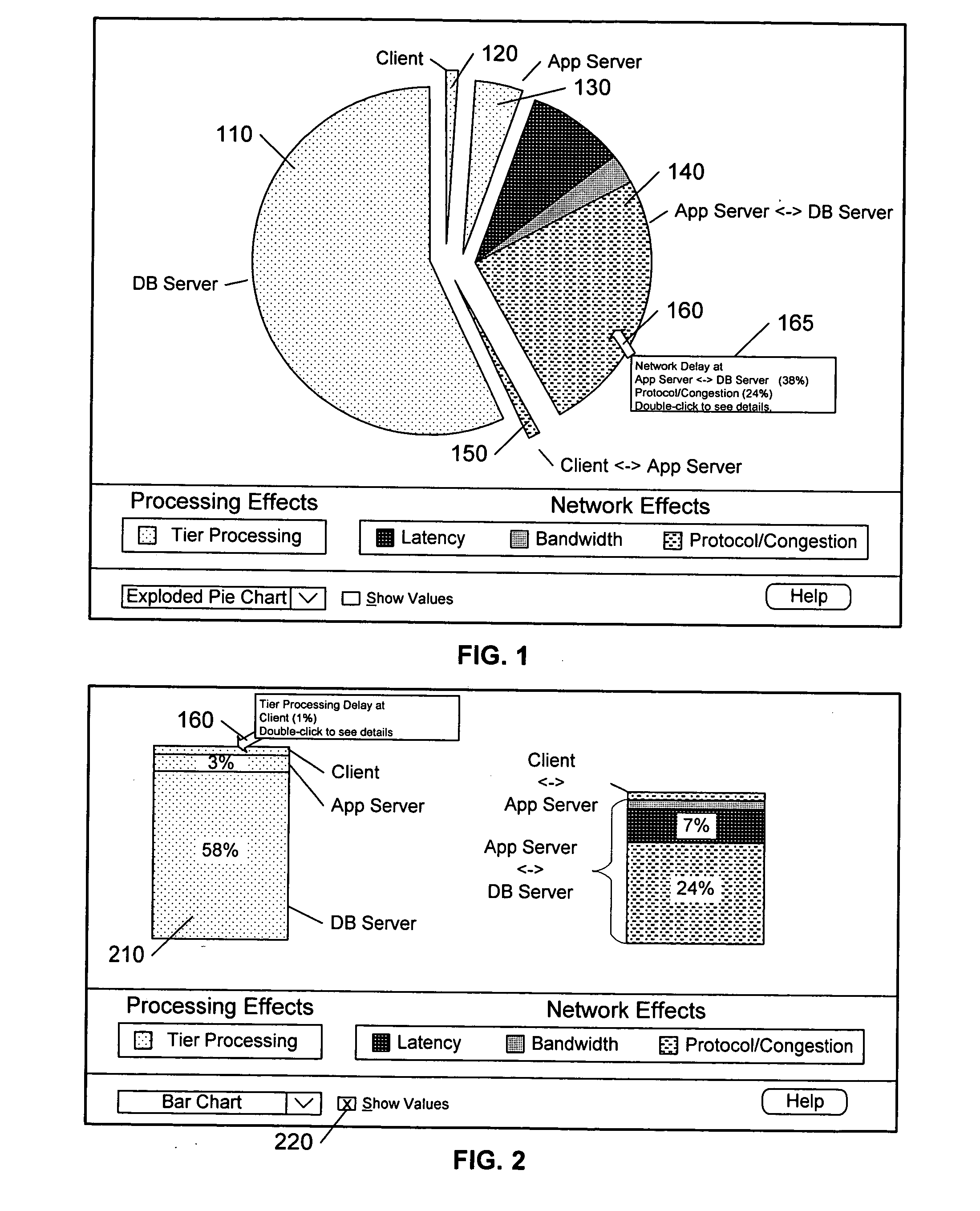

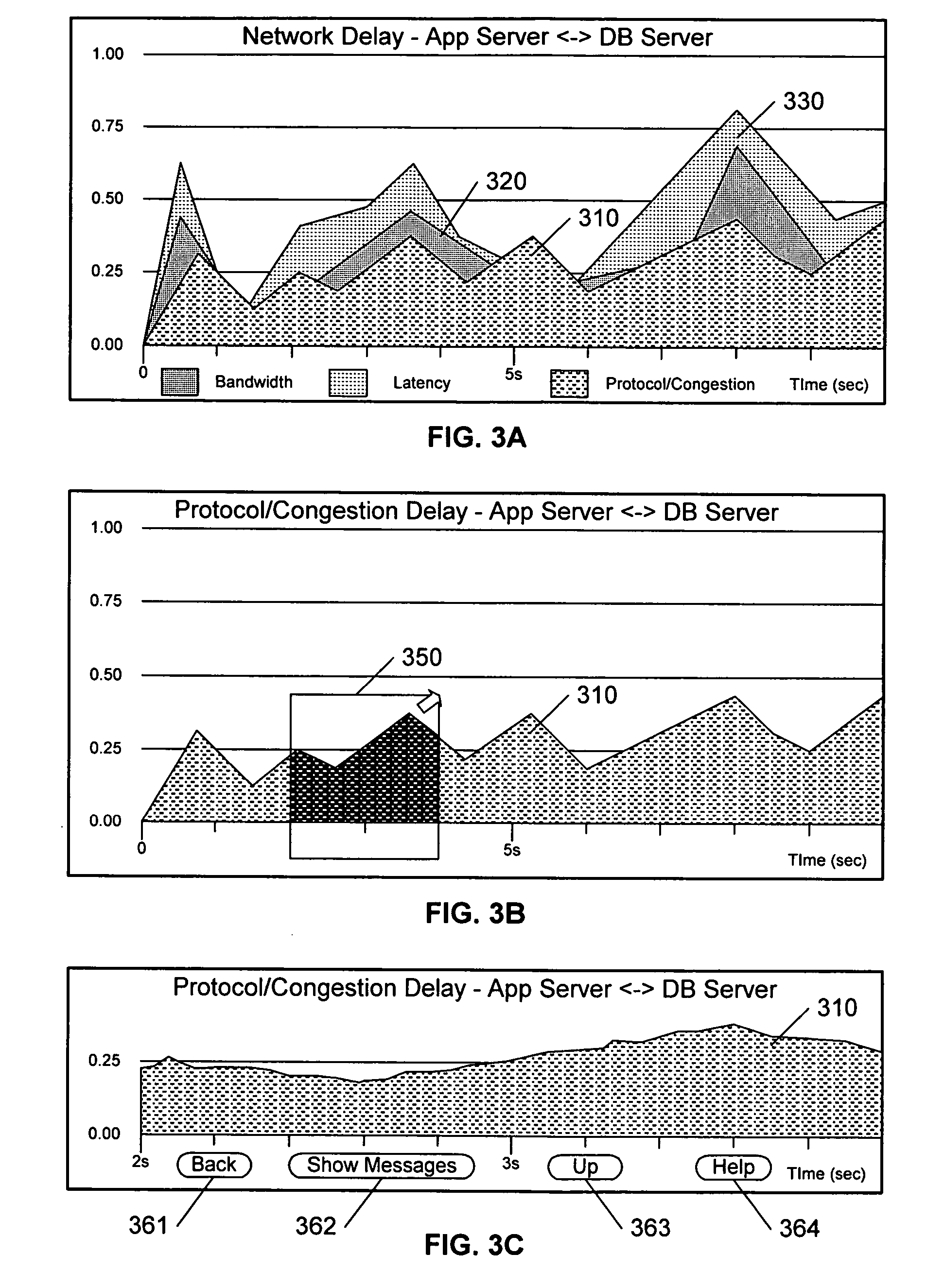

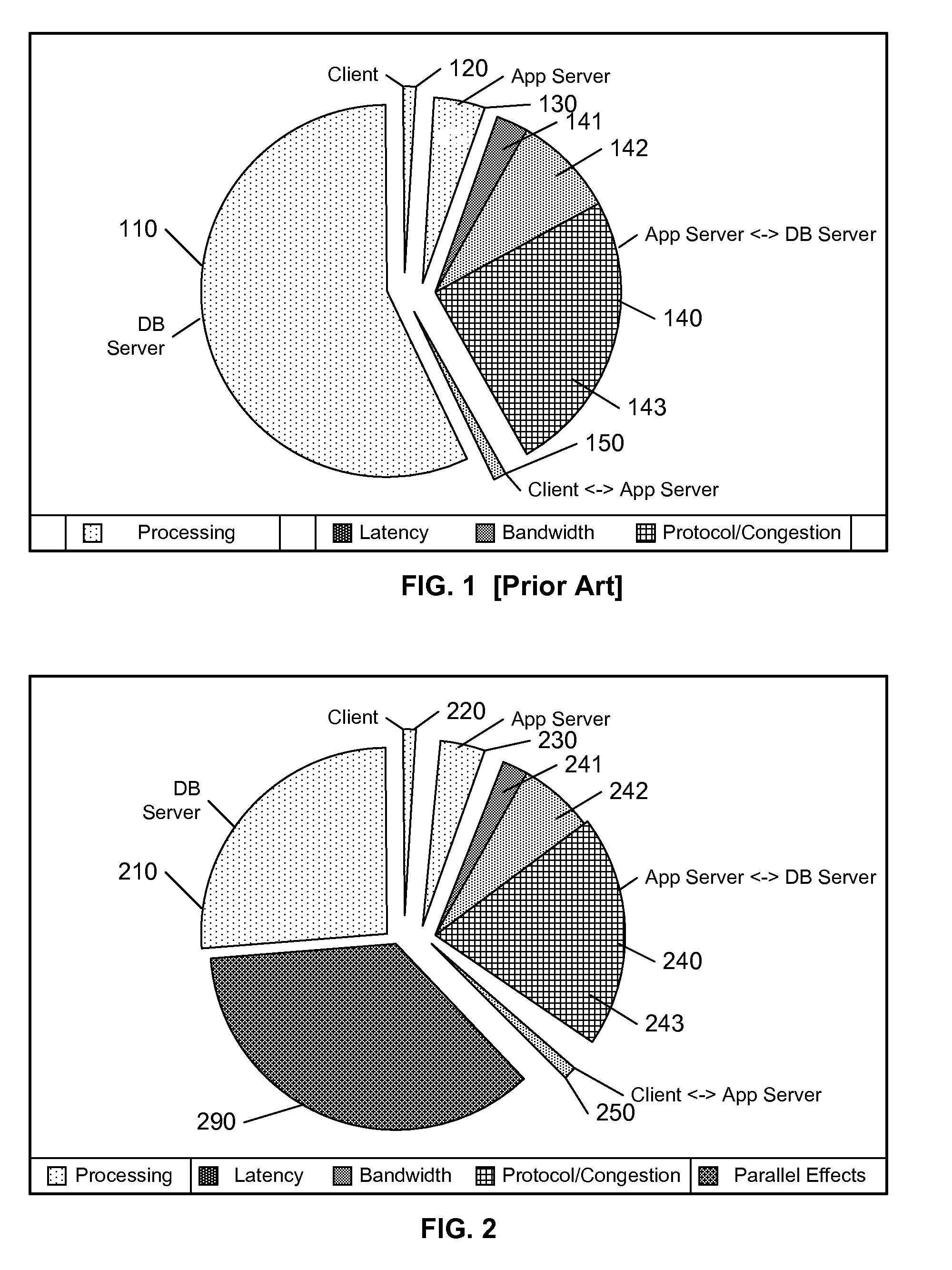

Application delay analysis

ActiveUS20070028142A1Easy to understandEasy to analyzeError preventionFrequency-division multiplex detailsPropagation delayGraphics

A graphic user interface facilitates the hierarchical analysis of timing parameters related to network-based applications. At the top level of the hierarchy, the user is presented a summary of the delays incurred while running an application, or while simulating the running of an application, organized by delay categories, including processing delays at each node, as well as propagation delays at each link between nodes. The interface enables a user to “drill down” into lower levels of the timing information hierarchy by ‘clicking’ on currently displayed information. The information is presented in a form most appropriate to the level of analysis. The presentation forms include, for example, pie-charts, multi-variable timing diagrams (in both absolute and relative forms), data exchange charts, and so on, and ‘zoom’ capabilities are provided as appropriate to the particular display form.

Owner:RIVERBED TECH LLC

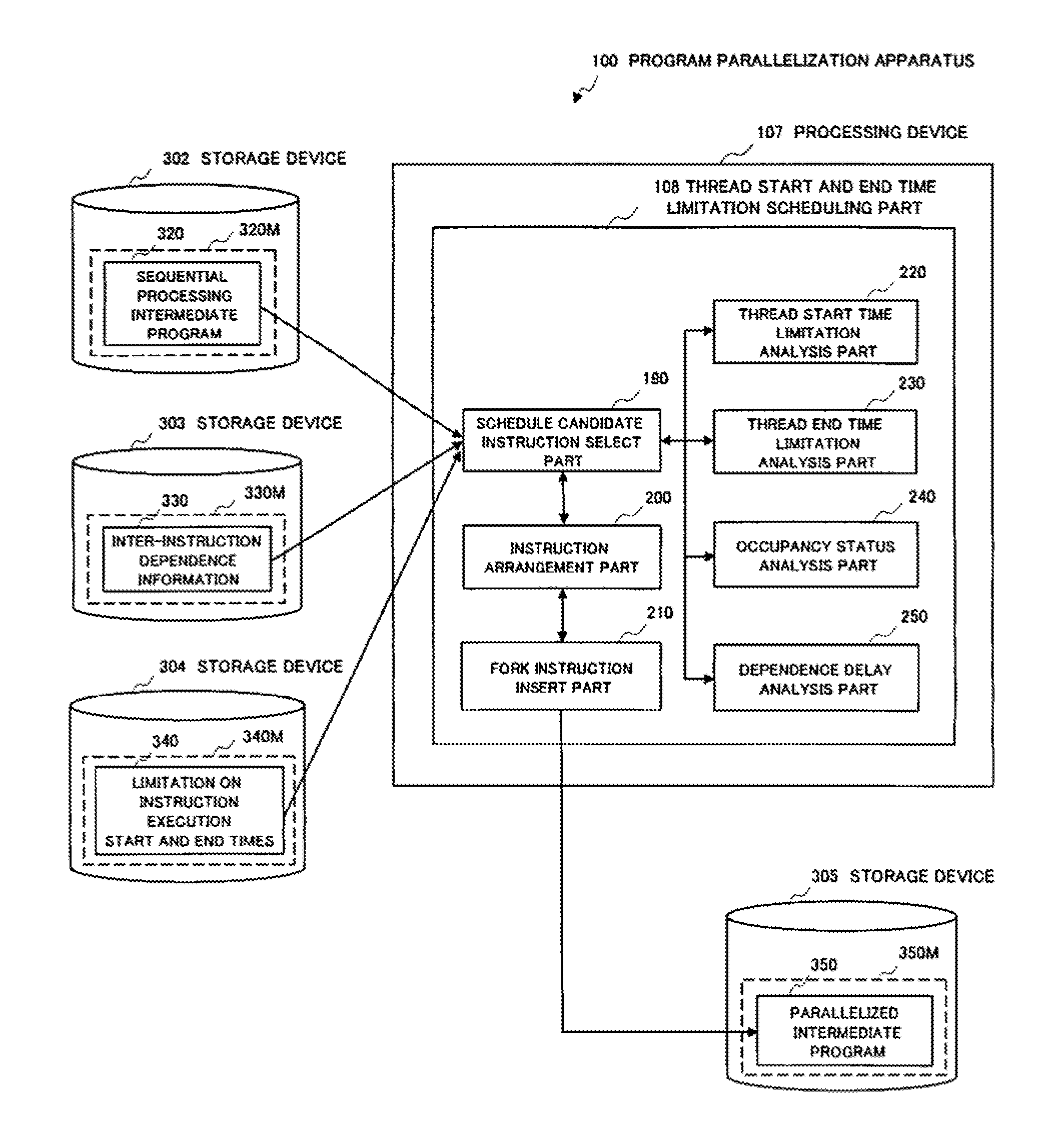

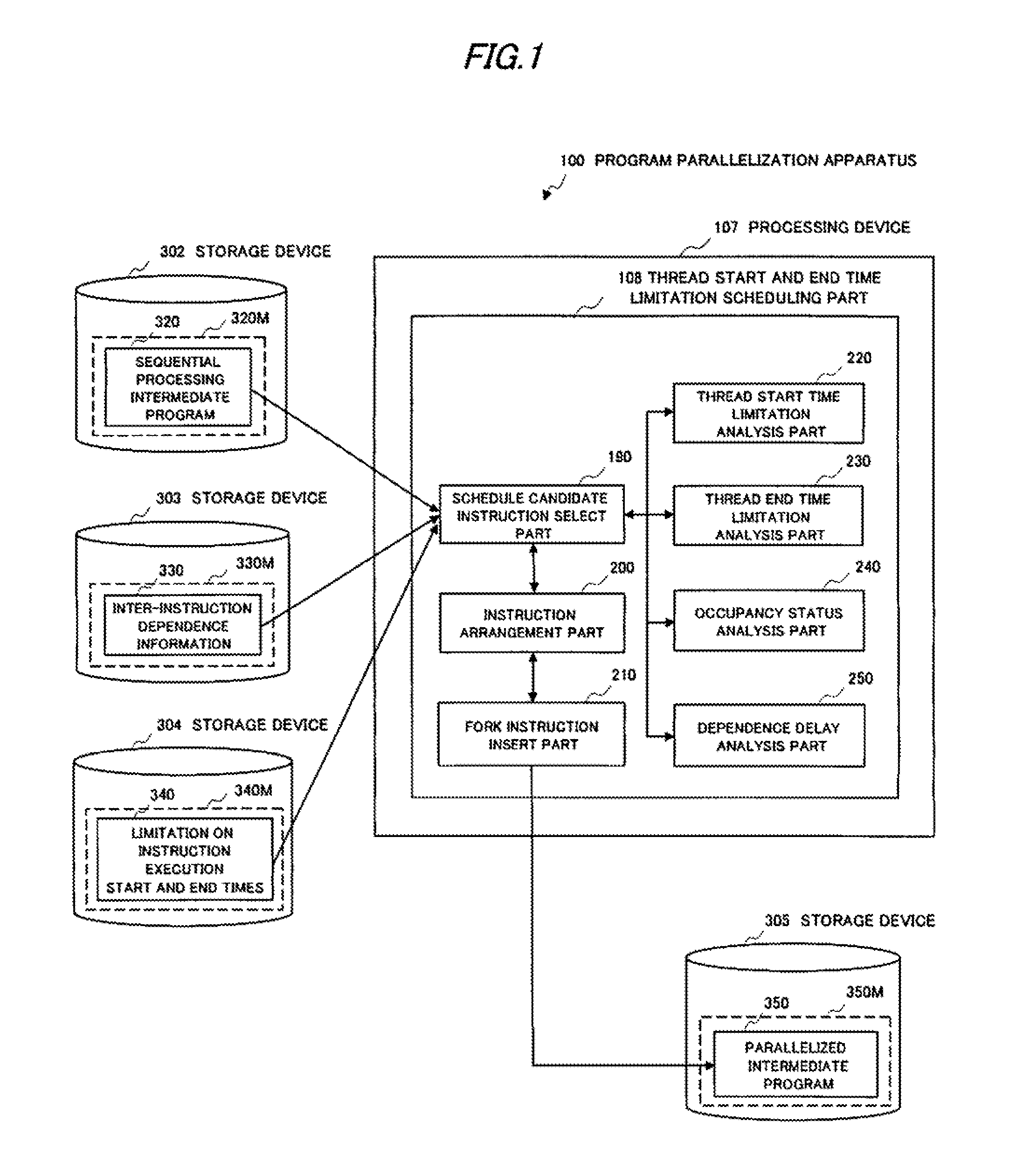

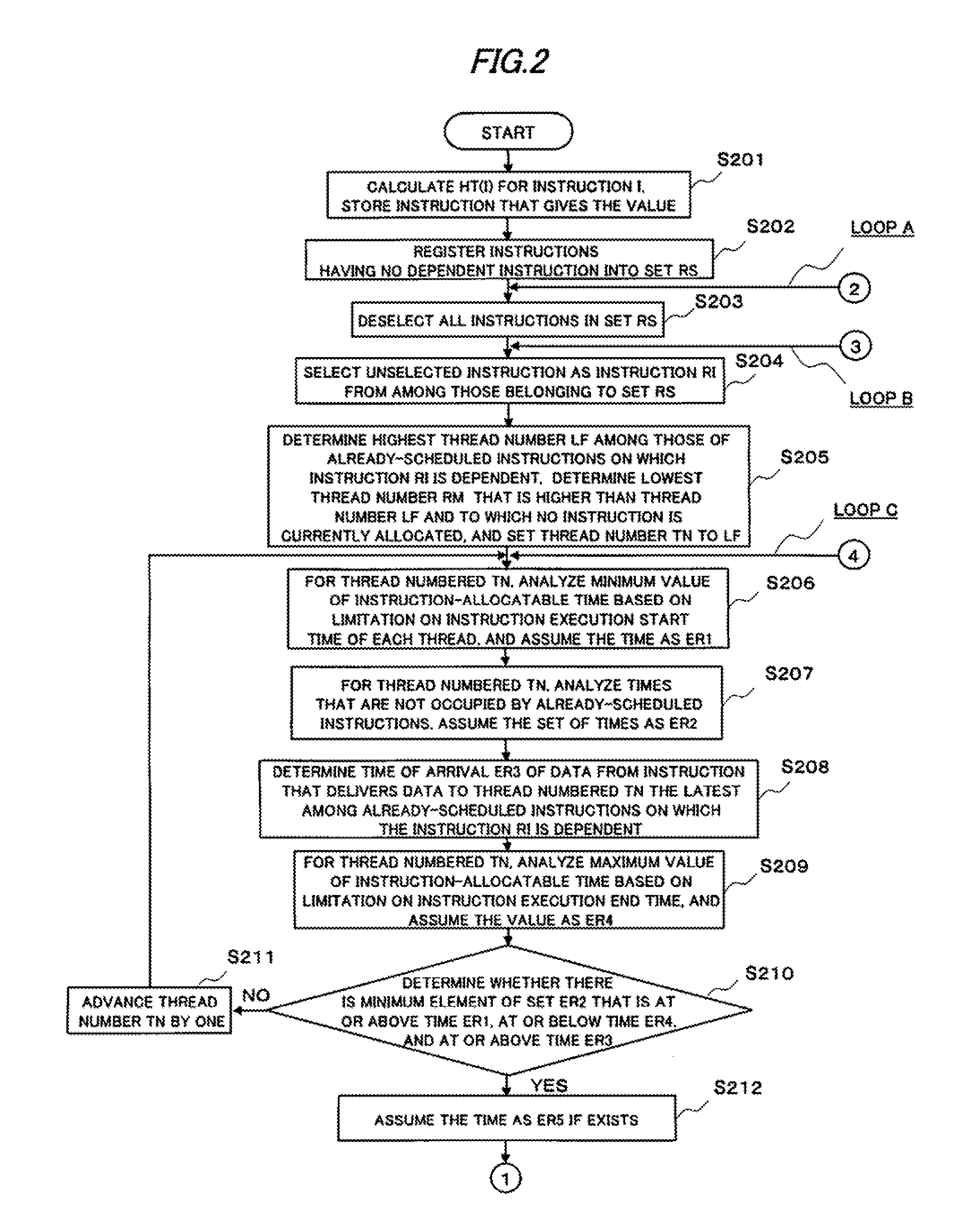

Program parallelization apparatus, program parallelization method, and program parallelization program

InactiveUS20110067015A1Reduce idle timeShort execution timeSoftware engineeringProgram controlStart timeParallel computing

A program parallelization apparatus which generates a parallelized program of shorter parallel execution time is provided. The program parallelization apparatus inputs a sequential processing intermediate program and outputs a parallelized intermediate program. In the apparatus, a thread start time limitation analysis part analyzes an instruction-allocatable time based on a limitation on an instruction execution start time of each thread. A thread end time limitation analysis part analyzes an instruction-allocatable time based on a limitation on an instruction execution end time of each thread. An occupancy status analysis part analyzes a time not occupied by already-scheduled instructions. A dependence delay analysis part analyzes an instruction-allocatable time based on a delay resulting from dependence between instructions. A schedule candidate instruction select part selects a next instruction to schedule. An instruction arrangement part allocates a processor and time to execute to an instruction.

Owner:NEC CORP

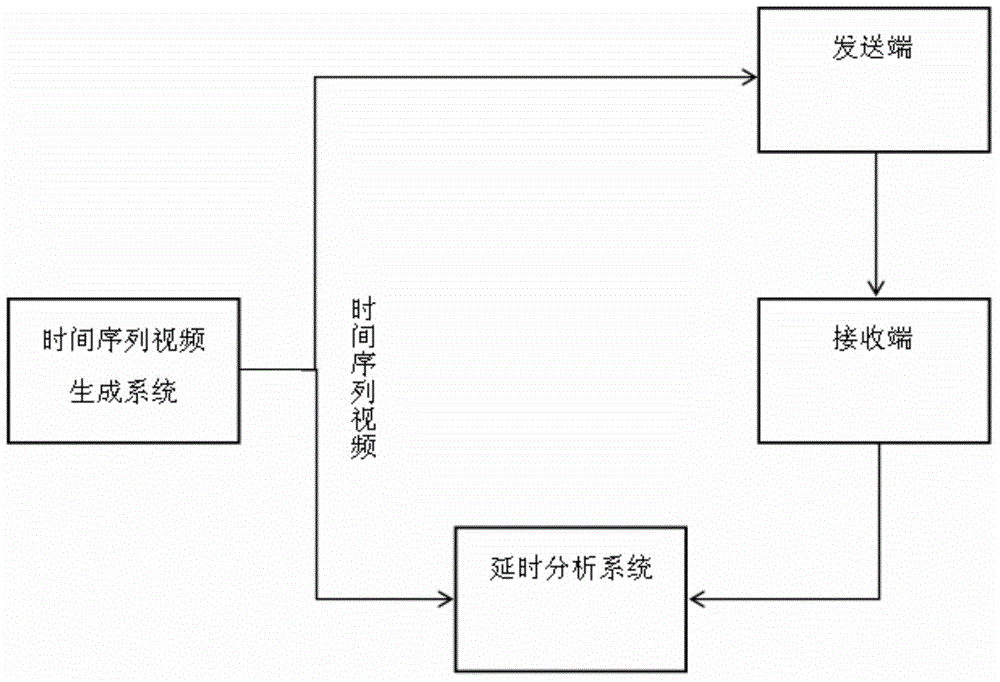

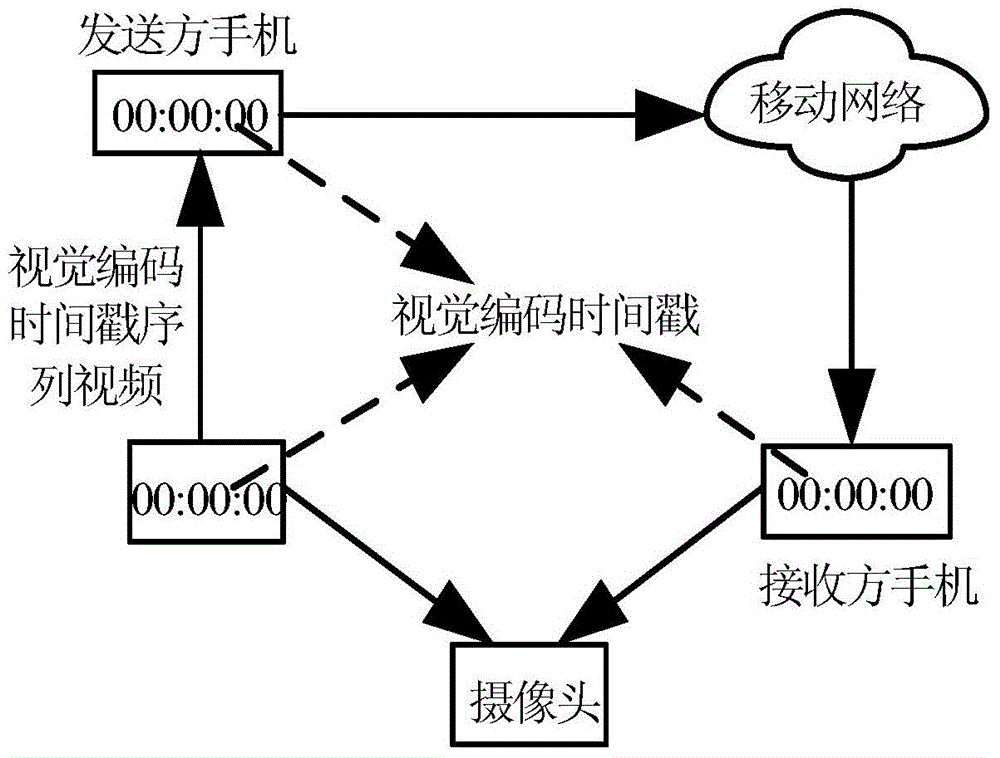

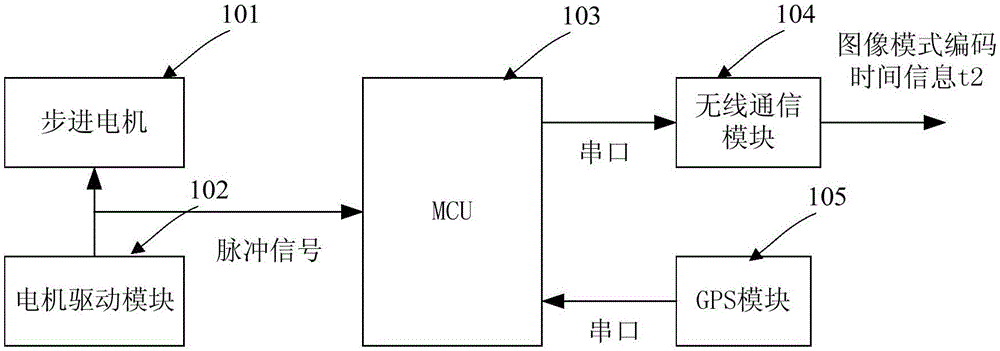

Method of measuring end-to-end delay of mobile phone?video?communication application

InactiveCN103826117AEasy to operateAvoiding the Difficulties of Synchronizing Different ClocksTwo-way working systemsTimestampDisplay device

The invention discloses a method of measuring end-to-end delay of mobile phone?video?communication application. Firstly, a section of visual coding timestamp sequence?video is generated and displayed on an LCD display; secondly, a sender mobile phone and a receiver mobile phone build video connection via video?communication application, the visual coding timestamp sequence?video shot by the sender is sent to the receiver, and the receivers displays the conversation content with the visual coding timestamp sequence?video included on a screen; thirdly, a high-definition camera is used for shooting the LCD display and the receiver screen at the same time; and finally, the acquired video data with the visual coding timestamps included is sent to a delay analysis system, the timestamp on each frame is recognized, time difference among the timestamps is calculated, and the end-to-end delay is obtained. According to the method disclosed by the invention, from?the?perspective?of?the?computer vision, the delay measurement problem is converted into the timestamp reorganization problem, the operation process is simple, the difficult problem of synchronization of different clocks is avoided, and accuracy of delay detection is improved.

Owner:ZHEJIANG UNIV

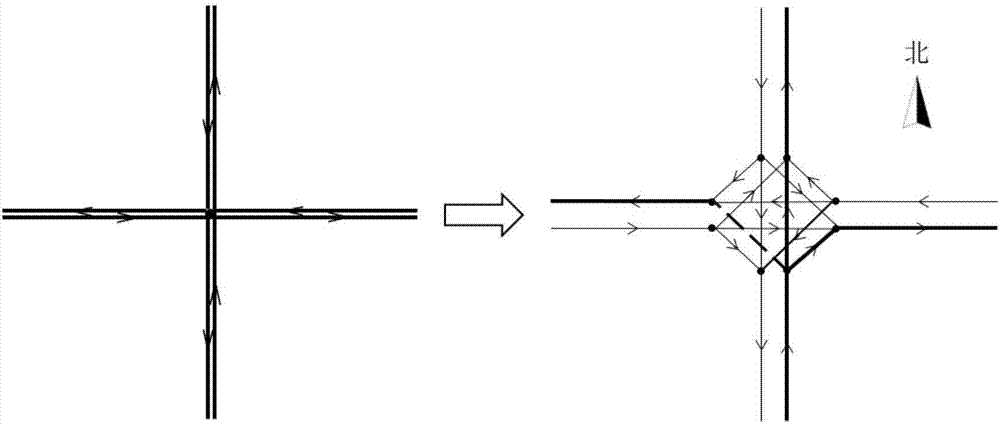

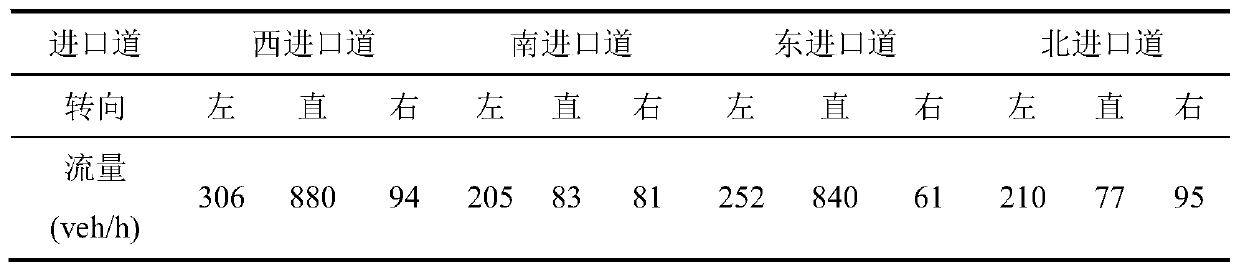

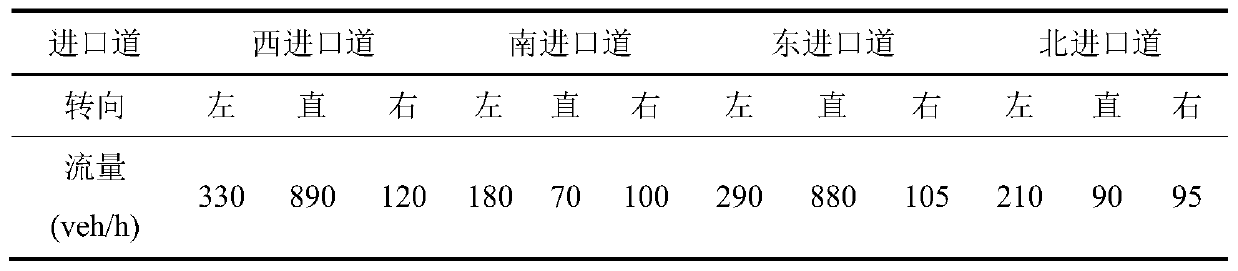

An urban road network generalized road right calculating method considering comprehensive traffic management measures

ActiveCN107038863ASimulation is accuratePrediction is accurateDetection of traffic movementTraffic capacityUrban Traffic Management and Control

The invention discloses an urban road network generalized road right calculating method considering comprehensive traffic management measures. The method comprises road section time impedance calculation with traffic management measures being taken into consideration and intersection delay calculation under a traffic control strategy, and specifically comprises road section basic traffic capacity analysis, influence correction of the traffic management measures on road section traffic capacity, road section time impedance analysis and correction of the traffic management measures on road section time impedance; and intersection entrance road lane group division based on turning relation, lane group motor basic traffic capacity analysis, influence correction of the traffic management measures on lane group traffic capacity and intersection delay analysis for traffic assignment. The method can reflect independent road rights of different types of vehicles in an urban road network, can enable simulation and prediction results to be more accurate, quantifies difference of different traffic management strategy combination schemes and provides powerful support for planning of current urban traffic management and control and formulation of traffic policies.

Owner:SOUTHEAST UNIV

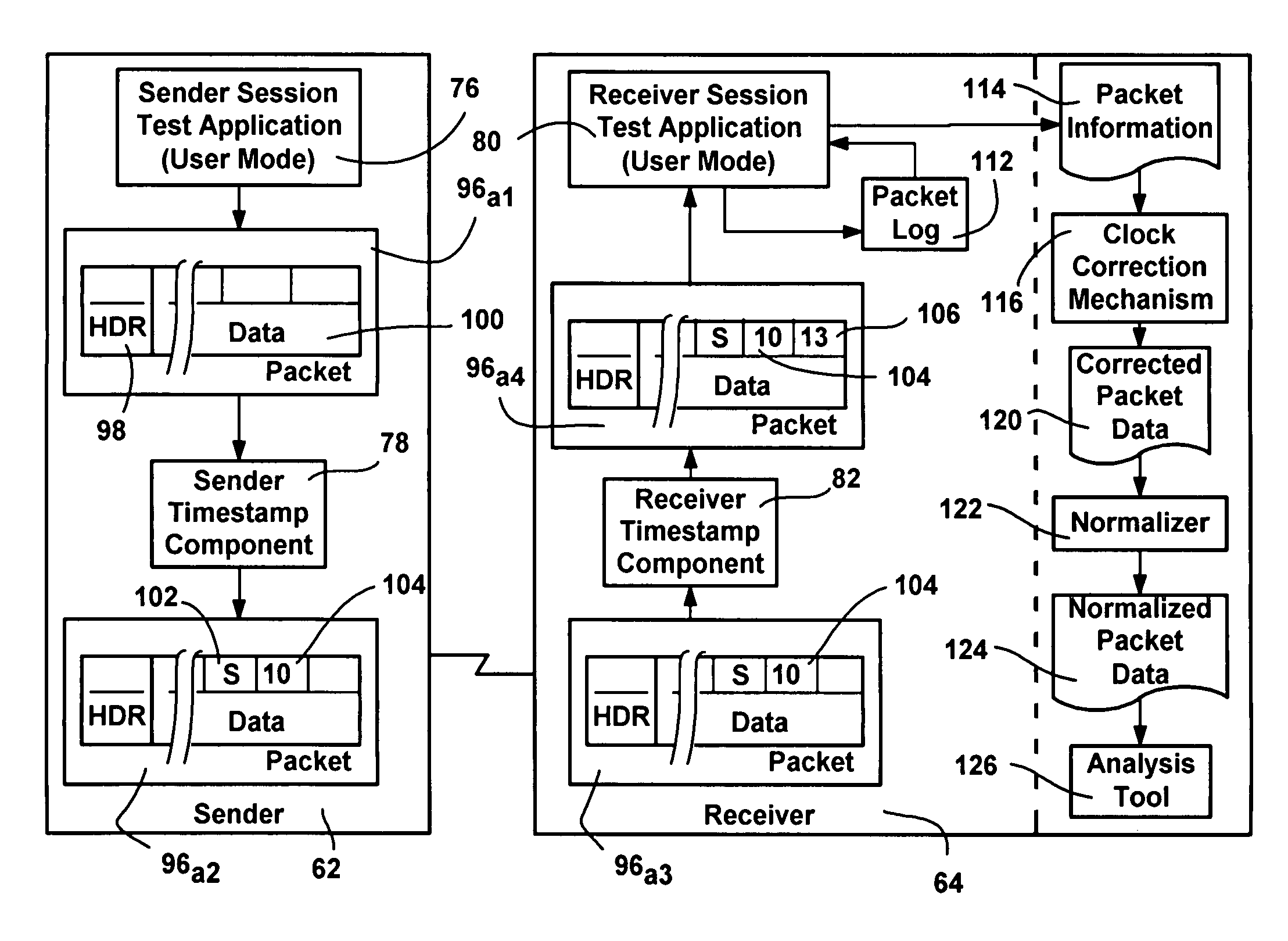

Method and system for accurately calculating latency variation on an end-to-end path in a network

InactiveUS6975656B1Improve accuracyTime-division multiplexWide area networksTemporal informationNetwork packet

A high-resolution, per-packet measurement tool for analyzing a computer network that operates by sending a predetermined number of packets from a sender machine to a receiver machine with measurement information inserted into the packet. The system kernel at the sending machine stamps a sequence number and the sender's local time into the data section of each packet. When packets arrive at the receiver machine, they are similarly stamped by the receiving machine's kernel with the receiving machine's local time. The maintained packet information serves as the basis for latency analysis. For example, one set of latencies can be obtained with QoS mechanisms turned on, and another set with QoS mechanisms turned off, whereby the benefits of the QoS mechanisms can be accurately determined. To analyze the latencies, the present invention normalizes each time and each latency into relative latency information. Clock skew and timer jumps may be handled as part of the normalization.

Owner:MICROSOFT TECH LICENSING LLC

Master-slave underwater robotic arm delay control method

ActiveCN106054599ASolve problems such as work interruptionMeet the needs of smooth and stable operationsAdaptive controlRobotic armControl signal

The invention relates to the technical field of robots, and provides a master-slave underwater robotic arm delay control method which can achieve coordinated control on the master arm and the salve arm of a master-slave underwater robotic arm in a bad operating environment and under the condition of transmission communication delay. The method comprises the following steps: giving the structure parameters of an underwater robotic arm, and making a delay analysis of the master and slave robotic arms according to a kinematics model of the underwater robotic arm; collecting hydrodynamic factors, and verifying whether the performance of the robotic arm meets the demand of the model according to the kinematics model of the underwater robotic arm; and delaying an action signal of the master arm, caching joint control signals at first n moments in an underwater controller, and calculating the ideal motion position of the joint of the slave arm at a moment n+1 based on a multi-power curve fitting method. The problem that an underwater robotic arm works intermittently due to a bad operating environment and transmission communication delay is solved.

Owner:HARBIN ENG UNIV

Video delay testing device in monitoring system

ActiveCN106851259ATroubleshoot Latency MeasurementsImprove technical levelClosed circuit television systemsVideo-signal generatorTime information

The invention provides a video delay testing device in a monitoring system. The device comprises a video signal generator, a video delay analysis unit and a synchronization link, wherein the video signal generator is used for generating a continuously changing time varying video signal and a timestamp of each frame of image and packaging and transmitting image mode information and time information to the delay analysis unit; the video delay analysis unit is used for identifying a frame mode of a decoded video to determine system time generated by the frame mode and subtracting frame mode occurrence time from the system time which is decoded and displayed currently to obtain video transmission delay of the system; and the synchronization link is used for realizing synchronization of the video signal generator and the video delay analysis unit. The device solves a problem of video delay measurement in an actual engineering application, provides the realizable video delay measurement device and method for related professional institutes and construction units, fills a blank of the measurement field and improves the technological level of the national security and protection system, especially the monitoring system.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

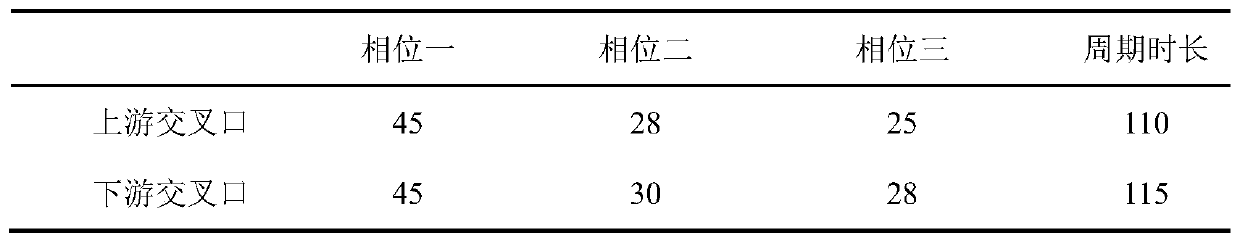

Signal control optimization method of bus transit lane at single-point intersection

InactiveCN110009918AConditions take precedenceImprove signal control schemeControlling traffic signalsArrangements for variable traffic instructionsBus laneGreen-light

The invention discloses a signal control optimization method of a bus transit lane at a single-point intersection. The signal control optimization method disclosed by the invention comprises the following steps: calculating an average vehicle delay at an intersection based on the Webster intersection delay analysis method; respectively solving a bus delay and a social vehicle delay, performing weighted averaging, and establishing an intersection comprehensive delay model after a bus weight is given; establishing a single-point intersection signal control model based on the minimum comprehensive delay; and designing a scheme of guiding the vehicles to accelerate / decelerate to arrive at the intersection at proper moments in combination with an optimized signal period time length and an optimized green light time length. According to the signal control optimization method disclosed by the invention, the minimum average vehicle delay is taken as the optimization target of the signal control, and based on the driving characteristics of bus fleets, the bus fleets can pass through the intersection, thereby realizing the priority of the buses and improving the traffic efficiency of the buses at the intersection.

Owner:WUHAN UNIV OF TECH

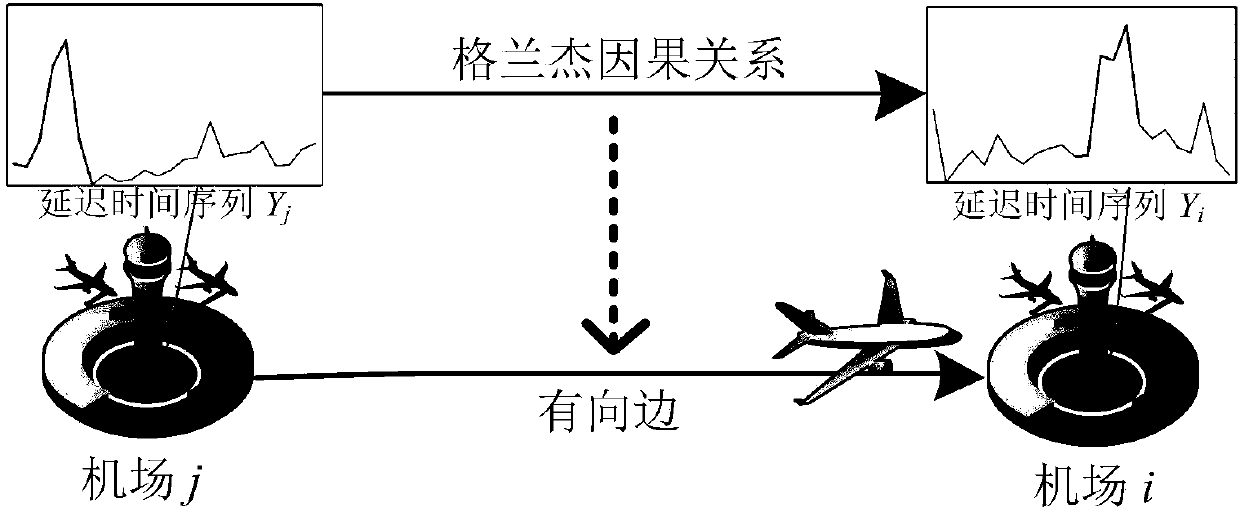

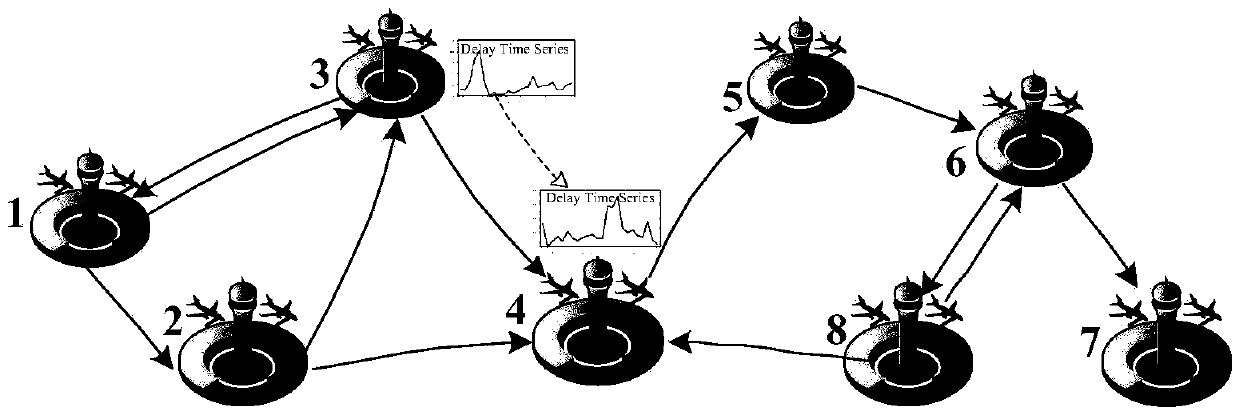

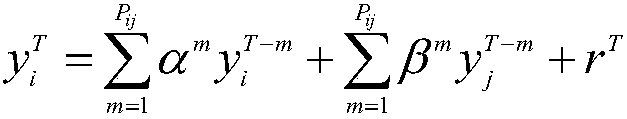

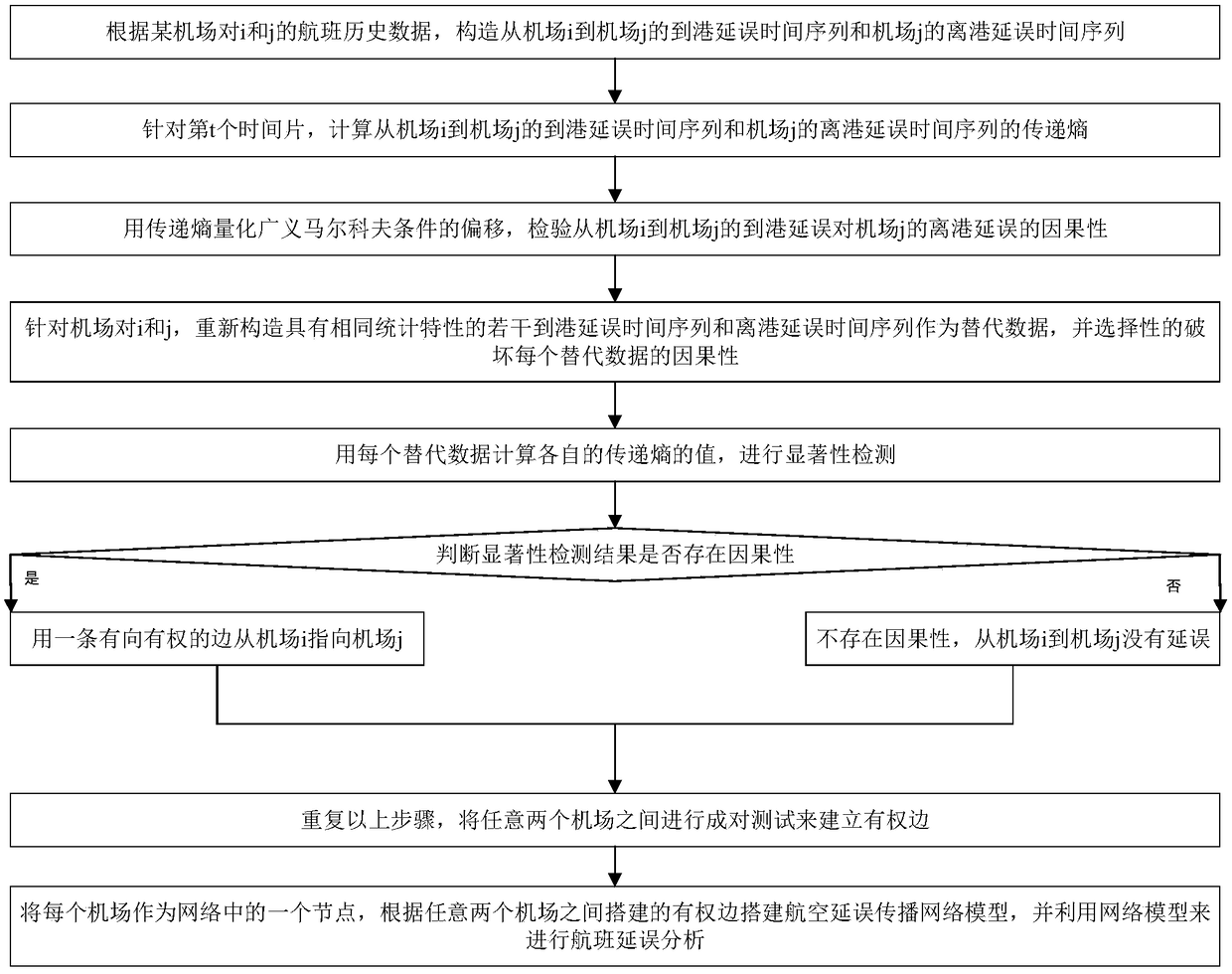

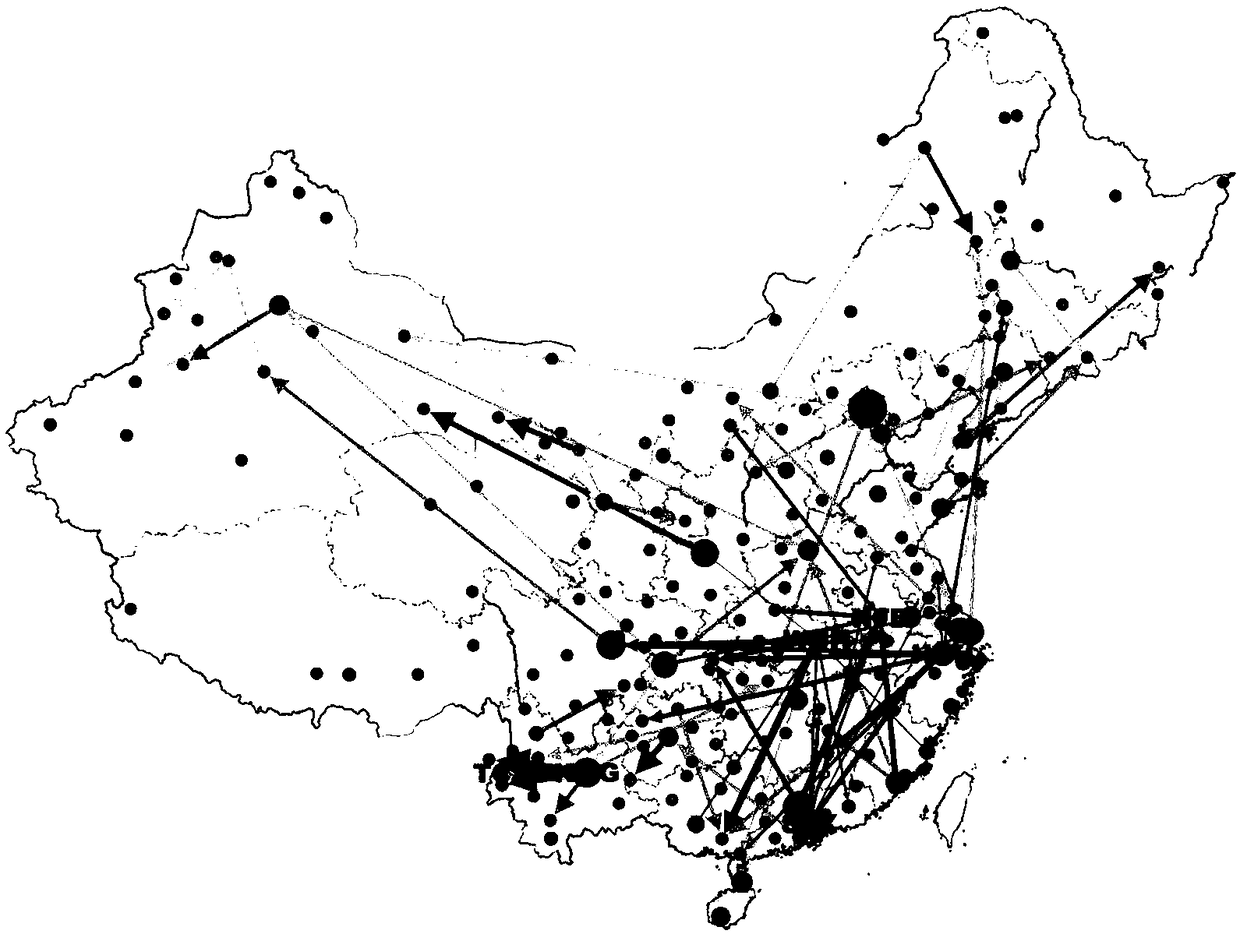

Flight delay causality network building method based on Granger test

ActiveCN108519988AReduce in quantityReduce delay propagationData processing applicationsKnowledge representationDelayed timeCivil aviation

The invention discloses a flight delay causality network building method based on a Granger test, pertaining to the technical field of delay analyses for civil aviation. The method comprises the following steps: firstly, acquiring a delay time sequence of each airport with the set time period according to historical data of flight of airports; then, taking each airport as a node for the network and testing a Granger causality of each pair of airports, when an airport I causes delay of an airport j by the test and establishing a directed edge from a node i to node j; and ultimately, repeating the above processes till selected airports are added to the network and making flight delay analyses by means of the obtained network. Through the established flight delay causality network, the numberof delay dissemination paths is analyzed for some large airports. Therefore, the delay dissemination range is narrowed, thereby effectively resolving a delay problem. The delays disseminated by an overall system are reduced. Therefore, loss caused by many flight delays is lowered.

Owner:BEIHANG UNIV

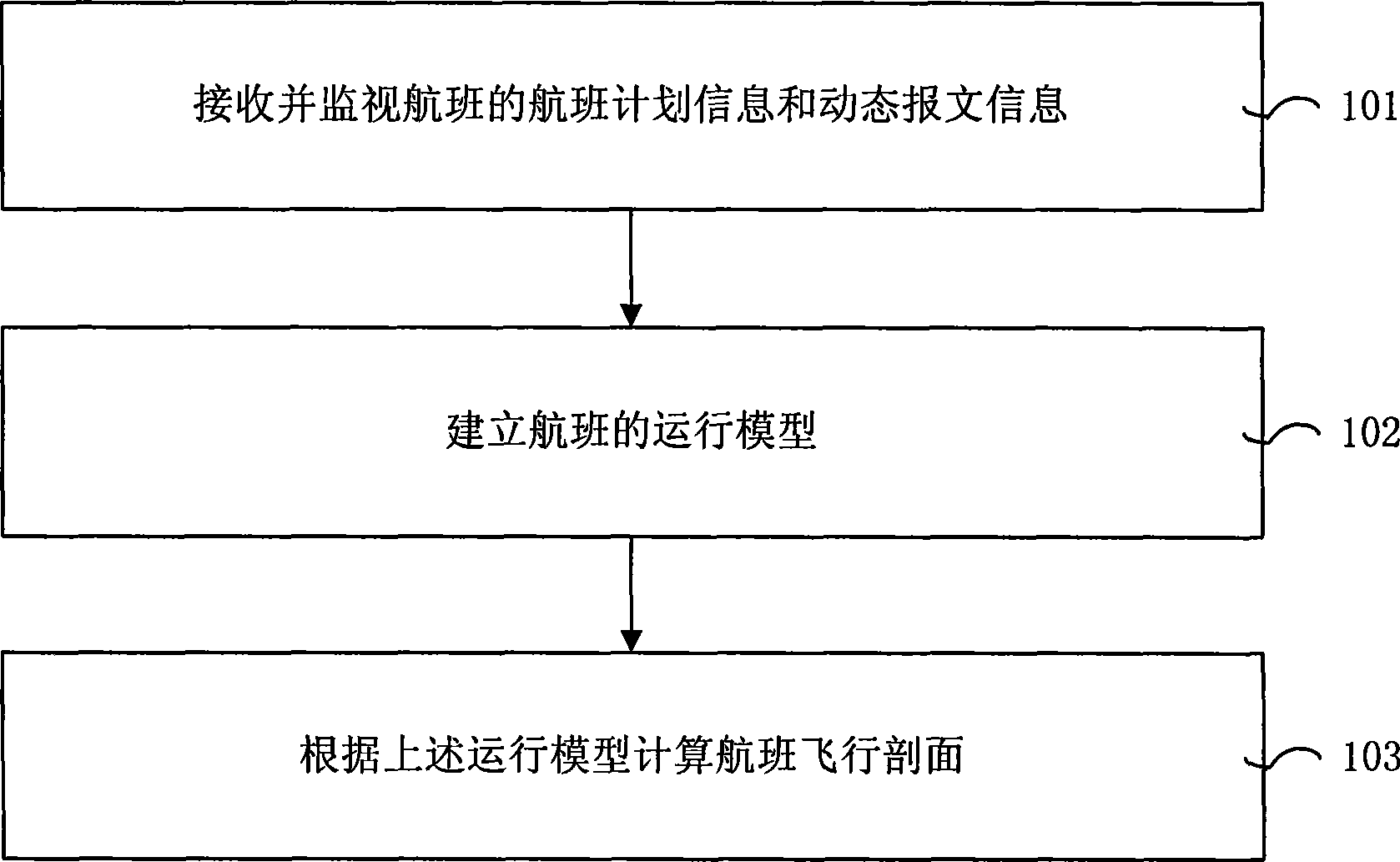

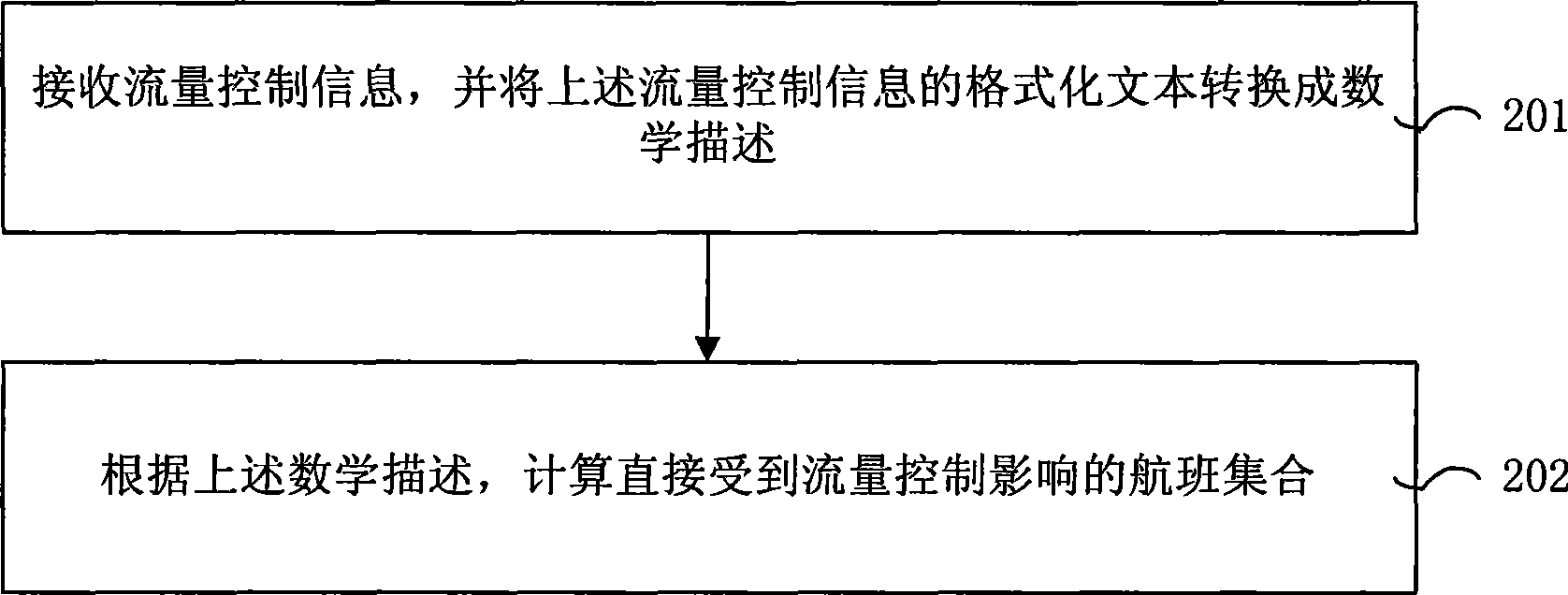

Statistical method and apparatus for airliner delay

The invention discloses a flight delay statistical method and a flight delay statistical device, wherein, the flight delay statistical method comprises: real-time data of flight operation is monitored, a flight operation model is built, and a flight flying section plane is computed; flow control information is received, format conversion of the information is realized, and flights that are directly influenced are computed according to the flight flying section plane; successive connecting information and station turnaround time of flights are summarized, flights that are indirectly influenced are computed, and the flight delay number is the sum of the flight numbers that are directly influenced and indirectly influenced. The flight delay statistical method and device can analyze the directly or indirectly influenced flights and the delay degrees thereof according to the flow control information of air traffic management, improve the accuracy of delay analysis and lower delay influence.

Owner:北京民航天宇科技发展股份有限公司 +2

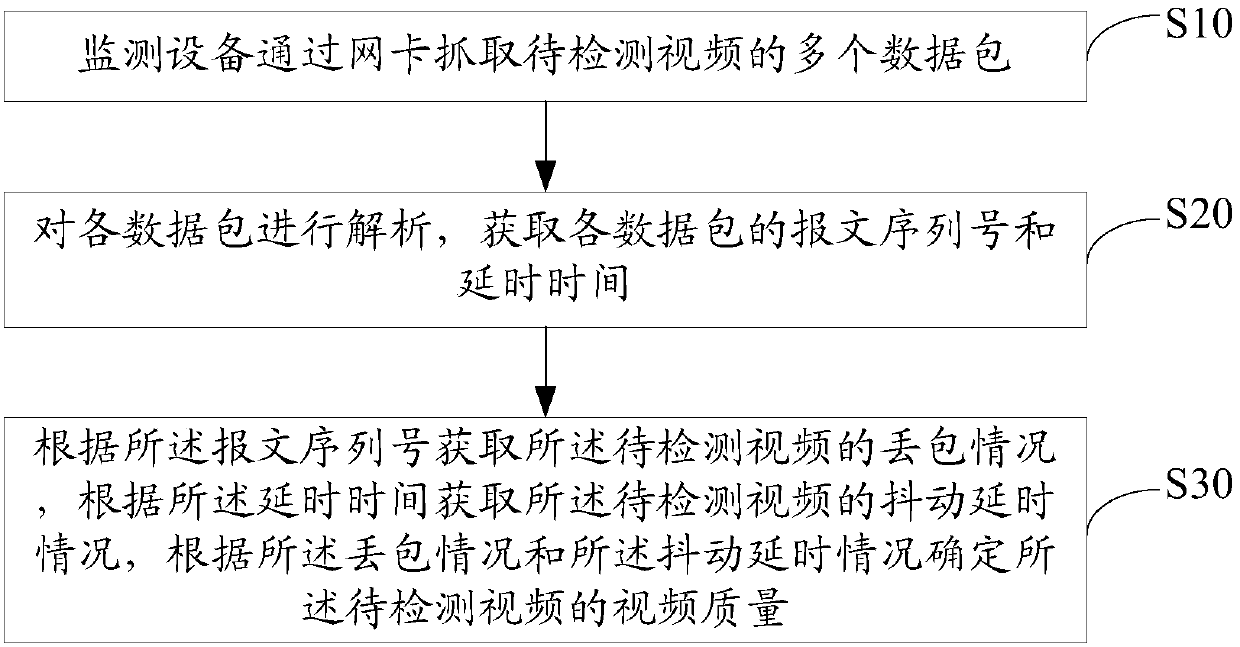

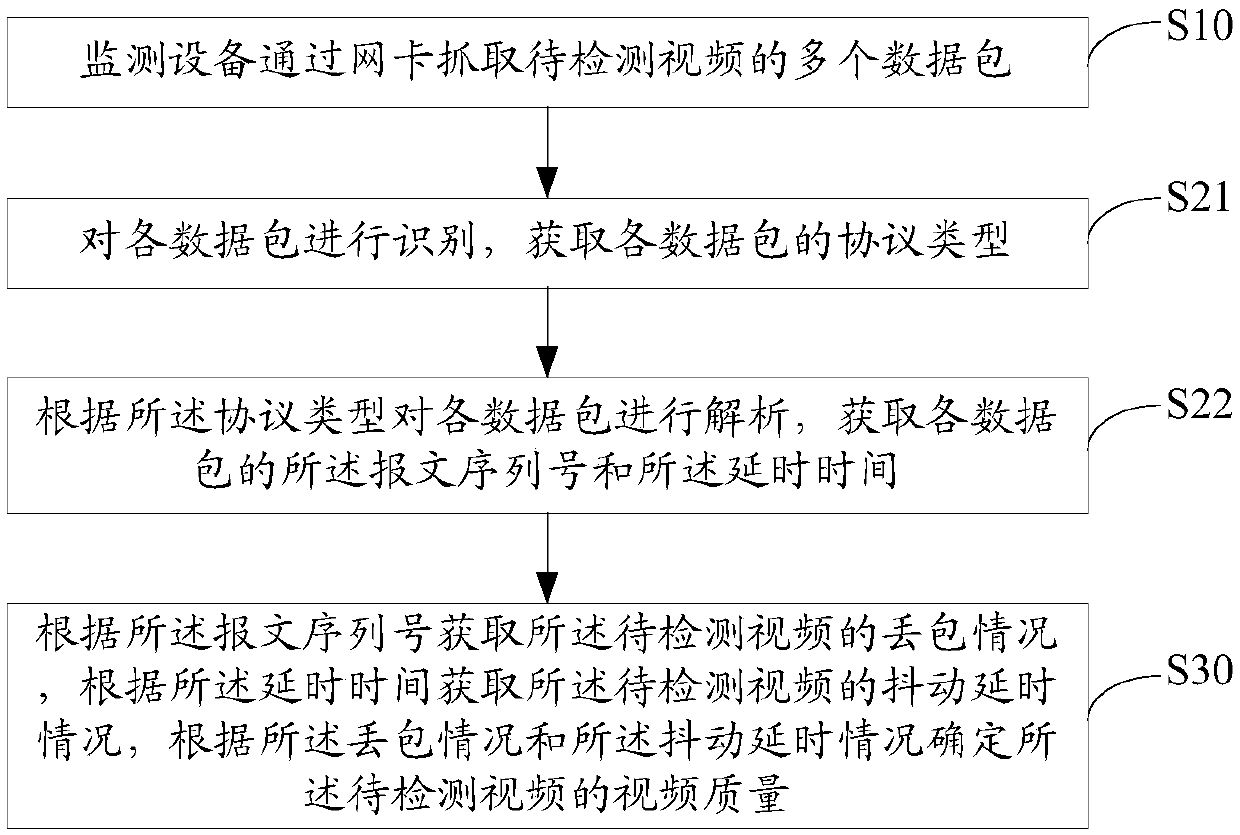

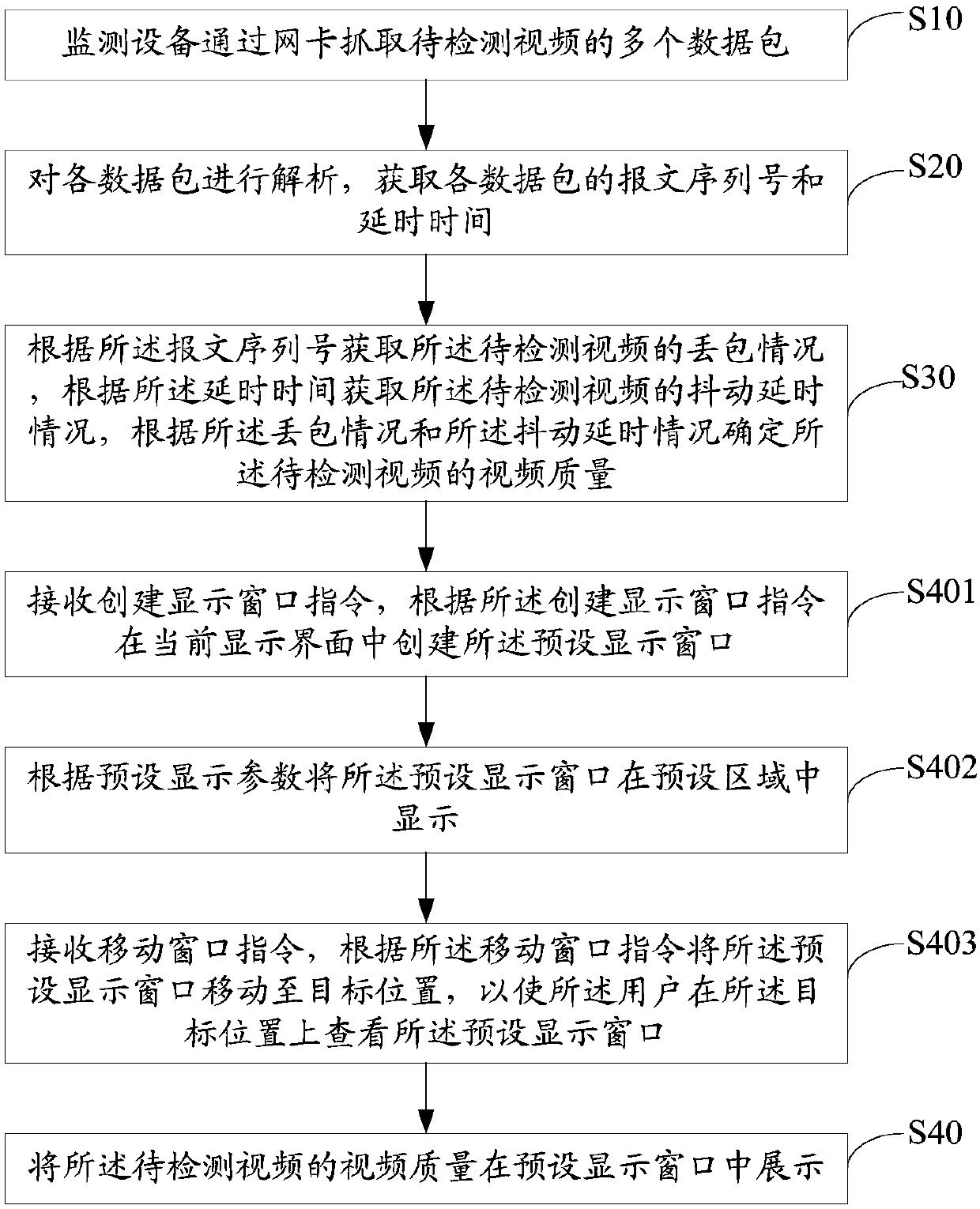

Video quality detection method, monitoring equipment and storage medium

InactiveCN107743228AHigh speedImprove efficiencyTelevision systemsTransmissionPacket lossDelayed time

The invention discloses a video quality detection method, monitoring equipment and a storage medium. The method includes the following steps: enabling monitoring equipment to capture multiple data packets of a video to be detected through a network card, parsing each data packet, acquiring a message sequence number and delay time of each data packet, acquiring the packet loss situation of the video to be detected according to the message sequence number, acquiring the jitter delay situation of the video to be detected according to the delay time, and determining the video quality of the videoto be detected according to the packet loss situation and the jitter delay situation. The monitoring equipment performs packet loss and delay analysis on the captured multiple data packets of the video to be detected, the video network transmission quality can be improved, the fault detection speed and efficiency can be increased, and the technical staff or non-technical staff can be rapidly and conveniently assisted to preliminarily investigate the quality problems of video services; and the video quality detection method is convenient and fast, and has wide applicability.

Owner:SHENZHEN SKYWORTH SOFTWARE

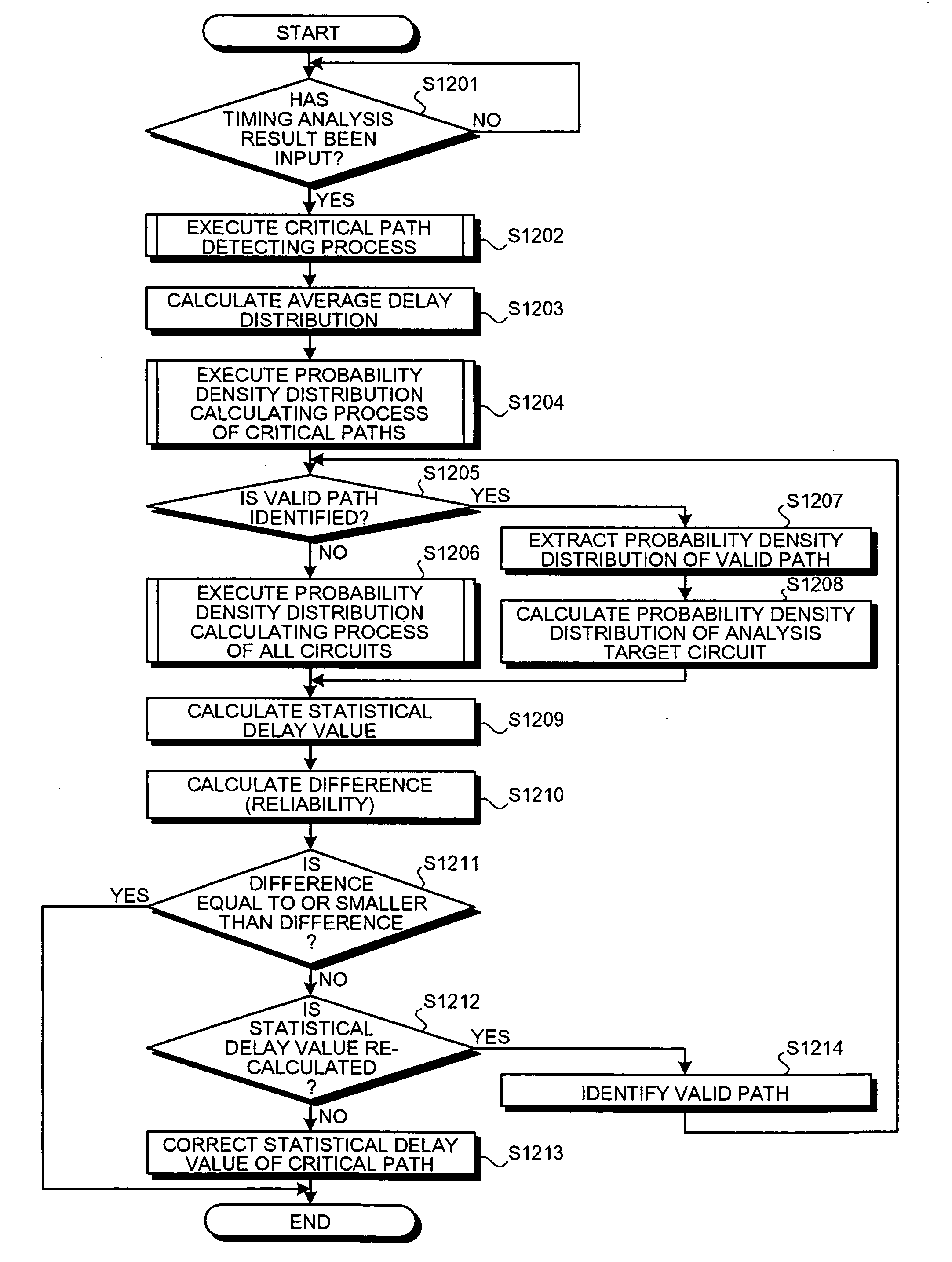

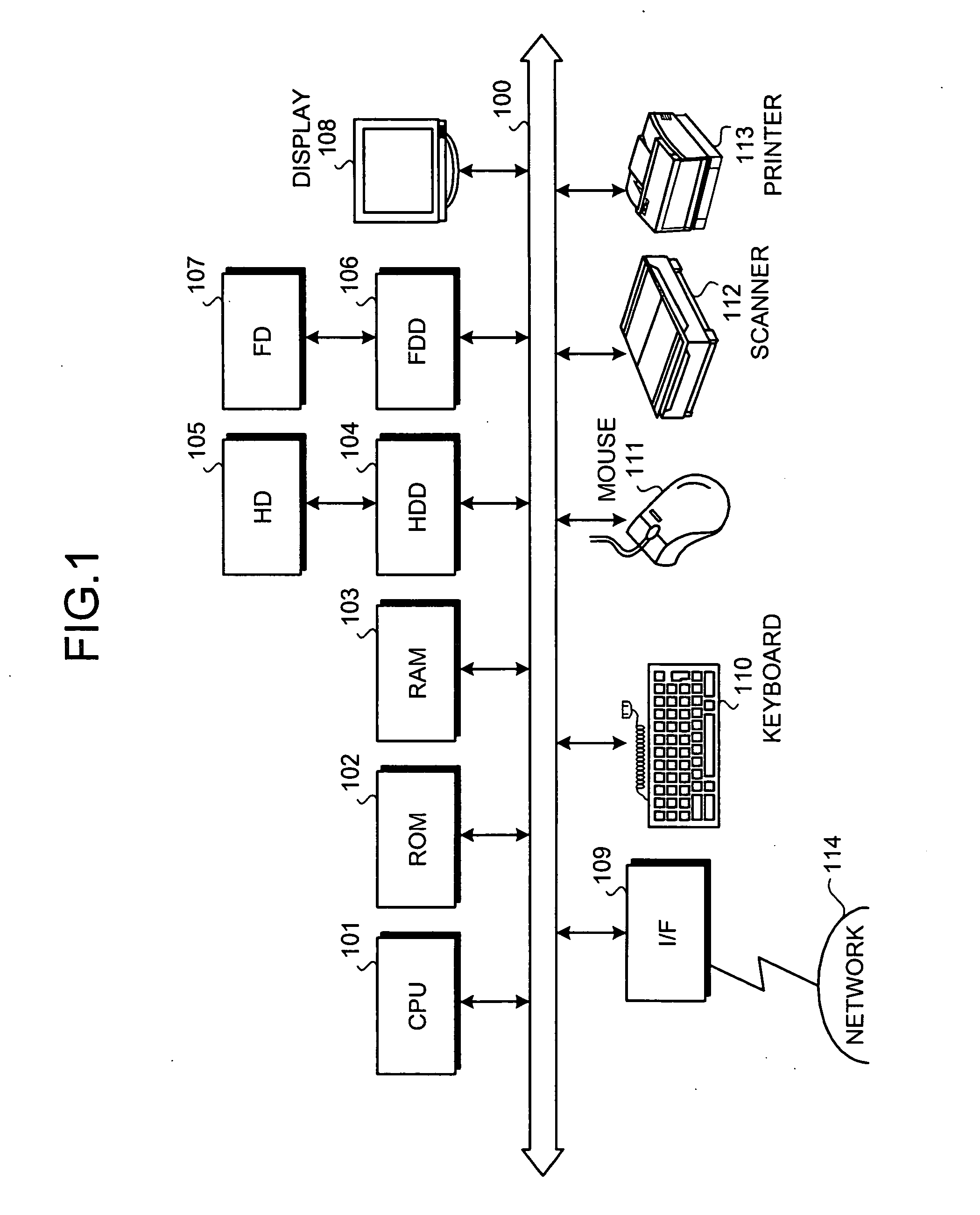

Delay analyzing method, delay analyzing apparatus, and computer product

InactiveUS20070204248A1Computer aided designSoftware simulation/interpretation/emulationDensity distributionCritical path method

A delay analyzing apparatus receives a result of timing analysis of a target circuit, and detects, from paths in the target circuit, critical paths based on the result of the timing analysis with a detecting unit. A first calculating unit calculates an average delay distribution of the paths other than the critical paths based on an average delay value of each of the critical paths. A second calculating unit calculates a probability density distribution of the critical paths, and a third calculating unit calculates a probability density distribution of all of the paths based on the average delay distribution. A fourth calculating unit calculates difference between a statistical delay value of the critical paths and a statistical delay value of all of the paths based on the probability density distribution of the critical paths and the probability density distribution of all of the paths.

Owner:FUJITSU LTD

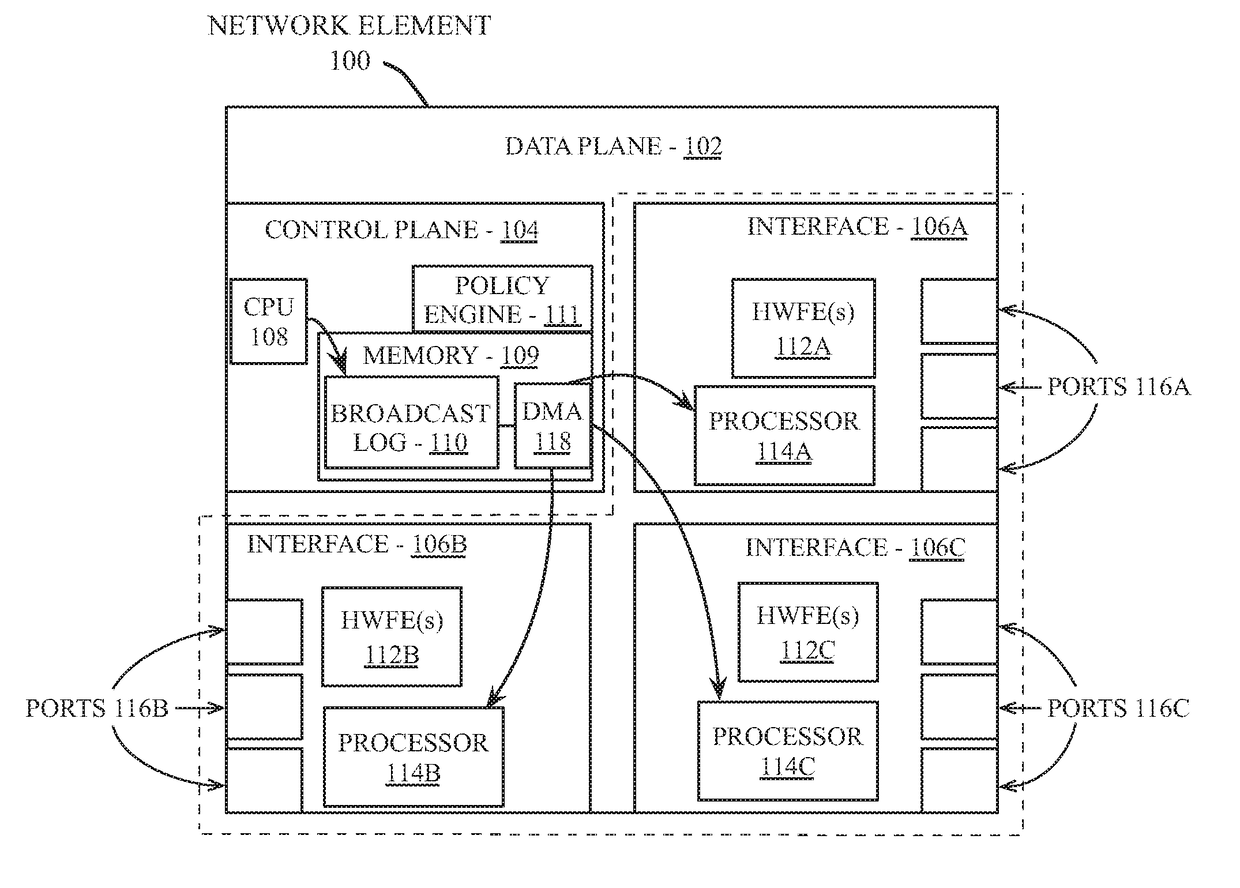

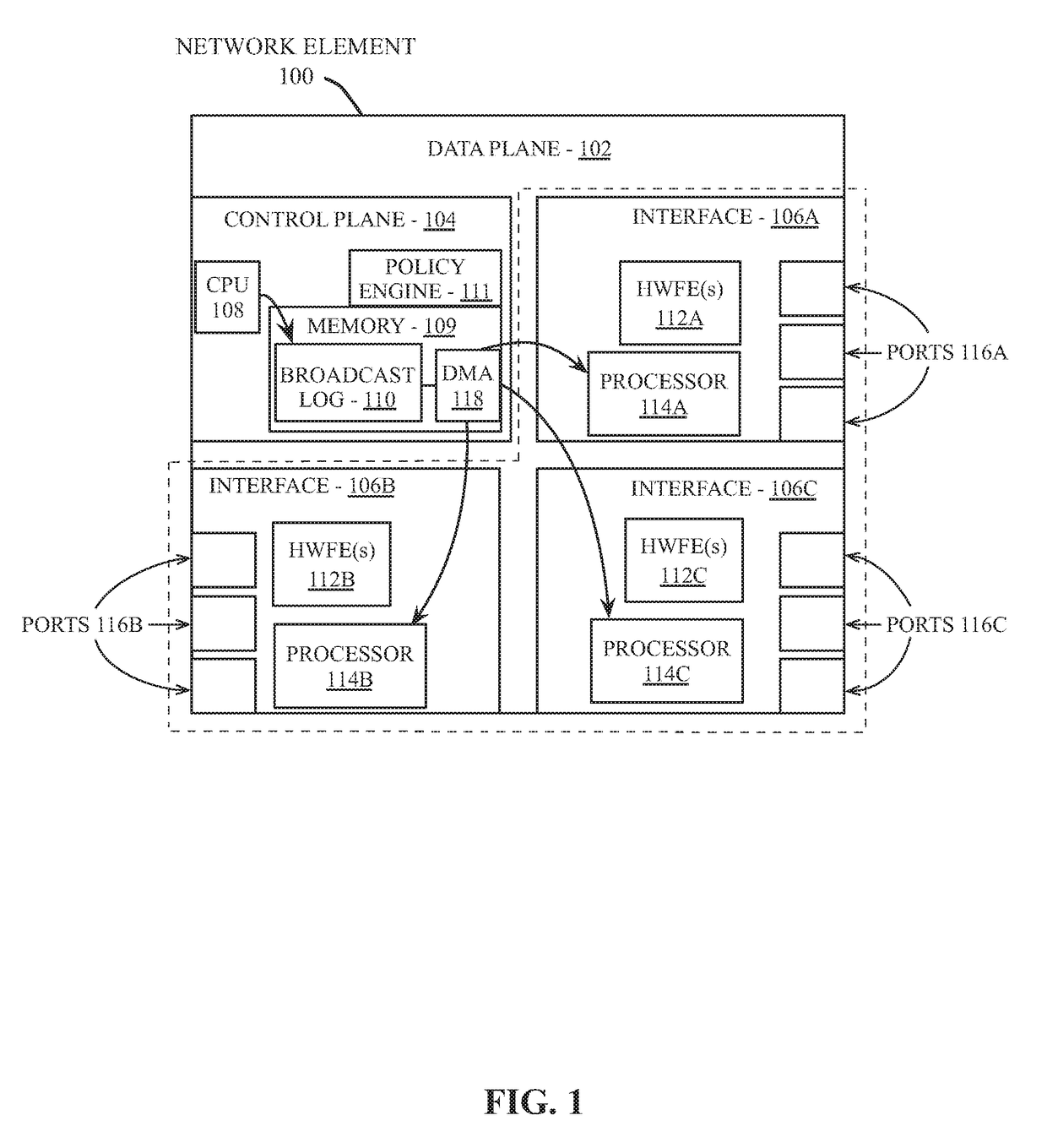

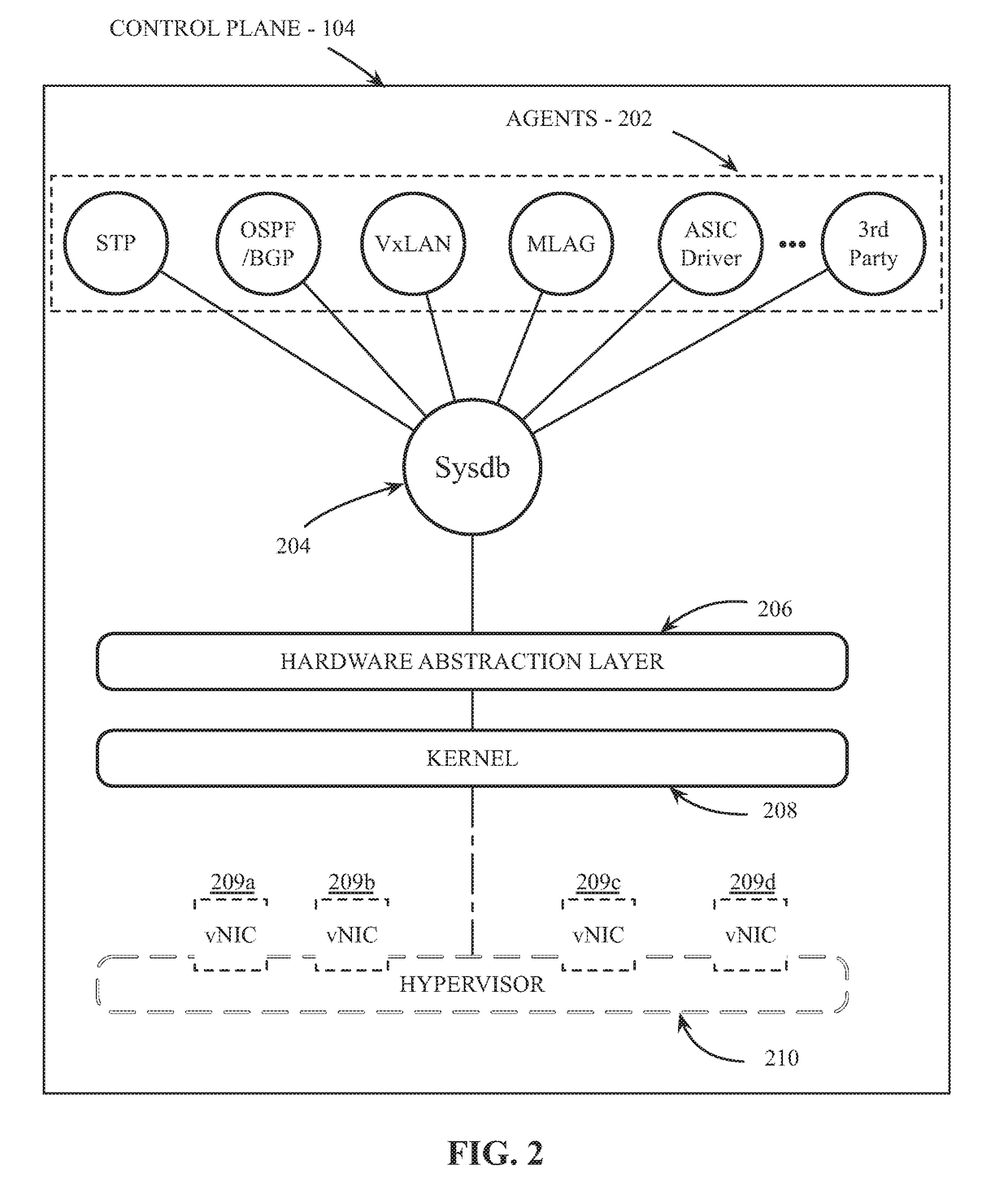

Hierarchical time stamping

Various embodiments are described herein, which provide a network element comprising a network port to receive production network data that is used for purposes other than testing the performance of a network, a data plane coupled to the network port, the data plane including a timing module to append a time stamp to a set of one or more time stamps included within the production network data, and a control plane coupled to the data plane, the control plane including a latency analyzer to analyze the set of one or more time stamps included within the production network data.

Owner:ARISTA NETWORKS

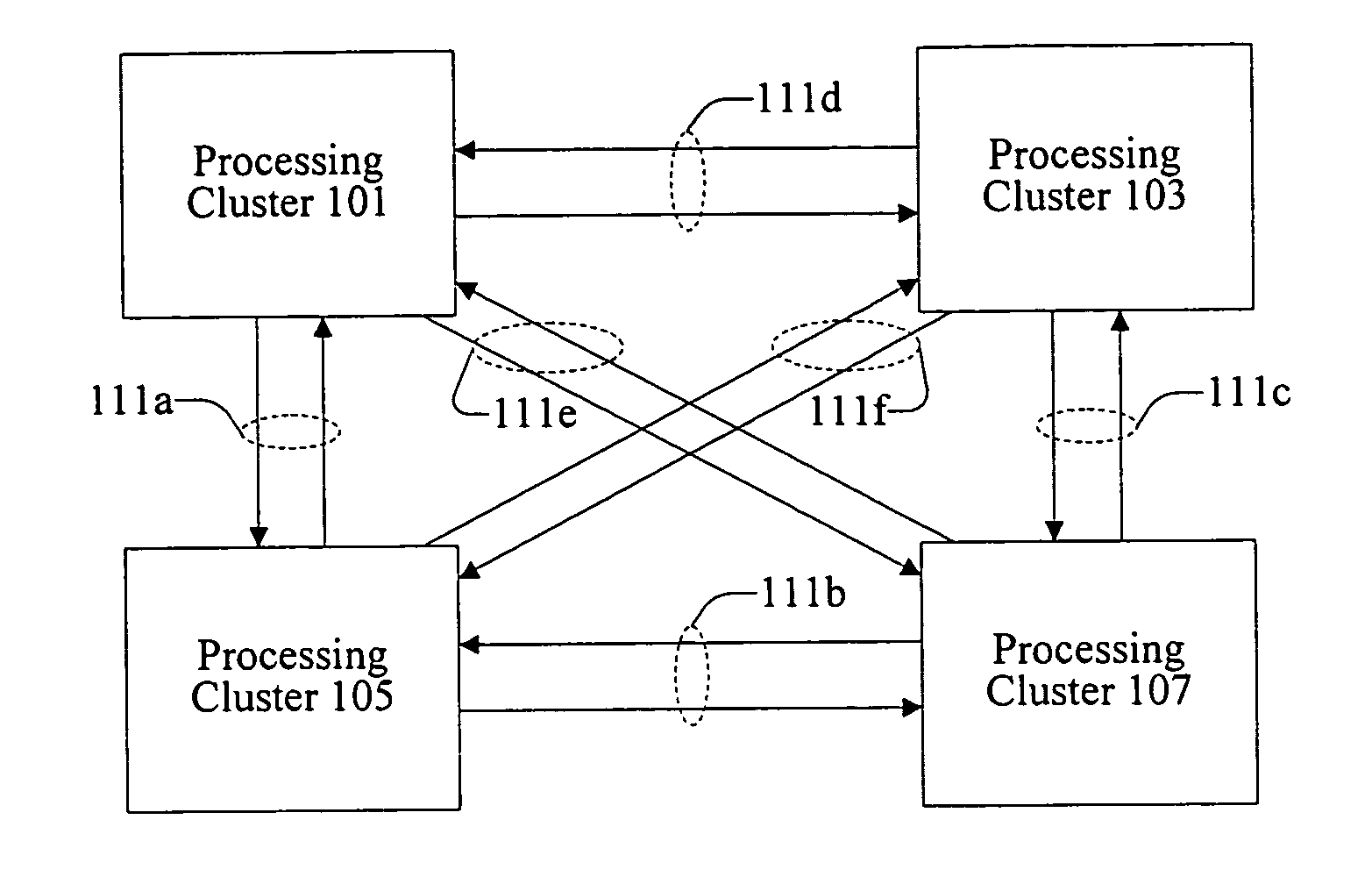

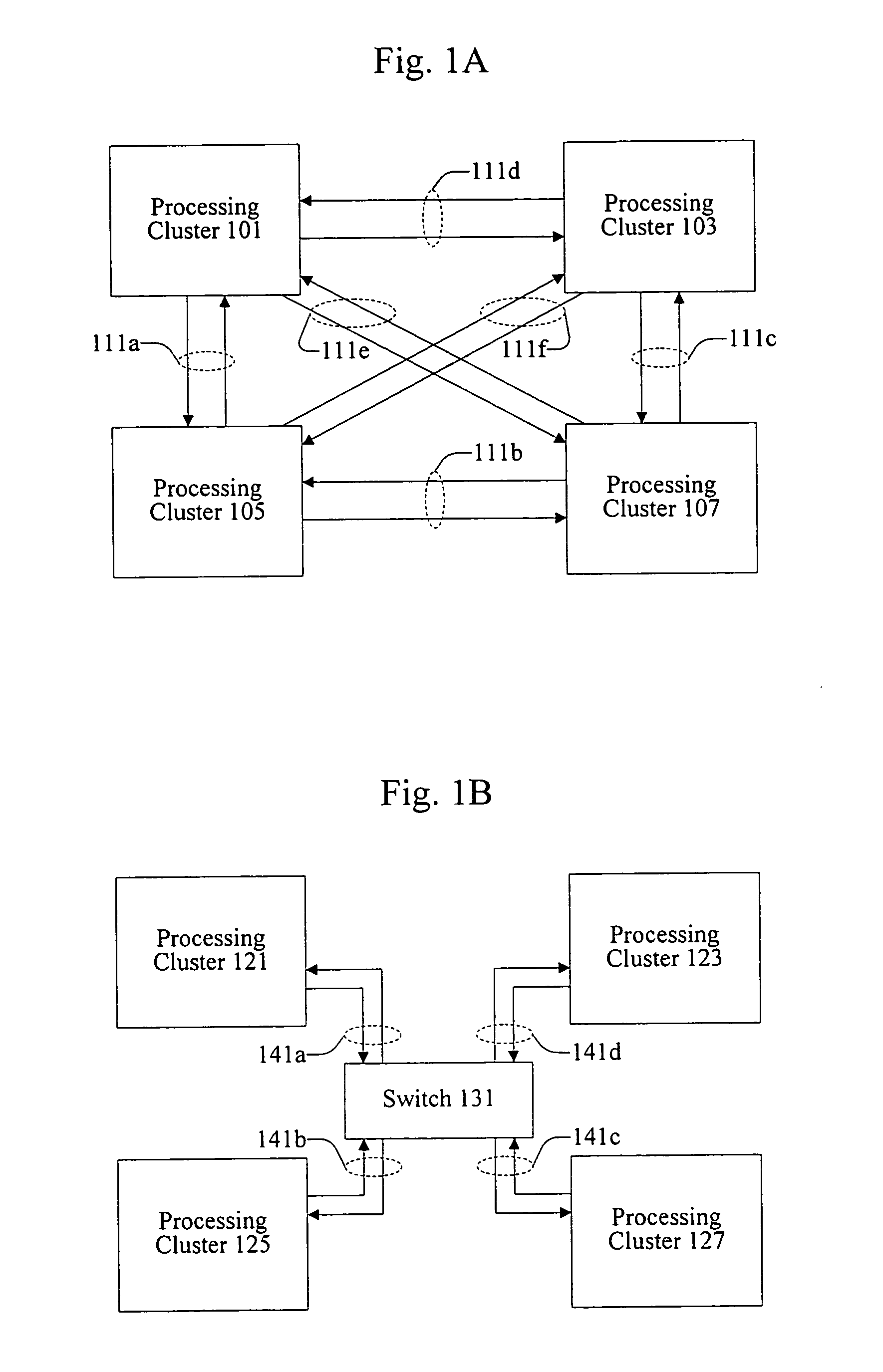

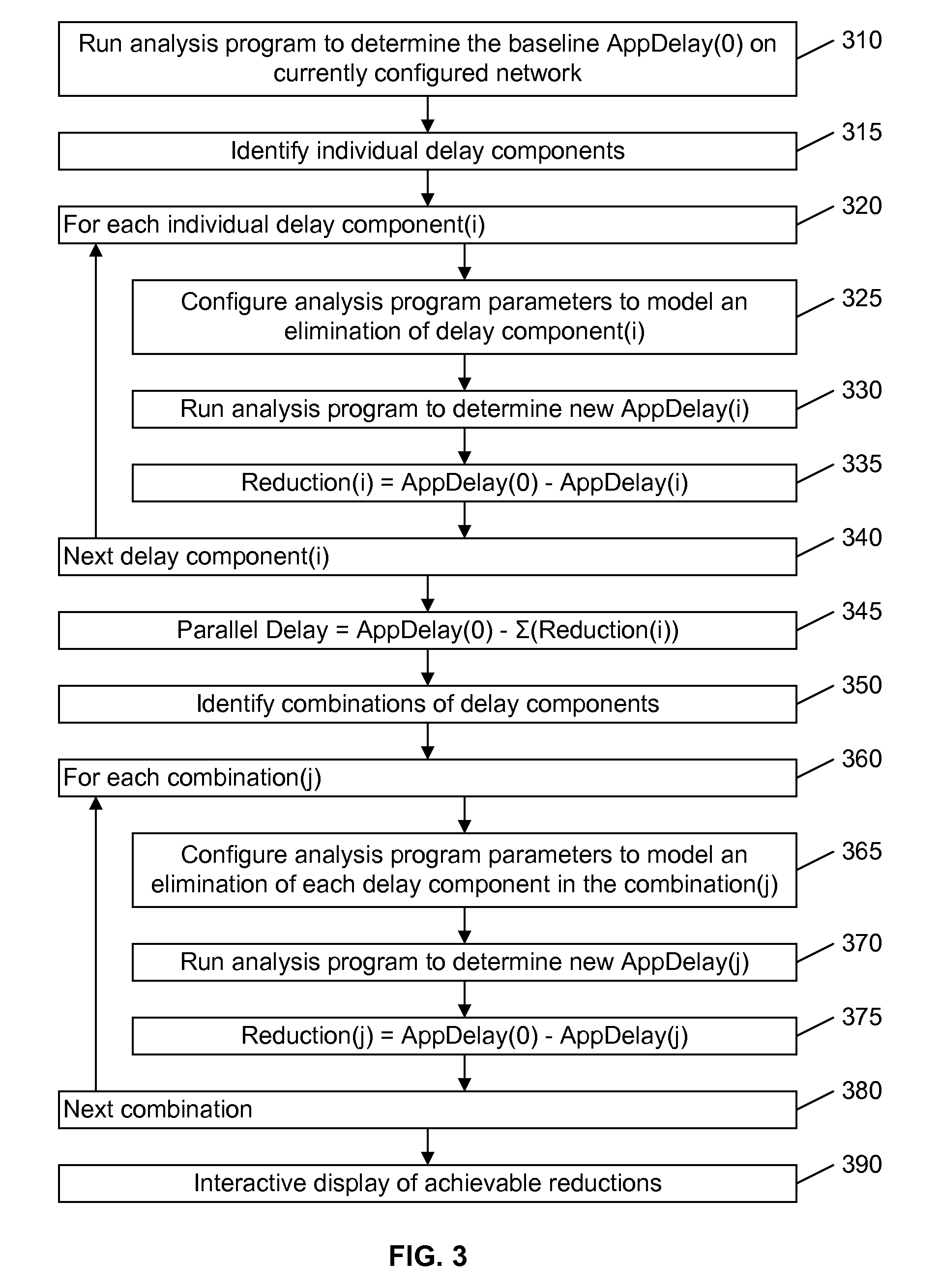

Network delay analysis including parallel delay effects

ActiveUS20080281961A1Easy to analyzeEasy to identifyError preventionTransmission systemsGraphicsDrill down

A multi-functional graphical user interface facilitates the analysis and assessment of application delays, including delays that occur on multiple paths. A trace file of an application's network events is processed to categorize the causes of delays incurred in the propagation and processing of these events. The system identifies the amount of delay (‘component delay’) that can be eliminated by eliminating each of the components of delay individually, as well as the amount of delay (‘parallel delay’) that can be eliminated by eliminating combinations of the delay components. A user interface displays the amount of reduction that can be achieved by eliminating each component delay individually and the amount of reduction that can be achieved by eliminating combinations of the individual component delays. To facilitate the analysis and assessment of these potential reductions, the interface allows the user to ‘drill down’ to view the individual delay components contained in each combination forming the parallel delays. In this manner, the user is provided a view of each of the delay components that would need to be addressed, either individually or in combination, to improve the overall application delay.

Owner:RIVERBED TECH LLC

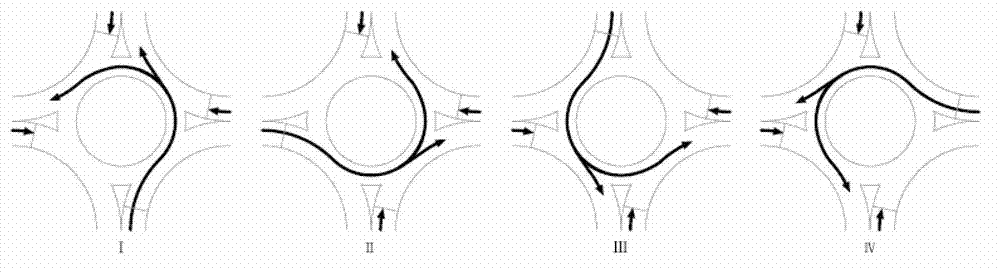

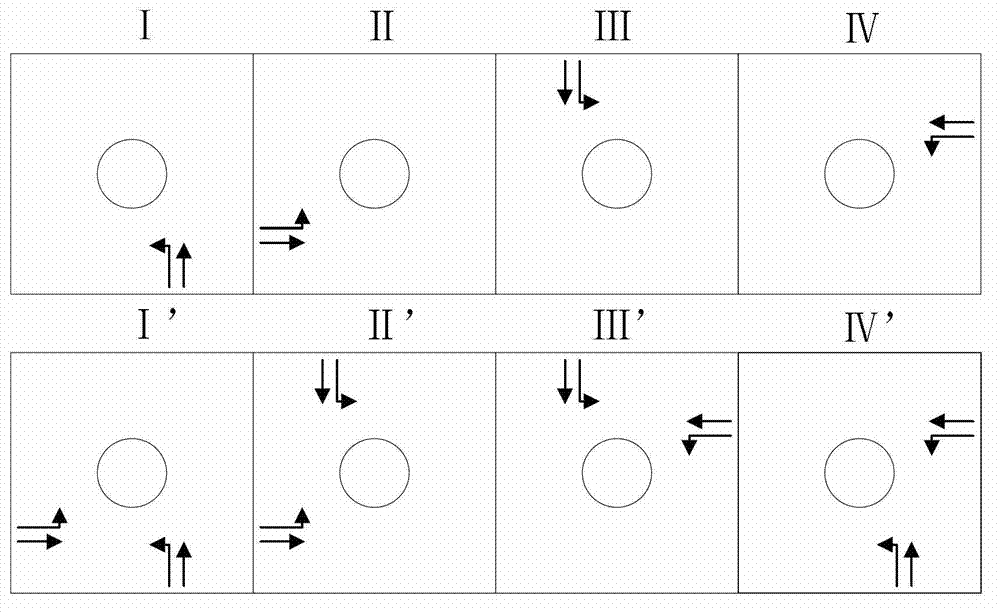

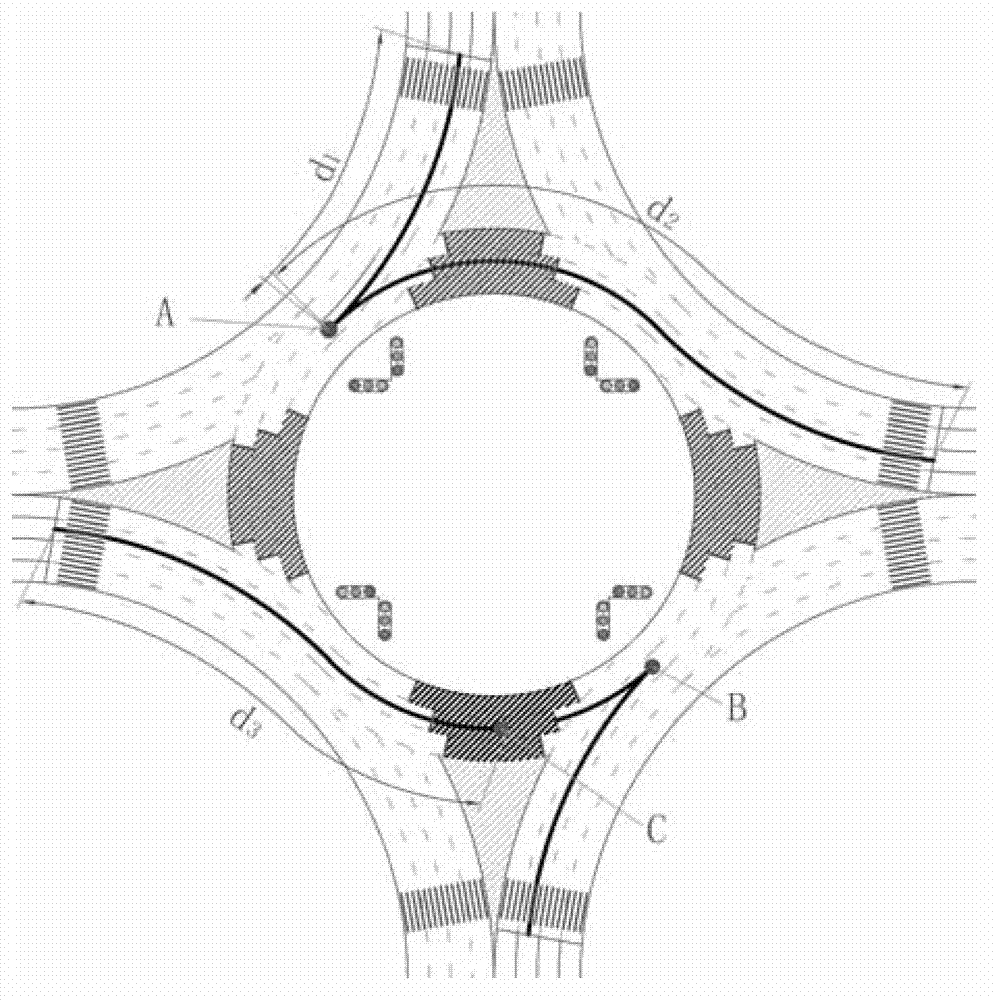

Four-road annular intersection design method based on single entrance release

InactiveCN103116992AImprove traffic capacityReduce delaysRoad vehicles traffic controlTraffic capacityEngineering

The invention provides a four-road annular intersection design method based on single entrance release. In terms of adjacent entrances and annular road trapezoid car storage area, an original single entrance release signal cycle model is modified, a modified four-road annular intersection single entrance release signal control mode is provided, signal phase of the control mode is coordinated, steps for phase coordination time difference calculation is elaborated, and preliminary discussion of application conditions of the control mode is provided one the basis of intersection traffic capacity and delay analysis. The traffic capacity and delay analysis results show that by the control mode, intersection traffic capacity is increased by more than 20%, and delay is reduced by more than 30%.

Owner:WUHAN UNIV OF TECH

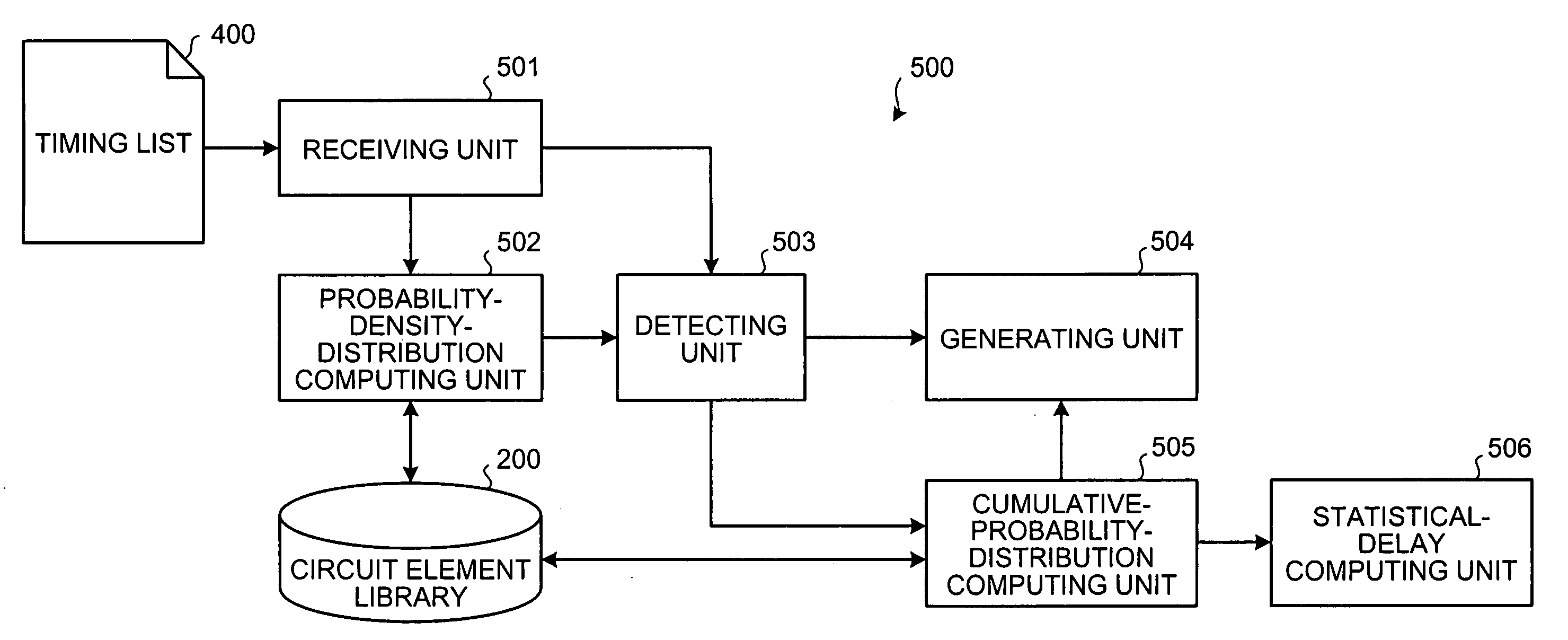

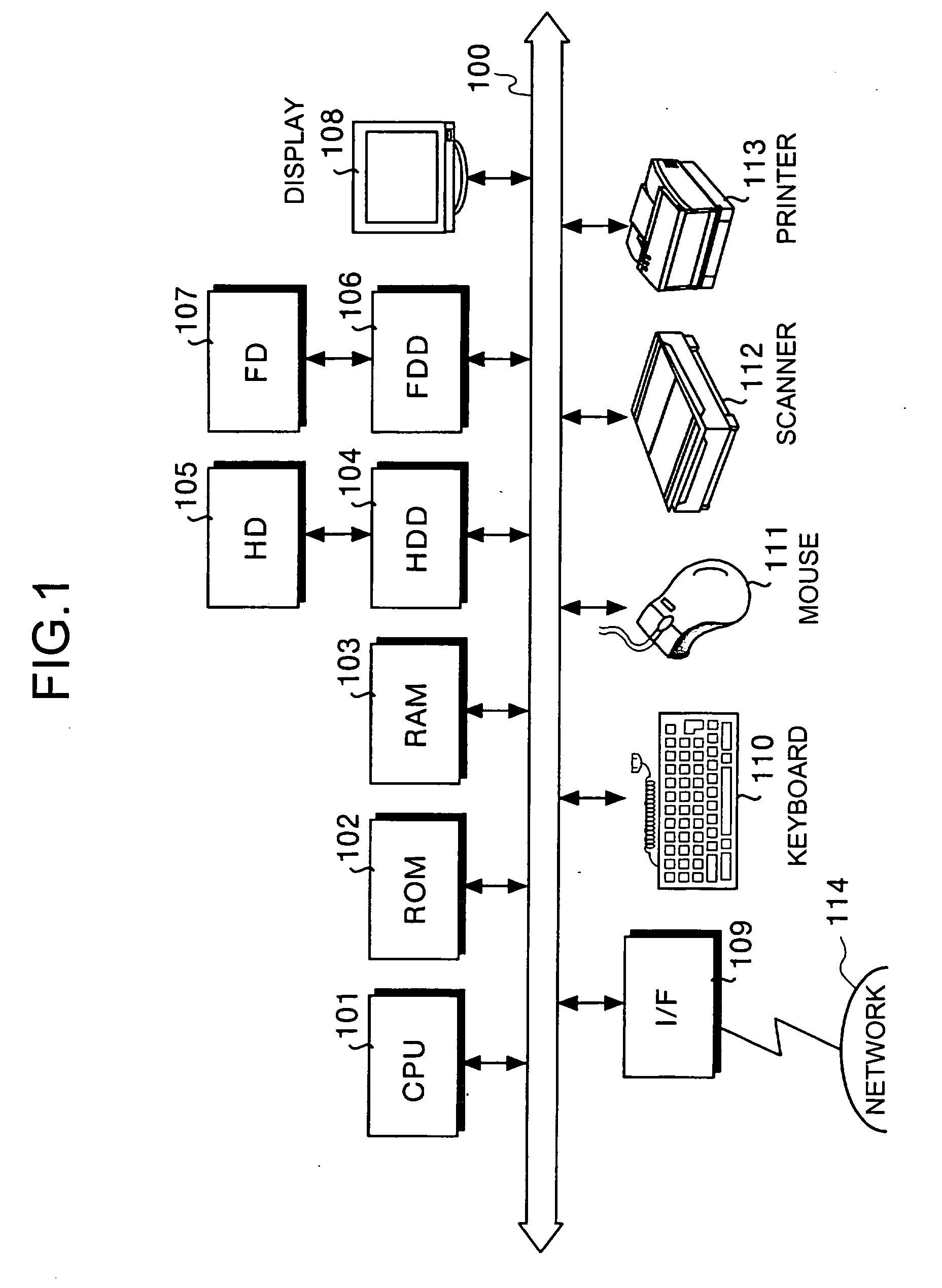

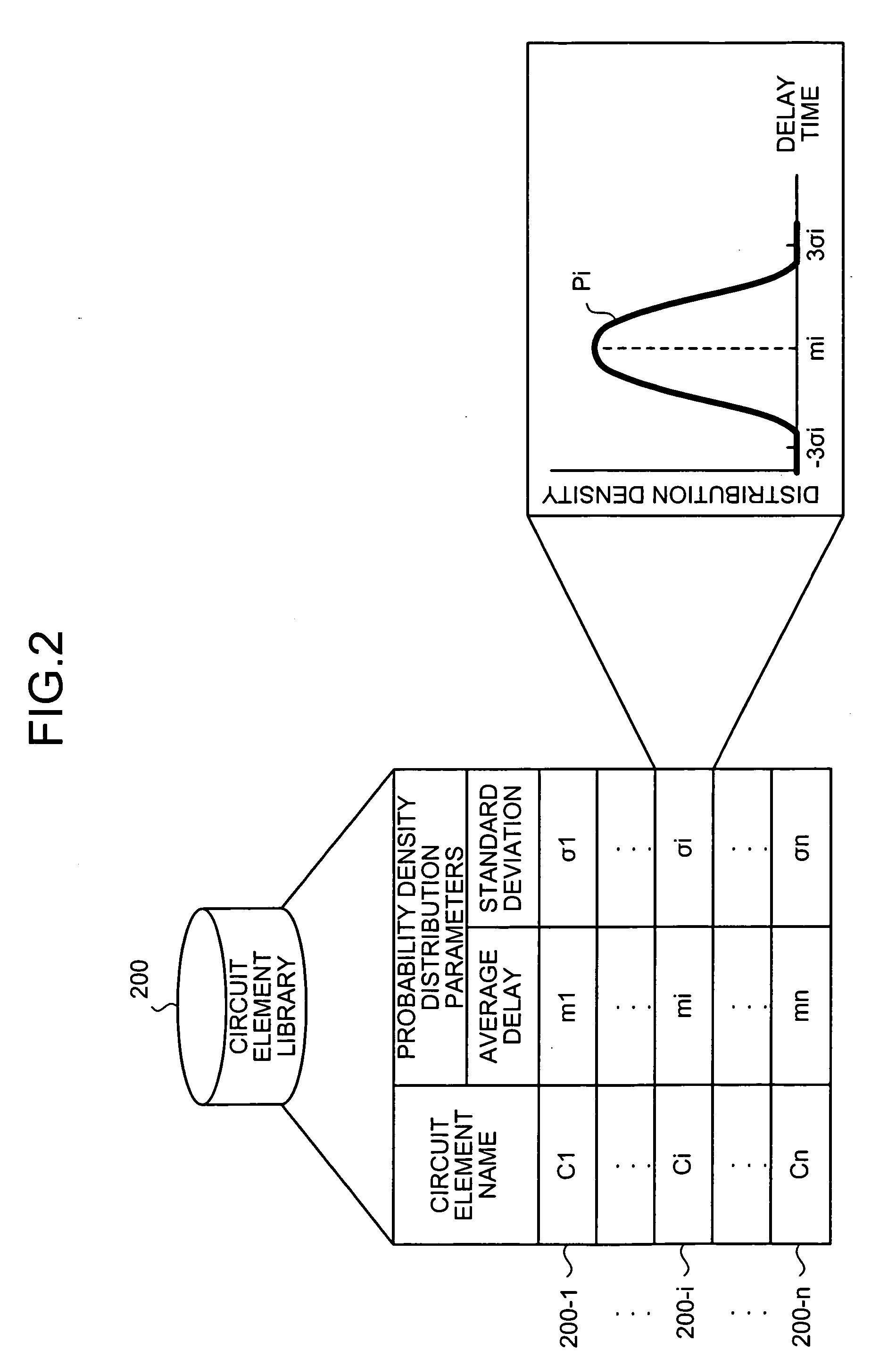

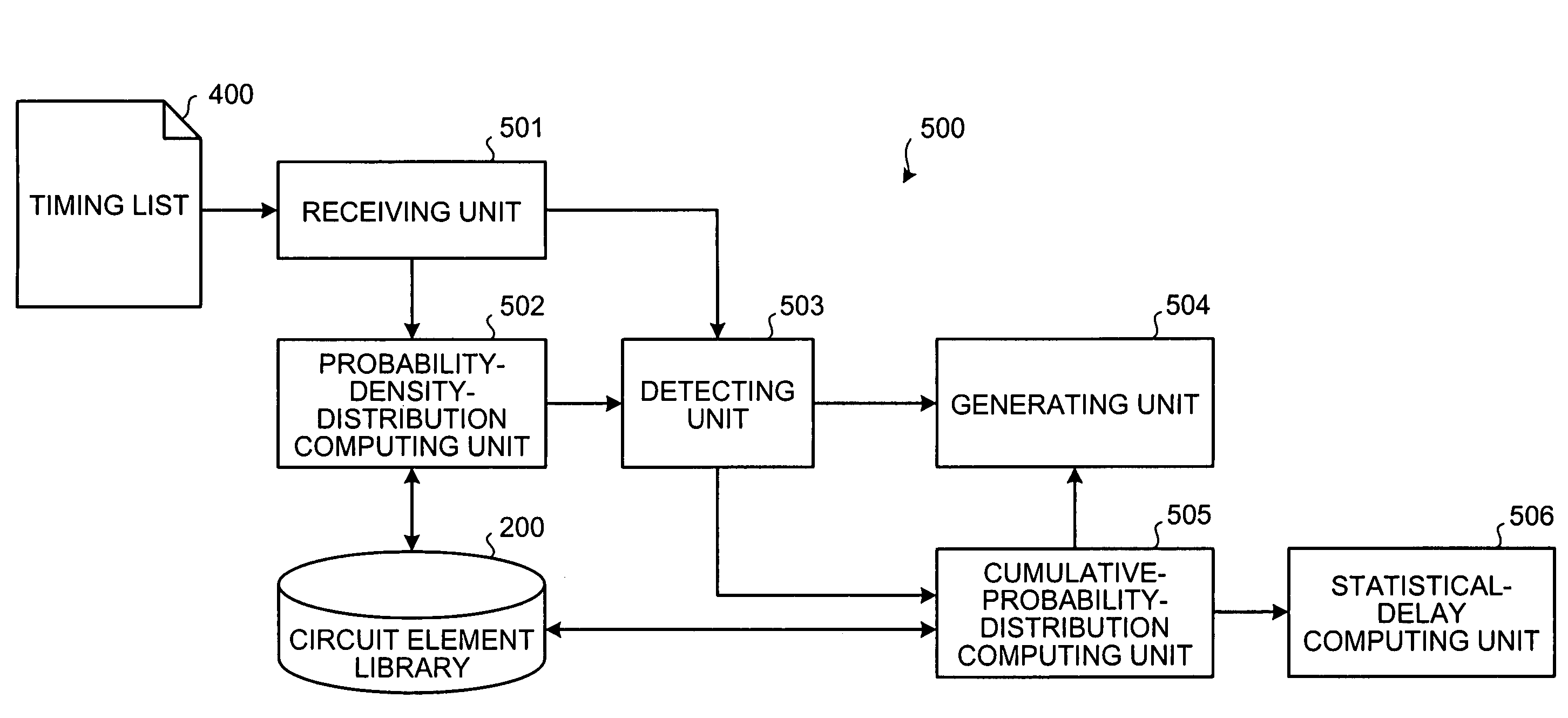

Delay analysis device, delay analysis method, and computer product

InactiveUS20070074138A1Solve problemsComputer aided designSoftware simulation/interpretation/emulationDensity distributionDelay analysis

A delay analysis device includes a receiving unit that receives a result of a timing analysis of a target circuit to be analyzed, a detecting unit that detects critical paths having delays within a predetermined range, a statistical-delay computing unit that computes a statistical delay of the target circuit based on a cumulative probability distribution of the delays of the critical paths, and a probability-density-distribution computing unit that computes a probability density distribution of delay of a critical path that has the greatest delay in the result. The detecting unit detects x number of critical paths having cumulative delays within computed probability density distribution.

Owner:FUJITSU LTD

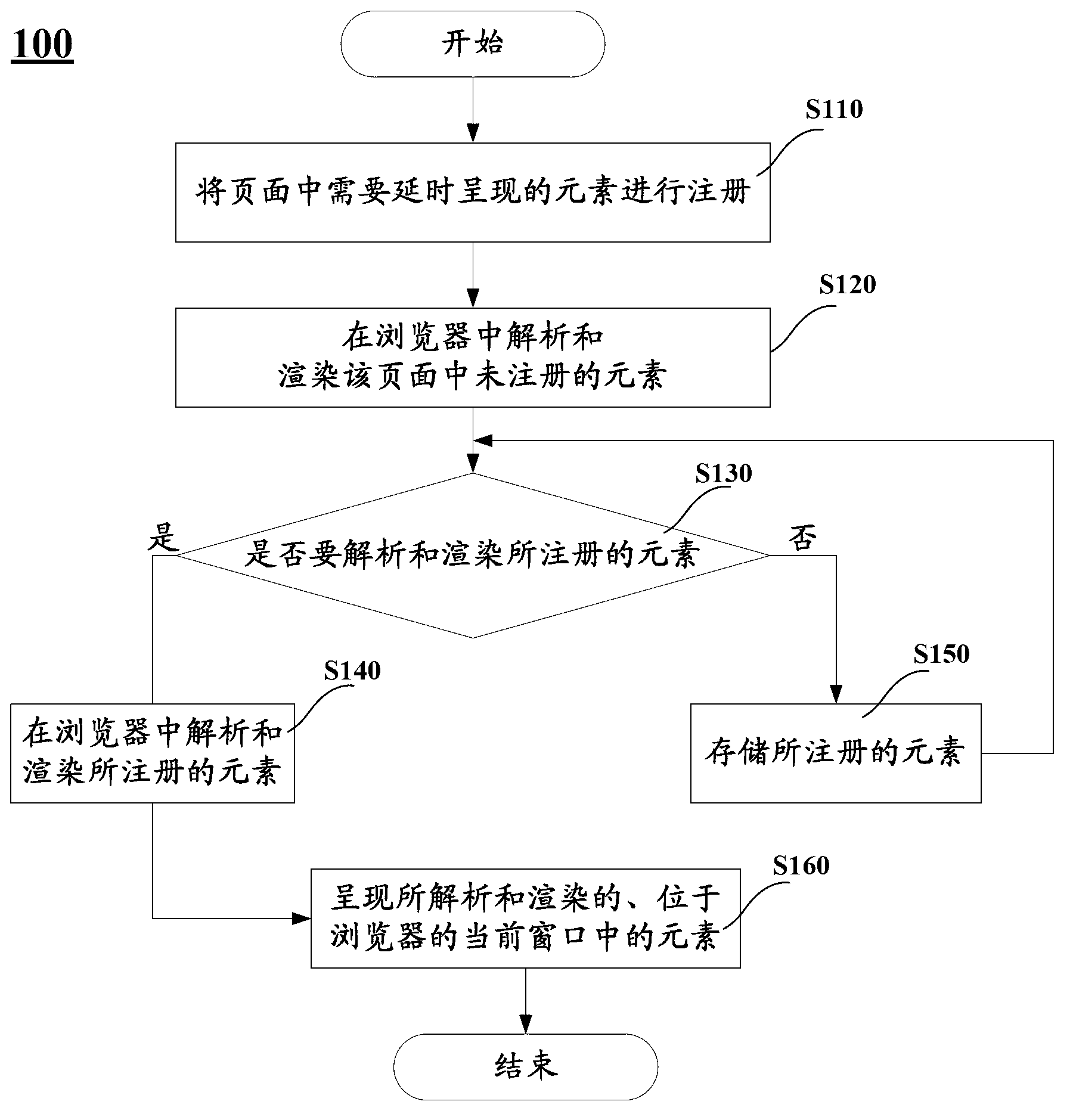

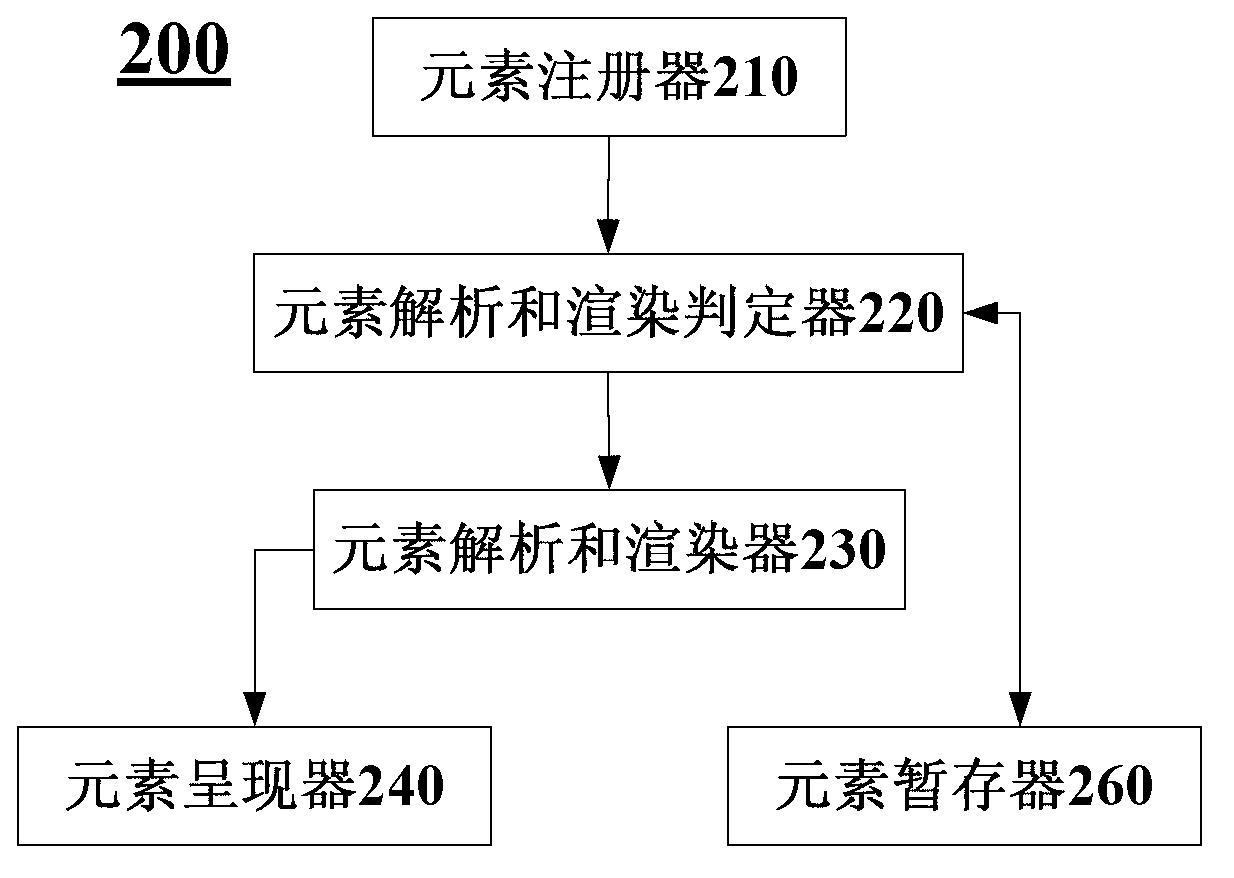

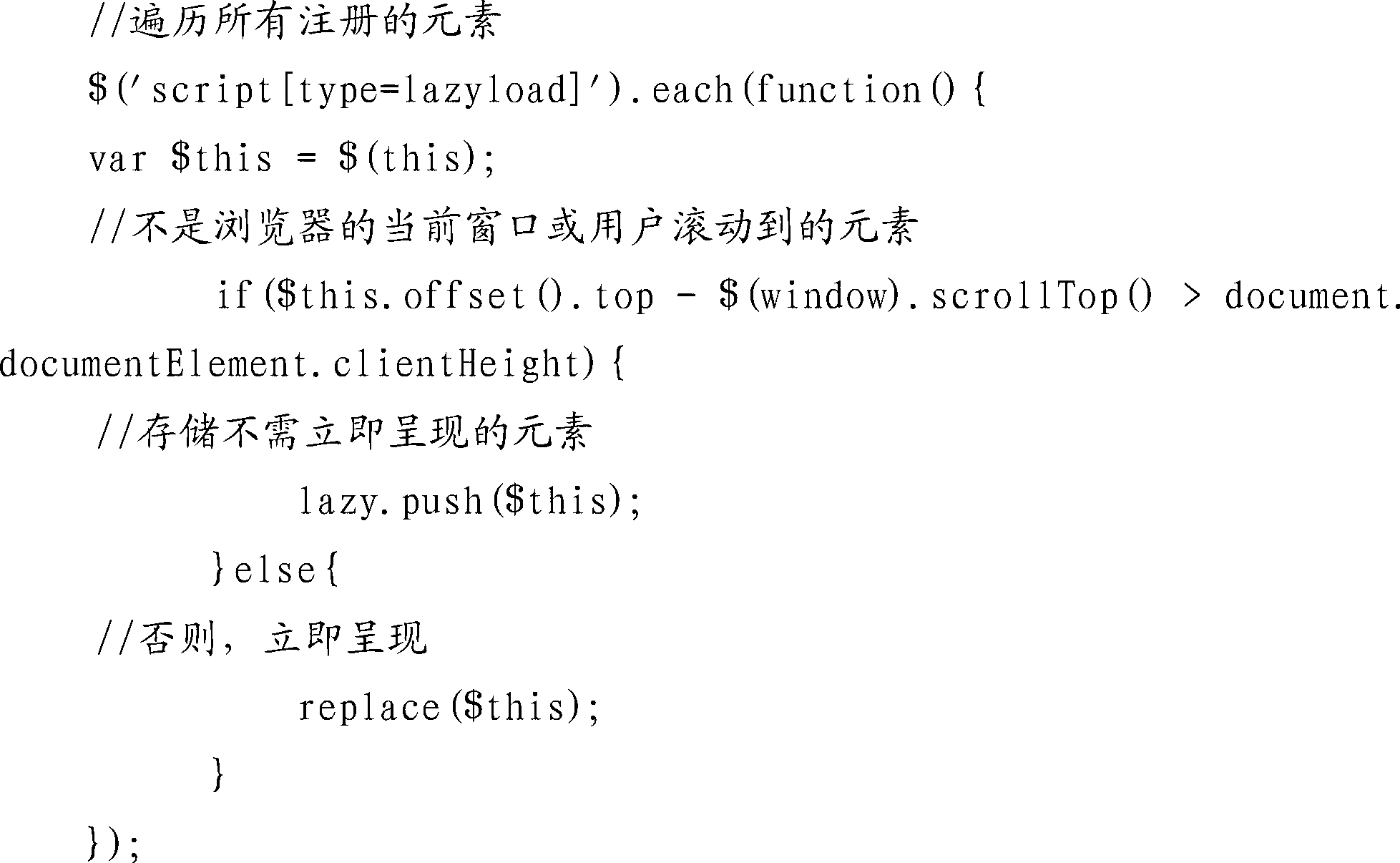

Method and device for processing page in browser

ActiveCN103019720AImprove display speedSpecific program execution arrangementsSpecial data processing applicationsDelayed presentationComputer science

The invention discloses a method and a device for processing a page in a browser. The method comprises the steps of: registering elements to be subject to delayed presentation in the page; analyzing and rendering unregistered elements of the page in the browser; judging whether the registered elements need to be analyzed and rendered, analyzing and rendering the registered elements if yes, otherwise, storing the registered elements; and presenting the rendered elements in the current window of the browser. Due to registering of the elements to be subject to delayed presentation and delay analysis, rendering and presentation of the registered elements to be subject to delayed presentation, images in the page can be subject to delayed presentation. Moreover, other elements of the page can be subject to delayed presentation. Therefore, the page display speed can be improved effectively.

Owner:BEIJING QIHOO TECH CO LTD

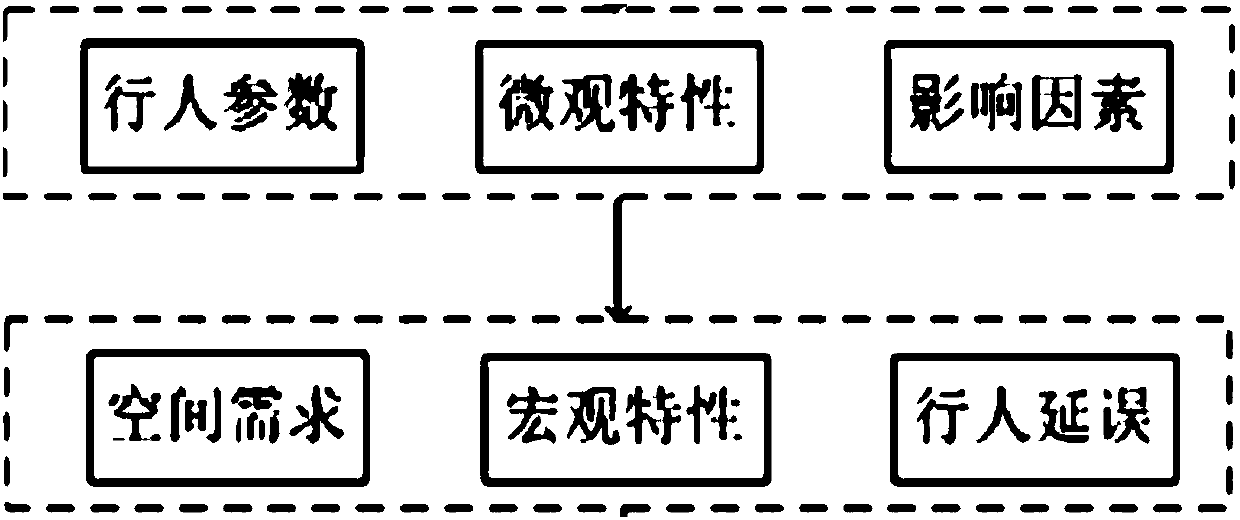

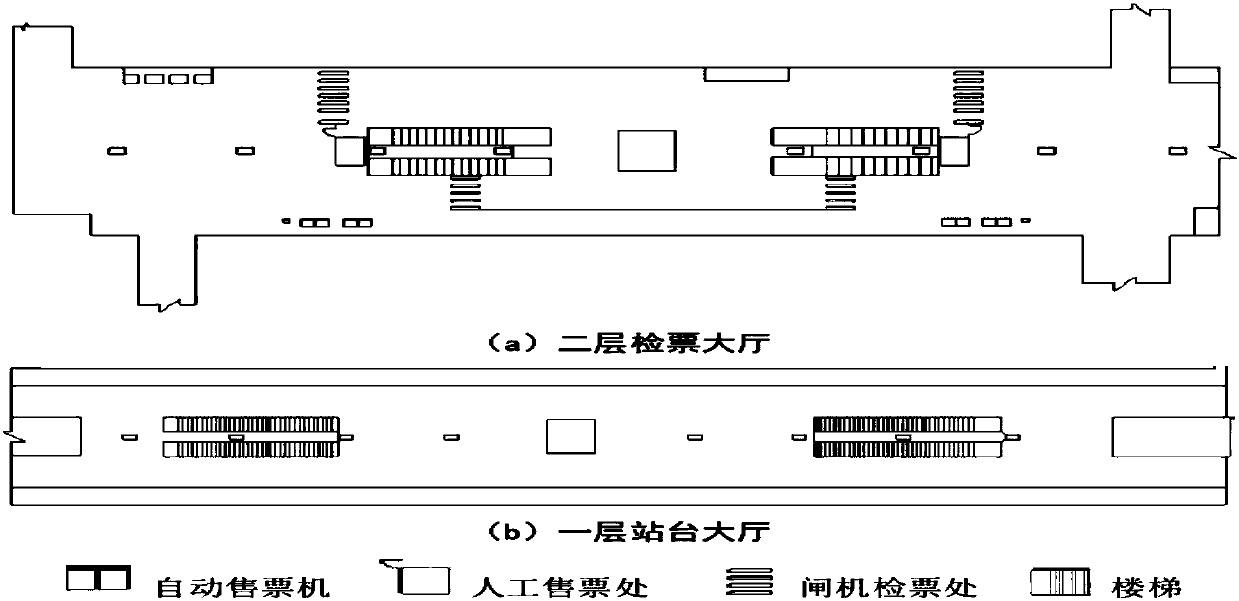

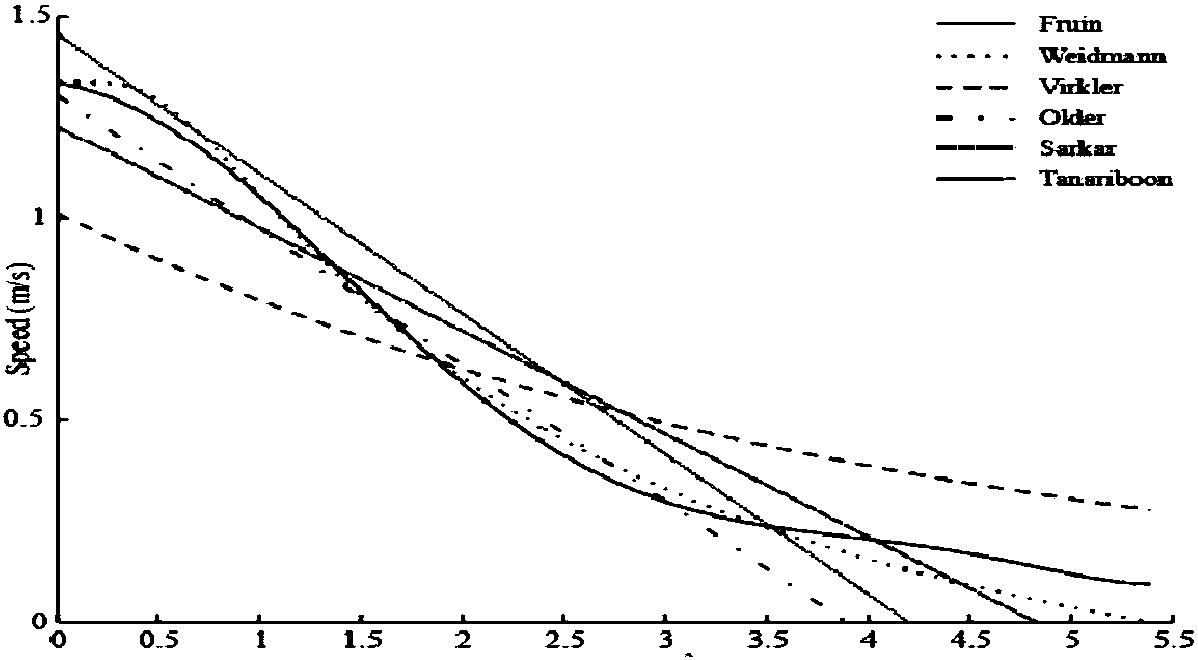

Passenger characteristic analysis method for track transportation junction

The present invention discloses a passenger characteristic analysis method for a track transportation junction. The method comprises the following steps: junction station pedestrian space demand analysis; junction station pedestrian flow macroscopic characteristic analysis; and pedestrian delay analysis. According to the analysis method disclosed by the present invention, pedestrian behavior characteristic theories, including a pedestrian flow microscopic theory, a pedestrian macroscopic theory and a statistic regression method, are applied to track transportation junction passenger characteristic analysis work, the pedestrian space demand is analyzed according to video information and an equation is obtained by means of curve fitting for the pedestrian flow macroscopic characteristic on different facilities, and a conclusion of whether a current facility meets a maximum traffic capacity or not is given out.

Owner:NANJING RAIL TRANSIT SYST

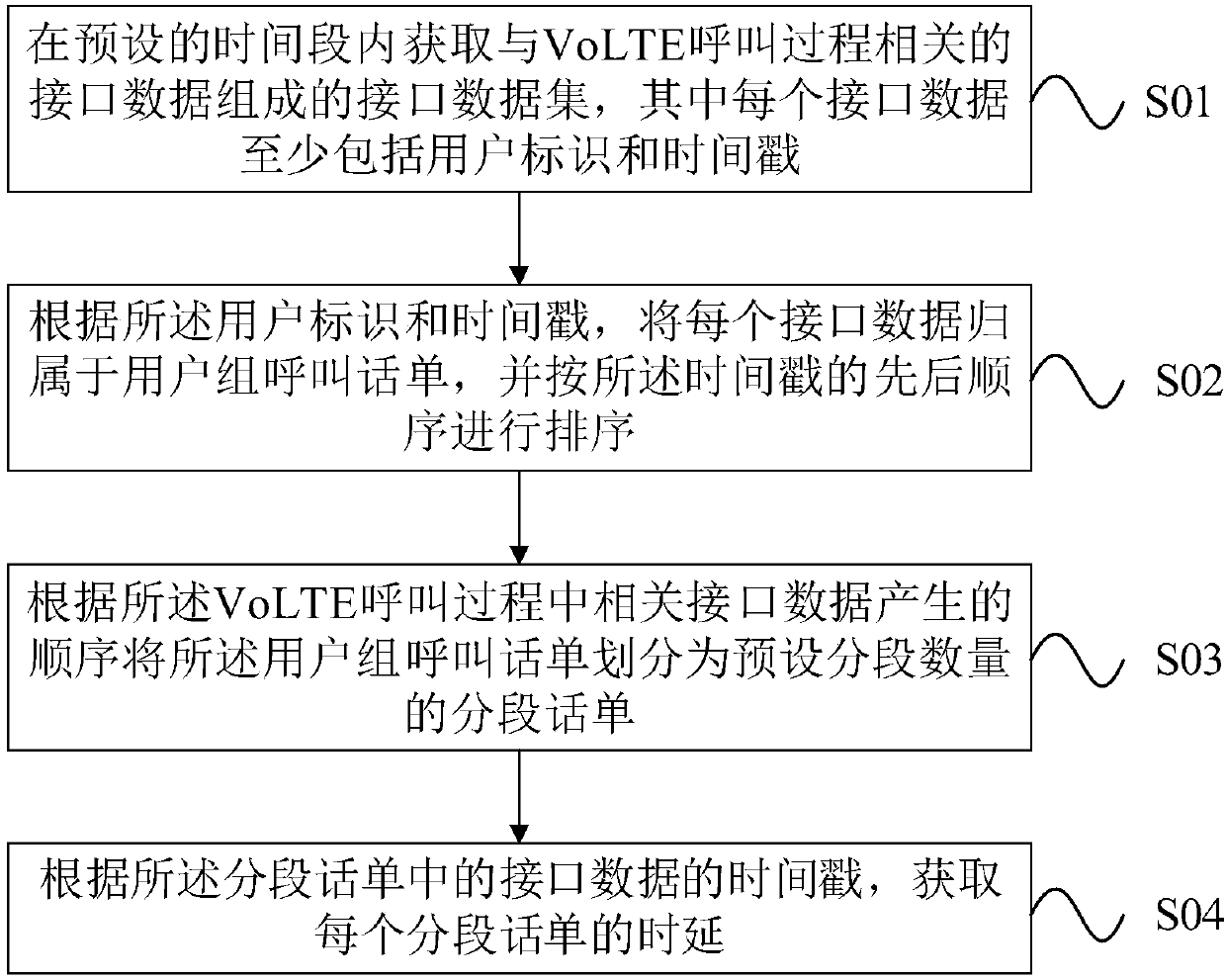

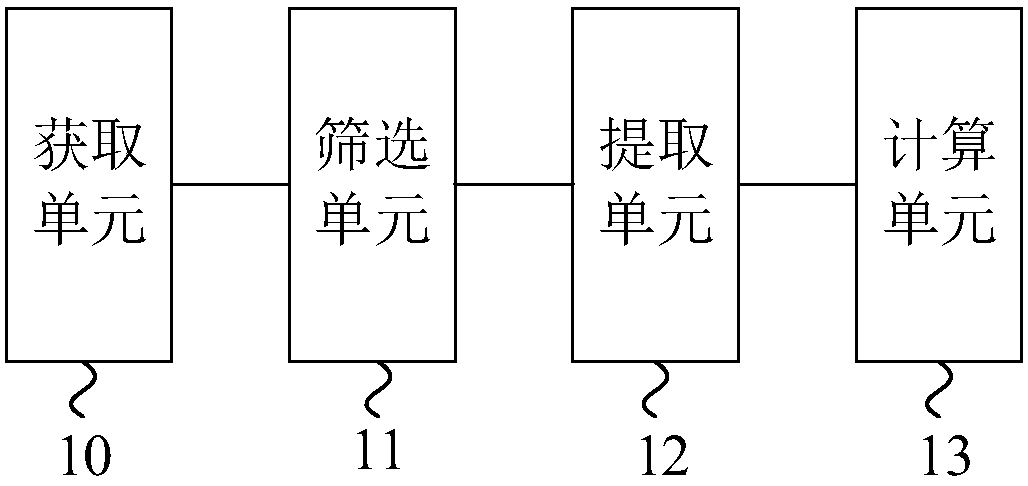

A VoLTE call delay analysis method and device

ActiveCN109818816AMeet maintenance requirementsAddress maintenance requirementsData switching networksWireless communicationData setTimestamp

The embodiment of the invention provides a VoLTE call delay analysis method and device. The method comprises the following steps: acquiring an interface data set related to a VoLTE calling process ina preset time period, wherein each interface data at least comprises a user identifier and a timestamp; according to the user identifier and the timestamp, each piece of interface data belonging to auser group calling bill, and sorting according to the sequence of the timestamps; dividing the user group call ticket into a preset number of segmented tickets according to the sequence generated by the related interface data in the VoLTE call process; According to the timestamps of the interface data in the segmented call tickets, obtaining the segmented call tickets; obtaining the time delay ofeach segmented call ticket, According to the embodiment of the invention, the user group call ticket corresponding to the VoLTE call process is formed by the collected interface data; and extracting akey segmented call ticket to calculate the segmented time delay so as to establish a VoLTE call multi-interface association analysis system and a multi-interface association analysis tool, thereby meeting the maintenance requirements of rapid positioning and problem solving.

Owner:CHINA MOBILE GROUP DESIGN INST +1

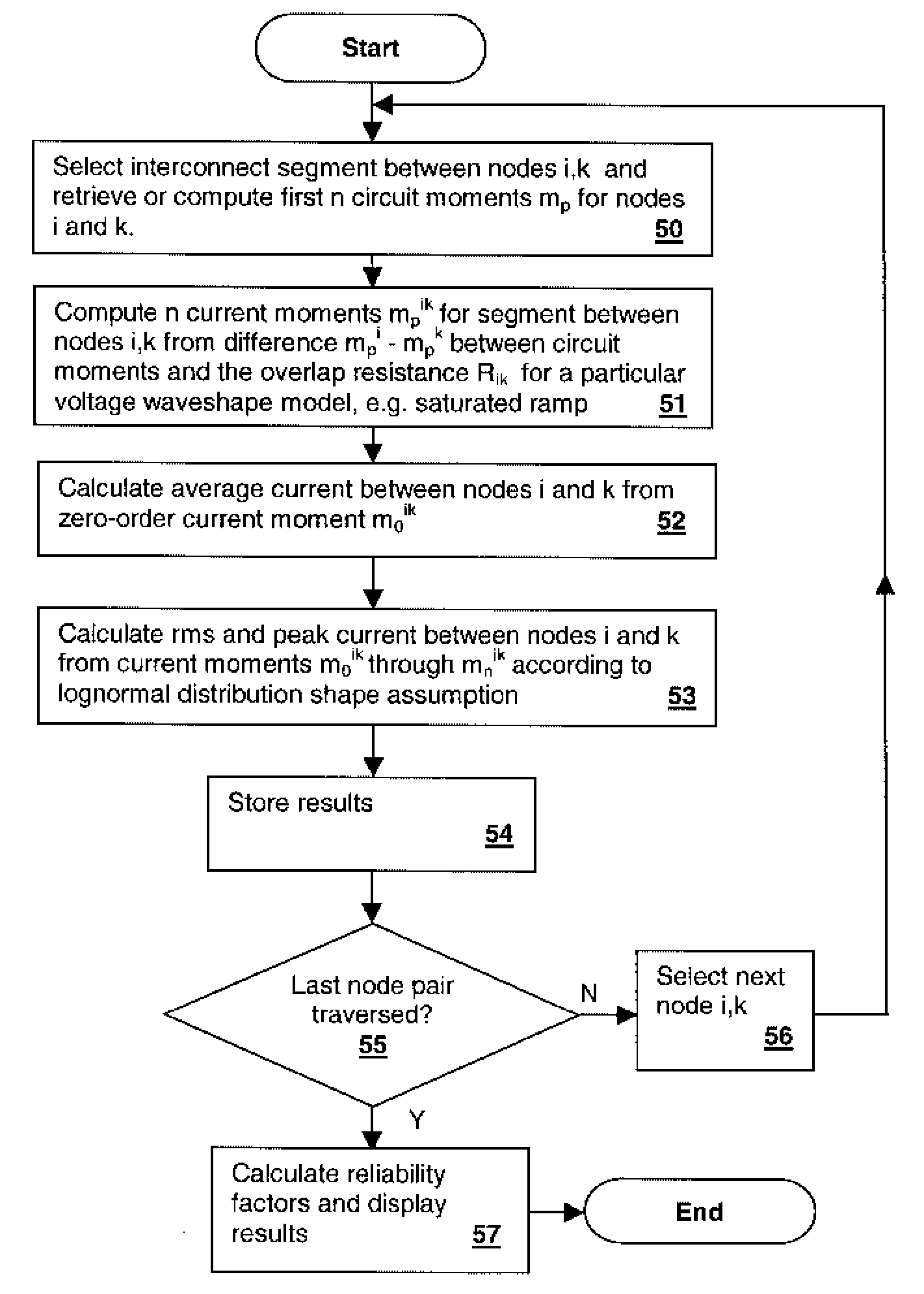

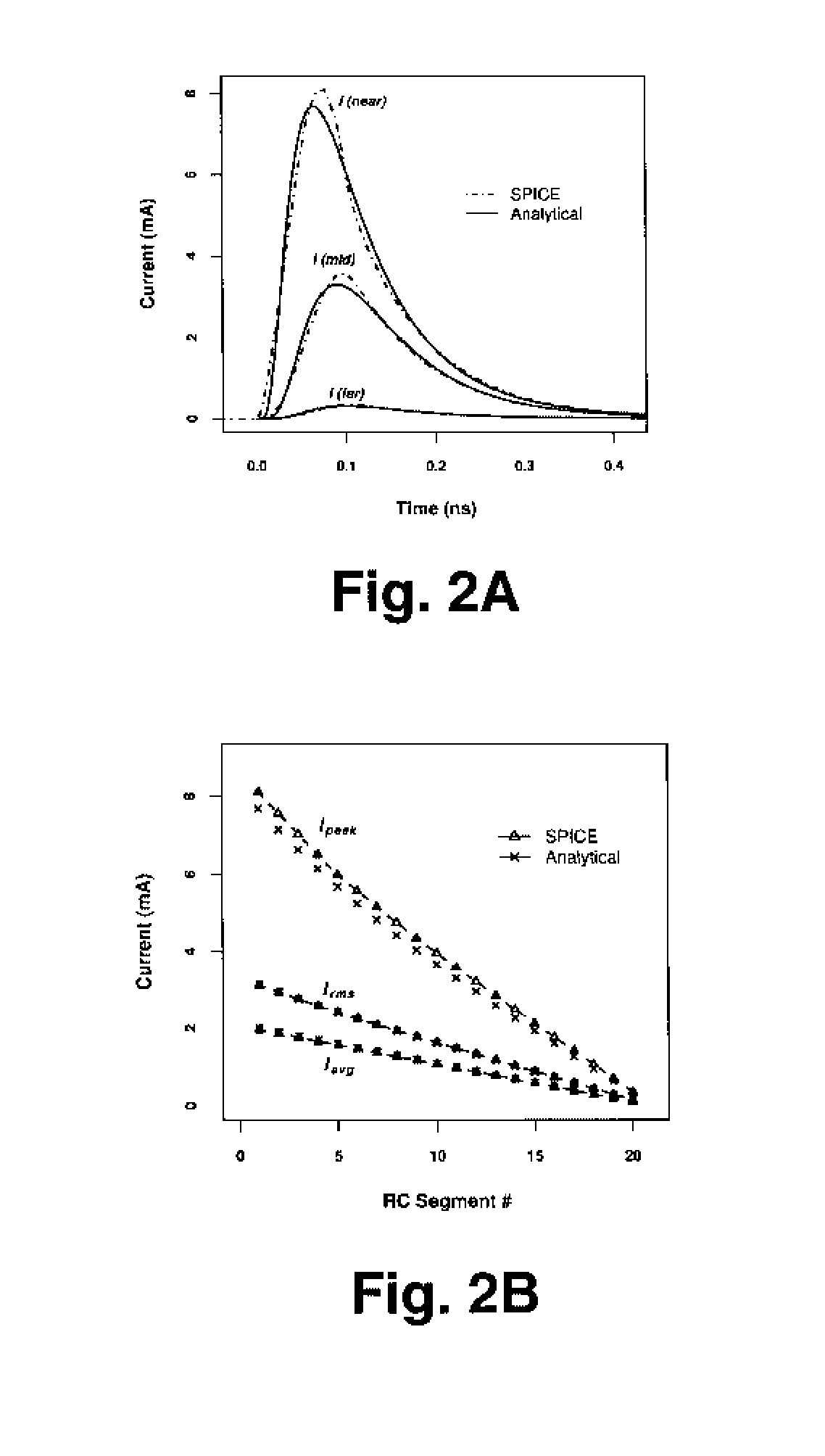

Moment-Based Method and System for Evaluation of Metal Layer Transient Currents in an Integrated Circuit

InactiveUS20080222579A1Accurately determinedSemiconductor/solid-state device testing/measurementDetecting faulty computer hardwareAverage currentEngineering

A moment-based method and system for evaluation of metal layer transient currents in an integrated circuit provides a computationally efficient evaluation of transient current magnitudes through each interconnect in the metal layer. The determinable magnitudes include peak, rms and average current, which can be used in subsequent reliability analyses. Interconnect path nodes are traversed and circuit moments are either retrieved from a previous interconnect delay analysis or are computed. For each pair of nodes, current moments are computed from the circuit moments. The average current is computed from the zero-order circuit moment and the peak and rms currents are obtained from expressions according to a lognormal or other distribution shape assumption for the current waveform at each node.

Owner:IBM CORP

Delay analysis device, delay analysis method, and computer product

InactiveUS7320118B2Computer aided designSoftware simulation/interpretation/emulationDensity distributionCritical path method

A delay analysis device includes a receiving unit that receives a result of a timing analysis of a target circuit to be analyzed, a detecting unit that detects critical paths having delays within a predetermined range, a statistical-delay computing unit that computes a statistical delay of the target circuit based on a cumulative probability distribution of the delays of the critical paths, and a probability-density-distribution computing unit that computes a probability density distribution of delay of a critical path that has the greatest delay in the result. The detecting unit detects x number of critical paths having cumulative delays within computed probability density distribution.

Owner:FUJITSU LTD

Method and apparatus for simulating packet delay variation of a multi-switch network

InactiveUS20090259445A1Analogue computers for electric apparatusVoltage-current phase angleTotal delayPacket generator

A packet delay variation simulation system has a packet generator, a packet delay variation generator, and a packet delay analyzer to analyze delayed packets. The packet delay variation generator has multiple delay distribution modules that use both a deterministic delay process and a statistical delay process packet for determining a packet's delay. The packet delay variation generator may utilize different probability density functions to describe various portions of measured packet data. That is, measured packet delay information is analyzed and information from this analysis is used to construct a total delay model for a network. The delay may include a pre-determined deterministic delay offset as well as one or more variable statistical delay offsets.

Owner:INTEL CORP

Method and apparatus for simulating packet delay variation of a multi-switch network

InactiveUS8094686B2Analogue computers for electric apparatusVoltage-current phase angleTotal delayPacket generator

A packet delay variation simulation system has a packet generator, a packet delay variation generator, and a packet delay analyzer to analyze delayed packets. The packet delay variation generator has multiple delay distribution modules that use both a deterministic delay process and a statistical delay process packet for determining a packet's delay. The packet delay variation generator may utilize different probability density functions to describe various portions of measured packet data. That is, measured packet delay information is analyzed and information from this analysis is used to construct a total delay model for a network. The delay may include a pre-determined deterministic delay offset as well as one or more variable statistical delay offsets.

Owner:INTEL CORP

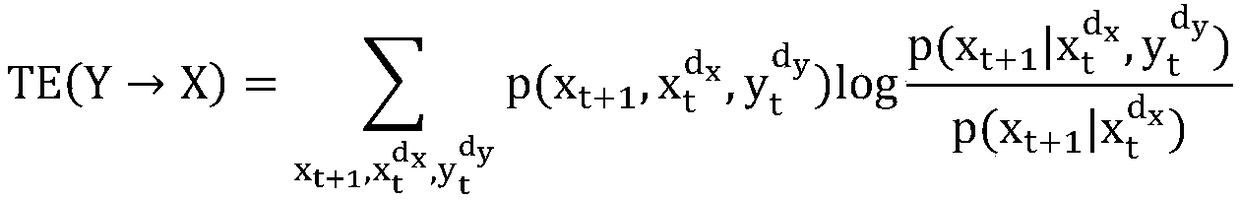

A quantitative analysis method of aviation delay propagation

The invention discloses a quantitative analysis method of aviation delay propagation, belonging to the technical field of aviation delay analysis. Firstly, the arrival delay time series from airport ito airport j and the departure delay time series of airport j are constructed, and the transfer entropy TE (Y(right arrow)X) of the t-th time slice is calculated to quantify the shift of the generalized Markov condition, and the causality of arrival delay to departure delay is tested. Then several arrival delay time series and departure delay time series with the same statistical characteristicsare reconstructed as substitute data, and the causality of each substitute data is destroyed; the transfer entropy (TE) is calculated with the substitute data, and the significance test is carried out. Pairs of tests are conducted between any two airports to establish the weighted edge, build the network model of aviation delay propagation, and use the network model to analyze flight delay. The invention only needs to analyze the causality between the delay time series, and can quantitatively calculate the delay propagation situation between the airports.

Owner:BEIHANG UNIV

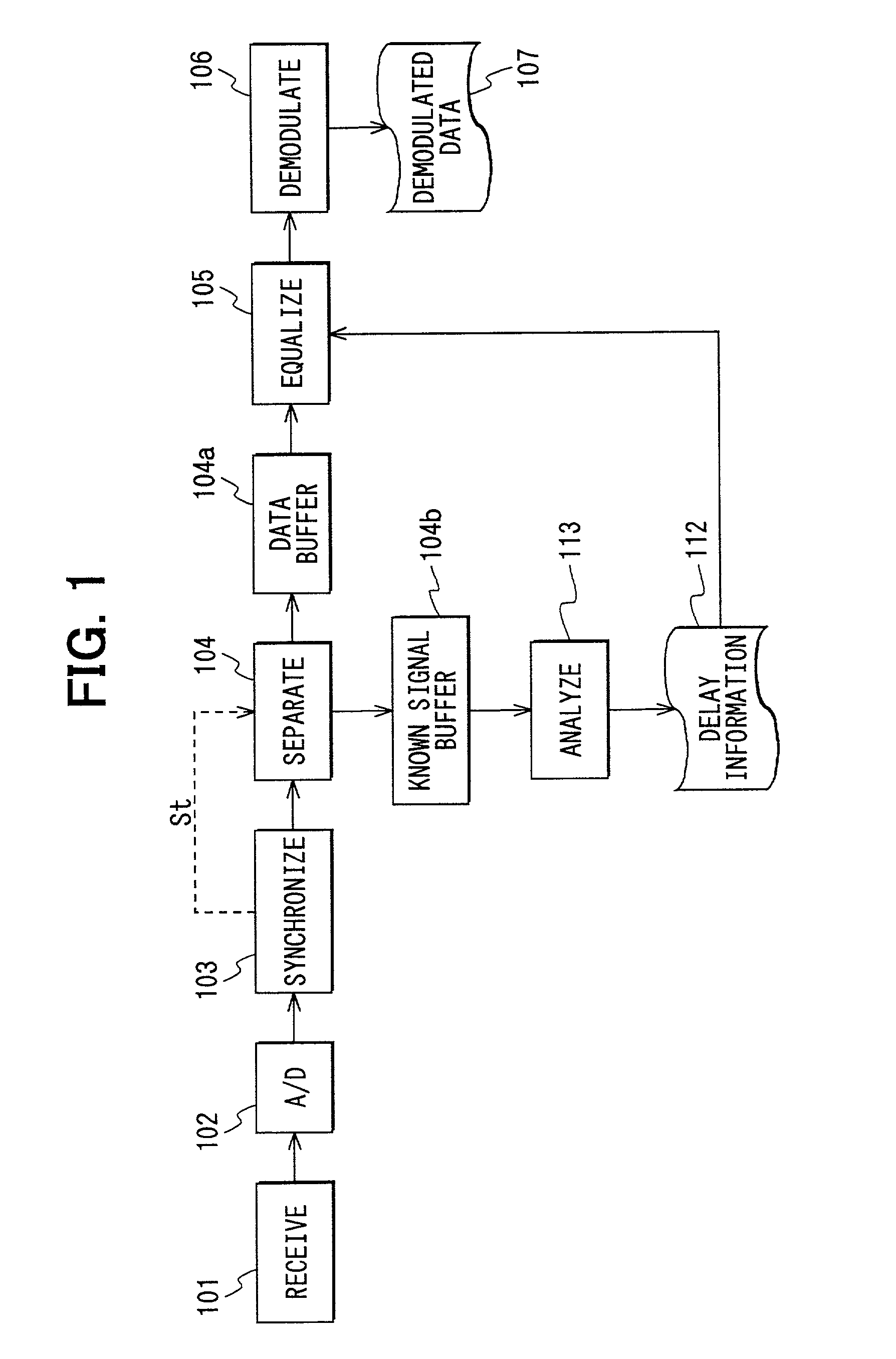

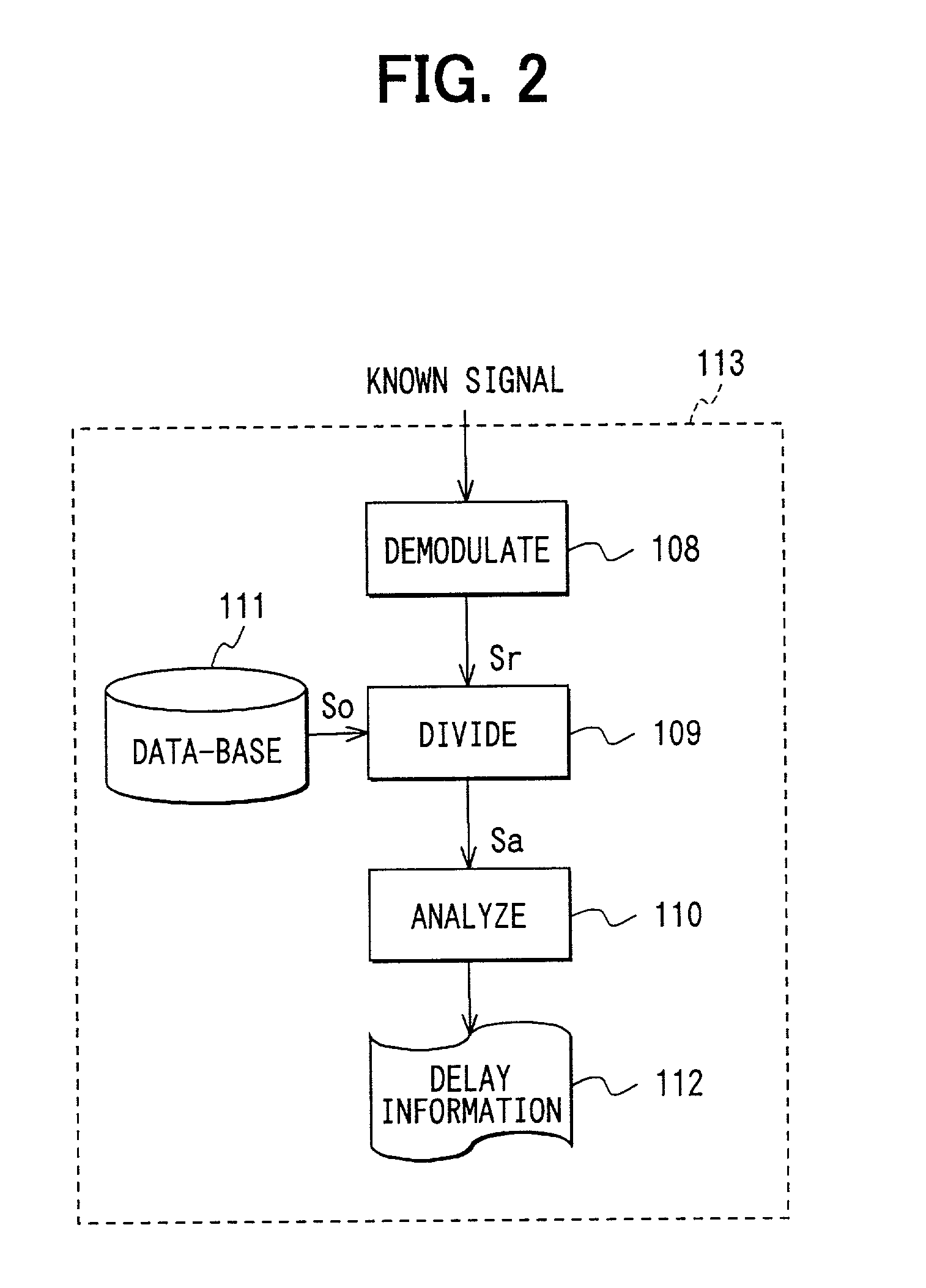

Communication device having delay information calculating function

InactiveUS7106817B2Improve efficiencySpatial transmit diversityTransmission control/equalisingMultiplexingCarrier signal

A communication device using orthogonal multiplexing carrier method for determining delay information of received radio waves. In this device, a known signal demodulator performs OFDM demodulation to output demodulated signal, and a divider performs a complex division of the demodulated signal with a data sector of known signal of a database for each sub-carrier. By the data section of the known signal, the computation result of the amount of shift can be determined for each of sub-carriers. A delay analytical calculation circuit uses the computation result of the amount of shift for sub-carriers to analyze the delayed waves. For delay analysis, ESPRIT method is used to determine delay information by means of computation result of the amount of shift for each sub-carrier.

Owner:DENSO CORP

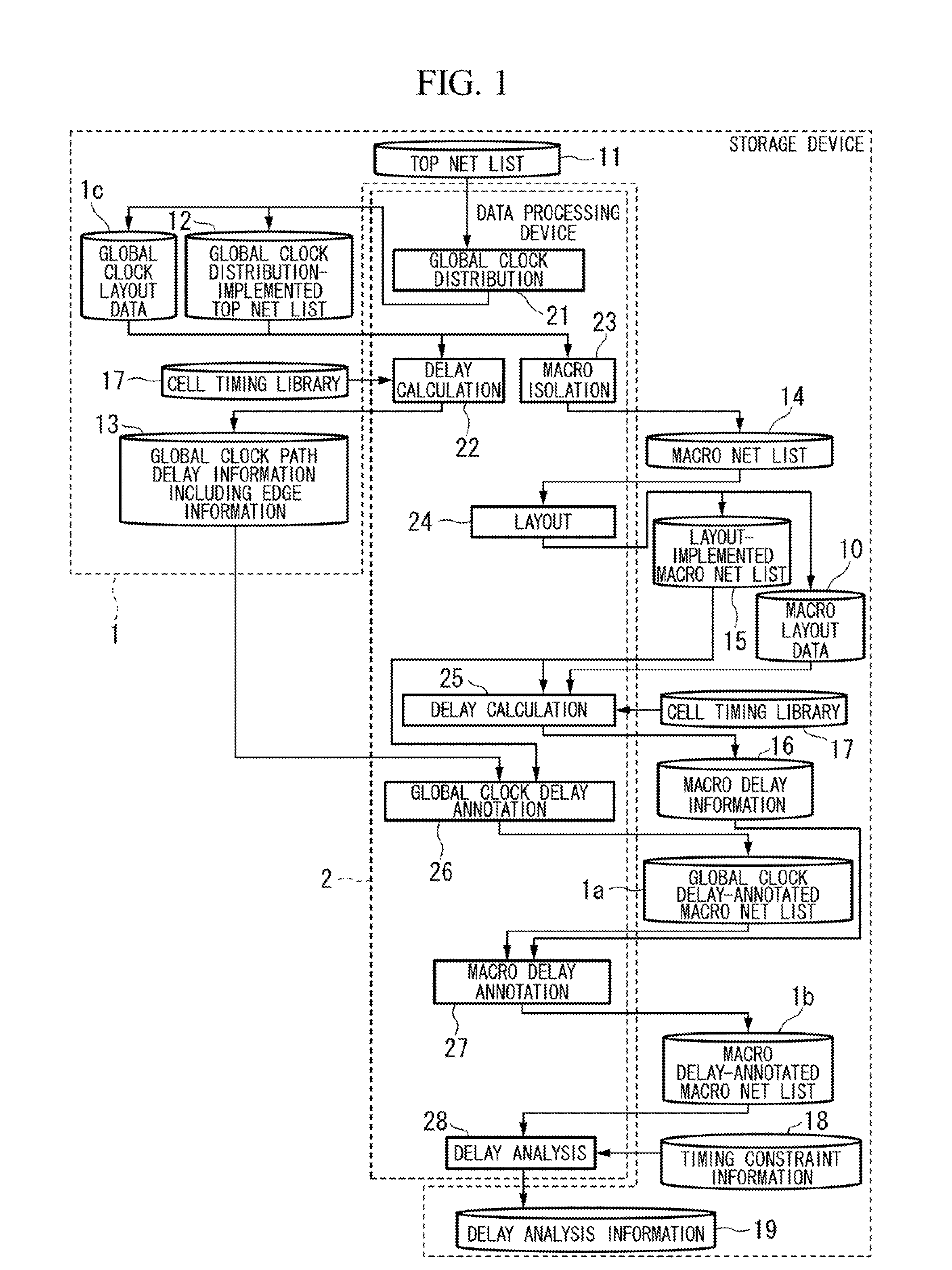

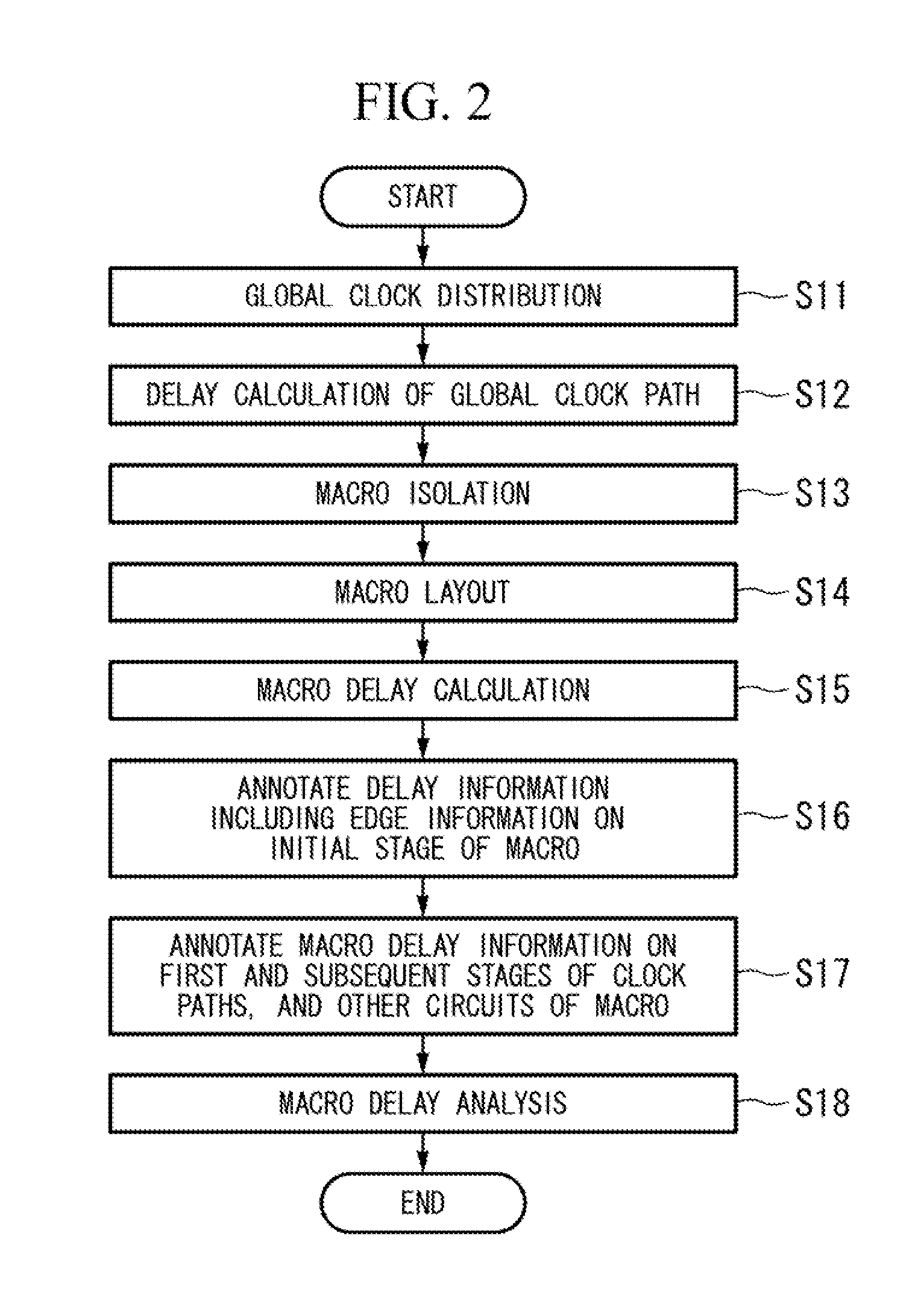

Delay analysis processing of semiconductor integrated circuit

InactiveUS20110046937A1The effect is outstandingOutstanding featuresComputer aided designSpecial data processing applicationsComputer scienceDelay analysis

A delay analysis device composed of a storage device and a data processing device analyzes a chip fabricating a semiconductor integrated circuit. Delay calculation is performed via an RC simulation with reference to a layout-implemented macro net list, macro layout data, and a cell timing library, thus producing macro delay information. An initial stage of a macro is annotated by the global clock path delay information including the edge information so as to produce a global clock delay-annotated macro net list, which is then converted into a macro delay-annotated net list. Based on the macro delay-annotated net list and timing constraint, the delay analysis device calculates delay times of signal paths and clock paths as well as clock skews with a high precision. It checks whether or not the relationship between the delay times of signal paths and clock paths meets the timing constraint, thus producing delay analysis information.

Owner:NEC CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com