Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

40results about How to "Secure margin" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

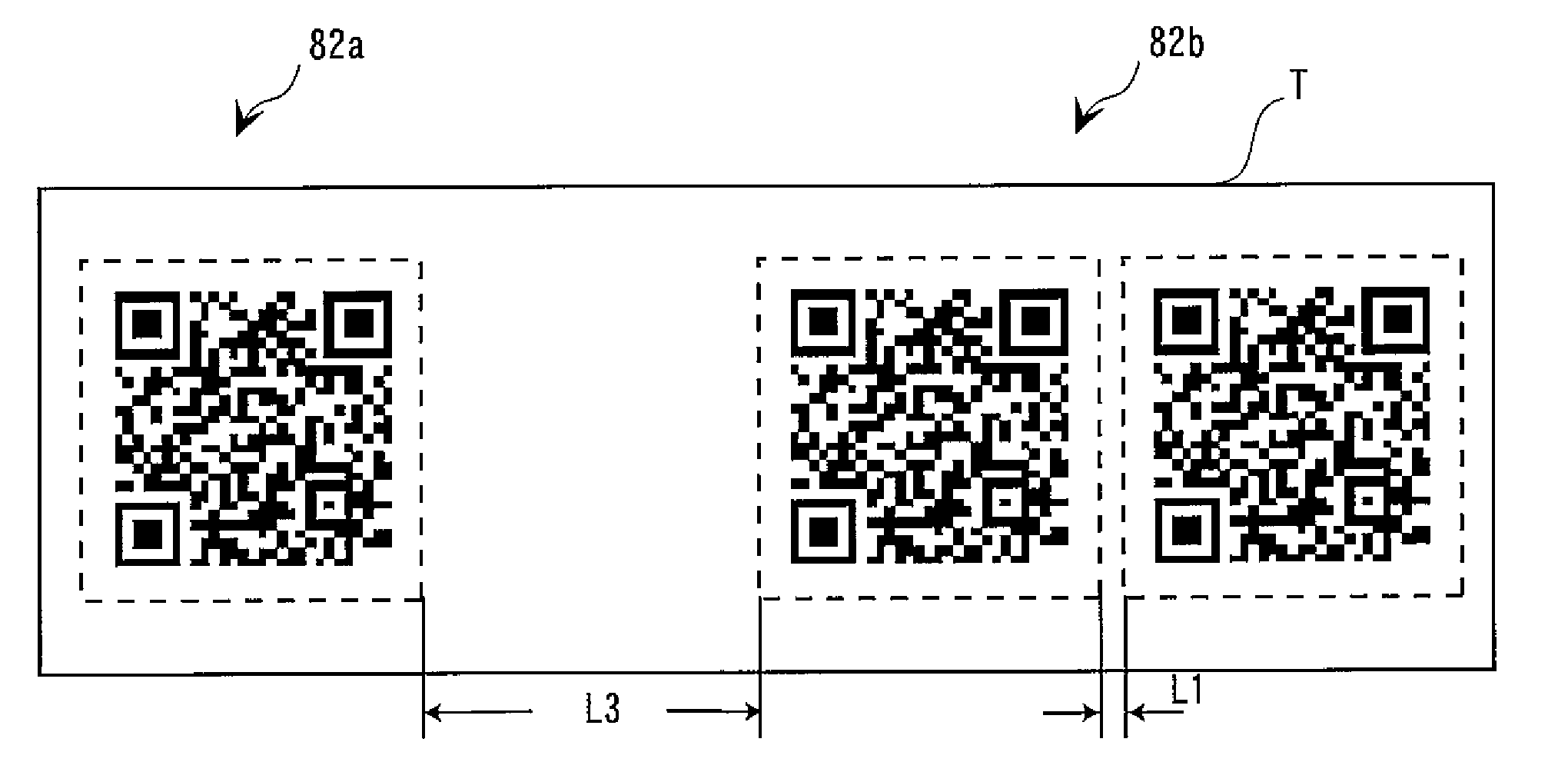

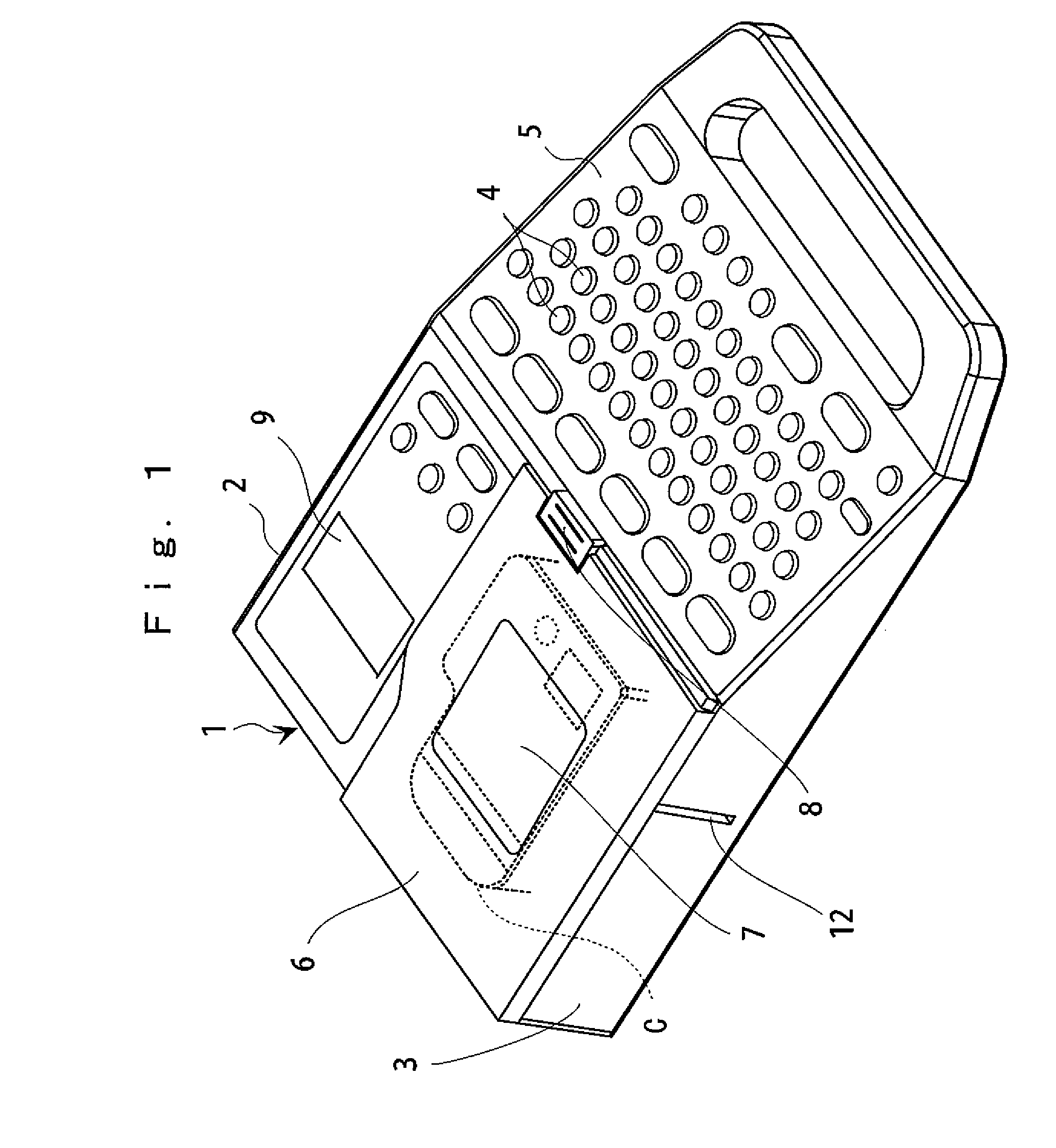

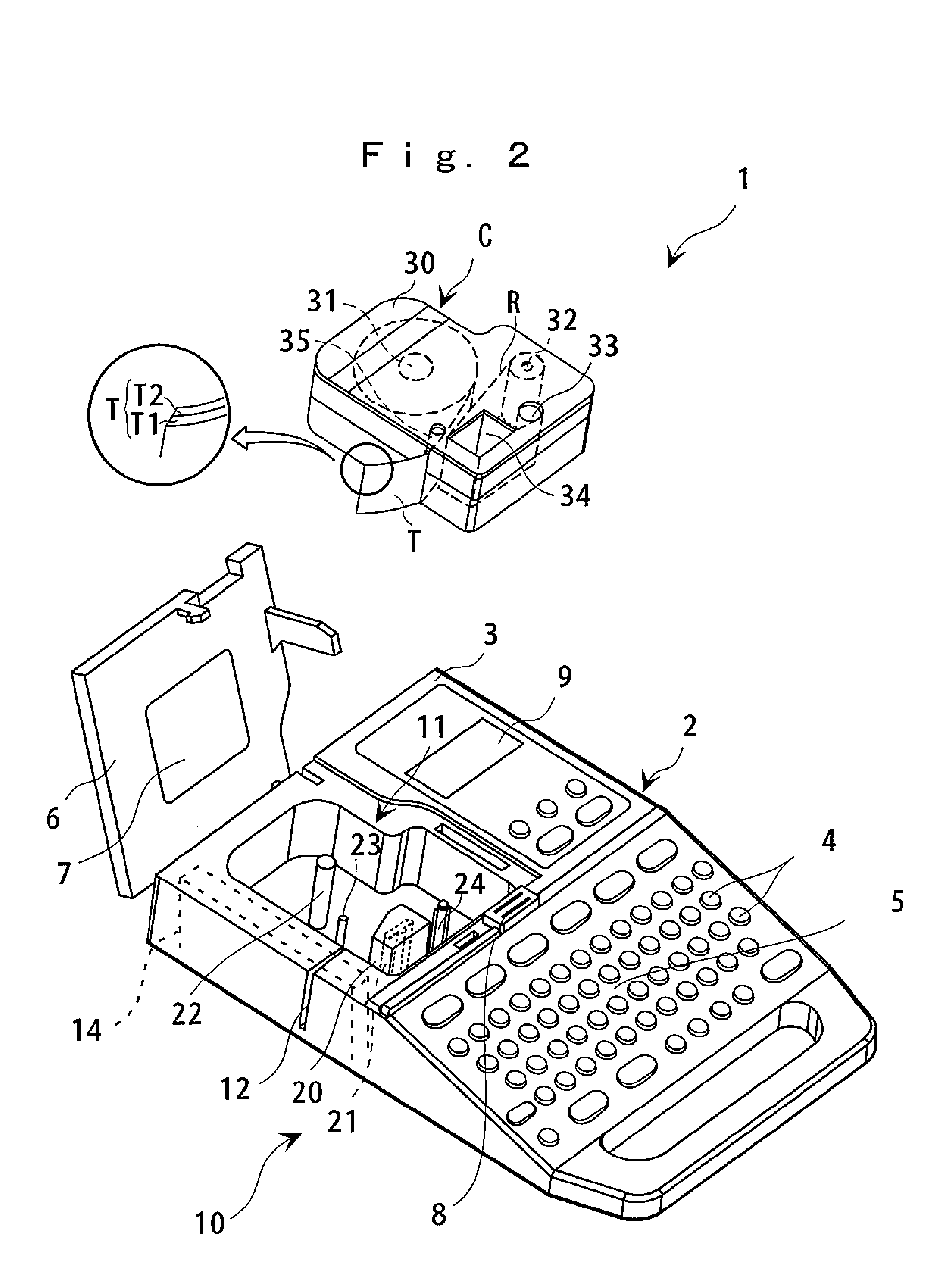

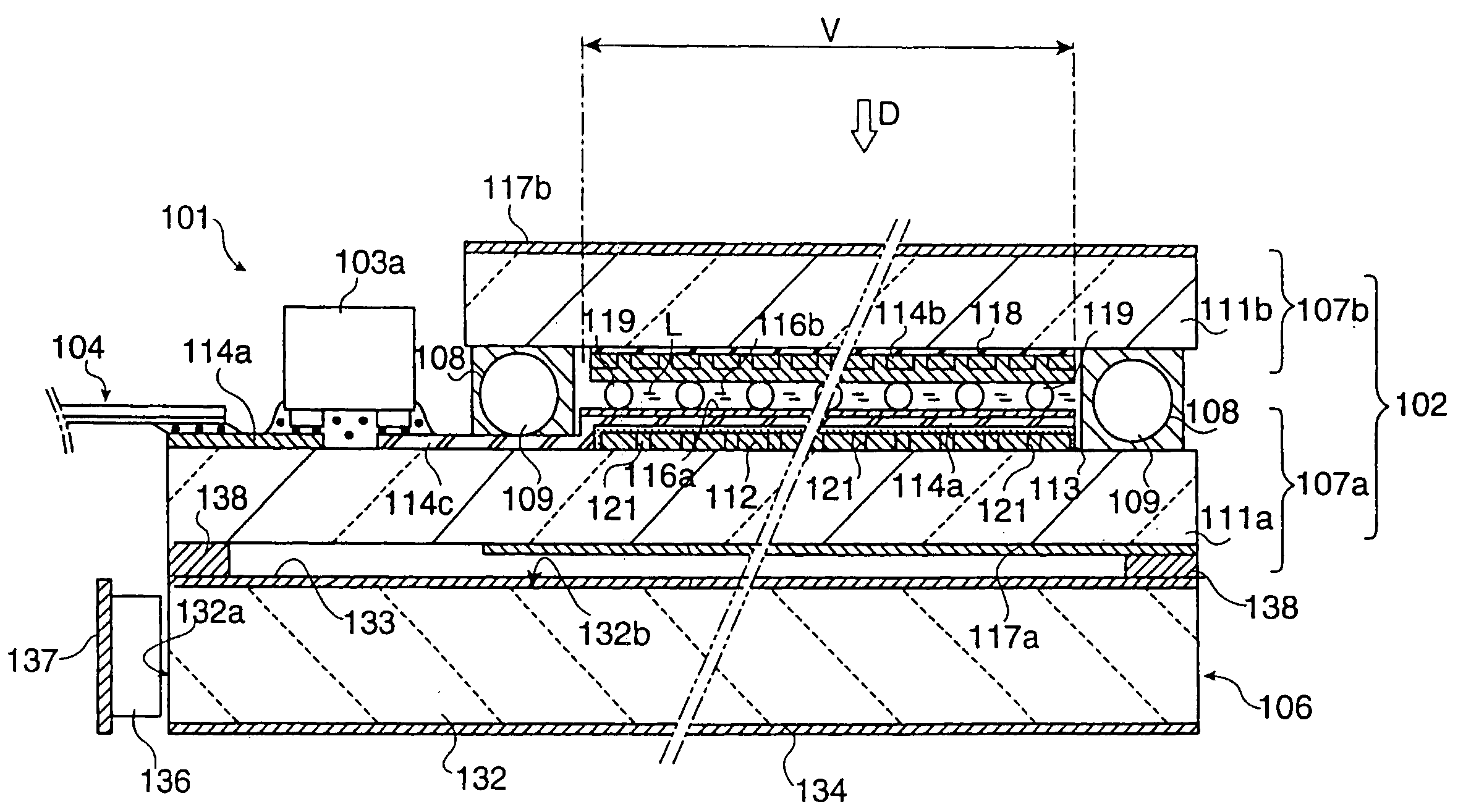

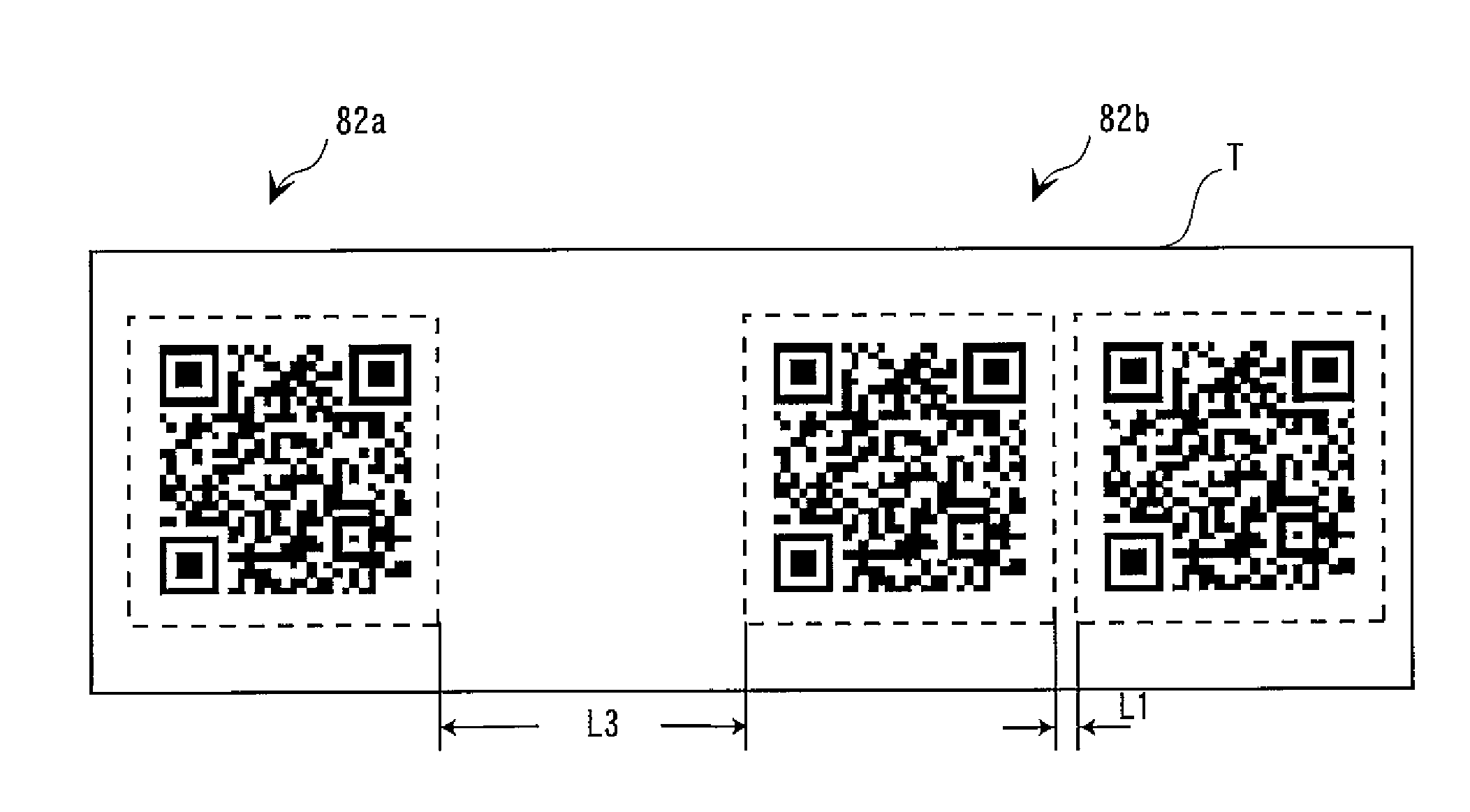

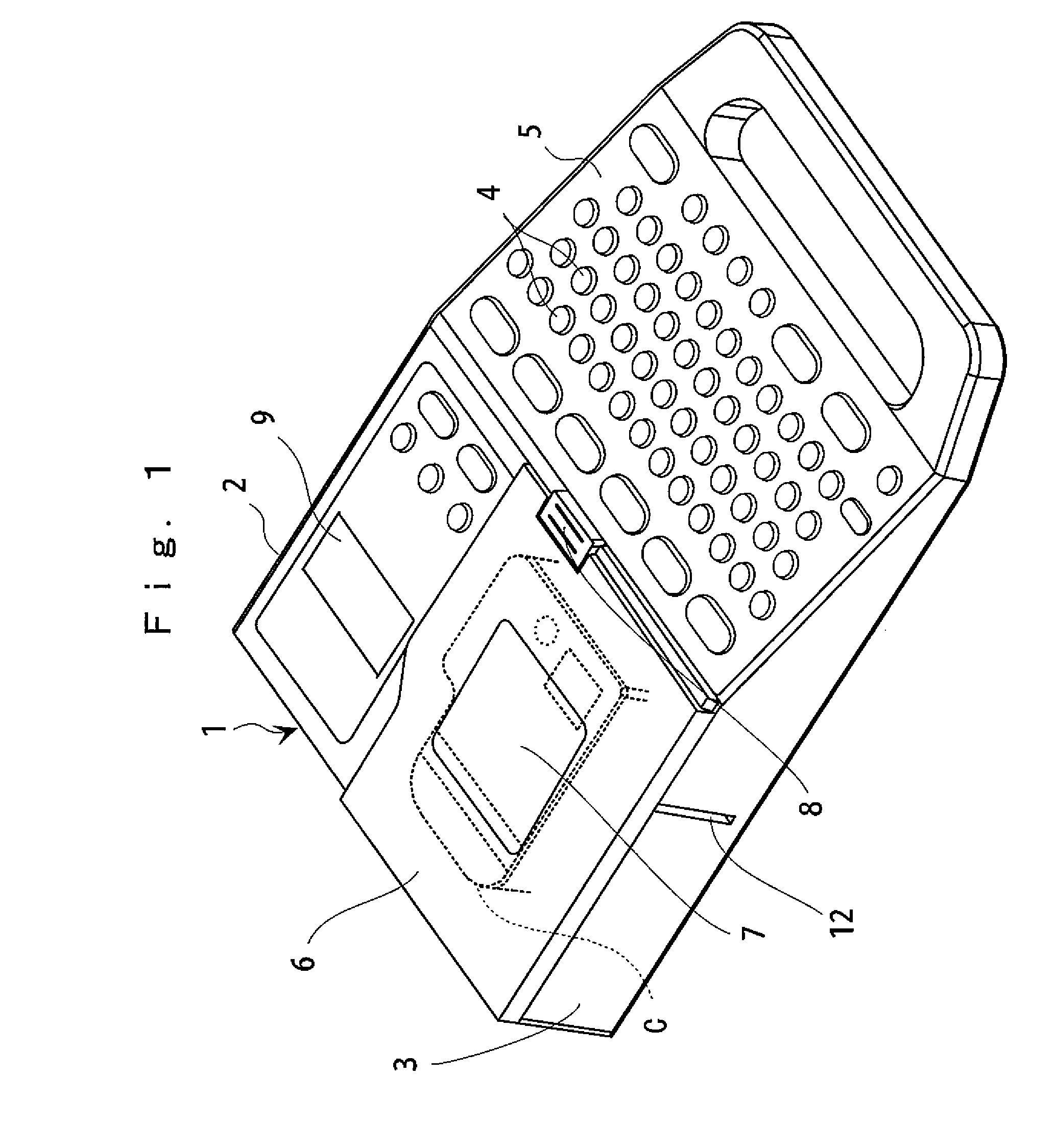

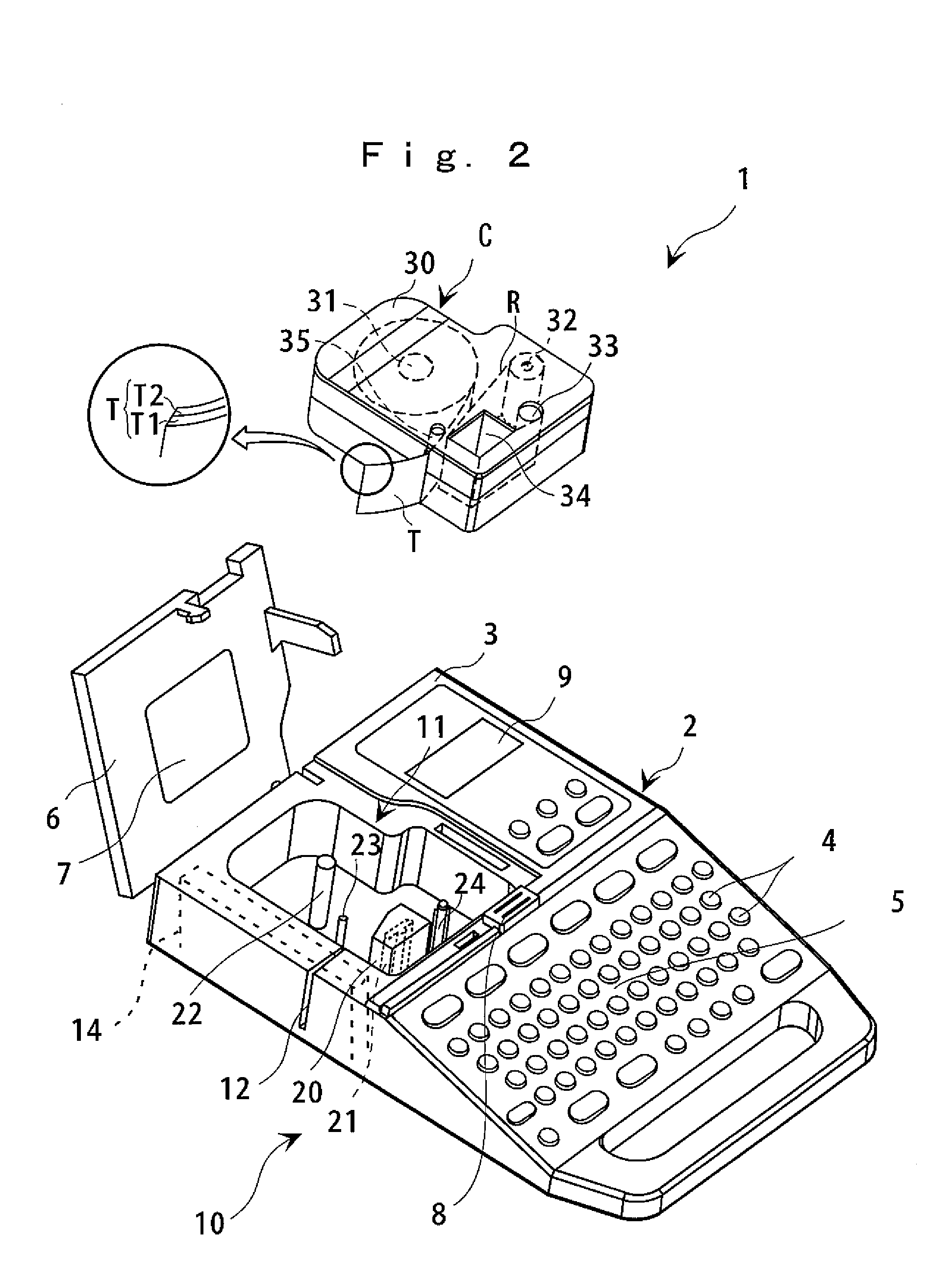

Printing Apparatus and Printing Method

InactiveUS20070187508A1Simple processEasy to implementCharacter and pattern recognitionTabulatorsComputer science

Owner:SEIKO EPSON CORP

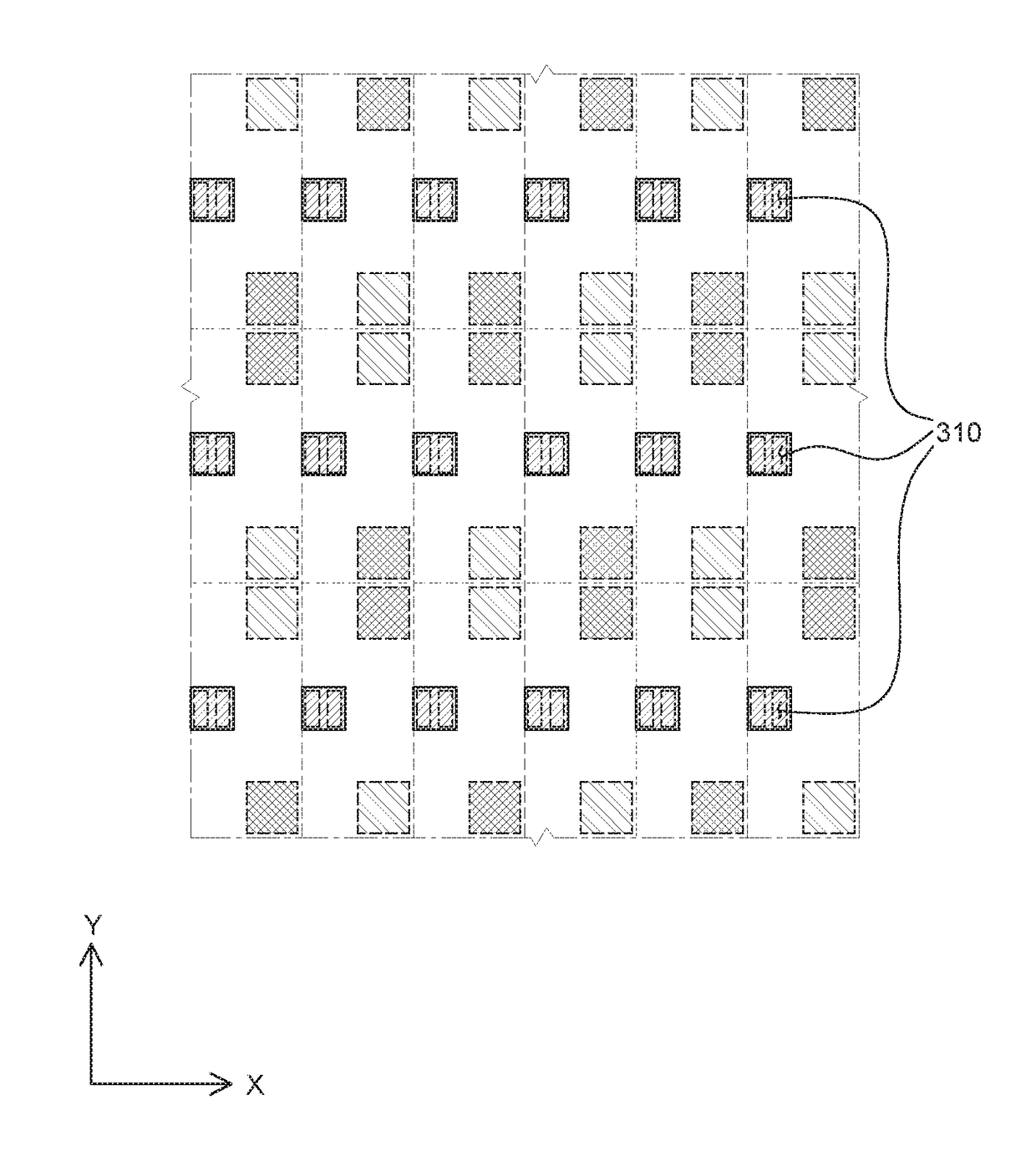

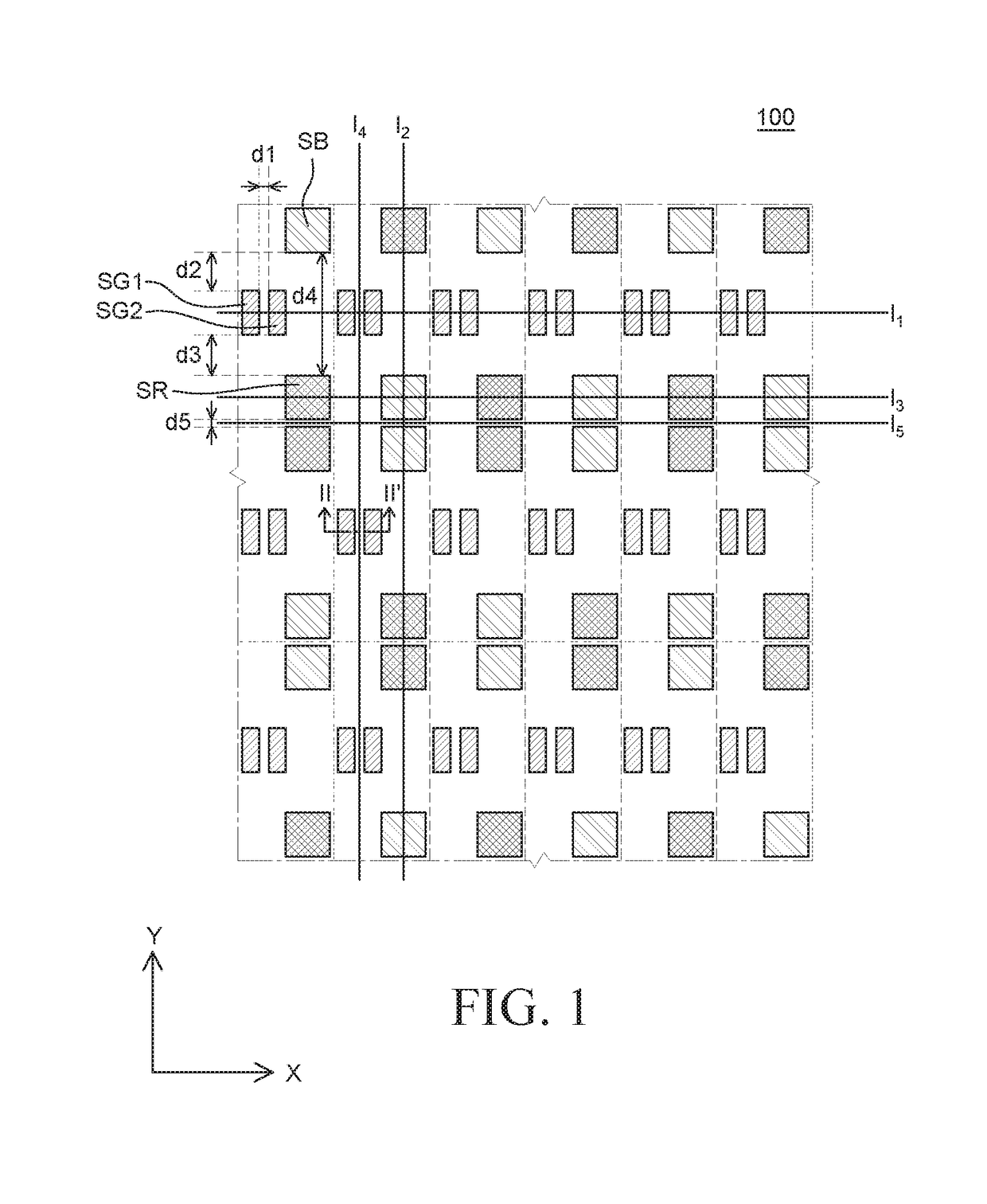

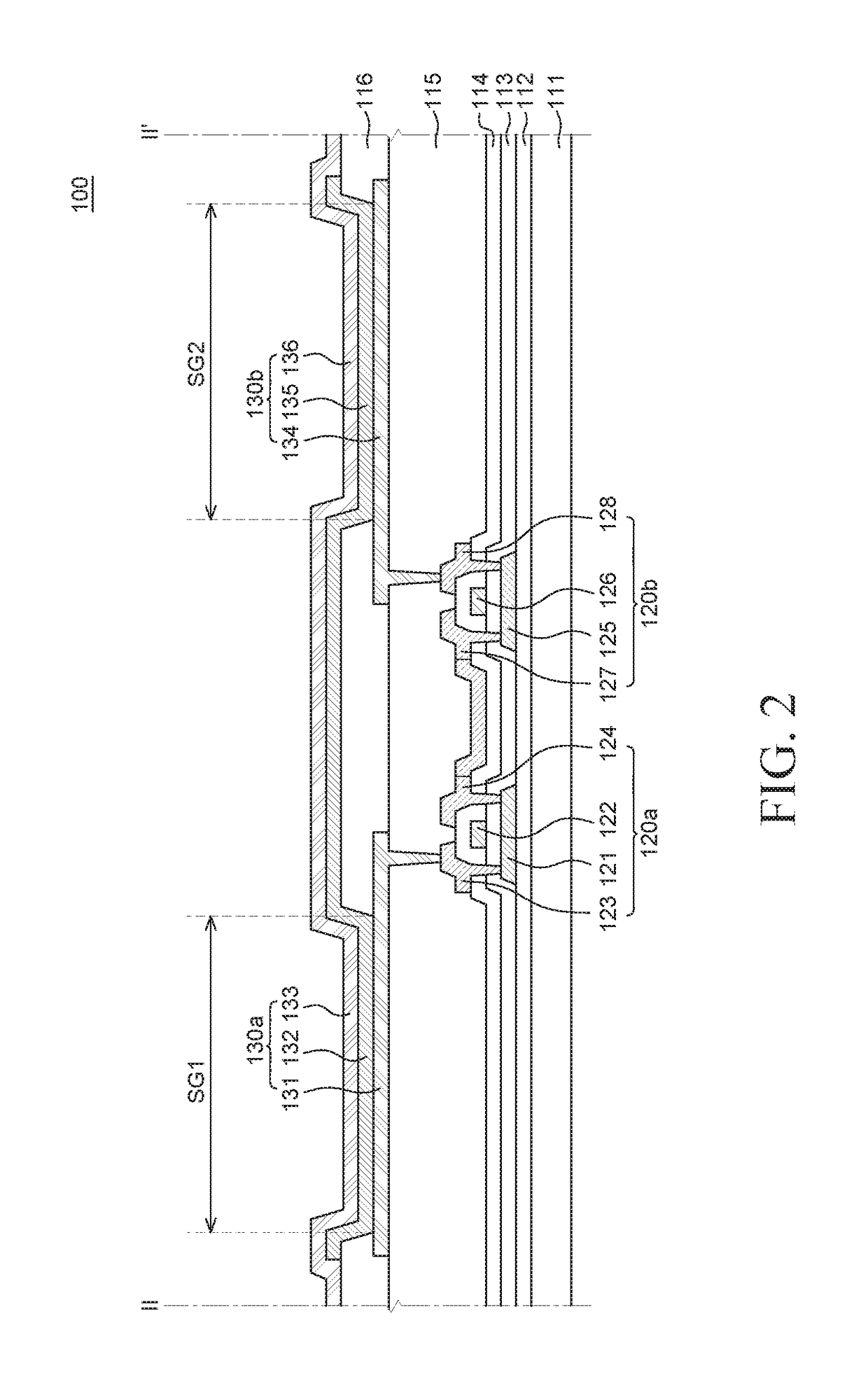

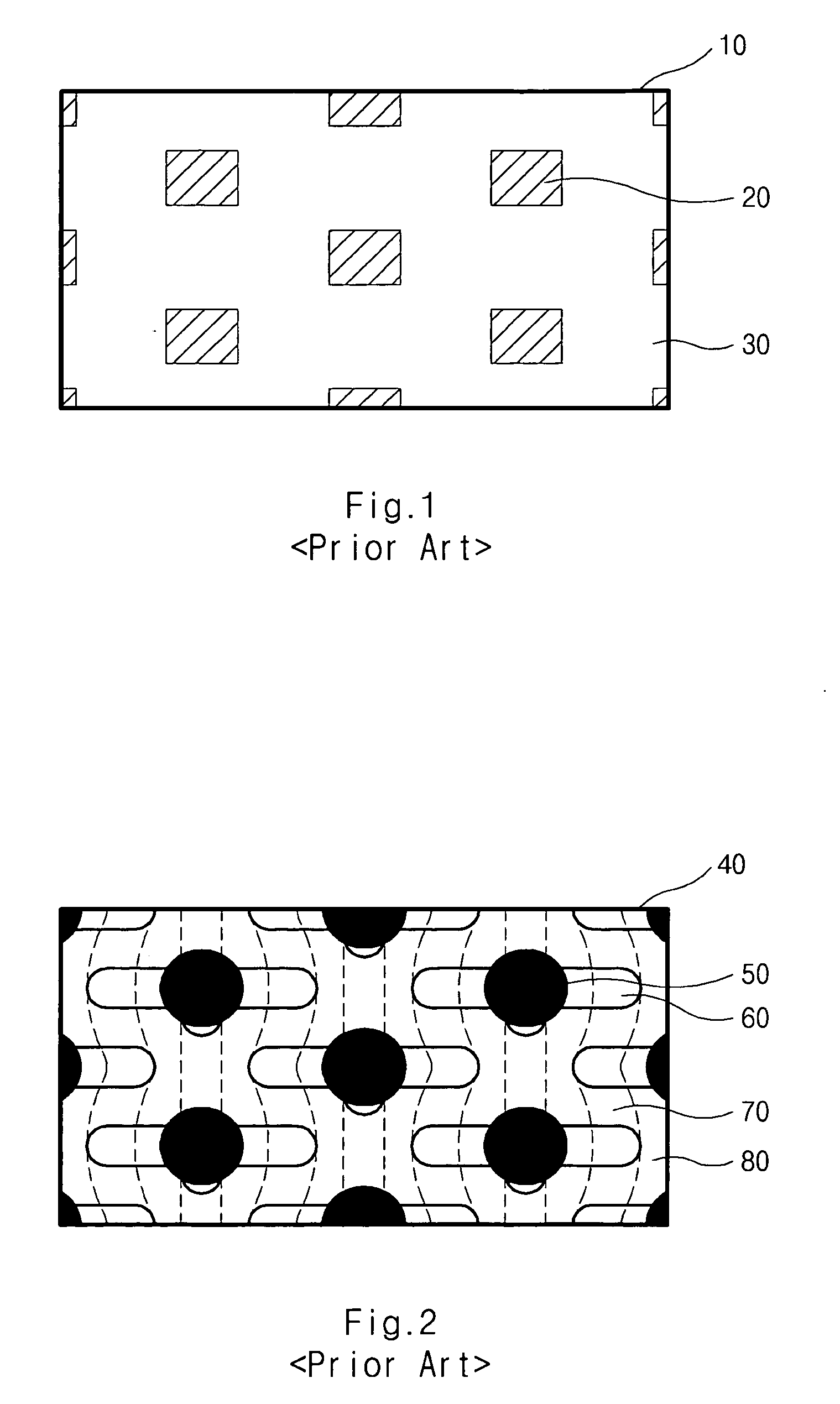

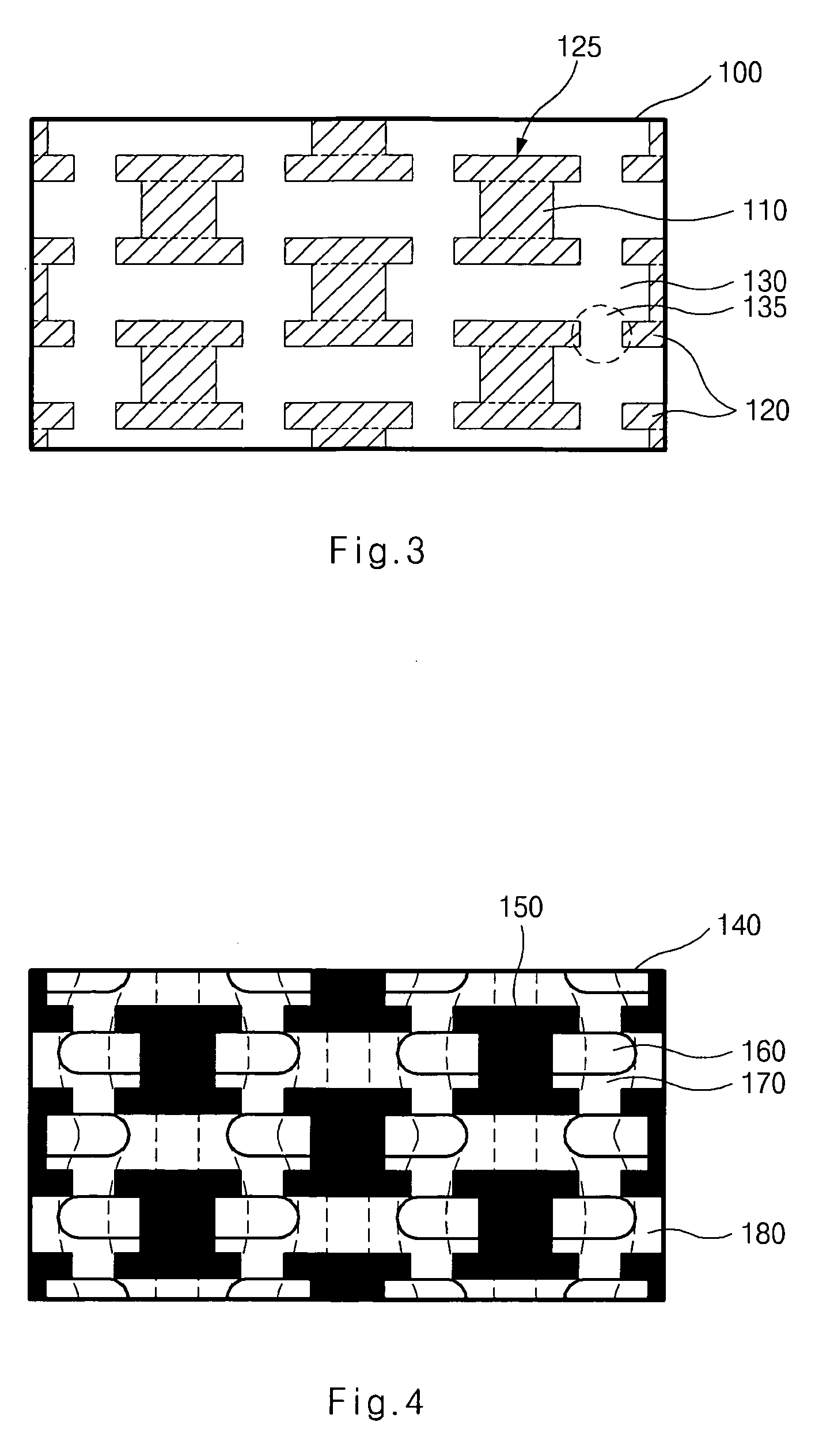

Organic light emitting display device

ActiveUS20170317150A1Increase in sizeSecure marginStatic indicating devicesSolid-state devicesDisplay deviceMaterials science

Discussed is an organic light emitting display device including a plurality of pixels, where red sub pixels and blue sub pixels of adjacent pixels are aligned in a first direction and are also aligned in a second direction, the second direction being a direction that intersects the first direction. Also, the green pixels of adjacent pixels are aligned in the first direction and are also aligned in the second direction. And the at least one green sub pixel of each pixel is disposed between the at least one red sub pixel and the at least one blue sub pixel of the each pixel, and the at least one green sub pixel is offset from the at least one red sub pixel and the at least one blue sub pixel in the first direction and the second direction in the each pixel.

Owner:LG DISPLAY CO LTD

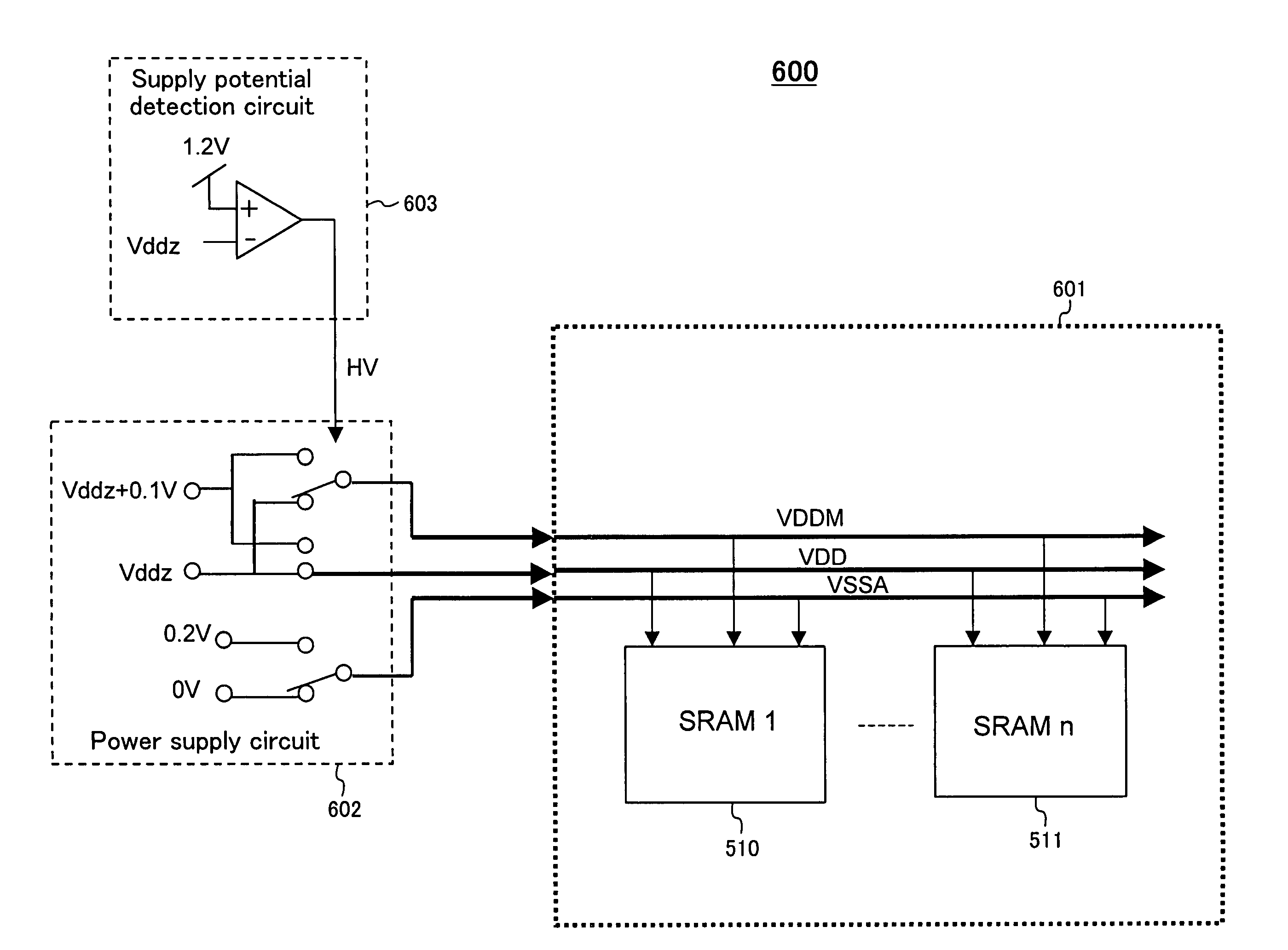

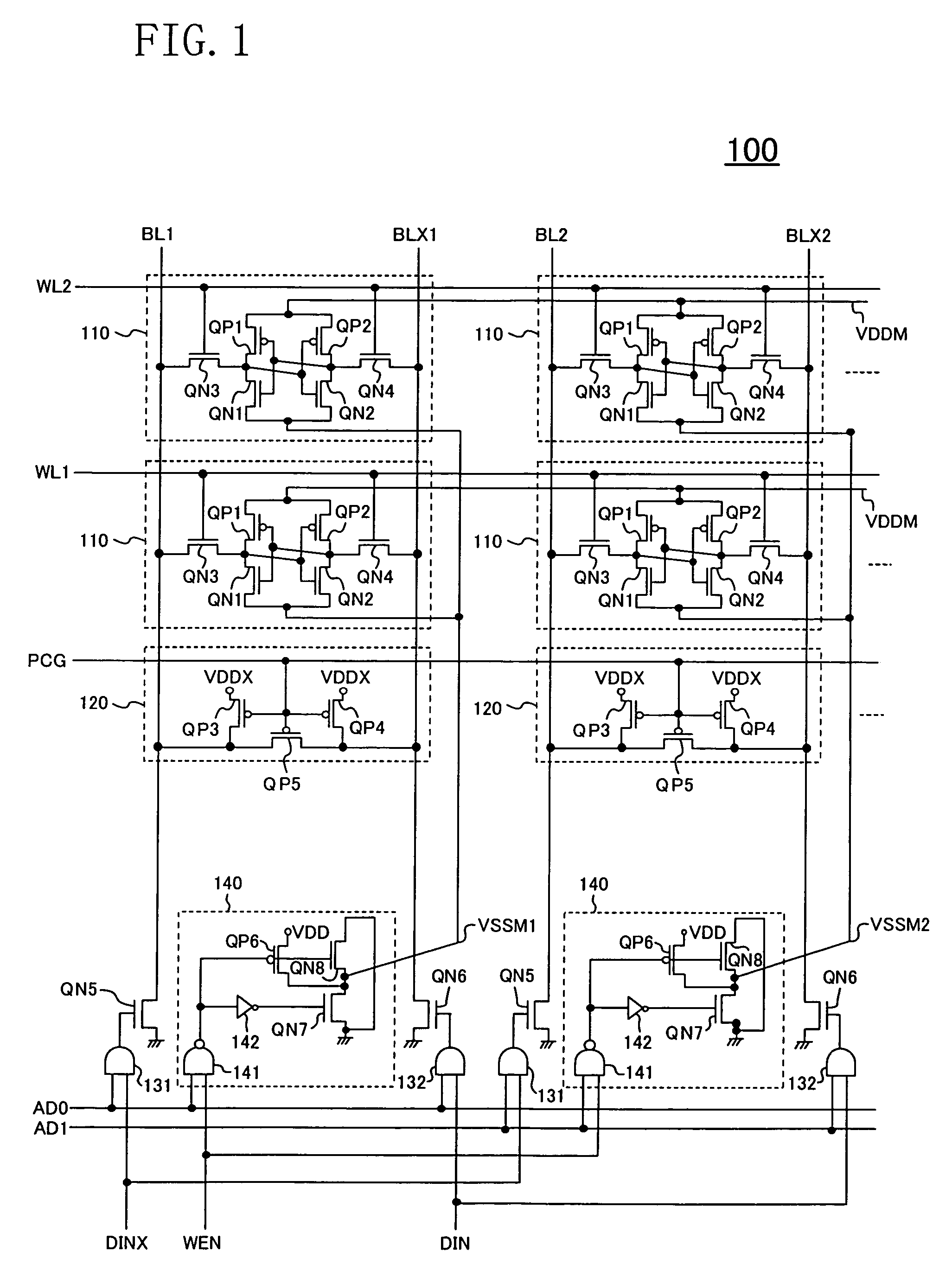

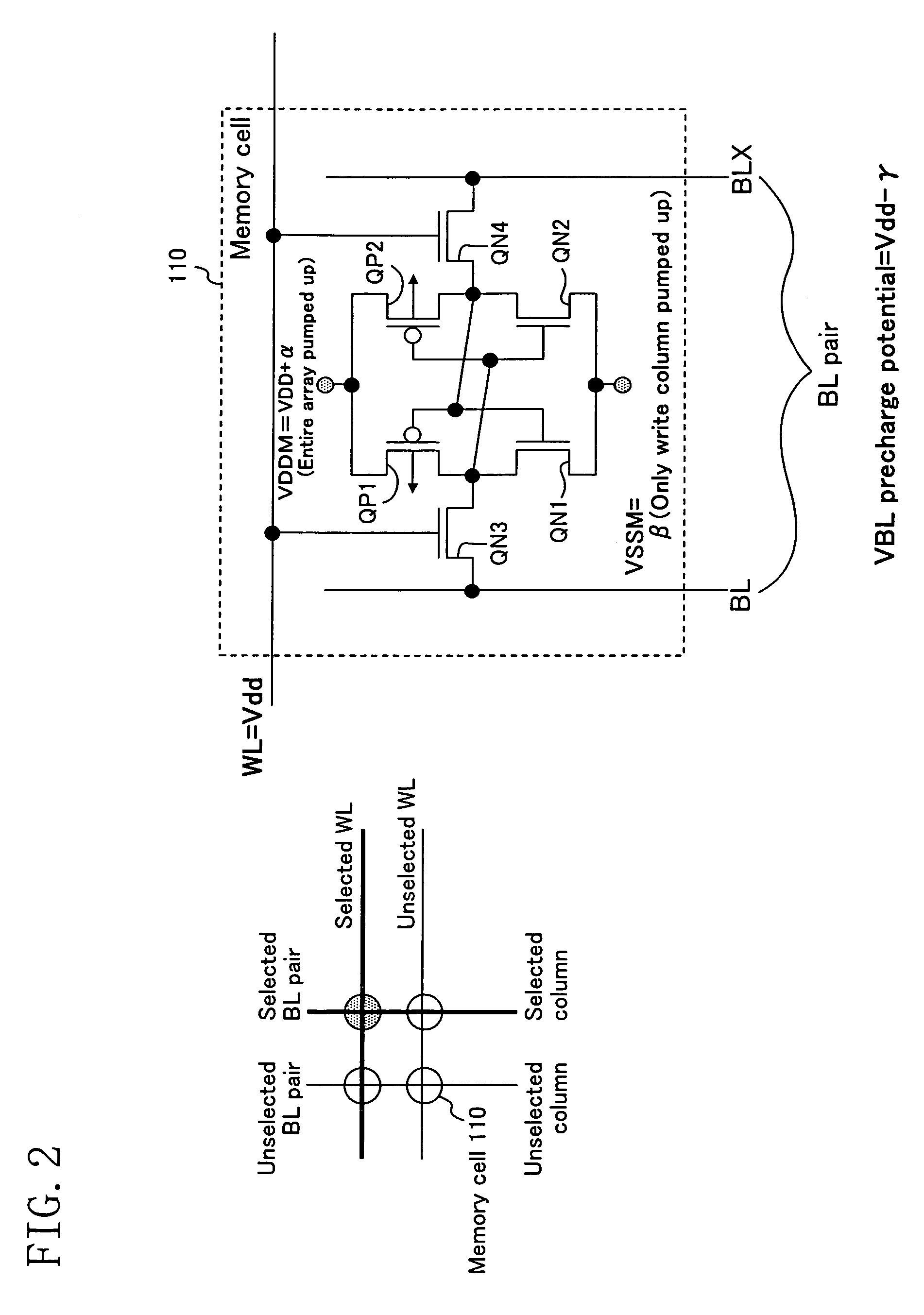

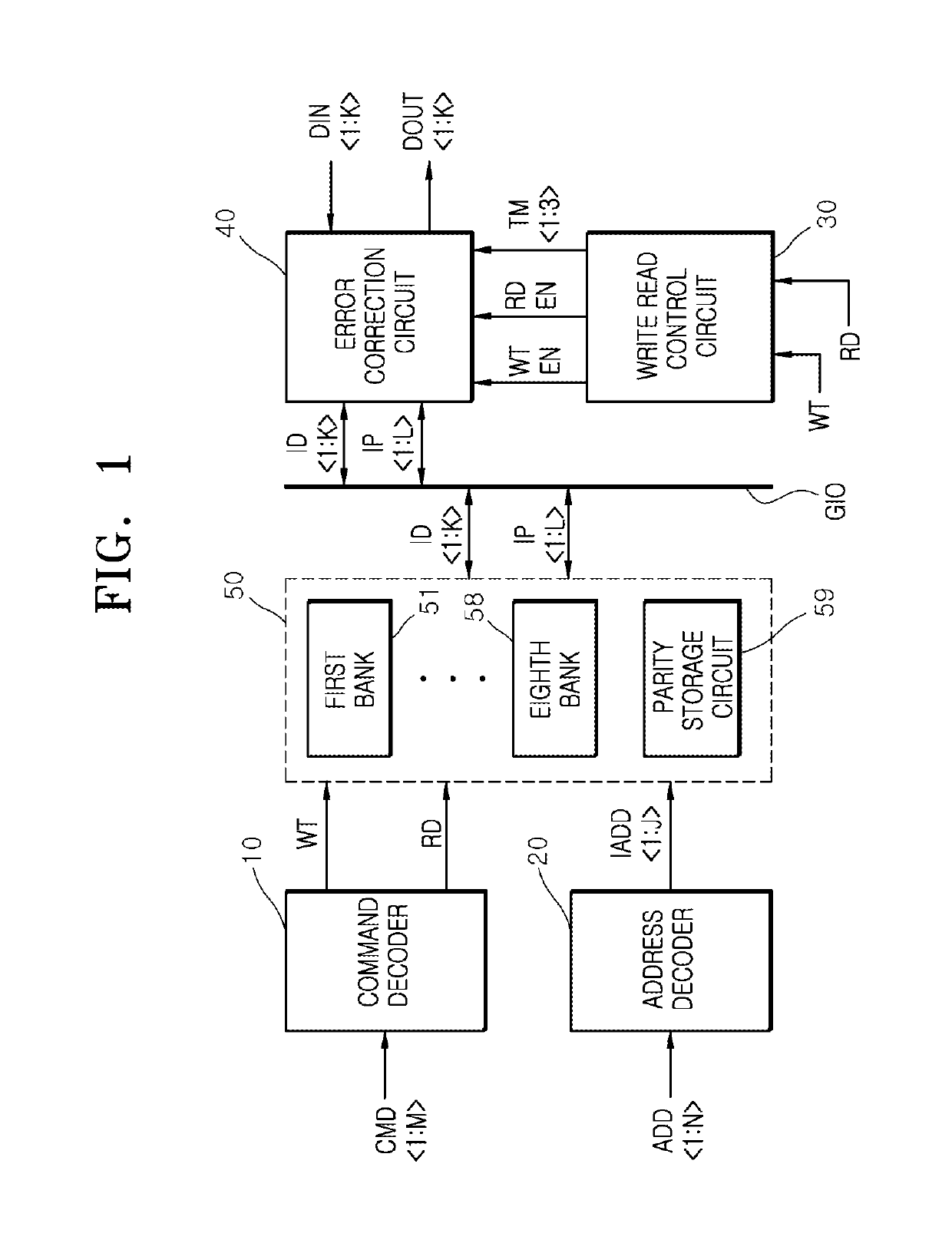

Semiconductor memory

ActiveUS7495948B2Reduce power consumptionGate-source potential of a memory cell transistor is decreasedRead-only memoriesDigital storageBit lineHemt circuits

In a semiconductor memory including word lines and bit lines arranged in a matrix and a plurality of memory cells provided at intersections of the word lines and the bit lines, a bit line precharge circuit is provided for controlling the potential of a low-data holding power supply coupled to memory cells provided on a corresponding one of the bit lines. In a write operation, the bit line precharge circuit controls the potential of a low-data holding power supply of a memory cell corresponding to a selected bit line to be higher than the potential of a low-data holding power supply of a memory cell corresponding to an unselected bit line.

Owner:SOCIONEXT INC

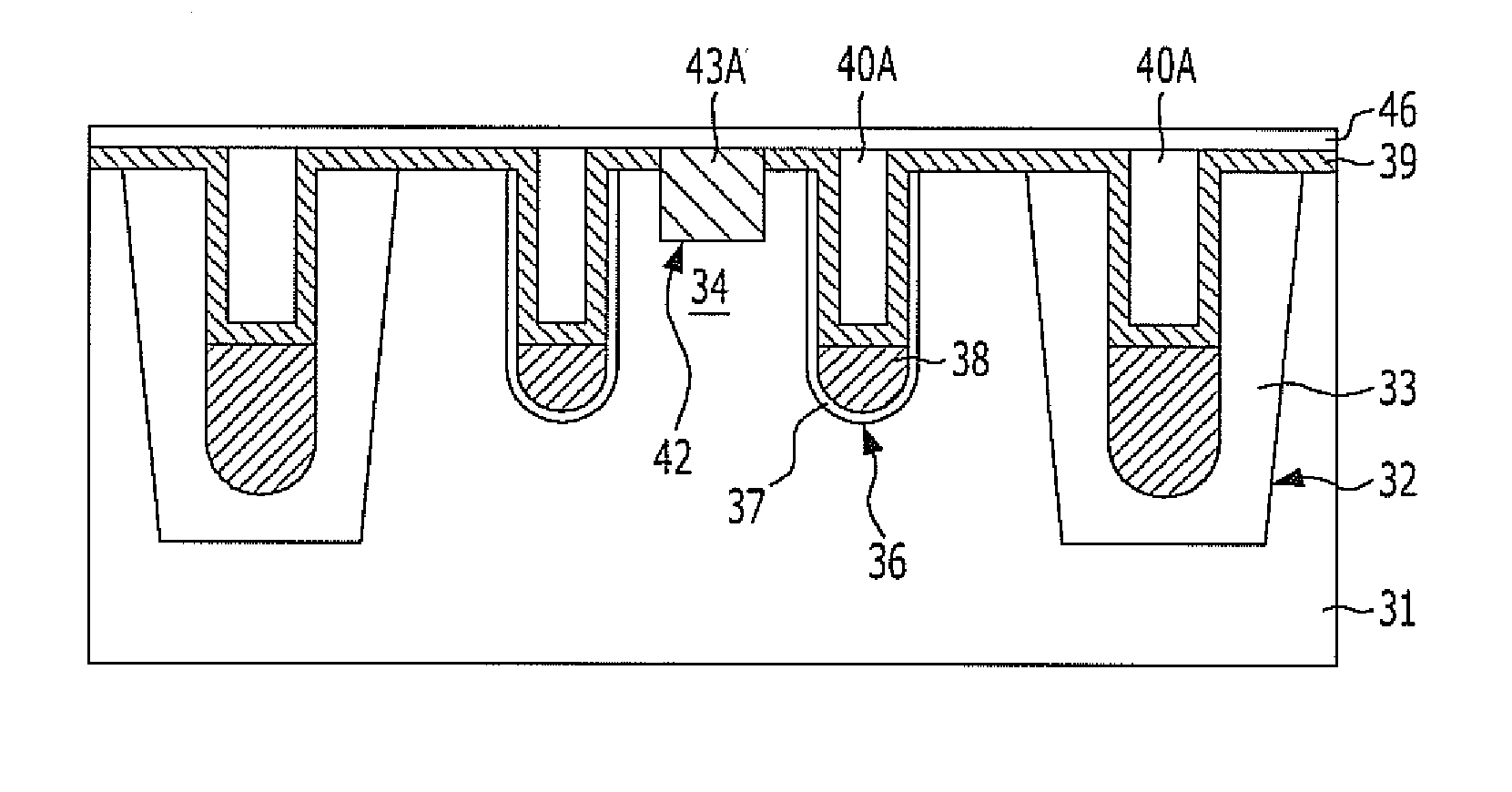

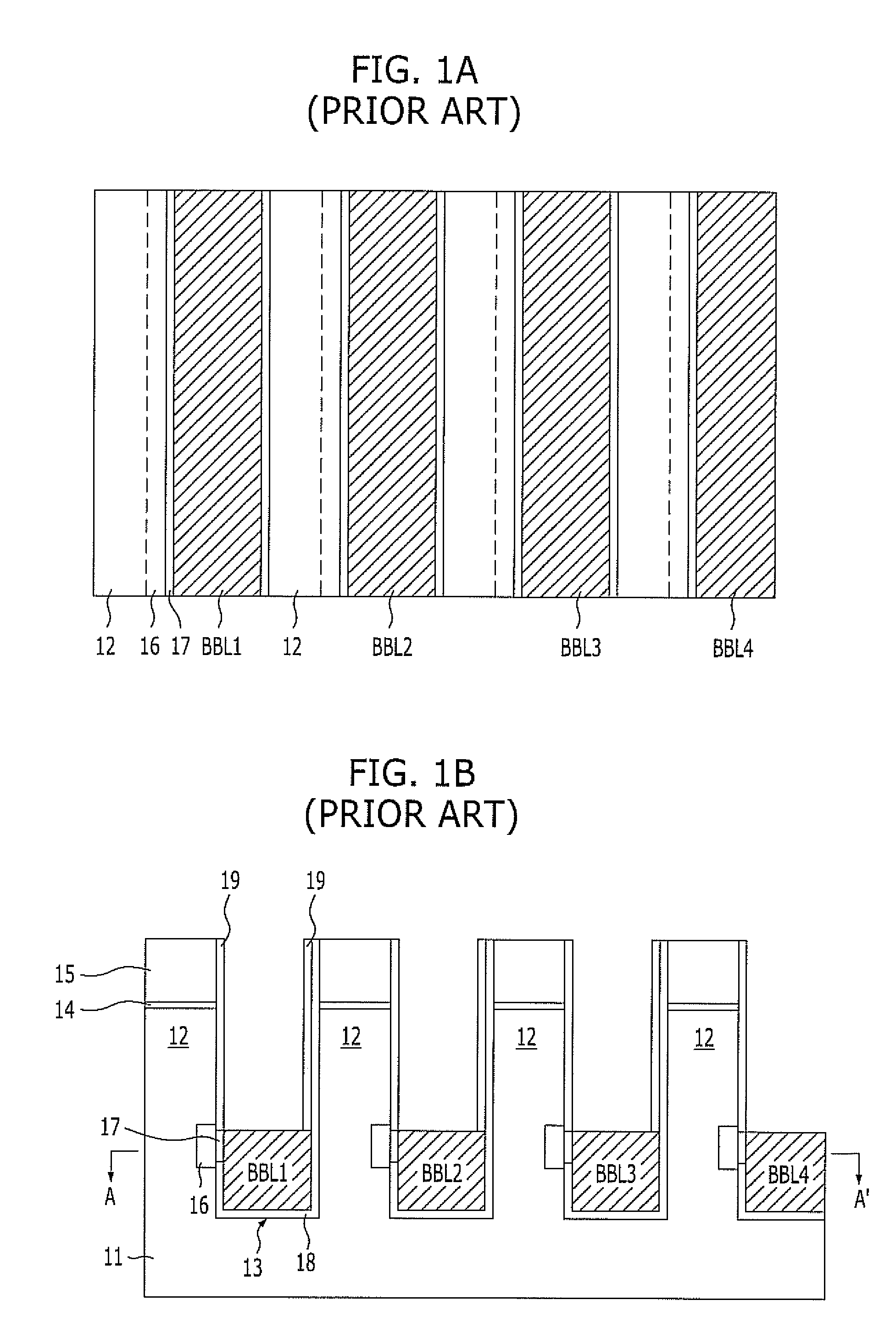

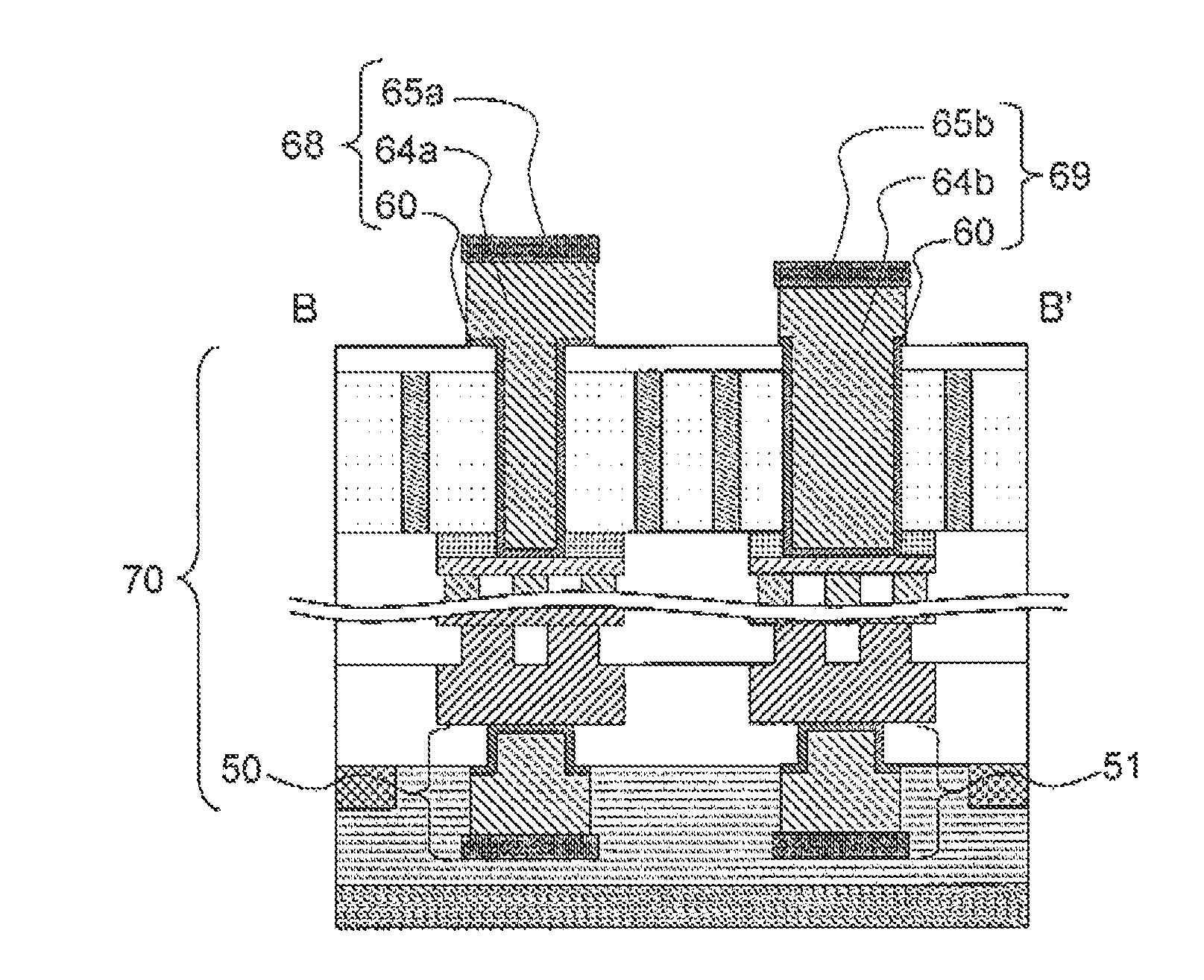

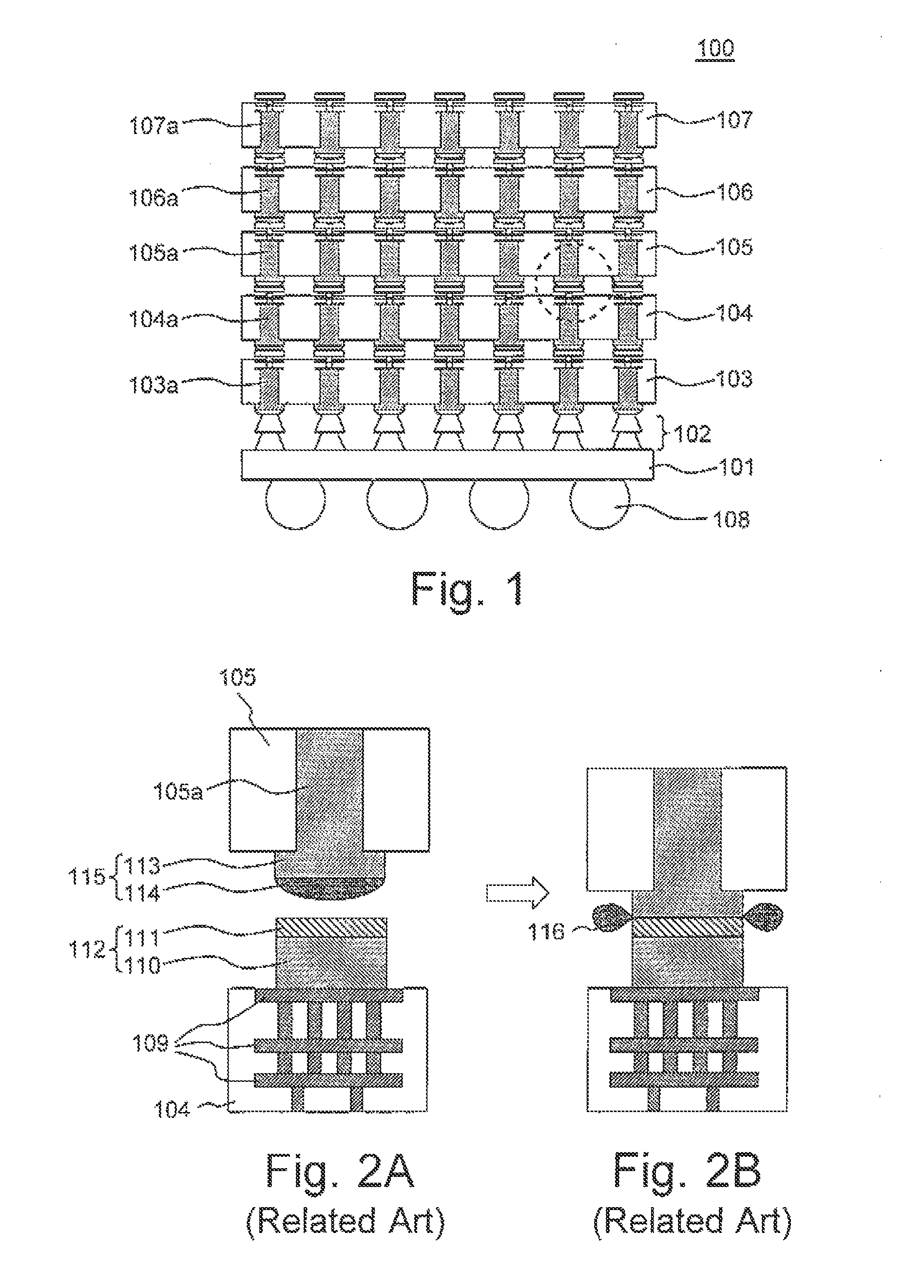

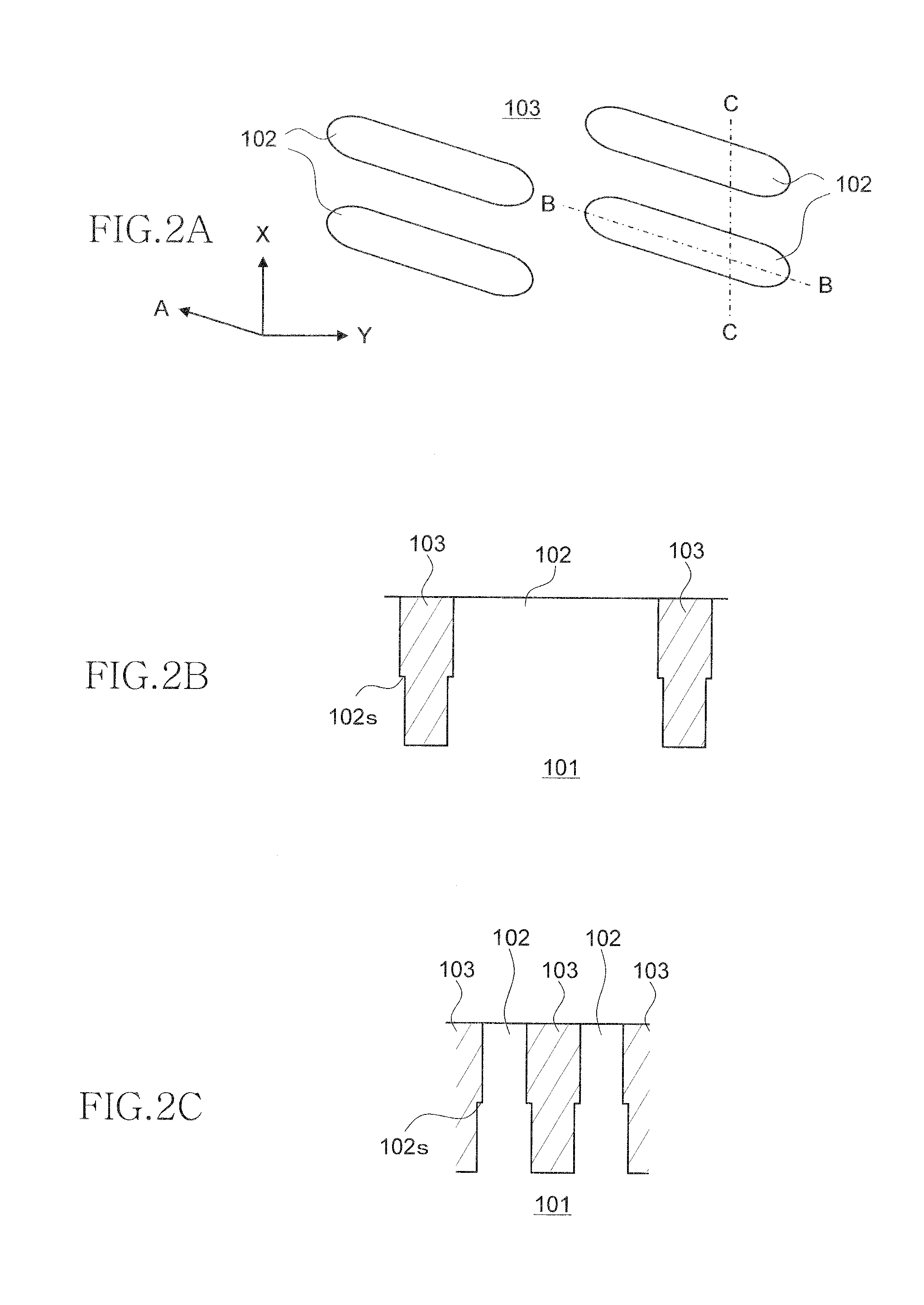

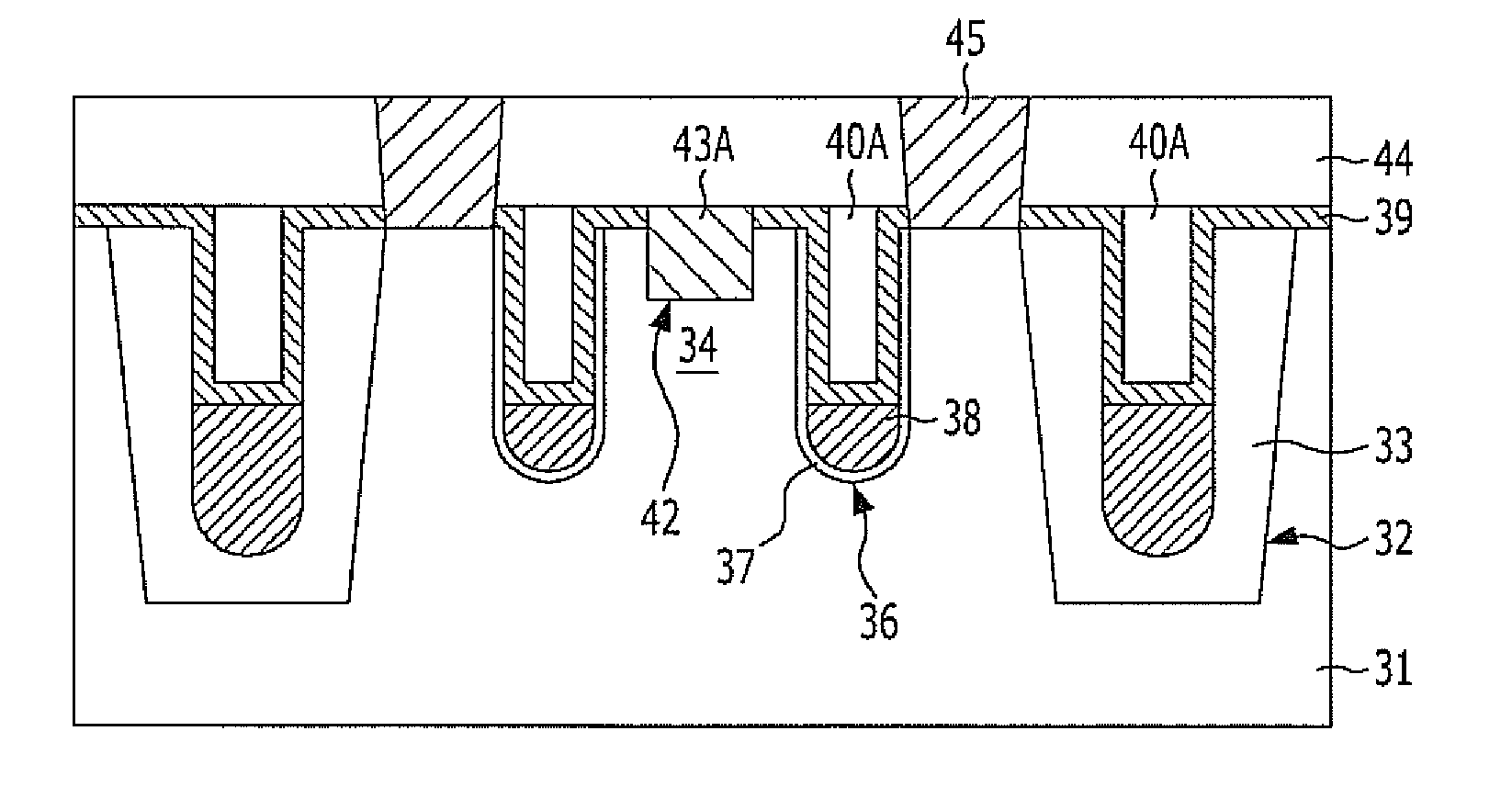

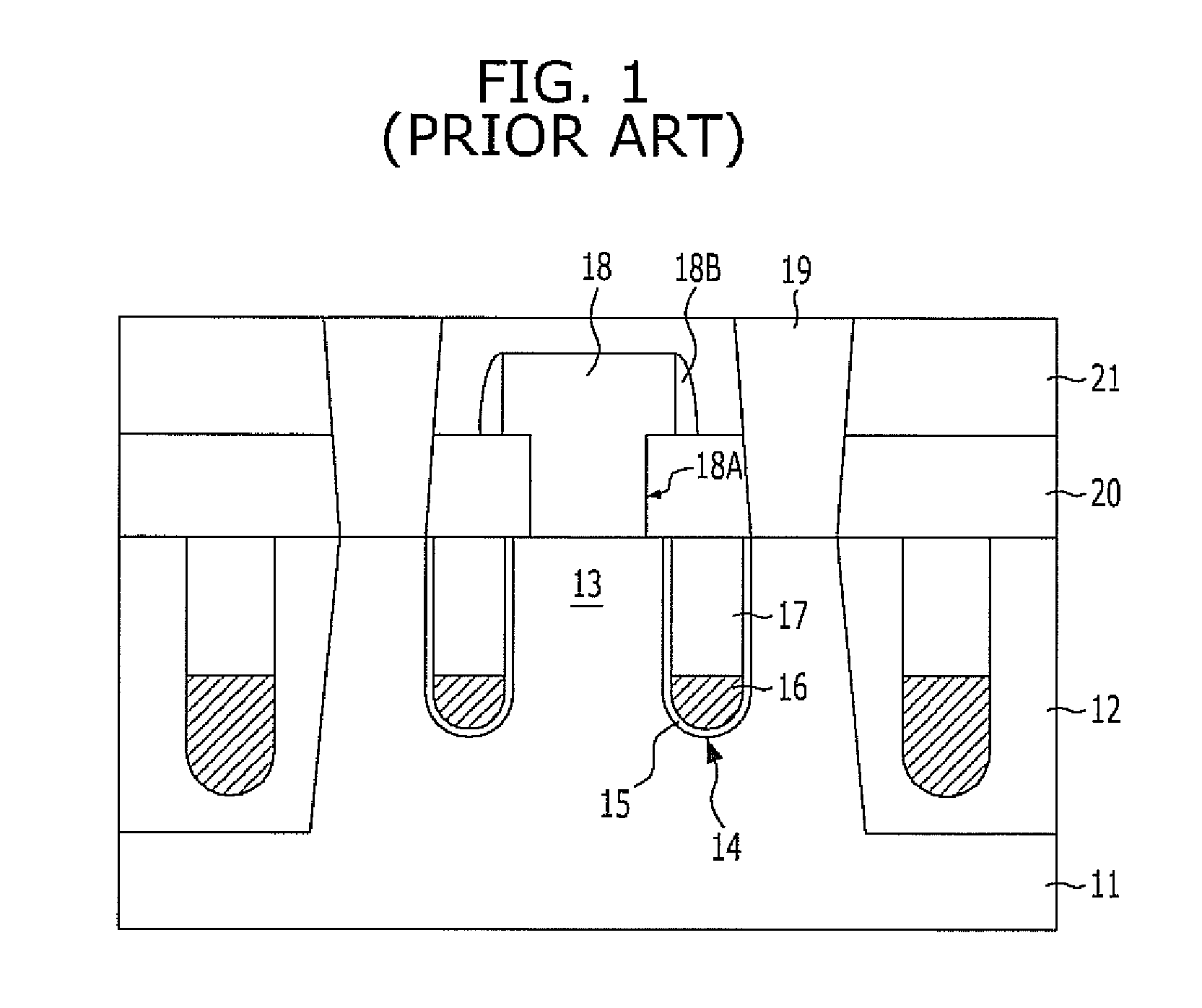

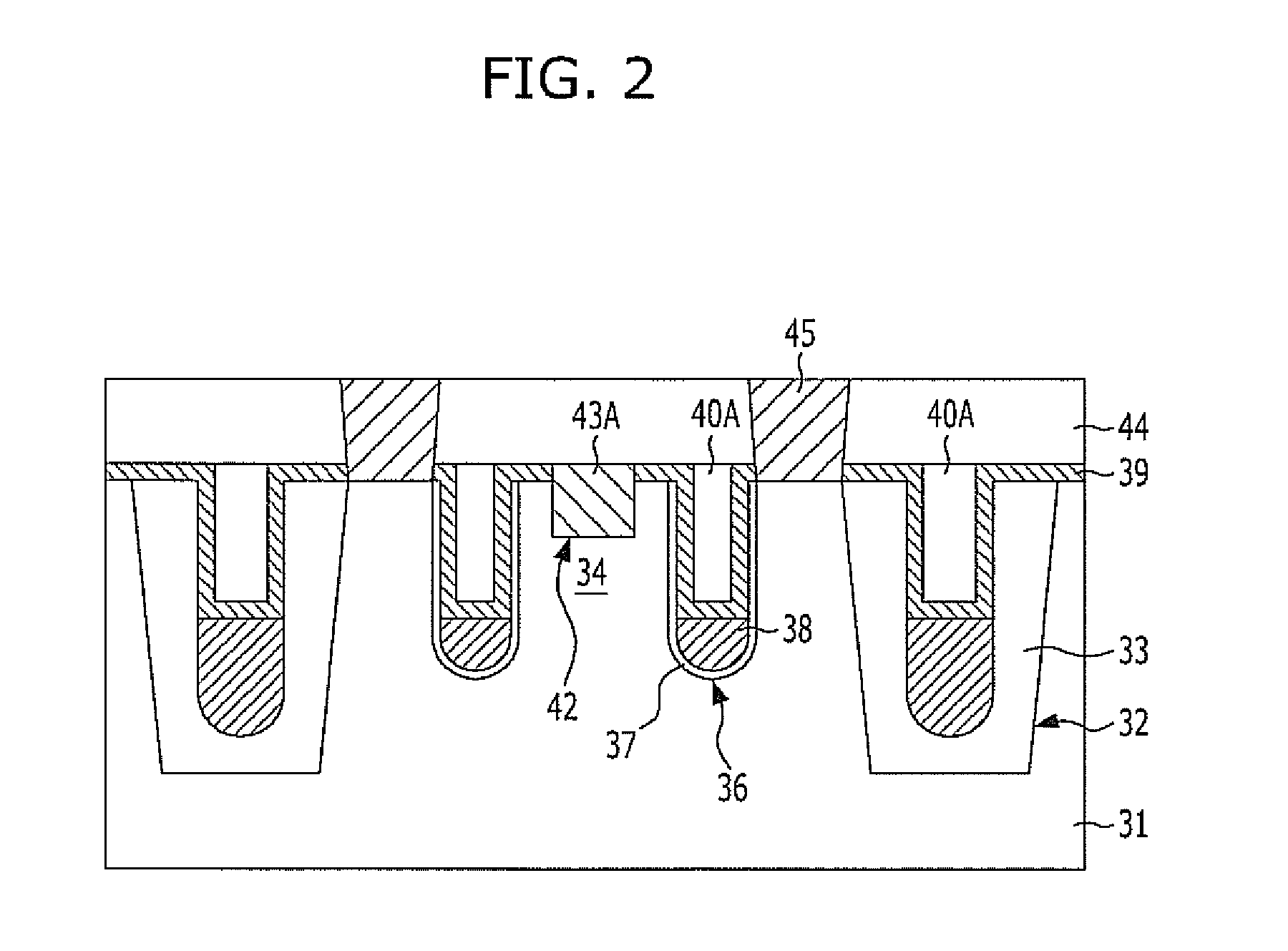

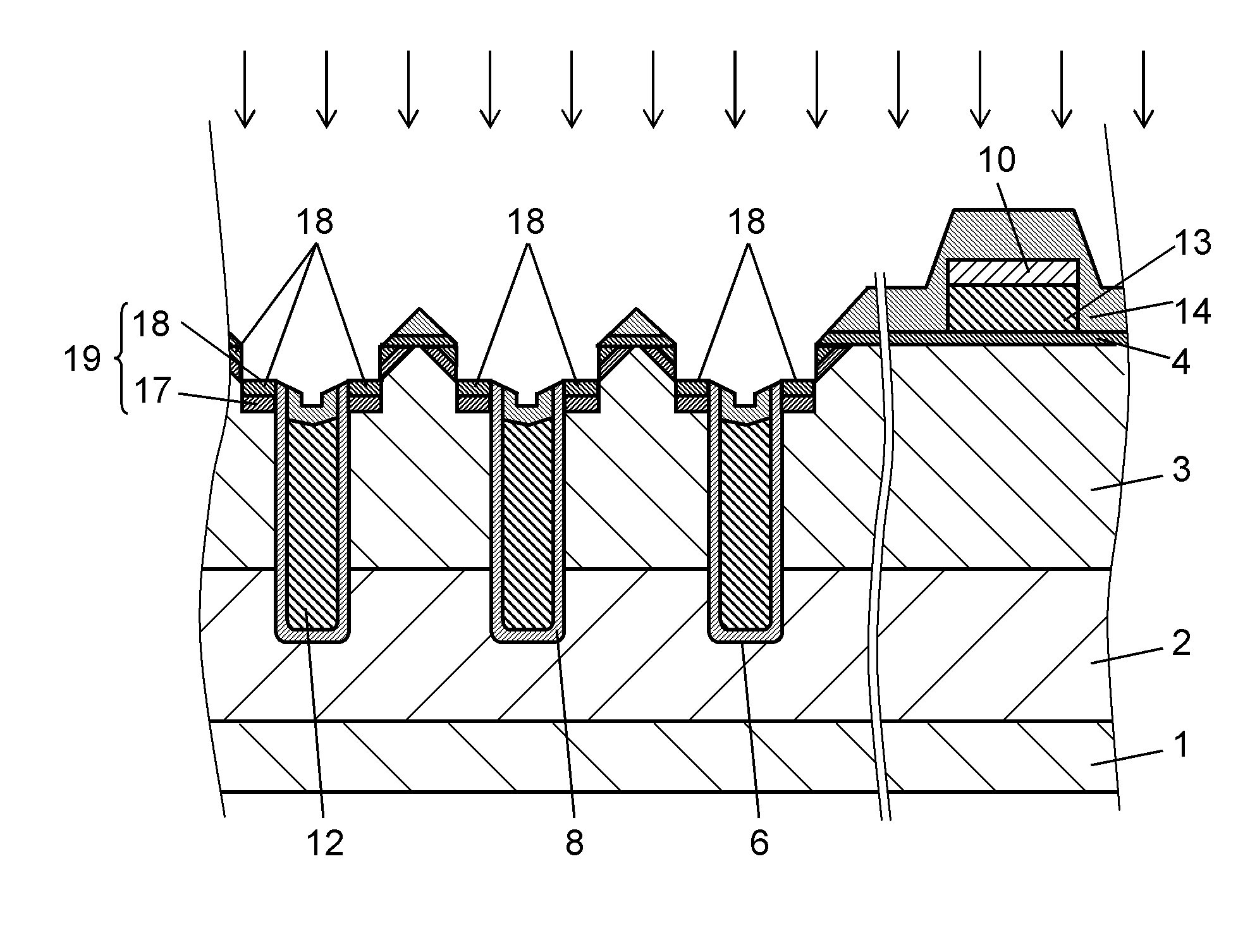

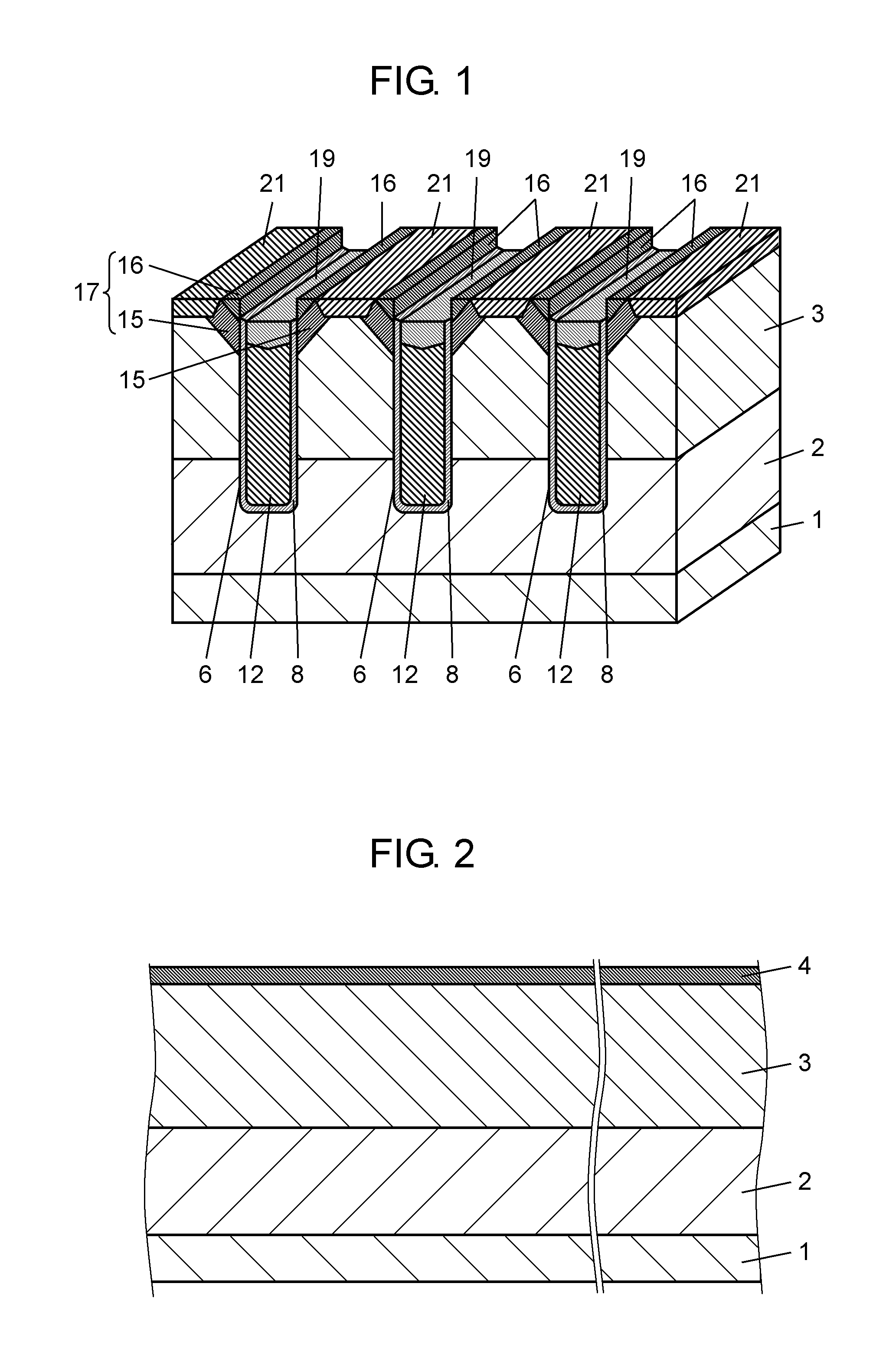

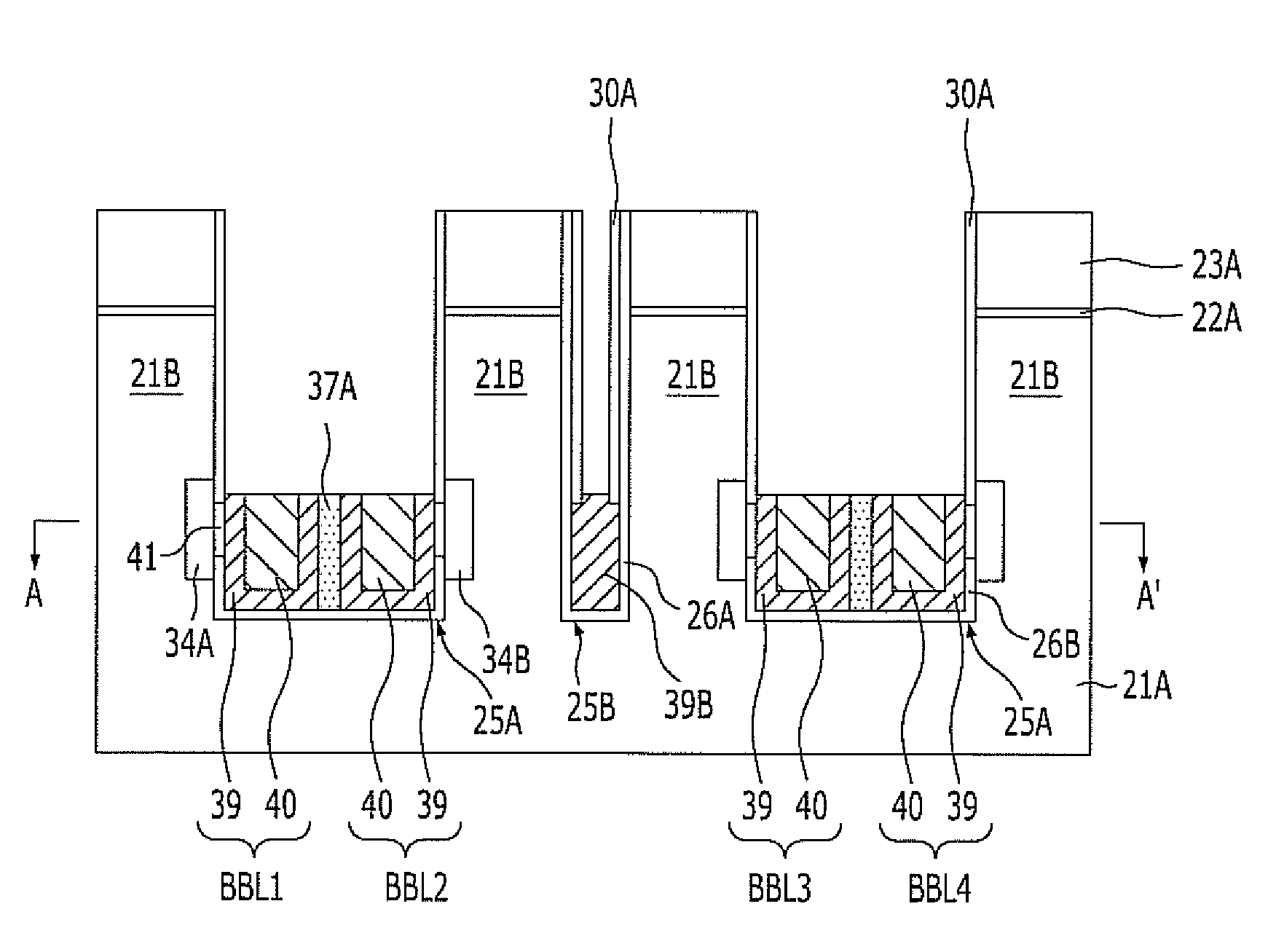

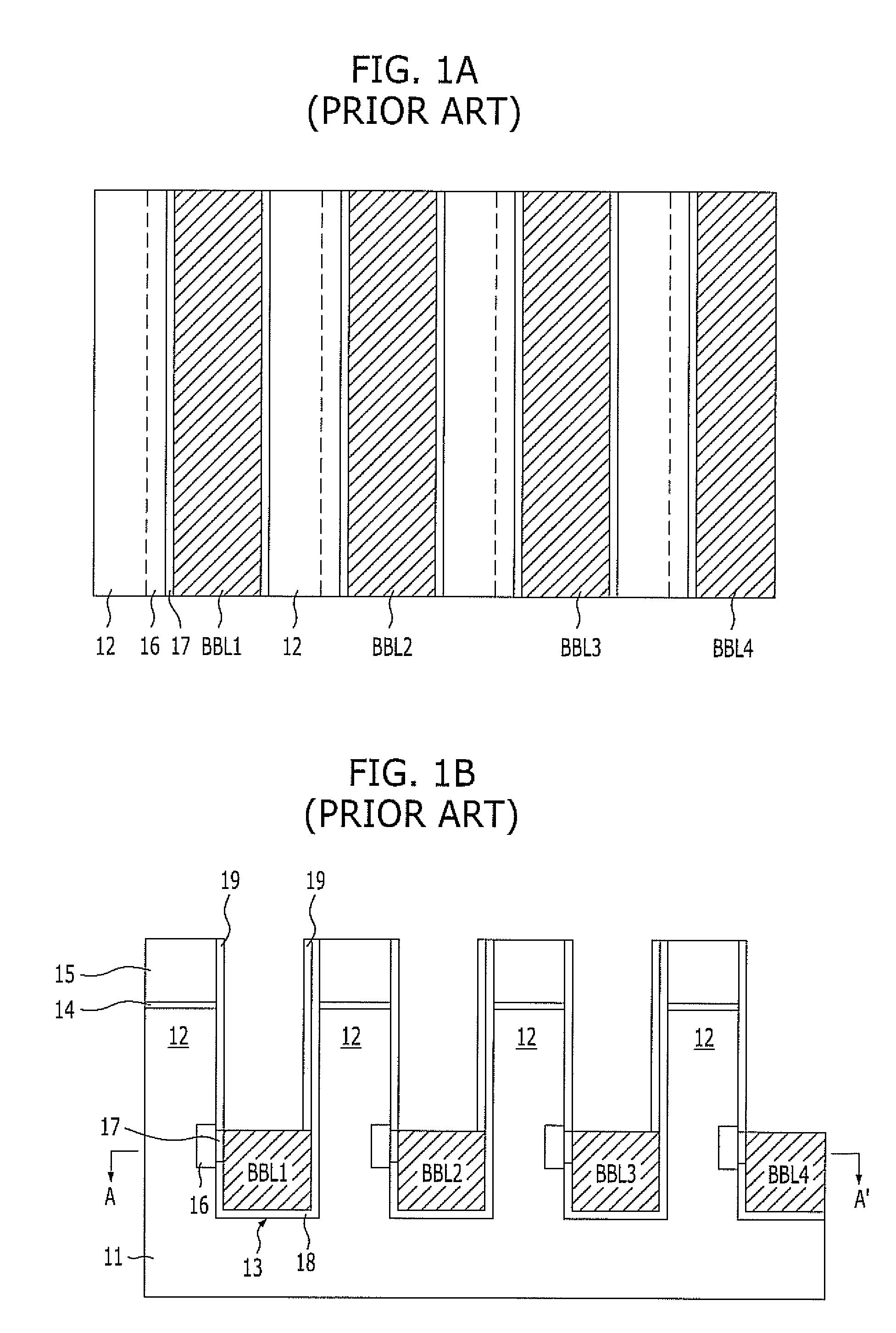

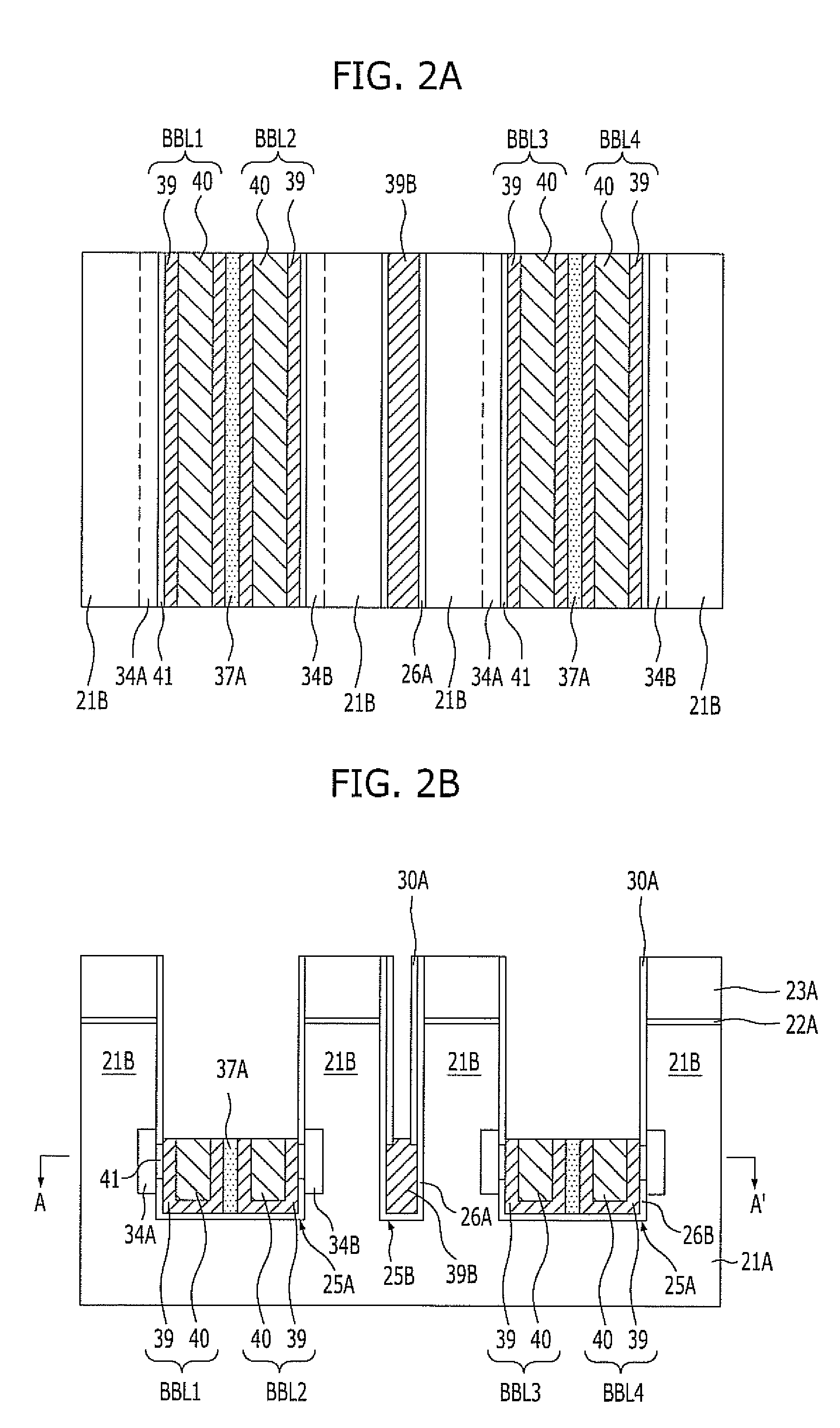

Semiconductor device with buried gates and buried bit lines and method for fabricating the same

InactiveUS20110101450A1Reduce resistancePrevent bridgingSolid-state devicesSemiconductor/solid-state device manufacturingBit lineSemiconductor

A semiconductor device includes: a plurality of first trenches formed inside a plurality of active regions; a plurality of buried gates configured to partially fill insides of the plurality of the first trenches; a plurality of second trenches formed to be extended in a direction crossing the plurality of the buried gates; and a plurality of buried bit lines configured to fill the plurality of the second trenches.

Owner:SK HYNIX INC

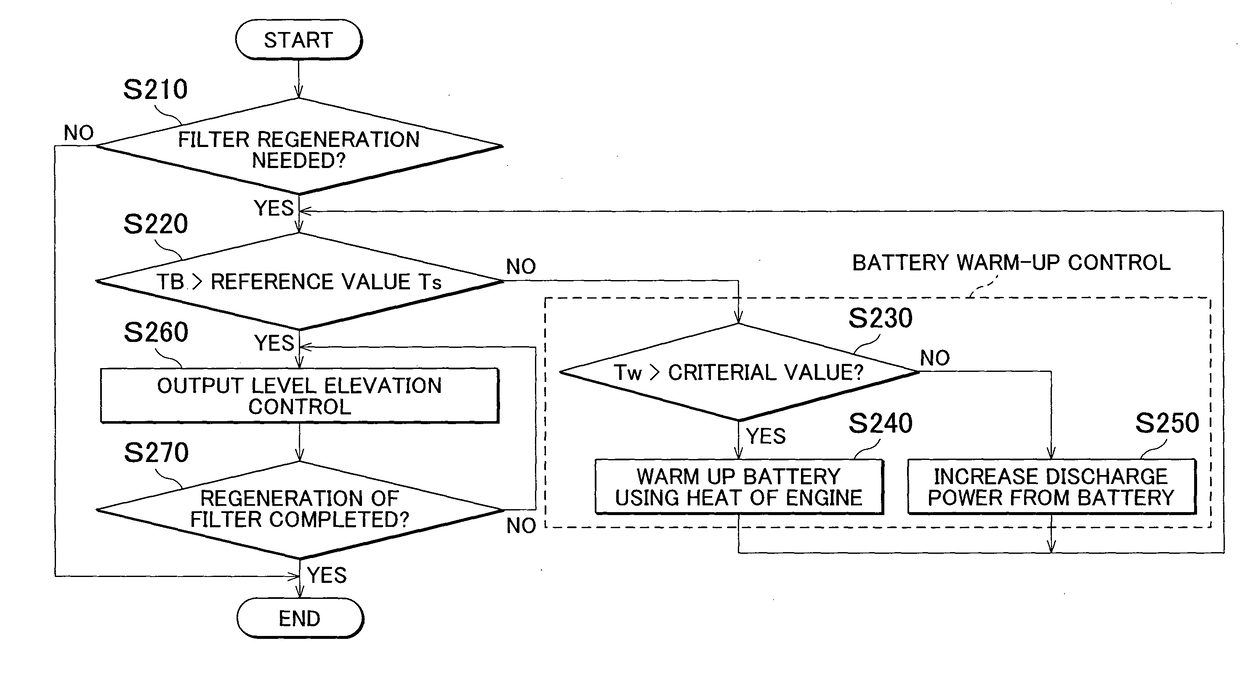

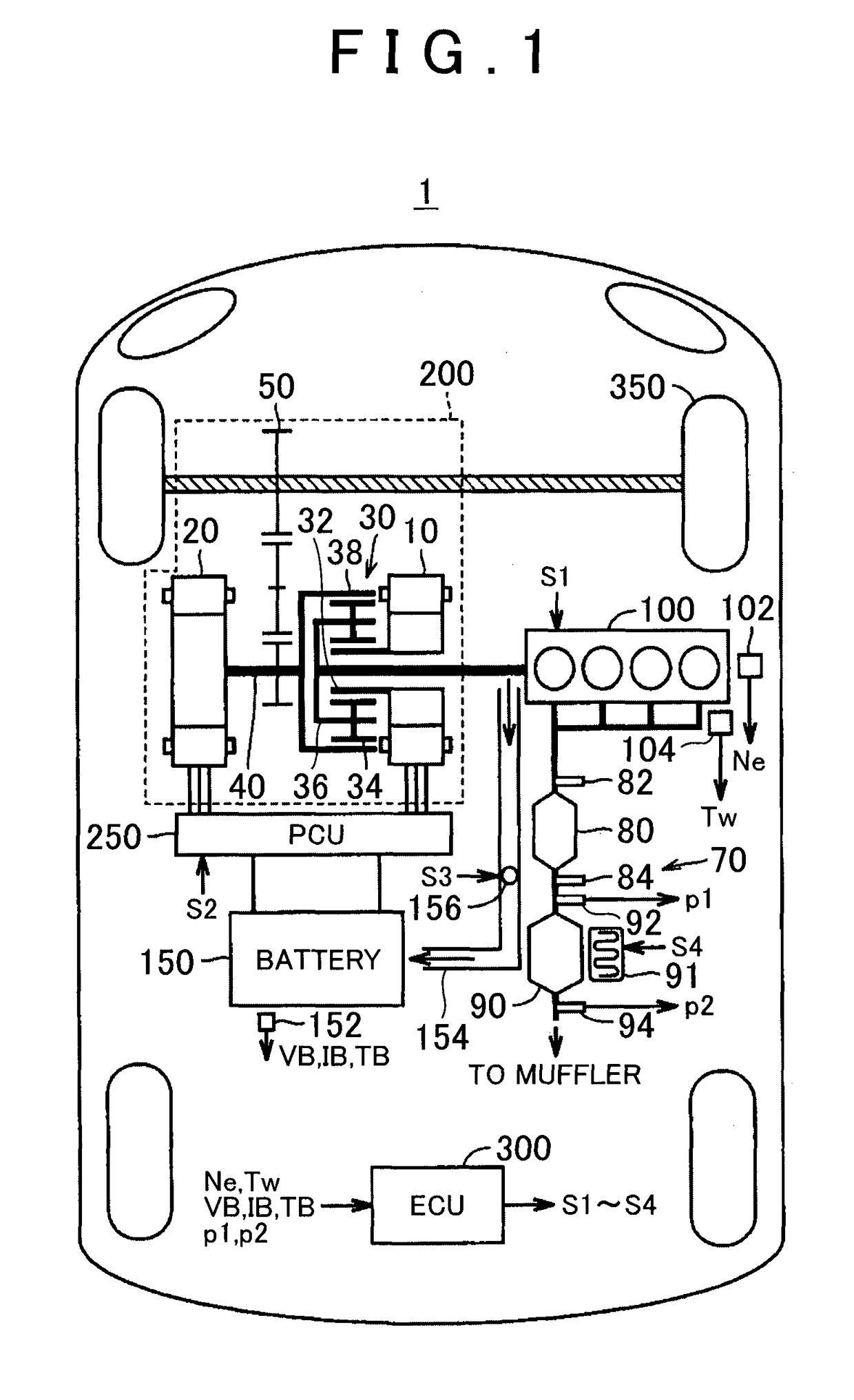

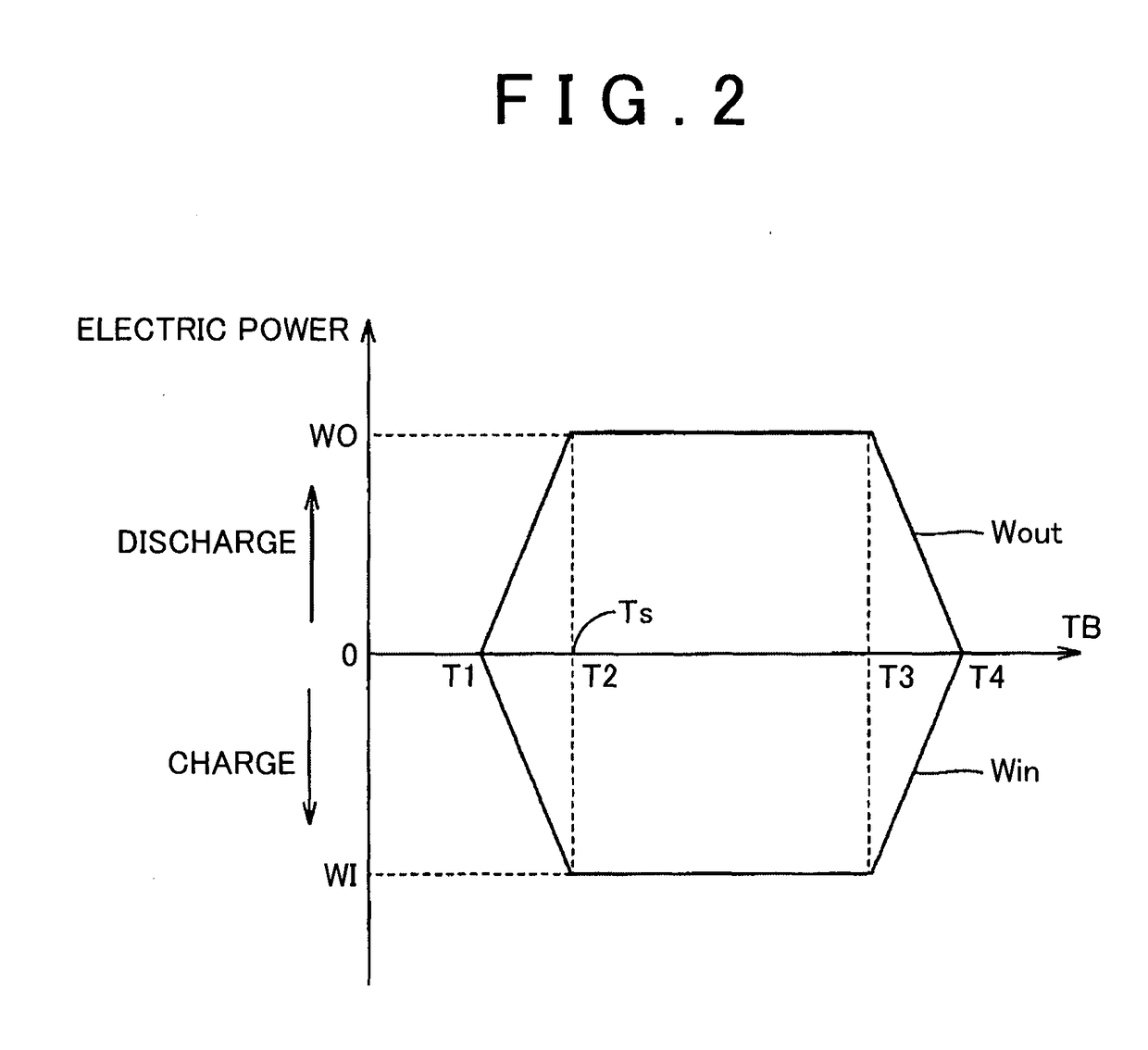

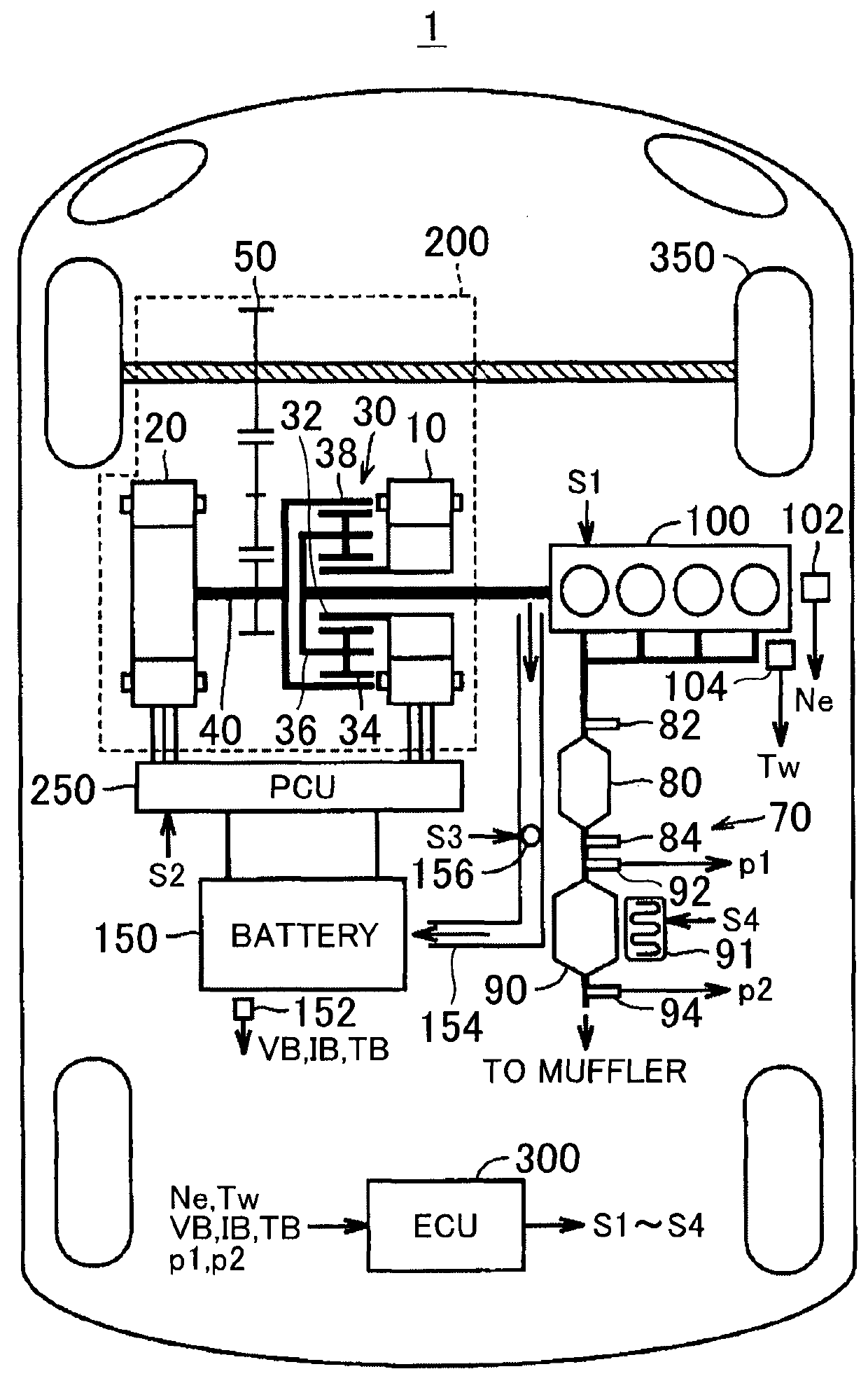

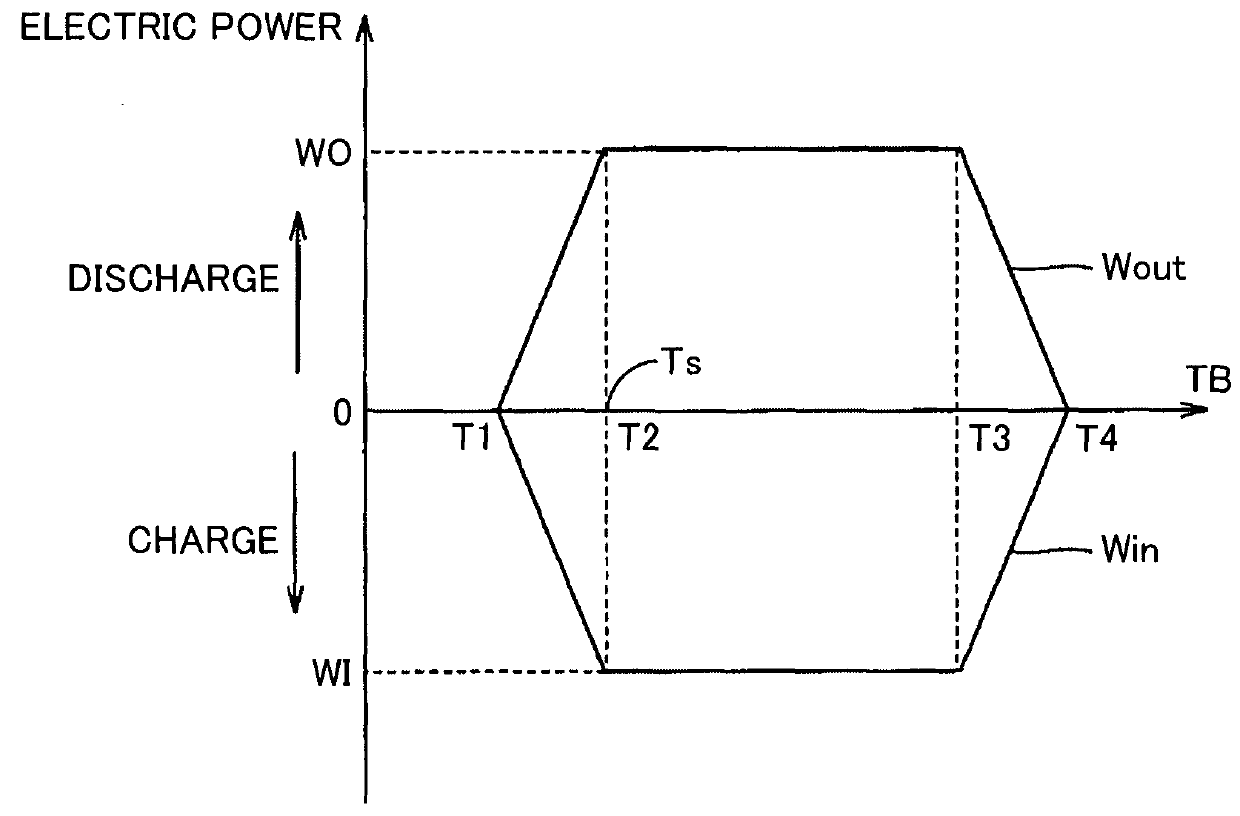

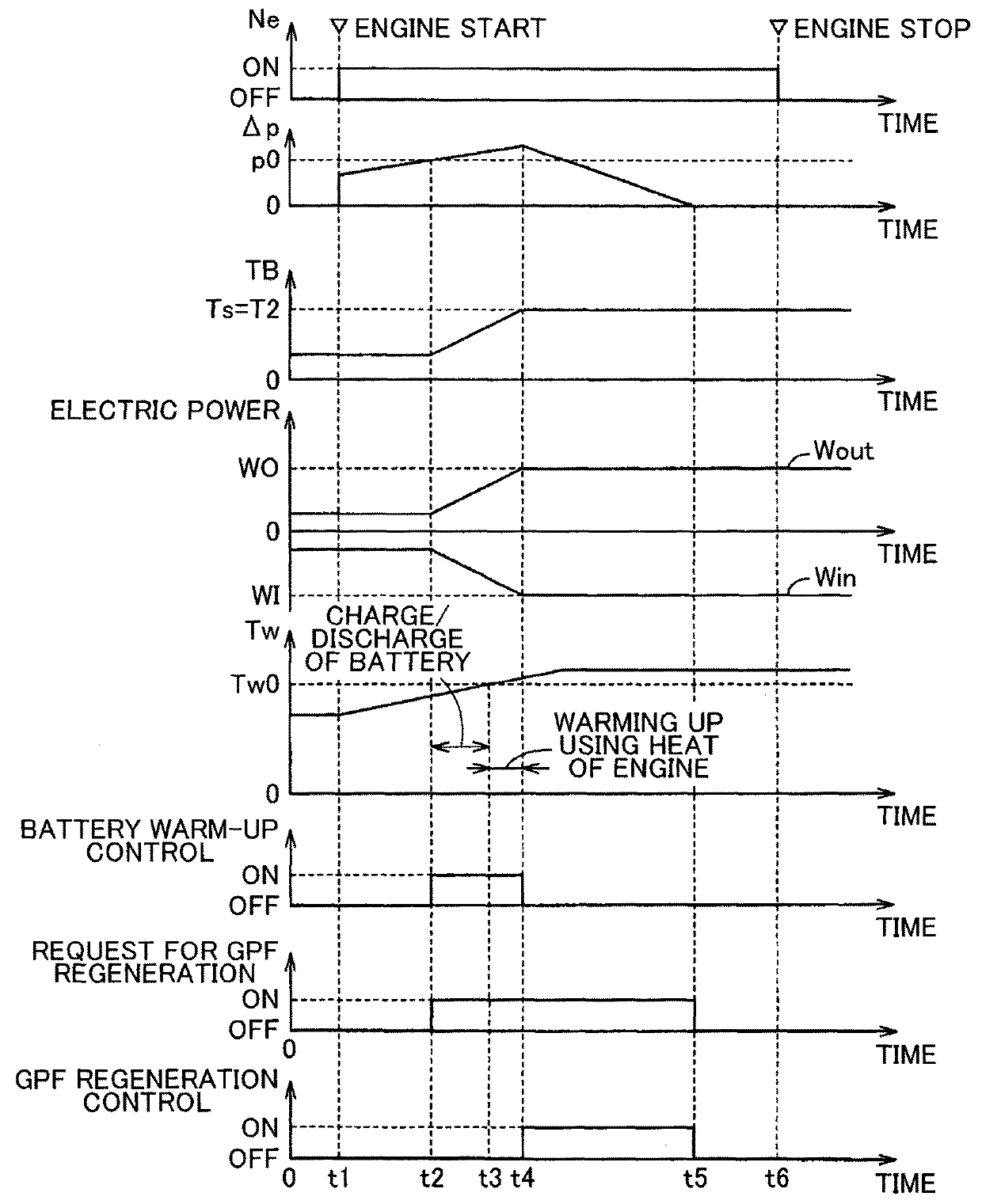

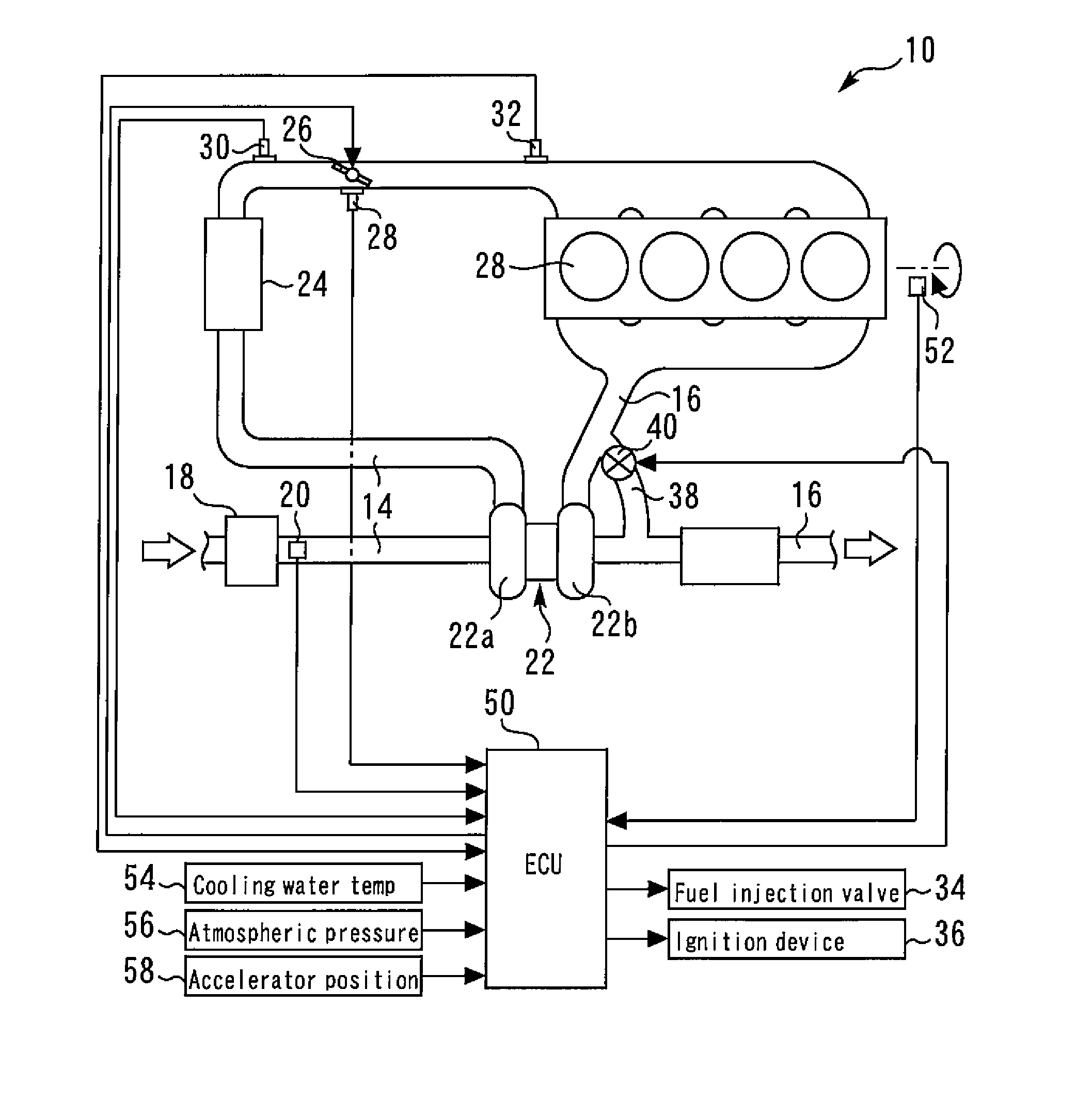

Hybrid vehicle and method of controlling the same

ActiveUS20170096136A1Charge-discharge efficiency be reduceReduce influenceHybrid vehiclesElectrical controlExhaust gasEngineering

A hybrid vehicle includes an internal combustion engine, a filter, an electrical storage device, a rotating electric machine, and a controller. The filter is configured to trap particulate matter in exhaust gas of the internal combustion engine. The rotating electric machine is configured to generate electric power using power from the internal combustion engine so as to charge the electrical storage device, and drive the internal combustion engine using electric power from the electrical storage device. The controller is configured to control the internal combustion engine and the rotating electric machine, so as to warm up the electrical storage device when regeneration control needs to be performed and when the temperature of the electrical storage device is lower than a reference value. The regeneration control is control for raising the temperature of the filter to a predetermined temperature so as to burn the particulate matter. The controller may be configured to execute the regeneration control when the temperature of the electrical storage device exceeds the reference value.

Owner:TOYOTA JIDOSHA KK

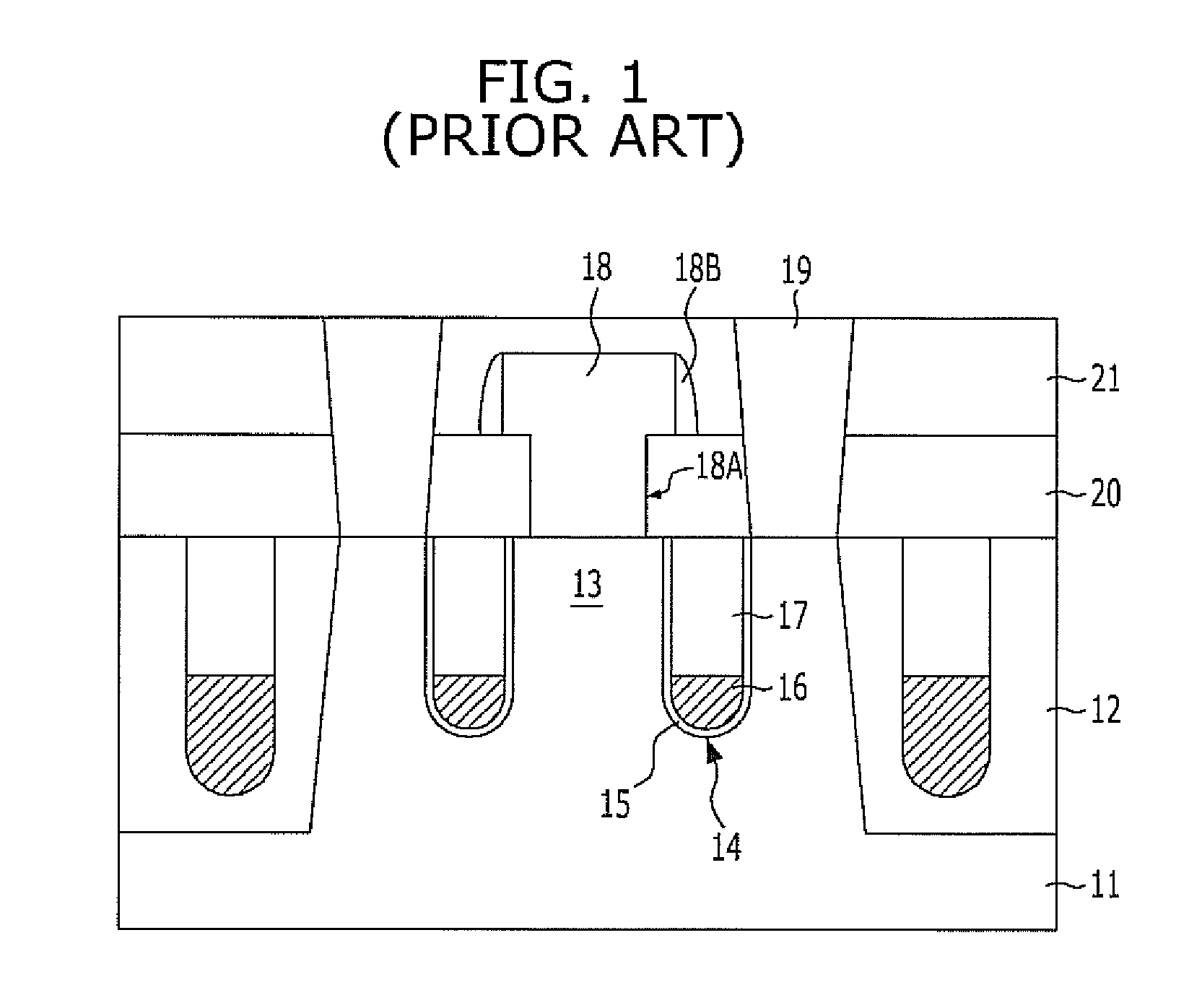

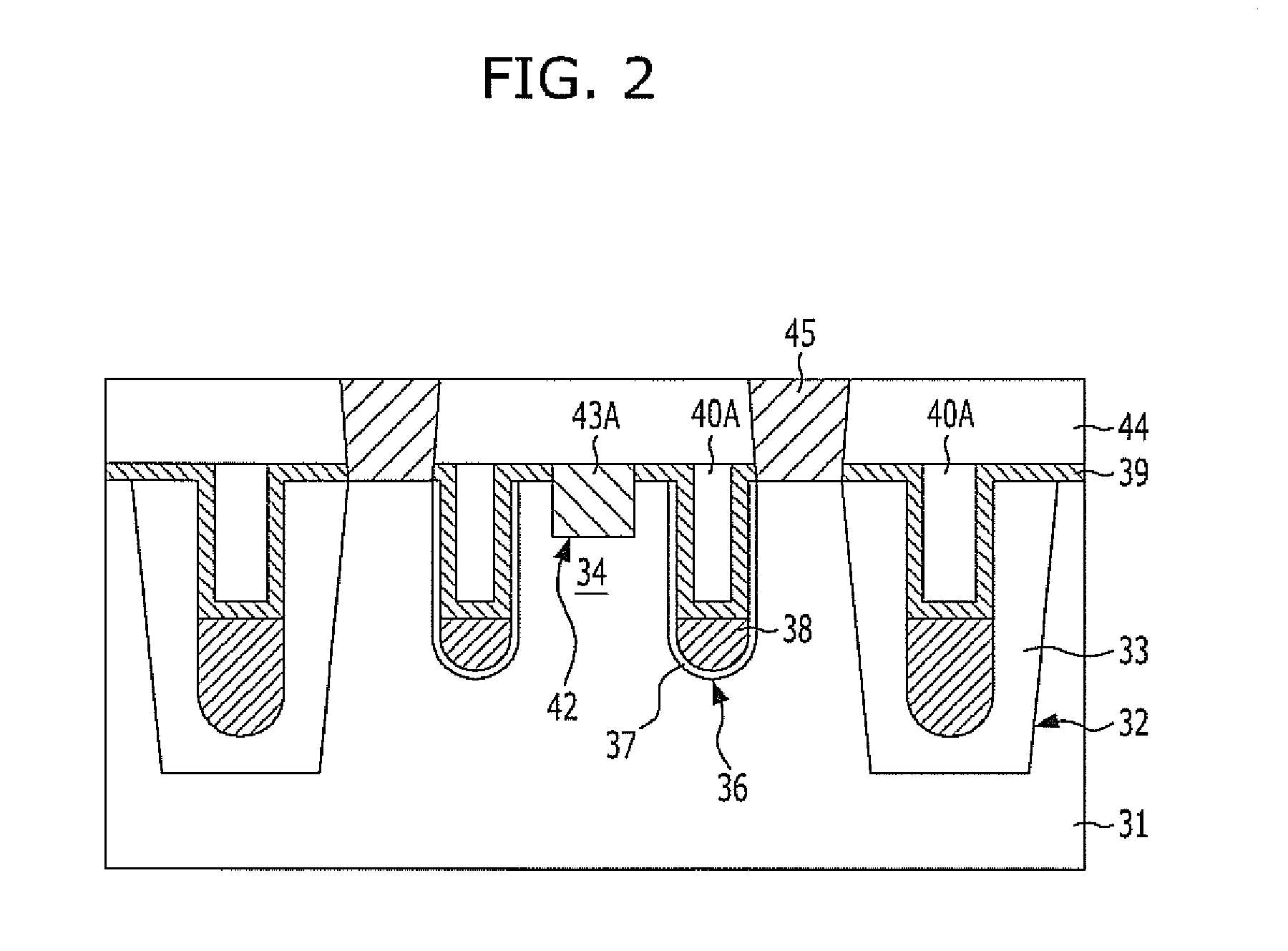

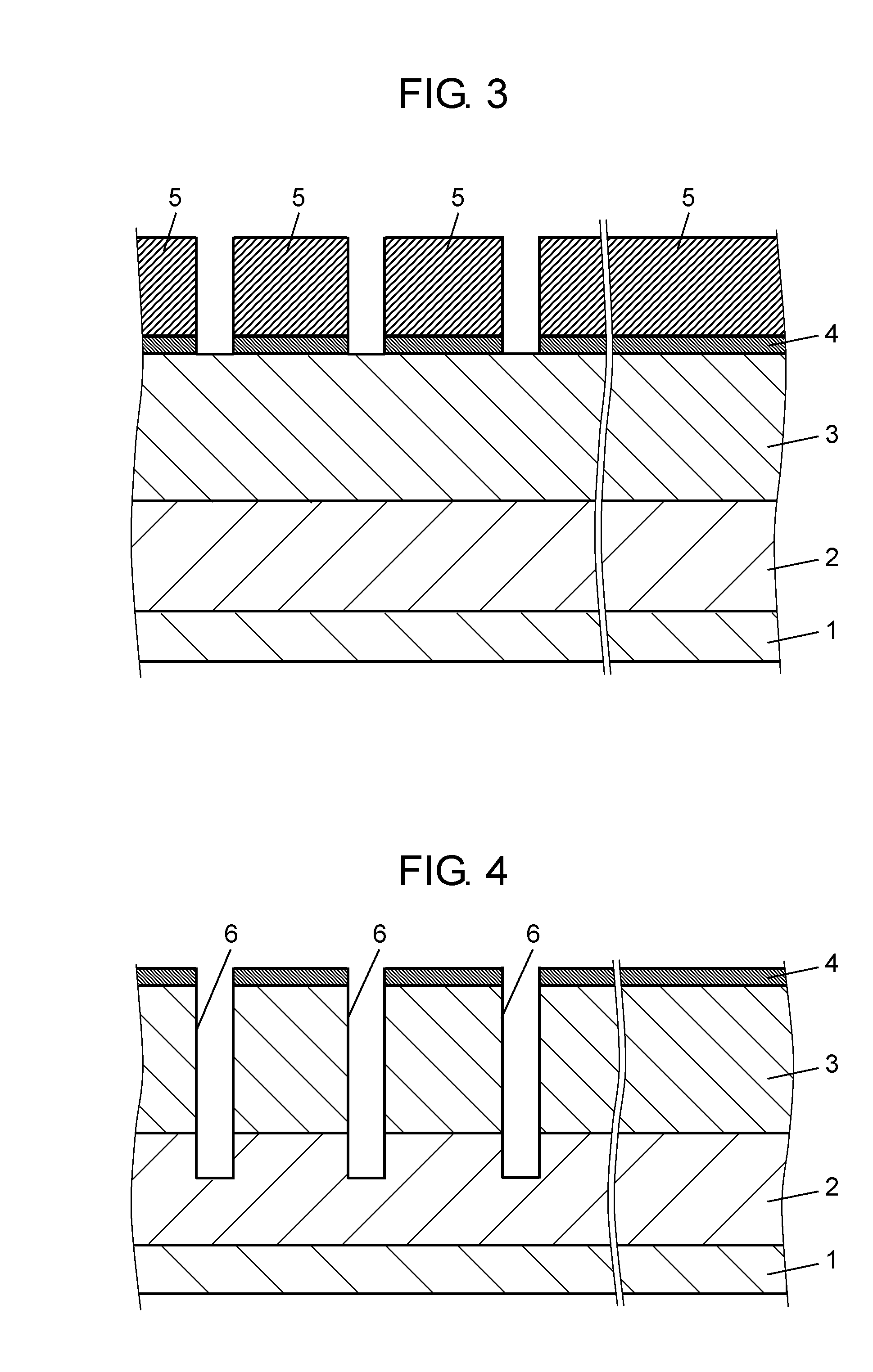

Semiconductor device with buried bit lines and method for fabricating the same

ActiveUS20110298046A1Stable characteristicsEnsure uniformitySolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceSemiconductor

A semiconductor device includes active regions separated by a trench, a separation layer dividing the trench, and buried bit lines buried in the trench with the separation layer interposed between the buried bit lines.

Owner:SK HYNIX INC

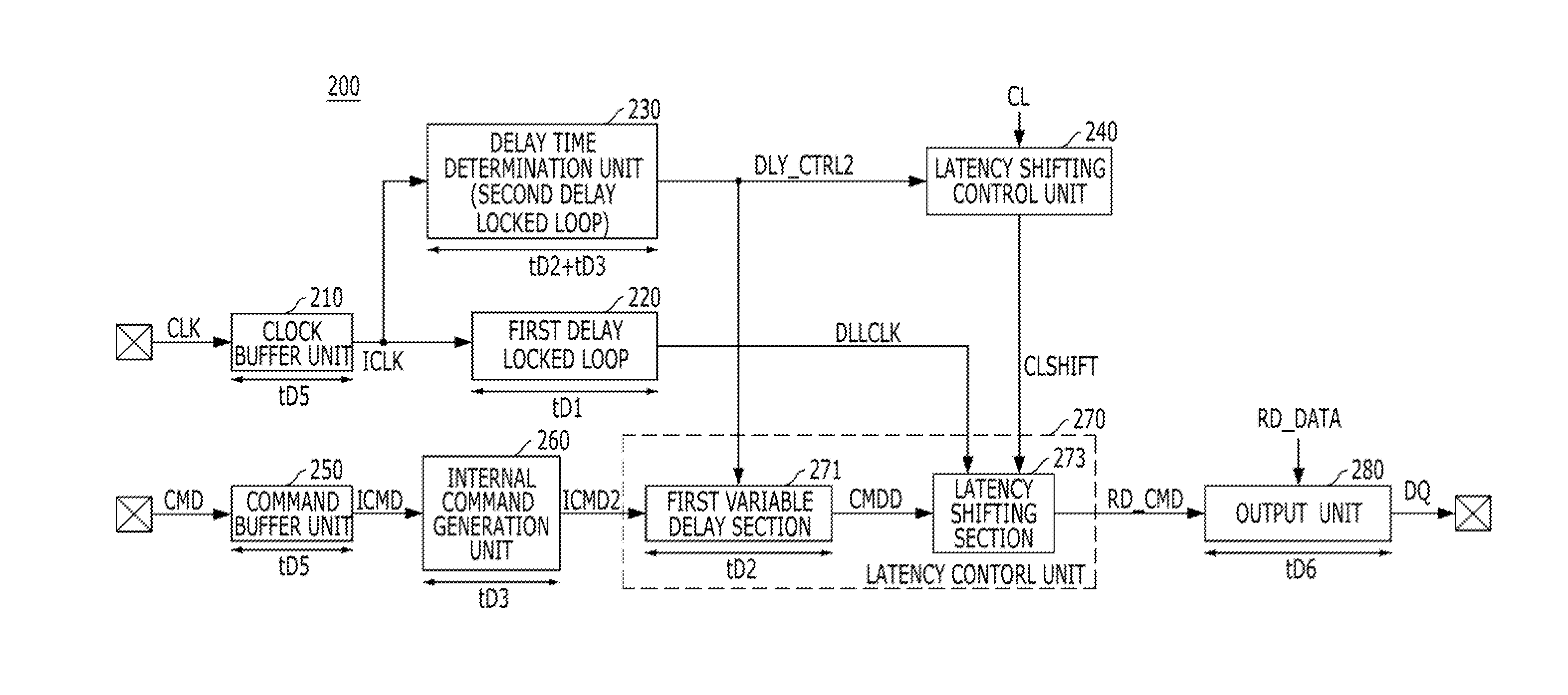

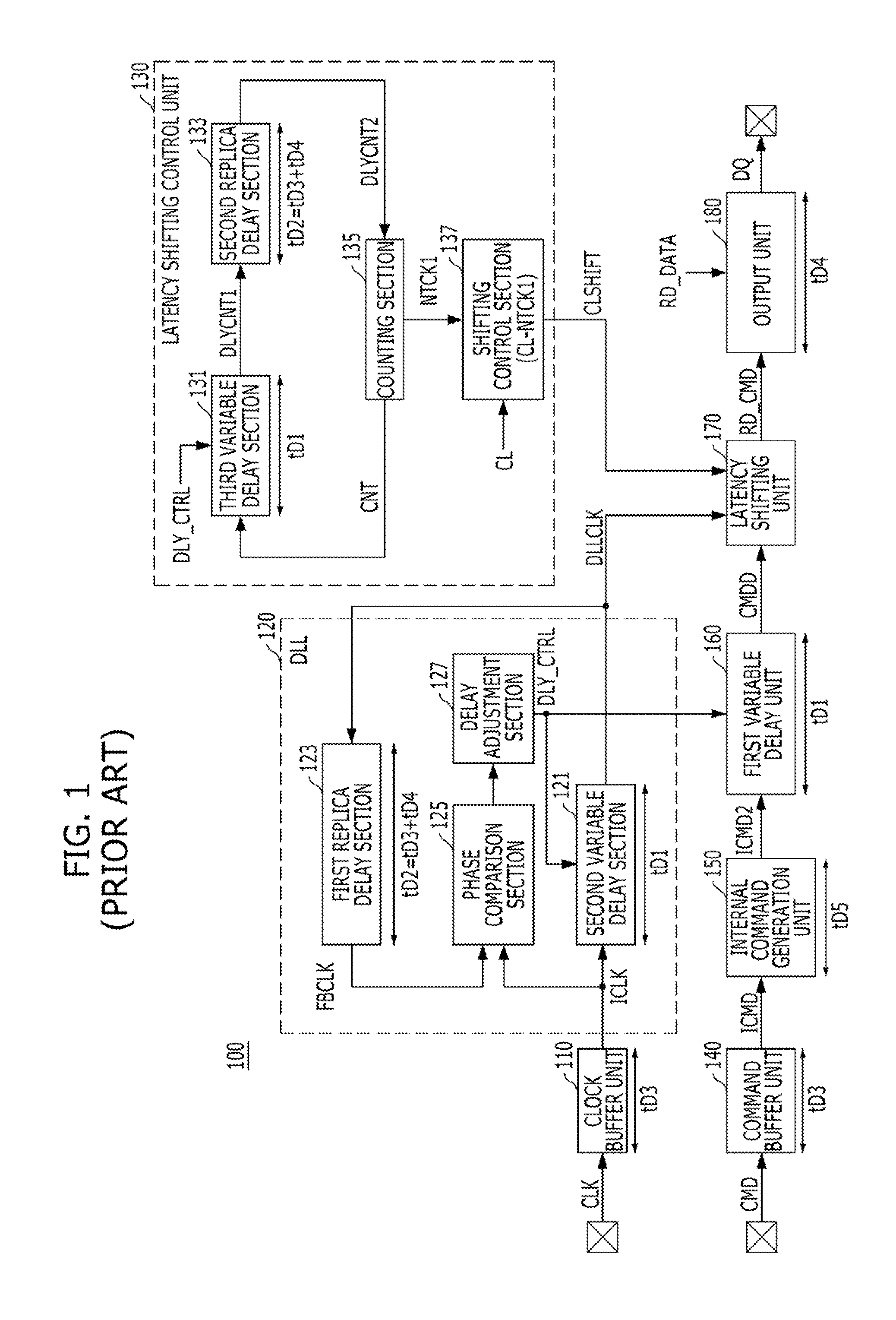

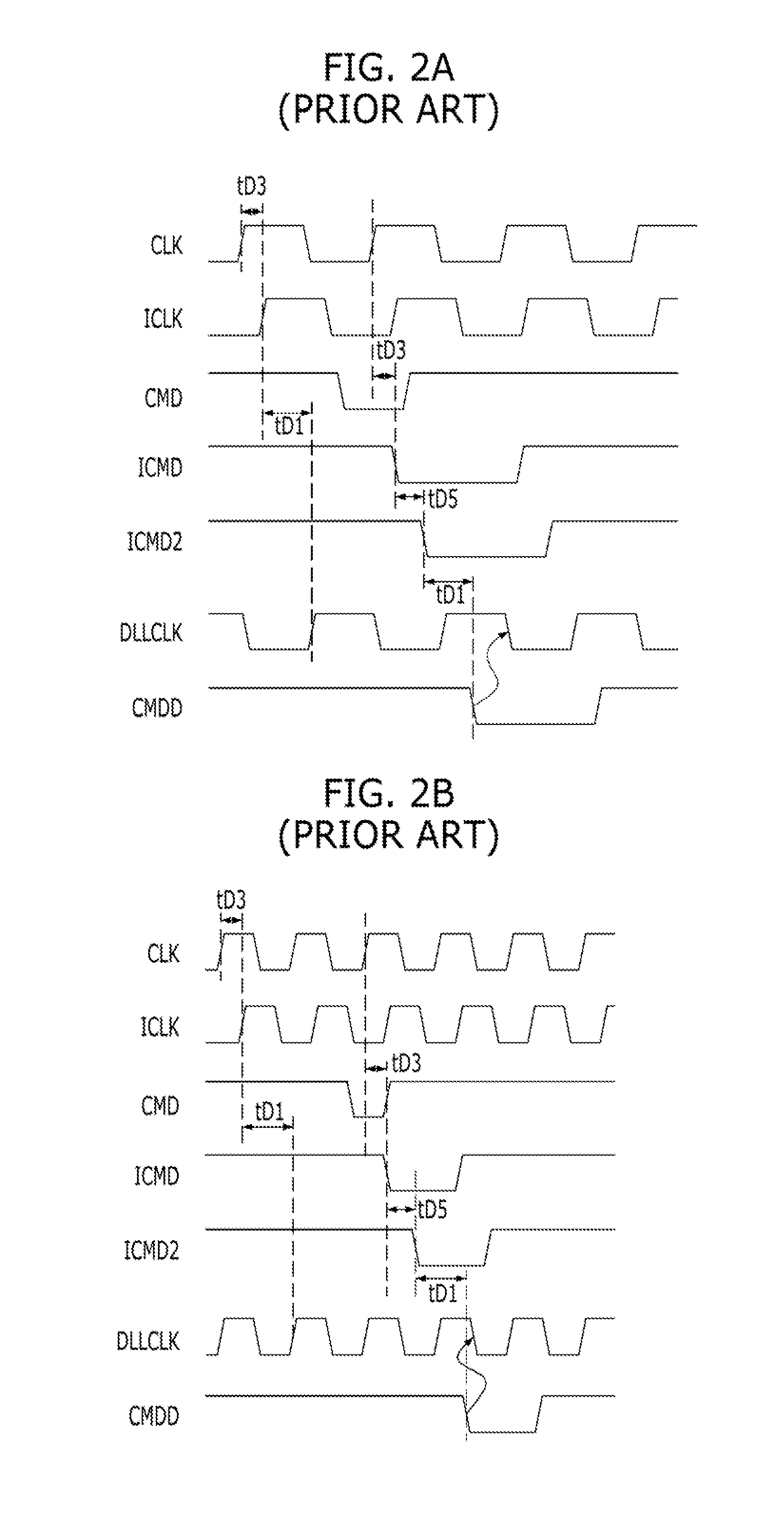

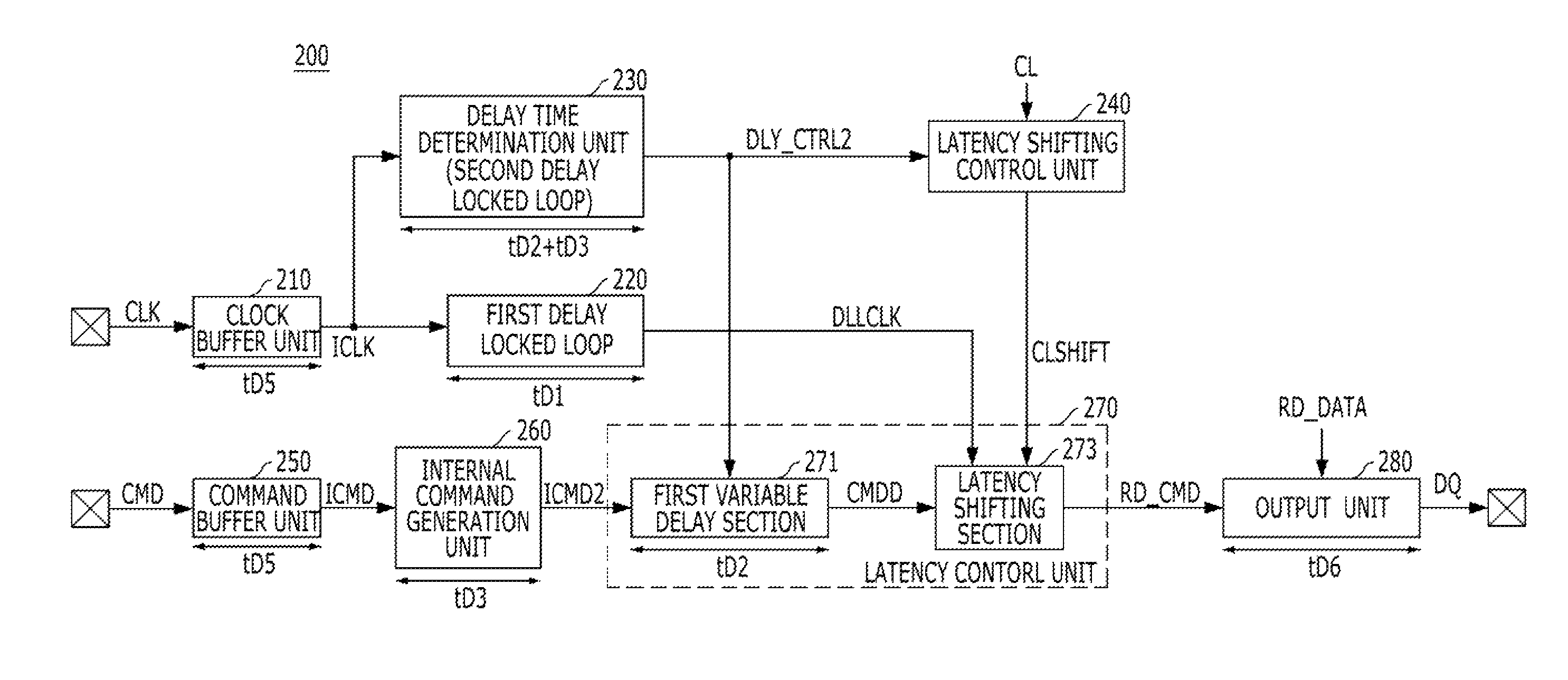

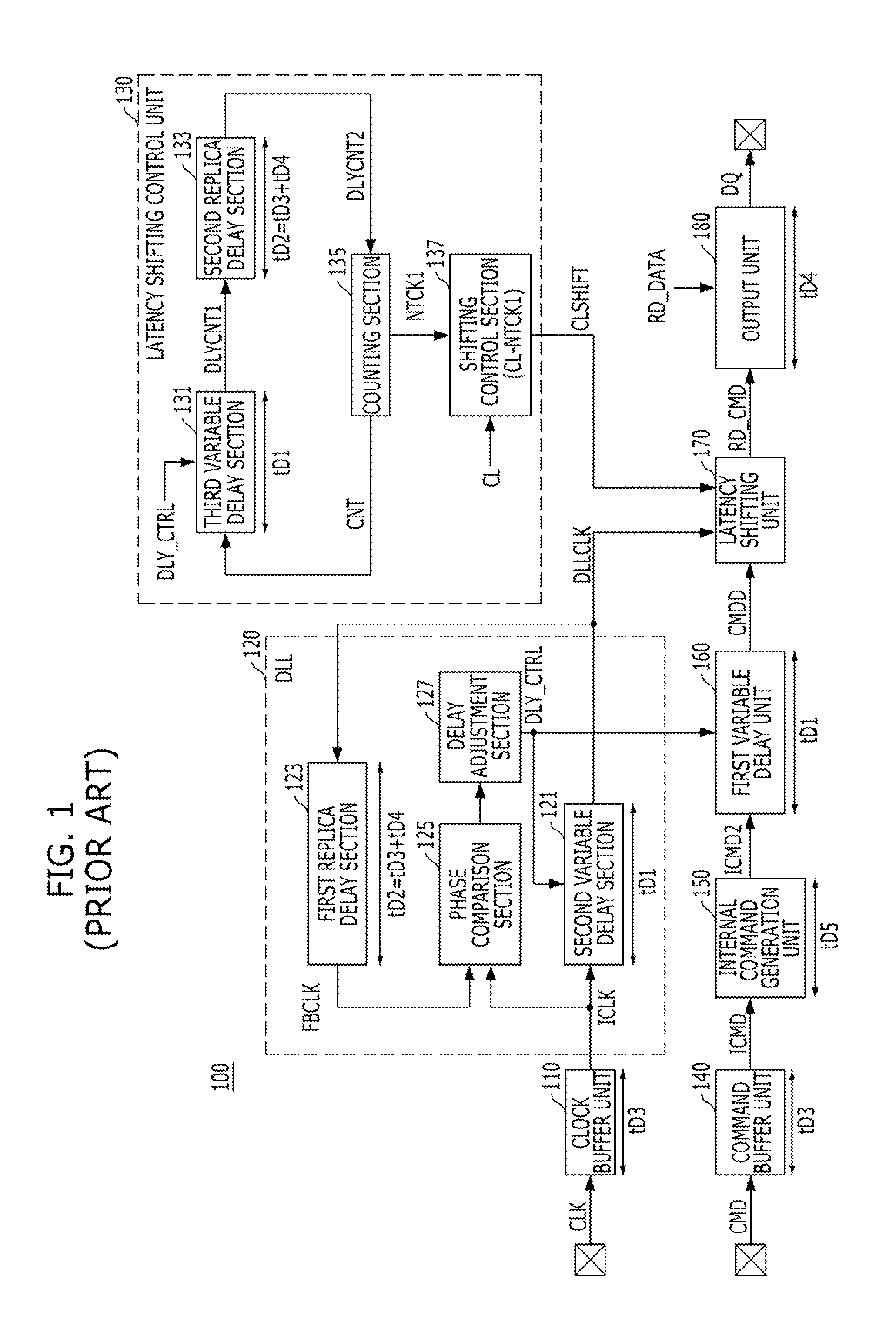

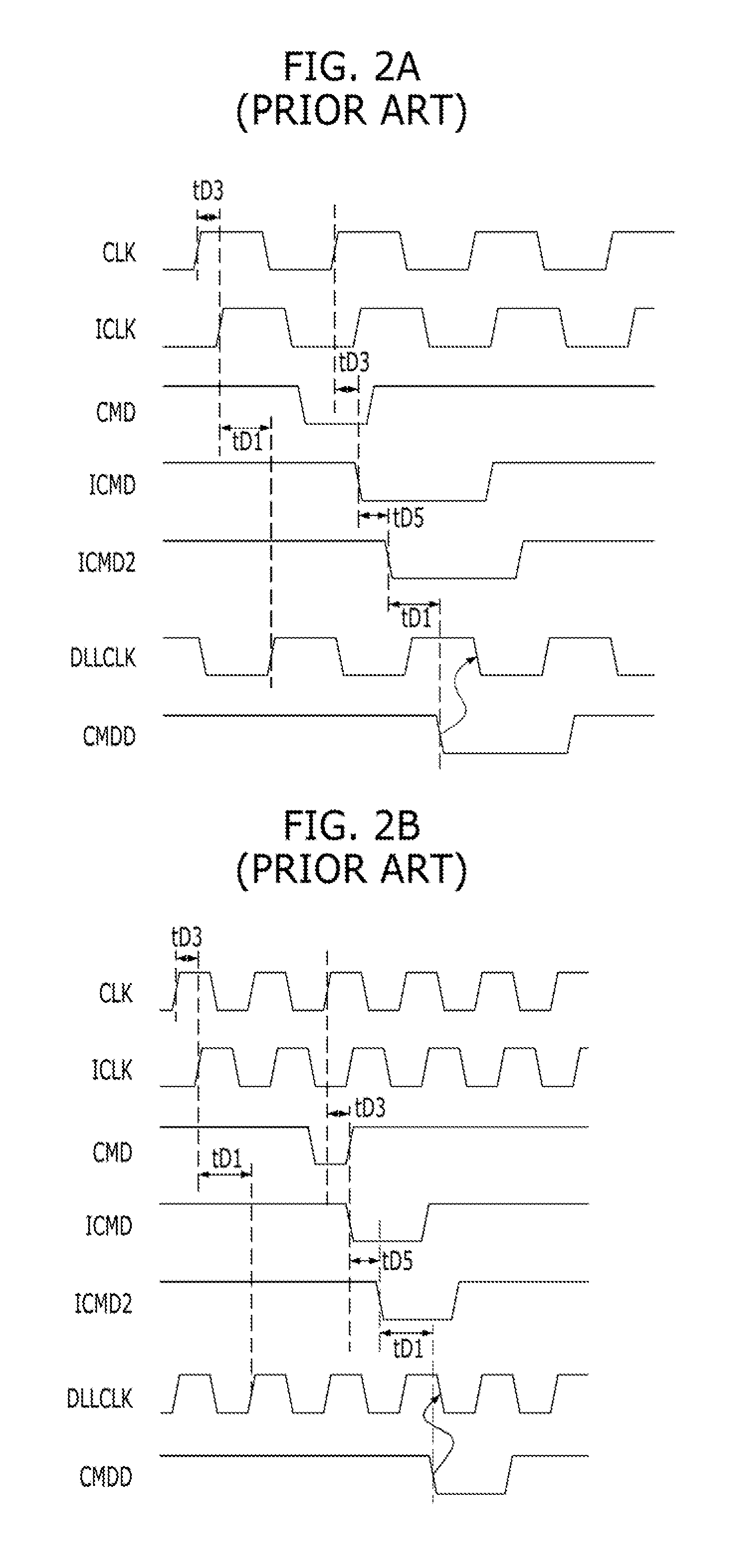

Synchronous semiconductor device having delay locked loop for latency control

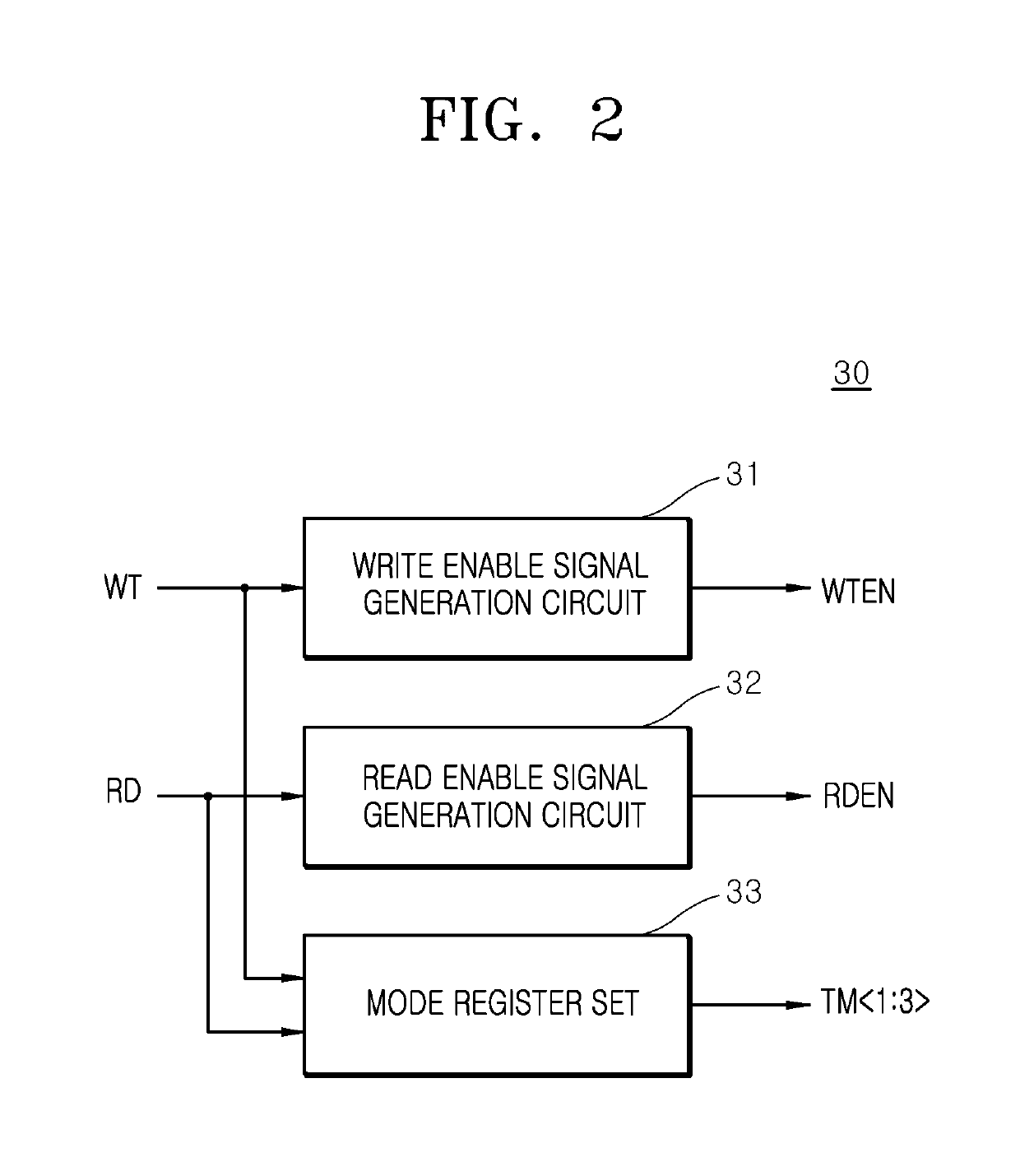

ActiveUS20140015575A1Secure marginPulse automatic controlDigital storageDelay-locked loopSemiconductor

A synchronous semiconductor device includes an internal command generation unit configured to generate an internal command corresponding to a source command, a delay locked loop configured to delay a source clock by a first delay time required for delay-locking to generate a delay locked clock, a delay time determination unit configured to determine a second delay time for delay-locking the internal command using the source clock, the second delay time being determined by reflecting a third delay time generated on a command path, and a latency control unit configured to shift the internal command by a shifting period, in which the second delay time is reflected, in response to the delay locked clock.

Owner:SK HYNIX INC

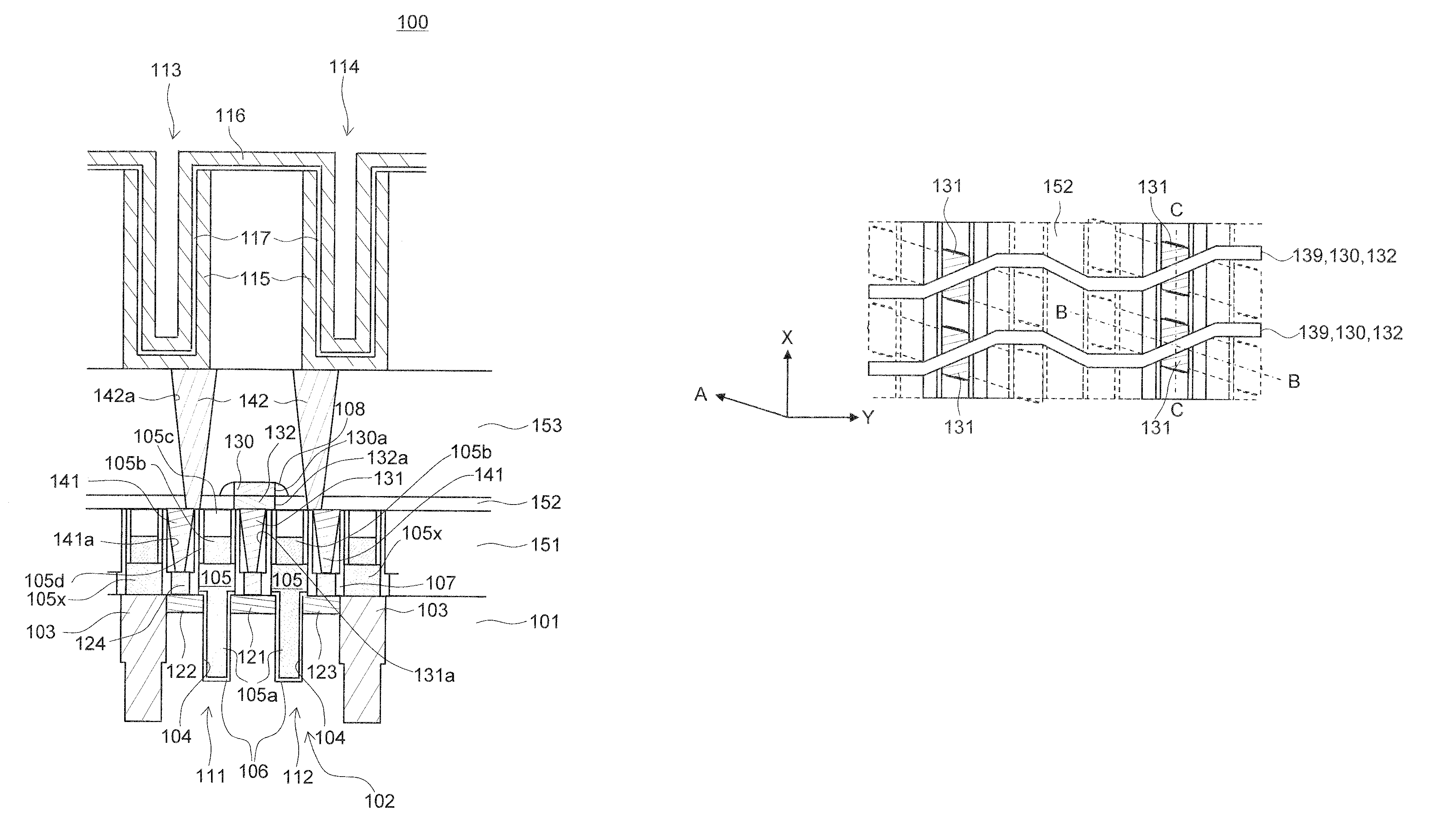

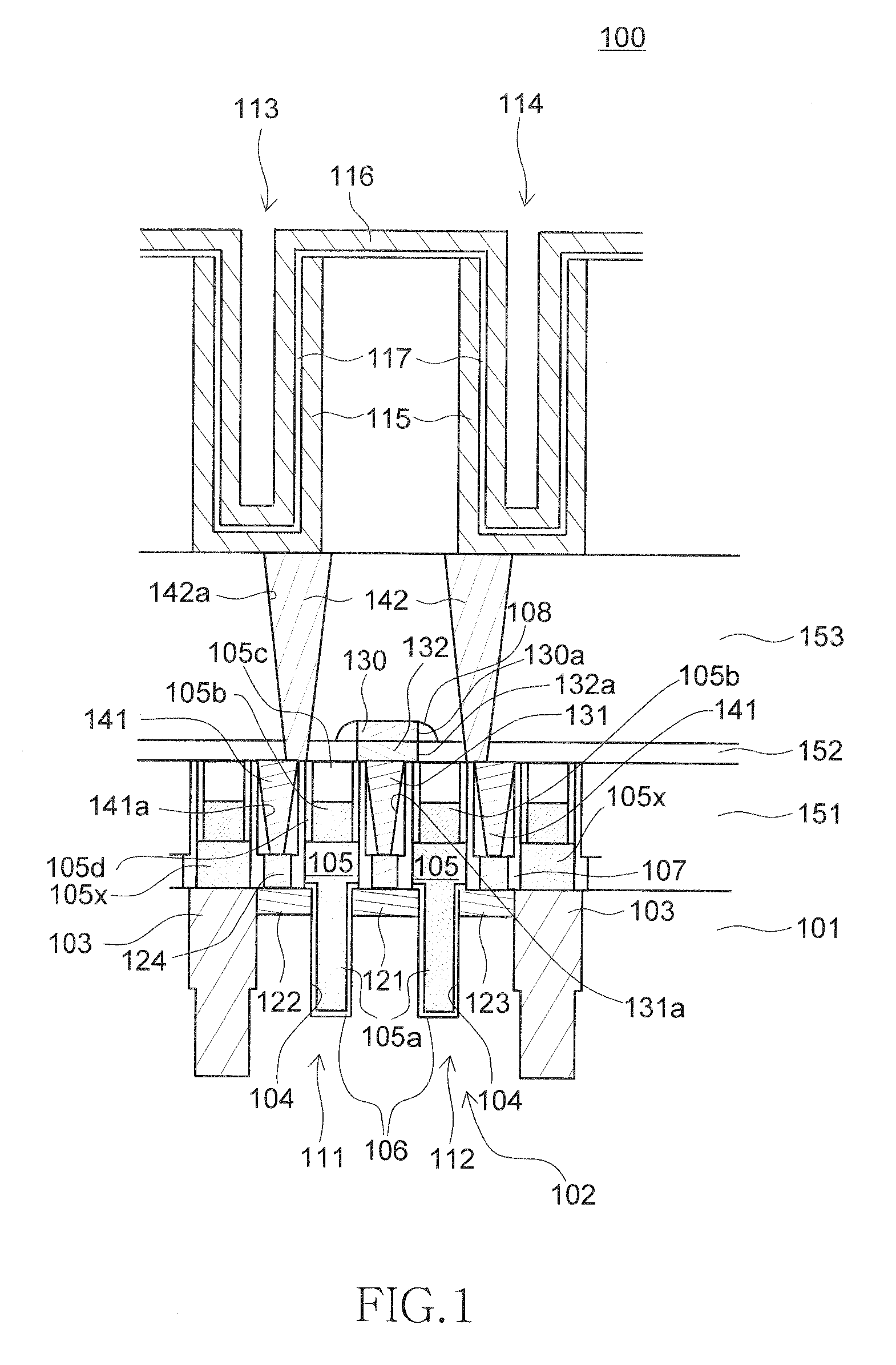

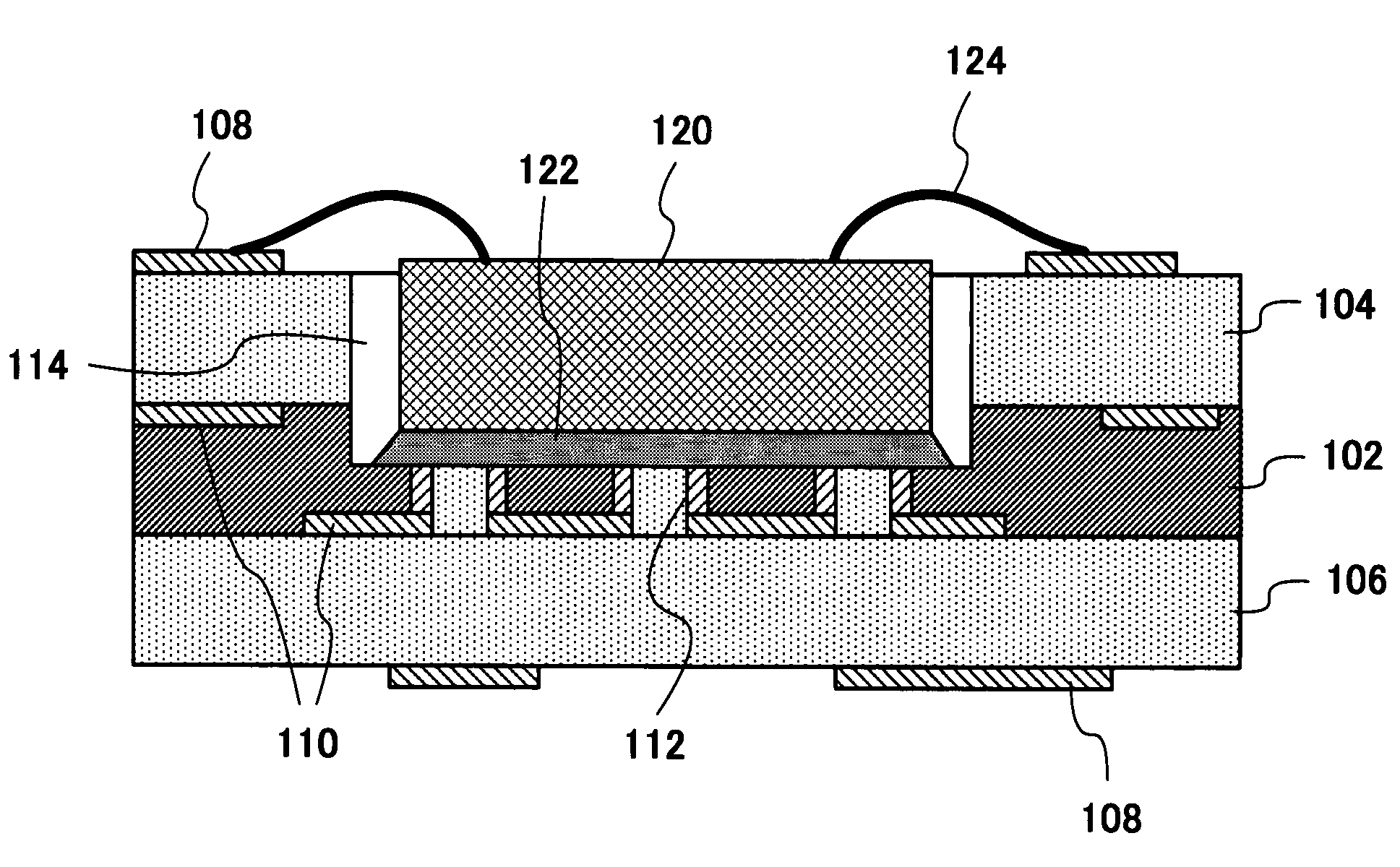

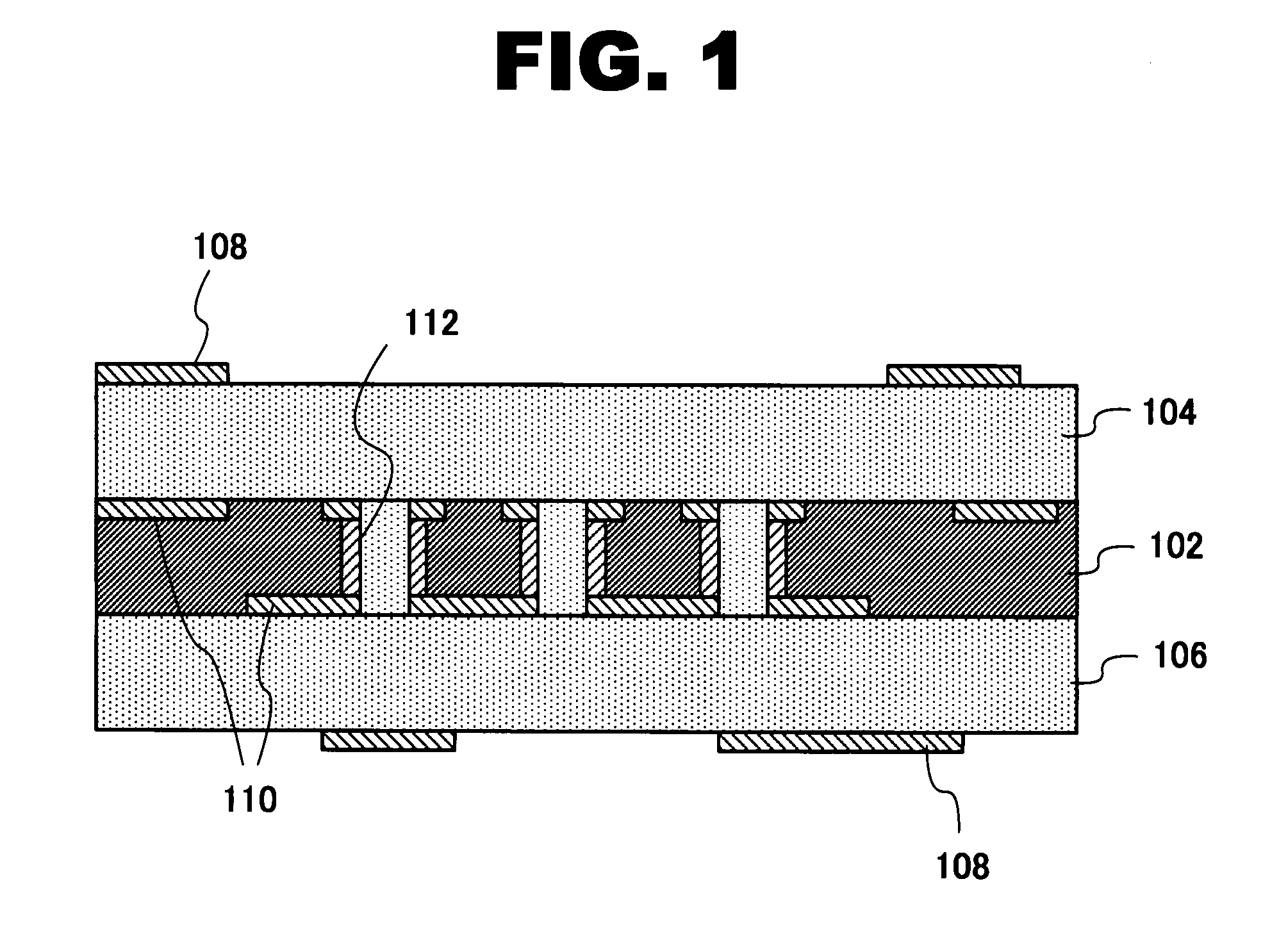

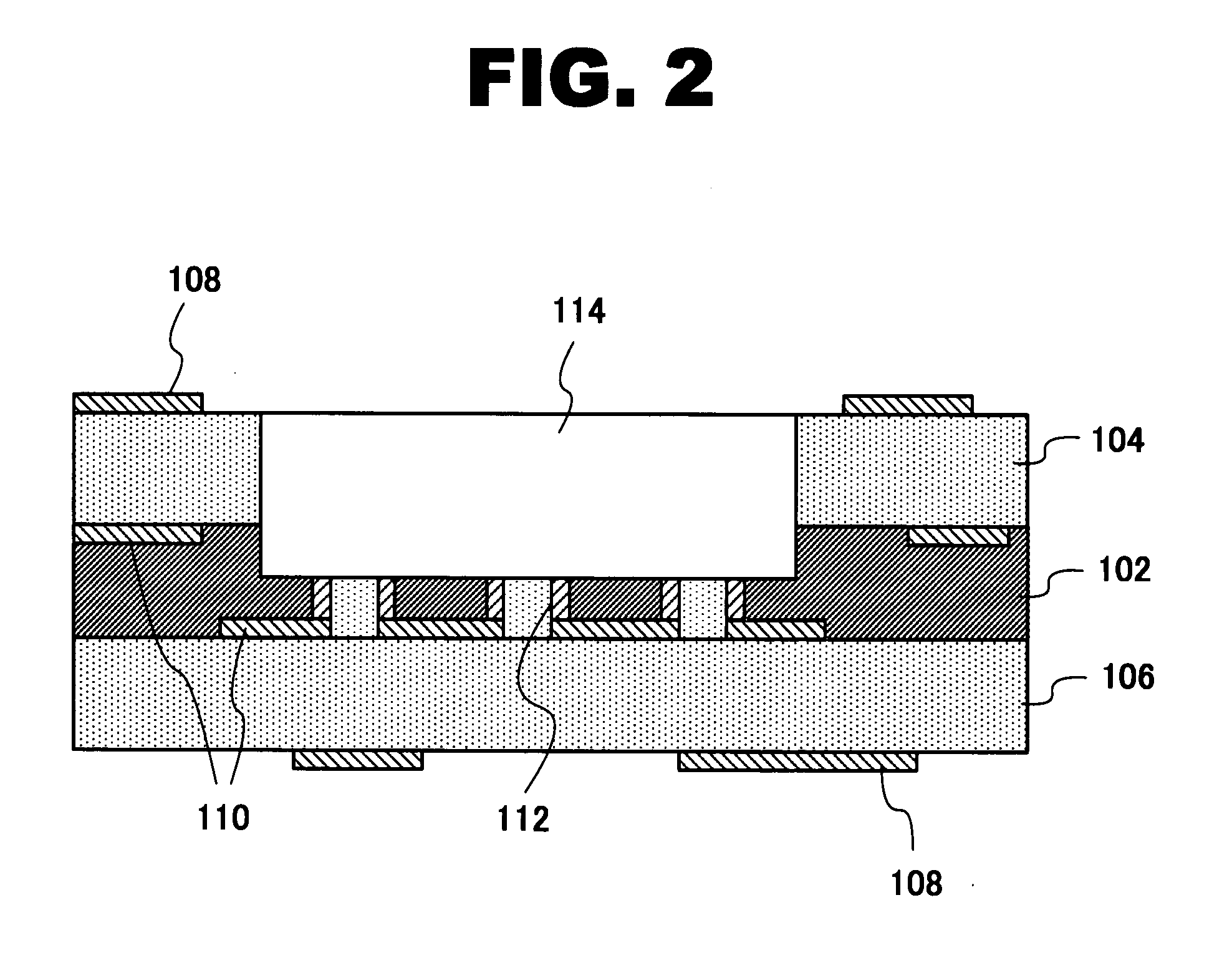

Semiconductor device

InactiveUS20130082382A1Inhibition of thinningSecure marginSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

First and second sub-bumps are provided on both surfaces of each substrate along with a usual bump structure (first and second main bumps), and at least one of the first and second sub-bumps is made greater in height than the first and second main bumps, so that the sub-bumps come into contact with one another earlier than the main bumps at the time of joining semiconductor chips, thereby securing margins of joint among the main bumps and suppressing the thin-filming of a layer, such as a solder layer, to be fluidized by heating.

Owner:PS4 LUXCO SARL

Semiconductor device and manufacturing method thereof

InactiveUS7851303B2Smooth connectionSecure marginTransistorSemiconductor/solid-state device detailsEngineeringContact electrode

A semiconductor device includes: a transistor having source and drain regions; first and second contact electrodes embedded in a first interlayer insulating film, and electrically connected to the source region and the drain region, respectively; a third electrode embedded in a second interlayer insulating film positioned in an upper layer of the first interlayer insulating film, and electrically connected to the first contact electrode; a wiring pattern embedded in a third interlayer insulating film positioned in an upper layer of the second interlayer insulating film, and electrically connected to the third contact electrode; and a fourth contact electrode embedded in at least the second and third interlayer insulating films, and electrically connected to the second contact electrode, wherein side surfaces of the wiring pattern along an extending direction of the wiring pattern coincide with side surfaces of the third contact electrode along an extending direction of the wiring pattern.

Owner:LONGITUDE SEMICON S A R L

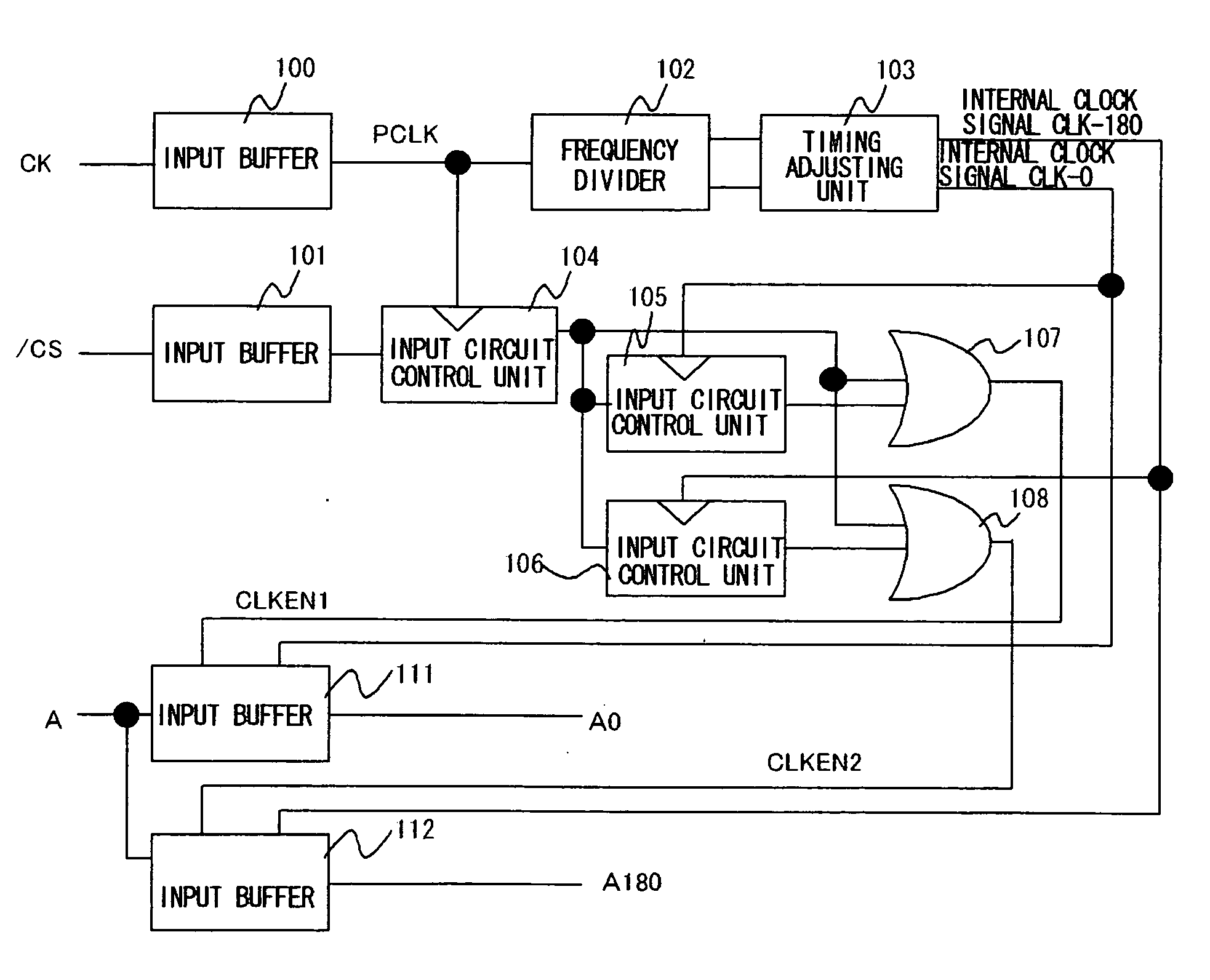

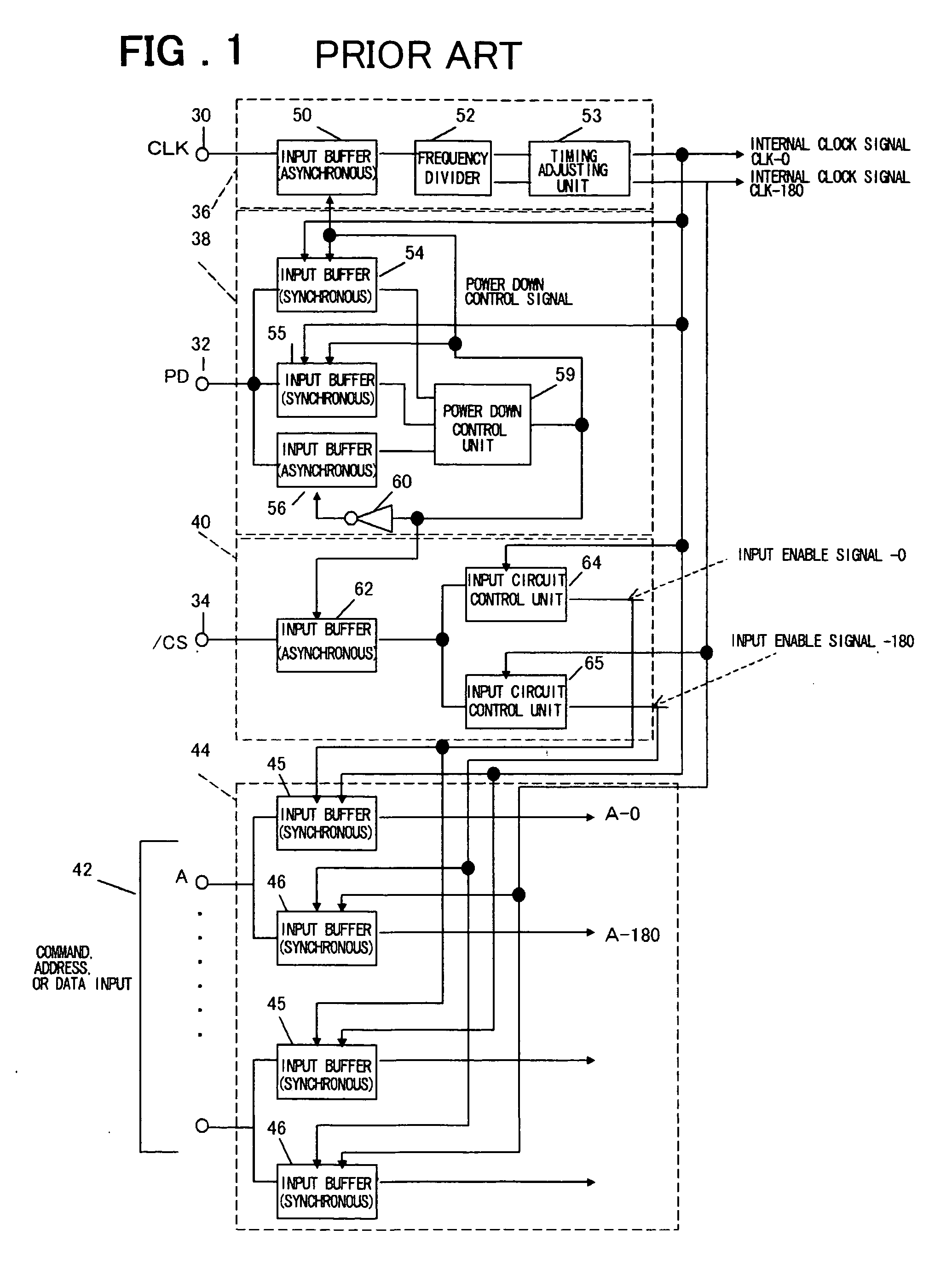

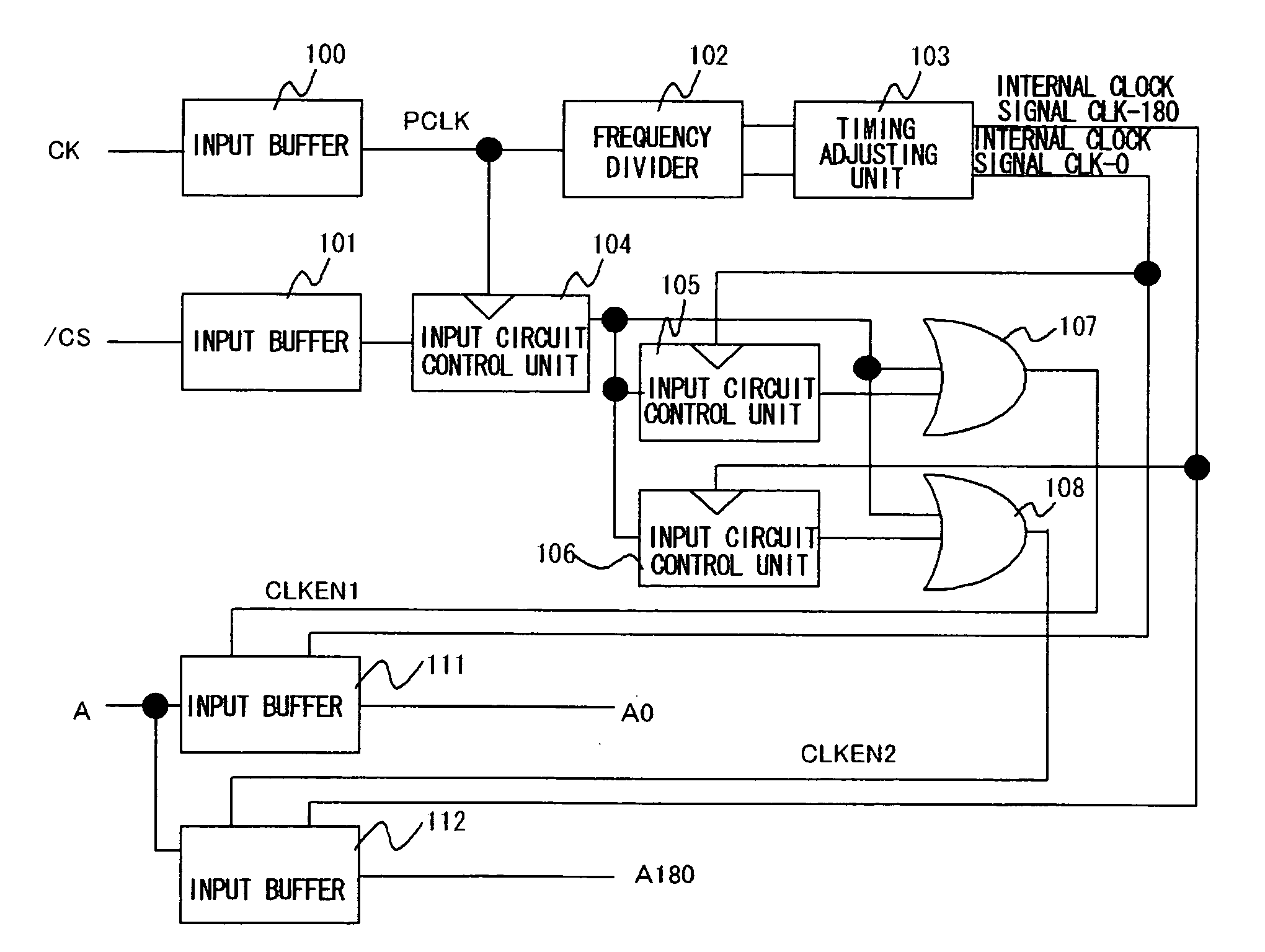

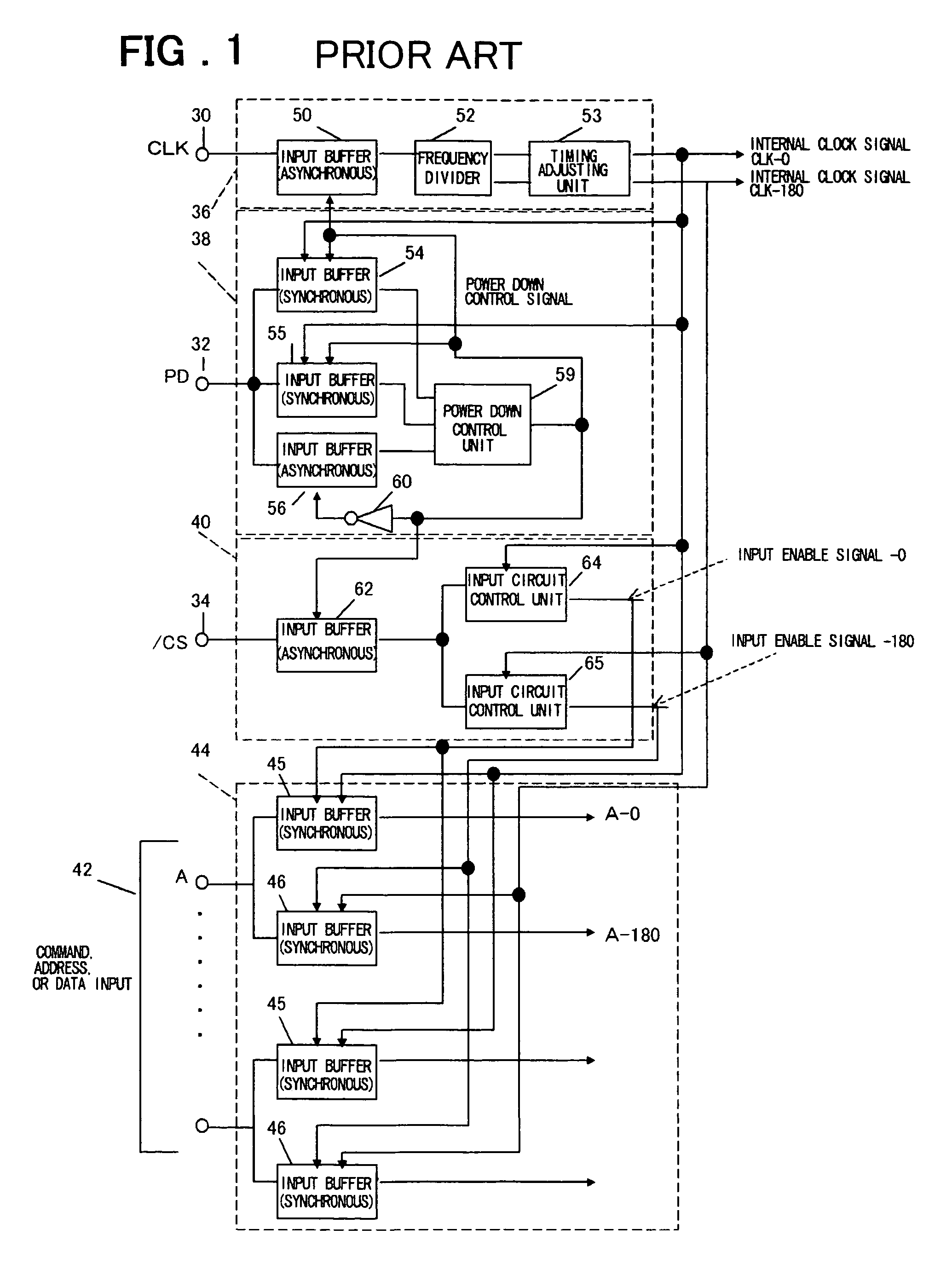

Synchronous type semiconductor device

ActiveUS20070101177A1Avoid misinformationReduce widthPulse automatic controlGenerating/distributing signalsDevice materialPhase difference

Disclosed is a synchronous semiconductor device including clock generation circuit that frequency divides a clock signal (PCLK) input from an input buffer and generates first and second internal clock signals having a predetermined phase difference from first and second frequency-divided clock signals of different phases, respectively, a first input circuit control unit that receives a chip select signal and samples the chip select signal in synchronization with the clock signal, second and third input circuit control units that sample an output of the first input circuit control unit in synchronization with the first and second internal clock signals, respectively, and first and second input circuits that receive a result of a logic operation between the output of the first input control unit and an output of the second input circuit control unit and a result of a logic operation between the output of the first input circuit control unit and an output of the third input circuit control unit as input enable signals, respectively, and sample an externally input signal in synchronization with the first and second internal clock signals, respectively based on enabling instructed by the input enable signals.

Owner:MICRON TECH INC

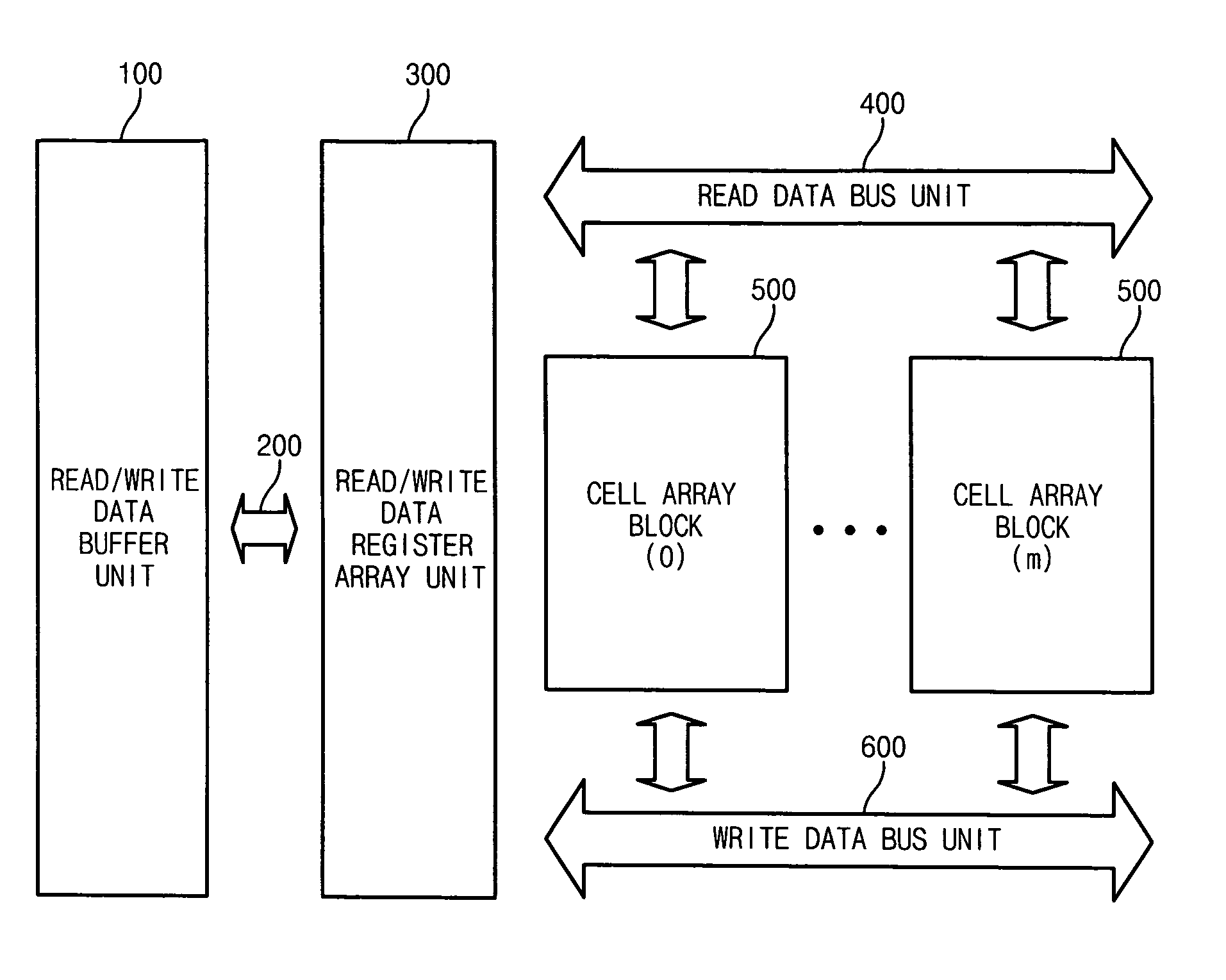

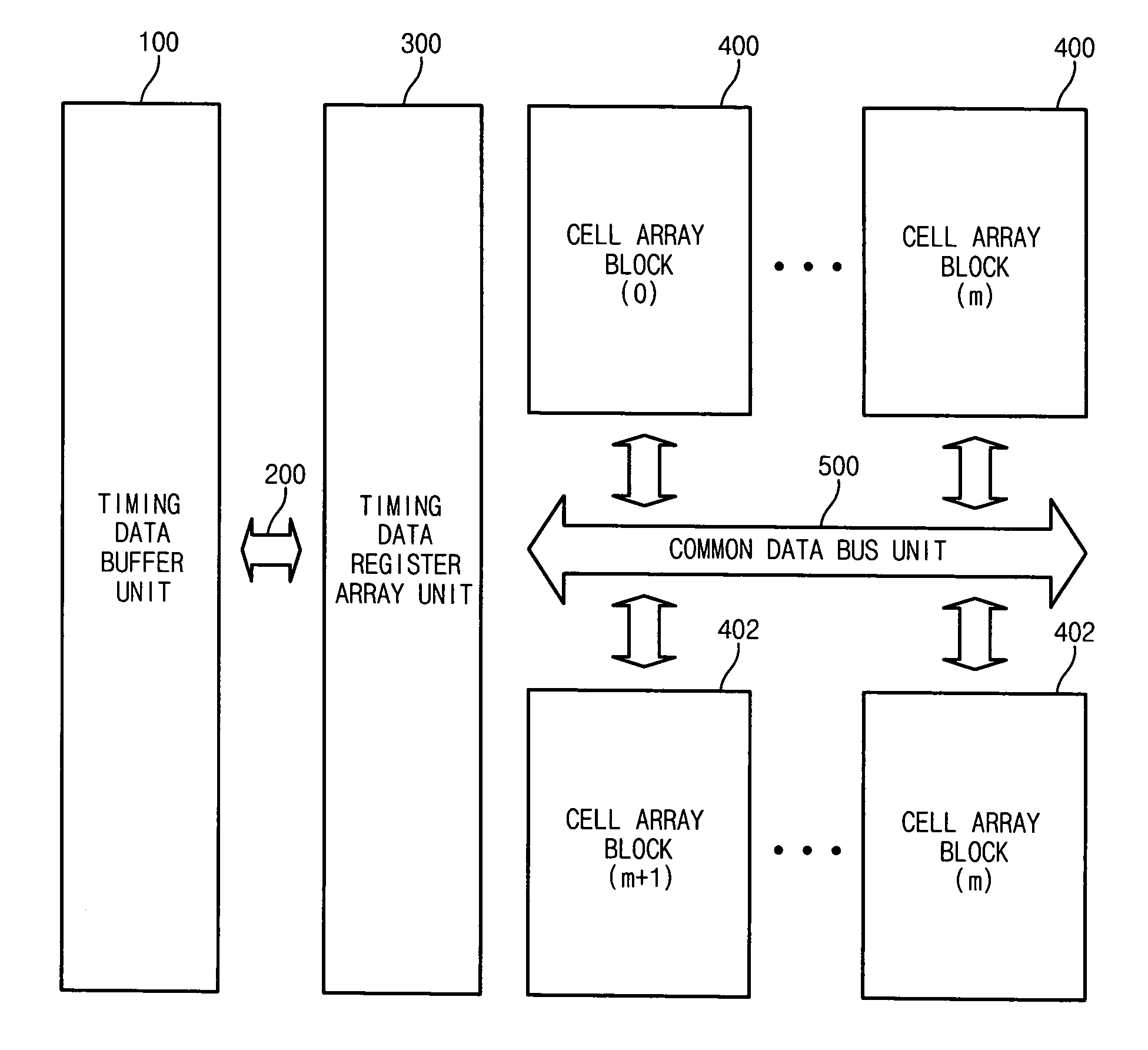

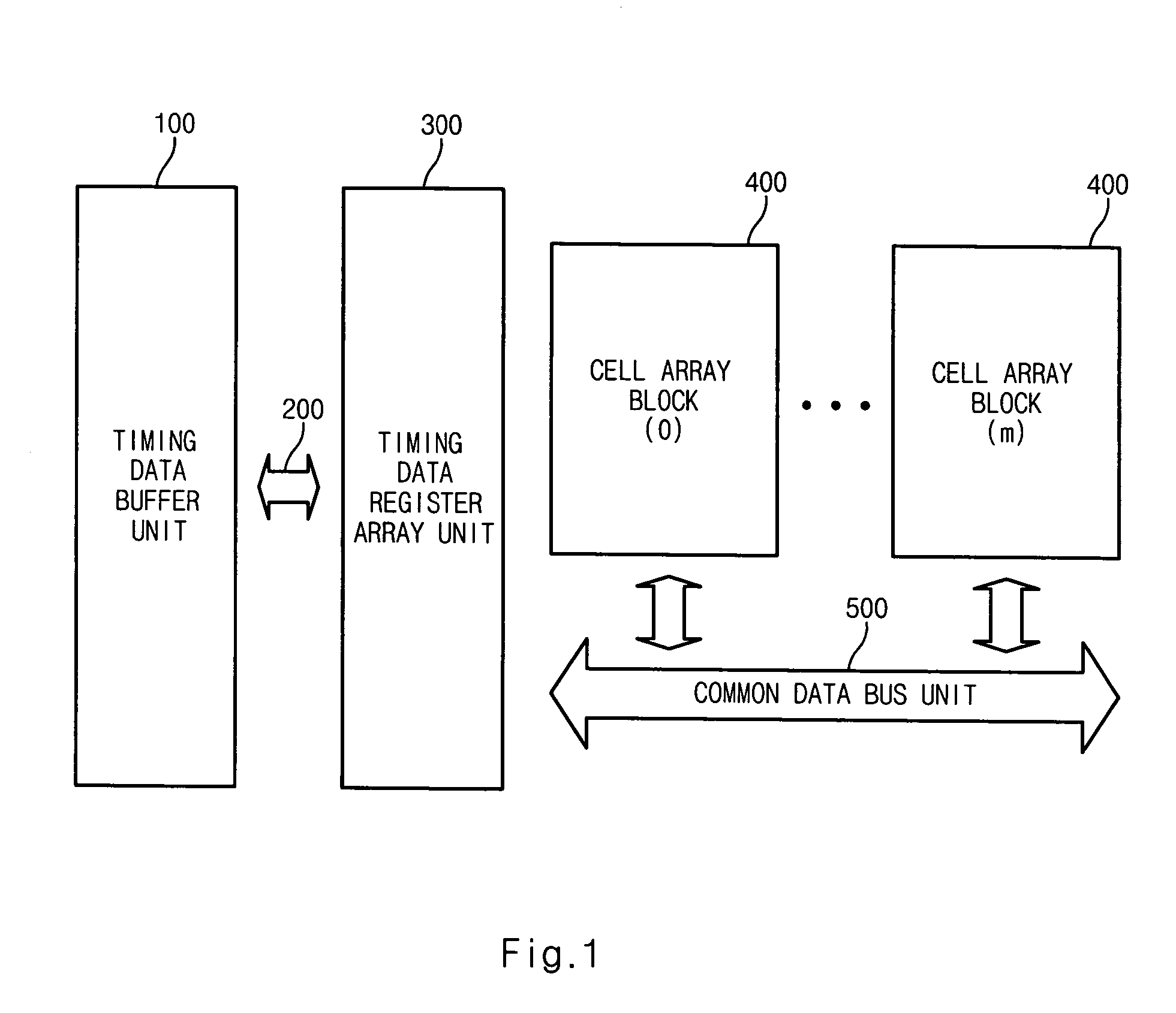

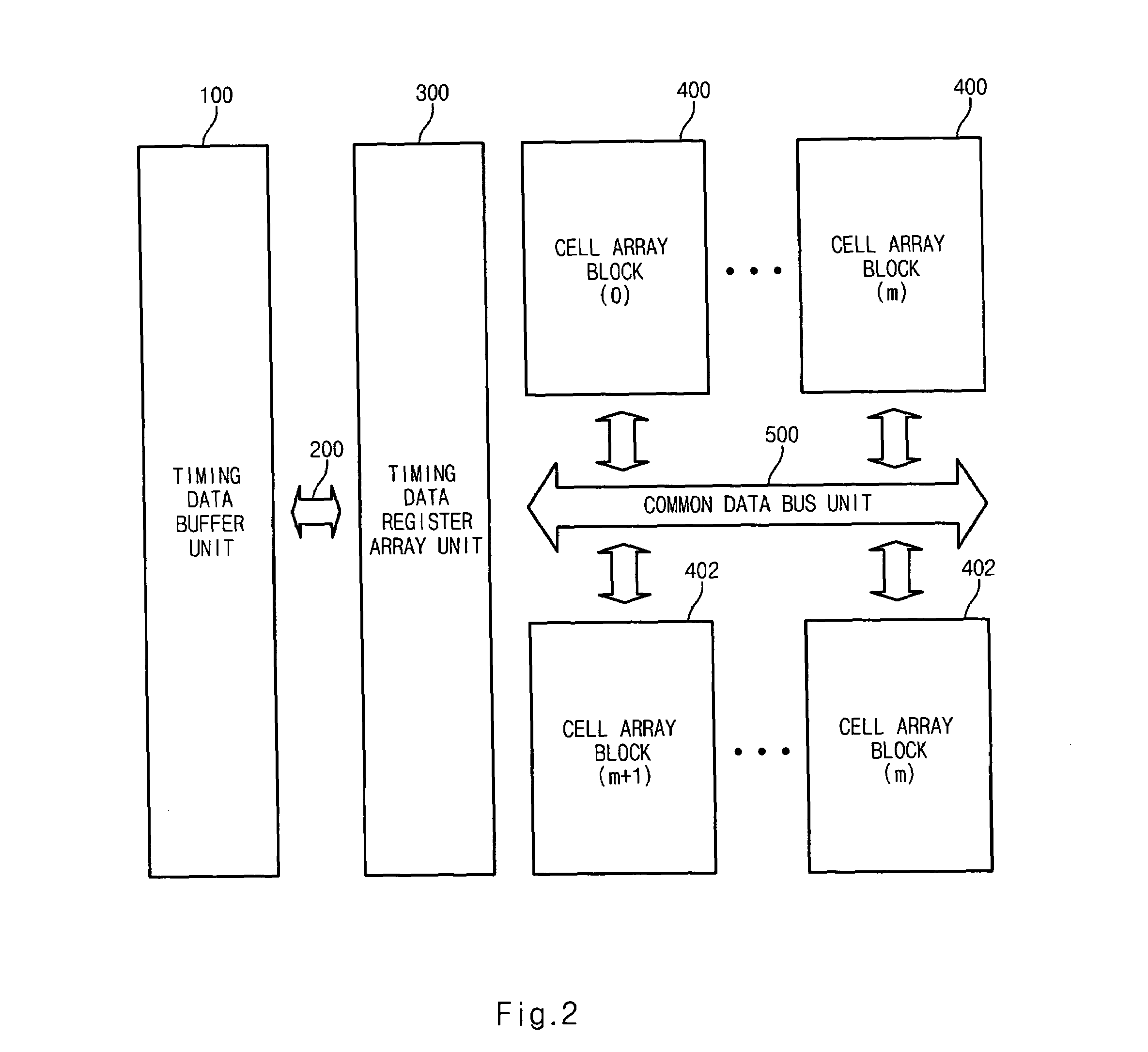

Nonvolatile ferroelectric memory device having a multi-bit control function

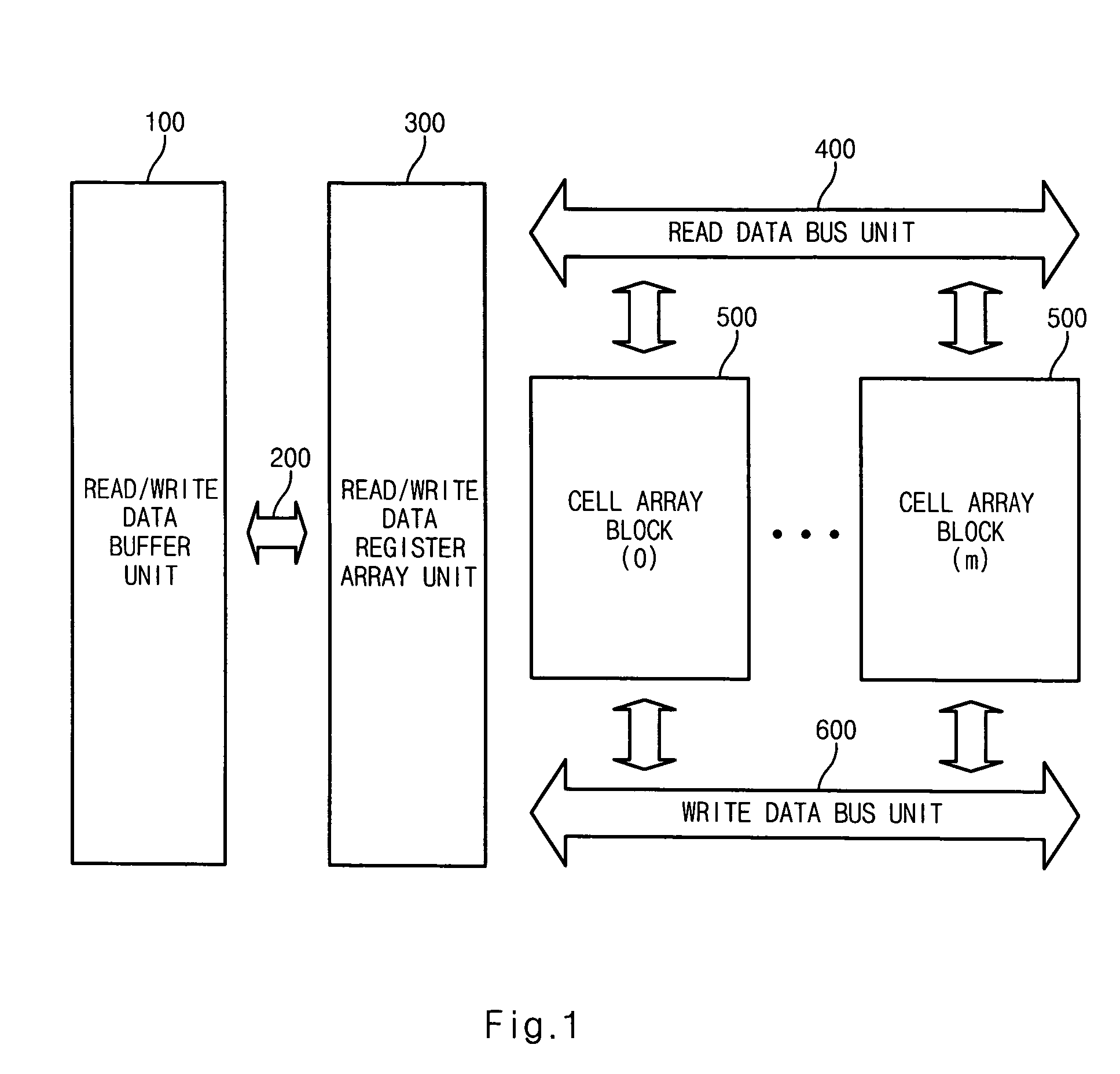

A nonvolatile ferroelectric memory device having a multi control function can amplify sensing voltage levels in a sensing critical voltage and determine a plurality of cell data when a plurality of reference timing strobes are applied on a basis of a time axis. In a read mode, a plurality of read data applied from a cell array block are stored in a read / write data register array unit through a common data bus unit. In a write mode, a plurality of read data stored in the read / write data register array unit or input data applied from a timing data buffer unit are stored in a cell array block through the common data bus unit. Here, since a plurality of sensing voltage levels are set in cell data, a plurality of sensed data bits can be stored in one cell.

Owner:SK HYNIX INC

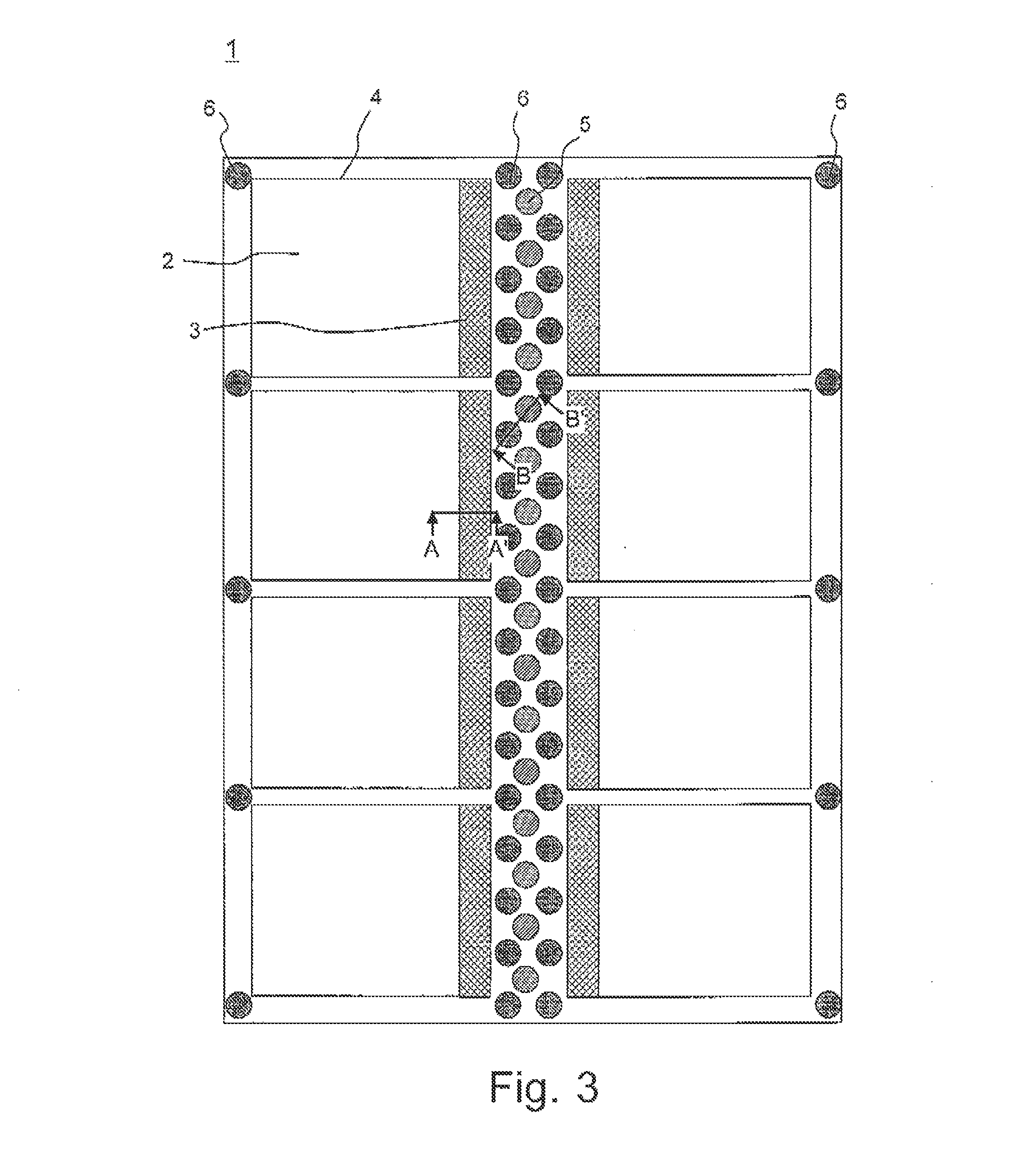

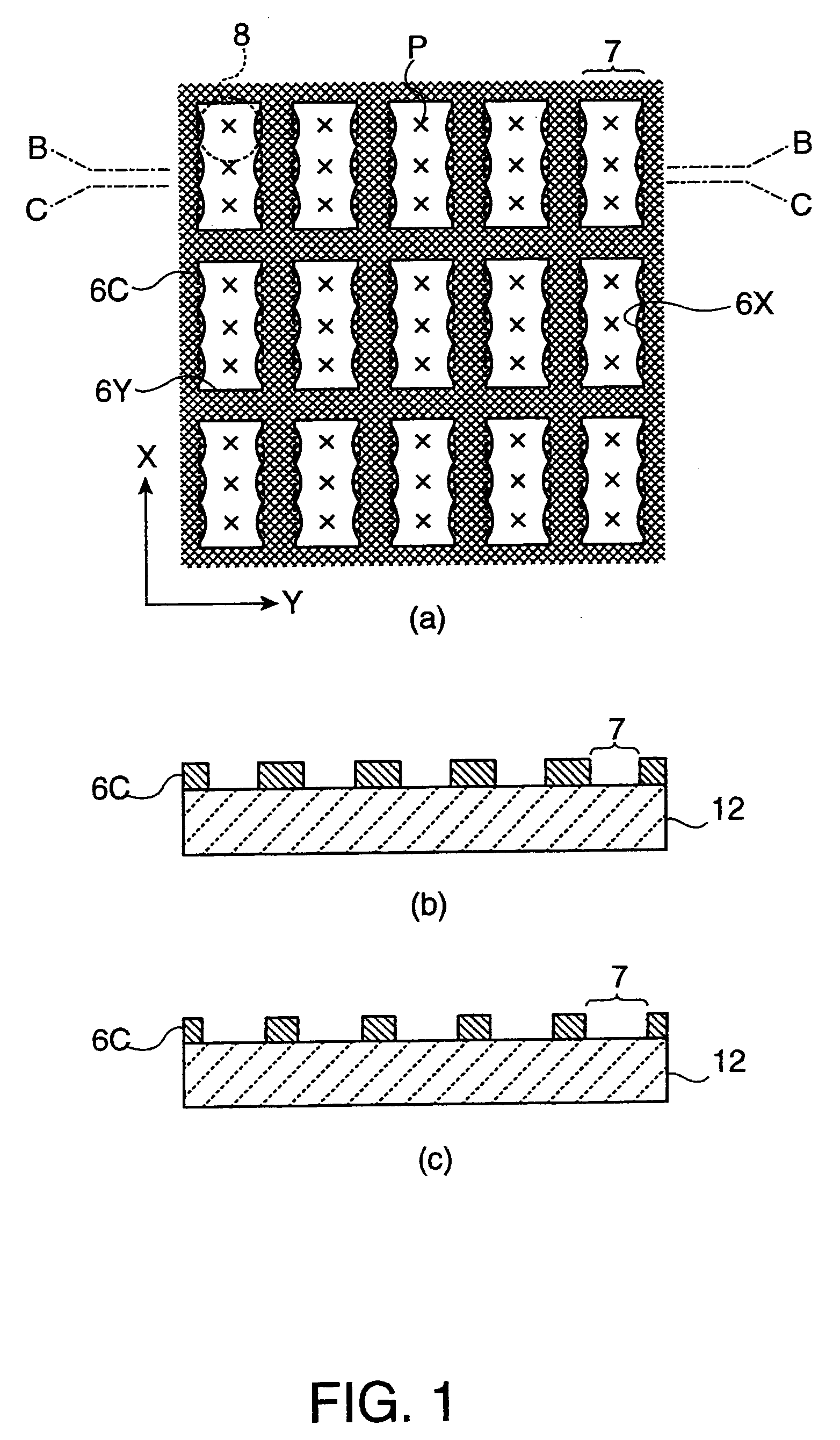

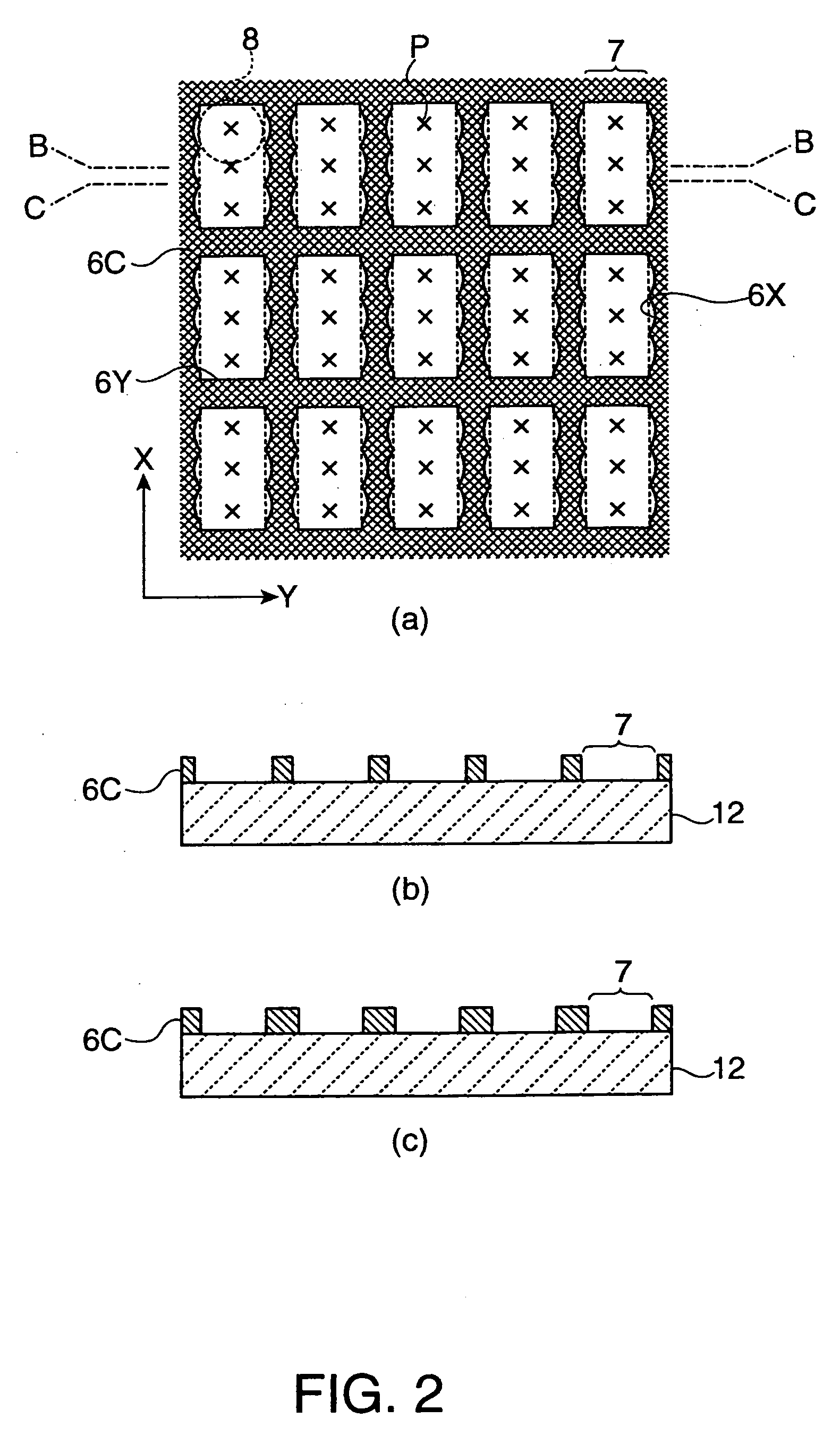

Method for disposing material by droplet ejection, display device, method for manufacturing display device, and electronic apparatus

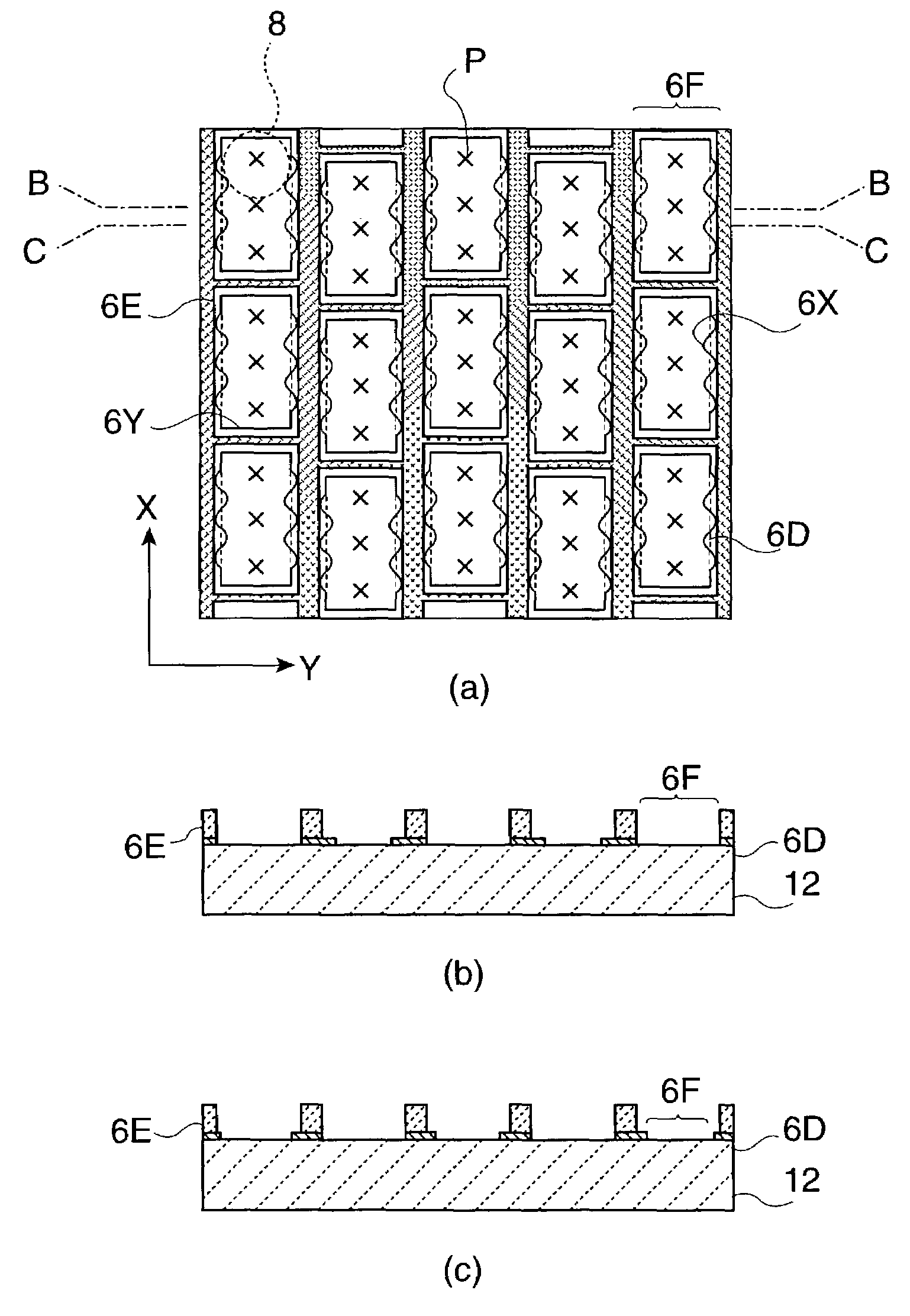

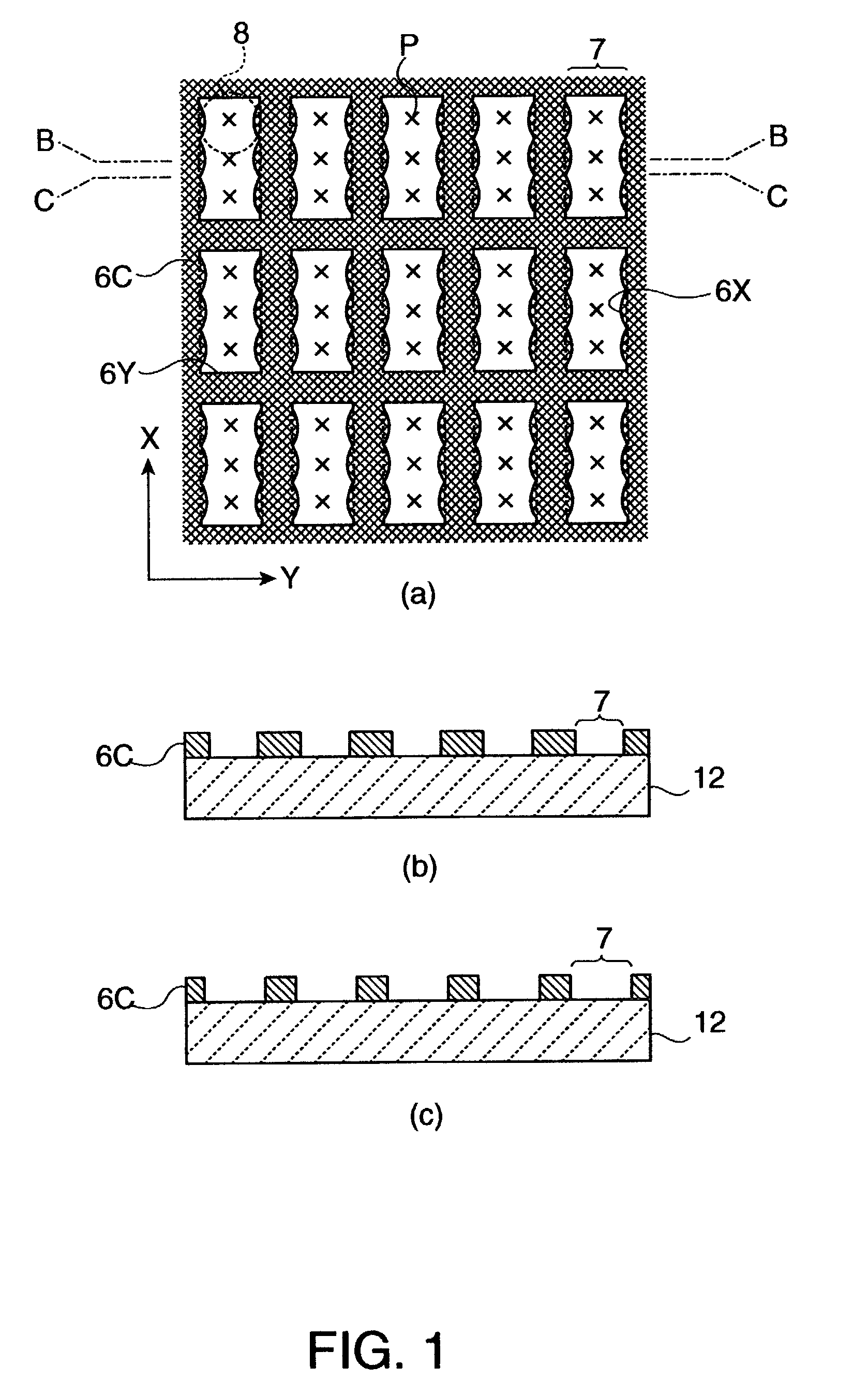

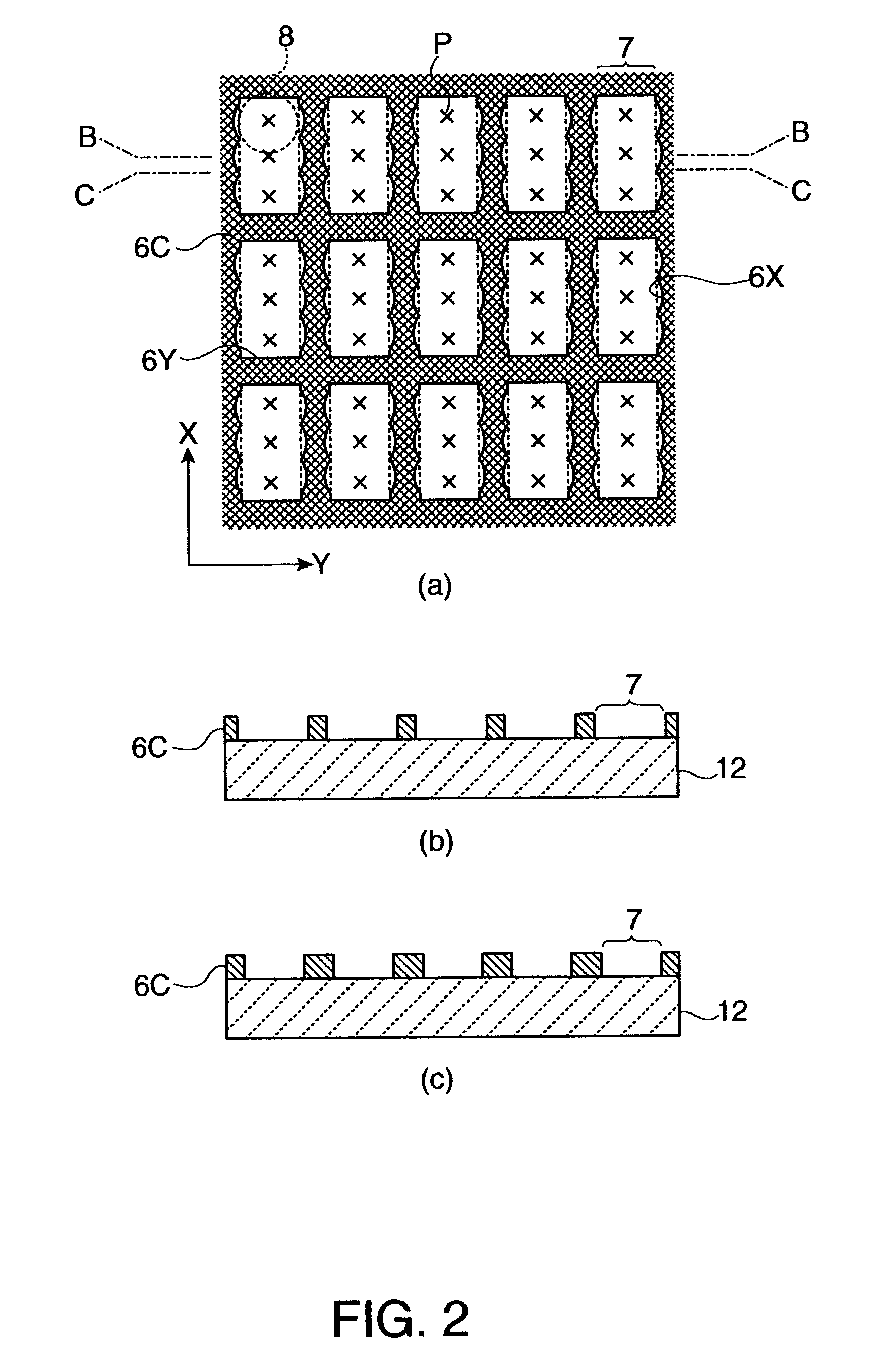

InactiveUS7459322B2Reduce widthSecure marginOptical filtersElectroluminescent light sourcesDisplay deviceEngineering

The invention provides a method for suppressing insufficient spread of droplets or mixing of the droplets in neighboring regions when a liquid material is disposed in the regions on a substrate by ejecting the droplets composed of the liquid material. In addition, for a display device, the structure in which insufficient spread of droplets or mixing of the droplets in neighboring regions can be suppressed and the manufacturing method therefor are provided. To accomplish the above, substantially square regions can be formed by a partition provided on a substrate. In each region, among internal surfaces and of the partition surrounding this region, the internal surfaces forming the long sides of the region have irregularities. In addition, the distance between parts of the partition opposing each other with one of regions provided therebetween is increased and decreased along the long side of the region. Furthermore, along the long side of the region, the width of the partition will be increased and decreased.

Owner:SEIKO EPSON CORP

Method for disposing material by droplet ejection, display device, method for manufacturing display device, and electronic apparatus

InactiveUS20090068351A1Suppressing insufficient spreadInsufficient spreadingOptical filtersElectroluminescent light sourcesDisplay deviceEngineering

The invention provides a method for suppressing insufficient spread of droplets or mixing of the droplets in neighboring regions when a liquid material is disposed in the regions on a substrate by ejecting the droplets composed of the liquid material. In addition, for a display device, the structure in which insufficient spread of droplets or mixing of the droplets in neighboring regions can be suppressed and the manufacturing method therefor are provided. To accomplish the above, substantially square regions can be formed by a partition provided on a substrate. In each region, among internal surfaces and of the partition surrounding this region, the internal surfaces forming the long sides of the region have irregularities. In addition, the distance between parts of the partition opposing each other with one of regions provided therebetween is increased and decreased along the long side of the region. Furthermore, along the long side of the region, the width of the partition will be increased and decreased.

Owner:SEIKO EPSON CORP

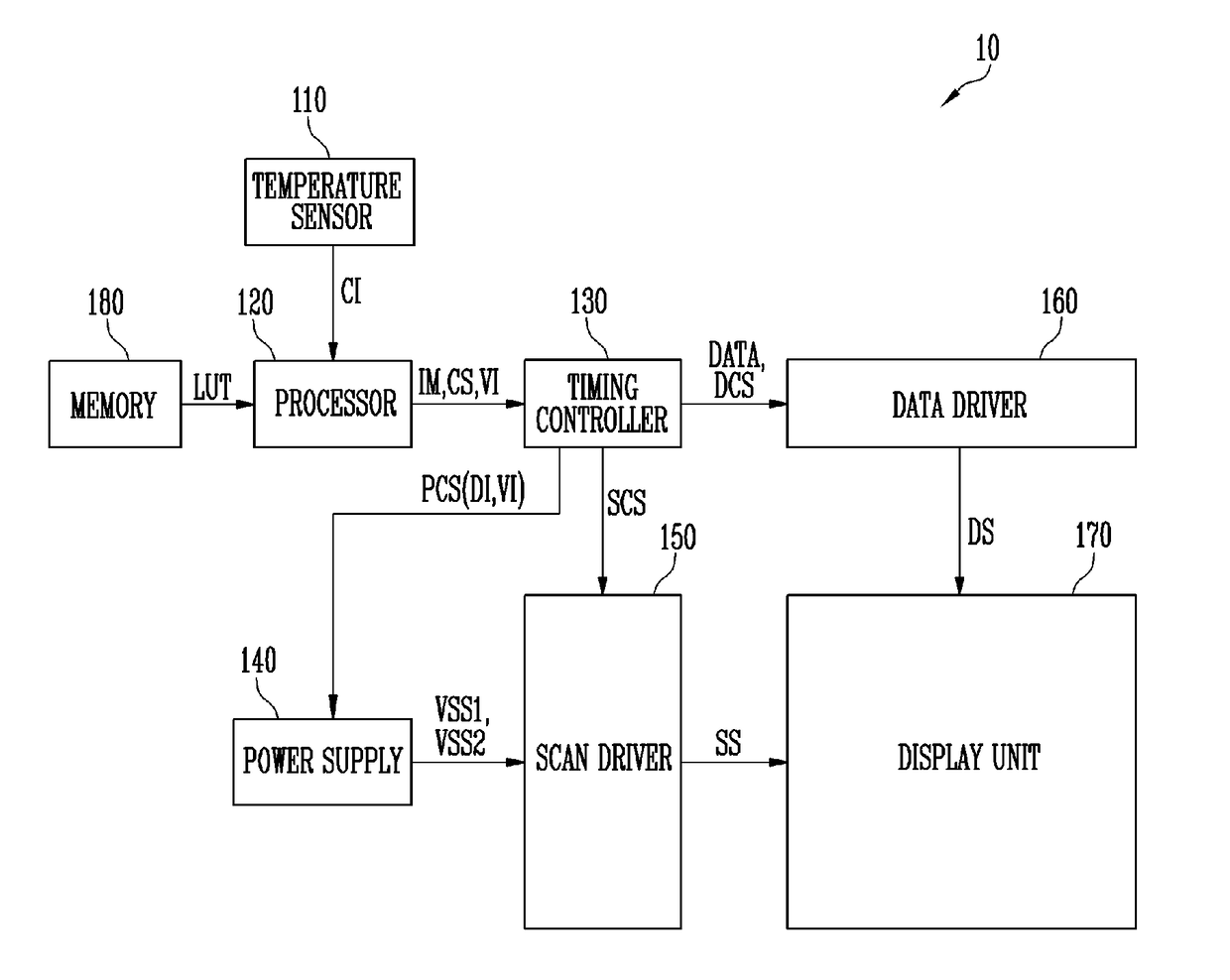

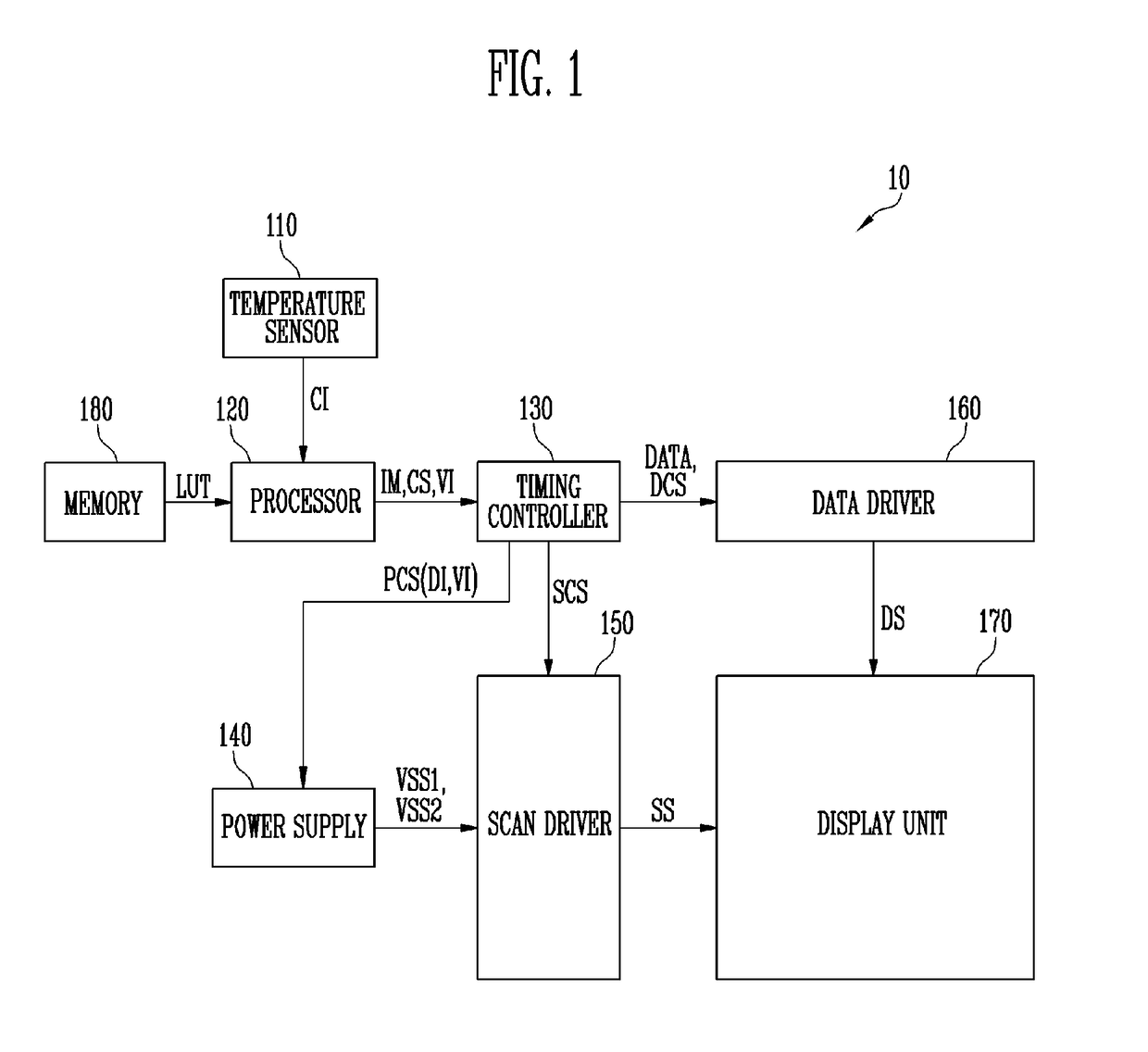

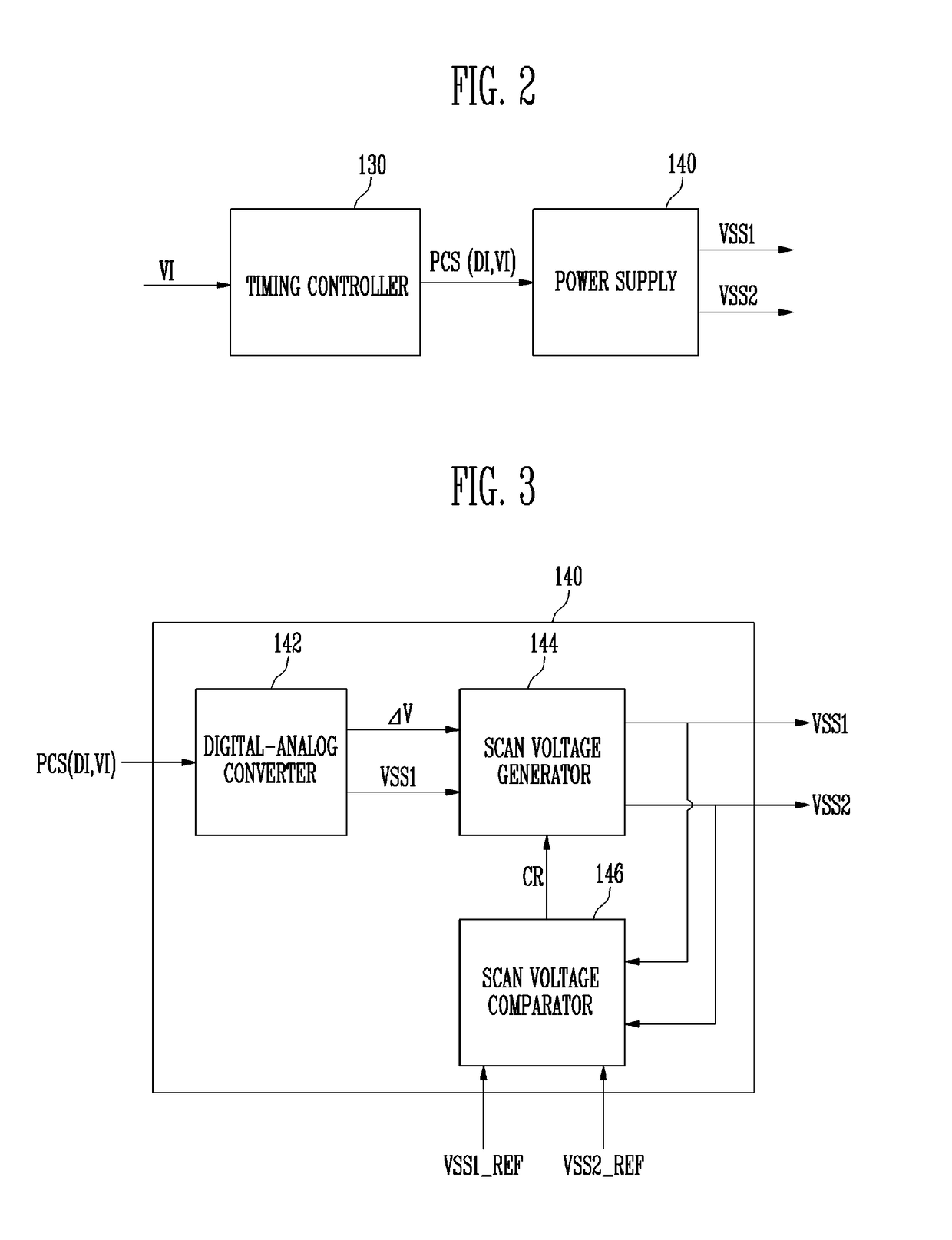

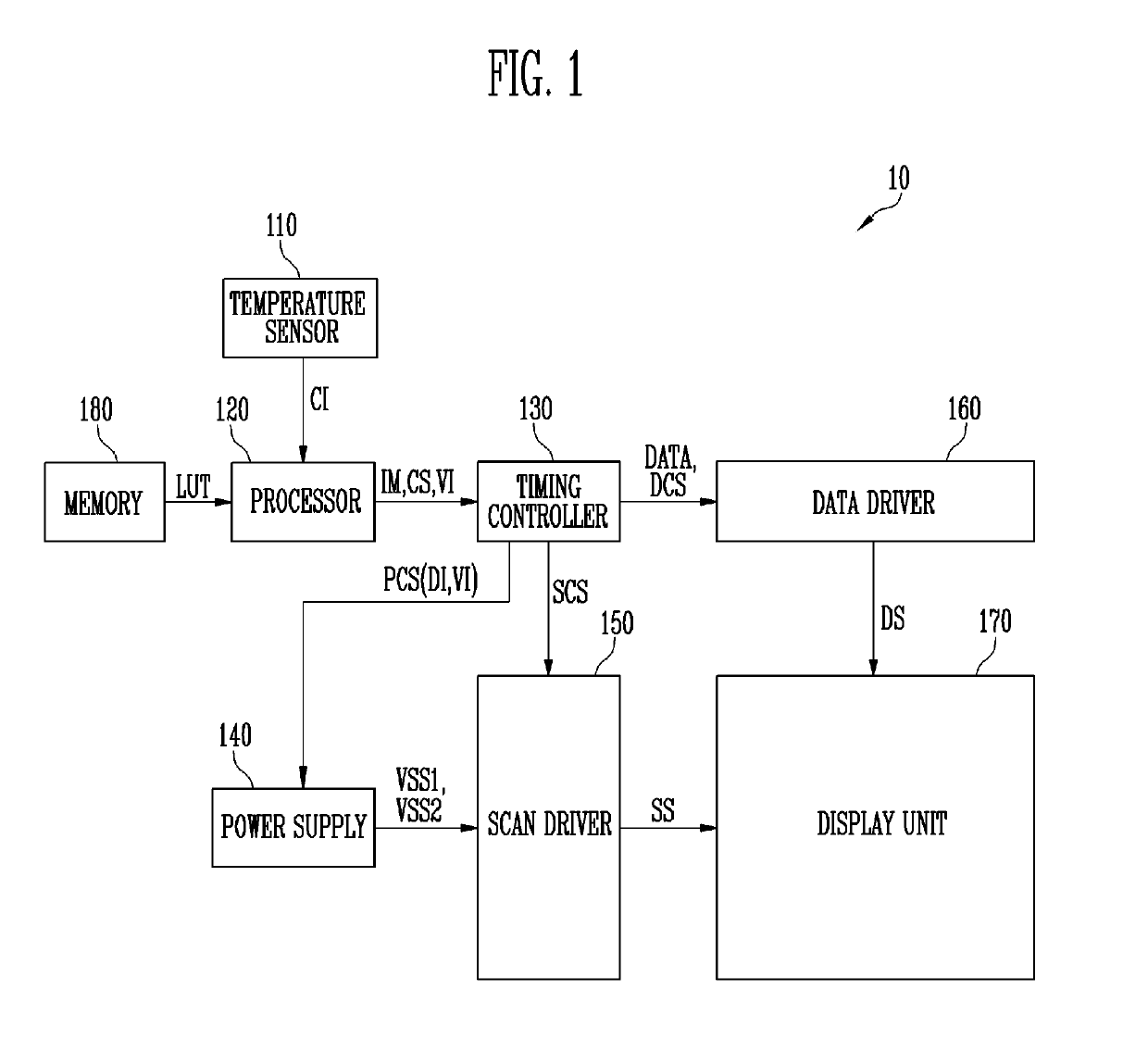

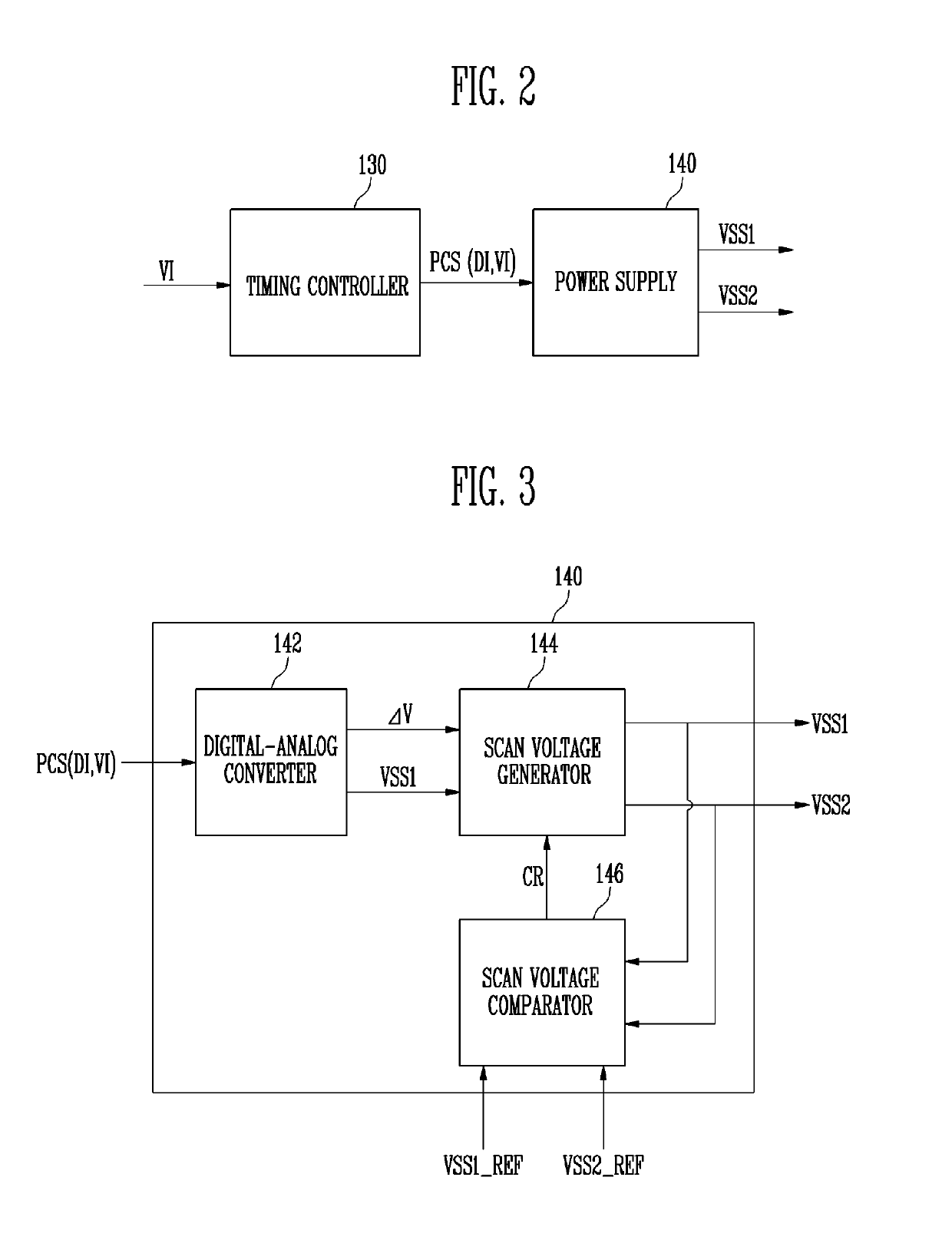

Display device and operating method thereof

A display device includes a display unit including pixels coupled to scan lines and data lines, a data driver which supplies a data signal to pixels through the data lines, a scan driver which generates a scan signal using a first scan voltage and a second scan voltage, and supplying the scan signal to the pixels through the scan lines, a processor which generates first scan voltage information by setting a first scan voltage level, based on an ambient temperature of the display device, a timing controller which generates a power control signal using the first scan voltage information and delta voltage information, and a power supply which generates the first scan voltage and a delta voltage using the power control signal, and generates the second scan voltage by dropping the delta voltage from the first scan voltage.

Owner:SAMSUNG DISPLAY CO LTD

Semiconductor device with buried gates and buried bit lines and method for fabricating the same

InactiveUS8487369B2Reduce resistancePrevent bridgingSolid-state devicesSemiconductor/solid-state device manufacturingBit lineEngineering

A semiconductor device includes: a plurality of first trenches formed inside a plurality of active regions; a plurality of buried gates configured to partially fill insides of the plurality of the first trenches; a plurality of second trenches formed to be extended in a direction crossing the plurality of the buried gates; and a plurality of buried bit lines configured to fill the plurality of the second trenches.

Owner:SK HYNIX INC

Nonvolatile ferroelectric memory device having a multi-bit control function

A nonvolatile ferroelectric memory device having a multi control function can determine a plurality of cell data in a reference timing strobe interval by setting a plurality of sensing voltage levels when cell data are sensed in a sensing critical voltage. In a read mode, a plurality of read data applied from a cell array block are stored in a timing data register array unit through a common data bus unit. In a write mode, a plurality of read data stored in the timing data register array unit or input data applied from a timing data buffer unit are stored in a cell array block through the common data bus unit. Here, since a plurality of sensing voltage levels are set in cell data, a plurality of sensed data bits can be stored in one cell.

Owner:SK HYNIX INC

Printing apparatus and printing method

InactiveUS7978363B2Easy to implementSecure marginDigitally marking record carriersCharacter and pattern recognitionComputer science

Owner:SEIKO EPSON CORP

Semiconductor device with vertical gate and method of manufacturing the same

ActiveUS20150011066A1Small on-resistanceReduce the gate electrode pitchTransistorSemiconductor/solid-state device manufacturingDevice materialEngineering

A gate electrode is formed in a trench reaching a drain region so as to leave a concave portion on the top of the trench. A first insulating film is formed, which fills the concave portion and of which the thickness increases as the distance from an end of the trench increases on the substrate surface on both sides of the trench. First and second source regions are formed in a self-alignment manner by introduction of impurities through the first insulating film.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

Synchronous type semiconductor device for high speed data processing

ActiveUS7681062B2Avoid misinformationReduce widthPulse automatic controlGenerating/distributing signalsPhase differenceChip select

Disclosed is a synchronous semiconductor device including clock generation circuit that frequency divides a clock signal (PCLK) input from an input buffer and generates first and second internal clock signals having a predetermined phase difference from first and second frequency-divided clock signals of different phases, respectively, a first input circuit control unit that receives a chip select signal and samples the chip select signal in synchronization with the clock signal, second and third input circuit control units that sample an output of the first input circuit control unit in synchronization with the first and second internal clock signals, respectively, and first and second input circuits that receive a result of a logic operation between the output of the first input control unit and an output of the second input circuit control unit and a result of a logic operation between the output of the first input circuit control unit and an output of the third input circuit control unit as input enable signals, respectively, and sample an externally input signal in synchronization with the first and second internal clock signals, respectively based on enabling instructed by the input enable signals.

Owner:MICRON TECH INC

Synchronous semiconductor device having delay locked loop for latency control

A synchronous semiconductor device includes an internal command generation unit configured to generate an internal command corresponding to a source command, a delay locked loop configured to delay a source clock by a first delay time required for delay-locking to generate a delay locked clock, a delay time determination unit configured to determine a second delay time for delay-locking the internal command using the source clock, the second delay time being determined by reflecting a third delay time generated on a command path, and a latency control unit configured to shift the internal command by a shifting period, in which the second delay time is reflected, in response to the delay locked clock.

Owner:SK HYNIX INC

Semiconductor device

InactiveUS20080079138A1Reduce manufacturing costSecure marginSemiconductor/solid-state device detailsPrinted circuit aspectsSemiconductor chipEngineering

A semiconductor device that mounts a semiconductor chip in a multilayer substrate, including, inner layer conductive patterns formed in the multilayer substrate; extending conductive portions formed to extend on inner layer conductive patterns in the thickness direction, in the chip mounting area into which the semiconductor chip is mounted; and a cutout portion that is formed by cutting the multilayer substrate, and into which the semiconductor chip is contained, in the chip mounting area. And, in the cutout portion, the underside surface of the semiconductor chip and the inner layer conductive patterns are connected via the extending conductive portions at a same potential.

Owner:LAPIS SEMICON CO LTD

Hybrid vehicle and method of controlling the same

ActiveUS10005450B2Reduce impactIncrease resistanceHybrid vehiclesElectrical controlParticulatesElectric machine

A hybrid vehicle includes an internal combustion engine, a filter, an electrical storage device, a rotating electric machine, and a controller. The filter is configured to trap particulate matter in exhaust gas of the internal combustion engine. The rotating electric machine is configured to generate electric power using power from the internal combustion engine so as to charge the electrical storage device, and drive the internal combustion engine using electric power from the electrical storage device. The controller is configured to control the internal combustion engine and the rotating electric machine, so as to warm up the electrical storage device when regeneration control needs to be performed and when the temperature of the electrical storage device is lower than a reference value. The regeneration control is control for raising the temperature of the filter to a predetermined temperature so as to burn the particulate matter. The controller may be configured to execute the regeneration control when the temperature of the electrical storage device exceeds the reference value.

Owner:TOYOTA JIDOSHA KK

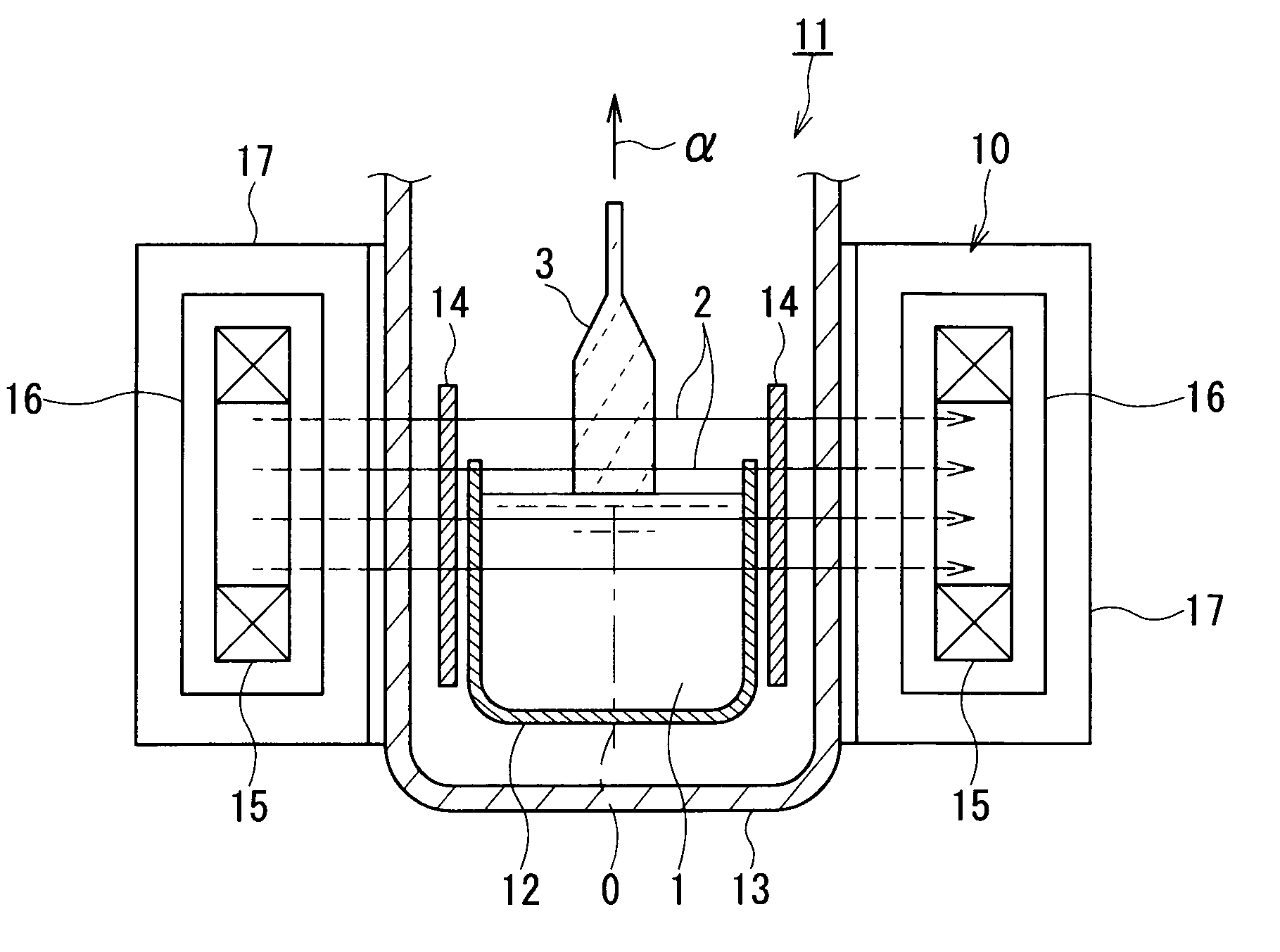

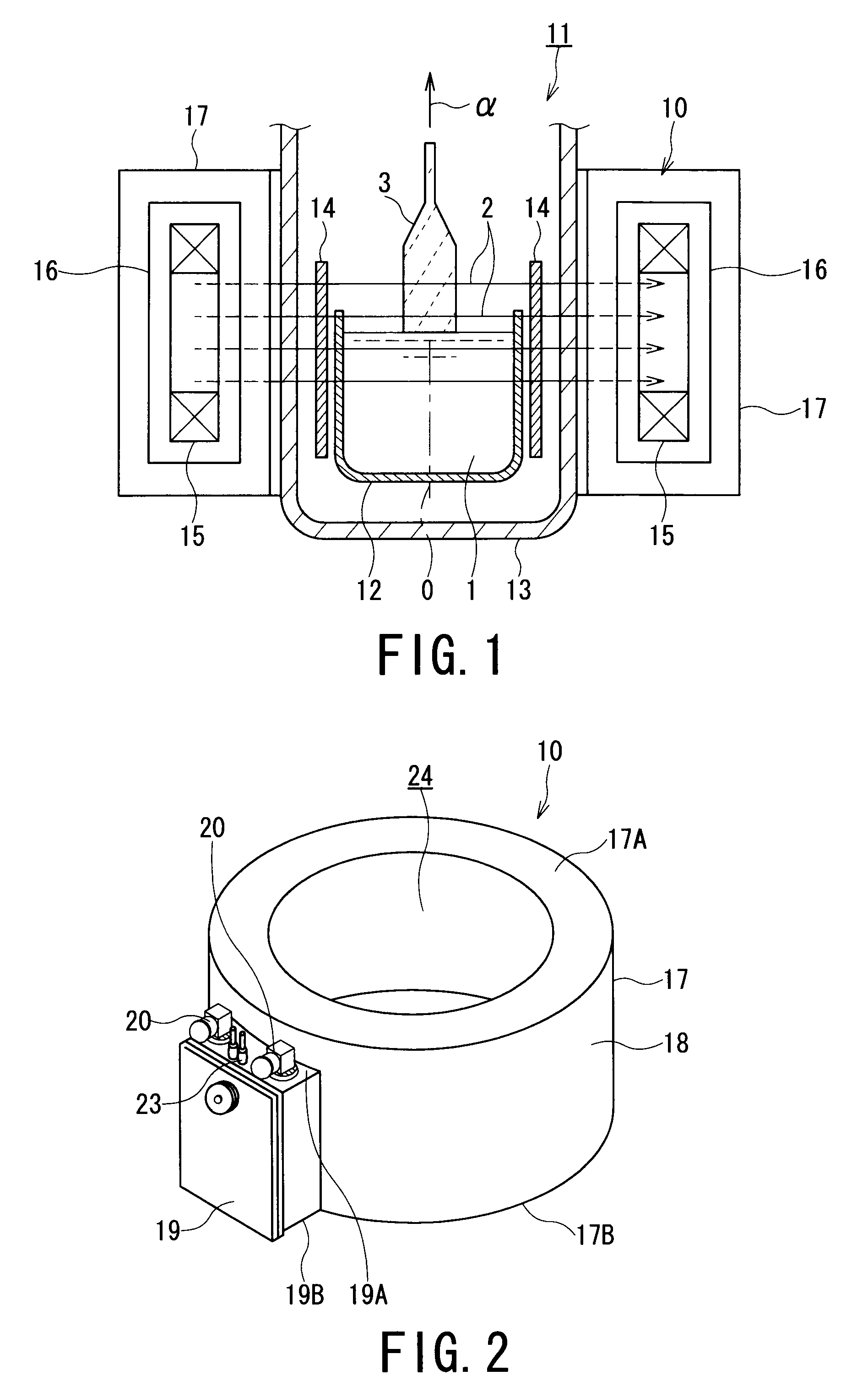

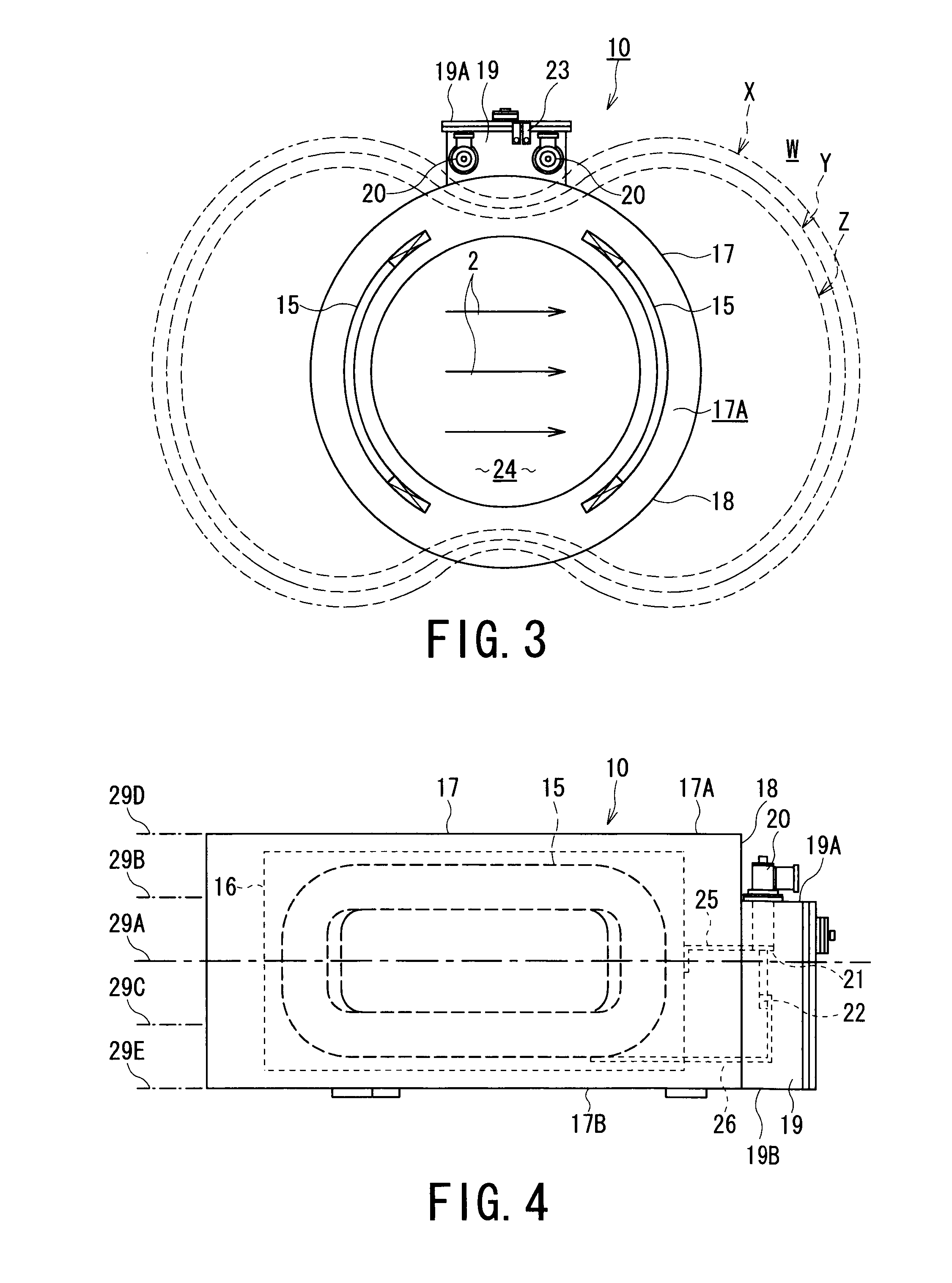

Superconducting magnet device for single crystal pulling apparatus

ActiveUS20110077161A1Suppress interferenceImprove workabilityPolycrystalline material growthSuperconductors/hyperconductorsCrucibleSuperconducting Coils

A superconducting magnet device for a single crystal pulling apparatus is arranged outside a pulling furnace containing a crucible for melting a single crystal material therein so as to apply a magnetic field to the melted single crystal material. The superconducting magnet device for a single crystal pulling apparatus includes a cryostat containing a superconducting coil therein, and a refrigerator port arranged on the outer circumferential surface of the cryostat and provided with a cryogenic refrigerator that cools the superconducting coil. The cryogenic refrigerator is provided in a region of the outer surface region of the cryostat at which the intensity of the magnetic field generated by the superconducting coil is weak.

Owner:KK TOSHIBA

Semiconductor device with buried bit lines and method for fabricating the same

ActiveUS8507342B2Stable characteristicsEnsure uniformitySolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceSemiconductor

A semiconductor device includes active regions separated by a trench, a separation layer dividing the trench, and buried bit lines buried in the trench with the separation layer interposed between the buried bit lines.

Owner:SK HYNIX INC

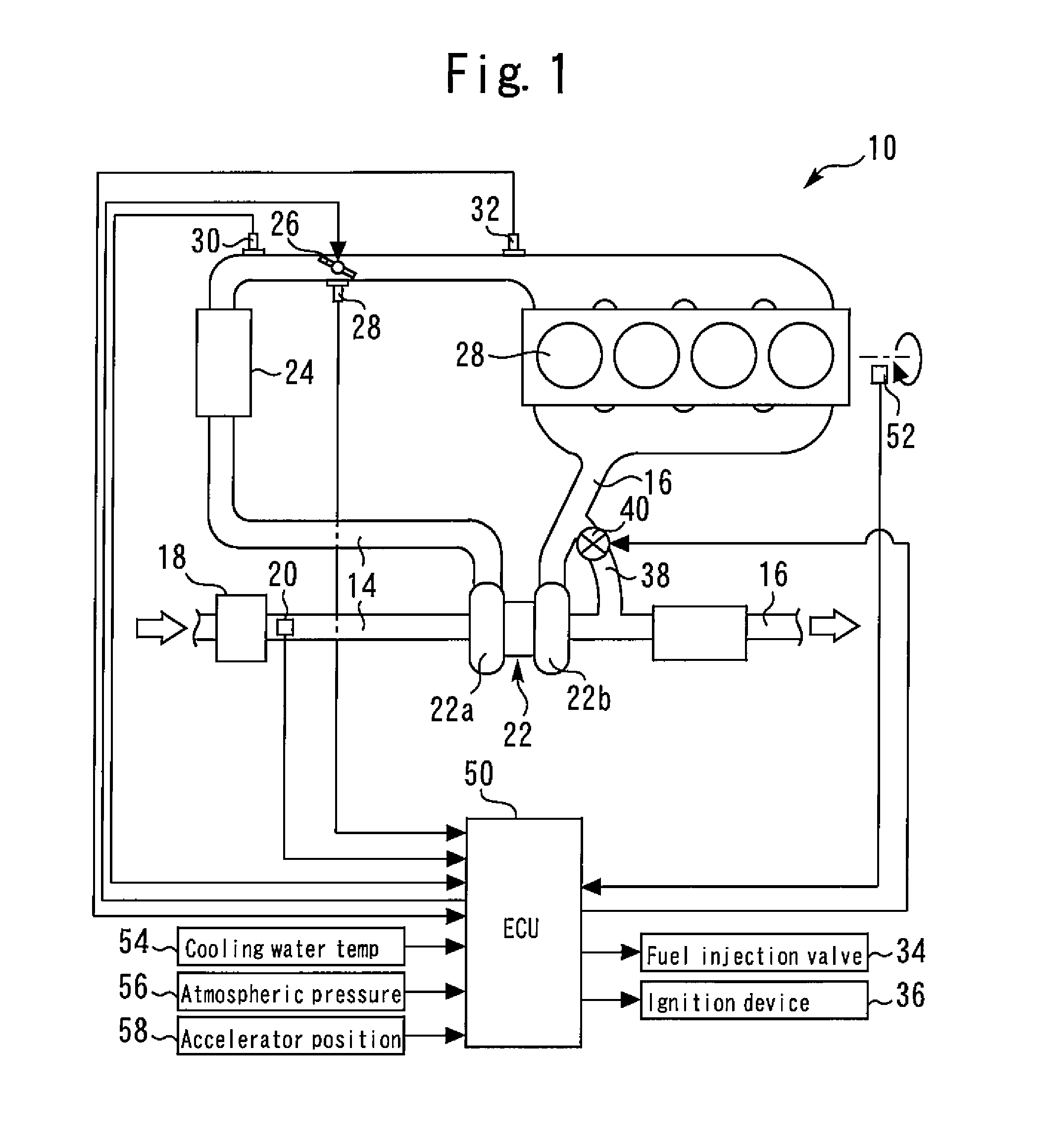

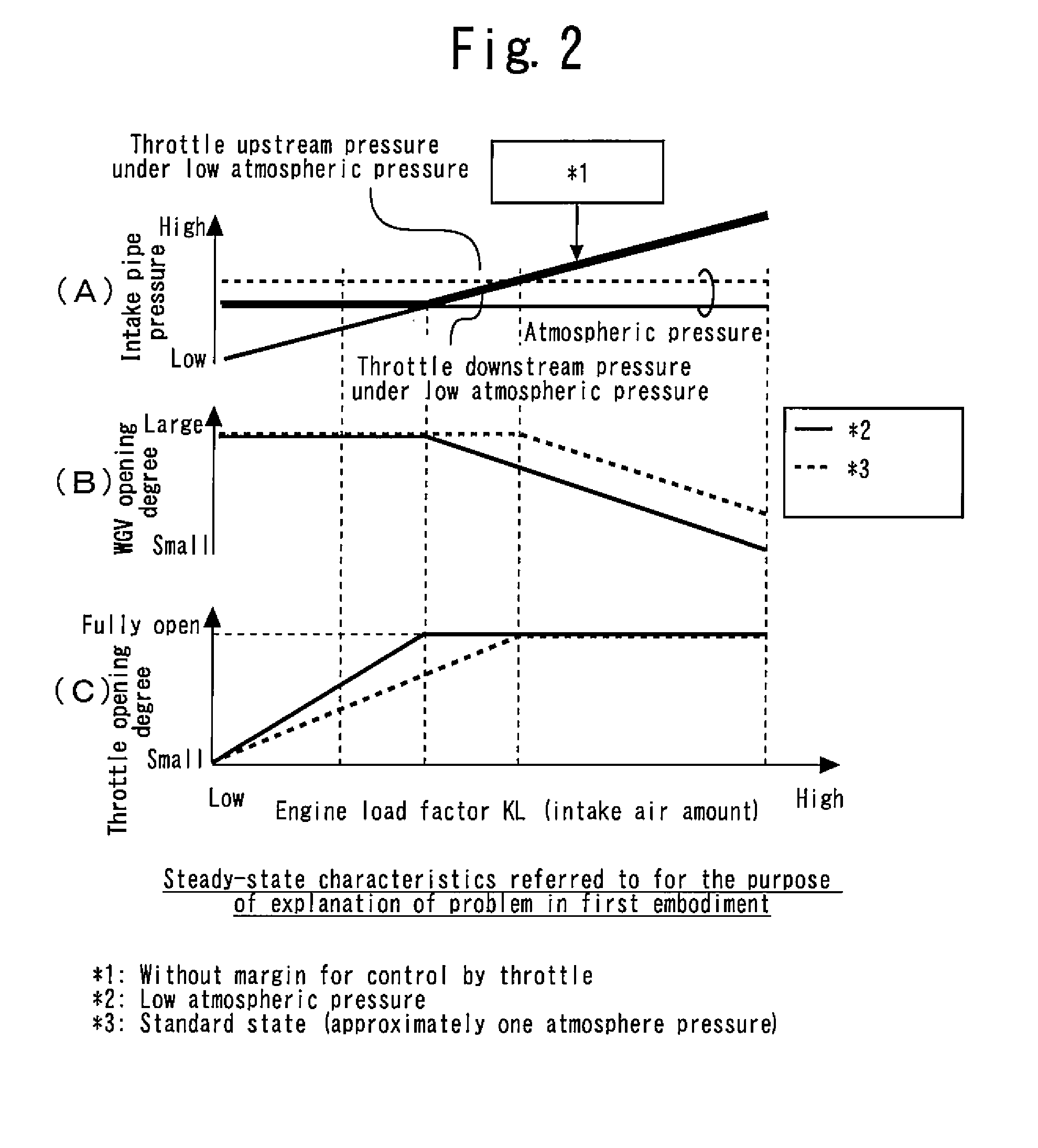

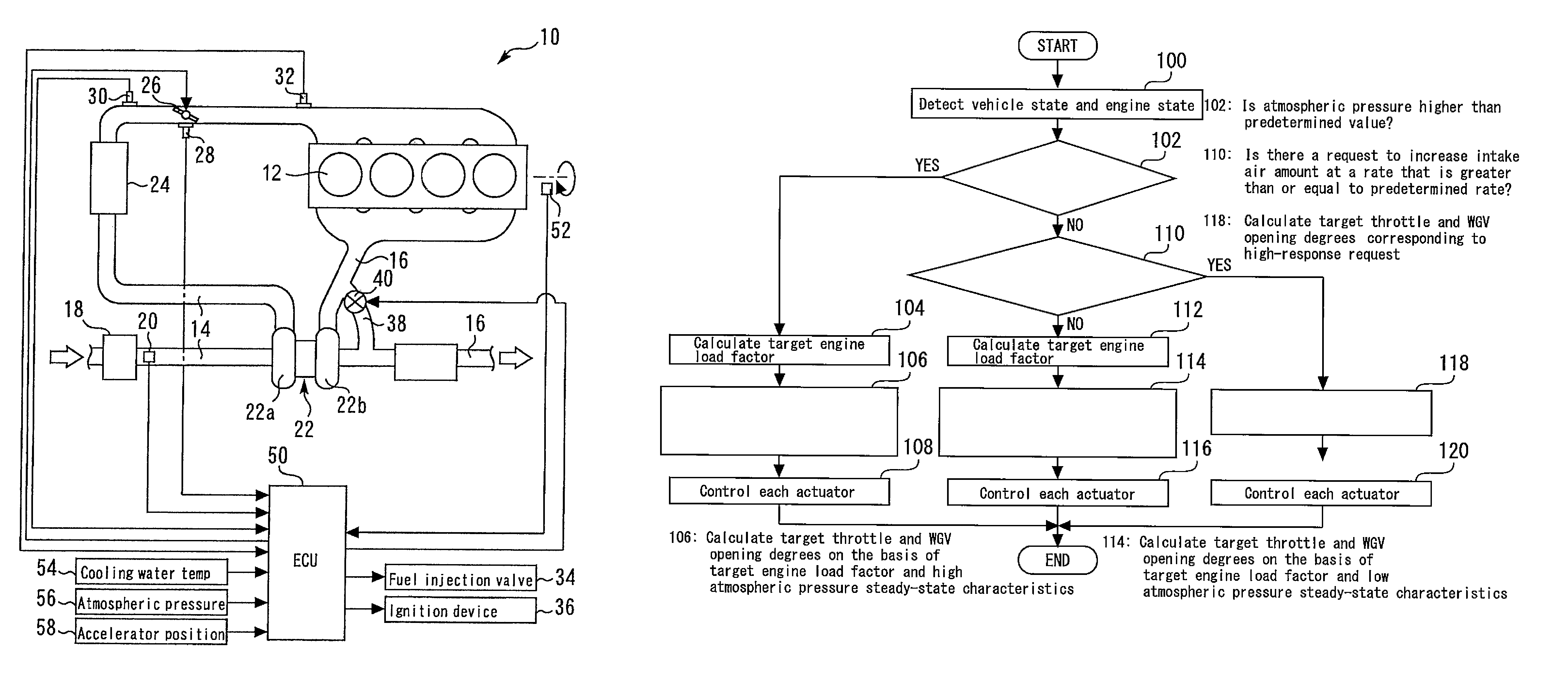

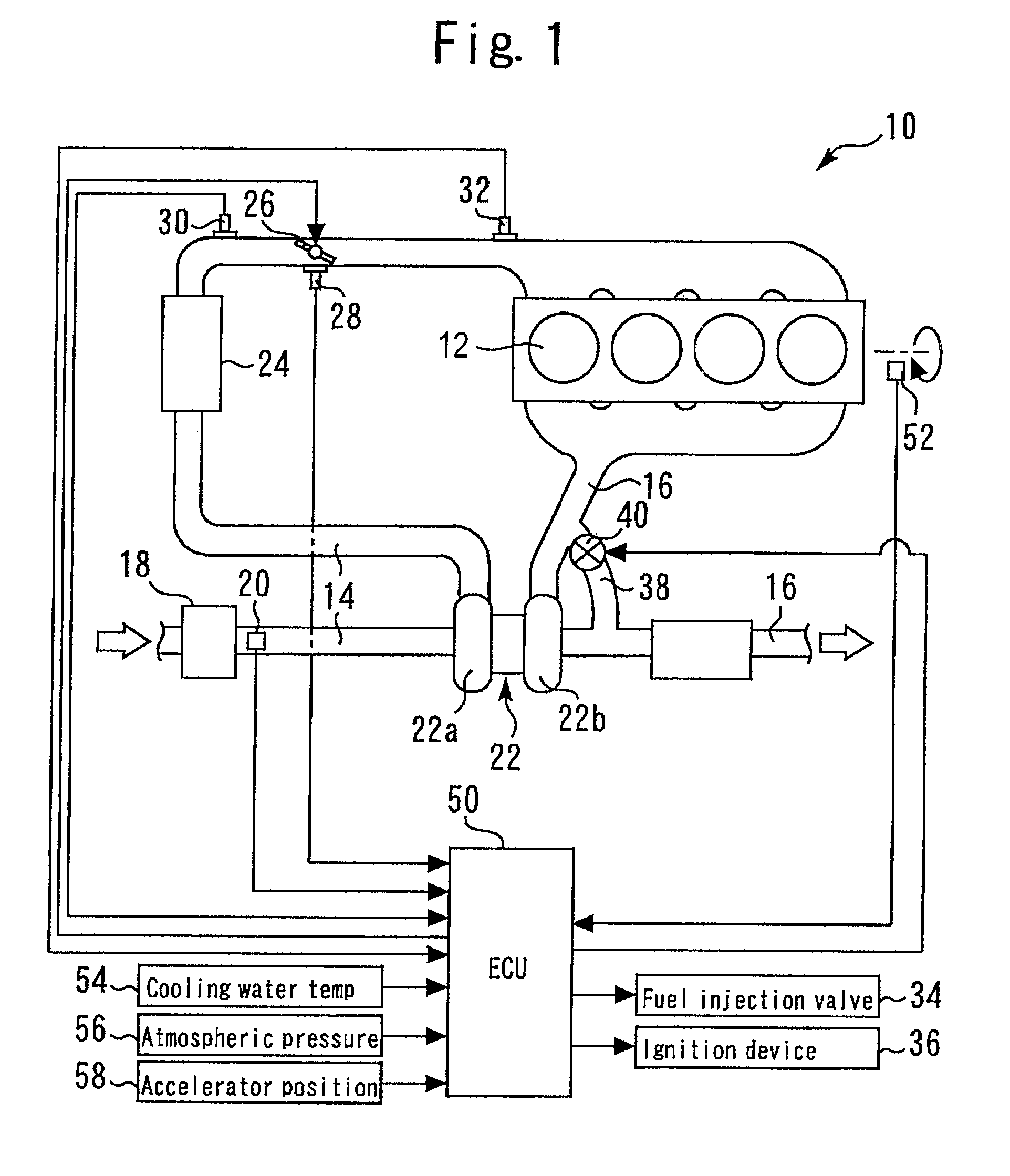

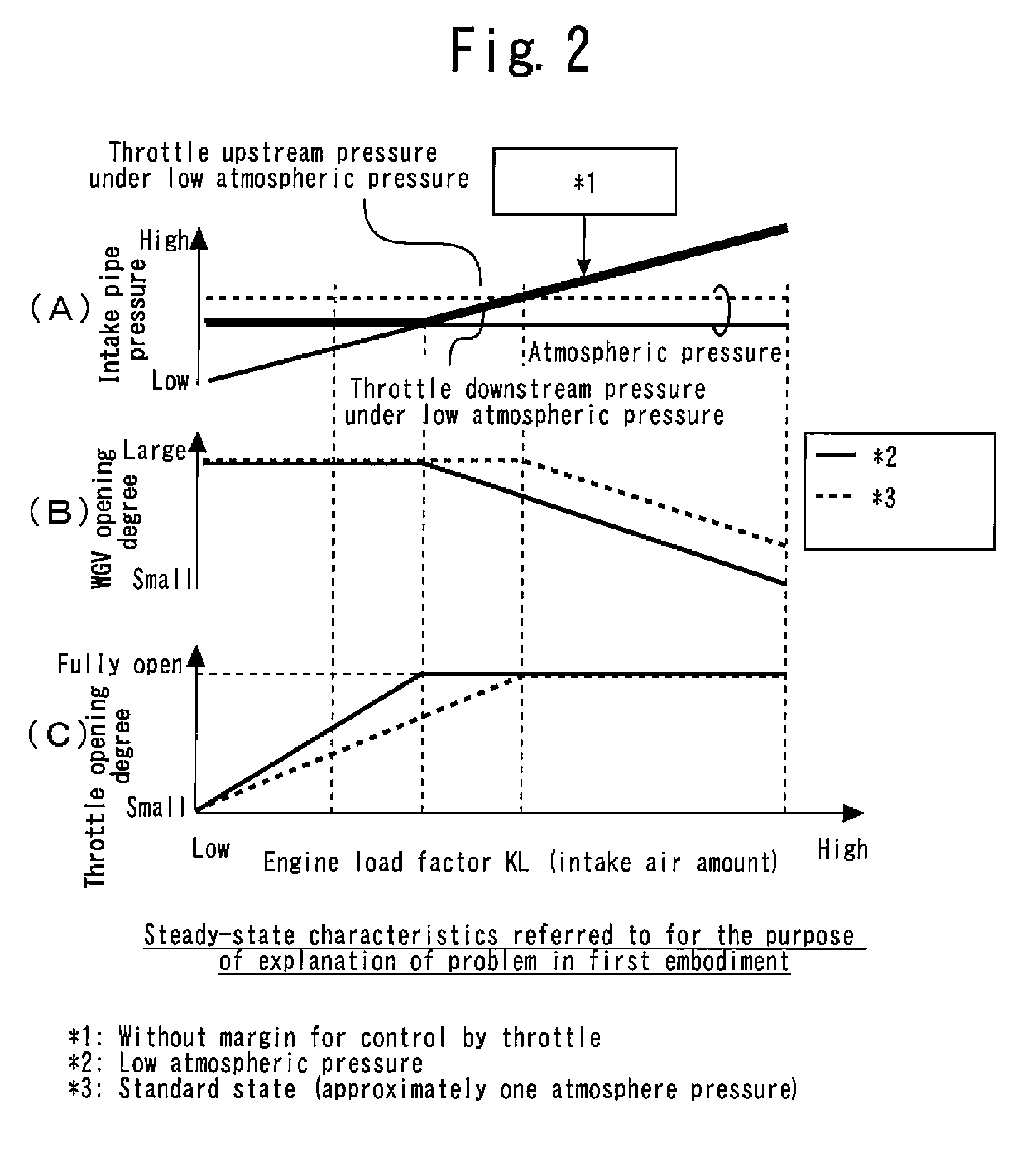

Control apparatus for internal combustion engine

ActiveUS20150013331A1Improve responsivenessLarge marginInternal combustion piston enginesEngine controllersExternal combustion engineHigh-pressure area

A control apparatus for an internal combustion engine of the present invention switches a steady-state characteristic that defines a relation between an engine load factor and a throttle opening degree between a high atmospheric pressure steady-state characteristic and a low atmospheric pressure steady-state characteristic in accordance with whether or not the atmospheric pressure is higher than a predetermined value. According to the low atmospheric pressure steady-state characteristic, a throttle opening degree corresponding to an identical engine load factor is set to a smaller value compared to the high atmospheric pressure steady-state characteristic in a medium load region, and the throttle opening degree is set so as to increase as the engine load factor increases towards a full load in a region on the side of a higher load factor than the medium load region.

Owner:TOYOTA JIDOSHA KK

Control apparatus for internal combustion engine

ActiveUS9416722B2Improve responsivenessLow levelInternal combustion piston enginesEngine controllersAtmospheric airHigh-pressure area

A control apparatus for an internal combustion engine of the present invention switches a steady-state characteristic that defines a relation between an engine load factor and a throttle opening degree between a high atmospheric pressure steady-state characteristic and a low atmospheric pressure steady-state characteristic in accordance with whether or not the atmospheric pressure is higher than a predetermined value. According to the low atmospheric pressure steady-state characteristic, a throttle opening degree corresponding to an identical engine load factor is set to a smaller value compared to the high atmospheric pressure steady-state characteristic in a medium load region, and the throttle opening degree is set so as to increase as the engine load factor increases towards a full load in a region on the side of a higher load factor than the medium load region.

Owner:TOYOTA JIDOSHA KK

Photo mask

InactiveUS20060234169A1Prevent crashSecure marginOriginals for photomechanical treatmentSilver halide emulsionsDevice materialSemiconductor

A photo mask comprises a H-type light-shield pattern. In an exposure process, a photo mask is used to form a STAR (Step Asymmetry Recess) gate region, thereby stably securing a storage node contact region and improving a refresh characteristic of a semiconductor device.

Owner:SK HYNIX INC

Semiconductor device

ActiveUS10379947B2Secure marginDigital storageRedundant data error correctionControl circuitComputer science

Owner:SK HYNIX INC

Semiconductor memory device and method of operating the same

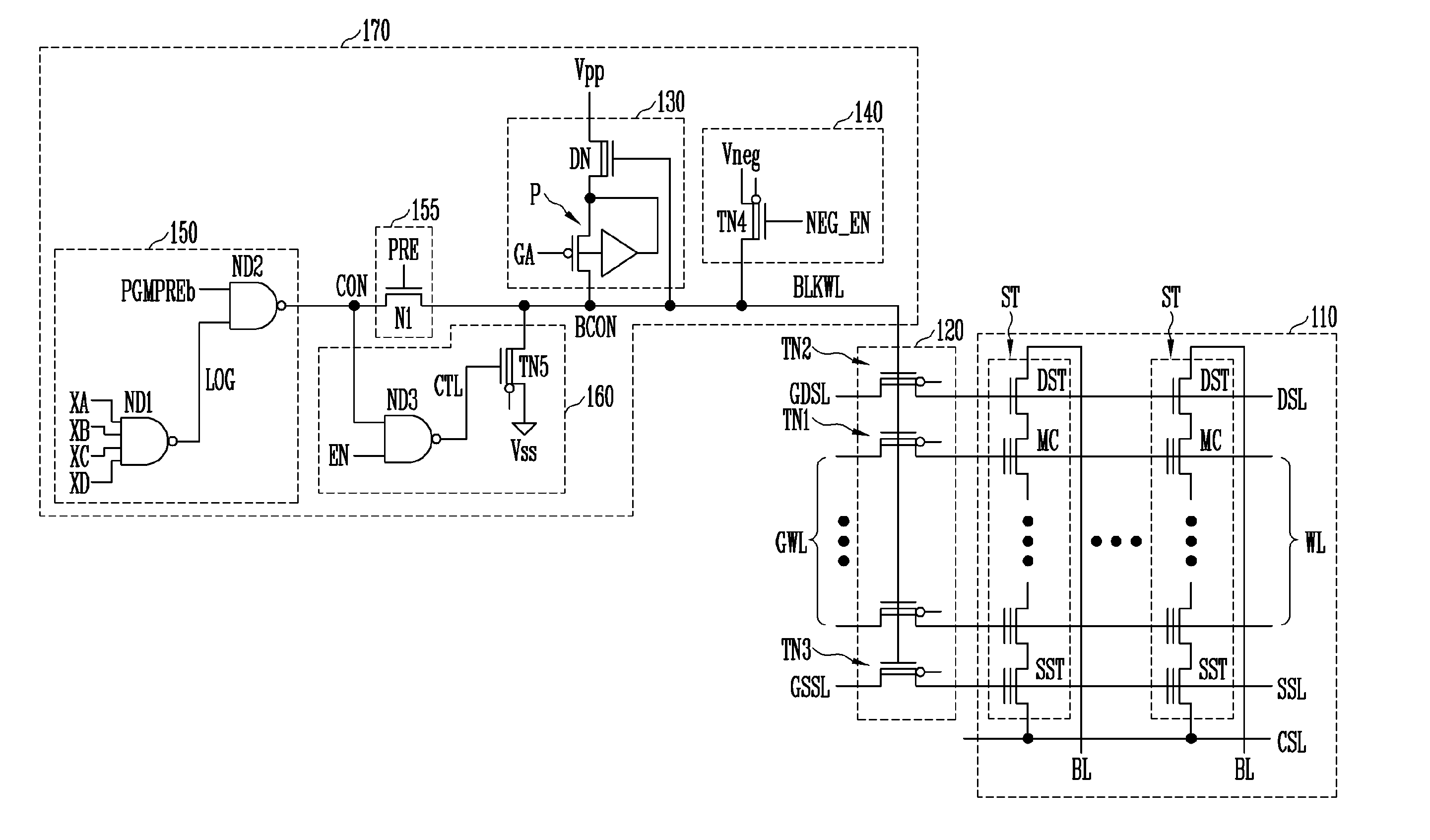

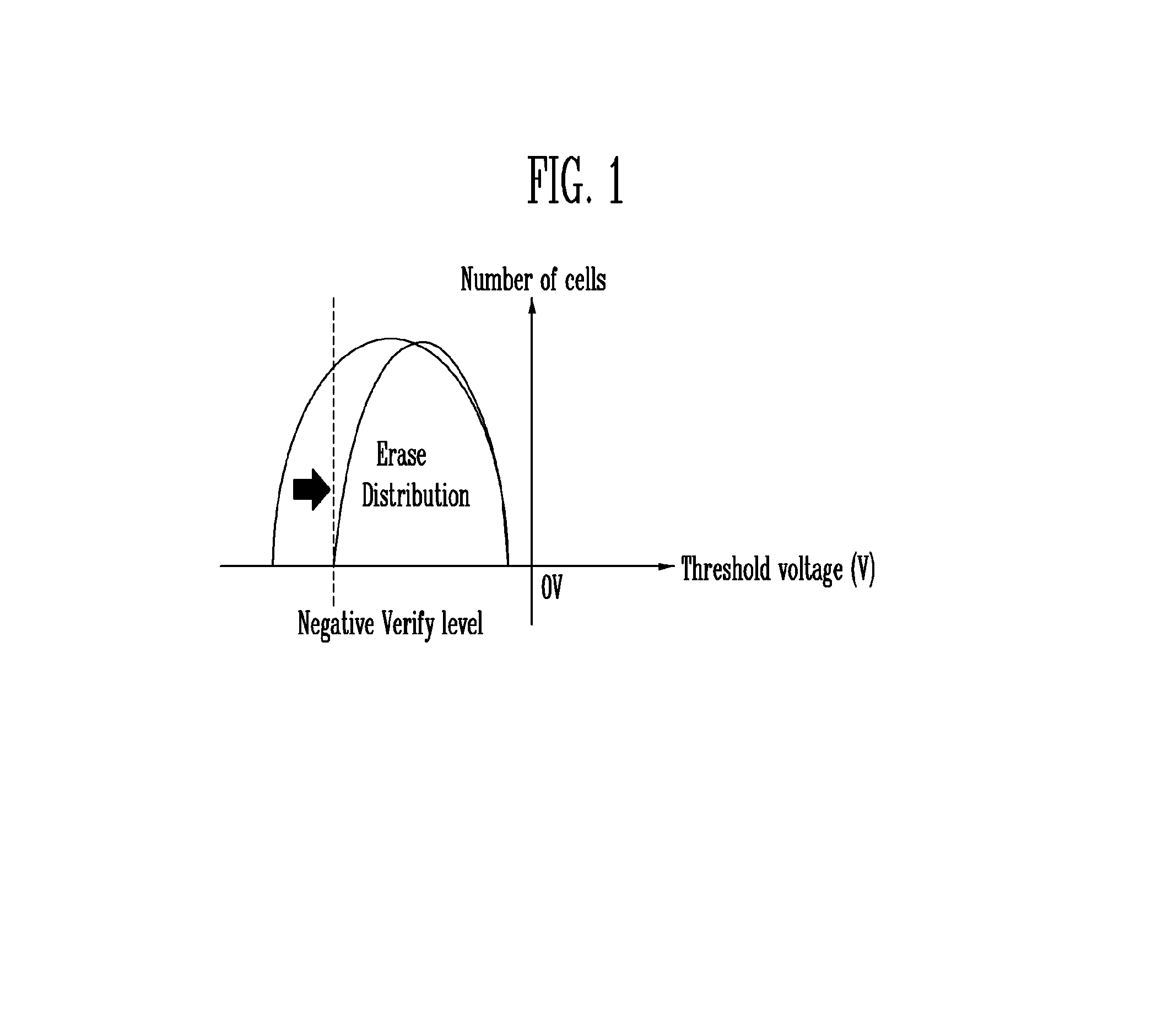

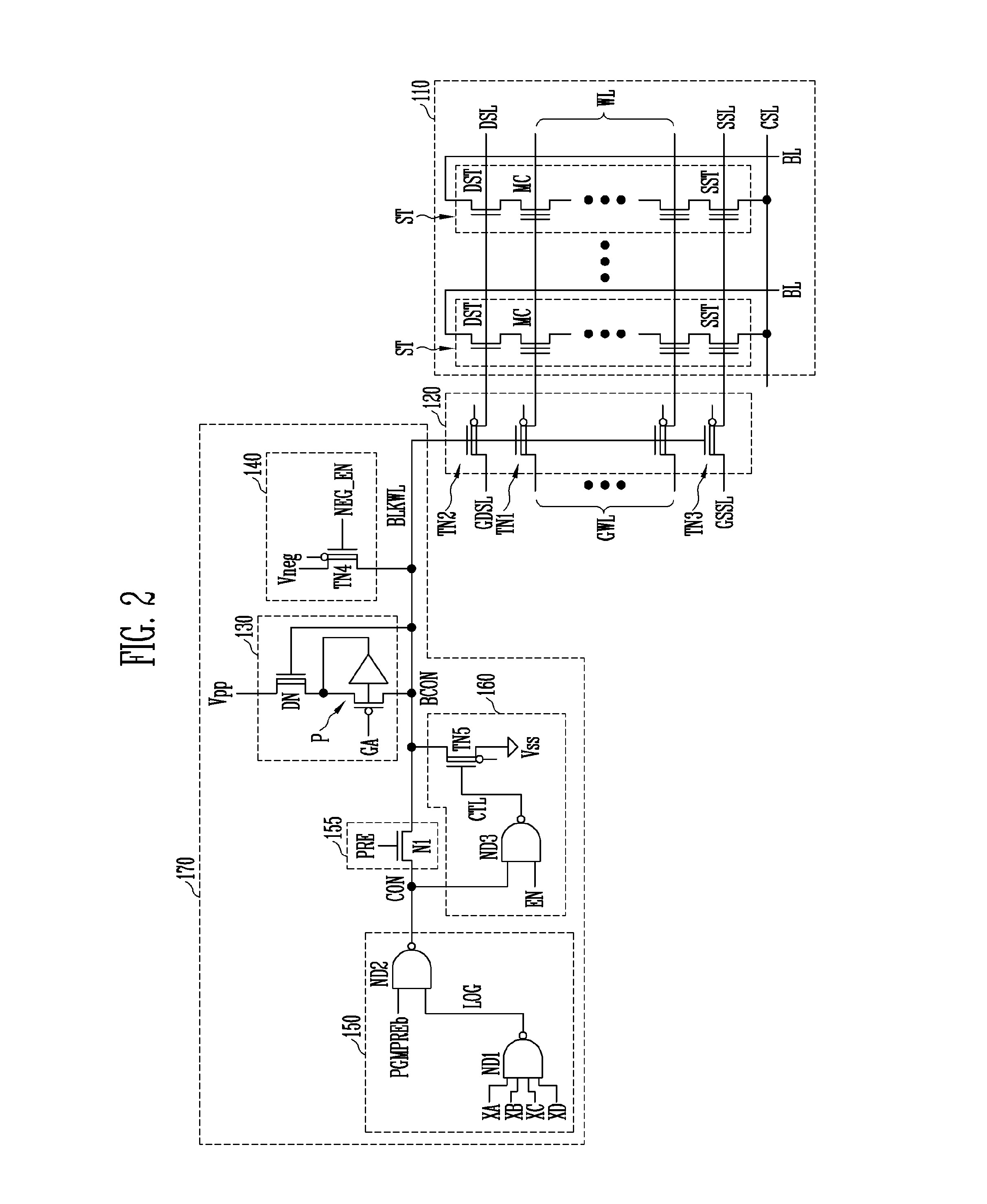

ActiveUS8520445B2Narrow distributionSecure marginRead-only memoriesDigital storageEngineeringSemiconductor

A memory device includes a block switch for transferring operating voltages, supplied to global lines, to local lines coupled to a memory cell array in response to the voltage level of a block selection signal and a negative voltage transfer circuit for transferring a negative voltage as the block selection signal in order to couple the global lines and the local lines when the operating voltage has a negative level and to disconnect the global lines and the local lines from each other when the block selection signal is disabled.

Owner:SK HYNIX INC

Display device controlling scan voltage level according to ambient temperature and operating method thereof

A display device includes a display unit including pixels coupled to scan lines and data lines, a data driver which supplies a data signal to pixels through the data lines, a scan driver which generates a scan signal using a first scan voltage and a second scan voltage, and supplying the scan signal to the pixels through the scan lines, a processor which generates first scan voltage information by setting a first scan voltage level, based on an ambient temperature of the display device, a timing controller which generates a power control signal using the first scan voltage information and delta voltage information, and a power supply which generates the first scan voltage and a delta voltage using the power control signal, and generates the second scan voltage by dropping the delta voltage from the first scan voltage.

Owner:SAMSUNG DISPLAY CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com