Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2769results about "Inspection/indentification of circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

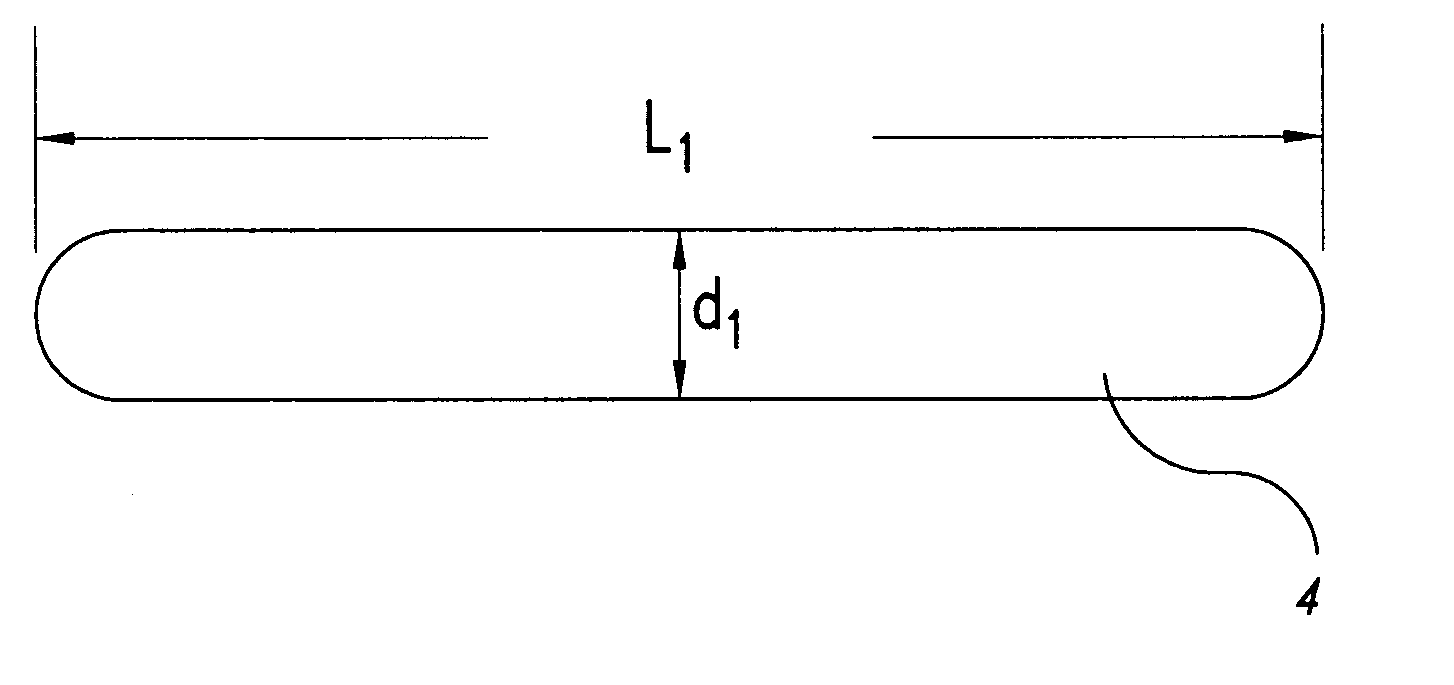

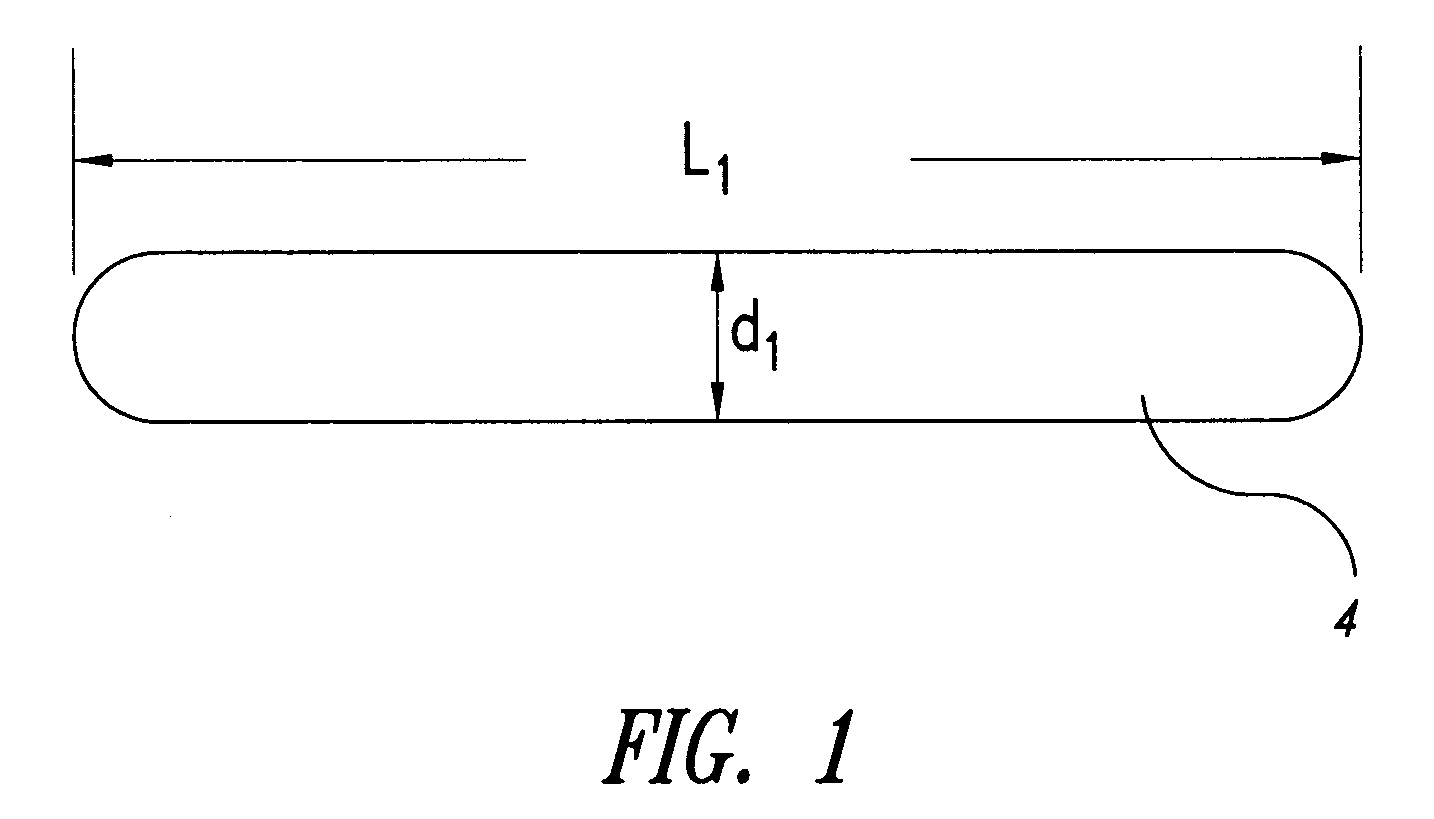

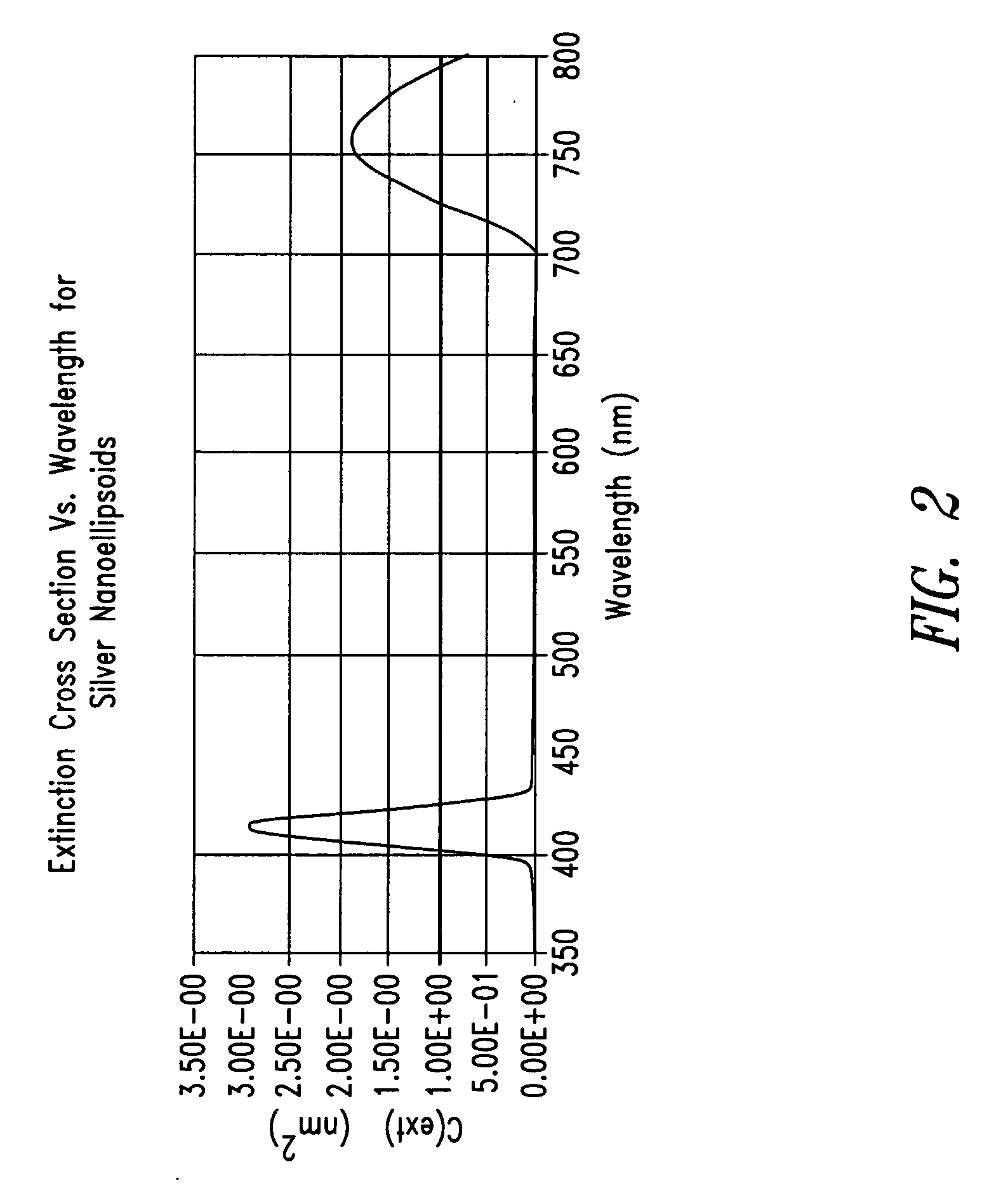

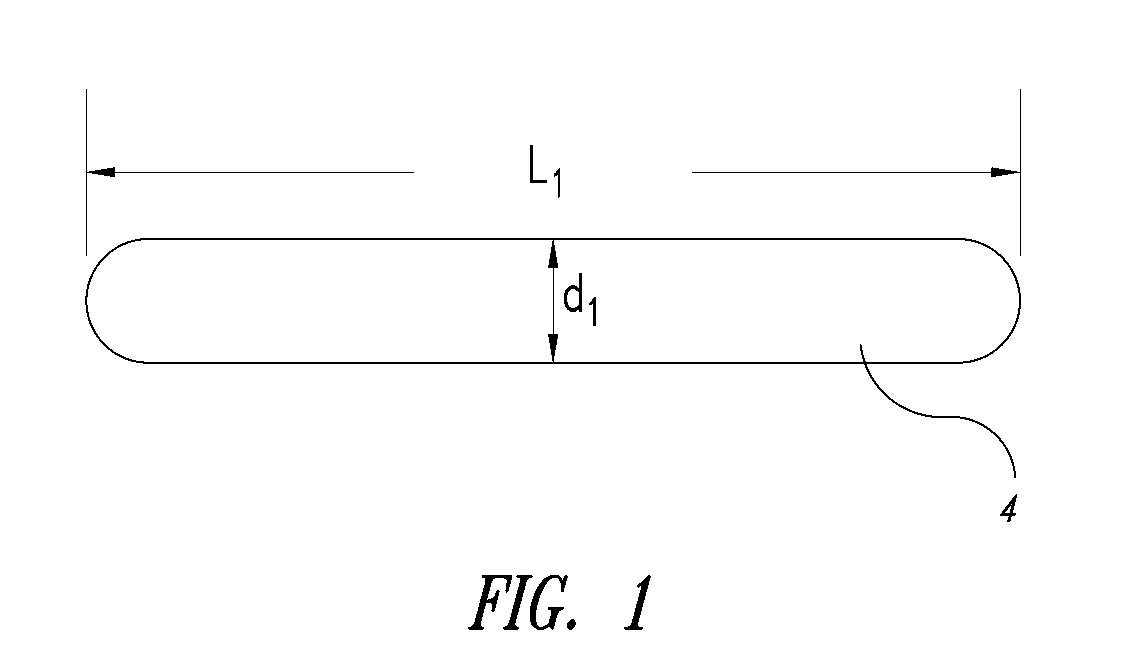

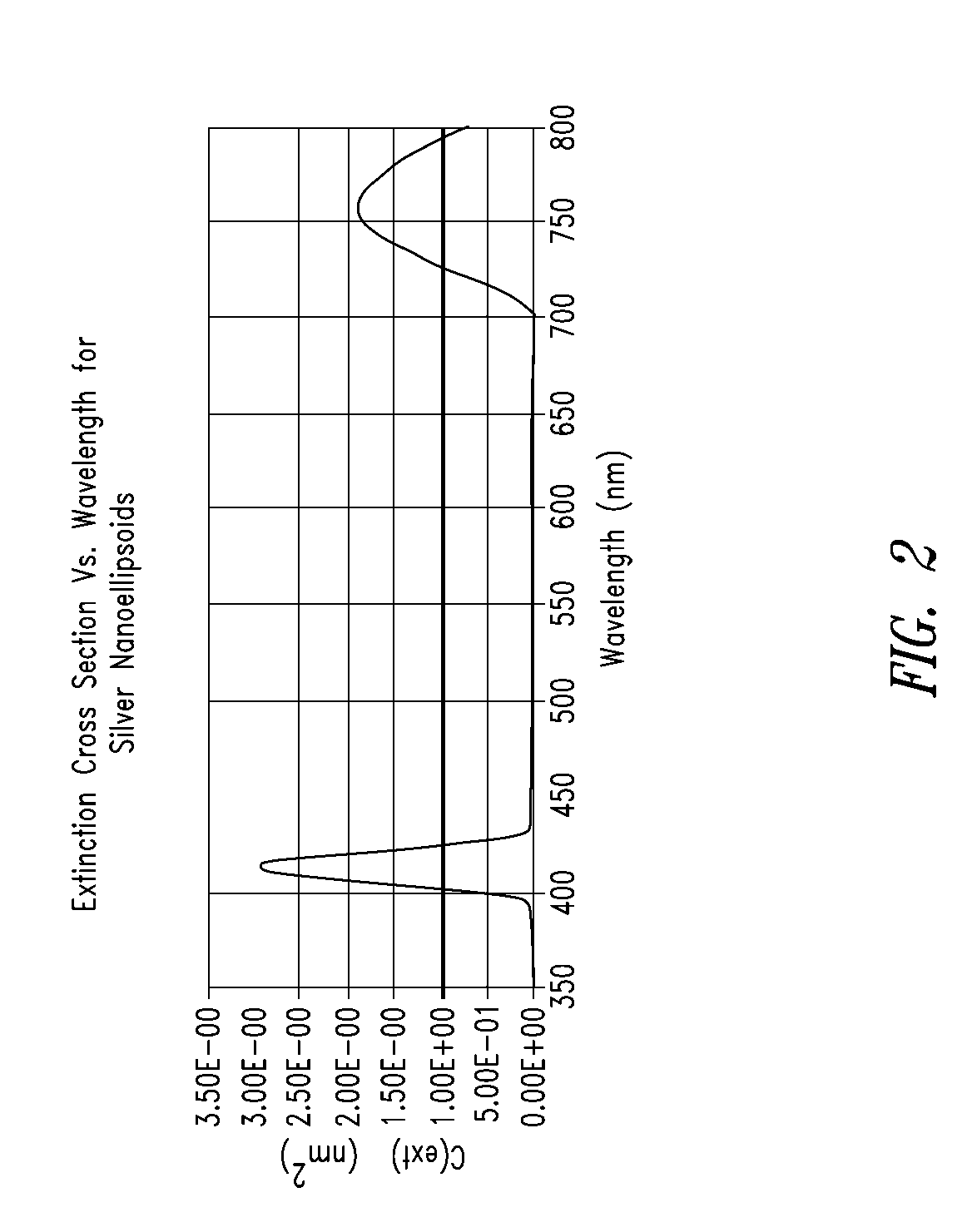

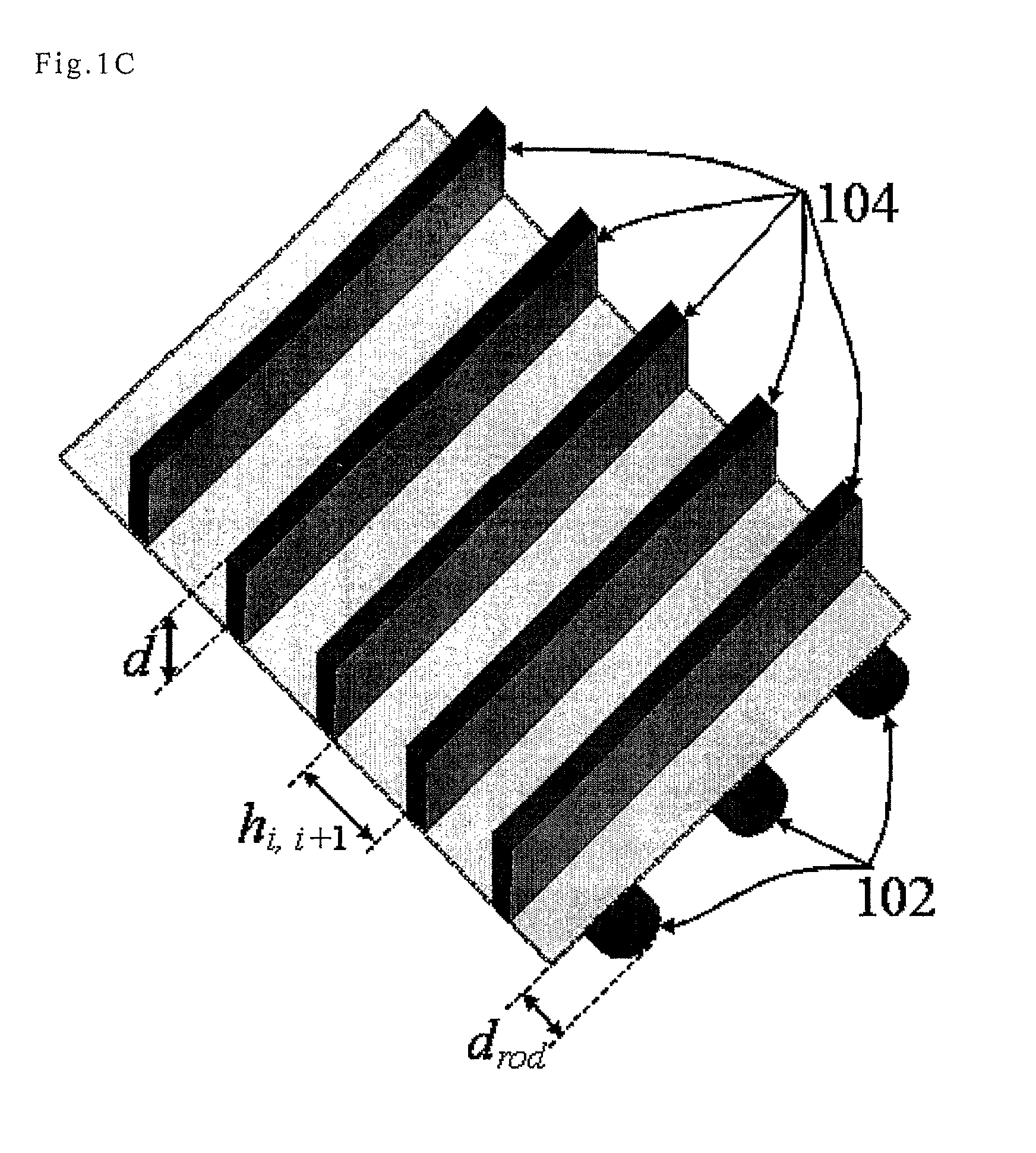

Nanowires-based transparent conductors

ActiveUS20070074316A1Improve drawing legibilityMaterial nanotechnologyFrom normal temperature solutionsElectrical conductorNanowire

Owner:CHAMP GREAT INTL

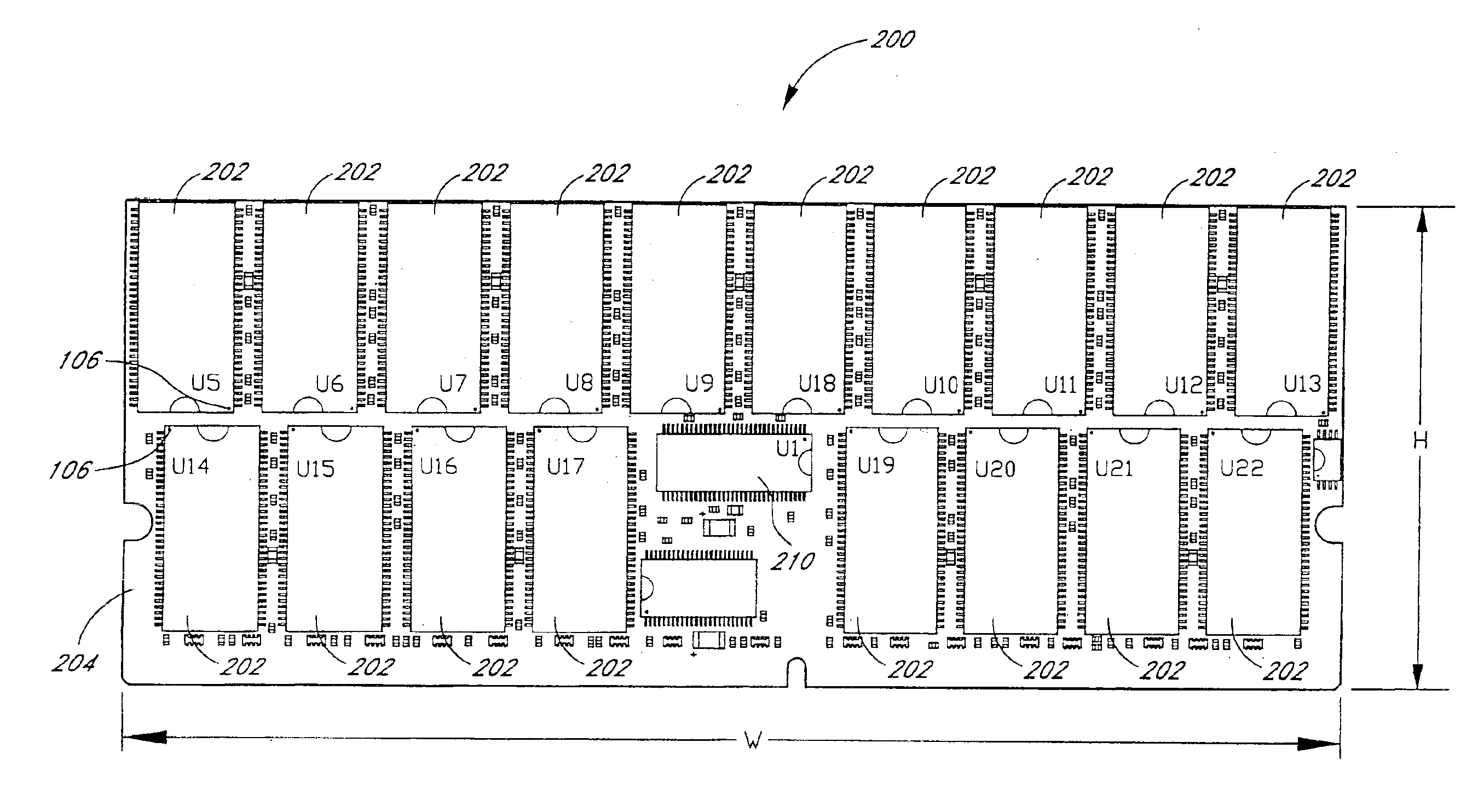

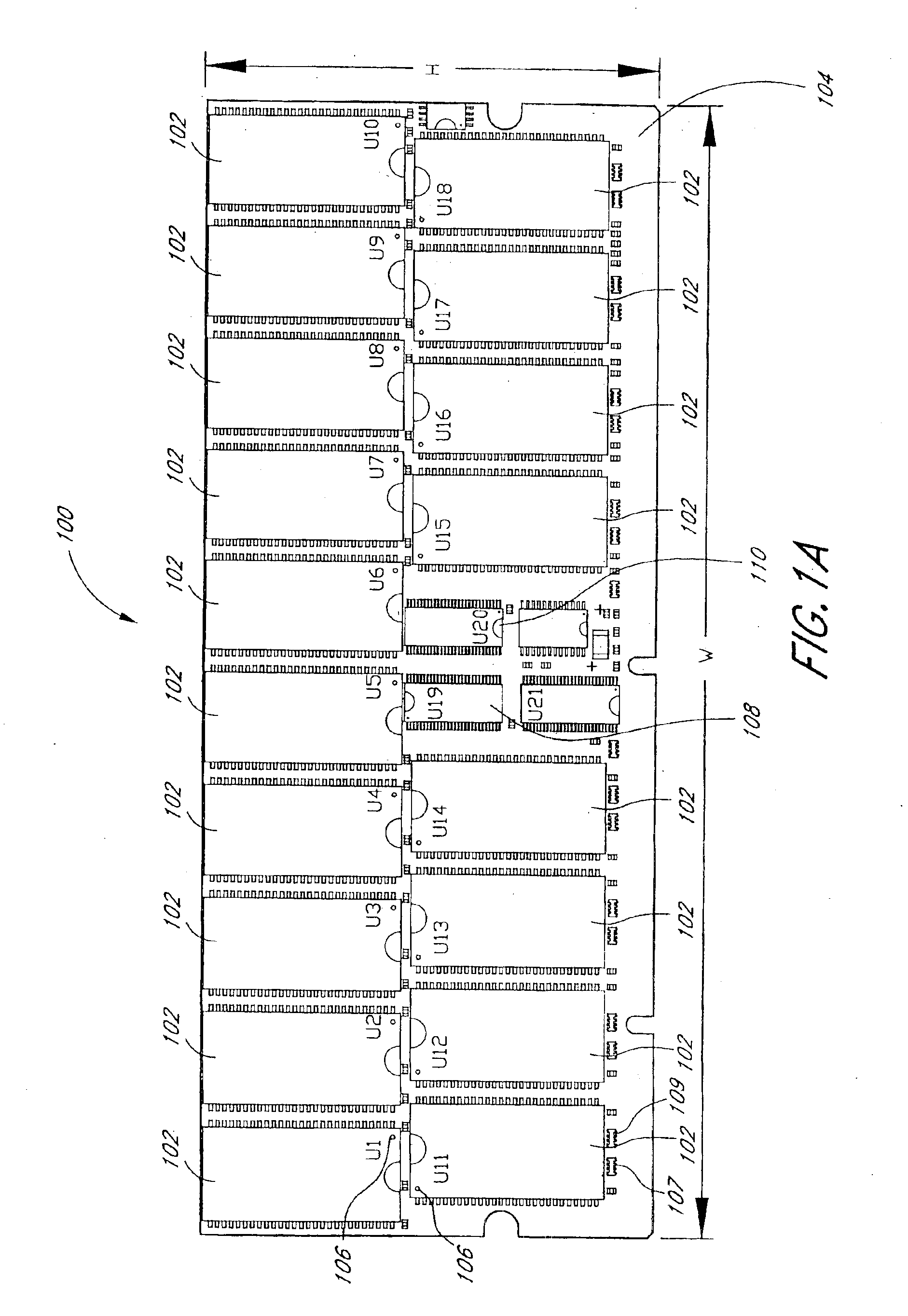

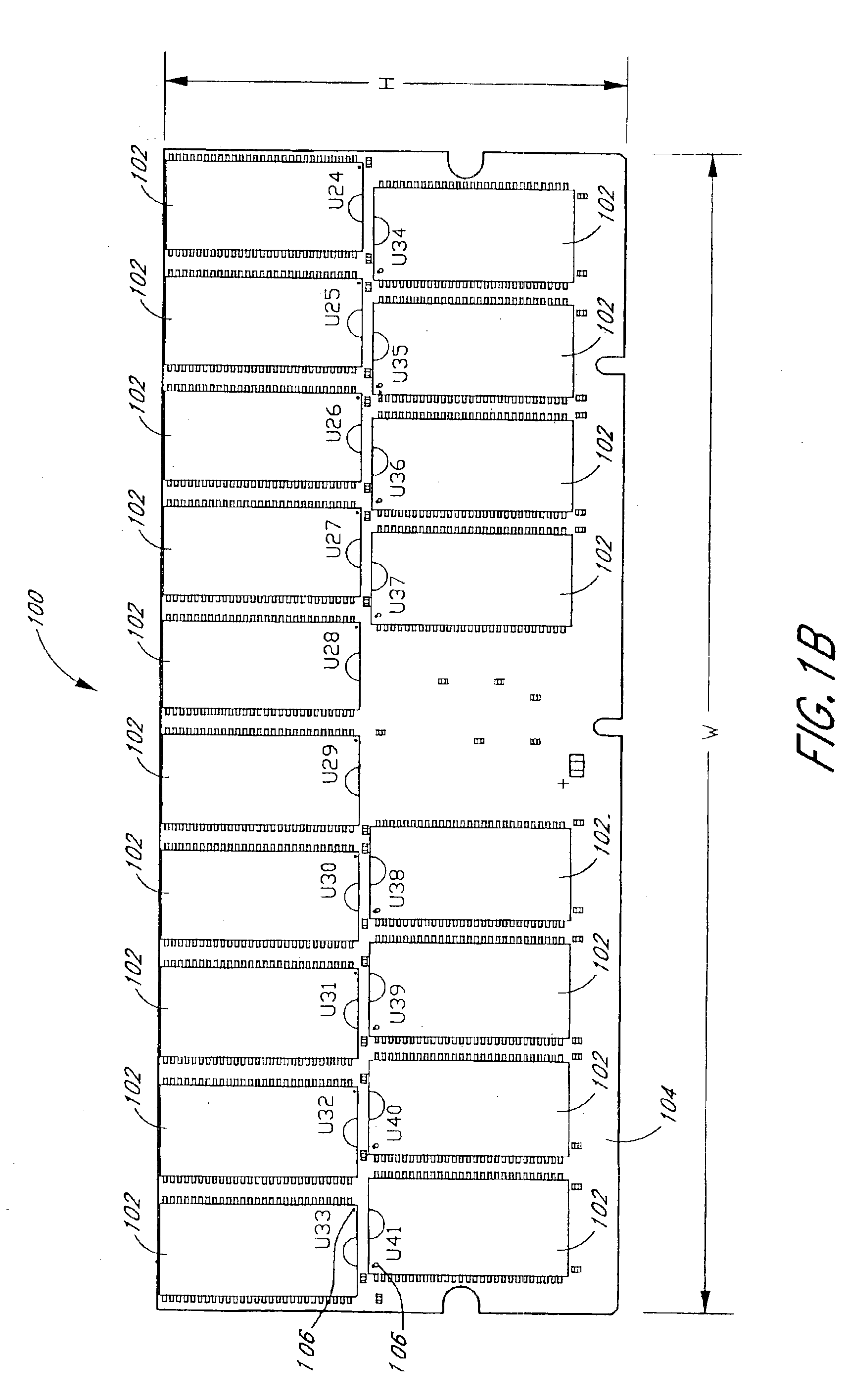

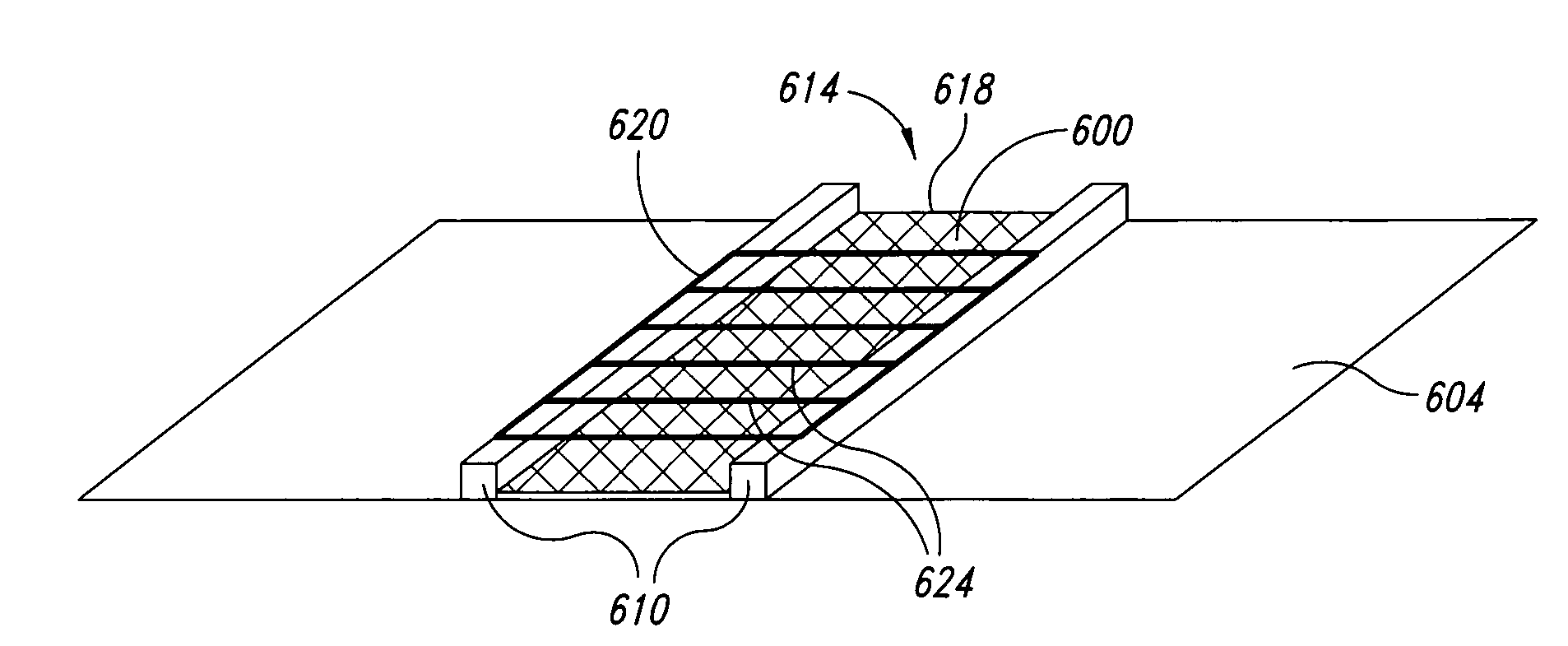

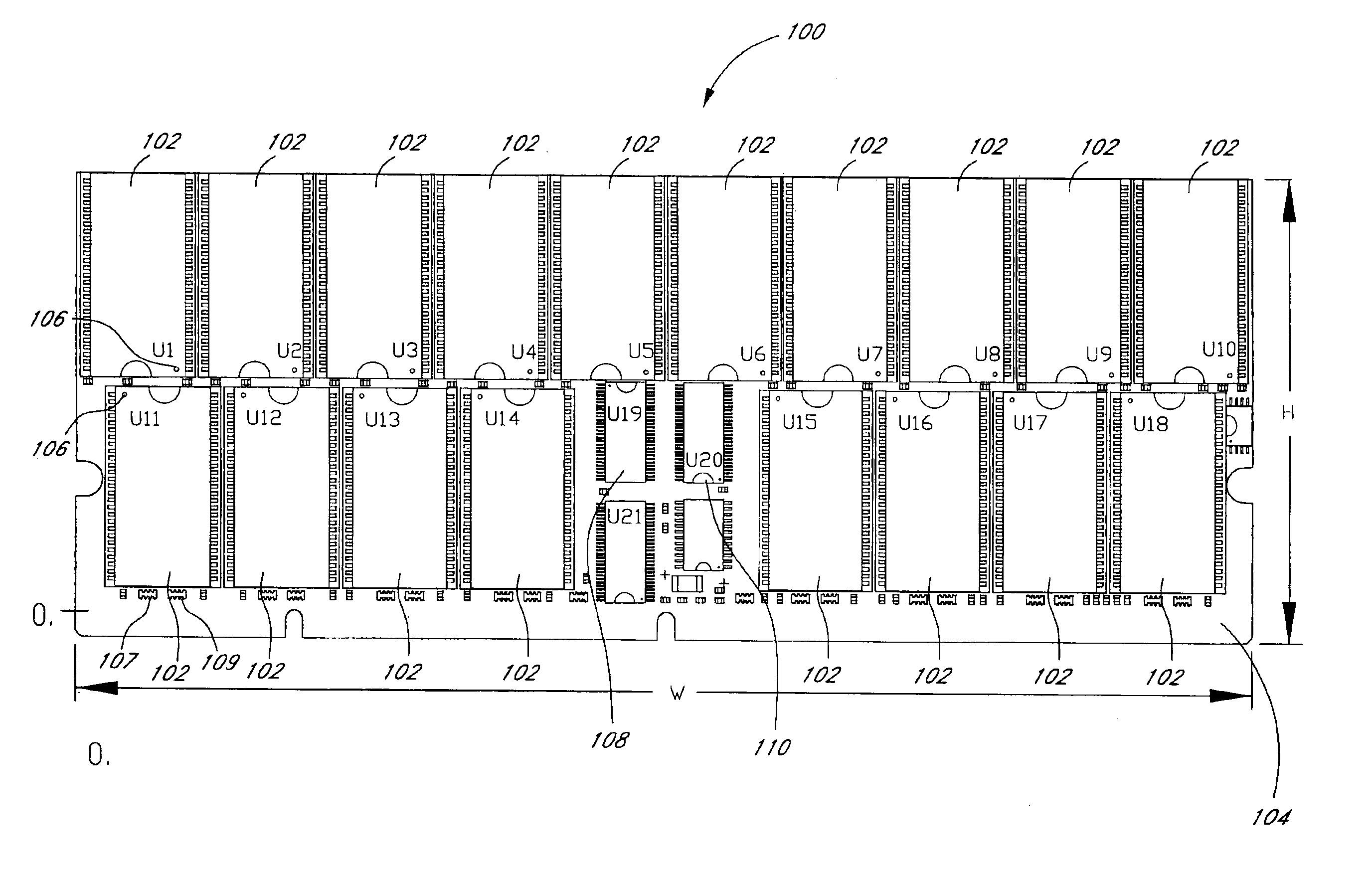

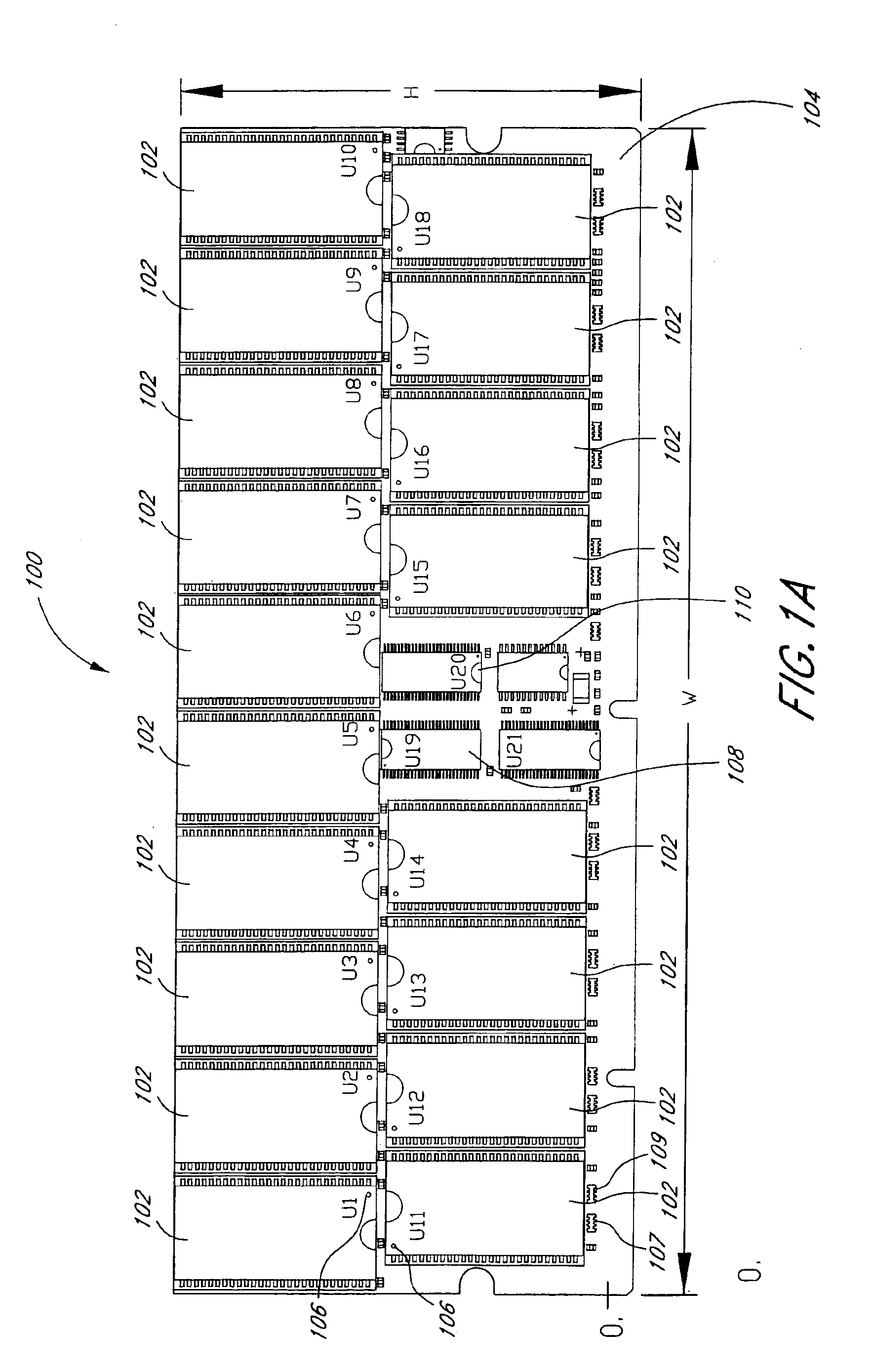

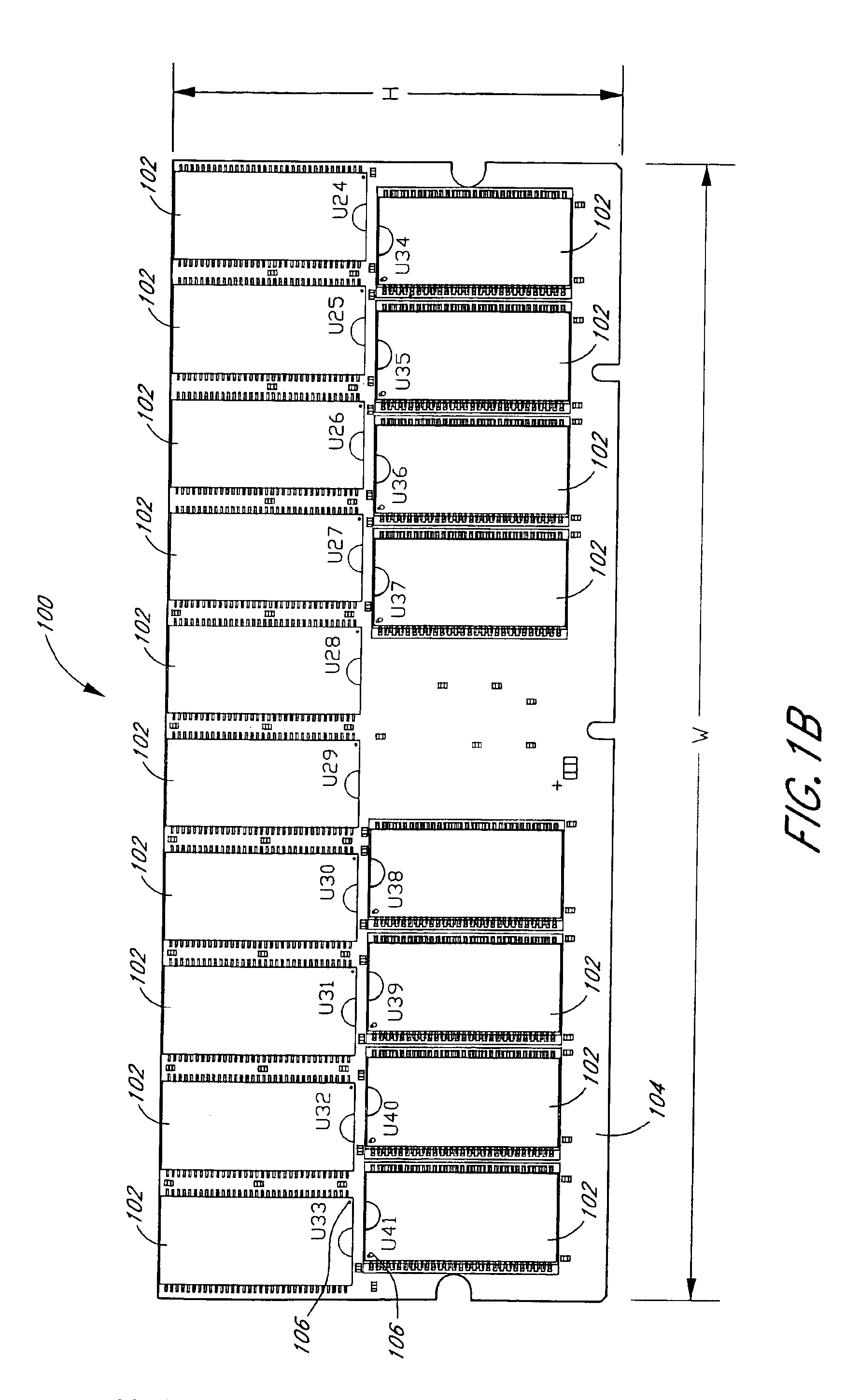

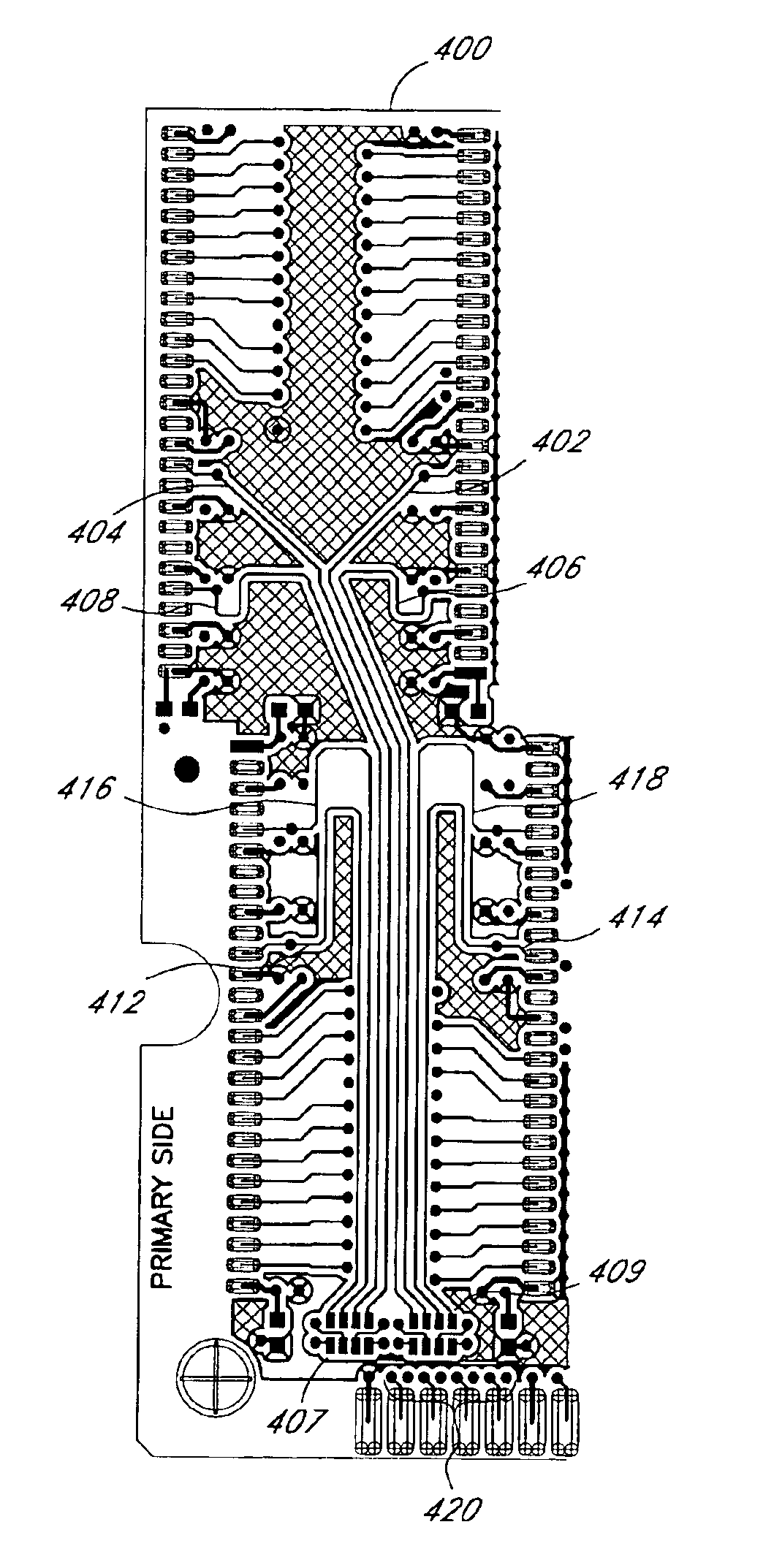

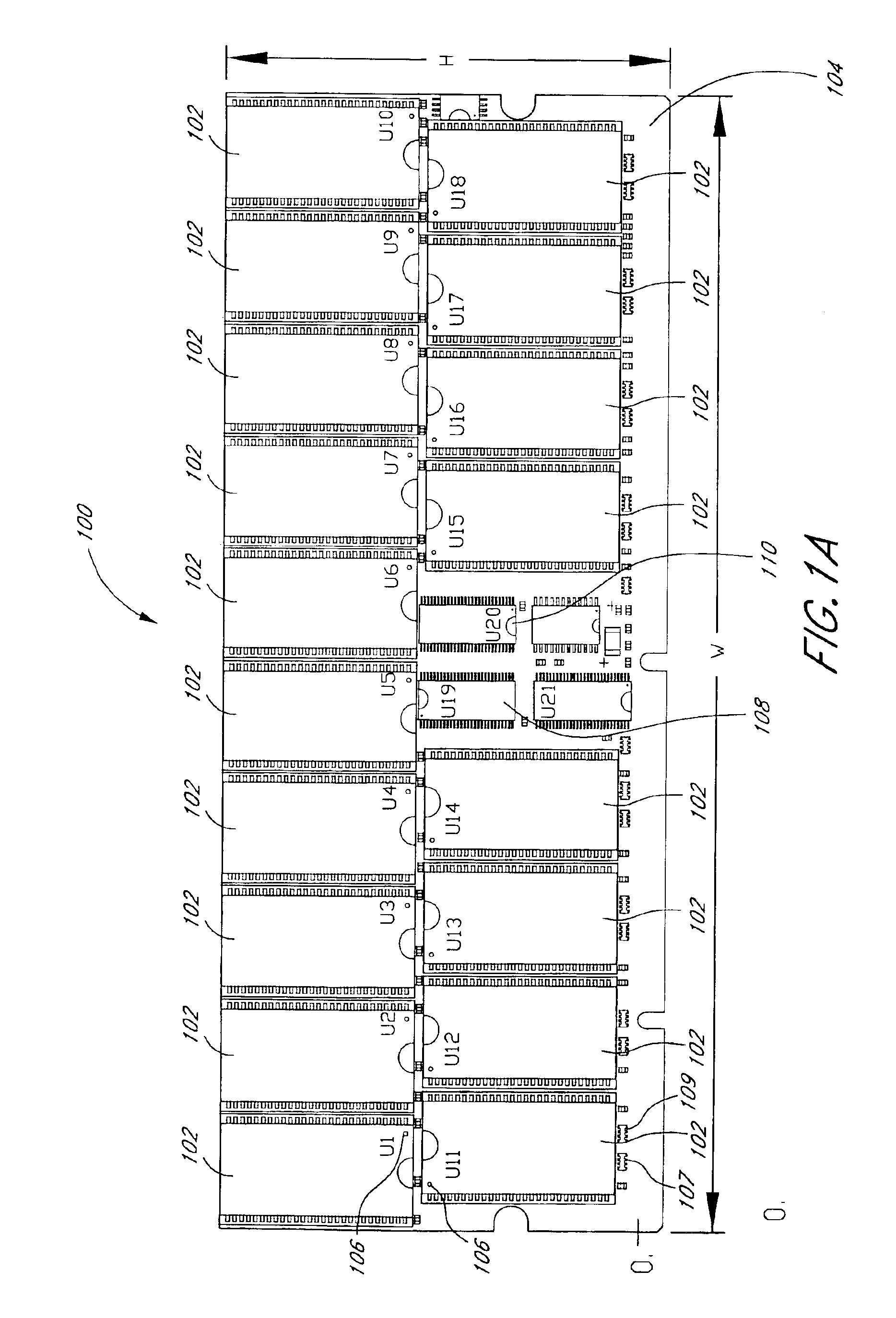

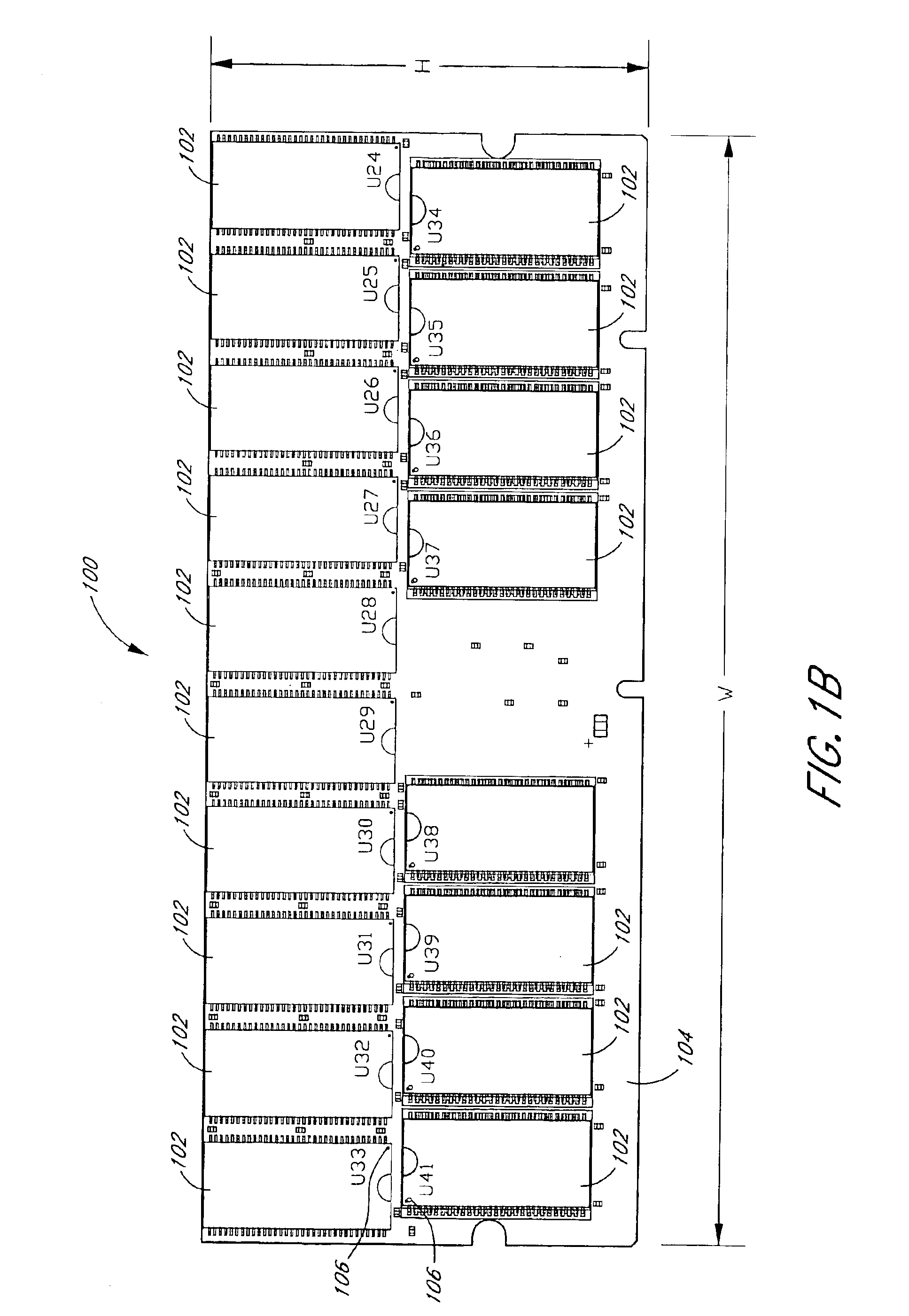

Arrangement of integrated circuits in a memory module

Integrated circuits utilizing standard commercial packaging are arranged on a printed circuit board to allow the production of 1-Gigabyte and 2-Gigabyte capacity memory modules. A first row of integrated circuits is oriented in an opposite orientation to a second row of integrated circuits. The integrated circuits in a first half of the first row and in the corresponding half of the second row are connected via a signal trace to a first register. The integrated circuits in a second half of the first row and in the corresponding half of the second row are connected to a second register. Each register processes a non-contiguous subset of the bits in each data word.

Owner:NETLIST INC

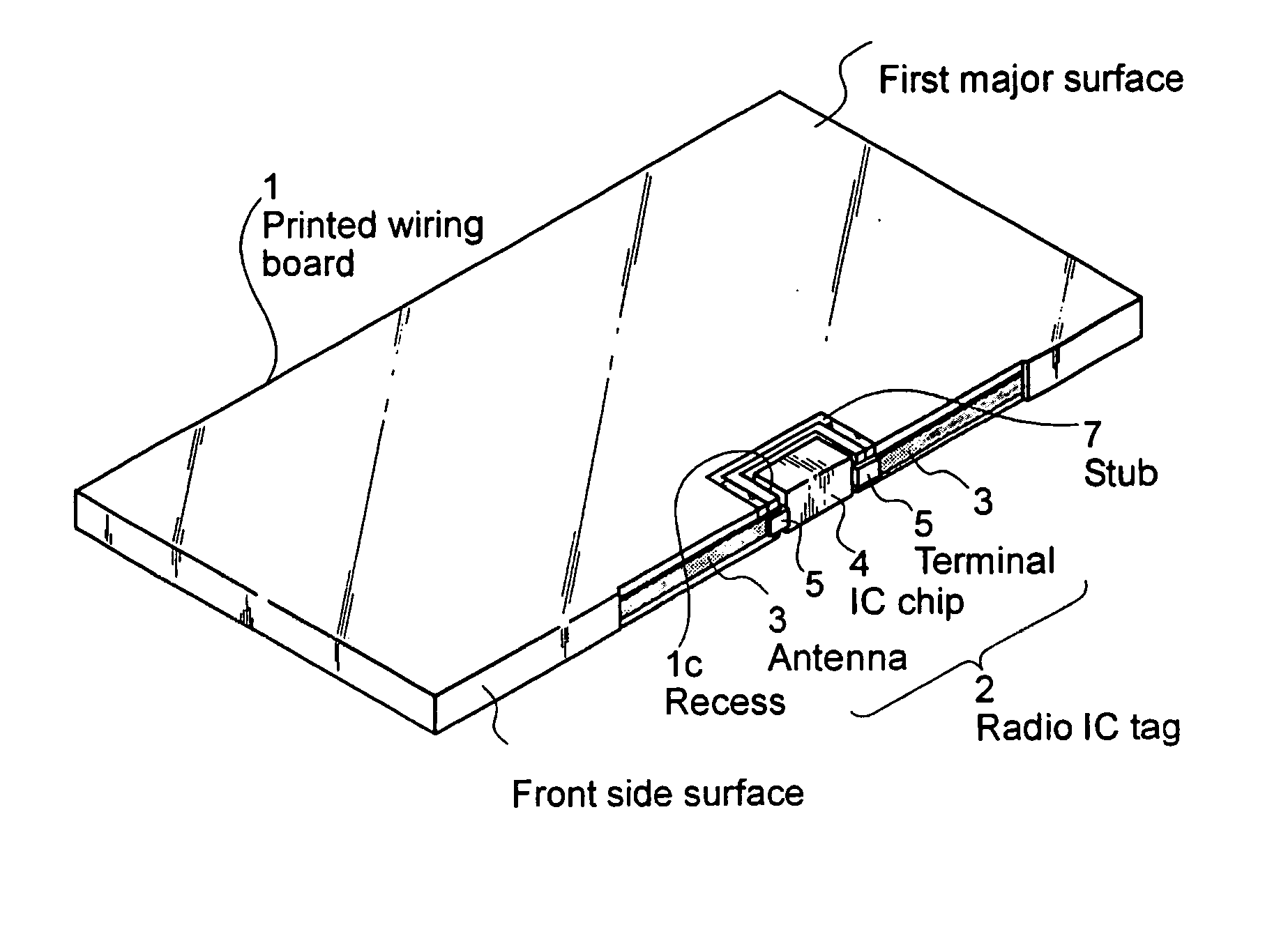

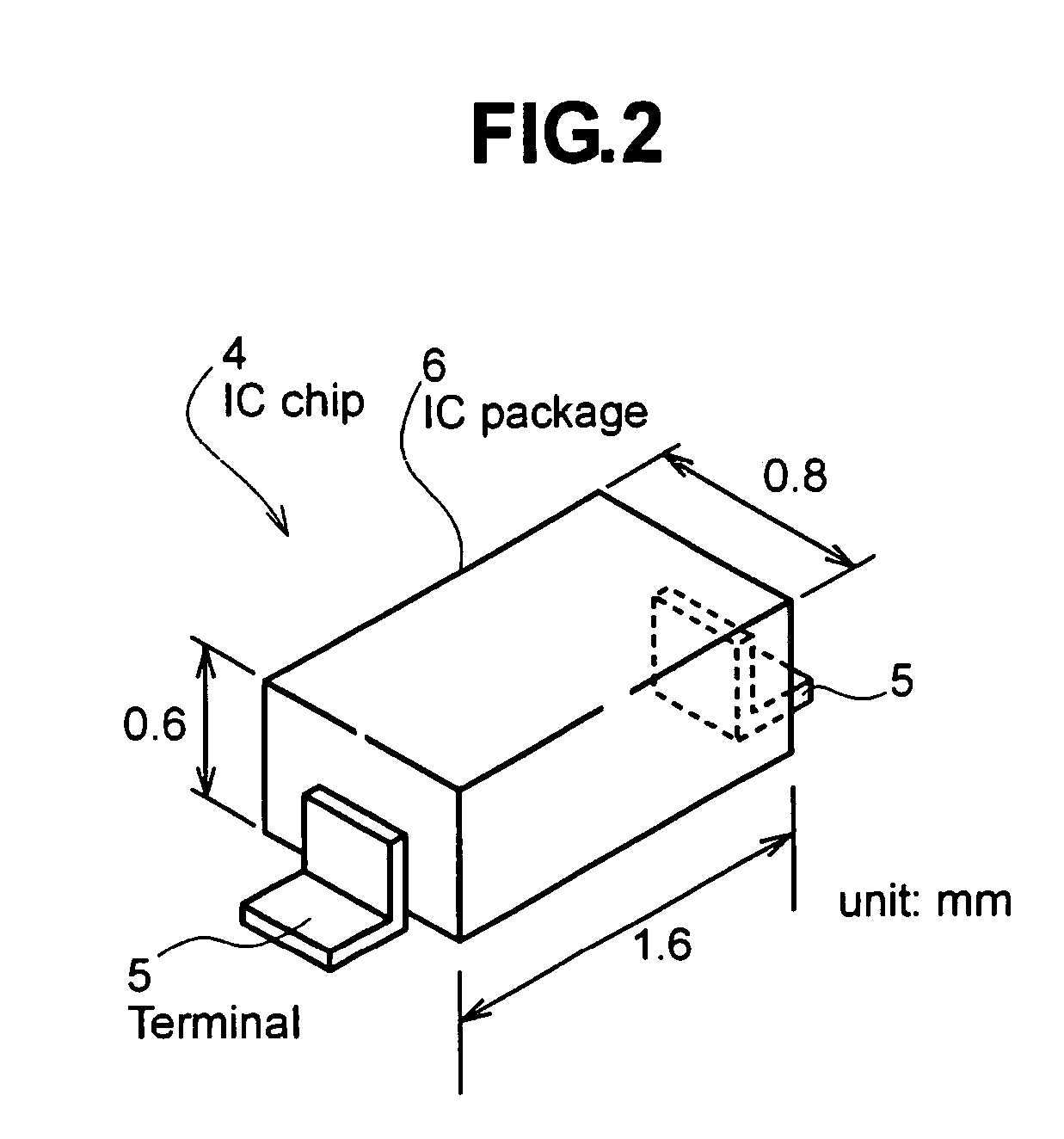

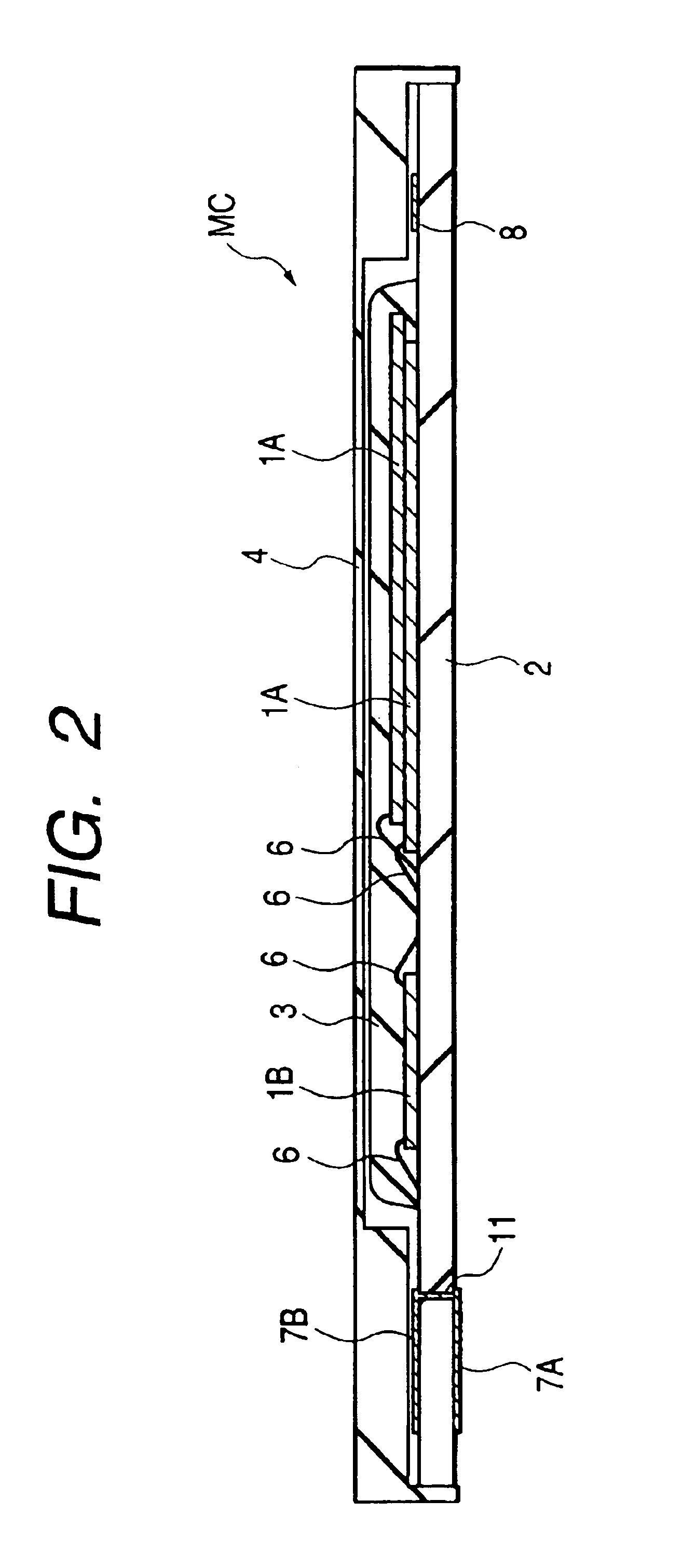

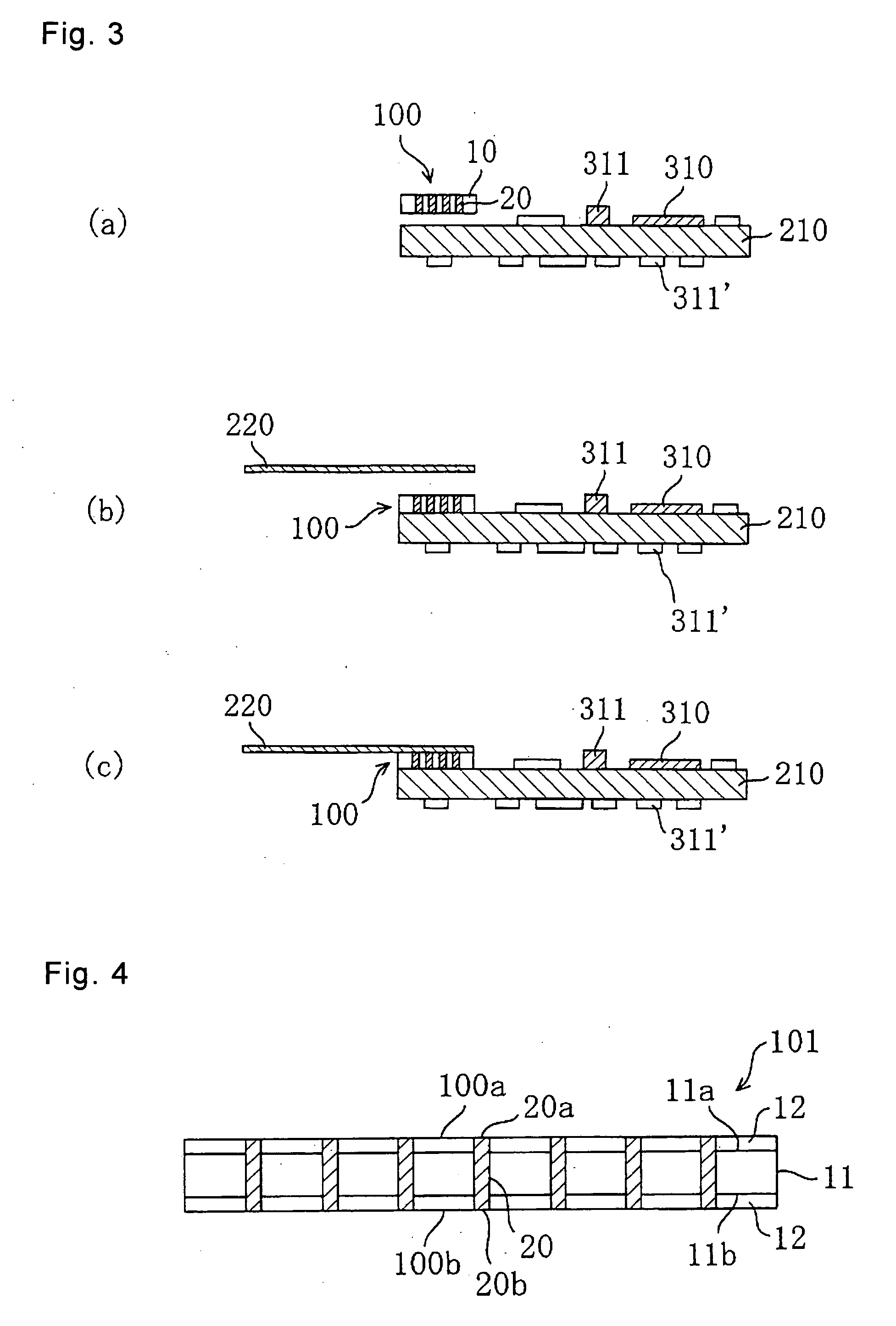

IC-tag-bearing wiring board and method of fabricating the same

InactiveUS20060001138A1Improve efficiencyEasy to useAntenna supports/mountingsSemiconductor/solid-state device detailsEngineeringDipole antenna

To improve electronic part packaging efficiency without sacrificing the transmission distance of a radio IC tag, a recess is formed in the front side surface of a printed wiring board. An IC chip is placed in the recess so that the IC chip does not protrude from the front side surface, a first major surface 1a and a second major surface of the printed wiring board. Antenna elements of an antenna are formed on the front side surface on the opposite sides, respectively, of the IC chip, and the antenna is connected to the IC chip. The antenna is a dipole antenna of a length equal to half the wavelength of radio waves to be radiated by the antenna.

Owner:HITACHI LTD

Nanowires-based transparent conductors

ActiveUS20080286447A1Material nanotechnologyFrom normal temperature solutionsNanowireElectrical conductor

Owner:CHAMP GREAT INTL

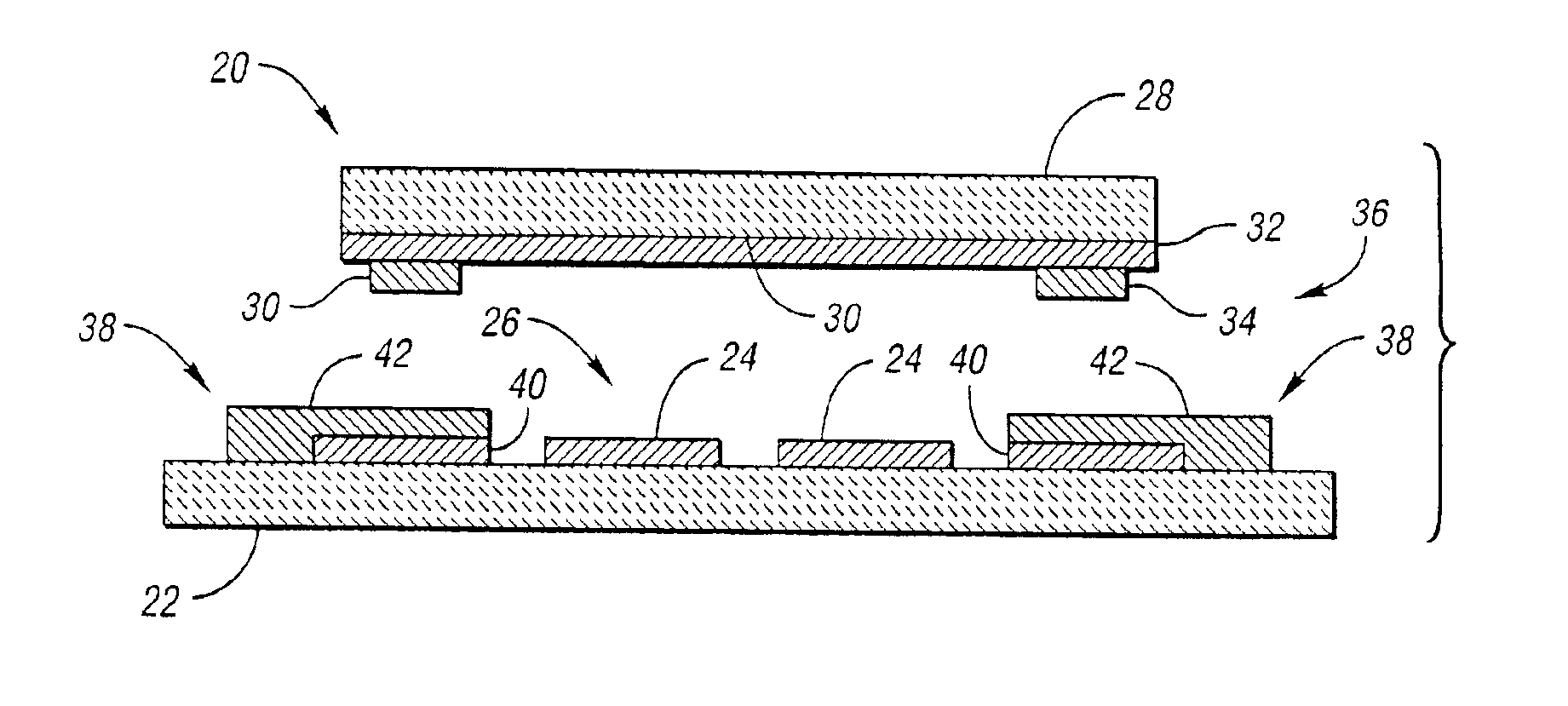

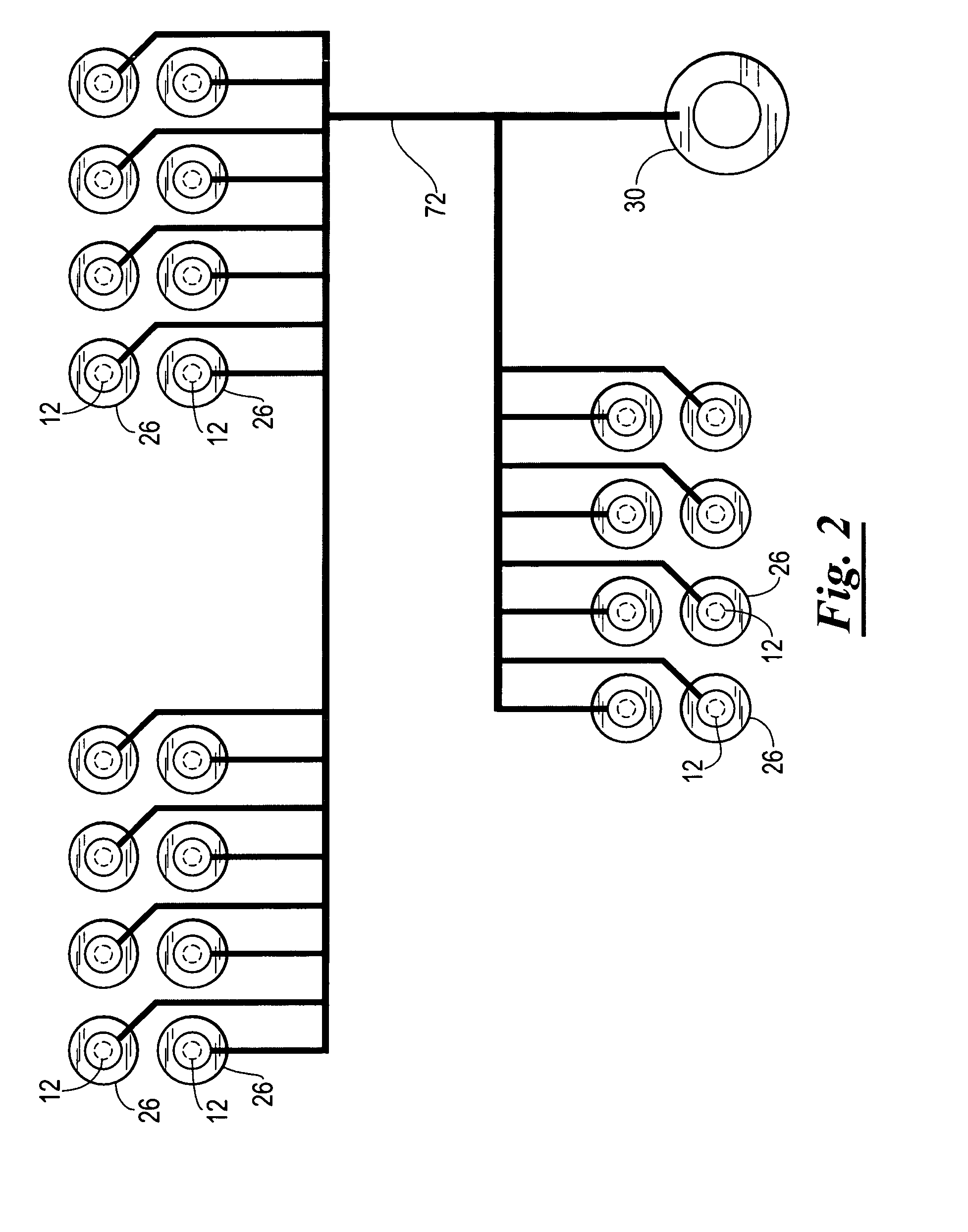

Arrangement of integrated circuits in a memory module

Integrated circuits utilizing standard commercial packaging are arranged on a printed circuit board to allow the production of 1-Gigabyte and 2-Gigabyte capacity memory modules. A first row of integrated circuits is oriented in an opposite orientation to a second row of integrated circuits. The integrated circuits in a first half of the first row and in the corresponding half of the second row are connected via a signal trace to a first register. The integrated circuits in a second half of the first row and in the corresponding half of the second row are connected to a second register. Each register processes a non-contiguous subset of the bits in each data word.

Owner:NETLIST INC

Arrangement of integrated circuits in a memory module

Integrated circuits utilizing standard commercial packaging are arranged on a printed circuit board to allow the production of 1-Gigabyte and 2-Gigabyte capacity memory modules. A first row of integrated circuits is oriented in an opposite orientation to a second row of integrated circuits. The integrated circuits in a first half of the first row and in the corresponding half of the second row are connected via a signal trace to a first register. The integrated circuits in a second half of the first row and in the corresponding half of the second row are connected to a second register. Each register processes a non-contiguous subset of the bits in each data word.

Owner:NETLIST INC

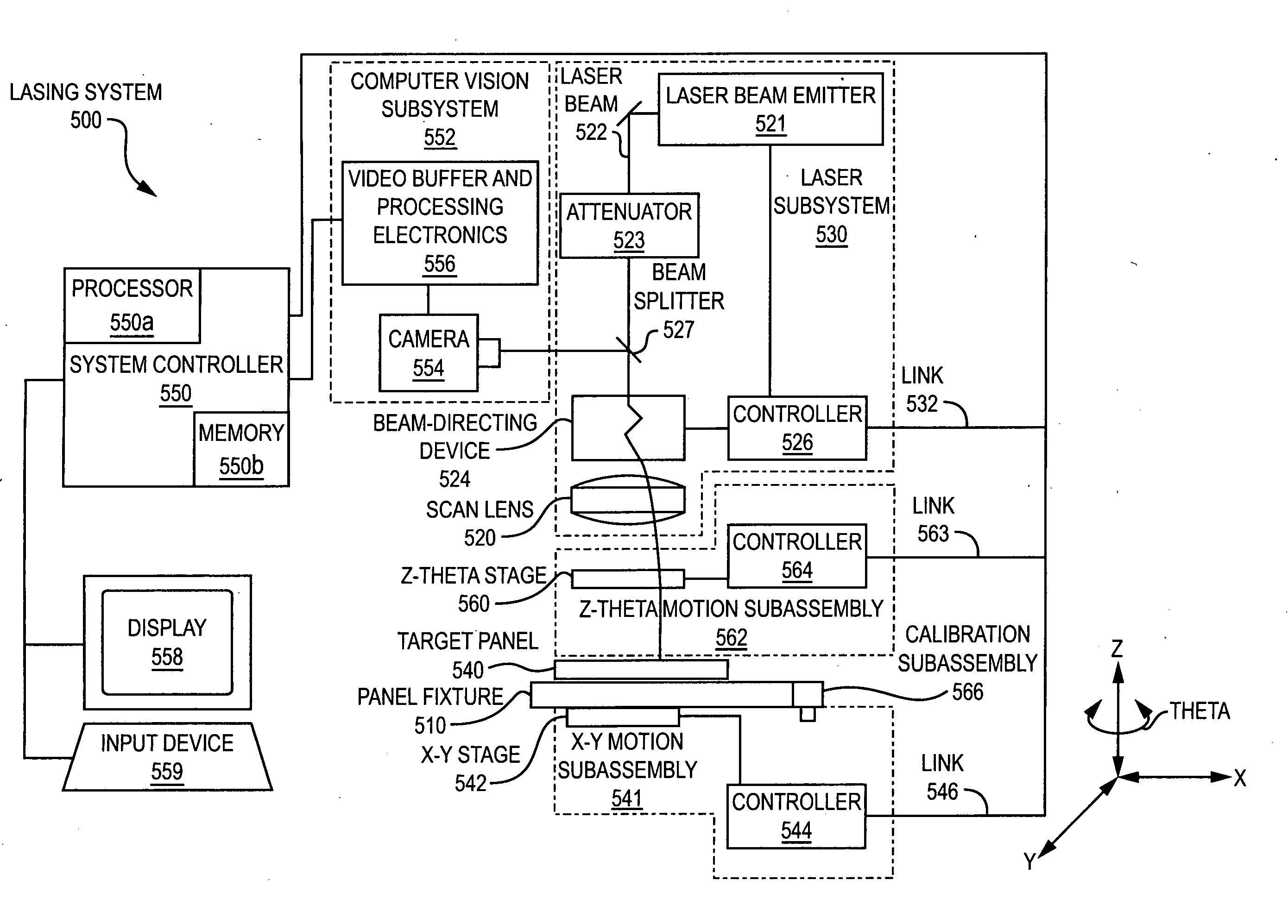

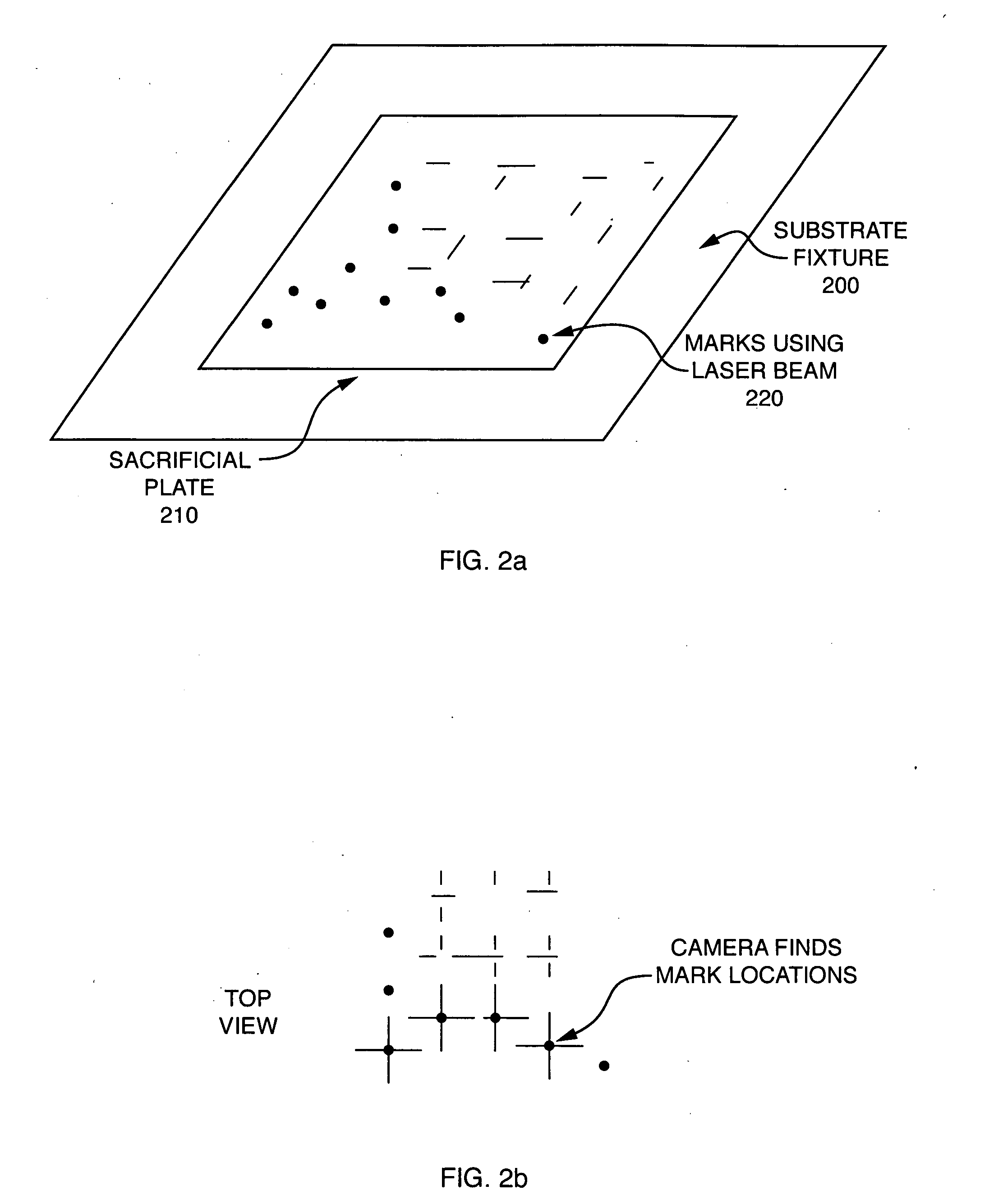

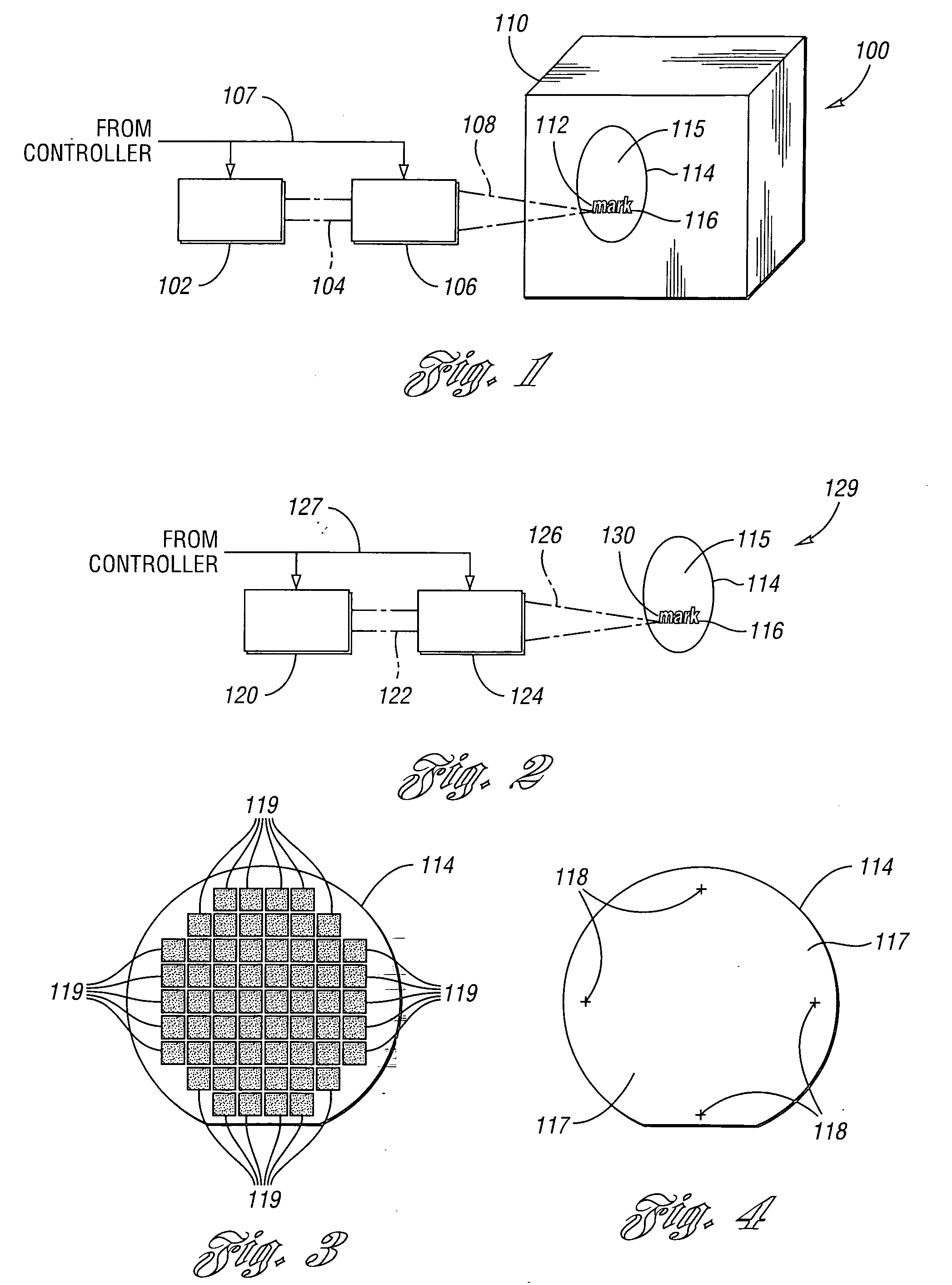

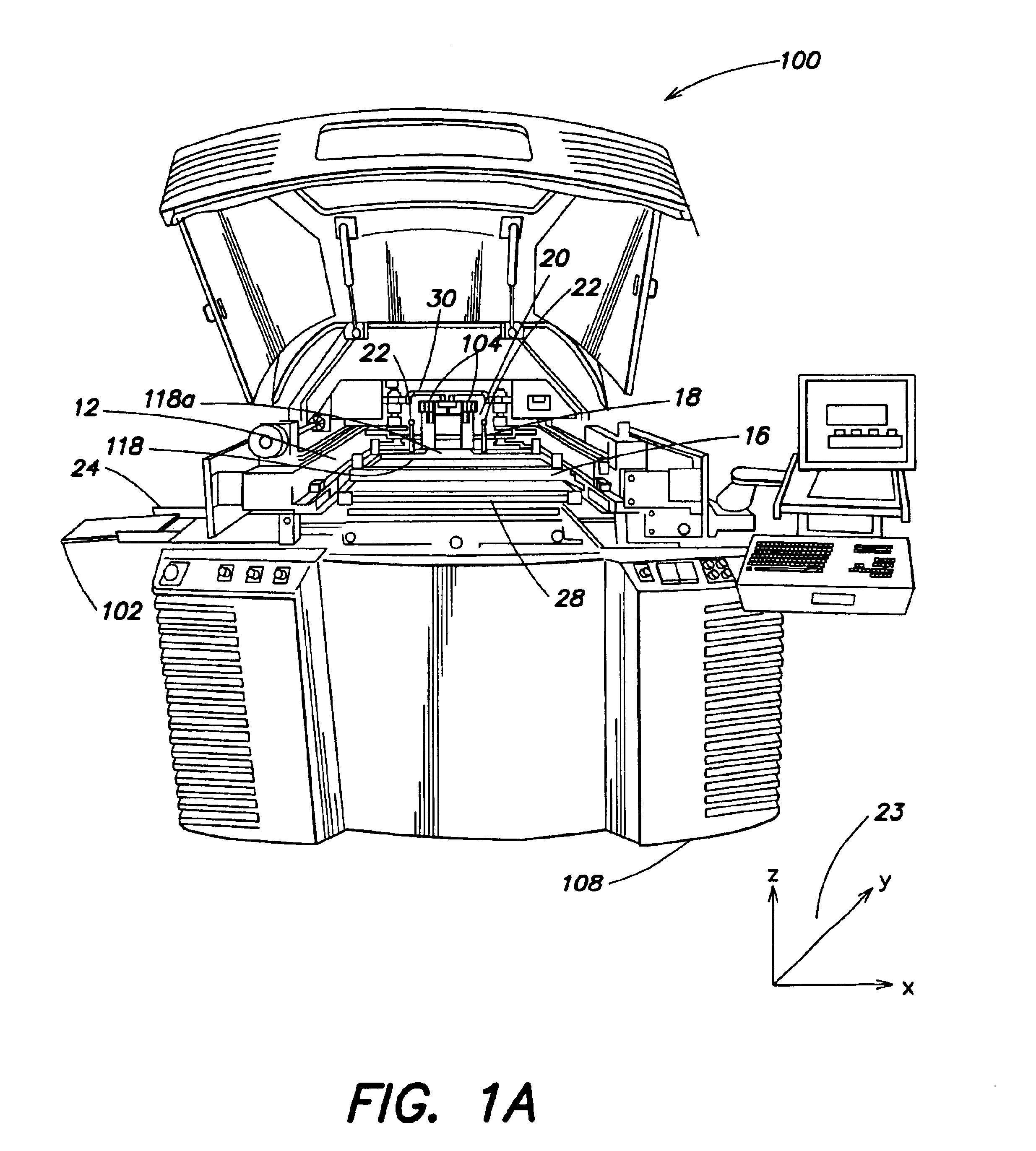

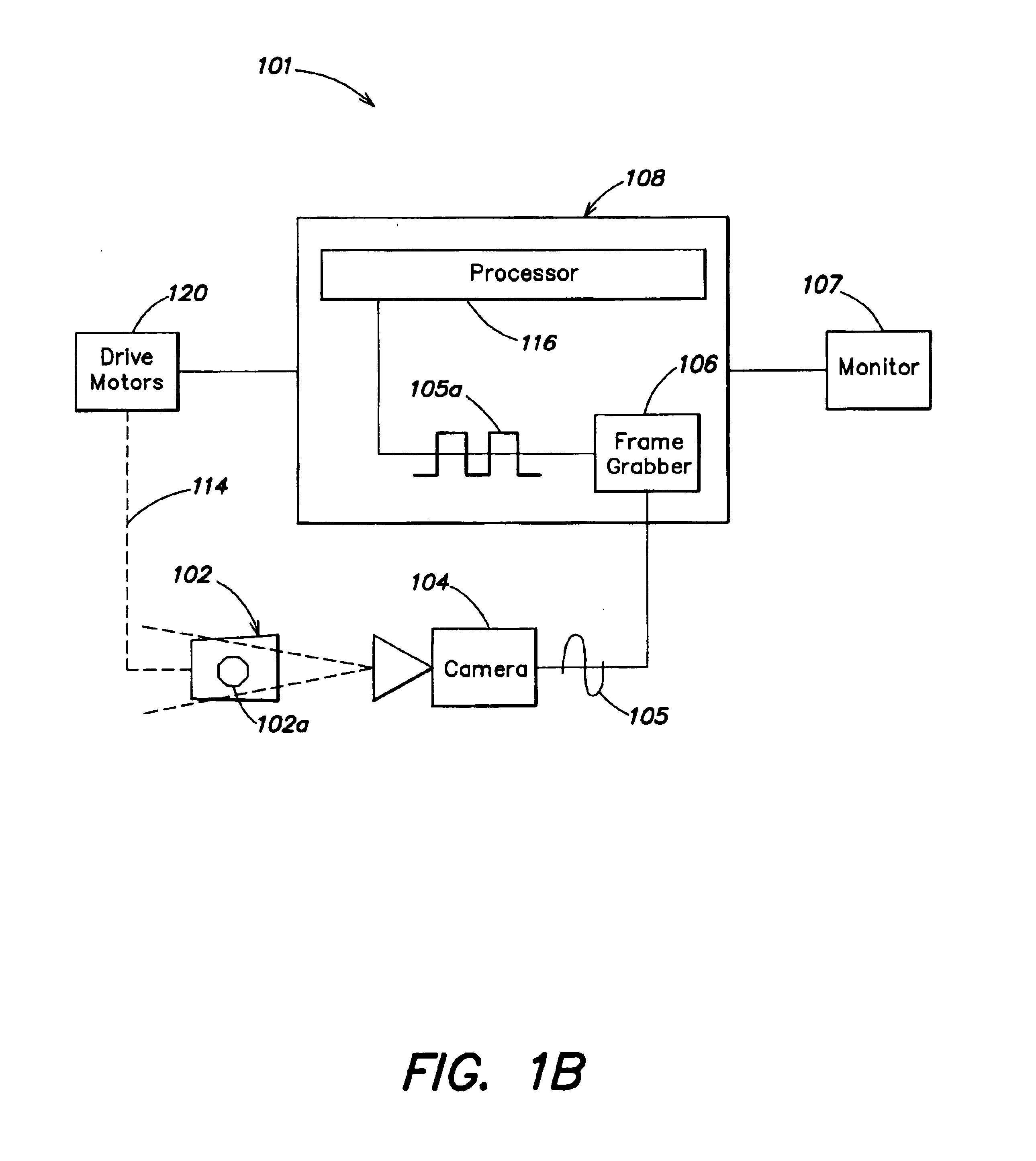

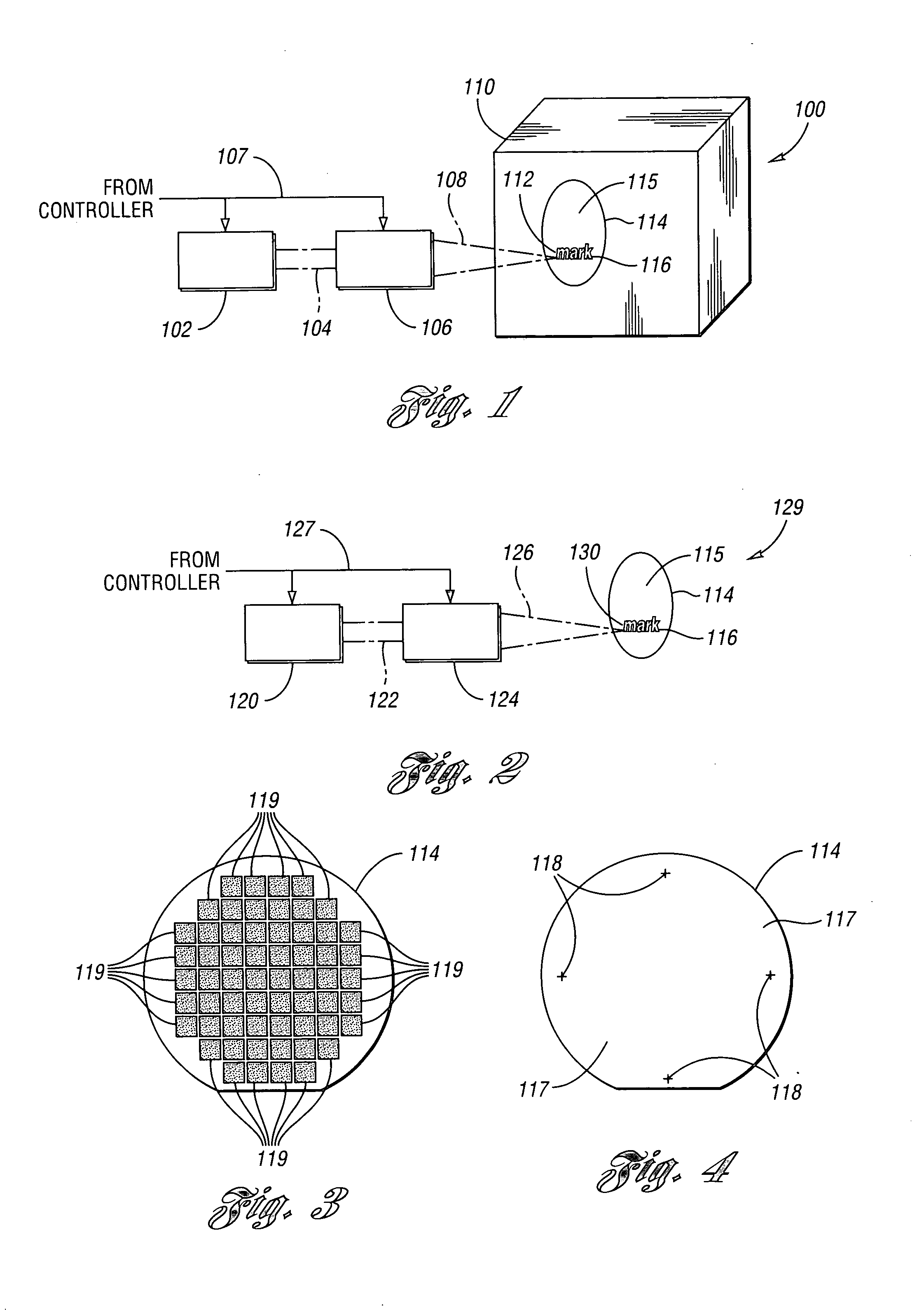

Laser trim motion, calibration, imaging, and fixturing techniques

InactiveUS20050205778A1Optimal lasing procedureOptimal procedureMaterial analysis using wave/particle radiationPrinted circuit aspectsBiomedical engineeringLaser trimming

A system for probing circuit elements, includes a panel fixture, probe holder and stage. The fixture has a platen surface to support a work piece having work piece surface. The work piece surface is substantially parallel to the platen surface and has a target element thereon. The probe holder is configured to support a probe for detecting a characteristic of the target element. A stage rotates the probe holder about an axis substantially orthogonal to the platen surface, to align the probe with probe locations associated with the circuit element, so that the characteristic of the circuit element can detected by the probe. Fixturing motion can be optimized for efficient work piece manufacturing. Calibration and vision subassemblies are also provided.

Owner:THE GSI GRP LLC

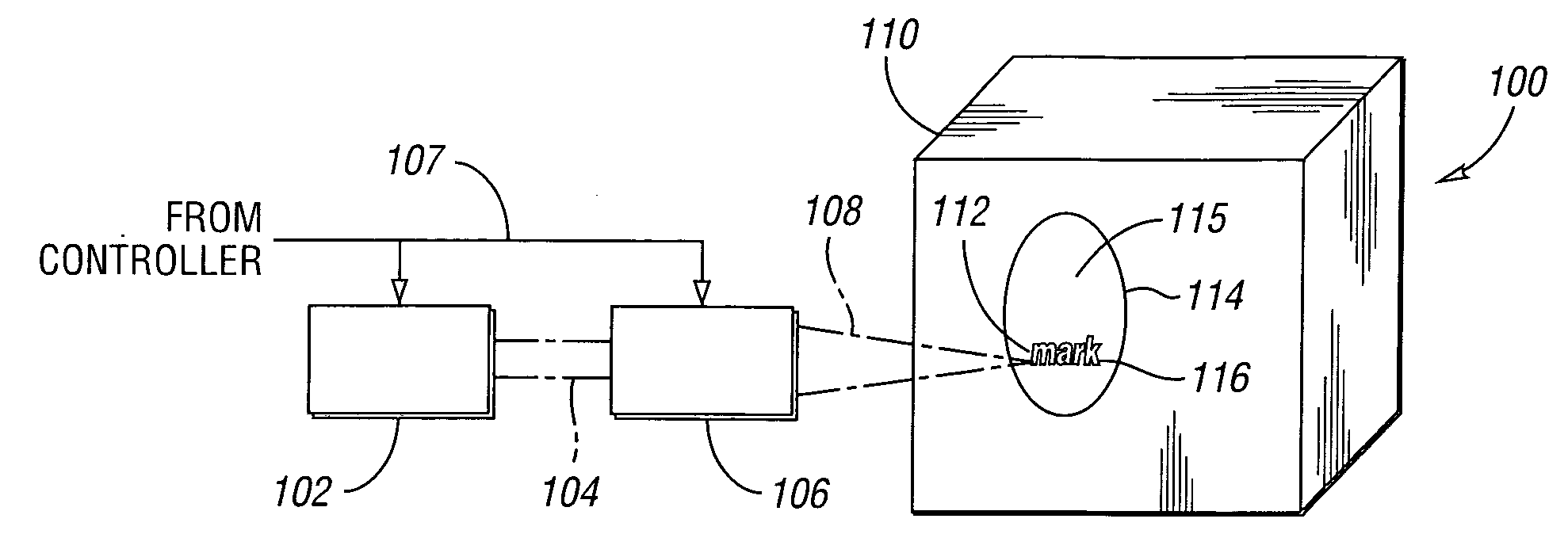

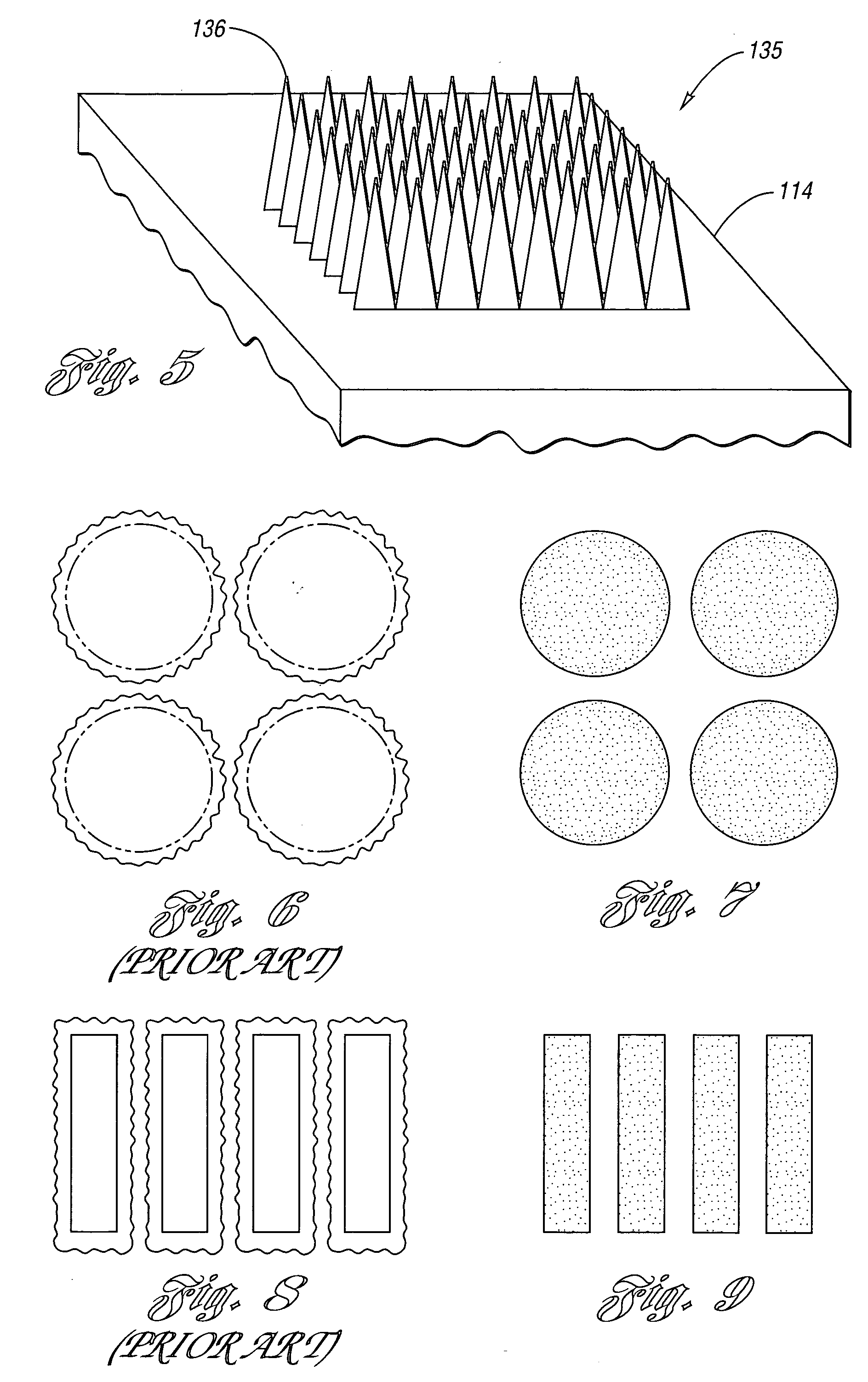

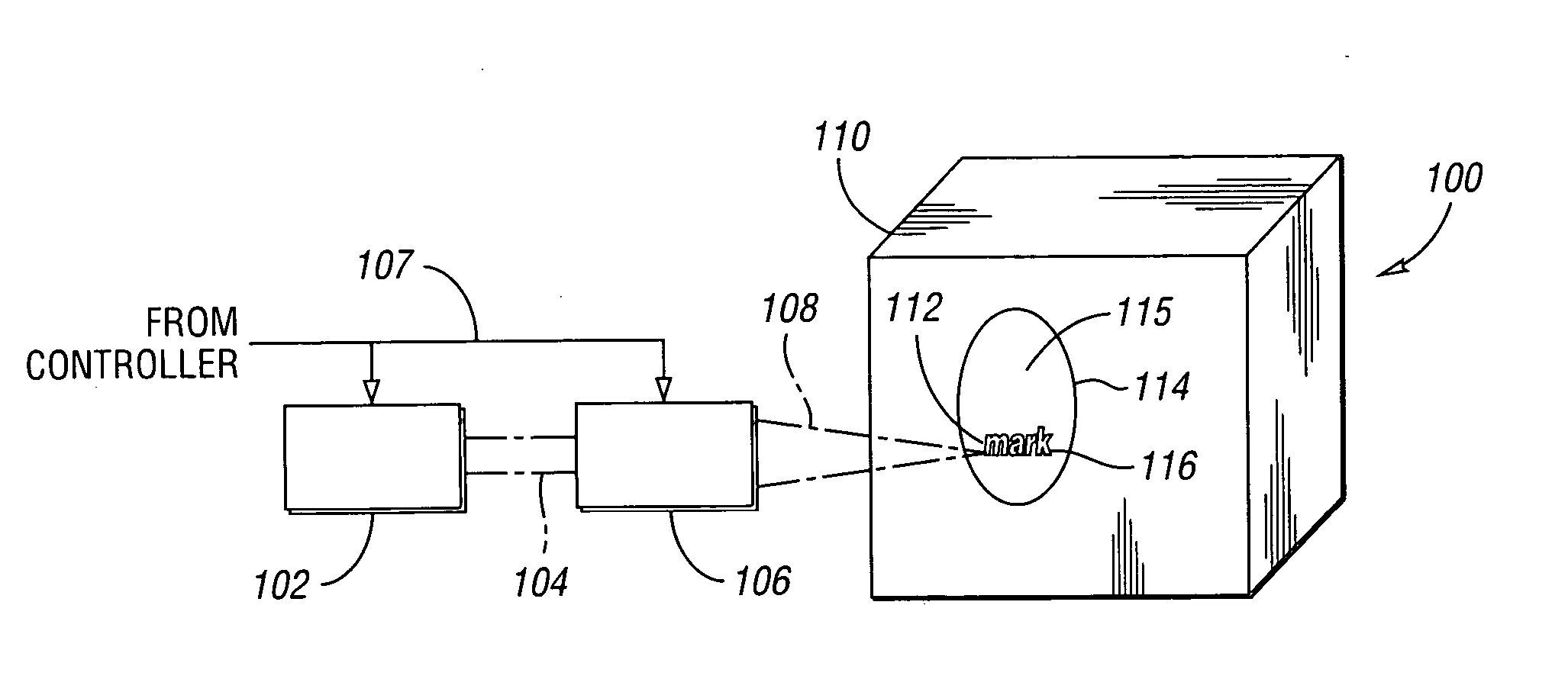

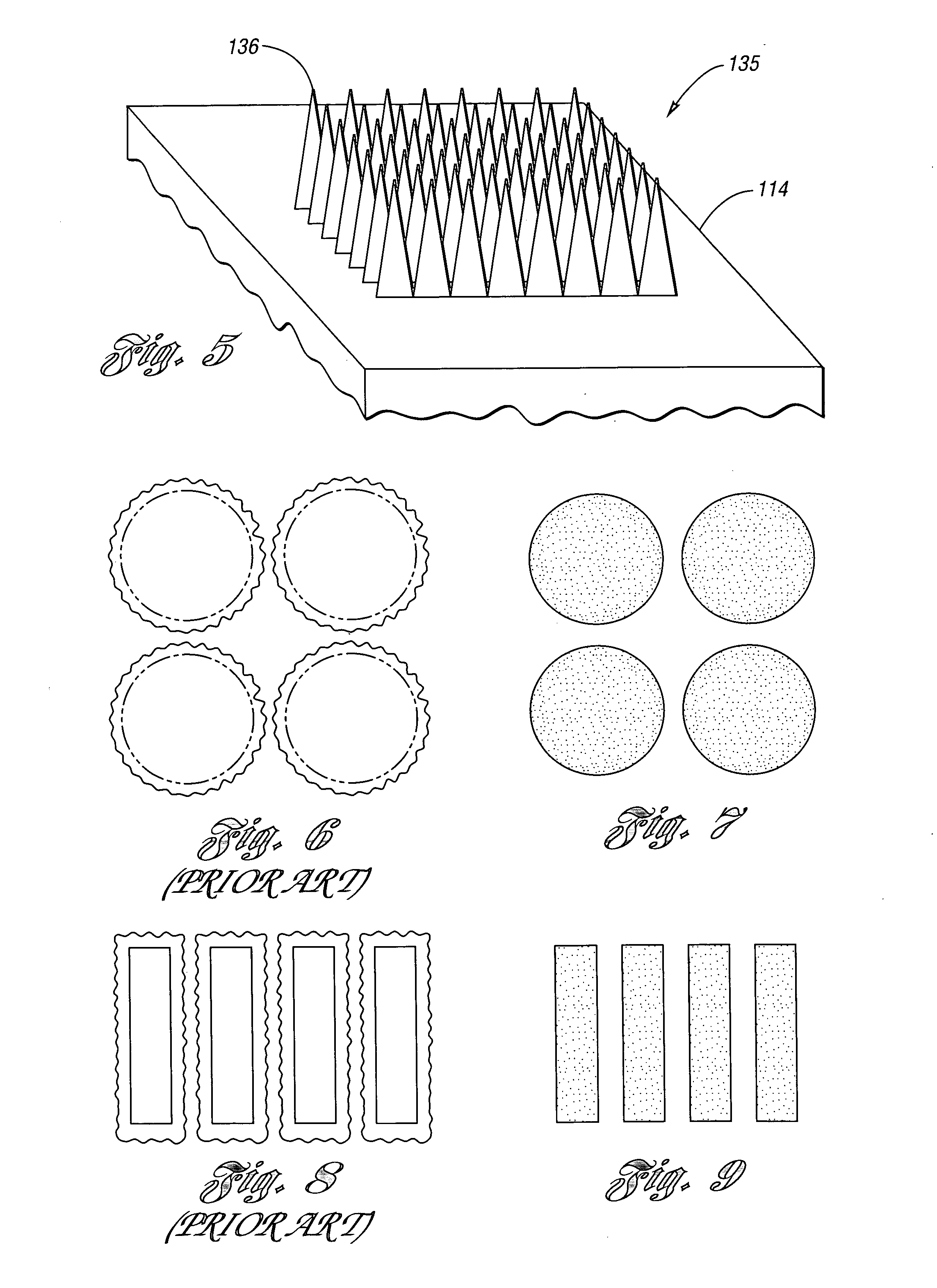

Laser-based method and system for processing targeted surface material and article produced thereby

InactiveUS20060000814A1Prevent unwanted changesSufficient total fluenceAdditive manufacturing apparatusSemiconductor/solid-state device detailsTarget surfaceSlag

A laser-based method and system for processing targeted surface material and article produced thereby are provided. The system processes the targeted surface material within a region of a workpiece while avoiding undesirable changes to adjacent non-targeted material. The system includes a primary laser subsystem including a primary laser source for generating a pulsed laser output including at least one pulse having a wavelength and a pulse width less than 1 ns. A delivery subsystem irradiates the targeted surface material of the workpiece with the pulsed laser output including the at least one pulse to texture the targeted surface material. The pulsed laser output has sufficient total fluence to initiate ablation within at least a portion of the targeted surface material and the pulse width is short enough such that the region and the non-targeted material surrounding the material are substantially free of slag.

Owner:ELECTRO SCI IND INC

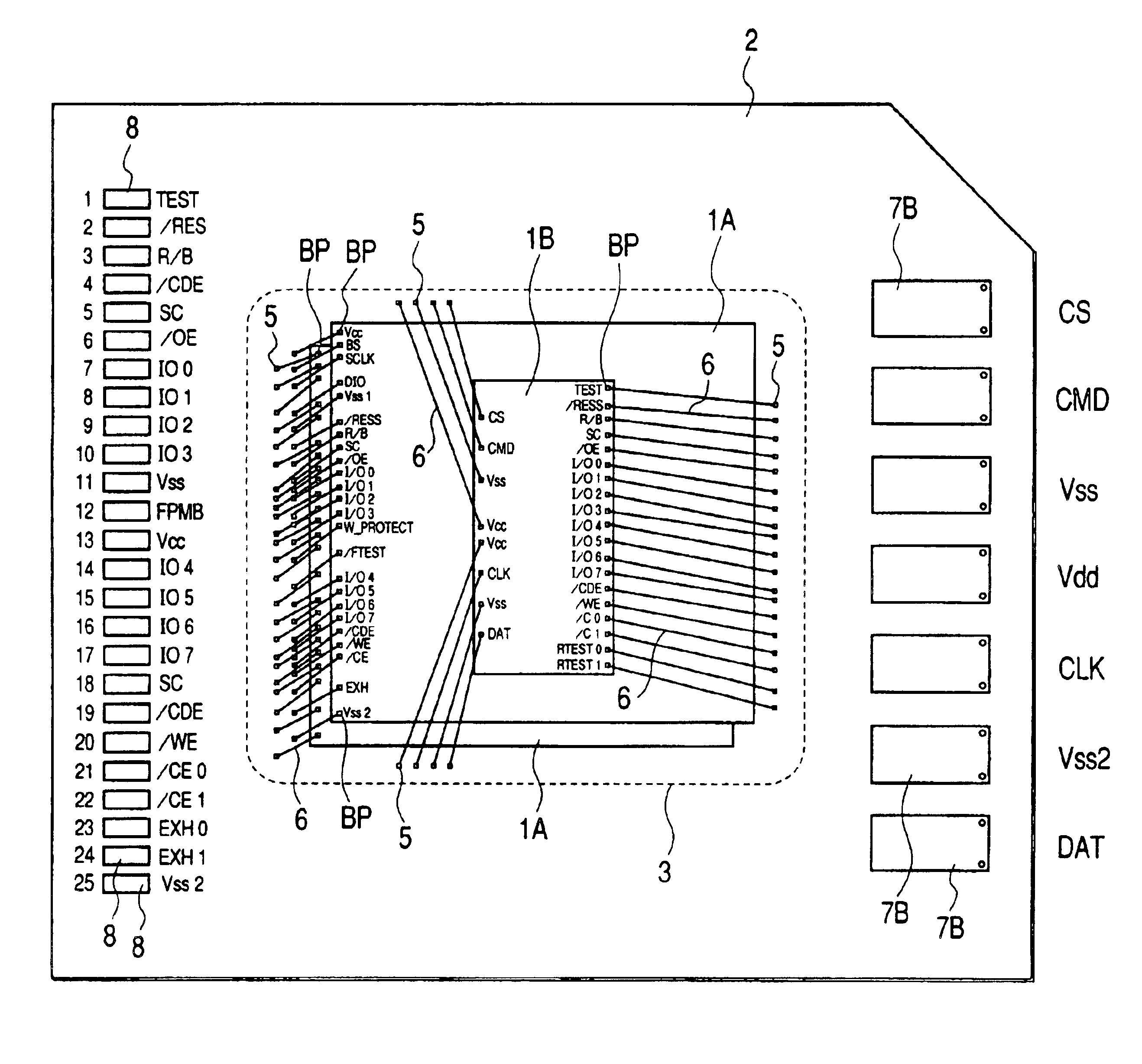

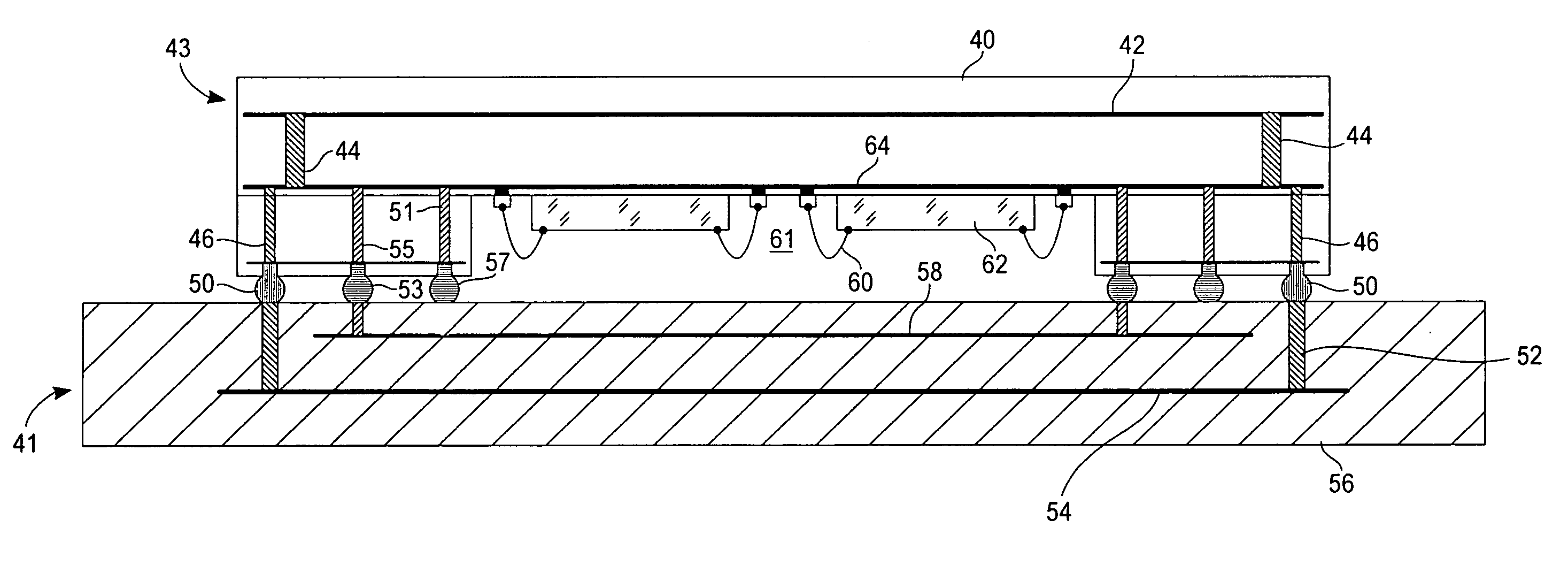

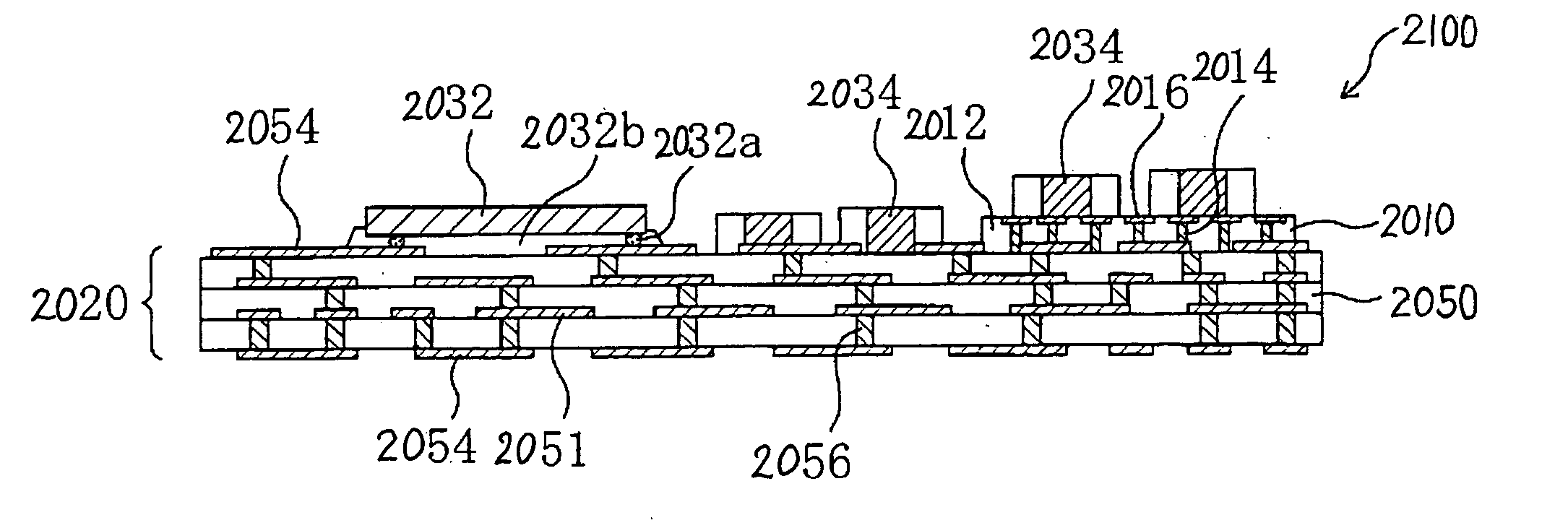

Semiconductor device and a method of manufacturing the same

InactiveUS7061105B2Reduce distanceIncrease in loop heightSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsMemory chipSemiconductor

Two memory chips mounted over a base substrate have the same external size and a flash memory of the same memory capacity formed thereon. These memory chips are mounted over the base substrate with one of them being overlapped with the upper portion of the other one, and they are stacked with their faces being turned in the same direction. The bonding pads BP of one of the memory chips are disposed in the vicinity of the bonding pads BP of the other memory chip. In addition, the upper memory chip is stacked over the lower memory chip in such a way that the upper memory chip is slid in a direction (X direction) parallel to the one side of the lower memory chip and in a direction (Y direction) perpendicular thereto in order to prevent partial overlapping of it with the bonding pads BP of the lower memory chip.

Owner:LONGITUDE LICENSING LTD

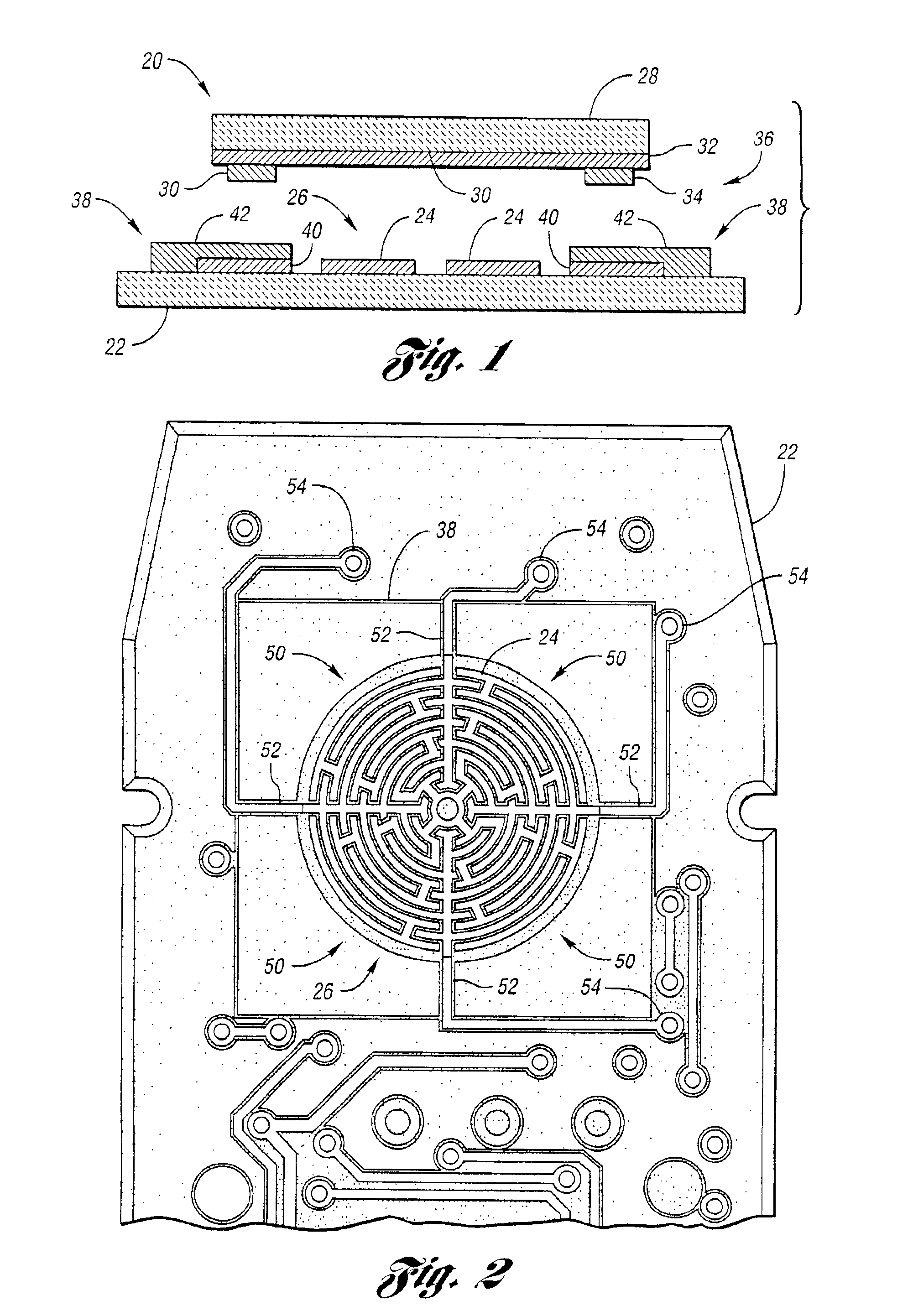

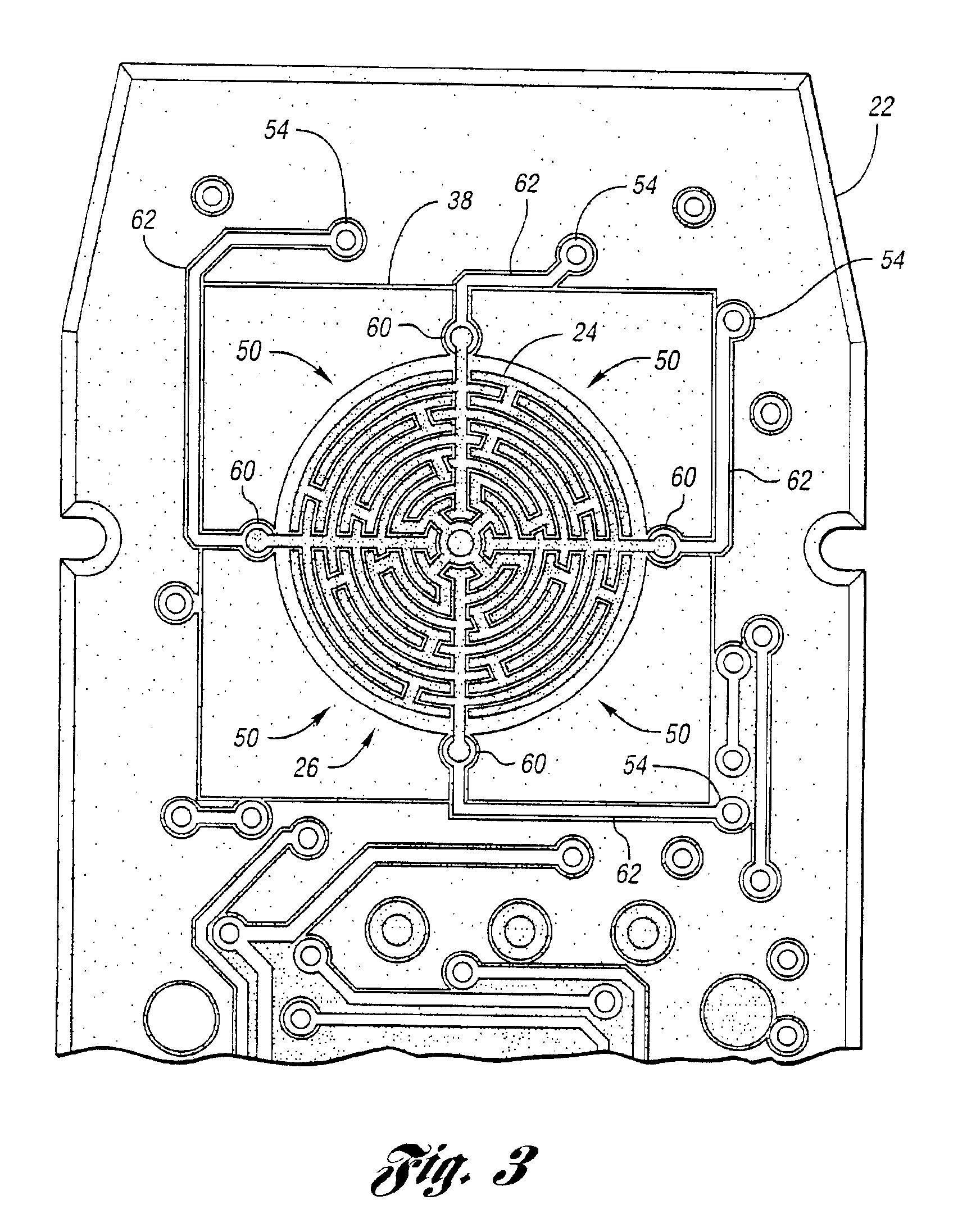

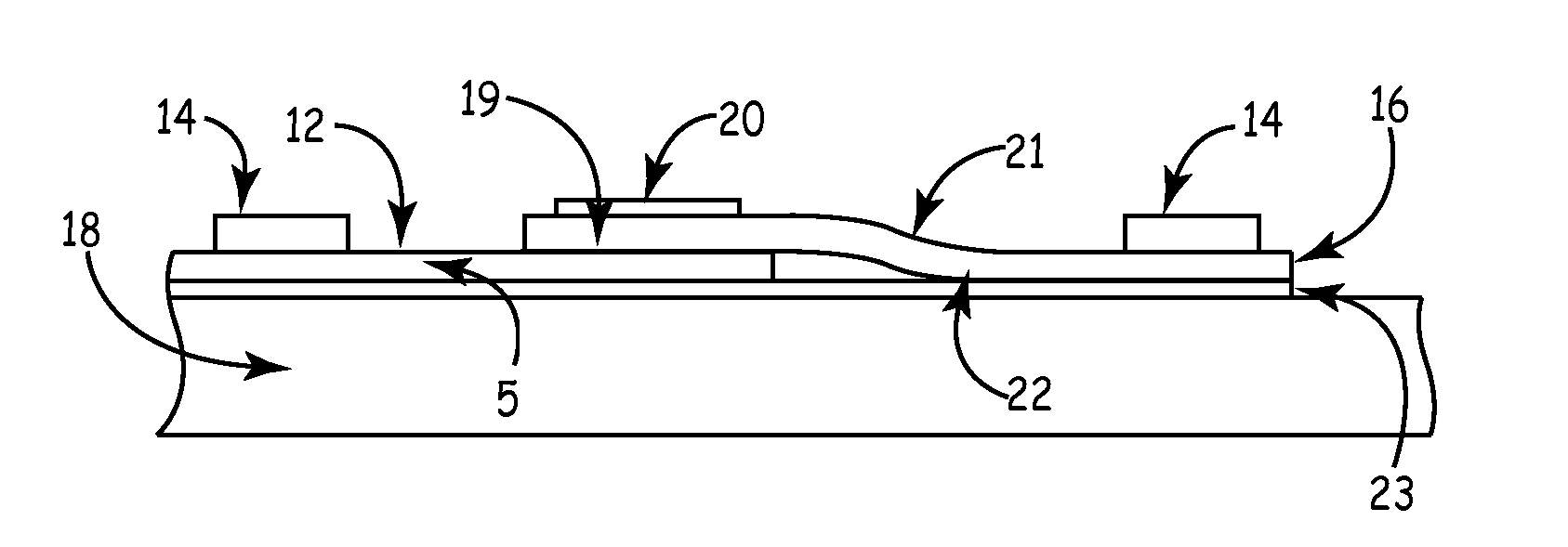

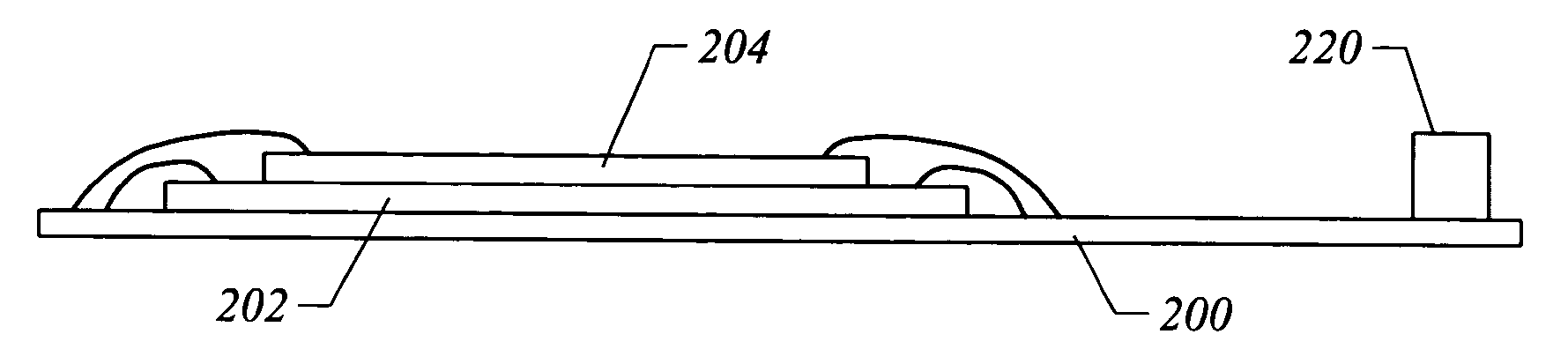

Electronic pressure sensitive transducer apparatus and method for manufacturing same

InactiveUS6909354B2Low costReduce complexityPrinted circuit assemblingPrinted circuit aspectsTransducerEngineering

The cost and complexity of an electronic pressure sensitive transducer are decreased by constructing such a transducer directly on a printed circuit board containing support electronics. Conductive traces are formed on the printed circuit board to define a contact area. A flexible substrate having an inner surface is positioned over the contact area. An adhesive spacer, substantially surrounding the contact area, attaches the flexible substrate to the printed circuit board. At least one resistive layer is deposited on the flexible substrate inner surface. In use, the resistive layer contacts at least two conductive traces in response to pressure applied to the flexible substrate to produce an electrical signal indicative of applied pressure.

Owner:INTERLINK ELECTRONICS

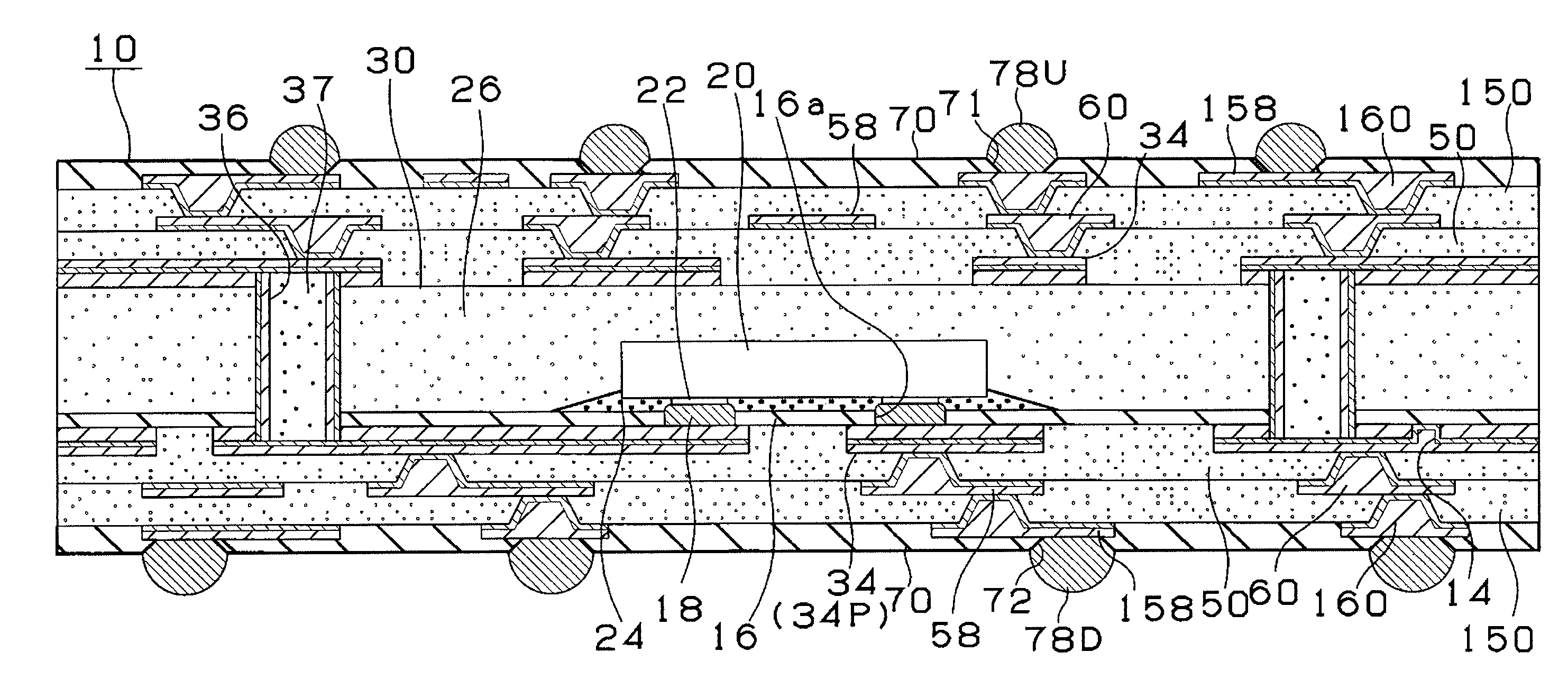

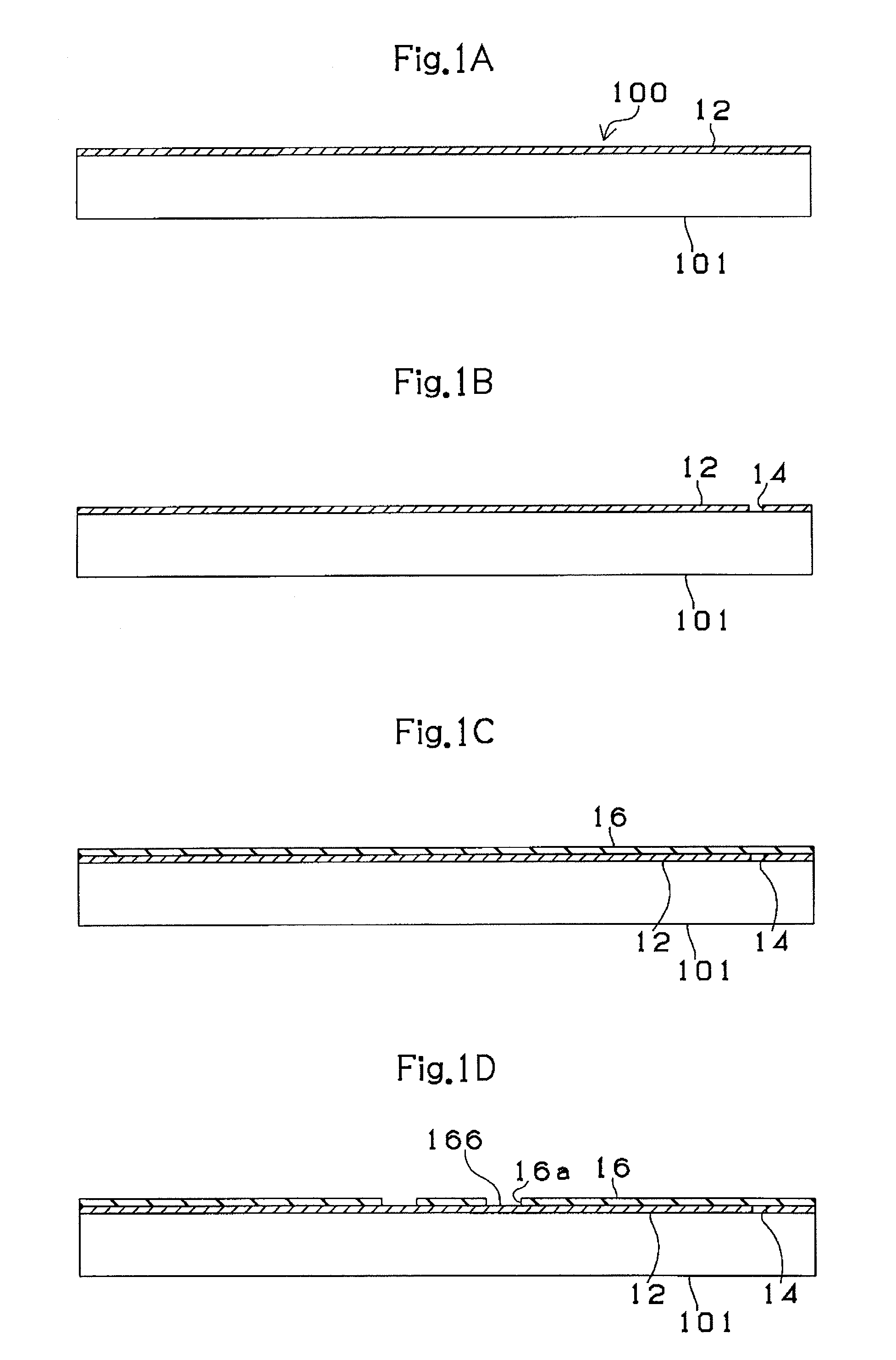

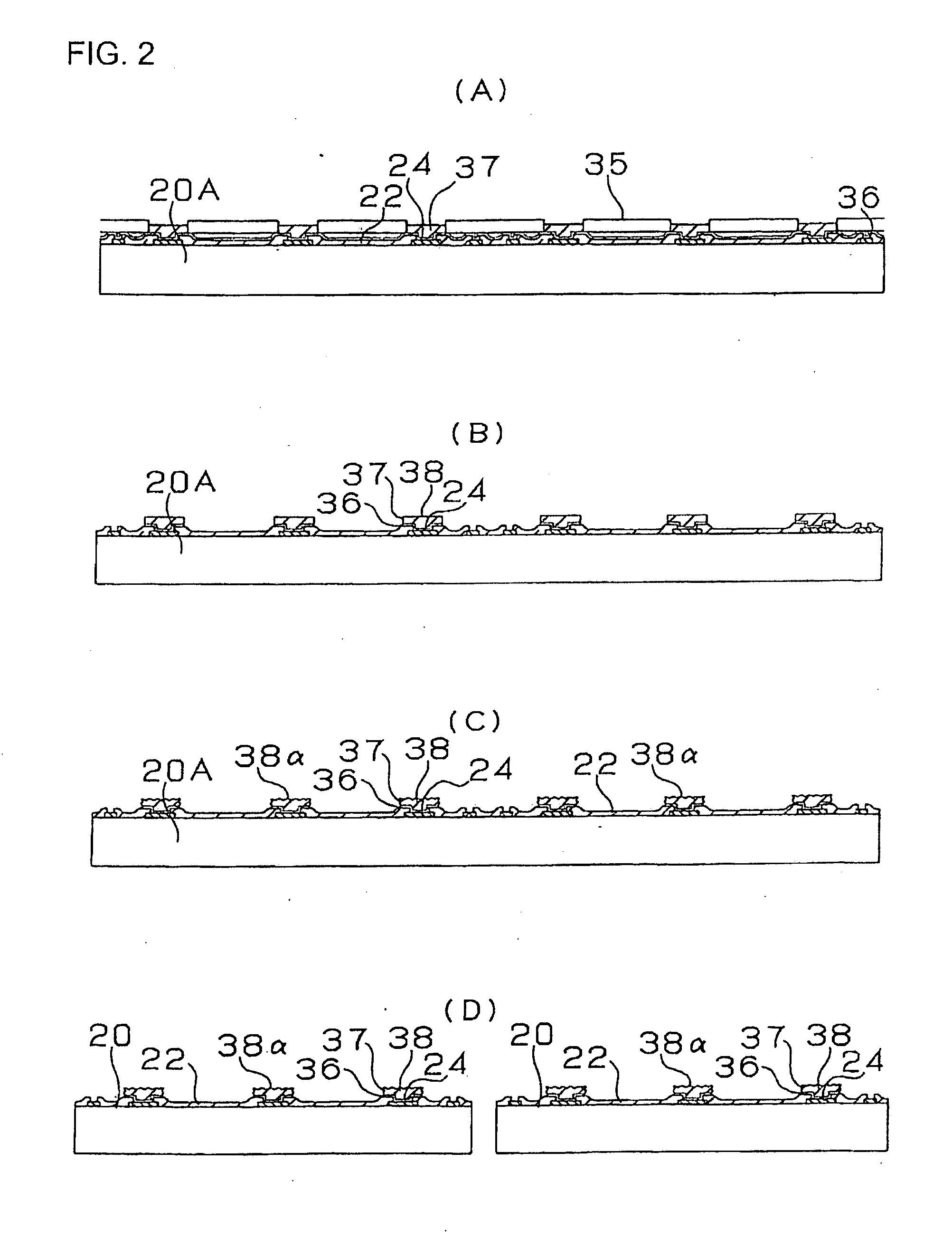

Printed wiring board with built-in electronic component and manufacturing method thereof

ActiveUS20090293271A1Printed circuit assemblingSemiconductor/solid-state device detailsInsulation layerMetal foil

A printed wiring board is manufactured by a method in which an alignment mark is formed in a metal foil, a bump is formed on the metal foil at a position determined based on the alignment mark, an electronic component is aligned with the bump based on the alignment mark, the electronic component is connected with the bump, and an insulation layer is formed over the electronic component.

Owner:IBIDEN CO LTD

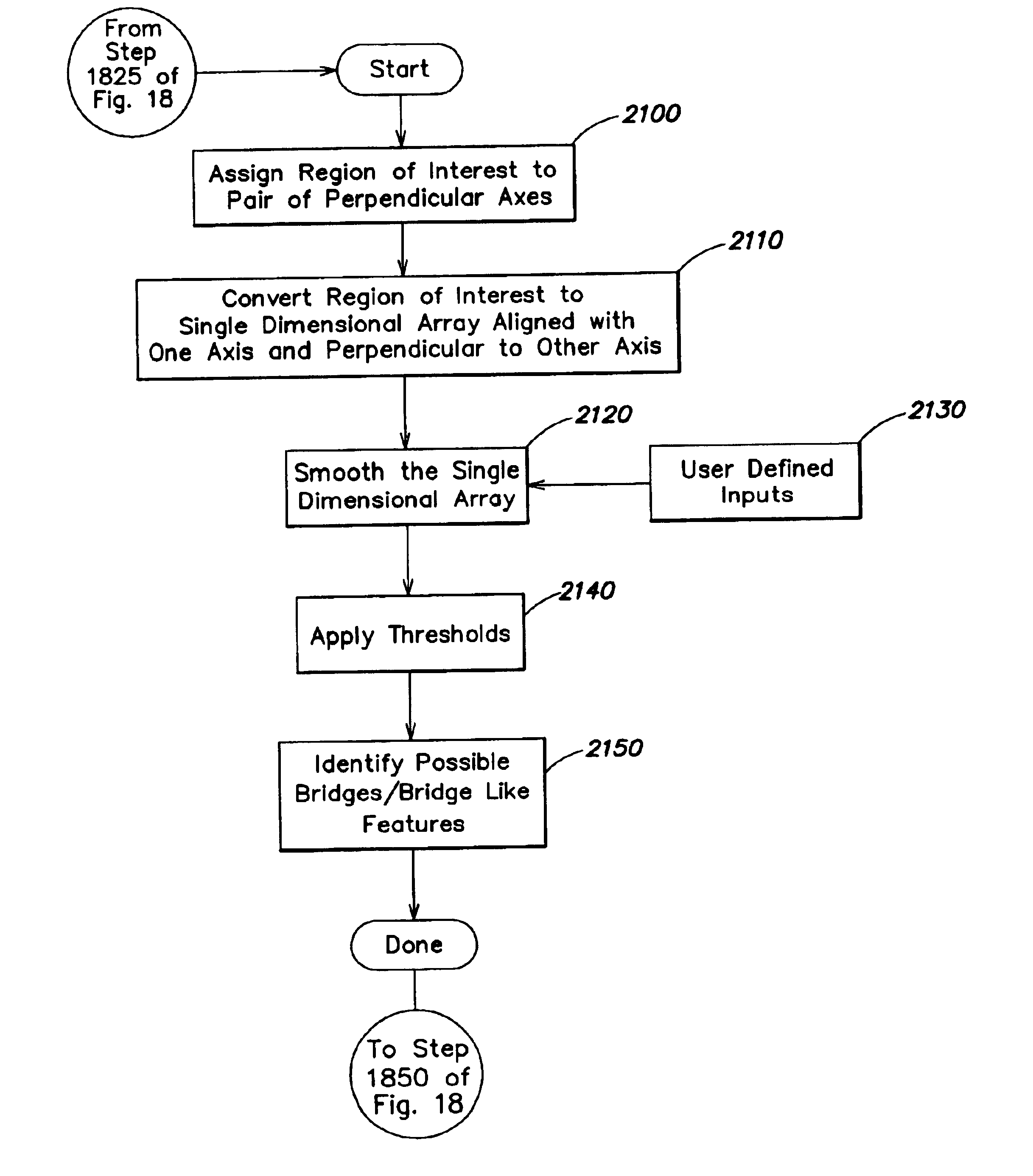

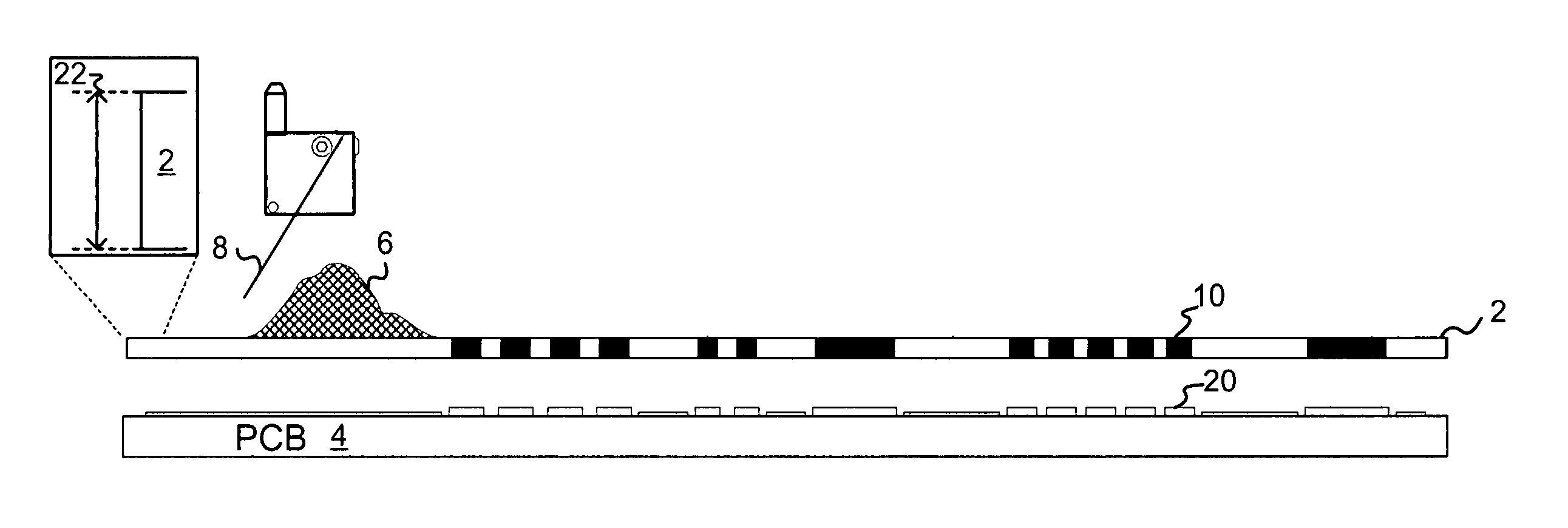

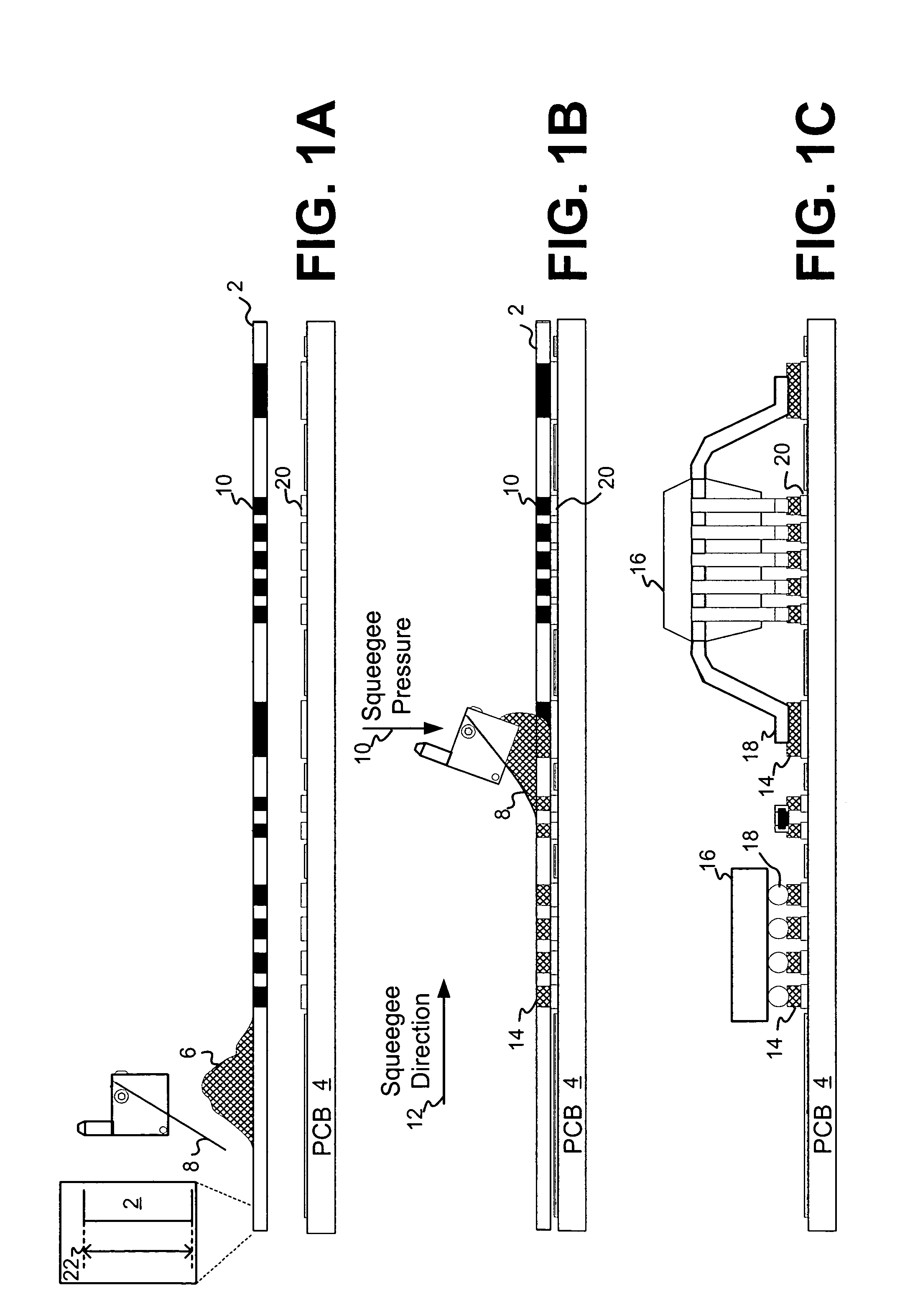

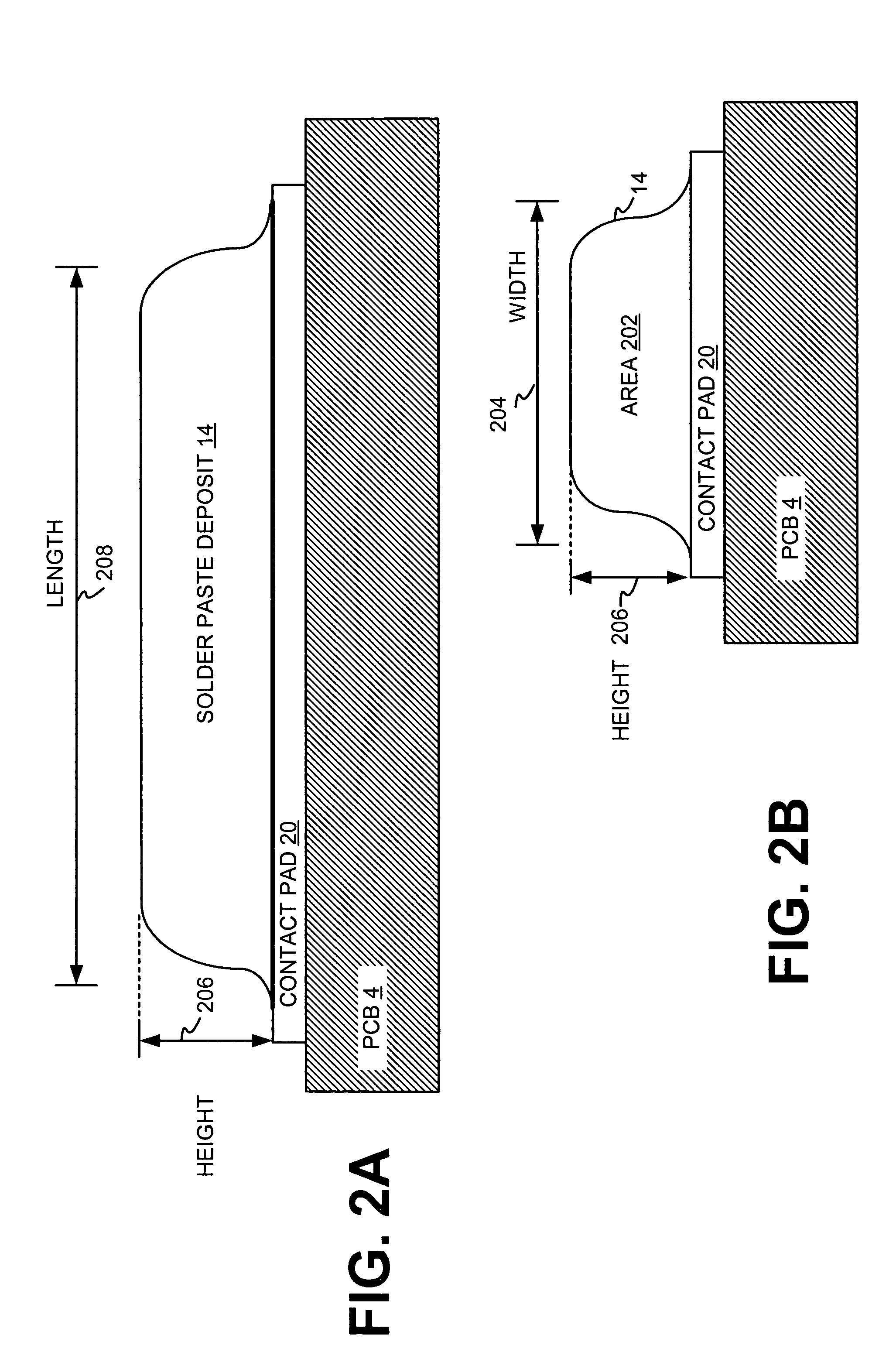

Systems and methods for detecting defects in printed solder paste

InactiveUS6891967B2Easy to detectEasy to controlImage enhancementImage analysisSolder pasteRegion of interest

A method of analyzing an image of a substance deposited onto a substrate, the image comprising a plurality of pixels, includes defining a region of interest in the image, associating the region of interest with first and second perpendicular axis, wherein a set of pixels in the image lie along the first axis, converting the pixels in the region of interest to a single dimensional array aligned with the first axis and projecting along the second axis, and applying at least one threshold to the single dimensional array, the threshold based at least in part on a predetermined limit.

Owner:KPS SPECIAL SITUATIONS FUND II LP

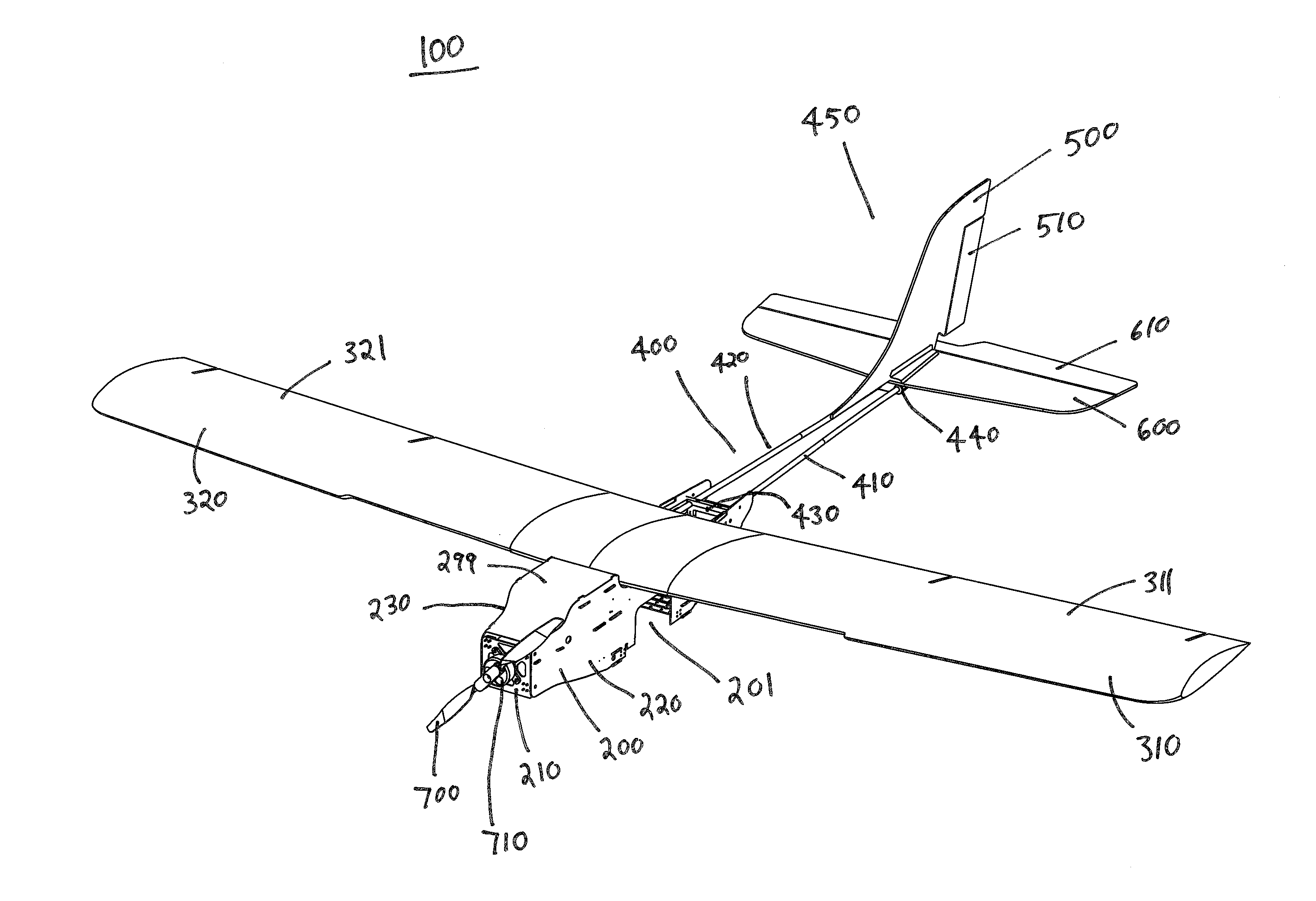

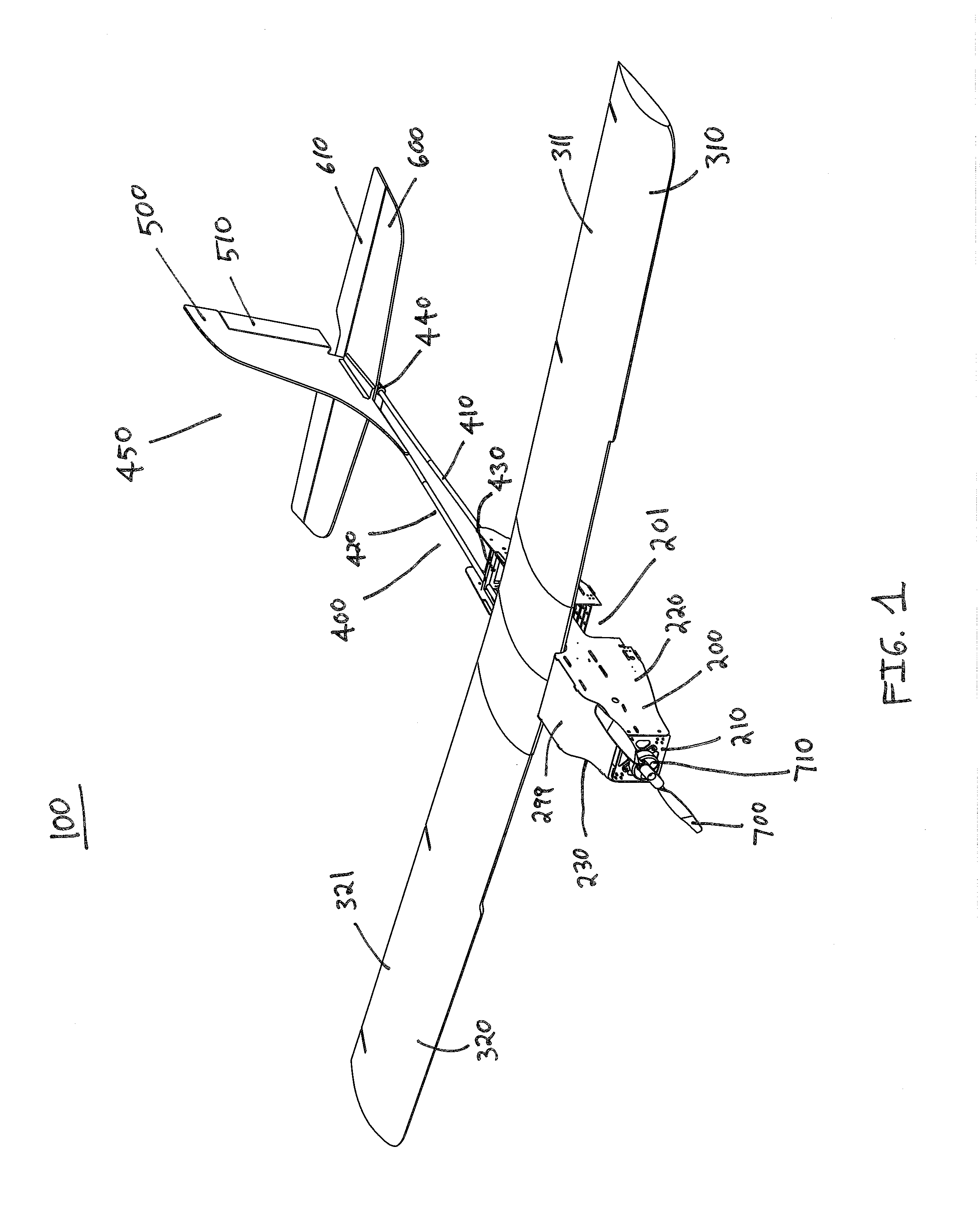

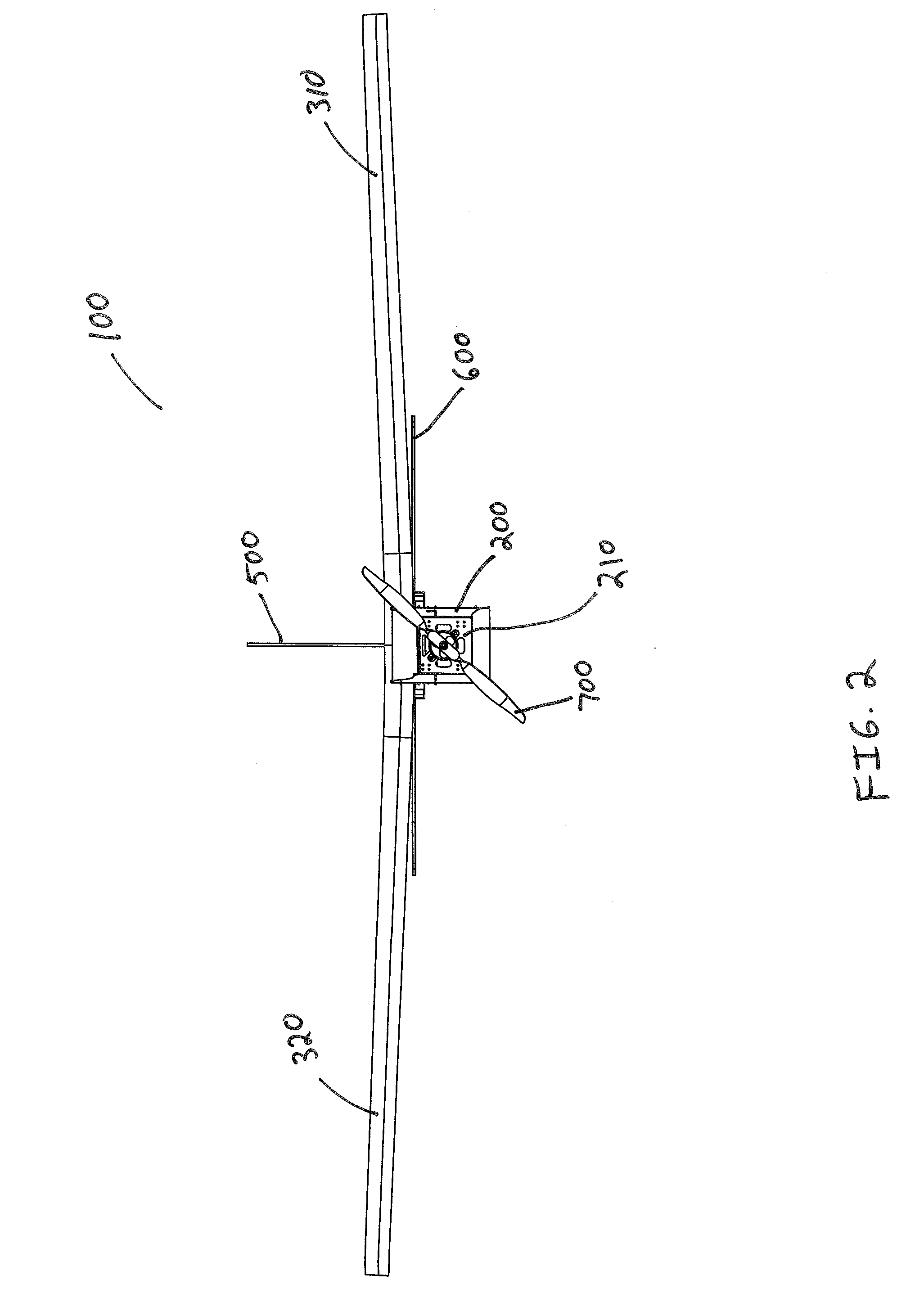

Unmanned aerial vehicle

An unmanned aerial vehicle, comprising: a fuselage having a first side board and a second side board spaced apart and connected by at least one transverse board; the first side board, the second side board, and the at least one transverse board being printed circuit boards; at least one of the first side board, the second side board, and the at least one transverse board having formed and mounted thereon conductive traces and at least one component, respectively, for controlling and monitoring the unmanned aerial vehicle; first and second wings mounted to the fuselage; and, a tail mounted to the fuselage.

Owner:PRECISIONHAWK

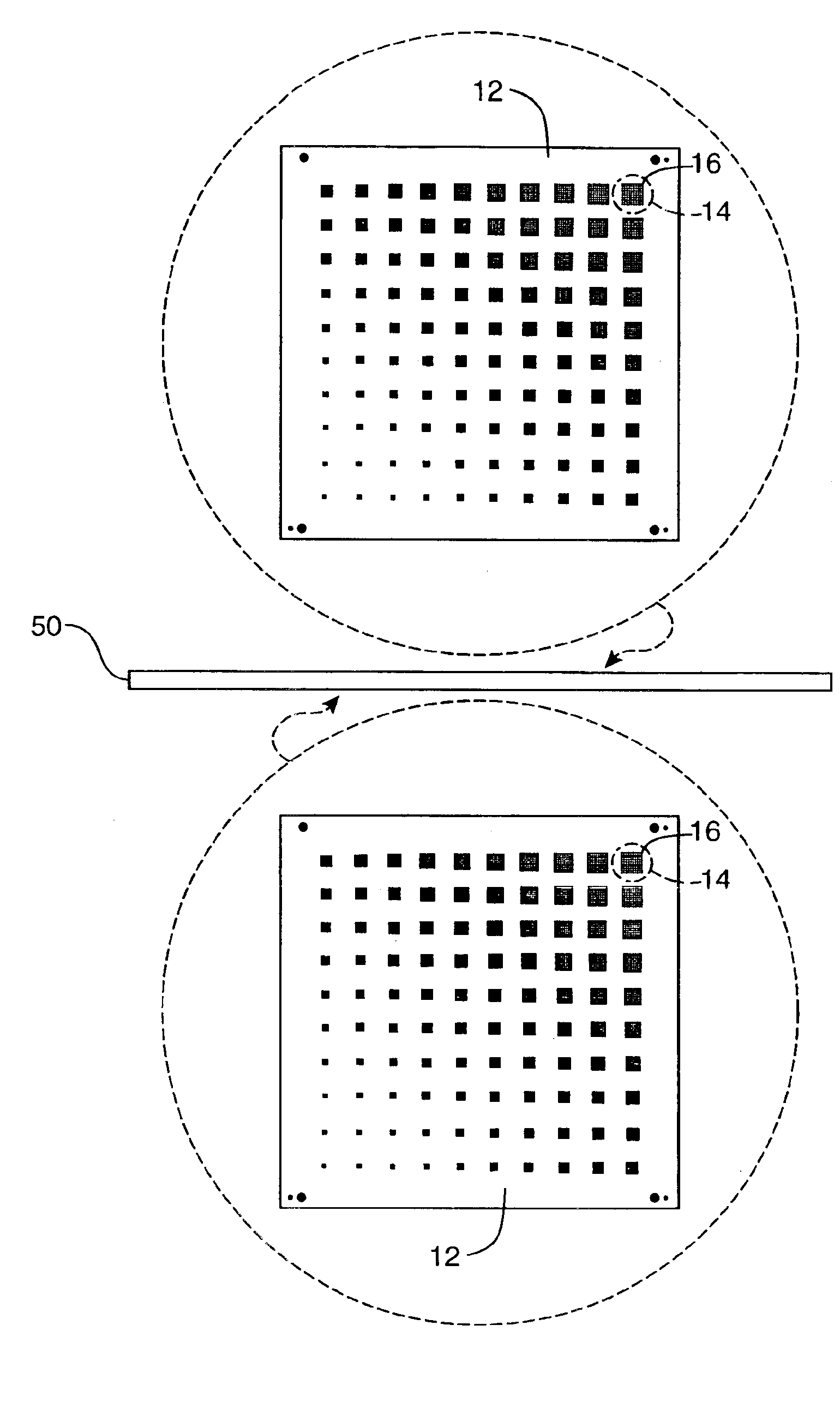

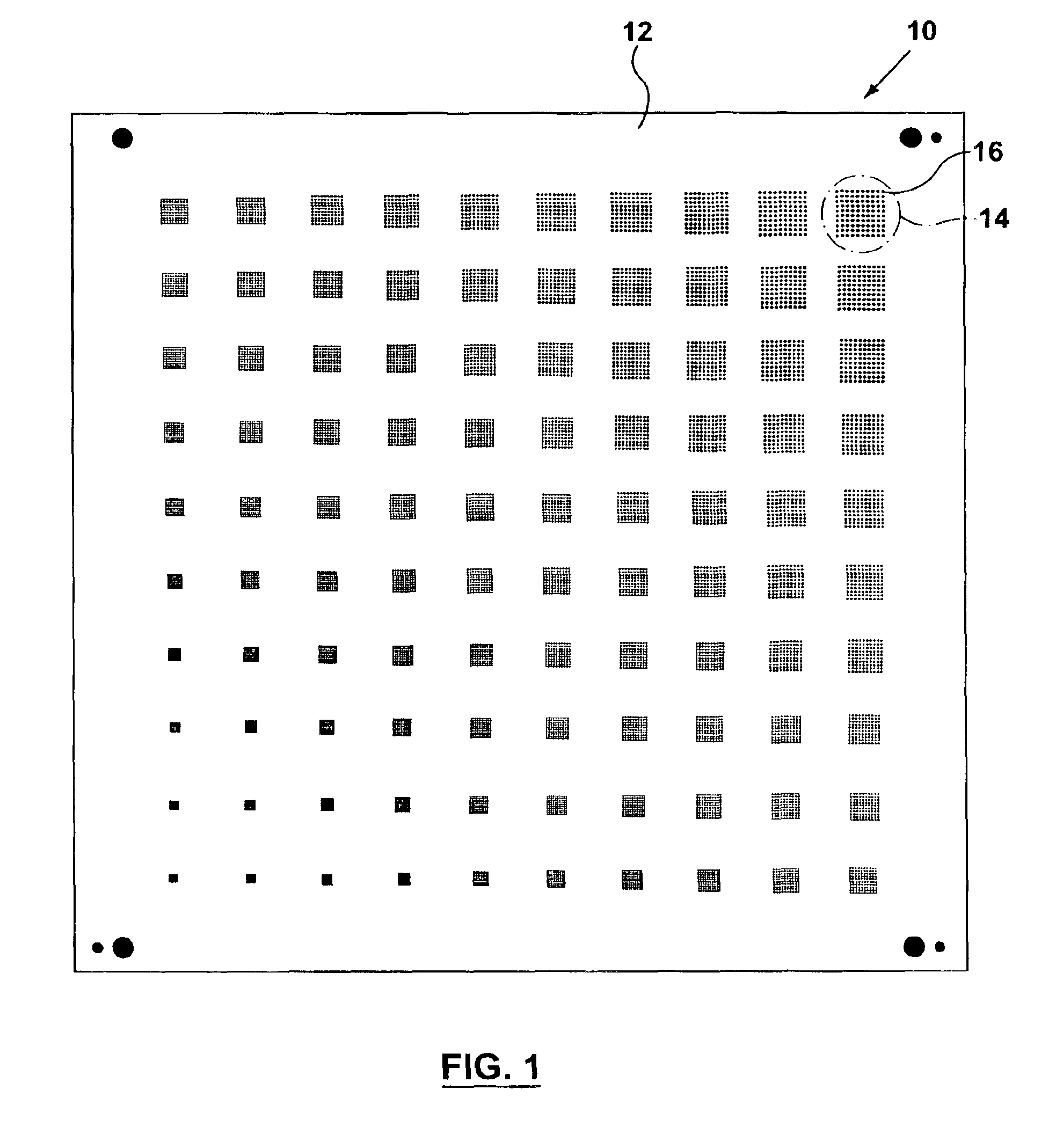

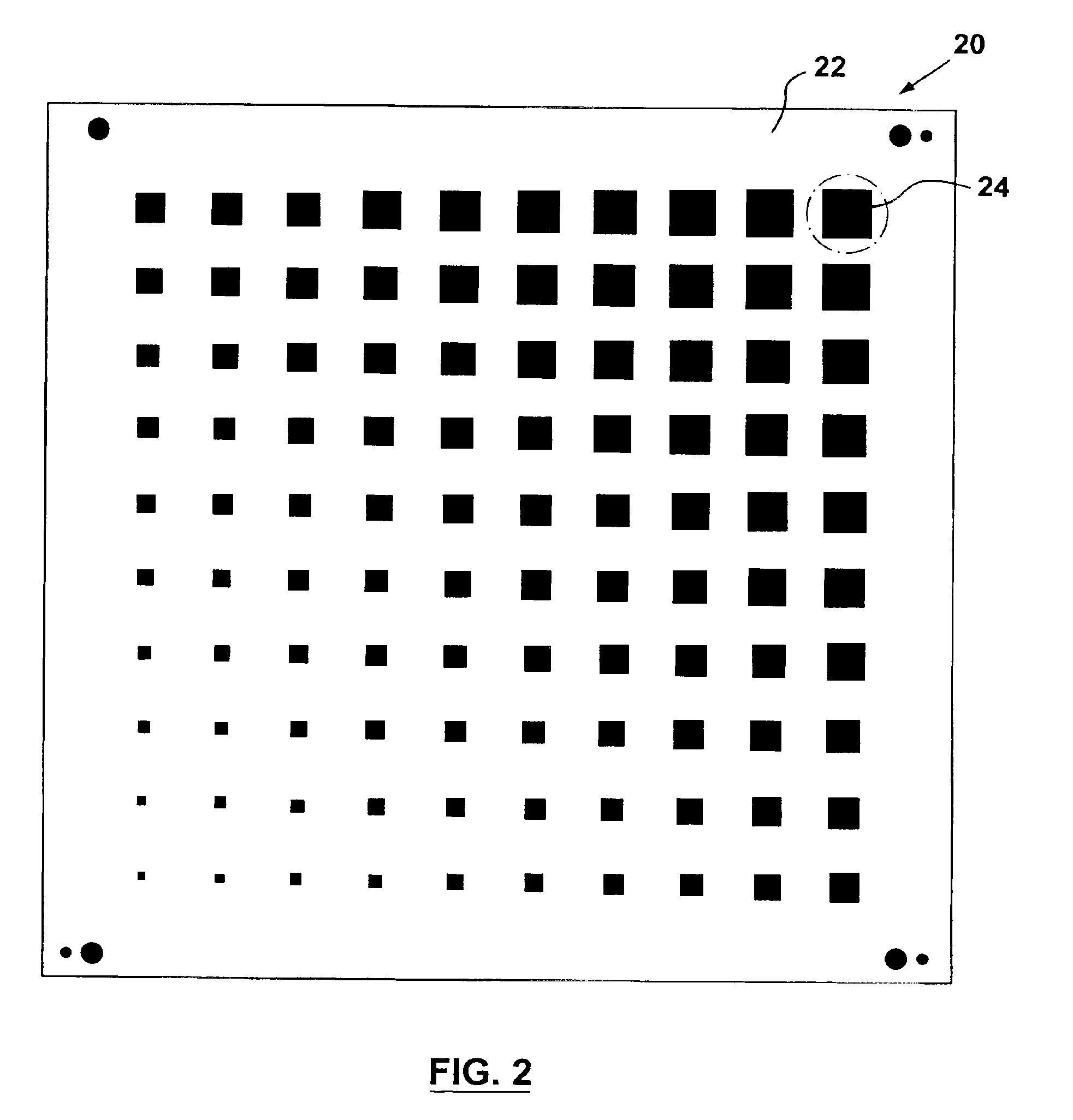

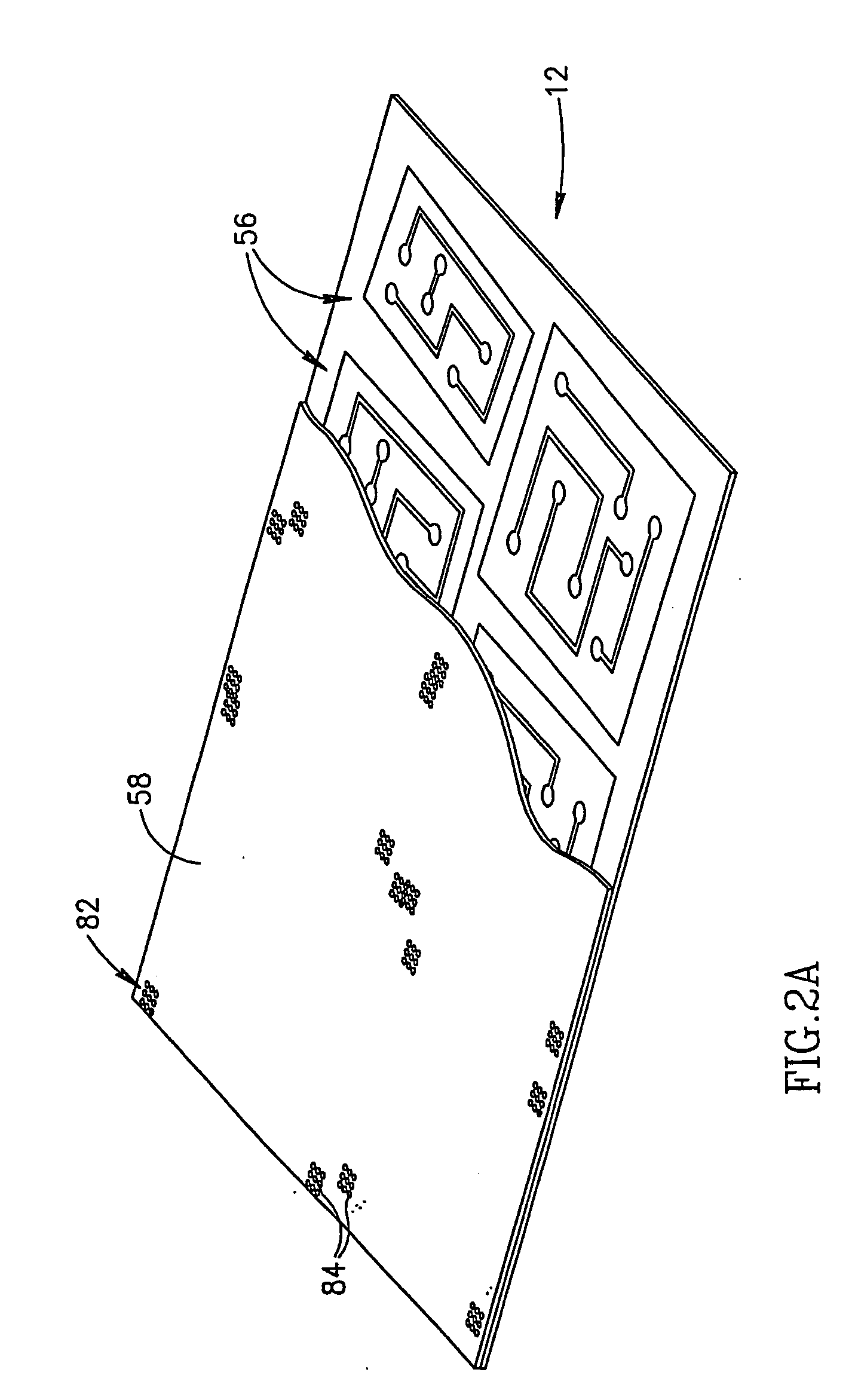

Surface mount technology evaluation board having varied board pad characteristics

ActiveUS6888360B1Final product manufacturePrinted circuit aspectsEngineeringSurface-mount technology

This invention provides an evaluation board for evaluating one or more aspects of a surface mount technology system. In one aspect, the evaluation board has a substrate with at least one surface. A plurality of board pad patterns, each including a plurality of board pads, is formed on the surface. The different board pad patterns may have different shaped, sized and spaced board pads, allowing the characteristics of a surface mount technology to be tested on some or all of the board pad patterns at the same time and under uniform conditions. In another aspect, the surface may have a plurality of area-filled board pads similarly allowing a surface mount technology to be tested on the various area-filled board pads.

Owner:MALIKIE INNOVATIONS LTD

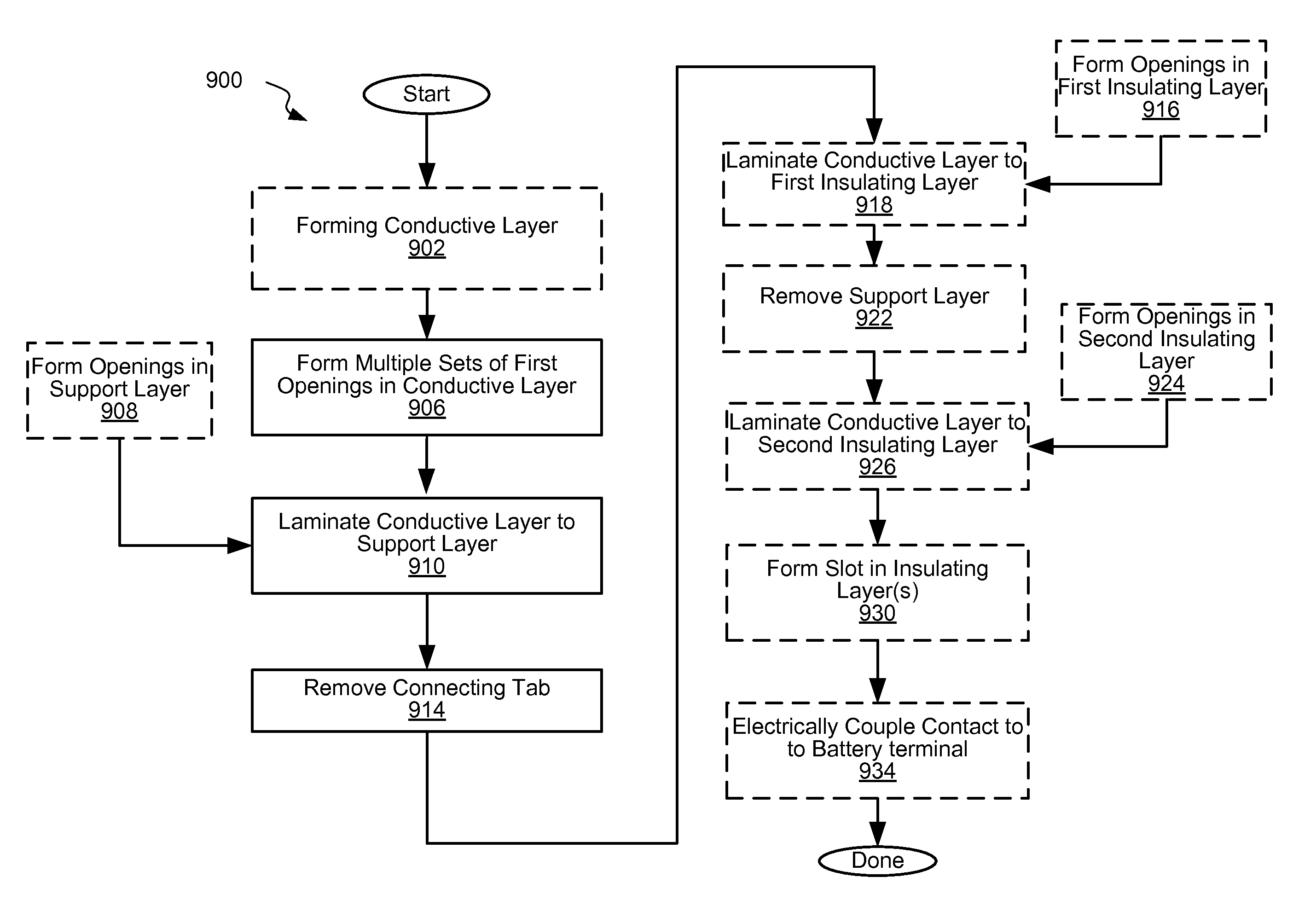

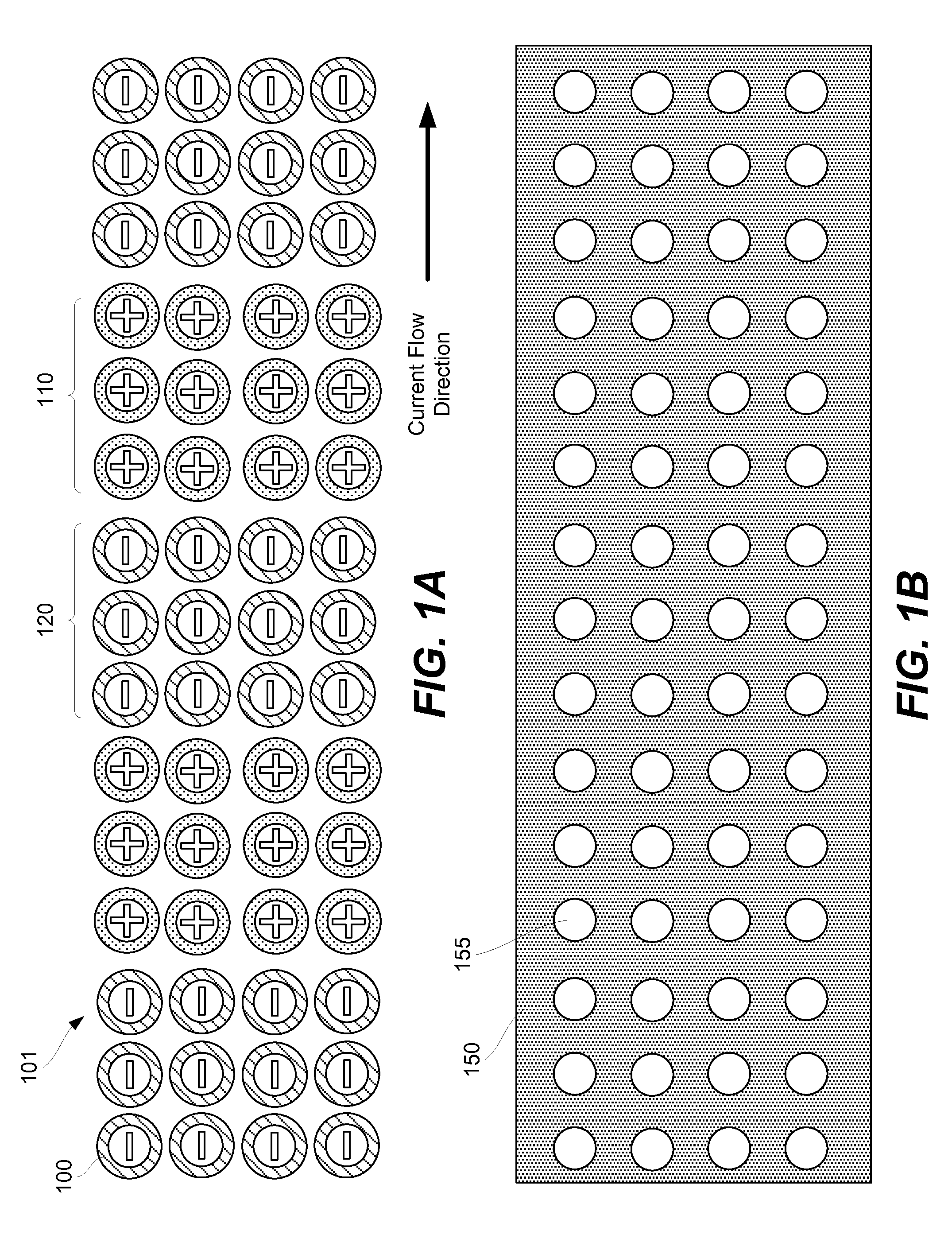

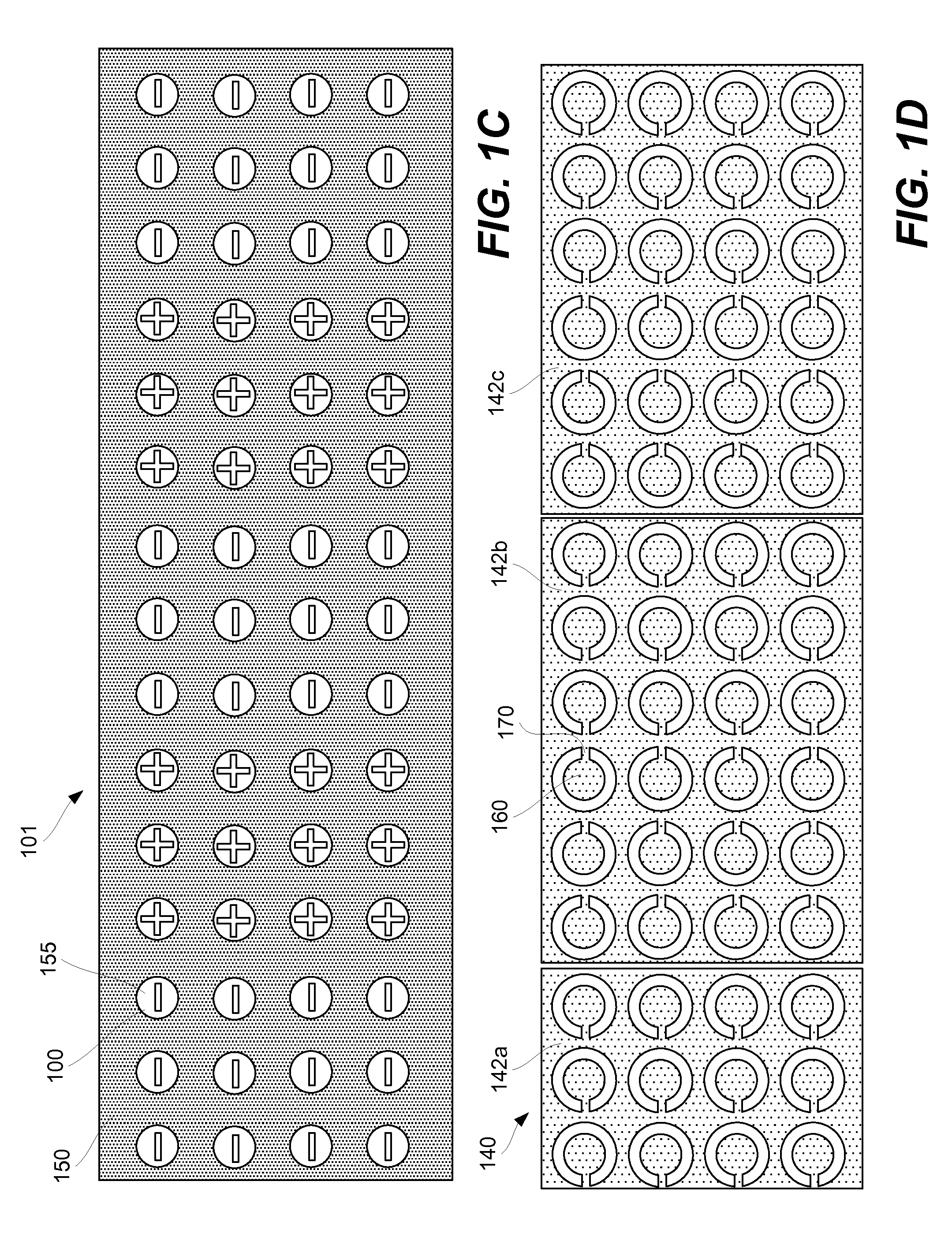

Interconnect for battery packs

ActiveUS9147875B1Increase flexibilityInhibited DiffusionBatteries circuit arrangementsElectrode manufacturing processesContact padElectrical connection

Provided are interconnect circuits for interconnecting arrays of battery cells and methods of forming these interconnect circuits as well as connecting these circuits to the battery cells. An interconnect circuit may include a conductive layer and one or more insulating layers. The conductive layer may be patterned with openings defining contact pads, such that each pad is used for connecting to a different battery cell terminal. In some embodiments, each contact pad is attached to the rest of the conductive layer by a fusible link formed from the same conductive layer as the contact pad. The fusible link controls the current flow to and from this contact pad. The insulating layer is laminated to the conductive layer and provides support to the contacts pads. The insulating layer may also be patterned with openings, which allow forming electrical connections between the contact pads and cell terminals through the insulating layer.

Owner:CELLINK

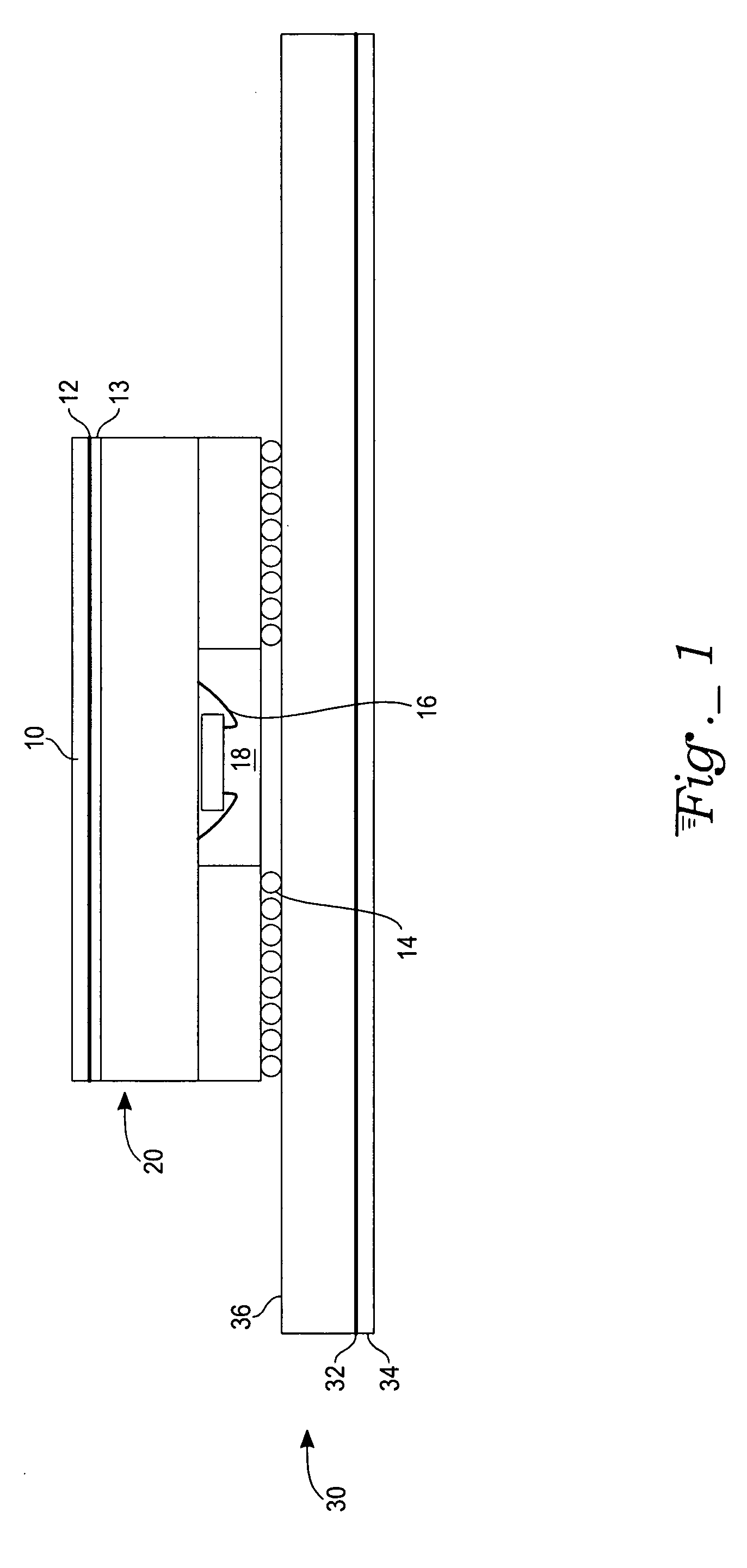

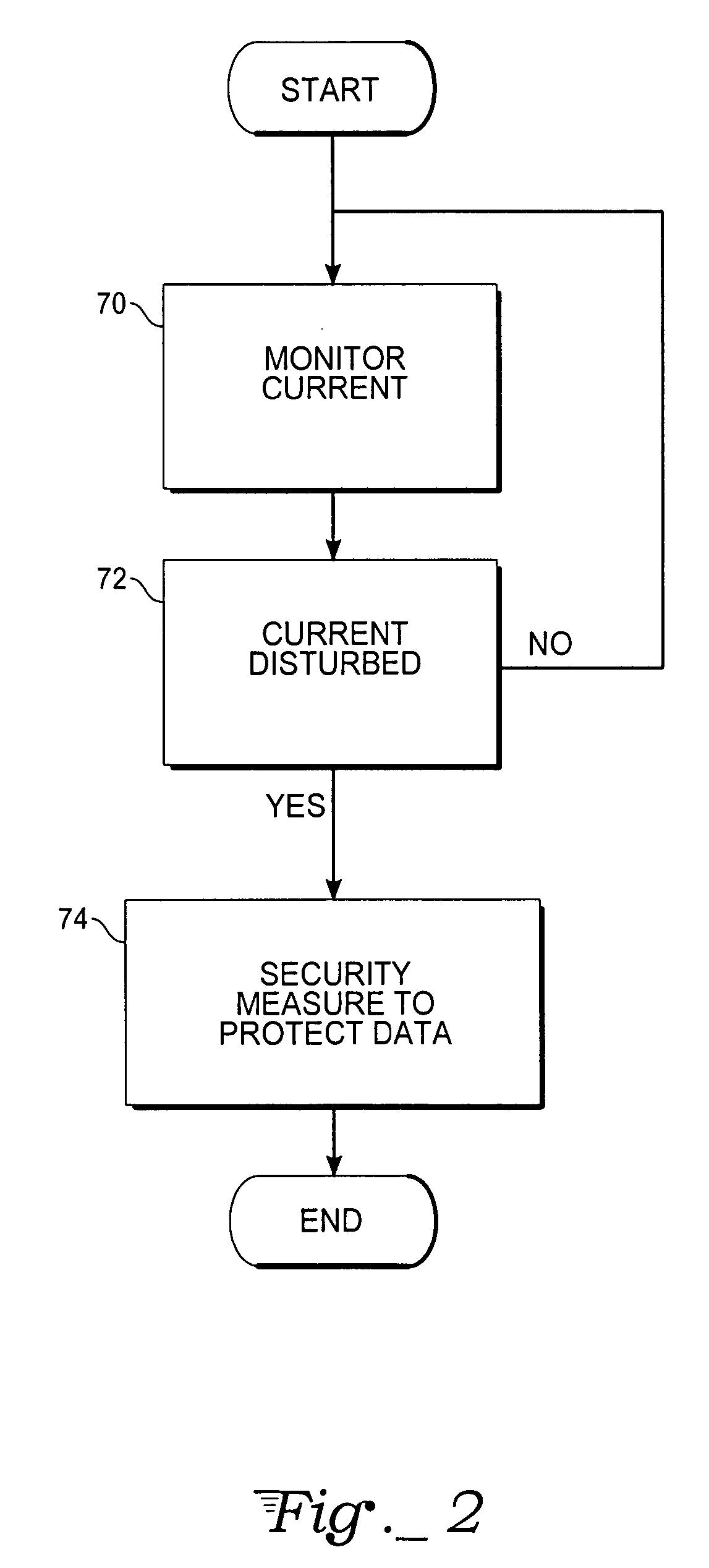

Security method for data protection

InactiveUS20070018334A1Avoid accessMagnetic/electric field screeningSemiconductor/solid-state device detailsEngineeringData storing

A method and device for data security including a printed circuit board and an integrated circuit each having a conductive trace layer shielded by a electrical shield layer. Tampering with either side of the device causes disturbance of a current flowing through a conductive trace layer used as an electrical shield. This triggers a security circuit to erase the data stored in the integrated circuit and stop data flow between the printed circuit board and the integrated circuit.

Owner:RAMBUS INC

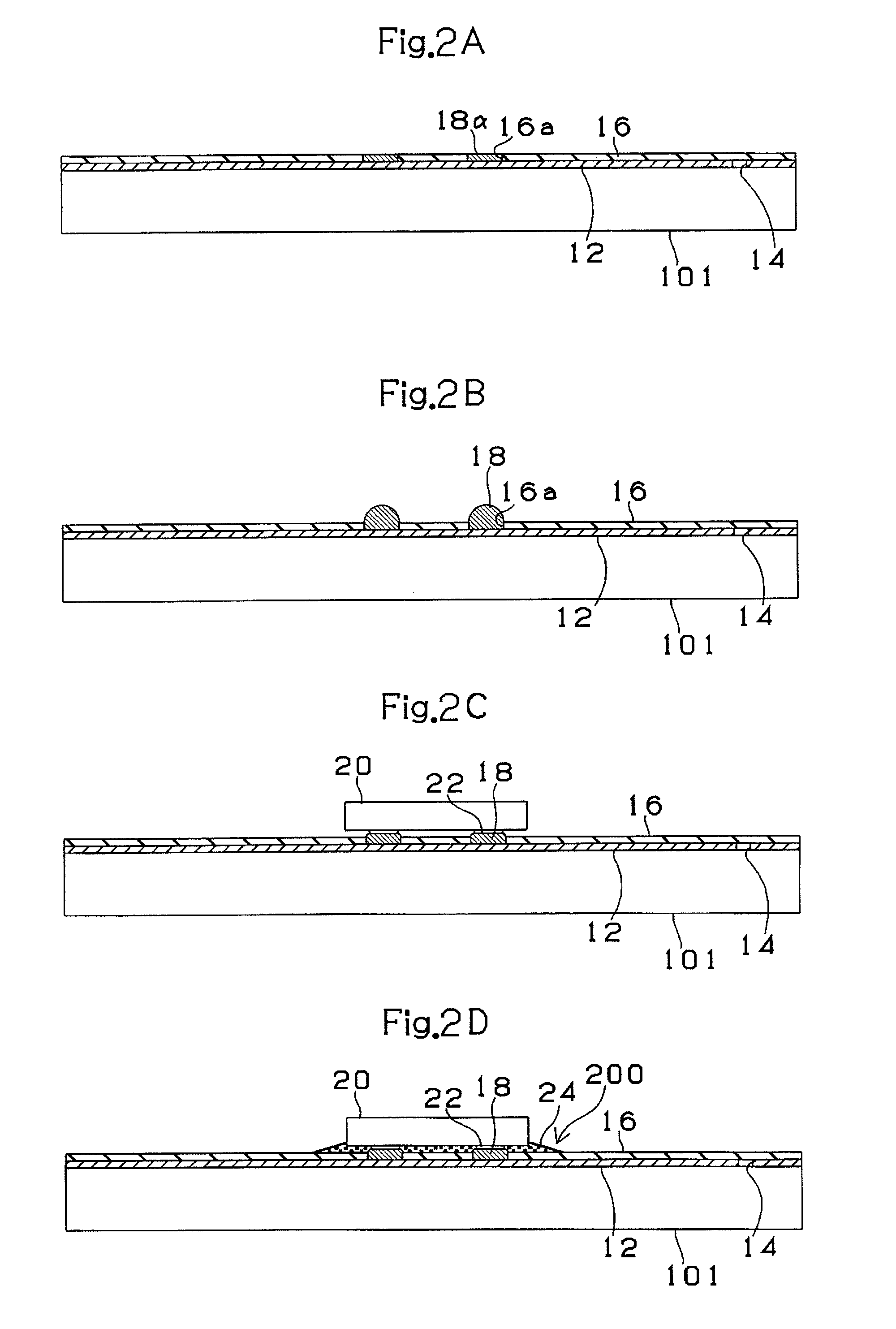

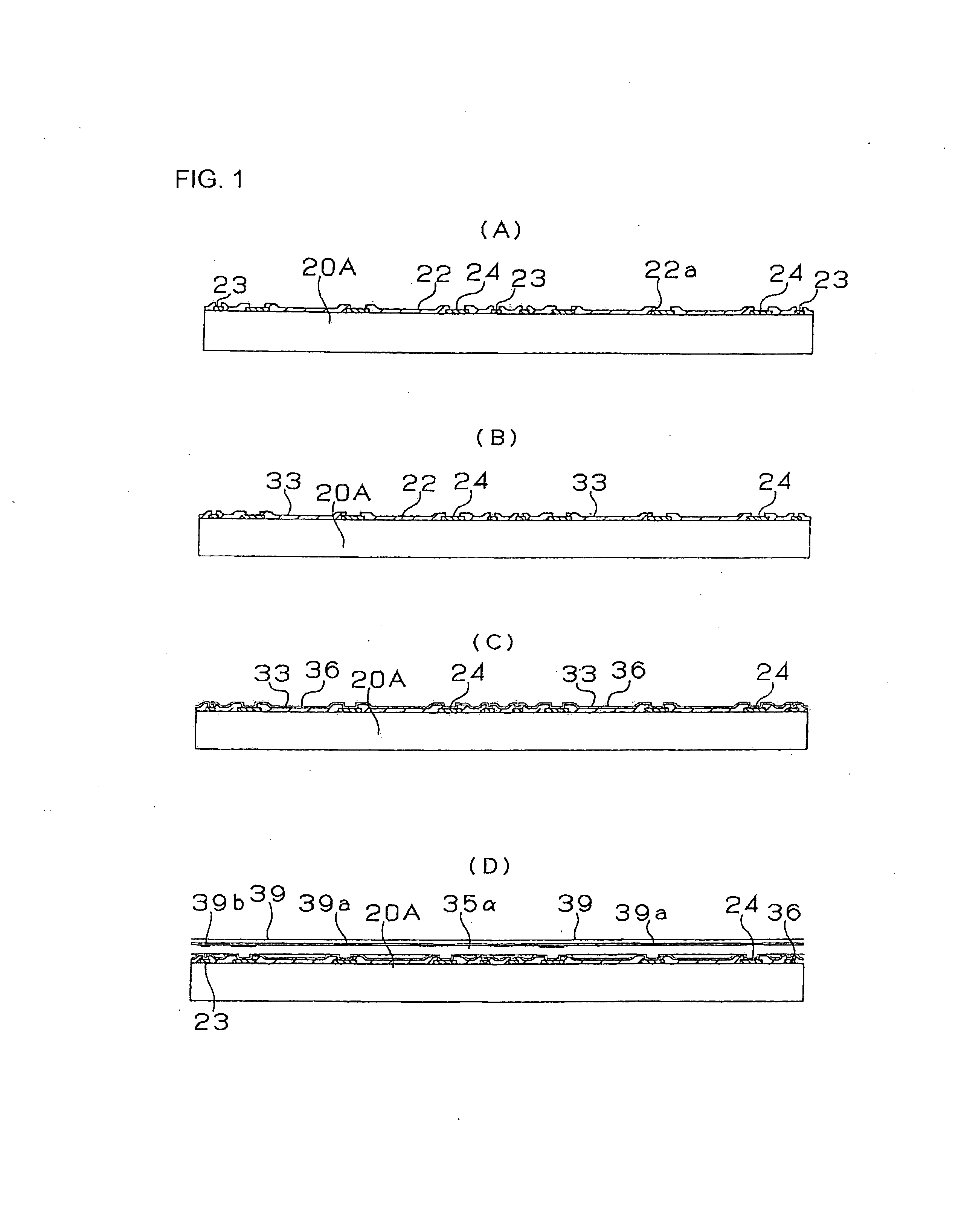

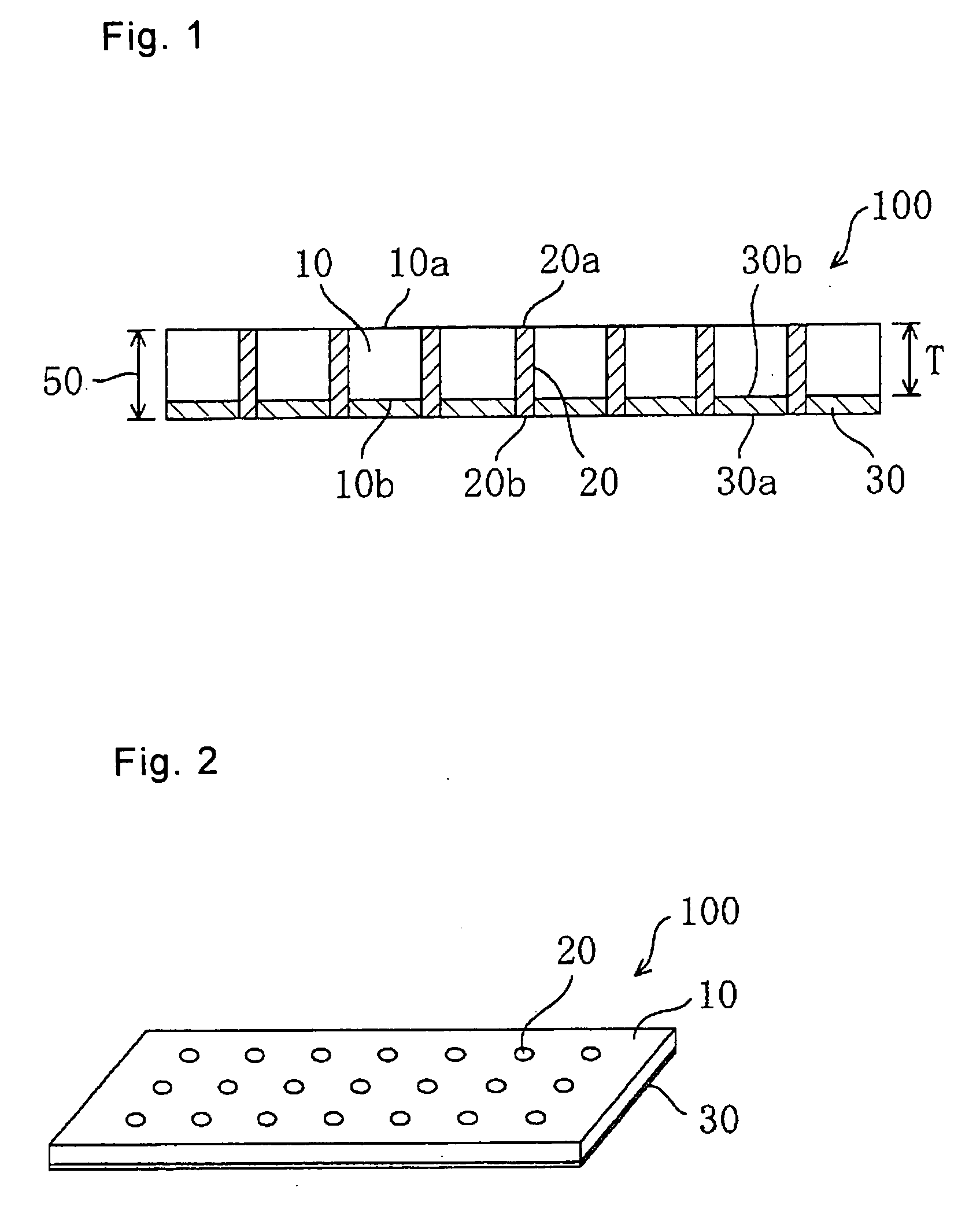

Method for manufacturing multilayer printed wiring board

ActiveUS20090244865A1Accurate connectionPrinted circuit assemblingFinal product manufactureElectrical conductorElectronic component

A method for manufacturing a multilayer printed wiring board having an electronic component housed therein includes forming a first conductor circuit on a first surface of a substrate. A first alignment mark is formed on the first surface of the substrate separate from the conductor circuit and forming a through bore in the substrate, the through bore extending from the first surface of the substrate to a second surface of the substrate. A seal member is disposed on the second surface of the substrate, the seal member sealing an opening on the second surface of the through bore to provide a sealed through bore. An electronic component is inserted in the sealed through bore using the first alignment mark on the first surface of the substrate.

Owner:IBIDEN CO LTD

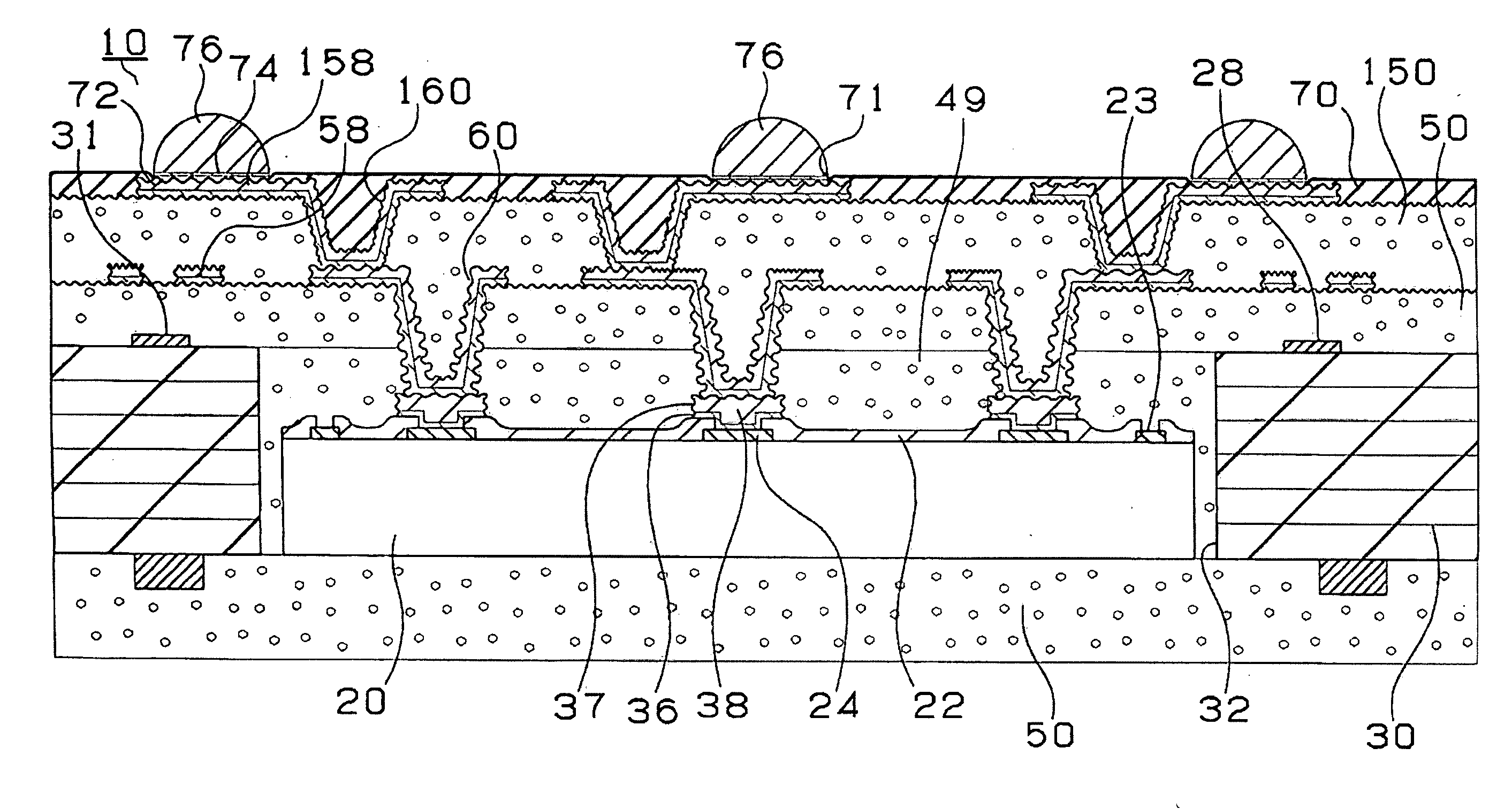

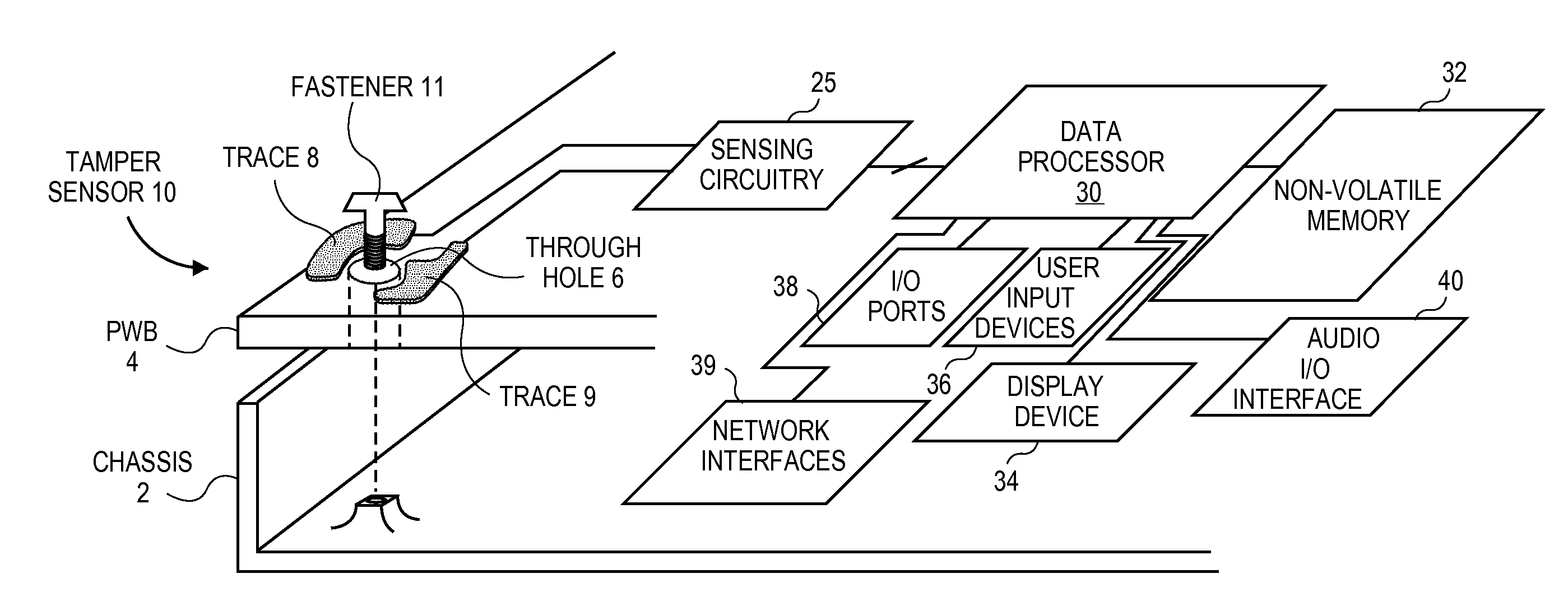

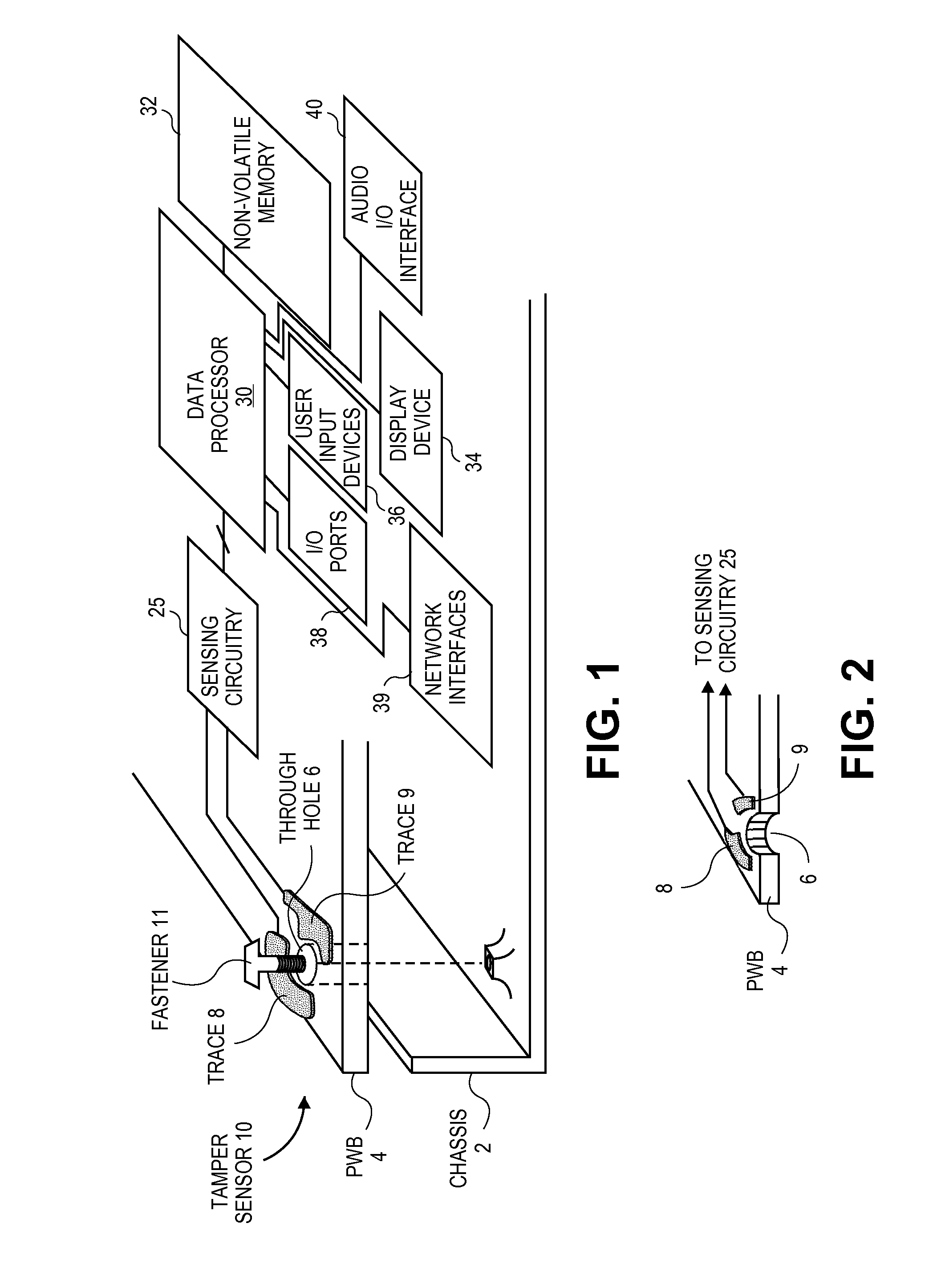

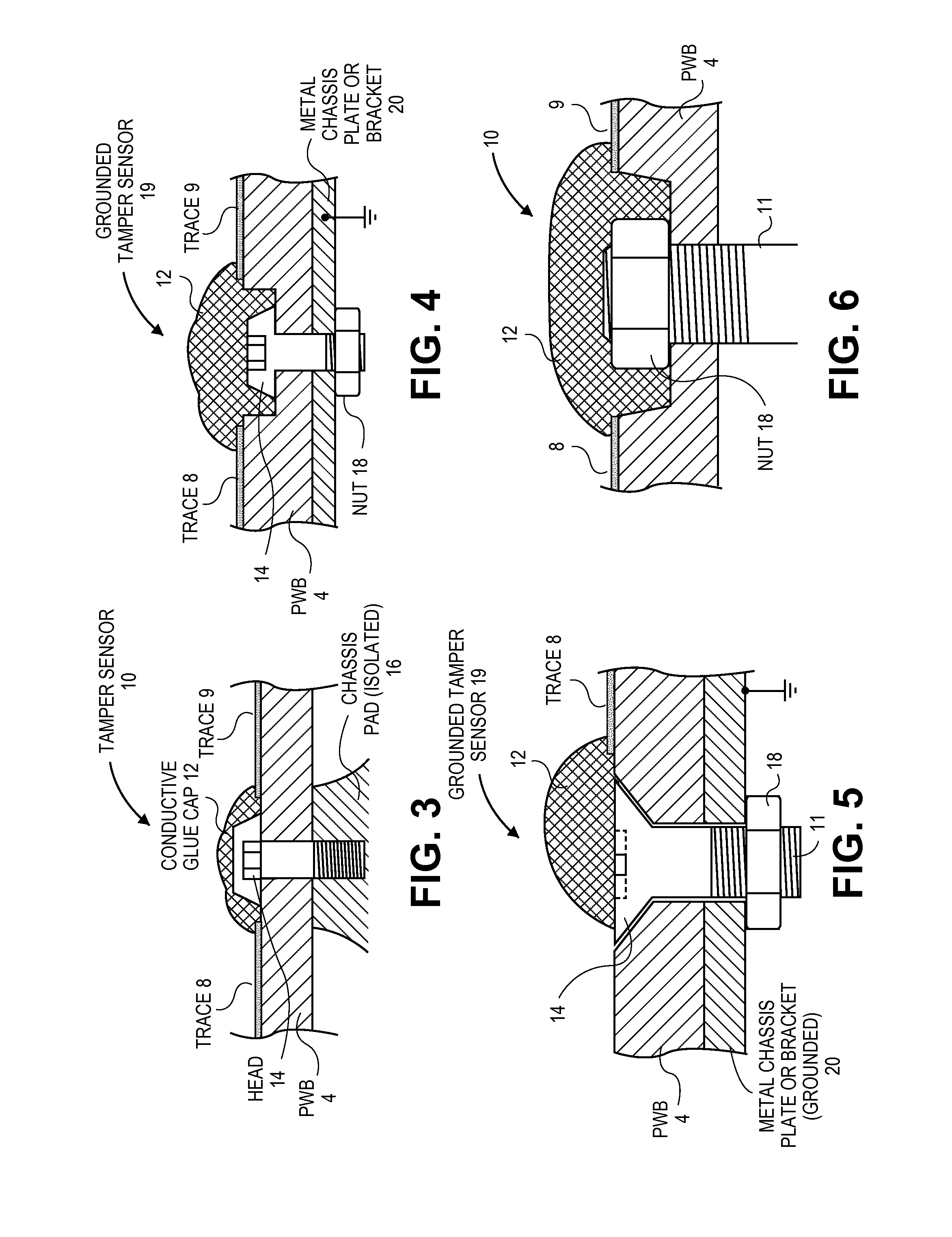

Mechanisms for detecting tampering of an electronic device

ActiveUS20110031985A1Electrical testingInternal/peripheral component protectionElectronic equipmentFastener

An electronic device has a chassis, and a printed wiring board (PWB) having a hole. A fastener is installed in the hole thereby securing the PWB to the chassis. A pair of conductive traces is formed in the PWB. A cap, being an amount of conductive glue, covers a part of the fastener and fills an electrically insulating gap between the two traces, to thereby form a conductive path that connects the two traces. A sensing circuit is coupled to the traces, to detect a change in impedance of the path and signal a tamper event alert. Other embodiments are also described and claimed.

Owner:APPLE INC

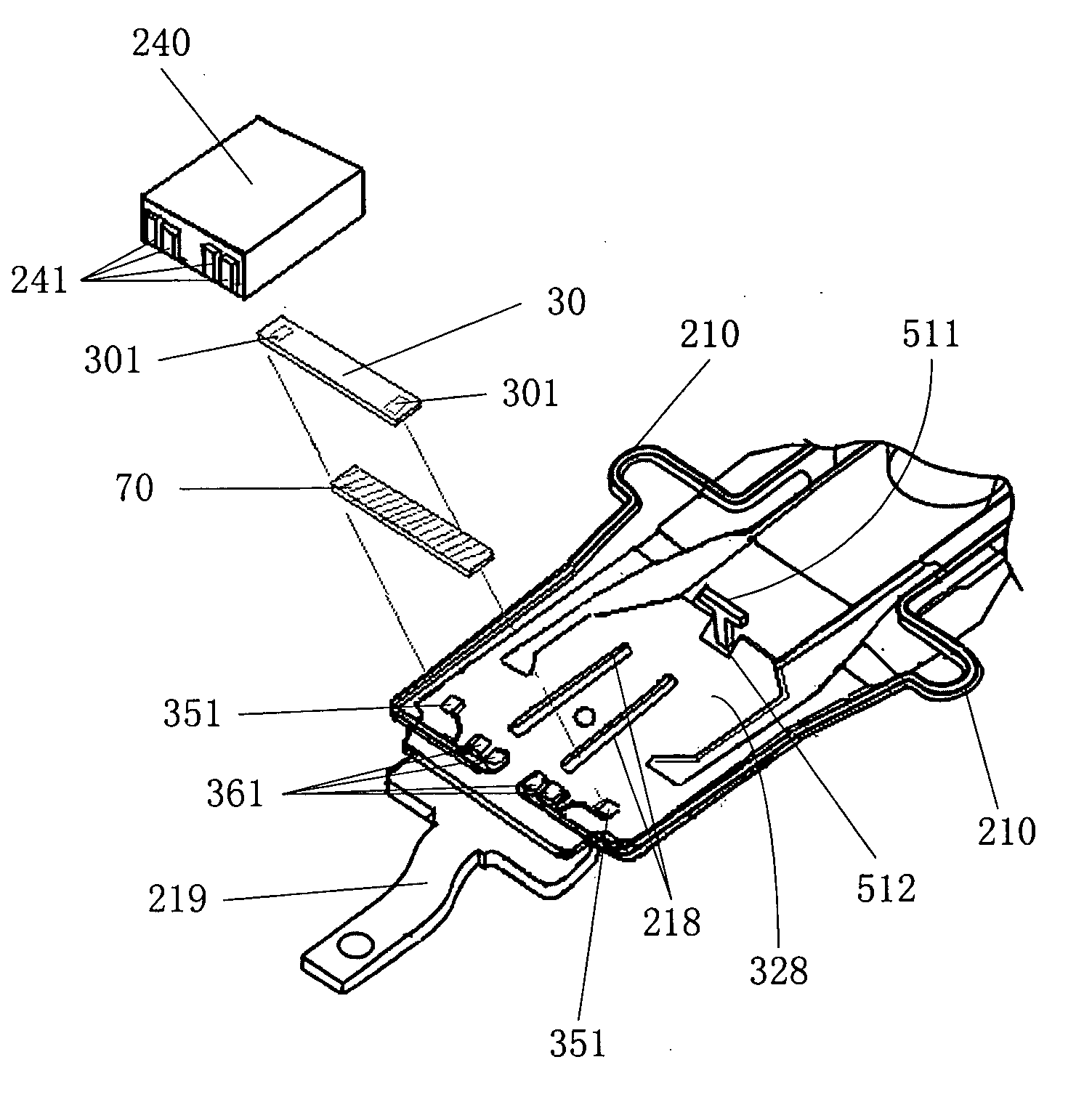

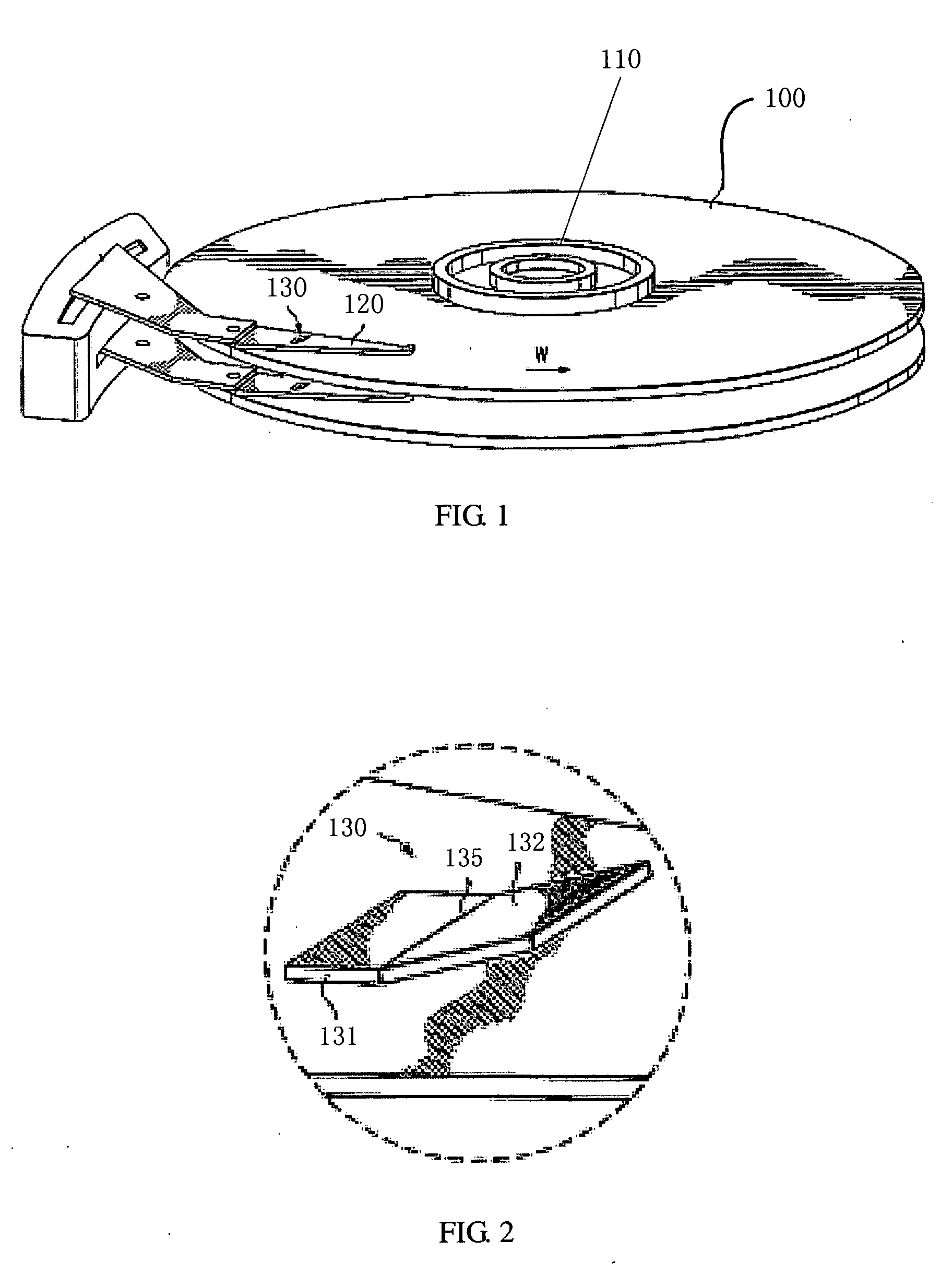

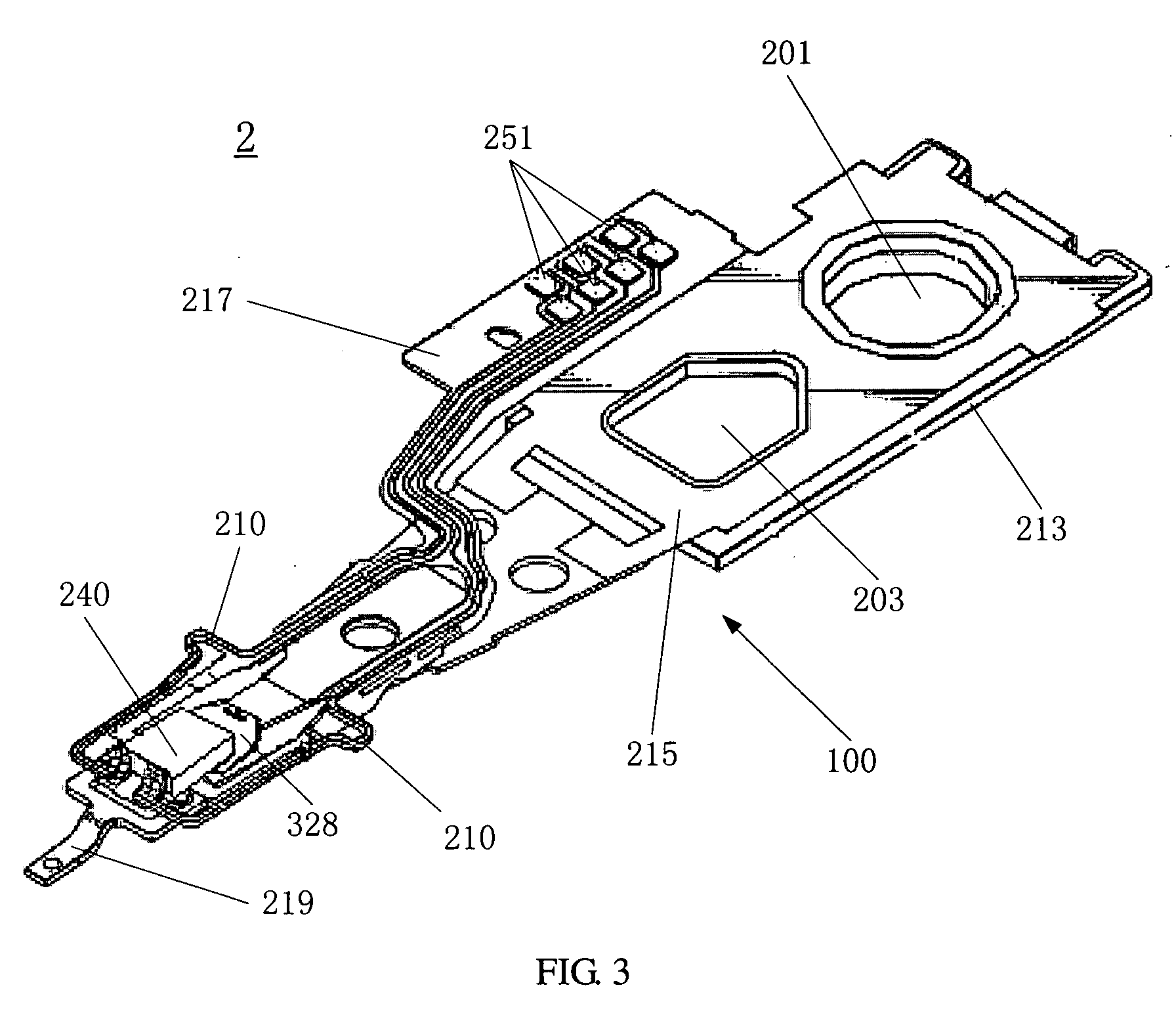

Head gimbal assembly with flying height controller, disk drive unit using the same, and flying height adjusting method and system thereof

InactiveUS20060082917A1Good flying height adjustment capabilityReduce weightElectrical connection between head and armDriving/moving recording headsControl systemFlying height

Owner:SAE MAGNETICS (HK) LTD

Laser-based method and system for processing targeted surface material and article produced thereby

ActiveUS20080011852A1Prevent unwanted changesSufficient total fluenceAdditive manufacturing apparatusSemiconductor/solid-state device detailsTarget surfaceSlag

Owner:ELECTRO SCI IND INC

Connector sheet and wiring board, and production processes of the same

InactiveUS20050057906A1Low costHigh wiring densityPrinted circuit assemblingPrinted electric component incorporationEngineeringElectrically conductive

There is provided a connector sheet which includes an insulation sheet substrate having a front surface and a rear surface opposing to the front surface, and electrically conductive members each passing through the sheet substrate along a thickness direction of the sheet substrate, and the front surface and the rear surface contain a thermoset resin, and have tackiness under a first condition and develop adhesiveness under a second condition which is different from the first condition.

Owner:PANASONIC CORP

Circuit boards interconnected by overlapping plated through holes portions

ActiveUS8007286B1Point-like light sourceSoldered/welded conductive connectionsEngineeringElectrical and Electronics engineering

In some embodiments, an interconnectable circuit board may include one or more of the following features: (a) a first electrically conductive pad located on a top of the circuit board, (b) a plated through hole on the conductive pad which passes through the circuit board, (c) a second electrically conductive pad coupled to the plated through hole; the second conductive pad capable of being electrically connected to a third electrically conductive pad attached to a top of a second interconnectable circuit board, (d) cut marks indicating safe locations for separating the circuit board, and (e) a second cut mark adjacent to the first cut mark where the area between the first and second cut mark can be utilized to make a safe cut through the circuit board.

Owner:METROSPEC TECH

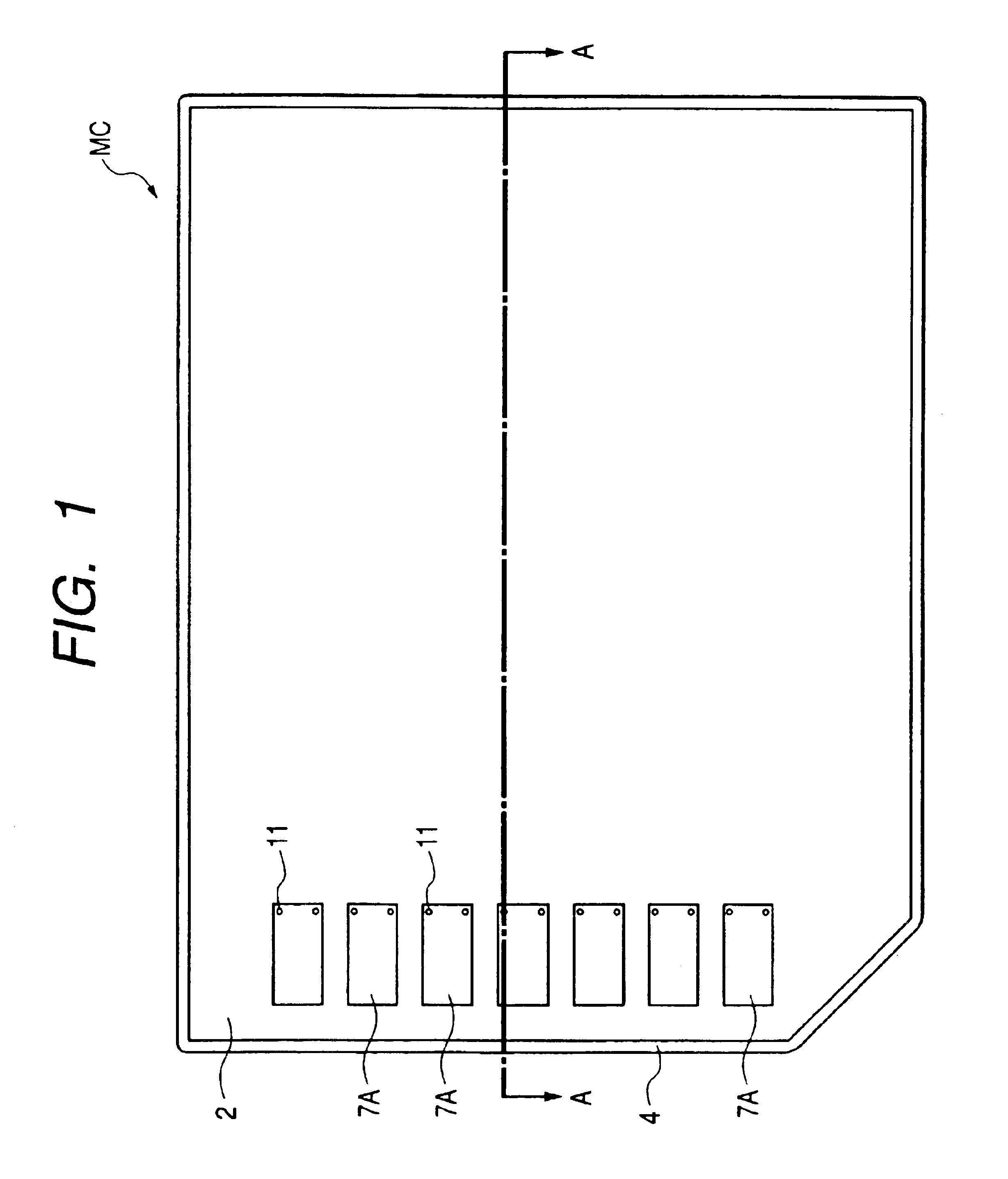

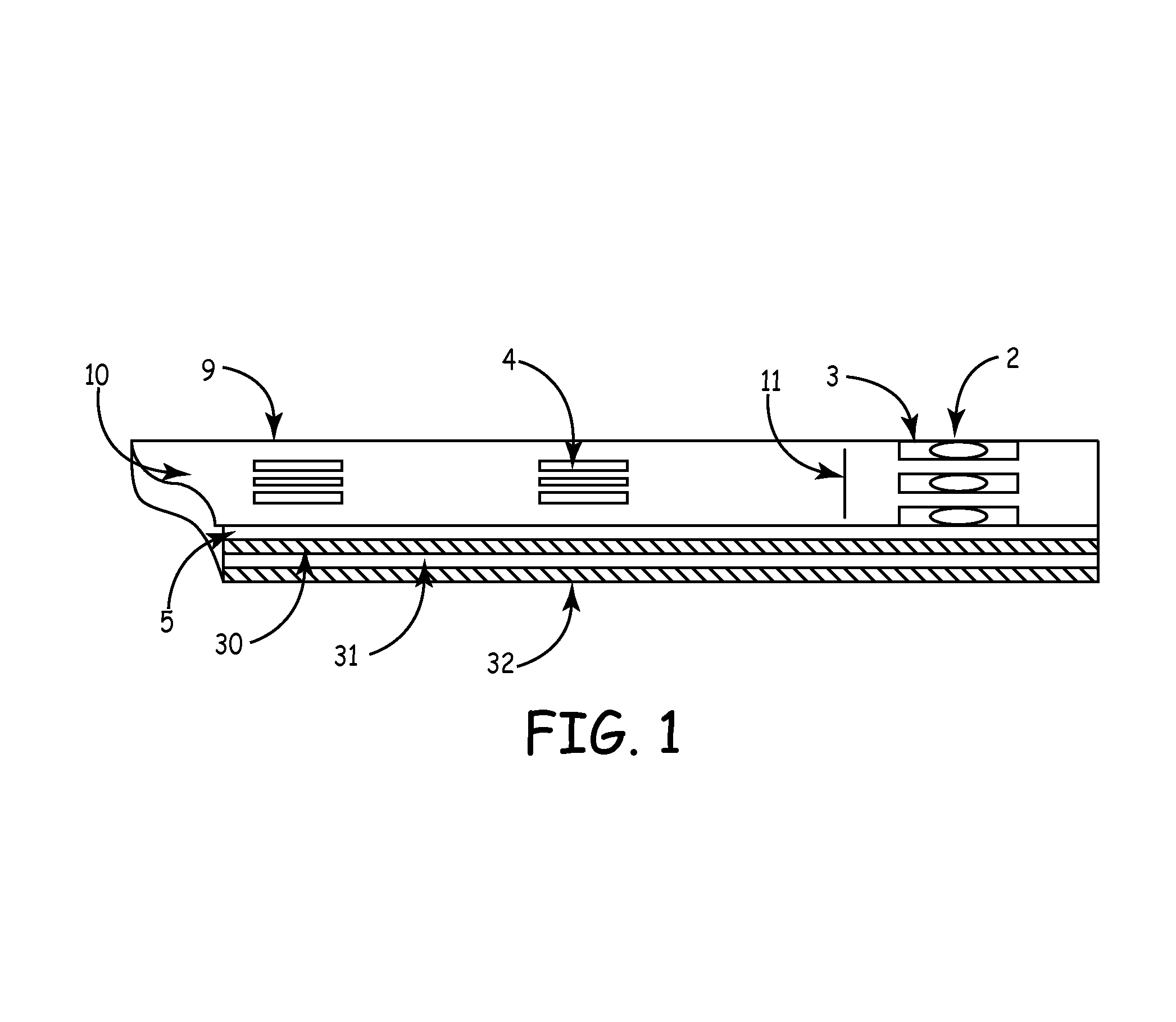

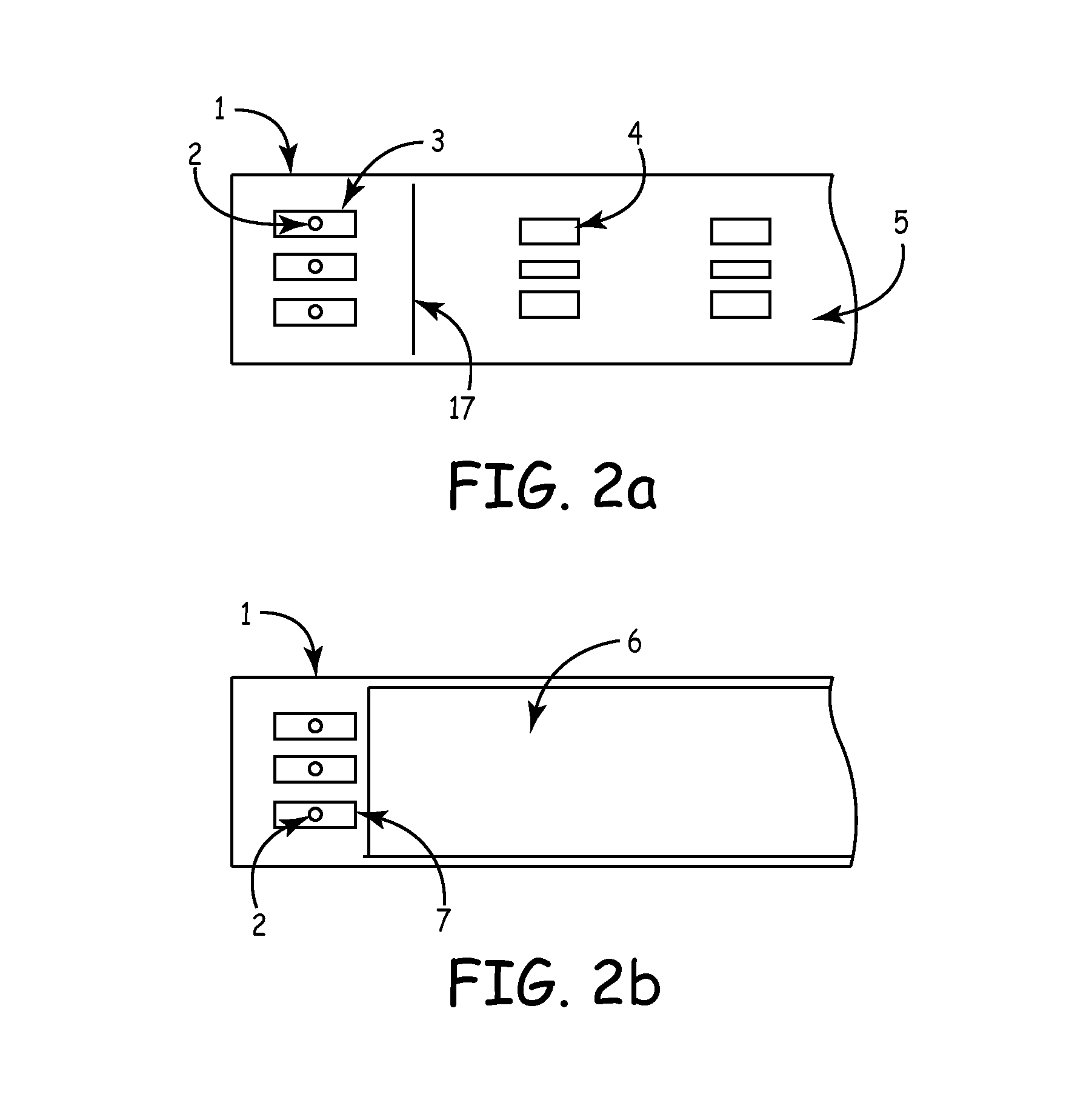

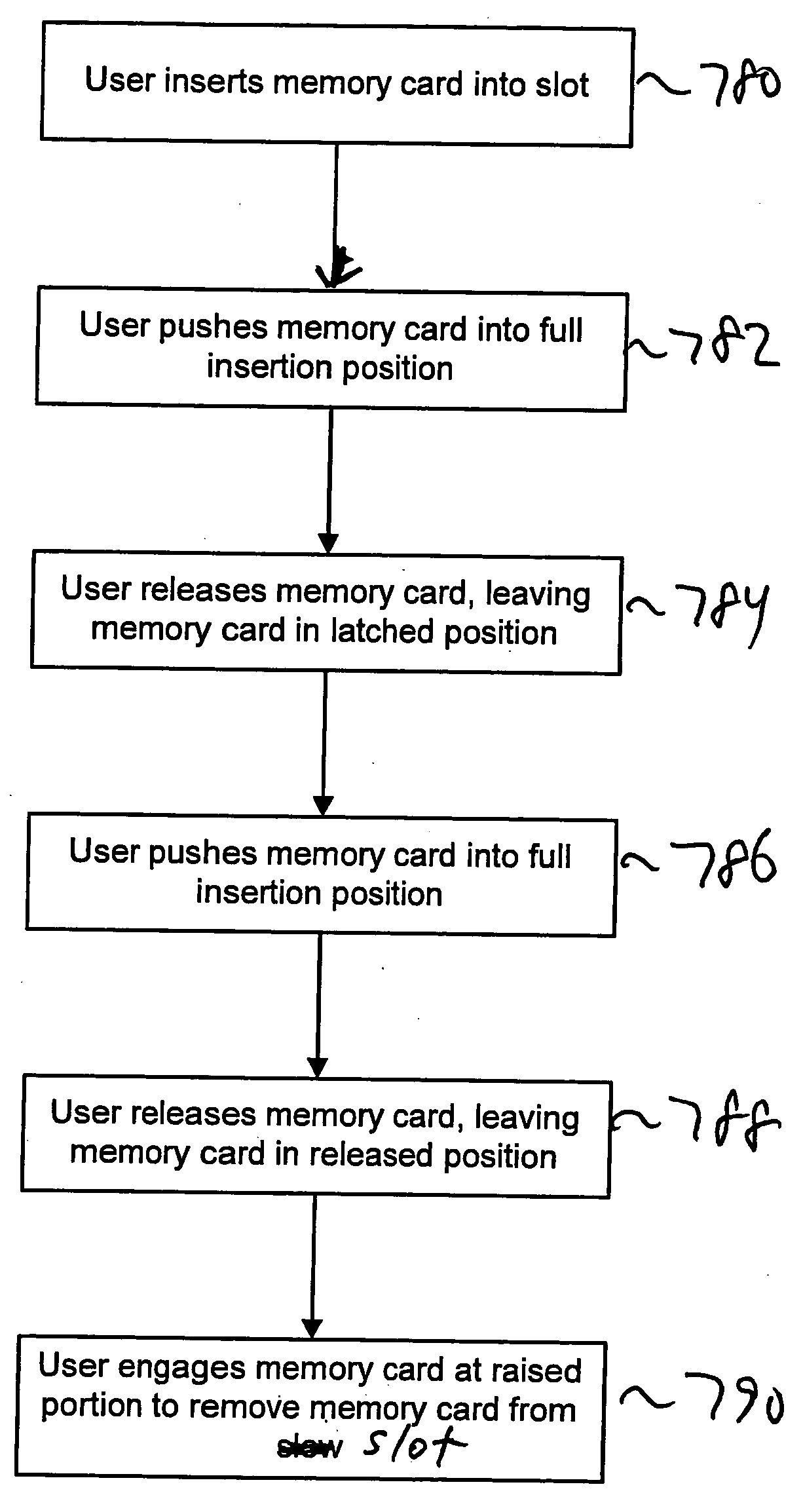

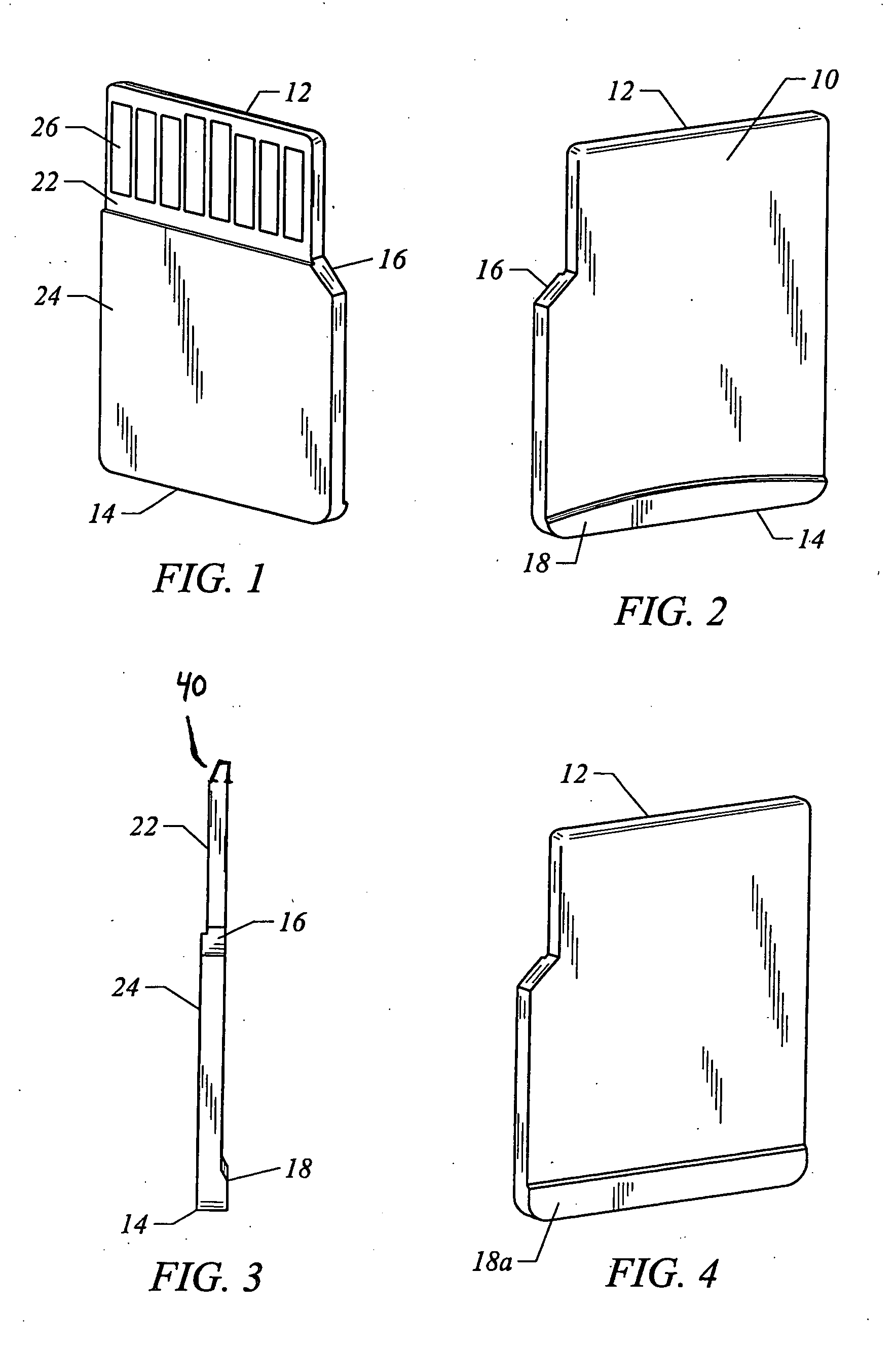

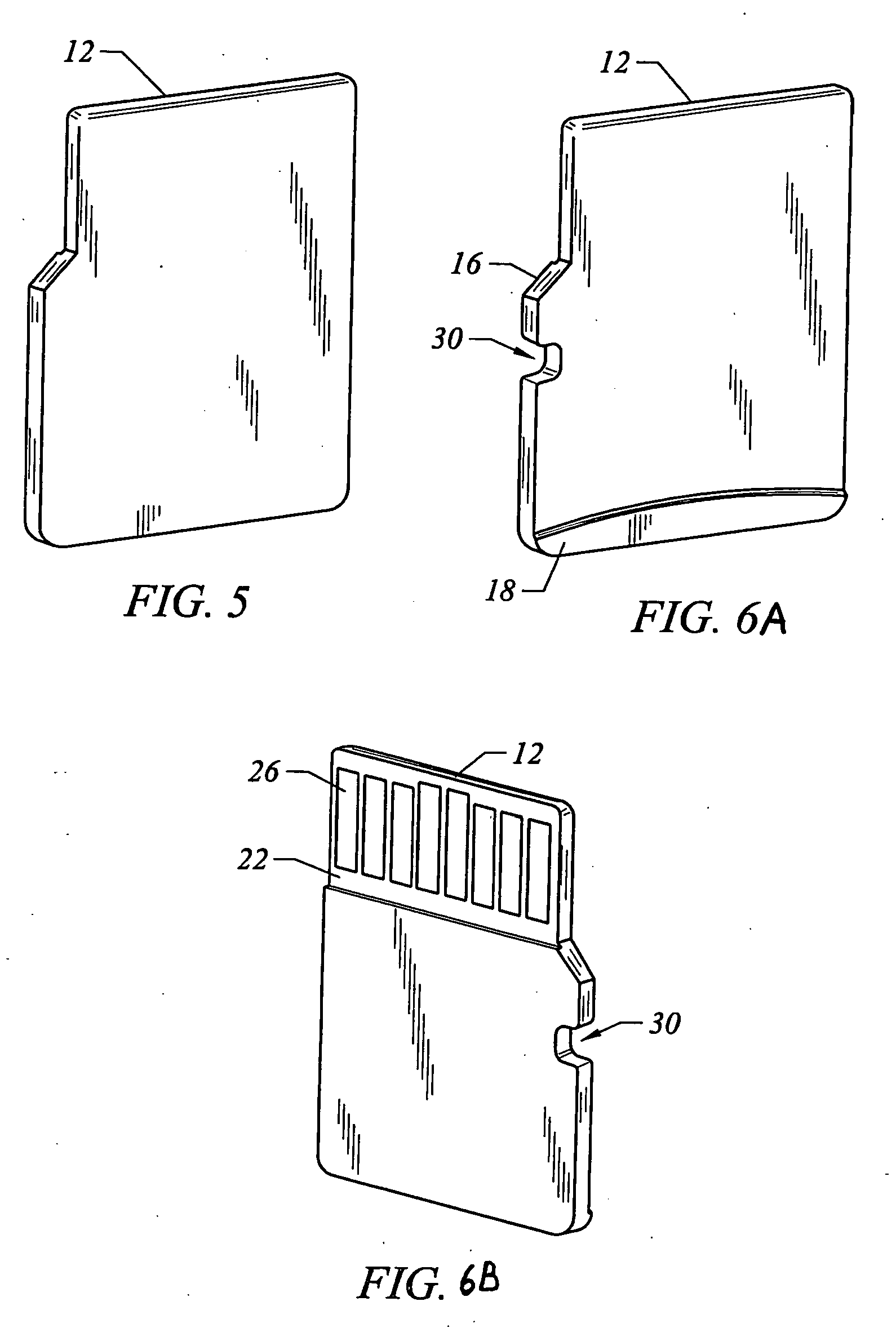

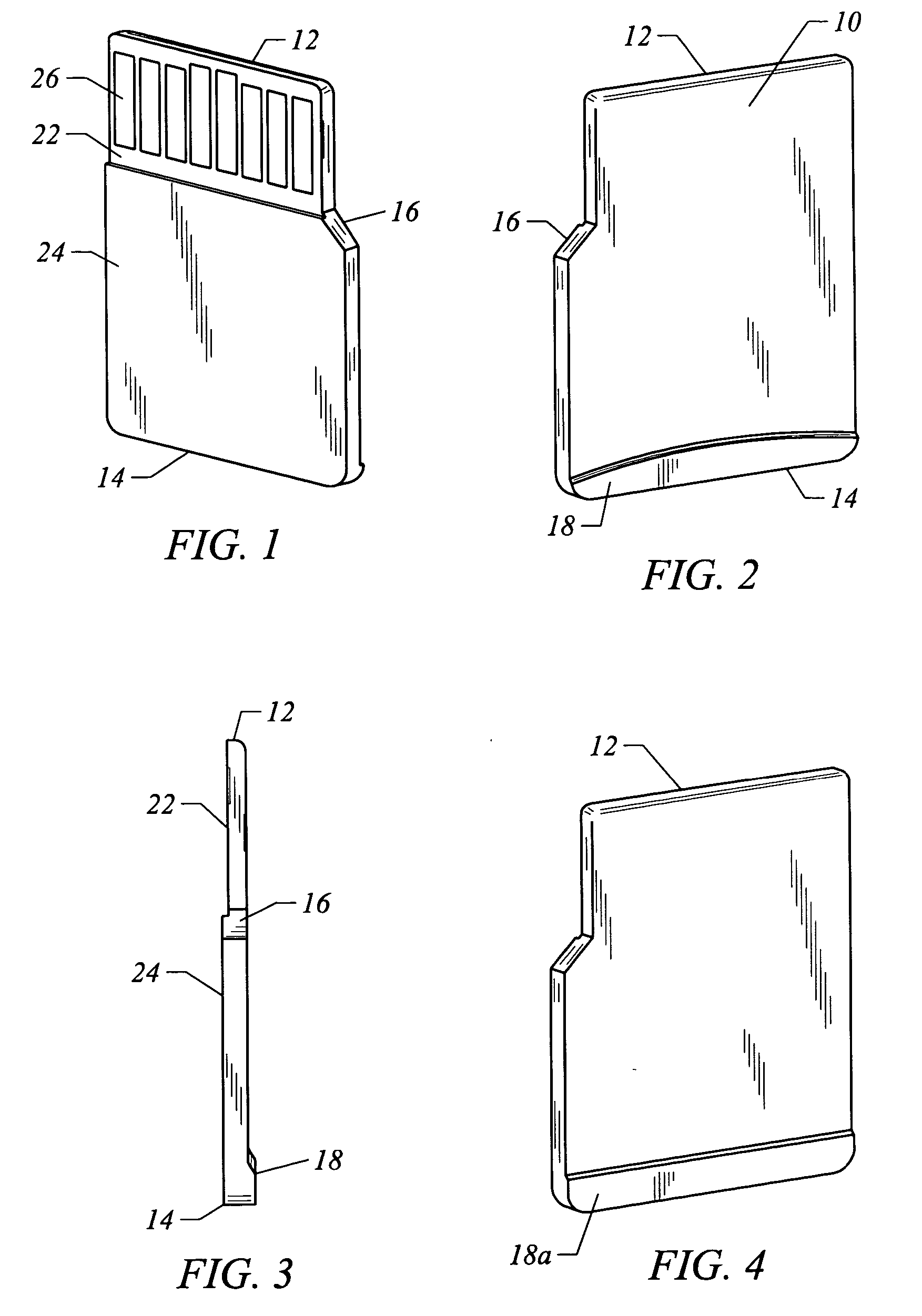

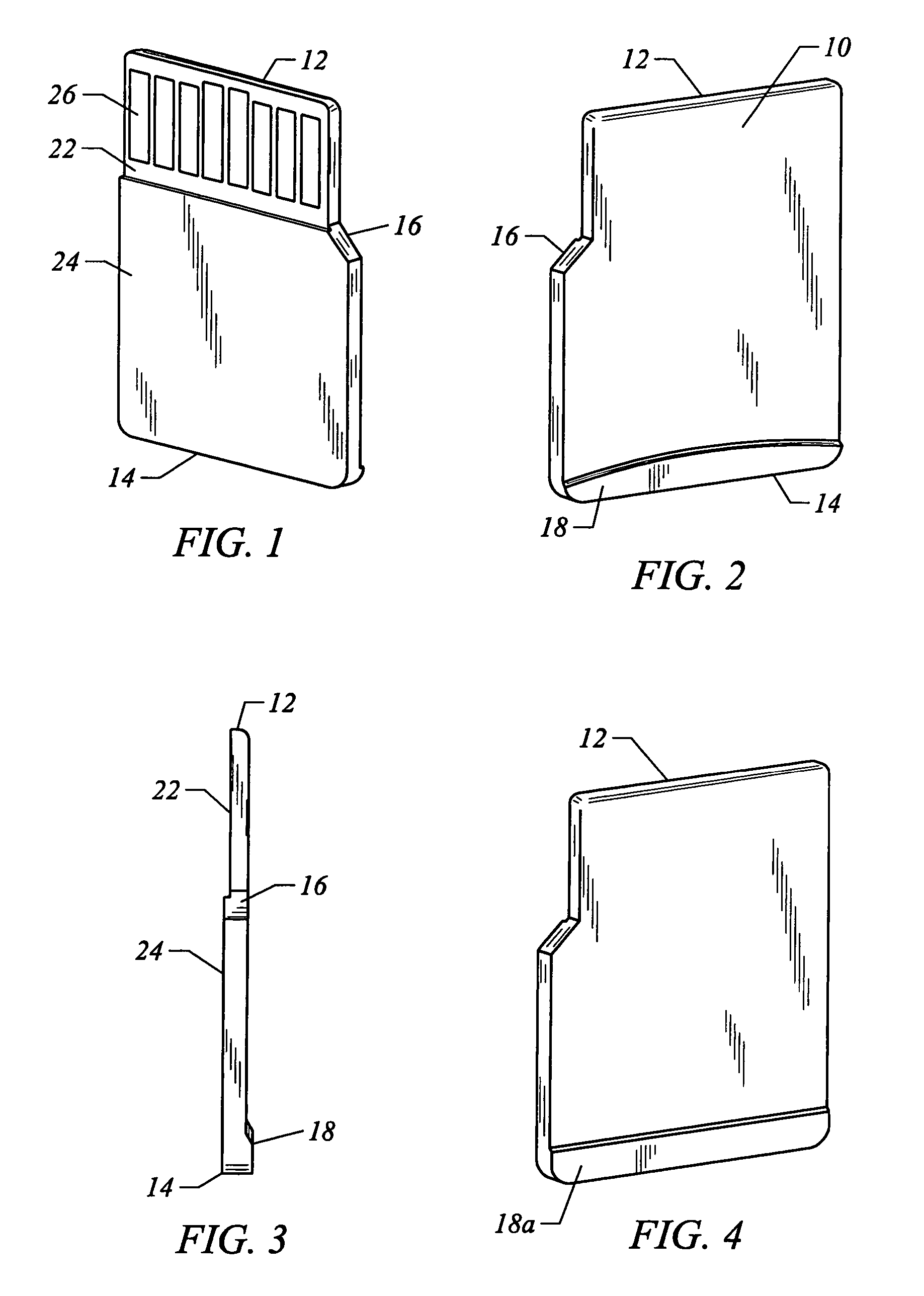

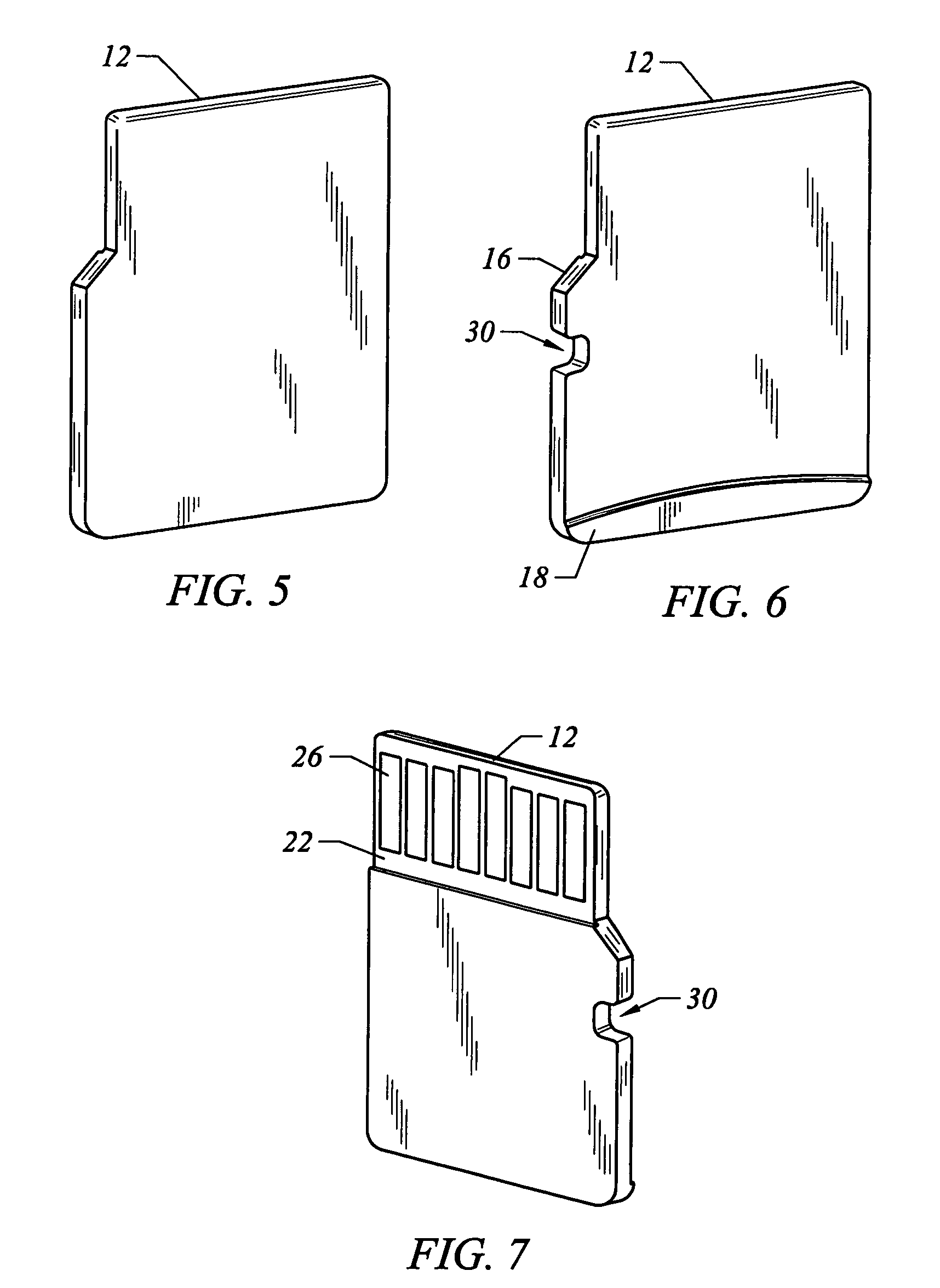

Memory card with and without enclosure

ActiveUS20050011671A1Easy to handleEasy to catchEngagement/disengagement of coupling partsConveying record carriersCapacitorMemory cards

The present invention, roughly described, pertains to a small memory card that includes features which allow the memory card to be more easily handled by a user. In various embodiments, the memory card can include a chamfer and / or a raised portion that allows the memory card to be more easily grabbed by a human hand (or mechanical device) and also provides additional room to store passive devices such as capacitors and / or resistors. Because different electronic devices use different types of memory cards, an adaptor is provided that allows the memory cards disclosed herein to be used in ports or connectors on electronic devices that are meant for other types of memory cards.

Owner:SANDISK TECH LLC

Peripheral card with hidden test pins

InactiveUS20050013106A1Avoid accessImprove overall utilizationElectronic circuit testingDigital data processing detailsEngineeringComputer case

A peripheral card includes a circuit board, various circuit elements on the circuit board, a set of user terminals, a set of test terminals, and an enclosure that covers a portion of the circuit board and the circuit elements. The enclosure does not cover the user terminals and test terminals. After the peripheral card is tested, the test terminals are covered with a conformal contact coating in order to prevent access to the test terminals.

Owner:SANDISK TECH LLC

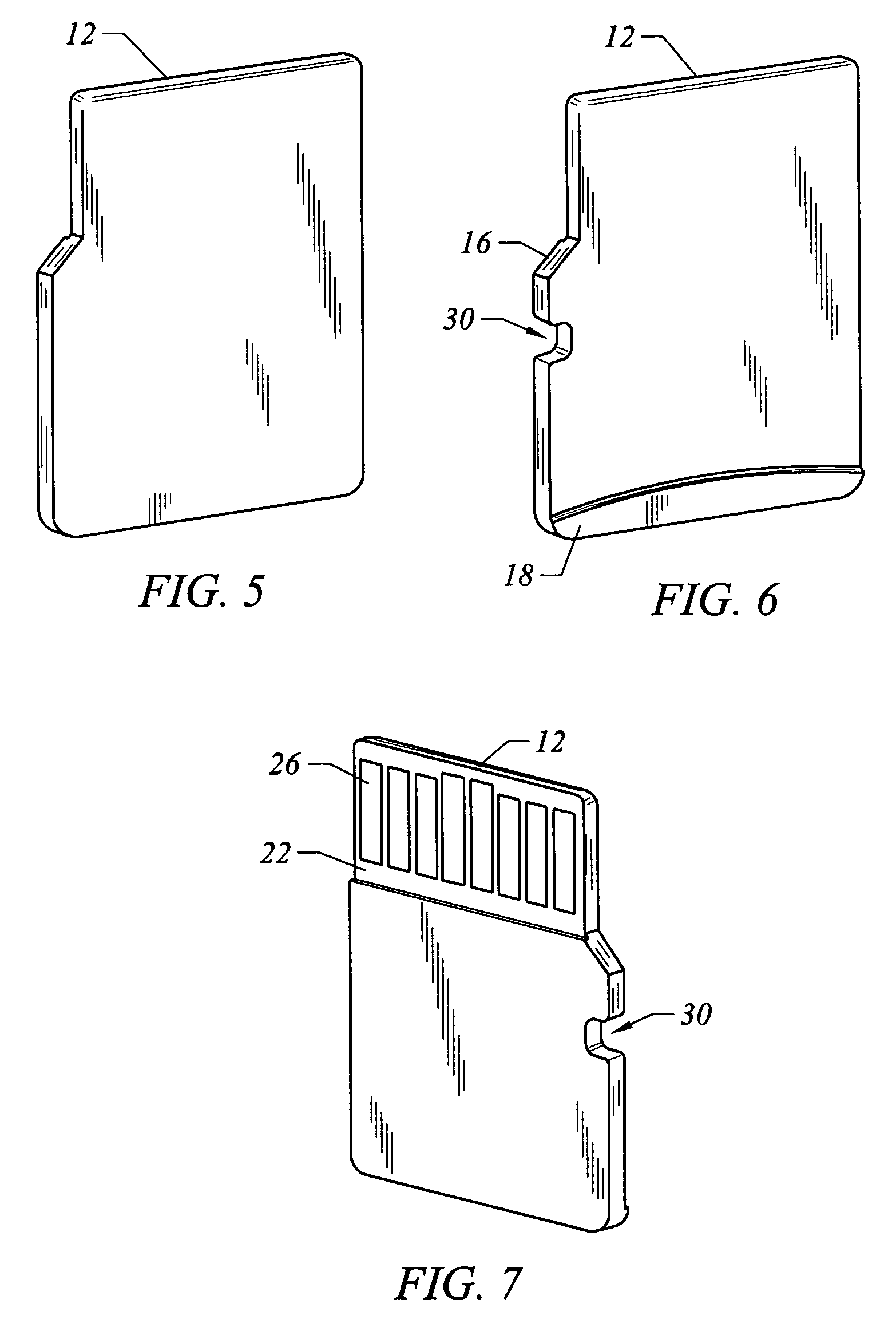

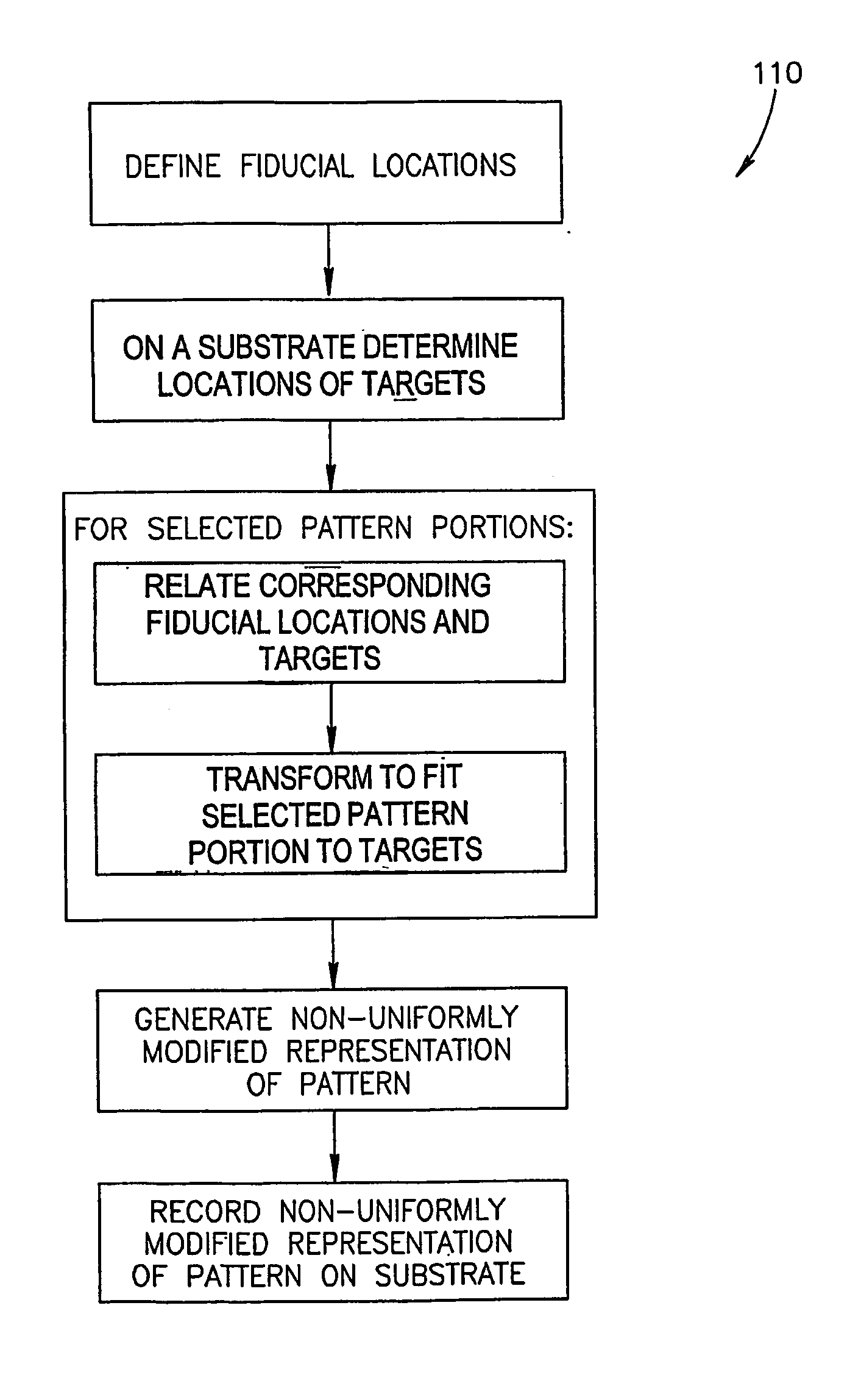

System and method for manufacturing printed circuit boards employing non-uniformly modified images

ActiveUS20050213806A1Non uniformCharacter and pattern recognitionCircuit board tools positioningEngineeringDigital control

A system and method for fabricating an electrical circuit in which a digital control image (46) is generated by non-uniformly modifying (44) a representation of an electrical circuit (40), such that an electrical circuit pattern (72) recorded on a substrate (12) using the digital control image (46) precisely fits an already formed electrical circuit portion (62).

Owner:ORBOTECH LTD

System and methods for data-driven control of manufacturing processes

Systems and methods for implementing hybrid, closed-loop control that generates control values for processes defined by a limited number of function evaluations and large amounts of process and measurement noise. The described control system is applied to a stencil printing process for applying solder paste to an electronic medium such as a printed circuit board or semiconductor wafer. The control system is defined by a hybrid approach. A first, coarse algorithm is used to rapidly produce the value of a stencil printer control value resulting in a solder paste deposit having a volume within predetermined acceptable limits. After the coarse algorithm no longer produces solder paste deposits closer to a desired volume, a second, more refined estimator is used to fine tune the process. An additional transitional algorithm may be added between the coarse algorithm and refined estimator. The coarse algorithm may be implemented with a constrained-conjugated gradient search, and the refined search may be a implemented using a least-squares affine estimator or a quadratic estimator. The transitional algorithm may be implemented using a block version of a least-squares affine estimator.

Owner:GEORGIA TECH RES CORP

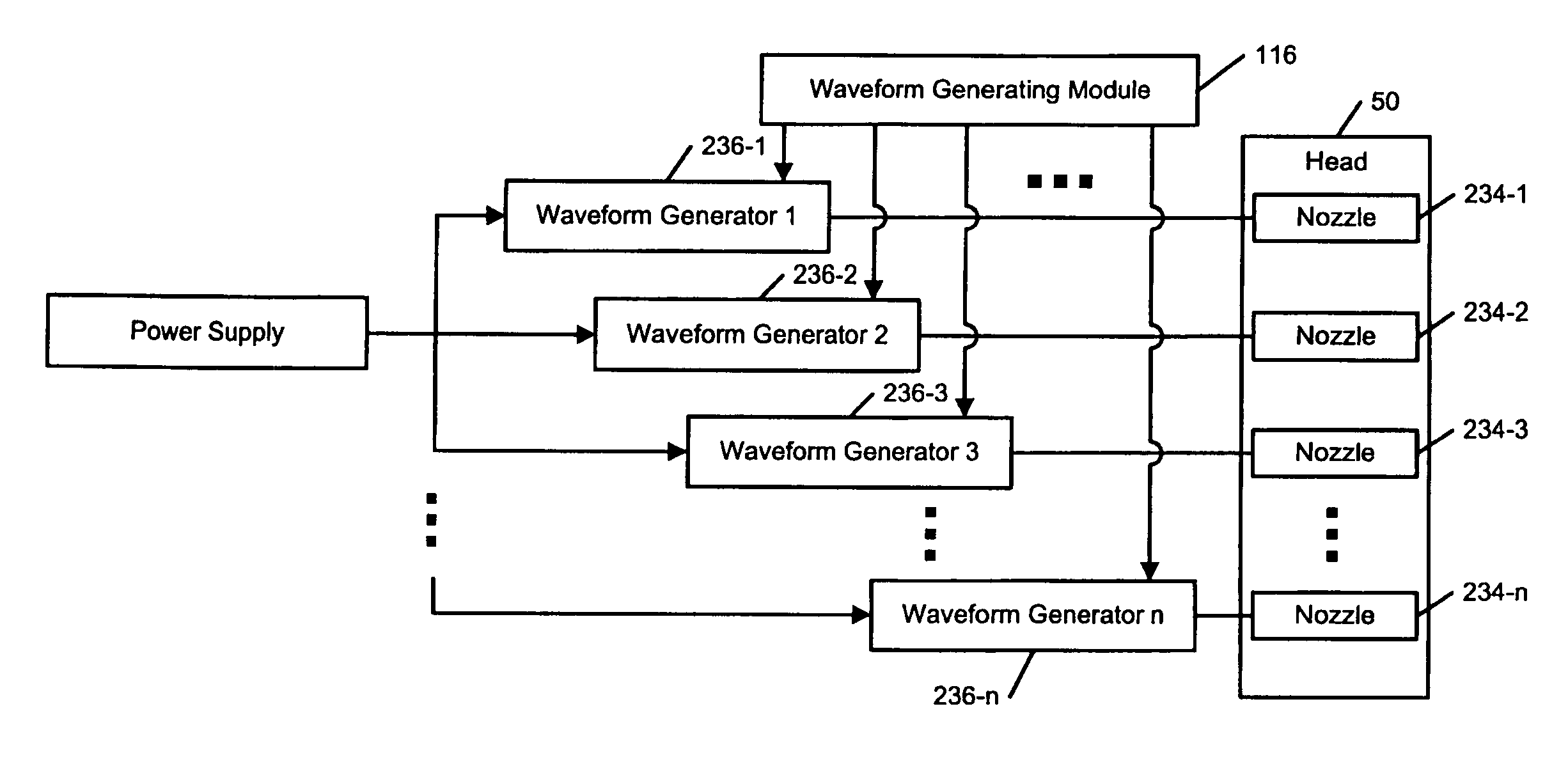

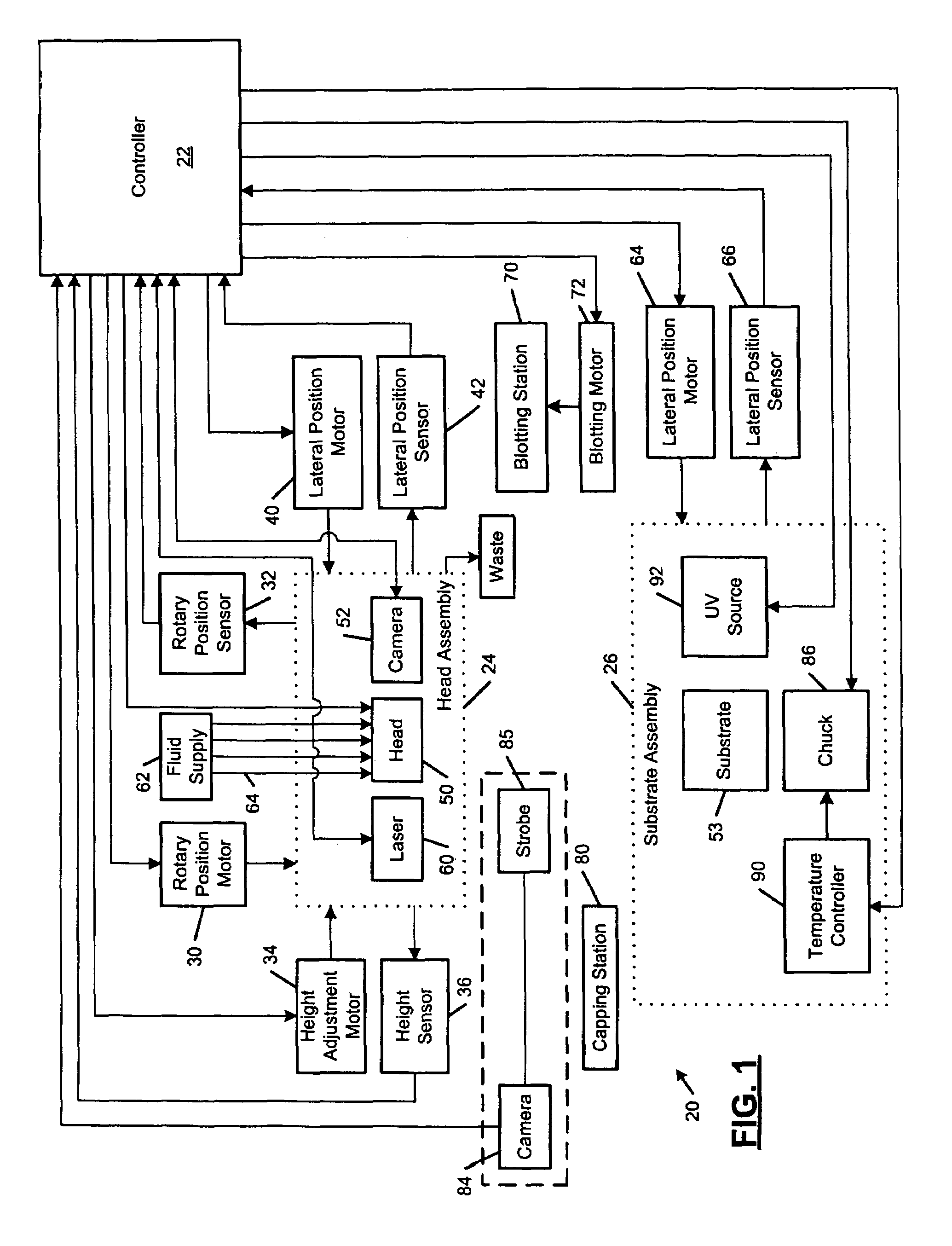

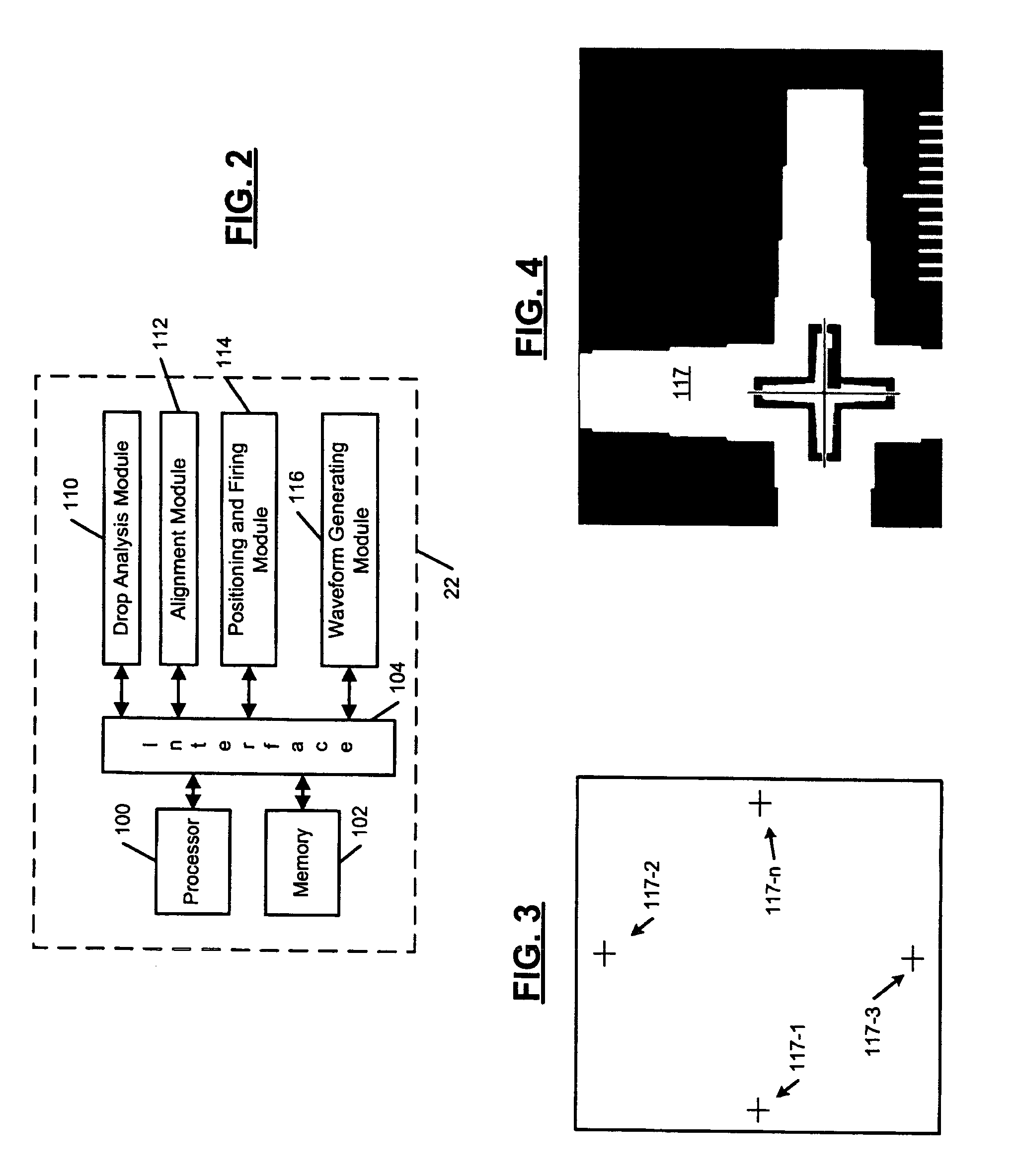

Industrial microdeposition system for polymer light emitting diode displays, printed circuit boards and the like

InactiveUS7270712B2Add featureCompensation changesInking apparatusSemiconductor/solid-state device detailsLED displayComputer module

A microdeposition system (20) and method deposits precise amounts of fluid material onto a substrate. A microdeposition head (50) includes a plurality of spaced nozzles. A positioning device controls a position of the microdeposition head relative to the substrate. A controller (22) includes a positioning module that communicates with the positioning device and that generates position control signals for the positioning device. A nozzle firing module communicates with the microdeposition head (50) and selectively generates nozzle firing commands to define features of at least one layer of an electrical device, such as resistors, traces and capacitors on a printed circuit board, polymer light emitting diodes, and light panels.

Owner:ULVAC INC

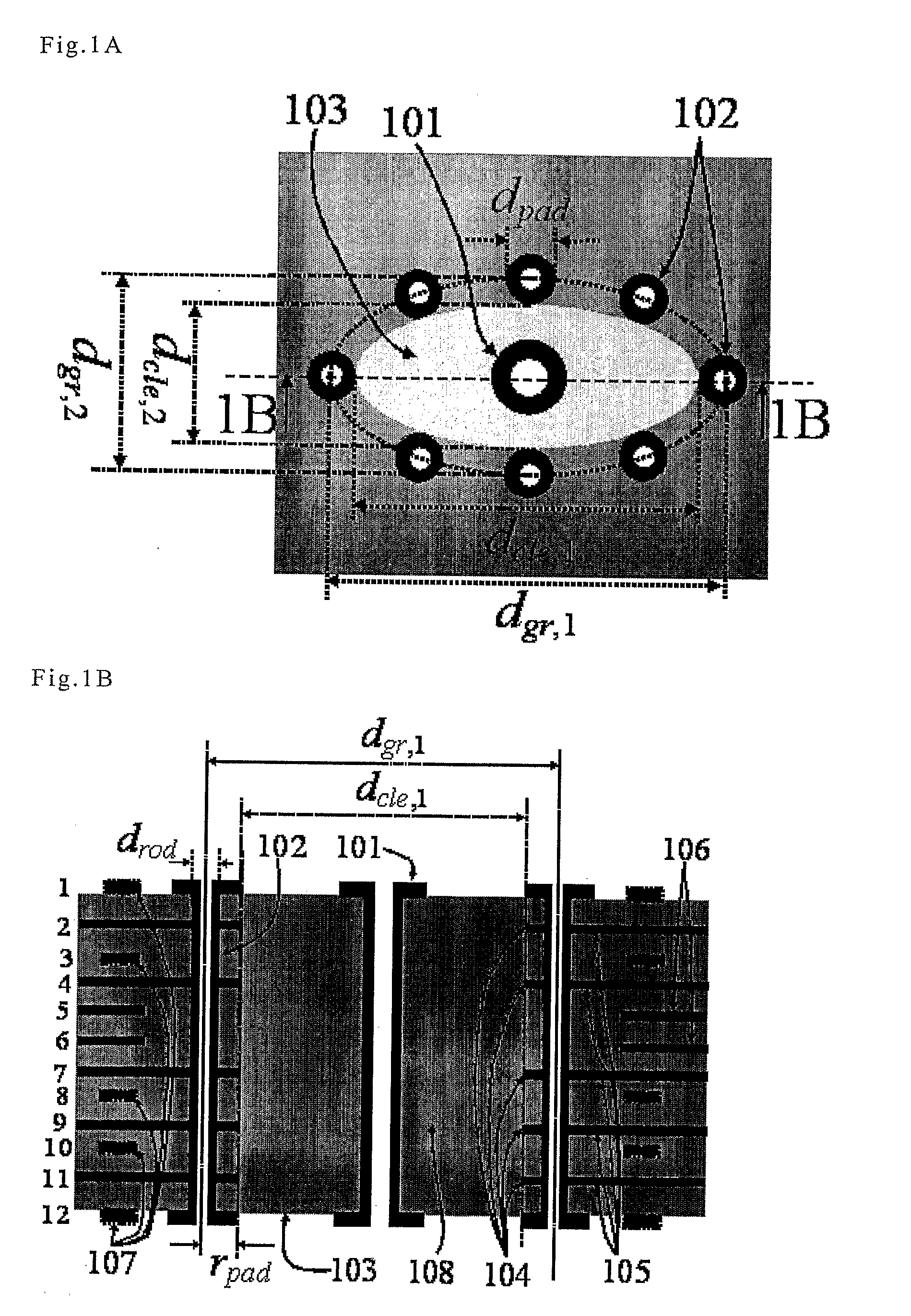

Via transmission lines for multilayer printed circuit boards

ActiveUS20070205847A1Improve performanceMultiple-port networksPrinted circuit aspectsElectrical conductorEngineering

A via transmission line for a multilayer printed circuit board (PCB) in which a wave guiding channel is formed by a signal via or a number of signal vias, an assembly of ground vias surrounding the signal via or corresponding number of coupled signal vias, a set of ground plates from conductor layers of the multilayer PCB, and a clearance hole. In this via transmission line, the signal via, or the number of signal vias forms an inner conductive boundary, ground vias and ground plates from conductor layers of the multilayer PCB form an outer conductive boundary, and the clearance hole provides both isolation of the inner conductive boundary from the outer conductive boundary and high-performance broadband operation of the via transmission line by means of the predetermined clearance hole cross-sectional shape and dimensions where the cross-sectional shape of the clearance hole is defined by the arrangement of ground vias in the outer conductive boundary and dimensions of the clearance hole are determined according to a method to minimize frequency-dependent return losses caused by specific corrugations of the outer conductive boundary formed by ground plates in the wave guiding channel of the via transmission line.

Owner:RENESAS ELECTRONICS CORP +1

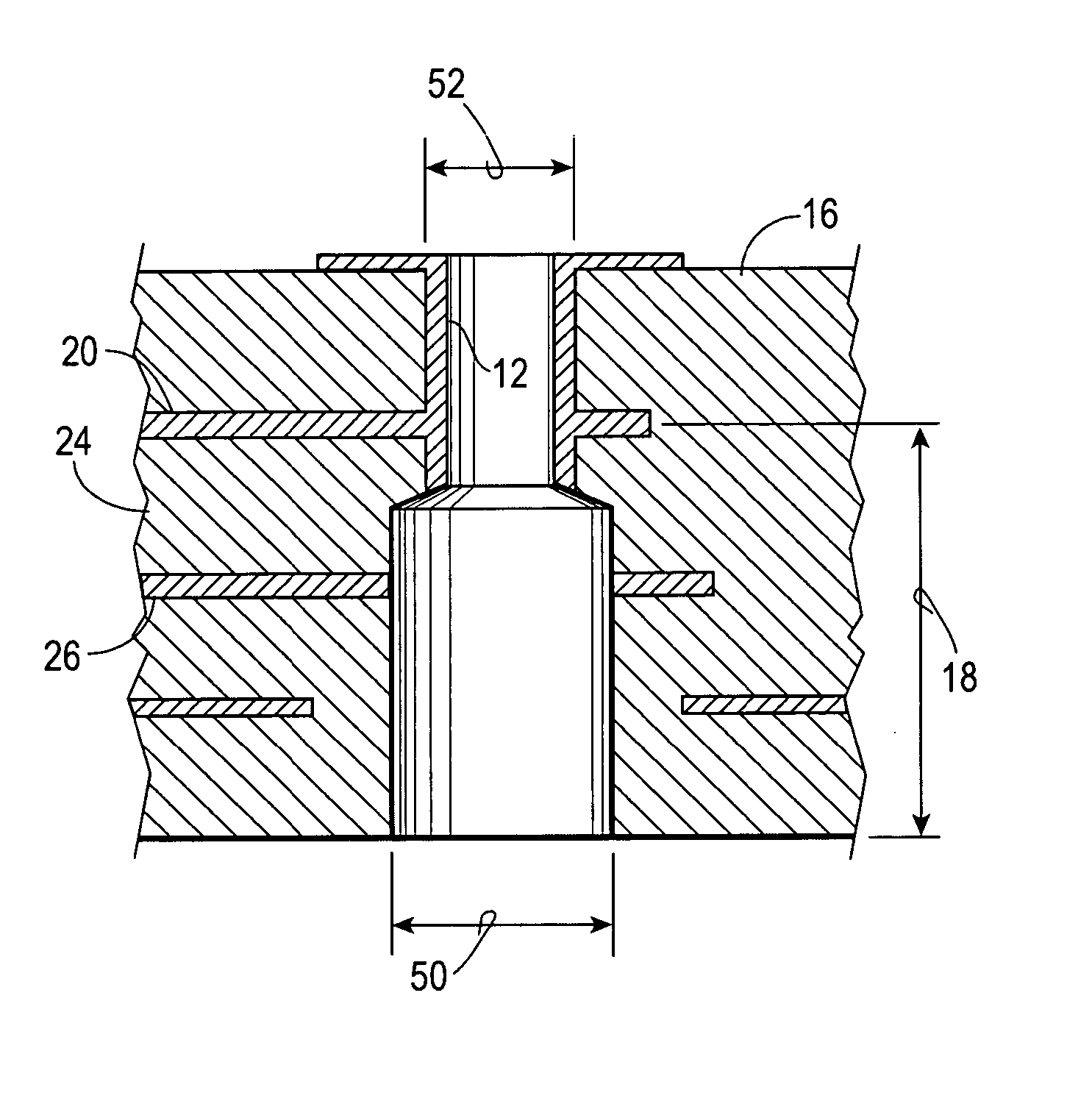

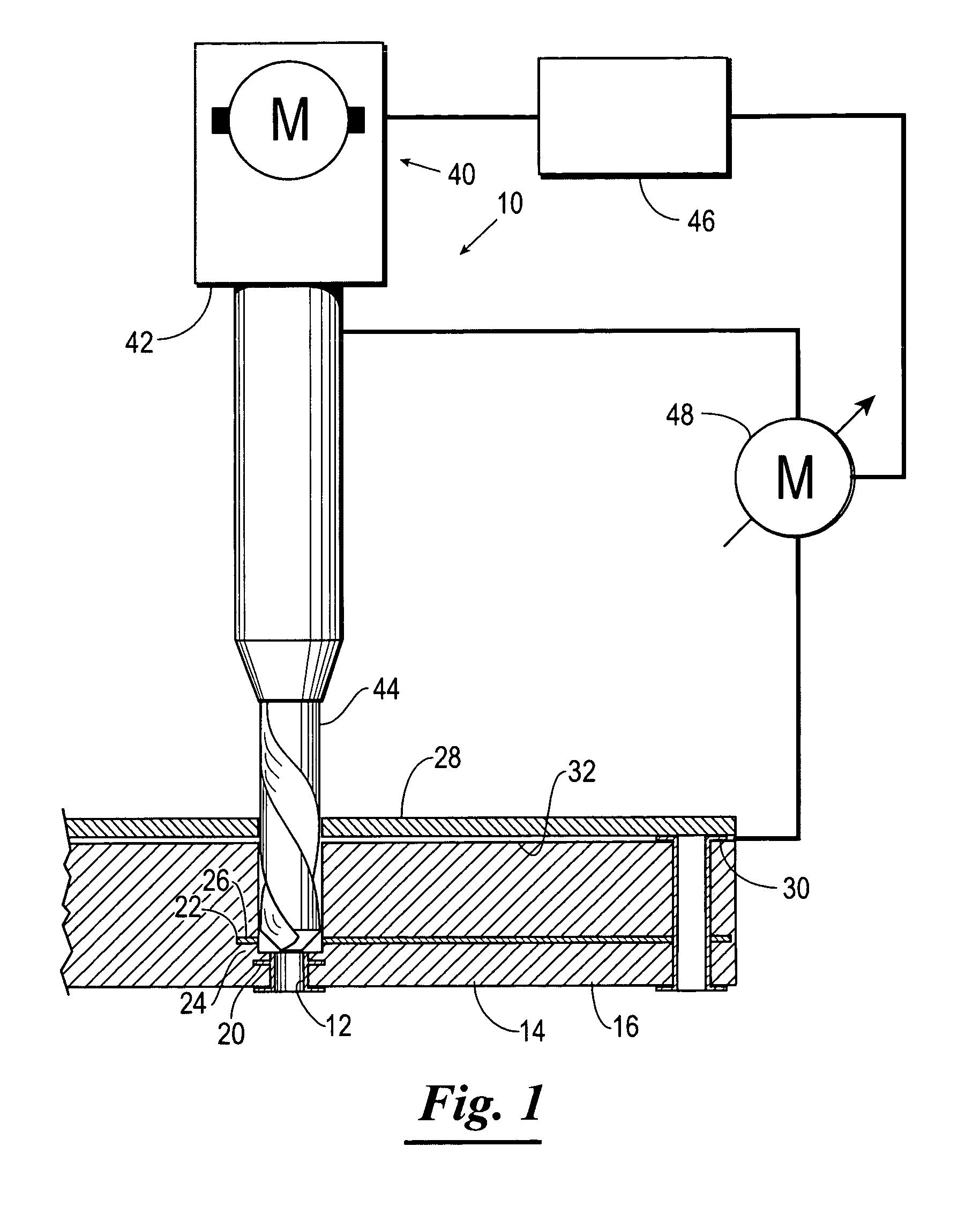

Closed loop backdrilling system

InactiveUS20050128672A1Thread cutting machinesElectrical connection printed elementsEpoxyContact pad

A multilayer circuit board is provided with at least one signal layer, at least one feedback layer, and at least one dielectric layer positioned between the signal layer and the feedback layer. The signal layer is connected to at least one plated hole. The feedback layer has a contact pad, which is positioned adjacent to the plated hole, but is electrically isolated from the plated hole. The contact pad is connected to a measurement unit. The dielectric layer is positioned between the signal layer and the contact pad of the feedback layer. A portion of the plated hole forms a stub portion, which extends a distance away from the signal layer and typically extends a distance away from the contact pad of the feedback layer. To remove the stub portion, a hole is bored or routed into the multilayer circuit board until electrical feedback is received by the measurement unit upon contact of a portion of the boring device with the contact pad. Upon receipt of the electrical feedback by the measurement unit, the boring device is retracted from the hole, and the hole formed by the boring device is filled with an epoxy, or other filler material.

Owner:VIASYST

Memory card with raised portion

ActiveUS7307848B2Improve overall utilizationLine/current collector detailsSemiconductor/solid-state device testing/measurementEngineeringComputer terminal

A peripheral card includes a circuit board, various circuit elements on the circuit board, a set of user terminals, a set of test terminals, and an enclosure that covers a portion of the circuit board and the circuit elements. The enclosure does not cover the user terminals and test terminals. After the peripheral card is tested, the test terminals are covered with a conformal contact coating in order to prevent access to the test terminals.

Owner:SANDISK TECH LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com