Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

57 results about "Write combining" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Write combining (WC) is a computer bus technique for allowing data to be combined and temporarily stored in a buffer – the write combine buffer (WCB) – to be released together later in burst mode instead of writing (immediately) as single bits or small chunks.

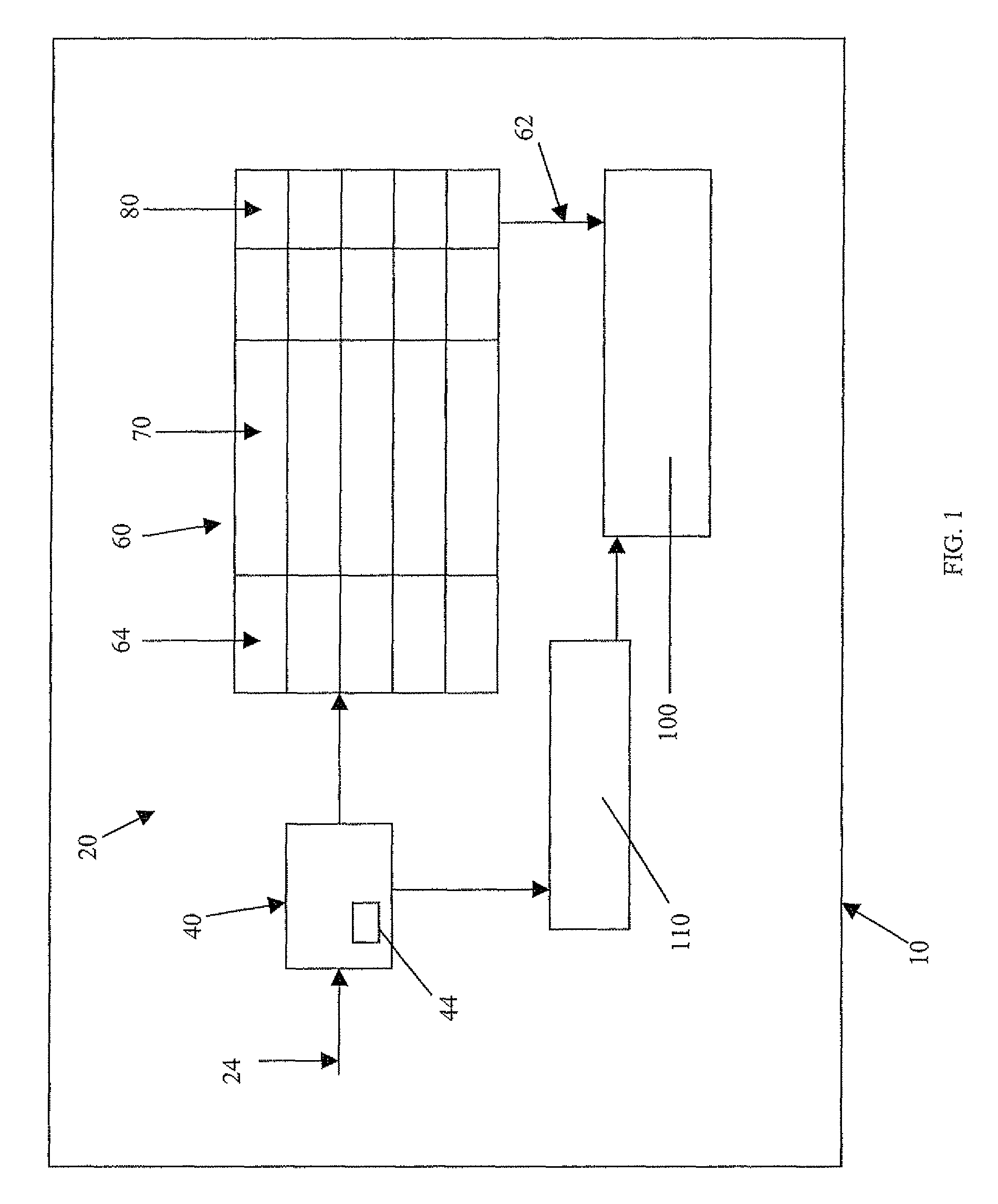

Method and system for optimizing write combining performance in a shared buffer structure

InactiveUS6122715AReduce in quantityIncrease bus bandwidthMemory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingData buffer

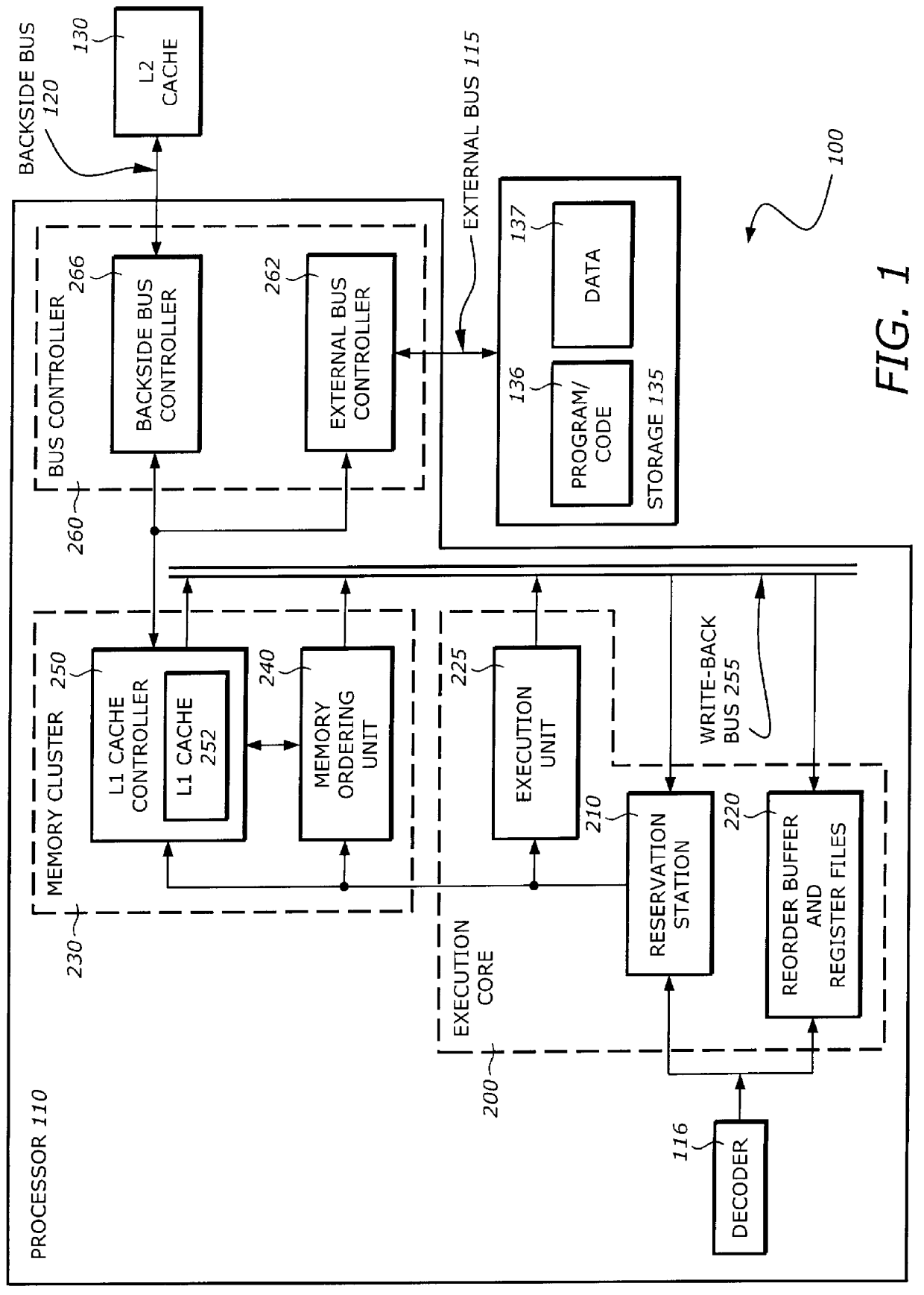

An apparatus and method of optimizing write combining operations using write combining buffers. A plurality of control fields are assigned to each of the write combining buffers. Each of the control fields has a value corresponding to one of a plurality of write combining states. A first of the plurality of write combining states transitions to a second of the plurality of write combining states in response to a write combining operation.

Owner:INTEL CORP

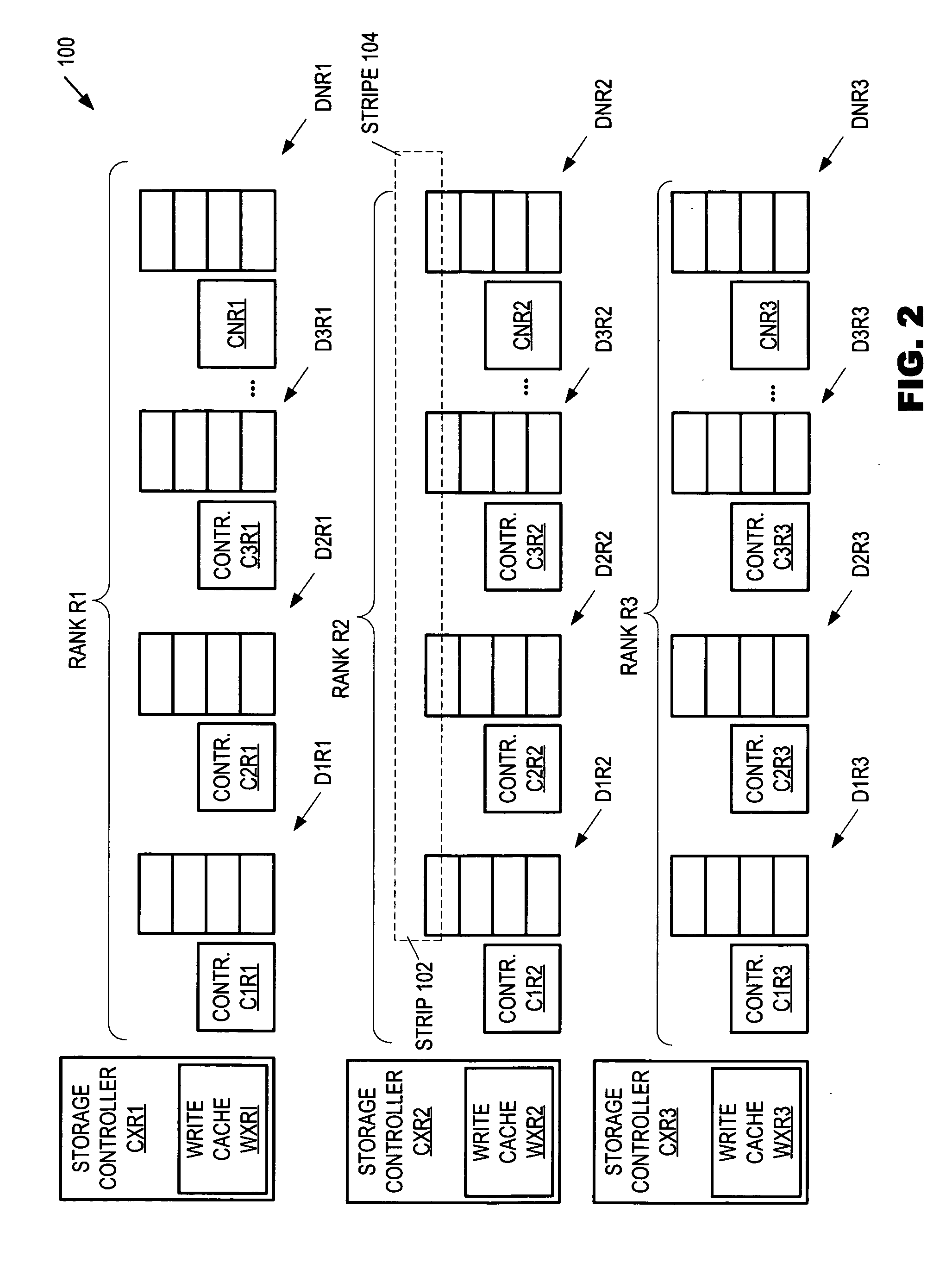

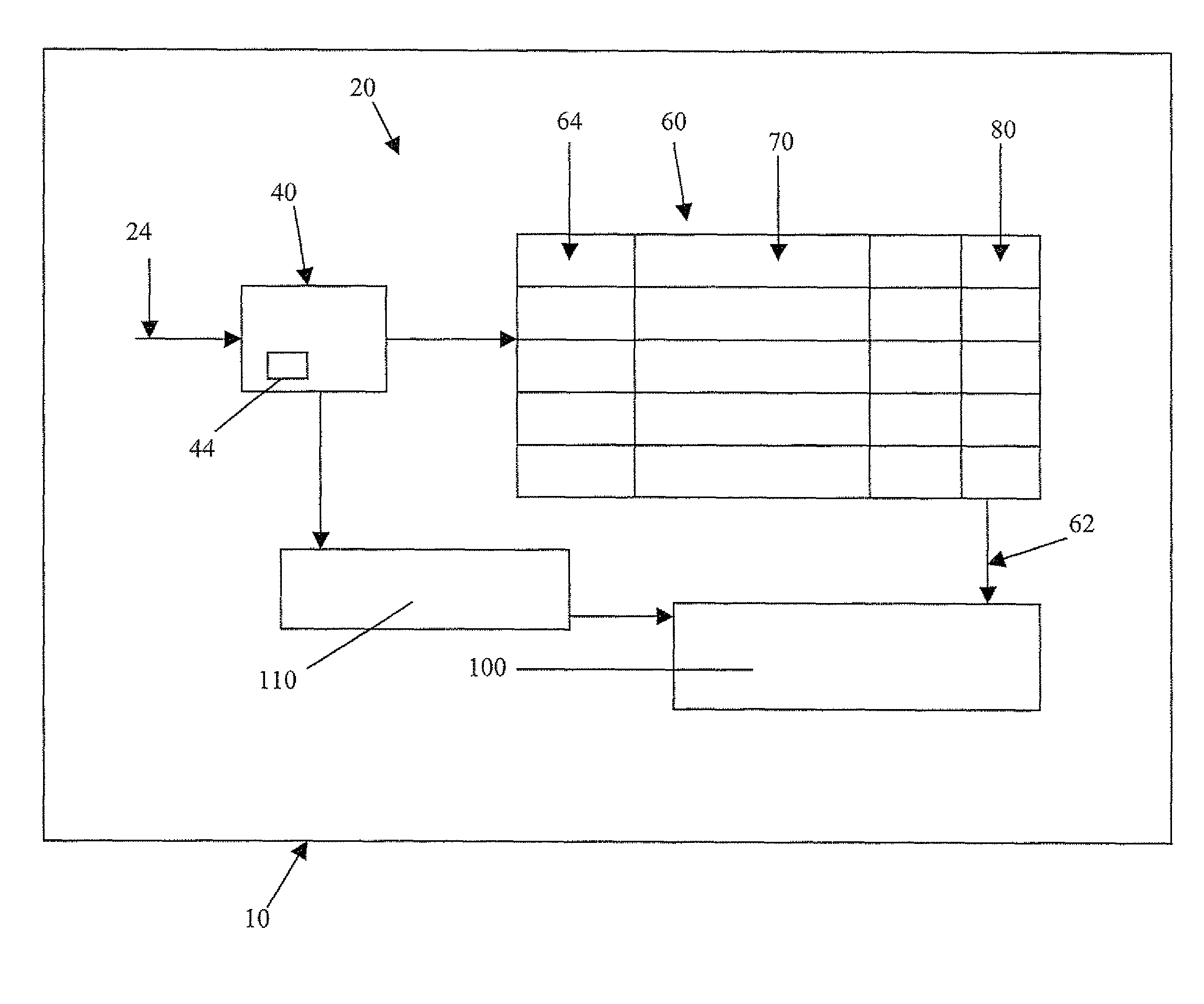

Wise ordering for writes-combining spatial and temporal locality in write caches

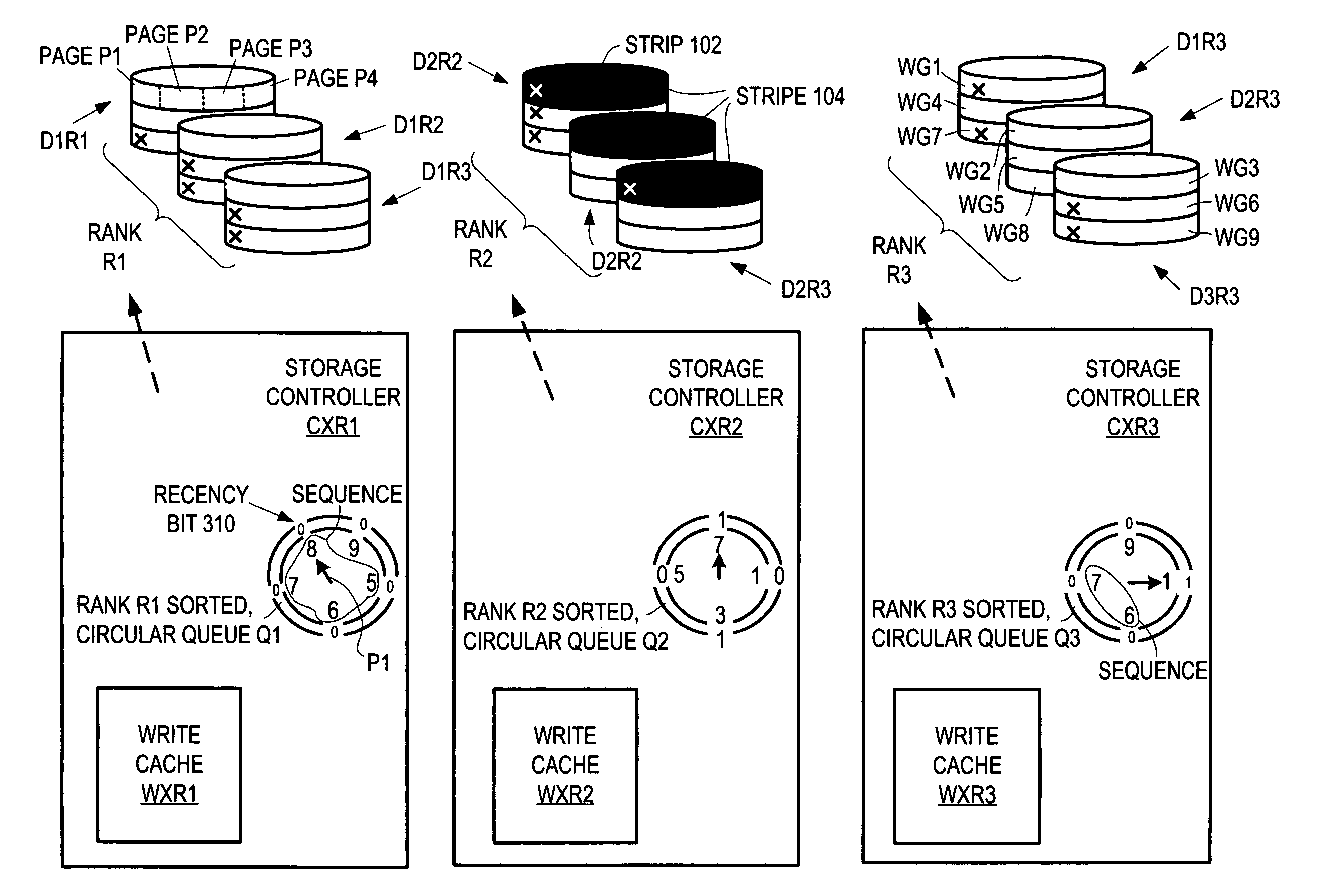

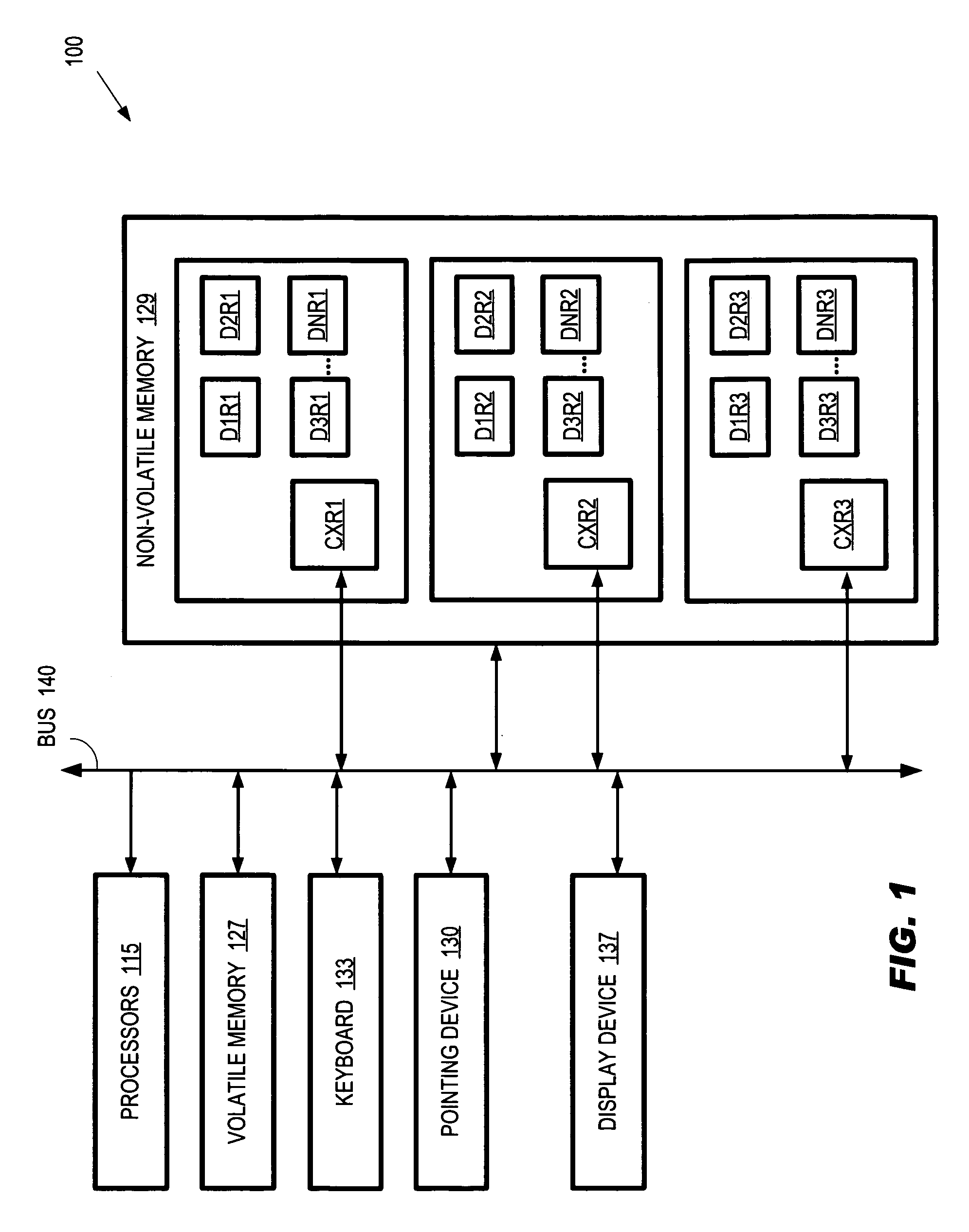

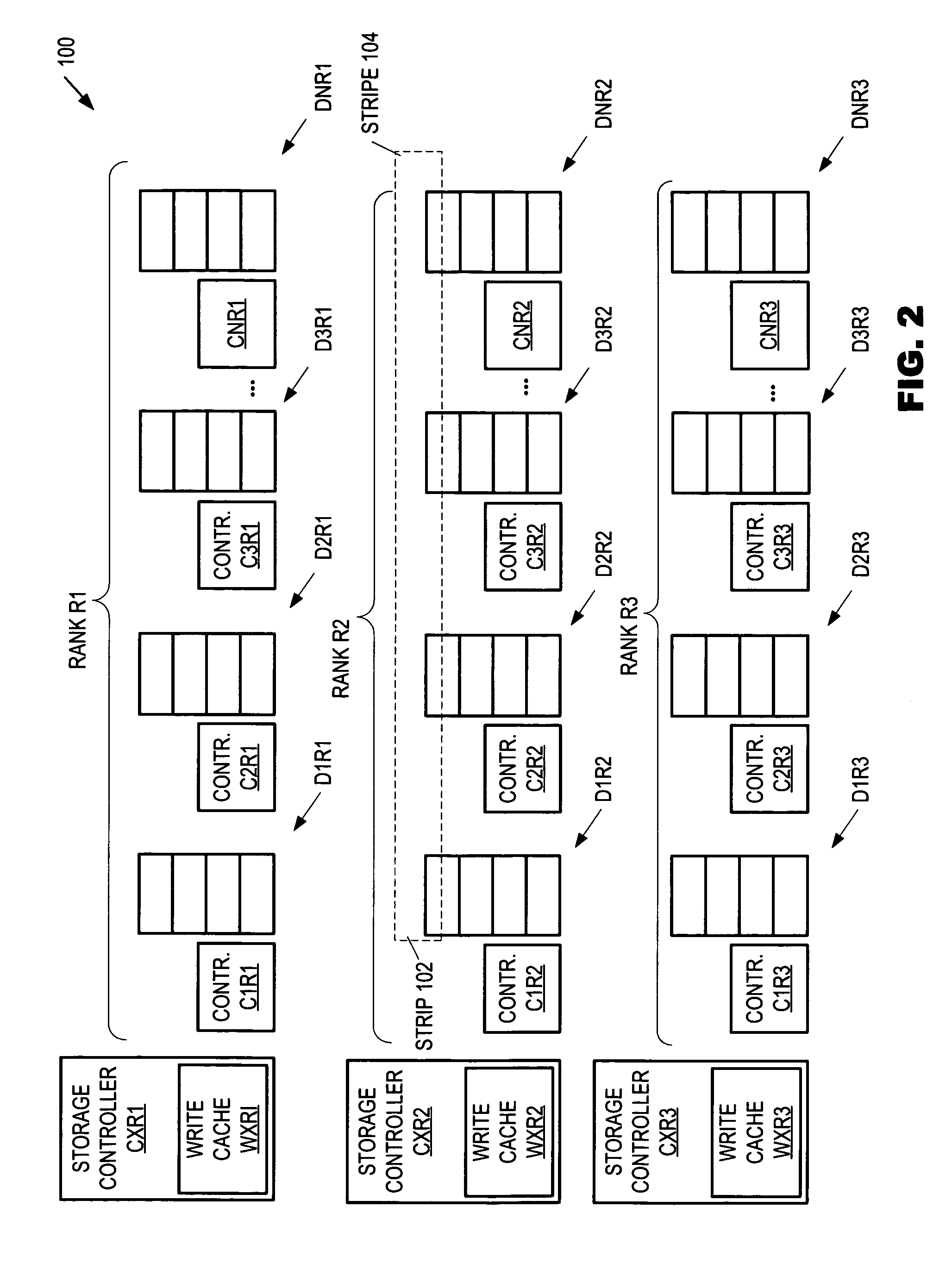

InactiveUS20070220201A1Reduce spacingIncrease the number ofMemory architecture accessing/allocationMemory systemsControl storeDisk array

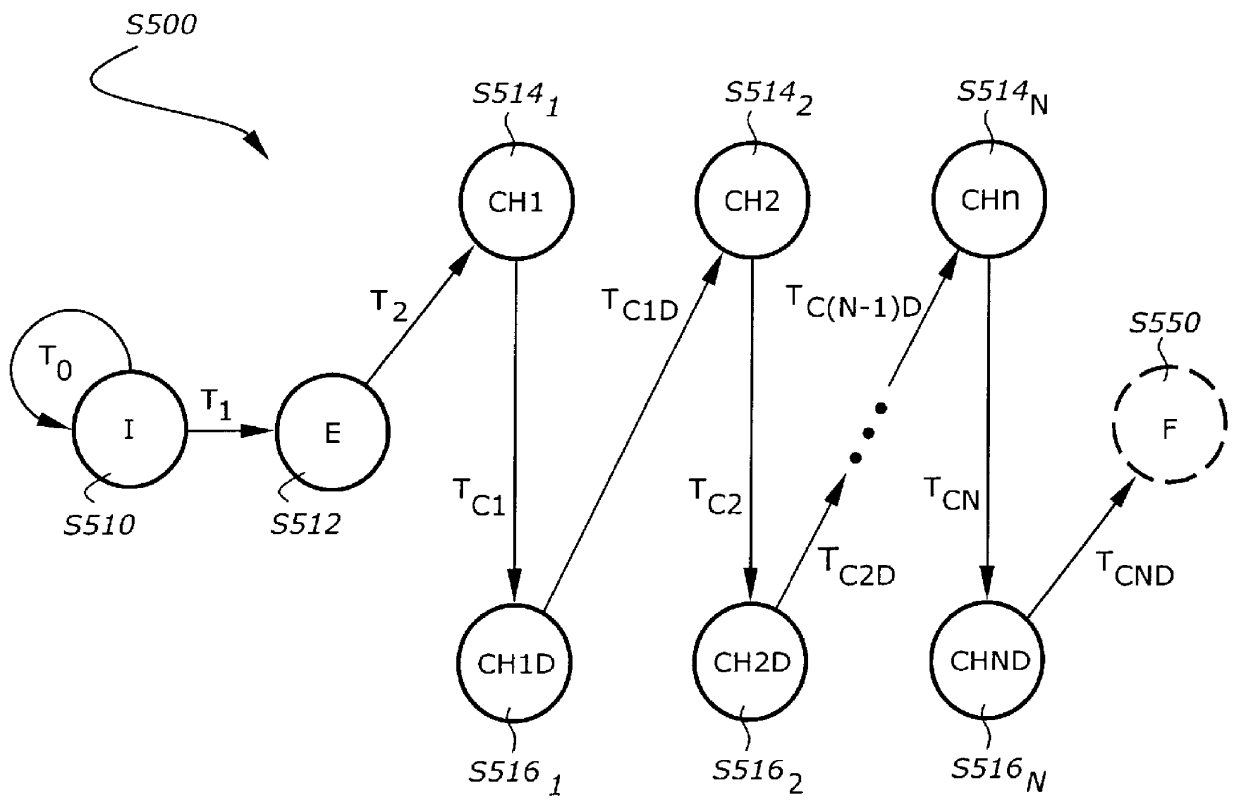

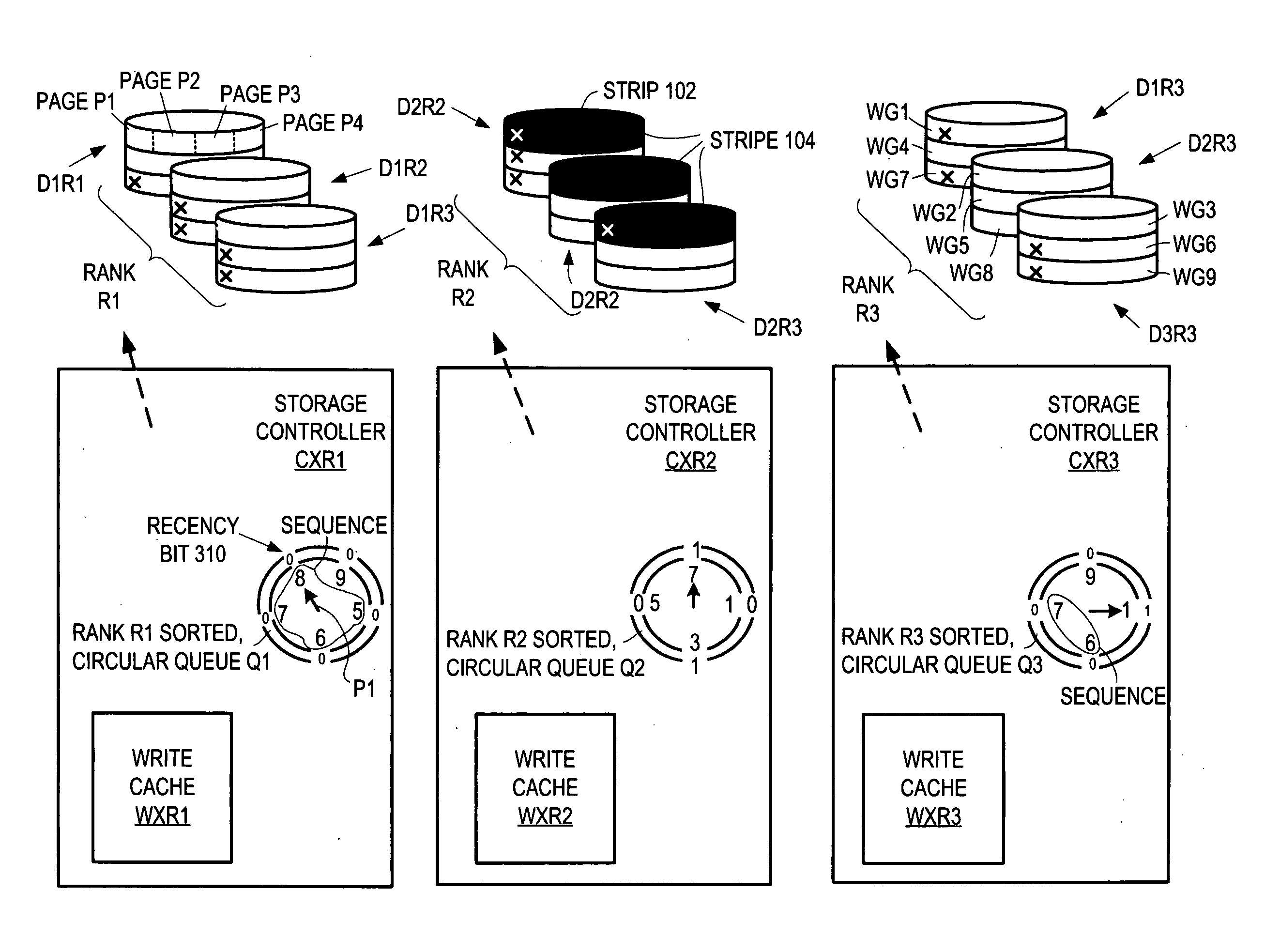

A storage system has a storage controller for an array of storage disks, the array being ordered in an sequence of write groups. A write cache is shared by the disks. The storage controller temporarily stores write groups in the write cache, responsive to write groups being written, and lists the write groups in order of their sequence in the array and in circular fashion, so that a lowest is listed next to a highest one of the write groups. The storage controller selects the listed write groups in rotating sequence. Such a write group is destaged from the write cache to the disk responsive to i) the selecting of the write group and ii) a state of a recency indicator for the write group, wherein the recency indicator shows recency of writing to the write group.

Owner:INTERMATIONAL MACHINERY CORPORATIO

Methods and Apparatuses for Flushing Write-Combined Data From A Buffer

Owner:TAHOE RES LTD

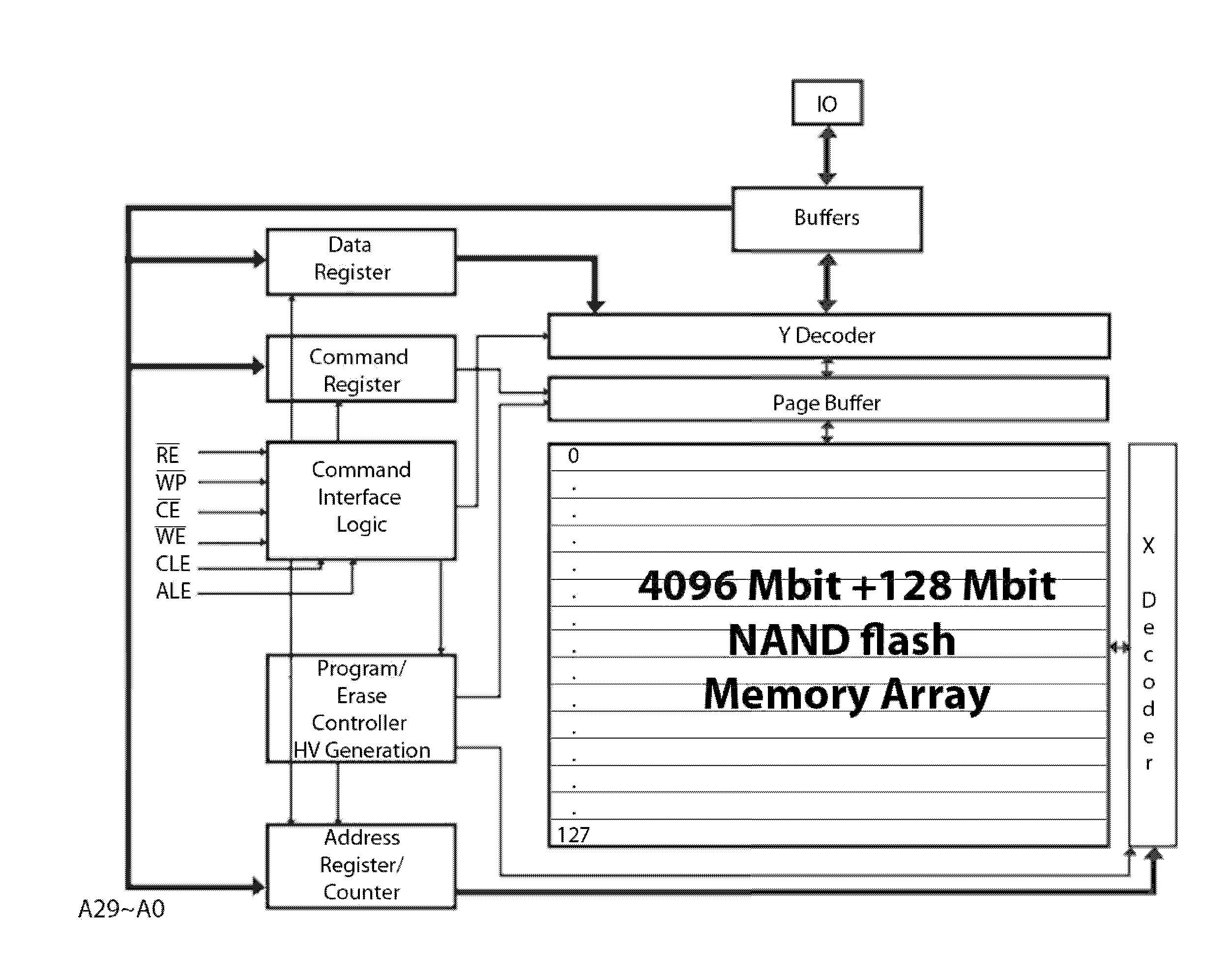

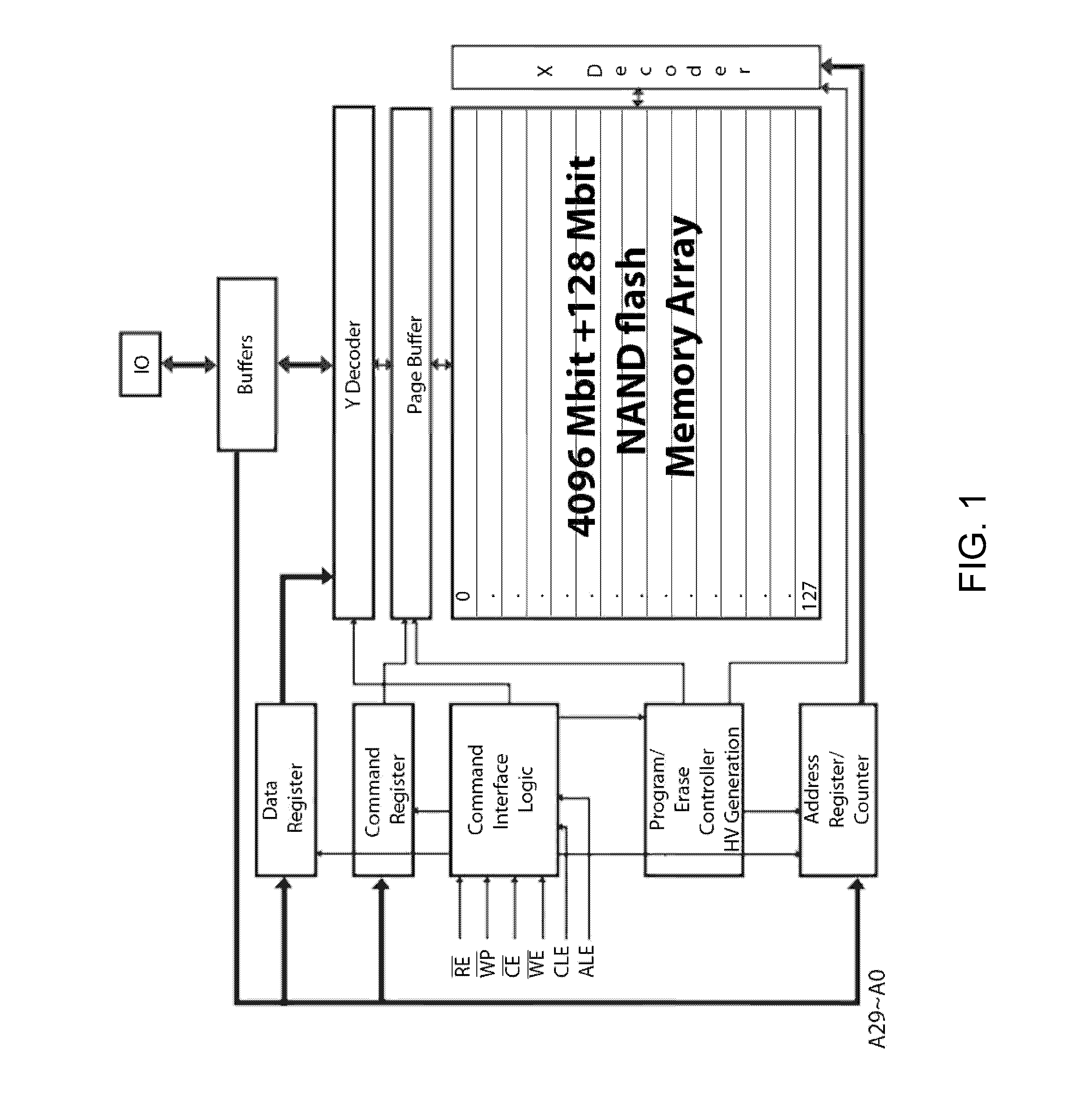

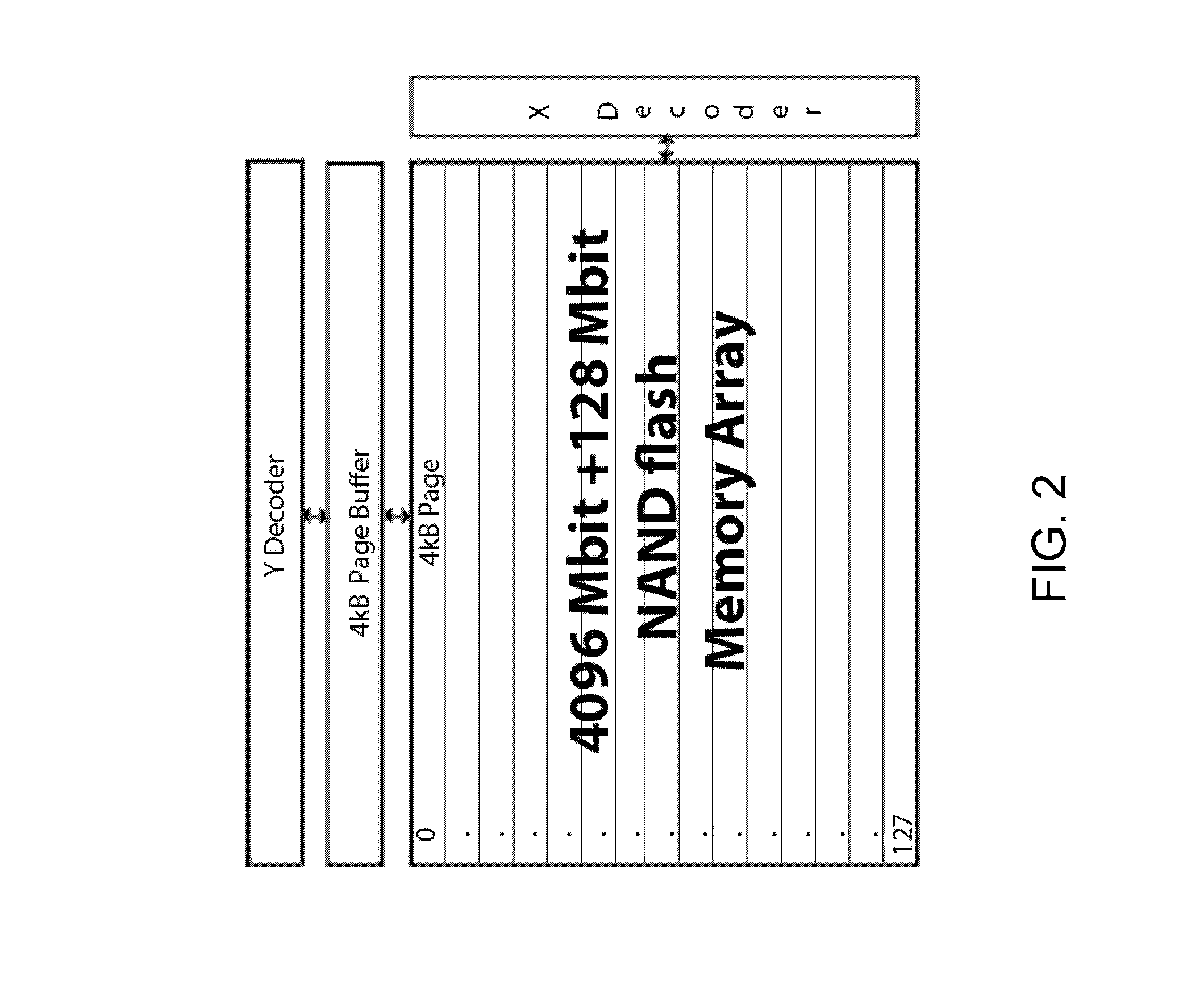

Page-buffer management of non-volatile memory-based mass storage devices

InactiveUS20130103889A1Improve access speedProvide flexibilityMemory architecture accessing/allocationMemory systemsMass storageFile system

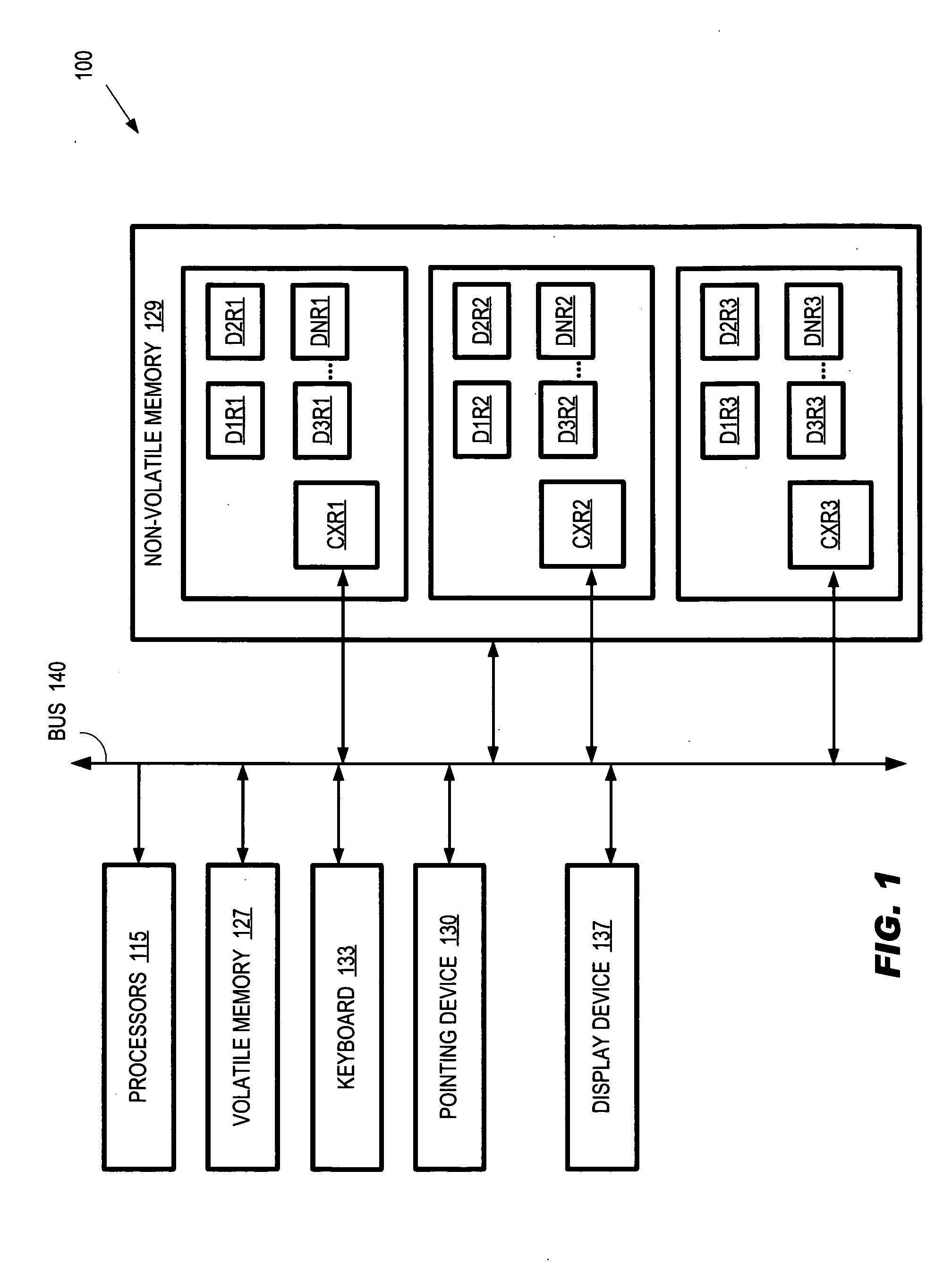

Mass storage devices and methods that use at least one non-volatile solid-state memory device, for example, one or more NAND flash memory devices, that defines a memory space for permanent storage of data. The mass storage device is adapted to be operatively connected to a host computer system having an operating system and a file system. The memory device includes memory cells organized in pages that are organized into memory blocks for storing data, and a page buffer partitioned into segments corresponding to a cluster size of the operating system or the file system of the host computer system. The size of a segment of the page buffer is larger than the size of any page of the memory device. The page buffer enables logically reordering multiple clusters of data fetched into the segments from pages of memory device and write-combining segments containing valid clusters.

Owner:KK TOSHIBA

Methodology and apparatus for implementing write combining

Write-combining in a computer system that uses a push model is set forth herein. In one embodiment, the method comprises creating one or more packets having a descriptor and the data associated with detected write transactions stored in the buffer assigned to a write-combinable range in response to a flush request to flush the buffer, and sending (pushing) these packets to the network I / O device.

Owner:TAHOE RES LTD

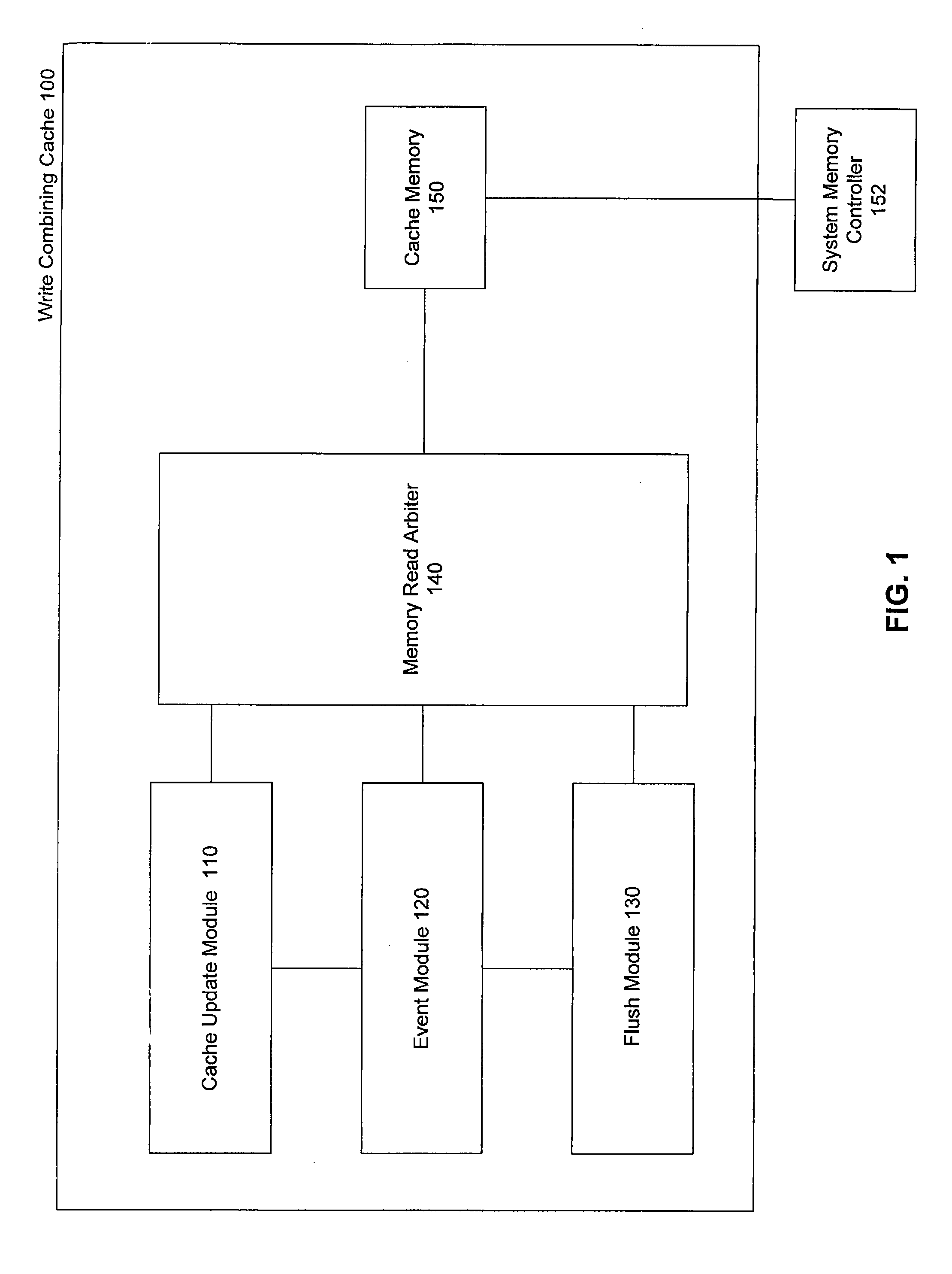

Write Combining Cache with Pipelined Synchronization

ActiveUS20090300288A1Avoid procrastinationMemory adressing/allocation/relocationParallel computingData storing

Owner:ADVANCED MICRO DEVICES INC

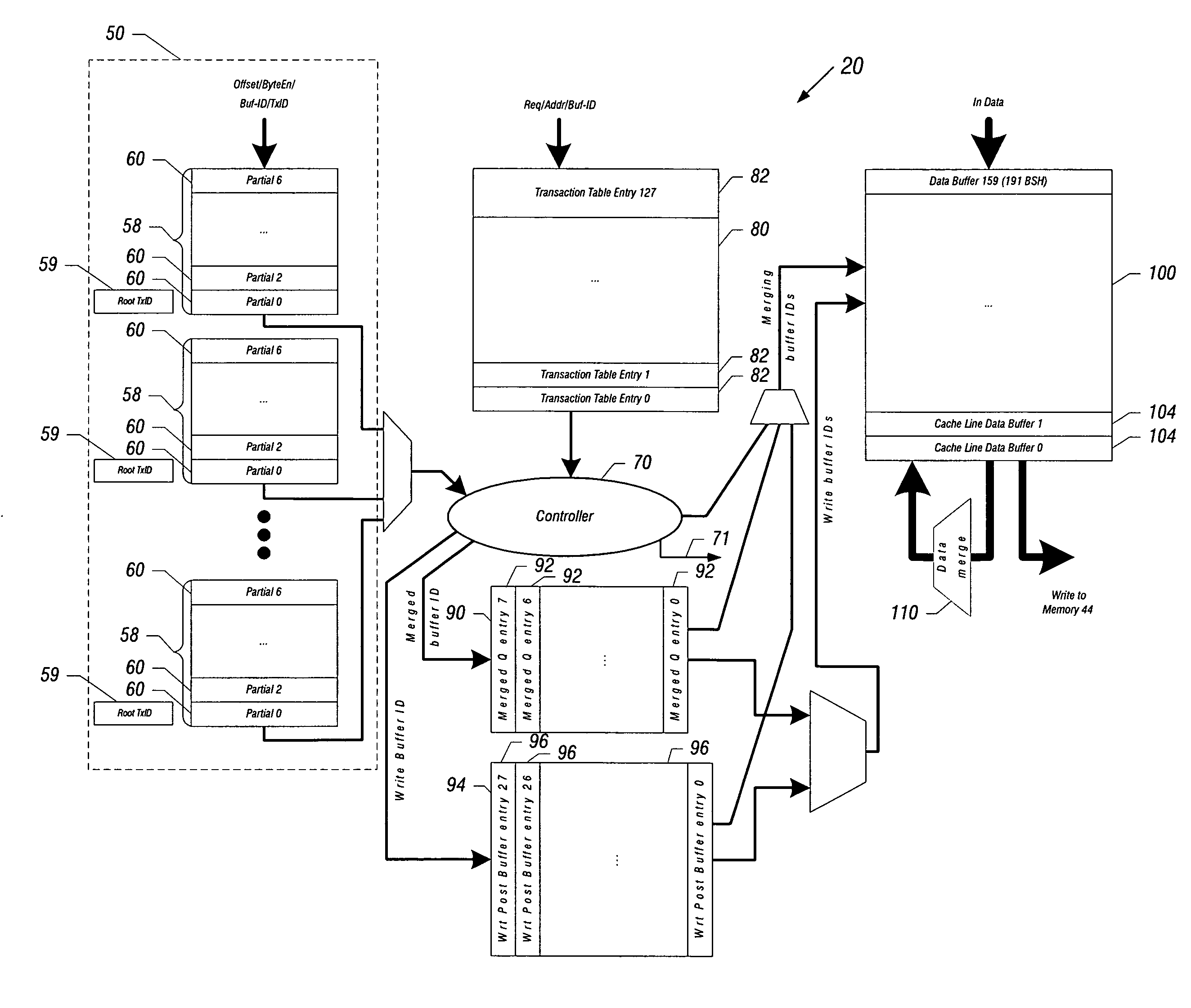

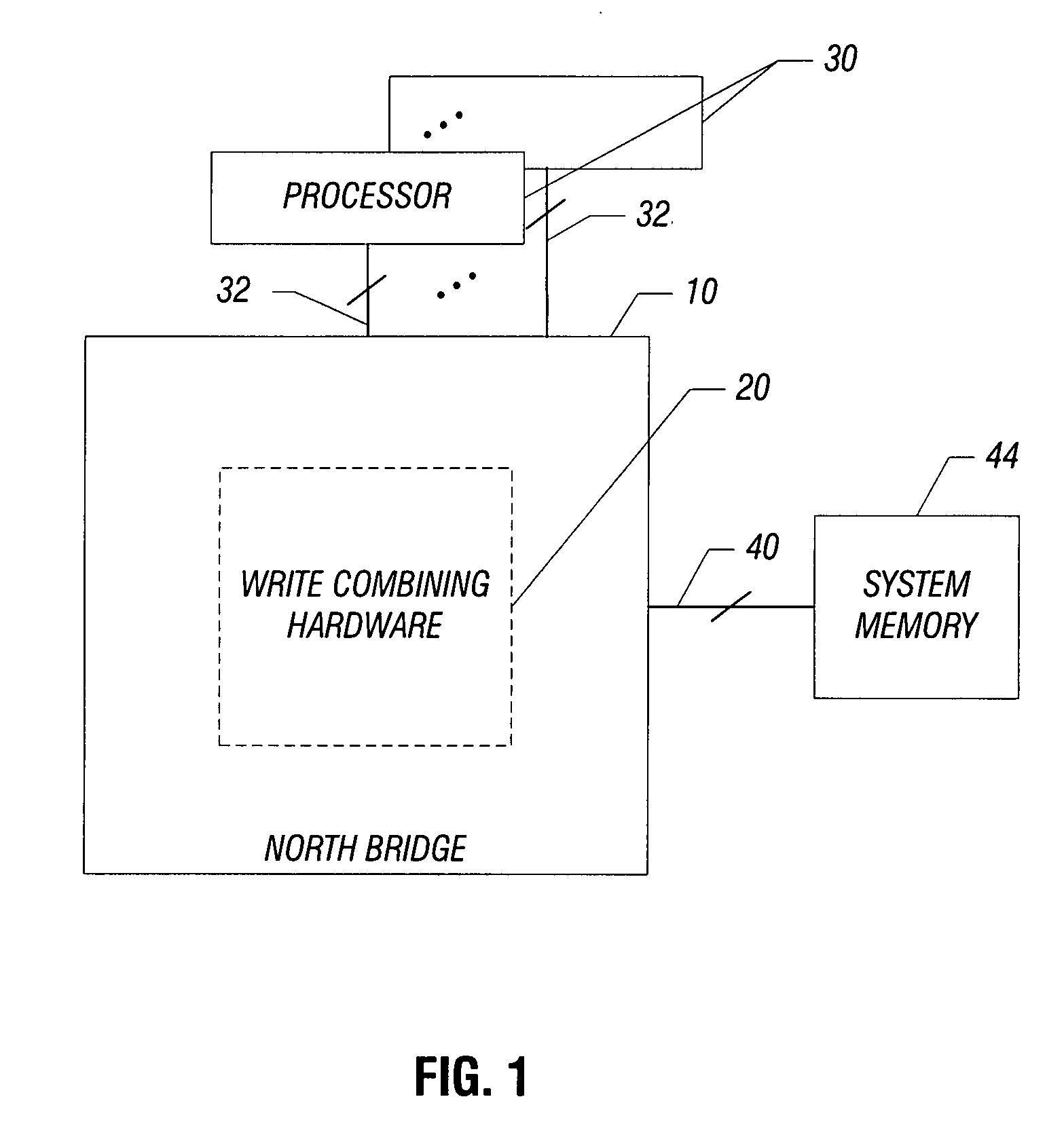

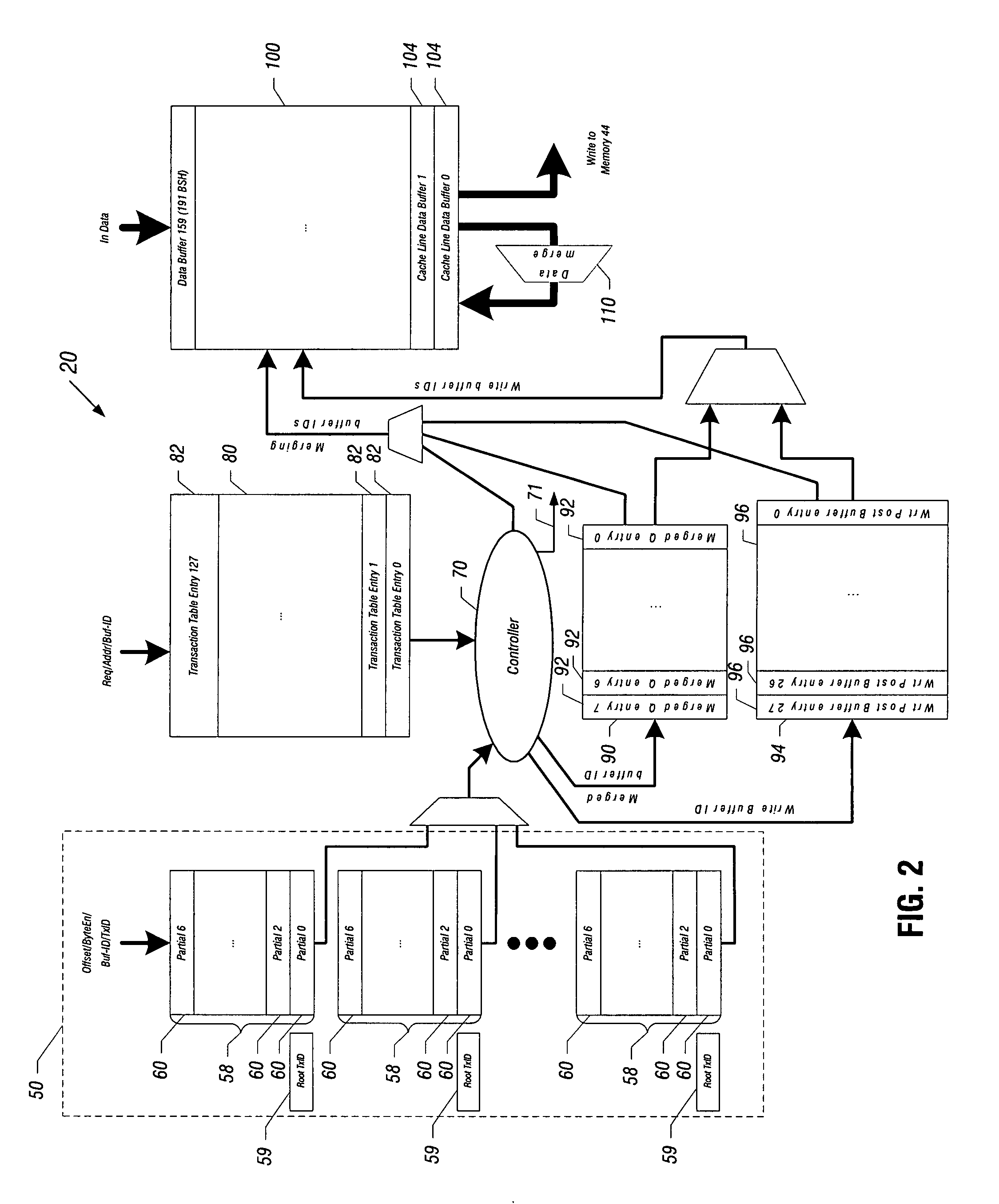

Technique and apparatus for combining partial write transactions

A bridge includes a memory to establish a transaction table and write combining windows. Each write combining window is associated with a cache line and is subdivided into subwindows; and each of the subwindows is associated with a partial cache line. The bridge includes a controller to determine whether an incoming partial write transaction conflicts with a transaction stored in the transaction table. If a conflict occurs, the controller uses the write combining windows to combine the partial write transaction with another partial write transaction if one of the partial write combining windows is available. The controller issues a retry signal to a processor originating the partial write transaction if none of the partial write combining windows are available.

Owner:INTEL CORP

Maximal length packets

InactiveUS20060168384A1Multiple digital computer combinationsInput/output processes for data processingData packReal-time computing

Detecting and flushing maximal length packets is set forth herein. In one embodiment, the method comprises receiving a flushing event and, in response to the flushing event, repeatedly detecting a maximum length packet of write data from a write combining storage area and flushing the detected maximum length packet to a target input / output (I / O) device over a bus. Each maximal length packet is a packet of maximum payload of write data that can be formulated within in the write combining storage area while adhering to packet protocol rules for the bus.

Owner:INTEL CORP

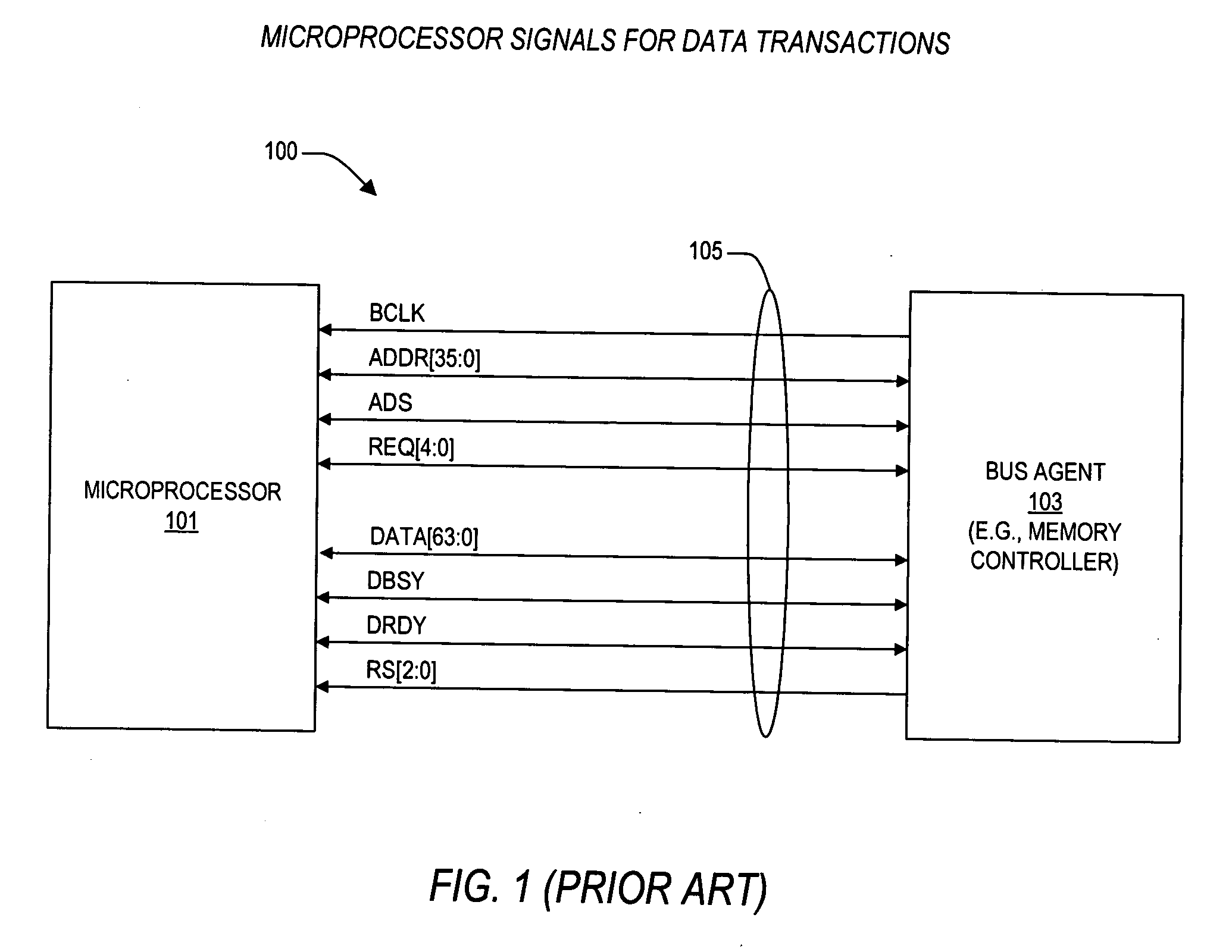

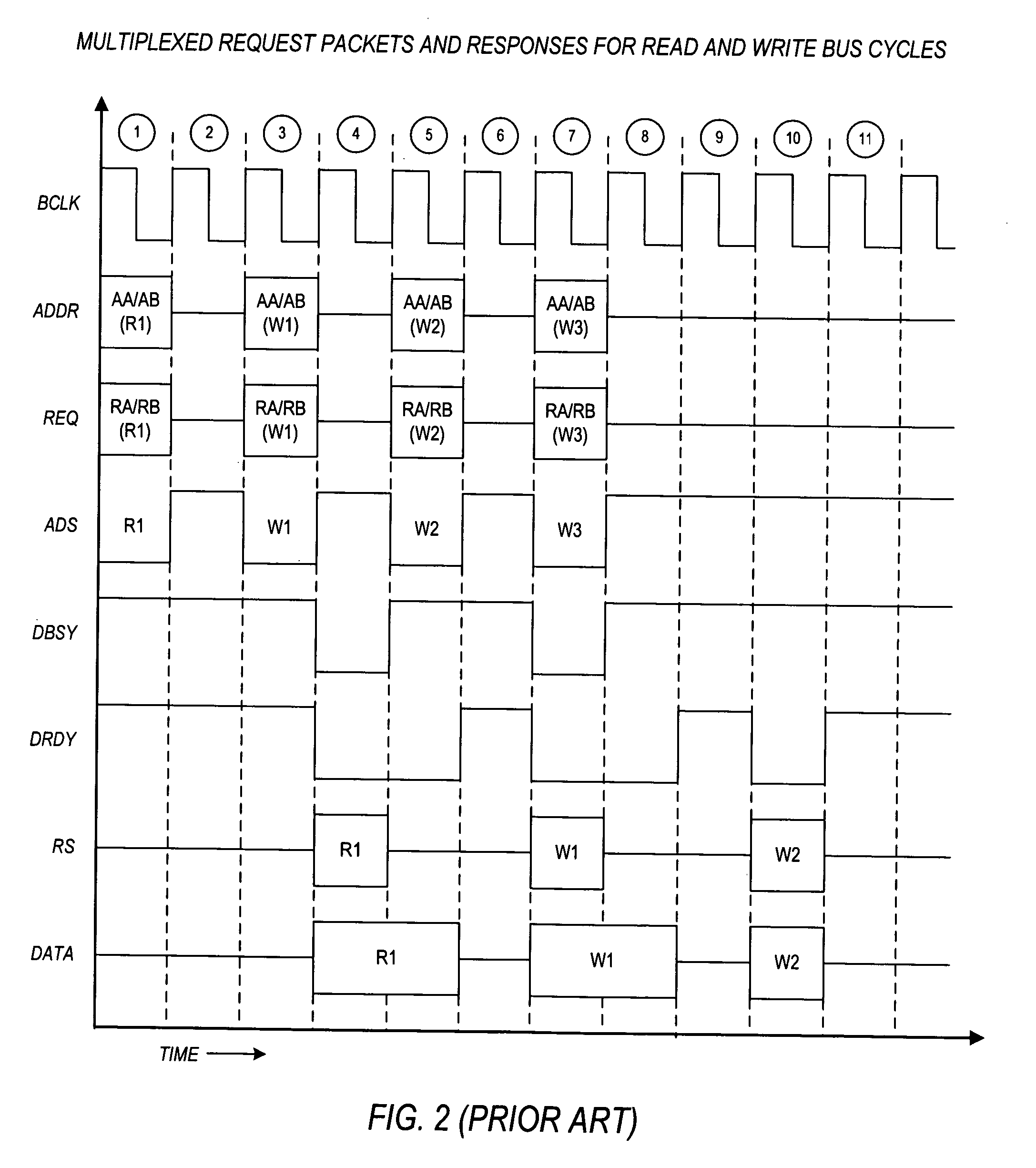

Apparatus and method for sparse line write transactions

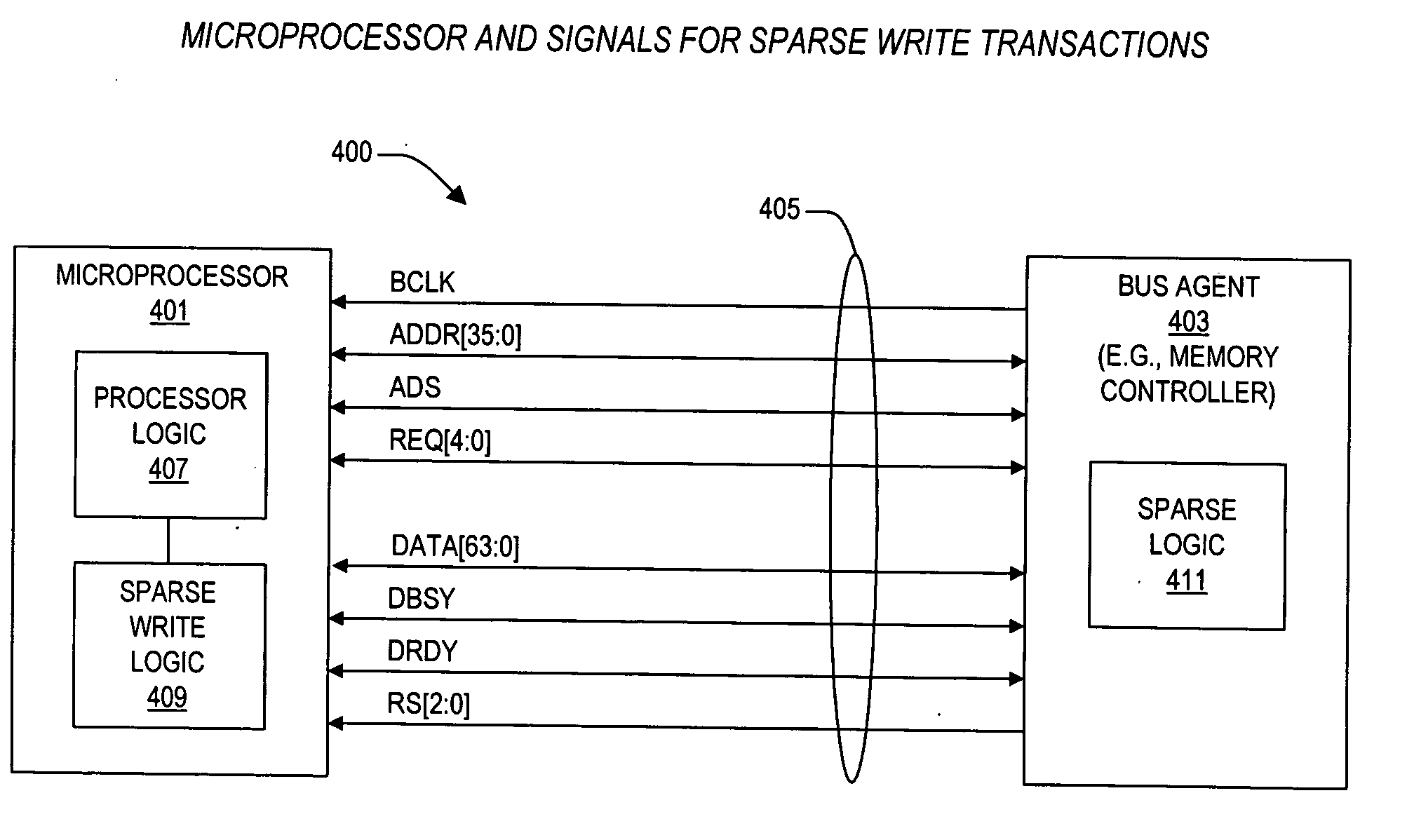

A microprocessor including processor logic and sparse write logic. The processor logic asserts address and request signals to provide an address and a request for a cache line memory write transaction. The sparse write logic causes the processor logic to modify a second part of the write request to specify the sparse write command value and to provide the corresponding enable bits. The sparse write-combined memory write transaction may be a quad-pumped cache line write transaction for writing eight quadwords in which each enable bit identifies a corresponding doubleword. A method of performing a sparse write-combined write transaction including providing an address and a request for a memory write transaction, indicating that the memory write transaction is a sparse write-combined write transaction, asserting enable signals for the sparse write-combined write transaction, and providing data for the sparse write-combined write transaction.

Owner:VIA TECH INC

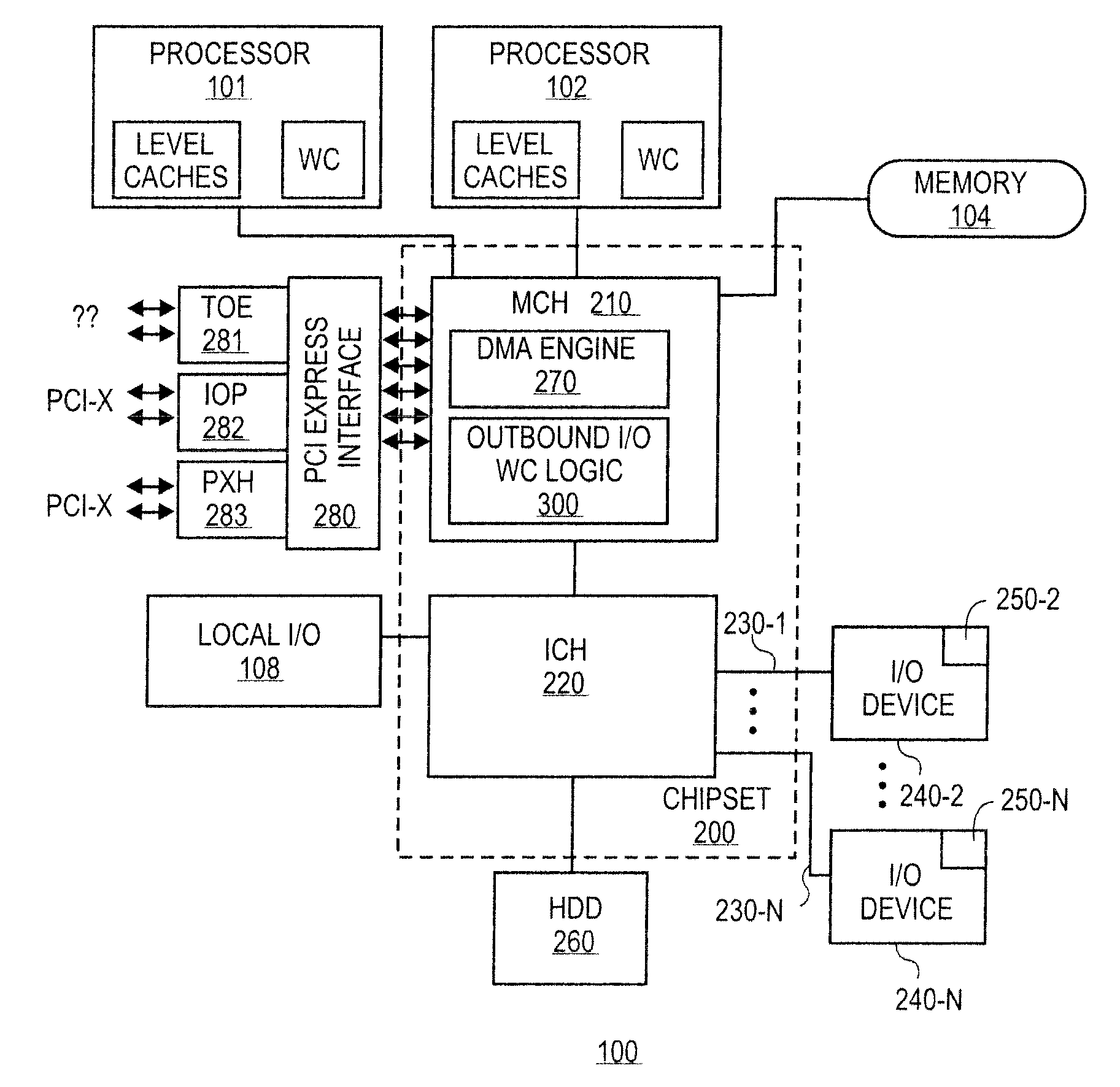

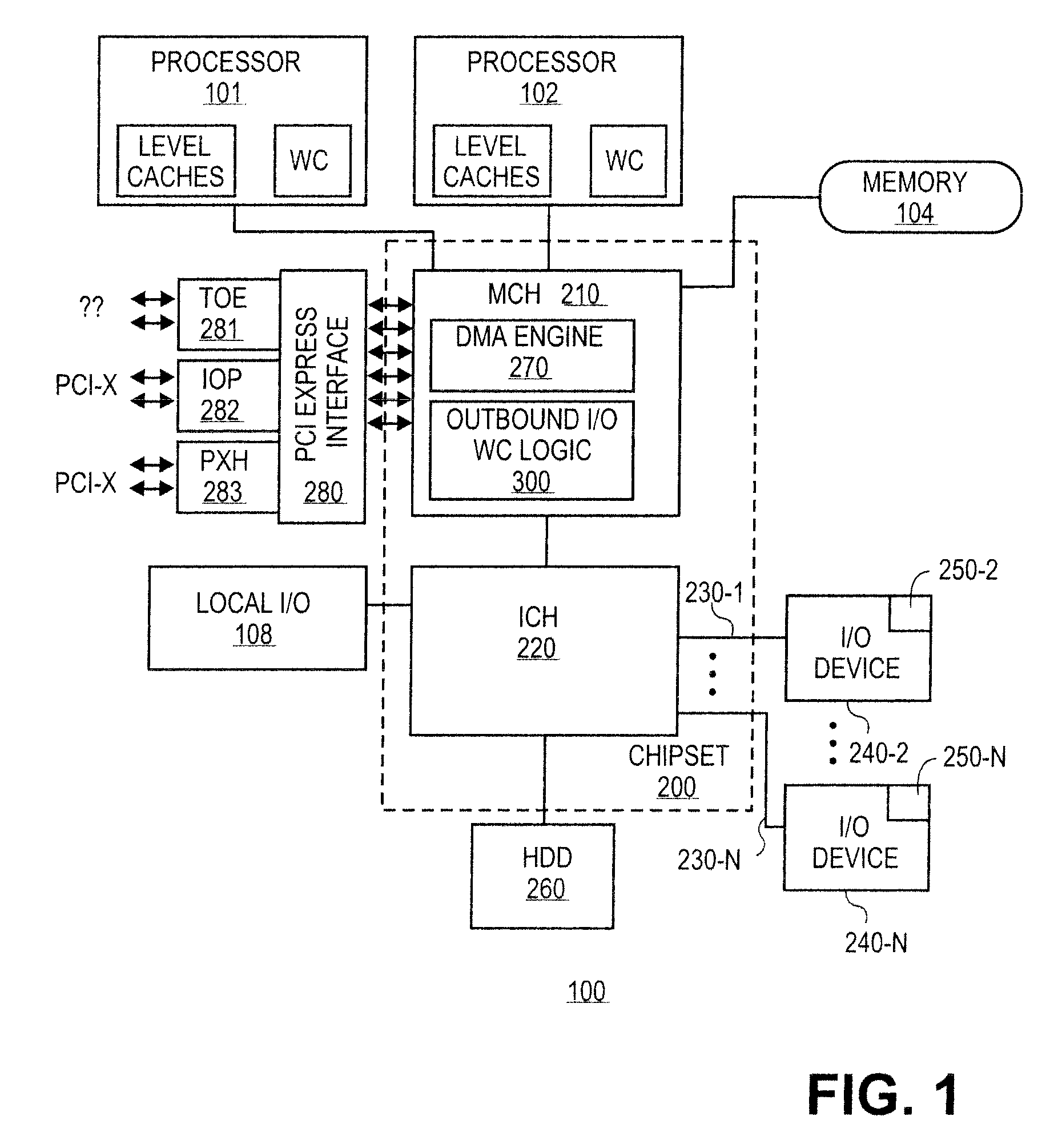

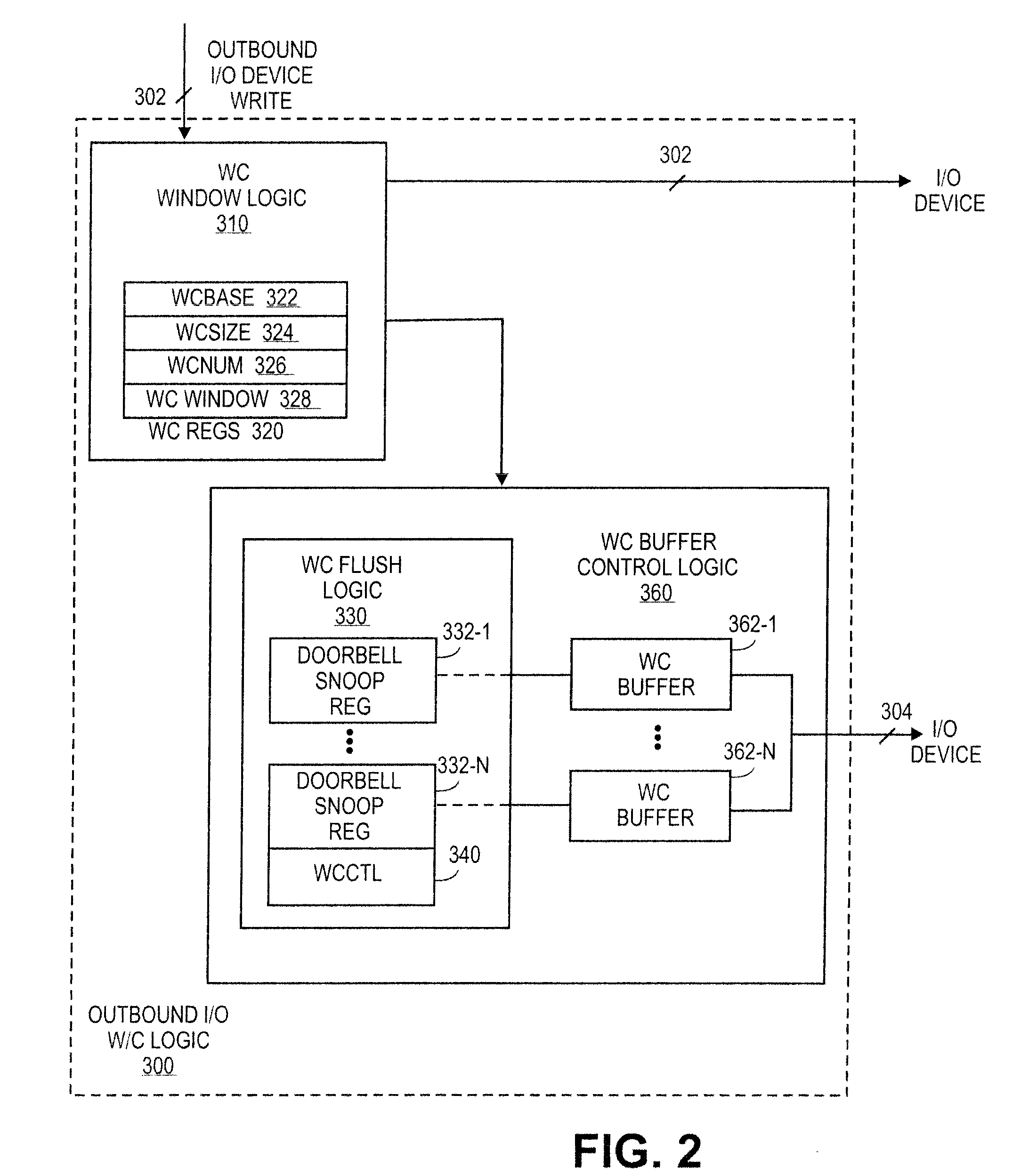

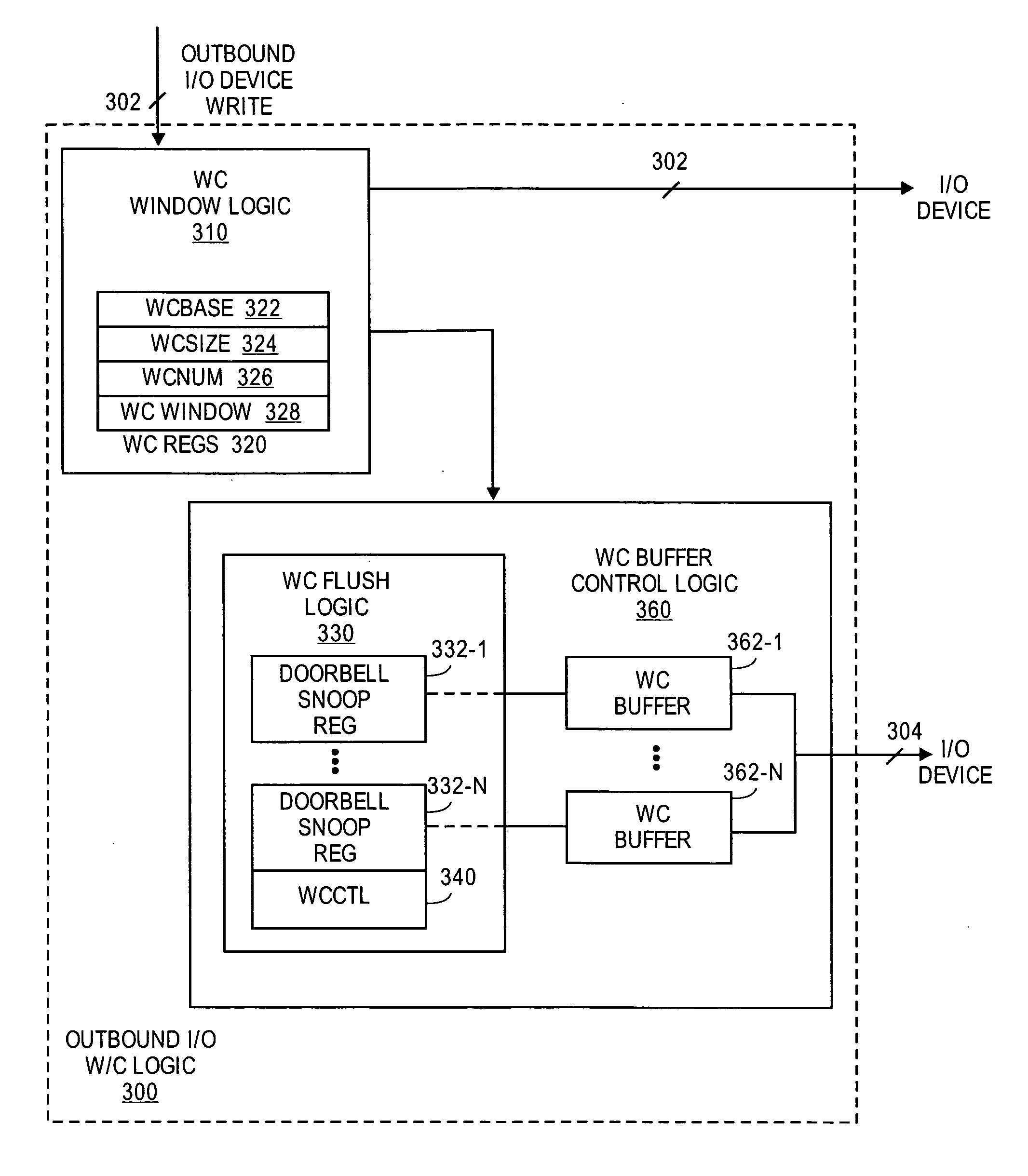

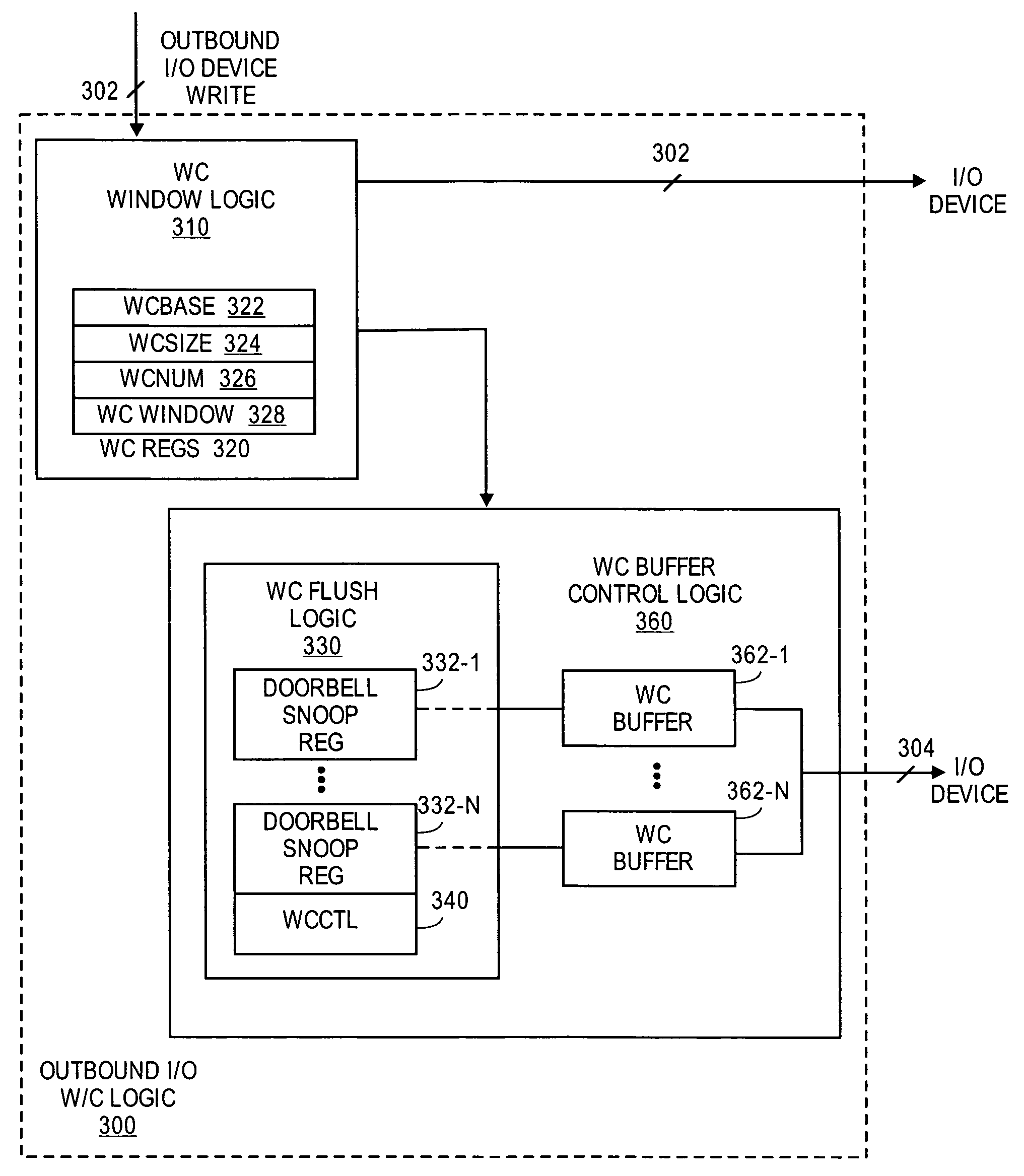

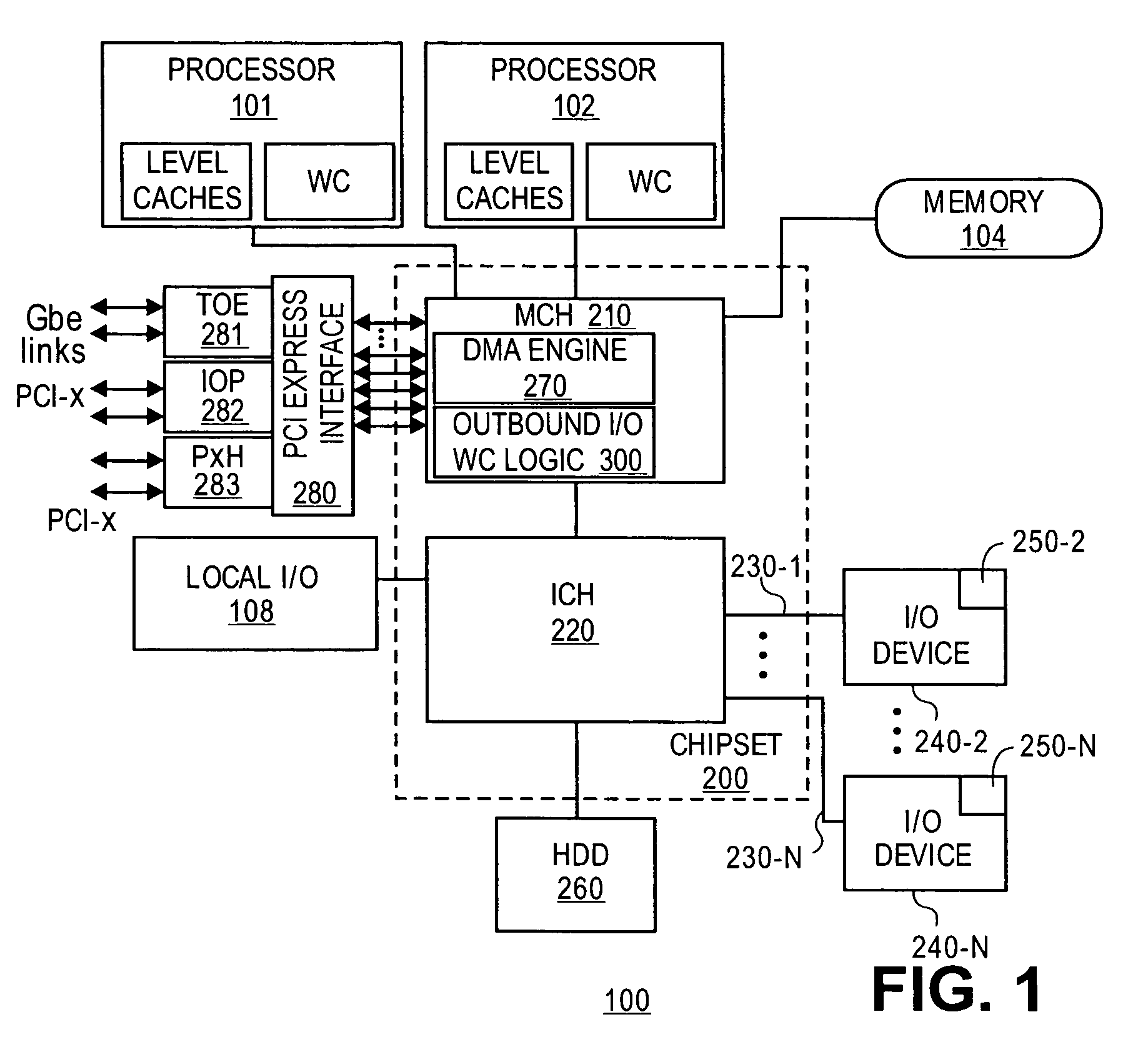

Apparatus and method for combining writes to I/O

InactiveUS7206865B2Input/output processes for data processingData conversionSpatial correlationData store

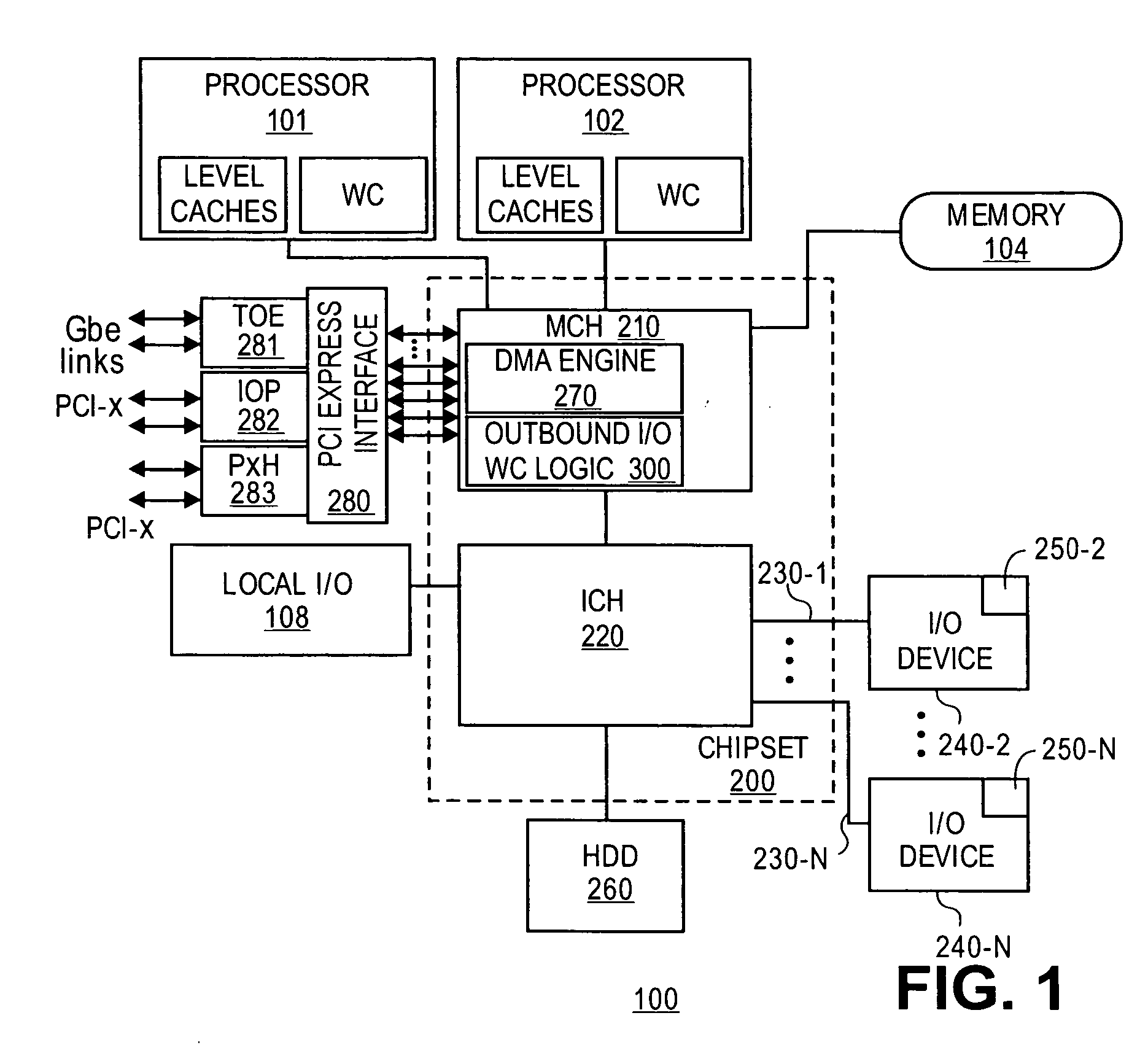

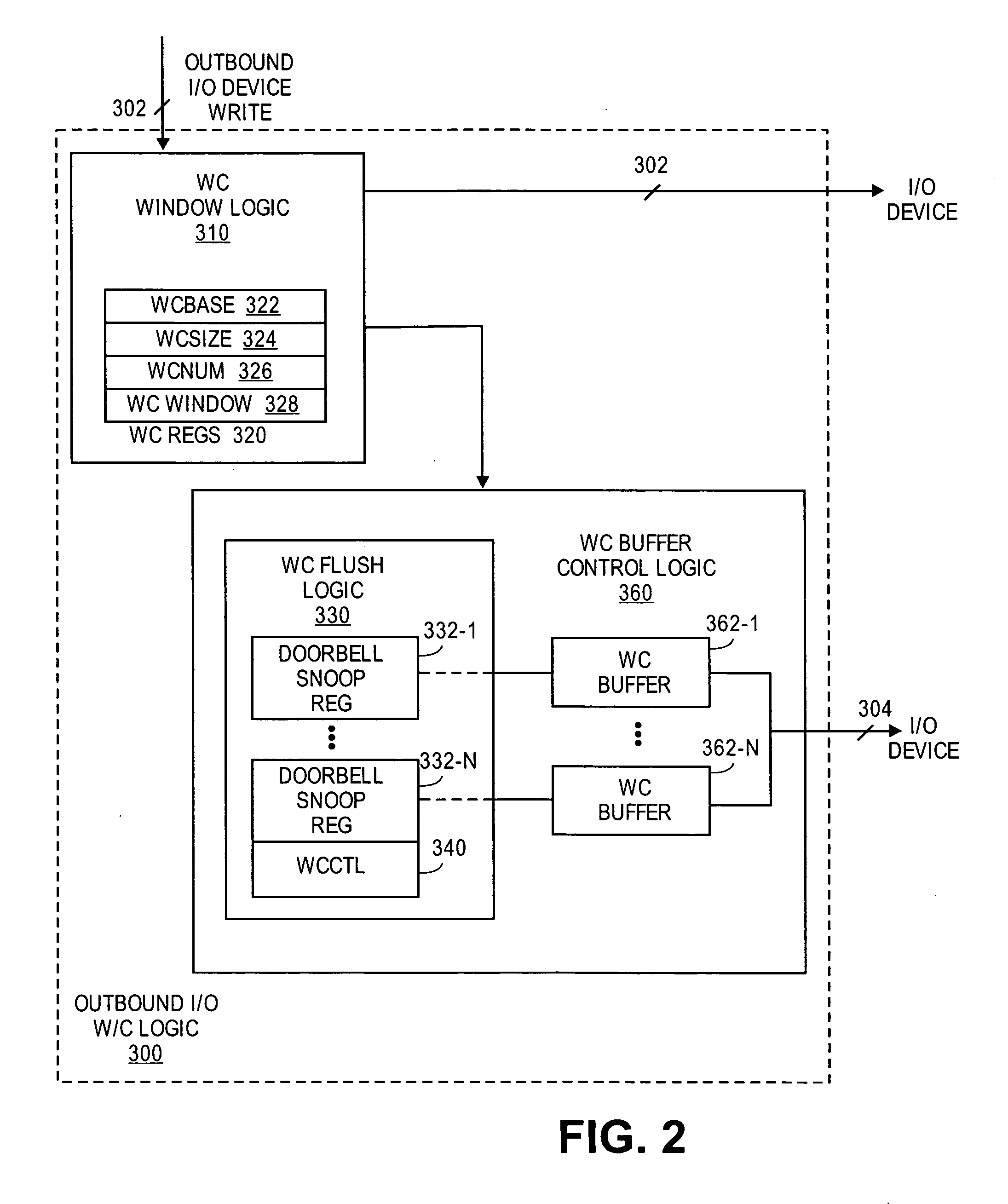

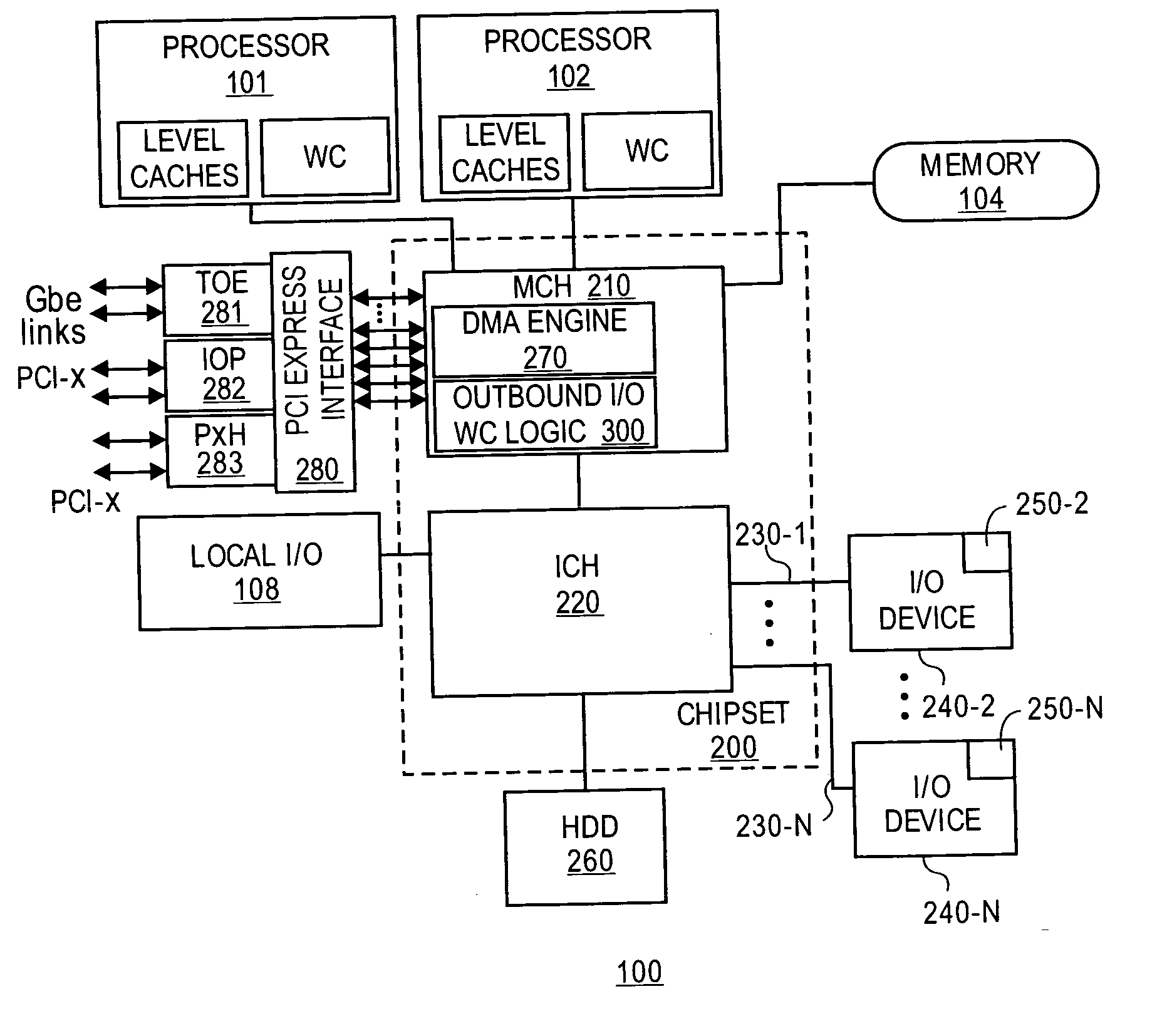

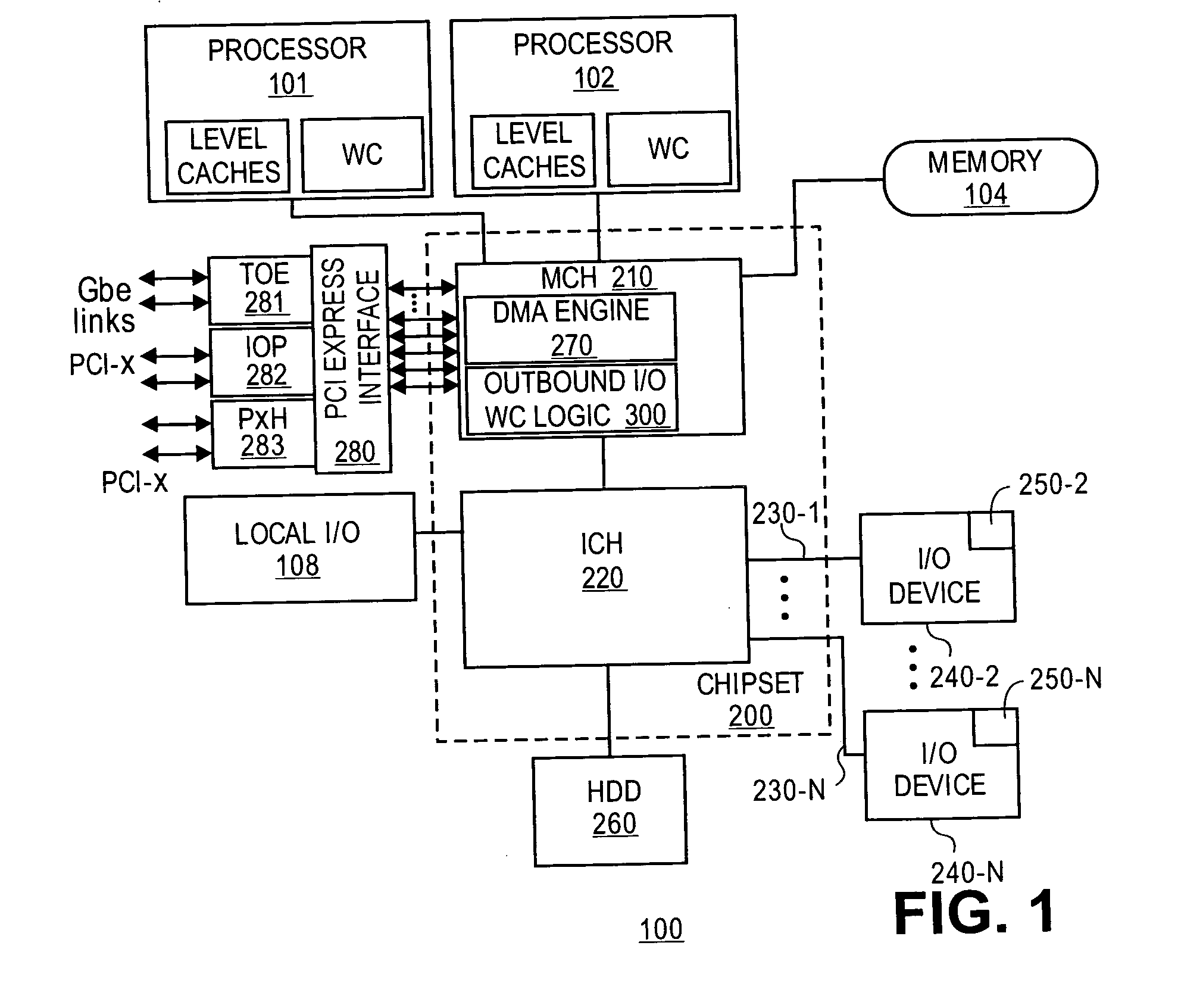

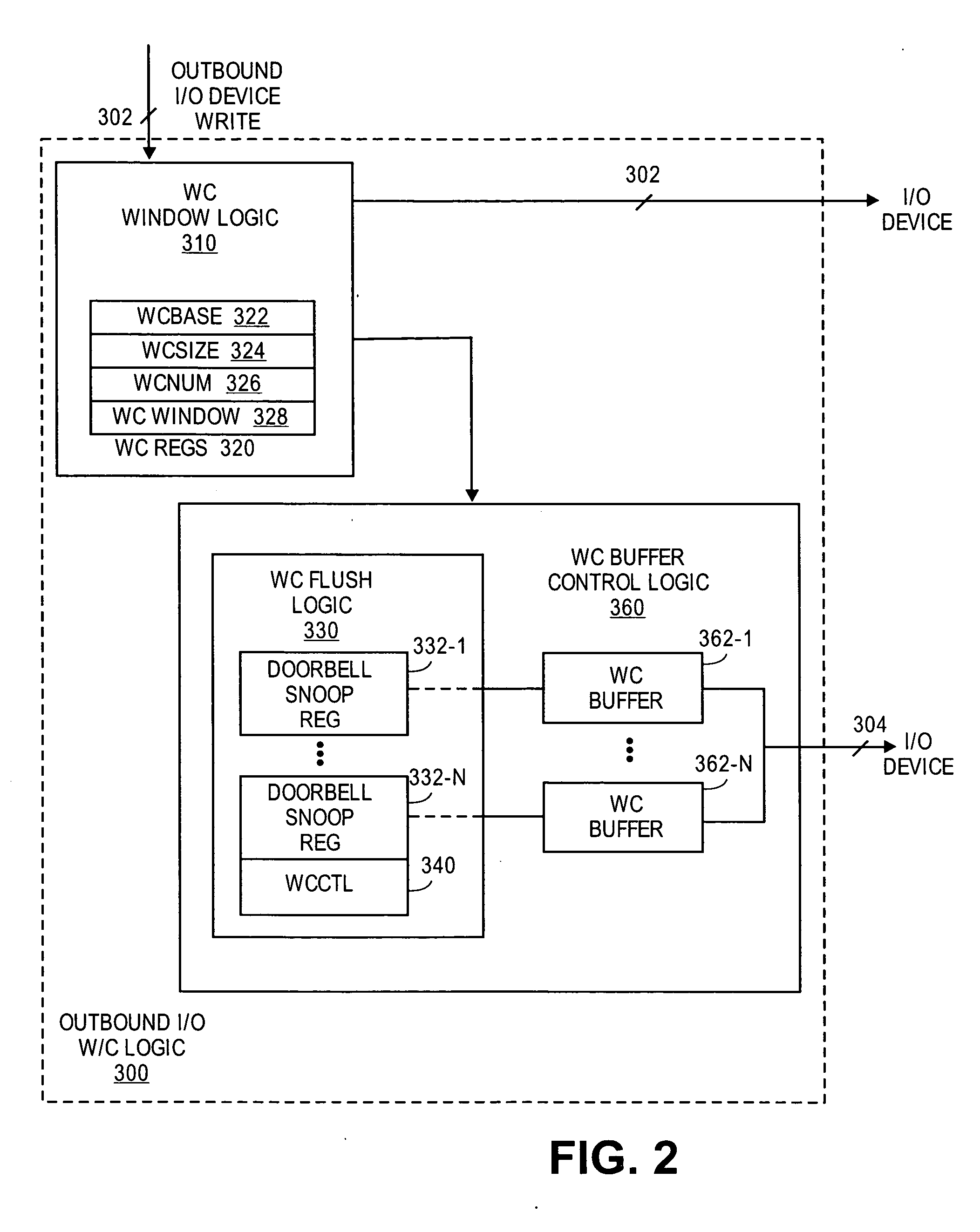

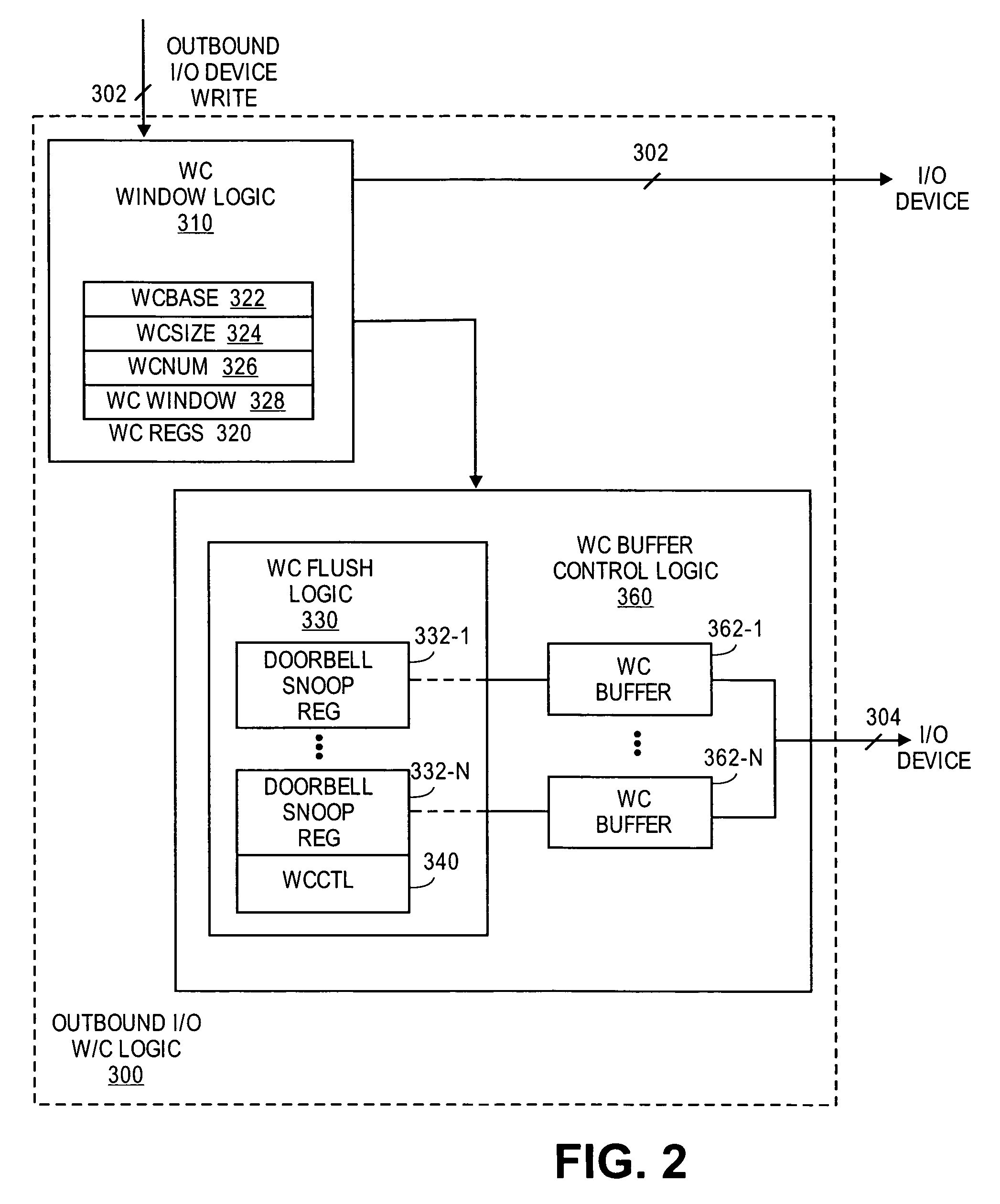

An apparatus and method for outbound I / O write-combining are described. In one embodiment the method includes the detection of a write transaction request directed to an I / O device. Once detected, it is determined whether an address associated with the detected write transaction falls within a predetermined write-combinable range of the memory mapped I / O space assigned to the I / O device. When the transaction address falls within a write-combinable range, data associated with the detected write transaction is stored within a buffer corresponding to the transaction address. Accordingly, one embodiment of the present invention provides write-combining for data written to an I / O port associated with a memory mapped I / O address space.

Owner:MICRON TECH INC

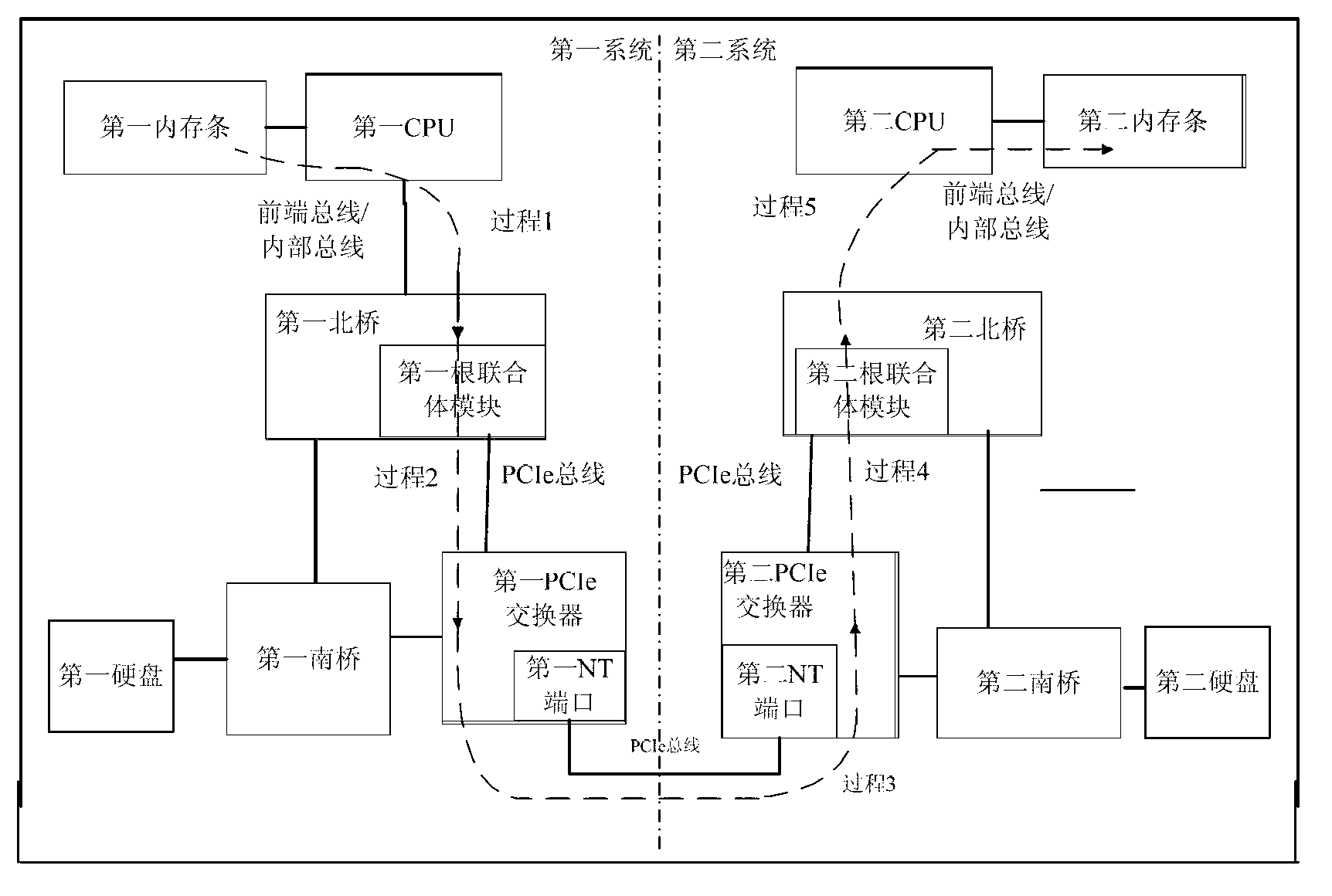

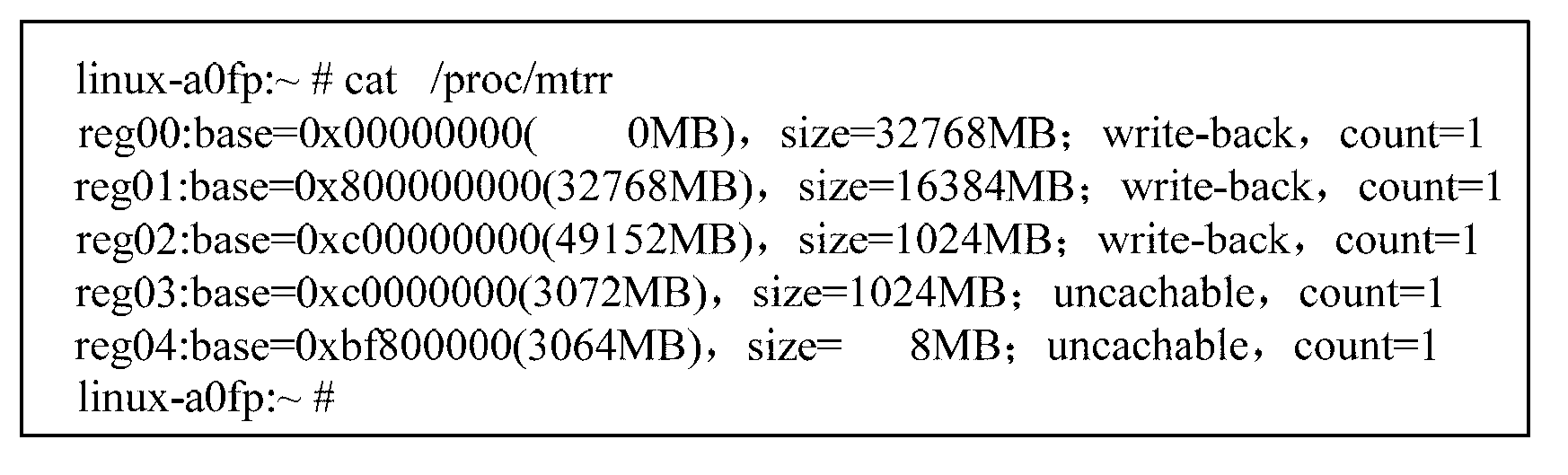

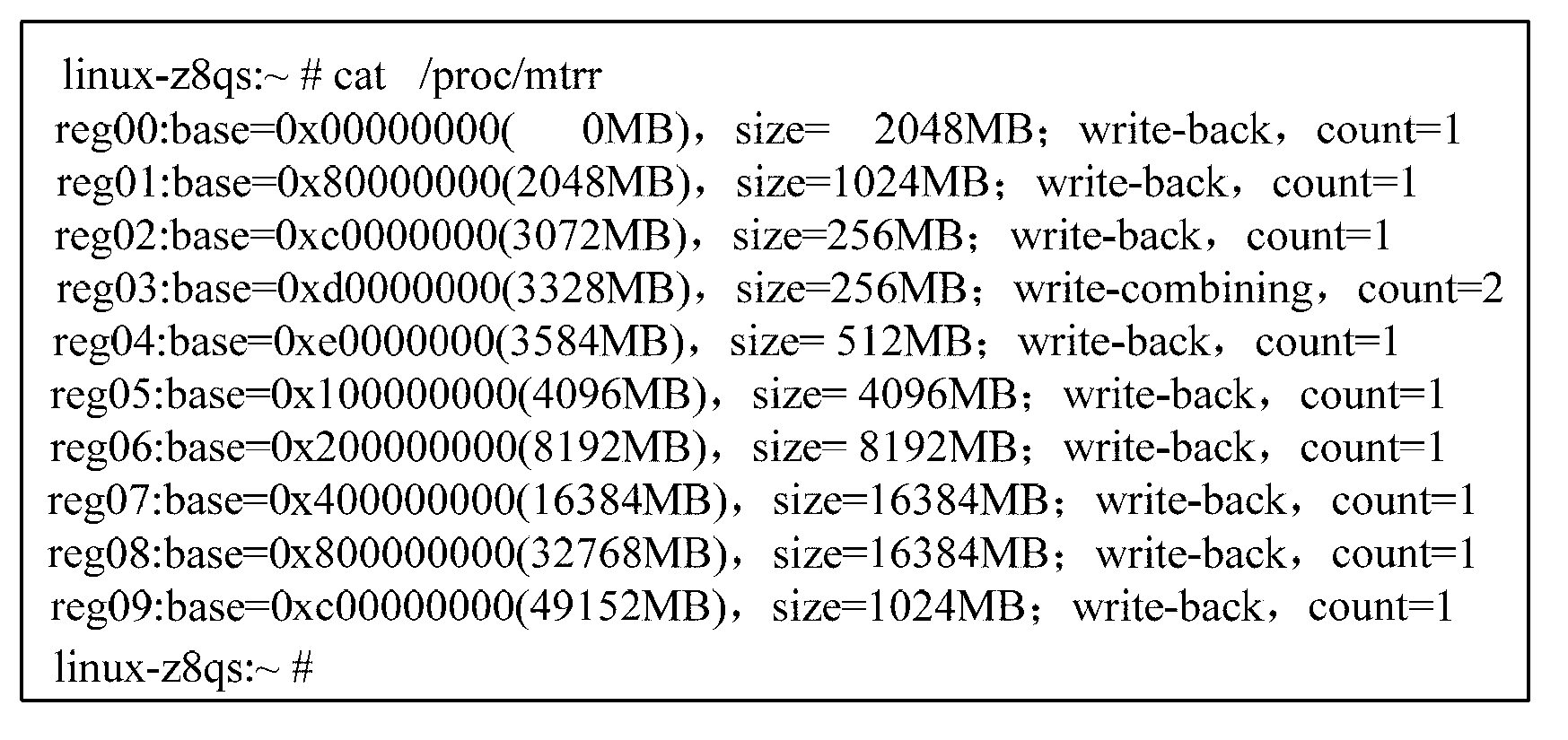

Allocation method and device of write combine attribute memory space

ActiveCN103019949AEasy to implementMemory architecture accessing/allocationMemory adressing/allocation/relocationDistribution methodParallel computing

The embodiment of the invention discloses an allocation method and an allocation device of a write combine attribute memory space. The allocation method comprises the following steps of: during resource scanning of equipment, determining types and sizes of resources required by each set of equipment; after the resource scanning of all equipment, determining the total size of a write combine memory space required by all first equipment; determining an initial address used for allocating the write combine memory space to the first equipment; and jointly allocating a memory space to all first equipment and allocating a sub memory space to each first equipment from the memory space. By using the allocation method and the allocation device of the write combine attribute memory space provided by the embodiment of the invention, the write combine attribute memory space can be more reliably allocated to the equipment and the allocation method is relatively simple.

Owner:HUAWEI TECH CO LTD

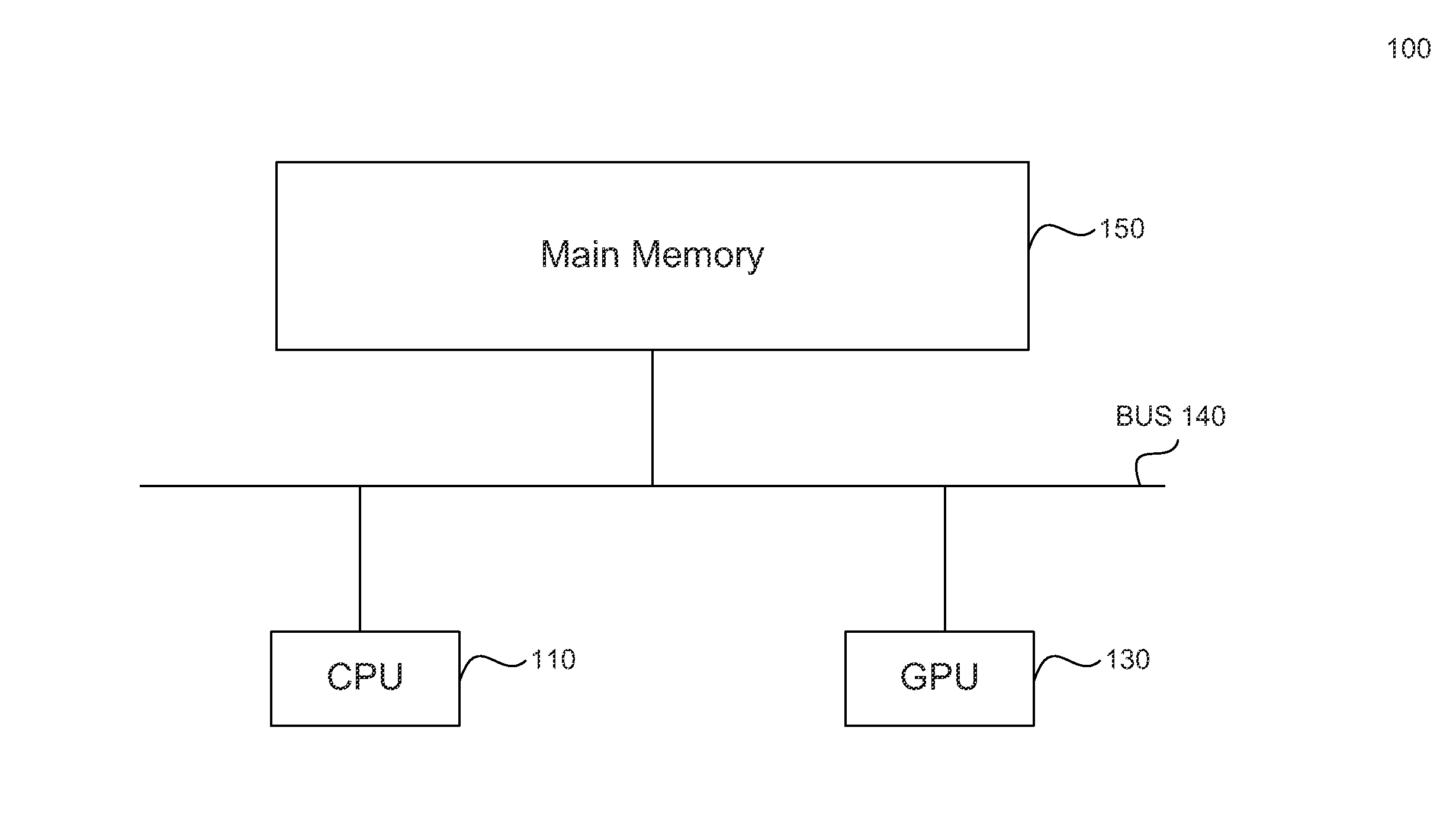

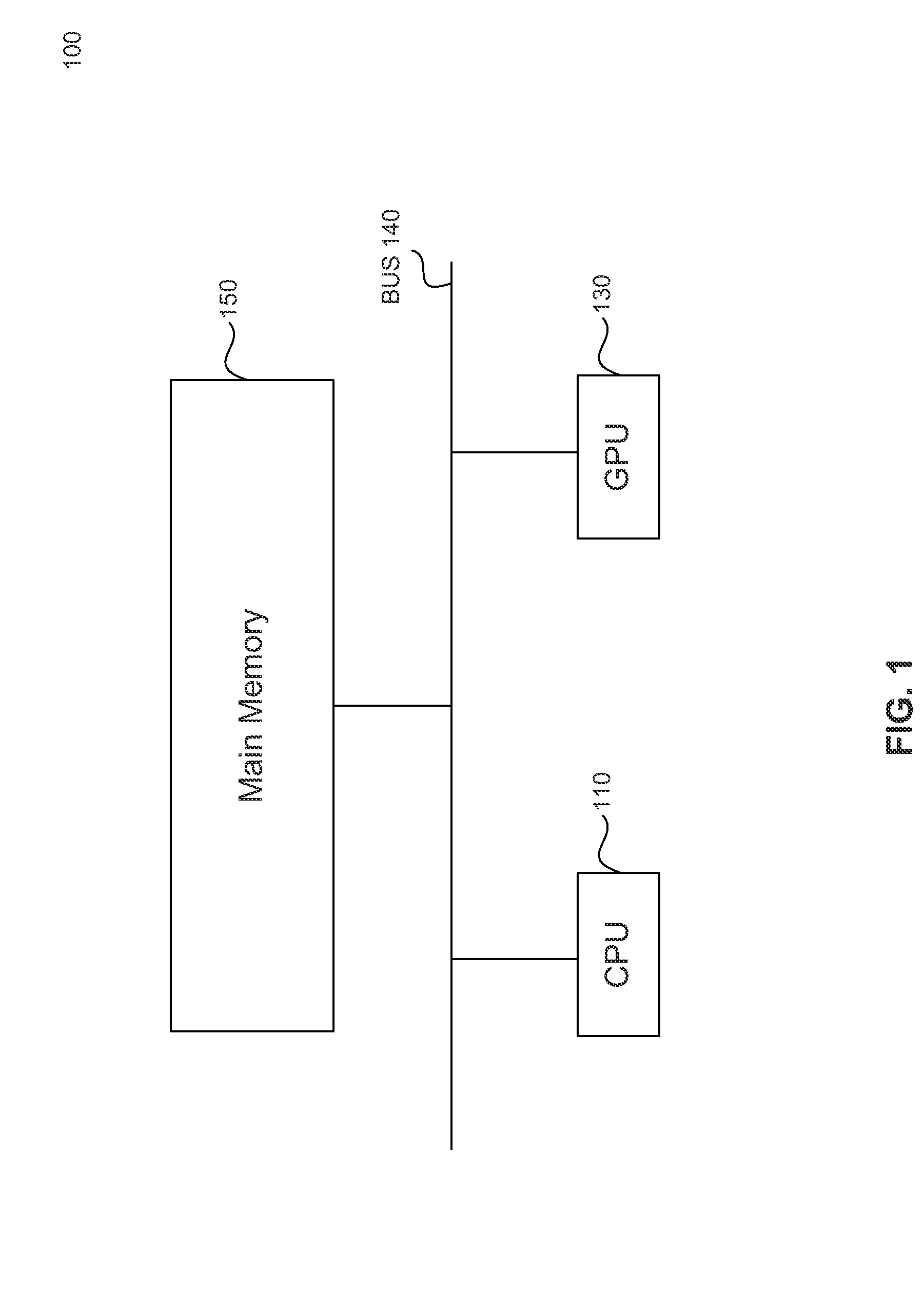

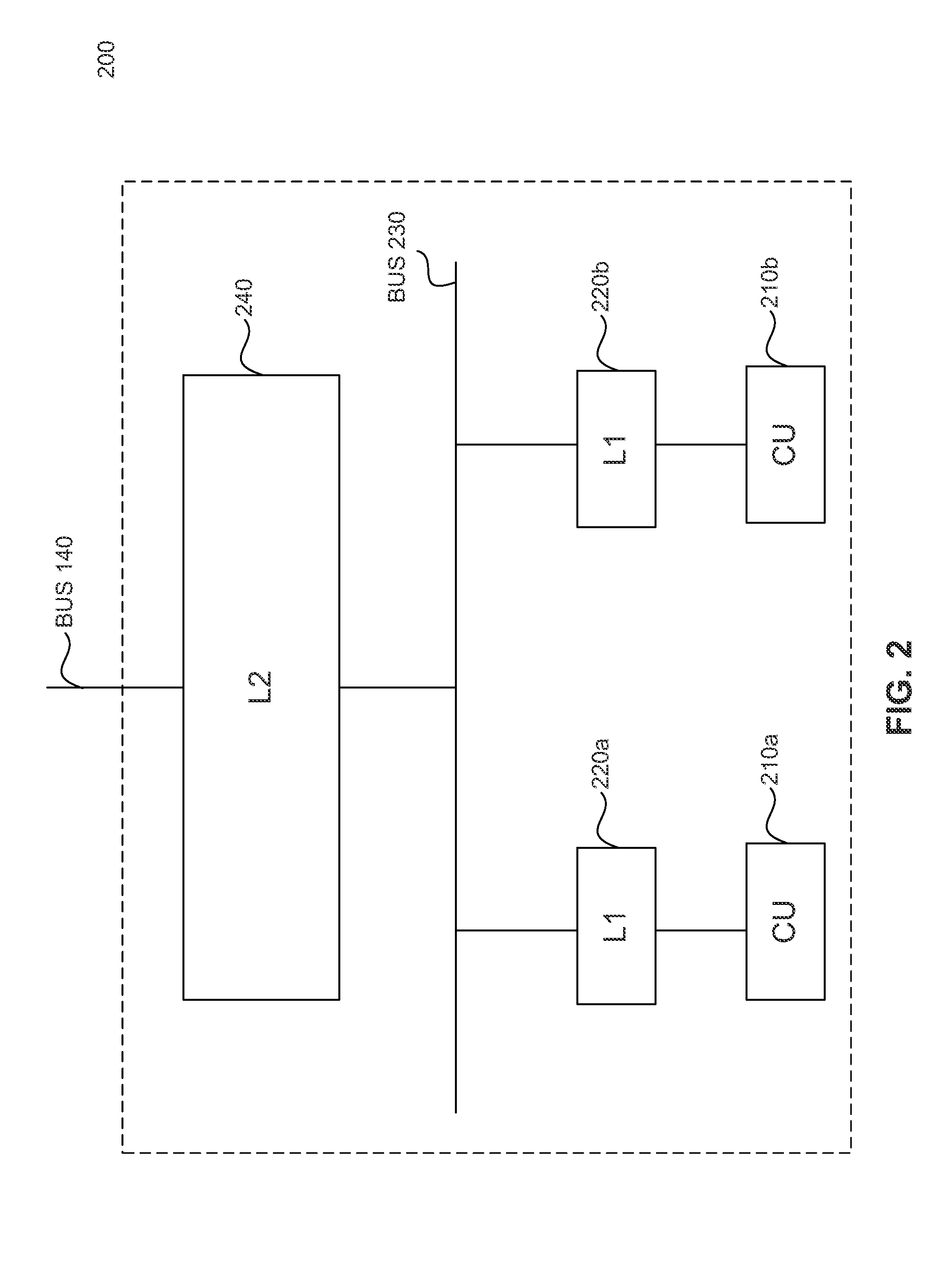

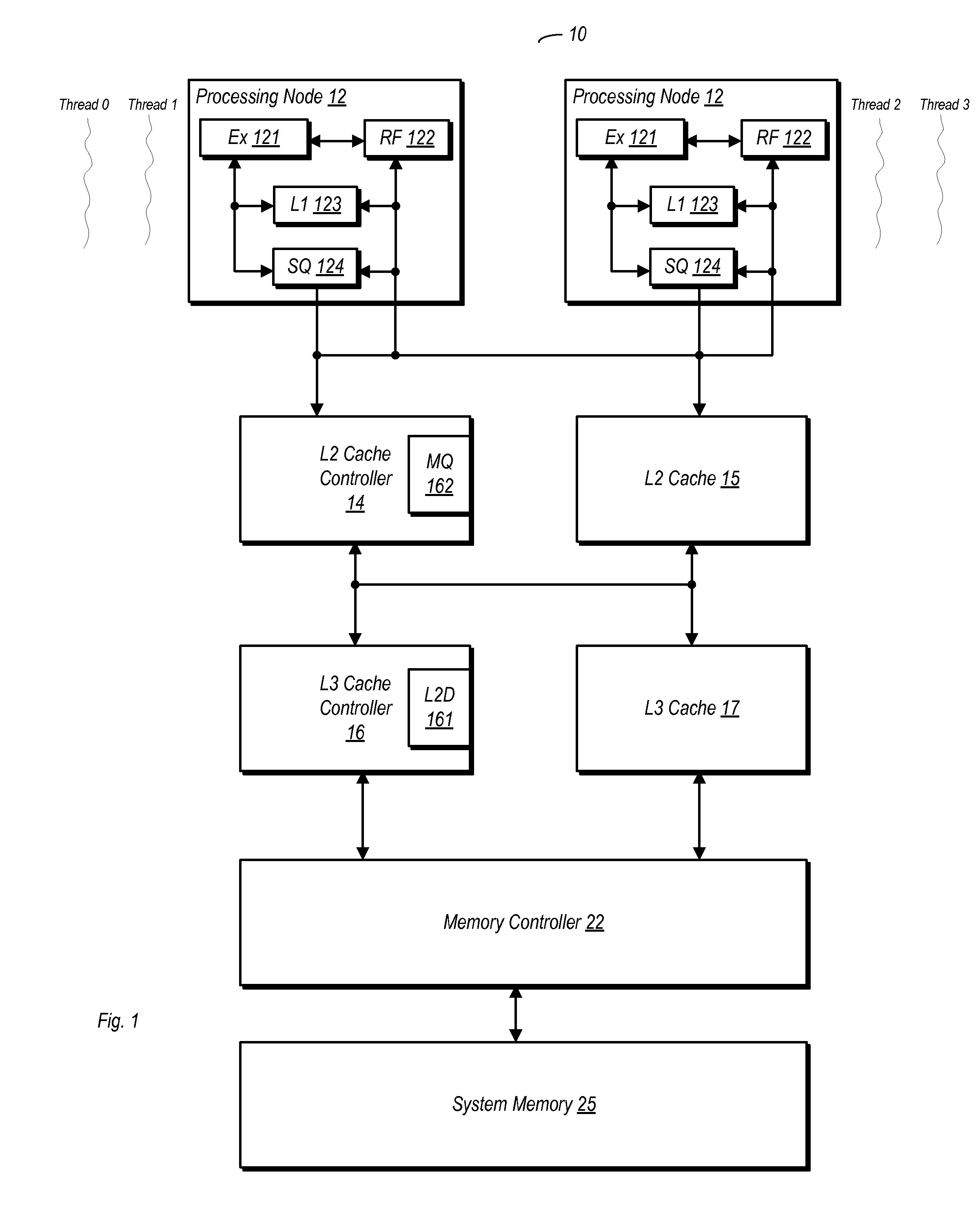

Hierarchical write-combining cache coherence

ActiveUS20150058567A1Easy to useImprove performanceMemory adressing/allocation/relocationEnergy efficient computingMemory hierarchyAs Directed

A method, computer program product, and system is described that enforces a release consistency with special accesses sequentially consistent (RCsc) memory model and executes release synchronization instructions such as a StRel event without tracking an outstanding store event through a memory hierarchy, while efficiently using bandwidth resources. What is also described is the decoupling of a store event from an ordering of the store event with respect to a RCsc memory model. The description also includes a set of hierarchical read-only cache and write-only combining buffers that coalesce stores from different parts of the system. In addition, a pool component maintains partial order of received store events and release synchronization events to avoid content addressable memory (CAM) structures, full cache flushes, as well as direct write-throughs to memory. The approach improves the performance of both global and local synchronization events and reduces overhead in maintaining write-only combining buffers.

Owner:ADVANCED MICRO DEVICES INC

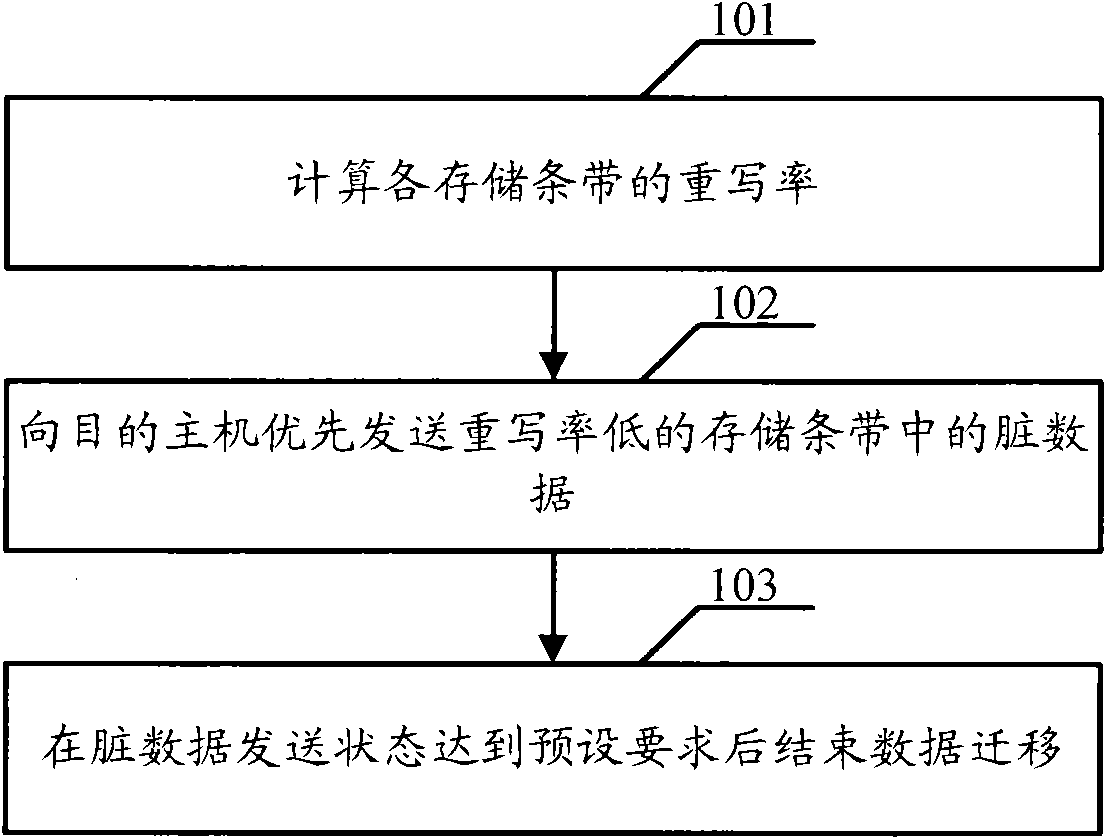

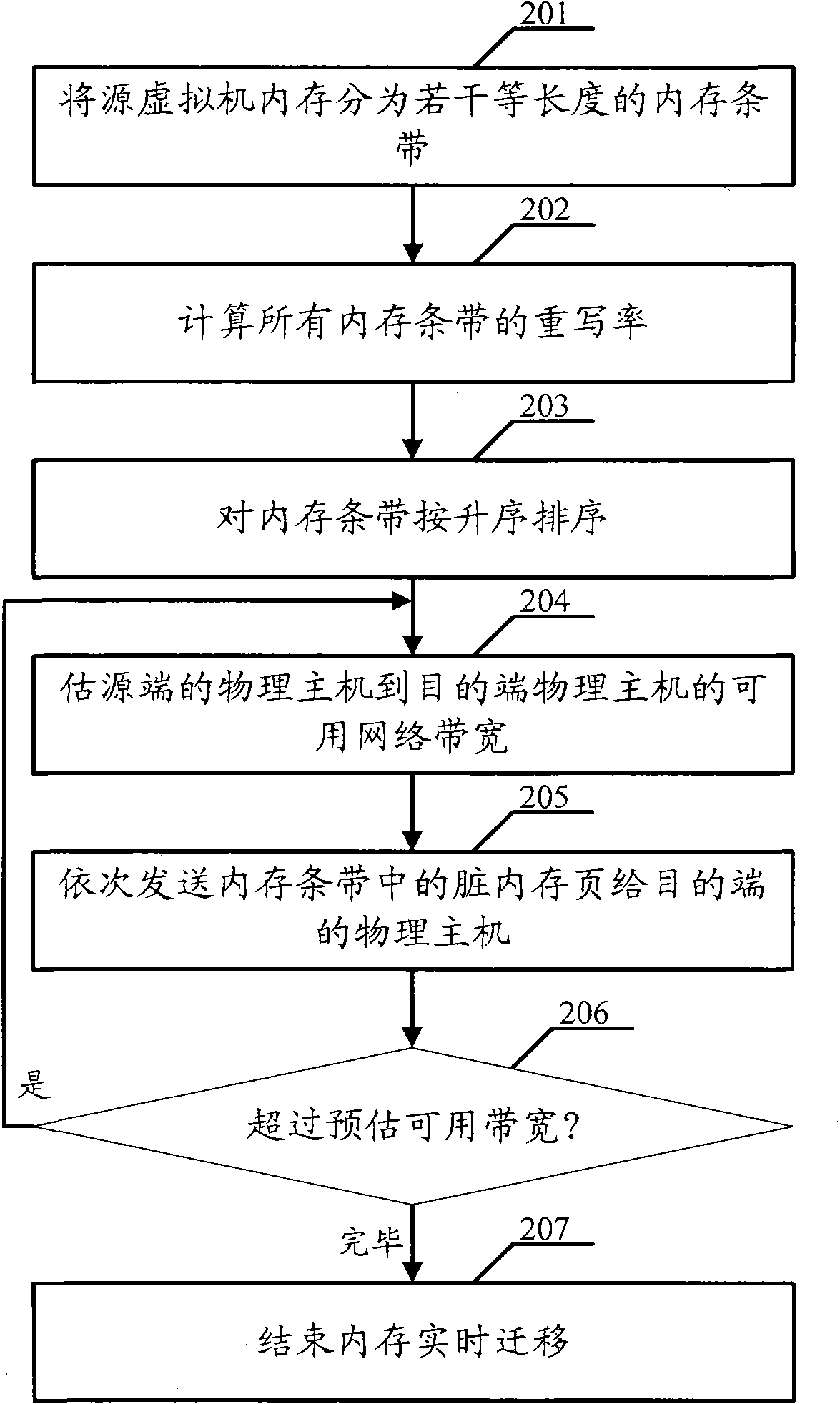

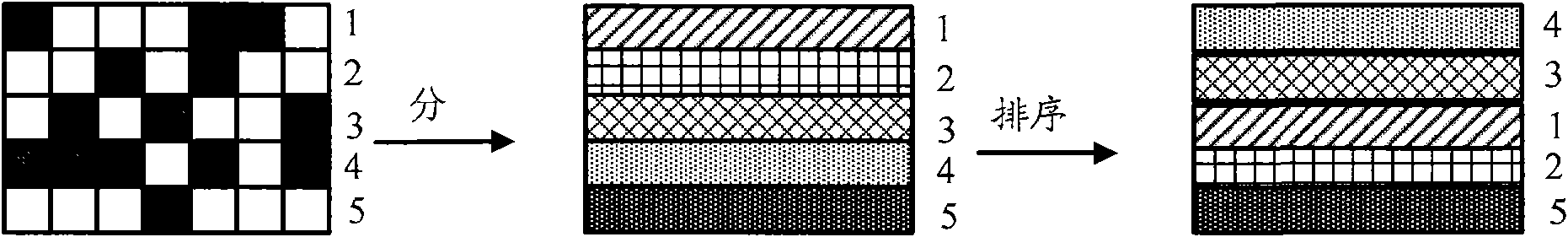

Data transfer method, device and system

ActiveCN102136993AReduce transfer volumeReduce transmissionData switching networksTransfer systemDirty data

The embodiment of the invention discloses a data transfer method, a data transfer device and a data transfer system. The method is implemented by the following steps of: calculating rewriting rates of each memory stripe, wherein the memory strips are obtained by segmenting a memory space required to perform data transfer; preferably transmitting dirty data in the memory stripes with low rewriting rates to a destination host; and finishing the data transfer after the transmission state of the dirty data reaches preset requirements. Due to the adoption of the technical means of segmenting the memory space required to perform the data transfer to obtain the memory stripes and preferably transmitting the dirty data in the memory stripes with the low rewriting rates to the destination host, the transmission of the dirty data, with relatively higher rewriting rates, of the memory space is delayed by utilizing a spatial locality principle and a temporal locality principle, and more memory writing operations are saved by writing combination to reduce the transmission of the dirty data and further reduce data traffic.

Owner:HUAWEI TECH CO LTD +1

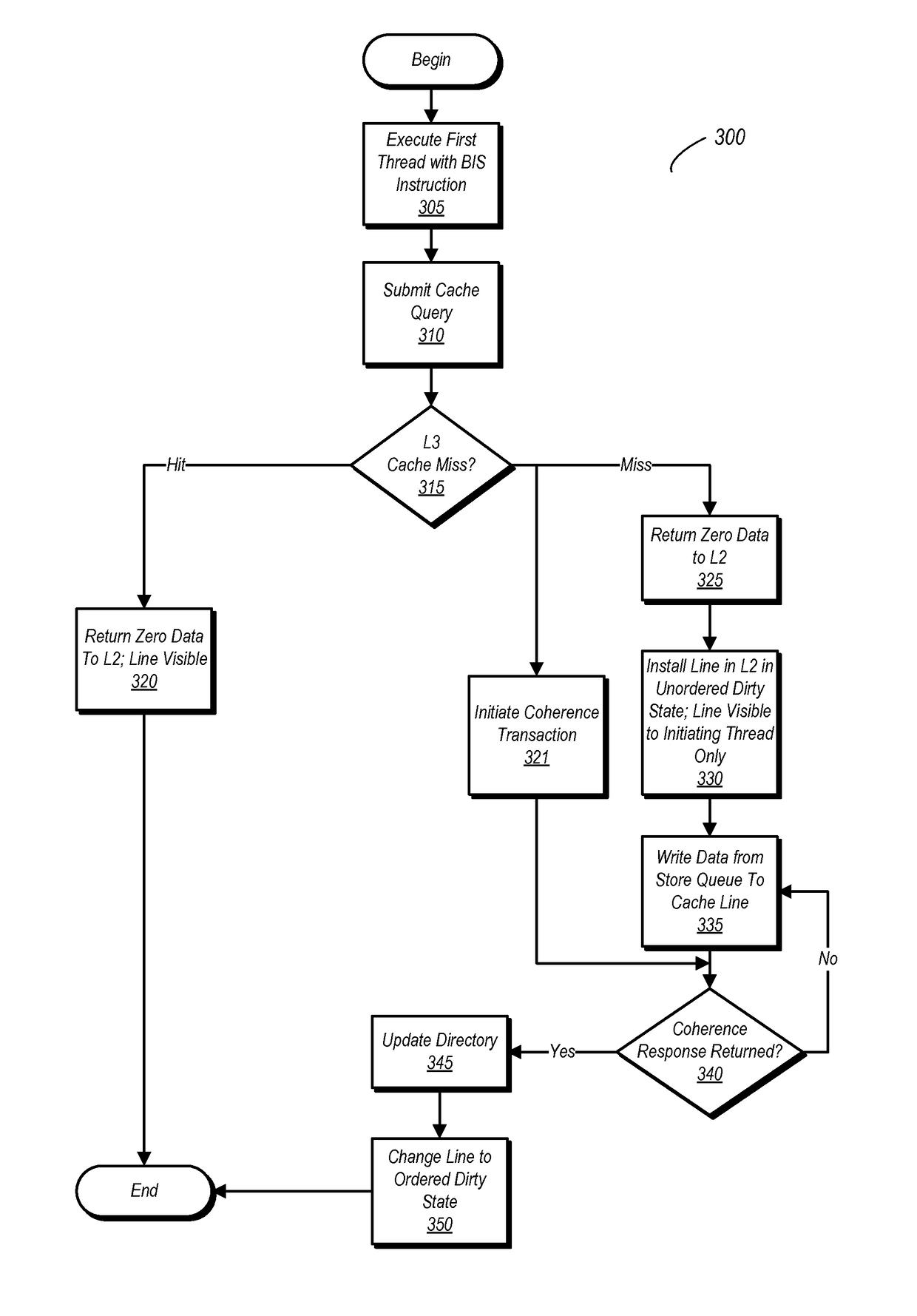

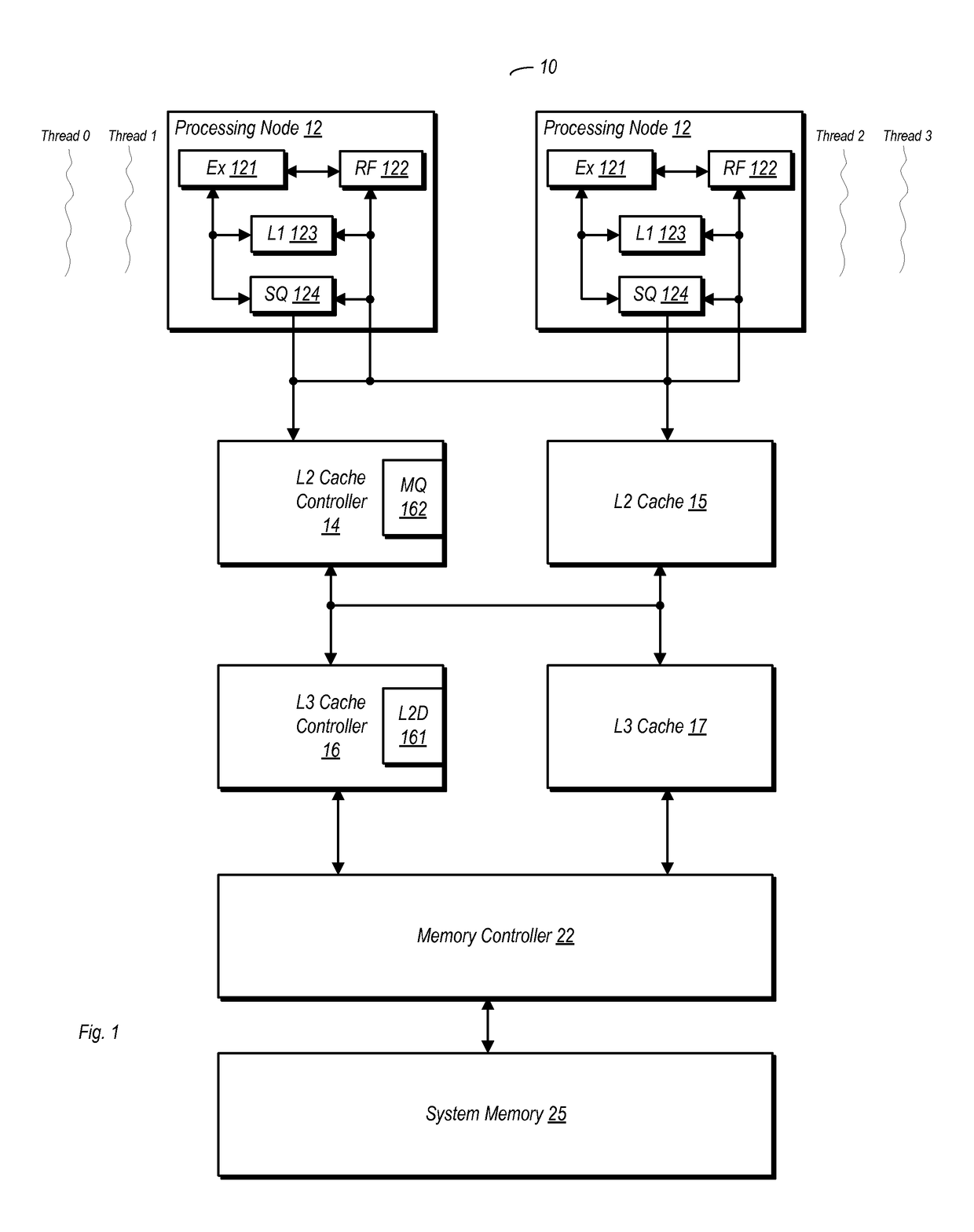

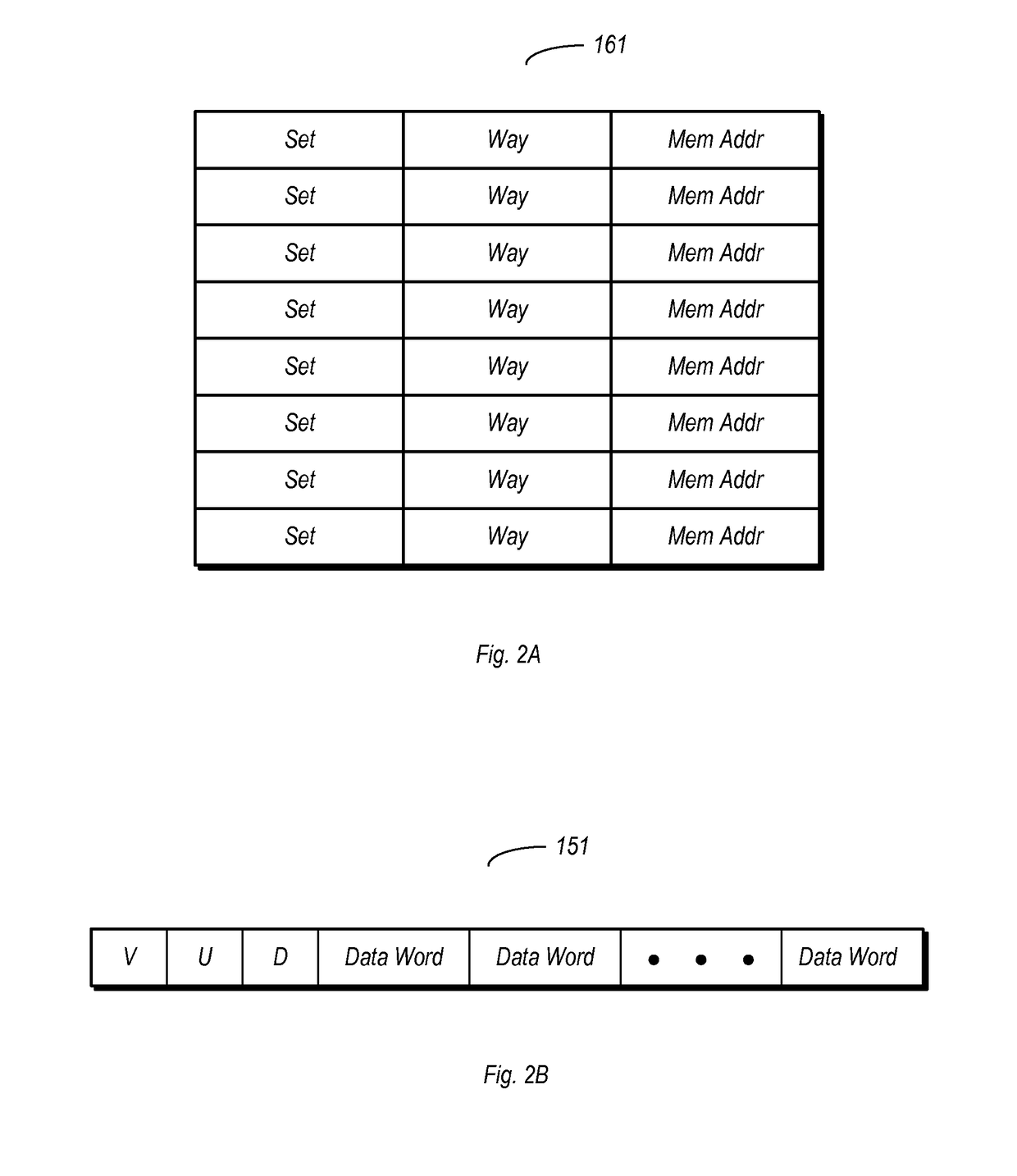

Non-Temporal Write Combining Using Cache Resources

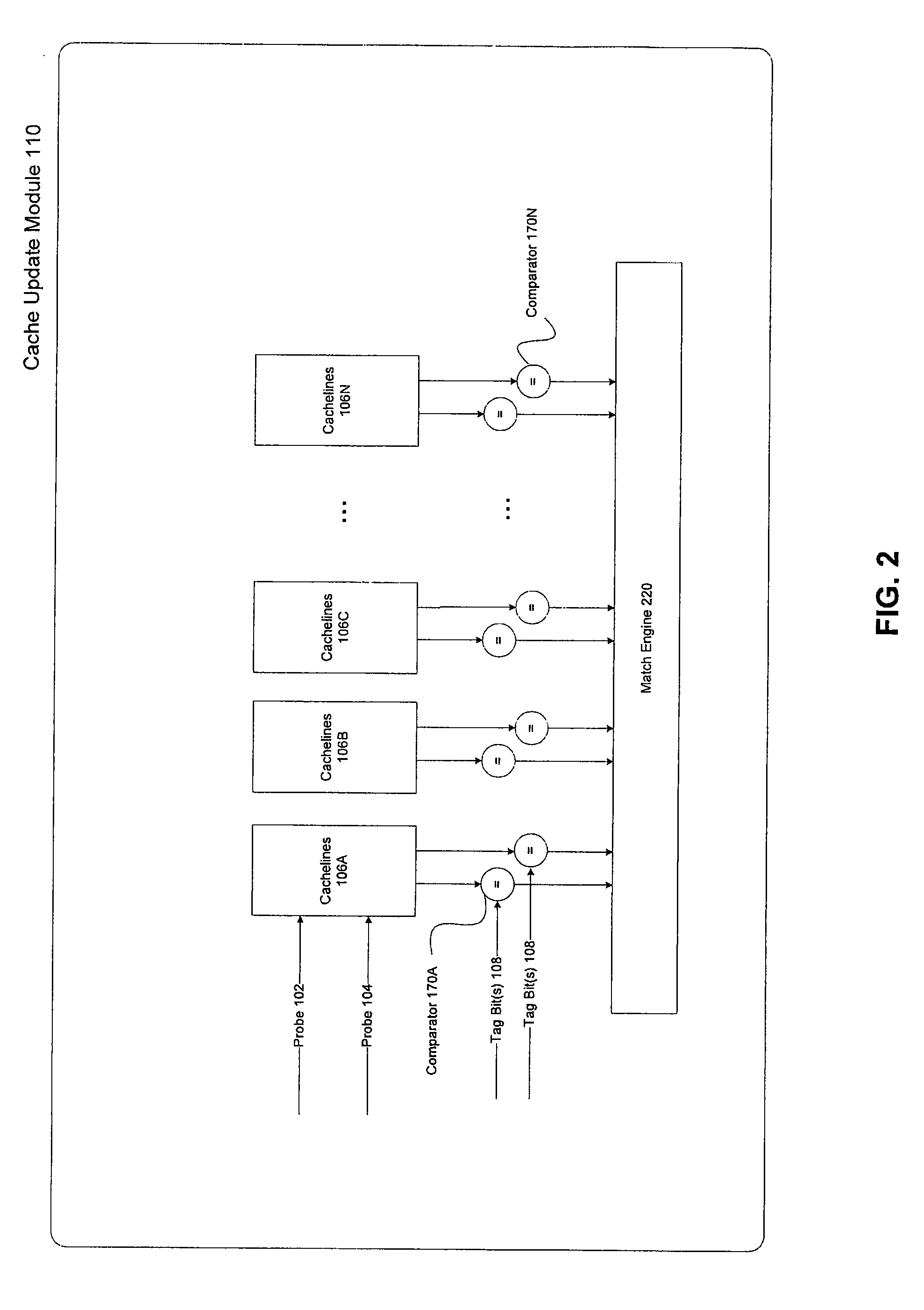

ActiveUS20160314069A1Memory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingCache coherence

A method and apparatus for performing non-temporal write combining using existing cache resources is disclosed. In one embodiment, a method includes executing a first thread on a processor core, the first thread including a first block initialization store (BIS) instruction. A cache query may be performed responsive to the BIS instruction, and if the query results in a cache miss, a cache line may be installed in a cache in an unordered dirty state in which it is exclusively owned by the first thread. The first BIS instruction and one or more additional BIS instructions may write data from the first processor core into the first cache line. After a cache coherence response is received, the state of the first cache line may be changed to an ordered dirty state in which it is no longer exclusive to the first thread.

Owner:ORACLE INT CORP

Wise ordering for writes-combining spatial and temporal locality in write caches

InactiveUS7574556B2Reduce spacingIncrease the number ofMemory architecture accessing/allocationMemory systemsControl storeDisk array

A storage system has a storage controller for an array of storage disks, the array being ordered in an sequence of write groups. A write cache is shared by the disks. The storage controller temporarily stores write groups in the write cache, responsive to write groups being written, and lists the write groups in order of their sequence in the array and in circular fashion, so that a lowest is listed next to a highest one of the write groups. The storage controller selects the listed write groups in rotating sequence. Such a write group is destaged from the write cache to the disk responsive to i) the selecting of the write group and ii) a state of a recency indicator for the write group, wherein the recency indicator shows recency of writing to the write group.

Owner:INTERMATIONAL MACHINERY CORPORATIO

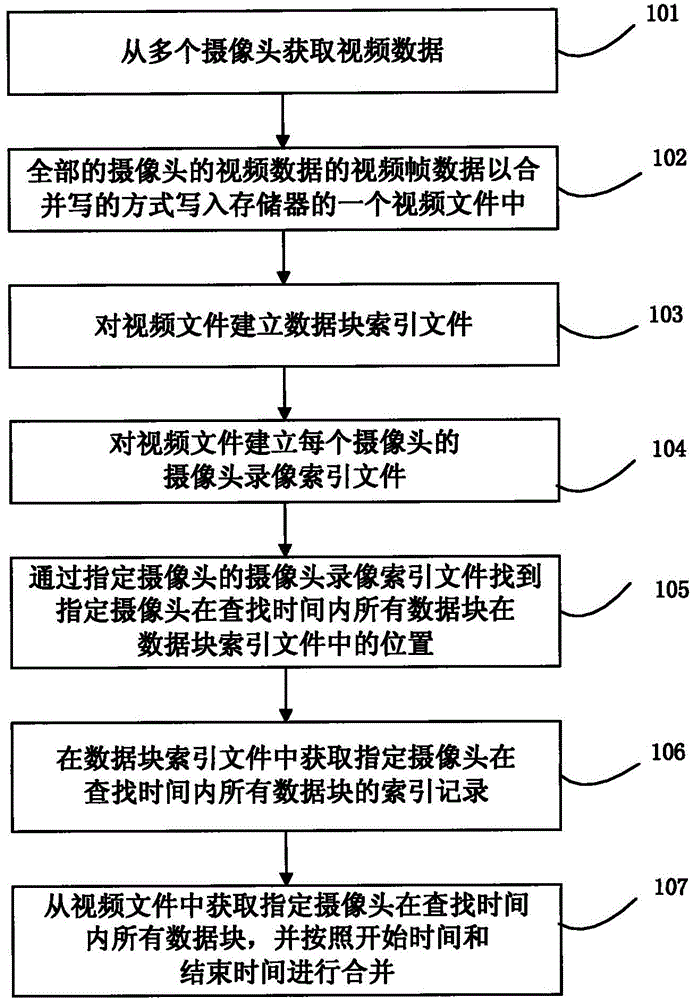

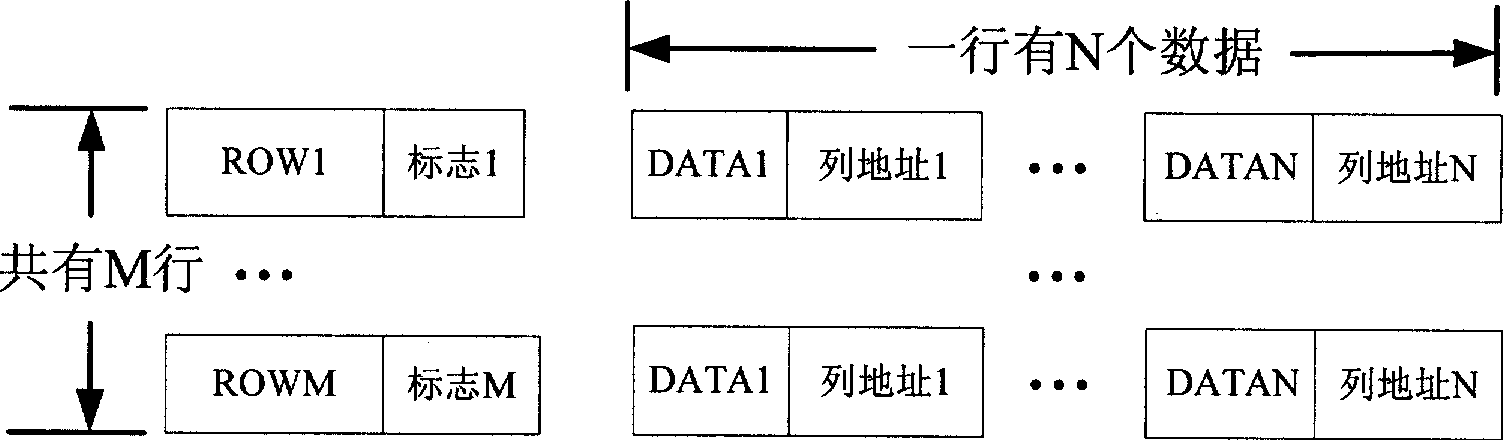

Multi-channel video data reading and writing method

InactiveCN104572764AReduce jump frequencyImprove reading and writing efficiencyVideo data retrievalSpecial data processing applicationsStart timeComputer graphics (images)

The invention discloses a multi-channel video data reading and writing method. The multi-channel video data reading and writing method comprises the steps of obtaining video data from multiple cameras, writing video frame data of the video data of all the cameras into one video file of a memory in a write combining way, establishing a data block indexing file and a camera video indexing file in the video file, finding the positions of all data blocks of one assigned camera in the data block indexing file within a search time through the camera video indexing file, obtaining indexing records of all the data blocks of the assigned camera within the search time from the data block indexing file, obtaining all the data blocks of the assigned camera within the search time from the video file, and merging according to the start time and the end time. By adopting the technical scheme, the jumping frequency of a magnetic-disc head can be reduced to a large extent, and the whole reading-writing efficiency of a magnetic disc is increased.

Owner:XIAN QUNFENG ELECTRONICS INFORMATION TECH

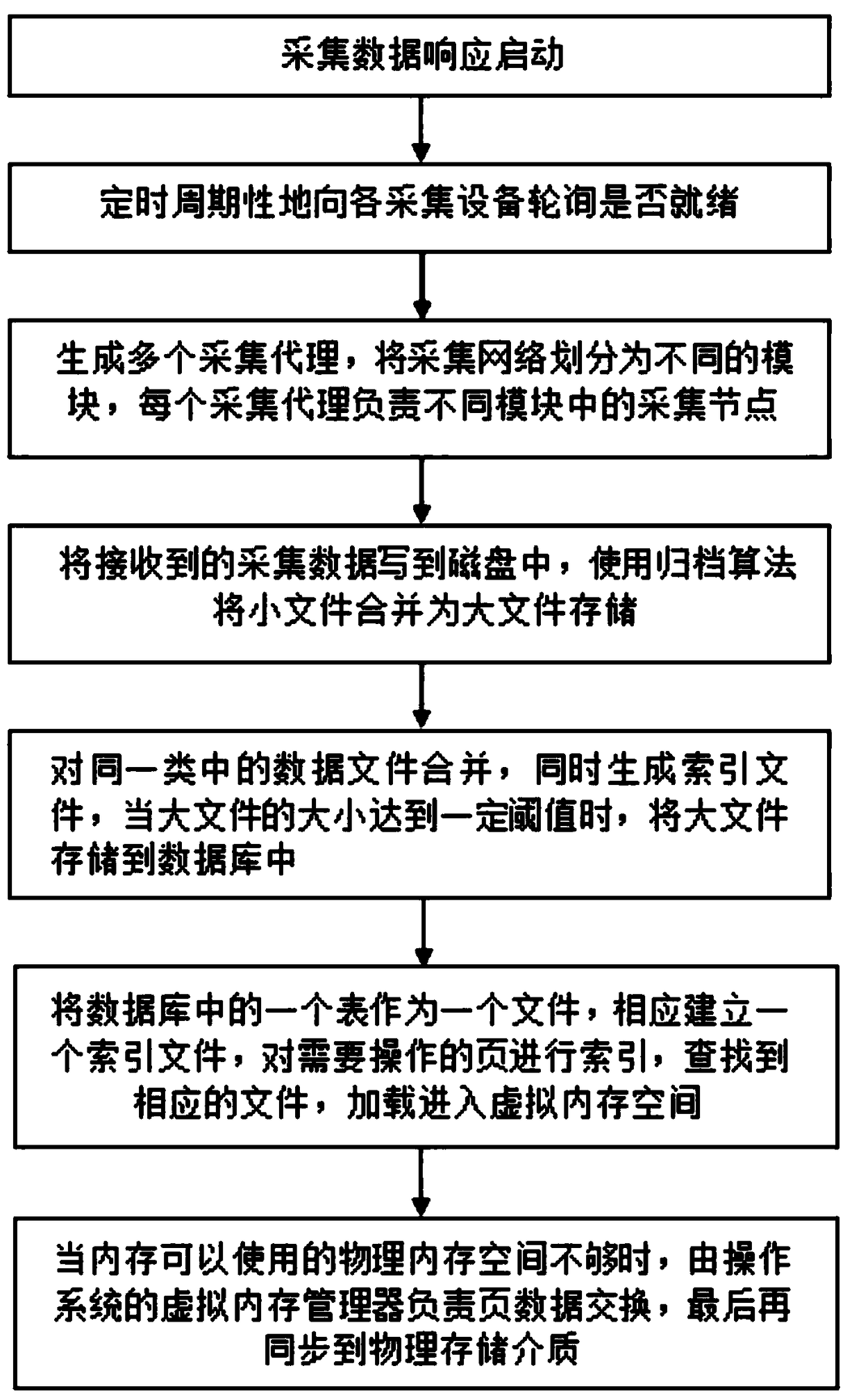

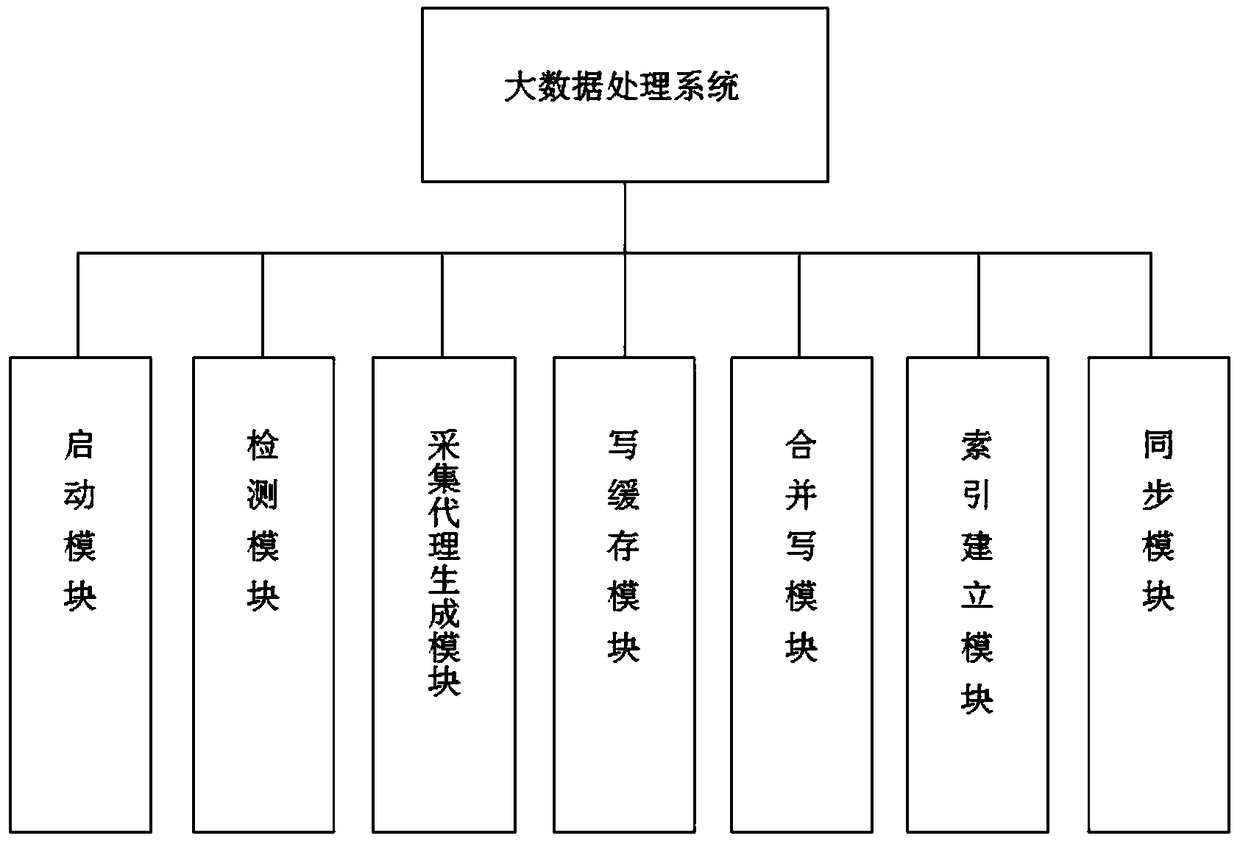

E-commerce platform big data processing method and system

ActiveCN108717457AAvoid unfriendlyBoost rateSpecial data processing applicationsOccupancy rateMemory footprint

The invention discloses an e-commerce platform big data processing method and an e-commerce platform big data processing system. Through generating multiple collection agents, a collection network isdivided into different modules, each collection agent is responsible for collection nodes in the different modules, a file system using a write cache as the bottom layer provides a high performance write caching service, a file set is divided into multiple classes, mass files are combined into a big file, and finally the big data is written into the file system for storing constantly. Through write caching and write combination, unfriendliness of writing of the mass files to the file system is avoided, and thus the write throughput rate and the memory occupancy rate are optimized.

Owner:苏州易康萌思网络科技有限公司

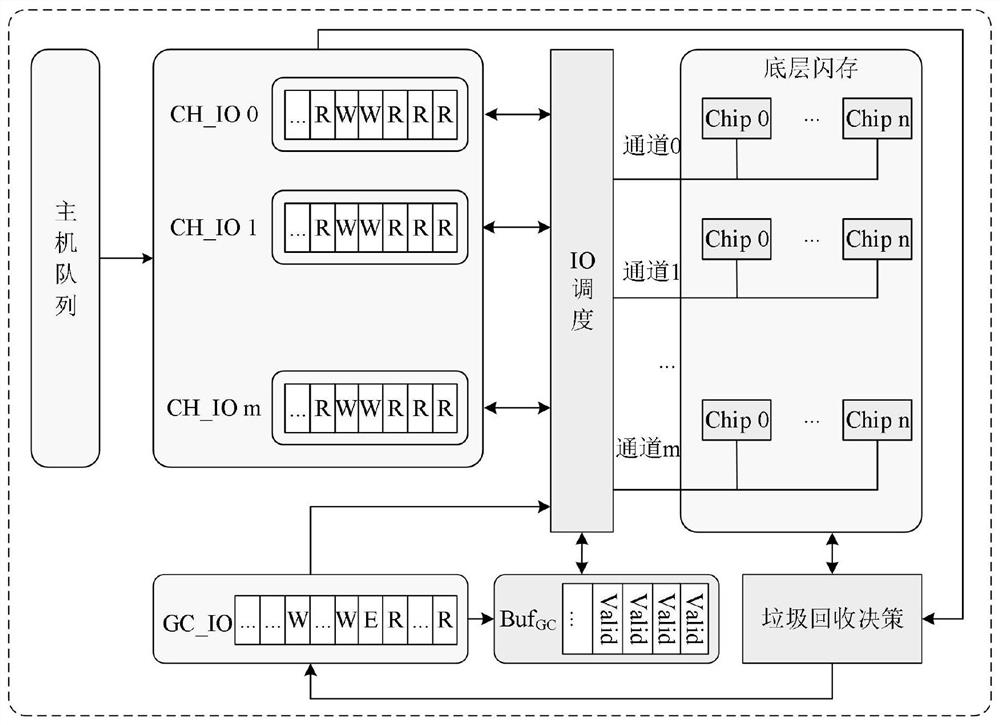

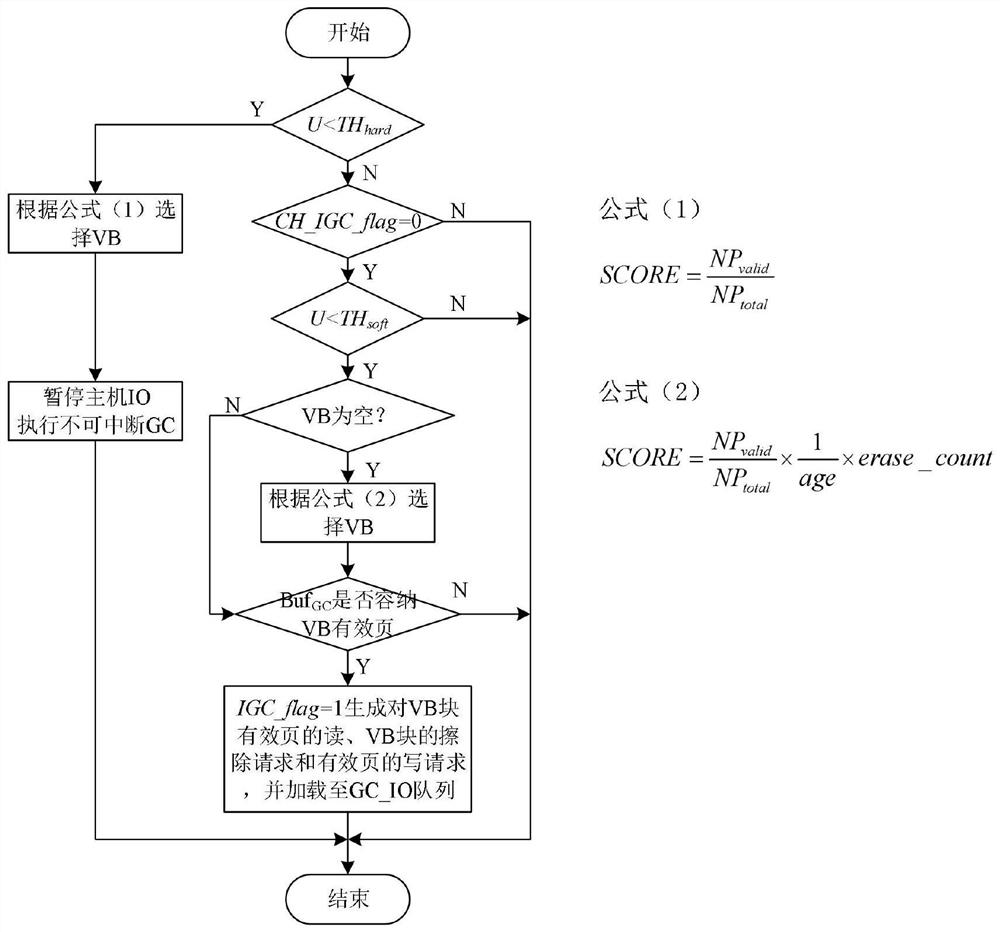

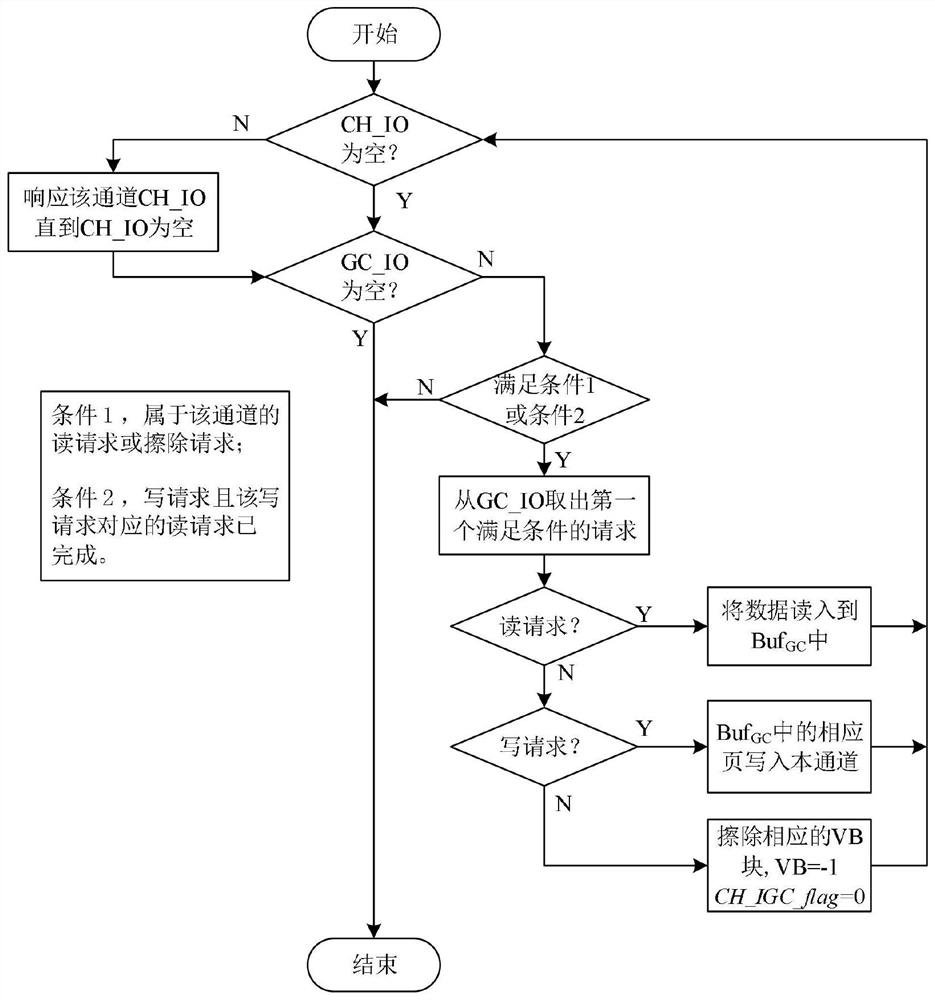

Solid state disk intelligent garbage recycling and scheduling method

ActiveCN111708713AEquilibrium recovery efficiencyUniform wearMemory architecture accessing/allocationInput/output to record carriersGarbage collectionComputer science

The invention provides a solid state disk intelligent garbage recycling and scheduling method. According to the method, the type of generated GC is determined through two levels of thresholds. Read-write erasing operation capable of interrupting garbage collection is combined with read-write IO of each channel for management, and available space is actively recycled by fully utilizing idle time ofeach channel. An interruptible garbage collection IO queue is set, a GC buffer area is used for temporarily storing and recycling effective pages of damaged blocks, the writing operation of the interruptible garbage collection effective pages is delayed, and the influence of GC on host IO is reduced. For non-interruptible GC, a greedy strategy is adopted for selection of damaged blocks, the blockwith the most invalid pages is selected, and GC efficiency is maximized. For interruptible GC, the recovery efficiency, the data updating frequency and the erasure frequency are comprehensively considered for selection of damaged blocks, and the garbage recovery efficiency and abrasion balance are considered. According to the method, the GC efficiency can be ensured, Meanwhile, the influence of GC on host IO is reduced.

Owner:HANGZHOU DIANZI UNIV

Methodology and apparatus for implementing write combining

Write-combining in a computer system that uses a push model is set forth herein. In one embodiment, the method comprises creating one or more packets having a descriptor and the data associated with detected write transactions stored in the buffer assigned to a write-combinable range in response to a flush request to flush the buffer, and sending (pushing) these packets to the network I / O device.

Owner:TAHOE RES LTD

High efficiency data buffering in a computer network device

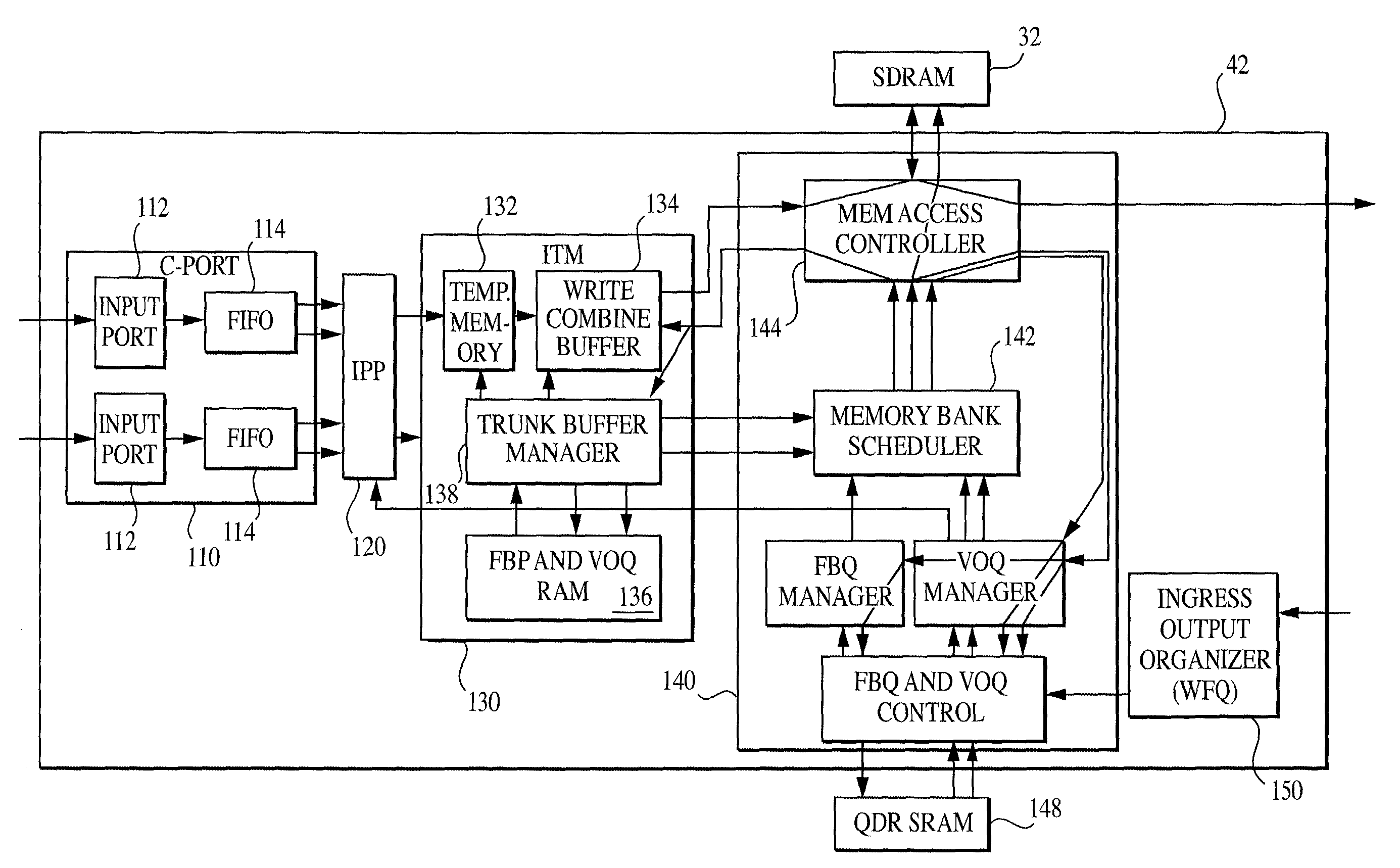

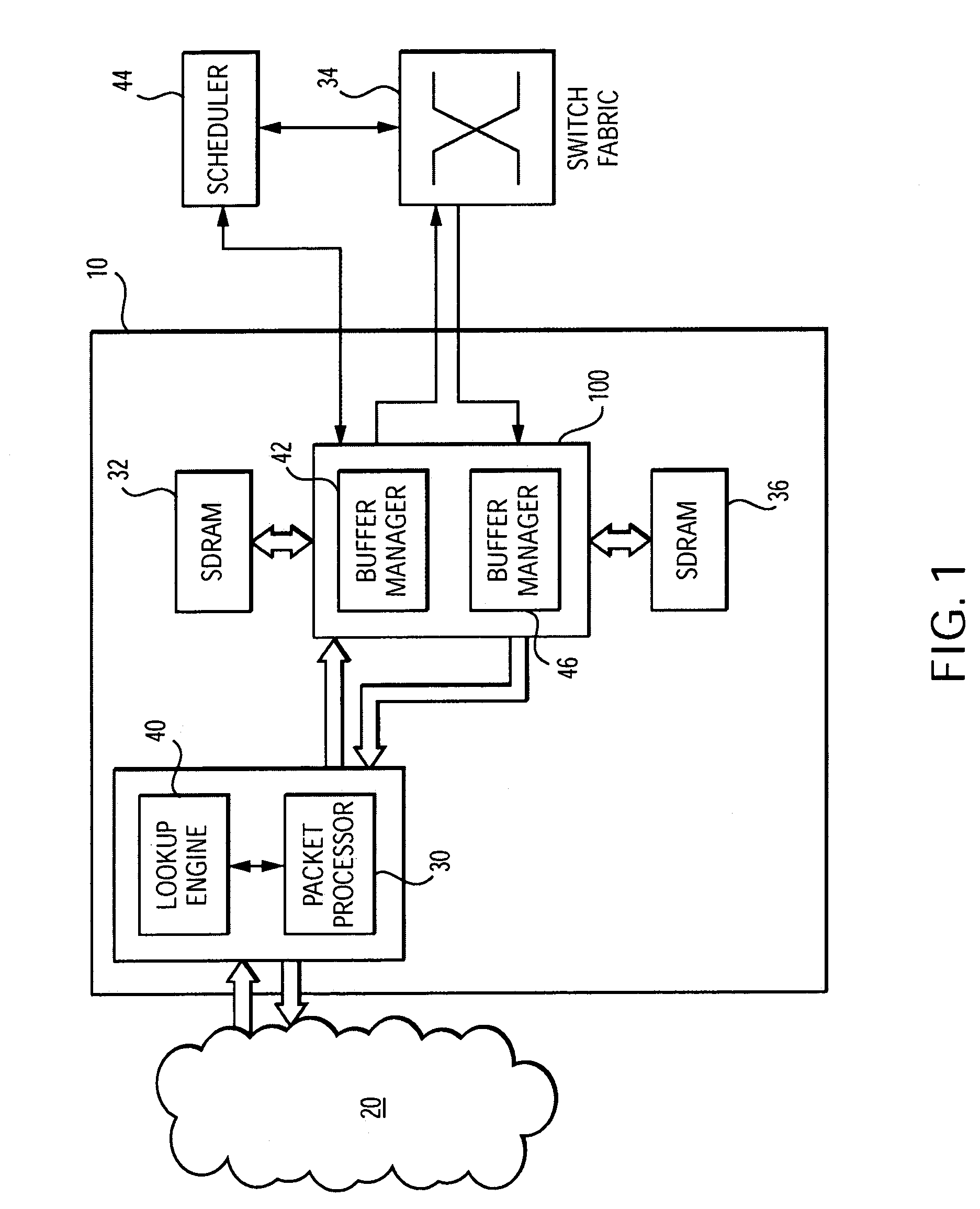

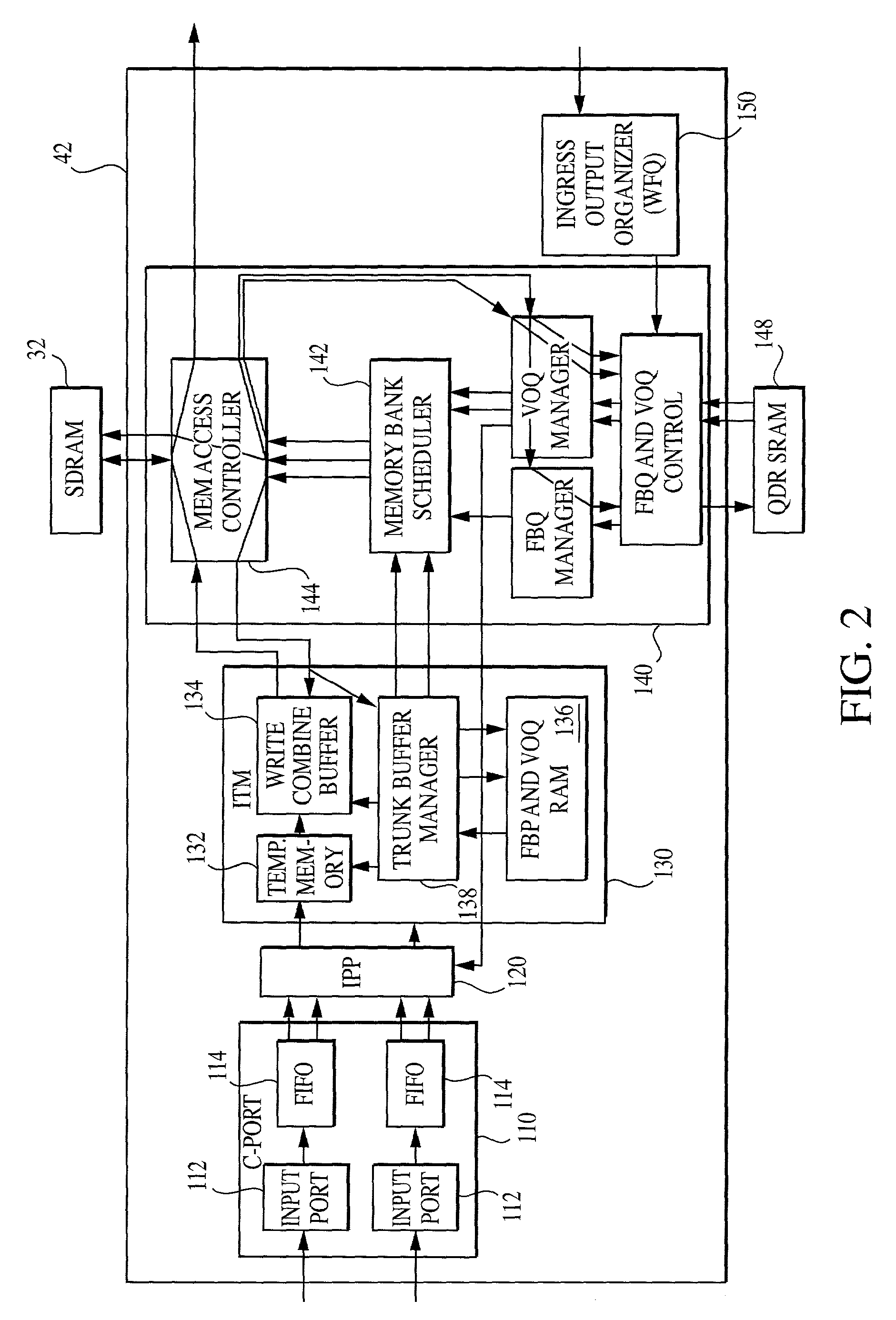

ActiveUS7346067B2Data switching by path configurationStore-and-forward switching systemsHigh speed memoryNetwork processing

A network processing device stores and aligns data received from an input port prior to forwarding the data to an output port. Data packets arrive at various input ports already having an output queue or virtual output queue assigned. A buffer manager groups one or more packets destined for the same output queue into blocks, and stores the blocks in a buffer memory. A linked list is created of the trunks, which is an ordered collection of blocks. The trunks are sent to a high speed second memory and stored together as a unit. In some embodiments the trunks are split on boundaries and stored in a high speed memory. Once the trunks are stored in the high speed second memory, the corresponding data is erased from the write combine buffer memory and the pointers that made up the linked list are returned to a free block pointer pool. The data can then be read from the high speed second memory very quickly, passed through a switching fabric, and placed back on the computer network for its next destination. In other embodiments, the trunk data is stored after passing through the switching fabric, before being placed back on the computer network.

Owner:DELL MARKETING CORP

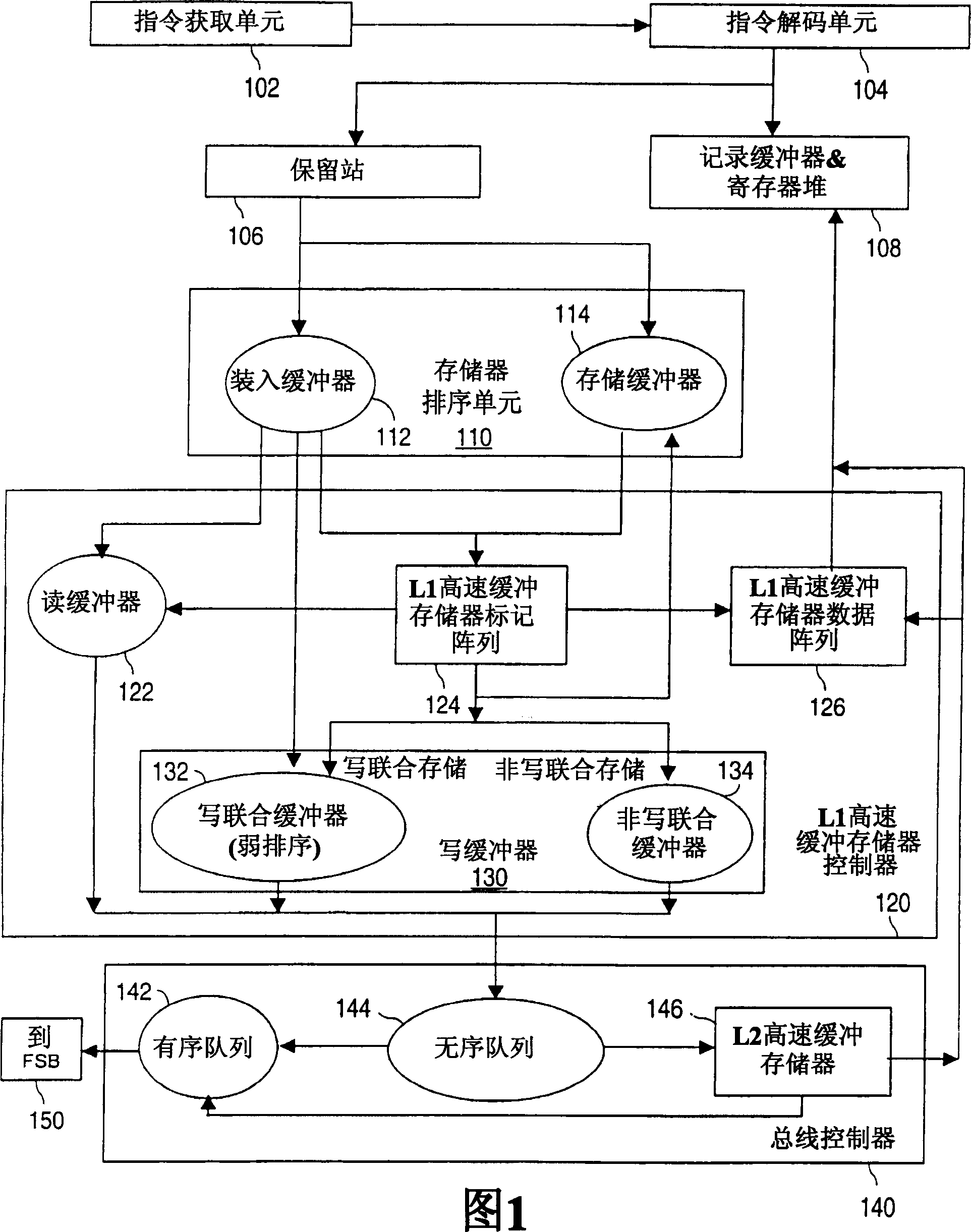

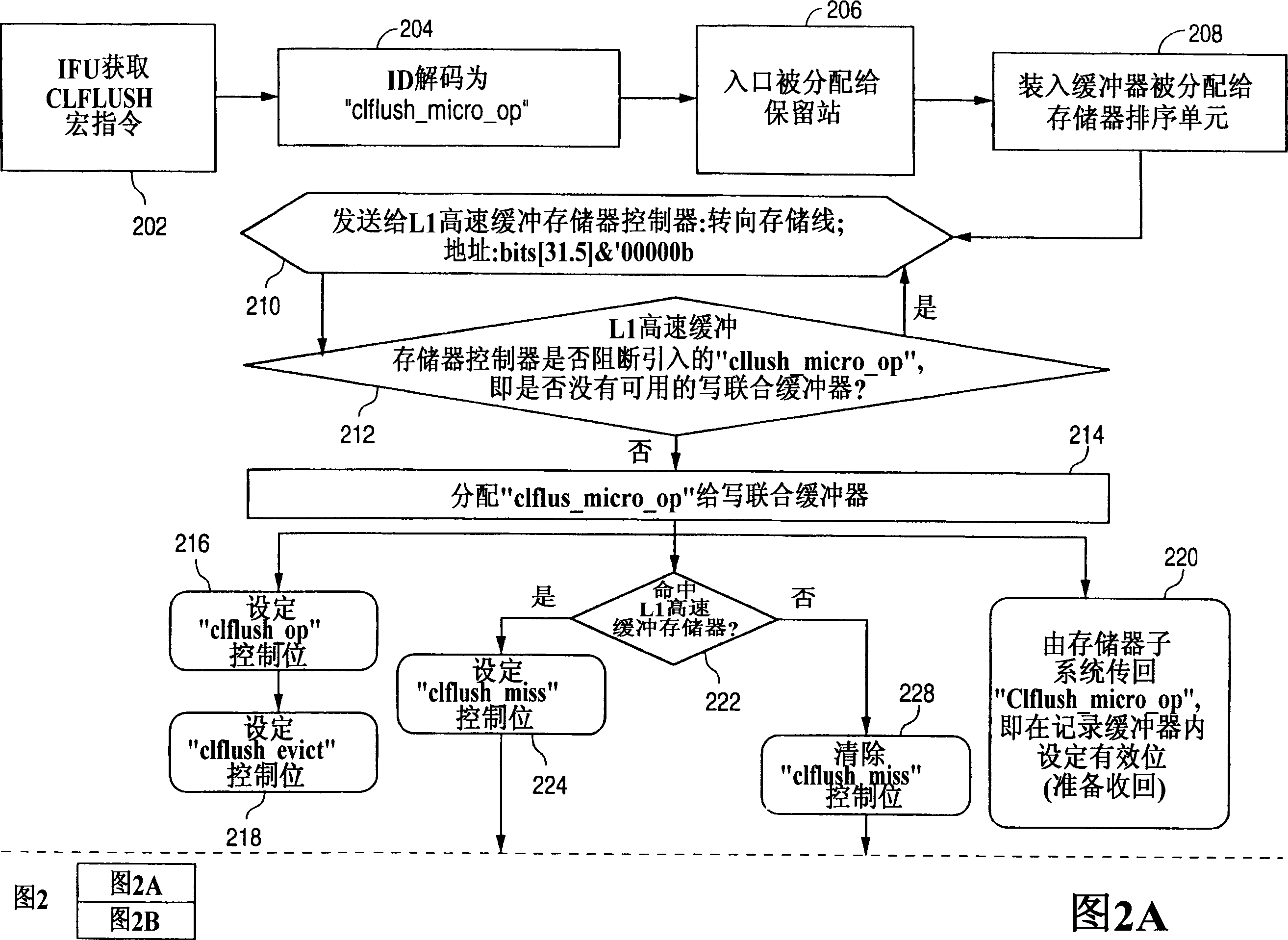

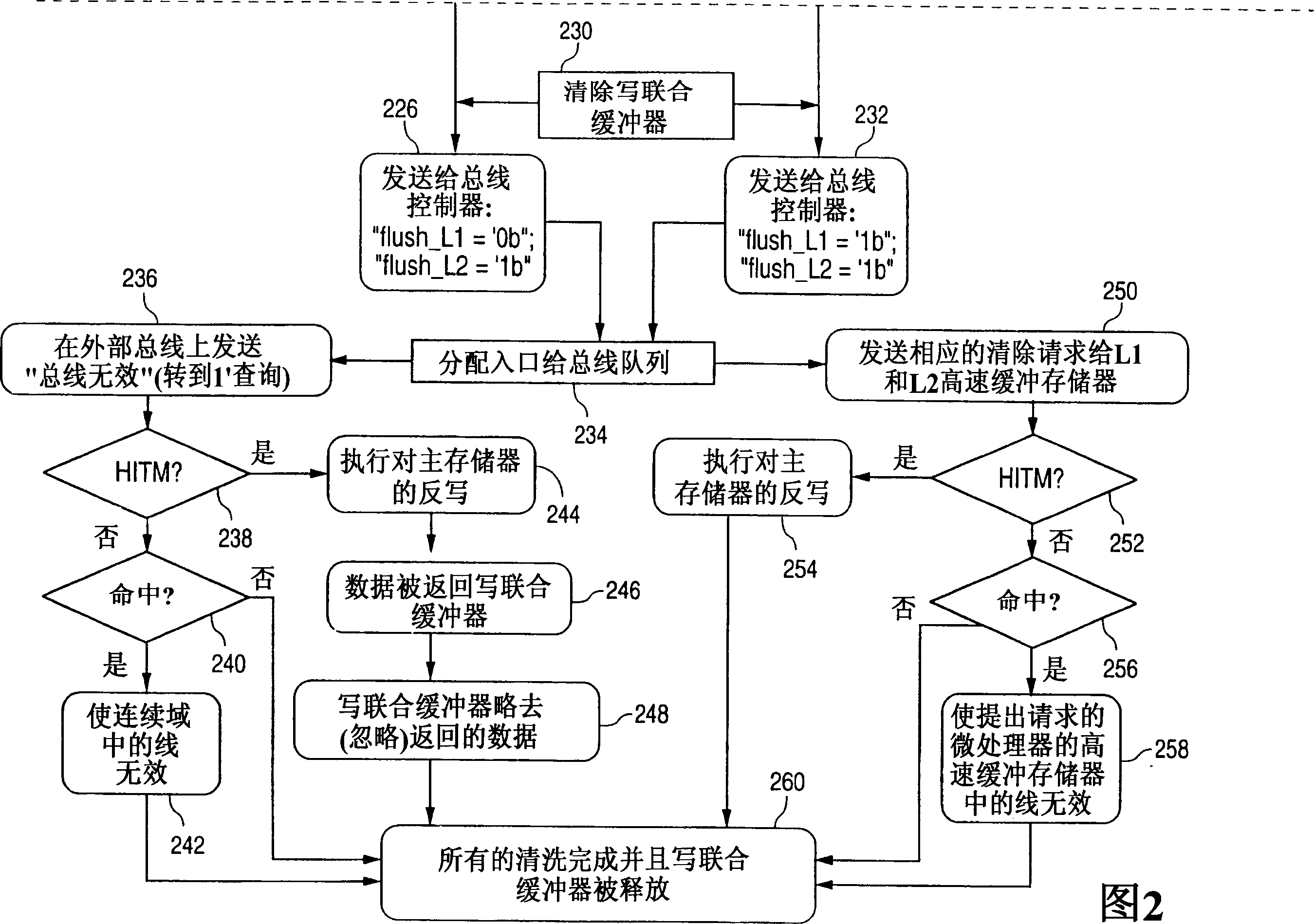

Cache line flush micro-architectural implementation method ans system

A system and method for flushing a cache line associated with a linear memory address from all caches in the coherency domain. A cache controller receives a memory address, and determines whether the memory address is stored within the closest cache memory in the coherency domain. If a cache line stores the memory address, it is flushed from the cache. The flush instruction is allocated to a write-combining buffer within the cache controller. The write-combining buffer transmits the information to the bus controller. The bus controller locates instances of the memory address stored within external and intel cache memories within the coherency domain; these instances are flushed. The flush instruction can then be evicted from the write-combining buffer. Control bits may be used to indicate whether a write-combining buffer is allocated to the flush instruction, whether the memory address is stored within the closest cache memory, and whether the flush instruction should be evicted from the write-combining buffer.

Owner:INTEL CORP

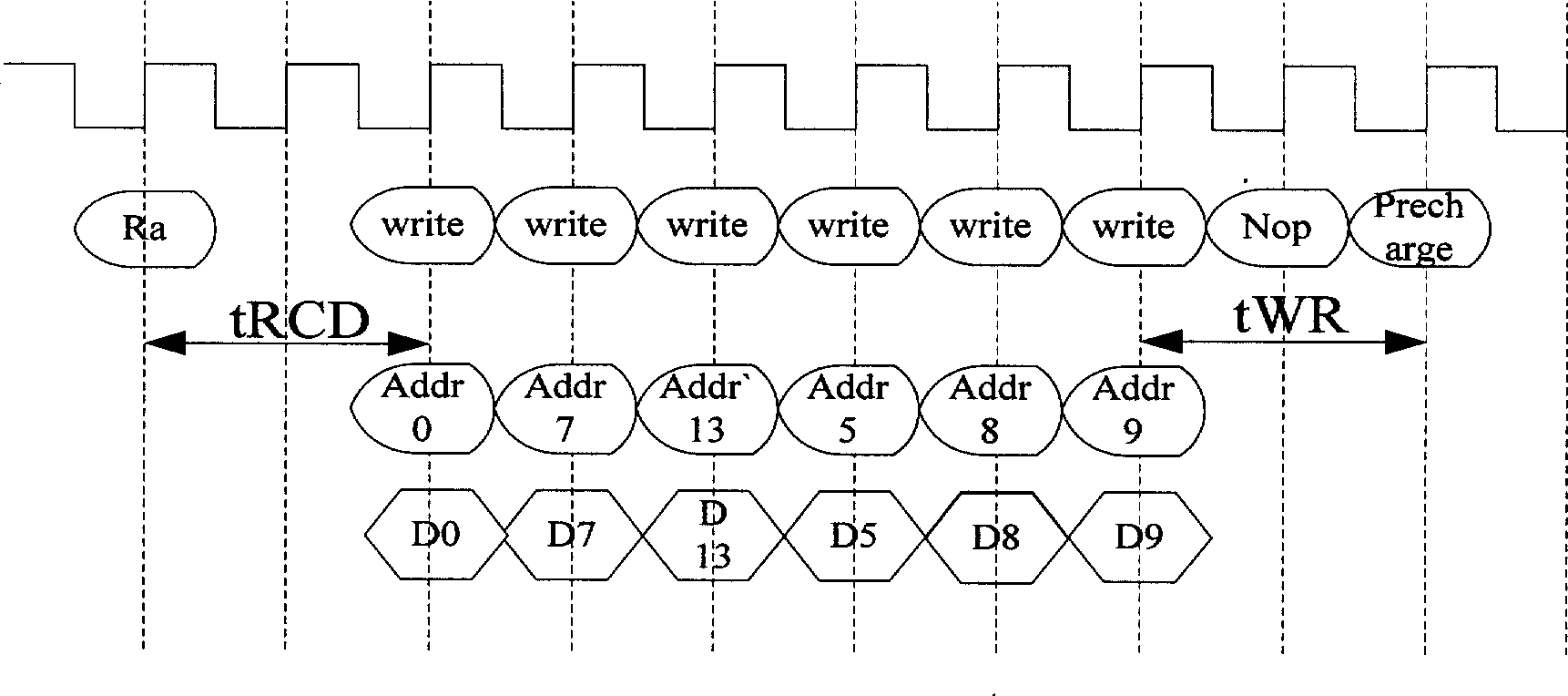

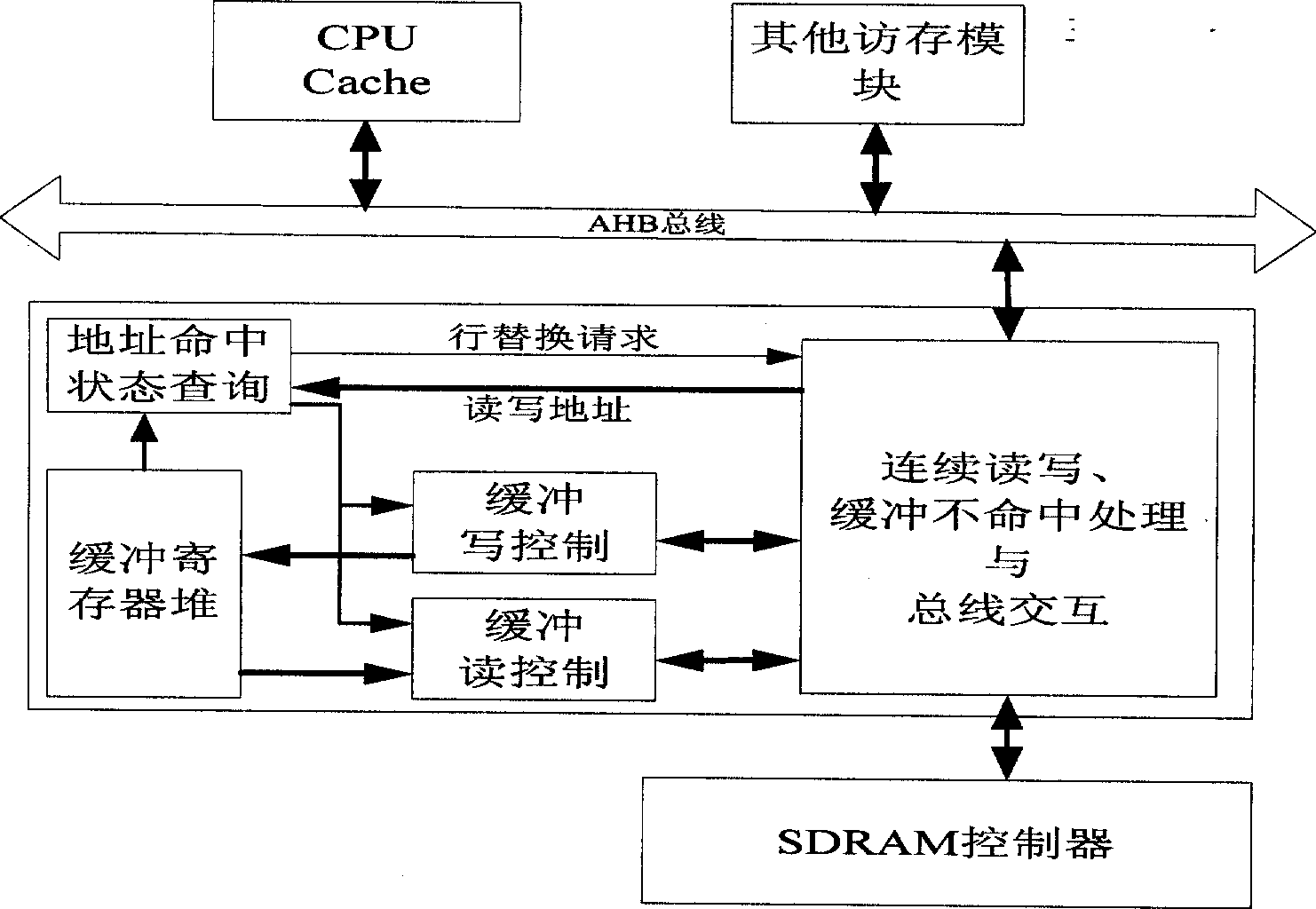

Write-through cache oriented SDRAM read-write method

InactiveCN101425044AImprove writing efficiencyImprove access efficiencyMemory adressing/allocation/relocationComputer architectureAccess time

The invention relates to an SDRAM read-write method and discloses an SDRAM read-write method facing write-penetrable cache. The invention mainly uses the characteristics of single write of a physical storage SDRAM to disclose a write-combined mechanism, thus reducing the access time of a CPU to memory data and simultaneously improving the access efficiency of the SDRAM. The method is applicable for being applied to the field of multimedia processing chip which has frequent access to the storage and is designed by using multicore SoC.

Owner:XI AN JIAOTONG UNIV

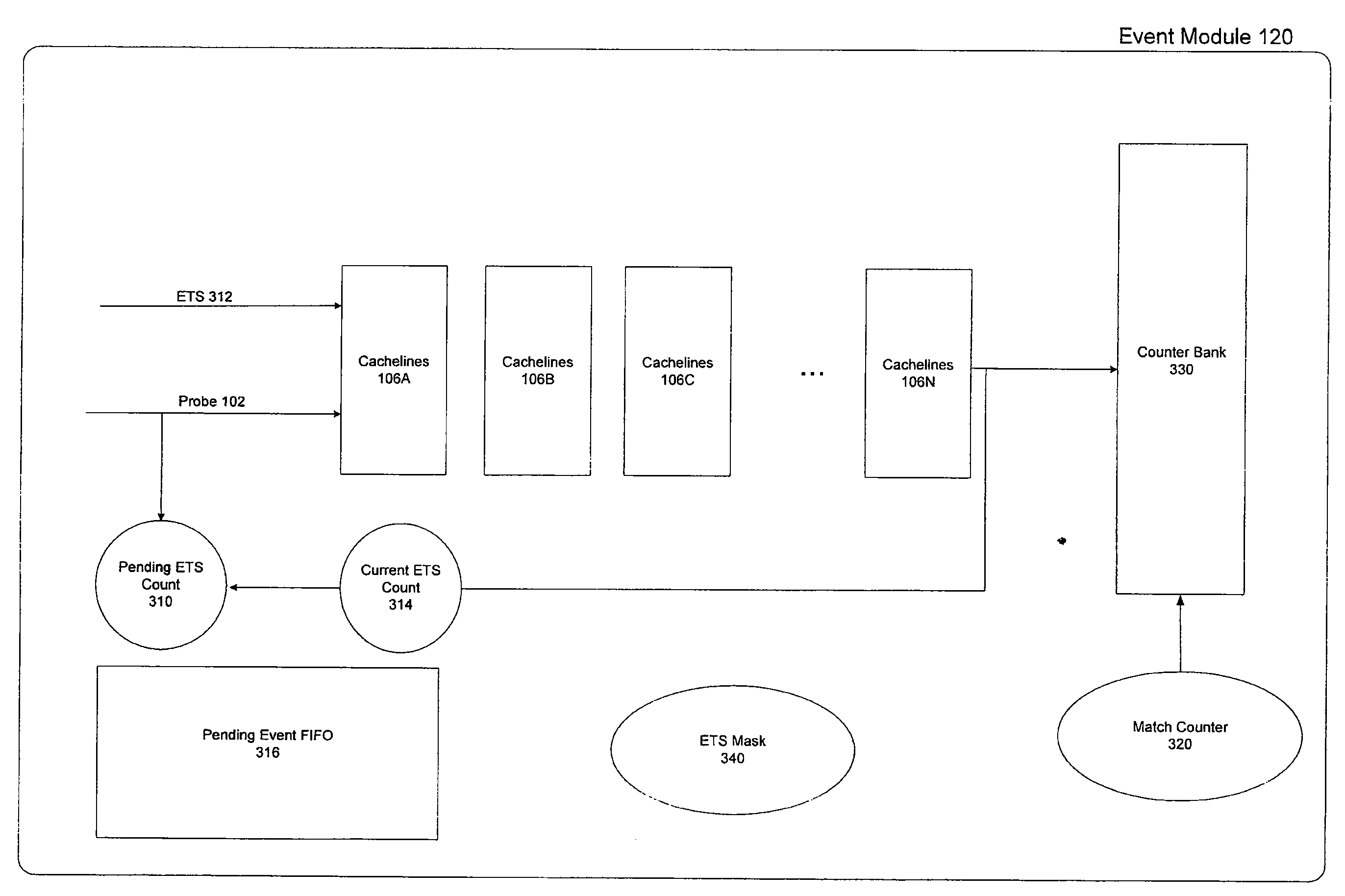

Write combining cache microarchitecture for synchronization events

ActiveUS20150046652A1Easy to useImprove performanceMemory adressing/allocation/relocationEnergy efficient computingMemory hierarchyAs Directed

A method, computer program product, and system is described that enforces a release consistency with special accesses sequentially consistent (RCsc) memory model and executes release synchronization instructions such as a StRel event without tracking an outstanding store event through a memory hierarchy, while efficiently using bandwidth resources. What is also described is the decoupling of a store event from an ordering of the store event with respect to a RCsc memory model. The description also includes a set of hierarchical read / write combining buffers that coalesce stores from different parts of the system. In addition, a pool component maintains partial order of received store events and release synchronization events to avoid content addressable memory (CAM) structures, full cache flushes, as well as direct write-throughs to memory. The approach improves the performance of both global and local synchronization events since a store event may not need to reach main memory to complete.

Owner:ADVANCED MICRO DEVICES INC

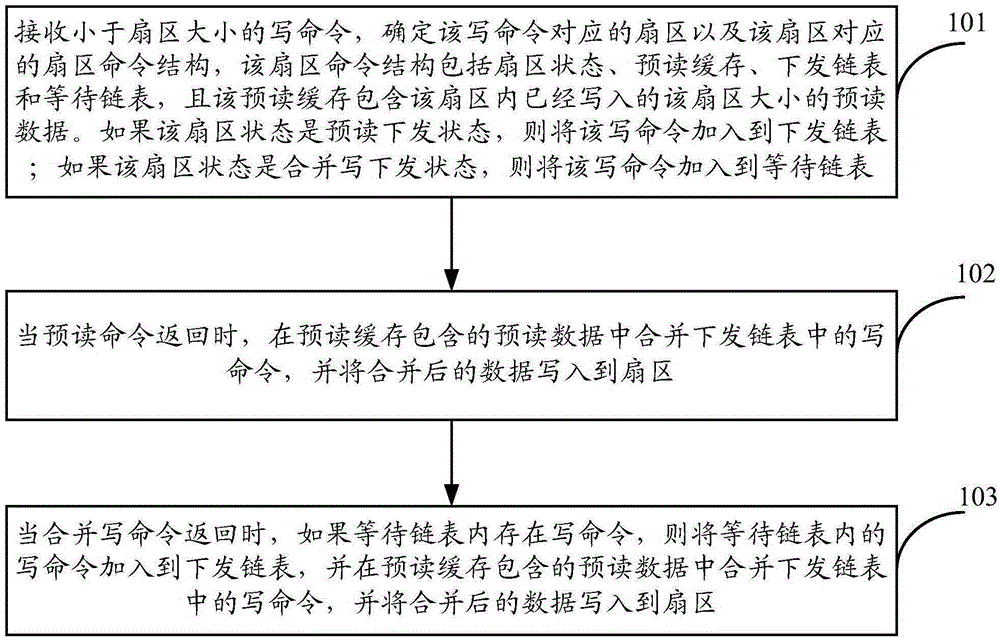

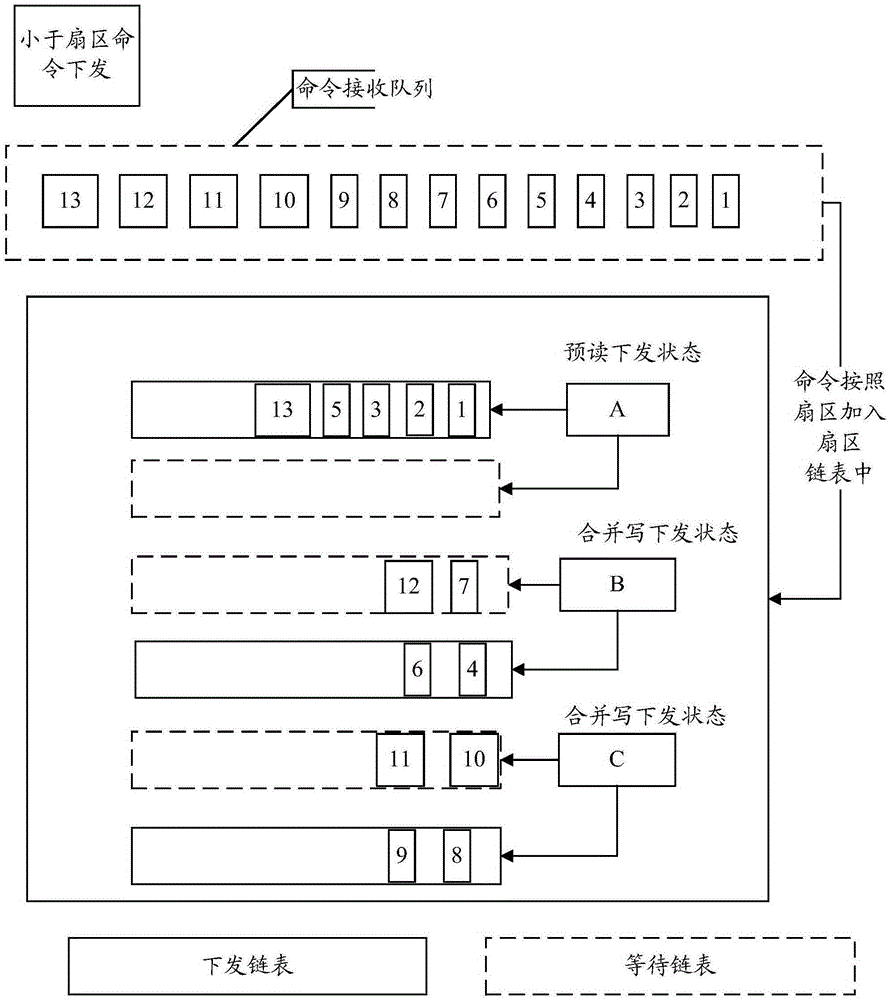

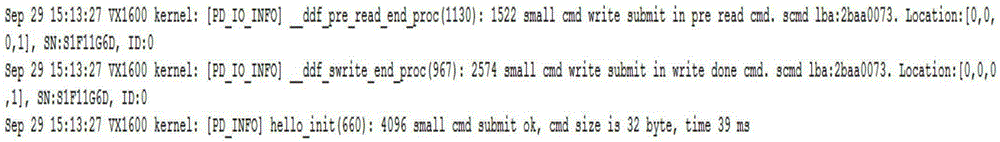

Control method and device for disk sectors

ActiveCN105302501ASave spaceEasy to handleInput/output to record carriersDisk sectorOperating system

Owner:ZHEJIANG UNIVIEW TECH CO LTD

Non-temporal write combining using cache resources

ActiveUS9892039B2Memory architecture accessing/allocationMemory systemsParallel computingCache coherence

A method and apparatus for performing non-temporal write combining using existing cache resources is disclosed. In one embodiment, a method includes executing a first thread on a processor core, the first thread including a first block initialization store (BIS) instruction. A cache query may be performed responsive to the BIS instruction, and if the query results in a cache miss, a cache line may be installed in a cache in an unordered dirty state in which it is exclusively owned by the first thread. The first BIS instruction and one or more additional BIS instructions may write data from the first processor core into the first cache line. After a cache coherence response is received, the state of the first cache line may be changed to an ordered dirty state in which it is no longer exclusive to the first thread.

Owner:ORACLE INT CORP

Extended write combining using a write continuation hint flag

InactiveUS8458282B2Reduce the amount of processingMultiple digital computer combinationsTransmissionComputer hardwareNetwork Computing System

A computing apparatus for reducing the amount of processing in a network computing system which includes a network system device of a receiving node for receiving electronic messages comprising data. The electronic messages are transmitted from a sending node. The network system device determines when more data of a specific electronic message is being transmitted. A memory device stores the electronic message data and communicating with the network system device. A memory subsystem communicates with the memory device. The memory subsystem stores a portion of the electronic message when more data of the specific message will be received, and the buffer combines the portion with later received data and moves the data to the memory device for accessible storage.

Owner:INT BUSINESS MASCH CORP

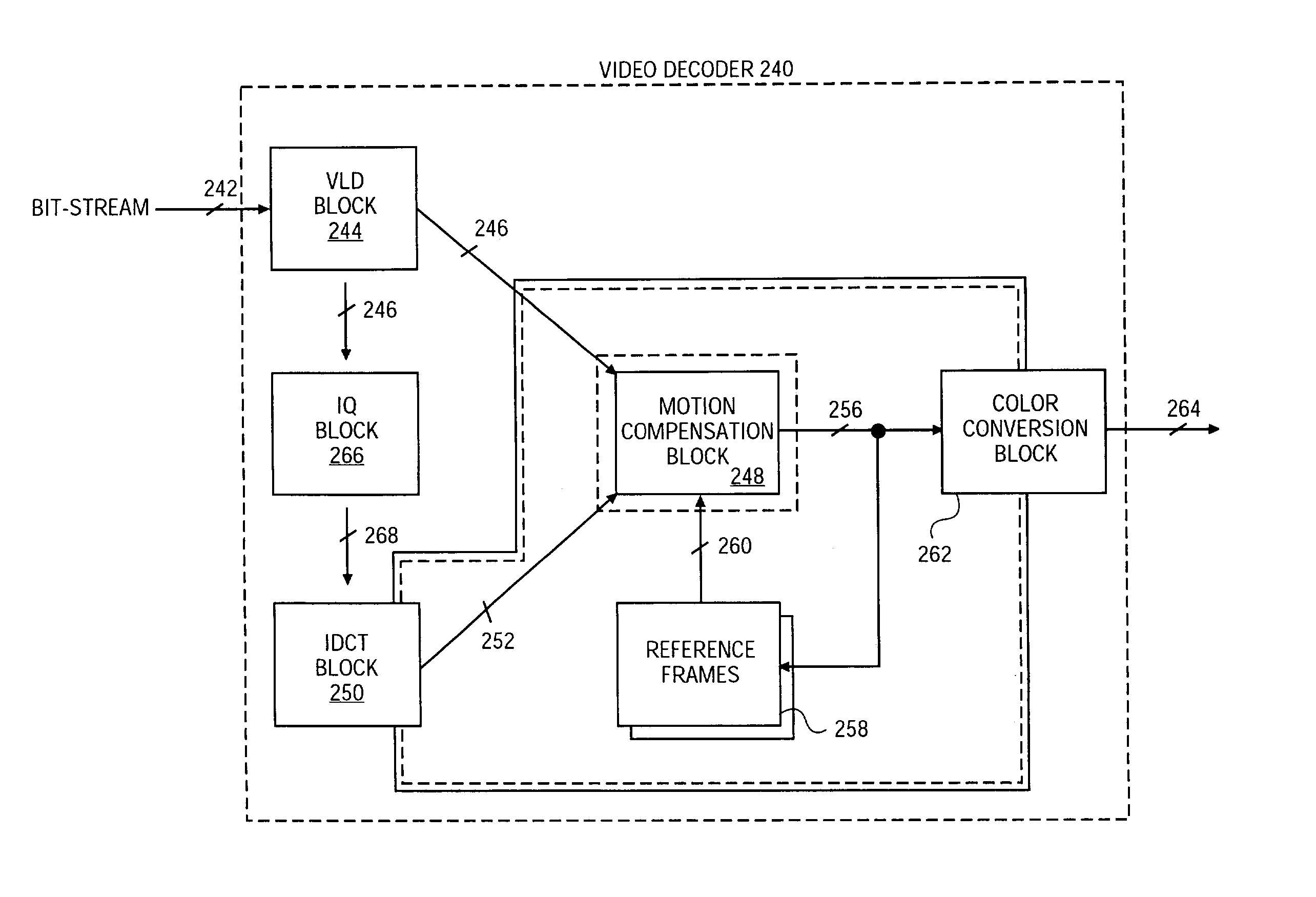

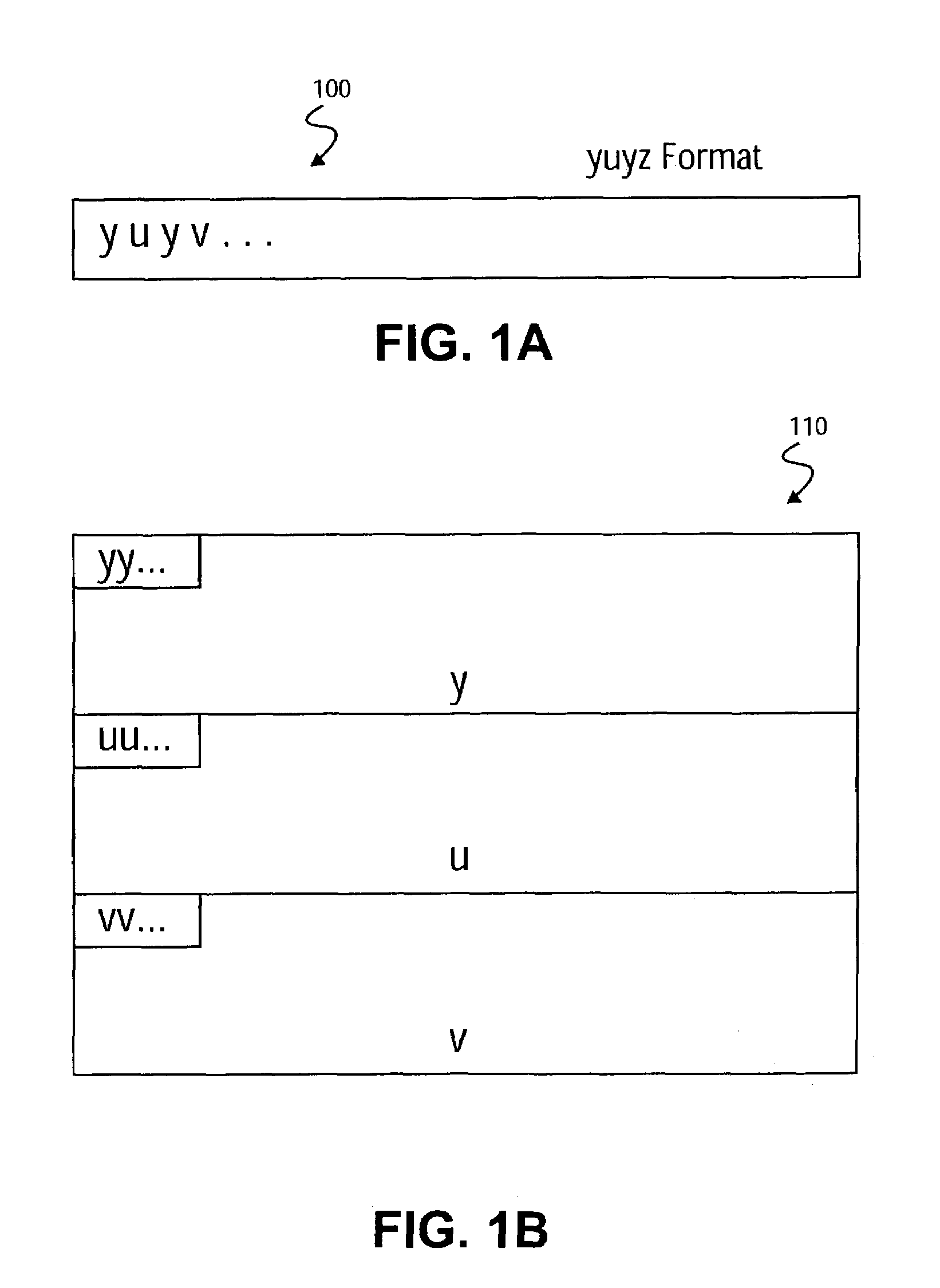

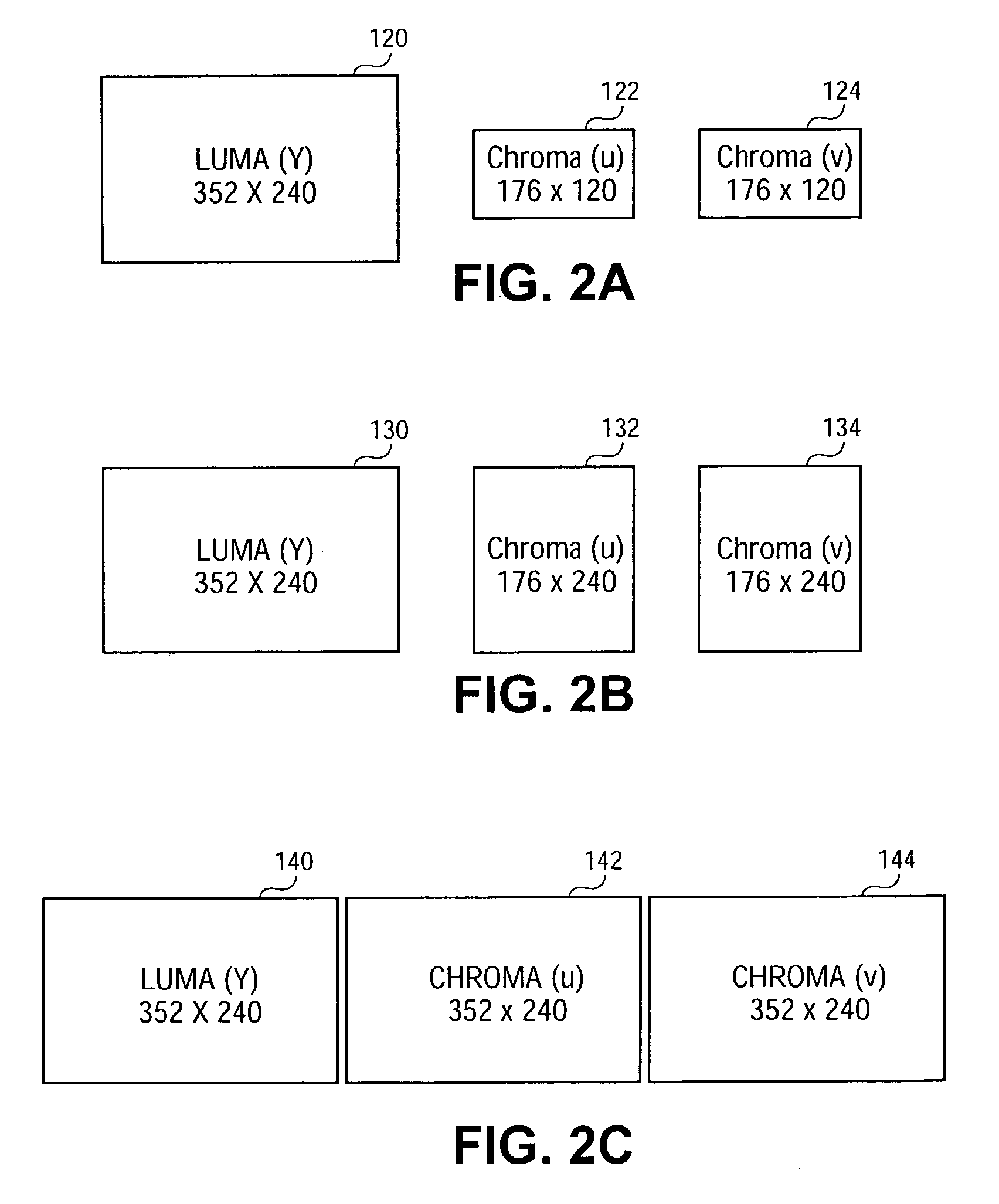

Method and apparatus for improved memory management of video images

InactiveUS7298782B2Picture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningComputer graphics (images)Video image

A novel storage format enabling a method for improved memory management of video images is described. The method includes receiving an image consisting of a plurality of color components. Once received, the plurality of color components is converted to a mixed format of planar format and packed format. The mixed packet format is implemented by storing one or more of the plurality of color components in a planar format and storing one or more of the plurality of color components in a packed format. A method for writing out video images is also described utilizing a write combining (WC) fame buffer. The decoding method motion compensates groups of macroblocks in order to eliminate partial writes from the WC frame buffer.

Owner:INTEL CORP

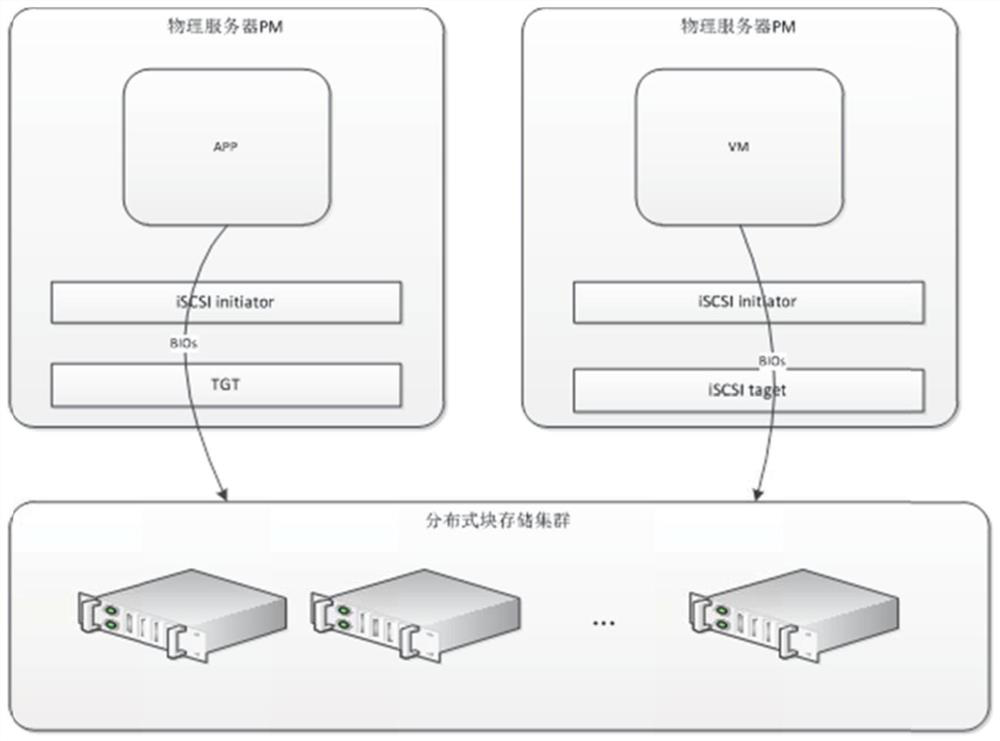

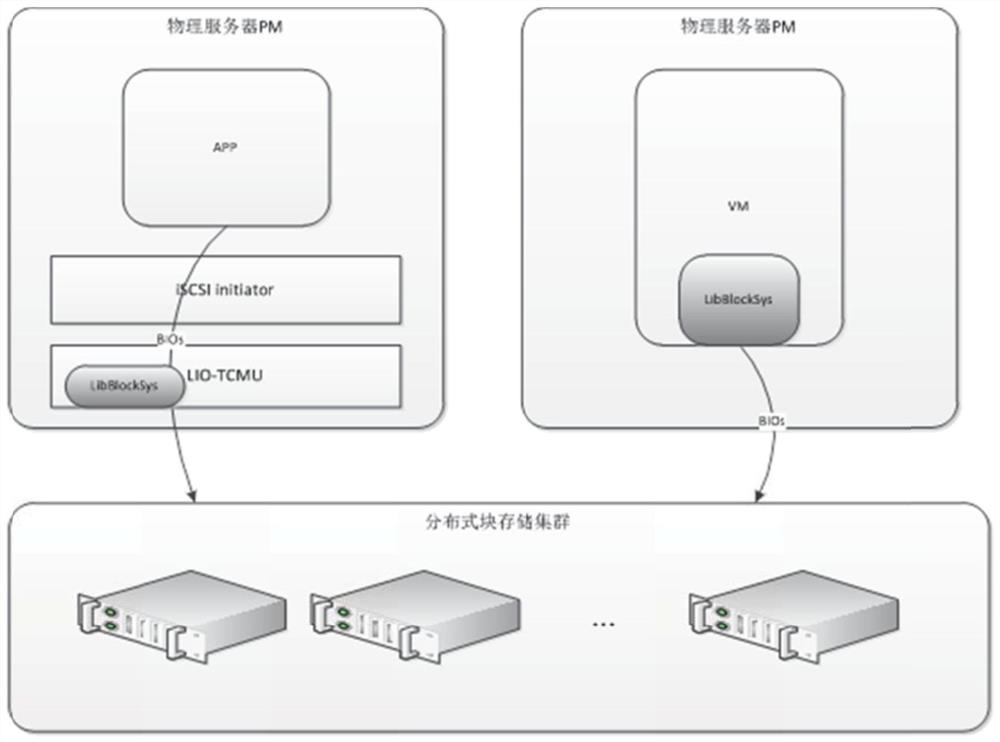

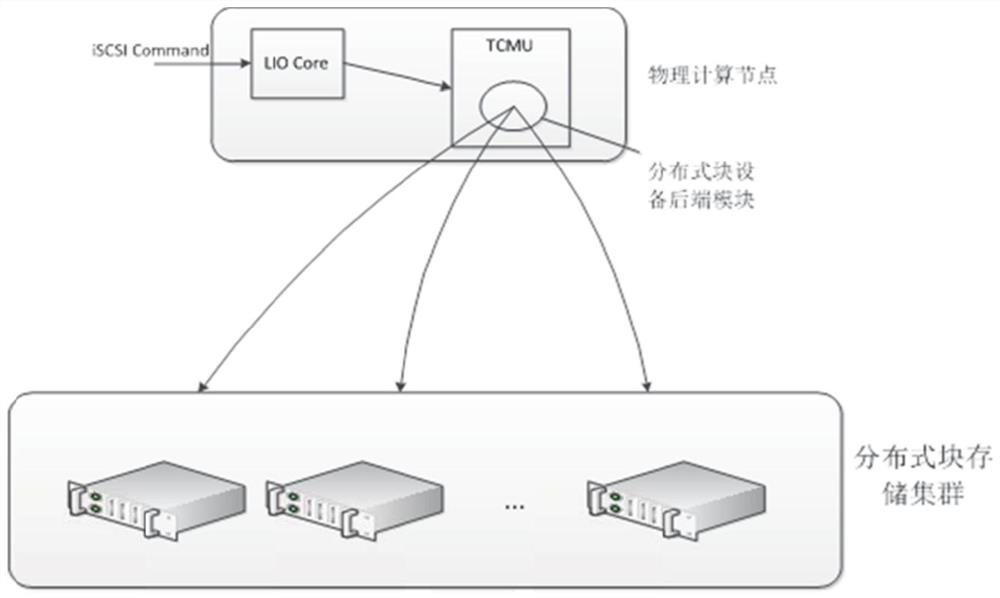

Method and system for accessing distributed block storage system in user mode

PendingCN112052291AImprove service capabilitiesImprove response speedDatabase distribution/replicationTransmissionData accessISCSI

The invention discloses a method and system for accessing a distributed block storage system in a user mode, an access module is arranged in an LIO TCMU of a computing node, and the method comprises the following steps: after the LIO TCMU is connected with an iSCSI initiator, receiving a data reading request from a data access party sent by the iSCSI initiator through the access module; determining whether target data corresponding to the data reading request exists in a cache of the access module or not; if so, returning the target data to the data access party; and otherwise, generating a corresponding thread in a pre-configured thread pool in the access module, so as to execute the thread to request target data corresponding to the data reading request from the distributed block storagecluster and return the target data to the data access party. The functions of caching, pre-reading, writing merging and the like are added to a client, so that tasks originally processed by the server are moved to the client, the service capacity and the response speed of the whole cluster are improved, and while the access performance is improved, the bandwidth overhead of the cluster is reduced, and services can be provided for more computing nodes.

Owner:SUNING CLOUD COMPUTING CO LTD

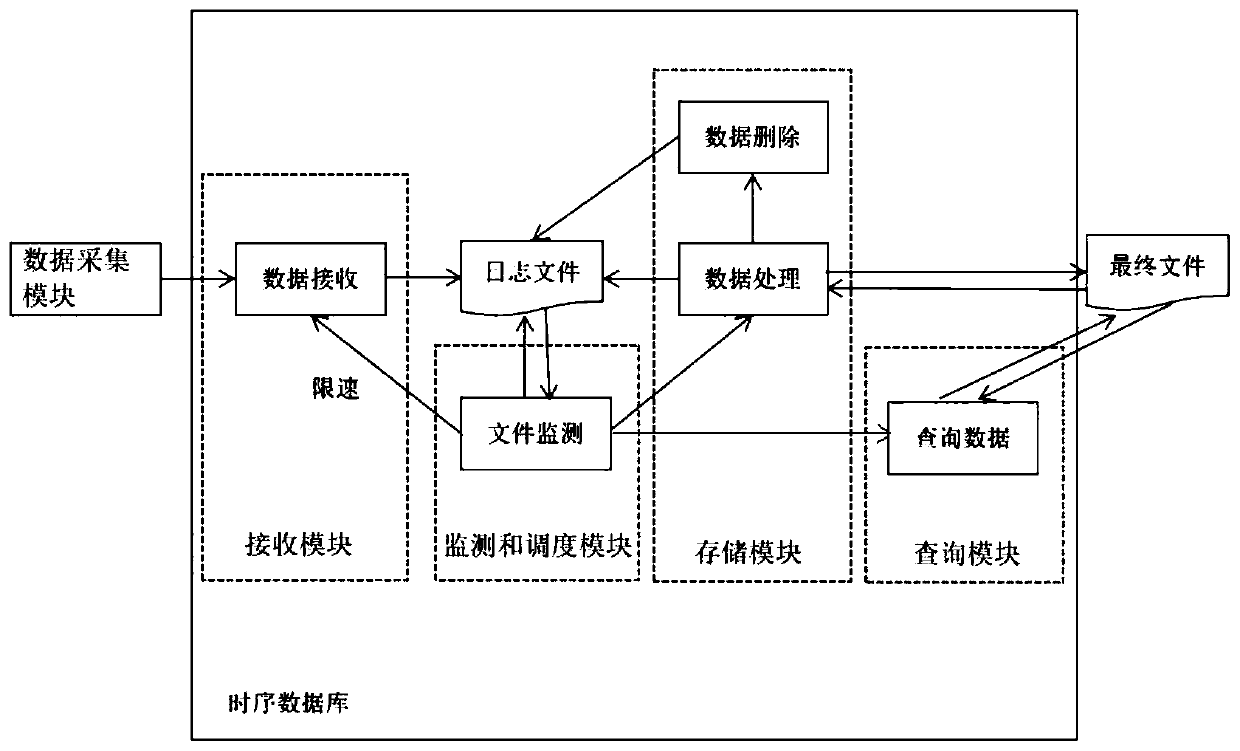

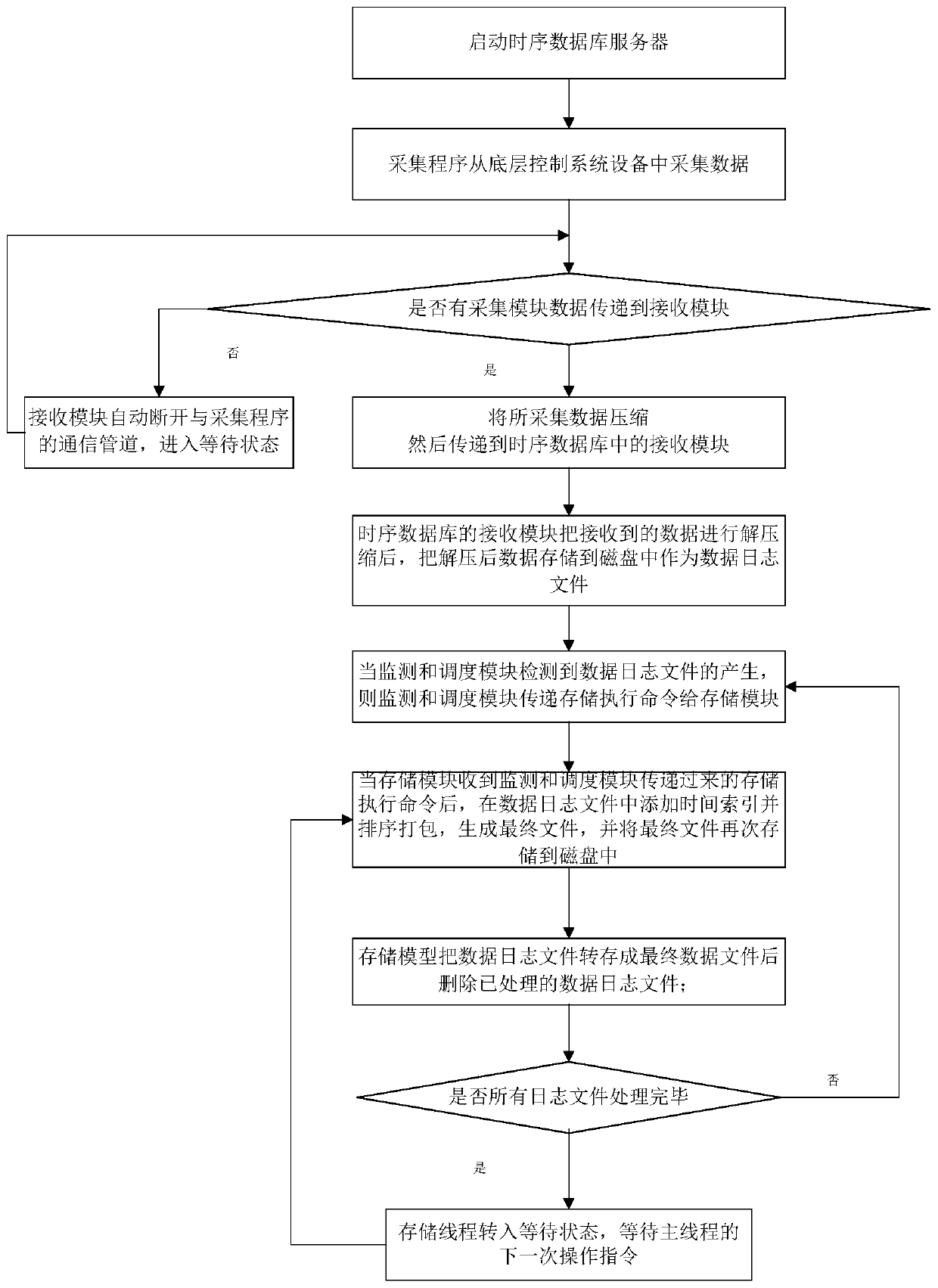

Data storage system and method

ActiveCN110609813AIntegrity guaranteedGuaranteed storage effectFile/folder operationsSpecial data processing applicationsData acquisition moduleData store

The invention provides a data storage system and a data storage method, and belongs to the field of data storage. The data storage system comprises a data collection module and a time sequence database. According to the data storage method, after a time sequence database receives data and before the data is written into a disk, the data is independently stored as a log, real storage operation is carried out after the log is successfully stored, and the data is written into the disk. If the whole storage operation is interrupted due to a certain reason, when the system is restarted, the storageoperation before interruption can be recovered according to the data of the data log file, and it is guaranteed that the received data cannot be lost. When real data storage operation is carried out,multiple random writes are combined into one sequential write operation, the frequency of calling disk write operation and the moving range of a magnetic head and a mechanical arm are reduced, and the highest disk write speed of a rotating speed hard disk is achieved. One data log file is deleted after the storage operation is completed, and the occupied hard disk space can be recycled.

Owner:BEIJING HUADIAN TIANREN ELECTRIC POWER CONTROL TECH

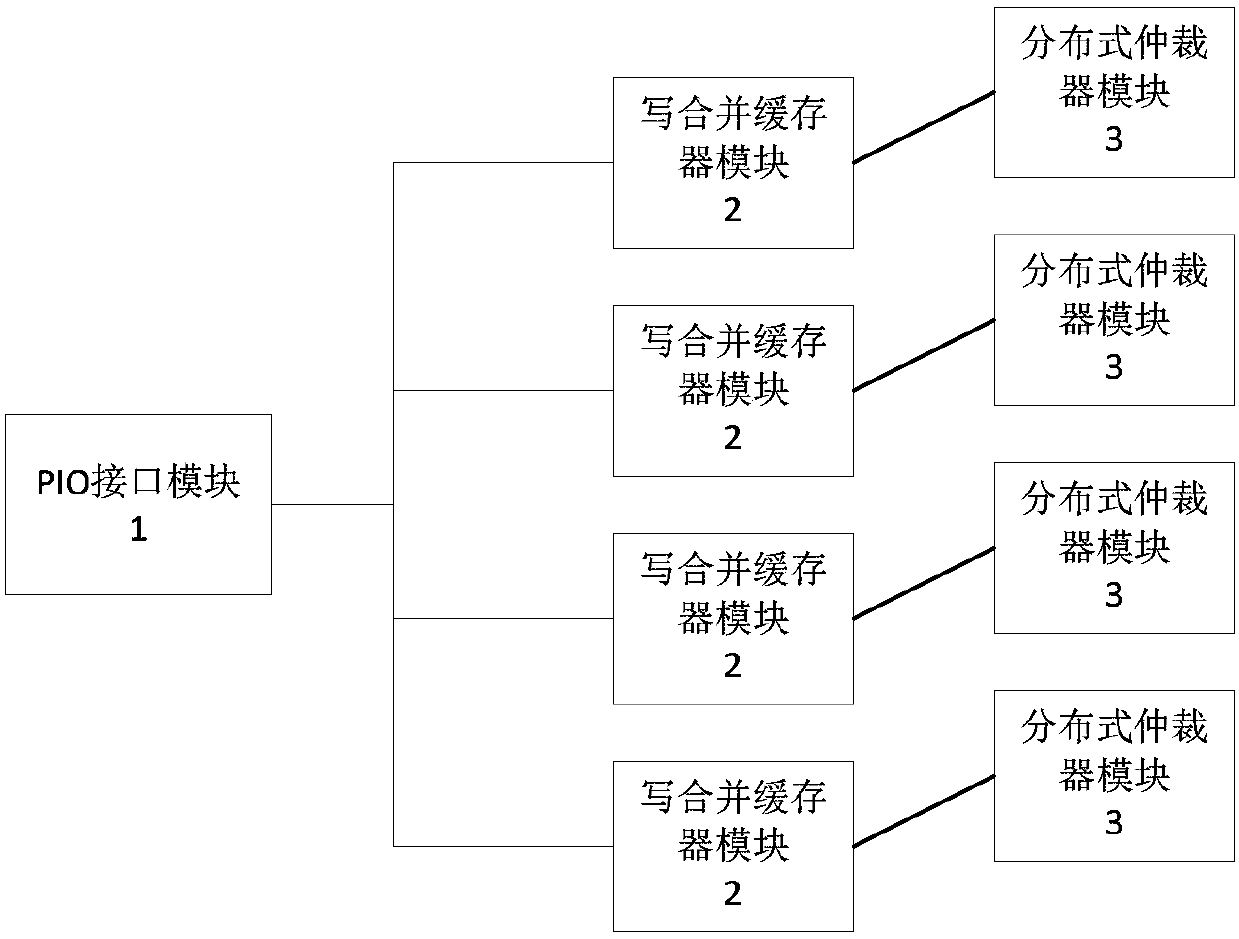

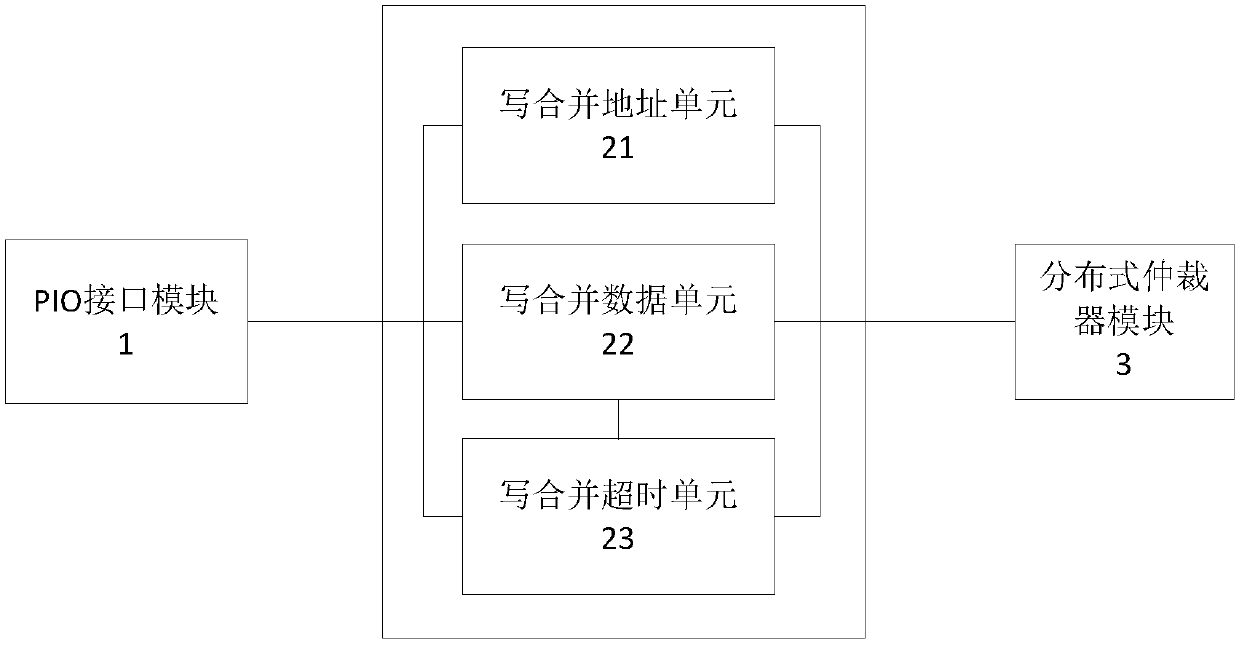

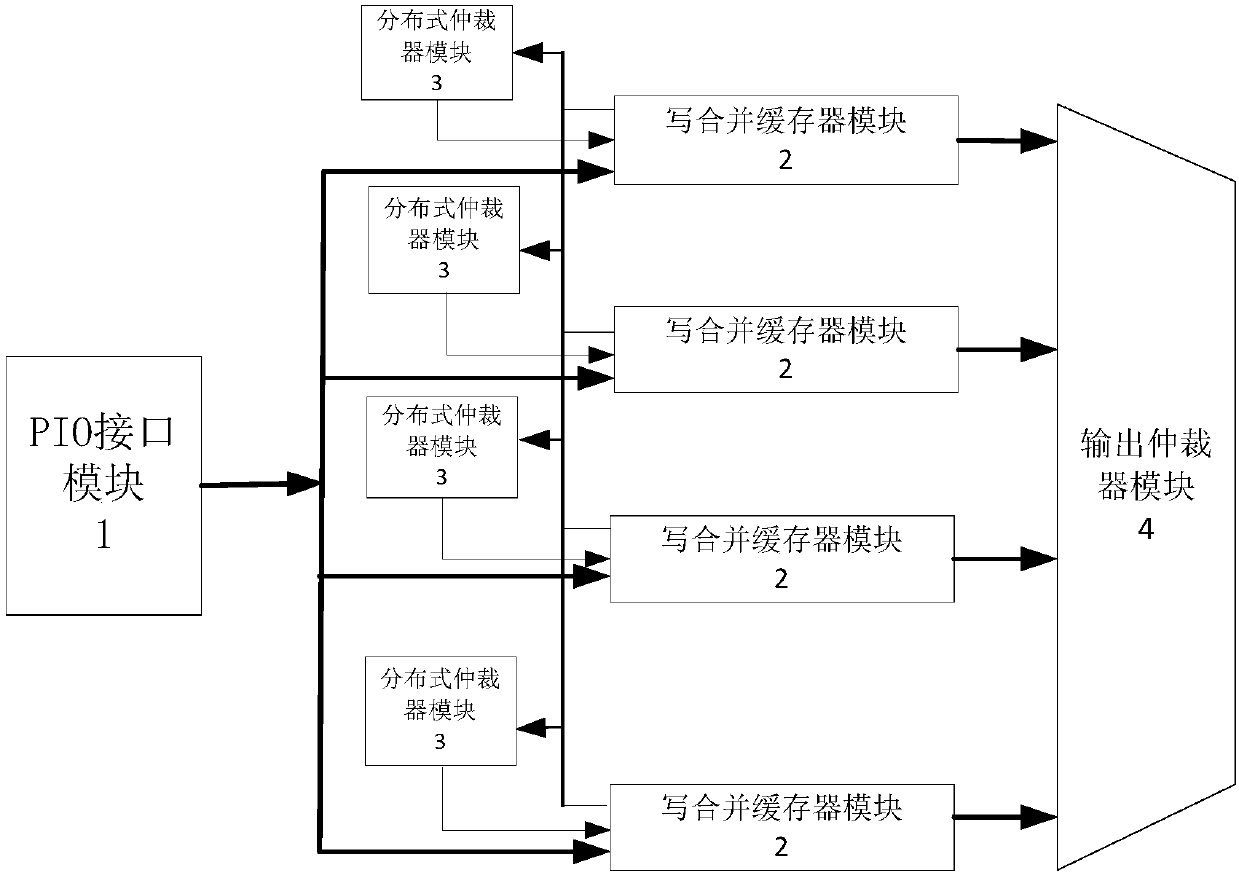

Programmable-input/output (PIO) writing merging device based on distributed arbitration and method

ActiveCN107861895AEasy to implementImprove scalabilityElectric digital data processingReal-time computingWrite combining

The embodiment of the invention provides a programmable-input / output (PIO) writing merging device based on distributed arbitration and a method, and belongs to the field of data communication. Each writing merging buffer module in at least one writing merging buffer module corresponds to a distributed arbiter module. A PIO interface module is used for processing received PIO writing requests intoa format which is suitable for the at least one writing merging buffer module, wherein the PIO writing requests include a writing address and written data. Each writing merging buffer module is used for receiving the PIO writing requests. The writing merging buffer module storing a buffer address which is the same as the writing address outputs a hit signal. Each distributed arbiter module is usedfor outputting an enabling signal to enable the corresponding writing merging buffer module to write the written data according to an address offset of the writing address when the hit signal is received. According to the device, realization is easy, expansibility is good, generality is high, and a data processing process can be simplified as much as possible.

Owner:深圳市楠菲微电子有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com