Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

42 results about "MIMD" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

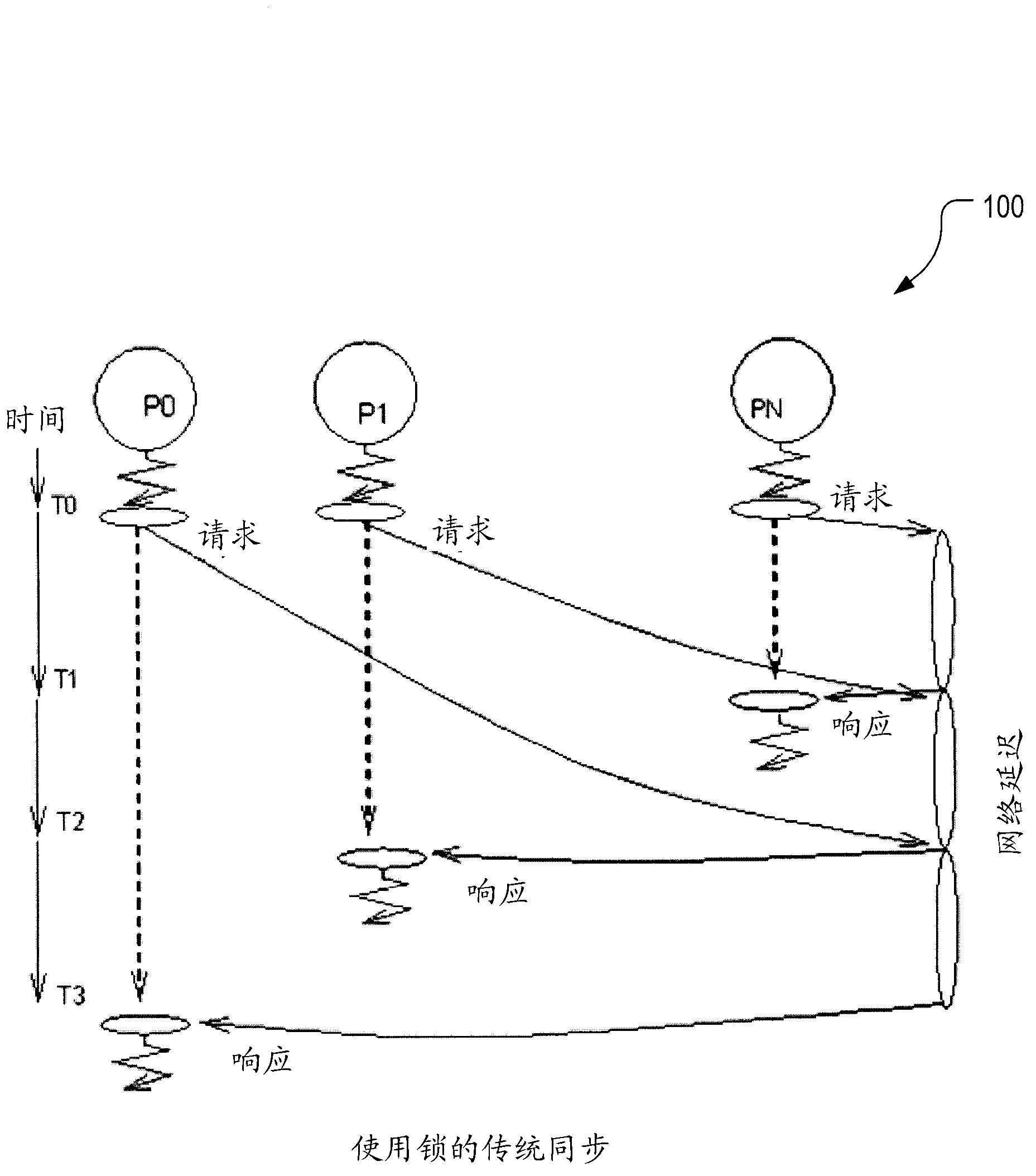

In computing, MIMD (multiple instruction, multiple data) is a technique employed to achieve parallelism. Machines using MIMD have a number of processors that function asynchronously and independently. At any time, different processors may be executing different instructions on different pieces of data. MIMD architectures may be used in a number of application areas such as computer-aided design/computer-aided manufacturing, simulation, modeling, and as communication switches. MIMD machines can be of either shared memory or distributed memory categories. These classifications are based on how MIMD processors access memory. Shared memory machines may be of the bus-based, extended, or hierarchical type. Distributed memory machines may have hypercube or mesh interconnection schemes.

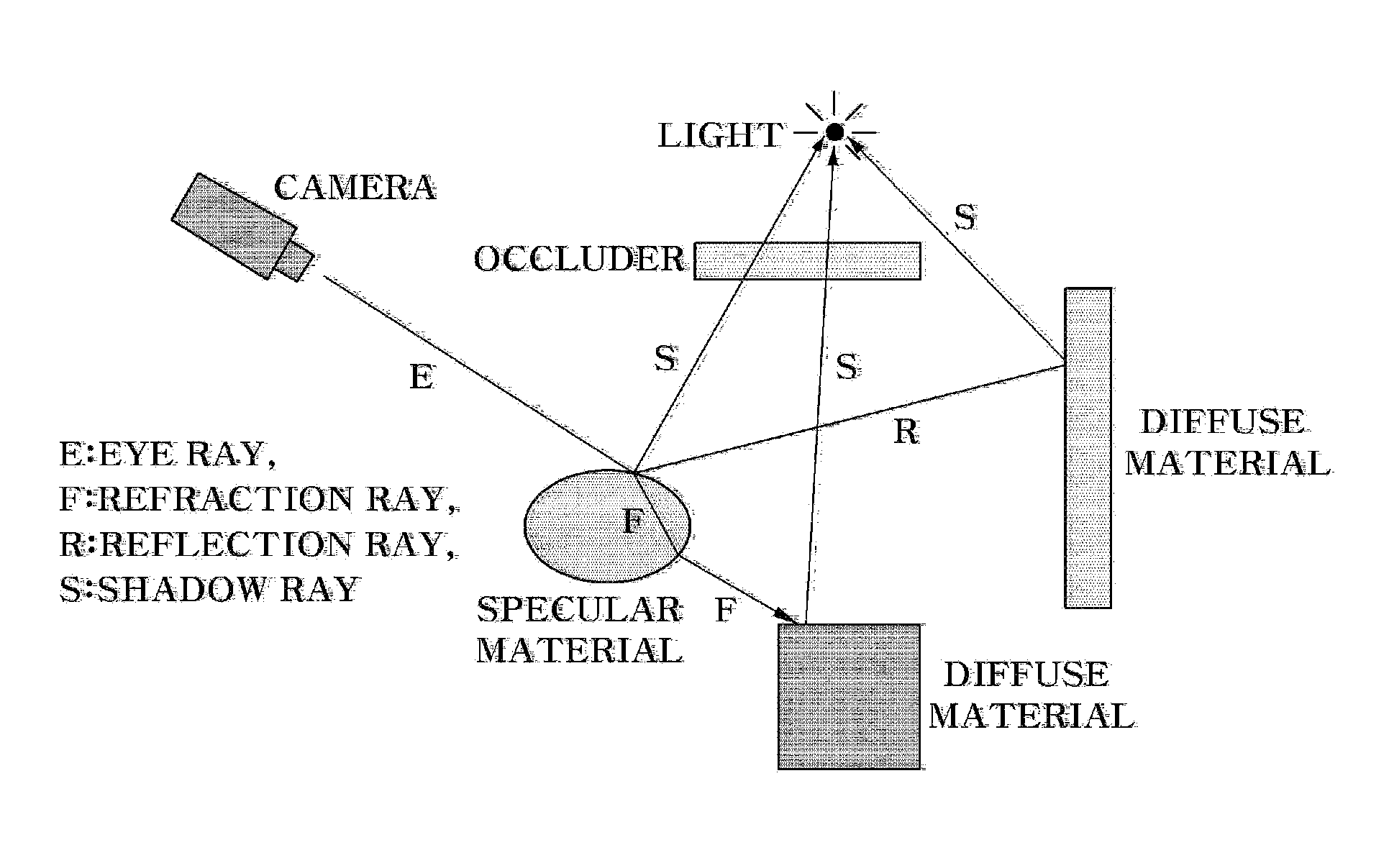

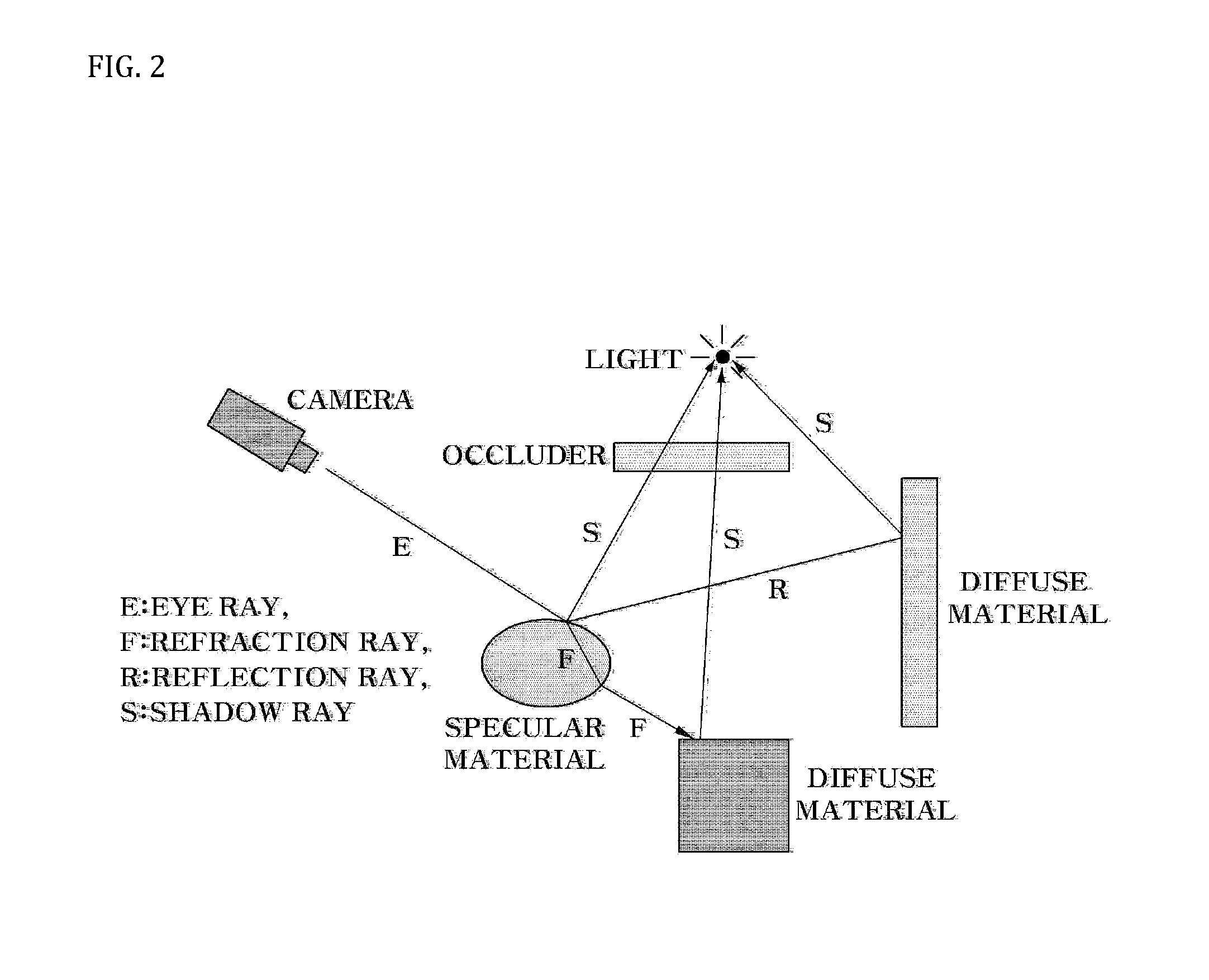

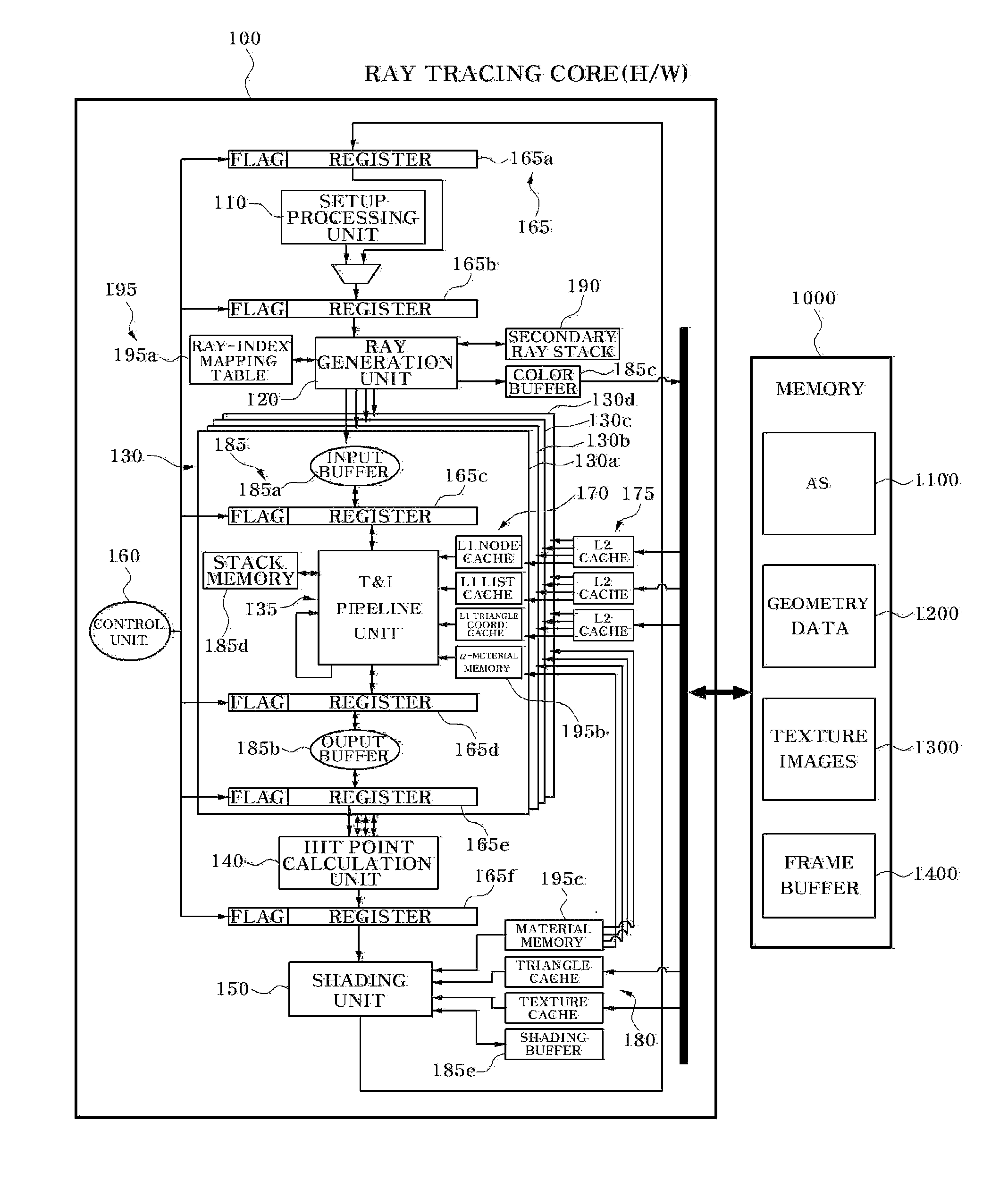

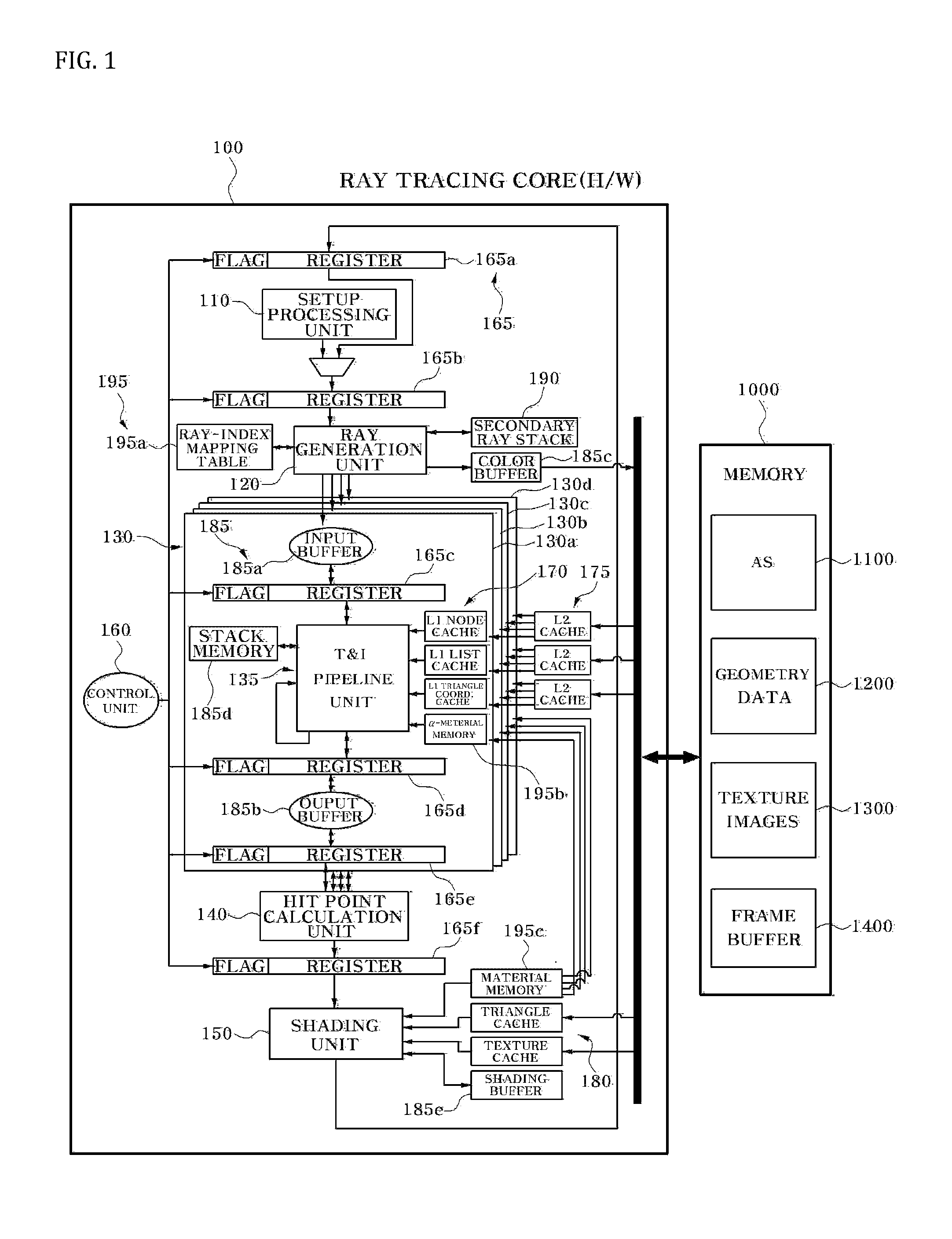

Ray tracing core and ray tracing chip having the same

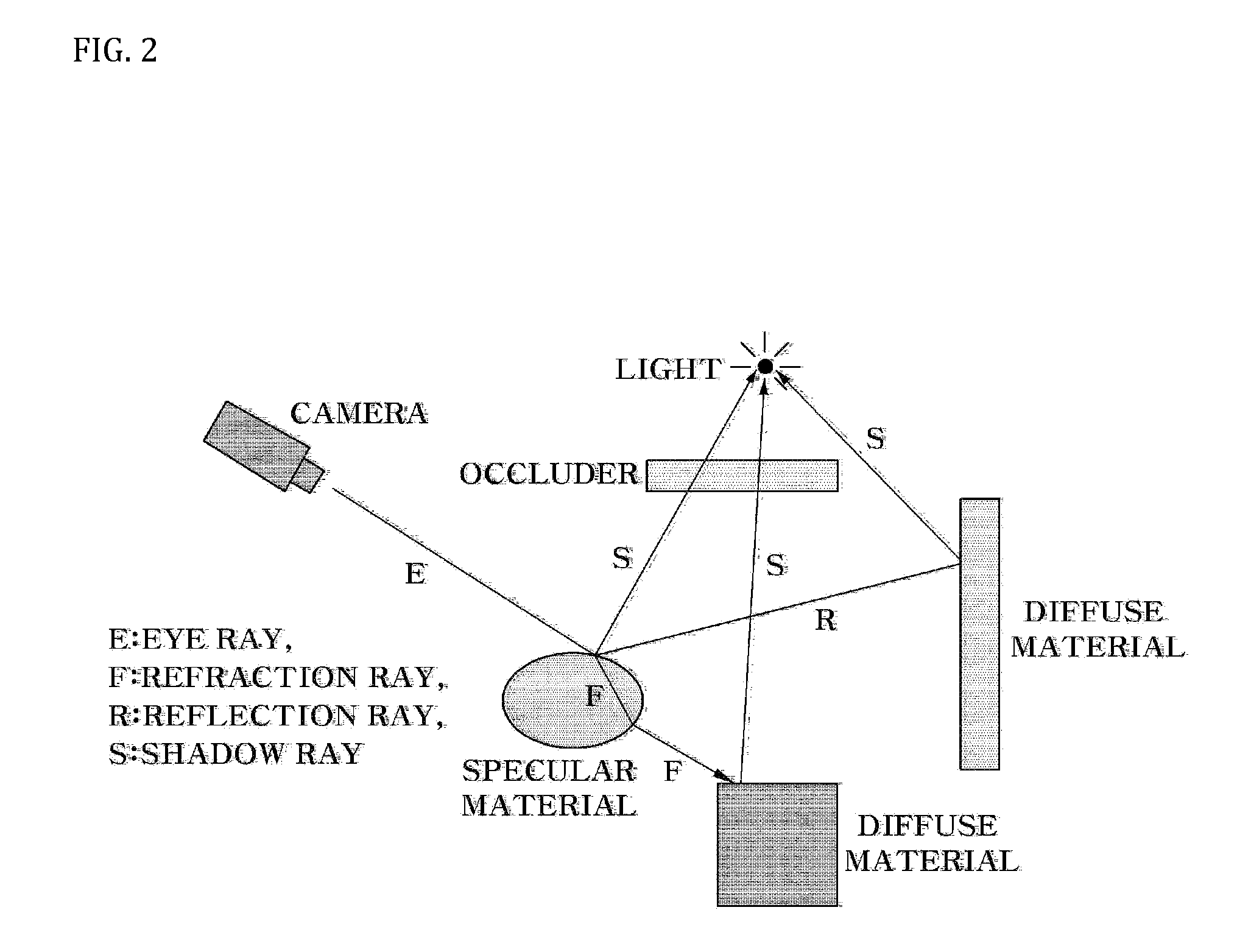

A ray tracing core comprising a ray generation unit and a plurality of T&I (Traversal & Intersection) units with MIMD (Multiple Instruction stream Multiple Data stream) architecture is disclosed. The ray generation unit generates at least one eye ray based on an eye ray generation information. The eye ray generation information includes a screen coordinate value. Each of the plurality of T&I units receives the at least one eye ray and checks whether there exists a triangle intersected with the received at least one eye ray. The triangle configures a space.

Owner:SILICONARTS

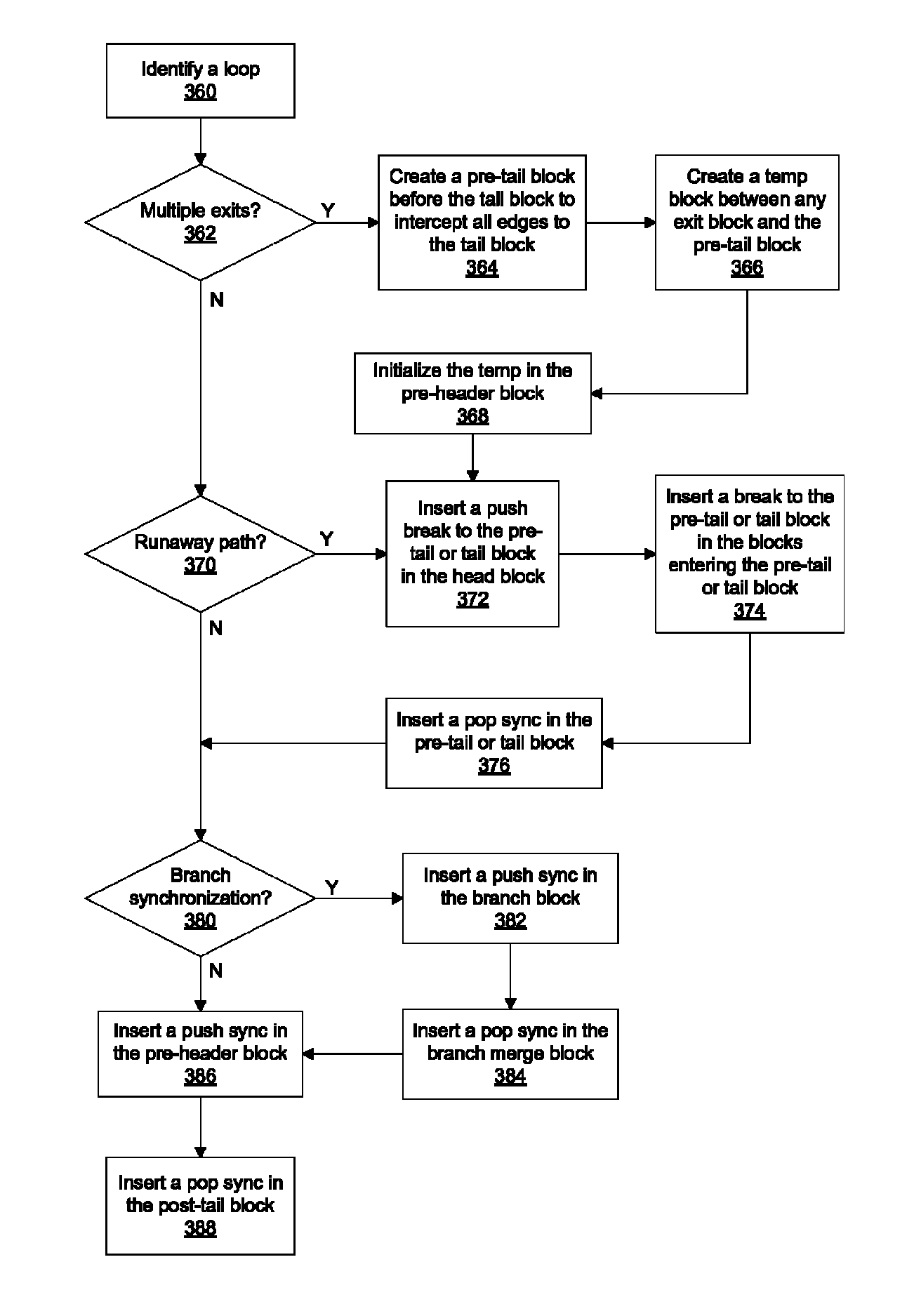

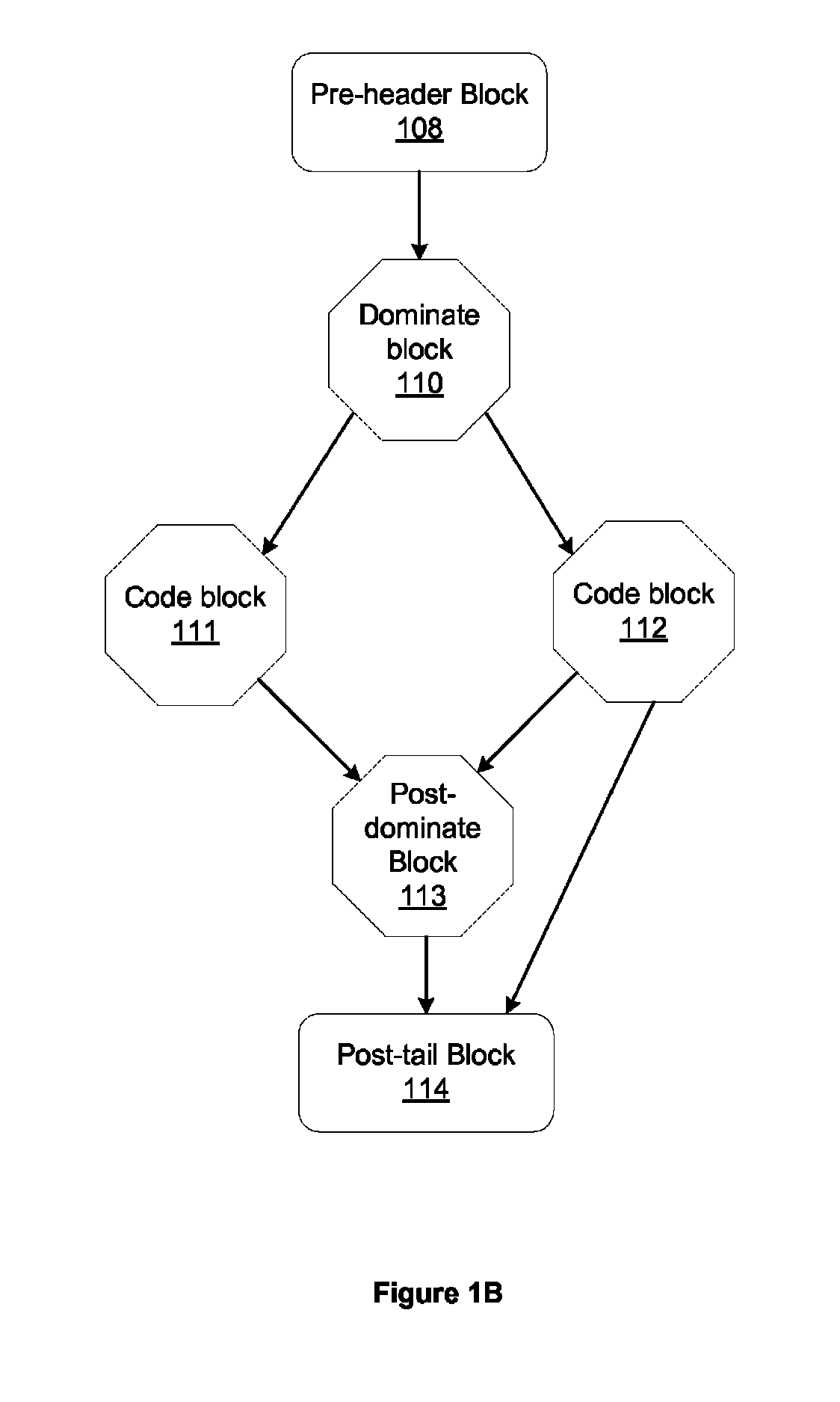

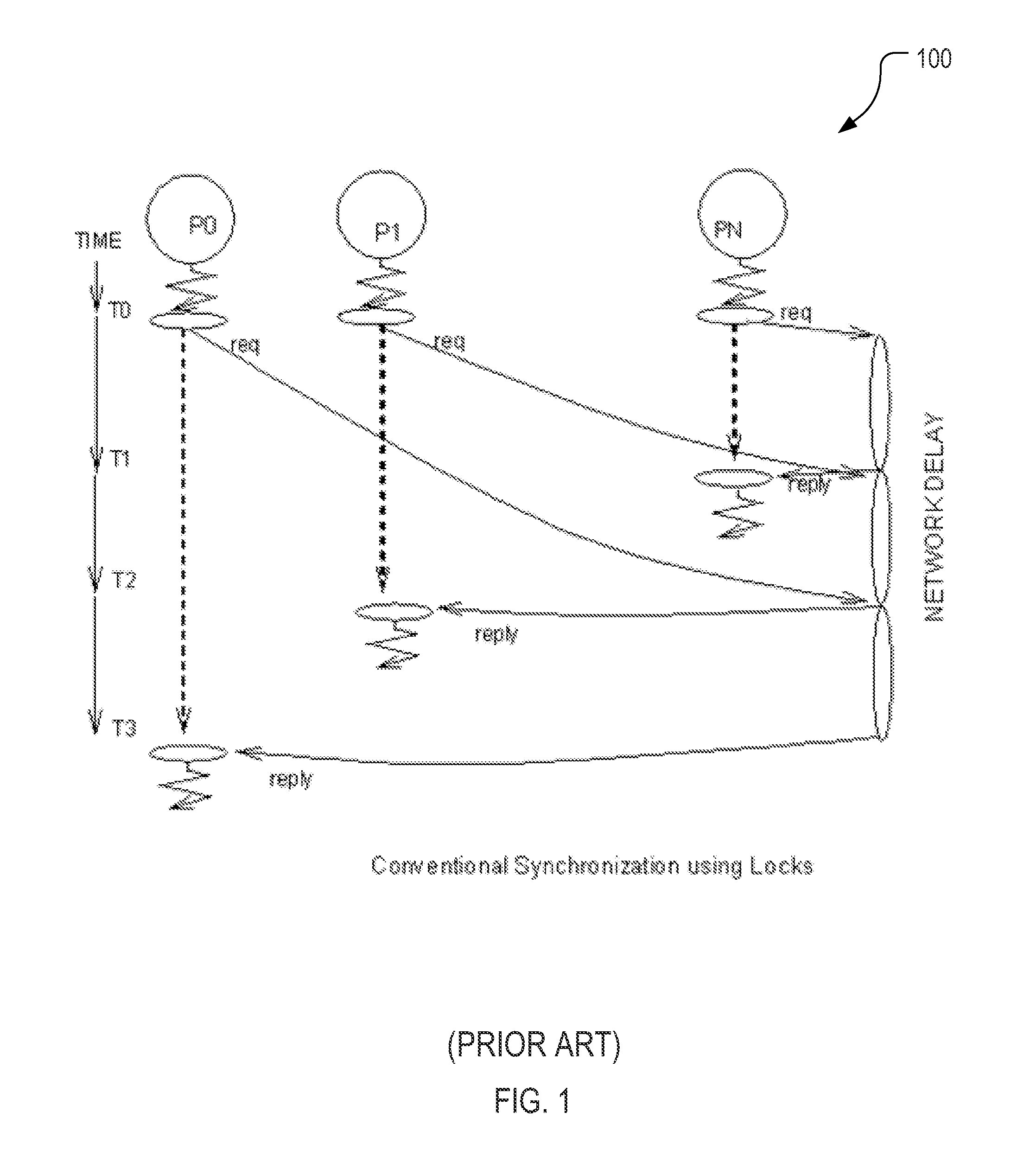

Insertion of multithreaded execution synchronization points in a software program

ActiveUS8381203B1Good benefitImprove performanceSoftware engineeringMultiprogramming arrangementsGraphicsMIMD

A compiler is configured to determine a set of points in a flow graph for a software program where multithreaded execution synchronization points are inserted to synchronize divergent threads for SIMD processing. MIMD execution of divergent threads is allowed and execution of the divergent threads proceeds until a synchronization point is reached. When all of the threads reach the synchronization point, synchronous execution resumes. The synchronization points are needed to ensure proper execution of the certain instructions that require synchronous execution as defined in some graphics APIs and when synchronous execution improves performance based on a SIMD architecture.

Owner:NVIDIA CORP

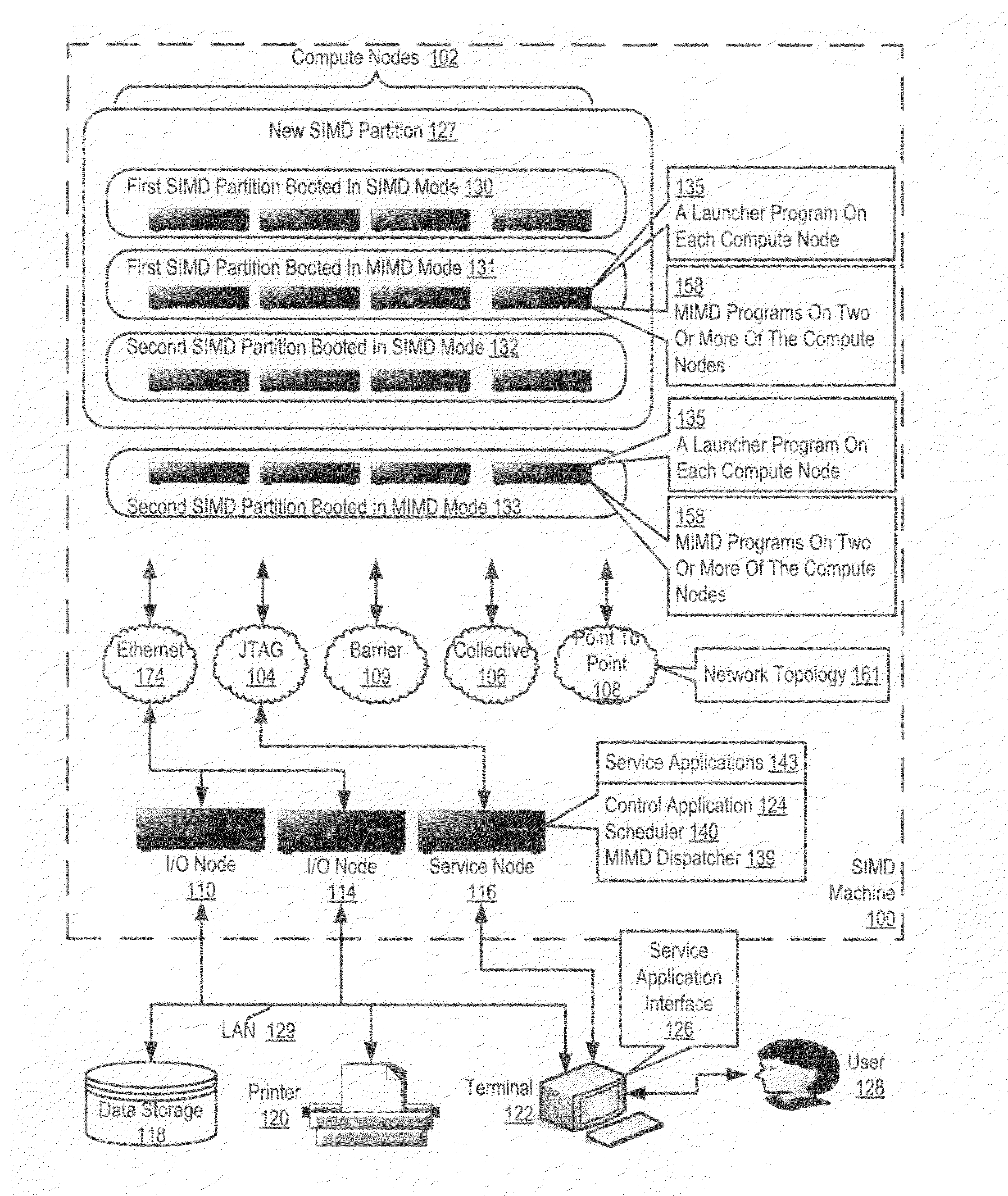

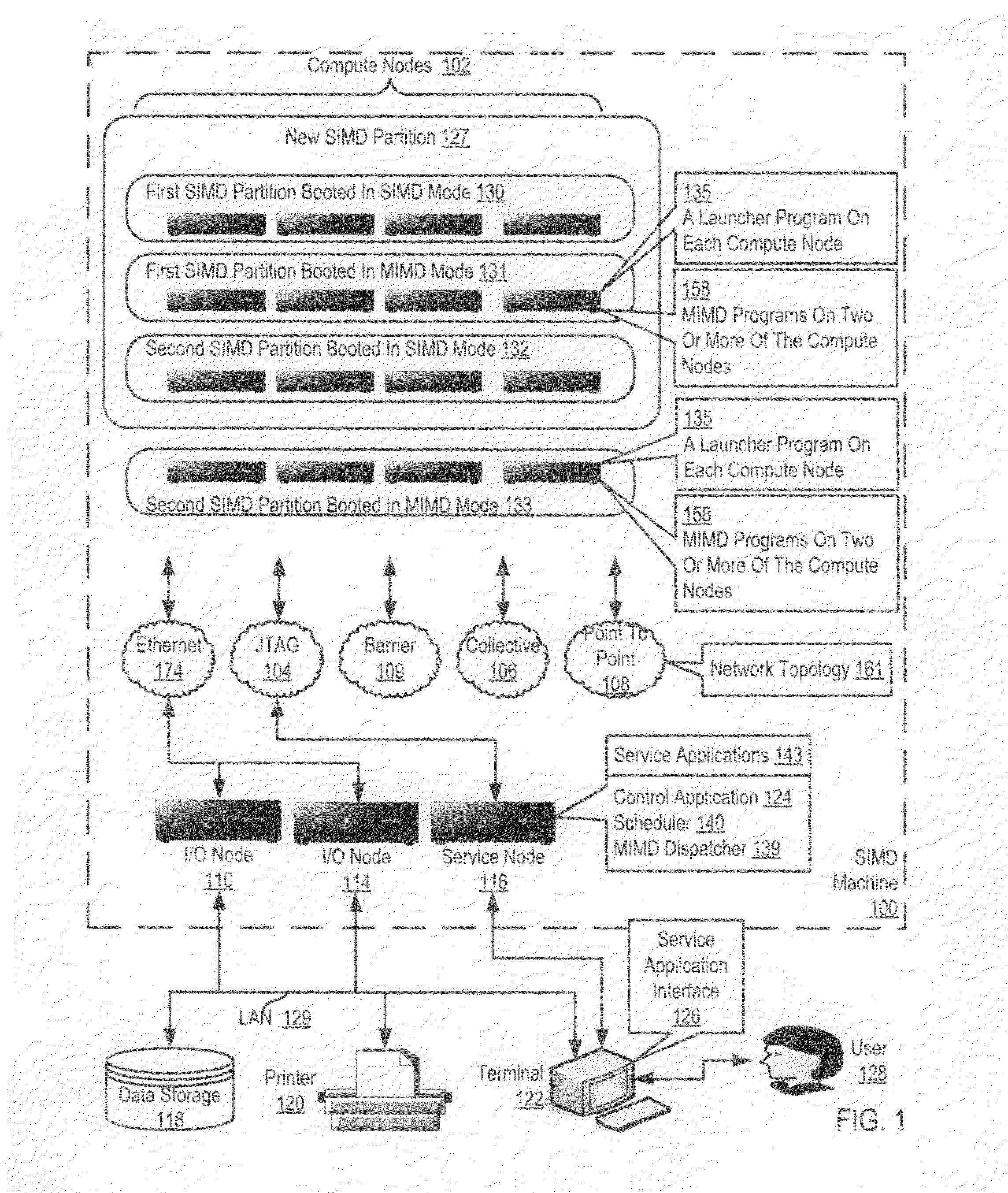

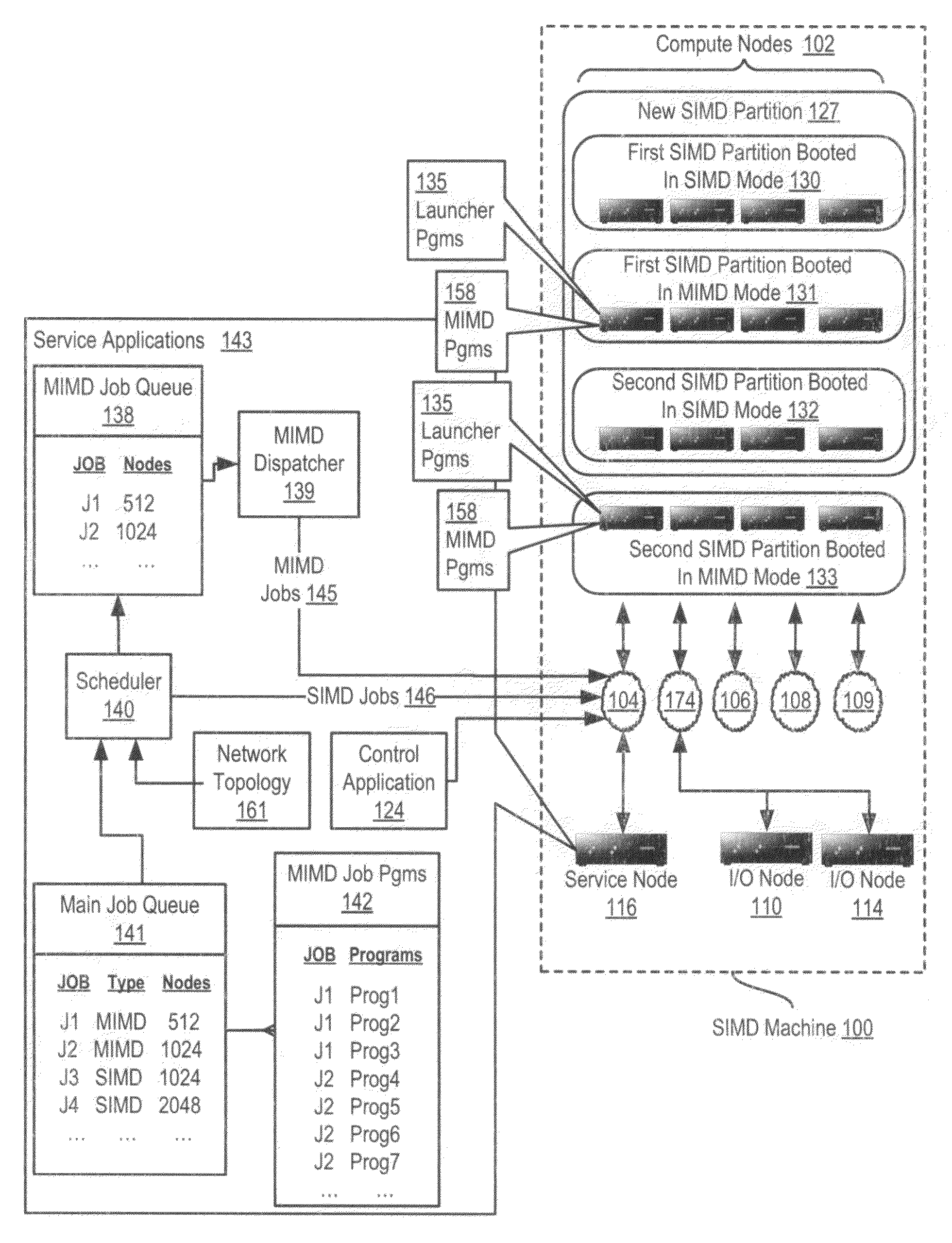

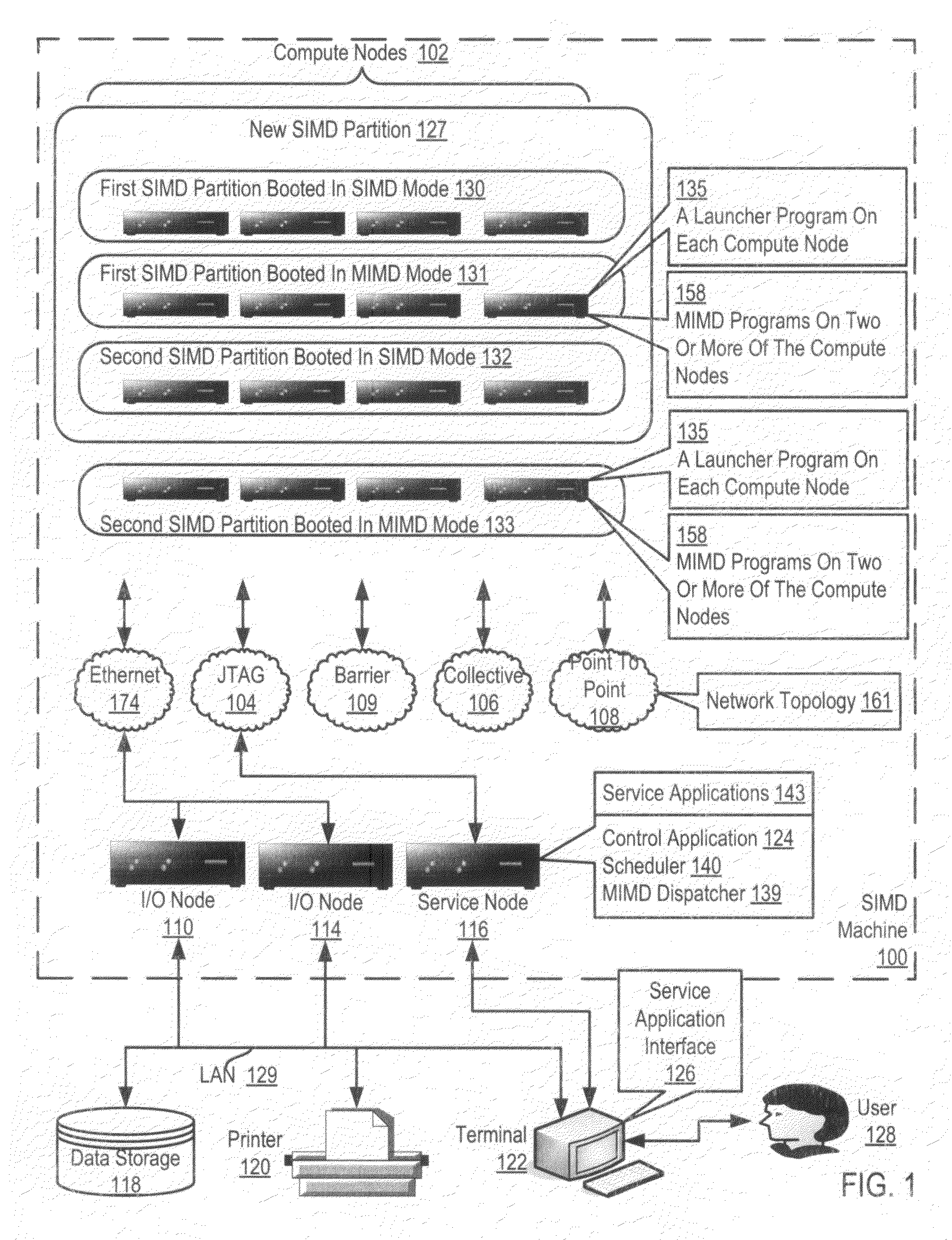

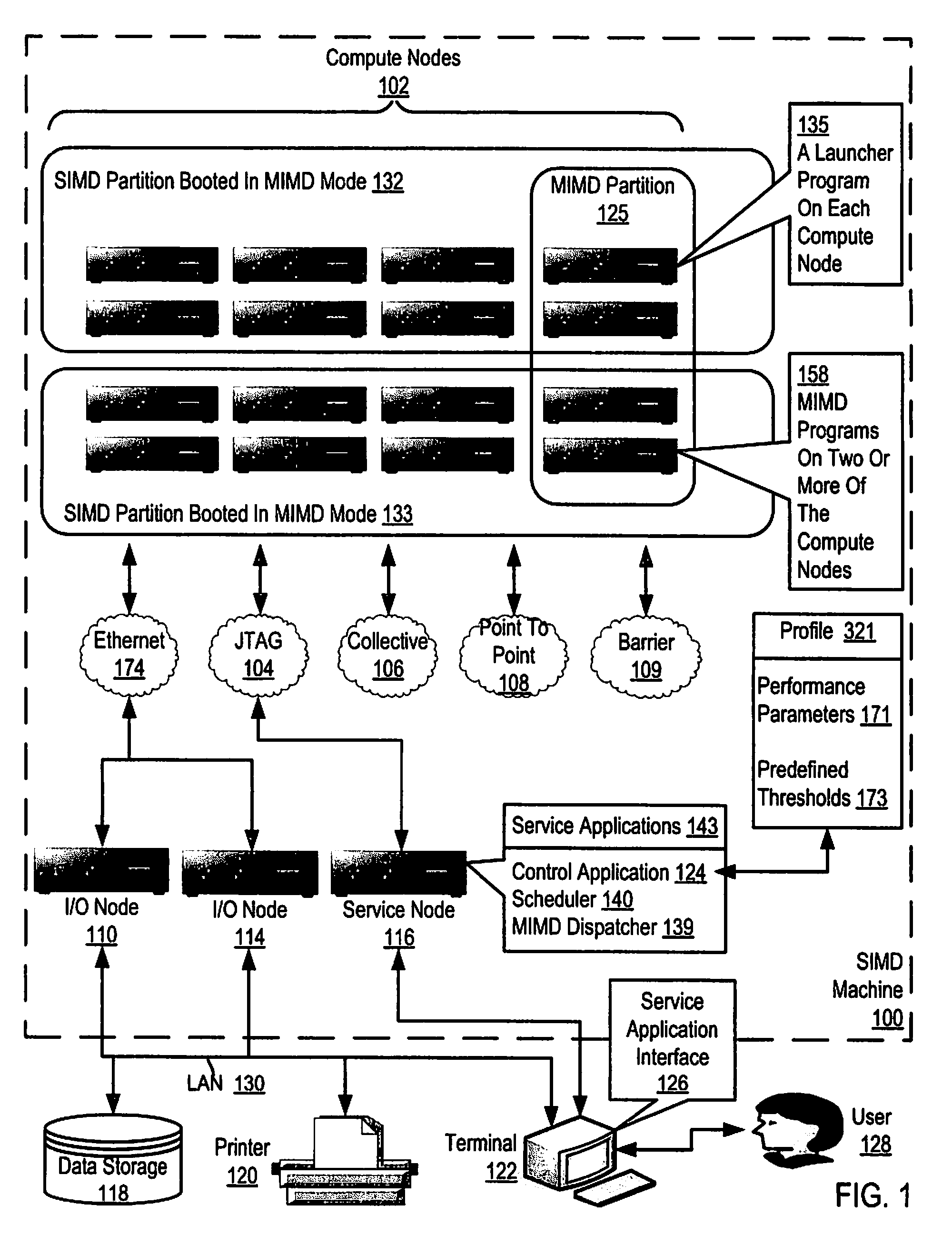

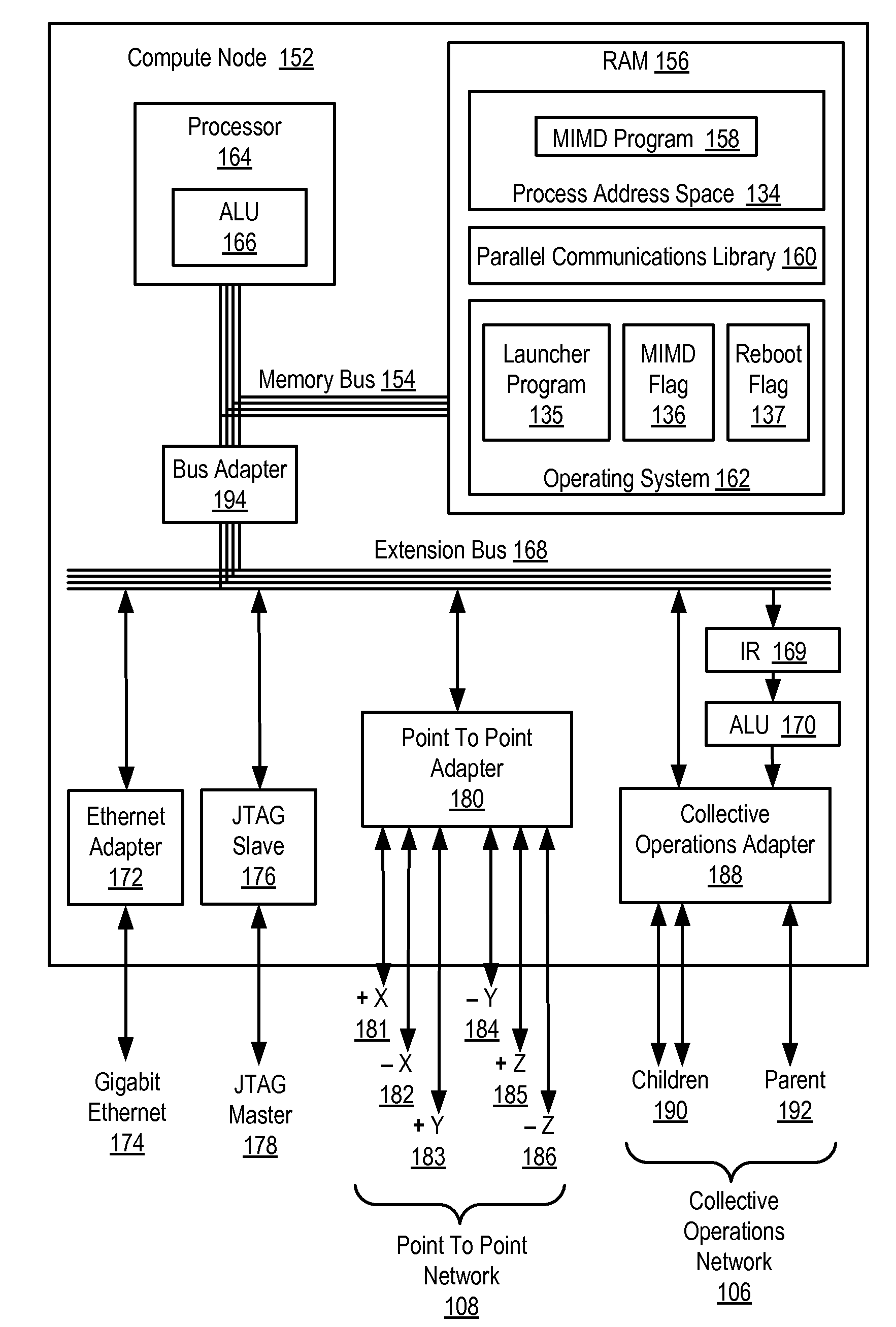

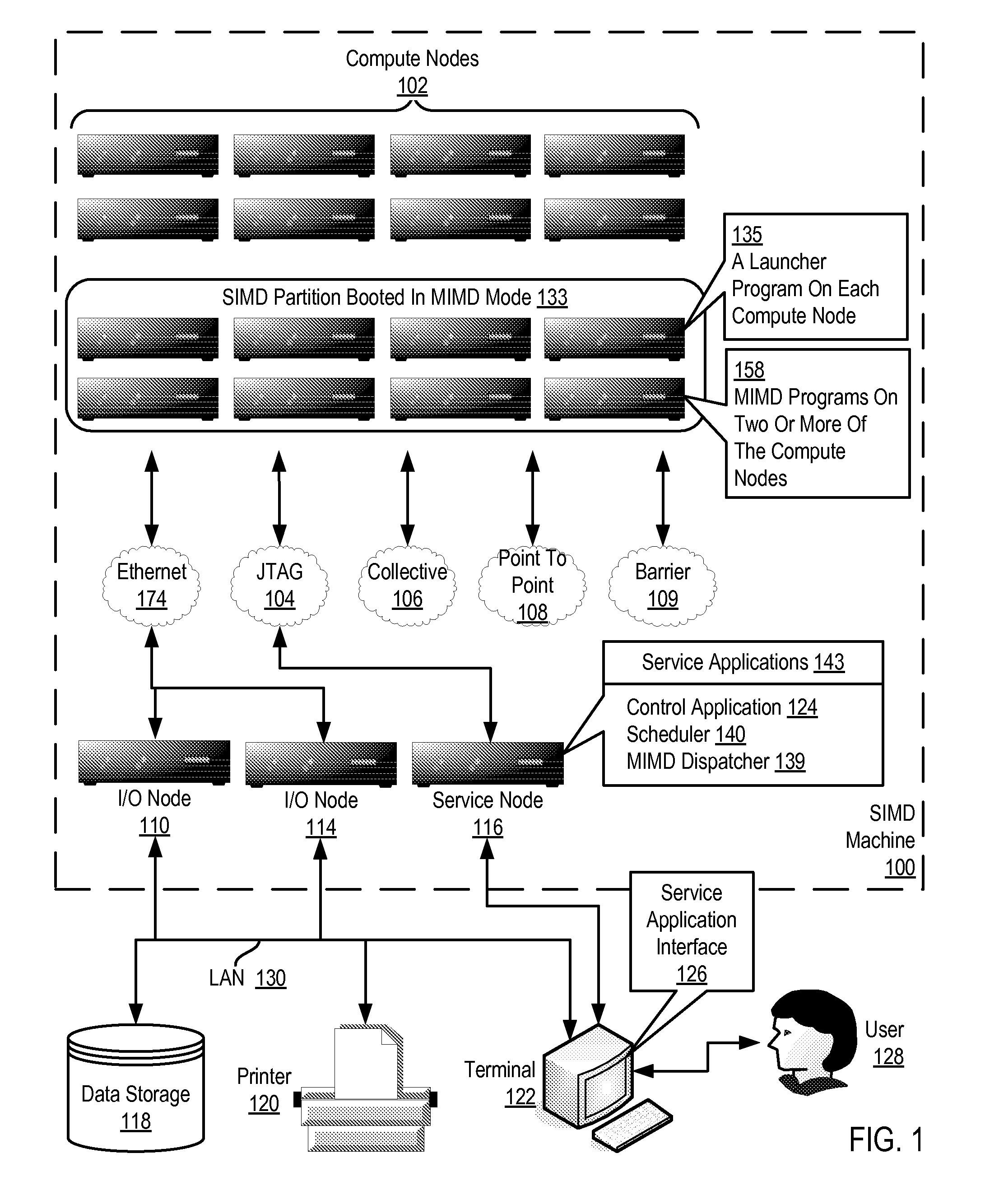

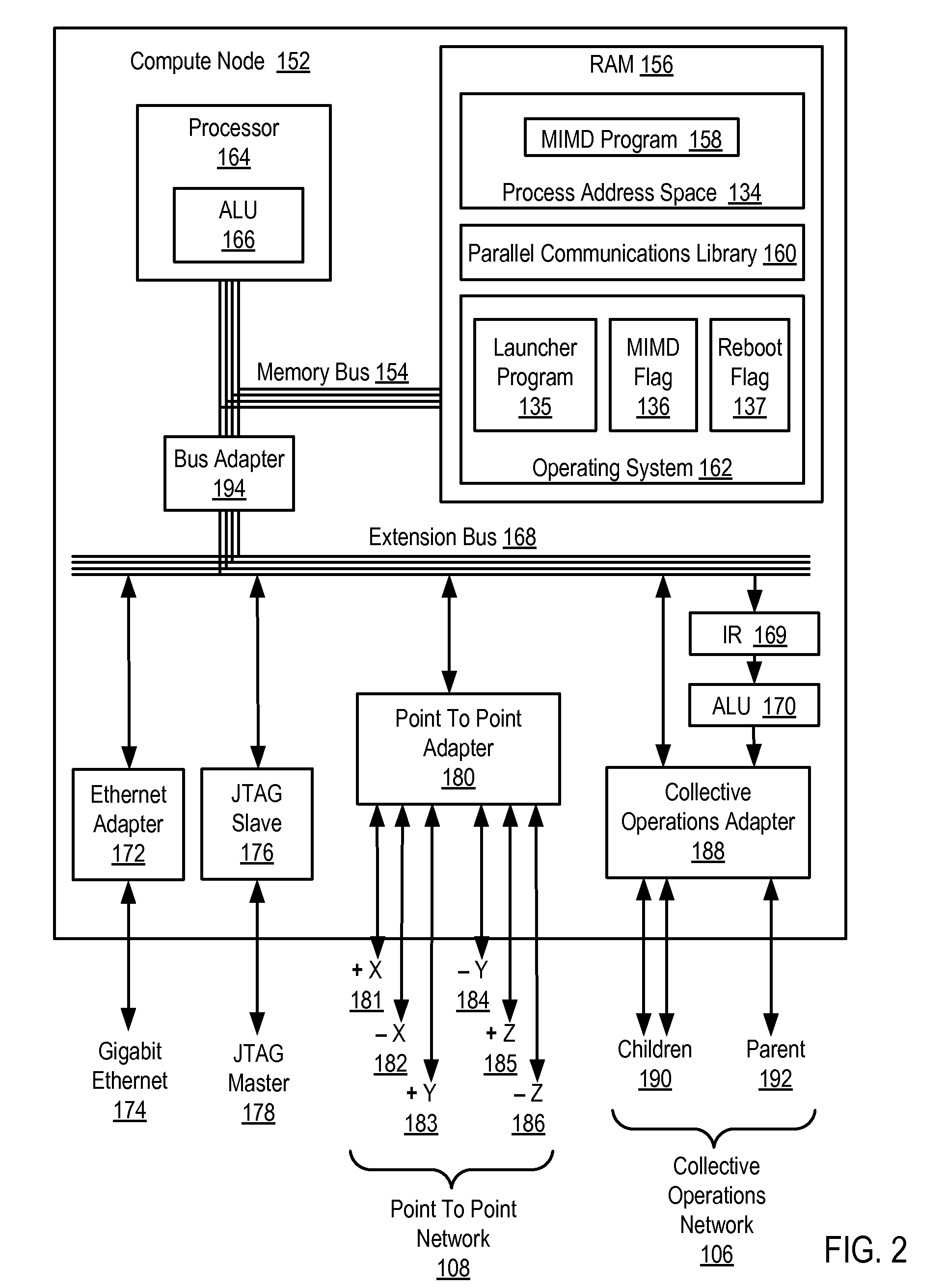

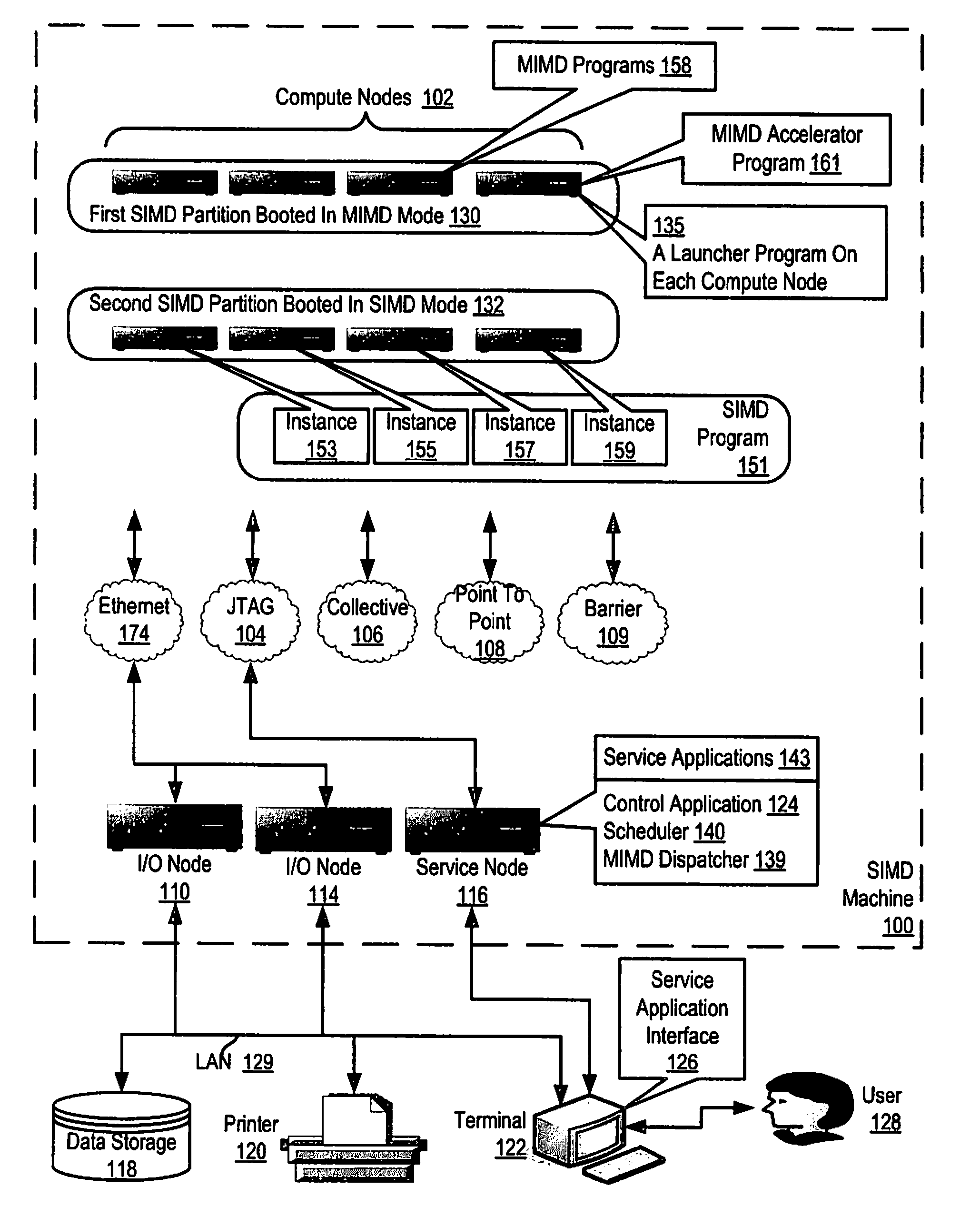

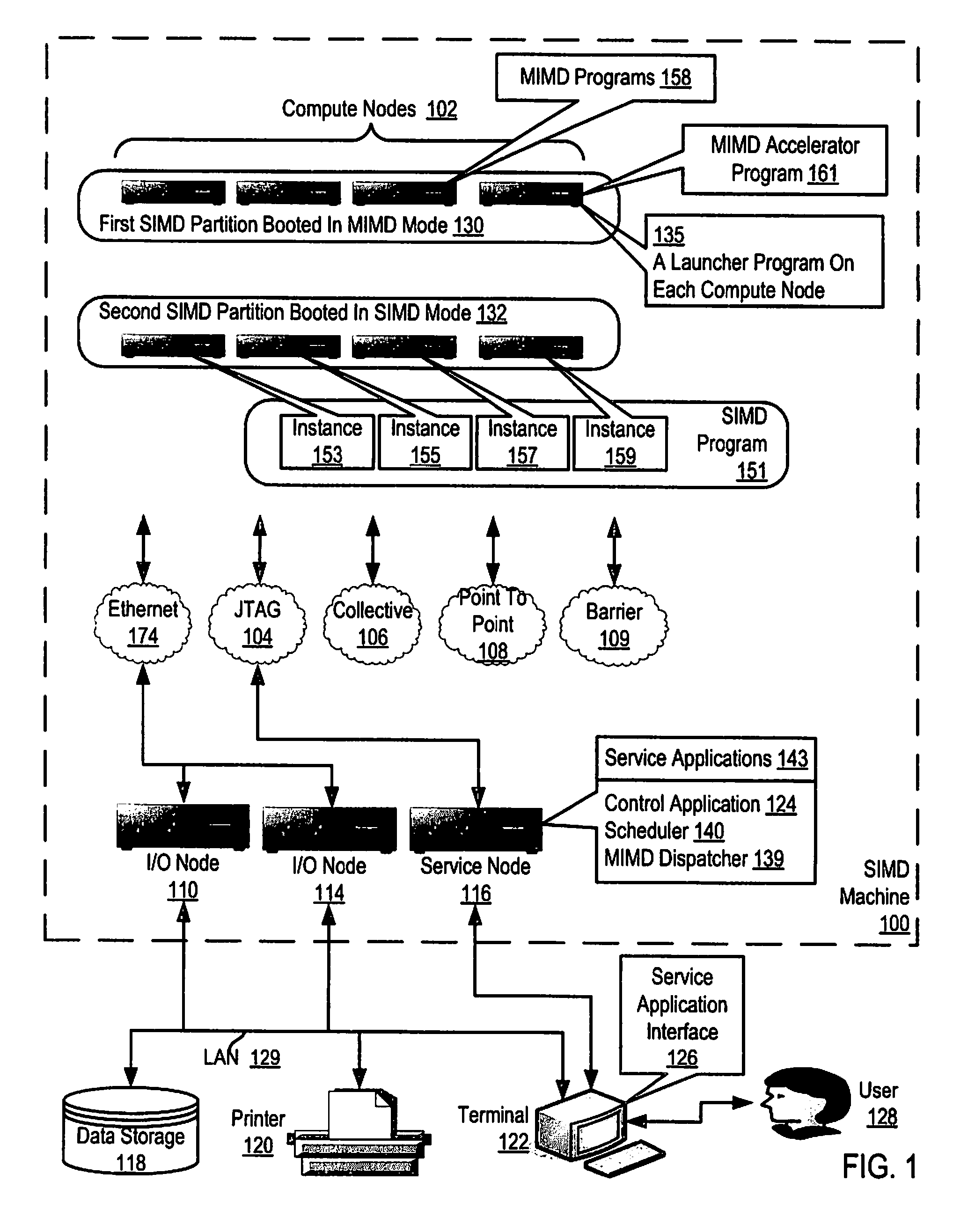

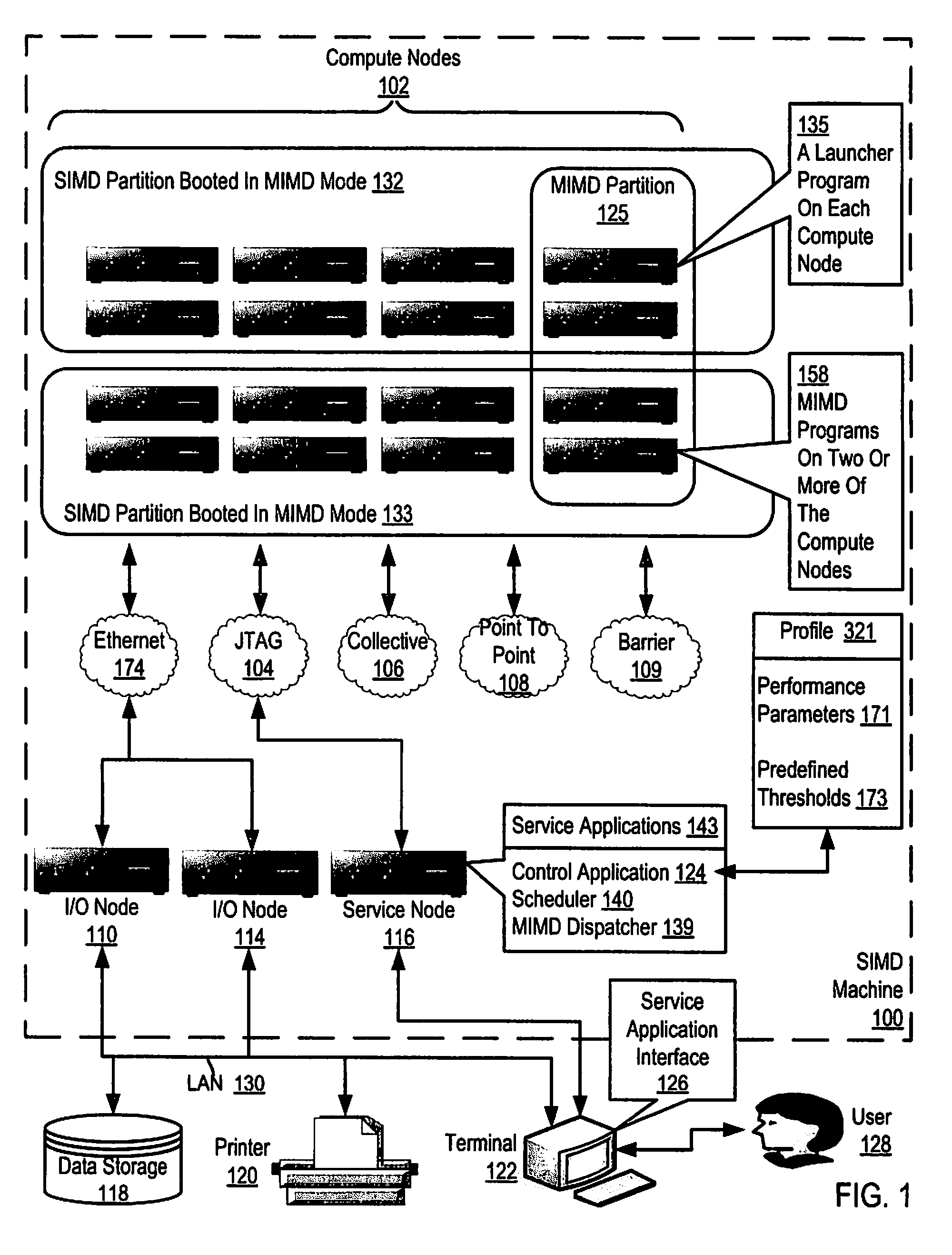

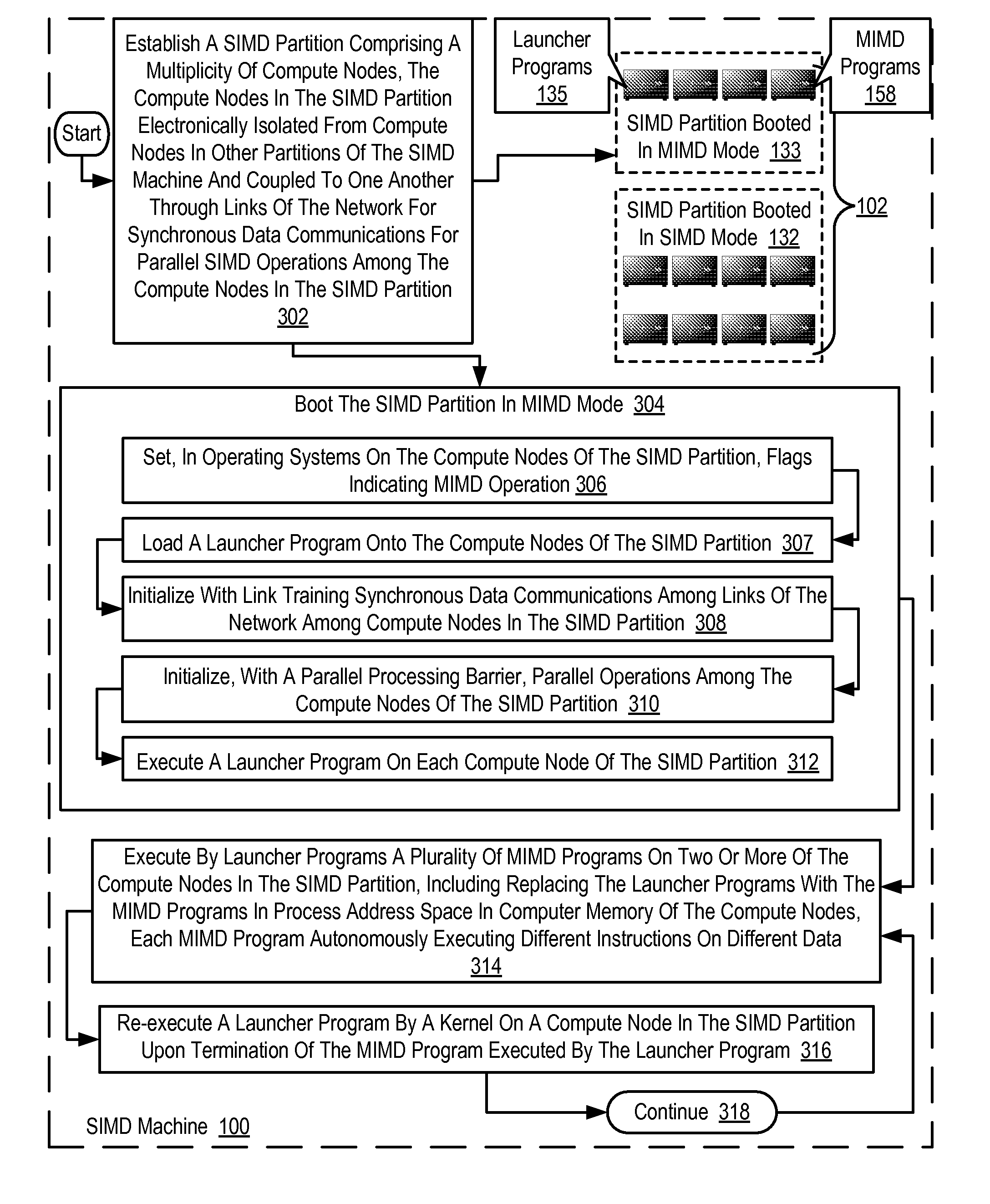

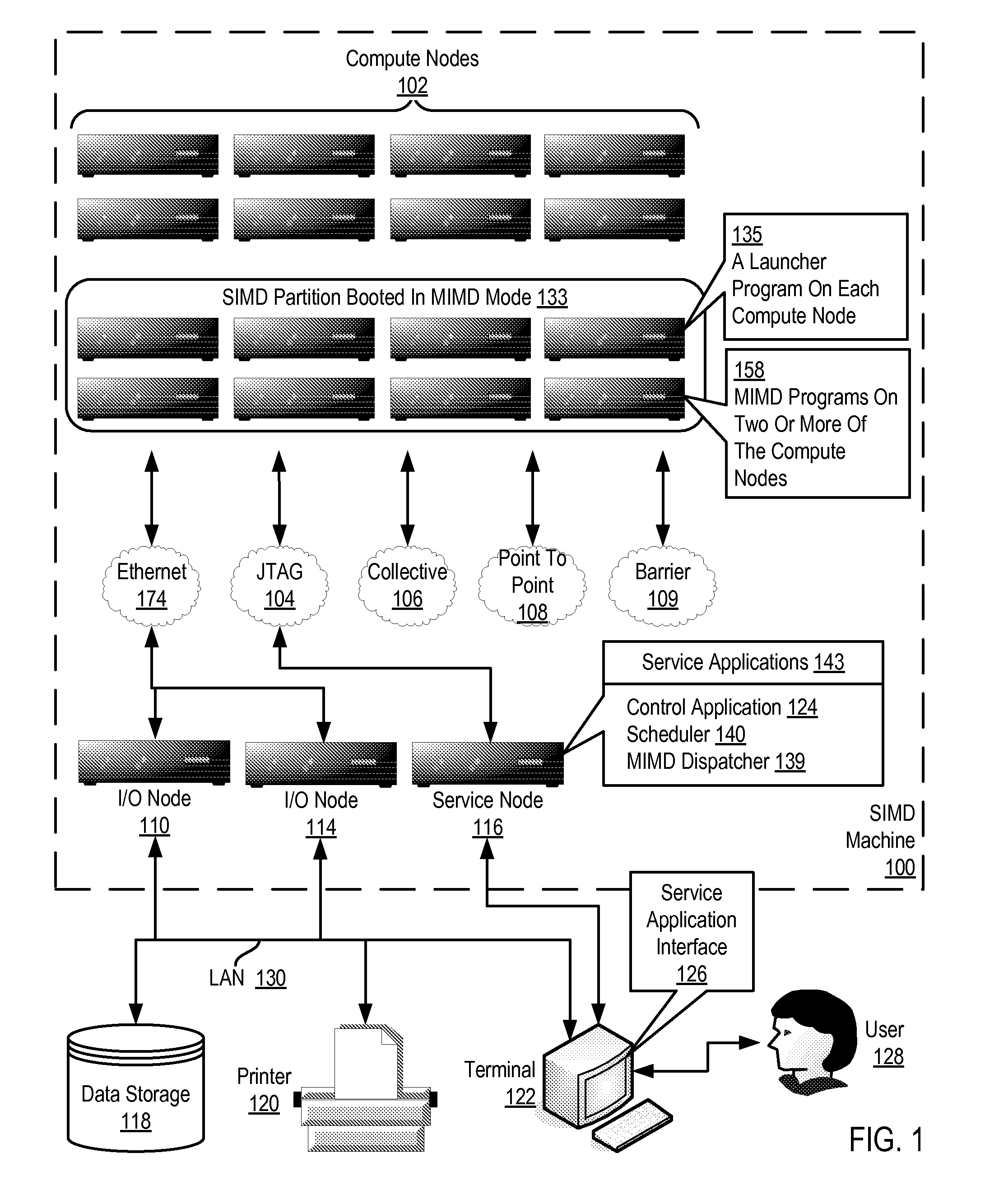

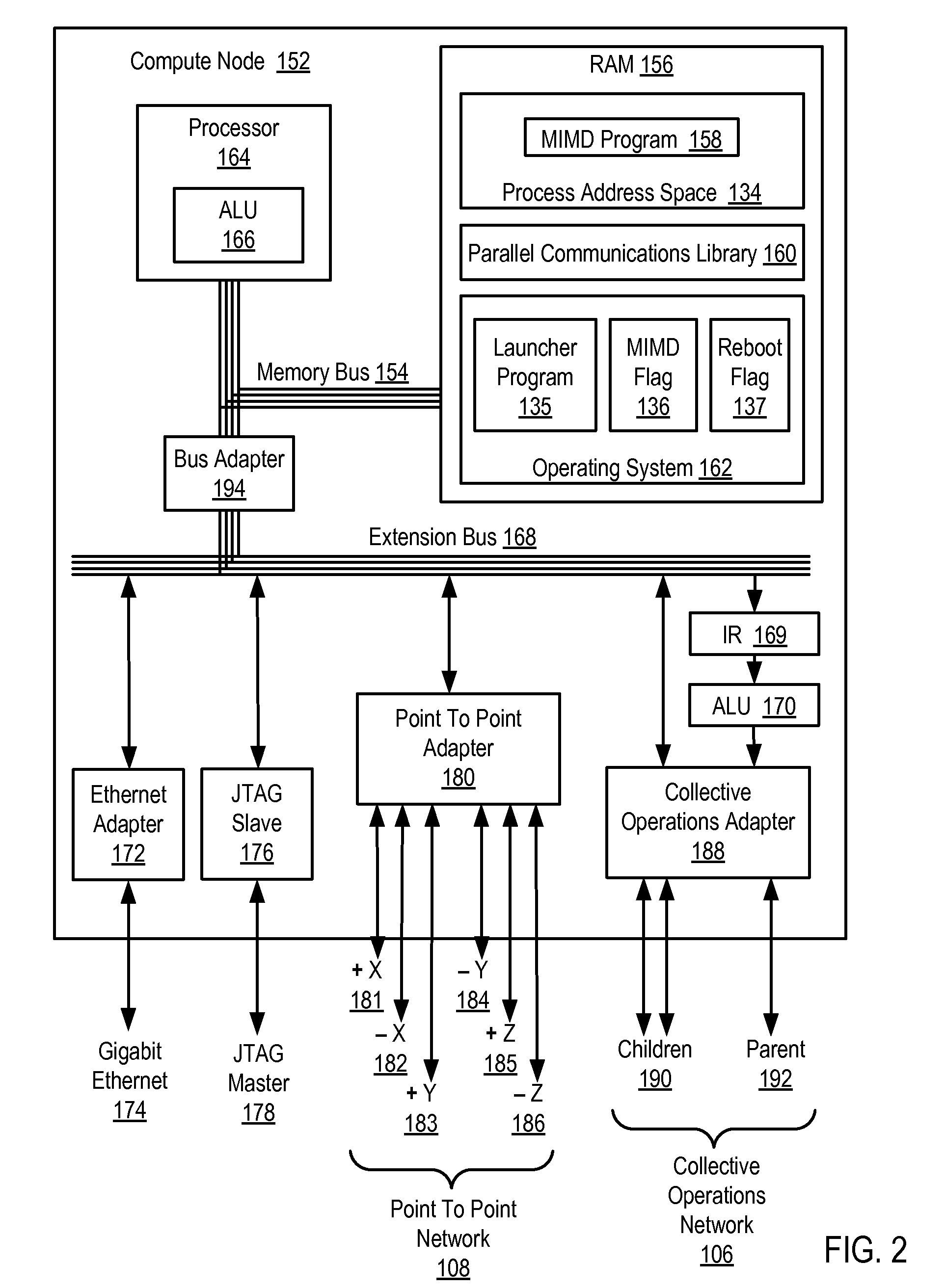

Executing Multiple Instructions Multiple Data ('MIMD') Programs on a Single Instruction Multiple Data ('SIMD') Machine

Executing MIMD programs on a SIMD machine, including establishing SIMD partitions on the SIMD machine; booting SIMD partitions in MIMD mode; executing MIMD programs on the compute nodes of a first SIMD partition booted in MIMD mode; re-executing a launcher program by an operating system on a compute node in the first SIMD partition booted in MIMD mode upon termination of the MIMD program executed by the launcher program; determining by a scheduler that the first SIMD partition booted in MIMD mode is required to establish a new SIMD partition large enough to run a SIMD program that is scheduled for execution; moving by the scheduler data processing operations from the first SIMD partition booted in MIMD mode to the second SIMD partition booted in MIMD mode; and establishing by the scheduler the new SIMD partition.

Owner:IBM CORP

Moving processing operations from one MIMD booted SIMD partition to another to enlarge a SIMD partition

Executing MIMD programs on a SIMD machine, including establishing SIMD partitions on the SIMD machine; booting SIMD partitions in MIMD mode; executing MIMD programs on the compute nodes of a first SIMD partition booted in MIMD mode; re-executing a launcher program by an operating system on a compute node in the first SIMD partition booted in MIMD mode upon termination of the MIMD program executed by the launcher program; determining by a scheduler that the first SIMD partition booted in MIMD mode is required to establish a new SIMD partition large enough to run a SIMD program that is scheduled for execution; moving by the scheduler data processing operations from the first SIMD partition booted in MIMD mode to the second SIMD partition booted in MIMD mode; and establishing by the scheduler the new SIMD partition.

Owner:IBM CORP

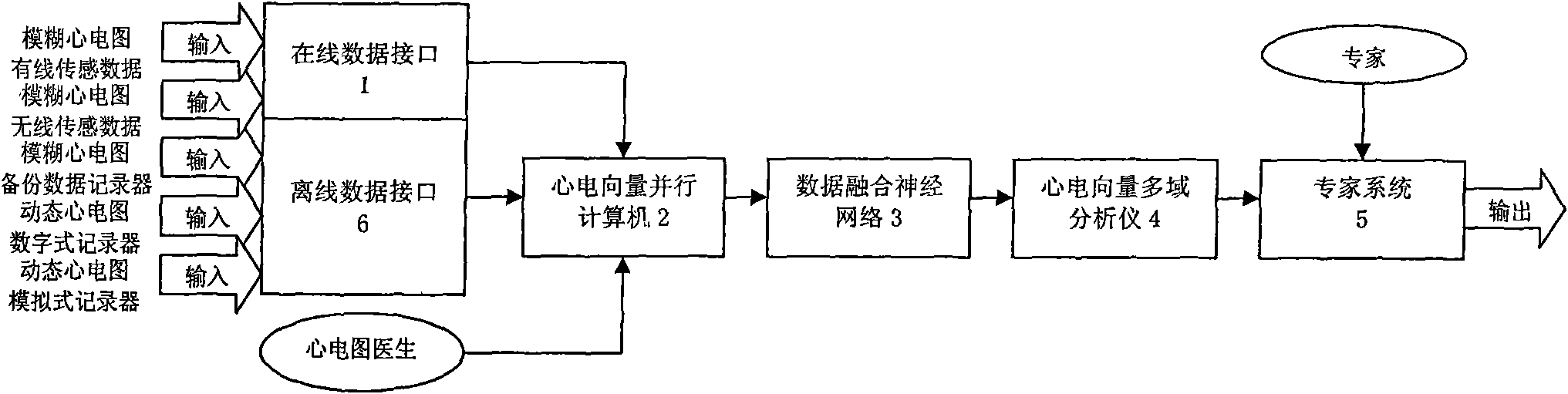

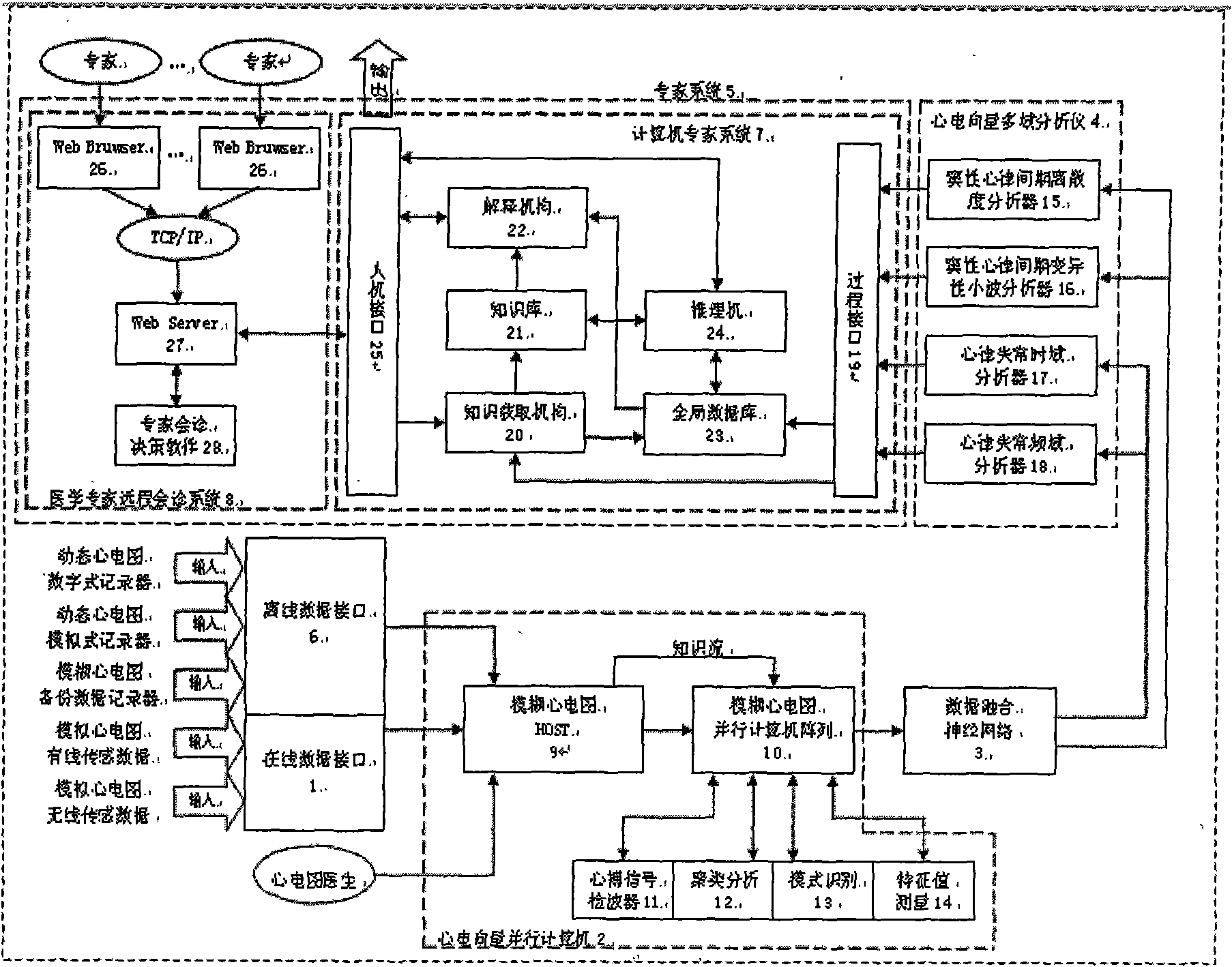

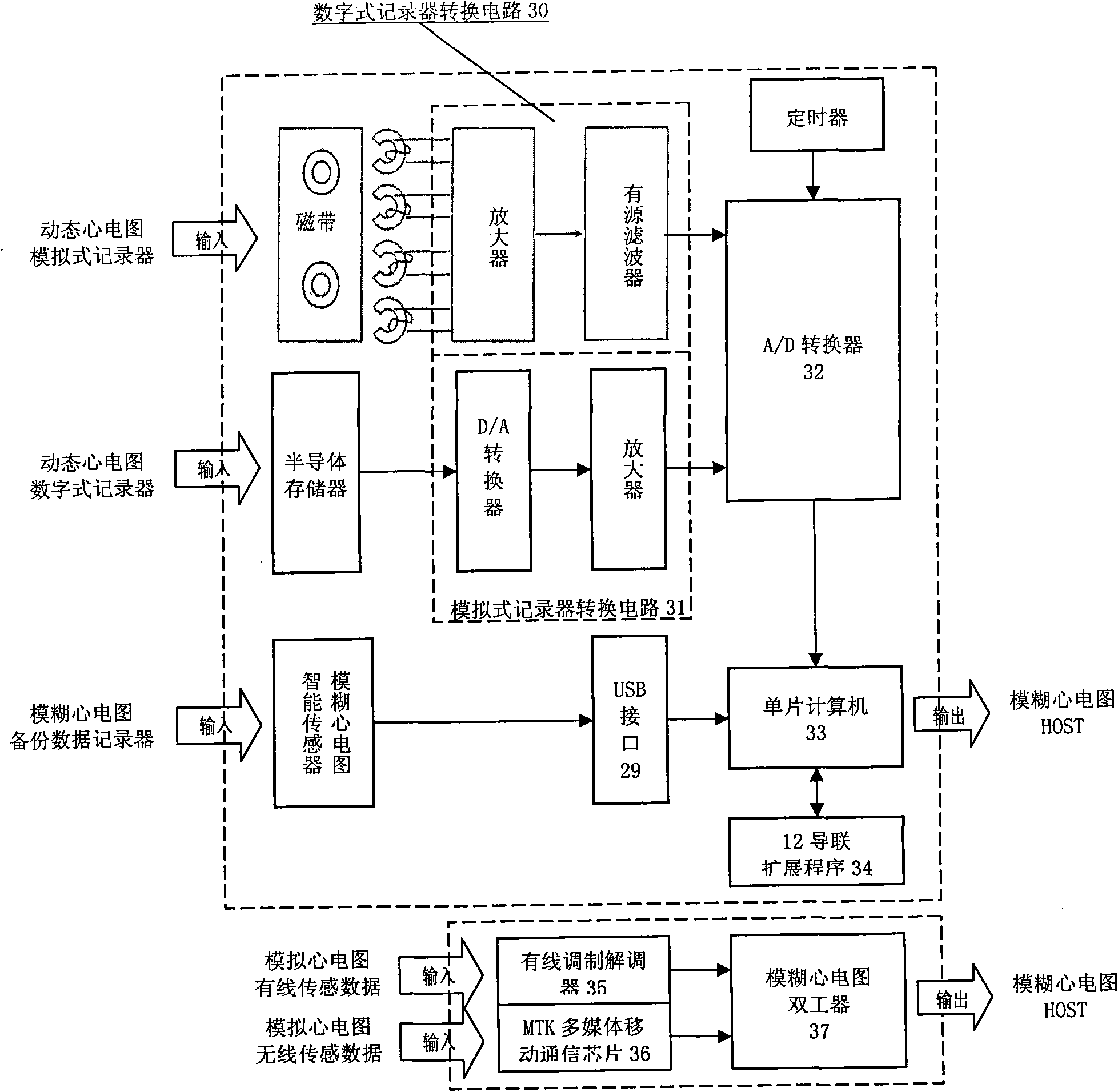

Intelligent blurry electrocardiogram on-line analyzer system

The invention discloses an intelligent blurry electrocardiogram on-line analyzer system, which consists of an on-line data interface, an electrocardial vector parallel computer, a data fusion nerve network, an electrocardial interval vector multi-domain analyzer, an expert system, an application software packet and an off-line data interface. By adopting the MIMD parallel computer, the multiplex nerve network analysis, multi-sensor time sequence data fusion and electrocardial vector multi-domain analysis for a 12 lead electrocardial vector, automatic analysis conclusion of a main blurry electrocardiogram and blurry electrocardiogram attached figure information comprising the information of blood pressure, pulse, blood oxygen, respiration, activity range and activity content and the like are integrated to form a diagnostic report of time domain analysis and frequency domain analysis of vital sign signals comprising a 12 lead electrocardiogram, time domain analysis of various electrocardial interval dispersions and wavelet analysis of various electrocardial interval variability.

Owner:陈跃军

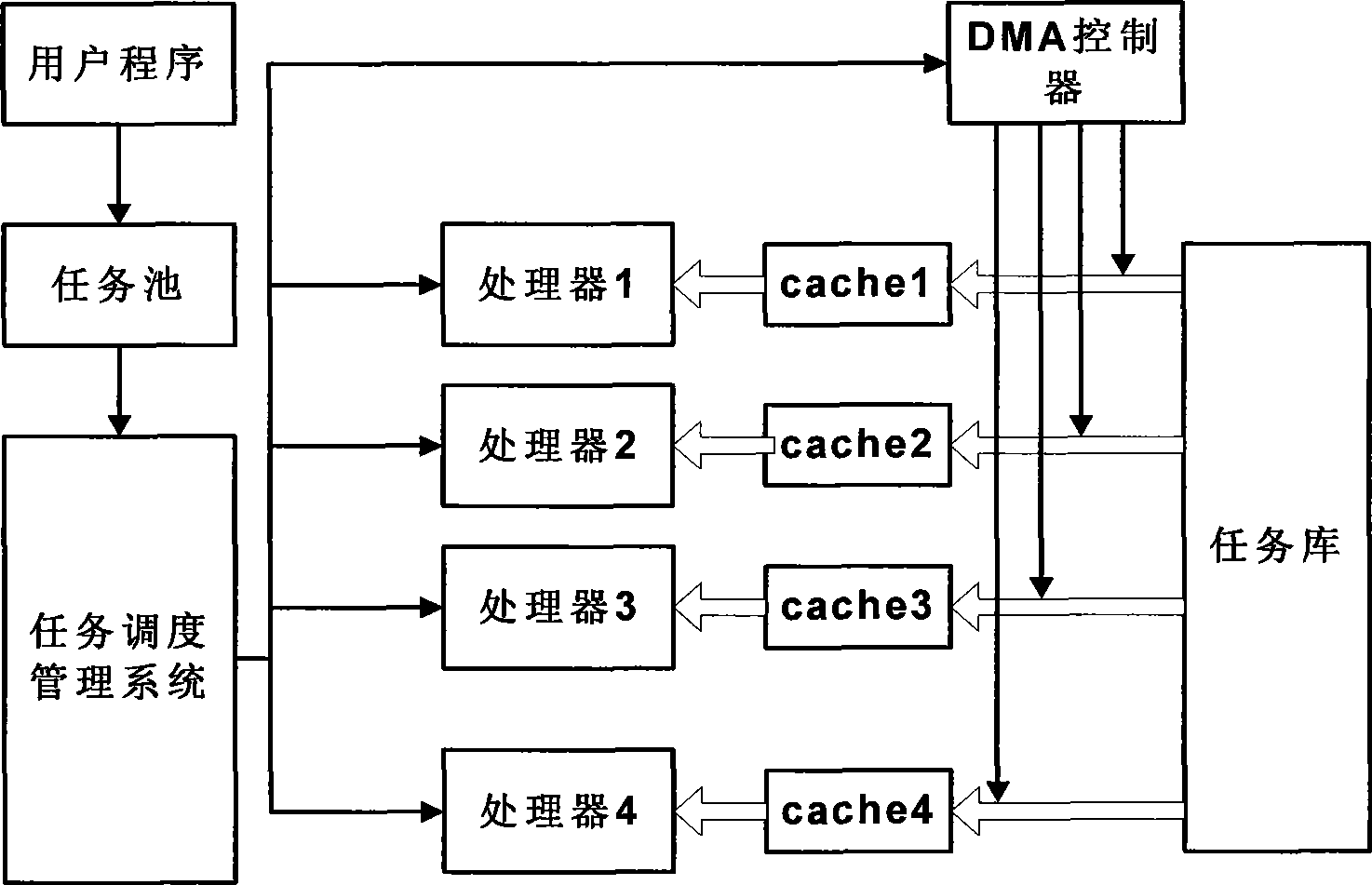

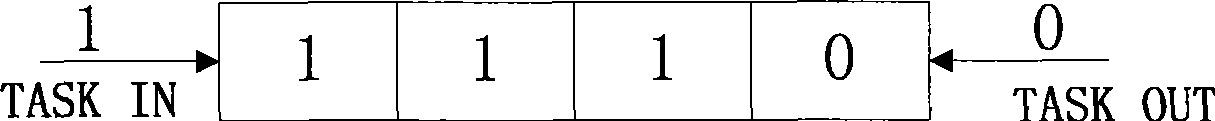

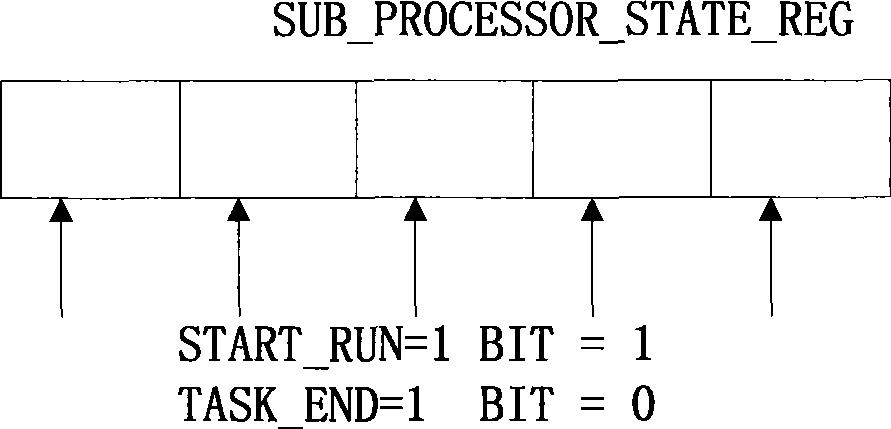

Single-chip multi-processor task scheduling and managing method

InactiveCN101387952AImplement parallel processingImprove processing speedResource allocationConcurrent instruction executionMIMDData stream

The invention relates to a dispatching method for the task management of a single-chip multiprocessor, which is based on a structural system of the multi-instruction multi-data-stream (MIMD) of a single-chip multiprocessor. The dispatching method performs task dispatching, task distribution, task management and sub-processor management for parallel tasks running in a system, and realizes the parallel treatment of the single-chip multiprocessor. The dispatching method for the task management of the single-chip multiprocessor can be applied to a single-chip multiprocessor system composed of various sub-processors which have independent local ROM, such as an MCU of an 8051 structural system. Further, the sub-processors can be homogeneous, and also can be heterogeneous.

Owner:SHANGHAI UNIV

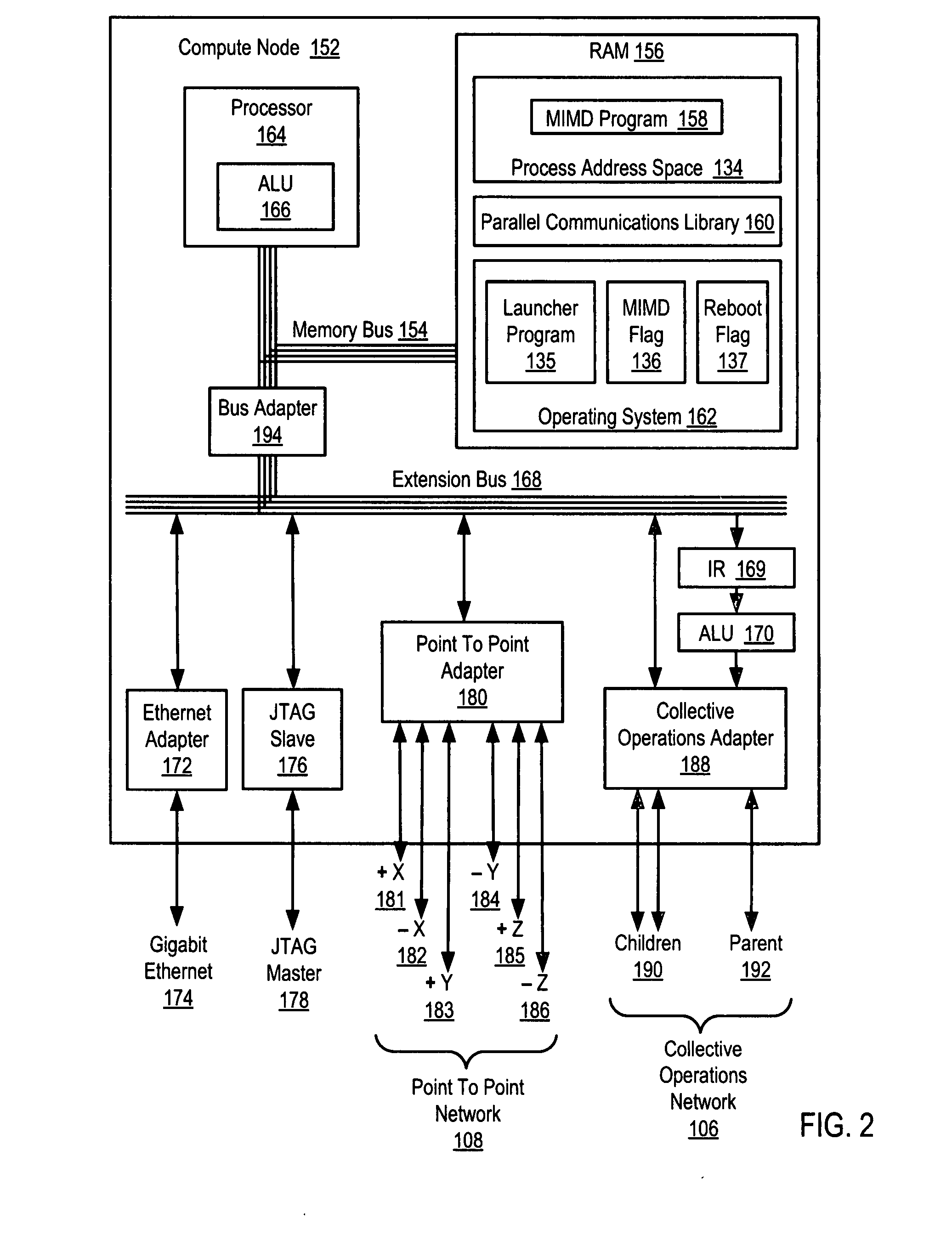

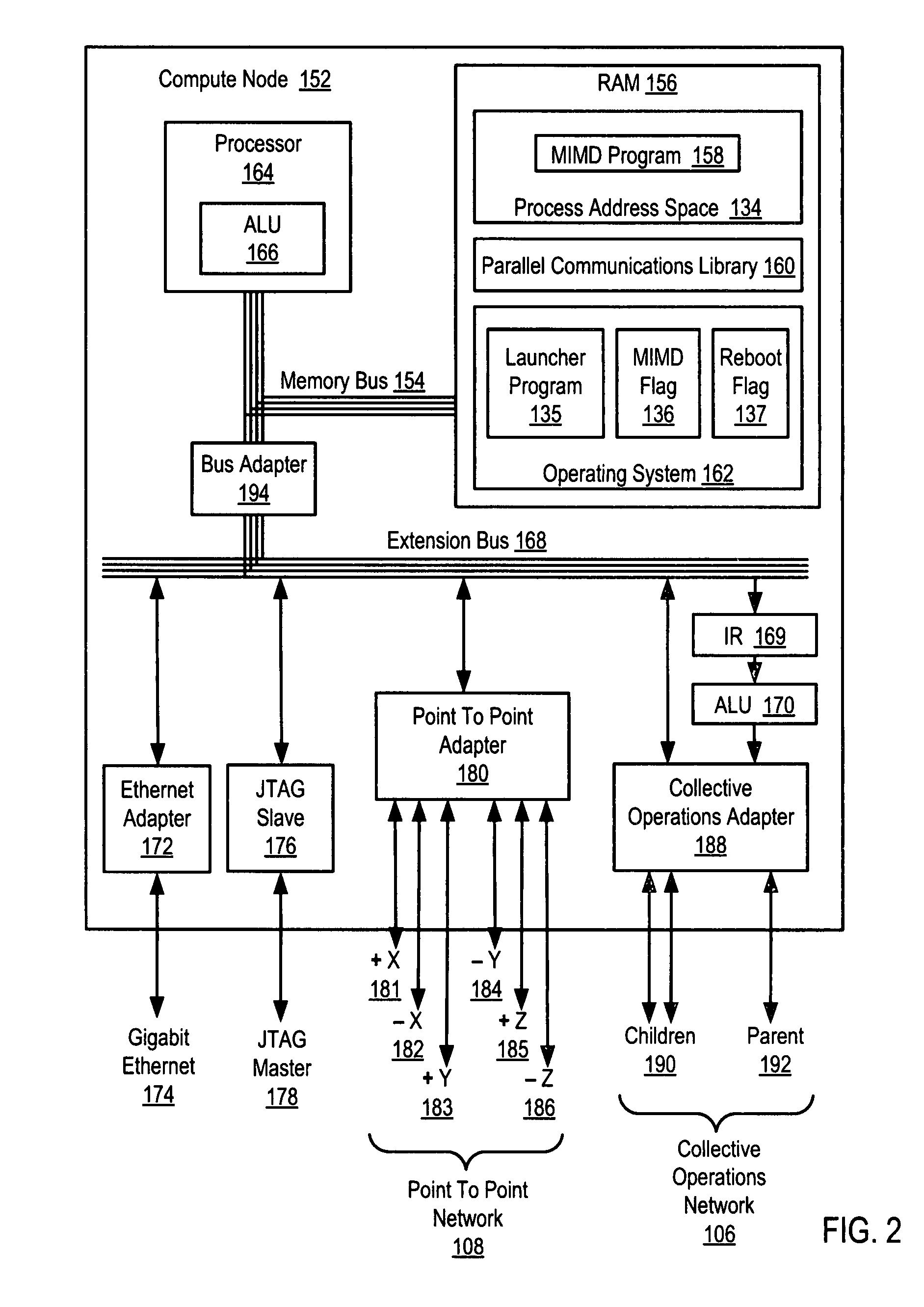

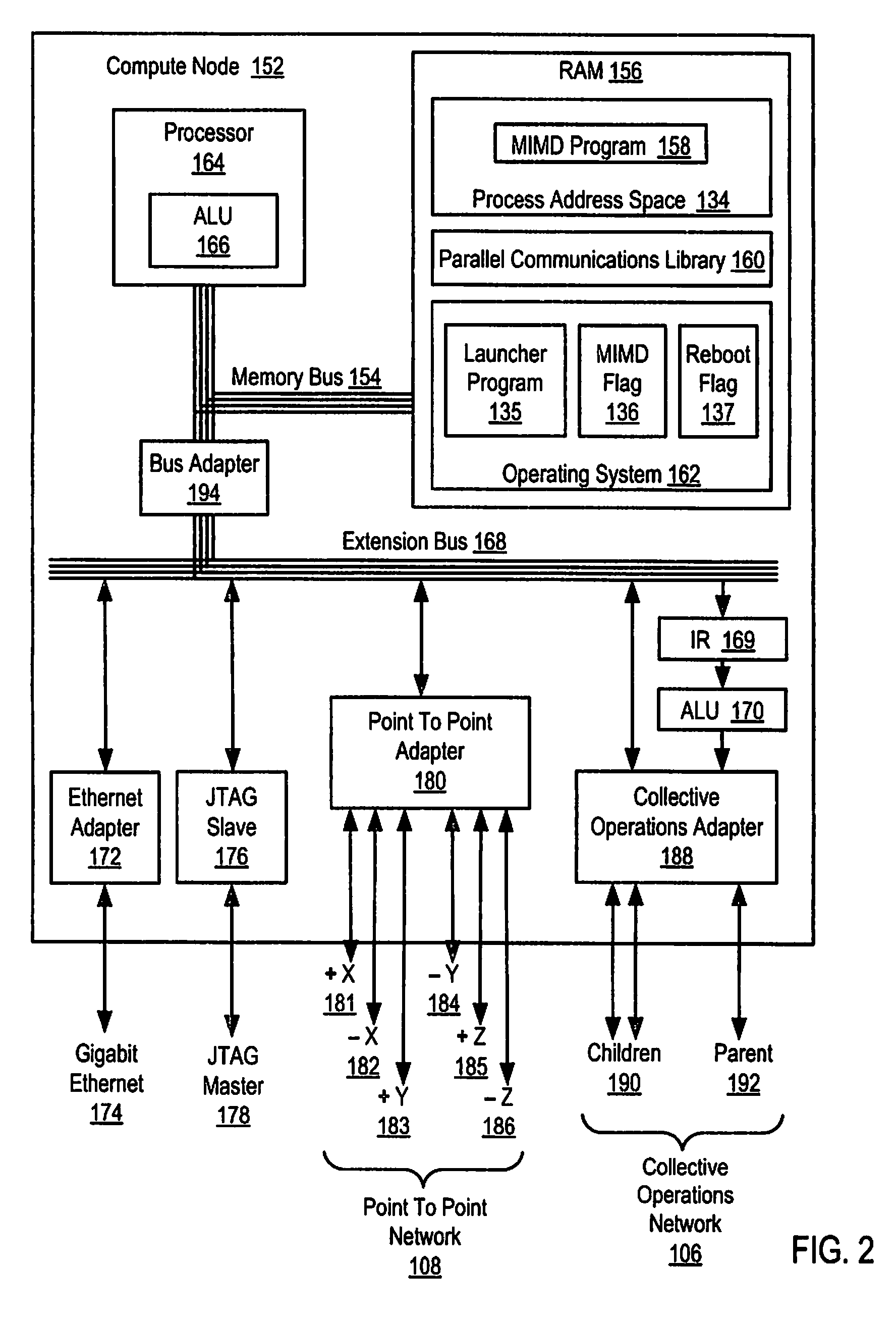

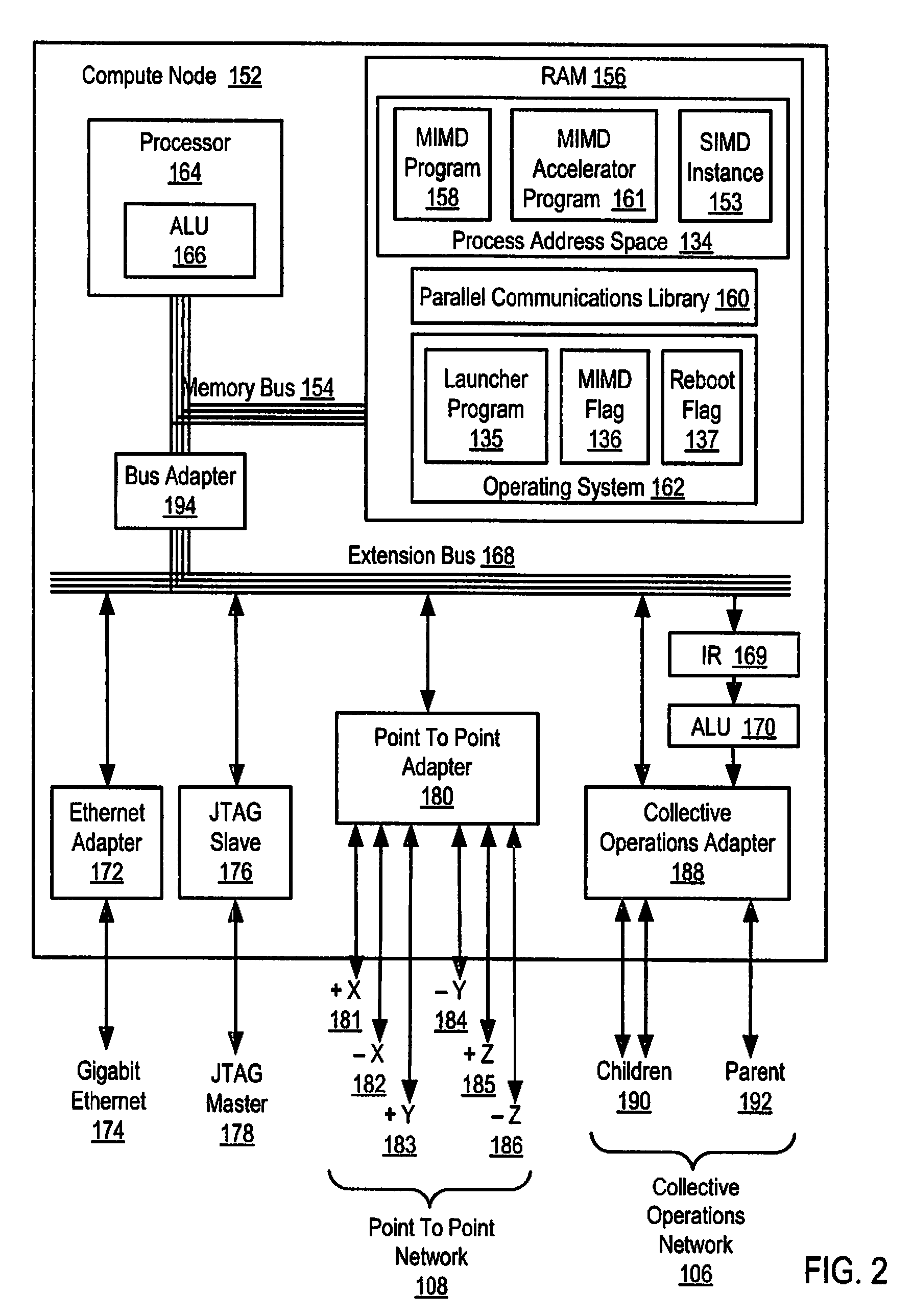

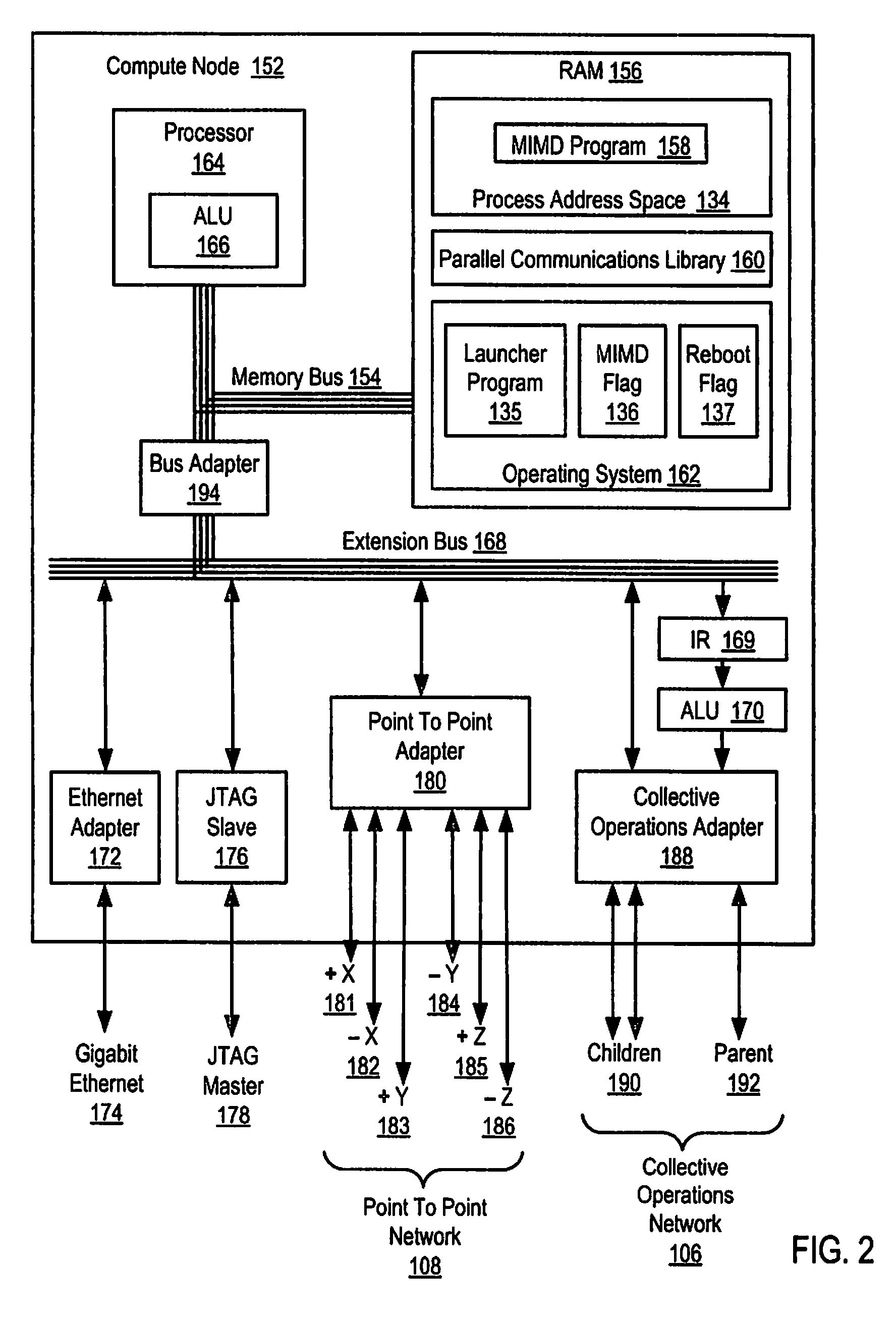

Executing Multiple Instructions Multiple Data ('MIMD') Programs on a Single Instruction Multiple Data ('SIMD') Machine

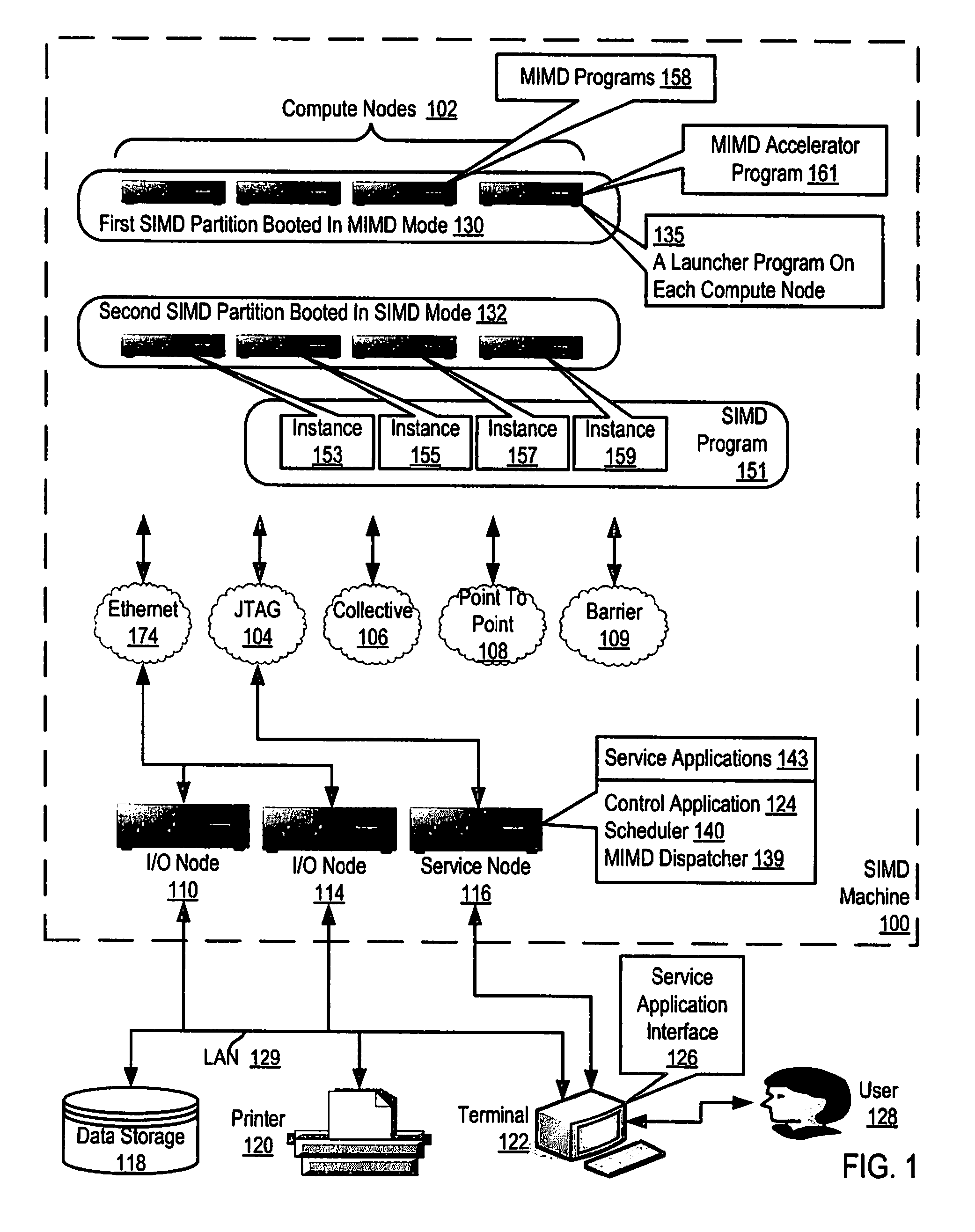

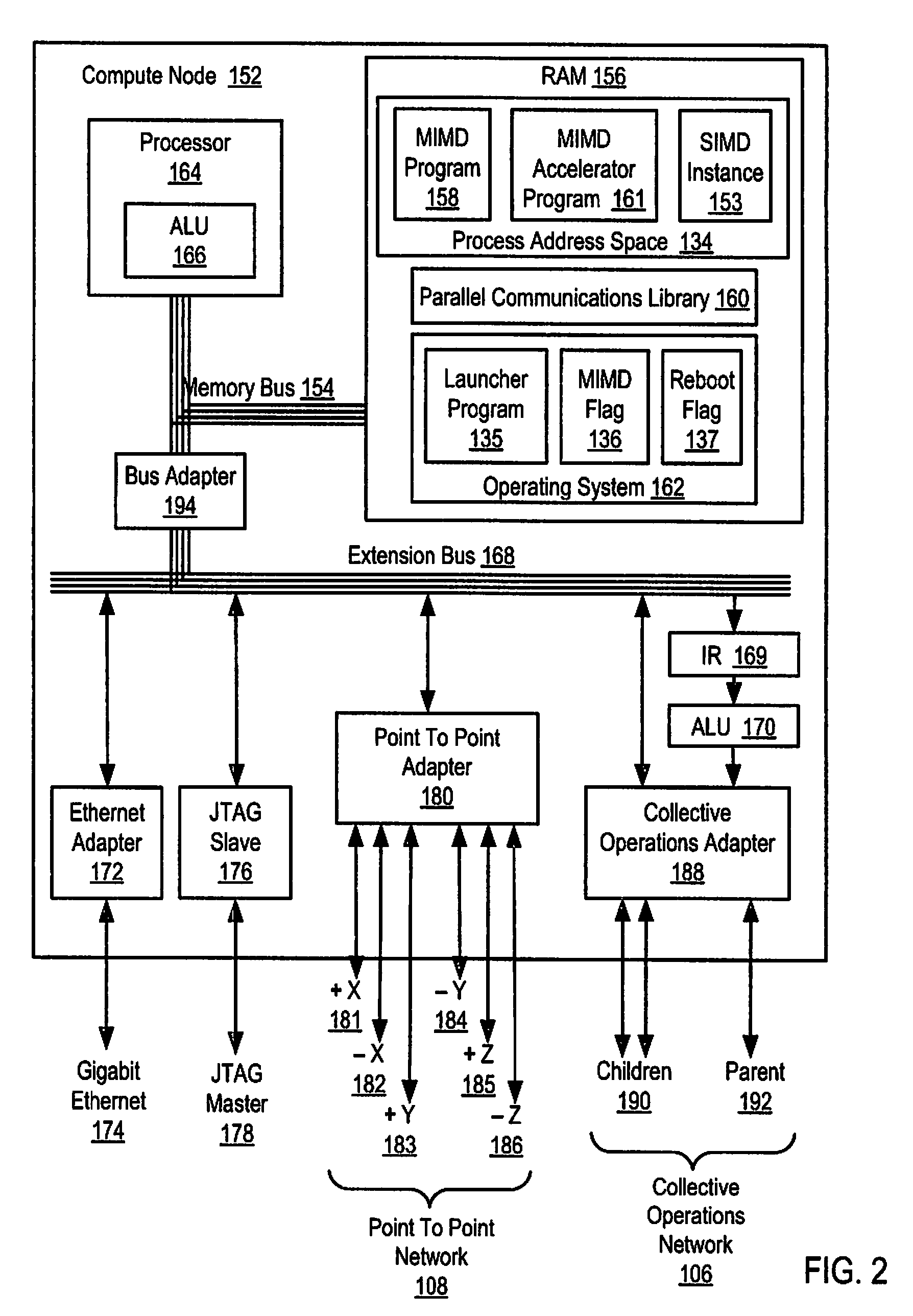

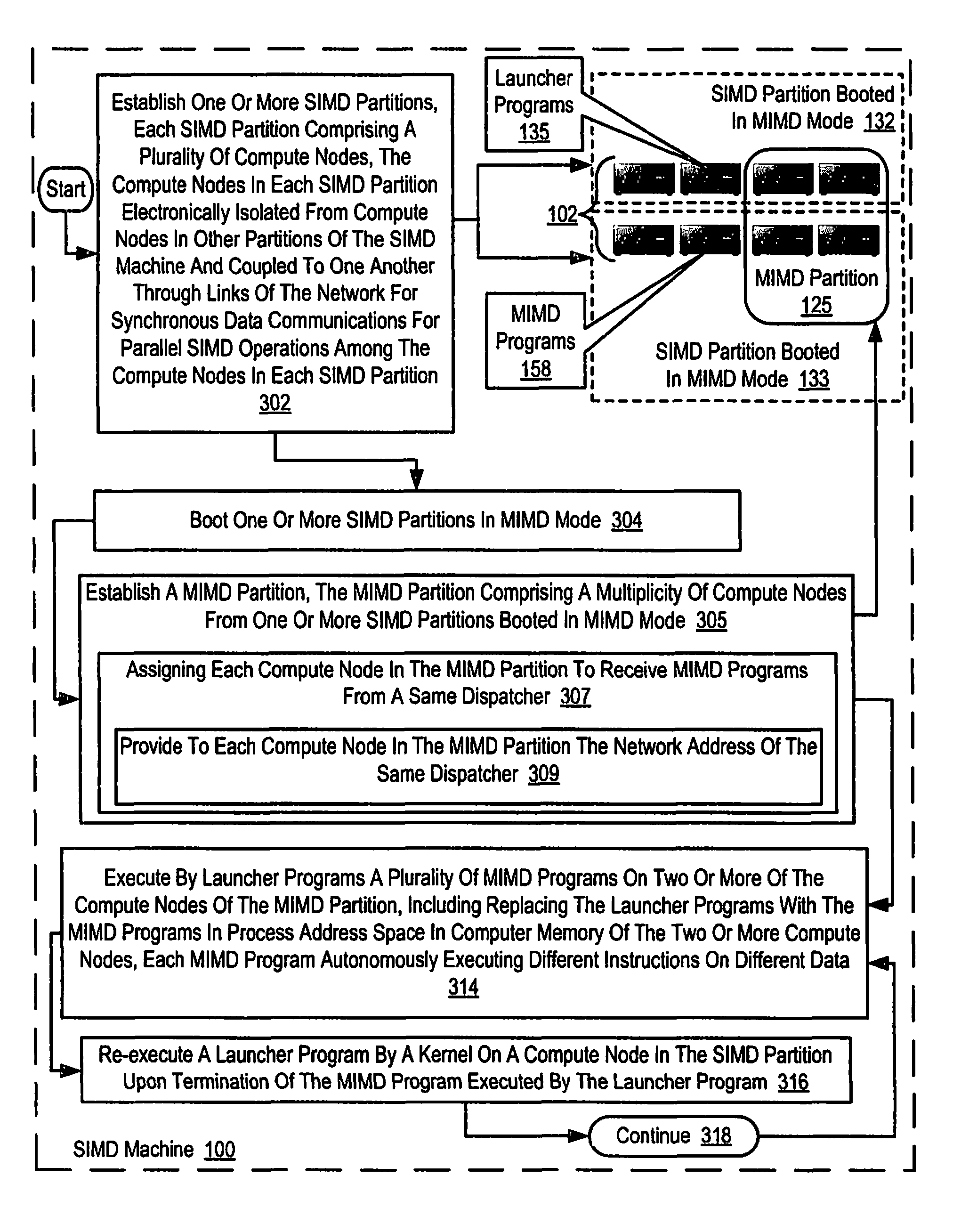

InactiveUS20080288746A1General purpose stored program computerMachine execution arrangementsMIMDTelecommunications link

Executing MIMD programs on a SIMD machine, the SIMD machine including a plurality of compute nodes, each compute node capable of executing only a single thread of execution, the compute nodes initially configured exclusively for SIMD operations, the SIMD machine further comprising a data communications network, the network comprising synchronous data communications links among the compute nodes, including establishing one or more SIMD partitions, booting one or more SIMD partitions in MIMD mode; establishing a MIMD partition; executing by launcher programs a plurality of MIMD programs on two or more of the compute nodes of the MIMD partition; and re-executing a launcher program by an operating system on a compute node in the MIMD partition upon termination of the MIMD program executed by the launcher program.

Owner:IBM CORP

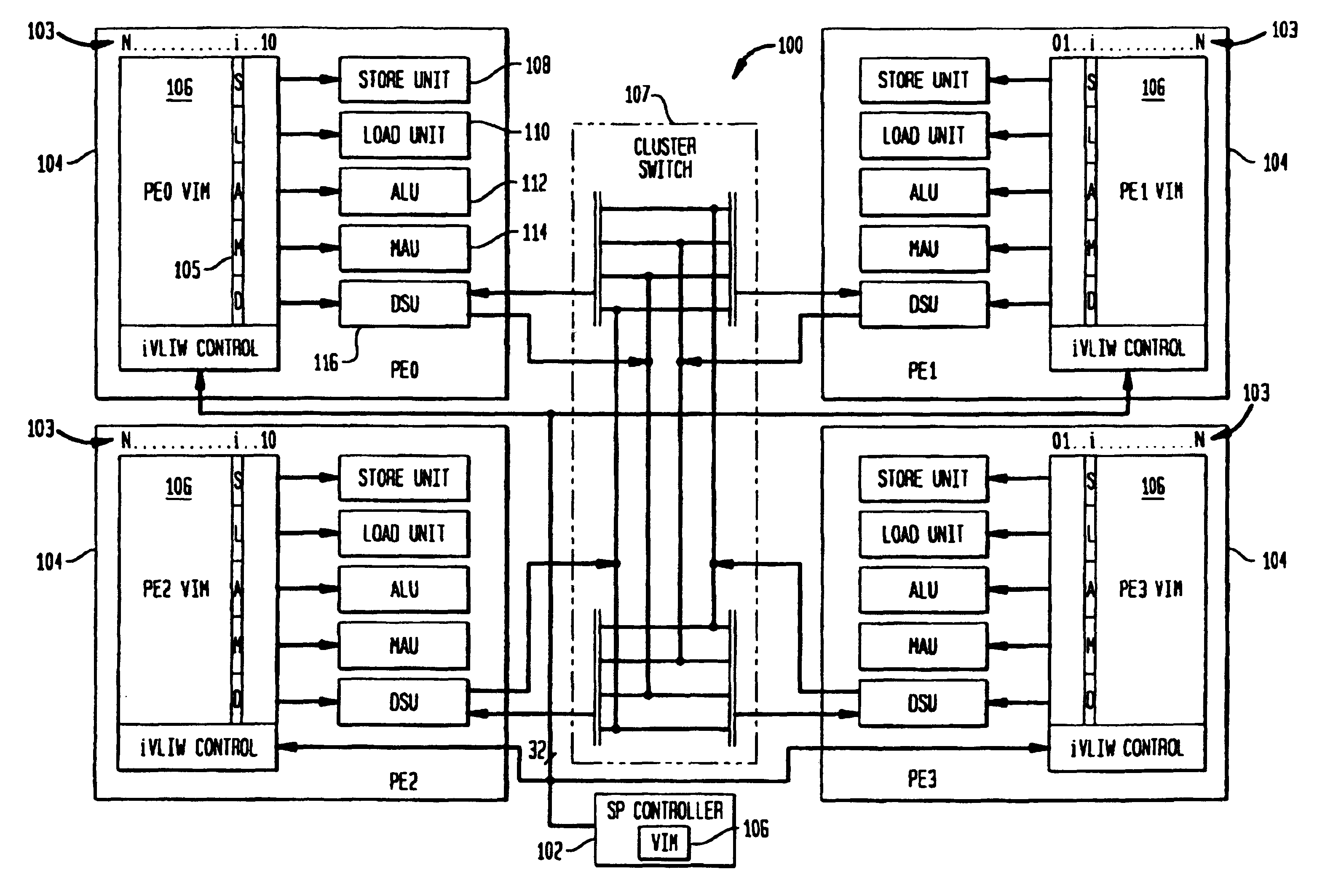

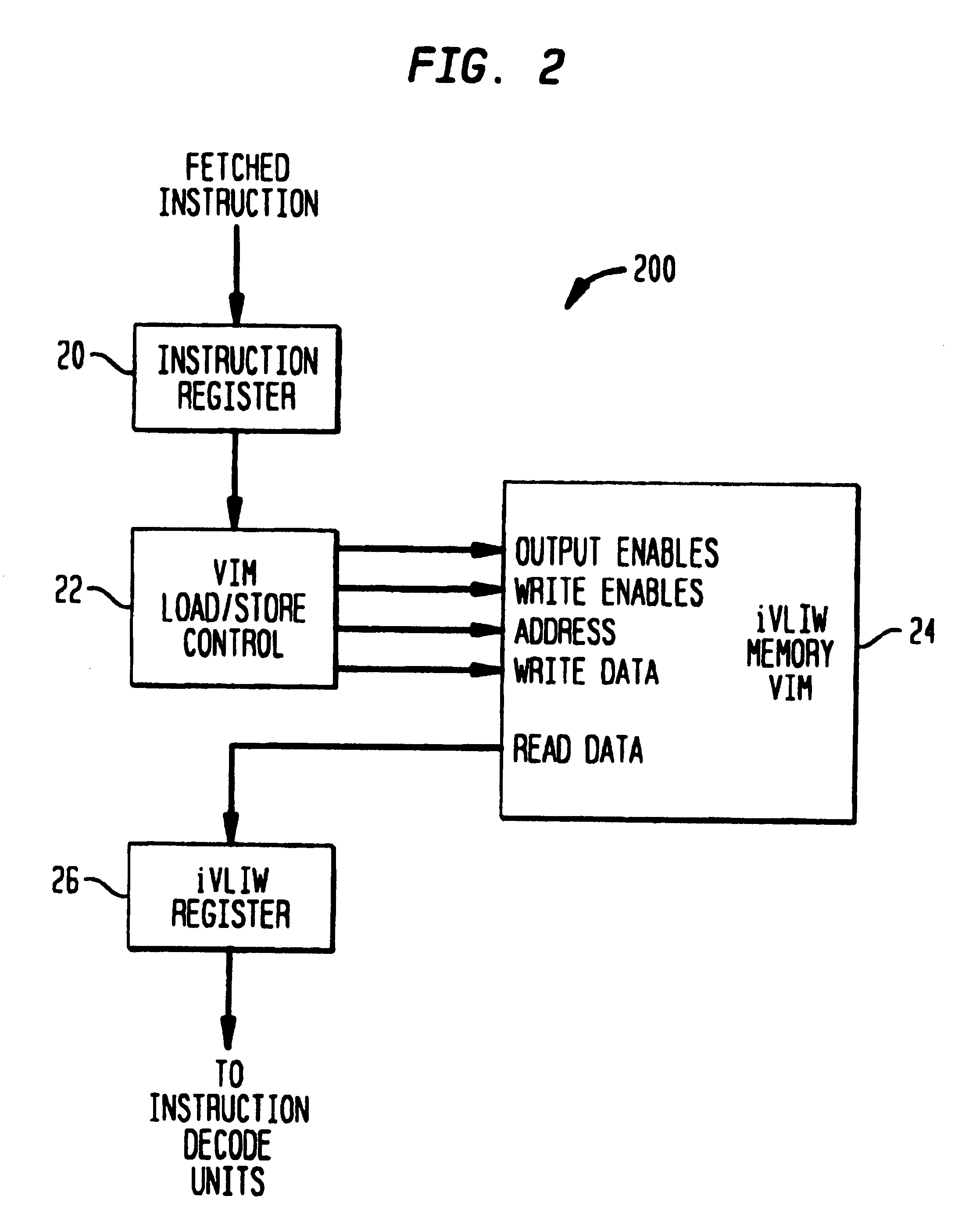

Methods and apparatus for efficient synchronous MIMD operations with IVLIW PE-TO-PE communication

InactiveUSRE41703E1Improve efficiencyReduce hardware costsInstruction analysisMultiple digital computer combinationsInstruction memoryMIMD

A SIMD machine employing a plurality of parallel processor (PEs) in which communications hazards are eliminated in an efficient manner. An indirect Very Long Instruction Word instruction memory (VIM) is employed along with execute and delimiter instructions. A masking mechanism may be employed to control which PEs have their VIMs loaded. Further, a receive model of operation is preferably employed. In one aspect, each PE operates to control a switch that selects from which PE it receives. The present invention addresses a better machine organization for execution of parallel algorithms that reduces hardware cost and complexity while maintaining the best characteristics of both SIMD and MIMD machines and minimizing communication latency. This invention brings a level of MIMD computational autonomy to SIMD indirect Very Long Instruction Word (iVLIW) processing elements while maintaining the single thread of control used in the SIMD machine organization. Consequently, the term Synchronous-MIMD (SMIMD) is used to describe the present approach.

Owner:ALTERA CORP

Executing Multiple Instructions Multiple Data ('MIMD') Programs on a Single Instruction Multiple Data ('SIMD') Machine

InactiveUS20090024830A1General purpose stored program computerElectric digital data processingTelecommunications linkOperational system

Executing Multiple Instructions Multiple Data (‘MIMD’) programs on a Single Instruction Multiple Data (‘SIMD’) machine, the SIMD machine including a plurality of compute nodes, each compute node capable of executing only a single thread of execution, the compute nodes initially configured exclusively for SIMD operations, the SIMD machine further comprising a data communications network, the network comprising synchronous data communications links among the compute nodes, including establishing a SIMD partition comprising a plurality of the compute nodes; booting the SIMD partition in MIMD mode; executing by launcher programs a plurality of MIMD programs on compute nodes in the SIMD partition; and re-executing a launcher program by an operating system on a compute node in the SIMD partition upon termination of the MIMD program executed by the launcher program.

Owner:IBM CORP

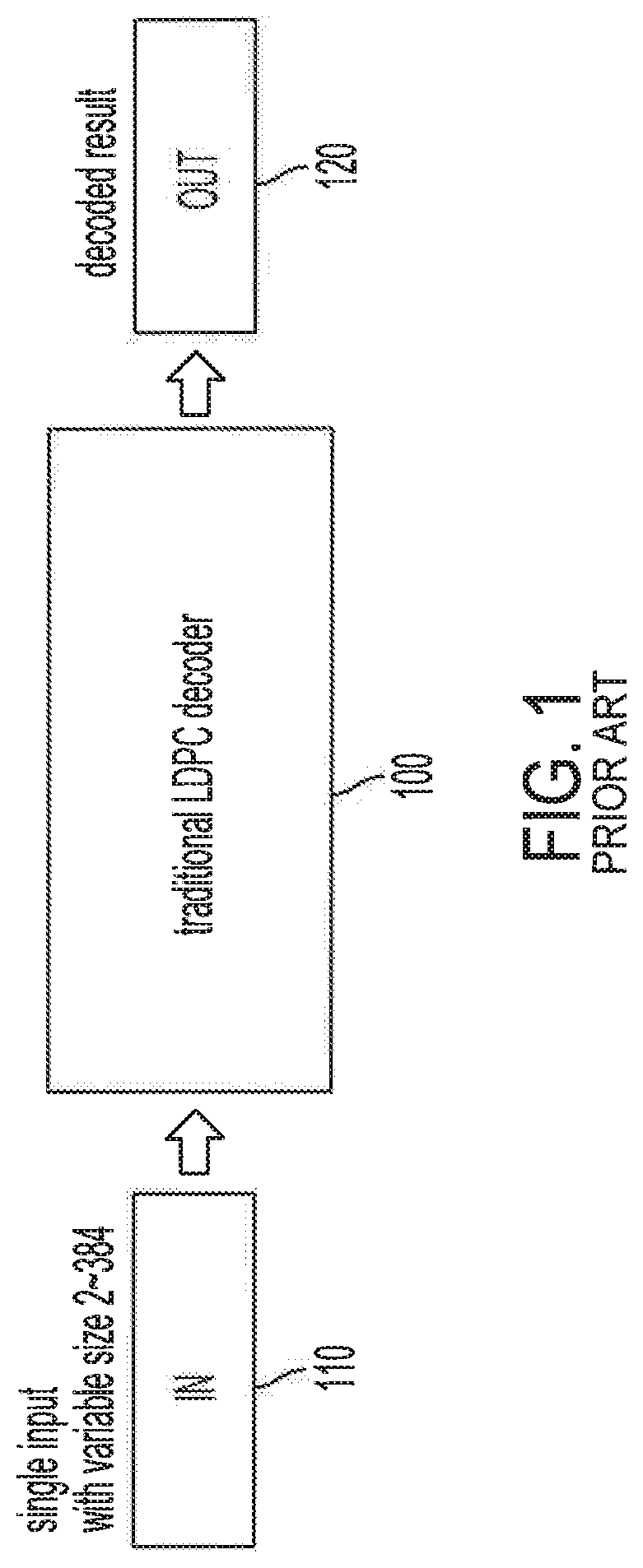

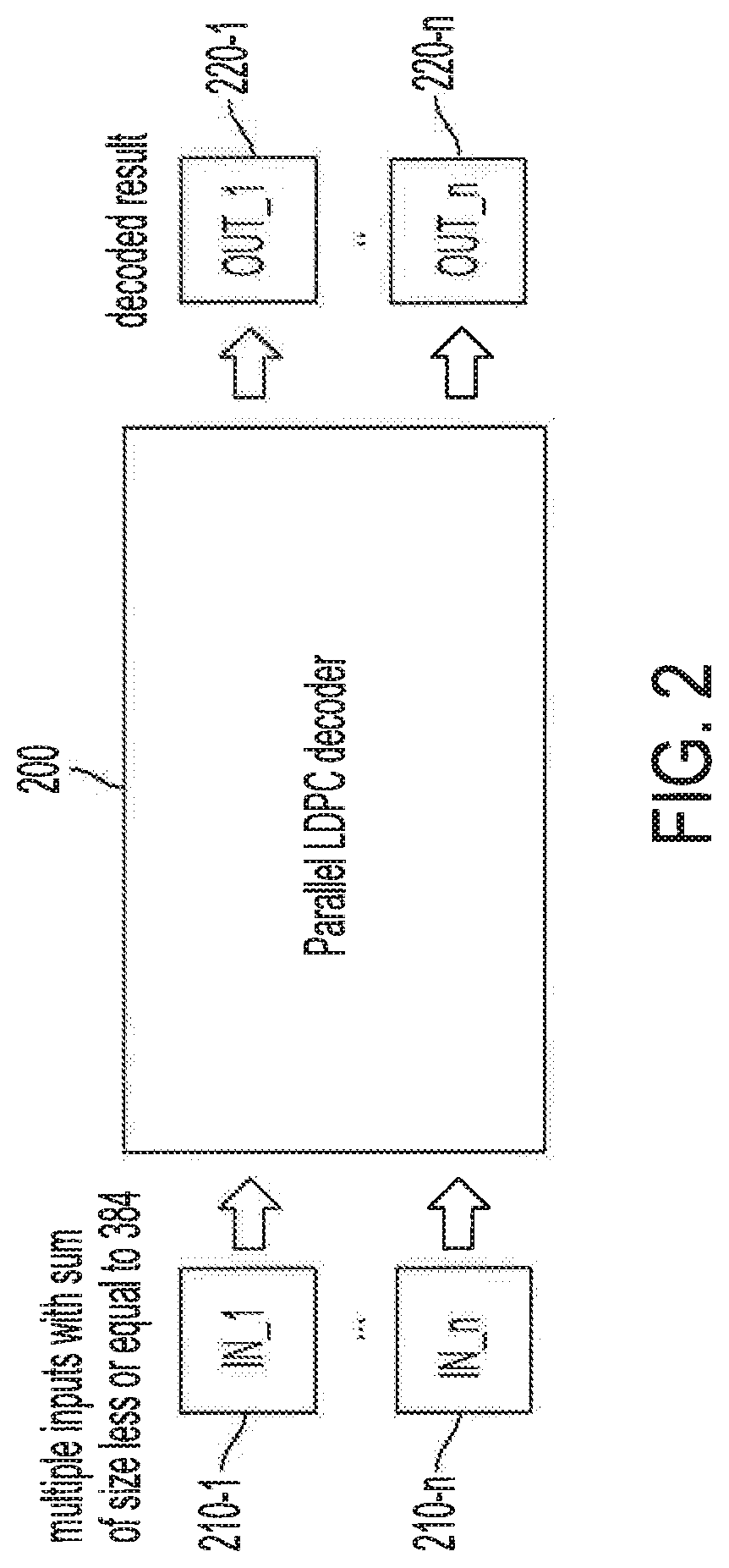

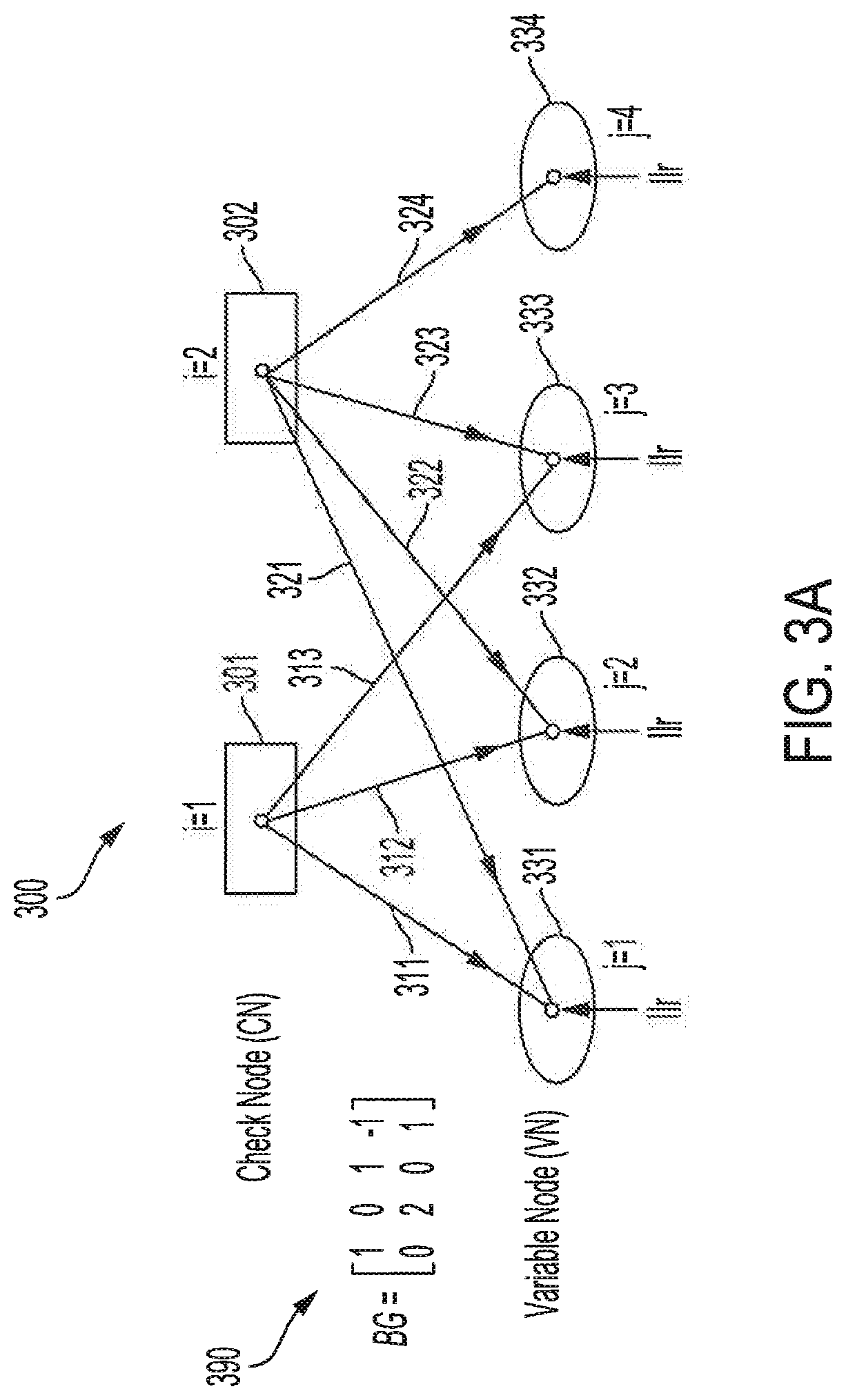

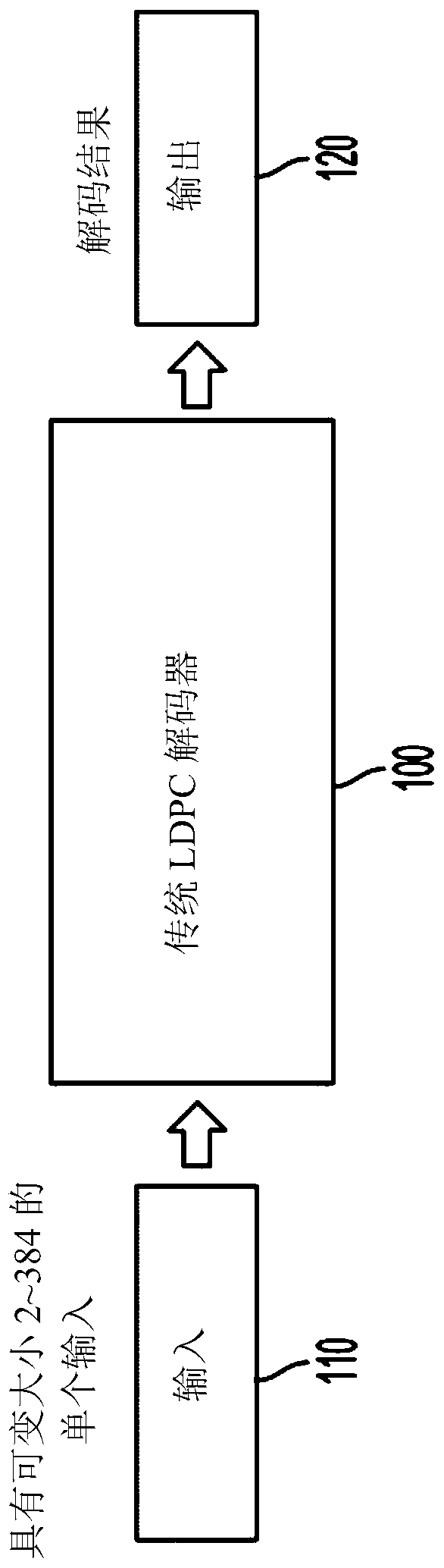

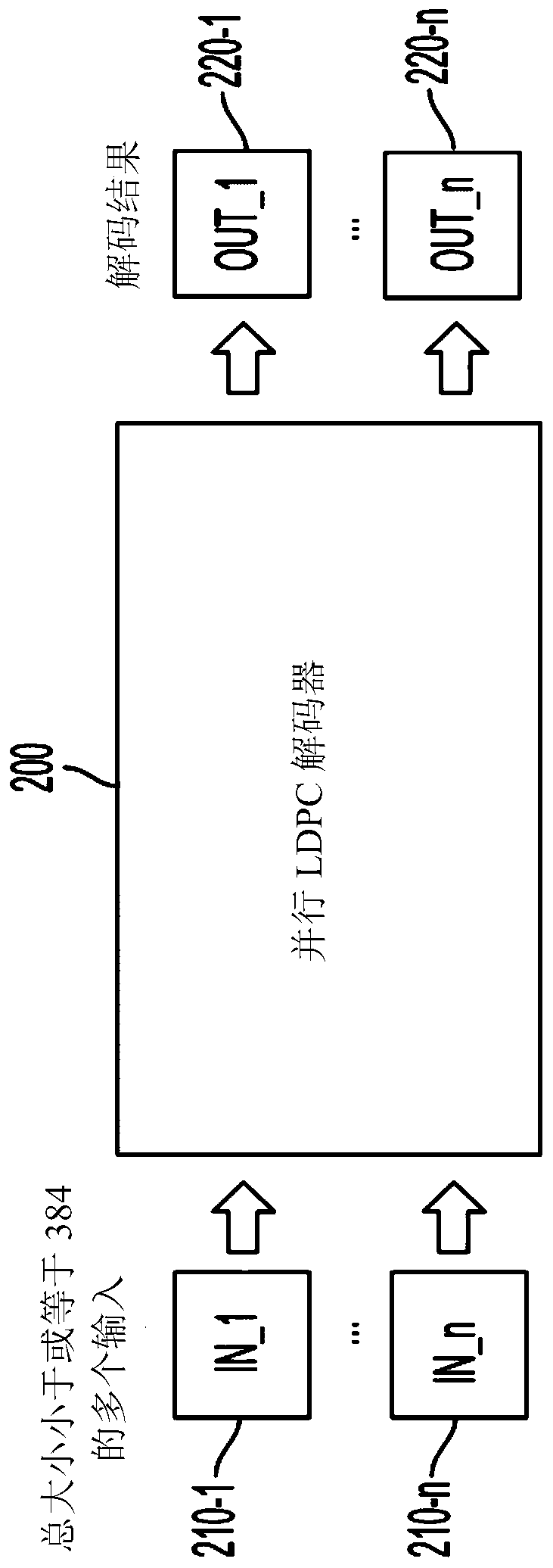

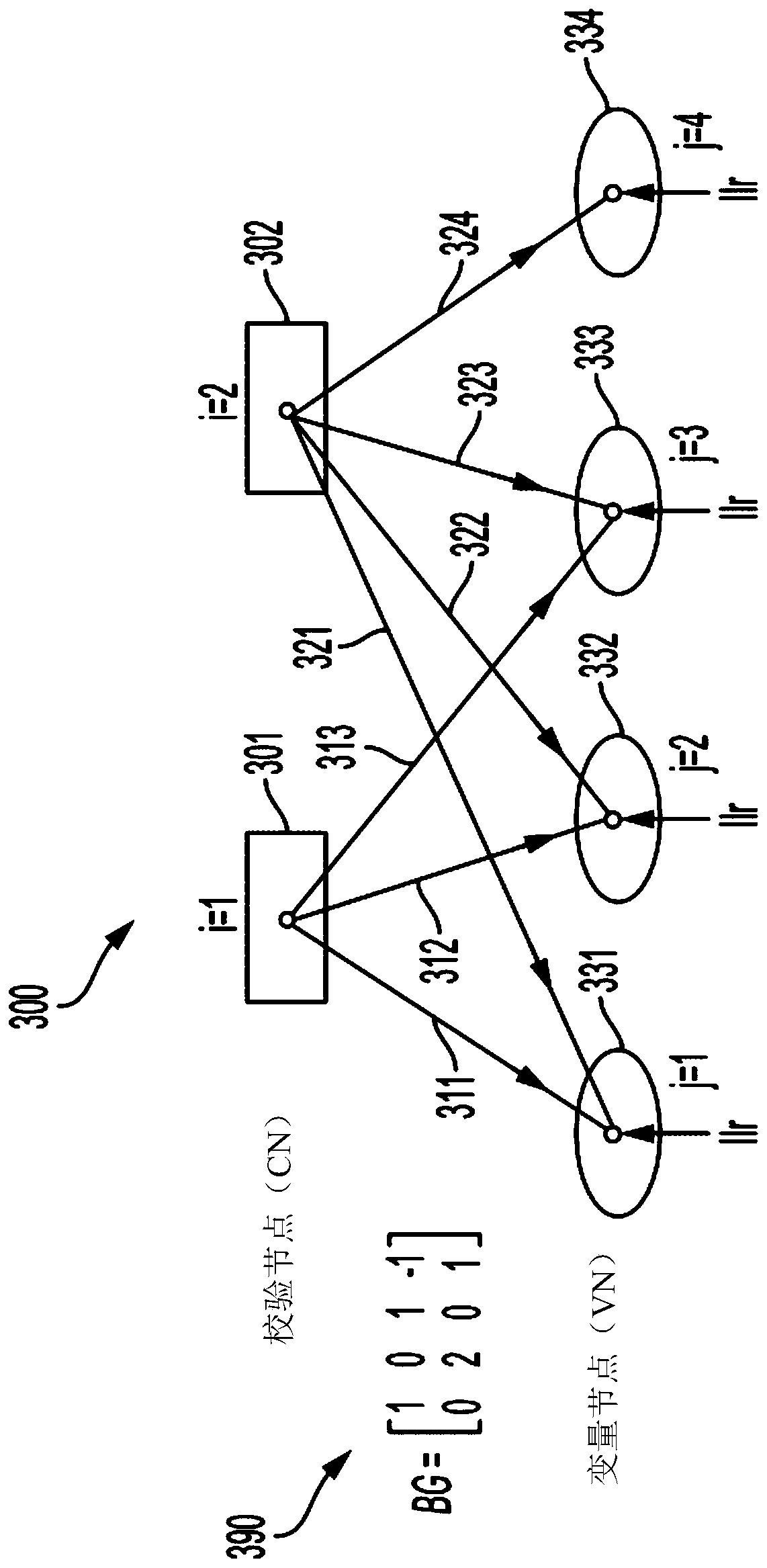

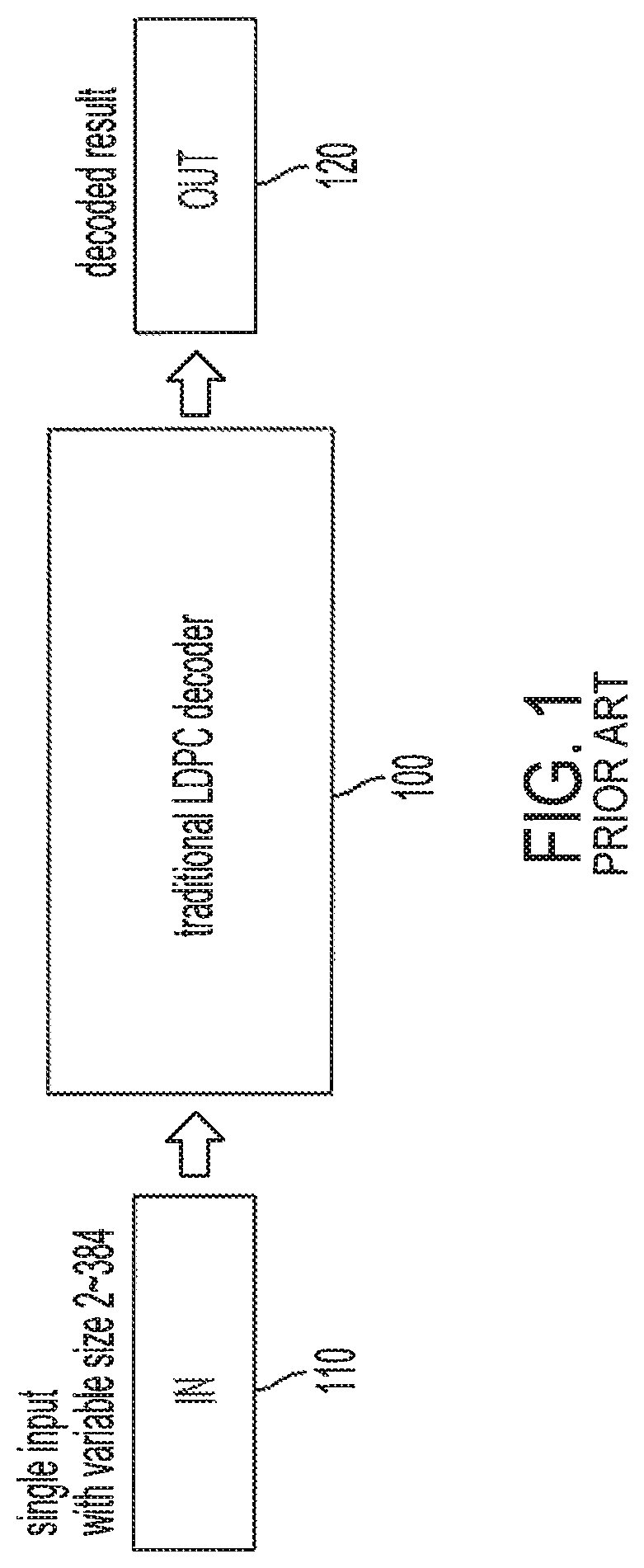

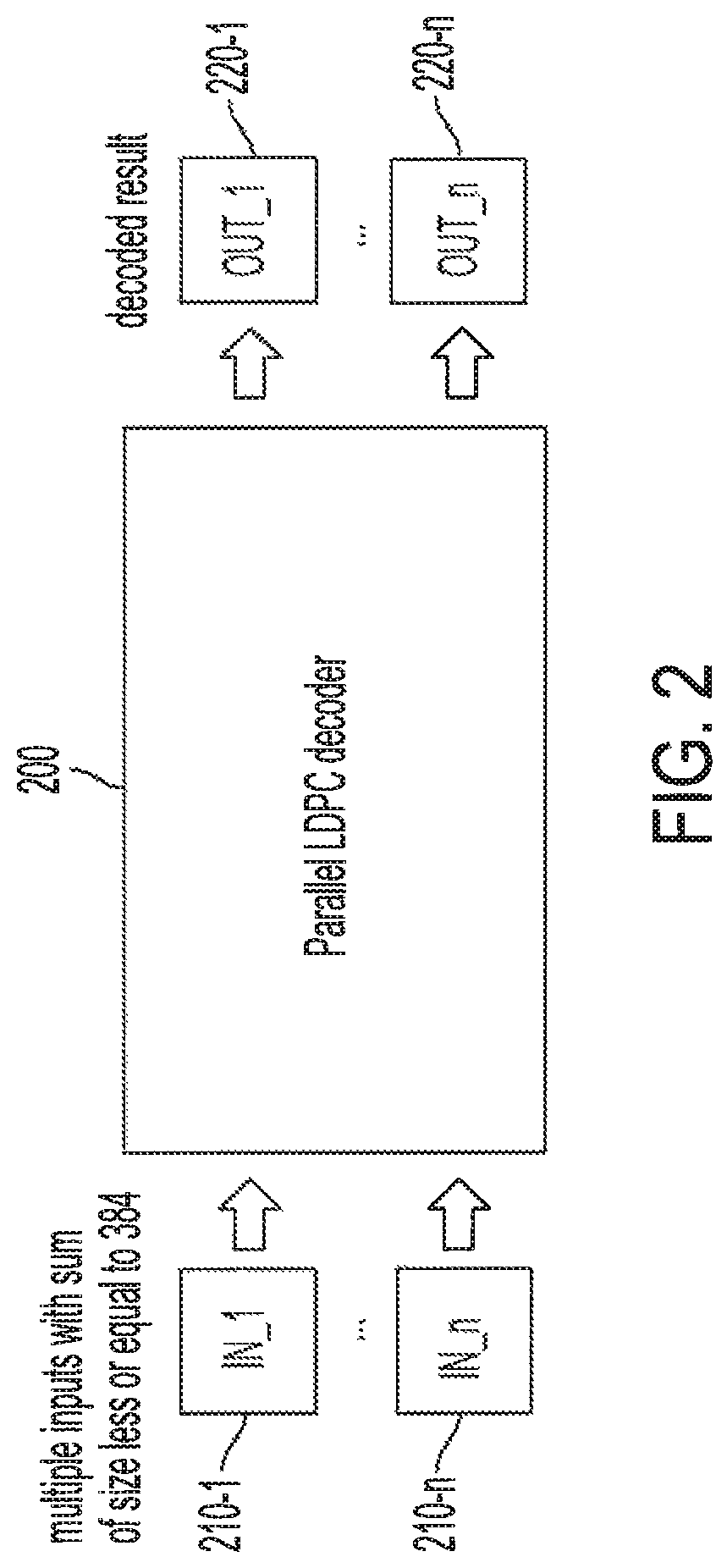

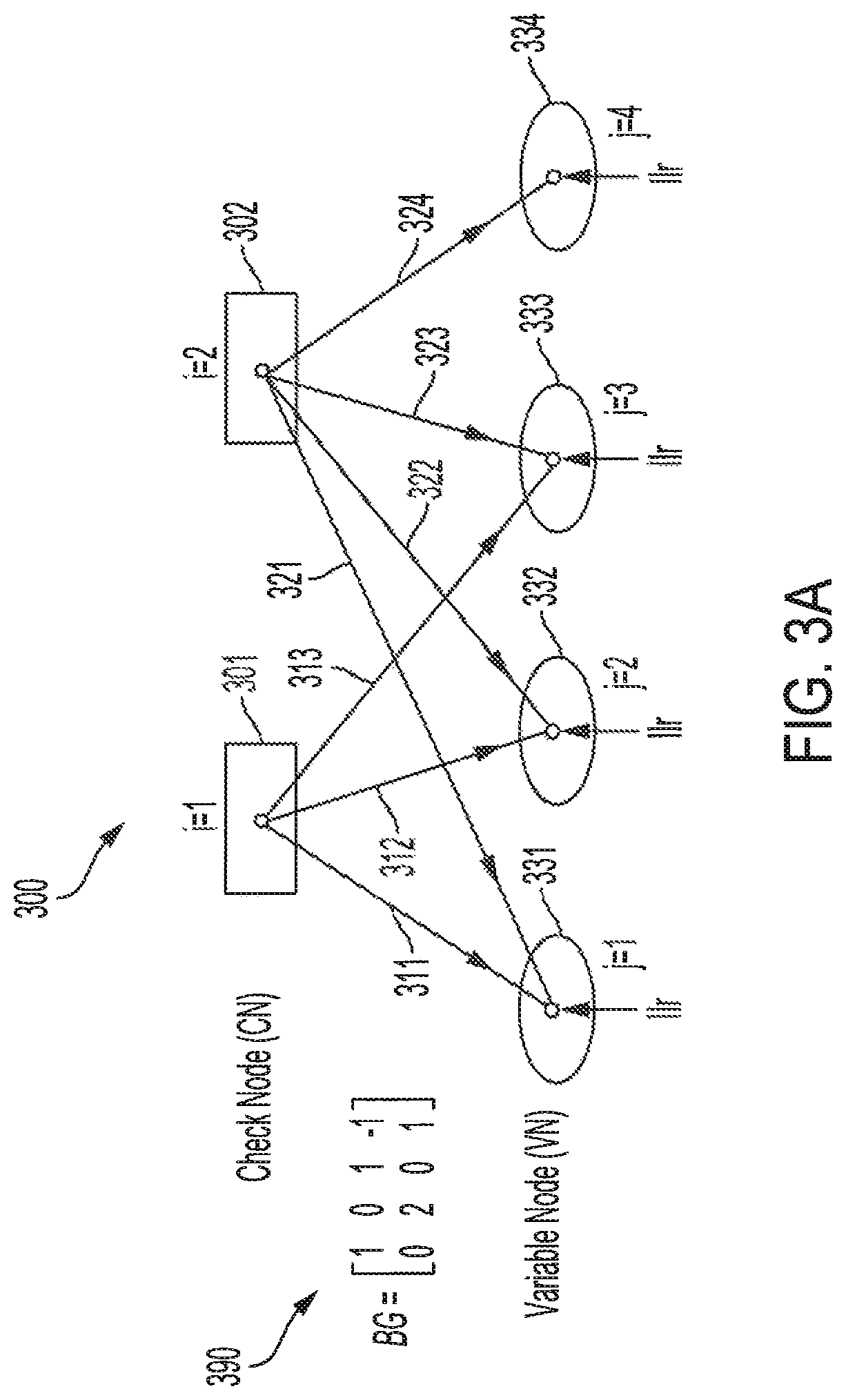

Parallel LDPC decoder

ActiveUS20200252080A1Efficient and flexible designEnhanced operational aspectError correction/detection using multiple parity bitsCode conversionCoding blockComputer architecture

Systems and methods providing low-density parity-check (LDPC) decoder configurations capable of decoding multiple code blocks in parallel are described. Parallel LDPC decoders of embodiments can be reconfigured to simultaneously decode multiple codewords with reconfigurable size. In operation of embodiments of a parallel LDPC decoder, a plurality of active portions of the decoder logic are configured for parallel processing of a plurality of code blocks, wherein each active region processes a respective code block. The decoder logic active portions of embodiments are provided using a reconfigurable segmented scalable cyclic shifter supporting multiple instruction, multiple data (MIMD), wherein multiple individual different data shifts are implemented with respect to a plurality of code blocks in an instance of data shifting operation. Multiple data shift commands may be utilized such that the plurality of code blocks have an individual shifting command to thereby implement different data shifting with respect to each code block.

Owner:HONG KONG APPLIED SCI & TECH RES INST

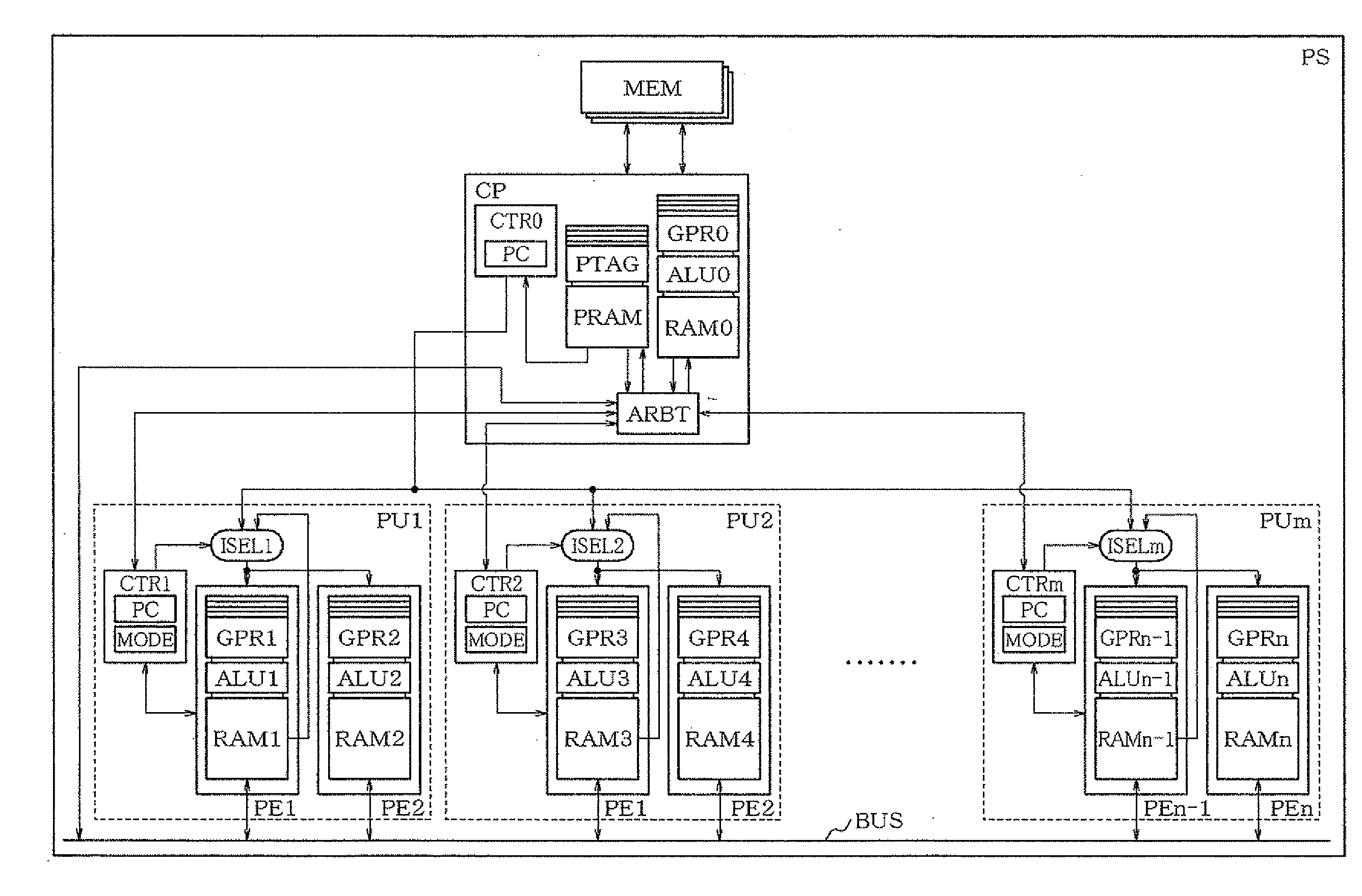

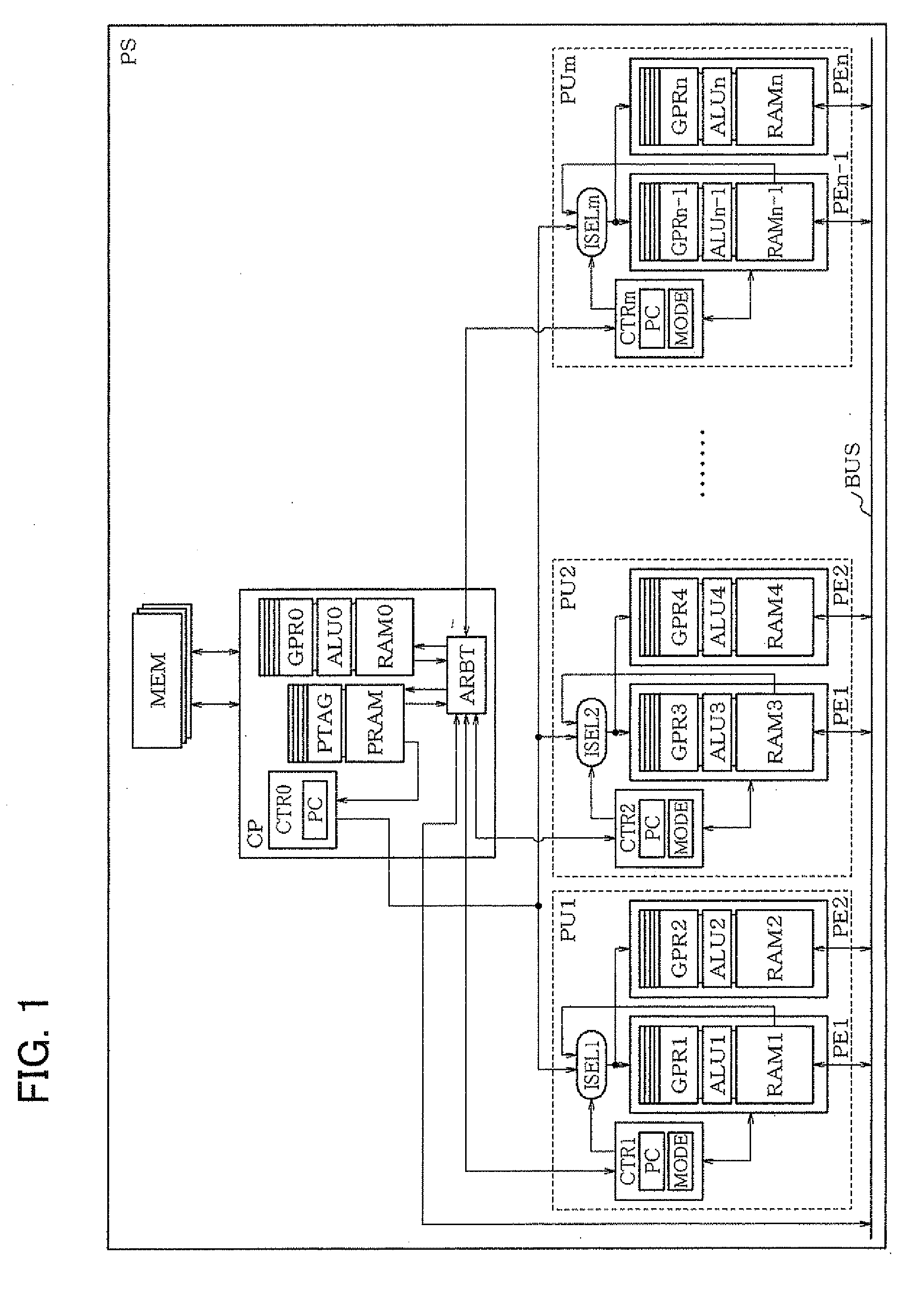

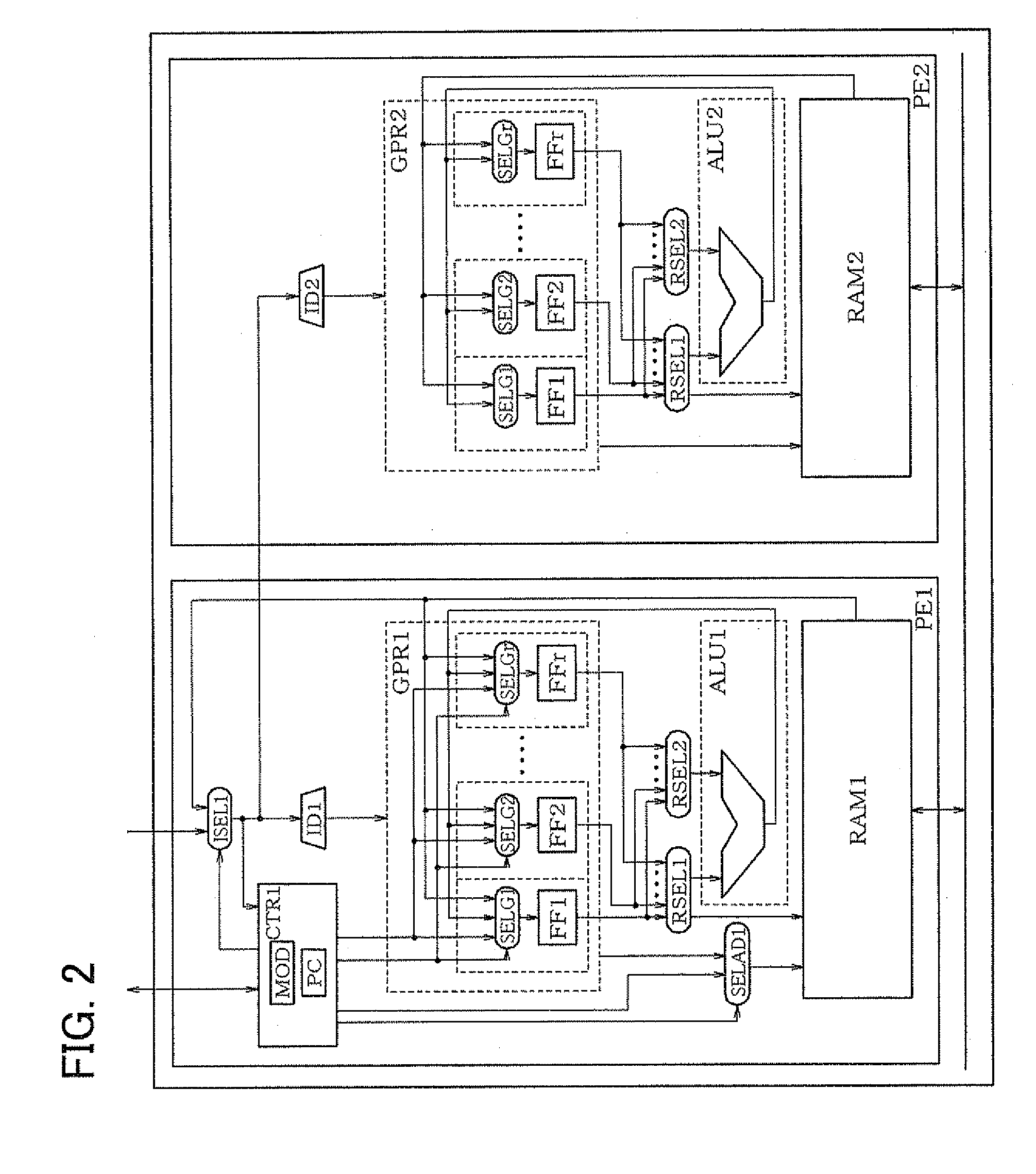

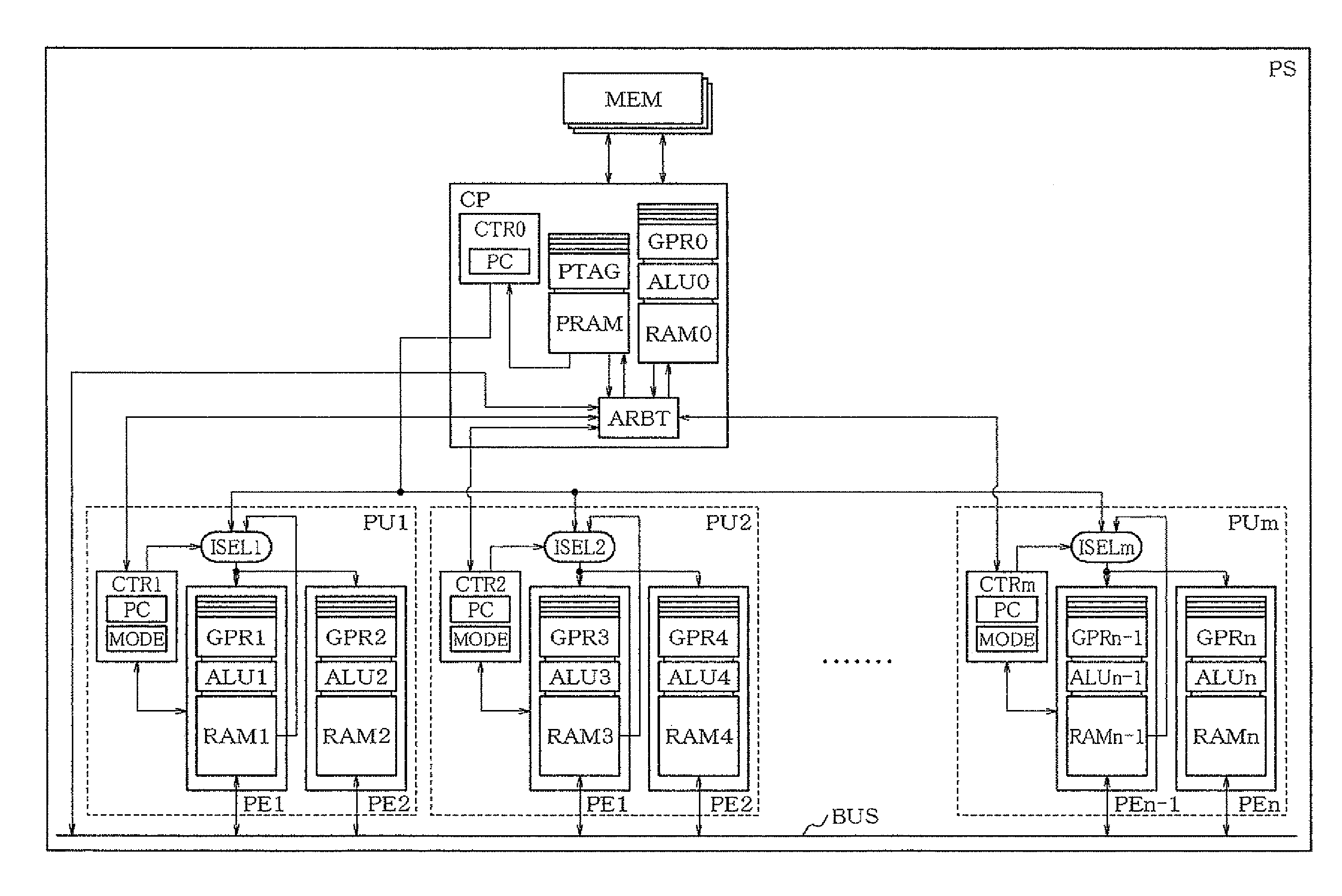

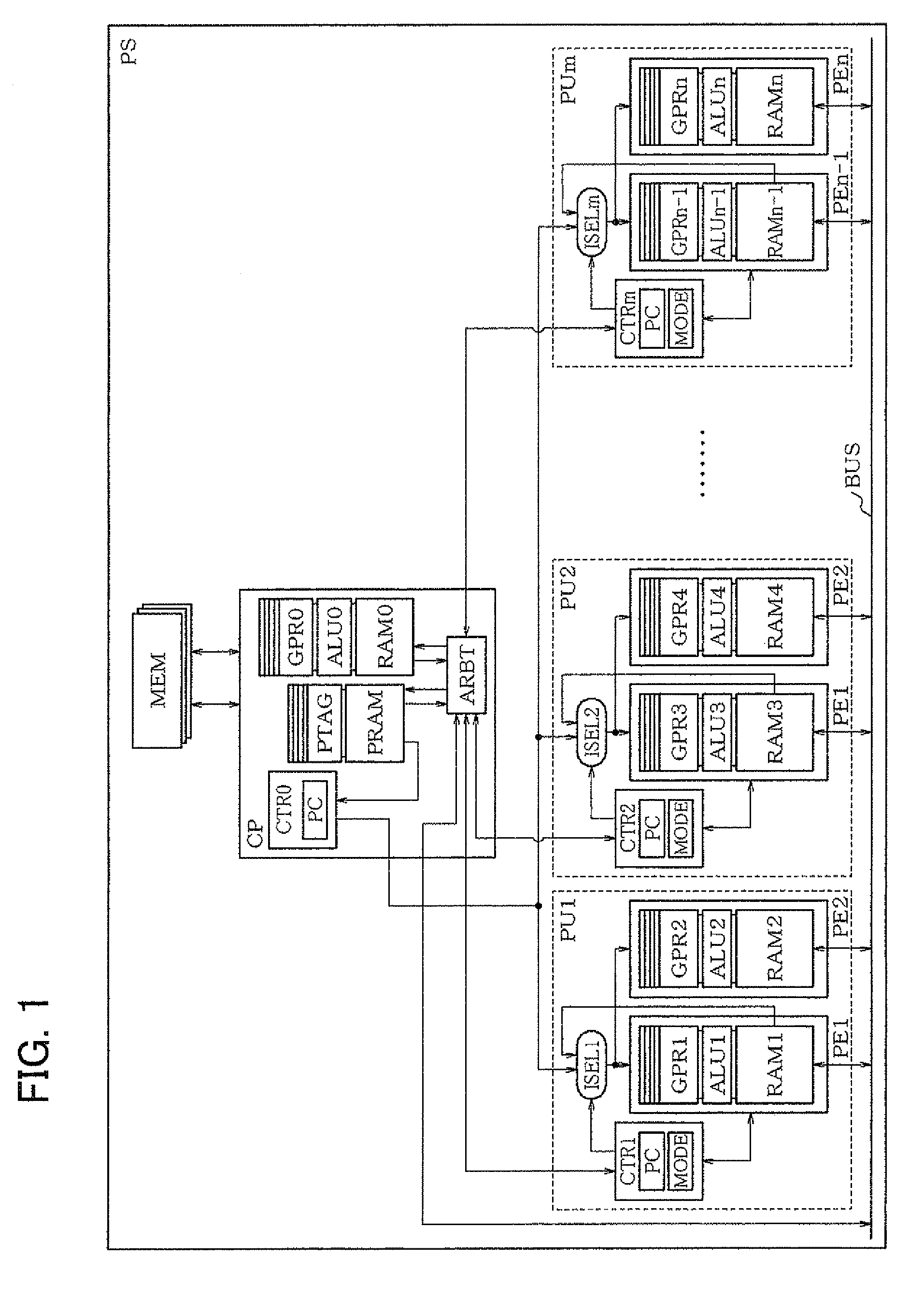

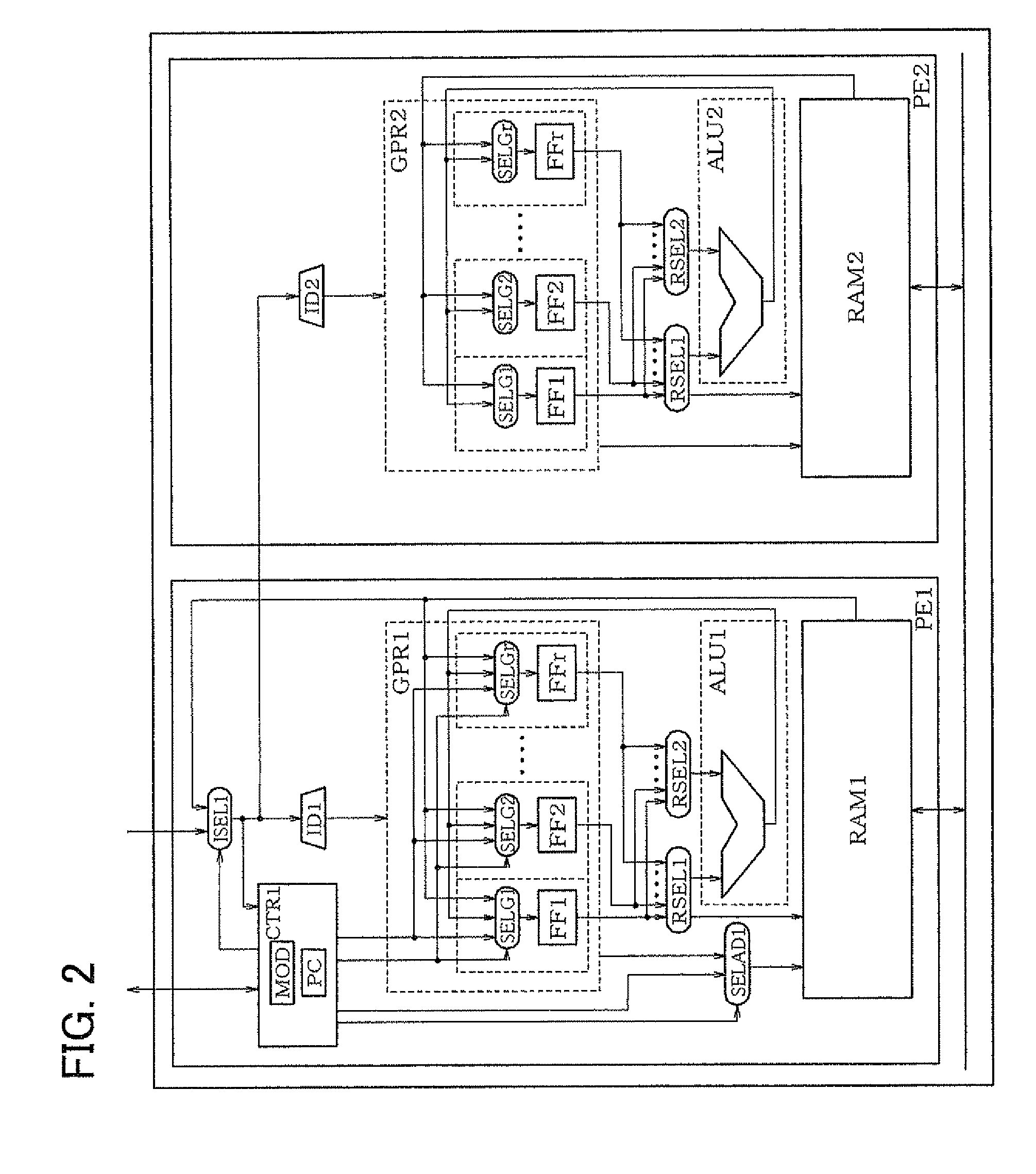

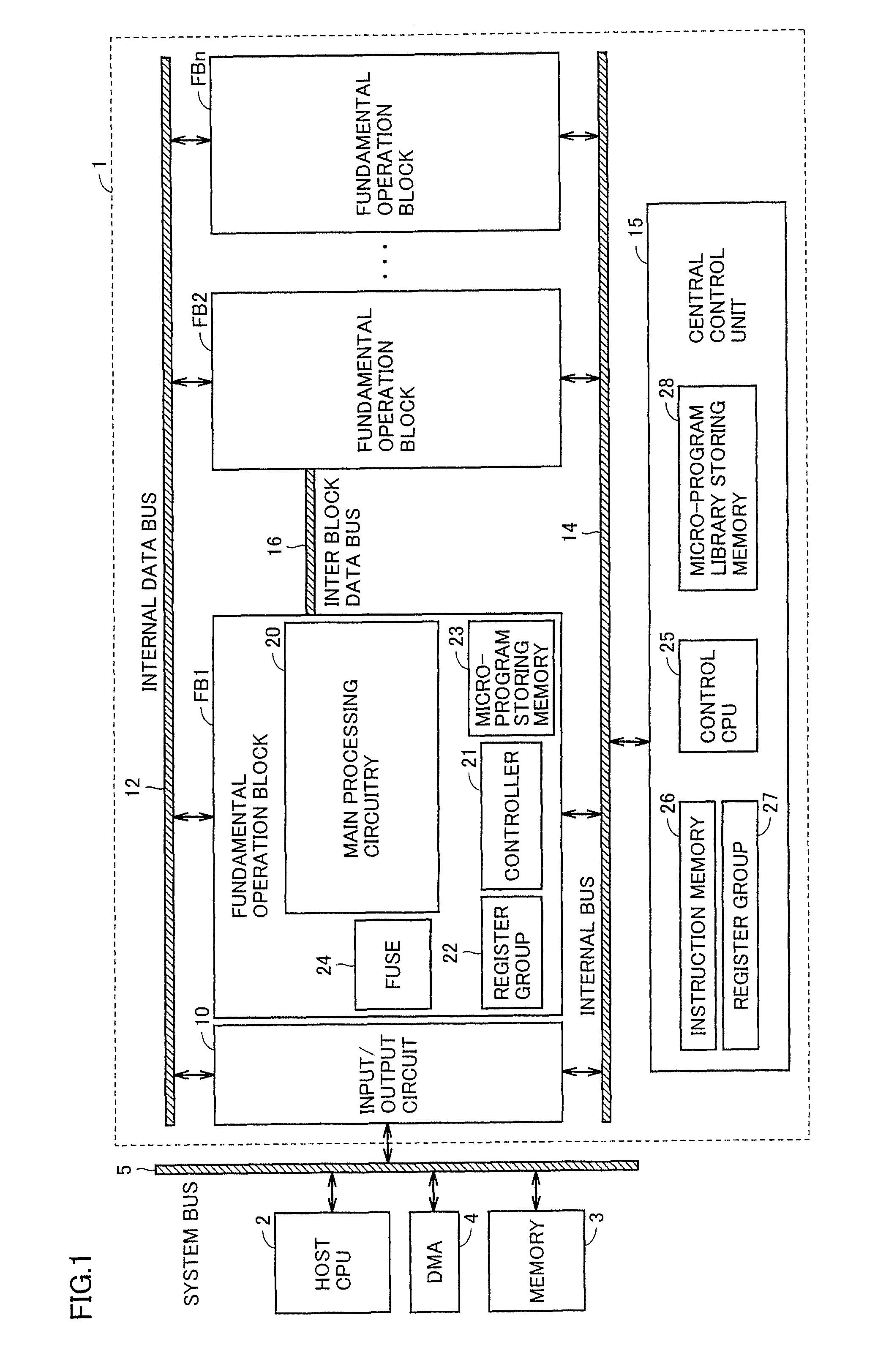

Processing elements, mixed mode parallel processor system, processing method by processing elements, mixed mode parallel processor method, processing program by processing elements and mixed mode parallel processing program

InactiveUS20090049275A1Circuit scale is not increasedLower performance requirementsMemory adressing/allocation/relocationMultiprogramming arrangementsGeneral purposeMIMD

Disclosed is a mixed mode parallel processor system in which N number of processing elements PEs, capable of performing SIMD operation, are grouped into M (=N÷S) processing units PUs performing MIMD operation. In MIMD operation, P out of S memories in each PU, which S memories inherently belong to the PEs, where P<S, operate as an instruction cache. The remaining memories operate as data memories or as data cache memories. One out of S sets of general-purpose registers, inherently belonging to the PEs, directly operates as a general register group for the PU. Out of the remaining S−1 sets, T set or a required number of sets, where T<S−1, are used as storage registers that store tags of the instruction cache.

Owner:NEC CORP

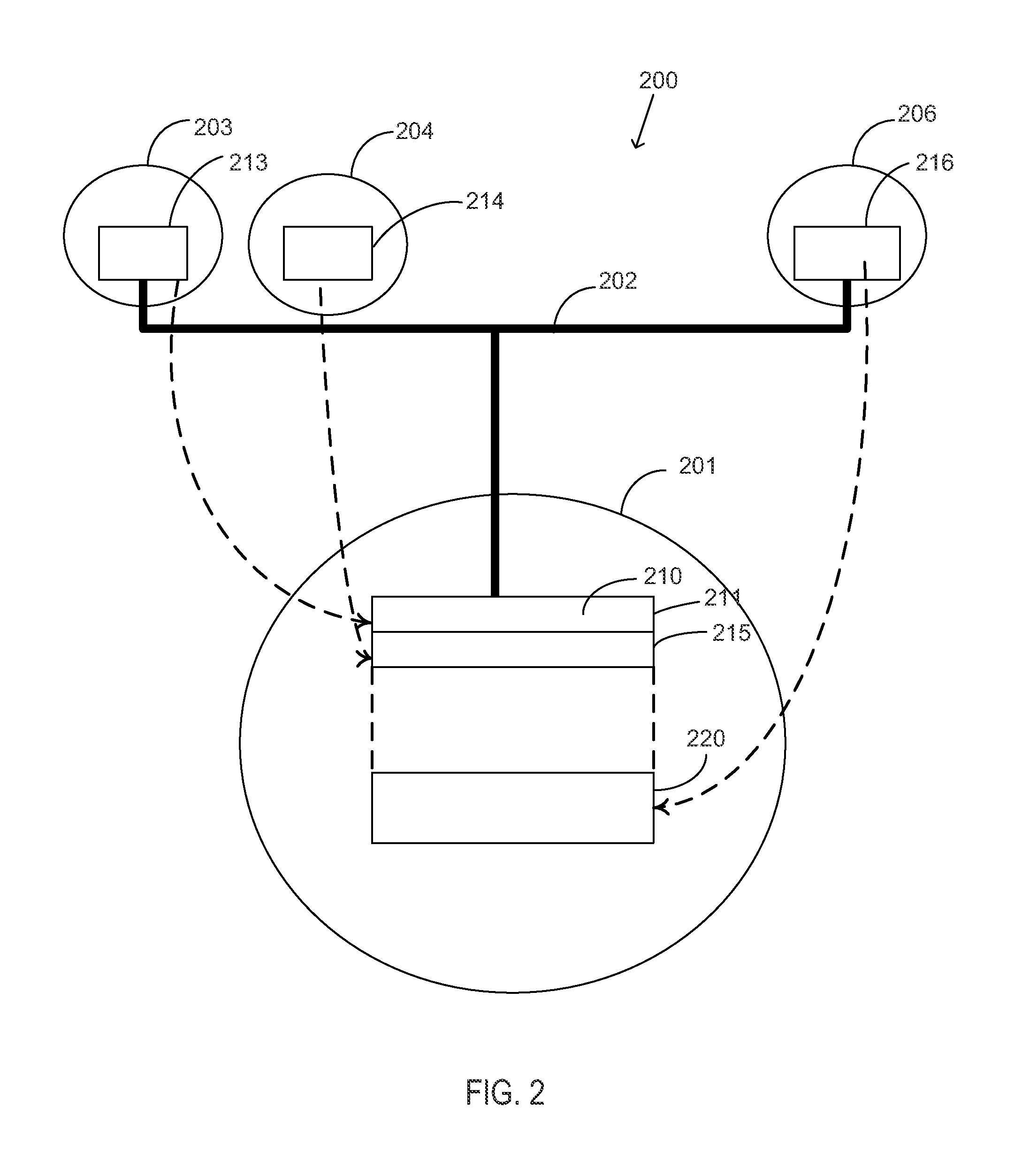

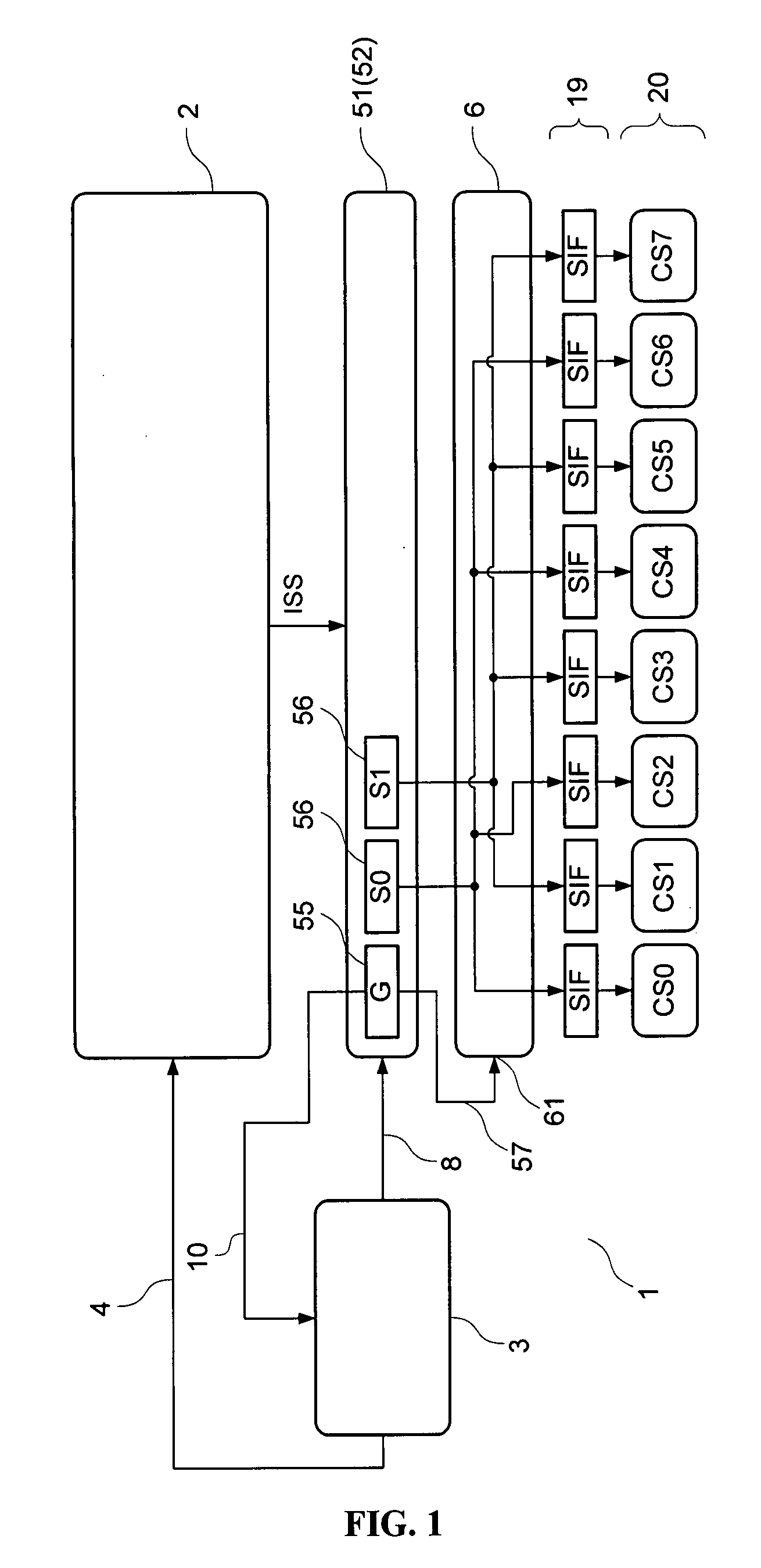

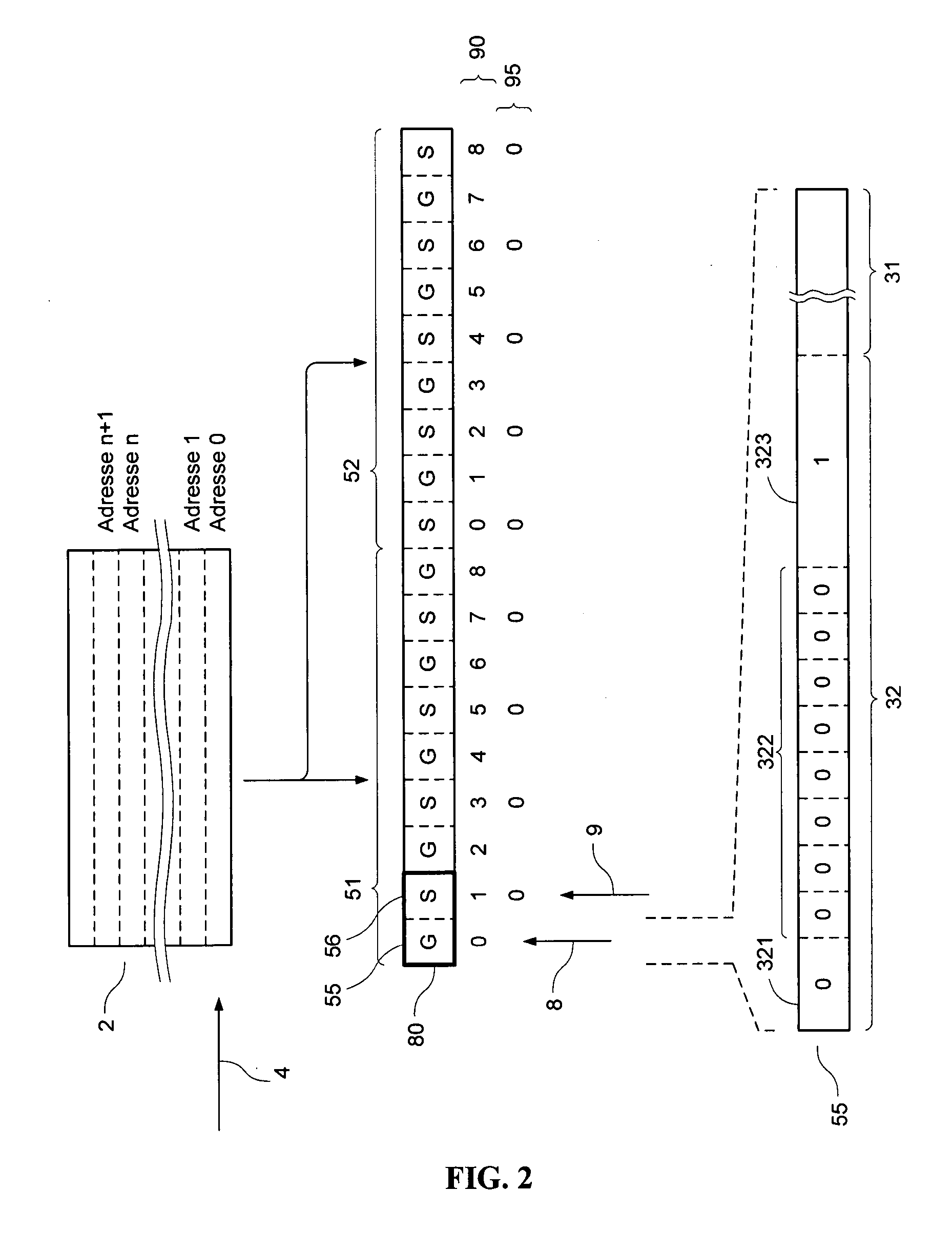

Method, system and apparatus for multi-level processing

InactiveUS20120096292A1Low costReduces synchronization waiting timeGeneral purpose stored program computerMultiprogramming arrangementsThree levelMIMD

A Multi-Level Processor 200 for reducing the cost of synchronization overhead including an upper level processor 201 for taking control and issuing the right to use shared data and to enter critical sections directly to each of a plurality of lower level processors 202, 203 . . . 20n at processor speed. In one embodiment the instruction registers of lower level parallel processors are mapped to the data memory of upper level processor 201. Another embodiment 1300 incorporates three levels of processors. The method includes mapping the instructions of lower level processors into the memory of an upper level processor and controlling the operation of lower level processors. A variant of the method and apparatus facilitates the execution of Single Instruction Multiple Data (SIMD) and single to multiple instruction and multiple data (SI>MIMD). The processor includes the ability to stretch the clock frequency to reduce power consumption.

Owner:CONVERSANT INTPROP MANAGEMENT INC

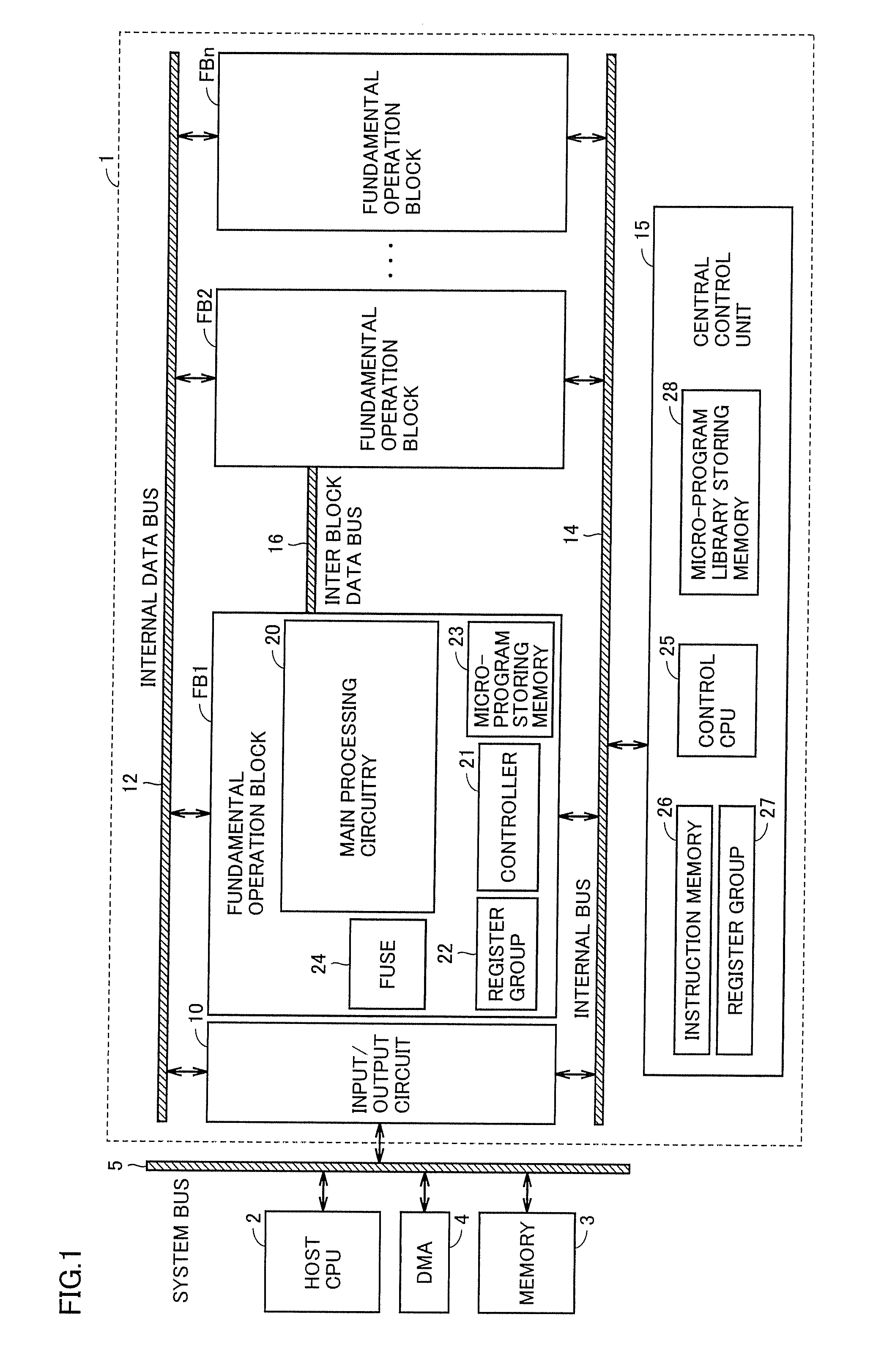

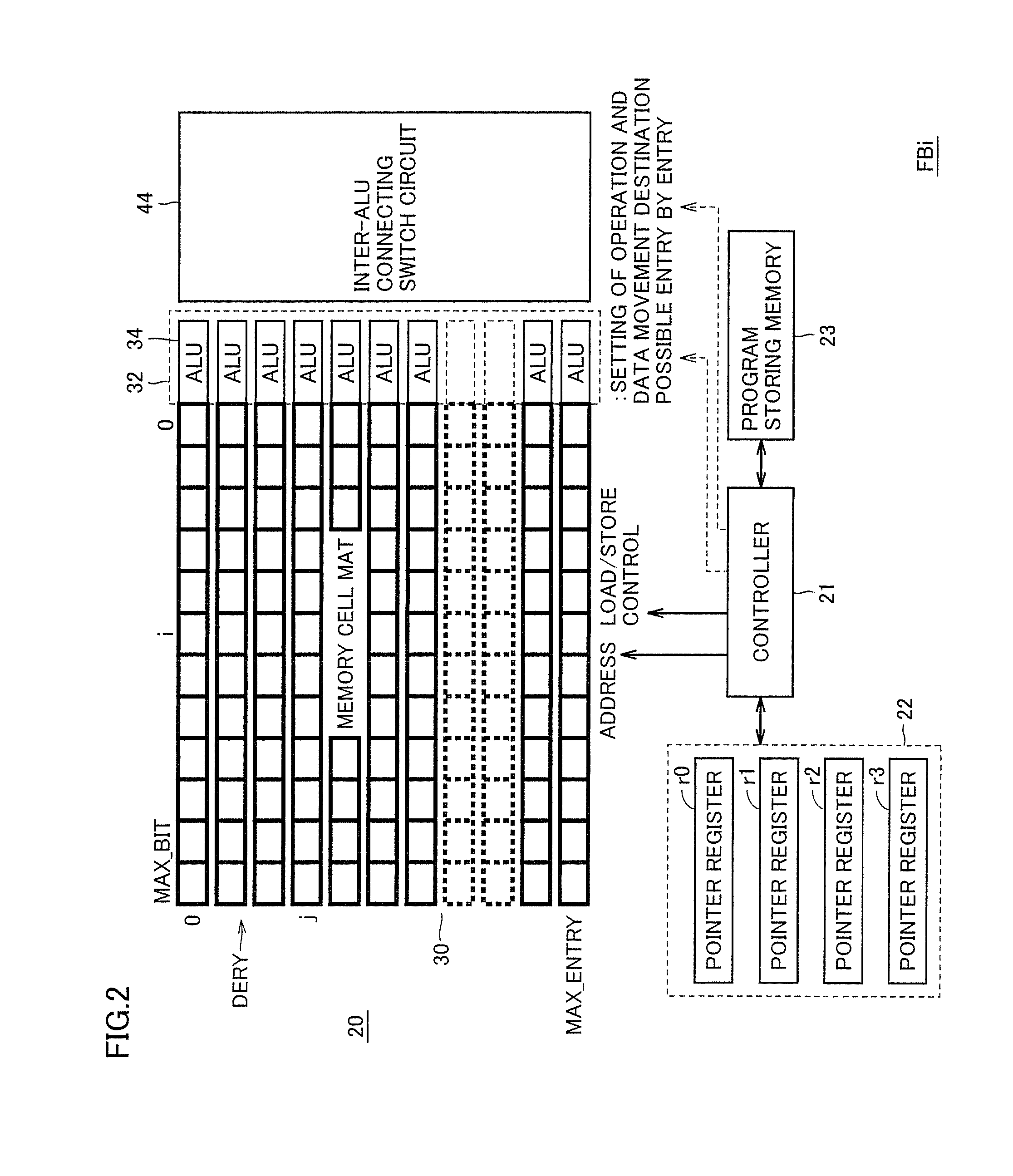

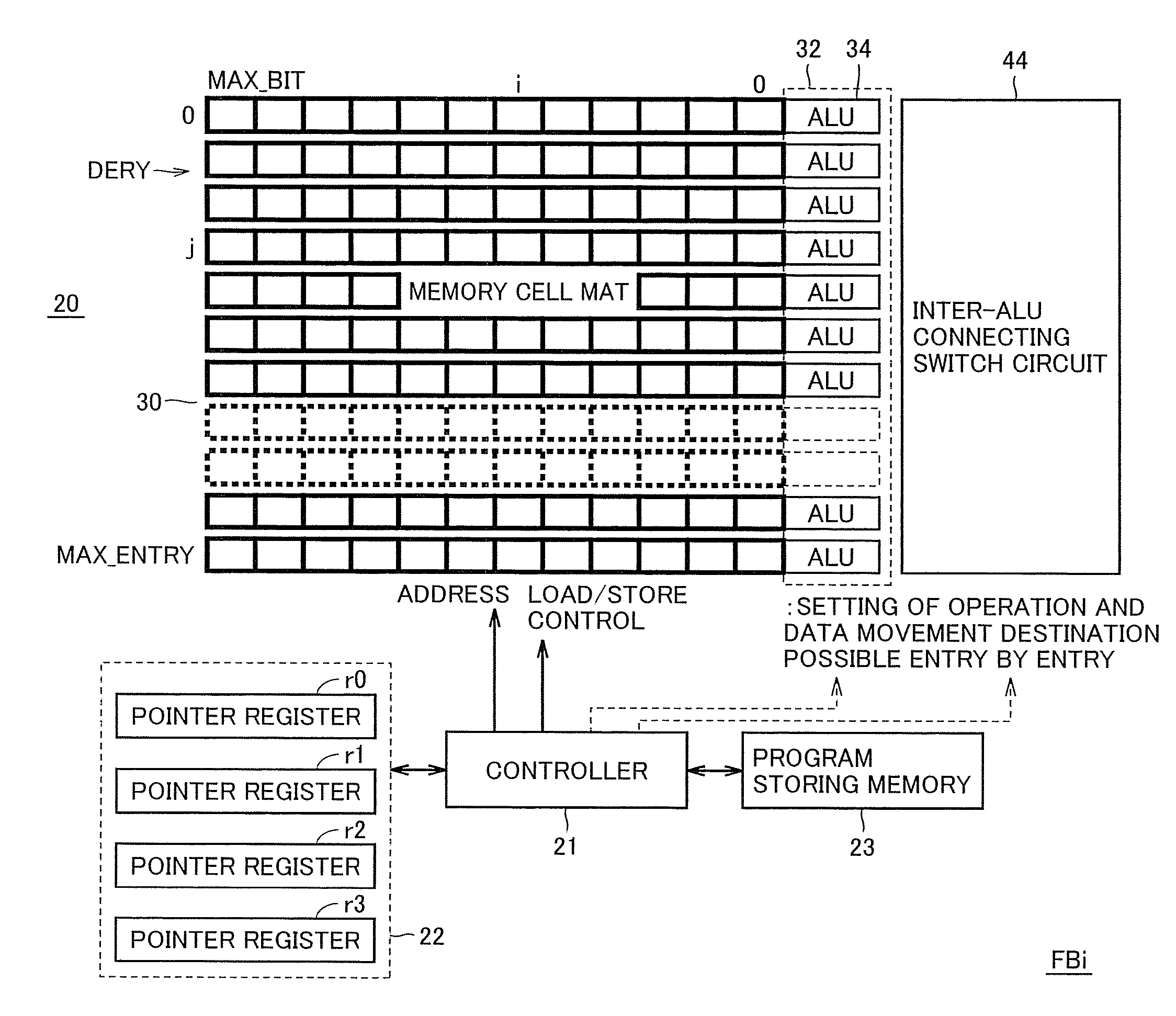

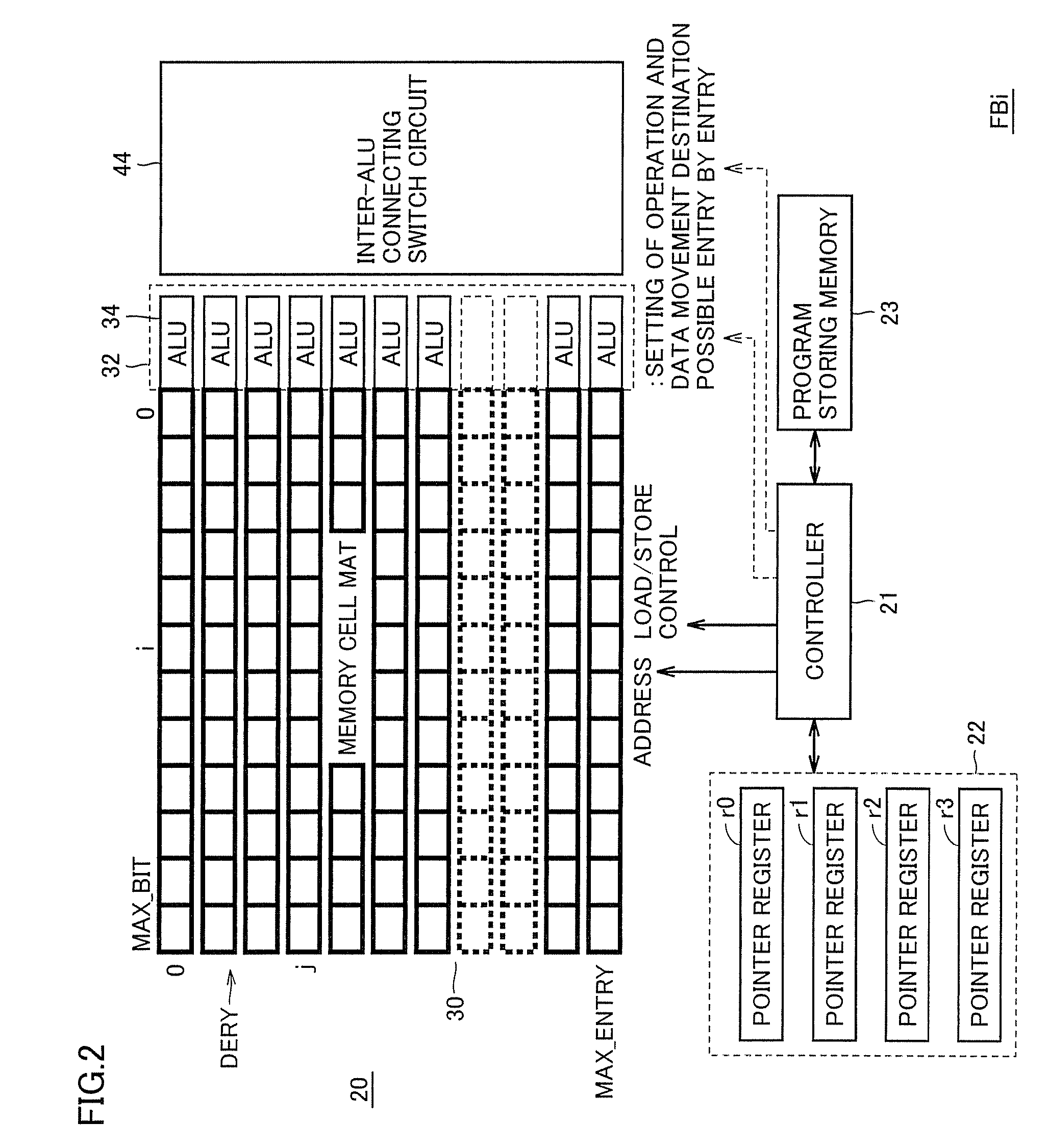

Parallel operation device allowing efficient parallel operational processing

InactiveUS20080052497A1Easy to handleLow degreeGeneral purpose stored program computerSpecific program execution arrangementsArithmetic logic unitMIMD

In arithmetic / logic units (ALU) provided corresponding to entries, an MIMD instruction decoder generating a group of control signals in accordance with a Multiple Instruction Multiple Data (MIME) instruction and an MIMD register storing data designating the MIME instruction are provided, and an inter-ALU communication circuit is provided. The amount and direction of movement of the inter-ALU communication circuit are set by data bits stored in a movement data register. It is possible to execute data movement and arithmetic / logic operation with the amount of movement and operation instruction set individually for each ALU unit Therefore, in a Single Instruction-Multiple Data type processing device, Multiple Instruction-Multiple Data operation can be executed at high speed in a flexible manner.

Owner:RENESAS ELECTRONICS CORP

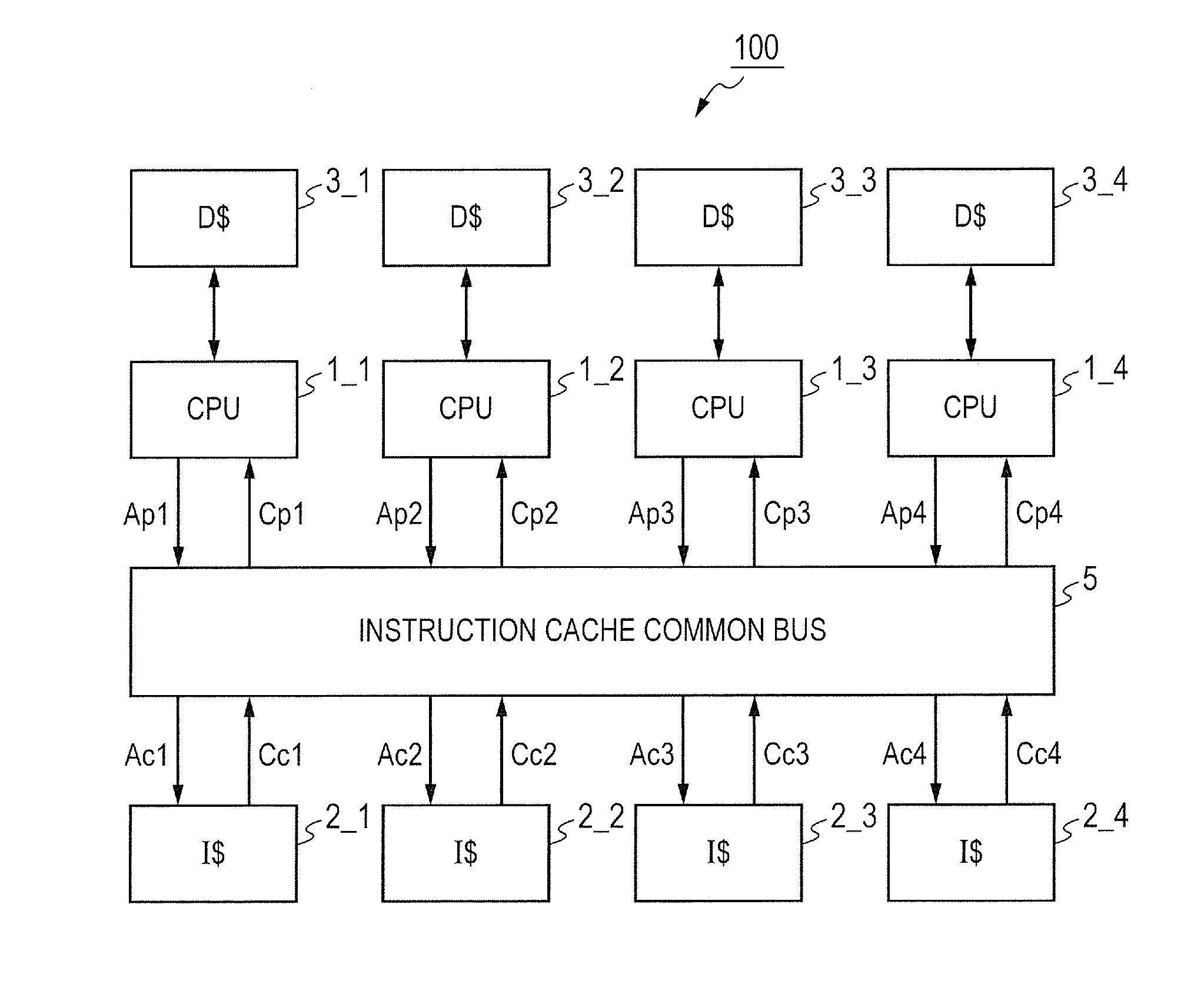

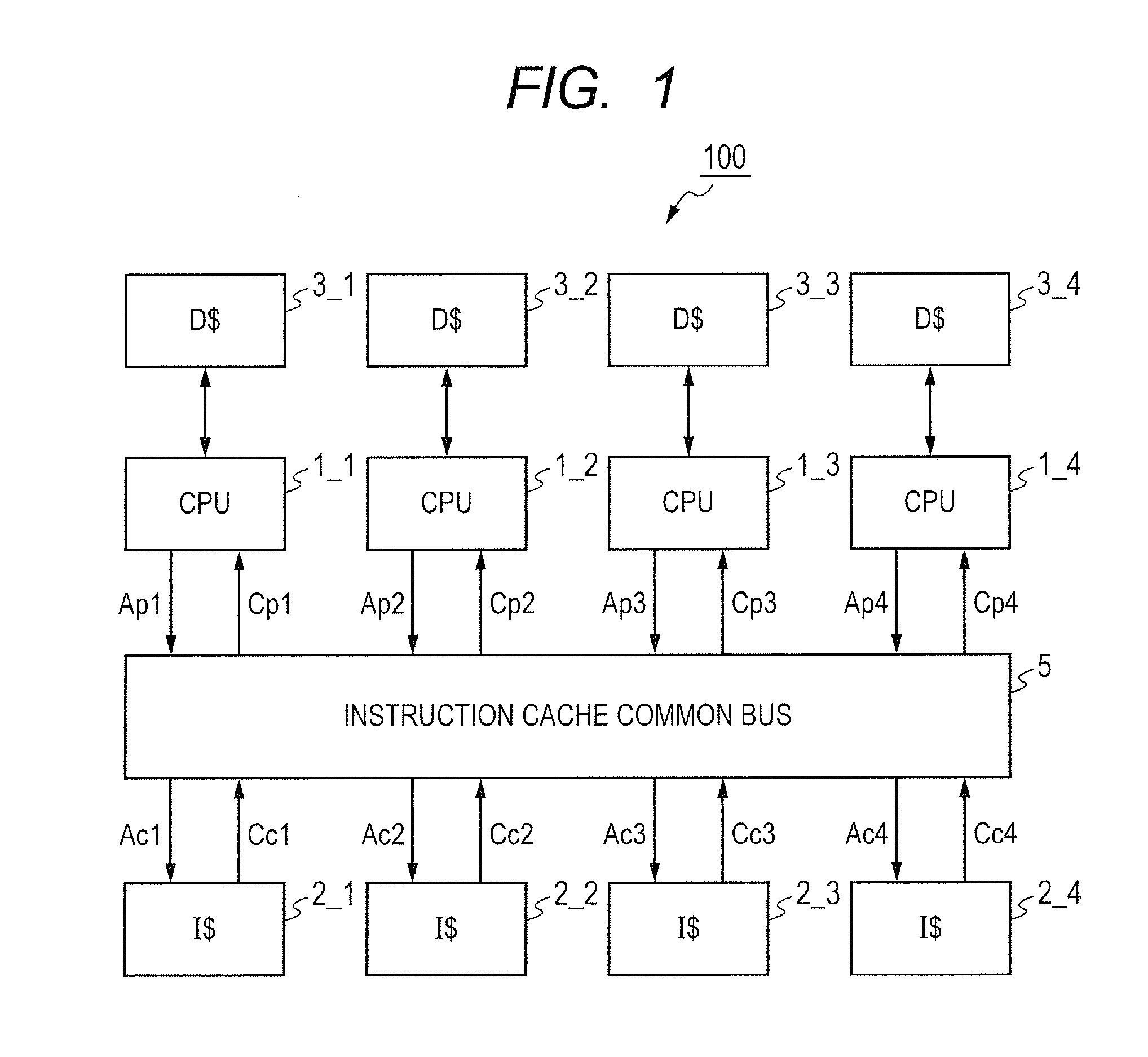

Processing elements grouped in MIMD sets each operating in SIMD mode by controlling memory portion as instruction cache and GPR portion as tag

InactiveUS7853775B2Lower performance requirementsReduce scaleMemory adressing/allocation/relocationMultiprogramming arrangementsGeneral purposeMIMD

Disclosed is a mixed mode parallel processor system in which N number of processing elements PEs, capable of performing SIMD operation, are grouped into M (=N÷S) processing units PUs performing MIMD operation. In MIMD operation, P out of S memories in each PU, which S memories inherently belong to the PEs, where P<S, operate as an instruction cache. The remaining memories operate as data memories or as data cache memories. One out of S sets of general-purpose registers, inherently belonging to the PEs, directly operates as a general register group for the PU. Out of the remaining S−1 sets, T set or a required number of sets, where T<S−1, are used as storage registers that store tags of the instruction cache.

Owner:NEC CORP

Executing Multiple Instructions Multiple Data ('MIMD') Programs on a Single Instruction Multiple Data ('SIMD') Machine

InactiveUS20090024831A1General purpose stored program computerMachine execution arrangementsMIMDData treatment

Executing MIMD programs on a SIMD machine, including establishing on the SIMD machine a plurality of SIMD partitions; booting a first SIMD partition in MIMD mode; executing, on a compute node of the first SIMD partition booted in MIMD mode, a MIMD accelerator program; executing a SIMD program in a second SIMD partition, one instance of the SIMD program executing on each compute node of the second SIMD partition, each instance of the SIMD program carrying out a portion of the data processing effected by the SIMD program; and accelerating, by an instance of the SIMD program through the MIMD accelerator program, a portion of the data processing of the instance of the SIMD program.

Owner:IBM CORP

Method, system and apparatus for multi-level processing

InactiveCN103154892AReduce bandwidth requirementsLow costGeneral purpose stored program computerMultiprogramming arrangementsThree levelMIMD

A Multi-Level Processor (200) for reducing the cost of synchronization overhead including an upper level processor (201) for taking control and issuing the right to use shared data and to enter critical sections directly to each of a plurality of lower level processors (202, 203...20n) at processor speed. In one embodiment the instruction registers of lower level parallel processors are mapped to the data memory of upper level processor (201). Another embodiment (1300) incorporates three levels of processors. The method includes mapping the instructions of lower level processors into the memory of an upper level processor and controlling the operation of lower level processors. A variant of the method and apparatus facilitates the execution of Single Instruction Multiple Data (SIMD) and single to multiple instruction and multiple data (SI>MIMD). The processor includes the ability to stretch the clock frequency to reduce power consumption.

Owner:CONVERSANT INTPROP MANAGEMENT INC

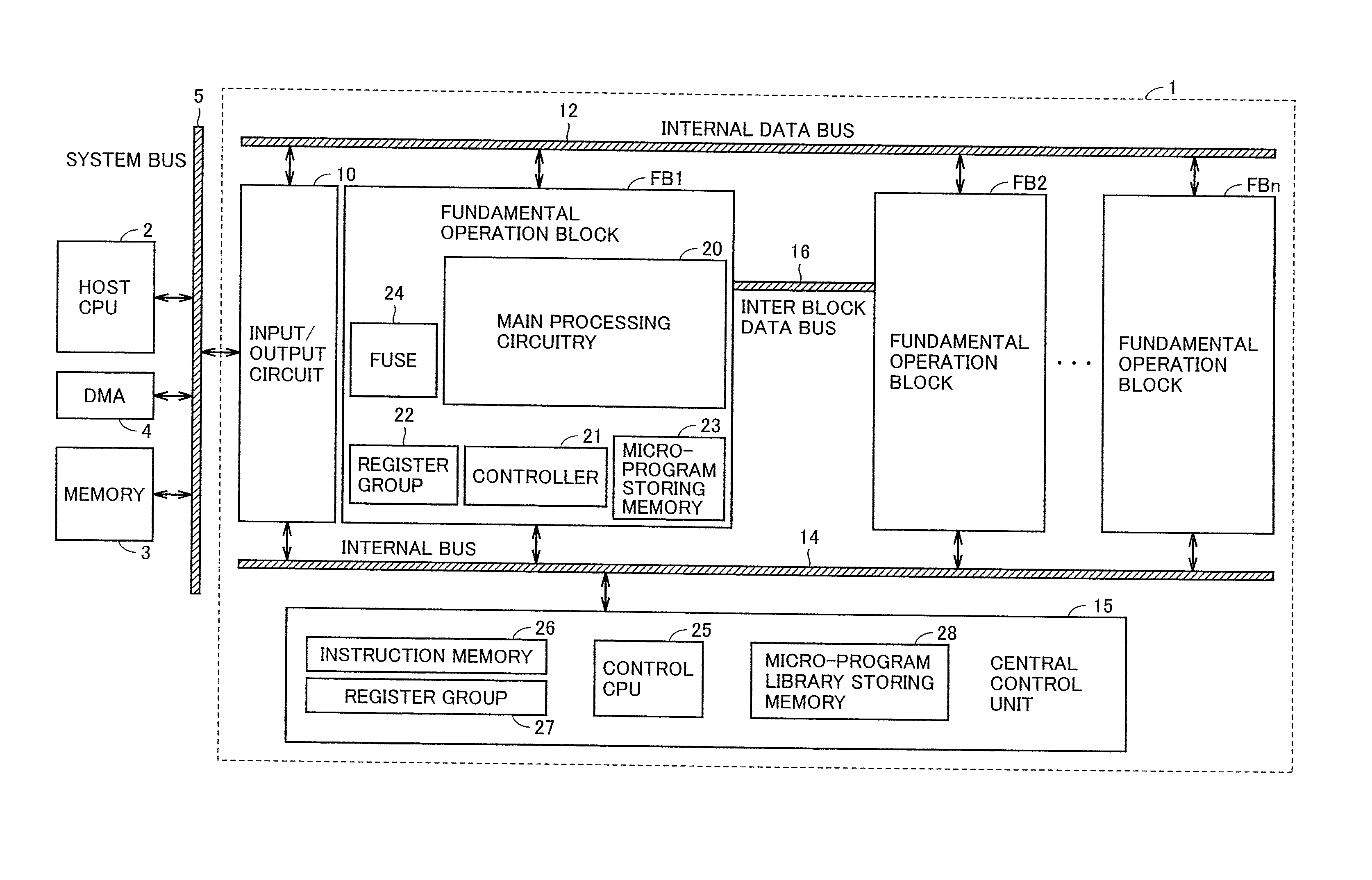

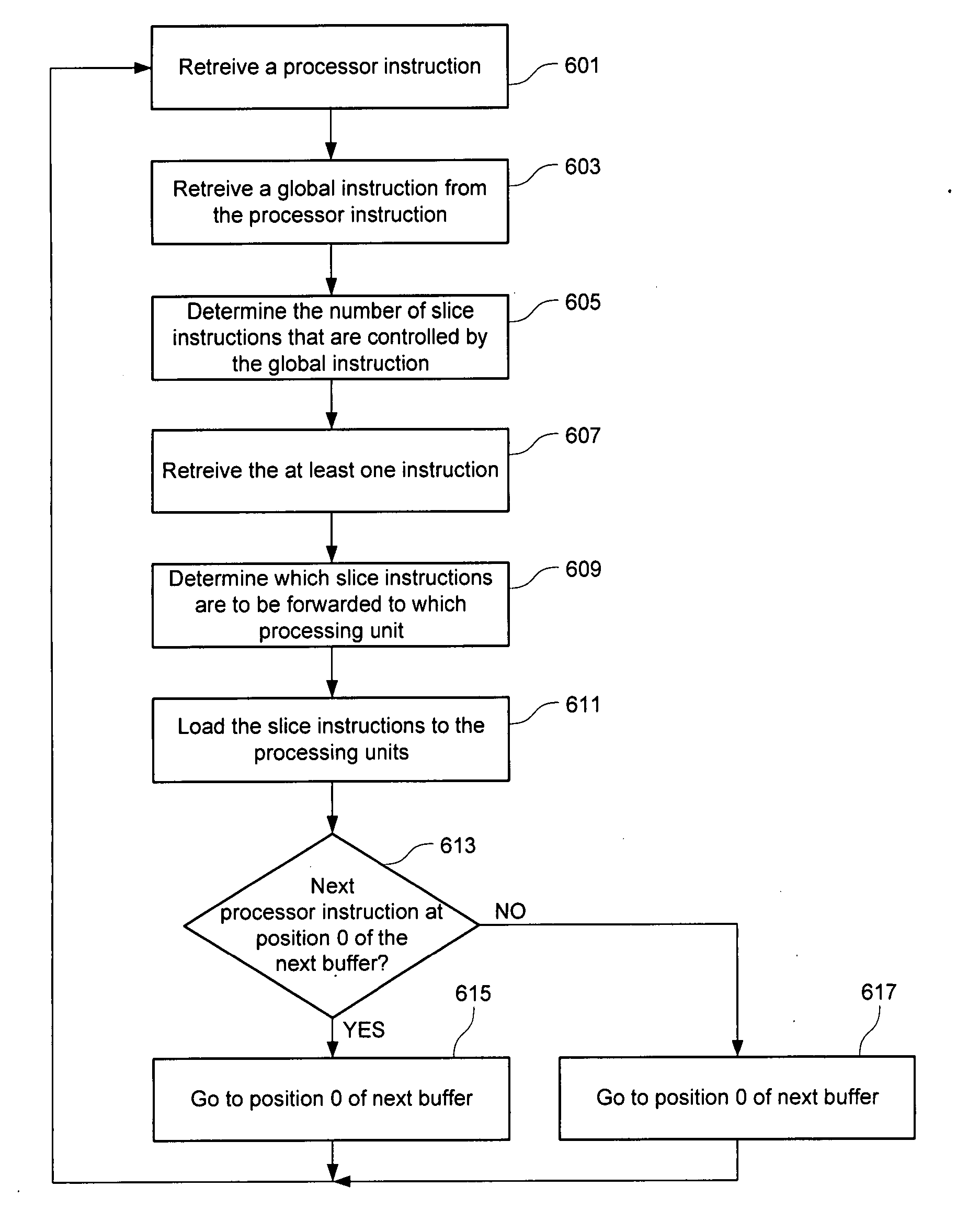

Arrangements for controlling instruction and data flow in a multi-processor environment

InactiveUS20070226468A1Digital computer detailsSpecific program execution arrangementsData streamMIMD

In one embodiment a method for controlling instruction flow in a multiprocessor environment is disclosed. The method can include retrieving at least one slice instruction that is executable by more than one processing unit in a plurality of processing units. The method can also retrieve a global instruction that indicates a processing unit from a plurality of processing units that will receive the at least one slice instruction and the method can load the at least one slice instruction to the more than one processing unit in response to the global instruction. Such instruction control can allow the system to operate in a single input multiple data (SIMD) mode, a multiple instruction multiple data (MIMD) mode or a hybrid thereof.

Owner:ON DEMAND MICROELECTRONICS

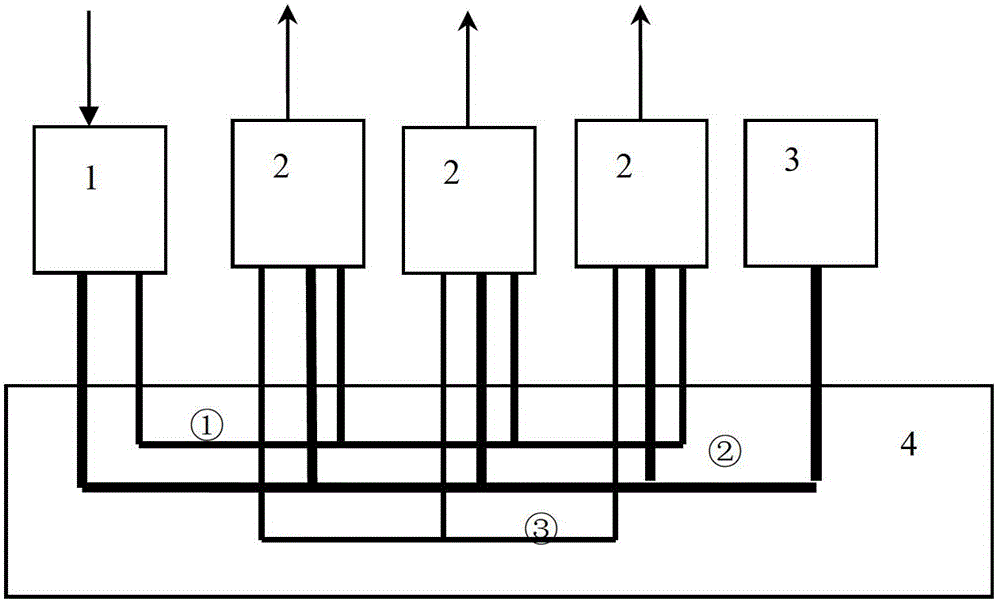

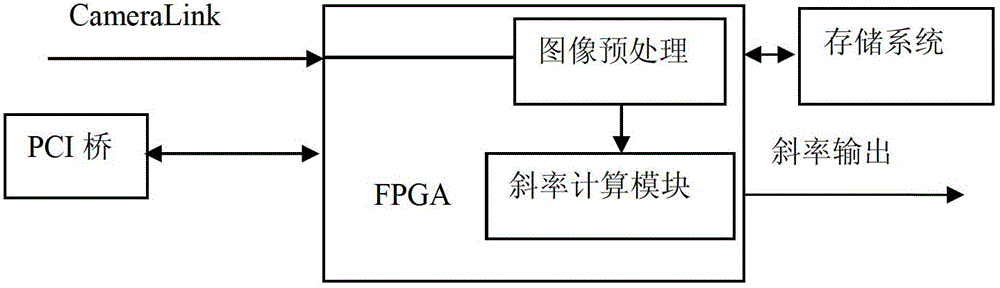

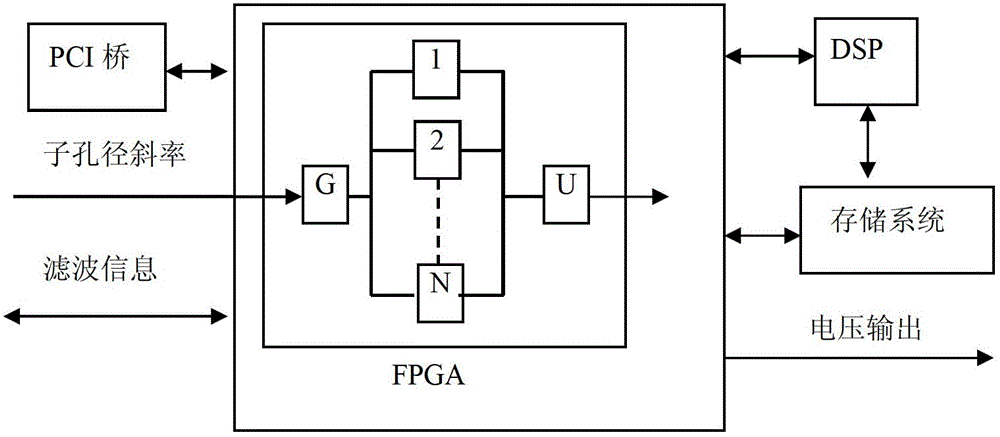

Wavefront signal processing platform of thousand-unit-level self-adaptive optical system

ActiveCN102722217AImprove engineering applicabilityMake up for integrationDigital dataOptical elementsProportion integration differentiationMIMD

The invention discloses a wavefront signal processing platform of a thousand-unit-level self-adaptive optical system. The wavefront signal processing platform of the thousand-unit-level self-adaptive optical system uses a wavefront error detecting module (1) to perform wavefront slope detection on a subspot; with a subaperture line as a pace, slope data is sent to three resetting control modules (2) in a broadcasting way through a set of local bus I on an interconnecting backplate (4); the three resetting control modules form an MIMD (multiple instruction multiple data) array machine to perform voltage solving and PID (proportion integration differentiation) control operation of a deformable mirror actuator; three paths of digital control voltages are output to an amplifying system of the deformable mirror actuator; data communication is realized among the three resetting control modules through another set of local bus III; and a signal processing platform uses a monitoring host (3) to load parameters and monitor signals of the wavefront error detecting module and the three resetting control modules through a PCI (peripheral component interconnecting) bus II. Compared with the conventional implementing way, the wavefront signal processing platform of the thousand-unit-level self-adaptive optical system has the characteristics of good timeliness, small volume and high integration.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

Parallel LDPC decoder

ActiveCN109952729ASave computing powerImprove experienceError preventionError correction/detection using multiple parity bitsCoding blockMIMD

Systems and methods are described for low density parity check (LDPC) decoder configurations capable of decoding multiple code blocks in parallel. The parallel LDPC decoder can be reset to simultaneously decode multiple codewords with a resettable size. While the parallel LDPC decoder is running, multiple active portions of the decoder logic are configured to process multiple code blocks in parallel, with each active region processing a respective code block. A decoder-restricted cyclic shifter that supports multiple instruction multiple data (MIMD) is used to provide a decoder logic active portion in which multiple separate different data shifts are performed on multiple code blocks while the data shift is running Bit. Multiple data shift commands can be used such that multiple code blocks have separate shift commands, thereby implementing different data shifts for each code block.

Owner:HONG KONG APPLIED SCI & TECH RES INST

Data processing device

InactiveUS20160041912A1Reduce power consumptionWithout peak performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationMIMDMulti processor

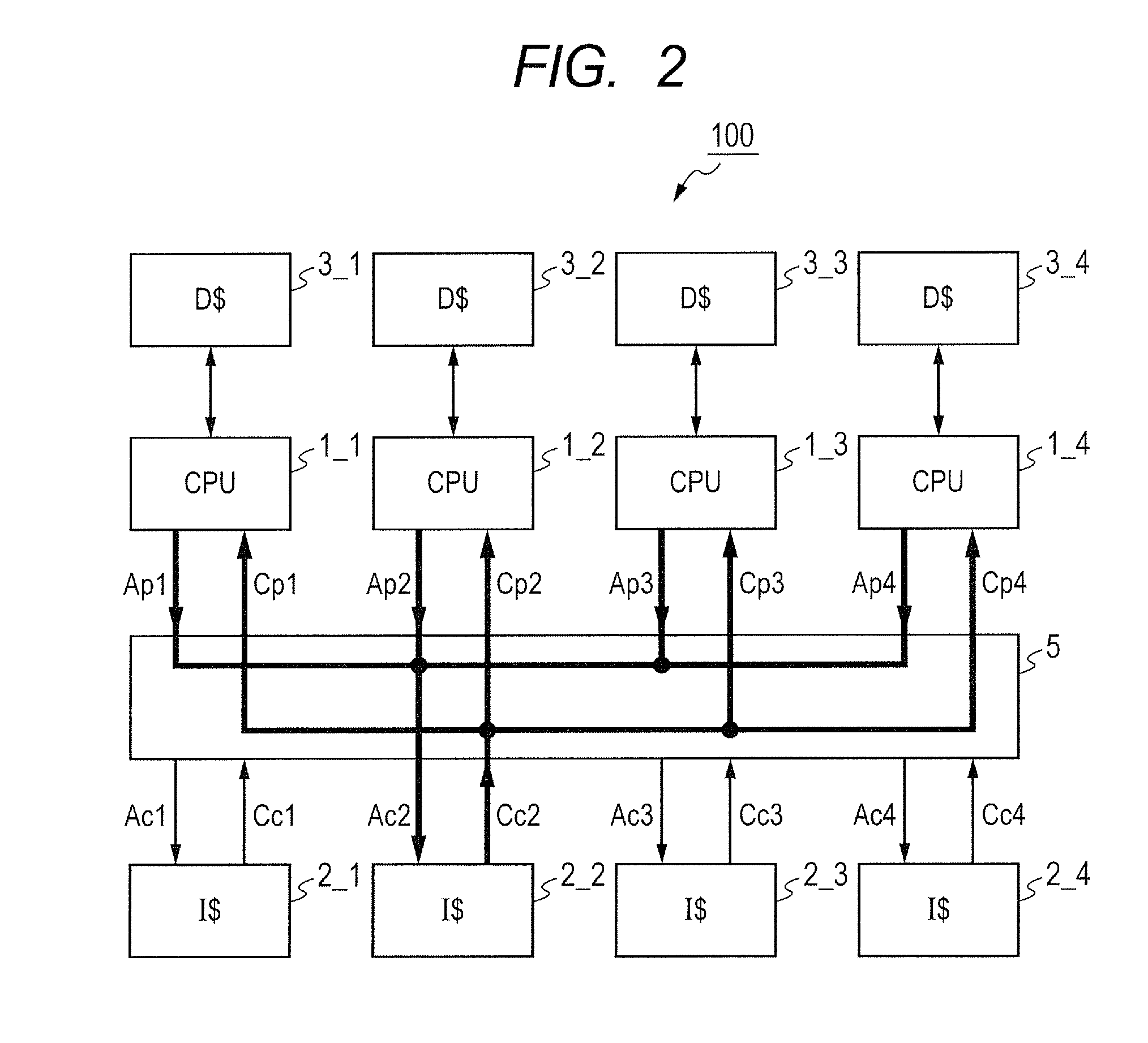

The disclosed invention enables the operation of an MIMD type, an SIMD type, or coexistence thereof in a multiprocessor system including a plurality of CPUs and reduces power consumption for instruction fetch by CPUs operating in the SIMD type. A plurality of CPUs and a plurality of memories corresponding thereto are provided. When the CPUs fetch instruction codes of different addresses from the corresponding memories, the CPUs operate independently (operation of the MIMD type). On the other hand, when the CPUs issue requests for fetching an instruction code of a same address from the corresponding memories, that is, operate in the SIMD type, the instruction code read from one of the memories by one access is parallelly supplied to the CPUs.

Owner:RENESAS ELECTRONICS CORP

Executing multiple instructions multiple date (‘MIMD’) programs on a single instruction multiple data (‘SIMD’) machine

Executing MIMD programs on a SIMD machine, including establishing on the SIMD machine a plurality of SIMD partitions; booting a first SIMD partition in MIMD mode; executing, on a compute node of the first SIMD partition booted in MIMD mode, a MIMD accelerator program; executing a SIMD program in a second SIMD partition, one instance of the SIMD program executing on each compute node of the second SIMD partition, each instance of the SIMD program carrying out a portion of the data processing effected by the SIMD program; and accelerating, by an instance of the SIMD program through the MIMD accelerator program, a portion of the data processing of the instance of the SIMD program.

Owner:IBM CORP

Re-executing launcher program upon termination of launched programs in MIMD mode booted SIMD partitions

InactiveUS7979674B2General purpose stored program computerMultiprogramming arrangementsMIMDTelecommunications link

Executing MIMD programs on a SIMD machine, the SIMD machine including a plurality of compute nodes, each compute node capable of executing only a single thread of execution, the compute nodes initially configured exclusively for SIMD operations, the SIMD machine further comprising a data communications network, the network comprising synchronous data communications links among the compute nodes, including establishing one or more SIMD partitions, booting one or more SIMD partitions in MIMD mode; establishing a MIMD partition; executing by launcher programs a plurality of MIMD programs on two or more of the compute nodes of the MIMD partition; and re-executing a launcher program by an operating system on a compute node in the MIMD partition upon termination of the MIMD program executed by the launcher program.

Owner:IBM CORP

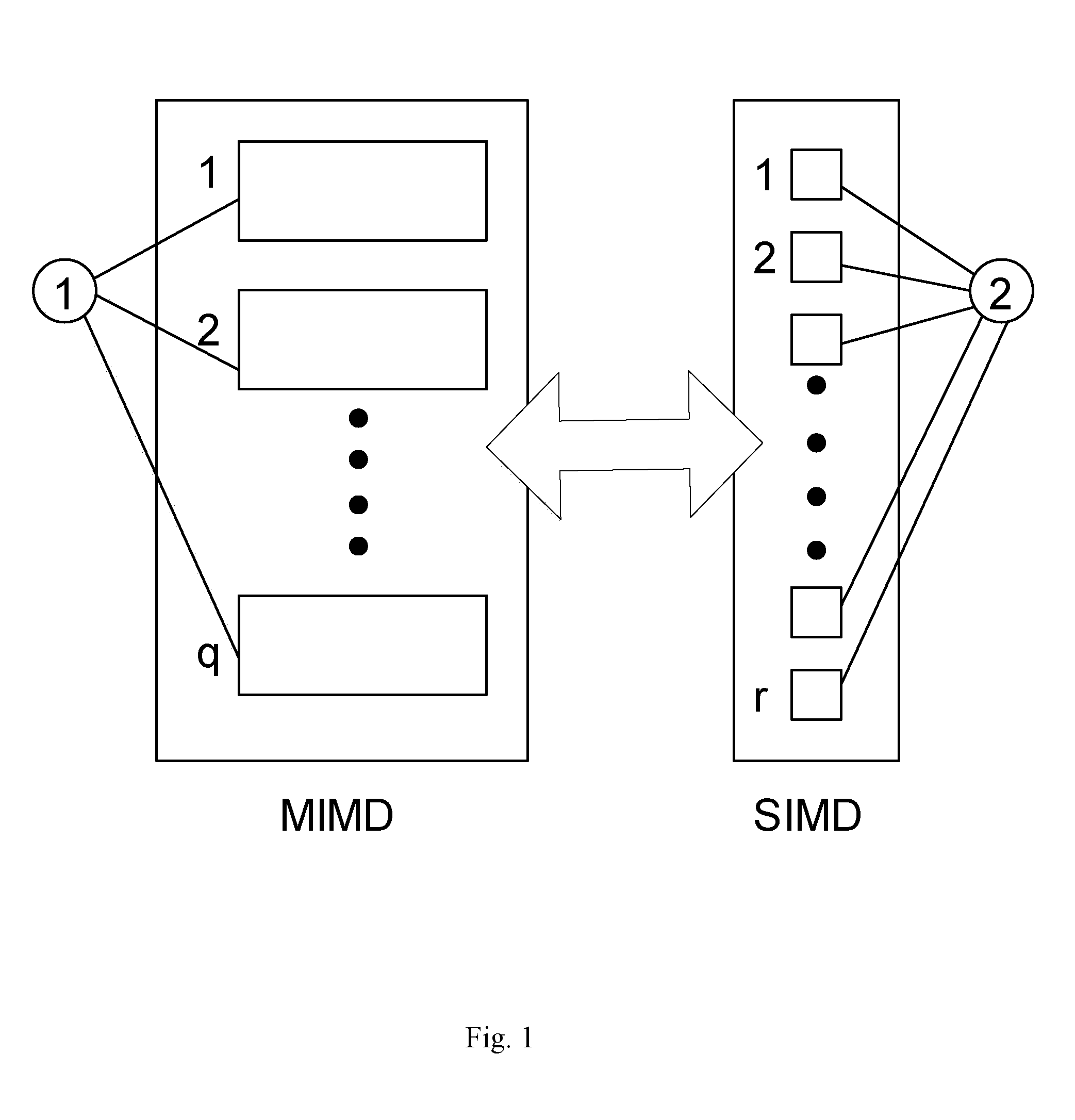

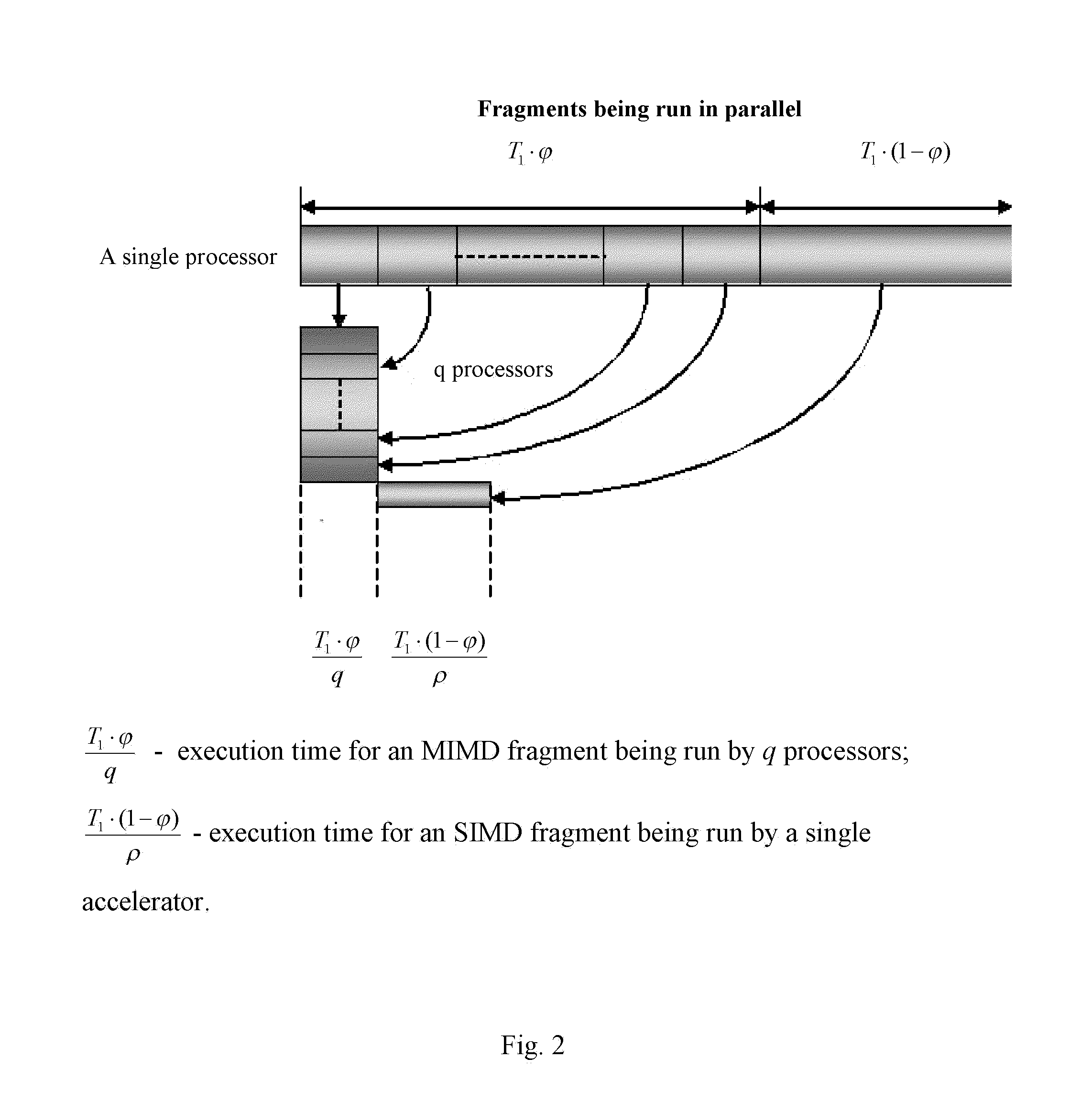

Method for determining the structure of a hybrid computing system

InactiveUS20130212356A1Reduced execution timeConcurrent instruction executionArchitecture with multiple processing unitsMIMDProgram fragment

A method comprises measuring the execution time T1 for a problem to be solved with a program being run by a single processor, measuring the execution time TM and TS of MIMD and SIMD program fragments being run by a single processor and a single accelerator correspondingly, determining the specific acceleration ρ of the execution time for an SIMD program fragment being run by a single accelerator in comparison with the execution time for the fragment being run by a single processor, determining a portion of the execution time for an MIMD fragment being run by a single processor and a portion of the execution time for an SIMD fragment being run by a single processor and adjusting the quantity of processors or accelerators comprised in a hybrid computing system structure according to the data obtained.

Owner:FEDERAL STATE UNITARY ENTERPRISE - AU - RUSN SCI RES INST OF EXPERIMENTAL PHYSICS - FSUE RVNC - VNIIEF

Executing Multiple Instructions Multiple Data (‘MIMD’) programs on a Single Instruction Multiple Data (‘SIMD’) machine

InactiveUS7831802B2General purpose stored program computerElectric digital data processingOperational systemMIMD

Executing Multiple Instructions Multiple Data (‘MIMD’) programs on a Single Instruction Multiple Data (‘SIMD’) machine, the SIMD machine including a plurality of compute nodes, each compute node capable of executing only a single thread of execution, the compute nodes initially configured exclusively for SIMD operations, the SIMD machine further comprising a data communications network, the network comprising synchronous data communications links among the compute nodes, including establishing a SIMD partition comprising a plurality of the compute nodes; booting the SIMD partition in MIMD mode; executing by launcher programs a plurality of MIMD programs on compute nodes in the SIMD partition; and re-executing a launcher program by an operating system on a compute node in the SIMD partition upon termination of the MIMD program executed by the launcher program.

Owner:INT BUSINESS MASCH CORP

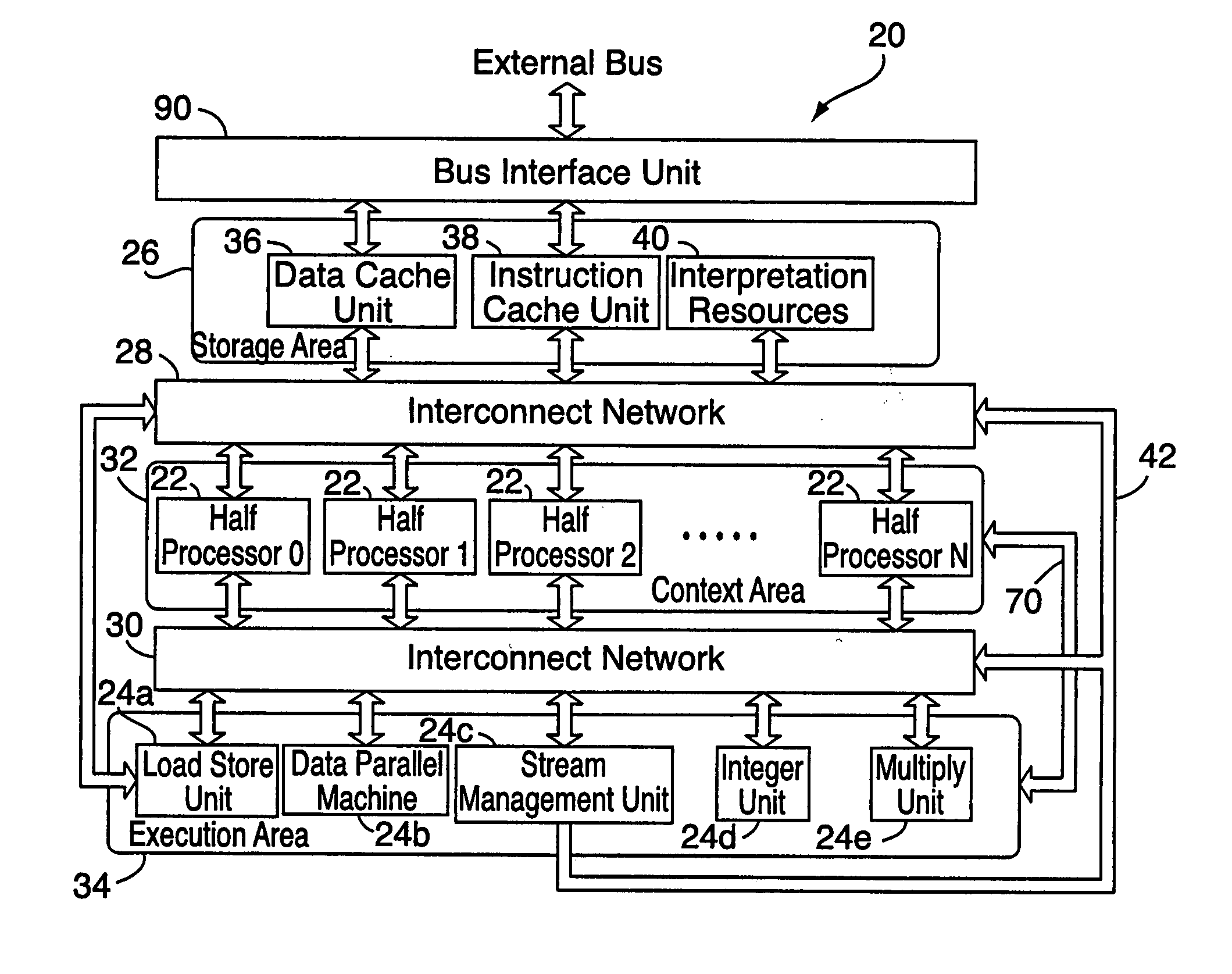

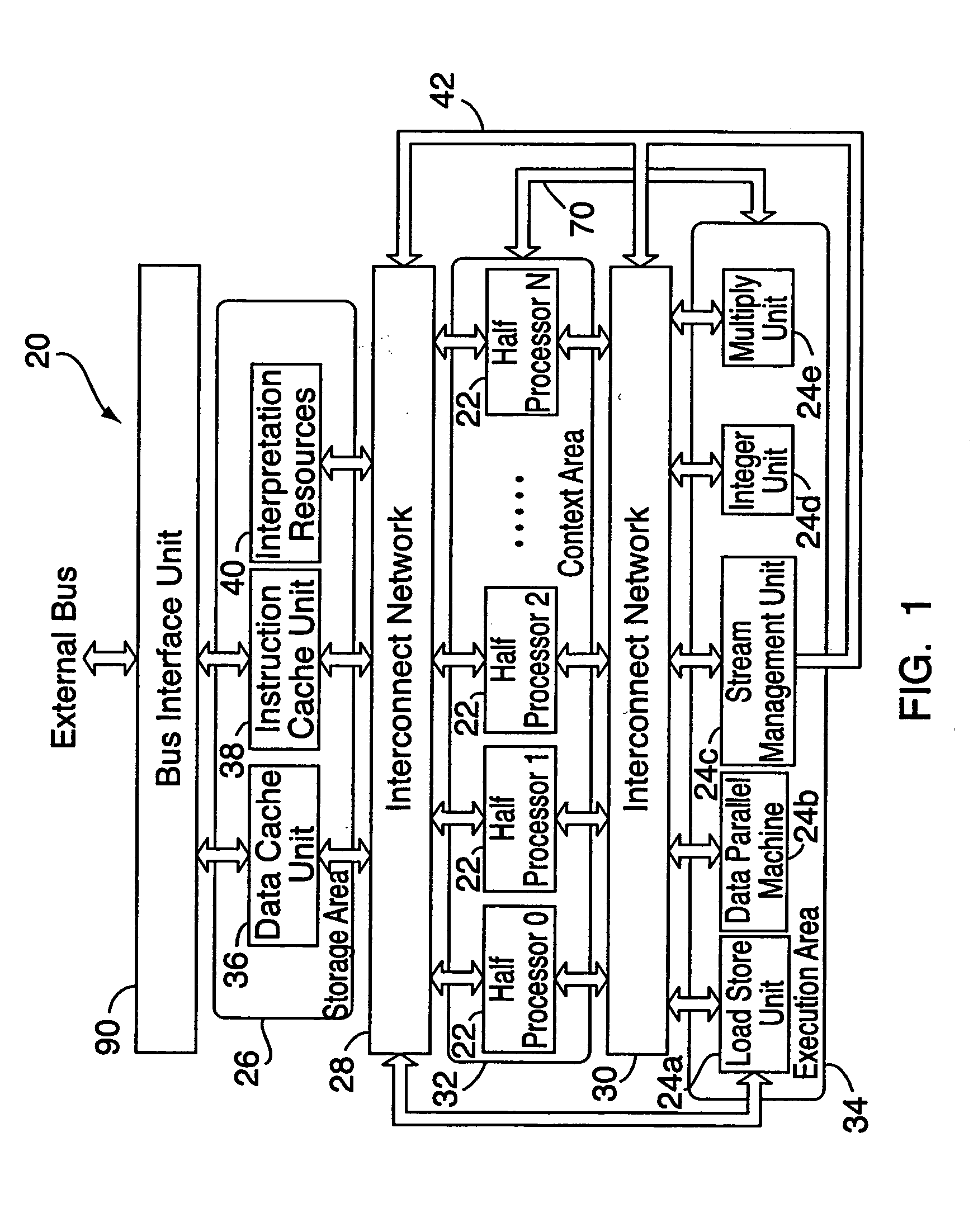

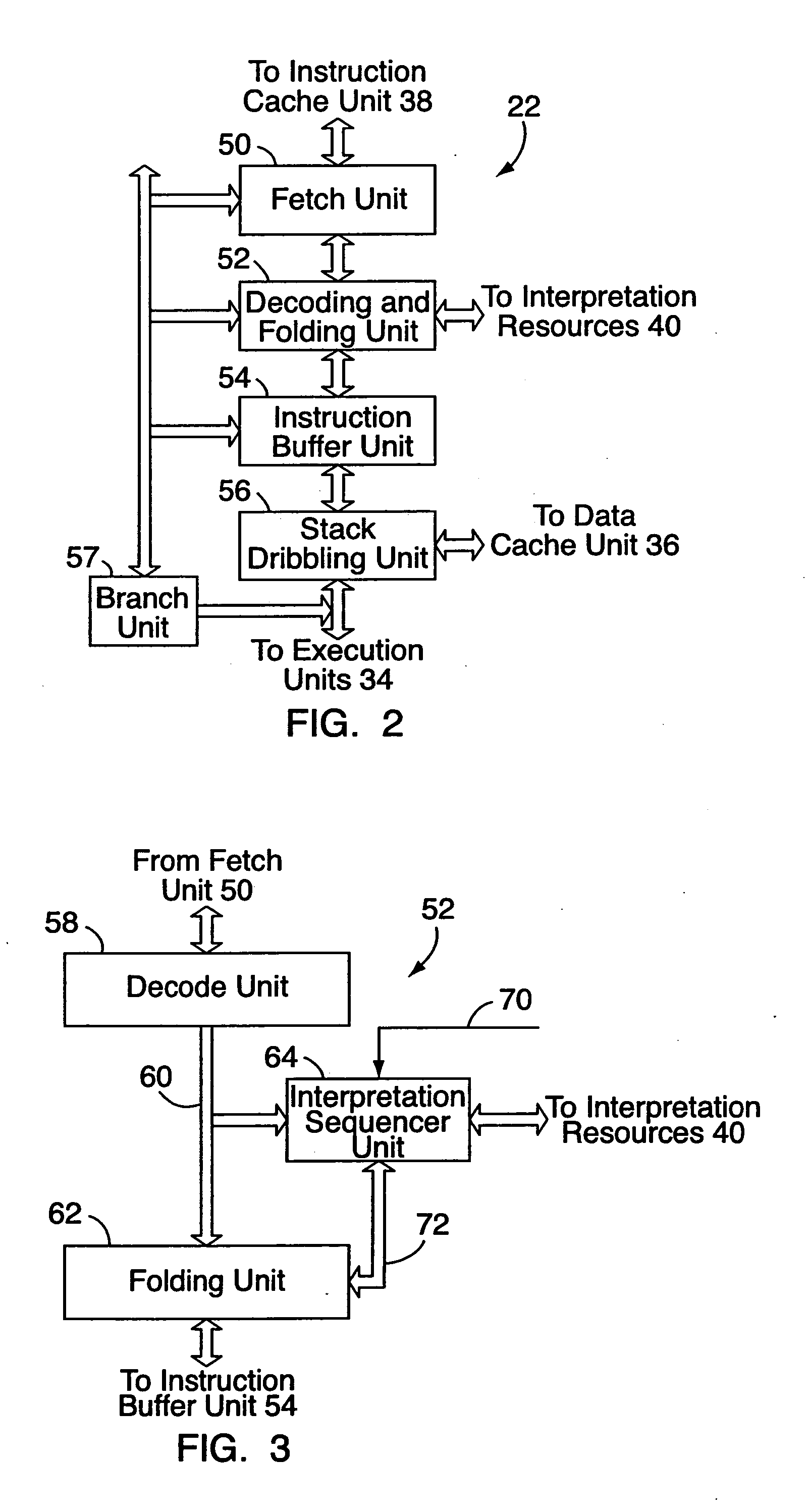

Highly scalable MIMD machine for java and .net processing

InactiveUS20070226454A1Degree of improvementImprove performanceRuntime instruction translationGeneral purpose stored program computerContext managementMIMD

An MIMD processor for Java and Net processing includes a plurality of “half-processors,” separate execution units, and memory caches. Each half-processor is an MIMD processing element having resources for instruction fetch and decode and for instruction stream context management, but excluding execution resources. In other words, the execution resources are removed from the processing elements (resulting in the half-processors) and provided as separate elements for being shared by all the half-processors. The execution units, memory caches, and half-processors are operably connected by two interconnection networks that use a priority-based communications scheme for administering shared access to the execution units and memory caches by the half-processors. The MIMD machine uses a Java and / or .Net instruction set and is capable of running both separate and combined Java and .Net instructions. An instruction stream management unit may be connected to the interconnection networks for controlling communications between the half-processors and shared resources.

Owner:S C UBICORE TECH

Parallel operation device allowing efficient parallel operational processing

InactiveUS7769980B2Easy to handleLow degreeSpecific program execution arrangementsMemory systemsMIMDProcessor register

In arithmetic / logic units (ALU) provided corresponding to entries, an MIMD instruction decoder generating a group of control signals in accordance with a Multiple Instruction-Multiple Data (MIMD) instruction and an MIMD register storing data designating the MIMD instruction are provided, and an inter-ALU communication circuit is provided. The amount and direction of movement of the inter-ALU communication circuit are set by data bits stored in a movement data register. It is possible to execute data movement and arithmetic / logic operation with the amount of movement and operation instruction set individually for each ALU unit. Therefore, in a Single Instruction-Multiple Data type processing device, Multiple Instruction-Multiple Data operation can be executed at high speed in a flexible manner.

Owner:RENESAS ELECTRONICS CORP

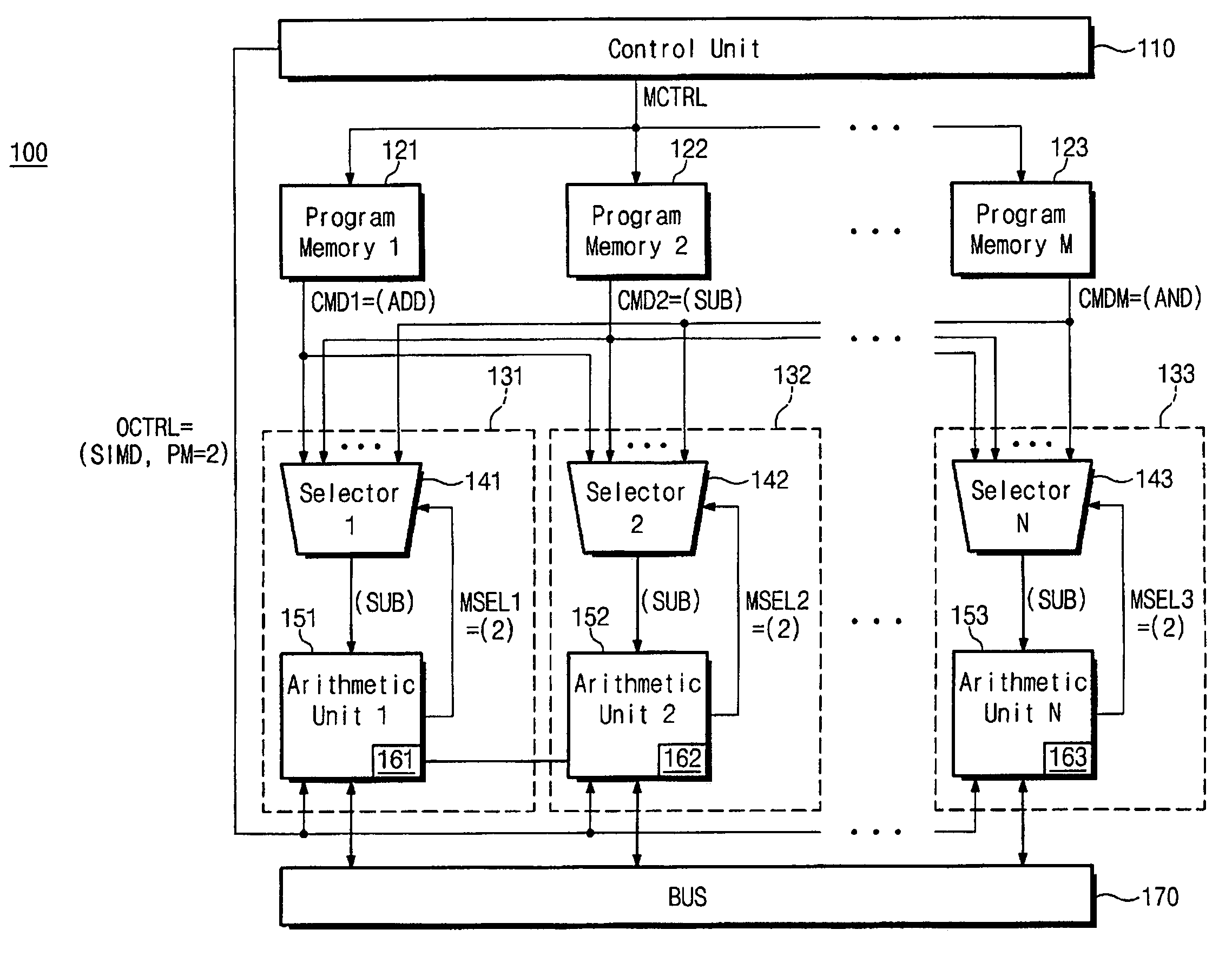

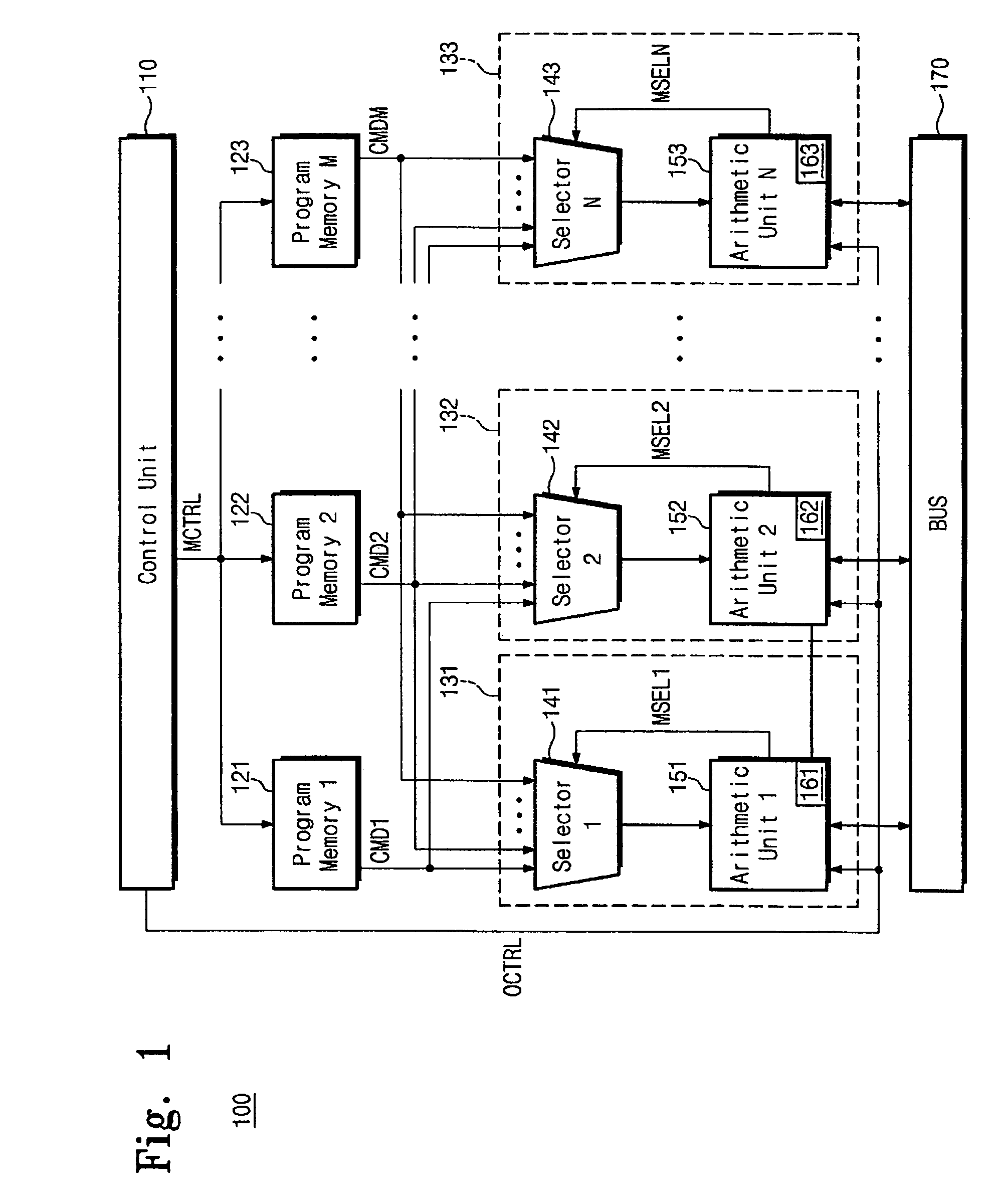

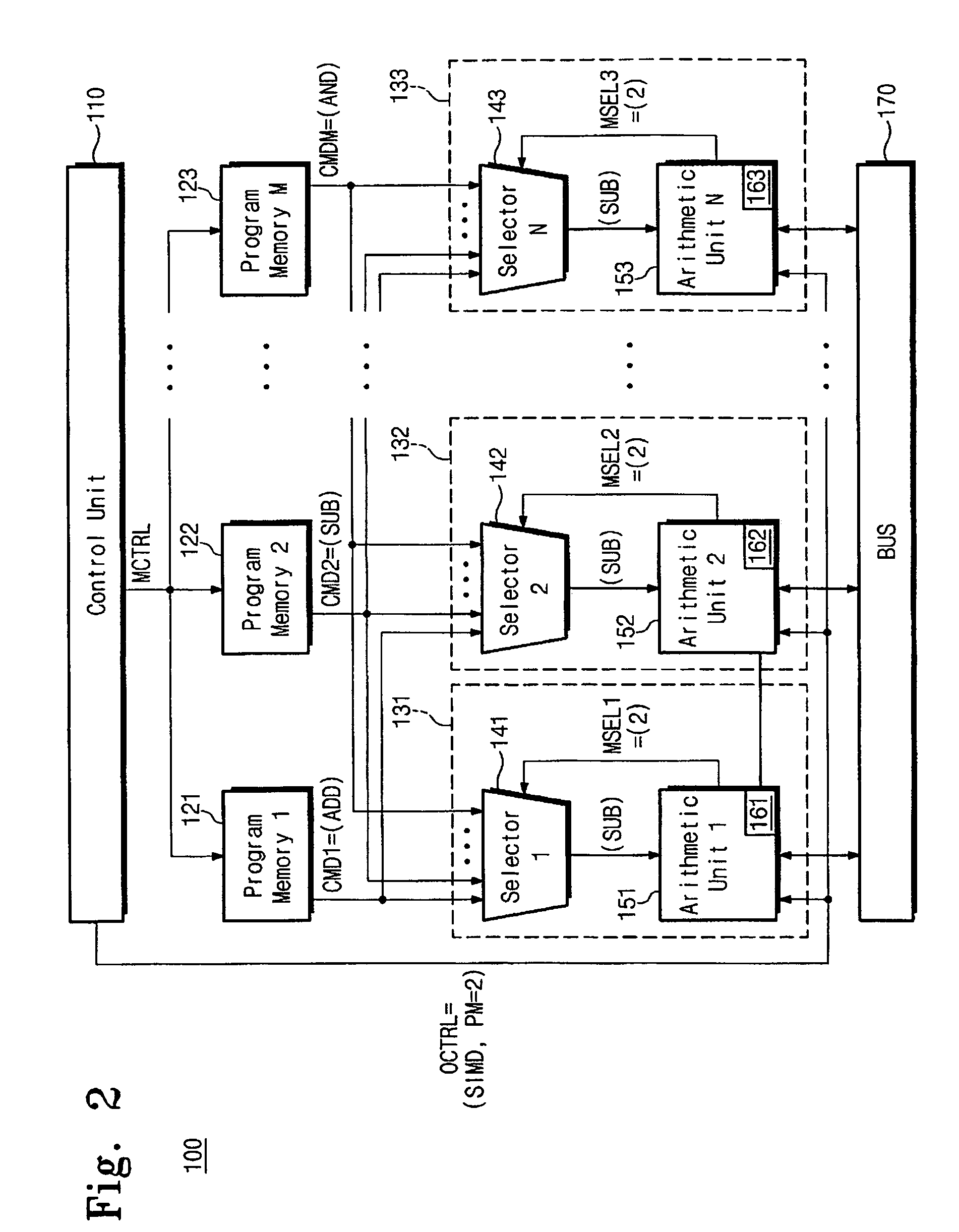

Arithmetic units responsive to common control signal to generate signals to selectors for selecting instructions from among respective program memories for SIMD / MIMD processing control

ActiveUS7814296B2Efficient changeProgram control using stored programsMultiprogramming arrangementsMIMDControl signal

Provided is a data processing circuit. A control unit outputs an operation control signal and a memory control signal. A plurality of program memories each outputs a command in response to the memory control signal. A plurality of arithmetic sections each selectively performs any one of the commands from the plurality of program memories in response to the operation control signal. Operation modes of the data processing circuit can be flexibly changed according to operation environments.

Owner:ELECTRONICS & TELECOMM RES INST

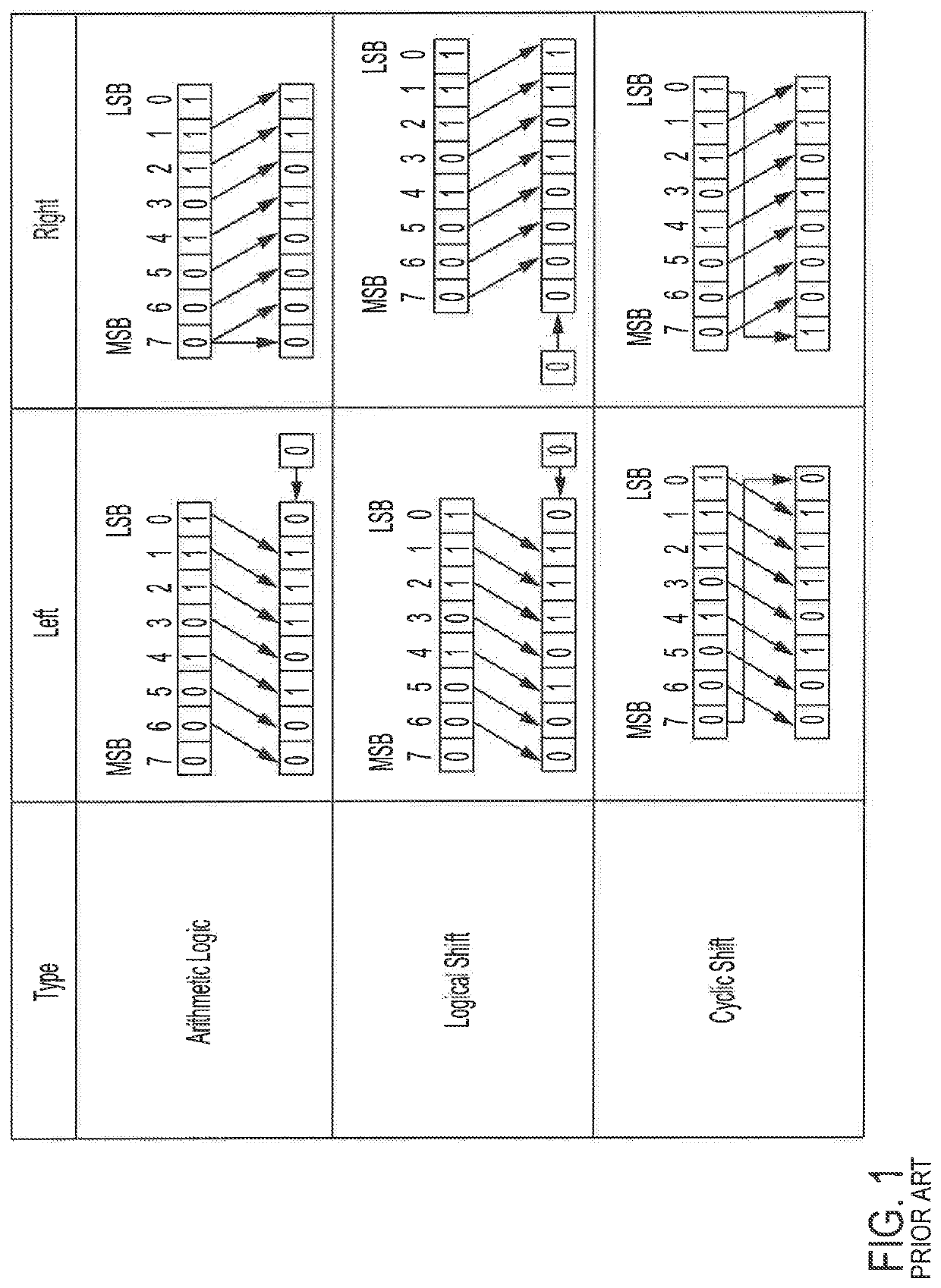

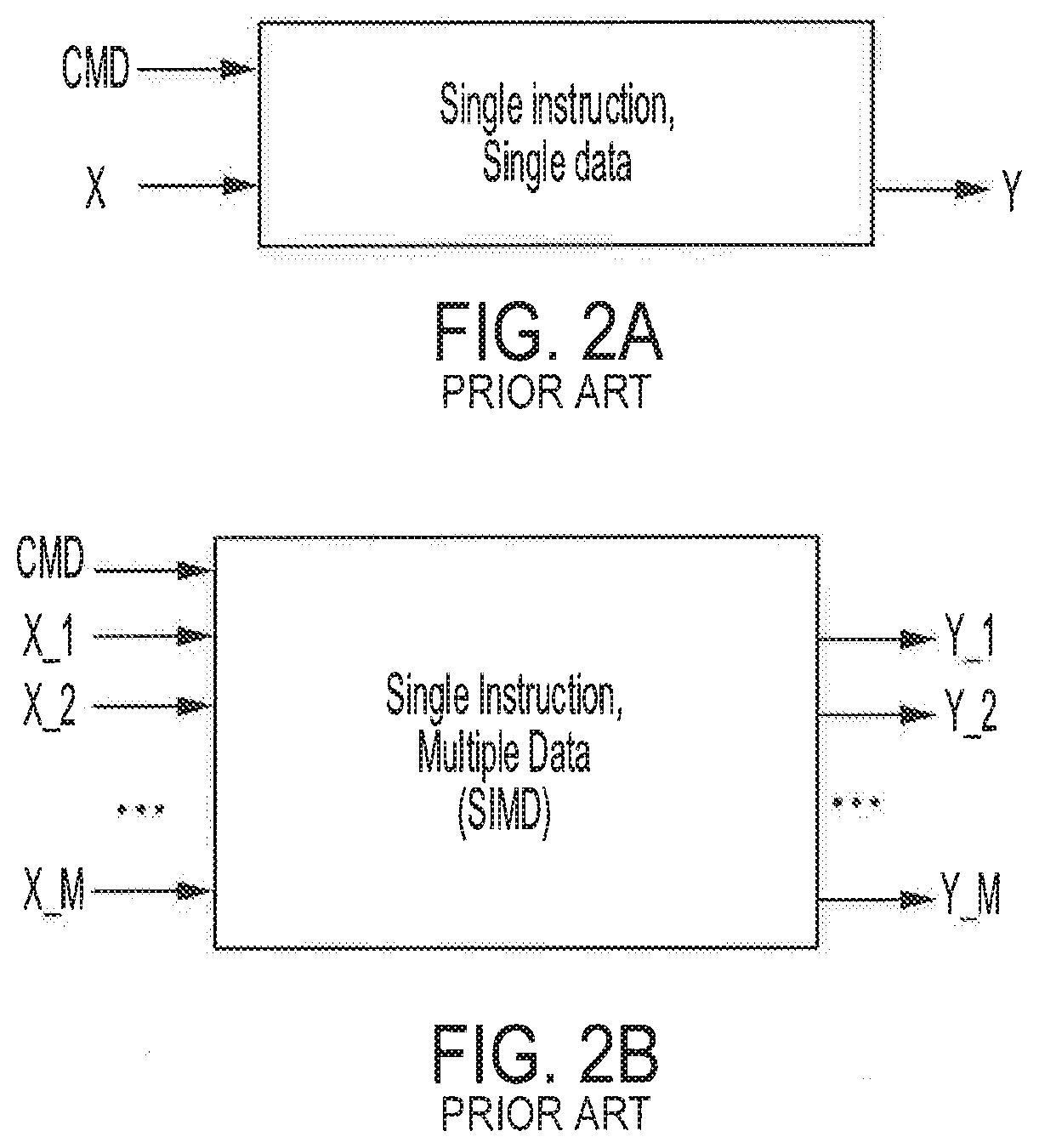

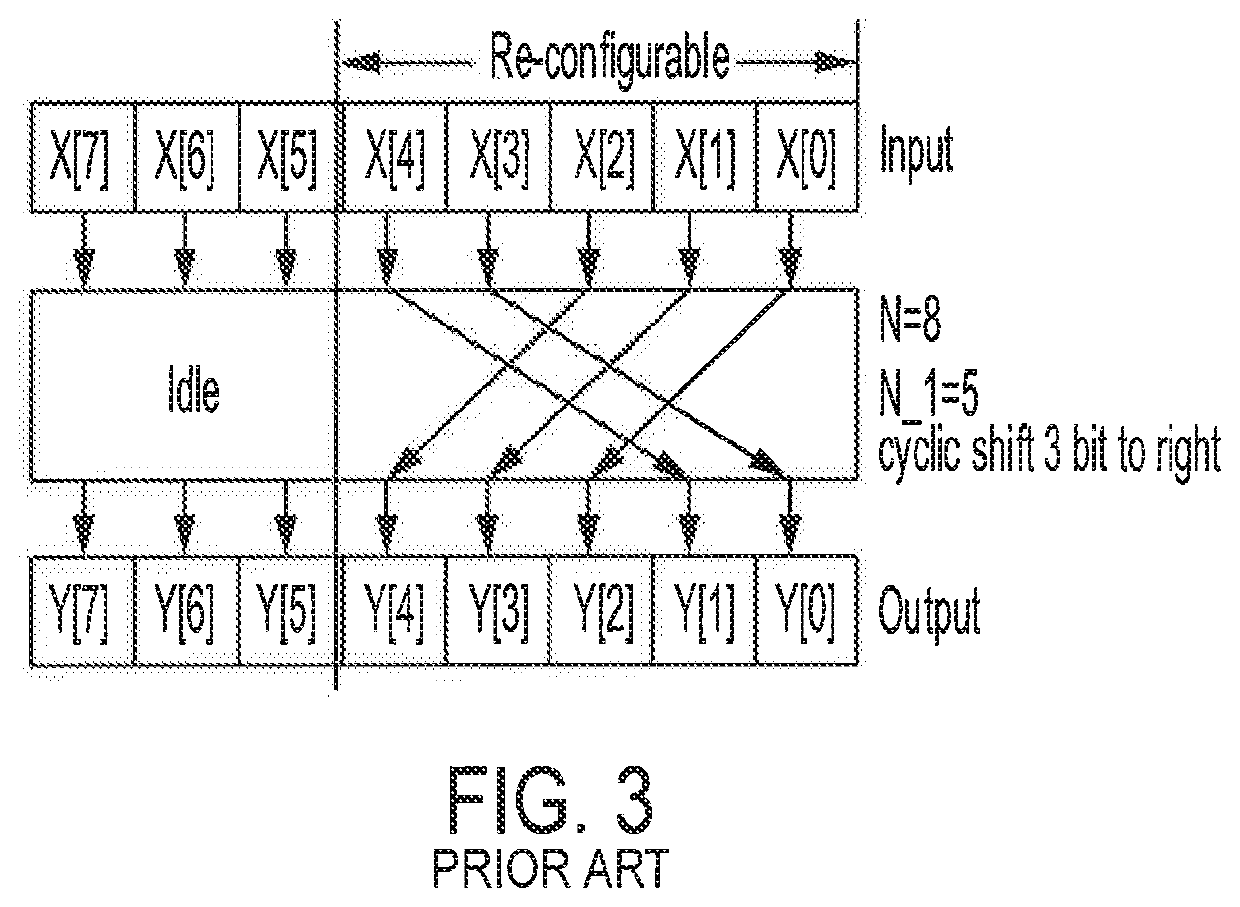

Reconfigurable segmented scalable shifter

ActiveUS20200249909A1Flexible and efficient utilization of hardwareCode conversionConcurrent instruction executionComputer architectureMIMD

Systems and methods that provide reconfigurable shifter configurations supporting multiple instruction, multiple data (MIMD) are described. Shifters implemented according to embodiments support multiple data shifts with respect to an instance of data shifting, wherein multiple individual different data shifts are implemented at a time in parallel. Reconfigurable segmented scalable shifters of embodiments, in addition being reconfigurable for scalability in supporting data shifting with respect to various bit lengths of data, are configured to support data shifting of differing bit lengths in parallel. The data shifters of embodiments implement segmentation for facilitating data shifting with respect to differing bit lengths. Different data shift commands may be provided with respect to each such segment, thereby facilitating multiple data shifts in parallel with respect to various bit lengths of data. Reconfigurable segmented scalable shifter configurations provide for fully reconfigurable data width and shift command of each message of input data.

Owner:HONG KONG APPLIED SCI & TECH RES INST

Parallel LDPC decoder

ActiveUS10826529B2Efficient and flexible designEnhanced operational aspectError correction/detection using multiple parity bitsCode conversionCoding blockComputer architecture

Owner:HONG KONG APPLIED SCI & TECH RES INST

Ray tracing core and ray tracing chip having the same

A ray tracing core comprising a ray generation unit and a plurality of T&I (Traversal & Intersection) units with MIMD (Multiple Instruction stream Multiple Data stream) architecture is disclosed. The ray generation unit generates at least one eye ray based on an eye ray generation information. The eye ray generation information includes a screen coordinate value. Each of the plurality of T&I units receives the at least one eye ray and checks whether there exists a triangle intersected with the received at least one eye ray. The triangle configures a space.

Owner:SILICONARTS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com