Parallel LDPC decoder

A decoder and code block technology, applied in the field of decoding and correcting encoded data, can solve the problems of not providing flexible design, low configuration efficiency, etc., achieve effective processing and power consumption, flexible design, and promote flexibility and efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

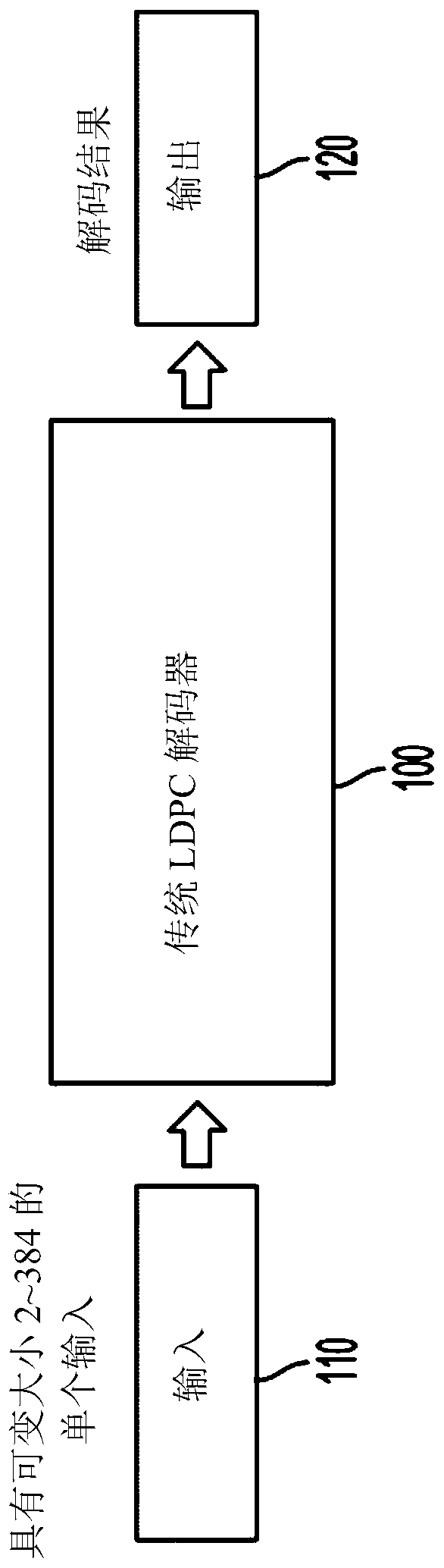

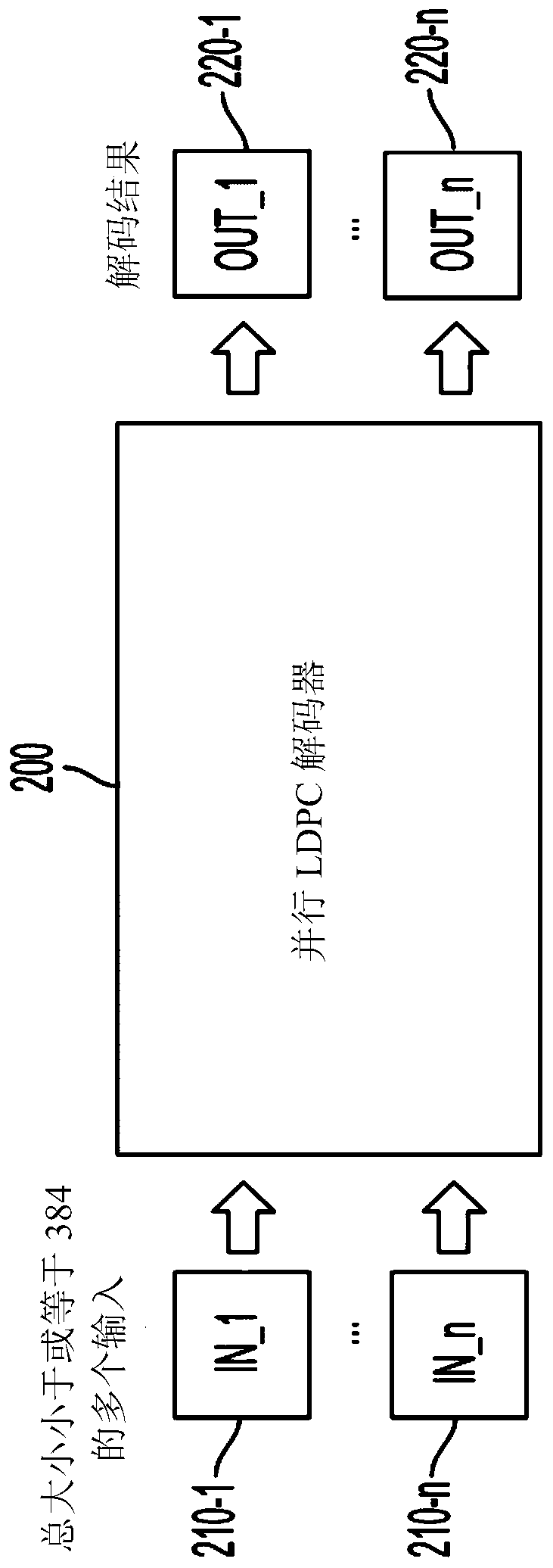

[0026] Figure 1 shows a conventional LDPC decoder, which is typically used by receivers in 5G cellular networks to decode data encoded using QC-LDPC codes for data correction. Accordingly, the conventional LDPC decoder 100 of FIG. 1 includes a 5G LDPC error-correcting code decoder that receives encoded bits (eg, in log-likelihood ratios (LLRs)) from a noise signal 110 and outputs decoded bits as a decoding result 120 . At runtime, conventional LDPC decoder 100 employs hierarchical decoding logic to iteratively process the parity check equations with respect to the coded bits of a single code block for which valid codewords satisfy all the parity check equations. It can be understood from the foregoing that the conventional LDPC decoder 100 can only decode one code block at a time.

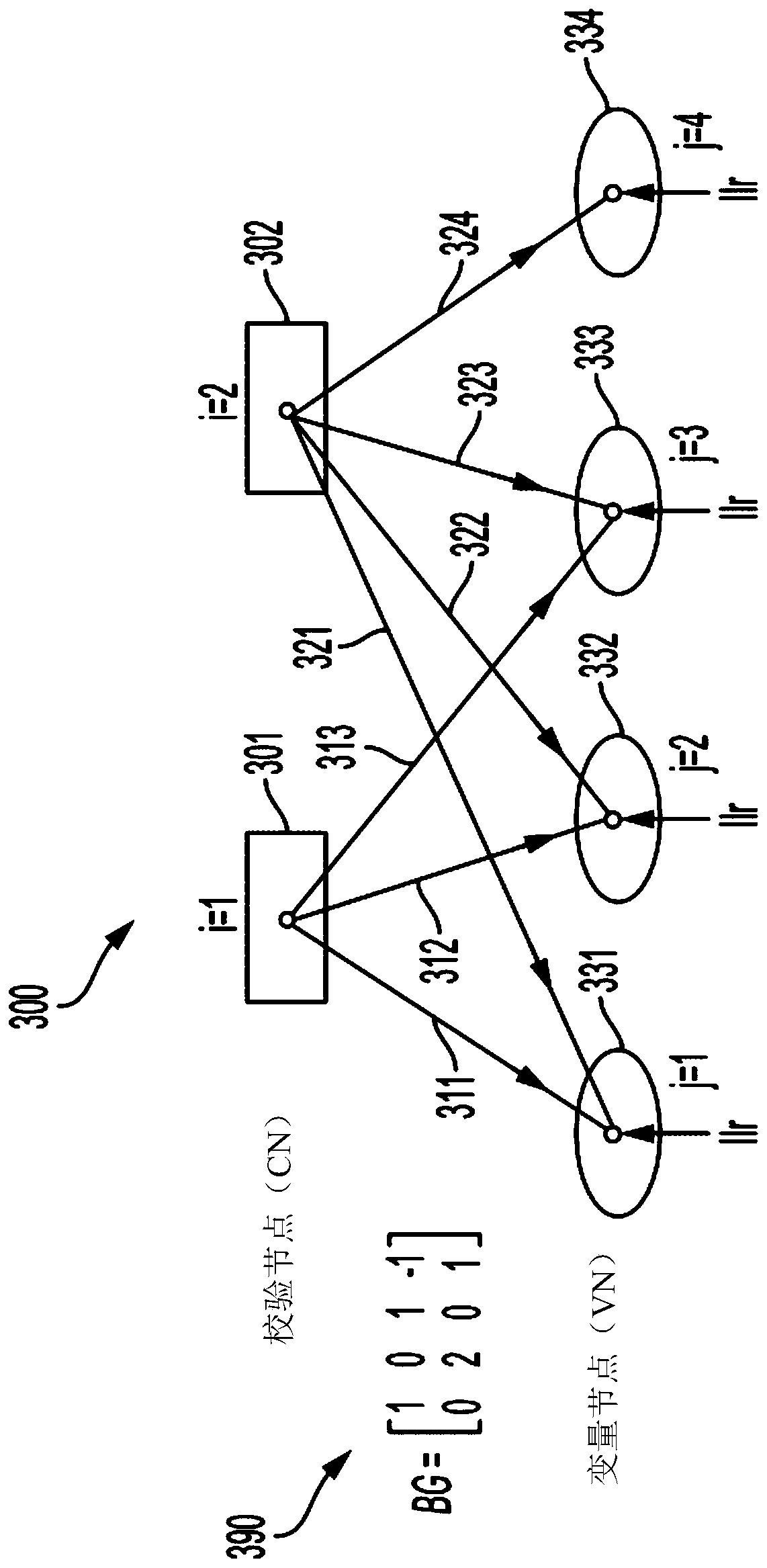

[0027] At runtime, the LDPC decoder input is a code block whose size depends on various factors. In a 5G cellular network according to current standards, base graph (base graph, BG) matrices BG1 a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com