Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

33results about How to "Simple circuit implementation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

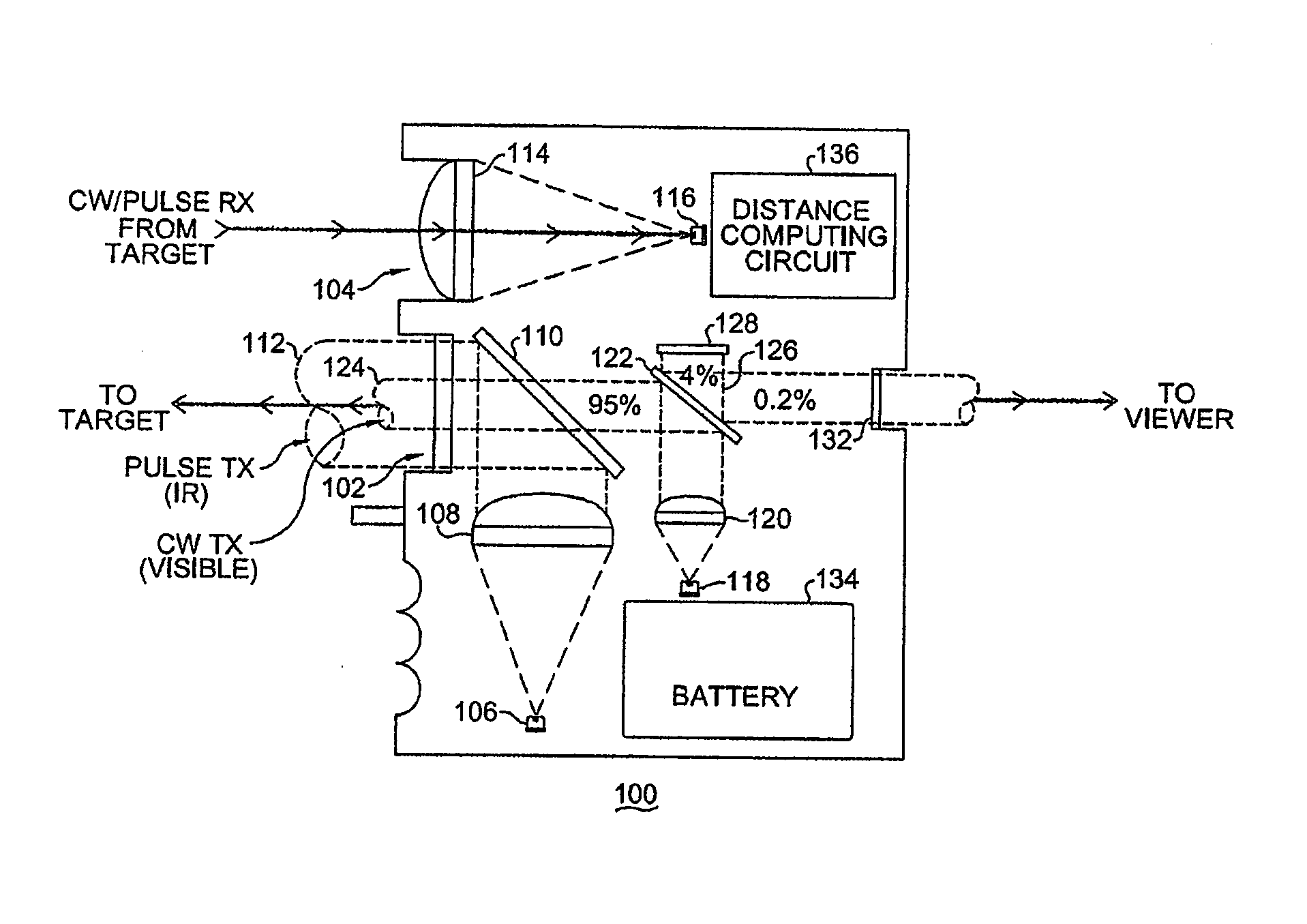

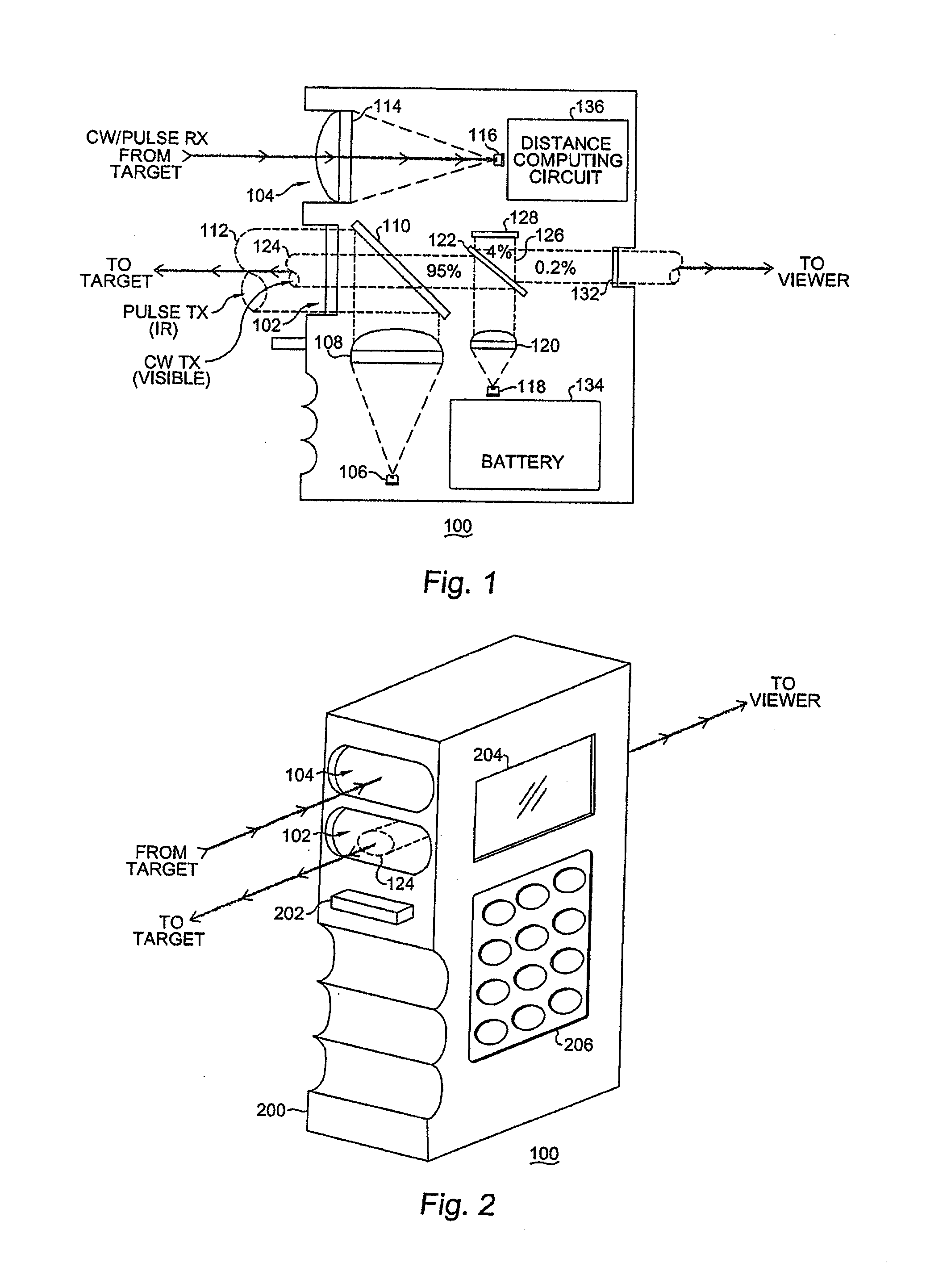

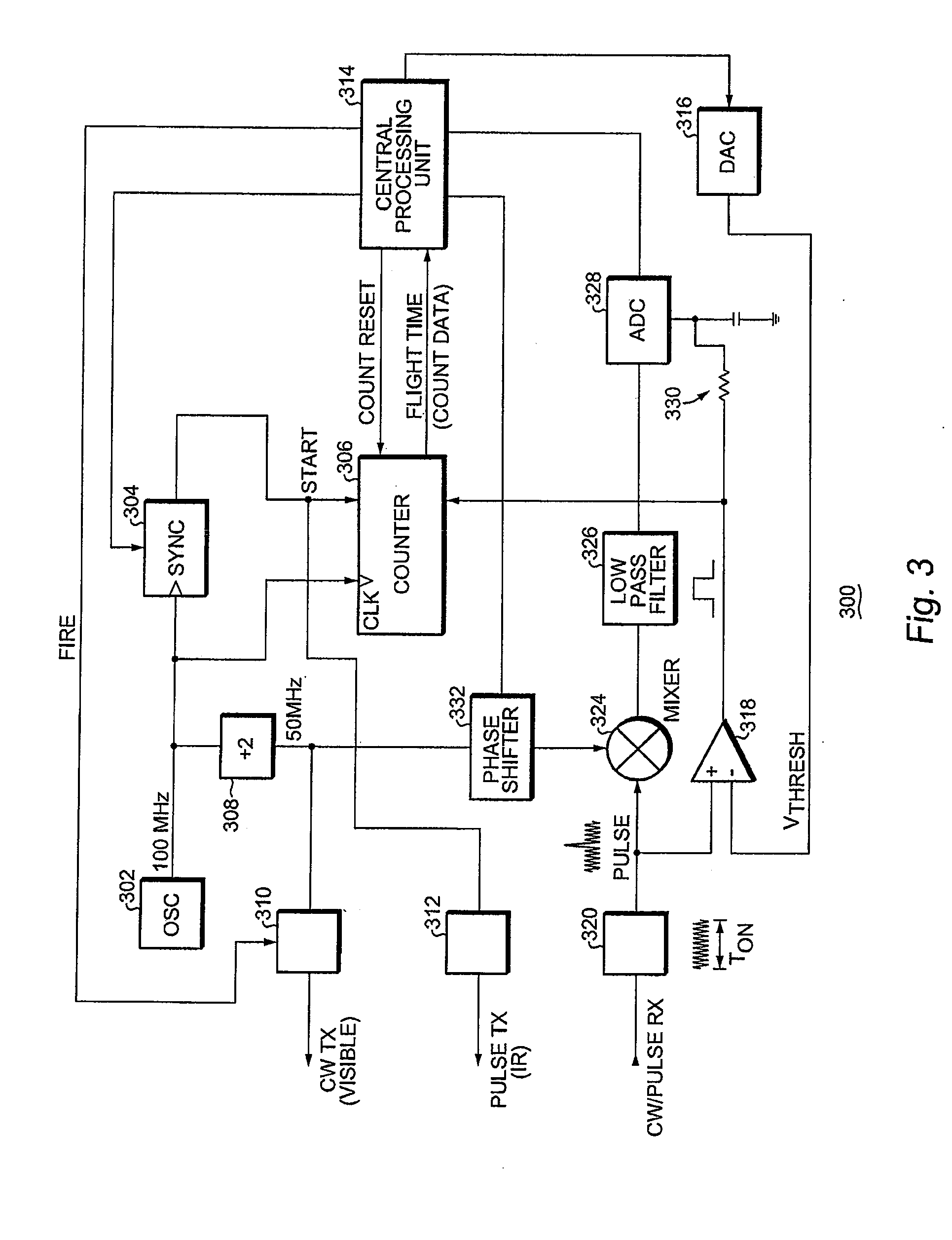

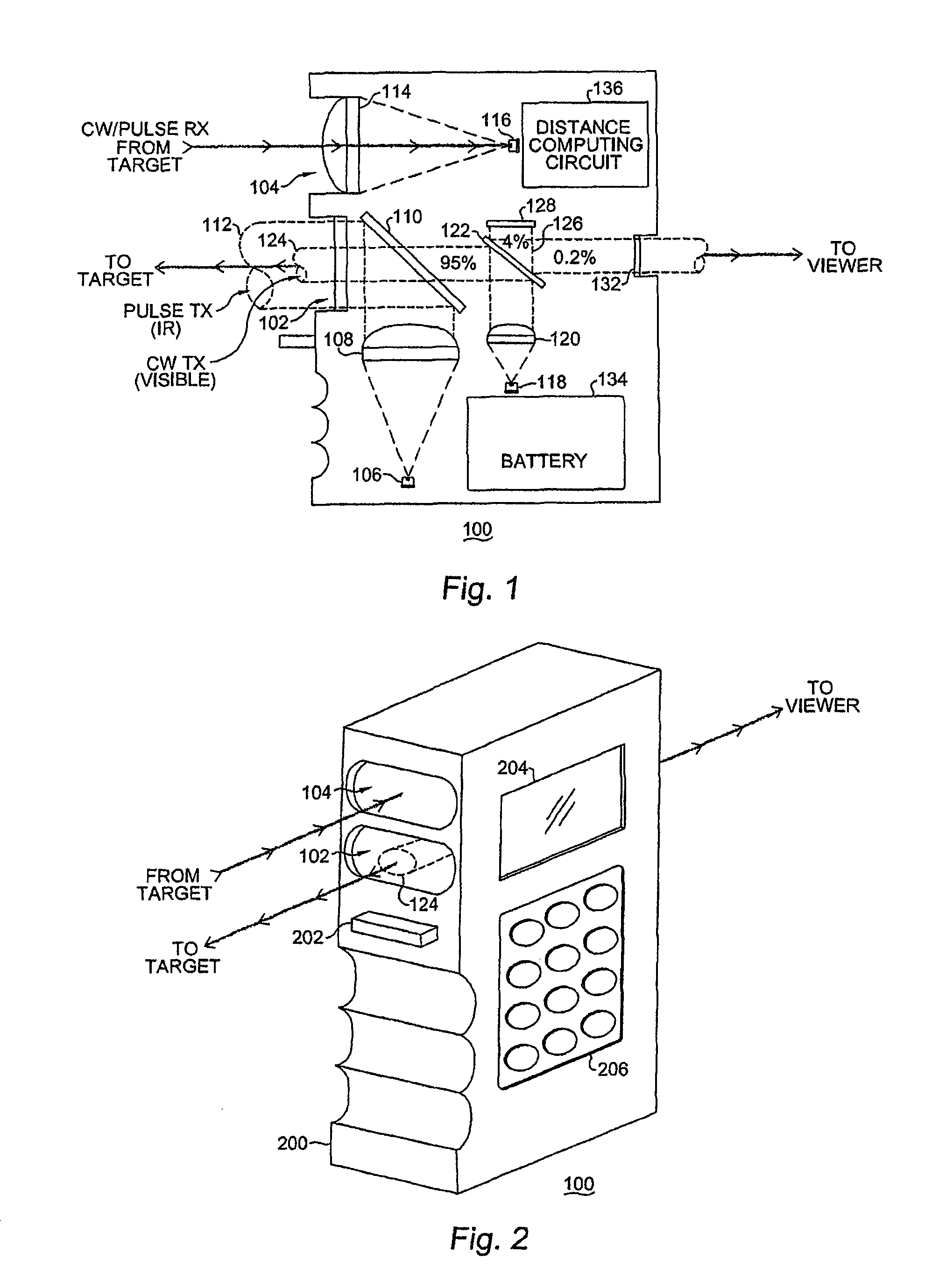

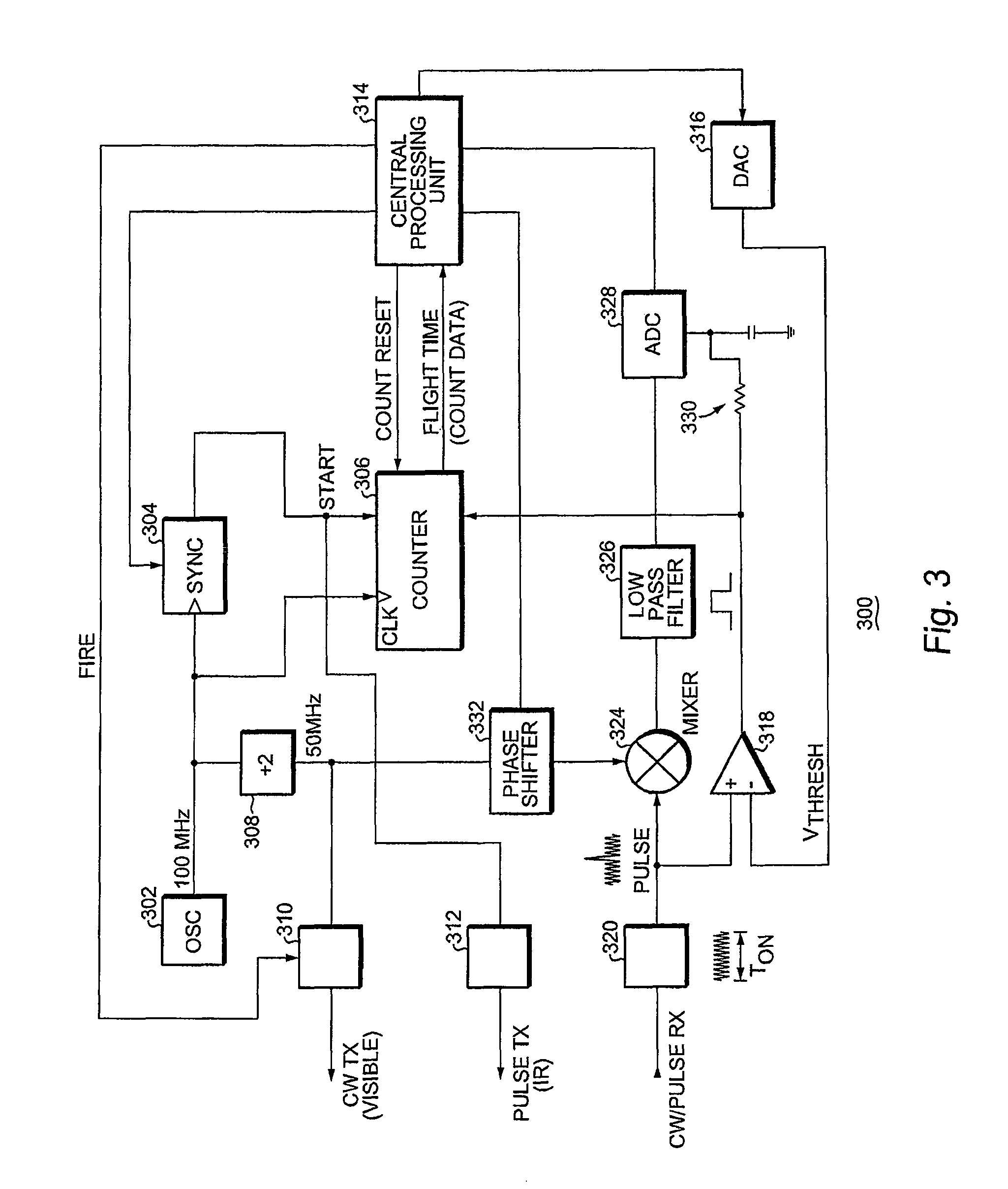

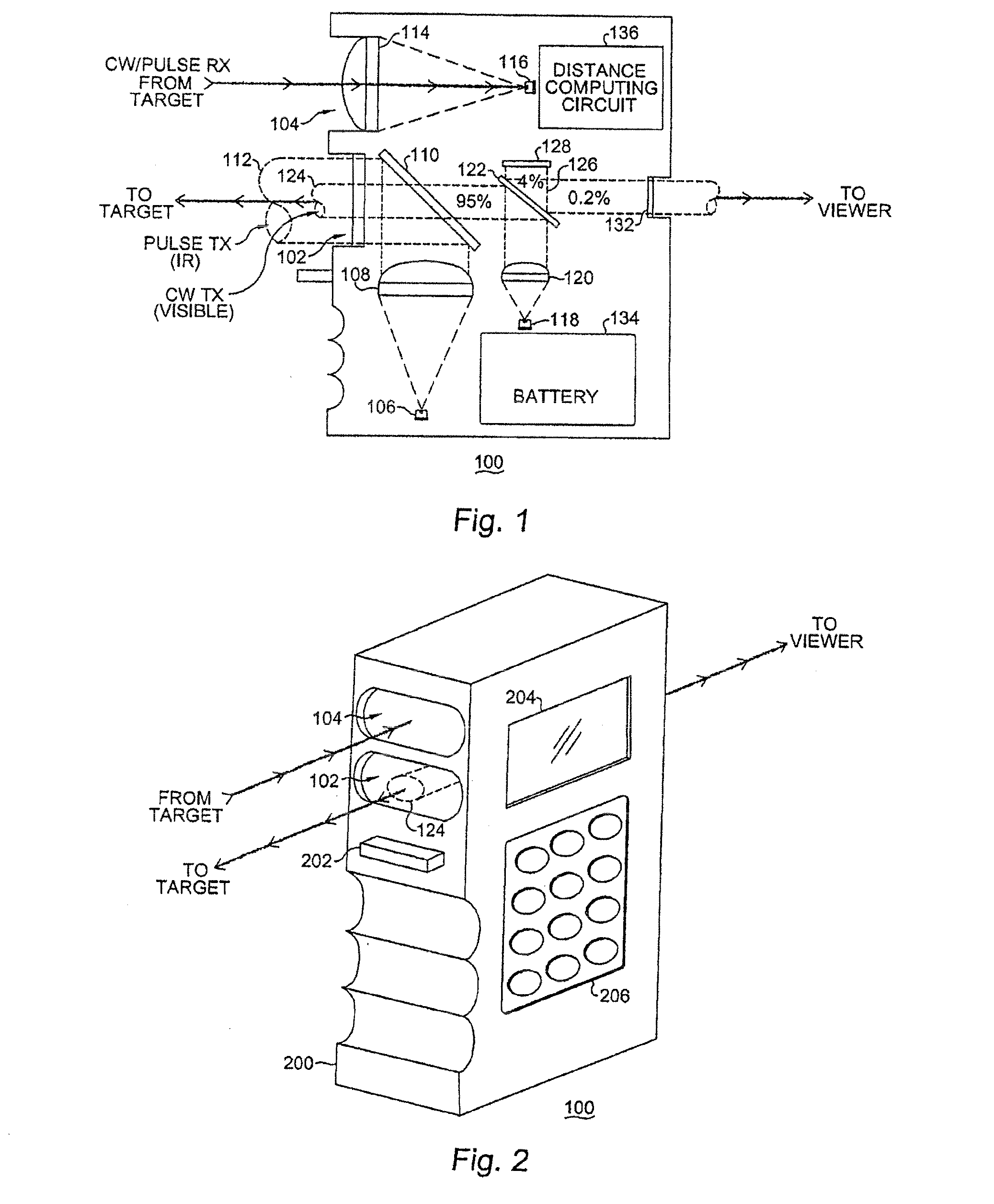

System and method for a rangefinding instrument incorporating pulse and continuous wave signal generating and processing techniques for increased distance measurement accuracy

ActiveUS20140071432A1Improve ranging accuracyEfficient solutionOptical rangefindersActive open surveying meansAmbiguityContinuous wave signal

A system and method for a rangefinding instrument incorporating pulse and continuous wave signal generating and processing techniques for increased distance measurement accuracy. The use of the former technique effectively solves the ambiguity issues inherent in the latter while allowing for relatively simple circuit implementations. Thus, a potentially more accurate phase-based distance measurement technique can be utilized which is also completely independent of the maximum range to the target.

Owner:LASER TECH INC +1

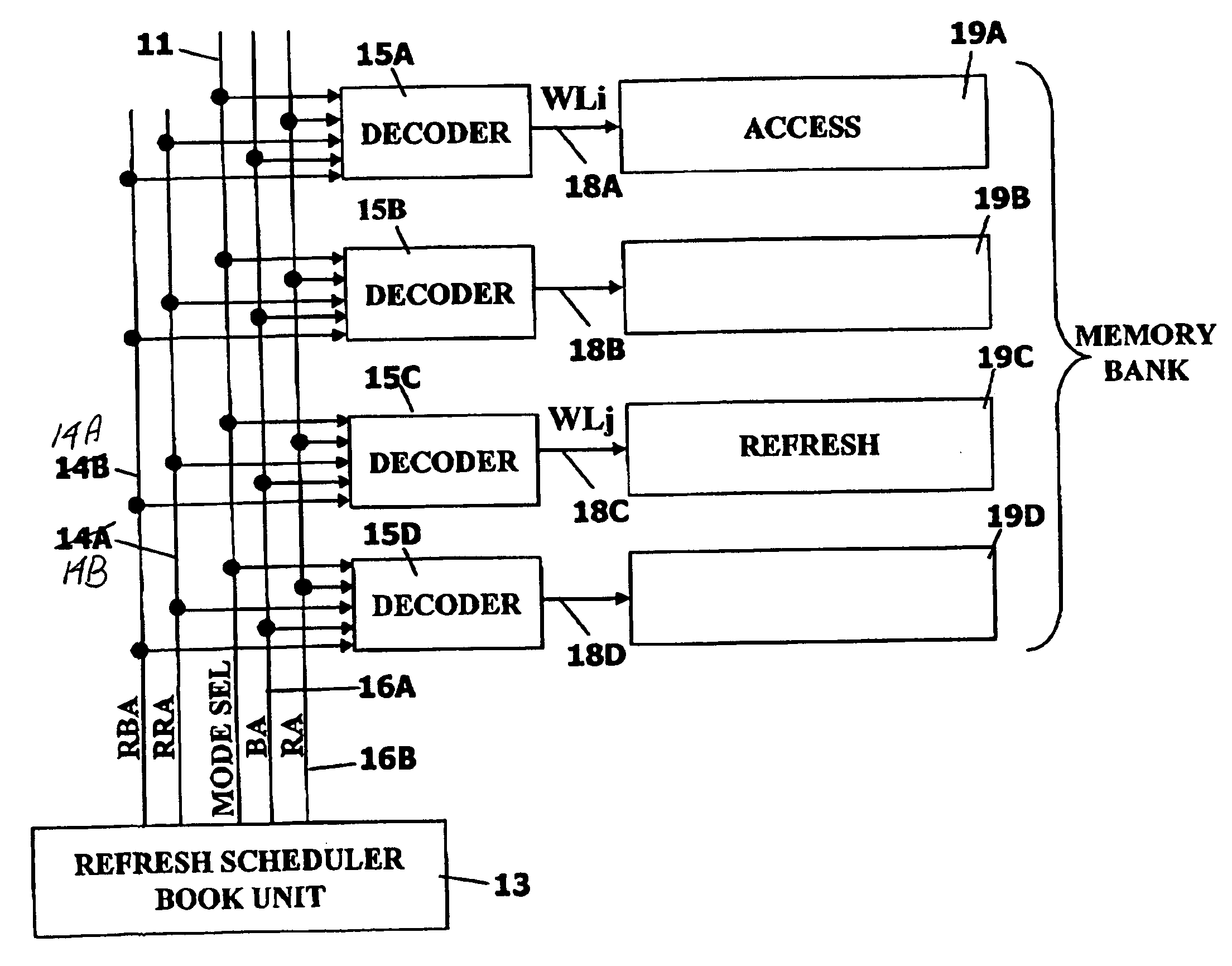

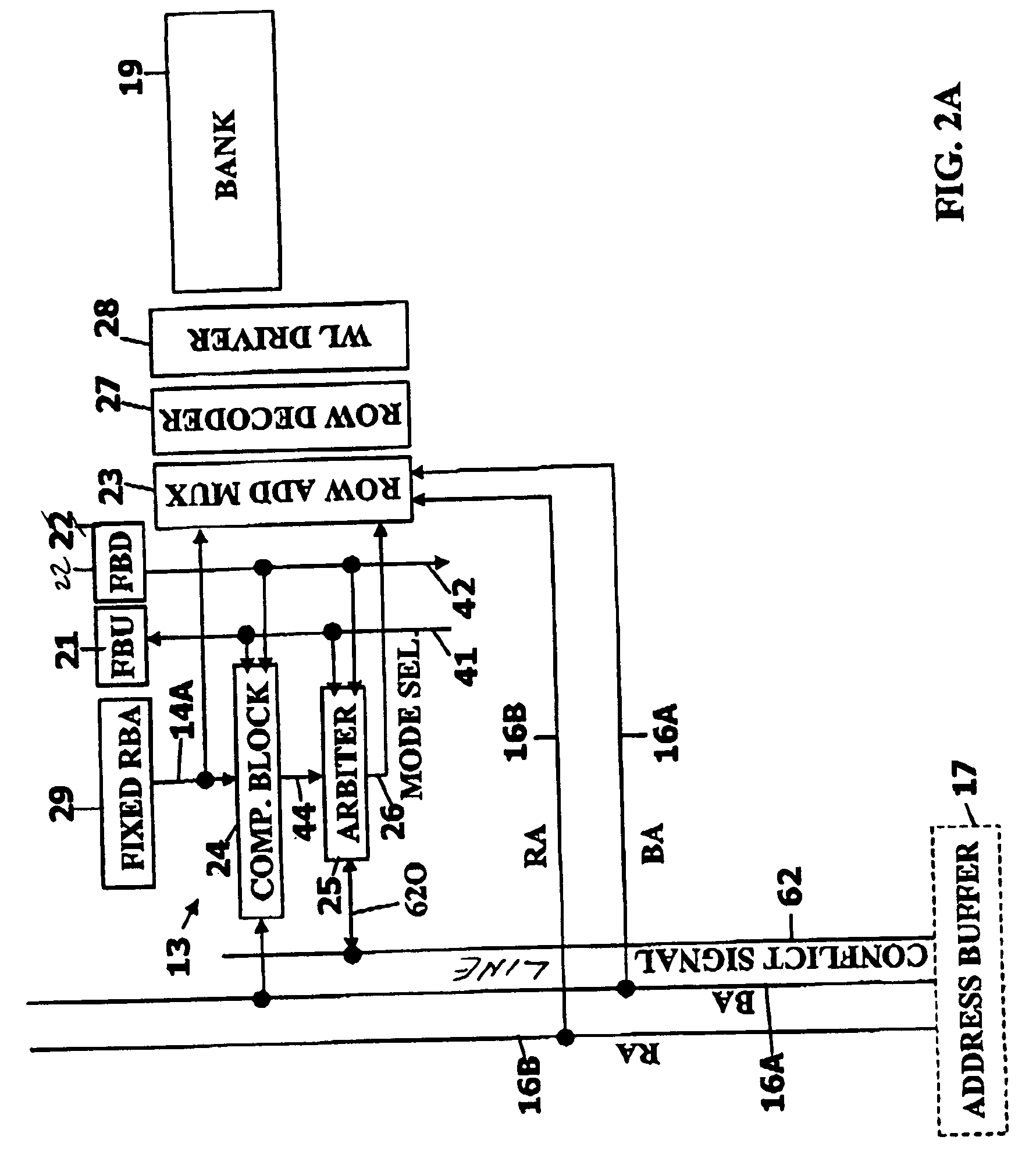

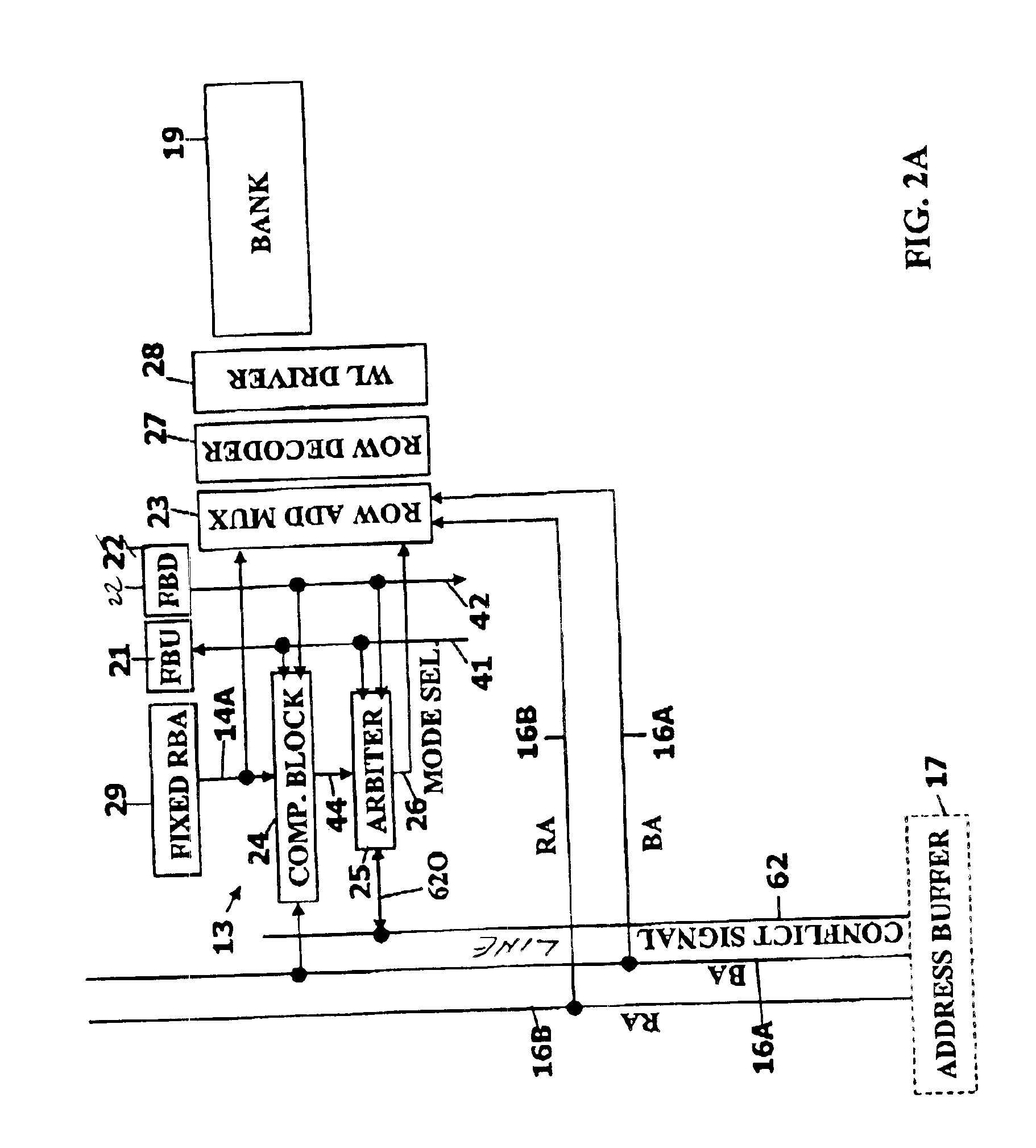

Dynamic random access memory with smart refresh scheduler

ActiveUS20050013185A1Simple circuit implementationMinimizes a penalty from schedulingDigital storageMemory bankEmbedded system

In a DRAM, which includes a plurality of memory banks, there is a pair of separate flag bit registers for each bank with the flag bit registers that are shifted up / down respectively. A comparator for each bank provides a comparator output. An arbiter for each bank is connected to receive a flag bit up signal and a flag bit down signal from the flag bit registers for that bank and the comparator output from the comparator for that bank. The arbiters are connected to receive a conflict in signal and to provide a conflict out signal. The pair of flag bit registers represent a refresh status of each bank and designate memory banks or arrays that are ready for a refresh operation.

Owner:GLOBALFOUNDRIES US INC

Dynamic random access memory with smart refresh scheduler

ActiveUS6954387B2Simple circuit implementationMinimizes a penalty from schedulingDigital storageStatic random-access memoryMemory bank

Owner:GLOBALFOUNDRIES U S INC

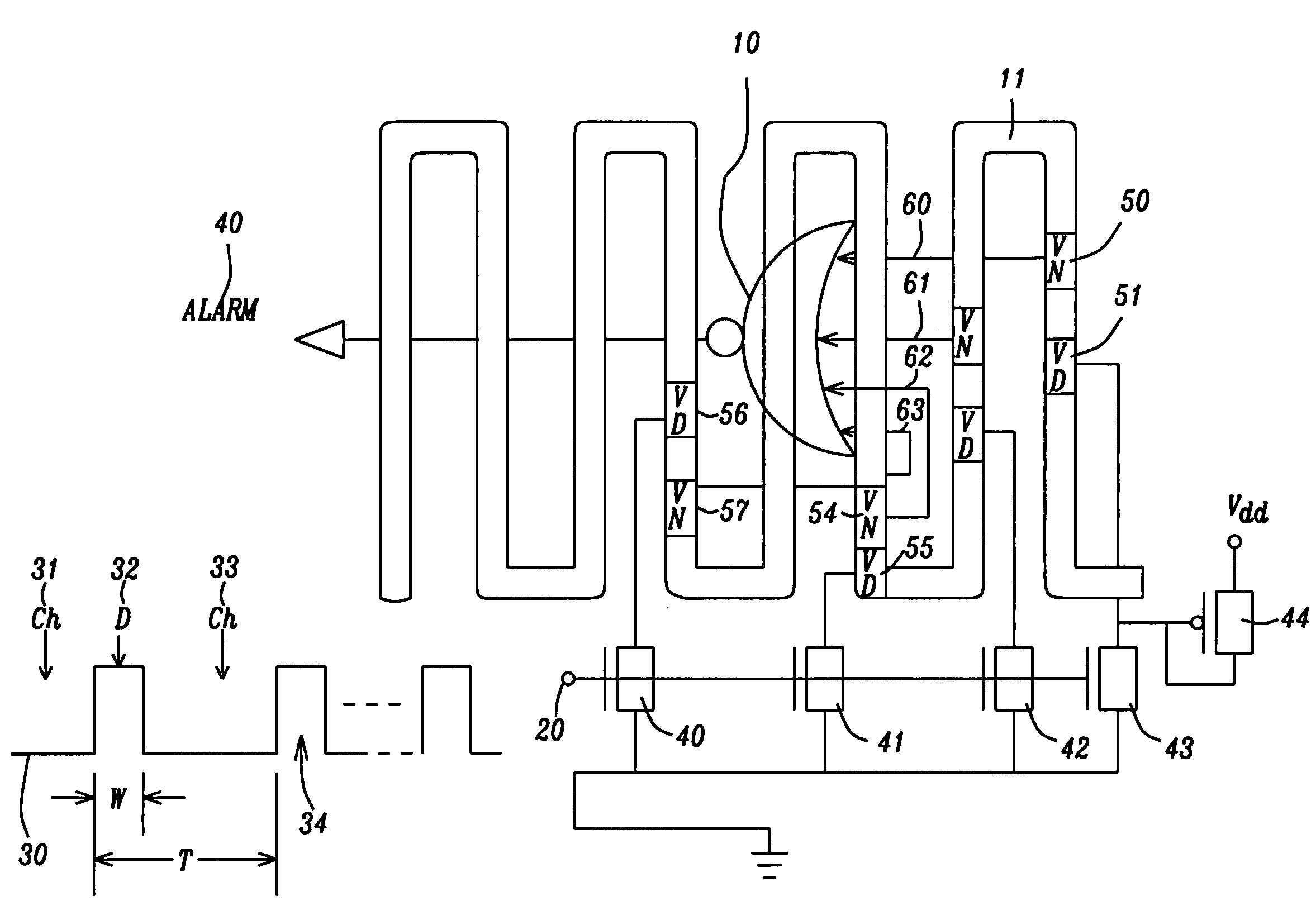

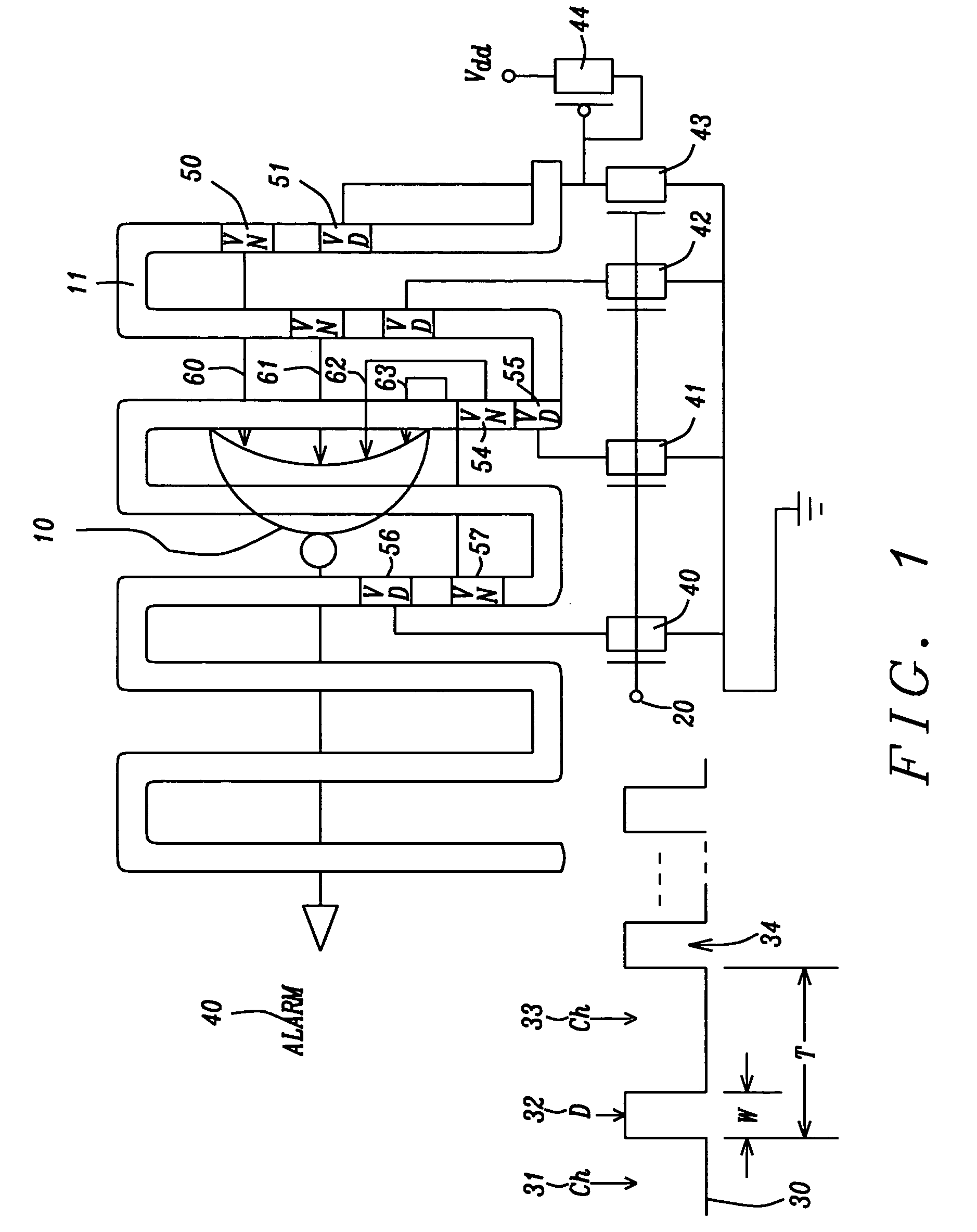

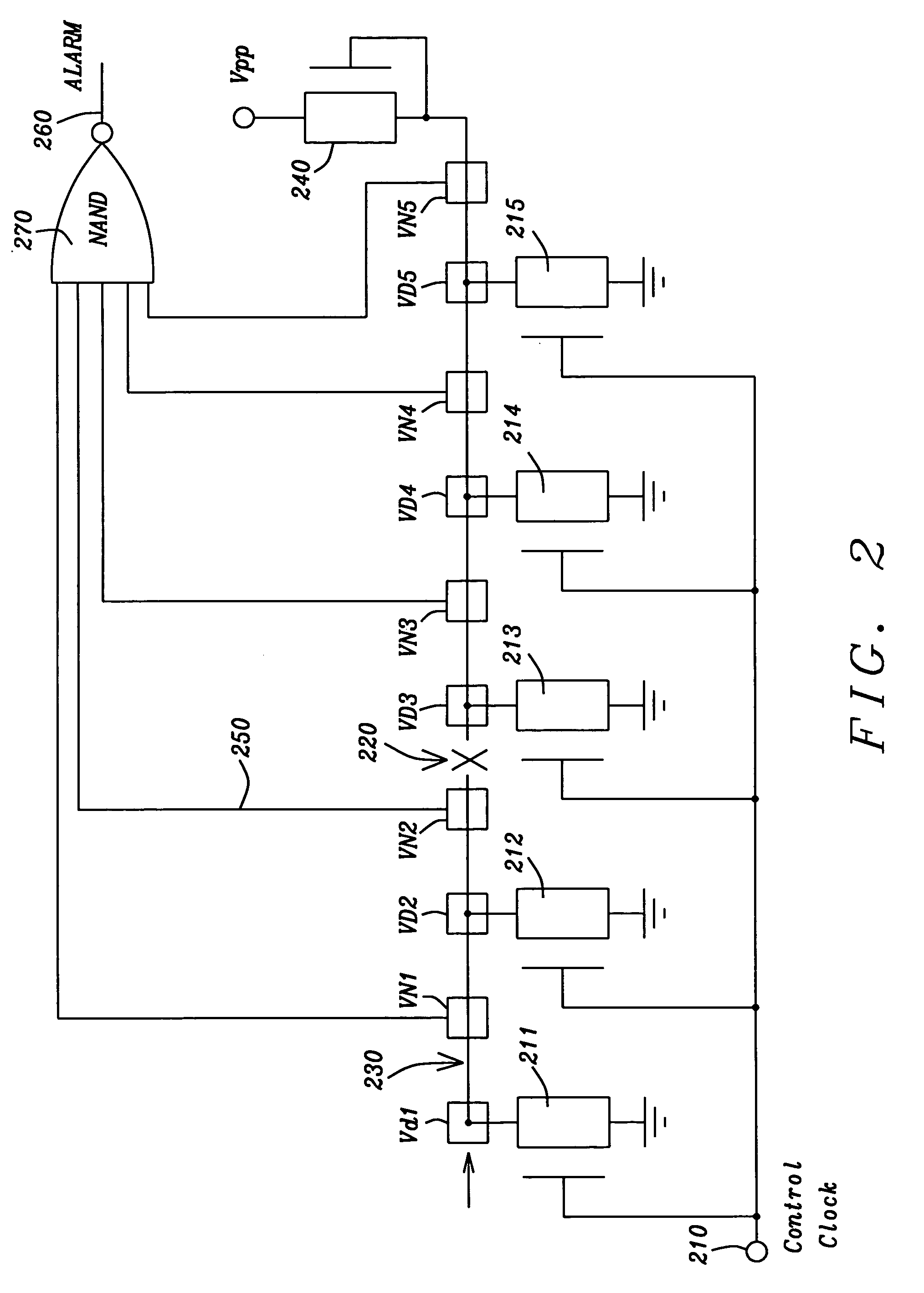

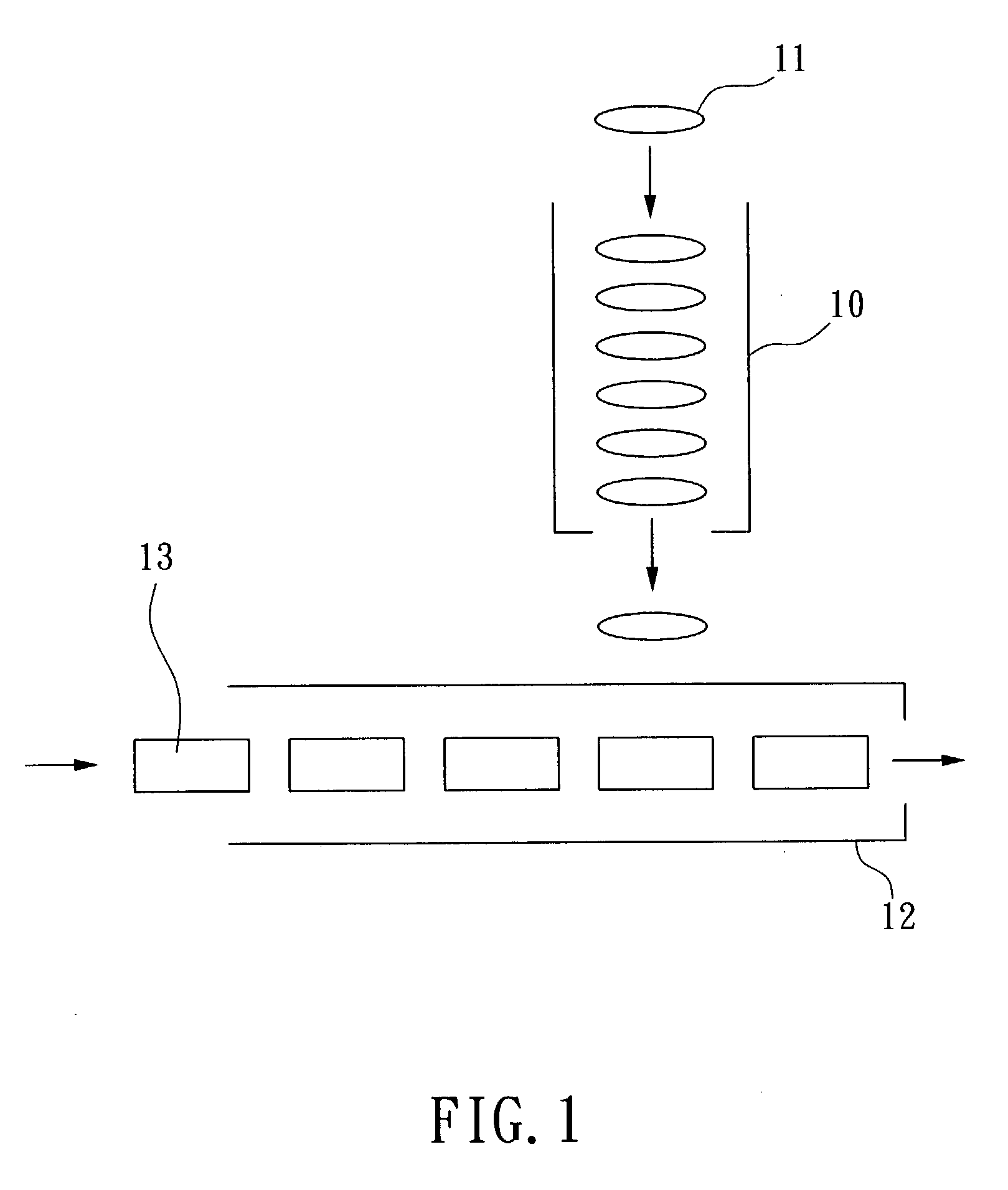

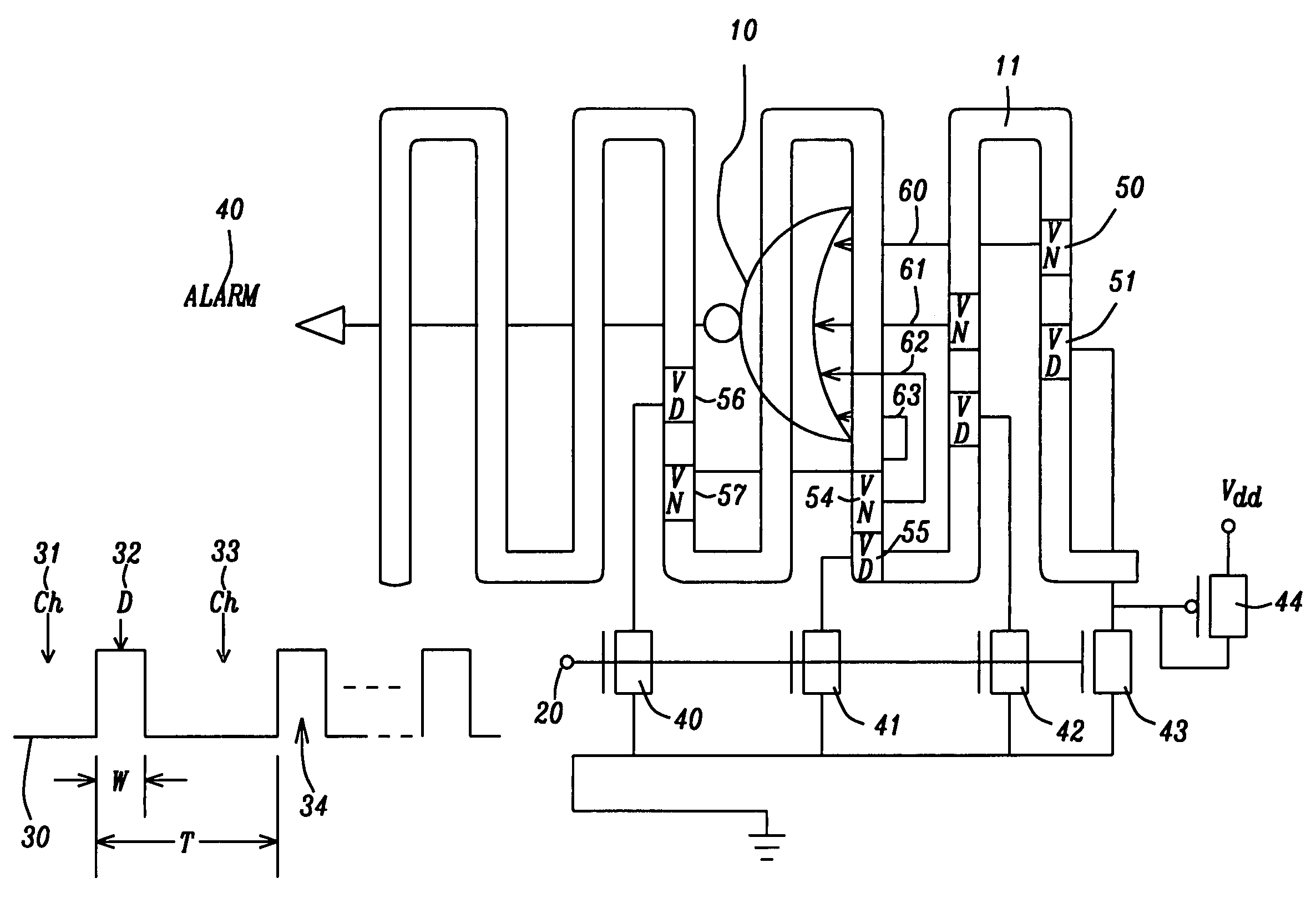

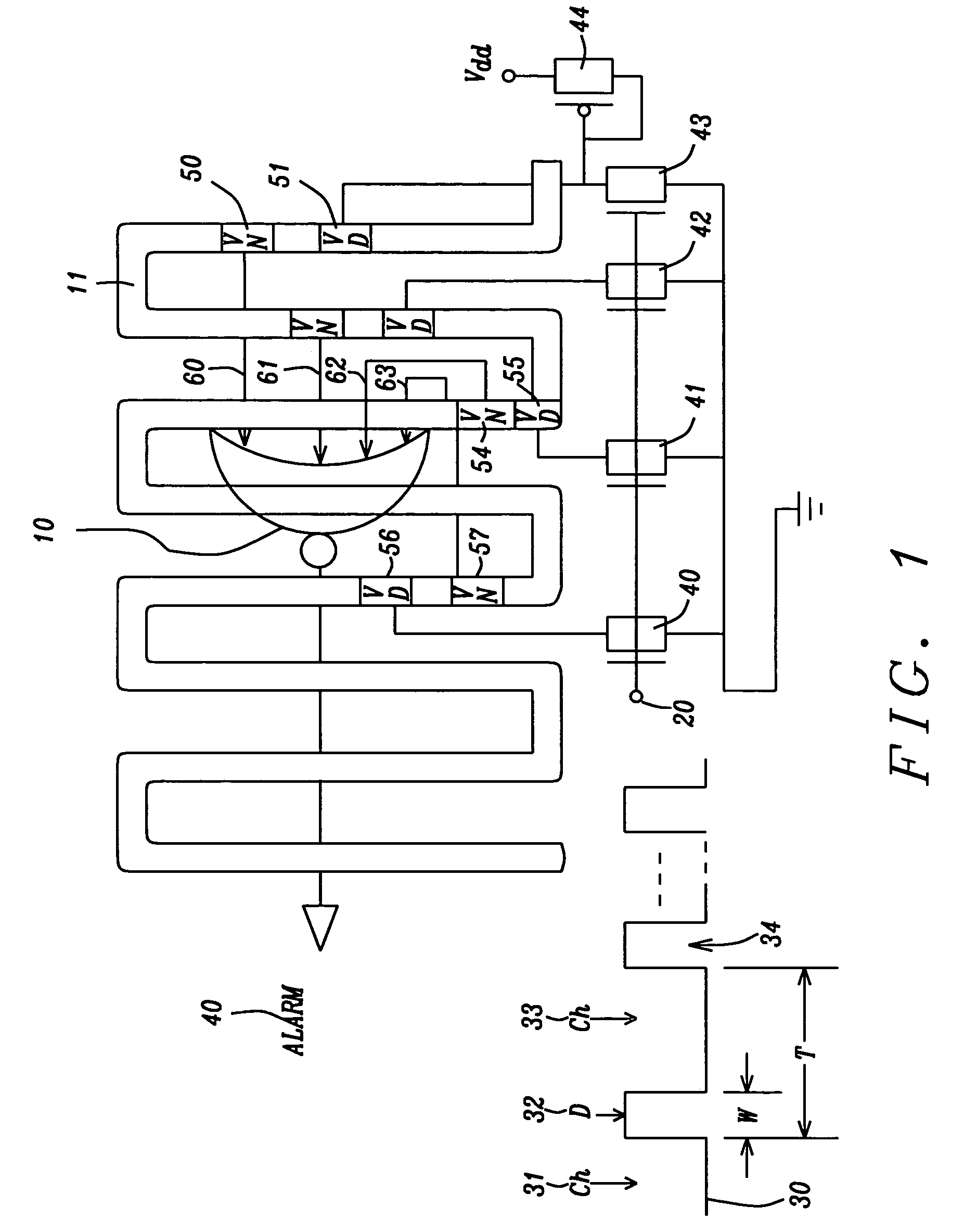

Die anti-tampering sensor

InactiveUS20060044138A1Low powerSimple circuit implementationSemiconductor/solid-state device detailsSolid-state devicesProgrammable read-only memoryNAND gate

This sensor circuit and method for defending against tampering with an integrated circuit die uses metal wire loops to protect the circuitry. In addition, these metal wire loops have several via pairs along its length. One of the vias of the via pair goes to a NAND gate which detects a break in a section of a metal wire loop. A second via of the via pair is used to periodically discharge a metal wire loop to remove residual charge, in preparation for charging the metal wire loop and detecting any uncharged section. A given integrated circuit can have one or more metal wire loops on top of the circuitry to be protected. Each metal wire loop has one or more NAND gates. These outputs of the NAND gates can be fed into OR gates to produce an overall signal which activates an alarm or other security action such as erasure of electrically erasable programmable read only memory (EEPROM).

Owner:KARMIC DESIGN USA

System and method for a rangefinding instrument incorporating pulse and continuous wave signal generating and processing techniques for increased distance measurement accuracy

ActiveUS9354051B2Efficient solutionHigh measurement accuracyOptical rangefindersActive open surveying meansAmbiguityContinuous wave signal

A system and method for a rangefinding instrument incorporating pulse and continuous wave signal generating and processing techniques for increased distance measurement accuracy. The use of the former technique effectively solves the ambiguity issues inherent in the latter while allowing for relatively simple circuit implementations. Thus, a potentially more accurate phase-based distance measurement technique can be utilized which is also completely independent of the maximum range to the target.

Owner:LASER TECH INC +1

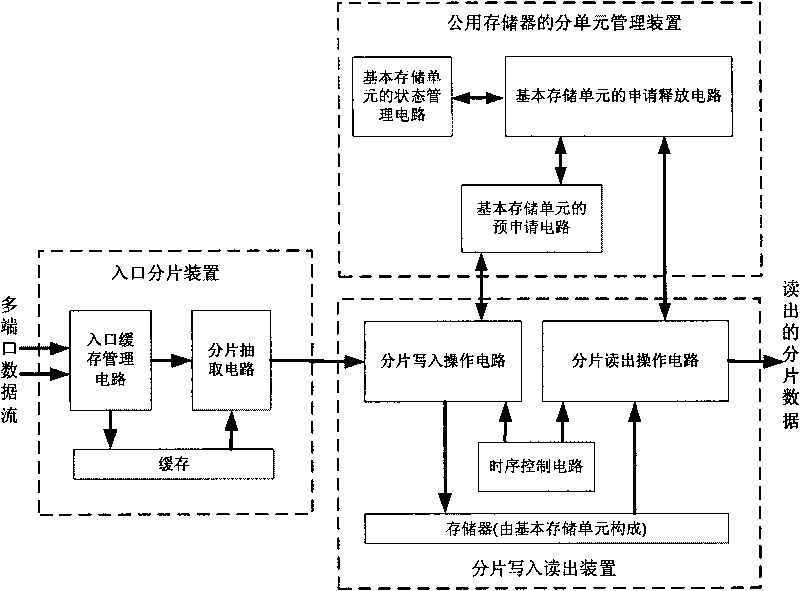

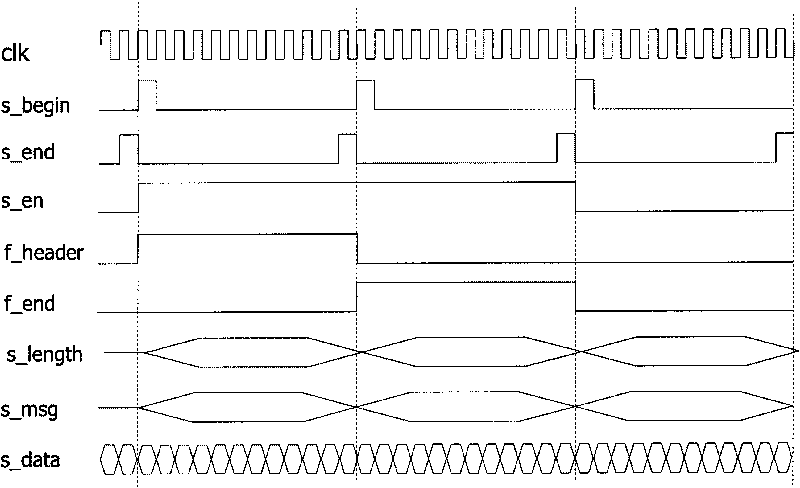

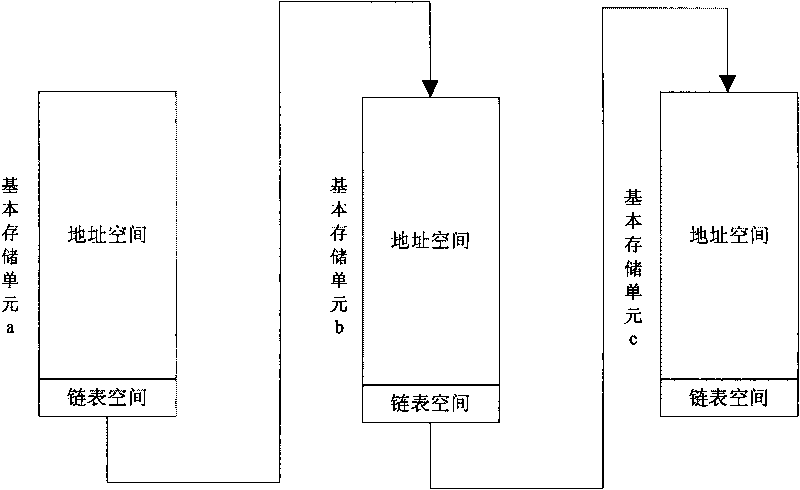

Data frame storage management device

InactiveCN101692655AAvoid reading and writing conflictsSimple circuit implementationData switching networksWhole systemsSequence signal

The invention discloses a data frame storage management device, and relates to data frame processing technology. The data frame storage management device comprises three parts, namely an inlet fragmentation device, a fragmentation write and read device and a sub-unit management device of a public storage, wherein the inlet fragmentation device caches a data stream, extracts the data stream in a fragmentation mode into fragmented data and sends the fragmented data to the fragmentation write and read device; the fragmentation write and read device writes the fragmented data into the storage according to sequence signals of a timing control circuit, or reads the fragmented data from the storage; and the sub-unit management device of the public storage controls the read-write operation of the fragmentation write-in and read-out device. The data frame storage management device divides the storage into a plurality of basic storage units which serve as basic units for storage, can be allocated with addresses based on a source port and also can be allocated with addresses in a sharing way, the independent use of the addresses is achieved by applying for a release mechanism, the write and read of the data are completed by adopting a sequence isolation method, and the conflict between the read and write is avoided, so the circuits of the whole system are realized simply.

Owner:FENGHUO COMM SCI & TECH CO LTD

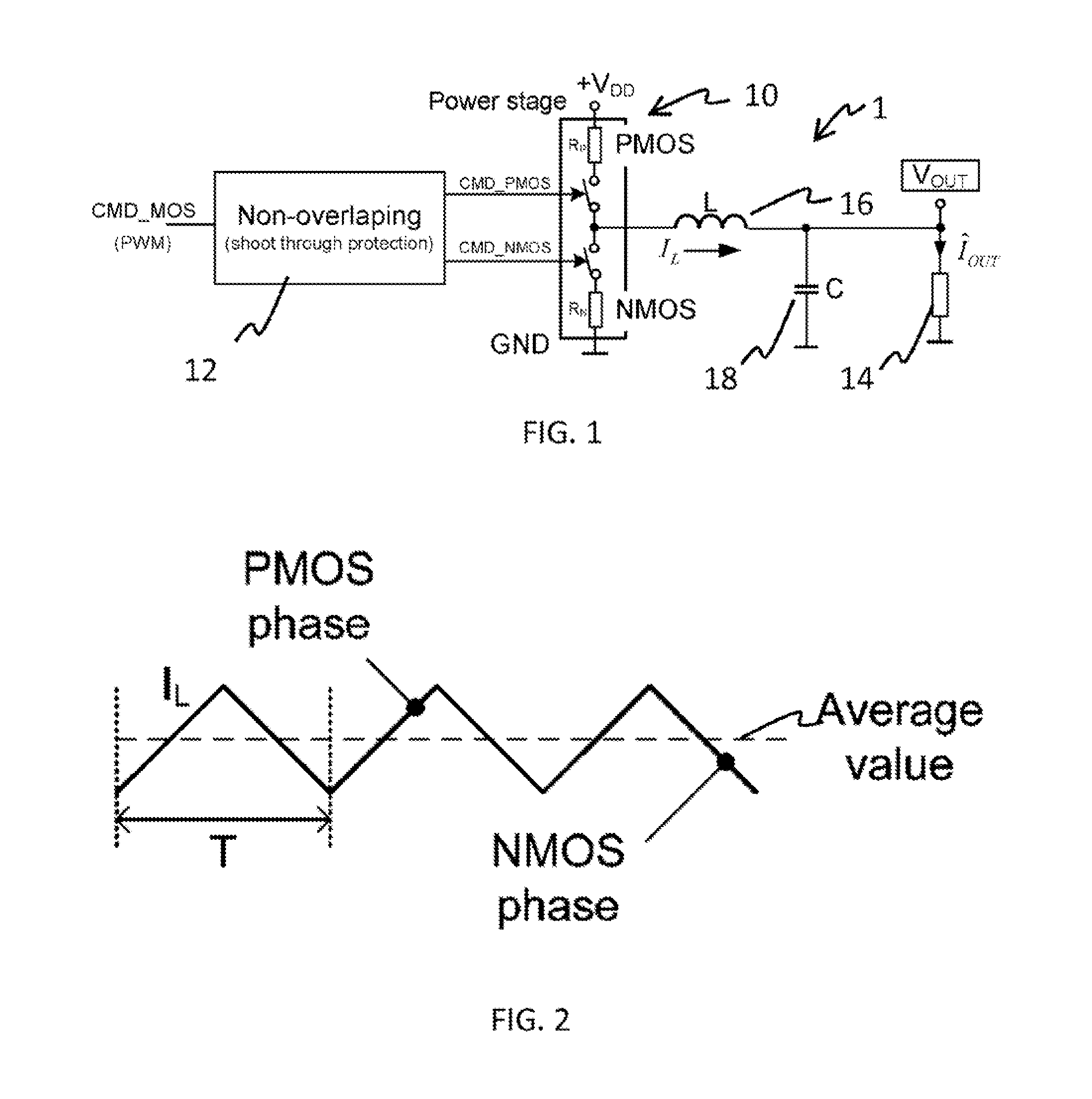

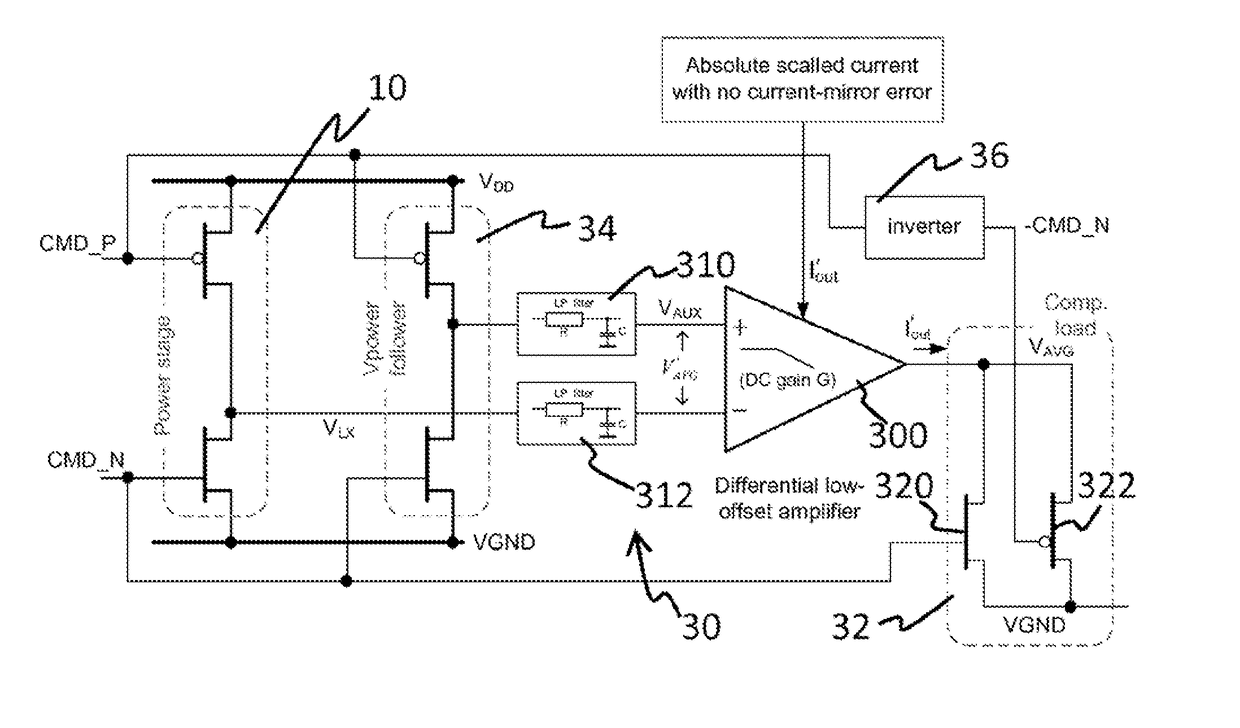

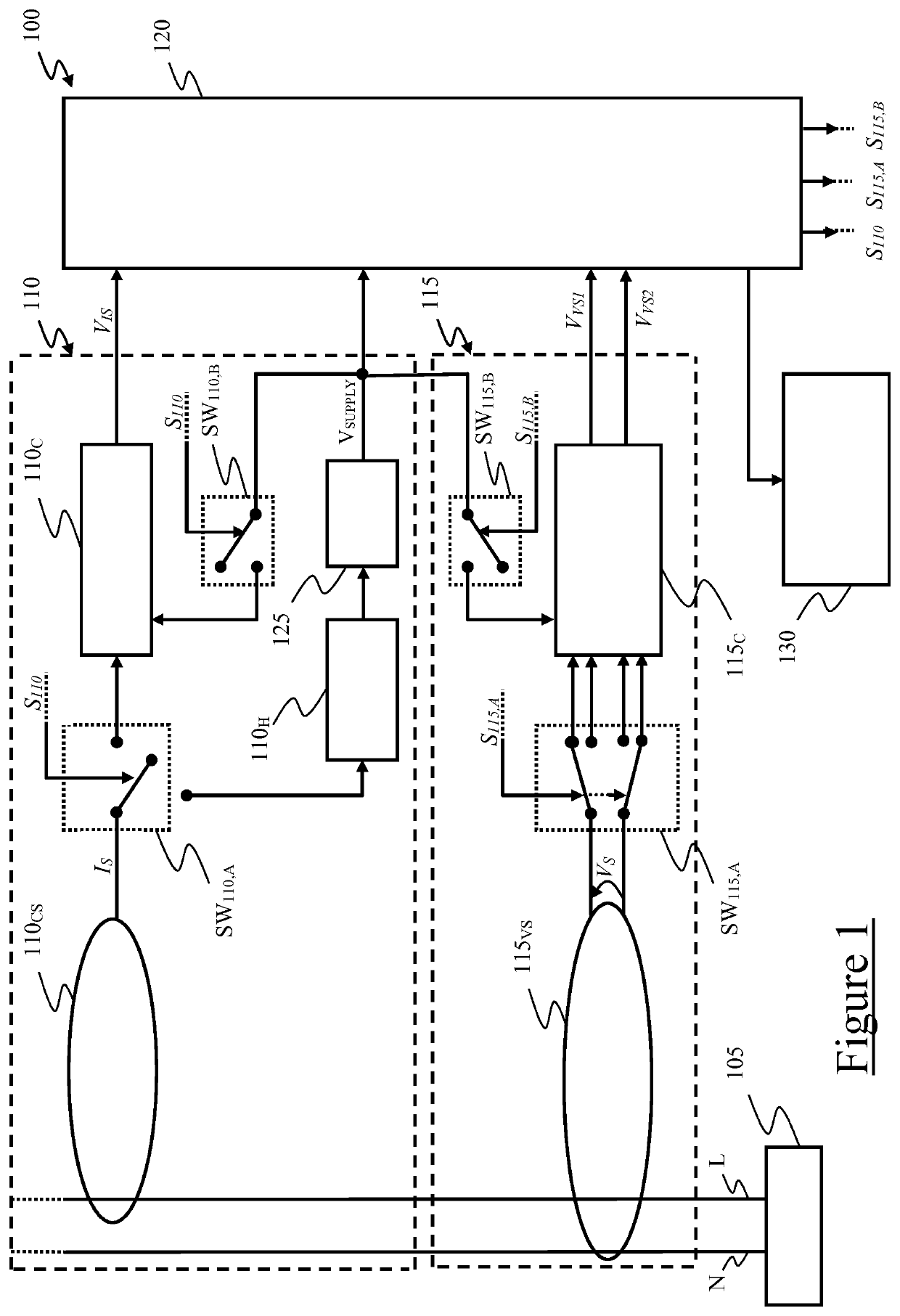

Absolute value current-sensing circuit for step-down dc-to-dc converters with integrated power stage

ActiveUS20150285843A1Accurate measurementSimple circuit implementationPhotovoltaic monitoringEfficient power electronics conversionVoltage dropElectrical current

It is proposed a system for measuring an output current ÎOUT of a DC-to-DC converter, the DC-to-DC converter comprising a transistor power stage. The system comprises:a voltage measuring circuit, connected to the output of the power stage of the DC-to-DC converter, for measuring an average voltage drop VAVG′ on impedances RDS(P,N) of the transistors of the power stage;an impedance RComposite, connected to an output of the voltage measuring circuit providing a current IOUT′, the impedance RComposite reproducing the impedances RDS(P,N) of the transistors of the power stage and being traversed by the current IOUT′ such that ÎOUT=VAVG / (G·k·RComposite)=IOUT′ / (G·k) wherein G·k is a scaling ratio.

Owner:TELEFON AB LM ERICSSON (PUBL)

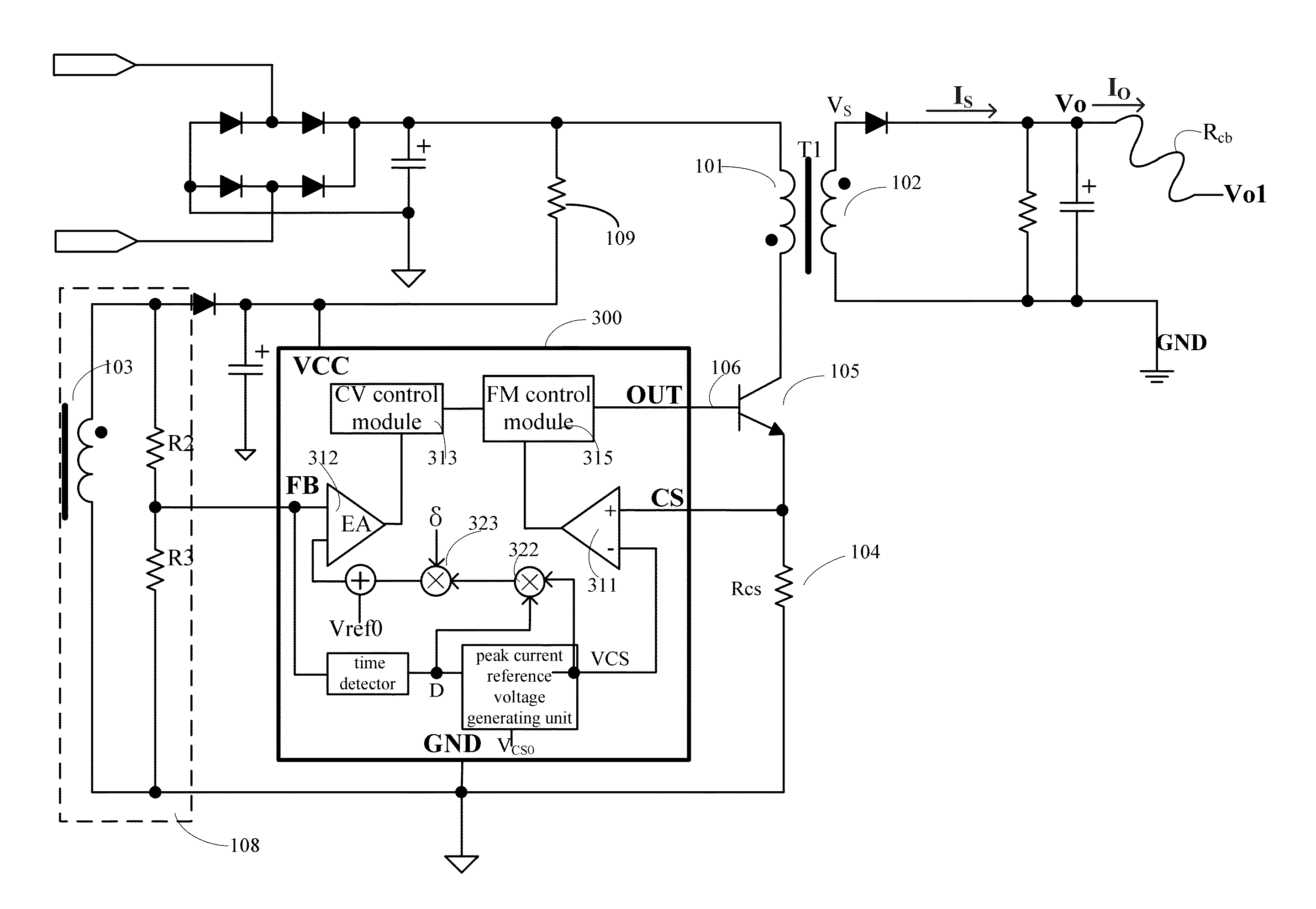

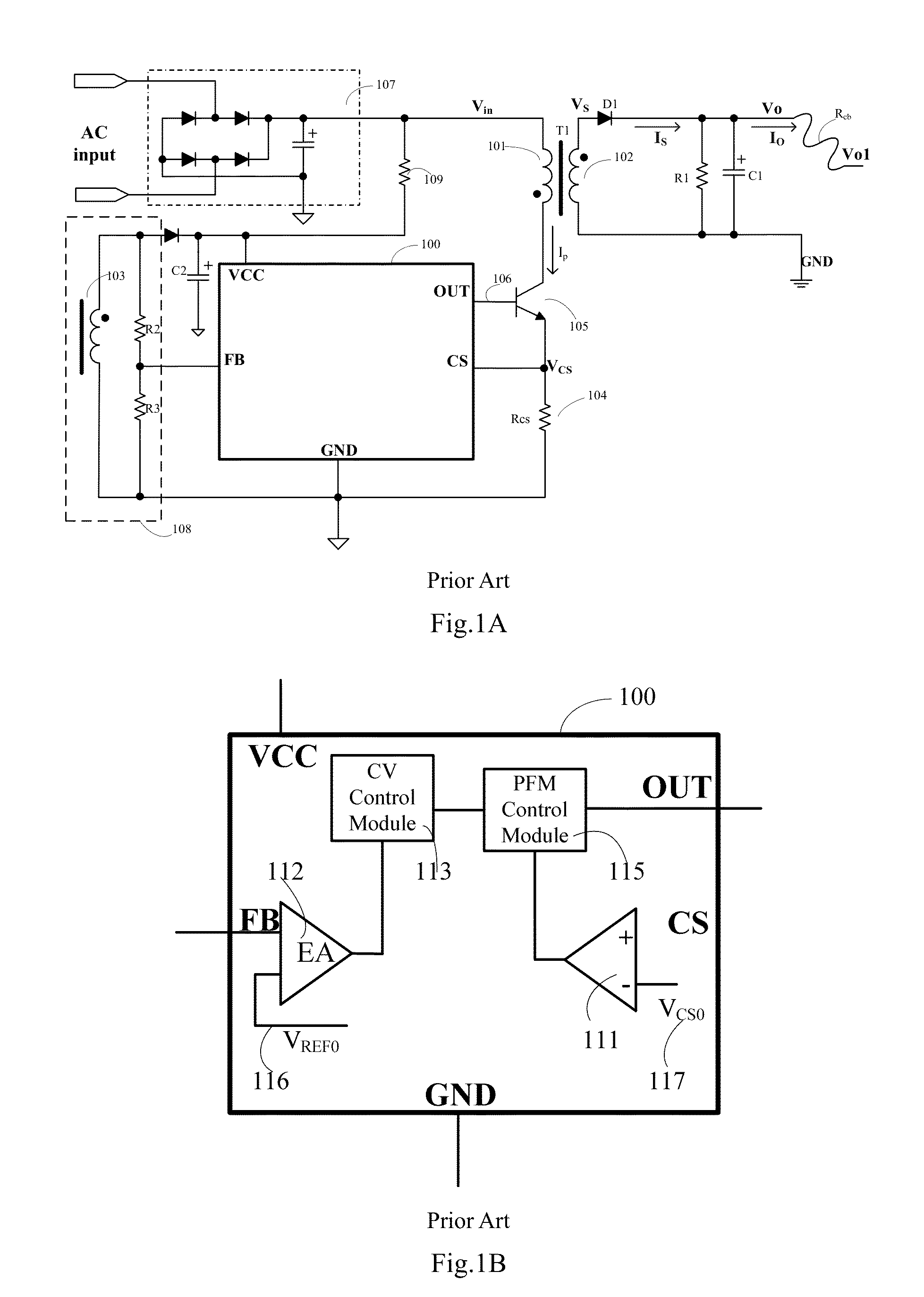

Primary-side regulated modulation controller with improved transient response and audile noise

ActiveUS8599581B2Simple circuit implementationImprove conversion efficiencyDc-dc conversionElectric variable regulationPeak currentPeak value

A switching mode power supply, and a primary-side controlled PFM converter using the primary-side regulated PFM controller are discussed. In present embodiment, the primary side cycle by cycle switch peak current is no longer a constant. The time detector is added to monitor the waveform of primary-side sample voltage and then generate the duty cycle. The transfer function should be selected to satisfy a specific relationship of switching frequency and switch peak current against with output loading current. The new design shows higher switching frequency but lower value of switch peak current at light load condition. This resolves the audible noise and poor transient response issue from the prior art PFM controller.

Owner:FREMONT MICRO DEVICES CORP

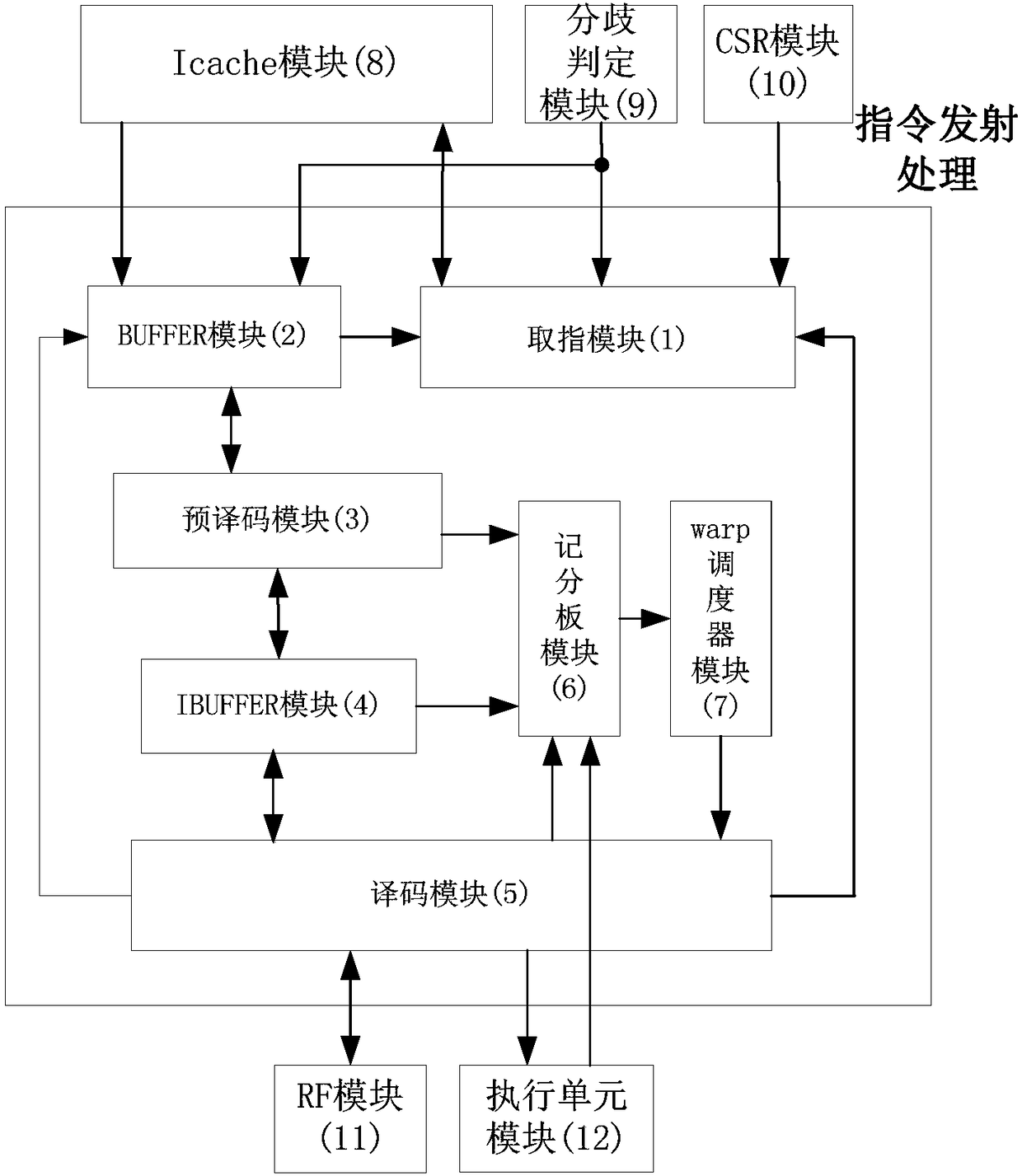

Instruction issue processing circuit of uniform dyeing device array

ActiveCN108133452AImprove execution efficiencySimple circuit implementationProcessor architectures/configurationDetails involving image processing hardwareAsic technologyIntegrated circuit

The invention belongs to the technical field of integrated circuits, and provides an instruction issue processing circuit of a uniform dyeing device array. The circuit comprises an instruction fetching module 1, a BUFFER module 2, a pre-decoding module 3, an IBUFFER module 4, a decoding module 5, a scoreboard module 6 and a warp scheduler module 7. The circuit has the technical effect that 1 at least 8 instructions are fetched from an Icache at each time, so that the frequency of accessing the Icache is reduced to a certain extent and the instruction execution efficiency can be improved; 2, buffers and ibuffers of a plurality of warps are independently realized by registers, so that the logic can be reused and the circuit realization is simple; and 3, the pre-decoding module and the decoding module realize corresponding decoding functions of two instructions in different stages, circuits in an instruction issue processing mechanism circuit have the modules, and the manner that multiplewarps correspond to multiple modules is not adopted so that the circuit realization is simple and resources are saved.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

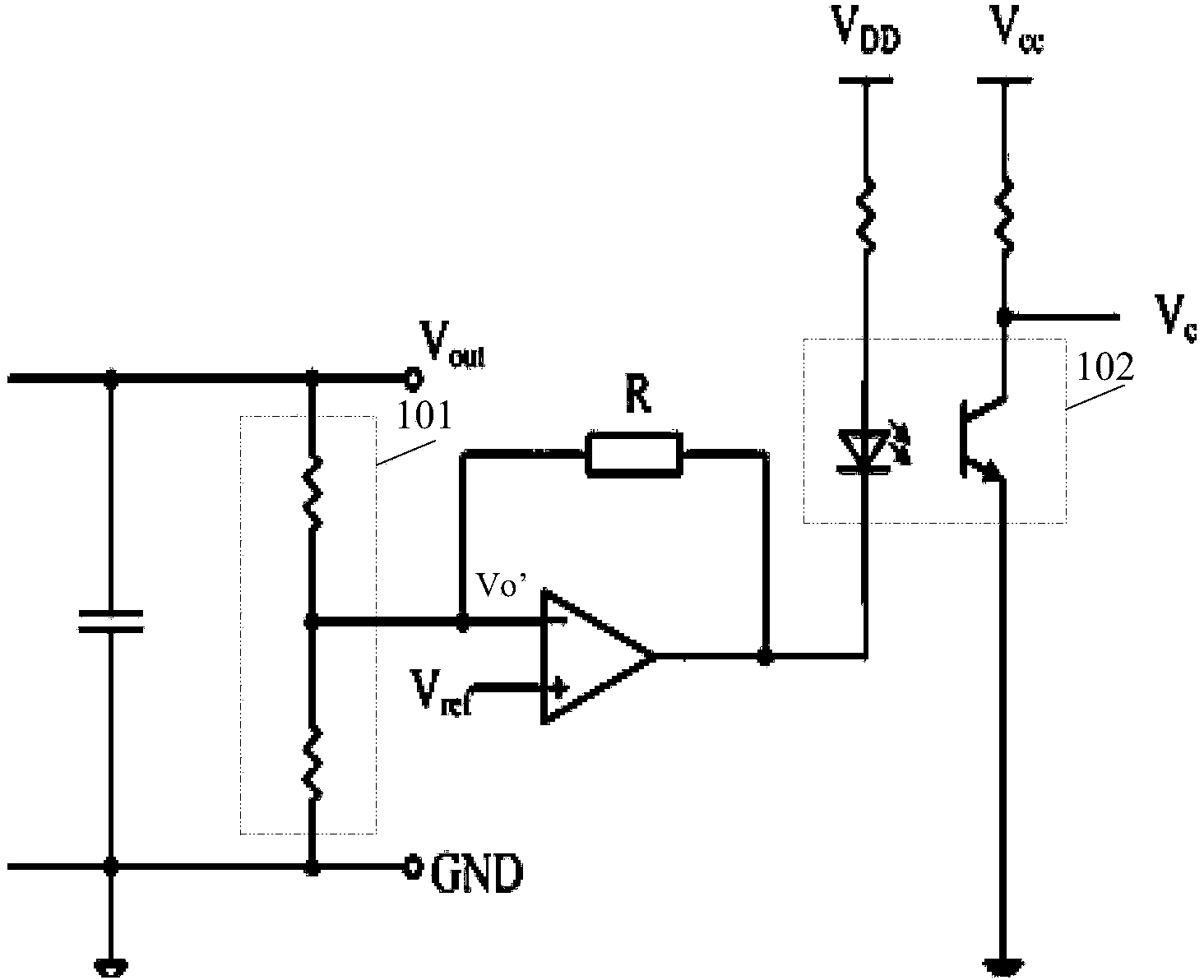

Voltage detection method and circuit and switching power supply with voltage detection circuit

ActiveCN103472283ASimple circuit implementationReduce circuit costApparatus without intermediate ac conversionVoltage/current isolationCapacitanceSwitching power

The invention relates to the field of electrons and discloses a voltage detection method and circuit and a switching power supply with the voltage detection circuit. The voltage detection method comprises the steps of generating first current according to first voltage and transformed resistance, using the first current to charge a detection capacitor within a first time period of each switching period, and using preset second current to charge the detection capacitor within a second time period of each switching period, wherein the current directions of the second current and the first current flowing through the detection capacitor are opposite, and voltage at two ends of the detection capacitor at the finish moment of the second time period of each switching period is detection voltage, so that the current output valve state of the switching power supply is determined according to the detection voltage.

Owner:SILERGY SEMICON TECH (HANGZHOU) CO LTD

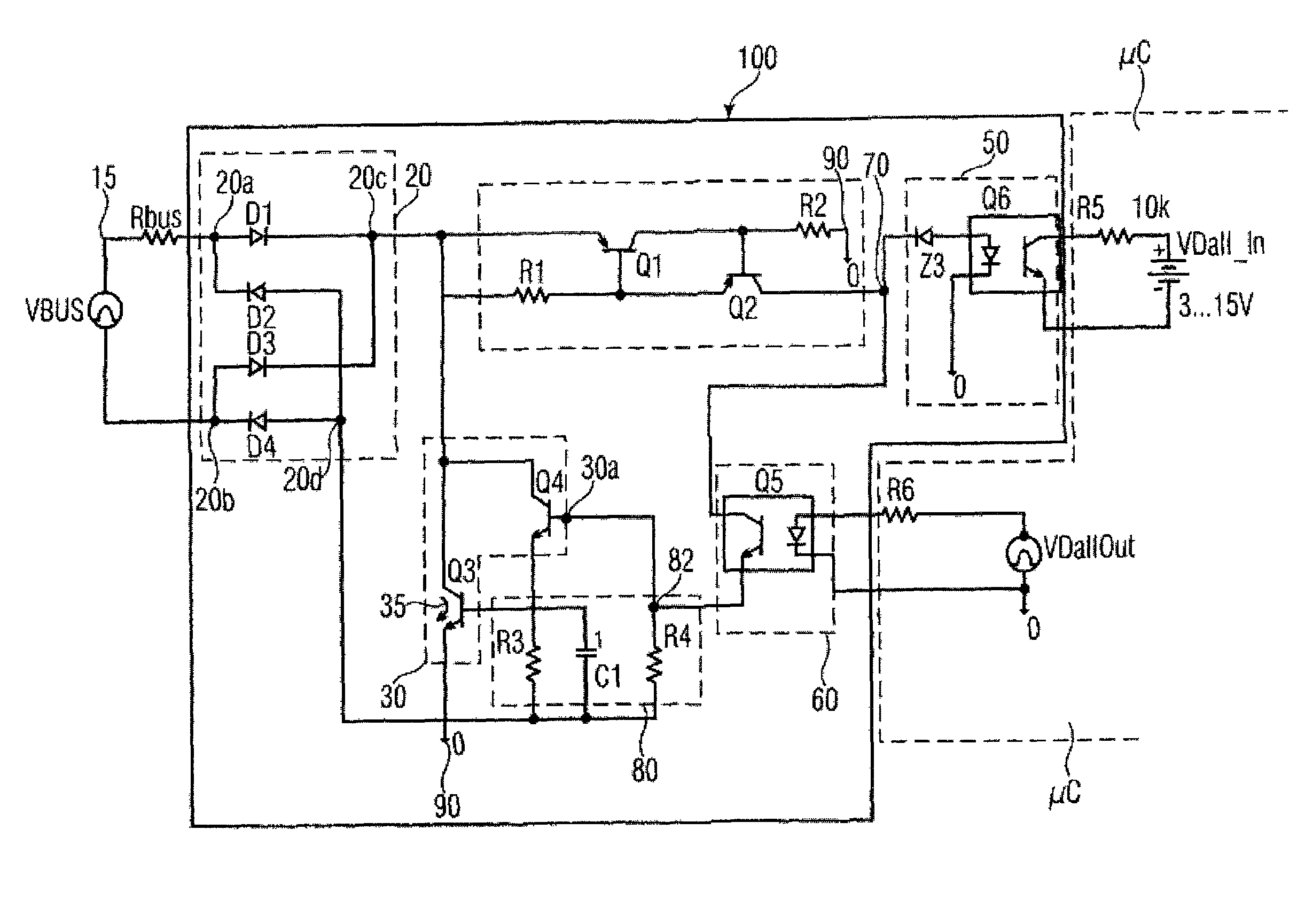

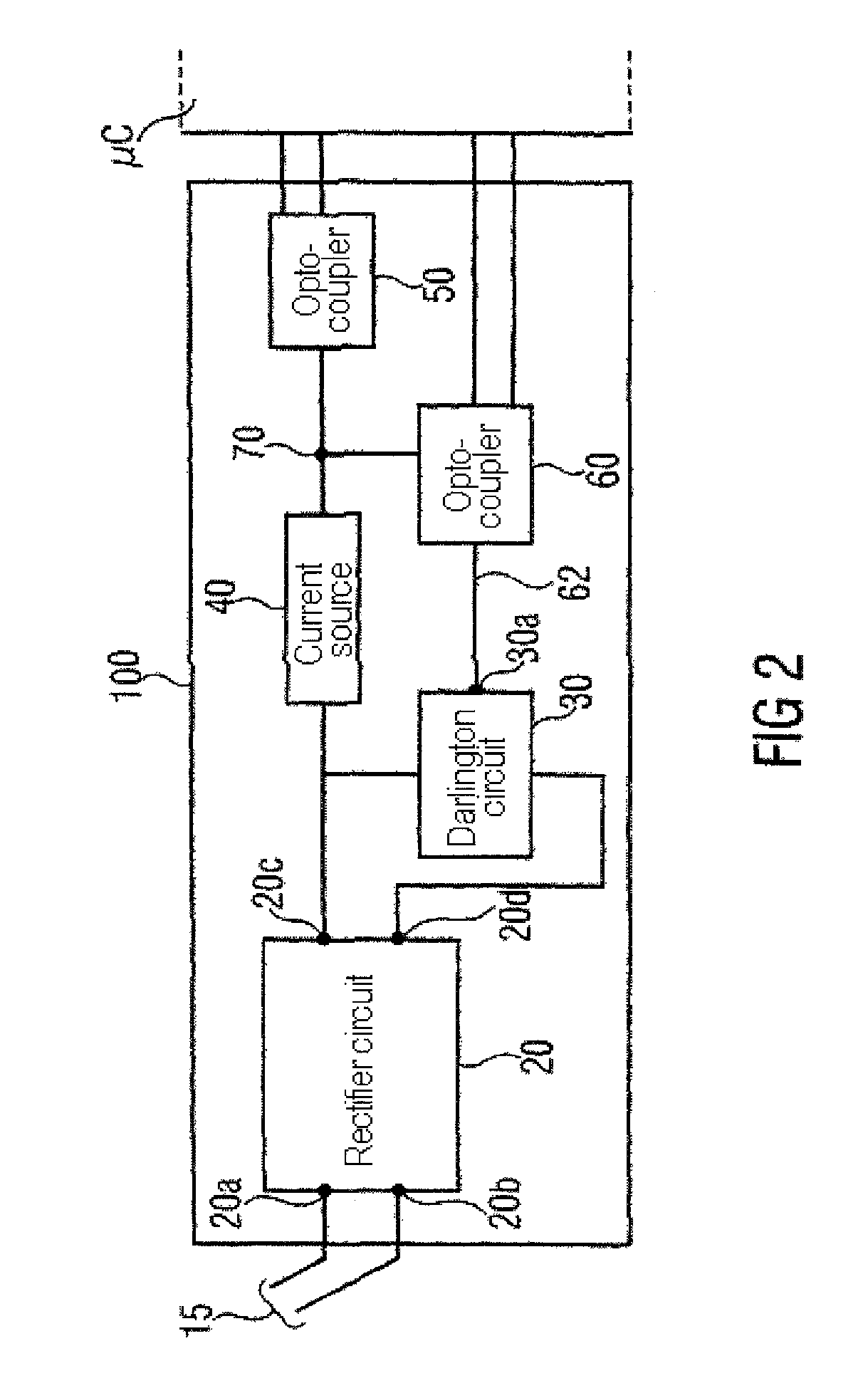

Surge-proof interface circuit

InactiveUS8810148B2High dielectric strengthAdequate current gainElectric light circuit arrangementSubstation equipmentControl signalInterface circuits

In examples of the embodiment, a surge-proof interface circuit (100) comprises a rectifier circuit (20) which is configured to produce a rectified rectifier output voltage at the rectifier output terminals (20c, 20d), in accordance with a rectifier input voltage at the rectifier input terminals (20a, 20b), and a Darlington circuit (30) which comprises at least two transistors (Q3, Q4). Said Darlington circuit (30) comprises a current path (35) which can be controlled on the output side in accordance with a control signal (62) and said current path (35) which can be controlled on the output side is coupled between the rectifier output connections (20c, 20d).

Owner:TRIDONIC

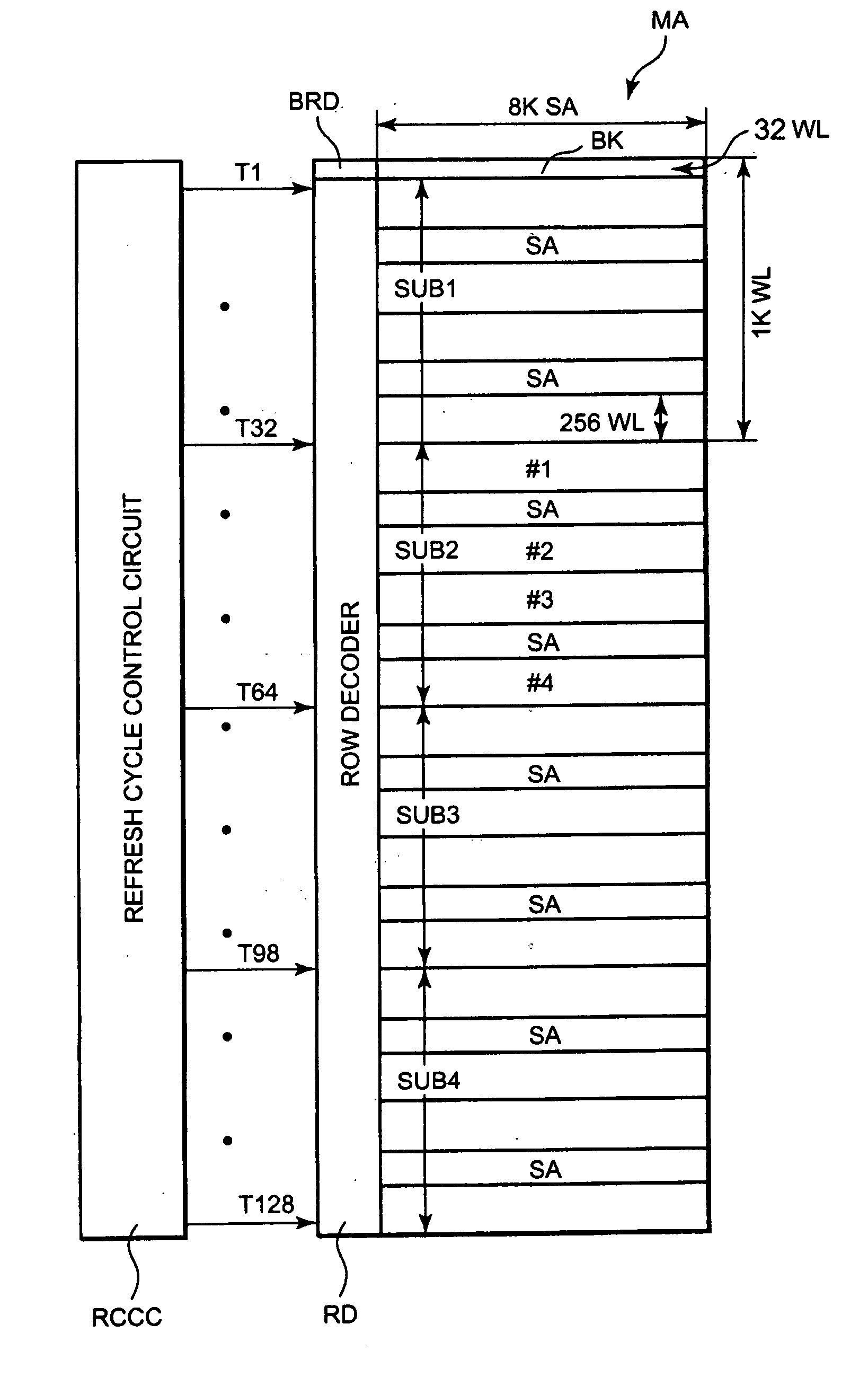

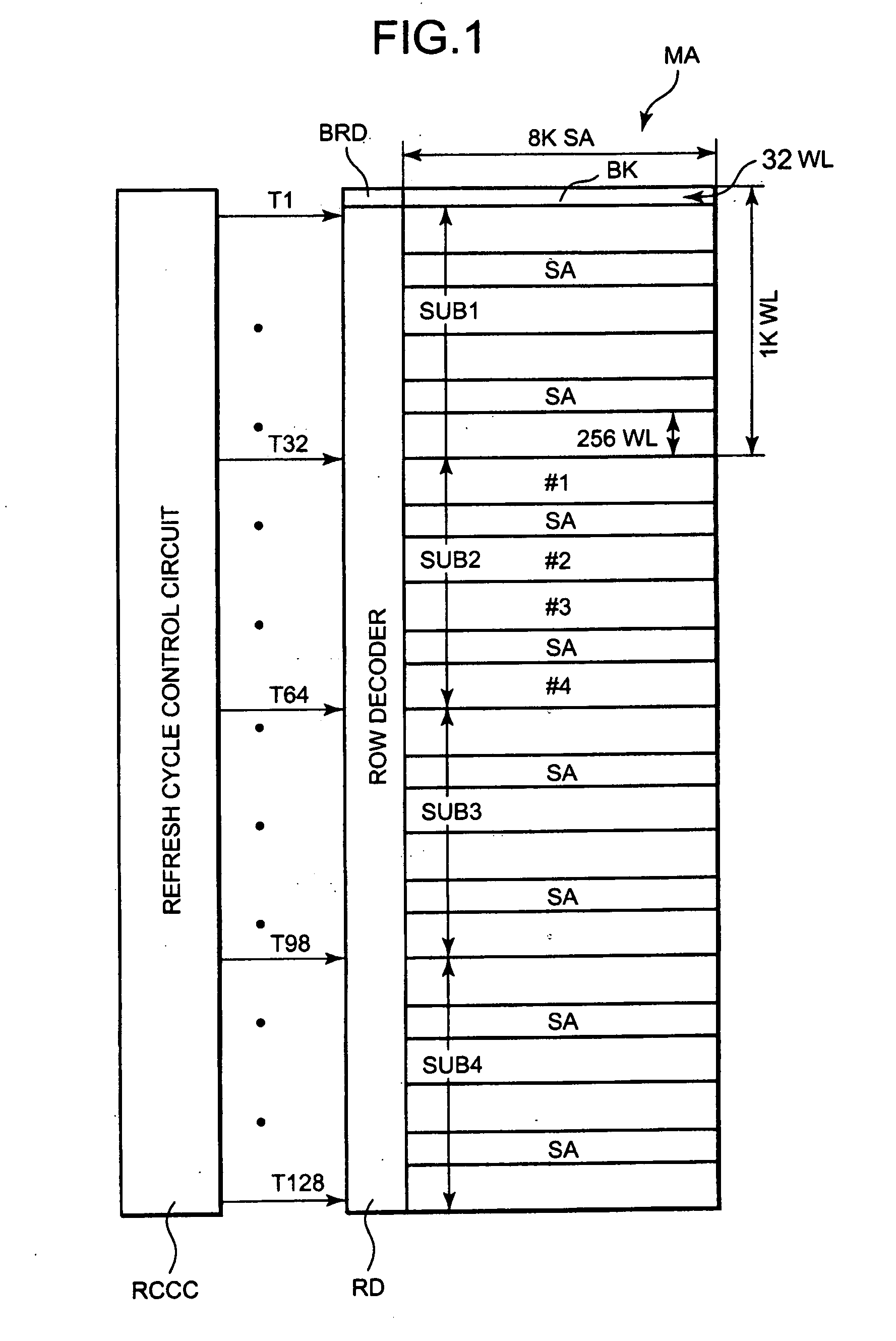

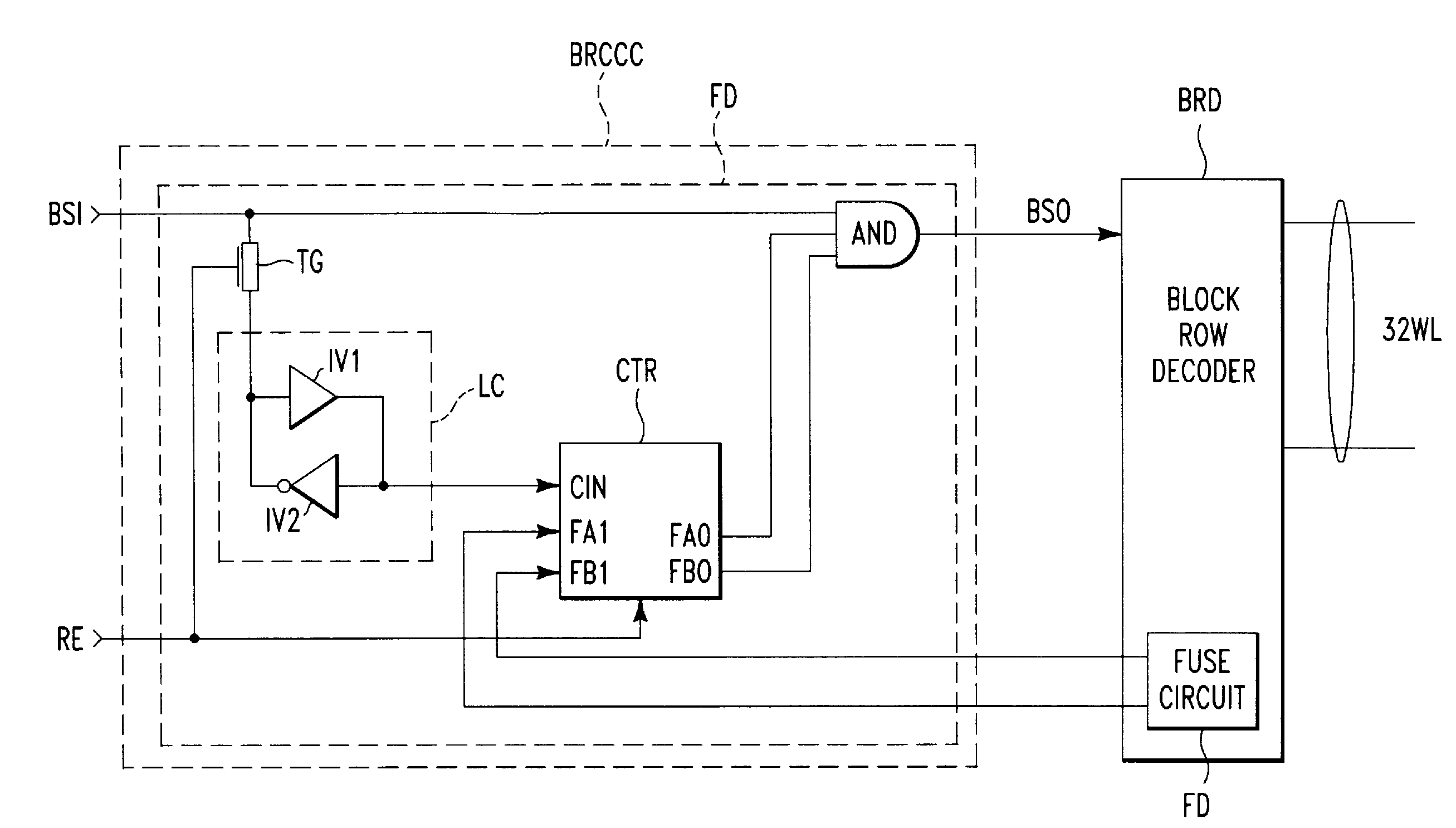

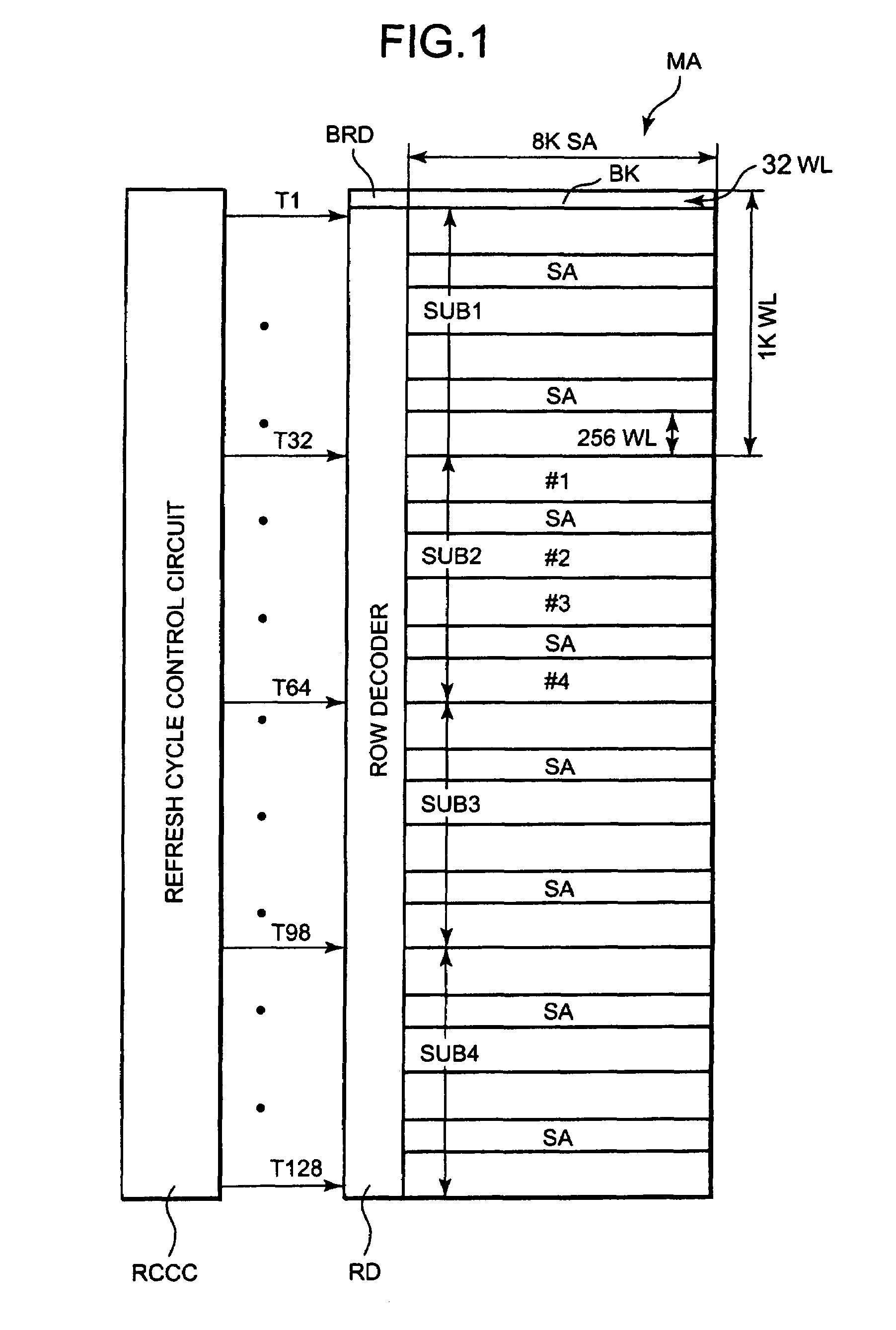

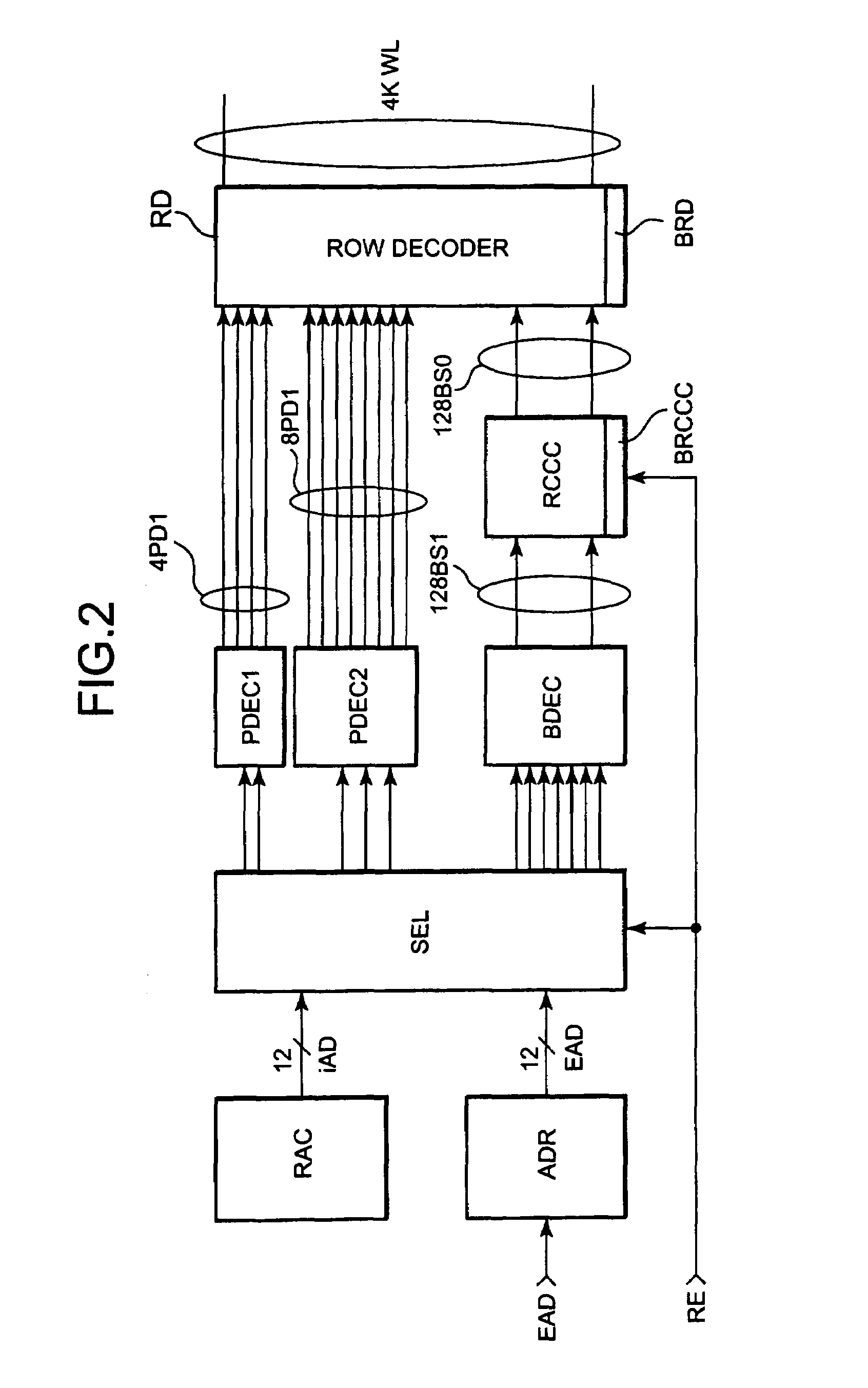

Dynamic semiconductor storage device

InactiveUS20060250873A1Reduced refresh currentSimple circuit configurationRead-only memoriesDigital storageEngineeringHemt circuits

To achieve, by a simple circuit configuration, a DRAM that permits refresh current to be effectively reduced by selectively setting refresh cycles. A memory cell array is divided into 64 subarrays, and each subarray is further divided into 8 blocks. A refresh cycle control circuit has a fuse circuit for setting a frequency dividing ratio of 1 or 1 / 2, a frequency divider that divides the frequency of a predecode signal by the set frequency dividing ratio, fuse circuits for setting a frequency dividing ratio of 1 or 1 / 4, and frequency dividers for dividing predecode signals by the set frequency dividing ratio. The refresh cycle control circuit is capable of setting a 64-ms or 128-ms refresh cycle for the 64 subarrays and a 64-ms or 256-ms refresh cycle for 512 blocks.

Owner:IBM CORP

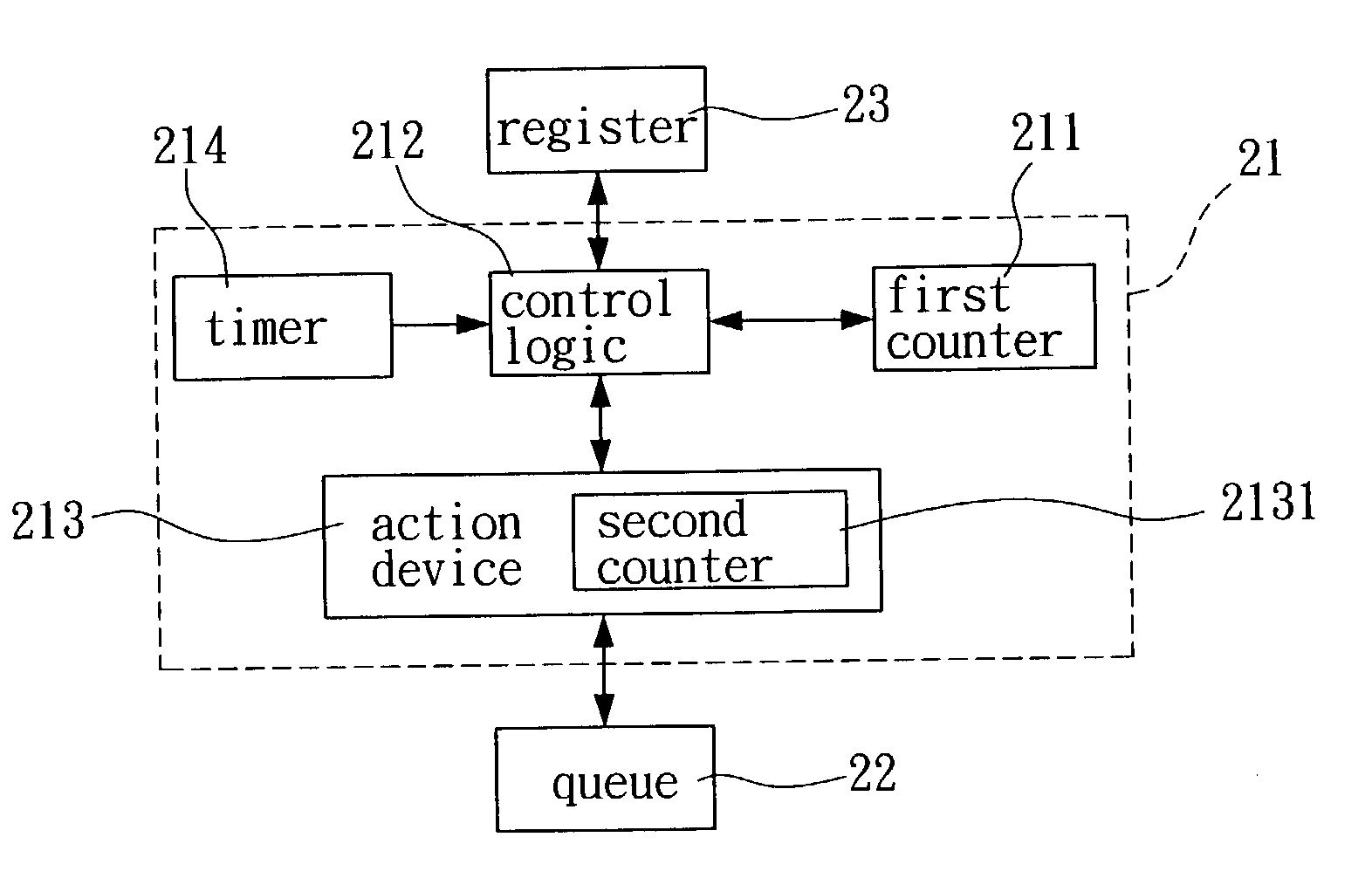

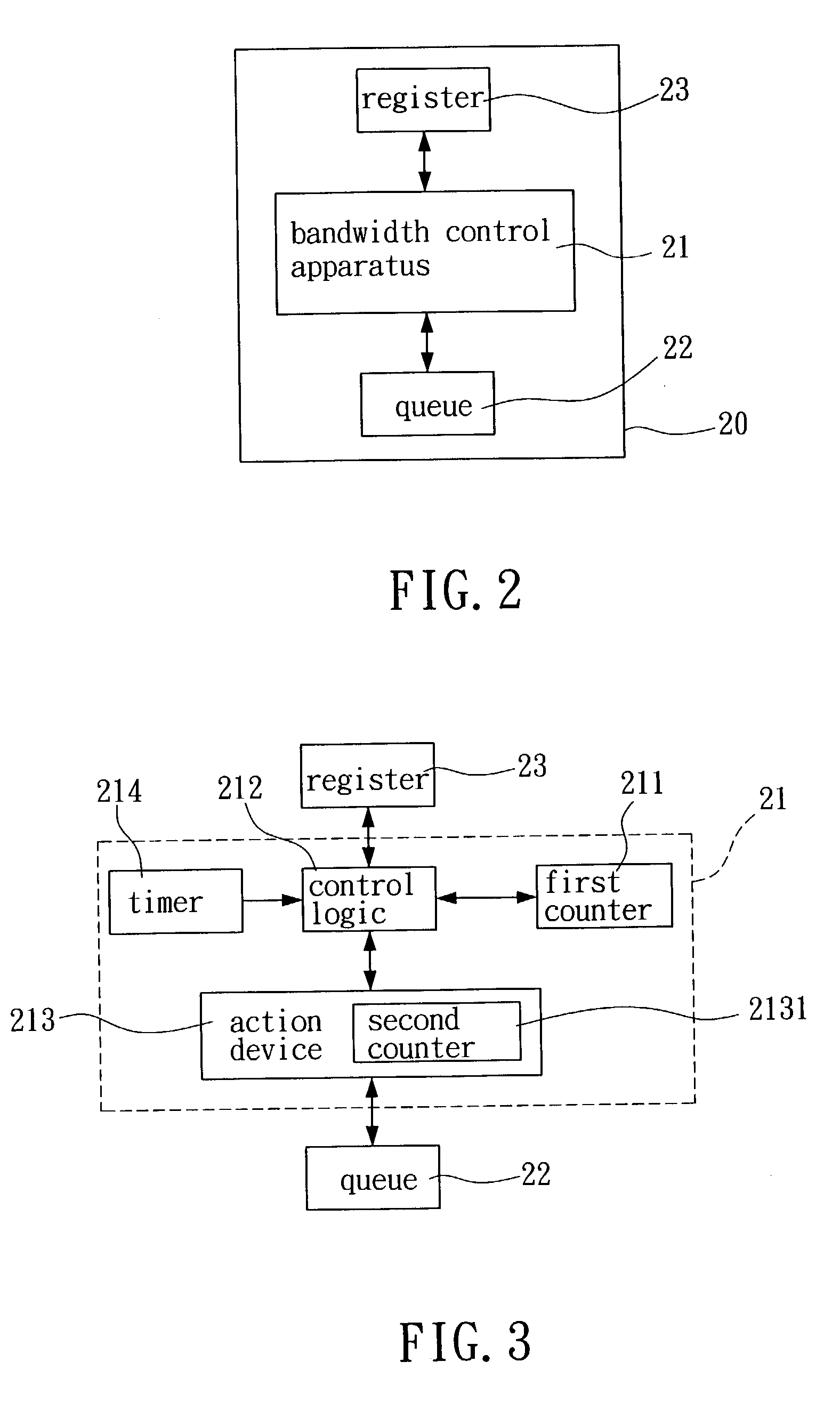

Apparatus and method for bandwidth control

ActiveUS20030123391A1Simplifies counting operationEasy to controlError preventionFrequency-division multiplex detailsEngineeringNetwork switch

The present invention provides an apparatus and method for bandwidth control used in a network switch controller. The apparatus and method achieve the goals of simplifying circuits and controlling bandwidth precisely by simplification of counting operations required by bandwidth control and a design of dual counters. The apparatus comprises: a first counter; a control logic for executing a operation of adding or subtracting the first counter by one based on an increment / decrement signal and for determining if a packet is allowed to enter a queue of the switch controller based on a value of the first counter; an action device for performing actions of inputting / outputting the packet to / from the queue, wherein the action device comprises a second counter which is increased by one when a byte is inputted, the second counter is reset to zero and generates the increment signal to the control logic when increased to one unit bytes; and a timer for generating the decrement signal to the control logic every unit time. The method employs the above apparatus to input packets and decreases the first counter by one to limit data volume allowed to input during one unit time to one unit bytes.

Owner:REALTEK SEMICON CORP

Die anti-tampering sensor

InactiveUS7119703B2Low powerSimple circuit implementationSemiconductor/solid-state device detailsSolid-state devicesElectricityProgrammable read-only memory

This sensor circuit and method for defending against tampering with an integrated circuit die uses metal wire loops to protect the circuitry. In addition, these metal wire loops have several via pairs along its length. One of the vias of the via pair goes to a NAND gate which detects a break in a section of a metal wire loop. A second via of the via pair is used to periodically discharge a metal wire loop to remove residual charge, in preparation for charging the metal wire loop and detecting any uncharged section. A given integrated circuit can have one or more metal wire loops on top of the circuitry to be protected. Each metal wire loop has one or more NAND gates. These outputs of the NAND gates can be fed into OR gates to produce an overall signal which activates an alarm or other security action such as erasure of electrically erasable programmable read only memory (EEPROM).

Owner:KARMIC DESIGN USA

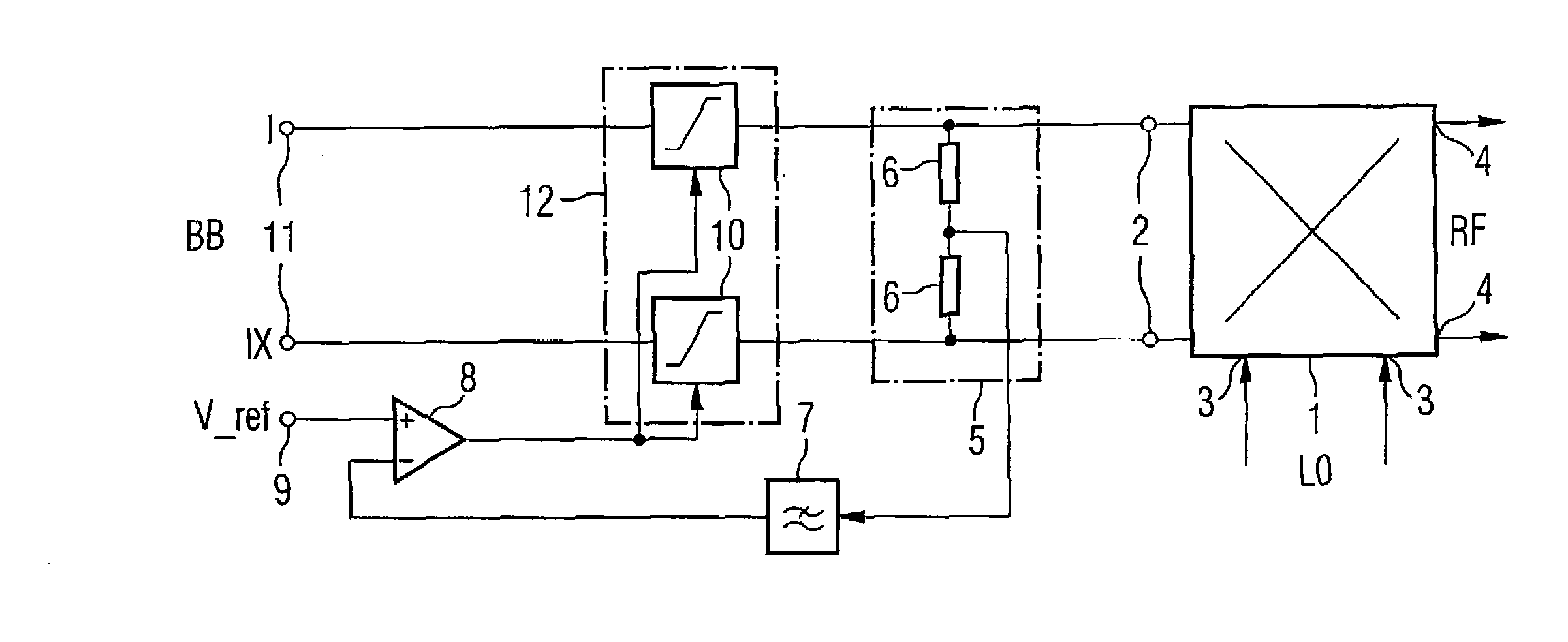

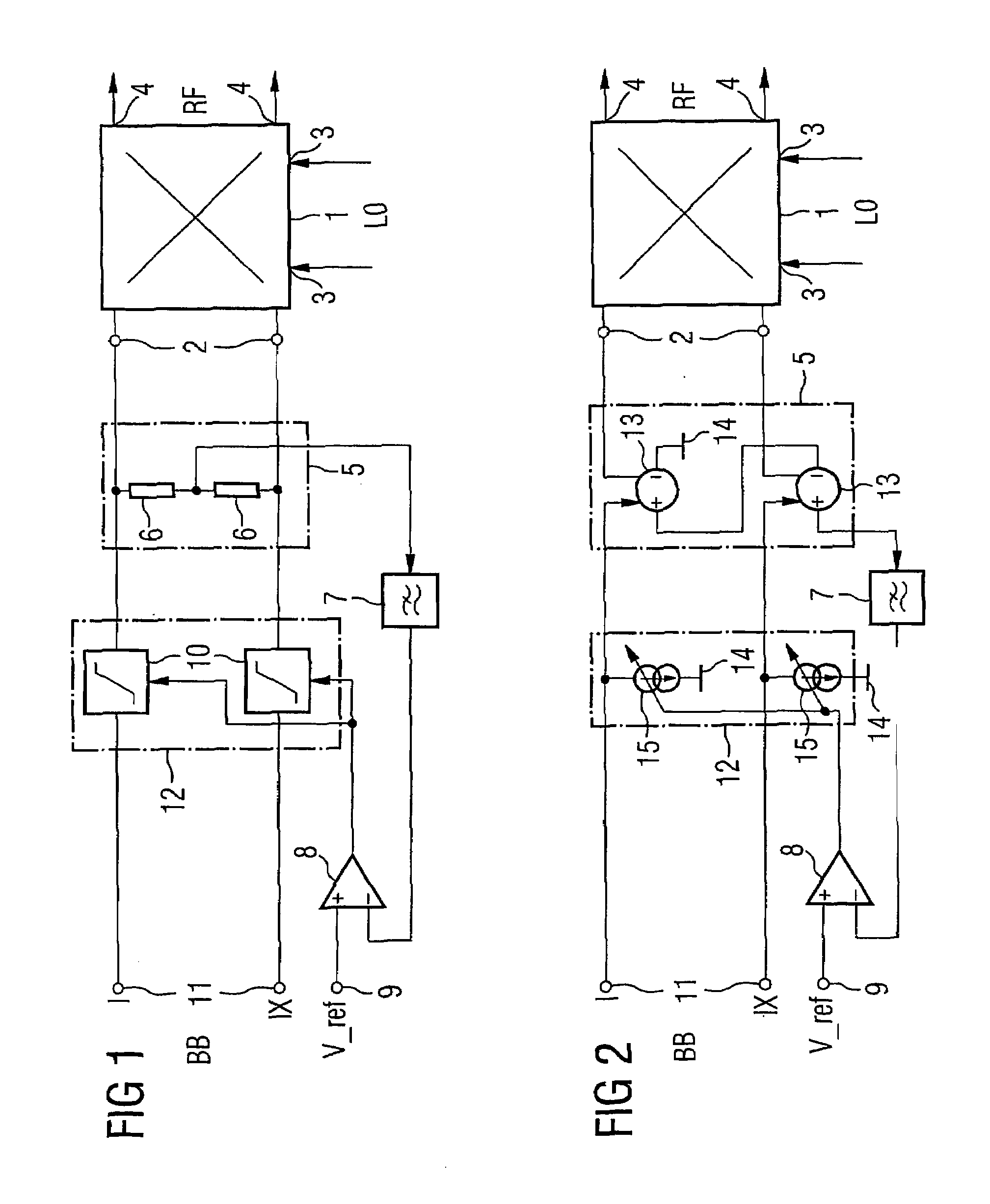

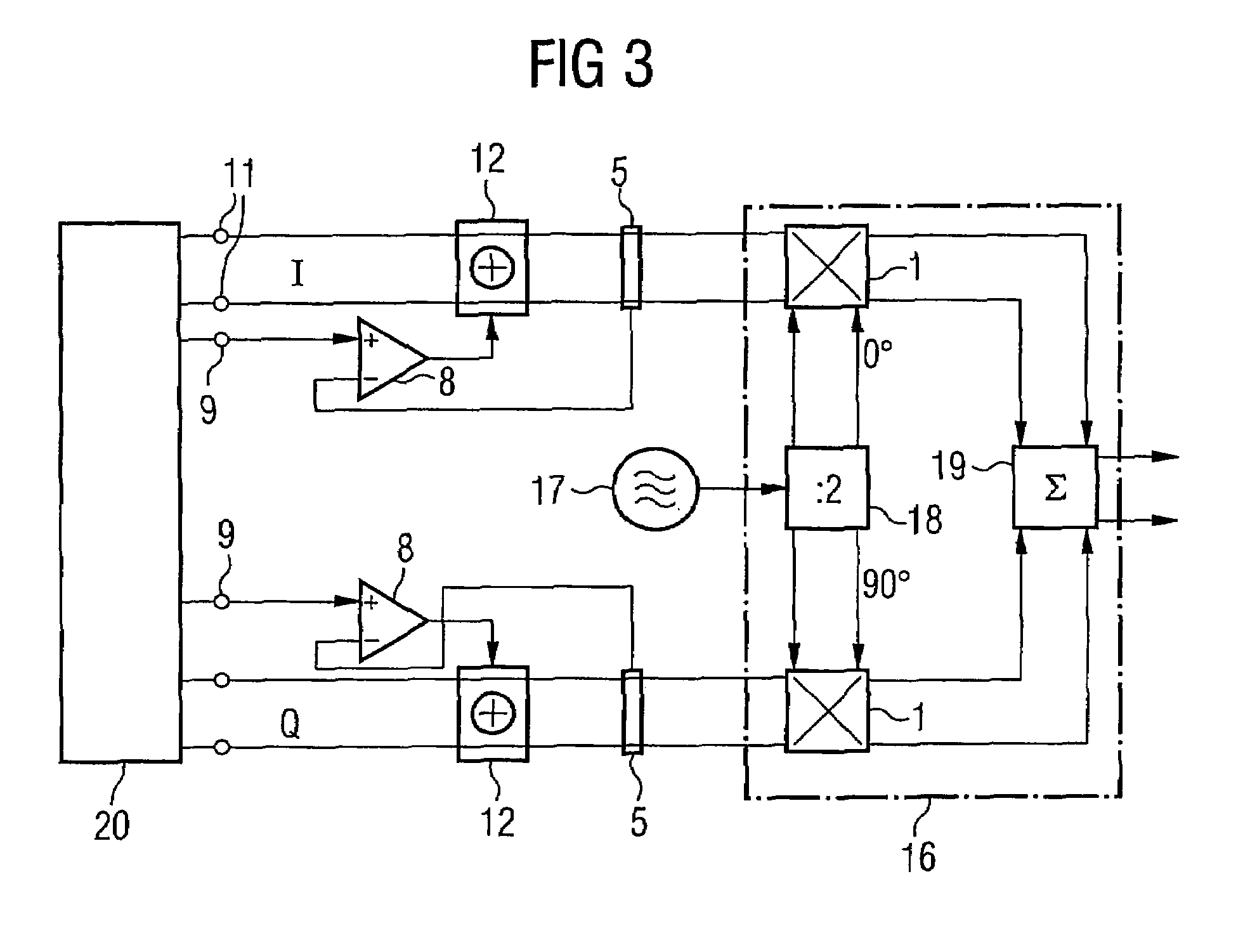

Circuit arrangement for regulating a DC signal component and mobile radio transmitter

InactiveUS7689181B2Simple circuit implementationImprove stabilityResonant long antennasMultiple carrier systemsFrequency mixerEngineering

In a circuit arrangement for regulating a DC signal component of a signal that is input to a frequency mixer, the regulation comprises a detector which detects the DC component of the input signal. A comparator compares the DC component with a reference value, and drives an apparatus for influencing the DC component based on the comparison.

Owner:INTEL CORP

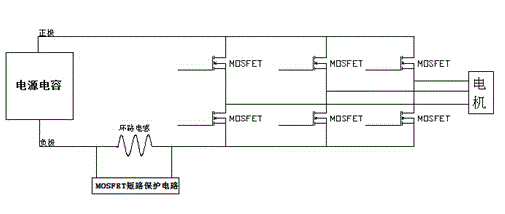

Short-circuit protection method for transistor in control circuit

InactiveCN104600677ASimple circuit implementationGood linearityEmergency protective circuit arrangementsShort circuit protectionInductor

The invention provides a short-circuit protection method for a transistor in a control circuit. The short-circuit protection method comprises the steps of acquiring induced electromotive force U at two ends of a section of a loop inductor of the circuit where the transistor is located, comparing the induced electromotive force U with pre-determined reference voltage Vref, enabling a transistor short-circuit protection circuit to output a control signal for controlling a drive signal of the transistor to change if the induced electromotive force U at two ends of the loop inductor is larger than the pre-determined reference voltage Vref, and enabling the transistor to be disconnected so as to achieve transistor short-circuit protection.

Owner:CHANGZHOU GLOBE

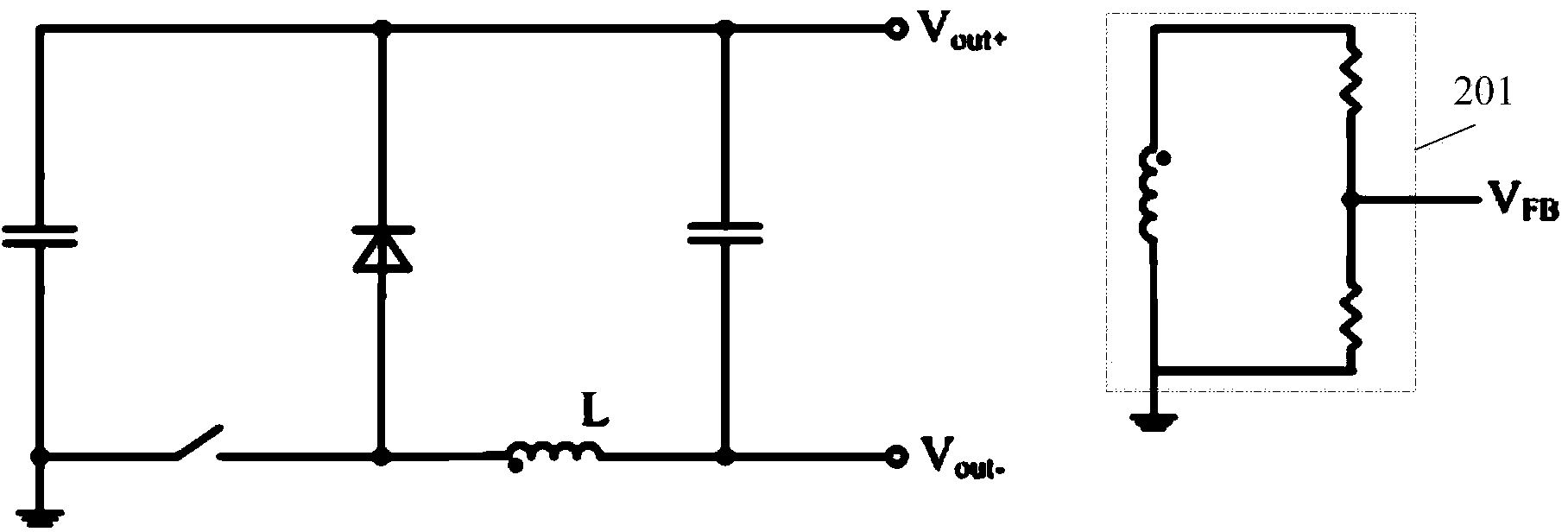

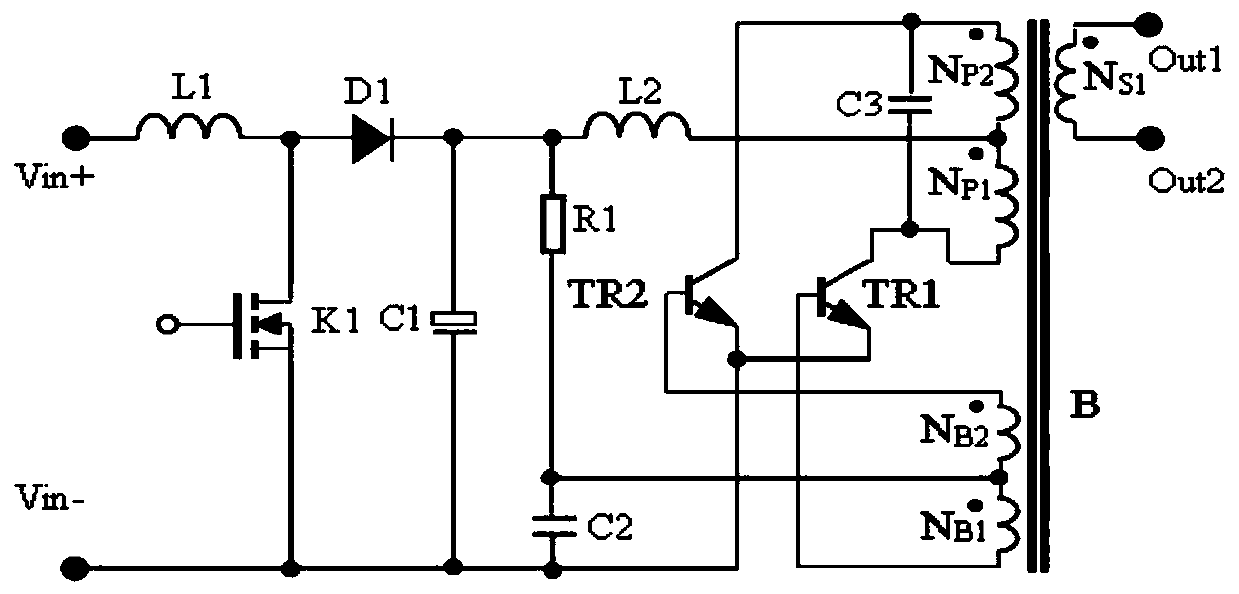

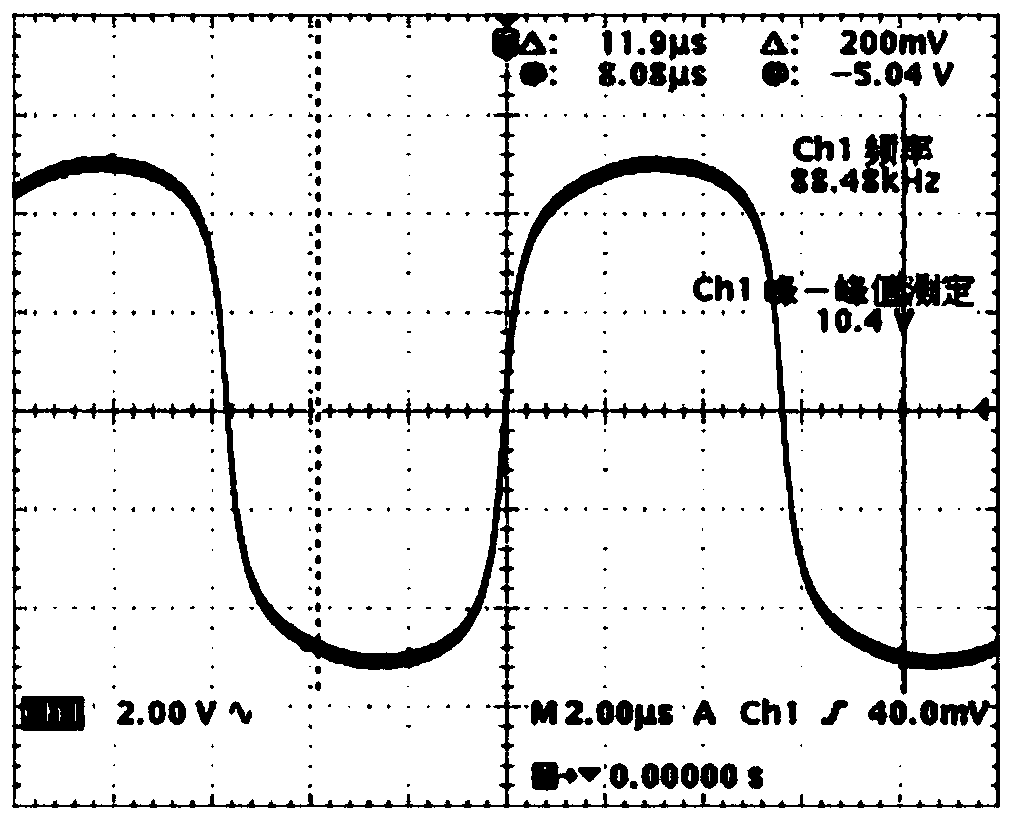

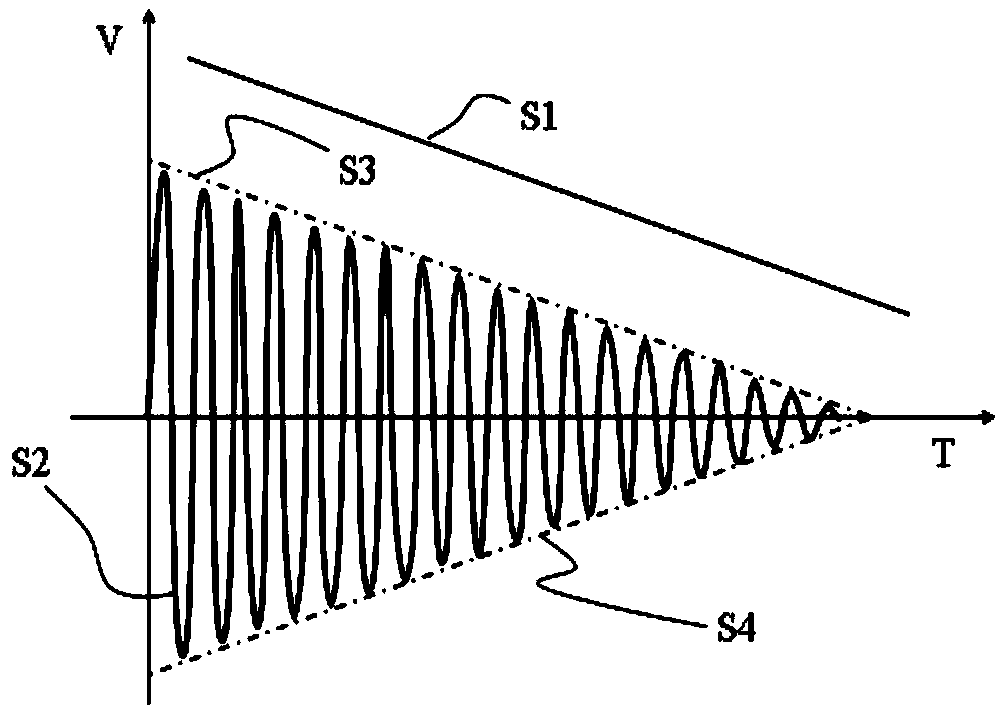

Power circuit and photovoltaic power generation system including power circuit

ActiveCN109525110AReduce radiationSimple circuit implementationDc-dc conversionSingle network parallel feeding arrangementsPeak valuePower circuits

The invention discloses a power circuit and a photovoltaic power generation system including the power circuit. The power circuit is a two-stage topological power circuit. The first stage is a BOOST circuit which processes an input low-voltage direct current into a direct voltage of which the output voltage decreases with time. The second stage is a CCFL conversion circuit. Because the CCFL conversion circuit works in open loop, the peak value of the sinusoidal alternating current output by the CCFL conversion circuit is directly proportional to the working voltage of the CCFL conversion circuit. The voltage decreases with time, namely, the peak value of the sinusoidal alternating current output by the CCFL conversion circuit decreases with time. Thus, the effective value of the sinusoidalalternating current also decreases with time, and an attenuated sinusoidal alternating current voltage is obtained. The voltage acts on the two ends of an activated photovoltaic string, which makes the voltage waveform delta(U) / dealt(t) output by the power circuit small. Therefore, the service life of the photovoltaic string is prolonged, and the radiation to the environment is low. Moreover, thepower circuit of the invention is simple to realize and low in cost.

Owner:MORNSUN GUANGZHOU SCI & TECH

Dynamic semiconductor storage device

InactiveUS7313045B2Simple circuit configurationTotal current dropRead-only memoriesDigital storageRefresh cycleHemt circuits

To achieve, by a simple circuit configuration, a DRAM that permits refresh current to be effectively reduced by selectively setting refresh cycles. A memory cell array is divided into 64 subarrays, and each subarray is further divided into 8 blocks. A refresh cycle control circuit has a fuse circuit for setting a frequency dividing ratio of 1 or 1 / 2, a frequency divider that divides the frequency of a predecode signal by the set frequency dividing ratio, fuse circuits for setting a frequency dividing ratio of 1 or 1 / 4, and frequency dividers for dividing predecode signals by the set frequency dividing ratio. The refresh cycle control circuit is capable of setting a 64-ms or 128-ms refresh cycle for the 64 subarrays and a 64-ms or 256-ms refresh cycle for 512 blocks.

Owner:INT BUSINESS MASCH CORP

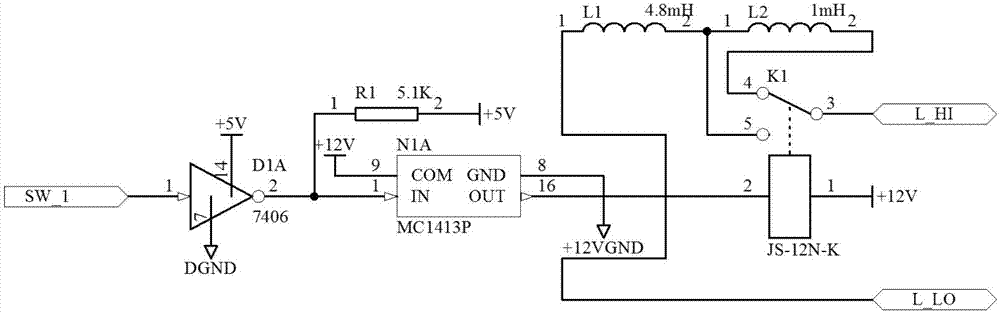

Inductive proximity sensor analog inductance output circuit

PendingCN107024233ASimple circuit implementationLow costConverting sensor output electrically/magneticallyElectrical connectionHemt circuits

The present invention discloses an inductive proximity sensor analog inductance output circuit, and aims to provide an analog inductance output circuit which is high in reliability and stable in performance, and enables the faults to be reduced. The inductive proximity sensor analog inductance output circuit of the present invention is realized by the following technical scheme that a series connection point of an inductance coil L1 and an inductance coil L2 is electrically connected with a normally open contact 5 of a relay K1, the other end of the inductance coil L2 is connected with a common end contact 3 of a relay via a normally-closed contact 4 of the relay K1, the common end contact 3 is electrically connected with the positive end L_HI of an analog inductance circuit output end, and the other end of the inductance coil L1 is electrically connected with the negative end L_LO of the analog inductance circuit output end, thereby forming an inductance switching gating switch circuit; the inductance switching gating switch circuit gates the inductance coil L1 of 4.8 mH, or gates the inductance coil L1 of 4.8 mH and the inductance coil L2 of 1 mH which are connected in series, and selects to output a 4.8 mH or 5.8 mH inductance value as an analog inductance value to output to a corresponding detection unit.

Owner:CHENGDU KAITIAN ELECTRONICS

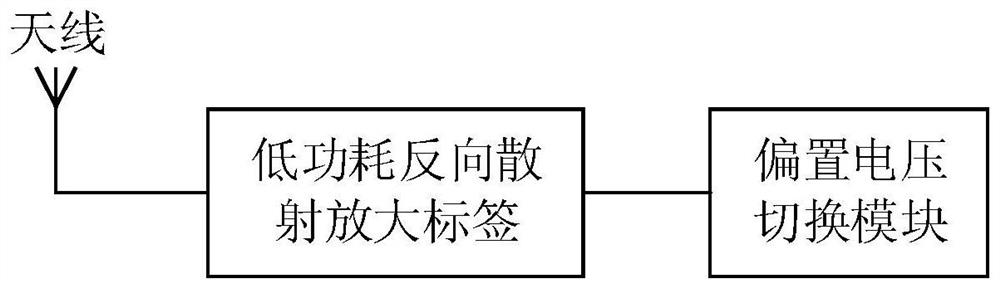

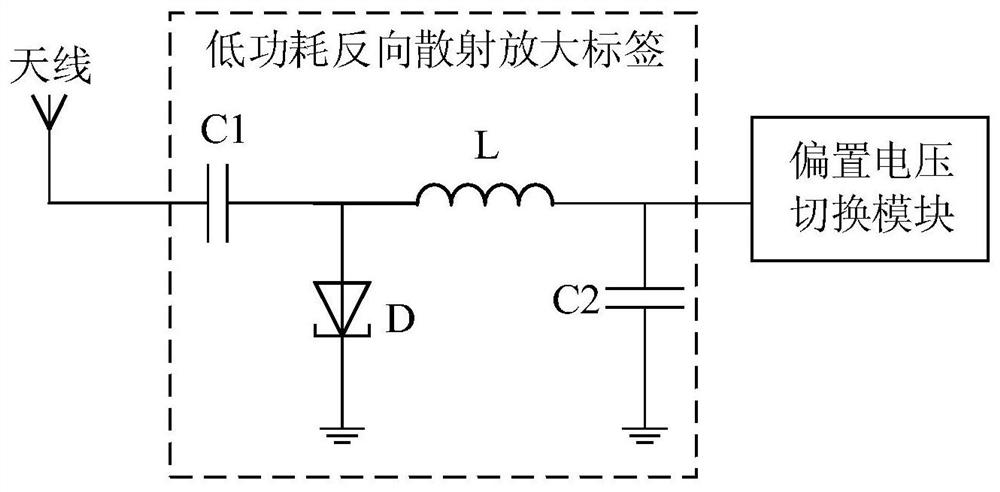

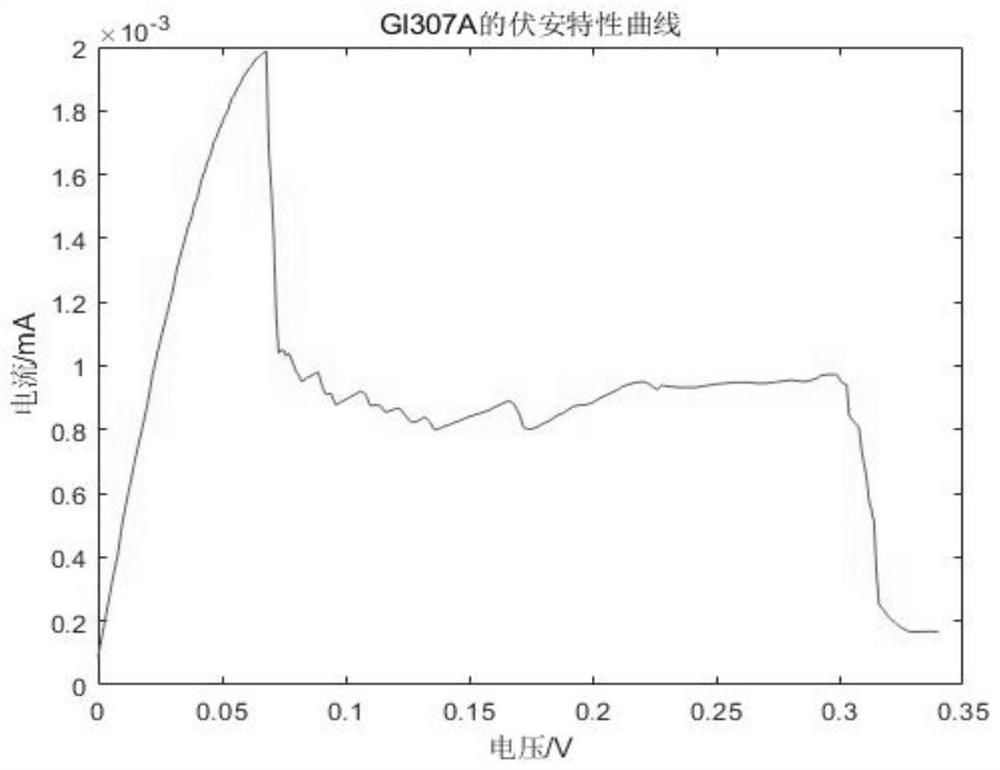

BPSK modulation circuit based on low-power-consumption backscattering amplification tag and method thereof

ActiveCN113055328ASimple circuit implementationAchieve modulationPhase-modulated carrier systemsShort range communication serviceHemt circuitsSwitching power

The invention discloses a BPSK modulation circuit and method based on a low-power-consumption backscattering amplification tag, the circuit comprises an antenna, the low-power-consumption backscattering amplification tag and a bias voltage switching module, wherein the antenna is used for receiving an incident excitation signal; the bias voltage switching module is used for providing different bias voltages; the low-power-consumption backscattering amplification tag is respectively connected with the antenna and the bias voltage switching module and is used for amplifying the incident excitation signal according to the different bias voltages and outputting a scattering signal; and the antenna is also used for sending the scattering signal. The bias voltage switching module performs switching power supply on the low-power-consumption backscattering amplification tag, and utilizes different impedances presented by the low-power-consumption backscattering amplification tag under different bias voltages to change phase information of a scattering coefficient of the low-power-consumption backscattering amplification tag so as to realize BPSK modulation, and the circuit is simple to realize.

Owner:XIDIAN UNIV

System and method for a rangefinding instrument incorporating pulse and continuous wave signal generating and processing techniques for increased distance measurement accuracy

ActiveUS20160238697A1Efficient solutionHigh measurement accuracyOptical rangefindersActive open surveying meansAmbiguityContinuous wave signal

A system and method for a rangefinding instrument incorporating pulse and continuous wave signal generating and processing techniques for increased distance measurement accuracy. The use of the former technique effectively solves the ambiguity issues inherent in the latter while allowing for relatively simple circuit implementations. Thus, a potentially more accurate phase-based distance measurement technique can be utilized which is also completely independent of the maximum range to the target.

Owner:LASER TECH INC +1

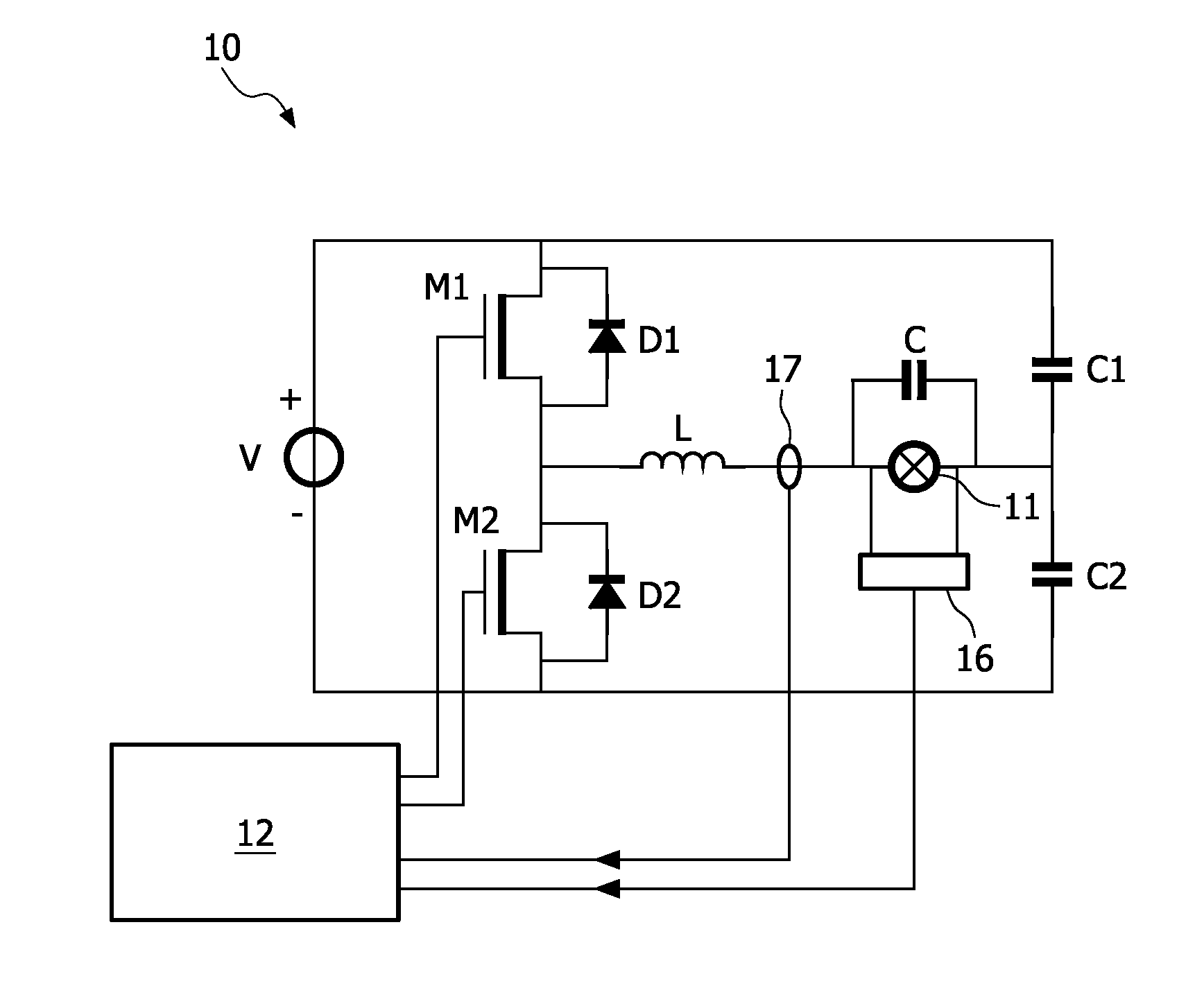

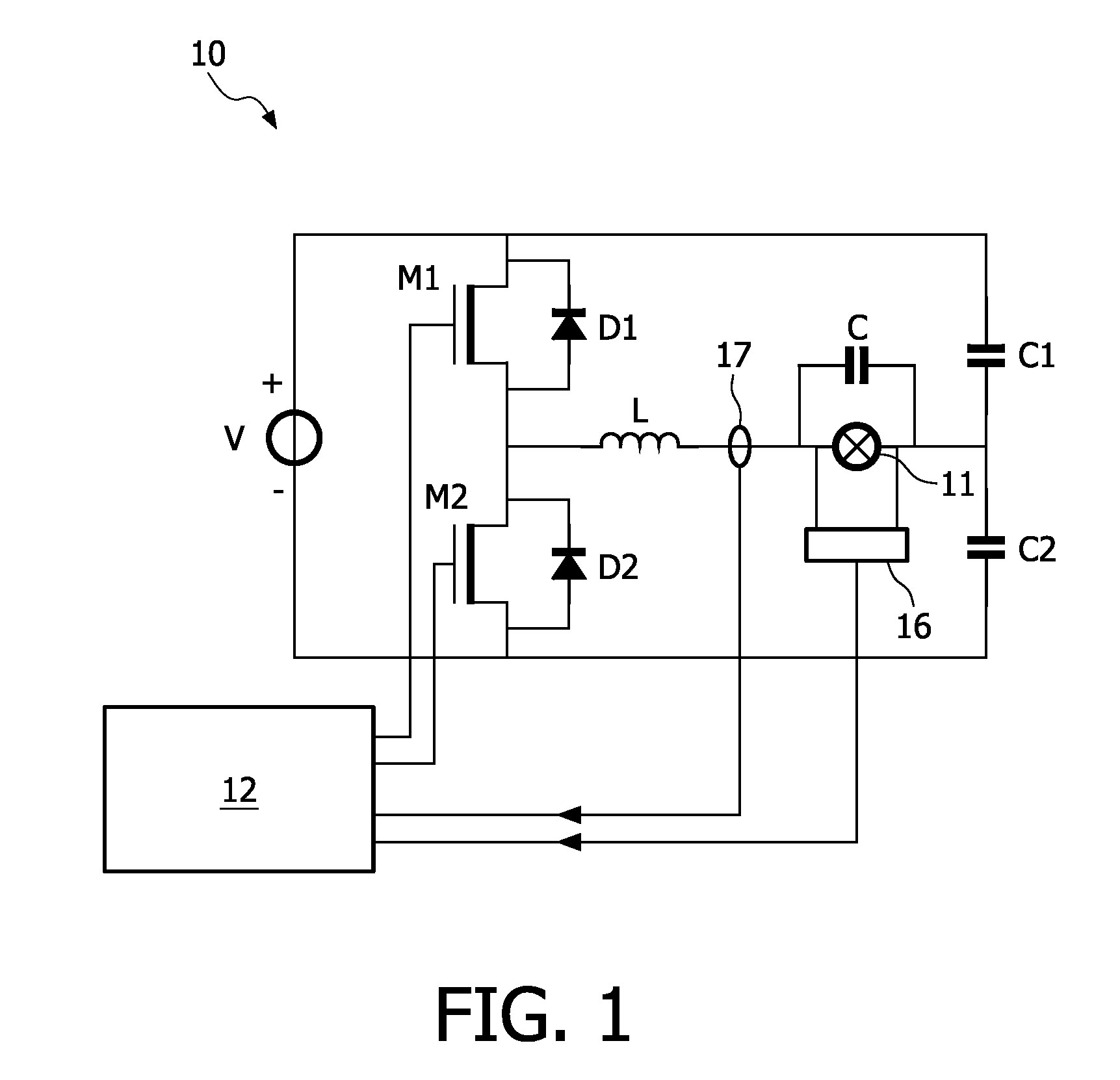

Device for driving a gas discharge lamp

InactiveUS20100176738A1Precision productionSimple componentsElectrical apparatusElectric light circuit arrangementGas-discharge lampEngineering

A driver (10) for driving a gas discharge lamp (11) comprises at least two controllable switches (M1, M2) and a controller (12) for controlling the switches. The controller has a first operative state in which one switch (M1) is conductive while the other switch (M2) is non-conductive, and has a second operative state in which said other switch (M2) is conductive while said first switch (M1) is non-conductive. The controller comprises a memory device (20) comprising a plurality of memory elements (21) each containing a binary value (“0”; “1”), wherein the value of the last memory element (21(N)) determines the operative state of the controller. Responsive to a clock signal (SQL) generated by a clock device (30), the memory device shifts the contents of each memory element (21(i)) to a subsequent memory element (21(i+1)) and shifts the contents of the last memory element (21(N)) to the first memory element (21(1)).

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

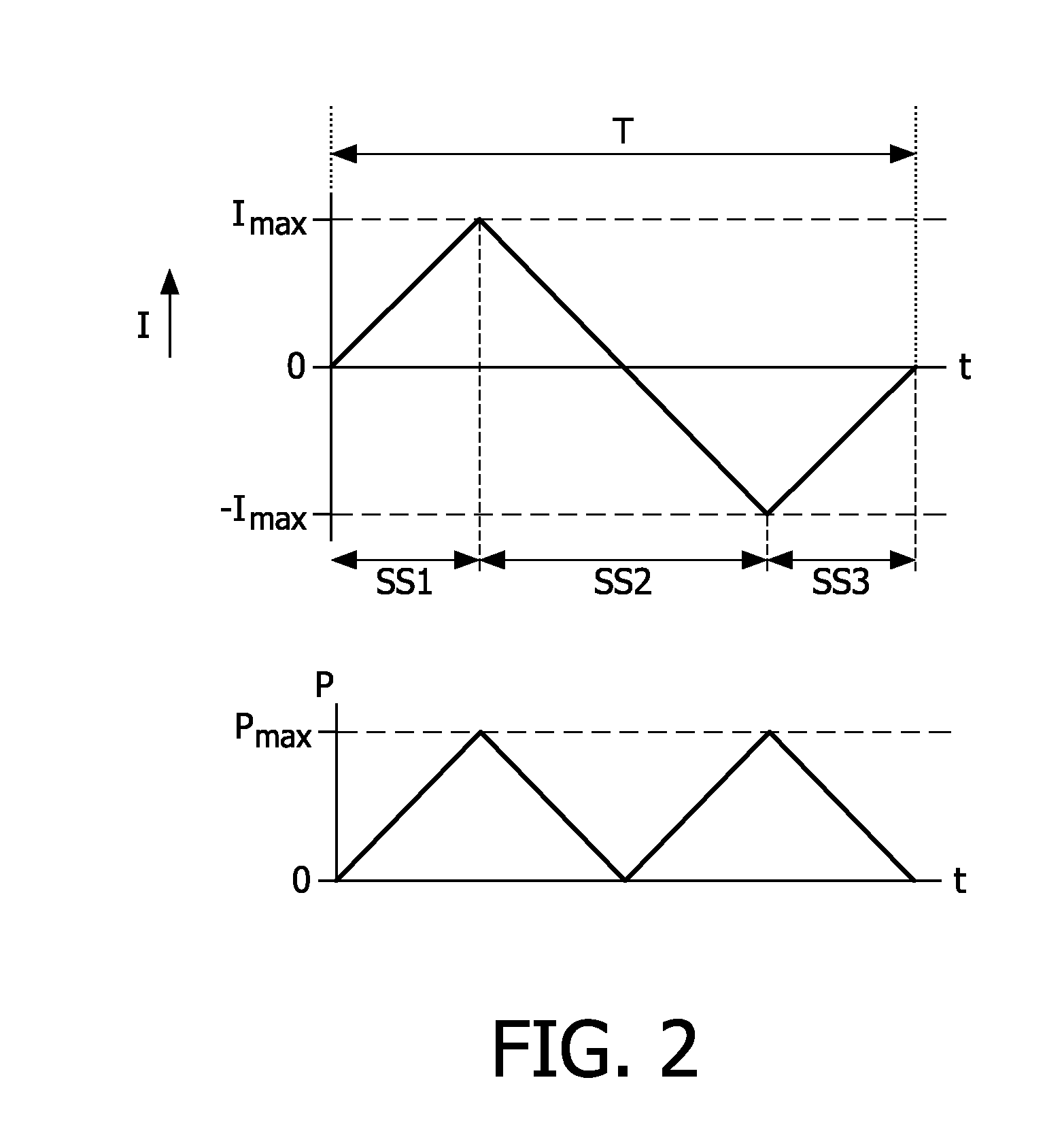

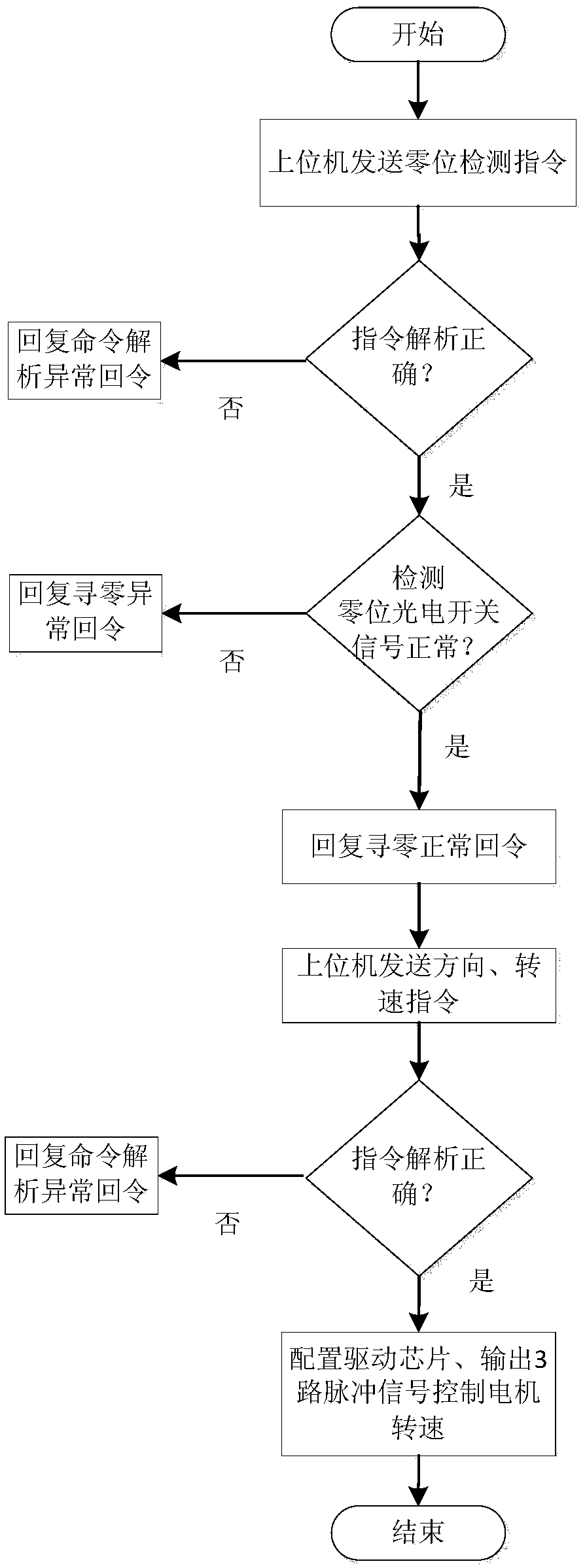

Universal stepping motor driving device

InactiveCN109672375ASimple circuit implementationEasy to useDynamo-electric converter controlControl functionElectricity

The invention relates to a universal stepping motor driving device, and belongs to the technical field of motor driving devices. Three way of stepping motors can be driven at the same time, and the circuit of the device is easy to realize. A single-chip microcomputer can communicate with an upper computer through a serial port. The control function of the upper computer is achieved, and the deviceis flexible and convenient to use. A zero-searching function is achieved, and absolute position information can be obtained after power-on.

Owner:TIANJIN JINHANG INST OF TECH PHYSICS

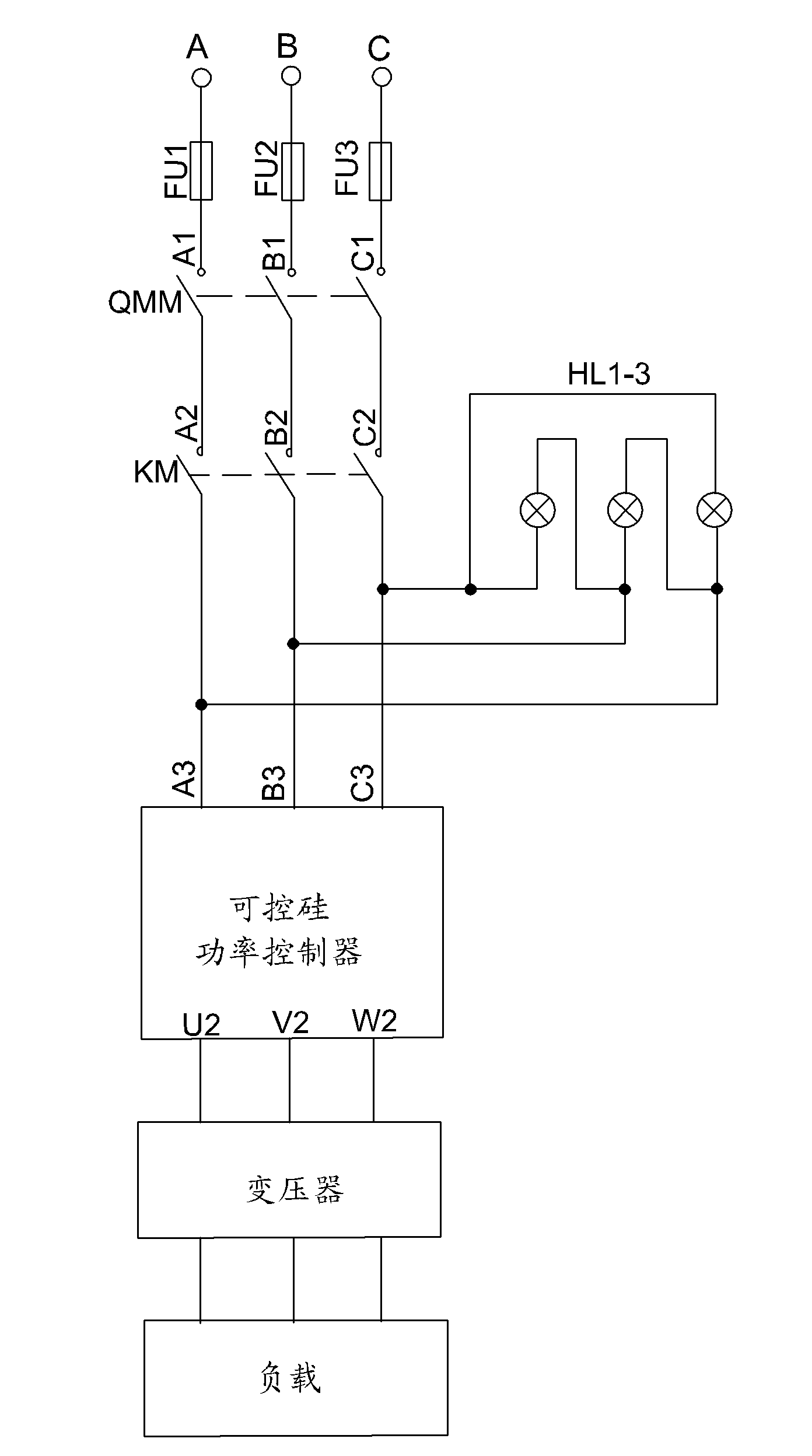

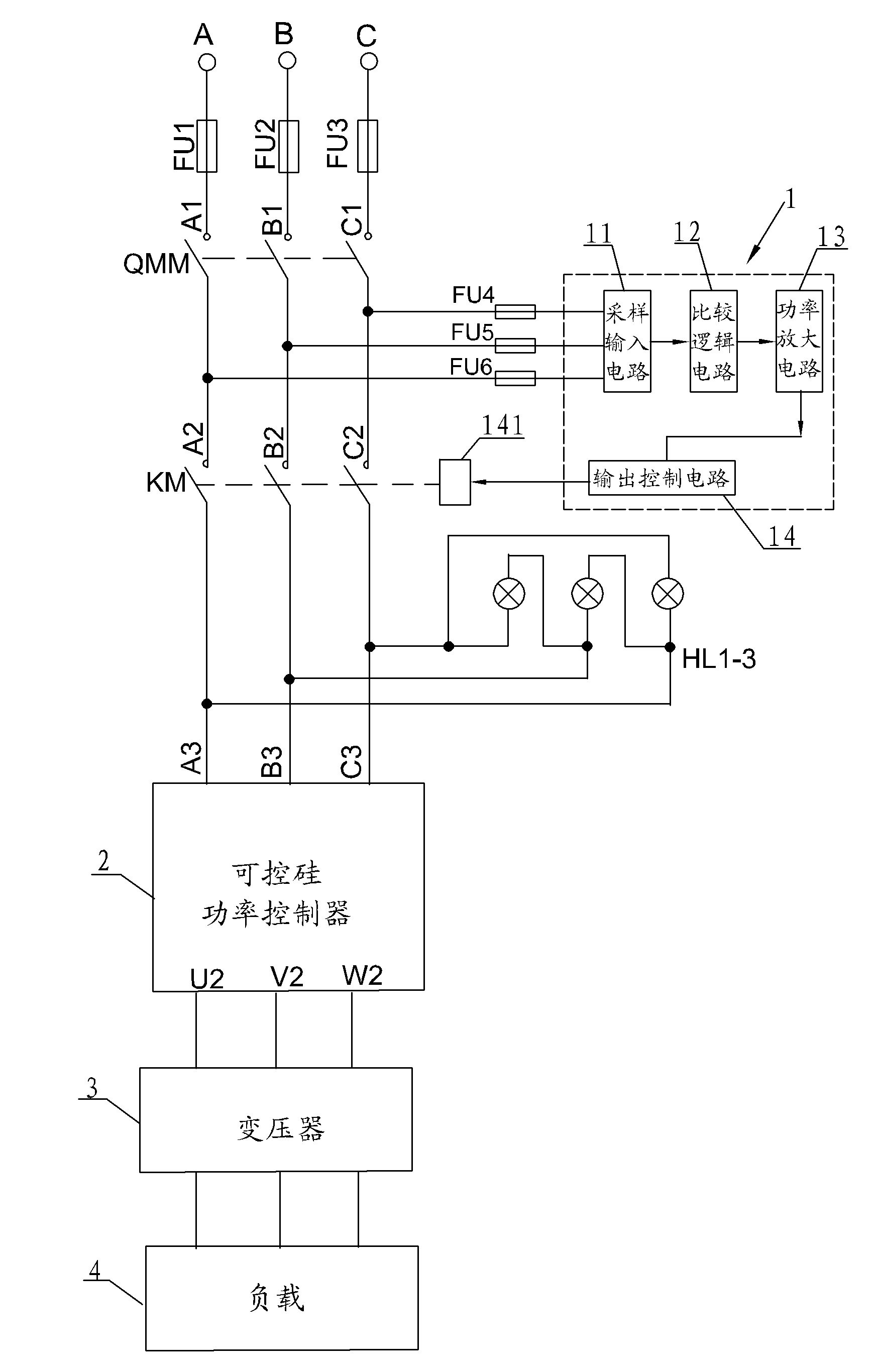

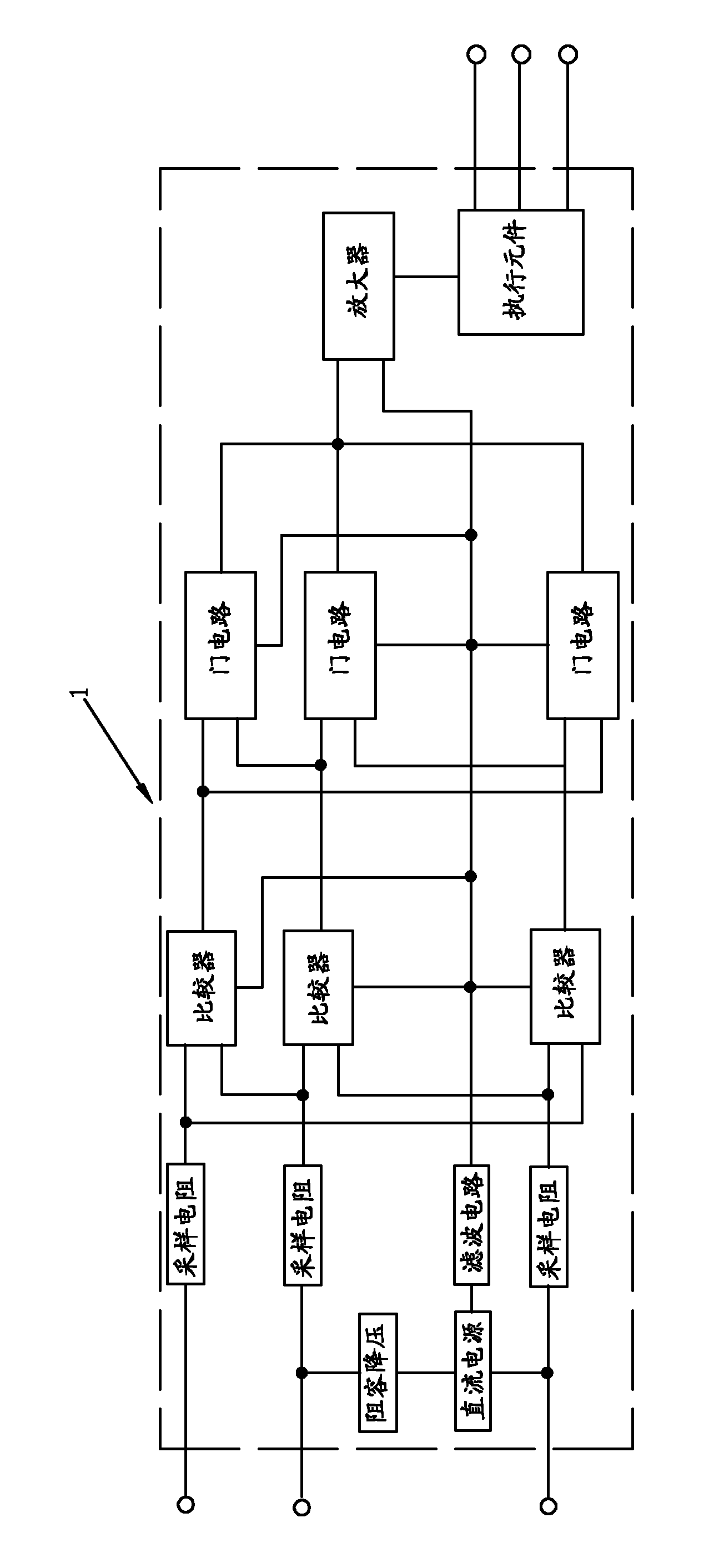

Thyristor pressure regulator with phase sequence protection

InactiveCN102064710ASimple circuit implementationRealize automatic on-off controlConversion without intermediate conversion to dcEmergency protective arrangements for automatic disconnectionContactorThree-phase

The invention relates to a thyristor pressure regulator with phase sequence protection. The thyristor pressure regulator comprises three phases of incoming circuit branches, a silicon controlled power controller and a transformer which are connected in sequence by output phases and the thyristor pressure regulator also comprises a phase sequence protection unit, wherein the phase sequence protection unit comprises a sampling input circuit, a comparison logic circuit and an output control circuit; the sampling input circuit is connected with the three phases of incoming circuit branches respectively and is used for acquiring the voltage of each phase; the comparison logic circuit is connected with the output ends of the sampling input circuit; the output control circuit is connected with the output end of the comparison logic circuit; the comparison logic circuit receives the voltage signal output by the sampling input circuit, compares the voltage signal with the preset standard voltage value and outputs the electrical signal to the output control circuit if the received voltage signal is abnormal; the output control circuit drives a contactor to act to disconnect a load and a main power source, thus completing the phase sequence protection function; and the phase sequence protection unit has the advantage of simple circuit realization, can be modularly designed with the existing pressure regulators and is especially applicable to the industrial control field.

Owner:张家港市中亚特种变压器制造有限公司

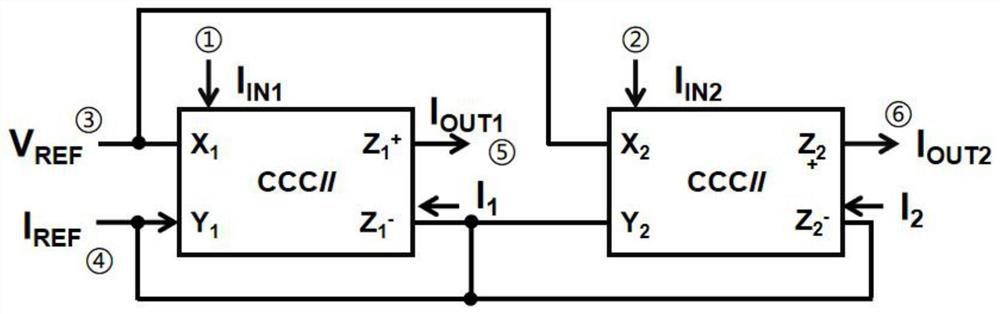

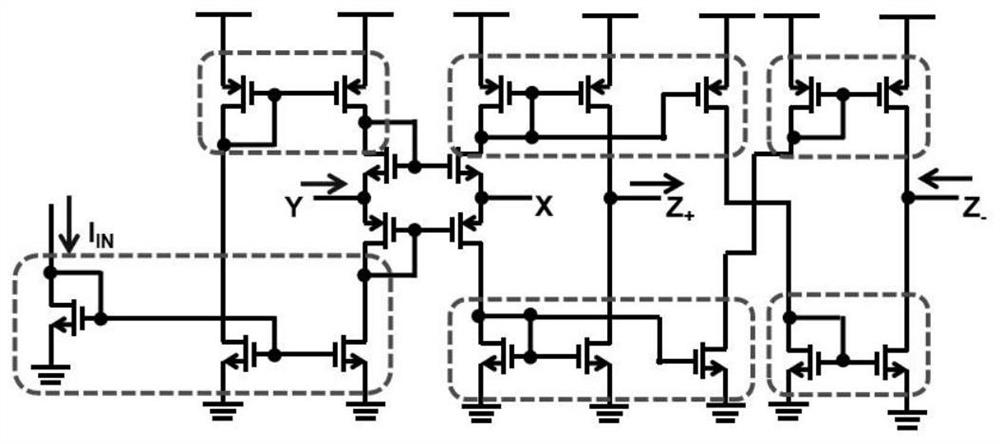

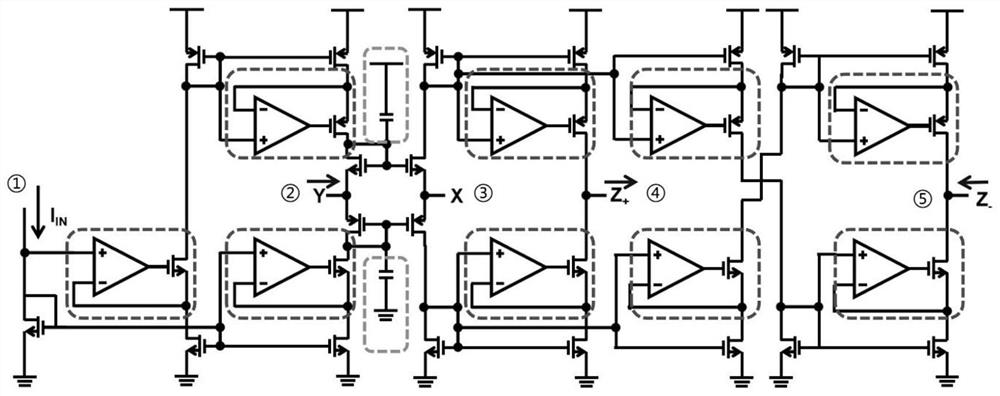

An analog current distributor for current regulation

ActiveCN113467568BReduce circuit costSimple circuit implementationElectric variable regulationCurrent regulationVoltage reference

The present invention provides an analog current distributor for current regulation, which specifically includes two improved CCCII circuits, namely a first CCCII circuit and a second CCCII circuit, and the voltage signal ports X of the first CCCII circuit and the second CCCII circuit are both connected to Reference voltage V REF , the current signal port Y and the current signal port Z of the first CCCII circuit and the second CCCII circuit are both connected to the reference current I REF , the analog current divider can also include a plurality of improved CCCⅡ circuits to realize multiple outputs. The sum of the output current of the analog current divider proposed by the present invention is equal to the input reference current, and the ratio of the output current can be referenced by other inputs. The current proportional control can control a more precise output current and can be used for more precise current signal (below uA level) processing.

Owner:SHENZHEN GRADUATE SCHOOL TSINGHUA UNIV

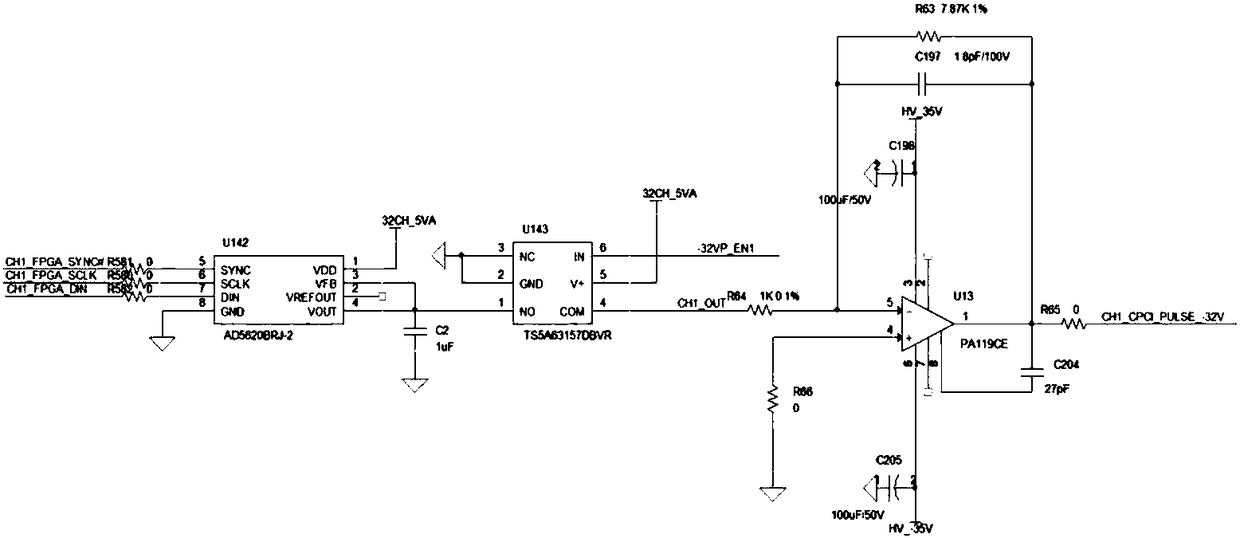

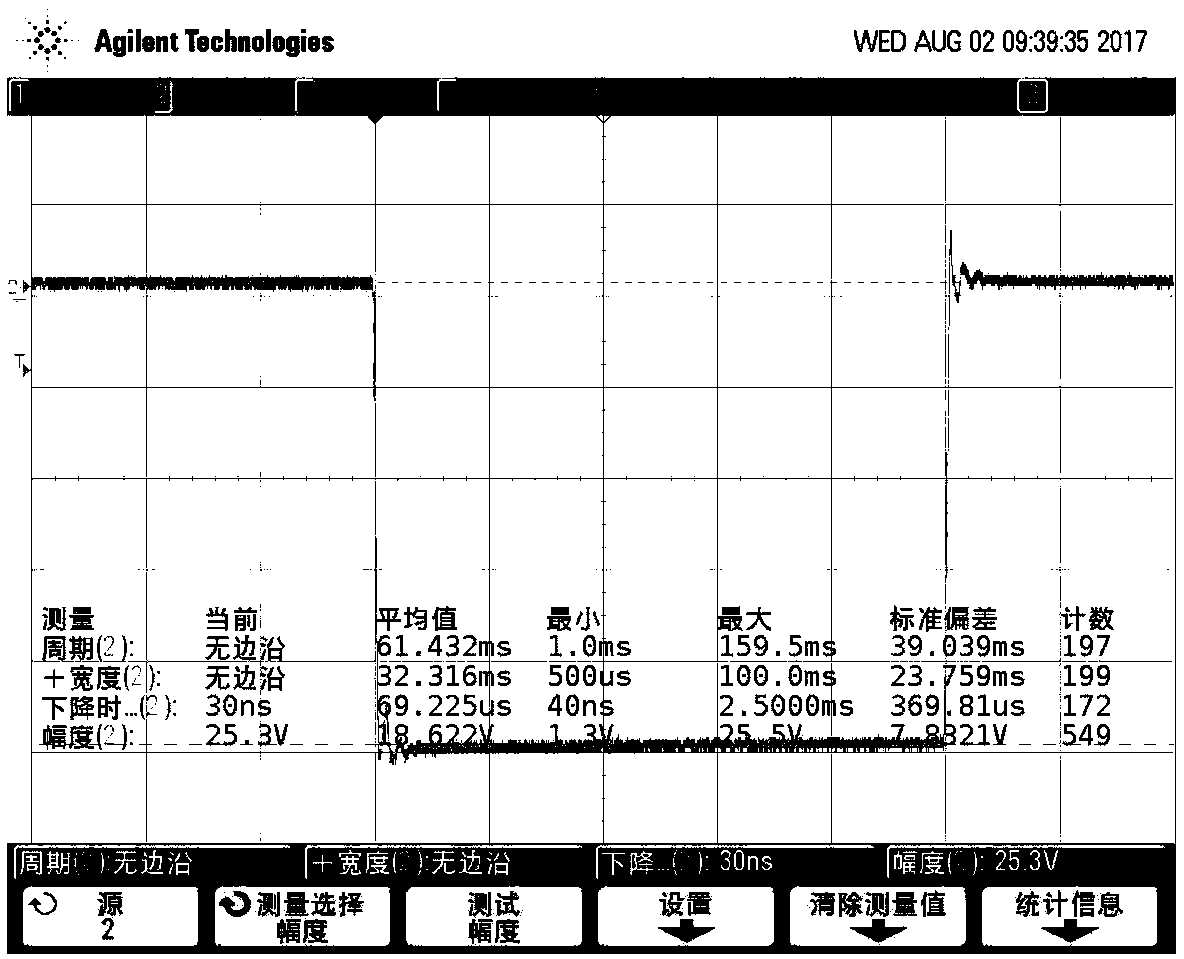

High-voltage fast-edge negative pulse generator

InactiveCN109085395ASimple circuit implementationImprove reliabilityElectrical measurement instrument detailsElectrical testingPhysicsVoltage amplitude

The invention discloses a high-voltage fast-edge negative pulse generator. According to the high-voltage fast-edge negative pulse generator, based on control of FPGA, the output voltage amplitude is adjusted by adjusting resistance values of a resistor R1 and a resistor R2; by adjusting a capacitor C1, the falling edge time of the negative pulse generator can be well realized within 30ns, and thewaveform amplitude is stable and the wave line is small; circuit implementation of the negative pulse generator is simple, reliability is high, and the cost is lower, and thus arrangement of the voltage amplitude, the pulse width and the falling edge time can be realized advantageously; and the signal precision is high, thus the high-voltage fast-edge negative pulse generator can be widely used inthe high demanding nanosecond industrial measurement field, and the effective measurement precision is improved.

Owner:CHINA SOUTH IND GRP AUTOMATION RES INST

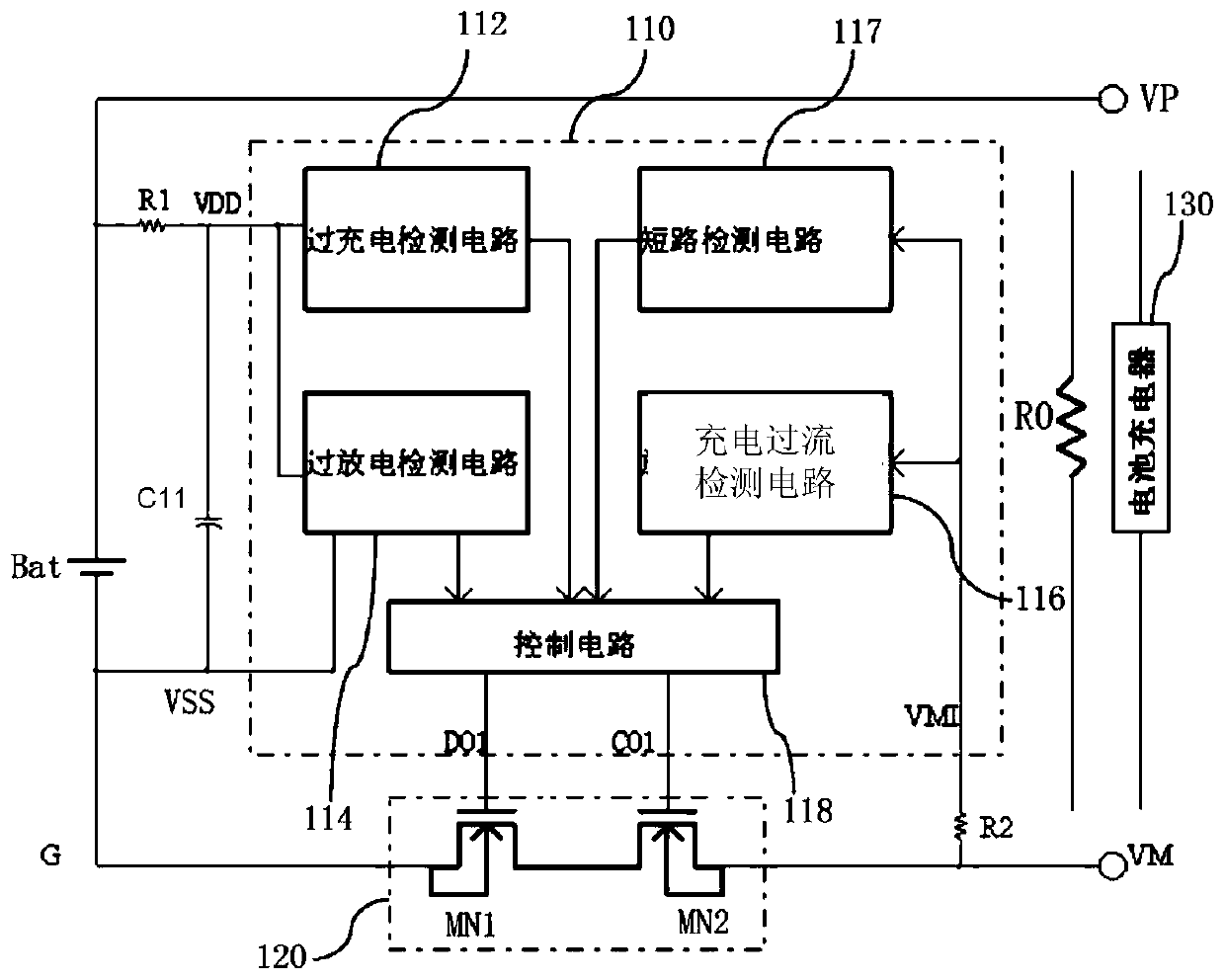

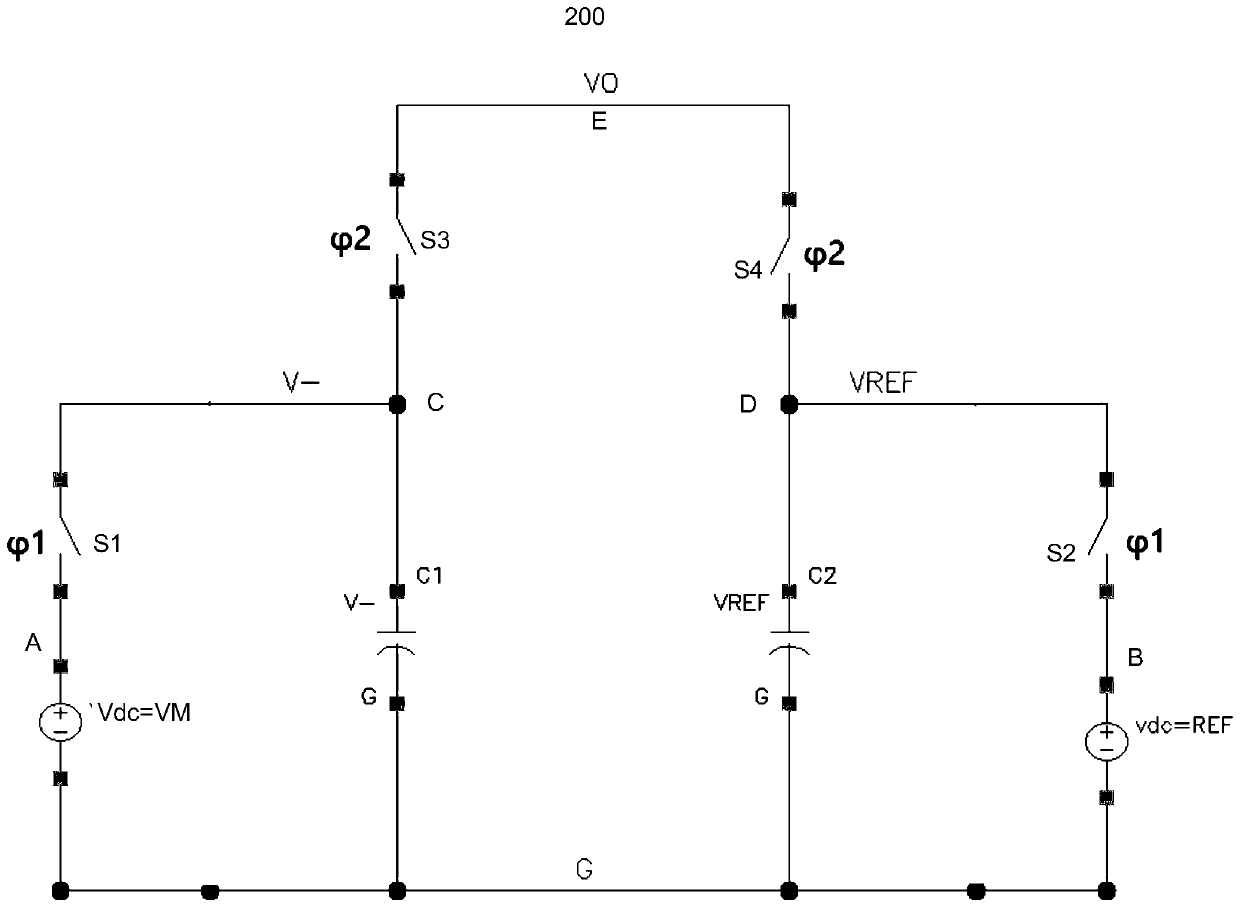

Negative voltage detection circuit and battery protection circuit

ActiveCN110108918ASimple circuit implementationEasy to implementEmergency protective circuit arrangementsVoltage measurements onlyElectrical batteryCapacitance

The invention discloses a negative voltage detection circuit and a battery protection circuit. The negative voltage detection circuit comprises a first capacitor connected between a first node and a grounding end, a second capacitor connected between a second node and the grounding end, a detection voltage end for receiving detection voltage, a reference voltage end for receiving reference voltagewhich is positive voltage, a first switch connected between the detection voltage end and the first node, a second switch connected between the reference voltage end and the second node, a third switch connected between the first node and the third node, a fourth switch connected between the second node and the third node, and a comparator comprising a first input end connected with the third node, a second input end connected with the grounding end and an output end for outputting a comparison result. Compared with the prior art, the negative voltage detection circuit of the invention can realize negative voltage comparison, and the circuit is simple to realize.

Owner:NANJING ZGMICRO CO LTD

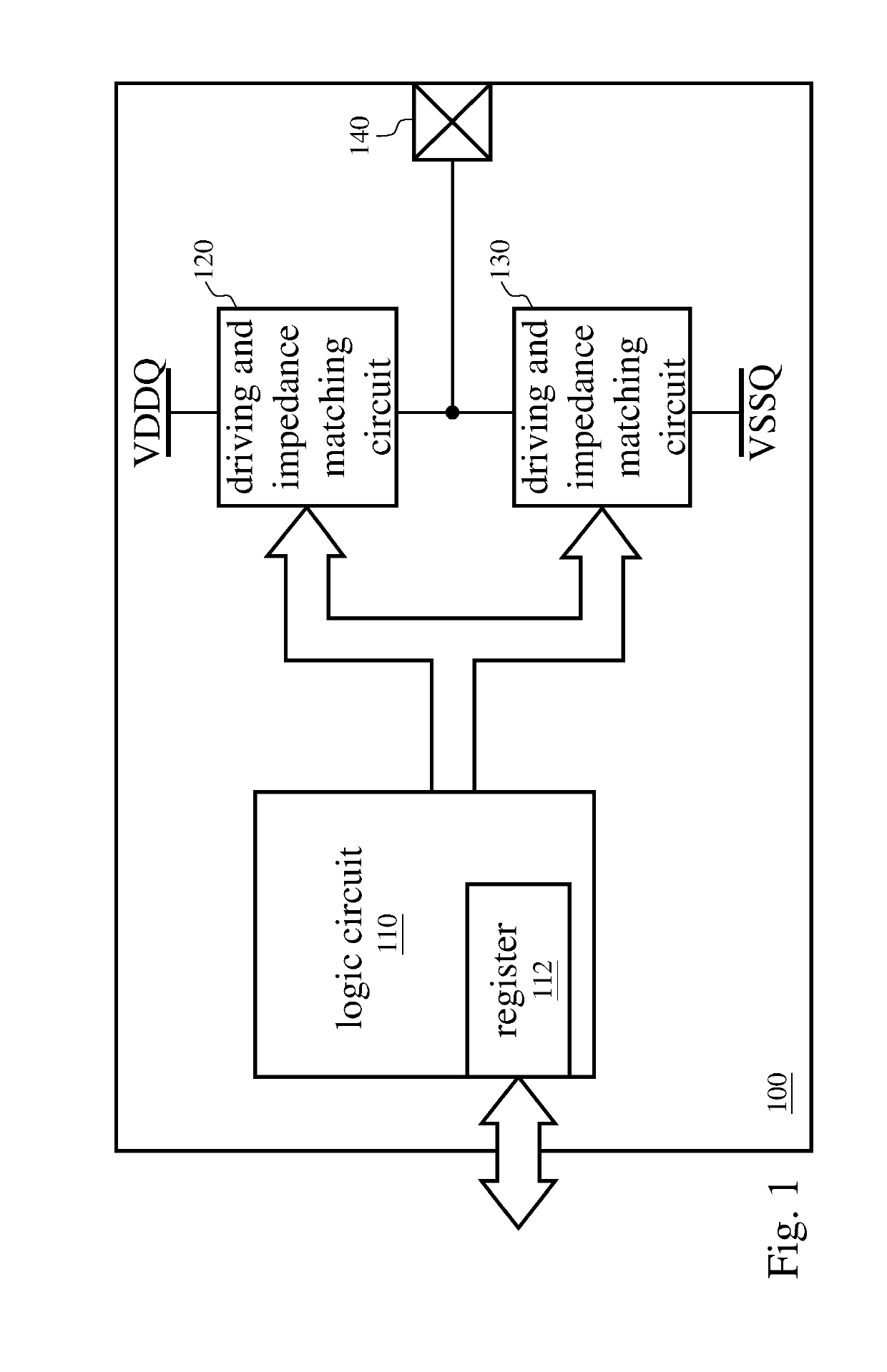

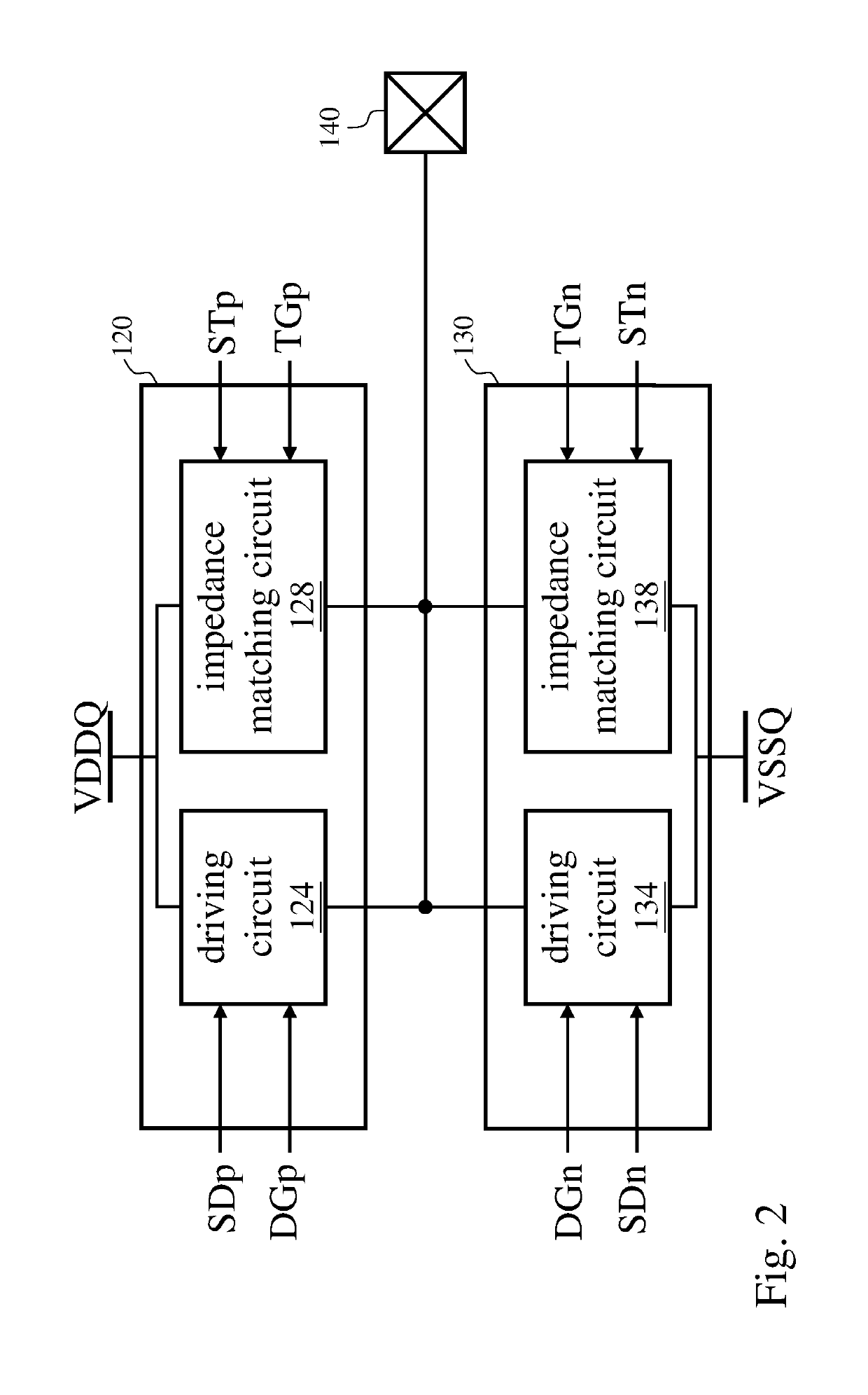

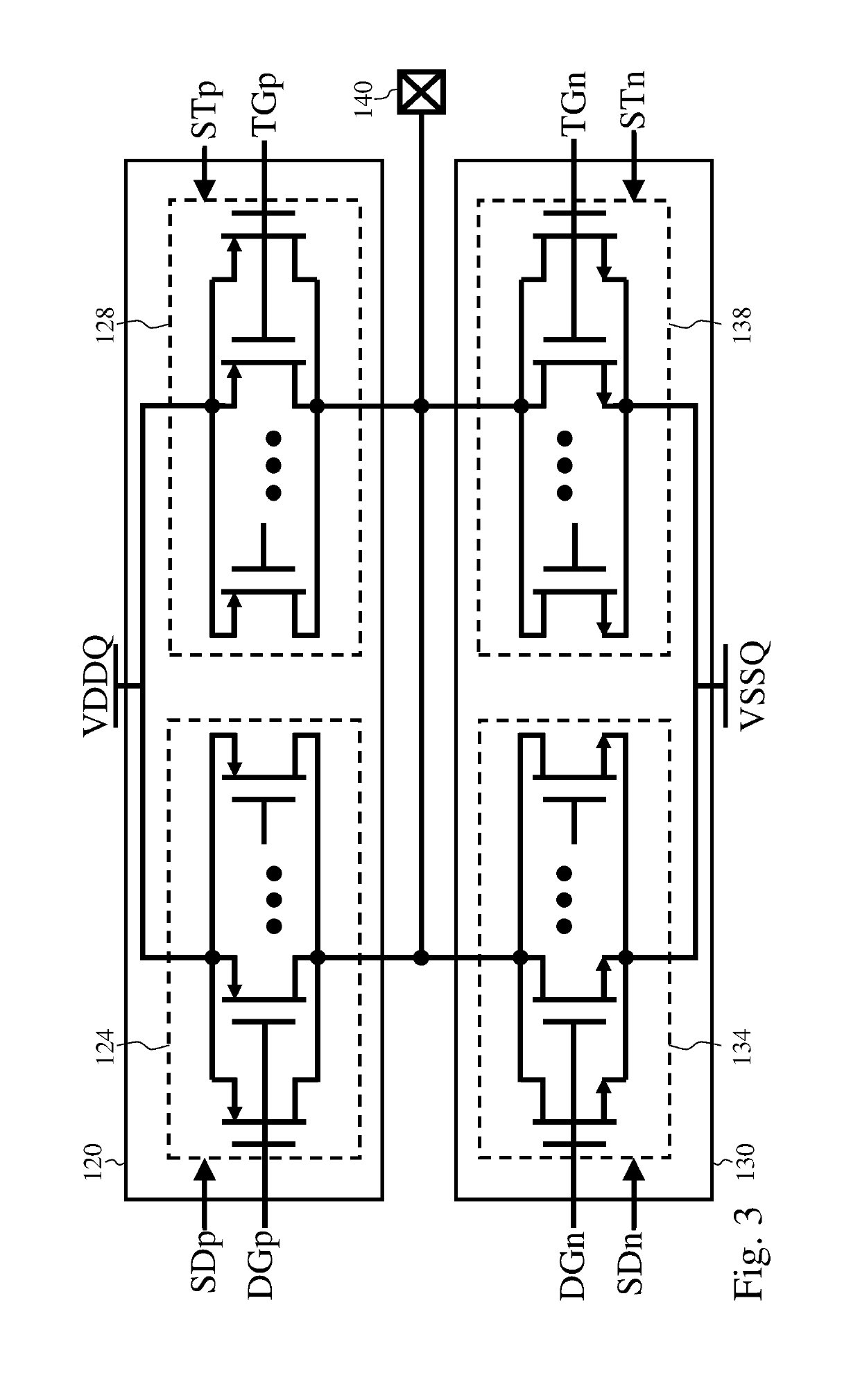

Memory controller

ActiveUS20190140867A1Simple circuit implementationReduce areaMultiple-port networksImpedence matching networksControl signalImpedance matching

A memory controller adjusts impedance matching of an output terminal and outputs a control signal that controls a memory through the output terminal. The memory controller includes a first driving and impedance matching circuit, a second driving and impedance matching circuit, and a logic circuit. The logic circuit, which is coupled to the first driving and impedance matching circuit and the second driving and impedance matching circuit, sets a first impedance and a first driving capability of the first driving and impedance matching circuit, sets a second impedance and a second driving capability of the second driving and impedance matching circuit, and enables the first driving and impedance matching circuit to cause the control signal to have a first level or enables the second driving and impedance matching circuit to cause the control signal to have a second level different from the first level.

Owner:REALTEK SEMICON CORP

Absolute value current-sensing circuit for step-down DC-to-DC converters with integrated power stage

ActiveUS9709608B2Accurate measurementWithout affecting efficiency of DC-to-DCPhotovoltaic monitoringEfficient power electronics conversionPower flowVoltage drop

Owner:TELEFON AB LM ERICSSON (PUBL)

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com