Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

90results about "Conversion with storage device usage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

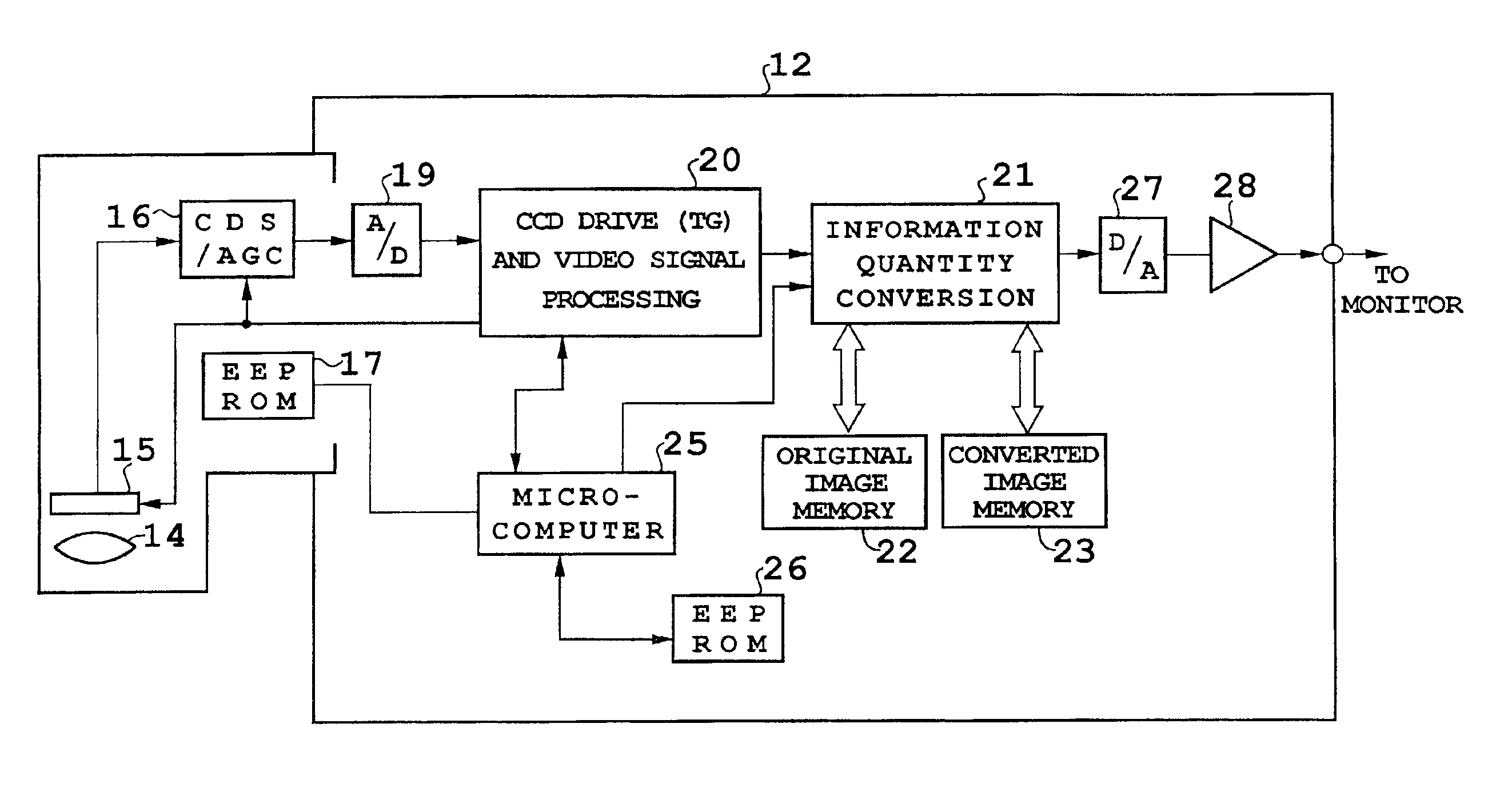

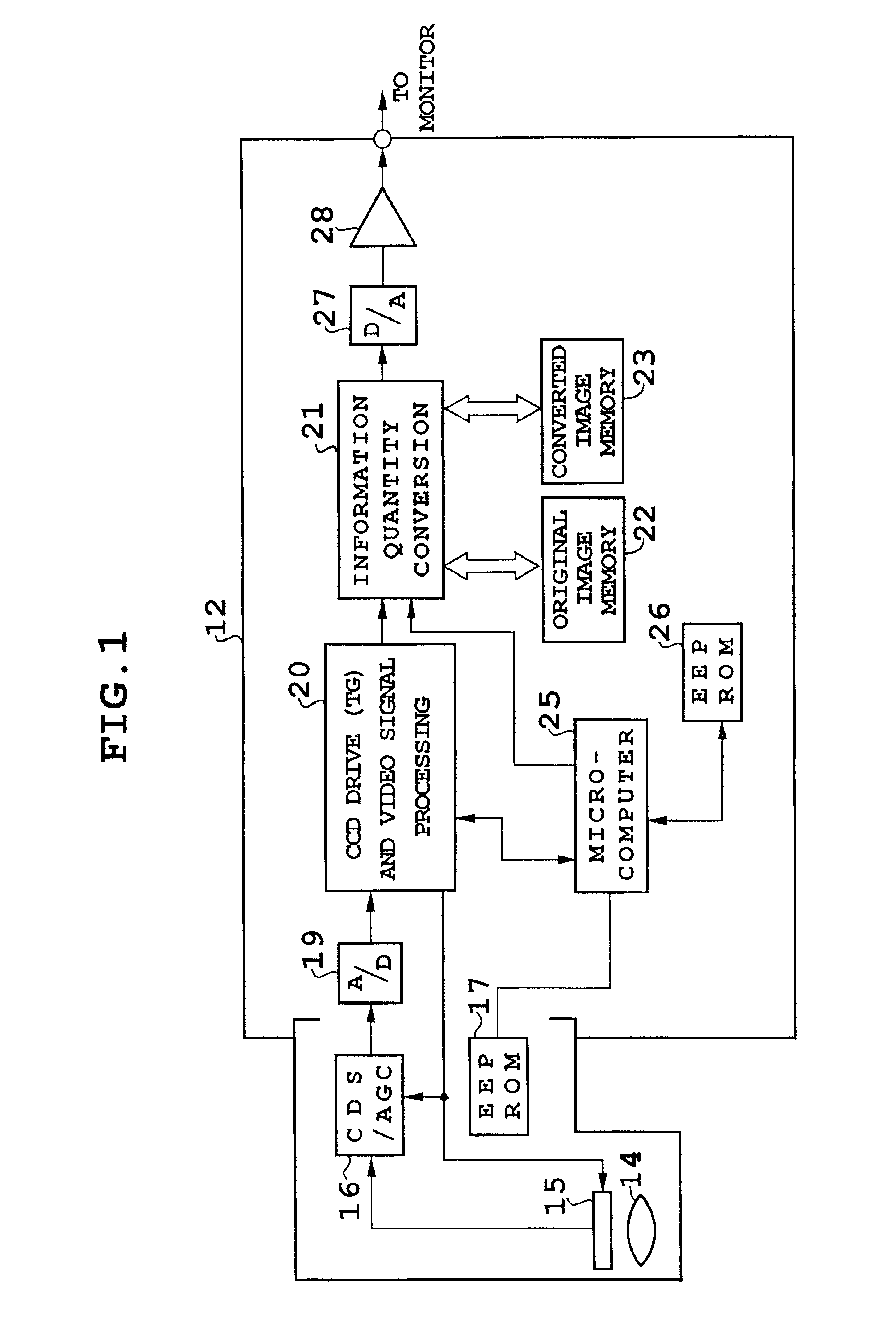

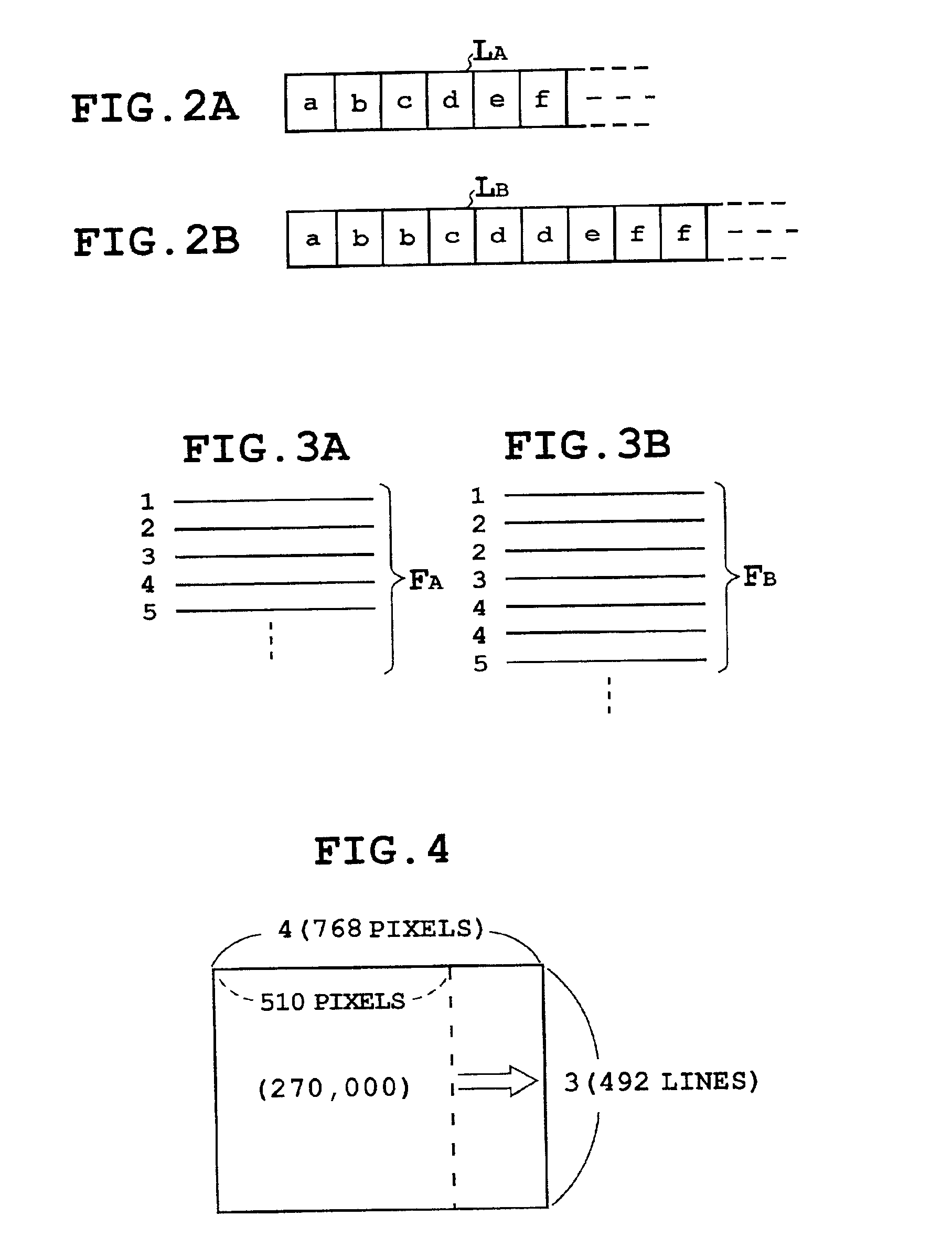

Electronic endoscopic apparatus connectable with electronic endoscope having different number of pixels

InactiveUS6876380B2Easy to implementAvoid noiseTelevision system detailsTelevision system scanning detailsSignal processing circuitsInformation quantity

An electronic endoscopic apparatus having various sorts of electronic endoscopes mounting a CCD with a different number of pixels, for example, 410,000 pixels, 270,000 pixels or 190,000 pixels that are connectable to a processor. A CCD drive and signal processing circuit drives all the CCDs at a frequency set up for the CCD with 410,000 pixels, and an information quantity conversion circuit expands an image acquired by the CCD with 270,000 pixels or 190,000 pixels by pixel interpolation in a horizontal direction or a vertical direction to form an image with an aspect ratio of 4 to 3. Also, a video signal acquired in an NTSC system is converted into a video signal of a PAL system by using a television standard conversion circuit, thereby displaying an excellent PAL video without any bar noise.

Owner:FUJI PHOTO OPTICAL CO LTD

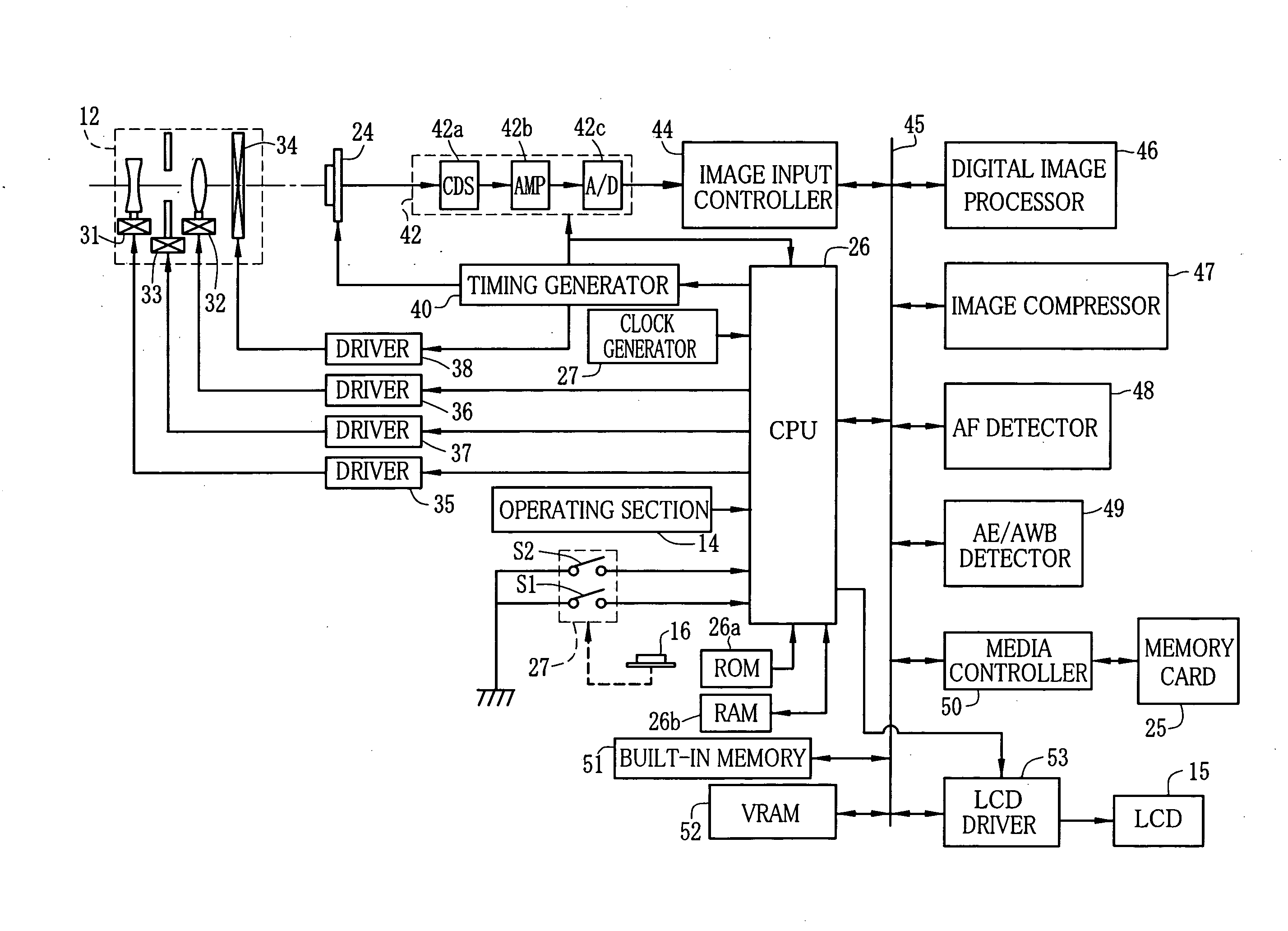

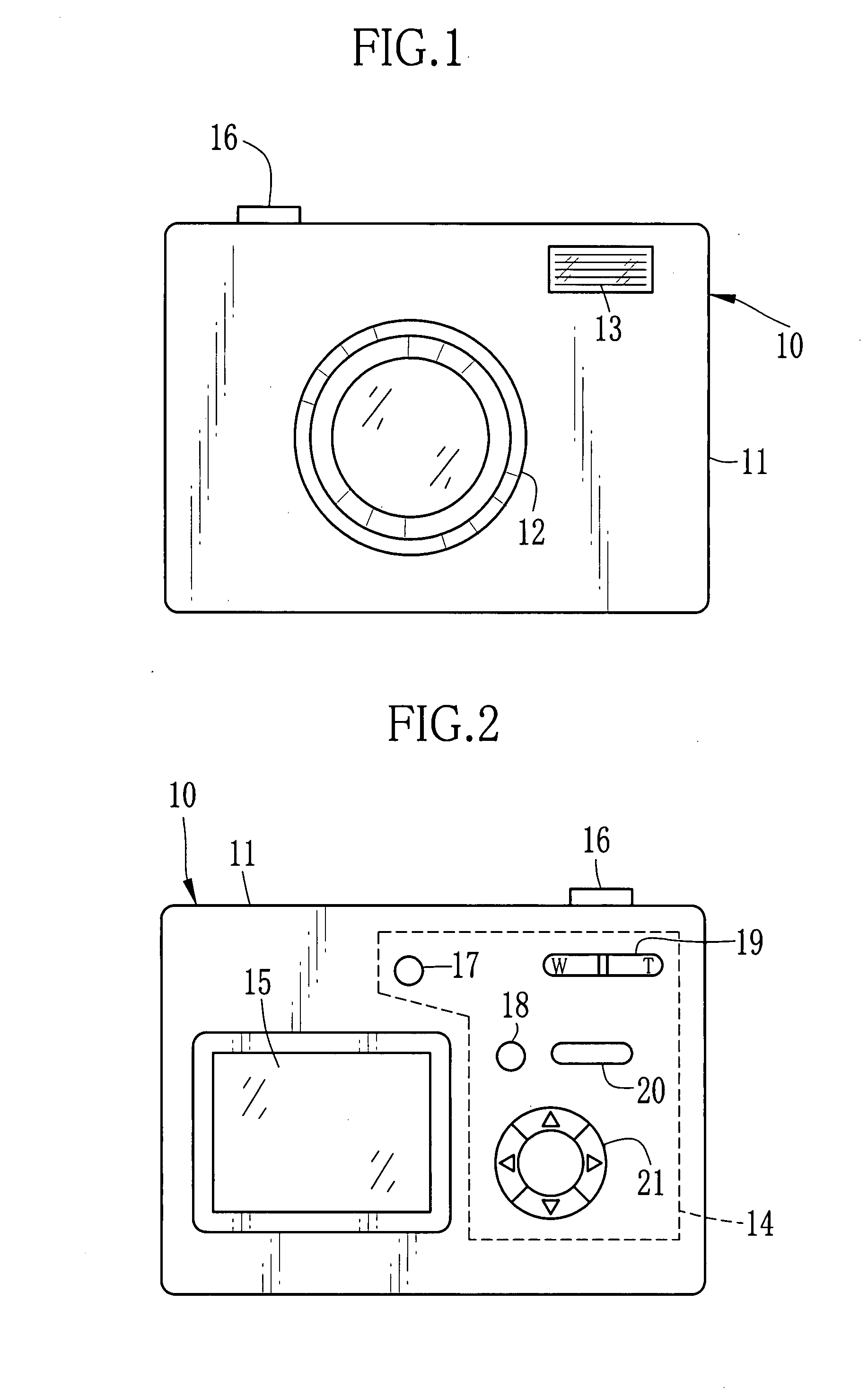

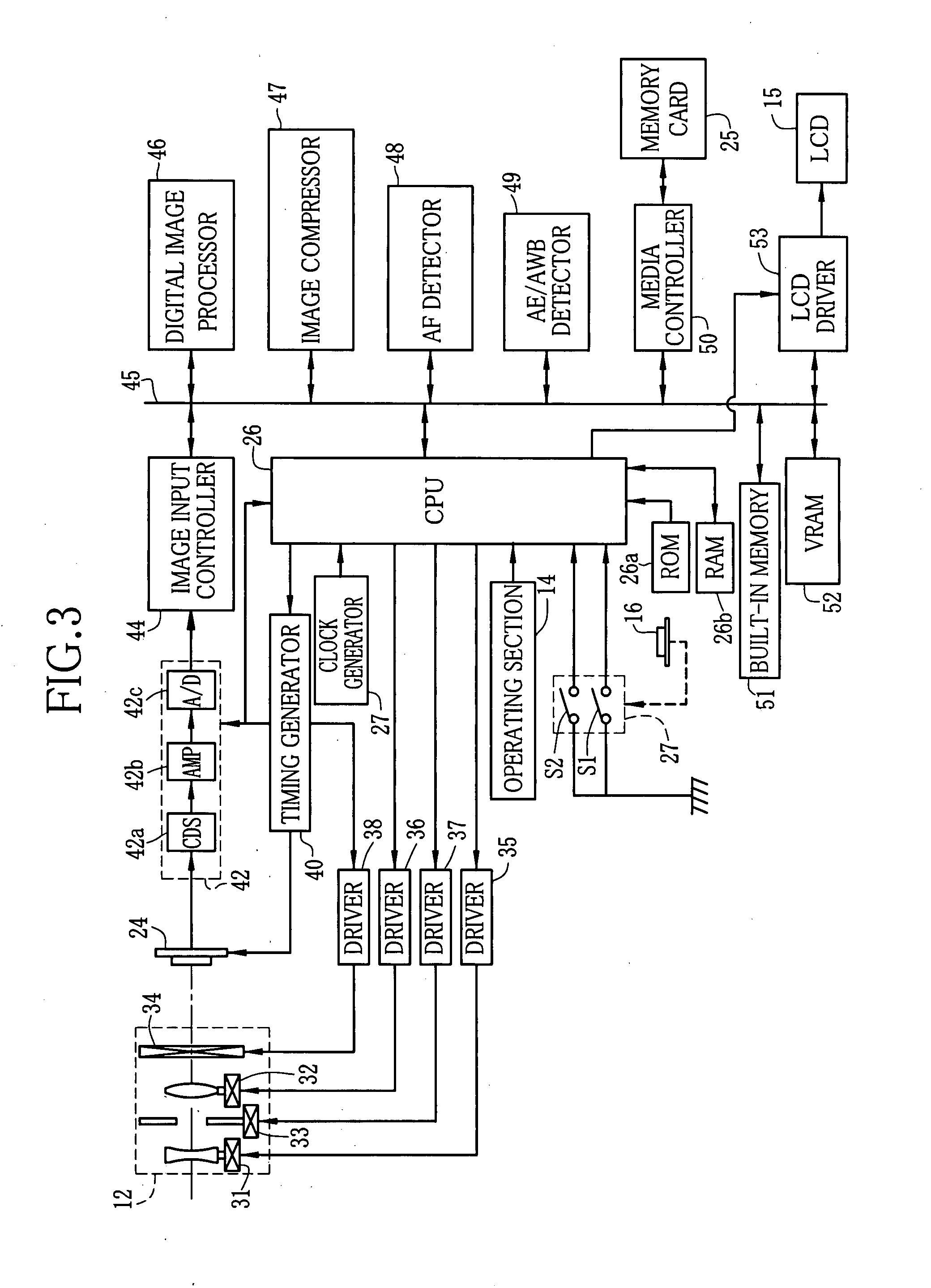

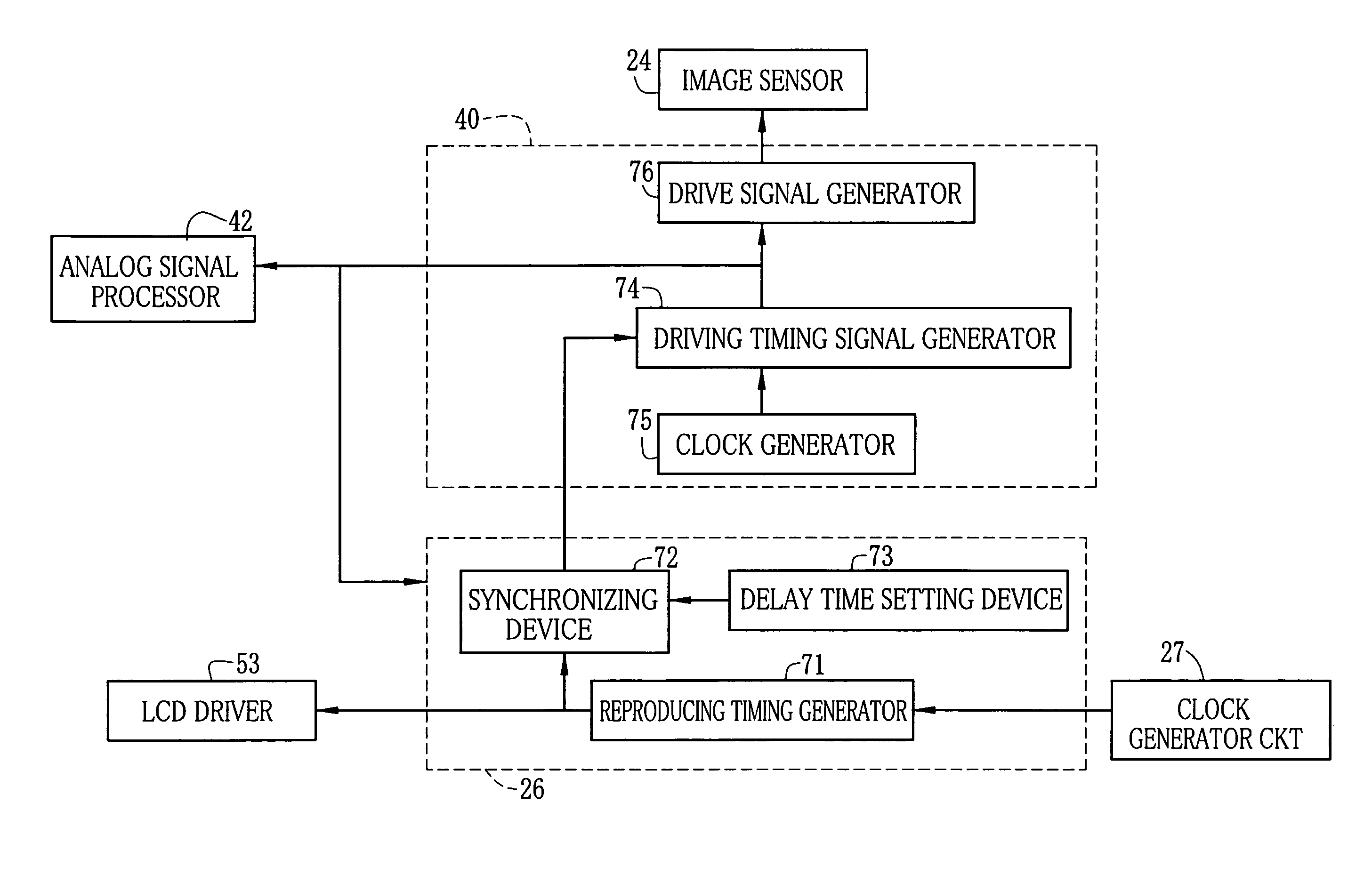

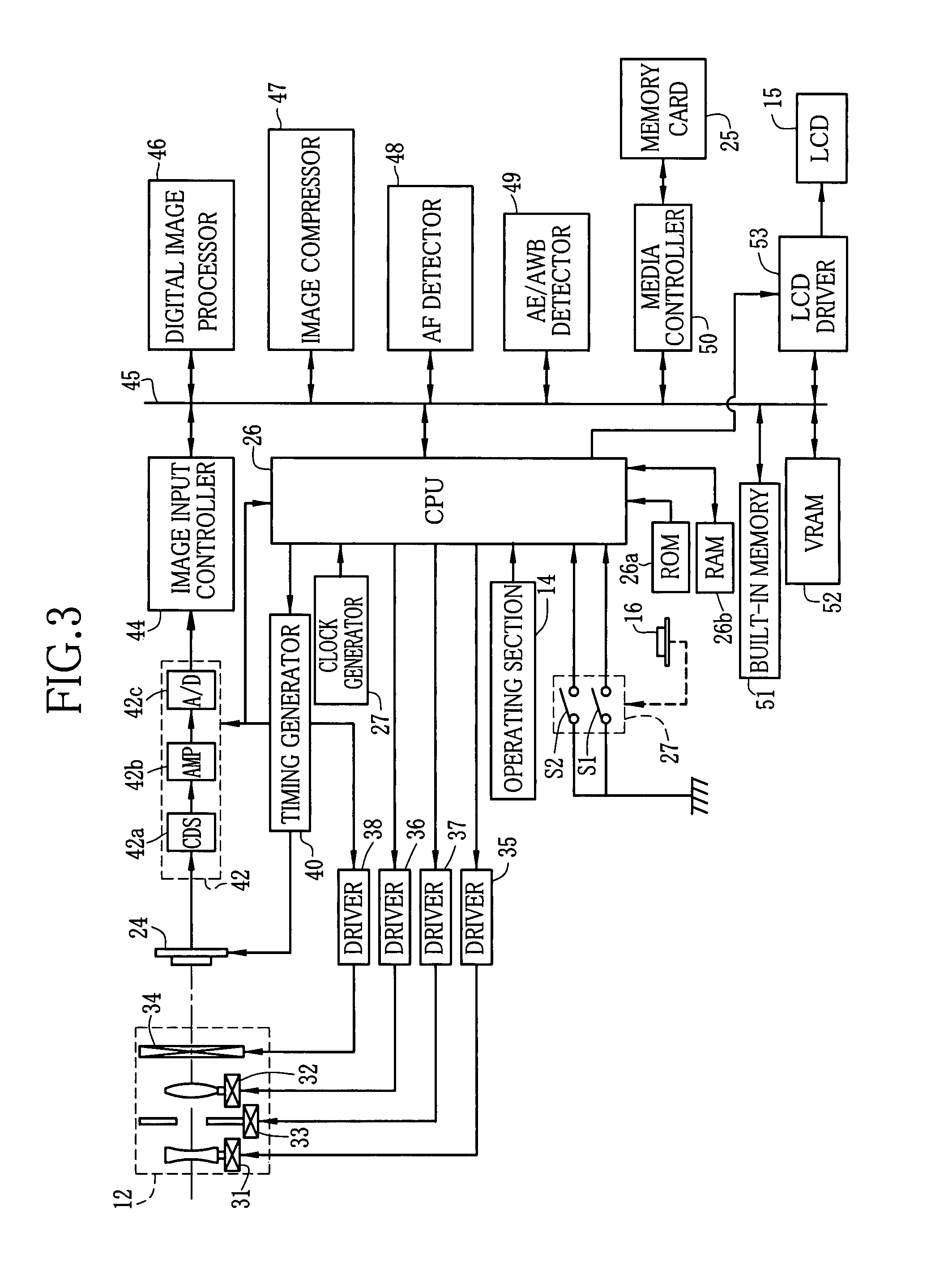

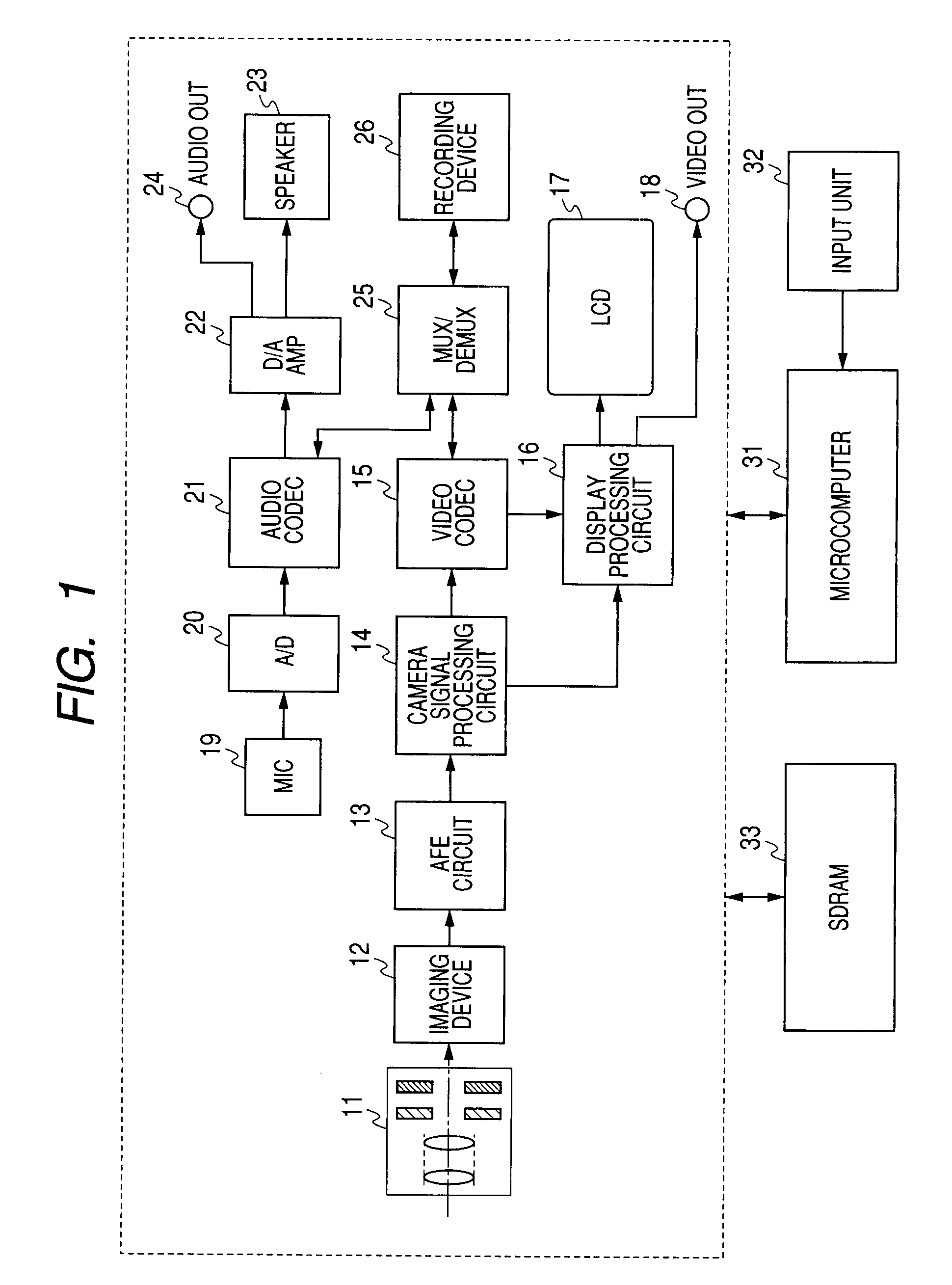

Imaging apparatus

InactiveUS20070211153A1Reduce time lagTelevision system detailsColor television detailsPhase differenceImaging equipment

An LCD driver starts reading a digital image signal of one frame from a VRAM in response to a reproduction timing signal. A driving timing signal generator generates a driving timing signal in response to a synchronizing signal, whose phase is shifted by a delay time from the reproduction timing signal. So a phase difference corresponding to the delay time is provided between the driving timing signal and the reproduction timing signal. Synchronously with the driving timing signal, an image sensor is driven to shoot a subject and output an analog image signal of one frame. After being converted into a digital form, the image signal is written in the VRAM sequentially from the first line of one frame. The phase difference is determined so that the LCD driver starts reading the image signal sequentially from the first line, immediately after the first line is written in the VRAM.

Owner:FUJIFILM CORP

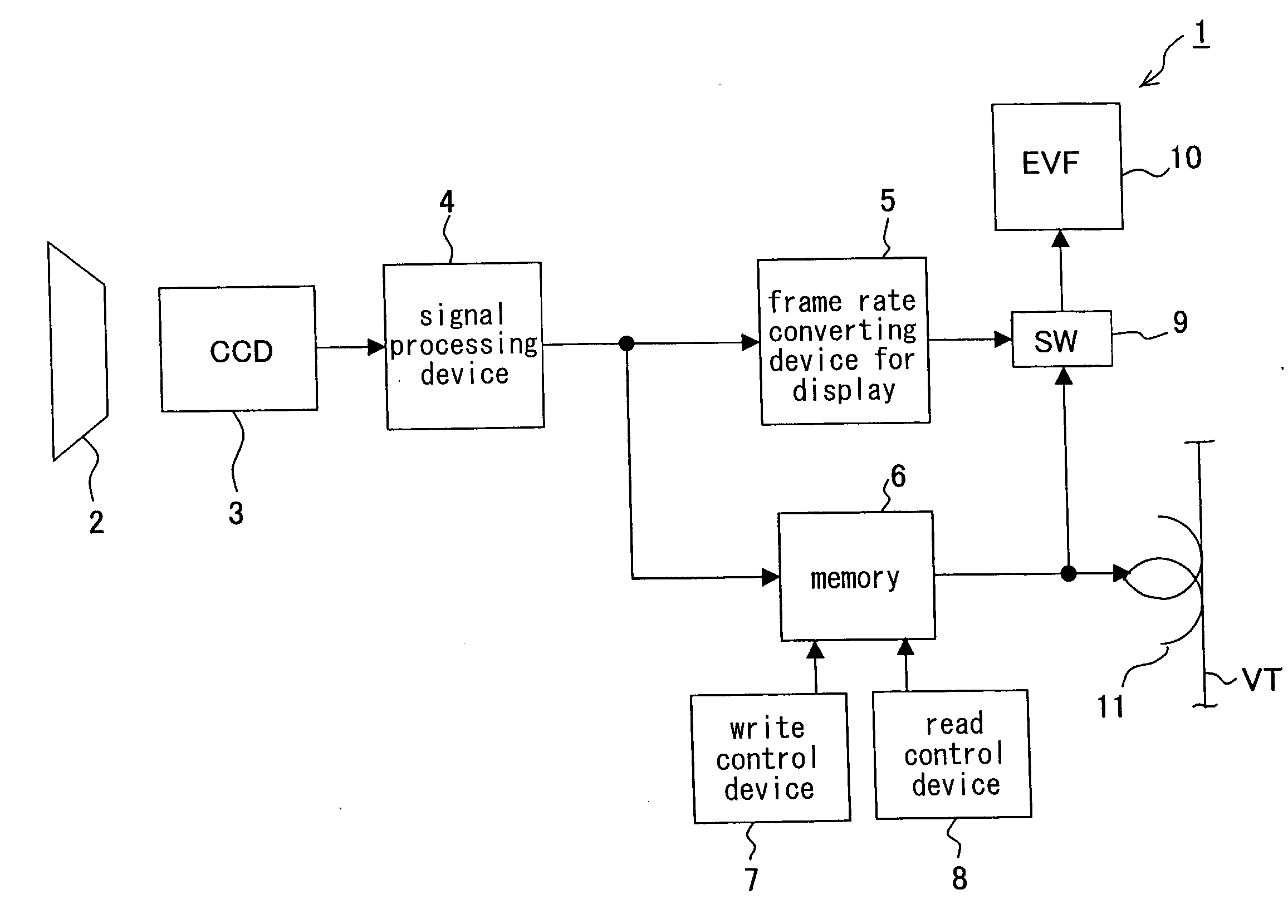

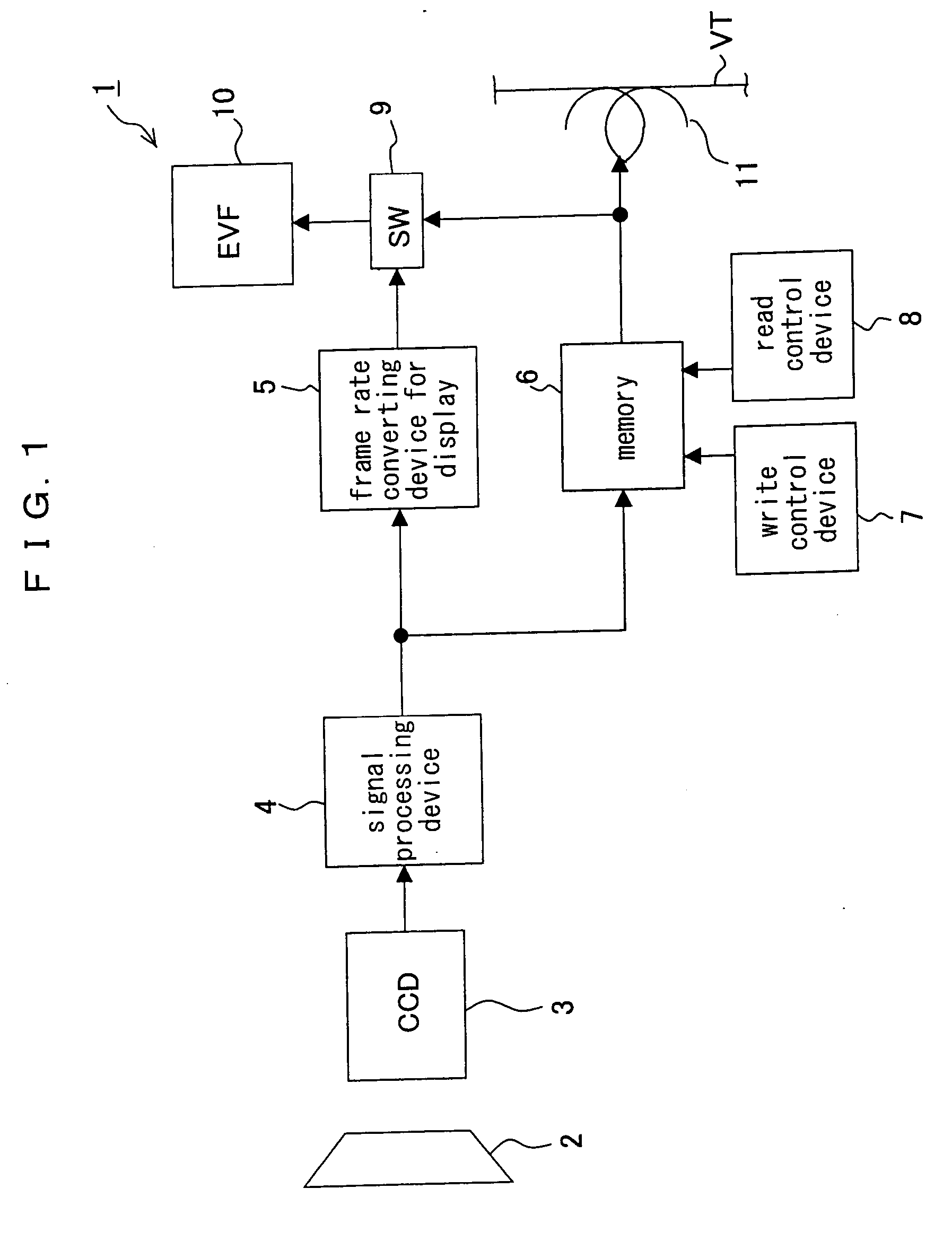

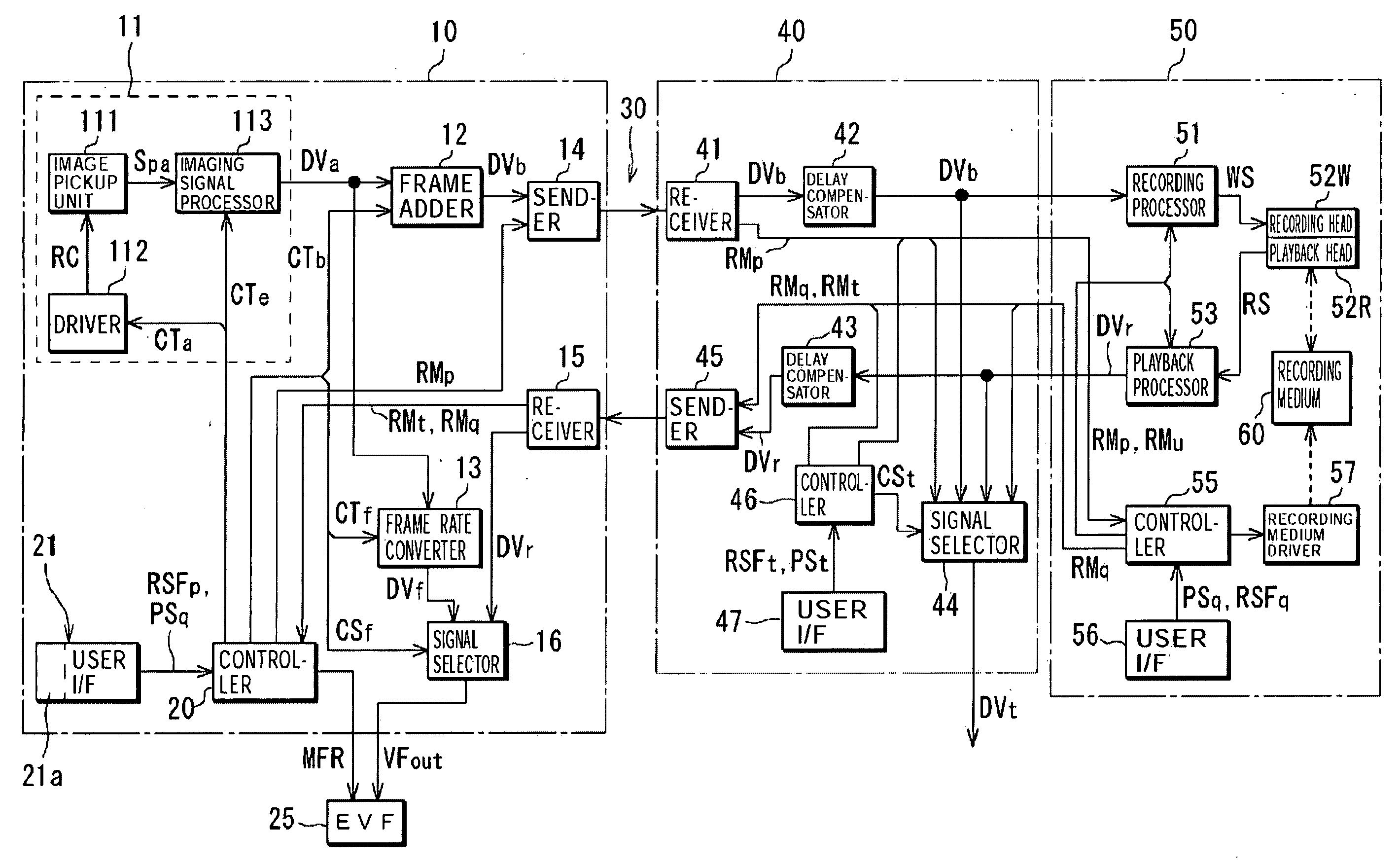

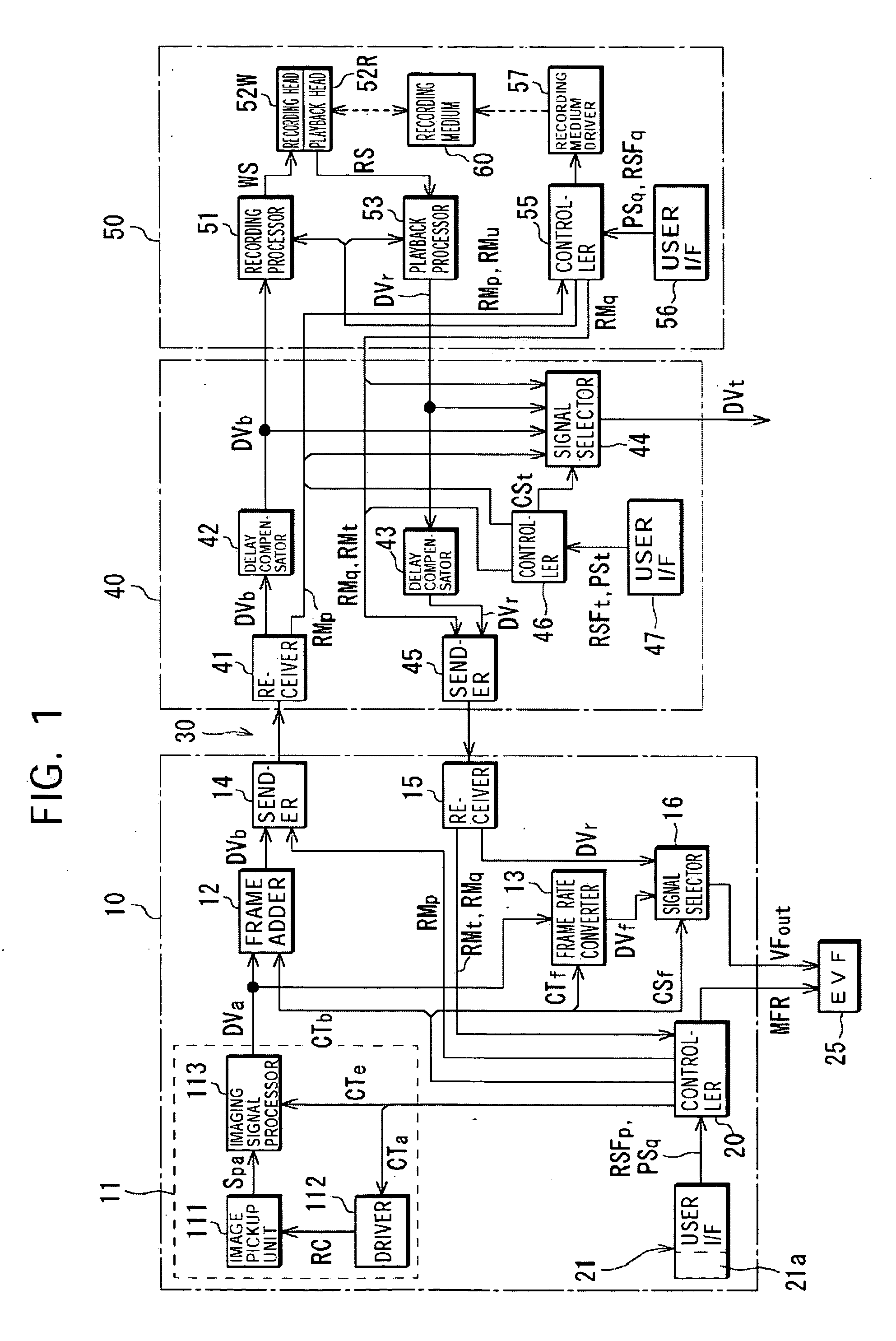

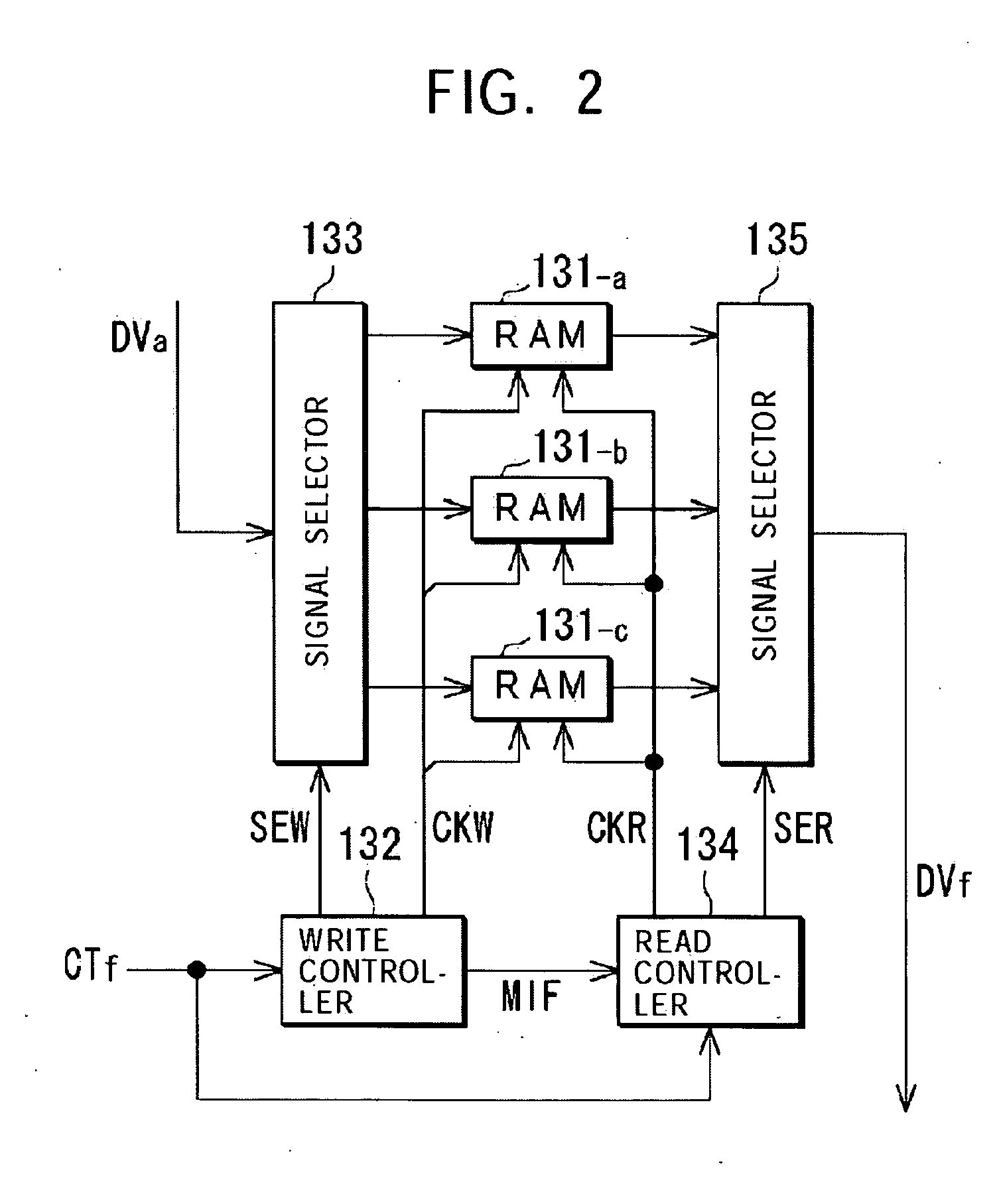

Television camera

ActiveUS20060147187A1Increase in sizeWeight increaseTelevision system detailsRecord information storageComputer hardwareComputer science

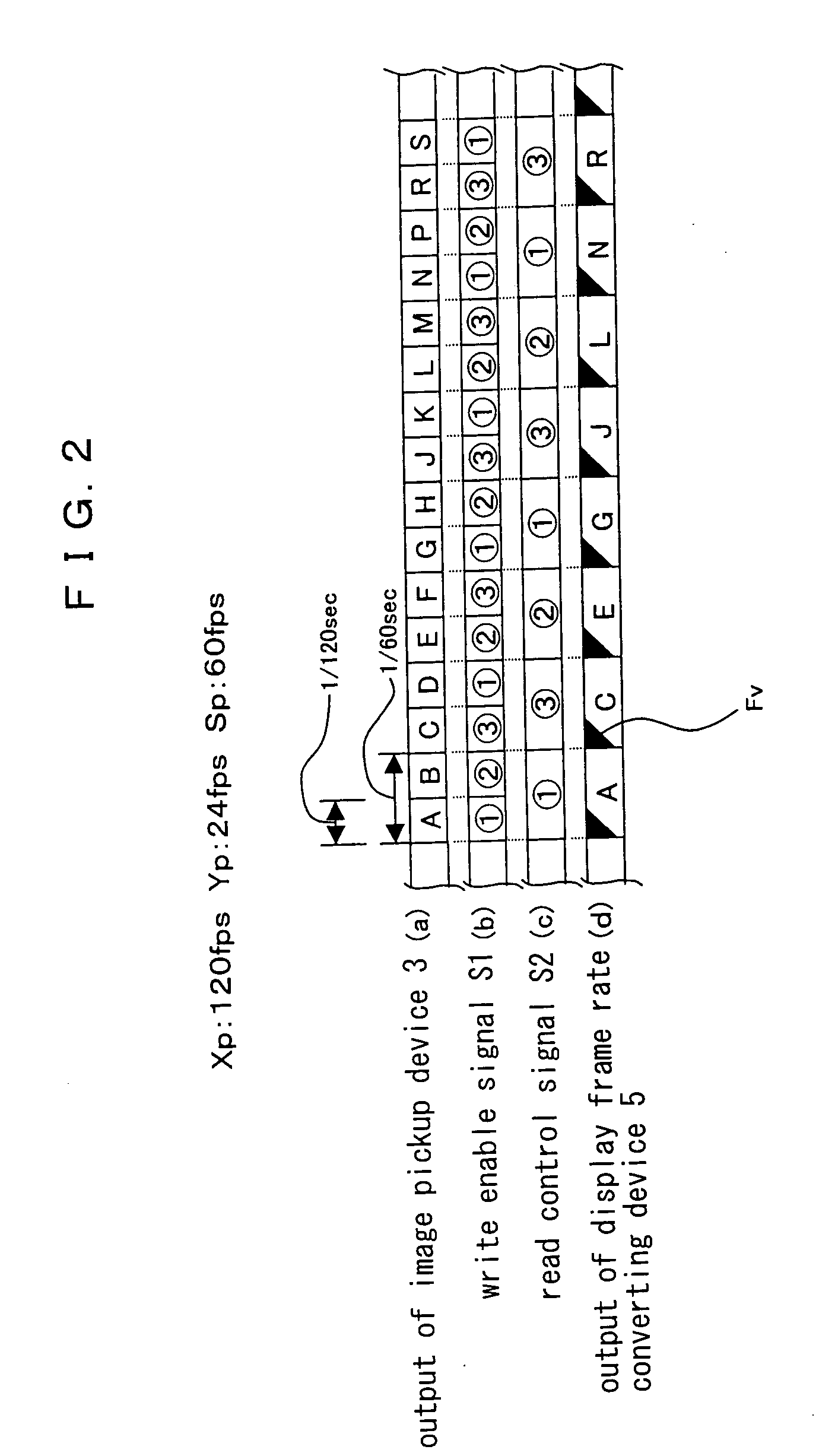

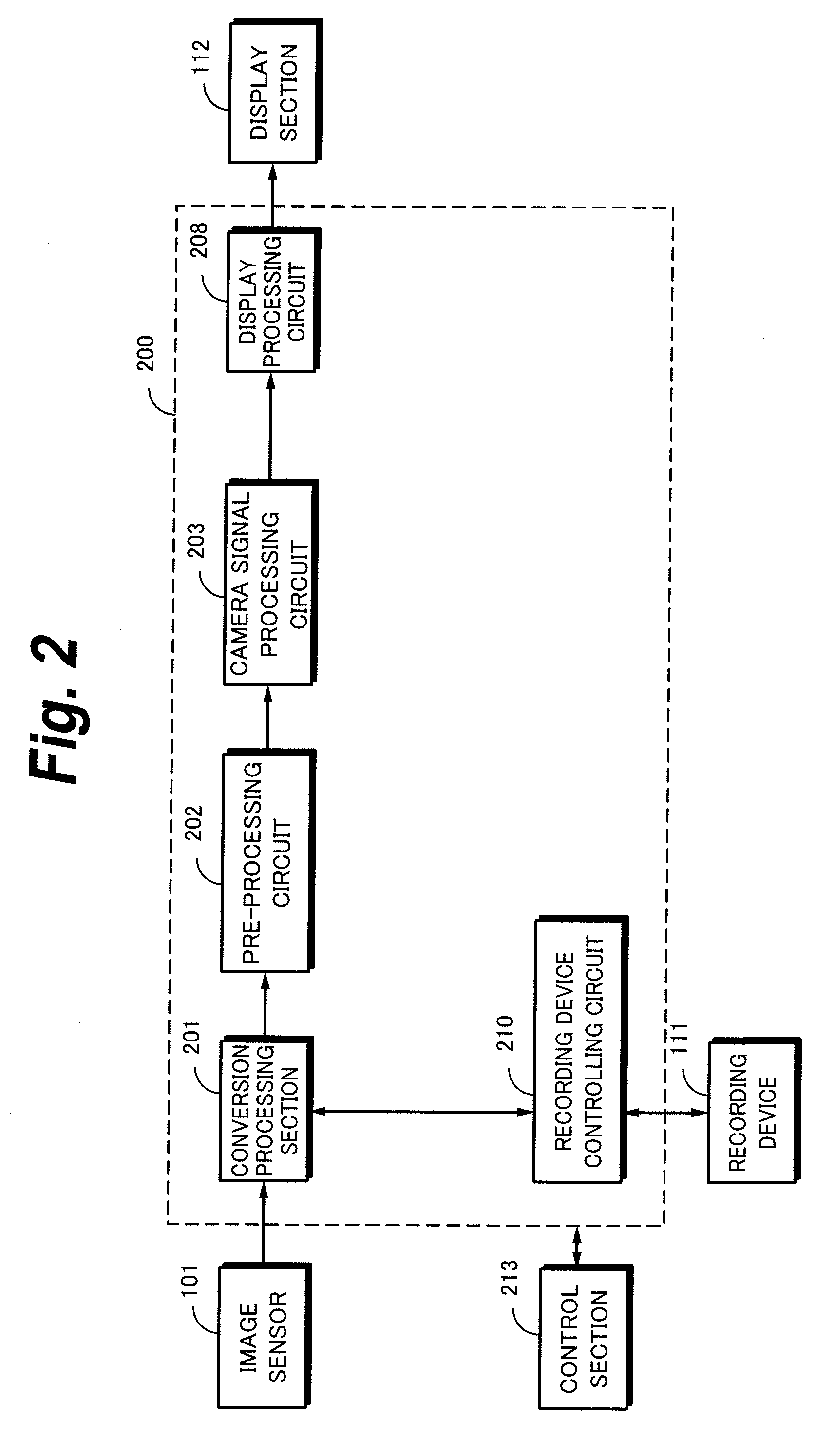

A first video signal having a first frame rate optionally settable is generated by an image pickup device, and the first video signal is memorized in a memory and outputted from the memory. A write control device controls the write of the first video signal with respect to the memory, and a read control device controls the read of the video signal with respect to the memory. The write control device writes respective first frame data constituting the first video signal in the memory in each cycle determined by the first frame rate of the first video signal. The read control device reads the first frame data as a second video signal. The second video signal is formed from sequentially arranging the first frame data in a partially duplicating manner in a standard video signal having a standard frame rate based on a determined arrangement rule. The predetermined arrangement rule is an arrangement rule employed when respective frame data constituting a video signal having a second frame rate equal to or lower than the standard frame rate are arranged in a duplicating manner in the standard video signal. In the foregoing manner, an time elongation / contraction effect on an image can be speedily and inexpensively obtained.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

Image capturing apparatus and image capturing method

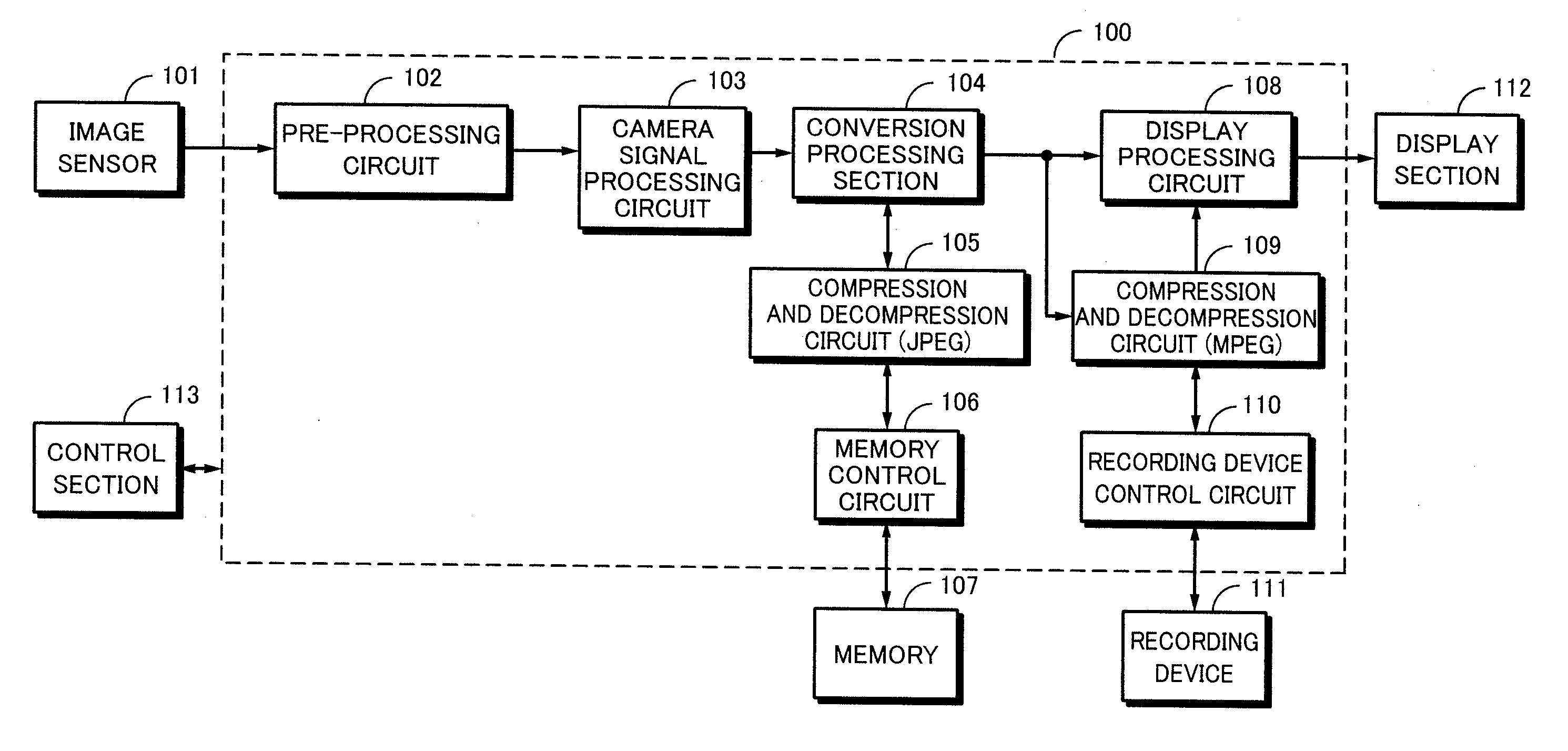

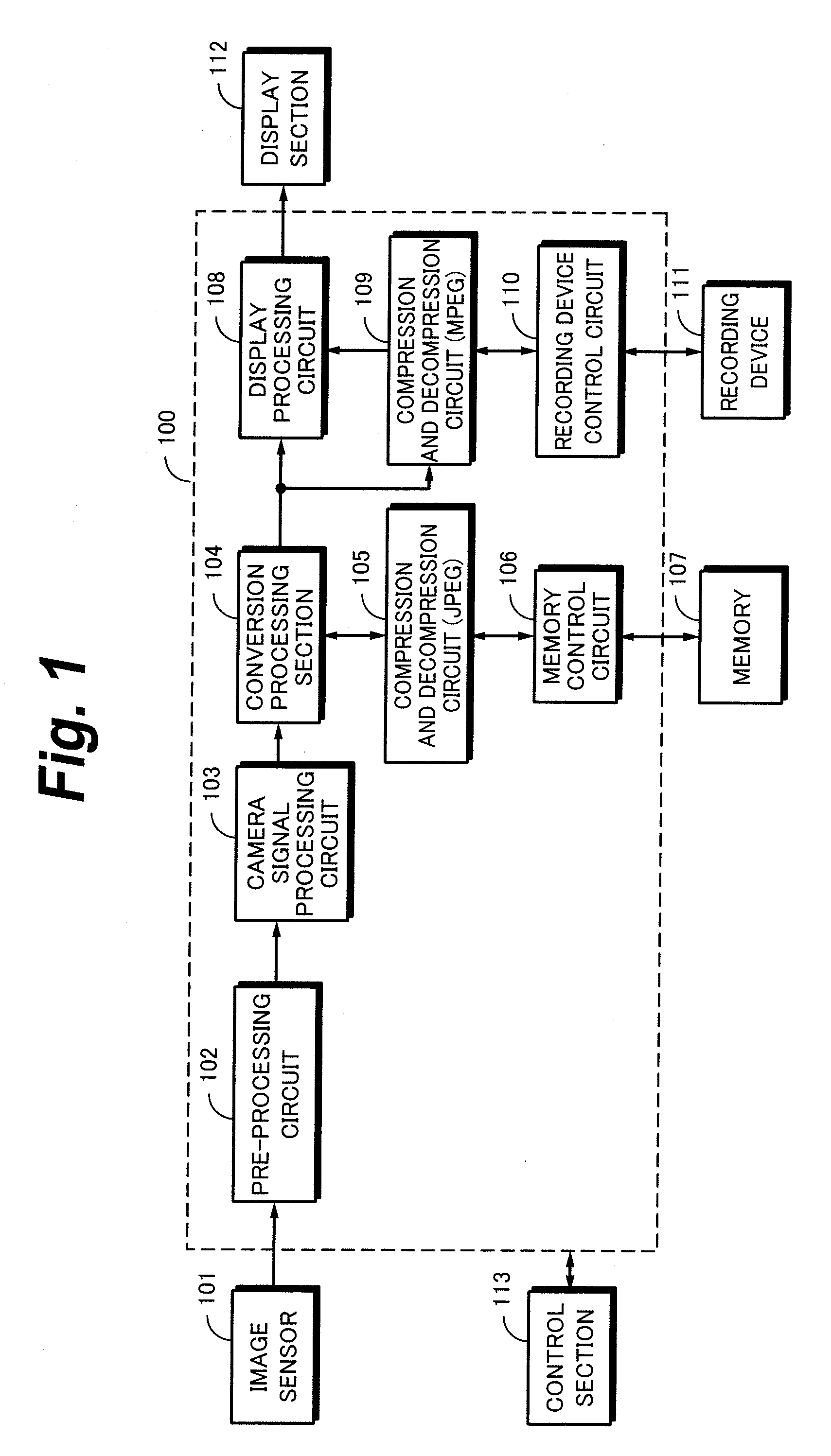

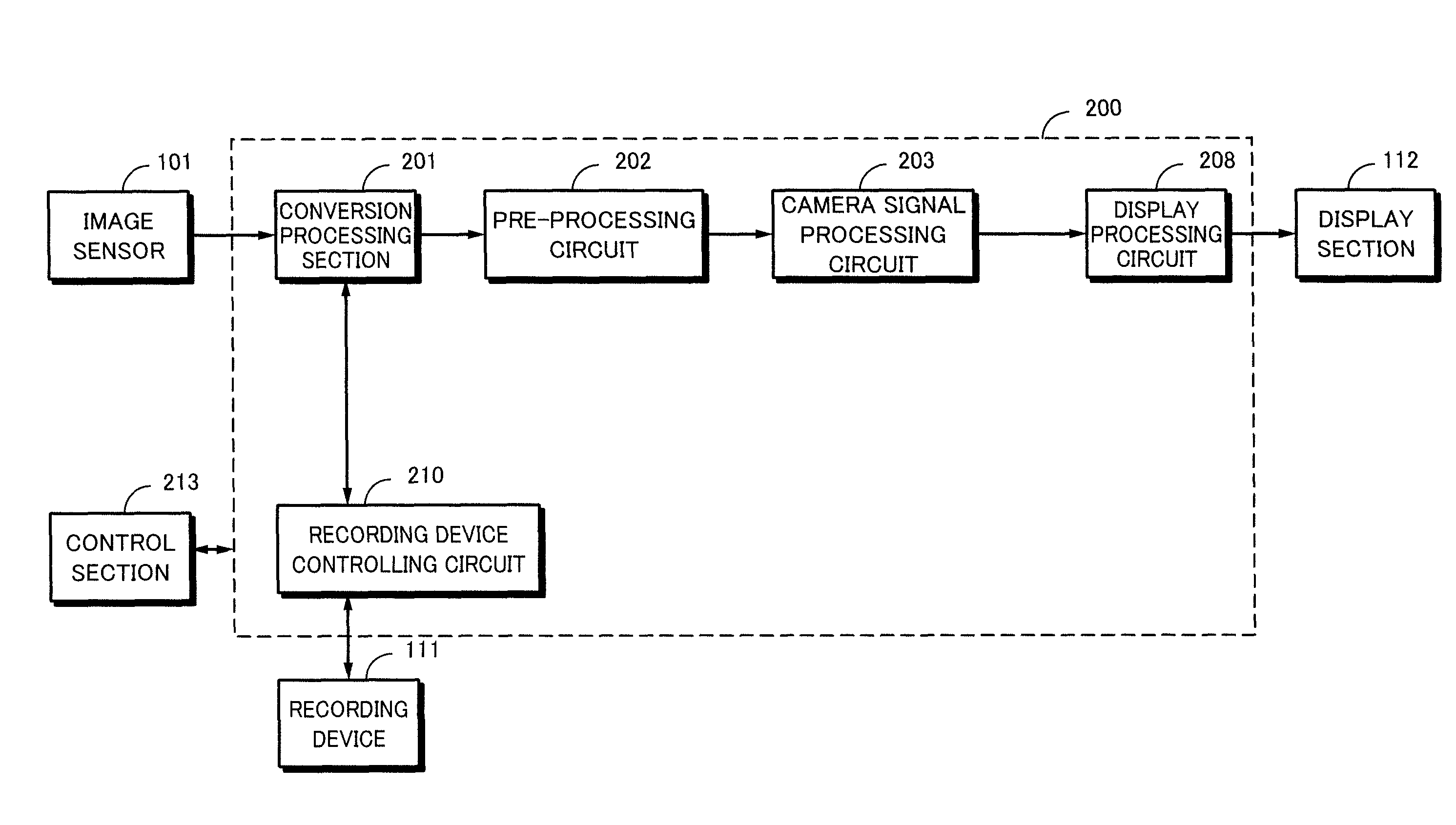

ActiveUS20100061707A1Circuit scale be reducedReduce power consumptionTelevision system detailsTelevision system scanning detailsComputer hardwareSignal processing circuits

In a high speed image capturing state, a camera signal processing circuit is not needed to perform a signal process at a high screen rate, but at a regular screen rate. In the high speed image capturing mode, raw data of 240 fps received from an image sensor 101 are recorded on a recording device 111 through a conversion processing section 201 and a recording device controlling circuit 210. Raw data that have been decimated and size-converted are supplied to a camera signal processing circuit 203 through a pre-processing circuit 202 and an image being captured is displayed on a display section 112 with a signal for which a camera process has been performed. In a reproducing state, raw data are read from the recording device 111 at a low screen rate according to a display performance of the display section 112 and the raw data that have been read are processed are processed by the pre-processing circuit 202 and the camera signal processing circuit 203 and a reproduced image is displayed by the display section 112.

Owner:SONY CORP

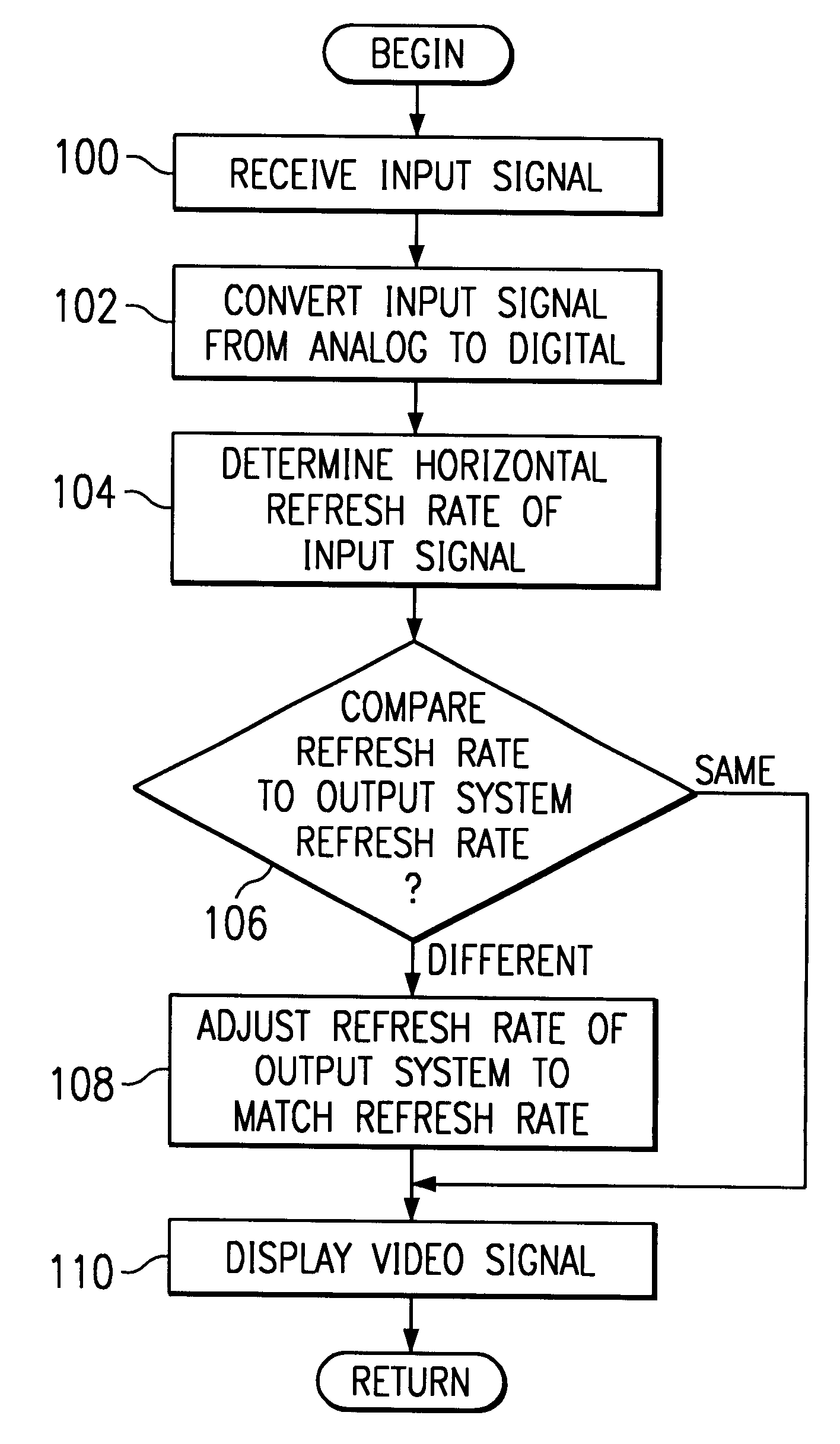

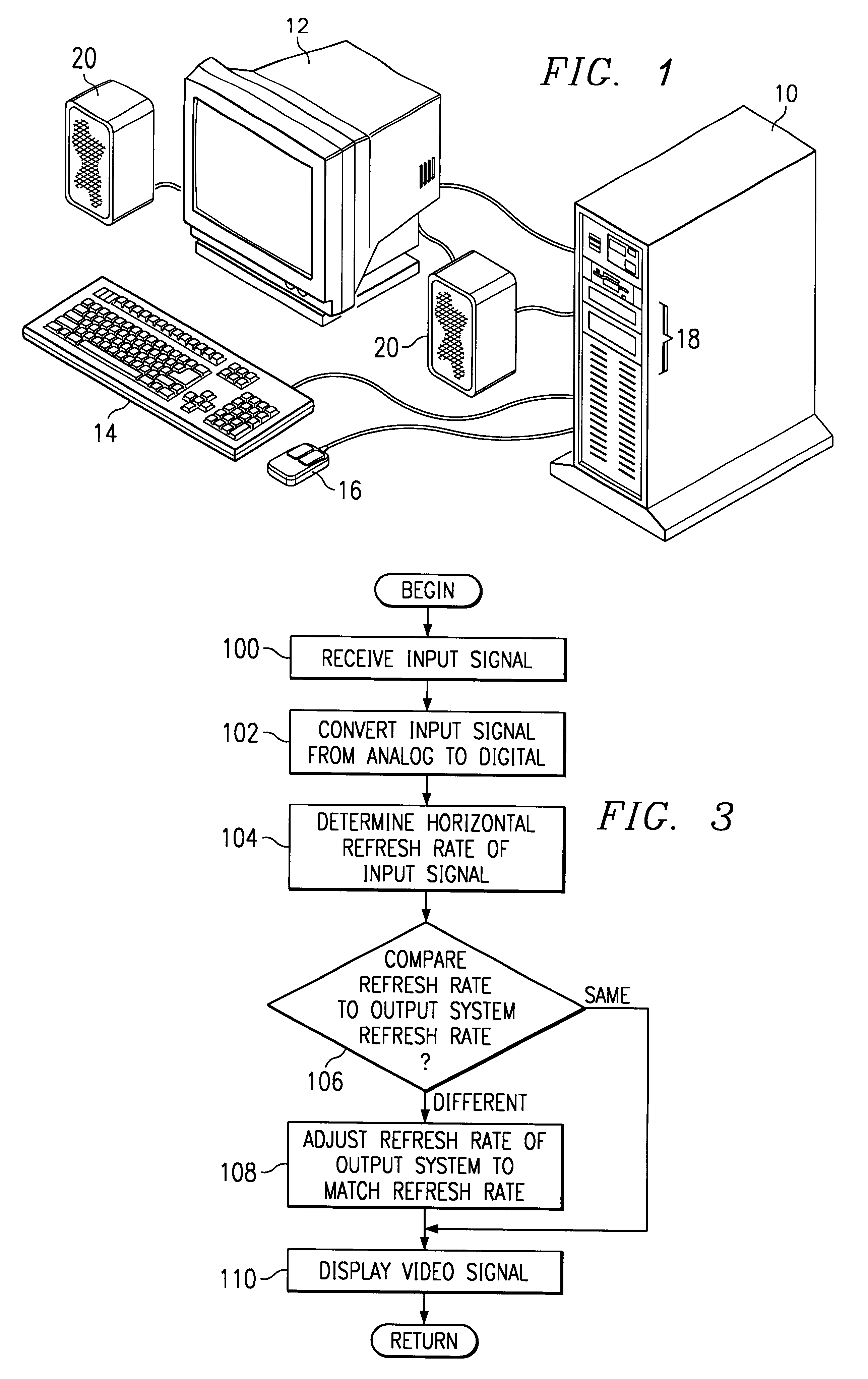

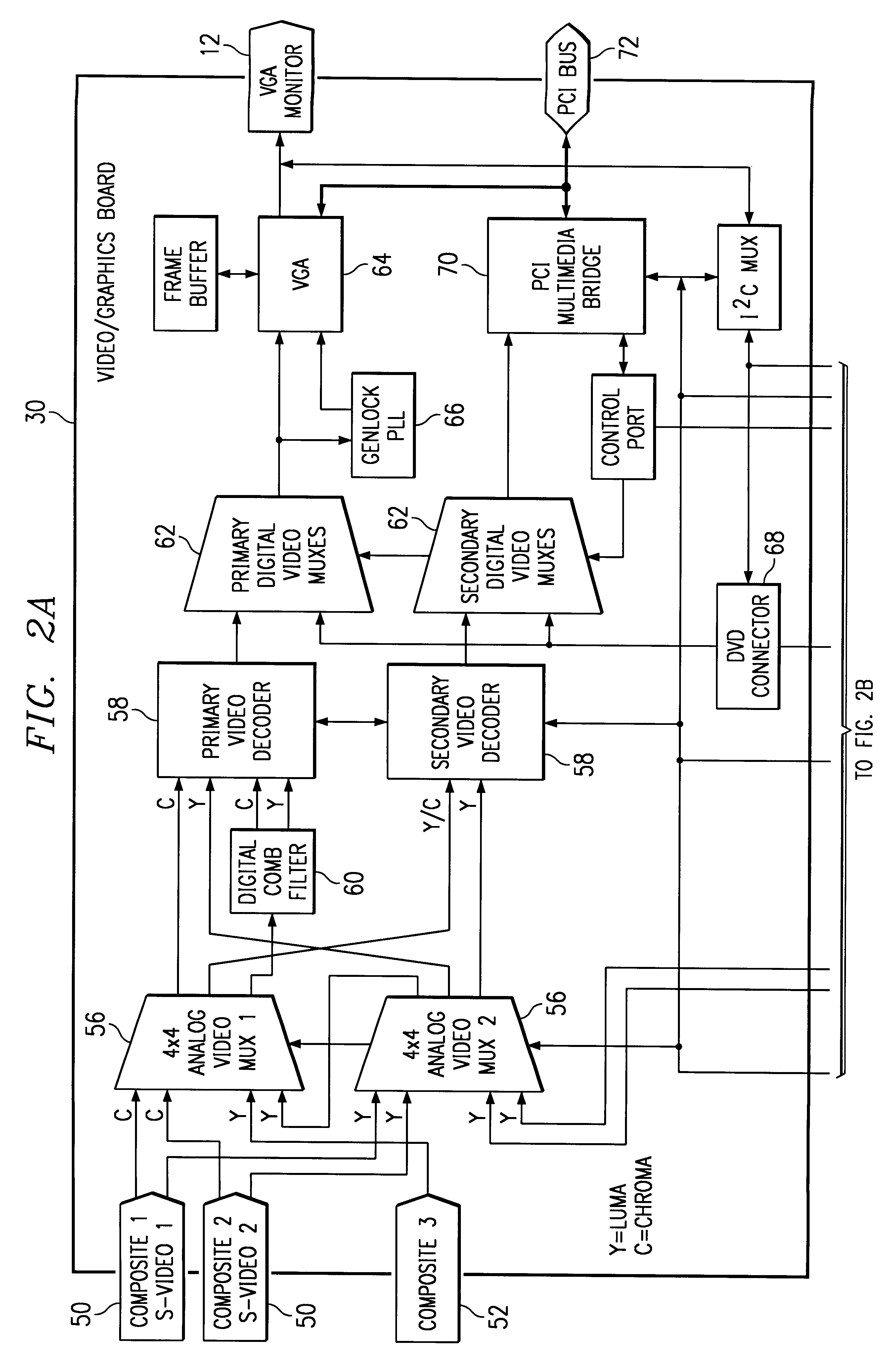

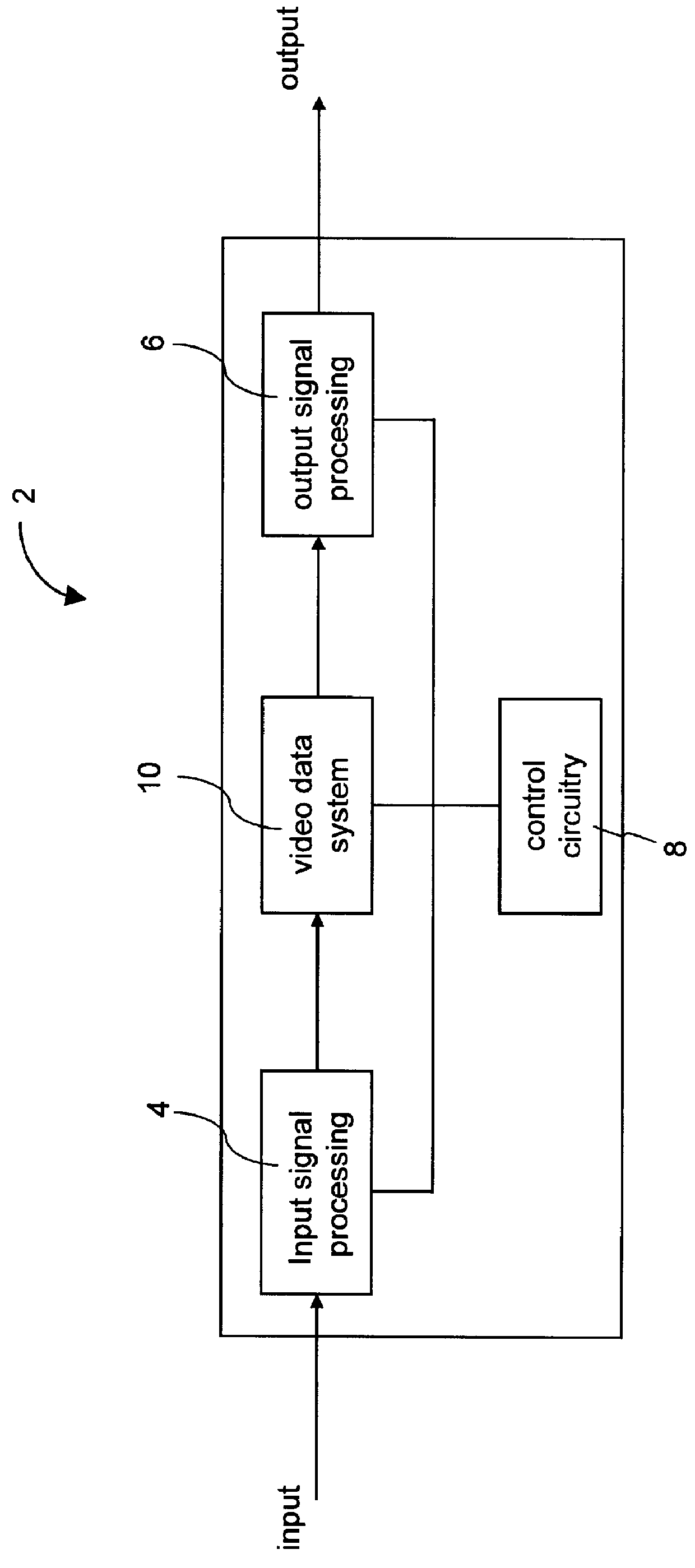

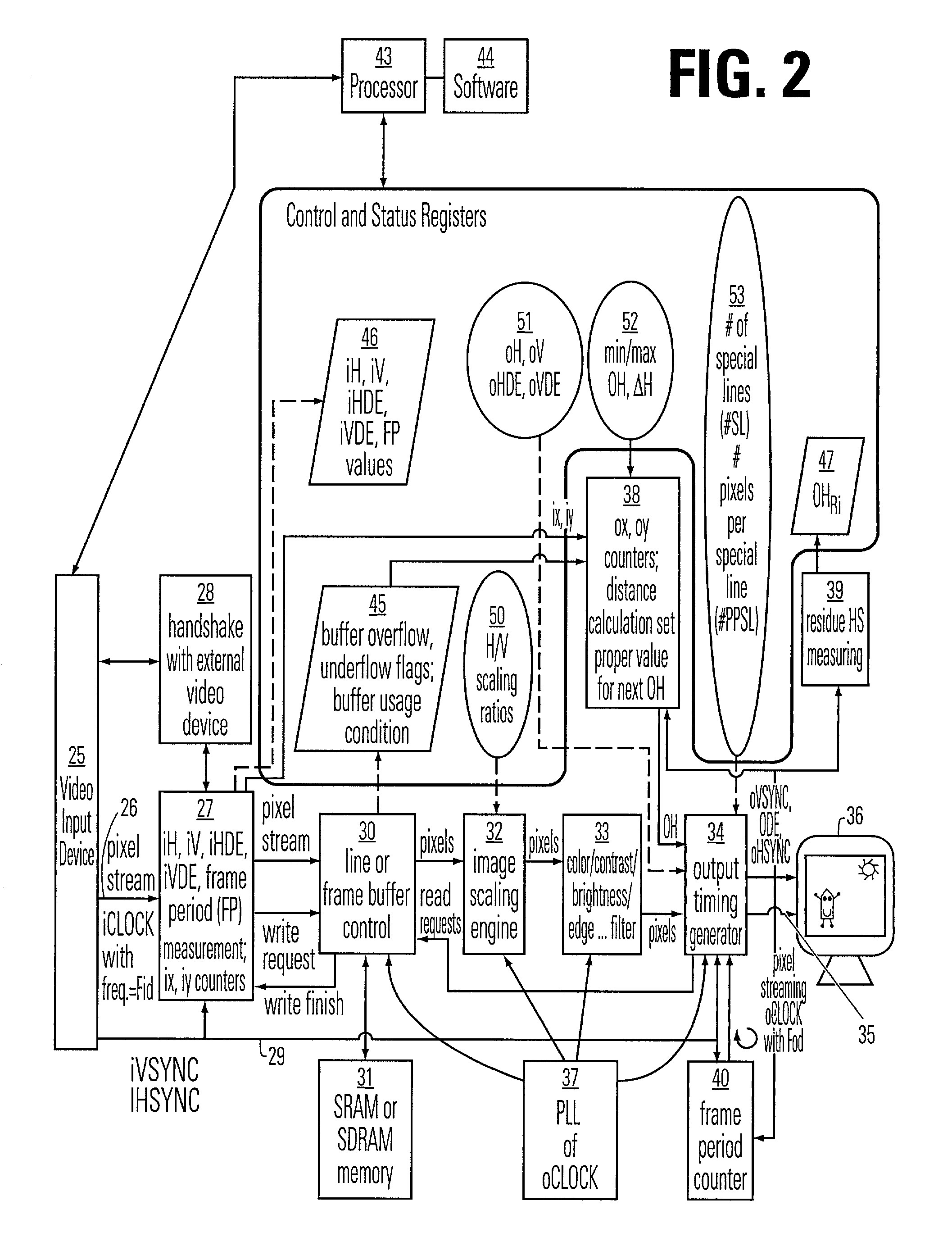

Apparatus for providing video resolution compensation when converting one video source to another video source

InactiveUS6295090B1Television system detailsTelevision system scanning detailsImage resolutionVideo processing

An apparatus and system for providing video processing is disclosed. Within the system and the apparatus there is an analog video signal input means, which is connected to a video signal output means, which are both coupled to a video resolution compensation means. The analog video signal input means provides decoding of a first signal type received by the input means. The first signal type operates at a first refresh rate. The video signal output means receives the decoded first signal type and converts the decoded first signal type into a second signal type, which has a second refresh rate. This second signal type typically is compatible for viewing on a display incompatible with the first signal type. Then, the video resolution compensation means modifies the second refresh rate associated with the decoded second signal type so as to be compatible with the first refresh rate and displayable on the video monitor.

Owner:HEWLETT PACKARD DEV CO LP

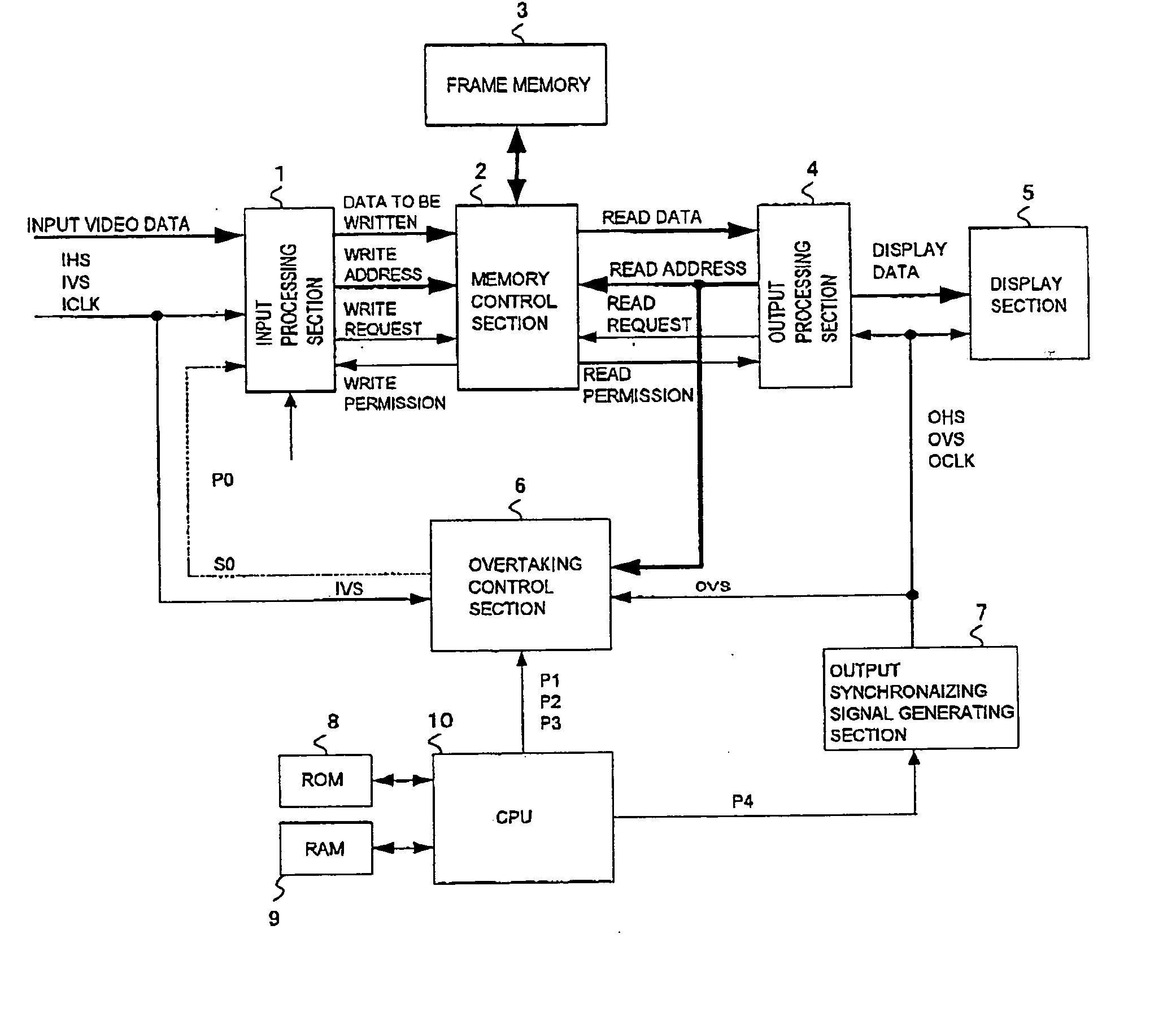

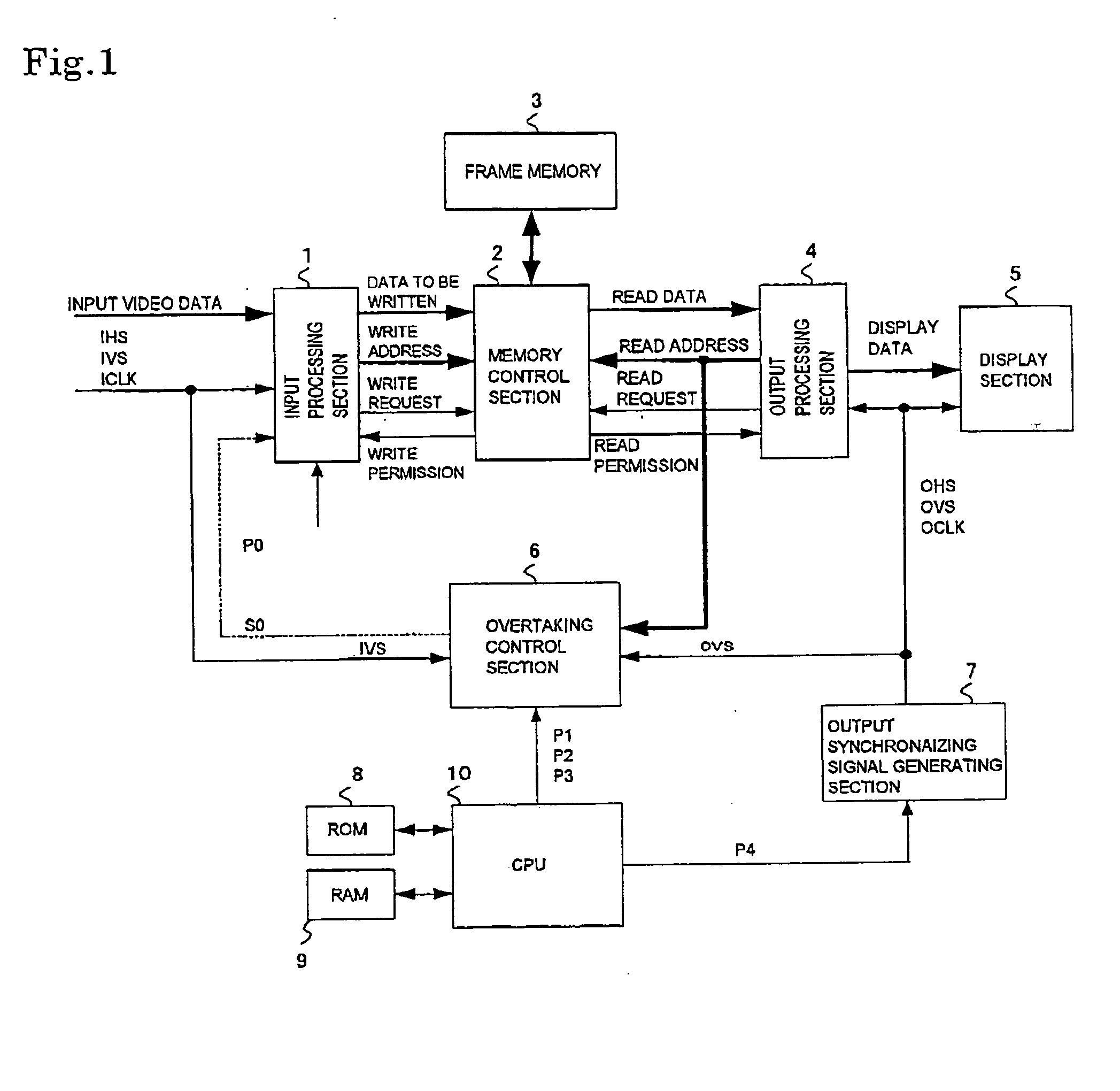

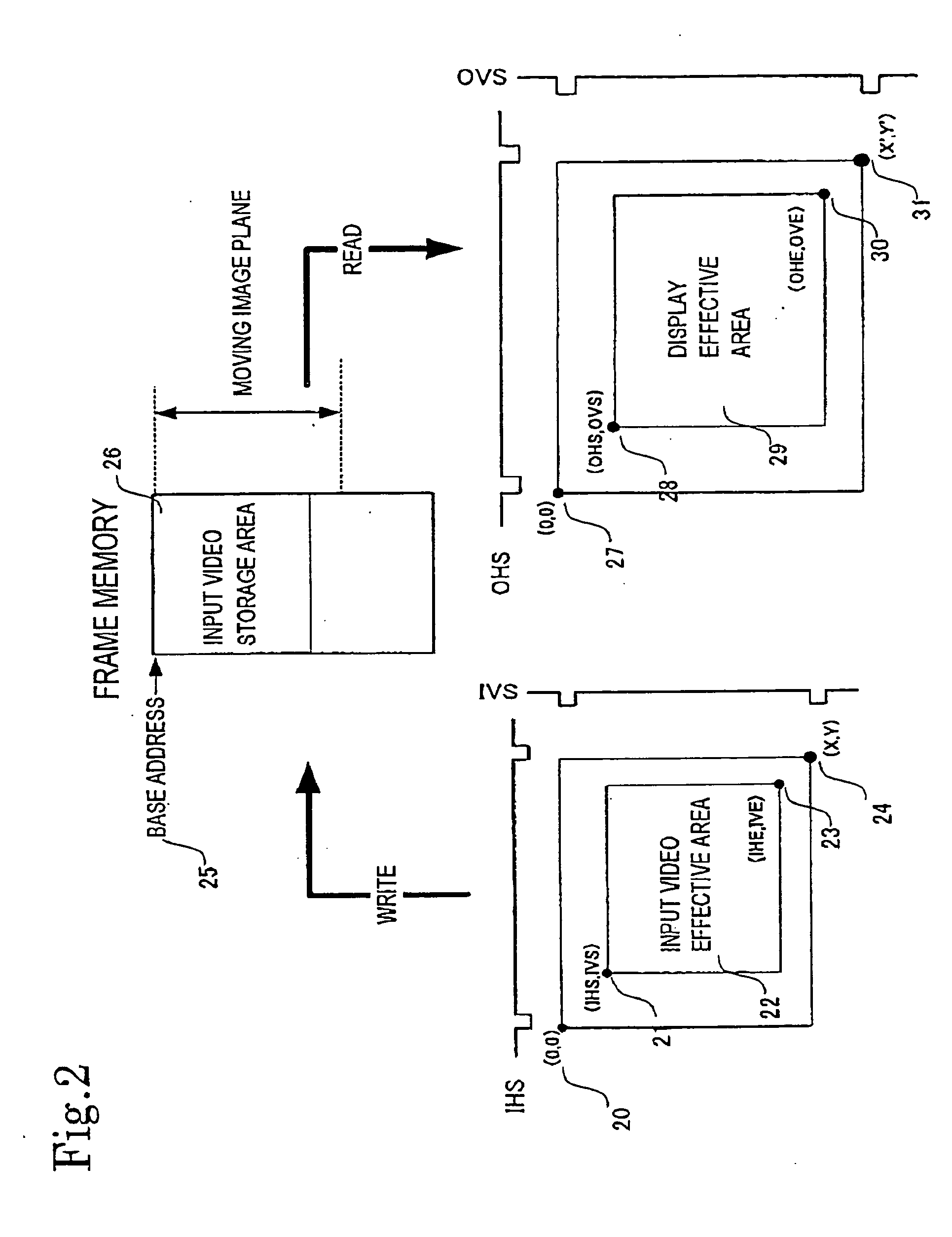

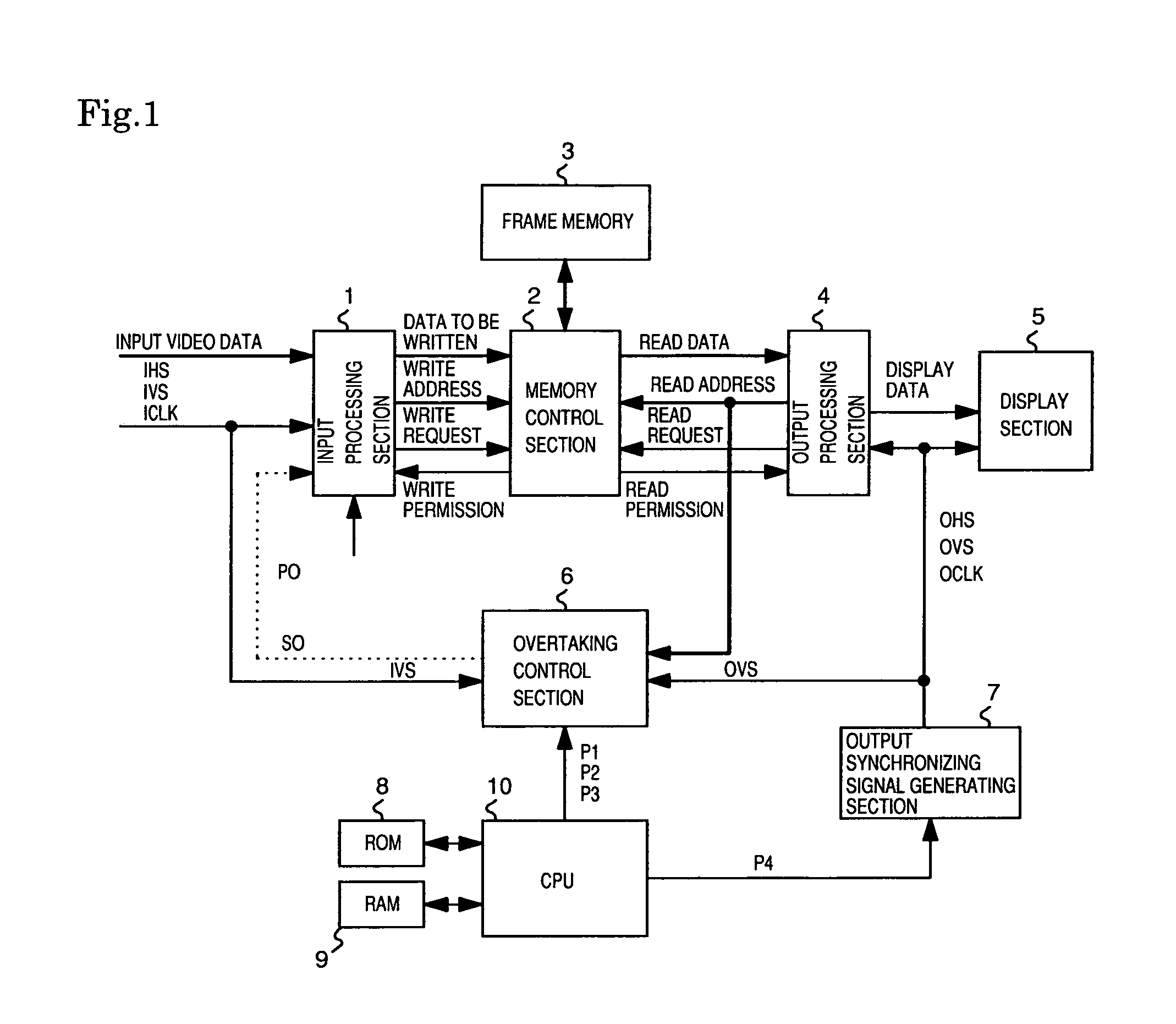

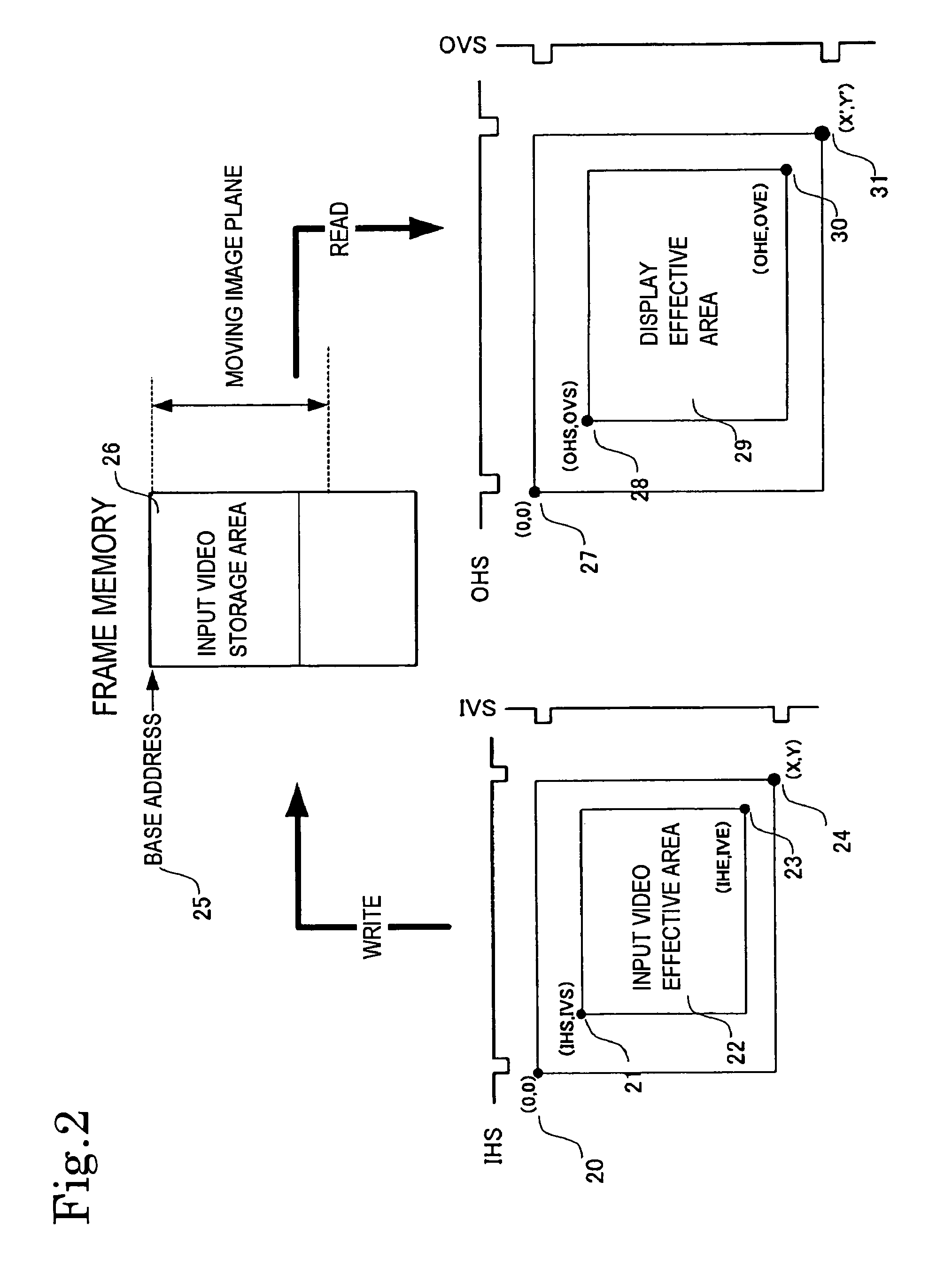

Frame rate conversion device, overtaking prediction method for use in the same, display control device and video receiving display device

InactiveUS20050105001A1Improve accuracyAvoid interferenceTelevision system detailsPulse modulation television signal transmissionComputer hardwareOvertaking

An overtaking prediction method of, when input and output of data to and from a common memory are being performed with an input frame frequency and an output frame frequency made different from each other, predicting a frame in which overtaking occurs between the input and the output of the data to and from the memory. The overtaking prediction method includes a step of predicting the frame in which the overtaking occurs between the input and the output of the data, on the basis of a first parameter corresponding to a difference amount between a progress speed of a write address and a progress speed of a read address and a second parameter corresponding to a difference between a write address and a read address at an overtaking prediction point and to an offset address difference amount between an input offset address and an output offset address.

Owner:CANON KK

Imaging apparatus with memory for storing camera through image data

InactiveUS7710468B2Reduce time lagTelevision system detailsColor television detailsPhase differenceDelayed time

An LCD driver starts reading a digital image signal of one frame from a VRAM in response to a reproduction timing signal. A driving timing signal generator generates a driving timing signal in response to a synchronizing signal, whose phase is shifted by a delay time from the reproduction timing signal. So a phase difference corresponding to the delay time is provided between the driving timing signal and the reproduction timing signal. Synchronously with the driving timing signal, an image sensor is driven to shoot a subject and output an analog image signal of one frame. After being converted into a digital form, the image signal is written in the VRAM sequentially from the first line of one frame. The phase difference is determined so that the LCD driver starts reading the image signal sequentially from the first line, immediately after the first line is written in the VRAM.

Owner:FUJIFILM CORP

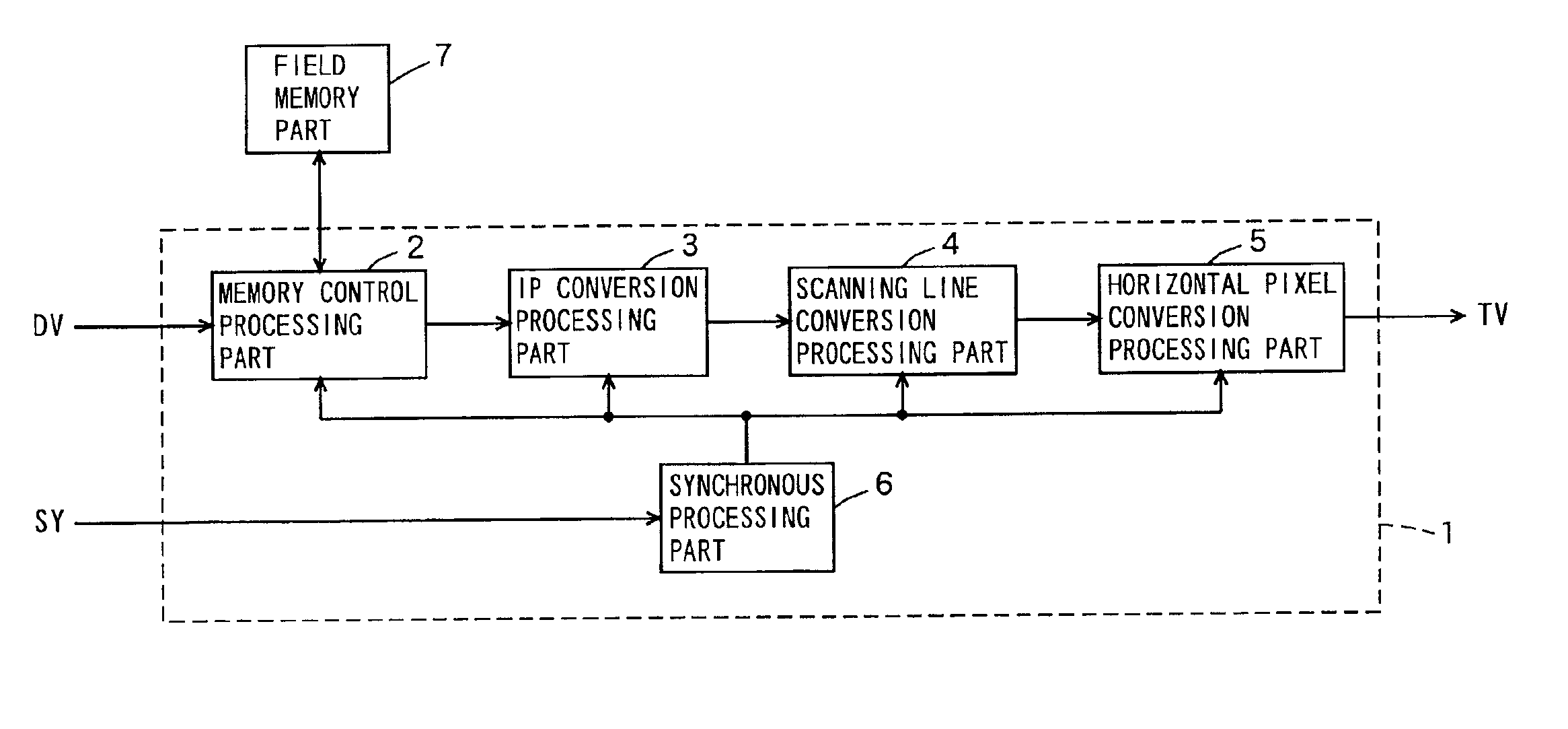

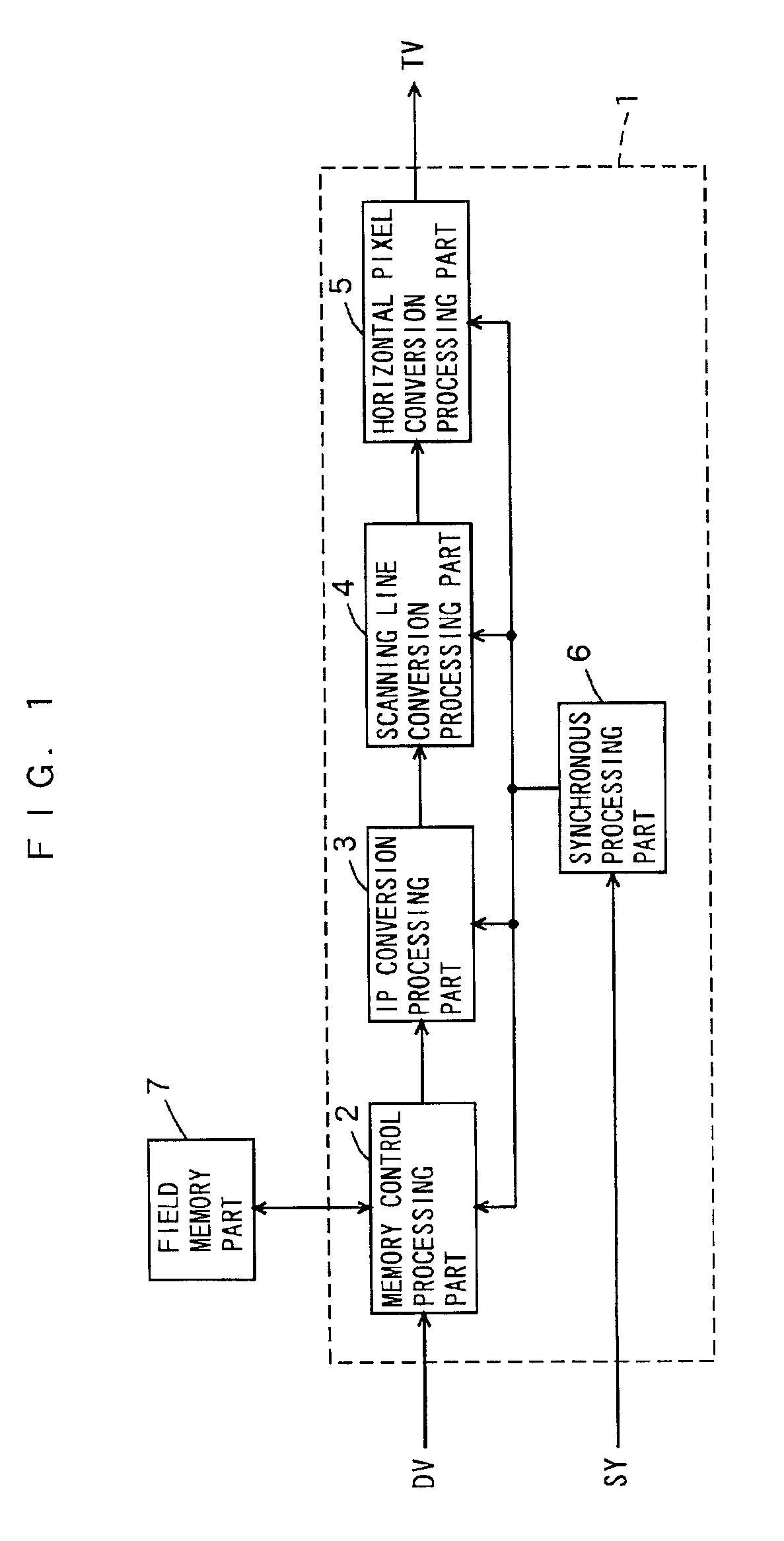

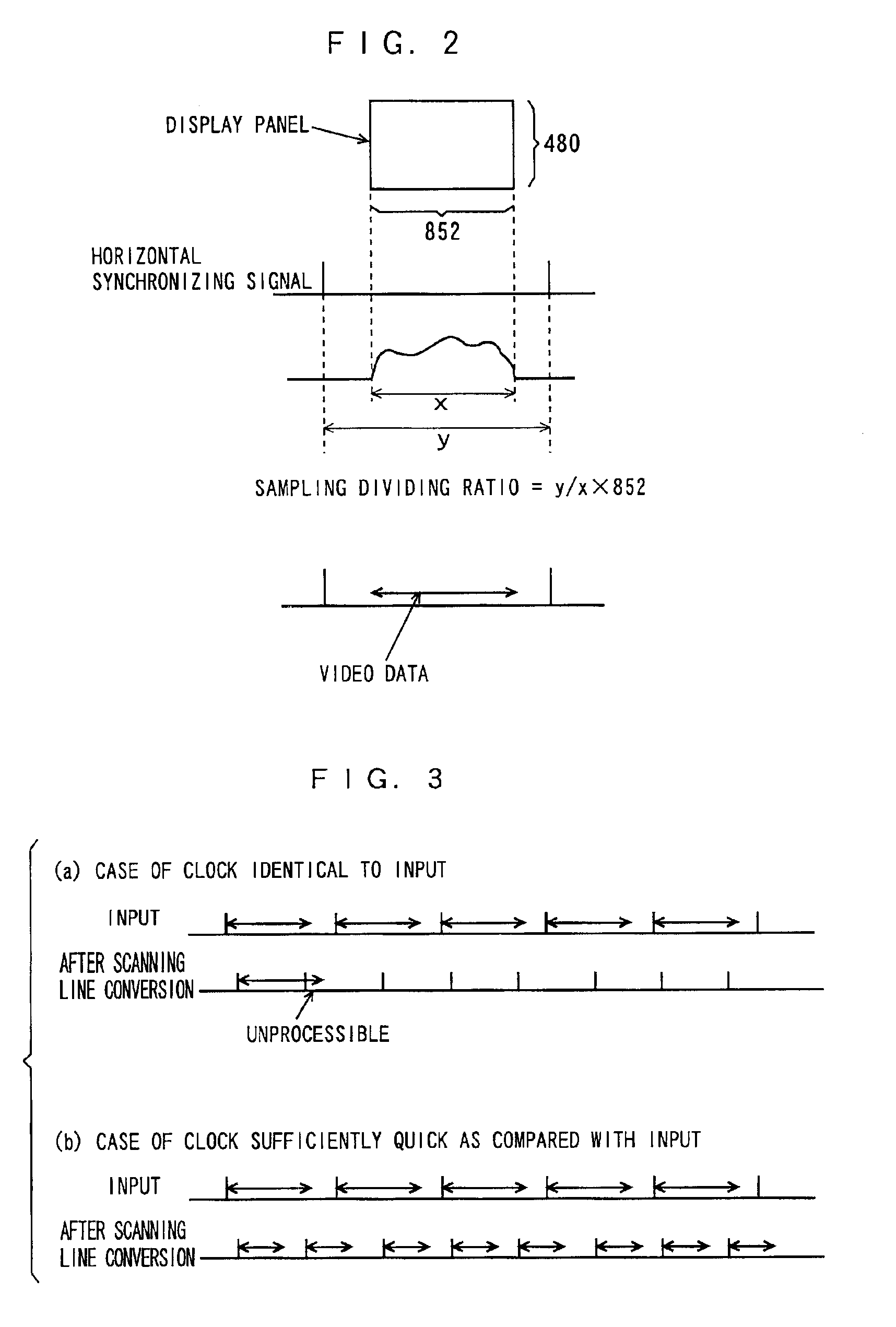

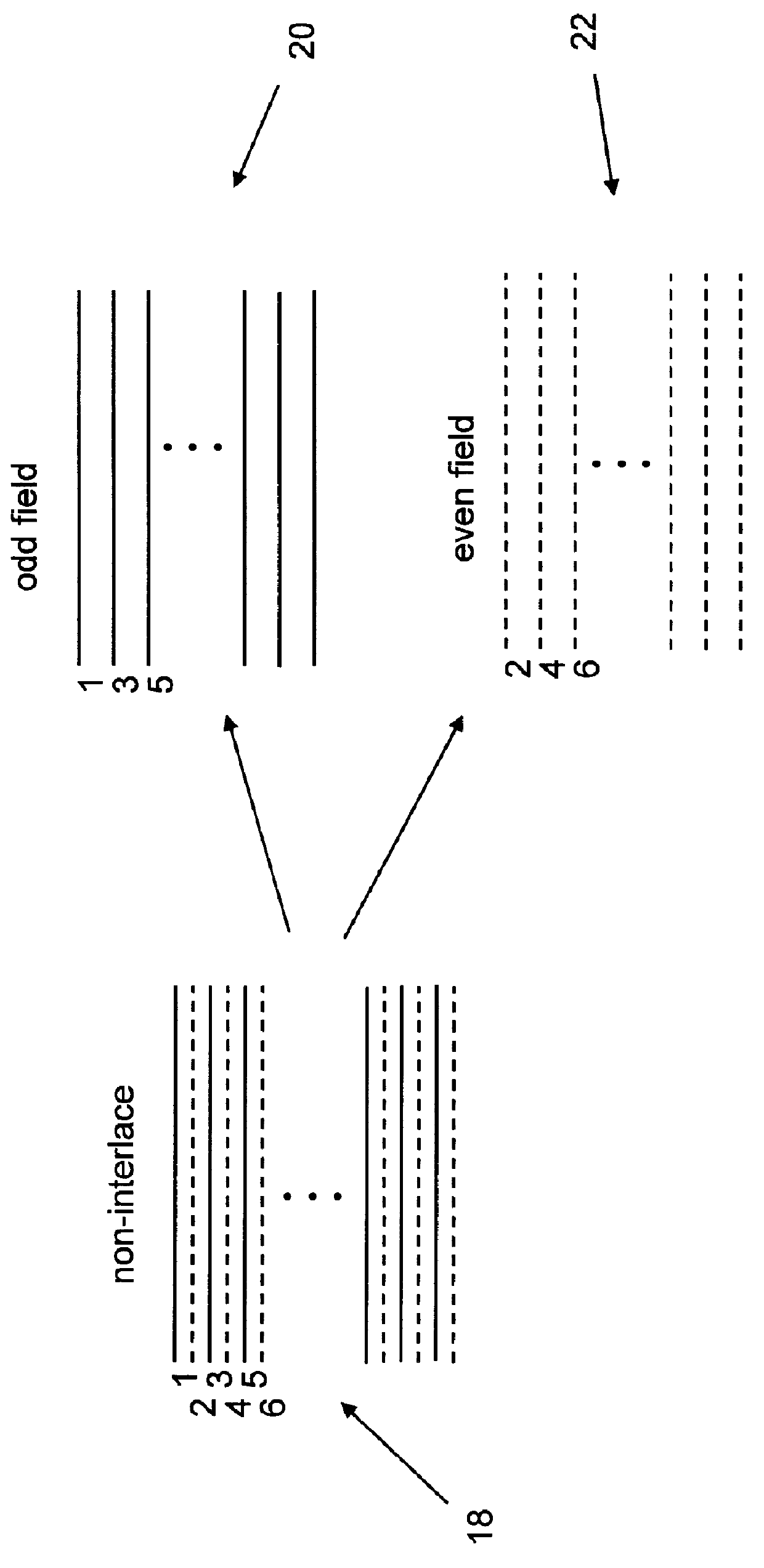

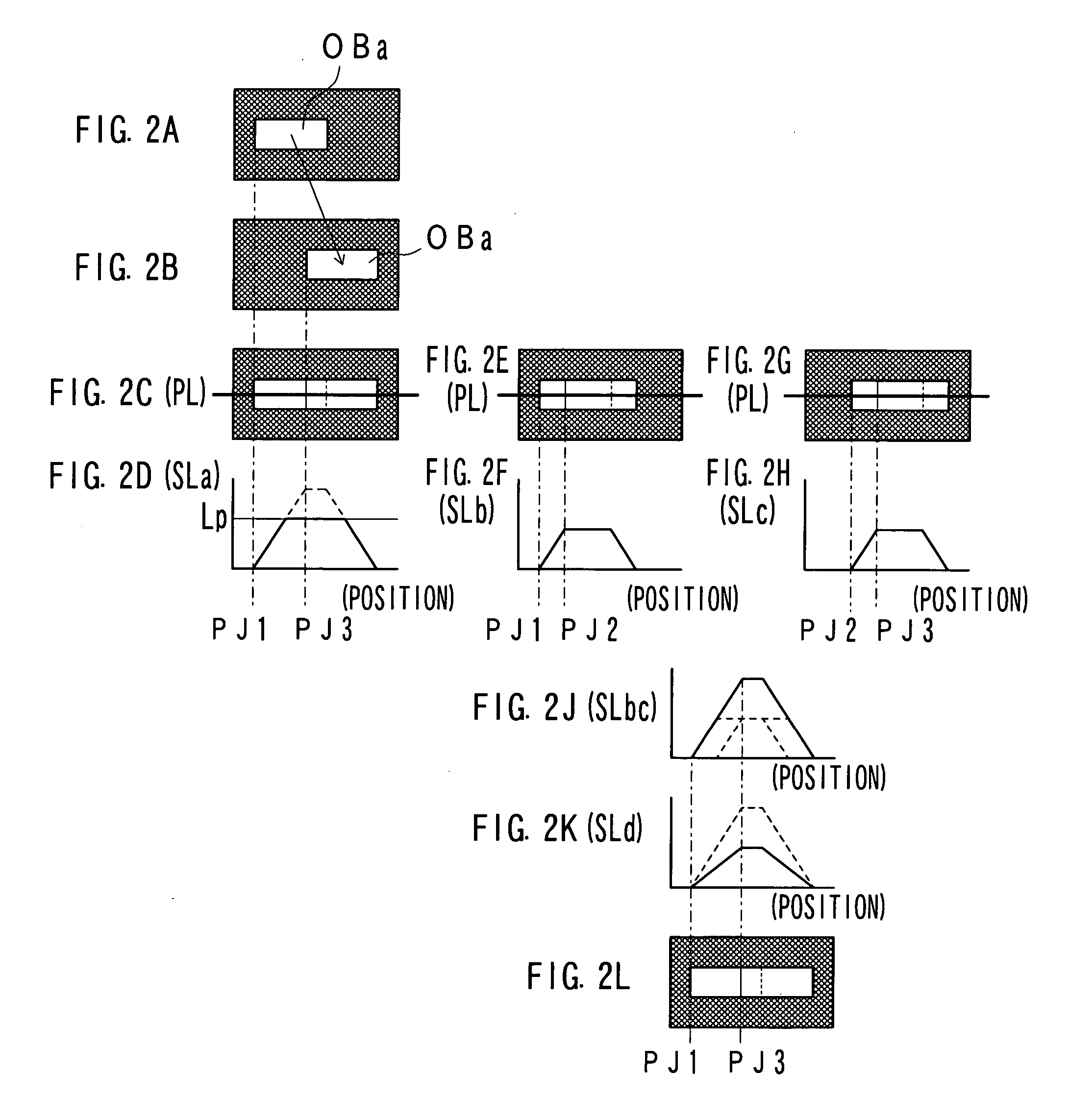

Video signal conversion device and video signal conversion method

InactiveUS6876395B1Television system detailsTelevision system scanning detailsFrequency conversionData storing

Video data of a field necessary for I / P conversion and scanning line conversion is stored in a field memory part (7), vertical frequency conversion is performed by a memory control processing part (2), I / P conversion is performed by an I / P conversion processing part (3), scanning line conversion is performed by a scanning line conversion part (4) and horizontal pixel conversion is performed by a horizontal pixel conversion processing part (5) with the data stored in the field memory part, and a synchronous processing part (6) supplies a prescribed clock, a horizontal synchronizing signal and a vertical synchronizing signal to each block. A single system performs vertical frequency conversion, I / P conversion, scanning line conversion and horizontal pixel conversion.

Owner:PANASONIC CORP

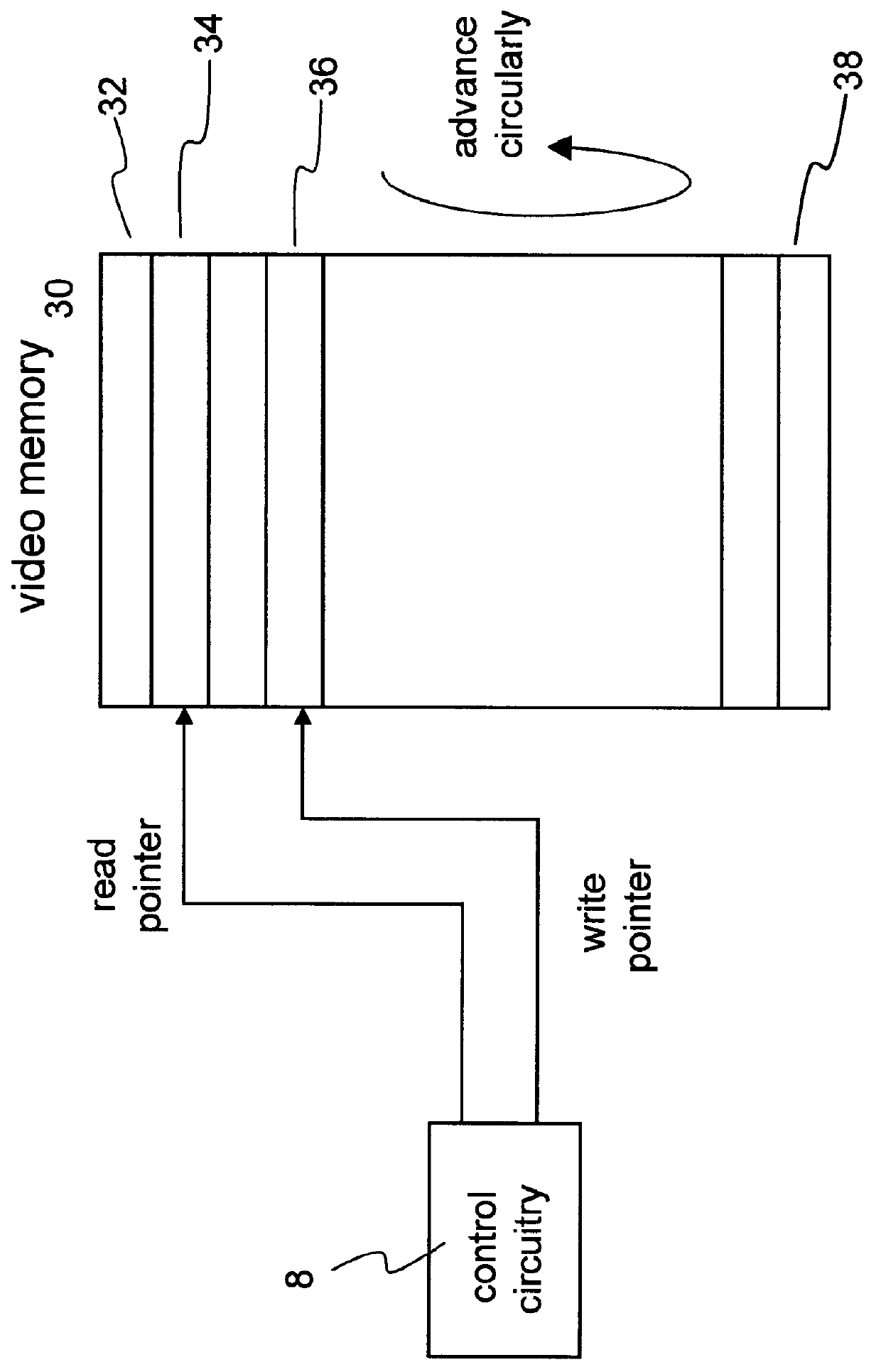

Method and apparatus for reducing video data memory in converting VGA signals to TV signals

InactiveUS6141055AEfficient reuseReduce memory capacityTelevision system detailsColor signal processing circuitsComputer architectureFrame time

It is disclosed herein that a system for reducing video data memory in VGA-to-TV converters that convert computer video signals to TV compliant signals for display on regular TV screens. By closely tracking two pointers, one being a write pointer responsible for writing incoming video data into the video data memory and the other being a read pointer responsible for reading out the stored video data in the video data memory, the memory is efficiently used for buffering the video data. To ensure that the read pointer always retrieves the valid video data at its own speed, an address monitoring process is provided to monitor the address difference between the write pointer and the read pointer. When the monitoring process detects that the read pointer may soon surpass the write pointer, a control process is placed on the write pointer to prevent the read pointer from passing over the write pointer. Depending on the speed difference between the write and read pointers, the writer pointer is either paused for a frame time or assigned to a secondary write pointer that writes data into the memory just visited by the read pointer. The efficient use of the memory makes it possible to reduce the memory capacity to a minimum so as to reduce the cost of manufacturing the converters.

Owner:ALTECH INT CORP

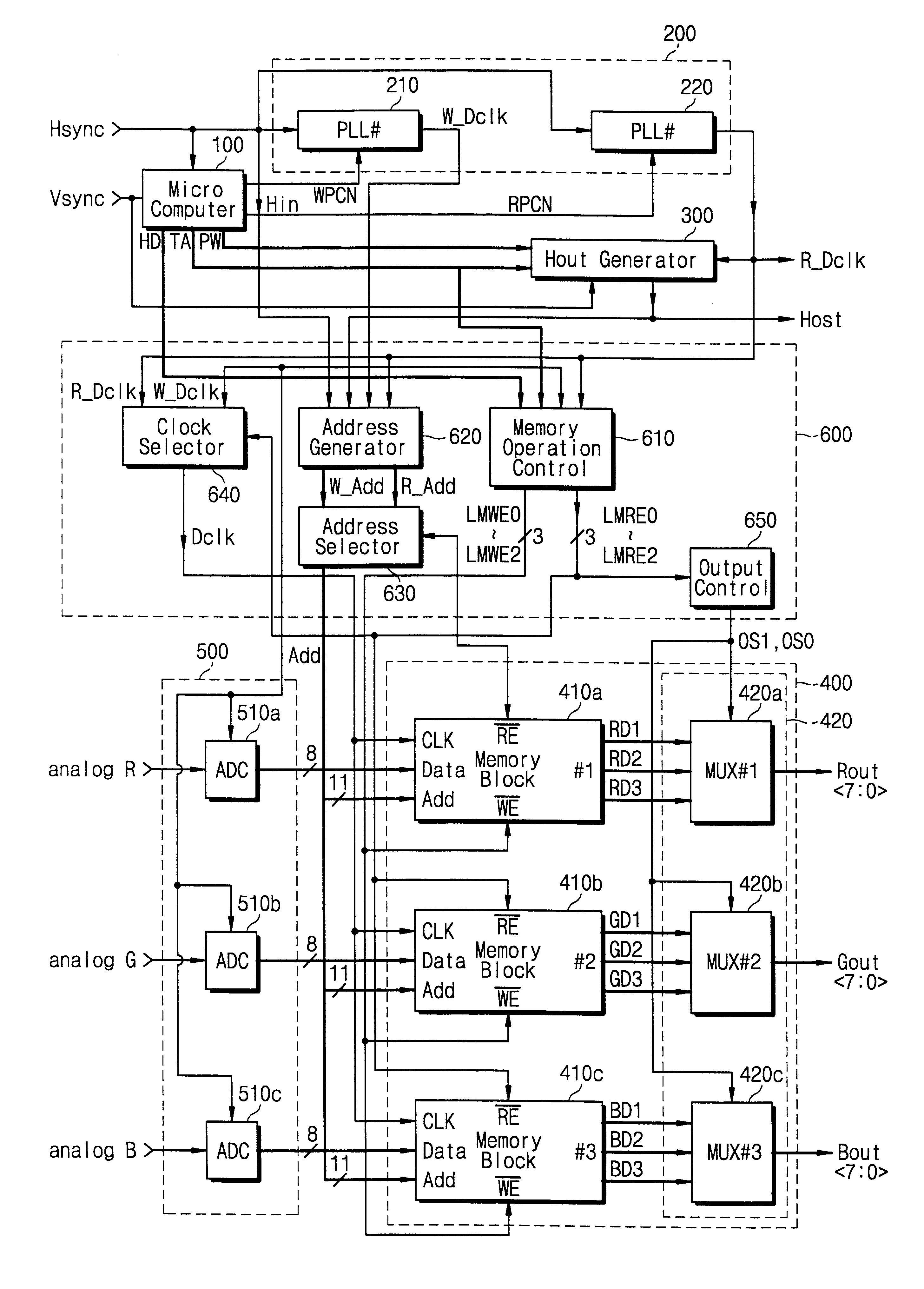

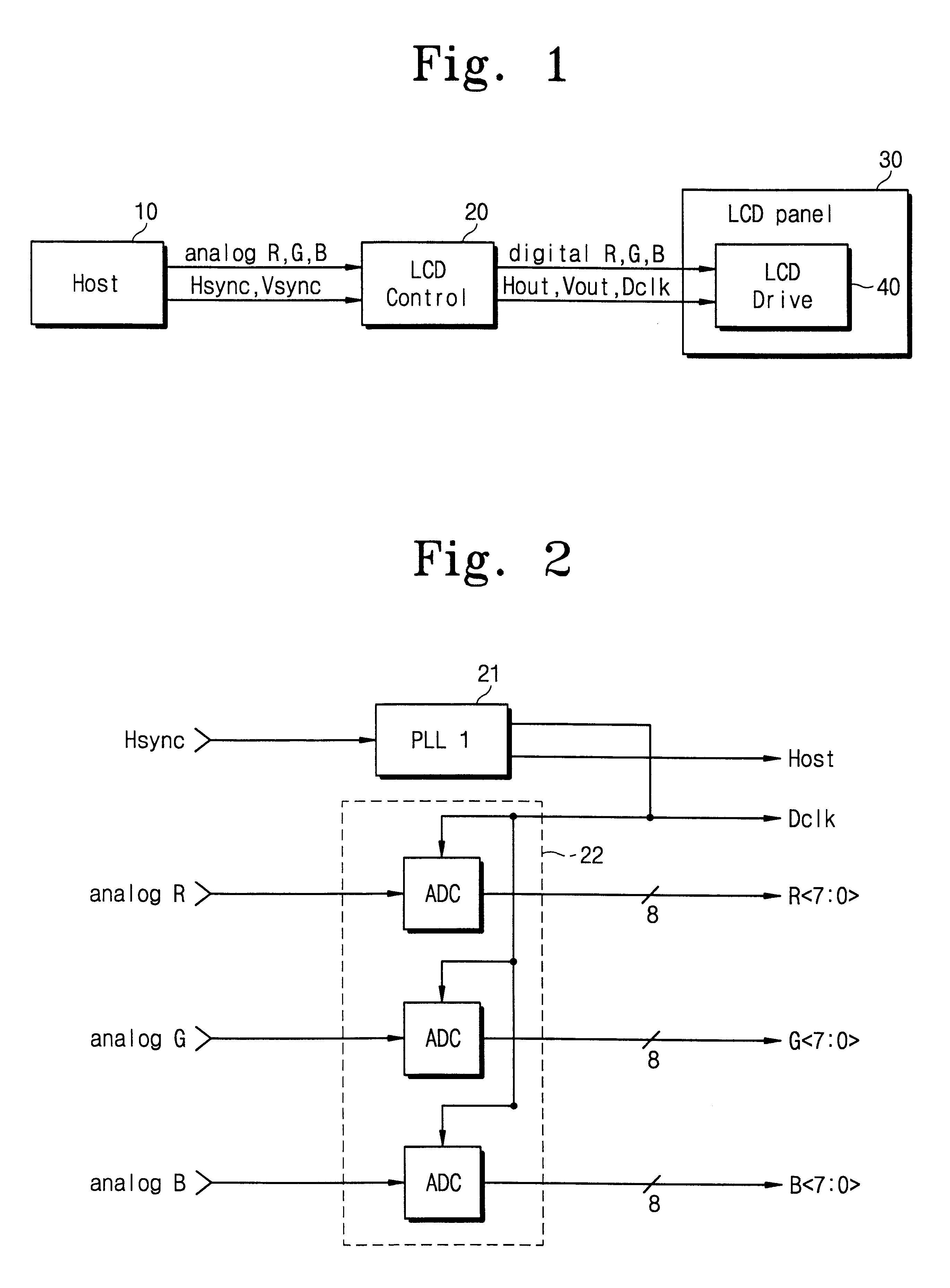

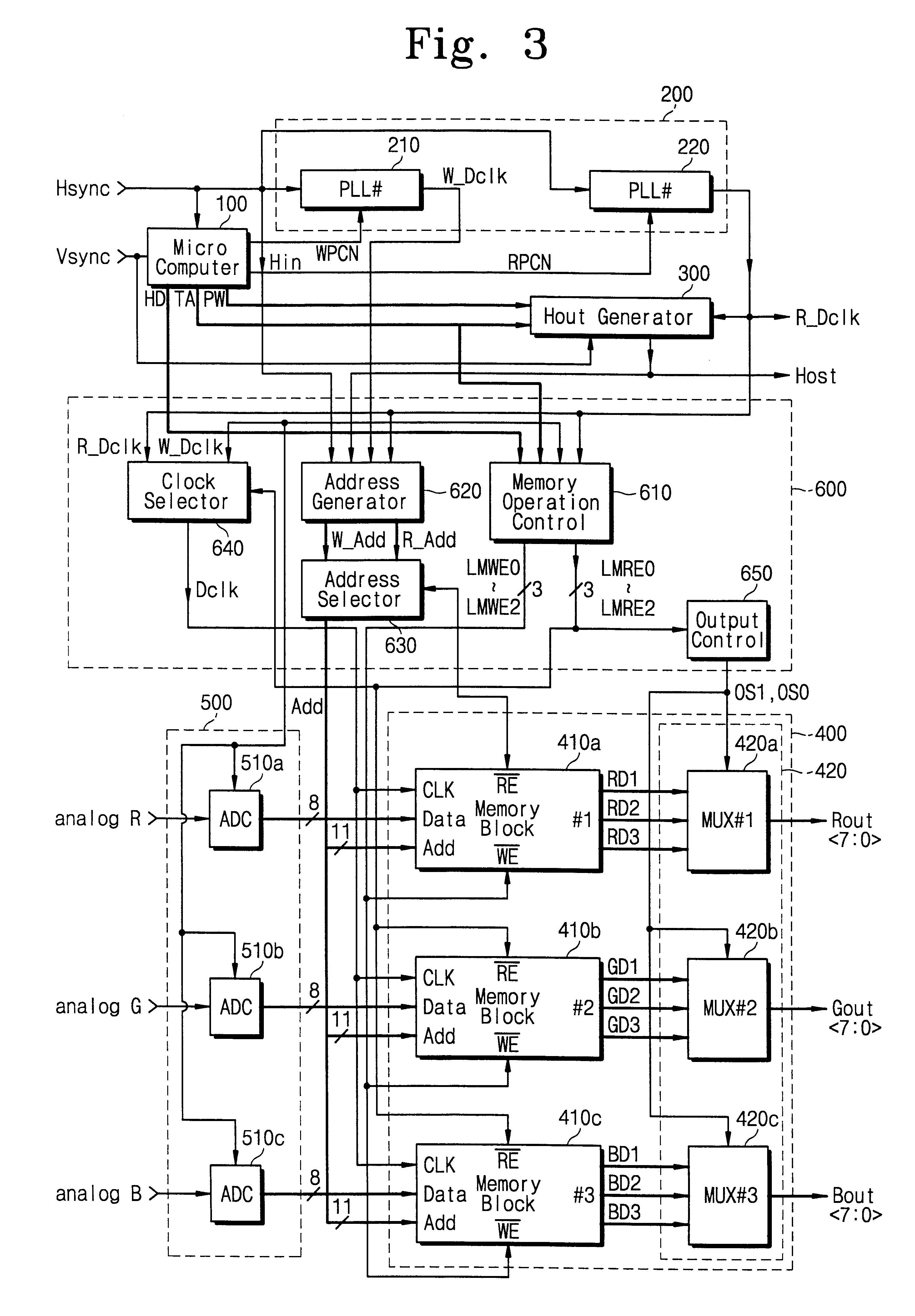

Video signal converting apparatus with display mode conversion and a display device having the same

InactiveUS6219023B1Television system detailsColor television with pulse code modulationDigital videoDisplay device

A video signal converting apparatus converts a low-resolution video signal from a host into a different-resolution video signal capable of being displayed on the entire screen of a high-resolution supporting display device. The apparatus has a memory for storing the digital video signals and a horizontal output generator. The horizontal output generator receives first and second data signals and a horizontal synchronization signal and generates a horizontal output signal for enabling the digital video signals corresponding to each horizontal line of the second display to be stored or read from the memory. A number of pixels per cycle of the horizontal output signal is equal to a value of the first data signal, and a number of pixels per pulse width of the horizontal output signal is equal to a value of the second data signal. The apparatus has a memory controller for controlling reading and storing operations of the memory in accordance with the horizontal and vertical synchronization signals, the horizontal output signal, the first data signal, a third data signal determined according to frequencies of the horizontal and vertical synchronization signals, a first pixel clock signal for a write operation of the memory and a second pixel clock signal for a read operation of the memory.

Owner:SAMSUNG ELECTRONICS CO LTD

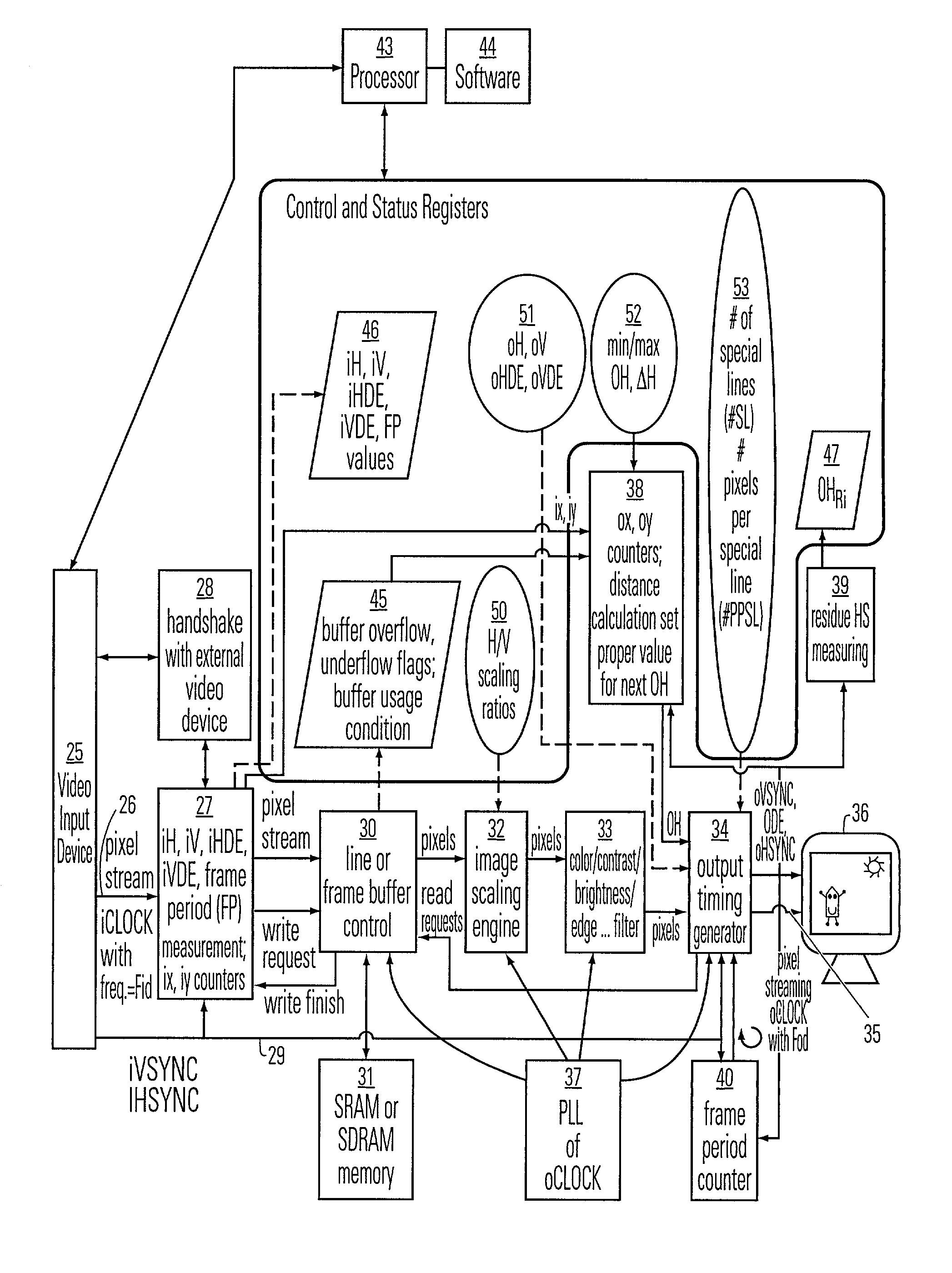

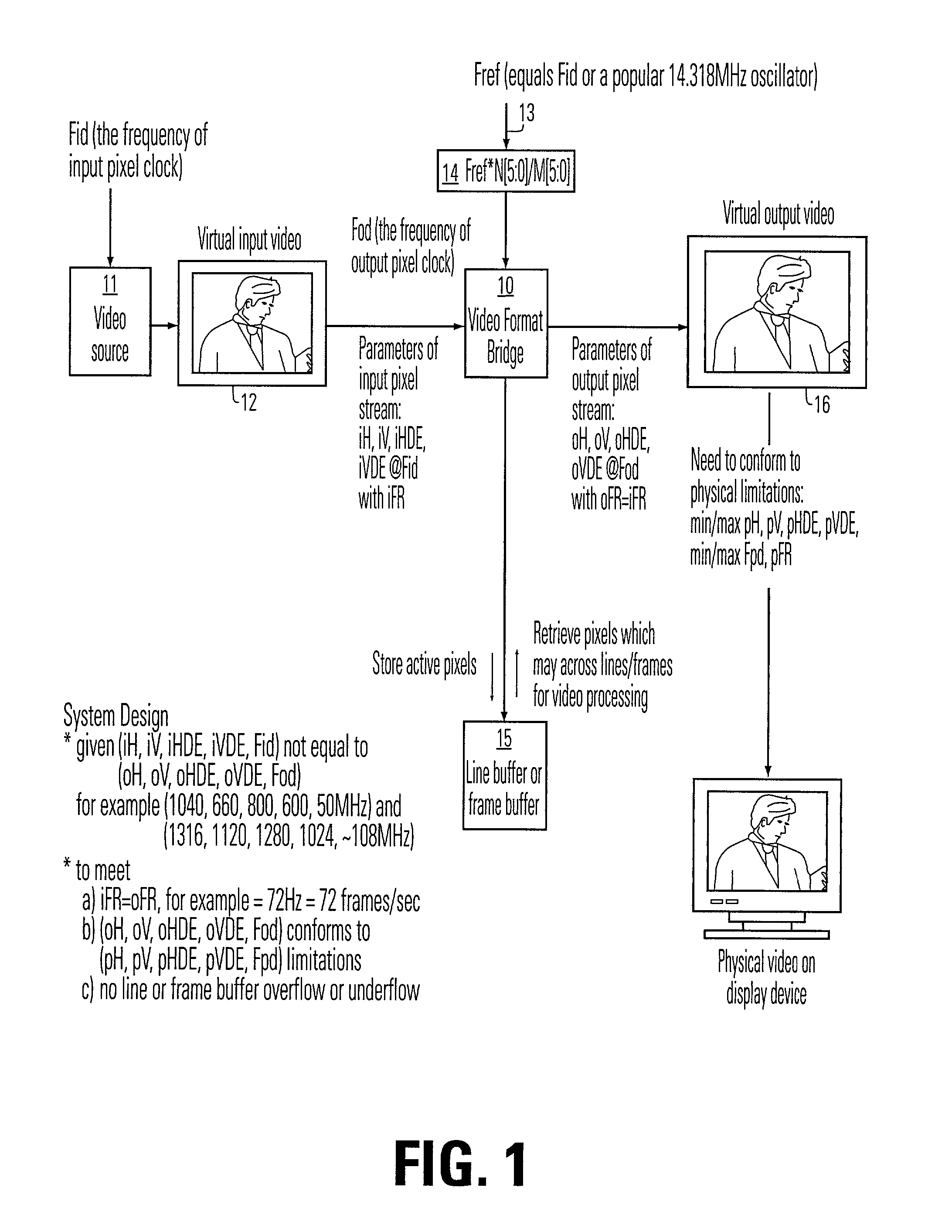

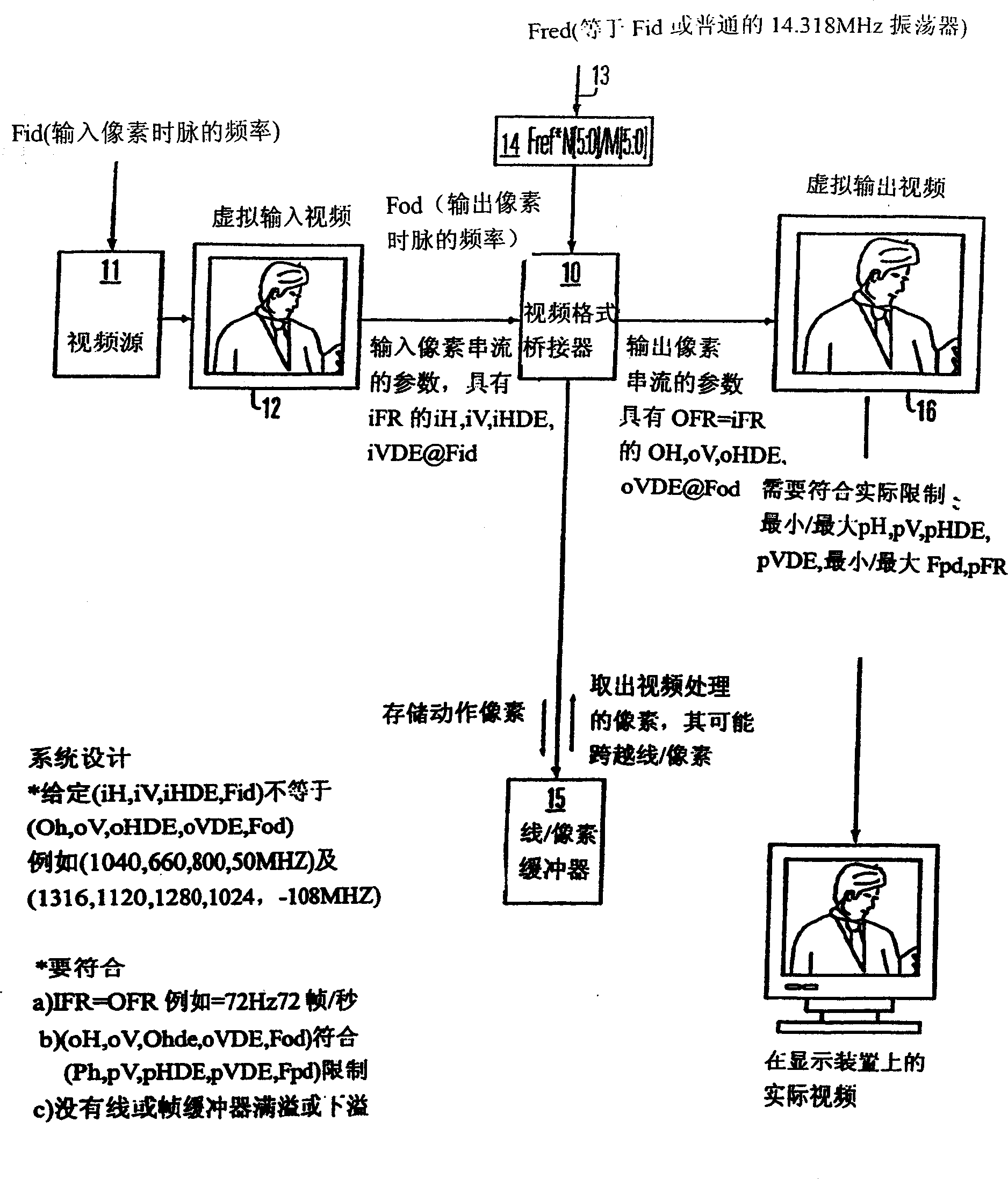

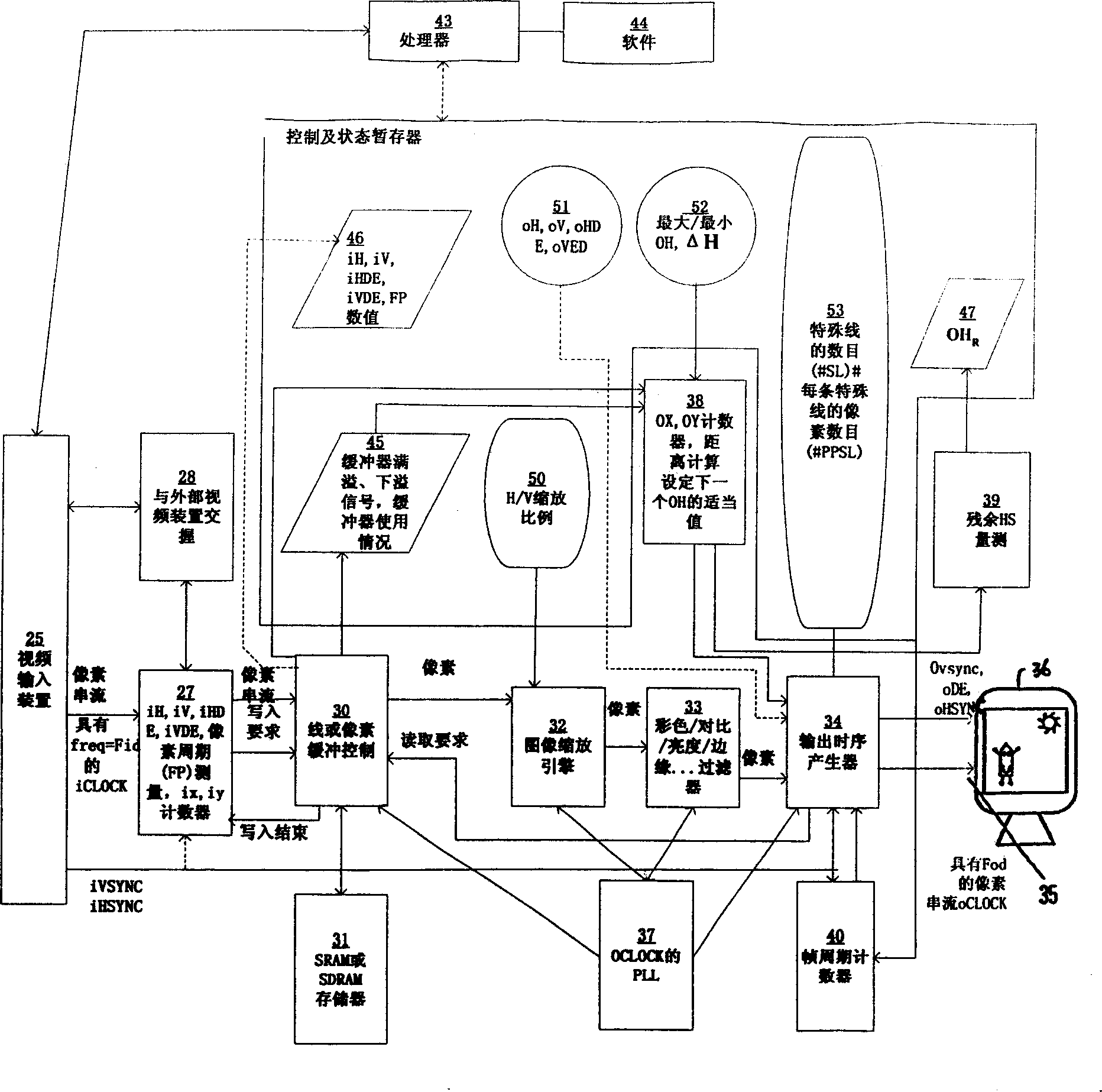

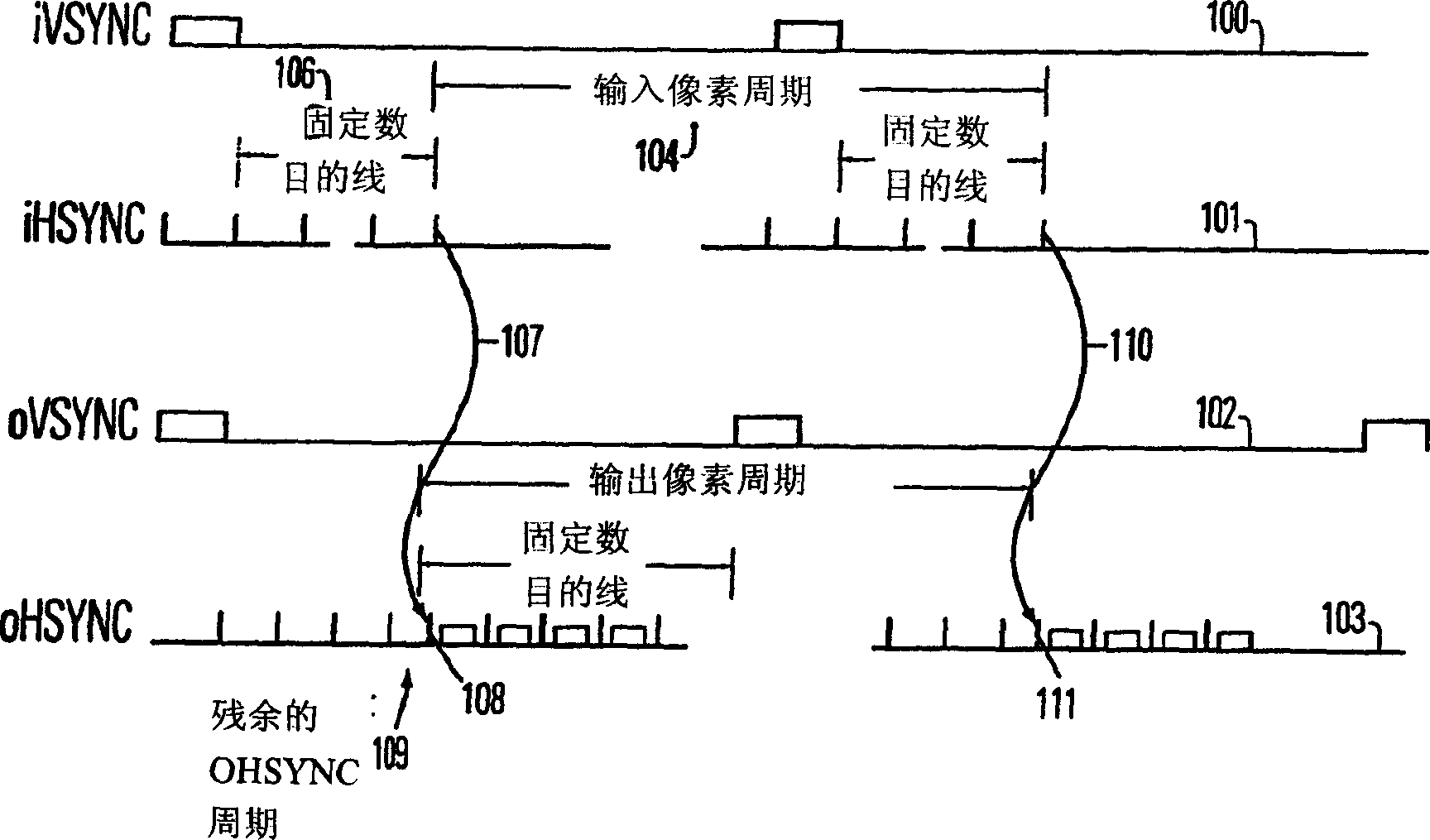

Methods and apparatus for bridging different video formats

InactiveUS7071992B2More precisionHandling problemPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningClock rateOutput device

A video format bridge employs a plurality of techniques to insure that the line buffer does not suffer underflow or overflow conditions, and that the output frame rate matches the input frame rate. The bridge handles the problem of residue lines, addresses fluctuations in the input and output clock rates, and allows adjustment of the ratio of the input and output the number of lines per frame or number of pixels per line so that output device specifications are not exceeded. A single integrated circuit may provided which is adapted to perform a plurality of techniques, and includes resources by which the user is able to enable and disable such techniques as needed for the particular bridging operation being executed. Bridge logic produces an output video stream which has an output frame rate matching the input frame rate, and in which the output frame has at least one of a variable number of pixels per line within an output frame, and / or a variable number of lines per frame among output frames in a set of more than one output frames.

Owner:MAGIC PIXEL

Image pickup apparatus and control method therefor

InactiveUS20050036055A1Television system detailsColor television detailsComputer hardwareInformation control

An image signal generator generates an imaging signal having a frame rate that is controlled to be variable. A frame rate converter generates a monitor image signal. Upon receiving communication information from an external source, a controller controls the operations of the image signal generator and the frame rate converter on the basis of the communication information. When an instruction to specify the frame rate of the monitor image signal is given from a user interface, the controller controls the frame rate converter to generate a monitor image signal having a specified frame rate by giving priority to this instruction over the communication information.

Owner:SONY CORP

High speed image capturing apparatus and method

ActiveUS8849090B2Easy to operateLow costTelevision system detailsColor signal processing circuitsComputer hardwareSignal processing circuits

In a high speed image capturing state, a camera signal processing circuit is not needed to perform a signal process at a high screen rate, but at a regular screen rate. In the high speed image capturing mode, raw data of 240 fps received from an image sensor 101 are recorded on a recording device 111 through a conversion processing section 201 and a recording device controlling circuit 210. Raw data that have been decimated and size-converted are supplied to a camera signal processing circuit 203 through a pre-processing circuit 202 and an image being captured is displayed on a display section 112 with a signal for which a camera process has been performed. In a reproducing state, raw data are read from the recording device 111 at a low screen rate according to a display performance of the display section 112 and the raw data that have been read are processed are processed by the pre-processing circuit 202 and the camera signal processing circuit 203 and a reproduced image is displayed by the display section 112.

Owner:SONY CORP

Video signal conversion processing apparatus and method

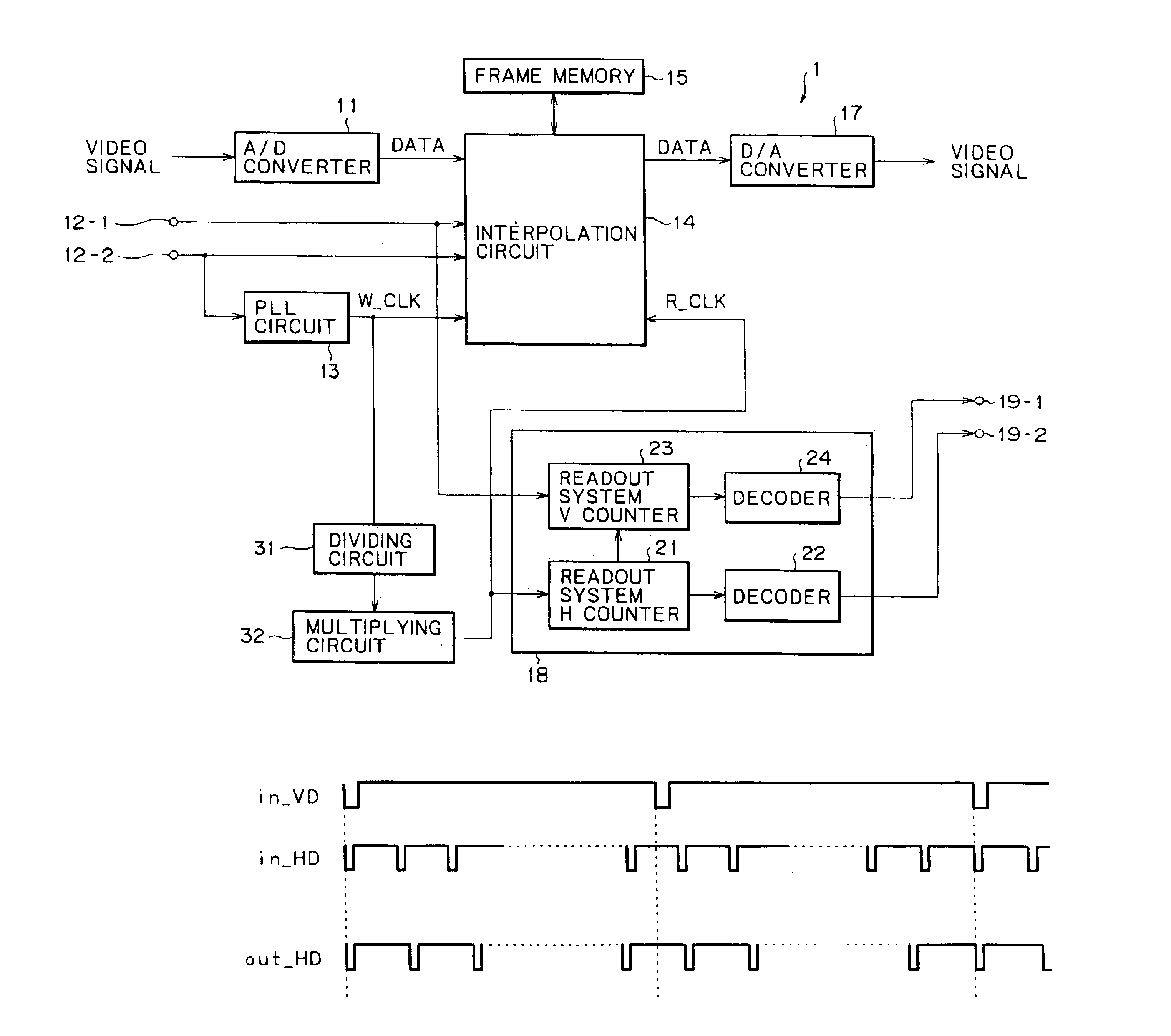

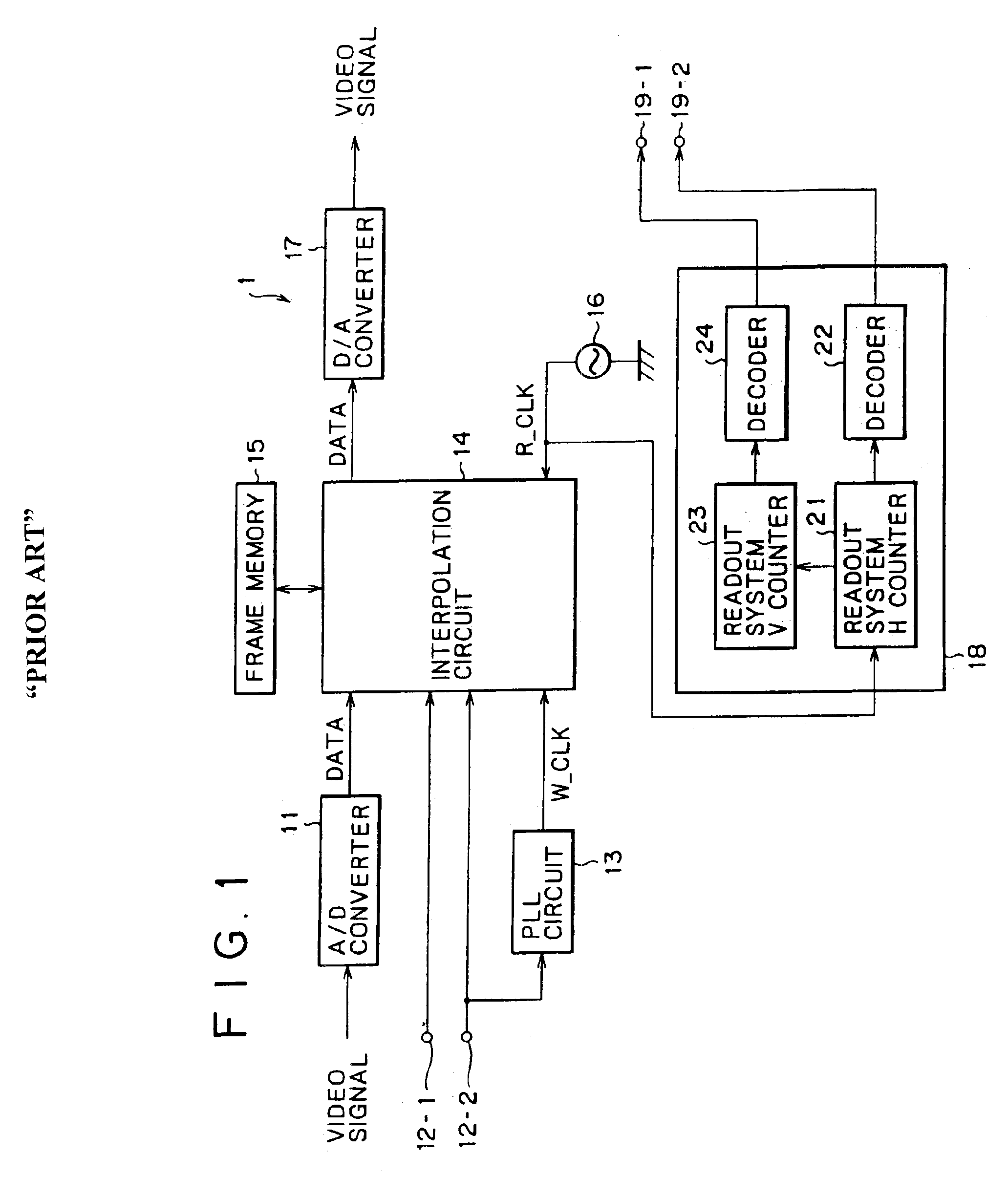

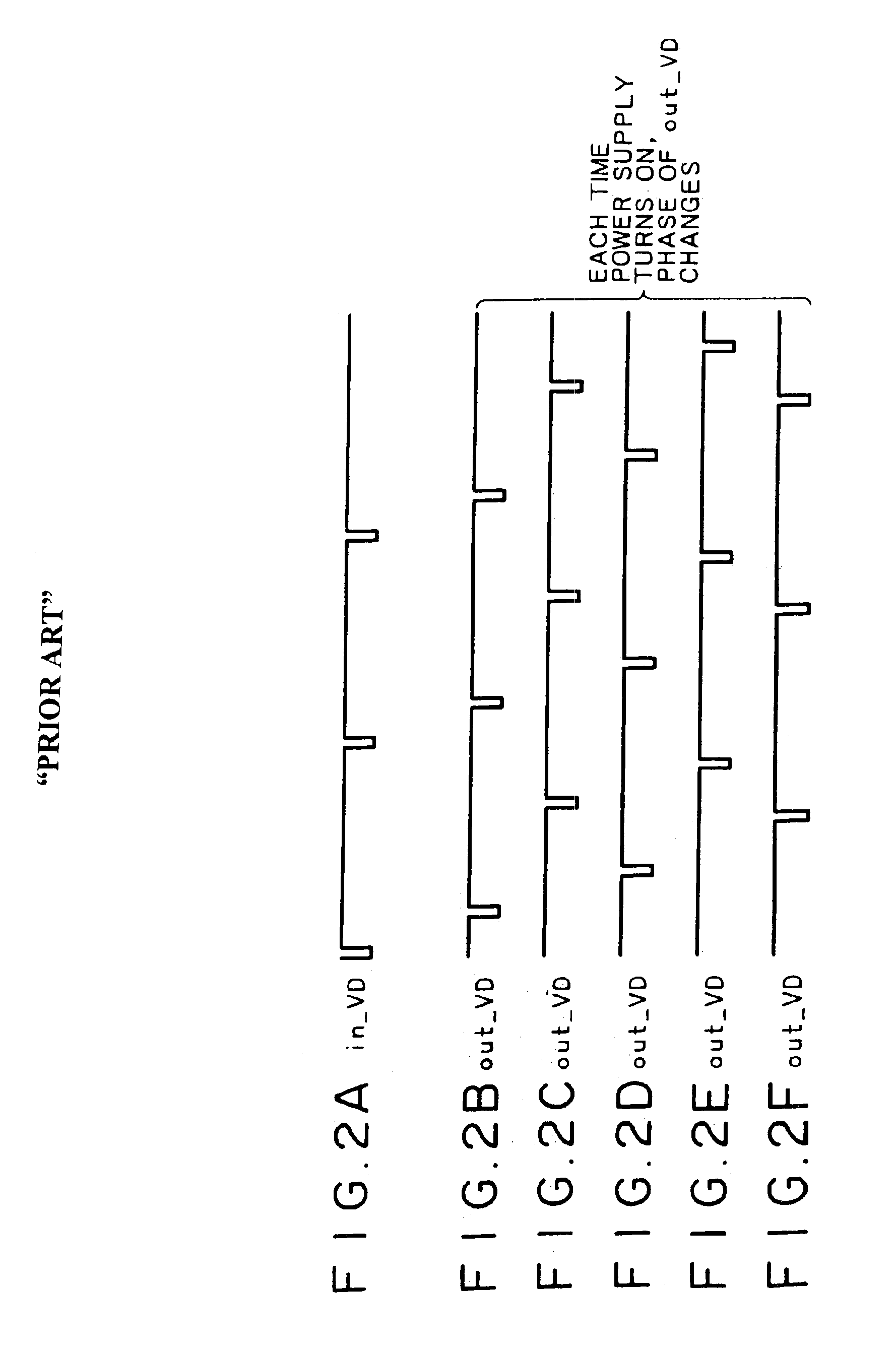

InactiveUS6891572B2High precisionImprove accuracyTelevision system detailsPulse automatic controlDividing circuitsComputer science

A signal processing apparatus and method for up or down conversion of an interlace signal with a high degree of accuracy. The frequency of a write system clock supplied from a PLL circuit is divided by N by a dividing circuit and then multiplied by M by a multiplying circuit to produce a readout system clock. An interpolation circuit writes a video signal into a frame memory in synchronism with the write system clock from the PLL circuit, and reads out the video signal in synchronism with the readout system clock from the multiplying circuit.

Owner:SONY CORP

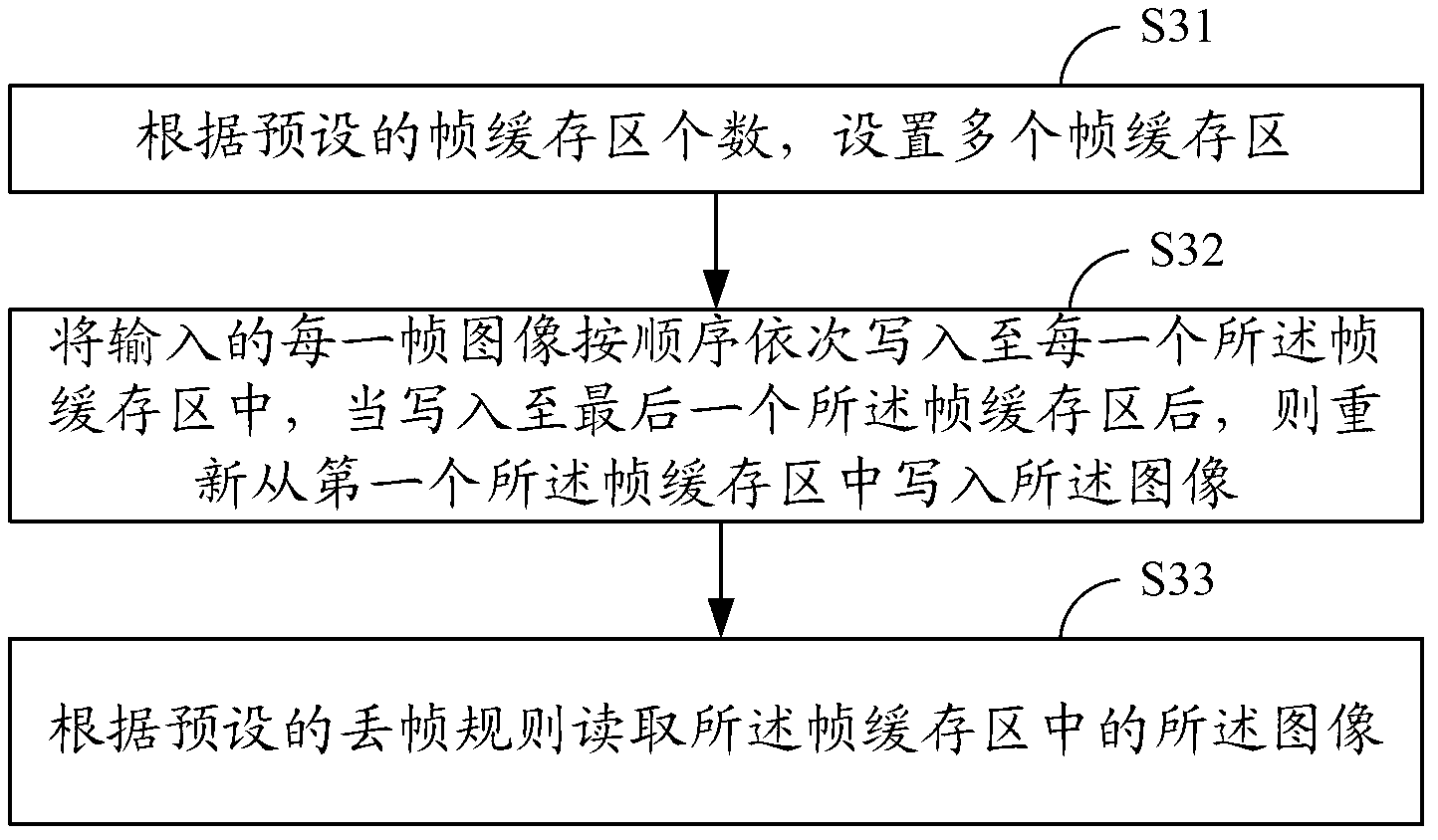

Frame dropping method and system of video image

ActiveCN103269421AImprove stuck phenomenonPulse modulation television signal transmissionConversion with storage device usageVideo imageComputer science

The invention provides a frame dropping method of a video image. The frame dropping method comprises the following steps that a plurality of frame buffer caches are arranged according to the number of preset frame buffer catches; input frame images are sequentially written into the frame buffer caches, and when the last frame buffer cache is written, the frame images are written from the first frame buffer cache again; the images in the frame buffer caches are read out according to preset frame loss rules. The invention further correspondingly provides a frame dropping system of the video image. When the frame dropping system is used for conducting frame dropping processing on the video image, the blocking phenomenon of a moving image is effectively improved.

Owner:GUANGDONG VTRON TECH CO LTD

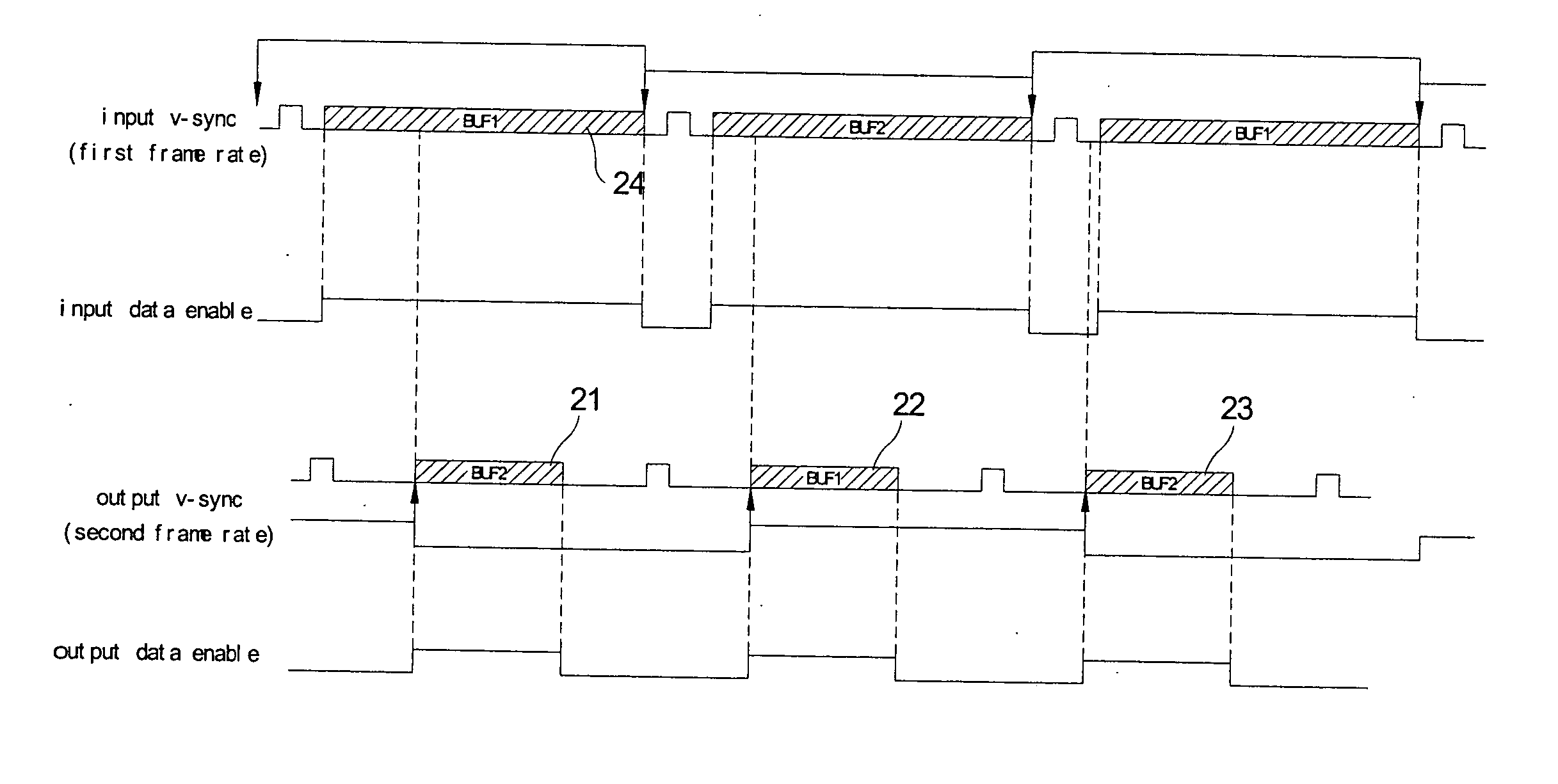

Method for frame rate conversion

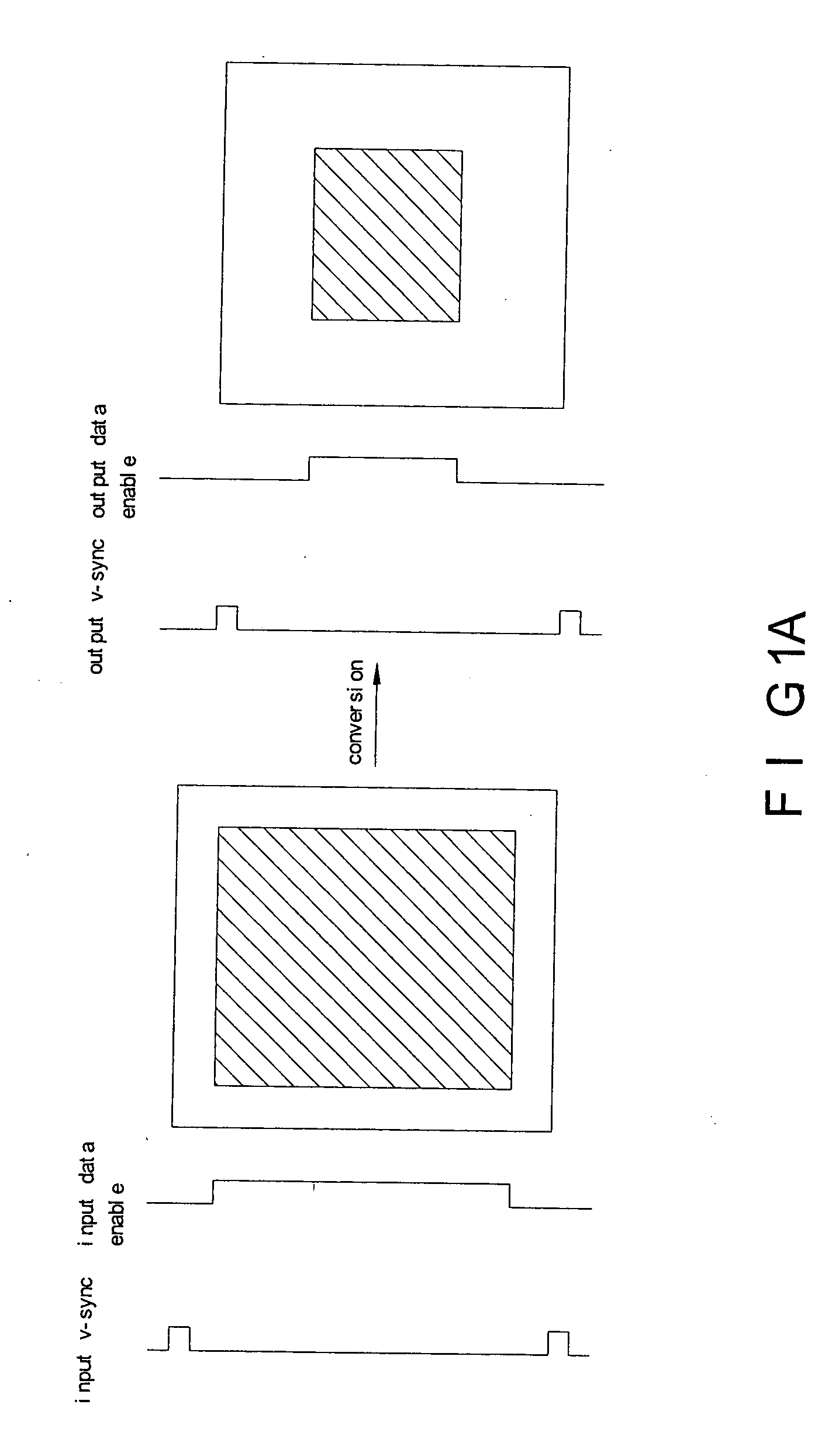

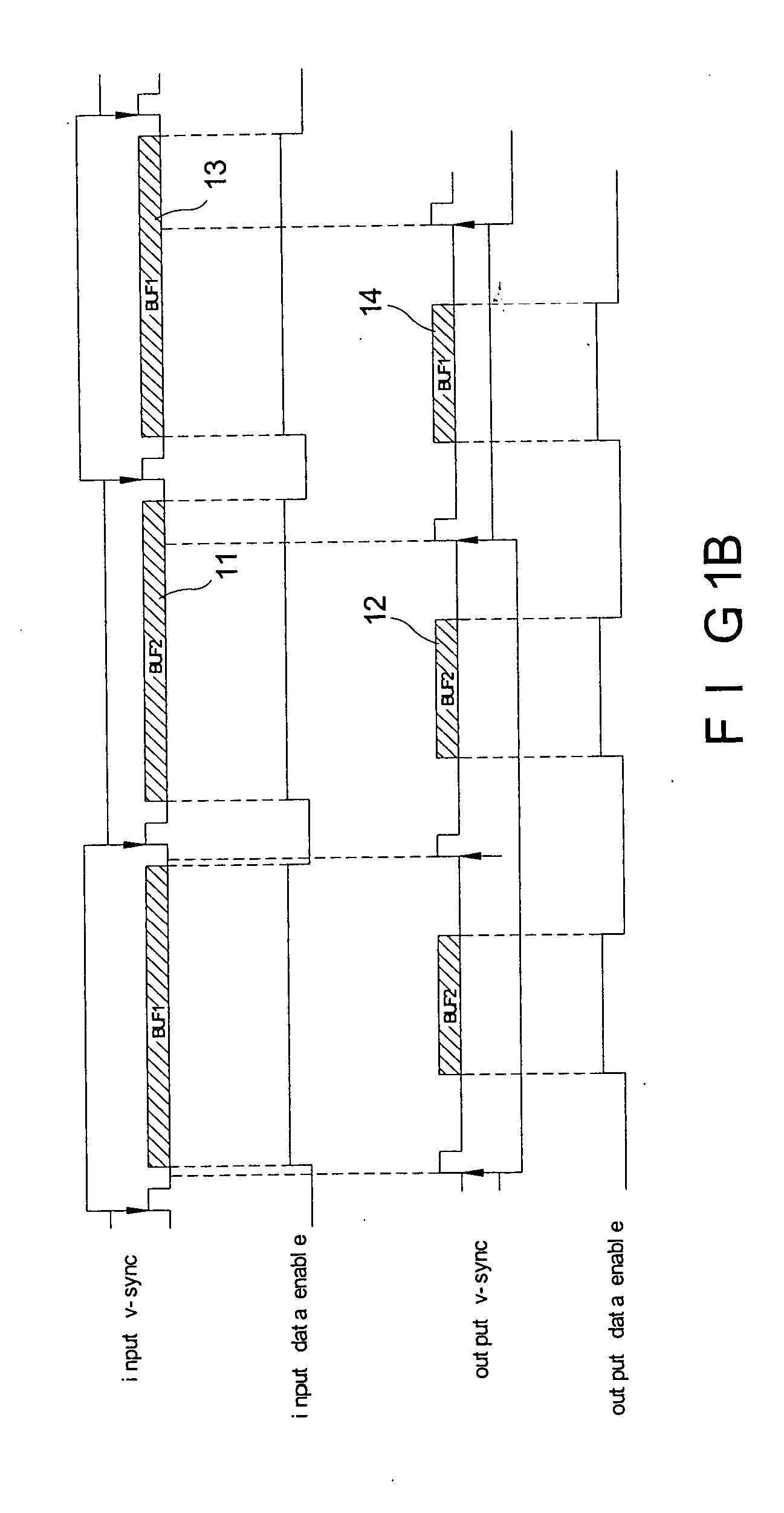

ActiveUS20060050075A1Good time pointConvenient timeCathode-ray tube indicatorsConversion with storage device usageAccess timeComputer science

A method for converting a frame rate of a video signal comprising a data enable signal by means of a first buffer and a second buffer is disclosed. The method comprises: alternatively accessing the first buffer and the second buffer according to a first frame rate; determining an accessing time point of the first and the second buffers according to the data enable signal; and accessing the buffer, which is one of the first and the second buffers and not accessed at the accessing time point, according to a second frame rate, wherein the second frame rate is faster than the first frame rate.

Owner:REALTEK SEMICON CORP

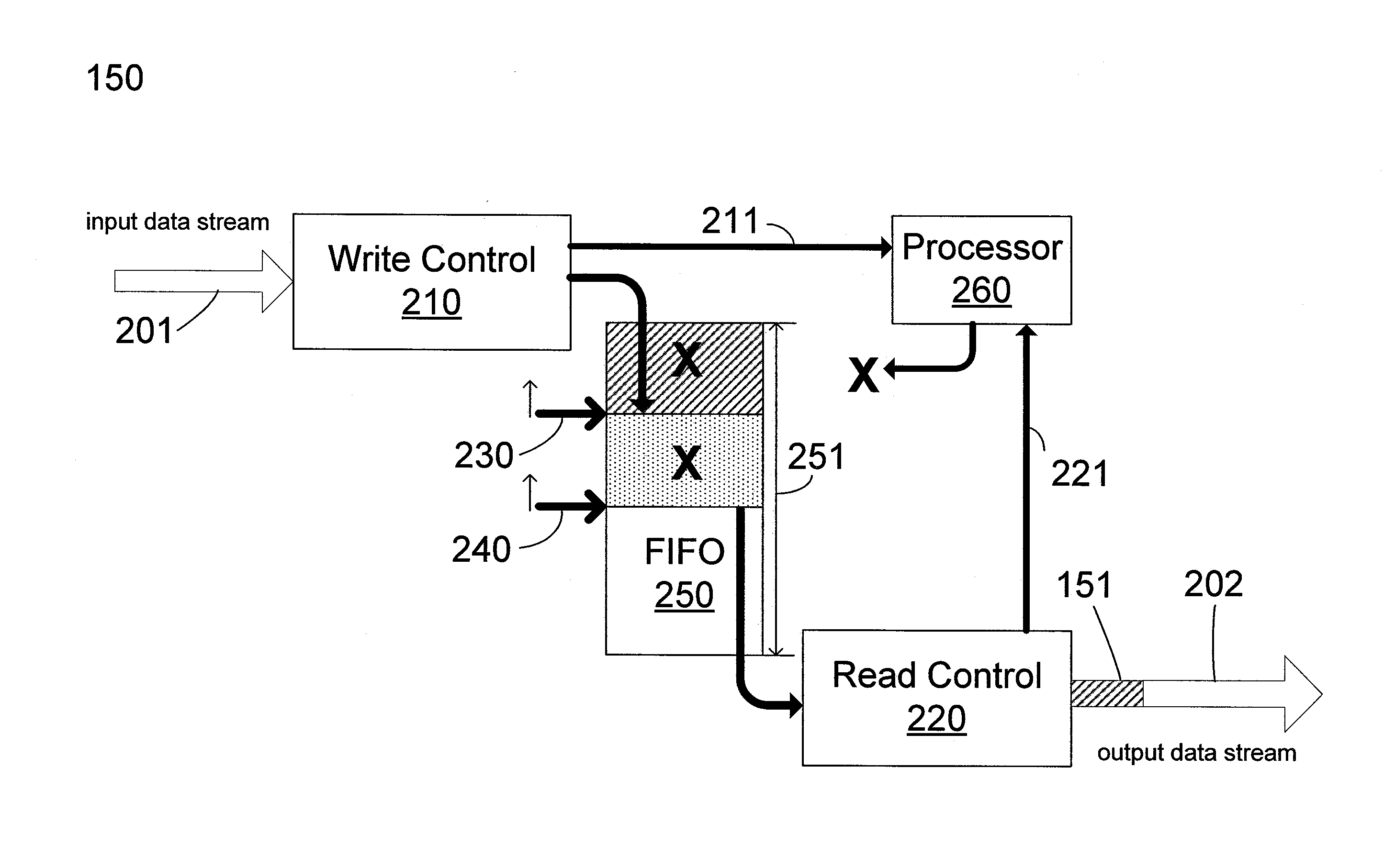

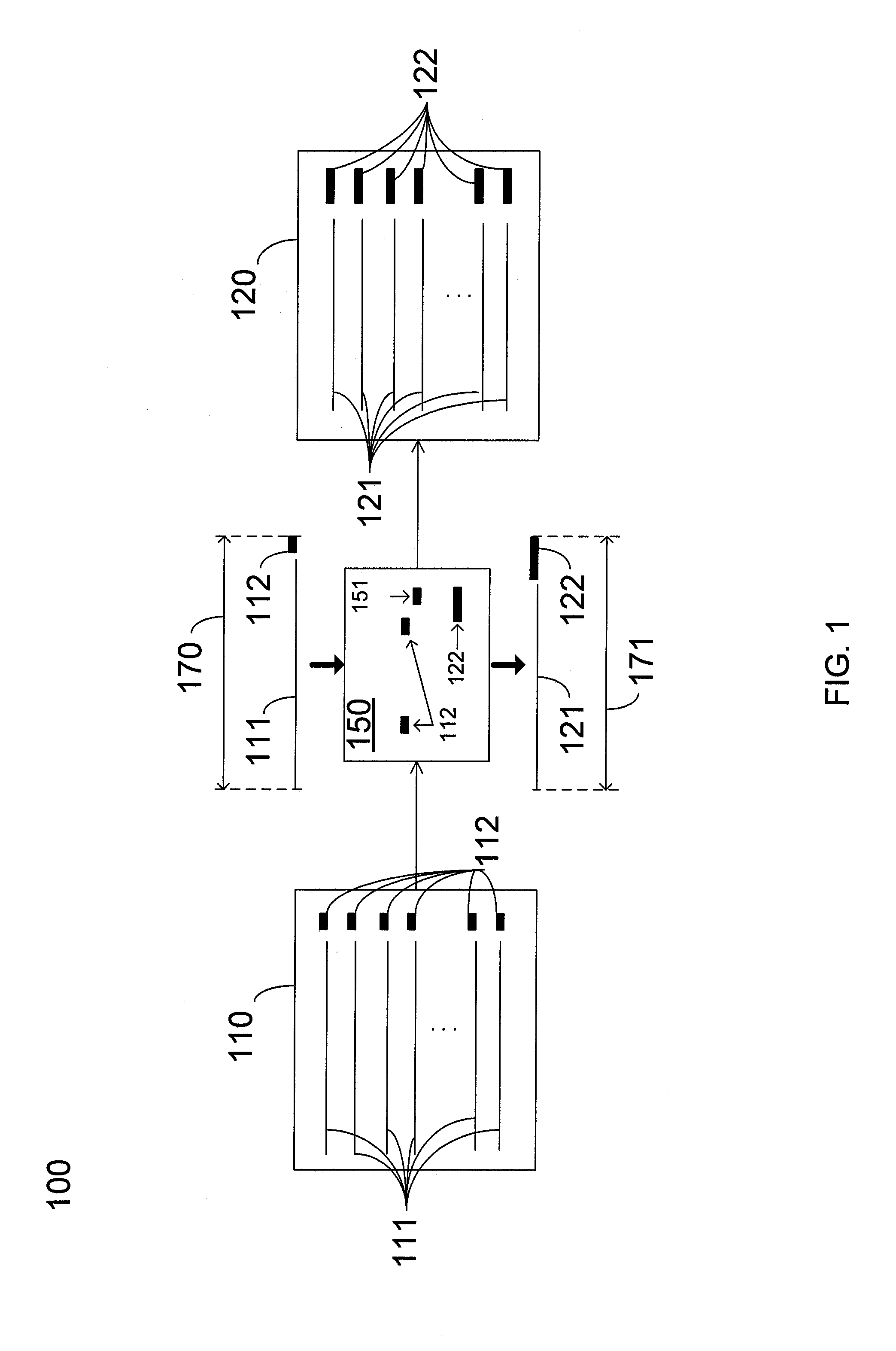

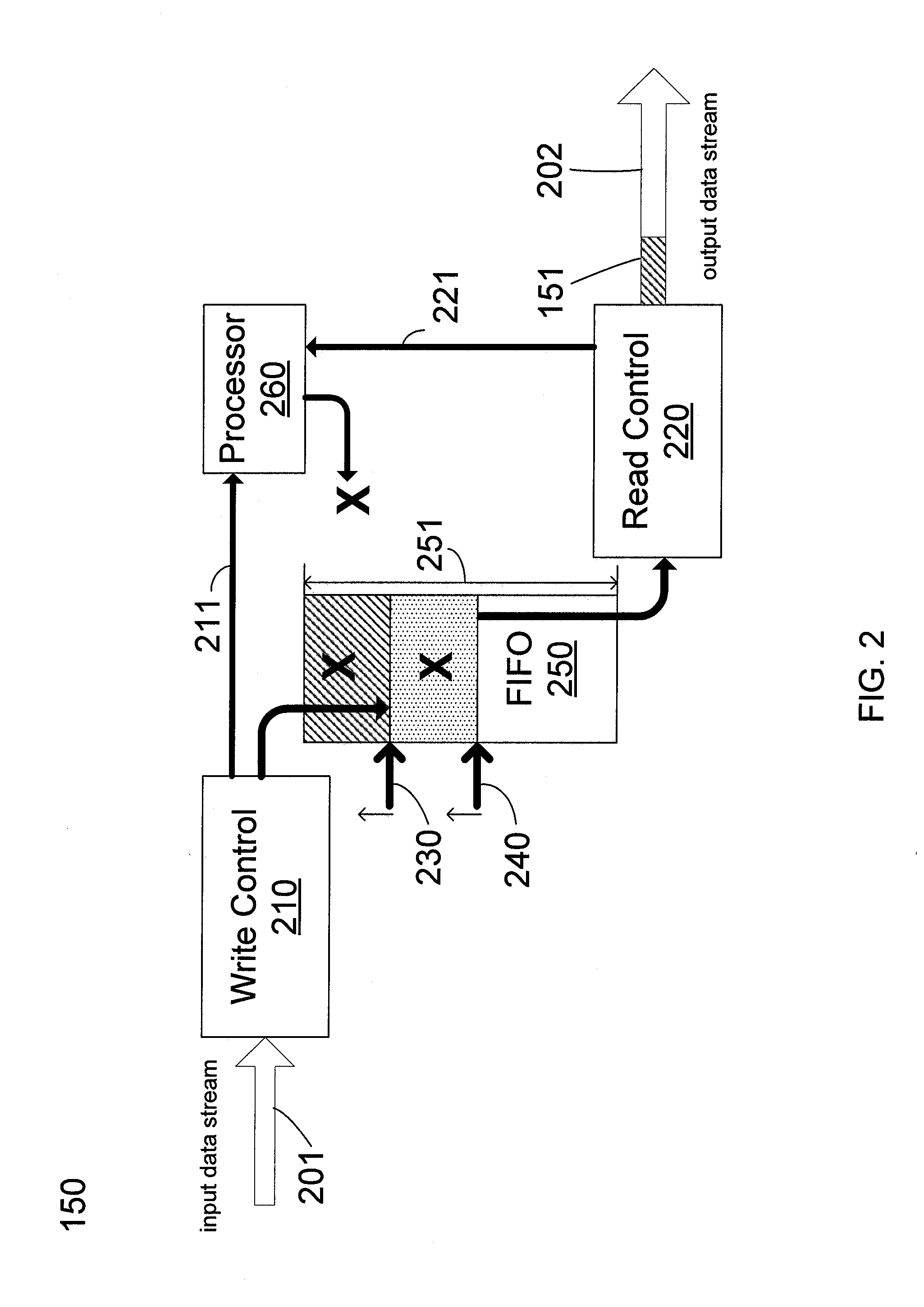

Data rate buffering in display port links

ActiveUS20110249192A1Television system detailsPicture reproducers using cathode ray tubesData streamData rate

Rate matching for use in data links between a source device and a sink device is provided. A rate matching device includes a first-in-first-out (FIFO) buffer having a write pointer and a read pointer; a write control having a write clock to write an input data stream from the source device onto the FIFO buffer using the write pointer; a read control having a read clock to read data from the FIFO buffer using a read pointer, insert data to an output data stream and transmitting the data stream to the sink device; a processor to provide a bit number based on the write clock period and the read clock period, wherein the read control inserts blanking data into the output data stream while the read pointer is stopped in the FIFO buffer to allow the write pointer to move ahead by the bit number provided by the processor. Some embodiments are thus able to avoid buffer overflow or underflow scenarios.

Owner:SYNAPTICS INC

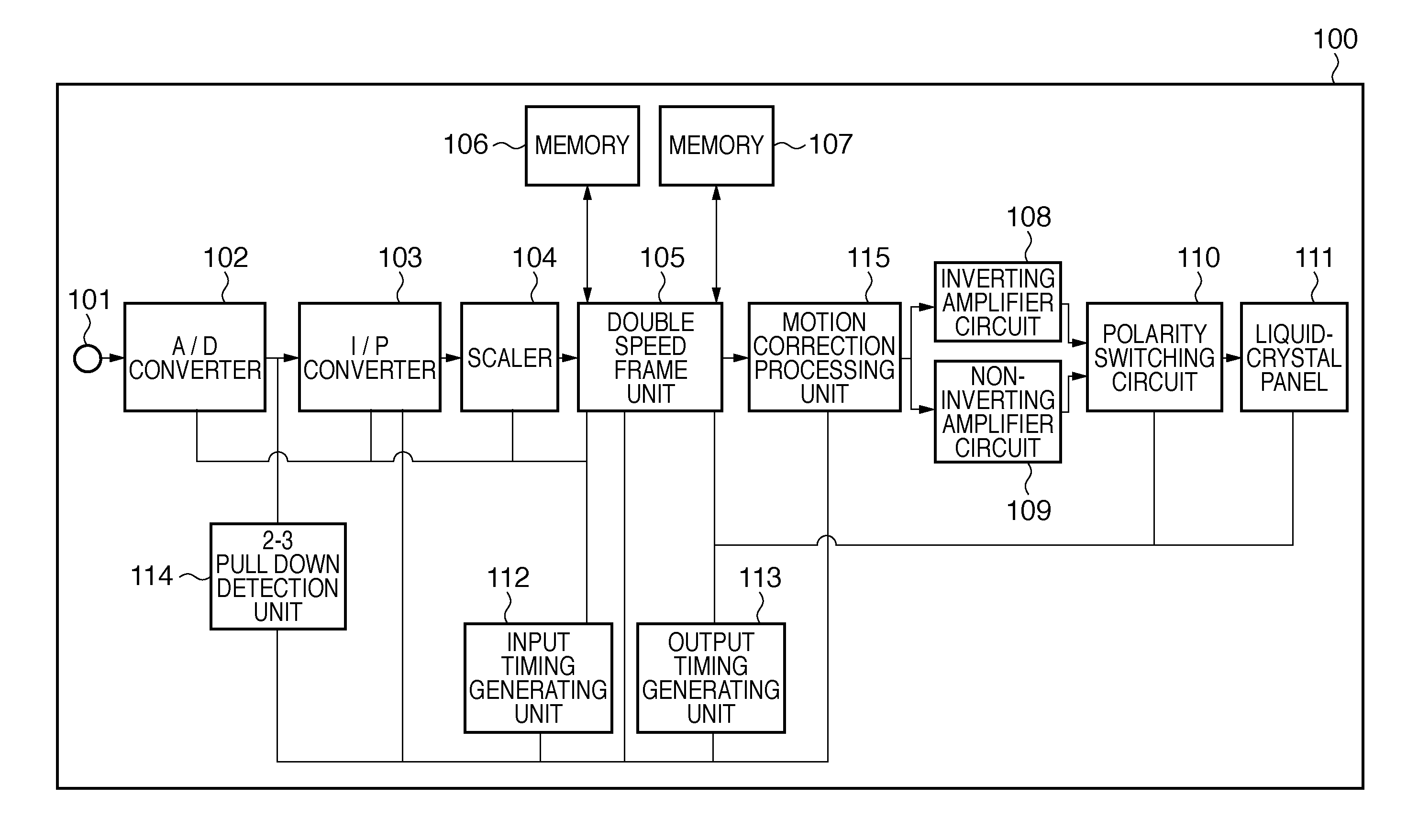

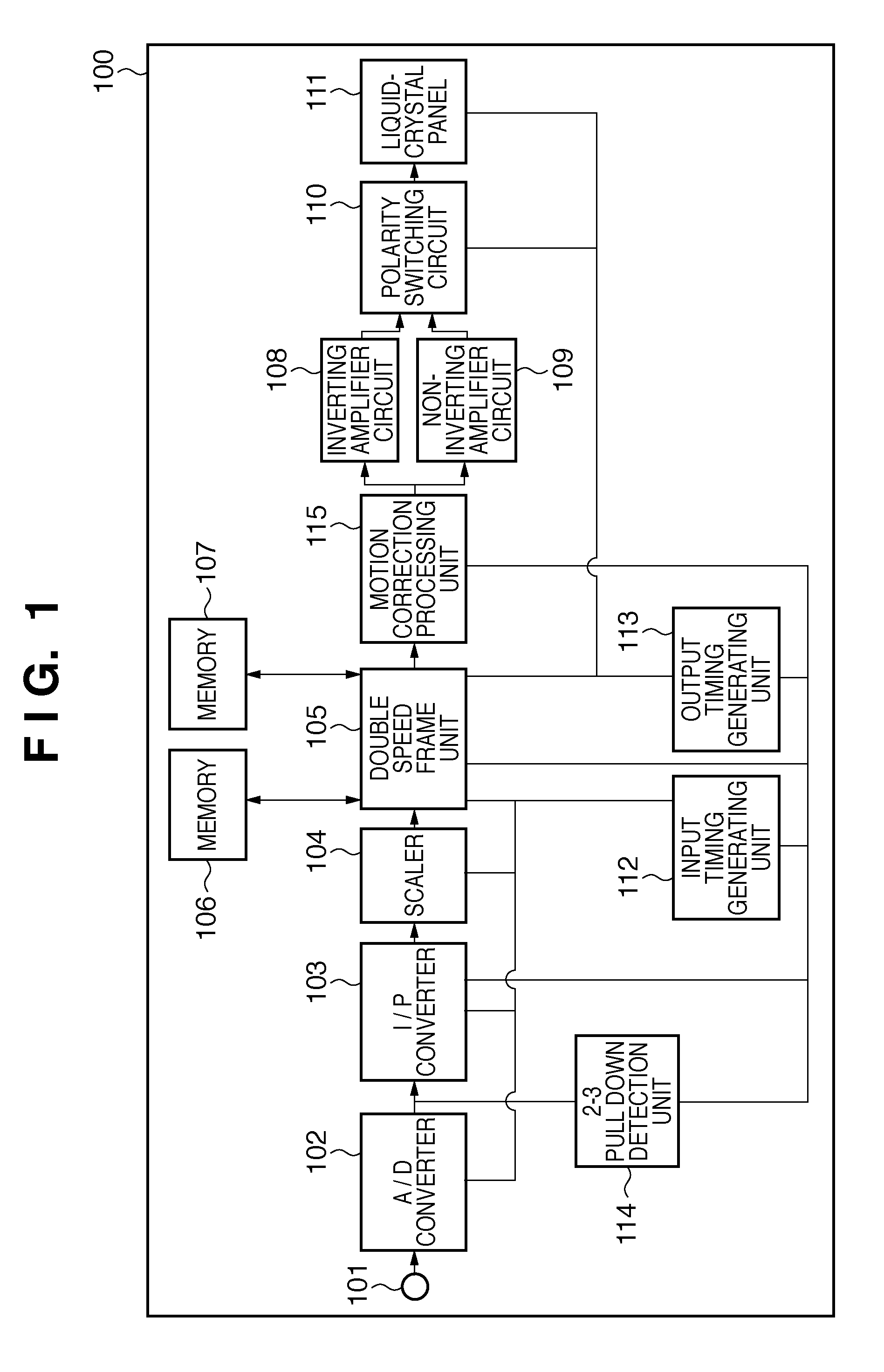

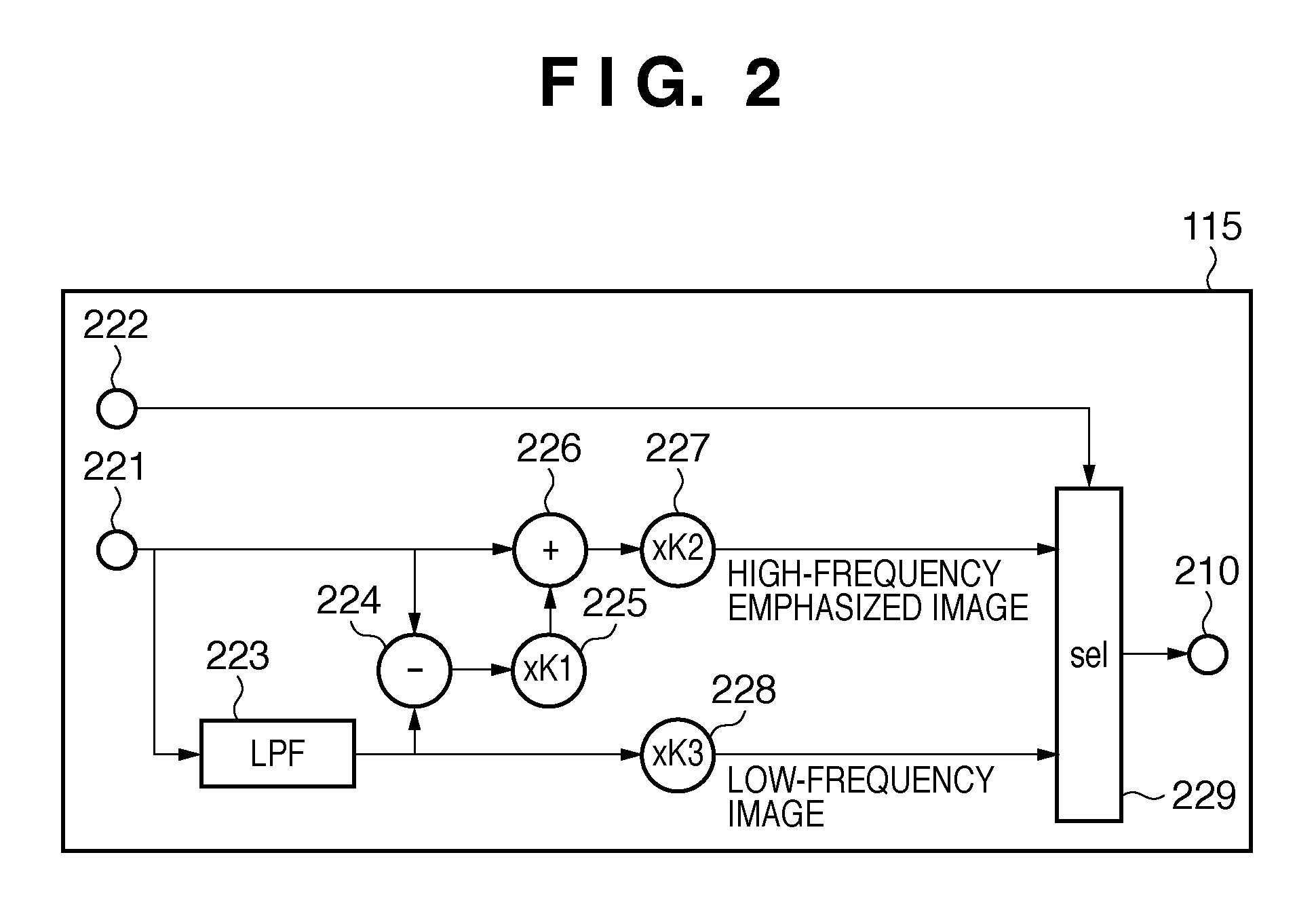

Display apparatus and driving method thereof

InactiveUS20090310018A1Improve image qualityEnsure reliabilityTelevision system scanning detailsPicture reproducers using cathode ray tubesComputer graphics (images)Video image

A display apparatus and a driving method thereof capable of assuring reliability in frame inversion driving and improving cinema video image quality are provided. To accomplish this, a display apparatus of the embodiment replaces at least one of a plurality of frame images obtained by doubling the frame rate, with a different image before display. Specifically, the display apparatus replaces at least one of the double-speed converted plural frame images with a high-frequency emphasized image and at least one with a low-frequency component image, and displays the frame images. Furthermore, the display apparatus replaces an image at the border between cinema images with a different image before displaying.

Owner:CANON KK

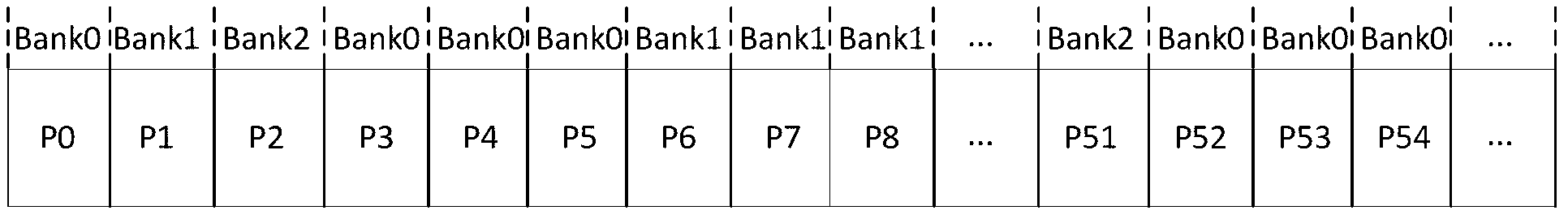

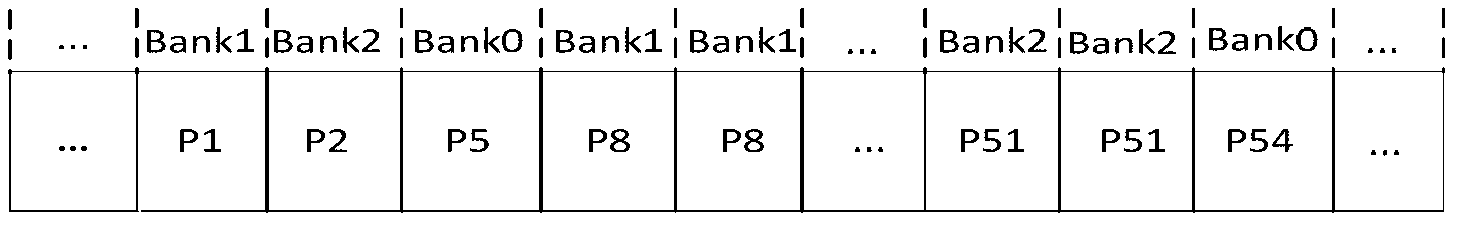

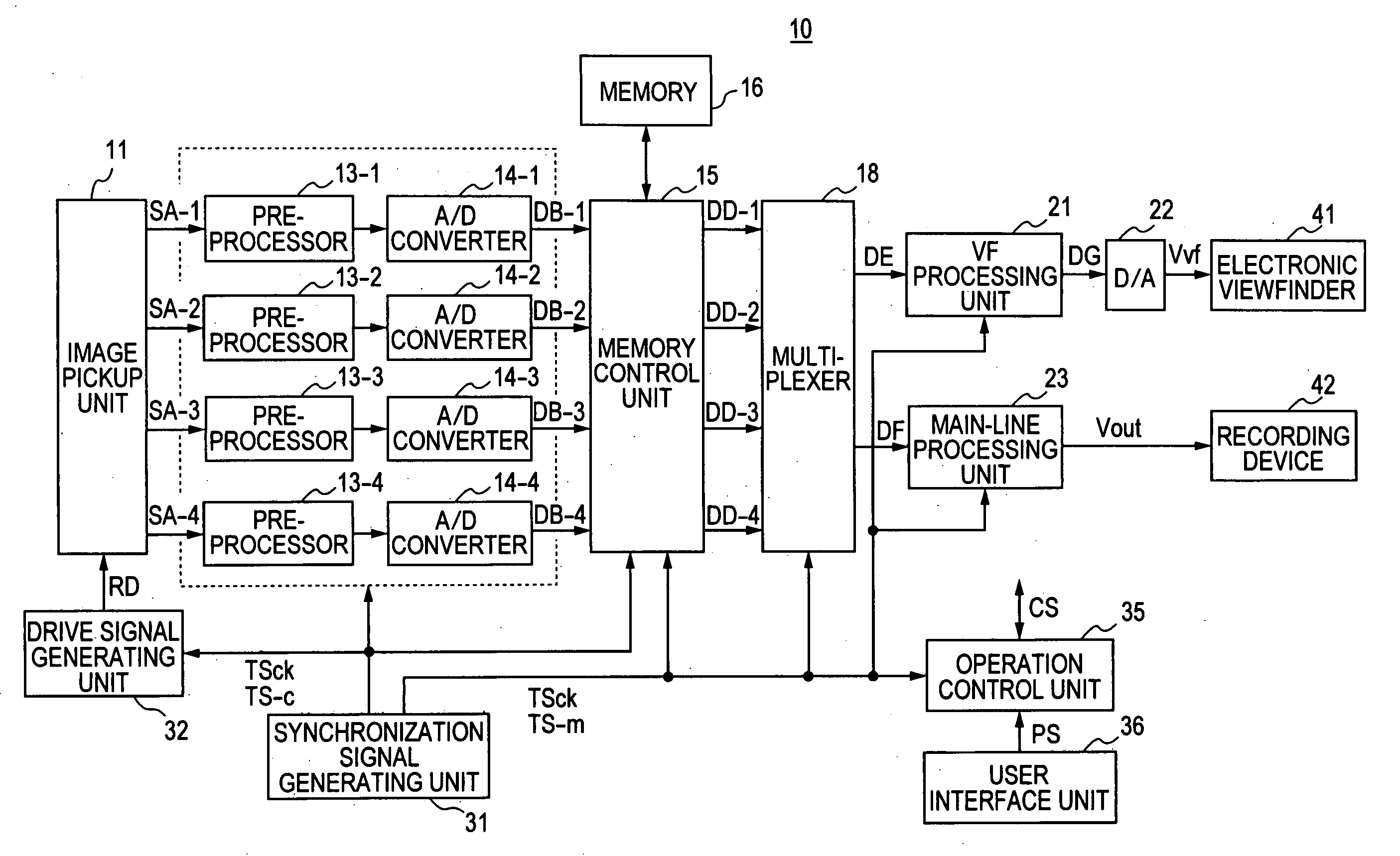

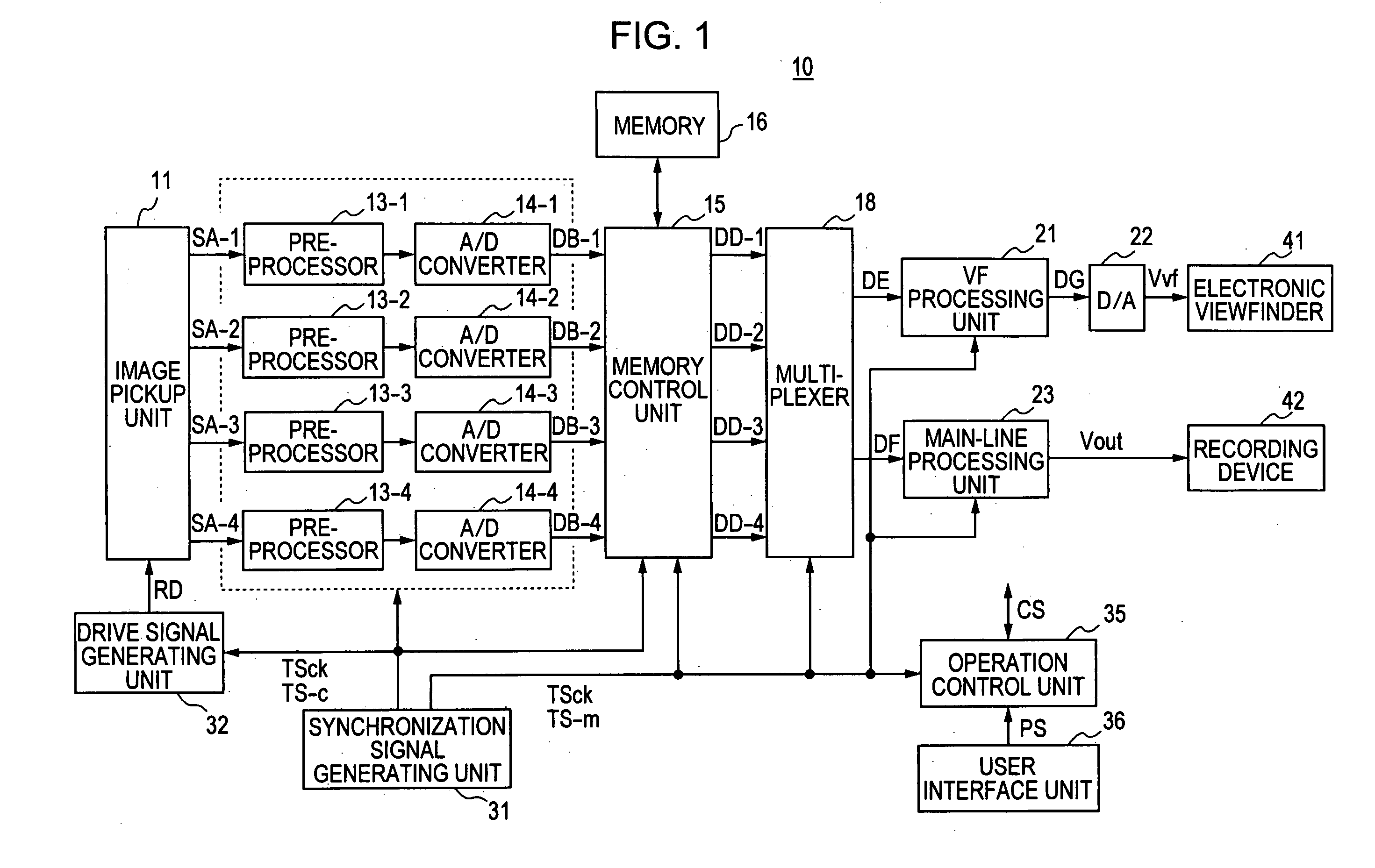

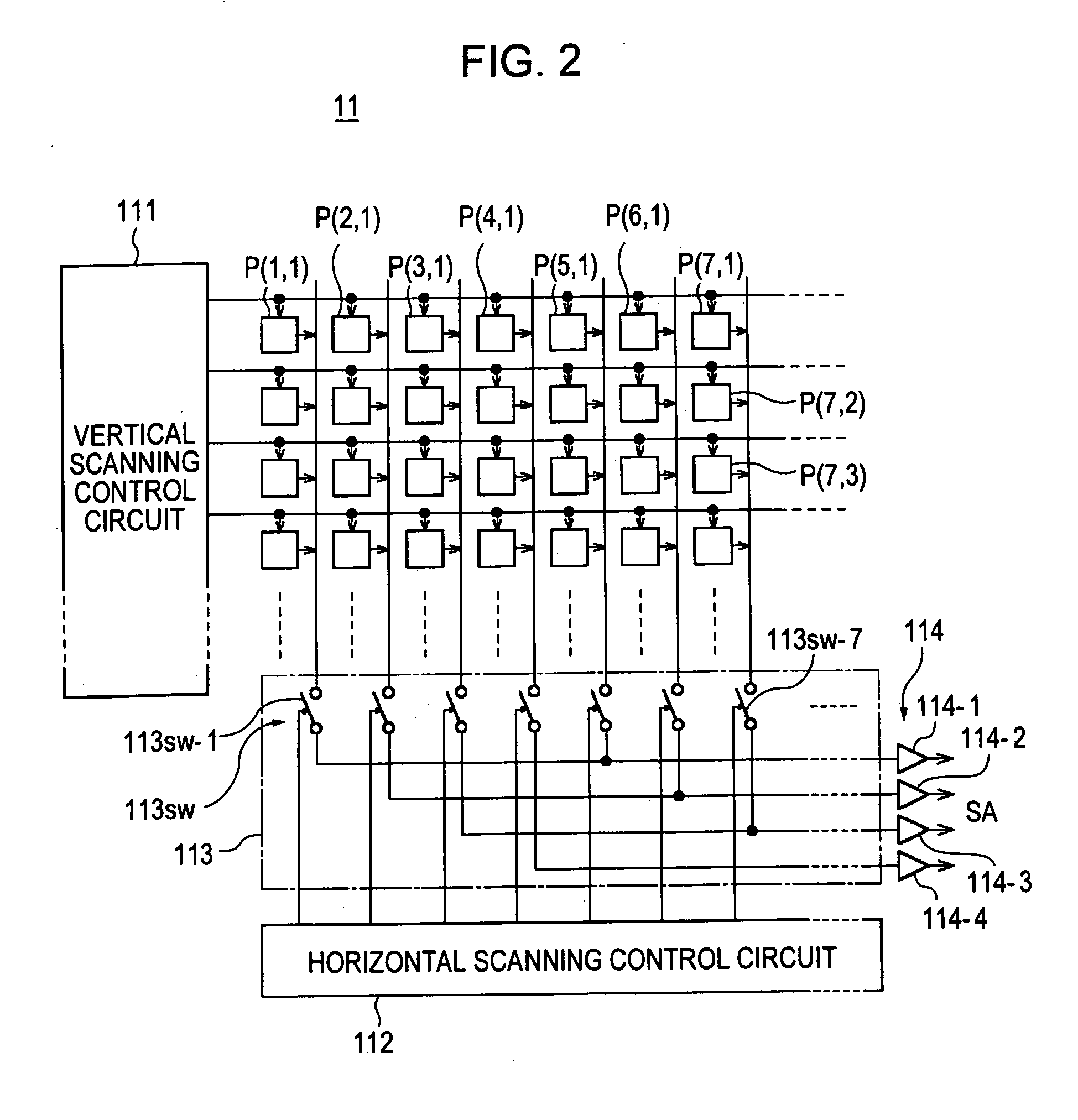

Image pickup apparatus and image pickup method

InactiveUS20060132622A1Easy to readRead rate is decreasedTelevision system detailsColor television detailsDigital imageComputer science

An image pickup apparatus includes an image pickup device generating image signals of picked up images; a converting unit converting the image signals generated by the image pickup device to digital image signals; a memory storing the image signals obtained by the converting unit; and a memory control unit controlling writing the image signals in the memory and reading the image signals from the memory. The memory control unit assigns bands of the memory in order to simultaneously perform writing image signals in the memory and reading the image signals from the memory for displaying picked up images and / or reading the image signals from the memory for recording picked up images at different frame rates.

Owner:SONY CORP

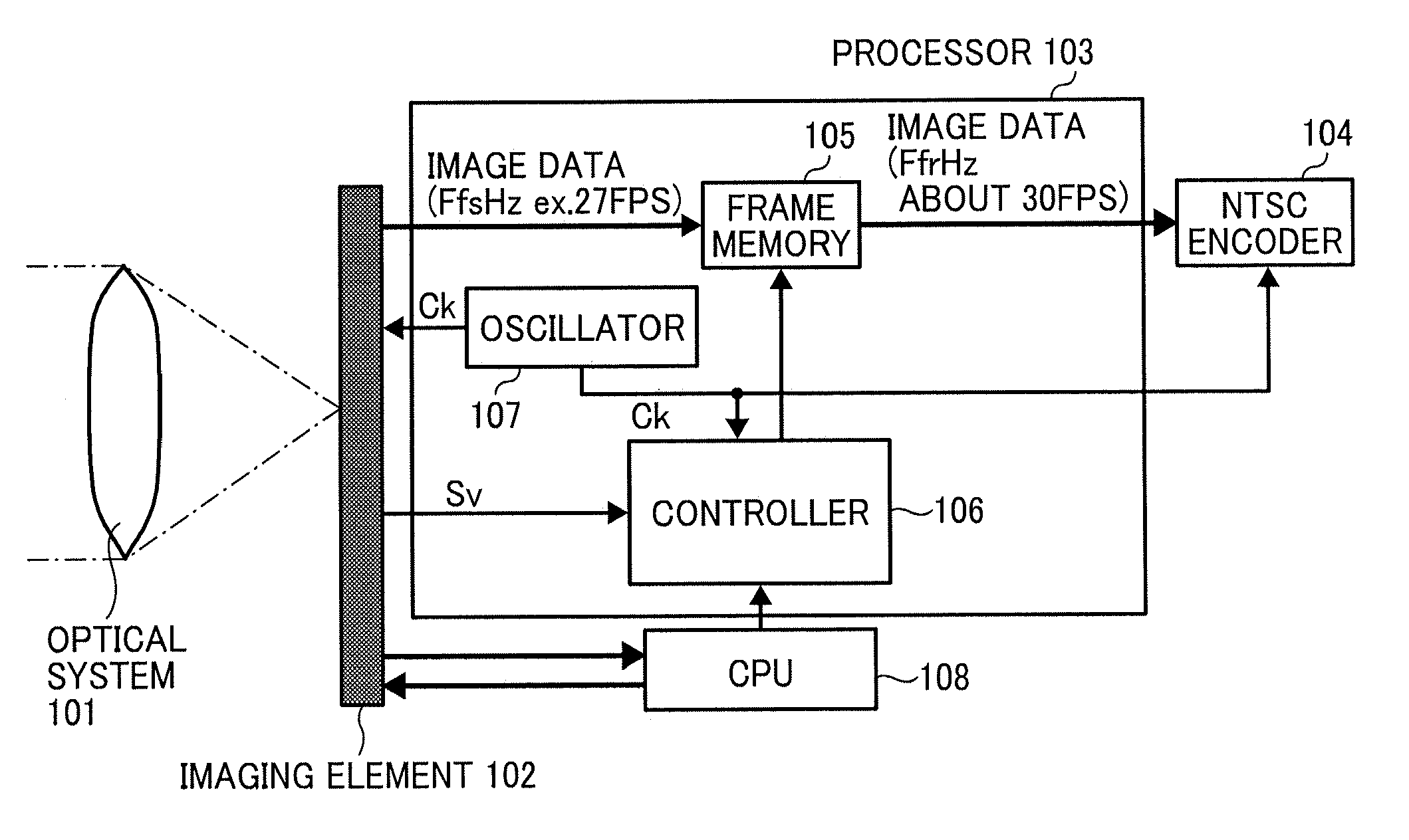

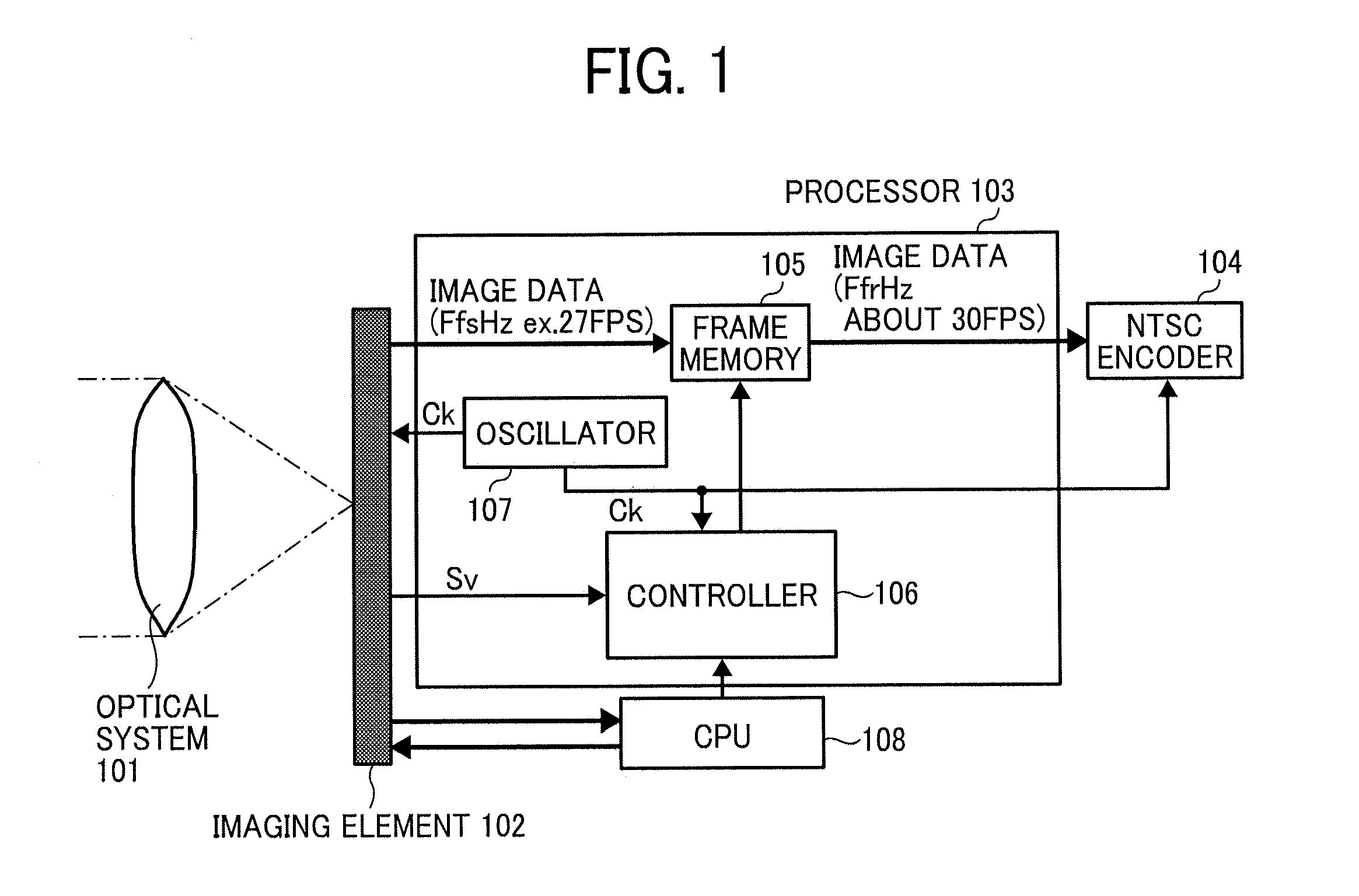

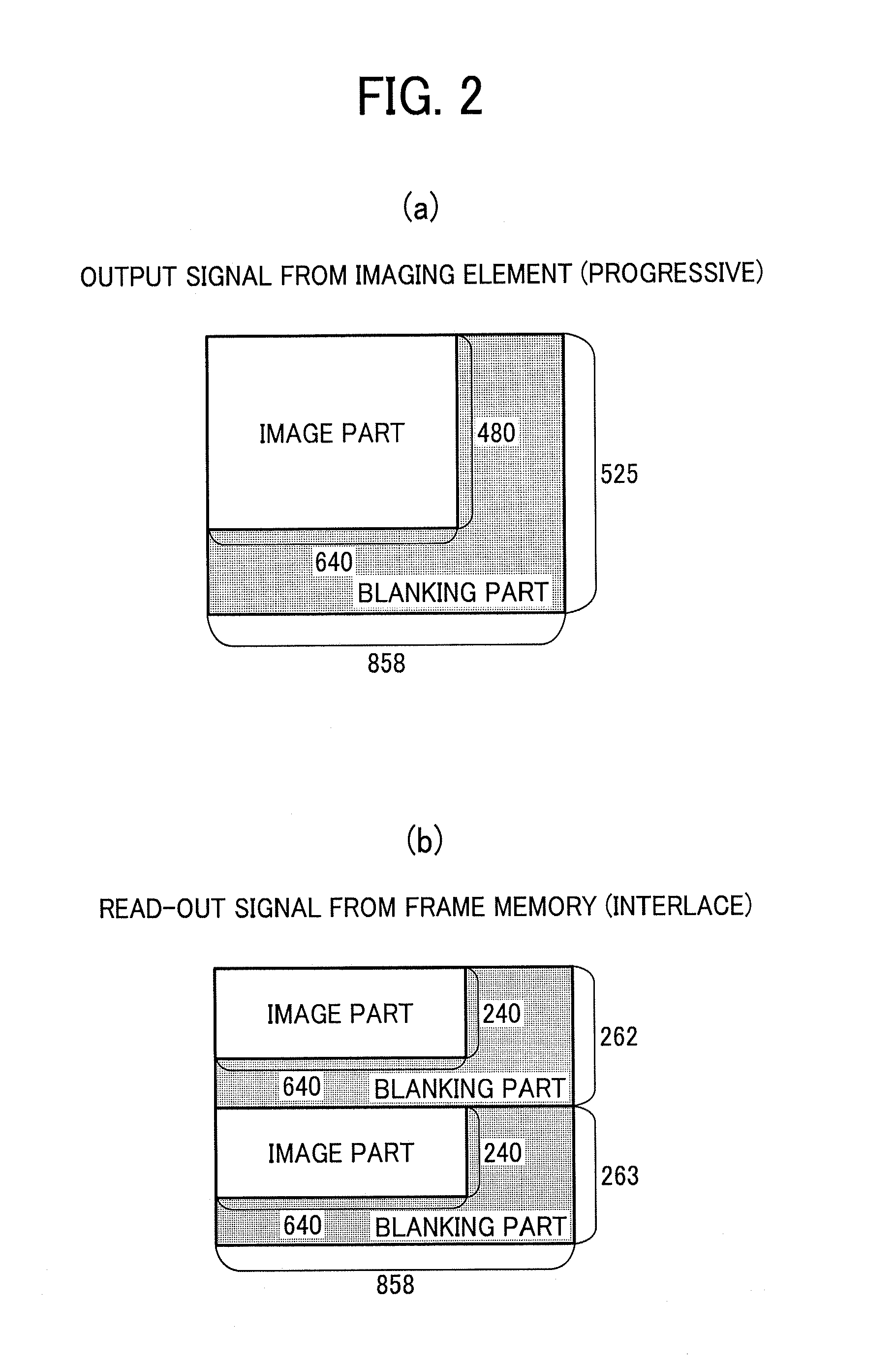

Imaging apparatus

ActiveUS20110128408A1Avoid it happening againSimple configurationTelevision system detailsColor television detailsImaging equipmentImaging data

An imaging apparatus, including an optical system forming an image of an optical image of an object; an imaging element imaging the optical image and producing image data at a frame frequency Ffs out of a frame frequency Ffr of NTSC system; a frame memory storing the image data; and a controller progressively writing the image data in the frame memory and interlacedly reading out the image data from the frame memory at the frame frequency Ffr of NTSC system. The frame memory is divided into at least three areas comprising a writing-in area and a read-out area, wherein the controller sequentially switches the areas of the frame memory and progressively writes one frame of image data in each area and interlacedly reads out one frame of image data from each area in sequence.

Owner:RICOH KK

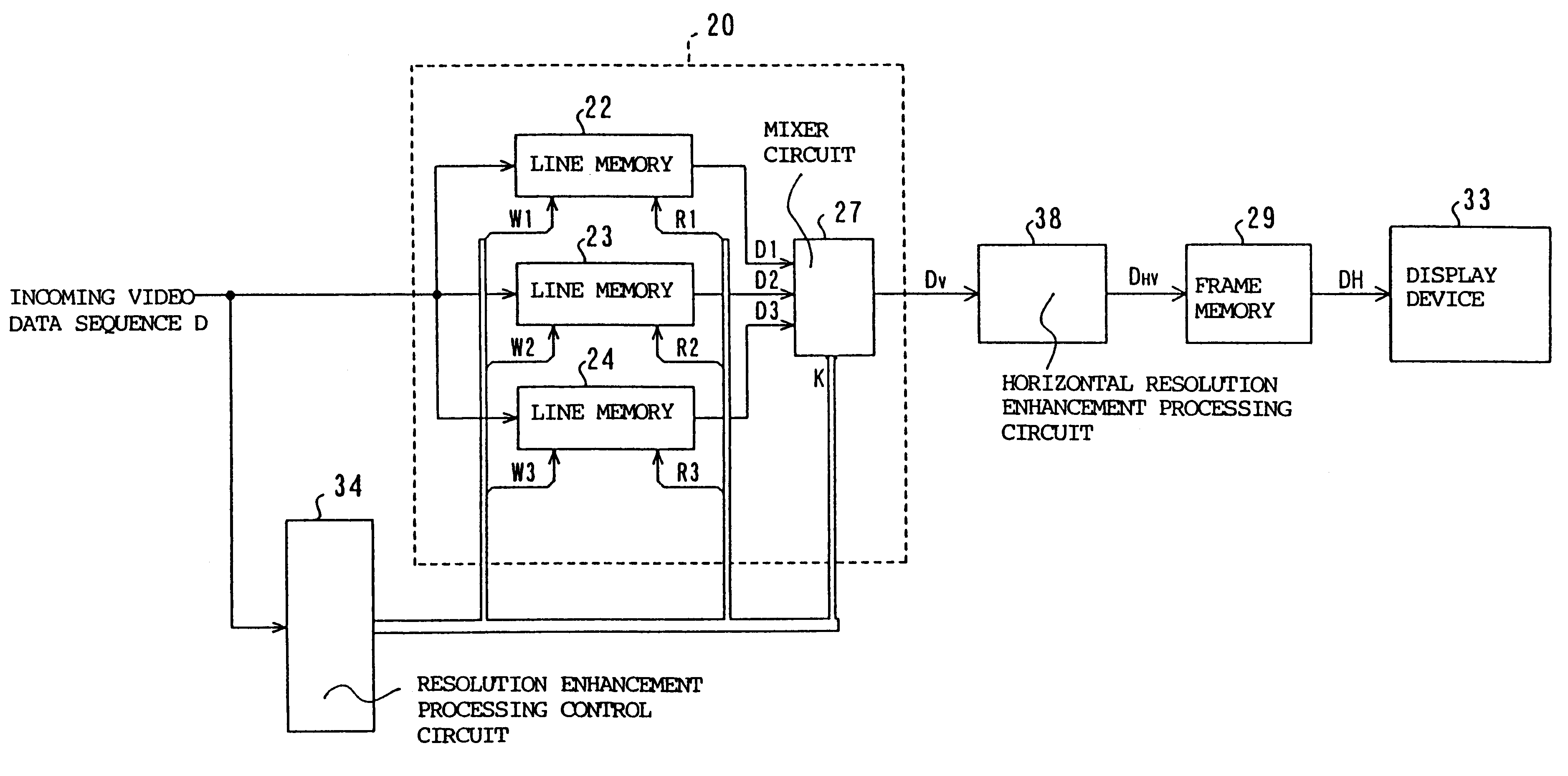

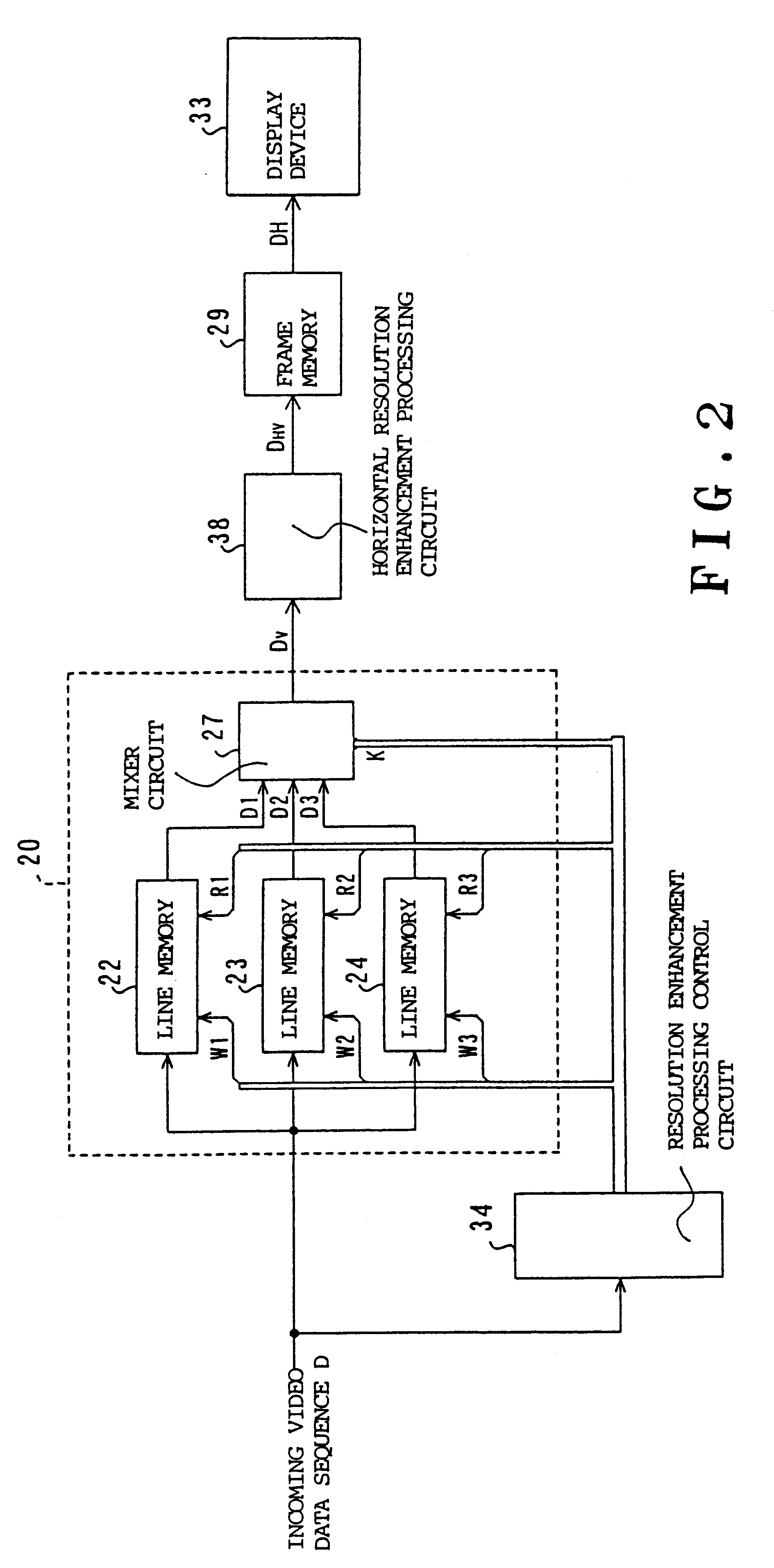

Video signal processing apparatus with resolution enhancing feature

InactiveUS6710810B1High resolutionSmall apparatus scaleTelevision system detailsColor signal processing circuitsPattern recognitionImage resolution

An apparatus for enhancing the resolution of video data in a reduced scale of apparatus, and a video signal processing apparatus for freely setting the number of video data sequences for enhancing the resolution, is created from one horizontal scanning line portion of an incoming video data sequence, without changing the circuit configuration. The resolution enhancement processing apparatus stores every one horizontal line portion of each video data in an incoming video data sequence sequentially in a plurality of memories. A first video data group and a second video data group of horizontal scanning line portion of different scan periods are read repetitively N times within one horizontal scan period. The first video data group and the second video data group are mixed at varying mixing ratios to generate a video data sequence which has the vertical resolution enhanced by a factor of N.

Owner:PANASONIC CORP

Imaging apparatus and imaging method

ActiveUS20050162529A1Television system detailsTelevision system scanning detailsImaging processingImaging equipment

Owner:SONY CORP

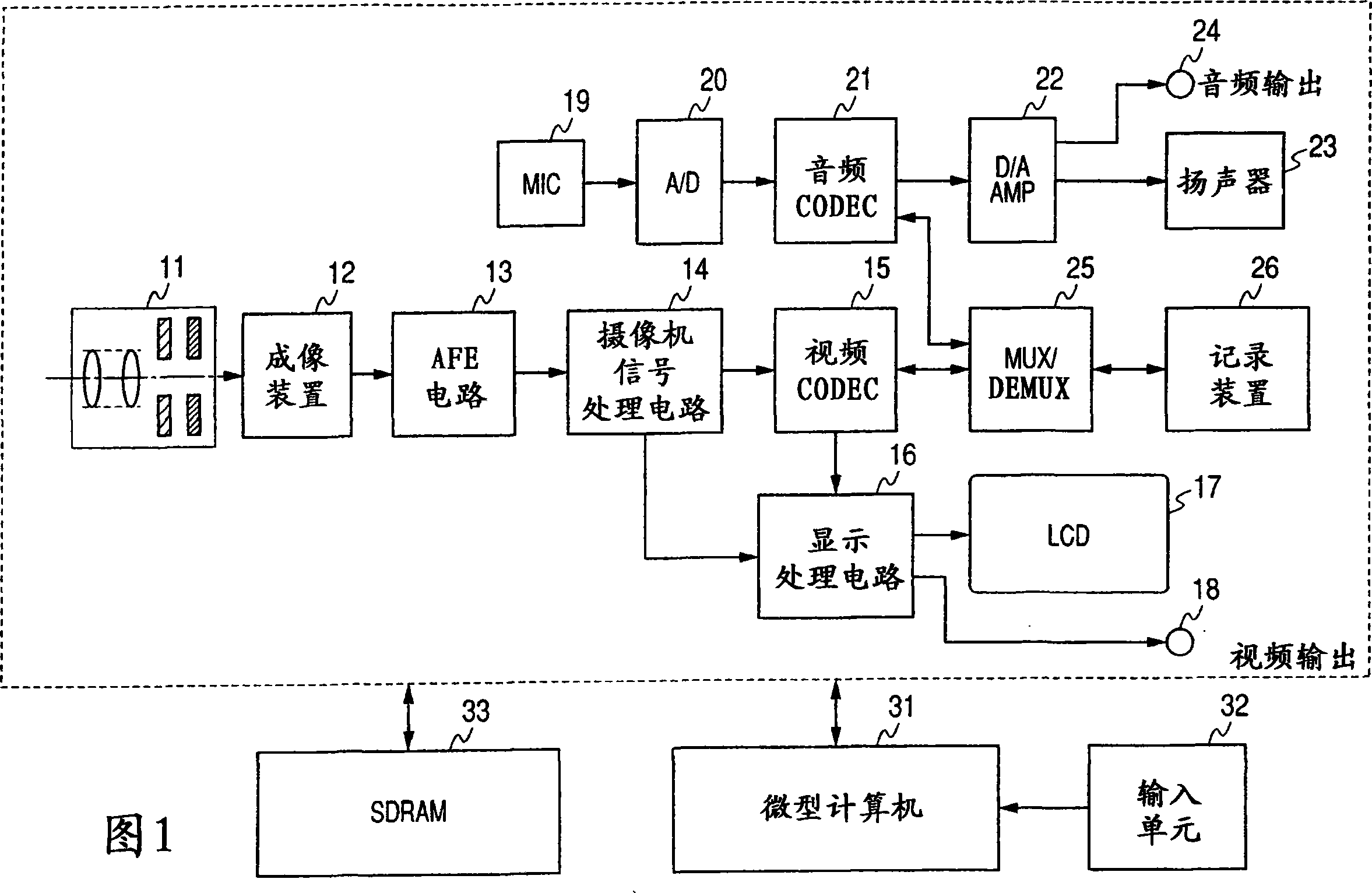

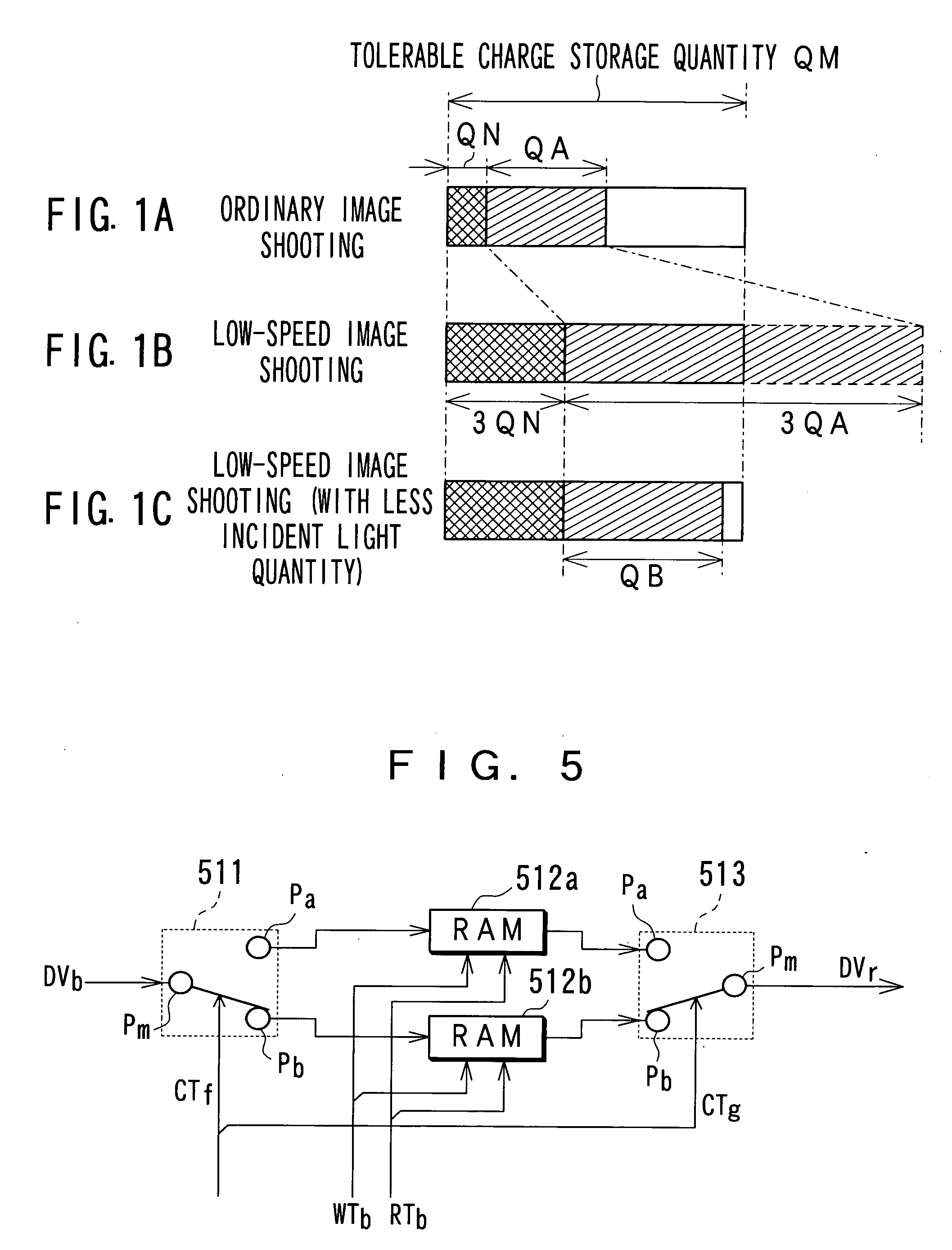

Picture processing apparatus, imaging apparatus and method of the same

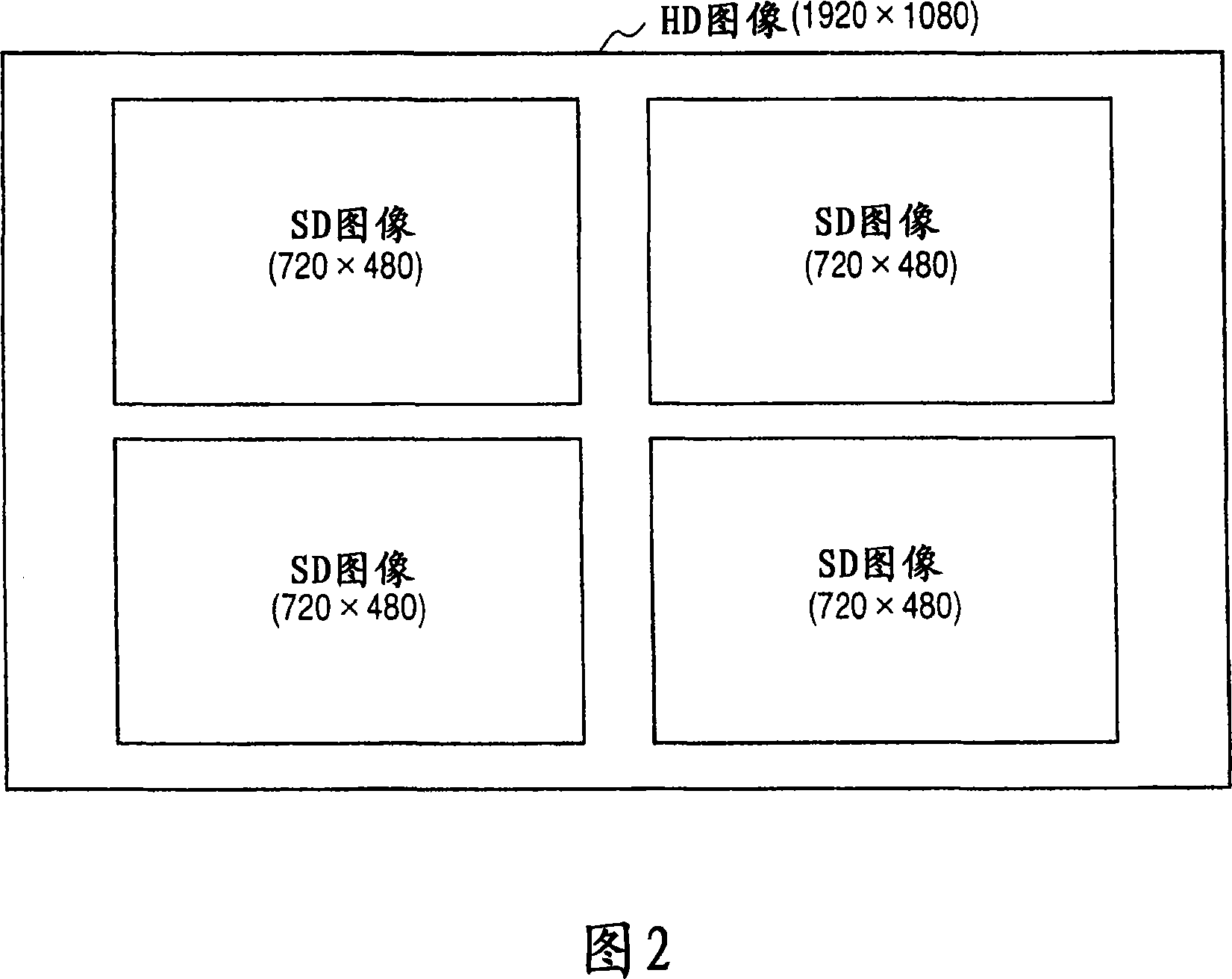

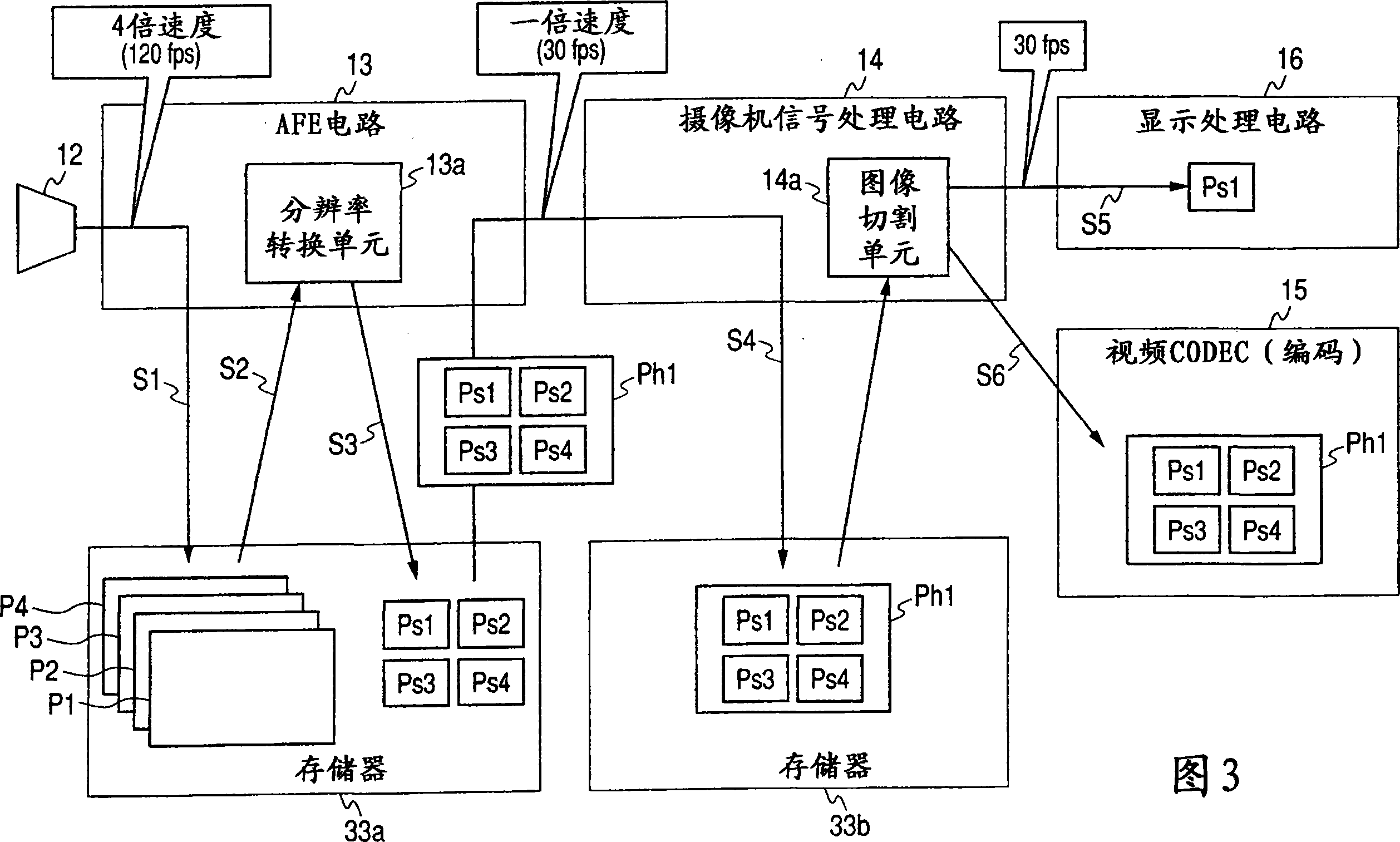

InactiveCN101094322ASuppress manufacturing costTelevision system detailsColor television detailsLow speedComputer graphics (images)

An imaging apparatus which images pictures using a solid-state imaging device includes a picture conversion unit converting pictures imaged at a high-speed screen rate by the solid-state imaging device into a picture in which n-pieces (''n'' is an integer of 2 or more) of continuous imaged pictures are arranged in one screen and outputting the converted picture at a low-speed screen rate which is 1 / n of the high-speed screen rate, a signal processing unit performing predetermined picture-quality compensation processing to the picture from the picture conversion unit, a display picture cutting unit cutting one of n-pieces of imaged pictures from pictures processed by the signal processing unit and outputting the picture at the low-speed screen rate, and a display processing unit generating picture signals for displaying the picture outputted from the display picture cutting unit at a display device.

Owner:SONY CORP

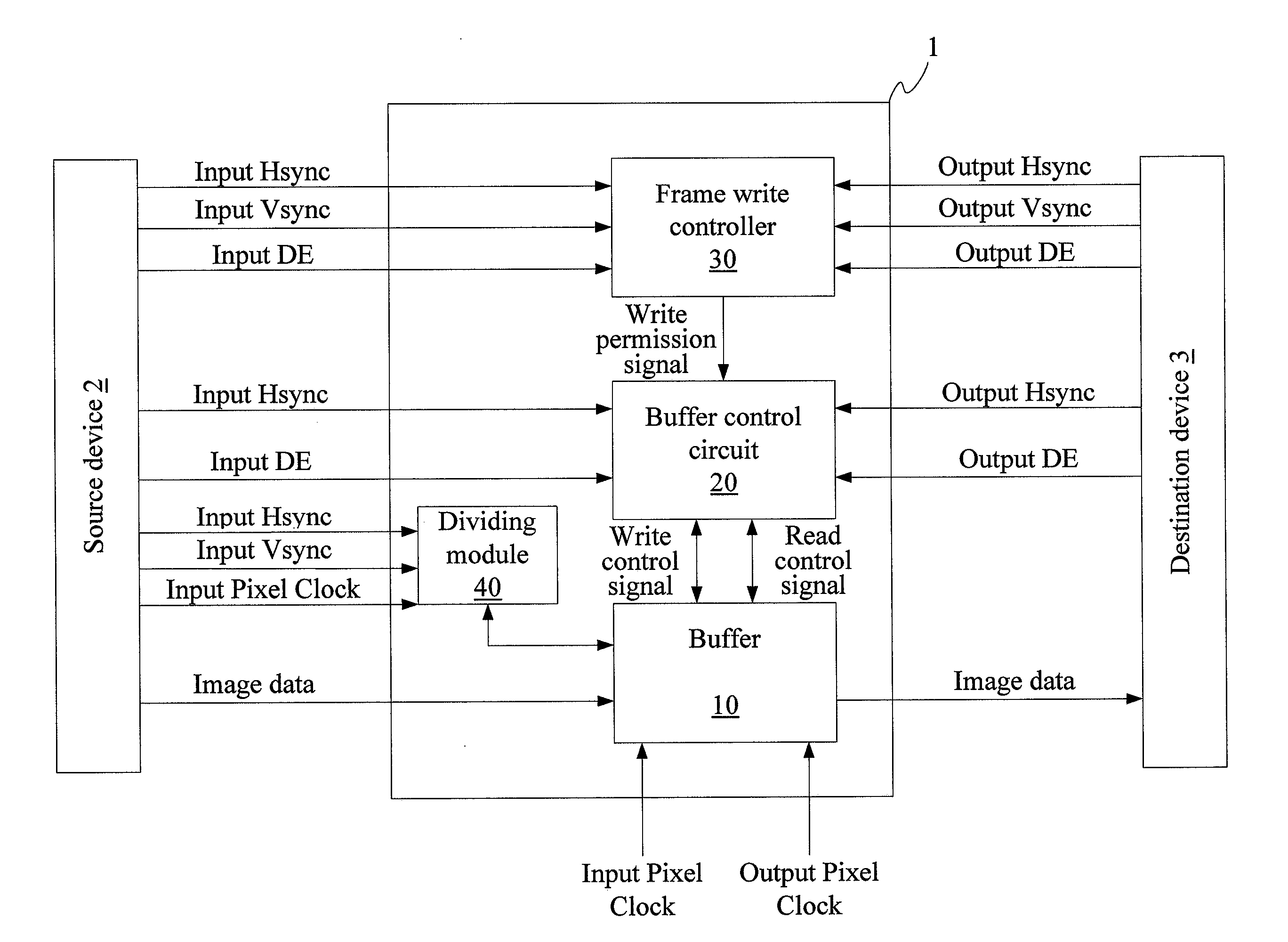

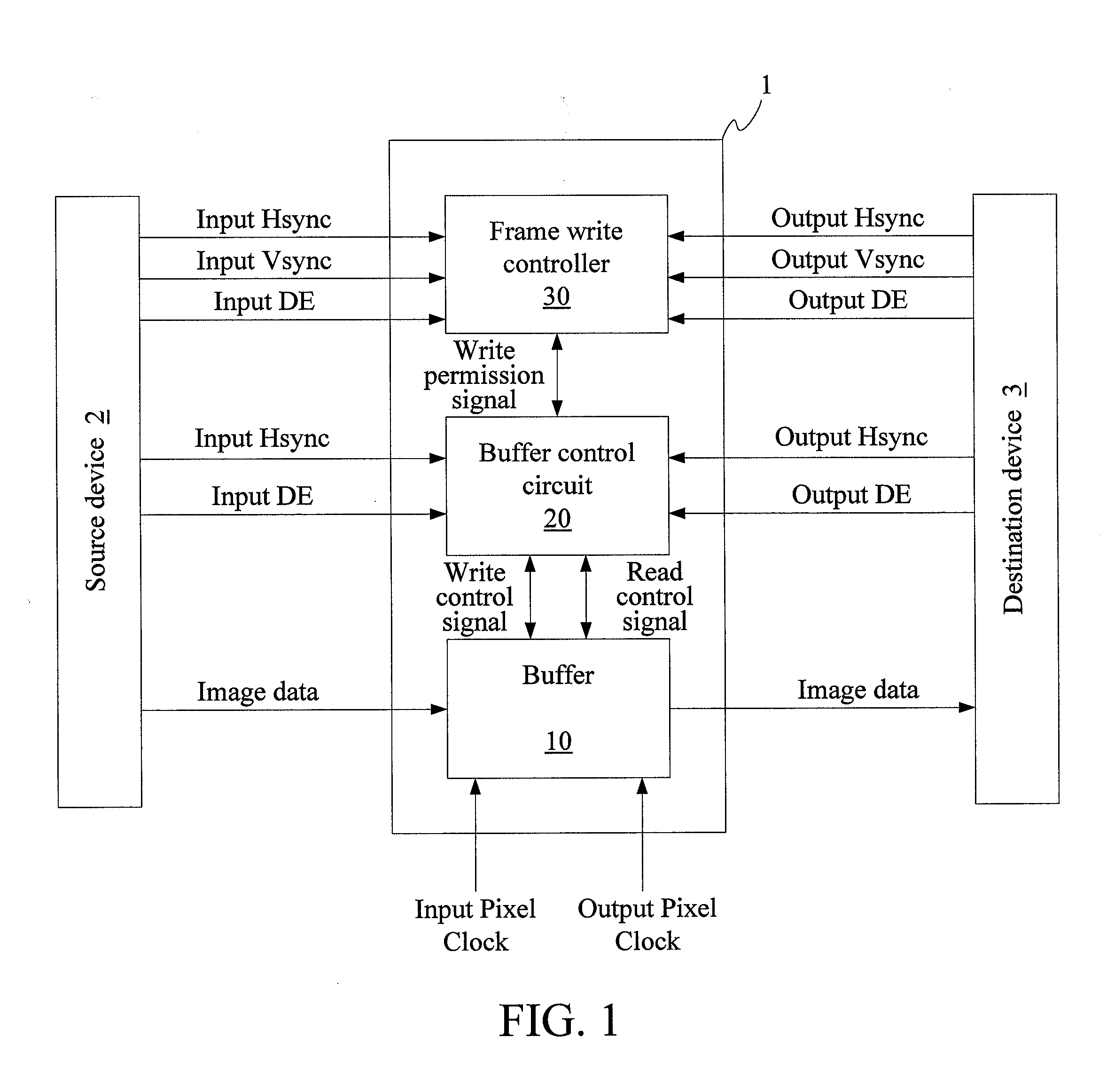

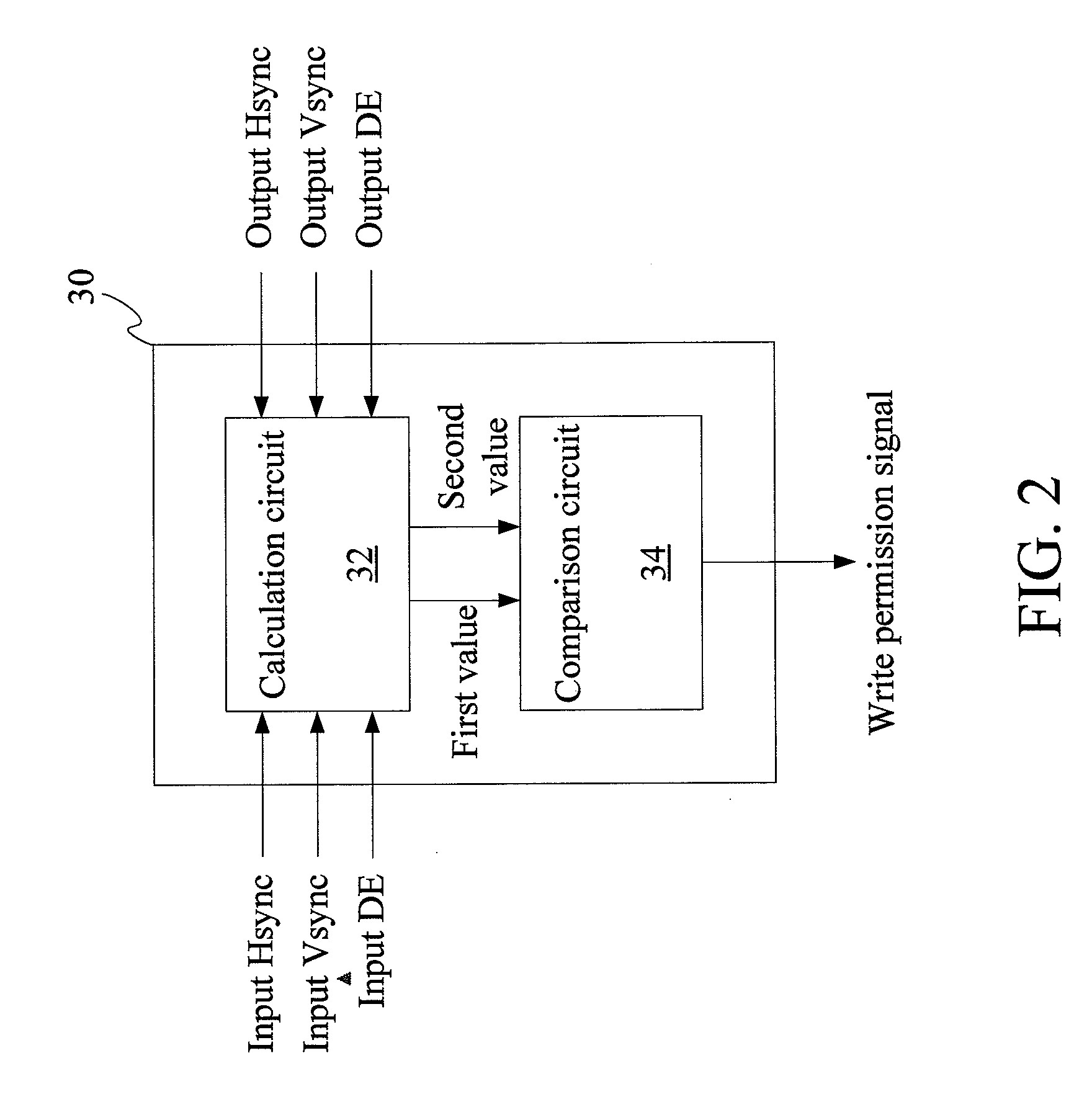

Device and method for controlling frame input and output

ActiveUS20100188574A1Effectively alleviatedTelevision system detailsPicture reproducers using cathode ray tubesComputer hardwareControl signal

A device and method for controlling frame input and output are applied to the reception of image data from a source device and output of the image data to a destination device, the device includes a buffer, a buffer control circuit, and a frame write controller. The input pixel clock is not equal to the output pixel clock. The frame write controller generates a write permission signal according to the Input DE and the Output DE. The buffer control circuit generates a write control signal according to the Input DE and the write permission signal, and generates a read control signal according to the Output DE. The buffer receives the image data from the source device according to the write control signal and the input pixel clock, and outputs the image data to the destination device according to the read control signal and the output pixel clock.

Owner:REALTEK SEMICON CORP

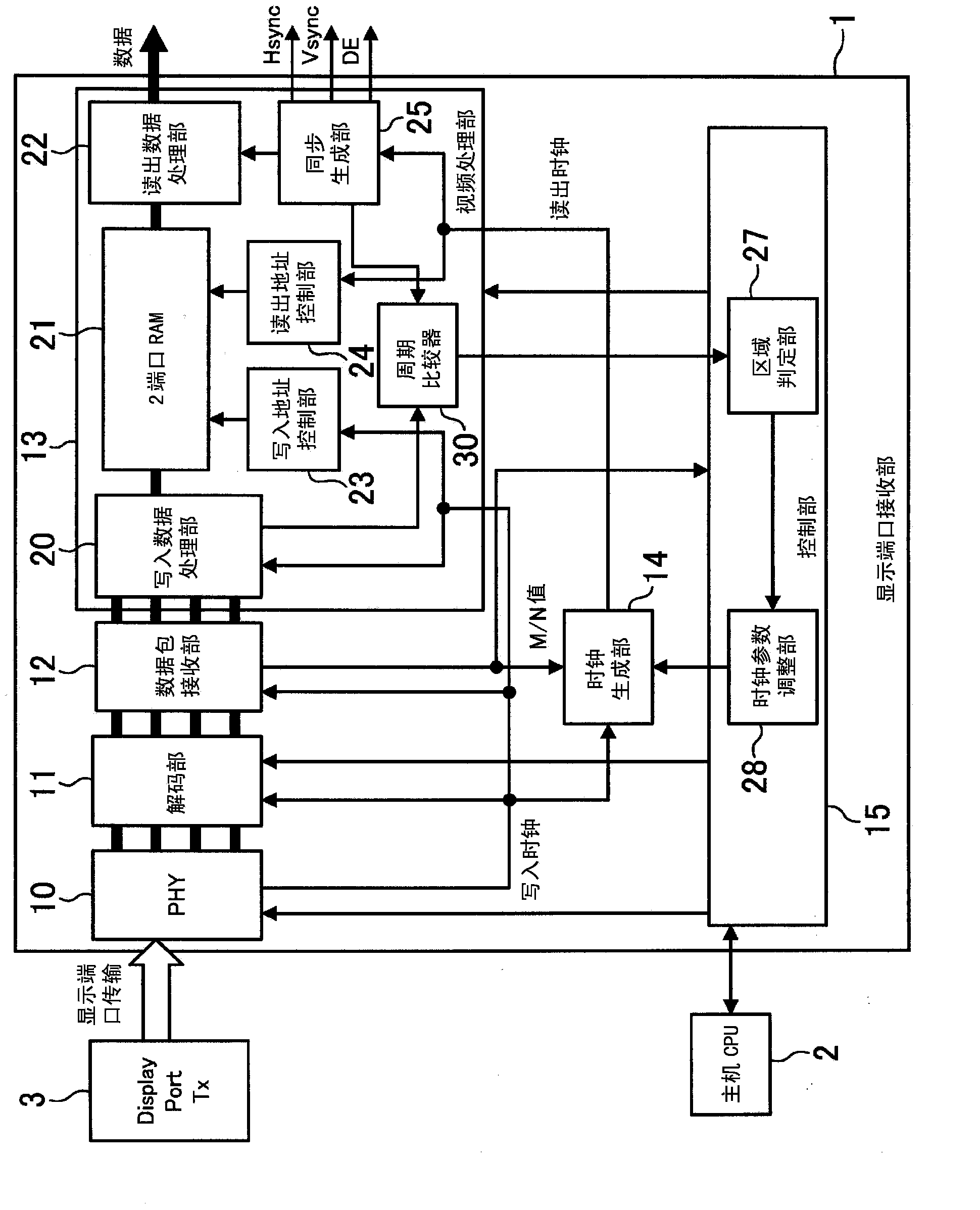

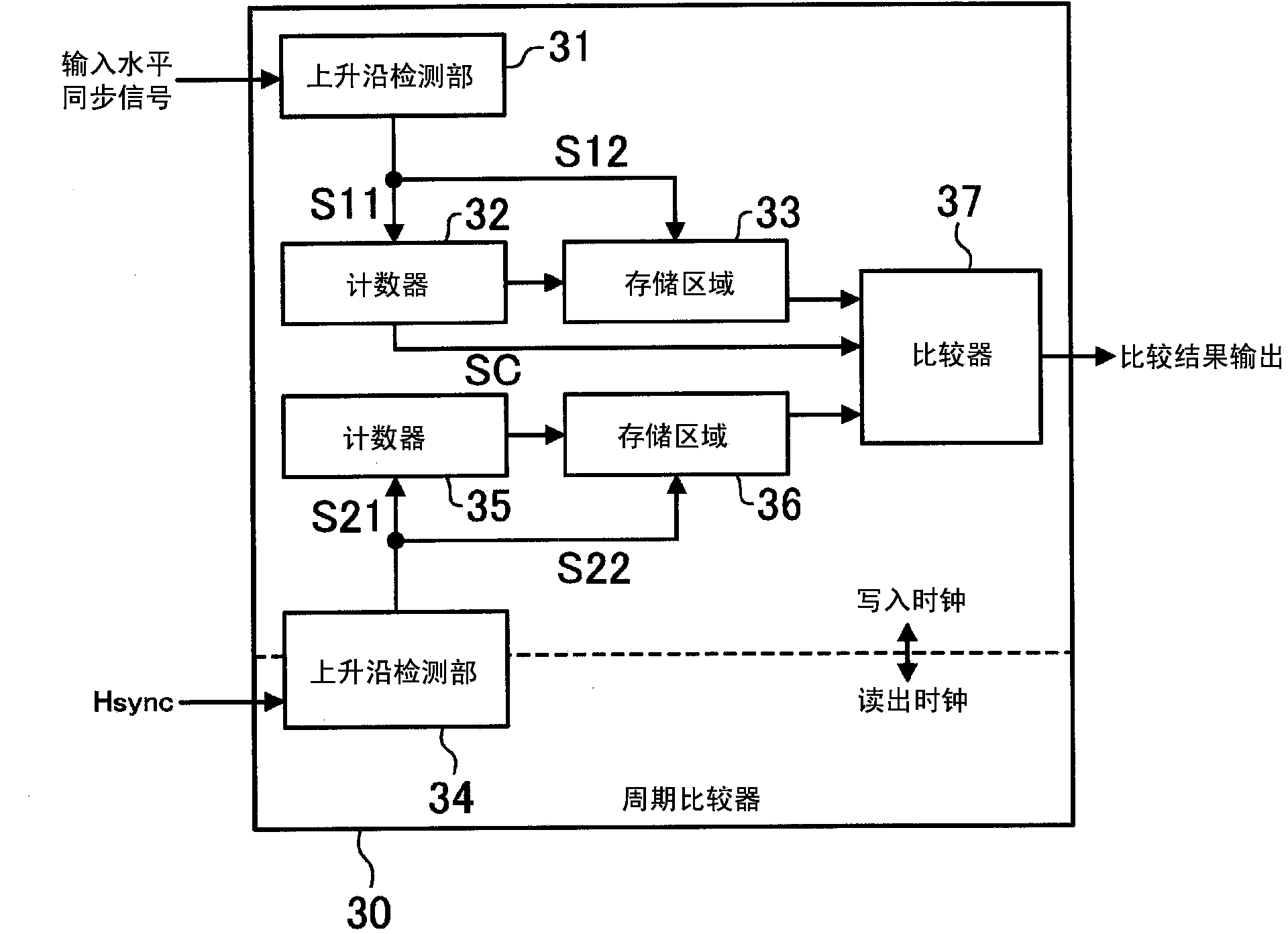

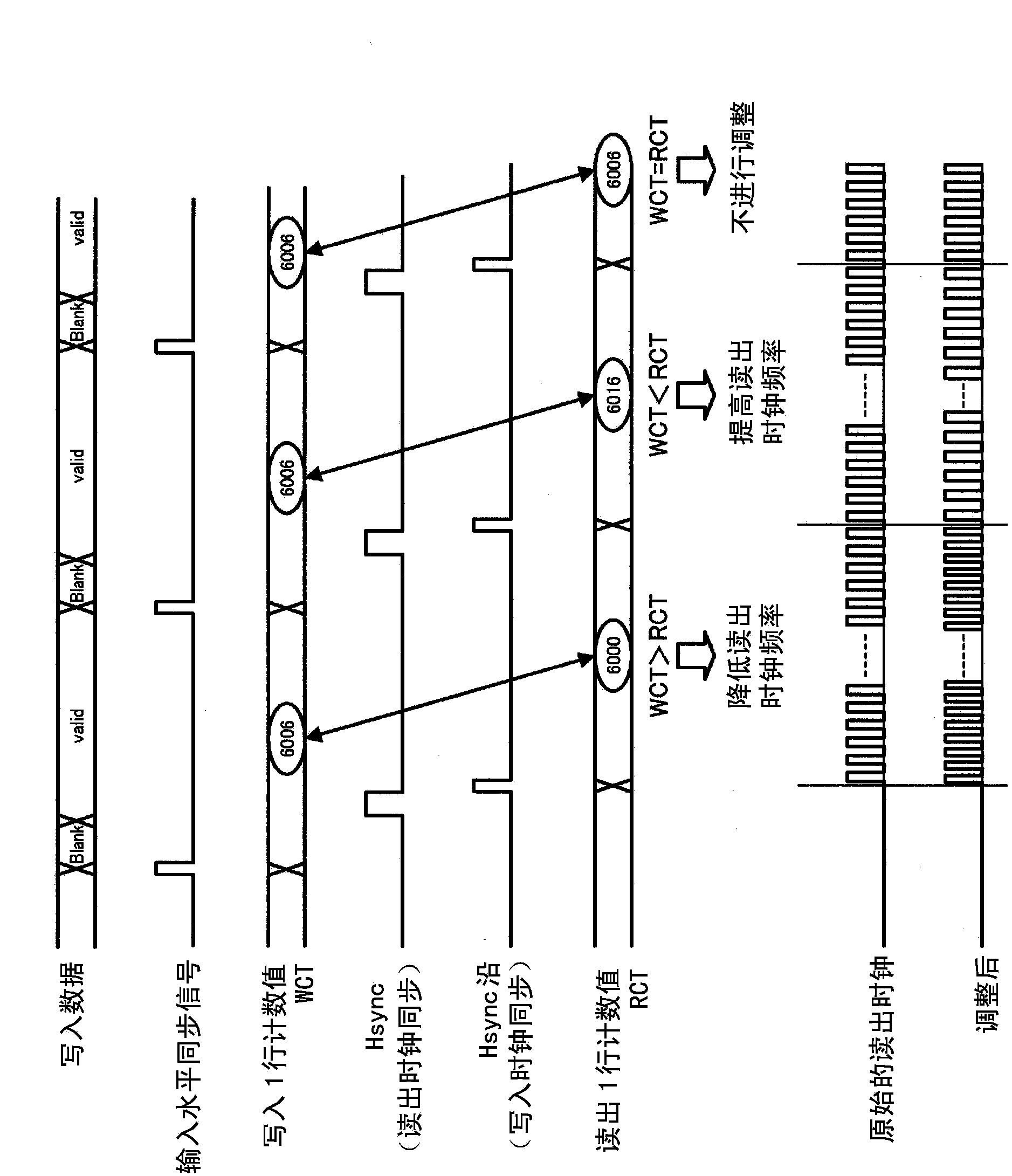

Clock transfer circuit, video processing system, and semiconductor integrated circuit

ActiveCN104380650ASmall sizeAvoid quality lossTelevision system detailsCathode-ray tube indicatorsImaging processingVideo processing

A clock transfer circuit receives input data synchronized with a first clock and outputs the received input data as output data synchronized with a second clock having a different frequency. A write address control unit (23) operates in synchronization with the first clock and supplies a write address to a memory (21). A read address control circuit (24) operates in synchronization with the second clock and supplies a read address to the memory (21). A frequency comparator (30) compares the input data with the output data in the frequency of a predetermined event. Based on this comparison result, clock adjustment units (14, 15) adjust the frequency of the second clock.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

Picture processing apparatus, imaging apparatus and method of the same

InactiveUS20070296826A1Suppress manufacturing costMiniaturizationTelevision system detailsColor television detailsLow speedComputer graphics (images)

An imaging apparatus which images pictures using a solid-state imaging device includes a picture conversion unit converting pictures imaged at a high-speed screen rate by the solid-state imaging device into a picture in which n-pieces (“n” is an integer of 2 or more) of continuous imaged pictures are arranged in one screen and outputting the converted picture at a low-speed screen rate which is 1 / n of the high-speed screen rate, a signal processing unit performing predetermined picture-quality compensation processing to the picture from the picture conversion unit, a display picture cutting unit cutting one of n-pieces of imaged pictures from pictures processed by the signal processing unit and outputting the picture at the low-speed screen rate, and a display processing unit generating picture signals for displaying the picture outputted from the display picture cutting unit at a display device.

Owner:SONY CORP

Method and device for bridging different video formats

InactiveCN1487739ASemiconductor/solid-state device detailsSolid-state devicesUnit sizeComputer science

The video format bridging device has no overflow and underflow and output frame rate matched with input frame rate ensured via several technological measures. The bridging device can settle residual line problem and input and output pulse frequency variation problem, and can regulate the ratio between the input and output line numbers each frame and ratio between the input and output pixel numbers each line within the output unit size. One single IC is provided for several technological aims, including enabling or disabling some specific bridging operation. The bridging logic produces serial output video signal flow in the output frame rate matching with the input frame rate, and the output frames have at least one frame with lines having different pixels and / or one set of several frame with different line numbers.

Owner:MAGIC PIXEL

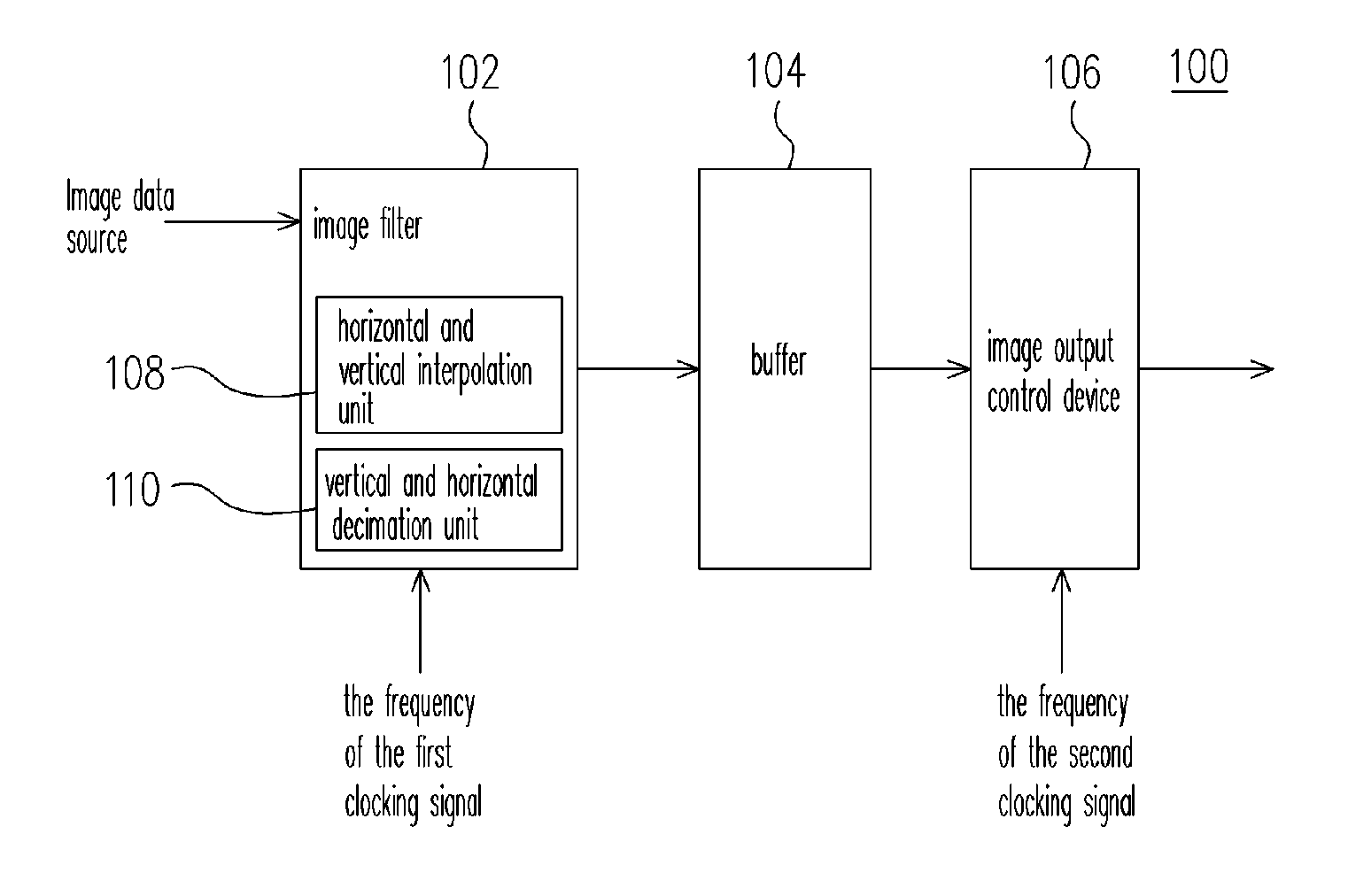

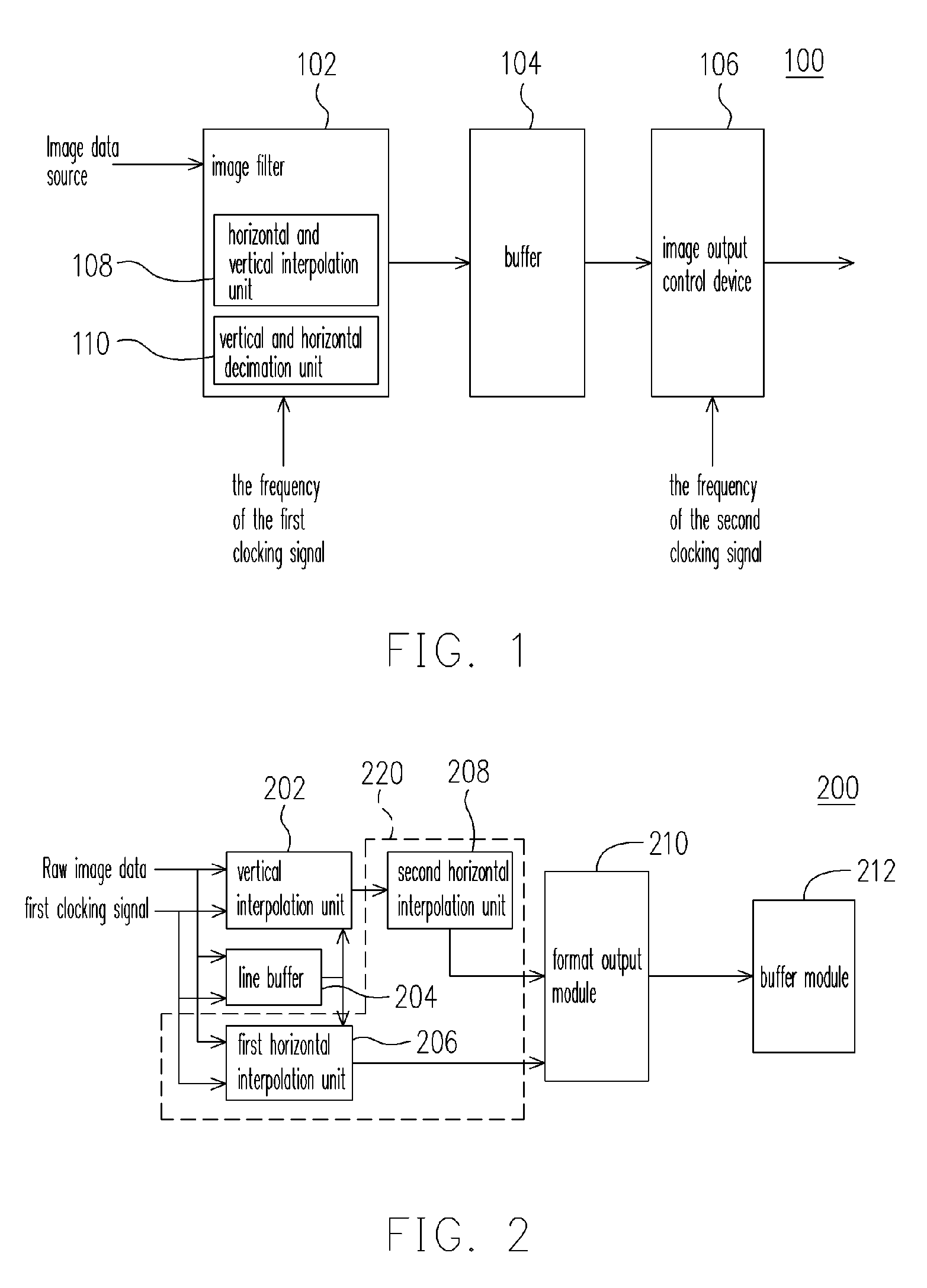

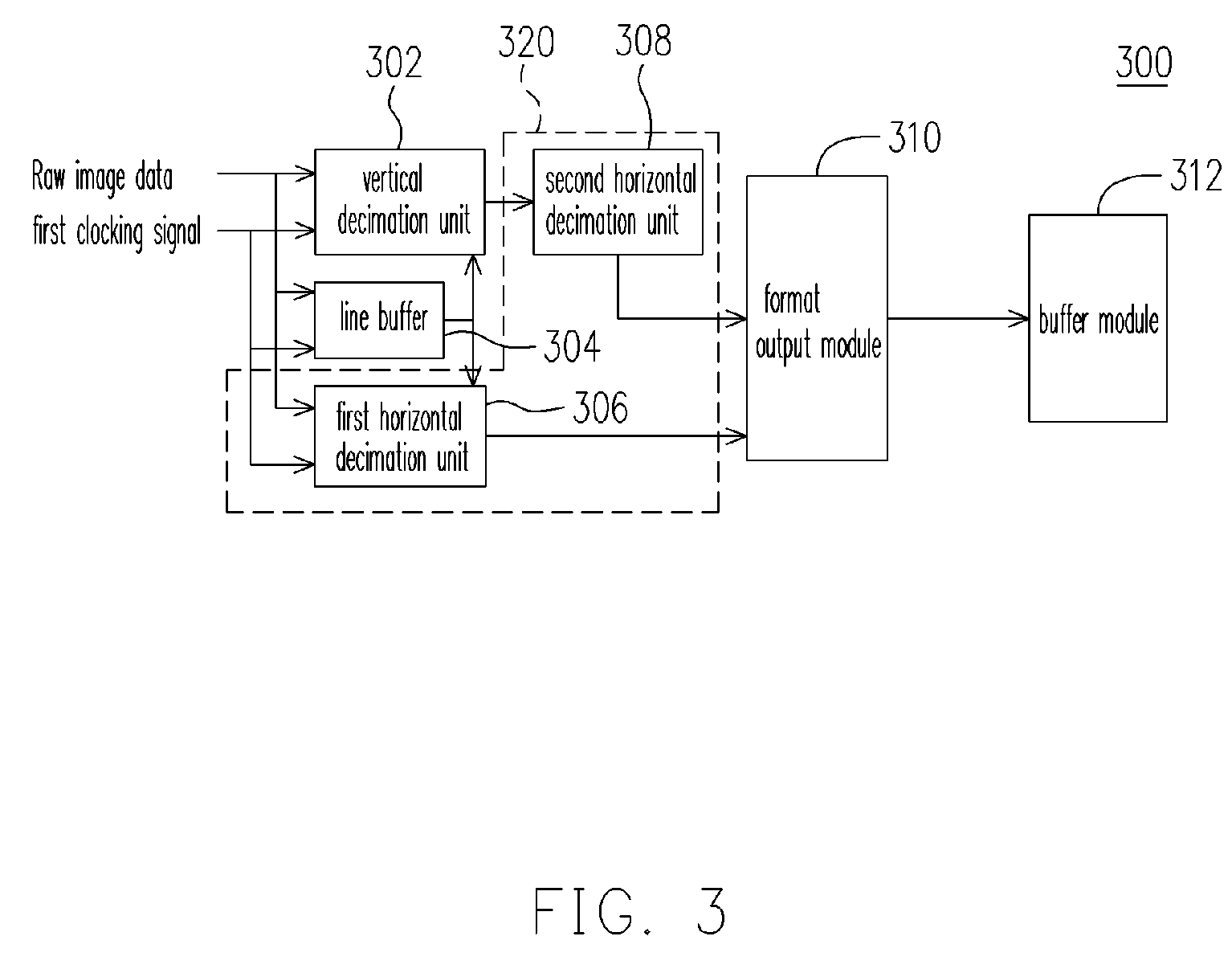

Synchronous image-switching device and method thereof

InactiveUS20060077201A1Reduce power consumptionReduce operating frequencyCathode-ray tube indicatorsConversion with storage device usageClock rateSource image

A synchronous image-switching device and switching method thereof are provided. The synchronous image-switching device comprises an image filter for generating target image data according to the frequency of a first clocking signal, a buffer for holding the target image and an image output control device for outputting the target image according to the frequency of a second clocking signal. Because the synchronous switching device of the present invention allows the clocking frequency of the source image to be different from that of the target image, images can be switched synchronously and power consumption of the switching operation can be reduced.

Owner:BEYOND INNOVATION TECH

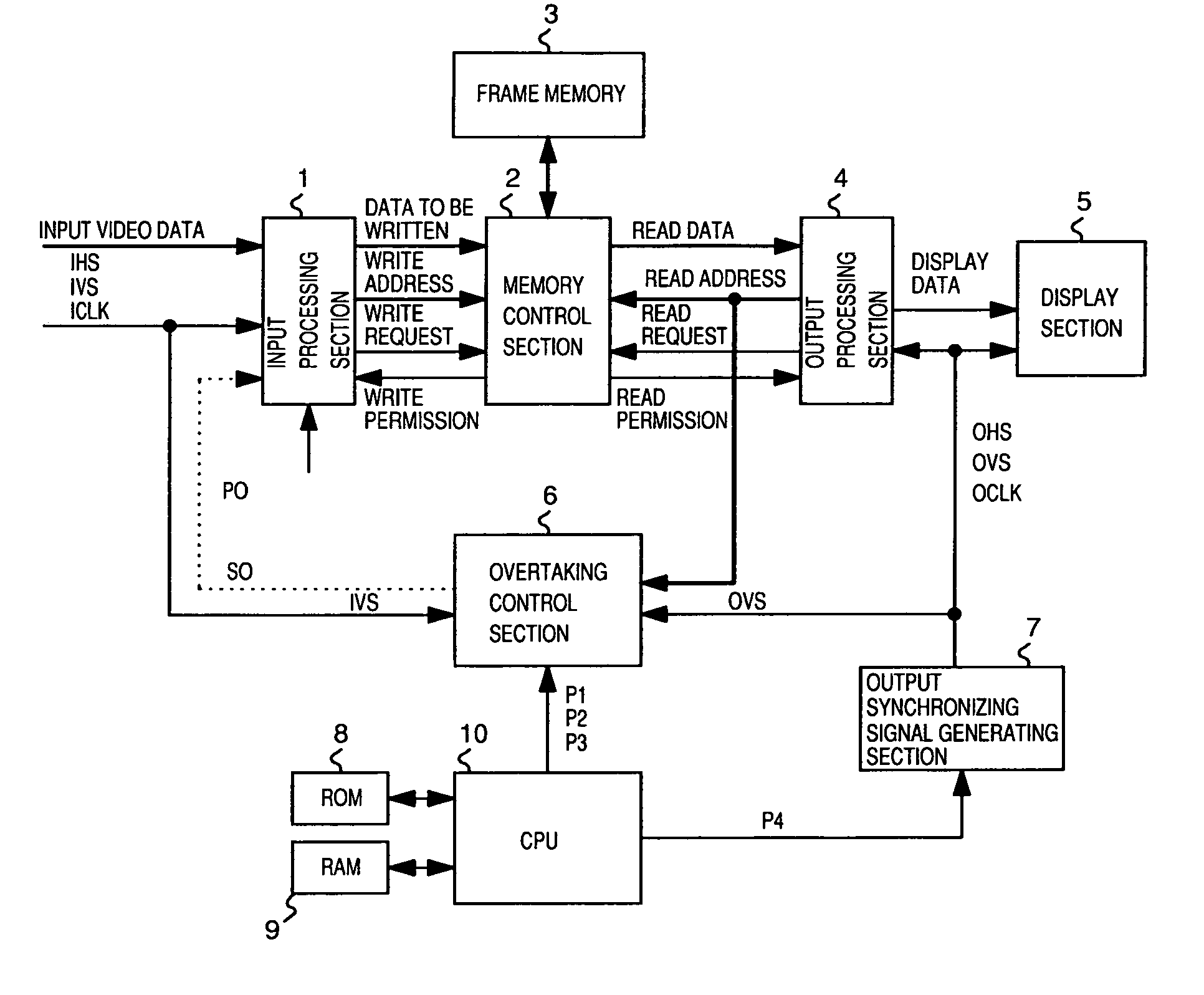

Frame rate conversion device, overtaking prediction method for use in the same, display control device and video receiving display device

InactiveUS7336317B2Improve accuracyAvoid interferenceTelevision system detailsPulse modulation television signal transmissionComputer hardwareDisplay device

An overtaking prediction method of, when input and output of data to and from a common memory are being performed with an input frame frequency and an output frame frequency made different from each other, predicting a frame in which overtaking occurs between the input and the output of the data to and from the memory. The overtaking prediction method includes a step of predicting the frame in which the overtaking occurs between the input and the output of the data, on the basis of a first parameter corresponding to a difference amount between a progress speed of a write address and a progress speed of a read address and a second parameter corresponding to a difference between a write address and a read address at an overtaking prediction point and to an offset address difference amount between an input offset address and an output offset address.

Owner:CANON KK

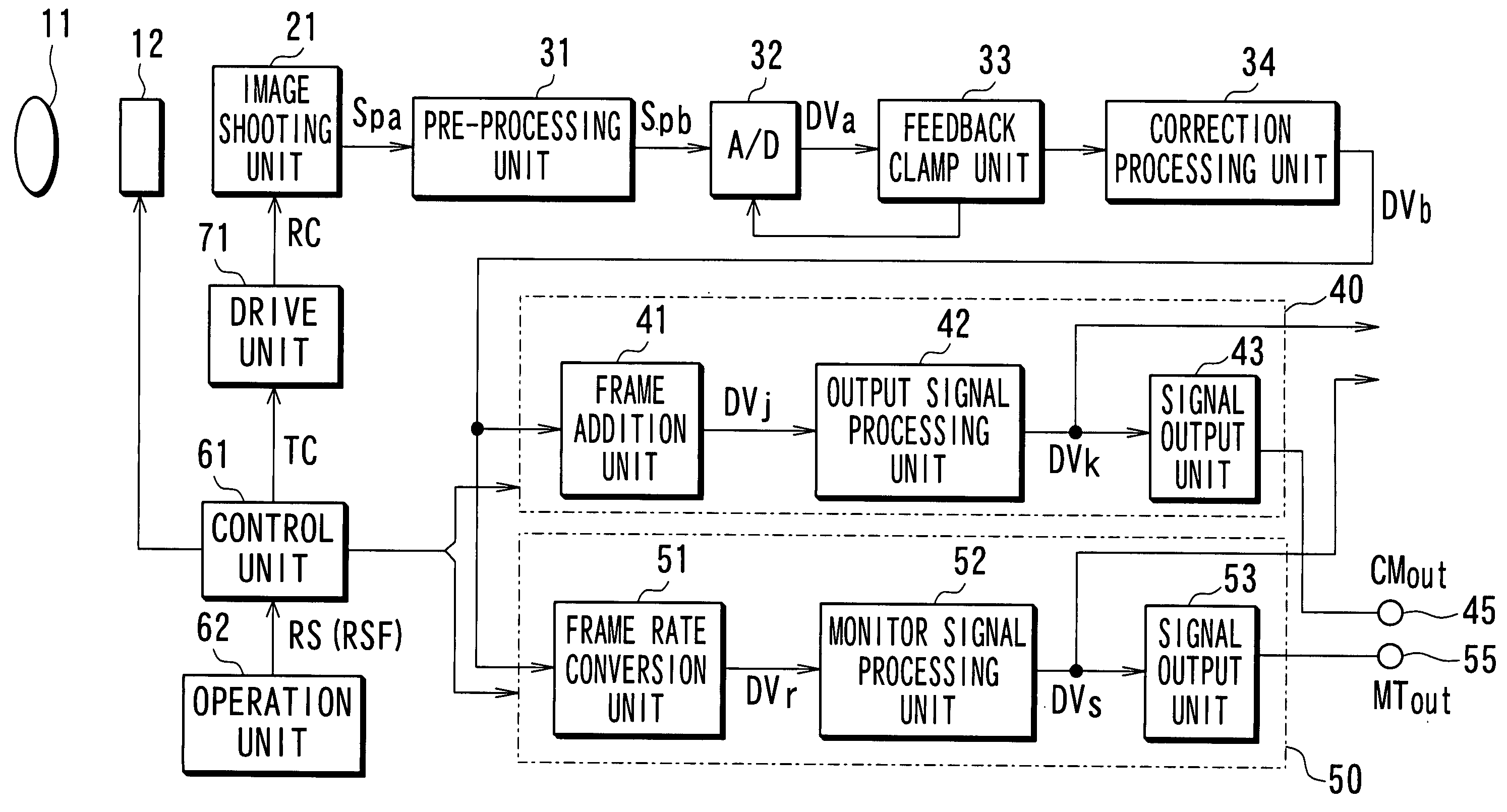

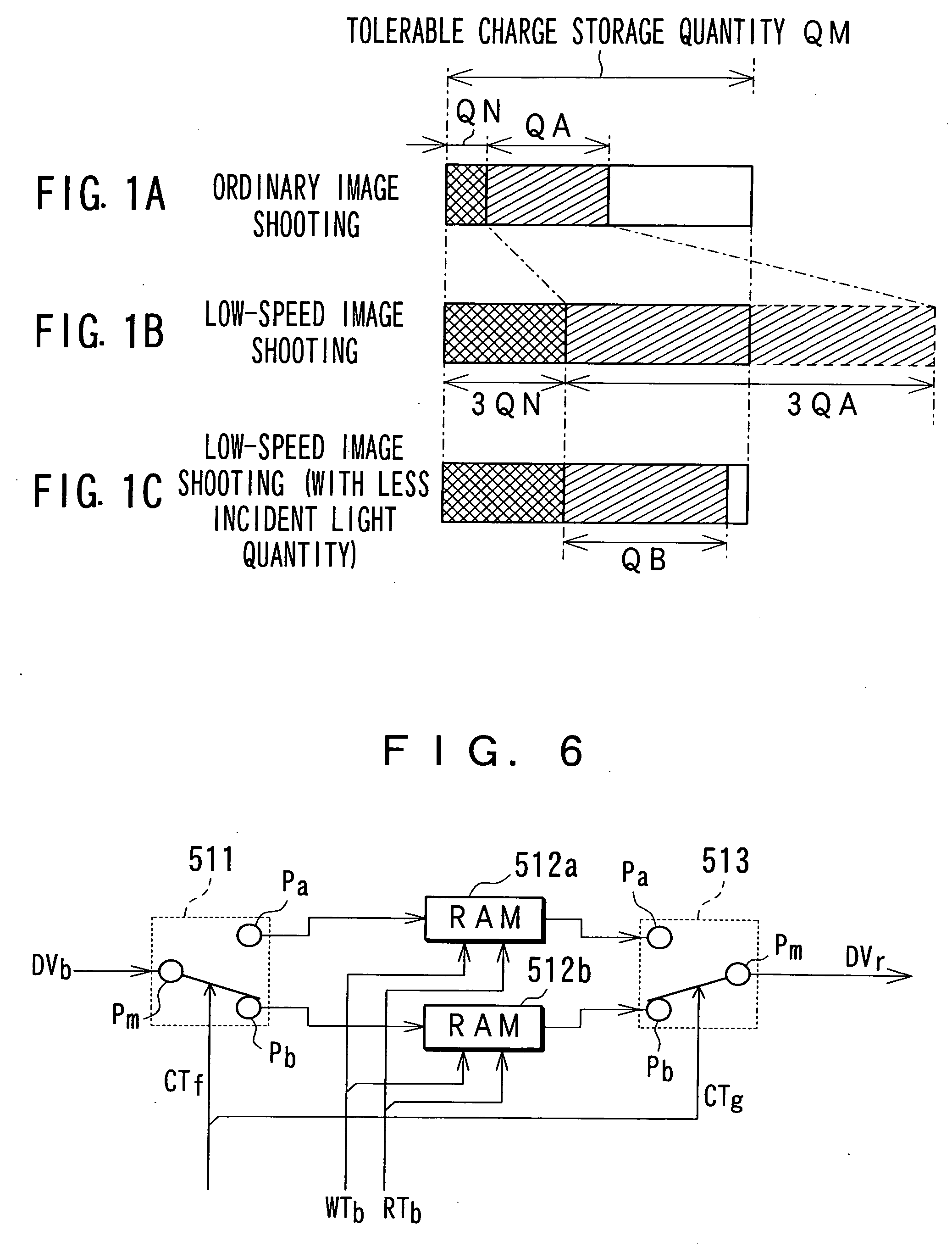

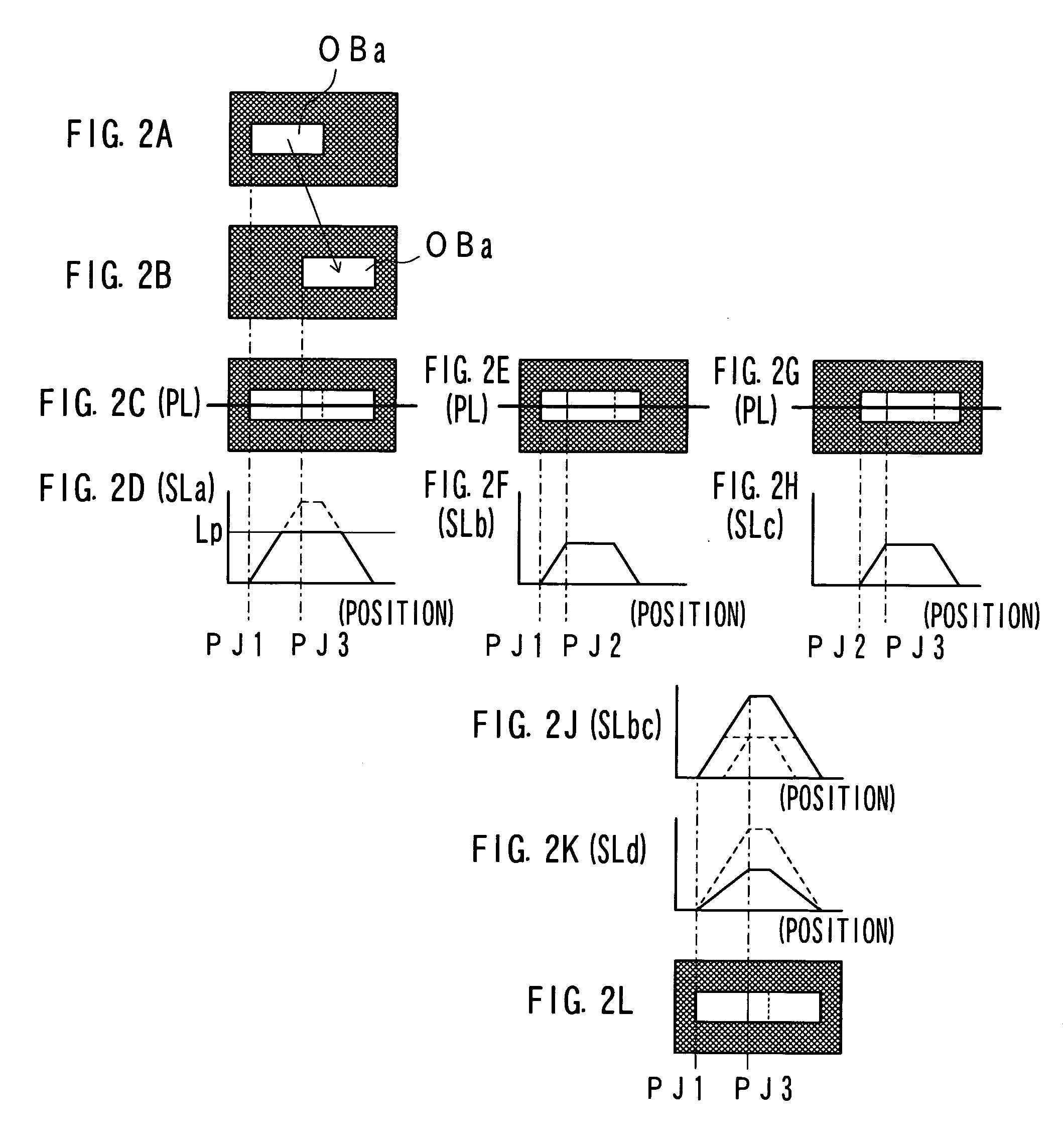

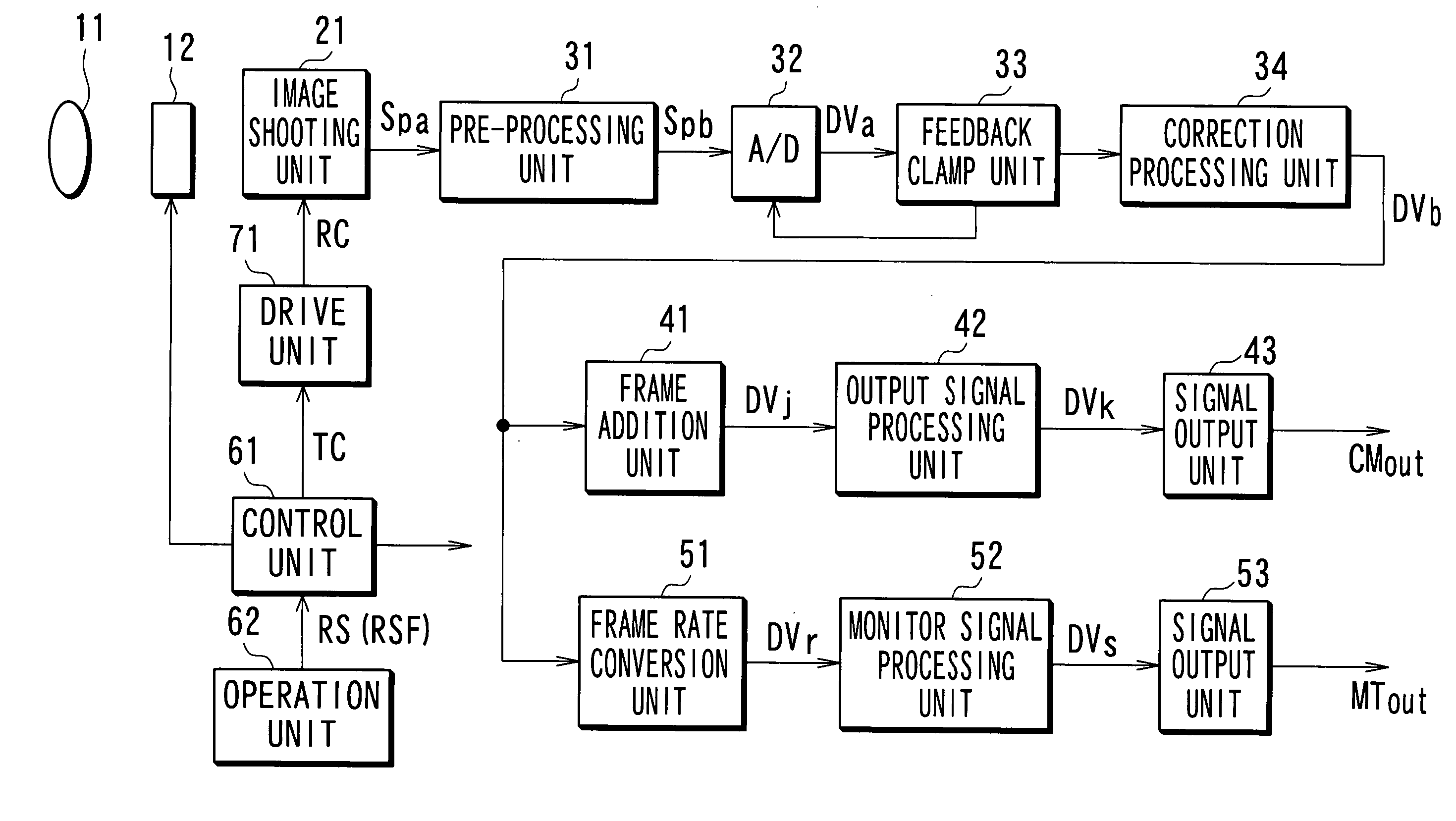

Imaging apparatus and imaging method

ActiveUS20050012827A1Restriction of variation rangeTelevision system detailsTelevision system scanning detailsLow speedImaging equipment

An image shooting unit 21 generates an image signal Spa having an image shooting frame rate. A frame addition unit 41 performs frame addition on the image signal DVb having the image shooting frame rate. Control unit 61 controls drive unit 71 and the frame addition unit 41 based on a frame rate setting signal RSF from operation unit 62, and controls a variation of the image shooting frame rate in image shooting unit 21 and / or a switch of the number of additive frames in the frame addition unit 41, thus allowing an image signal DVj having a desired frame rate to be output from the frame addition unit 41. Thus, increasing the additive frame in number even without decreasing the image shooting frame rate at a low-speed shooting of the image allows such an image signal DVj shot at the low speed to be obtained.

Owner:SONY CORP

Popular searches

Surgery Endoscopes Picture reproducers using projection devices Picture reproducers using solid-state color display Closed circuit television systems Color motion picture films scanning Signal generator with optical-mechanical scanning Television with combined individual color signal Building rescue Conversion involving interpolation processes

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com