Clock transfer circuit, video processing system, and semiconductor integrated circuit

A clock conversion and circuit technology, applied in electrical digital data processing, TV system components, standard conversion, etc., can solve problems such as memory control address flaws, and achieve the effect of reducing memory size and preventing quality degradation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

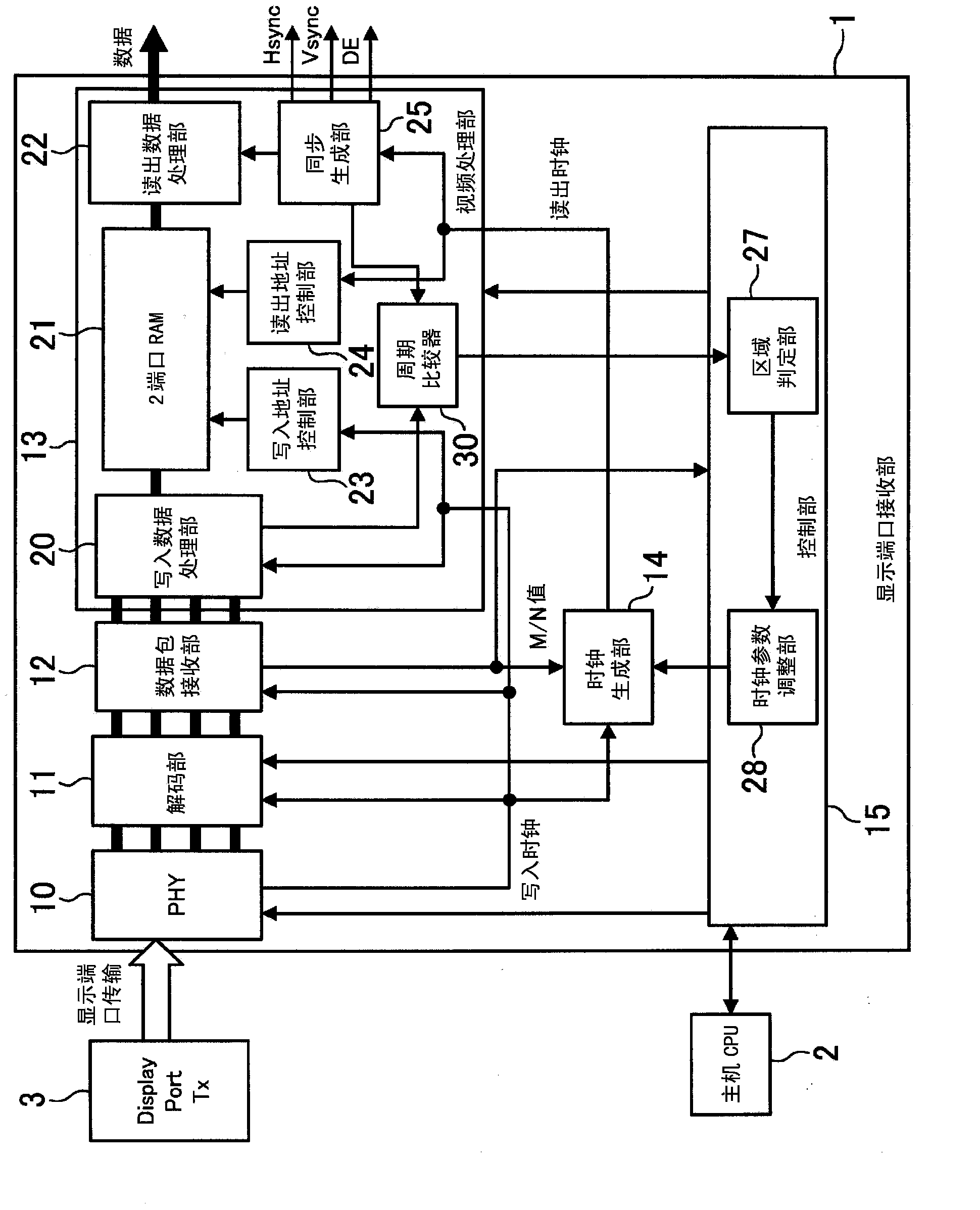

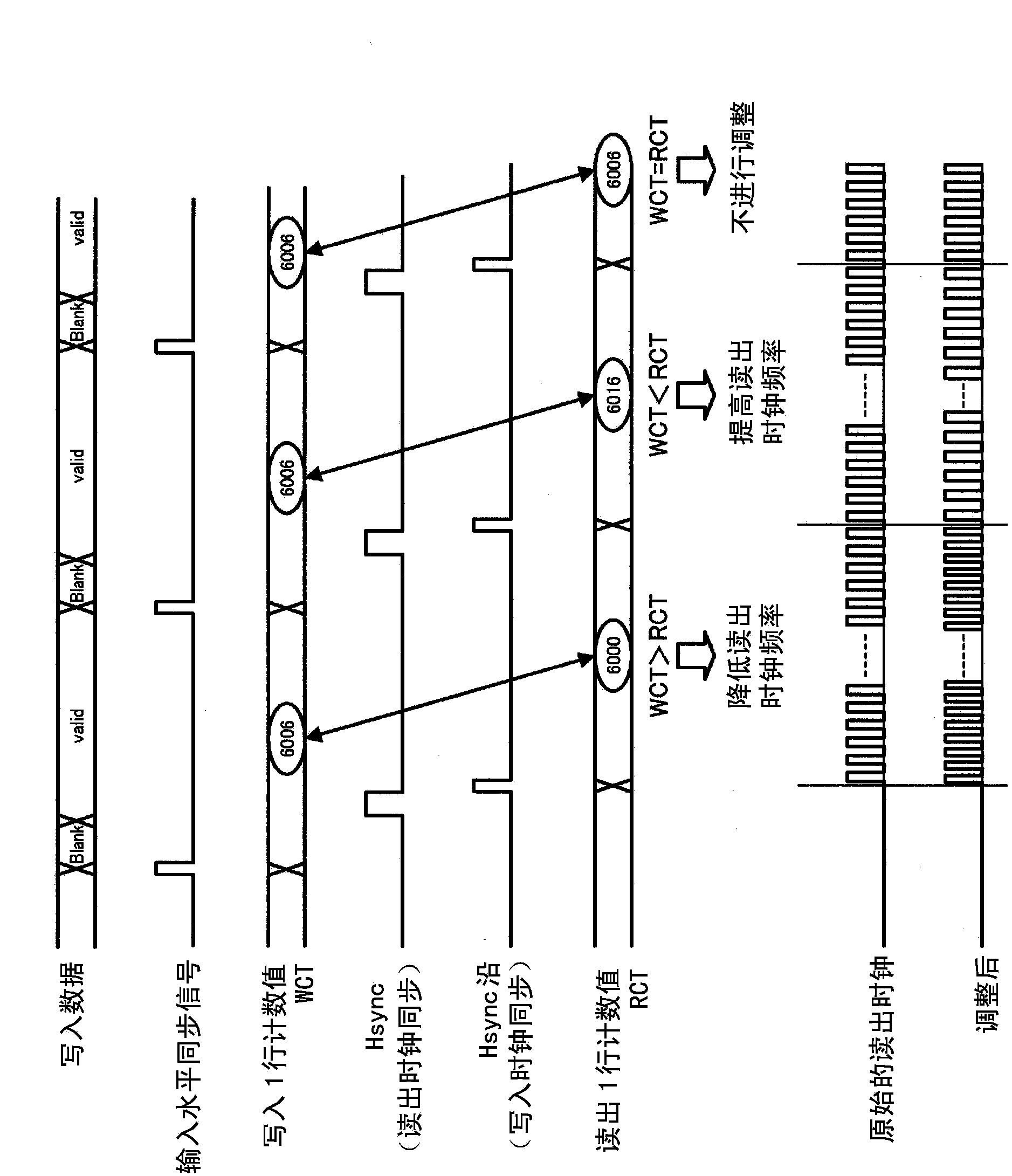

[0036] figure 1 It is a figure which shows the structure of the video processing system of Embodiment 1. in figure 1 In the display port (DisplayPort) receiving unit 1 is controlled by the host (HOST) CPU2, and data is transmitted from the transmitting device 3 through the display port transmission. In the display port receiving unit 1, the data transmitted by the PHY unit 10 is received, and after the decoding (Decode) unit 11 decodes the data, the packet receiving unit 12 receives various data packets. The video processing unit 13 receives the received image data, performs data rearrangement and clock conversion, and outputs video data Data, a horizontal synchronization signal Hsync, a vertical synchronization signal Vsync, and a data valid enable signal DE.

[0037] In the display port, the receiving side generates a read clock based on the write clock based on the clock generation parameters sent from the transmitting side. The clock generation unit 14 receives the clock gen...

Embodiment approach 2

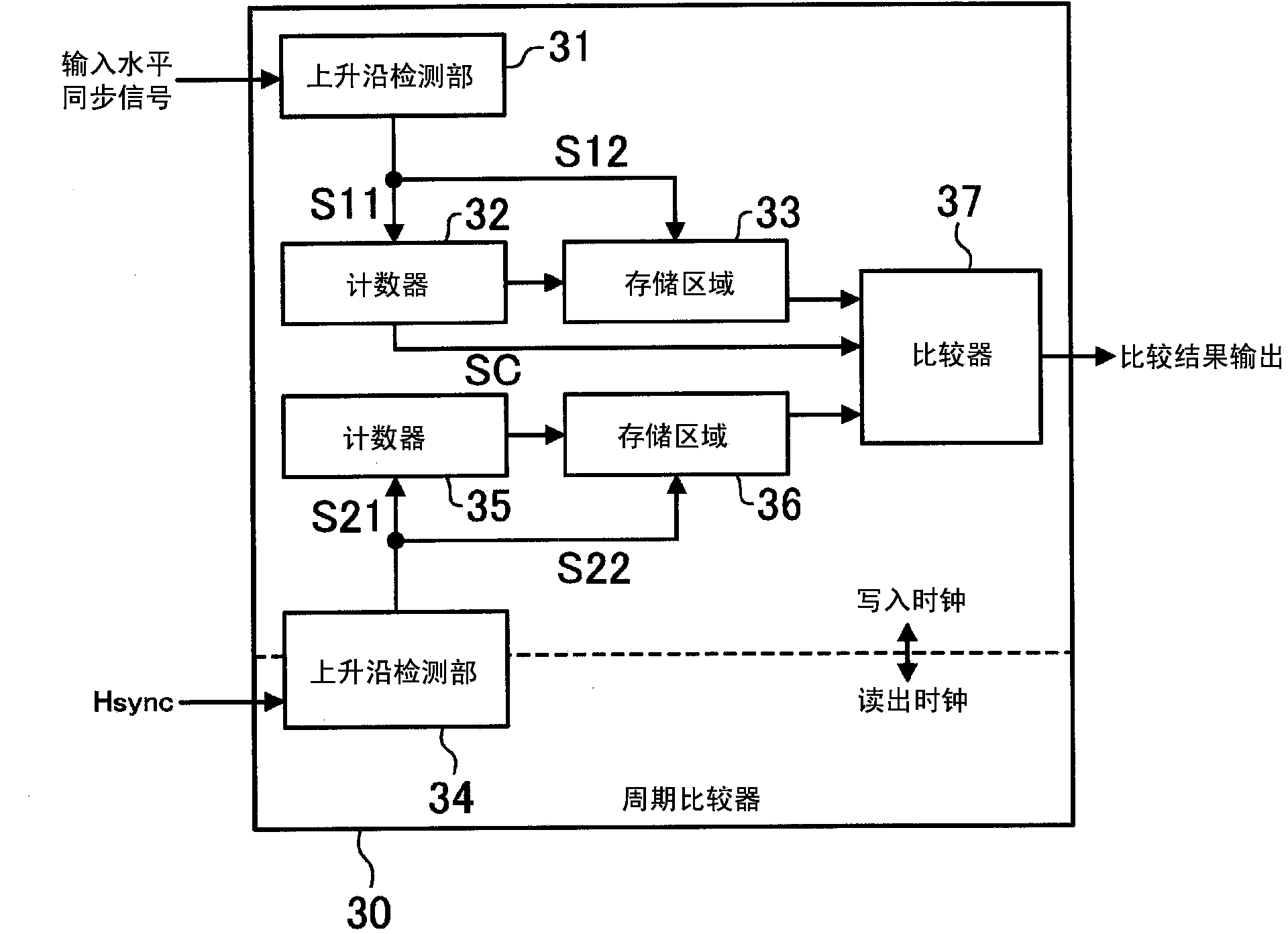

[0064] The configuration and operation of the video processing system in the second embodiment are the same as those in the first embodiment. However, the structure and operation of the period comparator 30 are different.

[0065] Picture 9 This is an example of the structure of the period comparator in the second embodiment. Picture 9 The cycle comparator 30 receives the input horizontal synchronization signal and the input vertical synchronization signal from the write data processing unit 20, and receives the Hsync as the output horizontal synchronization signal and the Vsync as the output vertical synchronization signal from the synchronization generation unit 25. The selector 42 as the first selector selects either one of the input horizontal synchronization signal or the input vertical synchronization signal, and supplies it to the rising edge detection unit 31. The selector 43 as the second selector selects and outputs either Hsync or Vsync, and supplies it to the rising...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com