Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

191 results about "Switched capacitor array" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

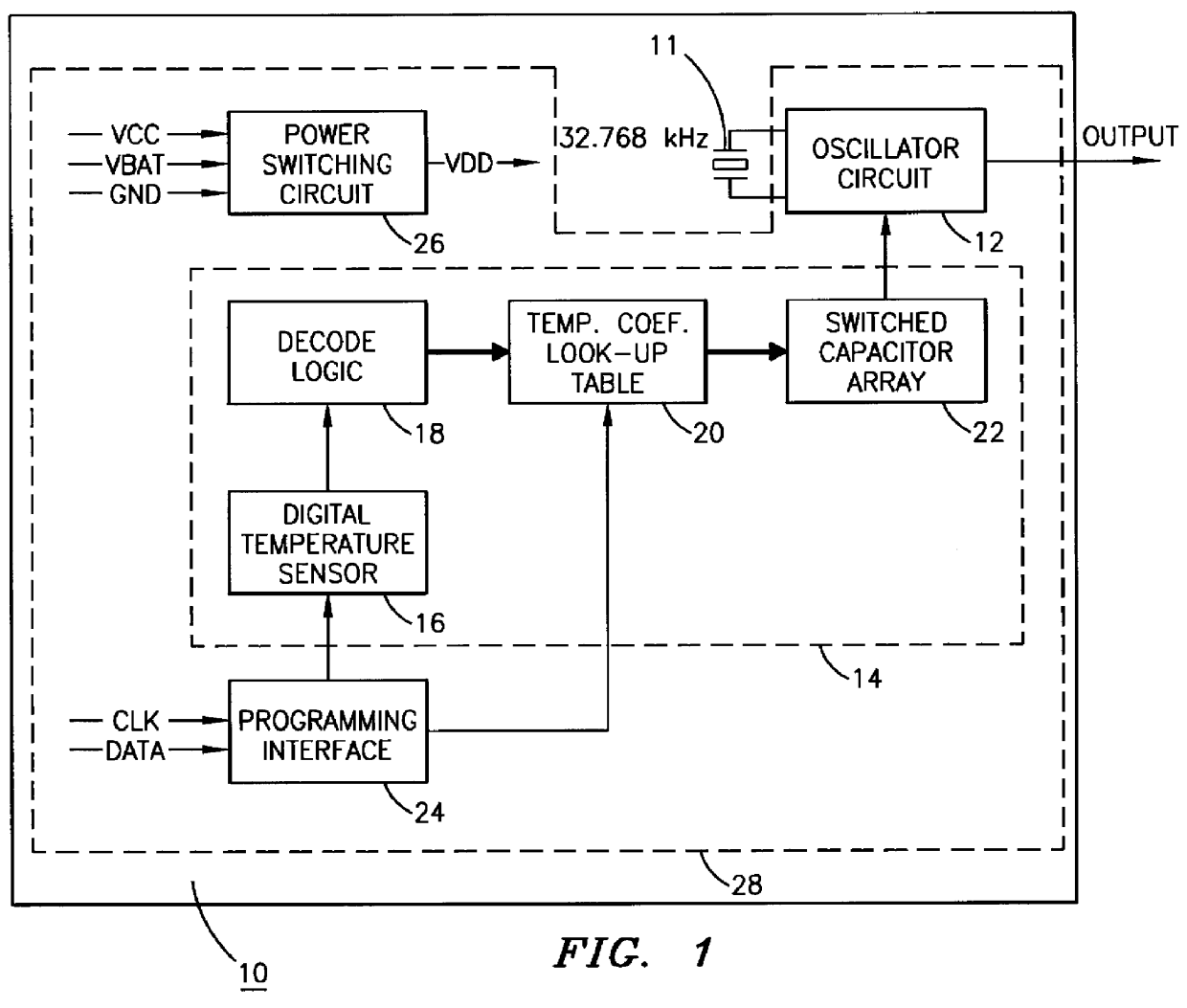

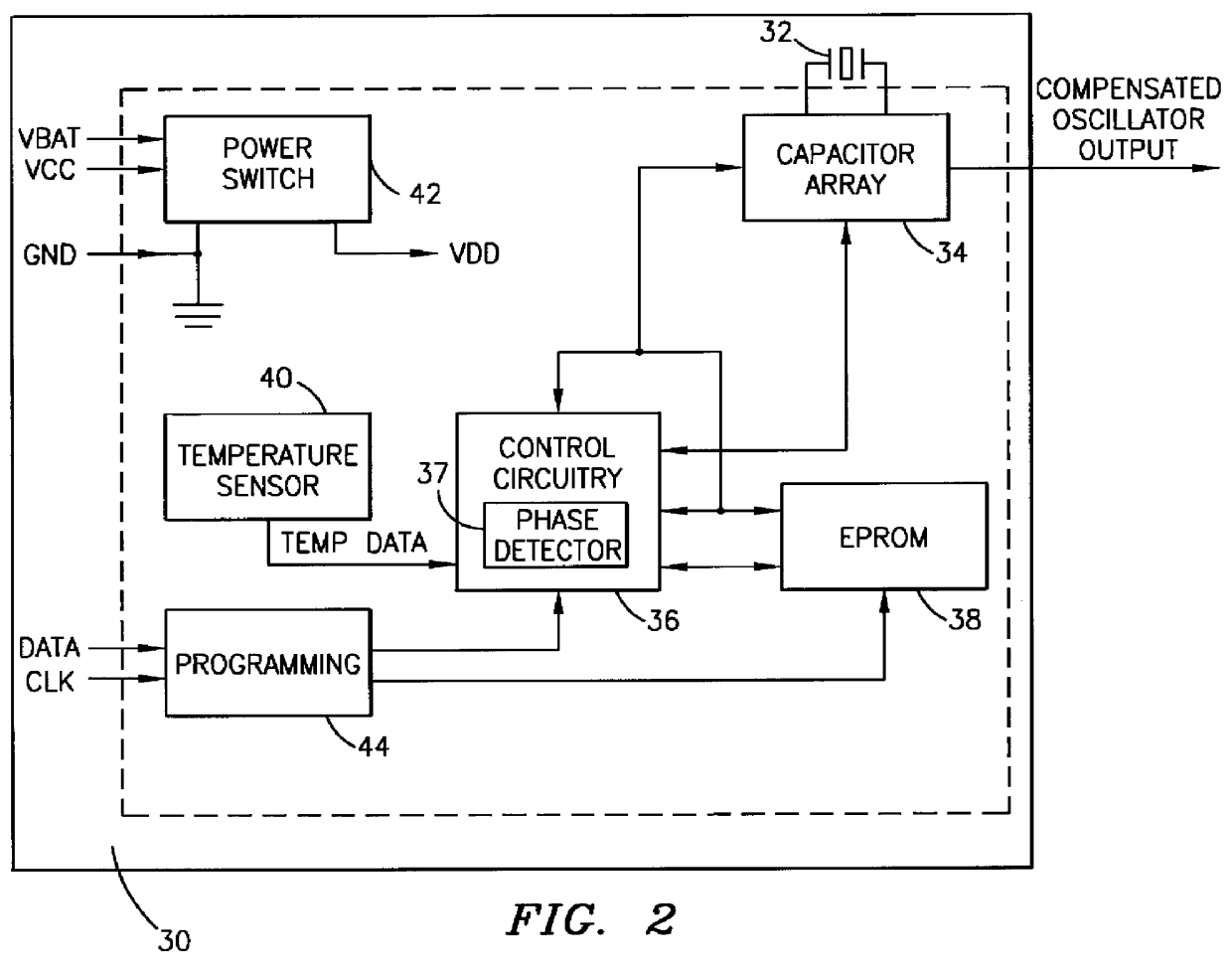

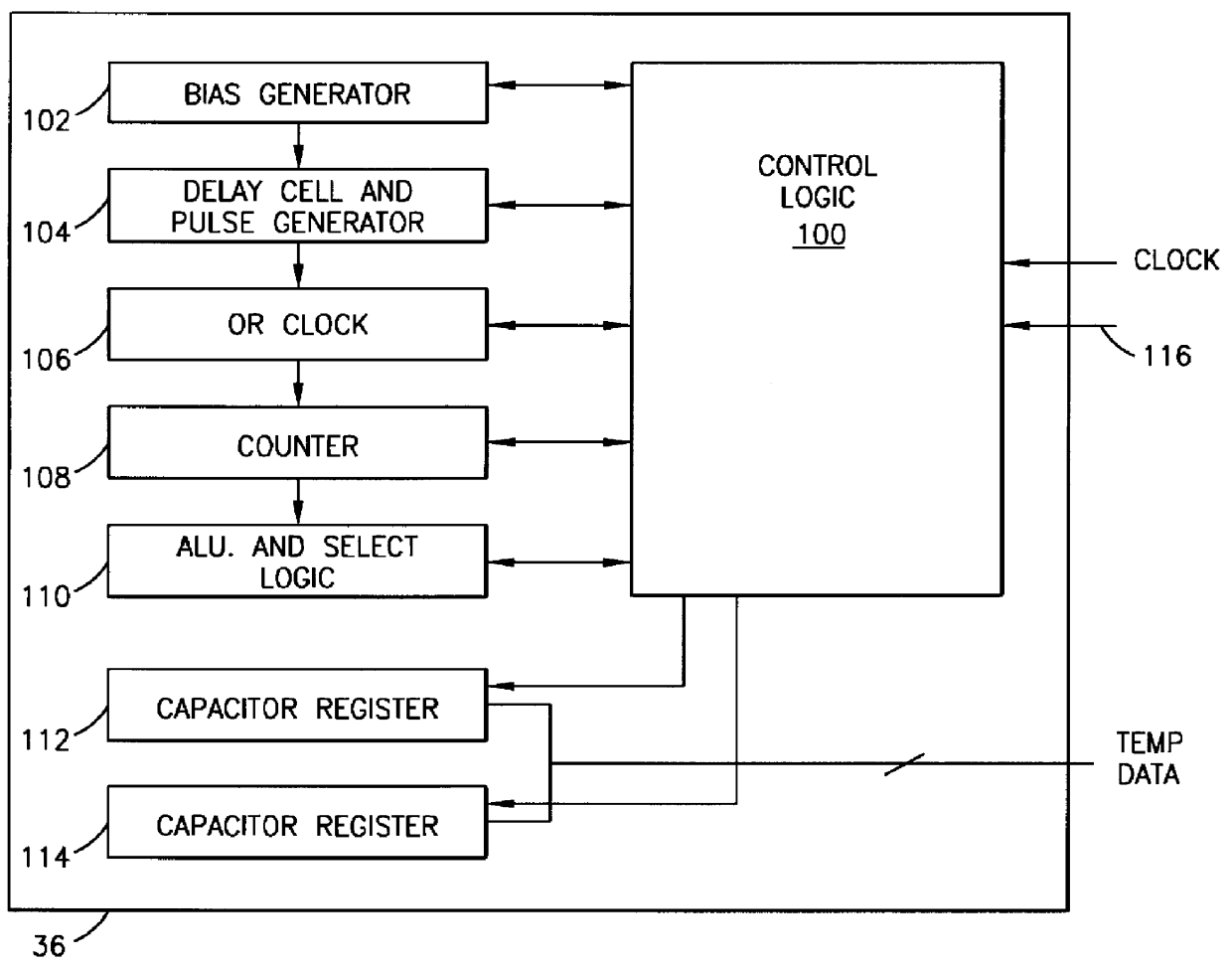

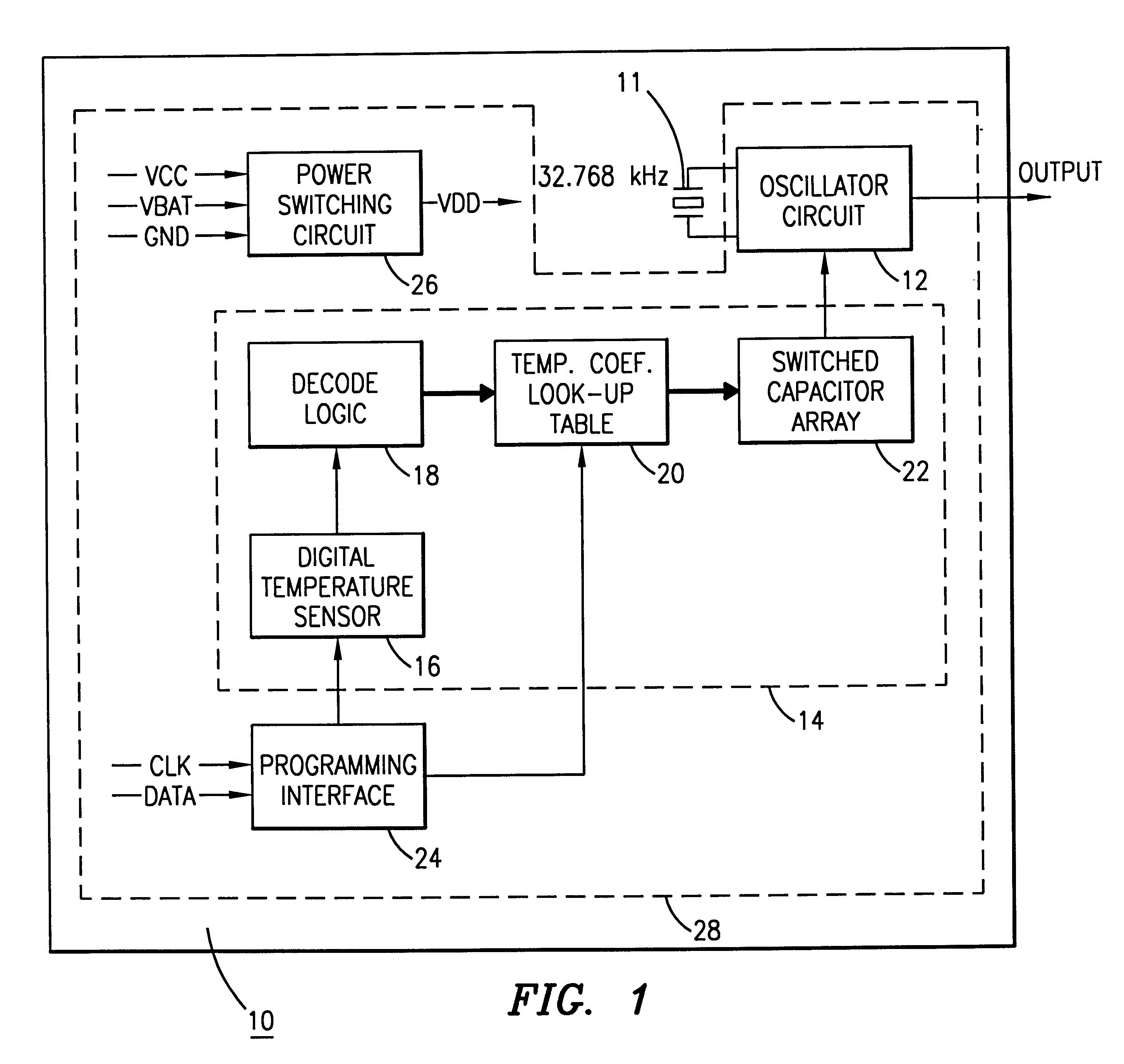

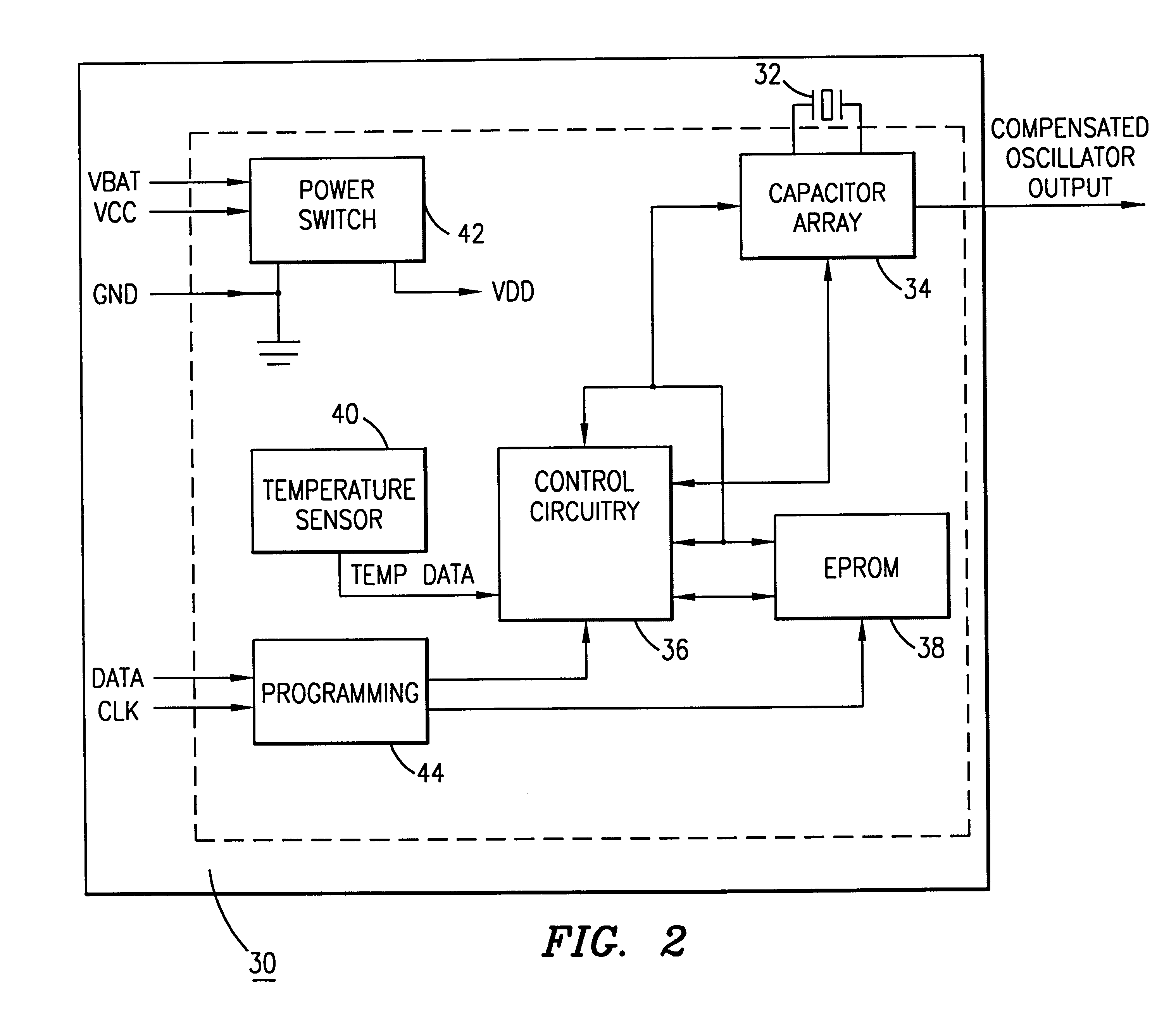

Temperature compensated crystal oscillator

A temperature compensated crystal oscillation circuit adapted to be contained within a small device package and providing an output frequency accuracy of approximately + / -2 ppm over a temperature range or less than 2 minutes per year over the temperature range. The device includes crystal and a single integrated circuit wherein the integrated circuit has a temperature sensing circuit with a digital output, control circuitry, a memory circuit and a switched capacitor array for compensating the oscillation of the crystal oscillator over temperature.

Owner:MAXIM INTEGRATED PROD INC

Method for calibrating a temperature sensitive oscillator

A temperature compensated crystal oscillation circuit adapted to be contained within a small device package and providing an output frequency accuracy of approximately + / -2 ppm over a temperature range or less than 2 minutes per year over the temperature range. The device includes crystal and a single integrated circuit wherein the integrated circuit has a temperature sensing circuit with a digital output, control circuitry, a memory circuit and a switched capacitor array for compensating the oscillation of the crystal oscillator over temperature.

Owner:MAXIM INTEGRATED PROD INC

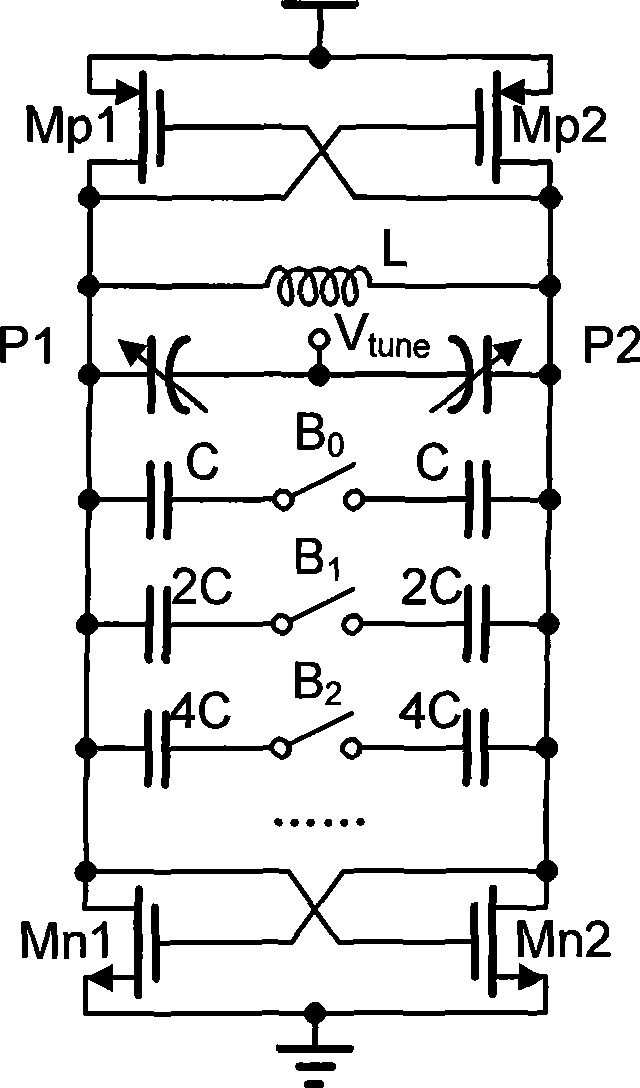

Voltage control oscillator with low tuning gain variance

InactiveCN101483434ACounteract the effects of tuning gainRealize the designPulse automatic controlOscillations generatorsCapacitanceControl signal

The present invention discloses an LC voltage-controlled oscillator with low tuning gain variation. The LC voltage-controlled oscillator comprises a parallel inductance-capacitance resonance circuit, two pairs of transistors which are crossly coupled and connected, a pressure controlled variable capacitor, a switch variable capacitor array and a switching capacitor array. The variation range of pressure controlled variable capacitor is adjusted through the switch variable capacitor array for counteracting the effect of oscillation frequency to tuning gain. The invention adjusts the magnitude of variable capacitor switched into the resonant circuit with a digital control signal according to the variation of oscillation frequency, and changes the regulation range of equivalent variable capacitor along with the difference of sub-band thereby counteracting the effect of oscillation frequency change to the tuning gain of voltage controlled oscillator, realizing the design of wideband voltage controlled oscillator with low tuning gain variation, and simultaneously not adding additional power consumption.

Owner:SHANGHAI RUIXIE MICROELECTRONICS TECH

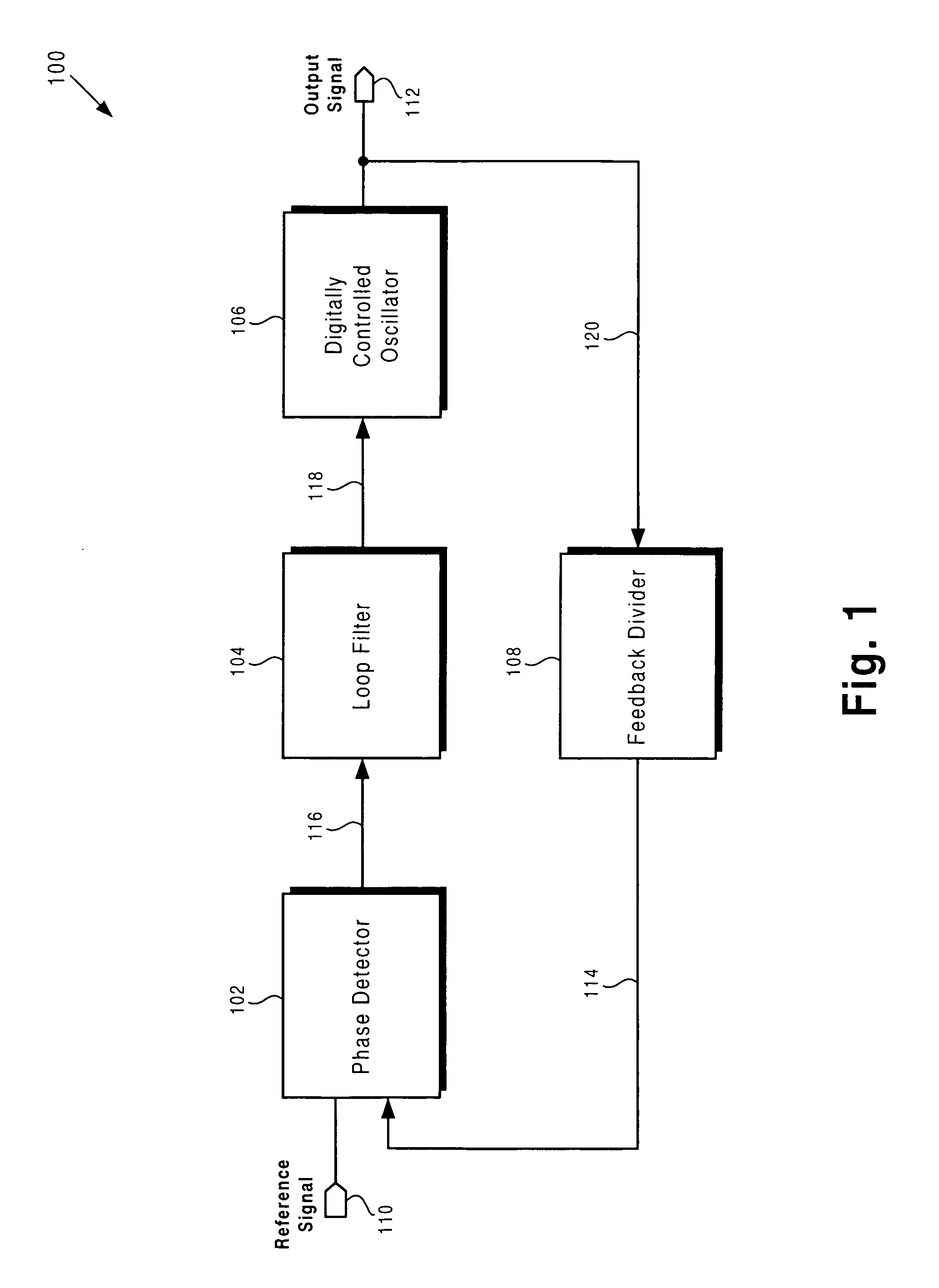

Wideband Digitally Controlled Injection-Locked Oscillator

A novel and useful digitally controlled injection-locked RF oscillator with an auxiliary loop. The oscillator is injection locked to a time delayed version of its own resonating voltage (or its second harmonic) and its frequency is modulated by manipulating the phase and amplitude of injected current. The oscillator achieves a narrow modulation tuning range and fine step size of an LC tank based digitally controlled oscillator (DCO). The DCO first gets tuned to its center frequency by means of a conventional switched capacitor array. Frequency modulation is then achieved via a novel method of digitally controlling the phase and amplitude of injected current into the LC tank generated from its own resonating voltage. A very linear deviation from the center frequency is achieved with a much lower gain resulting in a very fine resolution DCO step size and high linearity without needing to resort to oversampled noise shaped dithering.

Owner:SHORT CIRCUIT TECH LLC

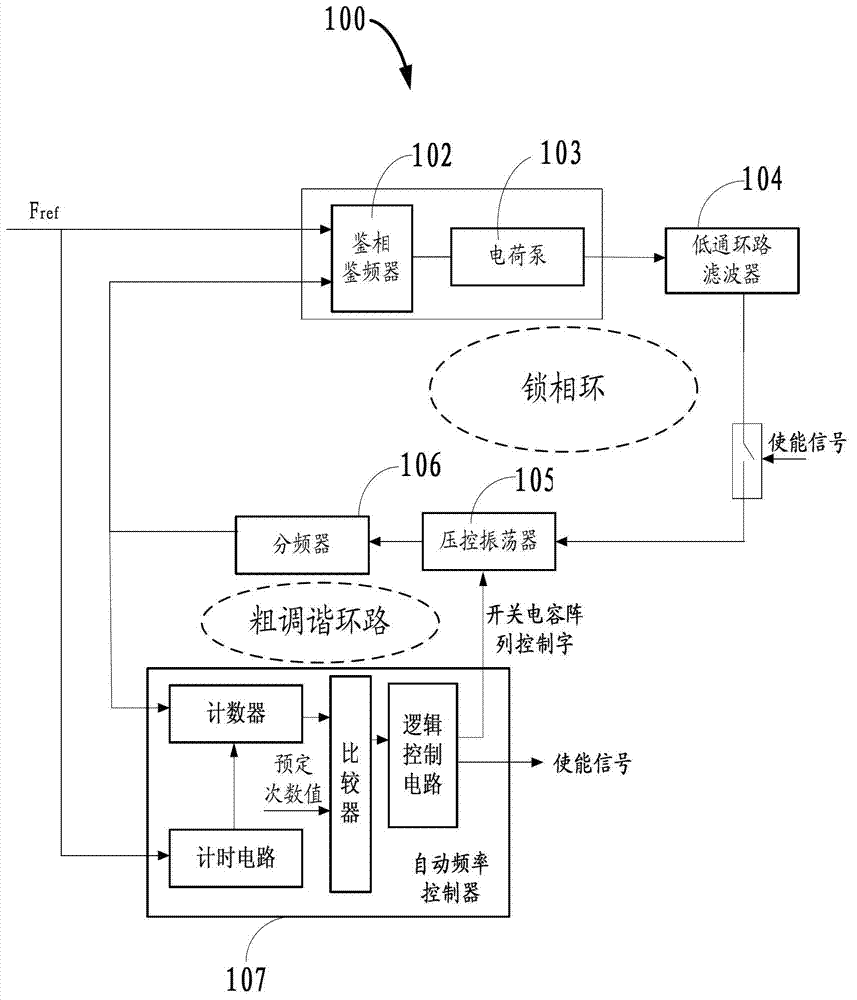

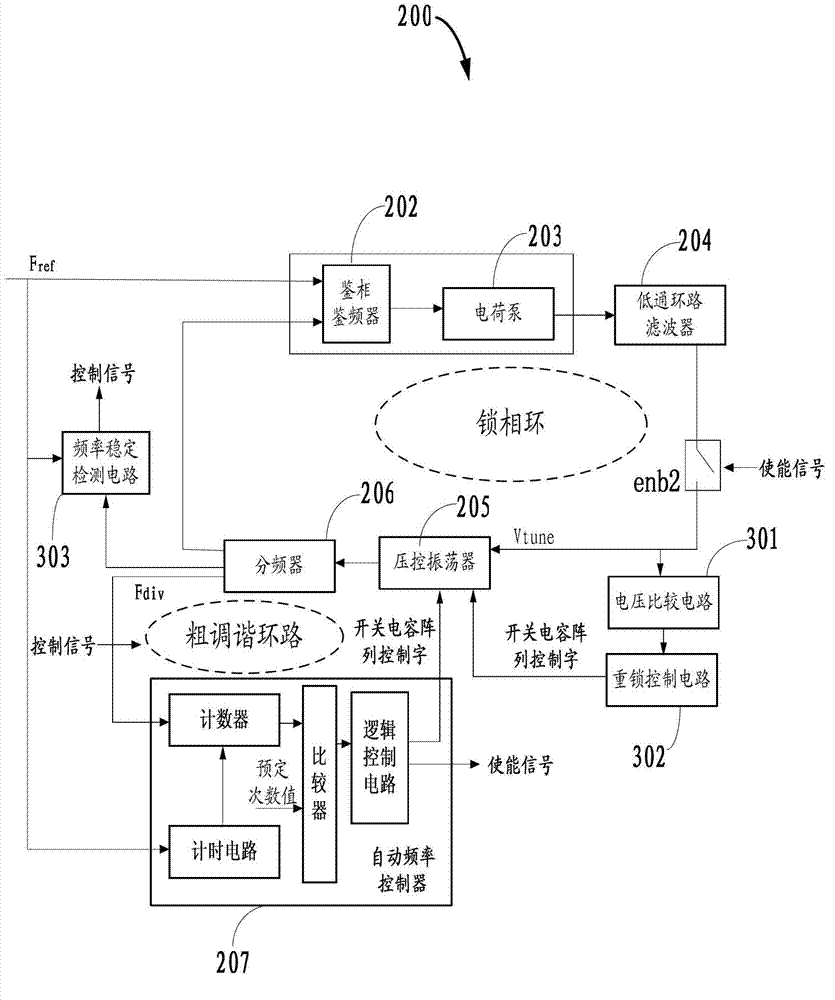

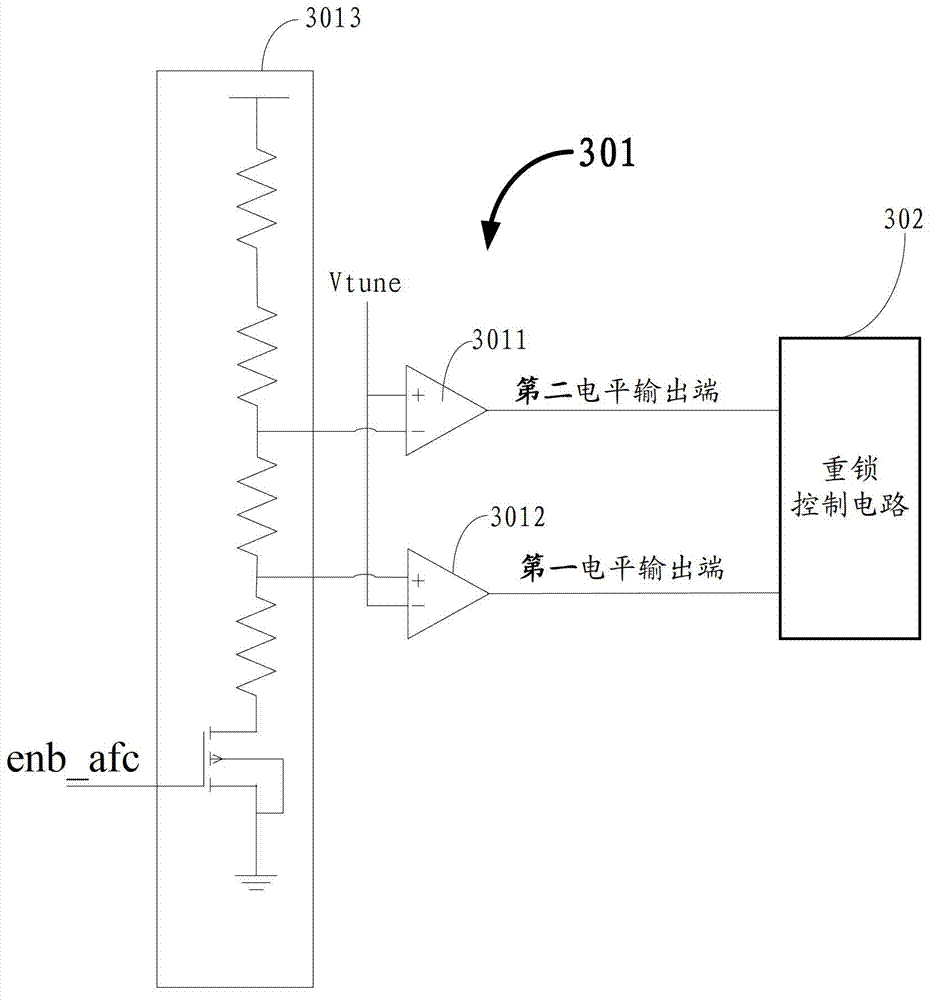

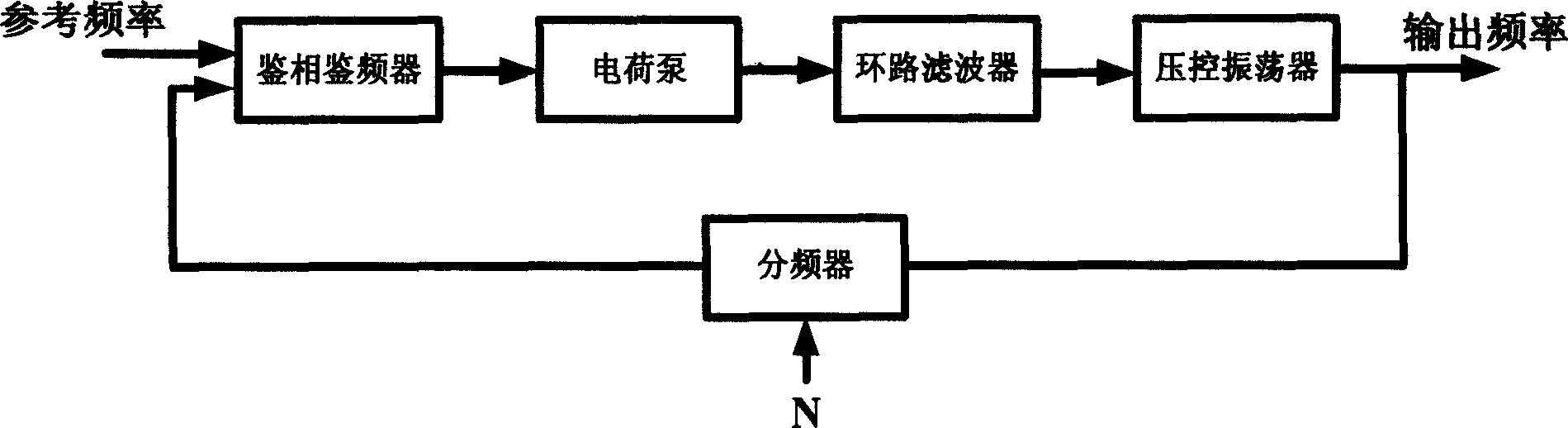

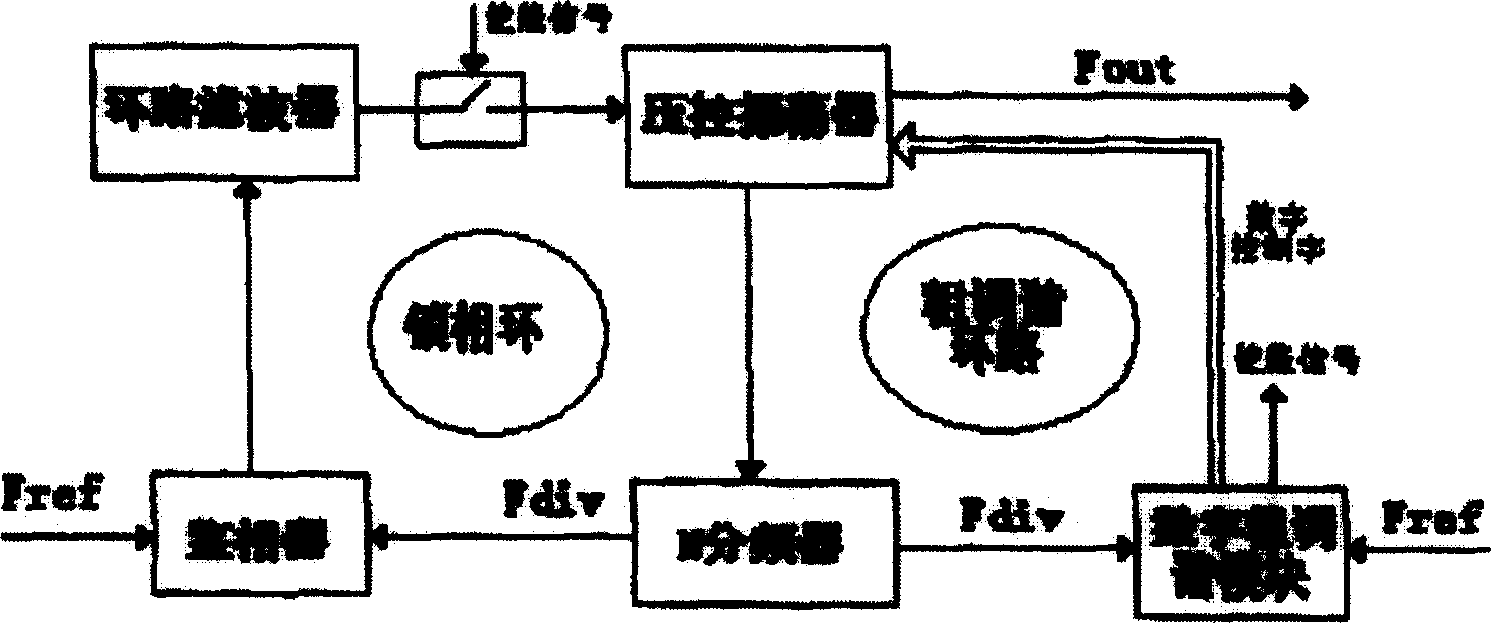

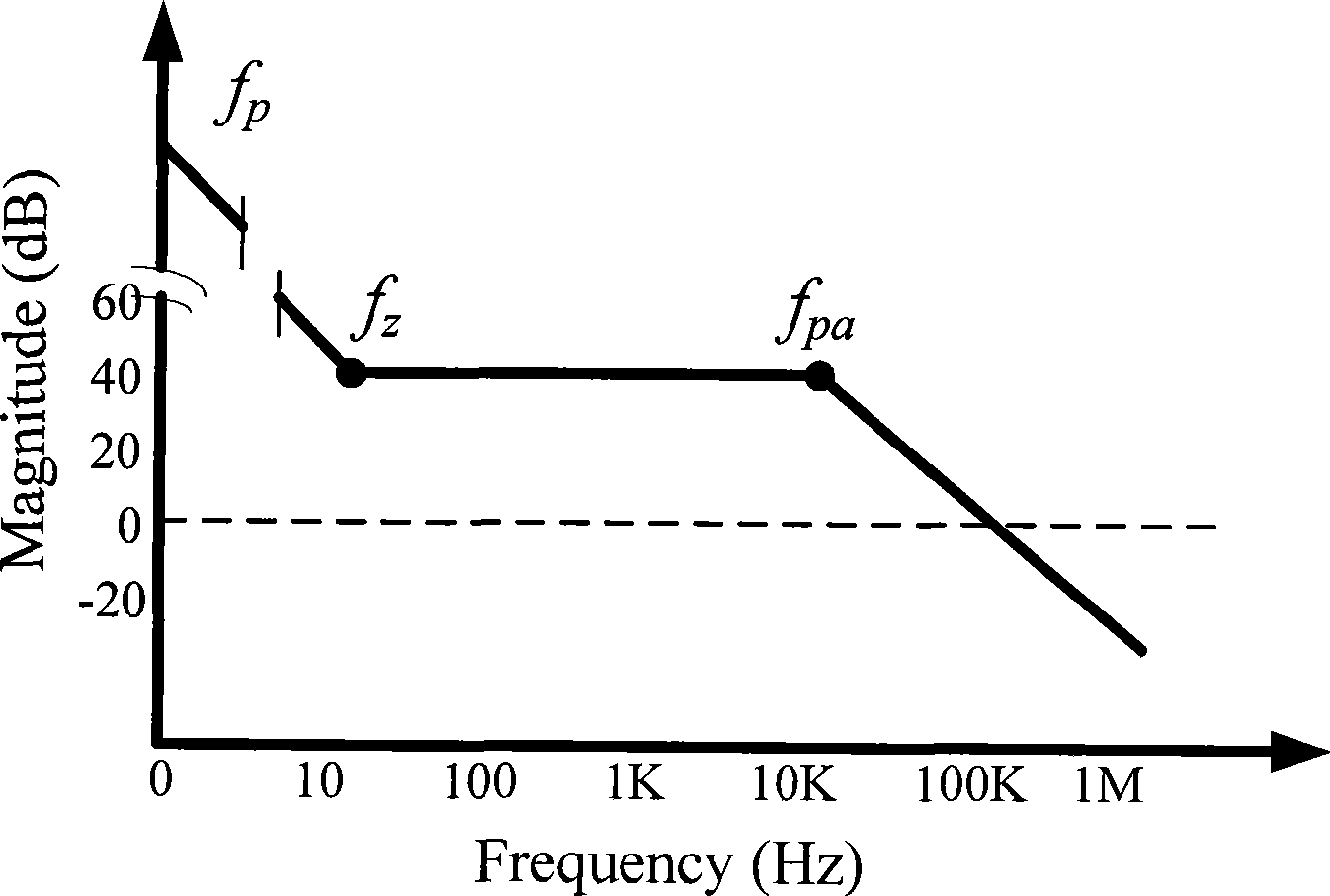

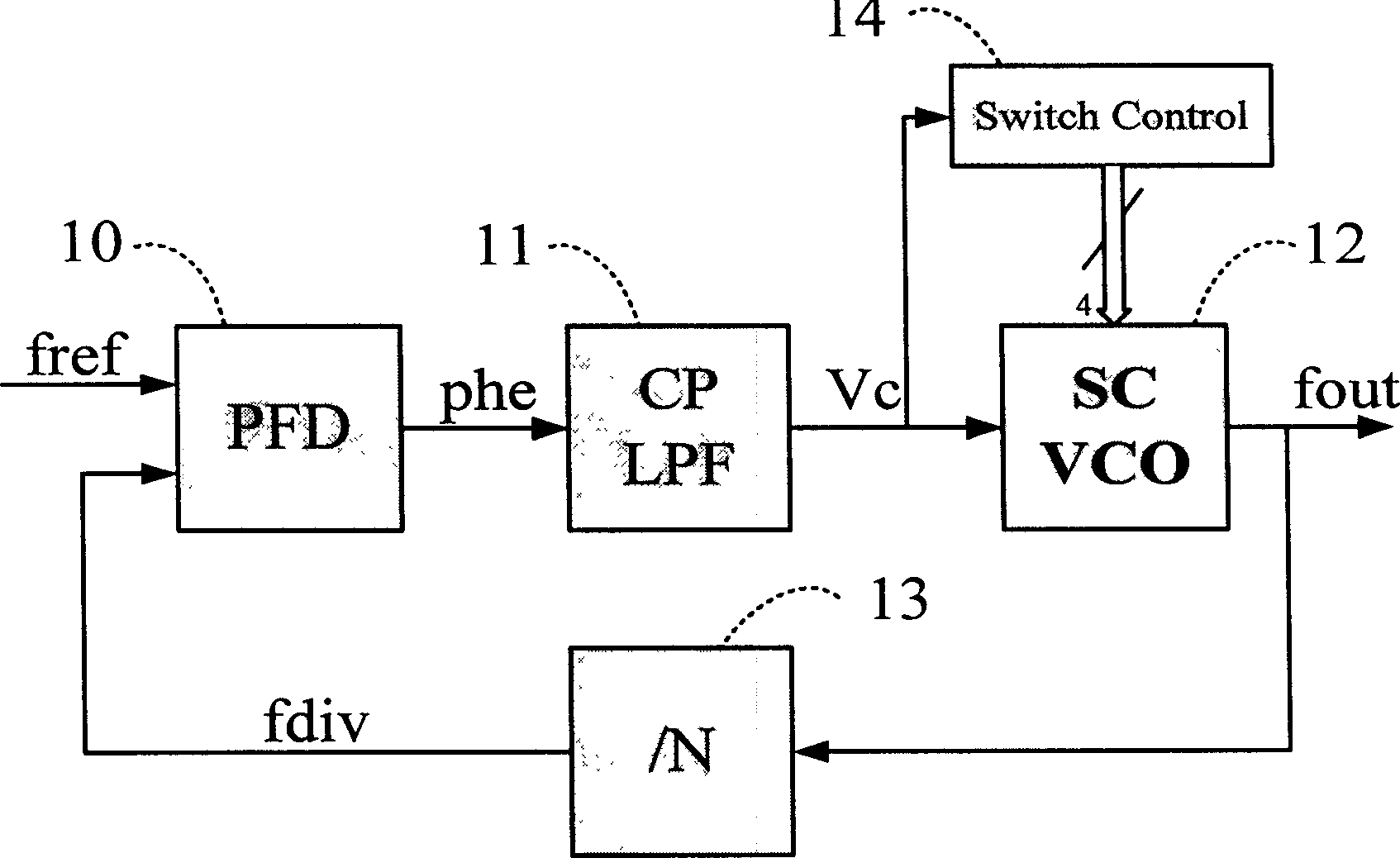

Phase-locked loop frequency synthesizer and phase-locked loop loss lock detecting and adjusting method

ActiveCN102868399AAvoid failureAvoid Reference Harmonic Energy IncreasePulse automatic controlDiscriminatorLoop filter

The invention discloses a phase-locked loop frequency synthesizer which comprises a phase detection discriminator, a charge pump, a low-pass loop filter, a voltage controlled oscillator with a switched capacitor array, a frequency divider, an automatic frequency controller, a voltage comparison circuit and a relock control circuit, wherein the voltage comparison circuit judges whether tuning voltage Vtune output to the voltage controlled oscillator by the low-pass loop filter is in the preset voltage range in real time when the phase-locked loop frequency synthesizer is at the phase-locked loop loss lock detection stage; and the relock control circuit dynamically adjusts a value of a control word of the switched capacitor array of the voltage controlled oscillator according to the comparison result of the voltage comparison circuit. The invention also discloses a corresponding phase-locked loop loss lock detecting and adjusting method. By the phase-locked loop frequency synthesizer and the phase-locked loop loss lock detecting and adjusting method, increase of reference harmonic energy can be avoided; interference is reduced, and the coarse tuning time is shortened.

Owner:GUANGZHOU RUNXIN INFORMATION TECH

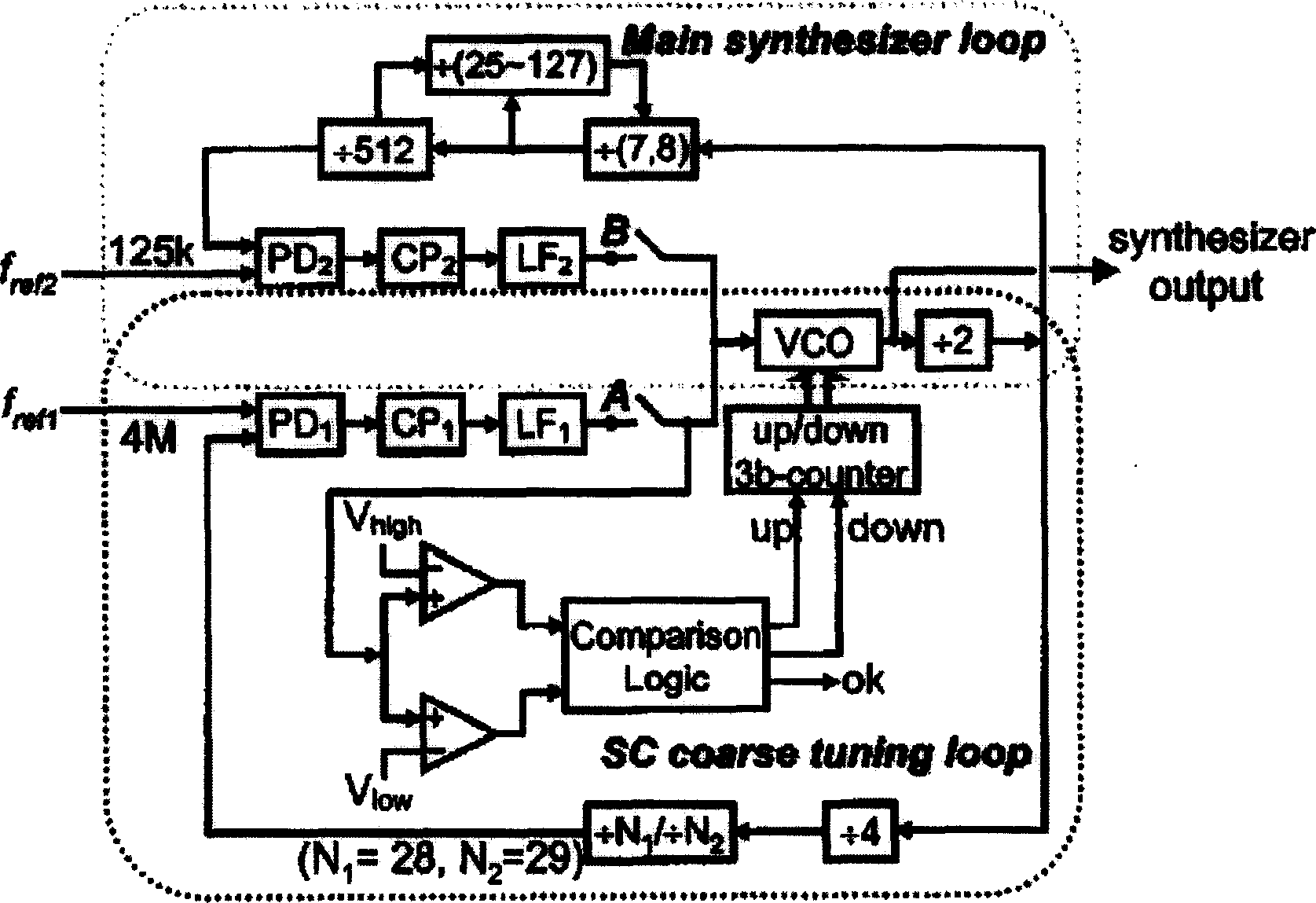

Double-loop frequency synthesizer and method for tuning coarse loop

InactiveCN1731681ASmall range of variationReduce gainPulse automatic controlDiscriminatorLoop filter

Owner:PEKING UNIV

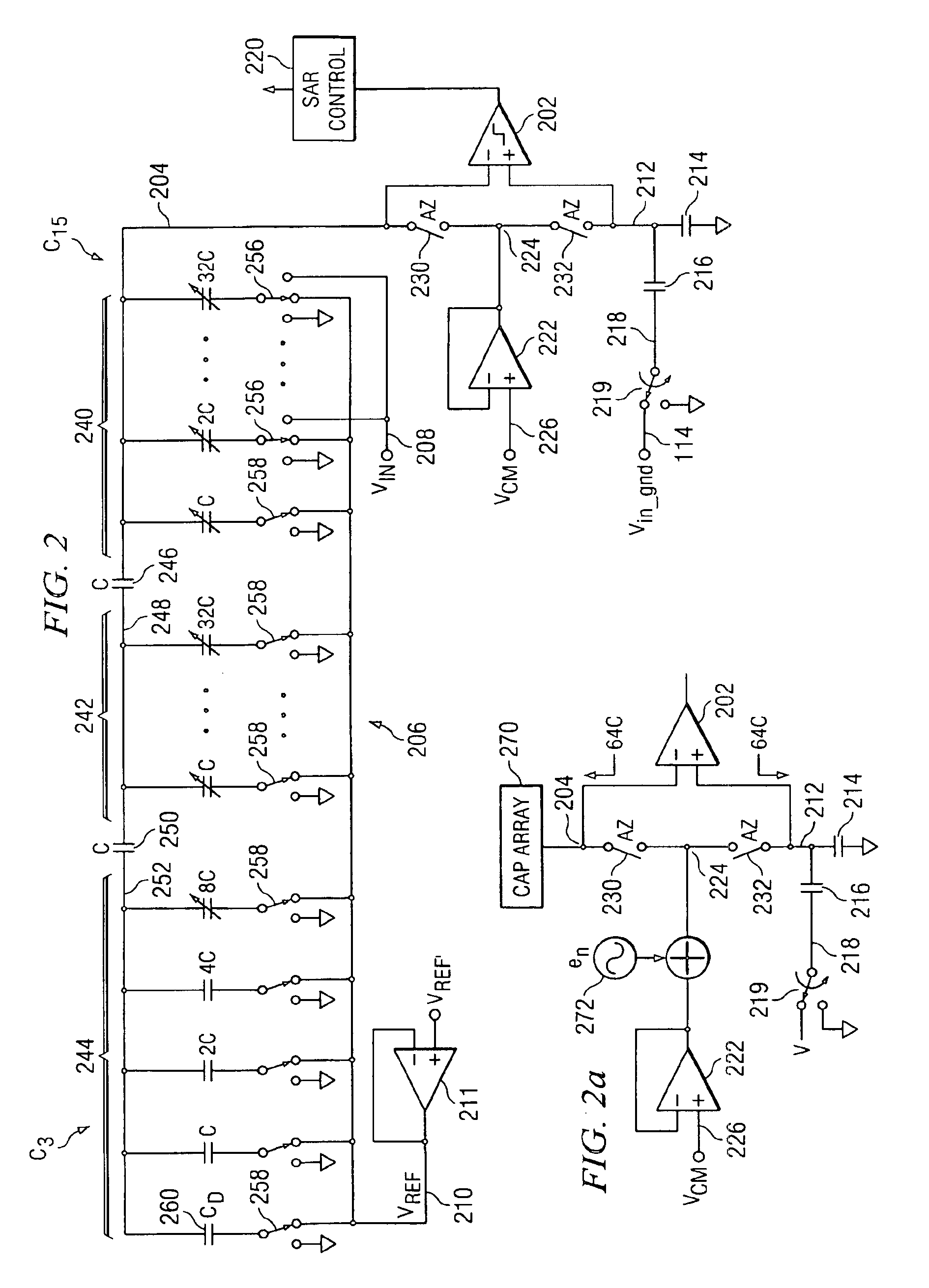

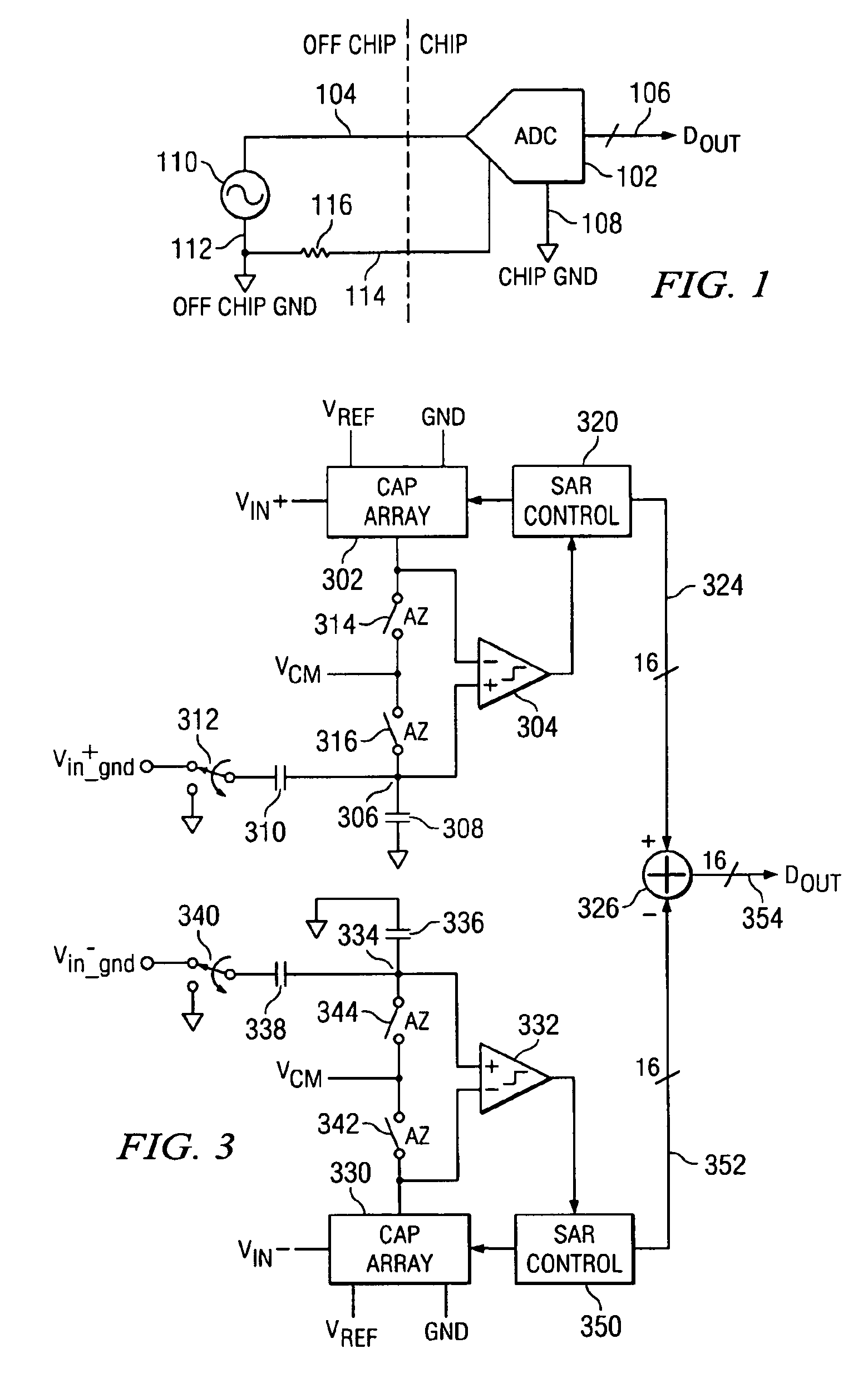

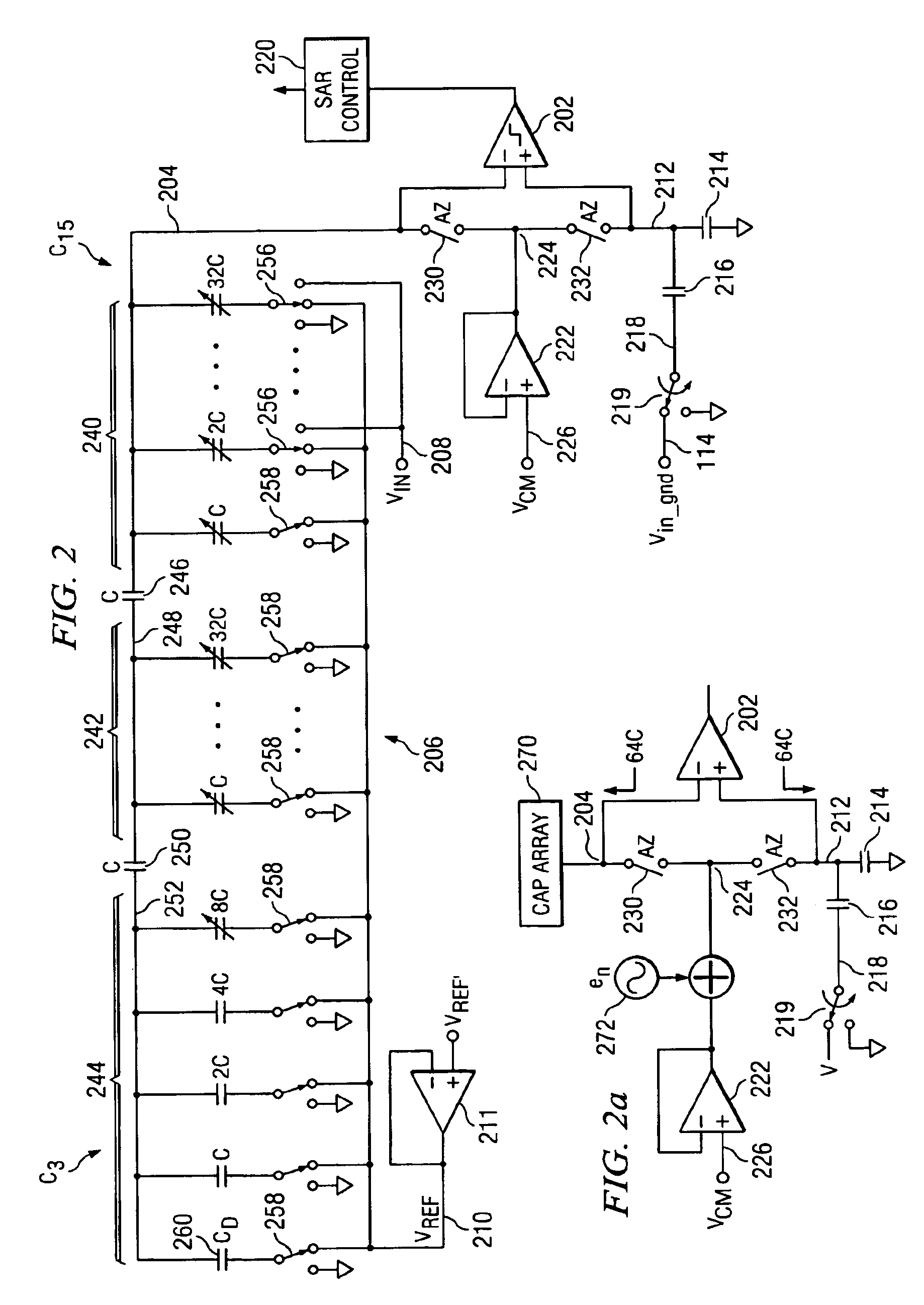

Capacitor calibration in SAR converter

InactiveUS6891487B2Electric signal transmission systemsResistors with plural resistive elementsVoltage referenceSwitched capacitor

Capacitor calibration in SAR converter. A method for calibrating a switched capacitor array in a SAR data converter is disclosed, which array includes a plurality of primary capacitors having a common node plate interfaced to a common node and a switched plate interfaced to a switch that is operable to be switched between first and second reference voltages. A comparator having an input connected to the common node and a reference input connected to a comparator reference node receives a comparator reference voltage. In a first calibration step for calibrating one of the primary capacitors, a reference capacitor is provided and then, the switched plate of the select primary capacitor is connected to the first reference voltage, the switched plate of the other capacitors and the reference capacitor are connected to the second reference voltage, and the common node and the comparator reference node are driven with a driver to dispose a first voltage thereon. In a second calibration step, the common node is allowed to float, the switched plate of the select primary capacitor is connected to the second reference voltage, the switched plate of the reference capacitor is connected to the first reference voltage, and the voltage on the common node is compared to the first voltage on the comparator reference node. A determination is then made as to whether the voltage on the common node is greater than the first voltage. A plurality of trim capacitors are provided and, if in the second calibration step, the voltage on the common node was determined to be greater than the first voltage, then one of the trim capacitors is disposed in parallel with the select one of the primary capacitors and then the first and second calibrating steps are repeated.

Owner:SILICON LAB INC

Single package temperature compensated electronic device

A temperature compensated crystal oscillation circuit adapted to be contained within a small device package and providing an output frequency accuracy of approximately + / -2 ppm over a temperature range or less than 2 minutes per year over the temperature range. The device includes crystal and a single integrated circuit wherein the integrated circuit has a temperature sensing circuit with a digital output, control circuitry, a memory circuit and a switched capacitor array for compensating the oscillation of the crystal oscillator over temperature.

Owner:MAXIM INTEGRATED PROD INC

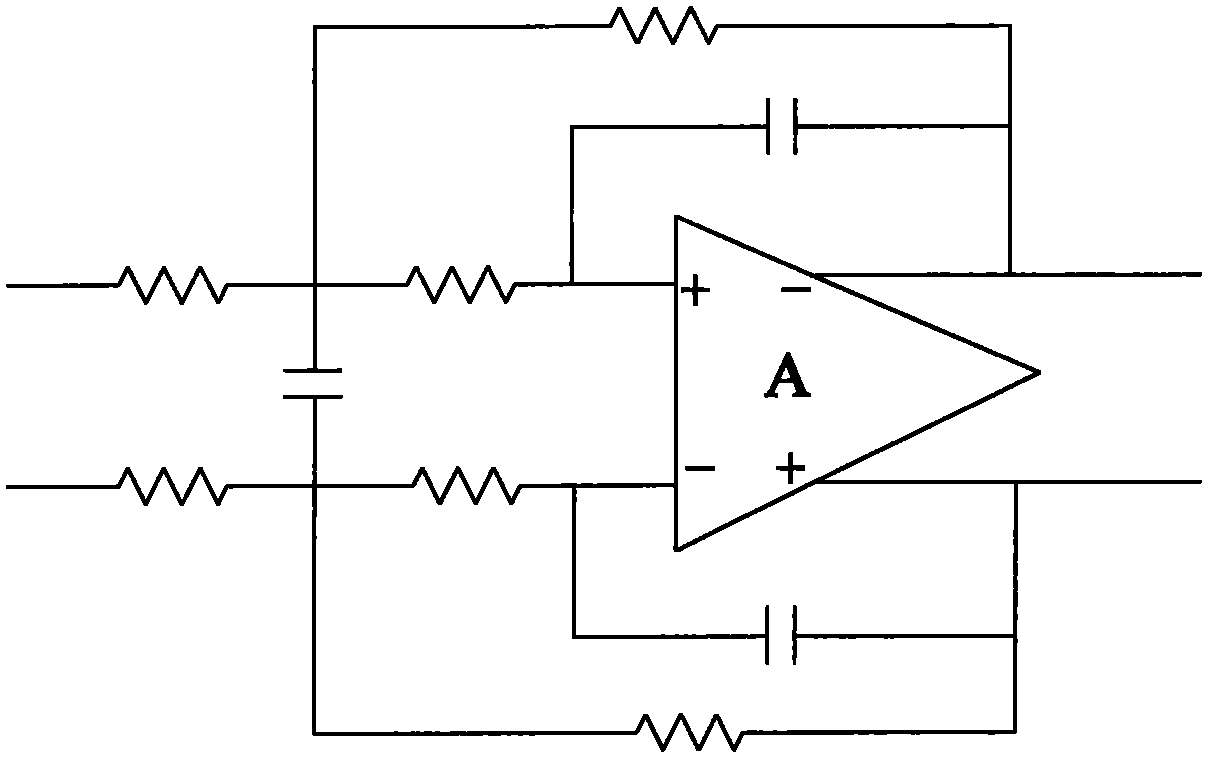

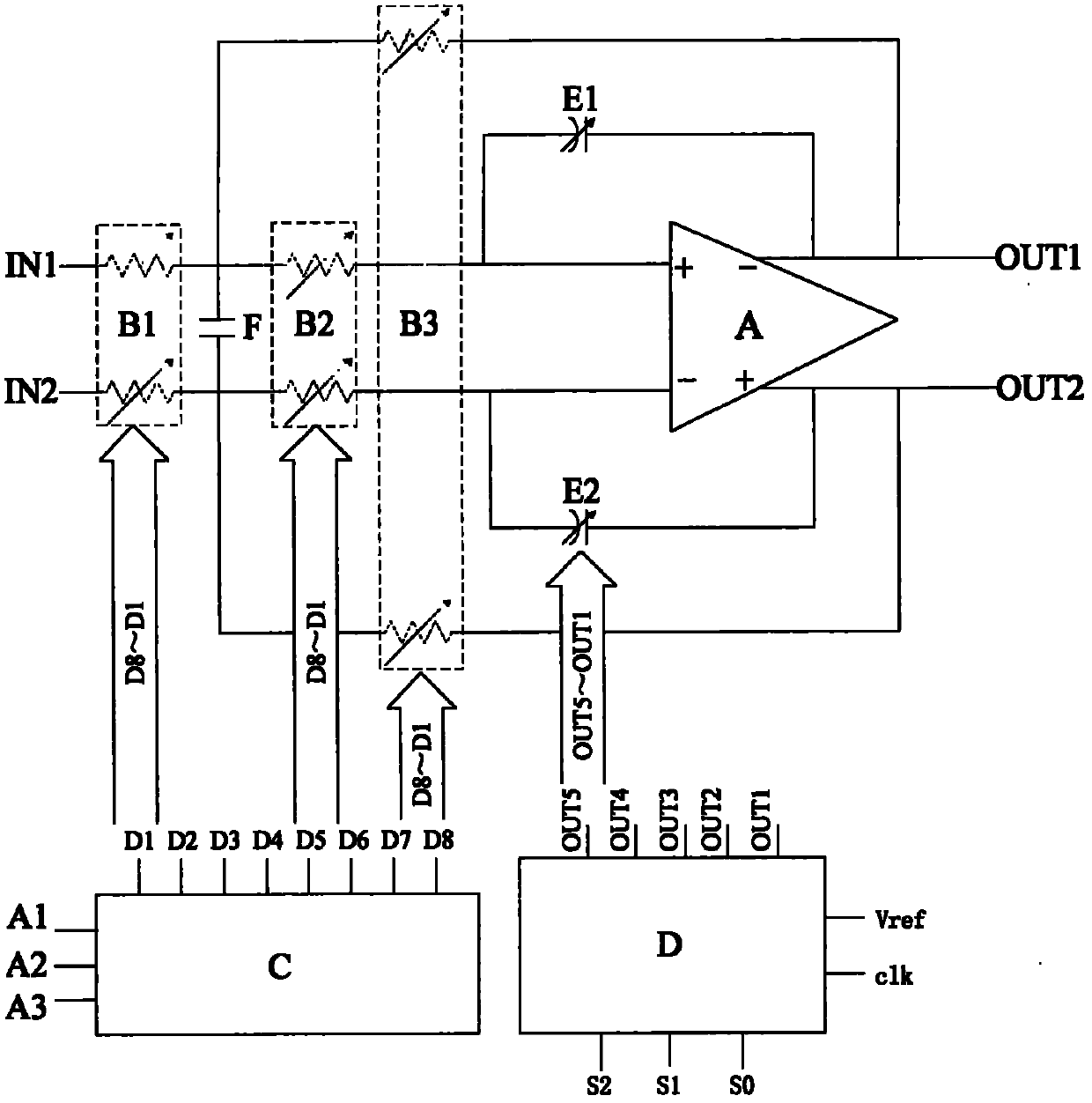

Automatic frequency calibration channel selection filter for multi-frequency multi-mode wireless transceiver

The invention discloses an automatic frequency calibration channel selection filter for a multi-frequency multi-mode wireless transceiver, which comprises a fully differential operational amplifier, three switch resistance arrays, a decoder, an automatic frequency calibration circuit, two switch capacitance arrays and a capacitor. The filter can be applied to multi-frequency multi-mode wireless transceivers which support wireless local area network, global mobile communication, radio frequency identification and time division synchronous code division multiple accesses. The filter supports eight different frequency bands, reduces the implementation cost of the system and improves the integrity of the system. The automatic frequency calibration circuit of the filter can realize the accurate adjustment of a cut-off frequency, and the error is within 3 percent.

Owner:EAST CHINA NORMAL UNIVERSITY

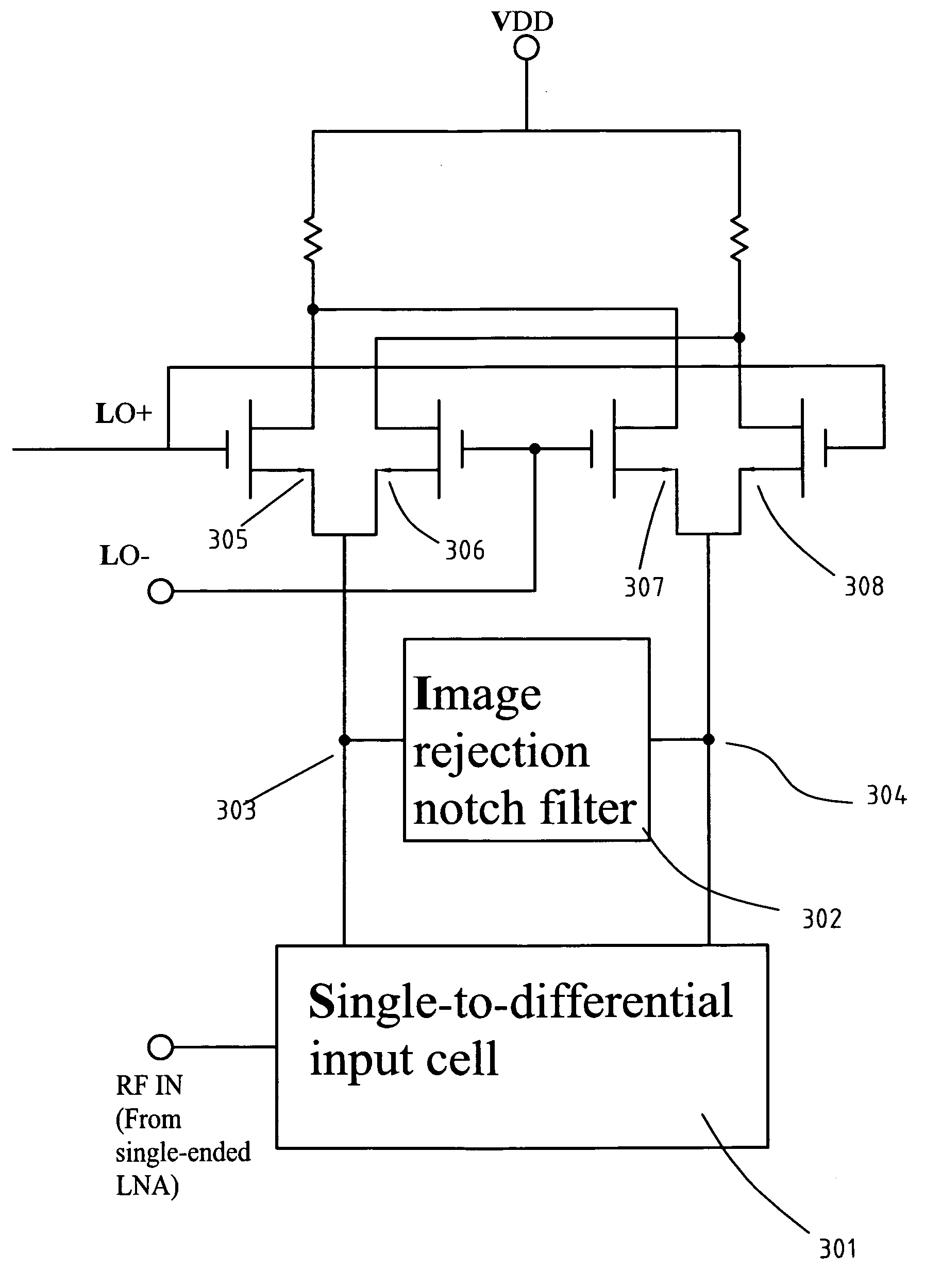

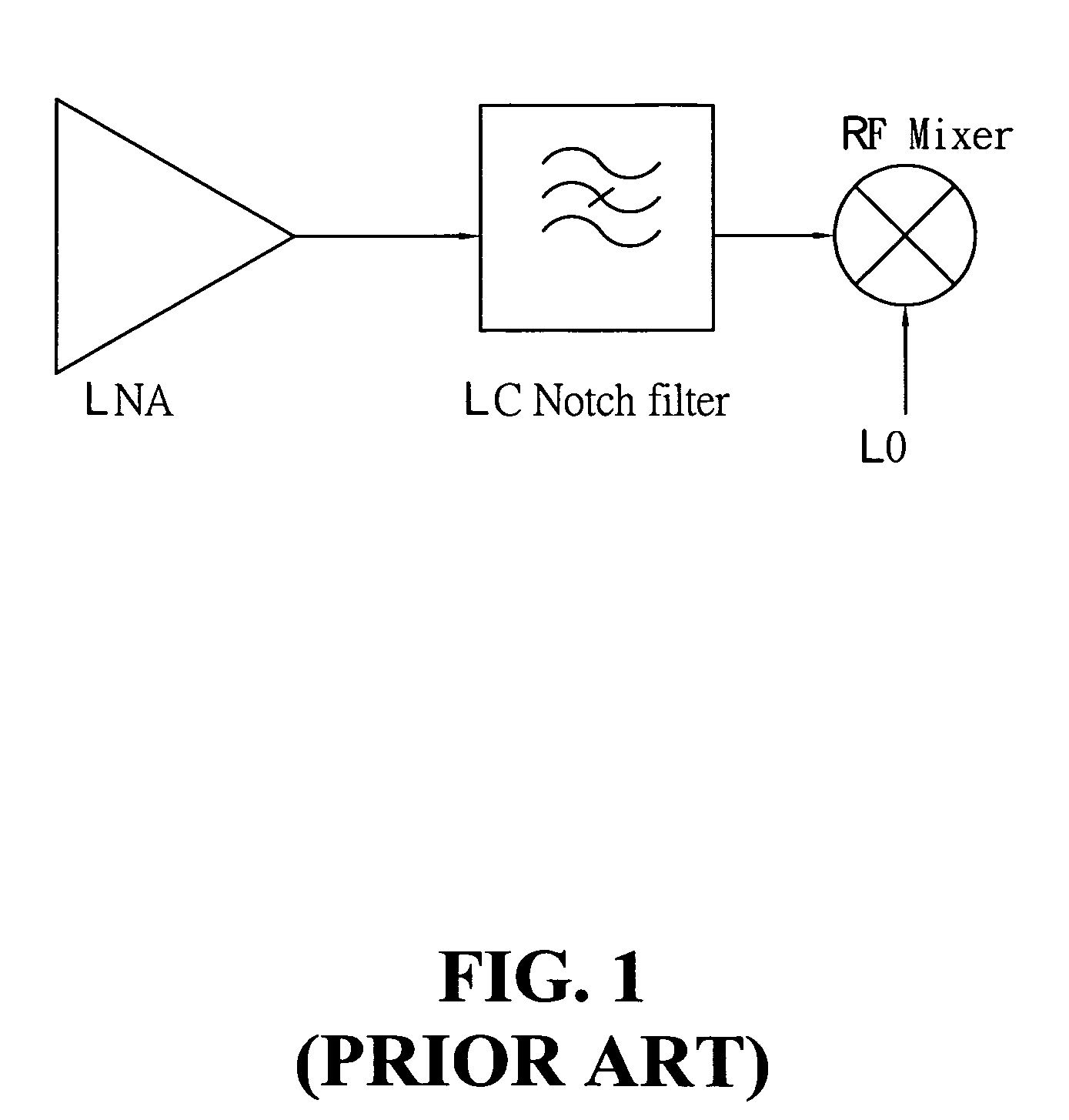

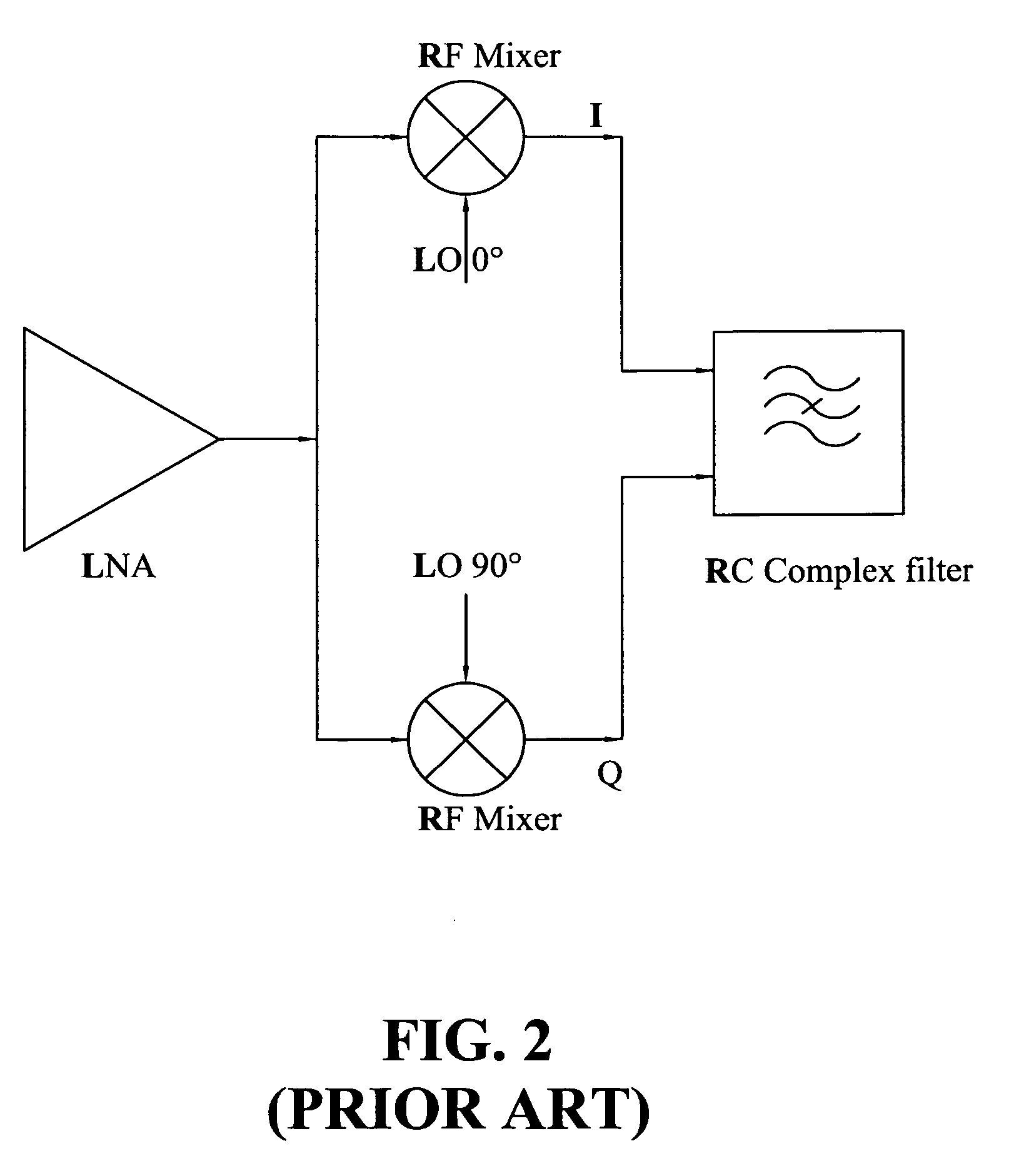

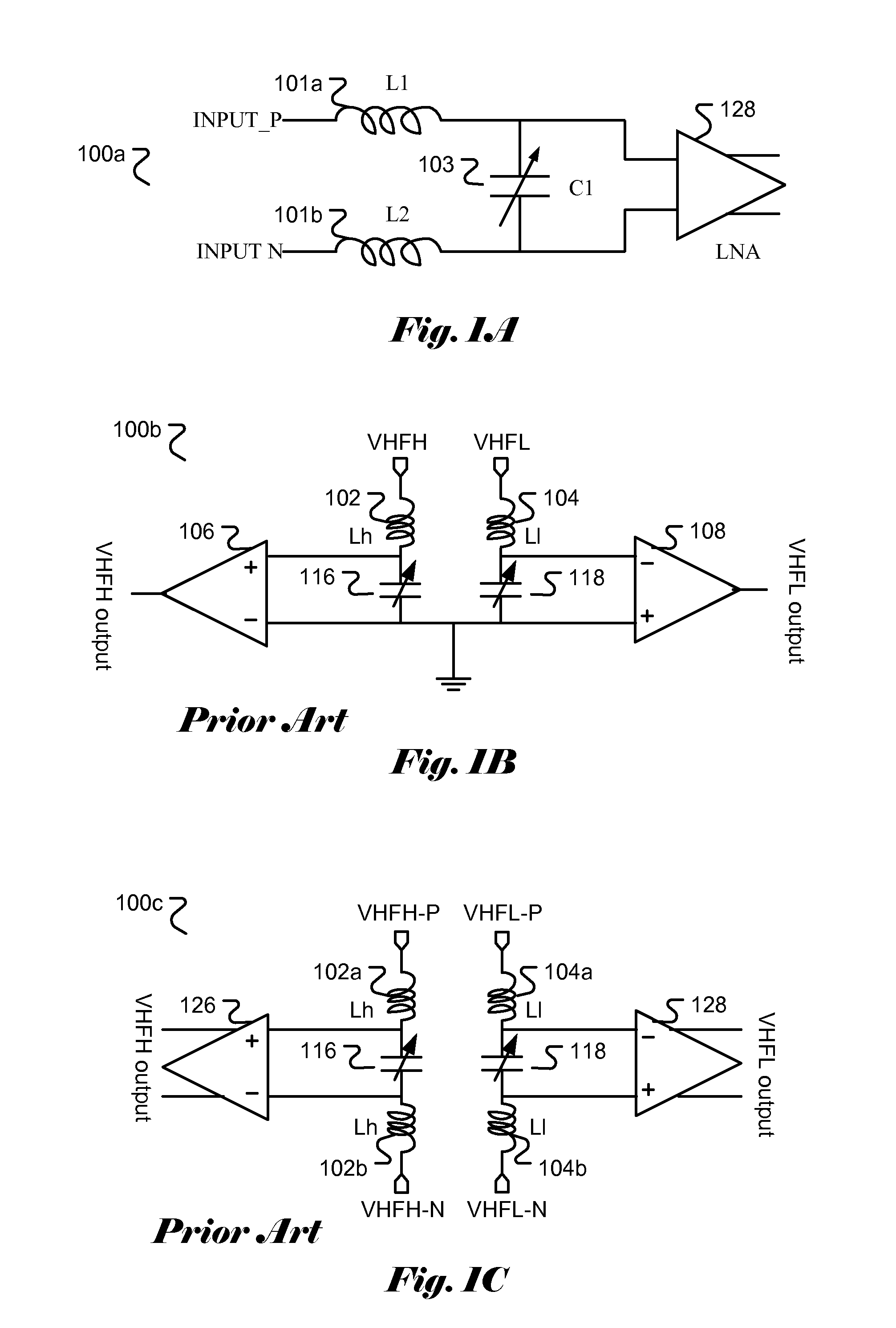

Radio frequency mixer with notch filter

InactiveUS20060128340A1Overcomes drawbackModulation transference by semiconductor devices with minimum 2 electrodesAmplifier with semiconductor-devices/discharge-tubesGilbert cellFrequency mixer

A mixer with integrated filter for single-ended image rejection is provided, including a single-end to differential (S-to-D) converter, an image rejection notch filer and four Gilbert cell switches. The mixer uses the S-to-D converter as the input cell of the mixer to replace a conventional differential pair circuit. With the converter, the mixer is directly connected to the single-ended LNA, and the output voltage swing of the LNA will be transferred into a differential signal. The image rejection filter is placed between the S-to-D converter and the Gilbert cell switches to filter the image signal from the converter. Thus, only the desired RF signal passing through the Gilbert cell switches will be converted to IF. The notch filter in the mixer of the present invention includes a third-order LC filter and a Q-enhanced circuit. The third-order LC filter has a switch capacitor array to tune both the desired frequency and the image frequency simultaneously. The Q-enhanced circuit includes a programmable current control to adjust the bandwidth and the image rejection of the notch filter.

Owner:MUCH IP

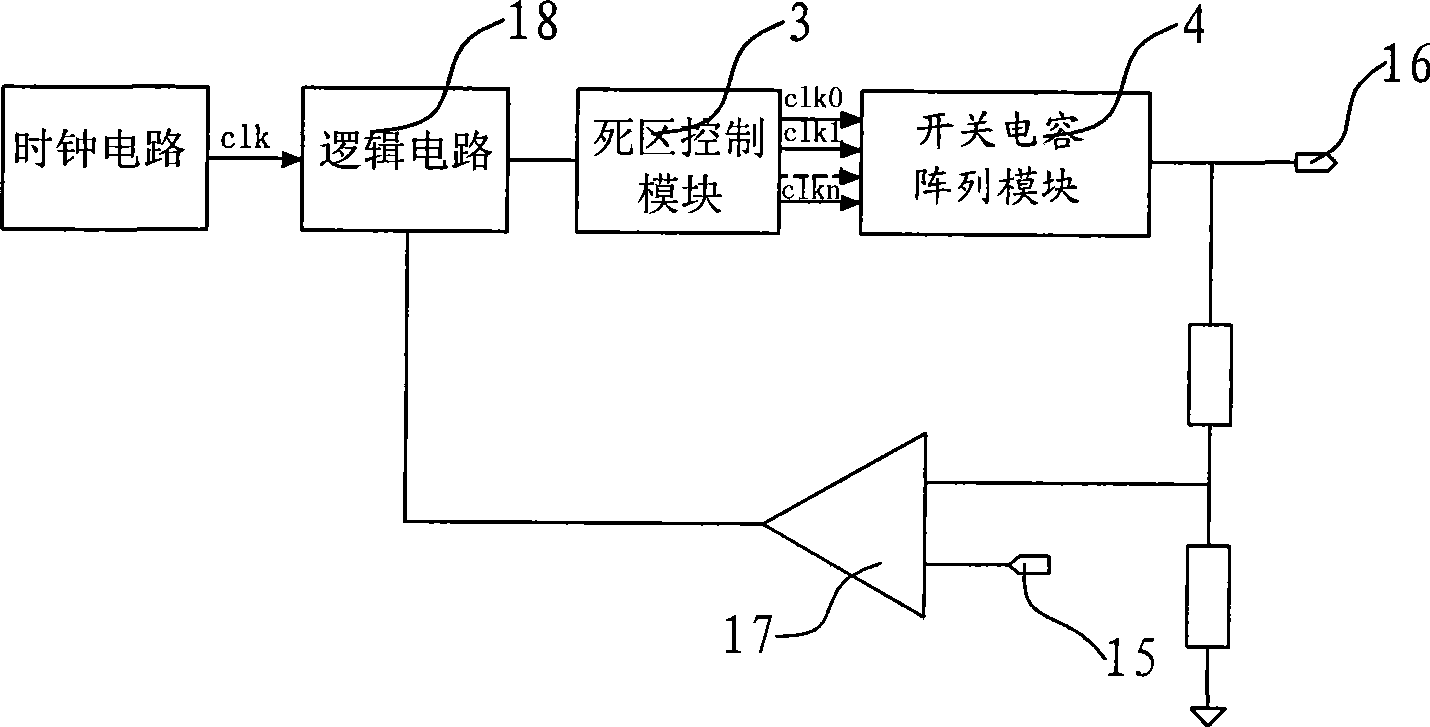

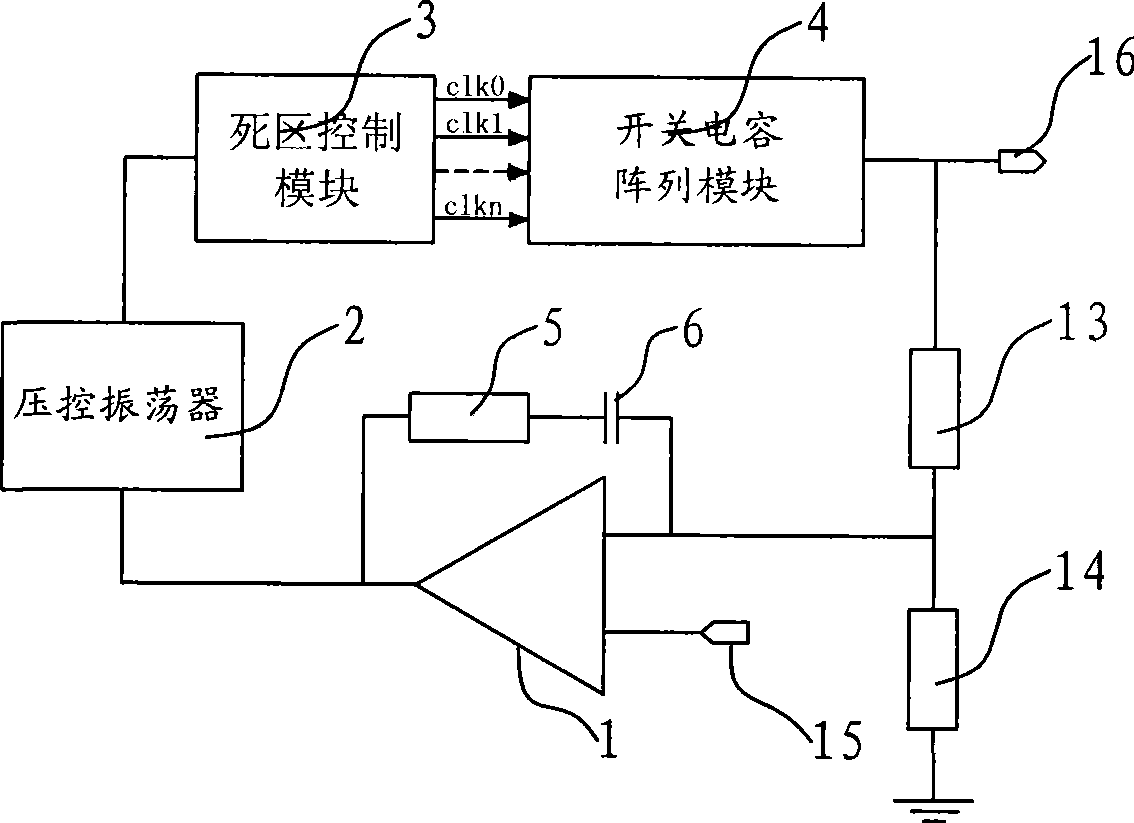

Switching capacitor type DC-DC converter

InactiveCN101478234AImprove efficiencySmall output rippleApparatus without intermediate ac conversionDc dc converterEngineering

The invention provides a switched capacitor DC-DC converter. The switched capacitor DC-DC converter comprises an output sampling branch, a dead area control module for generating the dead area and outputting multiunit clock signals which has the same frequency as the input clock, a switched capacitor array module for receiving multiunit clock signals which are not overlapped and sent by the dead area control module, an error amplifier for receiving the voltage signal from the output sampling branch and the reference voltage signals, and a voltage controlled oscillator for receiving the output voltage signals of the error amplifier and for outputting the clock signals with corresponding frequency. The voltage controlled oscillator sends the clock signals to the dead control module. The frequency variation of the clock signals is in proportion to the output voltage variation of the error amplifier. The converter has low output voltage ripple and high efficiency in full load range.

Owner:ZHEJIANG UNIV +1

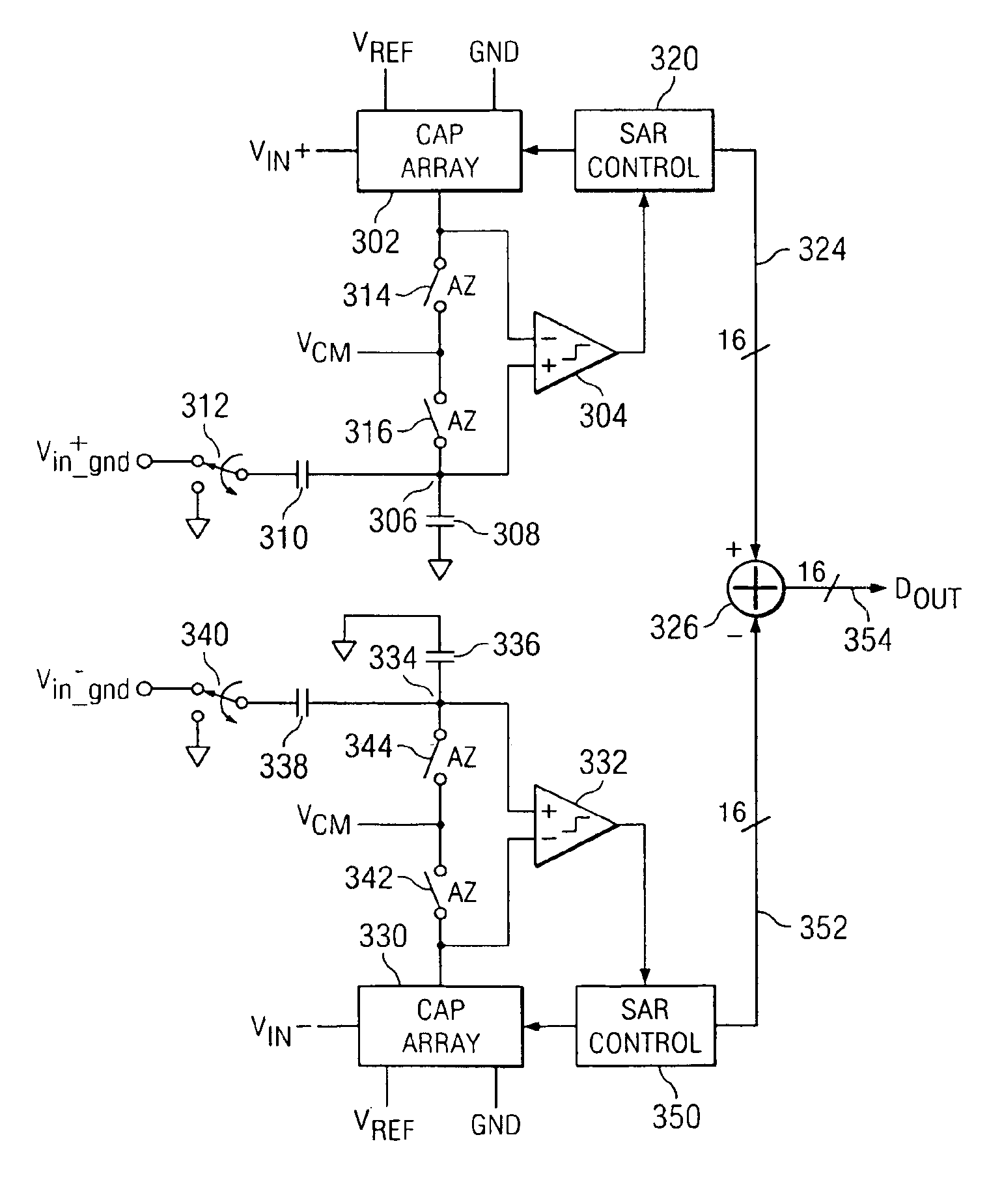

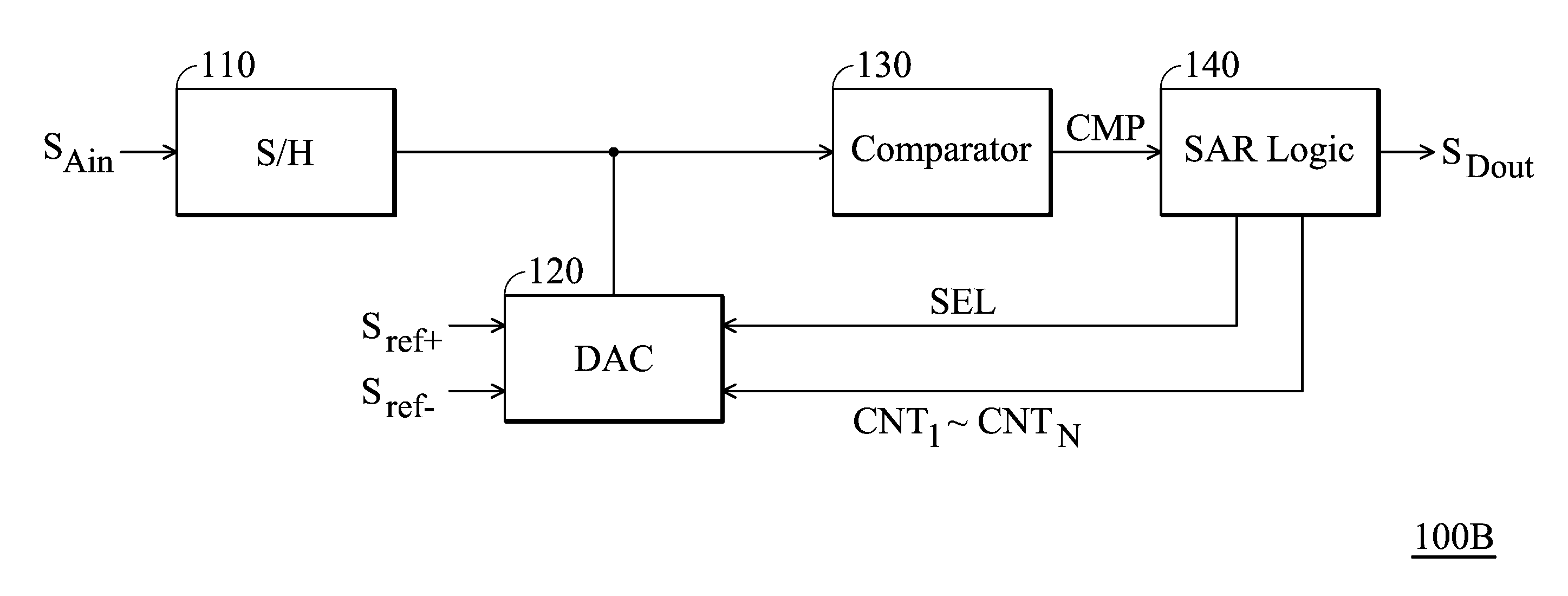

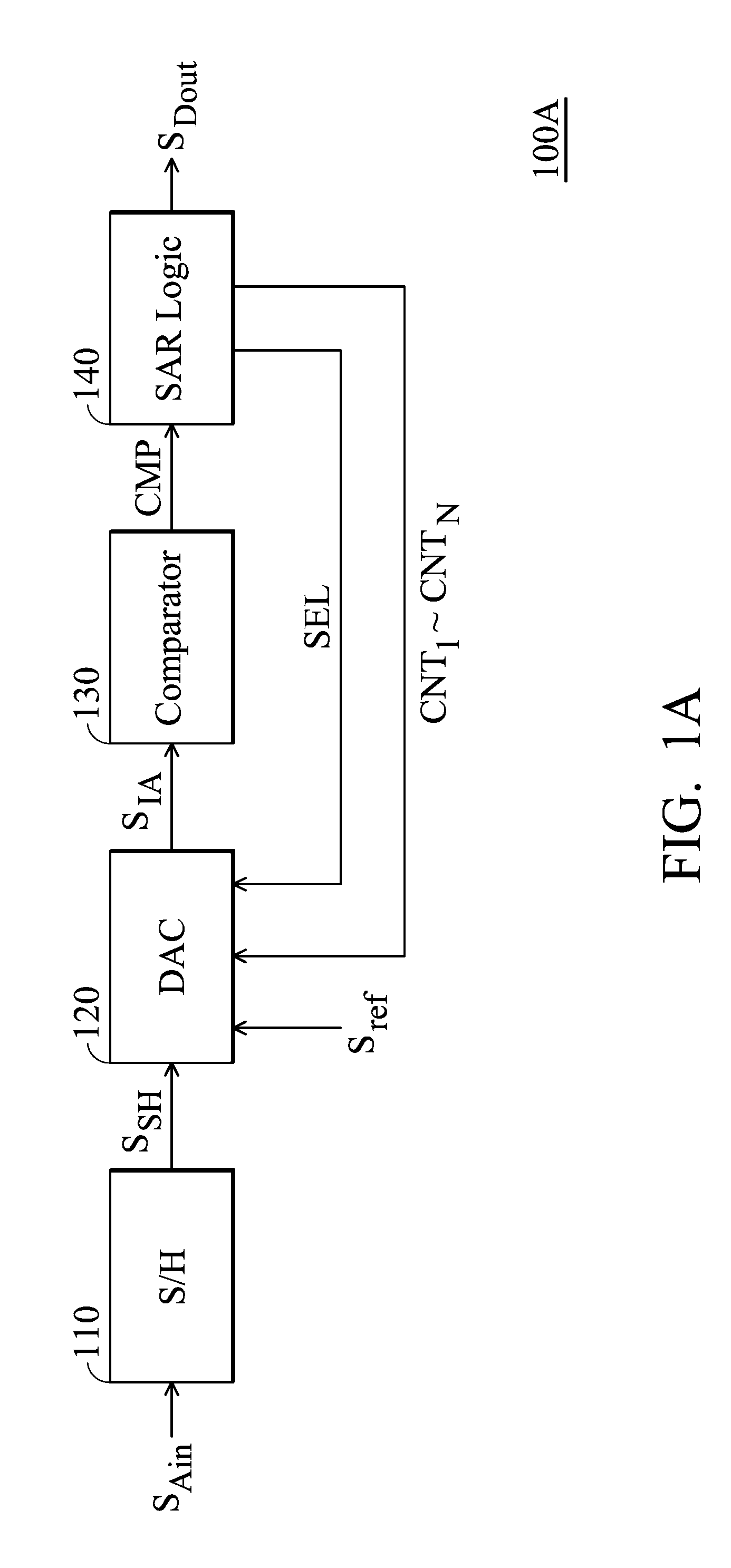

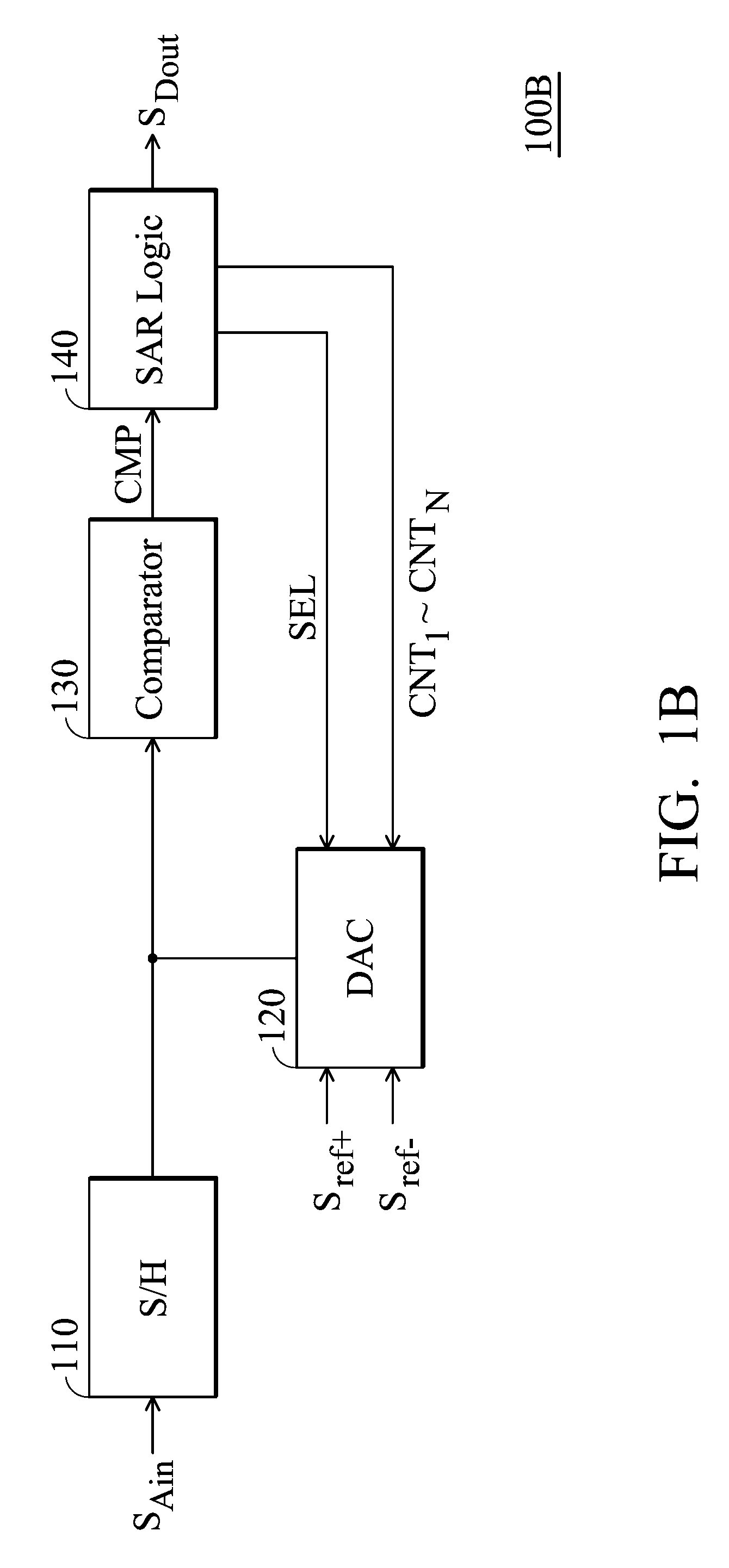

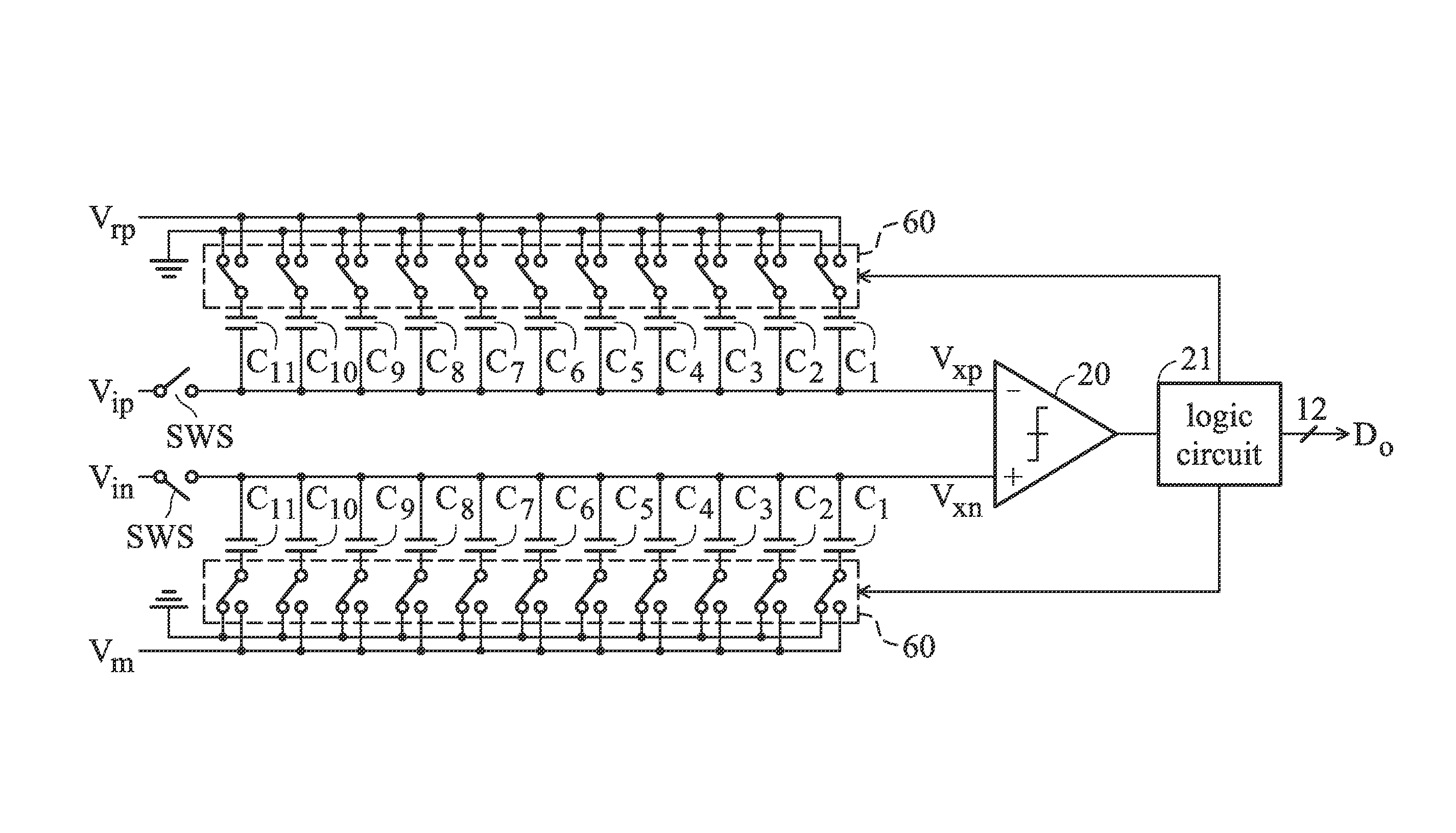

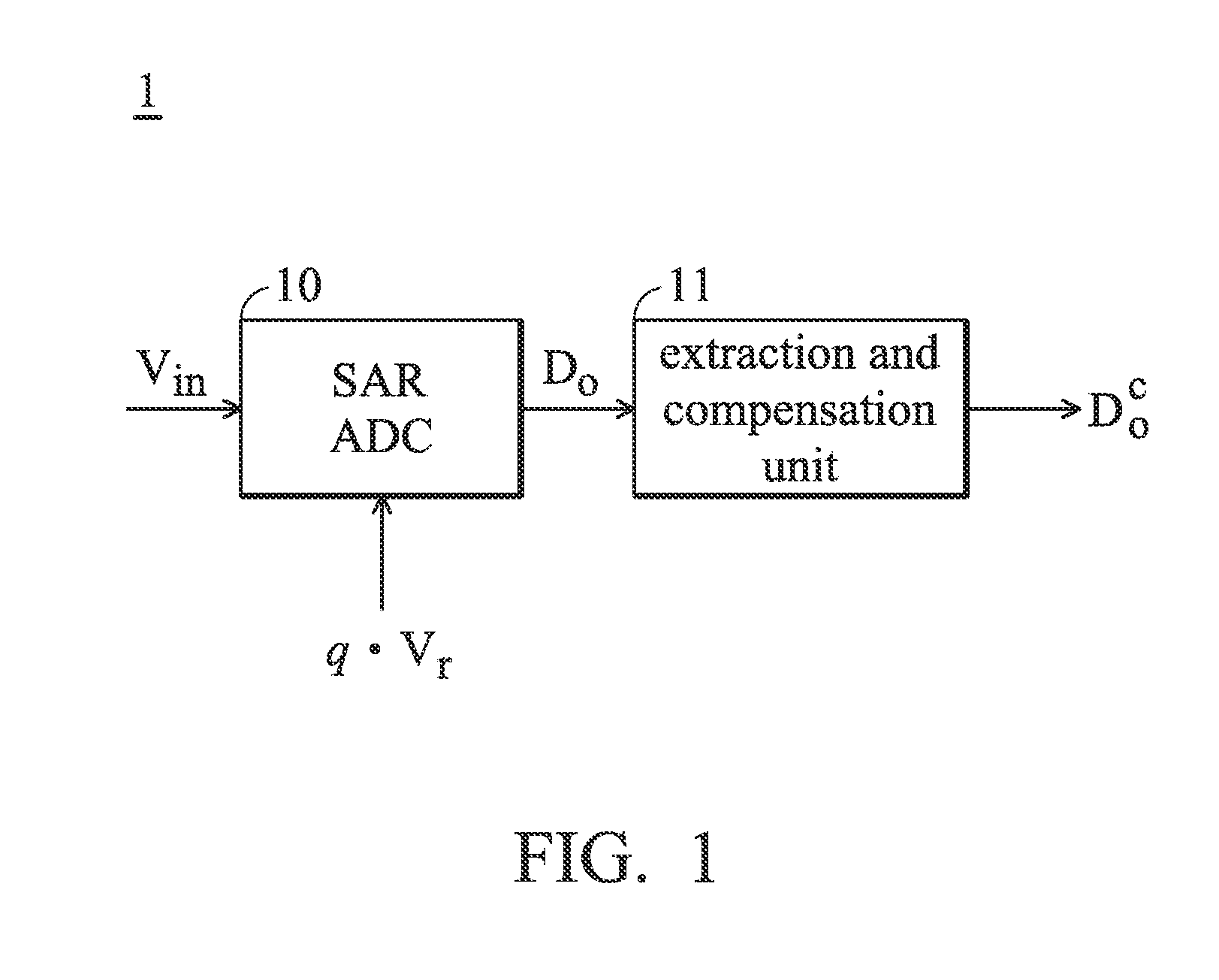

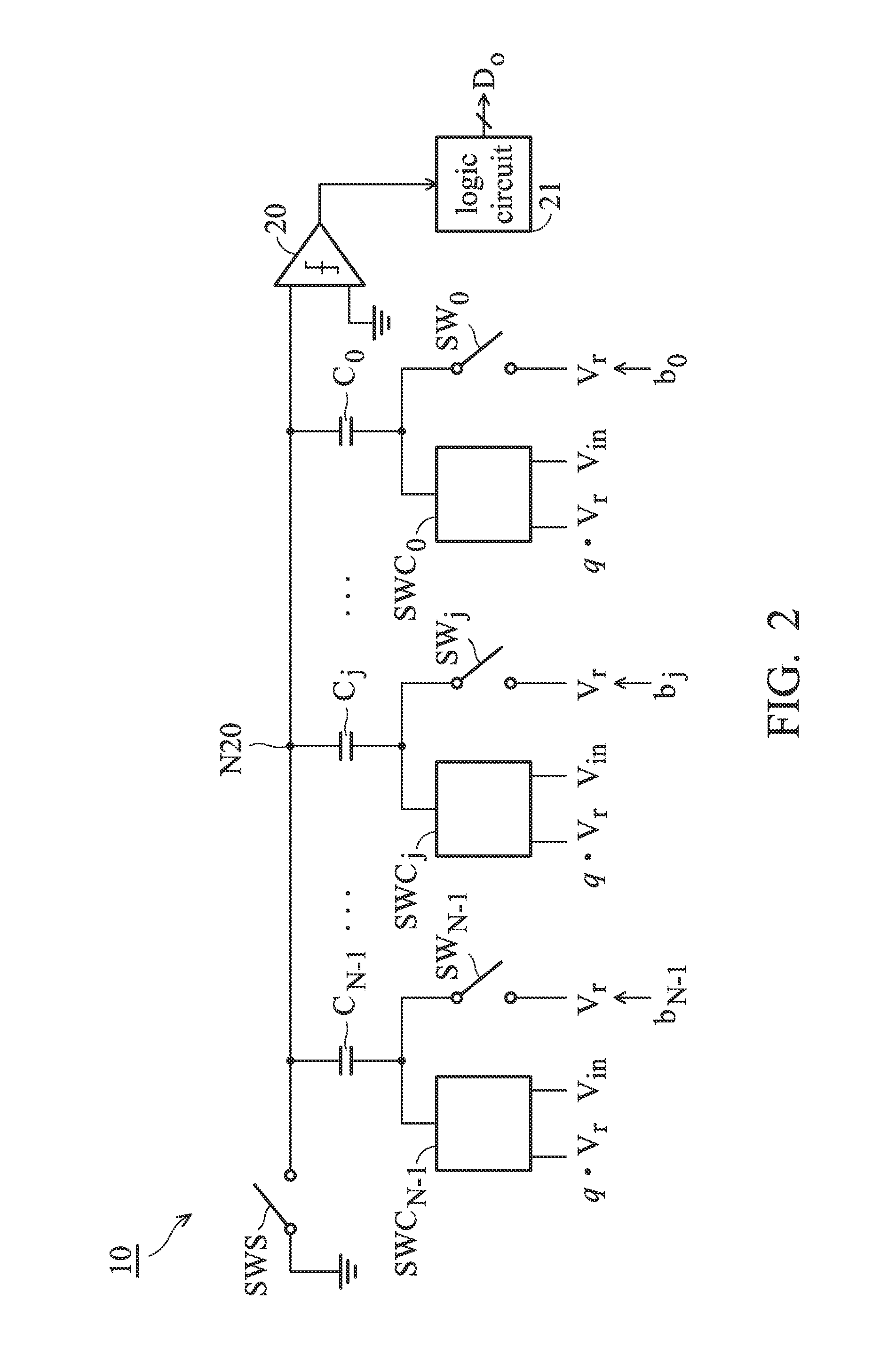

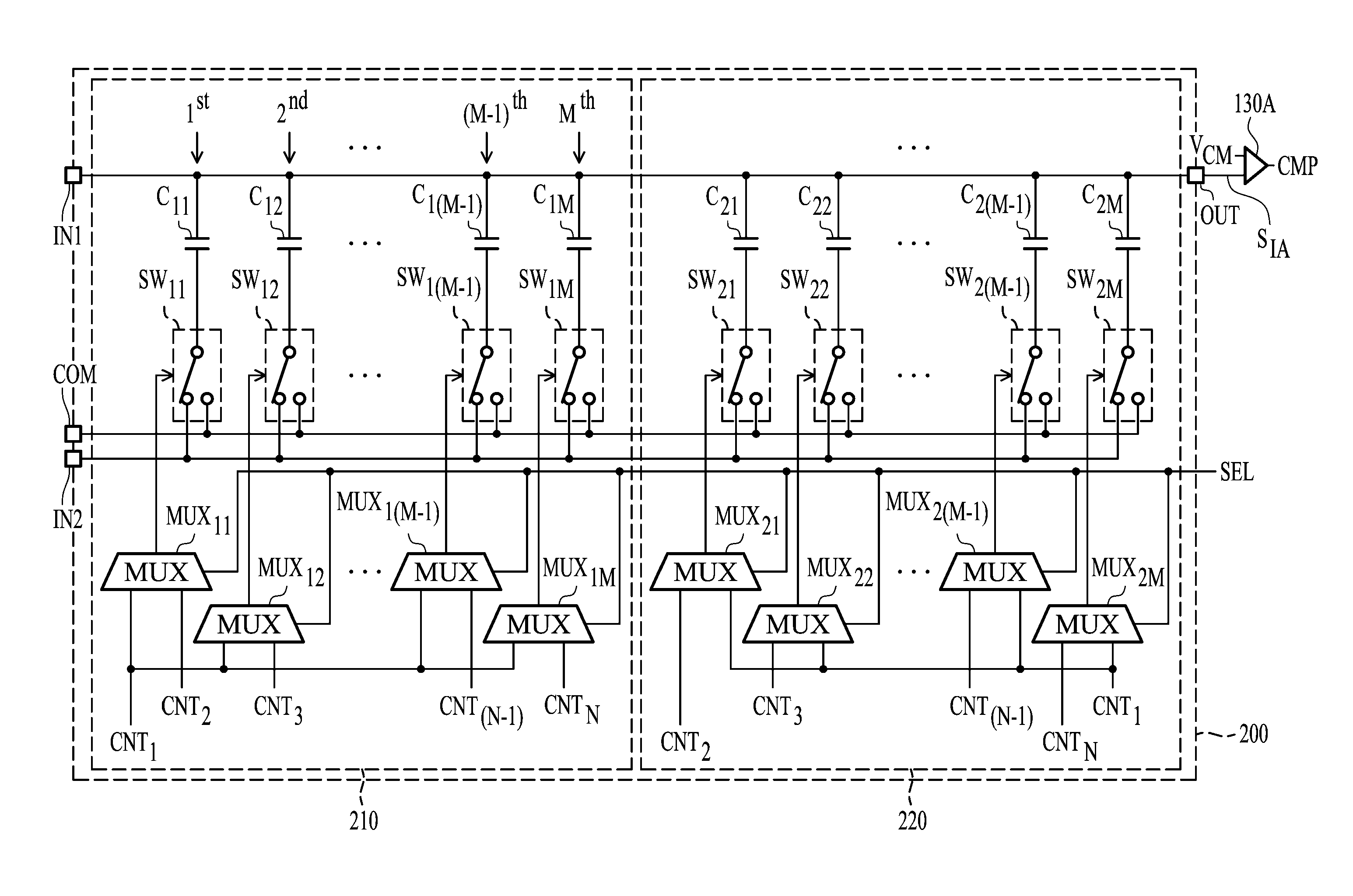

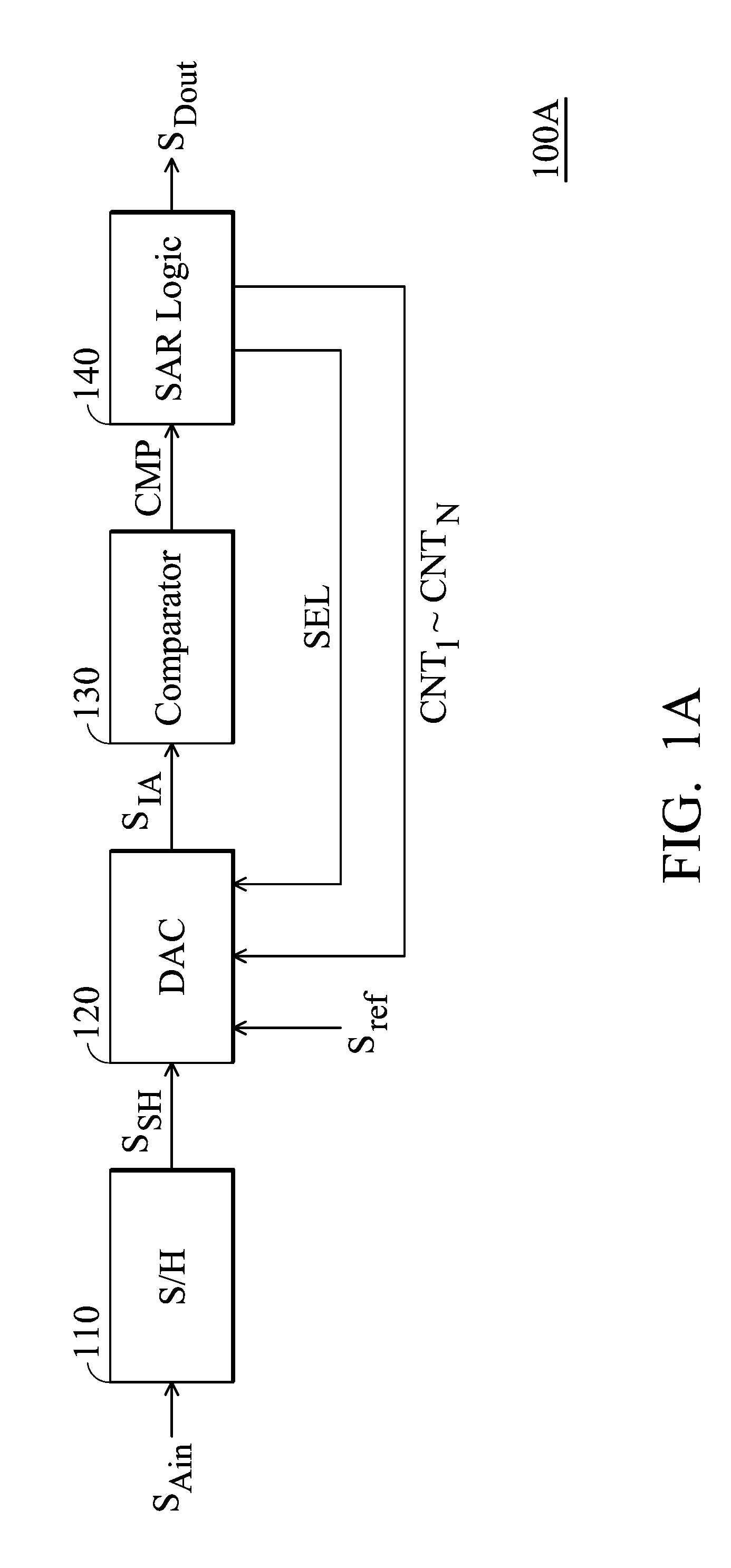

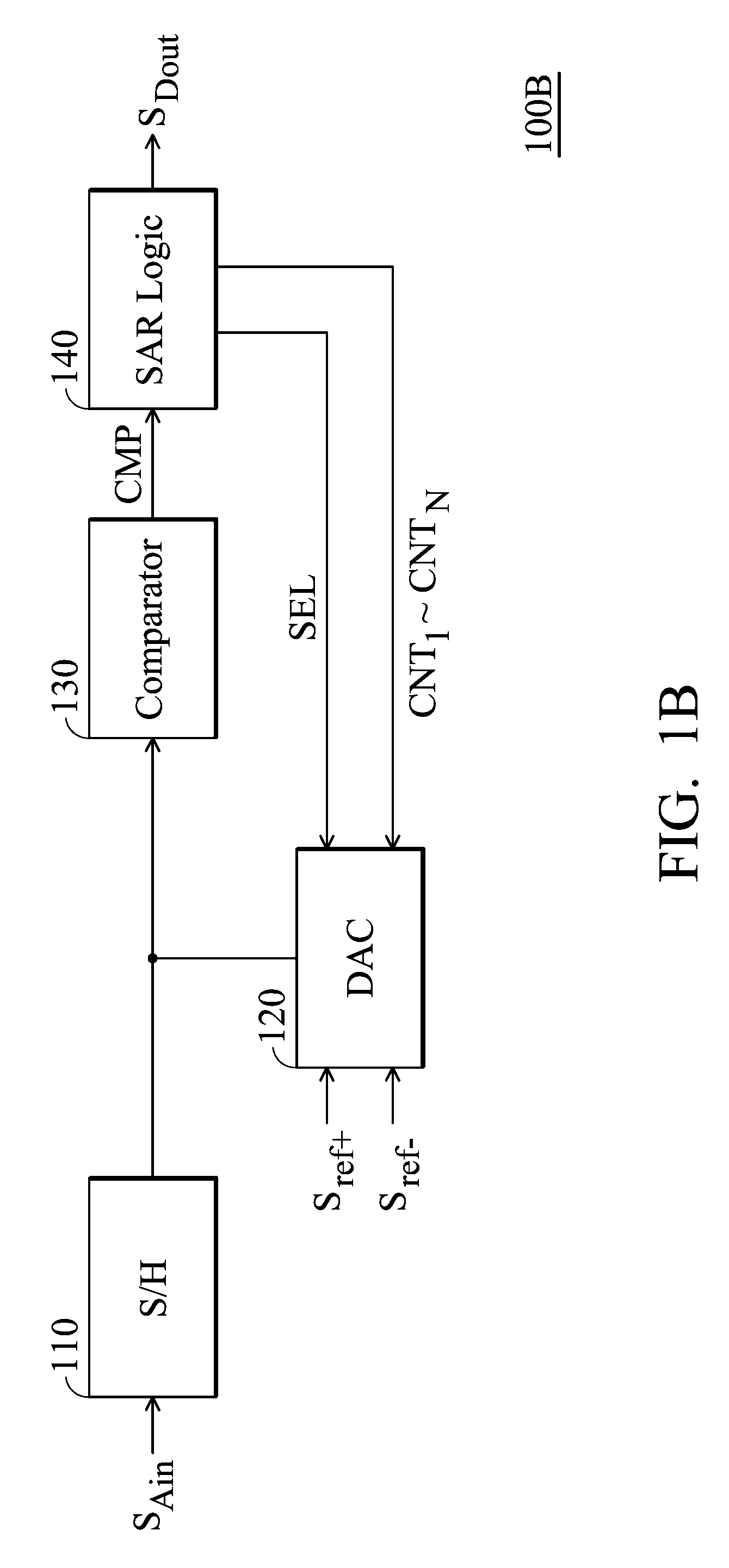

Successive approximation register analog to digital converter and conversion method thereof

InactiveUS20120326900A1Electric signal transmission systemsAnalogue-digital convertersCapacitanceAnalog signal

A SAR ADC is provided. A DAC provides an intermediate analog signal according to an analog input signal, a most significant bit capacitance and a plurality of significant bit capacitances smaller than the most significant bit capacitance. A first switched capacitor array selectively provides the most significant bit capacitance or the significant bit capacitances according to a select signal. Sum of the significant bit capacitances is equal to the most significant bit capacitance. The second switched capacitor array provides the significant bit capacitances when the first switched capacitor array provides the most significant bit capacitance, and provides the most significant bit capacitance when the first switched capacitor array provides the significant bit capacitances. A comparator provides a comparison result according to the intermediate analog signal. A SAR logic provides an digital output signal according to the comparison result.

Owner:MEDIATEK INC

Successive approximation register analog to digital converters

ActiveUS9287891B1Correction errorElectric signal transmission systemsAnalogue/digital conversion calibration/testingCapacitanceAnalog signal

A SAR ADC is provided. A DAC provides an intermediate analog signal according to an analog input signal, a most significant bit capacitance and a plurality of significant bit capacitances smaller than the most significant bit capacitance. A first switched capacitor array selectively provides the most significant bit capacitance or the significant bit capacitances according to a select signal. Sum of the significant bit capacitances is equal to the most significant bit capacitance. The second switched capacitor array provides the significant bit capacitances when the first switched capacitor array provides the most significant bit capacitance, and provides the most significant bit capacitance when the first switched capacitor array provides the significant bit capacitances. A comparator provides a comparison result according to the intermediate analog signal. A SAR logic provides an digital output signal according to the comparison result.

Owner:MEDIATEK INC

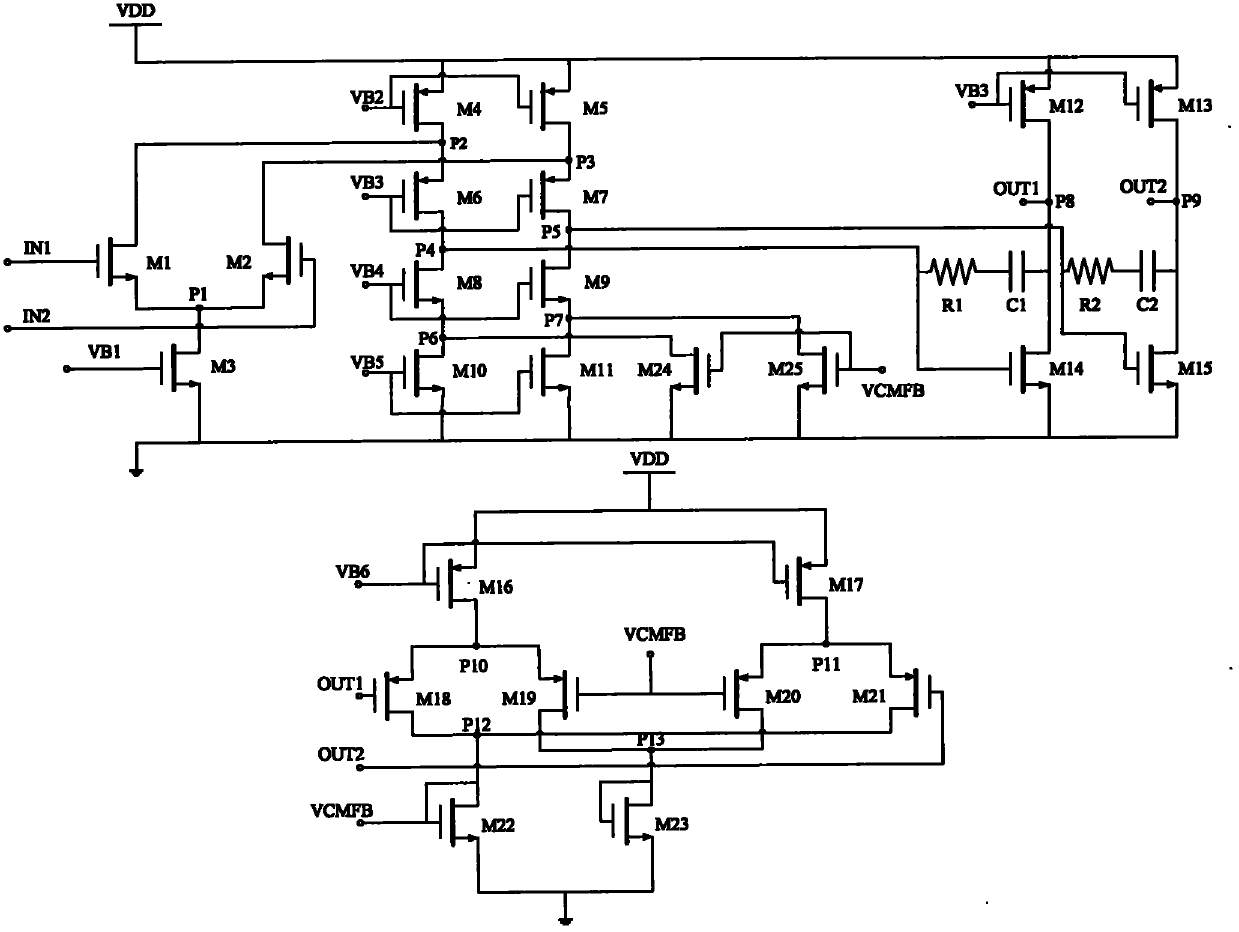

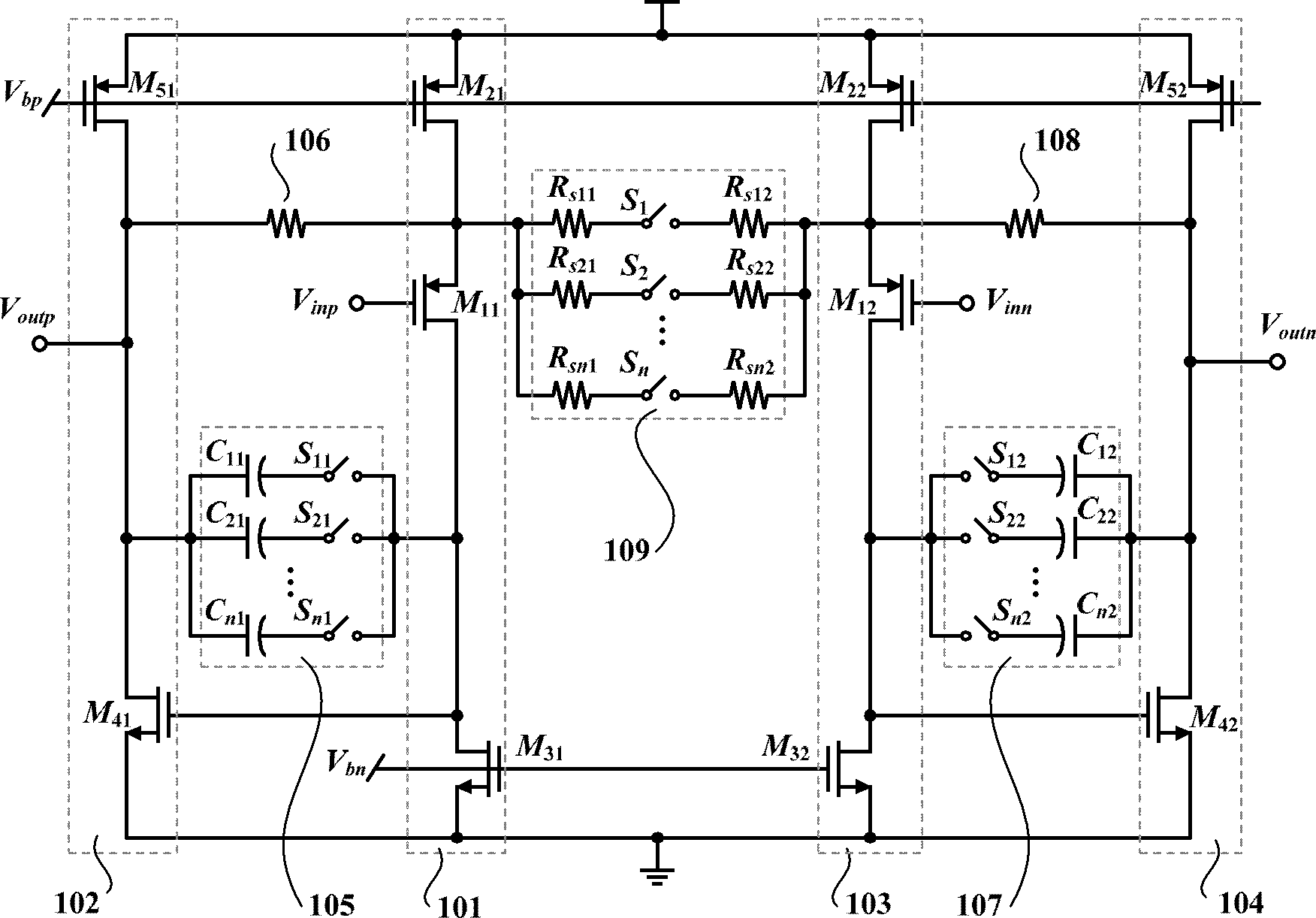

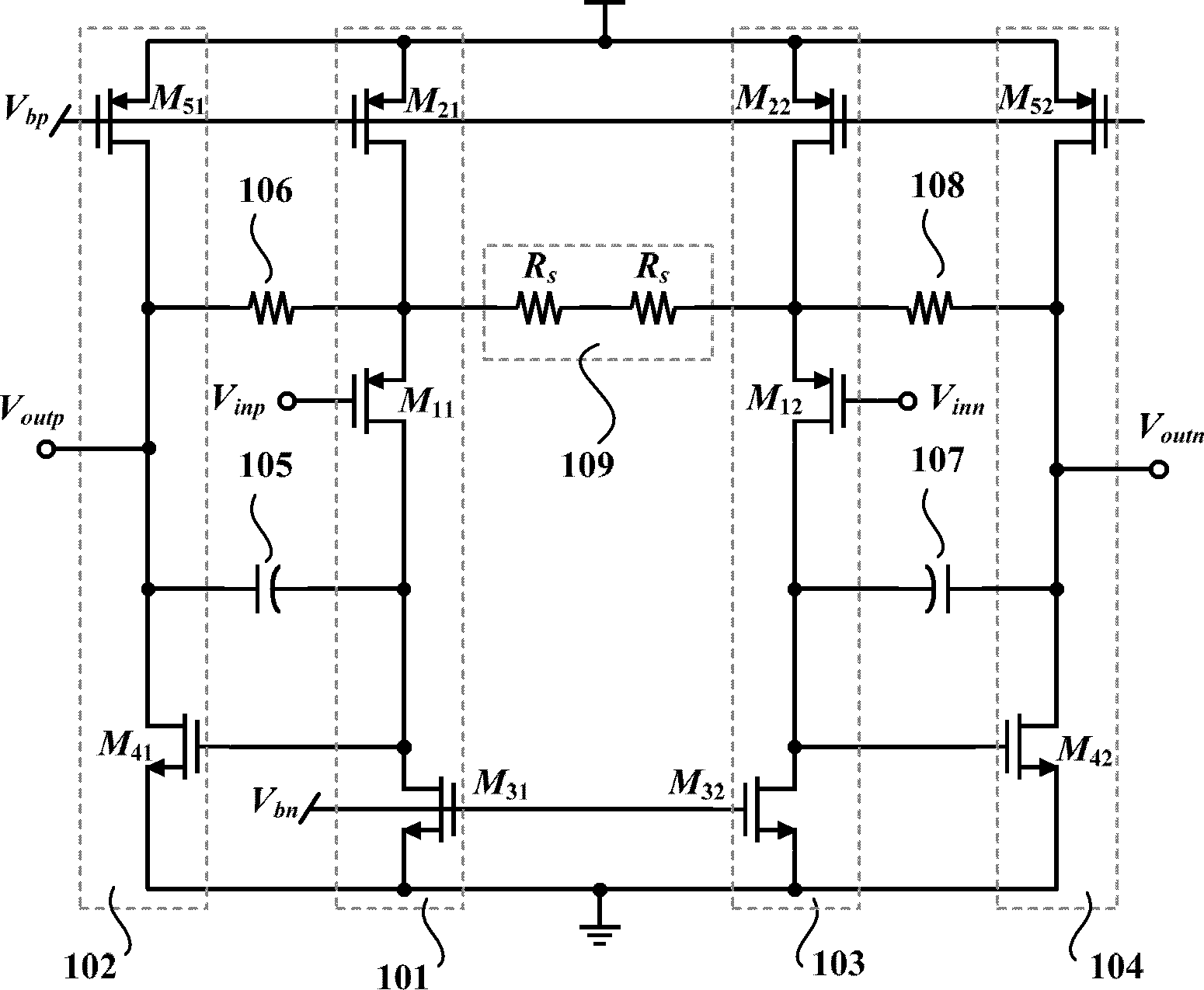

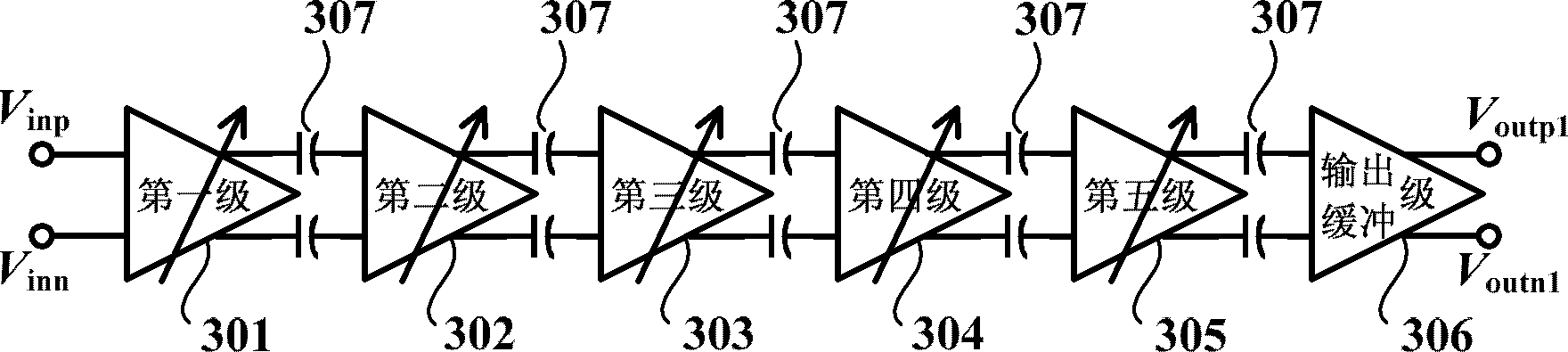

Programmable gain amplification circuit and programmable gain amplifier

ActiveCN103051298AImprove linearityHigh bandwidthAmplifier modifications to reduce non-linear distortionDifferential amplifiersClosed loop feedbackCoupling

The invention provides a programmable gain amplification circuit and a programmable gain amplifier. The programmable gain amplification circuit is of a symmetrical fully-differential circuit structure and comprises two differential branch circuits of the same structure, each differential branch circuit respectively comprises a differential input stage connected with a common source structure of a signal input end and a differential output stage connected with a common source structure of a signal output end, and a switching capacitor array is connected between the differential input stage and the differential output stage and connected with a feedback resistor to form a closed loop feedback circuit. The differential input stage of one differential branch circuit is connected with the differential input stage of the other differential branch circuit through a switching resistor array to form a source degeneracy structure. The programmable gain amplifier comprises a plurality of programmable gain amplification circuits connected through an alternating current coupling mode and an output buffer stage applied to a receiving end. The programmable gain amplifier can provide a large gain regulation range and can meet requirements of linearity and bandwidth.

Owner:锐立平芯微电子(广州)有限责任公司

SAR with partial capacitor sampling to reduce parasitic capacitance

InactiveUS6977607B2Reduce parasitic capacitanceElectric signal transmission systemsResistors with plural resistive elementsParasitic capacitanceVoltage reference

SAR with partial capacitor sampling to reduce parasitic capacitance. An analog-to-digital convertor is disclosed with reduced parasitic capacitance on the input during a sampling operation. A charge-redistribution, binary-weighted switched-capacitor array is included having a plurality of array capacitors that each have a commonly connected plate interfaced to a first common node and a switched plate, the switched plate operable to be switched between first and second reference voltages during a redistribution phase and select ones of the capacitors additionally operable to be switched to the input during a sampling phase. Each of the array capacitors has a parasitic capacitance associated therewith. A compensation capacitor having a common plate is connected to the first common node and a switched plate, the compensation capacitor operable to be switched to the input during the sampling phase and to the first reference voltage during the redistribution phase. The compensation capacitor has a parasitic capacitance less than the parasitic capacitance of the combination of all of the non select ones of the array capacitors. A comparator compares the voltage on the first common node to a compare reference voltage during the redistribution phase. A successive approximation controller is provided for switching the switched plate of the array capacitors between the first and second reference voltages in accordance with a successive approximation algorithm during the redistribution phase.

Owner:SILICON LAB INC

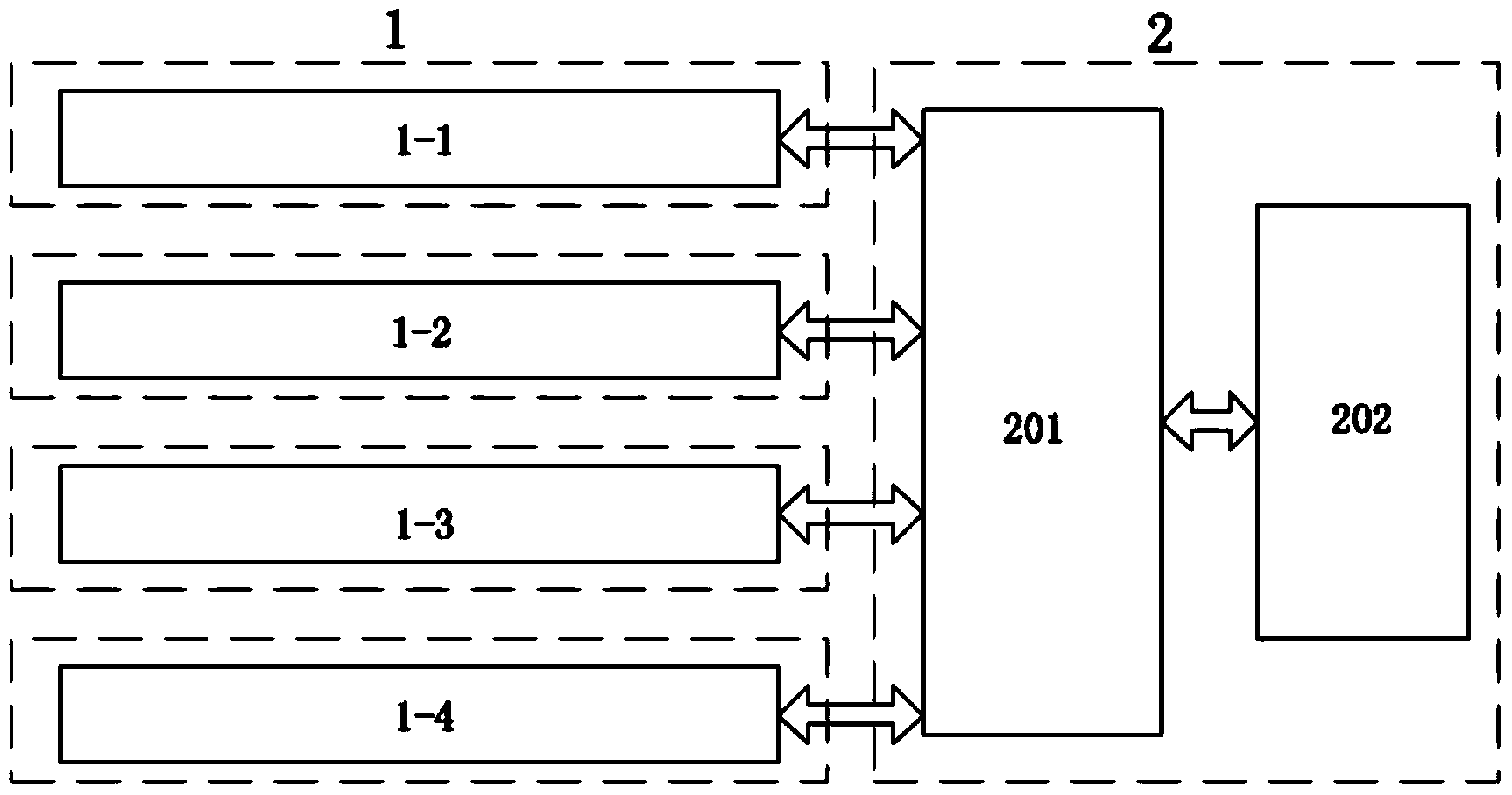

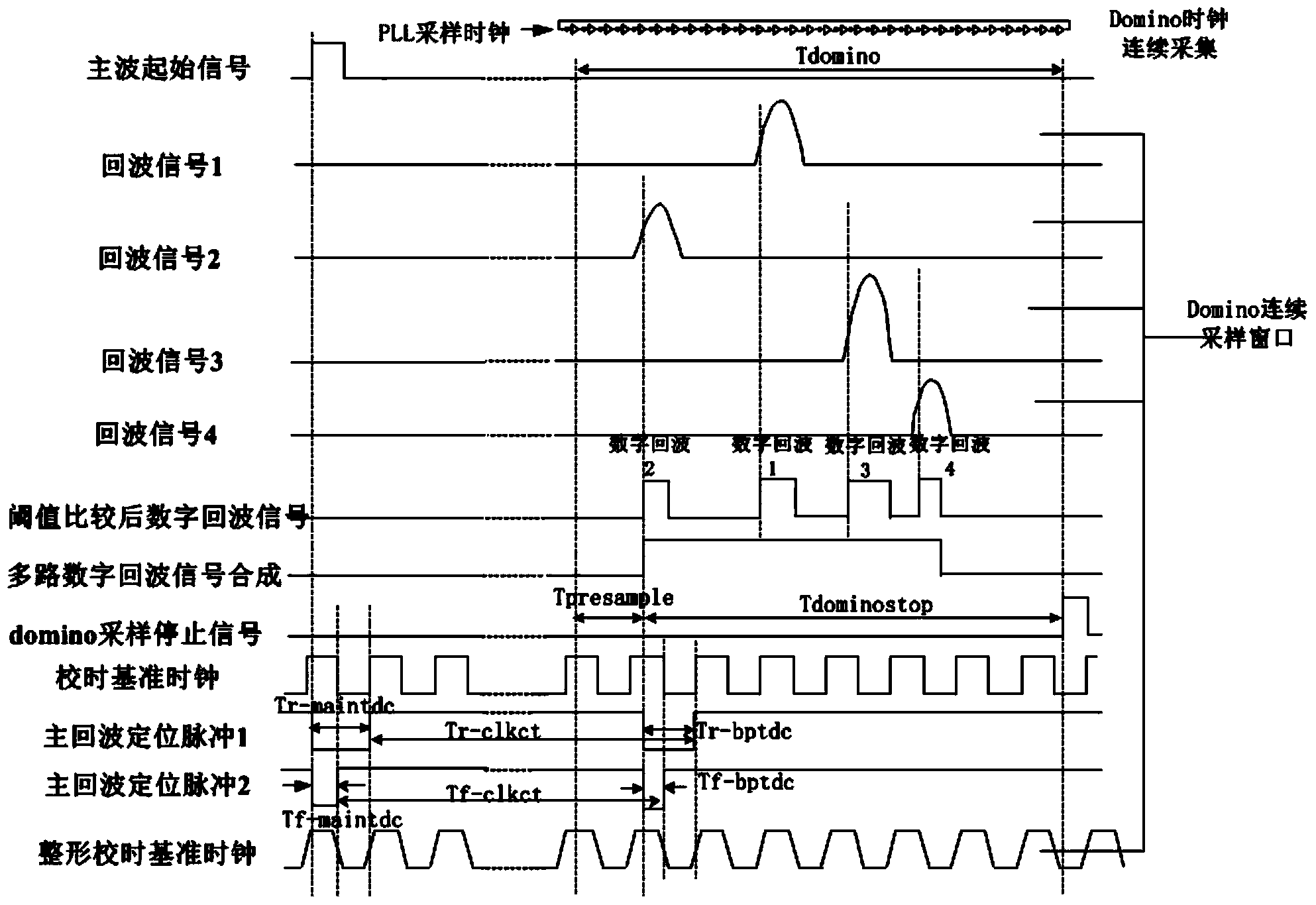

Time frequency synchronization calibration method of SCA-based multi-channel high-speed acquisition system

ActiveCN103762975AGuaranteed synchronicityPhase coincidencePulse automatic controlCapacitanceWaveform analysis

The invention discloses a time frequency synchronization calibration method of an SCA-based multi-channel high-speed data acquisition system. The SCA-based multi-channel high-speed acquisition system is composed of a waveform acquisition and time measurement module assembly and a comprehensive processor module, a high-speed switch capacitor array in an SCA chip is used for storing an analog signal and reading the analog signal through a slow-speed clock, then the analog signal is subjected to digital quantification through a high-accuracy low-speed AD to be stored into a buffer unit, and online real-time calibration can be achieved while multi-channel waveform acquisition and time measurement are completed. The time frequency synchronization calibration method is simple in calibration process, the calibration result is good in adaptability, the system calibration error is small, the measurement accuracy is superior to 80ps, and the method is particularly suitable for the technical field of whole waveform analysis.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

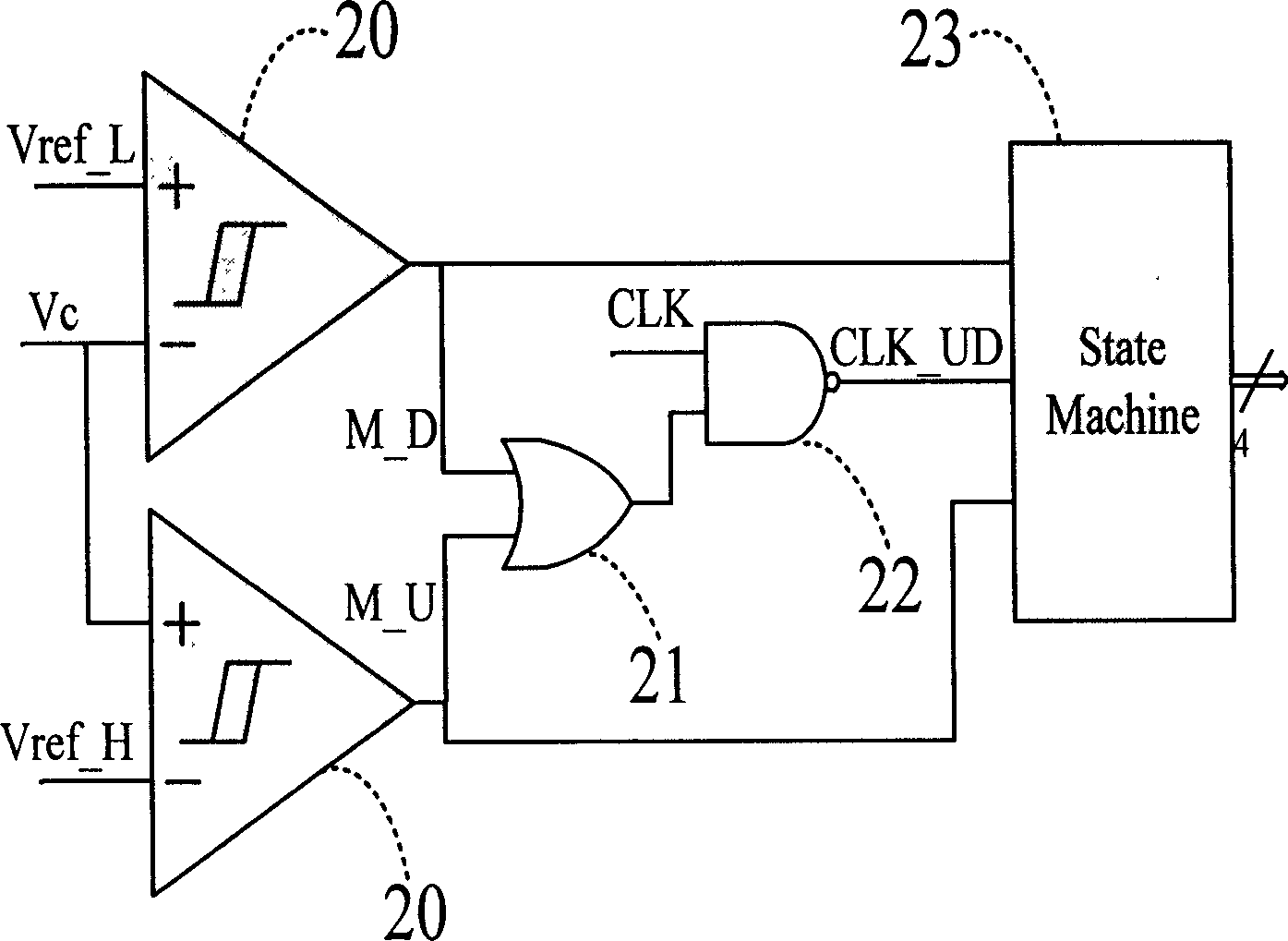

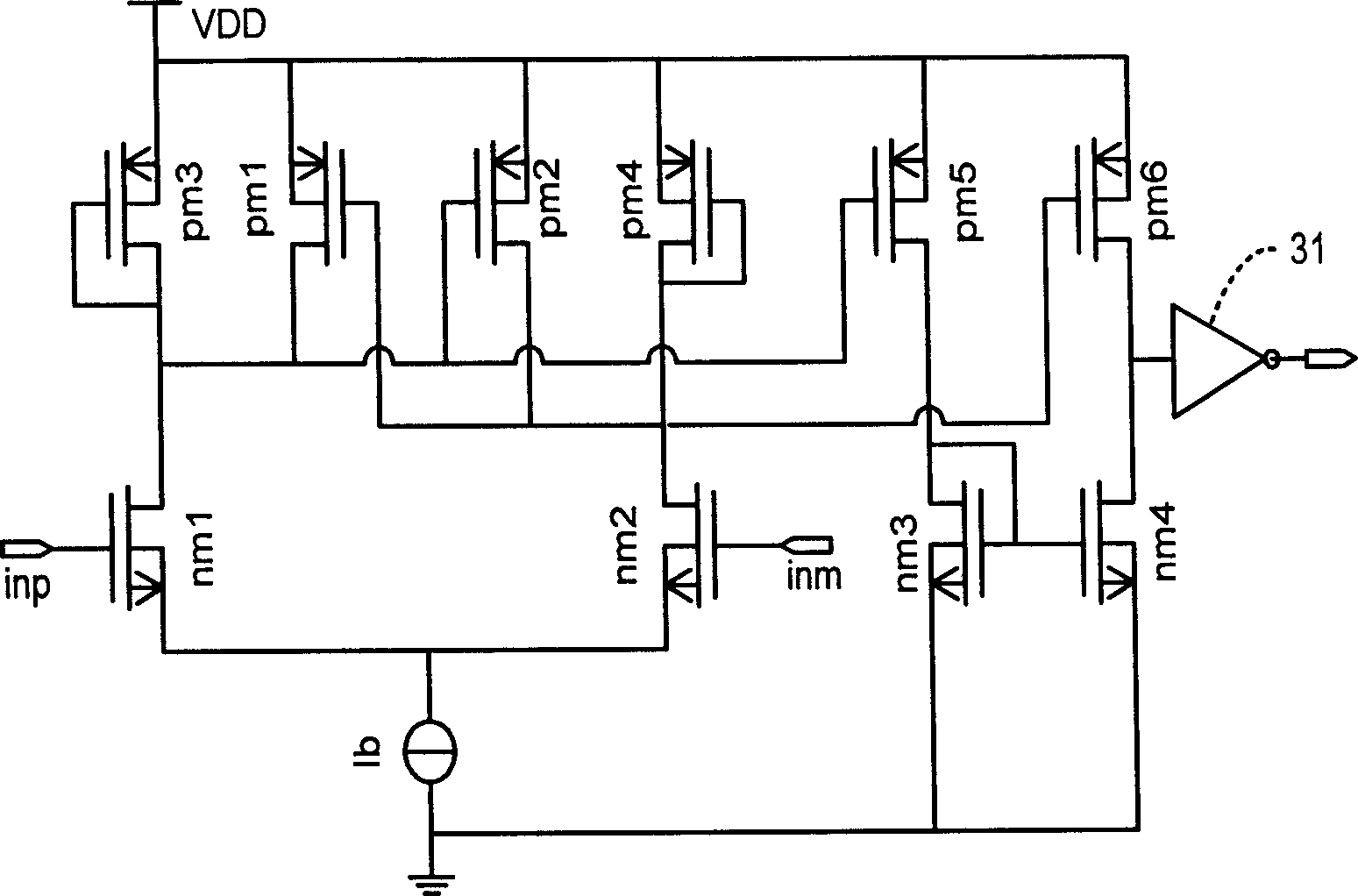

Automatic regulating method and circuit for phase locking loop frequency synthesizer switch capacitor

This invention relates to an automatic adjusting method and a realization circuit for the switch of a phase-locking loop frequency synthesizer switch capacitance, which changes the LC resonance structure of the voltage-controlled oscillator in a phase-locking loop frequency synthesizer to a structure of a variable capacitor and switch capacitor array and adds a switch capacitance control module for testing the voltage variance of the voltage-controlled oscillator to control the load of the switch capacitor and regulate the central frequency of the oscillator to get even better performance of synthesizers, said control module is composed of two hysteresis comparators and a FSM for regulating the switch, the input of the comparator is control voltage having high and low threshold voltages, the FSM controls the switch of the switch capacitor array.

Owner:张海清

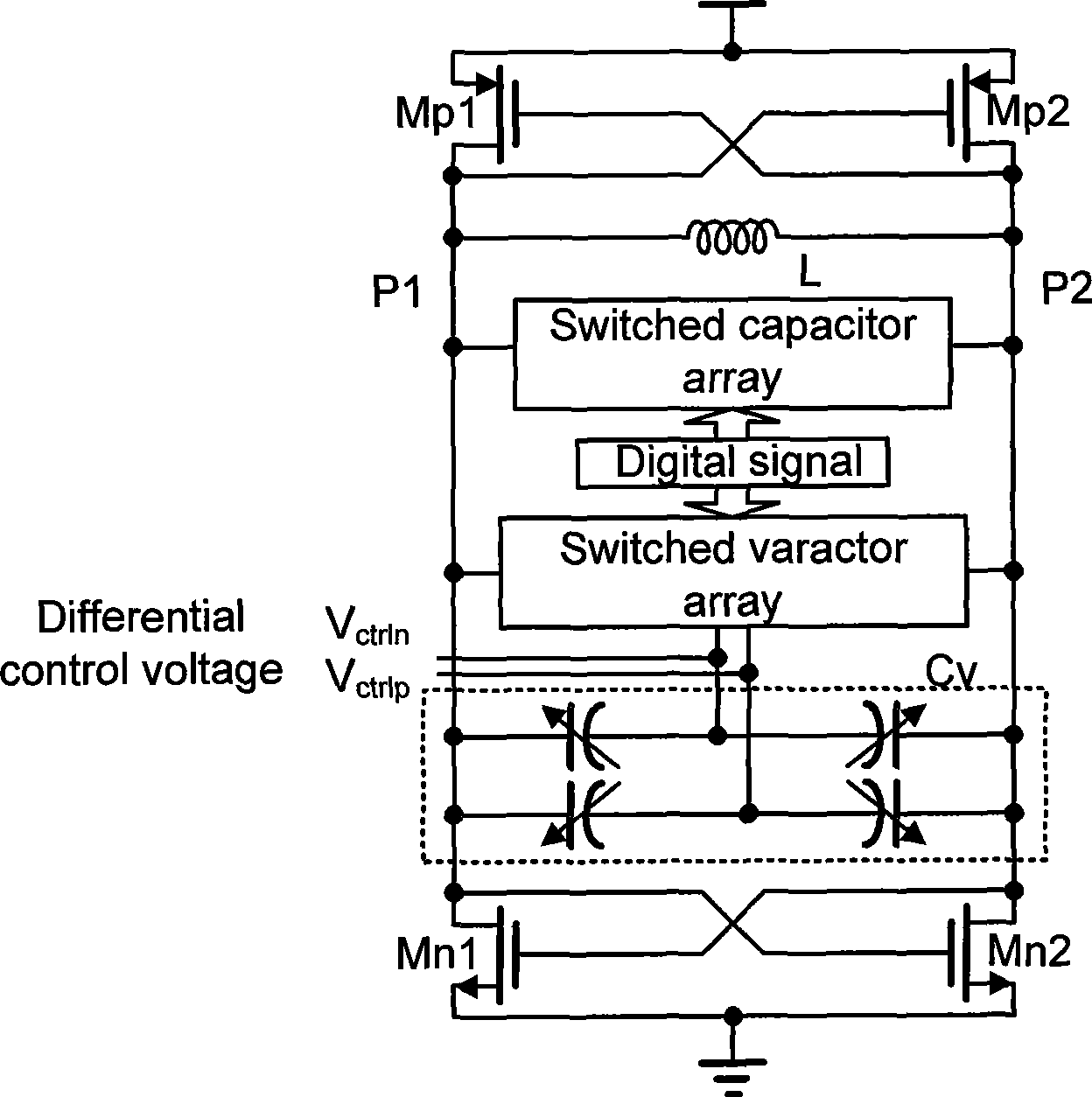

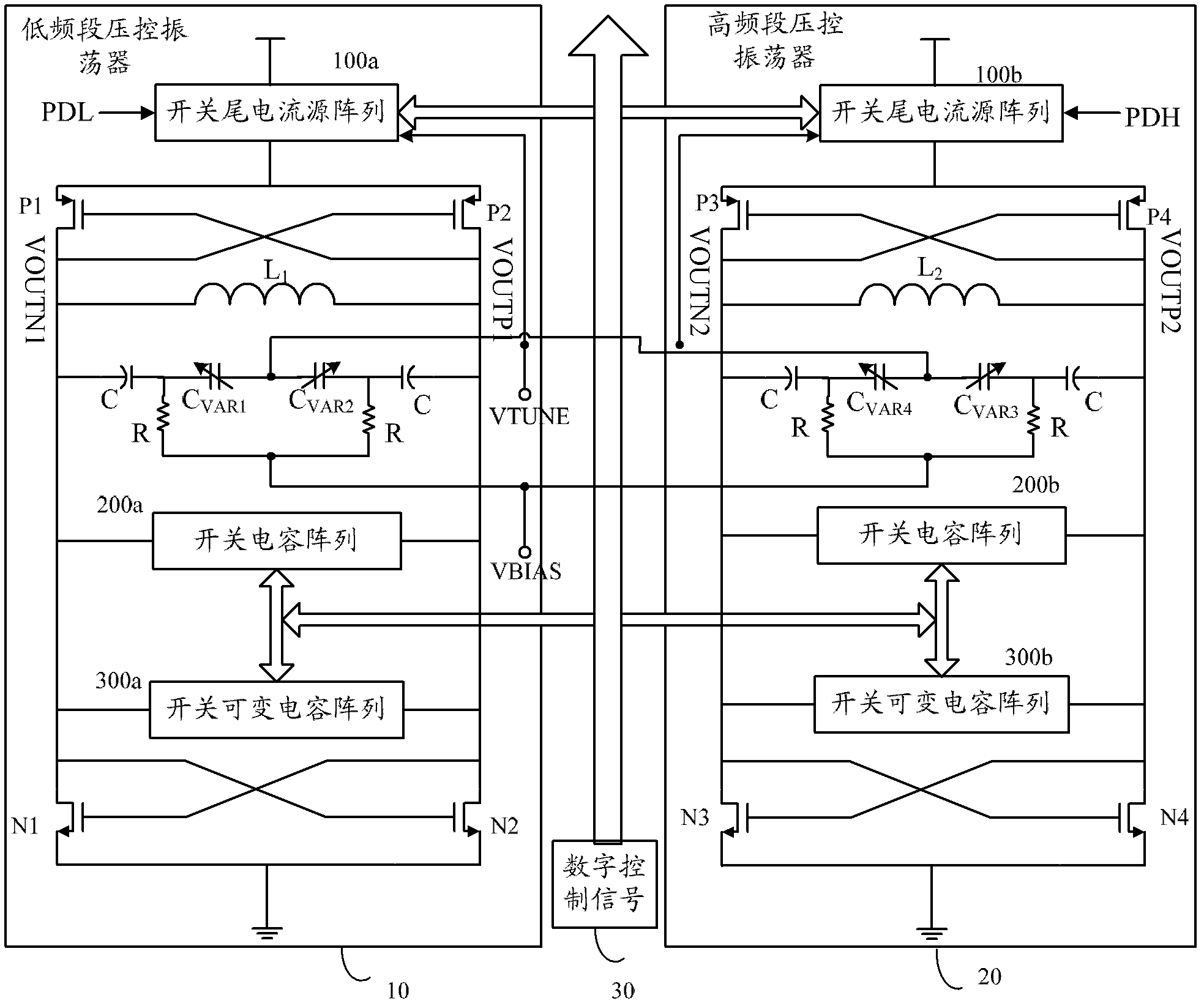

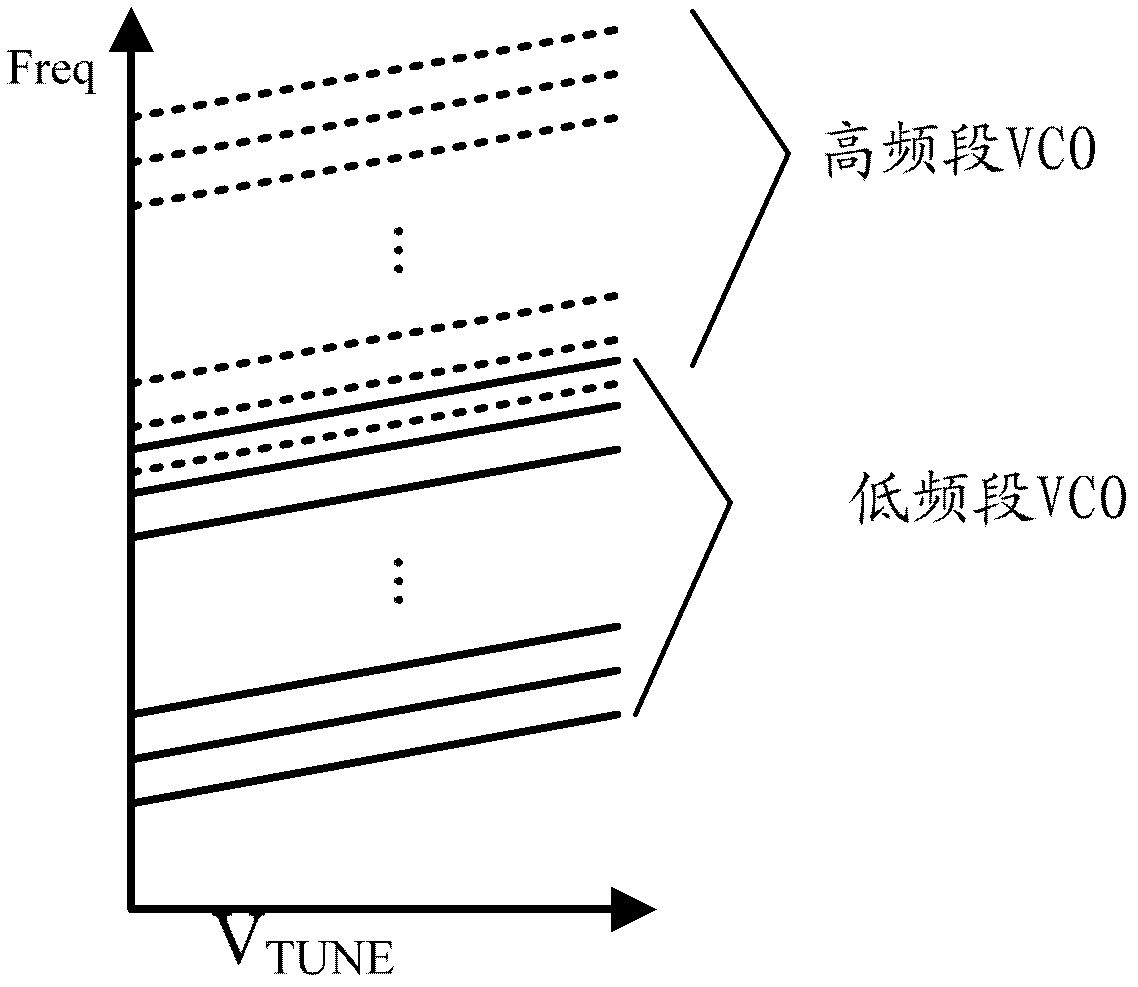

Dual-mode broadband voltage controlled oscillator

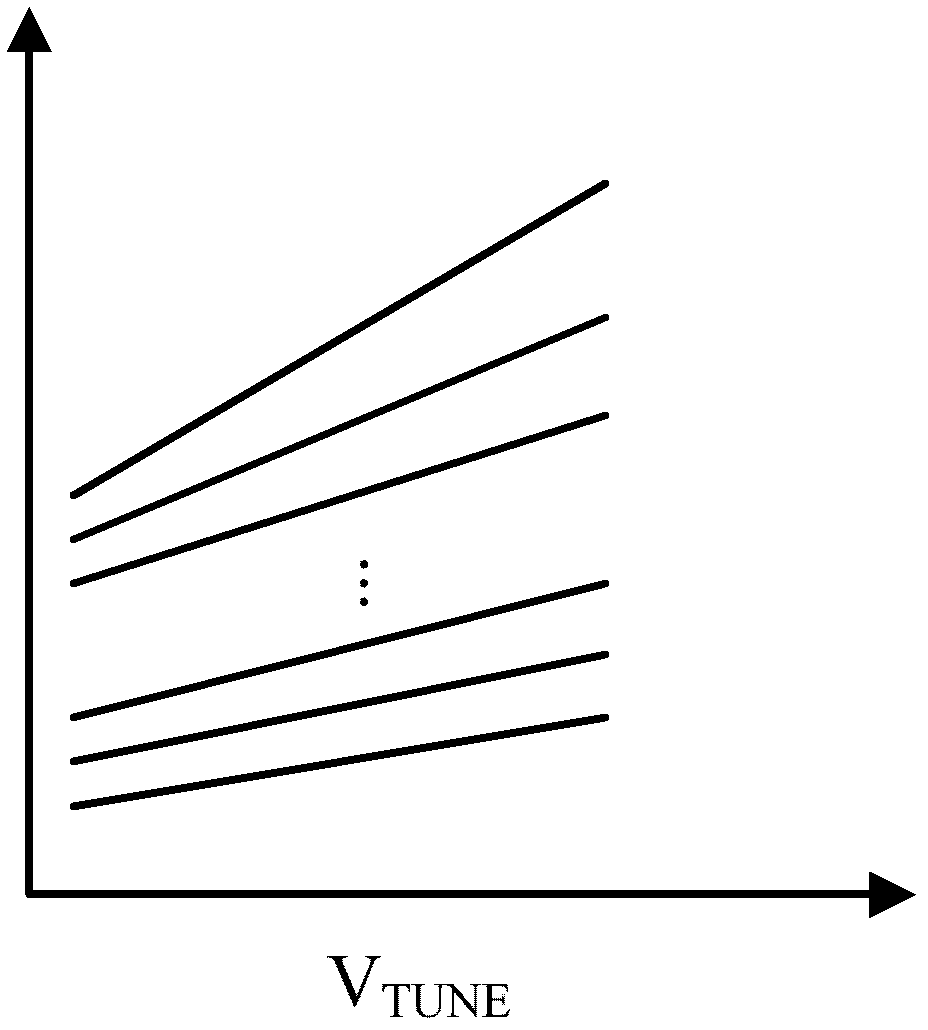

The invention provides a dual-mode broadband voltage controlled oscillator which comprises two voltage controlled oscillator parts working at a high frequency band and a low frequency band respectively, wherein each voltage controlled oscillator part comprises an inductor, two variable capacitors, a negative resistance circuit, a switch variable capacitor array, a switch capacitor array, and a switch tail current source array. In each voltage controlled oscillator part, the inductor is connected between two output ends of the voltage controlled oscillator part; one end of each variable capacitor is connected with control voltage, and the other end of each variable capacitor is connected with bias voltage through a blocking capacitor and a resistor; the negative resistance circuit is formed by a cross-coupled NMOS (n-channel metal oxide semiconductor) pair and a cross-coupled PMOS (p-channel metal oxide semiconductor) pair; the switch variable capacitor array is controlled by digital control words, and used for controlling the tuning range of each tuning curve; the switch capacitor array is controlled by the digital control words; the maximum capacitance in the switch capacitor array and the switch variable capacitor array codetermines the starting point of each tuning curve; the switch tail current source array is controlled by the digital control words and the control voltage together, and used for generating tail current; and the tail current is in direct proportion to output swing amplitude of the voltage controlled oscillator part. The oscillator is stable in output swing amplitude, and wider in tuning range.

Owner:SOI MICRO CO LTD

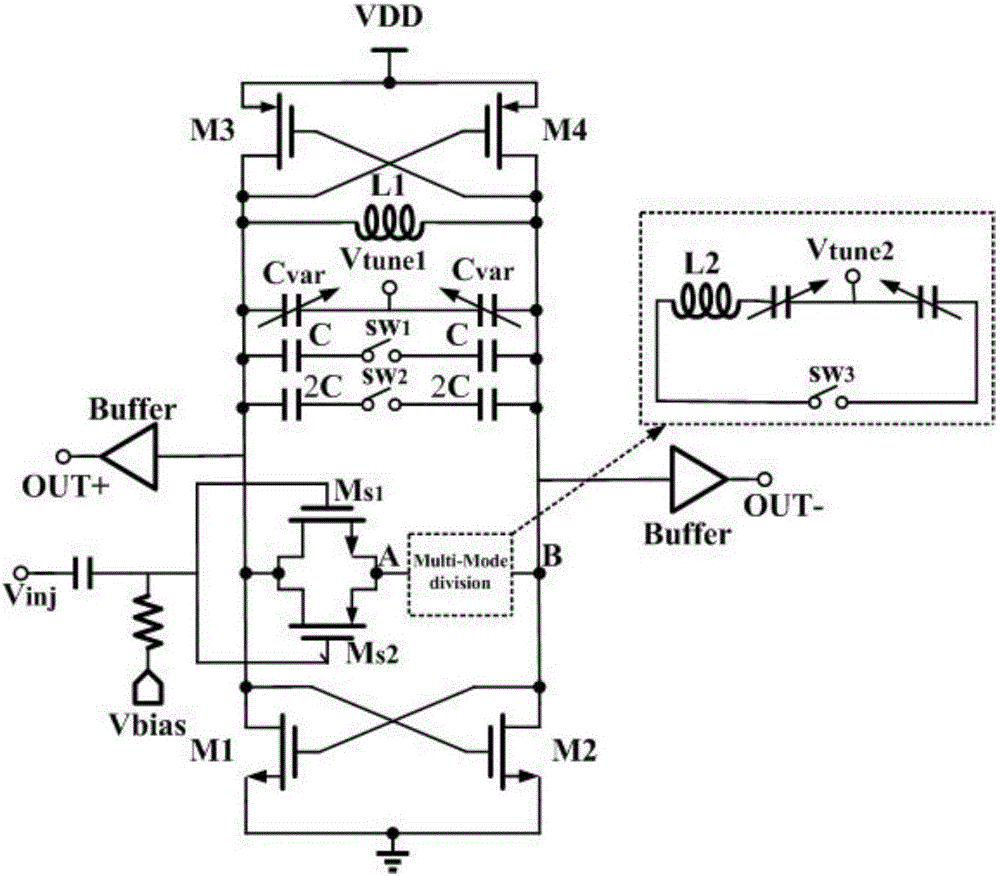

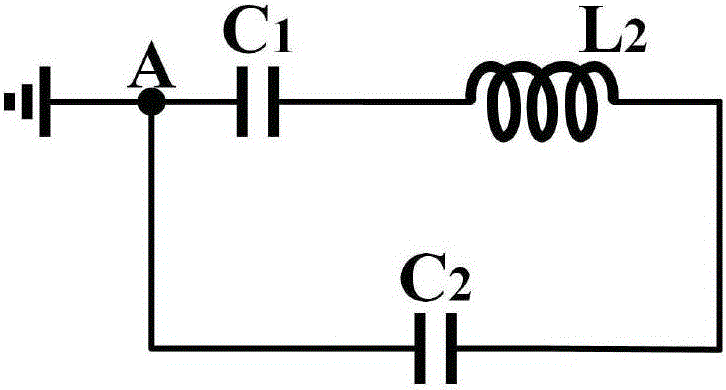

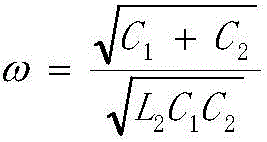

Multimode frequency division type injection locking frequency divider

The invention relates to a multimode frequency division type injection locking frequency divider comprising a negative resistance unit, a tuning unit, a signal injection unit and a differential output buffer, wherein the negative resistance unit is a complementary cross coupling geminate transistor negative resistance unit composed of four MOS tubes M1, M2, M3, M4; the tuning unit constitutes a resonant cavity with variable tuning frequency by a peak inductor L1, a voltage controlled variable capacitor Cvar and a 2bit switched capacitor array in a parallel manner; the signal injection unit is composed of double MOS tubes Ms1, Ms2 connected in parallel and a multimode switching unit; and a frequency division signal is injected into an oscillator in a parallel double-MOS tube direct injection mode, the tuning frequency of the resonant cavity is changed by the voltage controlled variable capacitor and the switched capacitor array, the frequency division ratio is changed, the harmonic energy is reinforced by the serially connected peak inductor L1, and the locking range is expanded.

Owner:TIANJIN UNIV

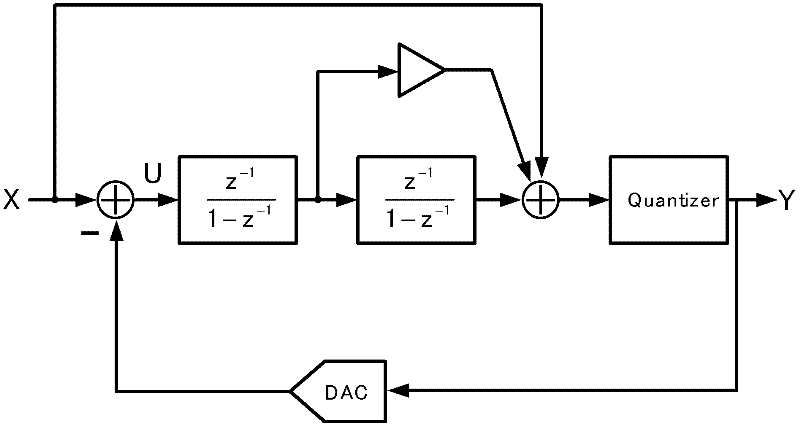

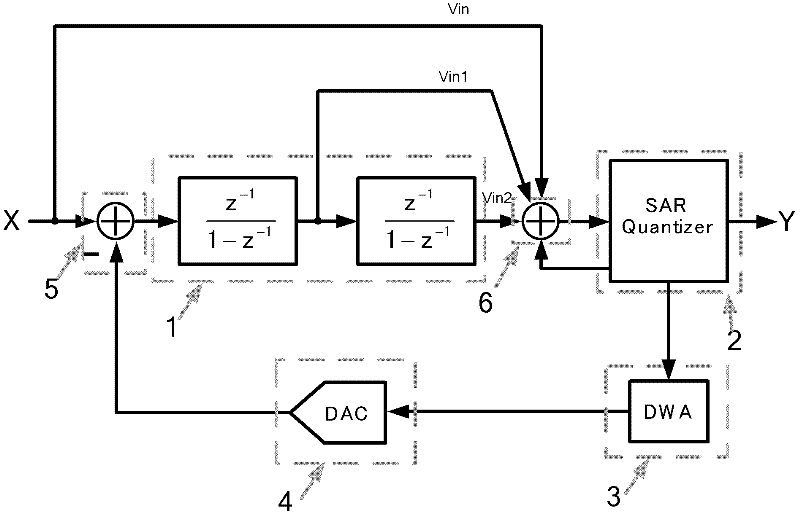

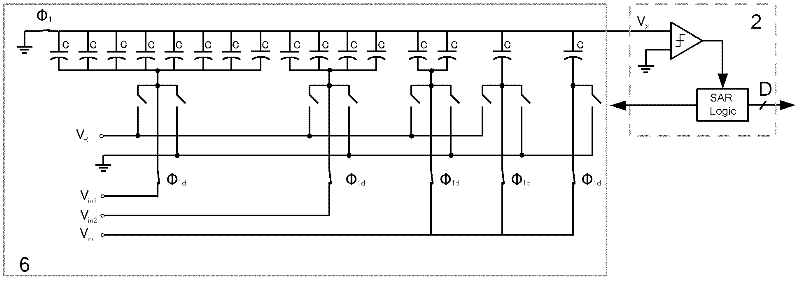

Second-order feedforward Sigma-Delta modulator based on successive comparison quantizer

InactiveCN102545901AReduce power consumptionReduce areaAnalogue/digital conversionElectric signal transmission systemsCapacitanceMulti input

The invention discloses a second-order feedforward Sigma-Delta modulator based on a successive comparison quantizer. The Sigma-Delta modulator comprises two integrators (1) based on a switched capacitor structure in the prior art, one multi-bit successive comparison quantizer (2), one digital circuit (3) transforming into a temperature code from a binary code based on the data weighed average algorithm, one feedback digital to analog converter (4) based on a capacitor, a first adder unit (5) for computing difference between an input signal and an output signal of the feedback digital to analog converter, and a second adder unit (6) which is directly formed by a multi-input sampling switched capacitor array of the successive comparator on a feedforward path, wherein the adder unit replaces the existing extra analog adder functional circuit or a digital adder functional circuit. The obtained Sigma-Delta modulator of the invention has the advantages of ultra-low power consumption and high resolution ratio.

Owner:BEIJING UNIV OF TECH

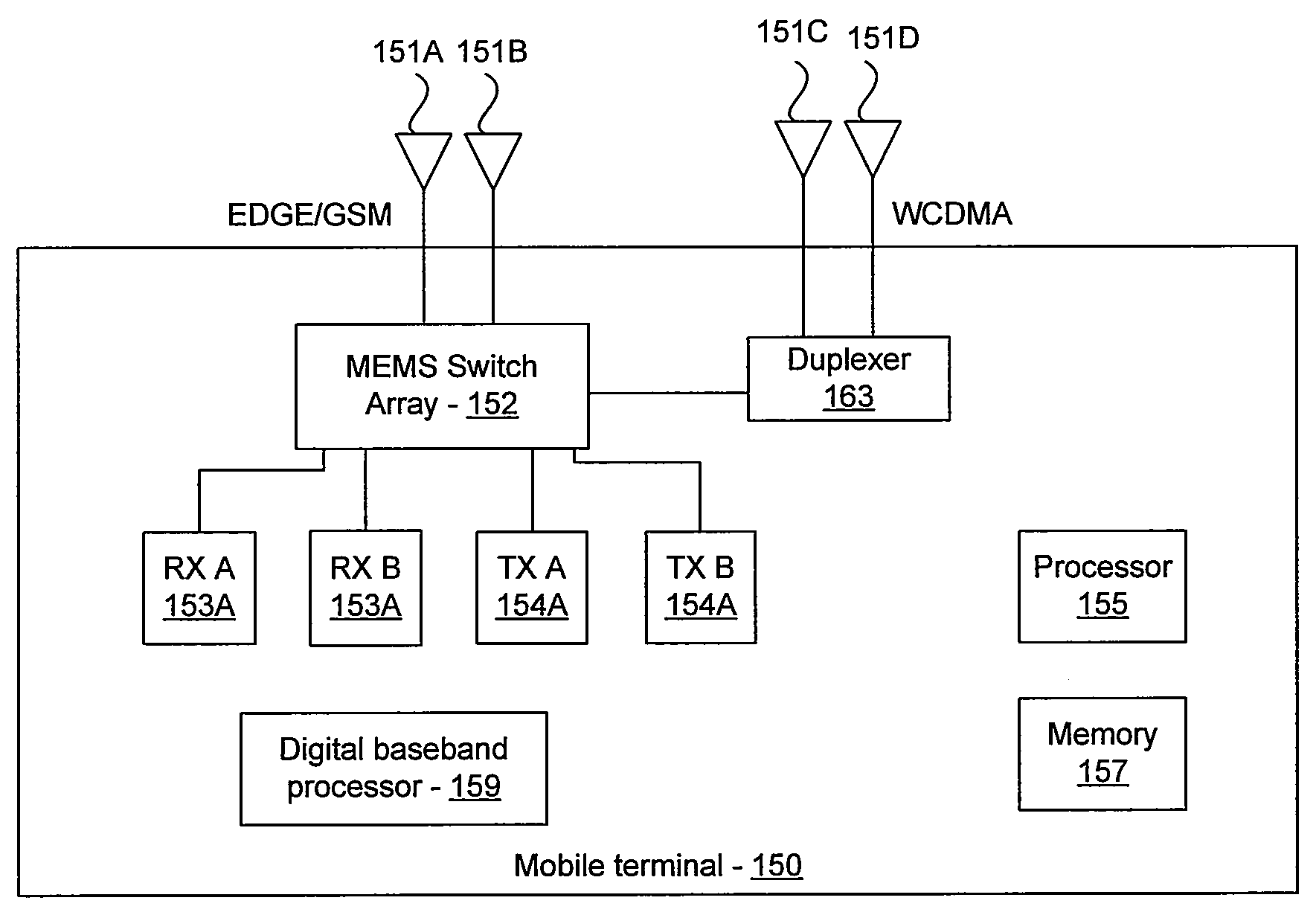

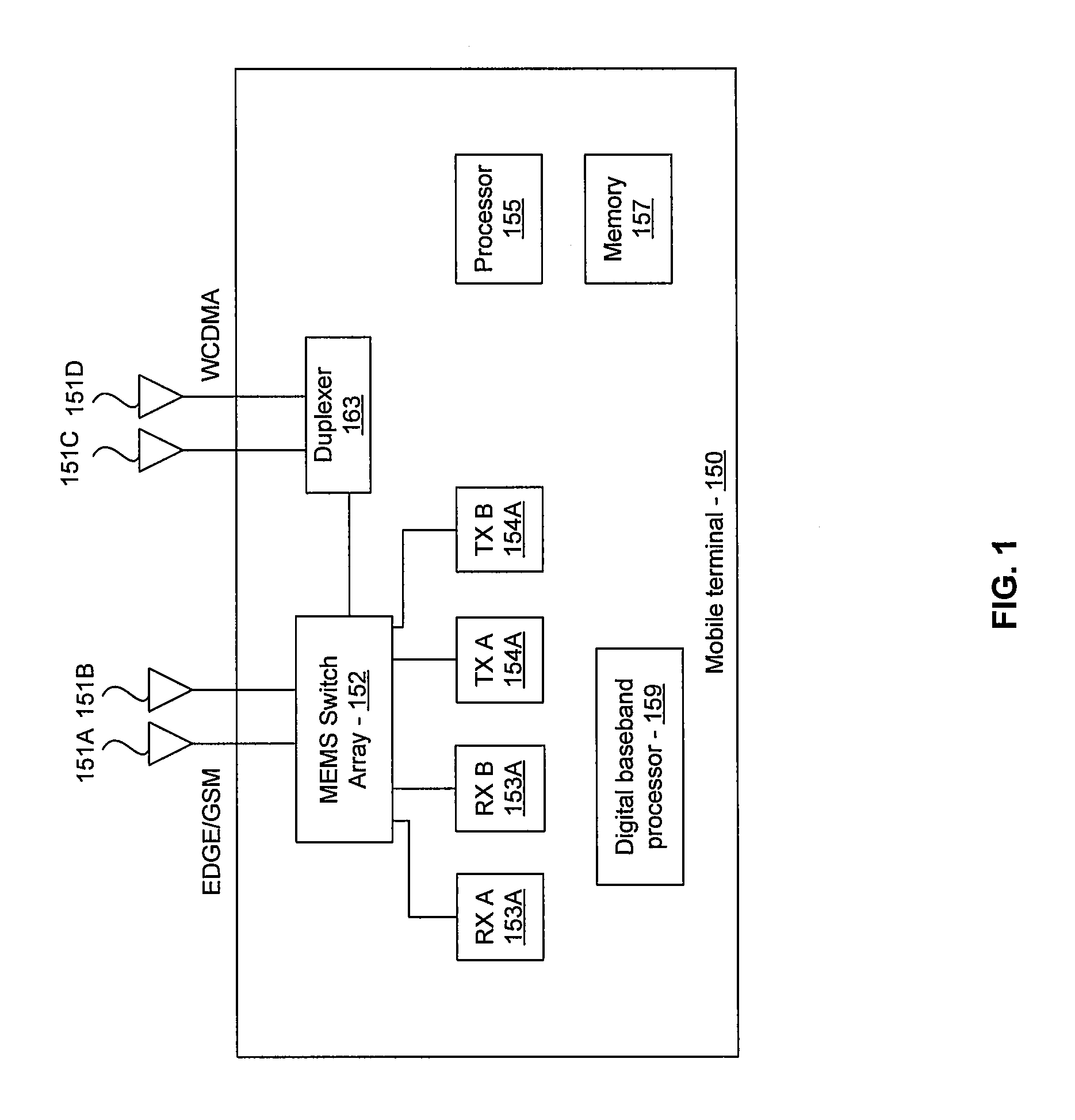

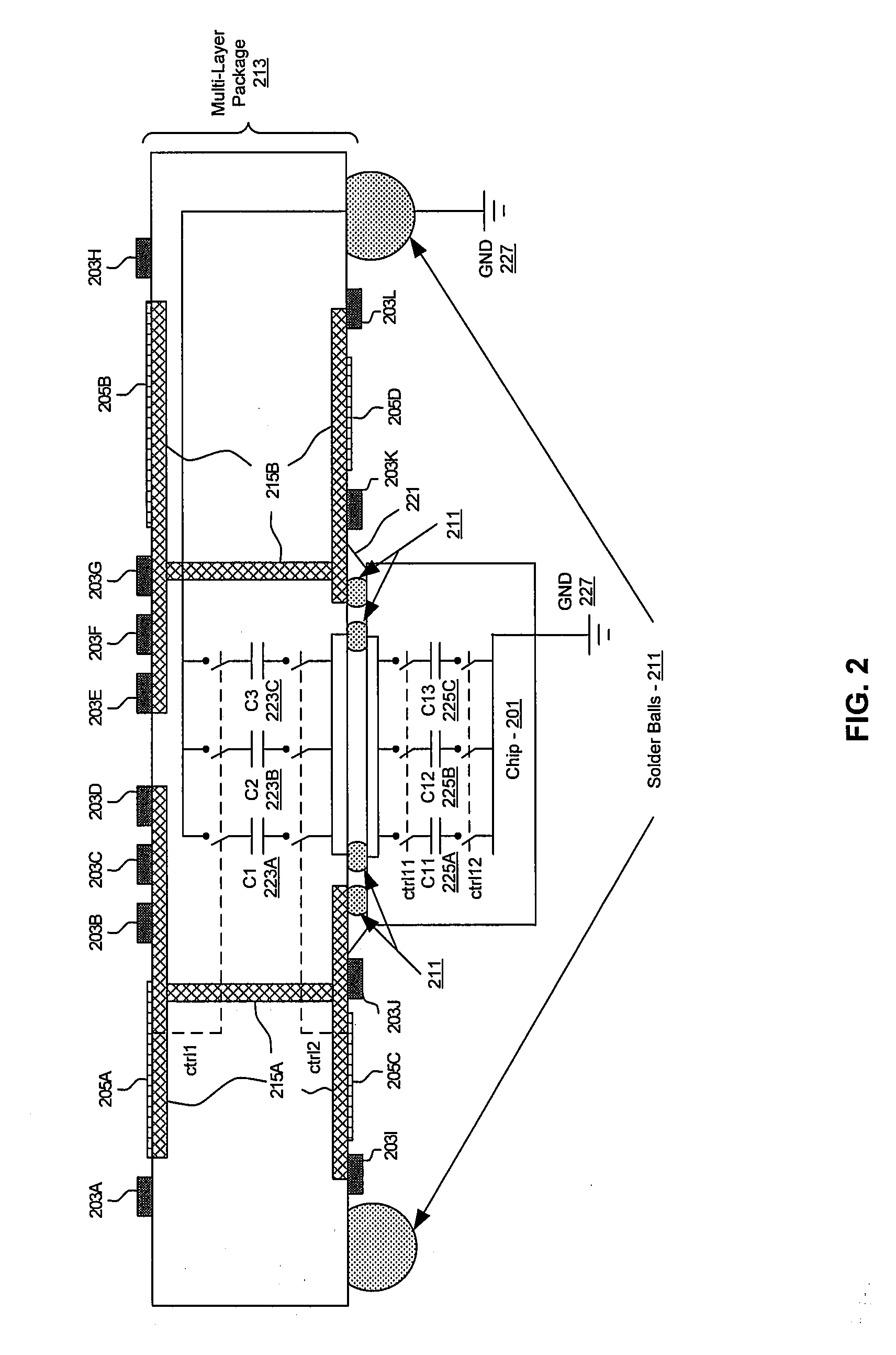

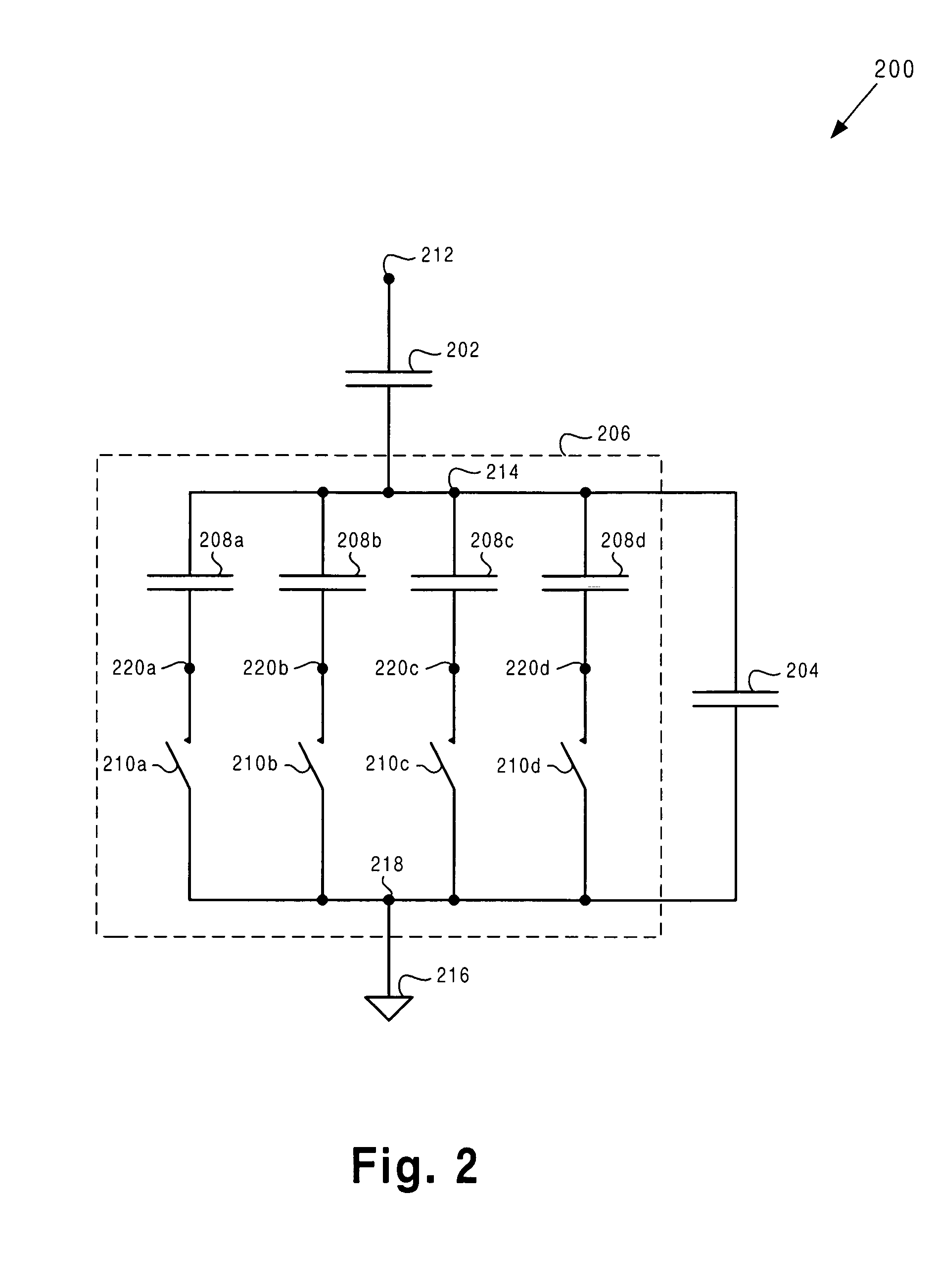

Method and system for increased resolution switching using MEMS and switched capacitors

ActiveUS20090156137A1Electrostatic/electro-adhesion relaysSubstation equipmentCapacitanceImage resolution

Certain aspects of a method and system for increased resolution switching using MEMS and switched capacitors may include a mobile terminal that includes an integrated circuit bonded to a multi-layer package. A capacitance of a first switched capacitor array in the multi-layer package may be tuned via one or more MEMS switches integrated in and / or on the multi-layer package. A capacitance of a second switched capacitor array in the integrated circuit may be tuned via one or more NMOS switches. A plurality of signals may be transmitted and / or received via one or more antennas in the mobile terminal.

Owner:AVAGO TECH INT SALES PTE LTD

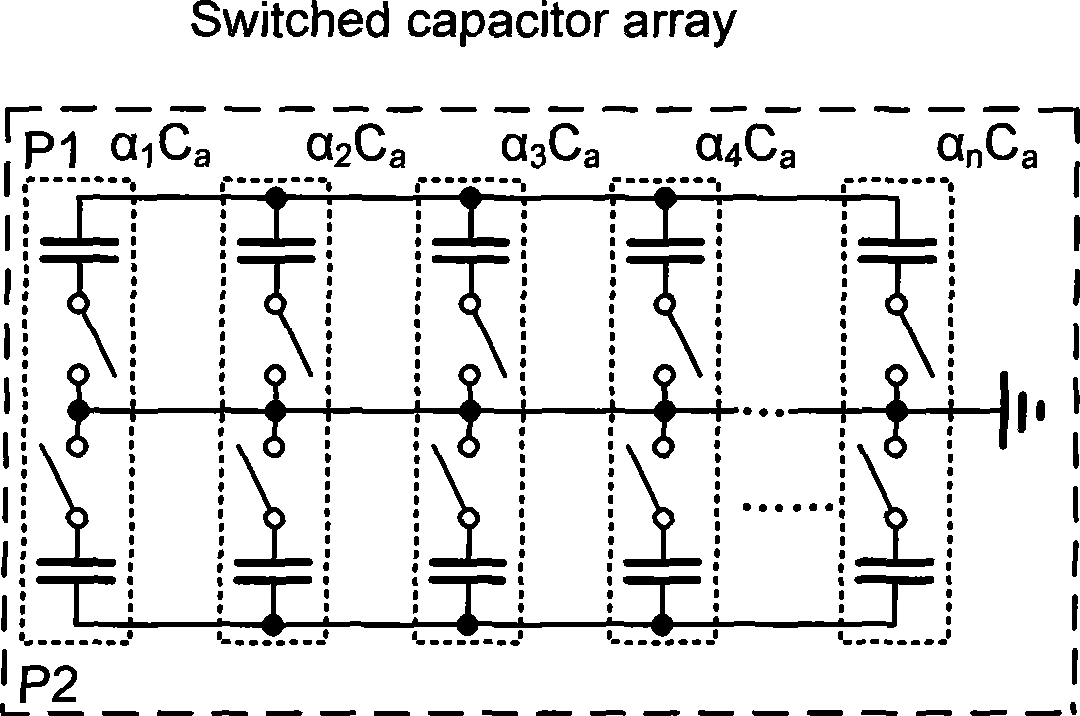

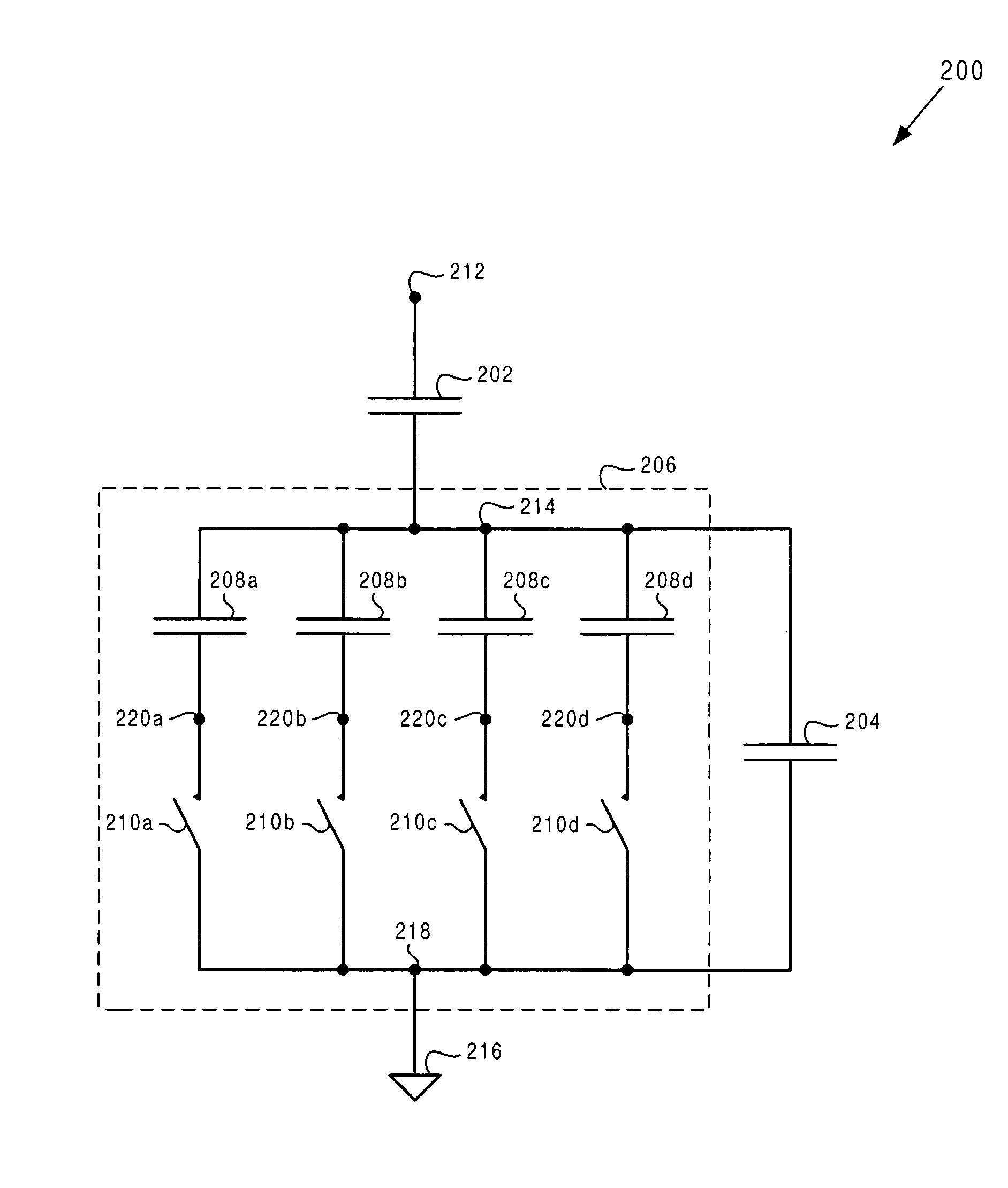

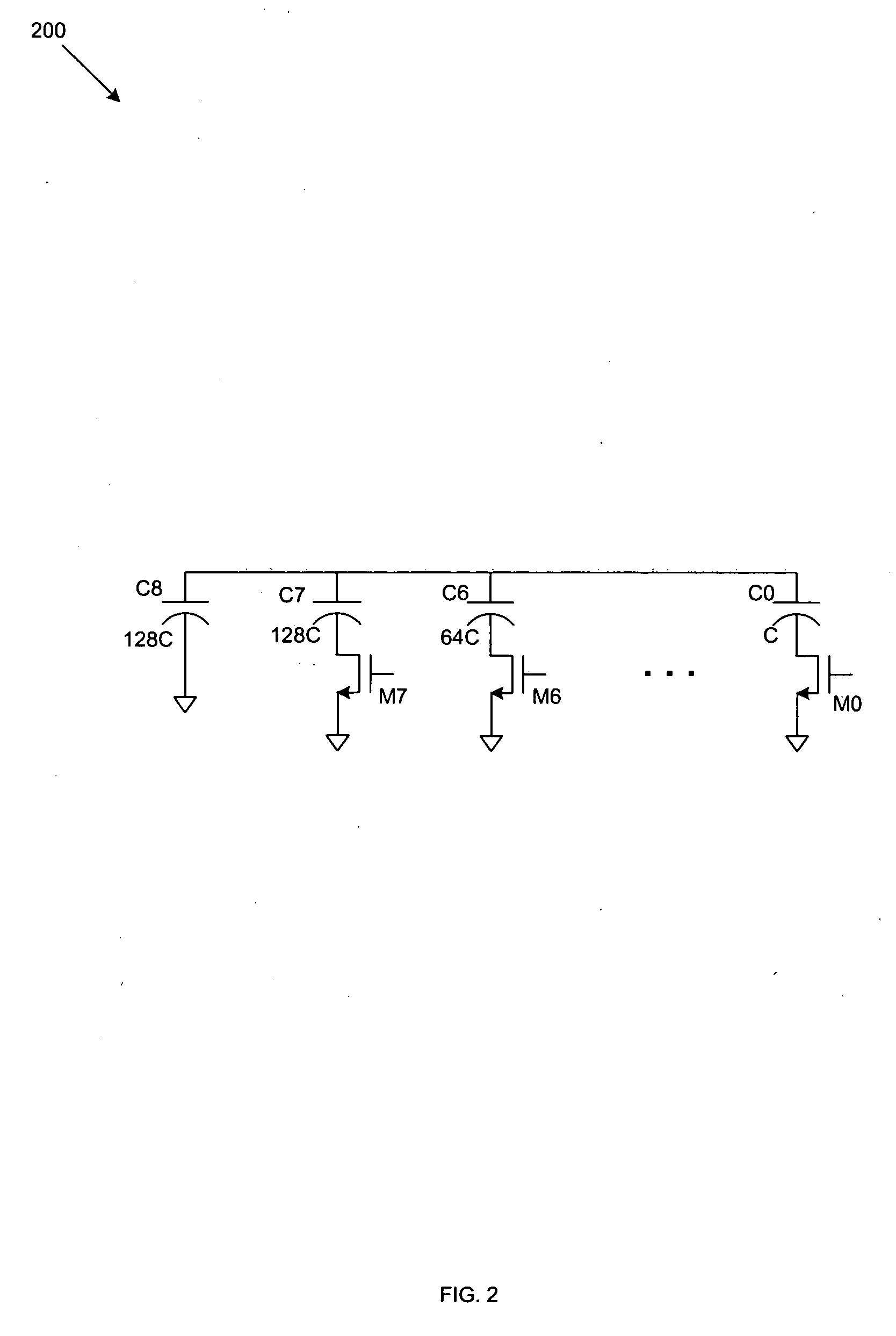

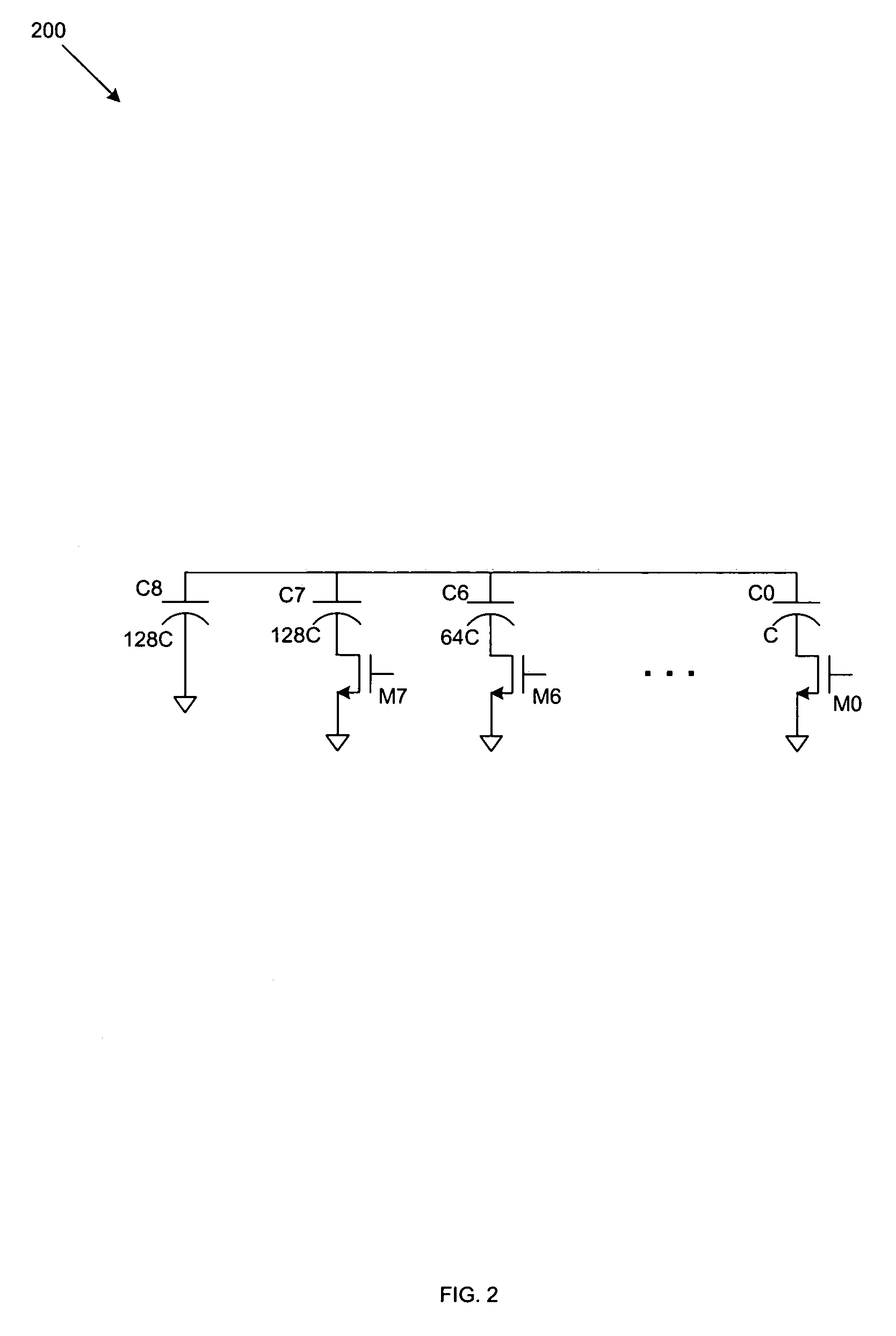

Capacitive tuning network for low gain digitally controlled oscillator

ActiveUS7212073B2Angle modulation by variable impedencePulse automatic controlCapacitanceNumerically controlled oscillator

According to one exemplary embodiment, a digitally controlled oscillator includes a capacitive tuning network, where the capacitive tuning network controls a frequency of an output signal of the digitally controlled oscillator. The capacitive tuning network includes a switched capacitor array, where a change of a first capacitance of the switched capacitor array causes the capacitive tuning network to change by a second capacitance, and where the first capacitance is larger than the second capacitance. According to this exemplary embodiment, the capacitive tuning network further includes a first capacitor coupled in parallel with the switched capacitor array. The first capacitor has a third capacitance, which is larger than the first capacitance. The capacitive tuning network further includes a second capacitor coupled in series with the first capacitor and the switched capacitor array. The second capacitor can have a fourth capacitance, where the third capacitance is larger than the fourth capacitance.

Owner:SKYWORKS SOLUTIONS INC

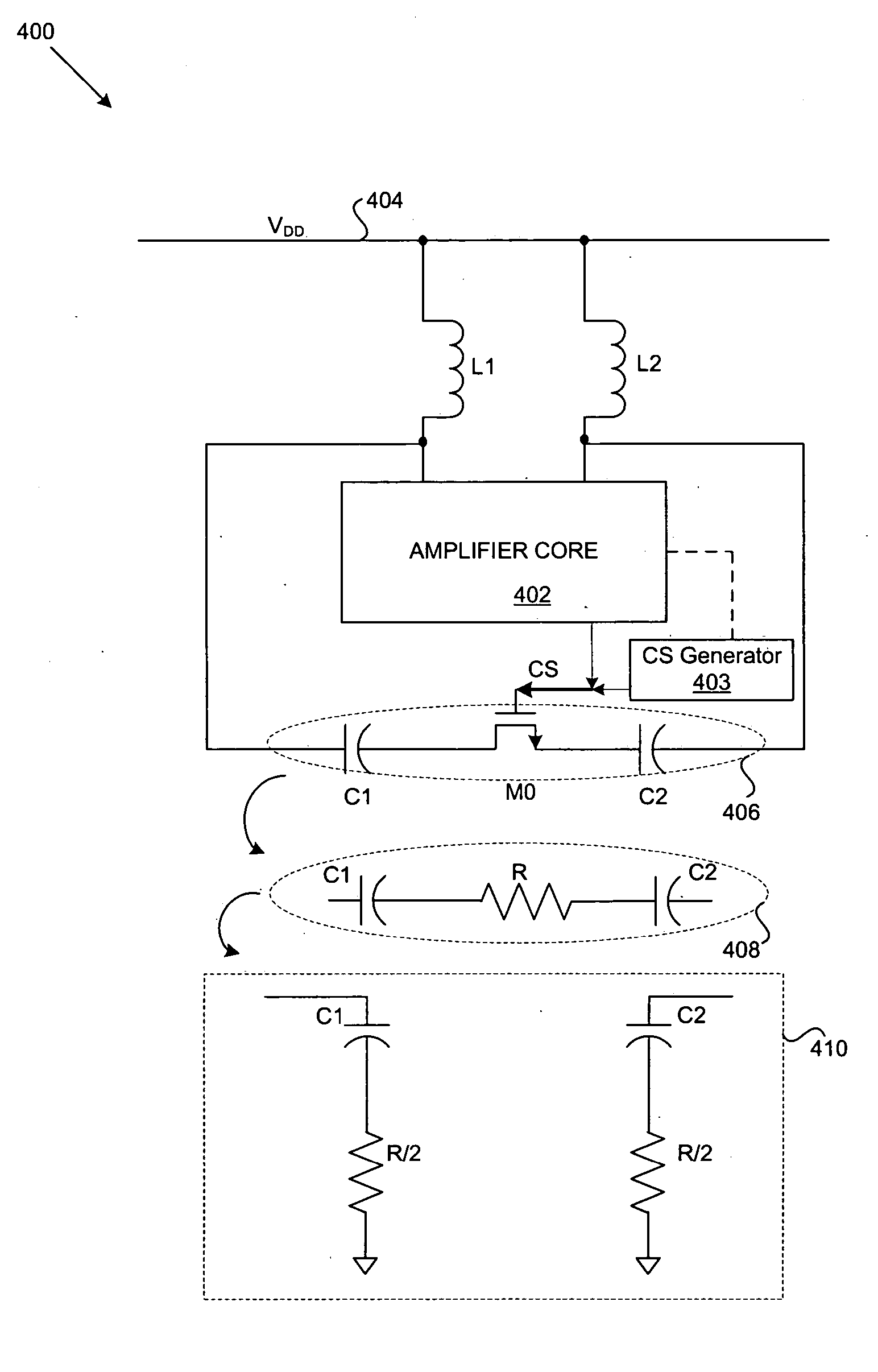

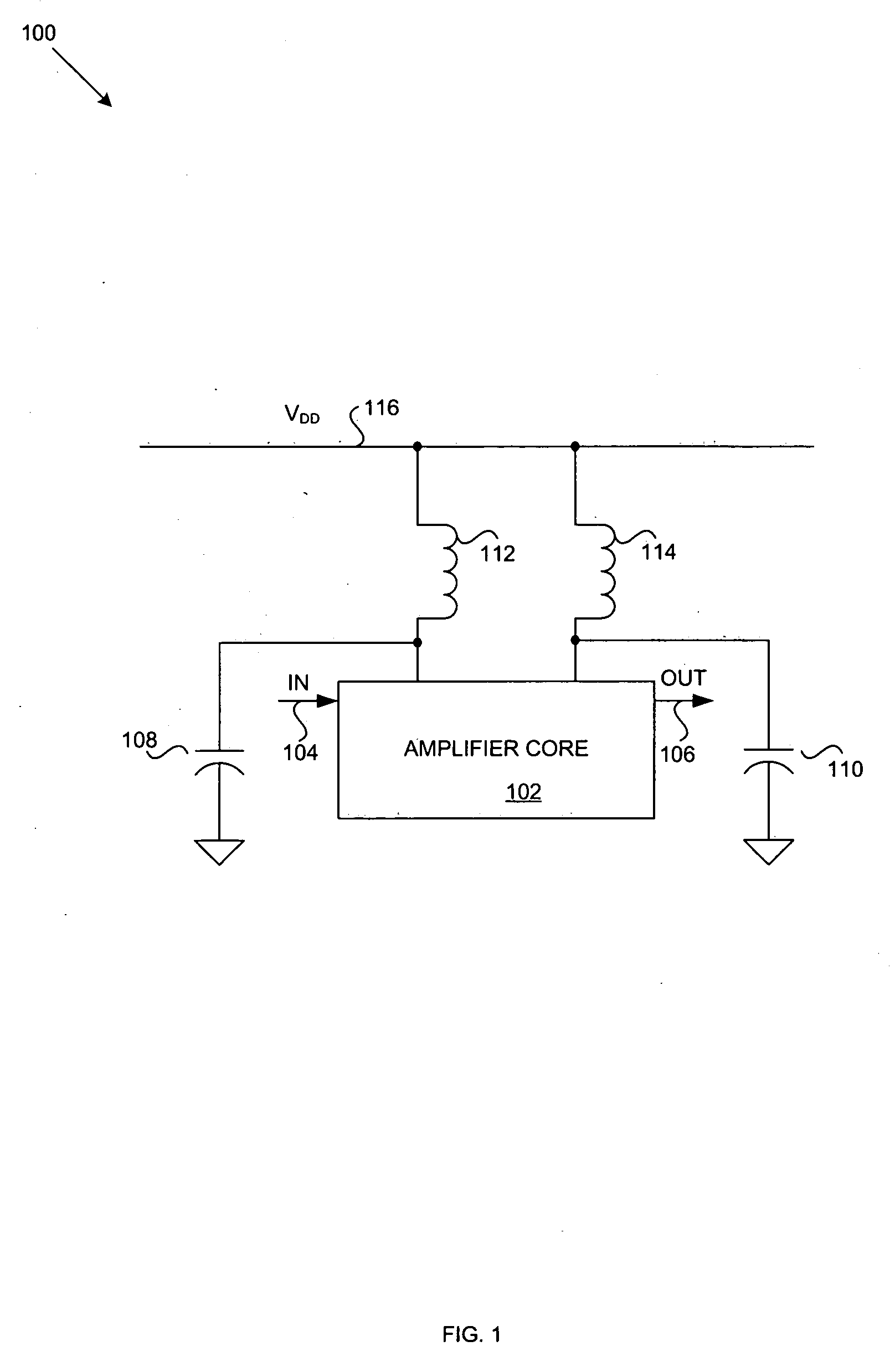

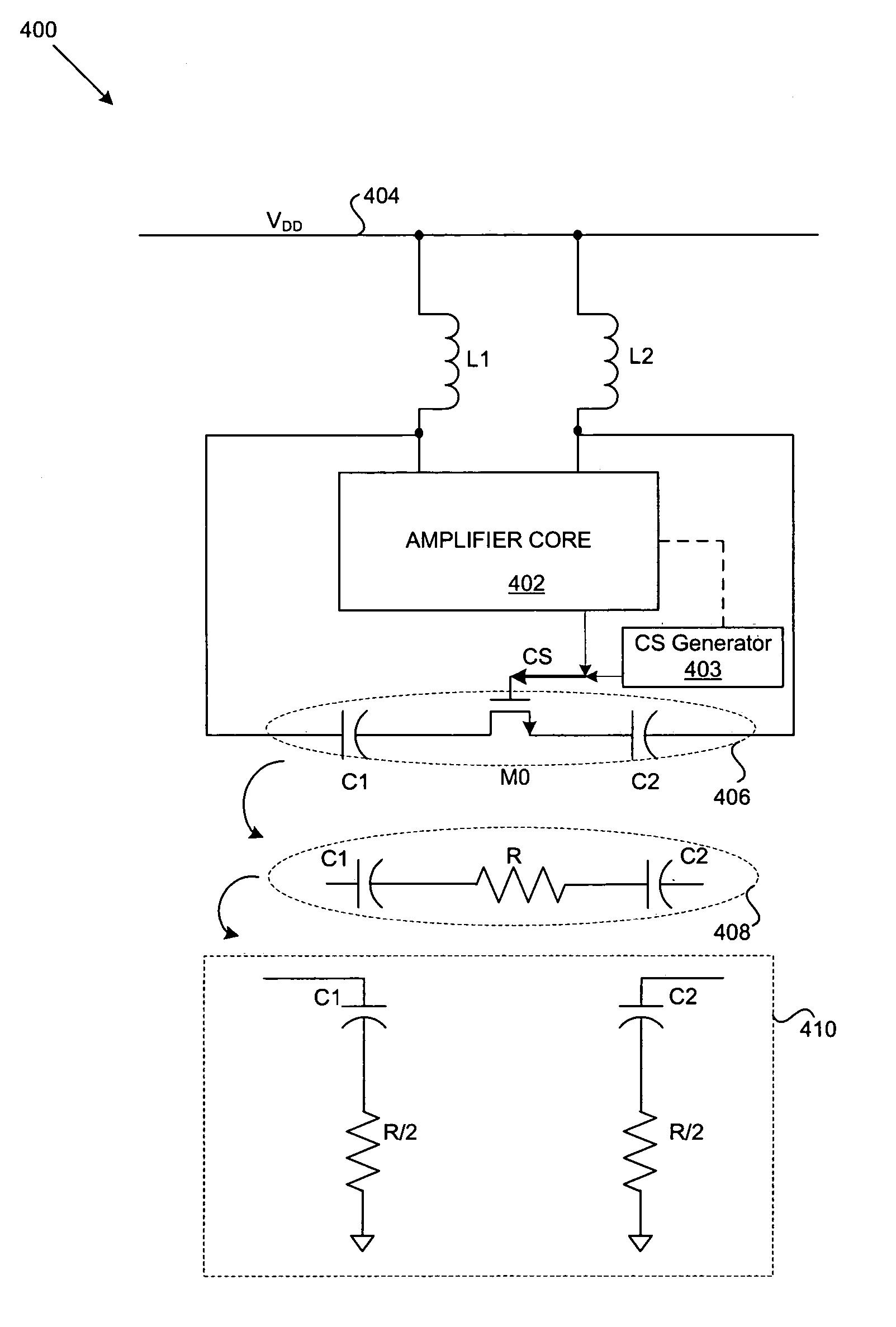

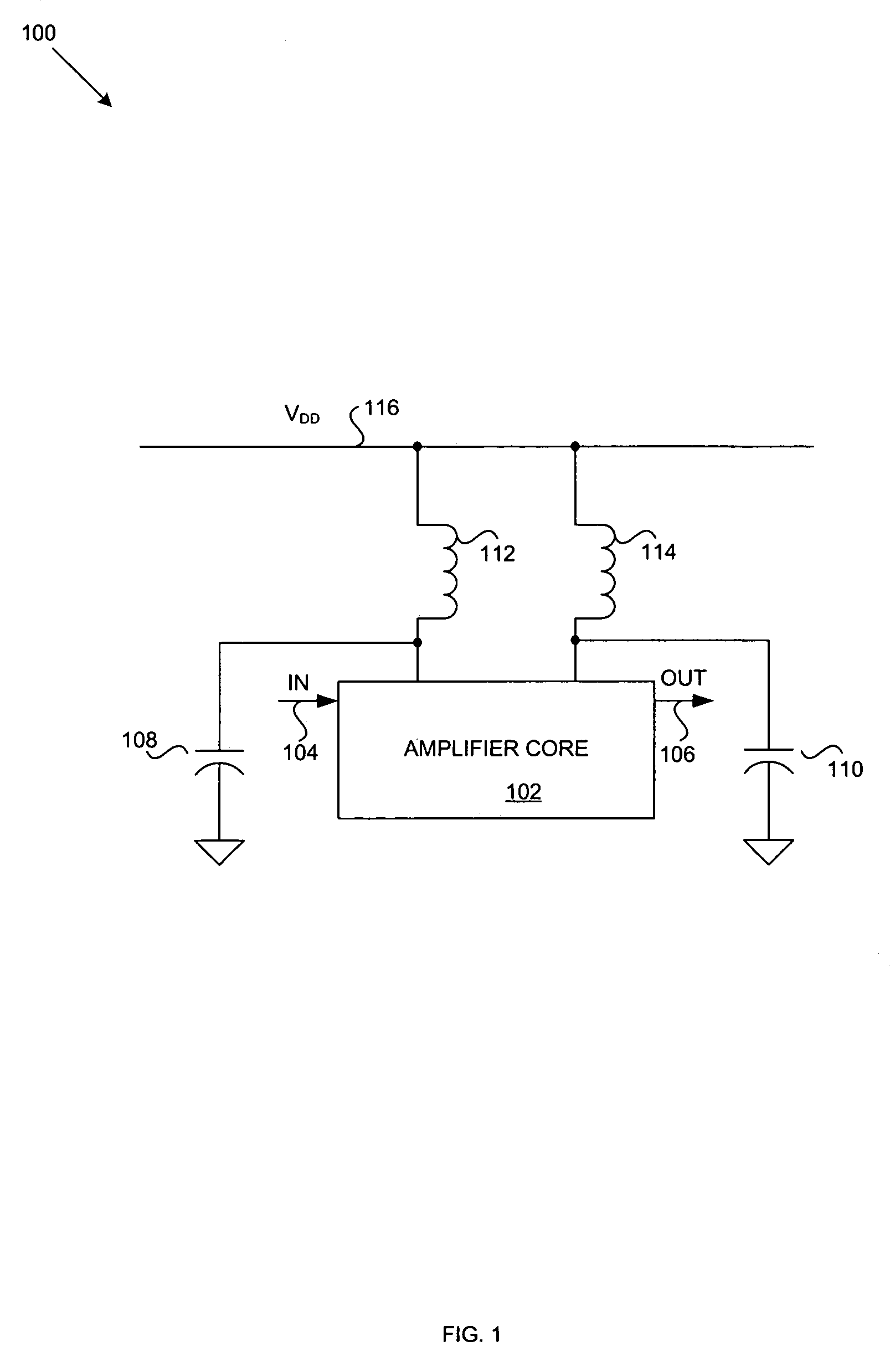

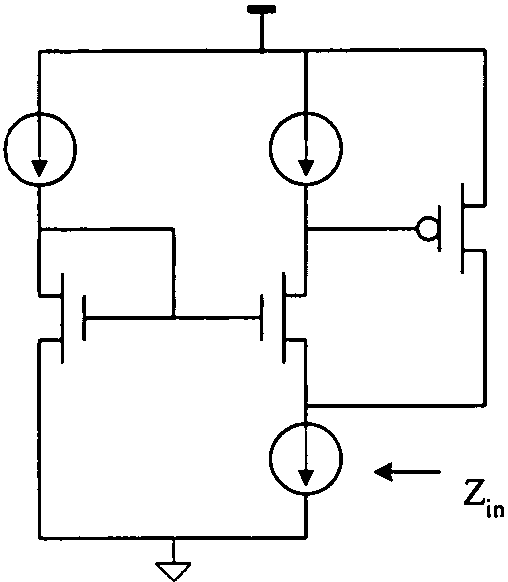

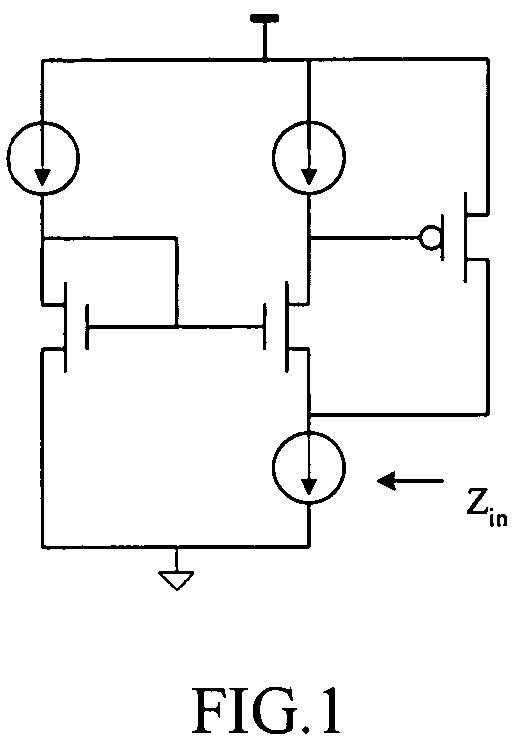

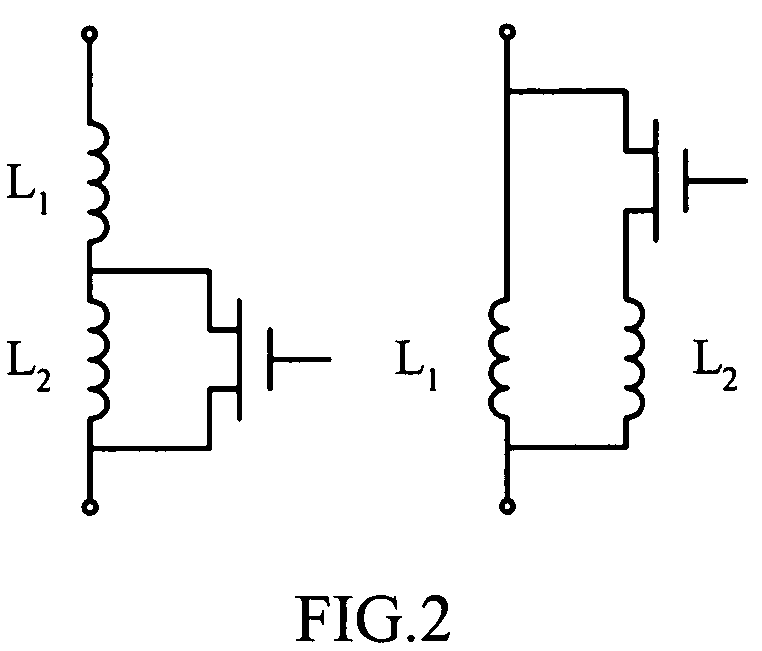

Method and system for a differential switched capacitor array for a voltage controlled oscillator (VCO) or a local oscillator (LO) buffer

InactiveUS20060091968A1Q-factor can be increasedReduce resistanceGenerator stabilizationElectric pulse generatorAudio power amplifierControl signal

Methods and systems for increasing an amplifier circuit's Q factor are disclosed herein. The method may comprise coupling a first LC tank to a source of a single switching transistor and coupling a second LC tank to a drain of the single switching transistor. A gate of the single switching transistor may be controlled by an amplifier core coupled to the first LC tank and the second LC tank. A resistance of the first LC tank and the second LC tank may be decreased by about one half, which increases the Q factor by about two. The gate of the single switching transistor may be controlled by a control signal generator coupled to the amplifier core. The first LC tank and / or the second LC tank may be tuned to a frequency of about 3.4 GHz to 4 GHz. The single switching transistor may comprise an NMOS transistor.

Owner:AVAGO TECH INT SALES PTE LTD

Successive approximation register analog to digital converter and conversion method thereof

InactiveUS8508400B2Electric signal transmission systemsAnalogue-digital convertersCapacitanceAnalog signal

A SAR ADC is provided. A DAC provides an intermediate analog signal according to an analog input signal, a most significant bit capacitance and a plurality of significant bit capacitances smaller than the most significant bit capacitance. A first switched capacitor array selectively provides the most significant bit capacitance or the significant bit capacitances according to a select signal. Sum of the significant bit capacitances is equal to the most significant bit capacitance. The second switched capacitor array provides the significant bit capacitances when the first switched capacitor array provides the most significant bit capacitance, and provides the most significant bit capacitance when the first switched capacitor array provides the significant bit capacitances. A comparator provides a comparison result according to the intermediate analog signal. A SAR logic provides an digital output signal according to the comparison result.

Owner:MEDIATEK INC

Method and system for a differential switched capacitor array for a voltage controlled oscillator (VCO) or a local oscillator (LO) buffer

InactiveUS7071790B2Reduce resistanceIncreasing the Q factorPulse automatic controlGenerator stabilizationAudio power amplifierControl signal

Methods and systems for increasing an amplifier circuit's Q factor are disclosed herein. The method may comprise coupling a first LC tank to a source of a single switching transistor and coupling a second LC tank to a drain of the single switching transistor. A gate of the single switching transistor may be controlled by an amplifier core coupled to the first LC tank and the second LC tank. A resistance of the first LC tank and the second LC tank may be decreased by about one half, which increases the Q factor by about two. The gate of the single switching transistor may be controlled by a control signal generator coupled to the amplifier core. The first LC tank and / or the second LC tank may be tuned to a frequency of about 3.4 GHz to 4 GHz. The single switching transistor may comprise an NMOS transistor.

Owner:AVAGO TECH INT SALES PTE LTD

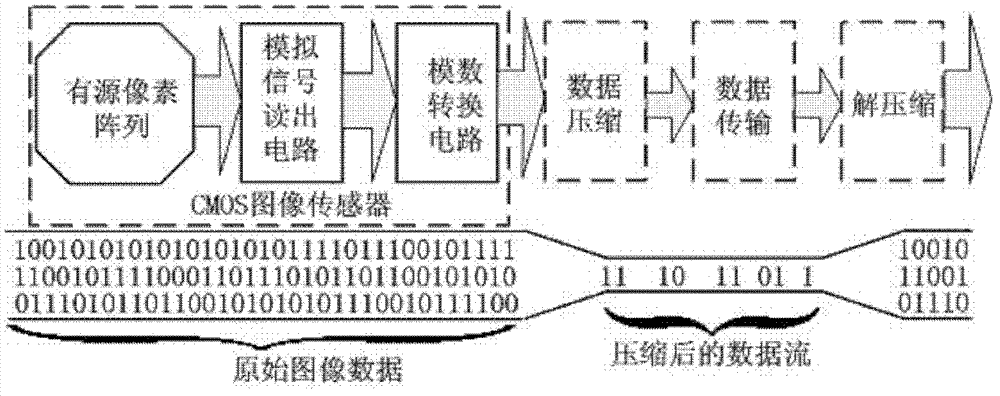

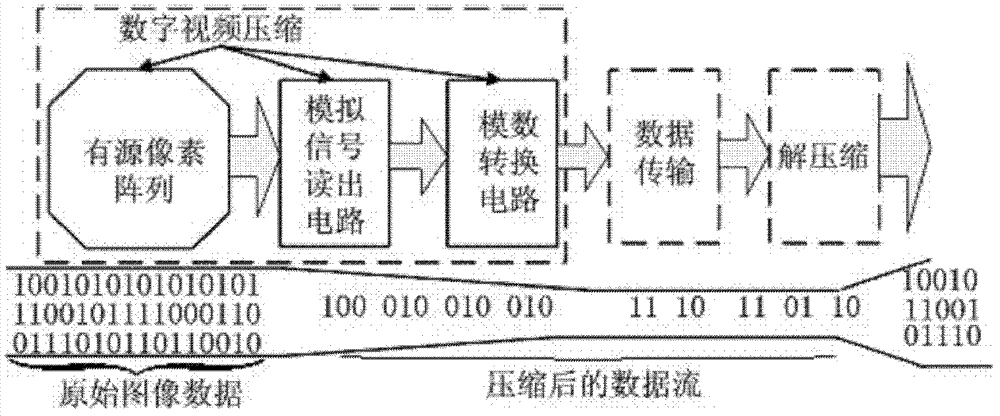

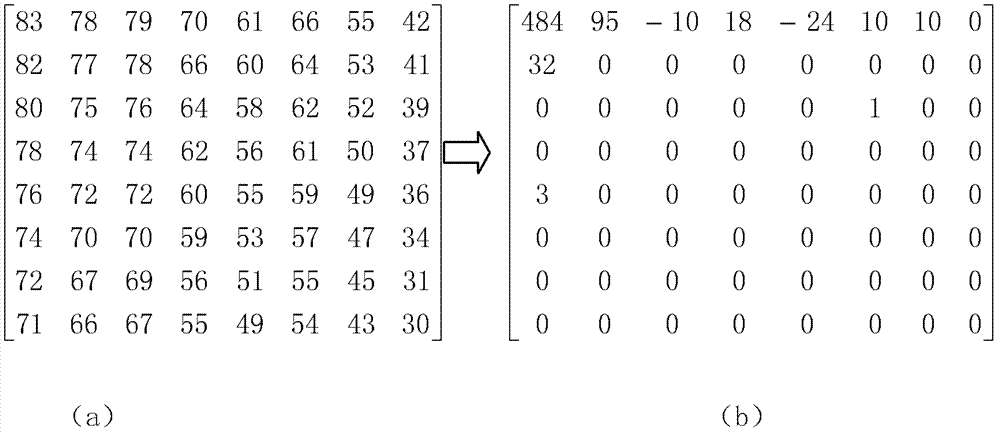

CMOS (complementary metal-oxide-semiconductor transistor) image sensor for realizing two-dimensional discrete cosine transformation

InactiveCN102710906AImprove efficiencyReduce areaTelevision system detailsColor television detailsCapacitanceSwitched capacitor array

The invention relates to the field of the integrated circuit design of micro-electronics and the field of encoding and compressing of a digital image. A CMOS (complementary metal-oxide-semiconductor transistor) image sensor structure for realizing 2D-DCT (two-dimensional-discrete cosine transformation) is provided so that the 2D-DCT is finished in a process of obtaining an image; and compared with the traditional processing flow, the area and power consumption for introducing a 2D-DCT module which is extra used are reduced on the basis of not reducing the sensing quality of the image. The technical scheme disclosed by the invention is as follows: the CMOS image sensor for realizing the two-dimensional discrete cosine transformation comprises a pixel array, a read-out circuit, a switch capacitance array, a multi-path selector MUX (multiplexer), a DPGA (digital programmable gain amplifier), an ADC (analogue-to-digital converter) and a control time sequence circuit and further comprises an analogue accumulator; and the ADC is internally and additionally provided with a switch control module 2, a register 2, a capacitance access and a digital accumulator. The CMOS image sensor disclosed by the invention is mainly applied to encoding and compressing the image sensor.

Owner:TIANJIN UNIV

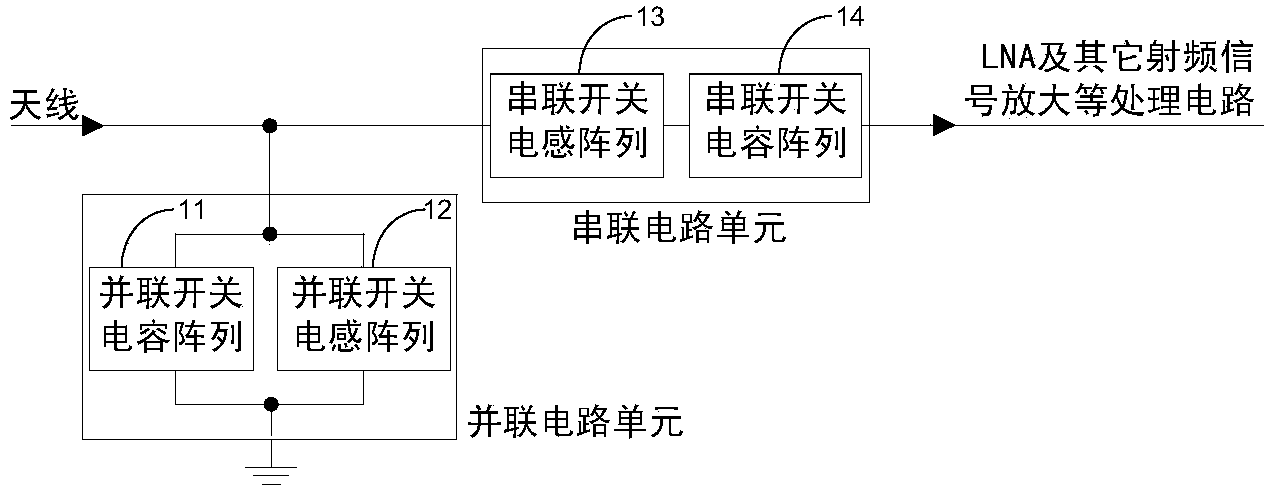

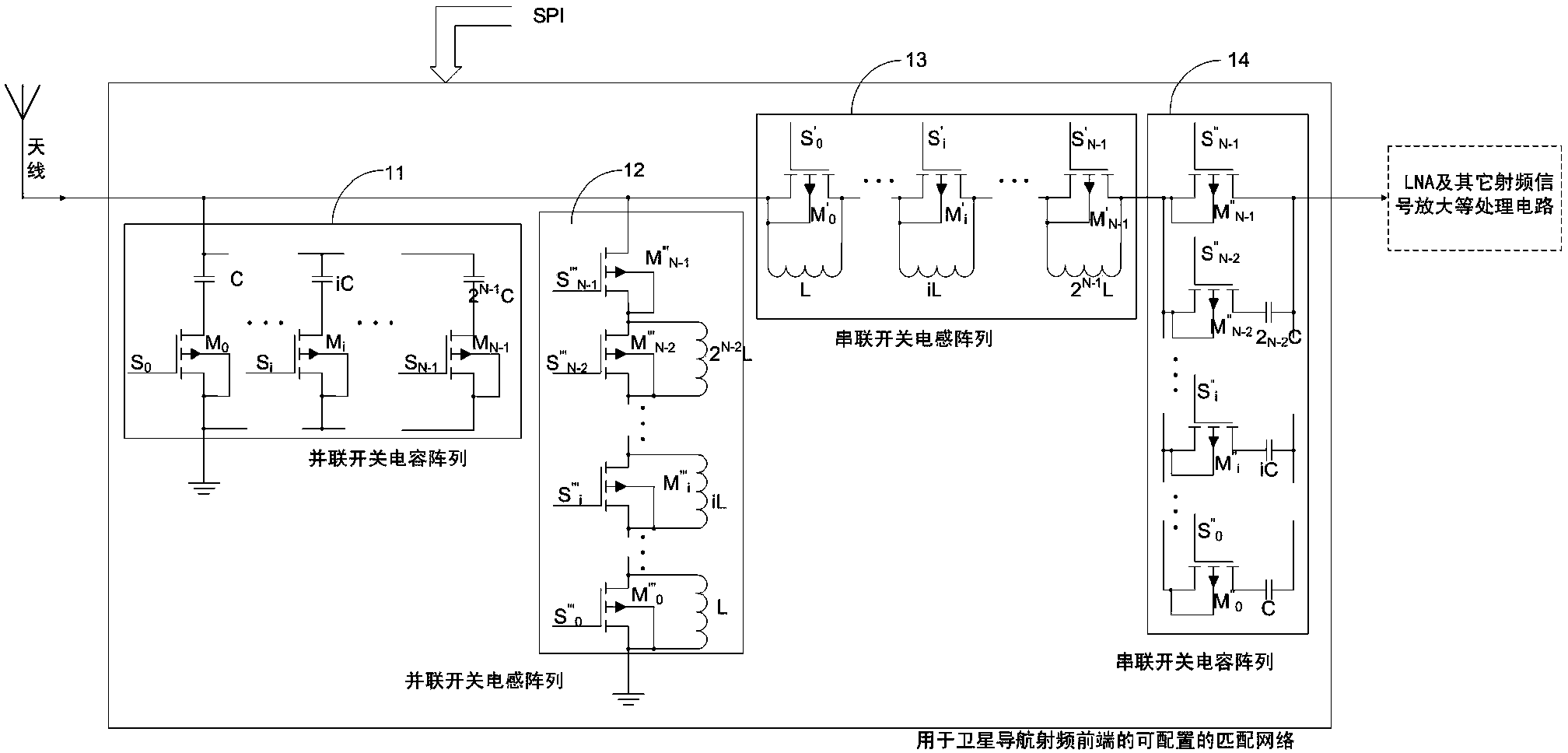

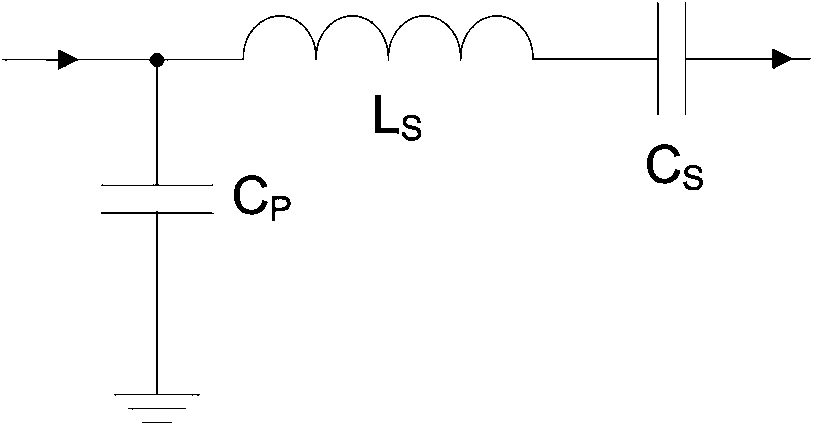

Configurable matching network used at satellite navigation radio frequency front end

ActiveCN103454654AReduce in quantityEasy to operateSatellite radio beaconingInput impedanceEngineering

The invention discloses a configurable matching network used at a satellite navigation radio frequency front end. The configurable matching network comprises a set of parallel switch capacitor arrays, a set of parallel switch inductance arrays, a set of series switch inductance arrays and a set of series switch capacitor arrays. The configurable matching network can be used for matching impedance of various satellite navigation radio frequency receiver ports, changes equivalent capacitance or equivalent inductance value of a corresponding array through regulating and controlling the switch capacitor arrays and the switch inductance arrays, and is further matched with input impedance. The invention provides a matching tuning technology combining digit and analog and a digital signal control simulation circuit to realize matching of impedance. The configurable matching network is used inside an integrated circuit of a satellite navigation radio frequency receiver, realizes matching of networks through sending orders, is good in performance, convenient and quick to operate, saves time and cost for a developing process, and has a good application prospect.

Owner:NO 54 INST OF CHINA ELECTRONICS SCI & TECH GRP

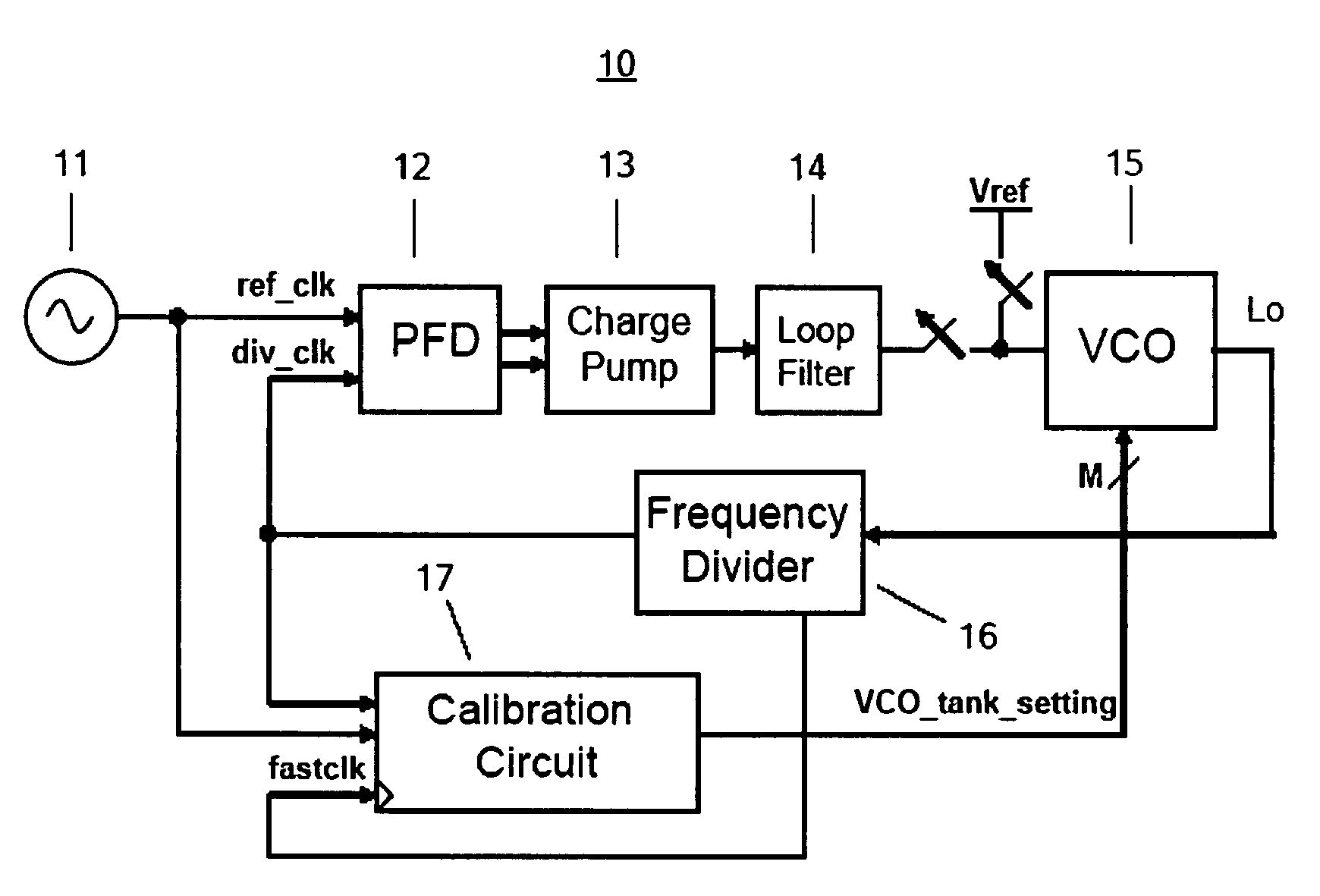

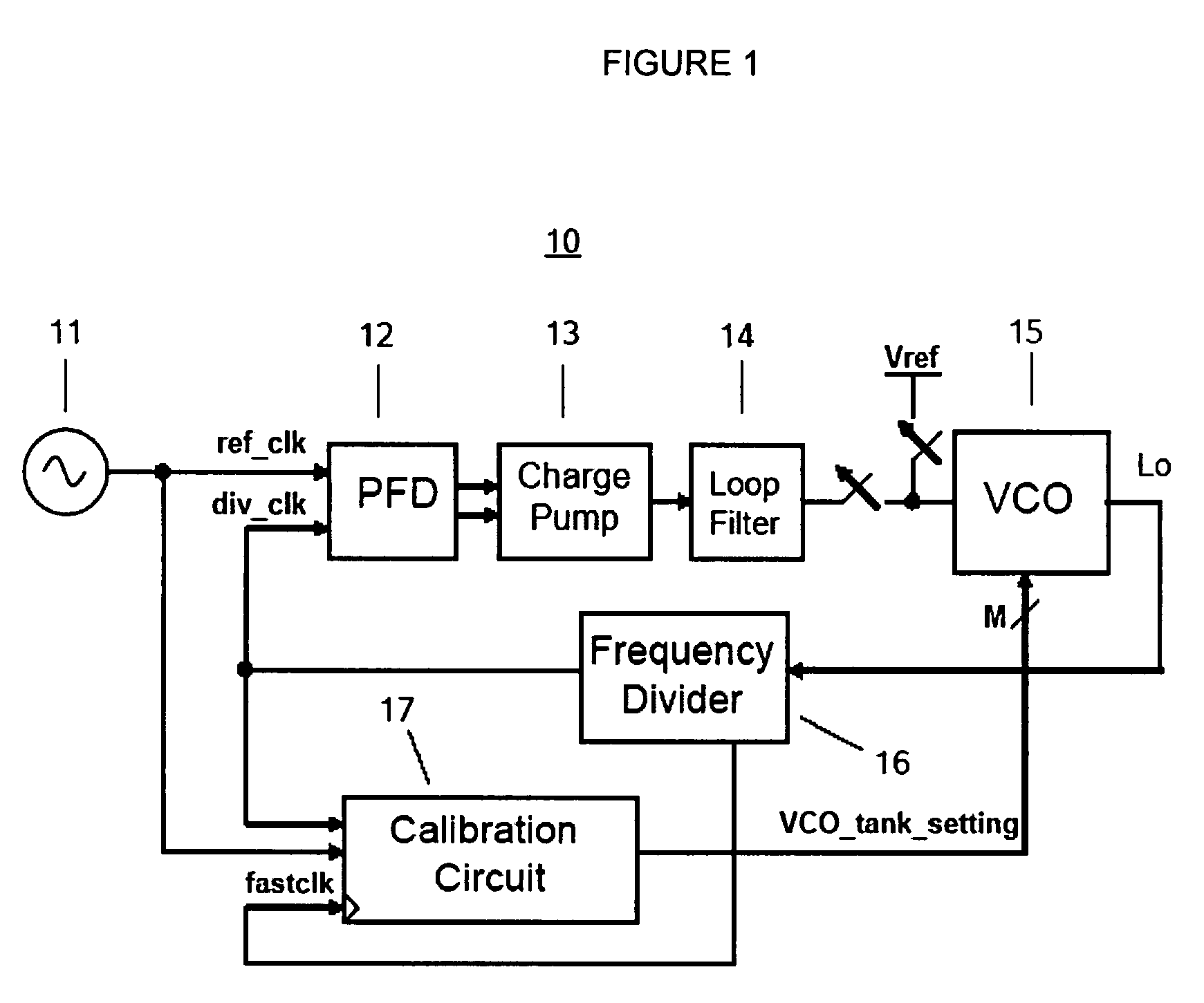

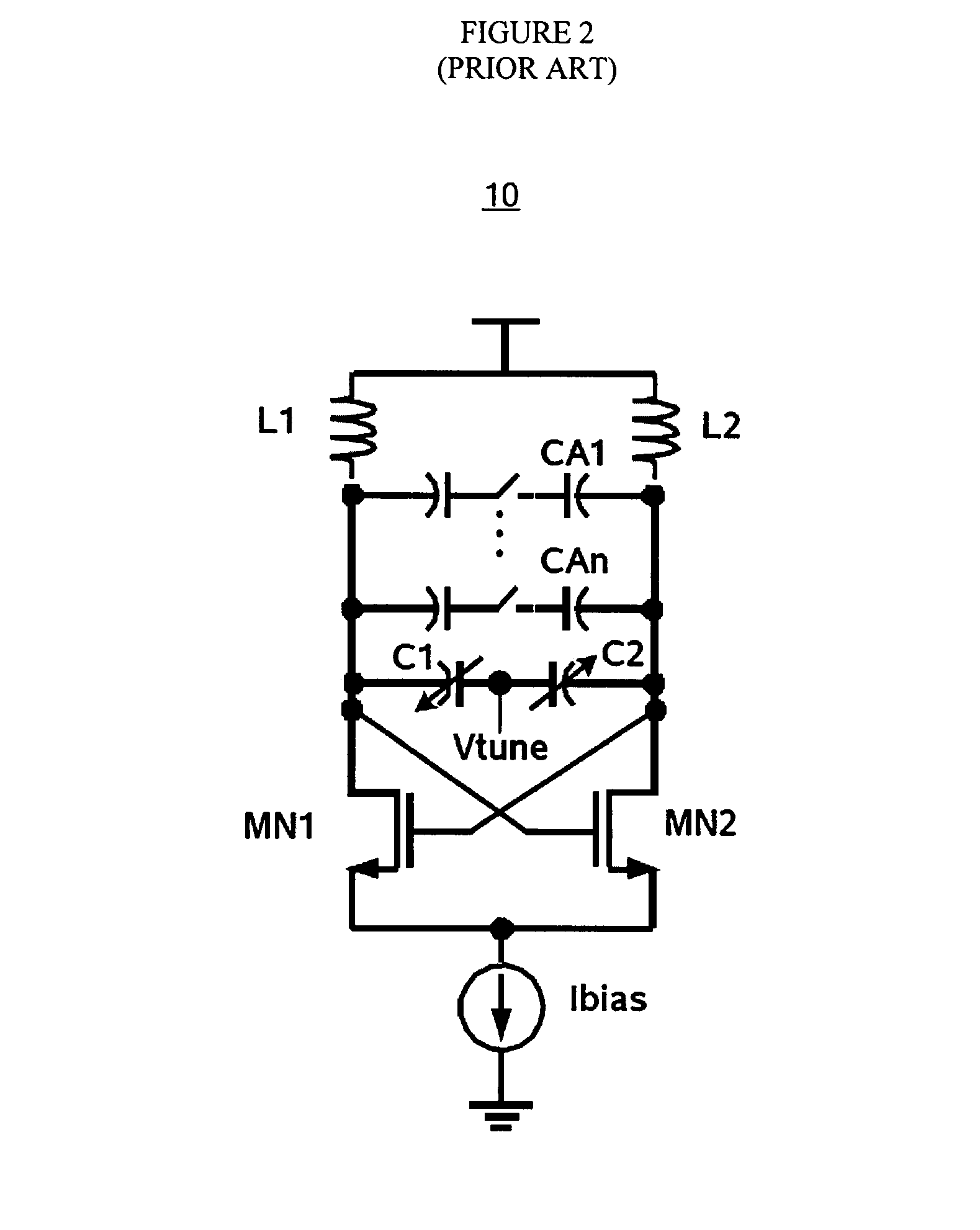

Frequency calibration for frequency synthesizers

ActiveUS7474159B2Angle modulation by variable impedencePulse automatic controlFrequency synthesizerSwitched capacitor

A calibration circuit (17) for calibrating a frequency synthesizer (10) having a voltage-controlled oscillator (VCO) (15) with a plurality of switched-capacitor arrays (CA1-CAn). The calibration circuit (17) counts a predetermined number of periods of the reference-clock signal (ref_clk) and divide-clock signal (div_clk) of the frequency synthesizer using a fast clock signal (fastclk). The fast-clock signal (fastclk) has a frequency greater than either the reference-clock signal (ref_clk) or the divide-clock signal (div_clk), enabling significantly faster calibration of the frequency synthesizer (10) than would be possible using the reference-clock signal (ref_clk). The calibration circuit (17) compares the count of the periods of the reference-clock signal (ref_clk) and the divide-clock signal (div_clk) and varies the tank signal of the VCO (VCO_tank_setting) until the count of the periods is substantially equal.

Owner:MICROCHIP TECH INC

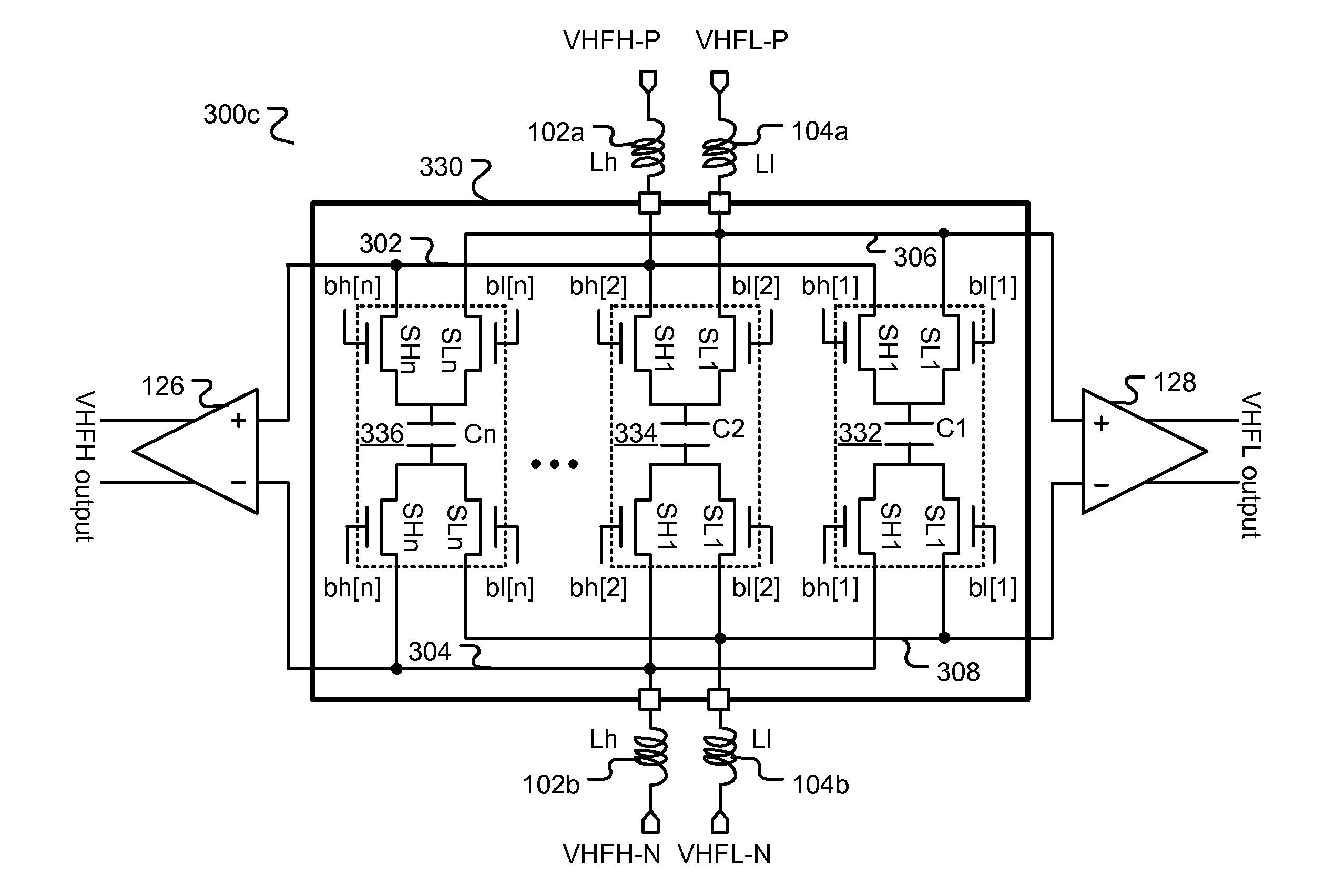

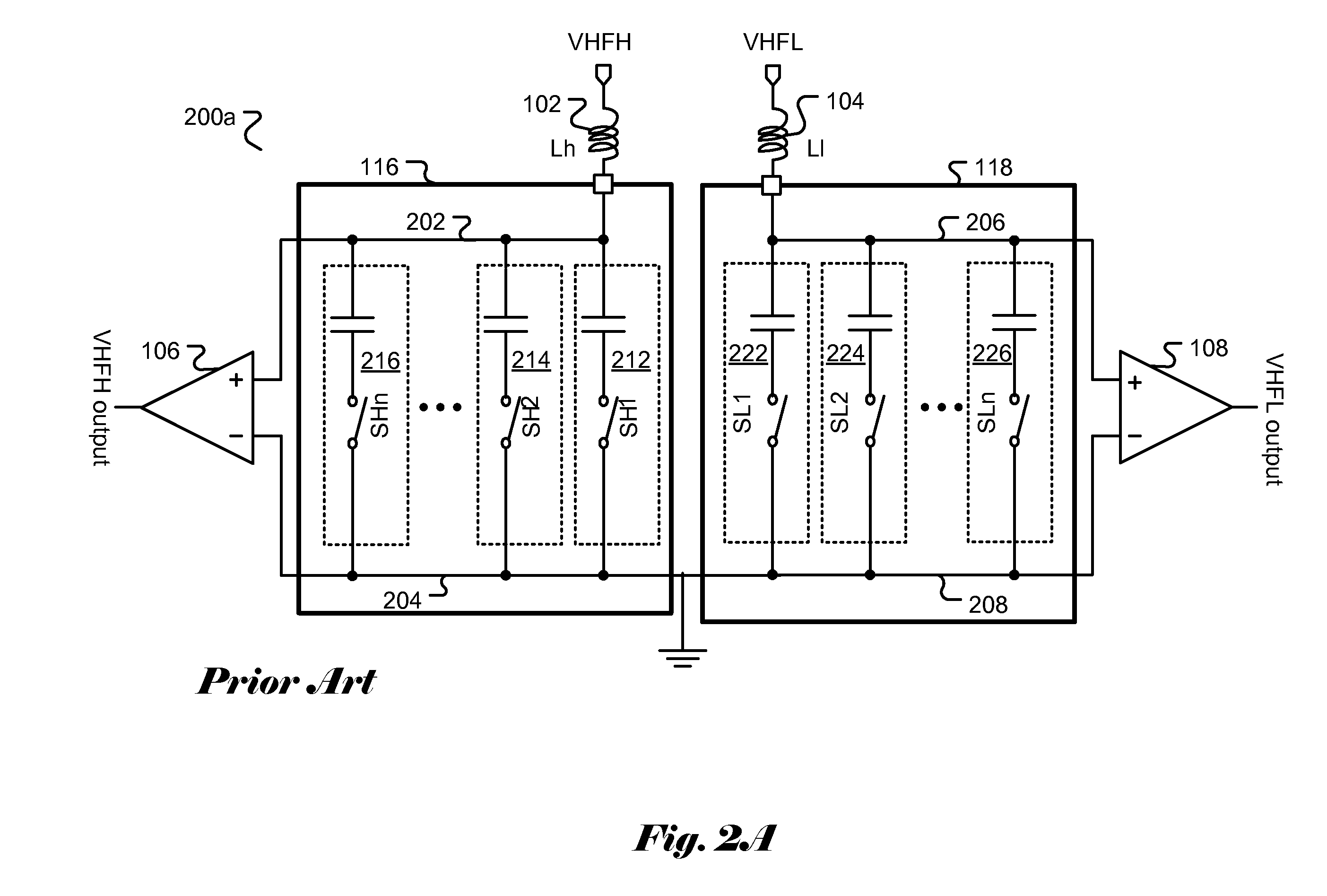

System and method for tuning-capacitor-array sharing

ActiveUS20110316654A1Multiple-port networksDiscontinuous tuning for band selectionCapacitanceRadio receiver

A system and method for sharing a switched capacitor array (SCA) by two tuning circuits are disclosed. In a multiple-band radio receiver, there is a need to use multiple tuning circuits for signals in different bands. The tuning circuit typically comprised an adjustable capacitance device and other tuning components, where the adjustable capacitance device is often implemented in SCA. The present invention discloses a system and method comprising n sections of capacitor elements where each capacitor element comprises a capacitor and switches to selectively connect the capacitor to one of the tuning circuit. Consequently, the SCA can be shared by the two tuning circuits. The control bits for the switched may be provided from a programmable control register.

Owner:QUINTIC MICROELECTRONICS WUXI

Dual-mode voltage controlled oscillator using integrated variable inductors

A novel form of an integrated variable inductor uses an on-chip transformer together with a variable capacitor. The variable capacitor can either be a varactor or a switched capacitor array and is connected to the secondary coil of the transformer. By changing the capacitance at the secondary coil of a transformer, the equivalent inductance looking into the primary coil of the transformer can be adjusted. With another capacitor in parallel to the primary coil, two different modes of resonance inherently exist, and a very wide frequency tuning range can be achieved by combining the two modes.

Owner:THE HONG KONG UNIV OF SCI & TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com