Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

37 results about "Memory timings" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

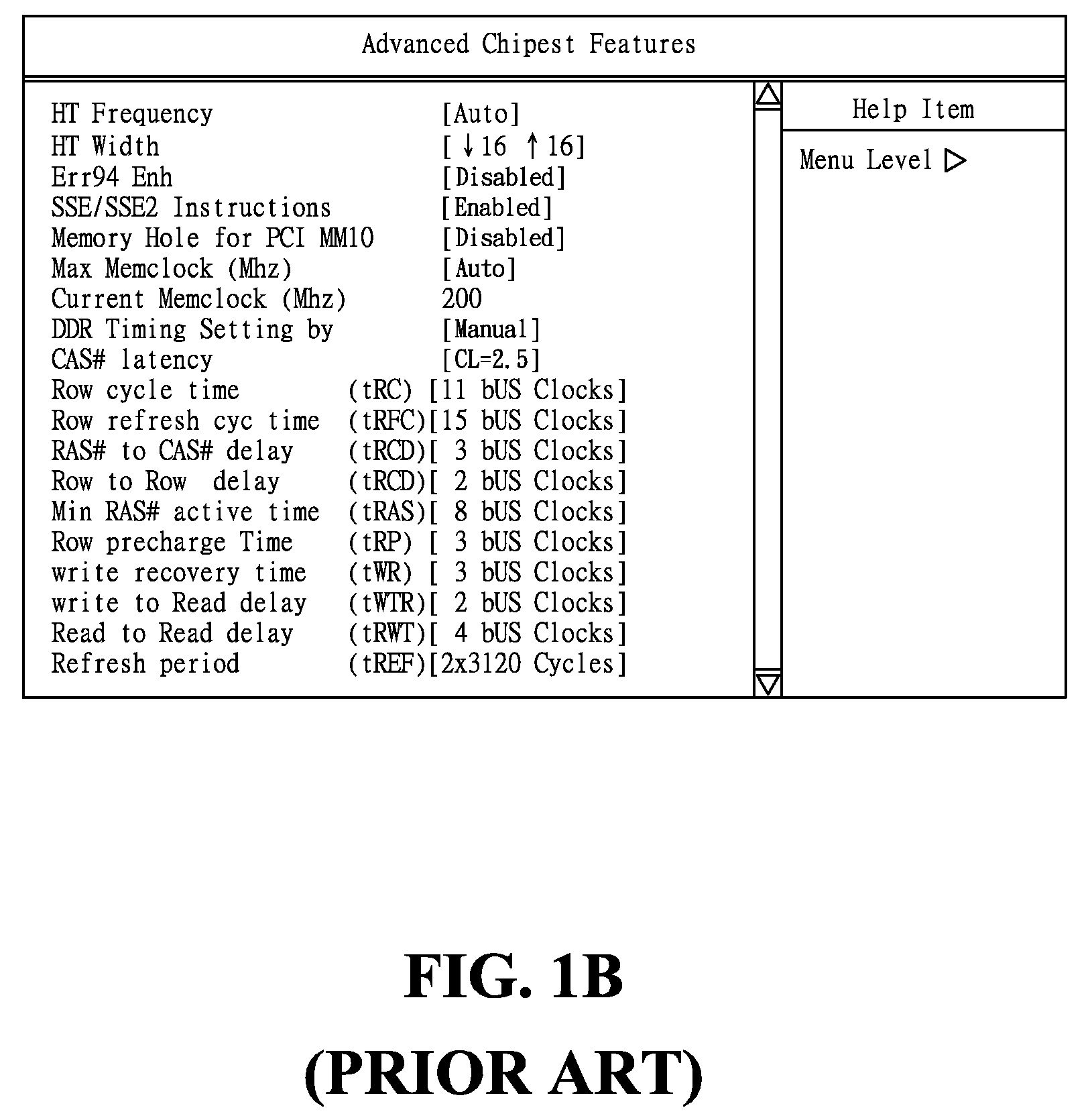

Memory timings or RAM timings describe the performance of synchronous dynamic random-access memory (SDRAM) using four parameters: CL, TRCD, TRP, and TRAS in units of clock cycles; they are commonly written as four numbers separated with dashes, e.g. 7-8-8-24. The fourth (tRAS) is often omitted, or a fifth, the Command rate, sometimes added (normally 2T or 1T, also written 2N, 1N). These parameters specify the latencies (time delays) that affect speed of random access memory. Lower numbers usually imply faster performance. What determines absolute system performance is actual latency time, usually measured in nanoseconds.

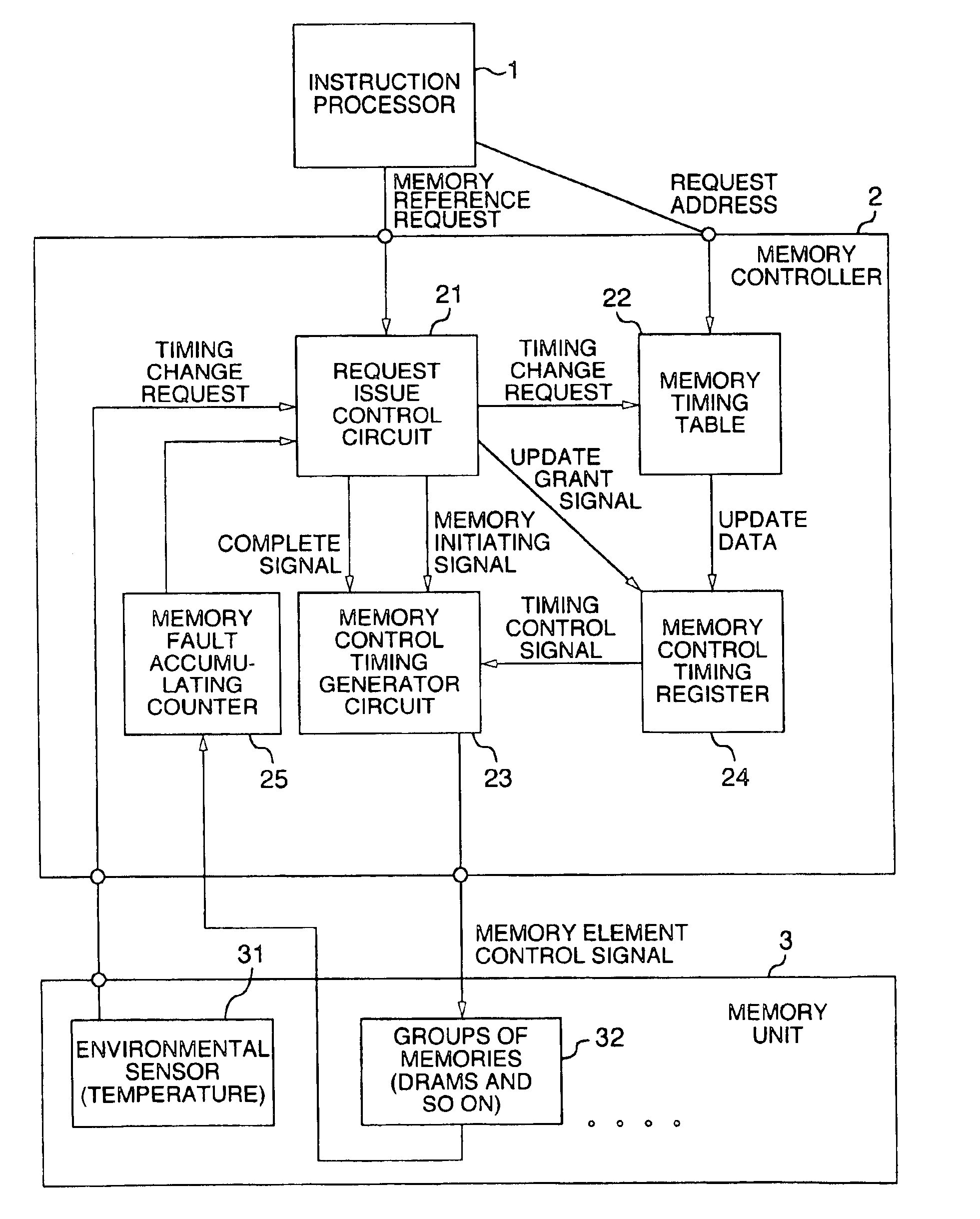

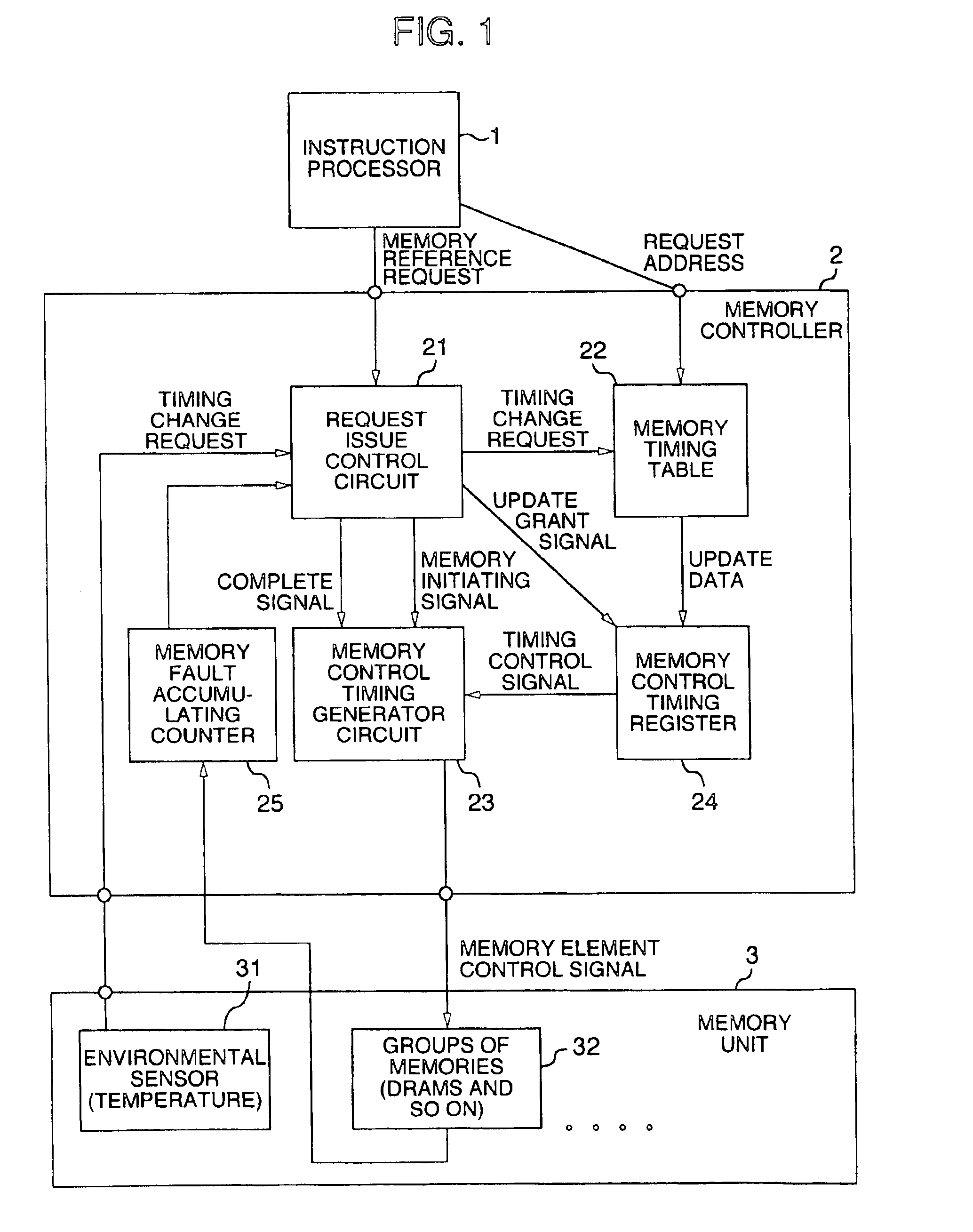

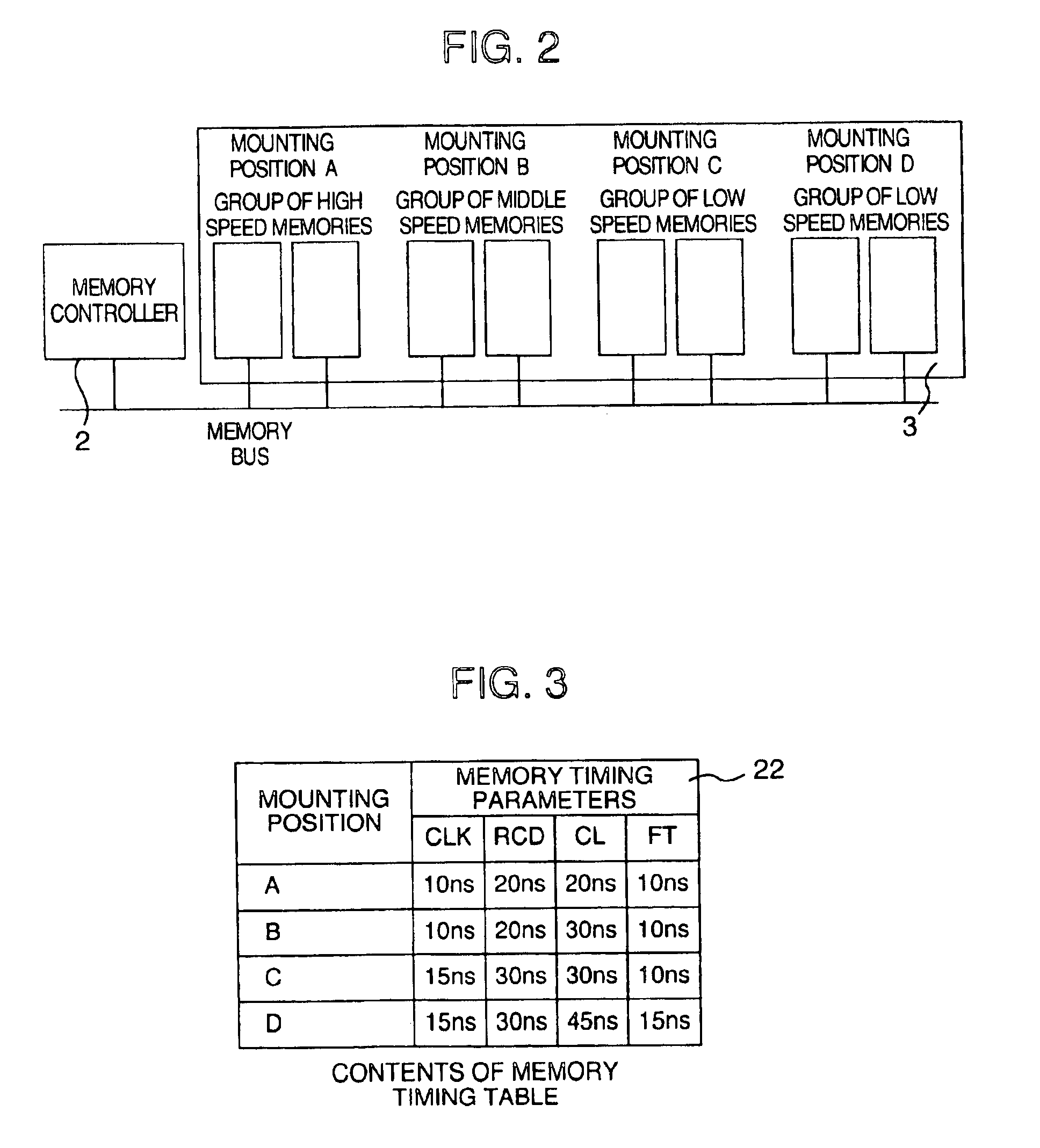

Information processing system with memory element performance-dependent memory control

InactiveUS6877078B2Improve performanceGuaranteed uptimeMemory adressing/allocation/relocationHardware monitoringInformation processingMemory controller

An information processing system which self-detects a change in the actual performance of memory elements due to mounting positions, change in environment, and aging changes to enable the memory elements to stably operate at the highest possible performance without shutting down the system. For implementing an optimal memory access for each of memory elements mounted in a memory unit, a memory controller is provided with a memory timing table which stores operation timings corresponding to the respective memory elements. The timing table is updated in response to an instruction from an apparatus for monitoring the memory operation, and the updated table is applied to a processing request after the update instruction. The apparatus for monitoring the memory operation includes an environmental sensor disposed around the memory elements, a counter for accumulating error information which is generated each time the memory unit is accessed, and so on.

Owner:HITACHI LTD

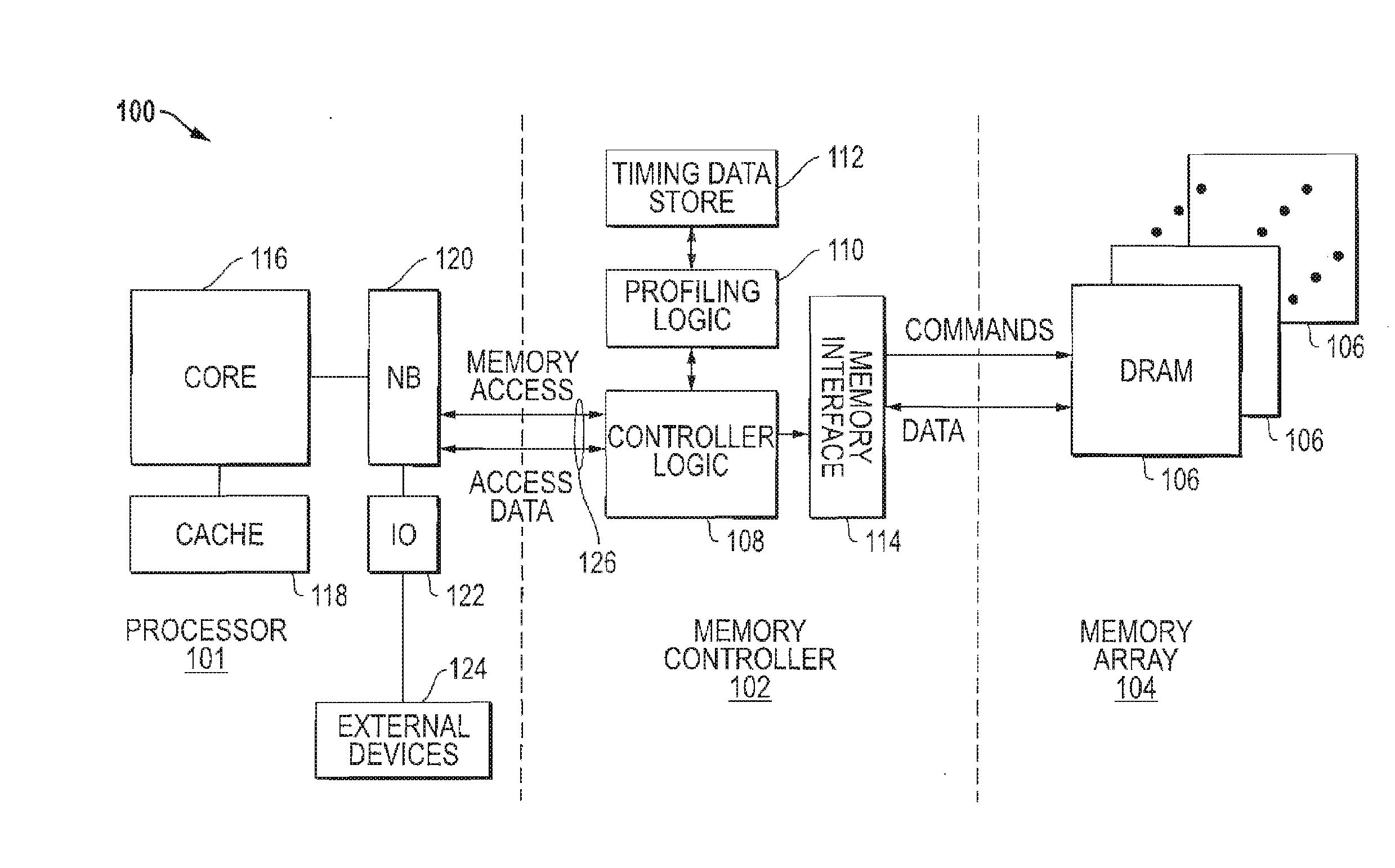

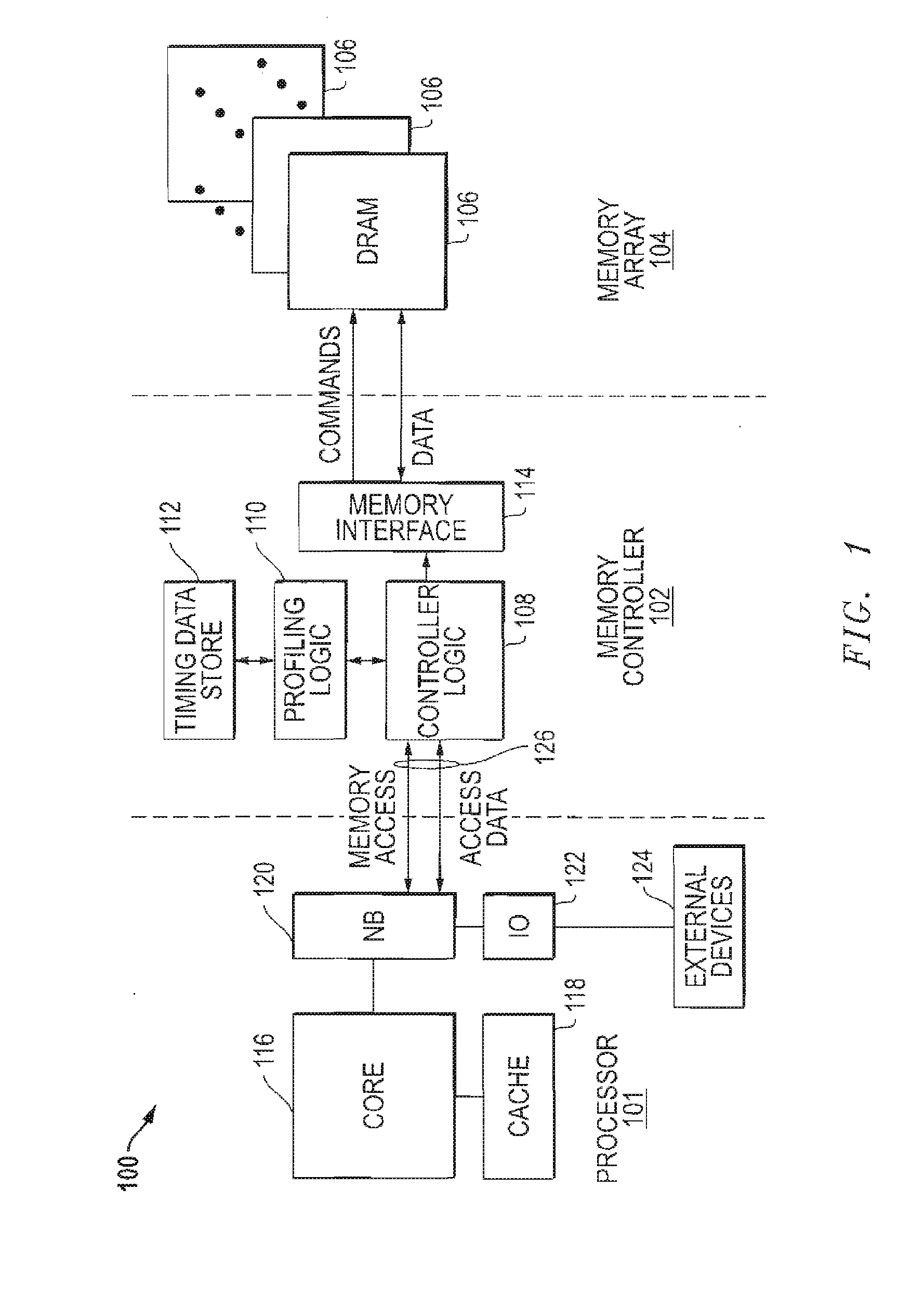

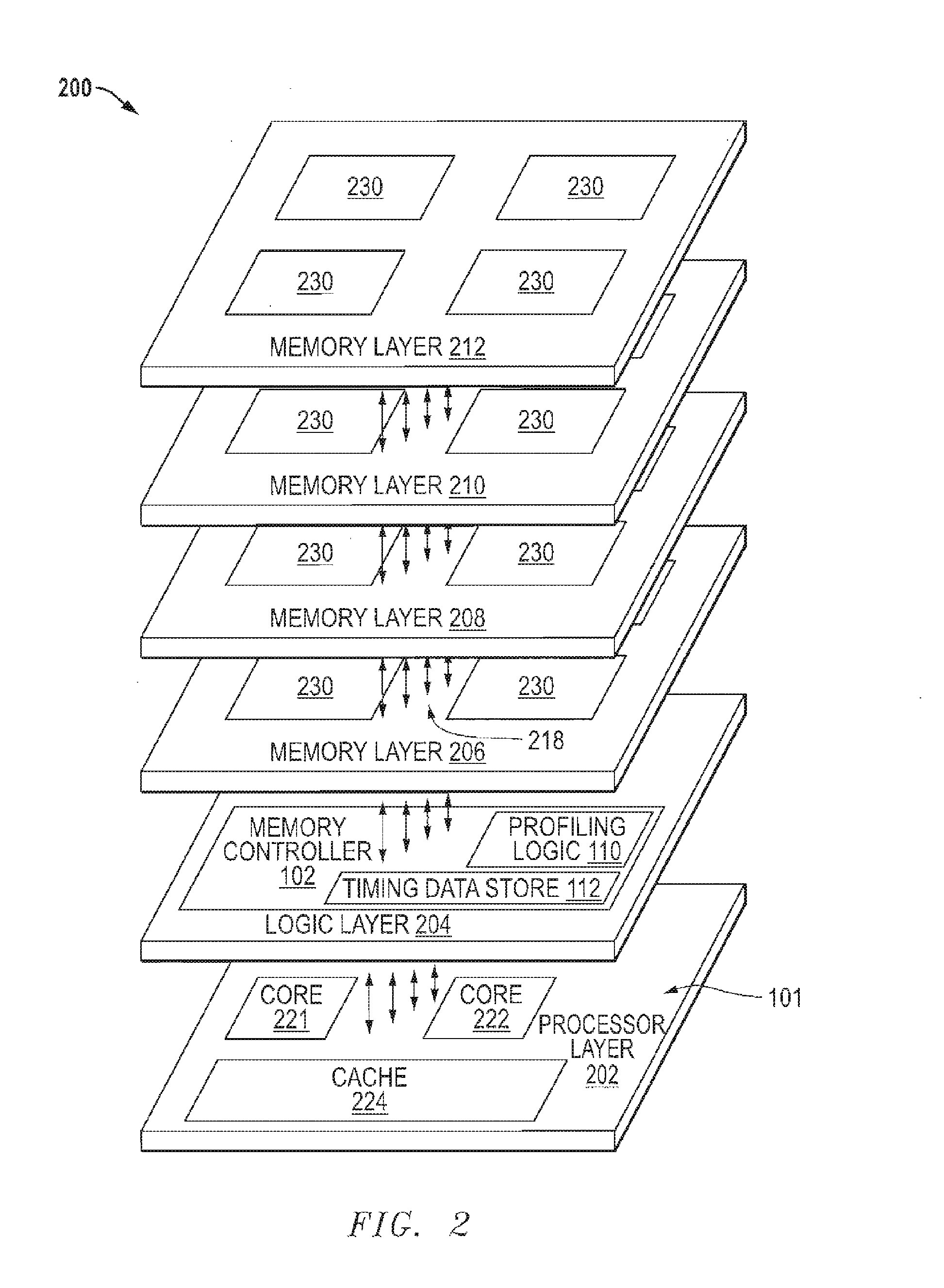

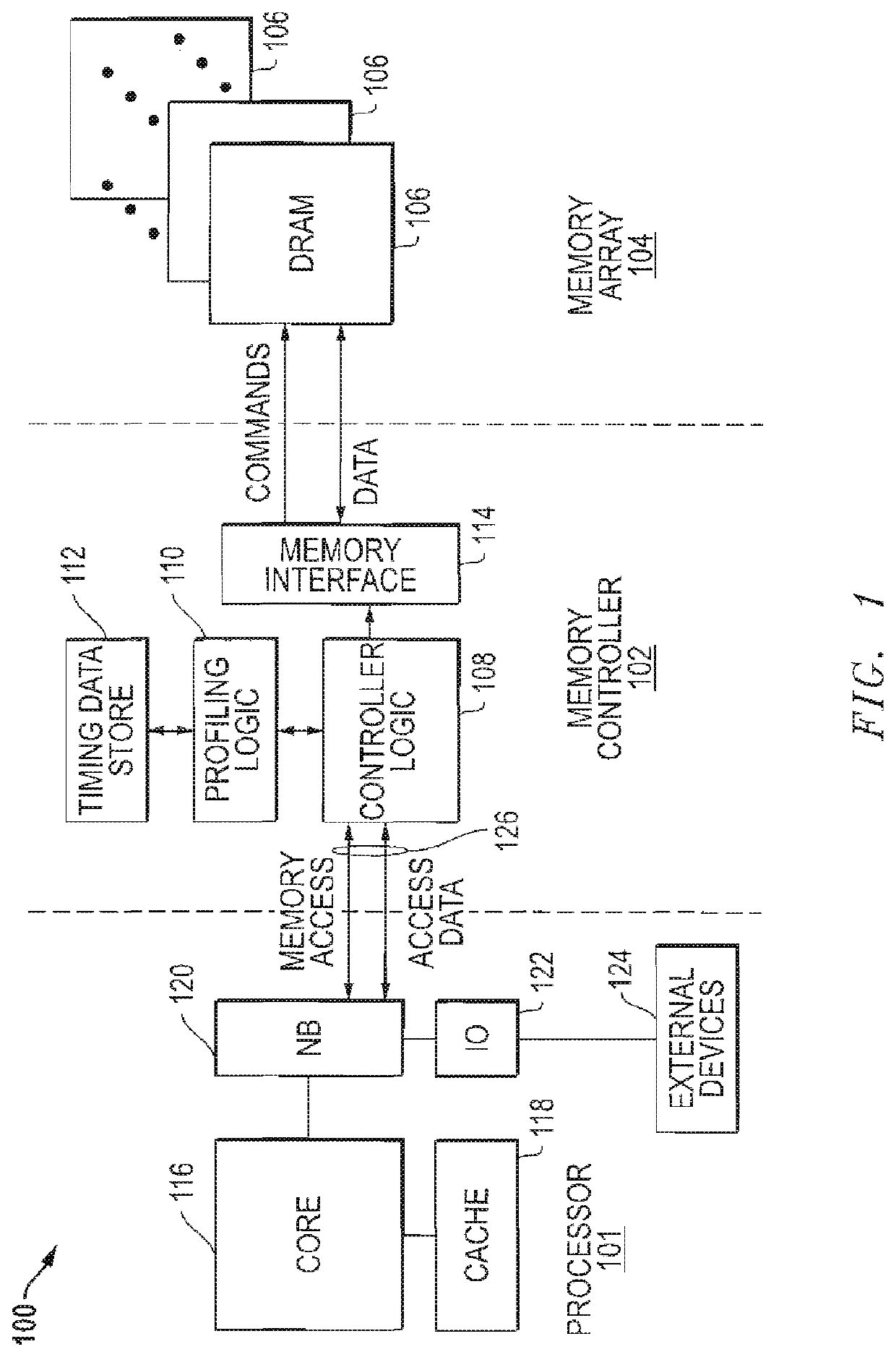

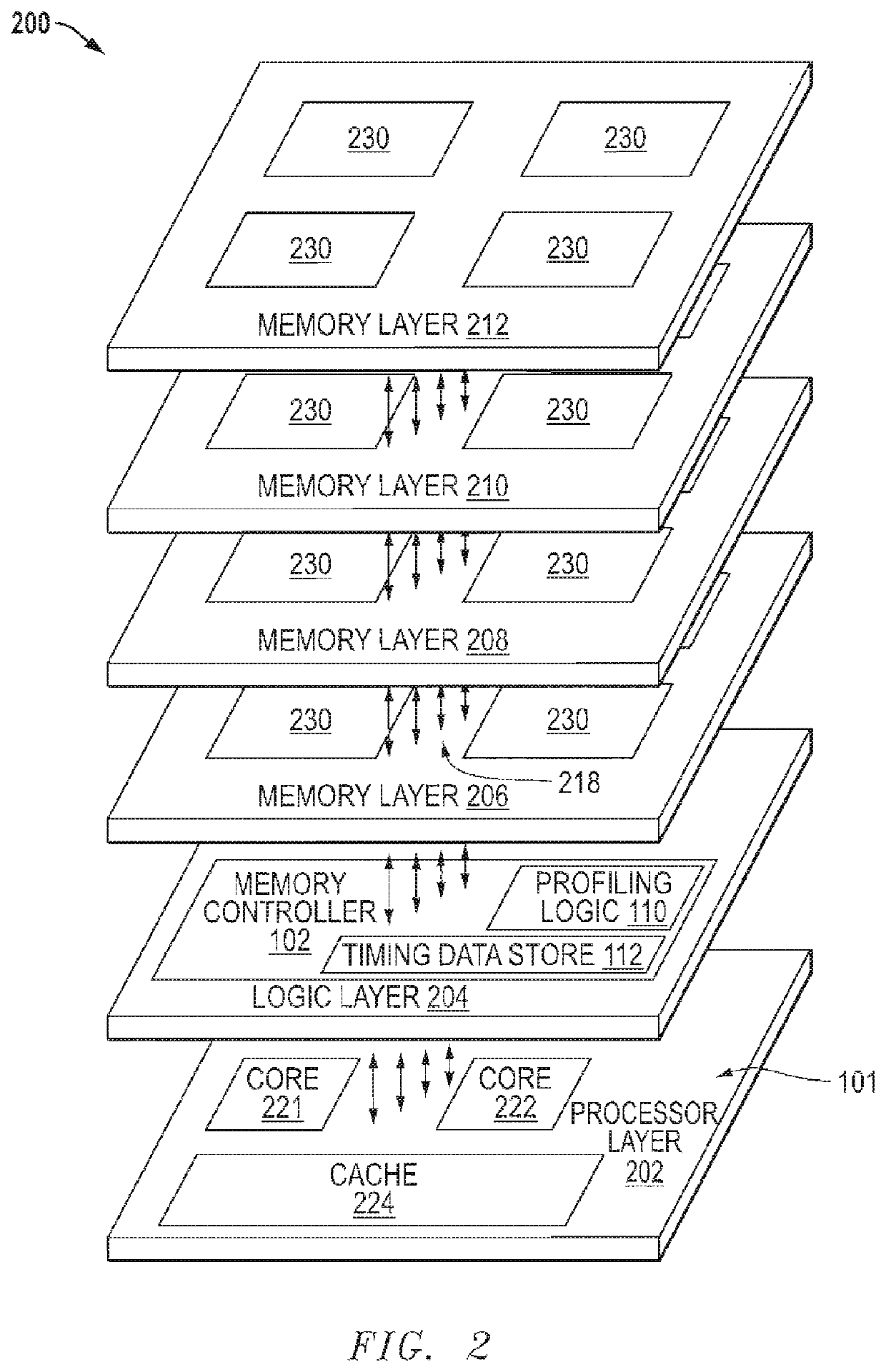

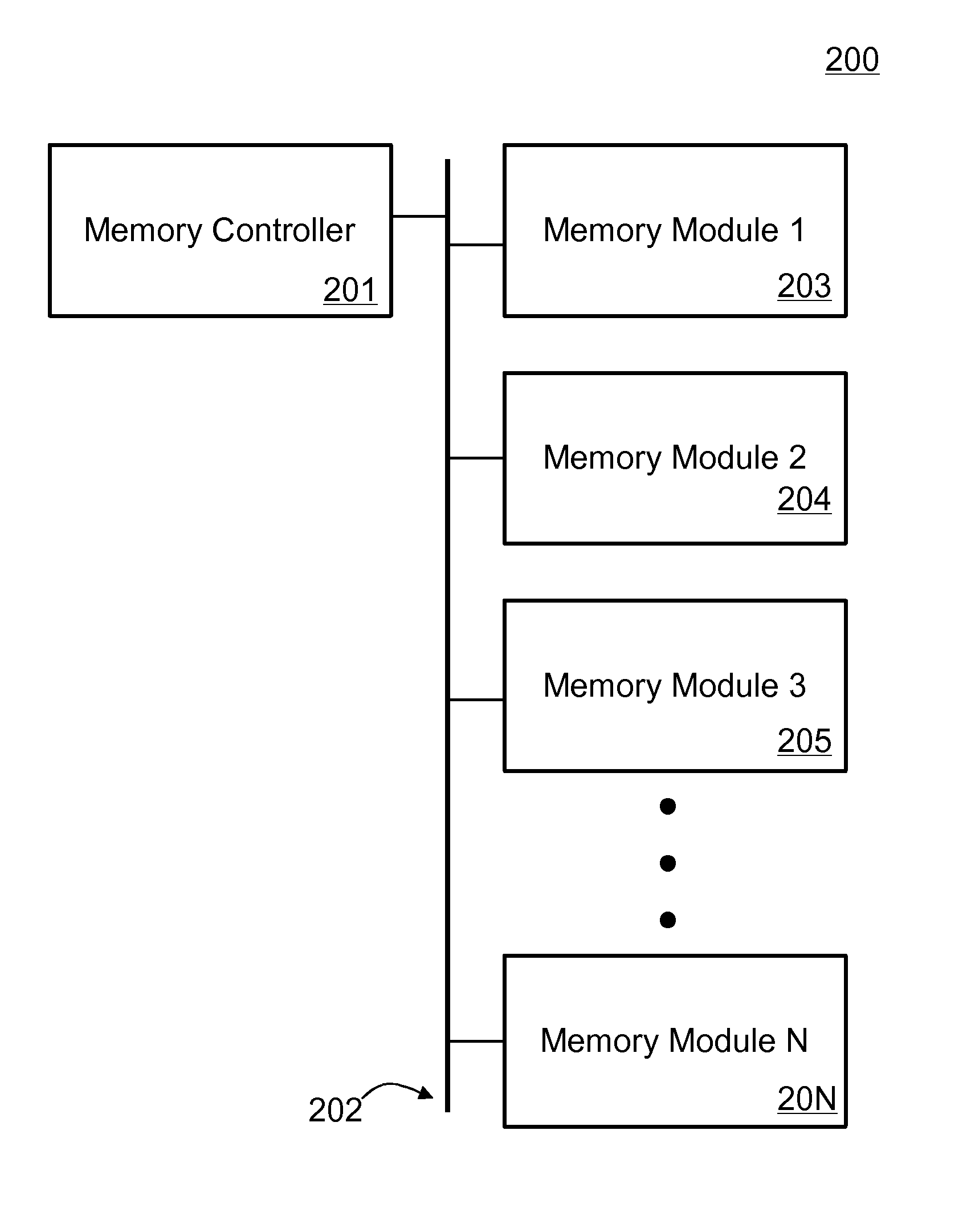

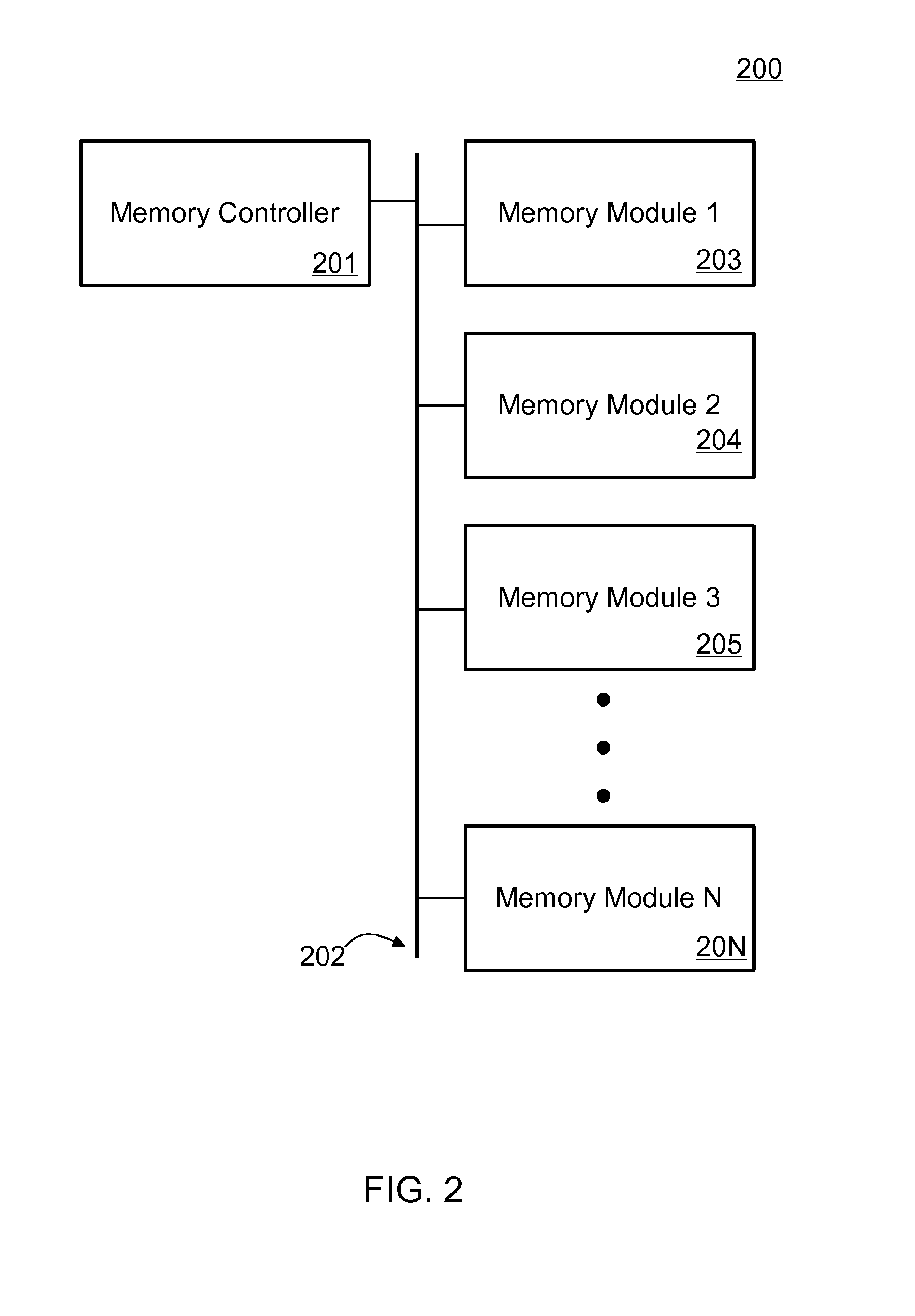

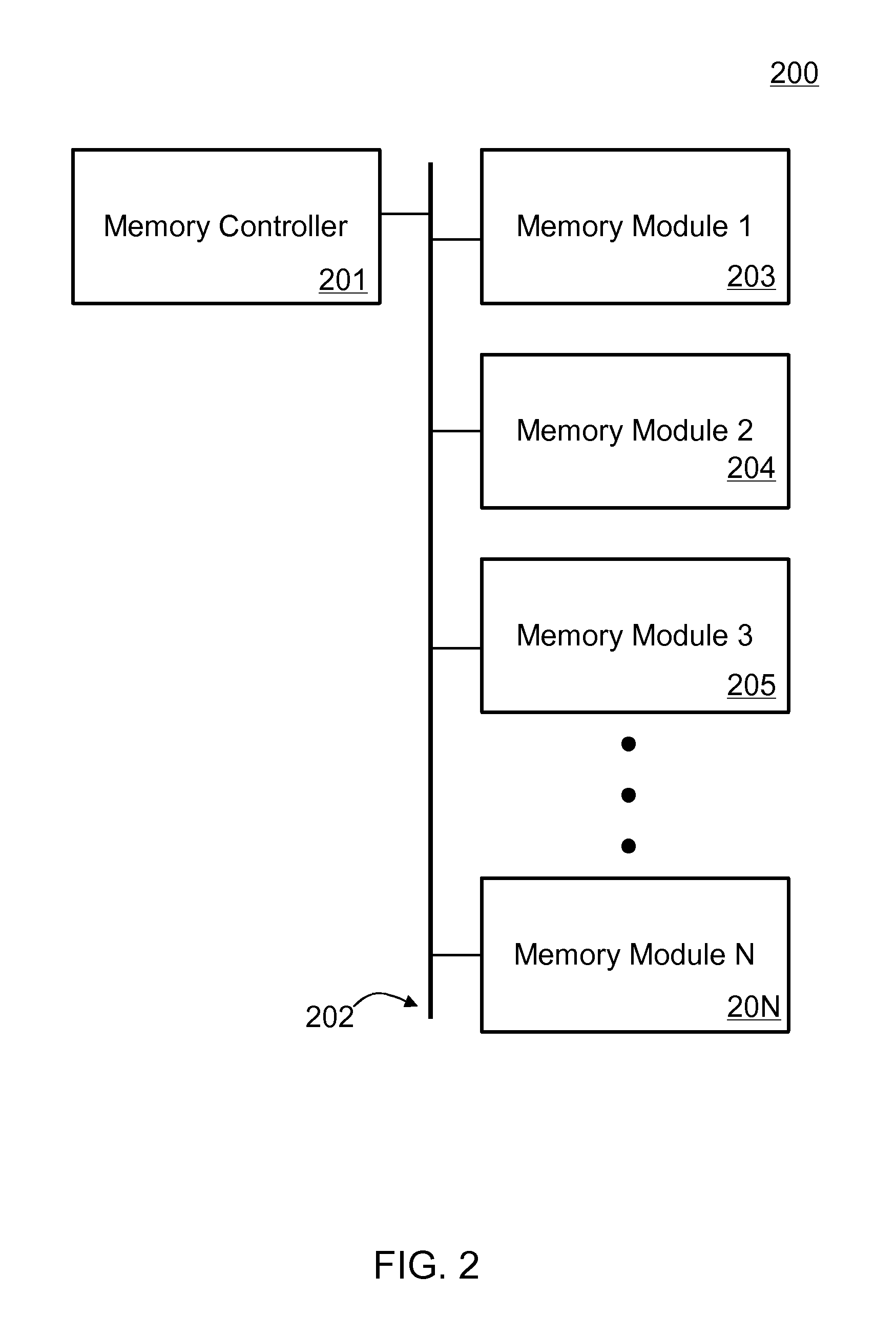

Memory system with region-specific memory access scheduling

ActiveUS20160124873A1Memory architecture accessing/allocationMemory adressing/allocation/relocationComputer hardwareMemory controller

An integrated circuit device includes a memory controller coupleable to a memory. The memory controller to schedule memory accesses to regions of the memory based on memory timing parameters specific to the regions. A method includes receiving a memory access request at a memory device. The method further includes accessing, from a timing data store of the memory device, data representing a memory timing parameter specific to a region of the memory cell circuitry targeted by the memory access request. The method also includes scheduling, at the memory controller, the memory access request based on the data.

Owner:ADVANCED MICRO DEVICES INC

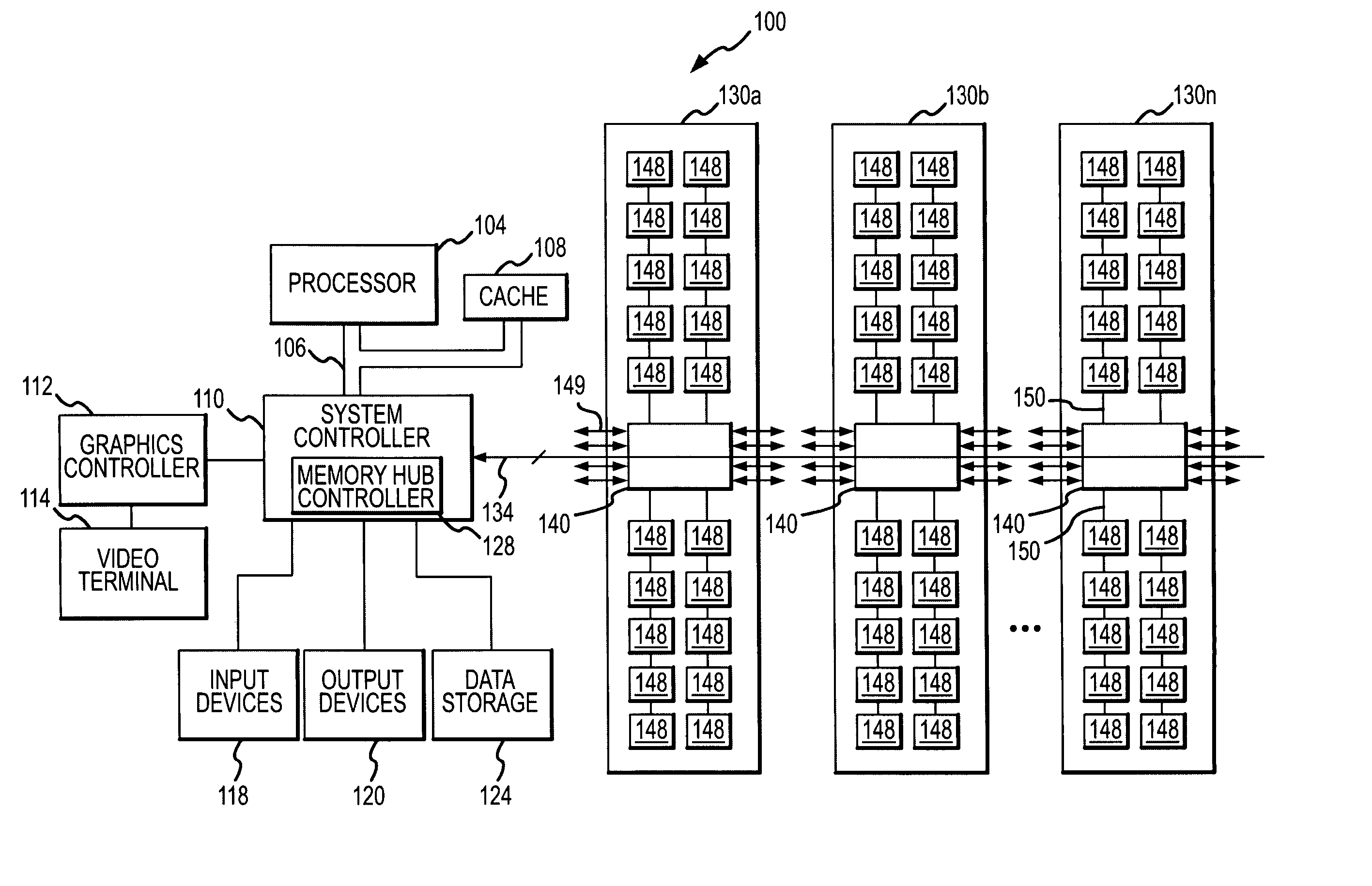

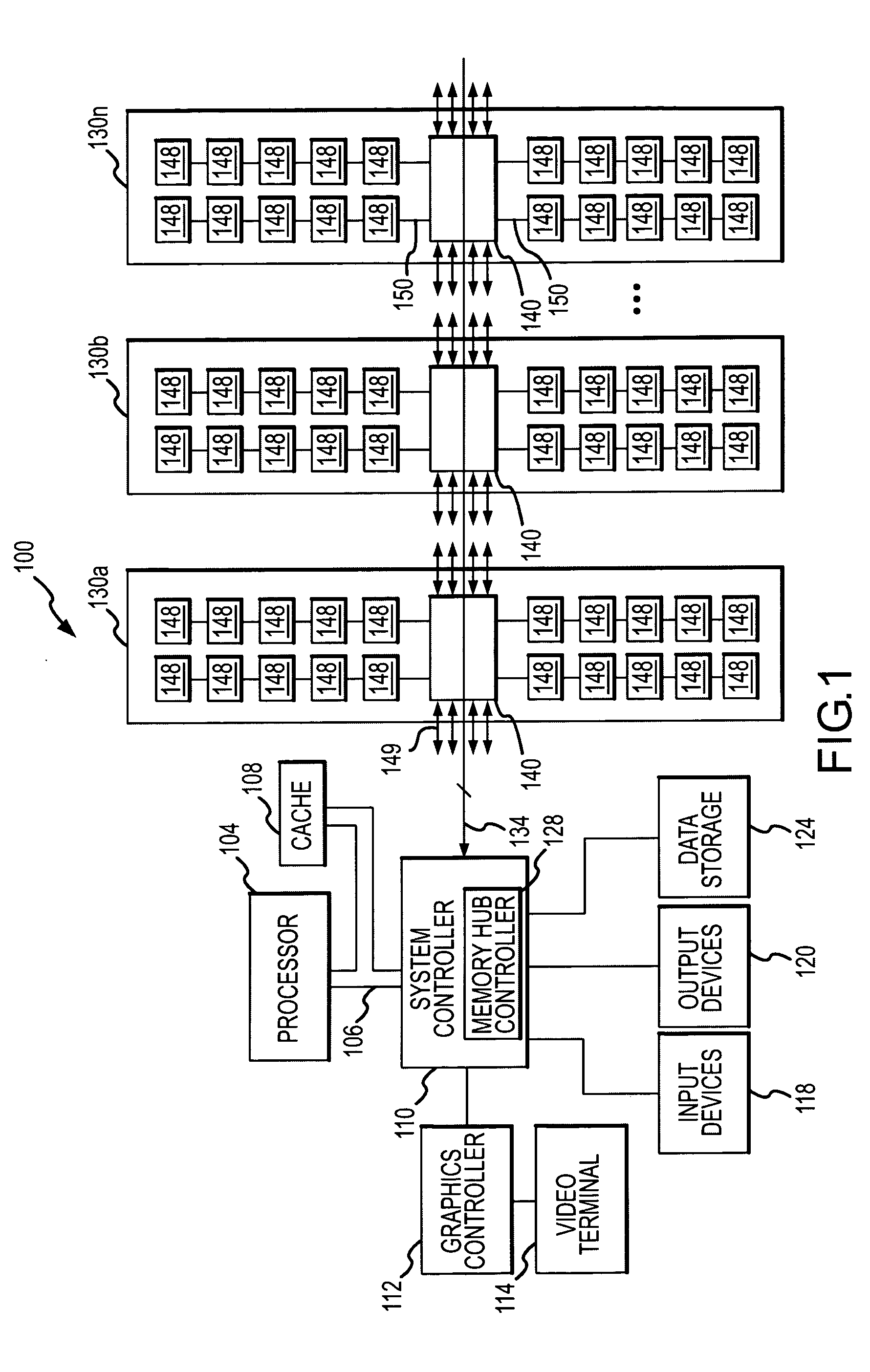

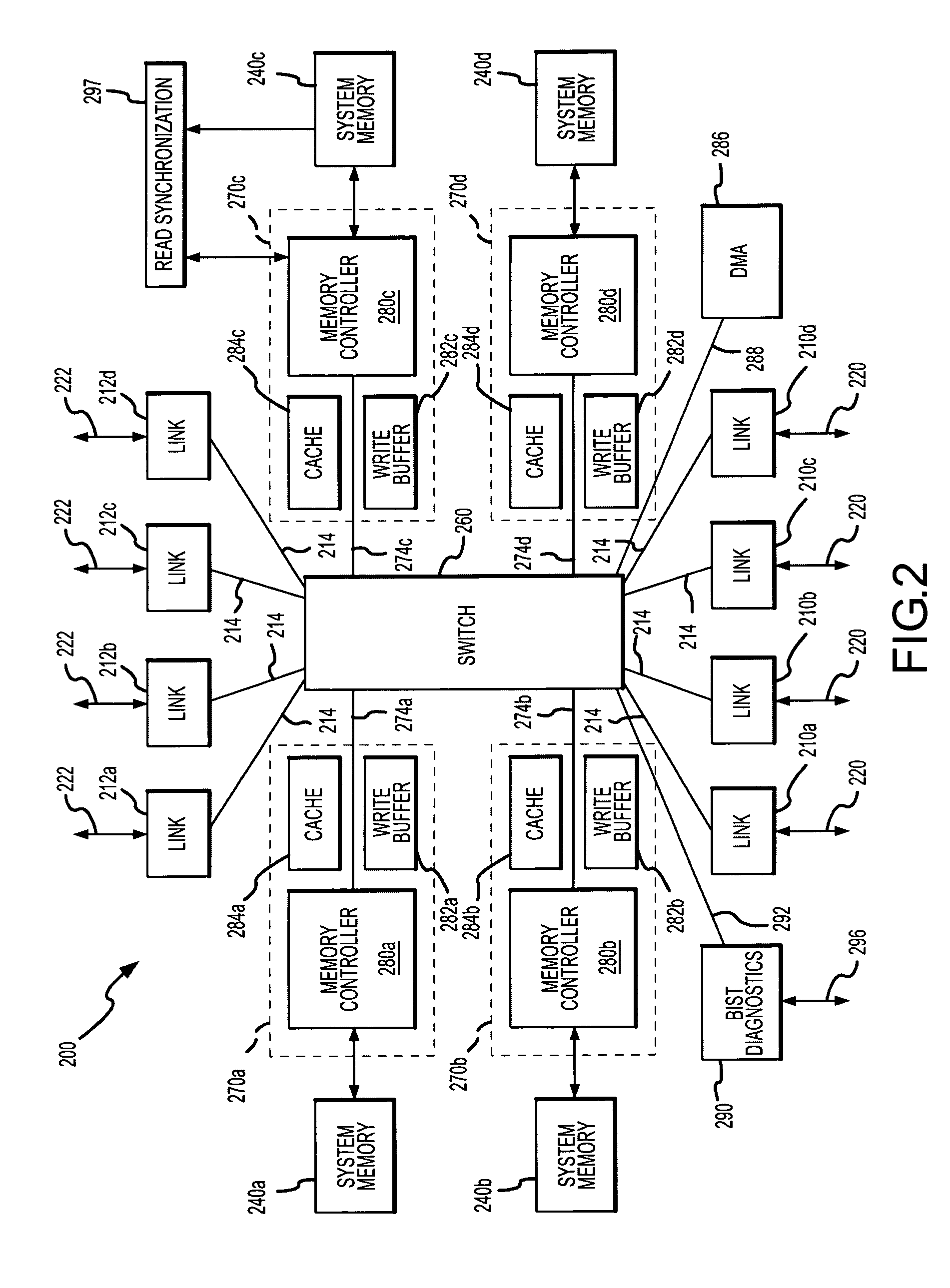

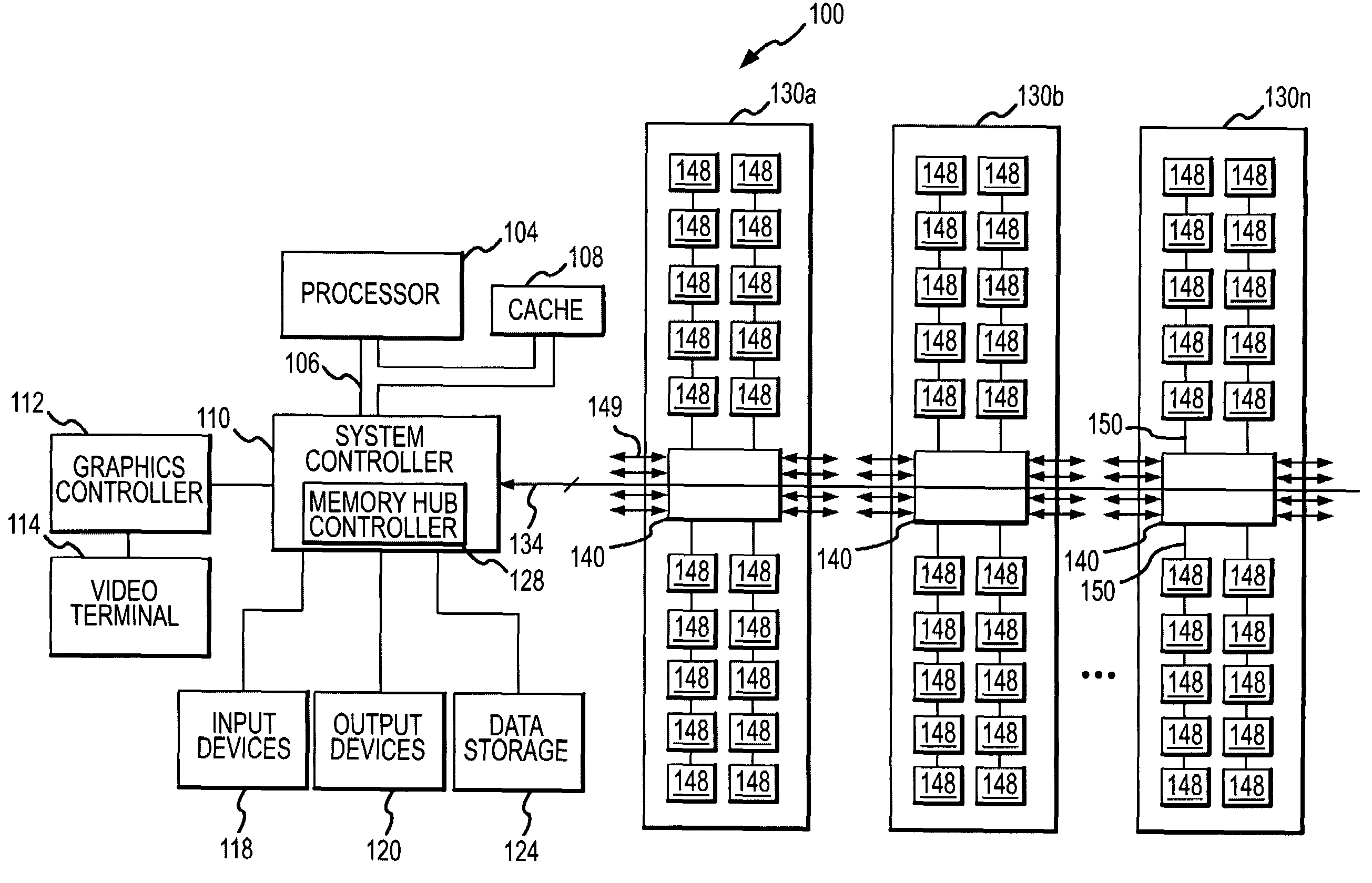

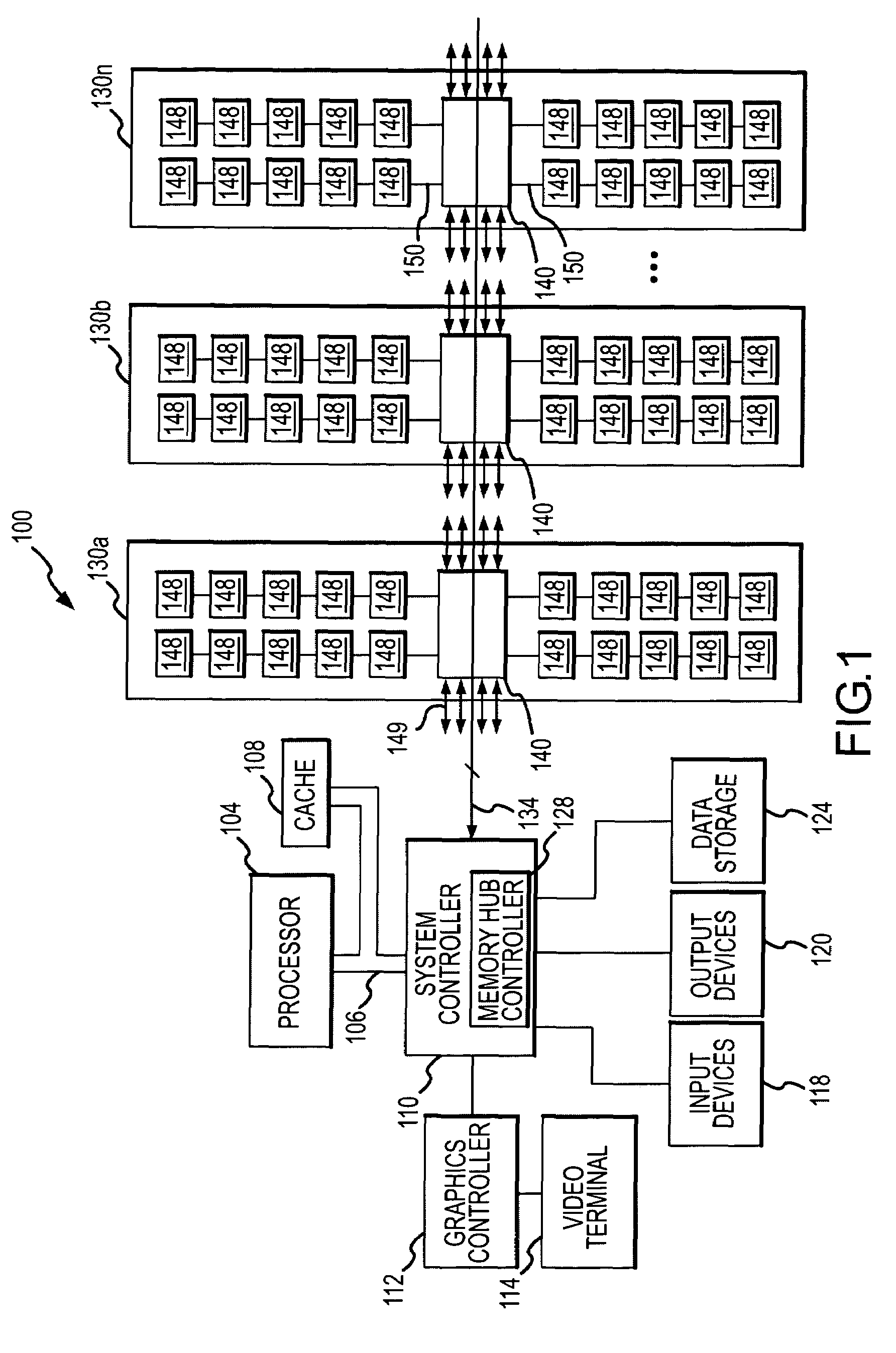

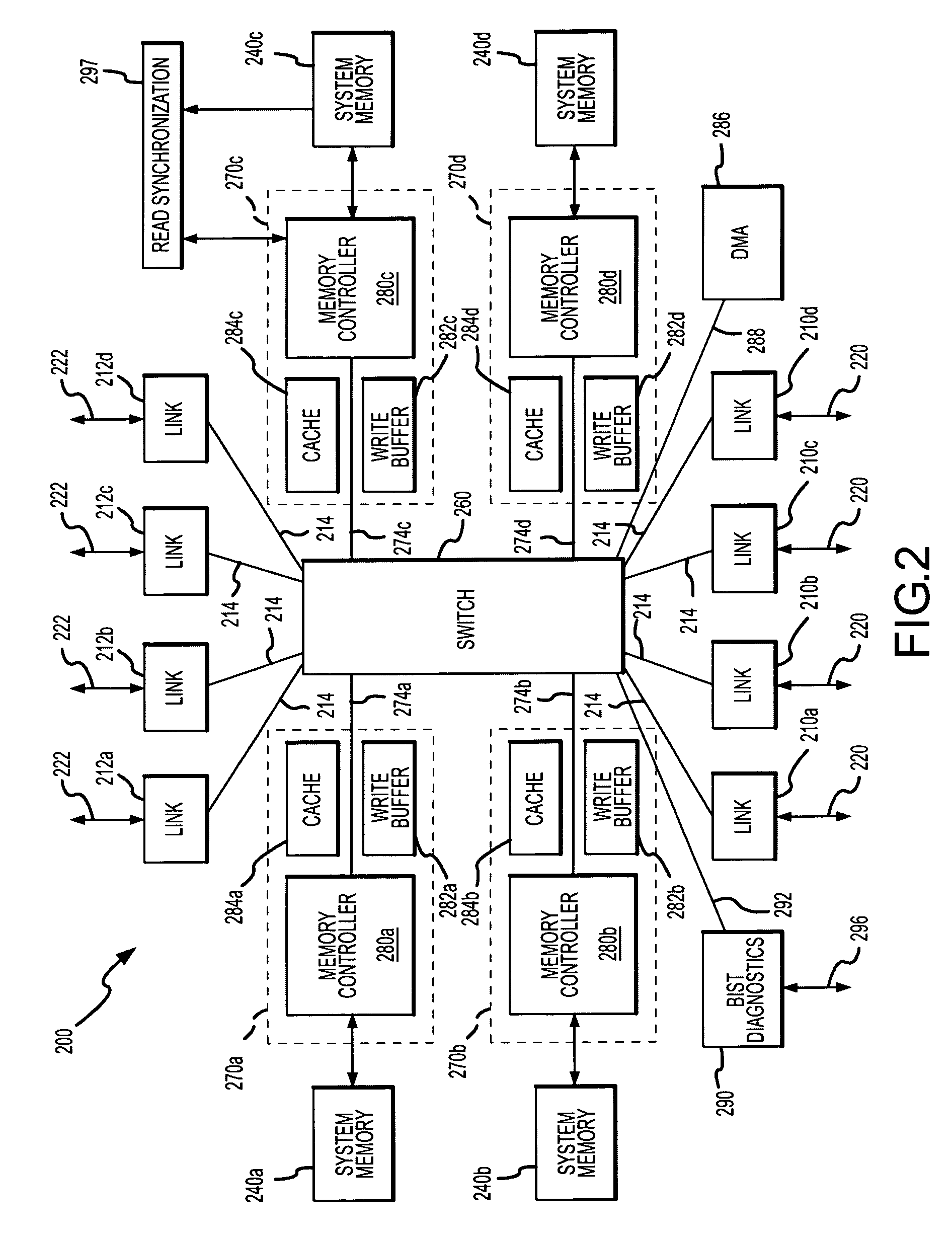

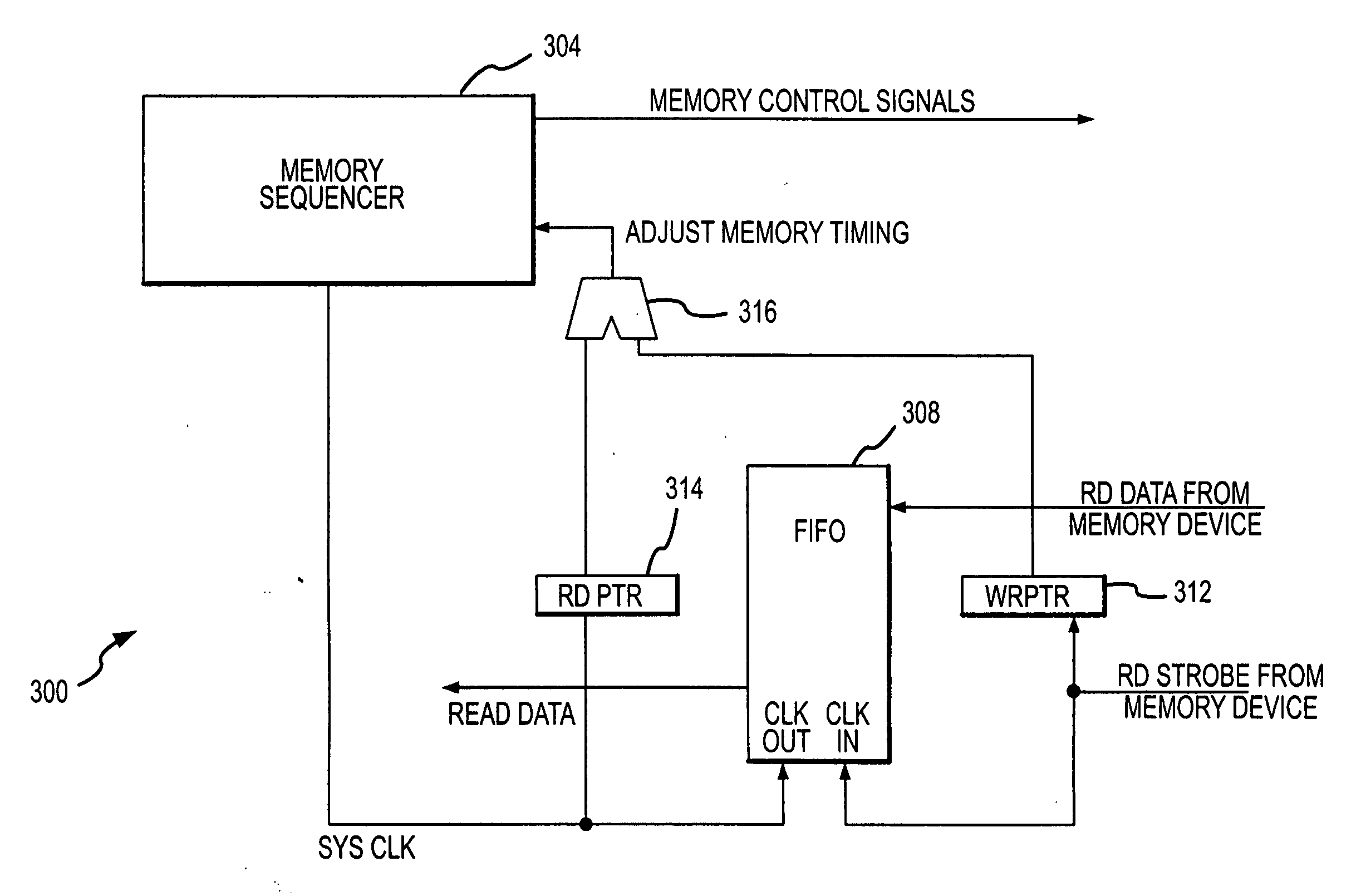

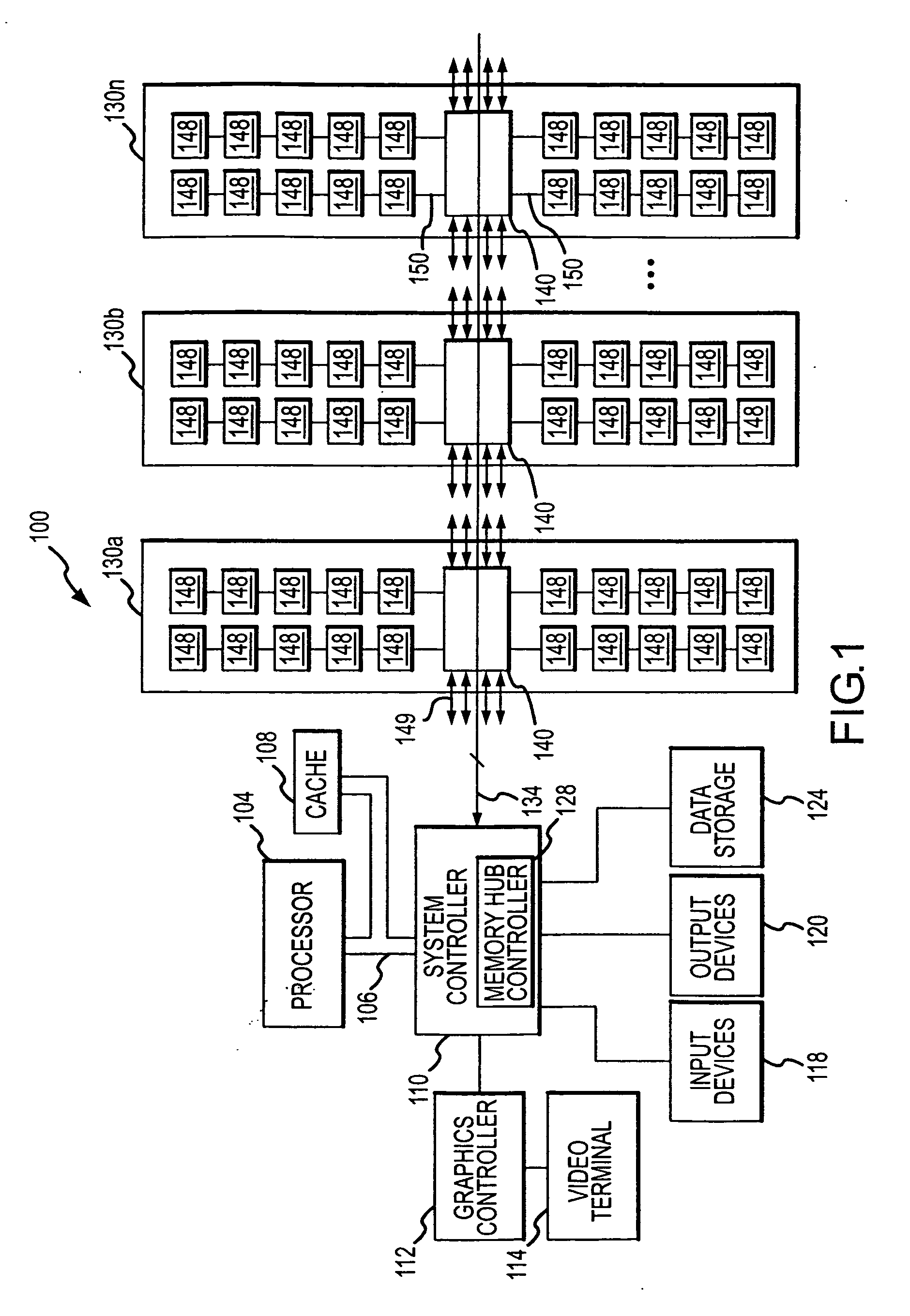

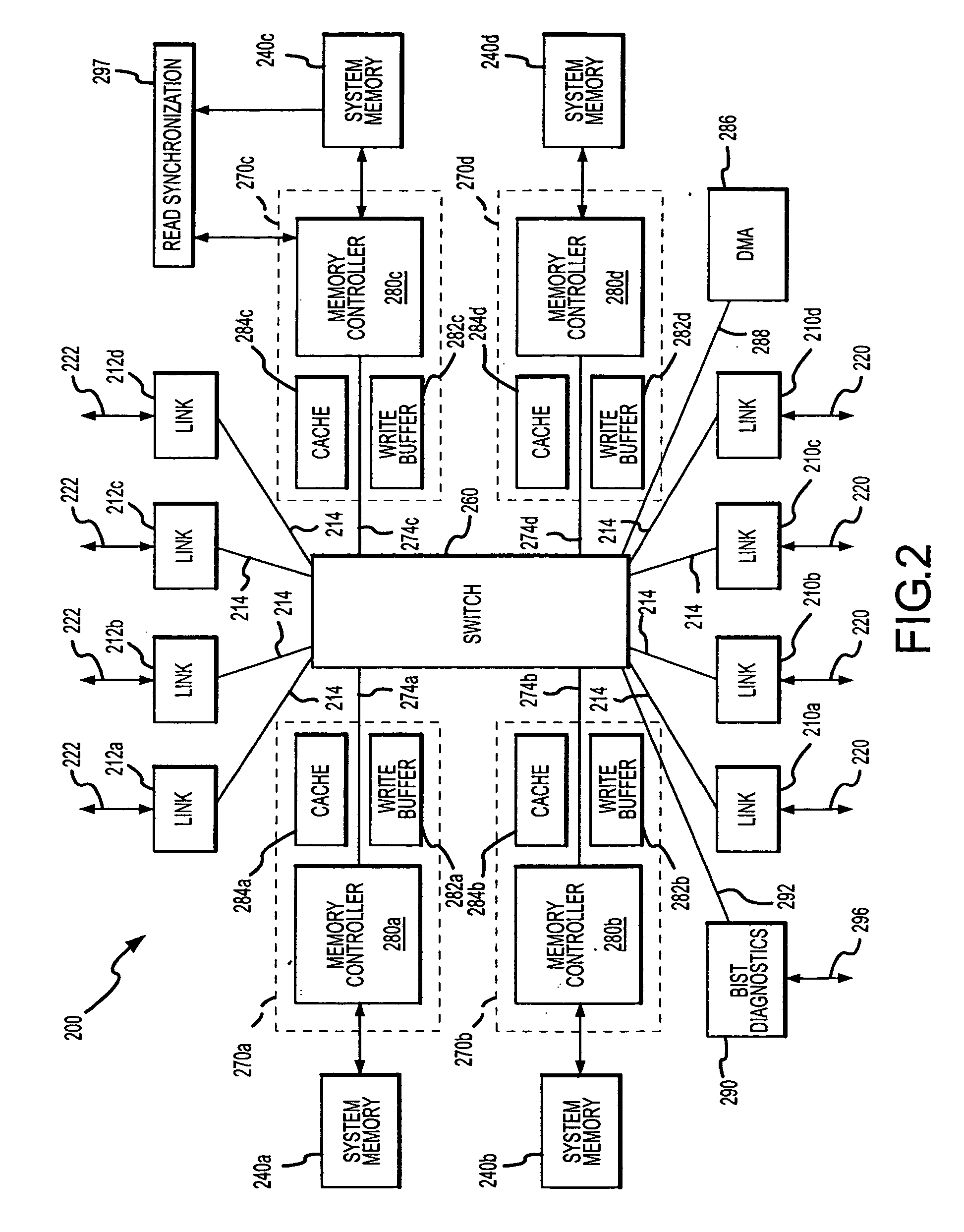

System and method for read synchronization of memory modules

A memory module includes several memory devices coupled to a memory hub. The memory hub includes several link interfaces coupled to respective processors, several memory controller coupled to respective memory devices, a cross-bar switch coupling any of the link interfaces to any of the memory controllers, a write buffer and read cache for each memory device and a read synchronization module. The read synchronization module includes a write pointer, a read pointer and a buffer. The write pointer is incremented in response to the receipt of read data. The read pointer increments in response to coupling of the read data from the memory hub. A comparator compares the read pointer an the write pointer, and the comparison is used to adjust the memory timing.

Owner:MICRON TECH INC

System and method for read synchronization of memory modules

A memory module includes several memory devices coupled to a memory hub. The memory hub includes several link interfaces coupled to respective processors, several memory controller coupled to respective memory devices, a cross-bar switch coupling any of the link interfaces to any of the memory controllers, a write buffer and read cache for each memory device and a read synchronization module. The read synchronization module includes a write pointer, a read pointer and a buffer. The write pointer is incremented in response to the receipt of read data. The read pointer increments in response to coupling of the read data from the memory hub. A comparator compares the read pointer an the write pointer, and the comparison is used to adjust the memory timing.

Owner:MICRON TECH INC

System and method for read synchronization of memory modules

A memory module includes several memory devices coupled to a memory hub. The memory hub includes several link interfaces coupled to respective processors, several memory controller coupled to respective memory devices, a cross-bar switch coupling any of the link interfaces to any of the memory controllers, a write buffer and read cache for each memory device and a read synchronization module. The read synchronization module includes a write pointer, a read pointer and a buffer. The write pointer is incremented in response to the receipt of read data. The read pointer increments in response to coupling of the read data from the memory hub. A comparator compares the read pointer an the write pointer, and the comparison is used to adjust the memory timing.

Owner:MICRON TECH INC

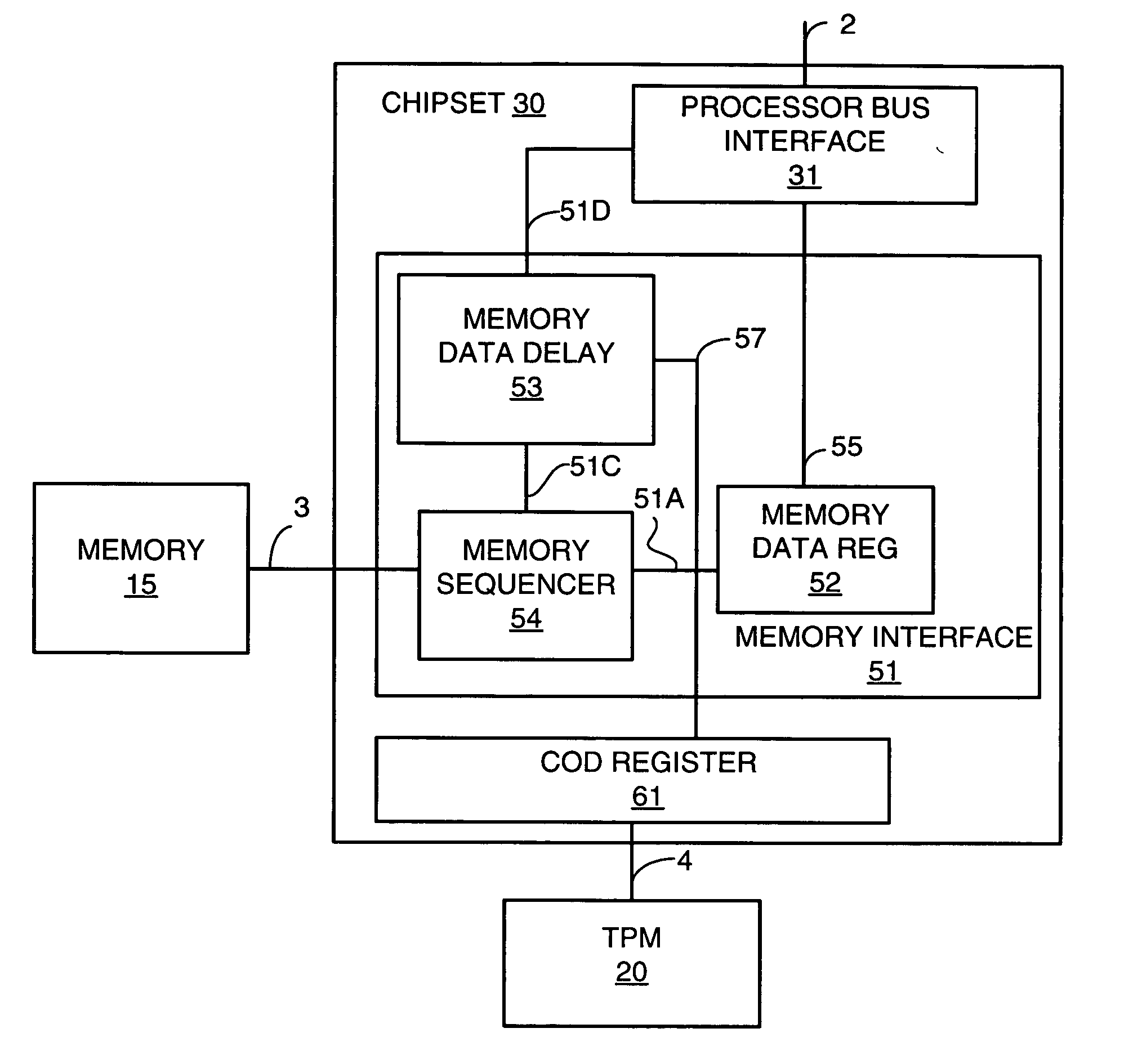

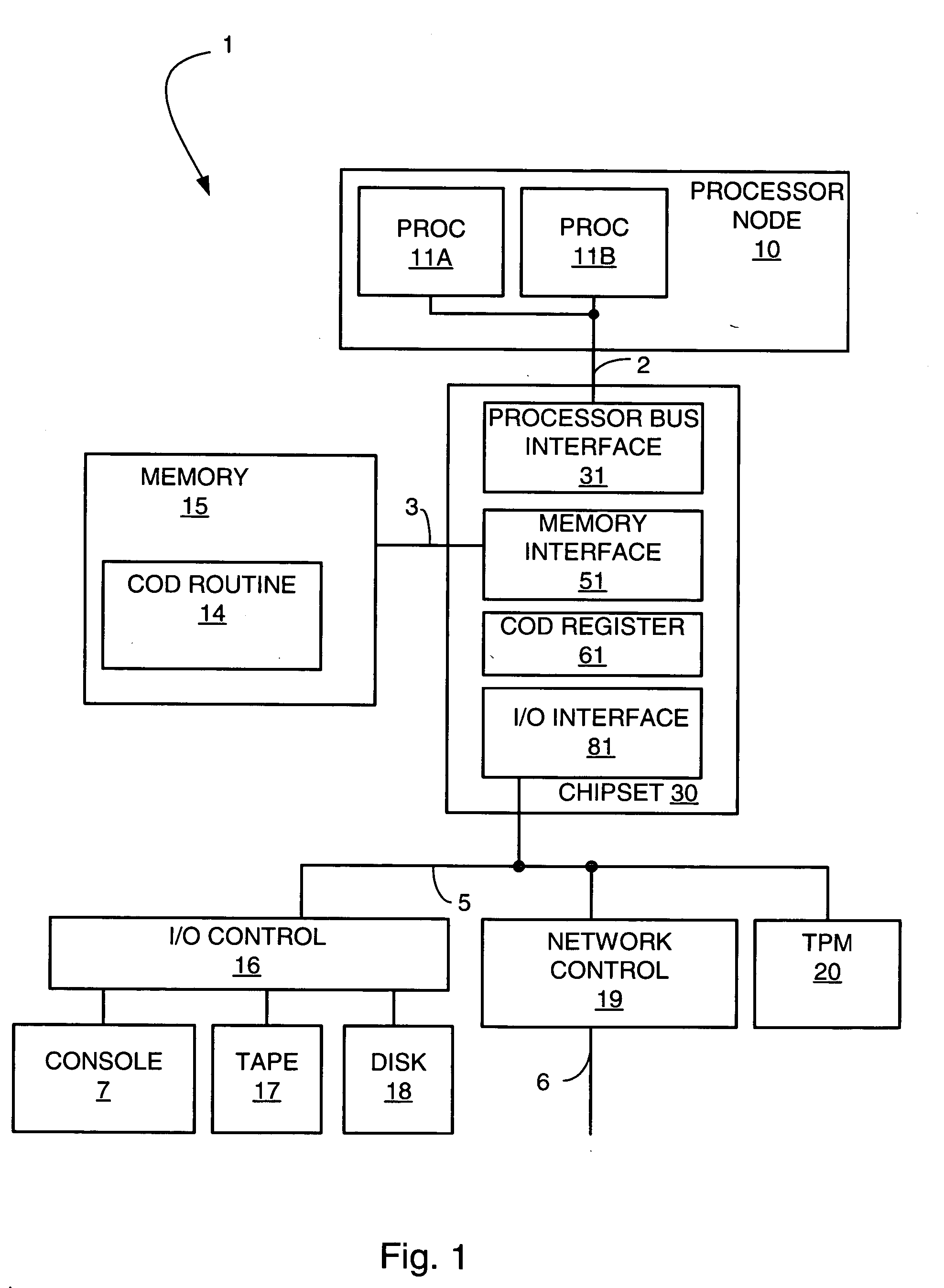

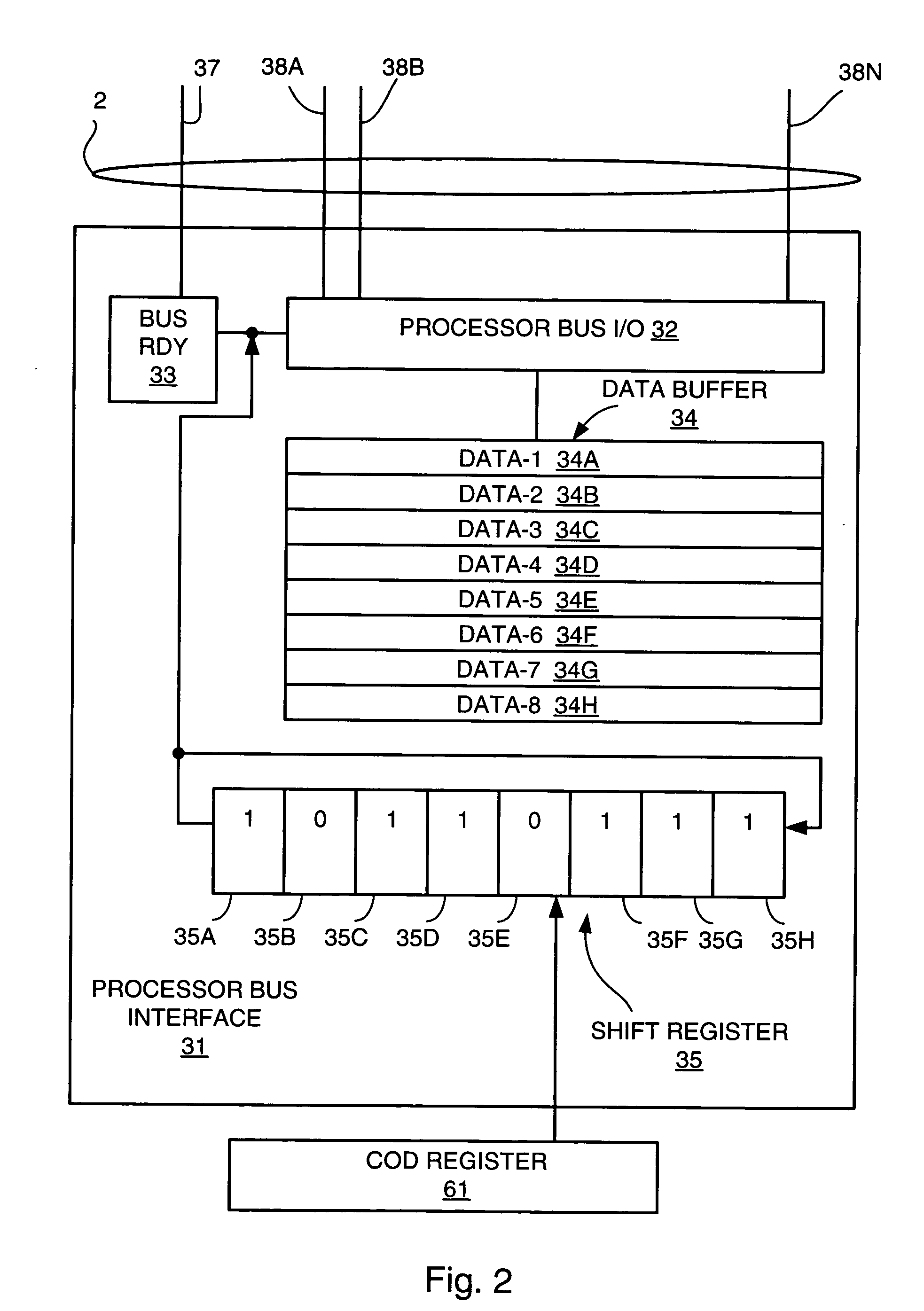

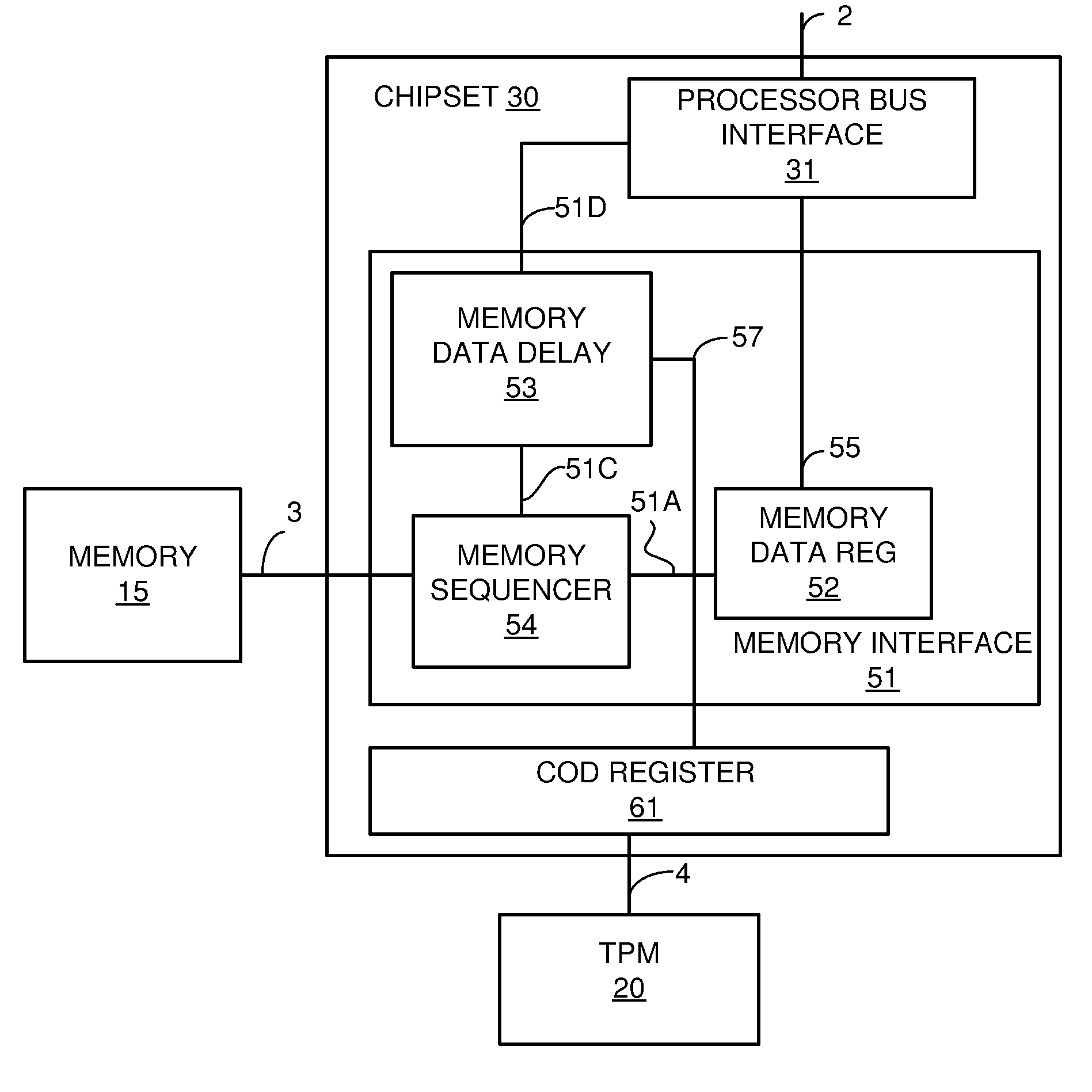

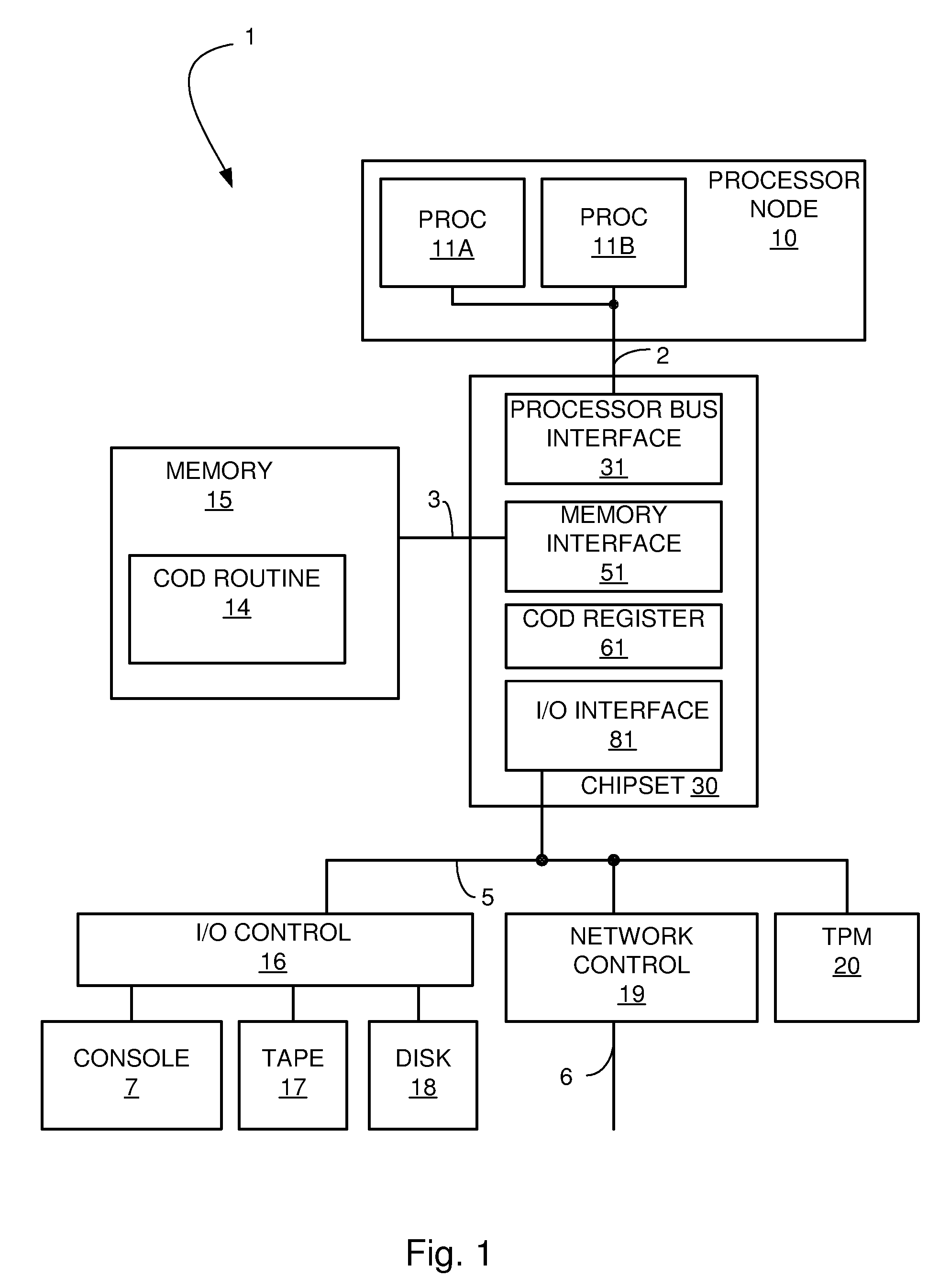

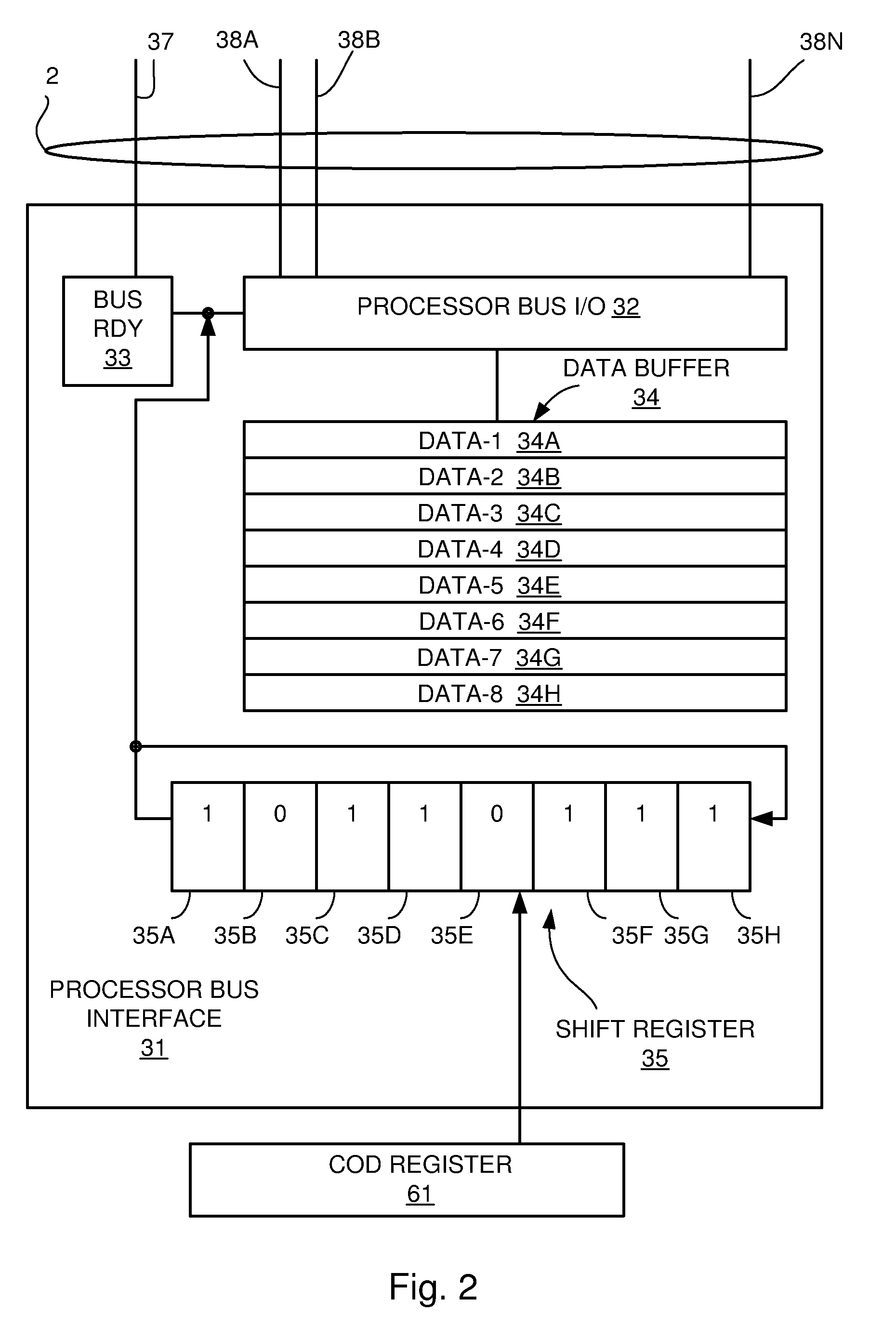

Capacity on demand using signaling bus control

ActiveUS20060136680A1Speed up and delay and bandwidth performanceSpeed up and delay latency and performanceGenerating/distributing signalsProgram controlBus masteringTerm memory

An apparatus and method is disclosed for providing capacity on demand using control to alter latency and / or bandwidth on a signaling bus in a computer system. If additional capacity is required, authorization is requested for additional capacity. If authorized, bandwidth of the signaling bus is increased to provide additional capacity in the computing system. Alternatively, upon authorization, latency of data transmissions over the signaling bus is reduced. In another alternative, upon authorization, memory timings are adjusted to speed up memory fetches and stores.

Owner:LENOVO GLOBAL TECH INT LTD

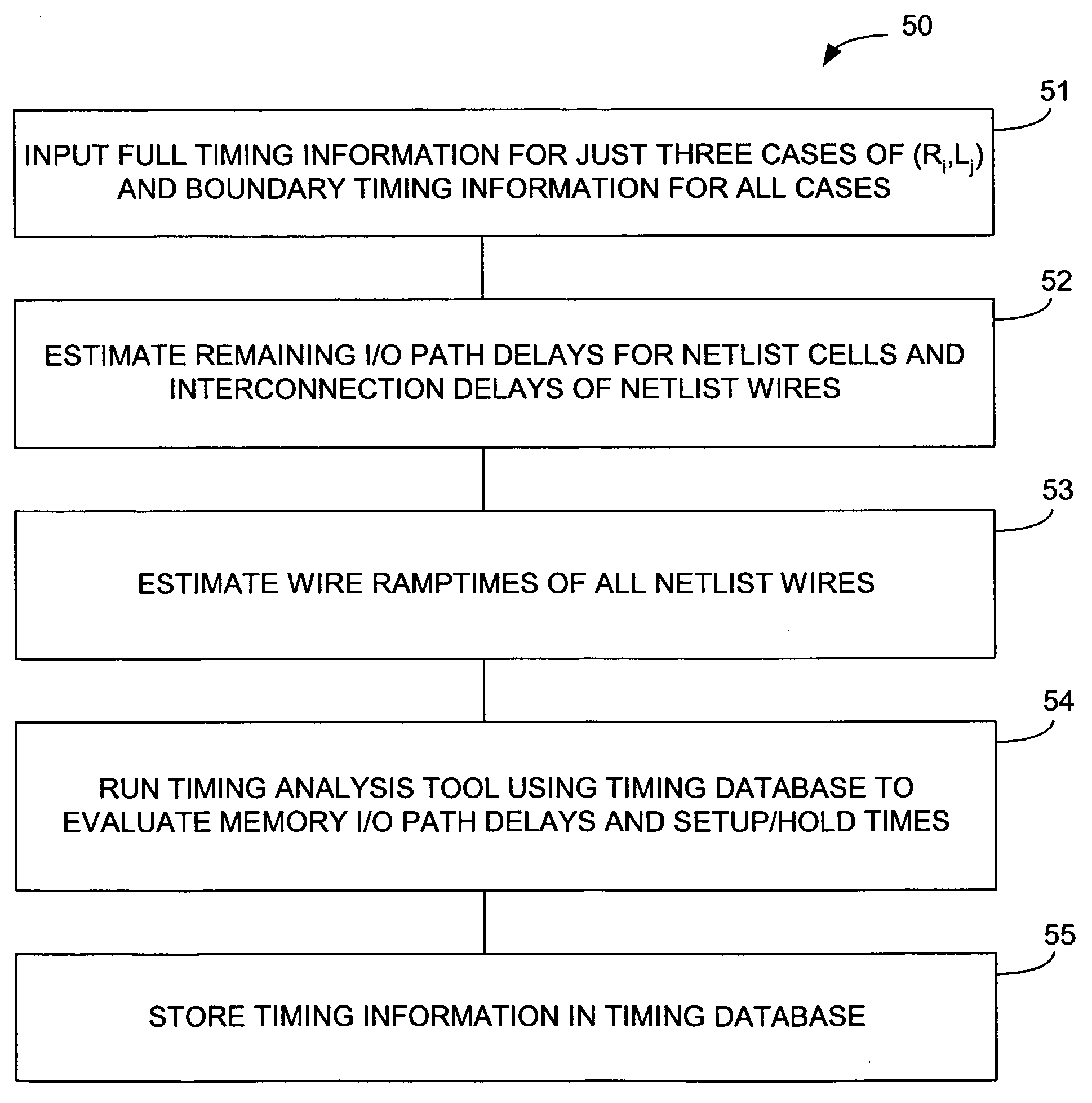

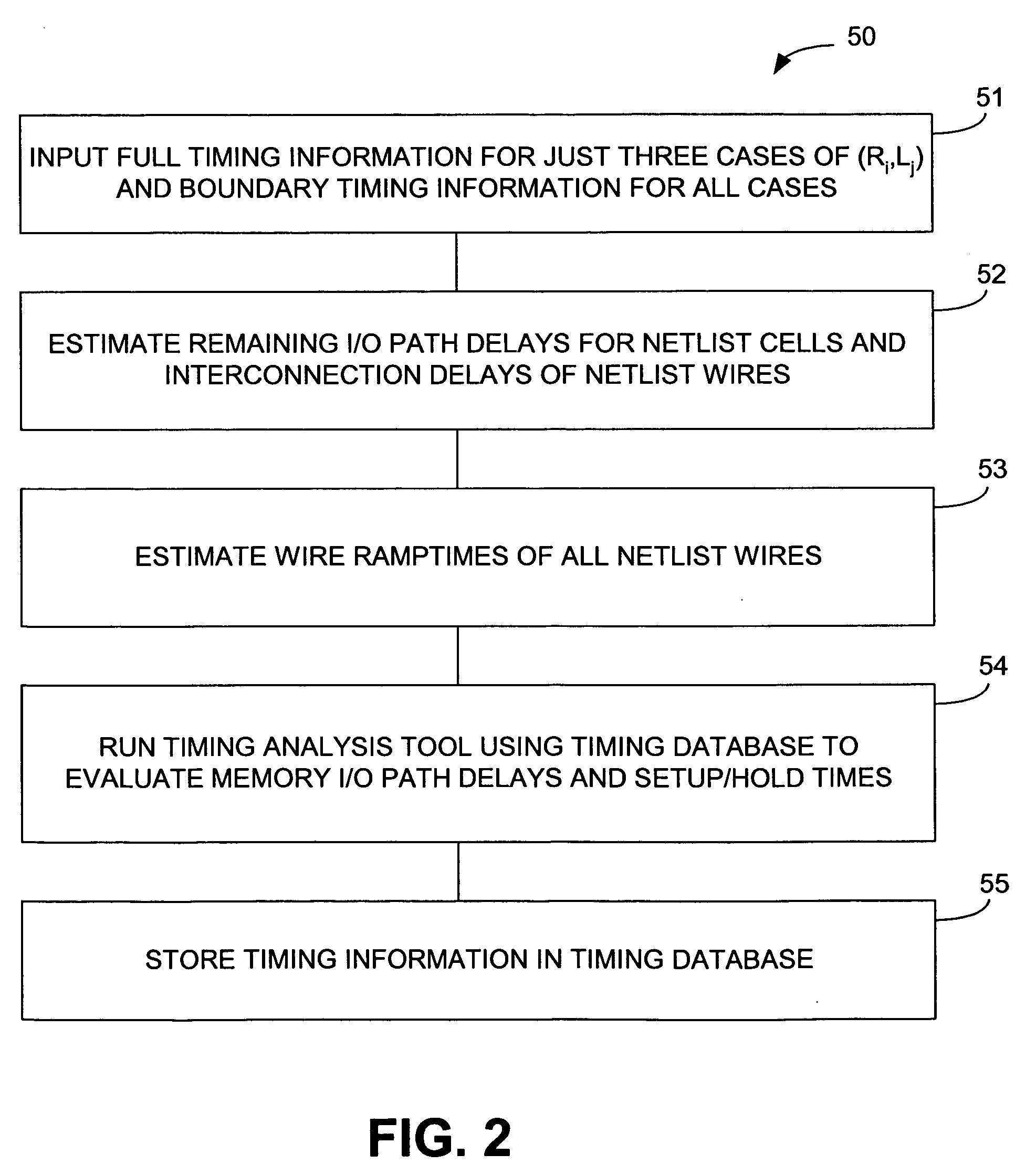

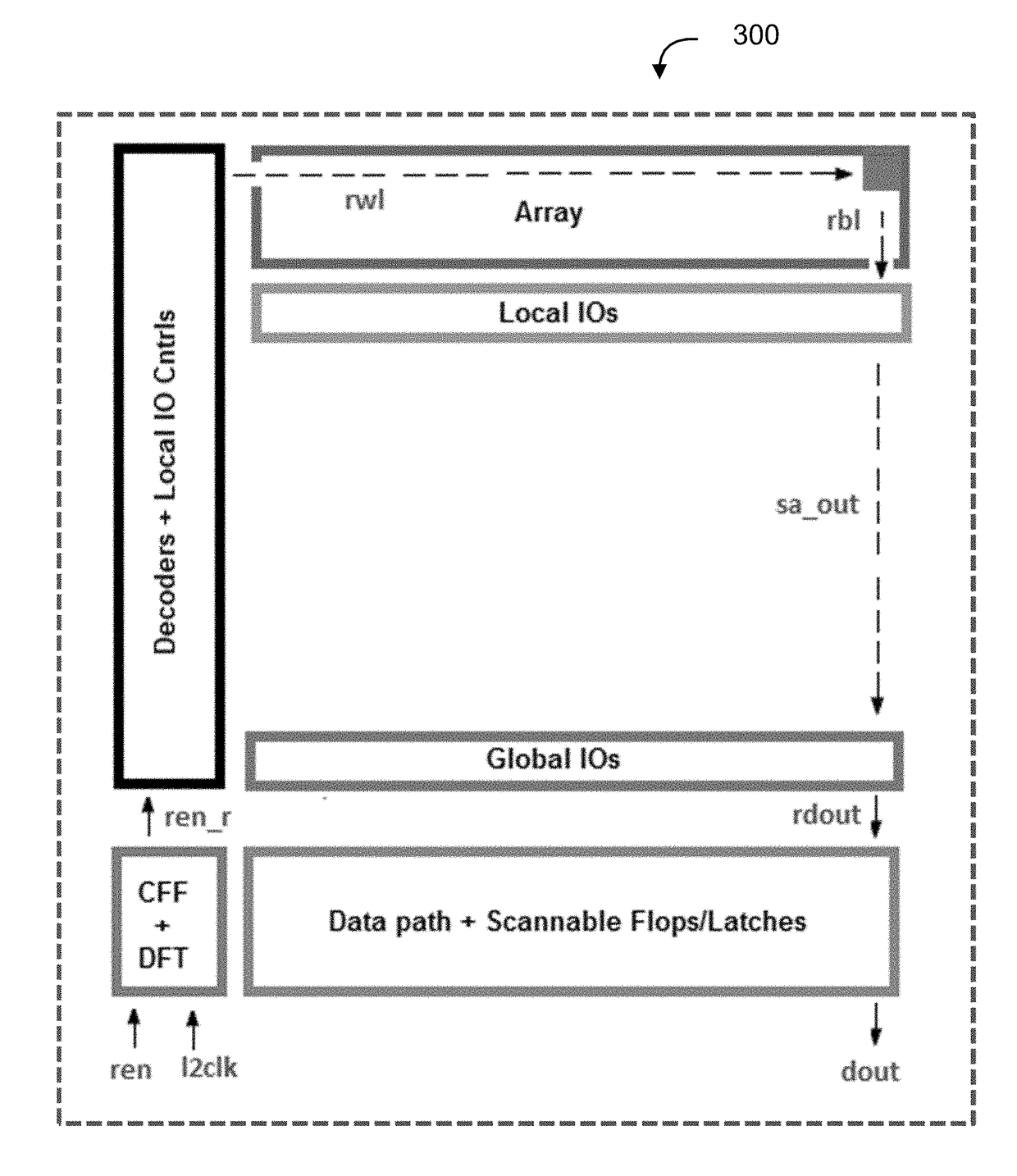

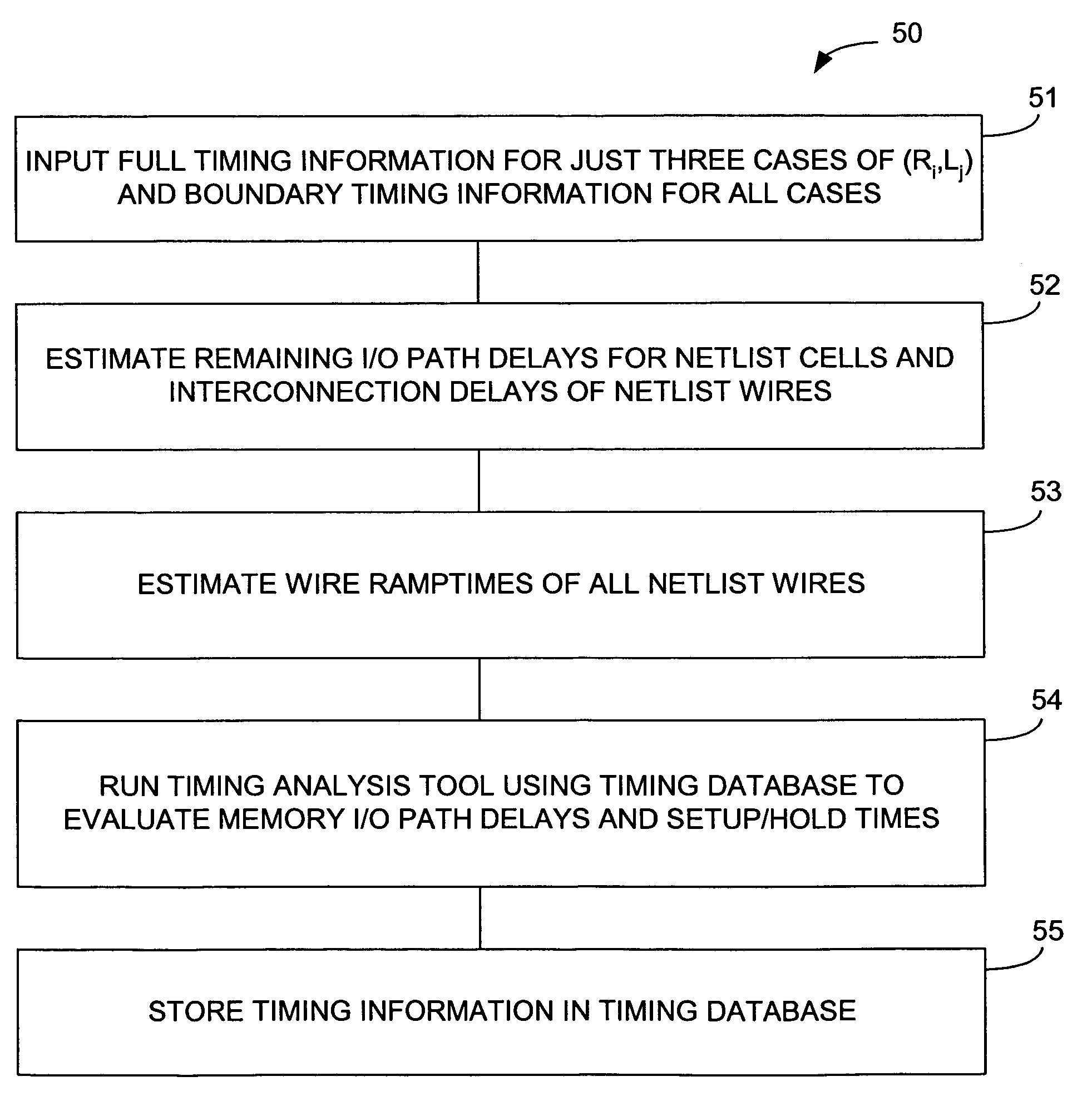

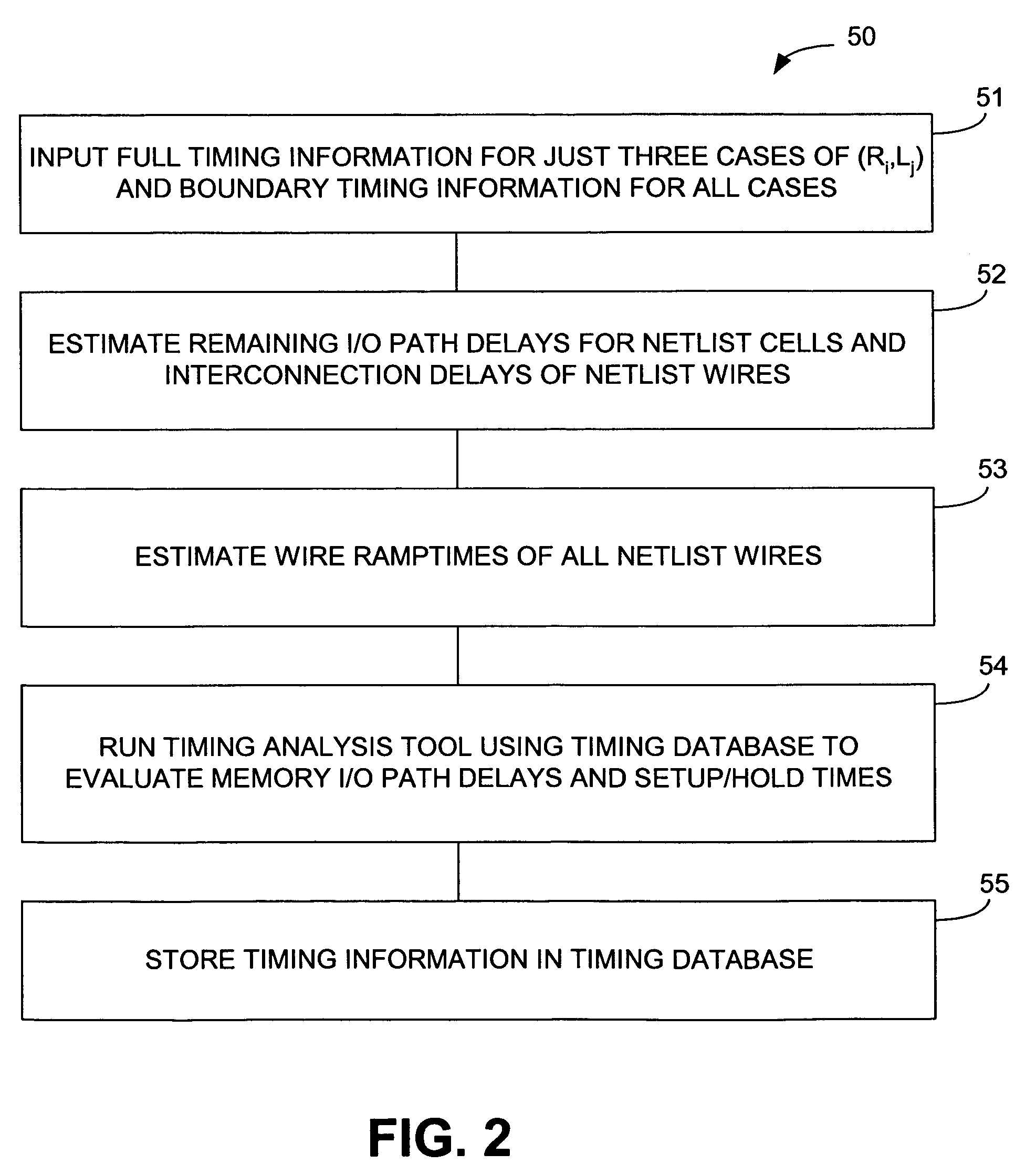

Memory timing model with back-annotating

InactiveUS7415686B2Static storageSoftware simulation/interpretation/emulationComputer moduleMemory timings

Owner:BELL SEMICON LLC

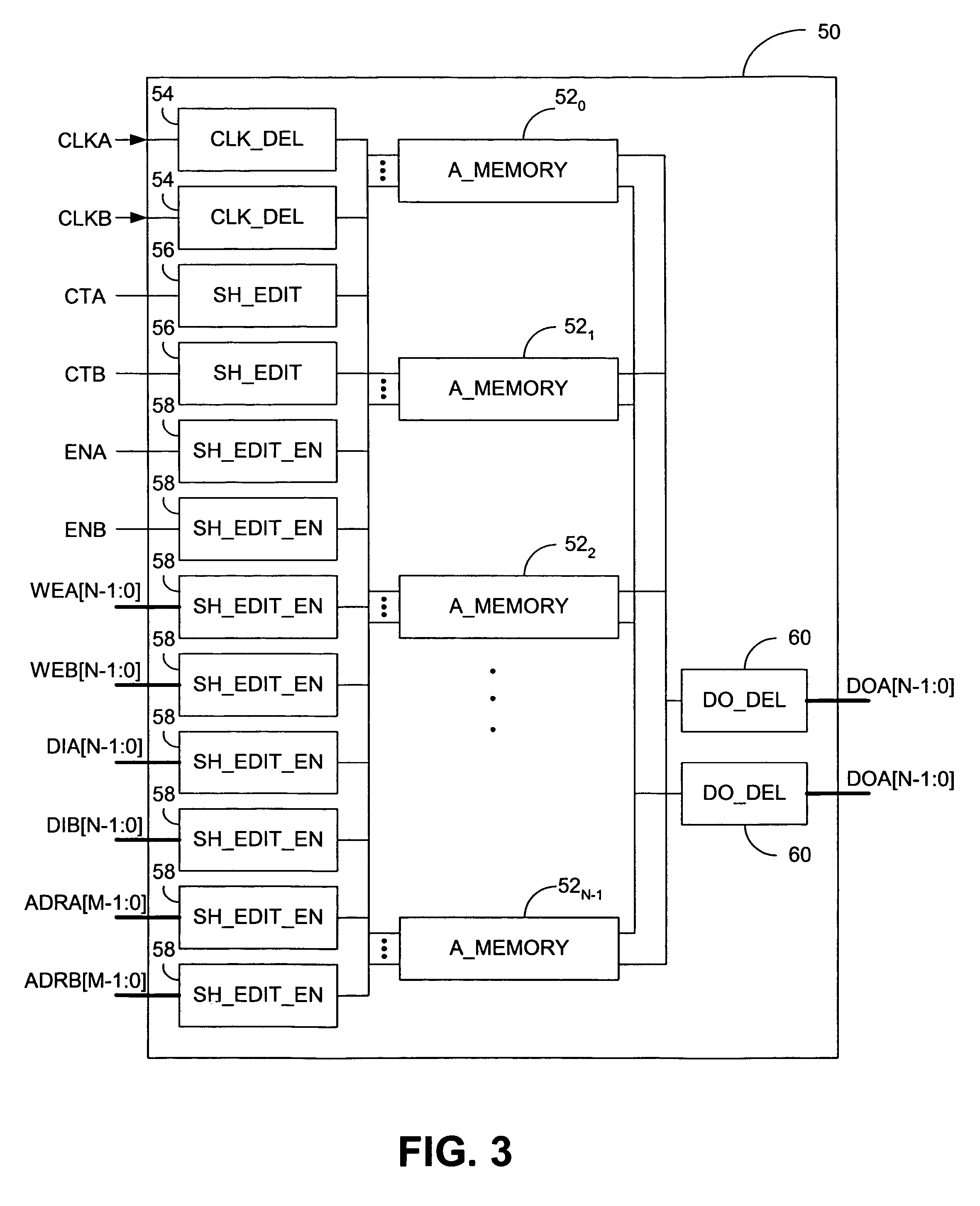

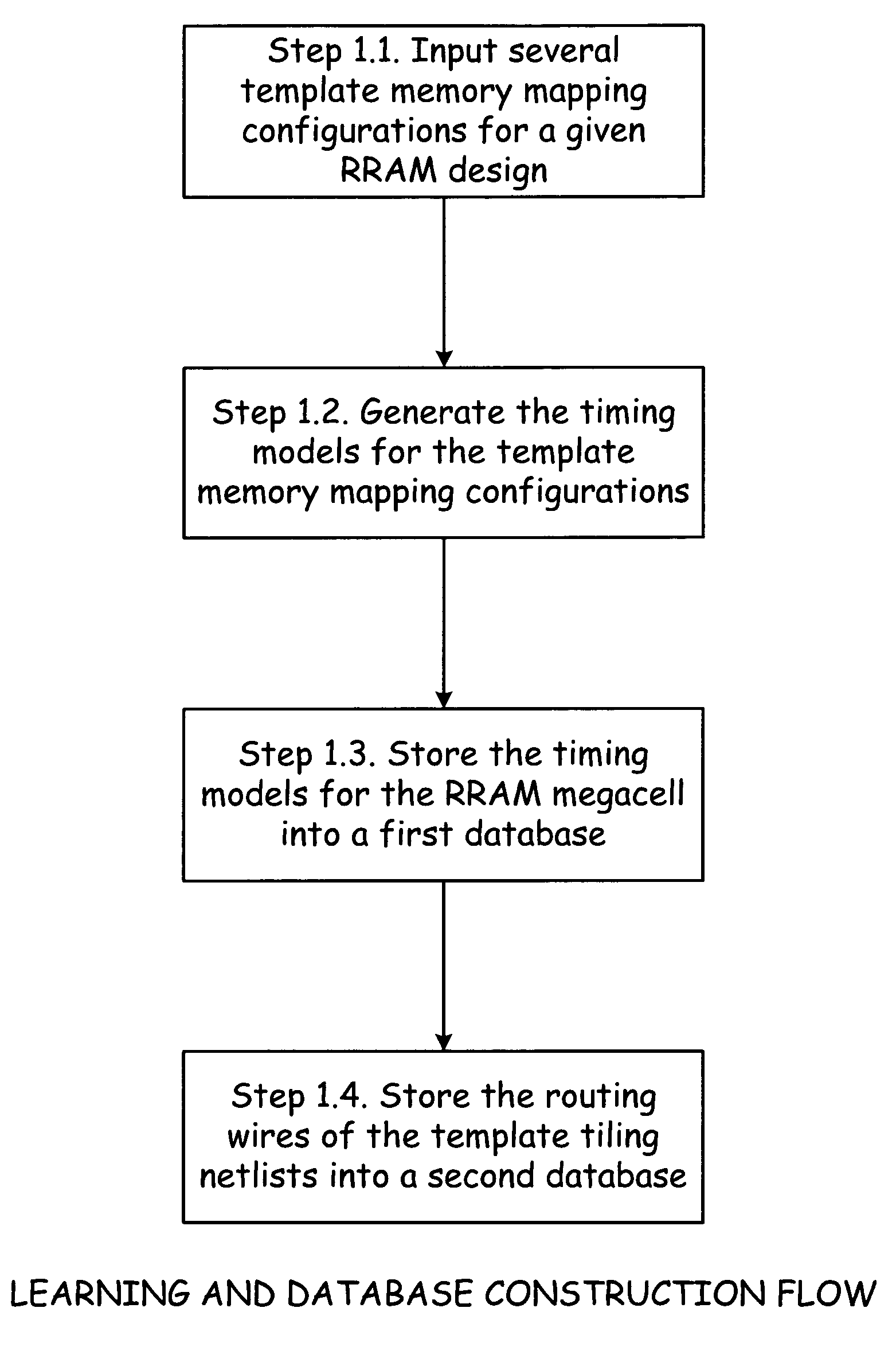

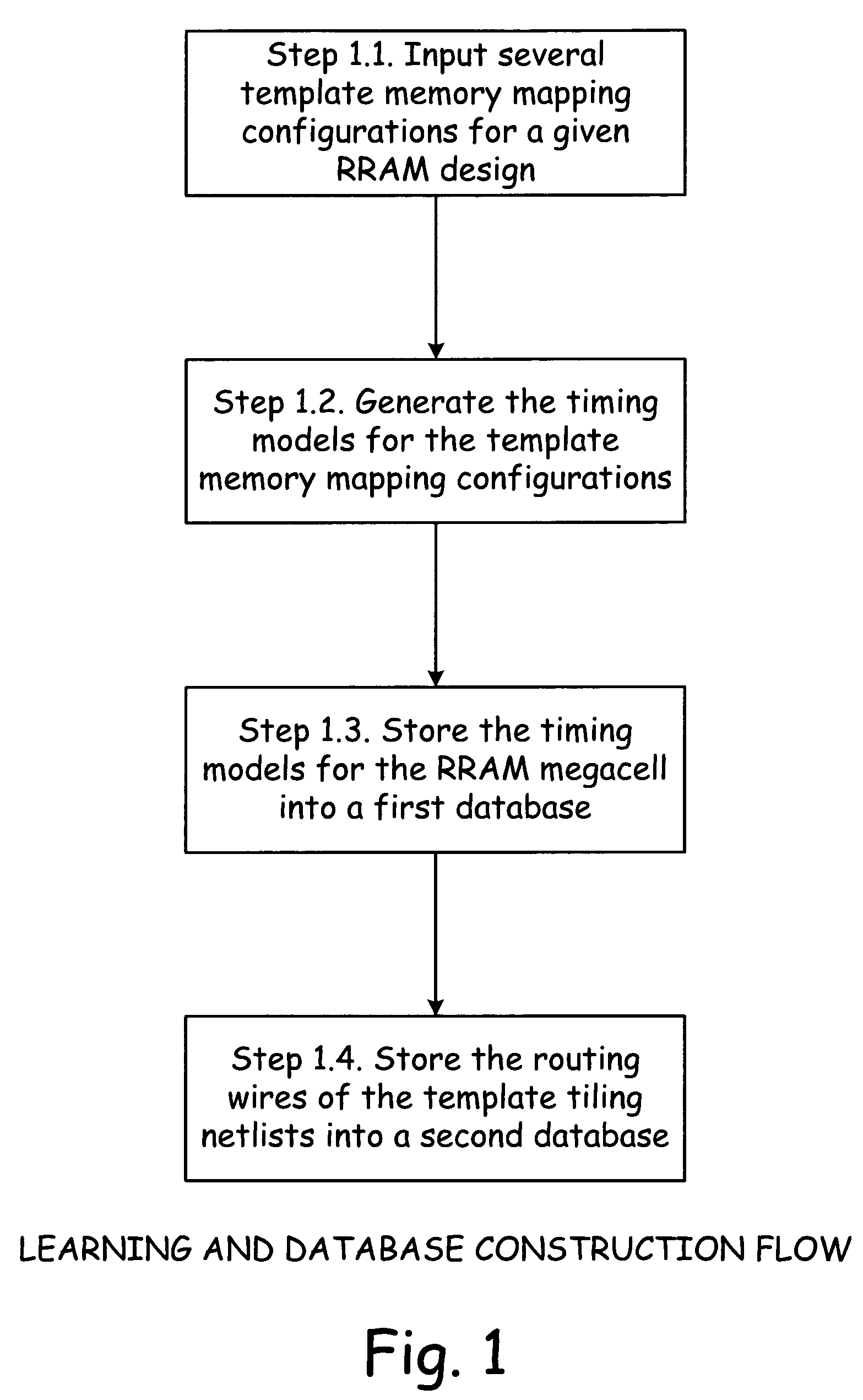

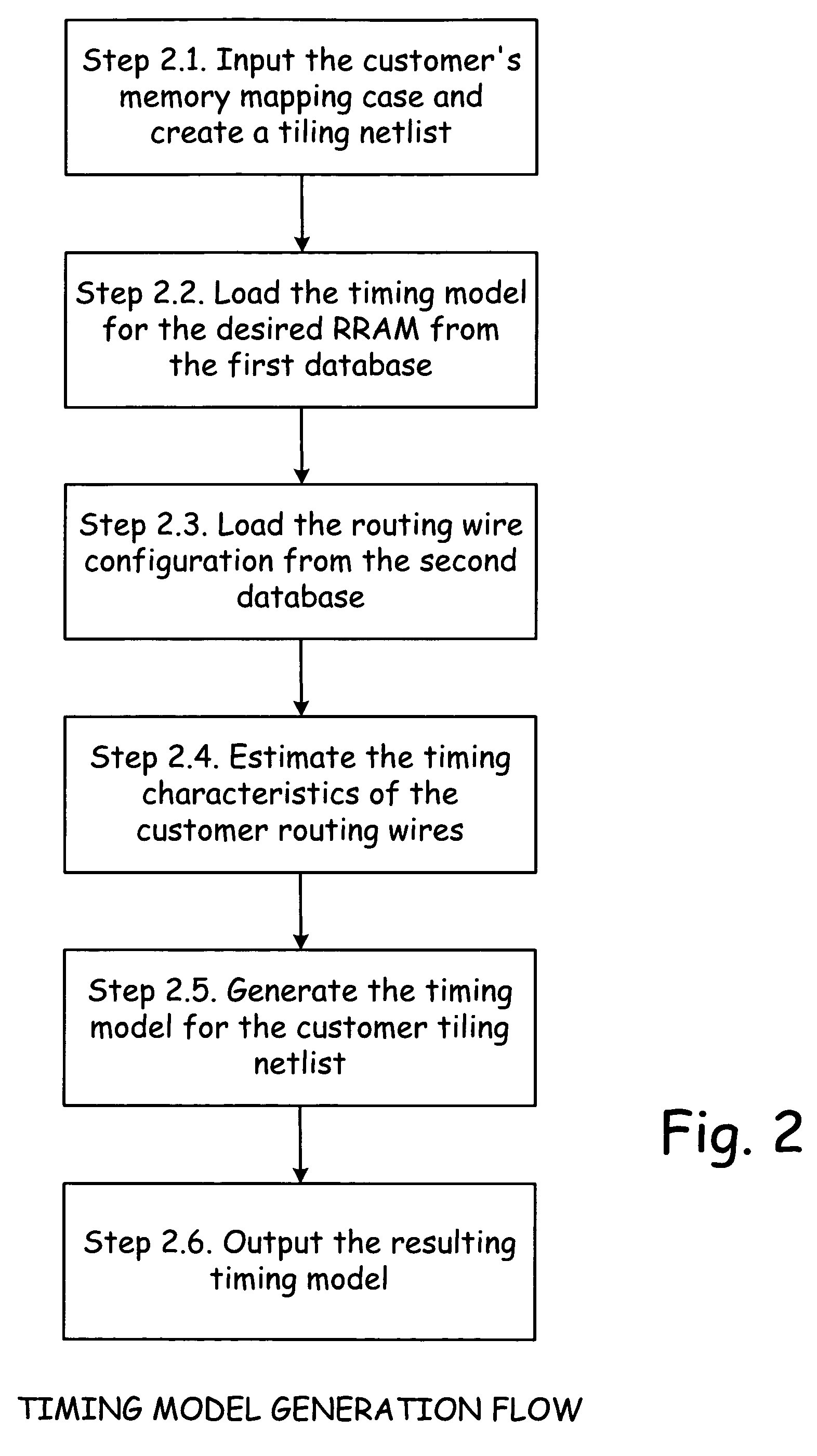

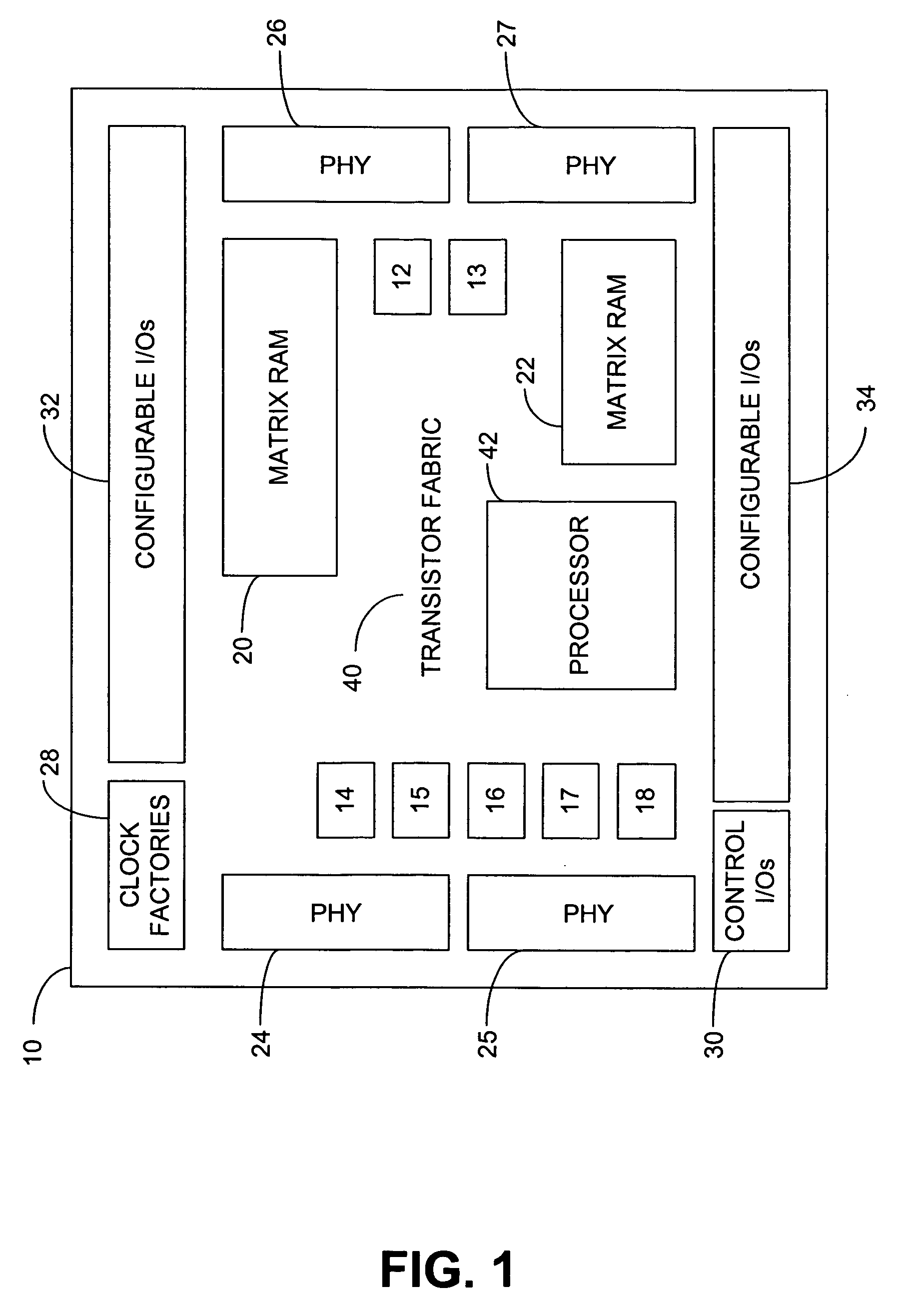

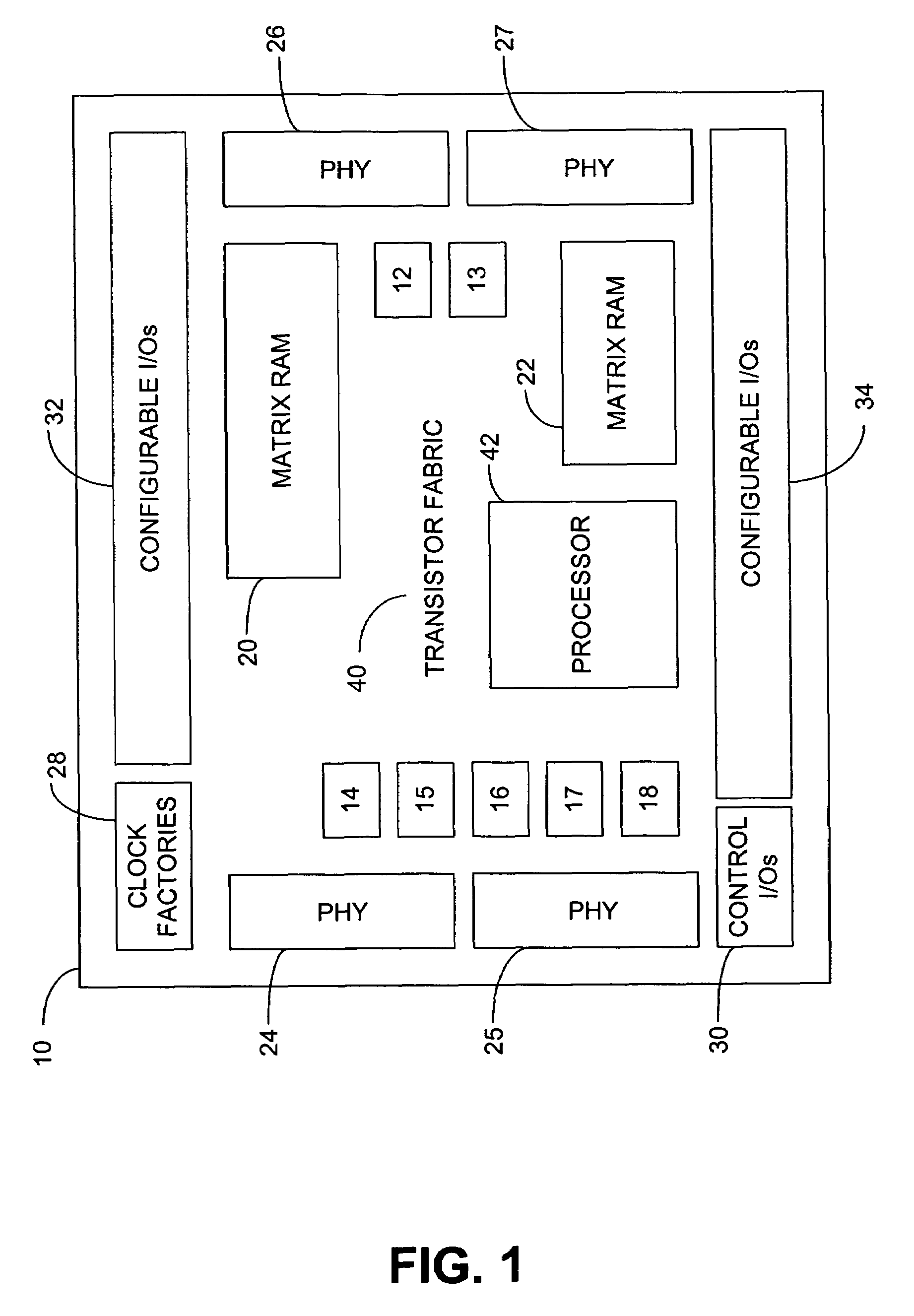

RRAM memory timing learning tool

ActiveUS7200826B2Small amount of timeComputer aided designSoftware simulation/interpretation/emulationComputer scienceNetlist

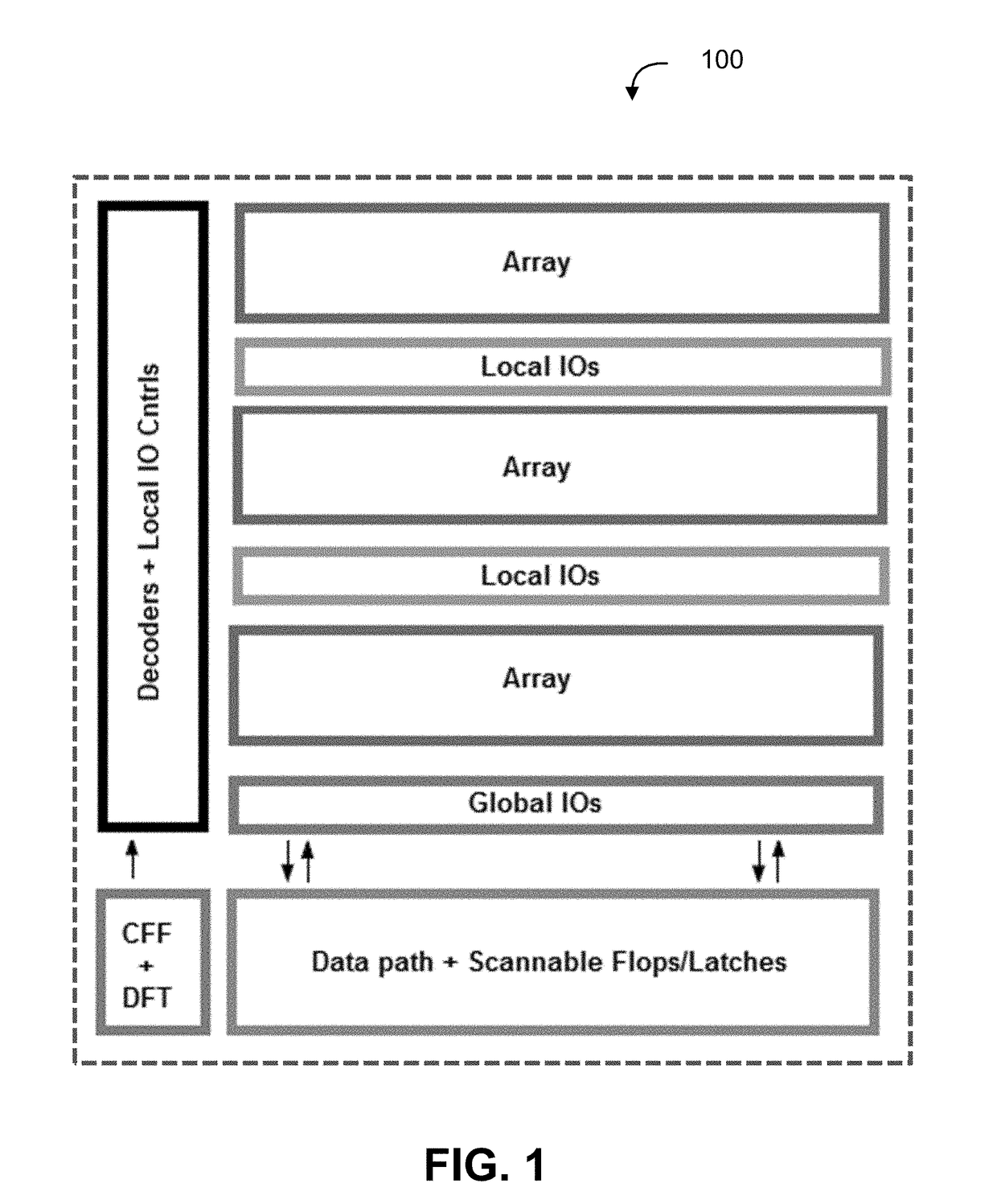

A method of generating a timing model for a customer memory configuration, by generating a plurality of template memory netlists for a given RRAM design. Timing models for the template memory netlists are produced and stored in a first database. The template memory netlists are stored in a second database. A netlist for the customer memory configuration is generated and compared to the template memory netlists to find a match. When a match is found, one of the timing models that is associated with the matching template memory netlist is used as the timing model for the customer memory configuration. When a match is not found, two of the template memory netlists that bound the customer netlist are found, according to at least one parameter, and the timing model for the customer memory configuration is interpolated based on the two bounding template memory netlists.

Owner:BELL SEMICON LLC

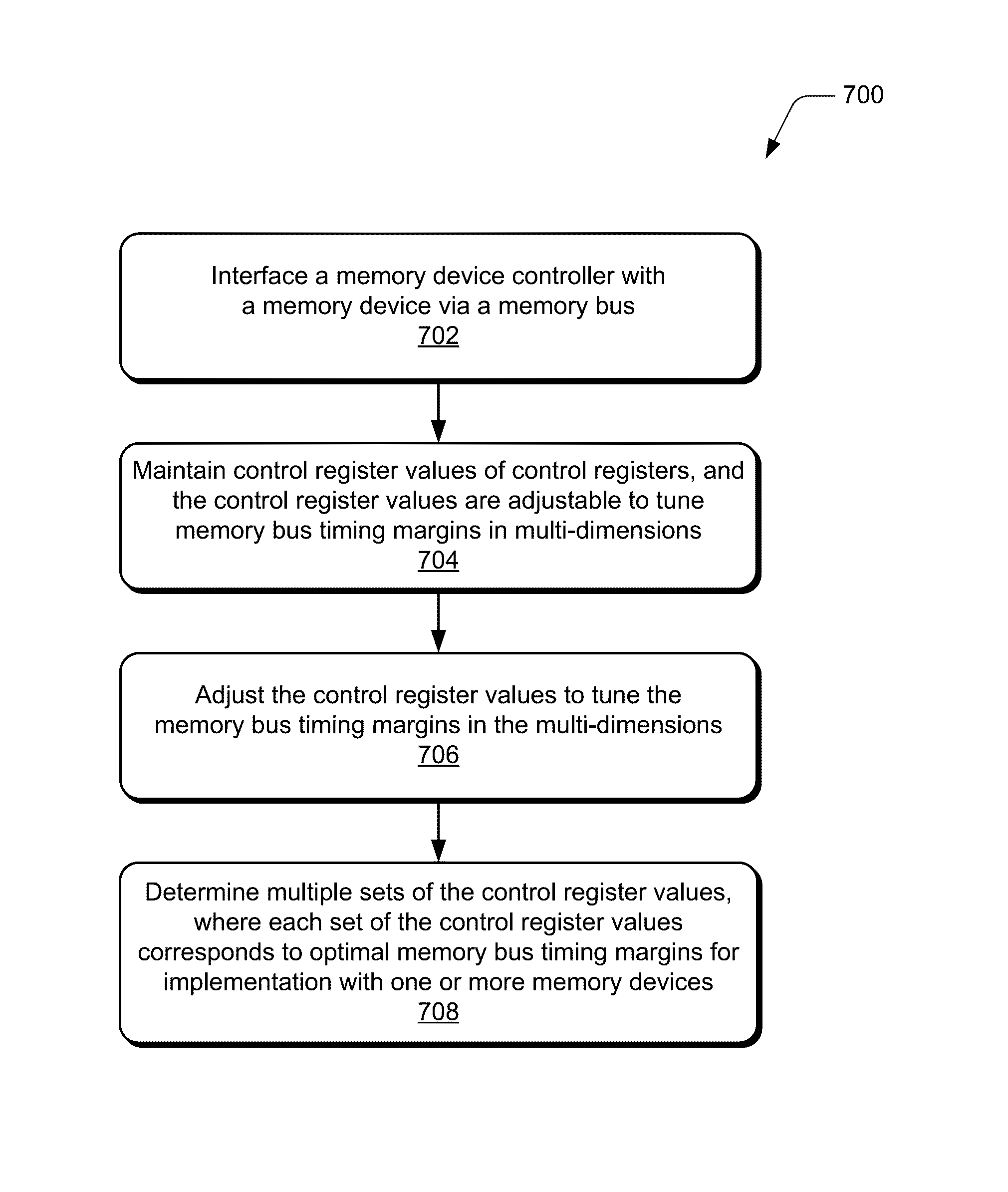

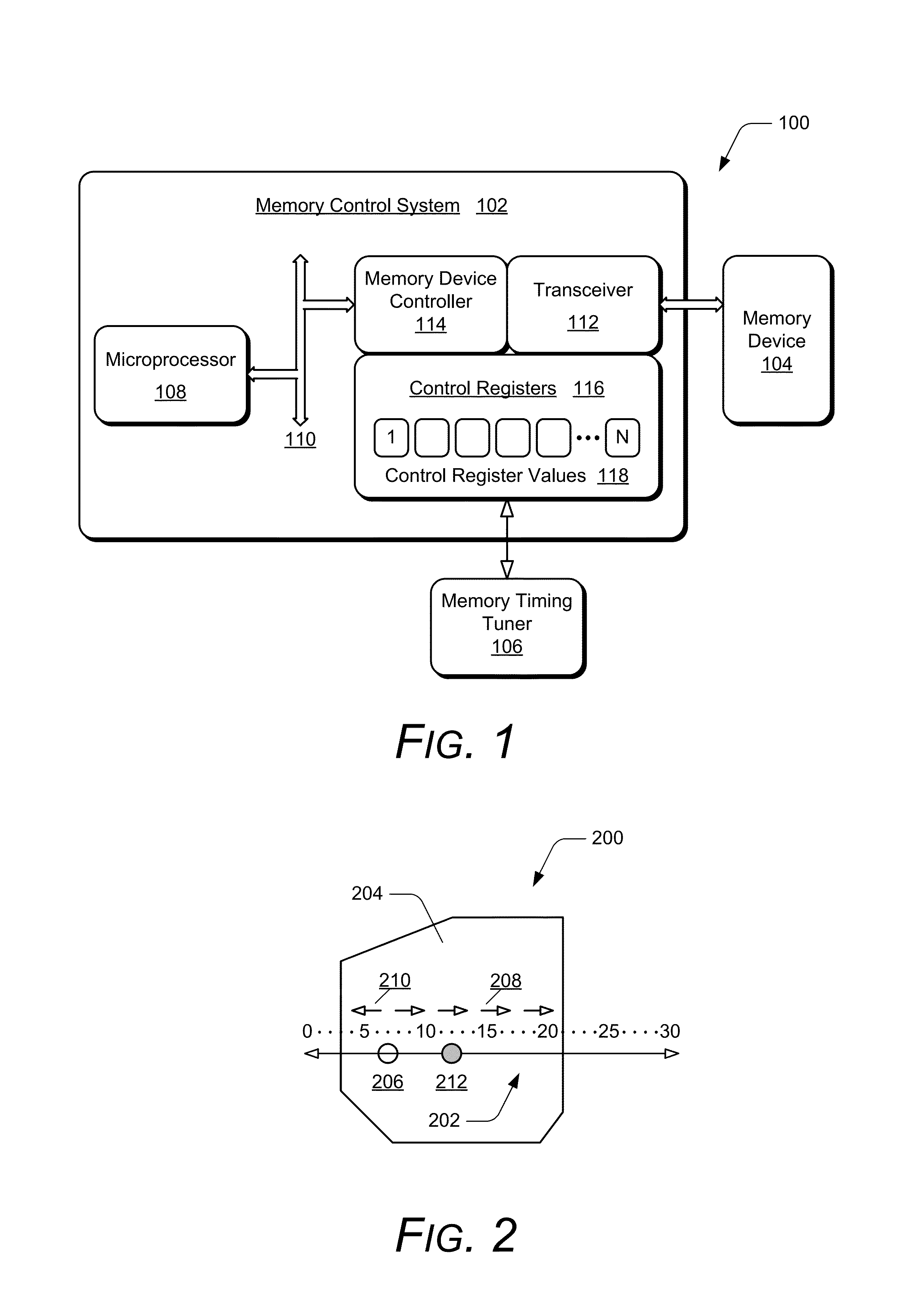

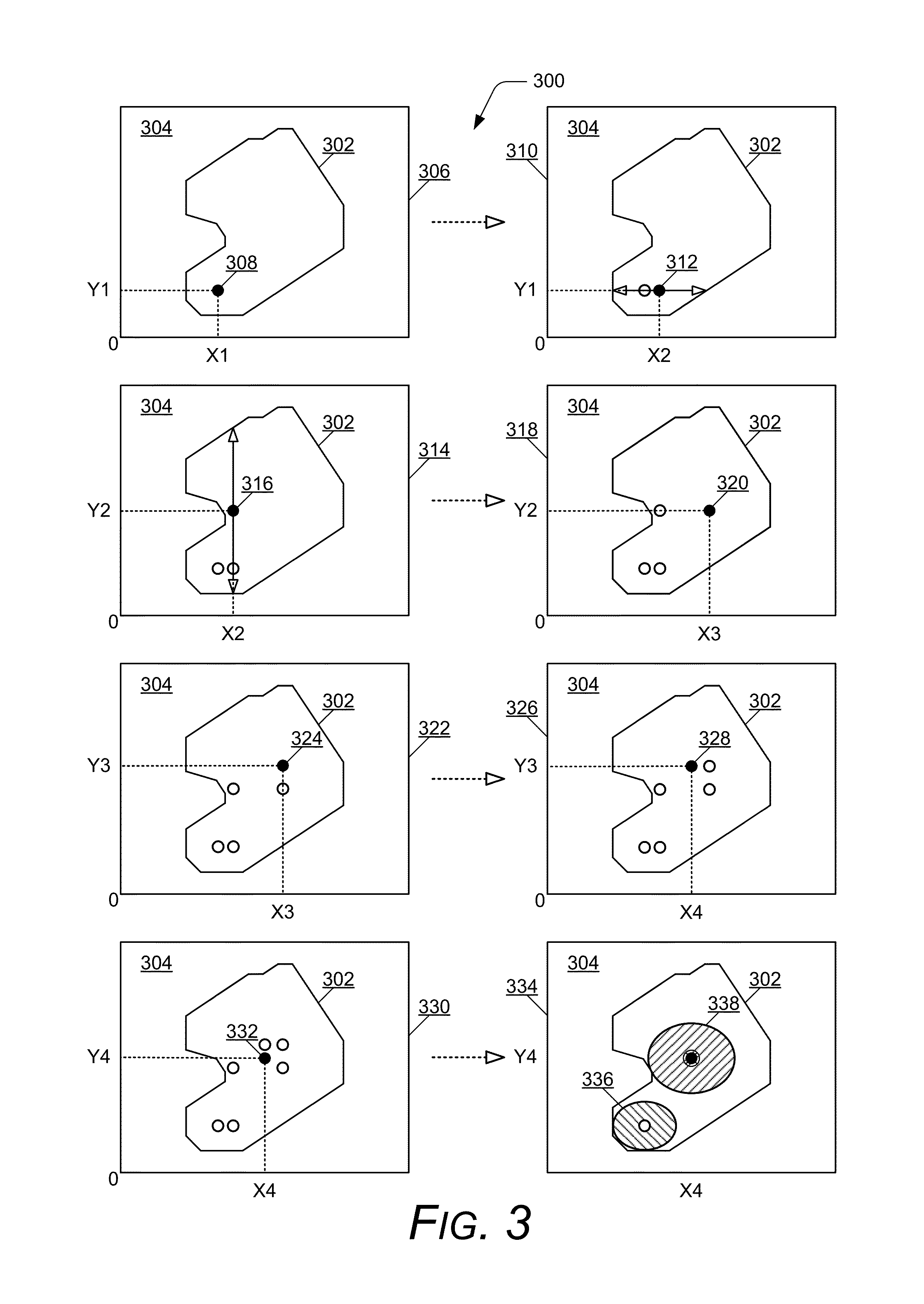

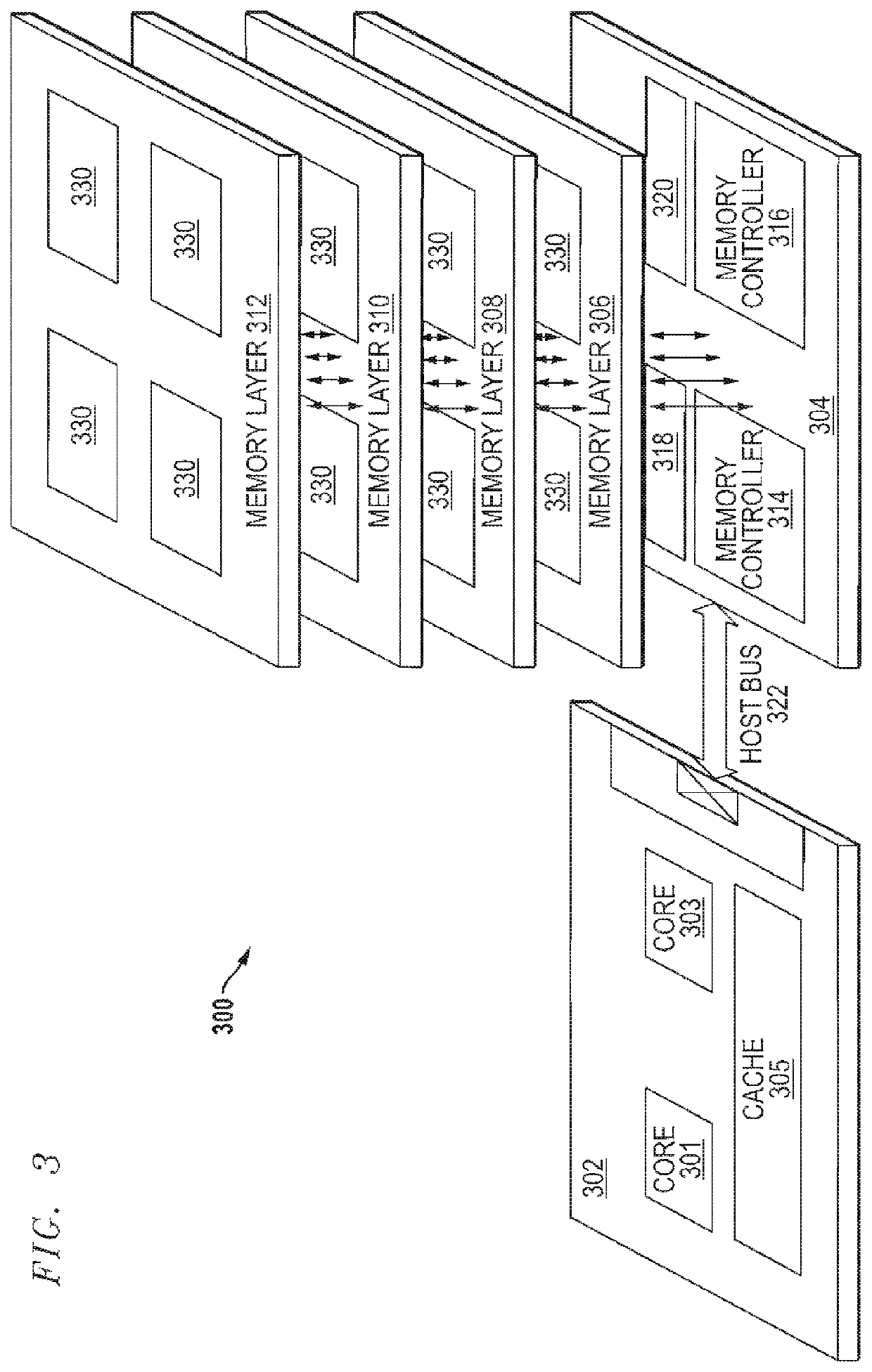

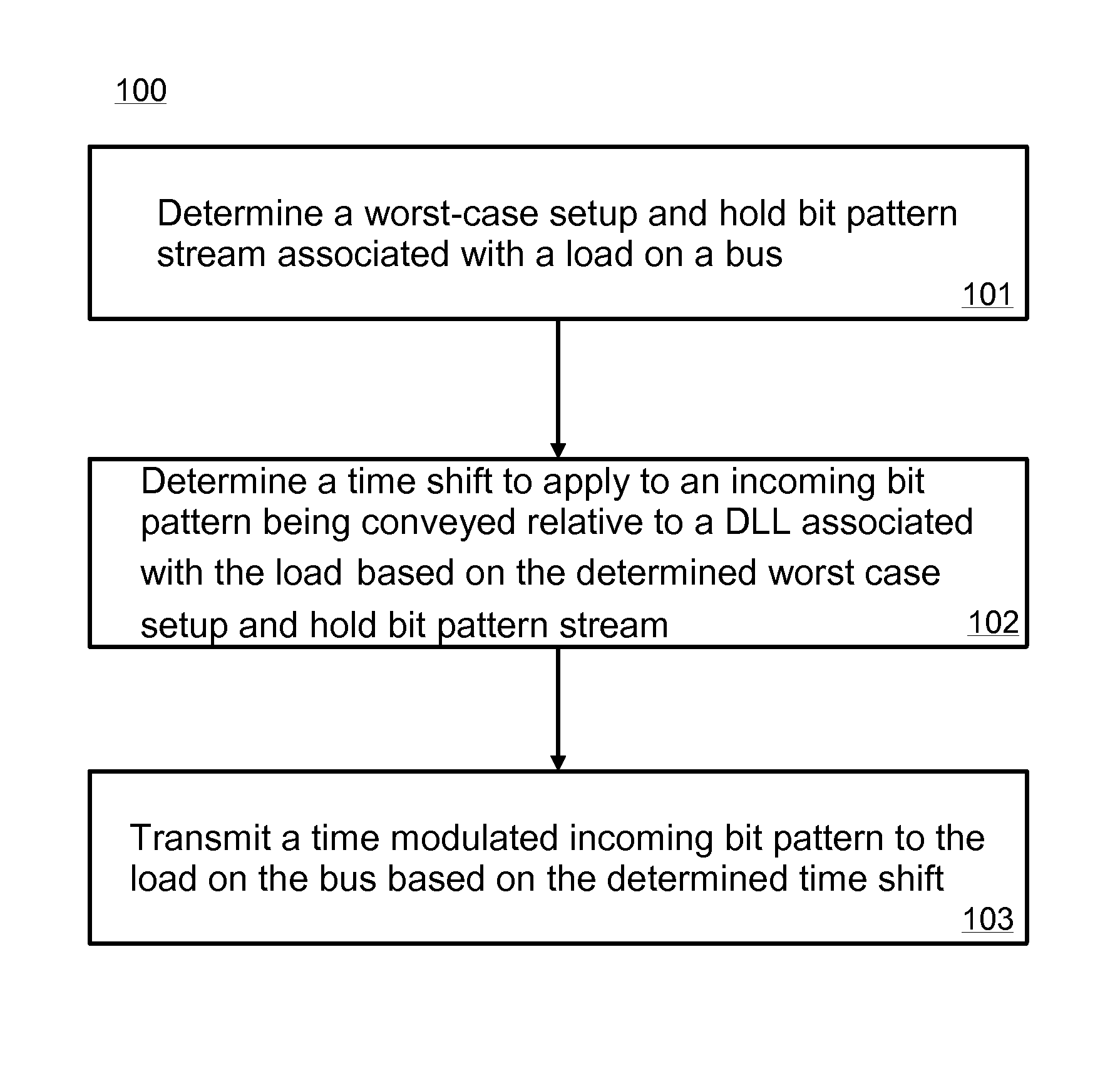

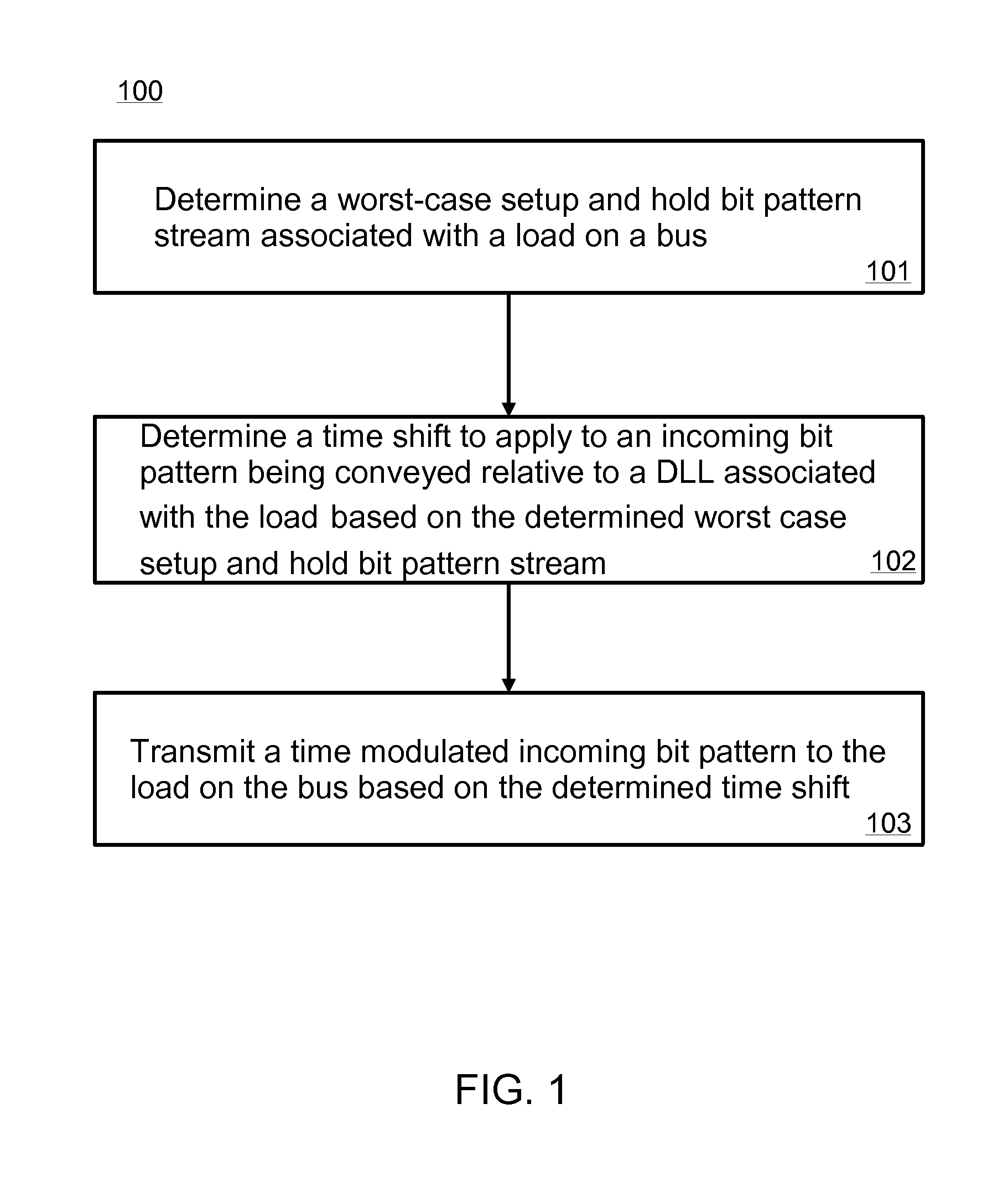

Multi-dimension memory timing tuner

In embodiments of a multi-dimension memory timing tuner, a memory device controller that can be interfaced with one or more memory devices is coupled to a memory device for data communication with the memory device via a bus, such as a data control system, system bus, or memory bus. Memory maintains values, such as a control register maintaining control register values, which are adjustable to tune bus timing margins in multi-dimensions. The bus timing margins are tunable for implementation of a memory device controller with one or more of the memory devices. A memory timing tuner is implemented to adjust the values to tune the bus timing margins in the multi-dimensions.

Owner:MARVELL ASIA PTE LTD

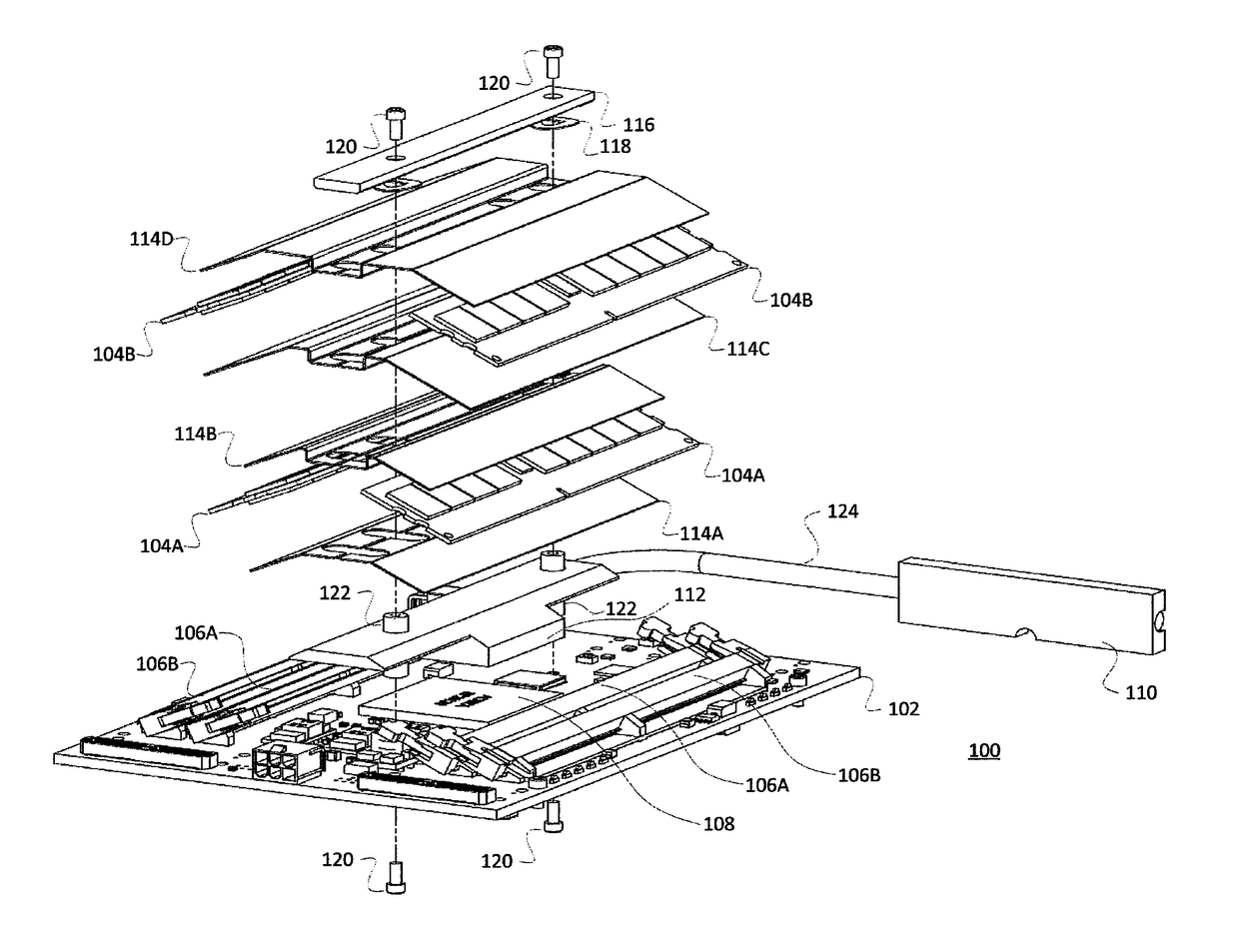

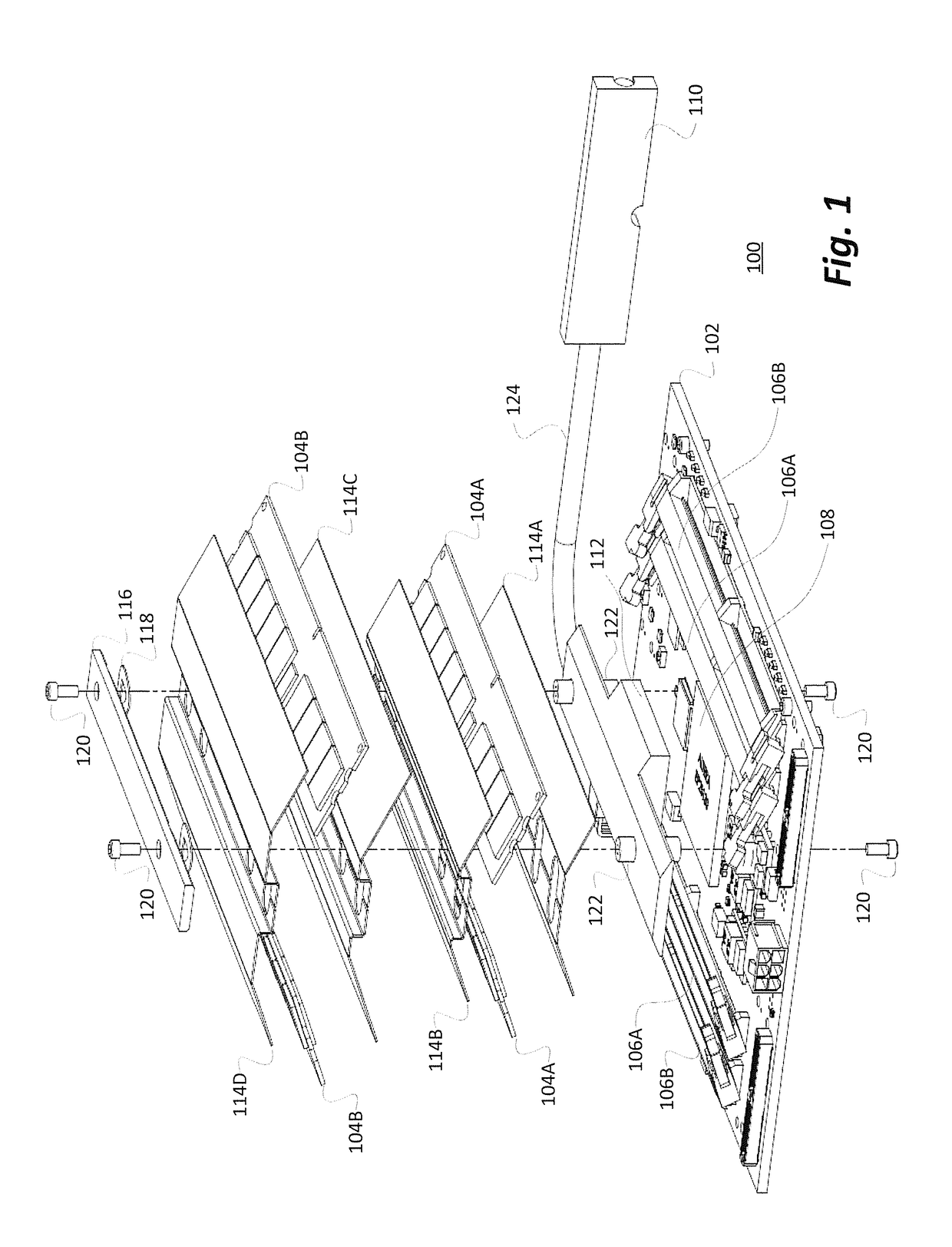

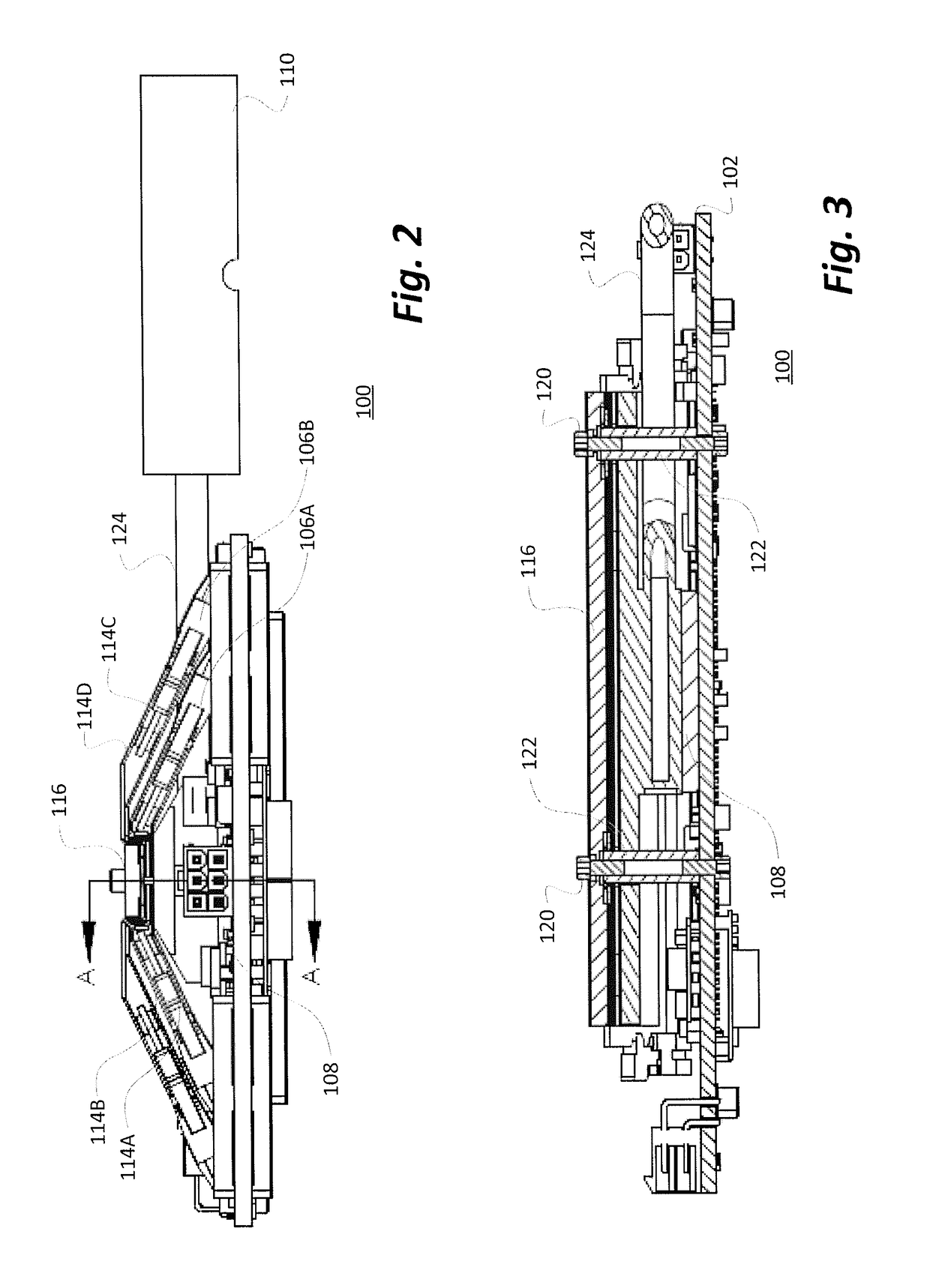

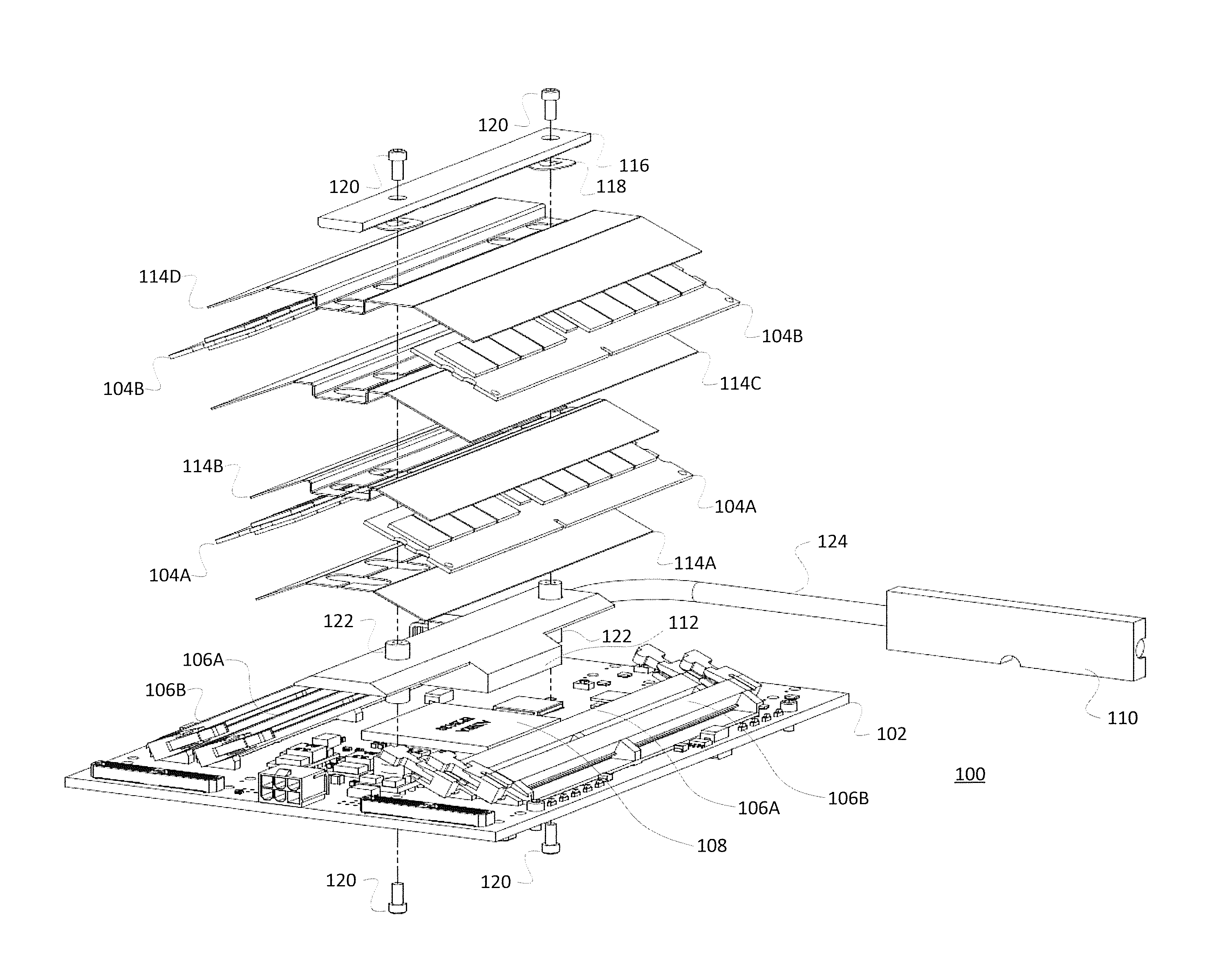

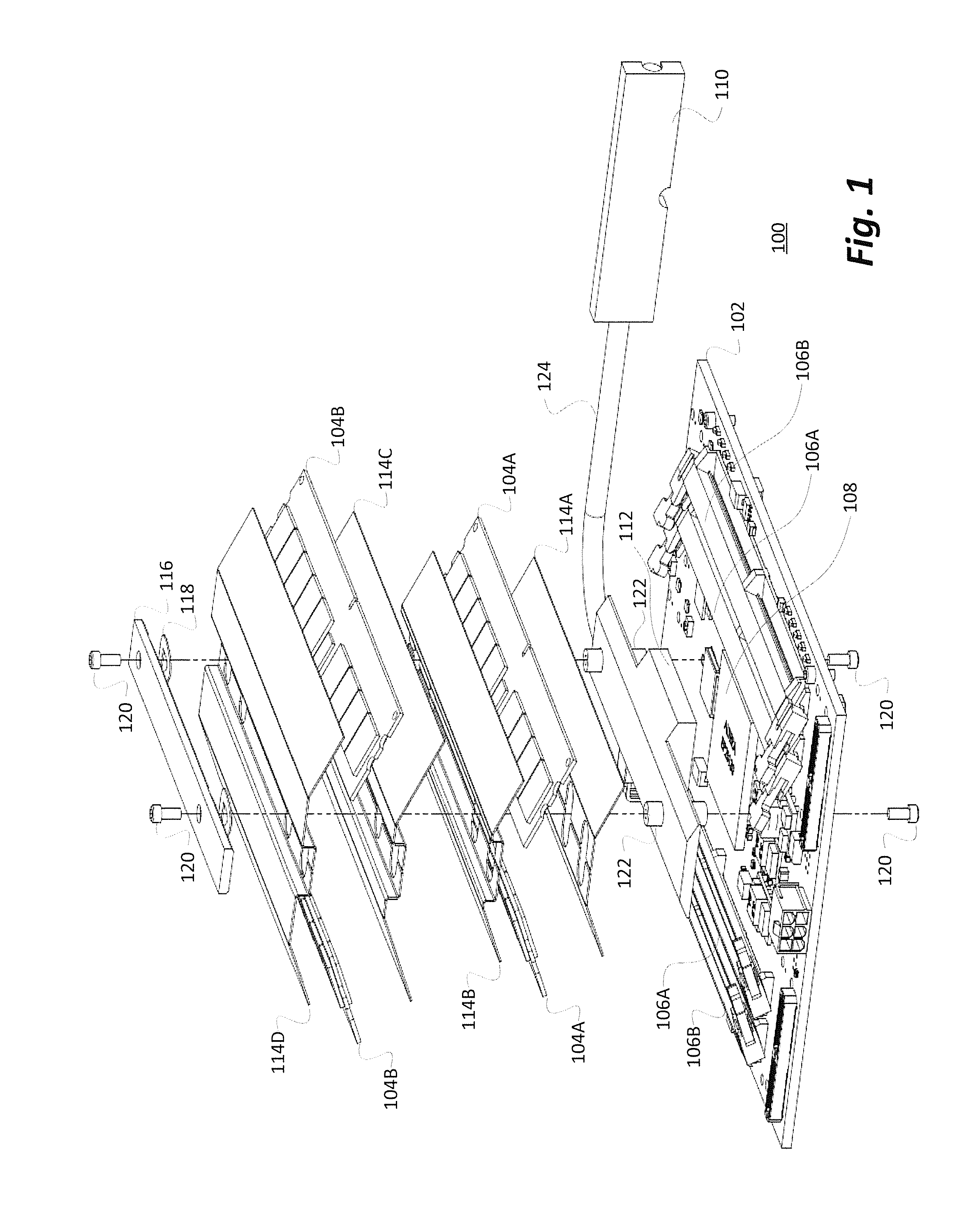

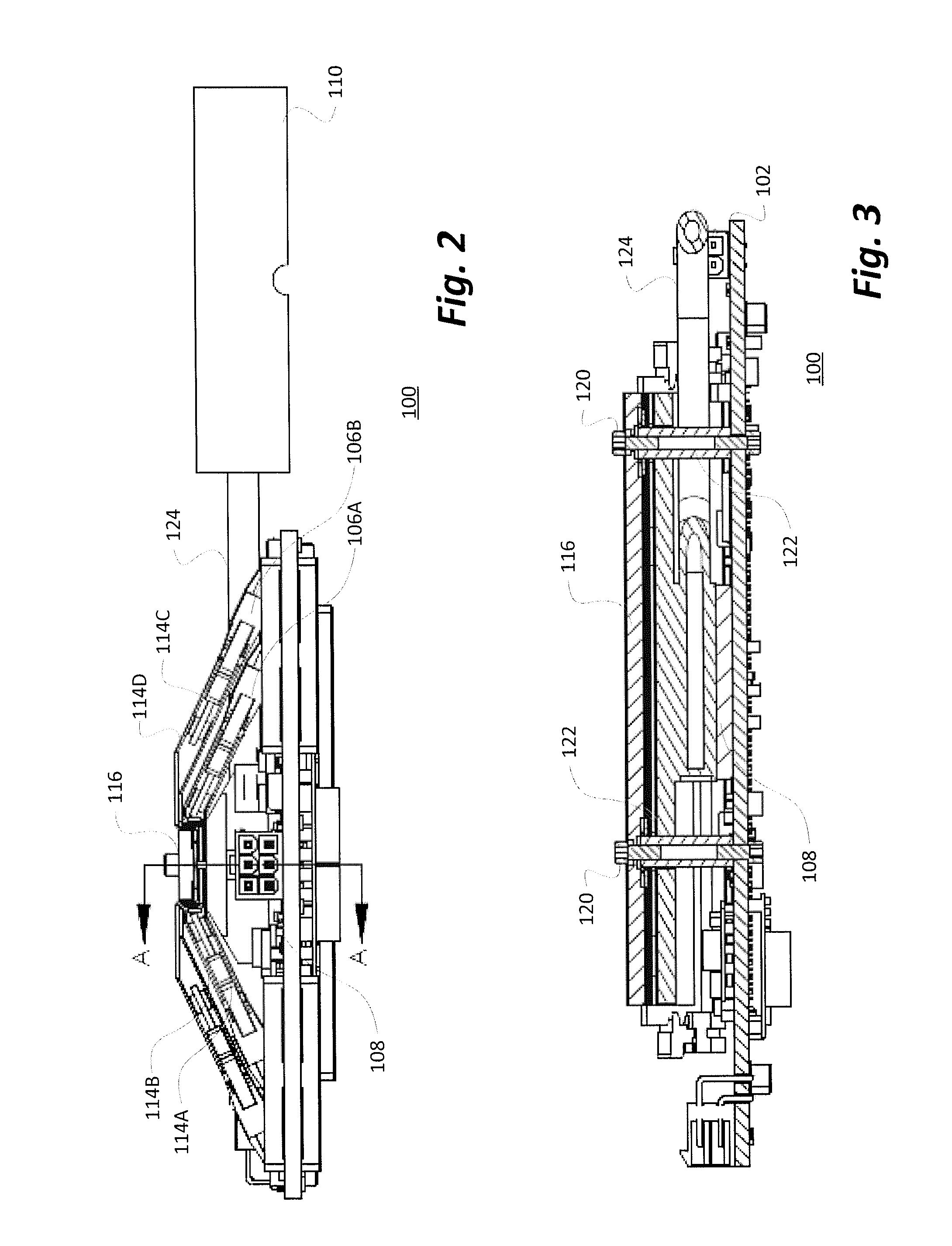

System and method for thermally coupling memory devices to a memory controller in a computer memory board

A system and method for thermally coupling memory devices, such as DIMM memory modules, to an associated memory controller such that both are cooled together at the same relative temperature. By maintaining all of the devices at a much more uniform temperature, memory timing issues are effectively eliminated. In accordance with an exemplary embodiment, the controller chip is physically located between two or more banks of memory, and is positioned under an adjoining heat sink while the memory DIMMs are positioned laterally of the controller chip in angled DIMM slots and are coupled to the controller chip with respective heat spreaders.

Owner:SRC COMP

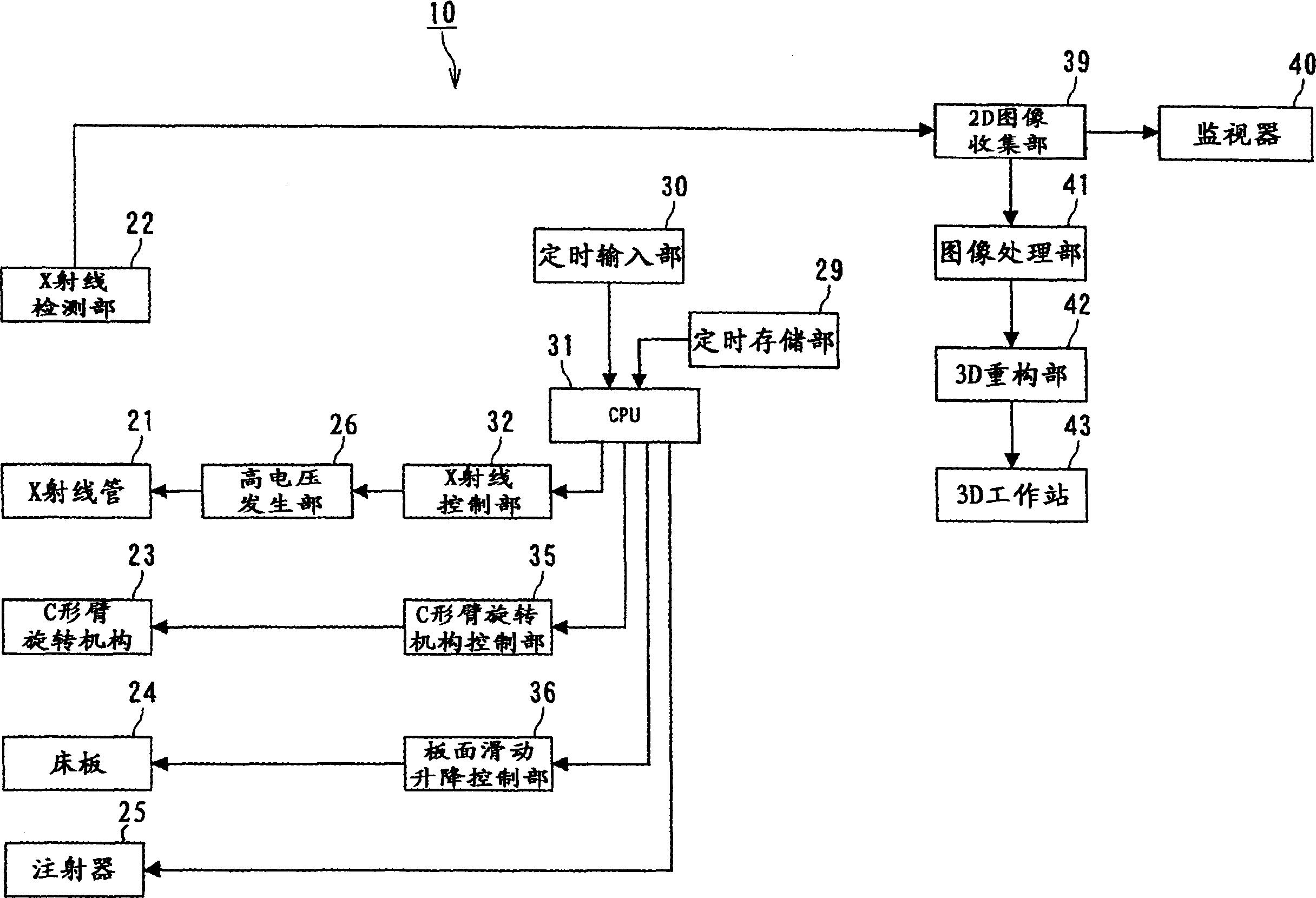

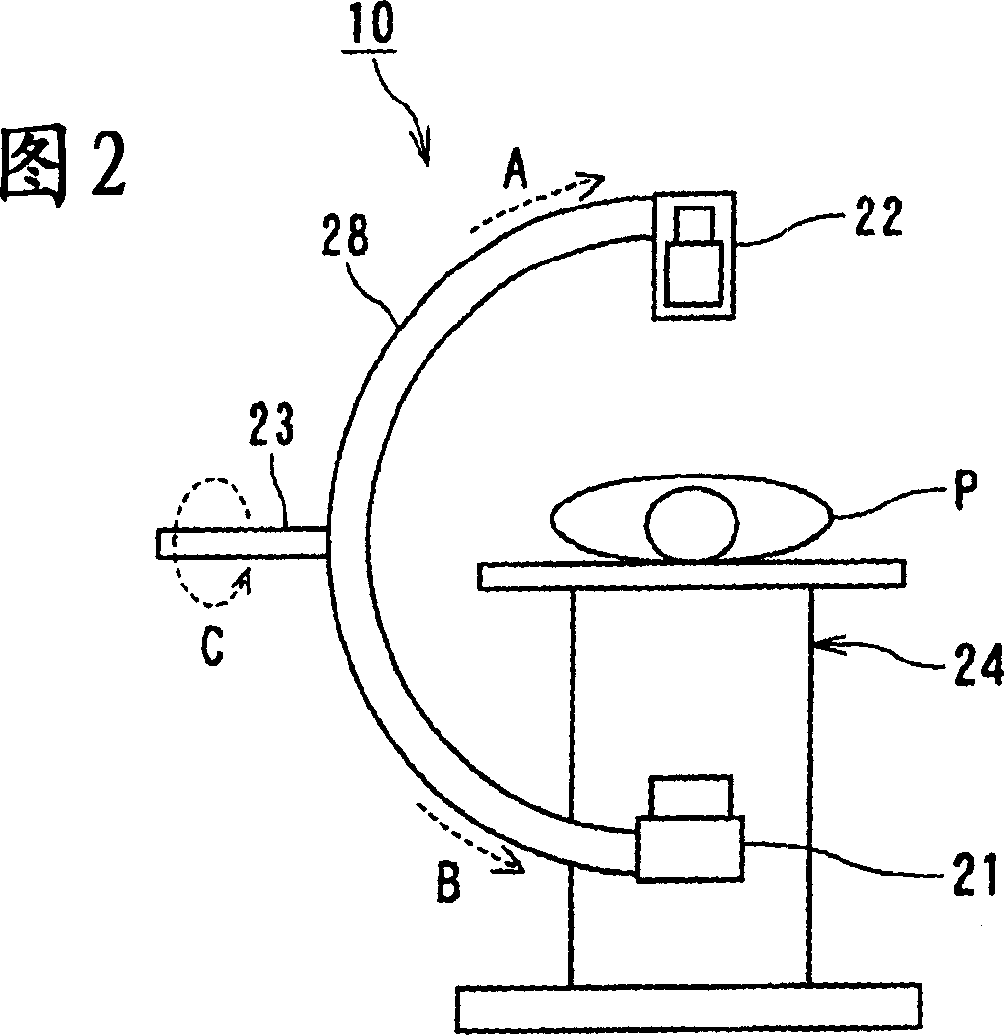

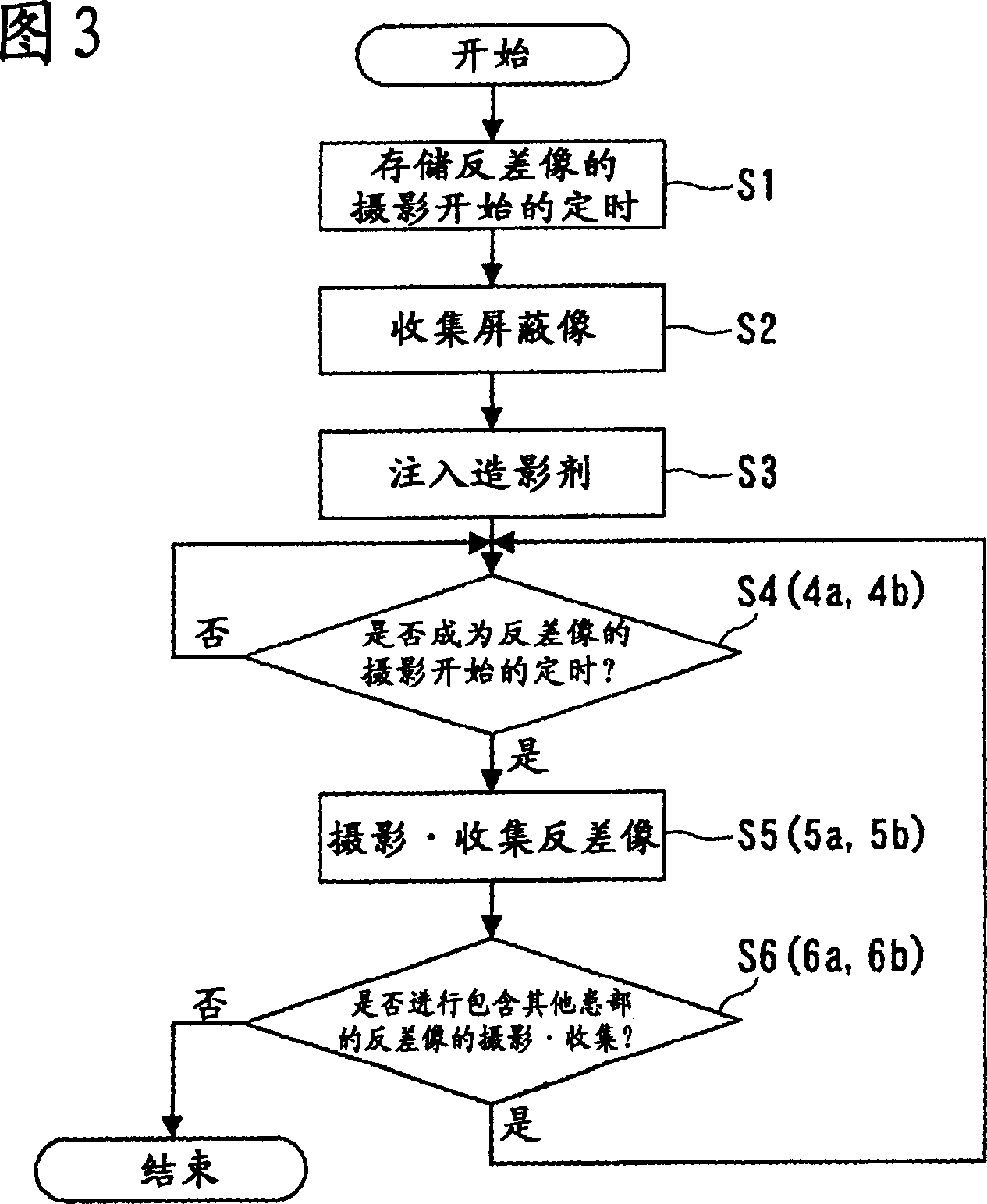

X-ray diagnostic imaging system and x-ray diagnostic imaging method

InactiveCN1723849AAbility to inhibit invasionEfficient photographyRadiation diagnosticsX-rayX ray image

The invention provides an X-ray image diagnostic device (10) used to photograph the necessary parts of patient P, collect all the image data of the shielded image and contrast image, and record and display the image data of the differential image of the shielded image and the contrast image. The device consists of a memory-timing part(39) and a CPU (31), wherein the memory-timing part(39) is used to record the timing of the start of the photograph of a first contrast image and a second contrast image; the CPU (31) is used to give instructions to carry out the photograph of the contrast image after the photograph of the contrast image to be stored at the timed memory part(39) starts. As the contrast medium is injected into the affected part, according to the instructions of the CPU (31), the photograph and the collection of the first contrast image is carried out, and then according to instructions of the CPU (31), the photograph and the collection of the second contrast image are carried out.

Owner:KK TOSHIBA +1

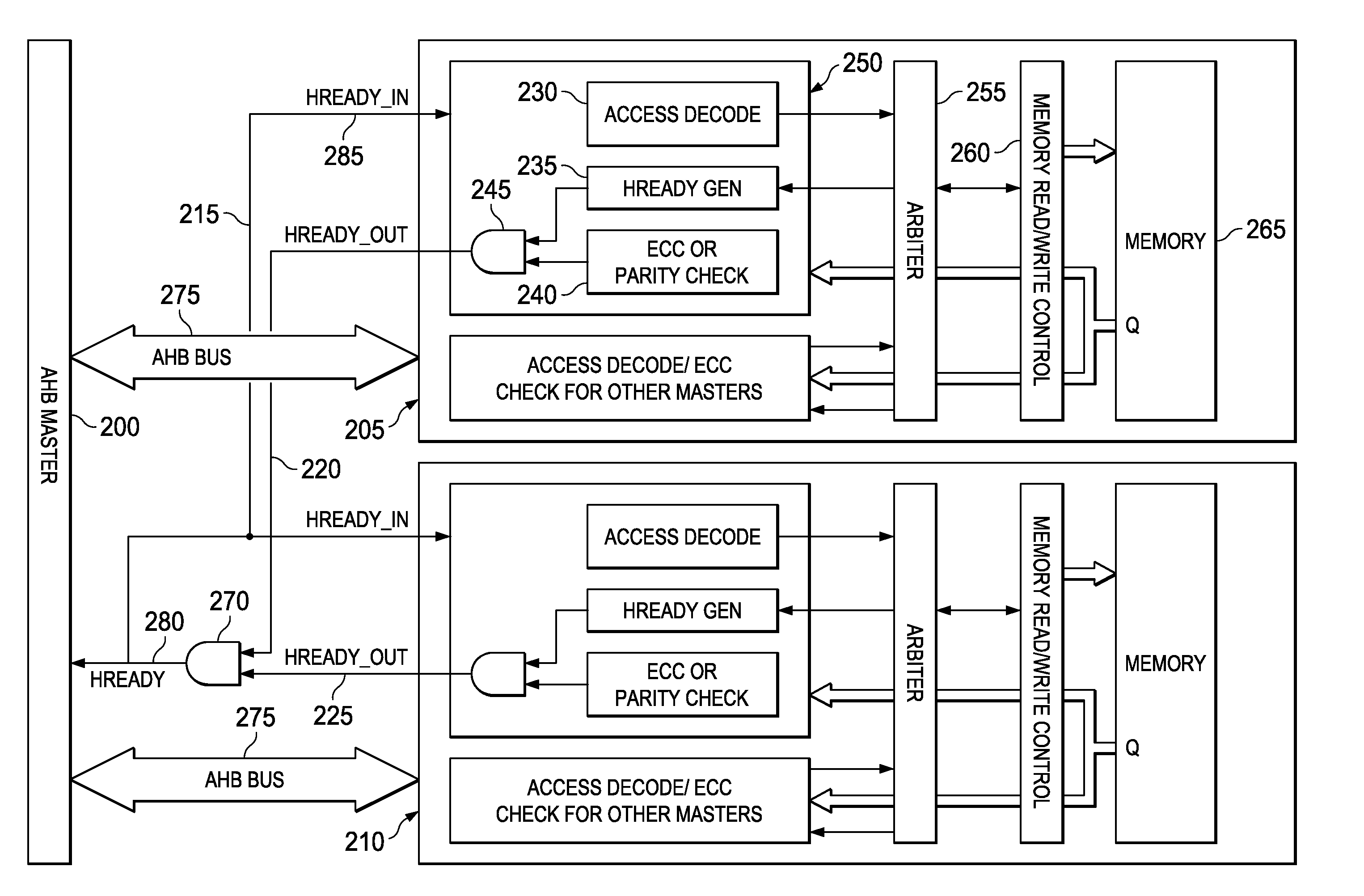

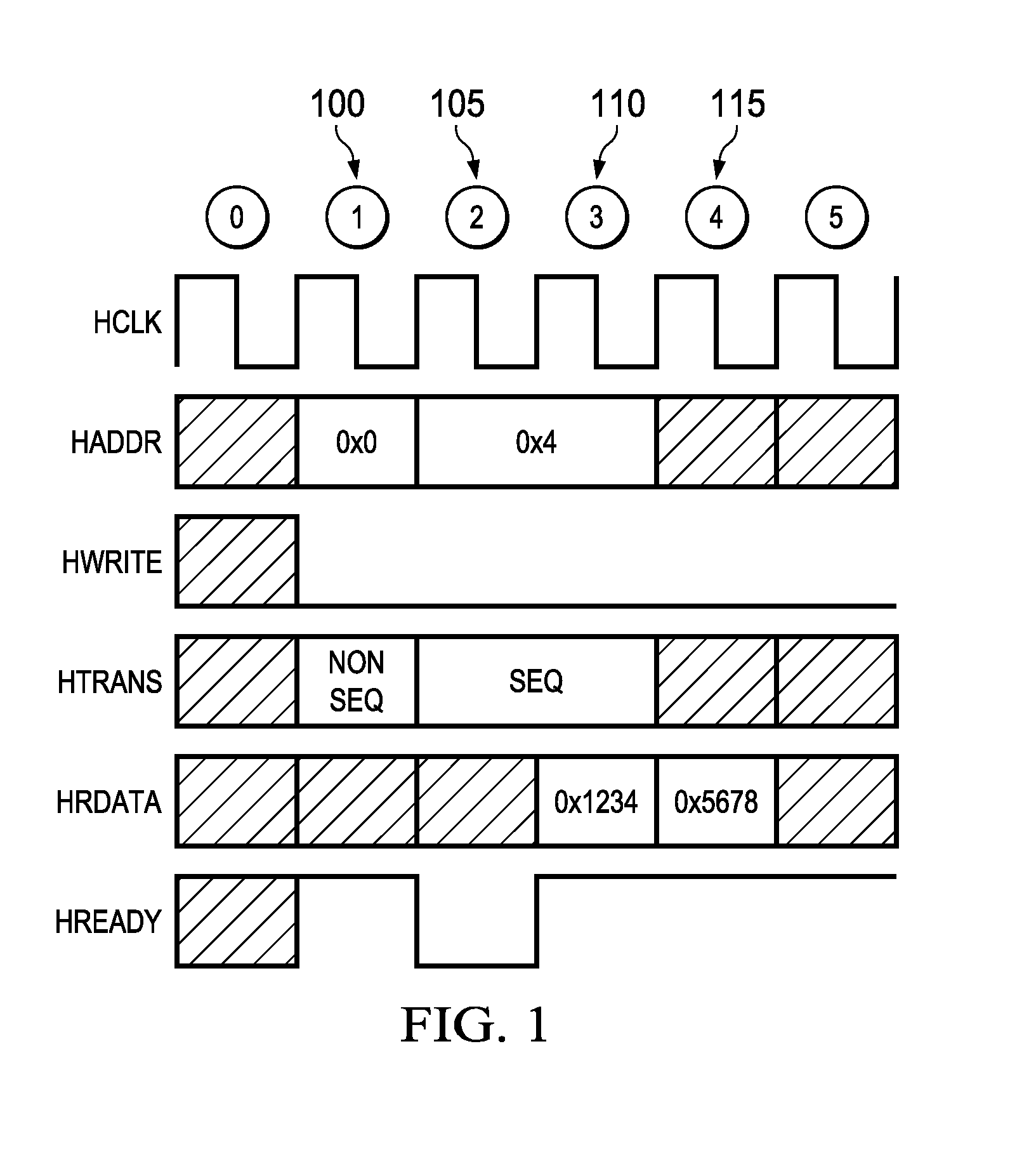

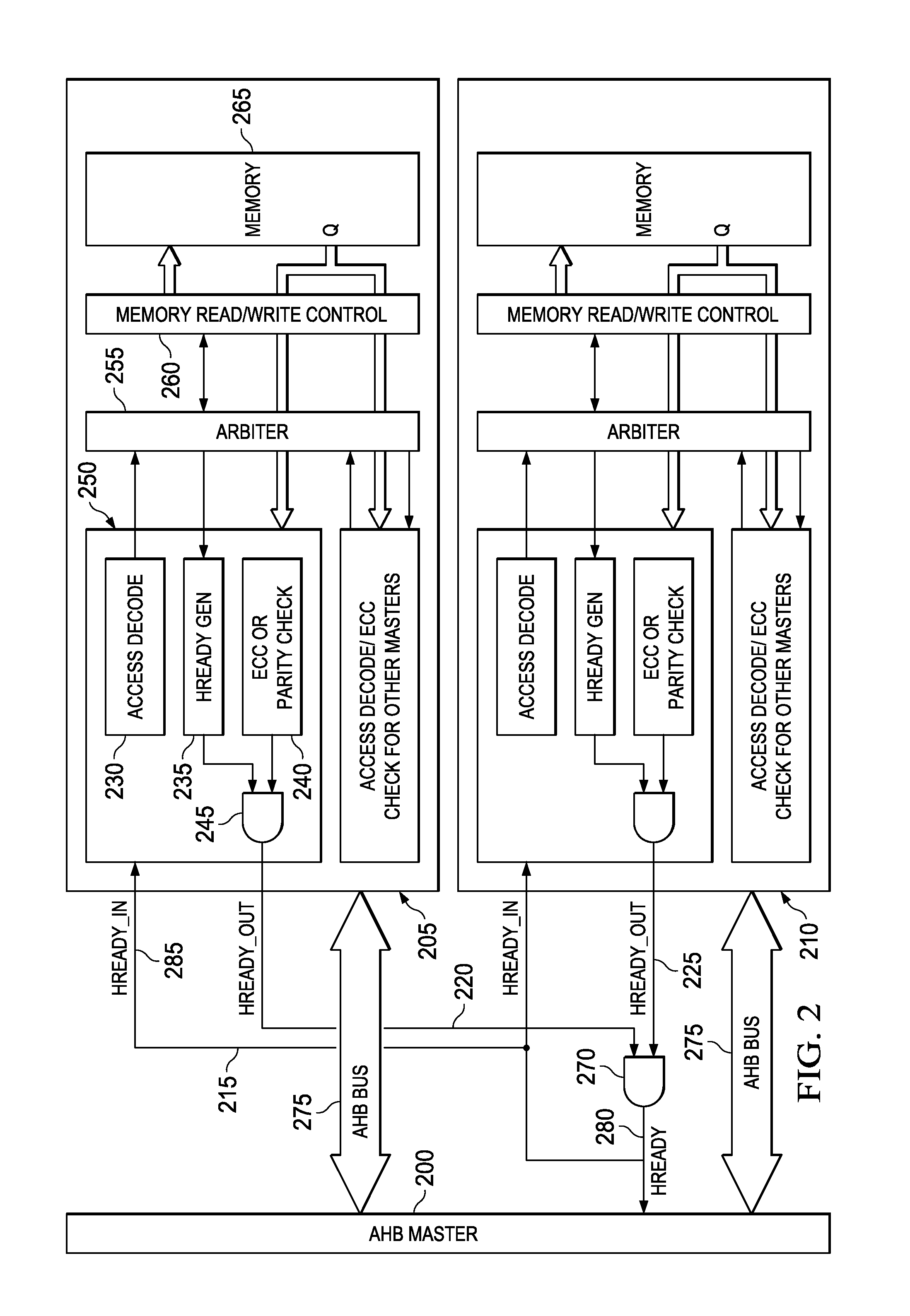

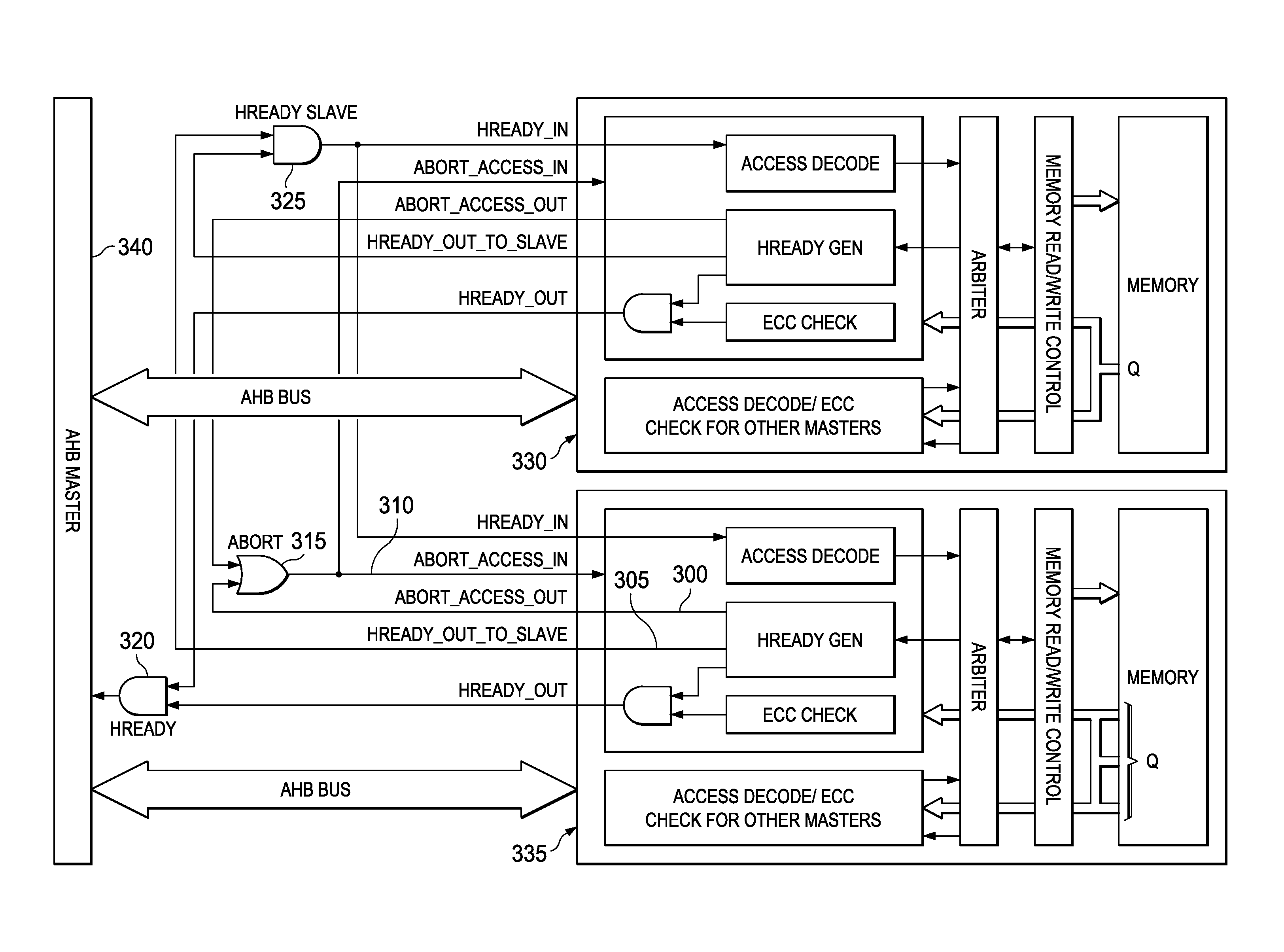

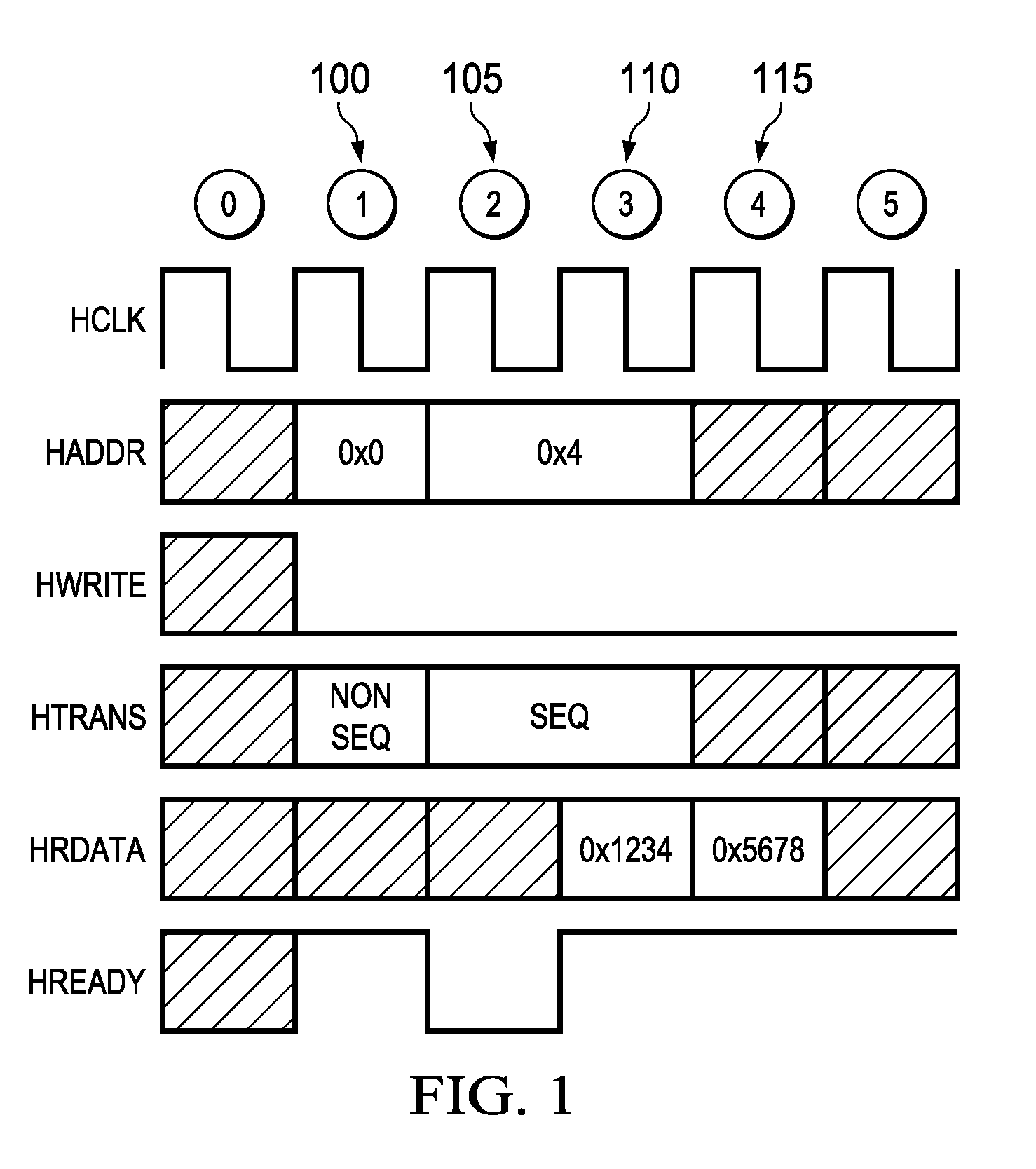

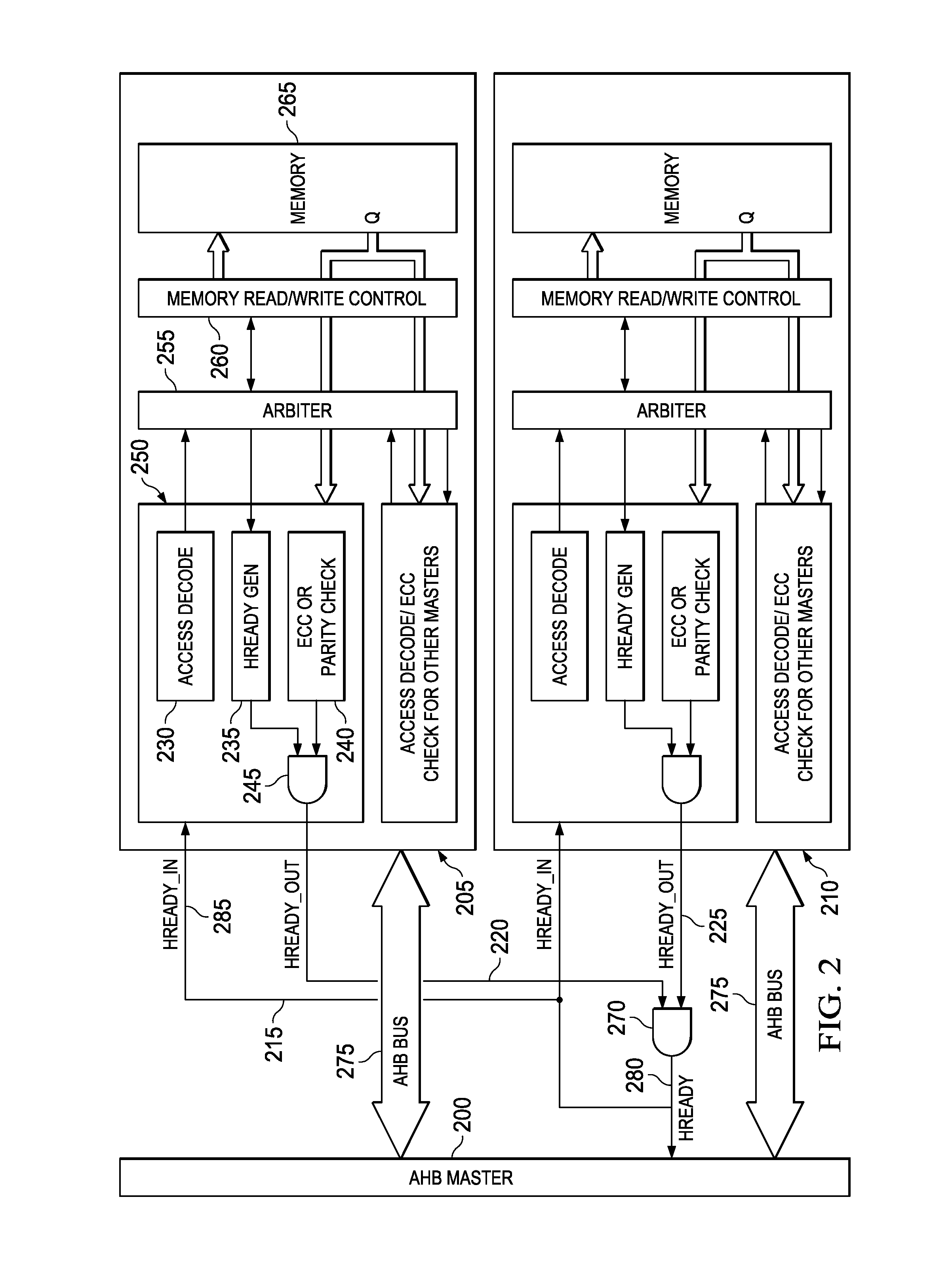

System and method for improving ECC enabled memory timing

A pipeline communication system includes a master and a plurality of slaves configured to communicate with each other. Each of the plurality of slaves includes a memory, and is configured to generate a first ready signal and a second ready signal. The first ready signal is configured to be provided only to the master and the second ready signal is configured to be provided only to each of the plurality of slaves. The second ready signal is generated independent of the error check in each of the plurality of slaves.

Owner:TEXAS INSTR INC

Method and apparatus for generating memory models and timing database

InactiveUS20070136704A1Software simulation/interpretation/emulationSpecial data processing applicationsTerm memoryResource based

A method and apparatus are provided for creating and using a memory timing database. A plurality of characterization memories are defined, which can be mapped to a memory resource. Each characterization memory has different memory parameters. A plurality of variants of tiling each characterization memory to the memory resource are also defined. Timing characteristics of each tiling variant of each characterization memory are stored in the memory timing database for the memory resource based on sets of input ramptimes and output loads.

Owner:BELL SEMICON LLC

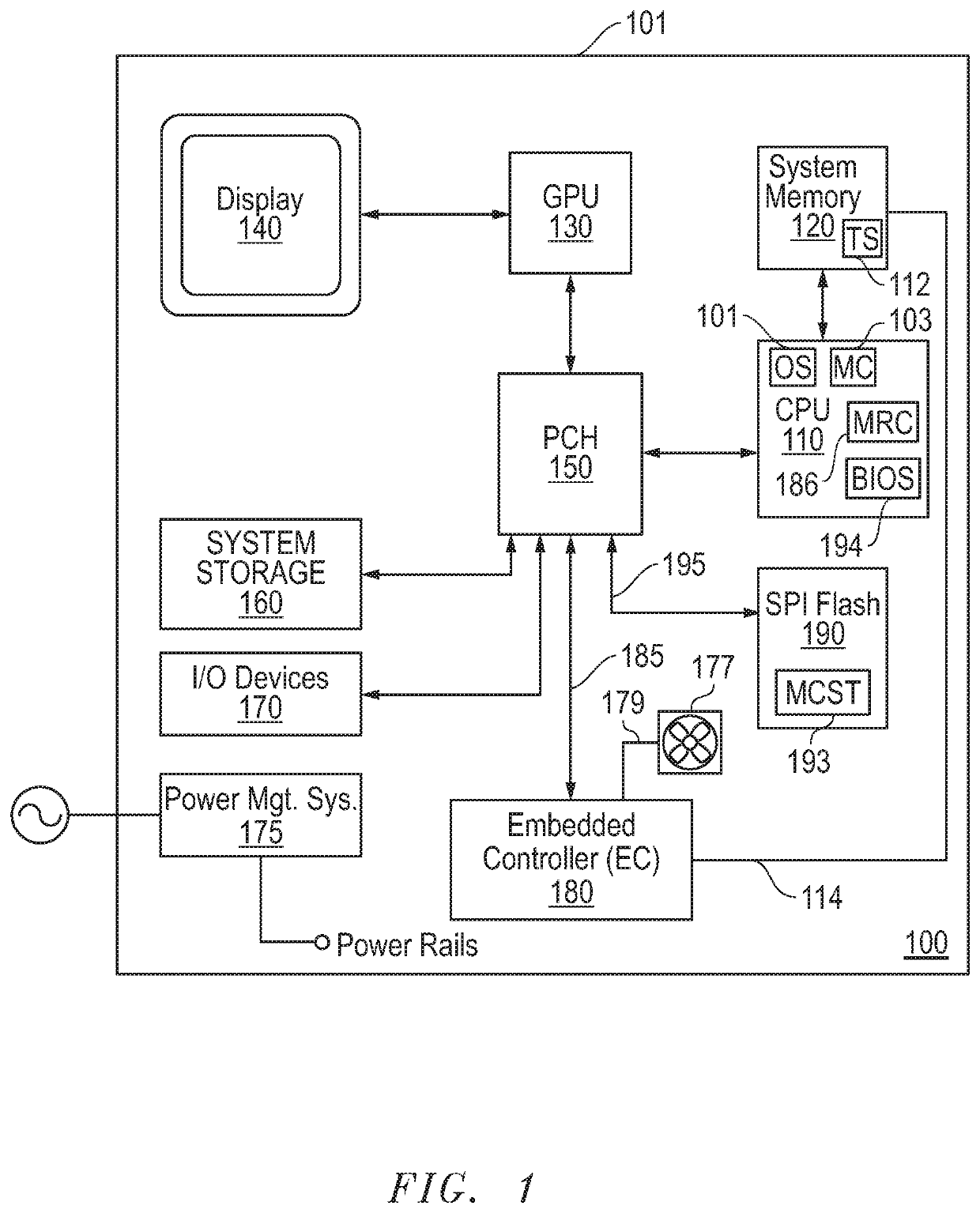

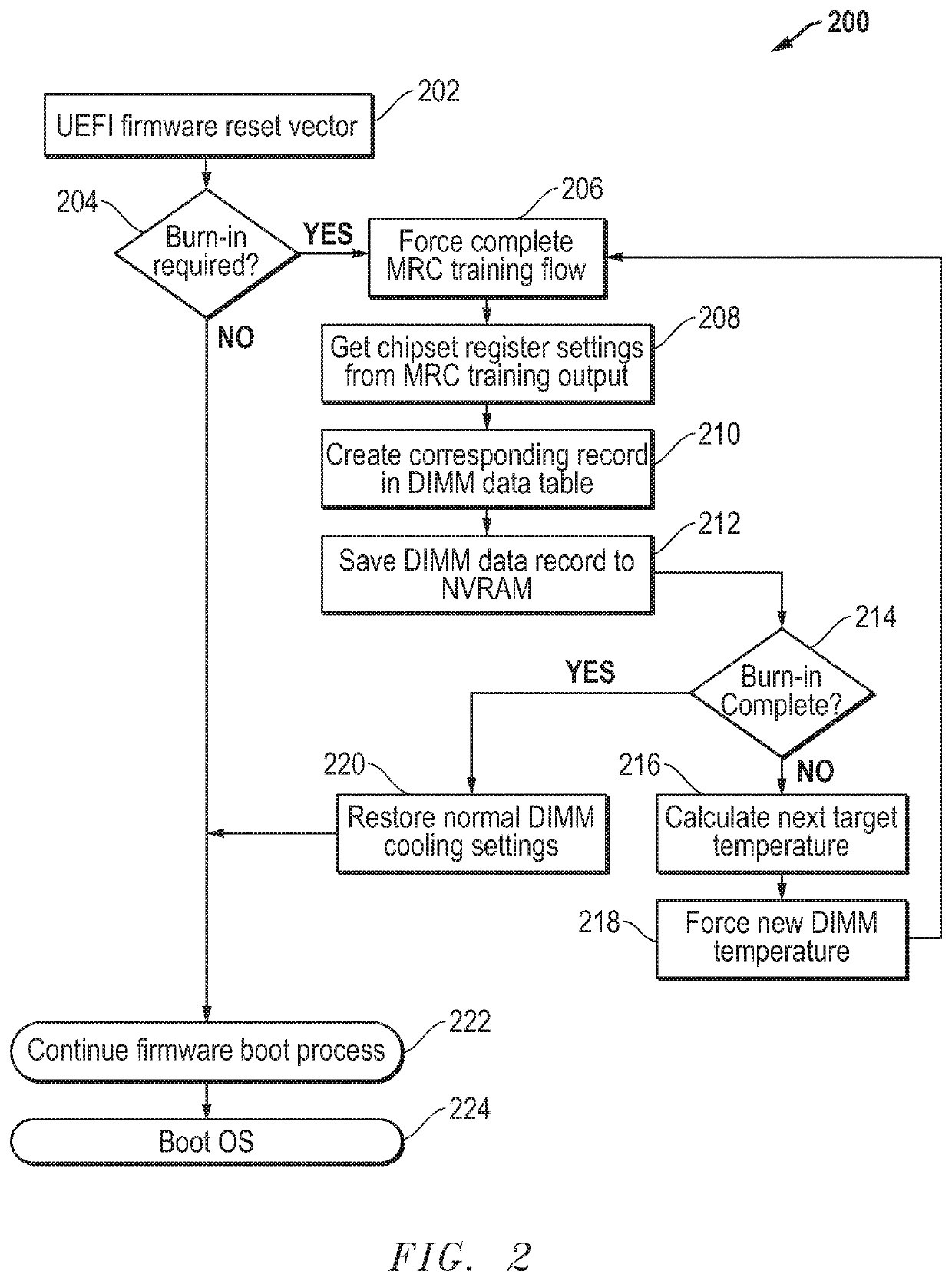

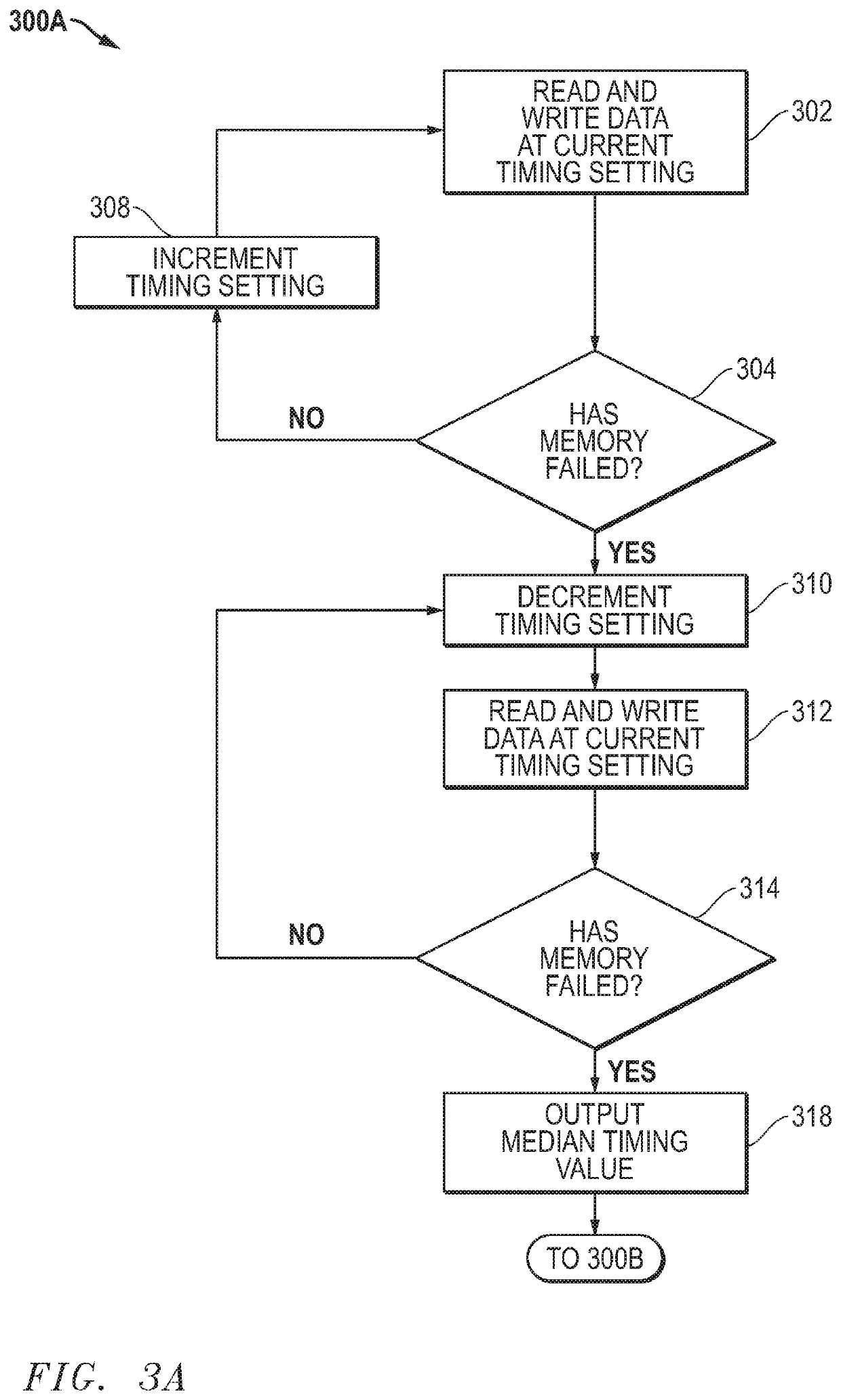

Systems And Methods For Creating And/Or Modifying Memory Configuration Settings

ActiveUS20200073568A1Reduces unnecessary product returnReduces repair attemptInput/output to record carriersStatic storageSoftware engineeringTerm memory

Systems and methods are provided for creating and / or modifying memory configuration settings (e.g., such as memory timing and memory drive voltage) for use at selected and / or varying memory temperature / s. The disclosed systems and methods may be implemented to create a relationship between optimized memory configuration settings for different memory temperatures during burn-in testing and / or on an ad-hoc basis.

Owner:DELL PROD LP

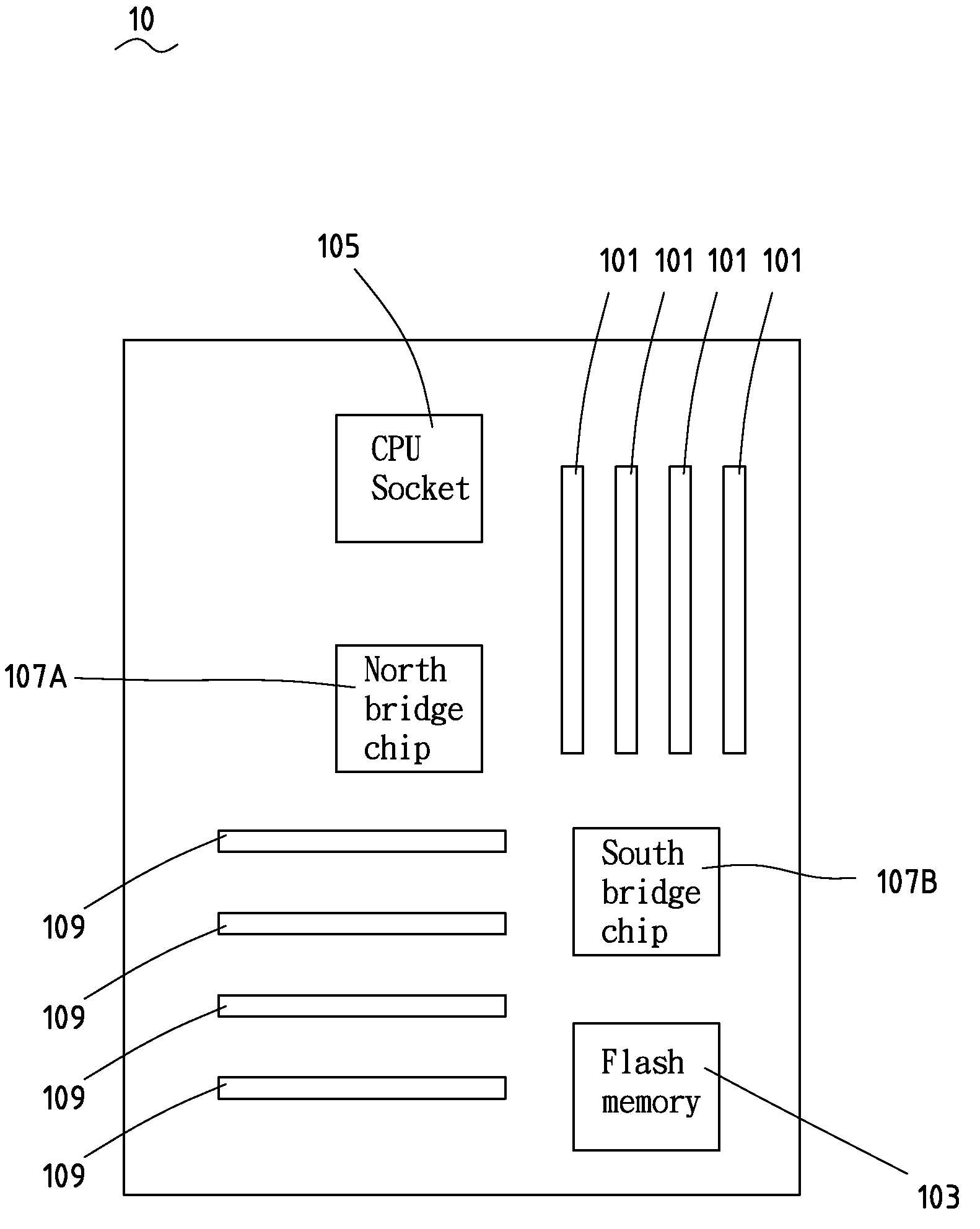

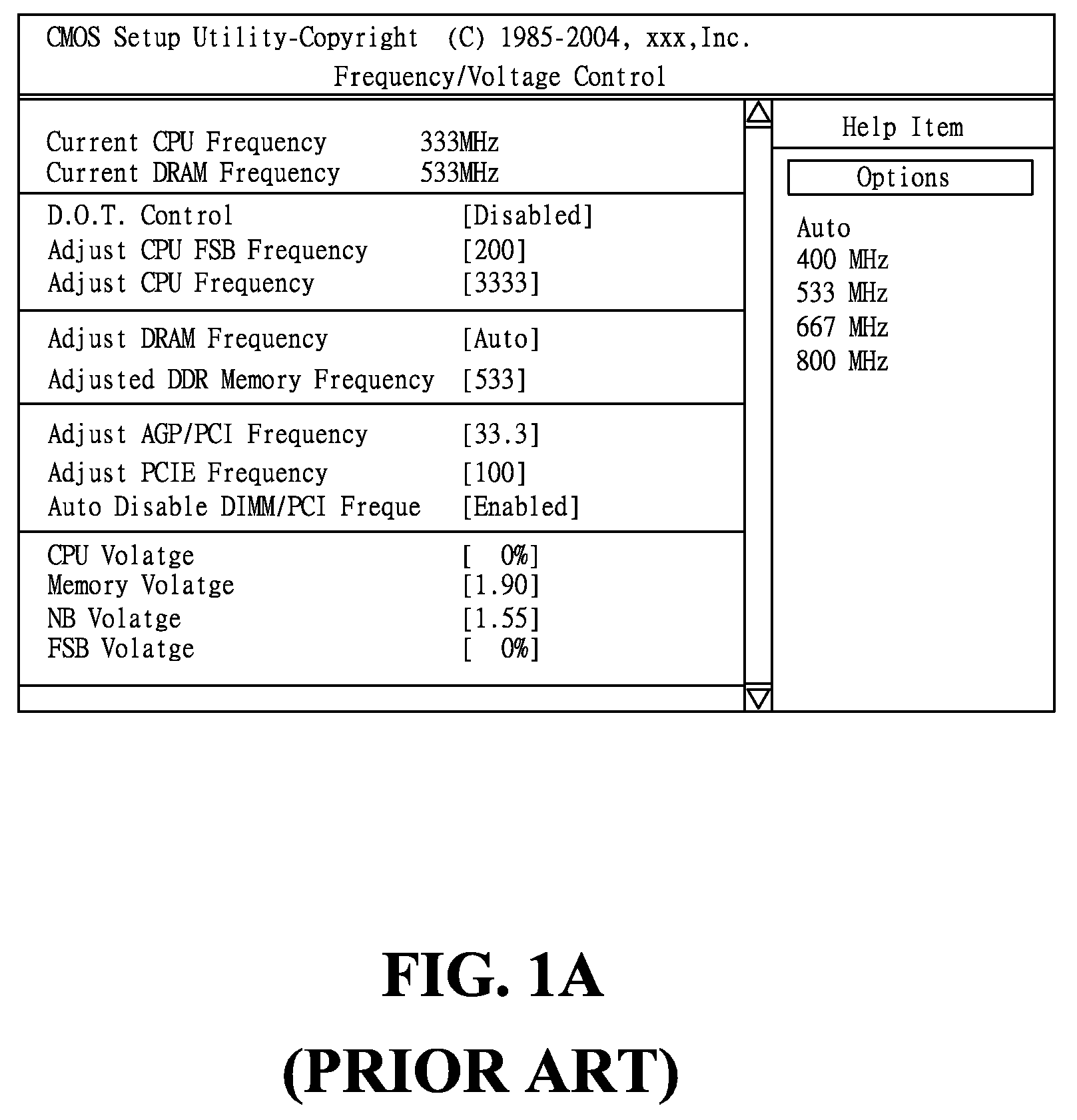

Computer motherboard

ActiveUS7865709B2Easy to modifyError detection/correctionDigital computer detailsComputer moduleBIOS

The present invention discloses a computer motherboard, which comprises: at least one memory module slot, a flash memory, a central processing unit socket; wherein, the memory module slot is used to plug at least one memory module; the flash memory is used to store BIOS programming codes, in which the BIOS programming codes are provided with at least one memory configuration programming codes for configuring the memory frequency and memory timing of the memory module; the central processing unit socket is used to plug the CPU, and the CPU is at least used to execute the memory configuration programming codes, so, after execution, they could provide a plurality of parameter options for memory frequency and memory timing of the memory modules to be selected one from them.

Owner:MICRO-STAR INTERNATIONAL +1

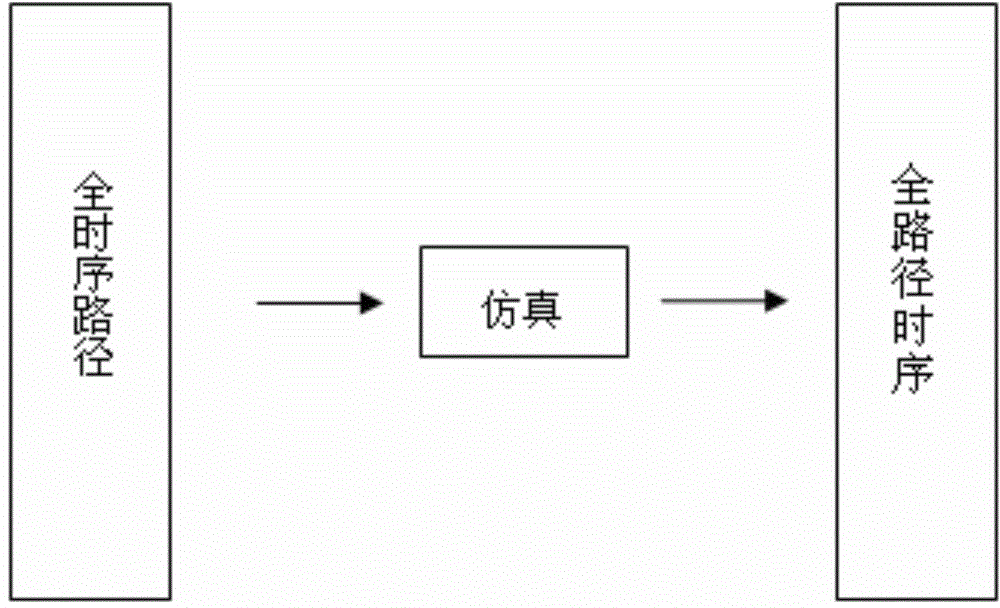

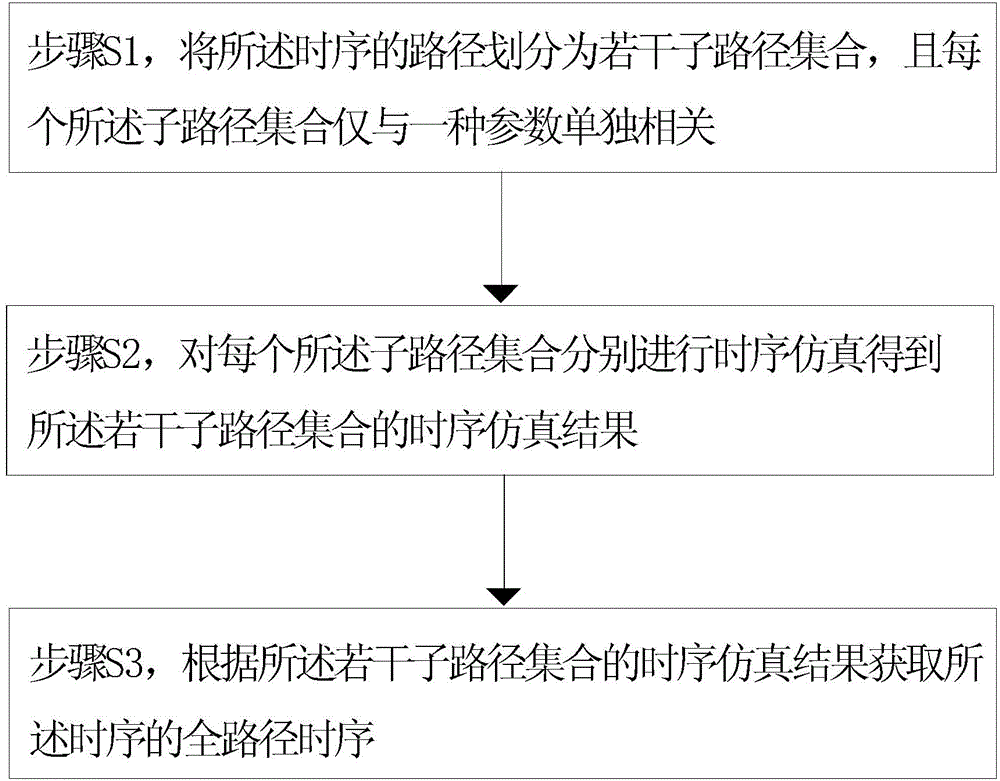

Memory compiler timing sequence simulation method

InactiveCN105824680ASoftware simulation/interpretation/emulationSpecial data processing applicationsResource consumptionMathematical model

The present invention relates to the technical field of memory timing sequence simulation, and especially relates to a memory compiler timing sequence simulation method. A timing sequence path is divided, each subpath set is only individually related to one parameter, timing sequence simulation is carried out on each subpath set about the parameter individually related to each subpath set, then simulation results are calculated through a mathematical model to obtain a full path timing sequence of the timing sequence, so that the accurate simulation results are obtained, computing resource consumption is effectively reduced, and furthermore, timing sequence simulation efficiency is improved, and simulation cost is also reduced.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

Automatic timing-sensitive circuit extraction

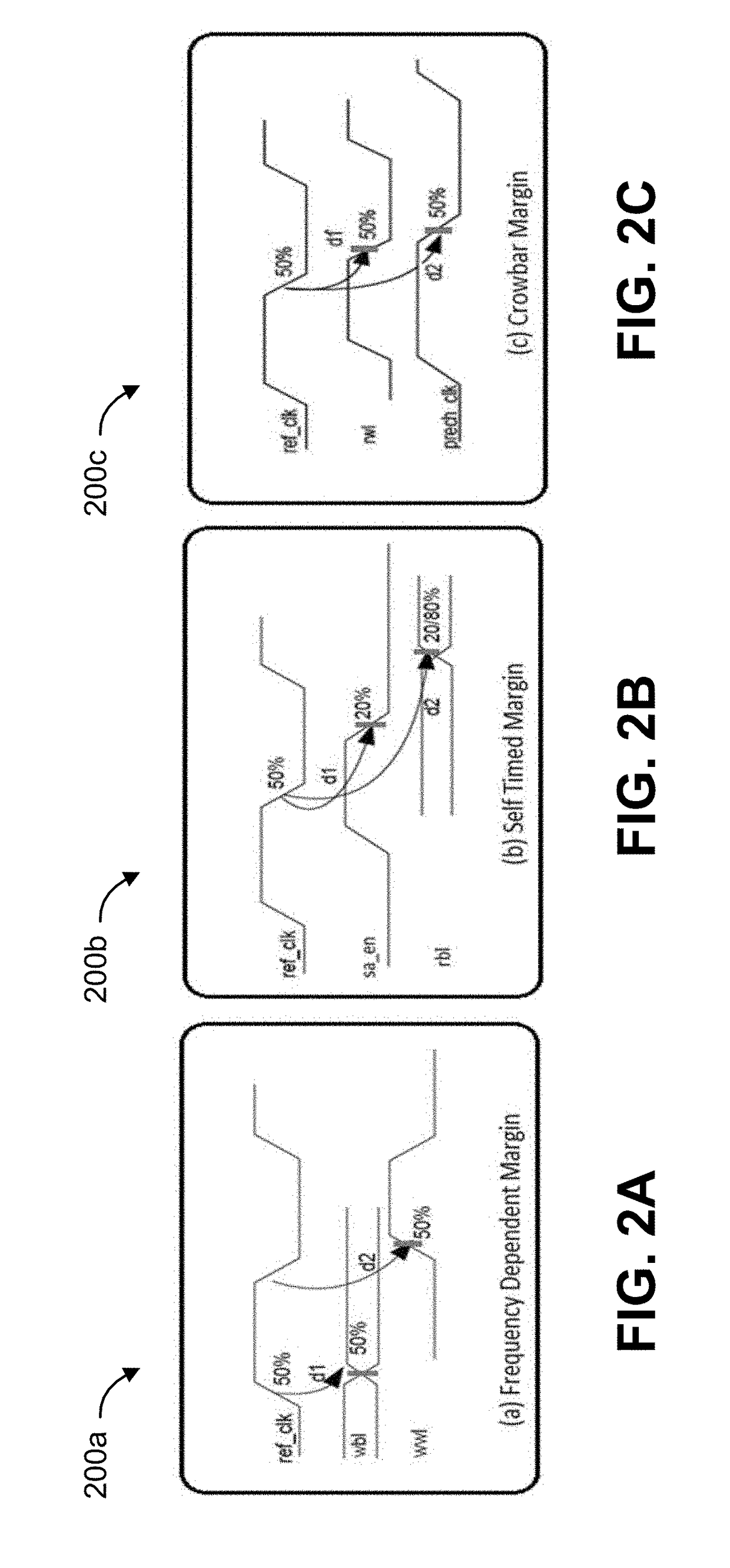

ActiveUS20180225399A1Quickly generate resultConstraint-based CADSpecial data processing applicationsTiming marginAlgorithm

Embodiments include systems and methods for automatic timing-sensitive circuit extraction for statistical timing margin analysis of custom designs. A timing-sensitive circuit extractor system can take pre- or post-layout netlists for integrated circuits and can automatically generate a timing-sensitive netlist. For example embodiments can generate a connectivity graph from the netlist and can traverse the graph with constraints defined according to measurement nodes to extract the timing-sensitive circuit. Memory timing checks and corresponding stimuli can generally be pre-defined, and a test-bench generator can generate appropriate parameters, stimuli, etc. Statistical simulations can then be performed to quickly generate results, which can be post-processed to obtain timing margin distributions and to flag out design errors.

Owner:ORACLE INT CORP

System and method for thermally coupling memory devices to a memory controller in a computer memory board

A system and method for thermally coupling memory devices, such as DIMM memory modules, to an associated memory controller such that both are cooled together at the same relative temperature. By maintaining all of the devices at a much more uniform temperature, memory timing issues are effectively eliminated. In accordance with an exemplary embodiment, the controller chip is physically located between two or more banks of memory, and is positioned under an adjoining heat sink while the memory DIMMs are positioned laterally of the controller chip in angled DIMM slots and are coupled to the controller chip with respective heat spreaders.

Owner:SRC COMP

Capacity on Demand Using Signaling Bus Control

ActiveUS20080114913A1Fine granularity of on demandImprove computing powerError detection/correctionTime-division multiplexBus masteringTerm memory

Owner:LENOVO GLOBAL TECH INT LTD

Method and apparatus for generating memory models and timing database

InactiveUS7584442B2Computer aided designSoftware simulation/interpretation/emulationResource basedMemory timings

A method and apparatus are provided for creating and using a memory timing database. A plurality of characterization memories are defined, which can be mapped to a memory resource. Each characterization memory has different memory parameters. A plurality of variants of tiling each characterization memory to the memory resource are also defined. Timing characteristics of each tiling variant of each characterization memory are stored in the memory timing database for the memory resource based on sets of input ramptimes and output loads.

Owner:BELL SEMICON LLC

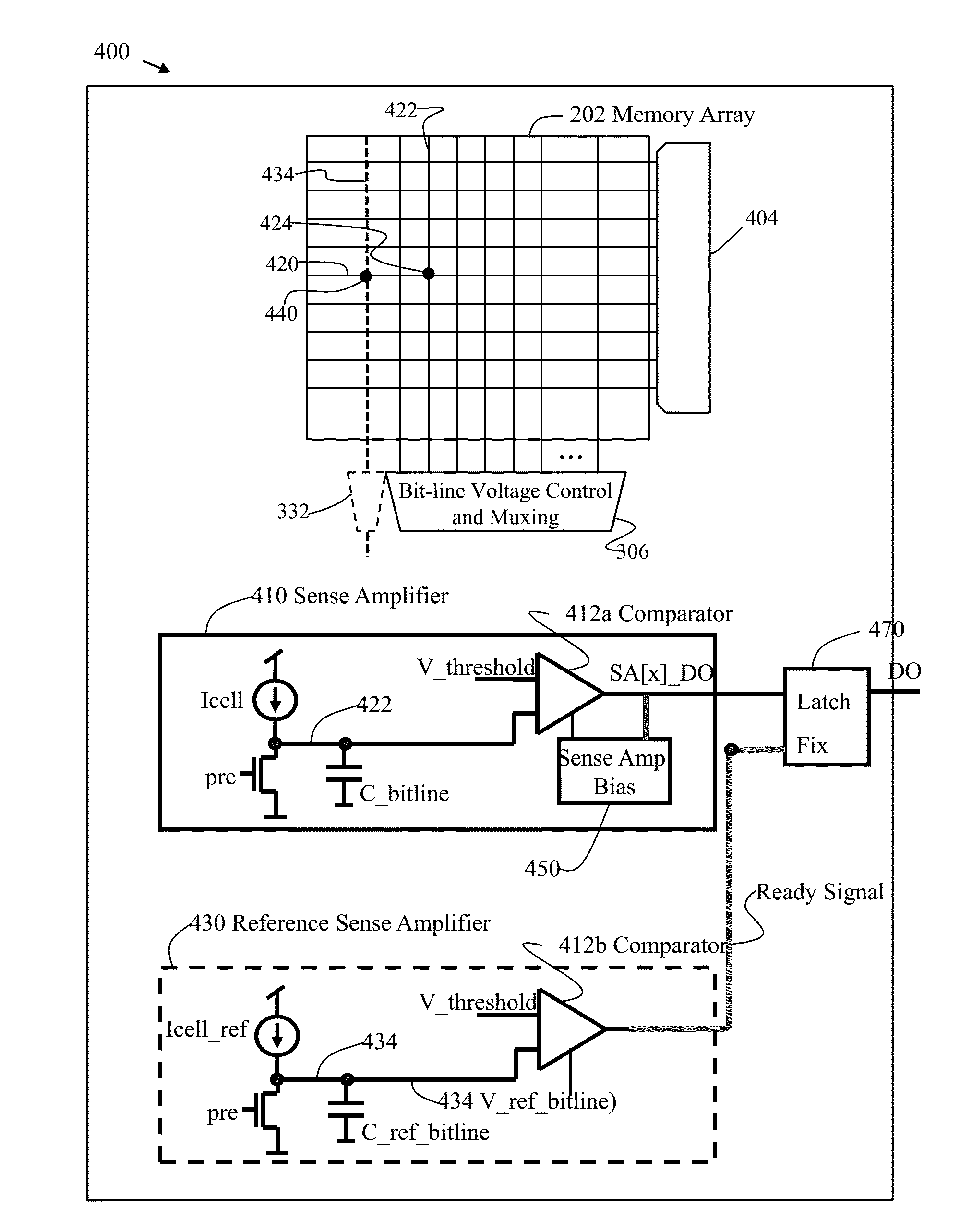

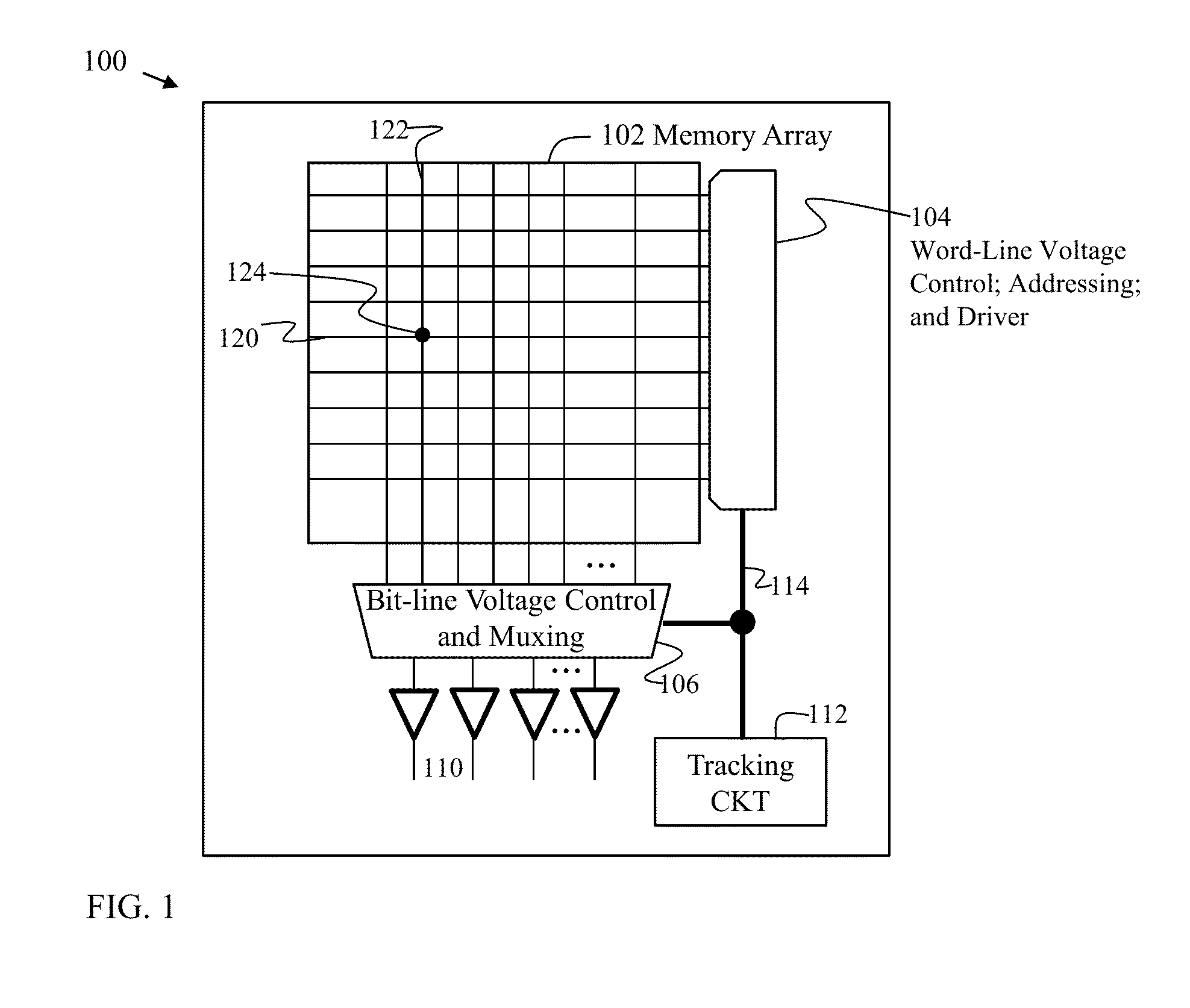

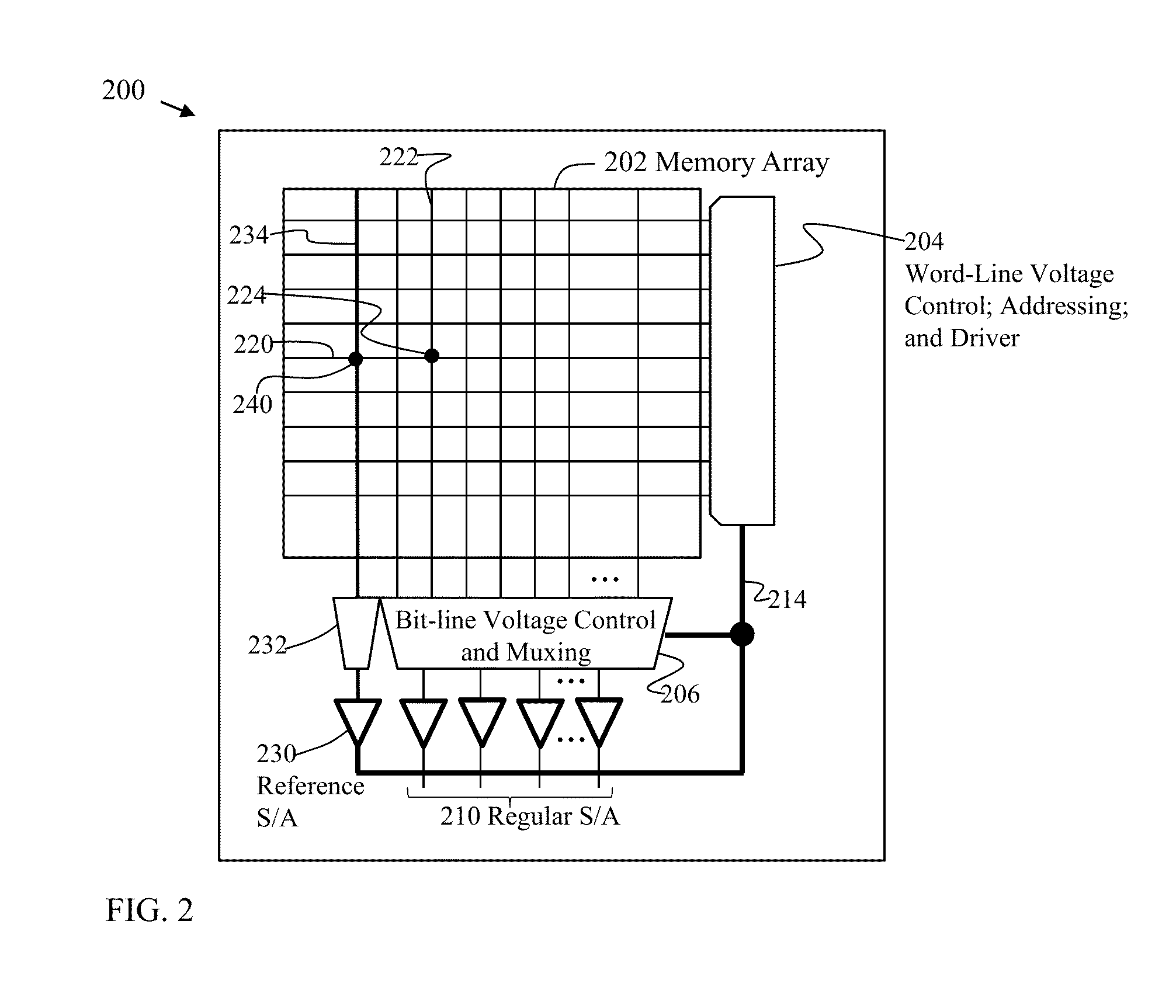

Memory timing circuit

A memory circuit including a memory cell configured to provide a charge, voltage, or current to an associated bit-line; a sense amplifier configured to sense the charge, voltage, or current on the bit-line; a word-line circuit configured to control a word-line of the memory cell; and a tracking circuit configured to track one or more conditions of the memory circuit and provide a timing control signal at an output operative to adaptively control the word-line circuit.

Owner:INFINEON TECH AG

Memory system with region-specific memory access scheduling

ActiveUS10956044B2Memory architecture accessing/allocationInput/output to record carriersComputer architectureMemory cell

An integrated circuit device includes a memory controller coupleable to a memory. The memory controller to schedule memory accesses to regions of the memory based on memory timing parameters specific to the regions. A method includes receiving a memory access request at a memory device. The method further includes accessing, from a timing data store of the memory device, data representing a memory timing parameter specific to a region of the memory cell circuitry targeted by the memory access request. The method also includes scheduling, at the memory controller, the memory access request based on the data.

Owner:ADVANCED MICRO DEVICES INC

System and method for improving ECC enabled memory timing

A pipeline communication system includes a master and a plurality of slaves configured to communicate with each other. Each of the plurality of slaves includes a memory, and is configured to generate a first ready signal and a second ready signal. The first ready signal is configured to be provided only to the master and the second ready signal is configured to be provided only to each of the plurality of slaves. The second ready signal is generated independent of the error check in each of the plurality of slaves.

Owner:TEXAS INSTR INC

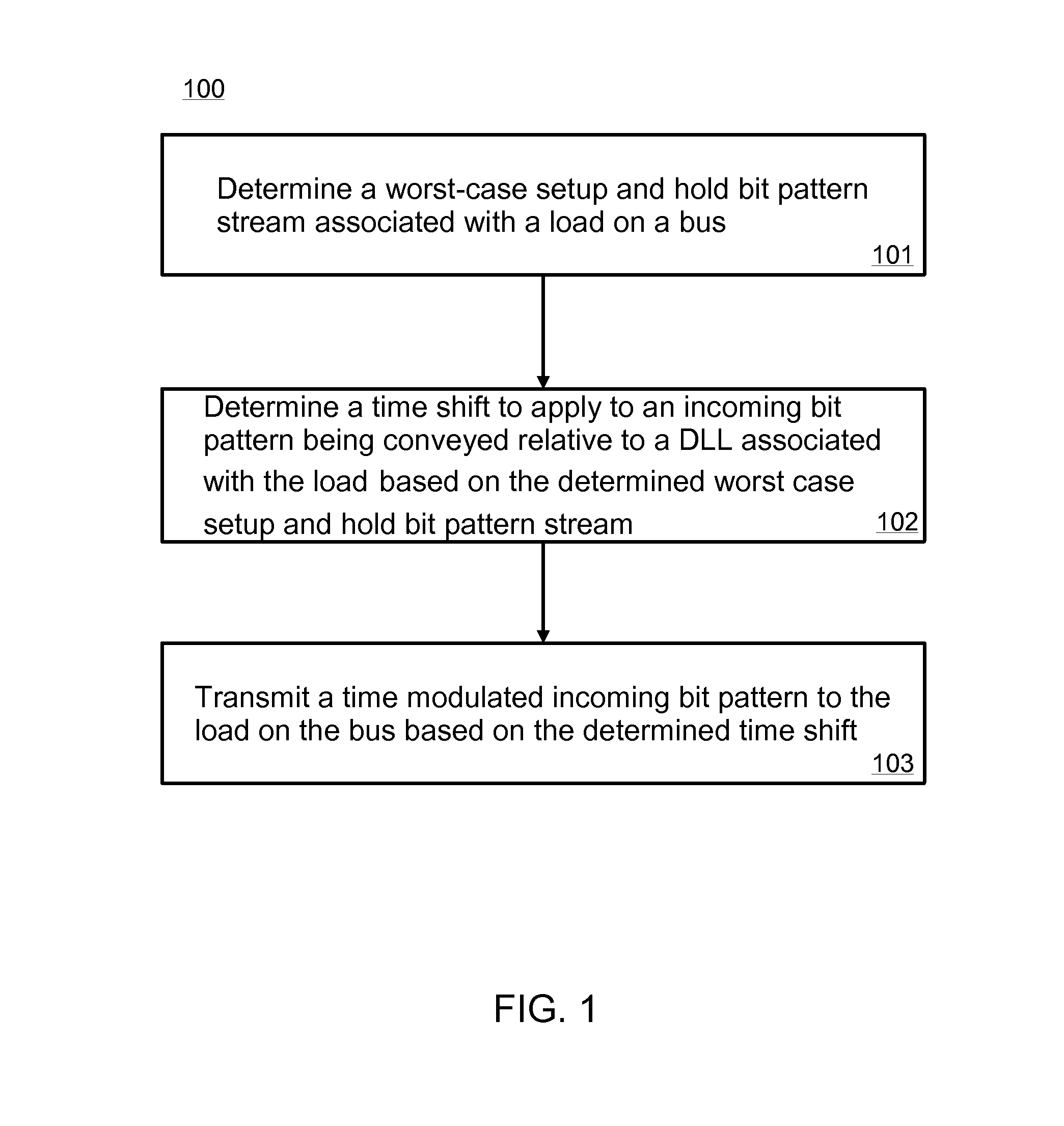

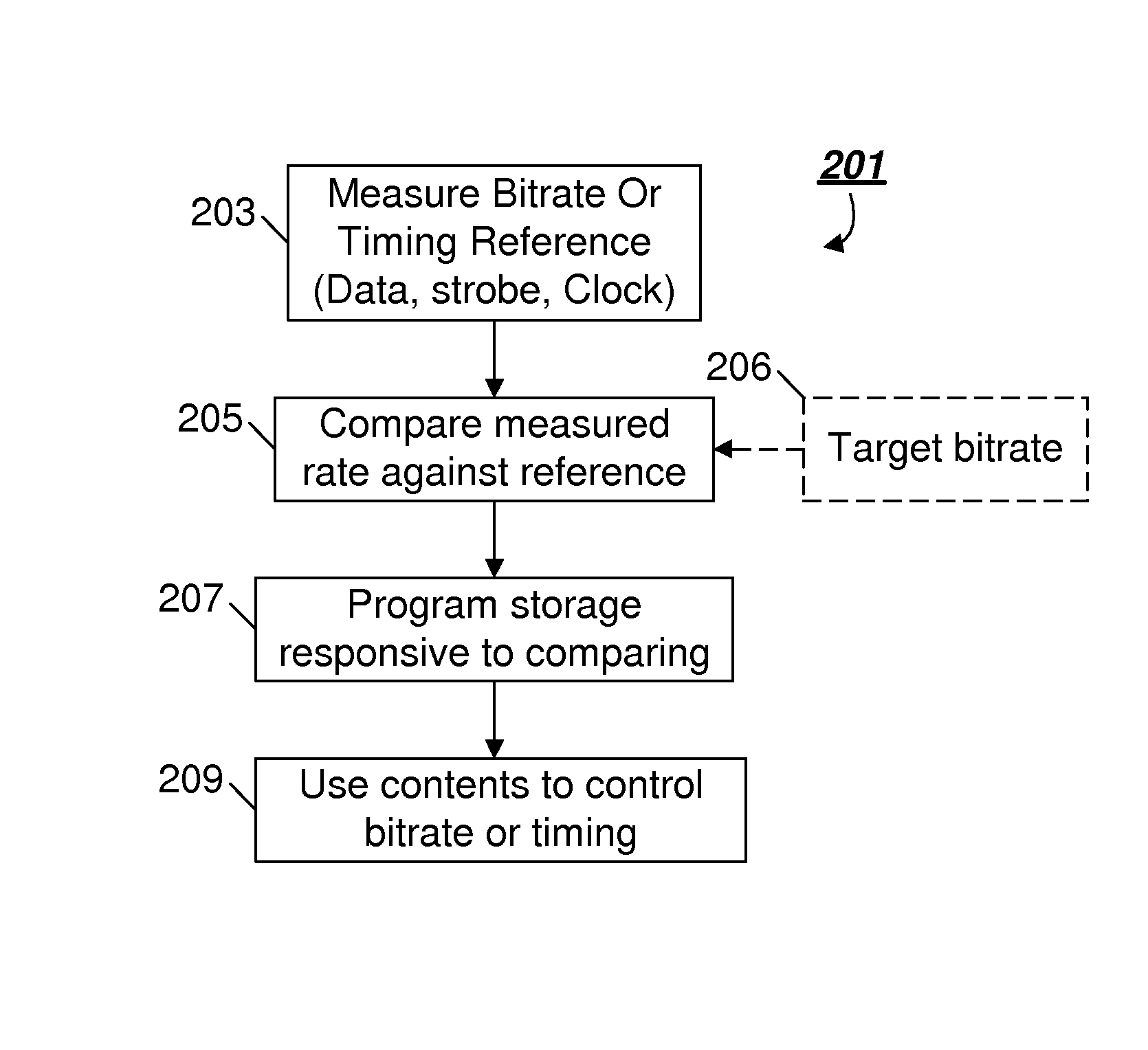

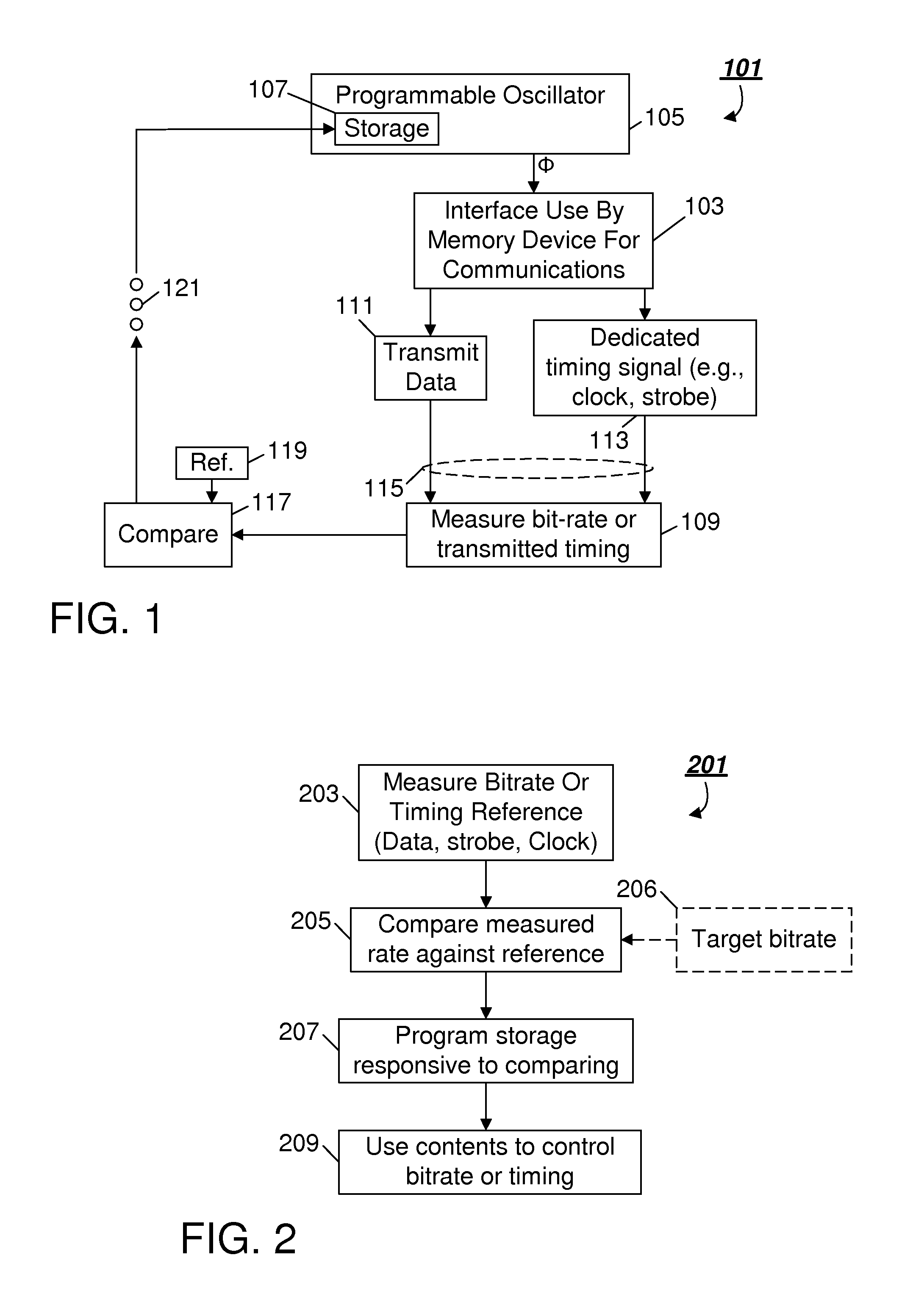

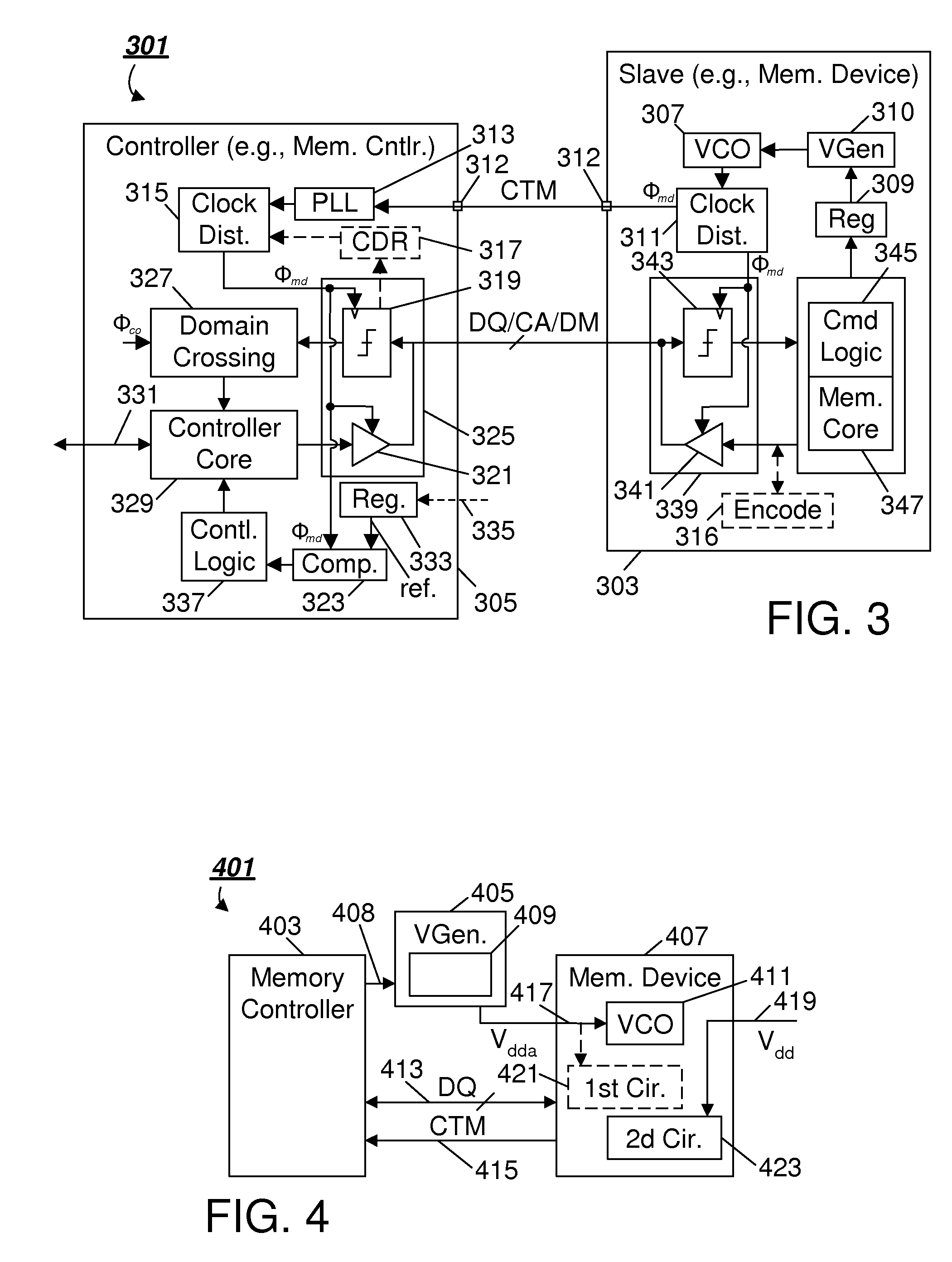

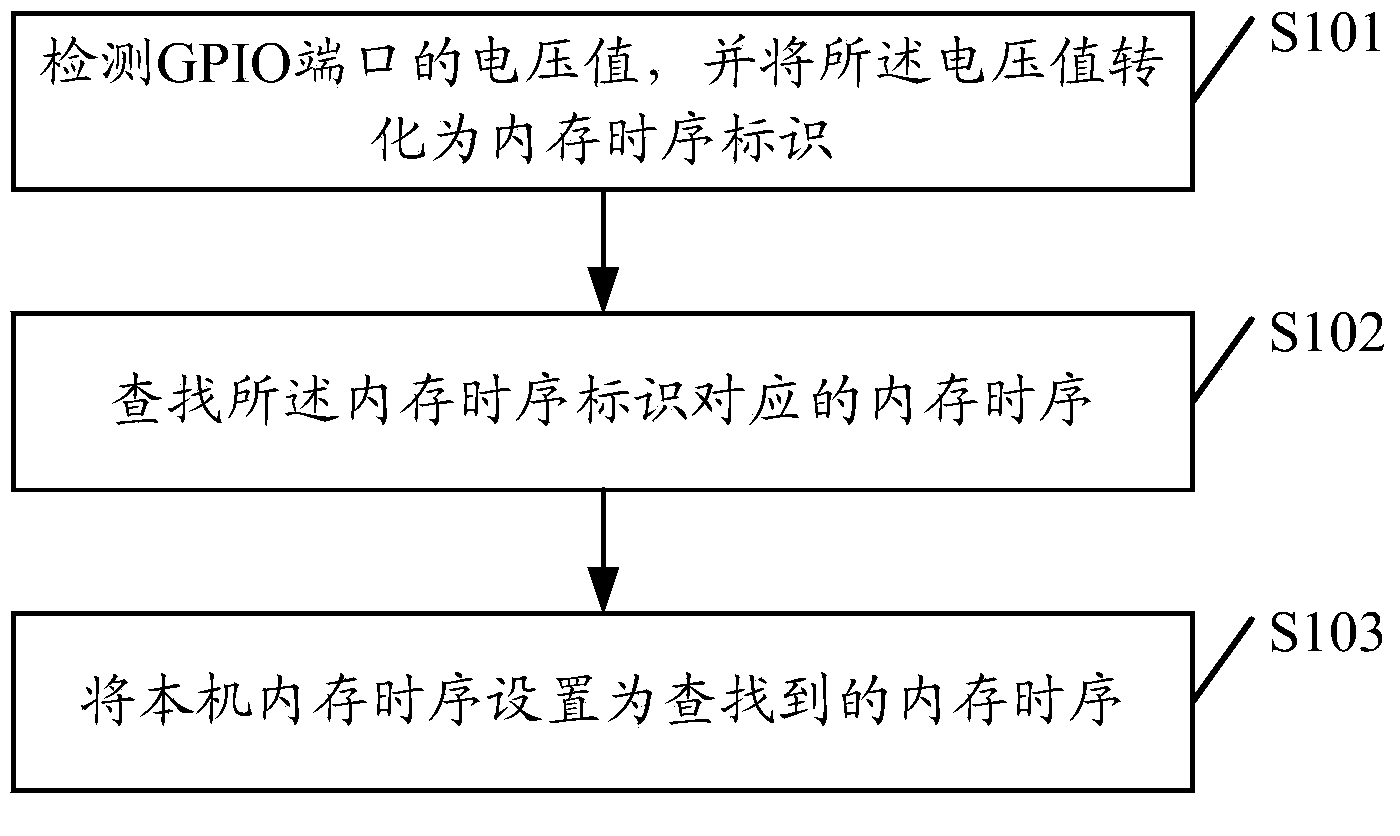

Regulation of memory IO timing using programmatic control over memory device IO timing

ActiveUS8930740B2Power supply for data processingGenerating/distributing signalsVoltage generatorProcessor register

Owner:RAMBUS INC

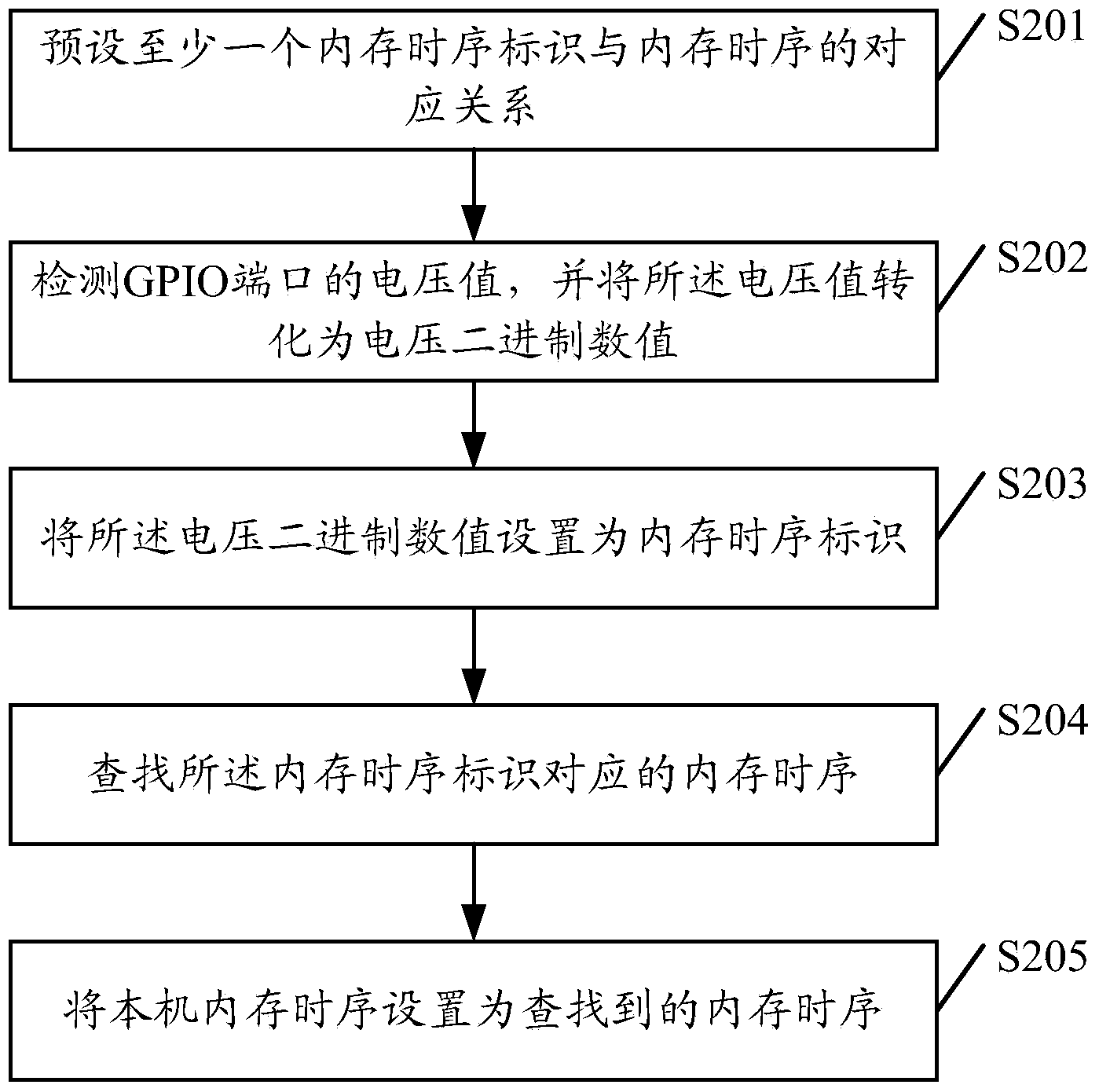

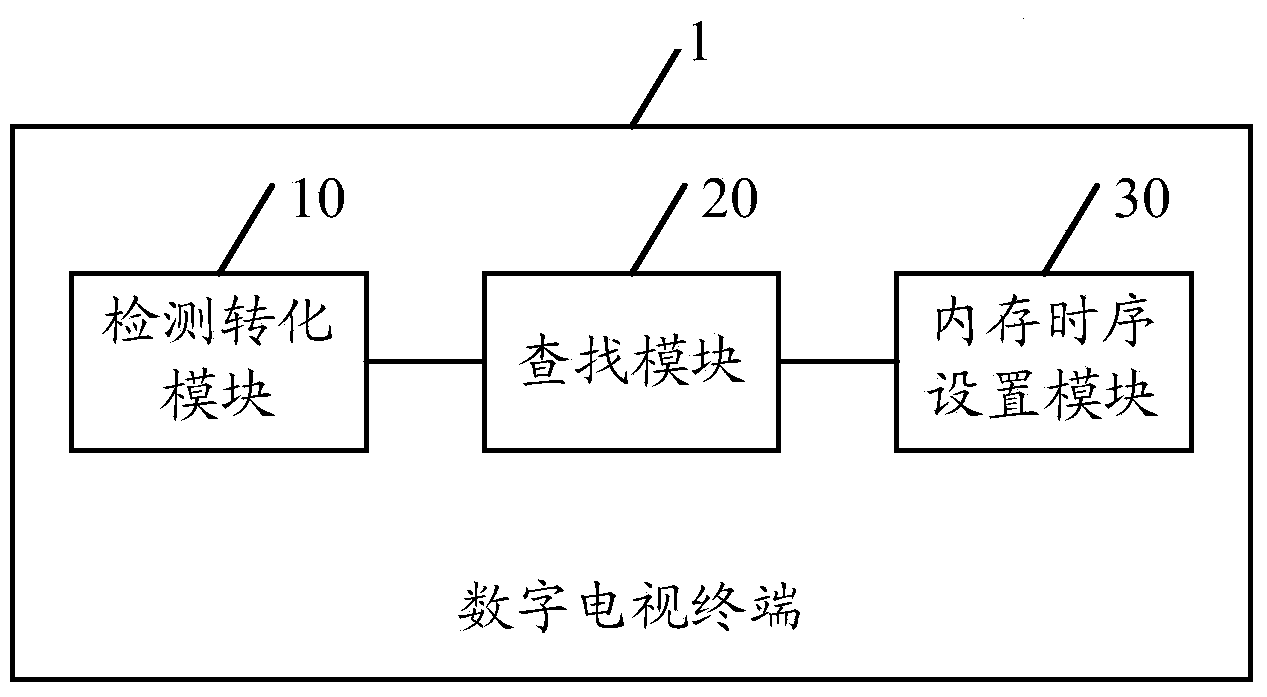

Method compatible with multiple memory timing sequences and digital television terminal

Owner:SHENZHEN COSHIP ELECTRONICS CO LTD

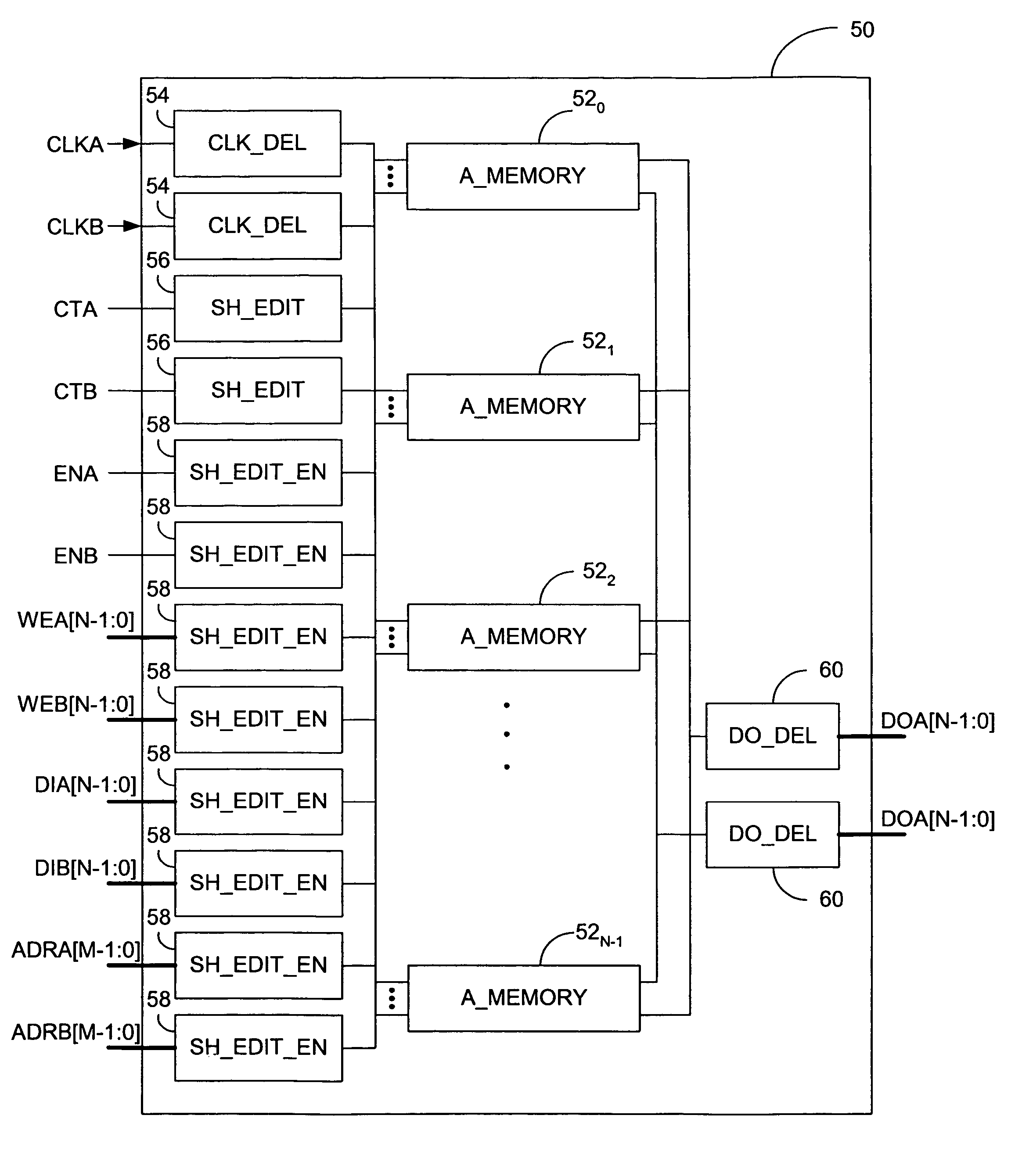

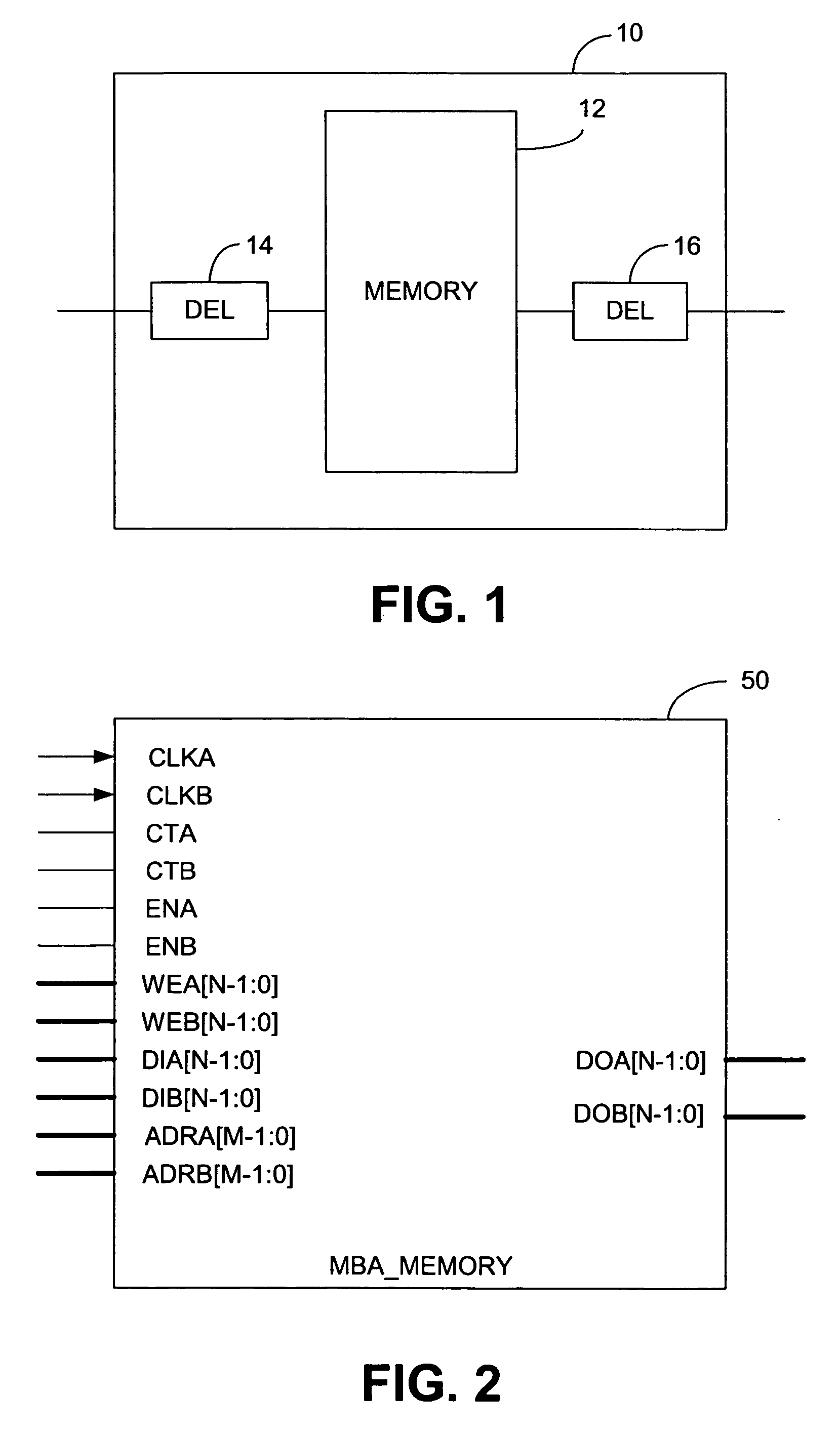

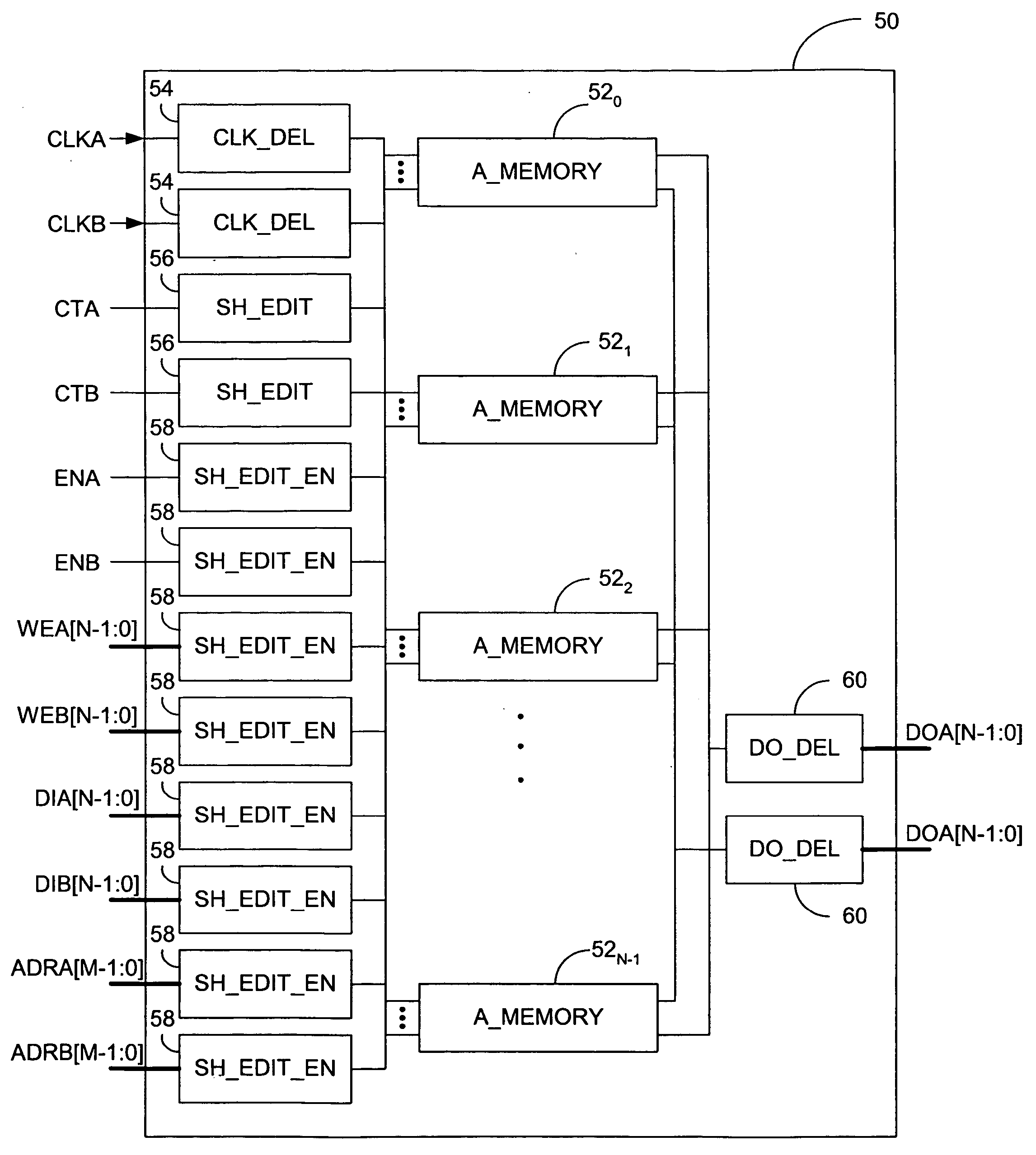

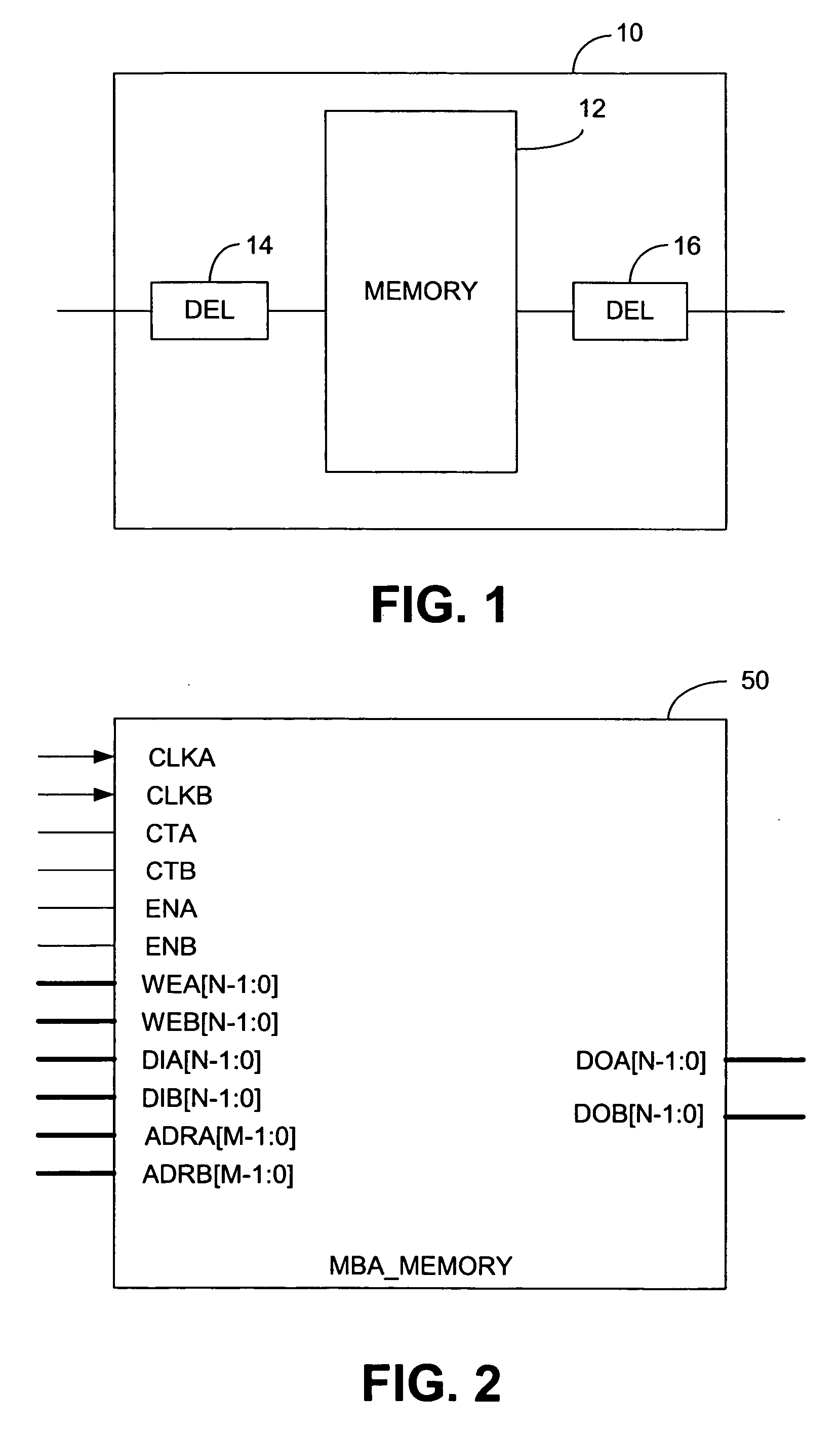

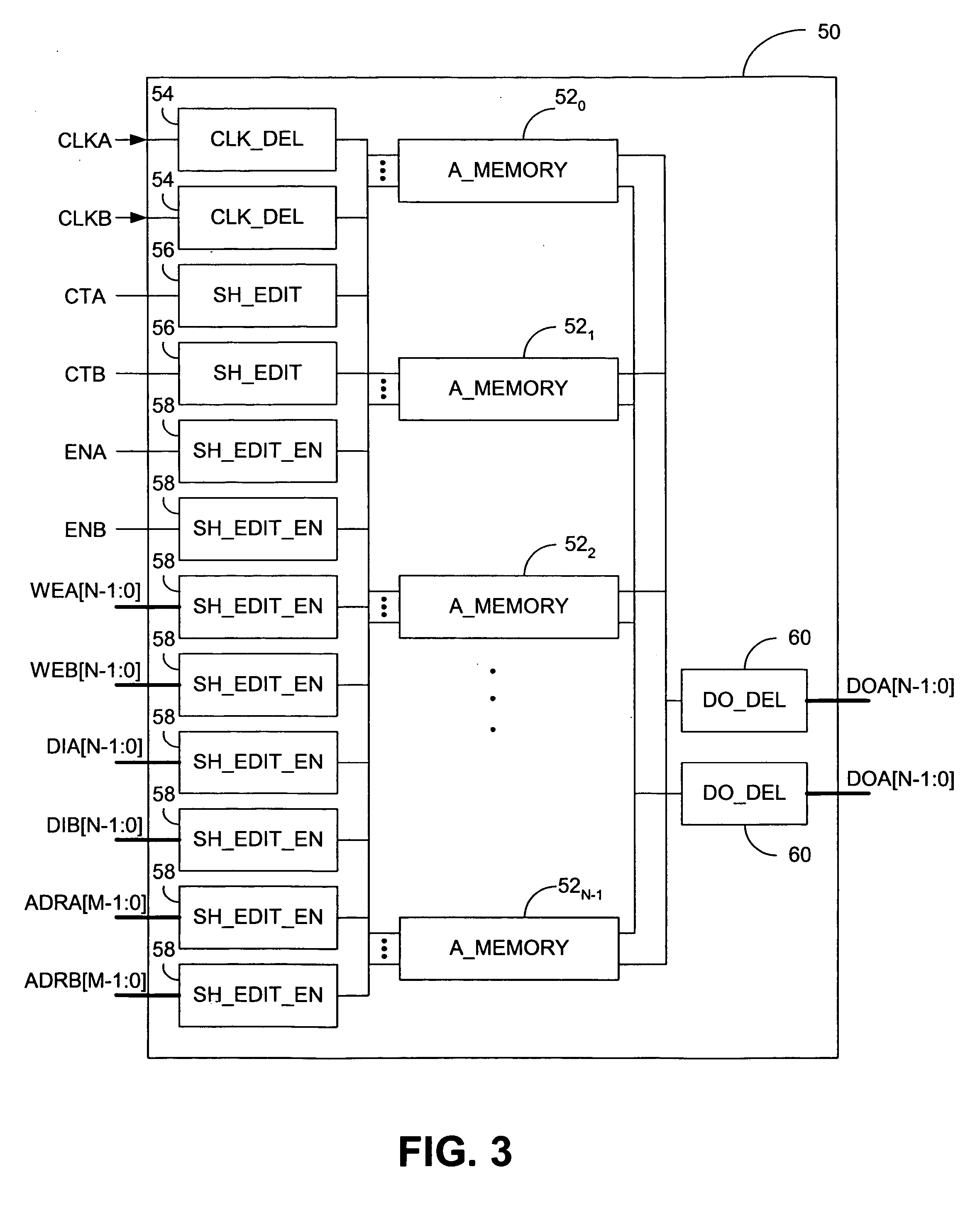

Memory timing model with back-annotating

InactiveUS20070143648A1Static storageSoftware simulation/interpretation/emulationTerm memoryMemory module

A memory timing model is provided, which includes an address input, a multiple-bit data input, a multiple-bit data output, a capacity C and a width N. N one-bit wide memory modules are instantiated in parallel with one another between respective bits of the data input and the data output. Each memory module has a capacity of C bits addressed by the address input.

Owner:BELL SEMICON LLC

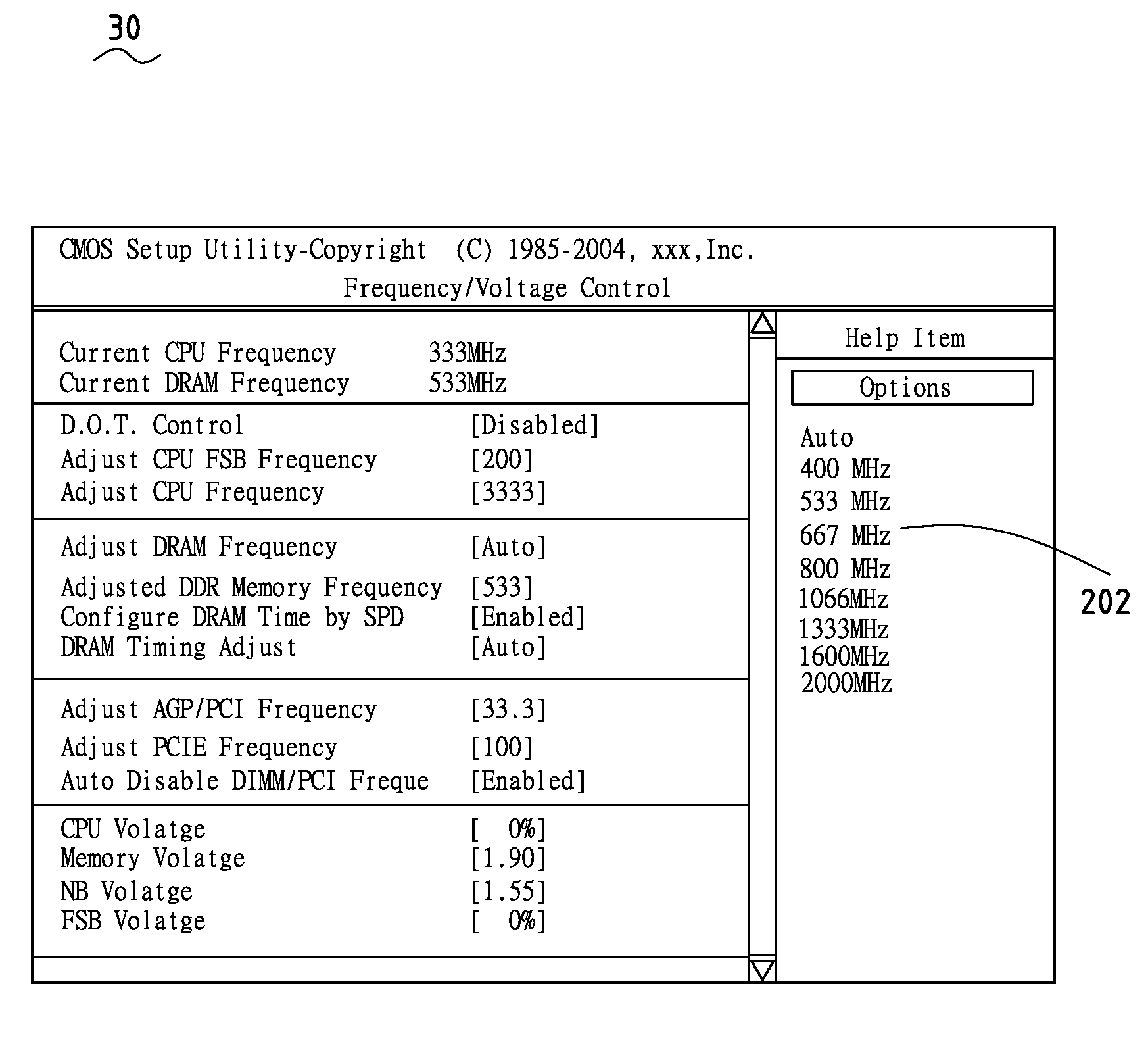

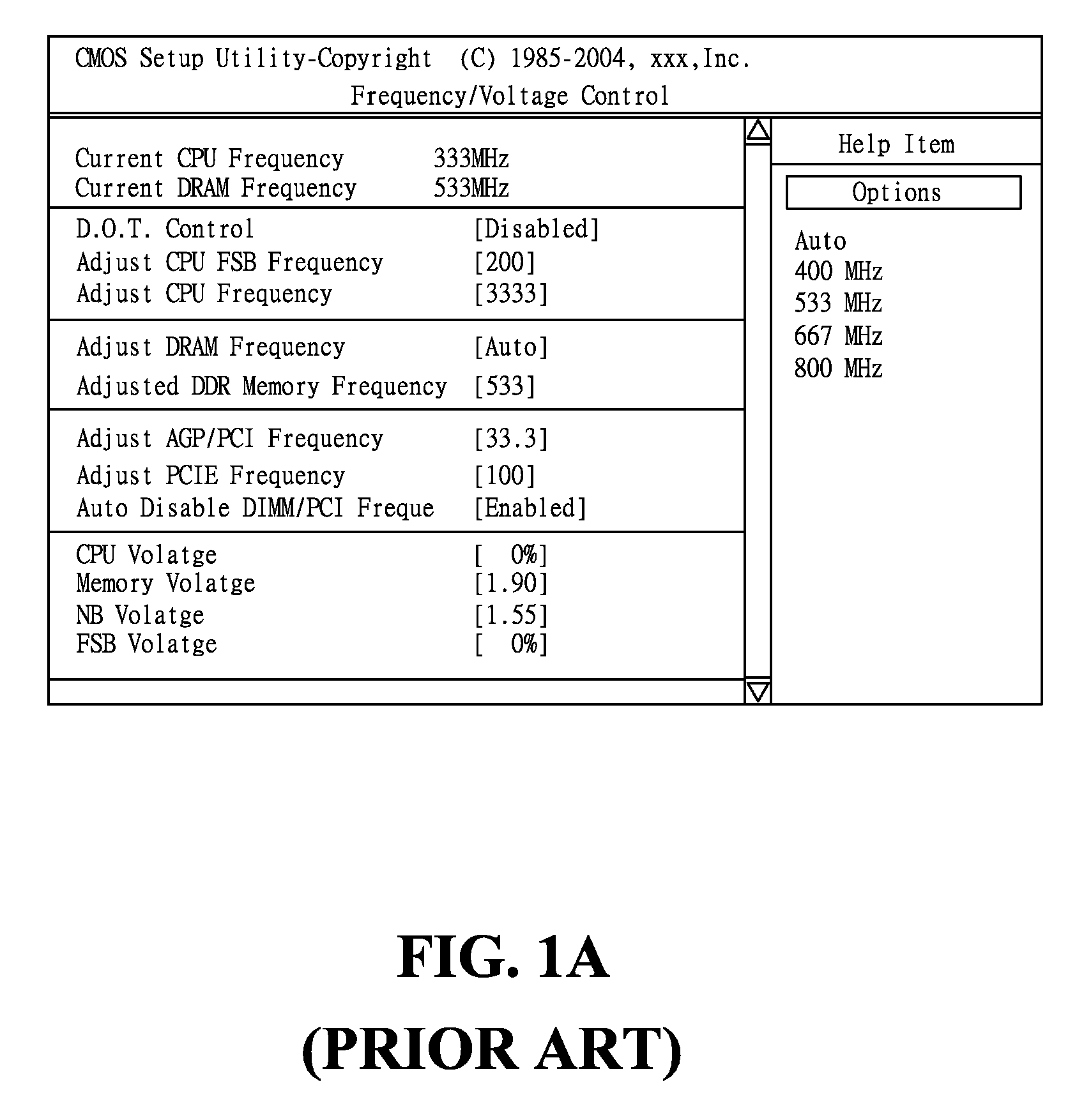

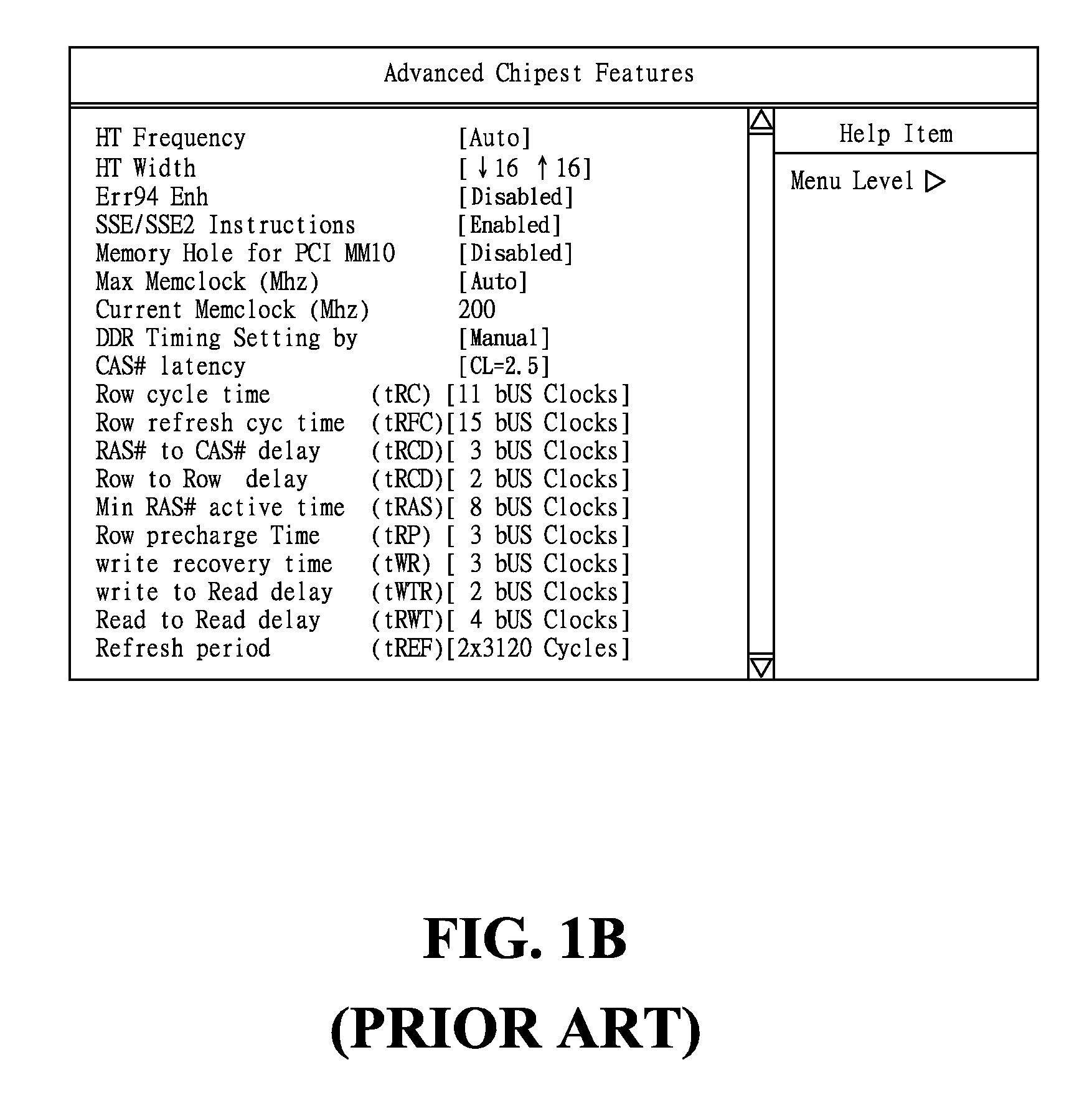

Computer motherboard

ActiveUS20090210687A1Easy to modifyError detection/correctionDigital computer detailsBIOSMemory module

The present invention discloses a computer motherboard, which comprises: at least one memory module slot, a flash memory, a central processing unit socket, wherein, the memory module slot is used to plug at least one memory module; the flash memory is used to store BIOS programming codes, in which the BIOS programming codes are provided with at least one memory configuration programming codes for configuring the memory frequency and memory timing of the memory module; the central processing unit socket is used to plug the CPU, and the CPU is at least used to execute the memory configuration programming codes, so, after execution, they could provide a plurality of parameter options for memory frequency and memory timing of the memory modules to be selected one from them.

Owner:MICRO-STAR INTERNATIONAL +1

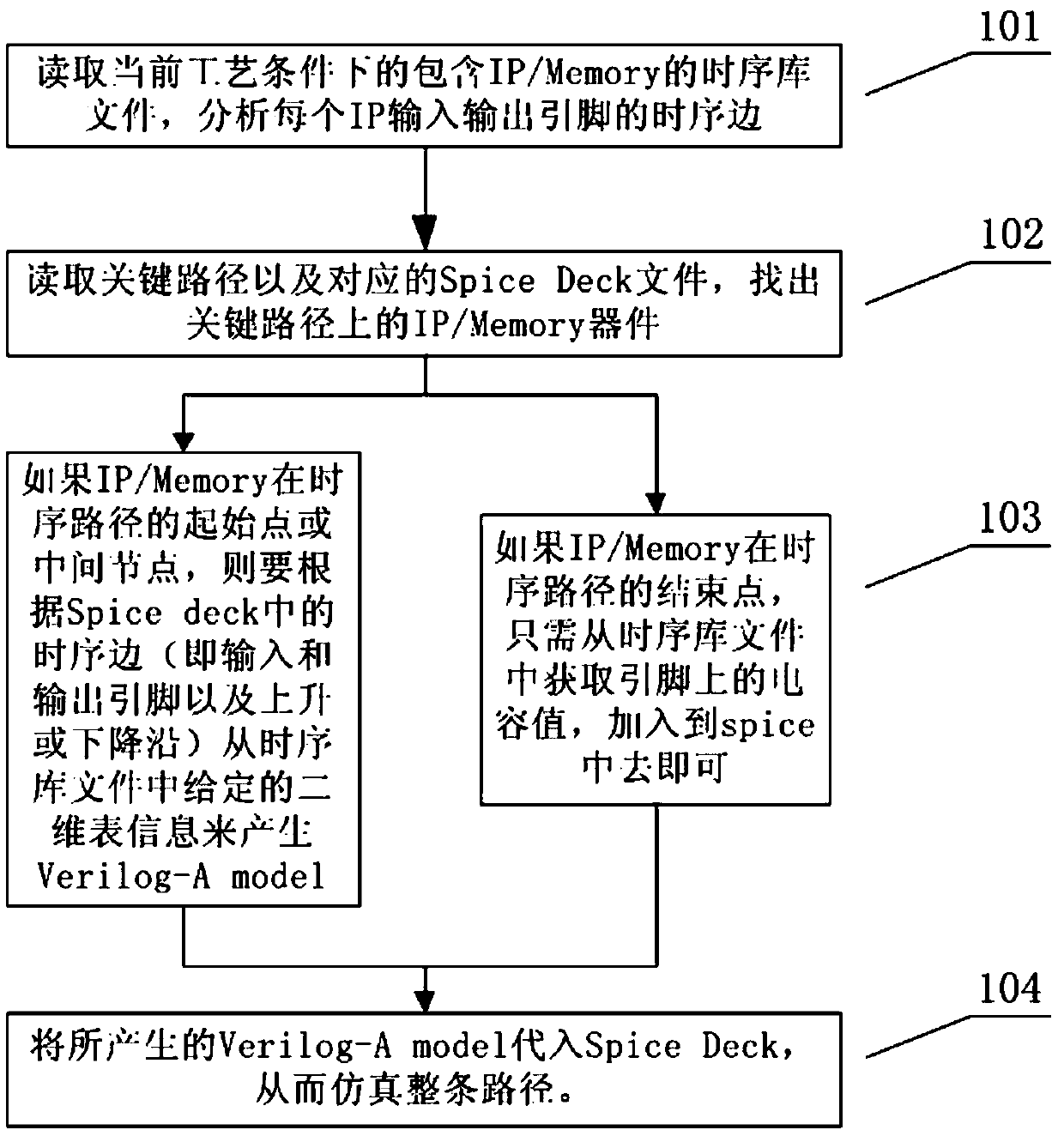

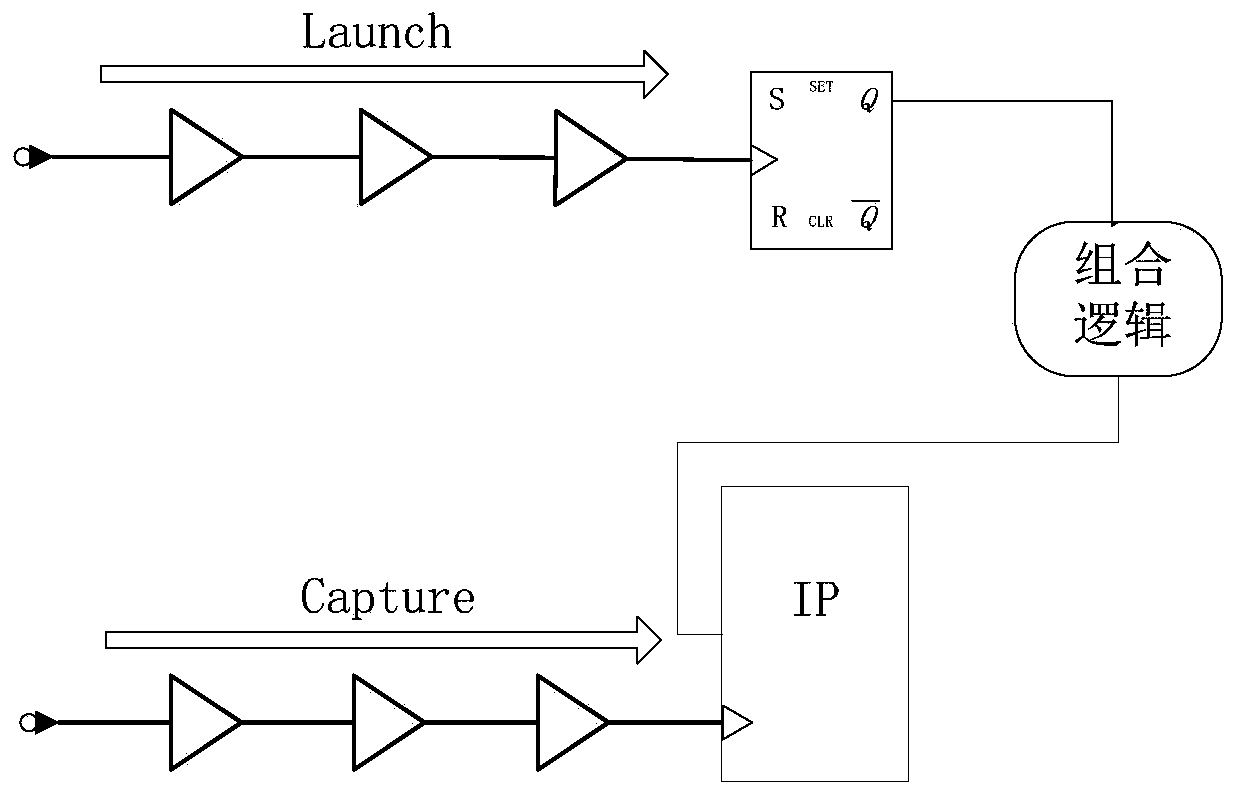

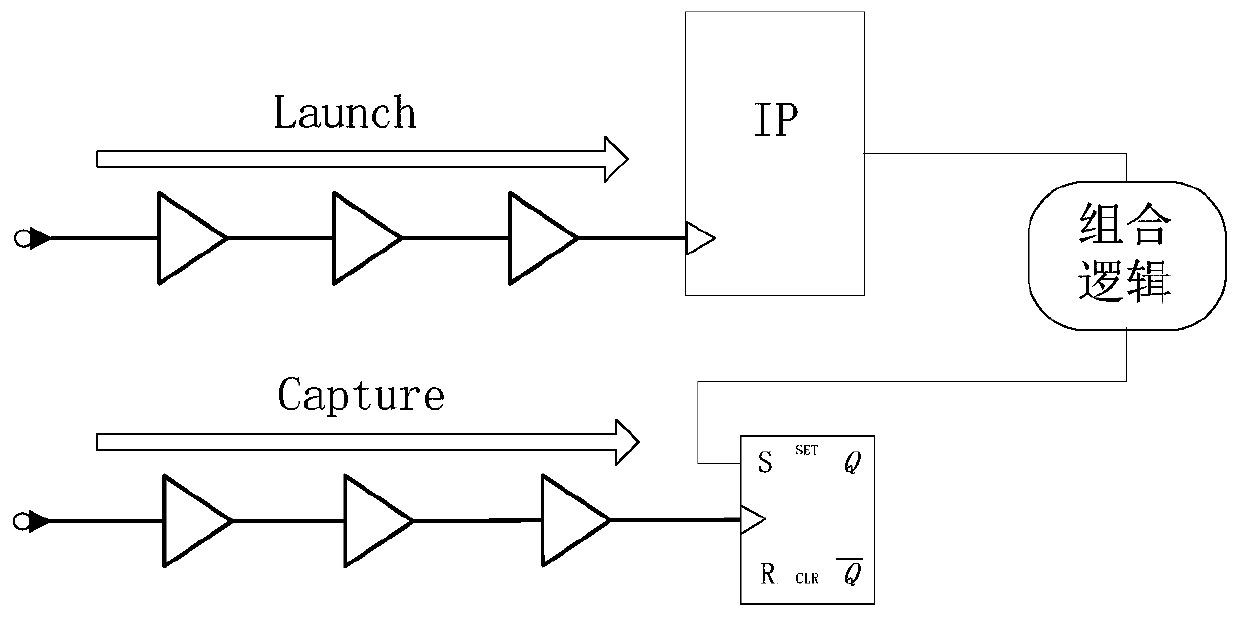

Spice simulation method including ip/memory timing path

ActiveCN107844678BAccuracy is not affectedImprove simulation speedComputer aided designSpecial data processing applicationsTime delaysEngineering

Provided is a spice simulation method containing an IP / Memory timing path. The method comprises the following steps: reading a IP / Memory-containing timing library file under a current technological condition and analyzing timing edges of input and output pins of each IP / Memory; reading a key path and a corresponding Spice Deck file and finding out an IP / Memory device in the key path; creating a Verilog-A model from given two-dimensional list information of the timing library file according to a timing edge of the Spice Deck in order to obtain time delay and output jump values of the device andobtaining capacitance values of the pins from the timing library file, and adding above values into the spice; taking the Verilog-A model into the Spice Deck so as to simulate an overall path. According to the method, simulation speed is increased evidently without affecting precision. Therefore, multiple paths containing IP / Memory can be simulated and can be widely accepted by many engineers inactual application.

Owner:北京华大九天科技股份有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com