Spice simulation method including ip/memory timing path

A simulation method and timing technology, which is applied in the fields of instrumentation, computing, and electrical digital data processing, etc., can solve problems such as restricting the application of spice simulation, inability to simulate timing paths, and difficulty in generating spice netlists.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

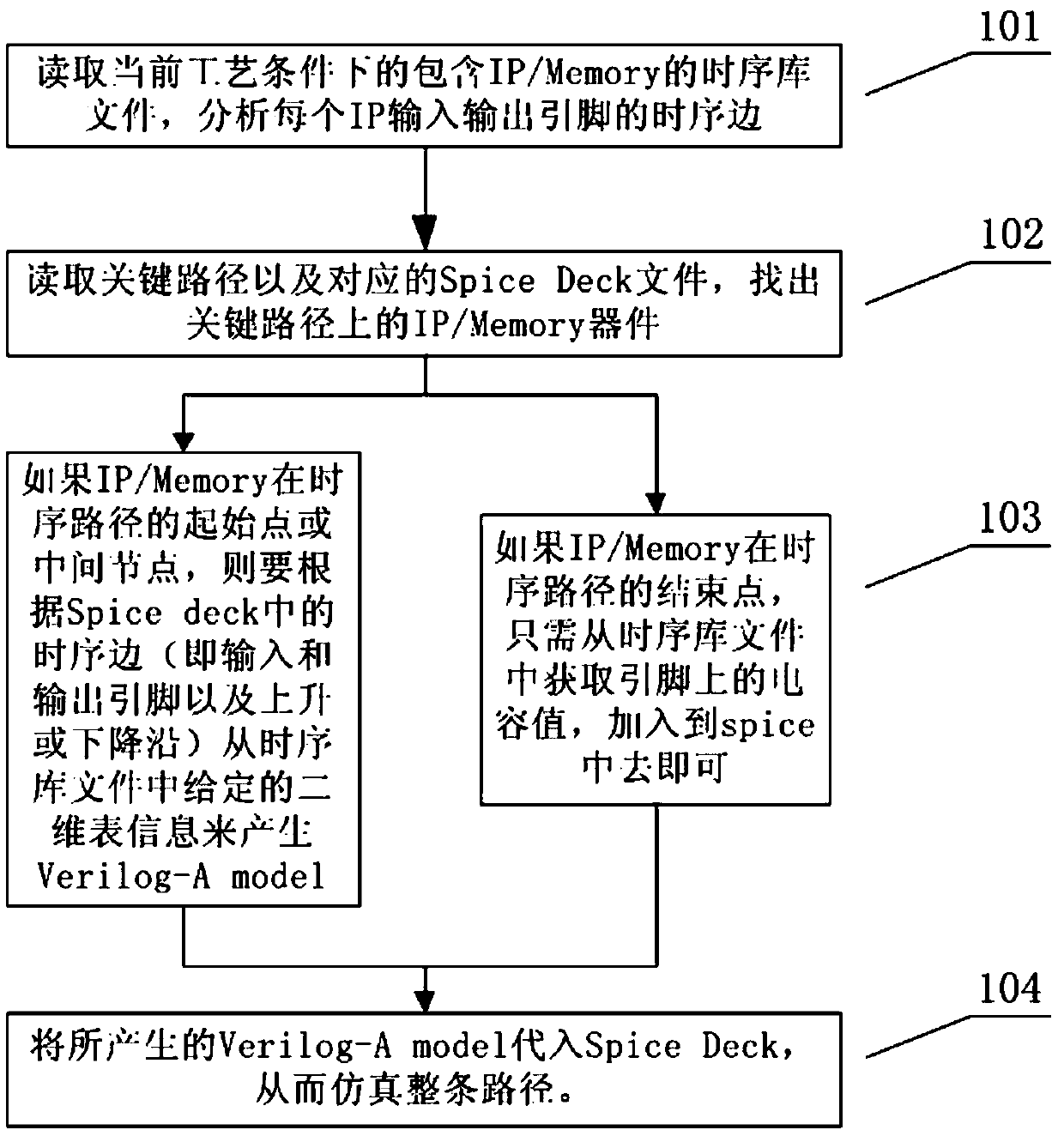

[0025] figure 1 It is a flow chart of the spice simulation method comprising IP / Memory timing path according to the present invention, which will be referred to below figure 1 , the spice simulation method including the IP / Memory timing path of the present invention is described in detail.

[0026] In step 101, the timing library file containing IP / Memory under the current process conditions is read, and the timing edge of each IP input and output pin is analyzed.

[0027] In step 102, the critical path and the corresponding Spice Deck file are read to find out the IP / Memory devices on the critical path.

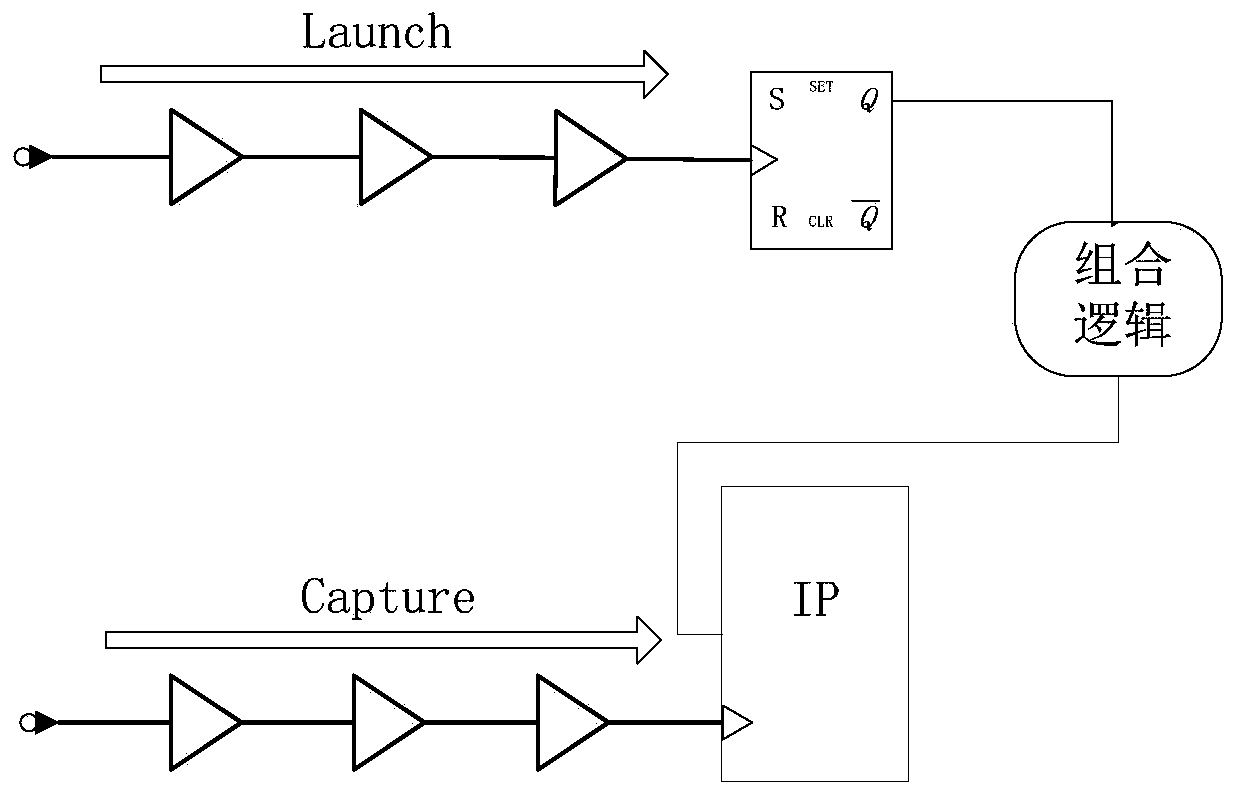

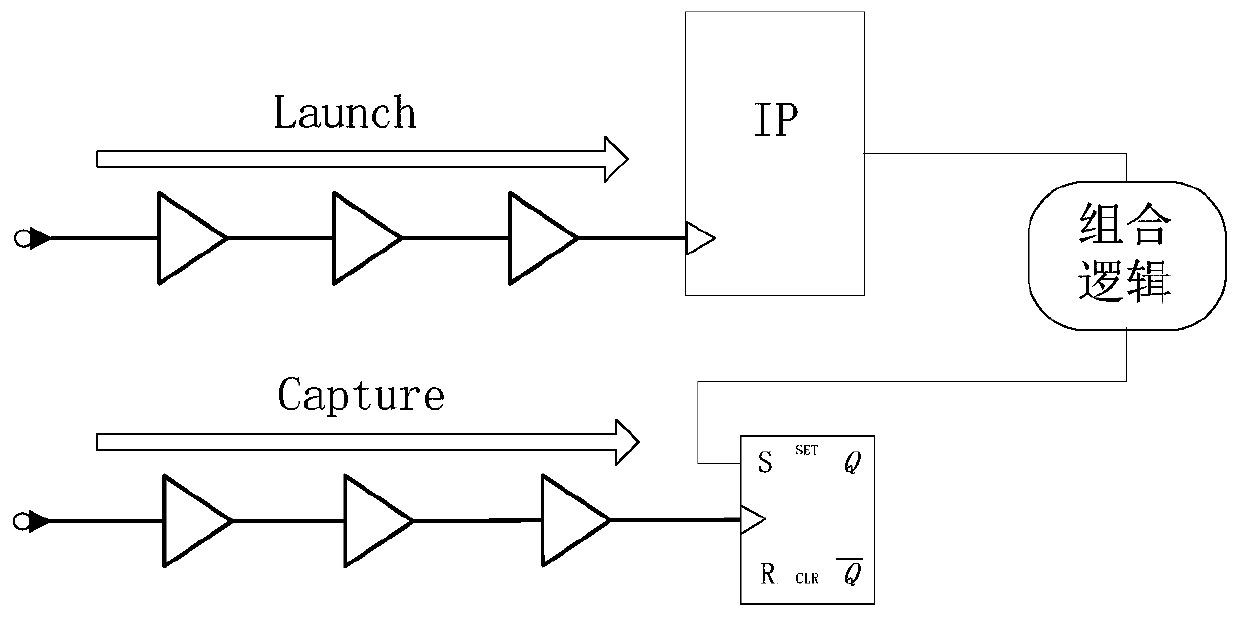

[0028] Among them, there are three positions of IP / Memory ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com